(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-323341

(P2006-323341A)

(43) 公開日 平成18年11月30日(2006.11.30)

| (51) Int.CI.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/36</b> (2006.01)  | G09G 3/36 | 2 H 093     |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 5 C 006     |

| <b>G02F 1/133</b> (2006.01) | G09G 3/20 | 5 C 080     |

|                             | G09G 3/20 | 6 2 3 X     |

|                             | G09G 3/20 | 6 2 1 B     |

審査請求 有 請求項の数 25 O L (全 24 頁) 最終頁に続く

|              |                              |            |                                |

|--------------|------------------------------|------------|--------------------------------|

| (21) 出願番号    | 特願2005-346689 (P2005-346689) | (71) 出願人   | 302062931                      |

| (22) 出願日     | 平成17年11月30日 (2005.11.30)     |            | N E C エレクトロニクス株式会社             |

| (31) 優先権主張番号 | 特願2005-119818 (P2005-119818) |            | 神奈川県川崎市中原区下沼部1753番地            |

| (32) 優先日     | 平成17年4月18日 (2005.4.18)       | (74) 代理人   | 100103894                      |

| (33) 優先権主張国  | 日本国 (JP)                     |            | 弁理士 家入 健                       |

|              |                              | (72) 発明者   | 橋本 義春                          |

|              |                              |            | 神奈川県川崎市中原区下沼部1753番地            |

|              |                              |            | N E C エレクトロニクス株式会社内            |

|              |                              | F ターム (参考) | 2H093 NA16 NA31 NA32 NA33 NA34 |

|              |                              |            | NA43 NC10 NC12 NC18 NC21       |

|              |                              |            | NC22 NC23 NC26 NC34 NC65       |

|              |                              |            | ND35 ND39 ND58                 |

最終頁に続く

(54) 【発明の名称】 液晶表示装置及びその駆動回路

## (57) 【要約】

【課題】液晶表示装置のデータ線駆動回路の回路規模の低減を図ること。

【解決手段】本発明の液晶表示装置は、複数の走査線4と、複数のデータ線3と、複数の走査線4と複数のデータ線3との各交点に設けられた画素5とを有する液晶表示装置であって、連続する複数のデータ線3と一の走査線4との各交点に設けられる画素5からなる画素グループを複数備え、各画素グループに含まれる全てのデータ線3には、信号を順次出力する時分割駆動によって同一極性の信号を出力し、互いに隣接する画素グループには逆極性の信号を出力し、各画素グループに含まれるデータ線3には、1フレーム毎に極性が反転した信号を出力する。

【選択図】 図5

**【特許請求の範囲】****【請求項 1】**

複数の走査線と、

複数のデータ線と、

前記複数の走査線と前記複数のデータ線との各交点に設けられた画素とを有する液晶表示装置であって、

連続する複数の前記データ線と一の前記走査線との各交点に設けられる画素からなる画素グループを複数備え、

各画素グループに含まれる全てのデータ線には、信号を順次出力する時分割駆動によって同一極性の信号を出力し、

互いに隣接する前記画素グループには逆極性の信号を出力し、

前記各画素グループに含まれるデータ線には、1フレーム毎に極性が反転した信号を出力する液晶表示装置。

**【請求項 2】**

前記データ線の極性が変化する前に前記データ線の電荷を電荷蓄積手段に蓄積することを特徴とする請求項1に記載の液晶表示装置。

**【請求項 3】**

各前記画素グループに含まれる夫々のデータ線は、当該画素グループに含まれるデータ線に時系列に信号を供給する信号線に選択的に接続されることを特徴とする請求項1又は2に記載の液晶表示装置。

**【請求項 4】**

各前記画素グループに含まれる前記複数のデータ線の本数は表示単位を構成する画素数の整数倍であることを特徴とする請求項1乃至3に記載の液晶表示装置。

**【請求項 5】**

基準電圧に対して極性の異なる正極のアナログ映像信号と負極のアナログ映像信号とを液晶表示装置のデータ線に出力する液晶表示装置の駆動回路であって、

1水平期間の所定の期間に前記正極のアナログ映像信号を第1の複数のデータ線に時分割に連続して出力すると同時に前記負極のアナログ映像信号を第2の複数のデータ線に時分割に連続して出力する液晶表示装置の駆動回路。

**【請求項 6】**

前記データ線の極性が変化する前に、前記データ線を前記基準電圧に近付くようにプリチャージすることを特徴とする請求項5に記載の液晶表示装置の駆動回路。

**【請求項 7】**

前記データ線の極性が変化する前に、前記データ線を前記基準電圧にプリチャージすることを特徴とする請求項5に記載の液晶表示装置の駆動回路。

**【請求項 8】**

前記基準電圧と前記基準電圧より高い第1の電圧とで規定される第1の電圧範囲で動作し、デジタル映像信号に応じて前記基準電圧に対して正極のアナログ映像信号を出力する正極D/A変換回路と、

前記基準電圧と前記基準電圧より低い第2の電圧とで規定される第2の電圧範囲で動作し、デジタル映像信号に応じて前記基準電圧に対して負極のアナログ映像信号を出力する負極D/A変換回路と、

前記正極D/A変換回路と前記データ線との間及び前記負極D/A変換回路と前記データ線との間に設けられ、前記第1の電圧以上である電圧と前記第2の電圧以下である電圧とで規定される第3の電圧範囲で動作し、前記正極D/A変換回路の出力端子を前記第1の複数のデータ線のうちのいずれかに選択的に接続し、前記負極D/A変換回路の出力端子を前記第2の複数のデータ線のうちのいずれかに選択的に接続する時分割選択回路と、

前記正極及び負極D/A変換回路と前記時分割選択回路との間に設け、前記データ線の極性が変化する前に前記データ線を前記基準電圧に近付くようにプリチャージするプリチャージ回路とを備える請求項5乃至7いずれかに記載の液晶表示装置の駆動回路。

10

20

30

40

50

**【請求項 9】**

1 水平期間の所定の期間に前記正極のアナログ映像信号を前記第1の複数のデータ線に時分割に連続して出力すると同時に前記負極のアナログ映像信号を前記第2の複数のデータ線に時分割に連続して出力し、前記データ線の極性が変化する前に、前記データ線が前記基準電圧にプリチャージされるように制御する制御回路を備える請求項6又は7に記載の液晶表示装置の駆動回路。

**【請求項 10】**

前記第3の電圧範囲で動作し、前記正極のアナログ映像信号または前記負極のアナログ映像信号を極性信号に応じて選択する極性選択回路をさらに備える請求項8に記載の液晶表示装置の駆動回路。

10

**【請求項 11】**

前記プリチャージ回路は、

複数のスイッチと、

第1及び第2の容量とを備え、

前記複数のスイッチ、前記時分割選択回路又は前記極性切換回路を制御して、プリチャージ期間の第1の期間に、前記第1の容量と前記第1の複数のデータ線を接続すると同時に前記第2の容量と前記第2の複数のデータ線を接続し、

プリチャージ期間の第2の期間に、前記第1及び第2の複数のデータ線を基準電圧に近く付くようにプリチャージし、

プリチャージ期間の第3の期間に、前記第1の容量と前記第2の複数のデータ線を接続すると同時に前記第2の容量と前記第1の複数のデータ線を接続することを特徴とする請求項8又は10に記載の液晶表示装置の駆動回路。

20

**【請求項 12】**

前記正極及び負極D/A変換回路に接続され、色単位を構成する各色ごとに調整可能である正極及び負極の階調電圧生成回路とをさらに備える請求項8に記載の液晶表示装置の駆動回路。

**【請求項 13】**

前記時分割選択回路は、前記データ線が配置されるパネル基板上に形成され、

前記正極D/A変換回路、負極D/A変換回路及びプリチャージ回路は、前記パネル基板とは異なる半導体基板上に形成される請求項8に記載の液晶表示回路の駆動回路。

30

**【請求項 14】**

前記時分割選択回路及びプリチャージ回路は、前記データ線が配置されるパネル基板上に形成され、

前記正極D/A変換回路及び負極D/A変換回路は、前記パネル基板とは異なる半導体基板上に形成される請求項8に記載の液晶表示回路の駆動回路。

40

**【請求項 15】**

基準電圧に対して極性の異なる正極のアナログ映像信号と負極のアナログ映像信号とを表示装置のデータ線に出力する液晶表示装置の駆動回路であって、

基板上の第1の連続領域に形成され、前記正極のアナログ映像信号を出力端子に出力する正極駆動回路と、

前記正極駆動回路と出力端子との間に設けられ、前記データ線の極性が正極から負極に変化する前に前記データ線を前記基準電圧近傍にプリチャージする正極プリチャージ回路と、

前記基板上の前記第1の連続領域と異なる第2の連続領域に形成され、前記負極のアナログ映像信号を出力端子に出力する負極駆動回路と、

前記負極駆動回路と出力端子との間に設けられ、前記データ線の極性が負極から正極に変化する前に前記データ線を前記基準電圧近傍にプリチャージする負極プリチャージ回路とを備える液晶表示装置の駆動回路。

**【請求項 16】**

前記正極のアナログ映像信号と前記負極のアナログ映像信号とを極性信号に応じて選択

50

する極性切換回路を備える請求項 1 5 に記載の液晶表示装置の駆動回路。

**【請求項 1 7】**

前記正極駆動回路及び正極プリチャージ回路は、第 1 の電圧 > 基準電圧であるような、前記第 1 の電圧と基準電圧とで規定される電圧範囲で動作する前記第 1 の連続領域に形成され、

前記負極駆動回路及び負極プリチャージ回路は、前記基準電圧 > 第 2 の電圧であるような、前記基準電圧と前記第 2 の電圧とで規定される電圧範囲で動作する前記第 2 の連続領域に形成され、

前記極性切換回路は、前記第 1 の電圧以上の電圧と前記第 2 の電圧以下の電圧とで規定される電圧範囲で動作する前記第 3 の連続領域に形成されている請求項 1 6 に記載の液晶表示装置の駆動回路。10

**【請求項 1 8】**

前記第 1 の連続領域、前記第 2 の連続領域及び前記第 3 の連続領域には、それぞれ M O S ドラジスタを形成し、

前記第 1 の連続領域及び前記第 2 の連続領域の M O S ドラジスタのゲート酸化膜の厚さは、前記第 3 の連続領域の M O S ドラジスタのゲート酸化膜の厚さよりも薄い請求項 1 7 に記載の液晶表示装置の駆動回路。10

**【請求項 1 9】**

前記第 1 の連続領域、前記第 2 の連続領域及び前記第 3 の連続領域には、それぞれ M O S ドラジスタを形成し、20

前記第 1 の連続領域及び前記第 2 の連続領域の前記 M O S ドラジスタのゲート長の長さは、前記第 3 の連続領域の M O S ドラジスタのゲート長よりも短い請求項 1 7 に記載の液晶表示装置の駆動回路。20

**【請求項 2 0】**

電圧調整範囲が、システムグランドより低く負極駆動回路又は負極 D / A 変換回路の低位電圧より高い直流電圧か、又はシステムグランドより高く正極駆動回路又は正極 D / A 変換回路の高位電圧より低い直流電圧を生成して前記液晶表示装置の共通電極に供給する電源回路を備える請求項 8 、 1 5 に記載の液晶表示装置の駆動回路。

**【請求項 2 1】**

基準電圧に対して極性の異なる正極のアナログ映像信号と負極のアナログ映像信号とを表示装置のデータ線に出力する液晶表示装置の駆動回路であって、30

基板上の第 1 の連続領域に形成され、前記正極のアナログ映像信号を、前記データ線に出力するための出力端子に出力する正極駆動回路と、

前記基板上の前記第 1 の連続領域と異なる第 2 の連続領域に形成され、前記負極のアナログ映像信号を、前記データ線に出力するための出力端子に出力する負極駆動回路と、

前記データ線に接続され、前記データ線の極性が正極から負極に変化する前に前記データ線を前記基準電圧近傍にプリチャージする正極プリチャージ回路と、

前記データ線に接続され、前記データ線の極性が負極から正極に変化する前に前記データ線を前記基準電圧近傍にプリチャージする負極プリチャージ回路とを備える液晶表示装置の駆動回路。40

**【請求項 2 2】**

前記正極のアナログ映像信号と前記負極のアナログ映像信号とを極性信号に応じて選択する極性切換回路を備える請求項 2 1 に記載の液晶表示装置の駆動回路。

**【請求項 2 3】**

基準電圧に対して極性の異なる正極のアナログ映像信号と負極のアナログ映像信号とを液晶表示装置のデータ線に出力し、デジタルの映像信号をアナログの映像信号に変換する D / A 変換回路を含むデータ線駆動回路を半導体基板上に集積化した液晶表示装置の駆動回路であって、

前記正極及び負極のアナログの映像信号の電圧範囲よりも広い電圧範囲の制御信号を前記半導体基板と異なる基板に形成された回路に供給する液晶表示装置の駆動回路。50

**【請求項 2 4】**

前記半導体基板と異なる基板に形成された回路は、前記データ線駆動回路から出力される連続した同一極性のアナログ映像信号を複数の前記データ線に時分割に選択して出力する時分割選択回路であることを特徴とする請求項 2 3 に記載の液晶表示装置の駆動回路。

**【請求項 2 5】**

前記半導体基板と異なる基板に形成された回路は、前記データ線の極性が変化する前に前記データ線の電荷を電荷蓄積手段に蓄積する電荷リサイクル回路であることを特徴とする請求項 2 3 に記載の液晶表示装置の駆動回路。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、液晶表示装置及びその駆動回路に関し、特にパネルの片側にのみ D / A 変換回路を含むデータ線駆動回路を配置してドット反転駆動するのに好適な液晶表示装置及び駆動回路に関する。

**【背景技術】****【0 0 0 2】**

公知の液晶表示装置において、データ線から TFT を介して画素に印加される電圧（以下、画素電圧という）の極性は、所定の期間ごとに反転する。つまり、画素は交流的に駆動される。ここで、極性とは、液晶の共通電極の電圧（com 電圧）を基準とした場合の画素電圧の正負を示す。このような駆動方法は、液晶材料が劣化するのを抑制するために適用されている。

**【0 0 0 3】**

例えば、隣り合う画素ごとに極性が異なるように隣り合うデータ線及び隣り合う走査線ごとに画素電圧の極性を反転するドット反転駆動方式や、隣り合うデータ線ごとに反転し、2 本走査線ごとに極性を反転する 2H ドット反転駆動方式などが知られ、これらの駆動方式により、フリッカなどが低減され画質が向上する。

**【0 0 0 4】**

また、特許文献 1 には、1 つの D / A 変換回路で複数のデータ線を時分割に駆動する回路が開示されている。特許文献 1 では、奇数番目のデータ線は上側のデータ線駆動回路に接続し、偶数番目のデータ線は下側のデータ線駆動回路に接続し、任意の水平期間（走査期間ともいう）に上側のデータ線駆動回路で正極のアナログ映像信号を出力すると同時に下側のデータ線駆動回路で負極のアナログ映像信号を出力し、次の水平期間では、上側のデータ線駆動回路で負極のアナログ映像信号を出力すると同時に下側のデータ線駆動回路で正極のアナログ映像信号を出力することでドット反転駆動を実現している。また、水平ブランкиング期間にデータ線を com 電圧に初期化する初期化回路を有し、書き込み時間、書き込む順序を制御して時分割駆動している。そして、データ線駆動回路の外部から供給される階調電圧は、1 水平期間ごとに反転させている。そのため、階調電圧を選択するスイッチ群は高圧素子で製造している。尚、特許文献 2 には、RGB 時分割駆動を行う構成が記載されている。

**【特許文献 1】特開平 8 - 129362 号公報****【特許文献 2】特開 2004 - 258485 号公報****【発明の開示】****【発明が解決しようとする課題】****【0 0 0 5】**

しかしながら、この従来の駆動回路にはいくつかの問題点がある。第 1 の問題点は、パネルの上下にデータ線駆動回路を実装する領域が必要となることである。このことによりパネルサイズが大きくなるため 1 枚のマザーガラスから取れるパネル数が減少する。また、データ線駆動回路に信号や電源を供給するフレキシブル基板の配線の面積が大きくなる。

**【0 0 0 6】**

10

20

30

40

50

第2の問題点は、階調電圧を選択するスイッチ群は高圧素子で製造するので、回路面積が増大することである。通常、電源電圧が高いと回路を構成する素子の耐圧を高くする必要があり、ゲート酸化膜T o xを厚く、ゲート長Lを長く、また素子間の距離を長くするなどしているため、回路面積が大きくなる。

【課題を解決するための手段】

【0007】

本発明の液晶表示装置は、複数の走査線と、複数のデータ線と、前記複数の走査線と前記複数のデータ線との各交点に設けられた画素とを有する液晶表示装置であって、連続する複数の前記データ線と一の前記走査線との各交点に設けられる画素からなる画素グループを複数備え、各画素グループに含まれる全てのデータ線には、信号を順次出力する時分割駆動によって同一極性の信号を出力し、互いに隣接する前記画素グループには逆極性の信号を出力し、前記各画素グループに含まれるデータ線には、1フレーム毎に極性が反転した信号を出力する。これによって回路規模を低減することができる。

【0008】

次に、本発明の液晶表示装置の駆動回路は、基準電圧に対して極性の異なる正極のアナログ映像信号と負極のアナログ映像信号とを液晶表示装置のデータ線に出力する液晶表示装置の駆動回路であって、1水平期間の所定の期間に前記正極のアナログ映像信号を第1の複数のデータ線に時分割に連続して出力すると同時に前記負極のアナログ映像信号を第2の複数のデータ線に時分割に連続して出力する。これによって回路規模を低減することができる。

【0009】

また、本発明の液晶表示装置の駆動回路は、基準電圧に対して極性の異なる正極のアナログ映像信号と負極のアナログ映像信号とを表示装置のデータ線に出力する液晶表示装置の駆動回路であって、基板上の第1の連続領域に形成され、前記正極のアナログ映像信号を出力端子に出力する正極駆動回路と、前記正極駆動回路と出力端子との間に設け、前記データ線の極性が正極から負極に変化する前に前記データ線を前記基準電圧にプリチャージする正極プリチャージ回路と、前記基板上の前記第1の連続領域と異なる第2の連続領域に形成され、前記負極のアナログ映像信号を出力端子に出力する負極駆動回路と、前記負極駆動回路と出力端子との間に設け、前記データ線の極性が負極から正極に変化する前に前記データ線を前記基準電圧にプリチャージする負極プリチャージ回路を備える。これにより高耐圧素子の使用を低減することができ、回路規模の低減を図ることができる。

【発明の効果】

【0010】

本発明によれば、液晶表示装置のデータ線駆動回路の回路規模の低減を図ることができる。

【発明を実施するための最良の形態】

【0011】

以下に、本発明を適用可能な実施の形態が説明される。以下の説明は、本発明の実施形態を説明するものであり、本発明が以下の実施形態に限定されるものではない。説明の明確化のため、以下の記載は、適宜、省略及び簡略化がなされている。又、当業者であれば、以下の実施形態の各要素を、本発明の範囲において容易に変更、追加、変換することが可能である。

【0012】

実施の形態1.

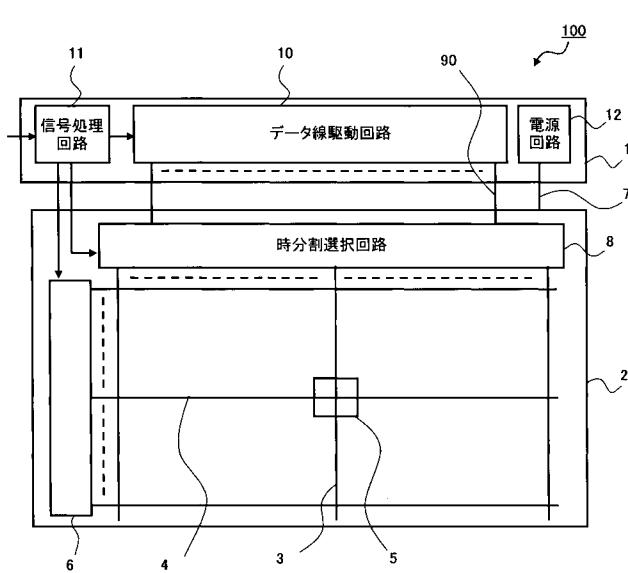

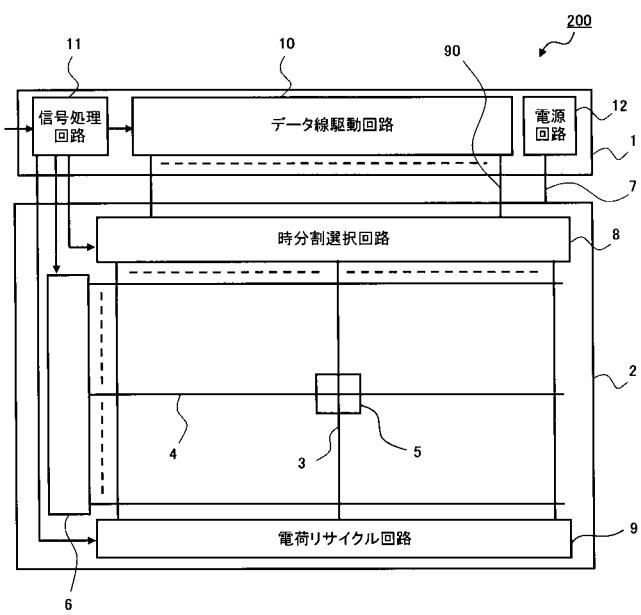

図1に本形態の液晶表示装置100のブロック図を示す。液晶パネルの基板2上には、複数のデータ線3と、データ線3と直交するように複数の走査線4とが形成され、その各交点にスイッチング素子としてのTFT(Thin Film Transistor)と液晶などを含む画素5が形成されている。画素5には、液晶に電界を印加する表示電極と共に共通電極が形成されている。表示電極にはデータ線3から画素の輝度(光の透過量)を制御するアナログ映像信号が供給され、共通電極には直流電圧(DC)のcom電圧が共通電極線7から供給さ

10

20

30

40

50

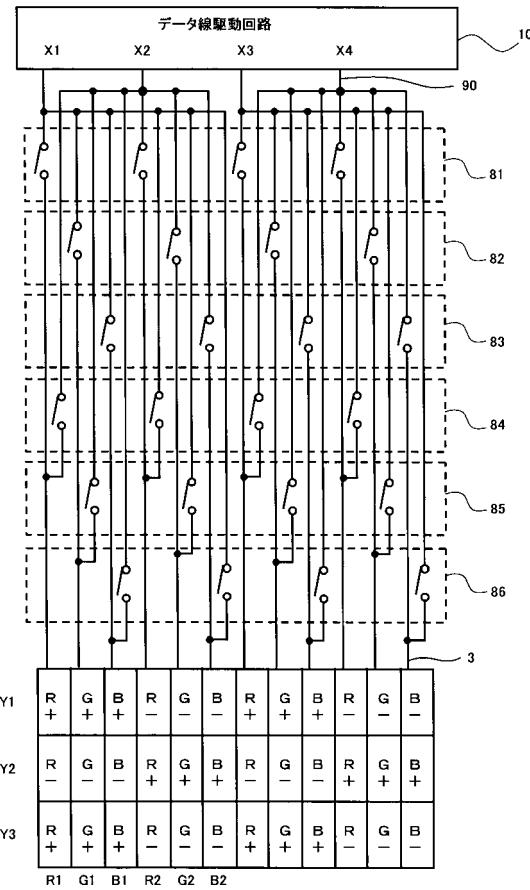

れる。さらに、基板 2 上には、走査線 4 を駆動する走査線駆動回路 6 と、データ線駆動回路 10 のデータ線 90 から供給されるアナログ映像信号を時分割に切り換える時分割選択回路 8 などが形成されている。

#### 【 0 0 1 3 】

また、基板 2 の片側のみにドライバ I C 1 が配置され、このドライバ I C 1 にデータ線駆動回路 10、信号処理回路 11、及び電源回路 12 が設けられている。データ線駆動回路 10 は、デジタル映像信号に対応してデータ線 3 及び画素 5 にアナログ映像信号を供給する。このデータ線駆動回路 10 は、上記のように、基板 2 の片側のみに配置し、また、後述する D / A 変換回路から出力されるアナログ映像信号の出力電圧精度の点から、相対精度の高いシリコンなどの半導体基板上にドライバ I C 1 として集積化することが好ましい。また、信号処理回路 11 などはマクロ化された回路を使用し自動レイアウトすることから多層配線が容易である半導体基板上に集積化するのが好ましい。10

#### 【 0 0 1 4 】

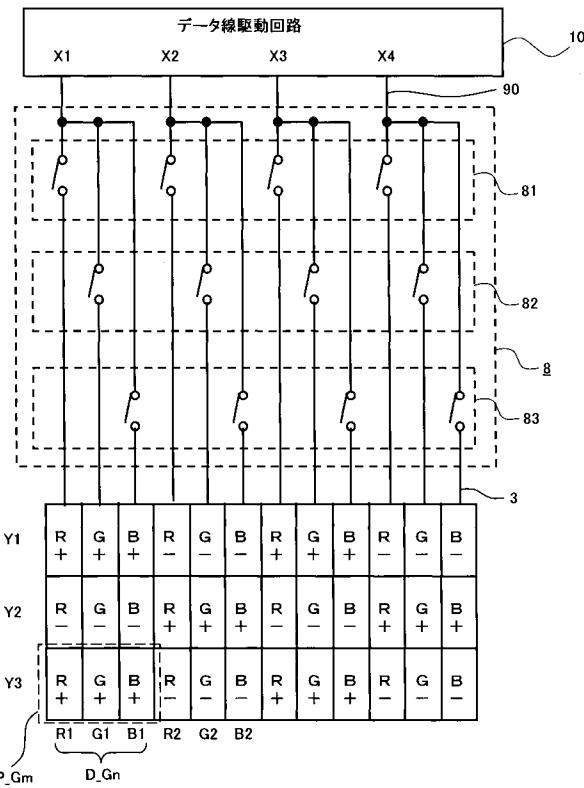

次に、図 2 に、本発明の液晶表示装置の駆動回路の一部である時分割選択回路 8 の詳細図を示す。データ線駆動回路 10 の 1 つの出力端子 X<sub>n</sub> (データ線 90) に対し、3 つのデータ線 3 が時分割スイッチ 81、82、83 を介して接続されている。ここでは、例として、3 分割駆動で説明するが分割数は 4 以上であってもよい。ただし、表示単位が 3 色である場合において分割数が 4 であった場合、一の色を構成する R G B の各信号が分割される場合がある。一の色を構成する R G B の各信号が異なる経路を通過することにより、経路による微細な特性の違いが与える影響によって、R G B 間のバランスに誤差が生じ、色むらの原因となる場合がある。一つの色を構成する表示単位が R G B の 3 色であり、表示単位を構成する画素数が 3 であることから、色むら等が発生しないように 6 分割や 9 分割など 3 の倍数の分割数であることが好ましい。20

#### 【 0 0 1 5 】

ここで、本明細書においては、データ線駆動回路 10 の同一の出力端子 X<sub>n</sub> から出力され、時分割選択回路 8 によって分割されるアナログ映像信号が供給される画素及びデータ線を夫々画素グループ、データ線グループと定義する。図 2 においては、R 1、G 1、B 1 の 3 本のデータ線が一つのデータ線グループ D\_G<sub>n</sub> であり、更に一のデータ線グループにおける一のライン Y 1、Y 2、Y 3 毎に画素グループ P\_G<sub>m</sub> が定義される。30

#### 【 0 0 1 6 】

また、時分割選択回路 8 は、前述したように基板 2 上に製造され、ドライバ I C 1 内部の信号処理回路 11 で制御される。時分割選択回路 8 の制御回路を基板 2 上に形成して制御してもよいが、データ線駆動回路 10 との制御信号の同期が取りやすいようにドライバ I C 1 内部の信号処理回路 11 で直接行うのが好ましい。40

#### 【 0 0 1 7 】

次に電源回路 12 について説明する。電源回路 12 は、ドライバ I C 1 の外部から供給される直流電源 V D C からデータ線駆動回路 10 や走査線駆動回路 6 に供給する電圧を生成する回路で、D C D C コンバータやレギュレータなどで構成され、データ線駆動回路 10 の正極の高位電源電圧 V P H、負極の低位電源電圧 V N L、走査線駆動回路 6 の高位電源電圧 V G H、低位電源電圧 V G Lなどを生成する。ここでは、データ線駆動回路 10 の正極の低位電源電圧及び負極の高位電源電圧をシステムグランド G N D とし、V P H = 5 V、V N L = - 5 V、V G H = 10 V、V G L = - 10 V として説明する。

#### 【 0 0 1 8 】

この電源回路 12 は、電源の出力インピーダンス特性などから基板 2 上に形成する T F T に比べ移動度が高く、多層配線が容易なシリコン基板上に集積化するのが好ましい。本実施の形態においては、ドライバ I C 1 として上記データ線駆動回路 10 及び信号処理回路 11 と共に集積化されている。

#### 【 0 0 1 9 】

また、電源回路 12 では、液晶の共通電極の電圧 (c o m 電圧) も生成している。c o m 電圧は、例えば G N D より低く、負極駆動回路の低位電圧より高い直流電圧か、又は G

N Dより高く、正極駆動回路の高位電圧より低い直流電圧とすることができる。これは、液晶パネルのTFTをオフにするとフィードスルー誤差が発生するために、その誤差を補正する必要があり、液晶の共通電極の電圧は-1Vなど直流電圧にする。フィードスルー誤差の量はパネルごとに異なるため、例えば、TFTがn型であれば、フィードスルー誤差は負側になりやすいのでGNDから-2V程度の範囲で微調整する。TFTがp型であれば、フィードスルー誤差は正側になりやすいのでGNDから+2V程度の範囲で微調整する。一般にn型のTFTが多いので、以降の説明ではn型のTFTでの説明をする。

#### 【0020】

c o m電圧は、正極の高位電圧V P Hと負極の低位電圧V N Lで動作するバッファで生成し、c o m電圧として2Vから-2Vの電圧を出力してもよい。なお、バッファは高圧素子で製造する。バッファをGNDと負側の電圧V N Lで動作させると、GNDの電圧が出力されにくくなるが、調整電圧範囲をGNDまで保証しないのであればバッファを中圧素子で製造してもよい。

#### 【0021】

また、c o m電圧は、GNDとV N Lとの間に抵抗分圧回路を設け、抵抗と抵抗との接続点にバイパスコンデンサを設ける簡単な構成の回路により生成するようにしてよい。

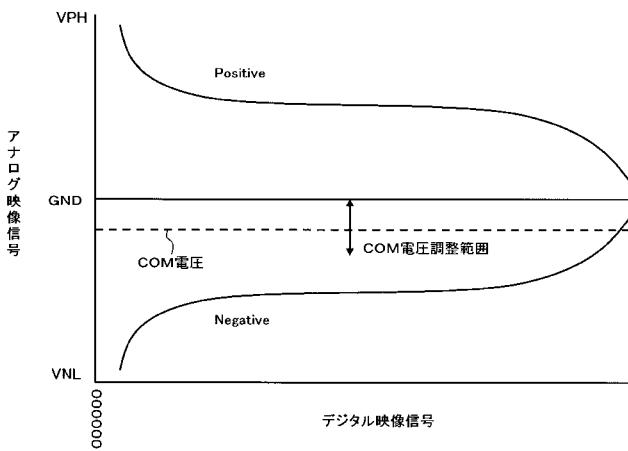

#### 【0022】

図3には、正極のガンマカーブ(P o s i t i v e)と負極のガンマカーブ(N e g a t i v e)及びc o m電圧の関係を示す。正極のガンマカーブはGND以上V P H以下の電圧で、負極のガンマカーブはV N L以上GND以下となるようにして、c o m電圧を-1±1Vの範囲で微調整する。微調整の範囲は便宜的に±1としたが、前述のようにGNDと負極の低位電圧V N Lで製造すれば、その範囲で調整可能である。このように、c o m電圧を、GND付近の電圧にすることで、電源回路12でのD C D Cコンバータの昇圧回数を削減して電源回路12の効率を向上させ、消費電力の低減を図ることができる。

#### 【0023】

次に、信号処理回路11について説明する。信号処理回路11に入力する信号は、少なくともデジタル映像信号D x、クロック信号C L K、垂直同期信号V s y n c、水平同期信号H s y n cを含み、これらの信号から信号処理回路11にて水平スタート信号S T H、ラッチ信号S T B、極性信号P O L、時分割スイッチ制御信号、垂直スタート信号S T Vなどの所望のタイミング信号を生成し、データ線駆動回路10の各回路、時分割選択回路8及び走査線駆動回路6等を制御している。基板2上の回路は、V G H、V G Lの電源電圧で動作させるので、基板2上に供給する各信号は、レベルシフトしたV G H、V G Lの信号を供給する。

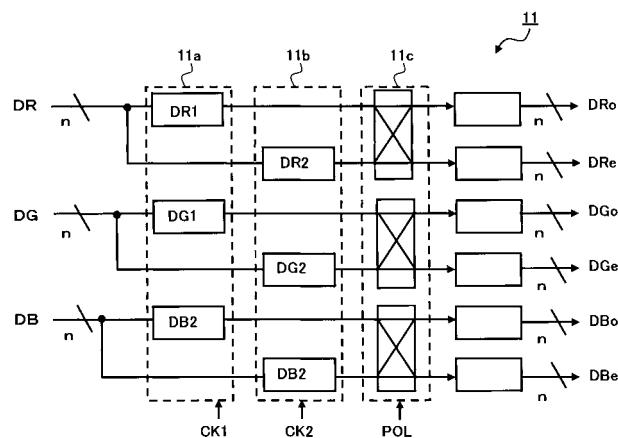

#### 【0024】

信号処理回路11は、クロックC K 1、C K 2のタイミングでデジタル映像信号D x(D R、D G、D B)をラッチするそれぞれラッチ回路11a、11bと、極性信号P O Lに応じてデータバスD R o、D G o、D B oとデータバスD R e、D G e、D B eとを切り換える切替回路11cとを有する。この信号処理回路11は、図4に示すように、外部から供給される1画素分(18ビット)のデジタル映像信号D x(D R、D G、D B)をラッチ回路11a及びラッチ回路11bで2クロック分つまり2画素分(36ビット)にまとめてからデータ線駆動回路10に出力している。図に示されるようにデジタル映像信号D xはデータバスD R o、D R e、D G o、D G e、D B o、D B eに出力される。また、切替回路11cが極性信号P O Lに応じて、デジタル映像信号D xのデータバスD R o、D G o、D B o、又はデータバスD R e、D G e、D B eへの出力を切り替える。これは、正極と負極のアナログの映像信号がデータ線駆動回路10内部で切り換えられるので、これに対応するようにデジタル映像信号D xのデータバスへの出力の入れ替えを行うためである。さらに、2画素分まとめてデータ線駆動回路10に供給することで、データ線駆動回路10でのクロック信号の周波数が半減し、高周波数の電磁波が発生しないという効果がある。

#### 【0025】

10

20

30

40

50

本発明のデータ線駆動回路10は、正極のアナログ映像信号と負極のアナログ映像信号をデータ線駆動回路10のそれぞれの出力端子X<sub>n</sub>から同時に出力する駆動回路である。ここで、正極、負極とは液晶の液晶共通電極の電圧（c o m電圧）を基準とした場合の画素電圧の正負を示すが、本形態においては、基準電圧をシステムグランドG N D（0 V）とした場合の画素電圧の正負として説明する。

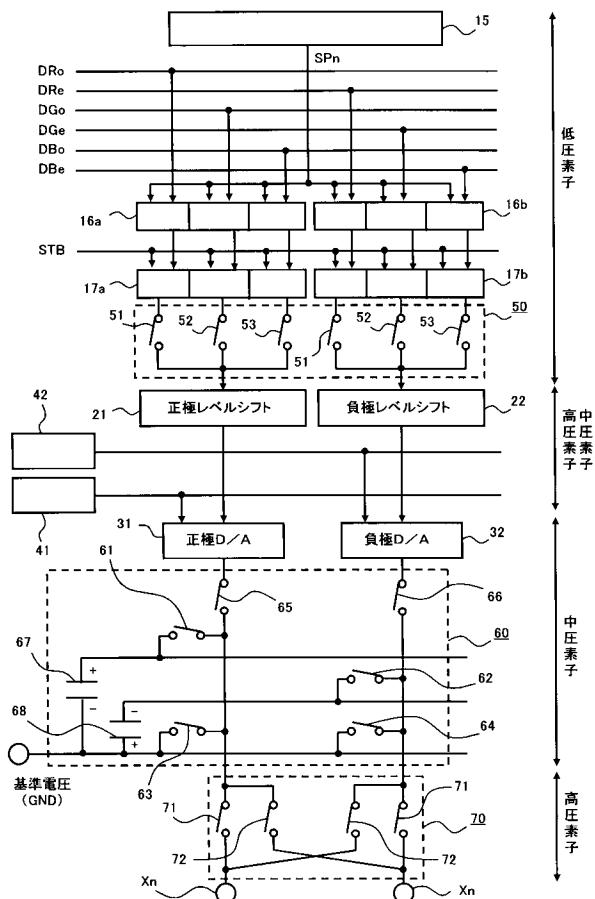

#### 【0026】

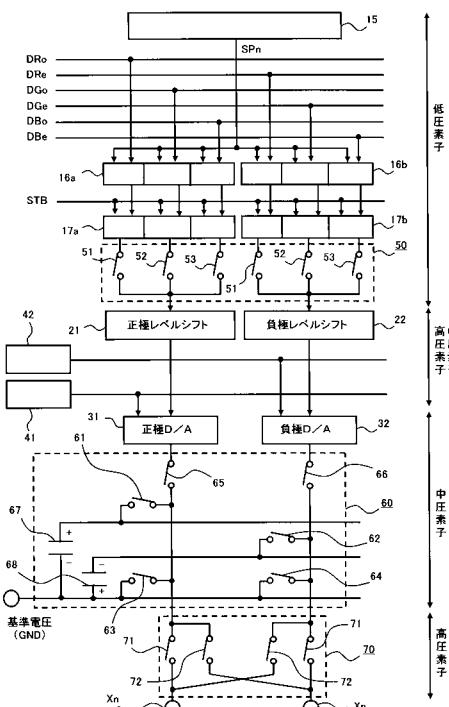

図5に、データ線駆動回路10のブロック図を示し、各部の構成について説明する。データ線駆動回路10は、少なくともデータラッチ回路17、正極レベルシフト回路21、負極レベルシフト回路22、正極D/A変換回路31、負極D/A変換回路32、正極階調電圧生成回路41、負極階調電圧生成回路42、及びプリチャージ回路60を含む回路で構成される。さらに、デジタル映像信号時分割回路50や、シフトレジスタ回路15や、データレジスタ回路16、フレームメモリ（図示なし）を内蔵してもよい。

#### 【0027】

データレジスタ回路16は正極データレジスタ回路16a、及び負極データレジスタ回路16bを有する。正極データレジスタ回路16aはデジタル映像信号D<sub>x</sub>のデータバスD R<sub>o</sub>、D G<sub>o</sub>、D B<sub>o</sub>に接続されており、シフトレジスタ回路15から入力されるサンプリング信号S P<sub>n</sub>に応じてデータバスD R<sub>o</sub>、D G<sub>o</sub>、D B<sub>o</sub>からのデジタル映像信号をラッチする。負極データレジスタ回路16bはデジタル映像信号D<sub>x</sub>のデータバスD R<sub>e</sub>、D G<sub>e</sub>、D B<sub>e</sub>に接続されており、シフトレジスタ回路15のサンプリング信号S P<sub>n</sub>に応じてデータバスD R<sub>e</sub>、D G<sub>e</sub>、D B<sub>e</sub>からのデジタル映像信号をラッチする。

#### 【0028】

データレジスタ回路16はデータラッチ回路17に接続されている。データラッチ回路17は正極データラッチ回路17a、負極データラッチ回路17bを有し、データレジスタ回路16でラッチしたデジタル映像信号D<sub>x</sub>を再度ラッチする。データラッチ回路17はデジタル映像信号時分割回路50に接続されている。デジタル映像信号時分割回路50は時分割スイッチ51、52、53を備え、これらのスイッチを切り換えることによって、データラッチ回路17でラッチされたデジタル映像信号D<sub>x</sub>を時系列に順次出力する。デジタル映像信号時分割回路50による当該時分割動作は、信号処理回路11から入力される制御信号により制御される。

#### 【0029】

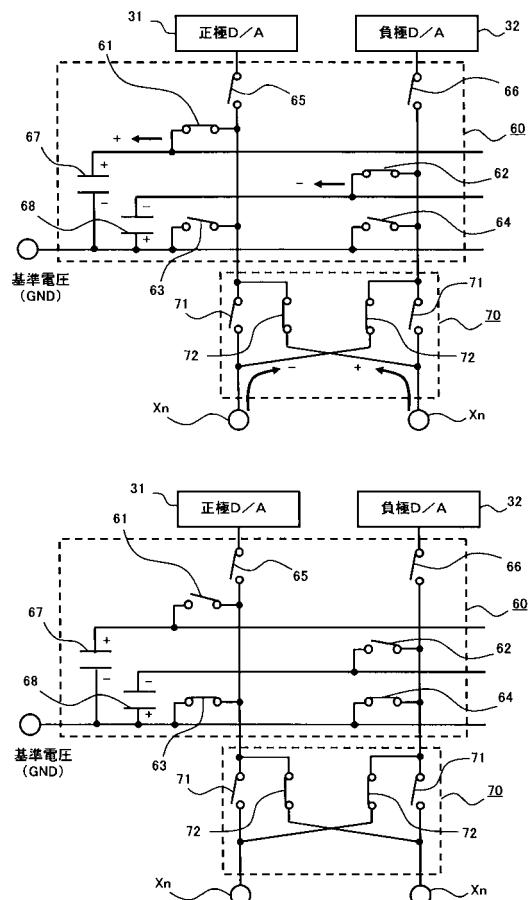

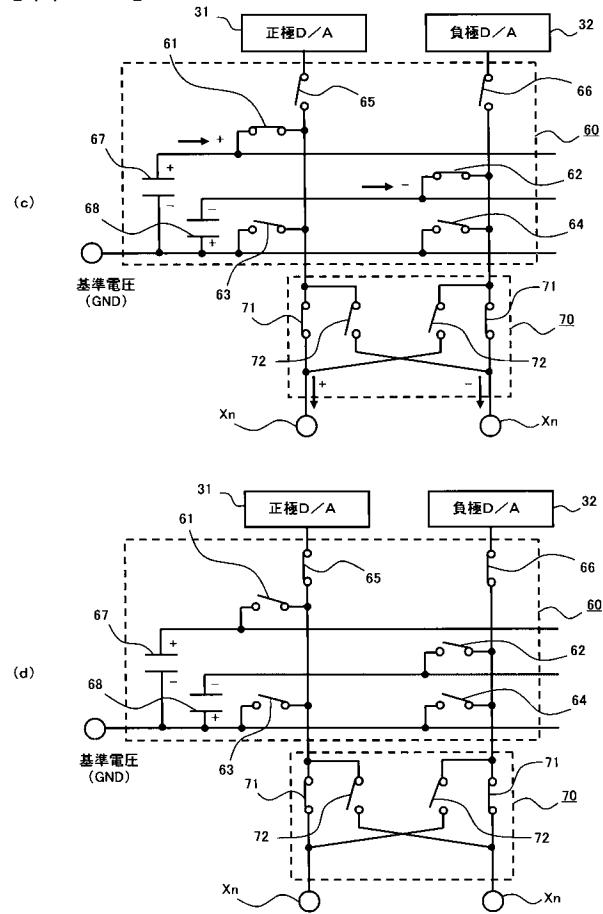

プリチャージ回路60は、少なくともデータ線を基準電圧にプリチャージするプリチャージスイッチ63、64と、D/A変換回路31、32と出力端子X<sub>n</sub>間の接続スイッチ65、66とを有する。更に本実施の形態においては、低消費電力に駆動するための電荷リサイクルスイッチ61、62と電荷リサイクル容量67、68を有する。そして、これらのスイッチは後述の中圧素子で形成する。電荷リサイクル容量67、68は、容量値が大きい方が電荷のリサイクル効果が向上するためドライバIC1の外部に設けるのが好ましい。ここで、電荷リサイクルスイッチ61、プリチャージスイッチ63及び接続スイッチ65は、G N DからV P L（5 V）の電圧範囲で動作し、電荷リサイクルスイッチ62、プリチャージスイッチ64及び接続スイッチ66は、V N L（-5 V）からG N Dの電圧範囲で動作する。これらの各スイッチは夫々の出力端子X<sub>n</sub>ごとに設けられるが、信号処理回路11から正極及び負極のレベルシフト回路21、22を介して一括して制御される。プリチャージスイッチ63、64は、M O Sトランジスタで構成するアナログスイッチ以外でもよく、例えば、ダイオードなどのp n接合素子であってもよい。

#### 【0030】

また、プリチャージ回路60と出力端子X<sub>n</sub>との間には、極性切換回路70を設ける。極性切換回路70は、各出力端子X<sub>n</sub>ごとに極性切換スイッチ71、72を有し、極性信号P O Lに応じて正極または負極のアナログ映像信号を選択する回路である。極性切換回路70では、奇数番目の出力端子X<sub>n</sub>に正極のアナログ映像信号を選択すると同時に偶数番目の出力端子X<sub>n</sub>には負極のアナログ映像信号を選択するか、または、奇数番目の出力端子X<sub>n</sub>に負極のアナログ映像信号を選択すると同時に偶数番目の出力端子X<sub>n</sub>には正極

10

20

30

40

50

のアナログ映像信号を選択するように、奇数番目の出力端子  $X_n$  と偶数番目の出力端子  $X_{n+1}$  との極性が互いに異なるように選択する。ここでも、出力端子ごとに設ける極性切換スイッチ 71、72 は、信号処理回路 11 から高圧レベルシフト回路 21、22 を介して一括して制御される。

#### 【0031】

階調電圧生成回路 41、42 は、複数の抵抗を直列に接続した抵抗分圧回路であって、ガンマ特性に適合するような所望の電圧を生成する。本発明においては、正極と負極のアナログ映像信号を同時に出力することから、正極階調電圧生成回路 41 と負極階調電圧生成回路 42 を設け、それぞれ、64 値の正極の階調電圧 ( $V_{P0} \sim V_{P63}$ ) と、負極の階調電圧 ( $V_{N0} \sim V_{N63}$ ) であって、RGB の色ごとに微調整された複数の階調電圧を時分割に出力することができる。階調電圧生成回路 41、42 は、正極と負極の 2 個あり、微調整レジスタにより RGB ごとの補正值を格納して微調整された正極及び負極の階調電圧を生成している。

#### 【0032】

正極 D/A 変換回路 31 は、デジタル映像信号  $D_x$  に応じて基準電圧に対して正極のアナログ映像信号を出力し、負極 D/A 変換回路 32 はデジタル映像信号  $D_x$  に応じて基準電圧に対して負極のアナログ映像信号を出力する。正極 D/A 変換回路 31 及び負極 D/A 変換回路 32 は、それぞれ後述の中圧素子で形成する。

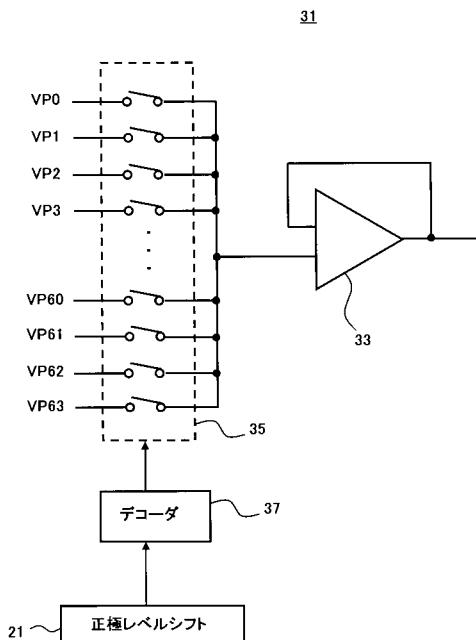

#### 【0033】

図 6 に、正極 D/A 変換回路 31 の詳細図を示す。正極 D/A 変換回路 31 は、増幅器 33 と、64 個のスイッチで構成するセレクタ 35 と、デコーダ 37 とで構成され、各回路は、GND から VPL (5V) の電圧範囲で動作する。セレクタ 35 の各スイッチには、正極階調電圧生成回路 41 から正極の階調電圧 ( $V_{P0} \sim V_{P63}$ ) が供給され、デジタル映像信号  $D_x$  に応じて、デコーダ 37 により 64 値の正極の階調電圧から 1 値の階調電圧が選択され、選択された階調電圧が増幅器 33 を介して出力される。

#### 【0034】

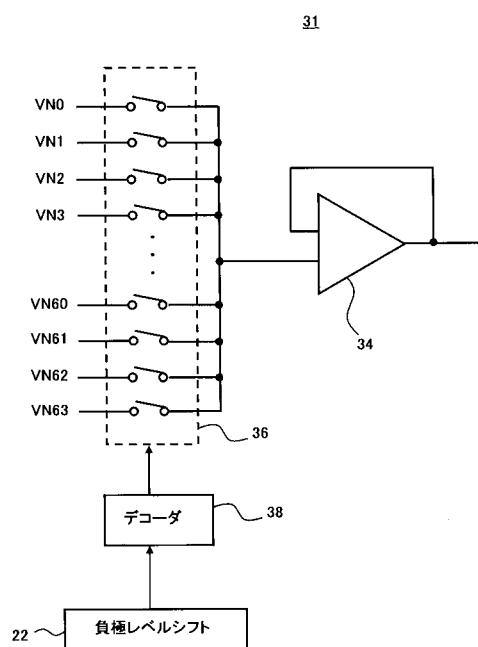

図 7 に、負極 D/A 変換回路 32 の詳細図を示す。負極 D/A 変換回路 32 は、増幅器 34 と、64 個のスイッチで構成するセレクタ 36 と、デコーダ 38 とで構成され、各回路は、VNL (-5V) から GND の電圧範囲で動作する。セレクタ 36 の各スイッチには、負極階調電圧生成回路 42 から負極の階調電圧 ( $V_{N0} \sim V_{N63}$ ) が供給され、デジタル映像信号  $D_x$  に応じて、デコーダ 38 により 64 値の負極の階調電圧から 1 値の階調電圧が選択され、選択された階調電圧が増幅器 34 を介して出力される。

#### 【0035】

なお、信号処理回路 11、データラッチ回路 17 などのロジック部は GND から VDD (2.5V) で動作している。そのため、データラッチ回路 17 又はデジタル映像信号時分割回路 50 と正極 D/A 変換回路 31 及び負極 D/A 変換回路 32 との間にはそれぞれ正極レベルシフト回路 21 又は負極レベルシフト回路 22 を設ける。正極レベルシフト回路 21 と負極レベルシフト回路 22 は、後述の中圧素子と高圧素子で形成する。

#### 【0036】

また、時分割選択回路 8 は、上述したようにデータ線駆動回路 10 の出力端子  $X_n$  と複数のデータ線 3 を複数のスイッチを介して接続する回路である。詳細には、図 2 に示すように出力端子  $X_1$  とデータ線 R1、G1、B1 との間に時分割スイッチ 81、82、83 を設ける。即ち、出力端子  $X_n$  とデータ線 Rn、Gn、Bn との間に時分割スイッチ 81、82、83 を設ける。この時分割駆動回路 8 は、走査線駆動回路 6 と同じ VGH、VGL の電源電圧で動作させる。

#### 【0037】

カラー表示の QVGA (240RGB × 320) 画素を 3 分割駆動するには、ドライバ IC 1 には正極 D/A 変換回路 31、負極 D/A 変換回路 32 などは 120 個ずつ設け、6 分割駆動では、60 個ずつ設ける。しかし、電荷リサイクル容量 67、68 は、液晶表示装置に 1 個ずつ設ければよい。この様に、正極、負極の駆動回路毎に時分割駆動を行

、時分割駆動されるデータ線グループ毎に極性反転させることにより、回路構成を単純化することができる。

#### 【0038】

次に動作について説明する。水平スタート信号 STH がシフトレジスタ回路 15 に入力されると、順に内部クロック信号 CK に同期したサンプリング信号 SPn が生成され、デジタル映像信号 Dx は、サンプリング信号 SPn に応じてデータレジスタ回路 16 にラッチされる。データレジスタ回路 16 でラッチされた、デジタル映像信号 Dx は、ラッチ信号 STB の入力に応答して、並列にデータラッチ回路 17 にラッチされる。データラッチ回路 17 は正極レベルシフト回路 21 又は負極レベルシフト回路 22 に接続されており、正極レベルシフト回路 21 又は負極レベルシフト回路 22 を介してそれぞれ正極 D/A 変換回路 31 又は負極 D/A 変換回路 32 に入力される。正極 D/A 変換回路 31 又は負極 D/A 変換回路 32 にて正極アナログ映像信号、負極アナログ映像信号に変換され、極性信号 POL に応じて正極アナログ映像信号と負極アナログ映像信号を選択する極性切換回路 70 及び時分割選択回路 8 を介し、正極及び負極のアナログ映像信号を各データ線 3 に供給する。10

#### 【0039】

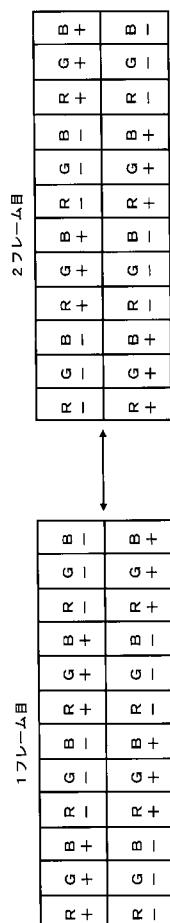

次に詳細な動作について説明する。尚、説明の明確化のため、図 8 に示すようにデータ線が 6 本 (R1, G1, B1, R2, G2, B2) で走査線が 2 本 (Y1, Y2) の場合について説明する。また、各データ線 (R1, G1, B1, R2, G2, B2) に対応するデジタル映像信号を (DR1, DG1, DB1, DR2, DG2, DB2) とする。そして、図 2 に示すように第 1 走査線 Y1 での各画素の極性は (+, +, +, -, -, -) 、第 2 走査線 Y2 での各画素の極性は (-, -, -, +, +, +) となるように RGB 画素反転駆動される。また、各画素は図 8 に示すように、1 フレームごとに各画素が反転するように駆動される。20

#### 【0040】

デジタル映像信号は、図 4 に示す信号処理回路 11 内部で、表示する画素に対応するように入れ換えられる。極性信号 POL が L の時は、デジタル映像信号 (DR1, DG1, DB1) はデータバス (DRo, DGo, DBo) に供給され正極データレジスタ回路 16a にラッチされ、デジタル映像信号 (DR2, DG2, DB2) はデータバス (DRe, DGe, DBe) に供給され負極データレジスタ回路 16b にラッチされ、反対に、極性信号 POL が H の時は、デジタル映像信号 (DR1, DG1, DB1) はデータバス (DRo, DGo, DBo) に供給され負極データレジスタ回路 16b にラッチされ、デジタル映像信号 (DR2, DG2, DB2) はデータバス (DRo, DGo, DBo) に供給され正極データレジスタ回路 16a にラッチされる。30

#### 【0041】

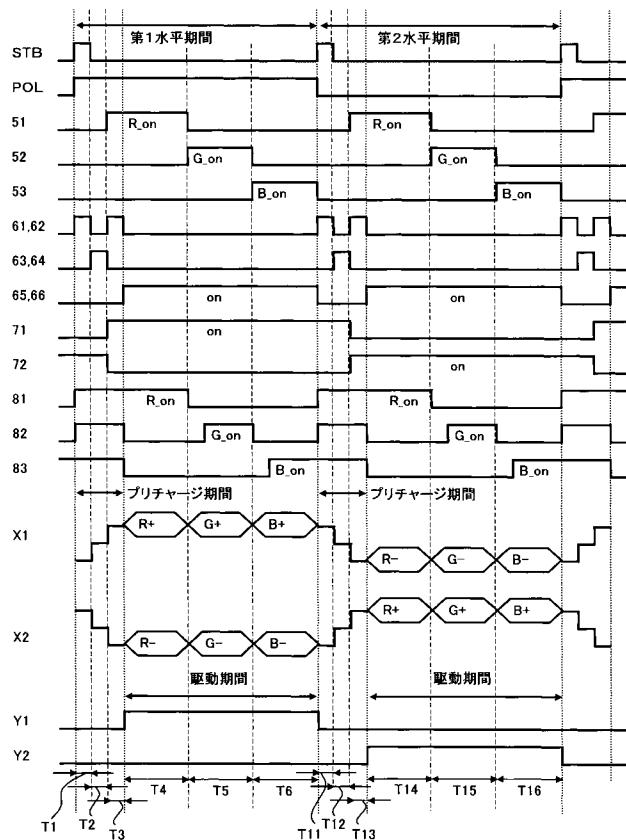

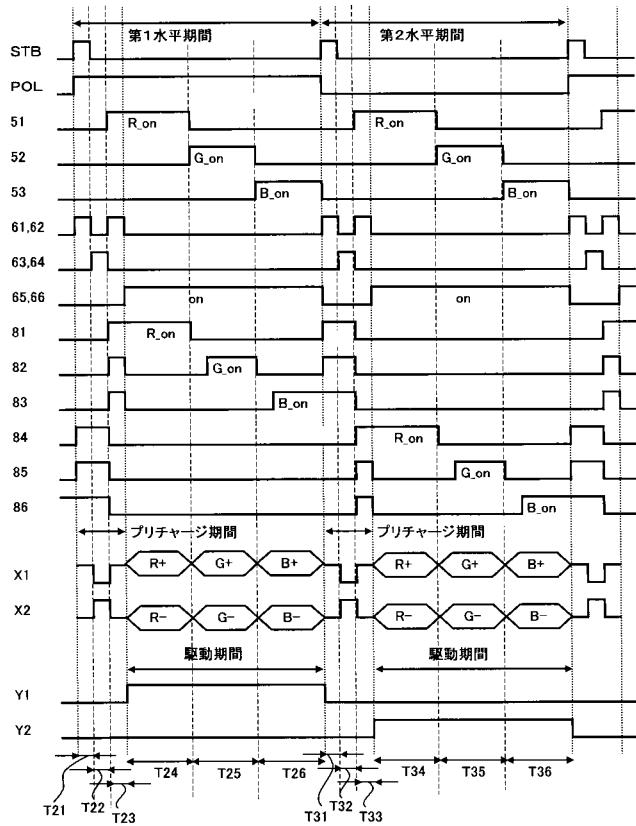

図 9 は信号処理回路 11 から出力される制御信号による、各部の動作を示すタイミングチャートである。図 9 のタイミングチャートおよび図 10、図 11 の電荷リサイクル動作模式図によれば、第 1 の水平期間の第 1 のプリチャージ期間 T1 に、電荷リサイクルスイッチ 61, 62、極性切換スイッチ 72 及び時分割スイッチ 81, 82, 83 をオン (図 10 の (a) の状態) し、前の水平期間に正極に駆動されたデータ線 (R2, G2, B2) の正極の電荷を電荷リサイクル容量 67 に充電し、同様に、負極に駆動されたデータ線 (R1, G1, B1) の負極の電荷を電荷リサイクル容量 68 に充電する。40

#### 【0042】

当該動作について更に詳細に説明する。画像信号として正極 D/A 変換回路 31 及び負極 D/A 変換回路 32 から出力端子 Xn を介してデータ線 3 に電圧が印加された後、プリチャージスイッチ 63, 64 が閉じられるまでは、正極 D/A 変換回路 31 及び負極 D/A 変換回路 32 から画素 5 に含まれる TFT との間に電荷が滞留している。そこで、出力端子 Xn を介してデータ線 3 に画素信号の電圧を印加した後、極性切換スイッチ 71, 72 をそのままの状態にして、時分割スイッチ 81, 82, 83 を閉じ、更に電荷リサイクルスイッチ 61, 62 を閉じることによって、データ線 3 に滞留している電荷が電荷リサ50

イクル容量 67、68 に回収される。

【0043】

次に、第1の水平期間の第2のプリチャージ期間T2に、プリチャージスイッチ63、64、極性切換スイッチ72及び時分割スイッチ81、82、83をオン(図10の(b)の状態)し、前の水平期間に正極に駆動されたデータ線3(R2、G2、B2)を基準電圧(GND)にプリチャージし、同様に、負極に駆動されたデータ線3(R1、G1、B1)を基準電圧(GND)にプリチャージして中和させる。この時、電荷リサイクルスイッチ61、62は開いた状態でプリチャージを行うので、電荷リサイクル容量67、68には電荷が保持される。

【0044】

次に、第1の水平期間の第3のプリチャージ期間T3に、電荷リサイクルスイッチ61、62、極性切換スイッチ71及び時分割スイッチ81、82、83をオン(図11の(c)の状態)し、第2のプリチャージ期間T2に基準電圧になっているデータ線3(R1、G1、B1)に電荷リサイクル容量67から正極の電荷を放電し、同様に、データ線3(R2、G2、B2)に電荷リサイクル容量68から負極の電荷を放電する。即ち、第1のプリチャージ期間T1において回収して電荷リサイクル容量67、68に保持した電荷を、極性切換スイッチ71、72を切り換えて開放することにより、当該電荷を回収したデータ線とは逆のデータ線3に放電する。こうすることにより、電荷の再利用が行われ、次に画素信号としてデータ線3に印加される電圧が、正極D/A変換回路31又は負極D/A変換回路32から印加される電圧に達するのに要する電力が低減される。

【0045】

次に、第1の水平期間の駆動期間に接続スイッチ65、66、極性切換スイッチ71をオン(図11の(d)の状態)し、時分割スイッチ81、82、83を切り換えることによりアナログ映像信号をデータ線3に出力する。即ち、第1の水平期間の第1の駆動期間T4に接続スイッチ65、66、極性切換スイッチ71及び時分割スイッチ81をオンしてデータ線R1に出力端子X1から正極のアナログ映像信号を出力し、データ線R2に出力端子X2から負極のアナログ映像信号を出力する。次に、第1の水平期間の第2の駆動期間T5に接続スイッチ65、66、極性切換スイッチ71及び時分割スイッチ82をオンしてデータ線G1に出力端子X1から正極のアナログ映像信号を出力し、データ線G2に出力端子X2から負極のアナログ映像信号を出力する。次に、第1の水平期間の第3の駆動期間T6に接続スイッチ65、66、極性切換スイッチ71及び時分割スイッチ83をオンしてデータ線B1に出力端子X1から正極のアナログ映像信号を出力し、データ線B2に出力端子X2から負極のアナログ映像信号を出力する。

【0046】

次に、第2の水平期間の第1のプリチャージ期間T11に、電荷リサイクルスイッチ61、62、極性切換スイッチ71及び時分割スイッチ81、82、83をオンし、第1の水平期間に正極に駆動されたデータ線3(R1、G1、B1)の正極の電荷を電荷リサイクル容量67に充電し、同様に、負極に駆動されたデータ線3(R2、G2、B2)の負極の電荷を電荷リサイクル容量68に充電する。次に、第2の水平期間の第2のプリチャージ期間T12に、プリチャージスイッチ63、64、極性切換スイッチ71及び時分割スイッチ81、82、83をオンし、第1の水平期間に正極に駆動されたデータ線3(R1、G1、B1)を基準電圧(GND)にプリチャージし、同様に、負極に駆動されたデータ線3(R2、G2、B2)を基準電圧(GND)にプリチャージして中和させる。次に、第2の水平期間の第3のプリチャージ期間T13に、電荷リサイクルスイッチ61、62、極性切換スイッチ72及び時分割スイッチ81、82、83をオンし、第2のプリチャージ期間T12に基準電圧になっているデータ線3(R2、G2、B2)に電荷リサイクル容量67から正極の電荷を放電し、同様に、データ線3(R1、G1、B1)に電荷リサイクル容量68から負極の電荷を放電する。

【0047】

次に、第2の水平期間の第1の駆動期間T14に接続スイッチ65、66、極性切換ス

10

20

30

40

50

イッチ72、時分割スイッチ81をオンしてデータ線R1に出力端子X1から負極のアナログ映像信号を出力し、データ線R2に出力端子X2から正極のアナログ映像信号を出力する。次に、第2の水平期間の第2の駆動期間T15に接続スイッチ65、66、極性切換スイッチ72及び時分割スイッチ82をオンしてデータ線G1に出力端子X1から負極のアナログ映像信号を出力し、データ線G2に出力端子X2から正極のアナログ映像信号を出力する。次に、第2の水平期間の第3の駆動期間T16に接続スイッチ65、66、極性切換スイッチ72及び時分割スイッチ83をオンしてデータ線B1に出力端子X1から負極のアナログ映像信号を出力し、データ線B2に出力端子X2から正極のアナログ映像信号を出力する。

## 【0048】

10

以上の動作によれば、正極D/A変換回路31及び電荷リサイクルスイッチ61、プリチャージスイッチ63、接続スイッチ65には、正極の電圧しか印加されず、また、負極D/A変換回路32及び電荷リサイクルスイッチ62、プリチャージスイッチ64、接続スイッチ66には、負極の電圧しか印加されない。よって、これらの素子は、後述の中圧素子(5V)で形成することができる。中圧素子では、高圧素子に比べゲート酸化膜が薄く、またゲート長が短いので回路面積を縮小することができる。

## 【0049】

20

また、フリッカの発生を抑制するには、com電圧の変動を抑制するのが効果的である。本形態のように、R1画素とR2画素のように画素が隣接していないとも、1回の書き込みにおいて、画素に同時に書き込まれる正極と負極のアナログ信号の総電荷量がほぼ同じであれば、正の電荷と負の電荷がうち消し合いcom電圧の変動は微少である。

## 【0050】

また、一連のプリチャージ動作により、データ線に蓄積された正極と負極の電荷の回収及び再利用を行い、最大で50%の電荷リサイクル効果が得られ、消費電力を低減することができる。

## 【0051】

30

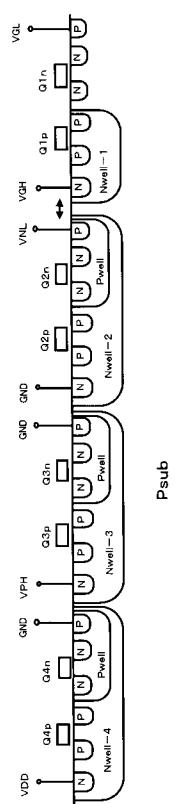

次に、本発明のドライバIC1を半導体製造装置で製造する例を説明する。本発明では、低電圧(2.5V)で動作する低圧素子、中電圧(5V)で動作する中圧素子、高電圧(20V)で動作する高圧素子を拡散プロセスで製造する例を説明する。尚、上記の電圧は例であって、低電圧<中電圧<高電圧の関係であれば、これら以外の電圧でもよい。但し、中圧素子には正極で用いられるものと負極で用いられるものがあり、高圧素子はその両方の電圧範囲で用いることが可能である。

## 【0052】

40

一般に、半導体集積回路におけるトランジスタなどのデバイス素子は、電圧が高いと素子面積が大きくなることが知られており、最小となるゲート長Lmin、ゲート幅Wmin、ゲート酸化膜厚Toxの関係は、Lmin(低圧素子) < Lmin(中圧素子) < Lmin(高圧素子)、Wmin(低圧素子) < Wmin(中圧素子) < Wmin(高圧素子)、Tox(低圧素子) < Tox(中圧素子) < Tox(高圧素子)である。よって、高圧素子をできるだけ使用しない回路構成にすることで、ドライバIC1のチップサイズを小さくすることができる。

## 【0053】

本形態では、信号処理回路11、データラッチ回路17などのロジック部は低圧素子で製造し、正極D/A変換回路31、負極D/A変換回路32、プリチャージ回路60は中圧素子で製造し、極性切換回路70と負極レベルシフト回路22の一部及び信号処理回路11の一部を高電圧素子で製造する。信号処理回路11の一部に高圧素子が使われるのではなく、走査線駆動回路6及び時分割選択回路8への制御信号はレベルシフト回路を介して入力されるからである。

## 【0054】

図12は半導体集積回路における基板及び基板上の素子の構成を示す断面図である。高圧(20V)基準で製造したN型トランジスタをQ1n、P型トランジスタをQ1p、中

50

圧(5V)基準で製造したN<sub>w</sub>e11-2上のN型トランジスタをQ2n、P型トランジスタをQ2pとし、N<sub>w</sub>e11-3上のN型トランジスタをQ3n、P型トランジスタをQ3pとし、低圧(2.5V)基準で製造したN<sub>w</sub>e11-4上のN型トランジスタをQ4n、P型トランジスタをQ4pとする。

#### 【0055】

基板(Psub)の電圧は最低電圧VGL = -10Vとして、信号処理回路11はN<sub>w</sub>e11-4上に、正極D/A変換回路31などはN<sub>w</sub>e11-3上に、負極D/A変換回路32などはN<sub>w</sub>e11-2上に製造し、極性切換回路70と負極レベルシフト回路22の一部、信号処理回路11の一部はPsubとN<sub>w</sub>e11-1上に製造する。ドライバIC1には、トランジスタ以外に抵抗や、コンデンサやダイオードなどのデバイス素子も設けられるが、それらの素子の耐圧も確保する。10

#### 【0056】

データ線駆動回路10は、複数のデータ線を駆動するため、D/A変換回路などが複数あり、動作電圧に応じてそれぞれの回路が、各N<sub>w</sub>e11の連続した領域に配置される。異電位のN<sub>w</sub>e11間隔は、数十μm程度必要であるため、同一の電圧範囲の回路は、連続したN<sub>w</sub>e11内に配置すると回路面積が小さくなる。

#### 【0057】

本形態では、極性切換回路70は、高圧素子(20V)で製造しているため、極性切換回路70を動作する電圧は、VGL = -10VとVPH = 5Vとの電圧範囲であってもよいし、VGL = -10VとVGH = 10Vとの電圧範囲であってもよいため、N<sub>w</sub>e11-1の電圧は、VPH = 5VまたはVGH = 10Vとする。20

#### 【0058】

本形態では、基板はP型半導体で説明したが、基板はN型半導体(Nsub)でもよい。この場合には、Nsubの電圧は最高電圧VGH = 10Vとすればよい。

#### 【0059】

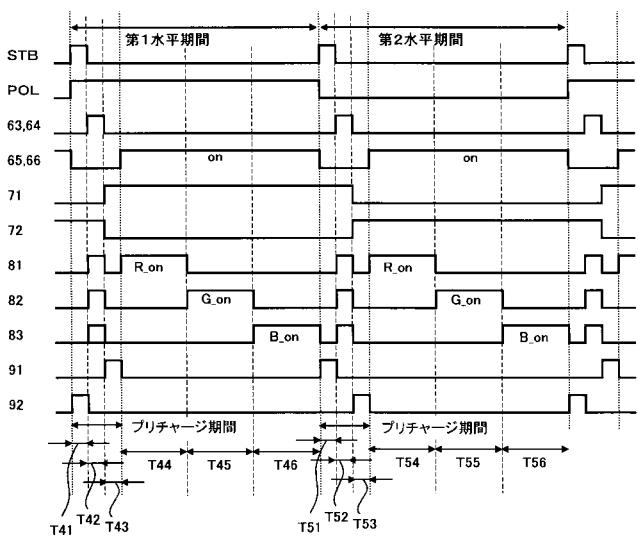

実施の形態2.

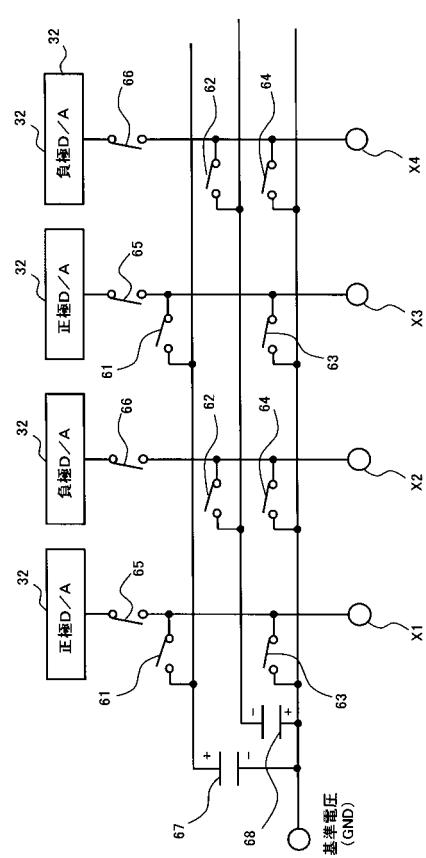

実施の形態1においては、極性切換回路70は、ドライバIC1に形成され、時分割選択回路8はパネル上に形成されていたが、極性切換の機能と時分割切換の機能を有する選択回路をパネル上に形成してもよい。本形態におけるドライバIC1のD/A変換回路部とプリチャージ回路部の詳細図を図13に示す。30

#### 【0060】

実施の形態1では、プリチャージ回路60と出力端子Xnとの間に極性切換回路70を設けていたが、本実施の形態では、プリチャージ回路60と出力端子Xnとを直接接続し、図14に示すように、時分割選択回路8は、データ線3ごとに2個のスイッチで構成し、それぞれのスイッチは、奇数番目の出力端子と偶数番目の出力端子に接続され、極性切換機能を含んでいる。その結果、パネル2上の時分割選択回路8を構成するスイッチ数は、実施の形態1に比べ2倍になっている。例えば、出力端子X1は、3本のデータ線(R1、G1、B1)にスイッチ81、82、83を介して接続されると共に3本のデータ線(R2、G2、B2)にスイッチ84、85、86を介して接続される。そして、出力端子X1に隣接する出力端子X2は、3本のデータ線(R2、G2、B2)にスイッチ81、82、83を介して接続されると共に3本のデータ線(R1、G1、B1)にスイッチ84、85、86を介して接続される。40

#### 【0061】

また、実施の形態1では、ドライバIC1の出力端子Xnからは正極または負極のアナログ映像信号が出力されたが、本形態では、奇数番目の出力端子からは正極のアナログ映像信号、偶数番目の出力端子からは負極のアナログ映像信号が出力される。いうまでもないが、奇数番目の出力端子からは負極のアナログ映像信号、偶数番目の出力端子からは正極のアナログ映像信号が出力される回路構成でもよい。

#### 【0062】

本実施の形態では、電源回路12など高圧素子はパネル2上に形成し、データ線駆動回

路 1 0 及び信号処理回路 1 1 をドライバ I C 1 上に形成している。この構成によれば、正極または負極の D / A 変換回路からのアナログ映像信号は、実施の形態 1 では、接続スイッチ 6 5、6 6、極性切換スイッチ 7 1、7 2 及び時分割選択回路 8 に含まれるスイッチの計 3 個のスイッチを介して各データ線に出力されているが、本実施の形態では、接続スイッチ 6 5、6 6、時分割選択回路 8 に含まれるスイッチの計 2 個のスイッチを介して各データ線 3 にアナログ映像信号が出力されることにより、スイッチのオン抵抗が小さくなることで駆動時間を短くすることができる。

#### 【 0 0 6 3 】

また、ドライバ I C に含まれる高圧素子は、負極レベルシフト回路の一部のみとなり、ドライバ I C 1 のチップサイズを小さくすることができる。

10

#### 【 0 0 6 4 】

さらに、実施の形態 1 と同様に、プリチャージ回路 6 0 を構成する各スイッチ（6 1 ~ 6 6）は中圧素子で製造する。このプリチャージ回路 6 0 のスイッチは、ガラス基板などのパネル 2 上に形成するより半導体基板上に製造した方がトランジスタの能力が 1 衍以上よいため、プリチャージ時間を短くすることができる。プリチャージ時間が短くなるということは、相対的に駆動時間が長くなるので、分割数を増やして、D / A 変換回路の数を低減することができる。

#### 【 0 0 6 5 】

次に図 1 5 のタイミングチャートを用いて本実施の形態の動作について説明する。第 1 の水平期間の第 1 のプリチャージ期間 T 2 1 に、電荷リサイクルスイッチ 6 1、6 2、時分割スイッチ 8 4、8 5、8 6 をオンし、前の水平期間に正極に駆動されたデータ線（R 2、G 2、B 2）の正極の電荷を電荷リサイクル容量 6 7 に充電し、同様に、負極に駆動されたデータ線（R 1、G 1、B 1）の負極の電荷を電荷リサイクル容量 6 8 に充電する。次に、第 1 の水平期間の第 2 のプリチャージ期間 T 2 2 に、プリチャージスイッチ 6 3、6 4、時分割スイッチ 8 4、8 5、8 6 をオンし、前の水平期間に正極に駆動されたデータ線（R 2、G 2、B 2）を基準電圧（G N D）にプリチャージし、同様に、負極に駆動されたデータ線（R 1、G 1、B 1）を基準電圧（G N D）にプリチャージして中和させる。

20

#### 【 0 0 6 6 】

次に、第 1 の水平期間の第 3 のプリチャージ期間 T 2 3 に、電荷リサイクルスイッチ 6 1、6 2、時分割スイッチ 8 1、8 2、8 3 をオンし、第 2 のプリチャージ期間 T 2 2 に基準電圧になっているデータ線（R 1、G 1、B 1）に電荷リサイクル容量 6 7 から正極の電荷を放電し、同様に、データ線（R 2、G 2、B 2）に電荷リサイクル容量 6 8 から負極の電荷を放電する。こうすることにより、各データ線 3 に画素信号として印加した電荷の回収及び再利用を行う。

30

#### 【 0 0 6 7 】

次に、第 1 の水平期間の第 1 の駆動期間 T 2 4 に接続スイッチ 6 5、6 6、時分割スイッチ 8 1 をオンしてデータ線 R 1 に出力端子 X 1 から正極のアナログ映像信号を出力し、データ線 R 2 に出力端子 X 2 から負極のアナログ映像信号が出力される。次に、第 1 の水平期間の第 2 の駆動期間 T 2 5 に接続スイッチ 6 5、6 6、時分割スイッチ 8 2 をオンしてデータ線 G 1 に出力端子 X 1 から正極のアナログ映像信号を出力し、データ線 G 2 に出力端子 X 2 から負極のアナログ映像信号を出力する。次に、第 1 の水平期間の第 3 の駆動期間 T 2 6 に接続スイッチ 6 5、6 6、時分割スイッチ 8 3 をオンしてデータ線 B 1 に出力端子 X 1 から正極のアナログ映像信号を出力し、データ線 B 2 に出力端子 X 2 から負極のアナログ映像信号を出力する。

40

#### 【 0 0 6 8 】

次に、第 2 の水平期間の第 1 のプリチャージ期間 T 3 1 に、電荷リサイクルスイッチ 6 1、6 2、時分割スイッチ 8 1、8 2、8 3 をオンし、第 1 の水平期間に正極に駆動されたデータ線（R 1、G 1、B 1）の正極の電荷を電荷リサイクル容量 6 7 に充電し、同様に、負極に駆動されたデータ線（R 2、G 2、B 2）の負極の電荷を電荷リサイクル容量

50

68に充電する。次に、第2の水平期間の第2のプリチャージ期間T32に、プリチャージスイッチ63、64、時分割スイッチ81、82、83をオンし、第1の水平期間に正極に駆動されたデータ線(R1、G1、B1)を基準電圧(GND)にプリチャージし、同様に、負極に駆動されたデータ線(R2、G2、B2)を基準電圧(GND)にプリチャージして中和させる。次に、第2の水平期間の第3のプリチャージ期間T33に、電荷リサイクルスイッチ61、62、時分割スイッチ84、85、86をオンし、第2のプリチャージ期間に基準電圧になっているデータ線(R2、G2、B2)に電荷リサイクル容量67から正極の電荷を放電し、同様に、データ線(R1、G1、B1)に電荷リサイクル容量68から負極の電荷を放電する。

## 【0069】

10

次に、第2の水平期間の第1の駆動期間T34に接続スイッチ65、66、時分割スイッチ84をオンしてデータ線R2に出力端子X1から正極のアナログ映像信号を出力し、データ線R1に出力端子X2から負極のアナログ映像信号を出力する。次に、第2の水平期間の第2の駆動期間T35に接続スイッチ65、66、時分割スイッチ85をオンしてデータ線G2に出力端子X1端子から正極のアナログ映像信号を出力し、データ線G1に出力端子X2端子から負極のアナログ映像信号を出力する。次に、第2の水平期間の第3の駆動期間T36に接続スイッチ65、66、時分割スイッチ86をオンしてデータ線B2に出力端子X1から正極のアナログ映像信号を出力し、データ線B1に出力端子X2から負極のアナログ映像信号を出力する。各画素は図8に示すように、フレームごとに反転するように駆動される。

20

## 【0070】

実施の形態1及び2において、画素への書き込み順序は、R G Bで便宜説明してきたが、時分割スイッチ81、82、83をTFTで形成した場合に、当該TFTのリーク電流を考慮すると、G(緑)がR(赤)B(青)に比べて感度が高いので、R B GまたはB R Gの順のようにGを最後に書き込むことが好ましい。また、分割数は3で説明してきたが、3に限らない。この場合、RGB3色であることから分割数は3の倍数が好ましく、例えば、6分割であれば、1つのD/A変換回路でR1 R2 B1 B2 G1 G2などの順に同じ色の画素から優先して書き込むのが好ましい。R1 B1 G1 R2 B2 G2と書き込むとR1とR2との間にB1とG1の書き込み時間があるので、この間にTFTで形成された時分割スイッチのリーク電流により、R1画素の電圧が変動してしまい表示むらになるからである。

30

## 【0071】

また、分割数が多くなるほど、D/A変換回路が削減できるが、パネル上の表示むらが顕著に現れるので、1、2フレーム目(R1 R2 B1 B2 G1 G2)、3、4フレーム目(R2 R1 B2 B1 G2 G1)のように4フレームを1つの単位としてフレーム間で同一色の画素の書き込み順序を変えるのが好ましい。

40

## 【0072】

実施の形態3.

実施の形態2においては、極性切換の機能と時分割切換の機能を有する選択回路をパネル上に形成しているが、さらに、電荷リサイクルの回路もパネル上に形成してもよい。

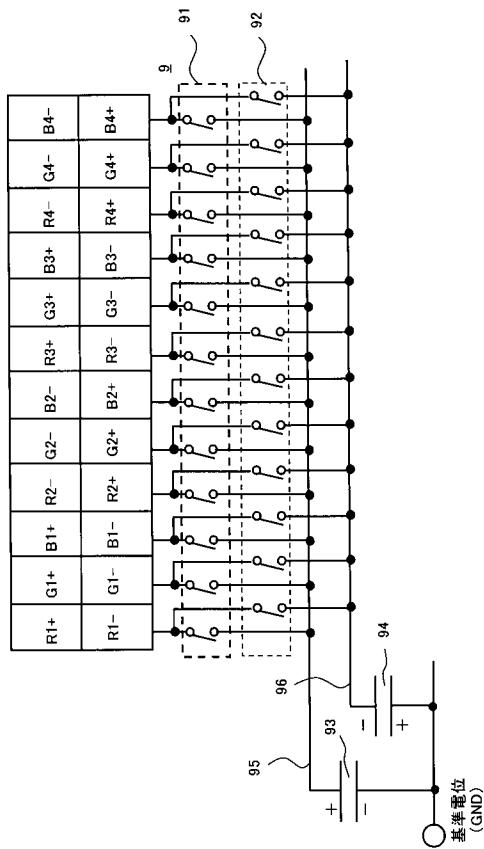

## 【0073】

図16に本形態の液晶表示装置200のブロック図を示す。液晶パネルの基板2上に、さらに電荷リサイクル回路9を形成する。電荷リサイクル回路9は、ドライバIC1上の信号処理回路11から出力される信号で制御される。次に電荷リサイクル回路9の詳細を図17を参照して説明する。電荷リサイクル回路9は、各データ線3ごとに並列に2個の電荷リサイクルスイッチ91、92を設け、電荷リサイクルスイッチ91、92の他端は、データ線グループごとに回収線95又は回収線96に接続される。回収線95及び96はそれぞれ電荷リサイクル容量93及び94に接続される。電荷リサイクルスイッチ91、92は水平期間の初めのプリチャージ期間に極性信号POLに応じて制御される。この電荷リサイクル回路9も、走査線駆動回路6や時分割駆動回路8と同じくVGH、VGL

50

の電源電圧で動作させる。

【0074】

電荷リサイクル回路9の動作について、図18のタイミングチャートを用いて説明する。第1の水平期間では極性信号POLがHである。そして、第1の水平期間の第1のプリチャージ期間T41にスイッチ81、82、83はターンオフ、スイッチ92をターンオンし、データ線3に蓄積された電荷を電荷リサイクル容量93に電荷を移動して電荷の回収を行う。次に、第1の水平期間の第2のプリチャージ期間T42にスイッチ92をターンオフ、スイッチ81、82、83をターンオンし、ドライバIC1内のプリチャージスイッチ63、64をターンオンし基準電圧にプリチャージする。次に、第1の水平期間の第3のプリチャージ期間T43にプリチャージスイッチ63、64をターンオフ、スイッチ81、82、83をターンオフ、スイッチ91をターンオンして電荷リサイクル容量94からデータ線3に電荷を移動して電荷の再利用を行う。10

【0075】

第2の水平期間では、極性信号POLがLとなる。そして、第2の水平期間の第1のプリチャージ期間T51にスイッチ81、82、83はターンオフ、スイッチ91をターンオンし、データ線3に蓄積された電荷を電荷リサイクル容量94に電荷を移動して電荷の回収を行う。次に、第2の水平期間の第2のプリチャージ期間T52に、スイッチ91をターンオフ、スイッチ81、82、83をターンオンし、ドライバIC1内のプリチャージスイッチ63、64をターンオンし基準電圧にプリチャージする。次に、第2の水平期間の第3のプリチャージ期間T53に、プリチャージスイッチ63、64をターンオフ、スイッチ81、82、83をターンオフ、スイッチ92をターンオンして電荷リサイクル容量93からデータ線に電荷を移動して電荷の再利用を行う。なお、駆動期間(T44～T46、T54～T56)における動作は実施の形態1と同様である。20

【0076】

本実施の形態においては、実施の形態1、2と同様に、パネルの片側にのみD/A変換回路を含む駆動回路を配置する構成とすることができます。データ線駆動回路の回路規模を低減することができる。また、正極D/A変換回路31には、正極の電圧しか印加されず、負極D/A変換回路32には、負極の電圧しか印加されない。よって、これらの素子は、中圧素子(5V)で形成することができ、高圧素子で形成するのに比ベゲート酸化膜が薄く、またゲート長が短くすることができ、回路面積を縮小することができる。30

【0077】

そして、本実施の形態においては、更に、電荷リサイクル回路9をドライバIC1の外部にすることで、ドライバIC1内部のGNDへのノイズが減少し、ドライバIC1内部の電源回路12にノイズが伝播することを防止することができるため、com電圧などが安定して良好な表示を得ることができる。

【0078】

また、実施の形態1、2及び3において、基準電圧はシステムグランドとして説明したが、システムグランドでなくてもよい。薄膜トランジスタTFT(Thin Film Transistor)のフィードスルー誤差分だけ電圧をシフトした電圧であってもよい。具体的には、TFTのフィードスルー誤差が-1Vであれば、com電圧をシステムグランドとし、ドライバIC1の基準電圧は1VとしてこれをドライバIC1の仮想GNDとする。つまり、正極の高位電源電圧VPH=6V、正極の低位電源電圧(仮想GND)=1V、負極の高位電源電圧(仮想GND)=1V、負極の低位電源電圧VNL=-4Vとしてもよい。40

【図面の簡単な説明】

【0079】

【図1】本発明の第1の実施形態における液晶表示装置のブロック図である。

【図2】本発明の第1の実施形態における時分割選択回路8の詳細図である。

【図3】本発明の第1の実施形態におけるデジタル入力信号とアナログ信号の相関図である。

【図4】本発明の第1の実施形態におけるデジタル映像信号の入れ換え回路の詳細図であ50

る。

【図5】本発明の第1の実施形態におけるデータ線駆動回路10のブロック図である。

【図6】本発明の第1の実施形態における正極D/A変換回路31の詳細図である。

【図7】本発明の第1の実施形態における負極D/A変換回路32の詳細図である。

【図8】本発明の第1の実施形態における画素の極性の模式図である。

【図9】本発明の第1の実施形態におけるタイミングチャートである。

【図10】本発明の第1の実施形態におけるプリチャージ動作の詳細図である。

【図11】本発明の第1の実施形態におけるプリチャージ動作の詳細図である。

【図12】本発明の第1の実施形態における半導体集積回路の断面図である。

【図13】本発明の第2の実施形態におけるデータ線駆動回路10の出力部の詳細図である。 10

【図14】本発明の第2の実施形態における時分割選択回路8の詳細図である。

【図15】本発明の第2の実施形態におけるタイミングチャートである。

【図16】本発明の第3の実施形態における液晶表示装置のブロック図である。

【図17】本発明の第3の実施形態における電荷リサイクル回路9の詳細図である。

【図18】本発明の第3の実施形態における電荷リサイクルのタイミングチャートである

。

#### 【符号の説明】

##### 【0080】

1 ドライバIC、2 液晶パネル基板、3 データ線、4 走査線、5 画素、 20

6 走査線駆動回路、7 共通電極線、8 時分割選択回路、9 電荷リサイクル回路、

10 データ線駆動回路、11 信号処理回路、11a、11b ラッチ回路、11c

切換回路、

12 電源回路、15 シフトレジスタ回路、16 データレジスタ回路、

16a 正極データレジスタ回路、16b 負極データレジスタ回路、

17 データラッチ回路、17a 正極データラッチ回路、

17b 負極データラッチ回路、21 正極レベルシフト回路、

22 負極レベルシフト回路、31 正極D/A変換回路、32 負極D/A変換回路、

33、34 増幅器、35、36 セレクタ、37、38 デコーダ、

41 正極階調電圧生成回路、42 負極階調電圧生成回路、 30

50 デジタル映像信号時分割回路、60 プリチャージ回路、

61、62、91、92 電荷リサイクルスイッチ、63、64 プリチャージスイッチ

、

65、66 接続スイッチ、67、68、93、94 電荷リサイクル容量、70 極性

切換回路、

71、72 極性切換スイッチ、

81、82、83、84、85、86 時分割スイッチ、

90 出力端子、100、200 液晶表示装置

【 図 1 】

【 図 2 】

【図3】

〔 四 4 〕

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 2 3 Y |

| G 0 9 G | 3/20  | 6 2 3 F |

| G 0 9 G | 3/20  | 6 2 3 R |

| G 0 9 G | 3/20  | 6 4 1 C |

| G 0 9 G | 3/20  | 6 4 2 L |

| G 0 9 G | 3/20  | 6 2 1 M |

| G 0 9 G | 3/20  | 6 8 0 G |

| G 0 2 F | 1/133 | 5 2 5   |

F ターム(参考) 5C006 AA16 AA22 AC11 AC27 AC28 AF42 AF43 AF44 AF46 AF51

AF53 AF61 AF69 AF71 AF83 AF84 AF85 BB16 BC02 BC03

BC11 BC20 BF03 BF04 BF14 BF24 BF43 BF46 EB04 EB05

FA41 FA47 FA56

5C080 AA10 BB05 CC03 DD03 DD22 DD26 DD27 DD28 EE29 EE30

FF11 JJ02 JJ03 JJ04 JJ05

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其驱动电路                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2006323341A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 公开(公告)日 | 2006-11-30 |

| 申请号            | JP2005346689                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 申请日     | 2005-11-30 |

| [标]申请(专利权)人(译) | NEC电子股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 申请(专利权)人(译)    | NEC电子公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| [标]发明人         | 橋本義春                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 发明人            | 橋本 義春                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| CPC分类号         | G09G3/3688 G09G3/3614 G09G2310/0235 G09G2310/0248 G09G2310/027 G09G2310/0297<br>G09G2320/0219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| FI分类号          | G09G3/36 G09G3/20.621.H G09G3/20.622.K G09G3/20.623.X G09G3/20.621.B G09G3/20.623.Y<br>G09G3/20.623.F G09G3/20.623.R G09G3/20.641.C G09G3/20.642.L G09G3/20.621.M G09G3/20.680.<br>G G02F1/133.525 G09G3/20.621.F G09G3/20.621.G G09G3/20.623.V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA31 2H093/NA32 2H093/NA33 2H093/NA34 2H093/NA43 2H093/NC10 2H093<br>/NC12 2H093/NC18 2H093/NC21 2H093/NC22 2H093/NC23 2H093/NC26 2H093/NC34 2H093/NC65<br>2H093/ND35 2H093/ND39 2H093/ND58 5C006/AA16 5C006/AA22 5C006/AC11 5C006/AC27 5C006<br>/AC28 5C006/AF42 5C006/AF43 5C006/AF44 5C006/AF46 5C006/AF51 5C006/AF53 5C006/AF61<br>5C006/AF69 5C006/AF71 5C006/AF83 5C006/AF84 5C006/AF85 5C006/BB16 5C006/BC02 5C006<br>/BC03 5C006/BC11 5C006/BC20 5C006/BF03 5C006/BF04 5C006/BF14 5C006/BF24 5C006/BF43<br>5C006/BF46 5C006/EB04 5C006/EB05 5C006/FA41 5C006/FA47 5C006/FA56 5C080/AA10 5C080<br>/BB05 5C080/CC03 5C080/DD03 5C080/DD22 5C080/DD26 5C080/DD27 5C080/DD28 5C080/EE29<br>5C080/EE30 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 2H193/ZA04 2H193/ZC02<br>2H193/ZC15 2H193/ZC20 2H193/ZF22 2H193/ZF36 2H193/ZF59 2H193/ZH40 |         |            |

| 优先权            | 2005119818 2005-04-18 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 其他公开文献         | <a href="#">JP4584131B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

### 摘要(译)

解决的问题：减小液晶显示装置的数据线驱动电路的电路规模。本发明的液晶显示装置包括多条扫描线4，多条数据线3和设置在多条扫描线4和多条数据线3的每个交叉点处的像素5。液晶显示装置包括多个像素组，每个像素组包括设置在多个连续数据线3和一条扫描线4的每个交叉点处的像素5，并且每个像素组中包括的所有数据线3包括通过时分驱动来输出相同极性的信号，该时分驱动依次输出信号，将相反极性的信号输出到彼此相邻的像素组，并且每个像素组中包括的数据线3的每一帧都具有极性。输出反相信号。[选择图]图5