(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-48083

(P2006-48083A)

(43) 公開日 平成18年2月16日(2006.2.16)

| (51) Int.CI.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/36</b> (2006.01)  | G09G 3/36 | 2 H 09 3    |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 5 C 00 6    |

| <b>G02F 1/133</b> (2006.01) | G09G 3/20 | 5 C 08 0    |

|                             | G09G 3/20 | 6 2 1 B     |

|                             | G09G 3/20 | 6 1 2 F     |

|                             | G09G 3/20 | 6 2 3 F     |

審査請求 有 請求項の数 42 O L (全 82 頁) 最終頁に続く

|              |                              |          |                     |

|--------------|------------------------------|----------|---------------------|

| (21) 出願番号    | 特願2005-296834 (P2005-296834) | (71) 出願人 | 000005108           |

| (22) 出願日     | 平成17年10月11日 (2005.10.11)     |          | 株式会社日立製作所           |

| (62) 分割の表示   | 特願平7-120017の分割               |          | 東京都千代田区丸の内一丁目6番6号   |

| 原出願日         | 平成7年5月18日 (1995.5.18)        | (74) 代理人 | 110000198           |

| (31) 優先権主張番号 | 特願平6-170696                  |          | 特許業務法人湘洋内外特許事務所     |

| (32) 優先日     | 平成6年7月22日 (1994.7.22)        | (72) 発明者 | 新田 博幸               |

| (33) 優先権主張国  | 日本国 (JP)                     |          | 神奈川県川崎市麻生区王禅寺1099番地 |

| (31) 優先権主張番号 | 特願平6-138499                  |          | 株式会社日立製作所システム開発研究所内 |

| (32) 優先日     | 平成6年6月21日 (1994.6.21)        | (72) 発明者 | ▲真▼野 宏之             |

| (33) 優先権主張国  | 日本国 (JP)                     |          | 神奈川県川崎市麻生区王禅寺1099番地 |

|              |                              |          | 株式会社日立製作所システム開発研究所内 |

最終頁に続く

(54) 【発明の名称】 液晶駆動回路及び液晶表示装置

## (57) 【要約】

【課題】液晶表示装置において、液晶ドライバを液晶パネルの片側に配置し実装面積を縮小しかつ列毎反転駆動を行うことにより高画質表示を可能とする目的とし、また、液晶駆動の基準電圧の交流化回路を液晶ドライバ内蔵することで電源回路の回路規模を縮小する目的とする。

【解決手段】入力される基準電圧と交流化信号から交流化駆動する2通りの交流化基準電圧を生成する電圧生成手段と表示データ、前記2通りの交流化基準電圧と交流化信号から液晶パネルに対して、各出力毎に交流化駆動の異なる液晶印加電圧に変換して出力する手段を持つ構成としたので、同一液晶ドライバ内の出力は互いに交流化のタイミングが異なる液晶駆動電圧とすることができます。

【選択図】 図1

図1

**【特許請求の範囲】****【請求項 1】**

複数の出力端子を持ち、

該複数の出力端子に対応した表示データを受け取り、

該表示データを表示電圧に変換し、

前記複数の出力端子に出力する駆動回路において、

前記表示電圧は同一の表示データに対して 2 つの異なる電圧を持ち、

該 2 つの異なる電圧は端子毎に一方の電圧となるように制御可能であることを特徴とする駆動回路。

**【請求項 2】**

請求項 1 記載の駆動回路の前記 2 つの異なる電圧は、基準電圧に対して基準電圧より高い電圧と、低い電圧の 2 つであることを特徴とする駆動回路。 10

**【請求項 3】**

請求項 1、2 記載の駆動回路であって、

前記複数の出力端子に対応した、前記 2 つの異なる電圧のどちらを選択するかを指示する極性信号を入力することを特徴とする駆動回路。

**【請求項 4】**

複数の出力端子と、

該複数の出力端子に対応した表示データを記憶するデータ記憶手段と、

該データ記憶手段の出力から前記複数出力端子に対応して、表示電圧を生成する電圧生成手段と、

該電圧生成手段の出力を前記複数の出力端子に出力する駆動回路において、

前記複数の出力端子に対応した極性データを記憶する極性記憶手段を設け、

前記電圧生成手段は、前記データ記憶手段の出力と該極性記憶手段の出力から、前記複数の出力端子に対応して、表示電圧を生成することを特徴とする駆動回路。 20

**【請求項 5】**

複数の出力端子と、

該複数の出力端子に対応した表示データと、

該表示データをラッチするラッチクロックと、

該ラッチしたデータの出力を指示する出力クロックと、

前記ラッチクロックにより、前記表示データをラッチする第 1 のラッチ手段と、前記出力クロックにより、該第 1 のラッチ手段の出力をラッチする第 2 のラッチ手段と、

該第 2 のラッチ手段の出力を表示電圧に変換し、該複数の出力端子に出力する電圧生成手段とを有する駆動回路において、

前記出力端子に対応して生成電圧の種類を示す極性信号を入力し、

該極性信号を前記ラッチクロックでラッチする第 1 の極性信号ラッチ手段と、

該第 1 の極性信号ラッチ手段の出力を出力クロックでラッチする第 2 の極性信号ラッチ手段を有し、

前記電圧生成手段は前記第 2 のラッチ手段の出力と該第 2 の極性ラッチ手段の出力を表示電圧に変換して、前記複数の出力端子に出力することを特徴とする駆動回路。 30

**【請求項 6】**

請求項 5 に記載の駆動回路において、

前記極性信号はプラス側とマイナス側をデジタル的に示し、

前記電圧生成手段は、前記第 2 の極性信号ラッチ手段の出力がプラス側を示す時は、基準電圧より高い電圧を生成し、マイナス側を示す時は、基準電圧より低い電圧を生成することを特徴とする駆動回路。 40

**【請求項 7】**

請求項 5、6 に記載の駆動回路において、

極性取り込み指示信号を入力し、極性信号ラッチ制御手段を有し、該極性取り込み指示信号により、該極性信号ラッチ制御手段は、前記第 1 の極性信号ラッチ制御手段に取り込み 50

を指示することを特徴とする駆動回路。

【請求項 8】

請求項 7 の前記取り込みの指示は、前記第 1 の極性信号ラッチ手段に与えるラッチ用のクロックを与えることで実現することを特徴とする駆動回路。

【請求項 9】

表示データを順次保持する保持手段と、

ライン表示同期信号に同期して液晶ドライバの有する出力データ線分の前記保持手段の表示データを同時に保持する保持手段と、

基準電圧と交流化信号から交流化駆動する 2 通りの交流化基準電圧を生成する電圧生成手段と、

前記保持手段に保持された表示データ、該 2 通りの交流化基準電圧と交流化信号から液晶パネルに対して、各出力毎に交流化駆動の異なる液晶印加電圧に変換して出力する手段とを有することを特徴とする液晶駆動回路。

10

【請求項 10】

請求項 9 記載の液晶駆動回路であって、

前記保持手段に保持された表示データ、前記基準電圧と前記交流化信号から前記液晶パネルに対して、1 出力毎に交流化駆動の異なる液晶印加電圧に変換して出力することを特徴とする液晶駆動回路。

20

【請求項 11】

請求項 9 記載の液晶駆動回路であって、

前記保持手段に保持された表示データ、前記基準電圧と前記交流化信号から前記液晶パネルに対して、複数の出力毎に交流化駆動の異なる液晶印加電圧に変換して出力することを特徴とする液晶駆動回路。

20

【請求項 12】

請求項 9 記載の液晶駆動回路であって、

交流化駆動の一方の交流化基準電圧を入力し、他方の交流化基準電圧を前記電圧生成手段が生成することを特徴とする液晶駆動回路。

30

【請求項 13】

請求項 9 記載の液晶駆動回路であって、

交流化駆動の一方の交流化基準電圧を入力し、他方の交流化基準電圧を前記電圧生成手段が基準電圧に対し対称に反転し生成することを特徴とする液晶駆動回路。

30

【請求項 14】

請求項 9 記載の液晶駆動回路であって、

交流化駆動の一方の交流化基準電圧を入力し、他方の交流化基準電圧を前記電圧生成手段が基準電圧分シフトし生成することを特徴とする液晶駆動回路。

40

【請求項 15】

表示データを順次保持する保持手段と、

ライン表示同期信号に同期して液晶ドライバの有する出力データ線分の該保持手段の表示データを同時に保持する保持手段と、

基準電圧は 2 通りの交流化基準電圧で、交流化信号で 2 通りの交流化基準電圧を切り換える電圧切り換え手段と、

前記保持手段に保持された表示データ、前記 2 通りの交流化基準電圧と交流化信号から液晶パネルに対して、各出力毎に交流化駆動の異なる液晶印加電圧に変換して出力する手段とを有することを特徴とする液晶駆動回路。

40

【請求項 16】

請求項 15 記載の液晶駆動回路であって、

前記保持手段に保持された表示データ、前記基準電圧と前記交流化信号から前記液晶パネルに対して、1 出力毎に交流化駆動の異なる液晶印加電圧に変換して出力することを特徴とする液晶駆動回路。

50

【請求項 17】

請求項 1 5 記載の液晶駆動回路であつて、

前記保持手段に保持された表示データ、前記基準電圧と前記交流化信号から前記液晶パネルに対して、複数の出力毎に交流化駆動の異なる液晶印加電圧に変換して出力することを特徴とする液晶駆動回路。

**【請求項 1 8】**

複数のデータ線および複数の走査線の交点位置にマトリックス状に配列した画素部を有する液晶パネルと、

該複数の走査線に順次電圧を印加する走査回路と、

上位装置からの表示データと基準電圧を受けて該表示データに対応した電圧を前記複数のデータ線に印加する液晶ドライバとを具備する液晶表示装置において、前記液晶ドライバは、請求項 1 から請求項 8 に記載の駆動回路であることを特徴とする液晶表示装置。 10

**【請求項 1 9】**

複数のデータ線および複数の走査線の交点位置にマトリックス状に配列した画素部を有する液晶パネルと、

該複数の走査線に順次電圧を印加する走査回路と、

上位装置からの表示データと基準電圧を受けて該表示データに対応した電圧を前記複数のデータ線に印加する液晶ドライバとを具備する液晶表示装置において、前記液晶ドライバは、請求項 9 から請求項 1 4 に記載の液晶駆動回路であることを特徴とする液晶表示装置。 20

**【請求項 2 0】**

複数のデータ線および複数の走査線の交点位置にマトリックス状に配列した画素部を有する液晶パネルと、

該複数の走査線に順次電圧を印加する走査回路と、

上位装置からの表示データと基準電圧を受けて該表示データに対応した電圧を前記複数のデータ線に印加する液晶ドライバとを具備する液晶表示装置において、前記液晶ドライバは、請求項 1 5 から請求項 1 7 に記載の液晶駆動回路であることを特徴とする液晶表示装置。 30

**【請求項 2 1】**

複数の出力端子を持ち、該複数の出力端子に対応した表示データを受け取り、該表示データを表示電圧に変換し、前記複数の出力端子に出力する駆動 L S I において、前記表示電圧は同一の表示データに対して、2つの異なる電圧を持ち、該2つの異なる電圧は端子毎に一方の電圧となるように制御可能であることを特徴とする液晶駆動 L S I。 30

**【請求項 2 2】**

前記2つの異なる電圧は、一方は入力した電圧であり、もう一方は反転基準電圧に対して前記入力した電圧を反転した電圧の2つであることを特徴とする請求項 2 1 記載の液晶駆動 L S I。

**【請求項 2 3】**

前記複数の出力端子に対応した、前記2つの異なる電圧のどちらを選択するかを指示する極性信号を入力することを特徴とする請求項 2 1 または 2 2 記載の液晶駆動 L S I。

**【請求項 2 4】**

表示データを順次保持する保持手段と、ライン表示同期信号に同期して液晶ドライバの有する出力データ線分の前記保持手段の表示データを同時に保持する保持手段と、基準電圧から交流化駆動する一方の階調電圧を生成する電圧生成手段と、前記保持手段に保持された表示データ、前記階調電圧と交流化信号と反転基準電圧から前記液晶パネルに対して、各出力毎に前記階調電圧を反転基準電圧に対して反転または非反転の制御を行い同一の表示データに対しての異なる液晶印加電圧を出力する出力手段とを有することを特徴とする液晶駆動 L S I。 40

**【請求項 2 5】**

前記保持手段に保持された表示データ、前記基準電圧と前記交流化信号から前記液晶パネルに対して、1出力毎に交流化駆動の異なる液晶印加電圧を出力することを特徴とする 50

請求項 2 4 記載の液晶駆動 L S I。

**【請求項 2 6】**

交流化駆動の一方の基準電圧を入力し、他方の基準電圧を液晶駆動 L S I で生成することを特徴とする請求項 2 4 記載の液晶駆動 L S I。

**【請求項 2 7】**

交流化駆動の一方の基準電圧を入力し、基準電圧から電圧生成手段で出力する階調数の階調電圧を生成し、交流化駆動の他方の階調電圧を出力手段で基準電圧に対し対称に反転して出力することを特徴とする請求項 2 6 記載の液晶駆動 L S I。

**【請求項 2 8】**

交流化駆動の一方の 9 レベル基準電圧を入力し、基準電圧から電圧生成手段で出力する 6 4 階調の階調電圧を生成し、交流化駆動の他方の 6 4 階調電圧を出力手段で基準電圧に対し対称に反転して出力することを特徴とする請求項 2 6 記載の液晶駆動 L S I。 10

**【請求項 2 9】**

複数のデータ線および複数の走査線の交点位置にマトリックス状に配列した画素部を有する液晶パネルと、前記複数の走査線に順次電圧を印加する走査駆動 L S I と、上位装置からの表示データと基準電圧を受けて該表示データに対応した電圧を前記複数のデータ線に印加する液晶ドライバとを備える液晶ディスプレイにおいて、前記液晶ドライバは、請求項 2 1, 2 2, 2 3, 2 4, 2 5, 2 6, 2 7 または 2 8 いずれか一に記載の液晶駆動 L S I であることを特徴とする液晶ディスプレイ。 20

**【請求項 3 0】**

前記走査駆動 L S I は、前記液晶ドライバのデジタル入力信号と同一の信号レベルのデジタル入力信号を直接入力することを特徴とする請求項 2 9 に記載の液晶ディスプレイ。 20

**【請求項 3 1】**

前記走査駆動 L S I は、入力段に入力するデジタル入力信号をレベルシフトするレベルシフト回路を設け、該レベルシフト回路でデジタル入力信号を該走査駆動 L S I の内部で動作する信号レベルにレベルシフトすることを特徴とする請求項 2 9 に記載の液晶ディスプレイ。 20

**【請求項 3 2】**

前記走査駆動 L S I は、基準信号を入力し、入力するデジタル入力信号の入力レベルを前記基準信号で制御可能なことを特徴とする請求項 2 9 に記載の液晶ディスプレイ。 30

**【請求項 3 3】**

前記出力端子との接続関係を変更可能に構成された複数の出力アンプ回路を備え、前記出力端子と前記出力アンプとの接続関係を、外部からの信号に従って切り替えることで、前記 2 つの異なる電圧を前記出力端子から出力することを特徴とする請求項 2 1 記載の液晶駆動 L S I。 30

**【請求項 3 4】**

非反転用の出力アンプのある出力端子に、また、反転用の出力アンプ回路を他のある出力端子に接続し、

前記出力端子と前記出力アンプとの接続関係を外部からの信号に従って交互に切り替えることで、前記出力端子から前記 2 つの異なる電圧を出力することを特徴とする請求項 2 1 記載の液晶駆動 L S I。 40

**【請求項 3 5】**

前記反転基準電圧よりも電圧の高い表示電圧を出力した出力端子と、前記反転基準電圧よりも電圧の低い表示電圧を出力した出力端子とを、表示電圧を次回出力する前に一旦接続すること、

を特徴とする請求項 2 2 記載の液晶駆動 L S I。

**【請求項 3 6】**

複数の出力端子を持ち、該複数の出力端子に対応した表示データを受け取り、該表示データを液晶駆動電圧に変換し、前記複数の出力端子に出力する駆動 L S I において、

前記液晶駆動電圧を、同一の表示データに対して電圧レベルの異なる 2 種類生成し、こ 50

のうちのいずれか一方を前記出力端子ごとに選択し出力すること、

を特徴とする液晶駆動 L S I。

**【請求項 3 7】**

前記 2 種類の液晶駆動電圧のうちの一方は、予め定められた基準電圧より電圧レベルが

高く、他方は該基準電圧より電圧レベルが低いこと、

を特徴とする請求項 3 6 記載の液晶駆動 L S I。

**【請求項 3 8】**

前記 2 種類の液晶駆動電圧のうち、一方は外部から入力されたものであり、他方は予め

定められた反転基準電圧に対して前記外部から入力された液晶駆動電圧を反転したもので

あること、

を特徴とする請求項 3 6 記載の液晶駆動 L S I。

**【請求項 3 9】**

前記前記液晶駆動電圧の選択は、外部から入力される交流化信号に従ってなされるもの

であること、

を特徴とする請求項 3 6 , 3 7 または 3 8 記載の液晶駆動 L S I。

**【請求項 4 0】**

複数の出力端子と、

表示データを順次保持する保持手段と、

前記保持手段に保持されている表示データを、別途入力されるライン表示同期信号に同

期して、上記出力端子の本数分だけ同時に保持する第 2 保持手段と、

20

別途生成された基準電圧から、複数レベルの電圧からなる階調電圧を生成する電圧生成

手段と、

前記階調電圧のうち前記第 2 保持手段に保持された表示データに対応したレベルの電圧

を前記出力端子毎に選択し、該選択した電圧を別途生成された反転基準電圧に対して反転

または非反転した後、前記出力端子から出力する出力手段と、

を有することを特徴とする

液晶駆動 L S I。

**【請求項 4 1】**

前記出力手段は、前記反転によって得られた電圧を出力する出力端子と、前記非反転に

よって得られた電圧を出力する出力端子とが、前記出力端子の配列上交互に位置するよう

に、前記反転または非反転を行うものであること、

30

を特徴とする請求項 4 0 記載の液晶駆動 L S I。

**【請求項 4 2】**

前記基準電圧は、外部から入力されるものであること、

を特徴とする請求項 4 0 記載の液晶駆動 L S I。

**【請求項 4 3】**

前記基準電圧は、9 レベルの電圧を含んで構成され、

前記階調電圧は、64 レベルの電圧を含んで構成されたものであること、

を特徴とする請求項 4 0 記載の液晶駆動 L S I。

**【請求項 4 4】**

複数のデータ線および複数の走査線の交点位置にマトリックス状に配列した画素部を有

する液晶パネルと、

40

前記複数の走査線に順次電圧を印加する走査駆動 L S I と、

上位装置から送られてくる表示データと、別途生成された基準電圧とを受けて、該表示

データに対応した電圧を生成し、該生成した電圧を前記複数のデータ線に印加する液晶ド

ライバと、を備え、

前記液晶ドライバは、請求項 3 6 , 3 7 , 3 8 , 3 9 , 4 0 , 4 1 , 4 2 または 4 3 記

載の液晶駆動 L S I であること、

を特徴とする液晶ディスプレイ。

**【請求項 4 5】**

前記走査駆動 L S I は、前記液晶ドライバのデジタル入力信号と同一レベルのデジタル

50

入力信号を、直接入力されていること、

を特徴とする請求項 4 4 記載の液晶ディスプレイ。

**【請求項 4 6】**

前記走査駆動 L S I は、入力段に入力されるデジタル入力信号を、該走査駆動 L S I 内部の動作信号レベルにまで、レベルシフトするレベルシフト回路を備えたこと、

を特徴とする請求項 4 4 記載の液晶ディスプレイ。

**【請求項 4 7】**

複数の出力端子と、

表示データを順次保持する保持手段と、

前記保持手段に保持されている表示データを、別途生成されるライン表示同期信号に同期して、上記出力端子の本数分だけ同時に保持する第 2 保持手段と、

別途生成された基準電圧と、別途生成された交流化信号とから、交流化駆動に用いられる交流化された 2 種類の交流化基準電圧を生成する電圧生成手段と、

前記交流化基準電圧を、前記第 2 保持手段に保持された表示データに対応したレベルの液晶駆動電圧に変換し、当該表示データに対応する出力端子からそれぞれ出力する出力手段と、

を有することを特徴とする液晶駆動 L S I 。

**【請求項 4 8】**

前記 2 種類の交流化基準電圧のうち、一方の交流化基準電圧に基づいて生成された液晶駆動電圧が出力される出力端子と、他方の交流化基準電圧に基づいて生成された液晶駆動電圧が出力される出力端子とは、上記出力端子の配列上予め定められた本数分ごとに交互に位置されていること、

を特徴とする請求項 4 7 記載の液晶駆動 L S I 。

**【請求項 4 9】**

上記予め定められた本数とは、1 本であること、

を特徴とする請求項 4 8 記載の液晶駆動 L S I 。

**【請求項 5 0】**

上記電圧生成手段は、別途生成された反転基準電圧を基準として一方の交流化基準電圧を反転し、該反転後の電圧を他方の交流化基準電圧とするものであること、

を特徴とする請求項 4 7 記載の液晶駆動 L S I 。

**【請求項 5 1】**

複数のデータ線および複数の走査線の交点位置にマトリックス状に配列した画素部を有する液晶パネルと、

前記複数の走査線に順次電圧を印加する走査回路と、

上位装置から送られてくる表示データと、別途生成された基準電圧とを受けて、該表示データに対応した電圧を生成し、該生成した電圧を前記複数のデータ線に印加する液晶ドライバと、を備え、

前記液晶ドライバは、請求項 4 0 , 4 1 , 4 2 , 4 3 または 4 4 記載の液晶駆動 L S I であること、

を特徴とする液晶ディスプレイ。

**【請求項 5 2】**

複数のデータ線および複数の走査線の交点位置にマトリックス状に配列した画素部を有する液晶パネルと、

前記複数の走査線に順次電圧を印加する走査回路と、

上位装置から送られてくる表示データと、別途生成された基準電圧とを受けて、該表示データに対応した電圧を前記複数のデータ線に印加する液晶ドライバと、を備え、

前記液晶ドライバは、請求項 4 7 , 4 8 , 4 9 または 5 0 に記載の液晶駆動 L S I であること、

を特徴とする液晶ディスプレイ。

**【発明の詳細な説明】**

10

20

30

40

50

## 【技術分野】

## 【0001】

本発明は、液晶駆動回路および液晶表示装置に関し、さらに詳しくは液晶ドライバにより液晶パネルを駆動させて、表示データを高画質でディスプレイさせる装置に関するものである。

## 【背景技術】

## 【0002】

従来の液晶表示装置を、具体的な例をいくつか挙げて説明する。なお、以下における従来例の説明において使用する符号は、各例ごとに独立したものである。従って、ある従来例の説明において使用した符号と同一の符号を、他の従来例の説明において全く異なる部分に付して使用する場合もある。10

## 【0003】

先ず第1の従来例を、図60、図61、図62、図63、図64、図65を用いて説明する。

## 【0004】

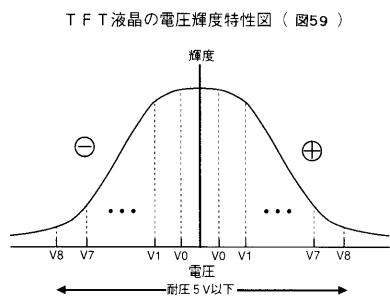

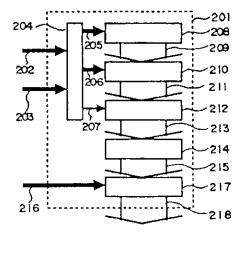

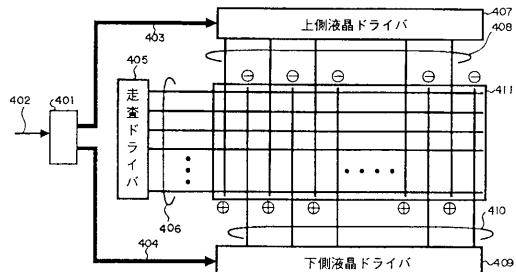

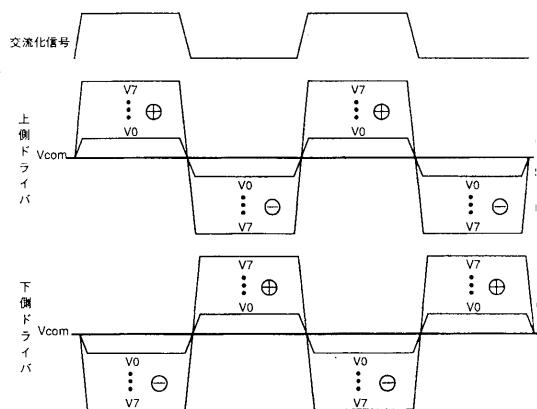

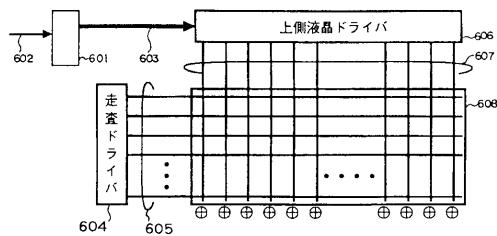

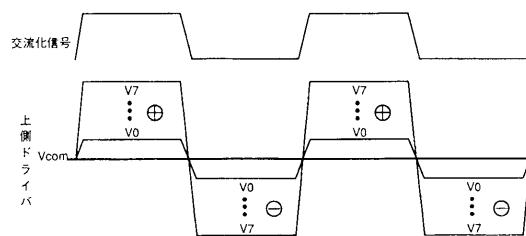

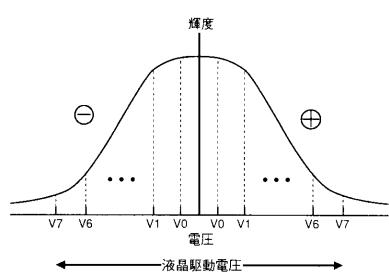

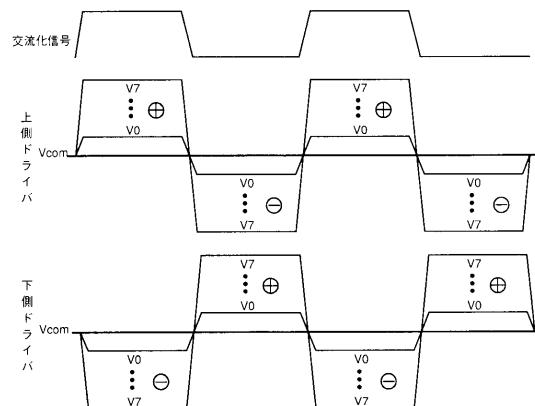

図60は従来の液晶ドライバの構成図、図61は液晶の電圧、輝度特性を示す図である。図62は液晶パネルの両側に液晶ドライバを配置した場合の液晶表示装置の構成図、図63は液晶基準電圧と交流化信号とのタイミング図である。図64は液晶パネルの片側に液晶ドライバを配置した場合の液晶表示装置の構成図、図65は液晶基準電圧と交流化信号とのタイミング図である。20

## 【0005】

図60において、201は液晶ドライバ、202はシステムから転送される表示データ、203は液晶ドライバを制御する制御信号群、204はタイミング制御回路、205は表示データ202のラッチタイミングを制御する制御信号、206は表示データ、207は表示を行うタイミング信号、208はラッチアドレス制御回路、209はラッチアドレス制御回路208で生成したラッチ信号群、210は表示データ206を順次ラッチするラッチ回路、211はラッチ回路210ラッチした表示データ、212は表示データ211をタイミング信号207で同時にラッチするラッチ回路、213はラッチ回路212にラッチした表示データ、214はロジック電圧レベルを液晶駆動電圧レベルに変換するレベルシフタ、215はレベルシフタ214で電圧レベルを変換した表示データ、216は液晶駆動電圧の基準電圧、217は基準電圧216を基に液晶駆動電圧を生成する液晶駆動回路、218は液晶パネルを駆動する液晶駆動信号群である。30

## 【0006】

図62において、401は液晶駆動の基準電圧を生成する電源回路、402は交流化のタイミングを示す交流化信号、403、404はそれぞれ交流化され、互いにタイミングが異なる基準電圧、405は液晶パネル411のゲート線を駆動する走査ドライバ、406は走査ドライバ405で駆動する液晶パネル411のゲート線、407は液晶パネル411の上側に配置したデータ線を駆動する液晶ドライバ、408は液晶ドライバ407が駆動するデータ線、409は液晶パネル411の下側に配置したデータ線を駆動する液晶ドライバ、410は液晶ドライバ409が駆動するデータ線、411は液晶パネルである。40

## 【0007】

図64において、601は液晶駆動の基準電圧を生成する電源回路、602は交流化のタイミングを示す交流化信号、603は交流化された基準電圧、604は液晶パネル608のゲート線を駆動する走査ドライバ、605は走査ドライバ604で駆動する液晶パネル608のゲート線、606は液晶パネル608の上側に配置したデータ線を駆動する液晶ドライバ、607は液晶ドライバ606が駆動するデータ線、608は液晶パネルである。

## 【0008】

次に、液晶ドライバの駆動動作について図60、図61を用いて説明する。図60にお50

いて、システムからの4画素、階調3ビット合計12ビットの表示データ202は順次転送され、4画素毎、40回合計160画素分の表示データがラッチャドレス制御回路208で生成されるラッチ信号209でラッチ回路210にラッチされる。ラッチされた表示データ211は走査ドライバのゲート選択信号に同期したタイミング信号207で160画素分同時にラッチ回路212にラッチされる。表示データ213はレベルシフタ214で電圧レベルが変換され、液晶駆動レベルに電圧変換された表示データ215に変換される。液晶駆動回路217では、基準電圧216のV7からV0の8レベルの内、表示データ215に対応した電圧レベルが選択され液晶駆動信号218として出力される。このようにすることで、液晶パネルを駆動することができる。

## 【0009】

10

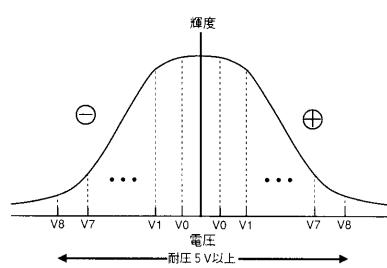

次に、図61を用いて液晶駆動電圧と表示輝度の説明をする。液晶は、共通電極に対して印加される電圧により表示輝度が異なり、V7からV0の8レベルの電圧を印加することで8階調表示を実現している。さらに、共通電極に対して正極性、負極性の同じ電圧が印加された場合は輝度が同じになり、液晶パネルの焼け付きを防止するため周期的に印加電圧を正極性、負極性とする交流駆動を行う必要がある。

## 【0010】

20

次に、液晶駆動装置の動作について、図62、図63、図64、図65を用いて説明する。図62は液晶ドライバを液晶パネルの上下に配置した場合の構成図であり、図63は交流化した基準電圧のタイミングを示した図である。電源回路401では交流化信号402に同期して交流化した上側ドライバ用基準電圧403と下側ドライバ用基準電圧404が生成される。上側液晶ドライバ用基準電圧403と下側液晶ドライバ用基準電圧404は、互いに正極性、負極性のタイミングが逆となっている。走査ドライバ405は1ラインずつ順次ゲート線406を選択し、選択されたラインを上側液晶ドライバと下側液晶ドライバが1列毎に駆動する。従って、走査ドライバ405で順次駆動する同一のゲート線上の液晶セルを1列毎に正極性、負極性交互に駆動することができる。

## 【0011】

30

また、図64は液晶ドライバを液晶パネルの上側のみに配置した場合の構成図であり、図65は交流化した基準電圧のタイミングを示した図である。電源回路601では交流化信号602に同期して交流化した基準電圧603を生成する。走査ドライバ604は1ラインずつ順次ゲート線605を選択し、選択されたラインを上側液晶ドライバが駆動する。従って、走査ドライバ604で順次駆動する同一のゲート線上の液晶セルは1ライン全て同一に正極性または負極性の駆動となる。

## 【0012】

40

液晶パネルの列毎反転駆動（液晶セルを列毎に正極性、負極性交互に駆動）は、液晶セルの印加電圧が交互に反転するため、液晶駆動時の電流が小さくなり、列毎反転駆動を行わない場合に比べ表示品質が良くなるという利点をもっている。そこで従来の液晶ドライバは、液晶ドライバを液晶パネルの上下に配置していた。一方、液晶表示装置は高画質表示だけでなく、小型軽量化の要求が強い。液晶ドライバを片側に配置することは、この小型軽量化を容易にする。しかし液晶ドライバを液晶パネルの片側に配置した場合、液晶ドライバは基準電圧216に基づき液晶駆動電圧を生成しているので、同一液晶ドライバ内の各出力は交流化のタイミングが同じとなる。従って、列毎反転駆動を行うことができず、液晶パネルの列毎反転駆動を行う場合に比較して表示品質が劣化する問題があった。

## 【0013】

別の従来例を、図67、図68、図69、図70、図71を用いて説明する。

## 【0014】

この例では、（株）日立製作所のデータドライバ（高耐圧データドライバHDD6310T）を用いるものとする。なお、該データドライバの詳細については、日立LCDコントローラ／ドライバLSIデータブック（株式会社日立製作所半導体事業本部19994年3月発行の933頁から947頁）に記載されている。

## 【0015】

50

図67はデータドライバHD66310Tを液晶パネルの両側に配置した場合の液晶表示装置の構成図、図68は走査回路の詳細を示したブロック図、図69は液晶ドライバLSIのプロセス耐圧を示す図、図70は液晶の電圧、輝度特性を示す図、図71は液晶基準電圧と交流化信号とのタイミング図である。

#### 【0016】

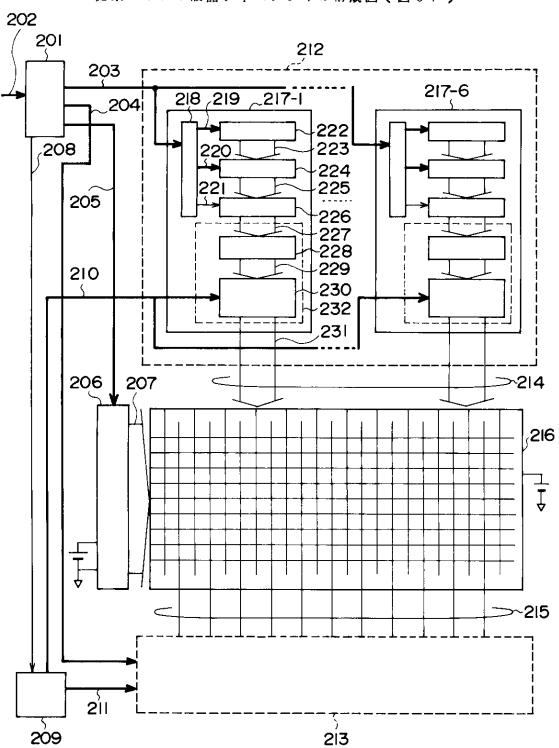

図67において、符号201を付したのは、液晶表示コントローラである。同様に、符号202はシステムからの表示データ、表示同期信号、203は液晶パネルの上側に配置した上側データドライバ212への表示データ、表示同期信号、204は液晶パネルの下側に配置したデータドライバ213への表示データ、表示同期信号、205は走査回路の表示同期信号、206は走査回路、207は走査回路206で順次選択されるゲート駆動信号を指している。10

#### 【0017】

また、符号208は交流同期信号、209は電源回路、210は上側データドライバ212への液晶駆動電圧の基準電圧、211は下側データドライバ213への液晶駆動電圧の基準電圧、212は上側データドライバ、213は下側データドライバ、214は上側データドライバ212の液晶駆動電圧、215は下側ドライバ213の出力する液晶駆動電圧、216は640×3(R、G、B)×480ドットの液晶パネルを指している。

#### 【0018】

上側データドライバ212は、出力を160本備えたデータドライバ217を6個備えている。以下、各データドライバ217をその配置順に、217-1、217-2、…、217-6と呼ぶ。また、図面上明らかではないが、下側データドライバ213も、同様に、160出力のデータドライバ217を6個備えている。つまり、この例ではデータドライバを合計12個（上側データドライバ212が6個、下側データドライバ213が6個）備えている。なお、以下の説明においては、下側データドライバ213を構成する6個のデータドライバを、それぞれ、217-1'、217-2'、…、217-6'と呼ぶ。20

#### 【0019】

データドライバ217内において符号218を付したのはタイミング制御回路である。同様に、符号219はタイミング信号群、220は表示データ、221は表示のタイミングを示す表示タイミング信号、222はラッチアドレス制御回路、223はラッチアドレス制御回路222で生成したラッチ信号群、224は表示データ220を順次ラッチするラッチ回路、225はラッチ回路224でラッチした表示データ、226は表示データ225を表示タイミング信号221で同時にラッチするラッチ回路、227はラッチ回路226にラッチした表示データ、228はロジック電圧レベルを液晶駆動電圧レベルに変換するレベルシフタ、229はレベルシフタ228で電圧レベルを変換した表示データ、230は基準電圧210を基に液晶駆動電圧を生成する液晶駆動回路、231は液晶パネルを駆動する液晶駆動信号群を指している。30

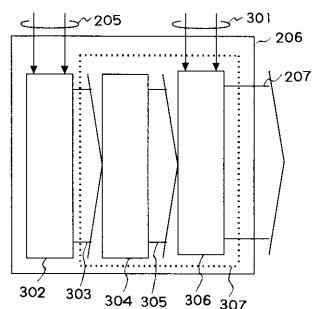

#### 【0020】

図68において、符号301は走査信号のオンレベル／オフレベルの電源電圧、302はシフトレジスタ、303はシフトレジスタ302のシフト出力信号、304はレベルシフト回路、305はシフト出力信号303をレベルシフト回路304で電圧レベル変換したシフト出力信号、306はシフト出力信号305に基づいて生成するゲート駆動回路を指している。40

#### 【0021】

次に、8階調表示を行う液晶パネル駆動動作について図67、図68を用いて説明する。

#### 【0022】

図67において、システムからの表示データ、表示同期信号202は、液晶表示コントローラ201で、12ビット(=4画素×階調3ビット)からなる表示データ、同期信号203、204に変換される。そして、表示データ、同期信号203は上側ドライバ21

10

20

30

40

50

2 へ、一方、表示データ、同期信号 204 は下側ドライバ 213 へ順次転送される。

【0023】

ラッチ回路 224 は、ラッチアドレス制御回路 222 で生成されるラッチ信号 223 で、表示データ 220 を、4 画素分づつラッチする。この例では、各ラッチ回路 224 が該ラッチ動作を 40 回繰り返すことで、1 つのラッチ回路 224（つまり、1 つのデータドライバ 217）当たり、160 画素分のデータをラッチしている。12 個のデータドライバ 217 のラッチ回路 224 がそれぞれ 160 画素分づつのデータを順次ラッチすることで、1 ライン分の表示データをラッチできる。各ラッチ回路 224 は、ラッチした表示データを表示データ 225 として出力する。

【0024】

各ラッチ回路 226 は、走査回路 206 のゲート選択信号に同期した表示同期信号 221 で、該表示データ 225 を同時にラッチする。つまり、640 画素分の表示データが同時にラッチされる。ラッチ回路 226 は、このラッチした表示データを、表示データ 227 としてレベルシフト回路 228 へ出力する。

【0025】

レベルシフト回路 228 は、液晶駆動レベルに合わせるように表示データ 227 の電圧レベルを変換し、表示データ 229 として出力する。

【0026】

液晶駆動回路 230 は、上側ドライバ用基準電圧 210（あるいは、下側ドライバ用基準電圧 211）に含まれている 8 種類の電圧レベルのうち、表示データ 229 に対応した電圧レベルを選択し、液晶駆動信号 231 として出力する。なお、上側ドライバ用基準電圧 210、下側ドライバ用基準電圧 211 は、電源回路 209 が交流同期信号 208 に基づいて生成するものであり、交流化された 8 種類のレベルの電圧（V7, V6, V5, V4, V3, V2, V1, V0）からなる。上側ドライバ用の基準信号 210 と、下側ドライバ用の基準信号 211 とでは、交流タイミングが異なっている。

【0027】

一方、走査回路 206 のシフトレジスタ 302（図 68 参照）は、表示同期信号 205 中の水平同期信号に同期して動作し、シフト出力信号 303 を出力する。レベルシフト回路 304 は、このシフト出力信号 303 の電圧レベルを液晶駆動レベルに電圧変換して、シフト出力信号 305 として出力する。

【0028】

ゲート駆動回路 306 は、シフト出力信号 305 に同期して 1 ライン毎に順次ゲート駆動信号 207 を生成し出力する。このゲート駆動信号 207 が、液晶パネル 213 のゲート線を、1 ラインづつ順次選択状態としてゆく。

【0029】

以上述べたとおり液晶パネルを 8 種類のレベルの電圧で駆動することで、表示データに対応した 8 階調表示を実現できる。

【0030】

次に、図 69 を用いて液晶駆動電圧と表示輝度との関係を説明をする。

【0031】

液晶は、共通電極に対して印加される電圧の大きさにより表示輝度が異なる。そのため、この共通電極に印加する電圧を変えることで、階調表示が可能である。例えば、図 67、図 68 を用いて説明した例では、8 種類のレベルの電圧（V7 ~ V0）の内のいずれかを表示データにあわせて選択し印加することで、8 階調表示を実現している。その一方で、印加される電圧の大きさが同じでありさえすれば、その電圧の正負に関わらず、液晶はその輝度が同じになる。つまり、共通電極に対して正極性、負極性の同じ電圧が印加された場合は、輝度が同じとなる。そのため、液晶パネルでは、周期的に印加電圧の極性（正極性 / 負極性）を変更する交流駆動を行うことで、液晶パネルの表示劣化につながる焼け付きを防止している。この交流駆動を行うために、現在の液晶パネルでは、液晶駆動電圧が 10V 以上となっている。

**【0032】**

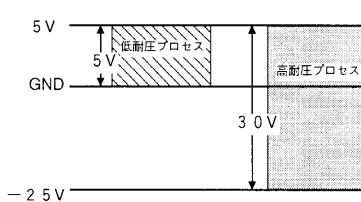

次に、この例で使用されているパネル液晶ドライバLSIのプロセスについて説明する。

**【0033】**

液晶ドライバは、通常、図70に示すように、デジタルロジック動作を行う低耐圧回路と、液晶駆動電圧で動作する高耐圧回路と、で構成されている。例えば、図65における破線232で囲んだ回路および図68における破線307で囲んだ回路が、高耐圧回路である。そのため、両者（高耐圧回路、低耐圧回路）を連携して動作させるためには、低耐圧回路からの信号を高耐圧回路の電圧レベルに変換するためのレベルシフト回路が必要である。

10

**【0034】**

次に、液晶駆動電圧の交流化のタイミングについて図67、図71を用いて説明する。

**【0035】**

基準信号210、211は、交流同期信号208に同期して電源回路209で生成されるものである。但し、上側ドライバ用の基準信号210と下側ドライバ用の基準信号211とでは、互いに異なるタイミングで交流化されている（図71参照）。従って、上側データドライバ212が正極性の液晶駆動電圧214を出力している間は、下側データドライバ213は負極性の液晶駆動電圧215を出力している。逆に、上側データドライバ212が負極性の液晶駆動電圧214を出力している間は、下側データドライバ213は正極性の液晶駆動電圧215を出力している。また、走査回路206は1ラインずつ順次ゲート線を選択している。そして、選択されたライン上の画素の内、奇数番目の画素は上側データドライバ212によって、一方、偶数番目の画素は下側データドライバ213によって駆動されている。これにより、同一のゲート線上の液晶セルは、1列置きに、異なった極性（正極性／負極性）の電圧で駆動されることになる。

20

**【0036】**

さらに別の従来例を図72を用いて説明する。

**【0037】**

この例では、図67～図71を用いて説明した従来例と同じ高耐圧データドライバを液晶パネルの上側のみに配置したものである。

30

**【0038】**

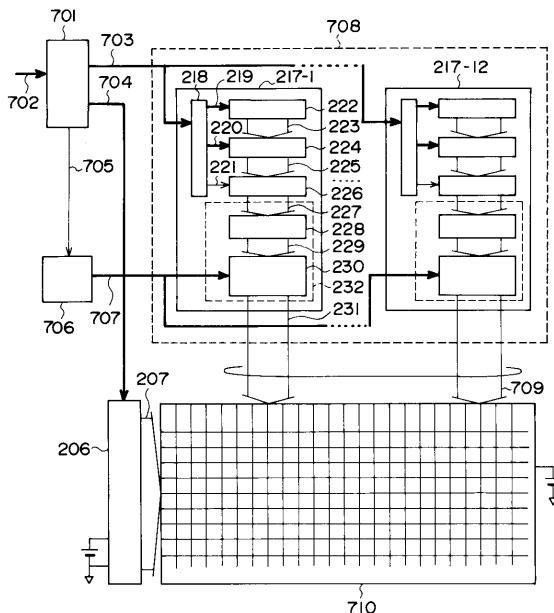

図72は、液晶駆動装置の構成図である。図72において、符号701を付したのは、液晶表示コントローラである。同様に、符号702はシステムからの表示データ、表示同期信号、703は液晶パネルの上側に配置したデータドライバの表示データ、表示同期信号、704は走査回路の表示同期信号を指す。また、符号705は交流同期信号、706は電源回路、707は上側に配置したデータドライバへの液晶駆動電圧の基準電圧、708は上側データドライバ、709は上側データドライバ708の出力する液晶駆動電圧、710は $640 \times 3$ （R、G、B） $\times 480$ ドットの液晶パネルを指す。

**【0039】**

上側データドライバ708は、160本の出力を有するデータドライバ217を12個備えている。以下、各データドライバ217を、その位置に応じてデータドライバ217-1、データドライバ217-2、……、データドライバ217-12と呼ぶ。

40

**【0040】**

次に、8階調表示を行う液晶パネル駆動動作について図72を用いて説明する。

**【0041】**

図72において、液晶表示コントローラ701は、システムからの表示データ、表示同期信号702を、合計12ビット（=4画素×階調3ビット）の表示データ、同期信号703に変換し、上側ドライバ708に順次転送する。

**【0042】**

上側ドライバ708内の各データドライバ217のラッチ回路224は、それぞれ、ラッチ信号223で、4画素毎に40回、合計160画素分の表示データをラッチする。な

50

お、ラッチ信号 223 は、ラッチアドレス制御回路 222 によって生成されるものである。12 個のデータドライバ 217 がそれぞれ 160 画素分の表示データをラッチすることで、1 ライン分の表示データをラッチ可能となっている。各ラッチ回路 224 は、ラッチしたデータを表示データ 225 として出力する。

#### 【0043】

ラッチ回路 226 は、走査回路 206 のゲート選択信号に同期した表示同期信号 221 で、該表示データ 225 を同時にラッチする。つまり、640 画素分の表示データが同時にラッチされる。ラッチ回路 226 は、このラッチした表示データを、表示データ 227 としてレベルシフト回路 228 へ出力する。

#### 【0044】

レベルシフト回路 228 は、液晶駆動レベルに合わせるように表示データ 227 の電圧レベルを変換し、表示データ 229 として出力する。

#### 【0045】

液晶駆動回路 230 は、上側ドライバ用基準電圧 210（あるいは、下側ドライバ用基準電圧 211）に含まれている 8 種類の電圧レベルの中から表示データ 229 に対応した電圧レベルを選択し、当該電圧レベルの電圧を液晶駆動信号 231 として出力する。なお、上側ドライバ用基準電圧 210、下側ドライバ用基準電圧 211 は、電源回路 706 が交流同期信号 705 に基づいて生成するものであり、交流化された 8 種類のレベルの電圧（V7, V6, V5, V4, V3, V2, V1, V0）からなる。

#### 【0046】

一方、走査回路 206 は、表示同期信号 704 の水平同期信号に同期して動作し、1 ライン毎に順次ゲート駆動信号 207 を生成する。このゲート駆動信号 207 が、液晶パネルのゲート線を、1 ラインづつ順次選択状態としてゆく。

#### 【0047】

以上述べたとおりこの例では、液晶パネル 710 を 8 レベルの電圧で駆動することで、表示データに対応した 8 階調表示を実現している。

#### 【0048】

次に、この例における液晶駆動電圧の交流化のタイミングについて図 71、図 72 を用いて説明する。

#### 【0049】

基準電圧 707 は、図 71 に示した上側ドライバ用の基準電圧 210 と同じように、交流同期信号 705 に同期して、電源回路 706 で生成されるものである。これにより、同一のゲート線上のすべての液晶セルは、その時々において定められる同一の極性（正極性または負極性）の電圧で駆動されることになる。

#### 【0050】

次にさらに別の従来技術を、図 73、図 74 を用いて説明する。

#### 【0051】

この例では、株式会社日立製作所性のデータドライバ（低耐圧データドライバ HD66330T）を用いている。なお、この低耐圧データドライバ HD66330T の詳細については、日立LCDコントローラ／ドライバ LSI データブック（株式会社日立製作所半導体事業本部 1999 年 3 月発行の 948 頁から 965 頁）に記載されている。

#### 【0052】

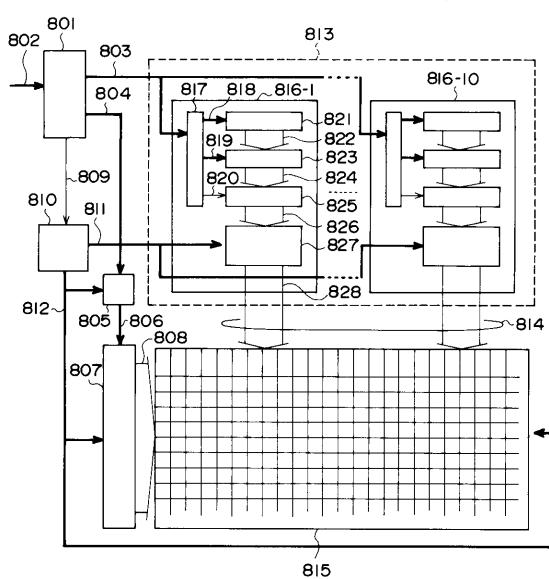

図 73 は従来のデータドライバ HD66330T を液晶パネルの上側に配置した場合の液晶表示装置の構成図、図 74 は液晶基準電圧と交流化信号とのタイミング図である。

#### 【0053】

図 73において、符号 801 を付したのは、液晶表示コントローラである。同様に符号 802 はシステムからの表示データ、表示同期信号、803 は液晶パネルの上側に配置したデータドライバへの表示データ、表示同期信号、804 は走査回路の表示同期信号、805 はレベルシフト回路、806 はレベルシフトした表示同期信号、807 は走査回路、808 は走査回路 807 が出力するゲート駆動信号を指す。また、符号 809 は交流同期

10

20

30

40

50

信号、810は電源回路、811は上側に配置したデータドライバへの液晶駆動電圧の基準電圧、812は交流基準電圧、813は上側データドライバ、814は上側データドライバ813の液晶駆動電圧、815は $640 \times 3$ (R、G、B)×480ドットの液晶パネルを指す。

#### 【0054】

上側データドライバ813は、192本の出力を有するデータドライバ816を、10個備えている。以下、各データドライバ816を、その配置位置に応じて、データドライバ816-1、データドライバ816-2、……、データドライバ816-10と呼ぶ。

#### 【0055】

符号817はタイミング制御回路、818はタイミング信号群、819は表示データ、820は表示のタイミングを示す表示タイミング信号、821はラッチアドレス制御回路、822はラッチアドレス制御回路821で生成したラッチ信号群、823は表示データ819を順次ラッチするラッチ回路、824はラッチ回路823でラッチした表示データ、825は表示データ824を表示タイミング信号820で同時にラッチするラッチ回路、826はラッチ回路825にラッチした表示データ、827は基準電圧811を基に液晶駆動電圧を生成する液晶駆動回路、828は液晶パネルを駆動する液晶駆動信号群を指す。

#### 【0056】

次に、この例において、対向電極交流駆動によって64階調表示を行う液晶パネル駆動動作について、図73、図74を用いて説明する。

#### 【0057】

図73において、液晶表示コントローラ801は、システムからの表示データ、表示同期信号802を、18ビット(=3画素×階調6ビット)の表示データ、同期信号803に変換し、これを上側ドライバ813に順次転送する。

#### 【0058】

上側ドライバ813のラッチ回路823は、ラッチアドレス制御回路821で生成されるラッチ信号822で、この表示データ、同期信号803を、3画素分づつ64回、合計192画素分をラッチする。合計10個のデータドライバ816が、順次、それぞれ192画素分のデータをラッチすることで、1ライン分の表示データがラッチ回路823にラッチされ、表示データ824として出力する。次に、各ラッチ回路825は、走査回路807のゲート選択信号に同期した表示同期信号820で、 $640 \times 3$ 画素分の該表示データ824を同時にラッチする。

#### 【0059】

液晶駆動回路827は、9種類の電圧レベルの電圧からなる上側ドライバ用基準電圧811の中から、表示データ826に対応した電圧レベルを選択し、当該電圧レベルの電圧を液晶駆動信号828として出力する。なお、上側ドライバ用基準電圧811は、電源回路810が交流同期信号809に基づいて生成するものであって、交流化された9種類の電圧レベルの電圧(V8, V7, V6, V5, V4, V3, V2, V1, V0)からなる。

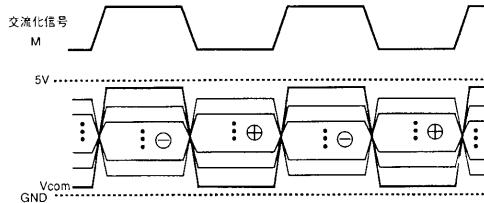

#### 【0060】

また、対向電極交流駆動は、図74に示す様に、データドライバが駆動する液晶駆動電圧に同期して、対向電極電圧(Vcom)をも交流化するものである。

#### 【0061】

この対向電極交流駆動では、対向電極をも交流化することで、データドライバの出力レベルが正極性、負極性ともに0Vから5Vの範囲内に収まる。そのため、データドライバを小チップサイズ化が可能な低耐圧回路で構成することができる。

#### 【0062】

しかしながら、このようにするとデータドライバと走査回路とで、入力信号のレベルが異なったものとなってしまう。そのため、表示同期信号804の電圧レベルを、レベルシ

10

20

30

40

50

フト回路 805 によって走査回路 807 に合わせて変換した上で、表示同期信号 806 として走査回路 807 に入力するようにしている。そして、走査回路 807 は、該表示同期信号 806 中の水平同期信号に同期して、1 ライン毎に順次ゲート駆動信号 808 を生成し出力する。該ゲート駆動信号 808 によって、液晶パネル 815 のゲート線が 1 ラインづつ順次選択状態とされる。

#### 【0063】

以上述べたようにこの例では 64 レベルの電圧で液晶パネルを駆動することで、表示データに対応した 64 階調表示を実現できる。

#### 【0064】

次に、液晶駆動電圧の交流化のタイミングについて図 74 を用いて説明する。

10

#### 【0065】

電源回路 810 は、図 74 に示すように、交流化信号（交流同期信号 809）に同期して基準信号 811 を生成する。これと並行して、電源回路 810 は、対向電極電圧（Vcom）をも該交流化信号に同期して交流化する。このように基準信号 811 と対向電極電圧との両方を交流化することで、該基準信号 811 の変動幅を 0V から 5V の範囲内に収めつつ、液晶にかかる電圧を交流化することができる。この例では、対向電極電圧（Vcom）を交流化しているため、同一のゲート線上の液晶セルに印加される電圧の極性（正極性／負極性）は、画素によって異なることはない。当該ゲート線上のいずれの画素にも、その時々において定まる一方の極性の電圧が印加される。

20

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0066】

図 60 乃至図 66 を用いて説明した従来技術には以下のようないくつかの課題があった。

#### 【0067】

上述したように、液晶表示装置には、携帯型機器へ搭載するため高画質化とともに小型軽量化が望まれている。本発明は、上記問題点に鑑みてなされたもので、この 2 つの要求を同時に満足する液晶表示装置を提供することを目的とする。即ち、高画質化のため、液晶セルを列毎に極性を反転して駆動する列毎反転駆動を行うことができ、また、液晶パネルを駆動する駆動回路の小型化、高密度実装のため、液晶ドライバを液晶パネルの片側に配置することのできる液晶表示装置を提供することを目的とする。

30

#### 【0068】

ところで、液晶パネルの列毎反転駆動（液晶セルを列毎に正極性、負極性交互に駆動）は、液晶セルの印加電圧が列毎交互に反転するため、液晶駆動時の共通電極に流れる電流が小さくなり、列毎反転駆動を行わない場合に比べ表示品質が良くなるという利点をもっている。このために、従来のデータドライバは、データドライバを液晶パネルの上下に配置していた。一方、液晶表示装置は高画質表示だけでなく、小型軽量化の要求が強い。データドライバを片側に配置することは、この小型軽量化を容易にする。

#### 【0069】

しかし、データドライバを液晶パネルの片側に配置した場合、データドライバは基準電圧 216 に基づき液晶駆動電圧を生成しているので、同一データドライバの内の各出力は交流化のタイミングが同じとなる。従って、列毎反転駆動を行うことができず、液晶パネルの列毎反転駆動を行う場合に比較して表示品質が劣化する問題があった。

40

#### 【0070】

また、液晶ディスプレイは、低価格化の要求が強い。回路部品の大きな割合を占めるデータドライバを低価格化するために、安価な汎用 5V 耐圧（低耐圧）プロセスを用いてチップ面積を小さくしチップ単価を安くしている。5V 耐圧のデータドライバを使用するために、図 66 に示す共通電極交流駆動を行っていた。共通電極交流駆動は、表示データに対応した液晶印加電圧の交流化と同じタイミングで共通電極を交流化することで、データドライバを 5V 耐圧の範囲内で動作させることができる。

#### 【0071】

50

しかし、共通電極交流駆動では、共通電極を交流するので、液晶印加電圧を列毎に反転することができない。そのため、共通電極に流れる電流が大きくなり、列毎反転駆動を行う場合に比較して表示品質が劣化する問題があった。この点を改善するため液晶パネル自身の特性を良くする必要があり、歩留り等の要因を考慮すると液晶ディスプレイとしての低価格化が困難になってきている。

#### 【0072】

また、液晶表示装置では基準電圧216を電源回路で交流化してデータドライバに入力しているため、電源回路の回路規模が大きくなり、液晶表示装置の周辺回路の小型化高密度実装化を困難にしていた。さらに、走査ドライバの入力信号、データドライバの入力信号のレベルを合わせるレベルシフト回路が外付けで、実装面積が増えるという問題もあった。上述したように、液晶ディスプレイには、携帯型機器へ搭載するため高画質化とともに小型軽量化、低価格化が望まれている。本発明は、上記問題に鑑みてなされたもので、これら三つの要求を同時に満足する液晶駆動LSIおよびそれを用いた液晶ディスプレイを提供することを目的とする。

#### 【0073】

具体的には、液晶ディスプレイの小型軽量化、すなわち、液晶パネルを駆動する駆動回路の小型化、高密度実装を行なうために、データドライバを液晶パネルの片側に配置しつつ、高画質化のために、液晶セルを列毎に極性を反転して駆動する列毎反転駆動を行うデータドライバとそれを用いた液晶ディスプレイを提供することを目的とする。

#### 【0074】

また、表示品質を劣化させないために共通電極交流駆動を行なわず、かつ、データドライバのチップ面積を小さくし、データドライバ、液晶ディスプレイのコストを下げる目的とする。

#### 【0075】

また、レベルシフト回路、交流化回路等、電源周辺回路の回路規模を削減して、小型で、高密度実装された液晶ディスプレイを提供することを目的とする。

#### 【0076】

さらに図67乃至図75を用いて説明した従来技術についても以下のような課題があった。

#### 【0077】

液晶表示装置に対しては、小型軽量化の要求が強い。図72のごとくデータドライバを片側に配置すれば、小型軽量化が容易になる。しかし、このような構成を採った場合、すべてのデータドライバ217は、同じ基準電圧707に基づいて液晶駆動電圧を生成することになる。そのため、すべてのデータドライバ217の出力について、その交流化のタイミングが同じとなる。つまり、その時々において各画素に印加される電圧の極性が、液晶パネルの同一ライン上の全ての画素について同じとなる。このときの画素部の電流方向を図75に示した。各画素に印加される電圧が、同一ライン上の画素について全て正極性となっている場合には、対向電極(Com)よりも駆動電圧の方が電位が高い。そのため、データドライバから各画素に対して電流が流れ込む。このため寄生抵抗の影響による画質の劣化が顕著になりやすいという問題があった。

#### 【0078】

また、液晶表示装置は、低価格化の要求が強い。これに応えるため、安価な汎用5V耐圧(低耐圧)プロセスを用いてチップ面積を小さくすることで、回路部品の大きな割合を占めるデータドライバの低コスト化を図っている。そして、このような5V耐圧(低耐圧)のデータドライバの使用を可能するために、対向電極交流駆動を行っていた。既に述べたとおり、対向電極交流駆動は、表示データに対応した液晶印加電圧の交流化と同じタイミングで対向電極電圧を交流化することで、データドライバを5V耐圧の範囲内で動作させることを可能としたものである。

#### 【0079】

しかし、この対向電極交流駆動では、図75に示すとおり、各画素にその時々において

10

20

30

40

50

印加される電圧の極性が、同一ライン上のすべて画素について同じとなってしまう。また、共通電極に流れる電流も大きくなってしまう。そのため、対向電極交流駆動を採用すると、寄生抵抗の影響による画質の劣化が顕著になりやすいという問題があった。さらに、この問題を改善するためには液晶パネル自身の特性を向上させなければならず、工程数、歩留り等の要因を総合的に考慮すると液晶表示装置全体としての低価格化が困難になっていた。

#### 【0080】

また、従来の液晶表示装置（図67～図75）では、基準電圧（210、211、707、811、812）を電源回路（209、706、810）で交流化していたため、電源回路の回路規模が大きくなり、液晶表示装置の周辺回路の小型化を困難にしていた。さらに、データドライバと走査回路との入力信号の電圧レベルを合わせるためにレベルシフト回路必要となり、液晶表示装置の周辺回路の小型化を困難にしていた。10

#### 【0081】

以上述べたとおり、液晶表示装置には小型機器へ搭載するため高画質化とともに小型軽量化、低価格化が望まれているにもかかわらず、これを実現するには問題があった。

#### 【0082】

本発明は、上記問題に鑑みてなされたもので、これらの3つの要求（高画質化、小型軽量化、低価格化）を同時に満足する液晶駆動LSIおよびそれを用いた液晶表示装置を提供することを目的とする。20

#### 【0083】

より具体的には、（1）データドライバを液晶パネルの片側に配置することによる液晶表示装置の小型軽量化（すなわち、液晶パネルを駆動する駆動回路の小型化、高密度実装）、（2）各画素に印加する電圧の極性を列毎に反転して駆動することによる高画質化、を可能としたデータドライバ、およびこれを用いた液晶表示装置を提供することを目的とする。20

#### 【0084】

また、チップ面積が小さく低コストなデータドライバ、およびこれを用いることで低価格化が可能な液晶表示装置を提供することを目的とする。

#### 【0085】

さらには、液晶表示装置の周辺回路（例えば、レベルシフト回路、交流化回路）の規模を削減した、小型高密度実装の液晶表示装置を提供することを目的とする。30

#### 【課題を解決するための手段】

#### 【0086】

まず、特許請求の範囲第1項～第20項において開示した発明について述べる。

#### 【0087】

本発明の液晶表示装置は、前記課題を解決するため、入力される基準電圧と交流化信号から交流化駆動する2通りの交流化基準電圧を生成する電圧生成手段と表示データ、前記2通りの交流化基準電圧と交流化信号から液晶パネルに対して、各出力毎に交流化駆動の異なる液晶印加電圧に変換して出力する手段を持つ。40

#### 【0088】

または、入力される基準電圧は2通りの交流化基準電圧で、交流化信号で2通りの交流化基準電圧を切り換える電圧切り換え手段と表示データ、前記2通りの交流化基準電圧と交流化信号から液晶パネルに対して、各出力毎に交流化駆動の異なる液晶印加電圧に変換して出力する手段を持つ。

#### 【0089】

または、入力される基準電圧から交流化駆動する2通りの交流化基準電圧を生成する電圧生成手段と表示データ、交流化信号を保持する保持手段と前記表示データ、前記2通りの交流化基準電圧と前記交流化信号から液晶パネルに対して、各出力毎に交流化信号に対応した液晶印加電圧に変換して出力する手段を持つ。

#### 【0090】

10

20

30

40

50

次に、特許請求の範囲第21項～第35項において開示した発明について述べる。

【0091】

本発明では、交流化駆動する一方の基準電圧から交流化駆動する一方の階調電圧を複数生成する電圧生成手段と、生成された複数の階調電圧から保持手段に保持された表示データに従って階調電圧を選択し、前記選択された階調電圧と交流化信号と反転基準電圧とから、前記液晶パネルに対して、前記選択された階調電圧を反転基準電圧に対して反転または非反転の制御を行い、同一の表示データに対して異なる液晶印加電圧を出力する出力手段とを、データドライバに設けた。

【0092】

さらに、データドライバの出力回路のみに高耐圧プロセスを用い、その他は低耐圧プロセスを用いる構成にした。 10

【0093】

さらに、走査ドライバに、入力段に入力するデジタル入力信号をレベルシフトするレベルシフト回路を設け、該レベルシフト回路でデジタル入力信号を走査ドライバの内部で動作する信号レベルにレベルシフトする。または、走査ドライバに、基準信号を入力し、入力するデジタル入力信号の入力レベルを前記基準信号で制御するようにした。

【0094】

また、複数の出力端子と複数の出力アンプとの接続関係を変更可能に構成しておく。例えば、ある出力端子には非反転用の出力アンプを、また、他のある出力端子には、反転用の出力アンプ回路を接続する。そして、外部からの信号に従ってこの接続関係を切り替えることで、前記2つの異なる電圧を前記出力端子から出力するようにした。 20

【0095】

さらに、前記反転基準電圧よりも電圧の高い表示電圧を出力した出力端子と、前記反転基準電圧よりも電圧の低い表示電圧を出力した出力端子とを、表示電圧を次回出力する前に一旦接続するようにした。

【0096】

特許請求の範囲第36～第52項において開示した発明について述べる。

【0097】

本発明の一の態様としては、複数の出力端子と、表示データを順次保持する保持手段と、前記保持手段に保持されている表示データを、別途入力されるライン表示同期信号に同期して、上記出力端子の本数分だけ同時に保持する第2保持手段と、別途生成された基準電圧から、複数レベルの電圧からなる階調電圧を生成する電圧生成手段と、前記階調電圧のうち前記第2保持手段に保持された表示データに対応したレベルの電圧を前記出力端子毎に選択し、該選択した電圧を別途生成された反転基準電圧に対して反転または非反転した後、前記出力端子から出力する出力手段と、を有することを特徴とする液晶駆動LSIが提供される。 30

【0098】

該液晶駆動LSIを用いて液晶表示装置を構成する場合には、走査駆動LSIは、入力段に入力されるデジタル入力信号を、該走査駆動LSI内部の動作信号レベルにまで、レベルシフトするレベルシフト回路を備えてもよい。

【0099】

さらに、データドライバは、出力回路のみを高耐圧プロセスを用い、その他は低耐圧プロセスを用いる構成とした。 40

【0100】

本発明の別の態様としては、複数の出力端子と、表示データを順次保持する保持手段と、前記保持手段に保持されている表示データを、別途生成されるライン表示同期信号に同期して、上記出力端子の本数分だけ同時に保持する第2保持手段と、別途生成された基準電圧と、別途生成された交流化信号とから、交流化駆動に用いられる交流化された2種類の交流化基準電圧を生成する電圧生成手段と、前記交流化基準電圧を、前記第2保持手段に保持された表示データに対応したレベルの液晶駆動電圧に変換し、当該表示データに対 50

応する出力端子からそれぞれ出力する出力手段と、を有することを特徴とする液晶駆動LSIが提供される。

【0101】

特許請求の範囲第1項～第20項までに開示した発明の作用を説明する。

【0102】

本発明の液晶表示装置は、入力される基準電圧と交流化信号から交流化駆動する2通りの交流化基準電圧を生成する電圧生成手段と表示データ、前記2通りの交流化基準電圧と交流化信号から液晶パネルに対して、各出力毎に交流化駆動の異なる液晶印加電圧に変換して出力する手段を持つので、同一液晶ドライバ内の出力は互いに、交流化のタイミングが異なる液晶駆動電圧とすることができます。10

【0103】

または、入力される基準電圧は2通りの交流化基準電圧で、交流化信号で2通りの交流化基準電圧を切り換える電圧切り換え手段と表示データ、前記2通りの交流化基準電圧と交流化信号から液晶パネルに対して、各出力毎に交流化駆動の異なる液晶印加電圧に変換して出力する手段を持つので、同一液晶ドライバ内の出力は互いに、交流化のタイミングが異なる液晶駆動電圧とすることができます。

【0104】

また、入力される基準電圧と交流化信号から交流化駆動する2通りの交流化基準電圧を生成する電圧生成手段を持つので、基準電圧を生成する電源回路の回路規模を小さくすることができます。20

【0105】

次に、特許請求の範囲第21項～第35項までに開示した発明の作用を説明する。

【0106】

上記の電圧生成手段と、出力手段によって、同一液晶ドライバ内の出力は互いに、交流化のタイミングが異なる液晶駆動電圧とすることができます。

【0107】

また、データドライバは、出力回路のみを高耐圧プロセスを用い、その他は低耐圧プロセスを用いる構成としたため、チップサイズの縮小を容易にすることができます。

【0108】

また、データドライバに入力される基準電圧は交流化するための片側の基準電圧のみであり、もう一方の基準電圧はデータドライバ内部で生成するため、基準電圧を生成する電源回路の回路規模を小さくすることができます。30

【0109】

また、走査ドライバの入力段に設けたレベルシフト回路で、デジタル入力信号を走査ドライバの内部で動作する信号レベルにレベルシフトすることが可能なため、外付けのレベルシフト回路を必要とせず、液晶ディスプレイの周辺回路の回路規模を低減することができます。

【0110】

また、走査ドライバは、基準信号を入力し、入力するデジタル入力信号の入力レベルを前記基準信号で制御可能であるため、外付けのレベルシフト回路を必要とせず、液晶ディスプレイの周辺回路の回路規模を低減することができます。40

【0111】

さらには、出力端子と出力アンプとの接続関係を変更可能に構成することで、2つの異なる電圧を出力端子から出力する。このようにすることで、必要な出力アンプの個数を減らすことができる。

【0112】

さらに、反転基準電圧よりも電圧の高い表示電圧を出力した出力端子と、反転基準電圧よりも電圧の低い表示電圧を出力した出力端子とを、表示電圧を次回出力する前に一旦接続することで、液晶パネル内の残留電荷を利用して液晶駆動電力を低減できる。

【0113】

10

20

30

40

50

特許請求の範囲第36項～第52項までに開示した発明の作用を説明する。

【0114】

電圧生成手段は、基準電圧から、複数レベルの電圧からなる階調電圧を生成している。第2保持手段は、保持手段に保持されている表示データを、ライン表示同期信号に同期して、出力端子の本数分だけ同時に保持する。出力手段は、階調電圧のうち2保持手段に保持された表示データに対応したレベルの電圧を前記出力端子毎に選択する。そして、この選択した電圧を反転基準電圧に対して反転または非反転した後、出力端子から出力する。

【0115】

あるいは、電圧生成手段は、基準電圧と、交流化信号とから、交流化駆動に用いられる交流化された2種類の交流化基準電圧を生成している。第2保持手段は、保持手段に保持されている表示データを、ライン表示同期信号に同期して、上記出力端子の本数分だけ同時に保持する。出力手段は、交流化基準電圧を、第2保持手段に保持された表示データに対応したレベルの液晶駆動電圧に変換する。そして、これを当該表示データに対応する出力端子からそれぞれ出力する。

【0116】

このように、電圧生成手段および出力手段によって、同一の液晶駆動LSI(データドライバ)内の出力を、互いに交流化のタイミングが異なる液晶駆動電圧とすることができます。また、交流駆動において必要となる2つの基準電圧のうち、一方は液晶駆動LSI(データドライバ)内部で生成するため、基準電圧を生成する電源回路の回路規模を小さくすることができる。

【0117】

液晶駆動LSI(データドライバ)は、出力回路のみに高耐圧プロセスを用い、その他は低耐圧プロセスを用いる構成としたため、チップサイズの縮小を容易にすることができます。

【0118】

また、走査ドライバの入力段に設けたレベルシフト回路で、デジタル入力信号を走査ドライバの内部で動作する信号レベルにレベルシフトすることが可能なため、外付けのレベルシフト回路を必要とせず、液晶ディスプレイの周辺回路の回路規模を低減することができる。

【発明の効果】

【0119】

本発明の液晶表示装置は、入力される基準電圧と交流化信号から交流化駆動する2通りの交流化基準電圧を生成する電圧生成手段と表示データ、前記2通りの交流化基準電圧と交流化信号から液晶パネルに対して、各出力毎に交流化駆動の異なる液晶印加電圧に変換して出力する手段を持つ構成としたので、同一液晶ドライバ内の出力は互いに、交流化のタイミングが異なる液晶駆動電圧とすることができます。従って液晶ドライバを片側に配置し実装面積を縮小し、高画質な列毎反転駆動を行うことができる。

【0120】

または、入力される基準電圧は2通りの交流化基準電圧で、交流化信号で2通りの交流化基準電圧を切り換える電圧切り換え手段と表示データ、前記2通りの交流化基準電圧と交流化信号から液晶パネルに対して、各出力毎に交流化駆動の異なる液晶印加電圧に変換して出力する手段を持つ構成としたので、同一液晶ドライバ内の出力は互いに、交流化のタイミングが異なる液晶駆動電圧とすることができます。このため液晶ドライバを片側に配置し実装面積を縮小し、高画質な列毎反転駆動を行うことができる。

【0121】

また、入力される基準電圧と交流化信号から交流化駆動する2通りの交流化基準電圧を生成する電圧生成手段を持つ構成としたので、基準電圧を生成する電源回路の回路規模を小さくすることができる。

【0122】

本発明によれば、同一液晶ドライバ内の出力は互いに、交流化のタイミングが異なる液

10

20

30

40

50

晶駆動電圧とすることができる。しかも、データドライバに入力される基準電圧は交流化するための片側の基準電圧のみでよい。もう一方の基準電圧は、データドライバ内部で生成する。つまり、本発明では、データドライバ自身が、交流化駆動において必要な2つの基準電圧を1つの基準電圧から生成して、互いに交流化のタイミングが異なる液晶駆動電圧を出力できる。そのため、基準電圧を生成する電源回路の回路規模を小さくすることができる。また、データドライバを液晶パネルの片側に配置し、小型化、高密度実装化を図ることができる。さらに実装面積を縮小しつつ、高画質な列毎反転駆動を行うことができる。周辺回路の回路規模を低減し、液晶ディスプレイの小型軽量化を容易にすることができます。

## 【0123】

10

また、本発明のデータドライバでは出力回路に高耐圧プロセスを用いているため、液晶駆動電圧は高耐圧電圧レベル(10V以上)が出力可能である。その結果、表示品質が良くない共通電極交流駆動を行わずに、高画質な列毎反転駆動を行うことができる。しかも、出力回路のみに高耐圧プロセスを用いているため、チップ面積の低減が容易であり、低価格化が可能である。

## 【0124】

20

また、走査ドライバの入力段に、デジタル入力信号をレベルシフトするレベルシフト回路を設けたことで、該レベルシフト回路によってデジタル入力信号を走査ドライバの内部で動作する信号レベルにレベルシフトすることができる。そのため、外付けのレベルシフト回路を必要とせず、液晶ディスプレイの周辺回路の回路規模を低減することができ、液晶ディスプレイの小型軽量化が容易である。

## 【0125】

また、走査ドライバは、基準信号を入力し、入力するデジタル入力信号の入力レベルを前記基準信号で制御可能であるため、外付けのレベルシフト回路を必要とせず、液晶ディスプレイの周辺回路の回路規模を低減することができるため、液晶ディスプレイの小型軽量化を容易にする。

## 【発明を実施するための最良の形態】

## 【0126】

30

以下、本発明を実施例を用いて説明する。

## 【0127】

以下において説明する10個の実施例のうち、第1～第5の実施例は特願平6-138499号の内容に対応するものである。また、第6，第7の実施例は、特願平6-138499号の内容に対応するものである(但し、一部内容の追加あり)。第8～第10の実施例は、本出願において新たに追加した実施例である。以下の説明において使用している符号は、下記グループ毎に独立したものである。

## 【0128】

40

グループ1：第1～第5の実施例

グループ2：第6，第7の実施例

グループ3：第8～第10の実施例

従って、異なるグループ間においては、同一の符号を異なる回路部分に重複して用いる場合もある。

## 【0129】

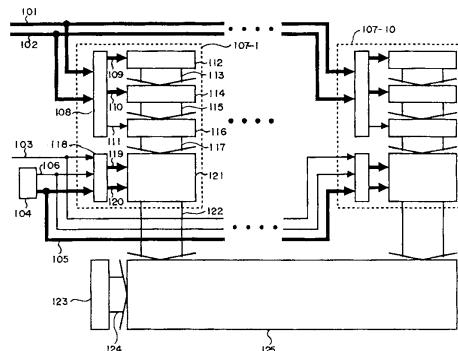

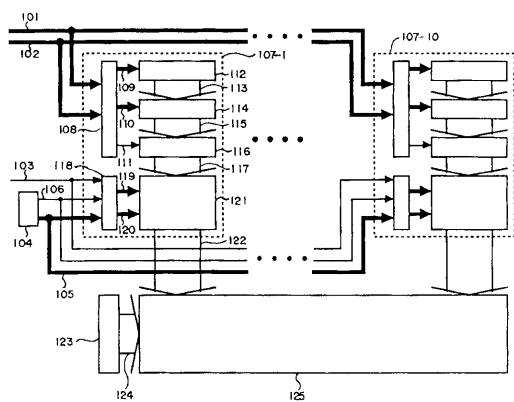

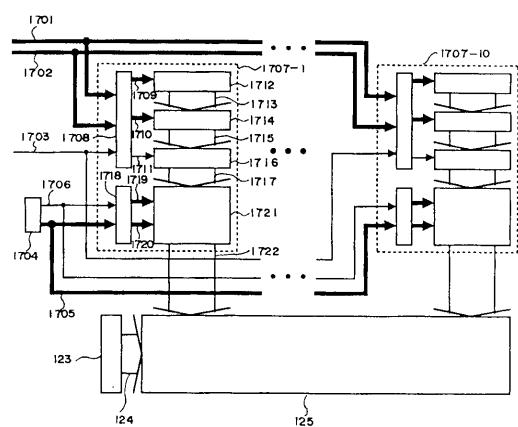

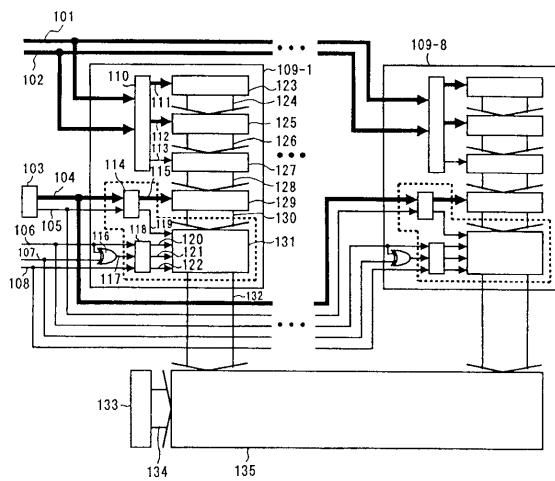

本発明の第1の実施例について、図1、図2、図3、図4を用いて説明する。

## 【0130】

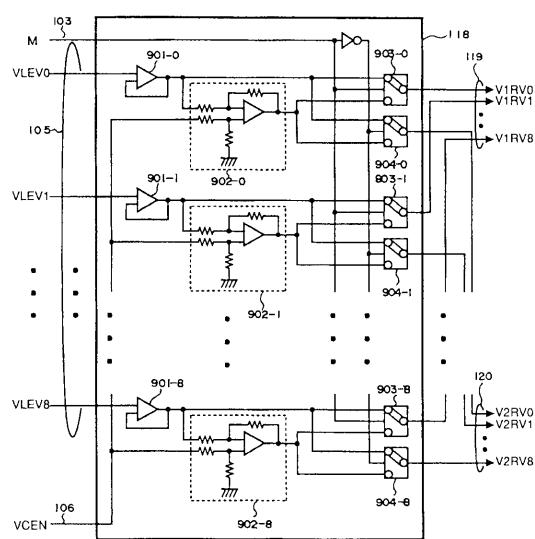

図1は本発明の液晶表示装置を示したブロック図、図2は液晶駆動回路のブロック図、図3は電圧生成回路のブロック図、図4は基準電圧と液晶駆動電圧のタイミングを示した図である。

## 【0131】

50

図1において、101はシステムから転送される表示データ、102は制御信号群、103は交流化のタイミングを示す交流化信号、104は液晶駆動電圧を生成するための基

準電圧を生成する電源回路、105、106は電源回路104で生成した直流の基準電圧である。107-1から107-10は192の出力数を有する液晶ドライバであり、108はタイミング制御回路、109はタイミング信号群、110は表示データ、111は表示のタイミングを示すタイミング信号、112はラッチアドレス制御回路、113はラッチアドレス制御回路112で生成したラッチ信号群、114は表示データ110を順次ラッチするラッチ回路、115はラッチ回路114でラッチした表示データ、116は表示データ115をタイミング信号111で同時にラッチするラッチ回路、117はラッチ回路116でラッチした表示データである。118は基準電圧105、106を基に液晶を交流駆動するための交流基準電圧を生成する電圧生成回路、119、120は電圧生成回路で生成した、交流化された交流基準電圧である。121は交流基準電圧119、120を基に表示データ117に対応した液晶駆動電圧を生成する液晶駆動回路、122は液晶駆動回路121で生成した液晶駆動電圧である。123は走査回路、124は走査回路123で順次選択されるゲート駆動信号、125は液晶パネルである。

10

20

30

40

50

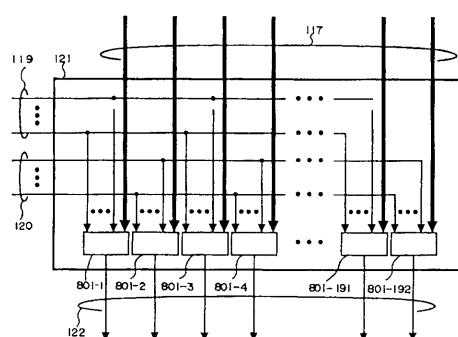

## 【0132】

図2において、801-1から801-192は各出力毎の液晶駆動回路である。

## 【0133】

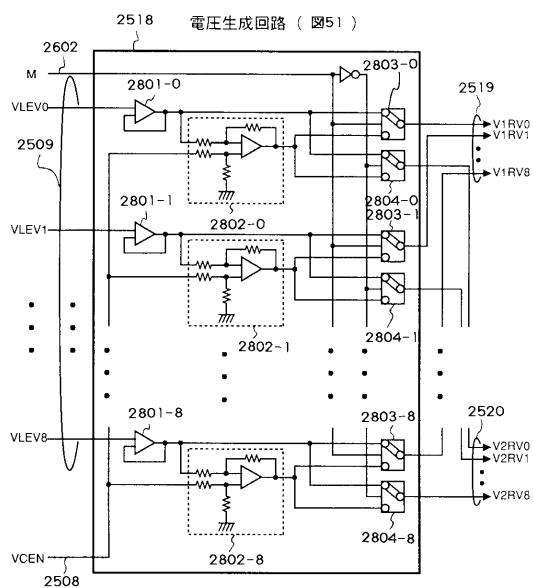

図3において、901-0から901-8はアンプバッファ回路、902-0から902-8は差動増幅回路、903-0から903-8、904-0から904-8は選択回路である。

## 【0134】

次に、液晶駆動回路の動作について説明する。図1において液晶ドライバ107-1から107-10は出力数が192であり、液晶パネル125は解像度 $640 \times RGB \times 480$ 画素であるため液晶ドライバは10個必要となる。表示データ101は3画素、階調6ビットの合計18ビットの表示データが順次転送され、制御信号群109から表示データ101に同期したラッチ信号113をラッチアドレス制御回路112で生成し、順次表示データ110をラッチ回路114にラッチする。ラッチ回路114は各6ビット192画素分のラッチ回路を持ち各液晶ドライバ107-1から107-10で1水平ライン分の表示データを順次ラッチすることができる。ラッチ回路114にラッチした表示データ115は、走査回路123のゲート選択信号124に同期したタイミング信号111で1水平ライン分同時にラッチ回路116にラッチする。ラッチした表示データ117は液晶駆動回路121に入力される。電圧生成回路118では、電源回路104で生成した基準電圧105、106と交流化信号103から互いに交流化タイミングの異なる交流基準電圧119、120が生成され液晶駆動回路121に入力される。液晶駆動回路121では表示データ117に対応した、交流基準電圧119、120を基に液晶駆動電圧122が生成され、液晶パネル125が駆動される。

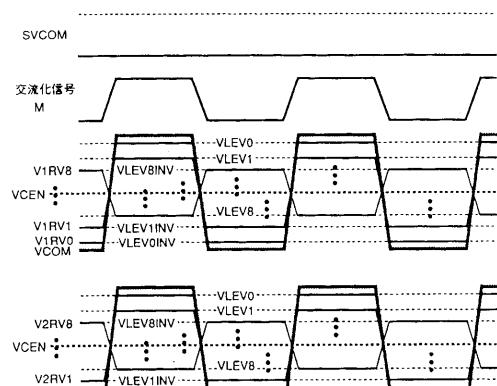

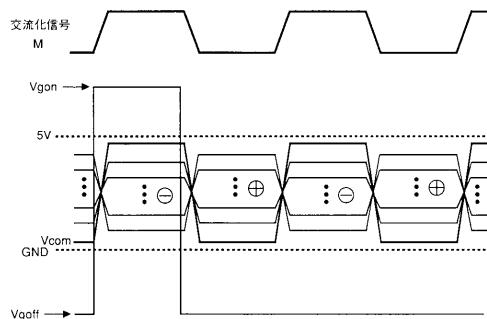

## 【0135】

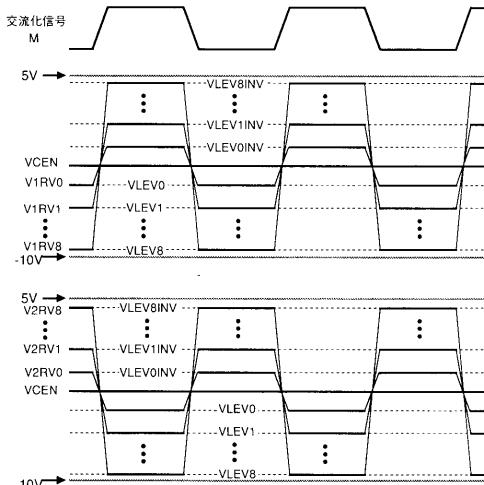

次に、電圧生成回路118の動作について図3、図4を用いて説明する。図3において、電源回路104からのVLEV0からVLEV8の9レベルの基準電圧105はそれぞれアンプバッファ回路901-0から901-8でバッファされ、差動増幅回路902-0から902-8、選択回路903-0から903-8、904-0から904-8に入力する。差動増幅回路902-0から902-8では、基準電圧(VCEN)106に対して基準電圧(VLEV0からVLEV8)105が反転され出力される。この関係を図4に示す。VLEV0からVLEV8はそれぞれVCENに対して反転したVLEV0INVからVLEV8INVの基準電圧となる。図9において選択回路903-0から903-8、904-0から904-8にはそれぞれ、アンプバッファ回路901-0から901-8の出力と差動増幅回路902-0から902-8からの出力が入力され、これらを交流化信号103で選択し、出力する。選択回路904-0から904-8には、反転した交流化信号が入力されるため、選択回路903-0から903-8と選択回路904-0から904-8で選択する電圧はそれぞれ逆となる。

## 【0136】

このタイミングを図4に示す。交流化信号(M)103がハイレベルの時、選択回路9

03-0から903-8で選択した交流化基準電圧(V1RV0からV1RV8)119はそれぞれVLEVOINVからVLEV8INVが出力され、選択回路904-0から904-8で選択した交流化基準電圧(V2RV0からV2RV8)120はそれぞれVLEVOからVLEV8が出力される。逆に、交流化信号(M)103がロウレベルの時、選択回路903-0から903-8で選択した交流化基準電圧(V1RV0からV1RV8)119はそれぞれVLEVOからVLEV8が出力され、選択回路904-0から904-8で選択した交流化基準電圧(V2RV0からV2RV8)120はそれぞれVLEVOINVからVLEV8INVが出力される。このようにして交流化のタイミングがお互いに異なる交流化基準電圧119、120が生成される。

#### 【0137】

次に、液晶駆動回路121について図2を用いて説明する。図2において、交流化基準電圧119、120は、192出力の各出力毎の液晶駆動回路801-1から801-192に交互に入力される。液晶駆動回路801-1から801-192では、特願平05-170647号に記載されているように、各出力6ビットの表示データ117と9レベルの交流化基準電圧119または120から64レベルの液晶駆動電圧を生成し、出力する。表示データ6ビットの内上位3ビットで9レベルの交流化基準電圧の2レベルを選択し、表示データ下位3ビットで選択した2レベルの電圧を8等分に分圧した8レベルの電圧から1レベルを選択することで64レベルの液晶駆動電圧を出力することができる。このようにすることで、液晶ドライバは出力毎に交流化のタイミングが互いに異なる液晶駆動電圧を生成することができ、液晶パネル125を列毎反転駆動することが可能となる。

#### 【0138】

また、本実施例では、各出力の液晶駆動回路に対し、1出力毎に交流化タイミングの異なる交流化基準電圧を切り換える構成としたが、2出力毎、または複数出力で交流化基準電圧を切り換えても良い。

#### 【0139】

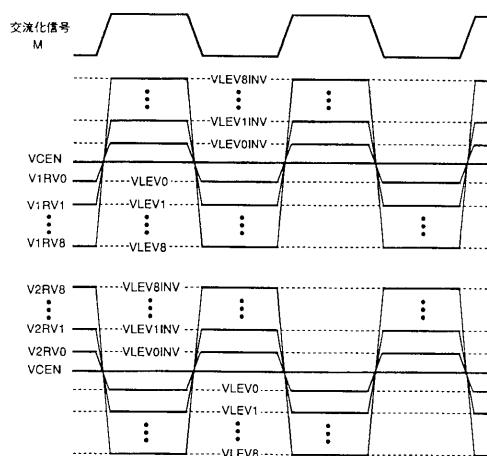

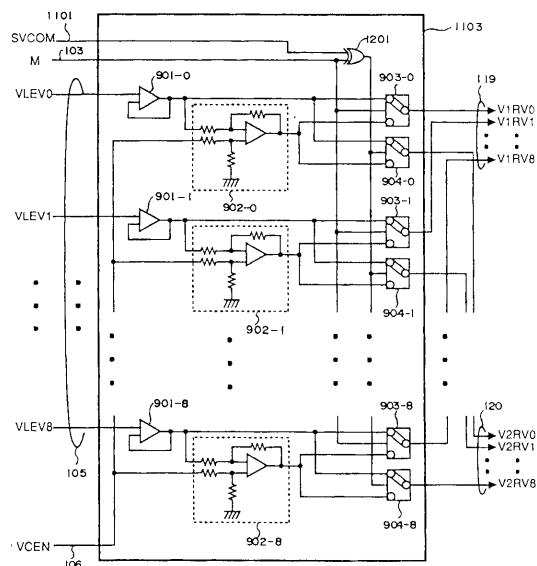

次に本発明の第2の実施例について、図2、図4、図5、図6、図7を用いて説明する。本実施例は、液晶パネルの共通電極交流駆動に対応するため、第1の実施例とは電圧生成回路が異なり、その他は同様である。図5は本発明の液晶表示装置を示したブロック図、図6は電圧生成回路のブロック図、図7は基準電圧と液晶駆動電圧のタイミングを示した図である。

#### 【0140】

図5において、1101は交流化基準電圧のタイミングを制御する制御回路、1102は液晶ドライバ、1103は基準電圧105、106を基に液晶を交流駆動するための交流基準電圧を生成する電圧生成回路である。

#### 【0141】

図6において、1201は交流化タイミングを切り換える切り換え回路である。

#### 【0142】

次に、液晶駆動回路の動作について説明する。図5において液晶ドライバ1102-1から1102-10は出力数が192であり、液晶パネル125は解像度640×RGB×480画素であるため液晶ドライバは10個必要となる。表示データ101は3画素、階調6ビットの合計18ビットの表示データが順次転送され、制御信号群109から表示データ101に同期したラッチ信号113をラッチアドレス制御回路112で生成し、順次表示データ110をラッチ回路114にラッチする。ラッチ回路114は各6ビット192画素分のラッチ回路を持ち各液晶ドライバ1102-1から1102-10で1水平ライン分の表示データを順次ラッチすることができる。ラッチ回路114にラッチした表示データ115は、走査回路123のゲート選択信号124に同期したタイミング信号111で1水平ライン分同時にラッチ回路116にラッチする。ラッチした表示データ117は液晶駆動回路121に入力される。電圧生成回路1103では、電源回路104で生成した基準電圧105、106と交流化信号103、制御信号1101から交流基準電圧119、120が生成され液晶駆動回路121に入力される。液晶駆動回路121では表示データ117に対応した、交流基準電圧119、120を基に液晶駆動電圧122が生

10

20

30

40

50

成され、液晶パネル 125 が駆動される。

#### 【0143】

次に、電圧生成回路 1103 の動作について図 4、図 6、図 7 を用いて説明する。図 6において、電源回路 104 からの VLEV0 から VLEV8 の 9 レベルの基準電圧 105 はそれぞれアンプバッファ回路 901-0 から 901-8 でバッファされ、差動增幅回路 902-0 から 902-8、選択回路 903-0 から 903-8、904-0 から 904-8 に入力する。差動增幅回路 902-0 から 902-8 では、基準電圧 (VCEN) 106 に対して基準電圧 (VLEV0 から VLEV8) 105 が反転され出力される。

#### 【0144】

この関係を図 4、図 7 に示す。これからわかるように、VREV0 から VREV8 はそれぞれ VCEN 10 に対して反転した VLEV0INV から VLEV8INV の基準電圧となる。選択回路 903-0 から 903-8、904-0 から 904-8 にはそれぞれ、アンプバッファ回路 901-0 から 901-8 の出力と差動增幅回路 902-0 から 902-8 からの出力が入力され、これらを交流化信号 103 で選択し、出力する。選択回路 904-0 から 904-8 には、交流化信号 (M) 103 と制御信号 (SVCOM) 1101 は切り換え回路 1201 で排他的論理和がとられるため、制御信号 (SVCOM) 1101 がハイレベルの場合は、選択回路 903-0 から 903-8 と選択回路 904-0 から 904-8 で選択する電圧はそれぞれ逆となり、制御信号 (SVCOM) 1101 がロウレベルの場合は、選択回路 903-0 から 903-8 と選択回路 904-0 から 904-8 で選択する電圧は同じとなる。つまり、基準電圧生成のタイミングは制御信号 (SVCOM) 1101 がハイレベルの場合は図 4 に示すように第 1 の実施例と同様となる。

#### 【0145】

制御信号 (SVCOM) 1101 がロウレベルの場合は、図 7 に示すように、交流化信号 (M) 103 がハイレベルの時、選択回路 903-0 から 903-8 で選択した交流化基準電圧 (V1RV0 から V1RV8) 119 はそれぞれ VLEV0INV から VLEV8INV が出力され、選択回路 904-0 から 904-8 で選択した交流化基準電圧 (V2RV0 から V2RV8) 120 も同様にそれぞれ VLEV0INV から VLEV8INV が出力され、交流化信号 (M) 103 がロウレベルの時、選択回路 903-0 から 903-8 で選択した交流化基準電圧 (V1RV0 から V1RV8) 119 はそれぞれ VLEV0 から VLEV8 が出力され、選択回路 904-0 から 904-8 で選択した交流化基準電圧 (V2RV0 から V2RV8) 120 も同様にそれぞれ VLEV0 から VLEV8 が出力される。共通電極交流駆動の場合、図 7 に示すように共通電極 (VCOM) を交流化するため、液晶ドライバの各出力の交流化タイミングは同一にする必要がある。したがって、制御信号 1101 を切り換えることで、交流化基準電圧 119、120 の交流化のタイミングを制御することができ、共通電極駆動にも容易に対応することができる。

#### 【0146】

液晶駆動回路 121 については第 1 の実施例と同様であり説明を省略する。

#### 【0147】

本発明の第 3 の実施例について、図 1、図 8、図 9 を用いて説明する。本実施例は、第 1 の実施例とは電圧生成回路が異なり、その他は同様である。図 8 は電圧生成回路のブロック図、図 9 は基準電圧と液晶駆動電圧のタイミングを示した図である。

#### 【0148】

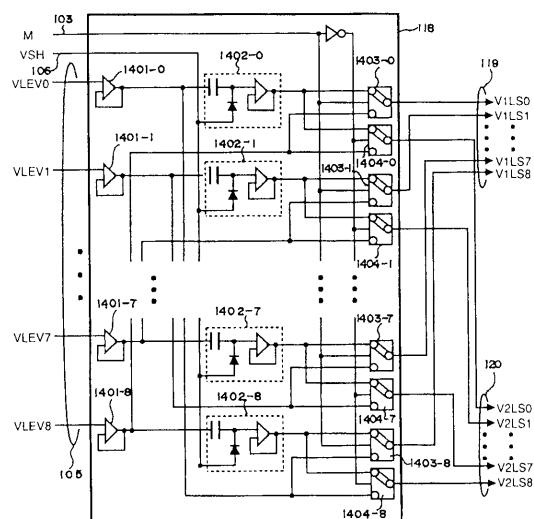

図 8 において、1401-0 から 1401-8 はアンプバッファ回路、1402-0 から 1402-8 はレベルシフト回路、1403-0 から 1403-8、1404-0 から 1404-8 は選択回路である。

#### 【0149】

次に、液晶駆動回路の動作について説明する。図 1 において液晶ドライバ 107-1 から 107-10 の動作は第 1 の実施例と同様である。

#### 【0150】

次に、本実施例の電圧生成回路 118 の動作について図 8、図 9 を用いて説明する。図 8 において、電源回路 104 からの VLEV0 から VLEV8 の 9 レベルの基準電圧 105 はそれぞ

10

20

30

40

50

れアンプバッファ回路 1401-0 から 1401-8 でバッファされ、レベルシフト回路 1402-0 から 1402-8、選択回路 1403-0 から 1403-8、1404-0 から 1404-8 に入力する。レベルシフト回路 1402-0 から 1402-8 では、基準電圧 (VLEV0からVLEV8) 105 が基準電圧 (VSH) 106 の電圧レベルに従いレベルシフトされ出力される。

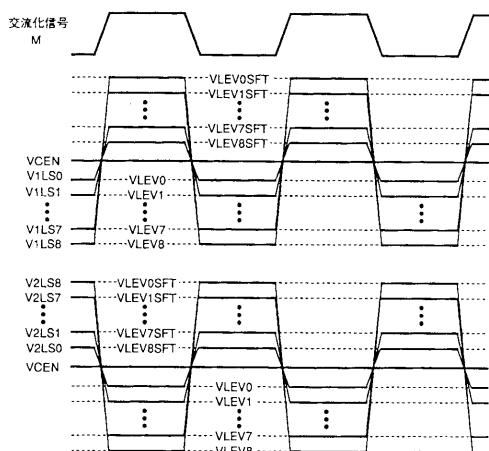

#### 【0151】

この関係を図9に示す。VREV0からVREV8はそれぞれ電圧レベルVSHだけレベルシフトしたVLEV0SFTからVLEV8SFTの基準電圧となる。選択回路 1403-0 から 1403-8、1404-0 から 1404-8 にはそれぞれ、アンプバッファ回路 1401-8 から 1401-0 の出力とレベルシフト回路 1402-0 から 1402-8 からの出力が入力され、これらを交流化信号 103 で選択し、出力する。選択回路 1404-0 から 1404-8 には、反転した交流化信号が入力されるため、選択回路 1403-0 から 1403-8 と選択回路 1404-0 から 1404-8 で選択する電圧はそれぞれ逆となる。このタイミングを図9に示す。交流化信号 (M) 103 がハイレベルの時、選択回路 1403-0 から 1403-8 で選択した交流化基準電圧 (V1LS0からV1LS8) 119 はそれぞれVLEV8SFTからVLEV0SFTが出力され、選択回路 1404-0 から 1404-8 で選択した交流化基準電圧 (V2LS0からV2LS8) 120 はそれぞれVLEV8SFTからVLEV0SFTが出力される。

#### 【0152】

逆に、交流化信号 (M) 103 がロウレベルの時、選択回路 1403-0 から 1403-8 で選択した交流化基準電圧 (V1LS0からV1LS8) 119 はそれぞれVLEV0からVLEV8が出力され、選択回路 1404-0 から 1404-8 で選択した交流化基準電圧 (V2LS0からV2LS8) 120 はそれぞれVLEV8SFTからVLEV0SFTが出力される。このようにして交流化のタイミングがお互いに異なる交流化基準電圧 119、120 が生成される。

#### 【0153】

次に、液晶駆動回路 121 の動作についても第1の実施例と同様である。このようにすることで、液晶ドライバは出力毎に交流化のタイミングがお互いに異なる液晶駆動電圧を生成することができ、液晶パネル 125 を列毎反転駆動することが可能となる。

#### 【0154】

本発明の第4の実施例について、図4、図10を用いて説明する。本実施例は第1の実施例とは電源回路、電圧生成回路が異なり、その他は同様である。

#### 【0155】

図10は本発明の液晶表示装置を示したブロック図である。

#### 【0156】

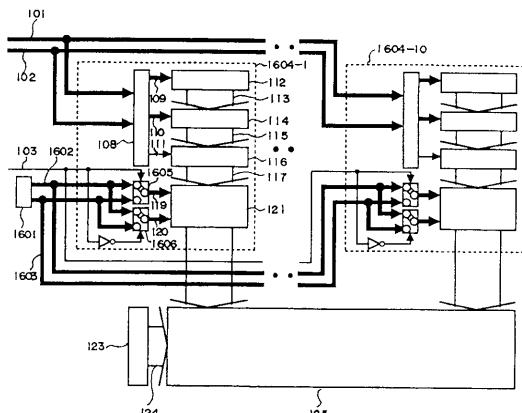

図10において、1601は液晶駆動電圧を生成するための基準電圧を生成する電源回路、1602、1603は電源回路 1601 で生成した基準電圧である。1604-1 から 1604-10 は出力数が 192 出力の液晶ドライバである。1605、1606は基準電圧 1602、1603 を交流化信号 103 で切り換え液晶を交流駆動するための交流基準電圧を生成する電圧選択回路である。

#### 【0157】

次に、液晶駆動回路の動作について説明する。図10において液晶ドライバ 1604-1 から 1604-10 は出力数が 192 であり、液晶パネル 125 は解像度  $640 \times RGB \times 480$  画素であるため液晶ドライバは 10 個必要となる。表示データ 101 は 3 画素、階調 6 ビットの合計 18 ビットの表示データが順次転送され、制御信号群 109 から表示データ 101 に動期したラッチ信号 113 をラッチアドレス制御回路 112 で生成し、順次表示データ 110 をラッチ回路 114 にラッチする。

#### 【0158】

ラッチ回路 114 は各 6 ビット 192 画素分のラッチ回路を持ち各液晶ドライバ 1604-1 から 1604-10 で 1 水平ライン分の表示データを順次ラッチすることができる。ラッチ回路 114 にラッチした表示データ 115 は、走査回路 123 のゲート選択信号 124 に同期したタイミング信号 111 で 1 水平ライン分同時にラッチ回路 116 にラッ

10

20

30

40

50

チする。ラッチした表示データ117は液晶駆動回路121に入力される。電圧選択回路1605、1606では、電源回路1601で生成した基準電圧1602、1603を交流化信号103で選択し、互いに交流化タイミングの異なる交流基準電圧119、120出力され液晶駆動回路121に入力される。液晶駆動回路121では表示データ117に対応した、交流基準電圧119、120を基に液晶駆動電圧122が生成され、液晶パネル125が駆動される。

#### 【0159】

次に、電圧選択回路1605、1606の動作について、図4を用いて説明する。電源回路1601からのVLEV0からVLEV8の9レベルの基準電圧1602とVLEV0INVからVLEV8INVの9レベルの基準電圧1603は、電圧選択回路1605、1606に入力され、これらを交流化信号103で選択し、出力する。選択回路1606には、反転した交流化信号が入力されるため、選択回路1605と選択回路1606で選択する電圧はそれ逆となる。このタイミングを図4に示す。交流化信号(M)103がハイレベルの時、選択回路1605で選択した交流化基準電圧(V1RV0からV1RV8)119はそれぞれVLEV0INVからVLEV8INVが出力され、選択回路1606で選択した交流化基準電圧(V2RV0からV2RV8)120はそれぞれVLEV0からVLEV8が出力される。

#### 【0160】

逆に、交流化信号(M)103がロウレベルの時、選択回路1605で選択した交流化基準電圧(V1RV0からV1RV8)119はそれぞれVLEV0からVLEV8が出力され、選択回路1606で選択した交流化基準電圧(V2RV0からV2RV8)120はそれぞれVLEV0INVからVLEV8INVが出力される。このようにして交流化のタイミングがお互いに異なる交流化基準電圧119、120が生成される。

#### 【0161】

液晶駆動回路121の動作については第1の実施例と同様であるので説明を省略する。

#### 【0162】

また、本実施例では、各出力の液晶駆動回路に対し、1出力毎に交流化タイミングの異なる交流化基準電圧を切り換える構成としたが、2出力毎、または複数出力で交流化基準電圧を切り換えて良い。

#### 【0163】

本発明の第5の実施例について、図11、図12、図13、図14を用いて説明する。

#### 【0164】

図11は本発明の液晶表示装置を示したブロック図、図12は液晶駆動回路のブロック図、図13は電圧生成回路のブロック図、図14は基準電圧と液晶駆動電圧のタイミングを示した図である。

#### 【0165】

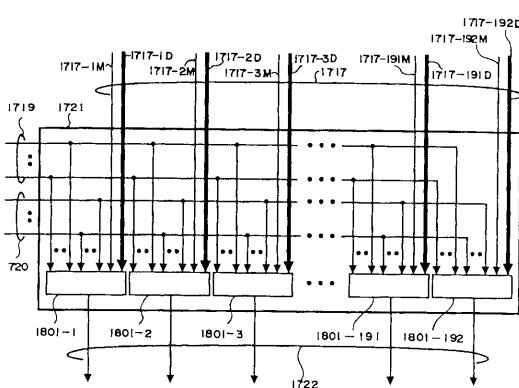

図11において、1701はシステムから転送される表示データ、1702は制御信号群、1703は交流化のタイミングを示す交流化信号、1704は液晶駆動電圧を生成するための基準電圧を生成する電源回路、1705、1706は電源回路1704で生成した直流の基準電圧である。1707-1から1707-10は出力数が192出力の液晶ドライバであり、1708はタイミング制御回路、1709はタイミング信号群、1710は表示データと交流化信号のデータバス、1711は表示のタイミングを示すタイミング信号、1712はラッチアドレス制御回路、1713はラッチアドレス制御回路1712で生成したラッチ信号群、1714はデータバス1710のデータを順次ラッチするラッチ回路、1715はラッチ回路1714でラッチした表示データと交流化信号のデータバス、1716はデータバス1715をタイミング信号1711で同時にラッチするラッチ回路、1717はラッチ回路1716でラッチした表示データと交流化信号のデータバスである。

#### 【0166】

1718は基準電圧1705、1706を基に液晶を交流駆動するための交流基準電圧を生成する電圧生成回路、1719、1720は電圧生成回路で生成した、正極性、負極性

10

20

30

40

50

性の基準電圧である。1721は基準電圧1719、1720を基に表示データと交流化信号のデータバス1717に対応した液晶駆動電圧を生成する液晶駆動回路、1722は液晶駆動回路1721で生成した液晶駆動電圧である。1723は走査回路、1724は走査回路1723で順次選択されるゲート駆動信号、1725は液晶パネルである。

#### 【0167】

図12において、1801-1から1801-192は各出力毎の液晶駆動回路、1717-1Mから1717-192Mはデータバス1717の各出力の交流化信号、1717-1Dから1717-192Dは各出力の表示データである。

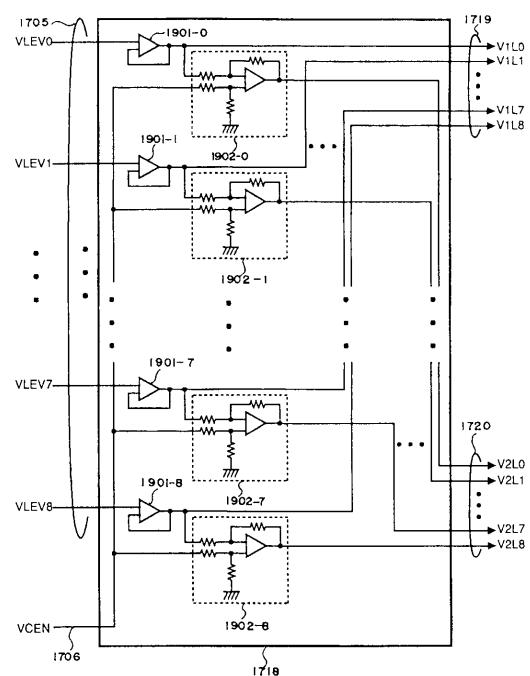

#### 【0168】

図13において、1901-0から1901-8はアンプバッファ回路、1902-0 10から1902-8は差動增幅回路である。

#### 【0169】

次に、液晶駆動回路の動作について説明する。図11において液晶ドライバ1707-1から1707-10は出力数が192であり、液晶パネル125は解像度640×RG 20B×480画素であるため液晶ドライバは10個必要となる。表示データ1701は3画素、階調6ビットの合計18ビット、交流化信号1703は3画素分の3ビットのデータが順次転送され、制御信号群1709から表示データ1701、交流化信号1703に同期したラッチ信号1713をラッチアドレス制御回路1712で生成し、順次データバス1710のデータをラッチ回路1714にラッチする。ラッチ回路1714は表示データ各6ビット、交流化信号各1ビットの192画素分のラッチ回路を持ち各液晶ドライバ1707-1から1707-10で1水平ライン分の表示データと交流化信号を順次ラッチすることができる。

#### 【0170】

ラッチ回路1714にラッチした表示データと交流化信号のデータバス1715は、走査回路1723のゲート選択信号1724に同期したタイミング信号1711で1水平ライン分同時にラッチ回路1716にラッチする。ラッチしたデータバス1717は液晶駆動回路1721に入力される。電圧生成回路1718では、電源回路1704で生成した基準電圧1705、1706から交流化の2レベルに対応したの異なる交流基準電圧1719、1720が生成され液晶駆動回路1721に入力される。液晶駆動回路1721では表示データ1717に対応した、交流基準電圧1719、1720を基に液晶駆動電圧1722が生成され、液晶パネル1725が駆動される。 30

#### 【0171】

次に、電圧生成回路1718の動作について図13、図14を用いて説明する。図13において、電源回路1704からのVLEV0からVLEV8の9レベルの基準電圧1705はそれぞれアンプバッファ回路1901-0から1901-8でバッファされ、差動增幅回路1902-0から1902-8に入力され、さらにV1L0からV1L8の基準電圧として出力される。差動增幅回路1902-0から1902-8では、基準電圧(VCEN)1706に対して基準電圧(VLEV0からVLEV8)1705が反転され、V2L0からV2L8の基準電圧として出力される。この関係を図14に示す。VLEV0からVLEV8は、バッファされ基準電圧V1L0からV1L8として出力し、それぞれVCENに対して反転した基準電圧V2L0からV2L8として出力する。 40

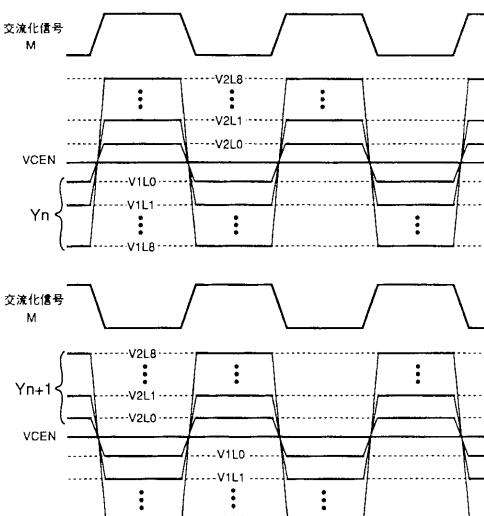

#### 【0172】

次に、液晶駆動回路1721について図12を用いて説明する。図12において、交流化基準電圧1719、1720は、192出力の各出力毎の液晶駆動回路1801-1から1801-192に入力される。液晶駆動回路1801-1から1801-192では、各出力6ビットの表示データと交流化信号のデータバス1717と9レベルの交流化基準電圧1719または1720から64レベルの液晶駆動電圧を生成し、出力する。交流化信号で交流化基準電圧1719または1720を選択し、さらに表示データ6ビットの内上位3ビットで9レベルの交流化基準電圧の2レベルを選択し、表示データ下位3ビットで選択した2レベルの電圧を8等分に分圧した8レベルの電圧から1レベルを選択することで64レベルの液晶駆動電圧を出力することができる。 50

## 【0173】

図14に示すように、n番目の出力端子Y<sub>n</sub>とn+1番目の出力端子Y<sub>n+1</sub>の交流化信号をお互いに反転することで交流化信号に対応して、出力端子Y<sub>n</sub>が交流化基準電圧1719(V1L0からV1L8)に対応した液晶駆動電圧を生成する時、出力端子Y<sub>n+1</sub>は交流化基準電圧1720(V2L0からV2L8)に対応した液晶駆動電圧を生成し、出力端子Y<sub>n</sub>が交流化基準電圧1720(V2L0からV2L8)に対応した液晶駆動電圧を生成する時、出力端子Y<sub>n+1</sub>は交流化基準電圧1719(V1L0からV1L8)に対応した液晶駆動電圧を生成する。

## 【0174】

このようにすることで、液晶ドライバは出力毎に交流化のタイミングをお互いに異なる液晶駆動電圧を生成することができ、液晶パネル1725を列毎反転駆動することが可能となる。さらに、表示データに同期して転送する交流化信号の設定を変えることで、2出力毎、または複数出力毎、ライン毎等に交流化のタイミングを容易に変えることができる。

## 【0175】

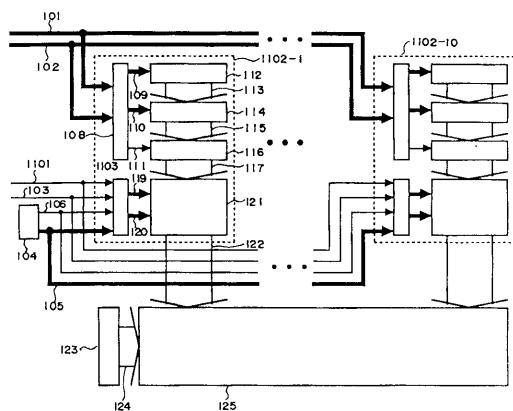

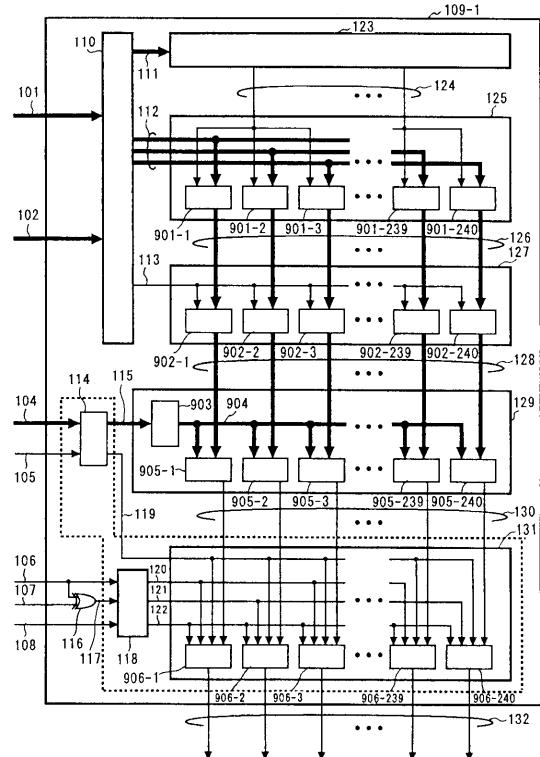

本発明の9レベルの基準電圧から64階調表示を行うデータドライバを用いた第6の実施例について、図15、図16、図17、図18、図19、図20、図21、図22、図23、図24、図25、図26、図27を用いて説明する。なお、本実施例でのデータドライバは、LSI化されているものとする。

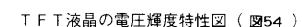

## 【0176】

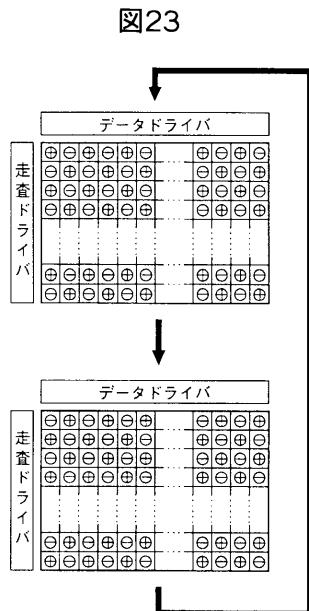

図15は本発明の液晶表示装置を示したブロック図、図16はデータドライバのブロック図、図17はデータドライバの階調電圧生成回路のブロック図、図18はデータドライバの出力回路のブロック図、図19は出力バッファ回路の構成図、図20は液晶印加電圧の交流タイミング図、図21はプロセス電圧を示す図、図15は列毎反転駆動を示す図、図23はドット毎反転駆動を示す図である。

## 【0177】

図15において、101はシステムから転送される表示データ、102は制御信号群、103は電源回路、104は液晶印加電圧の9レベルの基準電圧信号群、105は液晶印加電圧の交流化反転するための反転基準電圧、106は交流化のタイミングを示す交流化信号、107は列毎反転出力を制御する選択信号、108は出力回路の駆動制御を行う制御信号である。109-1から109-8は出力数が240出力のデータドライバであり、110はタイミング制御回路、111はタイミング信号群、112は表示データ、113は表示のタイミングを示す表示タイミング信号、114は基準電圧信号群104、反転基準電圧105を受けてバッファするバッファ回路、115、119はバッファ回路114が出力する基準電圧、反転基準電圧である。

## 【0178】

116は交流化信号106を選択信号107で反転か非反転の制御を行うEOR回路、117はEOR回路116が出力する交流化信号、118は交流化信号106、117、制御信号108を高耐圧プロセスの信号レベルにレベル変換するレベルシフタ回路であり、120は交流化信号106、121は交流化信号117、122は制御信号108をレベルシフタ回路118でレベル変換した信号である。123はラッチアドレス制御回路、124はラッチアドレス制御回路123で生成したラッチ信号群、125は表示データ112を順次ラッチするラッチ回路、126はラッチ回路125でラッチした表示データ、127は表示データ126を表示タイミング信号113で同時にラッチするラッチ回路、128はラッチ回路127でラッチした表示データである。

## 【0179】

129は9レベルの基準電圧115から64レベルの階調電圧を生成し、表示データに対応した1レベルの階調電圧を出力する階調電圧生成回路、130は階調電圧生成回路129で生成した階調電圧、131は交流化信号120、121に対応して反転基準電圧119を基準として階調電圧130を反転または非反転して出力する出力回路であり、制御信号122で出力電流を制御する。132は液晶駆動電圧である。133は走査回路、1

10

20

30

40

50

34は走査回路133で順次選択されるゲート駆動信号、135は640ドット×480ラインの液晶パネルである。

#### 【0180】

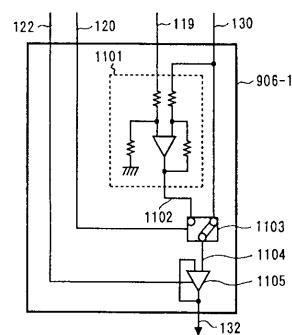

図16において、901-1から901-240はラッチ信号124で表示データをラッチするそれぞれ6ビットのラッチ回路、902-1から902-240は表示タイミング信号113で同時にラッチするそれぞれ6ビットのラッチ回路、903は9レベルの基準電圧115から64レベルの階調電圧を生成する階調電圧生成回路、904は階調電圧生成回路903で生成した64レベルの階調電圧、905-1から905-240は各出力毎に表示データ128に対応して階調電圧904から1レベルを選択する選択回路、906-1から906-240は各出力毎に交流化信号120または121に対応して階調電圧130を反転基準電圧119を基準に反転または非反転して出力する出力回路、132は液晶駆動電圧である。

10

#### 【0181】

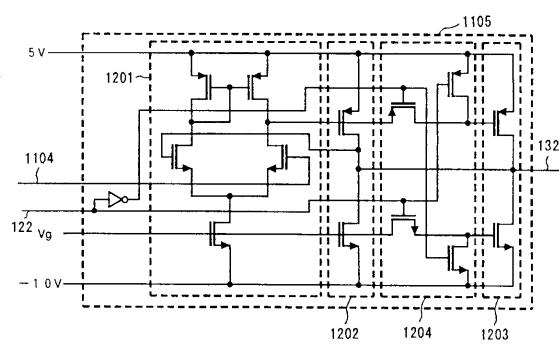

図18において、1101は反転増幅回路、1102は反転電圧、1103は選択回路、1104は選択回路1103で選択された出力電圧、1105は出力バッファ回路である。

#### 【0182】

図19において、1201は差動増幅回路、1202、1203は電流増幅回路、1204は電流増幅回路1203を制御信号122で有効にする選択回路である。

20

#### 【0183】

次に、データドライバの動作について説明する。図15においてデータドライバ109-1から109-8は出力数が240であり、液晶パネル135は解像度640×RGB×480画素であるためデータドライバは8個必要となる。タイミング制御回路110では、システムから転送される3画素、各階調6ビットの合計18ビットの表示データ101、水平同期信号、表示データ転送クロック等の制御信号群からデータドライバ内部の制御信号の生成やタイミング制御を行う。表示データ101はタイミング制御回路110でデータドライバ内部のタイミングに制御され表示データ112としてラッチ回路125に転送される。ラッチアドレス制御回路123では、タイミング制御回路110でデータドライバ内部のタイミングに制御された制御信号群111から表示データ112に同期したラッチ信号124を生成し、順次表示データ112をラッチ回路125にラッヂする。

30

#### 【0184】

ラッチ回路125は1出力あたり6ビット、240出力分のラッチ回路を持ち、データドライバ109-1から109-8で1水平ライン分の表示データを順次ラッヂすることができる。ラッチ回路125でラッヂした表示データ126は走査回路133のから出力されるゲート選択信号134に同期した表示タイミング信号113で1水平ライン分同時に、ラッチ回路127にラッヂする。ラッチ回路127は1出力あたり6ビット、240出力分のラッチ回路を持ち、データドライバ109-1から109-8で1水平ライン分の表示データを同時にラッヂすることができる。ラッチ回路127でラッヂした表示データ128は階調電圧生成回路129に転送される。電源回路103では、階調電圧生成のための9レベルの基準信号104と階調電圧を交流化のために反転する反転基準電圧105を生成する。バッファ回路114では、電源回路103から入力された基準電圧104、反転基準電圧105をバッファし基準電圧115、反転基準電圧119として階調電圧生成回路129と出力回路に出力される。

40

#### 【0185】

階調電圧生成回路129では、基準電圧115から64レベルの階調電圧を生成し、各出力毎に表示データに対応した階調電圧を1レベル選択し、出力回路131に出力する。交流化信号106は、交流化のタイミングを指示する信号で、選択信号107は交流化のタイミングを出力毎に変えるか否かを選択する信号で、交流化信号117は交流化信号106を選択信号107に対応して反転または非反転した信号である。制御信号108は出力回路131の駆動制御を行う信号である。表示データ101、制御信号群102、基準

50

電圧 104、反転基準電圧 105、交流化信号 106、選択信号 107、制御信号 108 の入力信号レベルはすべて 0V から 5V の信号レベルである。一方、液晶駆動電圧は交流駆動を行うため 15V 程度が必要である。

#### 【0186】

従って、液晶駆動電圧を出力する出力回路は高耐圧プロセス (15V 耐圧) を用いる必要があり、レベルシフタ 118 は交流化信号 106、117、制御信号 108 を高耐圧信号レベルにレベル変換して出力回路 131 に出力する。出力回路 131 では、階調電圧 130 を交流化信号 120、121 に対応して、反転基準電圧 105 に対して反転または非反転して、液晶駆動電圧 132 としてバッファ出力する。走査回路 133 は、液晶パネル 135 を 1 ライン毎に順次選択するゲート選択信号 134 を生成し、ゲート選択信号 134 に同期して出力される液晶駆動電圧 132 により液晶パネル 135 が駆動され、正極性または負極性の 64 レベルの階調電圧の内、表示データに対応した液晶駆動電圧の表示を行うことができる。10

#### 【0187】

次に、図 16、図 17、図 18、図 19、図 20、図 21、図 22、図 23 を用いて本発明のデータドライバの構成と動作を詳細に説明する。

#### 【0188】

図 16 はデータドライバ 109-1 の詳細なブロック図で、表示データ 101 はラッチアドレス制御回路 123 で生成したラッチ信号 124 で 3 画素毎に順次ラッチ回路 125 にラッチする。ラッチ回路 125 では、まず最初に 3 画素に対応した 6 ビットラッチ回路 901-1、901-2、901-3 に表示データ 112 がラッチされ、次に次の 3 画素に対応した 6 ビットラッチ回路 901-4、901-5、901-6 に表示データ 112 がラッチされ、同様に順次 3 画素毎、18 ビットの表示データをラッチし最後に 6 ビットラッチ回路 901-238、901-239、901-240 に表示データ 112 をラッチする。20

#### 【0189】

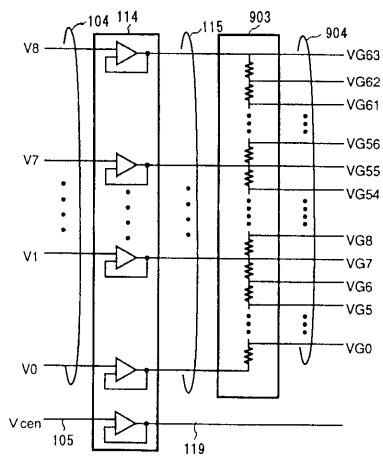

そして、8 個のデータドライバが順次表示データをラッチし、1 ライン分の表示データをラッチする。ラッチ回路 125 にラッチした表示データ 126 は表示タイミング信号 113 で 1 ライン分同時にラッチ回路 127 にラッチする。また、基準電圧 104 は 9 レベルの基準電圧であり、バッファ回路 114 でバッファして基準電圧 115 として出力される。そして、階調電圧生成回路 903 では、9 レベルの基準電圧 115 から 64 レベルの階調電圧を生成する。30

#### 【0190】

ここで図 17 を用いて階調電圧生成回路 903 について詳しく説明する。階調電圧生成回路 903 は、バッファ回路 114 でバッファされた 9 レベルの基準電圧 115 (V8 から V0) を抵抗素子を用いて分圧し、各基準電圧間を 8 分圧し、合計 64 レベルの階調電圧 904 (VG63 から VG0) を生成する。また、反転基準電圧 105 についてもバッファ回路 114 でバッファされ反転基準電圧 119 として出力される。

#### 【0191】

再び図 16 に戻り、階調電圧 904 は各出力に対応した階調電圧選択回路 905-1 から 905-240 に入力する。各階調電圧選択回路 905-1 から 905-240 では、各出力に対応した表示データ 128 に対応して表示データをデコードし、64 レベルの階調電圧 904 から 1 レベルを選択回路で選択し階調電圧 130 として出力される。つまり、電圧レベル 0V から 5V の基準電圧 104 から 0V から 5V の 64 レベルの階調電圧 904 を生成し、その中から表示データに対応した階調電圧 130 を出力毎に選択出力する。この階調電圧 130 は同じ表示データに対して正極性、負極性に交流駆動する正極性の液晶駆動電圧に対応している。40

#### 【0192】

また、交流化信号 106 と選択信号 107 は EOR 回路 116 に入力され、選択信号 107 が "Low" レベルのとき交流化信号 106 は反転されずに出力され、選択信号 10

7が”High”レベルのとき交流化信号106は反転されて出力される。つまり、交流化信号117は、選択信号107が”Low”レベルのとき交流化信号106と同じ信号で、選択信号107が”High”レベルのとき交流化信号106の反転信号となる。制御信号108は出力回路906-1から906-240の駆動電流の制御を指示する信号である。交流化信号106、117、制御信号108は、液晶駆動電圧レベル(5Vから-10V)で動作する出力回路131の信号レベルに電圧を合わせるためレベルシフト回路118でレベルシフトされ、それぞれ交流化信号120、121、制御信号122として出力される。

#### 【0193】

出力回路131では、各出力に対応した出力回路906-1から906-240で、正極性の階調電圧130、反転基準電圧119、交流化信号120、121と制御信号122が入力され、交流化信号に対応して反転基準電圧119を基準に階調電圧130を反転または非反転して出力し、液晶パネルを駆動する。ここで図18を用いて、出力回路906-1について詳しく説明する。出力回路906-1は反転増幅回路1101、選択回路1103、出力バッファ回路1105から構成されており、正極性の階調電圧130が反転増幅回路1101で反転基準電圧119に対して反転され反転電圧1102として出力される。この反転電圧1102は、正極性の階調電圧130を反転したものであり、同じ表示データに対して正極性、負極性に交流駆動する負極性の液晶駆動電圧に対応している。

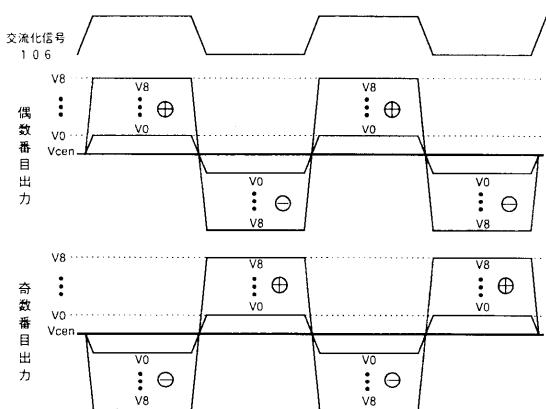

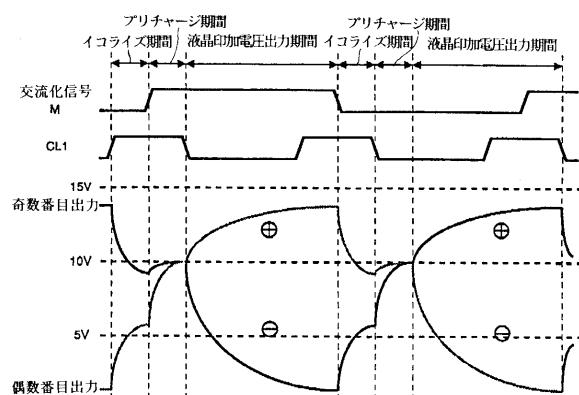

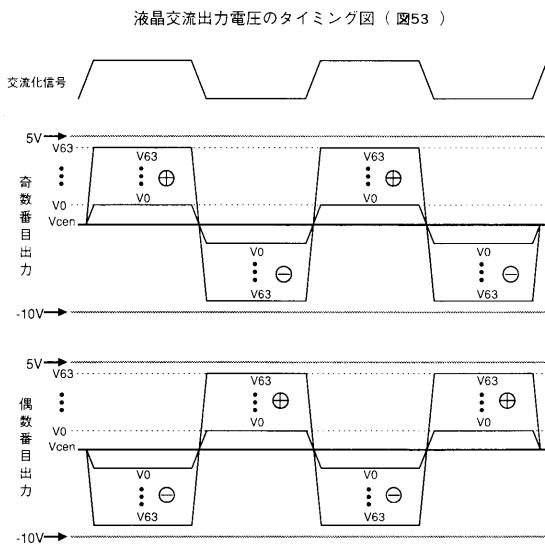

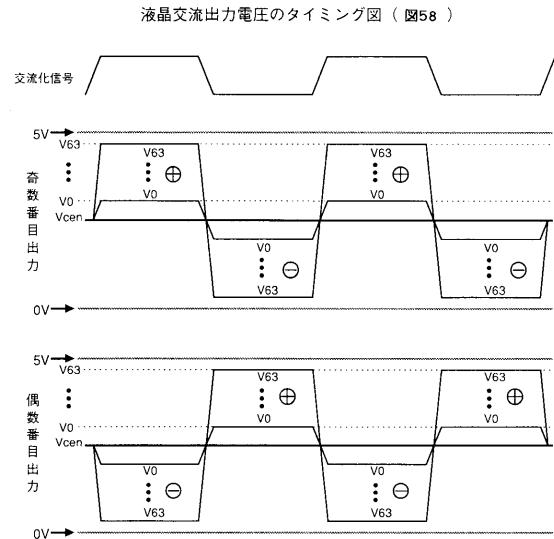

#### 【0194】

そして、階調電圧130と反転電圧1102は交流化信号120に対応して選択回路1103でどちらか一方が選択され出力電圧1104として出力され、出力バッファ回路1105でバッファされ液晶パネル135を駆動する。図20を用いて交流出力電圧のタイミングについて詳しく説明する。交流化信号120、121はそれぞれデータドライバ出力の偶数番目出力、奇数番目出力に1出力おきに対応している。従って、選択信号107を”High”レベルにすると交流化信号120、121は互いに反転した信号となるため、偶数番目出力と奇数番目出力では互いに交流化のタイミングが異なる。つまり、偶数番目出力が正極性の出力のとき、奇数番目出力は負極性の出力、逆に偶数番目出力が負極性の出力のとき、奇数番目出力は正極性の出力となる。また、選択信号107を”Low”レベルにすると交流化信号120、121は同極性の信号となるため、偶数番目出力と奇数番目出力では交流化のタイミングが同じになる。つまり、偶数番目出力が正極性の出力のとき、奇数番目出力も正極性の出力、逆に偶数番目出力が負極性の出力のとき、奇数番目出力も負極性の出力となる。そして、正極性、負極性の階調電圧は反転基準電圧119(Vcen)に対称に反転している。

#### 【0195】

また、図19に出力バッファ回路の構成図を示す。出力バッファ回路1105は出力電圧1104を差動増幅回路1201で受けて、液晶パネル135を駆動するために電流増幅回路1202、1203で電流を増幅して出力するボルテージフォロア回路である。制御信号122は電流増幅回路1203を制御する信号で、制御信号122を”High”レベルにすることで電流増幅回路1203を有効にし、電流増幅回路1202と合わせて大電流を出力することができ、制御信号122を”Low”レベルにすることで電流増幅回路1203を無効にし、電流増幅回路1202のみで電流を出力することができる。これにより、大出力電流が必要な期間は、電流増幅回路1202、1203で電流増幅を行い、大出力電流が必要でない期間は、電流増幅回路1203を無効にし電流増幅回路1202のみで電流増幅することで、電流増幅回路での消費電力を小さくすることができる。

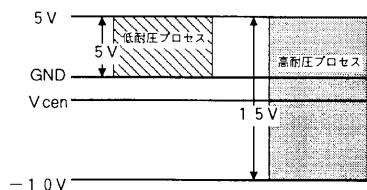

#### 【0196】

さらに、図15、図16のデータドライバの点線で囲んだ回路は、高耐圧プロセス(耐圧15V)であり、その他の回路部分は低耐圧プロセス(耐圧5V)である。図21に示すように、入力信号は全て低耐圧プロセスの動作範囲である5VからGNDとすることと、タイミング制御回路110、ラッチアドレス制御回路123、ラッチ回路125、12

10

20

30

40

50

7、階調電圧生成回路 129 をゲート長の小さい低耐圧プロセスとし、出力回路 131 のみをゲート長の大きな高耐圧プロセスとすることでチップ面積を小さくすることができる。現在、低耐圧プロセス（耐圧 5 V から 3 V 程度）は最新の微細プロセスであるゲート長 1.0 μm から 0.6 μm 程度であり、高耐圧プロセス（耐圧 30 V から 10 V 程度）はゲート長 5 μm から 2 μm 程度である。

#### 【0197】

従って、低耐圧プロセスより高耐圧プロセスの方が、同程度の能力の素子では、素子面積が数倍大きくなる。また、一般に出力回路は、静電破壊やラッチアップ対策のため低耐圧プロセスであってもゲート長が大きく設計する。従って、本実施例のデータドライバのように出力回路のみを高耐圧プロセスを用いることで、低耐圧プロセスのデータドライバに比べチップ面積の増加を極力小さくすることができ低価格化を図ることができる。10

#### 【0198】

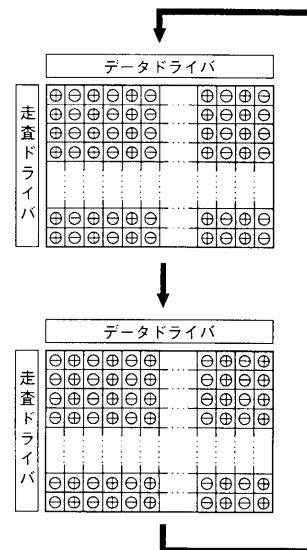

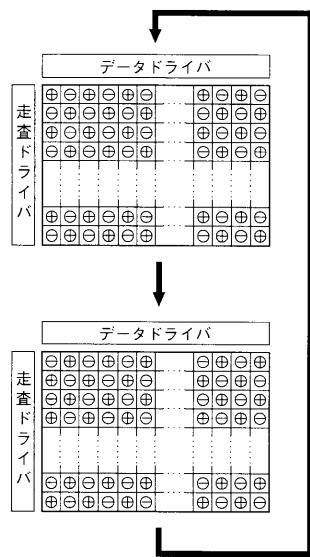

以上述べた本実施例のデータドライバを用いた液晶ディスプレイでは、図 22 に示すようにデータドライバを液晶パネルの片側に配置した場合でも、列毎反転駆動が可能となり、高画質表示を行うことができる。また、図 23 に示すように、ライン毎に交流化することで列毎反転駆動が可能となり、さらなる高画質表示を行うことができる。さらに、選択信号 107 の設定を変えることで共通電極駆動にも対応できる。

#### 【0199】

また、本実施例では、データドライバとして 240 出力のデータドライバについて説明したが、192 出力や 160 出力のデータドライバについても、ラッチアドレス制御回路やラッチ回路を出力数に対応した構成にすることで容易に実現できる。また、プロセスの耐圧についても、本実施例では低耐圧プロセスを 5 V 耐圧、高耐圧プロセスを 15 V 耐圧として説明したが、低耐圧プロセスについては 5 V 耐圧から 3 V 耐圧等の、高耐圧プロセスについては 30 V 耐圧から 10 V 耐圧等のプロセスを用いた場合についても本実施例と同様な効果を得ることができる。20

#### 【0200】

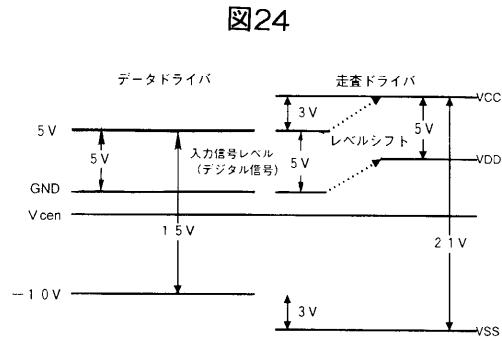

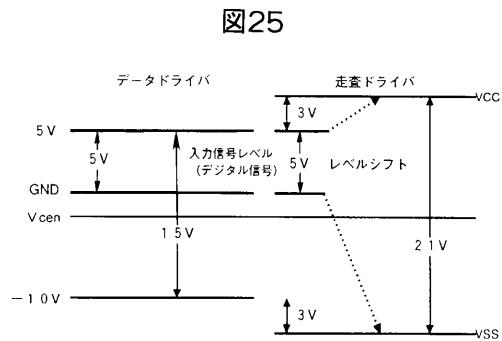

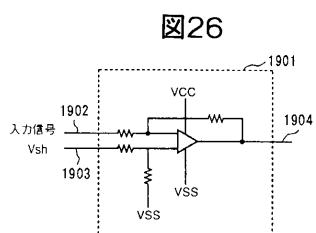

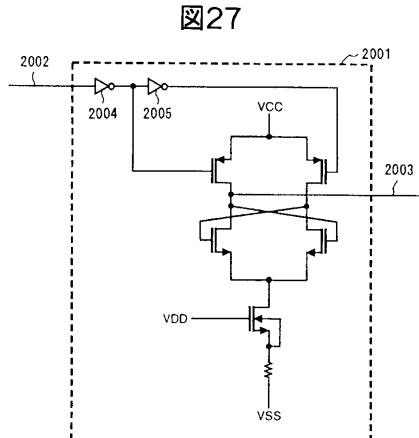

次に、本実施例の走査ドライバについて、図 24、図 25、図 26、図 27 を用いて説明する。図 24、図 25 はデータドライバ、走査ドライバの動作電圧レベルを示す図で、図 26、図 27 はレベルシフト回路の構成図である。

#### 【0201】

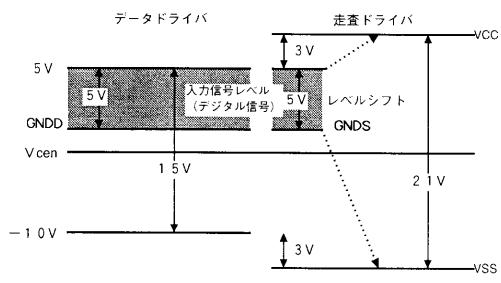

図 24 に示すように、データドライバと走査ドライバの動作電圧レベルは異なる。走査ドライバから出力されるゲート選択信号は液晶パネルの TFT の特性から、データドライバから出力する液晶印加電圧に対して上下に約 3 V 程度大きな電圧を与える必要がある。走査ドライバのデジタル信号の動作レベルは VCC - VDD 間の 5 V であるため、データドライバと走査ドライバのデジタル系の入力信号の電圧レベルに差が生じる。従来の液晶パネルではデジタル系の信号レベルをデータドライバの信号レベルとし、信号本数の少ない走査ドライバの入力信号は外付け回路でレベルシフトして信号レベルを合わせ走査ドライバに入力していた。これは液晶ディスプレイの周辺回路規模を大きくする要因となっていた。30

#### 【0202】

本実施例では、走査ドライバの入力信号の入力段にレベルシフト回路を内蔵することで、周辺回路の回路規模の削減を可能とする。図 26 はレベルシフト回路の構成例である。図 26 において、1901 は反転増幅回路を用いた 1 信号のレベルシフト回路、1902 は入力信号、1903 は反転増幅する反転基準電圧、1904 は入力信号 1902 を反転してレベルシフトした信号である。このレベルシフト回路 1901 では、入力信号の電圧レベルに合わせて反転基準信号 1903 を設定することで、種々の入力電圧レベルに対応することができる。また、図 27 はレベルシフト回路の他の構成例である。図 27 において、2001 はレベルシフト回路、2002 は入力信号、2003 は入力信号 2002 を非反転してレベルシフトした信号、2004、2005 はインバータ回路である。40

#### 【0203】

10

20

30

40

50

インバータ回路 2004 はスレシュホールド電圧を入力信号レベルの真ん中に設定し、振幅レベルは VCC - VSS である。インバータ回路 2005 の振幅レベルは VCC - VSS である。このレベルシフト回路 2001 では、レベルシフト回路 1901 のように基準電圧が必要でなく、反転、非反転のレベルシフトした信号を出力することができる。

#### 【0204】

また、図 25 に示すように、入力信号を VCC - VSS レベルにレベルシフトして、VCC - VSS の振幅レベルで回路動作を行うことでも周辺回路の回路規模の削減が可能である。これは走査ドライバの入力信号の入力段に、スレシュホールド電圧を入力信号レベルの真ん中に設定したインバータ回路を設けることで実現可能である。

#### 【0205】

以上、本実施例では、データドライバに関して、9 本の液晶基準電圧 104 はデータドライバの入力段にバッファ回路を内蔵しているため、駆動電流が少なく電源回路 103 の回路規模を小さくすることができる。

#### 【0206】

本発明の 9 レベルの基準電圧から 64 階調表示を行うデータドライバを用いた第 7 の実施例について、図 15、図 20、図 21、図 22、図 23、図 24、図 25、図 26、図 27、図 28、図 29、図 30 を用いて説明する。本実施例は、第 6 の実施例と階調電圧生成回路が異なり、他の回路は同様である。なお、第 6 の実施例と同様、本実施例でもデータドライバは LS1 化されているものとする。

#### 【0207】

図 28 はデータドライバのブロック図、図 29 はデータドライバの階調電圧生成回路のブロック図、図 30 はデータドライバの出力回路のブロック図である。

#### 【0208】

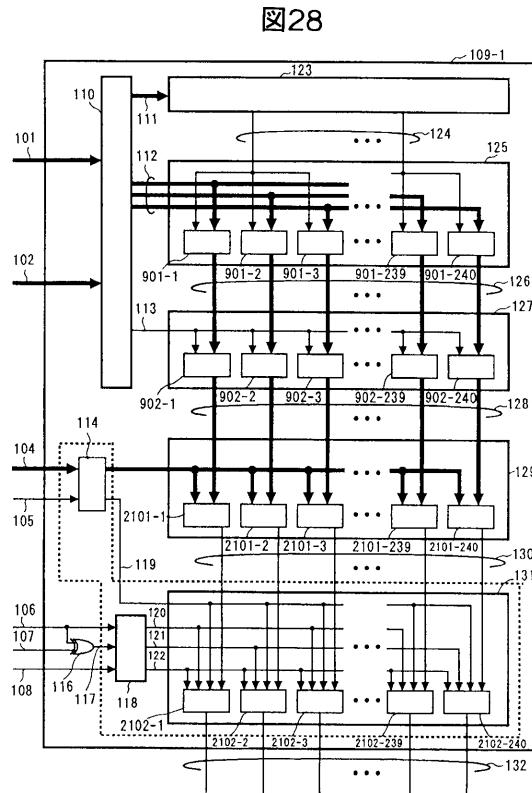

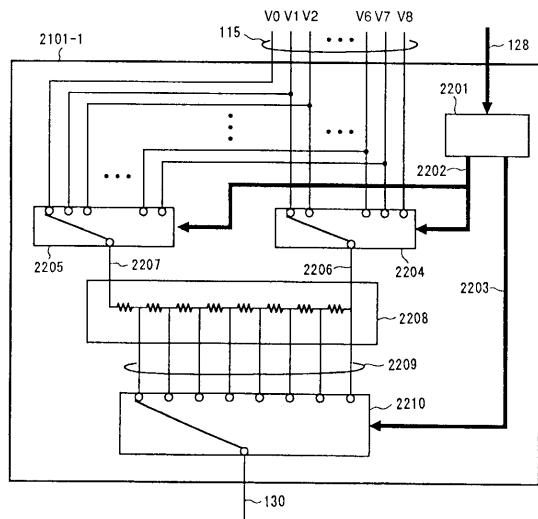

図 28において、2101-1 から 2101-240 は各出力毎に表示データ 128 に対応して基準電圧 115 から 1 レベルを選択する選択回路、2102-1 から 2102-240 は各出力毎に交流化信号 120 または 121 に対応して階調電圧 130 を反転基準電圧 119 を基準に反転または非反転して出力する出力回路、132 は液晶駆動電圧である。

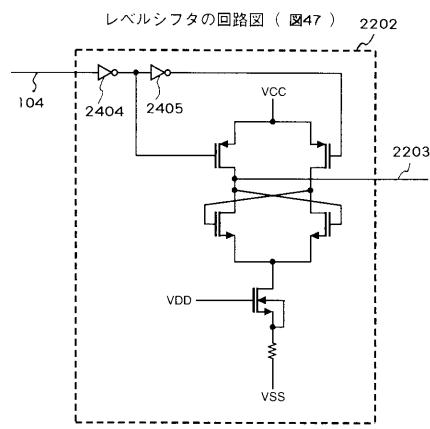

#### 【0209】

図 29において、2201 は表示データ 128 をデコードするデコーダ、2202 はデコーダ 2201 でデコードした表示データ上位 3 ビットのデコード信号、2203 はデコーダ 2201 でデコードした表示データ下位 3 ビットのデコード信号、2204 はデコード信号 2202 で 9 レベルの基準電圧 115 の内 V8 から V1 の 8 レベルから 1 レベルを選択する選択回路、2205 はデコード信号 2202 で 9 レベルの基準電圧 115 の内 V7 から V0 の 8 レベルから 1 レベルを選択する選択回路、2206、2207 はそれぞれ選択回路 2204、2205 で選択した選択電圧、2208 は選択電圧 2206、2207 の電圧間を 8 個の抵抗素子で 8 分圧する分圧回路、2209 は分圧回路 2208 で分圧された 8 レベルの階調電圧、2210 はデコード信号 2203 で 8 レベルの階調電圧 2209 から 1 レベルを選択する選択回路である。

#### 【0210】

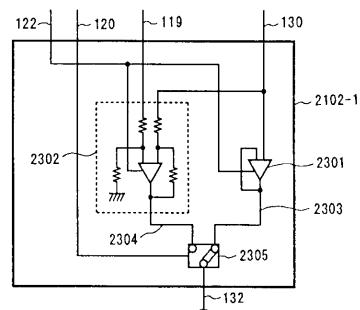

図 30において、2301 は非反転增幅回路、2302 は反転增幅回路、2303 は非反転增幅回路 2301 で増幅した正転電圧、2304 は反転增幅回路 2302 で増幅した反転電圧、2305 は選択回路である。

#### 【0211】

次に、データドライバの動作について説明する。図 15においてデータドライバ 109-1 から 109-8 は出力数が 240 であり、液晶パネル 135 は解像度  $640 \times RGB \times 480$  画素であるためデータドライバは 8 個必要となる。タイミング制御回路 110 では、システムから転送される 3 画素、各階調 6 ビットの合計 18 ビットの表示データ 101、水平同期信号、表示データ転送クロック等の制御信号群からデータドライバ内部の制御信号の生成やタイミング制御を行う。表示データ 101 はタイミング制御回路 110 で

10

20

30

40

50

データドライバ内部のタイミングに制御され表示データ112としてラッチ回路125に転送される。ラッチアドレス制御回路123では、タイミング制御回路110でデータドライバ内部のタイミングに制御された制御信号群111から表示データ112に同期したラッチ信号124を生成し、順次表示データ112をラッチ回路125にラッチする。

#### 【0212】

ラッチ回路125は1出力あたり6ビット、240出力分のラッチ回路を持ち、データドライバ109-1から109-8で1水平ライン分の表示データを順次ラッチすることができる。ラッチ回路125でラッチした表示データ126は走査回路133のから出力されるゲート選択信号134に同期した表示タイミング信号113で1水平ライン分同時に、ラッチ回路127にラッチする。ラッチ回路127は1出力あたり6ビット、240出力分のラッチ回路を持ち、データドライバ109-1から109-8で1水平ライン分の表示データを同時にラッチすることができる。ラッチ回路127でラッチした表示データ128は階調電圧生成回路129に転送される。電源回路103では、階調電圧生成のための9レベルの基準信号104と階調電圧を交流化のために反転する反転基準電圧105を生成する。

#### 【0213】

バッファ回路114では、電源回路103から入力された基準電圧104、反転基準電圧105をバッファし基準電圧115、反転基準電圧119として階調電圧生成回路129と出力回路に出力される。階調電圧生成回路129では、基準電圧115から64レベルの階調電圧を生成し、各出力毎に表示データに対応した階調電圧を1レベル選択し、出力回路131に出力する。交流化信号106は、交流化のタイミングを指示する信号で、選択信号107は交流化のタイミングを出力毎に変えるか否かを選択する信号で、交流化信号117は交流化信号106を選択信号107に対応して反転または非反転した信号である。制御信号108は出力回路131の駆動制御を行う信号である。表示データ101、制御信号群102、基準電圧104、反転基準電圧105、交流化信号106、選択信号107、制御信号108の入力信号レベルはすべて0Vから5Vの信号レベルである。

#### 【0214】

一方、液晶駆動電圧は交流駆動を行うため15V程度が必要である。従って、液晶駆動電圧を出力する出力回路は高耐圧プロセス(15V耐圧)を用いる必要があり、レベルシフタ118は交流化信号106、117、制御信号108を高耐圧信号レベルにレベル変換して出力回路131に出力する。出力回路131では、階調電圧130を交流化信号120、121に対応して、反転基準電圧105に対して反転または非反転して、液晶駆動電圧132としてバッファ出力する。走査回路133は、液晶パネル135を1ライン毎に順次選択するゲート選択信号134を生成し、ゲート選択信号134に同期して出力される液晶駆動電圧132により液晶パネル135が駆動され、正極性または負極性の64レベルの階調電圧の内、表示データに対応した液晶駆動電圧の表示を行うことができる。

#### 【0215】

次に、図28、図29、図30、図20、図21、図22、図23を用いて本発明のデータドライバの構成と動作を詳細に説明する。

#### 【0216】

図28はデータドライバ109-1の詳細なブロック図で、表示データ101はラッチアドレス制御回路123で生成したラッチ信号124で3画素毎に順次ラッチ回路125にラッチする。ラッチ回路125では、まず最初に3画素に対応した6ビットラッチ回路901-1、901-2、901-3に表示データ112がラッチされ、次に次の3画素に対応した6ビットラッチ回路901-4、901-5、901-6に表示データ112がラッチされ、同様に順次3画素毎、18ビットの表示データをラッチし最後に6ビットラッチ回路901-238、901-239、901-240に表示データ112をラッチする。

#### 【0217】

そして、8個のデータドライバが順次表示データをラッチし、1ライン分の表示データ

10

20

30

40

50

をラッチする。ラッチ回路 125 にラッチした表示データ 126 は表示タイミング信号 13 で 1 ライン分同時にラッチ回路 127 にラッチする。また、基準電圧 104 は 9 レベルの基準電圧であり、バッファ回路 114 でバッファして基準電圧 115 として出力される。また、反転基準電圧 105 についてもバッファ回路 114 でバッファされ反転基準電圧 119 として出力される。

#### 【0218】

基準電圧 115 は各出力に対応した階調電圧生成回路 2101-1 から 2101-240 に入力する。各階調電圧生成回路 2101-1 から 2101-240 では、各出力に対応した表示データ 128 と基準電圧 115 から表示データに対応した階調電圧を生成し階調電圧 130 として出力する。

10

#### 【0219】

ここで、図 29 を用いて階調電圧生成回路 2101 について詳しく説明する。64 階調を表わす 6 ビット表示データ 128 はデコーダ 2201 で、上位 3 ビットと下位 3 ビットをそれぞれ独立してデコードし、上位 3 ビットの 8 本のデコード信号 2202 は選択回路 2204、2205 に入力し、下位 3 ビットの 8 本のデコード信号 2203 は選択回路 2204 に入力する。選択回路 2204 では 9 レベルの基準電圧 115 (V8 から V0) の内 V8 から V1 の 8 レベルから 1 レベルをデコード信号 2202 に対応して選択し、2205 では 9 レベルの基準電圧 115 (V8 から V0) の内 V7 から V0 の 8 レベルから 1 レベルをデコード信号 2203 に対応して選択する。選択回路 2204、2205 でそれぞれ選択される選択電圧 2206、2207 の組合せは V8-V7、V7-V6、V6-V5、V5-V4、V4-V3、V3-V2、V2-V1、V1-V0 とする。

20

#### 【0220】

そして、分圧回路 2208 では選択電圧 2206、2207 の電圧間を 8 分圧し、選択電圧間に 8 レベルの階調電圧を生成する。選択回路 2210 では、分圧回路で生成した 8 レベルの階調電圧 2209 をデコード信号 2203 に対応して 1 レベルを選択し、階調電圧 130 として出力する。このように、選択電圧 2206、2207 の 8 組の組合せとそれを 8 分圧することで合計 64 レベルの階調電圧を生成することができる。つまり、電圧レベル 0V から 5V の基準電圧 104 から 0V から 5V の 64 レベルの階調電圧を生成し、その中から表示データに対応した階調電圧 130 を出力毎に選択出力する。この階調電圧 130 は同じ表示データに対して正極性、負極性に交流駆動する正極性の液晶駆動電圧に対応している。

30

#### 【0221】

また、交流化信号 106 と選択信号 107 は EOR 回路 116 に入力され、選択信号 107 が "Low" レベルのとき交流化信号 106 は反転されずに出力され、選択信号 107 が "High" レベルのとき交流化信号 106 は反転されて出力される。つまり、交流化信号 117 は、選択信号 107 が "Low" レベルのとき交流化信号 106 と同じ信号で、選択信号 107 が "High" レベルのとき交流化信号 106 の反転信号となる。制御信号 108 は出力回路 2102-1 から 2102-240 の駆動電流の制御を指示する信号である。交流化信号 106、117、制御信号 108 は、液晶駆動電圧レベル (5V から -10V) で動作する出力回路 131 の信号レベルに電圧を合わせるためレベルシフト回路 118 でレベルシフトされ、それぞれ交流化信号 120、121、制御信号 122 として出力される。

40

#### 【0222】

出力回路 131 では、各出力に対応した出力回路 2102-1 から 2102-240 で、正極性の階調電圧 130、反転基準電圧 119、交流化信号 120、121 と制御信号 122 が入力され、交流化信号に対応して反転基準電圧 119 を基準に階調電圧 130 を反転または非反転して出力し、液晶パネルを駆動する。ここで図 30 を用いて、出力回路 2102-1 について詳しく説明する。出力回路 2102-1 は非反転増幅回路 2301、反転増幅回路 2302、選択回路 2305 から構成されている。正極性の階調電圧 130 が非反転増幅回路 2301 で増幅され正転電圧 2303 として出力され、反転増幅回路

50

2302で反転基準電圧119に対して反転され反転電圧2304として出力される。

#### 【0223】

この反転電圧1102は、正極性の階調電圧130を反転したものであり、同じ表示データに対して正極性、負極性に交流駆動する負極性の液晶駆動電圧に対応している。そして、正転電圧2303と反転電圧2304は交流化信号120に対応して選択回路2305でどちらか一方が選択され出力電圧132として出力され、液晶パネル135を駆動する。図20を用いて交流出力電圧のタイミングについて詳しく説明する。交流化信号120、121はそれぞれデータドライバ出力の偶数番目出力、奇数番目出力に1出力おきに対応している。従って、選択信号107を”High”レベルにすると交流化信号120、121は互いに反転した信号となるため、偶数番目出力と奇数番目出力では互いに交流化のタイミングが異なる。10

#### 【0224】

つまり、偶数番目出力が正極性の出力のとき、奇数番目出力は負極性の出力、逆に偶数番目出力が負極性の出力のとき、奇数番目出力は正極性の出力となる。また、選択信号107を”Low”レベルにすると交流化信号120、121は同極性の信号となるため、偶数番目出力と奇数番目出力では交流化のタイミングが同じになる。つまり、偶数番目出力が正極性の出力のとき、奇数番目出力も正極性の出力、逆に偶数番目出力が負極性の出力のとき、奇数番目出力も負極性の出力となる。そして、正極性、負極性の階調電圧は反転基準電圧119(Vcen)に対称に反転している。

#### 【0225】

さらに、第6の実施例と同様に図15、図28のデータドライバの点線で囲んだ回路は、高耐圧プロセス(耐圧15V)であり、その他の回路部分は低耐圧プロセス(耐圧5V)である。図21に示すように、入力信号は全て低耐圧プロセスの動作範囲である5VからGNDとすることで、タイミング制御回路110、ラッチアドレス制御回路123、ラッチ回路125、127、階調電圧生成回路129をゲート長の小さい低耐圧プロセスとし、出力回路131のみをゲート長の大きな高耐圧プロセスとすることでチップ面積を小さくすることができる。現在、低耐圧プロセス(耐圧5Vから3V程度)は最新の微細プロセスであるゲート長1.0μmから0.6μm程度であり、高耐圧プロセス(耐圧30Vから10V程度)はゲート長5μmから2μm程度である。20

#### 【0226】

従って、低耐圧プロセスより高耐圧プロセスの方が、同程度の能力の素子では、素子面積が数倍大きくなる。また、一般に出力回路は、静電破壊やラッチャップ対策のため低耐圧プロセスであってもゲート長を大きく設計する。従って、本実施例のデータドライバのように出力回路のみを高耐圧プロセスを用いることで、低耐圧プロセスのデータドライバに比べチップ面積の増加を極力小さくすることができ低価格化を図ることができる。30

#### 【0227】

以上述べた本実施例のデータドライバを用いた液晶ディスプレイでは、第6の実施例と同様に、図22に示すようにデータドライバを液晶パネルの片側に配置した場合でも、列毎反転駆動が可能となり、高画質表示を行うことができる。また、図23に示すように、ライン毎に交流化することで列毎反転駆動が可能となり、さらなる高画質表示を行うことができる。さらに、選択信号107の設定を変えることで共通電極駆動にも対応できる。40

#### 【0228】

また、本実施例では、データドライバとして240出力のデータドライバについて説明したが、192出力や160出力のデータドライバについても、ラッチアドレス制御回路やラッチ回路を出力数に対応した構成にすることで容易に実現できる。また、プロセスの耐圧についても、本実施例では低耐圧プロセスを5V耐圧、高耐圧プロセスを15V耐圧として説明したが、低耐圧プロセスについては5V耐圧から3V耐圧等の、高耐圧プロセスについては30V耐圧から10V耐圧等のプロセスを用いた場合についても本実施例と同様な効果を得ることができる。

#### 【0229】

10

20

30

40

50

また、本実施例の走査ドライバについては第6の実施例と同様に入力信号の入力段に図26、図27に示したレベルシフト回路を設けることで、周辺回路の回路規模を小さくすることができる。

#### 【0230】

また、本実施例でも第6の実施例と同様に、データドライバに関する限り、9本の液晶基準電圧104はデータドライバの入力段にバッファ回路を内蔵しているため、駆動電流が少なく電源回路103の回路規模を小さくすることができる。

#### 【0231】

第6、第7の実施例では64階調のデータドライバについて述べたが、表示データを1画素あたり6ビットから8ビットにし、ラッチ回路の構成を1出力当たり8ビットとし、階調電圧生成回路の構成を256階調に対応するように変えることで、256階調やその他の階調数のデータドライバに対しても容易に実現することができる。

10

#### 【0232】

さらに、上述した第6、第7の実施例の低消費電力化と、小チップサイズ化を実現する出力回路の例を、図31、図32を用いて説明する。図31は出力波形のタイミングを示す図、図32は出力回路のブロック図である。

#### 【0233】

上述の第6、第7の実施例では、1出力ごとに正転、反転アンプ回路1組が必要であった。これに対し、この図32の例では、正転、反転アンプ回路1組を2出力で共有することで、チップサイズを小さくすることができる。

20

#### 【0234】

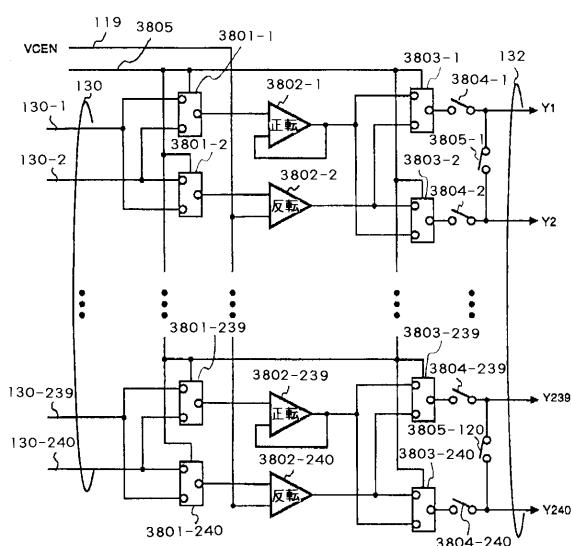

図32において、セレクタ3801は、階調電圧130-1~130-240のなかから、隣合う出力に対応した階調電圧を選択する。

#### 【0235】

正転アンプ回路および反転アンプ回路3802は、セレクタ3801で選択した階調電圧を、反転または正転し出力する。これらの動作を、出力端子Y1、Y2を例に採って詳細に説明する。

#### 【0236】

セレクタ3801-1は、出力端子Y1に対応した階調電圧130-1と、出力端子Y2に対応した階調電圧130-2とのうちのいずれかを選択し、正転アンプ回路3802-1に出力する。同様に、セレクタ3801-2は、出力端子Y1に対応した階調電圧130-1と、出力端子Y2に対応した階調電圧130-2とのうちのいずれかを選択し、反転アンプ回路3802-2に出力する。

30

#### 【0237】

また、セレクタ3803-1は、正転アンプ回路3802-1の出力と反転アンプ回路3802-2の出力とのうちのいずれかを選択し、該選択した方の出力を、出力端子Y1に出力する。同様に、セレクタ3803-2は、正転アンプ回路3802-1の出力と反転アンプ回路3802-2の出力とのうちのいずれかを選択し、該選択した方の出力を、出力端子Y2にそれぞれ出力する。

#### 【0238】

セレクタ3801、3803による選択状態は、交流化信号106に同期して切り替わる選択信号38005によって制御されている。出力端子Y1に階調電圧130-1が正転出力されるときには、出力端子Y2には階調電圧130-2が反転基準電圧119に対して反転出力される。逆に、出力端子Y1に階調電圧130-1が反転基準電圧119に対して反転出力される時には、出力端子Y2には階調電圧130-2が正転出力される。このように動作することで、隣合う出力端子ごとに交流タイミングが逆になっている液晶駆動電圧を出力することができる。

40

#### 【0239】

さらに、図31に示すように、液晶印加電圧を出力する前に、イコライズ期間を設ける。該イコライズ期間には、スイッチ回路3804-1~3804-2440で出力をハイ

インピーダンス状態にし、隣合う出力端子をスイッチ回路 3805-1 ~ 33805-2 40 を通じて接続する。これにより、液晶パネルのデータ線上に存在する正極性、負極性の電荷で、10V レベルへのプリチャージ動作を補助することができる。つまり、液晶パネル内の残留電荷を利用することで液晶駆動電力を低減できる。

#### 【0240】

本発明第8の実施例について、図33、図34、図35、図36、図37、図38、図39、図40、図41、図42、図43、図44、図45、図46、図47を用いて説明する。

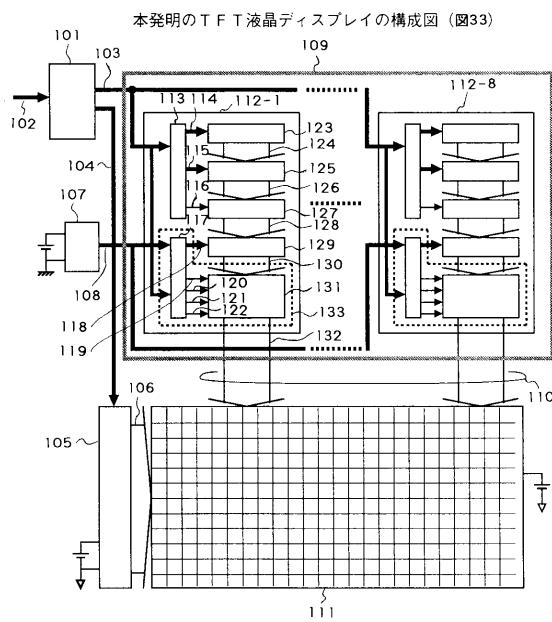

#### 【0241】

本実施例は、9レベルの基準電圧を用いて64階調表示を行うデータドライバを使用した液晶表示装置である。10

#### 【0242】

本実施例の液晶表示装置は、図33に示すとおり、大きく分けて、液晶表示コントローラ101と、走査回路105と、電源回路107と、データドライバ109と、640×3(R、G、B)×480ドットでの表示が可能な液晶パネル111と、から構成されている。

#### 【0243】

動作概要を説明する。

#### 【0244】

液晶表示コントローラ101は、液晶ドライバ用に、システムから入力される表示データ、表示同期信号102のタイミング制御を行なった上で、表示データと表示同期信号103としてデータドライバ109に転送する。なお、表示データ103は、1画素当たり階調6ビットを割り当てた、3画素分づつの合計18ビットのデータである。また、同様に、液晶コントローラ101は、システムから入力される表示データ、同期信号102から、表示データ、同期信号104を生成して走査回路105へ出力する。20

#### 【0245】

電源回路107は、9種類の電圧レベルの電圧からなる基準電圧108を発生し、データドライバ109に出力している。データドライバ109は、該基準電圧108に基づいて階調表示用に64階調の電圧を生成する。そして、表示データに対応して、出力ごとにいずれかを選択し、液晶パネル111へ液晶駆動電圧110として出力する。30

#### 【0246】

これと並行して走査回路105は、該表示データ、同期信号104に従って、液晶パネル111を構成しているゲート線の内の一本を順次選択してゆく。これにより、データドライバ109の出力している液晶駆動電圧110は、その時選択状態にされているゲート線に対応する行の画素にのみ印加されることとなる。走査回路105が選択するゲートを順次変更してゆくことで（すなわち、走査することで）、液晶パネル111全体に画像が表示されることになる。

#### 【0247】

次に、上記各部ごとにその構成および動作を詳細に説明する。

#### 【0248】

まず、データドライバ109について説明する。40

#### 【0249】

データドライバ109は、液晶表示コントローラ101等から入力される表示データ、表示同期信号103、基準電圧108に基づいて、液晶駆動電圧110を生成し、これを液晶パネル111に出力するものである。該データドライバ109は、240本の出力を有するデータドライバ112を8個備えて構成される。なお、各データドライバ112を、その配置位置に応じて、データドライバ112-1、データドライバ112-2、…、データドライバ112-8と呼ぶ場合がある。

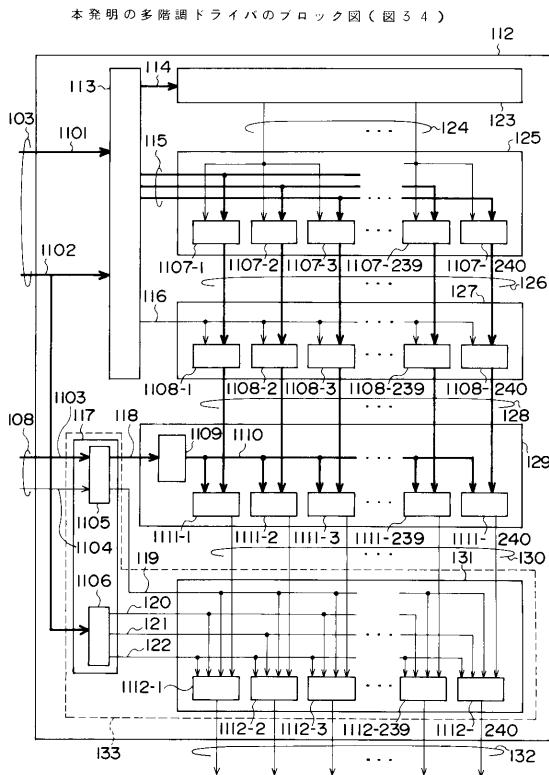

#### 【0250】

該データドライバ112は、図33、図34に示すとおり、タイミング制御回路11350

、入力バッファ回路 117、ラッチアドレス制御回路 123、ラッチ回路 125、ラッチ回路 127、階調電圧生成回路 129、出力回路 131 から、構成されている。

#### 【0251】

タイミング制御回路 113 は、表示データ、同期信号 103 のタイミングを制御することで、タイミング信号群 114、表示データ 115、ライン表示同期信号 116 を生成し、これらを、ラッチアドレス制御回路 123 などへ出力するものである。なお、表示データ、同期信号 103 は、表示データ 1101 と、制御信号 1102 とが含まれている。ライン表示同期信号 116 は、ゲート選択信号 106 に同期したものである。

#### 【0252】

ラッチアドレス制御回路 123 は、タイミング信号群 114 から、表示データ 115 に 10 同期したラッチ信号 124 を生成するものである。

#### 【0253】

ラッチ回路 125 は、表示データ 115 を順次ラッチするものである。該ラッチ回路 125 は、ラッチ信号 124 で、表示データ 115 をラッチするそれぞれ 6 ビットのラッチ回路 1107 を 240 個含んで構成されている。以下ラッチ回路 1107 をその配置位置に応じて、ラッチ回路 1107-1、ラッチ回路 1107-2 等と呼ぶ。該ラッチ回路 125 は、ラッチした表示データを、表示データ 126 として出力している。

#### 【0254】

ラッチ回路 127 は、表示データ 126 をライン表示同期信号 116 でラッチして、これを表示データ 128 として出力するものである。該ラッチ回路 127 は、それが 6 ビットのラッチ回路 1108 を、240 個備えて構成されている。各ラッチ回路 1108 は、ライン表示同期信号 116 で同時にラッチ動作を行うようになっている。

#### 【0255】

入力バッファ 117 は、アンプバッファ回路 1105 と、レベルシフト回路 1106 とからなる。

#### 【0256】

アンプバッファ回路 1105 は、電源回路 107 が生成する基準電圧 108 に含まれている 9 レベルの基準電圧 1103 を一旦バッファした後、基準電圧 118 として階調電圧生成回路 129 へ出力するものである。また、反転基準電圧 1104 を一旦バッファした後、反転基準電圧 119 として出力回路 131 へ出力している。既に述べたとおり、基準電圧 1103 に含まれている 9 レベルの電圧は、0V から 5V の範囲内にある。

#### 【0257】

レベルシフト回路 1106 は、制御信号群 1102 に含まれている交流化信号および出力駆動制御信号の電圧レベルを、低耐圧レベル (5V ~ 0V) から、液晶駆動電圧レベルである高耐圧レベル (5V ~ -10V) に変換するものである。そして、該変換後の交流化信号を、互いに極性の異なる 2 つの交流化信号 120、121 として出力するものである。また、変換後の出力駆動制御信号を、制御信号 122 として出力回路 131 に出力するものである。

#### 【0258】

階調電圧生成回路 129 は、9 レベルの基準電圧 118 から 64 レベルの階調電圧を生成するとともに、この中から表示データに対応した 1 レベルを選択し、これを階調電圧 130 として出力するものである。該階調電圧生成回路 129 は、階調電圧生成回路 110 と、240 個の選択回路 1111 と、からなる。

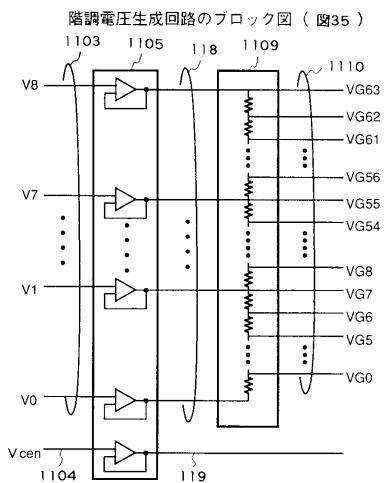

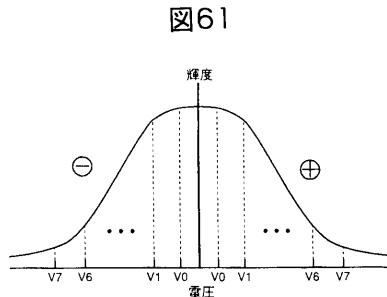

#### 【0259】

階調電圧生成回路 1109 は、9 レベルの基準電圧 118 から 64 レベルの階調電圧 1110 を生成するものである。図 35 に示すとおり、該階調電圧生成回路 1109 は、抵抗素子によって各基準電圧 118 (V8 ~ V0) 間を 8 分圧することで、合計 64 レベルの階調電圧 1110 (VG63 ~ VG0) を生成している。

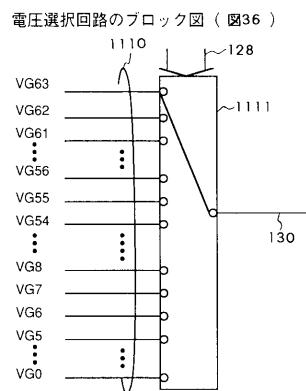

#### 【0260】

選択回路 1111 は、図 36 に示すとおり、表示データ 128 の内容に応じて、64 レ 50

ベルの階調電圧 1110 (VG0 ~ VG63) の中から各出力毎に 1 レベルを選択し、該選択した階調電圧を階調電圧 130 として出力するものである。

この階調電圧 130 は、正極性の液晶駆動電圧に対応している。

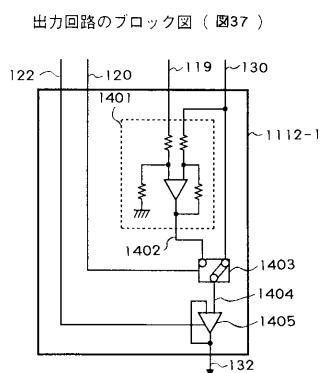

#### 【0261】

図 34 における出力回路 131 は、交流化信号 120, 121 に従いつつ、反転基準電圧 119 を基準として階調電圧 130 を反転または非反転して出力するものである。該出力回路 131 は、制御信号 122 に従ってその出力電流を変更する出力回路 1112 を 240 個備えて構成される。該出力回路 1112 は、交流化信号 120 (または交流化信号 121) に従いつつ、反転基準電圧 119 を基準として、各出力毎に階調電圧 130 を反転または非反転して出力するものである。該出力回路 1112 は、図 37 に示すとおり、反転增幅回路 1401 と、選択回路 1403 と、出力バッファ回路 1405 とから構成されている。10

#### 【0262】

反転增幅回路 1401 は、正極性の階調電圧 130 を、反転基準電圧 119 に対して反転し、反転電圧 1402 として出力する。該反転電圧 1402 は、負極性の液晶駆動電圧に対応したものである。

#### 【0263】

選択回路 1403 は、階調電圧 130 と反転電圧 1402 とのうちのいずれか一方を交流化信号 120 に従って選択し、該選択した方を出力電圧 1404 として出力バッファ回路 1405 へ出力するようになっている。20

#### 【0264】

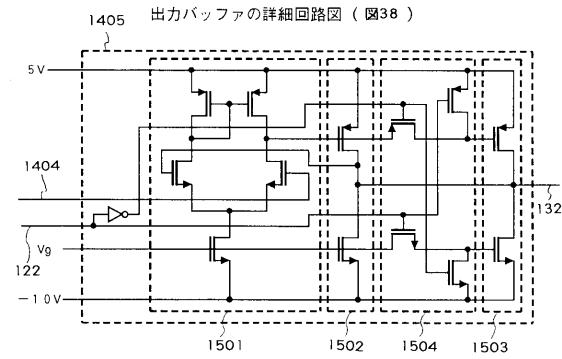

出力バッファ回路 1405 は、出力電圧 1404 の電流を増幅して出力するボルテージフォロア回路である。該出力バッファ回路 1405 は、電流増幅後の信号を、液晶駆動電圧 132 として液晶パネル 111 に出力している。該出力バッファ 1405 は、図 38 に示すとおり、差動增幅回路 1501 と、電流増幅回路 1502, 1503 と、選択回路 1504 とからなる。

#### 【0265】

出力バッファ 1405 は、差動增幅回路 1501 によって出力電圧 1404 を受け、その電流を電流増幅回路 1502, 1503 で増幅して出力するようになっている。

#### 【0266】

電流増幅回路 1503 はレベルシフト回路 1106 (図 34 参照) を通じて入力される制御信号 122 に従って動作している。制御信号 122 が "Low" レベルになると、電流増幅回路 1503 は無効になる。この場合には、電流増幅回路 1502 のみで電流を出力する。制御信号 122 が "High" レベルになると、電流増幅回路 1503 は有効になる。従って、この場合には、電流増幅回路 1503 および電流増幅回路 1502 によって大電流を出力することができる。従って、大出力電流が必要な期間には、電流増幅回路 1502 および電流増幅回路 1503 によって電流増幅を行い、大出力電流が必要でない期間には、電流増幅回路 1503 を無効にし電流増幅回路 1502 のみで電流増幅する。これにより、電流増幅回路での消費電力を小さくすることを可能としている。30

#### 【0267】

なお、交流駆動を行うためには、液晶駆動電圧としては 15V 程度が必要である。従って、該出力回路 131 としては高耐圧プロセス (15V 耐圧) を用いる必要がある。

#### 【0268】

次に、データドライバ 109 の動作を説明する。

#### 【0269】

図 33 において、液晶表示コントローラ 101 は、システムからの表示データ、表示同期信号 102 を、液晶ドライバ用にタイミング制御を行なう。そして、データドライバ 109 に 18 ビットの表示データ、表示同期信号 103 として転送する。

#### 【0270】

タイミング制御回路 113 は、表示データ、同期信号 103 を、データドライバ 109 50

内部の表示データ、タイミング制御信号に制御される。

【0271】

データドライバ109のラッチ回路125(図34参照)は、240画素分の表示データ115を、3画素分づつ80回に分けて、ラッチ信号124で順次ラッチする。つまり、まず最初に、3画素に対応したラッチ回路1107-1, 1107-2, 1107-3が、表示データ115をラッチする。続いて、次の3画素に対応したラッチ回路1107-4, 1107-5, 1107-6が、これに続く表示データ115をラッチする。これ以降のラッチ回路1107-7~1107-240も、同様に順次3画素分づつ、18ビットの表示データ115をラッチしてゆく。このようにデータドライバ112-1~112-8によって、合計1920画素、1ライン分の表示データがラッチされる。

10

【0272】

ラッチ回路127は、ライン表示同期信号116で1水平ライン分の表示データ126を同時にラッチする。ラッチ回路127は、ラッチした表示データ126を、表示データ128として階調電圧生成回路129に転送する。

【0273】

これと並行して、電源回路107(図33参照)は、基準電圧108を生成している。基準電圧108には、階調電圧生成のための9レベルの基準電圧1103と、と階調電圧を交流化のために反転するのに用いられる反転基準電圧1104が含まれている(図34参照)。

【0274】

図34における入力バッファ回路117では、電源回路107から入力された基準電圧1103を、バッファアンプ回路1105がバッファし、基準電圧118として階調電圧生成回路129に出力する。同様に、反転基準電圧1104についてもバッファアンプ回路1105がバッファし、反転基準電圧119として出力回路131に出力する。

20

【0275】

さらに、入力バッファ回路117では、レベルシフト回路1106が、制御信号103中の交流化信号1102の電圧レベルを、液晶駆動レベルに合わせるように変換し、互いに極性の反転した交流化信号120, 121を生成する。そして、これを出力回路131へ出力する。制御信号103中の出力制御信号についても同様に電圧レベルを変換した後、出力駆動制御信号122として出力回路131へ出力する。

30

【0276】

階調電圧生成回路129の階調電圧生成回路1109は、9レベルの基準電圧118から64レベルの階調電圧1110を生成する。電圧選択回路1111は、この中から、表示データ128に対応した階調電圧1110を各出力毎に1レベル選択し、それぞれ階調電圧130として出力回路131に出力する。

【0277】

出力回路131は、階調電圧130を交流化信号120、121に従いつつ、反転基準電圧105を基準として反転または非反転する。液晶駆動電圧132として出力する。なお、該液晶駆動電圧132の極性については、後ほど図41を用いて詳細に説明する。

40

【0278】

ところで、走査回路105は、表示同期信号104の水平同期信号に同期して1ライン毎に順次ゲート駆動信号106を生成し出力している。該ゲート駆動信号106によって、液晶パネル111のゲート線が1ライン順次選択状態とされている。従って、ゲート駆動信号106に同期して出力される液晶駆動電圧132は、その時選択状態とされているライン上の画素に印加されることとなる。つまり、液晶パネル111が駆動され、正極性または負極性の64レベルの階調電圧の内、表示データに対応した液晶駆動電圧の表示を行うことができる。

【0279】

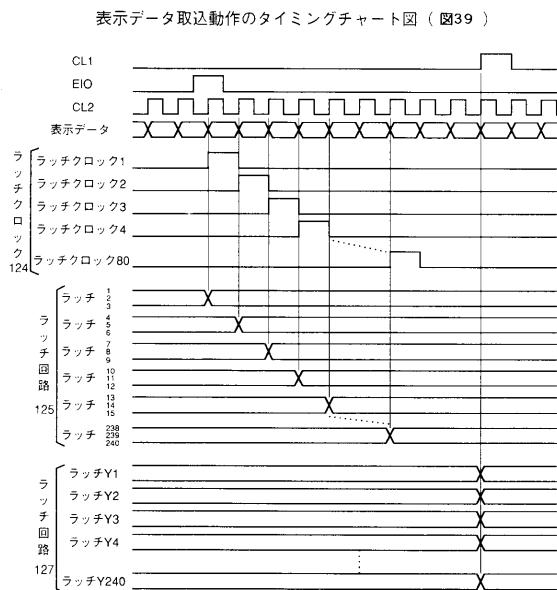

次に、表示データの取り込み動作を、図39を用いて改めて詳細に説明する。

【0280】

50

表示データ1101(図34参照)は、データ同期クロック(CL2)に同期してタイミング制御回路113に入力される。ラッチクロック124(ラッチクロック1~80)は、ラッチアドレス制御回路123によって、ドライバ有効信号(EIO)と、CL2とに同期して生成されている。なお、データ同期クロック(CL2)は、制御信号1102中に含まれているものである。

#### 【0281】

表示データ115は、ラッチ回路125(ラッチ回路1107-1~1107-240)によって、順次3画素毎にラッチされる。

#### 【0282】

1ライン分の表示データがラッチ回路125によってラッチされると、ラッチ回路127は、該1ライン分の表示データを、ライン表示同期信号116(CL1)で同時にラッチする。そして、最終的には、このラッチ回路127のラッチした表示データに対応した液晶駆動電圧が、出力回路131から出力される。10

#### 【0283】

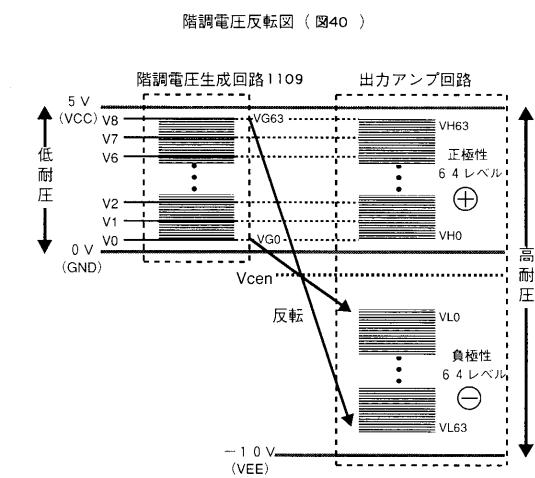

次に、階調電圧、交流出力電圧の電圧レベルとタイミングを、図40、図41を用いて詳しく説明する。

#### 【0284】

図40はデータドライバ112に入力される液晶駆動電圧の基準電圧1103と、その出力電圧(液晶駆動電圧132)との関係を示した図である。

#### 【0285】

基準電圧1103(V8~V0)の電圧レベルは、5V~0Vの範囲にある。各レベルの基準電圧1103は階調電圧生成回路1109によって分圧され、64レベルの階調電圧130(VG63~VG0)が生成される。該階調電圧130の電圧レベルも5V~0Vの範囲内にある。20

#### 【0286】

階調電圧130(VG63~VG0)は、出力回路131において、反転基準電圧119(Vcen)を基準に反転(VL63~VL0)されて、あるいは、非反転(VH63~VH0)で、液晶駆動電圧132として出力される。

#### 【0287】

VH63~VH0の電圧レベルは、階調電圧130(VG63~VG0)と同レベルの5V~0Vの範囲にある。VL63~VL0の電圧レベルは、反転基準電圧119(Vcen)を0Vから-5Vの範囲に設定することで、0Vから-10Vの範囲内となる。従って、階調電圧生成回路129までを低耐圧回路とし、図34中点線で囲んだ回路部分(すなわち、出力回路131, 入力バッファ117)のみを高耐圧回路とすることができる。さらに、低耐圧回路から高耐圧回路へ信号レベルを変換するレベルシフト回路が、交流化信号と出力駆動制御信号の2本の信号線の分だけでよい。30

#### 【0288】

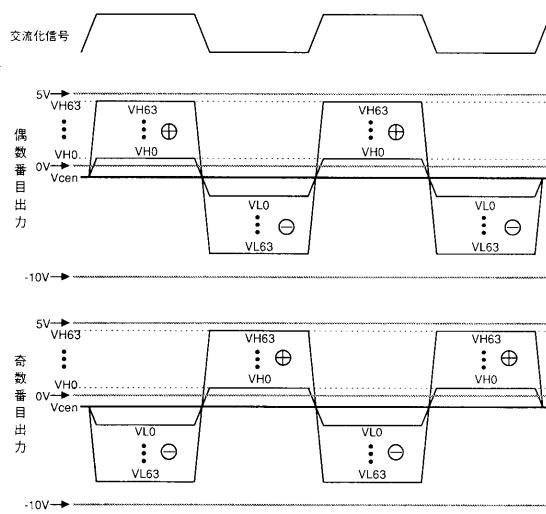

次に、データドライバ109の出力する液晶駆動電圧132の極性について、図41を用いて説明する。

#### 【0289】

交流化信号120は、データドライバ109の奇数番目の出力に対応している。一方、交流化信号121は、データドライバ109の偶数番目の出力に対応している。また、交流化信号121は、交流化信号120とは極性が異なっている。従って、データドライバ109の出力は、偶数番目の出力と、奇数番目の出力とで、互いに交流化のタイミングが異なる。偶数番目の出力が正極性となっているときには、奇数番目の出力は負極性の出力となっている。逆に偶数番目の出力が負極性となっている時には、奇数番目の出力は正極性となっている。40

#### 【0290】

現在、低耐圧プロセス(耐圧5V~3V程度)は、ゲート長が1.0μm~0.5μm程度の最新の微細プロセスである。これに対し、高耐圧プロセス(耐圧30V~10V程

度)は、ゲート長が  $5 \mu m \sim 2 \mu m$  程度である。従って、能力が同程度の素子について考えた場合、高耐圧プロセスの素子は、その素子面積が低耐圧プロセスの素子の数倍大きくなる。また、出力回路に低耐圧プロセスを採用している場合でも、静電破壊やラッチアップ対策のために、そのゲート長を大きく設計するのが通常である。図 4 0 に示すように、本実施例では入力信号の電圧レベルを全て低耐圧プロセスの動作範囲 ( $5 V \sim 0 V$  (GND)) 内としているため、高耐圧プロセスにする必要があるのは、出力回路 131 および入力バッファ 117 のみである。図 33、図 34 中、データドライバの点線で囲んだ回路部分は、高耐圧プロセス (耐圧  $15 V$ ) である。その他の回路部分は低耐圧プロセス (耐圧  $5 V$ ) である。従って、本実施例のデータドライバ 112 は、従来の低耐圧プロセスのデータドライバに比べても、チップ面積の増加を極力小さくすることができる。これは、

10 価格化につながる。

#### 【0291】

なお、ここでの説明では低耐圧プロセスを  $5 V$  耐圧、高耐圧プロセスを  $15 V$  耐圧として説明したが、低耐圧プロセスについては  $5 V$  耐圧から  $3 V$  耐圧等の、高耐圧プロセスについては  $30 V$  耐圧から  $10 V$  耐圧等のプロセスを用いた場合についても本実施例と同様な効果を得ることができる。

#### 【0292】

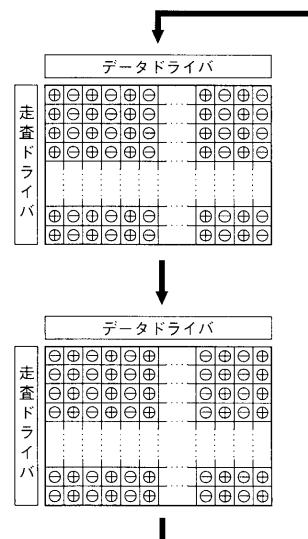

本実施例のデータドライバを用いた液晶ディスプレイでは、図 4 2 のごとく、データドライバを液晶パネルの片側に配置した場合でも、列毎反転駆動が可能となり、高画質表示を行うことができる。ここで言う”列毎反転駆動”とは、交流駆動のタイミングを、液晶パネル上の画素 1 列ごとに反転する駆動法である。

20

#### 【0293】

また、図 4 3 に示すように、液晶パネル上において隣り合う 4 つの画素で交流駆動タイミングを反転するドット毎反転駆動が可能となり、さらなる高画質表示を行うことができる。ここでいう”ドット毎反転駆動”とは、交流駆動のタイミングを、液晶パネル上において隣り合う 4 つの画素間で反転する駆動法である。該駆動法においては、全ての画素についてその上下左右に隣接する画素と交流駆動のタイミングが反転している。

#### 【0294】

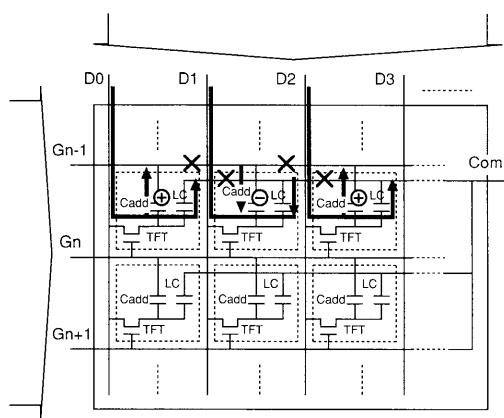

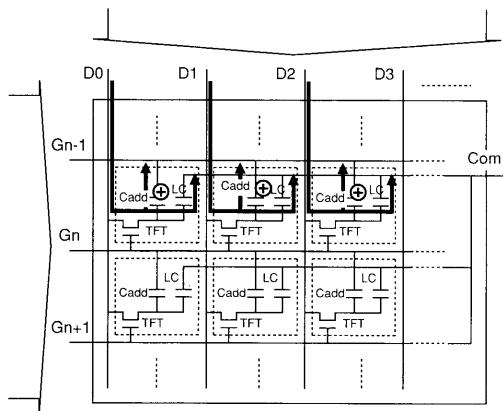

さらに、列毎反転駆動、ドット毎反転駆動では、図 4 4 に示すとおり、液晶パネル駆動時の電流の向きが隣り合う画素で逆となる。また、対向電極の電流の向きも隣り合う画素で、逆方向となる。従って、両者がその影響を互いに、打ち消し合うことで対向電極の電圧レベルが安定するため高画質表示が可能となる。

30

#### 【0295】

本実施例では、出力を 240 本有するデータドライバ 112 を採用していた。しかし、データドライバの出力数は、これに限定されるものではない。出力数が、192 本、160 本のデータドライバも、ラッチアドレス制御回路 123 等を、該出力の本数に対応した構成にすることで容易に実現できる。

#### 【0296】

また、本実施例では 64 階調のデータドライバについて述べたが、表示データを 1 画素あたり 8 ビット構成とするとともに、ラッチ回路の構成を 1 出力当たり 8 ビットに、また、階調電圧生成回路の構成を 256 階調に対応するように変えることで、256 階調やその他の階調数のデータドライバに対しても容易に実現することができる。

40

#### 【0297】

次に、本実施例 8 の走査回路 105 の構成および動作を、図 4 5、図 4 6、図 4 7 を用いて説明する。

#### 【0298】

図 4 6 に示すとおり、走査ドライバ 105 の出力するゲート選択信号 (ゲート駆動信号 106) としては、液晶パネルの TFT の特性から、データドライバ 112 の出力する液晶印加電圧 132 よりも上下に約  $3 V$  程度大きな電圧を与える必要がある。一方、走査ドライバ 105 のデジタル信号の動作レベルは、VCC - GND S 間の  $5 V$  である。そのため

50

め、データドライバ112への入力信号と、走査ドライバ105のデジタル系への入力信号とでは、その電圧レベルに差がある。従来の液晶パネルではデジタル信号の電圧レベルを、データドライバの電圧レベルに合わせていた。そして、走査ドライバへ入力されるデジタル信号については、外付けの回路によってレベルシフトすることで、該走査ドライバの電圧レベルに合わせていた。しかし、このような外付けの回路を使用することは、液晶ディスプレイの周辺回路規模が大きくなる要因となっていた。本実施例では、走査ドライバ105の入力段にレベルシフト回路を内蔵することで、周辺回路の回路規模の削減を可能としている。

#### 【0299】

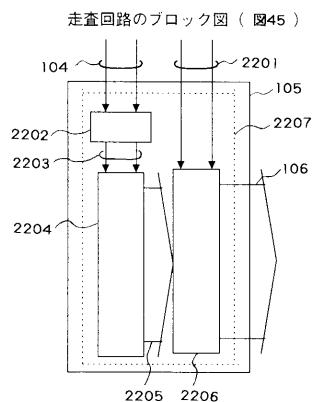

本実施例の走査回路105は、図45に示すとおり、レベルシフト回路2202、シフトレジスタ2204、ゲート駆動回路2206からなる。10

#### 【0300】

レベルシフト回路2202は、図47に示すとおり、インバータ回路2404、2405等を含んで構成されている。インバータ回路2404は、スレッシュホールド電圧を入力信号レベルの真ん中に設定されており、その出力信号の振幅レベルはVCC-VSSである。インバータ回路2405の振幅レベルはVCC-VSSである。表示同期信号2203は、入力信号104を非反転してレベルシフトしたものである。

#### 【0301】

走査回路105の動作を説明する。

#### 【0302】

図45において、レベルシフト回路2202は、表示同期信号104の電圧レベルを変換して、表示同期信号2203としてシフトレジスタ2204に出力する。シフトレジスタ2204は、該表示同期信号2203（水平同期信号）に同期してシフト動作することで、シフト出力信号2205を生成し出力している。ゲート駆動回路2206には、電源電圧2201が入力されている。この電源電圧2201には、ゲートを選択状態とするためのオンレベルの電圧と、ゲートを非選択状態とするためのオフレベルの電圧と、が含まれている。ゲート駆動回路2206は、該電源電圧2201を用いてゲート駆動信号106を生成する。ゲート駆動回路2206は、該ゲート駆動信号106を、シフト出力信号2205に同期して、1ライン毎に順次生成している。20

#### 【0303】

本実施例ではデータドライバ112へ入力する液晶基準電圧108が直流の電圧でよいため、電源回路107にはアンプバッファが不要である。従って、電源回路107の回路規模を小さくすることが可能である。30

#### 【0304】

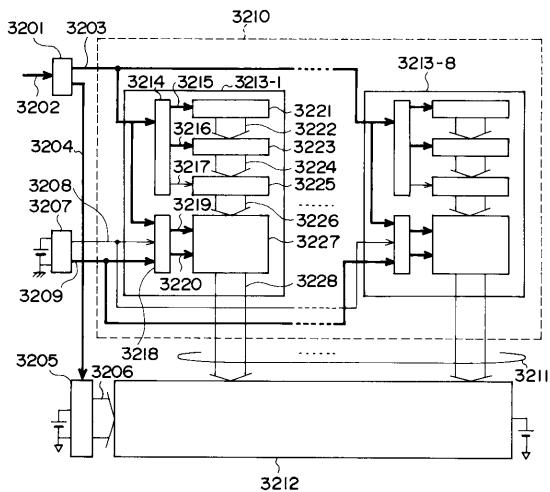

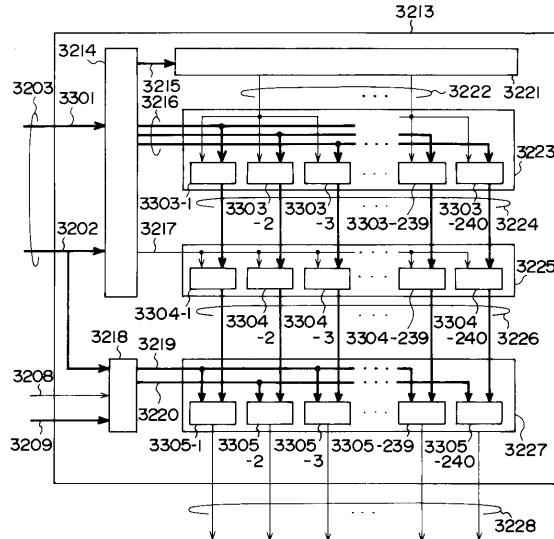

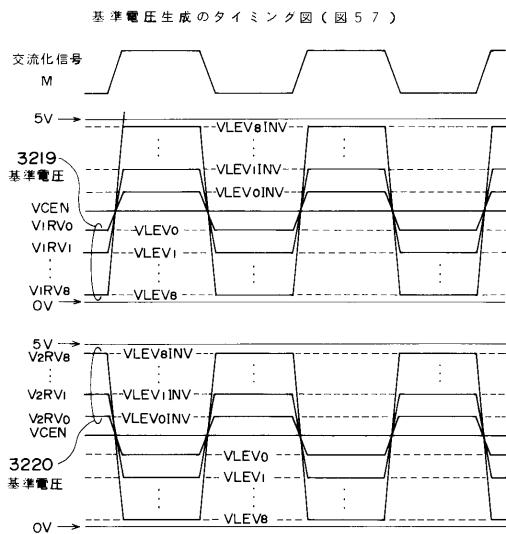

次に、本発明の第9の実施例について、図48、図49、図50、図51、図52、図53、図54を用いて説明する。本実施例は、9レベルの基準電圧から64階調表示を行うデータドライバを用いたものである。

#### 【0305】

本実施例の液晶表示装置は、大きく分けて、液晶表示コントローラ2501と、走査回路2505と、電源回路2507と、データドライバ2510と、640×3(R、G、B)×480ドットの液晶パネル2512と、から構成されている。40

#### 【0306】

動作概要を説明する。

#### 【0307】

液晶表示コントローラ2501は、システムから入力される表示データ、表示同期信号2502を、液晶ドライバ用にタイミング制御した上で、表示データ、表示同期信号2503としてデータドライバ2510に転送する。また、同様に、液晶コントローラ2501は、システムから入力される表示データ、同期信号2502から、表示データ、同期信号2504を生成して走査回路2505へ出力する。なお、表示データ2503は、1画素当たり階調6ビットを割り当てた、3画素分づつの合計18ビットのデータである。50

## 【0308】

電源回路2507は、9種類の電圧レベルの電圧からなる基準電圧2509を発生し、データドライバ2510に出力している。データドライバ2510は、該基準電圧2509に基づいて階調表示用に64階調の電圧を生成する。そして、表示データに応じていずれかの電圧を出力ごとに選択し、これを液晶駆動電圧2511として液晶パネル2512へ出力する。

## 【0309】

これと並行して走査回路2505は、表示データ、同期信号2504に従って、ゲート駆動信号2506を出力することで、液晶パネル2512を構成しているゲート線の内の一一本を順次選択してゆく。これにより、データドライバ2510の出力している液晶駆動電圧2511は、その時選択状態にされているゲート線に対応する行の画素にのみ印加されることとなる。走査回路2505が選択するゲートを順次変更してゆくことで(すなわち、走査することで)、液晶パネル2512全体に画像が表示されることになる。

## 【0310】

次に、上記各部ごとにその構成および動作を詳細に説明する。

## 【0311】

まず、データドライバ2510の詳細を説明する。

## 【0312】

データドライバ2510は、240本の出力を有するデータドライバ2513を、8個備えて構成されている。以下、各データドライバ2513をその配置位置に応じて、データドライバ2513-1、データドライバ2512-2等と呼ぶ。他の回路部分についても同様の呼び方をする。

## 【0313】

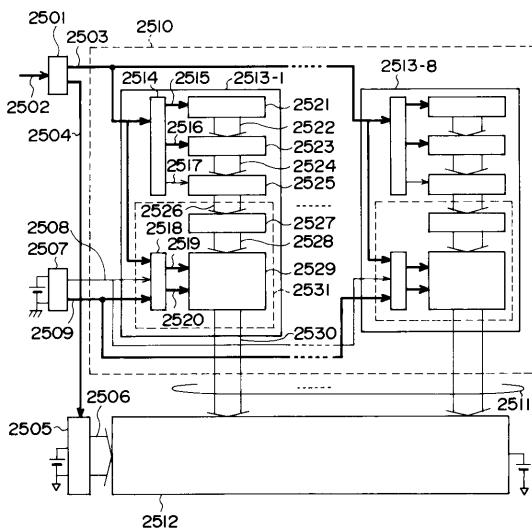

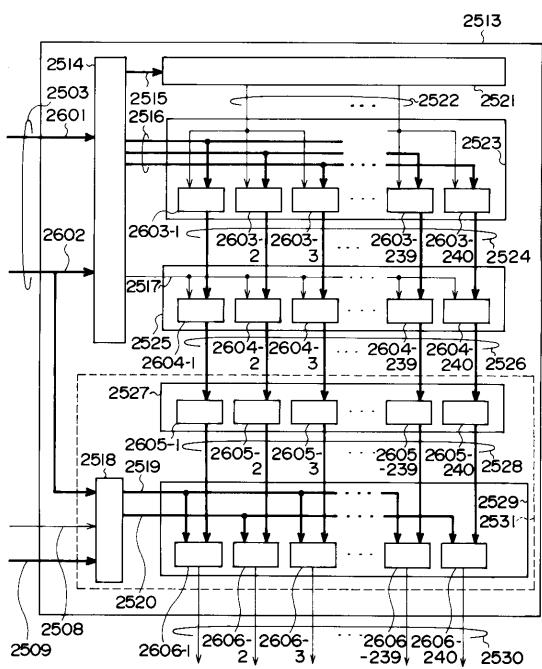

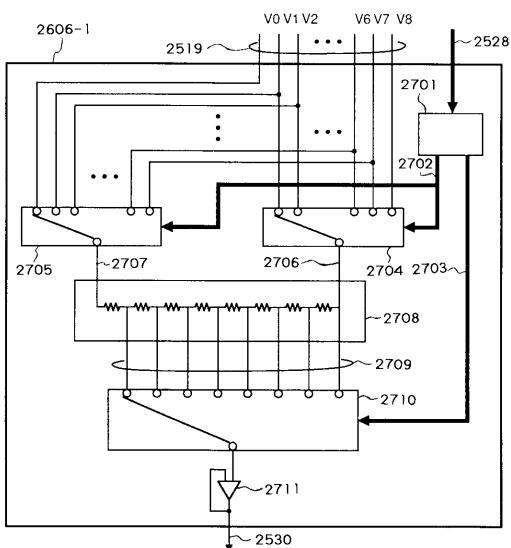

各データドライバ2513は、図49に示すとおり、タイミング制御回路2514と、電圧生成回路2518と、ラッチアドレス制御回路2521と、ラッチ回路2523と、ラッチ回路2525と、レベルシフト回路2527と、液晶駆動回路2529とからなる。

## 【0314】

タイミング制御回路2514は、表示データ、表示同期信号2503(表示データ2601、制御信号2602)に基づいて、タイミング信号2515、表示データ2516、ライン表示同期信号2517を生成出力するものである。

## 【0315】