(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-352479

(P2005-352479A)

(43) 公開日 平成17年12月22日(2005.12.22)

(51) Int.Cl.<sup>7</sup>

**G02F** 1/1368

**G02F** 1/1335

**G02F** 1/1343

**G02F** 1/1345

**H01L** 29/786

F 1

G02F 1/1368

G02F 1/1335 520

G02F 1/1343

G02F 1/1345

H01L 29/786

テーマコード(参考)

2 H 0 9 1

2 H 0 9 2

5 F 1 1 0

審査請求 有 請求項の数 42 O L (全 31 頁) 最終頁に続く

(21) 出願番号 特願2005-165711(P2005-165711)

(22) 出願日 平成17年6月6日(2005.6.6)

(31) 優先権主張番号 2004-041143

(32) 優先日 平成16年6月5日(2004.6.5)

(33) 優先権主張国 韓国(KR)

(71) 出願人 501426046

エルジー・フィリップス エルシーテー

カンパニー、リミテッド

大韓民国 ソウル、ヨンドゥンポーク、ヨ

イドードン 20

(74) 代理人 100064447

弁理士 岡部 正夫

(74) 代理人 100085176

弁理士 加藤 伸晃

(74) 代理人 100106703

弁理士 産形 和央

(74) 代理人 100094112

弁理士 岡部 謙

(74) 代理人 100096943

弁理士 白井 伸一

最終頁に続く

(54) 【発明の名称】 液晶表示装置及びその製造方法

## (57) 【要約】 (修正有)

【課題】 工程を単純化し、透過領域の開口率を増大し得る製造方法の提供。

【解決手段】 透明な第1導電層と不透明な第2導電層とが積層された二重構造で形成されたゲートラインと；前記ゲートラインの第1絶縁膜上の前記ゲートラインと交差して画素領域を画成するデーターラインと；薄膜トランジスターと；前記画素領域に前記第1導電層で形成された画素電極と；ストリッジキャバシターを形成するストリッジ上部電極と；前記薄膜トランジスター上の第2絶縁膜から前記第1絶縁膜まで貫通して、前記画素電極を露出させる透過ホールと；前記透過ホールのエッジ部を通じて露出されたドレン電極及びストリッジ上部電極を前記画素電極と接続させる反射電極と；を有することを特徴とする。

【選択図】 図4

## 【特許請求の範囲】

## 【請求項1】

第1及び第2基板と；透明な第1導電層と不透明な第2導電層が積層された二重構造にて前記第1基板上に形成されたゲートラインと；前記ゲートラインの上の第1絶縁膜と；前記ゲートラインと交差して画素領域を画成するデーターラインと；前記ゲートライン及びデーターラインと接続された薄膜トランジスターと；前記画素領域に前記第1導電層で形成された画素電極と；前記ゲートラインと前記第1絶縁膜の間にはさみ込まれ、かつ重なってストリッジキャパシターを形成するストリッジ上部電極と；前記薄膜トランジスターの上の第2絶縁膜から前記第1絶縁膜まで貫通して、前記画素電極を露出させる透過ホールと；前記透過ホールのエッジ部を通じて露出された前記薄膜トランジスターのドレイン電極及びストリッジ上部電極を前記画素電極と接続させる反射電極と；前記ゲートラインの第1導電層から伸長されたゲートペードと；前記第1導電層で形成されデーターリンクを通じて前記データーラインと接続されたデーターペードと；前記第1及び第2基板間の液晶層を備え；前記第1及び第2絶縁膜は前記ゲートペード及びデーターペード領域から除去されていることを特徴とする液晶表示装置。

10

【請求項2】

前記薄膜トランジスターと前記第2絶縁膜との間の第3絶縁膜をさらに備えることを特徴とする請求項1に記載の液晶表示装置。

### 【請求項3】

前記第3絶縁膜は、無機絶縁物質で形成されたことを特徴とする請求項2に記載の液晶表示装置。

20

#### 【請求項4】

前記透過ホールは、第3絶縁膜を貫通することを特徴とする請求項2に記載の液晶表示装置。

【請求項5】

前記第2絶縁膜は、有機絶縁膜で形成されたことを特徴とする請求項1に記載の液晶表示装置。

【請求項 6】

前記第2絶縁膜及びデーターラインと、第1絶縁膜を貫通して、前記データーラインの末端部分と重なるデーターリンクを露出させる第1コンタクトホールと；前記第1コンタクトホールを通じて前記データーラインと側面接続されるとともに、前記データーリンクと面接続された第1コンタクト電極をさらに備えることを特徴とする請求項1に記載の液晶表示装置

30

### 【請求項7】

前記第1コンタクト電極は、前記反射電極と同一の金属で形成されたことを特徴とする請求項6に記載の液晶表示装置

### 【請求項 8】

前記第1コンタクト電極は、シーリング材により密封される領域に形成されたことを特徴とする請求項6に記載の液量表示装置

徵文專題

前記反射電極及び前記第1コンタクト電極は、AlNd及びMoの二重層構造で形成されたことを特徴とする請求項6に記載の液晶表示装置

40

【説文頂 10】

前記ゲートライン及びデーターラインのうち、いずれか一つと接続された静電気防止素子をさらに備えることを特徴とする請求項1に記載の流用表示装置

」をどうに備え

【説文項 11】

前記静電気防止素子は、前記ゲートライン及びデーターラインのうち、いずれか一つと接続された第2薄膜トランジスター；前記第2薄膜トランジスターのゲート電極及びソース電極の間にダイオード形態で接続された第3薄膜トランジスターと；前記第2薄膜トランジスターのゲート電極及びドレイン電極の間にダイオード形態で接続された第4薄膜トランジスター。

50

ンジスターと；第2コンタクトホールを通じて前記第3薄膜トランジスターのソース電極及びゲート電極を接続させる第2コンタクト電極と；第3コンタクトホールを通じて前記第3または第4薄膜トランジスターのドレイン電極と前記第2薄膜トランジスターのゲート電極を接続させる第3コンタクト電極と；第4コンタクトホールを通じて前記第4薄膜トランジスターのソース電極及びゲート電極を接続させる第4コンタクト電極を備えることを特徴とする請求項10に記載の液晶表示装置。

【請求項12】

前記第2乃至第4薄膜トランジスターのゲート電極は、前記ゲートラインのように二重層構造で形成されたことを特徴とする請求項11に記載の液晶表示装置。

【請求項13】

前記第2乃至第4コンタクト電極は、前記反射電極と同一の金属で形成されたことを特徴とする請求項11に記載の液晶表示装置。

【請求項14】

前記第2乃至第4コンタクトホールは、前記第2絶縁膜から前記ソース電極またはドレイン電極と半導体パターン、前記第1絶縁膜と前記ゲート電極の第2導電層まで貫通して、前記ゲート電極の第1導電層を露出させることを特徴とする請求項11に記載の液晶表示装置。

【請求項15】

前記第2乃至第4コンタクト電極は、シーリング材により密封される領域に形成されたことを特徴とする請求項11に記載の液晶表示装置。

【請求項16】

前記反射電極と、第2乃至第4コンタクト電極は、AlNd及びMoの二重層構造で形成されたことを特徴とする請求項11に記載の液晶表示装置。

【請求項17】

前記第2絶縁膜は、エンボッシング表面を有することを特徴とする請求項1に記載の液晶表示装置。

【請求項18】

前記反射電極は、エンボッシング表面を有することを特徴とする請求項17に記載の液晶表示装置。

【請求項19】

第1及び第2基板を設ける段階と；第1マスクを利用して透明な第1導電層と不透明な第2導電層が積層された二重構造を有するゲートライン及びゲート電極と、前記第1導電層を有する画素電極を形成する段階と；前記ライン及び電極の上に第1絶縁膜を形成する段階と；第2マスクを利用して前記第1絶縁膜の上に半導体パターンを形成すると共に、データーライン、ソース電極、ドレイン電極、ストリッジ上部電極を含むソース／ドレインパターンを形成する段階と；第3マスクを利用して前記ソース／ドレインパターンの上に第2絶縁膜を形成し、前記第2絶縁膜から前記第1絶縁膜まで貫通する透過ホールを透過領域に形成する段階と；第4マスクを利用して前記透過ホールを通じて前記ドレイン電極及びストリッジ上部電極を前記画素電極と接続させる反射電極を反射領域に形成する段階と；前記第1及び第2基板の間に液晶層を形成する段階とを含むことを特徴とする液晶表示装置の製造方法。

【請求項20】

前記データーラインの前記半導体パターンの一部と重なることを特徴とする請求項19に記載の液晶表示装置の製造方法。

【請求項21】

前記反射領域は、前記画素電極の一部分と重なることを特徴とする請求項20に記載の液晶表示装置の製造方法。

【請求項22】

前記第2絶縁膜を形成する以前に、第3絶縁膜を形成する段階をさらに含むことを特徴とする請求項19に記載の液晶表示装置の製造方法。

10

20

30

40

50

**【請求項 2 3】**

前記第3絶縁膜は、無機絶縁物質で形成されたことを特徴とする請求項22に記載の液晶表示装置の製造方法。

**【請求項 2 4】**

前記透過ホールは、前記第3絶縁膜を貫通するように形成されたことを特徴とする請求項22に記載の液晶表示装置の製造方法。

**【請求項 2 5】**

前記第2絶縁膜は、有機絶縁物質で形成されたことを特徴とする請求項19に記載の液晶表示装置の製造方法。

**【請求項 2 6】**

前記第1マスクを利用して、前記ゲートラインの第1導電層から伸長されたゲートペードと、前記データーラインと接続されるデーターペードを形成する段階と；前記第3マスクを利用して、前記ゲートペード及びデーターペードが形成されたペード領域で前記第1及び第2絶縁膜を除去する段階とをさらに含むことを特徴とする請求項19に記載の液晶表示装置の製造方法。10

**【請求項 2 7】**

前記ゲートペード及びデーターペードは、同一の構造を有することを特徴とする請求項26に記載の液晶表示装置の製造方法。

**【請求項 2 8】**

前記第1マスクを利用して、前記データーペードから伸長されて、前記データーラインの末端部分と重なるデーターリンクを形成する段階と；前記第3マスクを利用して第2絶縁膜から前記データーラインを経由して前記第1絶縁膜まで貫通して、前記データーリンクを露出させる第1コントラクトホールを形成する段階と；前記第4マスクを利用して前記第1コントラクトホールを通じて前記データーライン及びデーターリンクを接続させる第1コントラクト電極を形成する段階とをさらに含むことを特徴とする請求項26に記載の液晶表示装置の製造方法。20

**【請求項 2 9】**

前記第1コントラクト電極は、シーリング材により密封される領域に形成されたことを特徴とする請求項28に記載の液晶表示装置の製造方法。

**【請求項 3 0】**

前記反射電極及び第1コントラクト電極は、AlNd及びMoの二重層構造で形成されたことを特徴とする請求項28に記載の液晶表示装置の製造方法。30

**【請求項 3 1】**

前記ゲートライン及びデーターラインのうち、いずれ一つと接続された第2薄膜トランジスター、前記第2薄膜トランジスターのゲート電極及びソース電極の間にダイオード形態で接続された第3薄膜トランジスター、前記第2薄膜トランジスターのゲート電極及びドレイン電極の間にダイオード形態で接続された第4薄膜トランジスターを含む静電気防止素子を形成する段階をさらに含むことを特徴とする請求項19に記載の液晶表示装置の製造方法。

**【請求項 3 2】**

前記静電気防止素子を形成する段階は、前記第1マスクを利用して前記二重構造を有する前記第2乃至第4薄膜トランジスターのゲート電極を形成する段階と；前記第2マスクを利用して前記第1絶縁膜の上に前記第2乃至第4薄膜トランジスターの半導体パターンとソース電極及びドレイン電極を形成する段階と；前記第3マスクを利用して第2乃至第4コントラクトホールを形成する段階と；前記第4マスクを利用して第2乃至第4コントラクト電極を形成する段階とを含むことを特徴とする請求項31に記載の液晶表示装置の製造方法。40

**【請求項 3 3】**

前記第2コントラクトホールは、前記第3薄膜トランジスターのゲート電極及びソース電極の重畠部に形成されたことを特徴とする請求項32に記載の液晶表示装置の製造方法。

**【請求項 3 4】**

10

20

30

40

50

前記第3コンタクトホールは、前記第3または第4薄膜トランジスターのドレイン電極と、前記第2薄膜トランジスターのゲート電極との重畠部に形成されたことを特徴とする請求項32に記載の液晶表示装置の製造方法。

【請求項 35】

前記第4コンタクトホールは、前記第4薄膜トランジスターのソース電極及びゲート電極の重なる部分に形成されたことを特徴とする請求項32に記載の液晶表示装置の製造方法。

【請求項 36】

前記第2コンタクト電極は、前記第2コンタクトホールを通じて前記第3薄膜トランジスターのソース電極及びゲート電極を接続させることを特徴とする請求項32に記載の液晶表示装置の製造方法。 10

【請求項 37】

前記第3コンタクト電極は、前記第3コンタクトホールを通じて前記第3または第4薄膜トランジスターのドレイン電極と、前記第2薄膜トランジスターゲート電極とを接続させることを特徴とする請求項32に記載の液晶表示装置の製造方法。

【請求項 38】

前記第4コンタクト電極は、前記第4コンタクトホールを通じて、前記第4薄膜トランジスターのソース電極及びゲート電極を接続させることを特徴とする請求項32に記載の液晶表示装置の製造方法。

【請求項 39】

前記第2乃至第4コンタクト電極は、シーリング材により密封される領域に形成されたことを特徴とする請求項32に記載の液晶表示装置の製造方法。 20

【請求項 40】

前記反射電極と前記第2乃至第4コンタクト電極は、AlNd及びMoの二重層構造で形成されたことを特徴とする請求項32に記載の液晶表示装置の製造方法。

【請求項 41】

前記第2絶縁膜は、エンボッシング表面を有することを特徴とする請求項19に記載の液晶表示装置の製造方法。

【請求項 42】

前記反射電極は、前記第2絶縁膜に対応してエンボッシング表面を有することを特徴とする請求項41に記載の液晶表示装置の製造方法。 30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は液晶表示装置に関し、特にその製造工程を単純化し得る液晶表示装置及びその製造法に関する。

【背景技術】

【0002】

液晶表示装置は、バックライトユニット(Back light unit)から入射された光を利用して画像を表示する透過型と、自然光のような外部光を反射させるによって画像を表示する反射型とに大別される。透過型はバックライトユニットの電力消耗が多く、反射型は外部光に依存することにより、暗い環境では画像を表示し得ない問題点がある。 40

【0003】

このような問題点を解決するために、バックライトユニットを利用する透過モードと外部光を利用する反射モードとが選択可能な半透過型液晶表示装置が出現した。半透過型液晶表示装置は、外部光が充分であれば反射モードに、不充分であればバックライトユニットを利用した透過モードに動作するようになるため、透過型より消費電力を減らすことができると共に、反射型とは相違に外部光の制約を受けないようになる。

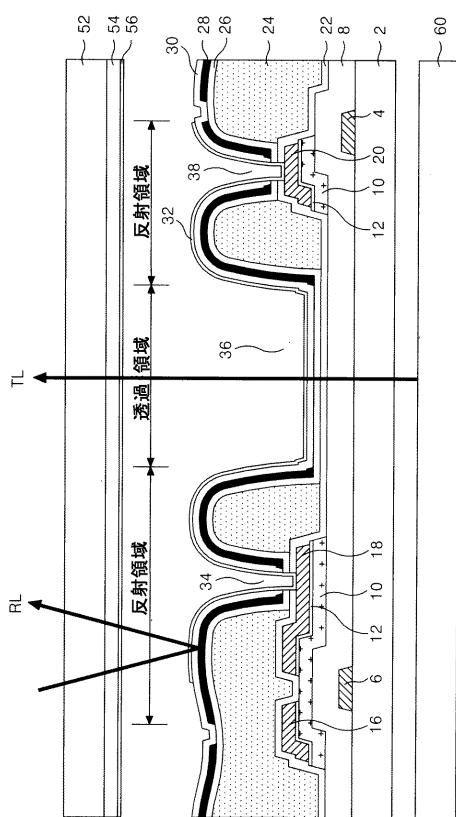

【0004】

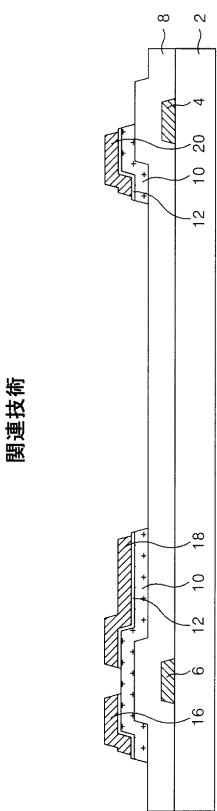

一般的に、半透過型液晶パネルは、図1に図示されたように、液晶層(図示なし)を間に置いて接合されたカラーフィルター基板及び薄膜トランジスター基板と、薄膜トランジ

ター基板の後部に配置されたバックライトユニット60とを備える。このような半透過型液晶パネルの各画素は、反射電極28が形成された反射領域と、反射電極28が形成されていない透過領域とに区分される。

【0005】

カラーフィルター基板は、上部基板52の上に形成されたブラックマトリックス(図示なし)及びカラーフィルター54、それらの上に積層された共通電極56及び配向膜(図示なし)で構成される。

【0006】

薄膜トランジスター基板は、下部基板2の上に形成されて、各画素領域を画成するゲートライン4及びデーターライン(図示なし)、ゲートライン4及びデーターラインと接続された薄膜トランジスター、画素領域に形成されて薄膜トランジスターと接続された画素電極32、各画素の反射領域に形成され画素電極32と重なる反射電極28を備える。

10

【0007】

薄膜トランジスターは、ゲートライン4と接続されたゲート電極6、データーラインと接続されたソース電極16、ソース電極16と対向するドレイン電極18、ゲート電極6とゲート絶縁膜8の間にはさみ込まれ、かつ重なって、ソース及びドレイン電極16,18の間のチャネルを形成する活性層10、その活性層10とソース及びドレイン電極16,18とのオーミック接触のためのオーミック接触層12を備える。このような薄膜トランジスターは、ゲートライン4のスキャン信号に応答して、データーライン上のビデオ信号が画素電極32に印加されて維持されるようとする。

20

【0008】

反射電極28は、カラーフィルター基板を通じて入射された外部光をカラーフィルター基板の方に反射させる。この際、反射電極28の下に形成された有機膜24の表面がエンボッシング(Embossing)形象を有し、その上の反射電極28もエンボッシング形象を有することによって散乱効果で反射効率が増大される。

30

【0009】

画素電極32は、薄膜トランジスターを通じて供給された画素信号により、共通電極56との間に電位差を発生させる。この電位差により誘電異方性を有する液晶が回転して、反射領域と透過領域各々の液晶層を経由する光の透過率を調節することによって、前記ビデオ信号により輝度が変化される。

30

【0010】

この場合、反射領域と透過領域において、液晶層を経由する光の経路の長さが同一になるように、透過領域において、相対的に厚い有機膜24に透過ホール36を形成するようになる。その結果、反射領域に入射された周辺光、即ち、反射光RLが液晶層の内で液晶層 反射電極28 液晶層を経由する経路と、透過領域に入射されたバックライトユニット60の透過光TLが液晶層を経由する経路との長さが同一であることにより、反射モードと透過モードとの透過効率が同じようになる。

40

【0011】

そして、薄膜トランジスター基板は、画素電極32に供給されたビデオ信号を安定に維持するために、画素電極32と接続されたストリッジキャパシターをさらに備える。ストリッジキャパシターは画素電極32と接続されたストリッジ上部電極20がゲートライン4とゲート絶縁膜8の間にはさみ込まれ、かつ重なることによって形成される。ストリッジ上部電極20の下には、工程上オーミック接触層12及び活性層10がさらに重なる。

【0012】

また、薄膜トランジスター基板は、薄膜トランジスターと有機膜24との間の第1保護膜2、有機膜24と反射電極28との間の第2保護膜26、反射電極28と画素電極32との間の第3保護膜30をさらに備えている。これによって、画素電極32は第1乃至第3保護膜22,26,30と有機膜24及び反射電極28を貫通する第1及び第2コンタクトホール34,38各々を通じて、ドレイン電極18及びストリッジ上部電極20と接続される。

【0013】

50

このような半透過型液晶パネルにおいて、薄膜トランジスター基板は、半導体工程を含むと共に、多数のマスク工程を必要とすることになり、製造工程が複雑となるため、液晶パネルの製造単価の上昇の重要な原因になっている。

#### 【0014】

以下、半透過型薄膜トランジスター基板の製造方法を図2a乃至図2fを参照して説明する。

#### 【0015】

図2aを参照すると、第1マスク工程を利用して、下部基板2上にゲートライン4、ゲート電極6を含むゲートパターンが形成される。

#### 【0016】

下部基板2上にスパッタリング方法などの蒸着方法によりゲート金属層が形成される。続いて、第1マスクを利用したフォトリソグラビ工程とエッチング工程によってゲート金属層がパターニングされることにより、ゲートライン4、ゲート電極8を含むゲートパターンが形成される。ゲート金属層としては、Al、Mo、Cr等の金属の単一層または二重層構造が利用される。

#### 【0017】

図2bを参照すると、ゲートパターンが形成された基板2上にゲート絶縁膜8が形成されるとともに、その上に第2マスク工程で活性層10及びオーミック接触層12を含む半導体パターンと；データーライン、ソース電極16、ドレイン電極18、およびストリッジ上部電極20を含むソース／ドレインパターンとが積層される。

#### 【0018】

ゲートパターンが形成された下部電極2上にPECVD、スパッタリングなどの蒸着方法により、ゲート絶縁膜8、非晶質シリコン層、不純物がドーピングされた非晶質シリコン層、そして、ソース／ドレイン金属層が順に形成される。ゲート絶縁膜8としては、酸化シリコン(SiO<sub>x</sub>)または窒化シリコン(SiN<sub>x</sub>)などの無機絶縁物質が、ソース／ドレイン金属層としては、Al、Mo、Crなどの金属の単一層または二重層構造が利用される。

#### 【0019】

そして、ソース／ドレイン金属層の上に、第2マスクを利用したフォトリソグラビ工程でフォトレジストパターンを形成するようとする。この場合、第2マスクとしては、薄膜トランジスターのチャンネル部に回折露光部を有する回折露光マスクを利用することにより、チャンネル部のフォトレジストパターンが他のソース／ドレインパターン部より低い高さを有するようとする。

#### 【0020】

続いて、フォトレジストパターンを利用したウェットエッチング工程によって、ソース／ドレイン金属層がパターニングされることにより、データーライン、ソース電極16、そのソース電極16と一体化されたドレイン電極18、ストリッジ電極20を含むソース／ドレインパターンが形成される。

#### 【0021】

次に、同一のフォトレジストパターンを利用したドライエッチング工程によって、不純物がドーピングされた非晶質シリコン層と非晶質シリコン層とが同時にパターニングされるにより、オミック接触層12と活性層10とが形成される。

#### 【0022】

そして、アッシング(Ashing)工程によって、チャンネル部において相対的に低い高さを有するフォトレジストパターンが除去された後、ドライエッチング工程によって、チャンネル部のソース／ドレ－パターン及びオーミック接触層12がエッチングされる。これによって、チャンネル部の活性層10が露出されるとともに、ソース電極16とドレイン電極18は分離される。

#### 【0023】

続いて、ストリップ工程によって、ソース／ドレインパターン上に残っているフォトレジストパターンが除去される。

10

20

30

40

50

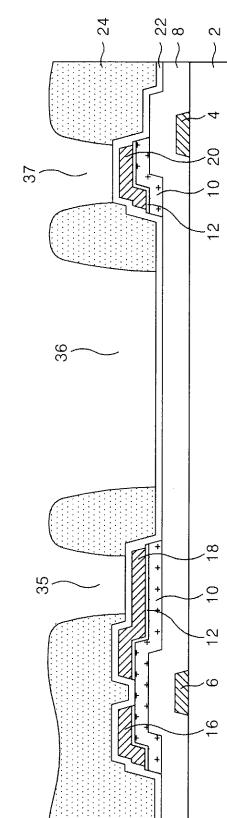

## 【0024】

図2cを参照すると、ソース／ドレインパターンが形成されたゲート絶縁膜8上に、第1保護膜22が形成されるとともに、その上に第3マスク工程で第1及び第2初期コンタクトホール35,37と透過ホール36とを有し、エンボッシング形状の表面を有する有機膜24が形成される。

## 【0025】

ソース／ドレインパターンが形成されたゲート絶縁膜8上に、第1保護膜22と有機膜24が順に形成される。第1保護膜22としては、ゲート絶縁膜8のような無機絶縁物質が、有機膜24としては、アクリルなどの感光性有機物質が利用される。

## 【0026】

次に、第3マスクを利用したフォトリソグラビ工程で有機膜24をパターニングすることにより、第3マスクの透過部に対応して、有機膜24を貫通する第1及び第2オープンホール35,37と透過ホール36とが形成される。この際に、第3マスクは、透過部を除いた残り部分が、遮断部と回折露光部が繰り返す構造を有し、これに対応して、残っている有機膜24は、段差を有する遮断領域(突出部)及び回折露光領域(溝部)が繰り返す構造にパターニングされる。続いて、突出部及び溝部が繰り返す有機膜24を焼成することにより、有機膜24の表面がエンボッシング形状を有するようになる。

## 【0027】

図2dを参照すると、エンボッシング形状を有する有機膜24の上に、第2保護膜26が形成されるとともに、その上に第4マスク工程で反射電極28が形成される。

## 【0028】

エンボッシング表面を有する有機膜24上に、第2保護膜26及び反射金属層がエンボッシング形状を維持して積層される。第2保護膜26としては、第1保護膜22のような無機絶縁物質が、反射金属層としては、AlNdなどの反射率の高い金属が利用される。

## 【0029】

続いて、第4マスクを利用したフォトリソグラビ工程及びエッチング工程で反射金属層がパターニングされることにより、各画素ごとに独立した、有機膜24の第1及び第2オープンホール35,37と透過ホール36でオープンされた反射電極28が形成される。

## 【0030】

図2eを参照すると、第5マスク工程で反射電極28を覆う第3保護膜30が形成されるとともに、第1乃至第3保護膜22,26,30を貫通する第1及び第2コンタクトホール34,38が形成される。

## 【0031】

反射電極28を覆う第3保護膜30が形成されるとともに、第5マスクを利用したフォトリソグラビ工程及びエッチング工程により、有機膜24の第1及び第2オープンホール35,37にて第1乃至第3保護膜22,26,30を貫通する第1及び第2コンタクトホール34,38が形成される。第1及び第2コンタクトホール34,38はそれぞれドレイン電極18とストリッジ上部電極20とを露出させる。第3保護膜30としては、第2保護膜26のように、無機絶縁物質が利用される。

## 【0032】

図2fを参照すると、第6マスク工程を利用して、第3保護膜30上に画素電極32が形成される。

## 【0033】

第3保護膜30上にスパッタリングなどの蒸着方法によって透明導電層が形成されるとともに、第6マスクを利用したフォトリソグラビ工程とエッチング工程により、透明導電層がパターニングされて、各画素領域に画素電極32が形成される。画素電極32は第1及び第2コンタクトホール34,38を通じてドレイン電極18及びストリッジ上部電極20と接続される。透明導電層としては、インジウム朱錫酸化物(Indium Tin Oxide: ITO)などが利用される。

## 【0034】

10

20

30

40

50

このように、従来の半透過型薄膜トランジスター基板では、6マスク工程で形成されるため、製造工程が複雑であるという欠点がある。また、従来の半透過型薄膜トランジスター基板としは、画素電極32と、ドレイン電極18及びストリッジ上部電極20各々との接続のために、第1及び第2コントラクトホール34,38のマージンを充分に確保しなければならない。このため、透過領域の開口率が減少するという問題がある。

【発明の開示】

【発明が解決しようとする課題】

【0035】

本発明の目的は、工程を単純化しながらも透過領域の開口率を増大し得る液晶表示装置及びその製造方法を提供することである。

10

【課題を解決するための手段】

【0036】

前記目的を達成するために、本発明の実施形態の液晶表示装置は、第1及び第2基板と；透明な第1導電層と不透明な第2導電層とが積層された二重構造にて、前記第1基板上に形成されたゲートラインと；前記ゲートラインの上の第1絶縁膜と；前記ゲートラインと交差して画素領域を画成するデーターラインと；前記ゲートライン及びデーターラインと接続された薄膜トランジスターと；前記画素領域に前記第1導電層で形成された画素電極と；前記ゲートラインと前記第1絶縁膜との間にはさみ込まれ、かつ重なって、スリッジキャパシターを形成するストリッジ上部電極と；前記トランジスター上の第2絶縁膜から前記第1絶縁膜まで貫通して前記画素電極を露出させる透過ホールと；前記透過ホールのエッジ部を通じて露出された前記薄膜トランジスターのドレイン電極及びストリッジ上部電極を前記画素電極と接続させる反射電極と；前記ゲートラインの第1導電層から伸長されたゲートペードと；前記第1導電層で形成されデーターリングを通じて前記データーラインと接続されたデーターペードと；前記第1及び第2基板間の液晶層とを備え；前記第1及び第2絶縁膜は前記ゲートペード及びデーターペード領域から除去されるようになっていることを特徴とする。

20

【0037】

本発明の実施形態の液晶表示装置の製造方法は、第1及び第2基板を設ける段階と；第1マスクを利用して透明な第1導電層と不透明な第2導電層とが積層された二重構造を有するゲートライン及びゲート電極と、前記第1導電層を有する画素電極を形成する段階と；前記ライン及び電極らの上に第1絶縁膜を形成する段階と；第2マスクを利用して前記第1絶縁膜の上に半導体パターンを形成すると共に、データーライン、ソース電極、ドレイン電極、ストリッジ上部電極を含むソース／ドレインパターンを形成する段階と；第3マスクを利用して前記ソース／ドレインパターン上に第2絶縁膜を形成し、前記第2絶縁膜から前記第1絶縁膜まで貫通する透過ホールを透過領域に形成する段階と；第4マスクを利用して前記透過ホールを通じて前記ドレイン電極及びストリッジ上部電極を前記画素電極と接続させる反射電極を反射領域に形成する段階と；前記第1及び第2基板の間に液晶層を形成する段階とを含む。

30

【発明の効果】

【0038】

本発明による液晶表示装置及びその製造方法では、二重構造のゲートパターンと、單一層構造の透明導電パターンをハーフトーンマスク(または回折マスク)を利用して、一つのマスク工程で形成することにより、工程を単純化できる。また、ハーフトーンマスク(または回折マスク)工程によって、二重構造ゲートパターンの第1及び第2導電層が階段形態で一定の段差を有するようになるため、第1及び第2導電層の急傾斜によるソース／ドレンパターンの断線を防止し得る。

40

【0039】

また、本発明による液晶表示装置及びその製造方法では、有機膜のパターニングの際、画素電極を露出させる透過ホールを形成し、透過ホールのエッジ部を経由する反射電極でドレイン電極及びストリッジ上部電極を画素電極と接続させる。これによって、工程を一

50

層単純化し得るだけでなく、ドレイン電極及びストリッジ上部電極を画素電極と接続させるための別のコンタクトホールが不要になるので、その分透過領域の開口率を増大し得る。

#### 【0040】

また、本発明による液晶表示装置及びその製造方法は、反射電極と同一の金属のコンタクト電極により、互いに異なる層に形成されたデーターリンク及びデーターラインを接続させるとともに、静電気防止素子の薄膜トランジスターを相互接続させる。これによって、4マスク工程で工程を単純化し得る。

#### 【0041】

加えて、本発明による液晶表示装置及びその製造方法は、反射電極及びコンタクト電極を二重構造に形成し、低コンタクト抵抗を有する第1反射金属層が透明導電層と接続させることによって、コンタクト抵抗を一層減少させることができる。

#### 【発明を実施するための最良の形態】

#### 【0042】

以下、図3乃至図18bを参照して本発明の望ましい実施例について説明する。

#### 【0043】

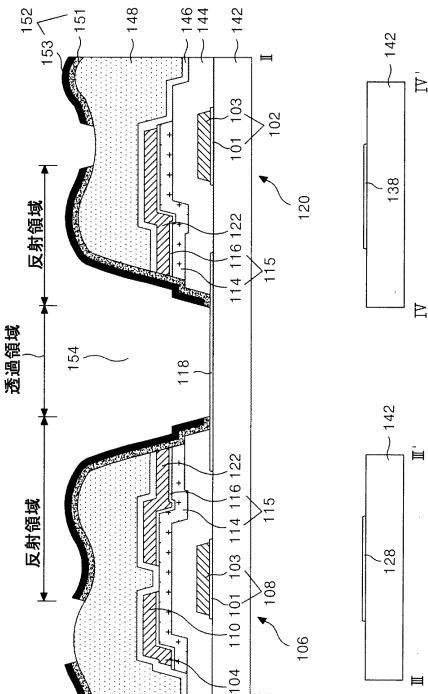

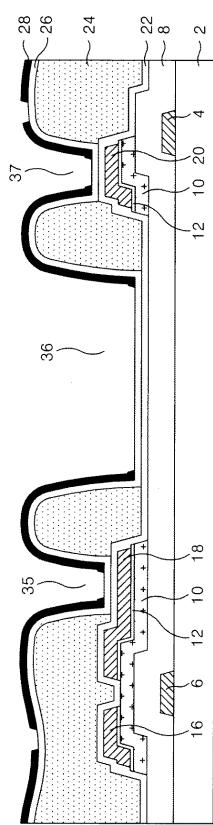

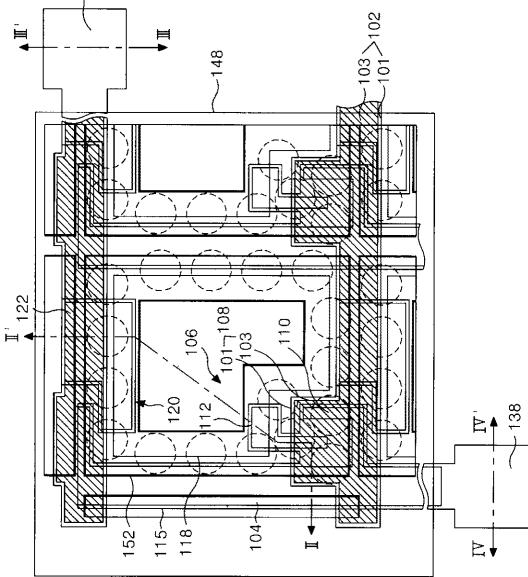

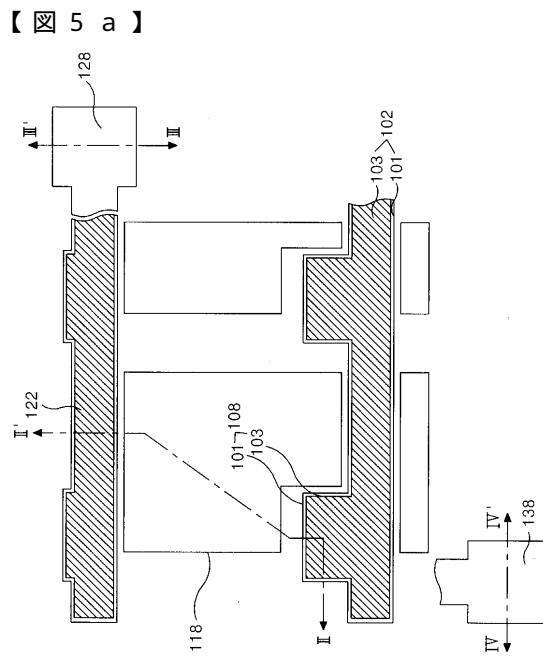

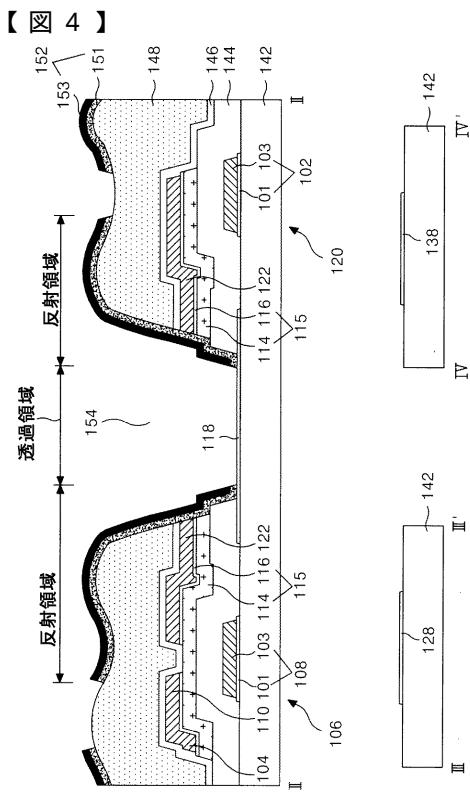

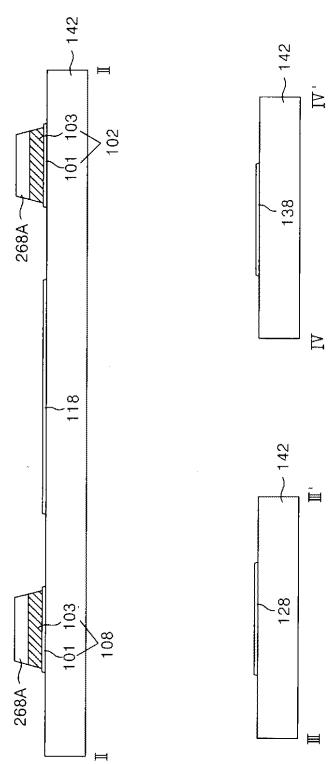

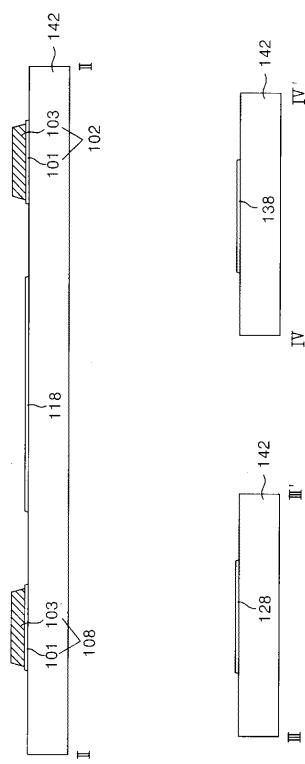

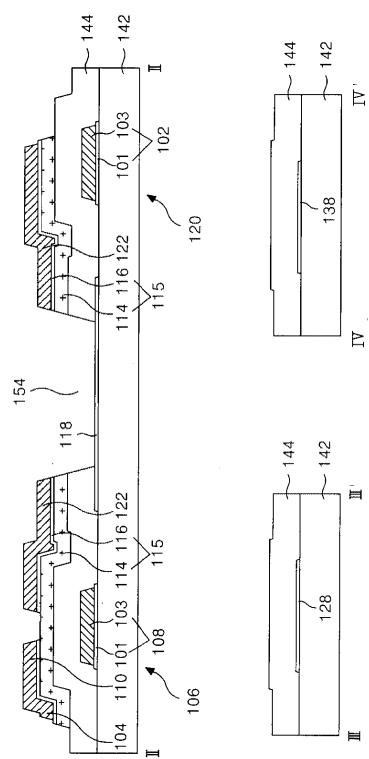

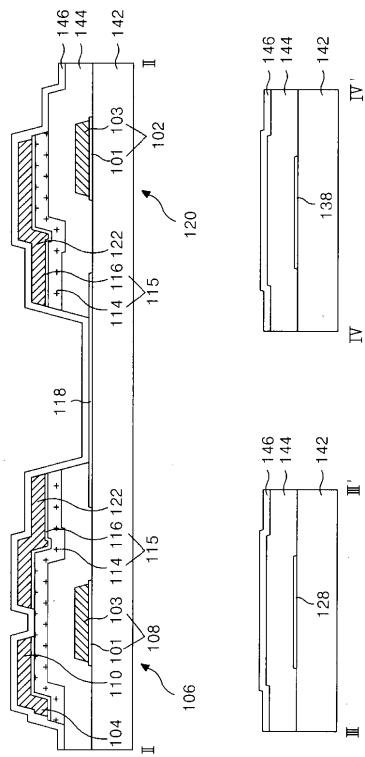

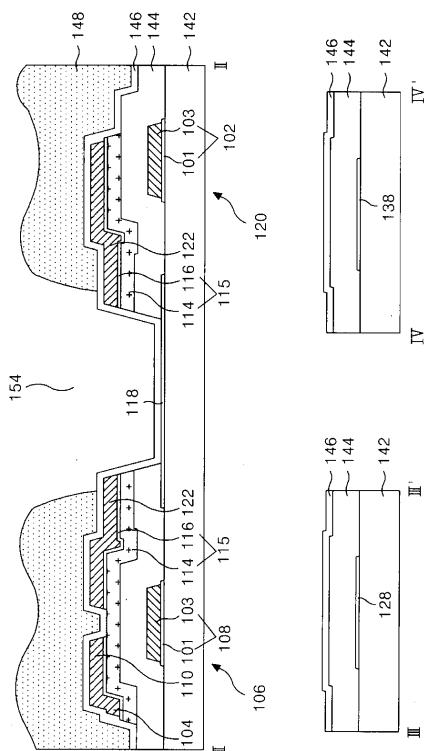

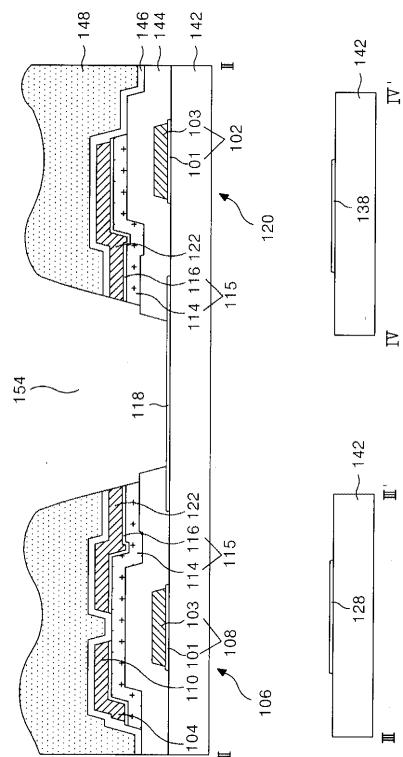

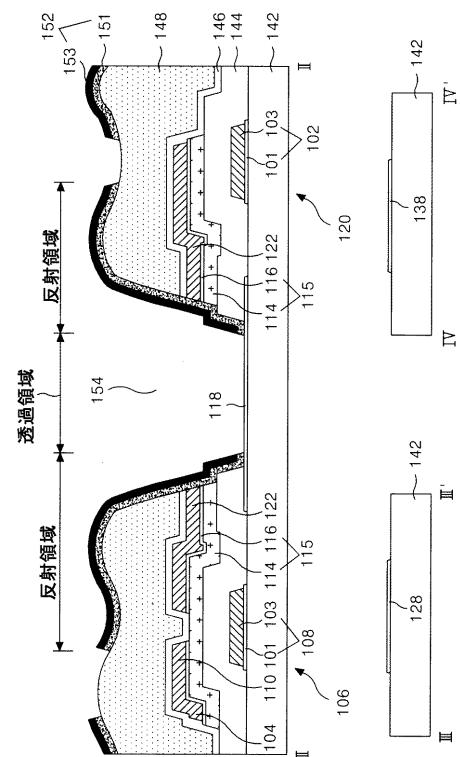

図3は本発明の実施形態の半透過型薄膜トランジスター基板を図示した平面図であり、図4は図3に図示された半透過型薄膜トランジスター基板をII-II'、III-III'、IV-IV'線に沿って切断して図示した断面図である。

#### 【0044】

図3と図4に図示された半透過型薄膜トランジスター基板は、下部基板142上にゲート絶縁膜144を間にさまれて交差して画素領域を画成するゲートライン102及びデーターライン104、そのゲートライン102及びデーターライン104と接続された薄膜トランジスター106、各画素の反射領域に形成された反射電極152、各画素領域に形成され、反射電極152を通じて薄膜トランジスター106と接続された画素電極118を備えている。そして、半透過型薄膜トランジスター基板は、反射電極153を通じて画素電極118に接続されたストリッジ上部電極122と前端ゲートライン102が重なって形成されたストリッジキャパシター120、ゲートライン102と接続されたゲートペード128、データーライン104と接続されたデーターペード138を備える。このような半透過型薄膜トランジスター基板で各画素領域は反射電極152が形成された反射領域と反射電極152が形成されない透過領域に区分される。

#### 【0045】

薄膜トランジスター106はゲートライン102と接続されたゲート電極108、データーライン104と接続されたソース電極110、ソース電極110と向かい合う画素電極118と接続されたドレイン電極112、ゲート絶縁膜144の間にさみ込まれ、かつゲート電極108と重なってソース電極110とドレイン電極112の間にチャンネルを形成する活性層114、ソース電極110及びドレイン電極112とのオーミック接触のためにチャンネル部を除いた活性層114上に形成されたオーミック接触層116を備える。このような薄膜トランジスター106はゲートライン102のスキャン信号に応答してデーターライン104上のビデオ信号が画素電極32, 118に印加されて維持されるようにする。

#### 【0046】

ここで、ゲートライン102及びゲート電極108は透明導電層101で成る第1導電層101と、その上に金属層で成る第2導電層103が積層された二重構造を有する。

#### 【0047】

そして、活性層114及びオーミック接触層116を含む半導体パターン115はデーターライン104とも重なるように形成される。

#### 【0048】

反射電極152は各画素の反射領域に形成されて外部光を反射させる。このような反射電極152は、その下の有機膜148の形状によってエンボッシング形状を有するようになることにより散乱効果で反射効率を増大させる。反射電極152は第1及び第2反射金属層151, 153が積層された二重構造を有する。第1反射金属層151には透明導電層である画素電極118との

10

20

30

40

50

コンタクト抵抗を減少させることができるMoなどのような金属が、第2反射金属層153にはAlNdなどのように反射率が高い金属が利用される。

#### 【0049】

画素電極118は、各画素領域に形成され透過ホール154のエッジ部を経由する反射電極152を通じてドレイン電極112と接続される。画素電極118は、ゲートライン102の第1導電層101のような透明導電層で形成され、透過領域で透過ホール154を通じて露出される。

#### 【0050】

画素電極118は、薄膜トランジスターを通じて供給された画素信号によりカラーフィルター基板(図示なし)の共通電極と電位差を発生させる。この電位差により誘電異方性を有する液晶が回転して反射領域と透過領域夫々の液晶層を経由する光の透過率が調節されるため、前記ビデオ信号によって輝度が異なるようになる。

#### 【0051】

透過ホール154は、透過領域で画素電極118上のゲート絶縁膜144と、薄膜トランジスター106上の保護膜146、有機膜148を貫通して形成される。これによって、反射領域と透過領域で液晶層を経由する光経路の長さが同一になるので、反射モードと透過モードの透過効率が同一になるようになる。

#### 【0052】

ストリッジキャパシター120は、画素電極118と接続されたストリッジ上部電極122がゲート絶縁膜144を間に置き前端ゲートライン102と重なって形成される。ストリッジ上部電極122は透過ホール154のエッジ部を経由する反射電極152を通じて画素電極118と接続され、ストリッジ上部電極122の下には半導体パターン115が更に重なる。

#### 【0053】

ゲートライン102はゲートペード128を通じてゲートドライバー(図示なし)と接続される。ゲートペード128はゲートライン102の第1導電層101が延長されて形成される。

#### 【0054】

データーライン104は、データーペード138を通じてデータードライバー(図示なし)と接続される。データーペード138はゲートペード128のように第1導電層101で形成される。このようなデーターペード138は別のコンタクト電極(図示せず)を通じてデーターライン104と接続される。

#### 【0055】

ゲートペード128及びデーターペード138が形成されたペード領域では、ゲート絶縁膜144、保護膜146、有機膜148が除去される。

#### 【0056】

このように、本発明の実施形態の半透過型薄膜トランジスター基板では、透過ホール154のエッジ部を経由する反射電極152を通じて画素電極118がドレイン電極112及びストリッジ上部電極122と接続される。これによって、画素電極118とドレイン電極112及びストリッジ上部電極122との接続のための別のコンタクトホールが不要になるため、その分だけ透過領域の開口率を増大し得るようになる。

#### 【0057】

そして、反射電極152のうち、透明導電層とのコンタクト抵抗の少ない第1反射金属層151が画素電極118と接続されるようになる。これによって、第1反射金属層151にはMoを、第2反射金属層153にはAlNdを、画素電極118にはITOを利用する場合、AlNdとITOはMoを通じてのみ接続するようになるため、Al2O3生成によるAlNdとITOとのコンタクト抵抗増加を防止することができるようになる。

#### 【0058】

このような構成を有する本発明の実施形態の薄膜トランジスター基板は次の通り5マスク工程で形成される。

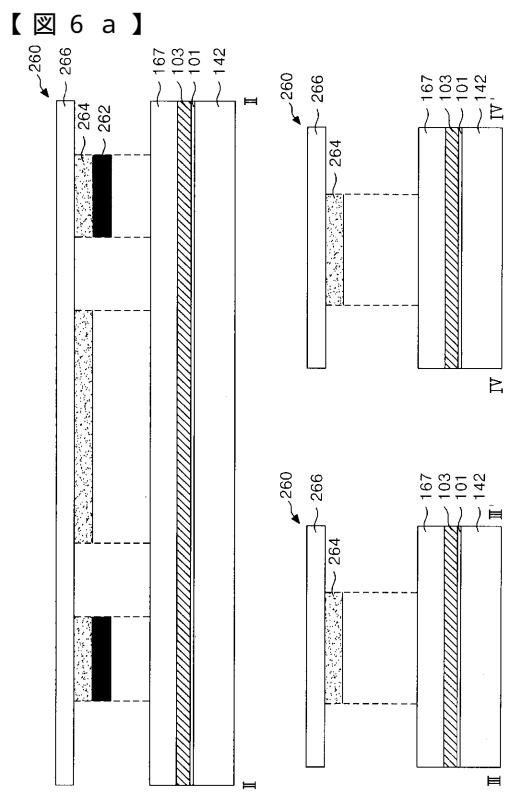

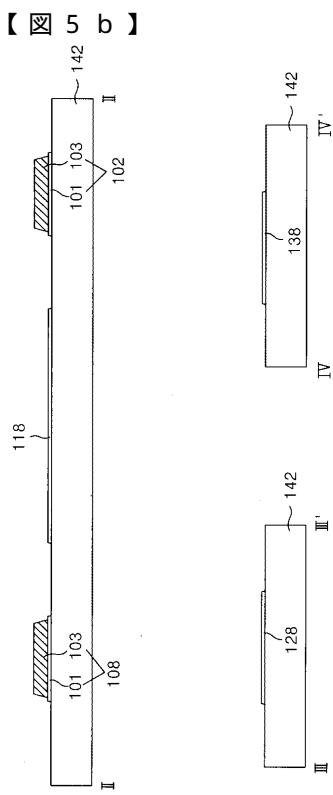

#### 【0059】

図5a及び図5bは、本発明の実施形態の半透過型薄膜トランジスター基板の製造方法のうち、第1マスク工程を説明するための平面図と断面図であり、図6a乃至図6eは第1マスク工

10

20

30

40

50

程を具体的に説明するための断面図である。

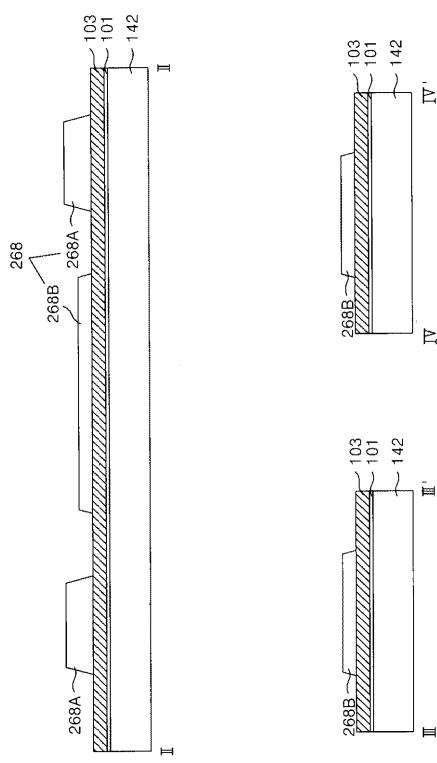

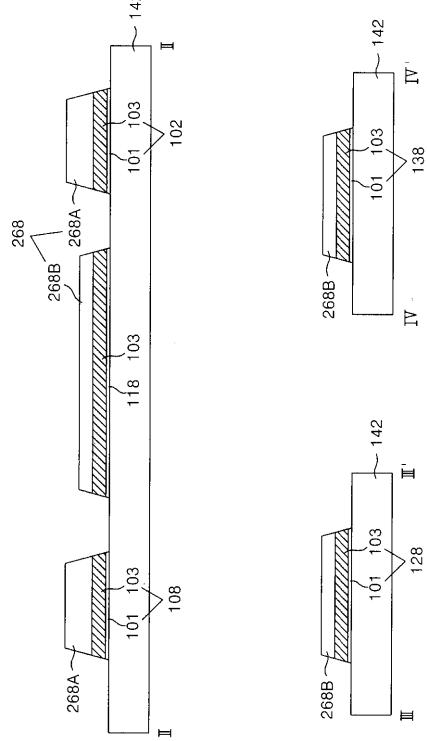

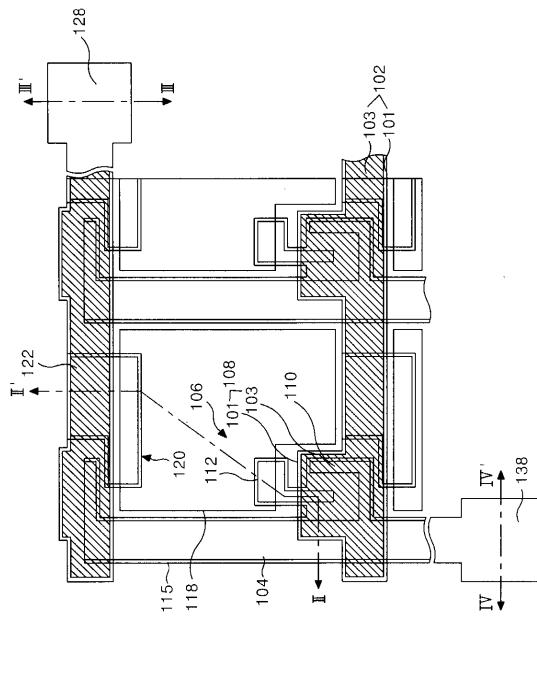

#### 【0060】

第1マスク工程において、下部基板142上にゲートライン102、ゲートライン102と接続されたゲート電極108を含むゲートパターンと、ゲートペード128、データーペード138、画素電極118を含む透明導電パターンとが形成される。ゲートパターンは、第1及び第2導電層101,103が積層された二重構造で、透明導電パターンはゲートパターンの第1導電層101と同一の単一層で形成される。このように二重構造を有するゲートパターンと、単一層構造を有する透明導電パターンは、ハーフトーン(Half Tone)マスクまたは回折マスクを利用することにより一つのマスク工程で形成される。以下ではハーフトーンマスクを利用した場合だけを例示して説明することにする。

10

#### 【0061】

具体的に、図6aに図示されたように、下部基板142の上にスパッタリング方法などの蒸着方法により、第1及び第2導電層101,103が積層されるとともに、その上にフォトレジスト167が形成される。第1導電層101としては、ITO、T0、TZ0などのような透明導電物質が、第2導電層103としては、Mo、Ti、Cu、Al(Nd)系などの金属物質が利用される。

#### 【0062】

次に、ハーフトーンマスク260を利用してフォトリソグラフィ工程で、フォトレジスト167を露光及び現象することにより、図6bに図示されるように、段差を有するフォトレジストパターン168が形成される。

20

#### 【0063】

ハーフトーンマスク260は、透明な石英( $\text{SiO}_2$ ; Quartz)基板266と、その上に形成された遮断層262及び部分透過層264を備える。部分透過層264と重なる遮断層262はゲートパターンが形成される領域に位置して紫外線UVを遮断することにより現象後に第1フォトレジストパターン268Aが残るようにする。遮断層262と重ならない部分の透過層264は透明導電パターンが形成される領域に位置して紫外線UVを部分的に透過させることにより現象後に第1フォトレジストパターン268Aより薄い第2フォトレジストパターン268Bが残るようにする。このために、遮断層262はCr、Cr<sub>0</sub>xなどのような金属で、部分透過層264はMoSi<sub>x</sub>などで形成される。

#### 【0064】

続いて、段差を有するフォトレジストパターン268を利用してエッチング工程において、第1及び第2導電層101,103をパターニングすることにより、図6cに図示される通り、二重構造のゲートパターンと、その上に第2導電層103が残っている透明導電パターンが形成される。

30

#### 【0065】

次に、酸素( $\text{O}_2$ )プラズマを利用してアッシング工程により、フォトレジストパターン268をアッシングすることにより、図6dに図示されるように、第1フォトレジストパターン268Aは厚さが薄くなり、第2フォトレジストパターン268Bは除去される。そして、アッシングされた第1フォトレジストパターン268Aを利用してエッチング工程で透明導電パターン上の第2導電層103が除去される。この際、アッシングされた第1フォトレジストパターン268Aに従ってパターニングされた第2導電層103の両側部がもう一度更にエッチングされることによりゲートパターンの第1及び第2導電層101,103は階段形態で一定の段差を有するようになる。これによって、第1及び第2導電層101,103の側面部が高い急傾斜を有する場合、その上で発生し得るソース/ドレイン金属層の断線不良を防止できることとなる。

40

#### 【0066】

そして、ストリップ工程でゲートパターン上に残存していた第1フォトレジストパターン268Aが図6eに図示される通りに除去される。

#### 【0067】

図7a及び図7bは、本発明の実施形態の薄膜トランジスター基板の製造方法のうち、第2マスク工程を説明するための平面図と断面図であり、図8a乃至図8eは、第2マスク工程を

50

具体的に説明するための断面図である。

【0068】

ゲートパターンと画素電極118とが形成された下部基板142の上に、ゲート絶縁膜144が形成され、その上に第2マスク工程でデーターライン104、ソース電極110、ドレイン電極112、ストリッジ上部電極122を含むソース／ドレインパターンと、ソース／ドレインパターンの背面に沿って重なる活性層114及びオーミック接触層116を含む半導体パターン115が形成される。このような半導体パターン115とソース／ドレインパターンは回折露光マスクを利用した一つのマスク工程で形成される。

【0069】

具体的に、図8aのように、ゲートパターンが形成された下部基板142の上に、ゲート絶縁膜144、非晶質シリコン層105、不純物( $n+$ または $p+$ )がドーピングされた非晶質シリコン層107、ソース／ドレイン金属層109が順に形成される。例えば、ゲート絶縁膜144、非晶質シリコン層105、不純物がドーピングされた非晶質シリコン層107はPECVD方法により、ソース／ドレイン金属層109はスパッタリング方法により形成される。ゲート絶縁膜144には酸化シリコンSiO<sub>x</sub>、窒化シリコンSiN<sub>x</sub>などの無機絶縁物質が、ソース／ドレイン金属層109にはCr、Mo、MoW、Al/Cr、Cu、Al(Nd)、Al/Mo、Al(Nd)/Al、Al(Nd)/Cr、Mo/Al(Nd)/Mo、Cu/Mo、Ti/Al(Nd)/Tiなどが利用され、二重層が例えばAl/Crである場合、Crを先ず形成した後にAlを形成することとなる。

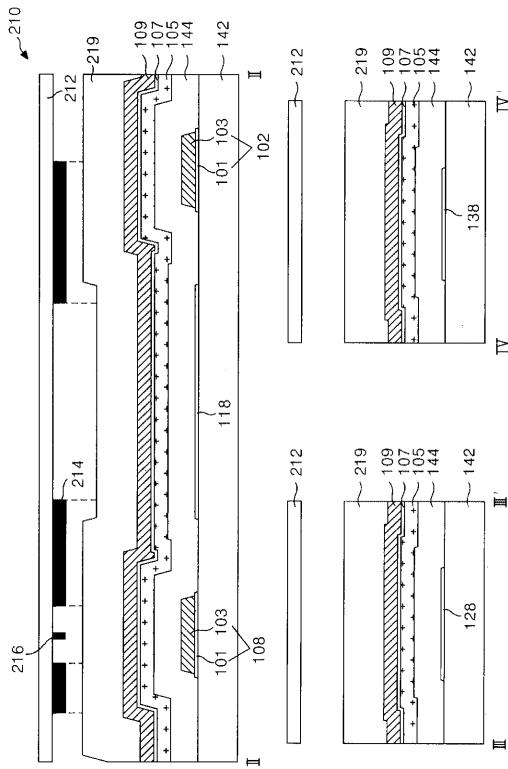

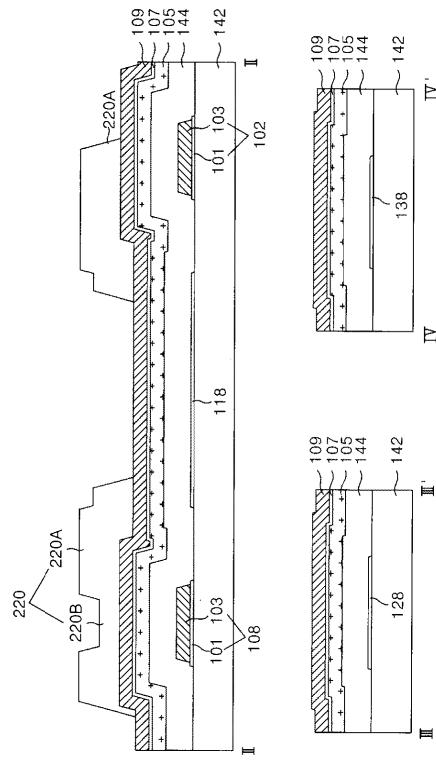

そして、ソース／ドレイン金属層109上にフォトレジスト219が塗布された後、回折露光マスク310を利用してフォトリソグラビ工程でフォトレジスト219を露光及び現象することにより、図8bに図示される通りに、段差を有するフォトレジストパターン220が形成される。

【0070】

回折露光マスク210は、透明な石英基板212と、その上にCr、CrO<sub>x</sub>などの金属層で形成された遮断層214及び回折露光用スリット216を備える。遮断層214は半導体パターン及びソース／ドレインパターンが形成される領域に位置して紫外線を遮断することにより現象後に第1フォトレジストパターン220Aが残るようにする。回折露光用スリット216は薄膜トランジスターのチャンネルが形成される領域に位置して紫外線を回折させることにより現象後に第1フォトレジストパターン220Aより薄い第2フォトレジストパターン220Bが残るようにする。

【0071】

続いて、段差を有するフォトレジストパターン220を利用してエッチング工程において、ソース／ドレイン金属層109がパターニングされることにより、図8cに図示されるように、ソース／ドレインパターンと、その下の半導体パターン115とが形成される。この場合、ソース／ドレインパターンのうちソース電極110とドレイン電極112は一体化された構造を有する。

【0072】

次に、酸素(O<sub>2</sub>)プラズマを利用してアッシング工程によってフォトレジストパターン220をアッシングすることにより、図8dに図示されたように、第1フォトレジストパターン220Aは薄くなり、第2フォトレジストパターン220Bは除去される。そして、アッシングされた第1フォトレジストパターン220Aを利用してエッチング工程において、第2フォトレジストパターン220Bの除去で露出されたソース／ドレインパターンと、その下のオーミック接触層116が除去されることによりソース電極110とドレイン電極112は分離され活性層114が露出される。これによって、ソース電極110とドレイン電極112の間には活性層114から成るチャンネルが形成される。この際に、アッシングされた第1フォトレジストパターン220Aに従ってソース／ドレインパターンの両側部が一度更にエッチングされることによりソース／ドレインパターンと半導体パターン115は階段形態で一定の段差を有するようになる。

【0073】

そして、ストリップ工程でソース／ドレインパターンの上に残存していた第1フォトレ

10

20

30

40

50

ジストパターン220Aが図8eに示す通り除去される。

【0074】

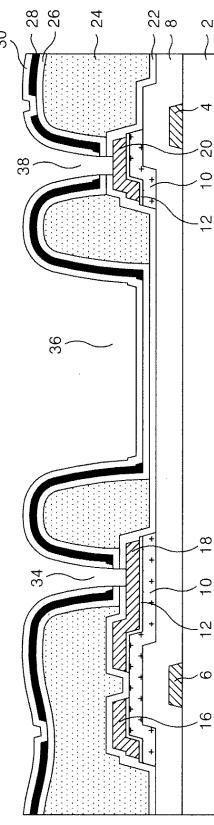

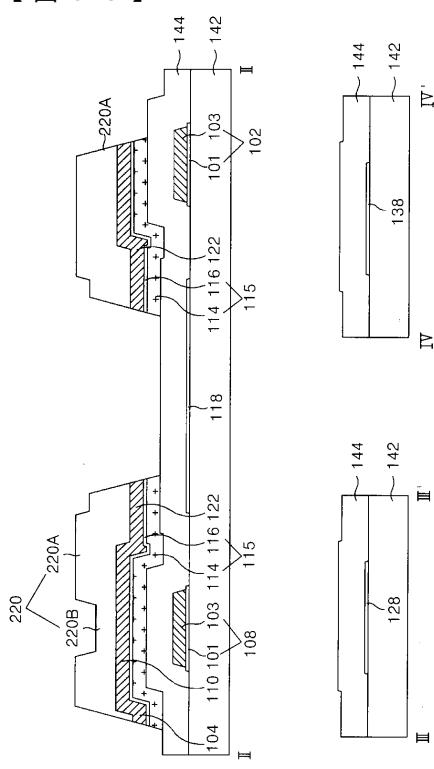

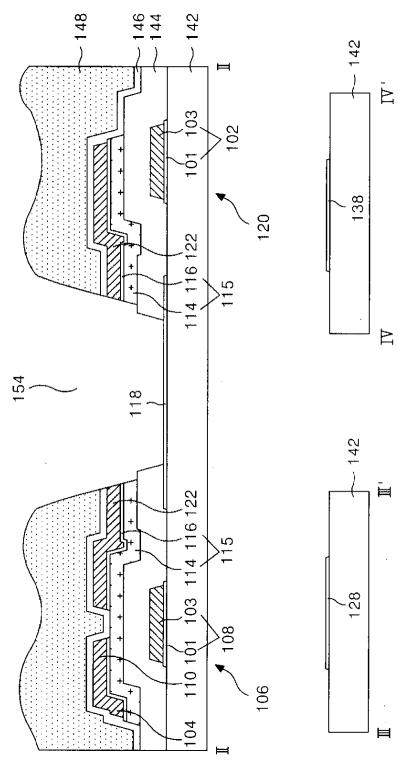

図9a及び図9bは、本発明の実施形態の薄膜トランジスター基板の製造方法のうち、第3マスク工程を説明するための平面図と断面図であり、図10a乃至図10cは、第3マスク工程を段階的に説明するための断面図である。

【0075】

第3マスク工程でソース／ドレインパターンが形成されたゲート絶縁膜144上に透過領域で透過ホール154を有する保護膜146及び有機膜148が形成される。

【0076】

図10aを参照すると、ソース／ドレインパターンが形成されたゲート絶縁膜144の上に、PECVDなどの蒸着方法で保護膜146が形成される。保護膜146としては、ゲート絶縁膜144のような無機絶縁物質が利用される。10

【0077】

図10bを参照すると、反射領域でエンボッシング表面を有し、透過領域で透過ホール154を有する有機膜148が保護膜146の上に形成される。具体的には、有機膜148はアクリルなどのような感光性有機物質をスピンドルコーティング方法で保護膜146上にコーティングすることにより形成される。

【0078】

次に、第3マスクを利用したフォトリソグラビ工程で有機膜148をパターニングすることにより、第3マスクの透過部に対応して、透過領域で有機膜148を貫通する透過ホール154が形成され、ゲートペード128及びデータペード138が形成されたペード領域の有機膜148が除去される。20

【0079】

また、第3マスクで透過部を除いた残り部分が、遮断部と回折露光部(または半透過部)が繰り返えす構造を有し、これに対応して、有機膜148は反射領域で段差を有する遮断領域(突出部)及び回折露光領域(溝部)が繰り返す構造でパターニングされる。続いて、突出部及び溝部が繰り返えされた有機膜148を塑性することにより反射領域で有機膜148の表面はエンボッシング現象を有するようになる。

【0080】

図10cを参照すると、有機膜148をマスクにして、その下の保護膜146及びゲート絶縁膜144をパターニングすることにより、透過ホール154はゲート絶縁膜144まで貫通するようになり、ペード領域の保護膜146及びゲート絶縁膜144が除去される。この場合、透過ホール154を通じて露出されたドレイン電極112及びストリッジ上部電極122とその下の半導体パターン115もエッチングされる。ここで、エッチング速度の差異に因りドレイン電極112及びストリッジ上部電極122とその下の半導体パターン115よりゲート絶縁膜144のエッジ部がやや突出された構造を有するようになる。このような透過ホール154は画素電極118の第2導電層103を露出させ、そのエッジ部はドレイン電極112及びストリッジ上部電極122の側面を露出させる。30

【0081】

図11a及び図11bは、本発明の実施形態の薄膜トランジスター基板の製造方法のうち第4マスク工程を説明するための平面図と断面図である。40

【0082】

第4マスク工程において各画素の反射領域に反射電極153が形成される。

【0083】

具体的に、エンボッシング表面を有する有機膜148の上に反射金属層がエンボッシング形状を維持して形成される。反射金属層はMoなどのように画素電極118とのコンタクト抵抗の少ない第1反射金属層151と、AlNなどのように反射率の高い第2反射金属層153が積層された二重構造に形成される。続いて、第4マスクを利用したフォトリソグラビ工程及びエッチング工程で、第1及び第2反射金属層151, 153がパターニングされることにより、各画素の反射領域ごとに反射電極152が形成される。このような反射電極152は透過ホール1550

4のエッジ部を経由して、ドレイン電極112と画素電極118とを接続させて、ストリッジ上部電極122と画素電極118とを接続させる。これによって、画素電極118とドレイン電極112及びストリッジ上部電極122との接続のための別のコンタクトホールが不要になるので、透過領域の開口率を増大させることができるようになる。また、反射電極152のうち第1反射金属層151が透明導電層である画素電極118と接続されるため、コンタクト抵抗を減少させることができるようになる。

#### 【0084】

このように、本発明の実施形態の半透過型薄膜トランジスター基板の製造方法は、画素電極118をハーフトーンまたは回折マスクを利用してゲートパターンのように形成し、反射電極152に画素電極118とドレイン電極112及びストリッジ上部電極122を接続させることにより一つのマスク工程を減らすことができるようになる。10

#### 【0085】

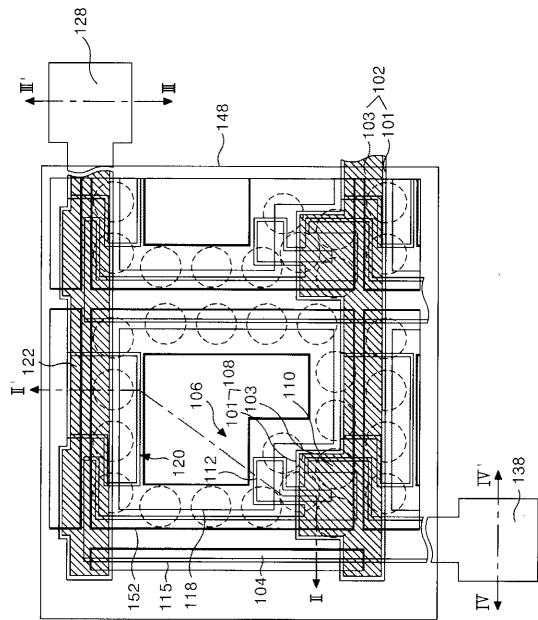

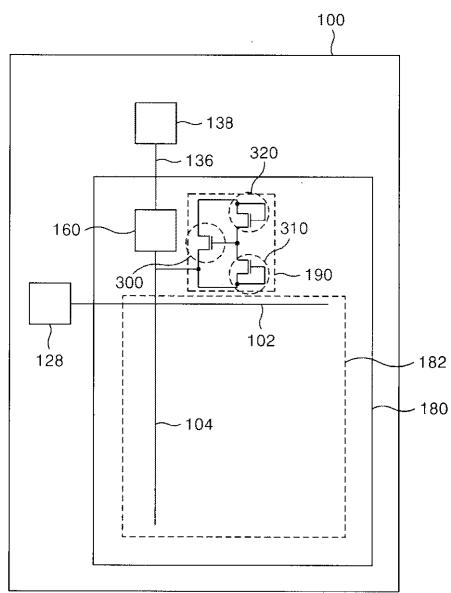

図12は、本発明の実施形態の半透過型薄膜トランジスター基板の周辺部を概略的に図示したものである。

#### 【0086】

図12に図示された半透過型薄膜トランジスター基板100は、ゲートペード128と同一層に形成されたデーターペード138をデーターライン104と接続させるためのコンタクト電極160を備える。言い換えると、コンタクト電極160はデーターペード138から伸長されたデーターリンク136とデーターライン104を接続させる。ここで、コンタクト電極160をアクティブ領域182に形成される反射電極152と同一の金属層AlNd、AlNd/Moで形成することにする。このようなコンタクト電極160は外部へ露出する場合、酸化作用で腐蝕する問題があるため、シーリング材180により密封される領域、即ち、シーリング材180とアクティブ領域182との間に位置して腐蝕を防止することができる。20

#### 【0087】

また、薄膜トランジスター基板100は、アクティブ領域182に流入される静電気を遮断するための静電気防止素子190を備える。静電気防止素子190は、データーライン104またはゲートライン102と接続され、相互接続関係を有する多数個の薄膜トランジスター300,310,320で構成される。静電気防止素子190は静電気などによる高電圧領域では低いインピーダンスを有するため、過電流が放電されるようにすることにより静電気の流入を遮断し、正常的な駆動環境では高いインピーダンスを有するため、データーライン104またはゲートライン102を通じて供給される駆動信号には影響を与えないようとする。このような静電気防止素子190は薄膜トランジスターら300,310,320を相互接続するために多数のコンタクト電極を必要とする。このような多数のコンタクト電極も反射電極152と同一の金属層(AlNd、AlNd/Mo)で形成されることとなる。これによって、静電気防止素子190もシーリング材180により密封される領域、即ち、シーリング材180とアクティブ領域182との間に形成される。30

#### 【0088】

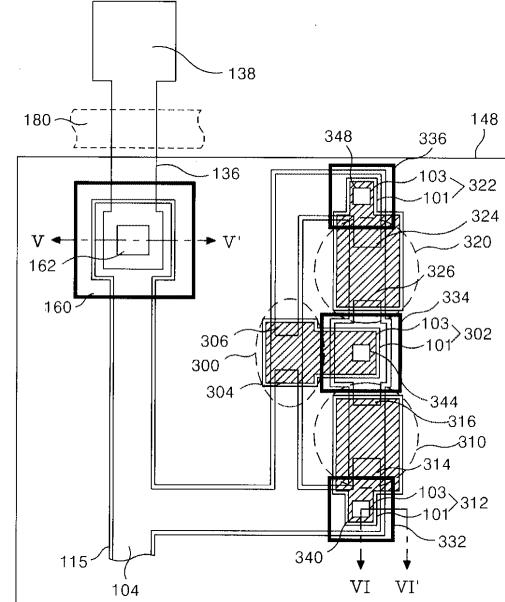

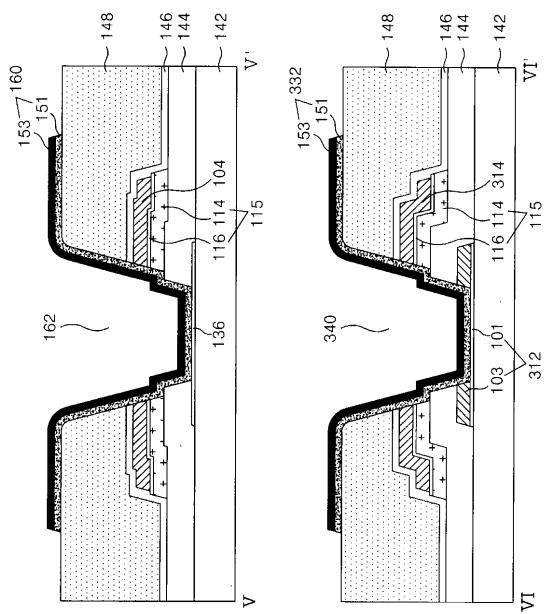

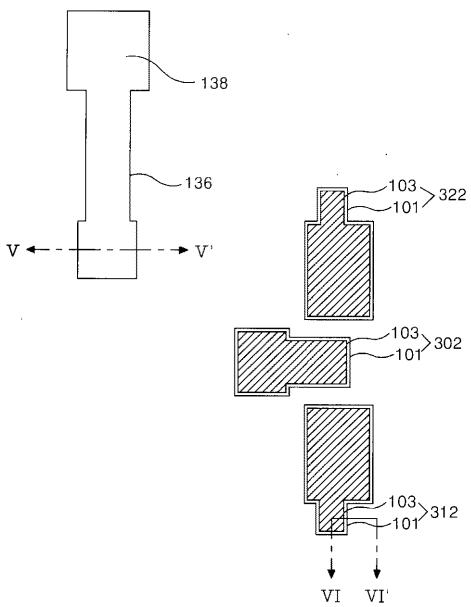

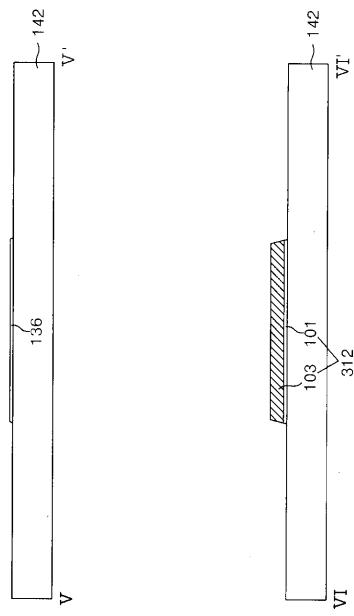

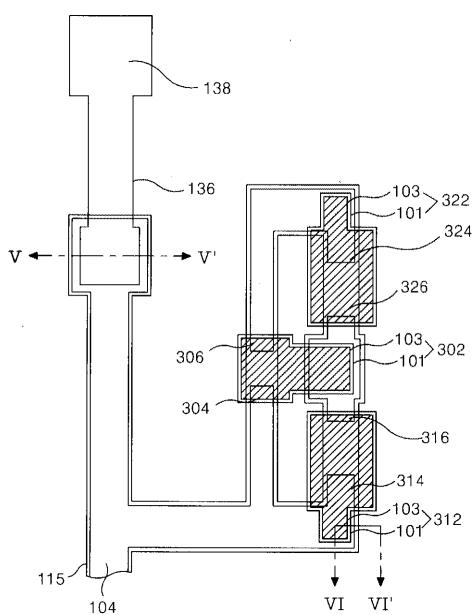

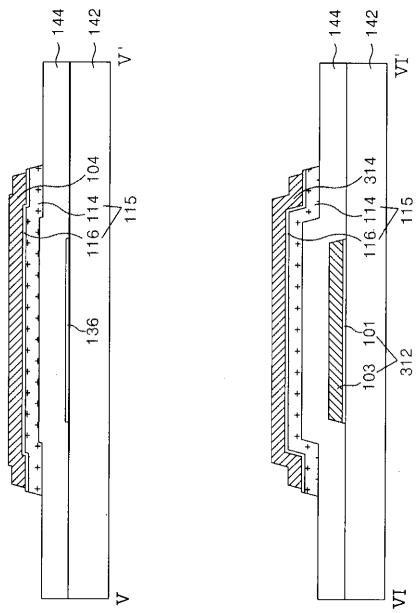

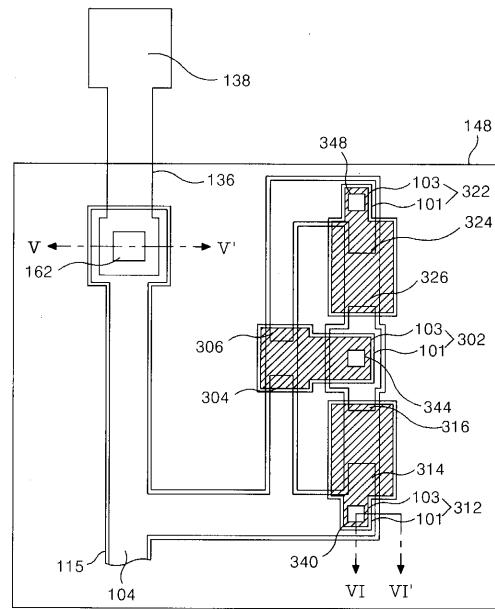

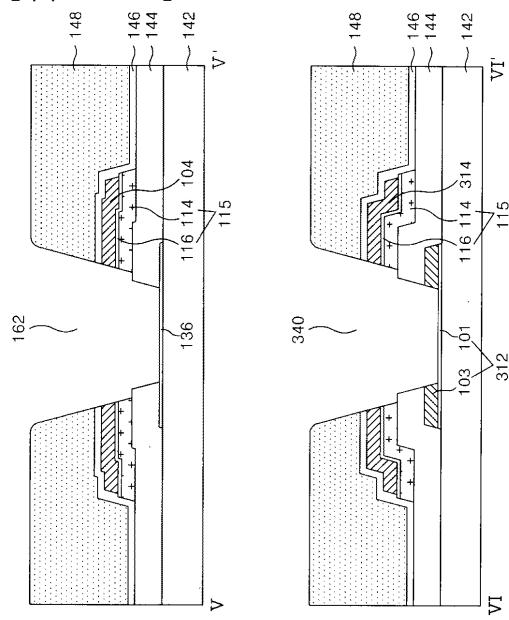

図13は、図12に図示されたデーターライン104と接続されたコンタクト電極160及び静電気防止素子190を具体的に図示した平面図であり、図14は図13に図示された薄膜トランジスター基板をV-V'、VI-VI'線に沿って切断して図示した断面図である。40

#### 【0089】

図13と図14に図示されたデーターリンク136は、データーペード138から延長されてシーリング材180で密封される領域に位置するデーターライン104の末端部分と重なる。データーリンク136はデーターペード138と同様に第1導電層101である透明導電層でのみ形成される。

#### 【0090】

第1コンタクト電極160は、データーリンク136とデーターライン104との重なる部分に形成された第1コンタクトホール162にかけて形成されて、データーライン104及びデーターリンク136を接続させる。第1コンタクトホール162は、有機膜148から保護膜146、データーライン104、半導体パターン115、ゲート絶縁膜144まで貫通してデーターリンク136を露50

出させる。これによって、第1コンタクト電極160は第1コンタクトホール162を通じて露出されたデーターライン104と側面接続され、データーリンク136とは面接続するようになる。データーライン104と接続された静電気防止素子は第2乃至第4薄膜トランジスター300,310,320を備える。

#### 【0091】

第2薄膜トランジスター300は、データーライン104と接続された第2ソース電極304と、その第2ソース電極304と対向する第2ドレイン電極306と、第2ソース及びドレイン電極304,306と半導体パターン115及びゲート絶縁膜144の間にはさみ込まれ、かつ重なる第2ゲート電極302を備える。ここで、第2ゲート電極302は第1及び第2導電層101,103の二重構造を有する。

10

#### 【0092】

第3薄膜トランジスター310は、第2薄膜トランジスターの第2ソース電極304と第2ゲート電極302との間にダイオード型で接続される。このために、第3薄膜トランジスター310は、前記第2ソース電極304と接続された第3ソース電極314と、その第3ソース電極314と対向する第3ドレイン電極316と、その第3ソース及びドレイン電極314,316と半導体パターン115及びゲート絶縁膜144を間に置き重なる第3ゲート電極312とを備える。ここで、第3ゲート電極312は第1及び第2導電層101,103の二重構造を有する。そして、第3ゲート電極312は、第2コンタクトホール340にかけて形成された第2コンタクト電極332を通じて第3ソース電極314と接続される。第2コンタクトホール340は、有機膜148、保護膜146、第3ソース電極314、半導体パターン115、ゲート絶縁膜144、第3ゲート電極312の第2導電層103を貫通して第3ゲート電極312の第1導電層101を露出させる。

20

#### 【0093】

第4薄膜トランジスター320は、前記第2薄膜トランジスターの第2ドレイン電極306と第2ゲート電極302との間にダイオード型で接続される。このために、第4薄膜トランジスター320は、前記第2ドレイン電極306と接続された第4ソース電極324と、その第4ソース電極324と対向された第4ドレイン電極326と、その第4ソース及びドレイン電極324,326と半導体パターン115及びゲート絶縁膜144の間にはさみ込まれ、かつ重なる、第4ゲート電極322とを備える。ここで、第4ゲート電極322は第1及び第2導電層101,103の二重構造を有する。第4ドレイン電極326は、第3ドレイン電極316と接続され、第3コンタクトホール344に亘って形成された第3コンタクト電極334を通じて第2ゲート電極302と接続される。また、第4ゲート電極322は第4コンタクトホール348に亘って形成された第4コンタクト電極336を通じて第4ソース電極324と接続される。第3コンタクトホール344は、有機膜148、保護膜146、第4ドレイン電極326、半導体パターン115、ゲート絶縁膜144、第2ゲート電極302の第1導電層103を貫通して形成され、第4コンタクトホール348は有機膜148、保護膜146、第4ソース電極324、半導体パターン115、ゲート絶縁膜144、第4ゲート電極322の第1導電層103を貫通して形成される。

30

#### 【0094】

ここで、第1乃至第4コンタクト電極160,332,334,336は前述した通り、反射電極152と共に第1及び第2反射金属層151,153が積層された二重構造を有する。これによって、第1乃至第4コンタクト電極160,332,334,336の第1反射金属層151が透明導電層である第1導電層103と接続されるため、コンタクト抵抗を減少させることができる。

40

#### 【0095】

このような構造を有する半透過型薄膜トランジスター基板は、前述した通り、4マスク工程で形成される。これを図15a乃至図19bを参照して説明する。

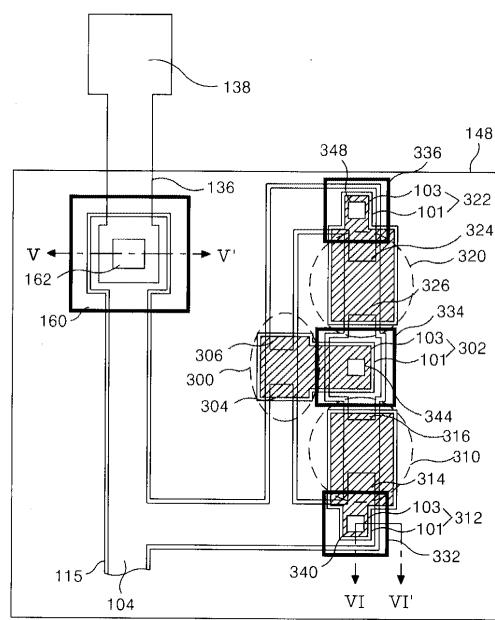

#### 【0096】

図15a及び図15bを参照すると、第1マスク工程で下部基板142上にデーターペード138と共にデーターリンク136、第2乃至第4ゲート電極302,312,322を含むゲートパターンが形成される。ここで、データーペード138及びデーターリンク136は、第1導電層101である透明導電層だけで形成され、第2乃至第4ゲート電極302,312,322を含むゲートパターンは第1及び第2導電層101,103が積層された二重構造を有する。このような第1マスク工程は、図5a

50

乃至図6eで前述した通り、ハーフトーンマスク(または回折マスク)を利用する。

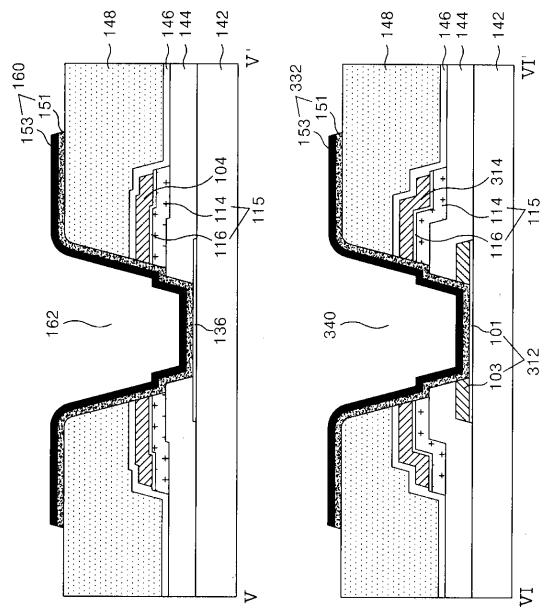

**【0097】**

図16a及び図16bを参照すると、第2マスク工程でゲート絶縁膜144と、活性層114及びオーミック接触層116を含む半導体パターン115と、データーライン104、第2乃至第4ソース電極304,314,324、第2乃至第4ドレイン電極306,316,326を含むソース／ドレインパターンが形成される。このような第2マスク工程は、図7a乃至図8eで前述した通りである。

**【0098】**

図17a及び図17bを参照すると、第3マスク工程で保護膜146及び有機膜148が形成され、有機膜148からゲート絶縁膜144まで貫通する第1コンタクトホール162と、第2乃至第3ゲート電極の第2導電層103まで貫通する第2乃至第4コンタクトホール340,344,348が形成される。このような第3マスク工程は図9a乃至図10cで前述した通りである。この場合、有機膜148はペード領域では除去され、画素領域のように反射電極152が形成されない部分ではエンボッシング表面を有しない。

**【0099】**

図18a及び図18bを参照すると、第4マスク工程で反射電極152と同一である二重構造の第1乃至第4コンタクト電極160,332,334,336が形成される。このような第4マスク工程は、図11a及び図11bで前述した通りである。

**【0100】**

以上説明した内容を通じて、当業者であれば本発明の技術思想を逸脱しない範囲で多様な変更及び修正が可能であることが分る。従って、本発明の技術的範囲は明細書の詳細な説明に記載された内容に限定されるものではなく、特許請求の範囲の記載により定められるべきものである。

**【図面の簡単な説明】**

**【0101】**

【図1】従来の半透過型液晶パネルの一部分を図示した断面図である。

【図2a】図1に図示された半透過型薄膜トランジスター基板の製造法を段階的に説明するための断面図である。

【図2b】図1に図示された半透過型薄膜トランジスター基板の製造法を段階的に説明するための断面図である。

【図2c】図1に図示された半透過型薄膜トランジスター基板の製造法を段階的に説明するための断面図である。

【図2d】図1に図示された半透過型薄膜トランジスター基板の製造法を段階的に説明するための断面図である。

【図2e】図1に図示された半透過型薄膜トランジスター基板の製造法を段階的に説明するための断面図である。

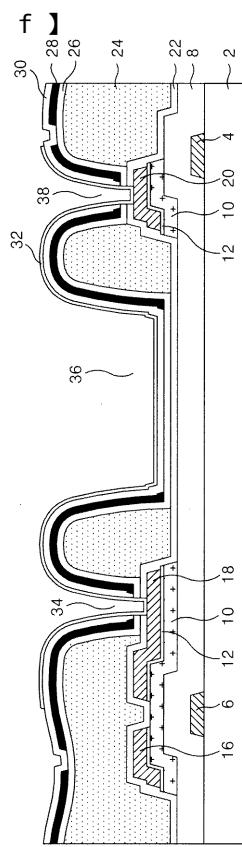

【図2f】図1に図示された半透過型薄膜トランジスター基板の製造法を段階的に説明するための断面図である。

【図3】本発明の実施形態の半透過型薄膜トランジスター基板を部分的に図示した平面図である。

【図4】図3に図示された半透過型薄膜トランジスター基板をII-II'、III-III'、IV-IV'線に沿って切断して図示した断面図である。

【図5a】本発明の実施形態の半透過型薄膜トランジスター基板の第1マスク工程を説明するための平面図である。

【図5b】本発明の実施形態の半透過型薄膜トランジスター基板の第1マスク工程を説明するための断面図である。

**【図6a】**本発明の第1マスク工程を具体的に説明するための断面図である。

**【図6b】**本発明の第1マスク工程を具体的に説明するための断面図である。

**【図6c】**本発明の第1マスク工程を具体的に説明するための断面図である。

**【図6d】**本発明の第1マスク工程を具体的に説明するための断面図である。

**【図6e】**本発明の第1マスク工程を具体的に説明するための断面図である。

10

20

30

40

50

【図7 a】本発明の実施形態の半透過型薄膜トランジスター基板の第2マスク工程を説明するための平面図である。

【図7 b】本発明の実施形態の半透過型薄膜トランジスター基板の第2マスク工程を説明するための断面図である。

【図8 a】本発明の第2マスク工程を具体的に説明するための断面図である。

【図8 b】本発明の第2マスク工程を具体的に説明するための断面図である。

【図8 c】本発明の第2マスク工程を具体的に説明するための断面図である。

【図8 d】本発明の第2マスク工程を具体的に説明するための断面図である。

【図8 e】本発明の第2マスク工程を具体的に説明するための断面図である。

【図9 a】本発明の実施形態の半透過型薄膜トランジスター基板の第3マスク工程を説明するための平面図である。 10

【図9 b】本発明の実施形態の半透過型薄膜トランジスター基板の第3マスク工程を説明するための断面図である。

【図10 a】本発明の第3マスク工程を具体的に説明するための断面図である。

【図10 b】本発明の第3マスク工程を具体的に説明するための断面図である。

【図10 c】本発明の第3マスク工程を具体的に説明するための断面図である。

【図11 a】本発明の実施形態の半透過型薄膜トランジスター基板の第4マスク工程を説明するための平面図である。 20

【図11 b】本発明の実施形態の半透過型薄膜トランジスター基板の第4マスク工程を説明するための断面図である。

【図12】本発明の実施形態の半透過型トランジスター基板の周辺部を主に概略的に図示した平面図である。 20

【図13】図12に図示されたデーターライン及びデーターリンクのコンタクト領域と静電気防止素子領域を具体的に図示した平面図である。

【図14】図13に図示された半透過型薄膜トランジスター基板をV-V'、VI-VI'線に沿って切断して図示した断面図である。 20

【図15 a】図14に図示された半透過型薄膜トランジスター基板の第1マスク工程を説明するための平面図である。

【図15 b】図14に図示された半透過型薄膜トランジスター基板の第1マスク工程を説明するための断面図である。 30

【図16 a】図14に図示された半透過型薄膜トランジスター基板の第2マスク工程を説明するための平面図である。

【図16 b】図14に図示された半透過型薄膜トランジスター基板の第2マスク工程を説明するための断面図である。

【図17 a】図14に図示された半透過型薄膜トランジスター基板の第3マスク工程を説明するための平面図である。

【図17 b】図14に図示された半透過型薄膜トランジスター基板の第3マスク工程を説明するための断面図である。 40

【図18 a】図14に図示された半透過型薄膜トランジスター基板の第4マスク工程を説明するための平面図である。

【図18 b】図14に図示された半透過型薄膜トランジスター基板の第4マスク工程を説明するための断面図である。

#### 【符号の説明】

##### 【0102】

2, 142 : 下部基板

4, 102 : ゲートライン

6, 108, 302, 312, 322 : ゲート電極

8, 144 : ゲート絶縁膜

10, 114 : 活性層

12, 116 : オーム接触層

|                                            |              |    |

|--------------------------------------------|--------------|----|

| 16 , 110 , 304 , 314 , 324 : ソース電極         |              |    |

| 20 , 112 , 306 , 316 , 326 : ドレイン電極        |              |    |

| 20 , 122 : ストリッジ上部電極                       |              |    |

| 22 , 26 , 30 , 146 : 保護膜                   |              |    |

| 24 , 148 : 有機膜                             |              |    |

| 28 , 152 : 反射電極                            |              |    |

| 32 , 118 : 画素電極                            |              |    |

| 34 , 38 , 162 , 340 , 344 , 348 : コンタクトホール |              |    |

| 35 , 37 : 開口部                              |              | 10 |

| 36 , 154 : 透過ホール                           |              |    |

| 52 : 上部基板                                  |              |    |

| 54 : カラーフィルター                              |              |    |

| 56 : 共通電極                                  |              |    |

| 100 : 薄膜トランジスター基板                          |              |    |

| 101 : 第1導電層                                |              |    |

| 108 : 第2導電層                                |              |    |

| 113 : 第3導電層                                |              |    |

| 106 , 300 , 310 , 320 : 薄膜トランジスター          |              |    |

| 115 : 半導体パターン                              |              |    |

| 128 : ゲートペード                               | 136 : データリンク | 20 |

| 138 : データペード                               |              |    |

| 151 : 第1反射金属層                              |              |    |

| 160 , 262 , 332 , 334 , 336 : コンタクト電極      |              |    |

| 180 : シーリング材                               |              |    |

| 182 : アクティブ領域                              |              |    |

| 190 : 静電気防止素子                              |              |    |

| 210 : 回折露光マスク                              |              |    |

| 212 , 266 : 石英基板                           |              |    |

| 214 , 262 : 遮断層                            |              |    |

| 216 : スリット                                 |              | 30 |

| 219 , 167 : フォトレジスト                        |              |    |

| 105 : 非晶質シリコン層                             |              |    |

| 107 : 不純物ドーピングされた非晶質シリコン層                  |              |    |

| 109 : ソース / ドレイン金属層                        |              |    |

| 168 , 220 : フォトレジストパターン                    |              |    |

| 153 : 第2反射金属層                              |              |    |

| 168A , 220A : 第1フォトレジストパターン                |              |    |

| 260 : ハーフトーンマスク                            |              |    |

| 168B , 220B : 第2フォトレジストパターン                |              |    |

| 264 : 部分透過層                                |              | 40 |

【図1】

関連技術

【図2 a】

【図2 b】

【図2 c】

【図2d】

関連技術

【図2e】

関連技術

【図2f】

関連技術

【図3】

【図 6 b】

【図 6 c】

【図 6 d】

【図 6 e】

【図 7 a】

【図 7 b】

【図 8 a】

【図 8 b】

【図 8 c】

【図 9 b】

【図 10 a】

【図 10 b】

【図 10 c】

【図 1 1 a】

【図 1 1 b】

【図 1 2】

【図 1 3】

【図 1 4】

【図 1 5 a】

【図 1 5 b】

【図 1 6 a】

【図 16 b】

【図 17 a】

【図 17 b】

【図 18 a】

【図 1 8 b】

---

フロントページの続き(51) Int.CI.<sup>7</sup>

F I

テーマコード(参考)

H 0 1 L 29/78 6 1 6 U

H 0 1 L 29/78 6 2 3 A

(74)代理人 100101498

弁理士 越智 隆夫

(74)代理人 100096688

弁理士 本宮 照久

(74)代理人 100104352

弁理士 朝日 伸光

(74)代理人 100128657

弁理士 三山 勝巳

(72)発明者 安炳哲

大韓民国 京畿道 安養市 東安區 坪村洞 899-2番地 ヒヤンチョン アパート 203

- 903号

(72)発明者 朴鍾佑

大韓民国 大邱廣域市 北區 太田洞 テベク 2-チャ アパート 102-205号

F ターム(参考) 2H091 FA16Y FB02 FB08 FC02 FC25 FD04 FD23 GA03 GA07 GA13

JA03 LA12 LA30

2H092 GA17 GA19 GA25 HA04 HA05 JA24 JB08 JB57 JB66 JB67

JB79 MA13 MA17 NA07 NA27 PA12

5F110 AA16 AA22 BB02 CC07 EE02 EE04 EE06 EE07 EE14 FF02

FF03 FF30 GG02 GG15 GG45 HK02 HK03 HK04 HK06 HK09

HK16 HK21 HK22 HK33 HK35 NN03 NN23 NN24 NN27 NN35

NN36 NN71 NN73 QQ01

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其制造方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP2005352479A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 公开(公告)日 | 2005-12-22 |

| 申请号            | JP2005165711                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 申请日     | 2005-06-06 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | Eruji. 菲利普斯杜天公司，有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 安炳哲<br>朴鍾佑                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | 安炳哲<br>朴鍾佑                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号         | G02F1/136 G02F1/1335 G02F1/1343 G02F1/1345 G02F1/1362 G02F1/1368 H01L29/786                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| CPC分类号         | G02F1/13458 G02F1/133555 G02F1/1362                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| FI分类号          | G02F1/1368 G02F1/1335.520 G02F1/1343 G02F1/1345 H01L29/78.617.L H01L29/78.616.U H01L29/78.623.A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| F-TERM分类号      | 2H091/FA16Y 2H091/FB02 2H091/FC02 2H091/FC25 2H091/FD04 2H091/FD23 2H091/GA03 2H091/GA07 2H091/GA13 2H091/JA03 2H091/LA12 2H091/LA30 2H092/GA17 2H092/GA19 2H092/GA25 2H092/HA04 2H092/HA05 2H092/JA24 2H092/JB08 2H092/JB57 2H092/JB66 2H092/JB67 2H092/JB79 2H092/MA13 2H092/MA17 2H092/NA07 2H092/NA27 2H092/PA12 5F110/AA16 5F110/AA22 5F110/BB02 5F110/CC07 5F110/EE02 5F110/EE04 5F110/EE06 5F110/EE07 5F110/EE14 5F110/FF02 5F110/FF03 5F110/FF30 5F110/GG02 5F110/GG15 5F110/GG45 5F110/HK02 5F110/HK03 5F110/HK04 5F110/HK06 5F110/HK09 5F110/HK16 5F110/HK21 5F110/HK22 5F110/HK33 5F110/HK35 5F110/NN03 5F110/NN23 5F110/NN24 5F110/NN27 5F110/NN35 5F110/NN36 5F110/NN71 5F110/NN73 5F110/QQ01 2H191/FA02 2H191/FA02Y 2H191/FA32 2H191/FA32Y 2H191/FA34 2H191/FA34Y 2H191/FD22 2H191/GA19 2H191/LA21 2H191/NA13 2H191/NA34 2H191/NA37 2H192/AA24 2H192/BC32 2H192/BC44 2H192/BC64 2H192/BC72 2H192/BC82 2H192/CB05 2H192/CC32 2H192/DA02 2H192/EA43 2H192/GA31 2H291/FA02Y 2H291/FA32Y 2H291/FA34Y 2H291/FD22 2H291/GA19 2H291/LA21 2H291/NA13 2H291/NA34 2H291/NA37 |         |            |

| 代理人(译)         | 臼井伸一<br>朝日伸光                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 优先权            | 1020040041143 2004-06-05 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 其他公开文献         | JP4268956B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

**摘要(译)**

解决的问题：提供一种能够通过简化工艺来增加透射区域的开口率的制造方法。以双层结构形成的栅线，其中堆叠有透明的第一导电层和不透明的第二导电层；以及在栅线的第一绝缘膜上与栅线相交的栅线。数据线限定像素区域；薄膜晶体管；由像素区域中的第一导电层形成的像素电极；形成存储电容器的存储上电极；在薄膜晶体管上的第二绝缘体。从膜穿透到第一绝缘膜以暴露像素电极的透明孔；连接漏极和存储上电极的反射电极，通过透明孔的边缘暴露到像素电极；它的特点是具有。[\[选择图\]图4](#)