(19)日本国特許庁 (JP)

(12) 公開特許公報 (A) (11)特許出願公開番号

特開2003 - 43513

(P2003 - 43513A)

(43)公開日 平成15年2月13日(2003.2.13)

| (51) Int.CI <sup>7</sup> | 識別記号 | F I            | テ-マコード (参考) |

|--------------------------|------|----------------|-------------|

| G 0 2 F 1/1343           |      | G 0 2 F 1/1343 | 2 H 0 9 0   |

| 1/1333                   | 505  | 1/1333         | 2 H 0 9 2   |

| 1/1368                   |      | 1/1368         | 5 F 1 1 0   |

| H 0 1 L 29/786           |      | H 0 1 L 29/78  | 612 C       |

審査請求 未請求 請求項の数 420 L (全 18数)

(21)出願番号 特願2002 - 156001(P2002 - 156001)

(22)出願日 平成14年5月29日(2002.5.29)

(31)優先権主張番号 2001 - 029811

(32)優先日 平成13年5月29日(2001.5.29)

(33)優先権主張国 韓国(KR)

(71)出願人 501426046

エルジー・フィリップス エルシーデー

カンパニー、リミテッド

大韓民国 ソウル,ヨンドゥンポ-ク,ヨイ

ド-ドン 20

(72)発明者 チェジースン

大韓民国 406-130,インチョン,ヨンス-

グ,ドンチュン-ドン,ハンヤン1チャ アバ

ートメント,111-607

(74)代理人 100064447

弁理士 岡部 正夫 (外10名)

最終頁に続く

(54)【発明の名称】 液晶表示装置用アレー基板及びその製造方法

(57)【要約】

【課題】 既存より保存静電容量を減少することなく、開口率を向上させることができる高画質、高精度液晶表示装置用アレー基板を提供する。

【解決手段】 液晶表示装置用アレー基板では、基板と；基板上部に第1方向に形成されたゲート配線と；ゲート配線と平行に一定間隔離隔されて形成され、ゲート配線と同一物質からなる共通配線と；ゲート配線及び共通配線上に形成されたゲート絶縁膜と；ゲート絶縁膜上に形成された半導体層と；半導体層とオーバーラップされて形成されたドレイン電極を含むと共に透明導電性物質からなる画素電極と；ドレイン電極と離隔されて形成されて透明導電性物質からなるソース電極と；ソース電極を露出させる第1コンタクトホールと画素電極を露出させる開口部とを有して画素電極及びソース電極上に形成された保護層と；第1コンタクトホールを通してソース電極と連結され、ゲート配線と交差する第2方向に形成されたデータ配線を含む液晶表示装置用アレー基板を提供する。

**【特許請求の範囲】**

【請求項 1】 基板と；前記基板上の第 1 の方向に形成されたゲート配線と；前記ゲート配線と平行に一定間隔をあいて離隔されて配置され、前記ゲート配線と同一物質で形成された共通配線と；前記ゲート配線及び共通配線上に形成されたゲート絶縁膜と；前記ゲート絶縁膜上に形成された半導体層と；前記半導体層とオーバーラップして配置されたドレイン電極を含むと共に透明導電性物質で形成された画素電極と；前記ドレイン電極と離隔されて配置されると共に透明導電性物質で形成されたソース電極と；前記ソース電極を露出させる第 1 コンタクトホールと前記画素電極を露出させる開口部とを有して前記画素電極及びソース電極上に形成された保護層と；前記第 1 コンタクトホールを通して前記ソース電極と接続され、前記ゲート配線と交差する第 2 の方向に形成されたデータ配線とを含むことを特徴とする液晶表示装置用アレー基板。

【請求項 2】 前記半導体層は、非晶質シリコンでなされたアクティブ層と、不純物非晶質シリコンでなされたオーミックコンタクト層と、チタン(Ti)、クロム(Cr)のうちのいずれか一つの金属層が順序に従って積層された構造を有し、前記ソース電極とドレイン電極との間の区間には前記アクティブ層が露出されていることを特徴とする請求項 1 に記載の液晶表示装置用アレー基板。

【請求項 3】 前記ゲート配線の端に前記データ配線と同一物質で形成されると共に前記ゲート配線と一定間隔オーバーラップして配置されて前記ゲート絶縁膜及び保護層に形成された第 2 コンタクトホールを通してゲート配線と接続されるゲートリンクと、前記画素電極と同一物質からなり前記保護層に形成された第 3 コンタクトホールを通して前記ゲートリンクと接続されるゲートパッドをさらに含むことを特徴とする請求項 1 に記載の液晶表示装置用アレー基板。

【請求項 4】 前記ゲートリンクは、前記ゲートパッドより広い幅を有することを特徴とする請求項 3 に記載の液晶表示装置用アレー基板。

【請求項 5】 前記データ配線の端部に位置して前記画素電極と同一物質で形成されて前記データ配線と一定間隔オーバーラップして配置されると共に第 4 コンタクトホールを通して前記データ配線と接続されるデータパッドをさらに含むことを特徴とする請求項 1 に記載の液晶表示装置用アレー基板。

【請求項 6】 前記オーバーラップされるデータ配線は、データパッドより大きな幅を有することを特徴とする請求項 5 に記載の液晶表示装置用アレー基板。

【請求項 7】 前記画素電極は、前記ゲート配線とオーバーラップして配置されることを特徴とする請求項 1 に記載の液晶表示装置用アレー基板。

【請求項 8】 前記第 1 コンタクトホールは、前記データ配線下部に位置することを特徴とする請求項 1 に記載の液晶表示装置用アレー基板。

【請求項 9】 前記透明導電性物質は、ITOであることを特徴とする請求項 1 に記載の液晶表示装置用アレー基板。

【請求項 10】 前記保護層は、アクリル樹脂であることを特徴とする請求項 1 に記載の液晶表示装置用アレー基板。

【請求項 11】 基板と；前記基板上に形成される共通電極と；前記基板上の第 1 の方向に形成されたゲート配線と；前記ゲート配線と、平行に一定間隔をあいて離隔されて配置され、前記ゲート配線と同一物質で形成されて、前記共通電極と接続される共通配線と；前記ゲート配線及び共通配線上に形成されたゲート絶縁膜と；前記ゲート絶縁膜上に形成された半導体層と；前記半導体層上に前記半導体層とオーバーラップされて形成されると共に透明導電性物質からなるドレイン電極を含む画素電極と；前記ドレイン電極と離隔されて形成されると共に透明導電性物質からなるソース電極と；前記ソース電極を露出させる第 1 コンタクトホールと前記画素電極を露出させる開口部とを有する保護層と；前記第 1 コンタクトホールを通して前記ソース電極と接続され、前記ゲート配線と交差する第 2 の方向に形成されたデータ配線とを含むことを特徴とする液晶表示装置用アレー基板。

【請求項 12】 前記半導体層は、非晶質シリコンからなるアクティブ層と、不純物非晶質シリコンからなるオーミックコンタクト層と、チタン(Ti)、クロム(Cr)のうちのいずれか一つの金属層が順序に従って積層された構造を有し、前記ソース電極とドレイン電極との間の区間で前記アクティブ層が露出されていることを特徴とする請求項 11 に記載の液晶表示装置用アレー基板。

【請求項 13】 前記ゲート配線の端に前記データ配線と同一物質で形成されると共に前記ゲート配線と一定間隔オーバーラップして配置されて、前記ゲート絶縁膜及び保護層に形成された第 2 コンタクトホールを通してゲート配線と接続されるゲートリンクと、前記画素電極と同一物質で形成されると共に前記保護層に形成された第 3 コンタクトホールを通して前記ゲートリンクと接続されるゲートパッドをさらに含むことを特徴とする請求項 11 に記載の液晶表示装置用アレー基板。

【請求項 14】 前記ゲートリンクは、前記ゲートパッドより広い幅を有することを特徴とする請求項 13 に記載の液晶表示装置用アレー基板。

【請求項 15】 前記データ配線の端部に位置して前記画素電極と同一物質で形成されると共に前記データ配線と一定間隔オーバーラップして配置されて、第 4 コンタクトホールを通して前記データ配線と接続されるデータパッドをさらに含むことを特徴とする請求項 11 に記載の液晶表示装置用アレー基板。

【請求項 16】 前記オーバーラップされるデータ配線

は、データパッドより大きな幅を有することを特徴とする請求項15に記載の液晶表示装置用アレー基板。

【請求項17】 前記画素電極は、前記ゲート配線とオーバーラップして配置されることを特徴とする請求項11に記載の液晶表示装置用アレー基板。

【請求項18】 前記第1コンタクトホールは、前記データ配線の下方に延在することを特徴とする請求項11に記載の液晶表示装置用アレー基板。

【請求項19】 前記透明導電性物質は、ITOであることを特徴とする請求項11に記載の液晶表示装置用アレー基板。

【請求項20】 前記保護層は、アクリル樹脂であることを特徴とする請求項11に記載の液晶表示装置用アレー基板。

【請求項21】 基板と；前記基板上の第1の方向に形成されてストレージ電極を含むゲート配線と；前記ゲート配線上に形成されたゲート絶縁膜と；前記ゲート絶縁膜上に形成された半導体層と；前記ゲート配線とオーバーラップして配置され、前記半導体層とオーバーラップして配置されたドレイン電極を含むと共に透明導電性物質で形成された画素電極と；前記ドレイン電極と離隔されて配置されて透明導電性物質で形成されたソース電極と；前記ソース電極を露出させる第1コンタクトホールと前記画素電極を露出させる開口部とを有する保護層と；前記第1コンタクトホールを通して前記ソース電極と接続され、前記ゲート配線と交差する第2の方向に形成されたデータ配線とを含むことを特徴とする液晶表示装置用アレー基板。

【請求項22】 前記半導体層は、非晶質シリコンからなるアクティブ層と、不純物非晶質シリコンからなるオーミックコンタクト層と、チタン(Ti)、クロム(Cr)のうちのいずれか一つの金属層が順序に従って積層された構造を有し、前記ソース電極とドレイン電極との間の区間で前記アクティブ層が露出されていることを特徴とする請求項21に記載の液晶表示装置用アレー基板。

【請求項23】 前記ゲート配線の端に前記データ配線と同一物質で形成されると共に前記ゲート配線と一定間隔オーバーラップして配置されて、前記ゲート絶縁膜及び保護層に形成された第2コンタクトホールを通してゲート配線と接続されるゲートリンクと、前記画素電極と同一物質からなり、前記保護層に形成された第3コンタクトホールを通して前記ゲートリンクと接続されるゲートパッドをさらに含むことを特徴とする請求項21に記載の液晶表示装置用アレー基板。

【請求項24】 前記ゲートリンクは、前記ゲートパッドより広い幅を有することを特徴とする請求項23に記載の液晶表示装置用アレー基板。

【請求項25】 前記データ配線の端部に位置して前記画素電極と同一物質で形成されると共に前記データ配線と一定間隔オーバーラップして配置され、第4コンタク

トホールを通して前記データ配線と接続されるデータパッドをさらに含むことを特徴とする請求項21に記載の液晶表示装置用アレー基板。

【請求項26】 前記オーバーラップされるデータ配線は、データパッドよりさらに大きな幅を有することを特徴とする請求項25に記載の液晶表示装置用アレー基板。

【請求項27】 前記画素電極は、前記ゲート配線とオーバーラップして配置されることを特徴とする請求項21に記載の液晶表示装置用アレー基板。

【請求項28】 前記第1コンタクトホールは、前記データ配線の下方に延在することを特徴とする請求項21に記載の液晶表示装置用アレー基板。

【請求項29】 前記透明導電性物質は、ITOであることを特徴とする請求項21に記載の液晶表示装置用アレー基板。

【請求項30】 前記保護層は、アクリル樹脂であることを特徴とする請求項21に記載の液晶表示装置用アレー基板。

【請求項31】 基板上にストレージ電極を含むゲート配線と、前記ゲート配線と平行に前記ゲートラインから一定間隔をおいて離隔された共通配線とを第1の方向に形成する段階と；前記ゲート配線及び共通配線上にゲート絶縁膜を形成する段階と；前記ゲート絶縁膜上に半導体層を形成する段階と；前記半導体層とオーバーラップして配置され、ドレイン電極を含むと共に透明導電性物質からなる画素電極と、前記ドレイン電極と離隔されて配置されると共に透明導電性物質からなるソース電極を形成する段階と；前記ソース電極を露出させる第1コンタクトホールと前記画素電極を露出させる開口部とを有する保護層を形成する段階と；前記第1コンタクトホールを通して前記ソース電極と接続され、前記ゲート配線と交差するデータ配線を第2の方向に形成する段階とを含むことを特徴とする液晶表示装置用アレー基板の製造方法。

【請求項32】 前記半導体層を形成する段階は、非晶質シリコンからなるアクティブ層と、不純物非晶質シリコンからなるオーミックコンタクト層と、チタン(Ti)、クロム(Cr)のうちのいずれか一つの金属層を順序に従って積層することによって形成され、前記ソース電極とドレイン電極との間の区間で前記アクティブ層が露出されるようにすることを特徴とする請求項31に記載の液晶表示装置用アレー基板の製造方法。

【請求項33】 前記ゲート配線の端に前記データ配線と同一物質で形成され、前記ゲート配線と一定間隔オーバーラップして配置されると共に前記ゲート絶縁膜及び保護層に形成された第2コンタクトホールを通してゲート配線と接続されるゲートリンクと、前記画素電極と同一物質からなり、前記保護層に形成された第3コンタクトホールを通して前記ゲートリンクと接続されるゲート

パッドを形成する段階をさらに含むことを特徴とする請求項31に記載の液晶表示装置用アレー基板の製造方法。

【請求項34】前記ゲートリリンクは、前記ゲートパッドより広い幅を有することを特徴とする請求項33に記載の液晶表示装置用アレー基板の製造方法。

【請求項35】前記データ配線の端部に位置して前記画素電極と同一物質で形成され、前記データ配線と一定間隔オーバーラップして配置されると共に第4コントラクトホールを通して前記データ配線と接続されるデータパッドを形成する段階をさらに含むことを特徴とする請求項31に記載の液晶表示装置用アレー基板の製造方法。

【請求項36】前記オーバーラップして配置されるデータ配線は、データパッドより大きな幅を有することを特徴とする請求項35に記載の液晶表示装置用アレー基板の製造方法。

【請求項37】前記画素電極は、前記ゲート配線とオーバーラップして配置されることを特徴とする請求項31に記載の液晶表示装置用アレー基板の製造方法。

【請求項38】前記第1コントラクトホールは、前記データ配線の下方に延在することを特徴とする請求項31に記載の液晶表示装置用アレー基板の製造方法。

【請求項39】前記透明導電性物質は、ITOであることを特徴とする請求項31に記載の液晶表示装置用アレー基板の製造方法。

【請求項40】前記保護層は、アクリル樹脂であることを特徴とする請求項31に記載の液晶表示装置用アレー基板の製造方法。

【請求項41】基板上に共通電極を形成する段階と；前記基板上にゲート配線と、前記ゲート配線と平行に一定間隔をおいて離隔されて配置されると共に前記共通電極に隣接して配置される共通配線とを第1方向に形成する段階と；前記ゲート配線及び共通配線上にゲート絶縁膜を形成する段階と；前記ゲート絶縁膜上に半導体層を形成する段階と；前記半導体層とオーバーラップして配置されるドレイン電極を含むと共に透明導電性物質からなる画素電極と、前記ドレイン電極と離隔されて配置されると共に透明導電性物質からなるソース電極を形成する段階と；前記ソース電極を露出させる第1コントラクトホールと前記画素電極を露出させる開口部とを有する保護層を形成する段階と；前記第1コントラクトホールを通して前記ソース電極と接続され、前記ゲート配線と交差する第2の方向に形成されたデータ配線を形成する段階とを含むことを特徴とする液晶表示装置用アレー基板の製造方法。

【請求項42】基板上の第1の方向に形成されると共にストレージ電極を含むゲート配線を形成する段階と；前記ゲート配線上にゲート絶縁膜を形成する段階と；前記ゲート絶縁膜上に半導体層を形成する段階と；前記半導体層とオーバーラップして配置されるドレイン電極を

含むと共に透明導電性物質からなる画素電極と、前記ドレイン電極と離隔されて配置されると共に透明導電性物質からなるソース電極とを形成する段階と；前記ソース電極を露出させる第1コントラクトホールと前記画素電極を露出させる開口部とを有する保護層を形成する段階と；前記ゲート配線と交差する第2の方向に前記第1のコントラクトホールを介して前記ソース電極と接続されたデータ配線を形成する段階とを含むことを特徴とする液晶表示装置用アレー基板の製造方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】本発明は液晶表示装置に係り、特に高保存容量と高開口率を有するアレー基板及びその製造方法に関する。

【0002】

【従来の技術】一般的な液晶表示装置は、液晶分子の光学的異方性と分極性質を利用する。液晶分子は構造が細くて長いために分子の配列に方向性を持っており、人為的に液晶に電界を印加して分子配列の方向を制御できる。

【0003】したがって、前記液晶の分子配列方向を任意に調節すると、液晶の分子配列が変わらるようになって、光学的異方性によってこの液晶の分子配列方向に光が屈折して画像情報を表現できる。

【0004】現在には薄膜トランジスタ(Thin Film Transistor; TFT)と画素電極が相互連結されて行列方式で配列された能動行列液晶表示装置(Active Matrix LCD: AM-LCD)が解像度及び動映像具現能力が優秀で最も注目されている。

【0005】このような液晶表示装置を構成する基本的な部品である液晶パネルの構造を説明すると次のとおりである。

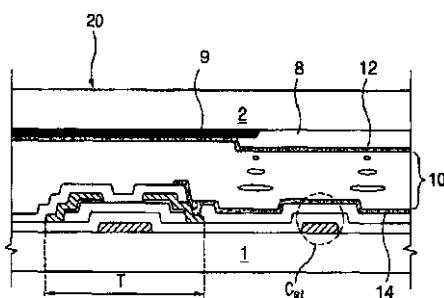

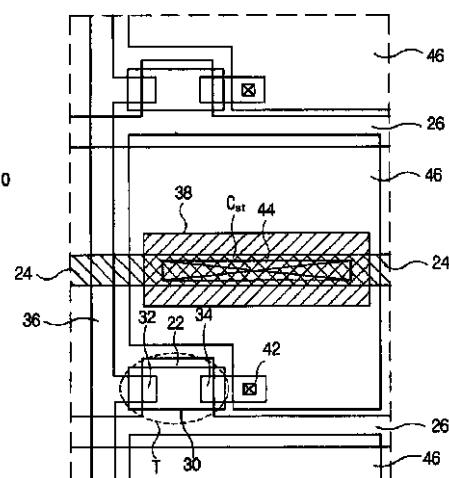

【0006】図1は、従来の液晶表示装置用液晶パネルを部分的に示した概略的な断面図である。

【0007】図示したように、液晶パネル20は、相互対向して一定間隔をおいて離隔されたカラーフィルタ基板である上部基板2及びアレー基板である下部基板1と、この上部及び下部基板2、1間に充填された液晶層10で構成される。

【0008】この上部基板2下部には液晶配列を制御できない部分の光を遮断するブラックマトリックス9と、色彩表現及び光を選択透過させるカラーフィルタ8が相互一定間隔オーバーラップされて形成されていて、その下部には液晶層10に電圧を印加する片側電極である共通電極12が形成されている。

【0009】前記下部基板1上部には光を透過させる領域で液晶層10に電圧を印加する他の片側電極である画素電極14が形成されていて、この画素電極14と連結されて、この画素電極14に電圧を掛けたり遮断するス

イッチの役割をする薄膜トランジスタTが形成されていて、前記画素電極14が形成された画素部内には1フレーム(frame)周期で液晶層10に印加された電圧を一定に維持する保存蓄電器(C<sub>ST</sub>; storage capacitor)が構成されている。

【0010】前記保存蓄電器C<sub>ST</sub>は、前段ゲート(previous gate)方式と、共通(common)方式に分けることができる。

【0011】前段ゲート方式は、画素電極と前段のゲート配線を一定間隔オーバーラップさせて、その間の蓄電器を保存蓄電器で用いる方式であって、共通方式は画素領域内に別途のキャパシタ電極を形成して、このキャパシタ電極と画素電極間の蓄電器を保存蓄電器で用いる方式である。

【0012】前記共通方式のキャパシタ電極は、上部基板の共通電極と連結して駆動する。

【0013】この際、開口率と収率の面では前段ゲート方式が良いし、画質の面では共通方式が優秀である。

【0014】しかし、最近では、高精度、高画質液晶表示装置の開発に関心が集中しており、前段ゲート方式と共通方式を複合的に採用する方式の保存蓄電器に対する研究が活発になされている。

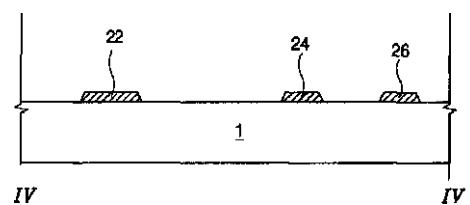

【0015】図2は、共通方式の保存蓄積容量を有する従来の液晶表示装置用アレー基板を部分的に示した概略的な平面図である。

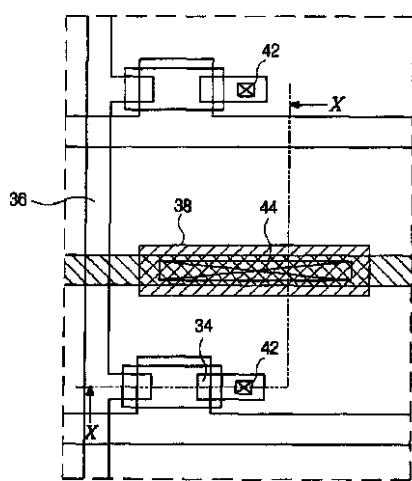

【0016】図示したように、ゲート電極22を含むゲート配線26が横方向に形成されていて、このゲート配線26と平行な方向に一定間隔をおいて離隔されている共通方式の共通配線24が形成されていて、前記ゲート電極22を覆う領域に半導体層30が形成されていて、前記半導体層30と一定面積オーバーラップされると共に、相互に離隔されてソース及びドレイン電極32、34が形成されていて、前記ソース電極32と連結されて前記ゲート配線26及び共通配線24と交差するデータ配線36が縦方向に形成されている。

【0017】前記ゲート配線26及びデータ配線36が交差する領域内で定義される画素領域には画素電極46が形成されていて、前記画素領域内には前記共通配線24とオーバーラップされる位置に一定面積を有し、前記データ配線36と同一物質で構成されたストレージ電極38が形成されている。

【0018】前記ゲート電極22、半導体層30、ソース電極32及びドレイン電極34を合わせて薄膜トランジスタTと呼ぶ。

【0019】前記ドレイン電極34と画素電極46は、第1コンタクトホール42によって連結されて、画素電極46とストレージ電極38は第2コンタクトホール44によって連結される。

【0020】図面に提示しなかったが、前記共通配線24とストレージ電極38間にゲート絶縁膜が介在され

て、前記ストレージ電極38と画素電極46間に前記薄膜トランジスタTの電気的特性を保護する役割をすると共に、上述した第1コンタクトホール42及び第2コンタクトホール44を有する保護層が位置する。

【0021】以下、前記共通配線24、ストレージ電極38と画素電極46間に形成される保存蓄電器に対してさらに詳細に説明する。

【0022】前記蓄電器は、次のような式により与えられる。

$$C = (A/d)$$

(C(capacitance): 静電容量、A: 絶縁体の誘電率、d: 電極の面積、d: 電極間の距離) ゲート絶縁膜が保護層より薄いので、共通配線24とストレージ電極38間に静電容量が共通配線24と画素電極46間に静電容量より大きい。したがって、前記ストレージ電極38の追加によって保存静電容量は増加する。

【0023】しかし、前記共通配線24とストレージ電極38は、不透明金属物質であるデータ配線36の物質で形成されるために、前記ストレージ電極38の追加は開口率を落とすという問題がある。

【0024】以下、前記液晶表示装置用アレー基板の製造工程を説明する。図3ないし12は、前記図2の従来の液晶表示装置用アレー基板の製造工程を示した概略的な平面図及び断面図である。前記製造工程では蒸着(deposition)、フォトリソグラフィ(photo lithography)、エッティング(etching)工程が何度も繰り返される。

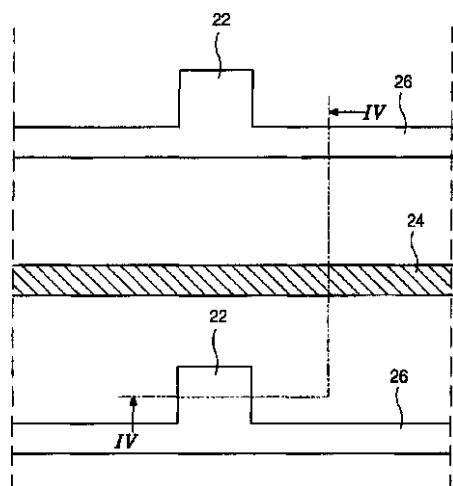

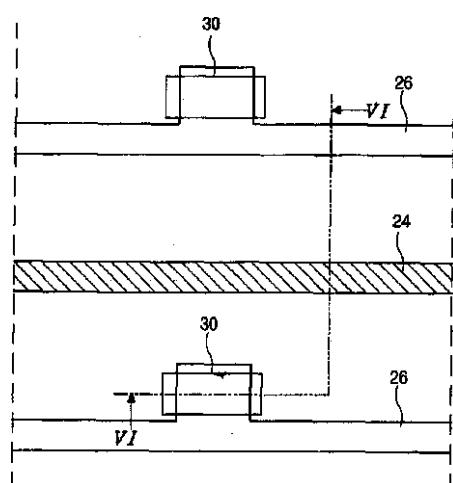

【0025】図3は、従来の液晶表示装置用アレー基板の製造工程を示した概略的な平面図であって、図4は従来の液晶表示装置用アレー基板の製造工程を示した概略的な断面図であるが、ゲート電極22を含むゲート配線26を横方向に、前記ゲート配線26と平行な方向に一定間隔をおいて離隔して共通配線24を形成する段階である。

【0026】前記ゲート配線26及び共通配線24をなす物質は、アルミニウムを含む二重金属層が主に利用される。

【0027】図5は、従来の液晶表示装置用アレー基板の製造工程を示した概略的な平面図であって、図6は従来の液晶表示装置用アレー基板の製造工程を示した概略的な断面図であるが、前記ゲート配線26及び共通配線24が形成された基板上に、ゲート絶縁膜28を基板全面にかけて形成した後、前記ゲート電極22と対応する前記ゲート絶縁膜28上の位置に非晶質シリコン(a-Si)でなされたアクティブ層30aと、不純物を添加した非晶質シリコン(n+a-Si)で形成されたオームикコンタクト層(ohmic contact layer)30bとで構成された半導体層30を形成する段階である。

【0028】前記オーミックコンタクト層30bは、その下部層をなすアクティブ層30aと後続工程で形成される金属層との間の接触抵抗を低める役割をするものであって、イオンドーピング(i on d o p i n g)工程を経て非晶質シリコンの電子移動度を高めた物質である。

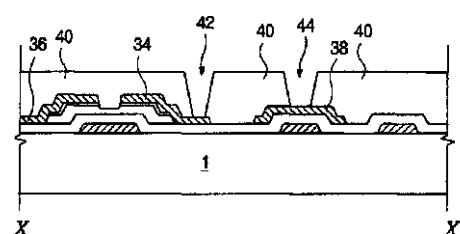

【0029】図7は、従来の液晶表示装置用アレー基板の製造工程を示した概略的な平面図であって、図8は従来の液晶表示装置用アレー基板の製造工程を示した概略的な断面図であるが、前記半導体層30が形成された基板上に、前記ゲート配線26及び共通配線24と交差する縦方向に、ソース電極32を含むデータ配線36と、前記ソース電極32と離隔されるドレイン電極34と、前記共通配線24と一定面積オーバーラップされ、前記画素領域内に位置するストレージ電極38を形成する段階である。

【0030】前記データ配線36及びドレイン電極34とストレージ電極38には、モリブデン(Mo)のような化学的耐蝕性が強い金属が主に利用される。

【0031】前記ソース電極32とドレイン電極34とを形成する段階では、前記ソース電極32とドレイン電極34との間の区間のオーミックコンタクト層30bを除去して、前記アクティブ層30aを露出させてチャネルchを形成する工程が含まれる。

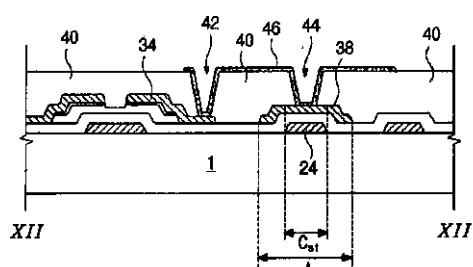

【0032】図9は、従来の液晶表示装置用アレー基板の製造工程を示した概略的な平面図であって、図10は従来の液晶表示装置用アレー基板の製造工程を示した概略的な断面図であるが、前記データ配線36及びストレージ電極38が形成された基板上の前記ドレイン電極34及びストレージ電極38と対応する位置に各々形成された第1コンタクトホール42及び第2コンタクトホール44を含む保護層40を形成する段階である。

【0033】図11は、従来の液晶表示装置用アレー基板の製造工程を示した概略的な平面図であって、図12は従来の液晶表示装置用アレー基板の製造工程を示した概略的な断面図であるが、前記保護層40が形成された基板上に、前記第1コンタクトホール42及び第2コンタクトホール44を通して各々ドレイン電極34及びストレージ電極38と連結される画素電極46を形成する段階である。

【0034】前記画素電極46をなす物質としてITO(I n d i u m T i n O x i d e)またはIZO(I ndium Zinc Oxide)が主に利用される。

【0035】前記第2コンタクトホール44は、前記画素電極46とストレージ電極38を連結させて、前記画素電極46によってストレージ電極38が電極としての役割をして、共通配線24と共に保存蓄電器C<sub>ST</sub>を形成する。

【0036】すなわち、前記画素電極46と連結されるストレージ電極38をさらに形成すると、このストレー

10

ジ電極38と共に通配線24間の距離が狭まって、既存の单一キャパシタ電極より保存蓄電容量を増やすことができる。

【0037】しかし、前記画素領域で不透明金属物質でなされたストレージ電極38が占める領域Aは開口率を落とす領域になる。

【0038】すなわち、このような保存蓄電器C<sub>ST</sub>構造を有する液晶表示装置用アレー基板では開口率と保存静電容量を同時に向上させることはむずかしい。

【0039】

【発明が解決しようとする課題】前記問題点を解決するために、本発明では従来のものより保存静電容量を減少させず、開口率を向上させることができる高画質、高精度液晶表示装置用アレー基板を提供することを目的にする。

【0040】すなわち、本発明では従来のものより開口率を向上させながら保存蓄電器の電極体間距離を狭めることができアレー工程を提案して、従来のIOP(ITO on passivation)構造に比べて保存静電容量を落とさずに、開口率を増やすことができるようにするものである。

【0041】

【課題を解決するための手段】前記目的を達成するためには、本発明の1つの態様によれば、基板と；前記基板上部の第1方向に形成されたゲート配線と；前記ゲート配線と平行に一定間隔をあいて離隔されて配置され、前記ゲート配線と同一物質で形成された共通配線と；前記ゲート配線及び共通配線の上に形成されたゲート絶縁膜と；前記ゲート絶縁膜上に形成された半導体層と；前記半導体層とオーバーラップされて形成されたドレイン電極を含むと共に透明導電性物質で形成された画素電極と；前記ドレイン電極と離隔されて配置されると共に透明導電性物質でなされたソース電極と；前記ソース電極を露出させる第1コンタクトホールと前記画素電極を露出させる開口部とを有すると共に前記画素電極及びソース電極の上に形成された保護層と；前記第1コンタクトホールを通して前記ソース電極と接続され、前記ゲート配線と交差する第2方向に形成されたデータ配線を含む液晶表示装置用アレー基板を提供する。

【0042】本発明の他の態様によれば、基板と；前記基板上に形成された共通電極と；前記基板上の第1の方向に形成されたゲート配線と；前記ゲート配線と平行に一定間隔をあいて離隔されて配置されると共に、前記ゲート配線と同一物質でなされて、前記共通電極と隣接して配置される共通配線と；前記ゲート配線及び共通配線上に形成されたゲート絶縁膜と；前記ゲート絶縁膜上に形成された半導体層と；前記半導体層上に透明導電性物質で形成されると共に、前記半導体層とオーバーラップして形成されたドレイン電極を含む画素電極と；前記ドレイン電極と離隔されて配置されると共に透明導電性物

50

質で形成されたソース電極と；前記ソース電極を露出させる第1コンタクトホールと前記画素電極を露出させる開口部とを有する保護層と；前記第1コンタクトホールを通して前記ソース電極と接続されると共に、前記ゲート配線と交差する第2の方向に形成されたデータ配線を含む液晶表示装置用アレー基板を提供する。

【0043】本発明のさらなる態様によれば、基板と；前記基板上の第1の方向に形成されると共にストレージ電極を含むゲート配線と；前記ゲート配線上に形成されたゲート絶縁膜と；前記ゲート絶縁膜上に形成された半導体層と；前記ゲート配線とオーバーラップして配置されると共に、前記半導体層とオーバーラップされて形成されたドレン電極を含んで透明導電性物質で形成された画素電極と；前記ドレン電極と離隔されて配置されると共に透明導電性物質で形成されたソース電極と；前記ソース電極を露出させる第1コンタクトホールと前記画素電極を露出させる開口部とを有する保護層と；前記第1コンタクトホールを通して前記ソース電極と接続され、前記ゲート配線と交差する第2の方向に形成されたデータ配線を含む液晶表示装置用アレー基板を提供する。

【0044】本発明のさらなる態様によれば、基板上のストレージ電極を含むゲート配線と、前記ゲート配線に平行に前記ゲート配線から一定間隔をおいて離隔された共通配線とを第1の方向に形成する段階と；前記ゲート配線及び共通配線上にゲート絶縁膜を形成する段階と；前記ゲート絶縁膜上に半導体層を形成する段階と；前記半導体層とオーバーラップするドレン電極を含むと共に透明導電性物質で形成された画素電極と、前記ドレン電極と離隔されて配置されると共に透明導電性物質で形成されたソース電極を形成する段階と；前記ソース電極を露出させる第1コンタクトホールと前記画素電極を露出させる開口部とを有する保護層を形成する段階と；前記第1コンタクトホールを通して前記ソース電極と接続されると共に、前記ゲート配線と交差するデータ配線を第2の方向に形成する段階とを含む液晶表示装置用アレー基板の製造方法を提供する。

【0045】本発明のさらなる態様によれば、基板上に共通電極を形成する段階と；前記基板上にゲート配線と前記ゲート配線と平行に一定間隔をおいて離隔されて配置されると共に、前記共通電極と隣接して配置される共通配線を第1の方向に形成する段階と；前記ゲート配線及び共通配線上にゲート絶縁膜を形成する段階と；前記ゲート絶縁膜上に半導体層を形成する段階と；前記半導体層とオーバーラップするドレン電極を含むと共に透明導電性物質からなる画素電極と、前記ドレン電極と離隔されて配置されると共に透明導電性物質からなるソース電極とを形成する段階と；前記ソース電極を露出させる第1コンタクトホールと前記画素電極を露出させる開口部とを有する保護層を形成する段階と；前記第1コ

ンタクトホールを通して前記ソース電極と接続されると共に、前記ゲート配線と交差する第2の方向に形成されたデータ配線を形成する段階とを含む液晶表示装置用アレー基板の製造方法を提供する。

【0046】本発明のさらなる態様によれば、基板上の第1の方向に形成されてストレージ電極を含むゲート配線を形成する段階と；前記ゲート配線上にゲート絶縁膜を形成する段階と；前記ゲート絶縁膜上に半導体層を形成する段階と；前記半導体層とオーバーラップするドレン電極を含むと共に透明導電性物質からなる画素電極と、前記ドレン電極と離隔されて配置されると共に透明導電性物質からなるソース電極を形成する段階と；前記ソース電極を露出させる第1コンタクトホールと前記画素電極を露出させる開口部とを有する保護層を形成する段階と；前記第1コンタクトホールを通して前記ソース電極と接続されると共に、前記ゲート配線と交差する第2の方向にデータ配線を形成する段階とを含む液晶表示装置用アレー基板の製造方法を提供する。

【0047】**【発明の実施の形態】**以下、本発明による望ましい実施例を図面を参照して説明する。本発明の液晶表示装置用アレーは、アレー製造工程中のソース及びドレン電極形成工程で透明導電性物質を利用してソース及びドレン電極と画素電極を形成して、保護層形成工程後にデータ配線を形成することによって、既存より保存蓄電器の電極体間の距離を狭めることを共通的な特徴とする。

【0048】<第1実施例>第1実施例では、上述したように従来のものより画素電極と单一キャパシタ電極間の距離を狭めることによって、第2のキャパシタ電極を省略した液晶表示装置用アレー基板及びその製造方法に関する。

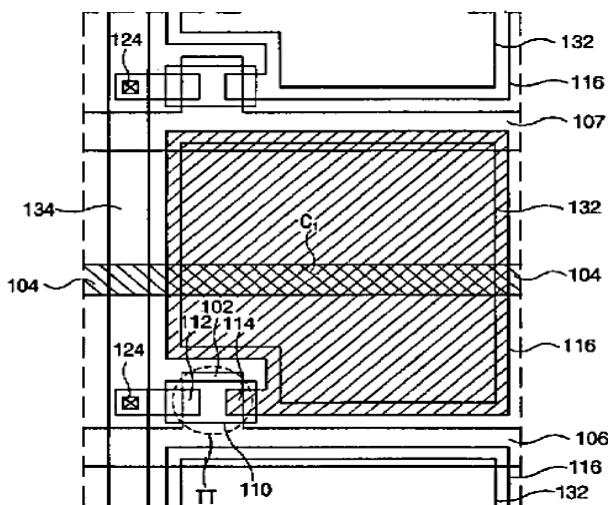

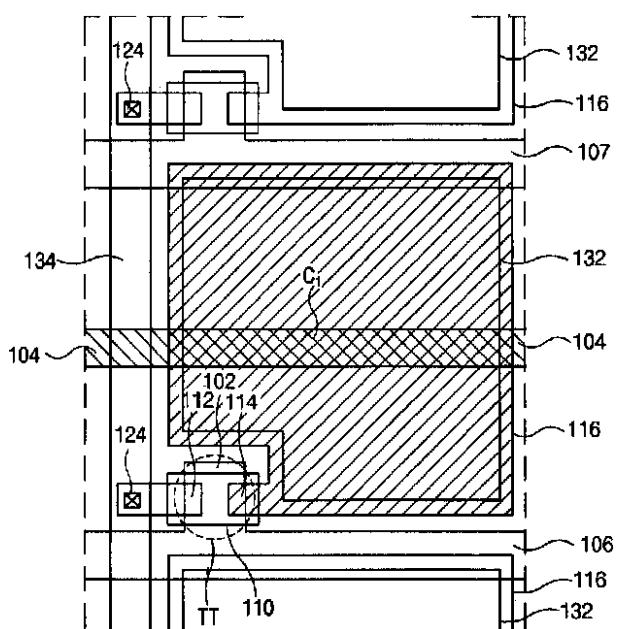

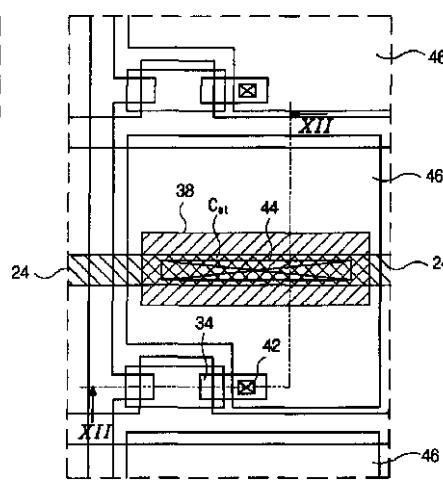

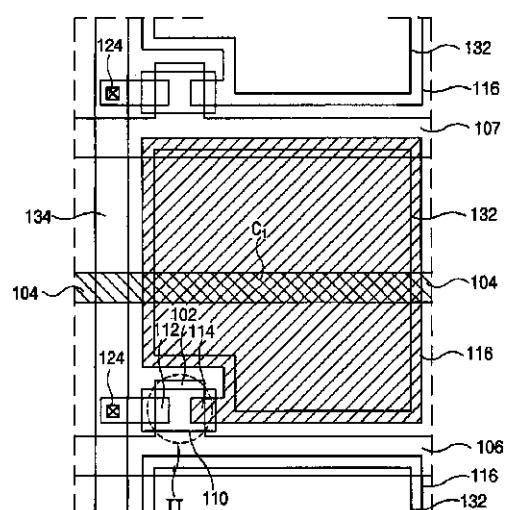

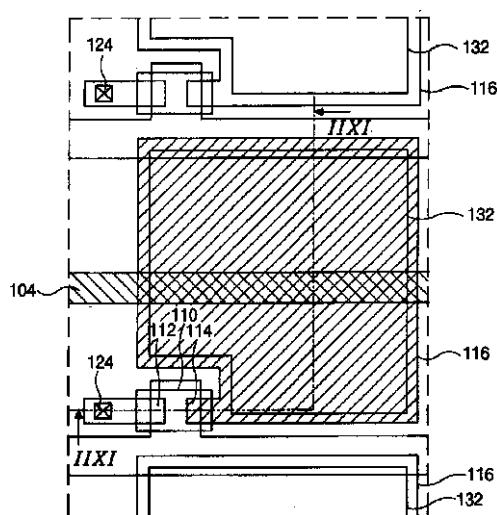

【0049】図13は、本発明の第1実施例による液晶表示装置用アレー基板の概略的な平面図である。

【0050】図示したように、ゲート電極102を含むゲート配線106が第1の方向に形成されていて、前記ゲート配線106と平行な方向に一定間隔をおいて離隔されて、前記ゲート配線106と同一物質からなる共通配線104が形成され、前記ゲート電極102を覆う位置に半導体層110が形成され、前記半導体層110とオーバーラップされ、相互に一定間隔をおいて離隔されたソース電極112とドレン電極114が形成されていて、前記ドレン電極114と接続されると共に、前記ドレン電極114と同一物質からなる画素電極116が形成されている。

【0051】そして、前記ゲート配線106及び共通配線104と交差する第2の方向にはデータ配線134が形成されていて、このデータ配線134は前記データ配線134上に位置する第1コンタクトホール124によって、前記ソース電極112と接続されている。

【0052】前記ゲート配線106とデータ配線134

が交差する領域は、画素領域として定義されるが、この画素領域と対応する面積を有し、前記画素電極116を露出させる開口部132が形成されている。

【0053】前記開口部132及び第1コンタクトホール124は、図示しなかった保護層に含まれる。

【0054】前記開口部132は、画素電極116で生成する電界の強さが弱まることを防止するために、前記画素領域上の保護層を除去した領域である。

【0055】そして、前記ソース電極112とドレイン電極114と画素電極116は、透明導電性物質で形成されるが、前記透明導電性物質としてはITO、IZO、ITZO(Indium Tin Zinc Oxide)を挙げることができ、このうち、外部回路との接触特性が優れたITOで形成することが最も望ましい。

【0056】しかし、前記透明導電性物質は、一般的なゲート配線及びデータ配線を形成する物質より抵抗率値が大きいので、前記半導体層110を構成することにおいて、前記半導体層110とソース電極112とドレイン電極114との間に透明導電性物質と半導体物質間の接触抵抗を緩和させることができるチタン(Ti)またはクロム(Cr)中いずれか一つの物質を緩衝層で含むことを特徴とする。

【0057】そして、前記画素電極116は、開口率向上目的で、前段のゲート配線106と一定面積オーバーラップされて構成される。

【0058】すなわち、前記第1実施例による液晶表示装置用アレー基板が有する保存蓄電器C<sub>1</sub>は、共通配線104と画素電極116間にオーバーラップされる網目紋が表示された領域であって、本発明では画素電極116の形成工程を保護層形成工程前に実行することによって、画素電極116と共に通配線104間の距離を狭めることができあり、別途のストレージ電極の形成をせずに既存水準の保存静電容量を確保しながら、従来に比べて開口率も向上させることができる効果を有する。

【0059】そして、本発明では前記ゲート電極102、半導体層110、ソース電極112、ドレイン電極114からなる薄膜トランジスタTを構成することにおいて、従来の薄膜トランジスタと比較した場合に、前記半導体層110の上部層に別途の緩衝層を形成する点と、前記ソース電極112とドレイン電極114とを透明導電性物質で形成する点と、前記ドレイン電極114を画素電極116から延長形成するという点と、前記ソース電極112をデータ配線134と別途の第1コンタクトホール124を通して接続するという点で異なる。

【0060】以下、前記実施例1による液晶表示装置用アレー基板の製造工程について説明する。

【0061】図14ないし23は、本発明の第1実施例による液晶表示装置用アレー基板を製造段階別に示した50

平面図及び断面図である。

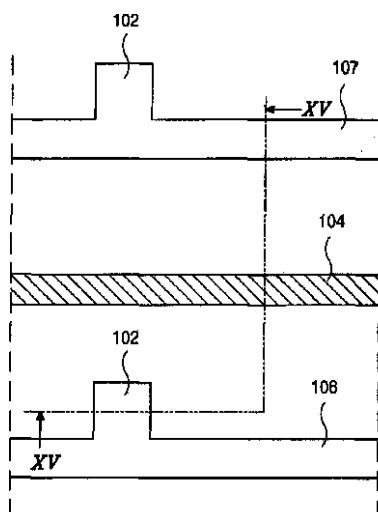

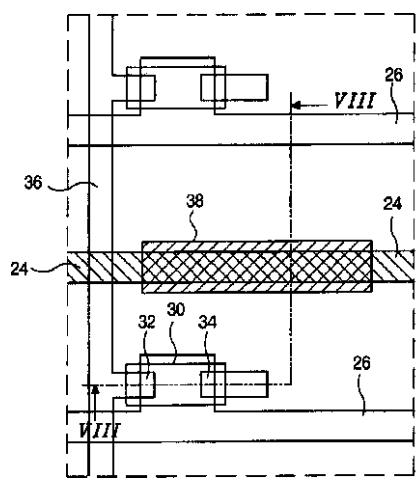

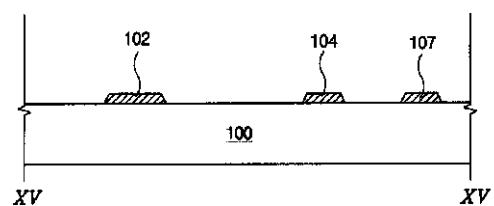

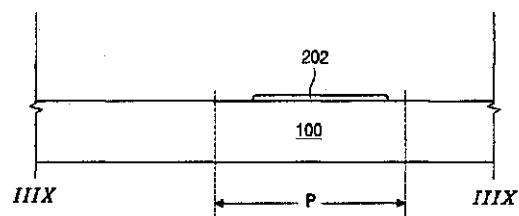

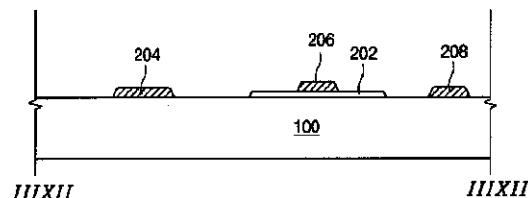

【0062】図14は、本発明の第1実施例による液晶表示装置用アレー基板の製造工程を示した概略的な平面図であって、図15は本発明の第1実施例による液晶表示装置用アレー基板の製造工程を示した概略的な断面図であり、透明基板100上の第1方向にゲート電極102を含むゲート配線106を、前記ゲート配線106と平行な方向に一定間隔をおいて離隔される共通配線104を形成する段階を示す。

【0063】前記ゲート配線106及び共通配線104は、下部層をアルミニウムネオジム(AlNd)で形成し、その上部層をモリブデン(Mo)のように化学的耐蝕性が強い金属で形成された二重層で形成することが望ましい。

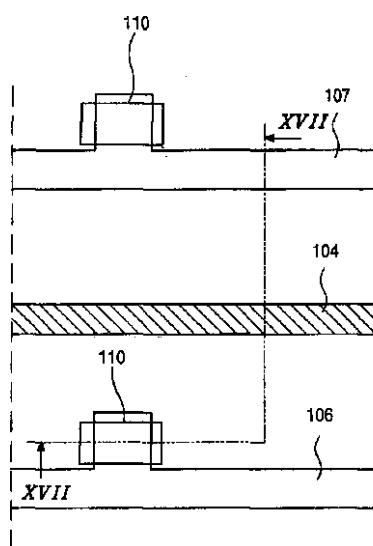

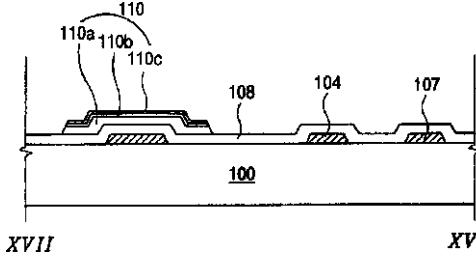

【0064】図16は、本発明の第1実施例による液晶表示装置用アレー基板の製造工程を示した概略的な平面図であって、図17は本発明の第1実施例による液晶表示装置用アレー基板の製造工程を示した概略的な断面図であり、前記ゲート配線106及び共通配線104が形成された基板上にゲート絶縁膜108及び別途の緩衝層110cを有する半導体層110を形成する段階を示す。

【0065】前記製造段階に対する最も望ましい工程例としては、前記ゲート配線106及び共通配線104が形成された基板上にシリコン窒化膜(SiNx)を蒸着してゲート絶縁膜108を形成して、連続的に非晶質シリコン(a-Si)、不純物非晶質シリコン(n+a-Si)をPECVD(Plasma Enhanced Chemical Vapor Deposition)を利用して蒸着した後、前記不純物非晶質シリコン上にチタン(Ti)またはクロム(Cr)中いずれか一つの金属物質をスパッタリング(sputtering)蒸着を利用して蒸着した後、前記非晶質シリコン、不純物非晶質シリコン、金属物質をパターニング(patterning)して各々アクティブ層110a、オーミックコンタクト層110b、緩衝層110cを形成する。

【0066】前記緩衝層110cは、追って前記半導体層110上に形成される透明導電性物質と前記半導体層110との間の接触抵抗を緩衝させるために形成するものである。

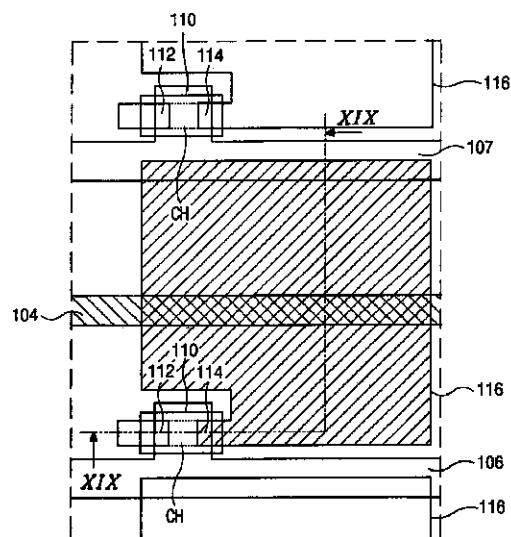

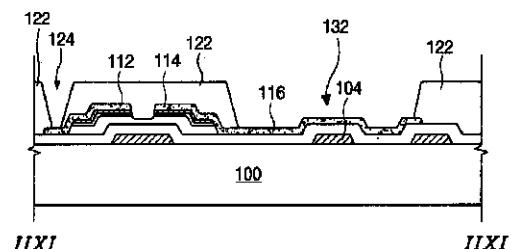

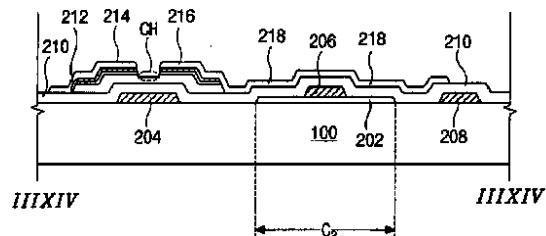

【0067】図18は、本発明の第1実施例による液晶表示装置用アレー基板の製造工程を示した概略的な平面図であって、図19は本発明の第1実施例による液晶表示装置用アレー基板の製造工程を示した概略的な断面図であり、前記緩衝層110cを含む半導体層110が形成された基板上に、透明導電性物質を利用してドレイン電極114を含む画素電極116と前記ドレイン電極114に対して一定間隔をおいて離隔されて配置されるソース電極112とを形成する段階を示す。

【0068】この段階では前記画素電極116の一部領

域を延ばしてドレイン電極114を形成することを特徴とする。

【0069】前記ソース電極112は、後続工程でデータ配線と接続される。前記ソース電極112とドレイン電極114と画素電極116を構成する物質は、透明導電性物質中ITOですることが最も望ましい。

【0070】前記断面図に示したように、前記透明導電性物質はドレイン電極114と画素電極116が連続でつながって形成されていて、前段のゲート配線106と一定間隔オーバーラップされるように形成する。

【0071】前記前段ゲート配線106とオーバーラップされて形成される蓄電器は、保存蓄電器としての目的よりむしろ開口率向上の目的を有する。

【0072】この段階では、ソース電極112とドレイン電極114と画素電極116を形成した後、前記ソース電極112とドレイン電極114との間に緩衝層110cとオーミックコンタクト層110bとを、前記ソース電極112とドレイン電極114と画素電極116のパターニング工程に伴うエッチング工程で除去してその下部層をなすアクティブ層110aを露出してチャネルCHを形成する段階をさらに含む。

【0073】前記エッチング工程は、乾式エッチング(dry etching)方式ですることが望ましい。

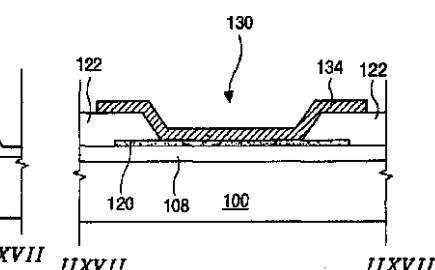

【0074】図20は、本発明の第1実施例による液晶表示装置用アレー基板の製造工程を示した概略的な平面図であって、図21は本発明の第1実施例による液晶表示装置用アレー基板の製造工程を示した概略的な断面図であり、前記ソース電極112とドレイン電極114と画素電極116が形成された基板上に、前記ソース電極112を一部露出させる第1コンタクトホール124及び前記画素電極116と対応する面積を有し、前記画素電極116を露出させる開口部132を有する保護層122を形成する段階を示す。

【0075】前記断面図を通して見る時、前記開口部132は、画素電極116上に形成された保護層122を除去して形成したものであって、前記画素電極116が電圧印加時に電界を形成して、この電界によって液晶が配列されるようになるので、前記画素電極116上に位置する保護層122を除去することによって、前記開口部132は、画素電極116によって生成する電界の強さが弱まることを防止する。

【0076】本発明で、前記画素電極116を保護層122を形成する前の工程で形成する理由は、上述したように蓄電器の容量は二電極体間の距離と比例関係であるために、画素電極116と共通配線104との間の間隔を狭めるためである。

【0077】すなわち、従来のアレー工程では保護層形成工程の次に画素電極工程が進められるので、画素電極と共に配線間にはゲート絶縁膜と保護層で構成された二重層の絶縁層が介在されて、前記電極体間の距離を狭め

るための方法として、データ配線物質でなされたストレージ電極を形成する方法が利用されることによって、このような構造による開口率低下を甘受しなければならなかった。

【0078】しかし、前記本発明による第1実施例では画素電極116の形成工程を保護層122の形成工程より先行して進めるので、別途のストレージ電極を形成しなくても既存のような水準の保存静電容量を確保すると同時に、開口率まで向上させることができる効果を有する。

【0079】前記保護層122は、絶縁物質でなされ、望ましくは段差特性が優秀なアクリル樹脂(acrylic resin)で形成する。

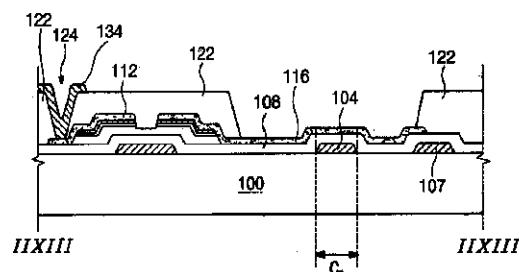

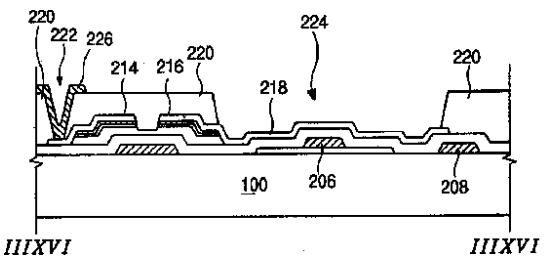

【0080】図22は、本発明の第1実施例による液晶表示装置用アレー基板の製造工程を示した概略的な平面図であって、図23は本発明の第1実施例による液晶表示装置用アレー基板の製造工程を示した概略的な断面図であり、前記保護層122が形成された基板上の、前記ゲート配線106及び共通配線104と交差する第2の方向に、前記第1コンタクトホール124を通してソース電極112と接続されるデータ配線134を形成する段階を示す。

【0081】前記データ配線134は、化学的耐蝕性が強く、機械的な強度が高いモリブデン(Mo)、ニッケル(Ni)、クロム(Cr)、タンクステン(W)中いずれか一つの金属で形成することが望ましい。

【0082】前記断面図で示したように、本発明では別途のストレージ電極の構成なしに、ゲート絶縁膜108でなされた単一層を絶縁体として、共通配線104と画素電極116を二電極体として保存蓄電器を構成することによって、従来のものの保存静電容量水準を維持しながらも、保存蓄電器C<sub>1</sub>形成領域を減らすことができる、従来より開口率を向上させることができる。

【0083】そして、前記液晶表示装置用アレー基板を外部回路と接続するために、前記ゲート配線及びデータ配線の端に各々ゲート及びデータパッドを構成する。

【0084】以下、記述される内容は前記図14ないし23による製造段階に示されるゲート及びデータパッド部構造に対する説明である。

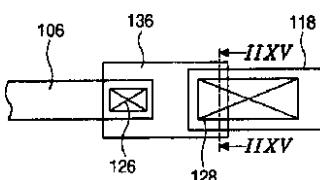

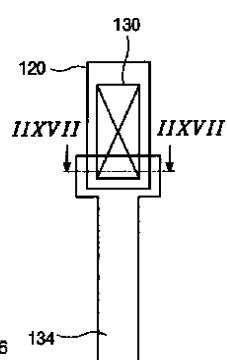

【0085】図24ないし27は、前記第1実施例によるゲート及びデータパッドの平面図及び断面図である。

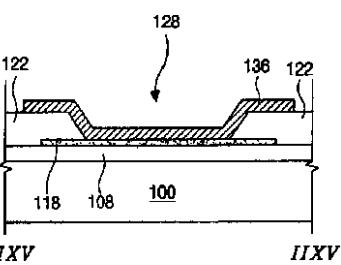

【0086】図24は、本発明の第1実施例による液晶表示装置用アレー基板のゲートパッドの概略的な平面図であって、図25は本発明の第1実施例による液晶表示装置用アレー基板のゲートパッドの概略的な断面図であるが、ゲート配線106の端部に一定間隔をあいて離隔されてゲートパッド118が形成されていて、このゲート配線106及びゲートパッド118はゲートリンク部136によって相互連結されている。

【0087】前記ゲートリンク部136とゲート配線1

06及びゲートリンク部136とゲートパッド118は各々第2コンタクトホール126及び第3コンタクトホール128を通して接続される。

【0088】前記第3コンタクトホール128は、その左側はゲート配線106とゲートパッド118を接続して、右側は前記ゲートパッド120と外部回路を接続する役割をする。

【0089】前記ゲートパッド118は、前記図18の画素電極形成工程で透明導電性物質で形成されることを特徴とし、前記ゲートリンク部136はデータ配線形成工程でデータ配線(図示せず)と同一物質で形成されることを特徴とする。

【0090】前記ゲートパッド118を前記画素電極形成工程で形成する理由は、画素電極(図18の116)を形成する透明導電性物質は一般的に外部回路との接続のためのパッド電極で利用されているため、別途のパッド電極を構成せずに前記ゲートパッド118を通して直ちに外部回路と接続するためである。

【0091】前記断面図は、前記ゲートリンク部136と接続されたゲートパッド118部の断面構造に係り、透明基板100上にはゲート絶縁膜108、ゲートパッド118、保護層122、ゲートリンク部136が順序どおり積層されるが、前記保護層122には前記ゲートパッド118を一部露出させる第3コンタクトホール128が形成されていて、前記第3コンタクトホール128を通して前記ゲートリンク部136はゲートパッド118と接続されている。

【0092】この際、前記ゲート配線106とゲートパッド118の安定した接続のために、前記ゲートリンク部136の幅はゲートパッド118幅より一定の幅だけ広く形成することが望ましい。

【0093】図26は、本発明の第1実施例による液晶表示装置用アレー基板のデータパッドの概略的な平面図であって、図27は本発明の第1実施例による液晶表示装置用アレー基板のデータパッドの概略的な断面図であるが、データ配線134が形成されていて、このデータ配線134の端部と一定間隔オーバーラップされてデータパッド120が形成されている。

【0094】前記データパッド120は、前記図24のゲートパッド118と同一の工程で同一物質で形成されることを特徴とする。

【0095】すなわち、前記データパッド120は、画素電極116の形成工程で形成されるので、前記データパッド120を形成した後に、前記データパッド120と連結されてデータ配線134を形成する。

【0096】前記データパッド120の部分においては、データ配線134とデータパッド120との間の安定した接続のために、前記データパッド120とオーバーラップするデータ配線134の端部を前記データパッ

ド120と一定の面積だけ重複するように形成すること

が望ましい。

【0097】前記データ配線134とデータパッド120は前記第4コンタクトホール130を通して接続され、前記第4コンタクトホール130は、前記データ配線134とデータパッド120との間の接続だけでなく、前記データパッド120と外部回路とを接続させる。

【0098】前記断面図では、透明基板100上にゲート絶縁膜108、データパッド120、保護層122、データ配線134が順序どおり積層されているが、前記保護層122にはデータ配線134とデータパッド120を連結させるデータパッドコンタクトホール130が形成されている。

【0099】このように、本発明によるゲート及びデータパッド部構造は、画素電極工程を保護層形成工程前に行うことによって、工程数の増加なしに各パッド部の積層構造を単純化させることができる長所を有する。

【0100】以下、前記第1実施例と保存蓄電器を異なるように構成する他の実施例について説明する。

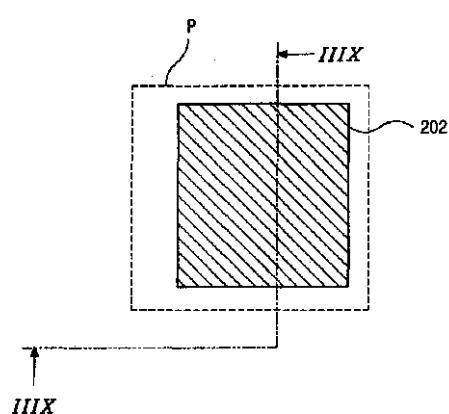

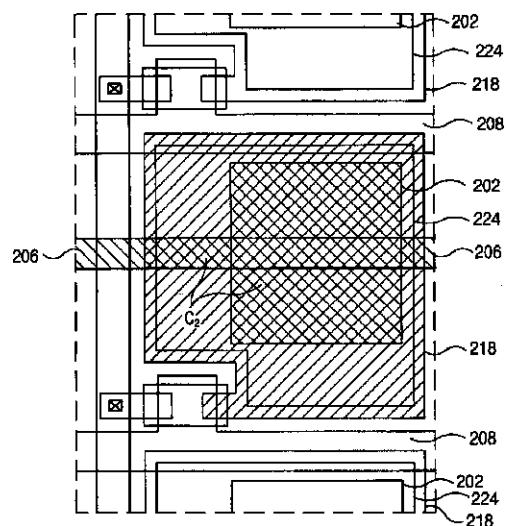

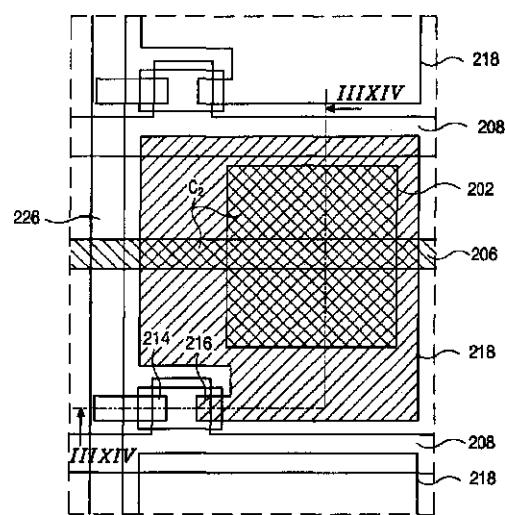

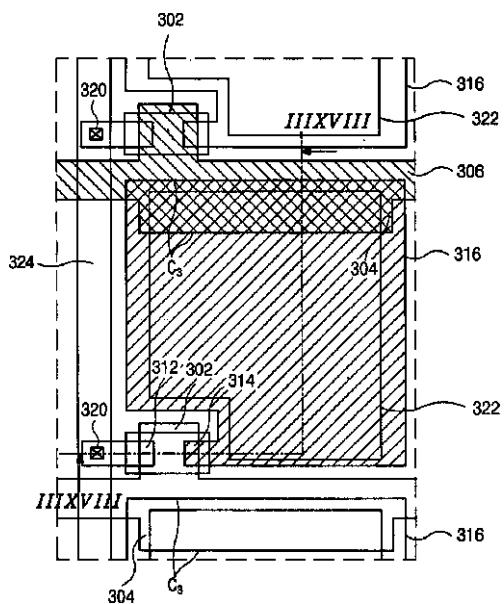

【0101】<第2実施例>図28は、本発明の第2実施例による液晶表示装置用アレー基板の概略的な平面図である。

【0102】図示したように、前記第2実施例による保存蓄電器C<sub>2</sub>は、画素領域内に位置し、透明導電性物質でなされた共通電極202と、この共通電極202と接続され、ゲート配線208と平行な方向に一定間隔を置いて離隔されて形成された共通配線206と、この共通配線206から絶縁体によって絶縁されて、前段ゲート配線208と一定面積オーバーラップすると共に、前記共通電極202を含む画素領域に形成されて、透明導電性物質からなる画素電極218によって構成される。

【0103】そして、前記画素電極218と対応する領域には前記画素電極218を露出させる開口部224が形成されている。

【0104】前記共通配線206は、図示していない上部基板の共通電極を通して電圧を印加される方式で駆動されて、この共通配線206と接続されるように形成された共通電極202に電圧を印加する。

【0105】すなわち、第2実施例では透明導電性物質からなる共通電極202を構成することによって、開口率を落とさずに、保存静電容量を大幅に増加させることができ効果を有する。

【0106】図面に提示しなかったが、前記共通配線206と画素電極218間に介在された絶縁体はゲート絶縁膜であり、前記開口部224は保護層に含まれる。

【0107】また、前記第2実施例による薄膜トランジスタ、ゲート及びデータ配線、ゲート及びデータパッドの構造は前記第1実施例と一緒に構成することができる。

【0108】以下、前記第2実施例の製造工程に対して

説明する。図29ないし図36は、本発明の第2実施例による液晶表示装置用アレー基板の製造工程を示した概略的な図面である。

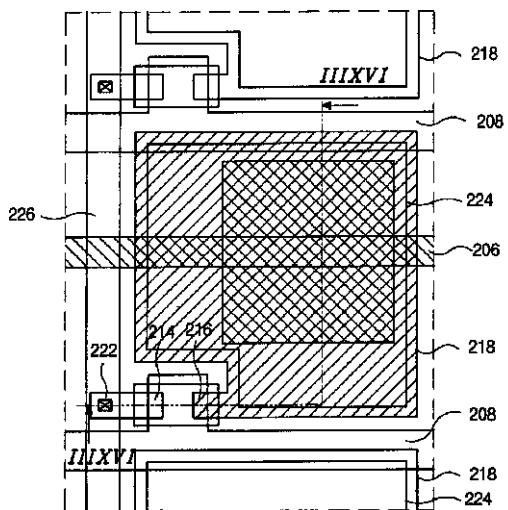

【0109】図29は、本発明の第2実施例による液晶表示装置用アレー基板の製造工程を示した概略的な平面図であって、図30は本発明の第2実施例による液晶表示装置用アレー基板の製造工程を示した概略的な断面図であり、透明基板100上の画素領域Pに透明導電性物質を利用して、一定面積を有する共通電極202を形成する段階を示す。

【0110】前記透明導電性物質はITOを使用することが最も望ましい。従来は開口率を考慮して共通配線の面積を開口率を大きく落とさない範囲で形成したが、前記第2実施例では透明導電性物質で共通電極202を形成することによって、前記第1実施例で有する開口率と同一の水準の開口率を維持し、保存静電容量をさらに増やすことができることを特徴とする。

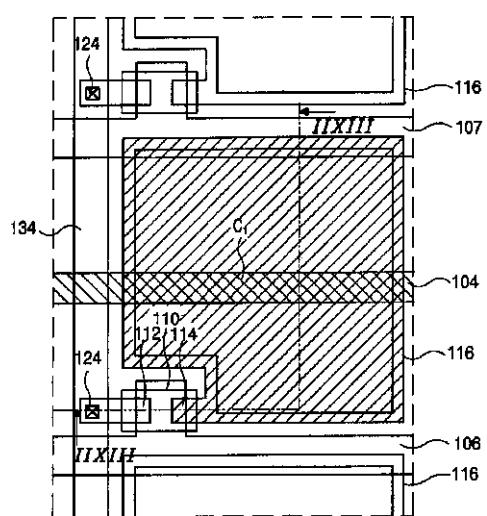

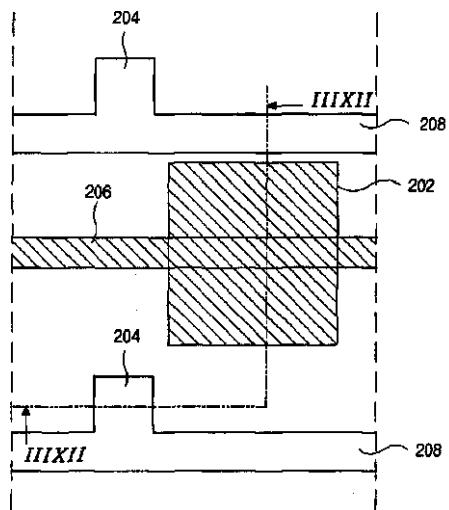

【0111】図31は、本発明の第2実施例による液晶表示装置用アレー基板の製造工程を示した概略的な平面図であって、図32は本発明の第2実施例による液晶表示装置用アレー基板の製造工程を示した概略的な断面図であり、前記共通電極202が形成された基板上の第1の方向にゲート電極204を含むゲート配線208及び前記ゲート配線208と平行な方向に一定間隔をおいて離隔され、前記共通電極202とオーバーラップする共通配線206を形成する段階を示す。

【0112】この際、断面図と同じく、前記共通配線206を前記共通電極202と接続されるように構成することを特徴とする。

【0113】この共通配線206は、共通方式で駆動されて、この共通配線206と接続された共通電極202に電圧を印加する。

【0114】図33は、本発明の第2実施例による液晶表示装置用アレー基板の製造工程を示した概略的な平面図であって、図34は本発明の第2実施例による液晶表示装置用アレー基板の製造工程を示した概略的な断面図であり、前記ゲート配線208及び共通配線206が形成された基板上にゲート絶縁膜210を形成して、このゲート絶縁膜210上のゲート電極204と対応する位置にチタン、ニッケルのいずれか一つの金属物質を上部層に含む半導体層212を形成して、前記半導体層212が形成された基板上に透明導電性物質を利用して前記半導体層212とオーバーラップして、相互に一定間隔をおいて離隔されたソース電極214とドレイン電極216とを形成して、このドレイン電極216と接続された画素電極218を形成する段階を示す。

【0115】前記断面図では、前記ゲート絶縁膜210及び半導体層212が形成された基板上に配置された透明導電性物質からなるソース電極214とドレイン電極216とを画素電極218の断面構造と連結させて図示

した。

【0116】前記段階でのゲート絶縁膜210、半導体層212、チャネルCHの形成工程は前記第1実施例による該工程と同一に適用することができる。

【0117】図35は、本発明の第2実施例による液晶表示装置用アレー基板の製造工程を示した概略的な平面図であって、図36は本発明の第2実施例による液晶表示装置用アレー基板の製造工程を示した概略的な断面図であり、前記ソース電極214とドレイン電極216と画素電極218が形成された基板上に第1コンタクトホール222及び開口部224を有する保護層220を形成して、前記第1コンタクトホール222を通してソース電極214と接続されると共に、前記ゲート配線208及び共通配線206と交差する第2の方向に延在するデータ配線226を形成する段階を示す。

【0118】前記第2実施例では透明導電性物質を使用して共通電極202を形成することにより従来のものより画素領域に相当な面積を有するように形成して、このような共通電極202に電圧を印加することができる共通配線206を構成することによって、前記平面図で網目紋で示した領域のように大容量の保存蓄電器C<sub>2</sub>を有することが可能であり、断面図に示したように、共通電極202は透明導電性物質で形成されるために、保存蓄電器C<sub>2</sub>形成領域中の共通配線206の形成領域Iのみが開口率減少領域になるので、結果として、前記第2実施例では共通電極202に対する別途の工程が要求されるが、従来のものより大容量の保存静電容量を確保しながらも開口率を向上させることができる長所を有する。

【0119】一方、図面に提示しないが、前記第2実施例によるゲート及びデータパッドは前記第1実施例と同一な構造にすることができる。

【0120】以下、本発明による第3実施例では前記第1、2実施例のように保護層を画素電極上部に形成する工程を適用しながら、保存蓄電器を前段ゲート方式で構成する実施例に関する。

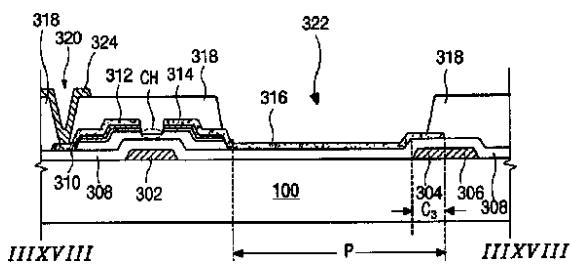

【0121】<第3実施例>図37は、本発明の第3実施例による液晶表示装置用アレー基板の概略的な平面図であって、前記第1、2実施例と重複される説明は省略して、保存蓄電器構造を中心に説明する。

【0122】図示したように、第1方向にゲート電極302及びこのゲート電極302と他の辺から延長形成されたストレージ電極304と、このストレージ電極304を覆いながら画素領域上に形成された画素電極316と、この画素電極316に接続されて形成されたドレン電極314と、このドレン電極314と一定間隔をおいて離隔されて形成されたソース電極312と、このソース電極312と第1コンタクトホール320に接続されたデータ配線324が形成されている。

【0123】前記画素電極316と対応する領域には画素電極316を露出させる開口部322が形成されてい

て、この開口部322は画素電極316の上部に形成された図示されていない保護層に形成されたものである。

【0124】図面に提示しなかったが、前記ストレージ電極304と画素電極316間にはゲート絶縁膜が介在されて前記網目紋で示した領域は、保存蓄電器C<sub>3</sub>をなす。

【0125】前記第3実施例では、前段ゲート方式で保存蓄電器を構成するために、上述したように共通方式保存蓄電器構造より開口率の点で有利であり、画素電極上に保護層を形成する構造によって、ストレージ電極と画素電極間の絶縁体をゲート絶縁膜単一層で構成するため、従来の前段ゲート方式より保存静電容量を向上させることができると有する。

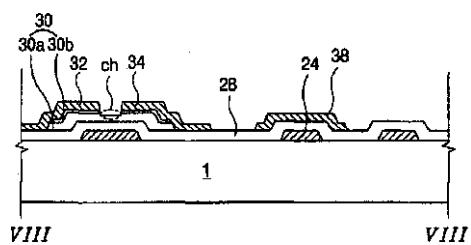

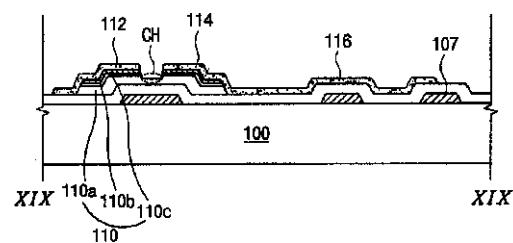

【0126】図38は、前記図37の切断線“I I I X VI I I - I I I X VI I I”によって切断された断面図であって、製造工程を示す図である。

【0127】図示したように、前記第3実施例によるストレージ電極304は、前段ゲート方式を取る場合には、画素領域P側に一定方向延長形成されることを特徴として、前記ストレージ電極304とオーバーラップしている画素電極316と保存蓄電器C<sub>3</sub>をなす。

【0128】そして、前記断面図を参照すると、前記第3実施例による製造工程は、ゲート電極302及びストレージ電極304を含むゲート配線306を形成する段階と、このゲート電極302とストレージ電極304とを含むゲート配線306上にゲート絶縁膜308を基板全面にかけて形成する段階と、このゲート絶縁膜308が形成された基板上のゲート電極302と対応する位置にチタン、ニッケル中いずれか一つの金属物質からなる上部層を含む半導体層310を形成する段階と、この半導体層310が形成された基板上に、透明導電性物質を利用して前記半導体層310と一部オーバーラップするドレン電極314を含む画素電極316とこのドレン電極314と一定間隔をおいて離隔されて配置されるソース電極312とを形成する段階と；前記ソース電極312とドレン電極314との間にチャネルCHを形成する段階と、前記ソース電極312及び画素電極316を各々露出させる第1コンタクトホール320及び開口部322を有する保護層318を形成する段階と、前記第1コンタクトホール320を通してソース電極312と接続されるデータ配線324を形成する段階とを含む。

【0129】図面に提示しなかったが、前記ゲート配線306とデータ配線324は、相互に交差する第1の方向と第2の方向に形成され、前記ゲート配線306とデータ配線324の端に形成されるゲート及びデータパッド部の構造は前記第1実施例構造と同様にすることができる。

【0130】しかし、本発明は前記実施例に限らず、本発明の趣旨に外れない範囲で多様に変更して実施でき \*50

\*る。

#### 【0131】

【発明の効果】このように、本発明による液晶表示装置用アレー基板ではゲート配線形成工程で共通電極を形成して、ソース及びドレン電極形成工程で、透明導電性物質を利用してソース及びドレン電極と画素電極を形成して、その次の工程で保護層を形成することによって、共通電極と画素電極間の距離を狭めることができて、保存静電容量を増やすことができ、これにより別途のストレージ電極を省略できるので、開口率を向上させることができて、ストレージ電極を形成する場合には透明導電性物質を利用して、保存静電容量を大幅に増加させると共に開口率を従来のものより向上させることができる。

【0132】また、前記製造工程を適用して、前段ゲート方式でストレージ電極を構成する場合にも、共通方式より開口率を向上させると共に、従来の前段ゲート方式よりストレージ電極と画素電極間の距離を狭めて、保存静電容量を向上させることができるので、本発明による液晶表示装置用アレー基板によると、画質特性と開口率と共に向上させることができて製品信頼性及び収率が向上されて、高画質、高精度製品を提供できる長所を有する。

#### 【図面の簡単な説明】

【図1】従来の液晶表示装置用液晶パネルを部分的に示した概略的な断面図。

【図2】共通方式の保存蓄積容量を有する従来の液晶表示装置用アレー基板を部分的に示した概略的な平面図。

【図3】従来の液晶表示装置用アレー基板の製造工程を示した概略的な平面図。

【図4】従来の液晶表示装置用アレー基板の製造工程を示した概略的な断面図。

【図5】従来の液晶表示装置用アレー基板の製造工程を示した概略的な平面図。

【図6】従来の液晶表示装置用アレー基板の製造工程を示した概略的な断面図。

【図7】従来の液晶表示装置用アレー基板の製造工程を示した概略的な平面図。

【図8】従来の液晶表示装置用アレー基板の製造工程を示した概略的な断面図。

【図9】従来の液晶表示装置用アレー基板の製造工程を示した概略的な平面図。

【図10】従来の液晶表示装置用アレー基板の製造工程を示した概略的な断面図。

【図11】従来の液晶表示装置用アレー基板の製造工程を示した概略的な平面図。

【図12】従来の液晶表示装置用アレー基板の製造工程を示した概略的な断面図。

【図13】本発明の第1実施例による液晶表示装置用アレー基板の概略的な平面図。

- 【図14】本発明の第1実施例による液晶表示装置用アレー基板の製造工程を示した概略的な平面図。

- 【図15】本発明の第1実施例による液晶表示装置用アレー基板の製造工程を示した概略的な断面図。

- 【図16】本発明の第1実施例による液晶表示装置用アレー基板の製造工程を示した概略的な平面図。

- 【図17】本発明の第1実施例による液晶表示装置用アレー基板の製造工程を示した概略的な断面図。

- 【図18】本発明の第1実施例による液晶表示装置用アレー基板の製造工程を示した概略的な平面図。

- 【図19】本発明の第1実施例による液晶表示装置用アレー基板の製造工程を示した概略的な断面図。

- 【図20】本発明の第1実施例による液晶表示装置用アレー基板の製造工程を示した概略的な平面図。

- 【図21】本発明の第1実施例による液晶表示装置用アレー基板の製造工程を示した概略的な断面図。

- 【図22】本発明の第1実施例による液晶表示装置用アレー基板の製造工程を示した概略的な平面図。

- 【図23】本発明の第1実施例による液晶表示装置用アレー基板の製造工程を示した概略的な断面図。

- 【図24】本発明の第1実施例による液晶表示装置用アレー基板のゲートパッドの概略的な平面図。

- 【図25】本発明の第1実施例による液晶表示装置用アレー基板のゲートパッドの概略的な断面図。

- 【図26】本発明の第1実施例による液晶表示装置用アレー基板のデータパッドの概略的な平面図。

- 【図27】本発明の第1実施例による液晶表示装置用アレー基板のデータパッドの概略的な断面図。

- 【図28】本発明の第2実施例による液晶表示装置用アレー基板の概略的な平面図。

- 【図29】本発明の第2実施例による液晶表示装置用ア\*

\*レー基板の製造工程を示した概略的な平面図。

【図30】本発明の第2実施例による液晶表示装置用アレー基板の製造工程を示した概略的な断面図。

【図31】本発明の第2実施例による液晶表示装置用アレー基板の製造工程を示した概略的な平面図。

【図32】本発明の第2実施例による液晶表示装置用アレー基板の製造工程を示した概略的な断面図。

【図33】本発明の第2実施例による液晶表示装置用アレー基板の製造工程を示した概略的な平面図。

10 【図34】本発明の第2実施例による液晶表示装置用アレー基板の製造工程を示した概略的な断面図。

【図35】本発明の第2実施例による液晶表示装置用アレー基板の製造工程を示した概略的な平面図。

【図36】本発明の第2実施例による液晶表示装置用アレー基板の製造工程を示した概略的な断面図。

【図37】本発明の第3実施例による液晶表示装置用アレー基板の概略的な平面図。

【図38】前記図37の切断線“*I I I X V I I I - I I I X V I I I*”によって切断された断面図。

20 【符号の説明】

102：ゲート電極

104：共通配線

106：ゲート配線

110：半導体層

112：ソース電極

114：ドレイン電極

116：画素電極

124：第1コンタクトホール

132：開口部

30 134：データ配線

【図1】

【図24】

【図2】

【図14】

【図3】

【図4】

【図5】

【図10】

【図7】

【図8】

【図15】

【図9】

【図11】

【図25】

【図26】

【図12】

【図13】

【図16】

【図17】

【図27】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図28】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【四三八】

フロントページの続き

(72)発明者 リー ジェ - キュン

大韓民国 435 - 040 , ギヨンギ - ド , グン

ポ - シ , サンボン - ドン , ウールック ジ

ユーコン アパートメント 707 - 1701

(72)発明者 ファン ヨン - サップ

大韓民国 440 - 302 , ギヨンギ - ド , スウ

オン - シ , ジヤンガン - グ , ジヨンジヤ 2

- ドン , ドンシン アパートメント , 207

- 804

F ターム(参考) 2H090 HA04 HA06 HB07 HD05 HD07

LA01

2H092 GA17 GA25 GA28 HA04 JA24

JB61 NA07 NA21

5F110 AA30 BB01 CC07 EE04 EE06

EE14 FF03 GG02 GG15 GG45

HK02 HK04 HK09 HK21 HK33

HK35 HM18 NN72 NN73 QQ09

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于液晶显示装置的阵列基板及其制造方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 公开(公告)号        | <a href="#">JP2003043513A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 公开(公告)日 | 2003-02-13 |

| 申请号            | JP2002156001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 申请日     | 2002-05-29 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | Eruji. 菲利普斯杜天公司，有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| [标]发明人         | チエジースン<br>リージエキュン<br>ファンヨンサップ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 发明人            | チエジースン<br>リージエキュン<br>ファンヨンサップ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| IPC分类号         | G02F1/1333 G02F1/1343 G02F1/136 G02F1/1362 G02F1/1368 H01L29/786                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| CPC分类号         | G02F1/13458 G02F1/1362 G02F1/136213                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| FI分类号          | G02F1/1343 G02F1/1333.505 G02F1/1368 H01L29/78.612.C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| F-TERM分类号      | 2H090/HA04 2H090/HA06 2H090/HB07 2H090/HD05 2H090/HD07 2H090/LA01 2H092/GA17 2H092/GA25 2H092/GA28 2H092/HA04 2H092/JA24 2H092/JB61 2H092/NA07 2H092/NA21 5F110/AA30 5F110/BB01 5F110/CC07 5F110/EE04 5F110/EE06 5F110/EE14 5F110/FF03 5F110/GG02 5F110/GG15 5F110/GG45 5F110/HK02 5F110/HK04 5F110/HK09 5F110/HK21 5F110/HK33 5F110/HK35 5F110/HM18 5F110/NN72 5F110/NN73 5F110/QQ09 2H190/HA04 2H190/HA06 2H190/HD05 2H190/HD07 2H190/LA01 2H192/AA24 2H192/CB05 2H192/CB61 2H192/CC32 2H192/CC44 2H192/DA02 2H192/DA12 2H192/DA42 2H192/DA63 2H192/DA65 2H192/FA65 |         |            |

| 优先权            | 1020010029811 2001-05-29 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

### 摘要(译)

解决的问题：提供一种用于高图像质量和高精度液晶显示装置的阵列基板，与现有基板相比，该阵列基板能够在不减小存储电容的情况下提高开口率。在用于液晶显示装置的阵列基板中，基板：在第一方向上形成在基板的上部上的栅极布线；平行于栅极布线并隔开一定距离地形成的公共布线。布线；形成在栅极布线和公共布线上的栅极绝缘膜；形成在栅极绝缘膜上的半导体层；形成为与半导体层和透明导电材料重叠的漏电极。源电极由透明导电材料制成并与漏电极分开；第一接触孔暴露出源电极，而开口暴露出像素电极。一种液晶显示装置，包括：形成在电极上的保护层；数据线，该数据线通过第一接触孔连接到源极并在与栅极线相交的第二方向上形成提供一种阵列基板供使用。