(19)日本国特許庁( J P )

# 公開特許公報 ( A ) (11)特許出願公開番号

特開2002 - 202527

(P2002 - 202527A)

(43)公開日 平成14年7月19日(2002.7.19)

(51) Int.CI<sup>7</sup>

識別記号

G 0 2 F 1/1368

1/1345

F I

G 0 2 F 1/1345

1/136

テマコード(参考)

2 H 0 9 2

500

審査請求 未請求 請求項の数 150 L (全 14数)

(21)出願番号 特願2000 - 399870(P2000 - 399870)

(71)出願人 000004237

日本電気株式会社

東京都港区芝五丁目7番1号

(22)出願日 平成12年12月28日(2000.12.28)

(71)出願人 000181284

鹿児島日本電気株式会社

鹿児島県出水市大野原町2080

(72)発明者 田中 宏明

東京都港区芝五丁目7番1号 日本電気株式会社内

(74)代理人 100081433

弁理士 鈴木 章夫

最終頁に続く

(54)【発明の名称】アクティブマトリクス型液晶表示装置

## (57)【要約】

【課題】 アクティブマトリクス基板に形成される走査線、信号線等の配線の構造を複雑化することなく、A1ヒロックを抑制し、かつ接続抵抗を低減して接続部の信頼性を向上する。

【解決手段】 透明絶縁性基板10上に薄膜トランジスタ14及び画素部13が形成されたアクティブマトリクス基板1を含むアクティブマトリクス型液晶表示装置において、前記薄膜トランジスタ14のゲート電極15及びこれに接続される走査線11は、TiN/Ti/A1構造、あるいは、TiN/A1/Ti構造、さらには、TiN/Ti/A1/Ti構造とする。A1膜に接してTi膜が存在することで、A1膜でのA1ヒロックの発生を抑制する。また、最上層にTiN膜が存在することで、走査線端子部22での表面腐食を抑制し、走査線端子部22での接続抵抗の増加を抑制するとともに、信頼性を高める。

## 【特許請求の範囲】

【請求項1】 透明絶縁性基板上に薄膜トランジスタ及び画素電極が形成されたアクティブマトリクス型液晶表示装置において、前記薄膜トランジスタのゲート電極及びこれに接続される走査線は、アルミニウム膜の上層と下層の少なくとも一方にチタン膜が形成され、かつ最上層には窒化チタン膜が形成された多層配線構造膜とされ、かつ前記窒化チタン膜は窒素濃度が25原子%以上であることを特徴とするアクティブマトリクス型液晶表示装置。

【請求項2】 透明絶縁性基板上に薄膜トランジスタ及び画素電極が形成されたアクティブマトリクス型液晶表示装置において、前記薄膜トランジスタのゲート電極及びこれに接続される走査線、前記画素電極に対向配置される共通電極及びこれに接続される共通線は、アルミニウム膜の上層と下層の少なくとも一方にチタン膜が形成され、かつ最上層には窒化チタン膜が形成された多層配線構造膜とされ、かつ前記窒化チタン膜は窒素濃度が25原子%以上であることを特徴とするアクティブマトリクス型液晶表示装置。

【請求項3】 透明絶縁性基板上に薄膜トランジスタ及び画素電極が形成されたアクティブマトリクス型液晶表示装置において、前記薄膜トランジスタのソース電極、ドレイン電極及びこれに接続される信号線は、アルミニウム膜の下層、または上層と下層の両方にチタン膜が形成され、かつ最上層には窒化チタン膜が形成された多層配線構造膜とされ、かつ前記窒化チタン膜は窒素濃度が25原子%以上であることを特徴とするアクティブマトリクス型液晶表示装置。

【請求項4】 透明絶縁性基板上に薄膜トランジスタ及び画素電極が形成されたアクティブマトリクス型液晶表示装置において、前記薄膜トランジスタのソース電極及びこれに接続される画素電極、ドレイン電極及びこれに接続される信号線は、アルミニウム膜の下層、または上層と下層の両方にチタン膜が形成され、かつ最上層には窒化チタン膜が形成された多層配線構造膜とされ、かつ前記窒化チタン膜は窒素濃度が25原子%以上であることを特徴とするアクティブマトリクス型液晶表示装置。

【請求項5】 透明絶縁性基板上に薄膜トランジスタ及び画素電極が形成されたアクティブマトリクス型液晶表示装置において、前記薄膜トランジスタのゲート電極及びこれに接続される走査線は、アルミニウム膜の上層と下層の少なくとも一方にチタン膜が形成され、前記薄膜トランジスタのソース電極、ドレイン電極及びこれに接続される信号線は、アルミニウム膜の下層、または上層と下層の両方にチタン膜が形成された多層配線構造膜とされ、その上で前記各線の最上層には窒化チタン膜が形成され、かつ前記窒化チタン膜

チタン膜は窒素濃度が25原子%以上であることを特徴とするアクティブマトリクス型液晶表示装置。

【請求項6】 透明絶縁性基板上に薄膜トランジスタ及び画素電極が形成されたアクティブマトリクス型液晶表示装置において、前記薄膜トランジスタのゲート電極及びこれに接続される走査線、前記画素電極に対向配置される共通電極及びこれに接続される共通線は、アルミニウム膜の上層と下層の少なくとも一方にチタン膜が形成され、前記薄膜トラン

ジスタのソース電極、ドレイン電極及びこれに接続される信号線は、アルミニウム膜の下層、または上層と下層の両方にチタン膜が形成された多層配線構造膜とされ、その上で前記各線の最上層には窒化チタン膜が形成され、かつ前記窒化チタン膜は窒素濃度が25原子%以上であることを特徴とするアクティブマトリクス型液晶表示装置。

【請求項7】 透明絶縁性基板上に薄膜トランジスタ及び画素電極が形成されたアクティブマトリクス型液晶表示装置において、前記

薄膜トランジスタのゲート電極及びこれに接続される走査線、前記画素電極に対向配置される共通電極及びこれに接続される共通線は、アルミニウム膜の上層と下層の少なくとも一方にチタン膜が形成され、前記薄膜トランジスタのソース電極及びこれに接続される画素電極、ドレイン電極及びこれに接続される信号線は、アルミニウム膜の下層、または上層と下層の両方にチタン膜が形成された多層配線構造膜とされ、その上で前記各線の最上層には窒化チタン膜が形成され、かつ前記窒化チタン膜は窒素濃度が25原子%以上であることを特徴とするアクティブマトリクス型液晶表示装置。

【請求項8】 前記走査線の端部は、外部に電気接続を行うために前記最上層の窒化チタン膜が露呈された走査線接続部が設けられていることを特徴とする請求項1，2，5，6又は7に記載のアクティブマトリクス型液晶表示装置。

【請求項9】 前記信号線の端部は、外部に電気接続を行うために前記最上層の窒化チタン膜が露呈された信号線接続部が設けられていることを特徴とする請求項3，4，5，6又は7に記載のアクティブマトリクス型液晶表示装置。

【請求項10】 前記共通線の端部は、外部に電気接続を行うために前記最上層の窒化チタン膜が露呈された共通線接続部が設けられていることを特徴とする請求項2，6又は7に記載のアクティブマトリクス型液晶表示装置。

【請求項11】 前記薄膜トランジスタは、前記ゲート電極と、前記ゲート電極を覆うように形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された島状の半導体層と、前記半導体層上にチャネルギャップを隔てて形成された前記ソース電極及びドレイン電極とで構成され

る逆スタガ型薄膜トランジスタとして構成されていることを特徴とする請求項1ないし10のいずれかに記載のアクティブマトリクス型液晶表示装置。

【請求項12】 前記多層配線構造膜は、下層から上層に向けて、アルミニウム膜、チタン膜、窒化チタン膜の構造であることを特徴とする請求項1, 2, 5ないし11のいずれかに記載のアクティブマトリクス型液晶表示装置。

【請求項13】 前記多層配線構造膜は、下層から上層に向けて、チタン膜、アルミニウム膜、窒化チタン膜の構造であることを特徴とする請求項1ないし11のいずれかに記載のアクティブマトリクス型液晶表示装置。 10

【請求項14】 前記多層配線構造膜は、下層から上層に向けて、チタン膜、アルミニウム膜、チタン膜、窒化チタン膜の構造であることを特徴とする請求項1ないし11のいずれかに記載のアクティブマトリクス型液晶表示装置。

【請求項15】 前記アルミニウム膜は、アルミニウム、またはアルミニウムを主体とする合金で構成されていることを特徴とする請求項1ないし14のいずれかに記載のアクティブマトリクス型液晶表示装置。 20

#### 【発明の詳細な説明】

##### 【0001】

【発明の属する技術分野】 本発明は透明基板上に画素電極と薄膜トランジスタ（以下、TFTと略称する）とを配列したアクティブマトリクス基板を備えるアクティブマトリクス型液晶表示装置に関し、特にその電極構造に関するものである。

##### 【0002】

【従来の技術】 アクティブマトリクス型液晶表示装置は、マトリクス配置された画素電極と、前記画素電極に印加する電圧を制御するために各画素電極に対応して設けられたTFTとを備えるアクティブマトリクス基板を備えており、このアクティブマトリクス基板と対向基板との間に液晶を挟み込み、電極間に印加した電圧で液晶を駆動して表示を行う構成とされている。前記アクティブマトリクス基板は、例えば、基板と垂直方向に電界を形成する縦電界型の液晶表示装置の場合には、透明なガラス基板の表面上にX方向に延びる複数本の走査線をY方向に所要の間隔で配列する。また、これと直交するようにY方向に延びる複数本の信号線をX方向に所要の間隔で配列する。そして、前記走査線と信号線で囲まれる領域に透明電極で構成される画素電極が配置され、かつ各画素電極に対応してそれぞれTFTが配置される。前記TFTはゲート電極が前記走査線に接続され、ドレン電極が前記信号線に接続され、ソース電極が前記画素電極に接続される。したがって、走査線と信号線にそれぞれ所要の電流が通流されたときに、当該走査線と信号線が交差する位置のTFTがオン動作し、画素電極に所要の電位を供給し、当該画素電極での表示を行うことに 40

なる。また、前記走査線の端部には走査線端子部が設けられ、前記信号線の端部には信号線端子部が設けられ、これらの走査線端子部及び信号線端子部には、駆動回路（ドライバ）に接続されているテープ状配線が接続される。

【0003】 このようなアクティブマトリクス基板において、液晶表示装置の大型化、高密度化の要求に伴い、画素電極の寸法を微細化するとともに、走査線及び信号線や共通線を電気抵抗の低い材料、構造で構成することが要求される。また、その一方で、走査線、信号線、共通線の端部は走査線端子部、信号線端子部、共通線端子部として図外の駆動回路のテープ状配線に接続を行う必要がある。したがってこれらの端子部は水分の浸入により接続部の信頼性が低下しないように接続信頼性の高い材料で構成する必要がある。

【0004】 このような要求から、例えば、特開平7-120789号公報（以下、第1の公報）には、下層のアルミニウムA1と上層の窒化チタン膜TiNからなる多層の配線構造が提案されている。この第1の公報に記載の配線構造では、下層のアルミニウムにより低抵抗化が図られ、上層の窒化チタン膜によりアルミニウムがプロセス中の薬液等に晒されて腐食することが防止でき、信頼性の高い接続構造を得ることが可能になる。しかしながら、このようなアルミニウムと窒化チタン膜の積層からなる配線構造では、プロセス中の熱工程でアルミニウムにA1ヒロックが発生し易い。周知のように、A1ヒロックは、アルミニウムの表面に発生する突起状物であり、アルミニウムが熱処理により圧縮応力を受け、この応力緩和のためにアルミニウム原子が拡散することによって生じる。このA1ヒロックの発生により、層間ショートのような不良を増大し、歩留り低下の要因となる。

【0005】 このようなA1ヒロックを防止する技術として、例えば、特開平7-58110号公報（以下、第2の公報）に記載の技術がある。この第2の公報に記載の技術は、配線の多層構造として、TiN/Ti/A1/TiON/Tiの構造膜とする。最上層のTiN膜は、反射防止及びコンタクト形成時にエッチング選択性をとるために、上層のTi膜は接続抵抗低減膜として、A1膜は配線材料膜として、TiONはシリコンに対する拡散バリア膜として、下層のTi膜は接続抵抗低減膜として形成している。

##### 【0006】

【発明が解決しようとする課題】 前記第2の公報に記載の技術は、上層に設けたTiN膜と下層に設けたTiON膜とでA1膜を挟み込むことで、A1ヒロック及びアロイピットの発生を防止している。しかしながら、第2の公報には、前記したTiN/Ti/A1/TiON/Tiの構造が有効であることが記載されているのみであり、これ以外の多層構造においてA1ヒロック防止が有

効であることについては特に記載されていない。そのため、配線を半導体層に接して形成しない場合、例えば、本発明が対象とする液晶表示装置のゲート電極のように、絶縁性基板上に直接配線構造を形成するような場合に、第2の公報に記載の多層構造が有効であるか否かは明確ではない。特に、下層のTiON膜は、シリコンに対する拡散バリア膜として機能しているが、絶縁性基板のように拡散バリア膜が不要とされる場合には、当該TiON膜はいたずらに配線構造を複雑化させる要因となる。また、第2の公報に記載の範囲では、A1膜の上層のTiN膜とTi膜、及び下層のTiON膜とTi膜の各組み合わせ構造が有効であることは明らかであるが、これらの膜の一部を省略した場合に、開示されているような作用効果が期待できるものであるかは明確ではない。

【0007】本発明の目的は、各配線の構造を複雑化することなく、A1ヒロックを抑制し、かつ接続抵抗を低減して接続部の信頼性を向上したアクティブマトリクス型液晶表示装置を提供するものである。

#### 【0008】

【課題を解決するための手段】本発明は、透明絶縁性基板上に薄膜トランジスタ及び画素電極が形成されたアクティブマトリクス基板を含むアクティブマトリクス型液晶表示装置において、前記薄膜トランジスタのゲート電極及びこれに接続される走査線、前記画素電極に対向配置される共通電極及びこれに接続される共通線の少なくとも一つは、アルミニウム膜の上層と下層の少なくとも一方にチタン膜が形成される。また、前記薄膜トランジスタのソース電極とドレイン電極及び前記ドレイン電極に接続される信号線は、アルミニウム膜の下層、または上層と下層の両方にチタン膜が形成される。その上で、最上層には窒化チタン膜が形成された多層配線構造膜とされ、前記窒化チタン膜は窒素濃度が25原子%以上であることを特徴とする。

【0009】前記本発明の第1の態様としては、前記ゲート電極及び走査線は、アルミニウム膜の上層と下層の少なくとも一方にチタン膜が形成された多層配線構造とされ、かつ最上層には窒化チタン膜が形成され、かつ前記窒化チタン膜は窒素濃度が25原子%以上である構成とする。また、第2の態様としては、前記ゲート電極及び走査線、前記共通電極及び共通線は、アルミニウム膜の上層と下層の少なくとも一方にチタン膜が形成された多層配線構造膜とされ、かつ最上層には窒化チタン膜が形成され、かつ前記窒化チタン膜は窒素濃度が25原子%以上である構成とする。第3の態様としては、前記ソース電極とドレイン電極及び信号線は、アルミニウム膜の下層または、上層と下層の両方にチタン膜が形成された多層配線構造膜とされ、かつ最上層には窒化チタン膜が形成され、かつ前記窒化チタン膜は窒素濃度が25原子%以上である構成とする。第4の態様としては、前記

ソース電極及び画素電極とドレイン電極及び信号線は、アルミニウム膜の下層または、上層と下層の両方にチタン膜が形成された多層配線構造膜とされ、かつ最上層には窒化チタン膜が形成され、かつ前記窒化チタン膜は窒素濃度が25原子%以上である構成とする。第5の態様としては、前記第1と第3の態様の特徴を備える構成とする。第6の態様としては、前記第2と第3の態様の特徴を備える構成とする。

【0010】前記多層配線構造膜は、例えば、TiN/Ti/A1構造膜とする。あるいは、TiN/A1/Ti構造膜とする。さらには、TiN/Ti/A1/Ti構造膜とする。また、A1はA1またはA1合金とする。

【0011】本発明のアクティブマトリクス型液晶表示装置によれば、A1膜に接してTi膜が存在することで、A1膜でのA1ヒロックの発生を抑制する。ドレン層に関してはA1膜と半導体膜の間にTi膜が存在することで、アロイピットの発生を抑制する。また、最上層にTiN膜が存在することで、走査線、信号線、共通線等の各接続部における腐食を抑制し、接続部での接続抵抗を低下するとともに、その信頼性を高めることができる。

#### 【0012】

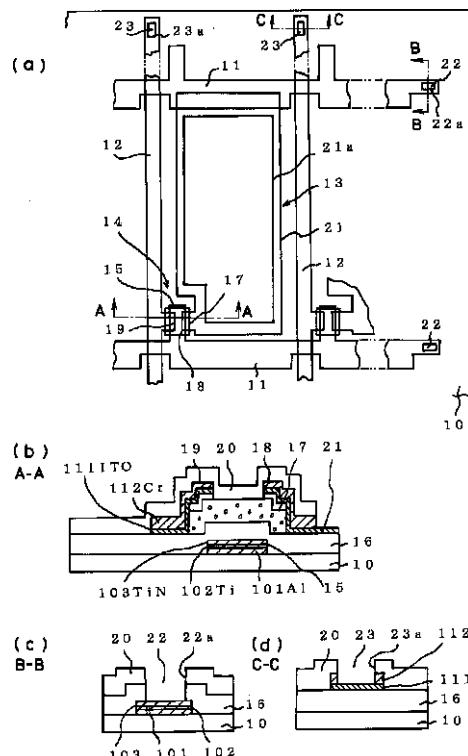

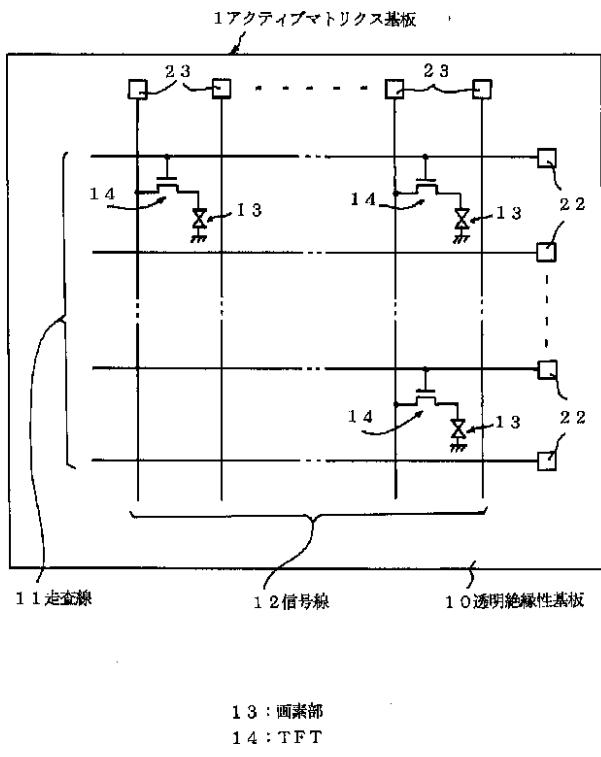

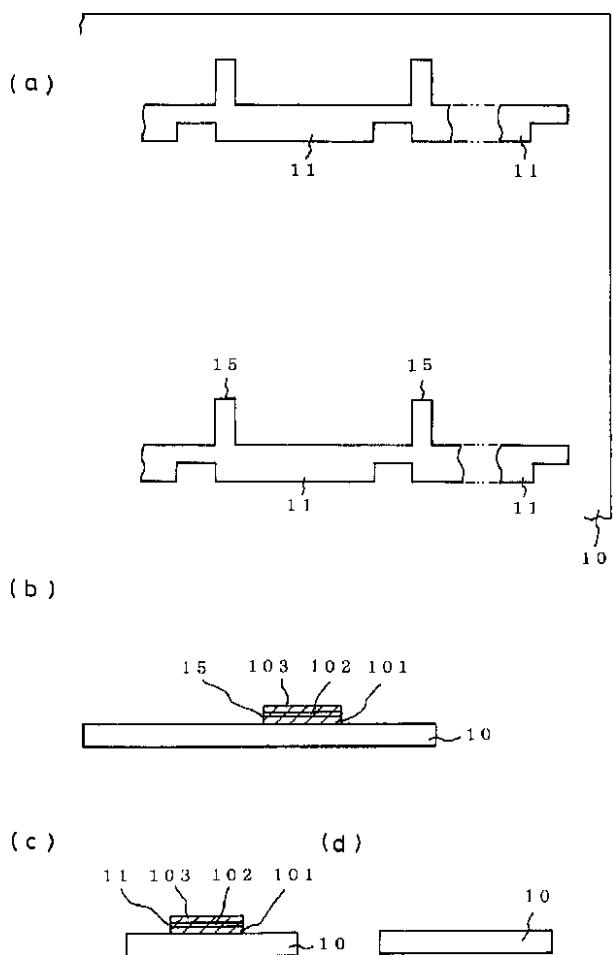

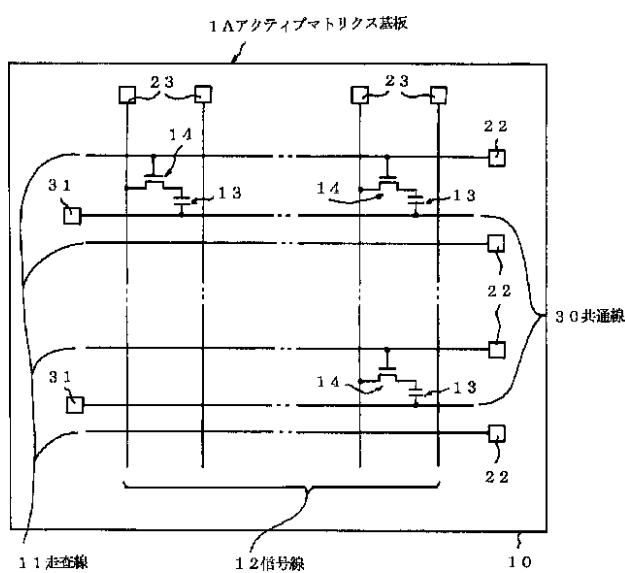

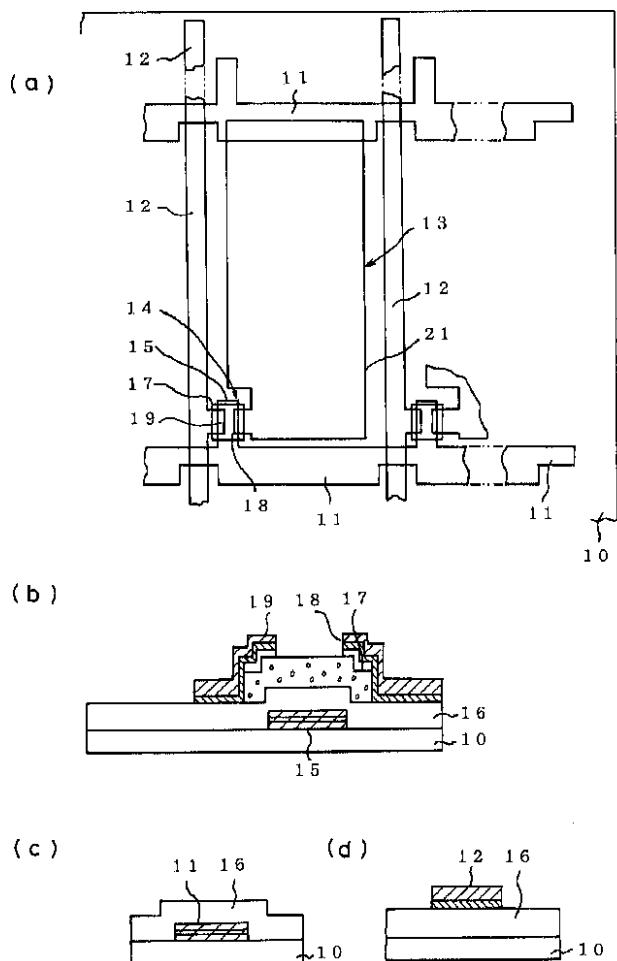

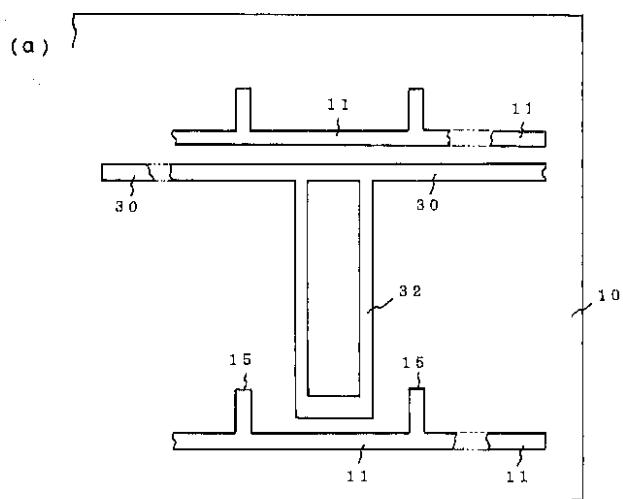

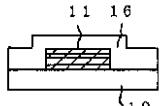

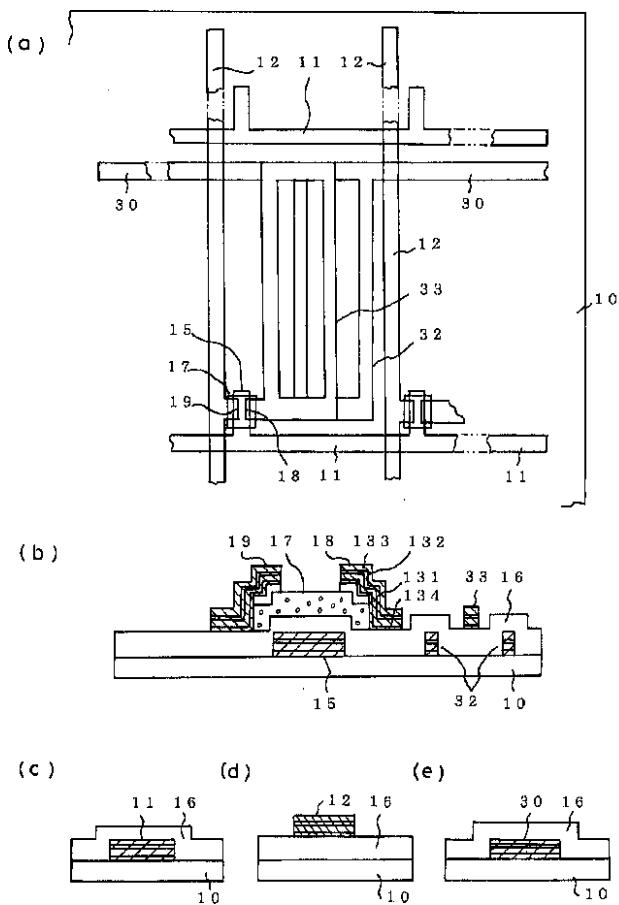

【発明の実施の形態】次に、本発明の実施形態を図面を参照して説明する。図1は本発明のアクティブマトリクス型液晶表示装置を縦電界型のアクティブマトリクス基板に適用した第1の実施形態の概略平面構成図である。また、図2はその一つの画素領域を示しており、同図(a)は平面レイアウト図であり、同図(b)~(d)はAA線、BB線、CC線の各断面図である。図1及び図2を参照すると、透明絶縁性基板10上に、X方向に延長された複数本の走査線11がY方向に所要の間隔で配置され、また、前記走査線11と直交するようにY方向に延長された複数本の信号線12がX方向に所要の間隔で配置されている。そして、前記走査線11と信号線12で囲まれた領域に画素部13とTFT14が形成されている。前記TFT14は、前記透明ガラス基板10の表面上に前記走査線11と同層に形成されたゲート電極15と、前記走査線11及びゲート電極15を覆うように形成されたゲート絶縁膜16と、前記ゲート絶縁膜16上において前記ゲート電極に対向して形成されたアイランド状の半導体層17と、前記半導体層17上に形成され、かつ前記信号線12と同層に形成された対をなすソース電極18及びドレイン電極19からなる逆スタガ型TFTとして構成される。さらにその上にパッセーション膜20が形成される。

【0013】また、前記画素部13は、前記ゲート絶縁膜16上に形成されたITO等の透明電極からなる画素電極21で構成される。前記画素電極21の大部分は前記パッセーション膜20に形成された表示窓としての

開口21a内に露出され、この露出された領域が表示領域として構成される。そして、前記ゲート電極15は前記走査線11に、前記ドレイン電極19は前記信号線12に、前記ソース電極18は画素電極21に接続される。また、前記走査線11の端部に設けられた走査線端子部22は、前記ゲート絶縁膜16及びパッシベーション膜20に形成された開口22aにおいて前記走査線11の端部が露出した構成とされる。同様に、前記信号線12の端部に設けられた信号線端子部23は、前記パッシベーション膜20に形成された開口23aにおいて前記信号線の端部が露出した構成とされる。

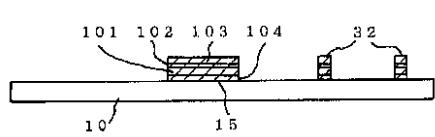

【0014】ここで、前記ゲート電極15と前記走査線11は一体の多層配線構造として構成されており、この第1の実施形態では、下層のA1膜101、その上層のTi膜102、最上層のTiN膜103からなる、TiN/Ti/A1構造膜とされている。前記TiN膜103は100nm、Ti膜102は50nm、A1膜101は200nmの膜厚に形成されている。また、前記ソース電極18とドレイン電極19及び信号線12は同じ多層配線構造として構成されており、この実施形態では、下層のITO膜111、その上層のCr膜112からなるCr/ITO構造膜とされている。そして、前記画素電極21と信号線端子部23では上層のCr膜112は部分的に除去されて下層のITO膜111のみで構成されており、これにより画素電極21では透明性が確保され、信号線端子部23では電気接続の信頼性が確保される。前記ITO膜111は50nm、Cr膜112は200nmの膜厚に形成されている。

【0015】図3～図6はそれぞれその主要な工程における図2と同様の図である。先ず、図3に示すように、ガラス等の透明絶縁性基板10上に、スパッタリング法により、順次A1膜101とTi膜102とTiN膜103を積層したTiN/Ti/A1構造膜を形成する。膜厚は前記したように、TiN/Ti/A1=100nm/50nm/200nmである。そして、第1PR(フォトレジスト)工程において前記TiN/Ti/A1構造膜上に所要のパターンの第1のフォトレジスト膜を形成し、露光、現像した上で、当該第1のフォトレジストをマスクにして前記TiN/Ti/A1構造膜をドライエッティングしてゲート電極15及び走査線11を形成する。

【0016】ここで、前記TiN膜103は、反応性スパッタリング法により形成し、ArガスとN<sub>2</sub>ガスとの流量比を調整し、窒素が25原子%以上含まれるようにする。例えば、圧力0.8Pa、Arガス流量225sccm、N<sub>2</sub>ガス流量150sccm、DC放電電力16kW、基板温度150℃、ギャップ115mmの成膜条件で行うことにより、窒素が25原子%以上含まれたTiN膜103を成膜することが可能である。

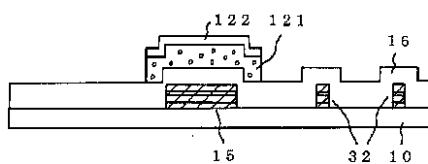

【0017】次いで、図4に示すように、全面にゲート

10

絶縁膜16としてSiN膜を400nmの厚さに形成する。その上に真性a-Si膜121を250nmの厚さに、その上にオーミック層としてリンを含むn<sup>+</sup>型a-Si膜122を50nmの厚さにそれぞれプラズマCVD法により形成する。そして、第2PR工程において第2のフォトレジスト膜を所要のパターンに形成し、露光、現像した上で、当該第2のフォトレジストをマスクにして前記n<sup>+</sup>型a-Si膜121、真性a-Si膜122を順次ドライエッティングを行い、前記ゲート電極15の直上に前記ゲート絶縁膜16を介してアイランド状の半導体層17を形成する。

20

【0018】次いで、図5に示すように、全面に透明電極としてのITO膜111を50nmの厚さに、さらにその上にCr膜112を200nmの厚さに順次スパッタ法により形成する。そして、第3のフォトレジスト膜を所要のパターンに形成し、露光、現像した上で、前記Cr膜112とITO膜111をウェットエッティングし、画素電極21、前記画素電極21と一体のソース電極18、ドレイン電極19、及び前記ドレイン電極19と一体の信号線12を形成する。

30

【0019】その上で、前記ソース電極18及びドレイン電極19をマスクにして、n<sup>+</sup>型a-Si膜122をドライエッティングする。このエッティングにより、前記半導体層17においては、前記ドレイン電極19及びソース電極18の間のn<sup>+</sup>型a-Si膜122がエッティングされてチャネルギャップが形成され、また前記ドレイン電極19及びソース電極18の直下にn<sup>+</sup>型a-Si膜122のオーミック層が形成される。これにより、前記TFT14が形成される。

40

【0020】次いで、図6に示すように、プラズマCVD法により、全面にパッシベーション膜20としてSiN膜を形成する。しかる上で、第4PRにより、前記画素電極21、走査線端子部22、信号線端子部23の各パッシベーション膜20を選択的に除去して開口21a, 22a, 23aを形成する。さらに、前記走査線端子部22では開口22aを形成する際に前記ゲート絶縁膜16を除去する。これにより、図2に示したように、走査線端子部22ではパッシベーション膜20及びゲート絶縁膜16の開口22a内に走査線11の端部が露出され、走査線端子部22が形成される。また、前記画素部13、信号線端子部23では、前記パッシベーション膜20の開口21a, 23aに露出されている前記Cr膜112を除去し、下層のITO膜111を露出する。これにより、画素部13及び信号線端子部23が形成される。

50

【0021】しかる上で、図示は省略するが、マトリクス配列された画素配列領域のパッシベーション膜20上に配向膜を形成し、アクティブマトリクス基板が完成される。さらに、前記アクティブマトリクス基板上に所要の間隔で対向基板を対向配置し、両者の間隔を封止して

液晶を充填することによりアクティブマトリクス型液晶表示装置が完成される。また、アクティブマトリクス基板10の周辺部に配置されている走査線端子部22、信号線端子部23に対して駆動回路のテープ状端子を接続することでアクティブマトリクス型液晶表示装置への電力供給が可能になり、液晶表示が可能になる。

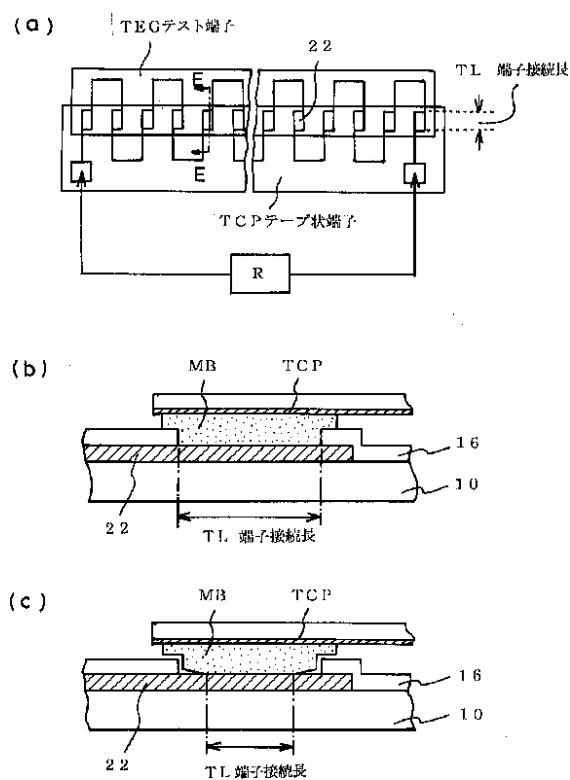

【0022】以上のように、本発明の第1の実施形態では、ゲート電極15及び走査線11を構成する多層配線として、TiN/Ti/A1構造膜を用いているので、A1ヒロックの発生を抑制する効果が高められる。図7は従来の第1公報に記載のTiN/A1構造膜と、本発明のTiN/Ti/A1構造膜におけるA1ヒロックの発生個数を比較した例である。ここでは、それぞれの多層配線を形成した後に、窒素ガス雰囲気で300、1時間の熱処理を行った後、配線面積1mm<sup>2</sup>内に目視により観察されたA1ヒロックの個数を示している。第1公報に記載の構造では、1mm<sup>2</sup>当たり、6410個のA1ヒロックが確認されているが、本実施形態では、1~26個のA1ヒロックが確認されているのみである。なお、同図には、TiN/Ti/A1構造膜の各膜厚を相違させた場合のA1ヒロックの個数についても示している。このように、第1の実施形態では、走査線としてTiN/Ti/A1構造膜を採用することで、走査線におけるA1ヒロックの発生を極めて有效地に抑制することが可能である。これは、TiをTiNとA1の間に形成すると、TiNでは不十分である物理的ヒロック抑制効果が向上することが理由であると推測される。ここで、TiN膜の膜厚を大きくすれば、A1ヒロックの抑制効果が高められることが判る。また、Ti膜の膜厚を増大してもA1ヒロックの抑制効果が高められることが判る。

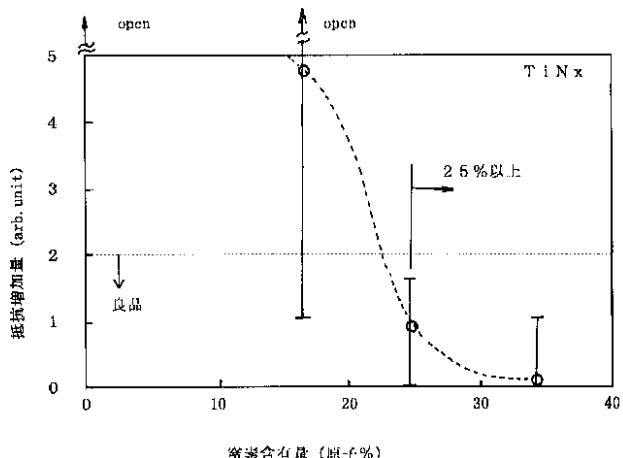

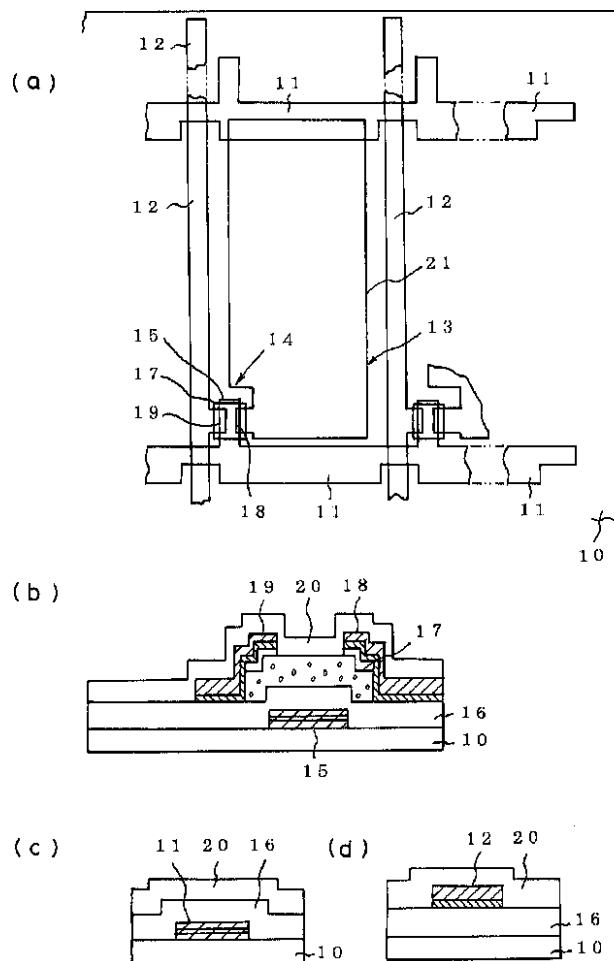

【0023】また、前記TiN/Ti/A1構造膜において、最上層のTiNにより、走査線端子部での電気接続の信頼性が向上する。すなわち、図8は、TiN/Ti/A1構造膜からなる走査線において、TiN膜の窒素含有%を相違したときの走査線端子部での接続抵抗の違いを示す図である。この走査線端子部22の接続抵抗は、図9(a)に模式的な配線構成図を、図9(b)にそのEE線に沿う断面図を示すように、前記走査線端子部22と同一規格でテスト用の複数個、ここでは2000個のダミー走査線端子部22を配列したテスト端子TEGを形成し、当該テスト端子TEGの各ダミー走査線端子部22にそれぞれテープ状端子TCPを接続する。ここで、両者の接続した長さTLを端子接続長とする。前記テスト端子TEGは、TiN膜の窒素含有%を相違したものをそれぞれ形成する。ここでは、窒素含有%が、15%、25%、30%のものを3種類形成した。また、前記テープ状端子TCPは、実際にアクティブマトリクス基板を駆動回路に接続する際に用いるテープ状端子と同じ規格で形成されたものである。そして、前記

テスト端子TEGとテープ状端子TCPとを金属接合材MBにより図9(a)のように直列に接続し、その両端の抵抗を測定する。

【0024】この状態で、温度85、湿度85%で1000時間の熱処理を施したときの抵抗値の変化を測定する。この熱処理により、図9(c)に示すように、走査線端子部22では開口部の周辺より接続不良部が進行するため、前記した端子接続長が短くなり、ダミー走査線端子部22での抵抗値が増加する。ここで、ダミー走査線端子部22での許容される端子接続長TLを0.1mmとしたときの抵抗増加量(arb.unit)を「2」とし、「2」を超えないものを良品とする。前記3種類のテスト端子TEGでの熱処理後の抵抗値は図8にプロットした通りであり、これを連続線で接続すると、同図の破線のようになる。そして、抵抗増加量が「2」以下となる窒素含有%を判定すると、窒素含有%が25%以上であれば、抵抗増加量をばらつきを含めて「2」以下に抑えることが可能となる。すなわち、TiN膜の窒素含有%を25%以上とすることで、腐食に対して接続抵抗の増加が少ない信頼性の高い走査線接続部を構成することが可能になる。

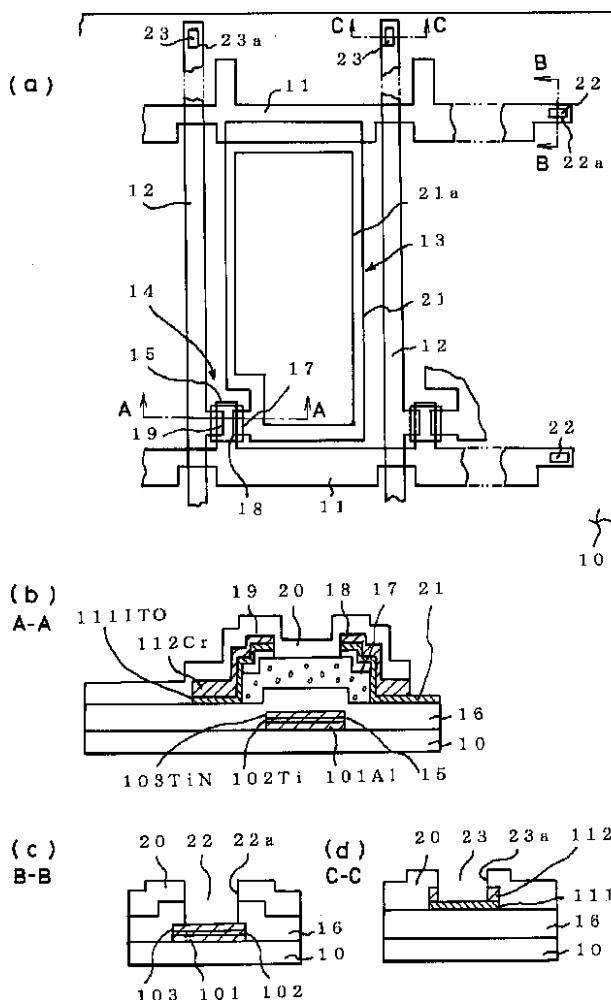

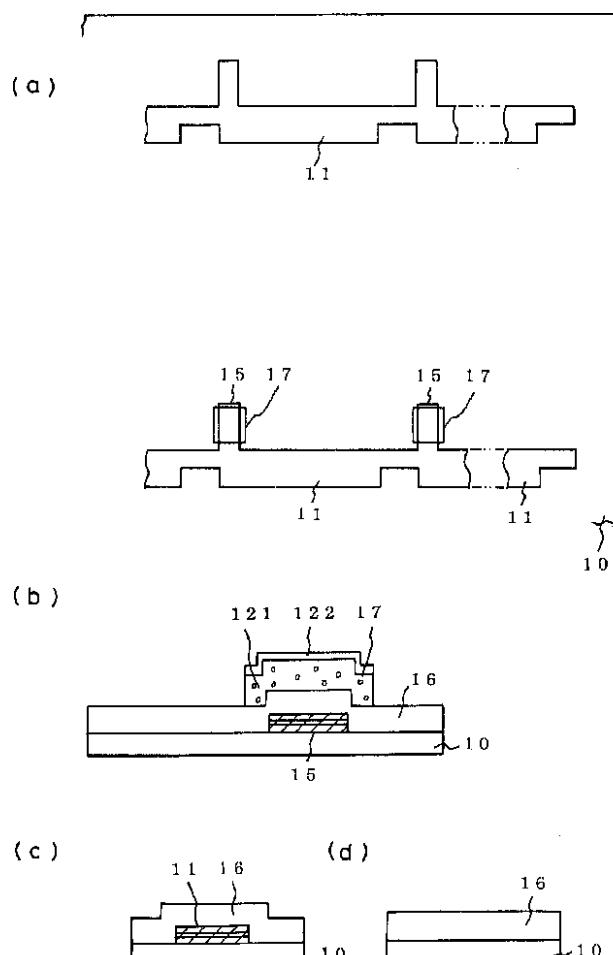

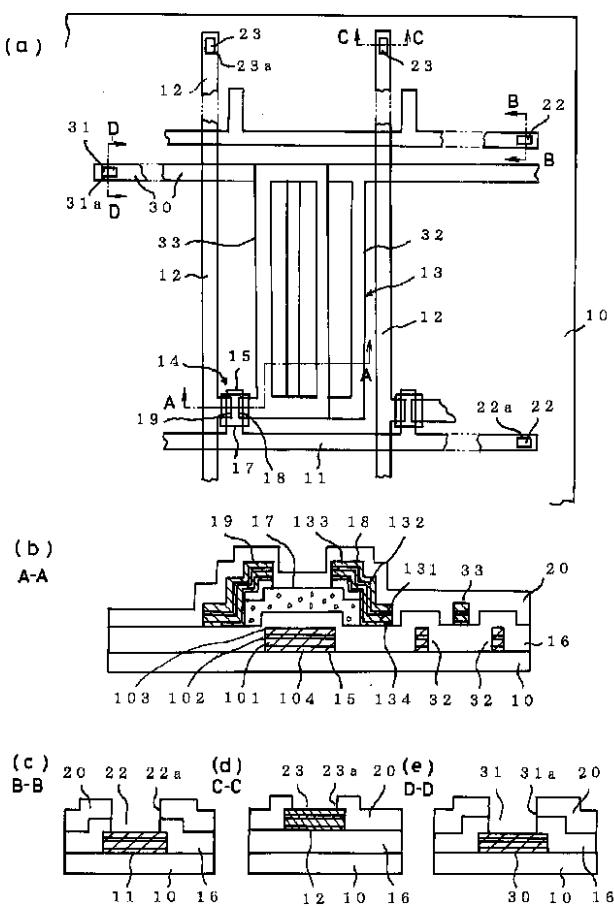

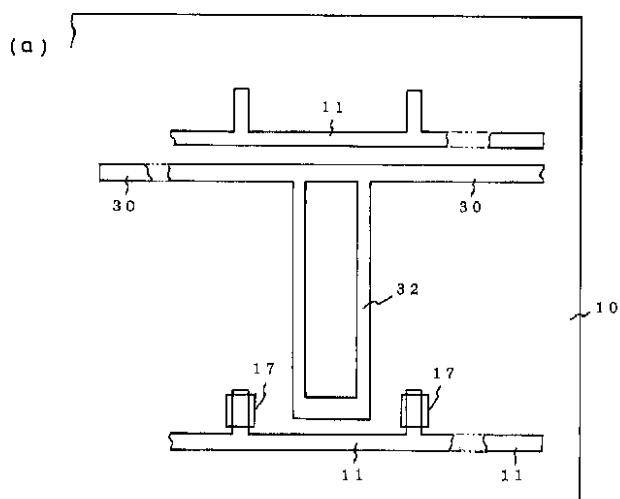

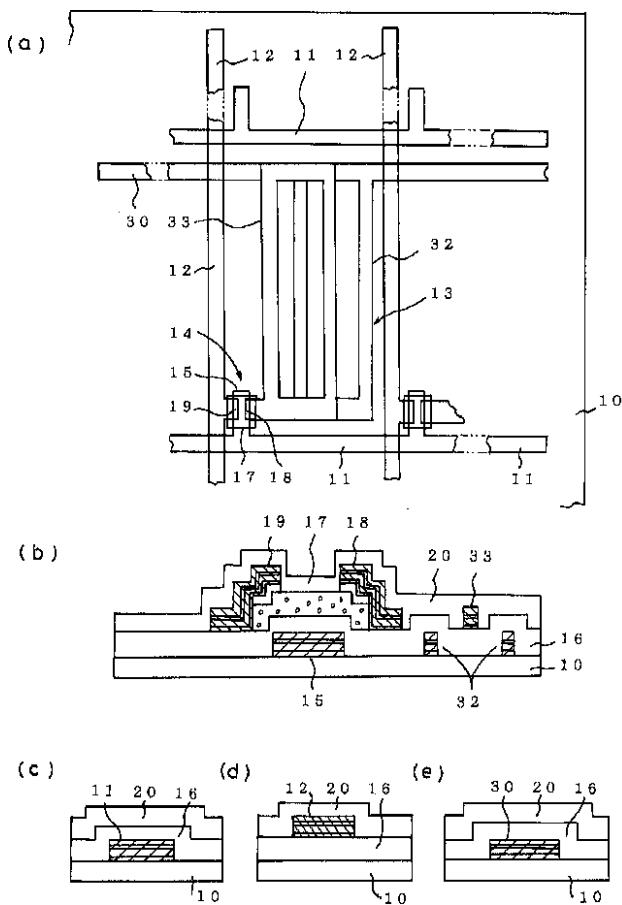

【0025】次に、本発明の第2の実施形態を説明する。この第2の実施形態は、本発明を横電界方式のアクティブマトリクス基板に適用した実施形態である。図10は当該アクティブマトリクス基板の概略構成図、図11は一つの画素領域を示し、同図(a)は平面レイアウト図、同図(b)~(e)はAA線、BB線、CC線、DD線の各断面図である。なお、第1の実施形態と等価な部分には同一符号を付してある。図10及び図11を参照すると、第2の実施形態のアクティブマトリクス基板1Aは、透明絶縁性基板10上に、X方向に延長された複数本の走査線11がY方向に所要の間隔で配置され、また、前記走査線11のY方向の間には、それぞれX方向に延長された共通線30が配置される。一方、前記走査線11及び共通線30と直交するようにY方向に延長された複数本の信号線12がX方向に所要の間隔で配置されている。そして、図10に示すように、前記走査線11、共通線30及び信号線12で囲まれた領域に画素部13が形成され、かつこの画素部13に隣接してTFT14が形成されている。前記TFT14は、第1の実施形態と同様であり、前記透明ガラス基板10の表面上に形成され、前記走査線11及び共通線30と同層に形成されたゲート電極15と、前記ゲート電極15及び前記走査線11と共に30を覆うように形成されたゲート絶縁膜16と、前記ゲート絶縁膜16において前記ゲート電極15に対向して形成されたアイランド状の半導体層17と、前記半導体層17上に形成され、かつ前記信号線12と同層に形成された対をなすソース電極18及びドレイン電極19から構成される。さらにその上にパッセンジーション膜20が形成される。

【0026】また、前記画素部13は、前記ゲート電極13と同じ層に形成された櫛状または枠状の共通電極32と、前記ゲート絶縁膜16の上層に形成された前記ソース電極18と同じ層に形成されて前記共通電極32とはピッチがずれた状態で形成された櫛状又は枠状の画素電極33で構成される。そして、前記ゲート電極15は前記走査線11に、前記ドレイン電極19は前記信号線12に、前記ソース電極18は前記画素電極33に、前記共通電極32は前記共通線30にそれぞれ接続される。また、前記走査線11の端部に設けられた走査線端子部22は、前記ゲート絶縁膜16及びパッシベーション膜20に形成された開口22aにおいて前記走査線11の端部が露出した構成とされる。同様に、前記信号線12の端部に設けられた信号線端子部23は、前記パッシベーション膜20に形成された開口23aにおいて前記信号線12の端部が露出した構成とされる。さらに、前記共通線30の端部に設けられた共通線端子部31は、前記ゲート絶縁膜16及びパッシベーション膜20に形成された開口31aにおいて前記共通線30の端部が露出した構成とされる。

【0027】ここで、前記ゲート電極15と前記走査線11、及び前記共通電極32と共通線30はそれぞれ多層配線構造として構成されており、この実施形態では、下層のTi膜104、その上のAl膜101、その上層のTi膜102、最上層のTiN膜103からなる、TiN/Ti/Al/Ti構造膜とされている。また、前記ドレイン電極19と信号線12、及び前記ソース電極18と画素電極33はそれぞれ一体の多層配線構造として構成されており、この実施形態では、前記走査線11及び共通線30と同様に、下層のTi膜134、その上のAl膜131、その上層のTi膜132、最上層のTiN膜133からなる、TiN/Ti/Al/Ti構造膜とされている。

【0028】図12～図15は各工程を説明するための図11と同様の図である。先ず、図12において、透明絶縁性基板10上にTi膜104、Al膜101、Ti膜102、TiN膜103を順次スパッタ法により形成し、TiN/Ti/Al/Ti構造膜を形成する。ここで前記TiN/Ti/Al/Ti構造膜の各膜厚は、50nm/50nm/200nm/50nmの膜厚である。そして、TiN/Ti/Al/Ti構造膜を第1PRでエッティングし、ゲート電極15及びこれにつながる走査線11と、枠型の共通電極32及びこれにつながる共通配線30を形成する。ここで、前記TiN膜103は、反応性スパッタリング法により形成し、ArガスとN<sub>2</sub>ガスとの流量比を調整し、窒素が25原子%以上含まれるようにする。この成膜条件は、例えば、第1の実施形態で説明した条件と同じ条件で良い。

【0029】次いで、図13に示すように、全面にゲート絶縁膜16としてSiN膜を400nmの厚さに形成50

する。また、その上に、真性a-Si膜121を250nmの厚さに、その上にオーミック層としてリンを含むn<sup>+</sup>型a-Si膜122を50nmの厚さにそれぞれプラズマCVD法により形成する。そして、第2PR工程において、第2のフォトレジスト膜を所要のパターンに形成し、露光、現像した上で、当該第2のフォトレジストをマスクにしてn<sup>+</sup>型a-Si膜122、真性a-Si膜121を順次ドライエッティングを行い、前記ゲート電極15上にゲート絶縁膜16を介してアイランド状の半導体層17を形成する。

【0030】さらに、図14に示すように、その上に、Ti膜134、Al膜131、Ti膜132、TiN膜133をスパッタ法により順次形成し、TiN/Ti/Al/Ti構造膜を前記走査線11の場合と同じ厚さに形成する。そして、形成したTiN/Ti/Al/Ti構造膜を第3PRでエッティングし、ドレイン電極19及びこれにつながる信号線12と、ソース電極18およびこれにつながる枠状の画素電極33とをそれぞれ形成する。ここで、前記TiN膜133は、反応性スパッタリング法により形成し、ArガスとN<sub>2</sub>ガスとの流量比を調整し、窒素が25原子%以上含まれるようにする。この際の成膜条件も前記走査線の形成時の成膜条件と同じでよい。

【0031】その上で、前記ソース電極18及びドレイン電極19をマスクにして、n<sup>+</sup>型a-Si膜122をドライエッティングする。このエッティングにより、前記半導体層17においては、前記ドレイン電極19及びソース電極18の間にチャネルギャップが形成され、また前記ドレイン電極19及びソース電極18の直下にn<sup>+</sup>型a-Si膜122のオーミック層が形成される。これにより、前記TFT14が形成される。

【0032】次いで、図15に示すように、プラズマCVD法により、全面にパッシベーション膜20としてSiN膜を形成する。その後、第4PRにより、前記走査線端子部22、共通線端子部31の各ゲート絶縁膜16とパッシベーション膜20、及び信号線端子部23のパッシベーション膜20を除去して開口22a, 31a, 23aを形成する。これにより、図11に示した構成となり、各開口22a, 31a, 23a内に走査線22、共通線30、信号線12の一部が露出され、各端子部22, 31, 23が形成される。次いで、図示は省略するが、マトリクス配列された画素領域のパッシベーション膜上に配向膜を形成し、アクティブマトリクス基板が形成される。さらに、前記アクティブマトリクス基板上に所要の間隔で対向基板を対向配置し、両者の間隔を封止して液晶を充填することによりアクティブマトリクス型液晶表示装置が完成される。また、アクティブマトリクス基板の周辺部に配置されている走査線端子部、信号線端子部に対して駆動回路のテープ状端子を接続することでアクティブマトリクス型液晶表示装置への電力供給が

可能になり、液晶表示が可能になる。

【0033】この第2の実施形態においては、走査線1、共通線30、信号線12にそれぞれTiN/Ti/A1/Ti構造膜を採用しているので、第1の実施形態と同様にA1ヒロックを抑制することが可能になる。すなわち、第1の実施形態と同様に、TiをTiNとA1の間に形成すると、TiNでは不十分である物理的ヒロック抑制効果が向上する。また、A1の下層にTiを形成すると、A1の結晶性が改善され、マイグレーションが起こり難く、ヒロックを抑制することが理由である。また、走査線端子部22、共通線端子部31、信号線端子部23の各端子部においても、第1の実施形態と同様な接続抵抗のテストを行った結果、図8に示したと同様に、TiN膜の窒素含有%を25%以上することで、腐食に対する信頼性の高い走査線接続部を構成することが可能になる。なお、この結果から、TiN膜の膜厚を相違させても、A1ヒロックの抑制効果には差が生じないことが確認できる。

【0034】以上の実施形態では、第1の実施形態においてTiN/Ti/A1構造膜の例を示し、第2の実施形態においてTiN/Ti/A1/Ti構造膜の例を示したが、TiN/A1/Ti構造膜を用いることも可能である。特に、このTiN/A1/Ti構造膜を用いた場合のA1ヒロックの数を図7に併せて示している。同図から判るように、A1ヒロックをほぼ0に抑制することが可能である。また、この構造においても、接続抵抗の低減の両効果が得られることが確認されている。さらに、本発明では、A1膜が純A1、あるいはA1合金で構成される場合においても同様な作用効果が得られることが確認されている。

### 【0035】

【発明の効果】以上説明したように本発明は、アクティブマトリクス基板の走査線、信号線、共通線の少なくとも一つを構成する配線構造として、最上層にTiN膜を有し、A1膜の上層または下層の少なくとも一方にTi膜を有する多層配線構造としているので、A1膜に接して設けられるTi膜が存在することで、A1膜でのA1ヒロックの発生を抑制し、最上層に存在するTiN膜によって、走査線、信号線、共通線等の各接続部における表面腐食を抑制し、接続部の接続抵抗を低下するとともに、その信頼性を高めることが可能になる。これにより、高密度化したアクティブマトリクス型液晶表示装置が実現できる。

### 【図面の簡単な説明】

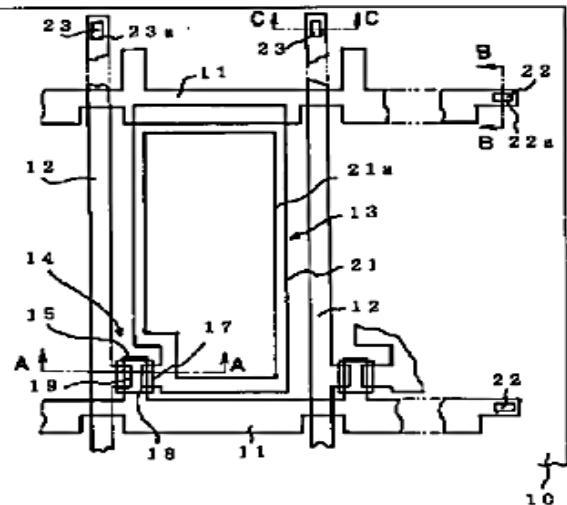

【図1】本発明の第1の実施形態にかかるアクティブマトリクス基板の概略構成図である。

【図2】図1のアクティブマトリクス基板の一画素領域と接続部の平面レイアウト図とそのAA線、BB線、CC線の各拡大断面図である。

【図3】第1の実施形態の製造工程1を示す図2と同様

の図である。

【図4】第1の実施形態の製造工程2を示す図2と同様の図である。

【図5】第1の実施形態の製造工程3を示す図2と同様の図である。

【図6】第1の実施形態の製造工程4を示す図2と同様の図である。

【図7】多層配線構造とA1ヒロックの個数の相関を示す図である。

10 【図8】TiNの窒素含有%と抵抗増加量との相関を示す図である。

【図9】端子部の接続抵抗のテスト方法と接続抵抗が増加した状態を示す図である。

【図10】本発明の第2の実施形態にかかるアクティブマトリクス基板の概略構成図である。

【図11】図10のアクティブマトリクス基板の一画素領域と接続部の平面レイアウト図とそのAA線、BB線、CC線、DD線の各拡大断面図である。

【図12】第2の実施形態の製造工程1を示す図11と同様の図である。

【図13】第2の実施形態の製造工程2を示す図11と同様の図である。

【図14】第2の実施形態の製造工程3を示す図11と同様の図である。

【図15】第2の実施形態の製造工程4を示す図11と同様の図である。

### 【符号の説明】

1, 1A アクティブマトリクス基板

10 透明絶縁性基板

30 11 走査線

12 信号線

13 画素部

14 TFT(薄膜トランジスタ)

15 ゲート電極

16 ゲート絶縁膜

17 半導体層(アイランド)

18 ソース電極

19 ドレイン電極

20 パッシベーション膜

21 画素電極

22 走査線端子部

23 信号線端子部

30 共通線

31 共通線端子部

32 共通電極

101 A1膜

102 Ti膜

103 TiN膜

104 Ti膜

111 ITO膜

50

- 112 Cr膜

121 真性a-Si膜

122 n<sup>+</sup>型a-Si膜

131 Al膜

- \*132 Ti膜

133 TiN膜

134 Ti膜

\*

【図1】

【図2】

【図7】

| 膜構造<br>(膜厚単位: nm)        | 熱処理                              | Al ヒロシタ数<br>(個/mm <sup>2</sup> ) |

|--------------------------|----------------------------------|----------------------------------|

| TiN(100)/Al(200)         |                                  | 6410                             |

| TiN(50)/Ti(50)/Al(200)   |                                  | 26                               |

| TiN(100)/Ti(50)/Al(200)  | N <sub>2</sub> 気圧<br>300°C, 1 hr | ~4                               |

| TiN(100)/Ti(100)/Al(200) |                                  | ~1                               |

| TiN(50)/Al(200)/Ti(30)   |                                  | 0                                |

| TiN(100)/Al(200)/Ti(30)  |                                  | 0                                |

【図8】

【図3】

【図4】

【図10】

【図5】

【図6】

【図9】

【図11】

【図12】

(b)

(c)

(d)

(e)

【図13】

(b)

(c)

(d)

(e)

【図14】

【図15】

フロントページの続き

(72)発明者 藤田 明

東京都港区芝五丁目7番1号 日本電気株式会社内

(72)発明者 木村 茂

東京都港区芝五丁目7番1号 日本電気株式会社内

(72)発明者 前田 明寿

東京都港区芝五丁目7番1号 日本電気株式会社内

(72)発明者 早瀬 貴介

鹿児島県出水市大野原町2080 鹿児島日本電気株式会社内

F ターム(参考) 2H092 HA04 JA26 JA34 JA37 JA41

JB24 JB33 KB04 MA05 MA08

MA18

|             |                                                                                                                                                                                                                                                                                      |         |            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)     | 有源矩阵型液晶显示装置                                                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号     | <a href="#">JP2002202527A</a>                                                                                                                                                                                                                                                        | 公开(公告)日 | 2002-07-19 |

| 申请号         | JP2000399870                                                                                                                                                                                                                                                                         | 申请日     | 2000-12-28 |

| 申请(专利权)人(译) | NEC公司<br>Kagoshimanihondenki有限公司                                                                                                                                                                                                                                                     |         |            |

| [标]发明人      | 田中宏明<br>藤田明<br>木村茂<br>前田明寿<br>早瀬貴介                                                                                                                                                                                                                                                   |         |            |

| 发明人         | 田中 宏明<br>藤田 明<br>木村 茂<br>前田 明寿<br>早瀬 貴介                                                                                                                                                                                                                                              |         |            |

| IPC分类号      | G02F1/1345 G02F1/136 G02F1/1362 G02F1/1368 H01L29/45 H01L29/49                                                                                                                                                                                                                       |         |            |

| CPC分类号      | H01L29/4908 G02F1/13458 G02F1/136286 G02F2001/13629 G02F2001/136295 H01L29/458                                                                                                                                                                                                       |         |            |

| FI分类号       | G02F1/1345 G02F1/136.500 G02F1/1368                                                                                                                                                                                                                                                  |         |            |

| F-TERM分类号   | 2H092/HA04 2H092/JA26 2H092/JA34 2H092/JA37 2H092/JA41 2H092/JB24 2H092/JB33 2H092 /KB04 2H092/MA05 2H092/MA08 2H092/MA18 2H192/AA24 2H192/BB02 2H192/BB72 2H192/BB86 2H192/CB05 2H192/CC02 2H192/CC17 2H192/CC32 2H192/CC42 2H192/CC72 2H192/DA02 2H192 /DA32 2H192/FA64 2H192/JA32 |         |            |

| 代理人(译)      | 铃木昭雄                                                                                                                                                                                                                                                                                 |         |            |

| 外部链接        | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                            |         |            |

## 摘要(译)

解决的问题：在不使形成在有源矩阵基板上的诸如扫描线和信号线之类的布线结构复杂的情况下，抑制Al小丘并减小连接电阻以提高连接部的可靠性。在包括在透明绝缘基板10上形成有薄膜晶体管14和像素部13的有源矩阵基板1的有源矩阵型液晶显示装置中，薄膜晶体管14的栅电极15和与其连接的扫描线。图11的结构具有TiN/Ti/Al结构，TiN/Al/Ti结构或TiN/Ti/Al/Ti结构。TiN膜作为最上层的存在抑制了Al膜中Al小丘的产生。此外，TiN膜作为最上层的存在抑制了扫描线端子部22处的表面腐蚀，抑制了扫描线端子部22处的连接电阻的增加，并提高了可靠性。