(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5369446号

(P5369446)

(45) 発行日 平成25年12月18日(2013.12.18)

(24) 登録日 平成25年9月27日(2013.9.27)

(51) Int.Cl.

F 1

G02F 1/1368 (2006.01)

G02F 1/1343 (2006.01)G02F 1/1368

G02F 1/1343

請求項の数 8 外国語出願 (全 23 頁)

(21) 出願番号 特願2008-33479 (P2008-33479)

(22) 出願日 平成20年2月14日 (2008.2.14)

(65) 公開番号 特開2008-203849 (P2008-203849A)

(43) 公開日 平成20年9月4日 (2008.9.4)

審査請求日 平成22年10月28日 (2010.10.28)

(31) 優先権主張番号 096106311

(32) 優先日 平成19年2月16日 (2007.2.16)

(33) 優先権主張国 台湾(TW)

(73) 特許権者 510134581

群創光電股▲ふん▼有限公司

InnoLux Corporation

台湾新竹科學工業園區苗栗縣竹南鎮科學路

160號

(74) 代理人 110000110

特許業務法人快友國際特許事務所

(72) 発明者 チーヤン シエ

台湾 744 タイナン サイエンス ベースト インダストリアル パーク タイナン カウンティー チーイェー ロード ナンバー1 チー メイ オプトエレクトロニクス コーポレーション内

最終頁に続く

(54) 【発明の名称】 液晶ディスプレイパネルとその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

薄膜トランジスタ基板を有する液晶ディスプレイパネルであって、

前記薄膜トランジスタ基板は、第1の走査線と、第2の走査線と、複数のピクセルと、

データ線と、蓄積容量ラインを備え、

前記第1の走査線は、前記薄膜トランジスタ基板上に配設されており、

前記第2の走査線は、前記薄膜トランジスタ基板上に前記第1走査線と平行に配設され

ており、

前記複数のピクセルのそれぞれは、第1のサブピクセルを有しており、

前記第1のサブピクセルは、前記第1の走査線と前記第2の走査線の間に配設されてい

るとともに、第1の薄膜トランジスタと第2の薄膜トランジスタと第3の薄膜トランジス

タとピクセル電極を有しており、

前記ピクセル電極は、互いに異なる信号を表示する第1の領域と第2の領域に分割され

ており、

前記第1の薄膜トランジスタは、そのゲートを通じて前記第1の走査線に電気的に接続

されるとともに、そのドレイン電極によって前記第1の領域に電気的に接続されてお

り、

前記第2の薄膜トランジスタは、そのゲートを通じて前記第1の走査線に電気的に接続

されるとともに、そのドレイン電極によって前記第2の領域に電気的に接続されてお

り、

10

20

前記第3の薄膜トランジスタは、そのゲートを通じて前記第2の走査線に電気的に接続されるとともに、そのドレイン電極によって前記第2の領域に電気的に接続されており、

前記データ線は、前記第1の薄膜トランジスタのソース電極及び前記第2の薄膜トランジスタのソース電極に接続されており、

前記蓄積容量ラインは、前記第1の走査線及び第2の走査線に平行に配設されているとともに、前記第3の薄膜トランジスタのソースと同一電位を有する電極と対になって補助キャパシタを構成し、

前記蓄積容量ラインから前記第1の走査線までの距離は、前記蓄積容量ラインから前記第2の走査線までの距離よりも長く、

前記第1の薄膜トランジスタのドレイン電極と第1走査線の間の寄生キャパシタを $C_{g_d1}$ 、前記第2の薄膜トランジスタのドレイン電極と第1走査線の間の寄生キャパシタを $C_{g_d2}$ としたときに、

$\frac{C_{g_d2}}{C_{g_d1}} = \frac{L_2}{L_1}$  (1)

を満たすことを特徴とする液晶ディスプレイパネル。

#### 【請求項2】

前記第1の走査線が前記第1の薄膜トランジスタのドレイン電極と同電位となる第1の電極に対向する第1対向領域と、前記第1の走査線が前記第2の薄膜トランジスタのドレイン電極と同電位となる第2の電極に対向する第2対向領域が、それぞれ設けられているとともに、

前記第1対向領域は、前記第2対向領域よりも狭いことを特徴とする請求項1に記載の液晶ディスプレイパネル。

#### 【請求項3】

前記第1の薄膜トランジスタのチャネル幅を $W_1$ 、前記第2の薄膜トランジスタのチャネル幅を $W_2$ 、前記第1の薄膜トランジスタのチャネル長を $L_1$ 、前記第2の薄膜トランジスタのチャネル長を $L_2$ としたときに、

$W_2 / L_2 = W_1 / L_1$  (2)

を満たすことを特徴とする請求項1に記載の液晶ディスプレイパネル。

#### 【請求項4】

前記蓄積容量ラインは、前記ピクセル電極と前記第2の走査線の間に配設されていることを特徴とする請求項1に記載の液晶ディスプレイパネル。

#### 【請求項5】

前記薄膜トランジスタ基板に対向配置されているとともに共通電極を有する対向基板と、

前記薄膜トランジスタ基板と前記対向基板の間に配設されている液晶層と、前記蓄積容量ラインに対向するように配設されているパターン化金属層をさらに備え、前記共通電極と前記ピクセル電極の第1の領域との間に、第1の液晶キャパシタが構成されており、

前記共通電極と前記ピクセル電極の第2の領域との間に、第2の液晶キャパシタが構成されており、

前記パターン化金属層の第1の部分は、前記ピクセル電極の第1の領域に電気的に接続されており、蓄積容量ラインと対になって第1の蓄積キャパシタを構成しており、

前記パターン化金属層の第2の部分は、前記ピクセル電極の第2の領域及び第3の薄膜トランジスタに電気的に接続されており、蓄積容量ラインと対になって第2の蓄積キャパシタを構成しており、

前記パターン化金属層の第3の部分は、第3の薄膜トランジスタに電気的に接続されており、蓄積容量ラインと対になって第1の補助キャパシタを構成しているとともに、前記第1の部分と対になって第2の補助キャパシタを構成しており、

前記第1のサブピクセルにおいて、前記第1の領域における蓄積キャパシタ $C_{st1}$ と液晶キャパシタ $C_{1c1}$ との比と、前記第2の領域における蓄積キャパシタ $C_{st2}$ と液

10

20

30

40

50

晶キャパシタ  $C_{1c2}$  との比が、

$$(C_{st1} / C_{1c1}) \quad (C_{st2} / C_{1c2}) \quad (3)$$

を満たすことを特徴とする請求項 1 に記載の液晶ディスプレイパネル。

【請求項 6】

前記複数のピクセルのそれぞれは、第 2 のサブピクセルと第 3 のサブピクセルをさらに有し、

前記第 1 のサブピクセルと前記第 2 のサブピクセルと前記第 3 のサブピクセルは、前記第 1 走査線に沿って互いに隣接して配設されており、

各サブピクセルの前記補助キャパシタを  $C_s$ 、各サブピクセルの液晶キャパシタを  $C_{1c}$ 、各サブピクセルの蓄積キャパシタを  $C_{st}$  としたときに、各サブピクセルが下記式の比  $R_a$ 、即ち、

$$R_a = C_s / (C_s + C_{1c} + C_{st}) \quad (4)$$

を有することを特徴とする請求項 1 に記載の液晶ディスプレイパネル。

【請求項 7】

前記比  $R_a$  は、0.1 以上 0.35 以下であることを特徴とする請求項 6 に記載の液晶ディスプレイパネル。

【請求項 8】

前記第 1 のサブピクセルは赤色のサブピクセルであり、前記第 2 のサブピクセルは緑色のサブピクセルであり、前記第 3 のサブピクセルは青色のサブピクセルであり、

前記赤色のサブピクセルにおける前記比  $R_a$  を  $R_{a1}$ 、前記緑色のサブピクセルにおける前記比  $R_a$  を  $R_{a2}$ 、前記青色のサブピクセルにおける前記比  $R_a$  を  $R_{a3}$  としたときに、

$$R_{a1} = R_{a2} = R_{a3} \quad (5)$$

を満たすことを特徴とする請求項 6 に記載の液晶ディスプレイパネル。

【発明の詳細な説明】

【技術分野】

【0001】

本出願は、2007年2月16日に出願された台湾国特許出願第096106311号に基づく利権を主張し、その出願の全ての内容はこの明細書中に参照により援用されている。

【0002】

本開示は、ディスプレイパネルとその製造方法に関し、特に、液晶ディスプレイ (LCD) パネルとその製造方法に関する。

【背景技術】

【0003】

LCD パネルは、普及の進んでいるディスプレイパネルの 1 種であり、解像度の高さ、重量の軽さ、厚みの薄さ、消費電力の低さといった利点を備えている。しかしながら、現在の LCD パネルには、解消されるべきいくつかの技術的課題が未だ存在している。例えば、使用者がディスプレイの正面から表示画像を見たときと、使用者がディスプレイの左右から斜めに表示画像を見たときで、表示画像のグレースケールレベルや輝度が変化するという、広視野角に係る問題が存在する。通常、ディスプレイの正面から見たときの表示画像の輝度は、ディスプレイの左右から斜めに見たときの表示画像よりも高くなる。従って、LCD 装置上の表示画像は、見る角度によってその輝度が変化し、結果として異なった混合色によって表示されることがある。即ち、色ずれ (カラーシフト) や色の彩度低下といった現象が生じてしまう。

【0004】

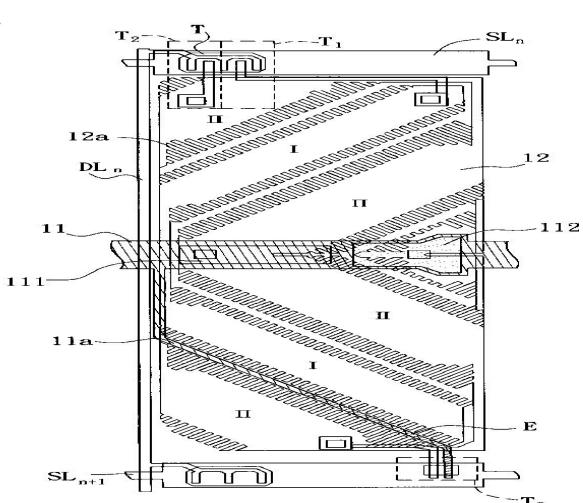

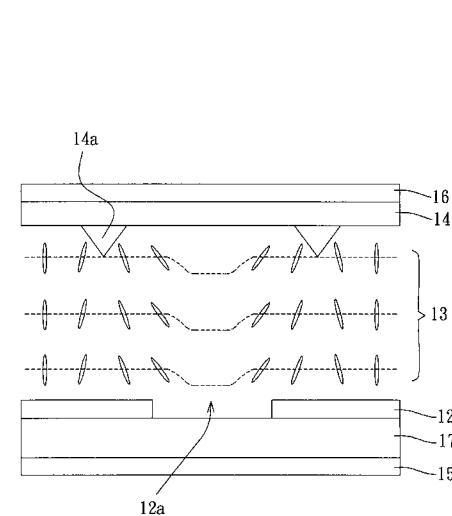

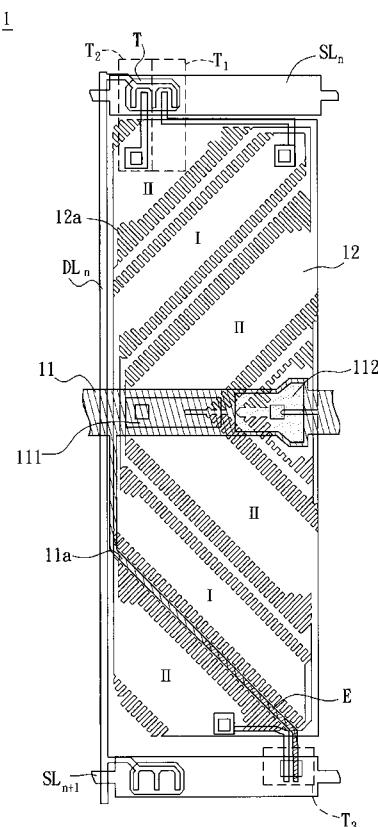

図 1、図 2 に示すように、従来のマルチドメイン垂直配向 (MVA) 型 LCD パネルのサブピクセル構造 1 は、少なくとも 1 つの薄膜トランジスタ (TFT) T、蓄積容量ライン 11、サブピクセル電極 12、液晶層 13、共通電極 14 を含んでいる。共通電極 14 は、カラーフィルタ基板 16 上に形成されている。サブピクセル電極 12 は、TFT 基板

10

20

30

40

50

15の誘電体層17上に形成されている。液晶層13は、サブピクセル電極12と共に通電極14の間に位置している。サブピクセル電極12は、2つの隣接する走査線SL<sub>n</sub>およびSL<sub>n+1</sub>の間に配設されている。サブピクセル電極12は、所定の形状パターンを形成するように、複数のスリット12aを有している。薄膜トランジスタTは、サブピクセル構造1の動作を制御する。また、蓄積キャパシタが、蓄積容量ライン11およびサブピクセル電極12の間に形成されている。

#### 【0005】

MVA型LCDパネルでは、上述したスリット12a又はアライメント突起14aが、TFT基板15又はカラーフィルタ基板16の上にそれぞれ形成される。それにより、液晶分子を複数の方向に配向させ、複数の配向ドメインを形成することによって、広視野角に係る問題を改善している。10

#### 【0006】

近年、広視野角に係る色ずれの問題をより効果的に改善するために、図2に示す他の技術が提案されている。図2に示すように、この技術では、サブピクセル電極12を第1の領域Iと第2の領域IIに分割し、それらの輝度比をグレースケールレベルに応じて調整しながら表示を行う。この効果を達成するために、通常は、隣接する走査線SL<sub>n+1</sub>が作動状態のときに、第3の薄膜トランジスタT<sub>3</sub>をオンさせることによって、補助キャパシタの電荷をサブピクセル電極12の第2の領域IIに通電させる。ここで、補助キャパシタは、蓄積容量ライン11から伸びる付加的相互接続部11aと、第3の薄膜トランジスタT<sub>3</sub>のソースと同一電位を有する電極Eとの対向配置によって構成される。その結果、第2の領域IIと第1の領域Iの間の輝度差が一定に維持され、色ずれの問題の発生が回避されるようになっている。20

#### 【0007】

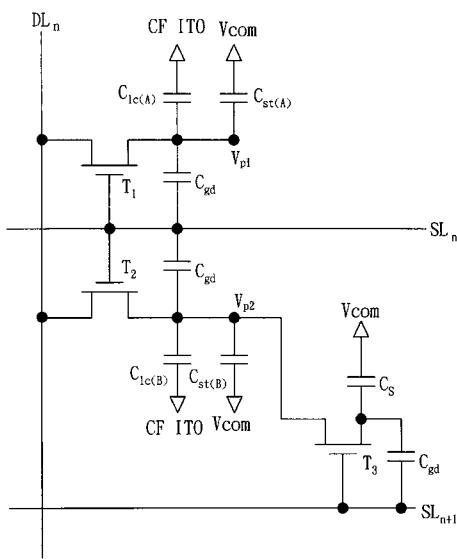

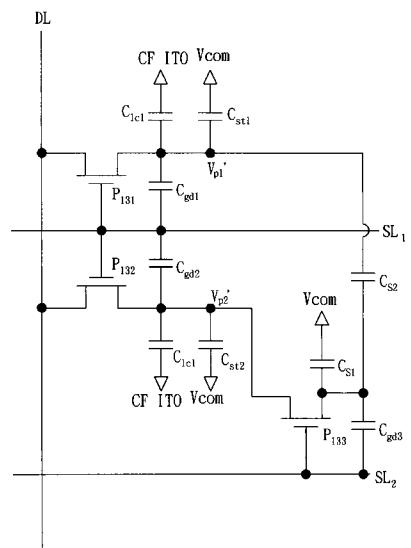

図3は、サブピクセル構造1の等価回路図を示す。液晶キャパシタC<sub>1c</sub>(A)は、サブピクセル電極12の第1の領域I(例えば明領域)と共に通電極14との対向配置によって構成されている。液晶キャパシタC<sub>1c</sub>(B)は、サブピクセル電極12の第2の領域II(例えば暗領域)と共に通電極14との対向配置によって構成されている。蓄積キャパシタC<sub>st</sub>(A)は、蓄積容量ライン11と、サブピクセル電極12の第1の領域Iにビアを介して電気的に接続されたキャパシタ電極112との対向配置によって構成されている。蓄積キャパシタC<sub>st</sub>(B)は、蓄積容量ライン11と、サブピクセル電極12の第2の領域IIにビアを介して電気的に接続されたキャパシタ電極111との対向配置によって構成されている。補助キャパシタC<sub>s</sub>は、蓄積容量ライン11の付加的相互接続部11aと、第3の薄膜トランジスタT<sub>3</sub>のソースと同一電位を有する電極Eとの対向配置によって構成されている。サブピクセル電極12の第1の領域Iと第2の領域IIは、共通電極14に対向して配設されている。サブピクセル電極12の第1の領域Iは、第1の薄膜トランジスタT<sub>1</sub>を介して、データ線DL<sub>n</sub>及びデータ線DL<sub>n</sub>と向かい合う走査線SL<sub>n</sub>に電気的に接続されている。サブピクセル電極12の第2の領域IIは、第1の薄膜トランジスタT<sub>1</sub>と向かい合う第2の薄膜トランジスタT<sub>2</sub>を介して、データ線DL<sub>n</sub>及びデータ線DL<sub>n</sub>と向かいあう走査線SL<sub>n</sub>に電気的に接続されている。また、サブピクセル電極12の第2の領域IIは、対応する第3の薄膜トランジスタT<sub>3</sub>を介して、隣接する走査線SL<sub>n+1</sub>及び補助キャパシタに電気的に接続されている。30

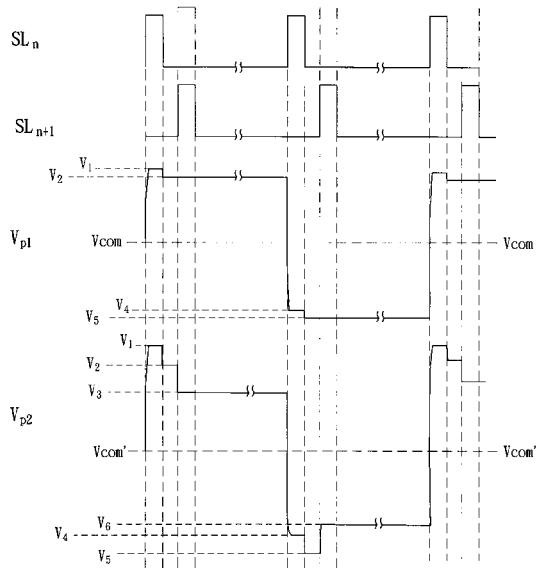

#### 【0008】

図4は、図3に示す走査線SL<sub>n</sub>、SL<sub>n+1</sub>及びノードV<sub>p1</sub>、V<sub>p2</sub>の動作(電位)を示すタイムチャートである。先ず、走査線SL<sub>n</sub>がサブピクセル電極12にシグナルを入力すると、第1の薄膜トランジスタT<sub>1</sub>および第2の薄膜トランジスタT<sub>2</sub>がオンし、正電位のサブピクセルデータがデータ線DLを介して入力される。このとき、ノードV<sub>p1</sub>及びV<sub>p2</sub>の電位は互いに等しい電位V<sub>1</sub>となる。走査線SL<sub>n</sub>からサブピクセル電極12へのシグナルの入力が中止されると、第1の薄膜トランジスタT<sub>1</sub>及び第2の薄膜トランジスタT<sub>2</sub>は瞬時にオフする。この時点において、ノードV<sub>p1</sub>及びV<sub>p2</sub>は、薄膜トランジスタT<sub>1</sub>及びT<sub>2</sub>のゲート-ドレインの間の寄生キャパシタ効果により、異なる40

るフィードスルー効果を受ける。その結果、ノード  $V_{p_1}$  及び  $V_{p_2}$  の電位は相互に異なる電位となる。そのノード  $V_{p_1}$  及び  $V_{p_2}$  の電位をそれぞれ  $V_2$  及び  $V_{21}$  とする。このとき、共通電圧  $V_{com}$  に対して相対的なそれらのレベル差は約  $V_2 - V_{21}$  となる。次いで、走査線  $SL_{n+1}$  がサブピクセル電極 12 にシグナルを入力すると、前のフレームはドット反転によって影響を受ける。そのことから、第 3 の薄膜トランジスタ  $T_3$  がオンすると、蓄積キャパシタ  $C_{st(B)}$  に保持された電荷が補助キャパシタ  $C_s$  を中性化し、ノード  $V_{p_1}$  の電圧レベルが  $V_2$  のままでノード  $V_{p_2}$  の電圧レベルのみが  $V_3$  に変化する。走査線  $SL_{n+1}$  がシグナルの入力を停止した場合、ノード  $V_{p_1}$  及び  $V_{p_2}$  の電位は、 $V_2$  及び  $V_3$  にそれぞれ維持される。次のフレーム期間では、走査線  $SL_n$  から再度シグナルが入力されて第 1 の薄膜トランジスタ  $T_1$  及び第 2 の薄膜トランジスタ  $T_2$  がオンし、負極性のサブピクセルデータがデータ線  $DL$  を介して入力され、ノード  $V_{p_1}$  及び  $V_{p_2}$  の電位が同時に  $V_4$  に等しくなる。走査線  $SL_n$  からシグナルの入力が停止されると、第 1 の薄膜トランジスタ  $T_1$  及び第 2 の薄膜トランジスタ  $T_2$  は瞬時にオフする。ノード  $V_{p_1}$  及び  $V_{p_2}$  の電位は、異なるフィードスルー効果を受けることにより、それぞれ  $V_5$  及び  $V_{51}$  に等しくなる。このとき、共通電圧  $V_{com}$  に対して相対的なそれらのレベル差は約  $V_5 - V_{51}$  となる。次いで、走査線  $SL_{n+1}$  がシグナルを入力して第 3 の薄膜トランジスタ  $T_3$  がオンすると、蓄積キャパシタ  $C_{st(B)}$  に保持された前のフレームの正極性の電荷が補助キャパシタ  $C_s$  に移動し、ノード  $V_{p_2}$  の電圧レベルが  $V_6$  に変化する。この間、ノード  $V_{p_1}$  の電圧レベルは  $V_5$  に維持される。走査線  $SL_{n+1}$  がシグナルの入力を停止すると、ノード  $V_{p_1}$  及び  $V_{p_2}$  の電位はそれぞれ  $V_5$  および  $V_6$  に等しくなる。

10

## 【0009】

特許文献 1 は、「SUBSTRATE FOR LIQUID CRYSTAL DISPLAY, LIQUID CRYSTAL DISPLAY HAVING THE SUBSTRATE, AND METHOD OF DRIVING THE DISPLAY」と題し、液晶表示装置用の基板、その基板を有する液晶表示装置、及びその液晶表示装置の駆動方法を開示しており、優れた表示性能を有する液晶表示装置用の基板と、それを有する液晶表示装置及びその駆動方法を提案している。また、特許文献 2 は、「Liquid Crystal Display Device」と題し、優れた表示性能を有する液晶表示装置を開示している。

20

【特許文献 1】米国特許出願公開第 2006/0215066 号明細書

【特許文献 2】米国特許出願公開第 2006/0290827 号明細書

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0010】

しかしながら、どの方法が利用されるかに関わらず、サブピクセル構造 1 中の蓄積容量ライン 11 は、サブピクセル電極 12 の中間位置に配設されている。キャパシタンスを調整するために、付加的相互接続部 11a を蓄積容量ライン 11 から付加的に形成する必要がある場合、蓄積容量ライン 11 の相互接続の困難性および負荷が増加することになり、開口比も低減することとなる。加えて、サブピクセル電極 12 が第 1 の領域（明領域）I 及び第 2 の領域（暗領域）II に分割され、明領域 I および暗領域 II が異なるフィードスルー効果を受ける場合、サブピクセル構造 12 の 2 つの領域によって表示されるシグナルは、シグナル中心点  $V_{com}$  と比して異なるレベルとなる。それにより、異なるフレームの間でシグナルはフリッキングを起こすことになり、また、液晶分子の極性化による残像が長時間に亘ることもある。

40

従って、相互接続構造を簡素に構成でき、ディスプレイ特性における低グレースケール領域の影響を低減させ、色ずれ現象を改善することが可能な LCD パネル、及びその製造方法が必要とされている。

## 【課題を解決するための手段】

## 【0011】

10

20

30

40

50

本明細書に開示される液晶ディスプレイパネルは、薄膜トランジスタ基板を有している。前記薄膜トランジスタ基板は、第1の走査線と、第2の走査線と、複数のピクセルと、データ線と、蓄積容量ラインを備えている。前記第1の走査線は、前記薄膜トランジスタ基板上に配設されている。前記第2の走査線は、前記薄膜トランジスタ基板上に前記第1走査線と平行に配設されている。前記複数のピクセルのそれぞれは、第1のサブピクセルを有している。前記第1のサブピクセルは、前記第1の走査線と前記第2の走査線の間に配設されているとともに、第1の薄膜トランジスタと第2の薄膜トランジスタと第3の薄膜トランジスタとピクセル電極を有している。前記ピクセル電極は、互いに異なる信号を表示する第1の領域と第2の領域に分割されている。前記第1の薄膜トランジスタは、そのゲートを通じて前記第1の走査線に電気的に接続されるとともに、そのドレイン電極によって前記第1の領域に電気的に接続されている。前記第2の薄膜トランジスタは、そのゲートを通じて前記第1の走査線に電気的に接続されるとともに、そのドレイン電極によって前記第2の領域に電気的に接続されている。前記第3の薄膜トランジスタは、そのゲートを通じて前記第2の走査線に電気的に接続されるとともに、そのドレイン電極によって前記第2の領域に電気的に接続されている。前記データ線は、前記第1の薄膜トランジスタのソース電極及び前記第2の薄膜トランジスタのソース電極に接続されている。前記蓄積容量ラインは、前記第1の走査線及び第2の走査線に平行に配設されており、前記第3の薄膜トランジスタのソースと同一電位を有する電極と対になって補助キャパシタを構成する。前記蓄積容量ラインから前記第1の走査線までの距離は、前記蓄積容量ラインから前記第2の走査線までの距離よりも長くなっている。ここで、前記第1の薄膜トランジスタのドレイン電極と第1走査線の間の寄生キャパシタを  $C_{g_d 1}$ 、前記第2の薄膜トランジスタのドレイン電極と第1走査線の間の寄生キャパシタを  $C_{g_d 2}$  としたときに、 $C_{g_d 2} - C_{g_d 1}$  を満たすことが好ましい。

10

20

## 【0012】

本明細書に開示される他の液晶ディスプレイパネルは、薄膜トランジスタ基板を有している。前記薄膜トランジスタ基板は、第1の走査線と、第2の走査線と、複数のピクセルと、データ線を備えている。前記第1の走査線は、前記薄膜トランジスタ基板上に配設されている。前記第2の走査線は、前記薄膜トランジスタ基板上に前記第1走査線と平行に配設されている。前記複数のピクセルのそれぞれは、第1のサブピクセルを有している。前記第1のサブピクセルは、前記第1の走査線と前記第2の走査線の間に配設されるとともに、第1の薄膜トランジスタと第2の薄膜トランジスタと第3の薄膜トランジスタとピクセル電極を有している。前記ピクセル電極は、互いに異なる信号を表示する第1の領域と第2の領域に分割されている。前記第1の薄膜トランジスタは、そのゲートを通じて前記第1の走査線に電気的に接続されるとともに、そのドレイン電極によって前記第1の領域に電気的に接続されている。前記第2の薄膜トランジスタは、そのゲートを通じて前記第1の走査線に電気的に接続されるとともに、そのドレイン電極によって前記第2の領域に電気的に接続されている。前記第3の薄膜トランジスタは、そのゲートを通じて前記第2の走査線に電気的に接続されるとともに、そのドレイン電極によって前記第2の領域に電気的に接続されている。前記データ線は、前記第1の薄膜トランジスタのソース電極及び前記第2の薄膜トランジスタのソース電極に接続されている。この液晶ディスプレイパネルには、前記第1の走査線が第1の薄膜トランジスタのドレイン電極に接続された第1の導電性パターン部に対向する第1対向領域と、前記第1の走査線が第2の薄膜トランジスタのドレイン電極に接続された第2の導電性パターン部に対向する第2対向領域が、それぞれ存在する。ここで、前記第1対向領域は、前記第2対向領域よりも狭くなっている。

30

40

## 【0013】

本明細書は、液晶ディスプレイパネルの製造方法を開示する。この製造方法は、薄膜トランジスタ基板に第1の走査線と第2の走査線を形成する工程と、第1の走査線に接続されたゲートと第1の走査線に対向するドレインを有する第1の薄膜トランジスタ及び第2の薄膜トランジスタを形成する工程と、第2の走査線に接続されたゲートを有する第3の

50

薄膜トランジスタを形成する工程と、薄膜トランジスタ基板に、第1の薄膜トランジスタ及び第2の薄膜トランジスタのソースに接続されたデータ線を形成する工程と、薄膜トランジスタ基板に、第1の走査線と第2の走査線の間に位置するピクセル電極を形成する工程と、薄膜トランジスタ基板を対向基板に組み付ける工程と、薄膜トランジスタ基板と対向基板の間に液晶層を形成する工程を備えている。ここで、前記ピクセル電極は、互いに異なる信号を表示する第1の領域と第2の領域に分割される。前記第1の薄膜トランジスタのドレインは、前記ピクセル電極の第1の領域に電気的に接続される。前記第2の薄膜トランジスタのドレインは、前記ピクセル電極の第2の領域に電気的に接続される。前記第3の薄膜トランジスタのドレインは、前記ピクセル電極の第2の領域に電気的に接続される。この製造方法では、前記第1の走査線が前記第1の薄膜トランジスタのドレイン及び前記ピクセル電極の第1の領域に対向する第1対向領域と、前記第1の走査線が前記第2の薄膜トランジスタのドレイン及び前記ピクセル電極の第2の領域に対向する第2対向領域を、それぞれ存在させるとともに、前記第1対向領域は前記第2対向領域よりも狭くする。

#### 【0014】

下記に開示される実施形態の付加的な特徴及び利点は、その一部が本明細書に記載されている一方、他の一部は開示された実施形態を実際に実施することによって明確に理解されるものである。開示される実施形態の付加的な特徴及び利点は、特許請求の範囲に記載された各要件及びそれらの組み合わせによって実現されるものである。

#### 【発明を実施するための最良の形態】

#### 【0015】

以下、添付の図面を参照しながら、発明を実施するための最良の形態を説明する。図面中、同一の構成要件には同一が符号されている。

#### 【0016】

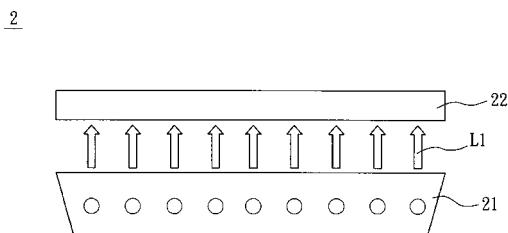

この実施形態における液晶ディスプレイ（LCD）装置2は、マルチドメイン垂直配向（MVA）液晶ディスプレイ装置である。ただし、この形態に制限されるものではなく、LCD装置2は、ツイステッドネマチックLCD装置、光学補償ベンド配向型（OCB）LCD装置、軸対称配向型（ASM）LCD装置、面内切替型（IPS）LCD装置であってもよい。

#### 【0017】

図5は、本発明の第1の実施形態によるLCD装置2の構造を示す概略図である。図5に示すように、LCD装置2は、バックライトモジュール21と、液晶ディスプレイ（LCD）パネル22を備えている。バックライトモジュール21は、LCDパネル22に隣接して配設されており、LCDパネル22を透過する光L1を発する。この実施形態のバックライトモジュール21は直下型バックライトモジュールであるが、これに制限されず、例えばエッジライト型バックライトモジュールであってもよい。バックライトモジュール21の光源は、冷陰極蛍光ランプ（CCFL）、発光ダイオード（LED）、有機エレクトロルミネッセント素子（OELD）、電界放出素子（FED）等であるとよい。

#### 【0018】

加えて、LCDパネル22は、薄膜トランジスタ基板（TFT基板）（図示せず）と、対向基板（例えば、カラーフィルタ基板）（図示せず）と、液晶層（図示せず）を有する。TFT基板は、対向基板に対向して配設されている。液晶層は、TFT基板と対向基板の間に配設されている。TFT基板は、複数のデータ線、複数の走査線、複数のピクセル、複数の蓄積容量ラインを有する。走査線は、蓄積容量ラインと平行に配置されている。ピクセルは、マトリックス状に配置されている。ここで、各ピクセルは、2つの隣接する走査線の間に配設されたサブピクセルを有している。

#### 【0019】

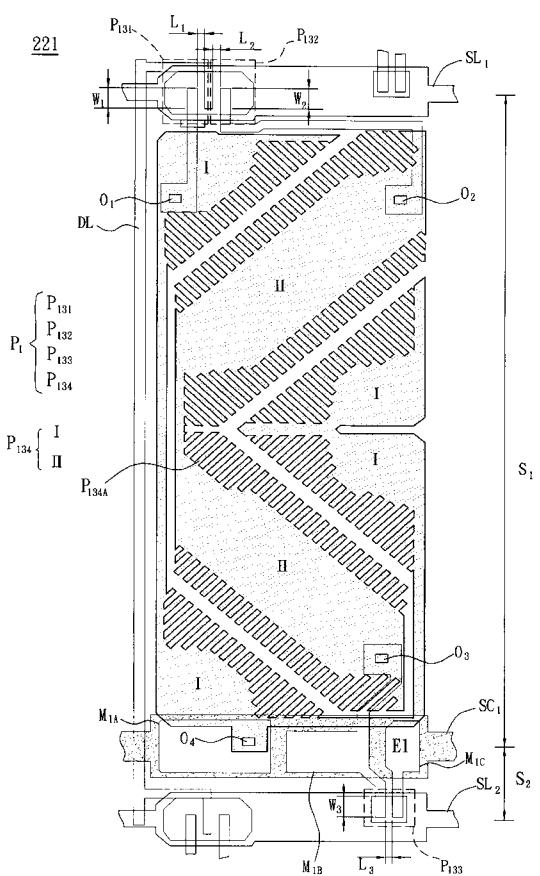

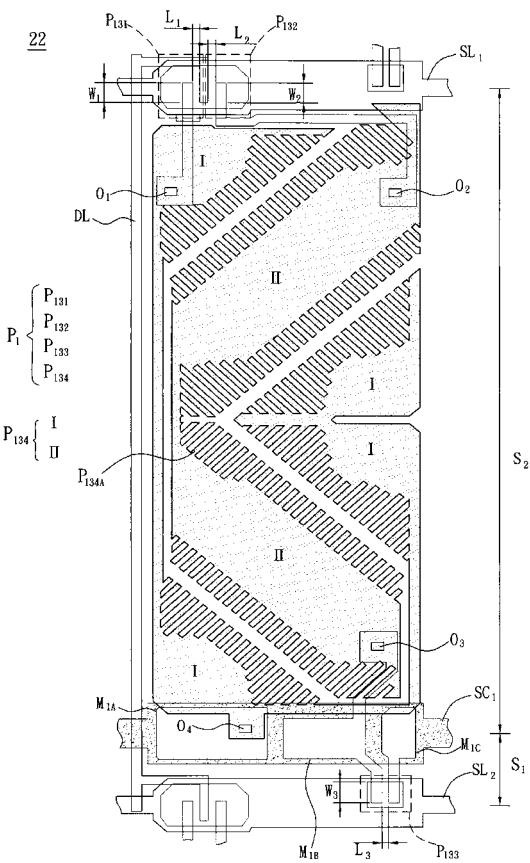

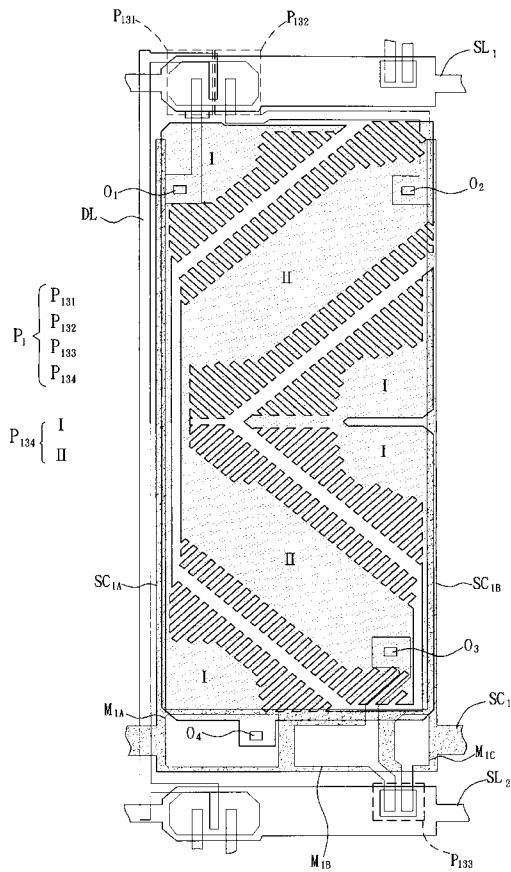

図6は、TFT基板のサブピクセル構造221を平面視した図である。図7は、対向基板のサブピクセル構造222を平面視した図である。図6に示すように、TFT基板のサブピクセル構造221は、第1のサブピクセルP<sub>1</sub>、データ線DL、第1の走査線SL<sub>1</sub>

10

20

30

40

50

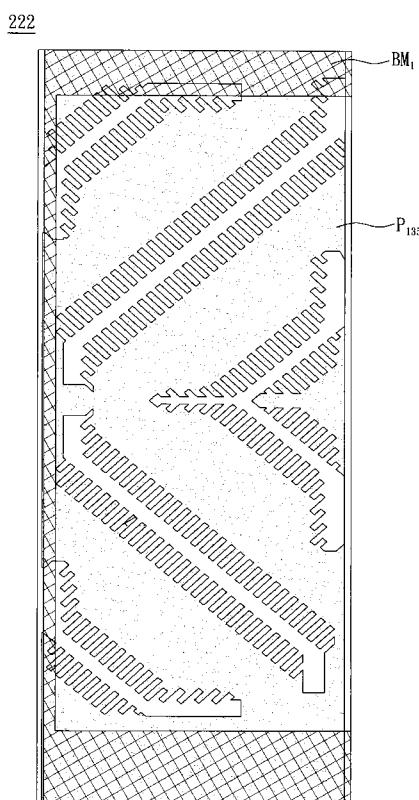

、第2の走査線 $S_{L_2}$ 、蓄積容量ライン $SC_1$ を有している。図7に示すように、対向基板のサブピクセル構造222は、共通電極 $P_{135}$ を有している。ここで、第1のサブピクセル $P_1$ は赤色、緑色、青色のいずれかのサブピクセル、あるいは、フルカラーピクセルにおける他の有色サブピクセルであり得る。

【0020】

第1のサブピクセル $P_1$ は、第1の薄膜トランジスタ $P_{131}$ 、第2の薄膜トランジスタ $P_{132}$ 、第3の薄膜トランジスタ $P_{133}$ およびピクセル電極 $P_{134}$ を有する。第1の薄膜トランジスタ $P_{131}$ 、第2の薄膜トランジスタ $P_{132}$ 、第3の薄膜トランジスタ $P_{133}$ 、蓄積容量ライン $SC_1$ およびピクセル電極 $P_{134}$ は TFT 基板上に形成されている。この実施形態では、補助キャパシタ $C_5$ を形成するために蓄積容量ライン $SC_1$ の構成を複雑なものにする必要がないように(例えば、蓄積容量ライン $SC_1$ に余剰な分岐を形成することによって、蓄積容量ライン $SC_1$ の構造を複雑なものとしないように)、蓄積容量ライン $SC_1$ と第1の走査線 $S_{L_1}$ の間の距離 $S_1$ は、蓄積容量ライン $SC_1$ と第2の走査線 $S_{L_2}$ の間の距離 $S_2$ よりも長くなっている。蓄積容量ライン $SC_1$ と第2の走査線 $S_{L_2}$ の間の距離 $S_2$ は、4 μm ~ 20 μmの範囲である。

10

【0021】

ピクセル電極 $P_{134}$ はまた、ピクセル電極 $P_{134}$ がパターンを伴って形成されると共に液晶分子が予め定められた傾斜角度を有するよう、複数のスリット $P_{134a}$ を有し得る。一方、例えばツイステッドネマチックLCD装置に適用される場合は、スリット $P_{134a}$ は省略され得る。ピクセル電極 $P_{134}$ は、第1の領域Iおよび第2の領域IIに分割されている。この実施形態において、第1の領域Iは明領域であり、および第2の領域IIは暗領域である。

20

【0022】

再度図6を参照すると、第1の薄膜トランジスタ $P_{131}$ は、第1の走査線 $S_{L_1}$ に電気的に接続されたゲート、第1のサブピクセル $P_1$ の第1の領域Iにビア $O_1$ を介して電気的に接続されたドレイン、およびデータ線 $DL$ に電気的に接続されたソースを有する。第2の薄膜トランジスタ $P_{132}$ は、第1の走査線 $S_{L_1}$ に電気的に接続されたゲート、第1のサブピクセル $P_1$ の第2の領域IIにビア $O_2$ を介して電気的に接続されたドレイン、およびデータ線 $DL$ に電気的に接続されたソースを有する。第3の薄膜トランジスタ $P_{133}$ は、第2の走査線 $S_{L_2}$ に電気的に接続されたゲート、第1のサブピクセル $P_1$ の第2の領域IIにビア $O_3$ を介して電気的に接続されたドレイン、および補助キャパシタの電極 $E_1$ に電気的に接続されたソースを有する。本願明細書において、第1の薄膜トランジスタ $P_{131}$ 、第2の薄膜トランジスタ $P_{132}$ および第3の薄膜トランジスタ $P_{133}$ は、第1のサブピクセル $P_1$ の第1の領域Iおよび第2の領域IIの作動を制御するためのものである。

30

【0023】

この実施形態において、第1の薄膜トランジスタ $P_{131}$ のゲートとドレインの間には第1の寄生キャパシタ $C_{gd1}$ が形成されており、第2の薄膜トランジスタ $P_{132}$ のゲートとドレインの間には第2の寄生キャパシタ $C_{gd2}$ が形成されており、第3の薄膜トランジスタ $P_{133}$ のゲートとドレインの間には第3の寄生キャパシタ $C_{gd3}$ が形成されている。

40

【0024】

フィードスルー電圧 $V_{feed\ through}$ については、下記の関係が知られている。

$$V_{feed\ through} = C_{gd1} \times (V_{gh} - V_{g1}) / (C_{st} + C_{lc} + C_{gd1})$$

それ故、第3の寄生キャパシタ $C_{gd3}$ を考慮することなく、2つのサブピクセルのフィードスルー電圧 $V_{feed\ through}$ を同一にするためには(第2の走査線 $S_{L_2}$ が起動(イネーブル)および停止(ディセーブル)とされるときに発生する第3の寄生キャパシタ $C_{gd3}$ の作用は相互にオフセットし得るため)、下記の関係が得られる。

$$\begin{aligned} C_{gd1} \times (V_{gh} - V_{g1}) / (C_{st1} + C_{lc1} + C_{gd1}) \\ = C_{gd2} \times (V_{gh} - V_{g1}) / (C_{st2} + C_{lc2} + C_{gd2}) \end{aligned}$$

50

上式において( $V_{g_h} - V_{g_1}$ )を消去すると、下記の関係が得られる。

$$\begin{aligned} C_{gd1} / [((C_{st1} / C_{1c1}) + 1 + (C_{gd1} / C_{1c1})) \times C_{1c1}] \\ = C_{gd2} / [((C_{st2} / C_{1c2}) + 1 + (C_{gd2} / C_{1c2})) \times C_{1c2}] \end{aligned}$$

ここで、( $C_{gd1} / C_{1c1}$ )および( $C_{gd2} / C_{1c2}$ )の各々の値は1よりはるかに小さく、無視し得る。従って、 $C_{st1} / C_{1c1} = C_{st2} / C_{1c2}$ であるとき、下記の関係が得られる。

$$C_{gd1} / [(2) \times C_{1c1}] = C_{gd2} / [(2) \times C_{1c2}]$$

しかしながら、明領域Iの面積/光束は、設計により暗領域IIのものより小さくされている。従って、 $C_{1c2} < C_{1c1}$ であり、 $C_{gd2} < C_{gd1}$ である。この場合、第1の薄膜トランジスタ $P_{131}$ および第2の薄膜トランジスタ $P_{132}$ は、下記の式(1)を満たす。

10

$$C_{gd2} < C_{gd1} \quad (1)$$

【0025】

加えて、薄膜トランジスタのソースおよびドレインの間に位置されており、半導体領域を含有する領域は、チャネル幅 $W$ として称される対応する幅を有し、およびソースおよびドレインの距離は、チャネル長さ $L$ として称される。上述の記載に基づく図6を再度参照すると、第1の薄膜トランジスタ $P_{131}$ は、第1のチャネル幅 $W_1$ および第1のチャネル長さ $L_1$ を有し；第2の薄膜トランジスタ $P_{132}$ は、第2のチャネル幅 $W_2$ および第2のチャネル長さ $L_2$ を有し；および第3の薄膜トランジスタ $P_{133}$ は、第3のチャネル幅 $W_3$ および第3のチャネル長さ $L_3$ を有する。

20

【0026】

第1の薄膜トランジスタ $P_{131}$ および第2の薄膜トランジスタ $P_{132}$ は下記の式(2)を満たす。

$$W_2 / L_2 < W_1 / L_1 \quad (2).$$

【0027】

この実施形態において、第2のチャネル幅 $W_2$ に対する第2のチャネル長さ $L_2$ の比は、第1のチャネル幅 $W_1$ に対する第1のチャネル長さ $L_1$ の比と等しい。

【0028】

図8に示すように、上述の要求を満たすため、「a：第1の薄膜トランジスタ $P_{131}$ のドレイン及び第1のサブピクセル $P_1$ の第1の領域I」と「b：第1の走査線 $SL_1$ 」とが対向し合う対向領域を、「c：第2の薄膜トランジスタ $P_{132}$ のドレイン及び第1のサブピクセル $P_1$ の第2の領域II」と「第1の走査線 $SL_1$ 」とが対向し合う対向領域よりも、小さくすることができる。この場合、例えば、第1の薄膜トランジスタ $P_{131}$ と第2の薄膜トランジスタ $P_{132}$ の形状は同一とする一方、第2の領域IIのピクセル電極 $P_{134}$ を第1の走査線 $SL_1$ と重なり合うように延伸させることができる(図8参照)。あるいは、第1の薄膜トランジスタ $P_{131}$ と第2の薄膜トランジスタ $P_{132}$ のチャネル長さ $L$ を同一にする一方、チャネル幅 $W$ について $W_2 > W_1$ となるように設計することもできる。そして、これらの手法を同時に用いて上記した式(1)を満足させることもできる。

30

【0029】

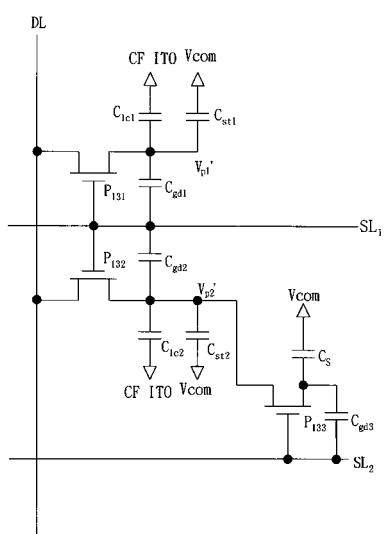

図6および図9を参照する。ここで、図9は図6の等価回路図である。この第2の実施形態において、LCDパネル22は、蓄積容量ライン $SC_1$ に対向して配設され、所定の形状を有するパターン化金属層 $M_1$ をさらに含む。パターン化金属層 $M_1$ の一部 $M_{1A}$ は、第1の領域Iにピア $O_4$ を介して電気的に接続されており、蓄積容量ライン $SC_1$ と対になって第1の蓄積キャパシタ $C_{st1}$ を構成している。パターン化金属層 $M_1$ の他の一部 $M_{1B}$ は、第3の薄膜トランジスタ $P_{133}$ および第2の領域IIにピア $O_3$ を介して電気的に接続されており、蓄積容量ライン $SC_1$ と対になって第2の蓄積キャパシタ $C_{st2}$ を構成している。パターン化金属層 $M_1$ のさらに別の一部 $M_{1C}$ は、第3の薄膜トランジスタ $P_{133}$ に電気的に接続されており、蓄積容量ライン $SC_1$ と対になって補助キャパシタ $C_S$ を構成している。

40

50

液晶キャパシタは、対向配置されたピクセル電極  $P_{134}$  と共通電極  $P_{135}$  によって形成されている。すなわち、第1のサブピクセル  $P_1$  の第1の領域Iと共通電極  $P_{135}$ との間に、第1の液晶キャパシタ  $C_{1c1}$  が構成されており、第1のサブピクセル  $P_1$  の第2の領域IIと共通電極  $P_{135}$ との間に、第2の液晶キャパシタ  $C_{1c2}$  が構成されている。

### 【0030】

この実施形態では、2つのサブピクセルに同一のフィードスルー電圧  $V_{feed\ through}$ を持たせるために、以下の関係が導かれる。

$$\begin{aligned} C_{gd1} / [((C_{st1} / C_{1c1}) + 1 + (C_{gd1} / C_{1c1})) \times C_{1c1}] \\ = C_{gd2} / [((C_{st2} / C_{1c2}) + 1 + (C_{gd2} / C_{1c2})) \times C_{1c2}] \end{aligned} \quad 10$$

ここで、( $C_{gd1} / C_{1c1}$ ) および ( $C_{gd2} / C_{1c2}$ ) の各々の値は、1よりはるかに小さく無視し得る。それ故、第1の薄膜トランジスタ  $P_{131}$  および第2の薄膜トランジスタ  $P_{132}$  が同一の設計サイズを有すると仮定（すなわち、 $C_{gd2} = C_{gd1}$  と仮定）すると以下の関係が導かれる。

$$1 / [((C_{st1} / C_{1c1}) + 1) \times C_{1c1}] = 1 / [((C_{st2} / C_{1c2}) + 1) \times C_{1c2}]$$

また、明領域Iの光束、即ち面積は、暗領域IIのものより小さく構成されている（即ち、 $C_{1c2} < C_{1c1}$ ）。それ故、下記の関係が成立する。

$$(C_{st1} / C_{1c1}) + 1 > (C_{st2} / C_{1c2}) + 1$$

従って、下記の関係が成立する。

$$(C_{st1} / C_{1c1}) > (C_{st2} / C_{1c2}) \quad 20$$

従って、第1の領域Iにおける蓄積キャパシタと液晶キャパシタとの比と、第2の領域IIにおける蓄積キャパシタと液晶キャパシタとの比が、下記の式(3)を満たしている。

$$C_{st1} / C_{1c1} > C_{st2} / C_{1c2} \quad (3)$$

### 【0031】

この実施形態では、第1の領域Iの面積を第2の領域IIより小さく設計すると共に、第1の領域Iおよび第2の領域IIが実質的に同一の蓄積キャパシタを有するよう設計することによって、 $C_{st1} / C_{1c1} > C_{st2} / C_{1c2}$  を達成することが可能である。

### 【0032】

加えて、各サブピクセルは、下記の式(4)を満たす比  $R_a$  を有する。

$$R_a = C_s / (C_s + C_{1c} + C_{st}) \quad (4)$$

ここで、この実施形態では、 $C_{1c} = C_{1c1} + C_{1c2}$  であることから、下記の関係が成立する。

$$C_{st} = C_{st1} + C_{st2}$$

明領域の面積と暗領域の面積の比が1:2に等しいときの、透過度の  $R_a$  への作用が以下に記載されている。透過度が、 $R_a = 0.15$  であるときに基準値(100%)と等しいと仮定すると、透過度は、 $R_a = 0.2$  であるとき95%に等しく；および透過度は、 $R_a = 0.25$  であるとき87.8%に等しい。それ故、上述の比は、好ましくは0.1~0.35の範囲である。簡潔に、比  $R_a$  は、サブピクセル全体の等価なキャパシタに対する補助キャパシタ  $C_s$  の比を表す。

### 【0033】

加えて、TFT基板のピクセルは、第2のサブピクセル（図示せず）および第3のサブピクセル（図示せず）をさらに含む。第1のサブピクセル  $P_1$ 、第2のサブピクセルおよび第3のサブピクセルは、第1の走査線  $SL_1$  に沿って互いに隣接して配設されている。本実施形態では、第1のサブピクセル  $P_1$  が赤色を表示するためのピクセル（R）であり、第2のサブピクセルが緑色を表示するためのピクセル（G）であり、および第3のサブピクセルが青色を表示するピクセル（B）であると仮定する。典型的に、高い色温度という仕様を満足すべきためには、ディスプレイの短波長での輝度出力を増加させる必要がある。例えば、ディスプレイの青色領域は、補助キャパシタが透過度の低下を生じさせることがから、減少させる必要がある。それ故、各サブピクセルの比  $R_a$  は式(5)を満たす。

$$R_a(R) = R_a(G) \quad R_a(B) \quad (5)$$

## 【0034】

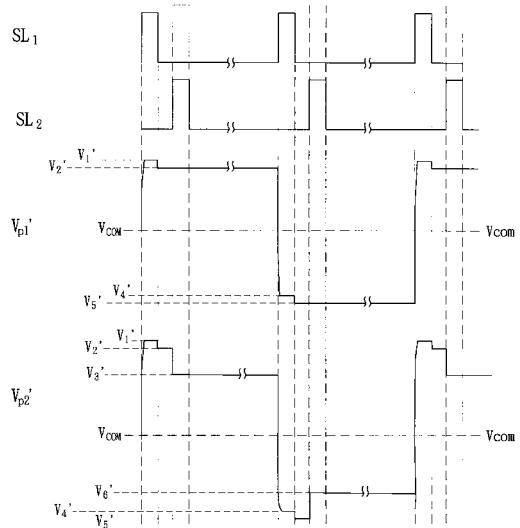

図10は、図9における、第1の走査線 $SL_1$ 、第2の走査線 $SL_2$ およびノード $V_{p_1}$ 、および $V_{p_2}$ のタイミングを示すタイミング図である。

## 【0035】

先ず、第1のフレームタイムにおいて、第1の走査線 $SL_1$ がシグナルを入力して第1の薄膜トランジスタ $P_{131}$ および第2の薄膜トランジスタ $P_{132}$ を起動し、およびノード $V_{p_1}$ 、および $V_{p_2}$ の電位が同時に $V_1$ に等しくなるよう、サブピクセルデータをデータ線 $DL$ を介して入力する。第1の走査線 $SL_1$ がシグナルの入力を停止した場合、第1の薄膜トランジスタ $P_{131}$ および第2の薄膜トランジスタ $P_{132}$ は瞬時に停止される。<sup>10</sup>しかしながら、薄膜トランジスタ $P_{131}$ と $P_{132}$ とのゲートおよびドレインの間の第1の寄生キャパシタ $C_{gd1}$ および第2の寄生キャパシタ $C_{gd2}$ は、本実施形態において、 $C_{gd2} - C_{gd1}$ または $W_2 / L_2 - W_1 / L_1$ となるよう設計されている。結果的に、ノード $V_{p_1}$ 、および $V_{p_2}$ の電位は、それぞれ、 $V_1$ から $V_2$ に変化される。換言すると、ノード $V_{p_1}$ 、および $V_{p_2}$ のピクセルシグナルと対向電圧 $V_{com}$ との間の電圧差を、フィードスルー効果と同一の作用により、安定に制御することが可能である。

## 【0036】

次いで、第2の走査線 $SL_2$ がシグナルを入力して、第2の蓄積キャパシタ $C_{st2}$ の電荷が第1の補助キャパシタ $C_{s1}$ を中性化し、ノード $V_{p_2}$ の電圧レベルが $V_3$ に変更され、およびノード $V_{p_1}$ の電圧レベルが第2の補助キャパシタ $C_{s2}$ により作用され、それ故、 $V_3$ に変更されるよう第3の薄膜トランジスタ $P_{133}$ を起動する。<sup>20</sup>次いで、第2のフレームタイムにおいては、例えば、第1の走査線 $SL_1$ が再度シグナルを入力して第1の薄膜トランジスタ $P_{131}$ および第2の薄膜トランジスタ $P_{132}$ を起動し、およびサブピクセルデータをデータ線 $DL$ を介して入力するとき、ノード $V_{p_1}$ 、および $V_{p_2}$ の電位が同時に $V_4$ に等しくなる。第1の走査線 $SL_1$ がシグナルの入力を停止した場合には、第1の薄膜トランジスタ $P_{131}$ および第2の薄膜トランジスタ $P_{132}$ は瞬時に停止する。しかしながら、第1の寄生キャパシタ $C_{gd1}$ および薄膜トランジスタ $P_{131}$ および $P_{132}$ のゲートおよびドレインの間の第2の寄生キャパシタ $C_{gd2}$ は、 $C_{gd2} - C_{gd1}$ または $W_2 / L_2 - W_1 / L_1$ となるよう本実施形態において特別に設計されている。<sup>30</sup>結果的に、ノード $V_{p_1}$ 、および $V_{p_2}$ の電位は、それぞれ、 $V_4$ から $V_5$ に変更される。換言すると、ピクセルシグナルと対向電圧 $V_{com}$ との間の電圧差を、フィードスルー効果と同一の作用により、安定に制御することが可能である。

## 【0037】

次いで、第2の走査線 $SL_2$ がシグナルを入力して、第2の蓄積キャパシタ $C_{st2}$ の電荷が第1の補助キャパシタ $C_{s1}$ を中性化し、およびノード $V_{p_2}$ の電圧レベルが $V_6$ に変更されるよう、第3の薄膜トランジスタ $P_{133}$ を起動する。

## 【0038】

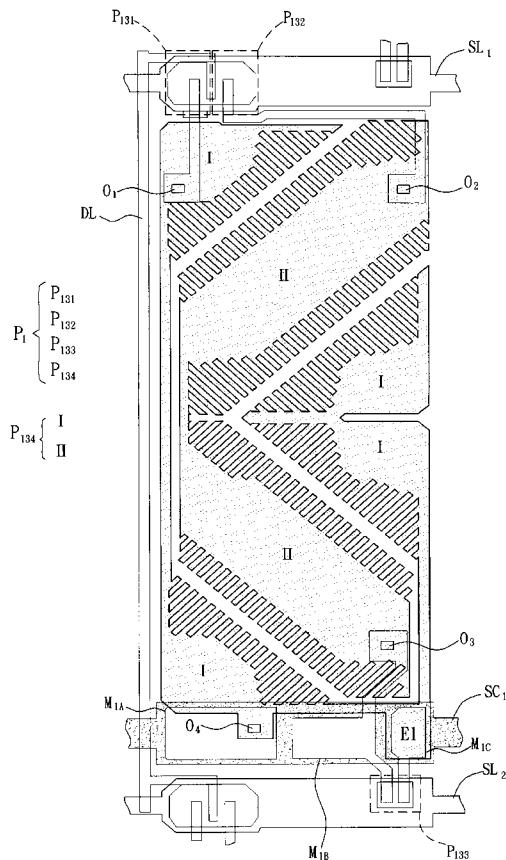

図11および12に示すように、この第3の実施形態においては、LCDパネル22のパターン化金属層 $M_1$ の一部 $M_{1c}$ が、ピクセル電極 $P_{134}$ の第1の領域 $I$ にも対向しており、第1の領域 $I$ と対になって第2の補助キャパシタ $C_{s2}$ を構成している。<sup>40</sup>

## 【0039】

図13に示すように、この第4の実施形態の蓄積容量ライン $SC_1$ は、2つの電気的延伸部 $SC_{1A}$ および $SC_{1B}$ をさらに有している。これらは、2つの電気的延伸部 $SC_{1A}$ および $SC_{1B}$ は、ピクセル電極 $P_{134}$ のデータ線 $DL$ に沿う縁部に対向して配設されている。電気的延伸部 $SC_{1A}$ および $SC_{1B}$ の各々の幅は、約 $4 \mu m$ とすることができる。

## 【0040】

上述した実施形態において、液晶分子の不規則な配向に起因する漏光現象を防止するた

めに、TFT基板221上のピクセル電極P<sub>134</sub>を覆うような黒色マトリックス層BM<sub>1</sub>（図7参照）を、対向基板のサブピクセル構造222に形成することができる。この場合、蓄積容量ラインSC<sub>1</sub>の電気的延伸部SC<sub>1A</sub>およびSC<sub>1B</sub>がピクセル電極P<sub>134</sub>の2つの側縁を部分的に覆っているため、対向基板およびTFT基板が組み合わされた場合に黒色マトリックス層BM<sub>1</sub>によって覆われる面積が減少されることになる。それ故、第1のサブピクセルP<sub>1</sub>の開口比が増加され得る。加えて、蓄積容量ラインSC<sub>1</sub>の電気的延伸部SC<sub>1A</sub>およびSC<sub>1B</sub>とピクセル電極P<sub>134</sub>との対向部分が、蓄積キャパシタC<sub>st</sub>の一部を構成し、蓄積キャパシタC<sub>st</sub>のキャパシタンスを増加させることができるとなる。

## 【0041】

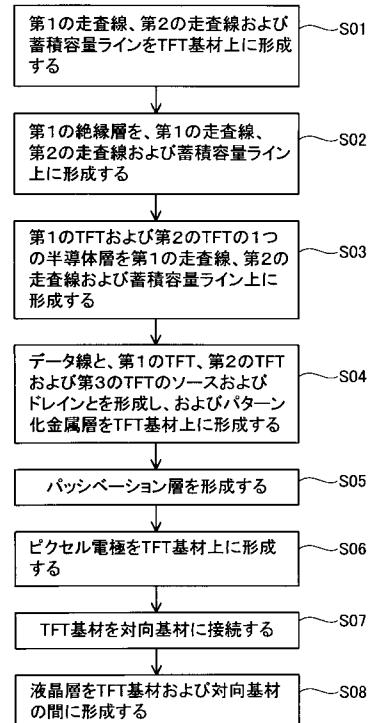

10

図14は、本発明の好ましい実施形態に基づくLCDパネルの製造方法を示している。この製造方法は、ステップS01～S08の工程を含んでいる。この図14に示す製造方法について、図6および図7を参照しながら説明する。

ステップS01においては、第1の走査線SL<sub>1</sub>、第2の走査線SL<sub>2</sub>および蓄積容量ラインSC<sub>1</sub>が、第1の金属層を用いてTFT基板221上に形成される。第1の金属層は、アルミニウム、モリブデン、銅、銀、またはこれらの合金の単一層または多重層などとすることができます。

ステップS02においては、第1の絶縁層が、第1の走査線SL<sub>1</sub>、第2の走査線SL<sub>2</sub>および蓄積容量ラインSC<sub>1</sub>上に形成される。第1の絶縁層は、窒化シリコン(SiNx)またはシリコンオキシド(SiOx)などの絶縁性材料を用いて形成することができます。

20

## 【0042】

ステップS03においては、第1の薄膜トランジスタP<sub>131</sub>および第2の薄膜トランジスタP<sub>132</sub>の1つの半導体層が第1の走査線SL<sub>1</sub>上に形成され、および第3の薄膜トランジスタP<sub>133</sub>の他の半導体層が第2の走査線SL<sub>2</sub>上に形成される。第1の薄膜トランジスタP<sub>131</sub>は、第1の走査線SL<sub>1</sub>に電気的に接続されたゲートを有し、第2の薄膜トランジスタP<sub>132</sub>は、第1の走査線SL<sub>1</sub>に電気的に接続されたゲートを有し、第3の薄膜トランジスタP<sub>133</sub>は、第2の走査線SL<sub>2</sub>に電気的に接続されたゲートを有する。

ステップS04においては、データ線DLと、第1の薄膜トランジスタP<sub>131</sub>、第2の薄膜トランジスタP<sub>132</sub>および第3の薄膜トランジスタP<sub>133</sub>のソースおよびドレインと、パターン化金属層M<sub>1</sub>が、第2の金属層を用いてTFT基板221上に形成される。第2の金属層は、アルミニウム、モリブデン、銅、銀、またはこれらの合金の単一層または多重層などによって形成することができる。ここで、蓄積容量ラインSC<sub>1</sub>を覆う第2の金属層の部分には、パターン化金属層M<sub>1A</sub>、M<sub>1B</sub>、M<sub>1C</sub>が形成される。

30

ステップS05においては、窒化シリコン(SiNx)またはシリコンオキシド(SiOx)などのパッシベーション層で各層を覆って第2の絶縁層が形成される。

## 【0043】

ステップS06においては、ピクセル電極P<sub>134</sub>がTFT基板221上に形成される。ピクセル電極P<sub>134</sub>は、第1の走査線SL<sub>1</sub>および第2の走査線SL<sub>2</sub>の間に配設されるとともに、第1の領域Iおよび第2の領域IIに分割される。第1の領域Iは、第1の薄膜トランジスタP<sub>131</sub>のドレインに第2の絶縁層のビアO<sub>1</sub>を介して電気的に接続される。第2の領域IIは、第2の薄膜トランジスタP<sub>132</sub>のドレインに第2の絶縁層のビアO<sub>2</sub>を介して電気的に接続される。第2の領域IIはまた、第3の薄膜トランジスタP<sub>133</sub>のドレインに第2の絶縁層のビアO<sub>3</sub>を介して電気的に接続される。パターン化金属層M<sub>1</sub>の一部M<sub>1A</sub>は、第1の領域IにビアO<sub>4</sub>を介して電気的に接続され、蓄積容量ラインSC<sub>1</sub>と対になって第1の蓄積キャパシタC<sub>st1</sub>を構成する。パターン化金属層M<sub>1</sub>の他の一部M<sub>1B</sub>は、第2の領域IIにビアO<sub>3</sub>を介して電気的に接続され、蓄積容量ラインSC<sub>1</sub>と対になって第2の蓄積キャパシタC<sub>st2</sub>を構成する。パターン化金属層M<sub>1</sub>のさらに他の一部M<sub>1C</sub>は、第3の薄膜トランジスタP<sub>133</sub>に電気的に接続

40

50

され、蓄積容量ライン  $S C_1$  と対になって第 1 の補助キャパシタ  $C_{S1}$  を構成する。なお、パターン化金属層  $M_1$  と第 1 の領域 I の部分によって、第 2 の補助キャパシタ  $C_{S2}$  を構成させることもできる。

ステップ S 07 においては、TFT 基板 221 が対向基板 222 に接続される。

最後に、ステップ S 08 において、TFT 基板 221 および対向基板 222 の間に液晶層が形成され、LCD パネル 22 が製造される。よく知られているように、ステップ S 07 と S 08 の順番は、変更することが可能である。

#### 【0044】

ステップ S 01 においては、蓄積容量ライン  $S C_1$  と第 1 の走査線  $S L_1$  間の距離  $S_1$  は、蓄積容量ライン  $S C_1$  と第 2 の走査線  $S L_2$  間の距離  $S_2$  よりも、長く設計することが好ましい。ここで、蓄積容量ライン  $S C_1$  と第 2 の走査線  $S L_2$  間の距離  $S_2$  は、 $4 \mu m \sim 20 \mu m$  の範囲とすることが好ましい。加えて、薄膜トランジスタ  $P_{131}$  および  $P_{132}$  は、ステップ S 04 において式 (1) を満たすように形成することが好ましい。

$$C_{g_{d2}} > C_{g_{d1}} \quad (1)$$

ここで、 $C_{g_{d1}}$  は、第 1 の薄膜トランジスタ  $P_{131}$  のゲートとドレインの間の寄生キャパシタを示す。 $C_{g_{d2}}$  は、第 2 の薄膜トランジスタ  $P_{132}$  のゲートとドレインの間の寄生キャパシタを示す。また、以下の式 (2) も満たすように形成されることが好ましい。

$$W_2 / L_2 > W_1 / L_1 \quad (2)$$

ここで、 $W_1$  は、第 1 の薄膜トランジスタ  $P_{131}$  のチャネル幅を示す。 $W_2$  は、第 2 の薄膜トランジスタ  $P_{132}$  のチャネル幅を示す。 $L_1$  は、第 1 の薄膜トランジスタ  $P_{131}$  のチャネル長さを示す。 $L_2$  は、第 2 の薄膜トランジスタ  $P_{132}$  のチャネル長さを示す。

#### 【0045】

また、ステップ S 04 において、「a：第 1 の薄膜トランジスタ  $P_{131}$  のドレインおよびライン  $L_{11}$ 」と「b：第 1 の走査線  $S L_1$ 」が対向し合う対向領域は、「c：第 2 の薄膜トランジスタ  $P_{132}$  のドレインおよび他のライン  $L_{12}$ 」と「d：第 2 の走査線  $S L_2$ 」が対向し合う対向領域よりも、小さくなるよう形成される。ここで、ライン  $L_{11}$  は、第 1 の薄膜トランジスタ  $P_{131}$  のドレインと同じ電位を有するものを示し、ライン  $L_{12}$  は、第 2 の薄膜トランジスタ  $P_{132}$  のドレインと同じ電位を有するものを示す。本発明の実施形態では、ライン  $L_{11}$  に、第 1 の薄膜トランジスタ  $P_{131}$  のドレインに電気的に接続されたすべての導電性パターン部が含まれる。例えば、ライン  $L_{11}$  には、ピクセル電極  $P_{134}$  の第 1 の領域 I、及び、その第 1 の領域 I を第 1 の薄膜トランジスタ  $P_{131}$  のドレインに接続するすべての導電性ラインが含まれる。同様に、ライン  $L_{12}$  は、第 2 の薄膜トランジスタ  $P_{132}$  のドレインに電気的に接続されたすべての導電性パターン部が含まれる。例えば、ライン  $L_{12}$  には、ピクセル電極  $P_{134}$  の第 2 の領域 II、及び、その第 2 の領域 II を第 2 の薄膜トランジスタ  $P_{132}$  のドレインに接続するすべての導電性ラインが含まれる。

#### 【0046】

加えて、ステップ S 07 において、第 1 の領域 I と第 2 の領域 II との比を形成する領域は式 (3) を満たす。

$$C_{st1} / C_{1c1} > C_{st2} / C_{1c2} \quad (3)$$

ここで、 $C_{st1}$  は第 1 の蓄積キャパシタを表し、 $C_{st2}$  は第 2 の蓄積キャパシタを表し、 $C_{1c1}$  は第 1 の液晶キャパシタを表し、 $C_{1c2}$  は第 2 の液晶キャパシタを表す。

#### 【0047】

加えて、ステップ S 01 において、蓄積容量ライン  $S C_1$  には、ピクセル電極  $P_{134}$  の縁部に対向し、データ線  $DL$  に沿う方向に配設された、1つ又は2つの電気的延伸部  $SC_{1A}$ 、 $SC_{1B}$  を形成することができる。ここで、電気的延伸部  $SC_{1A}$ 、 $SC_{1B}$  は、部分的にピクセル電極  $P_{134}$  と重なり合うように設けることができる。

10

20

30

40

50

## 【0048】

要約すれば、本発明に基づくLCDパネルおよびその製造方法では、蓄積容量ラインおよび第1の走査線の間の距離が、蓄積容量ラインおよび第2の走査線の間の距離よりも、長くなっている。それにより、本発明の実施形態に基づくLCD装置およびLCDパネルでは、蓄積容量ラインから追加的に延長される相互接続部を、簡素に構成することが可能となる。加えて、本発明の実施形態に基づくLCD装置およびLCDパネルでは、サブピクセルにおける $C_{g_d}$ および $C_{s_t} / C_{l_c}$ の値が調整されることによって、明領域と暗領域の間における $V_{c_m}$ に対するシグナルの相違に起因するフリッカの問題が解決される。さらに、上述の技術は、広い視野角を有するLCDパネルに適用することが可能であり、この場合、その色差補償能が増強され、色ずれ差の現象が改善されることにより、画像表示の品質を顕著に向上することが可能となる。

10

## 【0049】

以上、本発明について特定の実施形態を参照しながら説明したが、これらの記載は、限定的な意味で解釈されることを意図するものではない。開示された実施形態は種々に改良することが可能であり、それによる他の様々な実施形態は当業者にとって当然に理解されるものである。添付の特許請求の範囲には、本発明の真の範囲内に属するすべての改良が包含されるものである。以下に、本明細書に記載された発明を列記する。

## [発明1]

薄膜トランジスタ基板を有する液晶ディスプレイパネルであって、

前記薄膜トランジスタ基板は、第1の走査線と、第2の走査線と、複数のピクセルと、

データ線と、蓄積容量ラインを備え、

20

前記第1の走査線は、前記薄膜トランジスタ基板上に配設されており、

前記第2の走査線は、前記薄膜トランジスタ基板上に前記第1走査線と平行に配設され

ており、

前記複数のピクセルのそれぞれは、第1のサブピクセルを有しており、

前記第1のサブピクセルは、前記第1の走査線と前記第2の走査線の間に配設されてい

るとともに、第1の薄膜トランジスタと第2の薄膜トランジスタと第3の薄膜トランジス

タとピクセル電極を有しており、

前記ピクセル電極は、互いに異なる信号を表示する第1の領域と第2の領域に分割され

ており、

30

前記第1の薄膜トランジスタは、そのゲートを通じて前記第1の走査線に電気的に接続

されるとともに、そのドレイン電極によって前記第1の領域に電気的に接続されてお

り、

前記第2の薄膜トランジスタは、そのゲートを通じて前記第1の走査線に電気的に接続

されるとともに、そのドレイン電極によって前記第2の領域に電気的に接続されてお

り、

前記第3の薄膜トランジスタは、そのゲートを通じて前記第2の走査線に電気的に接続

されるとともに、そのドレイン電極によって前記第2の領域に電気的に接続されてお

り、

前記データ線は、前記第1の薄膜トランジスタのソース電極及び前記第2の薄膜トラン

ジスタのソース電極に接続されており、

40

前記蓄積容量ラインは、前記第1の走査線及び第2の走査線に平行に配設されていると

ともに、前記第3の薄膜トランジスタのソースと同一電位を有する電極と対になって補助

キャパシタを構成し、

前記蓄積容量ラインから前記第1の走査線までの距離は、前記蓄積容量ラインから前記

第2の走査線までの距離よりも長いことを特徴とする液晶ディスプレイパネル。

## [発明2]

前記第1の薄膜トランジスタのドレイン電極と第1走査線の間の寄生キャパシタを $C_{g_d_1}$

、前記第2の薄膜トランジスタのドレイン電極と第1走査線の間の寄生キャパシタを

$C_{g_d_2}$ としたときに、

50

$C_{g_d2}$   $C_{g_d1}$  (1)

を満たすことを特徴とする発明 1 に記載の液晶ディスプレイパネル。

[発明 3]

前記第 1 の走査線が前記第 1 の薄膜トランジスタのドレイン電極と同電位となる第 1 の電極に対向する第 1 対向領域と、前記第 1 の走査線が前記第 2 の薄膜トランジスタのドレイン電極と同電位となる第 2 の電極に対向する第 2 対向領域が、それぞれ設けられているとともに、

前記第 1 対向領域は、前記第 2 対向領域よりも狭いことを特徴とする発明 1 に記載の液晶ディスプレイパネル。

[発明 4]

10

前記第 1 の薄膜トランジスタのチャネル幅を  $W_1$ 、前記第 2 の薄膜トランジスタのチャネル幅を  $W_2$ 、前記第 1 の薄膜トランジスタのチャネル長を  $L_1$ 、前記第 2 の薄膜トランジスタのチャネル長を  $L_2$  としたときに、

$W_2 / L_2$   $W_1 / L_1$  (2)

を満たすことを特徴とする発明 1 に記載の液晶ディスプレイパネル。

[発明 5]

前記蓄積容量ラインは、前記ピクセル電極と前記第 2 の走査線の間に配設されていることを特徴とする発明 1 に記載の液晶ディスプレイパネル。

[発明 6]

20

前記薄膜トランジスタ基板に対向配置されているとともに共通電極を有する対向基板と、

前記薄膜トランジスタ基板と前記対向基板の間に配設されている液晶層と、

前記蓄積容量ラインに対向するように配設されているパターン化金属層をさらに備え、

前記共通電極と前記ピクセル電極の第 1 の領域との間に、第 1 の液晶キャパシタが構成されており、

前記共通電極と前記ピクセル電極の第 2 の領域との間に、第 2 の液晶キャパシタが構成されており、

前記パターン化金属層の第 1 の部分は、前記ピクセル電極の第 1 の領域に電気的に接続されており、蓄積容量ラインと対になって第 1 の蓄積キャパシタを構成しており、

前記パターン化金属層の第 2 の部分は、前記ピクセル電極の第 2 の領域及び第 3 の薄膜トランジスタに電気的に接続されており、蓄積容量ラインと対になって第 2 の蓄積キャパシタを構成しており、

前記パターン化金属層の第 3 の部分は、第 3 の薄膜トランジスタに電気的に接続されており、蓄積容量ラインと対になって第 1 の補助キャパシタを構成しているとともに、前記第 1 の部分と対になって第 2 の補助キャパシタを構成しており、

前記第 1 のサブピクセルにおいて、前記第 1 の領域における蓄積キャパシタ  $C_{s+t1}$  と液晶キャパシタ  $C_{1c1}$  との比と、前記第 2 の領域における蓄積キャパシタ  $C_{s+t2}$  と液晶キャパシタ  $C_{1c2}$  との比が、

$(C_{s+t1} / C_{1c1})$   $(C_{s+t2} / C_{1c2})$  (3)

を満たすことを特徴とする発明 1 に記載の液晶ディスプレイパネル。

30

[発明 7]

40

前記複数のピクセルのそれぞれは、第 2 のサブピクセルと第 3 のサブピクセルをさらに有し、

前記第 1 のサブピクセルと前記第 2 のサブピクセルと前記第 3 のサブピクセルは、前記第 1 走査線に沿って互いに隣接して配設されており、

各サブピクセルの補助キャパシタを  $C_s$ 、各サブピクセルの液晶キャパシタを  $C_{1c}$ 、各サブピクセルの蓄積キャパシタを  $C_{s+t}$  としたときに、各サブピクセルが下記式の比  $R_a$ 、即ち、

$R_a = C_s / (C_s + C_{1c} + C_{s+t})$  (4)

を有することを特徴とする発明 1 に記載の液晶ディスプレイパネル。

50

## [発明 8 ]

前記比  $R_a$  は、0.1以上0.35以下であることを特徴とする発明7に記載の液晶ディスプレイパネル。

## [発明 9 ]

前記第1のサブピクセルは赤色のサブピクセルであり、前記第2のサブピクセルは緑色のサブピクセルであり、前記第3のサブピクセルは青色のサブピクセルであり、

前記赤色のサブピクセルにおける前記比  $R_a$  を  $R_{a_1}$ 、前記緑色のサブピクセルにおける前記比  $R_a$  を  $R_{a_2}$ 、前記青色のサブピクセルにおける前記比  $R_a$  を  $R_{a_3}$  としたときに、

$$R_{a_1} = R_{a_2} = R_{a_3} \quad (5)$$

10

を満たすことを特徴とする発明7に記載の液晶ディスプレイパネル。

## [発明 10 ]

薄膜トランジスタ基板を有する液晶ディスプレイパネルであって、

前記薄膜トランジスタ基板は、第1の走査線と、第2の走査線と、複数のピクセルと、データ線を備え、

前記第1の走査線は、前記薄膜トランジスタ基板上に配設されており、

前記第2の走査線は、前記薄膜トランジスタ基板上に前記第1走査線と平行に配設されており、

前記複数のピクセルのそれぞれは、第1のサブピクセルを有しており、

前記第1のサブピクセルは、前記第1の走査線と前記第2の走査線の間に配設されるとともに、第1の薄膜トランジスタと第2の薄膜トランジスタと第3の薄膜トランジスタとピクセル電極を有し、

前記ピクセル電極は、互いに異なる信号を表示する第1の領域と第2の領域に分割されており、

前記第1の薄膜トランジスタは、そのゲートを通じて前記第1の走査線に電気的に接続されるとともに、そのドレイン電極によって前記第1の領域に電気的に接続されており、

前記第2の薄膜トランジスタは、そのゲートを通じて前記第1の走査線に電気的に接続されるとともに、そのドレイン電極によって前記第2の領域に電気的に接続されており、

前記第3の薄膜トランジスタは、そのゲートを通じて前記第2の走査線に電気的に接続されるとともに、そのドレイン電極によって前記第2の領域に電気的に接続されており、

前記データ線は、前記第1の薄膜トランジスタのソース電極及び前記第2の薄膜トランジスタのソース電極に接続されており、

前記第1の走査線が前記第1の薄膜トランジスタのドレイン電極に接続された第1の導電性パターン部に対向する第1対向領域と、前記第1の走査線が前記第2の薄膜トランジスタのドレイン電極に接続された第2の導電性パターン部に対向する第2対向領域が、それぞれ設けられているとともに、

前記第1対向領域は、前記第2対向領域よりも狭いことを特徴とする液晶ディスプレイパネル。

## [発明 11 ]

前記第1の導電性パターン部は、前記ピクセル電極の第1の領域を含み、前記第2の導電性パターン部は、前記ピクセル電極の第2の領域を含むことを特徴とする発明10に記載の液晶ディスプレイパネル。

## [発明 12 ]

前記第1の導電性パターン部は、第1の薄膜トランジスタのドレイン電極をさらに含み、前記第2の導電性パターン部は、第2の薄膜トランジスタのドレイン電極をさらに含み、

前記第1の薄膜トランジスタのドレイン電極と第1走査線の間の寄生キャパシタを  $C_g$

20

30

40

50

$C_{g d 2}$ としたときに、

$$C_{g d 2} / C_{g d 1} \quad (1)$$

を満たすことを特徴とする発明 10 に記載の液晶ディスプレイパネル。

[発明 13]

前記第 1 の薄膜トランジスタのチャネル幅を  $W_1$ 、前記第 2 の薄膜トランジスタのチャネル幅を  $W_2$ 、前記第 1 の薄膜トランジスタのチャネル長を  $L_1$ 、前記第 2 の薄膜トランジスタのチャネル長を  $L_2$ としたときに、

$$W_2 / L_2, W_1 / L_1 \quad (2)$$

を満たすことを特徴とする発明 10 に記載の液晶ディスプレイパネル。

10

[発明 14]

前記薄膜トランジスタ基板に対向配置されているとともに共通電極を有する対向基板と、

前記薄膜トランジスタ基板と前記対向基板の間に配設されている液晶層と、

前記蓄積容量ラインに対向するように配設されているパターン化金属層をさらに備え、

前記共通電極と前記ピクセル電極の第 1 の領域との間に、第 1 の液晶キャパシタが構成されており、

前記共通電極と前記ピクセル電極の第 2 の領域との間に、第 2 の液晶キャパシタが構成されており、

前記パターン化金属層の第 1 の部分は、前記ピクセル電極の第 1 の領域に電気的に接続されており、蓄積容量ラインと対になって第 1 の蓄積キャパシタを構成しており、

20

前記パターン化金属層の第 2 の部分は、前記ピクセル電極の第 2 の領域及び第 3 の薄膜トランジスタに電気的に接続されており、蓄積容量ラインと対になって第 2 の蓄積キャパシタを構成しており、

前記パターン化金属層の第 3 の部分は、第 3 の薄膜トランジスタに電気的に接続されており、蓄積容量ラインと対になって第 1 の補助キャパシタを構成しているとともに、前記第 1 の部分と対になって第 2 の補助キャパシタを構成しており、

前記第 1 サブピクセルにおいて、前記第 1 の領域における蓄積キャパシタ  $C_{s t 1}$  と液晶キャパシタ  $C_{1 c 1}$  との比と、前記第 2 の領域における蓄積キャパシタ  $C_{s t 2}$  と液晶キャパシタ  $C_{1 c 2}$  との比が、

$$(C_{s t 1} / C_{1 c 1}) \quad (C_{s t 2} / C_{1 c 2}) \quad (3)$$

を満たすことを特徴とする発明 10 に記載の液晶ディスプレイパネル。

30

[発明 15]

前記複数のピクセルのそれぞれは、第 2 のサブピクセルと第 3 のサブピクセルをさらに有し、

前記第 1 のサブピクセルと前記第 2 のサブピクセルと前記第 3 のサブピクセルは、前記第 1 走査線に沿って互いに隣接して配設されており、

各サブピクセルの補助キャパシタを  $C_s$ 、各サブピクセルの液晶キャパシタを  $C_{1 c}$ 、各サブピクセルの蓄積キャパシタを  $C_{s t}$  としたときに、各サブピクセルが下記式の比  $R_a$ 、即ち、

$$R_a = C_s / (C_s + C_{1 c} + C_{s t}) \quad (4)$$

を有しており、

前記第 1 のサブピクセルは赤色のサブピクセルであり、前記第 2 のサブピクセルは緑色のサブピクセルであり、前記第 3 のサブピクセルは青色のサブピクセルであり、

前記赤色のサブピクセルにおける前記比  $R_a$  を  $R_{a 1}$ 、前記緑色のサブピクセルにおける前記比  $R_a$  を  $R_{a 2}$ 、前記青色のサブピクセルにおける前記比  $R_a$  を  $R_{a 3}$  としたときに、

$$R_{a 1} = R_{a 2} = R_{a 3} \quad (5)$$

を満たすことを特徴とする発明 10 に記載の液晶ディスプレイパネル。

40

[発明 16]

50

液晶ディスプレイパネルの製造方法であって、

薄膜トランジスタ基板に、第1の走査線と第2の走査線を形成する工程と、

第1の走査線に接続されたゲートと第1の走査線に対向するドレインを有する第1の薄膜トランジスタ及び第2の薄膜トランジスタを形成する工程と、

第2の走査線に接続されたゲートを有する第3の薄膜トランジスタを形成する工程と、

薄膜トランジスタ基板に、第1の薄膜トランジスタ及び第2の薄膜トランジスタのソースに接続されたデータ線を形成する工程と、

薄膜トランジスタ基板に、第1の走査線と第2の走査線の間に位置するピクセル電極を形成する工程と、

薄膜トランジスタ基板を対向基板に組み付ける工程と、

薄膜トランジスタ基板と対向基板の間に液晶層を形成する工程を備え、

前記ピクセル電極は、互いに異なる信号を表示する第1の領域と第2の領域に分割され、

前記第1の薄膜トランジスタのドレインは、前記ピクセル電極の第1の領域に電気的に接続され、

前記第2の薄膜トランジスタのドレインは、前記ピクセル電極の第2の領域に電気的に接続され、

前記第3の薄膜トランジスタのドレインは、前記ピクセル電極の第2の領域に電気的に接続され、

前記第1の走査線が前記第1の薄膜トランジスタのドレイン及び前記ピクセル電極の第1の領域に対向する第1対向領域と、前記第1の走査線が前記第2の薄膜トランジスタのドレイン及び前記ピクセル電極の第2の領域に対向する第2対向領域を、それぞれ設けるとともに、前記第1対向領域は前記第2対向領域よりも狭くすることを特徴とする製造方法。

[発明 17]

前記薄膜トランジスタ基板に、蓄積容量ラインを形成する工程をさらに備え、

前記蓄積容量ラインは、前記第3の薄膜トランジスタに電気的に接続されるとともに、

前記第1の走査線と第2の走査線の間に配設され、

前記蓄積容量ラインから前記第1の走査線までの距離を、前記蓄積容量ラインから前記第2の走査線までの距離よりも長くすることを特徴とする発明16に記載の製造方法。

[発明 18]

前記蓄積容量ラインから前記第2の走査線までの距離を4μm以上20μm以下とする

ことを特徴とする発明17に記載の製造方法。

[発明 19]

前記蓄積容量ラインは、少なくとも一つの電気的延伸部を有し、

前記電気的延伸部は、前記ピクセル電極の前記データ線に沿って伸びる縁に対向する

ことを特徴とする発明17に記載の製造方法。

[発明 20]

前記薄膜トランジスタ基板に、前記蓄積容量ラインに対向するパターン化金属層を形成

する工程をさらに備え、

前記パターン化金属層の第1の部分は、前記ピクセル電極の第1の領域に電気的に接続

されており、蓄積容量ラインと対になって第1の蓄積キャパシタを構成し、

前記パターン化金属層の第2の部分は、前記ピクセル電極の第2の領域及び第3の薄膜

トランジスタに電気的に接続されており、蓄積容量ラインと対になって第2の蓄積キャパ

シタを構成し、

前記パターン化金属層の第3の部分は、第3の薄膜トランジスタに電気的に接続されて

おり、蓄積容量ラインと対になって第1の補助キャパシタを構成するとともに、前記第1

の部分と対になって第2の補助キャパシタを構成することを特徴とする発明17に記載の

製造方法。

[発明 21]

10

20

30

40

50

前記第1サブピクセルの第1の領域における蓄積キャパシタ  $C_{s+t_1}$  と液晶キャパシタ  $C_{1c_1}$  との比と、第2の領域における蓄積キャパシタ  $C_{s+t_2}$  と液晶キャパシタ  $C_{1c_2}$  との比が、

$$(C_{s+t_1} / C_{1c_1}) \quad (C_{s+t_2} / C_{1c_2}) \quad (3)$$

を満たすことを特徴とする発明 20 に記載の製造方法。

【図面の簡単な説明】

【0050】

【図1】従来のマルチドメイン垂直配向(MVA)LCDパネルのサブピクセル構造を示す側面図。

【図2】従来のMVALCDパネルのサブピクセル構造を示す外略図。

10

【図3】従来のMVALCDパネルのサブピクセル構造を示す等価回路図。

【図4】従来のMVA LCDパネルのサブピクセル構造のタイミング図。

【図5】第1の実施形態のLCDパネルを示す概略図。

【図6】第1の実施形態のLCDパネルのTFT基板のサブピクセル構造を示す概略図。

【図7】第1の実施形態のLCDパネルの対向基板のサブピクセル構造を示す概略図。

【図8】第2の実施形態のLCDパネルのTFT基板のサブピクセル構造を示す概略図。

【図9】第2の実施形態のLCDパネルのTFT基板のサブピクセルの等価回路図。

【図10】走査線と、図9に示すノードVP1'、VP2'のタイミング図。

【図11】第3の実施形態のLCDパネルのTFT基板のサブピクセル構造を示す概略図

。

20

【図12】第3の実施形態のLCDパネルのTFT基板のサブピクセルの等価回路図。

【図13】第4の実施形態のLCDパネルのTFT基板のサブピクセル構造であり、蓄積容量ラインが2つの電気的延伸部を有するサブピクセル構造を示す概略図。

【図14】実施形態のLCDパネルの製造方法を示すフローチャート。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(72)発明者 チエン , チエン - ホン

台湾 744 タイナン サイエンス - ベースト インダストリアル パーク タイナン カウン

ティ - チ - イエ - ロード ナンバー1 チ - メイ オプトエレクトロニクス コーポレー

ション内

審査官 藤田 都志行

(56)参考文献 特開2006-133577 (JP, A)

特開2004-163943 (JP, A)

特開平11-212107 (JP, A)

(58)調査した分野(Int.Cl. , DB名)

G 02 F 1 / 1368

G 02 F 1 / 1343

|                |                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示面板及其制造方法                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP5369446B2</a>                                                                                                                                                                                                                                                                                                                                                           | 公开(公告)日 | 2013-12-18 |

| 申请号            | JP2008033479                                                                                                                                                                                                                                                                                                                                                                          | 申请日     | 2008-02-14 |

| [标]申请(专利权)人(译) | 奇美电子<br>群创光电股份有限公司                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 申请(专利权)人(译)    | 奇美电子                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 当前申请(专利权)人(译)  | 群创光电股▲ふん▼有限公司                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| [标]发明人         | チーヤンシ工<br>チエンチエンホン                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 发明人            | チー-ヤン シ工<br>チエン,チエン-ホン                                                                                                                                                                                                                                                                                                                                                                |         |            |

| IPC分类号         | G02F1/1368 G02F1/1343                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| CPC分类号         | G09G3/3659 G02F1/136204 G02F2001/134345 G09G2300/0443 G09G2300/0447 G09G2300/0852                                                                                                                                                                                                                                                                                                     |         |            |

| FI分类号          | G02F1/1368 G02F1/1343                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| F-TERM分类号      | 2H092/GA13 2H092/GA29 2H092/JA26 2H092/JA30 2H092/JA31 2H092/JA32 2H092/JA40 2H092/JA46 2H092/JB05 2H092/JB24 2H092/JB33 2H092/JB41 2H092/JB46 2H092/JB63 2H092/JB64 2H092/JB69 2H092/KA12 2H092/KA18 2H092/KB04 2H092/KB24 2H092/NA01 2H092/NA23 2H192/AA24 2H192/BA25 2H192/BC24 2H192/BC31 2H192/CB12 2H192/CB52 2H192/CC04 2H192/CC24 2H192/DA12 2H192/EA22 2H192/GD61 2H192/JA13 |         |            |

| 优先权            | 096106311 2007-02-16 TW                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 其他公开文献         | JP2008203849A                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                             |         |            |

### 摘要(译)

要解决的问题：为了提供一种TFT-LCD，其中可以简化存储电容线的互连困难，可以减少从显示器的任一侧看到的灰度的影响，以及色移的现象可以改进。解决方案：液晶显示(LCD)面板包括以矩阵排列的像素，以及第一和第二扫描线以及存储电容线。每个像素具有第一子像素和第一至第三薄膜晶体管(TFT)，第一子像素设置在第一和第二扫描线之间，像素电极分成第一和第二区域。第一TFT电连接到第一扫描线和像素电极的第一区域。第二TFT电连接到像素电极的第一扫描线和第二区域。第三TFT电连接到像素电极的第二扫描线和第二区域。存储电容线电连接到第三TFT。存储电容线和第一扫描线之间的距离比存储电容线和第二扫描线之间的距离长。