(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5334552号

(P5334552)

(45) 発行日 平成25年11月6日(2013.11.6)

(24) 登録日 平成25年8月9日(2013.8.9)

(51) Int.CI.

F 1

G02F 1/1368 (2006.01)

G02F 1/1343 (2006.01)G02F 1/1368

G02F 1/1343

請求項の数 2 (全 24 頁)

(21) 出願番号 特願2008-312930 (P2008-312930)

(22) 出願日 平成20年12月9日 (2008.12.9)

(65) 公開番号 特開2010-8999 (P2010-8999A)

(43) 公開日 平成22年1月14日 (2010.1.14)

審査請求日 平成21年1月14日 (2009.1.14)

(31) 優先権主張番号 10-2008-0060328

(32) 優先日 平成20年6月25日 (2008.6.25)

(33) 優先権主張国 韓国 (KR)

(31) 優先権主張番号 10-2008-0082964

(32) 優先日 平成20年8月25日 (2008.8.25)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 501426046

エルジー ディスプレイ カンパニー リ

ミテッド

大韓民国 ソウル、ヨンドゥンポーク、ヨ

ウィーテロ 128

(74) 代理人 100094112

弁理士 岡部 譲

(74) 代理人 100064447

弁理士 岡部 正夫

(74) 代理人 100085176

弁理士 加藤 伸晃

(74) 代理人 100096943

弁理士 白井 伸一

(74) 代理人 100101498

弁理士 越智 隆夫

最終頁に続く

(54) 【発明の名称】 フリンジフィールドスイッチングモードの液晶表示装置用アレイ基板及びこれを含むフリンジフィールドスイッチングモードの液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に形成された多数のゲート配線と、

前記多数のゲート配線上に形成されるゲート絶縁膜と、

前記ゲート絶縁膜上に形成されて、前記多数のゲート配線と交差して多数の画素領域を定義する多数のデータ配線と、

前記ゲート配線及びデータ配線に連結されて、各画素領域に形成される薄膜トランジスタと、

板状で各画素領域に位置して、前記薄膜トランジスタの一部に連結される画素電極と、

前記画素電極と前記薄膜トランジスタとの上部に形成される第1保護層と、

前記第1保護層上に形成されて、各画素領域内のバー状の多数の第1開口部及び前記薄膜トランジスタに対応する第2開口部を有する共通電極とを含み、

前記多数の第1開口部の各々は、前記データ配線に平行な長軸と前記ゲート配線に平行な短軸とを有し、前記各第1開口部の中央部は、前記画素電極と重なって、前記各第1開口部の長軸の短側面の少なくとも一端は、前記画素電極の外側へと突出され、前記多数の第1開口部のうち、画素領域の最外角に位置する開口部の短軸の長側面の一端は、前記画素電極の外側へと突出され、

前記ゲート絶縁膜と前記画素電極との間に位置して、前記薄膜トランジスタの一部を露出させるコンタクトホールを有する第2保護層をさらに含み、前記第2保護層上の前記画素電極は、前記コンタクトホールを通じて前記薄膜トランジスタの一部に連結されること

10

20

を特徴とするフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板。

【請求項 2】

一つの画素領域内の前記画素電極に対応する前記第1開口部は、前記データ配線に沿つて、前記一つの画素領域に隣接する他の画素領域内の画素電極まで延びることを特徴とする請求項1に記載のフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、液晶表示装置に係り、特に、フリンジフィールド効果を有して回位の発生を抑制し、開口率及び透過率を向上させるフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板及びこれを含むフリンジフィールドスイッチングモードの液晶表示装置に関する。 10

【背景技術】

【0002】

一般的に、液晶表示装置は、液晶物質の光学的異方性と分極性質を利用して駆動する。液晶は、分子構造が細長く、配列に方向性を有しており、人為的に液晶に電場を印加して分子配列の方向を制御する。

従って、液晶分子の配列方向を人為的に調節すると、液晶分子の配列が変化し、光学的異方性によって液晶分子の配列方向に光が屈折して画像情報を表現する。 20

【0003】

現在は、薄膜トランジスタと薄膜トランジスタに連結された画素電極が行列方式で配列される能動行列の液晶表示装置((AM-LCD ; Active Matrix LCD)以下、「液晶表示装置」に略称する。)が、解像度及び動画の具現能力に優れており最も注目されている。

【0004】

また、液晶表示装置は、共通電極が形成されたカラーフィルター基板と画素電極が形成されたアレイ基板と、二つの基板の間に充填された液晶とで構成されて、このような液晶表示装置は、共通電極と画素電極との間の上下に印加される垂直電場によって駆動させる方法であって、透過率と開口率などの特性が優れている。

ところが、上下に印加される電場による液晶駆動は、視野角の特性が優れてない短所がある。 30

従って、このような短所を克服するために、視野角の特性が優れる横電界型の液晶表示装置が提案された。

【0005】

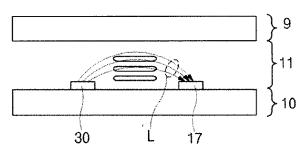

以下、図1を参照して、一般的な横電界型の液晶表示装置を詳しく説明する。

図1は、一般的な横電界型の液晶表示装置の断面を示した図である。

図1に示したように、カラーフィルター基板である上部基板9とアレイ基板である下部基板10が相互に離隔され向かい合っており、上部基板9及び下部基板10間に、液晶層11が介されている。

下部基板10上には、共通電極17と画素電極30が同一平面上に形成されており、この時、液晶層11は、共通電極17と画素電極30による水平電界Lによって作動する。 40

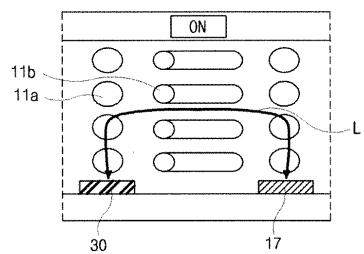

【0006】

図2Aと図2Bは、一般的な横電界型の液晶表示装置のオン(on)、オフ(off)動作を各々示した断面図である。

図2Aに示したように、液晶表示装置に電圧が印加されるオン(on)状態であって、共通電極17及び画素電極30に対応する位置の液晶11aの相変移はないが、共通電極17と画素電極30との間の区間に位置する液晶11bは、共通電極17と画素電極30との間に電圧が印加され形成される水平電界Lによって、水平電界Lと同一な方向に配列される。すなわち、横電界型の液晶表示装置は、液晶が水平電界によって移動するので、視野角が広い特性がある。 従って、横電界型の液晶表示装置を正面から見た時、上/下/右/ 50

左に約80～85度方向でも反転現象なしで見ることができる。

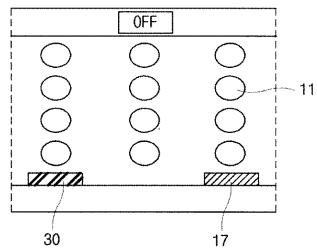

#### 【0007】

図2Bに示したように、液晶表示装置に電圧が印加されないオフ(off)状態であって、共通電極と画素電極との間に水平電界が形成されないので、液晶層11の配列状態が変わらない。

ところが、このような横電界型の液晶表示装置は、視野角を向上させる長所があるが、開口率及び透過率が低い短所もある。

従って、このような横電界型の液晶表示装置の短所を改善するために、フリンジフィールド(Fringe field)によって液晶が動作することを特徴とするフリンジフィールドスイッチングモードの液晶表示装置(fringe field switching mode LCD)が提案された。 10

#### 【0008】

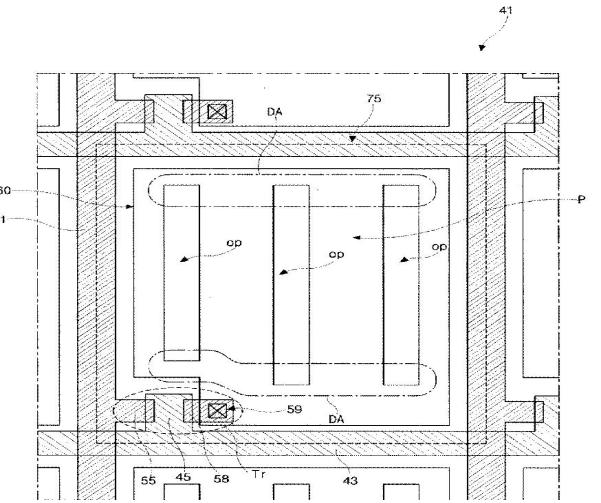

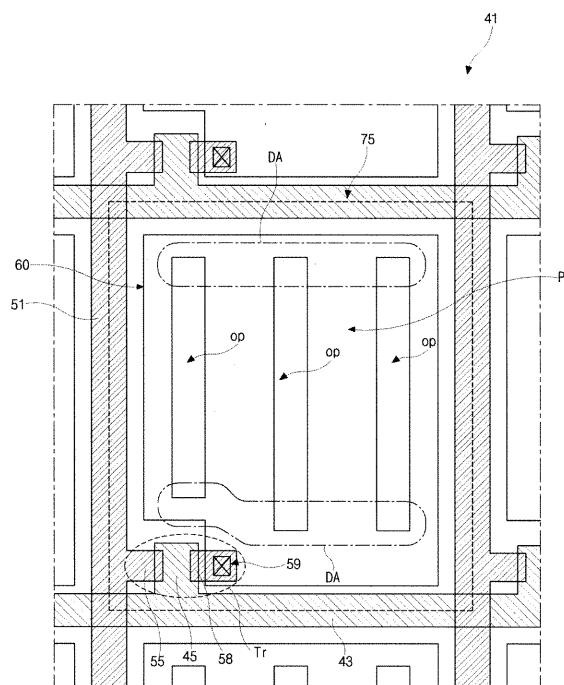

図3は、従来のフリンジフィールドスイッチングモードの液晶表示装置のアレイ基板の平面図である。

図3に示したように、一方向に多数のゲート配線43が延長して構成されており、このような多数のゲート配線43と交差して多数の画素領域Pを定義して多数のデータ配線51が構成されている。

#### 【0009】

また、多数の画素領域Pの各々には、データ配線51及びゲート配線43に連結されて、ゲート電極45とゲート絶縁膜(図示せず)と半導体層(図示せず)とソース電極55及びドレイン電極58とを含むスイッチング素子である薄膜トランジスタTrが形成される。 20

各画素領域Pには、ドレインコンタクトホール59を通じて薄膜トランジスタTrのドレイン電極58と電気的に連結されて、多数のバー(bar)状の開口部opを有するバー状の画素電極60が形成される。

また、多数の画素領域Pが形成された表示領域全面には、各画素領域Pに対応して板状の画素電極60と重なって共通電極75が形成される。この時、共通電極75は、表示領域全面に形成されるが、一つの画素領域に対応する部分を点線で示している。

#### 【0010】

このような構成のフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板41は、各画素領域Pに多数のバー状の開口部opを有する画素電極60と共に電圧が印加されることによってフリンジフィールドが形成される。 30

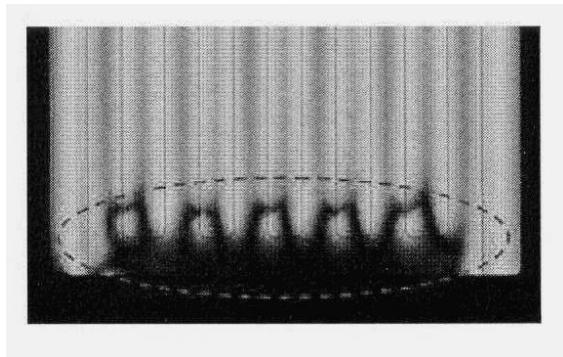

#### 【0011】

ところが、前述した構成の従来のフリンジフィールドスイッチング液晶表示装置用アレイ基板41は、共通電極75に対応して多数のバー状の開口部opを有する画素電極60、特に、多数の開口部opが完全に重なって形成されている。この場合、画素電極60と共に電圧が印加されることによってフリンジフィールドが形成されず、液晶分子が相互に異なる方向に動く境界部、すなわち、回位領域(DA; disclination area)が発生する。このような回位領域DAは、液晶表示装置が完全なオン(on)状態で光を透過させなくなって、図4(従来のフリンジフィールド液晶表示装置の開口部の一端に対するオン(on)状態での写真)に示したように、周辺に比べて不規則的に暗く表示される。

このような回位領域DAが発生する部分は、光が正常に透過しなくなり、実質的な透過率を低下させて、さらに、表示品質を低下させる要因になる。

#### 【0012】

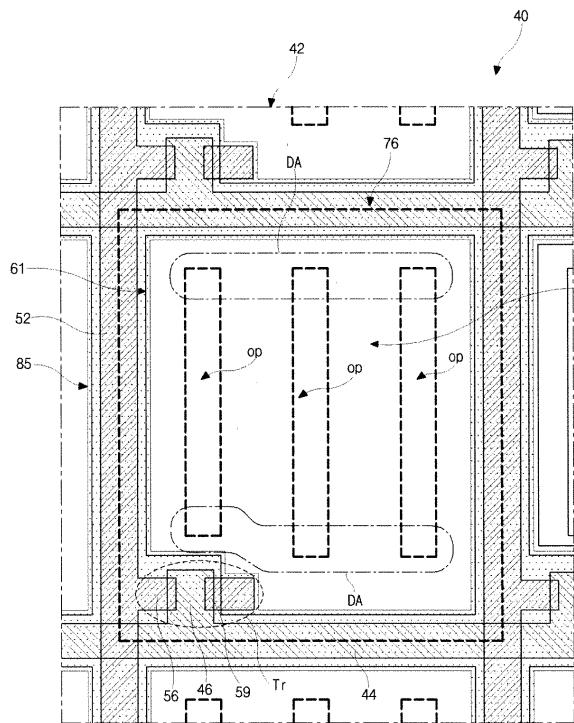

図5は、従来のフリンジフィールドスイッチングモードの液晶表示装置の平面図である。

図5に示したように、従来のフリンジフィールドスイッチングモードの液晶表示装置40は、第1基板42と第2基板(図示せず)、二つの基板(42、図示せず)間に介された液晶層(図示せず)で構成されている。

第1基板42には、一方向に多数のゲート配線44が延長して構成されており、このような多数のゲート配線44と交差して多数の画素領域Pを定義して多数のデータ配線52

10

20

30

40

50

が構成されている。

**【0013】**

また、多数の画素領域Pの各々には、データ配線52及びゲート配線44に連結されて、ゲート電極46とゲート絶縁膜(図示せず)と半導体層(図示せず)とソース電極56及びドレイン電極59とを含むスイッチング素子である薄膜トランジスタTrが形成される。

**【0014】**

各画素領域Pには、薄膜トランジスタTrのドレイン電極59と電気的に連結されて、多数のバー状の開口部opを有するバー状の画素電極61が形成される。この時、板状の画素電極61は、各画素領域Pの内側に、すなわち、各画素領域Pを定義するゲート配線44及びデータ配線52と重ならず、ゲート配線44及びデータ配線52から所定の幅離隔して形成される。このように、画素電極61をゲート配線44及びデータ配線52と重ならないように形成する理由は、ゲート絶縁膜(図示せず)を間に画素電極61と、ゲート配線44またはデータ配線52と重なる場合、寄生容量などが発生して、これは、各層間のカップリングによって画素電極61と共に電極76との間の電界歪曲が誘発される可能性があるので、これを防ぐためである。

**【0015】**

また、多数の画素領域Pが形成された表示領域全面には、各画素領域Pに対応して板状の画素電極61と重なって共通電極76が形成される。この時、共通電極76は、表示領域全面に形成されるが、一つの画素領域Pに対応する部分を点線で示している。

**【0016】**

このような構成のフリンジフィールドスイッチングモードの液晶表示装置の第1基板42は、各画素領域Pに多数のバー状の開口部opを有する画素電極61と共に電極76に電圧が印加されることによってフリンジフィールドが形成される。

**【0017】**

前述したように、ゲート配線44、データ配線52、薄膜トランジスタTr、画素電極61、共通電極76などが形成されている第1基板42をアレイ基板とする。

**【0018】**

また、前述した構造のアレイ基板に対応して、これと向い合う第2基板(図示せず)には、赤色R、緑色G、青色Bのカラーフィルターパターンを含むカラーフィルター層(図示せず)が形成されており、赤色R、緑色G、青色Bのカラーフィルターパターンは、各画素領域Pに対応して順に交互する。各画素領域Pの境界になるゲート配線44及びデータ配線52と薄膜トランジスタTrに対応してブラックマトリックス85が形成されている。

このようにカラーフィルター層とブラックマトリックス85などが形成されている第2基板をカラーフィルター基板とする。

**【0019】**

ところが、前述した構成の従来のフリンジフィールドスイッチング液晶表示装置40において、アレイ基板42は、共通電極76に対応して多数のバー状の開口部opを有する画素電極61、特に、多数の開口部opが完全に重なって形成されている。この場合、画素電極61と共に電極76の形態上、開口部opの長軸の両端では、電界が一定な一方向に形成されなくなって、液晶分子(図示せず)が相互に異なる方向に動く境界部、すなわち、回位領域DAが発生する。このような回位領域DAは、液晶表示装置が完全なオン(on)状態で光を透過させなくなって、周辺に比べて不規則的に暗く表示される。

**【0020】**

このような回位領域DAが発生する部分では、光が正常に透過しなくなって、表示品位が低下される。従って、回位が発生する部分に対応して、ゲート配線44に対応して形成されたブラックマトリックス85をさらに拡張し、すなわち、その幅をさらに広くしてカラーフィルター基板(図示せず)に構成することによって、回位が発生する部分から出射する光を遮断させている。

**【0021】**

10

20

30

40

50

ところが、このように、回位が発生する部分に対応してブラックマトリックス 85 を構成する場合、一つの画素領域 P 内で正常な光が透過する領域、すなわち、開口率が低下されて、さらに、光の実質的な透過率が低下される問題が発生する。

【発明の開示】

【発明が解決しようとする課題】

【0022】

本発明は、このような従来のフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板の問題を解決するために案出されており、回位発生領域を最小化したりまたはその発生を抑制したりすることによって透過率を向上させて、さらに、高品位の画像を提供することを目的とする。

10

【課題を解決するための手段】

【0023】

本発明のフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板は、前述したような目的を達成するために、基板上に形成された多数のゲート配線と、前記多数のゲート配線上に形成されるゲート絶縁膜と、前記ゲート絶縁膜上に形成されて、前記多数のゲート配線と交差して多数の画素領域を定義する多数のデータ配線と、前記ゲート配線及びデータ配線に連結されて、各画素領域に形成される薄膜トランジスタと、板状で各画素領域に位置して、前記薄膜トランジスタの一部に連結される画素電極と、前記画素電極と前記薄膜トランジスタの上部に形成される第1保護層と、前記第1保護層上に形成されて、各画素領域に対応してバー状の多数の開口部を有する共通電極とを含み、前記多数の開口部各々は、前記データ配線に平行な長軸と前記ゲート配線に平行な短軸を有し、前記各開口部の中央部は、前記画素電極と重なって、前記各開口部の長軸の短側面の少なくとも一端は、前記画素電極の外側へと突出されることを特徴とする。

20

【0024】

ここで、前記多数の開口部のうち、画素領域の最外角に位置する開口部の短軸の一端は、前記画素電極の外側へと突出される。

【0025】

前記画素電極は、前記ゲート絶縁膜と直接接触して形成されて、前記薄膜トランジスタのドレン電極と直接接触する。

30

【0026】

前記ゲート絶縁膜と前記画素電極間に位置して、前記薄膜トランジスタの一部を露出させるコンタクトホールを有する第2保護層をさらに含み、前記第2保護層上の前記画素電極は、前記コンタクトホールを通じて前記薄膜トランジスタの一部に連結される。

【0027】

前記多数の開口部各々は、前記データ配線各々に沿って隣接する多数の画素電極を横切る。

【0028】

前記共通電極は、前記薄膜トランジスタに対応する別途の開口部をさらに含む。

【0029】

また、本発明のフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板は、基板上に形成された多数のゲート配線と、前記多数のゲート配線上に形成されるゲート絶縁膜と、前記ゲート絶縁膜上に形成されて、前記多数のゲート配線と交差して多数の画素領域を定義する多数のデータ配線と、前記ゲート配線及びデータ配線に連結されて、各画素領域に形成される薄膜トランジスタと、板状で各画素領域に位置して、前記薄膜トランジスタの一部に連結される画素電極と、前記画素電極と前記薄膜トランジスタの上部に形成される保護層と、前記保護層上に形成されて、各画素領域に対応してバー状の多数の開口部を有する共通電極とを含み、前記多数の開口部各々は、前記データ配線に平行な長軸と前記ゲート配線に平行な短軸を有し、前記各開口部の中央部は、前記画素電極と重なって、前記多数の開口部のうち、画素領域の最外角に位置する開口部の短軸の一端は、前記画素電極の外側へと突出されることを特徴とする。

40

50

**【0030】**

さらに、本発明のフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板は、基板上に形成された多数のゲート配線と、前記多数のゲート配線上に形成されるゲート絶縁膜と、前記ゲート絶縁膜上に形成されて、前記多数のゲート配線と交差して多数の画素領域を定義する多数のデータ配線と、前記ゲート配線及びデータ配線に連結されて、各画素領域に形成される薄膜トランジスタと、板状で各画素領域に位置して、前記薄膜トランジスタの一部に連結されて前記ゲート配線の一部と重なる画素電極と、前記画素電極と前記薄膜トランジスタの上部に形成される保護層と、前記保護層上に形成されて、各画素領域に対応してバー状の多数の開口部を有する共通電極とを含み、前記多数の開口部各々は、前記データ配線に平行な長軸と前記ゲート配線に平行な短軸を有して、前記各開口部の長軸の短側面の少なくとも一端は、前記ゲート配線と前記画素電極とが重なった部分とさらに重なることを特徴とする。

**【0031】**

ここで、前記ゲート配線と前記画素電極が重なった部分は、前記ゲート配線の幅より小さい幅である。

**【0032】**

また、本発明のフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板は、基板上に形成された多数のゲート配線と、前記多数のゲート配線上に形成されるゲート絶縁膜と、前記ゲート絶縁膜上に形成されて、前記多数のゲート配線と交差して多数の画素領域を定義する多数のデータ配線と、前記ゲート配線及びデータ配線に連結されて、各画素領域に形成される薄膜トランジスタと、板状で各画素領域に位置して、前記薄膜トランジスタの一部に連結されて前記ゲート配線の一部と重なる画素電極と、前記画素電極と前記薄膜トランジスタの上部に形成される保護層と、前記保護層上に形成されて、各画素領域に対応してバー状の多数の開口部を有する共通電極とを含み、前記多数の開口部各々は、前記データ配線各々に沿って隣接する多数の画素電極を横切ることを特徴とする。

**【0033】**

さらに、本発明のフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板は、相互に向かい合う第1及び第2基板と、前記第1基板上に形成された多数のゲート配線と、前記多数のゲート配線上に形成されるゲート絶縁膜と、前記ゲート絶縁膜上に形成されて、前記多数のゲート配線と交差して多数の画素領域を定義する多数のデータ配線と、前記ゲート配線及びデータ配線に連結されて、各画素領域に形成される薄膜トランジスタと、板状で各画素領域に位置して、前記薄膜トランジスタの一部に連結される画素電極と、前記画素電極と前記薄膜トランジスタの上部に形成される保護層と、前記保護層上に形成されて、各画素領域に対応してバー状の多数の開口部を有する共通電極と、前記第2基板上に形成されて、前記画素領域各々を取り囲むブラックマトリックスと、前記第2基板上に形成されて、前記各画素領域に対応するカラーフィルター層と、前記第1及び第2基板間に位置する液晶層とを含み、前記多数の開口部各々は、前記データ配線に平行な長軸と前記ゲート配線に平行な短軸を有し、前記各開口部の中央部は、前記画素電極と重なって、前記各開口部の長軸の短側面の少なくとも一端は、前記画素電極の外側へと突出されることを特徴とする。

**【0034】**

ここで、前記多数の開口部各々は、前記データ配線各々に沿って隣接する多数の画素電極を横切る。

**【0035】**

また、本発明のフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板は、相互に向かい合う第1及び第2基板と、前記第1基板上に形成された多数のゲート配線と、前記多数のゲート配線上に形成されるゲート絶縁膜と、前記ゲート絶縁膜上に形成されて、前記多数のゲート配線と交差して多数の画素領域を定義する多数のデータ配線と、前記ゲート配線及びデータ配線に連結されて、各画素領域に形成される薄膜トランジスタと、板状で各画素領域に位置して、前記薄膜トランジスタの一部に連結される画素電極と

10

20

30

40

50

、前記画素電極と前記薄膜トランジスタの上部に形成される保護層と、前記保護層上に形成されて、各画素領域に対応してバー状の多数の開口部を有する共通電極と、前記第2基板上に形成されて、前記画素領域各自を取り囲むブラックマトリックスと、前記第2基板上に形成されて、前記各画素領域に対応するカラーフィルター層と、前記第1及び第2基板間に位置する液晶層とを含み、前記多数の開口部各自は、前記データ配線に平行な長軸と前記ゲート配線に平行な短軸を有し、前記各開口部の中央部は、前記画素電極と重なって、前記多数の開口部のうち、画素領域の最外角に位置する開口部の短軸の一端は、前記画素電極の外側へと突出されることを特徴とする。

#### 【0036】

さらに、本発明のフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板は、相互に向かい合う第1及び第2基板と、前記第1基板上に形成された多数のゲート配線と、前記多数のゲート配線上に形成されるゲート絶縁膜と、前記ゲート絶縁膜上に形成されて、前記多数のゲート配線と交差して多数の画素領域を定義する多数のデータ配線と、前記ゲート配線及びデータ配線に連結されて、各画素領域に形成される薄膜トランジスタと、板状で各画素領域に位置して、前記薄膜トランジスタの一部に連結されて前記ゲート配線の一部と重なる画素電極と、前記画素電極と前記薄膜トランジスタの上部に形成される保護層と、前記保護層上に形成されて、各画素領域に対応してバー状の多数の開口部を有する共通電極と、前記第2基板上に形成されて、前記ゲート配線を除いた前記データ配線と前記薄膜トランジスタに対応するブラックマトリックスと、前記第2基板上に形成されて、前記各画素領域に対応するカラーフィルター層と、前記第1及び第2基板間に位置する液晶層とを含み、前記多数の開口部各自は、前記データ配線に平行な長軸と前記ゲート配線に平行な短軸とを有して、前記各開口部の長軸の短側面の少なくとも一端は、前記ゲート配線と前記画素電極が重なった部分とさらに重なることを特徴とする。

10

#### 【0037】

ここで、前記ゲート配線と前記画素電極が重なった部分は、前記ゲート配線の幅より小さい幅である。

#### 【0038】

前記共通電極は、前記薄膜トランジスタに対応する別途の開口部をさらに含む。

#### 【0039】

また、本発明のフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板は、相互に向かい合う第1及び第2基板と、前記第1基板上に形成された多数のゲート配線と、前記多数のゲート配線上に形成されるゲート絶縁膜と、前記ゲート絶縁膜上に形成されて、前記多数のゲート配線と交差して多数の画素領域を定義する多数のデータ配線と、前記ゲート配線及びデータ配線に連結されて、各画素領域に形成される薄膜トランジスタと、板状で各画素領域に位置して、前記薄膜トランジスタの一部に連結されて前記ゲート配線の一部と重なる画素電極と、前記画素電極と前記薄膜トランジスタの上部に形成される保護層と、前記保護層上に形成されて、各画素領域に対応してバー状の多数の開口部を有する共通電極と、前記第2基板上に形成されて、前記ゲート配線を除いた前記データ配線と前記薄膜トランジスタに対応するブラックマトリックスと、前記第2基板上に形成されて、前記各画素領域に対応するカラーフィルター層と、前記第1及び第2基板間に位置する液晶層とを含み、前記多数の開口部各自は、前記データ配線各自に沿って隣接する多数の画素電極を横切ることを特徴とする。

30

#### 【0040】

ここで、前記共通電極は、前記薄膜トランジスタに対応する別途の開口部をさらに含む。

#### 【発明の効果】

#### 【0041】

本発明によるフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板は、バー状の開口部の両一端で回位発生が抑制されるため、透過率を向上させて、さらに、開口率を向上させる。

40

50

また、開口部の両一端で回位発生が抑制されることによって、高品位の画像を提供する。

ゲート配線とバー状の開口部の一端の間の領域を遮るためにブラックマトリックスが省略できるため、透過率及び開口率がさらに向上する。

また、画素電極を前段のゲート配線と所定の幅重なるように形成するため、電界発生領域をさらに拡張させて、より向上した開口率を得ることができる。

#### 【0042】

以下、添付した図面を参照して、本発明の望ましい実施例を説明する。

#### 【0043】

##### [第1実施例]

10

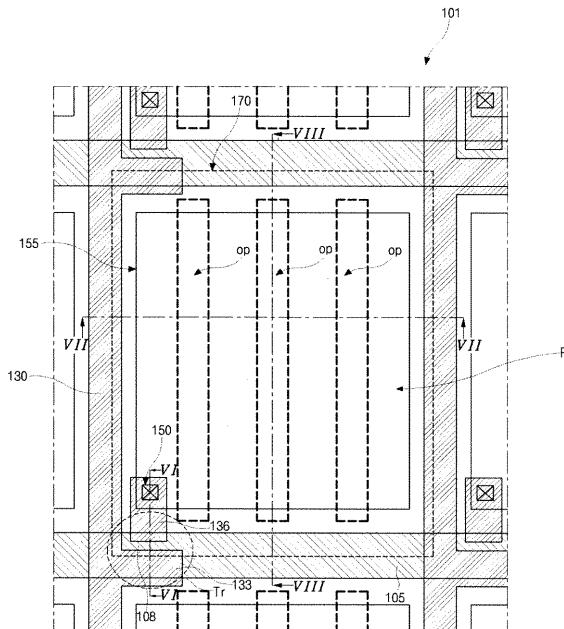

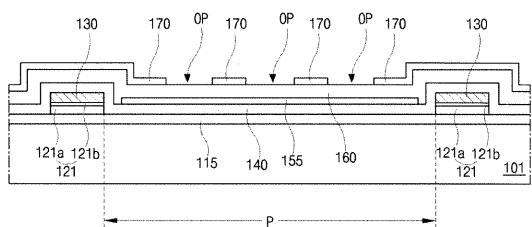

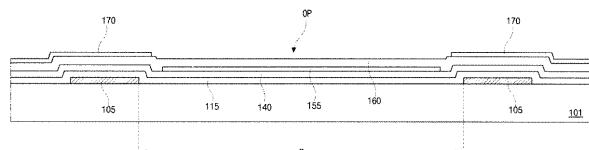

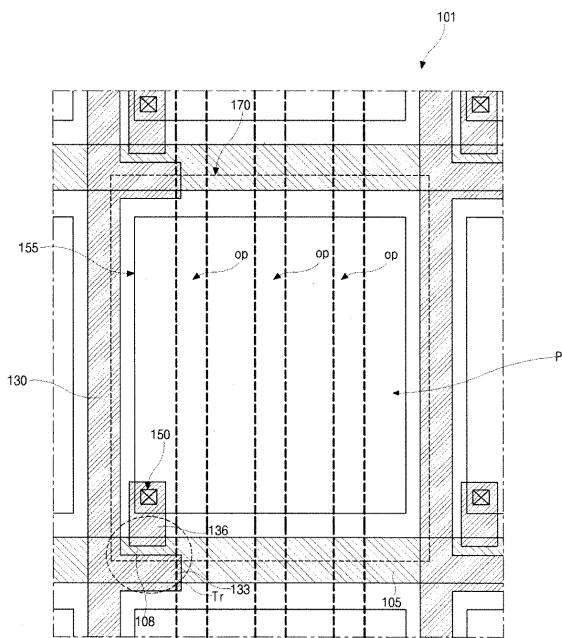

図6は、本発明の第1実施例によるフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板の一つの平面図であって、図7は、図6をVII-VII線に沿って切断した部分の断面図である。

また、図8は、図6をVIII-VIII線に沿って切断した部分の断面図であって、図9は、図6をVIIII-VIIII線に沿って切断した部分の断面図である。

#### 【0044】

説明の便宜上、多数の画素領域が形成される領域を表示領域、表示領域の外側のパッド部を含む領域を非表示領域で定義する。また、画素領域において、スイッチング素子である薄膜トランジスタが形成される部分をスイッチング領域で定義する。

#### 【0045】

20

図6を参照して本発明の第1実施例によるフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板の平面形態を説明する。

図6に示したように、第1方向に延長してゲート配線105が構成されており、第2方向に延長してゲート配線105と交差して画素領域Pを定義するデータ配線130が構成されている。

#### 【0046】

画素領域Pには、ゲート配線105及びデータ配線130に連結されて、ゲート電極108と、ゲート絶縁膜(図示せず)と、純粋非晶質シリコンのアクティブ層(図示せず)と、不純物非晶質シリコンのオーミックコンタクト層(図示せず)で構成される半導体層(図示せず)と、相互に離隔するソース電極133及びドレイン電極136とを含む薄膜トランジスタTrが形成されている。この時、図面において、一つの画素領域Pの開口率をさらに向上させるために、薄膜トランジスタTrは、ゲート配線105上に形成してゲート配線105自体をゲート電極108として構成しているが、これは一例であって、ゲート電極108は、ゲート配線105から分岐して形成される。

30

#### 【0047】

本発明の特徴的な部分として、画素領域Pの内部には、板状の画素電極155がドレインコンタクトホール150を通じて薄膜トランジスタTrのドレイン電極136と接触して形成される。また、多数の画素領域Pを含む表示領域全面には、多数のバー状の開口部opを有する共通電極170が形成される。多数のバー状の開口部opは、板状の画素電極155に対応する。この時、共通電極170は、表示領域全面に形成されて、図6では、説明の便宜上、一つの画素領域を点線で、図面符号170で示している。

40

#### 【0048】

本発明の特徴的な構成で画素領域P内に形成された板状の画素電極155に対応して形成される多数のバー状の開口部opのその長軸の両端の所定の幅は、画素電極155の外側に形成されている。すなわち、共通電極170内に形成された多数のバー状の開口部opは、その各々の開口部opの長軸の長さが画素電極155の長軸の長さよりさらに大きく形成されることによって画素電極155の外側に形成される。

このような構成のために、多数のバー状の開口部opは、基板101全面に形成される共通電極170に対してのみ構成される。

#### 【0049】

50

前述した構成によって、多数の各開口部 o p の長軸の両端においての短側面には、電界が形成されなかったりまたは非常に微弱だったりして、この部分に位置する液晶分子は、開口部の長側面による電界に影響を受けるため、一定な方向に動いて正常に駆動する。

従って、従来のような回位は発生することなく、または、回位発生部がゲート配線 105 と重なる部分に形成されたりして自然に回位発生部分が遮られ、開口率を向上させると同時に透過率も向上させる。

#### 【0050】

図 10 は、本発明の第 1 実施例の第 1 変形例によるフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板の平面図である。(第 1 実施例と同一な構成要素には、同一な図面符号で示している。)

図 10 に示したように、表示領域全体に形成された共通電極 170 内に形成された多数の開口部 o p は、データ配線 130 の延長方向に隣接する画素領域 P の間には、相互に連結された構造で形成される場合もある。すなわち、共通電極 170 内に形成された多数の開口部 o p は、表示領域全体において画素領域 P の区分なしにストライプ状でデータ配線 130 と並んで形成される場合もある。

#### 【0051】

この場合、第 1 実施例と同一な効果がある。すなわち、第 1 実施例の変形例による構成において、表示領域内の最外角に位置する画素領域(図示せず)を除いては開口部の長軸の両端が存在しない。

#### 【0052】

従って、最外角の画素領域(図示せず)を除いた各画素領域 P の内部には、多数の各開口部 o p の長軸の両端の短側面が存在しないので、両端の短側面による電界が全く形成されない。従って、この部分に位置する液晶分子は、開口部 o p の長側面による電界に影響を受けるため、一定な方向に動かされ正常に駆動して、回位は発生しない。この時、表示領域の最外角に位置する画素領域(図示せず)に対しては、第 1 実施例のように、ストライプ状の開口部の長軸の両端をその画素電極の一端の外側に位置させて形成することによって、回位発生を最小化したり抑制したりする。

#### 【0053】

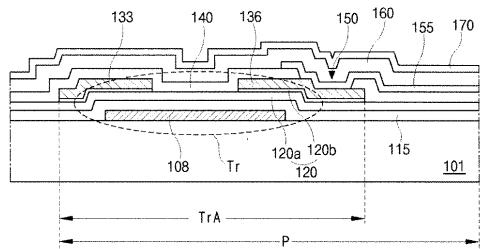

以下、図 7、図 8 及び図 9 を参照して本発明の第 1 実施例によるフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板の断面構造を説明する。第 1 実施例の変形例の場合、V I I I - V I I I 線に沿って切断した断面構造のみが異なるのであって、それ以外の断面構造は、第 1 実施例と同一であるため、相違点がある部分を簡単に説明する。

#### 【0054】

図 7、図 8 及び図 9 に示したように、本発明の第 1 実施例によるフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板は、透明な絶縁基板 101 上に低抵抗特性的ある金属物質、例えば、アルミニウム A1、アルミニウム合金 A1Nd、銅 Cu、銅合金、クロム Cr、モリブデン Mo のうちから選択される一つの金属物質で、第 1 方向に延長するゲート配線 105 と、これに連結されスイッチング領域 TrA にゲート電極 108 が形成されている。

#### 【0055】

尚、図面は、ゲート配線 105 とゲート電極 108 が单一層構造である一例を示しているが、二重層構造で形成される場合もある。二重層構造の場合、望ましくは、下部層は、低抵抗の金属物質であるアルミニウム A1、アルミニウム合金 A1Nd、銅 Cu、銅合金のうちから選択される一つの金属物質で構成されて、上部層は、モリブデン Mo で構成される。

#### 【0056】

また、ゲート配線 105 及びゲート電極 108 上に、基板 101 全面に無機絶縁物質、例えば、酸化シリコン SiO<sub>2</sub> または窒化シリコン SiN<sub>x</sub> でゲート絶縁膜 115 が形成されている。

10

20

30

40

50

## 【0057】

ゲート絶縁膜115上に、スイッチング領域TrAにゲート電極108に対応して純粋非晶質シリコンのアクティブ層120aと不純物非晶質シリコンのオーミックコンタクト層120bを含む半導体層120が形成されており、半導体層120の上部に、相互に離隔してソース電極133及びドレイン電極136が形成されている。この時、相互に離隔するソース電極133及びドレイン電極136間で、アクティブ層120aが露出される。

## 【0058】

また、ゲート絶縁膜115の上部には、ゲート配線105と交差して画素領域Pを定義するデータ配線130が第2方向に延長して形成されている。この時、薄膜トランジスタTrのソース電極133は、データ配線130に連結される。

10

## 【0059】

データ配線130とゲート絶縁膜115との間には、半導体層120を構成している同一な半導体物質で二重層構造の半導体パターン121(121a、121b)がさらに形成されている。このような半導体パターン121は、製造方法に基づいており、データ配線130の下部に形成されたりまたは省略されたりする。すなわち、半導体層120と、データ配線130とソース電極133及びドレイン電極136を1回のマスク工程によって同時に形成する場合は、データ配線130の下部に二重層構造の半導体パターン121が形成される。一方、半導体層120と、データ配線130とソース電極133及びドレイン電極136を相互に異なるマスク工程、すなわち、2回のマスク工程によって各々形成する場合は、データ配線130の下部に半導体パターンが形成されない。

20

## 【0060】

また、データ配線130と、薄膜トランジスタTrを覆って無機絶縁物質、例えば、酸化シリコンSiO<sub>2</sub>または窒化シリコンSiN<sub>x</sub>のうちから選択される一つまたは有機絶縁物質、例えば、ベンゾシクロブテンBCBまたはフォトアクリル(photo acryl)で、基板101全面に第1保護層140が形成される。

## 【0061】

図面では、無機絶縁物質で形成され、その下部の構成要素の段差を反映して形成された状態を示しているが、有機絶縁物質で形成される場合、その表面が平坦な状態になる。この時、第1保護層140は、薄膜トランジスタTrのドレイン電極136の一部を露出させるドレインコンタクトホール150を備える。

30

## 【0062】

ドレインコンタクトホール150を備えた第1保護層140上に、画素領域P毎に透明導電性物質、例えば、インジウムースズーオキサイドITOまたはインジウムージンクーオキサイドIZOでドレインコンタクトホール150を通じてドレイン電極136と接触して板状の画素電極155が形成される。

## 【0063】

尚、画素電極155は、薄膜トランジスタTrのドレイン電極136と直接接觸して、ゲート絶縁膜115上に、これと接觸するように形成して、ドレインコンタクトホール150を有する第1保護層140は、省略される。

40

## 【0064】

また、画素電極155上に、無機絶縁物質または有機絶縁物質で、基板101全面に第2保護層160が形成されており、第2保護層160上に、画素領域Pで構成される表示領域全面に、透明導電性物質で構成される板状の共通電極170が形成されている。この時、共通電極170は、各画素領域Pに形成された各画素電極155に対して画素電極155の長軸の長さよりさらに長い多数のバー状の開口部opがデータ配線130と並んで形成されることを特徴とする。すなわち、多数のバー状の開口部opは、各画素領域P内で一定間隔離隔して、その長軸の両端は、画素電極155の外側に形成される。

## 【0065】

第1実施例の変形例の場合、共通電極170内の多数の開口部opは、データ配線13

50

0が延長した方向に、相互に隣接する画素領域Pの間には連結され、すなわち、表示領域全体に対してストライプ状で形成される。従って、第1実施例の変形例の場合、図8においては、共通電極170が存在しない。

#### 【0066】

この場合、多数の開口部opは、表示領域の最外角に位置する画素領域(図示せず)に対してのみその長軸の一端が存在するので、この最外角の画素領域(図示せず)に対しては、その開口部opの一端を画素電極155の外側に位置させて形成する。

#### 【0067】

第1実施例の場合、図面においては、各画素領域Pに共通電極内にバー状の3個の開口部opが相互に同一な間隔に離隔して構成するように示されているが、効率的なフリンジフィールドの形成のために、各画素領域Pに対応する開口部opは、2個ないし10個程度の範囲内で適当な個数に形成されるものとする。このような開口部の個数は、第1実施例の変形例に対しても同様に適用されるものである。10

#### 【0068】

表示領域の外側の非表示領域には、ゲート配線105及びデータ配線130の一端が位置するゲート及びデータパッド部(図示せず)が構成されている。ゲート及びデータパッド部(図示せず)には、ゲート配線105及びデータ配線130に各々連結されたゲートパッド電極(図示せず)及びデータパッド電極(図示せず)が形成されており、共通電極170に共通電圧を印加するために、共通電極170に連結された共通パッド電極(図示せず)が形成されている。20

#### 【0069】

この時、ゲートパッド電極(図示せず)に対応する部分には、この上部に形成されたゲート絶縁膜115及び第1保護層140と第2保護層160が除去されゲートパッドコンタクトホール(図示せず)を備えることによってゲートパッド電極(図示せず)が露出されており、データパッド電極(図示せず)に対応する部分には、この上部に形成された第1保護層140と第2保護層160が除去されデータパッドコンタクトホール(図示せず)を備えることによってデータパッド電極(図示せず)が露出されている。

#### 【0070】

また、ゲート及びデータパッド部(図示せず)においては、第2保護層160上にゲート及びデータパッド電極(図示せず)と各々ゲート及びデータパッドコンタクトホール(図示せず)を通じて接触してゲート補助パッド電極(図示せず)及びデータ補助パッド電極(図示せず)が共通電極170を構成する同一な物質である透明導電性物質で形成されている。30

#### 【0071】

また、共通パッド電極(図示せず)は、ゲートパッド部(図示せず)またはデータパッド部(図示せず)のいずれかのパッド部に位置して、表示領域に形成された共通電極170が配線形態で延長して形成されている。

図面には示していないが、前述した構成のアレイ基板は、ブラックマトリックスとカラーフィルター層が形成されているカラーフィルター基板と、その間に液晶層が介された状態で合着されフリンジフィールドスイッチングモードの液晶表示装置を構成する。

#### 【0072】

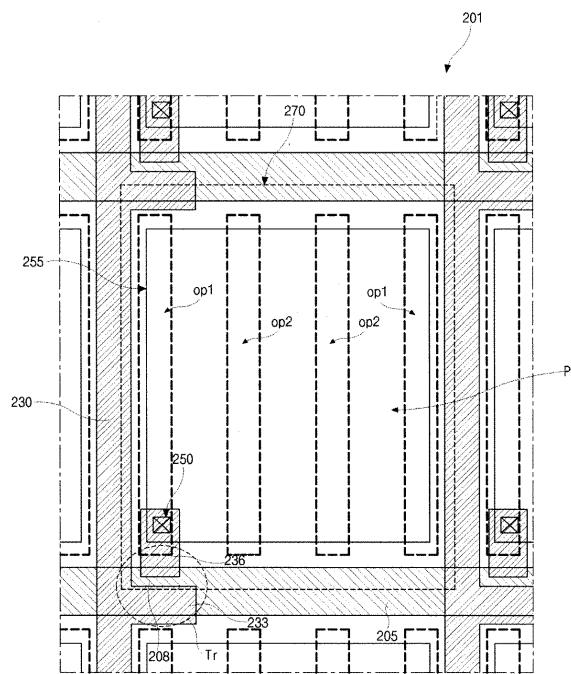

##### [第2実施例]

本発明の第2実施例によるフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板の場合、共通電極に形成された多数のバー状の開口部opと、これに対応する画素電極の位置関係のみが異なるのであって、それ以外の構成は上記第1実施例で述べた構成と同様であるため、相違点がある部分を説明する。この時、第1実施例と同一な構成要素に対しては、100を加えた図面符号で示している。

#### 【0073】

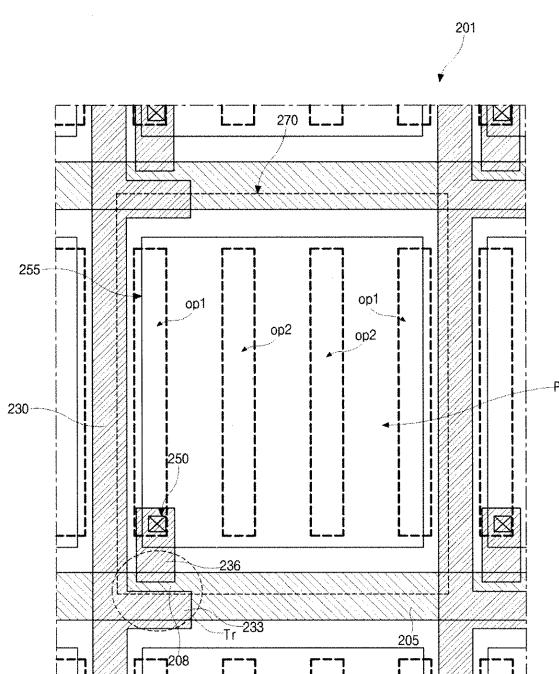

図11は、本発明の第2実施例によるフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板の平面図である。

図11に示したように、第1実施例と異なる構成は、画素電極255と共に電極270

10

20

30

40

50

内に形成された開口部  $o\ p\ 1$ 、 $o\ p\ 2$  にある。

**【0074】**

第1実施例の場合、板状の画素電極 155 に対応する共通電極 170 内に形成された多数の開口部  $o\ p$  の長軸の両端のみが画素電極 155 の外側に構成されているが、本発明の第2実施例の場合、多数の開口部  $o\ p\ 1$ 、 $o\ p\ 2$  の長軸の両端のみならず、多数の開口部  $o\ p\ 1$ 、 $o\ p\ 2$  のうちの画素領域 P の最外角に各々位置する開口部  $o\ p\ 1$  の短軸の長側面の一端まで画素電極 255 の外側に形成されている。

**【0075】**

このように画素領域 P 内の最外角に位置する 2 個の開口部  $o\ p\ 1$  各々の短軸の長側面の一端までも画素電極 255 の外側に形成した理由は、最外角の開口部  $o\ p\ 1$  に対してはフリンジフィールドによる電界が画素領域 P の中央部を向いて一方向のみに形成させるためである。10

従って、画素領域 P の最外角に位置する各開口部  $o\ p\ 1$  は、フリンジフィールドによる電界が一方向のみに形成されるため、液晶分子の動きを異にして発生される回位部分が最外角に形成された開口部  $o\ p\ 1$  に対応する部分には発生することなく、または、非常に微弱だったりして、使用者（ユーザー）には感じられない程度である。それ以外の構成要素は、第1実施例と同様であるため、説明を省略する。

**【0076】**

図 12 は、第2実施例の変形例によるフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板の一つの画素領域の平面図である。20

画素領域内の開口部  $o\ p\ 1$ 、 $o\ p\ 2$  の長軸の両一端に対しては画素電極 255 と重なるように、また、画素領域 P の最外角に位置する 2 個の開口部  $o\ p\ 1$  の短軸の長側面の一端に対してのみ画素電極 255 の外側に構成されるように形成する。これは、フリンジフィールドスイッチングモードの液晶表示装置のモデルによって回位が発生する部分が開口部  $o\ p\ 1$ 、 $o\ p\ 2$  の長軸の短側面の少なくとも一端部分または最外角に位置した開口部  $o\ p\ 1$  の短軸の長側面の一端であるためである。

**【0077】**

尚、このような第2実施例及び第2実施例の変形例に対しても第1実施例の変形例のように、多数の開口部  $o\ p\ 1$ 、 $o\ p\ 2$  は、データ配線 230 が延長する方向に相互に隣接する画素領域 P 間には、その長軸の両一端が相互に連結され表示領域全体に多数のストライプ状で形成される場合もある。30

図面には示していないが、前述した構成のアレイ基板は、ブラックマトリックスとカラー フィルター層が形成されているカラーフィルター基板と、その間に液晶層が介された状態で合着されフリンジフィールドスイッチングモードの液晶表示装置を構成する。

**【0078】**

以下に、構造的特徴の本発明の第1実施例によるフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板の製造方法を図 5、図 6、図 7 及び図 8 を参照して説明する。第2実施例及びその変形例の場合、その製造方法は、共通電極 270 内に形成される開口部  $o\ p\ 1$ 、 $o\ p\ 2$  の位置のみが異なるのであって、実質的に第1実施例と同様であるため、第1実施例によるフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板の製造方法のみを説明する。この時、説明の便宜上、各画素領域内に薄膜トランジスタ Tr が形成される領域をスイッチング領域 TrA で定義する。40

**【0079】**

図 7、図 8 及び図 9 に示したように、透明な絶縁基板 101 上に低抵抗特性の第1金属物質、例えば、アルミニウム Al、アルミニウム合金 AlNd、銅 Cu、銅合金、クロム Cr、モリブデン Mo のうちから選択された物質を全面に蒸着して第1金属層（図示せず）を形成して、これをフォトレジストの塗布、フォトマスクを利用して露光、露光されたフォトレジストの現像、第1金属層（図示せず）のエッチング及びフォトレジストのストリップ(strip)などの一連の単位工程を含むマスク工程を行って第1金属層（図示せず）をパターニングし、第1方向に延長する多数のゲート配線 105 と、スイッチング領域 TrA に50

、ゲート配線 105 に連結されたゲート電極 108 を形成する。この時、ゲートパッド部(図示せず)においては、ゲート配線 105 の一端に連結されて、ゲートパッド電極(図示せず)を形成する。

#### 【0080】

一方、図面では、ゲート配線 105 とゲート電極 108 は、単一層で形成するように示されているが、二つの金属物質、例えば、アルミニウム合金 AlNd 及びモリブデン Mo が各々下部層と上部層を構成する、二重層構造で形成することもできる。

#### 【0081】

ゲート配線 105 及びゲート電極 108 上に無機絶縁物質、例えば、酸化シリコン SiO<sub>2</sub> または窒化シリコン SiNx を蒸着して基板 101 全面にゲート絶縁膜 115 を形成する。次いで、ゲート絶縁膜 115 の上部で純粋非晶質シリコン層(図示せず)と不純物非晶質シリコン層(図示せず)を形成し、不純物非晶質シリコン層(図示せず)上に第 2 金属物質、例えば、アルミニウム Al、アルミニウム合金 AlNd、モリブデン Mo、銅 Cu、銅合金のうちの一つを蒸着して第 2 金属層(図示せず)を形成する。次いで、第 2 金属層(図示せず)上にフォトレジスト層(図示せず)を形成し、これをハーフトーン露光または回折露光を行って現像することにより、相互に厚さが異なる第 1 及び第 2 フォトレジストパターン(図示せず)を形成する。

#### 【0082】

第 1 及び第 2 フォトレジストパターン(図示せず)の外部に露出される第 2 金属層(図示せず)と、その下部の不純物及び純粋非晶質シリコン層(図示せず)をエッチングして除去することにより、ゲート配線 105 と交差して、第 2 方向に延長して多数の画素領域 P を定義する多数のデータ配線 130 を形成すると同時に、スイッチング領域 TrA においては、連結された状態のソースドレインパターン(図示せず)と、その下部でオーミックコンタクトパターン(図示せず)とアクティブ層 120a を形成する。この時、データパッド部(図示せず)においては、データ配線 130 の一端に連結されるデータパッド電極(図示せず)を形成する。

#### 【0083】

薄い厚さの第 2 フォトレジストパターン(図示せず)を除去して、これによって新しく露出されるソース・ドレインパターン(図示せず)の中央部と、その下部のオーミックコンタクトパターン(図示せず)をエッチングして除去することにより、相互に離隔するソース電極 133 及びドレイン電極 136 を形成して、ソース電極 133 及びドレイン電極 136 の下部でアクティブ層 120a を露出させるオーミックコンタクト層 120b を形成する。この時、スイッチング領域 TrA に順に積層されたゲート電極 108、ゲート絶縁膜 115、半導体層 120、相互に離隔するソース電極 133 及びドレイン電極 136 は、薄膜トランジスタ Tr を構成する。このような製造方法を行って、半導体層 120 とソース電極 133 及びドレイン電極 136 が一つのマスク工程によって形成されることにより、ソース電極 133 及びドレイン電極 136 と同一層に同一な物質で同一なマスク工程によって形成されるデータ配線 130 の下部にも、半導体層 120 を構成する同一な物質で二重層構造の半導体パターン 121(121a、121b) が形成される。

#### 【0084】

尚、変形例として、半導体層 120 とデータ配線 130 とソース電極 133 及びドレイン電極 136 は、2 回のマスク工程を行って形成されることもできる。すなわち、不純物及び純粋非晶質シリコン層(図示せず)をパターニングしてスイッチング領域 Tr にアクティブ層 120a とその上部でオーミックコンタクトパターン(図示せず)を形成し、オーミックコンタクトパターン(図示せず)の上部で第 2 金属層(図示せず)を形成する。

#### 【0085】

次いで、第 2 金属層(図示せず)をマスク工程を行ってパターニングすることにより、データ配線 130 とソース電極 133 及びドレイン電極 136 を形成して、ソース電極 133 及びドレイン電極 136 間に露出されたオーミックコンタクトパターン(図示せず)を除去してアクティブ層 120a を露出することにより、相互に離隔するオーミックコンタ

10

20

30

40

50

クト層 120b を形成することもできる。この時、データ配線の下部 130 には、二重層構造の半導体パターン 121 は、形成されない。

#### 【0086】

薄膜トランジスタ Tr とデータ配線 130 上に、全面に無機絶縁物質、例えば、酸化シリコン SiO<sub>2</sub> または窒化シリコン SiN<sub>x</sub> を蒸着したり、または有機絶縁物質、例えば、ベンゾシクロブテン BCB またはフォトアクリル(photo acryl)を塗布したりして、第 1 保護層 140 を形成し、これをパターニングすることによってドレイン電極 136 の一部を露出させるドレインコンタクトホール 150 を形成する。また、他の変形例の場合、第 1 保護層 140 は、省略される。

#### 【0087】

ドレインコンタクトホール 150 を有する第 1 保護層 140 上に透明導電性物質、例えば、インジウムースズーオキサイドITO またはインジウムージンクーオキサイドIZO を蒸着し、これをマスク工程を行ってパターニングすることにより、ドレインコンタクトホール 150 を通じてドレイン電極 136 と接触して各画素領域 P に分離された板状の画素電極 155 を形成する。一方、第 1 保護層 140 が省略された変形例の場合、ドレイン電極 136 と直接接触するバー状の画素電極 155 がゲート絶縁膜 115 上に形成される。

#### 【0088】

画素電極 155 上に無機絶縁物質、例えば、酸化シリコン SiO<sub>2</sub> または窒化シリコン SiN<sub>x</sub> を蒸着したり、または有機絶縁物質、例えば、フォトアクリル(photo acryl)またはベンゾシクロブテン BCB を塗布したりして第 2 保護層 160 を形成する。

#### 【0089】

次いで、第 2 保護層 160 を含み、その下部の第 1 保護層 140 とゲート絶縁膜 115 を除去することによって、ゲートパッド部(図示せず)においては、ゲートパッド電極(図示せず)を露出させるゲートパッドコンタクトホール(図示せず)を形成すると同時に、データパッド部(図示せず)においては、第 2 保護層 160 及び第 1 保護層 140 を除去することによって、データパッド電極(図示せず)を露出させるデータパッドコンタクトホール(図示せず)を形成する。

#### 【0090】

ゲート及びデータパッドコンタクトホール(図示せず)が形成された第 2 保護層 160 上に透明導電性物質、例えば、インジウムースズーオキサイドITO またはインジウムージンクーオキサイドIZO を蒸着してこれをパターニングすることにより、表示領域全面に板状の共通電極 170 を形成して、ゲート及びデータパッド部(図示せず)においては、ゲートパッドコンタクトホール(図示せず)を通じてゲートパッド電極(図示せず)と接触するゲート補助パッド電極(図示せず)と、データパッドコンタクトホール(図示せず)を通じてデータパッド電極(図示せず)と接触するデータ補助パッド電極(図示せず)を形成する。

#### 【0091】

この時、表示領域全面に形成された共通電極 170 は、パターニング時に、各画素領域 P に対応して、第 1 実施例(図 6 参照)または第 1 実施例の変形例(図 10 参照)、第 2 実施例(図 11 参照)と第 2 実施例の変形例(図 12 参照)のような形態で、多数のバー状の開口部 op を有して形成することによって、本発明の第 1 実施例及び第 1 実施例の変形例と、第 2 実施例及び第 2 実施例の変形例によるフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板 101 を完成する。

#### 【0092】

##### [第 3 実施例]

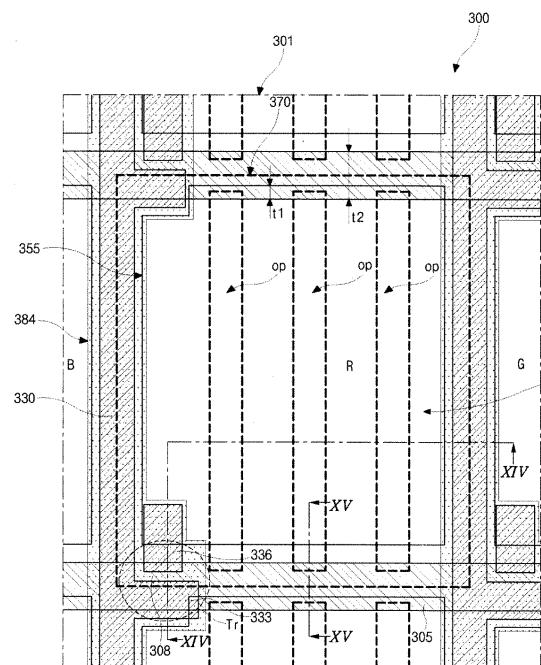

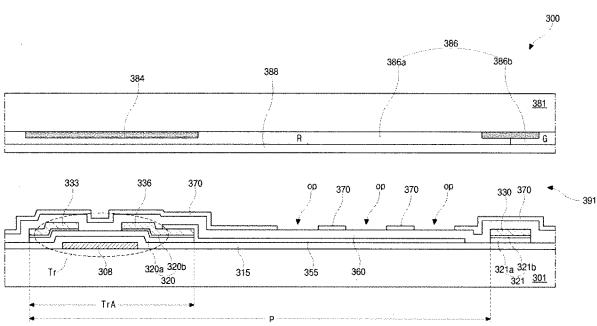

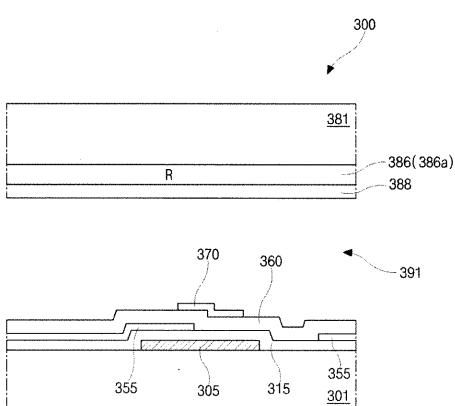

図 13 は、本発明の実施例によるフリンジフィールドスイッチングモードの液晶表示装置の平面図であって、図 14 は、図 13 を XIV-XIV 線に沿って切断した部分の断面図である。

#### 【0093】

図 15 は、図 13 を XV-XV 線に沿って切断した部分の断面図である。説明の便宜上

10

20

30

40

50

、多数の画素領域が形成された領域を表示領域として定義する。

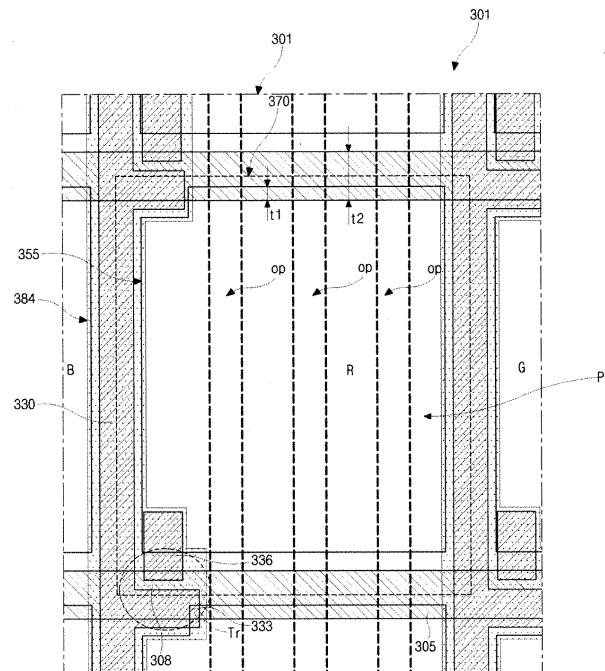

**【0094】**

図13に示したように、本発明の実施例によるフリンジフィールドスイッチングモードの液晶表示装置300は、第1基板301と第2基板(図示せず)、二つの基板(301、図示せず)間に介された液晶層(図示せず)を含んで構成されている。

**【0095】**

アレイ基板301は、第1方向にゲート配線305を延長して構成されており、また、第2方向に延長して、ゲート配線305と交差して画素領域Pを定義するデータ配線330が構成されている。

**【0096】**

画素領域Pには、ゲート配線305及びデータ配線330に連結されて、ゲート電極308と、ゲート絶縁膜(図示せず)と、純粋非晶質シリコンのアクティブ層(図示せず)と不純物非晶質シリコンのオーミックコンタクト層(図示せず)とで構成された半導体層(図示せず)と、相互に離隔するソース電極333及びドレイン電極336を含む薄膜トランジスタTrが形成されている。この時、図面において、薄膜トランジスタTrは、一つの画素領域Pの開口率をさらに向上させるためにゲート配線305上に形成して、ゲート配線305自体をゲート電極308として構成する一例を示しているが、ゲート電極308は、ゲート配線305から分岐して形成される。

**【0097】**

また、本発明の特徴的な部分として、画素領域Pの内側で板状の画素電極355が薄膜トランジスタTrのドレイン電極336と接触して同時に前段のゲート配線305と一部重なって形成されている。この時、板状の画素電極355と前段のゲート配線305との重なる幅t1は、望ましくは、ゲート配線305の幅t2の50%以下である。通常的に、ゲート配線305の幅t2は、8μmないし12μm程度であって、この場合、重なる最大の幅t1は、望ましくは、4μmないし6μm程度である。

**【0098】**

このように、前段のゲート配線305と画素電極355が重なる幅t1をゲート配線の幅t2の50%以下に形成する理由は、相互に隣接する画素電極305間のカップルリングによる電界歪曲を防ぐためである。従来の場合、電界歪曲を防ぐために、各画素領域の内側に位置させて画素電極を形成したが、シミュレーションの結果、画素電極355を前段のゲート配線305と特定範囲内で重ねて形成しても、画素電極355とゲート配線305が重なることによって生成された寄生容量または隣接する画素電極355間のカップルリングによる電界歪曲現象は、殆ど発生しなくなる。これに基づいて、重なった幅t1がゲート配線の幅t2の50%以下になる特定範囲で重ねて形成する。

**【0099】**

また、多数の画素領域Pを含む表示領域全面には、各画素領域P内に形成された板状の画素電極355に対応してバー状の多数の開口部opを有する共通電極370が形成されている。この時、共通電極370は、表示領域全面に形成されて、図13には、説明の便宜上、一つの画素領域Pに対して点線で、図面符号370で示している。

**【0100】**

画素領域P内に形成された板状の画素電極355に対応して形成されるバー状の多数の開口部opの長軸の両一端は、各々ゲート配線305と重ねて形成されることを特徴とする。この場合、共通電極370内に形成されたバー状の多数の開口部opは、従来より画素領域内でできるだけ長く形成されるため、透過率が向上する効果がある。

**【0101】**

前述した板状の画素電極355とバー状の多数の開口部opの形態によってバー状の多数の開口部opの一端で所定の幅の回位が発生するとしても、これは、不透明金属物質で形成されるゲート配線305に対応しては、その下部から射出される光が通過しなくなり光が透過されない領域になるため、自然に遮られる。

**【0102】**

10

20

30

40

50

図16は、本発明の変形例によるフリンジフィールドスイッチングモードの液晶表示装置の一つの画素領域の平面図である。(実施例3と同一な構成要素には、同一な図面符号で示す。)

図16に示したように、表示領域全体に形成された共通電極370内に形成されたバー状の多数の開口部opは、データ配線330の延長方向に隣接する画素領域Pの間には、相互に連結された構造で形成される。すなわち、共通電極370内に形成されたバー状の多数の開口部opは、表示領域全体において、画素領域Pの区分なしにストライプ状でデータ配線330と並んで形成される。

#### 【0103】

この場合、本発明の変形例による構成においては、表示領域内の最外角に位置する画素領域(図示せず)を除いては、開口部opの長軸の両一端が存在しない。これによって、最外角の画素領域(図示せず)を除いた各画素領域Pの内部には、多数の各開口部opの長軸の両端に短側面が存在しないので、両端の短側面がある場合に発生する電界が全く形成されない。

従って、この部分に位置する液晶分子(図示せず)は、開口部opの長側面による電界に影響を受けるため、一定な方向に動いて正常に駆動する。

#### 【0104】

前述したように、従来でのような回位は発生されなくなり、または、回位発生領域がゲート配線305に重なる部分に形成されたりするため、自然に回位発生部分がゲート配線305に遮られ、開口率を向上させると同時に、透過率を向上させる。

#### 【0105】

一方、図13を参照すると、バー状の多数の開口部opを含む共通電極370は、表示領域全面に形成されて、薄膜トランジスタTrに対応する部分では、バー状の多数の開口部opを形成したように、共通電極370の一部を除去するとしてもよい。これは、薄膜トランジスタTrのゲート電極308と重なることによって、寄生キャパシターを構成する薄膜トランジスタTrのスイッチング動作に悪影響を与えるので、これを防ぐためである。

#### 【0106】

このように、ゲート配線305、データ配線330、薄膜トランジスタTr、画素電極355、共通電極370などが形成されている第1基板301をアレイ基板とする。

#### 【0107】

尚、前述した構成の実施例及び変形例による第1基板301に対応して、各画素領域別に赤色R、緑色G、青色Bのカラーフィルターパターンが順に交互にカラーフィルター層(図示せず)とデータ配線330と薄膜トランジスタTrに対応してブラックマトリックス384を形成して、カラーフィルター層(図示せず)を覆って全面に形成されたオーバーコート層(図示せず)を含む第2基板(図示せず)が構成されている。

このように、カラーフィルター層、ブラックマトリックス384が形成されている第2基板をカラーフィルター基板とする。

#### 【0108】

また、第1基板301と第2基板(図示せず)間には、液晶層(図示せず)を備えている。この時、本発明のまた他の特徴的な構成のブラックマトリックス384は、従来の場合、ゲート及びデータ配線と薄膜トランジスタに対応して各画素領域を取り囲むように形成されるが、本発明の場合、ゲート配線305に対応する部分では省略され、データ配線330と薄膜トランジスタTrに対応する部分でのみ形成されることによって、画素領域Pの開口率を向上させる。

#### 【0109】

このように、本発明の実施例及び変形例において、ゲート配線305に対応してブラックマトリックス384を形成しない理由は、画素電極355を前段のゲート配線305と所定の幅重なって形成し、各画素領域P内でのバー状の多数の開口部opの両一端までゲート配線と重なるように形成(図13参照)するか、または、表示領域全体に対してストラ

10

20

30

40

50

イブ状で連結されて形成(図16参照)したりするので、各開口部o pの長軸の両一端での回位発生が最小化されたり、抑制されたりすることによって、ゲート配線305に対応してこれよりさらに広い幅の別途のブラックマトリックス384を形成しなくても、表示品質には問題ない。

#### 【0110】

以下、図14及び図15を参照して、本発明の実施例によるフリンジフィールドスイッチングモードの液晶表示装置の断面構造を説明する。

変形例の場合、開口部のゲート配線と重なる部分での断面構造のみが差であって、それ以外の断面構造は、実施例と同一であるため、相違点がある部分を簡単に説明する。この時、説明の便宜上、画素領域内に薄膜トランジスタが形成される領域をスイッチング領域で定義する。

10

#### 【0111】

図14及び図15に示したように、本発明の実施例によるフリンジフィールドスイッチングモードの液晶表示装置300におけるアレイ基板は、透明な絶縁基板301上に低抵抗特性の金属物質、例えば、アルミニウムA1、アルミニウム合金A1Nd、銅Cu、銅合金のうちから選択される一つの金属物質で、第1方向に延長するゲート配線305と、これに連結されスイッチング領域TrAにゲート電極308が形成される。

#### 【0112】

一方、図面において、ゲート配線305とゲート電極308は、単一層構造の一例を示しているが、二重層構造で形成される場合もある。二重層構造の場合、下部層は、低抵抗金属物質であるアルミニウムA1、アルミニウム合金A1Nd、銅Cu、銅合金のうちから選択される一つの金属物質で構成されて、上部層は、モリブデンMoで構成される。

20

また、ゲート配線305とゲート電極308上に、基板301全面に無機絶縁物質、例えば、酸化シリコンSiO<sub>2</sub>または窒化シリコンSiN<sub>x</sub>で構成されるゲート絶縁膜315が形成される。

#### 【0113】

ゲート絶縁膜315上にスイッチング領域TrAのゲート電極308に対応して、純粹非晶質シリコンのアクティブ層320aと不純物非晶質シリコンのオーミックコントラクト層320bを含む半導体層320が形成されており、半導体層320の上部に第2金属物質、例えば、モリブデンMo、クロムCr、アルミニウムA1、アルミニウム合金A1Nd、銅Cu、銅合金のうちいずれかの一つの物質で構成されて、相互に離隔するソース電極333及びドレイン電極336が形成されている。この時、相互に離隔するソース電極333及びドレイン電極336間にアクティブ層320aが露出されており、スイッチング領域TrAに順に積層されたゲート電極308とゲート絶縁膜315と半導体層320とソース電極333及びドレイン電極336は、薄膜トランジスタTrを構成する。

30

#### 【0114】

また、ゲート絶縁膜315の上部には、ゲート配線305と交差して画素領域Pを定義するデータ配線330が第2方向に延長して形成されている。この時、薄膜トランジスタTrのソース電極333は、データ配線330に連結されて、データ配線330とソース電極333及びドレイン電極336も二重層構造で構成されている。

40

#### 【0115】

また、データ配線330とゲート絶縁膜315の間には、半導体層320を構成する同一な半導体物質で、第1パターン321aと第2パターン321bの二重層構造の半導体パターン321がさらに形成されている。このような半導体パターン321は、アレイ基板301の製造方法に基づいており、データ配線330の下部に形成されたりまたは省略されたりする。すなわち、半導体層320と、データ配線330とソース電極333及びドレイン電極336を1回のマスク工程によって同時に形成する場合は、データ配線330の下部に二重層構造の半導体パターン321が形成されて、半導体層320と、データ配線330とソース電極333及びドレイン電極336を相互に異なるマスク工程、すなわち、2回のマスク工程によって各自形成する場合は、データ配線330の下部に半導体

50

パターン321が形成されない。

**【0116】**

尚、各画素領域P内には、ゲート絶縁膜315上に透明導電性物質、例えば、インジウムースズーオキサイドITOまたはインジウムージンクーオキサイドIZOで構成されて、ドレイン電極336と直接接触して板状の画素電極355が前段のゲート配線305と所定の幅重なって形成されている。この時、画素電極355と前段のゲート配線305が重なる幅は、望ましくは、ゲート配線の幅の50%以下である。

**【0117】**

また、データ配線330と薄膜トランジスタTr上に無機絶縁物質、例えば、酸化シリコンSiO<sub>2</sub>または窒化シリコンSiN<sub>x</sub>のうちから選択される一つまたは有機絶縁物質、例えば、ベンゾシクロブテンBCBまたはフォトアクリルで構成される保護層360が全面に形成されている。図面においては、無機絶縁物質で形成されその下部の構成要素の段差を反映して形成された状態を示しているが、有機絶縁物質で形成される場合、その表面が平坦な状態になる。

**【0118】**

保護層360上に、画素領域Pで構成された表示領域全面に透明導電性物質、例えば、インジウムースズーオキサイドITOまたはインジウムージンクーオキサイドIZOで構成される板状の共通電極370が形成されている。この時、共通電極370は、各画素領域Pに形成された各画素電極355に対してバー状の多数の開口部opがデータ配線330と並んで形成されている。図面においては、各画素領域Pに共通電極370内にバー状の多数の開口部opが相互に一定な間隔に離隔して3個(図14参照)構成されるように示しているが、効率的なフリンジフィールド形成のため、各画素領域Pに対応する開口部opは、2個ないし10個程度の範囲内で適当な個数で形成されるものとすればよい。

**【0119】**

尚、図14において、板状の共通電極370は、保護層360上に各画素領域P内の薄膜トランジスタTrを覆ってバー状の多数の開口部opを有するように示しているが、その変形例として、薄膜トランジスタTrに対応する部分では除去されて保護層360を露出して形成されるものとしてもよい。

**【0120】**

前述した構成の第1基板301に対応して、これと離隔して位置する第2基板381においては、その内側面にアレイ基板301のデータ配線330と薄膜トランジスタTrに対応してブラックマトリックス384が形成されている。また、ブラックマトリックス384を覆い、各画素領域Pに対応して赤色、緑色、青色のカラーフィルターパターン(386a、386b、図示せず)が順に交互にカラーフィルター層386を形成しており、カラーフィルター層386を覆い、透明な有機絶縁物質で全面にその表面が平坦なオーバーコート層388が形成されている。この時、オーバーコート層388が省略される場合もある。

**【0121】**

また、前述した構成の第1基板301と第2基板381との間の離隔領域には、液晶層391が介され本発明によるフリンジフィールドスイッチングモードの液晶表示装置300を構成する。

**【図面の簡単な説明】**

**【0122】**

**【図1】**一般的な横電界型の液晶表示装置の一部を概略的に示した断面図である。

**【図2A】**一般的な横電界型の液晶表示装置のオン(on)動作を示した断面図である。

**【図2B】**一般的な横電界型の液晶表示装置のオフ(off)動作を示した断面図である。

**【図3】**従来のフリンジフィールドスイッチングモードの液晶表示装置のアレイ基板の平面図である。

**【図4】**従来のフリンジフィールドスイッチングモードの液晶表示装置に回位の発生を示した写真である。

10

20

30

40

50

【図5】従来のフリンジフィールドスイッチングモードの液晶表示装置の平面図である。

【図6】本発明の第1実施例によるフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板の平面図である。

【図7】図6をV I - V I線に沿って切断した部分の断面図である。

【図8】図6をV I I - V I I線に沿って切断した部分の断面図である。

【図9】図6をV I I I - V I I I線に沿って切断した部分の断面図である。

【図10】本発明の第1実施例の変形例によるフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板の平面図である。

【図11】本発明の第2実施例によるフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板の平面図である。 10

【図12】本発明の第2実施例の変形例によるフリンジフィールドスイッチングモードの液晶表示装置用アレイ基板の平面図である。

【図13】本発明の第3実施例によるフリンジフィールドスイッチングモードの液晶表示装置の平面図である。

【図14】図13をX I V - X I V線に沿って切断した部分の断面図である。

【図15】図13をX V - X V線に沿って切断した部分の断面図である。

【図16】本発明の第3実施例の変形例によるフリンジフィールドスイッチングモードの液晶表示装置の平面図である。

【符号の説明】

【0123】

101：基板

105：ゲート配線

108：ゲート電極

130：データ配線

133：ソース電極

136：ドレイン電極

150：ドレインコンタクトホール

155：画素電極

170：共通電極

P：画素領域

o p：開口部

T r：薄膜トランジスタ

10

20

30

【図1】

【図2A】

【図2B】

【図3】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図4】

---

フロントページの続き

(74)代理人 100104352

弁理士 朝日 伸光

(74)代理人 100128657

弁理士 三山 勝巳

(72)発明者 ソン サンム

大韓民国 705-816 デグ ナムグ デミヨン7ドン 2151-19

(72)発明者 ファン インホ

大韓民国 110-827 ソウル ジョンノグ スンギン2ドン 649 ハンソパレス3チャ

ビー-102

(72)発明者 パク デイム

大韓民国 718-833 キョンブク チルゴックン ソクジョクミヨン ジュンリ 141

3ゴンダンミヨン アパート 113-808

(72)発明者 リュウ キヒヨン

大韓民国 427-806 キョンギ グワチヨンシ ジュンガンドン ジュゴン アパート 1

10-110

審査官 福田 知喜

(56)参考文献 特開2007-233317(JP,A)

特開2007-293155(JP,A)

特開2006-058908(JP,A)

特開2008-191669(JP,A)

特開2007-256905(JP,A)

特開2007-178979(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 1368

G 02 F 1 / 1343

G 02 F 1 / 1337

H 01 L 29 / 786

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于边缘场切换模式的液晶显示装置的阵列基板和包括其的边缘场切换模式的液晶显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">JP5334552B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 公开(公告)日 | 2013-11-06 |

| 申请号            | JP2008312930                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 申请日     | 2008-12-09 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 申请(专利权)人(译)    | Eruji显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 当前申请(专利权)人(译)  | Eruji显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| [标]发明人         | ソンサンム<br>ファンインホ<br>パクデイム<br>リュウキヒョン                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 发明人            | ソン サンム<br>ファン インホ<br>パク デイム<br>リュウ キヒョン                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| IPC分类号         | G02F1/1368 G02F1/1343                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| CPC分类号         | G02F1/133707 G02F2001/134372                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| FI分类号          | G02F1/1368 G02F1/1343 G02F1/1335.505                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| F-TERM分类号      | 2H092/GA13 2H092/GA29 2H092/HA04 2H092/JA26 2H092/JA46 2H092/JB24 2H092/JB33 2H092/JB52 2H092/JB57 2H092/KA05 2H092/KA12 2H092/KB14 2H092/KB24 2H092/NA01 2H092/PA08 2H092/PA09 2H191/FA02Y 2H191/FA14Y 2H191/FA94Y 2H191/FD22 2H191/FD26 2H191/GA05 2H191/GA19 2H191/GA22 2H191/LA19 2H191/LA21 2H192/AA24 2H192/BB12 2H192/BB52 2H192/BB66 2H192/BB73 2H192/BB84 2H192/BC31 2H192/CB05 2H192/CC04 2H192/CC32 2H192/CC72 2H192/EA22 2H192/EA43 2H192/JA33 2H291/FA02Y 2H291/FA14Y 2H291/FA94Y 2H291/FD22 2H291/FD26 2H291/GA05 2H291/GA19 2H291/GA22 2H291/LA19 2H291/LA21 |         |            |

| 代理人(译)         | 臼井伸一<br>朝日 伸光                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 审查员(译)         | 福田 知喜                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 优先权            | 1020080060328 2008-06-25 KR<br>1020080082964 2008-08-25 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 其他公开文献         | JP2010008999A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

**摘要(译)**

要解决的问题：提供一种用于边缘场切换模式的液晶显示装置的阵列基板，其抑制旋转的发生并提高开口率和透射率，以及包括阵列基板的边缘场切换模式的液晶显示装置。解决方案：在边缘场切换模式液晶显示装置阵列基板中，多个开口中的每一个具有与数据布线平行的长轴和与栅极布线平行的短轴，以及每个开口每个开口部分的长轴的短侧表面的至少一端突出到像素电极的外部，而中心部分与像素电极重叠。点域6