(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4543006号

(P4543006)

(45) 発行日 平成22年9月15日(2010.9.15)

(24) 登録日 平成22年7月2日(2010.7.2)

(51) Int.Cl.

F 1

|             |               |                  |      |          |

|-------------|---------------|------------------|------|----------|

| <b>G02F</b> | <b>1/1335</b> | <b>(2006.01)</b> | GO2F | 1/1335   |

| <b>G02F</b> | <b>1/13</b>   | <b>(2006.01)</b> | GO2F | 1/13 505 |

| <b>G02F</b> | <b>1/137</b>  | <b>(2006.01)</b> | GO2F | 1/137    |

| <b>G02F</b> | <b>1/1343</b> | <b>(2006.01)</b> | GO2F | 1/1343   |

請求項の数 26 (全 16 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2006-140733 (P2006-140733)  |

| (22) 出願日     | 平成18年5月19日 (2006.5.19)        |

| (65) 公開番号    | 特開2007-178979 (P2007-178979A) |

| (43) 公開日     | 平成19年7月12日 (2007.7.12)        |

| 審査請求日        | 平成18年5月19日 (2006.5.19)        |

| (31) 優先権主張番号 | 10-2005-0131564               |

| (32) 優先日     | 平成17年12月28日 (2005.12.28)      |

| (33) 優先権主張国  | 韓国 (KR)                       |

|           |                                                                               |

|-----------|-------------------------------------------------------------------------------|

| (73) 特許権者 | 501426046<br>エルジー ディスプレイ カンパニー リ<br>ミテッド<br>大韓民国 ソウル, ヨンドゥンパーク, ヨ<br>イドードン 20 |

| (74) 代理人  | 100110423<br>弁理士 曾我 道治                                                        |

| (74) 代理人  | 100084010<br>弁理士 古川 秀利                                                        |

| (74) 代理人  | 100094695<br>弁理士 鈴木 憲七                                                        |

| (74) 代理人  | 100111648<br>弁理士 梶並 順                                                         |

最終頁に続く

(54) 【発明の名称】 液晶表示素子及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1基板上に互いに直交して、赤色(R)を表示するRのサブピクセル、緑色(G)を表示するGのサブピクセル、青色(B)を表示するBのサブピクセル、白色(W)を表示するWのサブピクセルを定義するゲート配線及びデータ配線と、

前記ゲート配線及びデータ配線の交差地点に配置される薄膜トランジスタと、

前記R、G、B、Wサブピクセル内に備えられるプレート形の第1共通電極と、

前記薄膜トランジスタに接続され、前記第1共通電極と絶縁されて複数のスリットを有する画素電極と、

前記第1基板に対向合着され、前記第1基板との空間に液晶層が備えられる第2基板と、

前記第2基板上にWサブピクセルにのみ形成されるプレート形の第2共通電極とを備え、

前記Wサブピクセル内の前記液晶層は、広視野角モードの場合、前記R、G、Bサブピクセル内の前記液晶層と同一のFFSモードで駆動され、狭視野角モードの場合、前記R、G、Bサブピクセル内の前記液晶層が前記FFSモードで駆動されるのとは異なり、垂直電界で駆動される

ことを特徴とする液晶表示素子。

## 【請求項 2】

前記第2基板上に、前記R、G、Bサブピクセルに対応するR、G、Bのカラーフィル

10

20

タ層をさらに備えることを特徴とする請求項 1 に記載の液晶表示素子。

**【請求項 3】**

前記 R、G、B カラーフィルタ層と前記第 2 共通電極との間の前記 R、G、B カラーフィルタ層を含む全面に設けられたオーバーコート層をさらに備え、前記 W サブピクセルには、前記第 2 基板と前記第 2 共通電極との間に前記オーバーコート層が形成されることを特徴とする請求項 2 に記載の液晶表示素子。

**【請求項 4】**

前記広視野角モードの場合、前記 R、G、B、W サブピクセル内の前記画素電極と前記第 1 共通電極との間に形成されるフリンジフィールドによってホワイトまたはブラック状態が表示されることを特徴とする請求項 1 に記載の液晶表示素子。 10

**【請求項 5】**

前記第 2 共通電極には、電圧が印加されないか、または、前記第 1 共通電極と同じ電圧が印加されることを特徴とする請求項 4 に記載の液晶表示素子。

**【請求項 6】**

前記狭視野角モードの場合、前記 W サブピクセルの前記第 1 共通電極と前記第 2 共通電極との間に形成される前記垂直電界によって W サブピクセルの光が透過しないことを特徴とする請求項 1 に記載の液晶表示素子。

**【請求項 7】**

前記狭視野角モードの場合、前記 W サブピクセルの前記画素電極には、前記第 1 共通電極と同じ電圧が印加されるか、または、しきい値電圧未満の電界が印加されることを特徴とする請求項 1 に記載の液晶表示素子。 20

**【請求項 8】**

前記 W サブピクセルの前記第 2 共通電極には、前記第 1 共通電極に対して電位差が発生するように一定の電圧が印加されることを特徴とする請求項 1 に記載の液晶表示素子。

**【請求項 9】**

前記 W サブピクセルの前記第 1 共通電極と前記第 2 共通電極との間には、1 ~ 4 V または -4 ~ -1 V の電位差が発生することによって垂直電界が形成されることを特徴とする請求項 8 に記載の液晶表示素子。

**【請求項 10】**

前記第 2 共通電極に印加される電圧は、直流電圧または交流電圧であることを特徴とする請求項 8 に記載の液晶表示素子。 30

**【請求項 11】**

前記第 1 基板及び前記第 2 基板の内側面には配向膜がさらに備えられ、その外側面には、上部 / 下部偏光板がそれぞれさらに付着されることを特徴とする請求項 1 に記載の液晶表示素子。

**【請求項 12】**

前記配向膜は、前記上部 / 下部偏光板のいずれか一つの偏光板の偏光軸と同じ方向に配向処理されることを特徴とする請求項 11 に記載の液晶表示素子。

**【請求項 13】**

前記 R、G、B、W のサブピクセルは、クワッドタイプまたはストライプタイプで配置されることを特徴とする請求項 1 に記載の液晶表示素子。 40

**【請求項 14】**

前記画素電極の少なくとも 1 つのスリットは、前記ゲート配線またはデータ配線のいずれか一つと同じ方向に配置されることを特徴とする請求項 1 に記載の液晶表示素子。

**【請求項 15】**

前記画素電極、前記第 1 共通電極及び前記第 2 共通電極は、透明な導電層であることを特徴とする請求項 1 に記載の液晶表示素子。

**【請求項 16】**

前記第 2 共通電極は、互いに一体化して連結され、銀ドットを介して前記第 1 基板から電圧が供給されることを特徴とする請求項 1 に記載の液晶表示素子。 50

## 【請求項 17】

第1基板上に第1共通電極を形成する段階と、

前記第1基板上にゲート配線及びデータ配線を交差させて、赤色(R)を表示するRのサブピクセル、緑色(G)を表示するGのサブピクセル、青色(B)を表示するBのサブピクセル、白色(W)を表示するWのサブピクセルを定義し、両配線の交差地点に薄膜トランジスタを形成する段階と、

前記薄膜トランジスタを含む全面に保護膜を形成する段階と、

前記保護膜上に前記薄膜トランジスタに接続され、複数のスリットを有する画素電極を形成する段階と、

前記Wサブピクセルに限定して第2共通電極が形成された第2基板を、前記第1基板に10

対向合着させる段階と、

前記第1基板及び前記第2基板間に液晶層を形成する段階と

を備え、

前記Wサブピクセル内の前記液晶層は、広視野角モードの場合、前記R、G、Bサブピクセル内の前記液晶層と同一のFFSモードで駆動され、狭視野角モードの場合、前記R、G、Bサブピクセル内の前記液晶層が前記FFSモードで駆動されるのとは異なり、垂直電界で駆動される

ことを特徴とする液晶表示素子の製造方法。

## 【請求項 18】

前記第2基板上に第2共通電極を形成する以前に、

20

前記第2基板上にブラックマトリクスを形成する段階と、

前記ブラックマトリクス上部のR、G、B、Wの各サブピクセルに、R、G、B、Wカラーフィルタ層を形成する段階と、

前記カラーフィルタ層を含む全面にオーバーコート層を形成する段階と

をさらに備えることを特徴とする請求項17に記載の液晶表示素子の製造方法。

## 【請求項 19】

前記Wカラーフィルタ層は、前記オーバーコート層を形成する段階と同時に形成することを特徴とする請求項18に記載の液晶表示素子の製造方法。

## 【請求項 20】

前記Wカラーフィルタ層と前記オーバーコート層は、同一物質からなることを特徴とする請求項19に記載の液晶表示素子の製造方法。

30

## 【請求項 21】

前記第2共通電極は、透明な導電層から形成することを特徴とする請求項17に記載の液晶表示素子の製造方法。

## 【請求項 22】

前記第2共通電極は、ITO(Indium Tin Oxide)またはIZO(Indium Zinc Oxide)から形成することを特徴とする請求項21に記載の液晶表示素子の製造方法。

## 【請求項 23】

前記第2共通電極は、実質的にWサブピクセルの大きさと同一に形成することを特徴とする請求項17に記載の液晶表示素子の製造方法。

40

## 【請求項 24】

前記第2共通電極を形成する段階において、

前記第2共通電極を互いに一体化して連結し、アクティブ領域の外周まで延在する第2共通配線をさらに形成することを特徴とする請求項17に記載の液晶表示素子の製造方法。

## 【請求項 25】

前記第2共通配線をパネル隅に形成される銀ドットとコンタクトさせて、前記第1基板の駆動回路に電気的に接続させる段階をさらに備えることを特徴とする請求項24に記載の液晶表示素子の製造方法。

50

**【請求項 2 6】**

前記ゲート配線を形成する段階において、

前記第1共通電極にコンタクトする第1共通配線をさらに形成することを特徴とする請求項17に記載の液晶表示素子の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、液晶表示素子（LCD：Liquid Crystal Display Device）及びその製造方法に係り、特に、FFS（Fringe Field Switching）モードで広視野角に加えて狭視野角を実現するためにRGBW-4サブピクセル構造においてホワイトサブピクセルを視野制御目的として用いる液晶表示素子及びその製造方法に関する。 10

**【背景技術】****【0002】**

近来、アクティブマトリクス液晶表示素子は、その性能の急速な発展に伴い、平板TV、携帯用コンピュータ、モニターなどに広範囲に使用されている。

**【0003】**

このアクティブマトリクス液晶表示素子の中でもツイステッドネマチック（TN：Twisted Nematic）方式の液晶表示素子が主として用いられている。ツイステッドネマチック方式とは、両基板にそれぞれ電極を備え、液晶ダイレクタが90度ツイストするように配列した後、電極に電圧を加えて液晶ダイレクタを駆動することをいう。 20

**【0004】**

ツイステッドネマチック方式の液晶表示素子は、優れたコントラストと色再現性を提供するという点から脚光を浴びているが、視野角が狭いという慢性的な問題を抱えている。

**【0005】**

このようなTN方式における視野角問題を解決するために、対向電極と画素電極を透明伝導体で形成しながら対向電極と画素電極間の間隔を狭く形成し、これら対向電極と画素電極との間に形成されるフリンジフィールドによって液晶分子を動作させるFFSモードが提案された。 30

**【0006】**

以下、FFSモード液晶表示素子について具体的に説明する。

**【0007】**

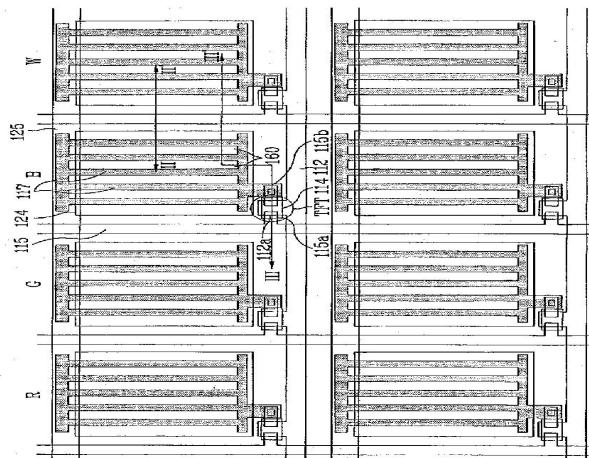

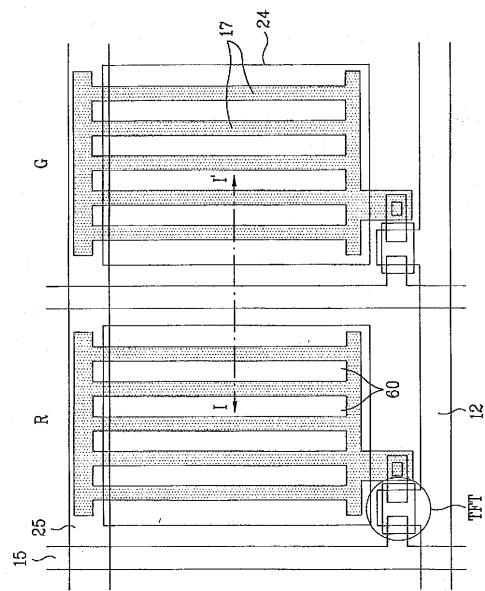

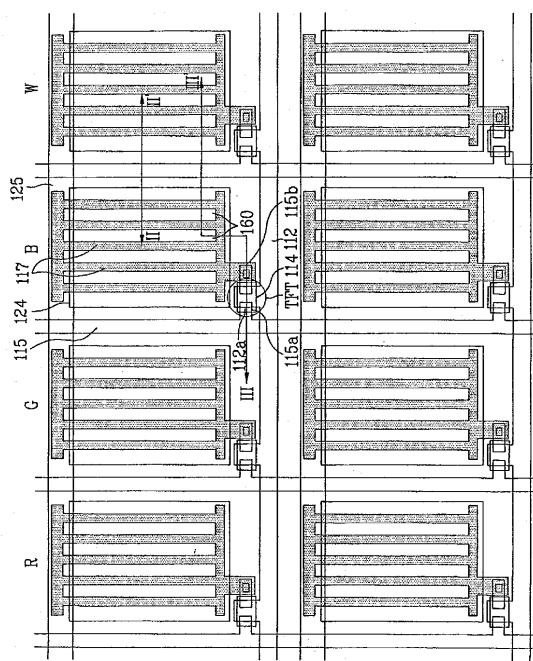

図1は、従来技術によるFFSモード液晶表示素子を示す平面図であり、図2は、図1のI-I'線断面図である。

**【0008】**

まず、FFSモード液晶表示素子のTFTアレイ基板11には、図1及び図2に示すように、不透明な金属から形成され、互いに直交してサブピクセルを定義するゲート配線12及びデータ配線15と、ゲート配線12と平行に配置される共通配線25と、ゲート配線12及びデータ配線15の交差地点で電圧のオン／オフをスイッチングする薄膜トランジスタと、透明な金属から形成され、絶縁膜によって絶縁され、かつ、画素領域内で互いにオーバーラップされる対向電極24及び画素電極17とが形成されている。ここで、対向電極24と共に配線25は互いにコンタクトする。 40

**【0009】**

具体的に、対向電極24は、画素領域内でプレート形に形成され、画素電極17は、データ配線方向に複数個に分岐され、分岐された隣接した画素電極の間にはスリット60が存在する構造となっている。ここで、対向電極24にはVcom信号が伝達され、画素電極17には薄膜トランジスタを通過したピクセル信号が伝達されることで、対向電極24と画素電極17との間にフリンジフィールドが発生する。

**【0010】**

スリット 60 の幅は、略  $2 \sim 6 \mu\text{m}$  範囲の値を有し、画素電極 17 と対向電極 24 との間に形成されるフリンジフィールドによって液晶が駆動される。すなわち、電圧非印加時にラビングによって初期配向されていた液晶が、フリンジフィールドによって回転し光を透過させるようになる。

#### 【0011】

一方、このような TFT アレイ基板 11 には、液晶層 31 を介在してカラーフィルタ層アレイ基板 21 が対向して合着されるが、このカラーフィルタ層アレイ基板 21 には、一定の順序に配列されて色を具現する赤色 (R)、緑色 (G)、青色 (B) のカラーフィルタ層 23 と、R、G、B セルの区画と光遮断の役割を担うブラックマトリクス 22 とが形成される。

10

#### 【0012】

カラーフィルタ層 23 は、各サブピクセルが一つの色素を持つように形成されるが、それぞれ独立して駆動され、これらの組み合わせにより 1 画素の色が表示される。

#### 【0013】

このような液晶表示素子のカラーフィルタ層 23 は、その配列方法によって、ストライプ配列、モザイク配列、デルタ配列、クワッド配列などに区分され、このような R、G、B の配列は、液晶表示パネルの大きさ、カラーフィルタの形状及び色配列によって様々に配列することができる。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

20

#### 【0014】

しかしながら、上述した従来の液晶表示素子には、次の問題点があった。

従来の FFS モード液晶表示素子については、広視野角を図る一方で、近くにいる人への個人情報流出を防ぐために狭視野角への変換も要求されているが、このような視野制御のためには、素子内に視野制御層を追加するか、上板全体に視野制御用電極を新たに追加形成する。しかしながら、かかる技術は、視野制御効果が微少であり、視野制御効果の上昇のために変形または追加された電極構造の範囲を拡大する場合に、開口率の面で極めて不利であり、かつ、狭視野角時に正面コントラスト比 (CR : Contrast Ratio) までも大きく低下するという問題があった。

#### 【0015】

30

なお、上記技術はいずれも、新しい電極層の挿入及び信号印加によって駆動方法が複雑になるという最大の問題があった。

#### 【0016】

本発明は上記の問題点を解決するためのもので、その目的は、RGBW-4 サブピクセルのうちホワイトサブピクセルについて、広視野角のときには RGB の隣接サブピクセルと同様に FFS モードで駆動し、狭視野角のときにのみ隣接サブピクセルと違い垂直電界を形成するようにすることによって、FFS モードで広視野に加えて狭視野角を実現することができる液晶表示素子及びその製造方法を提供することにある。

#### 【課題を解決するための手段】

#### 【0017】

40

上記目的を達成するために、本発明に係る液晶表示素子は、第 1 基板上に互いに直交して、赤色 (R) を表示する R のサブピクセル、緑色 (G) を表示する G のサブピクセル、青色 (B) を表示する B のサブピクセル、白色 (W) を表示する W のサブピクセルを定義するゲート配線及びデータ配線と、前記ゲート配線及びデータ配線の交差地点に配置される薄膜トランジスタと、前記 R、G、B、W サブピクセル内に備えられるプレート形の第 1 共通電極と、前記薄膜トランジスタに接続され、前記第 1 共通電極と絶縁されて複数のスリットを有する画素電極と、前記第 1 基板に対向合着され、前記第 2 基板との空間に液晶層が備えられる第 2 基板と、前記第 2 基板上に W サブピクセルにのみ形成されるプレート形の第 2 共通電極とを備え、前記 W サブピクセル内の前記液晶層は、広視野角モードの場合、前記 R、G、B サブピクセル内の前記液晶層と同一の FFS モードで駆動され、狭

50

視野角モードの場合、前記 R、G、B サブピクセル内の前記液晶層が前記 FFS モードで駆動されるのとは異なり、垂直電界で駆動されることを特徴とする。

#### 【0018】

一方、本発明に係る液晶表示素子の製造方法は、第1基板上に第1共通電極を形成する段階と、前記第1基板上にゲート配線及びデータ配線を交差させて、赤色（R）を表示するRのサブピクセル、緑色（G）を表示するGのサブピクセル、青色（B）を表示するBのサブピクセル、白色（W）を表示するWのサブピクセルを定義し、両配線の交差地点に薄膜トランジスタを形成する段階と、前記薄膜トランジスタを含む全面に保護膜を形成する段階と、前記保護膜上に前記薄膜トランジスタに接続され、複数のスリットを有する画素電極を形成する段階と、前記Wサブピクセルに限定して第2共通電極が形成された第2基板を前記第1基板に対向合着させる段階と、前記第1基板及び前記第2基板間に液晶層を形成する段階とを備え、前記Wサブピクセル内の前記液晶層は、広視野角モードの場合、前記R、G、B サブピクセル内の前記液晶層と同一のFFS モードで駆動され、狭視野角モードの場合、前記R、G、B サブピクセル内の前記液晶層が前記FFS モードで駆動されるのとは異なり、垂直電界で駆動されることを特徴とする。

10

#### 【0019】

ここで、本願発明は、RGBW - 4 サブピクセルのうちホワイトサブピクセル（Wサブピクセル）を用いて広・狭視野角を制御することを特徴としており、Wサブピクセルについてのみ第2基板（カラーフィルタ層アレイ基板）に第2共通電極をさらに形成することによって、広視野角のときには第2基板の第2共通電極に第1基板（薄膜トランジスタアレイ基板）の第1共通電極と同じ電圧が印加されるか、電圧が印加されないフローティング状態となるようにする一方、狭視野角のときには第2基板の第2共通電極と第1基板の第1共通電極間に1 ~ 4 Vまたは-4 ~ -1 V範囲の電位差が発生するように電圧を印加する。

20

#### 【0020】

すなわち、R、G、B、Wの4個のサブピクセルによって一つの画素を構成する液晶表示素子において、R、G、Bサブピクセルは、常にFFSモードで駆動し、Wサブピクセルは、広視野角のときにFFSモードで駆動することで、視野角を広め、狭視野角のときには垂直電界を形成して視野角を減少させる。

30

#### 【発明の効果】

#### 【0021】

本発明による液晶表示素子及びその製造方法によれば、次の効果が得られる。

#### 【0022】

第1に、RG BW - 4 サブピクセルのうちホワイトサブピクセルに対して、広視野角のときには、RGBの隣接サブピクセルと同様にFFSモードで駆動させて視野角を広めるほか、ホワイト輝度も補償する一方、狭視野角のときには、隣接画素と違い垂直電界を形成するECBモードで駆動されるようによることによって視野角を減少させ、個人情報の保護を図る。

#### 【0023】

第2に、既存の視野角制御技術に比べて、Wサブピクセルの上板にのみ共通電極をさらに形成すればいいので、製造コストの削減及び工程の単純化が図られる。そして、上板にさらに形成された共通電極について、広視野角のときにはフローティングさせるか、下板の共通電極と同じ電圧が流れるようにし、また、狭視野角のときには下板の共通電極と一定の電位差を有するように駆動すればいいので、駆動面においても容易である。

40

#### 【発明を実施するための最良の形態】

#### 【0024】

以下、添付の図面を参照しつつ、本発明に係る液晶表示素子及びその製造方法の好適な実施形態について詳細に説明する。

#### 【0025】

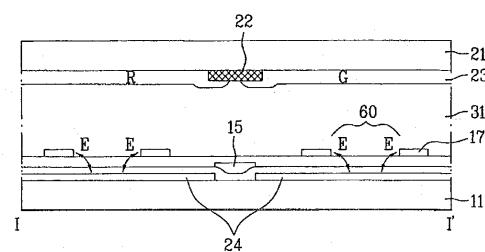

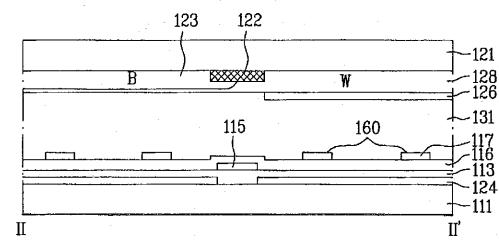

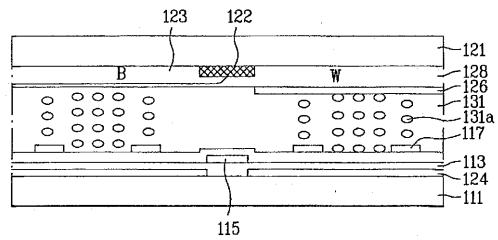

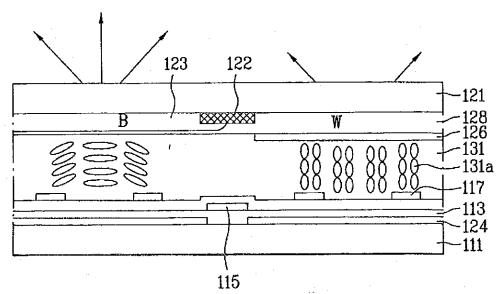

図3は、本発明によるFFSモード液晶表示素子の平面図であり、図4は、図3のII

50

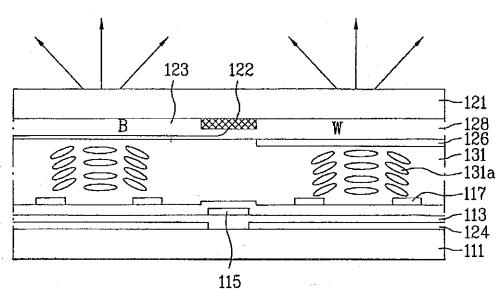

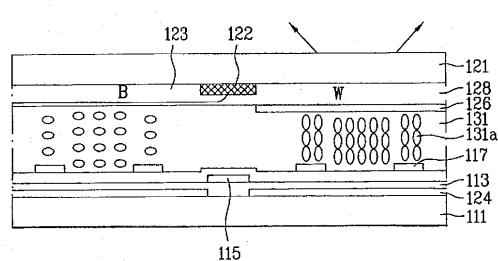

- I I ' 線断面図であり、図 5 は、本発明によるカラーフィルタ層アレイ基板のパターン配置図である。

#### 【 0 0 2 6 】

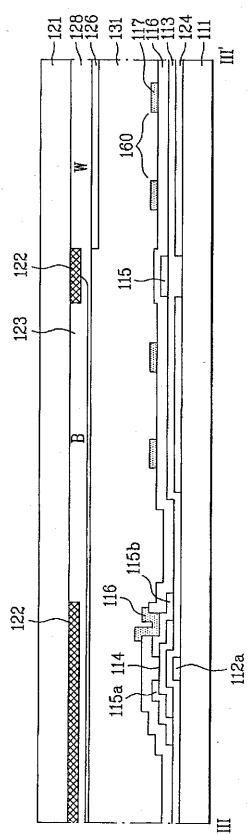

また、図 6 A 及び図 6 B は、本発明による液晶表示素子の広視野角モードを説明するための断面図であり、図 7 A 及び図 7 B は、本発明による液晶表示素子の狭視野角モードを説明するための断面図であり、図 8 A 乃至図 8 D は、図 3 の I I I - I I I ' 線における工程断面図である。

#### 【 0 0 2 7 】

まず、本発明による液晶表示素子は、図 3 及び図 4 に示すように、互いに対向して合着され、それによる空間に液晶層 131 が封入される TFT アレイ基板 111 及びカラーフィルタ層アレイ基板 121 から構成される。ここで、TFT アレイ基板 111 には、R、G、B、W の各サブピクセルに、スイッチング機能を行う薄膜トランジスタ、フリンジフィールドを形成する第 1 共通電極 124 及び画素電極 117 が備えられており、カラーフィルタ層アレイ基板 121 には、W サブピクセルにのみ視野角を制御するための第 2 共通電極 126 が形成されている。10

#### 【 0 0 2 8 】

すなわち、R、G、B サブピクセルは、フリンジフィールドが形成されることから広視野角または狭視野角の制御にかかわらず FFS モードが具現され、W サブピクセルは、広視野角と狭視野角を制御するための視野角制御用サブピクセルとして働く。広視野角モードでは、W サブピクセルを R、G、B サブピクセルのように FFS モードに具現して視野角を向上させ、狭視野角モードでは、W サブピクセルに垂直電界を形成しコントラスト比を落とすことによって視野角を減少させる。20

#### 【 0 0 2 9 】

このとき、R、G、B、W サブピクセルの配置によって、R、G、B、W のサブピクセルが四角形状に配列されて、 $2 \times 2$  構造のサブピクセルが一つの画素を構成するクワッドタイプと、R、G、B、W のサブピクセルが順次に配列されて、4 個のサブピクセルが一つの画素を構成するストライプタイプとに区分される。

具体的には、TFT アレイ基板 111 には、ゲート絶縁膜 113 によって互いに絶縁され、互いに直交するゲート配線 112 及びデータ配線 115 によって R、G、B、W のサブピクセルが定義され、このゲート配線とデータ配線との交差地点には薄膜トランジスタ (TFT) が形成され、各サブピクセル内には Vcom 信号が印加され、該サブピクセル内部に一体として形成されたプレート形の第 1 共通電極 124 及び薄膜トランジスタのドレイン電極 115b にコンタクトしてピクセル信号が印加され、第 1 共通電極 124 と絶縁されて複数個のスリット 160 を持つ画素電極 117 が形成される。これらスリット 160 を介して第 1 共通電極と画素電極との間にフリンジフィールドが形成され液晶層 131 を駆動させるようになる。30

#### 【 0 0 3 0 】

第 1 共通電極 124 及び画素電極 117 は、ITO (Indium Tin Oxide) または IZO (Indium Zinc Oxide) のような透明導電物質を蒸着しパテーニングして形成する。ここで、第 1 共通電極は、ゲート配線層の下部に形成されるか、または、データ配線層の上部に形成される。第 1 共通電極がデータ配線の上部に形成される場合、絶縁膜を介して画素電極と絶縁されるように形成する。40

画素電極のスリット 160 は、その長軸がゲート配線またはデータ配線方向に配置されるように形成可能であり、左右視野角を狭めるためにはデータ配線方向に形成する。R、G、B、W サブピクセルの全体に対して同じ方向に画素電極のスリットが配置されるようになる。

#### 【 0 0 3 1 】

そして、第 1 共通電極 124 は、第 1 共通配線 125 にコンタクトして Vcom 信号を受信し、この第 1 共通配線 125 は、ゲート配線と平行に形成されてアクティブ領域の外周から Vcom 信号を受信する。50

## 【0032】

画素電極117は、保護膜116を貫通して薄膜トランジスタのドレイン電極115bにコンタクトしてピクセル信号を受信する。

## 【0033】

一方、薄膜トランジスタは、電圧のオン／オフを制御するスイッチング機能を担うもので、ゲート配線112から分岐したゲート電極112aと、ゲート配線112を含む全面に形成されたゲート絶縁膜113と、ゲート電極上部のゲート絶縁膜上に非晶質シリコン(a-Si)を蒸着して形成された半導体層114と、データ配線115から分岐して半導体層114上に形成されるソース／ドレイン電極115a, 115bとで構成される。

## 【0034】

このような薄膜トランジスタアレイ基板111は、液晶層131を介在してカラーフィルタ層アレイ基板121に対向して合着される。このカラーフィルタ層アレイ基板121には、R、G、Bセル間の区画と光遮断の役割を担うブラックマトリクス122と、一定の順序に配列されて色を具現する赤色(R)、緑色(G)、青色(B)、ホワイト(W)のカラーフィルタ層123と、Wサブピクセルの視野角を制御するためにWサブピクセルにのみ形成される第2共通電極126とが備えられる。この第2共通電極126は、透明な導電物質からなり、Wサブピクセル内にプレート形に形成する。

10

## 【0035】

ここで、第2共通電極126には、第1基板の第1共通電極とは異なるVcom信号が印加されなければならず、このため、図5に示すように、Wサブピクセルにのみ形成された第2共通電極126を一体化して連結する第2共通配線127がさらに備えられ、この第2共通配線は、アクティブ領域の外周まで延在する。第2共通配線127は、画素の縁部に形成して、画像の表示される領域を遮光しないようにし、ゲート配線と平行に形成することができる。このような第2共通配線にVcom信号を印加するためには、これを第1基板の外部駆動回路に接続しなければならず、これら両者は、パネル隅に配置されて上、下板を電気的に接続する銀ドット191を介して互いに接続する。

20

## 【0036】

一方、カラーフィルタ層を構成するR、G、B、Wの色は、それぞれ独立して駆動され、これらの組み合わせによって1画素の色が表示される。このとき、Wサブピクセルには、カラーフィルタ層を形成することなくW色を具現しても良く、R、G、Bの顔料を混ぜないレジストを使ってR、G、Bのカラーフィルタ層工程と同時に形成しても良い。

30

## 【0037】

Wサブピクセルに対してカラーフィルタ層工程を行わない場合には、R、G、Bサブピクセルの段差とWサブピクセルの段差が異なってくるが、該カラーフィルタ層を含む全面にオーバーコート層128を平坦に形成することによって、基板全面に対する表面段差不均一を解消することができる。このとき、第2共通電極126は、Wサブピクセルのオーバーコート層128上に形成する。

## 【0038】

このように本発明による液晶表示素子は、R、G、Bのサブピクセルを配置する以外に、顔料を含まないホワイトパターンWのサブピクセルをさらに構成し、R、G、B、Wピクセルを配置することで一つの画素を構成する。こうすると、R、G、Bサブピクセルには、顔料が含まれたカラーフィルタ層を形成することから透過率が落ちるのに対し、Wサブピクセルには、顔料が含まれないので全体画素の透過率が向上する。

40

## 【0039】

一方、TFTアレイ基板とカラーフィルタ層アレイ基板の内側面には、液晶分子を望む方向に初期配列させるために配向膜がさらに備えられ、これら両基板の外側面には自然光を偏らせるための偏光板がさらに備えられる。ここで、TFTアレイ基板の外側面に付着される下部偏光板の偏光軸とカラーフィルタ層アレイ基板の外側面に付着される上部偏光板の偏光軸は、互いに直交するように構成され、配向膜は、上、下部偏光板のいずれか一つの偏光板の偏光軸と水平に配向処理する。

50

## 【0040】

画面では、TFTアレイ基板の内側面に備えられる配向膜を上板偏光板の偏光軸と水平な方向に配向処理することによって、液晶分子が画素電極スリットの長さ方向に初期配列されるようとする。

## 【0041】

このように構成される本発明による液晶表示素子は、RGBサブピクセルについては、広視野角か狭視野角かにかかわらず、同一電圧(FFS駆動電圧)を印加して同じ透過特性を有するようにし、視野角制御用Wサブピクセルについては、広視野角か狭視野角かによって相異なる電圧を印加して視野角が制御されることを特徴とする。

## 【0042】

まず、液晶表示素子を広視野角モードで駆動する場合には、R、G、B、WサブピクセルをいずれもFFSモードで駆動するが、図6Aに示すように、第1共通電極124及び画素電極117にいかなる電圧も印加しなかった場合には、液晶分子131aが初期配列状態を維持するので、液晶分子の初期配列方向と垂直な下部偏光板の偏光軸を通って入射した光が液晶層131を通過できず、ブラック状態が具現される。

## 【0043】

そして、図6Bに示すように、第1共通電極124にVcom電圧を印加し、画素電極にピクセル電圧を印加した場合、第1共通電極と画素電極との間にフリンジフィールドが形成されるので、液晶分子131aがフリンジフィールドによって水平方向に動く。したがって、下部偏光板の偏光軸を通過した光が液晶層から上部偏光板の偏光軸を通過し、ホワイト状態が具現される。

## 【0044】

このときに、Wサブピクセルの第2共通電極126は、フリンジフィールド形成過程に関与しないように、電圧が印加されないフローティング状態にするか、または、第1共通電極と同じ電圧を印加して垂直に形成される電界がほとんど形成されないようにする。

## 【0045】

このように広視野角モードでは、WサブピクセルもR、G、Bサブピクセルと同様にFFSモードで動作するので、広視野角の実現ができ、同時にホワイト輝度補償効果も満足させることが可能になる。

## 【0046】

一方、液晶表示素子を狭視野角モードで駆動する場合には、R、G、Bサブピクセルは、FFSモードで駆動するのに対し、Wサブピクセルは、それ以上輝度補償ピクセルとして機能できず、単に視野角制御の機能のみを行うことになる。この場合、広視野角モードと違い、第2共通電極126が電界形成過程に関与する。

## 【0047】

まず、図7Aに示すように、R、G、Bサブピクセルの第1共通電極124及び画素電極117にいかなる電圧も印加せず、Wサブピクセルの第2共通電極126に、第1共通電極との間で垂直電界が形成されるように一定の電圧を印加した場合、R、G、Bサブピクセル中の液晶分子131aは、初期配列状態を維持するので、液晶分子の初期配列方向と垂直な下部偏光板の偏光軸から入射した光が液晶層131を通過できず、ブラック状態を具現し、Wサブピクセル内の液晶分子131aは、第1共通電極124と第2共通電極126との間に形成される垂直電界によって垂直方向にチルトして光を透過させなくなる。しかし、正面からは、ホワイト状態であろうと、または、ブラック状態であろうとも光を観察できないが、Wサブピクセルの左、右視野角方向では光漏れが発生することになる。すなわち、Wサブピクセルにのみ垂直電界を形成することによってブラック状態での狭視野角を具現する。

## 【0048】

これにより、ブラック状態の左、右視野角方向から光が多く漏れるのを観察できるが、4個のサブピクセルが1画素を構成するという点から、観測者がパネルを左、右視野角から観察するとブラック輝度が急激に上昇し、コントラスト比(CR)が落ちるという結果

10

20

30

40

50

が得られ、したがって、素子の視野角が減少することとなる。

#### 【0049】

一方、R、G、Bサブピクセルの第1共通電極124にV<sub>com</sub>信号を印加し、画素電極117にピクセル信号を印加し、Wサブピクセルの第2共通電極に、第1共通電極との間に垂直電界が形成されるように一定電圧を印加した場合、図7Bに示すように、R、G、Bサブピクセルの第1共通電極と画素電極との間にフリンジフィールドが形成され、この電界によって液晶分子131aは、横方向に動き、下部偏光板の偏光軸から入射した光が液晶層131を通過してホワイト状態を具現し、Wサブピクセル中の液晶分子は、第1共通電極124と第2共通電極126との間に形成される垂直電界によって垂直方向にチルトし光を透過させなくなる。この場合にも、Wサブピクセルの正面では光を観察できないが、左、右視野角方向では光漏れが発生するので視野角が減少することになる。すなわち、R、G、Bサブピクセルに対して横電界を形成し、Wサブピクセルに対して垂直電界を形成することによって、ホワイト状態での狭視野角を具現する。10

#### 【0050】

このとき、狭視野角を具現するための、Wサブピクセルの画素電極117のピクセル電圧としては、第1共通電極に印加されるV<sub>com</sub>電圧と等しいか、しきい値電圧未満の電圧が印加され、第1共通電極124は、広視野角モードにおける電圧と同じ電圧が印加され、第2共通電極126は、第1共通電極に対して1～4Vまたは-4～-1Vの電位差が発生するように印加される。このとき、第2共通電極に印加されるV<sub>com</sub>電圧は、直20流あるいは交流のどちらも可能である。

#### 【0051】

このように本発明による液晶表示素子は、広視野角モードを具現しようとする場合には、R、G、B、Wサブピクセル全体に対してFFSモードを適用し、狭視野角モードを具現しようとする場合には、R、G、Bサブピクセルに対してはFFSモードを適用し、Wサブピクセルに対しては、第1基板及び第2基板間に垂直電界を形成し、液晶分子をツイストさせるのではなくチルトさせることによって光が透過しないようにする。20

#### 【0052】

以下、本発明の液晶表示素子の製造方法について、より具体的に説明する。

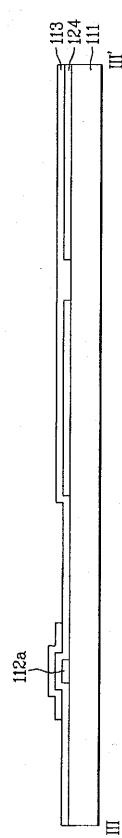

まず、図8Aに示すように、絶縁基板の全面にITO(Indium Tin Oxide)またはIZO(Indium Zinc Oxide)のような透明導電物質を蒸着し、Wサブピクセルに残るようにターニングしてプレート形の第1共通電極124を形成する。30

#### 【0053】

その後、第1共通電極124を含む全面に、低い比抵抗を有する銅(Cu)、アルミニウム(Al)、アルミニウム合金(AlNd)、モリブデン(Mo)、モリブデン-タンゲステン(MoW)などの金属を蒸着したのちパターニングすることで、ゲート配線(図3の112)、ゲート電極112a及び第1共通配線(図3の125)を形成する。

#### 【0054】

このとき、第1共通配線125は、ゲート配線112と平行に形成し、第1共通電極124にコンタクトするように形成する。第1共通配線は、アクティブ領域の外周まで延在し、TFTアレイ基板の外部駆動回路に接続される。40

#### 【0055】

そして、本実施の形態では、ゲート配線層形成の前に第1共通電極を形成したが、これに限定されるものではなく、ゲート配線層形成の以後、または、データ配線層形成の後に形成しても良い。

#### 【0056】

続いて、ゲート電極112aを含む全面に、シリコン酸化物(SiO<sub>x</sub>)またはシリコン窒化物(SiNx)などの無機絶縁物質を、通常、プラズマ強化型化学蒸気蒸着(PECVD: Plasma Enhanced Chemical Vapour Deposition)方法で蒸着してゲート絶縁膜113を形成し、このゲート絶縁膜を含む全面50

に、非晶質シリコンを蒸着しフォトエッチング工程でパターニングすることで、ゲート電極 112a 上部に半導体層 114 を形成する。

#### 【0057】

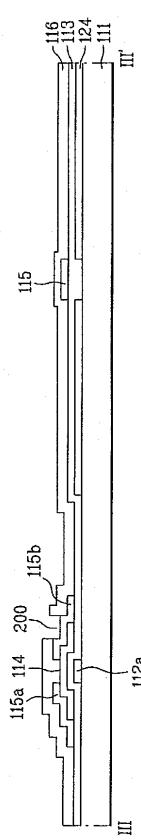

続いて、図 8B に示すように、半導体層 114 を含む全面に、銅 (Cu)、アルミニウム (Al)、アルミニウム合金 (AlNd)、モリブデン (Mo)、モリブデン・タンゲステン (MoW) などの低抵抗金属を蒸着したのちパターニングすることで、データ配線 115 及びソース / ドレイン電極 115a, 115b を形成する。

#### 【0058】

このとき、データ配線 115 は、ゲート配線 112 と交差するように形成して R、G、B、W のサブピクセルを定義し、ソース / ドレイン電極 115a, 115b は、半導体層 114 の両端にオーバーラップするように形成して薄膜トランジスタを完成する。10

#### 【0059】

その後、データ配線 115 を含む全面に、シリコン窒化物質、シリコン酸化物質などの無機材料を蒸着するか、または、BCB (Benzocyclobutene)、アクリル樹脂などの有機材料を塗布して保護膜 116 を形成し、薄膜トランジスタのドレイン電極が露出されるように保護膜を選択的に除去してコンタクトホール 200 を形成する。

#### 【0060】

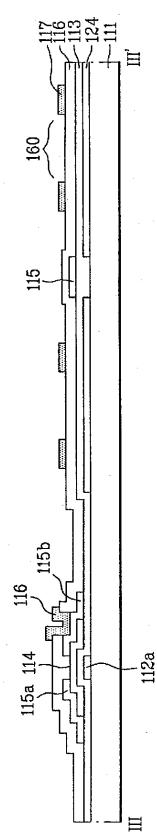

続いて、図 8C に示すように、保護膜 116 を含む全面に ITO または IZO のような透明導電物質を蒸着したのちパターニングすることで、スリット 160 を有する画素電極 117 を形成する。このとき、各サブピクセルに形成された画素電極 117 は、互いに一体化して連結されてコンタクトホール (図 8B の 200) を介してドレイン電極 115b にコンタクトする。20

#### 【0061】

続いて、図 8D に示すように、カラーフィルタ層アレイ基板 121 には、ブラックマトリクス 122、カラーフィルタ層 123、オーバーコート層 128 及び第 2 共通電極 126 が形成される。ここで、カラーフィルタ層アレイ基板上に Cr などの反射率の高い物質を蒸着し、光漏れが発生する領域、例えば、サブ画素周縁と薄膜トランジスタが配置される箇所に残るようパターニングしてブラックマトリクスを形成する。

#### 【0062】

その後、ブラックマトリクス 122 を含む全面に、顔料を含有したカラーレジストを塗布しパターニングしてカラーフィルタ層を形成する。このとき、赤色 (R)、緑色 (G)、青色 (B) を表すカラーレジストを使用するが、通常、赤色カラーレジストを塗布及びパターニングして R サブピクセルに R カラーフィルタ層を形成し、緑色カラーレジストを塗布及びパターニングして G サブピクセルに G カラーフィルタ層を形成した後、最後に青色カラーレジストを塗布及びパターニングして B サブピクセルに B カラーフィルタ層を形成する。30

#### 【0063】

続いて、R、G、B カラーフィルタ層 123 を含む全面に、アクリル樹脂などの有機絶縁物質を平坦に塗布してオーバーコート層 128 を形成する。このオーバーコート層は、顔料を含有しなく、よって、W - サブピクセルではホワイト色を具現する。カラーフィルタ層を形成するついでに、ホワイト色カラーレジストを塗布及びパターニングして W サブピクセルに W カラーフィルタ層を別に形成しても良いが、上記のように W サブピクセルに形成されるオーバーコート層を W カラーフィルタ層にしてもよい。40

#### 【0064】

その後、オーバーコート層 128 を含む全面に、ITO、IZO のような透明導電物質を蒸着しパターニングすることで、W サブピクセルにのみ第 2 共通電極 126 を形成する。第 2 共通電極は、視野角制御のためのもので、W サブピクセルの大きさで形成する。

#### 【0065】

この時、第 2 共通電極を一体化して連結する第 2 共通配線 (図 5 の 127) を同時に形成するが、第 2 共通配線は、アクティブ領域外周まで延在し、後続工程でパネル隅に形成50

される銀ドット（図5の191）を介してTFTアレイ基板の外部駆動回路に電気的に接続される。

【0066】

最後に、薄膜トランジスタアレイ基板の周縁にシール材を形成し、アクティブ領域にスペーサを均一に散布した後、カラーフィルタ層アレイ基板121を対向して合着させ、これら両板間に液晶層131を形成することで、本発明による液晶表示素子を完成する。

【図面の簡単な説明】

【0067】

【図1】従来技術によるFFSモード液晶表示素子を示す平面図である。

【図2】図1のI-I'線断面図である。

10

【図3】本発明によるFFSモード液晶表示素子を示す平面図である。

【図4】図3のII-II'線断面図である。

【図5】本発明によるカラーフィルタ層アレイ基板のパターン配置図である。

【図6A】本発明による液晶表示素子の広視野角モードを説明するための断面図である。

【図6B】本発明による液晶表示素子の広視野角モードを説明するための断面図である。

【図7A】本発明による液晶表示素子の狭視野角モードを説明するための断面図である。

【図7B】本発明による液晶表示素子の狭視野角モードを説明するための断面図である。

【図8A】図3のIII-III'切断線における工程断面図である。

【図8B】図3のIII-III'切断線における工程断面図である。

【図8C】図3のIII-III'切断線における工程断面図である。

20

【図8D】図3のIII-III'切断線における工程断面図である。

【符号の説明】

【0068】

111 TFTアレイ基板、112 ゲート配線、112a ゲート電極、113 ゲート絶縁膜、114 半導体層、115 データ配線、115a ソース電極、115b ドレイン電極、116 保護膜、117 画素電極、121 カラーフィルタ層アレイ基板、122 ブラックマトリクス、123 カラーフィルタ層、124 第1共通電極、125 第1共通配線、126 第2共通電極、127 第2共通配線、128 オーバーコート層、131 液晶層、131a 液晶分子、160 スリット。

【図1】

【図2】

【図4】

【図5】

【図3】

【図6 A】

【図6 B】

【図7 A】

【図 7 B】

【図 8 A】

【図 8 B】

【図 8 C】

【図 8 D】

---

フロントページの続き

(72)発明者 陳 賢碩

大韓民国京畿道安養市東安區飛散洞 1109-4、セトビヨル・アパートメント 608-911

(72)発明者 張 亨錫

大韓民国京畿道城南市盆唐區野塔洞ジャンミミヨルヒョンデ・アパートメント 803-201

審査官 奥田 雄介

(56)参考文献 特開平11-030783(JP,A)

特開平09-325346(JP,A)

特開2005-182067(JP,A)

特開2007-079525(JP,A)

特開2007-178948(JP,A)

特開2002-365657(JP,A)

特開2004-354407(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 1335

G 02 F 1 / 13

G 02 F 1 / 1343

G 02 F 1 / 137

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其制造方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">JP4543006B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2010-09-15 |

| 申请号            | JP2006140733                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 申请日     | 2006-05-19 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | Eruji飞利浦杜迪股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 当前申请(专利权)人(译)  | Eruji显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| [标]发明人         | 陳賢碩<br>張亨錫                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 发明人            | 陳 賢碩<br>張 亨錫                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G02F1/1335 G02F1/13 G02F1/137 G02F1/1343                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| CPC分类号         | G02F1/1362 G02F1/1323 G02F1/133514 G02F1/134363 G02F2001/134381 G02F2201/52 G09G3/3607 G09G3/3648 G09G2300/0452 G09G2320/028                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | G02F1/1335 G02F1/13.505 G02F1/137 G02F1/1343                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| F-TERM分类号      | 2H088/EA02 2H088/EA22 2H088/EA23 2H088/EA64 2H088/HA02 2H088/HA12 2H088/MA01 2H088/MA20 2H091/GA02 2H091/HA05 2H091/LA19 2H091/LA30 2H092/GA14 2H092/GA37 2H092/HA14 2H092/JA26 2H092/JA46 2H092/JB13 2H092/JB52 2H092/KA05 2H092/KA07 2H092/KA12 2H092/KA19 2H092/KB05 2H092/KB14 2H092/KB22 2H092/KB24 2H092/KB26 2H092/MA08 2H092/NA01 2H092/PA08 2H092/QA09 2H191/FA09 2H191/GA04 2H191/HA04 2H191/HA15 2H191/LA25 2H191/LA40 2H191/NA73 2H191/NA77 2H291/FA09 2H291/GA04 2H291/HA04 2H291/HA15 2H291/LA25 2H291/LA40 2H291/NA73 2H291/NA77 |         |            |

| 代理人(译)         | 英年古河<br>Kajinami秩序                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 优先权            | 1020050131564 2005-12-28 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 其他公开文献         | JP2007178979A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

## 摘要(译)

要解决的问题：提供一种液晶显示装置，其采用RGBW-4子像素结构中的白色子像素作为视图控制组件，以在FFS中实现窄视角以及宽视角（边缘场切换）模式，并提供制造显示装置的方法。 $\Sigma$ SOLUTION：显示装置包括：栅极线和数据线彼此交叉以在第一基板上限定R，G，B，W的子像素；薄膜晶体管，设置在栅极线和数据线的每个交叉处；平面第一公共电极，设置在R，G，B，W子像素内；像素电极，具有多个狭缝，连接到薄膜晶体管并与第一公共电极绝缘；第二基板，与第一基板相对并连接，其中液晶层形成在它们之间的空间中；板形第二公共电极126形成在第二基板上并对应于每个W子像素。 $\checkmark$

【 図 3 】