(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4391928号

(P4391928)

(45) 発行日 平成21年12月24日(2009.12.24)

(24) 登録日 平成21年10月16日(2009.10.16)

(51) Int.Cl.

G02F 1/1339 (2006.01)

F 1

G02F 1/1339 500

請求項の数 19 (全 28 頁)

(21) 出願番号 特願2004-360409 (P2004-360409)

(22) 出願日 平成16年12月13日 (2004.12.13)

(65) 公開番号 特開2005-242310 (P2005-242310A)

(43) 公開日 平成17年9月8日 (2005.9.8)

審査請求日 平成16年12月13日 (2004.12.13)

(31) 優先権主張番号 2004-013194

(32) 優先日 平成16年2月26日 (2004.2.26)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 501426046

エルジー ディスプレイ カンパニー リ

ミテッド

大韓民国 ソウル, ヨンドゥンポーク, ヨ

イドードン 20

(74) 代理人 100110423

弁理士 曽我 道治

(74) 代理人 100084010

弁理士 古川 秀利

(74) 代理人 100094695

弁理士 鈴木 憲七

(74) 代理人 100111648

弁理士 梶並 順

最終頁に続く

(54) 【発明の名称】 液晶表示装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

互いに対向する第1基板及び第2基板と、

前記第1基板上に画素領域を定義し、互いに直交する複数個のゲートライン及びデータ

ラインと、

前記ゲートライン及び前記データラインの各交差部に形成された、ゲート電極、ソース

電極、ドレイン電極及び半導体層を含んでなる複数個の薄膜トランジスターと、

相対的に段差の高い、前記薄膜トランジスターの上に相応した部分に形成され、前記第

1基板と前記第2基板とを加圧により貼り合せる段階において収縮する厚みが0.2 μm

乃至0.4 μmとなる高さを有する第1カラムスペーサーと、

相対的に段差の低い、前記ゲートラインの上に相応した部分に、前記第1基板と前記第

2基板とを加圧により貼り合せる段階において前記ゲートラインの上の保護膜の表面と0

.2 μm以内の間隔で離隔する高さを有するように形成された第2カラムスペーサーと、

前記第1基板と前記第2基板との間に形成された液晶層と

を含んでなる液晶表示装置において、

収縮前における前記第1カラムスペーサーの高さは、前記第2カラムスペーサーの高さ

と同一に形成される

ことを特徴とする液晶表示装置。

## 【請求項 2】

前記第1カラムスペーサーは、前記第1基板上の対応する表面を押して前記液晶層のセ

10

20

ルギャップを維持することを特徴とする請求項 1 に記載の液晶表示装置。

【請求項 3】

前記第 2 カラムスペーサーは、前記第 1 基板または前記第 2 基板に外力が加えられる時に、前記第 1 基板のゲートライン上に接触することを特徴とする請求項 1 に記載の液晶表示装置。

【請求項 4】

前記第 2 カラムスペーサーの第 1 高さは、前記第 1 基板または前記第 2 基板に圧力が加えられる時に第 2 高さに減ることを特徴とする請求項 1 に記載の液晶表示装置。

【請求項 5】

前記第 2 基板上にはカラーフィルターアレイが更に形成されることを特徴とする請求項 1 に記載の液晶表示装置。 10

【請求項 6】

前記各画素領域内に交互に形成された複数個の共通電極及び画素電極を更に含んでなることを特徴とする請求項 5 に記載の液晶表示装置。

【請求項 7】

前記カラーフィルターアレイは、

前記各ゲートライン及びデータラインを含む金属配線及び薄膜トランジスターに対応する第 2 基板に形成されたブラックマトリックス層と、

前記ブラックマトリックス層を含む前記第 2 基板上に形成されたカラーフィルター層と、 20

前記カラーフィルター層の上部に形成されたオーバーコート層と

を含んでなることを特徴とする請求項 5 に記載の液晶表示装置。

【請求項 8】

前記第 1 カラムスペーサーは、前記ソース電極に対応して形成されることを特徴とする請求項 1 に記載の液晶表示装置。

【請求項 9】

前記第 1 カラムスペーサーは、前記ドレイン電極に対応して形成されることを特徴とする請求項 1 に記載の液晶表示装置。

【請求項 10】

前記第 1 カラムスペーサーは、前記ゲート電極の上部に対応して形成されることを特徴とする請求項 1 に記載の液晶表示装置。 30

【請求項 11】

前記第 1 カラムスペーサーは、前記薄膜トランジスターと画素電極とのコンタクト領域に対応して形成されることを特徴とする請求項 7 に記載の液晶表示装置。

【請求項 12】

前記第 1 基板の前記液晶層と対向しない背面全面に ITO 膜を更に含むことを特徴とする請求項 1 に記載の液晶表示装置。

【請求項 13】

前記第 1 カラムスペーサー及び前記第 2 カラムスペーサーは、前記ブラックマトリック層上の相応した部分に形成されることを特徴とする請求項 7 に記載の液晶表示装置。 40

【請求項 14】

前記各画素領域内に形成された複数個の画素電極を更に含んで構成されることを特徴とする請求項 5 に記載の液晶表示装置。

【請求項 15】

前記カラーフィルターアレイは、

前記各ゲートライン及びデータラインを含む金属配線及び薄膜トランジスター形成部に対応して形成されたブラックマトリックス層と、

前記ブラックマトリックス層を含む第 2 基板上に形成されたカラーフィルター層と、

前記カラーフィルター層上に形成された共通電極と

を含んで構成されることを特徴とする請求項 14 に記載の液晶表示装置。 50

## 【請求項 16】

前記第1カラムスペーサーは、前記一つの薄膜トランジスターと前記一つの画素電極とのコンタクトする領域に対応して形成されることを特徴とする請求項15に記載の液晶表示装置。

## 【請求項 17】

前記第1カラムスペーサー及び前記第2カラムスペーサーは、前記ブラックマトリックス層形成部位に対応して形成されることを特徴とする請求項15に記載の液晶表示装置。

## 【請求項 18】

前記第1基板及び前記第2基板の互いに対向する表面に形成される複数個の配向膜を更に含むことを特徴とする請求項1に記載の液晶表示装置。

10

## 【請求項 19】

前記第1基板上に画素領域を定義し、互いに垂直に交差する複数個のゲートライン及びデータラインを形成する段階と、

前記ゲートライン及び前記データラインの各交差部に形成された、ゲート電極、ソース電極、ドレイン電極及び半導体層を含んでなる複数個の薄膜トランジスターを形成する段階と、

前記第1基板と互いに対向する第2基板上に、カラーフィルターアレイを形成する段階と、

前記カラーフィルターアレイの上に、前記薄膜トランジスターの上に相応した部分に第1カラムスペーサーを形成するとともに、前記ゲートラインの上に相応した部分に前記第1カラムスペーサーと同一の高さで第2カラムスペーサーを形成する段階と、

20

前記第1基板と前記第2基板との間に液晶層を形成する段階と、

前記第1カラムスペーサーの収縮する厚さが0.2μm乃至0.4μmとなるように、そして前記第2カラムスペーサーが前記ゲートライン上の保護膜の表面と0.2μm以内の間隔で離間されるように、前記第1基板と前記第2基板とを貼り合せる段階と

を含んでなることを特徴とする液晶表示装置の製造方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、液晶表示装置に関し、特にTFT基板の段差の異なる部分にカラムスペーサーを備えて不良を改善した液晶表示装置及びその製造方法に関する。

30

## 【背景技術】

## 【0002】

情報化社会の発達と共に、表示装置に対する要求も多様な形態で求められており、これに応じて最近、LCD (Liquid Crystal Display Device)、PDP (Plasma Display Panel)、ELD (Electro Luminescent Display)、VFD (Vacuum Fluorescent Display)など様々な平板表示装置が研究され、一部は、既に各種装備の表示装置に活用されている。

## 【0003】

その中で、現在、画質が優れており、軽量薄型、低消費電力の特徴及び長所を有することから、移動型画像表示装置の用途でCRT (Cathode Ray Tube)に替わってLCDが最も多用されており、ノートブックコンピューターのモニターのような移動型の用途以外にも、放送信号を受信してディスプレイするテレビ及びコンピューターのモニターなどで多様に開発されている。

40

## 【0004】

このような液晶表示装置が一般の画面表示装置として多様な所で使用されるには、軽量薄型、低消費電力の特長を維持しながらも、大型画面において高精細、高輝度を有する高品質な画像をどれだけ実現できるかにかかっているといつても過言ではない。

## 【0005】

50

以下、添付した図面を参照して、従来の液晶表示装置及び液晶表示装置のセルギャップを維持するスペーサーについて説明する。

【0006】

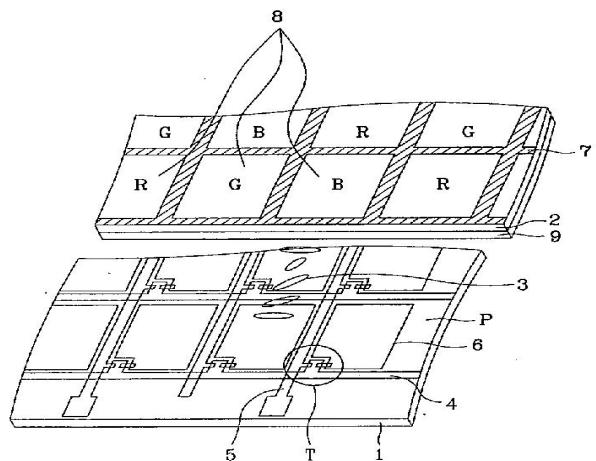

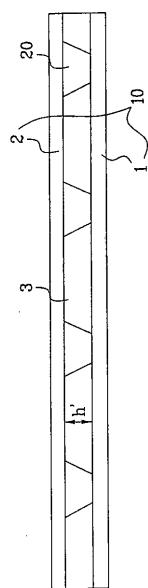

図1は、一般的な液晶表示装置を示す拡大斜視図である。液晶表示装置は、図1に示したように、一定の空間を有して貼り合せられた第1基板1及び第2基板2と、前記第1基板1及び第2基板2の間に注入された液晶層3とで構成されている。

【0007】

より具体的に説明すると、前記第1基板1には、画素領域Pを定義するために、一定の間隔を有して一方向に複数個のゲートライン4と、前記ゲートライン4と垂直方向に一定の間隔を有して複数個のデータライン5とが配列されている。そして、前記各画素領域Pには画素電極6が形成され、前記各ゲートライン4と各データライン5が交差する部分に薄膜トランジスターTが形成され、前記薄膜トランジスターが前記ゲートラインの信号に従って前記データラインのデータ信号を前記各画素電極に印加する。

【0008】

そして、前記第2基板2には前記画素領域Pを除いた部分の光を遮断するためのブラックマトリックス層7が形成され、前記各画素領域に対応する部分には色相を表現するためのR、G、Bカラーフィルター層8が形成され、前記カラーフィルター層8上には画像を表現するための共通電極9が形成されている。

【0009】

上記のような液晶表示装置は、前記画素電極6と共通電極9の間の電界によって、前記第1基板1と第2基板2との間に形成された液晶層3が配向され、前記液晶層3の配向程度によって液晶層3を透過する光の量を調節して画像を表現できる。

【0010】

このような液晶表示装置をTNモード液晶表示装置と言い、前記TNモード液晶表示装置は、視野角が狭いという短所を有しており、このようなTNモードの短所を克服するためにIPS(in-plane switching)モード液晶表示装置が開発された。

【0011】

前記IPSモード液晶表示装置は、第1基板の画素領域に画素電極と共通電極を一定の距離を有して互いに平行に形成し、前記画素電極と共通電極との間で基板と平行に電界が発生するようにし、この電界によって液晶層が配向されるようにしたものである。

【0012】

以下、従来のIPSモードの液晶表示装置の製造方法について説明する。

【0013】

一般的な液晶表示装置の製造方法は、第1基板と第2基板との間に液晶層を形成する方法による液晶注入方式製造方法と、液晶滴下方式製造方法とに区分できる。まず、液晶注入方式の液晶表示装置の製造方法は次の通りである。

【0014】

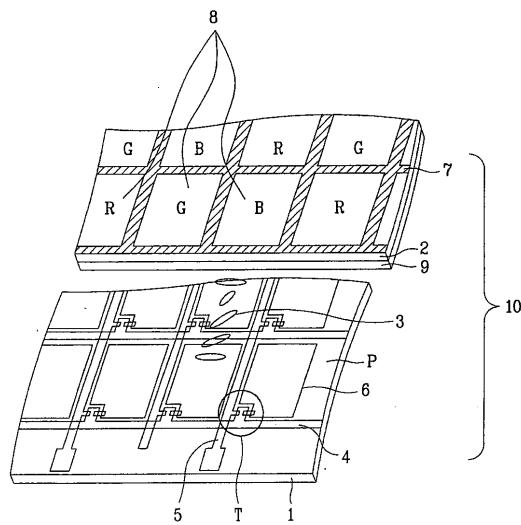

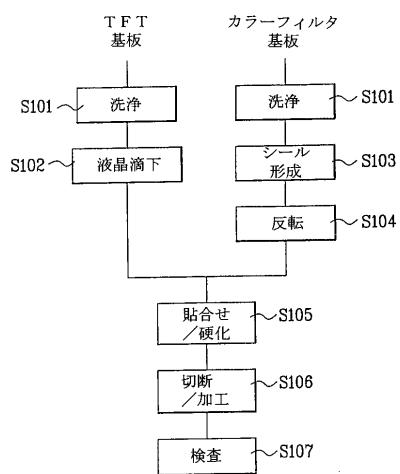

図2は一般的な液晶注入方式の液晶表示装置の製造方法を示したフローチャートである。

液晶表示装置は、大きく、アレイ工程、セル工程、モジュール工程などに区分される。

アレイ工程は、前述したように、前記TFT基板に互いに垂直となる方向に形成されたゲートライン及びデータラインと、前記ゲートラインに平行に形成された共通ラインと、前記ゲートラインとデータラインが交差する部分に形成された薄膜トランジスターと、前記共通ラインから画素領域に延長される共通電極と、前記薄膜トランジスターのドレン電極に連結され、前記共通電極の間に前記共通電極と平行に形成された画素電極などを備えているTFTアレイを形成し、カラーフィルター基板にブラックマトリックス層、カラーフィルター層、及びオーバーコート層などを備えたカラーフィルターアレイを形成する工程である。

【0015】

この時、前記アレイ工程は、一つの基板に一つの液晶パネルを形成するのではなく、一つの大型ガラス基板に複数個の液晶パネルを設計して、各液晶パネル領域にそれぞれTFT

10

20

30

40

50

アレイ、及びカラーフィルターアレイを形成する。このように、TFTアレイが形成されたTFT基板と、カラーフィルターアレイが形成されたカラーフィルター基板とはセル工程ラインに移動する。

【0016】

次に、前記TFT基板とカラーフィルター基板上に配向物質を塗布し、液晶分子が均一な方向性を有するようにするための配向工程(ラビング工程)(S10)をそれぞれ進める。ここで、前記配向工程S10は、配向膜塗布前の洗浄、配向膜印刷、配向膜塑性、配向膜検査、ラビング工程の順に進められる。

【0017】

次に、前記TFT基板及びカラーフィルター基板をそれぞれ洗浄(S20)する。そして、前記TFT基板又はカラーフィルター基板上にセルギャップを一定に維持するためのボールスペーサーを散布(30)し、前記各液晶パネル領域の外郭部に両基板を貼り合わせるためのシールパターンを形成する(S40)。この時、シールパターンは、液晶を注入するための液晶注入口パターンを有するように形成される。

10

【0018】

ここで、ボールスペーサーは、プラスチックボールや弾性体プラスチック微粒子で形成されたものである。前記シールパターンが間に位置するように、前記TFT基板とカラーフィルター基板とを向き合わせて両基板を貼り合わせ、前記シールパターンを硬化させる(S50)。その後、前記貼り合せ及び硬化されたTFT基板、及びカラーフィルター基板を各単位液晶パネル領域別に切断し、加工(S60)して、一定のサイズの単位液晶パネルを製作する。

20

【0019】

その後、それぞれの単位液晶パネルの液晶注入口を介して液晶を注入し、注入完了後に前記液晶注入口をシーリング(S70)して液晶層を形成する。そして、各単位液晶パネルの外観及び電気的な不良検査(S80)を進め、液晶表示装置を製作する。

【0020】

ここで、前記液晶注入工程について簡略に説明する。まず、注入する液晶物質を入れてある容器と、液晶を注入する液晶パネルとをチャンバー内部に位置させ、前記チャンバーの圧力を真空状態に維持することで、液晶物質の中や容器の内側に付いている水分を除去し、気泡を脱泡すると同時に前記液晶パネルの内部空間を真空状態にする。

30

【0021】

そして、所望の真空状態で前記液晶パネルの液晶注入口を、液晶物質を入れてある容器に浸す、あるいは接触させた後に、前記チャンバー内部の圧力を真空状態から大気圧状態にし、前記液晶パネル内部の圧力と、チャンバーの圧力との差によって液晶注入口を介して液晶物質が前記液晶パネルの内部に注入されるようにする。

【0022】

しかしながら、かかる液晶注入方式の液晶表示装置の製造方法においては次のような問題点がある。

【0023】

第一に、単位パネルにカッティングした後、両基板の間を真空状態に維持して液晶注入口を液晶液に浸して液晶を注入するため、液晶注入に多くの時間が必要とされ、生産性が低下する。

40

【0024】

第二に、大面積の液晶表示装置を製造する場合、液晶注入式で液晶を注入すると、パネル内に液晶が完全に注入されず不良の原因となる。

【0025】

第三に、上記のように工程が複雑で、多くの時間を要するので、複数個の液晶注入設備が要求され、たくさんの空間が必要とされる。したがって、このような液晶注入方式の問題点を克服するために、両基板のうち一方の基板に液晶を滴下させた後、両基板を貼り合せる液晶滴下型液晶表示装置の製造方法が開発された。

50

## 【0026】

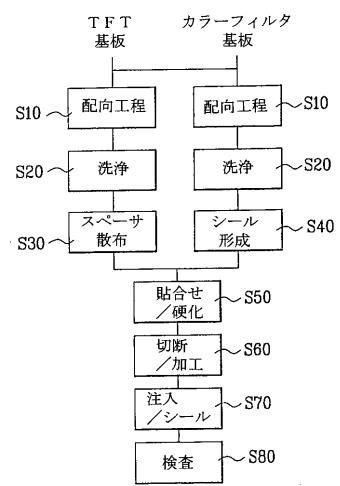

図3は、液晶滴下型液晶表示装置の製造方法を示したフローチャートである。即ち、液晶滴下方式の液晶表示装置の製造方法は、両基板を貼り合わせる前に両基板のうち何れか一方の基板に適定量の液晶を滴下した後、両基板を貼り合わせる方法である。従って、液晶注入方式と同様にセルギャップ維持のためにポールスペーサーを使用する場合は、滴下した液晶が広がる時に前記ポールスペーサーが液晶の拡散方向に移動して、スペーサーが一方に片寄るので、正確なセルギャップの維持が不可能となる。それゆえ、液晶滴下方式では、ポールスペーサーを使用せず、スペーサーが基板に固定される固定スペーサー（カラムスペーサー、又はパターンドスペーサー）を使用しなければならない。

## 【0027】

10

即ち、図3に示したように、アレイ工程において、カラーフィルター基板にブラックマトリックス層、カラーフィルター層、及び共通電極を形成し、前記共通電極上に感光性樹脂を形成し、選択的に除去して前記ブラックマトリックス層上にカラムスペーサーを形成する。勿論、前記カラムスペーサーは、フォト工程、又はインクジェット工程によって形成できる。そして、前記カラムスペーサーを含むTFT基板、及びカラーフィルター基板の全面に配向膜を塗布し、その配向膜をラビング処理する。

## 【0028】

このように、配向工程が完了したTFT基板と、カラーフィルター基板をそれぞれ洗浄（S101）した後、前記TFT基板とカラーフィルター基板のうち一方の基板上の一定の領域に液晶を滴下し（S102）、他方の基板の各液晶パネル領域の外郭部にディスペンシング装置を用いてシールパターンを形成する（S103）。この時、前記両基板のうち一方の基板に液晶を滴下し、且つシールパターンをも形成しても良い。

20

## 【0029】

そして、前記液晶が滴下されていない基板を反転（裏返して向き合うようにする）し（S104）、前記TFT基板とカラーフィルター基板とを押圧して貼り合せ、前記シールパターンを硬化させる（S105）。

## 【0030】

次に、単位液晶パネル別に前記した貼り合せ基板を切断及び加工する（S106）。そして、前記加工された単位液晶パネルの外観及び電気的な不良検査（S107）を進めることで、液晶表示素子を製作する。

30

## 【0031】

かかる液晶滴下方式の製造方法においては、カラーフィルター基板上にカラムスペーサーを形成し、TFT基板に液晶を滴下して両基板を貼り合せてパネルを形成する。この際、前記カラムスペーサーは、カラーフィルター基板に固定されており、TFT基板と接触する。そして、前記TFT基板と接触する部位は、ゲートライン又はデータラインの何れか一方の単一配線に対応して、カラーフィルター基板上で一定の高さを与えて形成される。

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0032】

40

しかしながら、以下ではこのような液晶滴下方式で形成された液晶表示素子のカラムスペーサーと、貼り合せ時に前記カラムスペーサーによってパネルに生じる問題点を考察してみる。

## 【0033】

第一に、従来の液晶滴下方式で形成された液晶表示装置の場合、カラムスペーサーは、ゲートライン又はデータラインに対応してカラーフィルター基板に形成される。この場合、カラムスペーサーは、段差のない単一の配線領域（ゲートライン又はデータライン）に同一の高さに形成する。

## 【0034】

従来の液晶表示装置の場合、同一の高さに該当するTFT基板に対応してカラムスペーサ

50

ーが貼り合せられた時、カラムスペーサーが両基板間を支持する支持力が低いため重力不良を引き起こした。一般的に、液晶表示装置を高温状態に放置し続けると、液晶が高温で膨張する性質によって膨らむ現象が発生する。特に、パネルを立てていた場合には、このような現象は、地面に近いパネルの角側でより深刻化する。このような現象を重力不良という。

【0035】

図4Aは、カラムスペーサーが形成されたカラーフィルター基板を示す構造断面図である。図4Bは、TFT基板とカラーフィルター基板との貼り合せ時の形状を示す構造断面図である。

【0036】

図4Aに示したように、複数個のカラムスペーサー20がそれぞれ所定の間隔で離隔して前記カラーフィルター基板2のブラックマトリックス層(図示せず)領域上に対応して形成される。この場合、前記それぞれのカラムスペーサー20は、 $h$ の高さに形成される。このように、カラムスペーサー20が形成されたカラーフィルター基板2を図4Bに示したようにTFT基板1と貼り合せると、加圧時の圧力で前記カラムスペーサー20は、セルギャップを表す高さ $h'$ で収縮する。

【0037】

図4A及び図4Bに示したように、貼り合せ後に前記パネル10内の前記カラムスペーサー20は、セルギャップ $h'$ の高さに収縮するが、このように、実際カラムスペーサーの形成高さ $h$ と、セルギャップ $h'$ との差に当たる厚さ( $h - h'$ )だけ、カラムスペーサー20は、高温時の液晶の膨張力に比べてTFT基板1とカラーフィルター基板2の支持力を有する。ここで、実際のカラムスペーサーの形成高さ $h$ と、セルギャップ $h'$ との差に該当する厚さ( $h - h'$ )は、重力マージンを意味する。

【0038】

従来の液晶表示装置の場合、このような同一の段差に対応する単一の配線領域にカラムスペーサーが形成され、前記厚さ( $h - h'$ )が約 $0.1\mu\text{m} \sim 0.15\mu\text{m}$ 以内に限定され、重量マージンが非常に低く又、パターニングで形成されるカラムスペーサー間の高さの差のため全体パネルで領域別重力不良の不均一も観察された。

【0039】

第二に、カラムスペーサーは、一方の基板には固定され、他方の基板と接触する面が球状でないため、前記ボールスペーサーに比べて基板に接触する面積が広く、基板との摩擦力が大きい。従って、カラムスペーサーが形成された液晶表示装置の画面を擦る場合、長時間染みが発生する。

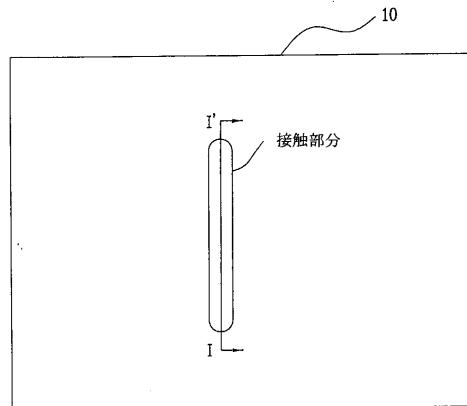

【0040】

図5A及び図5Bは、タッチスポットが生じる部位の状態を示した平面図及び断面図である。図5Aに示したように、液晶パネル10を所定の方向に指でタッチした状態でずらすと、図5Bに示したように、液晶パネル10の上部基板2は、指のずれた方向に所定の間隔でシフトする。この時、円柱状のカラムスペーサー20が上下部の基板1、2に触れ、その接触面積が大きくなるため、カラムスペーサー20と対向基板(下部基板1)との間に発生する摩擦力が大きい。よって、カラムスペーサー20の間の液晶3は、元の状態に戻り難くそのまま残っているため、不透明に見える染みが継続的に観察される。

【0041】

また、所定の方向に指がタッチされた時、図5Bに示したように、最後の接触部位に液晶3が集まり、その部位が膨らむような形状となる。この場合、前記液晶が集まり、膨らんでいる部位は、カラムスペーサー20の高さに定義される他の部位のセルギャップ( $h_2$ )よりセルギャップ( $h_1$ )が高くなり、液晶3の配列が不均一となるので光の漏れが生じる。

【0042】

また、パネル10面上に指がずれながらタッチされた部位では液晶が散らばるため、その部位に液晶が残らず、ブラック状態で薄っすらとした染みが生じるので、このような染み

10

20

30

40

50

は、パネル面の輝度が落ちる要因となる。

【0043】

第三に、液晶注入方式に用いられるボールスペーサーは、多くの量が散布され、又球状になつてあり、パネルの所定の領域を押した時、該当部位のボールスペーサーが横に滑り、押圧に対する耐性があるに対し、カラムスペーサーは、画素領域を除いた部分に選択的に形成されるため、カラムスペーサーが形成されない部分を押した場合、基板の撓みが生じ易く、又押した部位のセルギャップが維持されずに崩れる現象である押圧不良も観察される。

【0044】

本発明は上記の問題点を解決するために案出されたもので、TFT基板の段差の異なる部分にそれぞれカラムスペーサーを具備して不良を改善した液晶表示装置及びその製造方法を提供することにその目的がある。

10

【課題を解決するための手段】

【0045】

上記目的を達成するための本発明に係る液晶表示装置は、互いに対向する第1基板及び第2基板と、前記第1基板上に画素領域を定義し、互いに直交する複数個のゲートライン及びデータラインと、前記ゲートライン及び前記データラインの各交差部に形成された、ゲート電極、ソース電極、ドレイン電極及び半導体層を含んでなる複数個の薄膜トランジスターと、相対的に段差の高い、前記薄膜トランジスターの上に相応した部分に形成され、前記第1基板と前記第2基板とを加圧により貼り合せる段階において収縮する厚みが0.2μm乃至0.4μmとなる高さを有する第1カラムスペーサーと、相対的に段差の低い、前記ゲートラインの上に相応した部分に、前記第1基板と前記第2基板とを加圧により貼り合せる段階において前記ゲートラインの上の保護膜の表面と0.2μm以内の間隔で離隔する高さを有するように形成された第2カラムスペーサーと、前記第1基板と前記第2基板との間に形成された液晶層とを含んでなる液晶表示装置において、収縮前における前記第1カラムスペーサーの高さは、前記第2カラムスペーサーの高さと同一に形成されることを特徴とする。

20

【0047】

前記第1カラムスペーサーは、前記第1基板上の対応する表面を押して前記液晶層のセルギャップを維持する。

30

【0050】

前記第2カラムスペーサーは、前記第1基板または前記第2基板に外力が加えられる時に、前記第1基板のゲートライン上に接触する。

【0052】

前記第2カラムスペーサーの第1高さは、前記第1基板または前記第2基板に圧力が加えられる時に第2高さに減る。

【0053】

前記第2基板上にはカラーフィルターアレイが更に形成される。

【0054】

前記各画素領域内に交互に形成された複数個の共通電極及び画素電極を更に含んでなる。

40

【0055】

前記カラーフィルターアレイは、前記各ゲートライン及びデータラインを含む金属配線及び薄膜トランジスターに対応する第2基板に形成されたブラックマトリックス層と、前記ブラックマトリックス層を含む前記第2基板上に形成されたカラーフィルター層と、前記カラーフィルター層の上部に形成されたオーバーコート層とを含んでなる。

【0056】

前記第1カラムスペーサーは、前記ソース電極に対応して形成される。

【0057】

50

前記第1カラムスペーサーは、前記ドレイン電極に対応して形成される。

【0058】

前記第1カラムスペーサーは、前記ゲート電極の上部に対応して形成される。

【0059】

前記第1カラムスペーサーは、前記薄膜トランジスターと画素電極とのコンタクト領域に対応して形成される。

【0060】

前記第1基板の前記液晶層と対向しない背面全面にITO膜を更に含む。

【0062】

前記第1カラムスペーサー及び前記第2カラムスペーサーは、前記ブラックマトリック層上の相応した部分に形成される。 10

【0063】

前記各画素領域内に形成された複数個の画素電極を更に含んで構成される。

【0064】

前記カラーフィルターアレイは、前記各ゲートライン及びデータラインを含む金属配線及び薄膜トランジスター形成部に対応して形成されたブラックマトリックス層と、前記ブラックマトリックス層を含む第2基板上に形成されたカラーフィルター層と、前記カラーフィルター層上に形成された共通電極とを含んで構成される。

【0068】

前記第1カラムスペーサーは、前記一つの薄膜トランジスターと前記一つの画素電極とのコンタクトする領域に対応して形成される。 20

【0069】

前記第1カラムスペーサー及び前記第2カラムスペーサーは、前記ブラックマトリックス層形成部位に対応して形成される。

【0070】

前記第1基板と前記第2基板の互いに対応する表面に形成される複数個の配向膜を更に含む。

【0083】

上記目的を達成するための本発明に係る液晶表示装置の製造方法は、前記第1基板上に画素領域を定義し、互いに垂直に交差する複数個のゲートライン及びデータラインを形成する段階と、前記ゲートライン及び前記データラインの各交差部に形成された、ゲート電極、ソース電極、ドレイン電極及び半導体層を含んでなる複数個の薄膜トランジスターを形成する段階と、前記第1基板と互いに対応する第2基板上に、カラーフィルターアレイを形成する段階と、前記カラーフィルターアレイの上に、前記薄膜トランジスターの上に相応した部分に第1カラムスペーサーを形成するとともに、前記ゲートラインの上に相応した部分に前記第1カラムスペーサーと同一の高さで第2カラムスペーサーを形成する段階と、前記第1基板と前記第2基板との間に液晶層を形成する段階と、前記第1カラムスペーサーの収縮する厚さが0.2μm乃至0.4μmとなるように、そして前記第2カラムスペーサーが前記ゲートライン上の保護膜の表面と0.2μm以内の間隔で離間されるように、前記第1基板と前記第2基板とを貼り合せる段階とを含んでなることを特徴とする。 30

【発明の効果】

【0088】

本発明の液晶表示装置及びその製造方法には次のような効果がある。

【0089】

第一に、カラムスペーサーを押圧不良が発生しない程度の適切な密度で形成して、パネルのセルギャップが崩れる押圧不良を防止できる。即ち、一つの画素にセルギャップ維持用カラムスペーサーの外に別途のカラムスペーサーを更に形成して、押圧不良による押圧むらを解決する。

【0090】

50

第二に、TFT基板の互いに異なる段差を有する部位に対応して、同一の高さにカラムスペーサーを形成することで、一部のカラムスペーサーは、TFT基板と触れるようにし、一部のカラムスペーサーは、貼り合せ時の圧力でTFT基板に対応して接して押され、前記TFT基板に接して押された高さだけカラムスペーサーが収縮して、その高さだけ重力マージンとして作用できる。

#### 【0091】

第三に、段差の低いTFT基板の部位に対応するカラムスペーサーは、実際には、アレイ形成後、貼り合せ時にのみTFT基板と押されずちょうど接触するか、或いは 0.2 μm範囲以内で離隔されたり押されたりするように形成される。即ち、前記カラムスペーサーと対向基板との間の互いに押される力を減らして、TFT基板とカラムスペーサーとの間の摩擦力を低め、これによってパネルタッチ時に発生するタッチむらを改善できる。10

#### 【0092】

第四に、TFT設計に従いTFT基板の段差によって、段差の相対的に高い部分と相対的に低い部分とが定められ、その部位に対応するようにそれぞれ第1カラムスペーサー及び第2カラムスペーサーを同一の高さに形成するもので、別途のスペーサー形成工程の変更なしにTFT基板の設計構造が有する特性を用いて重力不良が改善される。

#### 【0093】

第五に、セルギャップを維持するためのカラムスペーサーを段差の高い部位に所定の厚さ以上が押されるように形成することにより、カラーフィルター基板上に形成されるカラムスペーサーのパターニング時にカラムスペーサー間の段差によってパネルに領域別に発生する重力不良の不均一を十分に補うことができる。20

#### 【発明を実施するための最良の形態】

#### 【0094】

以下、本発明に係る液晶表示装置及びその製造方法について、添付の図面に基づいて詳細に説明する。

#### 【0095】

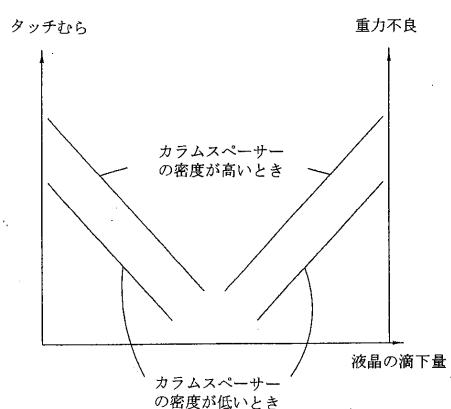

図6は、液晶滴下量及びカラムスペーサーの密度変化に伴うタッチむら及び重力不良を示したグラフである。大面積の液晶表示装置の製造において、工程時間短縮などの利点から液晶滴下方式で製造し、又上下部基板間の支持体でカラムスペーサーを用いるが、図6に示したように、このようなカラムスペーサーの密度は、液晶の滴下量と共に、パネルの不良程度を左右する大きな要因となる。30

#### 【0096】

大面積液晶表示装置で主に発生する不良として、重力不良、タッチむら、押圧不良などがある。まず、重力不良は、パネルを立てた時に、地面に近い方に液晶が片寄り、その部位が液晶の高温上昇に伴い膨張する性質によって、地面に近いパネルの角側が高温状態で膨らむ現象をいう。

#### 【0097】

タッチむらは、液晶パネル面が手やペンで所定の方向に触れた時、前記手やペンが触れた部分が摩擦力によって復元されず、その触れた部分に液晶が散らばる現状をいう。この時、復元されていない部分は、液晶が集まらず、ブラック状態で光漏れ不良が現れる。これは、触れた時に上下部基板間の所定の方向にシフト現象が起こるが、カラムスペーサーに触れる基板間の摩擦力が大きいために元の状態に戻らないためである。40

#### 【0098】

押圧不良は、カラムスペーサーが上下部基板の間で小密度に分布されている場合、前記カラムスペーサーが形成されていない部位を所定の力を加えて押した時、回復されずにセルギャップが崩れる状態をいう。

#### 【0099】

以上で説明したような不良は、互いに独立的な要素によって存在するものではなく、互いに相間関係をもって発生する。特に、重力不良とタッチむらは、液晶滴下量に対して互いにトレードオフの関係にあって、ある不良だけを改善させる方向に液晶滴下量を合わせる50

べきではなく、両方の不良が適切な水準に合わせられるように液晶滴下量を決定すべきである。

【0100】

このように適正量に液晶滴下量が決定された時に、パネル不良を左右するものはカラムスペーサーの密度である。即ち、カラムスペーサーの密度が相対的に低い時には、重力不良やタッチむらが共に改善され得るもの、低密度で分布されているために、カラムスペーサーが形成されていない部位のパネルが押された時に、外圧に対する耐性が弱く、崩れたセルギャップを回復できない押圧不良が発生しやすい。従って、適正水準のカラムスペーサーを上下部基板の間に分布させることが、押圧不良の改善のための重要なポイントである。

10

【0101】

本発明の液晶表示装置及びその製造方法は、段差のある TFT 基板の互いに異なる段差を有する部位別に相応させ、カラーフィルター基板上にカラムスペーサーを形成することにその特徴があるので、セルギャップを維持する他に画素内に別途のカラムスペーサーを更に形成して、外圧によってセルギャップが崩れる押圧不良を防止する。

【0102】

また、前記セルギャップの外に形成された別途のカラムスペーサーは、所定の範囲内で対向基板と触れたり、離隔されたり押されたりするように形成することで、前記別途のカラムスペーサーと対向基板との間の接触力を最小化してタッチむらを改善する。

20

【0103】

また、液晶が高温で膨張する特性から発生する重力不良の場合には、カラムスペーサーの形成時の厚さと、貼り合せ時の厚さとの差の分に当たる厚さに対して、重力マージンがあることに勘案して、一方のカラムスペーサーを貼り合せる時に段差の高い部分に対応して所定の厚さ以上更に押されるように形成して、前記所定の厚さだけの重力マージンを有するように形成する。また、このように一方のカラムスペーサーによって対向基板が所定の厚さ以上更に押された分だけ画素別に十分重力マージンを有することで、パターニングで形成されるカラムスペーサーの高さの差で発生するパネルの領域別重力不良の不均一を改善できる。

【0104】

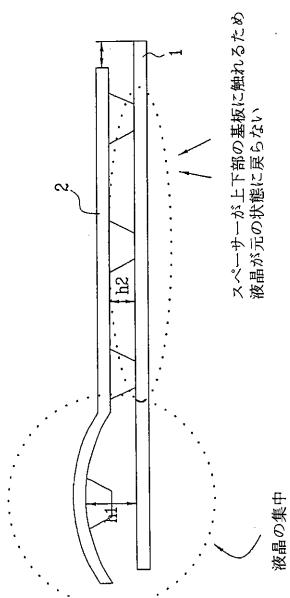

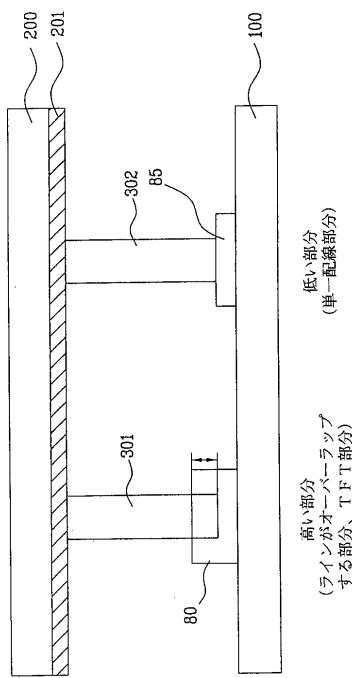

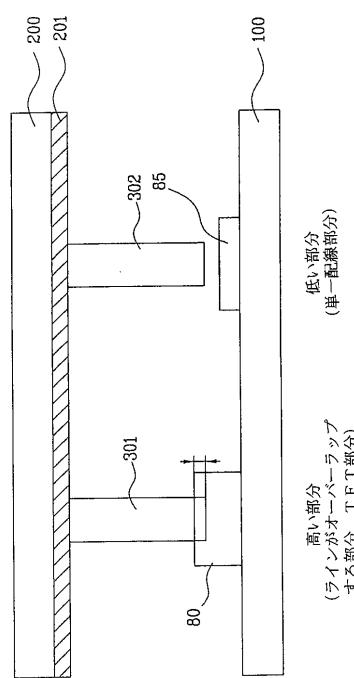

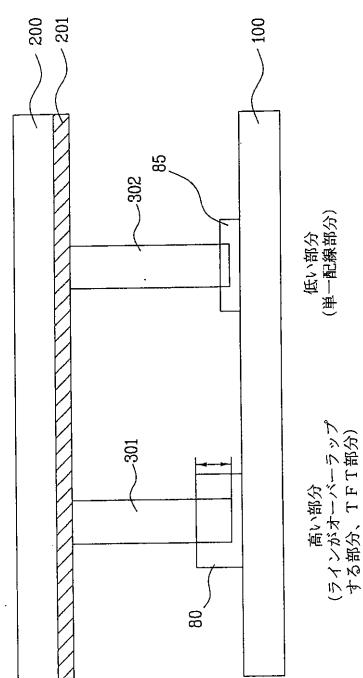

図 7A 乃至図 7C は、本発明の液晶表示装置を概略的に示す構造断面図である。図 7A において、本発明の液晶表示装置は、段差が互いに異なる領域を具備した第 1 基板 100 と、これに対向する第 2 基板 200 と、前記第 1 基板 100 の段差の高い部分 80 に形成される第 1 カラムスペーサー 301 と、前記第 1 基板 100 の段差の低い部分 85 に形成される第 2 カラムスペーサー 302 を含んでなる。

30

【0105】

ここで、前記第 1 カラムスペーサー 301 及び第 2 カラムスペーサー 302 は、ブラックマトリックス層 201 領域の上部に形成され、その高さは同一にする。

【0106】

前記第 1 基板 100 は、TFT アレイが形成される下部基板で、ゲートラインとデータラインとの交差部、或いは薄膜トランジスター (TFT) 形成部が段差の高い部分 80 に該当し、ゲートラインあるいはデータラインの単一配線領域が相対的に段差の低い部分 85 に該当する。

40

【0107】

本発明の液晶表示装置は、それぞれ第 1 カラムスペーサー 301 及び第 2 カラムスペーサー 302 の位置が前記第 1 基板 100 (TFT 基板) の設計によって変更可能である。この時、前記第 1 カラムスペーサー 301 は、ゲートラインとデータラインとの交差部、或いは薄膜トランジスター形成部のように相対的に段差の高い部分 80 に形成することで、単一のゲートラインやデータラインのように、段差の低い部分 85 に対応して形成される第 2 カラムスペーサー 302 に比べて、その下部に一層の金属ライン及び、又は半導体層などが更に含まれるので、第 1 基板 100 を押しながら収縮する厚さの程度が大きい。こ

50

の時、収縮する厚さは、重力マージンに作用する。

【0108】

実験の結果、第1カラムスペーサー301が対応する第1基板100の相対的に段差の高い部分80の段差がおよそ0.2μm～0.6μmの範囲にある時、従来に比べて重力不良を改善できる効果があることが分かる。この時、前記第2カラムスペーサー302は、図7Aに示したように、第1基板100と単に接するように形成されるか、図7Bに示したように、所定の範囲以内で離隔して形成されるか、図7Cに示したように、所定の範囲以内に押されるように形成される。

【0109】

ここで、前記第2カラムスペーサー302が第1基板100を押して離隔した程度は、約±0.2μm以内に限定する。これは、前記第2カラムスペーサー302が0.2μm以上で前記第1基板100を更に押した場合にはタッチむらをもたらし、前記第2カラムスペーサー302が0.2μm以上第1基板100と離隔した場合には、外圧加圧時にセルギヤップが崩れて押圧不良をもたらすためである。

10

【0110】

この場合、前記第1カラムスペーサー301及び前記第2カラムスペーサー302の配置程度は、要求される重力不良補償量によって相対的に段差の差が小さいか大きい部位に変更できる。

【0111】

即ち、パネルが置かれる環境が安定していれば、図7Bに示したように、第1カラムスペーサー301のみ約0.2μm乃至0.4μmの厚さで第1基板100を押すように形成し、第2カラムスペーサー302を離隔させて形成しても充分に重力不良に対する耐性を有する。この場合、第2カラムスペーサー302の離隔程度は、0.2μm以内にして、外圧に対する耐性を充分に持たせる。

20

【0112】

反面、パネルが置かれる環境が高低温の激しい変化など劣悪であれば、図7Cに示したように、第1カラムスペーサー301を0.4μm乃至0.6μmの範囲に重力マージンを有するように形成して、液晶の膨張力に対して十分な重力マージンを有するように形成しなければならない。この場合、第2カラムスペーサー302の第1基板の押圧程度は、0.2μm以内にして、前記第2カラムスペーサー302と第1基板100との間の摩擦力の増加を防止しなければならない。これは、タッチむらが発生しないようにするためにある。

30

【0113】

前記第1カラムスペーサー301及び前記第2カラムスペーサー302は、前記第2基板200に形成され、開口率の低下を防ぐために、第1基板100に対しては、ゲートライインやデータラインの配線領域、或いは薄膜トランジスター形成部に対応させ、第2基板200に対しては、ブラックマトリックス層201に対応させて形成される。

【0114】

前記第1カラムスペーサー301及び前記第2カラムスペーサー302は、前記第2基板200上に同一の高さに形成されたとしても、貼り合せ時に第1カラムスペーサー301が相対的に段差の高い領域80に対応するので、第1カラムスペーサー301は、第1カラムスペーサー301及び第2カラムスペーサー302とが対応する部位間の段差の差の分だけ収縮し、貼り合せ後には相対的に、より低い高さに形成されたものとして見える。

40

【0115】

以上で、それぞれ第2カラムスペーサー302が単に接していたり、所定の間隔で離隔したり、所定の間隔で押されている場合について説明したが、その全てに対して、本発明の液晶表示装置は、重力マージンの改善効果を有する。

【0116】

前記第2カラムスペーサー302の対応程度は、第1基板100に発生する段差の低い部

50

分 8 5 の段差によっても決定されるが、その他にカラムスペーサー形成のためのパターニング時に各カラムスペーサー間の高さの差によっても発生する。

【 0 1 1 7 】

本発明は、このようなパターニング時に高さの差が発生したそれぞれの場合に対応したもので、前記カラムスペーサーのパターニング時に高さの差によって発生するパネル内の重力不良の不均一を補える。

【 0 1 1 8 】

以下では、上述した本発明の具体的な実施形態について説明する。一方、段差を有する TFT 基板は、使用されるマスク数によってその構成及び製造工程が変わるので、以下では 5 マスク、4 マスク工程の順に順次に説明する。

10

【 0 1 1 9 】

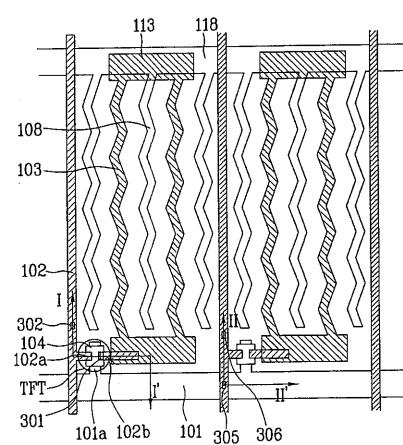

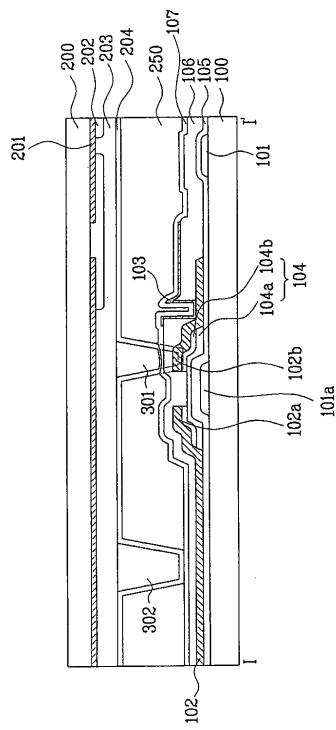

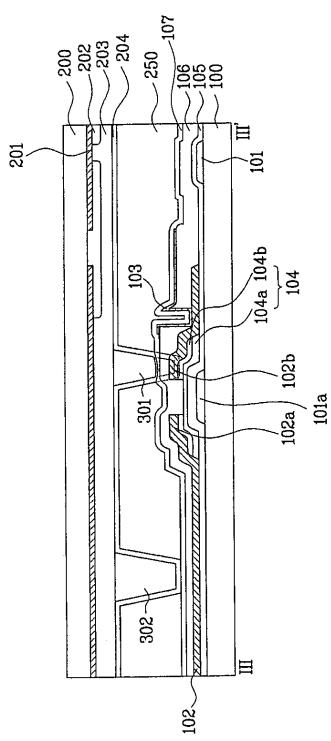

第 1 実施形態 図 8 は、本発明の第 1 実施形態を具体的に IPS モードで具現した液晶表示装置を示す平面図である。図 9 は、本発明の第 1 実施形態に係る液晶表示装置を示す図 8 の I - I' 線上の構造断面図である。図 8 及び図 9 に示したように、本発明の第 1 実施形態に係る液晶表示装置は、一定の空間を有して貼り合せられた第 1 基板 100 及び第 2 基板 200 と、前記第 1 基板 100 と前記第 2 基板 200 との間に注入された液晶層 250 とで構成されている。

【 0 1 2 0 】

前記第 1 基板 100 上には、垂直に交差して画素領域を定義する複数個のゲートライン 101 及びデータライン 102 と、前記ゲートライン 101 とデータライン 102 が交差する各画素領域に交互に形成された画素電極 103 及び共通電極 108 と、前記各ゲートライン 101 とデータライン 102 が交差する部分に形成された薄膜トランジスターとを含んでなる。そして、前記ゲートライン 101 と平行するように画素内に配置された共通ライン 118 と、前記画素電極 103 から延長され、共通ライン 118 の上部にオーバーラップしたキャパシター電極 113 とが更に具備されている。

20

【 0 1 2 1 】

具体的に、前記共通ライン 118 及び共通電極 108 は、一体型で形成され、前記ゲートライン 101 と同時に形成され、Cu、Al、Cr、Mo、Ti などの低抵抗金属で形成される。

【 0 1 2 2 】

30

そして、前記画素電極 103 は、前記共通電極 108 と交互に形成されるが、これらの電極を前記データライン 102 と同時に形成することもでき、或いは互いに異なる層に形成することもできる（図面には互いに異なる層に形成された場合を図示している）。この時、前記共通電極 108 及び前記画素電極 103 を、交互に一直線状に形成する、あるいは図 8 の図示したように、ジグザグ状に形成しても構わない。

【 0 1 2 3 】

前記共通電極 108 と前記画素電極 103との間には、両パターンを分離するために絶縁膜が更に具備されるが、ゲート絶縁膜又は保護膜と同一の成分のシリコン窒化物、又はシリコン酸化物からなる絶縁膜である。

【 0 1 2 4 】

40

前記薄膜トランジスターは、ゲート電極 101a と、所定の幅で前記ゲート電極 101a の上部を覆う半導体層 104 と、前記ゲート電極 101a の両側に対応して形成されたソース / ドレイン電極 102a、102b とからなる。

【 0 1 2 5 】

第 1 基板 100 の製造を、図 9 に示したように 5 マスク工程法によって詳しく説明するところである。まず、前記第 1 基板 100 上に Mo、Al、又は Cr などのような金属物質をスパッタリング方法で全面蒸着した後、第 1 マスク（図示せず）を介してパターニングして、複数個のゲートライン 101 及び前記ゲートライン 101 から突出する形状にゲート電極 101a を形成する。これと同一の工程で、前記ゲートライン 101 と平行に共通ライン 118 を形成し、前記共通ライン 118 からジグザグパターンとして突出する

50

共通電極 108 を形成する。

【0126】

次に、前記ゲートライン 101 を含む第1基板 100 上に SiNx などの絶縁物質を全面蒸着してゲート絶縁膜 105 を形成する。次に、前記ゲート絶縁膜 105 上に前記ゲート電極 101a を覆う形状で半導体層 104 を形成する。

【0127】

ここで、前記半導体層 104 は、前記ゲート絶縁膜 105 上に非晶質シリコン層 104a 、及び燐 (P) が高濃度でドーピングされた n+ 層 104b を連続的に蒸着した後、第2マスク (図示せず) を介して前記 n+ 層 104b 、非晶質シリコン層 104a を同時にパターニングして形成する。

10

【0128】

次に、Mo、Al、又はCr などのような金属物質をスパッタリング方法で全面蒸着し、第3マスク (図示せず) を用いてパターニングして、データライン 102 及び前記ゲート電極 101a の両側にソース電極 102a 、ドレイン電極 102b を形成する。ここで、前記ソース電極 102a は、前記データライン 102 から突出して形成される。

【0129】

このような金属パターニング工程で、前記ソース電極 102a 、ドレイン電極 102b の下部に n+ 層 104b までオーバーエッチングが行われるようにして、前記 n+ 層 104b が前記ゲート電極 101a の上部から除去されるようにする。従って、前記非晶質シリコン層が前記ゲート電極 101a の上部から露出されるが、この露出部位が薄膜トランジスター (TFT) のチャンネル領域に定義される領域である。ここで、前記非晶質シリコン層と、n+ 層とからなる層が半導体層 104 である。

20

【0130】

次に、前記半導体層 104 を含んでソース電極 102a と、ドレイン電極 102b などが形成されたゲート絶縁膜 105 上に化学気相蒸着 (CVD) 方式によって SiNx 材質の保護膜 106 を全面蒸着する。このような保護膜 106 の材料としては、主に SiNx などの無機物質が適用されており、最近、液晶セルの開口率を向上させるために、BCB (Benzocyclo Butene) 、SOG (Spin On Glass) 、又はアクリルなどの誘電率の低い有機物質が使用されている。

30

【0131】

次に、第4マスク (図示せず) を介して前記ドレイン電極 102b 上の保護膜 106 の一部を選択的にエッチングして、ドレイン電極 102b の一部を露出させるコンタクトホールを形成する。

【0132】

次に、前記保護膜 106 上に前記コンタクトホールを十分に埋め込むように透明な電極物質をスパッタリングして蒸着した後、第5マスク (図示せず) を介してパターニングして、前記画素領域内に前記共通電極 108 と前記画素電極 103 を交互にジグザグパターンとして形成する。ここで、前記共通ライン 118 上の前記画素電極 103 には、キャパシター電極 113 が接続される。

40

【0133】

このように第1基板 100 が形成される場合、薄膜トランジスターが形成された部位、及びゲートライン 101 とデータライン 102 とがオーバーラップした部分が、ゲートライン 101 又はデータライン 102 が形成された部分よりも相対的に高い段差を有する。

【0134】

前記第1基板 100 と対向する前記第2基板 200 上には、画素領域を除いた部分 (ゲートライン及びデータライン領域、薄膜トランジスター領域) の光を遮断するためのブラックマトリックス層 201 を形成し、前記画素領域に対応して色相を表現するための R、G 、B カラーフィルター層 202 を形成し、前記ブラックマトリックス層 201 と、カラーフィルター層 202 の上部の全面にオーバーコート層 203 を形成する。

【0135】

50

次に、前記共通電極 203 の上部の所定の部分、つまり第 1 基板 100 上の互いに異なる段差に相応する部位に、同一の高さの複数個のカラムスペーサー 301、302 を形成する。

【0136】

本発明の第 1 実施形態では、第 1 カラムスペーサー 301 を前記第 1 基板 100 の薄膜トランジスターが形成された部分に相応する位置に形成し、第 2 カラムスペーサー 302 を、第 1 基板 100 のデータライン 102 が形成された部分に相応する位置に形成する。この時、前記第 1 カラムスペーサー 301 及び第 2 カラムスペーサー 302 は、同一の高さで形成される。

【0137】

段差の高い第 1 基板 100 に対応して形成された前記第 1 カラムスペーサー 301 は、液晶層 250 のセルギャップを維持する工程後、貼り合せ時の加圧によって第 1 基板 100 に対して約 0.2 μm 乃至 0.6 μm の厚さに押される。このような第 1 カラムスペーサー 301 は、スペーサー固有のセルギャップ維持の機能を担当し、又、前記第 1 基板 100 に押された厚さだけの重力マージンを有する。

【0138】

そして、同一の高さに形成される第 2 カラムスペーサー 302 は、貼り合せ後に相対的に段差の低い部分の第 1 基板 100 に対応するので、第 1 カラムスペーサー 301 に比べて第 1 基板 100 に対する押圧程度が弱い。図 9 では、第 1 基板 100 と単に接するように図示したが、場合によって 0.2 μm 以内の範囲で第 1 基板 100 と離隔する（図 7B に相当）、あるいは第 1 基板 100 に押されるように（図 7C に相当）形成され得る。

【0139】

前記第 2 カラムスペーサー 302 は、セルギャップ維持機能の外に、外部でパネル面を押す外圧に対して耐性を有する用途で形成されたもので、前記第 2 カラムスペーサー 302 が対応する第 1 基板 100 上の部位は、前記第 1 カラムスペーサー 301 に対応する部分と一定の段差以上を確保して、前記第 1 基板 100 が 0.2 μm 以上の厚さにならないように形成する。これは、セルギャップ維持機能の外に、別途に形成された第 2 カラムスペーサー 302 が 0.2 μm 以上の厚さで第 1 基板 100 に押される場合、前記第 2 カラムスペーサー 302 と第 1 基板 100 との間の摩擦力が大きくなり、タッチむらが生じ得るからである。

【0140】

ここで、前記第 1 カラムスペーサー 301 及び前記第 2 カラムスペーサー 302 が対応する第 1 基板 100 の段差の差によって、相対的に第 1 カラムスペーサー 301 が第 2 カラムスペーサー 302 に比べ更に凹むように押圧の厚さが決定される。

【0141】

一方、第 1 基板 100 及び第 2 基板 200 のアレイをそれぞれ形成して、これを貼り合せた後、前記第 1 カラムスペーサー 301 は、スペーサー固有の機能であるセルギャップを維持し、貼り合せ時の加圧によって前記ドレイン電極 102b 部位と、前記データライン 102 の単一の形成部位との段差の差に該当するだけの高さが低まり、その高さだけ第 1 基板 100 及び第 2 基板 200 を支持するようになり、重力マージンを有する。また、前記第 2 カラムスペーサー 302 は、カラムスペーサーの密度を高め、押圧不良によって第 2 基板 200 の構造物が変性しないように押圧に対する耐性を向上させる。

【0142】

前記第 1 カラムスペーサー 301 及び前記第 2 カラムスペーサー 302 は、有機絶縁膜、感光性有機樹脂を形成した後、これを選択的に除去して形成できる。このような第 1 カラムスペーサー 301 及び第 2 カラムスペーサー 302 は、第 1 基板 100 に対応するゲートライン又はデータラインなどの金属物質に比べて硬度の低い有機性物質からなり、第 1 基板 100 及び第 2 基板 200 を貼り合せた後には、段差の高い部分に対応した第 1 カラムスペーサー 301 は、先に第 1 基板 100 と触れ合い、その部位が弾性体のように押されて高さの変化が生じる。

10

20

30

40

50

## 【0143】

ここで、貼り合せ時の加圧力は、前記第2カラムスペーサー302が第1基板100に約±0.2 μm以内に接する程度である。この時、貼り合せ後に相対的に収縮した前記第1カラムスペーサー301の厚さは、重力マージンに作用する。図面によれば、前記第1カラムスペーサー301は、前記単一のデータライン102上に対応して形成された第2カラムスペーサー302に比べて相対的に半導体層(104=104a+104b)とゲート絶縁膜105が更に形成された部位に対応して形成されるので、第1カラムスペーサー301の押圧程度は、半導体層(104=104a+104b)とゲート絶縁膜105の厚さに該当する(図9において、第2カラムスペーサー302は、第1基板100の構造物と押されず接する程度に図示している)。

10

## 【0144】

このように、それぞれTFTアレイが形成された第1基板100と、第1カラムスペーサー301及び第2カラムスペーサー302を含むカラーフィルターアレイが形成された第2基板200との表面には、それぞれ第1配向膜107及び第2配向膜204を形成した後、ラビング処理をする。ここで、ラビング処理とは、布を均一の圧力や速度で第1配向膜107及び第2配向膜204の表面と摩擦させることで、第1配向膜107及び第2配向膜204の表面の高分子チェーンが一定の方向に整列されるようにして液晶の初期配向方向を決定する工程をいう。

## 【0145】

この際、前記第2カラムスペーサー302の上部に形成された第2配向膜204部位は、貼り合せ後に對向する第1配向膜107と触れる部位で、接触時相対的に第2カラムスペーサー302に比べて配向膜の成分が柔らかい特性によって押される。

20

## 【0146】

前記第1カラムスペーサー301及び第2カラムスペーサー302の数は、押圧不良が発生しないように適正な水準に設定する。この時、過度な数のカラムスペーサーがパネル内に分布すると、高温状態時に、地面に近いパネルの角部分が膨らむ重力不良が発生する、あるいは、パネル面を指でタッチした時、カラムスペーサーと対応する第1基板100が触れる面積が大きくなり、摩擦力の上昇によってそのタッチした部分に液晶が再び回復されず、ブラック状態で光漏れを起こすタッチむらが発生する。従って、カラムスペーサーの数を適切に効率よく分布することが重要なポイントである。

30

## 【0147】

前記第2カラムスペーサー302は、第1カラムスペーサー301と共に一つの画素内に形成されることで、パネル内に分布される全体カラムスペーサーの密度を高めることができ、押圧不良を予防することができる。又、貼り合せ後に對向する第1基板100を押さずに単に隣接した程度に触れ合っているか、0.2 μm範囲以内に第1基板100に離隔又は押されるように形成され、第2カラムスペーサー302と、第1基板100との間の摩擦力を減らすことで、タッチむらを緩和することができる。

## 【0148】

又、第1カラムスペーサー301及び第2カラムスペーサー302が単一の画素内に共存することでカラムスペーサーの密度を適正な水準に維持させ、又第1カラムスペーサー301を相対的に段差の高い部分に対応させ貼り合せた後、第1基板100に対して押された厚さだけ高さの変化を起こし、その分だけ第1基板100及び第2基板200間の支持力を高めて重力不良を改善させることができる。

40

## 【0149】

本発明は、このように第1基板100の表面が有する段差を用いて、前記段差を有する部位に対応させ、第1カラムスペーサー301及び第2カラムスペーサー302を形成するものであって、第1カラムスペーサー301は、セルギャップを維持し、且つ重力不良を改善する用途として用いられ、第2カラムスペーサー302は、押圧不良、タッチむらなどの不良を改善する用途として用いられる。

## 【0150】

50

ここで、相対的に段差の高い部分に対応して形成される第1カラムスペーサー301は、セルギャップ維持として機能し、相対的に段差の低い部分に対応して形成される第2カラムスペーサー302と共に構成された液晶表示装置は、第1カラムスペーサー301のみ単独に分布した形態の液晶表示装置に比べて、前記第2カラムスペーサー302が前記第1基板100と触れ合ったり、所定の範囲以内に離隔又は押されたりするように形成され、タッチ時にも両基板の間に摩擦力の発生を緩和させ、元の状態に復元するのに無理がなくなる。

【0151】

前述した第1基板100の段差の最高地点は、TFTアレイ設計によって変更され得るし、ここでは薄膜トランジスターのドレイン電極102b部位に図示して説明した。その他に、ドレイン電極102bと画素電極とのコンタクト領域、又は薄膜トランジスターのソース電極102aなどの部位も設計によって最高地点に用いられ得る。

10

【0152】

そして、前記第2基板200の背面には、パネルで発生する静電気を防止するために全面にITO膜を更に含んでなることができる。

【0153】

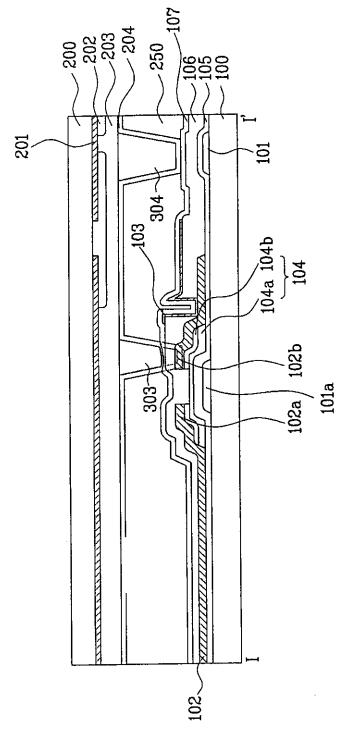

第2実施形態 図10は、本発明の第2実施形態に係る液晶表示装置を示す図8のI-I'線上的構造断面図である。図10に示したように、本発明の第2実施形態に係る液晶表示装置は、第1カラムスペーサー301が前記第1基板100の薄膜トランジスターが形成された部分に相応する位置に形成される。そして、第2カラムスペーサー302は、前記第1基板100に形成されたゲートライン101の相応する部位に形成されるもので、残りの構造は、第1実施形態の構造と一致し、又、このような第1カラムスペーサー303及び第2カラムスペーサー304の機能は、同一である。

20

【0154】

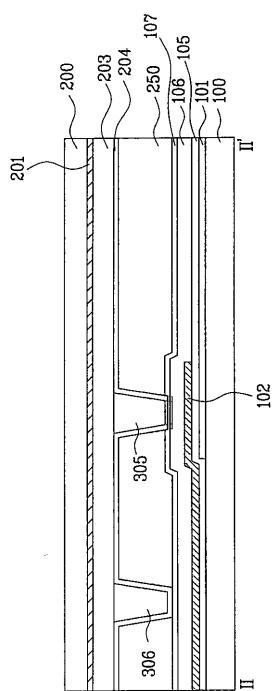

第3実施形態 図11は、本発明の第3実施形態に係る液晶表示装置を示す図8のII-II'線上的構造断面図である。図11に示したように、本発明の第3実施形態に係る液晶表示装置は、第1基板100の段差の高い部位をゲートライン101とデータライン102の交差部として、第1カラムスペーサー305をゲートライン101とデータライン102の交差領域に形成し、前記第2カラムスペーサー306を相対的に段差の低いデータライン102上に形成する。

30

【0155】

第1実施形態及び第2実施形態と同様に、前記第1カラムスペーサー305及び第2カラムスペーサー306は、第1基板100の互いに異なる段差を有する部位にそれぞれ対応して形成され、押圧不良、タッチむら、重力不良を最小化する機能を果たす。

【0156】

図示してはいないが、他の実施形態で前記第1カラムスペーサー305は、第3実施形態と同様にゲートライン101とデータライン102の交差部に対応して形成し、前記第2カラムスペーサー306のみゲートライン101に対応するように若干の構造変更をしても、前記ゲートライン101とデータ102の高さが同一であるという仮定下に前述した第3実施形態と同一の効果が得られる。

40

【0157】

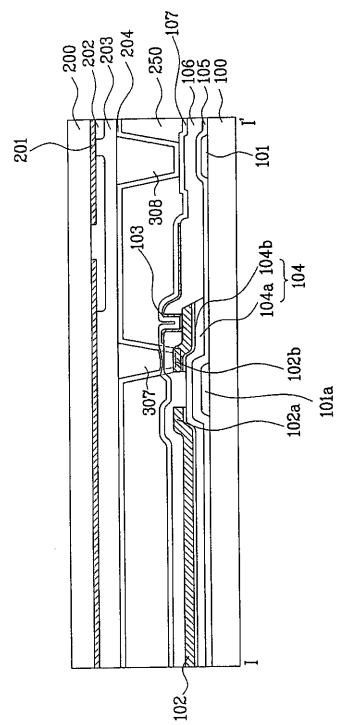

第4実施形態 図12は、本発明の第4実施形態に係る液晶表示装置を示した図8のI-I'線上的構造断面図である。図12に示したように、4マスク製造法で示した第4実施形態に係る本発明の液晶表示装置の製造方法を説明すると次の通りである。

【0158】

図12において、まず、前記第1基板100上にMo、Al、又はCrなどのような金属物質をスパッタリング方法で全面蒸着した後、第1マスク(図示せず)を介してパターニングして、複数個のゲートライン101及び前記ゲートライン101から突出する形状にゲート電極101aを形成する。これと同一の工程で、前記ゲートライン101と平行に共通ライン118を形成し、前記共通ライン118からジグザグパターンとして突出する

50

共通電極 108 を形成する。

【0159】

次に、前記ゲートライン 101 を含む第1基板 100 の全面にゲート絶縁膜 105、非晶質シリコン層 104a、n+層 104b、ソース／ドレイン電極層（102 と同一層）を順に蒸着して形成する。

【0160】

次に、第2マスク（図示せず）を用いて、まず始めに、前記ソース／ドレイン電極層、n+層 104b、非晶質シリコン層 104a を選択的に除去して、データライン 102 と、前記データライン 102 からドレイン電極形成部まで突出したパターンを形成する。この時、前記パターニングしたソース／ドレイン電極層の下部には、n+層 104b、非晶質シリコン層 104a が同一の幅で形成されている。10

【0161】

そして、前記第2マスクを用いて、次に、半導体層のチャンネルの上部に対応する部位のソース／ドレイン金属層及びn+層 104 を同一の幅で除去して、互いに離隔したソース／ドレイン電極 102a、102b 及びチャンネルが定義された半導体層 104a、104b を形成する。

【0162】

前記第2マスクは、回折マスクで、透過部については、前記感光膜が全部除去されており、前記半透過部については、前記感光膜が所定の厚さに除去されている。この時、前記遮断部は、前記感光膜の初期コーティングの厚さをそのまま維持する。ここで、前記遮断部は、ソース／ドレイン電極 105a、105b 部位と、データライン形成部位に対応して定義され、前記半透過部は、前記ソース電極 105a とドレイン電極 105b との間のチャンネル部位に対応して定義される。20

【0163】

次に、前記半導体層 104 を含んでソース電極 102a と、ドレイン電極 102b などが形成されたゲート絶縁膜 105 上に化学気相蒸着（CVD）方式によって SiNx 材質の保護膜 106 を全面蒸着する。このような保護膜 106 の材料としては、主に SiNx などの無機物質が適用されており、最近、液晶セルの開口率を向上させるために、BCB（Benzocyclo Butene）、SOG（Spin On Glass）、又はアクリルなどの誘電率の低い有機物質が使用されている。30

【0164】

次に、第3マスク（図示せず）を介して前記ドレイン電極 102b 上の保護膜 106 の一部を選択的にエッチングして、ドレイン電極 102b の一部を露出させるコンタクトホールを形成する。

【0165】

次に、前記保護膜 106 上に前記コンタクトホールを十分に埋め込むように透明な電極物質をスパッタリングして蒸着した後、第4マスク（図示せず）を介してパターニングして、前記画素領域内に前記共通電極 108 と交互に画素電極 103 を形成する。

【0166】

前記第1基板 100 と対向する前記第2基板 200 上には、画素領域を除いた部分（ゲートライン及びデータライン領域、薄膜トランジスター領域）の光を遮断するためのブラックマト40

リックス層 201 を形成し、前記画素領域に対応して色相を表現するための R、G、B カラーフィルター層 202 を形成し、前記ブラックマトリックス層 201 と、カラーフィルター層 202 の上部の全面にオーバーコート層 203 を形成する。

【0167】

次に、前記オーバーコート層 203 の上部の所定の部分、つまり第1基板 100 上の互いに異なる段差に相応する部位に同一の高さの複数個の第1カラムスペーサー 307 及び第2カラムスペーサー 308 を形成する。従って、前記第1カラムスペーサー 307 は、前記第1基板 100 上の高い段差を有する薄膜トランジスターと画素電極との接触領域に対50

応して、第2基板200上に形成される。そして、前記第2カラムスペーサー308は、前記第1基板100上の低い段差を有するゲートライン配線領域に対応して、第2基板200上に形成される。ここで、前記第1カラムスペーサー307は、スペーサー固有の機能のセルギャップ維持の機能をし、前記第2カラムスペーサー308は、カラムスペーサーの密度を高めて押圧不良に対する補償の機能を果たす。

【0168】

この時、前記第1カラムスペーサー307及び第2カラムスペーサー308は、薄膜トランジスターのドレイン電極102bと、画素電極103とが接触する部位に相応する第1カラムスペーサー307が前記第1基板100及び第2基板200を支持する程度の高さに同一に形成される。このような高さに第1カラムスペーサー307及び第2カラムスペーサー308が形成されると、貼り合せ後に前記第1カラムスペーサー307は、第1基板100を押し、第1カラムスペーサー307及び第2カラムスペーサー308が対応する第1基板100の段差の差に該当する厚さだけ高さが収縮し、前記第2カラムスペーサー308は、前記第1基板100と触れ合う。

10

【0169】

図示した図面で第1カラムスペーサー307及び第2カラムスペーサー308を、特にそれぞれ薄膜トランジスター形成部位とゲートライン領域に対応して形成した理由は、開口率の損傷を与えないブラックマトリックス層201がこれを遮るためである。

【0170】

このように、前記第1カラムスペーサー307及び第2カラムスペーサー308は、前述したカラムスペーサー製造工程で形成される。又、第1カラムスペーサー307及び第2カラムスペーサー308を、第2基板200のブラックマトリックス層201の部位内に形成することで、カラムスペーサーの形成によって開口率が落ちないようにする。

20

【0171】

このようにしてTFTアレイが形成された第1基板100と、カラーフィルターアレイが形成された第2基板200との表面に、それぞれ第1配向膜107及び第2配向膜204を形成した後ラビング処理をする。ここで、ラビング処理とは、布を均一の圧力や速度で第1配向膜107及び第2配向膜204の表面と摩擦させることで、第1配向膜107及び第2配向膜204の表面の高分子チェーンが一定の方向に整列されるようにして液晶の初期配向方向を決定する工程をいう。

30

【0172】

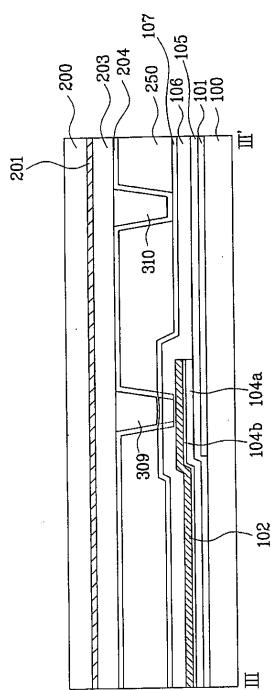

第5実施形態 図13は、本発明の第5実施形態に係る液晶表示装置を示す図8のII-II'線上の構造断面図である。図13に示したように、本発明の第5実施形態に係る液晶表示装置は、第1カラムスペーサー309がゲートライン101とデータライン102の交差領域に、第2カラムスペーサー310がゲートライン308の上部に対応して形成される点を除いては前記第4実施形態と同一の方法で形成され、同一の効果を持つ。

【0173】

この場合、第5実施形態に係る液晶表示装置は、4マスクで製造されるため、データライン102のパターニングと、n+層102b及び非晶質シリコン層104aのパターニングとが同一のマスクを用いて行われ、前記チャンネルに対応する部位を除いてはデータライン102の金属が残った部位は、前記半導体層104a、104bが共に積層される。

40

【0174】

従って、ゲートライン101とデータライン102の交差部は、単一のゲートライン101が形成される部位に比べて非晶質シリコン層104a、n+層、データライン102が更に形成されており、相対的にゲートライン101の部位に比べて前述した非晶質シリコン層104a、n+層、データライン102を積層した厚さだけ更に高い段差を有している。

【0175】

従って、第1カラムスペーサー309を前記ゲートライン101とデータライン102の

50

交差部に対応させ形成し、第2カラムスペーサー310を单一のゲートライン101の部位に形成すると、第1カラムスペーサー309は、第2カラムスペーサー310に比べて非晶質シリコン層104a、n+層、データライン102を積層した厚さ分だけ多く押される。

【0176】

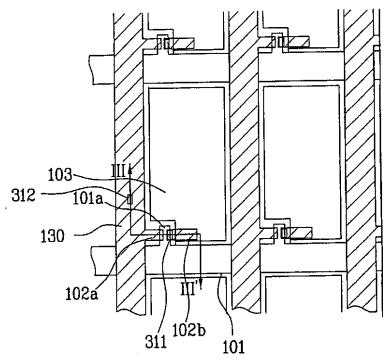

第6実施形態 図14は、本発明の液晶表示装置をTNモードで具現する時にこれを示す平面図である。図15は、本発明の第6実施形態に係る図9のI I I ~ I I I'線上の構造断面図である。図14及び図15において、第6実施形態に係る液晶表示装置は、一定の空間を有して貼り合せられた第1基板100及び第2基板200と、前記第1基板100と第2基板200との間に注入された液晶層250とで構成されている。 10

【0177】

前記第1基板100上には垂直に交差して画素領域を定義する複数個のゲートライン101及びデータライン102と、前記ゲートライン101とデータライン102が交差する各画素領域に形成された画素電極103と、前記各ゲートライン101とデータライン102が交差する部分に形成された薄膜トランジスターとを含んでなる。

【0178】

前記薄膜トランジスターは、ゲート電極101aと、所定の幅で前記ゲート電極101aの上部を覆う半導体層104と、前記ゲート電極101aの両側に対応して形成されたソースノードライン電極102a、102bとからなる。

【0179】

このようなTNモードの液晶表示装置が前述したIPSモードの液晶表示と異なる点は、第1基板100内の画素領域内に画素電極が一つのパターンで形成されることや、前記第2基板100上にオーバーコート層(図9の203参照)の代わりに、共通電極205が全面に形成されることで、その他の構造及び製造方法は、前述した第1実施形態乃至第5実施形態で説明したものと同様である。 20

【0180】

以下、第6実施形態に係る液晶表示装置の製造方法について説明する。

【0181】

まず、前記第1基板100上にMo、Al、又はCrなどの金属物質をスパッタリング方法で全面蒸着した後、第1マスク(図示せず)を介してパターニングして、複数個のゲートライン101及び前記ゲートライン101から突出する形状にゲート電極101aを形成する。 30

【0182】

次に、前記ゲートライン101を含む第1基板100上にSiNxなどの絶縁物質を全面蒸着してゲート絶縁膜105を形成する。次に、前記ゲート絶縁膜105上に前記ゲート電極101aを覆う形状で半導体層104を形成する。ここで、前記半導体層104は、前記ゲート絶縁膜105上に非晶質シリコン層104a、及び磷(P)が高濃度でドーピングされたn+層104bを連続的に蒸着した後、第2マスク(図示せず)を介して前記n+層104b、非晶質シリコン層104aを同時にパターニングして形成する。 40

【0183】

次に、Mo、Al、又はCrなどの金属物質をスパッタリング方法で全面蒸着した後、第3マスク(図示せず)を用いてパターニングして、データライン102及び前記ゲート電極101aの両側にソース電極102a、ドライン電極102bを形成する。ここで、前記ソース電極102aは、前記データライン102から突出して形成される。

【0184】

このような金属パターニング工程で、前記ソース電極102a、ドライン電極102bの下部にn+層104bまでオーバーエッチングが行われるようにして、前記n+層104bが前記ゲート電極101aの上部から除去されるようにする。従って、前記非晶質シリコン層が前記ゲート電極101aの上部から露出されるが、その露出部位が薄膜トランジスター(TFT)のチャンネル領域に定義される領域である。ここで、前記非晶質シリコ 50

ン層と、 $n +$ 層とからなるのが半導体層104である。

【0185】

次に、前記半導体層104を含んでソース電極102aと、ドレイン電極102bなどが形成されたゲート絶縁膜105上に化学気相蒸着(CVD)方式によってSiNx材質の保護膜106を全面蒸着する。このような保護膜106の材料としては、主にSiNxなどの無機物質が適用されており、最近、液晶セルの開口率を向上させるために、BCB(Benzo Cyclo Butene)、SOG(Spin On Glass)、又はアクリルなどの誘電率の低い有機物質が使用されている。

【0186】

次に、第4マスク(図示せず)を介して前記ドレイン電極102b上の保護膜106の一部を選択的にエッチングして、ドレイン電極102bの一部を露出させるコンタクトホールを形成する。

10

【0187】

次に、前記保護膜106上に前記コンタクトホールを十分に埋め込むように透明電極物質をスパッタリングして蒸着した後、第5マスク(図示せず)を介してパターニングして、画素領域に画素電極103を形成する。

【0188】

このように、第1基板100が形成される場合、薄膜トランジスターが形成された部位と、ゲートライン101とデータライン102とがオーバーラップした部分がゲートライン101又はデータライン102が形成された部分より相対的に高い段差を有する。

20

【0189】

前記第1基板100と対向する前記第2基板200上には、画素領域を除いた部分(ゲートライン及びデータライン領域、薄膜トランジスター領域)の光を遮断するためのブラックマトリックス層(図9の201参照)を形成し、前記画素領域に対応して色相を表現するためのR、G、Bカラーフィルター層(図9の202参照)を形成し、前記ブラックマトリックス層201と、カラーフィルター層202の上部の全面に共通電極(図9の203位置に準じる)を形成する。

【0190】

次に、前記共通電極203の上部の所定の部位、つまり第1基板100上の互いに異なる段差に相応する部位に同一の高さの複数個の第1カラムスペーサー311及び第2カラムスペーサー312を形成する。

30

【0191】

本発明の第6実施形態では、第1カラムスペーサー311を前記第1基板100の薄膜トランジスターが形成された部分に相応する位置に形成し、第2カラムスペーサー312を、第1基板100のデータライン102が形成された部分に相応する位置に形成する。

【0192】

以上では、IPSモードの第1実施形態をTNモードに適用した第6実施形態に係る液晶表示装置の製造方法についてのみ記述したが、同一の方式でIPSモードの第2乃至第5実施形態に係る方法もTNモードに適用できる。

【0193】

40

以上、これまで説明した本発明の液晶表示装置及びその製造方法は、それぞれ互いに異なる段差を有する第1基板(TFT基板)の地点に相応して同一の高さのカラムスペーサーを形成する点を特徴としており、ここで、互いに異なる段差は、それぞれ第1基板のアレイ形成工程に用いられる製法によって変更されることもある。

【0194】

上述した実施形態では、前記互いに異なる段差は、前記第2基板(カラーフィルター基板)のブラックマトリックス層上に第1基板の部位で最も高い地点と、最も低い地点とにそれぞれ相応して第1カラムスペーサー及び第2カラムスペーサーを形成した。このような高さの最高、最低地点は、製造工程法によって変更可能なもので、前記第1カラムスペーサーは、第1基板と接触し、第2カラムスペーサーは、第1基板と所定の間隔で離隔して

50

いることを満たせば同一の効果を達成できる。

【図面の簡単な説明】

【0195】

【図1】一般的な液晶表示装置を示す拡大斜視図である。

【図2】液晶注入型液晶表示装置の製造方法のフローチャートである。

【図3】液晶滴下型液晶表示装置の製造方法のフローチャートである。

【図4A】カラムスペーサーが形成されたカラーフィルター基板を示す構造断面図である。

【図4B】TFT基板とカラーフィルター基板との貼り合せ時の形状を示す構造断面図である。

10

【図5A】タッチむらが生じる部位の形状を示す平面図である。

【図5B】タッチむらが生じる部位の形状を示す断面図である。

【図6】液晶滴下量及びカラムスペーサーの密度変化に伴うタッチむら及び重力不良を示すグラフである。

【図7A】本発明の液晶表示装置を概略的に示す構造断面図である。

【図7B】本発明の液晶表示装置を概略的に示す構造断面図である。

【図7C】本発明の液晶表示装置を概略的に示す構造断面図である。

【図8】本発明の第1実施形態を具体的にIPSモードで具現した液晶表示装置を示す平面図である。

【図9】本発明の第1実施形態に係る液晶表示装置を示す図8のI-I'線上の構造断面図である。

20

【図10】本発明の第2実施形態に係る液晶表示装置を示す図8のI-I'線上の構造断面図である。

【図11】本発明の第3実施形態に係る液晶表示装置を示す図8のII-II'線上の構造断面図である。

【図12】本発明の第4実施形態に係る液晶表示装置を示す図8のI-I'線上の構造断面図である。

【図13】本発明の第5実施形態に係る液晶表示装置を示す図8のII-II'線上の構造断面図である。

【図14】本発明の液晶表示装置をTNモードで具現する時にこれを示す平面図である。

30

【図15】本発明の第6実施形態に係る図9のIII-III'線上の構造断面図である。

【符号の説明】

【0196】

100 第1基板、101 ゲートライン、101a ゲート電極、102 データライン、102a ソース電極、102b ドレイン電極、103 画素電極、104a 非晶質シリコン層、104b n+層、105 ゲート絶縁膜、106 保護膜、107 第1配向膜、200 第2基板、201 ブラックマトリックス層、202 カラーフィルター層、203 共通電極、204 第2配向膜、250 液晶層、301~312 カラムスペーサー。

40

【図1】

【図2】

【図3】

【図4A】

【図4B】

【図5A】

【図5B】

【図6】

【図 7 A】

【図 7 B】

【図 7 C】

【図 8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

---

フロントページの続き

(72)発明者 林 京男

大韓民国慶尚北道漆谷郡若木面701、オソン・アパートメント 102-412

審査官 小濱 健太

(56)参考文献 特開2003-156750 (JP, A)

特開2002-341354 (JP, A)

特開平10-160920 (JP, A)

特開2000-298282 (JP, A)

特開2002-169166 (JP, A)

特開2001-100652 (JP, A)

特開2002-182220 (JP, A)

特開2005-189662 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1339

|                |                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其制造方法                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">JP4391928B2</a>                                                                                                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2009-12-24 |

| 申请号            | JP2004360409                                                                                                                                                                                                                                                                                                                                                                                       | 申请日     | 2004-12-13 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | Eruji飞利浦杜迪股份有限公司                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 当前申请(专利权)人(译)  | Eruji显示有限公司                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| [标]发明人         | 林京男                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 发明人            | 林 京男                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| IPC分类号         | G02F1/1339 G02F1/133 G02F1/1335 G02F1/136 H01L29/786                                                                                                                                                                                                                                                                                                                                               |         |            |

| CPC分类号         | G02F1/13394                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| FI分类号          | G02F1/1339.500                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| F-TERM分类号      | 2H089/LA09 2H089/LA10 2H089/LA16 2H089/LA19 2H089/MA03X 2H089/NA14 2H089/NA15 2H089/NA17 2H089/NA22 2H089/PA06 2H089/QA01 2H089/QA02 2H089/QA14 2H189/DA07 2H189/DA14 2H189/DA32 2H189/DA38 2H189/DA39 2H189/DA43 2H189/DA48 2H189/DA49 2H189/EA06X 2H189/FA16 2H189/FA65 2H189/GA10 2H189/GA13 2H189/HA04 2H189/HA06 2H189/HA14 2H189/HA16 2H189/JA05 2H189/JA14 2H189/LA03 2H189/LA10 2H189/LA15 |         |            |

| 代理人(译)         | 英年古河<br>Kajinami秩序                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 优先权            | 1020040013194 2004-02-26 KR                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 其他公开文献         | JP2005242310A                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                          |         |            |

## 摘要(译)

一种液晶显示装置及其制造方法，其中通过在TFT基板的台阶的不同部分中设置柱状衬垫来改善缺陷。根据本发明的液晶显示装置包括：第一基板，具有相对高的电平差的第一区域和具有相对低的电平差的第二区域；以及第一区域，对应于第一区域在第一基板和第二基板之间，第一基板包括第一柱状间隔物，第二区域包括第二柱状间隔物，第二基板与第二区域对应，第二基板与第一基板接合并且在其上形成液晶层。[选定图]图7A。

【图 1】