(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-133410

(P2007-133410A)

(43) 公開日 平成19年5月31日(2007.5.31)

(51) Int.CI.

G02F 1/1343 (2006.01)

G02F 1/1368 (2006.01)

F 1

G02F 1/1343

G02F 1/1368

テーマコード(参考)

2 H 0 9 2

審査請求 未請求 請求項の数 14 O L (全 20 頁)

(21) 出願番号 特願2006-305998 (P2006-305998)

(22) 出願日 平成18年11月10日 (2006.11.10)

(31) 優先権主張番号 10-2005-0108016

(32) 優先日 平成17年11月11日 (2005.11.11)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 303016487

ビオイ ハイディス テクノロジー カン

パニー リミテッド

大韓民国京畿道利川市夫鉢邑牙美里山13

6-1

(74) 代理人 100075557

弁理士 西教 圭一郎

(74) 代理人 100072235

弁理士 杉山 翔至

(74) 代理人 100142332

弁理士 井上 真司

(72) 発明者 金 ▲秉▼ 勲

大韓民國 京畿道 富川市 素砂區 範朴

洞 現代 ホーム タウン アパートメン

ト 406-1503

最終頁に続く

(54) 【発明の名称】半透過型液晶表示装置のアレイ基板製造方法

(57) 【要約】 (修正有)

【課題】半透過型液晶表示装置の透過領域でのコンタクト抵抗を改善させ、反射領域での反射率特性を改善させることができるアレイ基板製造方法を提供する。

【解決手段】ガラス基板上にハーフトーン露光技術を適用した第1マスク工程で、ゲートライン及び共通電極ラインを形成すると共に、透過領域に配置されるITOのプレート型カウンタ電極及び反射領域に配置されるエンボシングパターンを形成するステップと、同じ露光技術の第2マスク工程で、共通電極ライン部の第1ビアホールとアクティブパターンを形成するステップと、同じ露光技術の第3マスク工程で、Mo-A1-Moの3層膜からなるソース/ドレーン電極を含むデータラインを形成すると共に、反射領域にボトム側Mo-A1の2層膜からなる反射電極を形成するステップと、第4マスク工程で第2ビアホールを、第5マスク工程でITOのスリット型画素電極を形成するステップを含む。

【選択図】図4 L

## 【特許請求の範囲】

## 【請求項 1】

画素部が薄膜トランジスタ領域、反射領域及び透過領域に区画されたガラス基板上にITO膜とゲート用金属膜を順次に形成するステップと、

前記ゲート用金属膜とITO膜に対し、ハーフトーン露光技術を適用した第1マスク工程及びエッチング工程を進行してゲート電極を含んだゲートライン及び共通電極ラインを形成すると共に、透過領域に配置されるITOのプレート型カウンタ電極及び反射領域に配置されるエンボーシングパターンを形成するステップと、

前記ゲート電極を含んだゲートライン、共通電極ライン、カウンタ電極及びエンボーシングパターンが形成されたガラス基板の全面上にゲート絶縁膜と非晶質シリコン膜及びドーピングされた非晶質シリコン膜を順次に形成するステップと、

前記ドーピングされた非晶質シリコン膜と非晶質シリコン膜及びゲート絶縁膜に対し、ハーフトーン露光技術を適用した第2マスク工程及びエッチング工程を進行して共通電極ラインを露出させる第1ビアホールを形成すると共に、薄膜トランジスタ領域にアクティブパターンを形成するステップと、

前記第1ビアホール及びアクティブパターンを含んだゲート絶縁膜上にボトム-Mo膜とA1膜及びトップ-Mo膜が順次に形成された3層膜を形成するステップと、

前記3層膜に対し、ハーフトーン露光技術を適用した第3マスク工程及びエッチング工程を進行してボトム-Mo膜とA1膜及びトップ-Mo膜の3層膜からなるソース/ドレーン電極を含んだデータラインを形成して薄膜トランジスタを構成すると共に、反射領域に配置されるボトム-Mo膜とA1膜との2層膜からなる反射電極を形成するステップと、

前記ソース/ドレーン電極及び反射電極が形成された結果物の全面上に保護膜を形成するステップと、

前記保護膜に対し、第4マスク工程及びエッチング工程を進行してソース/ドレーン電極を露出させる第2ビアホールを形成するステップと、

前記第2ビアホールを含んだ保護膜上にITO膜を形成するステップと、

前記ITO膜に対し、第5マスク工程及びエッチング工程を進行してソース/ドレーン電極とコンタクトされると共に、透過領域及び反射領域の全てに配置されるスリット型の画素電極を形成するステップと、

を含むことを特徴とする半透過型液晶表示装置のアレイ基板製造方法。

## 【請求項 2】

前記ゲート電極を含んだゲートライン及び共通電極ラインとエンボーシングパターンを形成するステップは、

前記ゲート用金属膜上にハーフトーン露光工程を適用してカウンタ電極形成領域を遮る部分がゲート電極を含んだゲートライン形成領域と共に電極ライン形成領域及びエンボーシングパターン形成領域を遮る部分より相対的に薄い厚さを有する第1感光膜パターンを形成するステップと、

前記第1感光膜パターンをエッチングマスクとして利用してゲート用金属膜とITO膜をエッチングしてゲート電極を含んだゲートラインと共に電極ライン及びエンボーシングパターンを形成するステップと、

前記第1感光膜パターンに対し、カウンタ電極形成領域を遮る部分が除去されるよう アッシングするステップと、

前記アッシングされた第1感光膜パターンをエッチングマスクとして利用してカウンタ電極上のゲート用金属膜を除去するステップと、

残留した第1感光膜パターンを除去するステップと、

から構成されることを特徴とする請求項1に記載の半透過型液晶表示装置のアレイ基板製造方法。

## 【請求項 3】

前記第1ビアホール及びアクティブパターンを形成するステップは、

10

20

30

40

50

前記ドーピングされた非晶質シリコン膜上にハーフトーン露光工程を適用して透過領域を遮る部分がアクティブパターン形成領域及び反射電極形成領域を遮る部分より相対的に薄い厚さを有する第2感光膜パターンを形成するステップと、

前記第2感光膜パターンをエッチングマスクとして利用してドーピングされた非晶質シリコン膜と非晶質シリコン膜及びゲート絶縁膜をエッチングして共通電極ラインを露出させる第1ピアホールを形成するステップと、

前記第2感光膜パターンに対し、透過領域上に形成された部分が除去されるようにアッシングするステップと、

前記アッシングされた第2感光膜パターンをエッチングマスクとして利用してドーピングされた非晶質シリコン膜と非晶質シリコン膜をエッチングしてアクティブパターンを形成するステップと、

残留した第2感光膜パターンを除去するステップと、

から構成されることを特徴とする請求項1に記載の半透過型液晶表示装置のアレイ基板製造方法。

#### 【請求項4】

前記ソース／ドレーン電極を含んだデータラインと反射電極を形成するステップは、

前記ボトム-Mo膜とAl膜及びトップ-Mo膜が順次に形成された3層膜上にハーフトーン露光工程を適用して反射電極形成領域を遮る部分がソース／ドレーン電極を含んだデータライン形成領域を遮る部分より相対的に薄い厚さを有する第3感光膜パターンを形成するステップと、

前記第3感光膜パターンをエッチングマスクとして利用して3層膜をエッチングしてソース／ドレーン電極を含んだデータラインを形成するステップと、

前記第3感光膜パターンに対し、反射電極形成領域に形成された第3感光膜パターンが除去されるようにアッシングするステップと、

前記アッシングされた第3感光膜パターンをエッチングマスクとして利用して反射領域のトップ-Mo膜をエッチングしてボトム-Mo膜とAl膜との2層膜からなる反射電極を形成するステップと、

残留した第3感光膜パターンを除去するステップと、

から構成されることを特徴とする請求項1に記載の半透過型液晶表示装置のアレイ基板製造方法。

#### 【請求項5】

前記ボトム-Mo膜は、500～700厚さで形成し、前記Al膜は1400～1600厚さで形成し、そして、前記トップ-Mo膜は100～200厚さで形成することを特徴とする請求項1に記載の半透過型液晶表示装置のアレイ基板製造方法。

#### 【請求項6】

前記反射電極は前記エンボーシングパターンによりエンボーシングを有するように形成されることを特徴とする請求項1に記載の半透過型液晶表示装置のアレイ基板製造方法。

#### 【請求項7】

前記透過領域及び反射領域は各々カウンタ電極と画素電極及び反射電極と画素電極との間の水平電界によるFFSモードで駆動されることを特徴とする請求項1に記載の半透過型液晶表示装置のアレイ基板製造方法。

#### 【請求項8】

画素部が薄膜トランジスタ領域、反射領域及び透過領域に区画されたガラス基板上にITO膜とゲート用金属膜を順次に形成するステップと、

前記ゲート用金属膜上にITO膜を形成するステップと、

前記ITO膜に対し、第1マスク工程及びエッチング工程を進行して透過領域にITOのプレイ型カウンタ電極を形成するステップと、

前記カウンタ電極が形成されたガラス基板上にゲート用金属膜を形成するステップと、

前記ゲート用金属膜に対し、第2マスク工程及びエッチング工程を進行してゲート電極を含んだゲートラインと共に電極ライン及び反射領域に配置されるエンボーシングパター

10

20

30

40

50

ンを形成するステップと、

前記ゲート電極を含んだゲートライン、共通電極ライン、カウンタ電極及びエンボーシングパターンが形成されたガラス基板の全面上にゲート絶縁膜と非晶質シリコン膜及びドーピングされた非晶質シリコン膜を順次に形成するステップと、

前記ドーピングされた非晶質シリコン膜と非晶質シリコン膜及びゲート絶縁膜に対し、ハーフトーン露光技術を適用した第3マスク工程及びエッチング工程を進行して共通電極ラインを露出させる第1ビアホールを形成すると共に、薄膜トランジスタ領域にアクティブパターンを形成するステップと、

前記第1ビアホール及びアクティブパターンを含んだゲート絶縁膜上にボトム-Mo膜とA1膜及びトップ-Mo膜が順次に形成された3層膜を形成するステップと、

前記3層膜に対し、ハーフトーン露光技術を適用した第4マスク工程及びエッチング工程を進行してボトム-Mo膜、A1膜及びトップ-Mo膜の3層膜からなるソース/ドレーン電極を含んだデータラインを形成して薄膜トランジスタを構成すると共に、反射領域に配置されるボトム-Mo膜とA1膜の2層膜からなる反射電極を形成するステップと、

前記ソース/ドレーン電極及び反射電極が形成された結果物の全面上に保護膜を形成するステップと、

前記保護膜に対し、第5マスク工程及びエッチング工程を進行してソース/ドレーン電極を露出させる第2ビアホールを形成するステップと、

前記第2ビアホールを含んだ保護膜上にITO膜を形成するステップと、

前記ITO膜に対し、第6マスク工程及びエッチング工程を進行してソース/ドレーン電極とコンタクトされるシリット型の画素電極を形成するステップと、

を含むことを特徴とする半透過型液晶表示装置のアレイ基板製造方法。

#### 【請求項9】

画素部が薄膜トランジスタ領域、反射領域及び透過領域に区画されたガラス基板上にゲート用金属膜を形成するステップと、

前記ゲート用金属膜に対し、第1マスク工程及びエッチング工程を進行してゲート電極を含んだゲートライン及び共通電極ラインを形成すると共に、反射領域に配置されるエンボーシングパターンを形成するステップと、

前記ゲート電極を含んだゲートラインと共に共通電極ライン及びエンボーシングパターンが形成されたガラス基板の全面上にゲート絶縁膜と非晶質シリコン膜及びドーピングされた非晶質シリコン膜を順次に形成するステップと、

前記ドーピングされた非晶質シリコン膜と非晶質シリコン膜及びゲート絶縁膜に対し、ハーフトーン露光技術を適用した第2マスク工程及びエッチング工程を進行して共通電極ラインを露出させる第1ビアホールを形成すると共に、薄膜トランジスタ領域にアクティブパターンを形成するステップと、

前記第1ビアホール及びアクティブパターンを含んだゲート絶縁膜上にボトム-Mo膜とA1膜及びトップ-Mo膜が順次に形成された3層膜を形成するステップと、

前記3層膜に対し、ハーフトーン露光技術を適用した第3マスク工程及びエッチング工程を進行してボトム-Mo膜、A1膜及びトップ-Mo膜の3層膜からなるソース/ドレーン電極を含んだデータラインを形成して薄膜トランジスタを構成すると共に、反射領域に配置されるボトム-Mo膜とA1膜の2層膜からなる反射電極を形成するステップと、

前記ソース/ドレーン電極及び反射電極が形成された結果物の全面上に保護膜を形成するステップと、

前記保護膜に対し、第4マスク工程及びエッチング工程を進行してソース/ドレーン電極を露出させる第2ビアホールを形成するステップと、

前記ITO膜を形成するステップと、

前記ITO膜に対し、第5マスク工程及びエッチング工程を進行してソース/ドレーン電極とコンタクトされると共に、透過領域に配置される画素電極を形成するステップと、

を含むことを特徴とする半透過型液晶表示装置のアレイ基板製造方法。

#### 【請求項10】

10

20

30

40

50

前記第1ピアホール及びアクティブパターンを形成するステップは、

前記ドーピングされた非晶質シリコン膜上にハーフトーン露光工程を適用して透過領域を遮る部分がアクティブパターン形成領域及び反射電極形成領域を遮る部分より相対的に薄い厚さを有する第2感光膜パターンを形成するステップと、

前記第2感光膜パターンをエッチングマスクとして利用してドーピングされた非晶質シリコン膜と非晶質シリコン膜及びゲート絶縁膜をエッチングして共通電極ラインを露出させる第1ピアホールを形成するステップと、

前記第2感光膜パターンに対し、透過領域上に形成された部分が除去されるようにアッシングするステップと、

前記アッシングされた第2感光膜パターンをエッチングマスクとして利用してドーピングされた非晶質シリコン膜と非晶質シリコン膜をエッチングしてアクティブパターンを形成するステップと、

残留した第2感光膜パターンを除去するステップと、

から構成されることを特徴とする請求項9に記載の半透過型液晶表示装置のアレイ基板製造方法。

#### 【請求項11】

前記ソース／ドレーン電極を含んだデータラインと反射電極を形成するステップは、

前記ボトム-Mo膜とA1膜及びトップ-Mo膜が順次に形成された3層膜上にハーフトーン露光工程を適用して反射電極形成領域を遮る部分がソース／ドレーン電極を含んだデータライン形成領域を遮る部分より相対的に薄い厚さを有する第3感光膜パターンを形成するステップと、

前記第3感光膜パターンをエッチングマスクとして利用して3層膜をエッチングしてソース／ドレーン電極を含んだデータラインを形成するステップと、

前記第3感光膜パターンに対し、反射電極形成領域に形成された第3感光膜パターンが除去されるようにアッシングするステップと、

前記アッシングされた第3感光膜パターンをエッチングマスクとして利用して反射領域のトップ-Mo膜をエッチングしてボトム-Mo膜とA1膜との2層膜からなる反射電極を形成するステップと、

残留した第3感光膜パターンを除去するステップと、

から構成されることを特徴とする請求項9に記載の半透過型液晶表示装置のアレイ基板製造方法。

#### 【請求項12】

前記ボトム-Mo膜は500～700厚さで形成し、前記A1膜は1400～1600厚さで形成し、そして、前記トップ-Mo膜は100～200厚さで形成することを特徴とする請求項9に記載の半透過型液晶表示装置のアレイ基板製造方法。

#### 【請求項13】

前記反射電極は前記エンボーシングパターンによりエンボーシングを有するように形成されることを特徴とする請求項9に記載の半透過型液晶表示装置のアレイ基板製造方法。

#### 【請求項14】

前記透過領域及び反射領域はTNモードで駆動されることを特徴とする請求項9に記載の半透過型液晶表示装置のアレイ基板製造方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半透過型液晶表示装置のアレイ基板製造方法に関し、より詳しくは、透過領域でのコンタクト抵抗を低めると共に、反射領域での高反射率特性を有するようにながら工程単純化をなした半透過型液晶表示装置のアレイ基板製造方法に関する。

#### 【背景技術】

#### 【0002】

液晶表示装置は電極が形成されている2枚の基板とその間に介されている液晶層を含み

10

20

30

40

50

、電極に電圧を印加して液晶層の液晶分子を再配列させることにより透過される光量を調節して所定の画像を具現する。

#### 【0003】

このような液晶表示装置はバックライトのような光源を利用して画像を表示する透過型液晶表示装置と、自然光など外部からの入射光を光源として利用する反射型液晶表示装置とに分けられる。前記透過型液晶表示装置はバックライトを光源として利用するので暗い周辺環境でも明るい画像を具現できるが、バックライトの使用により消費電力が高いという短所がある。一方、前記反射型液晶表示装置はバックライトを使用しなくて周辺環境の自然光などを利用するので、消費電力は小さいが、周辺環境が暗い時には使用が不可能であるという短所がある。

10

#### 【0004】

そこで、画素部を透過領域と反射領域とに分けることにより、室内や外部光源が存在しない暗い所では自体の内蔵光源を利用して画像を表示する透過型に作動し、室外の高照度環境では外部の入射光を反射させて画像を表示する反射型に作動する半透過型液晶表示装置が提案された。

#### 【0005】

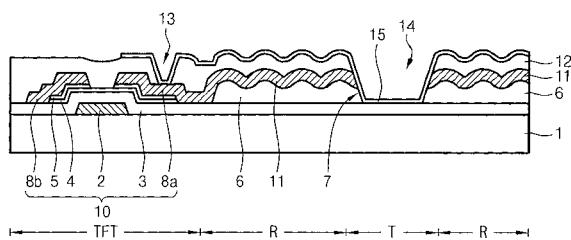

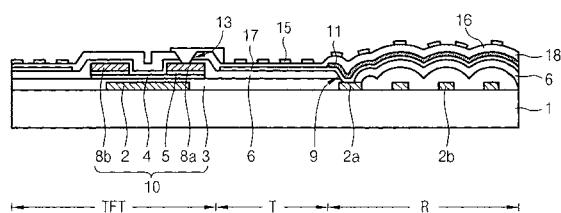

図1は、大韓民国特許公開2004-0070716に提案された従来の半透過型TNモード液晶表示装置のアレイ基板を示す断面図であって、これを参照してその製造方法を説明すれば次の通りである。

20

#### 【0006】

図示のように、画素部が薄膜トランジスタ領域(TFT)、反射領域(R)及び透過領域(T)に区画されたガラス基板1上にゲート用金属膜を蒸着した後、これをパターニングして薄膜トランジスタ領域(TFT)に配置されるゲート電極2を含んで画素部の境界に横方向に配列される複数のゲートライン(図示していない)を形成する。次に、前記ゲート電極2を含んだゲートラインを覆うように基板1の全面上にゲート絶縁膜3を形成する。

#### 【0007】

次に、前記ゲート絶縁膜3上に非ドーピングの非晶質シリコン膜とドーピングされた非晶質シリコン膜を順次に形成した後、これらをパターニングして薄膜トランジスタ領域(TFT)に配置されるアクティブパターンを形成する。次に、薄膜トランジスタ領域(TFT)及び透過領域(T)を除外した反射領域(R)のゲート絶縁膜部分上に、その表面に複数の凹凸を含む有機絶縁膜6を選択的に形成する。この際、前記透過領域(T)には有機絶縁膜6のパターニング過程で前記有機絶縁膜6を貫通する第1開口部7が形成される。

30

#### 【0008】

次に、アクティブパターン及び有機絶縁膜6が形成された基板結果物上にソース/ドレーン用金属膜を蒸着した後、これをパターニングして画素部の境界に実質的にゲートラインと直交する縦方向に配列される複数のデータライン(図示していない)を形成すると共に、薄膜トランジスタ領域(TFT)に配置されるソース/ドレーン電極8a、8bを形成する。次に、ソース電極8aとドレーン電極8bとの間のドーピングされた非晶質シリコン層部分をエッチングしてオーミック層5を形成すると共に、非ドーピングの非晶質シリコン層からなるチャネル層4を形成し、その結果として、薄膜トランジスタ領域(TFT)に薄膜トランジスタ10を構成する。ここで、前記データラインの形成時には反射領域(R)の有機絶縁膜6上に、例えば、薄膜トランジスタ10のソース電極8aと一体型からなる反射電極11と共に形成する。

40

#### 【0009】

次に、薄膜トランジスタ10及び反射電極11を覆うように基板結果物上に保護膜12を形成した後、前記保護膜12をエッチングしてソース電極8aを露出させるビアホール13を形成すると共に、透過領域(T)上に形成された保護膜部分を除去して第2開口部14を形成する。次に、前記保護膜12上にITO膜を蒸着した後、これをパターニングしてビアホール13を通じてソース電極8aとコンタクトされる画素電極15を形成し、その結果として、アレイ基板の製造を完成する。

50

**【 0 0 1 0 】**

前記において、前述の従来の半透過型液晶表示装置は反射電極をソース／ドレーン用金属膜を使用して形成するので、前記ソース／ドレーン用金属膜として反射率が高い金属を採択している。例えば、従来には Al、Al 合金、Ag、Ag 合金の中、いずれか一つの単一層や、Cr、Ti、MoW の中のいずれか一つの下部層と Al、Ag の中のいずれか一つの上部層から構成される二重層でソース／ドレーン電極及び反射電極を形成している。

**【 0 0 1 1 】**

ところが、Al 系列の金属は画素電極物質であるITOとコンタクト抵抗が高いので、点灯されないか、点灯されてもムラ及び輝度低下が発生する等、画面品位の低下を誘発することになる。一方、Ag 系列の金属はITOとのコンタクト抵抗が低くて Al 系列金属を適用する場合での問題は解決できるが、高価なので製品の生産費用を考慮する際、その利用が実質的に困難である。10

**【 0 0 1 2 】**

結局、ソース／ドレーン用金属膜で反射電極を形成する従来の半透過型液晶表示装置は ITO 膜とのコンタクト抵抗問題及び費用問題により実質的に希望する製品の具現に困難がある。

**【 0 0 1 3 】**

一方、従来の半透過型液晶表示装置はそのアレイ基板製作の際、一般的に 8 ~ 11 枚のマスクを必要とする。これは 5 ~ 8 枚のマスクを必要とする透過領域の形成に比べて反射領域の形成がレジン膜へのビア形成、エンボーシング形成及び反射電極形成が更に遂行されなければならないことと関連して、最小 3 枚のマスクを更に必要とするためである。20

**【 0 0 1 4 】**

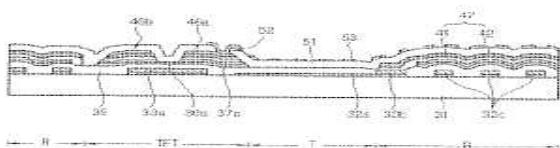

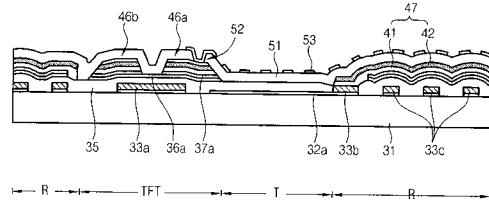

具体的に、図 2 は従来の半透過型 TN (Twisted Nematic) モード液晶表示装置のアレイ基板を示す断面図であって、この構造の場合はゲート電極 2 を含んだゲートライン及び共通電極ラインを形成するための第 1 マスク工程、アクティブパターンを形成するための第 2 マスク工程、ソース／ドレーン電極 8a、8b を含んだデータラインを形成するための第 3 マスク工程、ソース／ドレーン電極 8a、8b を露出させるビア形成のための第 4 マスク工程、ITO の画素電極 15 を形成するための第 5 マスク工程、レジン膜 6 へのビア 13 形成のための第 6 マスク工程、反射領域 (R) へのエンボーシング 16 形成のための第 7 マスク工程、そして、前記反射領域 (R) への反射電極 11 形成のための第 8 マスク工程が順次に遂行されることにより製造される。30

**【 0 0 1 5 】**

ここで、前記反射領域 (R) の形成はレジン膜 6 へのビア 13 形成、エンボーシング 16 形成、そして、反射電極 11 形成により透過領域 (T) の形成に比べて少なくとも 3 枚のマスクを更に必要とする。

**【 0 0 1 6 】**

図 3 は、従来の半透過型 FFS (Fringe Field Switching) モード液晶表示装置のアレイ基板を示す断面図であって、この構造の場合はゲート電極 2 を含んだゲートラインと共通電極ライン 2a 及び反射領域 (R) へのエンボーシングパターン 2b を形成するための第 1 マスク工程、アクティブパターンを形成するための第 2 マスク工程、ソース／ドレーン電極 8a、8b を含んだデータラインを形成するための第 3 マスク工程、共通電極ライン 2a を露出させるビア 9 形成のための第 4 マスク工程、透過領域 (T) へのプレート型力 ウンタ電極 17 を形成するための第 5 マスク工程、反射領域 (R) への反射電極 11 を形成するための第 6 マスク工程、ソース／ドレーン電極 8a、8b を露出させるビア 13 形成のための第 7 マスク工程、そして、透過領域 (T) 及び反射領域 (R) へのスリット型画素電極 15 を形成するための第 8 マスク工程が順次に遂行することにより製造される。40

**【 0 0 1 7 】**

ここで、FFS モードの場合、反射領域 (R) の形成は透過領域 (T) の形成に比べて共通電極ライン 2a を露出させるレジン膜 6 へのビア 9 形成及び反射電極 11 形成のために50

少なくとも 2 枚のマスクが更に必要であり、それで、基板の全体としては 8 枚以上のマスクを必要とする。

【 0 0 1 8 】

したがって、従来の半透過型液晶表示装置はそのアレイ基板製作時に少なくとも 8 枚以上のマスクを必要とし、周知のように、各マスク工程はその自体で感光膜塗布工程、既に塗布された感光膜に対するマスクを利用した露光工程及び露光した感光膜に対する現像工程、そして、ソフトベーク、ハードベークなどの熱工程を含むので、結果として、8 枚以上のマスクを必要とする従来の半透過型液晶表示装置のアレイ基板製造方法は非常に複雑であるだけでなく、費用面でも望ましくない。

【 0 0 1 9 】

図 2 及び図 3 において、未説明符号 1 はガラス基板、3 はゲート絶縁膜、4 はチャネル層、5 はオーミック層、10 は薄膜トランジスタ、11a は Al 金属膜、11b は Mo 金属膜、12 は保護膜、そして、14a は開口部を各々表す。

【 0 0 2 0 】

【特許文献 1】大韓民国特許出願公開第 2004 - 0070716 号明細書

【発明の開示】

【発明が解決しようとする課題】

【 0 0 2 1 】

従って、本発明は前記のような従来の諸問題を解決するために案出したものであって、ソース / ドレーン用金属膜で反射電極と共に形成しながらも透過領域でのコンタクト抵抗を改善させると共に、反射領域での反射率特性を改善させることができる半透過型液晶表示装置のアレイ基板製造方法を提供することをその目的とする。

【 0 0 2 2 】

また、本発明は透過領域でのコンタクト抵抗を改善させると共に、反射領域での反射率特性を改善させることによって安定した動作がなされるようになると共に、優れる画面品位を確保することができる半透過型液晶表示装置のアレイ基板製造方法を提供することを他の目的とする。

【 0 0 2 3 】

その上、本発明はマスク工程数を減らすことによって、工程単純化をなすと共に、製造費用を低減できる半透過型液晶表示装置のアレイ基板製造方法を提供することを又他の目的とする。

【課題を解決するための手段】

【 0 0 2 4 】

前記の目的の達成のために、本発明は、画素部が薄膜トランジスタ領域、反射領域及び透過領域に区画されたガラス基板上に ITO 膜とゲート用金属膜を順次に形成するステップと、前記ゲート用金属膜と ITO 膜に対し、ハーフトーン露光技術を適用した第 1 マスク工程及びエッチング工程を進行してゲート電極を含んだゲートライン及び共通電極ラインを形成すると共に、透過領域に配置される ITO のプレート型カウンタ電極及び反射領域に配置されるエンボッシングパターンを形成するステップと、前記ゲート電極を含んだゲートライン、共通電極ライン、カウンタ電極及びエンボッシングパターンが形成されたガラス基板の全面上にゲート絶縁膜と非晶質シリコン膜及びドーピングされた非晶質シリコン膜を順次に形成するステップと、前記ドーピングされた非晶質シリコン膜と非晶質シリコン膜及びゲート絶縁膜に対し、ハーフトーン露光技術を適用した第 2 マスク工程及びエッチング工程を進行して共通電極ラインを露出させる第 1 ビアホールを形成すると共に、薄膜トランジスタ領域にアクティブパターンを形成するステップと、前記第 1 ビアホール及びアクティブパターンを含んだゲート絶縁膜上にボトム - Mo 膜と Al 膜及びトップ - Mo 膜が順次に形成された 3 層膜を形成するステップと、前記 3 層膜に対し、ハーフトーン露光技術を適用した第 3 マスク工程及びエッチング工程を進行してボトム - Mo 膜と Al 膜及びトップ - Mo 膜の 3 層膜からなるソース / ドレーン電極を含んだデータラインを形成して薄膜トランジスタを構成すると共に、反射領域に配置されるボトム - Mo 膜と

10

20

30

40

50

A1膜との2層膜からなる反射電極を形成するステップと、前記ソース／ドレーン電極及び反射電極が形成された結果物の全面上に保護膜を形成するステップと、前記保護膜に対し、第4マスク工程及びエッチング工程を進行してソース／ドレーン電極を露出させる第2ビアホールを形成するステップと、前記第2ビアホールを含んだ保護膜上にITO膜を形成するステップと、前記ITO膜に対し、第5マスク工程及びエッチング工程を進行してソース／ドレーン電極とコンタクトされると共に、透過領域及び反射領域の全てに配置されるスリット型の画素電極を形成するステップと、を含むことを特徴とする半透過型液晶表示装置のアレイ基板製造方法を提供する。

#### 【0025】

ここで、前記ゲート電極を含んだゲートライン及び共通電極ラインとエンボーシングパターンを形成するステップは、前記ゲート用金属膜上にハーフトーン露光工程を適用してカウンタ電極形成領域を遮る部分がゲート電極を含んだゲートライン形成領域と共通電極ライン形成領域及びエンボーシングパターン形成領域を遮る部分より相対的に薄い厚さを有する第1感光膜パターンを形成するステップと、前記第1感光膜パターンをエッチングマスクとして利用してゲート用金属膜とITO膜をエッチングしてゲート電極を含んだゲートラインと共通電極ライン及びエンボーシングパターンを形成するステップと、前記第1感光膜パターンに対し、カウンタ電極形成領域を遮る部分が除去されるようにアッシングするステップと、前記アッシングされた第1感光膜パターンをエッチングマスクとして利用してカウンタ電極上のゲート用金属膜を除去するステップと、残留した第1感光膜パターンを除去するステップと、から構成されることを特徴とする。

10

20

30

40

#### 【0026】

前記第1ビアホール及びアクティブパターンを形成するステップは、前記ドーピングされた非晶質シリコン膜上にハーフトーン露光工程を適用して透過領域を遮る部分がアクティブパターン形成領域及び反射電極形成領域を遮る部分より相対的に薄い厚さを有する第2感光膜パターンを形成するステップと、前記第2感光膜パターンをエッチングマスクとして利用してドーピングされた非晶質シリコン膜と非晶質シリコン膜及びゲート絶縁膜をエッチングして共通電極ラインを露出させる第1ビアホールを形成するステップと、前記第2感光膜パターンに対し、透過領域上に形成された部分が除去されるようにアッシングするステップと、前記アッシングされた第2感光膜パターンをエッチングマスクとして利用してドーピングされた非晶質シリコン膜と非晶質シリコン膜をエッチングしてアクティブパターンを形成するステップと、残留した第2感光膜パターンを除去するステップと、から構成されることを特徴とする。

#### 【0027】

前記ソース／ドレーン電極を含んだデータラインと反射電極を形成するステップは、前記ボトム-Mo膜とA1膜及びトップ-Mo膜が順次に形成された3層膜の上にハーフトーン露光工程を適用して反射電極形成領域を遮る部分がソース／ドレーン電極を含んだデータライン形成領域を遮る部分より相対的に薄い厚さを有する第3感光膜パターンを形成するステップと、前記第3感光膜パターンをエッチングマスクとして利用して3層膜をエッチングしてソース／ドレーン電極を含んだデータラインを形成するステップと、前記第3感光膜パターンに対し、反射電極形成領域に形成された第3感光膜パターンが除去されるようにアッシングするステップと、前記アッシングされた第3感光膜パターンをエッチングマスクとして利用して反射領域のトップ-Mo膜をエッチングしてボトム-Mo膜とA1膜との2層膜からなる反射電極を形成するステップと、残留した第3感光膜パターンを除去するステップと、から構成されることを特徴とする。

#### 【0028】

前記ボトム-Mo膜は、500～700厚さで形成し、前記A1膜は1400～1600厚さで形成し、そして、前記トップ-Mo膜は100～200厚さで形成することを特徴とする。

#### 【0029】

前記反射電極は前記エンボーシングパターンによりエンボーシングを有するように形成

50

されることを特徴とする。

【0030】

前記透過領域及び反射領域は各々カウンタ電極と画素電極及び反射電極と画素電極間の水平電界によるFFSモードで駆動されることを特徴とする。

【0031】

また、前記のような目的の達成のために、本発明は、画素部が薄膜トランジスタ領域、反射領域及び透過領域に区画されたガラス基板上にITO膜とゲート用金属膜を順次に形成するステップと、前記ゲート用金属膜上にITO膜を形成するステップと、前記ITO膜に対し、第1マスク工程及びエッチング工程を進行して透過領域にITOのプレイ型カウンタ電極を形成するステップと、前記カウンタ電極が形成されたガラス基板上にゲート用金属膜を形成するステップと、前記ゲート用金属膜に対し、第2マスク工程及びエッチング工程を進行してゲート電極を含んだゲートラインと共に通電極ライン及び反射領域に配置されるエンボーシングパターンを形成するステップと、前記ゲート電極を含んだゲートライン、共通電極ライン、カウンタ電極及びエンボーシングパターンが形成されたガラス基板の全面上にゲート絶縁膜と非晶質シリコン膜及びドーピングされた非晶質シリコン膜を順次に形成するステップと、前記ドーピングされた非晶質シリコン膜と非晶質シリコン膜及びゲート絶縁膜に対し、ハーフトーン露光技術を適用した第3マスク工程及びエッチング工程を進行して共通電極ラインを露出させる第1ビアホールを形成すると共に、薄膜トランジスタ領域にアクティブパターンを形成するステップと、前記第1ビアホール及びアクティブパターンを含んだゲート絶縁膜上にボトム-Mo膜とA1膜及びトップ-Mo膜が順次に形成された3層膜を形成するステップと、前記3層膜に対し、ハーフトーン露光技術を適用した第4マスク工程及びエッチング工程を進行してボトム-Mo膜、A1膜及びトップ-Mo膜の3層膜からなるソース/ドレーン電極を含んだデータラインを形成して薄膜トランジスタを構成すると共に、反射領域に配置されるボトム-Mo膜とA1膜の2層膜からなる反射電極を形成するステップと、前記ソース/ドレーン電極及び反射電極が形成された結果物の全面上に保護膜を形成するステップと、前記保護膜に対し、第5マスク工程及びエッチング工程を進行してソース/ドレーン電極を露出させる第2ビアホールを形成するステップと、前記第2ビアホールを含んだ保護膜上にITO膜を形成するステップと、前記ITO膜に対し、第6マスク工程及びエッチング工程を進行してソース/ドレーン電極とコンタクトされるスリット型の画素電極を形成するステップと、を含むことを特徴とする半透過型液晶表示装置のアレイ基板製造方法を提供する。

【0032】

その上、前記のような目的の達成のために、本発明は、画素部が薄膜トランジスタ領域、反射領域及び透過領域に区画されたガラス基板上にゲート用金属膜を形成するステップと、前記ゲート用金属膜に対し、第1マスク工程及びエッチング工程を進行してゲート電極を含んだゲートライン及び共通電極ラインを形成すると共に、反射領域に配置されるエンボーシングパターンを形成するステップと、前記ゲート電極を含んだゲートラインと共に通電極ライン及びエンボーシングパターンが形成されたガラス基板の全面上にゲート絶縁膜と非晶質シリコン膜及びドーピングされた非晶質シリコン膜を順次に形成するステップと、前記ドーピングされた非晶質シリコン膜と非晶質シリコン膜及びゲート絶縁膜に対し、ハーフトーン露光技術を適用した第2マスク工程及びエッチング工程を進行して共通電極ラインを露出させる第1ビアホールを形成すると共に、薄膜トランジスタ領域にアクティブパターンを形成するステップと、前記第1ビアホール及びアクティブパターンを含んだゲート絶縁膜上にボトム-Mo膜とA1膜及びトップ-Mo膜が順次に形成された3層膜を形成するステップと、前記3層膜に対し、ハーフトーン露光技術を適用した第3マスク工程及びエッチング工程を進行してボトム-Mo膜、A1膜及びトップ-Mo膜の3層膜からなるソース/ドレーン電極を含んだデータラインを形成して薄膜トランジスタを構成すると共に、反射領域に配置されるボトム-Mo膜とA1膜の2層膜からなる反射電極を形成するステップと、前記ソース/ドレーン電極及び反射電極が形成された結果物の全面上に保護膜を形成するステップと、前記保護膜に対し、第4マスク工程及びエッティング

10

20

30

40

50

工程を進行してソース／ドレーン電極を露出させる第2ビアホールを形成するステップと、前記第2ビアホールを含んだ保護膜上にITO膜を形成するステップと、前記ITO膜に対し、第5マスク工程及びエッチング工程を進行してソース／ドレーン電極とコンタクトされると共に、透過領域に配置される画素電極を形成するステップと、を含むことを特徴とする半透過型液晶表示装置のアレイ基板製造方法を提供する。

#### 【0033】

ここで、前記第1ビアホール及びアクティブパターンを形成するステップは、前記ドーピングされた非晶質シリコン膜上にハーフトーン露光工程を適用して透過領域を遮る部分がアクティブパターン形成領域及び反射電極形成領域を遮る部分より相対的に薄い厚さを有する第2感光膜パターンを形成するステップと、前記第2感光膜パターンをエッチングマスクとして利用してドーピングされた非晶質シリコン膜と非晶質シリコン膜及びゲート絶縁膜をエッチングして共通電極ラインを露出させる第1ビアホールを形成するステップと、前記第2感光膜パターンに対し、透過領域上に形成された部分が除去されるようにアッシングするステップと、前記アッシングされた第2感光膜パターンをエッチングマスクとして利用してドーピングされた非晶質シリコン膜と非晶質シリコン膜をエッチングしてアクティブパターンを形成するステップと、残留した第2感光膜パターンを除去するステップと、から構成されることを特徴とする。

#### 【0034】

前記ソース／ドレーン電極を含んだデータラインと反射電極を形成するステップは、前記ボトム-Mo膜とAl膜及びトップ-Mo膜が順次に形成された3層膜の上にハーフトーン露光工程を適用して反射電極形成領域を遮る部分がソース／ドレーン電極を含んだデータライン形成領域を遮る部分より相対的に薄い厚さを有する第3感光膜パターンを形成するステップと、前記第3感光膜パターンをエッチングマスクとして利用して3層膜をエッチングしてソース／ドレーン電極を含んだデータラインを形成するステップと、前記第3感光膜パターンに対し、反射電極形成領域に形成された第3感光膜パターンが除去されるようにアッシングするステップと、前記アッシングされた第3感光膜パターンをエッチングマスクとして利用して反射領域のトップ-Mo膜をエッチングしてボトム-Mo膜とAl膜との2層膜からなる反射電極を形成するステップと、残留した第3感光膜パターンを除去するステップと、から構成されることを特徴とする。

#### 【0035】

前記ボトム-Mo膜は500～700厚さで形成し、前記Al膜は1400～1600厚さで形成し、そして、前記トップ-Mo膜は100～200厚さで形成することを特徴とする。

#### 【0036】

前記反射電極は前記エンボッシングパターンによりエンボッシングを有するように形成されることを特徴とする。

前記透過領域及び反射領域はTNモードで駆動されることを特徴とする。

#### 【発明の効果】

#### 【0037】

以上のように、本発明はソース／ドレーン用金属膜で反射電極を形成するものの、前記ソース／ドレーン用金属としてMo-Al-Moの3層膜を適用しながら選択的に反射領域でのトップ-Moを除去することによって、反射領域での優れる反射率特性を確保することができることは勿論、薄膜トランジスタ領域で良好な電気的コンタクトがなされるようになることができ、それで、製品の画面品位を向上させることができる。

#### 【0038】

また、本発明はハーフトーン露光技術を利用して略5～6枚のマスク工程を利用することだけでアレイ基板を製作することによって、8～11枚のマスクを必要とする従来に比べてマスク数を減らすことができ、それによって、低減されたマスク数及び工程数だけ製造費用を減らすことができることは勿論、工程単純化をなすことができる。

#### 【発明を実施するための最良の形態】

10

20

30

40

50

## 【0039】

以下、添付の図面を参照しつつ本発明の望ましい実施形態を詳細に説明する。

まず、本発明はソース／ドレーン及び反射電極を形成するための物質でM<sub>0</sub>-A<sub>1</sub>-M<sub>0</sub>の3層膜を適用するものの、反射領域ではトップ-M<sub>0</sub>を除去して反射度が高いA<sub>1</sub>金属膜が露出されるようにし、薄膜トランジスタ領域では前記トップ-M<sub>0</sub>がそのまま存在するようにする。このようにすれば、本発明は反射領域での優れる反射度を確保できることは勿論、薄膜トランジスタ領域での良好な電気的コンタクトがなされるようになることができ、それで、製品の画面品位を向上させることができるのでなく、安価のM<sub>0</sub>とA<sub>1</sub>を使用することからコスト高も防止することができる。

## 【0040】

また、本発明はハーフトーン(Half Tone)露光技術を利用して半透過型液晶表示装置のアレイ基板を製作する。このようにすれば、本発明は略5～6枚のマスク工程を利用することだけでもアレイ基板の製作が可能なので、減少したマスク数及び工程数だけ製造費用を低減できることは勿論、工程単純化をなすことができる。

## 【0041】

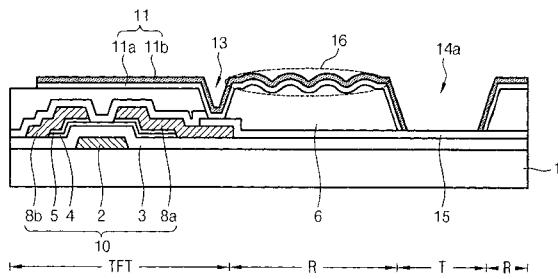

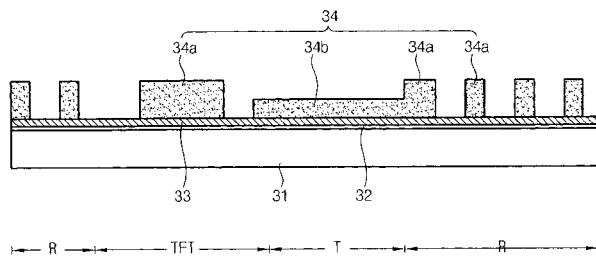

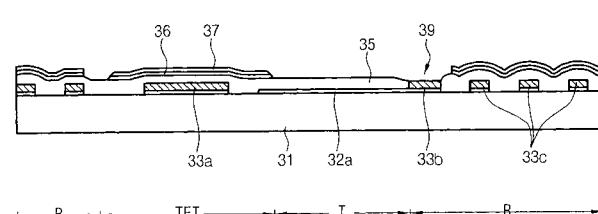

図4A乃至図4Lは、本発明の一実施形態に係る半透過型FFSモード液晶表示装置のアレイ基板製造方法を示す工程別断面図であって、これを詳しく説明すれば、次の通りである。

## 【0042】

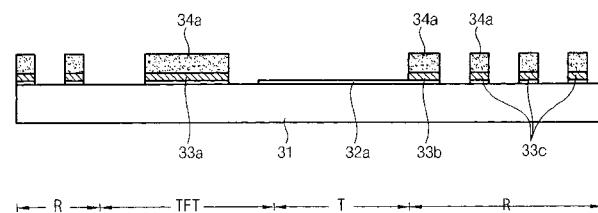

図4Aを参照すれば、画素部が薄膜トランジスタ領域(TFT)、反射領域(R)及び透過領域(T)に区画されたガラス基板31上にITO膜32とゲート用金属膜33を順次に蒸着する。次に、図示してはいないが、第1マスクを利用して前記ゲート用金属膜33上にゲート電極を含んだゲートライン形成領域及び共通電極ライン形成領域と反射領域(R)でのエンボーシング形成のためのエンボーシングパターン形成領域を遮りながら透過領域(R)でのカウンタ電極形成領域を遮る第1感光膜パターン34を形成する。この際、前記第1感光膜パターン34はハーフトーン露光工程を適用してカウンタ電極形成領域を遮る第1感光膜パターン部分34bが、その以外の部分、即ち、ゲート電極を含んだゲートライン形成領域と共に共通電極ライン形成領域及びエンボーシングパターン形成領域を遮る第1感光膜パターン部分34aより相対的に薄い厚さを有するように形成する。

## 【0043】

図4Bを参照すれば、エッチングマスクとして第1感光膜パターンを利用してゲート用金属膜及びITO膜をエッチングし、これを通じて、ゲート電極33aを含んだゲートライン(図示していない)及び共通電極ライン33bを形成すると共に、反射領域(R)にエンボーシングパターン33cを形成する。次に、前記結果物に対し、アッシング(ashing)工程を進行して透過領域(R)に形成された第1感光膜パターン部分を除去する。この際、前記ゲート電極33aを含んだゲートラインと共に共通電極ライン33b及びエンボーシングパターン33c上の第1感光膜パターン部分34aは透過領域(T)のカウンタ電極形成領域上に形成された第1感光膜パターン部分より相対的に厚く形成されたので、完全に除去されなくて一部が残留する。

## 【0044】

図4Cを参照すれば、残留した第1感光膜パターン34aをエッチングマスクとして利用して露出された透過領域(T)上のゲート用金属膜を除去し、これを通じて前記透過領域(T)にITO膜からなるプレート型のカウンタ電極32aを形成する。

## 【0045】

図4Dを参照すれば、公知の工程によって残留した第1感光膜パターンを除去する。次に、ゲート電極33aを含んだゲートライン、共通電極ライン33b、エンボーシングパターン33c及びカウンタ電極32aが形成されたガラス基板31の全面上にゲート絶縁膜35とアクティブ層、即ち、非晶質シリコン層36とドーピングされた非晶質シリコン層37を順次に形成する。この際、反射領域(R)にエンボーシングパターン33cが形成されていることによって、前記反射領域(R)に形成されたゲート絶縁膜35及びアク

10

20

30

40

50

ティップ層 3 6、3 7 は、その表面が屈曲することになる。

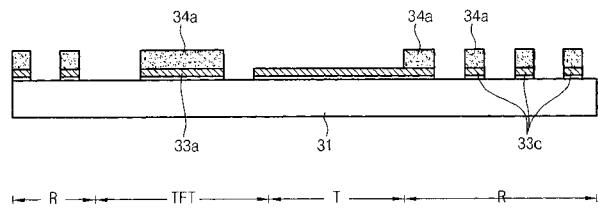

【0046】

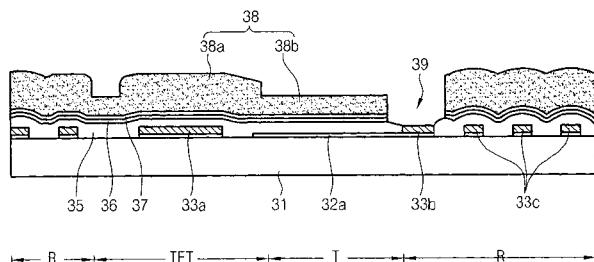

図 4 E を参照すれば、第 2 マスクを利用してドーピングされた非晶質シリコン層 3 7 上に共通電極ライン 3 3 b の上部領域を露出させる第 2 感光膜パターン 3 8 を形成する。この際、前記第 2 感光膜パターン 3 8 はハーフトーン露光技術を適用して透過領域 (T) を遮るように形成された部分 3 8 b がアクティブパターン形成領域及び反射電極形成領域を遮る部分 3 8 a より相対的に薄い厚さを有するように形成する。次に、エッティングマスクとして前記第 2 感光膜パターン 3 8 を利用してアクティブ層 3 6、3 7 及びゲート絶縁膜 3 5 をエッティングして共通電極ライン 3 3 b を露出させる第 1 ビアホール 3 9 を形成する。

10

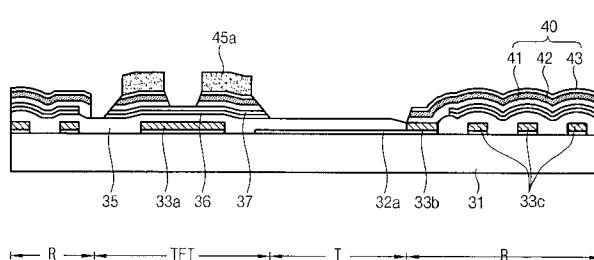

【0047】

図 4 F を参照すれば、前記第 1 ビアホール 3 9 が形成された結果物に対し、アッシング工程を進行して透過領域 (T) 上に形成された第 2 感光膜パターン部分を除去する。この際、前記透過領域 (T) の以外の領域に形成された第 2 感光膜パターンは相対的に厚く形成されていたので、完全に除去されなくて一部が残留する。

【0048】

図 4 G を参照すれば、残留した第 2 感光膜パターンをエッティングマスクとして利用してドーピングされた非晶質シリコン膜とその下の非晶質シリコン膜をエッティングしてアクティブパターンを形成する。次に、前記エッティングマスクとして利用された第 2 感光膜パターンを除去する。

20

【0049】

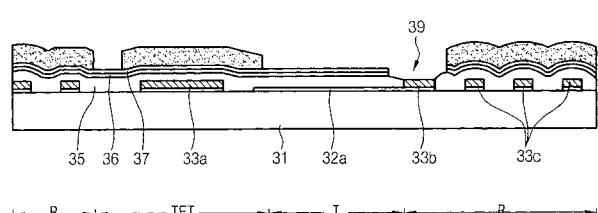

図 4 H を参照すれば、アクティブパターン及び第 1 ビアホール 3 9 が形成された結果物の全面上にソース / ドレーン用金属膜 4 0 を形成する。ここで、前記ソース / ドレーン用金属膜 4 0 は 3 層膜構造で形成し、実質的な配線物質である第 2 層膜としては電気伝導度が優れるだけでなく、反射率が優れる A 1 系列の膜を適用し、前記 A 1 系金属膜の下に配置される第 1 層膜は前記 A 1 系金属膜がゲート絶縁膜 3 5 と不要な反応が起こることが抑制されるように M o 系列の金属膜を利用し、そして、A 1 系金属膜上に配置される第 3 層膜は画素電極物質である I T O との電気的連結が容易であるように、M o 系列の金属膜を利用する。例えば、M o - A 1 - M o の 3 層構造においてボトム - M o 膜 4 1 は 500 ~ 700 、望ましくは、600 の厚さで、A 1 膜 4 2 は 1400 ~ 1600 、望ましくは、1500 の厚さで、そして、トップ - M o 膜 4 3 は後続工程でのその除去が容易であるように 100 ~ 200 の厚さで形成する。

30

【0050】

この際、前記 3 層構造のソース / ドレーン用金属膜 4 0 は第 1 ビアホール 3 9 を通じて共通電極ライン 3 3 b と連結される。また、反射領域 (R) に形成されたソース / ドレーン用金属膜部分は下地層が表面屈曲を有していることによって、それ自身も表面屈曲、即ち、エンボーシング 4 4 を有することになる。

【0051】

引き続き、第 3 マスクを利用して前記ソース / ドレーン用金属膜 4 0 上にソース / ドレーン電極を含んだデータライン形成領域及び反射電極形成領域を露出させる第 3 感光膜パターン 4 5 を形成する。この際、前記第 3 感光膜パターン 4 5 はハーフトーン露光技術を適用して反射電極形成領域に部分 4 5 b が、それ以外の領域に形成された部分 4 5 a より相対的に薄い厚さを有するように形成する。

40

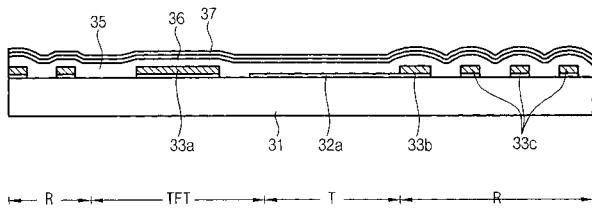

【0052】

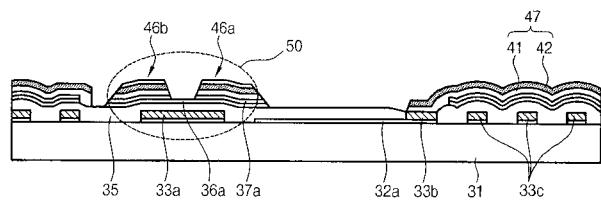

図 4 I を参照すれば、エッティングマスクとして前記第 3 感光膜パターンを利用して 3 層構造のソース / ドレーン用金属膜を湿式エッティングしてソース / ドレーン電極 4 6 a、4 6 b を含んだデータライン ( 図示していない ) を形成する。この際、反射領域 (R) には 3 層構造のソース / ドレーン用金属膜が残留する。次に、前記ソース / ドレーン電極 4 6 a、4 6 b が形成された結果物に対し、アッシング工程を進行して透過領域 (T) 上に形成された第 3 感光膜パターン部分を除去する。この際、前記透過領域 (T) の以外の領域

50

に形成された第3感光膜パターンは相対的に厚く形成されていたので、完全に除去されなくて一部が残留する。

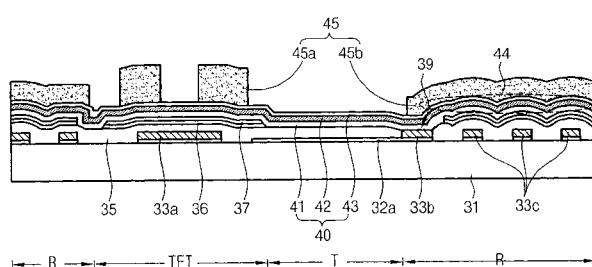

【0053】

図4Jを参照すれば、局部的に残留した第3感光膜パターンをエッチングマスクとして利用して結果物に対して乾燥式エッチングを進行し、これを通じて、反射領域(R)でのトップ-Moを除去してボトム-Mo膜41とAl膜42の2層膜からなる反射電極47を形成し、これと同時に、薄膜トランジスタ領域(TFT)でのドーピングされた非晶質シリコン層をエッチングしてオーミック層37aとチャネル層36aを形成して薄膜トランジスタ50を構成する。次に、前記局部的に残留した第3感光膜パターンを除去する。

【0054】

ここで、本発明に係る反射領域(R)での反射電極47はボトム-Mo膜41とAl膜42の2層膜からなり、特に、上部にAl膜42が配置されるので、優れる反射率特性を有する。また、本発明に係る薄膜トランジスタ領域(TFT)でのソース/ドレーン電極46a、46bはボトム-Mo膜41とAl膜42及びトップ-Mo膜43の3層膜からなり、特に、上部にMo膜が配置されるので、後続に形成されるITO画素電極と良好な電気的コントラクトをなすことができる。

【0055】

図4Kを参照すれば、反射電極47及び薄膜トランジスタ50が形成された結果物の全面上にシリコン窒化膜のような無機絶縁物質からなる保護膜51を約2000の厚さで形成する。次に、第4マスクを利用して前記保護膜51をエッチングして、例えば、薄膜トランジスタ50のソース電極46aの上部を露出させる第4感光膜パターン(図示していない)を形成した後、前記第4感光膜パターンをエッチングマスクとして利用して前記保護膜51をエッチングし、これを通じて、前記薄膜トランジスタ50のソース電極46aを露出させる第2ビアホール52を形成する。次に、前記エッチングマスクとして利用された第4感光膜パターンを除去する。

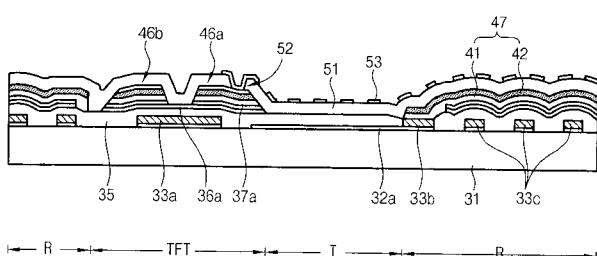

【0056】

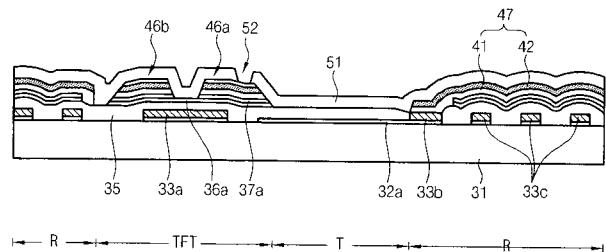

図4Lを参照すれば、第2ビアホール52が設けられた保護膜51の上にITO膜を蒸着する。次に、前記ITO膜の上に第5マスクを利用して透過領域(T)での第1画素電極形成領域及び反射領域(R)での第2画素電極形成領域を遮る第5感光膜パターンを形成した後、このような第5感光膜パターンをエッチングマスクとして利用してITO膜をエッチングして透過領域(T)及び反射領域(R)にスリット型の画素電極53を形成する。

【0057】

その後、前記第5感光膜パターンを除去して本発明の一実施形態に係る半透過型FFSモード液晶表示装置のアレイ基板の製造を完成する。

【0058】

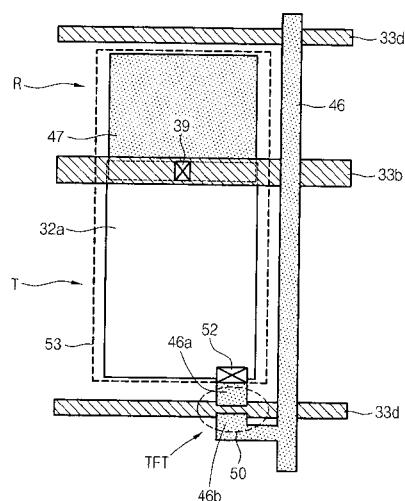

図5は、図4Lに対応する平面図であって、図示のように、ゲートライン33dとデータライン46が交差するように配列されており、共通電極ライン33bが前記ゲートライン33dと平行するように配列されており、前記ゲートライン33dとデータライン46の交差部には薄膜トランジスタ50が配置されており、透過領域(T)にはITOのカウンタ電極32aが配置されており、反射領域(R)には第1ビアホール39を通じて共通電極ライン33bとコントラクトされるように反射電極47が配置されている。

【0059】

そして、ゲートライン33dとデータライン46により区画された画素領域内にはITOの画素電極53が配置されている。

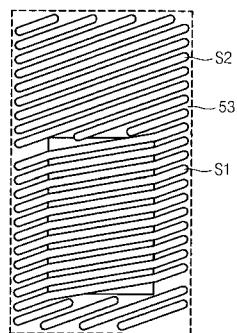

【0060】

ここで、前記画素電極53は、図6に示すように、反射領域(R)及び透過領域(T)の全てで、ゲートライン33dに対して一定の傾きを有する複数のスリットS1、S2を備えたスリット型構造からなり、特に、透過領域(T)でのスリットS1は、屈曲部分を有し、反射領域(R)でのスリットS2よりも、ゲートライン33dに対して小さい傾きを

成す部分を有するように備えられる。

【0061】

前述のような本発明の一実施形態に係る半透過型FFSモード液晶表示装置のアレイ基板製造方法によれば、反射電極47をソース／ドレーン用金属膜で形成しながらも反射領域(R)での反射電極47はMoとAlの2層膜からなるようによることによって、優れる反射率特性を表すようによることができ、また、薄膜トランジスタ領域(TFT)ではMo-Al-Moの3層膜からなるようによることによつて、ITOの画素電極と良好なコントラクトがなされるようによることができる。

【0062】

併せて、本発明の方法によれば、5枚のマスクを使用してアレイ基板を製造するので、最小8枚のマスクを使用しなければならない従来技術に比べて少なくとも3枚以上のマスクを減らすことができ、これによつて、製造費用を低減できることは勿論、工程を単純化することができる。

【0063】

一方、前述の本発明の一実施形態ではゲート電極を含んだゲートライン、共通電極ライン、エンボーシングパターン及びITOのカウンタ電極をハーフトーン技術を適用した第1マスク工程を通じて形成したが、本発明の他の実施形態として一つのマスクを利用してITOのカウンタ電極を形成した後、もう一つのマスクを利用して残りのゲート電極を含んだゲート電極、共通電極ライン及びエンボーシングパターンを形成し、以後、前述の本発明の一実施形態と同一な後続工程を進行してアレイ基板を製作することができる。

【0064】

この場合、本発明の他の実施形態は総数6枚のマスクを必要とすることになり、したがつて、従来技術に比べて2枚のマスクを減らすことができるので、相変らず製造費用を低減できることは勿論、工程単純化をなすことができる。

【0065】

また、前述の実施形態は透過領域及び反射領域が各々カウンタ電極と画素電極との間及び反射電極と画素電極との間の水平電界により駆動されるFFSモードについて説明したものであるが、本発明は半透過型TNモード液晶表示装置のアレイ基板製造方法にも適用可能である。

【0066】

即ち、詳細に図示及び説明してはいないが、TNモードはFFSモードとは異なり、ITOのカウンタ電極の形成が必要でないので、前述の一実施形態における第1マスクを利用した工程進行の際、ハーフトーン露光技術を適用しなくてもよく、併せて、第5マスクを利用した工程進行の際、画素電極は反射領域には形成しなく、透過領域のみに形成すればよい。それ以外の残りの第2マスク工程、第3マスク工程及び第4マスク工程は一実施形態と同じ方法で進行する。

【0067】

その上、前述の本発明の一実施形態ではソース／ドレーン電極を含んだデータライン及び反射電極を形成するための第3マスク工程の際、ハーフトーン露光技術を適用して反射領域でのトップ-Moを選択的に除去したが、典型的な露光技術を適用して反射領域でのトップ-Moを除去することは勿論、薄膜トランジスタ領域でのトップ-Moの除去も可能である。これは純粋Alの場合はITOとのコントラクト抵抗が高くて問題を起こすが、純粋Alの上にMoを蒸着した後、前記Moを除去することになれば、スパッタによりAlの表面に打込まれたMo粒子は完全に除去されずに残留するところ、このようなAlにITOをコントラクトさせる場合は、表面Mo粒子によりコントラクト抵抗を低めることができるためである。

【0068】

以上、ここでは、本発明を特定の実施形態に關連して図示及び説明したが、本発明がそれに限るのではなく、特許請求範囲は本発明の精神と分野から外れない限度内で本発明が多様に改造及び変形できるということを当業界で通常の知識を有する者であれば容易に分

10

20

30

40

50

かる。

**【図面の簡単な説明】**

**【0069】**

【図1】従来の半透過型TN(Twisted Nematic)モード液晶表示装置のアレイ基板を示す断面図である。

【図2】従来の他の半透過型TNモード液晶表示装置のアレイ基板を示す断面図である。

【図3】従来の半透過型FFS(Fringe Field Switching)モード液晶表示装置のアレイ基板を示す断面図である。

【図4A】本発明の一実施形態に係る半透過型FFSモード液晶表示装置のアレイ基板製造方法を説明するための工程別断面図である。

10

【図4B】本発明の一実施形態に係る半透過型FFSモード液晶表示装置のアレイ基板製造方法を説明するための工程別断面図である。

【図4C】本発明の一実施形態に係る半透過型FFSモード液晶表示装置のアレイ基板製造方法を説明するための工程別断面図である。

【図4D】本発明の一実施形態に係る半透過型FFSモード液晶表示装置のアレイ基板製造方法を説明するための工程別断面図である。

【図4E】本発明の一実施形態に係る半透過型FFSモード液晶表示装置のアレイ基板製造方法を説明するための工程別断面図である。

【図4F】本発明の一実施形態に係る半透過型FFSモード液晶表示装置のアレイ基板製造方法を説明するための工程別断面図である。

20

【図4G】本発明の一実施形態に係る半透過型FFSモード液晶表示装置のアレイ基板製造方法を説明するための工程別断面図である。

【図4H】本発明の一実施形態に係る半透過型FFSモード液晶表示装置のアレイ基板製造方法を説明するための工程別断面図である。

【図4I】本発明の一実施形態に係る半透過型FFSモード液晶表示装置のアレイ基板製造方法を説明するための工程別断面図である。

【図4J】本発明の一実施形態に係る半透過型FFSモード液晶表示装置のアレイ基板製造方法を説明するための工程別断面図である。

【図4K】本発明の一実施形態に係る半透過型FFSモード液晶表示装置のアレイ基板製造方法を説明するための工程別断面図である。

30

【図4L】本発明の一実施形態に係る半透過型FFSモード液晶表示装置のアレイ基板製造方法を説明するための工程別断面図である。

【図5】図4Lに対応する平面図である。

【図6】画素電極53を示す平面図である。

**【符号の説明】**

**【0070】**

31 ガラス基板

32 ITO膜

32a カウンタ電極

33 ゲート用金属膜

33a ゲート電極

33b 共通電極ライン

33c エンボーシングパターン

33d ゲートライン

34 第1感光膜パターン

35 ゲート絶縁膜

36 非晶質シリコン膜

37 ドーピングされた非晶質シリコン膜

38 第2感光膜パターン

39 第1ビアホール

40

50

- 4 0 ソース／ドレーン用金属膜

4 1 第1層膜

4 2 第2層膜

4 3 第3層膜

4 4 エンボーシング

4 5 第3感光膜パターン

4 6 データライン

4 6 a ソース電極

4 6 b ドレーン電極

4 7 反射電極

5 0 薄膜トランジスタ

5 1 保護膜

5 2 ビアホール

5 3 画素電極

10

【 図 1 】

【 図 2 】

【 四 3 】

【 4 A 】

【図4B】

【図4D】

【図4C】

【図4E】

【図4F】

【図4H】

【図4G】

【図4I】

【図4 J】

【図4 L】

【図4 K】

【図5】

【図6】

---

フロントページの続き

(72)発明者 林 三 鎬

大韓民國 ソウル市 江東區 岩寺洞 セオンサ ヒュンダイ アパートメント 105 - 150

1

F ターム(参考) 2H092 GA14 GA15 GA16 GA17 GA25 GA29 HA04 HA06 JA26 JA28

JA34 JA37 JA41 JA46 JB04 JB05 JB07 JB56 KA05 KA12

KA18 KB04 KB13 KB25 MA16 NA01 NA27 NA28 PA06 PA12

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 透反液晶显示装置的阵列基板的制造方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2007133410A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 公开(公告)日 | 2007-05-31 |

| 申请号            | JP2006305998                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 申请日     | 2006-11-10 |

| [标]申请(专利权)人(译) | Bioi高盘科技有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 申请(专利权)人(译)    | Bioi Heidis科技有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| [标]发明人         | 金秉勳<br>林三鎬                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 发明人            | 金 ▲秉▼勳<br>林 三 鎬                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G02F1/1343 G02F1/1368                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| CPC分类号         | G02F1/133555 G02F1/134309 G02F2001/136231                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| FI分类号          | G02F1/1343 G02F1/1368 G02F1/1335.520                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| F-TERM分类号      | 2H092/GA14 2H092/GA15 2H092/GA16 2H092/GA17 2H092/GA25 2H092/GA29 2H092/HA04 2H092 /HA06 2H092/JA26 2H092/JA28 2H092/JA34 2H092/JA37 2H092/JA41 2H092/JA46 2H092/JB04 2H092/JB05 2H092/JB07 2H092/JB56 2H092/KA05 2H092/KA12 2H092/KA18 2H092/KB04 2H092 /KB13 2H092/KB25 2H092/MA16 2H092/NA01 2H092/NA27 2H092/NA28 2H092/PA06 2H092/PA12 2H191/FA34Y 2H191/GA05 2H191/GA10 2H191/GA19 2H191/HA06 2H191/HA15 2H191/LA13 2H191 /LA21 2H191/NA13 2H191/NA29 2H191/NA34 2H191/NA37 2H192/AA24 2H192/BB13 2H192/BB73 2H192/BC31 2H192/BC64 2H192/BC74 2H192/BC82 2H192/CB05 2H192/CB42 2H192/CB82 2H192 /CC04 2H192/CC42 2H192/CC72 2H192/HA44 2H291/FA34Y 2H291/GA05 2H291/GA10 2H291/GA19 2H291/HA06 2H291/HA15 2H291/LA13 2H291/LA21 2H291/NA13 2H291/NA29 2H291/NA34 2H291 /NA37 |         |            |

| 代理人(译)         | 井上 真司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 优先权            | 1020050108016 2005-11-11 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 其他公开文献         | <a href="#">JP4902317B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

### 摘要(译)

解决的问题：提供一种阵列基板的制造方法，该方法能够提高半透射半反射型液晶显示装置的透射区域的接触电阻并提高反射区域的反射率特性。在第一掩模工艺中形成栅极线和公共电极线，在第一掩模工艺中，在玻璃基板上应用半色调曝光技术，并且布置在透射区域和反射区域中布置的ITO的板型对电极。使用相同的曝光技术形成压花图案，使用相同的曝光技术在第二掩模工艺中在公共电极线部分中形成第一通孔和有源图案，以及使用相同的曝光技术的第三掩模工艺中的Mo-形成包括由Al-Mo三层膜组成的源/漏电极并在反射区域中形成由底层Mo-Al两层膜组成的反射电极的数据线的步骤，以及第四掩模步骤 该方法包括在第五掩模工艺中在第二通孔中形成ITO的狭缝型像素电极。[选择图]图4L