(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-361949

(P2004-361949A)

(43) 公開日 平成16年12月24日(2004.12.24)

(51) Int.Cl.<sup>7</sup>

G02F 1/1368

G02F 1/1362

G09F 9/30

G09F 9/35

F 1

G02F 1/1368

G02F 1/1362

G09F 9/30 338

G09F 9/35

テーマコード(参考)

2H092

5C094

審査請求 未請求 請求項の数 14 O L (全 17 頁)

(21) 出願番号 特願2004-160998 (P2004-160998)

(22) 出願日 平成16年5月31日 (2004.5.31)

(31) 優先権主張番号 2003-034677

(32) 優先日 平成15年5月30日 (2003.5.30)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

大韓民国京畿道水原市靈通区梅灘洞 416

(74) 代理人 100094145

弁理士 小野 由己男

(74) 代理人 100106367

弁理士 稲積 朋子

(72) 発明者 李 祖勳

大韓民国京畿道龍仁市器興邑書川里 705

番地イエヒヨンマウル現代ホームタウン1

04棟1205号

(72) 発明者 倉 學 ▲スン▼

大韓民国ソウル市江南区逸院洞カチマウル

アパート1006棟315号

最終頁に続く

(54) 【発明の名称】薄膜トランジスタ表示板及びこれを含む液晶表示装置

## (57) 【要約】

【課題】 本発明の課題は、水平電界駆動方式の液晶表示装置の開口率を向上させることにある。その他の課題は、水平電界を印加するための電極の数を容易に調節することができる液晶表示装置を提供することにある。

【解決手段】 薄膜トランジスタ表示板は、絶縁基板上に、ゲート電極を含み一部傾いた部分を有するゲート線及び維持電極線が形成されており、ゲート線を覆うゲート絶縁膜上には、半導体層が形成されている。ゲート絶縁膜上には、少なくとも一部分が半導体層上に位置し、ゲート線と交差してゲート線の傾いた部分と共に梯形パターンの画素領域を定義するデータ線、及びデータ線から分離されてゲート線を中心に対向するドレーン電極と、維持電極線と重畳して維持蓄電器を構成する画素電極線とが形成されている。データ線及びドレーン電極で遮られない半導体層を覆う保護膜上には、ドレーン電極と電気的に連結されている線形の画素電極、及び画素電極と交互に配置されて形成され、縁部は画素電極の縁部と互いに一定の間隔を置いて互いに平行な線形の共通電極が形成されている。

**【特許請求の範囲】****【請求項 1】**

絶縁基板と、

前記絶縁基板上に形成され、ゲート電極を含み一部傾いた部分を有するゲート線と、

前記ゲート線を覆うゲート絶縁膜と、

前記ゲート絶縁膜上に形成されている半導体層と、

少なくとも一部は前記半導体層上に位置し、前記ゲート線と交差して前記ゲート線の傾いた部分と共に梯形パターンの画素領域を定義するデータ線、及び前記データ線と分離されて前記ゲート線を中心に対向するドレーン電極と、

前記データ線及びドレーン電極で遮られない半導体層を覆う保護膜と、

10

前記保護膜上に形成され、画素領域に少なくとも二つ以上配置され、前記ドレーン電極と電気的に連結されている線形の画素電極と、

前記保護膜上に前記画素電極と交互に配置されて形成され、端部は前記画素電極の端部と互いに一定の間隔を置いて互いに平行な線形の共通電極とを含む、薄膜トランジスタ表示板。

**【請求項 2】**

前記ゲート線は、前記画素領域の境界で屈曲している、請求項 1 に記載の薄膜トランジスタ表示板。

**【請求項 3】**

前記共通電極及び前記画素電極は、前記ゲート線の傾いた部分と平行に配列されている 20

、請求項 1 に記載の薄膜トランジスタ表示板。

**【請求項 4】**

前記基板上に形成され、前記データ線と平行に延在した維持電極線をさらに含む、請求項 1 に記載の薄膜トランジスタ表示板。

**【請求項 5】**

複数の前記画素電極を連結し、前記維持信号線と重畠して維持蓄電器を構成する画素電極線をさらに含む、請求項 4 に記載の薄膜トランジスタ表示板。

**【請求項 6】**

前記共通電極及び前記画素電極は、透明な導電物質からなる、請求項 1 に記載の薄膜トランジスタ表示板。

30

**【請求項 7】**

前記保護膜下に形成され、前記画素領域に順に配列されている赤、緑、青の色フィルターをさらに含む、請求項 1 に記載の薄膜トランジスタ表示板。

**【請求項 8】**

請求項 1 の前記薄膜トランジスタ表示板と、

前記薄膜トランジスタ表示板と対向する対向表示板と、

前記薄膜トランジスタ表示板と前記対向表示板との間に形成されている液晶物質層とを含む、液晶表示装置、

**【請求項 9】**

前記対向表示板の周囲に形成され、前記液晶物質層を封止する封止材をさらに含む、請求項 8 に記載の液晶表示装置。

40

**【請求項 10】**

前記対向表示板の周囲、前記封止材の内側に形成され、表示領域を定義するブラックマトリックスをさらに含む、請求項 9 に記載の液晶表示装置、

**【請求項 11】**

前記ブラックマトリックスは、有機物質からなり、写真エッチング工程でパターニングされる、請求項 10 に記載の液晶表示装置。

**【請求項 12】**

前記ブラックマトリックスと同一な層からなる基板間隔材をさらに含む、請求項 11 に記載の液晶表示装置。

50

**【請求項 1 3】**

前記ブラックマトリックス及び前記基板間隔材は、互いに異なる高さを有する、請求項12に記載の液晶表示装置。

**【請求項 1 4】**

前記ブラックマトリックスには、他の部分より厚さの薄いトレンチが形成されている、請求項11に記載の液晶表示装置。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は薄膜トランジスタ表示板とこれを含む液晶表示装置、及びこれに用いられる薄膜トランジスタ表示板に関し、特に、液晶分子に水平電界を印加するために同一な基板に形成された電極及び電界印加手段である薄膜トランジスタを有する薄膜トランジスタ表示板及びこれを含む液晶表示装置に関する。 10

**【背景技術】****【0 0 0 2】**

水平電界液晶駆動方式の従来の技術は、特許文献1に示されている。

**【0 0 0 3】**

しかし、特許文献1に示されている液晶表示装置では、水平電界を印加するための共通電極及び画素電極のうち、共通電極と共に連結されて共通信号を伝達する維持信号線とが互いに隣接する部分の画素の上部及び下部で液晶駆動の歪曲が発生する。このような歪曲を補うためにブラックマトリックスを広く形成するので、開口率が減少する問題が発生する。 20

**【0 0 0 4】**

また、画素電極に電圧を印加するデータ線とこれと平行な画素電極または共通電極との間にカッピング効果または歪曲した駆動が発生して光が漏れ、これにより、クロストークが発生する問題がある。これを補うためにデータ線に隣接する共通電極を必要以上に広く形成するので、開口率を減少させる要因となる。

**【0 0 0 5】**

そして、共通電極及び画素電極は、データ線と平行にゲート線及びデータ線で囲まれた画素の長さ方向と平行に形成されているので、電極の数を増やすのは容易なことではない。 30

**【特許文献1】米国特許第5,598,285号明細書****【発明の開示】****【発明が解決しようとする課題】****【0 0 0 6】**

本発明の課題は、水平電界駆動方式の液晶表示装置の開口率を向上させることにある。本発明の他の課題は、水平電界を印加するための電極の数を容易に調節することができる液晶表示装置を提供することにある。

**【課題を解決するための手段】****【0 0 0 7】**

このような技術的課題を解決するために、本発明では、ゲート線及びデータ線の交差により定義された梯形パターンの画素領域に、共通電極がゲート線と互いに平行に配列され、維持信号線がデータ線と平行に形成され、液晶分子がこれらと垂直に初期配向されている。 40

**【0 0 0 8】**

本発明の実施例による薄膜トランジスタ表示板は、絶縁基板上に、ゲート電極を含み一部傾いた部分を有するゲート線が形成されており、ゲート線を覆うゲート絶縁膜上には、半導体層が形成されている。ゲート絶縁膜上には、少なくとも一部分が半導体層上に位置し、ゲート線と交差してゲート線の傾いた部分と共に梯形パターンの画素領域を定義するデータ線、及びデータ線から分離されてゲート線を中心に対向するドレーン電極が形成されている。データ線及びドレーン電極で遮られない半導体層を覆う保護膜上には、画素領 50

域に少なくとも二つ以上配置され、ドレーン電極と電気的に連結されている線形の画素電極及び、画素電極と交互に配置されて形成され、縁部は画素電極の縁部と互いに一定の間隔を置いて互いに平行な線形の共通電極が形成されている。

#### 【0009】

ここで、共通電極及び画素電極は、ゲート線の傾いた部分と平行に配列されている。

#### 【0010】

基板上に形成され、データ線と平行に延在した維持電極線及び複数の画素電極を連結し、維持信号線と重畳して維持蓄電器を構成する画素信号線をさらに含むことができる。

#### 【0011】

共通電極及び前記画素電極は、透明な導電物質からなるのが好ましく、保護膜下に形成され、画素領域に順に配列されている赤、緑、青の色フィルターをさらに含むことができる。10

#### 【0012】

このような本発明の実施例による薄膜トランジスタ表示板は、これと対向する対向表示板、及びこれらの間に形成されている液晶物質層を含む。対向表示板は、その周囲に形成され、液晶物質層を封止する封止材及び、封止材の内側に形成され、表示領域を定義するブラックマトリックスをさらに含む。

#### 【0013】

ブラックマトリックスは、有機物質からなることができ、対向表示板は、ブラックマトリックスと同一な層からなる基板間隔材をさらに含むことができる。この時、ブラックマトリックス及び基板間隔材は、互いに異なる高さを有することができ、ブラックマトリックスには、他の部分より厚さの薄いトレーナーが形成されることができる。20

#### 【発明の効果】

#### 【0014】

本発明の実施例のように、維持電極線をデータ線と平行に、画素の長さ方向に形成することにより、開口率を向上させることができ、光漏れ現象を減らすことができる。また、梯形(台形)パターンの画素領域の辺と共通電極及び画素電極とを平行に配列することにより、画素領域の角部まで画像を表示することができ、画素の表示能力を極大化することができる。また、共通電極及び画素電極を画素の長さ方向に配列することにより、これらの数を容易に調節することができる。さらに、色フィルターを薄膜トランジスタ表示板に配置することにより、画素の開口率を極大化することができる。さらに、画素電極及び共通電極を透明な導電物質で形成することにより、画素の透過率を向上させることができる。30

#### 【発明を実施するための最良の形態】

#### 【0015】

添付した図面を参照して、本発明の実施例に対して本発明が属する技術分野における通常の知識を有する者が容易に実施できるように詳細に説明する。しかし、本発明は多様な形態で実現することができ、ここで説明する実施例に限定されない。

#### 【0016】

図面は、各種の層及び領域を明確に表現するために厚さを拡大して示している。明細書全体を通じて類似した部分については同一な図面符号を付けている。層、膜、領域、板などの部分が他の部分の“上に”あるとする時、これは他の部分の“すぐ上に”ある場合に限らず、その中間に更に他の部分がある場合も含む。逆に、ある部分が他の部分の“すぐ上に”あるとする時は、中間に他の部分がないことを意味する。40

#### 【0017】

以下、本発明の実施例による薄膜トランジスタ表示板及びこれを含む液晶表示装置について、図面を参照して詳細に説明する。

#### 【0018】

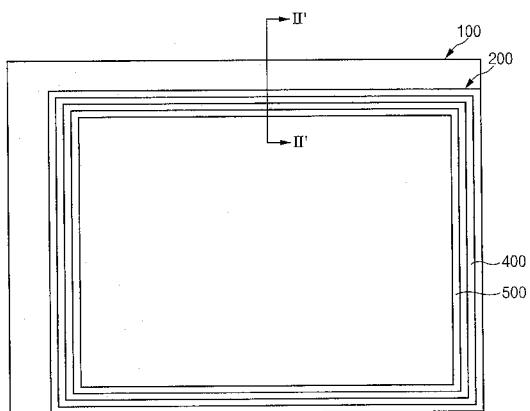

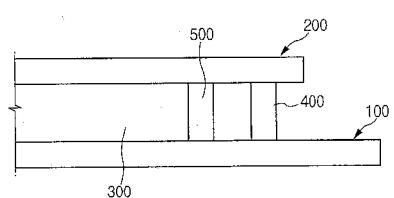

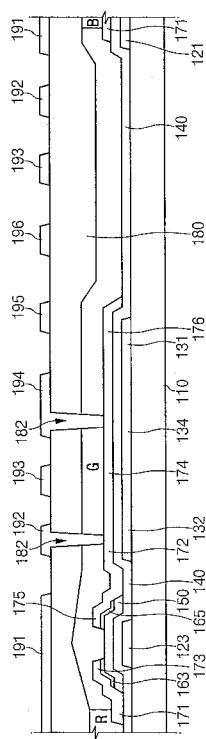

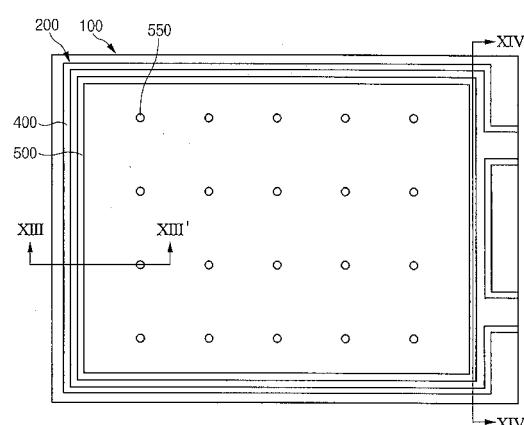

図1は本発明の実施例による液晶表示装置の構造を示した配置図であり、図2は図1のII-II'線による断面図である。50

## 【0019】

図1及び図2のように、互いに対向する下部及び上部表示板100、200、これらの間に形成されている液晶物質層300、下部及び上部表示板100、200の間に形成され、二つの表示板100、200の面に対してほぼ平行に配列されている液晶分子を含む液晶物質層300を封止する封止材400、及び封止材400の内側に形成され、画像が表示される表示領域を定義して表示領域周囲での光漏れを遮断するブラックマトリックス500を含む。この時、ブラックマトリックスは有機物質からなり、下部及び上部表示板100、200の間隔を平行に維持する基板間隔材の機能を有することができる。

## 【0020】

ここで、上部表示板200は対向表示板ともいい、これには製造工程時にブラックマトリックス500及び封止材400を形成する。また、下部表示板100は薄膜トランジスタ表示板ともいい、これには信号線、薄膜トランジスタなどを形成する。ブラックマトリックス500及び封止材400のうちの一つまたは全てを薄膜トランジスタ表示板100に形成することもできる。

## 【0021】

詳細には、本発明の実施例による液晶表示装置用薄膜トランジスタ表示板には、梯形(台形)パターンの画素領域を定義するゲート線及びデータ線が配置されており、液晶分子を駆動するための共通電極及び画素電極が互いに平行に配置されている。この時、共通電極に連結されている維持信号線は、データ線と平行に画素領域の長さ方向に延在している。また液晶分子は、データ線及び維持信号線と垂直に初期配向される。また、データ線と共に画素領域を定義するゲート線は、データ線と交差する部分と、梯形パターンの画素領域を定義し共通電極と平行に延在する部分とを含む。

## 【0022】

まず、本発明の第1実施例による液晶表示装置用薄膜トランジスタ表示板について説明する。

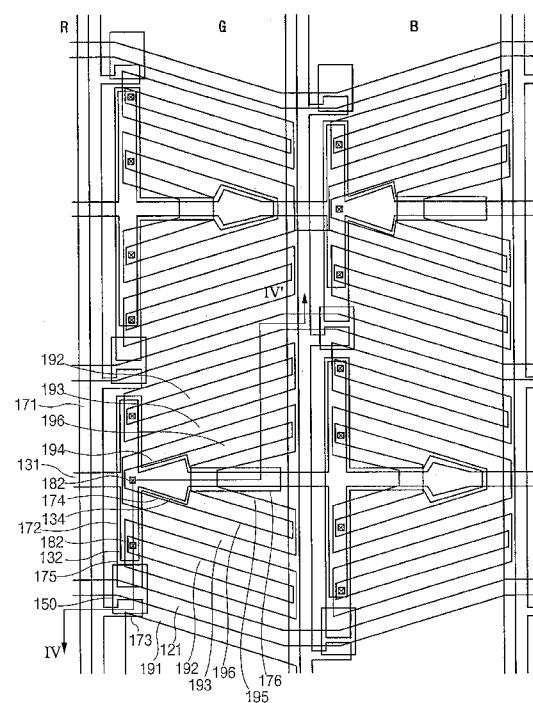

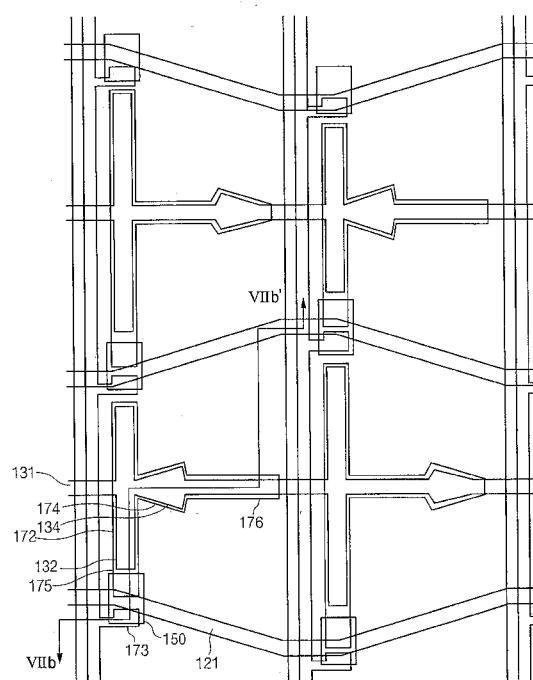

## 【0023】

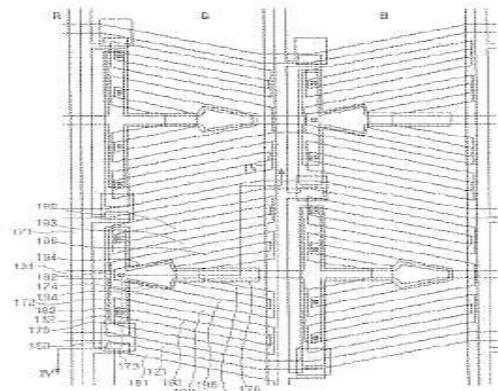

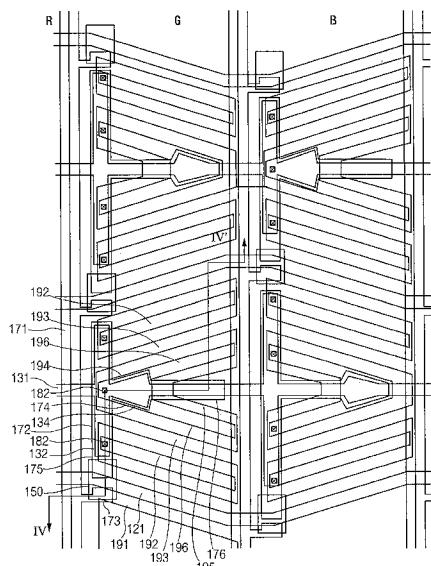

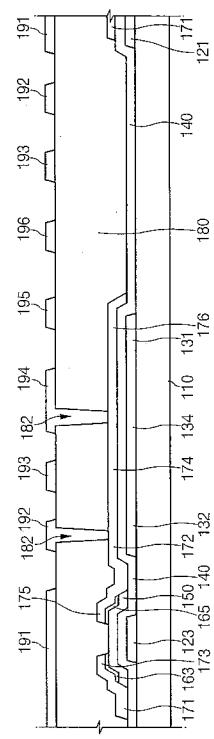

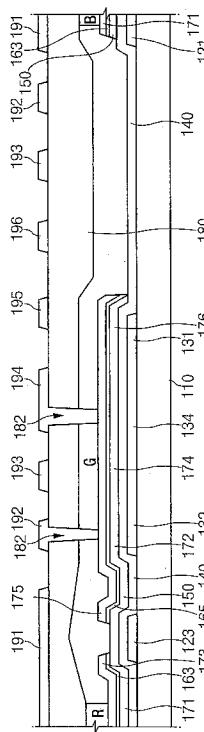

図3は本発明の第1実施例による液晶表示装置用薄膜トランジスタ表示板における単位画素の構成を簡略に示した配置図であり、図4は3の薄膜トランジスタ表示板のIV-IV'線による断面図である。

## 【0024】

図1乃至図3のように、絶縁基板110上に、主に横方向に延在している複数のゲート線121が形成されている。ゲート線121は、低い比抵抗の物質、例えば銀や銀合金またはアルミニウムやアルミニウム合金からなる単一膜からなることができる。これとは異なって、ゲート線121は、前記物質を含む少なくとも一つの膜と他の物質との接触特性に優れたパッド用の少なくとも一つの膜とを含む多層膜からなることもできる。ゲート線121の一端部付近に位置した部分(図示せず)は、外部からのゲート信号をゲート線に伝達し、各ゲート線121の一部123は薄膜トランジスタのゲート電極123を構成して分枝の形態を有することができる。この時、ゲート線121は、後に形成されるデータ線171と交差して梯形パターンの画素領域を定義するために、画素領域の境界で屈曲している。画素領域を定義するゲート線121の一部は、画素領域の図3中縦方向に延在するデータ線171に対して傾斜を有して交差している。このゲート線121の一部は、共通電極191、193、195の辺及び画素電極192、194、196と平行に形成されている。そして、ゲート線121の残りは、図3中横方向に延在して、図3中縦方向に延在するデータ線171と直交する。よって、ゲート線121とデータ線171とにより定義される画素領域は、梯形(台形)パターンを有する。また、ゲート線121と同一な層である絶縁基板110上には、画素領域の中央から図3中の横方向(図3中、データ線171と交差する方向)に延在している第1維持電極線131、及び画素領域の縁部から縦方向(図3中、データ線171方向に延在している第2維持電極線132が形成されている。この時、第1維持電極線131には、他の維持電極線部分より広い幅を有する第1拡張部134が連結されている。ここで、第1拡張部134は、第1維持電極線及び第2

10

20

30

40

50

維持電極線 131、132と共に、後に形成される複数の画素電極 196を連結する第2画素電極線 172と、これと連結された第1画素電極線 176及び第2拡張部 174と重畠して、維持蓄電器を構成する。第1拡張部 134及び第2拡張部 174は、画素領域の中央に形成されている。ここで、第1拡張部 134と第1維持電極線及び第2維持電極線 131、132とを一度に説明する際には、これらを維持信号線として記載する。

## 【0025】

そして、窒化ケイ素 (SiNx) などからなるゲート絶縁膜 140がゲート線 121及び維持信号線 131、132、134を覆っている。

## 【0026】

ゲート電極 125のゲート絶縁膜 140上には、水素化非晶質シリコンなどからなる島状半導体 150が形成されており、半導体 150の上部には、シリサイドまたはn型不純物が高濃度にドーピングされているn+水素化非晶質シリコンなどからなる複数対の抵抗性接触体 163、165が形成されている。各対の抵抗性接触部材 163、165は、該当ゲート線 121を中心にして互いに分離されている。この時、半導体 150及び抵抗性接触部材 163、165は、後に形成されるデータ線 171に沿って線形のパターンを有することができ、データ線 171及びドレーン電極 175と同一なパターンを有することができる。

## 【0027】

抵抗性接触部材 163、165及びゲート絶縁膜 140上には、複数のデータ線 171及び複数のドレーン電極 175が形成されている。データ線 171及びドレーン電極 175は、アルミニウムまたは銀のような低抵抗の導電物質からなる導電膜を含む。データ線 171は、主に図3中の縦方向に延在してゲート線 121と交差して梯形パターンの画素領域を定義する。データ線 171の複数の枝 173は、各対の抵抗性接触部材 163、165のうちの一つ 163の上部まで延在して、薄膜トランジスタのソース電極 173を構成する。データ線 171の一端付近に位置する部分(図示せず)は、外部からの画像信号をデータ線 171に伝達する。薄膜トランジスタのドレーン電極 175は、データ線 171と分離されて、ゲート電極 123に対してソース電極 173の反対側抵抗性接触部材 165の上部に位置する。また、ゲート絶縁膜 140上には、複数の第1及び第2維持電極線 131、132と各々重畠する第1及び第2画素電極線 176、172、及び第1拡張部 134と重畠する第2拡張部 174が形成されている。第2画素電極線 172は、ドレーン電極 175と連結されている。ここでも、第1画素電極線及び第2画素電極線 176、172と第2拡張部 174とは、画素信号線として記載する。

## 【0028】

データ線 171、ドレーン電極 175、及び画素信号線 172、174、176と、これらにより遮られない半導体 150との上部には、赤(R)、緑(G)、青(B)の色フィルターが順に形成されている。赤(R)、緑(G)、青(B)の色フィルターは互いに接しているが、互いに一定の間隔を置いてデータ線 171の上部で離隔していることもできる。また、互いに重なってブラックマトリックスの機能を有することができるが、この時、赤(R)、緑(G)、青(B)の色フィルターの縁部はテーパ構造を有するのが好ましい。

## 【0029】

一方、赤(R)、緑(G)、青(B)の色フィルターの下部には、半導体 150を覆う窒化ケイ素または酸化ケイ素からなる絶縁膜が追加されることがある。

## 【0030】

赤(R)、緑(G)、青(B)の色フィルターの上部には、窒化ケイ素または平坦化特性に優れた有機物質からなる下部保護膜 180が形成されている。保護膜 180には、第2画素電極線 172を露出する複数の接触孔 182が形成されている。

## 【0031】

保護膜 180上には、複数の共通電極 191、193、195、及びこれらと平行に対向する複数の画素電極 192、194、196が形成されている。つまり、互いに対向する共通電極 191、193、195の辺と画素電極 192、194、196の辺とは実質

10

20

30

40

50

的に平行で、画素領域を定義するゲート線 121 の一部と平行に配列されている。画素領域を定義するゲート線 121 の一部は、共通電極 191、193、195 の辺及び画素電極 192、194、196 と平行であるが、ゲート線 121 の残りは、図 3 中横方向に延在して、図 3 中縦方向に延在するデータ線 171 と交差する。ここで、画素電極 192、194、196 は、接触孔 182 を通じて第 2 画素電極線 172 と連結され、共通電極 191、193、195 は平面形態を有する。

#### 【0032】

図示してはいないが、保護膜 180 上には、液晶分子を配向するための配向膜が形成されている。

#### 【0033】

この時、ゲート電極 123、ゲート絶縁膜 140、半導体 150、抵抗性接触部材 163、165、ソース及びドレーン電極 173、175 は、薄膜トランジスタを構成する。

#### 【0034】

共通電極 191、193、195 及び画素電極 192、194、196 は、同一な層に配置されているが、各々ゲート線 121 またはデータ線 171 と同一な層に配置することもでき、これらは共に同一な層に配置されているが、互いに異なる層に配置することもできる。この時、配向膜で電極 191、192、193、194、195、196 の段差による配向不良が生じるのを防止するために、電極 191、192、193、194、195、196 は、2,000 以下の厚さであるのが好ましい。

#### 【0035】

液晶分子を初期配向するラビング方向は、データ線 171 または維持電極線 132 と垂直であるのが好ましい。

#### 【0036】

一方、ゲート絶縁膜 140 及び保護膜 180 には、外部の駆動回路からゲート信号及びデータ信号をゲート線及びデータ線に伝達するために、ゲート線 121 及びデータ線 171 の一端部上に接触孔が形成されている。この時、電極 191、192、193、194、195、196 と同一な層には、接触孔を通じてゲート線 121 及びデータ線 171 の一端部と連結される接触補助部材が追加されることができる。

#### 【0037】

ここで、電極 191、192、193、194、195、196 及び接触補助部材は、透明な導電物質である ITO または IZO からなることができる。

#### 【0038】

このような本発明の第 1 実施例による液晶表示装置用薄膜トランジスタ表示板では、画素領域を増加させる分だけ開口率を向上させることができる。

#### 【0039】

また、低誘電率を有する有機物質からなる保護膜 180 または色フィルターが、電極 191、192、193、194、195、196 とゲート線 121 及びデータ線 171 との間に配置され、これらの間で発生する側方電界 (lateral field) を弱化させることにより、これらを互いに重畳させて配置することができるので、画素の開口率を極大化することができる。

#### 【0040】

また、薄膜トランジスタ表示板に赤 (R)、緑 (G)、青 (B) の色フィルターを配置し、製造工程時の誤整列 (mis-align) に対する誤差 (margin) を最少化することにより、開口率が減少するのを防止することができる。また、透明な導電物質からなる電極 191、192、193、194、195、196 を画素に配置することにより、画素の透過率を極大化することができる。

#### 【0041】

第 2 維持電極線 132 が、データ線 171 と平行に画素の長さ方向に延在しており、液晶分子がデータ線 171 に垂直に液晶分子が初期配向されるようにラビングされている。よって、データ線 171 及び第 2 維持電極線 132 に電圧差が発生し、液晶分子が駆動さ

10

20

40

50

れても初期配向の方向と同一な方向に駆動されて暗く表示するので、側面クロストークが発生しない。

【0042】

従来の構造とは異なって、共通電極191、193、195及び画素電極192、194、196を、データ線171と平行な画素領域の長さ方向に配列することにより、電極191、192、193、194、195、196の数を容易に調節することができる。

【0043】

また、画素領域の最外角に配置されている画素電極及び共通電極が、ゲート線121及びデータ線171により定義される画素領域の辺と平行に配置されているので、画素領域の角部まで画像を表示することができる。また、テクスチャ(texture)により表示不良が生じる画素領域の中央に第1及拡張部及び第2拡張部134、174を含む維持蓄電器を配置することにより、画素の透過率が低下するのを防止することができる。これにより、画素の透過率を極大化することができると同時に、表示特性を向上させることができる。

【0044】

以下、本発明の第1実施例による液晶表示装置用薄膜トランジスタ表示板の製造方法について、図5a乃至9b、図3、及び図4を参照して詳細に説明する。

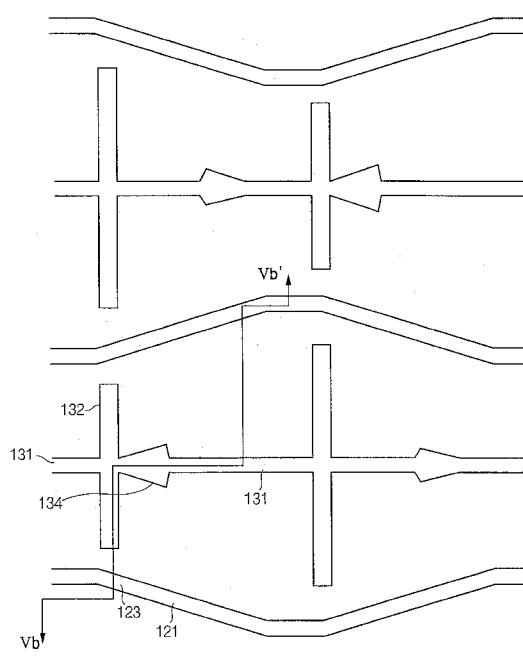

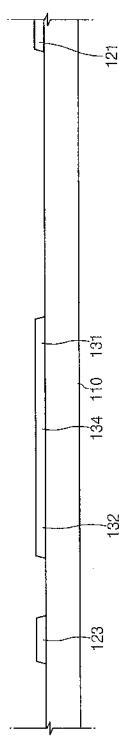

【0045】

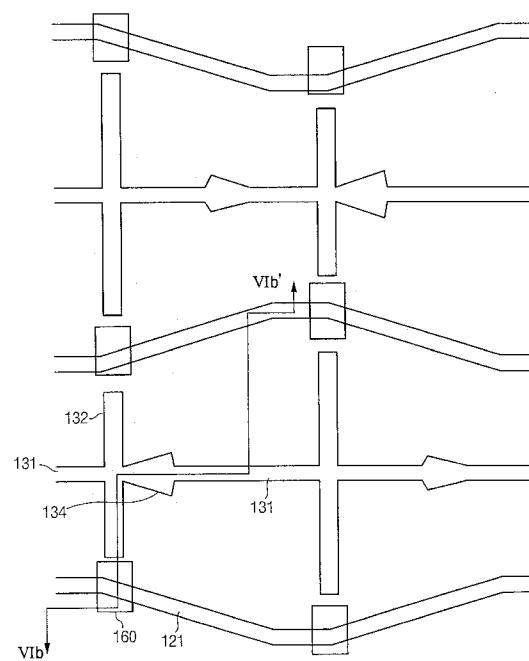

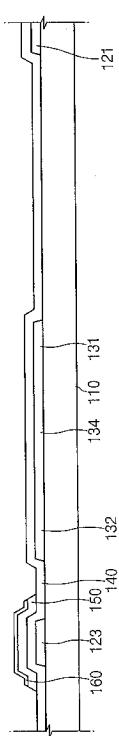

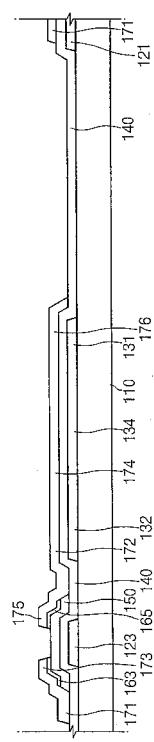

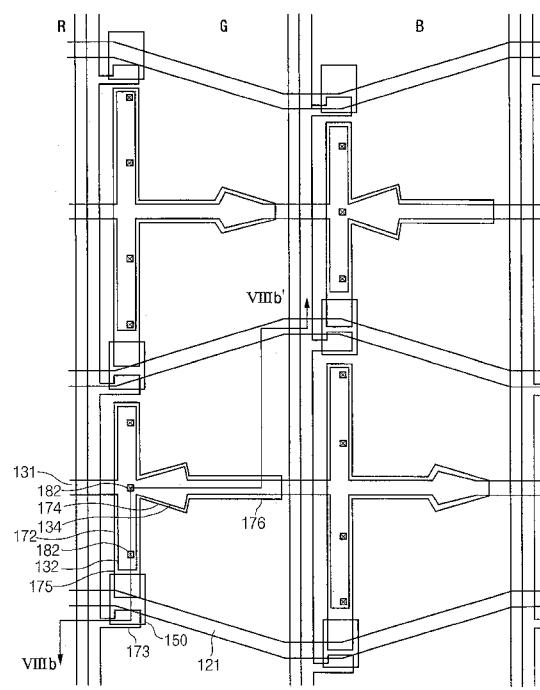

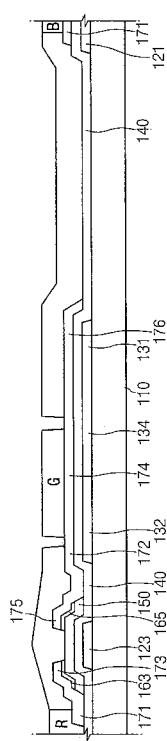

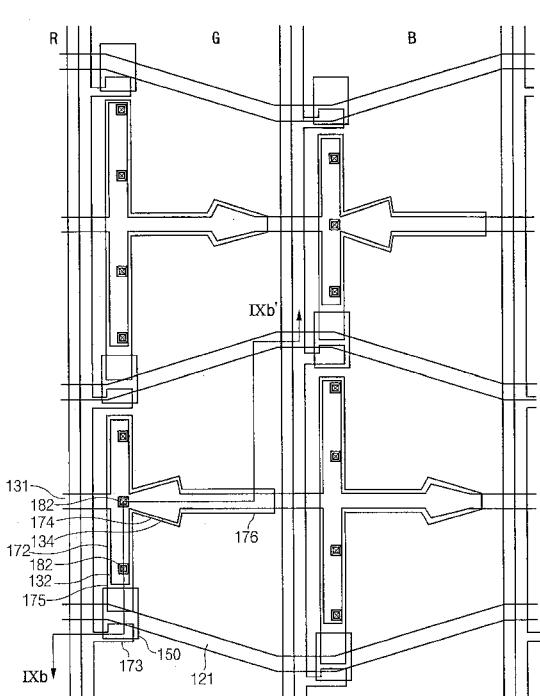

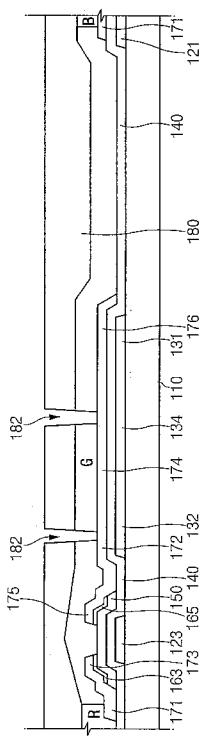

図5a乃至図9aは本発明の一実施例による液晶表示装置用薄膜トランジスタ表示板を製造する方法の各段階における薄膜トランジスタ表示板の配置図であり、図5b乃至9bは図5a乃至図9aの薄膜トランジスタ表示板をVb-Vb'、Vlb-Vlb'、VIIb-VIIb'、VIIIb-VII 20 Ib'及びIXb-IXb'によって切断した断面図である。

【0046】

まず、図5a及び5bに示されているように、絶縁基板110上に、ゲート線121、123及び維持信号線131、132、134を写真エッチング工程で形成する。

【0047】

次に、図6a及び6bのように、ゲート絶縁膜140、非晶質シリコン層、ドーピングされた非晶質シリコン層の3層膜を連続積層し、上の二つの層を写真エッチングして、ゲート絶縁膜140上に、複数の線状半導体150及び複数の線状にドーピングされた非晶質シリコン(doped amorphous silicon island)160を形成する。

【0048】

次に、図7a及び7bのように、複数のソース電極173を含む複数のデータ線171、複数のドレーン電極175、複数の画素信号線172、174、176を写真エッチング工程で形成する。次に、データ線171及びドレーン電極175で遮られないドーピングされた非晶質シリコン160部分を除去して、ドーピングされた非晶質シリコン160を各々線状及び島状抵抗性接触部材163、165に分離する一方で、両者の半導体150部分を露出する。次に、露出された半導体150の表面を安定化するために酸素プラズマ処理を実施するのが好ましい。

【0049】

次に、層間絶縁膜(図示せず)を形成した後、図8a乃至8bに示されているように、赤、緑、青の顔料を含む感光性有機物質をそれぞれ順に塗布し、写真エッチング工程だけで第2画素電極線172を露出する複数の開口部を有する赤、緑、青の色フィルターR、G、Bを順に形成する。

【0050】

次に、図9a及び図9bのように、平坦化特性に優れた絶縁物質からなる保護膜180を積層し、写真エッチング工程でゲート絶縁膜140と共にパターニングして、接触孔182をテーパ構造に形成する。第2画素電極線172を露出する接触孔182は、カラーフィルターR、G、Bに形成されている開口部の内側に位置したり、外側に位置することができる。

【0051】

次に、図3及び図4に示されているように、1,500乃至500の厚さのITO 50

またはIZO層を蒸着し、写真エッチング工程で複数の電極191、192、193、194、195、196、及びゲート線121及びデータ線171の端部に連結される複数の接触補助部材を形成する。

#### 【0052】

一方、本発明の第1実施例では、薄膜トランジスタ表示板に色フィルターを形成したが、そうしないこともできる。これについて、図面を参照して具体的に説明する。

#### 【0053】

図10は本発明の第2実施例による薄膜トランジスタ表示板の構造を示した断面図である。大部分の構造は図4と同じである。ところが、赤、緑、青の色フィルターを備えていない。この実施例では色フィルターを対向表示板200に備えている。

10

#### 【0054】

図11を参照して本発明の第3実施例による液晶表示装置の構造について詳細に説明する。

#### 【0055】

図11は本発明の第3実施例による液晶表示装置用薄膜トランジスタ表示板の構造を示した断面図である。大部分の構造は図4と同じである。ところが、第3実施例では、データ線171、ドレーン電極175、及び画素信号線172、174、176の下部に複数の線状半導体150及び複数の抵抗性接触部材163、165が形成されている。

#### 【0056】

線状半導体150は、薄膜トランジスタのチャンネル領域(C)を除いて、複数のデータ線171、複数のドレーン電極175、及び画素信号線172、174、176とほとんど同一な平面パターンである。即ち、薄膜トランジスタのチャンネル領域で、データ線171とドレーン電極175とは互いに分離されているが、線状半導体150はここで切れずに連結されて薄膜トランジスタのチャンネルを形成する。抵抗性接触部材163、165は、各々データ線171、ドレーン電極175、及び画素信号線172、174、176と同一なパターンである。

#### 【0057】

データ線171、ドレーン電極175、及び画素信号線172、174、176と半導体150及び抵抗性接触部材163、165とは、テーパ構造を有する。

20

#### 【0058】

このような本発明の第3実施例による液晶表示装置用基板の製造方法では、半導体層150及び抵抗性接触部材163、165とデータ線171、ドレーン電極175、及び画素信号線172、174、176とを一つの感光膜パターンを用いた写真エッチング工程でパターニングする。この時、感光膜パターンは、互いに異なる厚さを有する二つの部分を含むが、その一つの部分は薄膜トランジスタのチャンネル領域に位置し、配線領域に位置した他の部分より厚さが薄い。ここで、二つの部分は、半導体層150をパターニングするためのエッティングマスクであり、厚い部分はデータ線171、ドレーン電極175、及び画素信号線172、174、176をパターニングするためのエッティングマスクである。

#### 【0059】

一つの感光膜パターンを用いた写真エッチング工程で位置によって感光膜パターンの厚さを異ならせるためには、様々な方法がある。例えば、光マスクに透明領域(transparent area)及び遮光領域(light blocking area)の他に半透明領域(translucent area)を設ける方法がある。半透明領域にはスリット(slit)パターン、格子パターン(lattice pattern)、または透過率が中間であったり厚さが中間である薄膜が備わる。スリットパターンである場合には、スリットの幅やスリット間の間隔が写真エッチング工程に使用する露光器の分解能(resolution)より小さいのが好ましい。他の例として、リフローが可能な感光膜を用いる方法がある。つまり、透明領域及び遮光領域だけを有する通常のマスクにおいて、リフロー可能な感光膜パターンを形成した後にリフローさせて感光膜が残留しない領域に流すことによって、薄い部分を形成することができる。

40

50

## 【0060】

次に、本発明の実施例による液晶表示装置の薄膜トランジスタ表示板と対向する対向表示板の構造について具体的に説明する。

## 【0061】

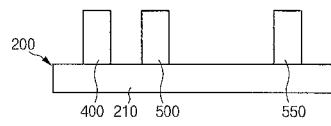

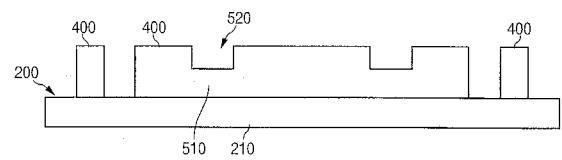

図12は本発明の実施例による液晶表示装置を組立てる前の対向表示板の構造を示した平面図であり、図13及び図14は図12のXII-XII'及びXIII-XIII'線による断面図である。

## 【0062】

図12乃至図14のように、本発明の実施例による液晶表示装置用対向表示板には、上部絶縁基板210上の周囲の液晶物質を封止するための封止材400が形成されており、封止材400の内側には、表示領域を定義し、周囲で漏れる光を遮断するためのブラックマトリックス500が形成されている。また、上部絶縁基板210の上部の表示領域には、薄膜トランジスタ表示板100と対向表示板200との間隔を均一に支持するための基板間隔材550が形成されている。

## 【0063】

封止材400は、薄膜トランジスタ表示板100を組立てて液晶表示装置を完成させる前には液晶物質を注入するための液晶注入口を有し、完成した後には他の封止材を利用して封止する。

## 【0064】

ブラックマトリックス500及び基板間隔材550は、黒色顔料を含む有機物質からなり、封止材400の液晶注入口に対応するブラックマトリックス500には、他の部分より厚さの薄いトレンチ520が形成されている。これは液晶注入時に液晶注入が容易に行われるようするためで、他の部分、特にトレンチ520が形成されている部分の向かい側のブラックマトリックス500に追加して配置される。

## 【0065】

図13では、基板間隔材550及びブラックマトリックス500が示されているが、基板間隔材550は、薄膜トランジスタ表示板で生じる段差を考慮してブラックマトリックス500より薄く形成することができ、そのために、半透明領域にスリットパターン、格子パターン、または透過率が中間であったり厚さが中間である薄膜が備えられたマスクを用いた写真エッチング工程でパターニングするのが好ましい。ブラックマトリックス500にトレンチ520を形成する工程でも同様な方法でパターニングする。

## 【0066】

一方、本発明の実施例では、基板間隔材550及びブラックマトリックス500を有機物質から形成したが、金属または金属酸化膜から形成することもできる。

## 【0067】

このような本発明の実施例による液晶表示装置の構造では、色フィルターを薄膜トランジスタ表示板に形成し、対向表示板にはブラックマトリックスだけを形成することにより、誤整列による誤差を考慮しなくてもすむ。また、対向基板200の周囲に配置されたブラックマトリックス500が、液晶物質が封止材400と直接接触するのを防止し、液晶物質が封止材400によって汚染されるのを防止することができる。

## 【0068】

このような薄膜トランジスタ表示板及び対向表示板は、この他にも様々な変形した形態及び方法で製造することができる。

## 【0069】

以上、本発明の好ましい実施例について詳細に説明したが、本発明の権利範囲はこれに限定されるわけではなく、請求の範囲で定義している本発明の基本概念を利用した当業者の多様な変形及び改良形態もまた本発明の権利範囲に属する。

## 【図面の簡単な説明】

## 【0070】

【図1】本発明の実施例による液晶表示装置の構造を示した平面図である。

10

20

30

40

50

【図2】図1の液晶表示装置のII-II'線による断面図である。

【図3】本発明の第1実施例による液晶表示装置用薄膜トランジスタ表示板の構造を示した配置図である。

【図4】図3のIV-IV'線による断面図である。

【図5a】本発明の第1実施例による液晶表示装置用薄膜トランジスタ表示板の製造方法をその工程順に示した断面図である。

【図5b】図5aのVb-Vb'線による断面図である。

【図6a】本発明の第1実施例による液晶表示装置用薄膜トランジスタ表示板の製造方法をその工程順に示した断面図である。

【図6b】図6aのVIb-VIb'線による断面図である。

【図7a】本発明の第1実施例による液晶表示装置用薄膜トランジスタ表示板の製造方法をその工程順に示した断面図である。

【図7b】図7aのVIIb-VIIb'線による断面図である。

【図8a】本発明の第1実施例による液晶表示装置用薄膜トランジスタ表示板の製造方法をその工程順に示した断面図である。

【図8b】図8aのVIIIb-VIIIb'線による断面図である。

【図9a】本発明の第1実施例による液晶表示装置用薄膜トランジスタ表示板の製造方法をその工程順に示した断面図である。

【図9b】図9aのIXb-IXb'線による断面図である。

【図10】本発明の第2及び第3実施例による液晶表示装置用薄膜トランジスタ表示板の構造を示した断面図である。

【図11】本発明の第2及び第3実施例による液晶表示装置用薄膜トランジスタ表示板の構造を示した断面図である。

【図12】本発明の実施例による液晶表示装置を組立てる前の対向表示板の構造を示した平面図である。

【図13】図12のXII-XII'線による断面図である。

【図14】図12のXIII-XIII'線による断面図である。

【符号の説明】

【0071】

100、200 表示板

110 絶縁基板

121、123 ゲート線

131、132 維持電極線

140 ゲート絶縁膜

171 データ線

175 ドレーン電極

192、194、196 画素電極

191、193、195 共通電極

300 液晶物質層

400 封止材

500 ブラックマトリックス

520 トレンチ

550 基板間隔材

10

20

30

40

【 図 1 】

【 図 2 】

【 図 4 】

【 図 3 】

【図 5 a】

【図 5 b】

【図 6 a】

【図 6 b】

【図 7 a】

【図 7 b】

【図 8 a】

【図 8 b】

【図 9 a】

【 図 9 b 】

【 図 1 0 】

【 図 1 1 】

【 図 1 2 】

【 図 1 3 】

### 【図14】

---

フロントページの続き

(72)発明者 韓 銀 姫

大韓民国ソウル市江南区道谷1洞948-29番地302号

(72)発明者 金 兌 奥

大韓民国ソウル市廣津区九宜3洞現代プライムアパート1棟2606号

F ターム(参考) 2H092 GA12 GA13 GA14 GA21 GA24 GA25 GA26 JA24 JB01 JB11

JB61 JB66 NA01 NA07 QA05

5C094 AA06 AA16 AA60 BA03 BA43 CA19 DA13 EA04 EA07 ED03

FA10

【要約の続き】

【選択図】 図3

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 薄膜晶体管阵列面板和包括其的液晶显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 公开(公告)号        | JP2004361949A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 公开(公告)日 | 2004-12-24 |

| 申请号            | JP2004160998                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 申请日     | 2004-05-31 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| [标]发明人         | 李昶勳<br>倉學スン<br>韓銀姫<br>金兌奐                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 发明人            | 李昶勳<br>倉學▲スン▼<br>韓銀姫<br>金兌奐                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G02F1/1368 G02F1/1343 G02F1/136 G02F1/1362 G09F9/30 G09F9/35 H01L21/77 H01L21/84 H01L27/12 H01L27/13                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| CPC分类号         | H01L27/124 G02F1/133707 G02F1/134363 G02F1/136227 G02F2001/134318 G02F2001/13606 G02F2001/136222 G02F2201/40 H01L27/1255                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| FI分类号          | G02F1/1368 G02F1/1362 G09F9/30.338 G09F9/35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| F-TERM分类号      | 2H092/GA12 2H092/GA13 2H092/GA14 2H092/GA21 2H092/GA24 2H092/GA25 2H092/GA26 2H092/JA24 2H092/JB01 2H092/JB11 2H092/JB61 2H092/JB66 2H092/NA01 2H092/NA07 2H092/QA05 5C094/AA06 5C094/AA16 5C094/AA60 5C094/BA03 5C094/BA43 5C094/CA19 5C094/DA13 5C094/EA04 5C094/EA07 5C094/ED03 5C094/FA10 2H192/AA24 2H192/AA43 2H192/AA45 2H192/BB03 2H192/BB52 2H192/BB53 2H192/BB73 2H192/BC31 2H192/CB05 2H192/CB46 2H192/CC15 2H192/DA13 2H192/DA15 2H192/DA32 2H192/DA42 2H192/EA32 2H192/EA42 2H192/EA67 2H192/FA65 2H192/GD23 2H192/HA33 2H192/HA43 2H192/HA44 2H192/JA33 |         |            |

| 优先权            | 1020030034677 2003-05-30 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 其他公开文献         | JP4776893B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

## 摘要(译)

本发明的目的是提高水平电场驱动型液晶显示装置的开口率。另一个目的是提供一种能够容易地调节用于施加水平电场的电极的数量的液晶显示装置。薄膜晶体管面板包括栅极线和具有部分倾斜部分的存储电极线，该存储电极线包括形成在绝缘基板上的部分栅极，并且半导体层形成在覆盖该栅极线的栅极绝缘膜上。形成。栅极绝缘膜的至少一部分位于半导体层上，并且数据线以及与数据线分开的栅极线的倾斜部分与栅极线的倾斜部分一起限定梯形图案的像素区域。形成彼此面对的漏极电极和与存储电极线重叠以形成存储电容器的像素电极线。在覆盖没有被数据线和漏极阻挡的半导体层的保护膜上，交替地形成有与漏极电连接的线性像素电极和与漏极电连接的像素电极。从电极的边缘以规则的间隔彼此平行地形成线性公共电极。[选择图]图3