(19) 日本国特許庁 (JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-302466

(P2004-302466A)

(43) 公開日 平成16年10月28日(2004.10.28)

(51) Int. Cl. 7

F

### テーマコード（参考）

GO2F 1/1343

GO2F 1/1343

2H088

GO2F 1/1333

GO2F 1/1333 505

2H090

GO2F 1/137

GO2F 1/137

2H092

GO9F 9/30

GO 9 F 9/30

5C094

審査請求 有 請求項の数 37 O.L. (全 35 頁)

|              |                            |

|--------------|----------------------------|

| (21) 出願番号    | 特願2004-93398 (P2004-93398) |

| (22) 出願日     | 平成16年3月26日 (2004. 3. 26)   |

| (31) 優先権主張番号 | 2003-019781                |

| (32) 優先日     | 平成15年3月29日 (2003. 3. 29)   |

| (33) 優先権主張国  | 韓国 (KR)                    |

| (31) 優先権主張番号 | 2003-019783                |

| (32) 優先日     | 平成15年3月29日 (2003. 3. 29)   |

| (33) 優先権主張国  | 韓国 (KR)                    |

| (31) 優先権主張番号 | 2003-021118                |

| (32) 優先日     | 平成15年4月3日 (2003. 4. 3)     |

| (33) 優先権主張国  | 韓国 (KR)                    |

(71) 出願人 599127667

エルジー フィリップス エルシーティー

カンパニー リミテッド

大韓民国 ソウル, ヨンドンポーク,

ヨイドードン 20

(74) 代理人 100057874

弁理士 曽我 道照

(74) 代理人 100110423

弁理士 曽我 道治

(74) 代理人 100084010

弁理士 古川 秀利

(74) 代理人 100094695

弁理士 鈴木 憲七

(74) 代理人 100111648

弁理士 樋並 順

### 最終頁に続く

(54) 【発明の名称】 水平電界印加型液晶表示装置及びその製造方法

(57) 【要約】

【課題】マスク工程数を節減することができる薄膜トランジスタアレイ基板及びその製造方法を提供する。

【解決手段】基板上に形成されたゲートライン、共通ライン、データライン、薄膜トランジスタ、画素領域に形成されて共通ラインと接続される共通電極、薄膜トランジスタと接続されて画素領域に共通電極と水平電界を形成する画素電極、ゲートラインに含まれた少なくとも一つの導電層で形成されるゲートパッド、データラインに含まれた少なくとも一つの導電層で形成されるデータパッド、共通ラインに含まれた少なくとも一つの導電層で形成される共通パッド、ゲートパッド、データパッド及び共通パッドを露出させる保護膜を具備する薄膜トランジスタアレイ基板と、薄膜トランジスタアレイ基板と合着されてその間に液晶が満たされるようにするカラーフィルターアレイ基板と、薄膜トランジスタアレイ基板の露出したパッドと接続される導電性フィルムとを具備する。

### 【選択図】図5

**【特許請求の範囲】****【請求項 1】**

基板上に形成されたゲートラインと、前記ゲートラインと平行に形成された共通ラインと、前記ゲートライン及び前記共通ラインとゲート絶縁膜を間に置いて交差して画素領域を決めるデータラインと、前記ゲートライン及び前記データラインの交差部に形成された薄膜トランジスタと、前記画素領域に形成されて、前記共通ラインと接続された共通電極と、前記薄膜トランジスタと接続され、前記画素領域に前記共通電極と水平電界を形成するように形成された画素電極と、前記ゲートラインに含まれた少なくとも一つの導電層で形成されたゲートパッドと、前記データラインに含まれた少なくとも一つの導電層で形成されたデータパッドと、前記共通ラインに含まれた少なくとも一つの導電層で形成された共通パッドと、前記ゲートパッド、前記データパッド、及び前記共通パッドを露出させる保護膜とを具備する薄膜トランジスタアレイ基板と、前記薄膜トランジスタアレイ基板と合着されて、その間に液晶が満たされるようにするカラーフィルターアレイ基板と、前記薄膜トランジスタアレイ基板の露出したパッドと接続された導電性フィルムとを具備することを特徴とする水平電界印加型液晶表示装置。10

**【請求項 2】**

前記ゲートライン及び前記共通ラインは、主導電層と、その主導電層の断線防止のための補助導電層とを具備することを特徴とする請求項 1 記載の水平電界印加型液晶表示装置。20

**【請求項 3】**

前記ゲートパッド及び前記共通パッドは、前記主導電層と前記補助導電層を具備し、前記補助導電層は露出した構造を有することを特徴とする請求項 2 記載の水平電界印加型液晶表示装置。20

**【請求項 4】**

前記ゲートパッド及び前記共通パッドは、前記補助導電層を具備することを特徴とする請求項 2 記載の水平電界印加型液晶表示装置。

**【請求項 5】**

前記主導電層は、低抵抗金属であるアルミニウム系金属、銅、モリブデン、クロム、タンゲステンの中から少なくとも一つの金属を含み、前記補助導電層は、チタンを含むことを特徴とする請求項 2 記載の水平電界印加型液晶表示装置。30

**【請求項 6】**

前記データラインは、主導電層と、その主導電層の断線防止のための補助導電層を具備することを特徴とする請求項 1 記載の水平電界印加型液晶表示装置。

**【請求項 7】**

前記データパッドは、前記主導電層と前記補助導電層を具備し、前記補助導電層は露出した構造を有することを特徴とする請求項 6 記載の水平電界印加型液晶表示装置。

**【請求項 8】**

前記データパッドは、前記補助導電層を具備することを特徴とする請求項 6 記載の水平電界印加型液晶表示装置。

**【請求項 9】**

前記主導電層は、低抵抗金属であるアルミニウム系金属、銅、モリブデン、クロム、タンゲステンの中から少なくとも一つの金属を含み、前記補助導電層はチタンを含むことを特徴とする請求項 6 記載の水平電界印加型液晶表示装置。40

**【請求項 10】**

前記基板のエッティング防止のためのエッティング防止層をさらに具備することを特徴とする請求項 1 記載の水平電界印加型液晶表示装置。

**【請求項 11】**

前記エッティング防止層は、フッ酸系エッチャントに対して強い透明オキサイド系物質を含むことを特徴とする請求項 10 記載の水平電界印加型液晶表示装置。

**【請求項 12】**

10

20

30

40

50

前記エッチング防止層は、 $TiO_2$ 及び $Al_2O_3$ の中からいずれかを含むことを特徴とする請求項1記載の水平電界印加型液晶表示装置。

【請求項13】

前記薄膜トランジスタは、前記ゲートラインと接続されたゲート電極と、前記データラインと接続されたソース電極と、前記ソース電極と対向されるドレーン電極と、前記ゲート電極と前記ゲート絶縁膜を間に置いて重畳されて、前記ソース電極及び前記ドレーン電極の間にチャンネル部を形成する半導体層を具備することを特徴とする請求項1記載の水平電界印加型液晶表示装置。

【請求項14】

前記ドレーン電極と前記画素電極は、同一な導電層から構成されることを特徴とする請求項13記載の水平電界印加型液晶表示装置。 10

【請求項15】

前記共通ラインの一部からなるストレージ下部電極と、前記ゲート絶縁膜上に前記ストレージ下部電極と重畳されるように形成され、前記画素電極と同一な導電層から構成されるストレージ上部電極を具備するストレージキャパシタをさらに具備することを特徴とする請求項13記載の水平電界印加型液晶表示装置。

【請求項16】

前記半導体層は、前記データライン、前記ソース電極、前記ドレーン電極、前記画素電極、及び前記ストレージ上部電極に沿って前記ゲート絶縁膜上に形成されることを特徴とする請求項15記載の水平電界印加型液晶表示装置。 20

【請求項17】

前記画素電極は、前記共通電極と並行するように形成されて前記共通電極と水平電界を成すフィンガー部と、前記フィンガー部と連結されて、前記ゲートラインと並行するように形成される水平部とを含むことを特徴とする請求項13記載の水平電界印加型液晶表示装置。

【請求項18】

前記半導体層は、少なくとも前記画素電極のフィンガー部と同一な幅を持つように形成されることを特徴とする請求項17記載の水平電界印加型液晶表示装置。

【請求項19】

前記ゲートパッド、前記データパッド、前記共通パッド、及び前記画素電極を露出させる保護膜をさらに具備することを特徴とする請求項18記載の水平電界印加型液晶表示装置。 30

【請求項20】

ゲートラインとデータラインの交差部に形成された薄膜トランジスタと、その薄膜トランジスタと接続された画素電極、前記画素電極と水平電界を形成する共通電極、その共通電極と接続された共通ラインを含み、前記ゲートラインに含まれる少なくとも一つの導電層で形成されたゲートパッド、前記データラインに含まれる少なくとも一つの導電層で形成されたデータパッド、及び前記共通ラインに含まれる少なくとも一つの導電層で形成された共通パッドが保護膜を通じて露出した構造を持つ薄膜トランジスタアレイ基板を用意する段階と、前記薄膜トランジスタアレイ基板と対向するようにカラーフィルターアレイ基板を用意する段階と、前記薄膜トランジスタアレイ基板と前記カラーフィルターアレイ基板を合着する段階と、前記露出したゲートパッド、データパッド、及び共通パッドに導電性フィルムを接続させる段階とを含むことを特徴とする水平電界印加型液晶表示装置の製造方法。 40

【請求項21】

前記薄膜トランジスタアレイ基板を用意する段階は、基板上に前記ゲートライン、そのゲートラインと接続された前記薄膜トランジスタのゲート電極、そのゲートラインと平行な前記共通ライン、前記共通電極、前記ゲートパッド、及び前記共通パッドを含む第1導電パターン群を形成する段階と、前記第1導電パターン群が形成された前記基板上にゲート絶縁膜を形成する段階と、前記データライン、そのデータラインと接続された前記薄膜 50

トランジスタのソース電極、そのソース電極と対向される前記薄膜トランジスタのドレン電極、そのドレン電極と接続され、前記共通電極と平行な画素電極、及び前記データパッドを含む第2導電パターン群と、前記薄膜トランジスタのチャンネルを含み、前記第2導電パターン群に沿う半導体層を形成する段階と、前記半導体層及び前記第2導電パターン群が積層された前記ゲート絶縁膜上に前記ゲートパッド、前記データパッド、及び前記共通パッドを露出させる保護膜を形成する段階とを含むことを特徴とする請求項20記載の水平電界印加型液晶表示装置の製造方法。

【請求項22】

前記第1及び第2導電パターン群の中から少なくともいずれかは、主導電層と、その主導電層の断線防止のための補助導電層の二層構造で形成されることを特徴とする請求項21記載の水平電界印加型液晶表示装置の製造方法。 10

【請求項23】

前記保護膜を形成する段階は、前記ゲートパッド及び前記共通パッドの補助導電層を露出させる段階を含むことを特徴とする請求項22記載の水平電界印加型液晶表示装置の製造方法。

【請求項24】

前記保護膜を形成する段階は、前記保護膜及び前記ゲート絶縁膜を貫くコンタクトホールを形成し、前記ゲートパッド及び前記共通パッドの補助導電層を露出させる段階を含むことを特徴とする請求項22記載の水平電界印加型液晶表示装置の製造方法。

【請求項25】

前記保護膜を形成する段階は、前記保護膜、前記ゲート絶縁膜、前記ゲートパッド及び前記共通パッドの主導電層を貫くコンタクトホールを形成し、前記ゲートパッド及び前記共通パッドの補助導電層を露出させる段階を含むことを特徴とする請求項22記載の水平電界印加型液晶表示装置の製造方法。 20

【請求項26】

前記保護膜を形成する段階は、前記データパッドの補助導電層を露出させる段階を含むことを特徴とする請求項22記載の水平電界印加型液晶表示装置の製造方法。

【請求項27】

前記保護膜を形成する段階は、前記保護膜を貫くコンタクトホールを形成し、前記データパッドの補助導電層を露出させる段階を含むことを特徴とする請求項22記載の水平電界印加型液晶表示装置の製造方法。 30

【請求項28】

前記保護膜を形成する段階は、前記保護膜と前記データパッドの主導電層を貫くコンタクトホールを形成し、前記データパッドの補助導電層を露出させる段階を含むことを特徴とする請求項22記載の水平電界印加型液晶表示装置の製造方法。

【請求項29】

前記主導電層は、低抵抗金属であるアルミニウム系金属、銅、モリブデン、クロム、タンゲステンの中から少なくとも一つの金属を含み、前記補助導電層は、チタンを含むことを特徴とする請求項22記載の水平電界印加型液晶表示装置の製造方法。

【請求項30】

前記第2導電パターン群を形成する段階は、前記共通ラインと前記ゲート絶縁膜を間に置いて重疊されるストレージ上部電極を形成する段階をさらに含むことを特徴とする請求項20記載の水平電界印加型液晶表示装置の製造方法。 40

【請求項31】

前記薄膜トランジスタアレイ基板を用意する段階は、基板を用意する段階と、前記基板上に前記エッチング防止層を形成する段階をさらに含むことを特徴とする請求項20記載の水平電界印加型液晶表示装置の製造方法。

【請求項32】

前記エッチング防止層は、フッ酸系エッチャントに対して強い透明オキサイド系物質を含むことを特徴とする請求項31記載の水平電界印加型液晶表示装置の製造方法。 50

## 【請求項 3 3】

前記エッチング防止層は、 $TiO_2$ 及び $Al_2O_3$ の中からいずれかを含むことを特徴とする請求項 3 2 記載の水平電界印加型液晶表示装置の製造方法。

## 【請求項 3 4】

前記薄膜トランジスタアレイ基板を用意する段階は、基板上に前記ゲートライン、そのゲートラインと接続された前記薄膜トランジスタのゲート電極、そのゲートラインと平行な前記共通ライン、前記共通電極、前記ゲートパッド、及び前記共通パッドを含む第1導電パターン群を形成する段階と、前記第1導電パターン群が形成された前記基板上にゲート絶縁膜を形成する段階と、前記データライン、そのデータラインと接続された前記薄膜トランジスタのソース電極、そのソース電極と対向される前記薄膜トランジスタのドレン電極、そのドレン電極に含まれる少なくとも一つの導電層で形成されて、前記共通電極と水平電界を成すフィンガー部を持つ画素電極、前記データパッドを含む第2導電パターン群と、前記薄膜トランジスタのチャンネル部を形成し、前記画素電極と重畠される半導体層を形成する段階と、前記半導体層及び前記第2導電パターン群を覆うように前記ゲート絶縁膜上に保護膜を形成する段階と、少なくとも前記画素電極のフィンガー部において、前記画素電極と同一な幅を持つように前記半導体層をパターニングする段階とを含むことを特徴とする請求項 2 0 記載の水平電界印加型液晶表示装置の製造方法。

10

## 【請求項 3 5】

前記保護膜を形成する段階は、前記保護膜を貫くコンタクトホールを形成して前記データパッドの補助導電層を露出させることと同時に、前記保護膜及び前記ゲート絶縁膜を貫く貫通ホールを形成して前記画素電極の補助導電層及び前記画素電極と重畠される半導体層を露出させる段階を含むことを特徴とする請求項 3 4 記載の水平電界印加型液晶表示装置の製造方法。

20

## 【請求項 3 6】

前記保護膜を形成する段階は、前記保護膜と前記主導電層を貫くコンタクトホールを形成して前記データパッドの補助導電層を露出させることと同時に、前記保護膜及び前記ゲート絶縁膜と前記主導電層を貫く貫通ホールを形成して前記画素電極の補助導電層及び前記画素電極と重畠される半導体層を露出させる段階を含むことを特徴とする請求項 3 4 記載の水平電界印加型液晶表示装置の製造方法。

30

## 【請求項 3 7】

前記半導体層をパターニングする段階は、前記画素電極をマスクとして前記半導体層を乾式エッチングする段階を含むことを特徴とする請求項 3 4 記載の水平電界印加型液晶表示装置の製造方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0 0 0 1】

本発明は水平電界を利用する液晶表示装置に関するもので、特にマスク工程の数を減らすことができる水平電界印加型液晶表示装置及びその製造方法に関するものである。

## 【背景技術】

## 【0 0 0 2】

液晶表示装置は電界を利用して液晶の光透過率を調節することで画像を表示するようになる。このような液晶表示装置は液晶を駆動させる電界の方向によって垂直電界型と水平電界型に大別される。

40

## 【0 0 0 3】

垂直電界型液晶表示装置は、上部基板上に形成された共通電極と下部基板上に形成された画素電極が互いに対向されるように配置され、これらの間に形成される垂直電界によって TN (Twisted Nematic) モードの液晶を駆動するようになる。このような垂直電界型液晶表示装置は、開口率が大きい長所を持つ反面、視野角が 90 度程度で狭い短所を持つ。

## 【0 0 0 4】

50

水平電界型液晶表示装置は、下部基板に並行するように配置された画素電極と共に電極の間の水平電界によってインプレーンスイッチ (In Plane Switch; IPS) モードの液晶を駆動するようになる。このような水平電界型液晶表示装置は、視野角が 160 度程度で広い長所を持つ。以下、水平電界型液晶表示装置に対して詳細に説明することにする。

#### 【0005】

水平電界型液晶表示装置は、互いに対向して合着された薄膜トランジスタアレイ基板（下板）及びカラーフィルターアレイ基板（上板）と、二つの基板の間でセルギャップを一定に維持させるためのスペーサーと、スペーサーによって用意された液晶空間に満たされた液晶を具備する。

#### 【0006】

薄膜トランジスタアレイ基板は、画素単位の水平電界形成のための多数の信号ライン及び薄膜トランジスタと、その上に液晶配向のために塗布された配向膜から構成される。カラーフィルターアレイ基板は、カラー具現のためのカラーフィルター及び光漏れ防止のためのブラックマトリックスと、それらの上に液晶配向のために塗布された配向膜から構成される。

#### 【0007】

このような液晶表示装置において、薄膜トランジスタアレイ基板は、半導体工程を含むことと同時に、多数のマスク工程を要することによって、製造工程が複雑で、液晶パネル製造単価上昇の主な原因になっている。これを解決するために、薄膜トランジスタアレイ基板は、マスク工程数を減らす方向に発展している。これは、一つのマスク工程が薄膜蒸着工程、洗浄工程、フォトリソグラフィ工程、エッチング工程、フォトレジスト剥離工程、検査工程などの多くの工程を含んでいるからである。これによって、最近では、薄膜トランジスタアレイ基板の標準マスク工程だった 5 マスク工程から一つのマスク工程を減らした 4 マスク工程が台頭している。

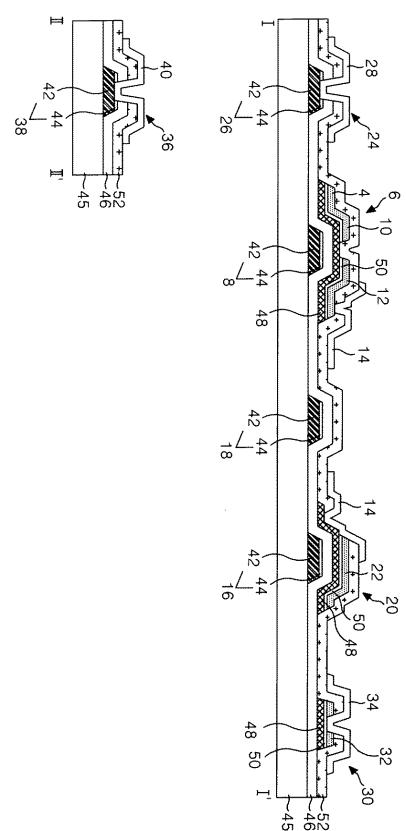

#### 【0008】

図 1 は従来の 4 マスク工程を利用した水平電界型液晶表示装置の薄膜トランジスタアレイ基板を示す平面図で、図 2 は図 1 で線 I - I'、II - II' に沿って切断した薄膜トランジスタアレイ基板を示す断面図である。

#### 【0009】

図 1 及び図 2 を参照すれば、従来の水平電界型液晶表示装置の薄膜トランジスタアレイ基板は、下部基板 45 上に交差されるように形成されたゲートライン 2 及びデータライン 4 と、その交差部毎に形成された薄膜トランジスタ 6 と、その交差構造で用意された画素領域に水平電界を成すように形成された画素電極 14 及び共通電極 18 と、共通電極 18 と接続された共通ライン 16 を具備する。また、従来の薄膜トランジスタアレイ基板は、画素電極 14 と共通ライン 16 の重畠部に形成されたストレージキャパシタ 20 と、ゲートライン 2 と接続されたゲートパッド 24 と、データライン 4 と接続されたデータパッド 30 と、共通ライン 16 と接続された共通パッド 36 とをさらに具備する。

#### 【0010】

ゲートライン 2 は薄膜トランジスタ 6 のゲート電極 8 にゲート信号を供給する。データライン 4 は薄膜トランジスタ 6 のドレーン電極 12 を通じて画素電極 14 に画素信号を供給する。ゲートライン 2 とデータライン 4 は交差構造に形成されて画素領域 5 を定義する。

#### 【0011】

共通ライン 16 は画素領域 5 を間に置いてゲートライン 2 と並行するように形成されて液晶駆動のための基準電圧を共通電極 18 に供給する。

#### 【0012】

薄膜トランジスタ 6 はゲートライン 2 のゲート信号に応答してデータライン 4 の画素信号が画素電極 14 に充電されて維持されるようにする。このため、薄膜トランジスタ 6 は、ゲートライン 2 に接続されたゲート電極 8 と、データライン 4 に接続されたソース電極 10 と、画素電極 14 に接続されたドレーン電極 12 とを具備する。また、薄膜トランジ

10

20

30

40

50

スタ 6 はゲート電極 8 とゲート絶縁膜 4 6 を間に置いて重畳されながら、ソース電極 1 0 とドレーン電極 1 2 との間にチャンネルを形成する活性層 4 8 をさらに具備する。活性層 4 8 はデータライン 4 、データパッド下部電極 3 2 及びストレージ電極 2 2 と重畳されるように形成される。このような活性層 4 8 上には、データライン 4 、ソース電極 1 0 、ドレーン電極 1 2 、データパッド下部電極 3 2 及びストレージ電極 2 2 とのオーミック接触のためのオーミック接触層 5 0 がさらに形成される。

【 0 0 1 3 】

画素電極 1 4 は、保護膜 5 2 を貫く第1コンタクトホール 1 3 を通じて薄膜トランジスタ 6 のドレーン電極 1 2 と接続されるように、画素領域 5 に形成される。特に、画素電極 1 4 はドレーン電極 1 2 と接続されて隣接のゲートライン 2 と並行するように形成された第1水平部 1 4 A と、共通ライン 1 6 と重畳されるように形成された第2水平部 1 4 B と、第1及び第2水平部 1 4 A , 1 4 B の間に共通電極 1 8 と並行するように形成されたフィンガー部 1 4 C とを具備する。

【 0 0 1 4 】

共通電極 1 8 は、共通ライン 1 6 と接続されるように画素領域 5 に形成される。特に、共通電極 1 8 は画素領域 5 で画素電極 1 4 のフィンガー部 1 4 C と並行するように形成される。

【 0 0 1 5 】

これによって、薄膜トランジスタ 6 を通じて画素信号が供給される画素電極 1 4 と、共通ライン 1 6 を通じて基準電圧が供給される共通電極 1 8 との間には、水平電界が形成される。特に、画素電極 1 4 のフィンガー部 1 4 C と共通電極 1 8 との間には、水平電界が形成される。このような水平電界によって薄膜トランジスタアレイ基板とカラーフィルターアレイ基板との間から水平方向に配列された液晶分子が誘電異方性によって回転するようになる。液晶分子の回転程度によって画素領域 5 を透過する光透過率が変わることで画像を具現するようになる。

【 0 0 1 6 】

ストレージキャパシタ 2 0 は、共通ライン 1 6 と、ゲート絶縁膜 4 6 、活性層 4 8 、及びオーミック接触層 5 0 を間に置いてその共通ライン 1 6 と重畳されるストレージ電極 2 2 と、そのストレージ電極 2 2 と保護膜 5 0 を貫く第2コンタクトホール 2 1 を通じて接続される画素電極 1 4 から構成される。このようなストレージキャパシタ 2 0 は、画素電極 1 4 に充電された画素信号が次の画素信号が充電されるまで安定的に維持されるようする。

【 0 0 1 7 】

ゲートライン 2 はゲートパッド 2 4 を通じてゲートドライバー（図示せず）と接続される。ゲートパッド 2 4 は、ゲートライン 2 から伸長されるゲートパッド下部電極 2 6 と、ゲート絶縁膜 4 6 及び保護膜 5 2 を貫く第3コンタクトホール 2 7 を通じてゲートパッド下部電極 2 6 と接続されるゲートパッド上部電極 2 8 から構成される。

【 0 0 1 8 】

データライン 4 はデータパッド 3 0 を通じてデータドライバー（図示せず）と接続される。データパッド 3 0 は、データライン 4 から延長されるデータパッド下部電極 3 2 と、保護膜 5 2 を貫く第4コンタクトホール 3 3 を通じてデータパッド下部電極 3 2 と接続されるデータパッド上部電極 3 4 から構成される。

【 0 0 1 9 】

共通ライン 1 6 は共通パッド 3 6 を通じて外部の基準電圧源（図示せず）から基準電圧を供給受けるようになる。共通パッド 3 6 は、共通ライン 1 6 から延長される共通パッド下部電極 3 8 と、ゲート絶縁膜 4 6 及び保護膜 5 2 を貫く第5コンタクトホール 3 9 を通じて共通パッド下部電極 3 8 と接続される共通パッド上部電極 4 0 から構成される。

【 0 0 2 0 】

このような構成を持つ薄膜トランジスタアレイ基板の製造方法を4マスク工程を利用して詳細に説明すれば図 3 A 乃至図 3 D に図示される。

10

20

30

40

50

## 【0021】

図3Aを参照すれば、第1マスク工程を利用して下部基板45上にゲートライン2、ゲート電極8、ゲートパッド下部電極26、共通ライン16、共通電極18及び共通パッド下部電極38を含む第1導電パターン群が形成される。

## 【0022】

これを詳細に説明すれば、下部基板45上にスパッタリング方法などの蒸着方法を用いて第1金属層42と第2金属層44が順次蒸着されることで二重構造のゲート金属層が形成される。次いで、第1マスクを利用したフォトリソグラフィ工程とエッチング工程を用いてゲート金属層がパターニングされることでゲートライン2、ゲート電極8、ゲートパッド下部電極26、共通ライン16、共通電極18及び共通パッド下部電極38を含む第1導電パターン群が形成される。ここで、第1金属層42としては、アルミニウム系金属などが利用され、第2金属層44としては、クロムCrまたはモリブデンMoなどの金属が利用される。

## 【0023】

図3Bを参照すれば、第1導電パターン群が形成された下部基板45上にゲート絶縁膜46が形成される。そして、第2マスク工程を利用してゲート絶縁膜46上に活性層48及びオーミック接触層50を含む半導体パターンと、データライン4、ソース電極10、ドレーン電極12、データパッド下部電極32、ストレージ電極22を含む第2導電パターン群が形成される。

## 【0024】

これを詳細に説明すれば、第1導電パターン群が形成された下部基板45上にPECVD、スパッタリングなどの蒸着方法を用いてゲート絶縁膜46、第1及び第2半導体層、及びデータ金属層が順次形成される。ここで、ゲート絶縁膜46の材料としては、酸化シリコーンSiO<sub>x</sub>または窒化シリコーンSiN<sub>x</sub>などの無機絶縁物質が利用される。第1半導体層は不純物がドーピングされない非晶質シリコーンが利用され、第2半導体層はN型またはP型の不純物がドーピングされた非晶質シリコーンが利用される。データ金属層としては、モリブデンMo、チタン、タンタル、モリブデン合金(Mo alloy)などが利用される。

## 【0025】

引き継いで、データ金属層上に第2マスクを利用したフォトリソグラフィ工程でフォトトレジストパターンを形成するようになる。この場合、第2マスクとしては薄膜トランジスタのチャンネル部に回折露光部を有する回折露光マスクを利用することで、チャンネル部のフォトトレジストパターンが他の領域部のフォトトレジストパターンより低い高さを持つようにする。

## 【0026】

チャンネル部の高さが異なるフォトトレジストパターンを利用した湿式エッチング工程でデータ金属層がパターニングされることにより、データライン4、ソース電極10、そのソース電極10と一体化されたドレーン電極12、ストレージ電極22を含むデータパターンが形成される。

## 【0027】

次に、同一なフォトトレジストパターンを利用した乾式エッチング工程で第1及び第2半導体層が同時にパターニングされることでオーミック接触層50と活性層48が形成される。

## 【0028】

そして、アッシング(Ashing)工程でチャンネル部において相対的に低い高さを持つフォトトレジストパターンが除去された後、乾式エッチング工程でチャンネル部の一体化されたソース電極及びドレーン電極とオーミック接触層50がエッチングされる。これによって、チャンネル部の活性層48が露出して、ソース電極10とドレーン電極12が分離する。

## 【0029】

10

20

30

40

50

引き継いで、ストリップ工程で第2導電パターン群上に残っていたフォトレジストパターンが除去される。

【0030】

図3Cを参照すれば、第2導電パターン群が形成されたゲート絶縁膜46上に第3マスク工程を利用して第1乃至第5コンタクトホール13, 21, 27, 33, 39を含む保護膜52が形成される。

【0031】

詳細に説明すれば、データパターンが形成されたゲート絶縁膜46上にPECVDなどの蒸着方法を用いて保護膜52が全面形成される。引き継いで、保護膜52が第3マスクを利用したフォトリソグラフィ工程とエッチング工程でパターニングされることにより、第1乃至第5コンタクトホール13, 21, 27, 33, 39が形成される。第1コンタクトホール13は保護膜52を貫いてドレーン電極12を露出させ、第2コンタクトホール21は保護膜52を貫いてストレージ電極22を露出させる。第3コンタクトホール27は保護膜52及びゲート絶縁膜46を貫いてゲートパッド下部電極26を露出させ、第4コンタクトホール33は保護膜52を貫いてデータパッド下部電極32を露出させ、第5コンタクトホール39は保護膜52及びゲート絶縁膜46を貫いて共通パッド下部電極38を露出させる。ここで、データ金属としてモリブデンMoのような乾式エッチング比の大きい金属が利用される場合、第1コンタクトホール13、第2コンタクトホール21、第4コンタクトホール33のそれぞれはドレーン電極12、ストレージ電極22、データパッド下部電極32まで貫いてそれらの側面を露出させるようになる。

10

20

30

40

【0032】

保護膜52の材料としては、ゲート絶縁膜46のような無機絶縁物質や誘電常数が小さなアクリル(acryl)系有機化合物、BCBまたはPFCBなどの有機絶縁物質が利用される。

【0033】

図3Dを参照すれば、第4マスク工程を利用して保護膜52上に画素電極14、ゲートパッド上部電極28、データパッド上部電極34、共通パッド上部電極40を含む第3導電パターン群が形成される。

【0034】

これを詳細に説明すれば、保護膜52上にスパッタリングなどの蒸着方法で透明導電膜が塗布される。引き継いで、第4マスクを利用したフォトリソグラフィ工程とエッチング工程を通じて透明導電膜がパターニングされることで画素電極14、ゲートパッド上部電極28、データパッド上部電極34、共通パッド上部電極40を含む第3導電パターン群が形成される。画素電極14は第1コンタクトホール13を通じてドレーン電極12と電気的に接続され、第2コンタクトホール21を通じてストレージ電極22と電気的に接続される。ゲートパッド上部電極28は第3コンタクトホール37を通じてゲートパッド下部電極26と電気的に接続される。データパッド上部電極34は第4コンタクトホール33を通じてデータ下部電極32と電気的に接続される。共通パッド上部電極40は第5コンタクトホール39を通じて共通パッド下部電極38と電気的に接続される。

【0035】

ここで、透明導電膜の材料としては、インジウム-スズ-オキサイド(Indium Tin Oxide: ITO)、スズ-オキサイド(Tin Oxide: T0)、インジウム-亜鉛-オキサイド(Indium Zinc Oxide: IZO)またはインジウム-スズ-亜鉛-オキサイド(Indium Tin Zinc Oxide: ITZO)などが利用される。

【0036】

このように、従来の水平電界印加型薄膜トランジスタアレイ基板及びその製造方法は、4マスク工程を採用することで5マスク工程を利用した場合より製造工程数を減らすことと同時に、それに比例して製造単価を節減することができるようになる。しかし、4マスク工程もやはり製造工程が複雑で原価節減に限界があるので、製造工程をさらに単純化して製造単価をさらに減らすことが要求される。

50

**【発明の開示】****【発明が解決しようとする課題】****【0037】**

本発明の目的は構造及びマスク工程数を節減することができる水平電界印加型液晶表示装置及びその製造方法を提供するものである。

**【課題を解決するための手段】****【0038】**

前記目的を達成するために、本発明に係る水平電界印加型液晶表示装置は、基板上に形成されたゲートライン、前記ゲートラインと平行に形成された共通ライン、前記ゲートライン及び前記共通ラインとゲート絶縁膜を間に置いて交差して画素領域を決めるデータライン、前記ゲートライン及び前記データラインの交差部に形成された薄膜トランジスタ、前記画素領域に形成されて前記共通ラインと接続される共通電極、前記薄膜トランジスタと接続されて前記画素領域に前記共通電極と水平電界を形成するように形成された画素電極、前記ゲートラインに含まれた少なくとも一つの導電層で形成されたゲートパッド、前記データラインに含まれた少なくとも一つの導電層で形成されたデータパッド、前記共通ラインに含まれた少なくとも一つの導電層で形成された共通パッド、前記ゲートパッド、前記データパッド、及び前記共通パッドを露出させる保護膜を具備する薄膜トランジスタアレイ基板と、前記薄膜トランジスタアレイ基板と合着されてその間に液晶が満たされるようにするカラーフィルタアレイ基板と、前記薄膜トランジスタアレイ基板の露出したパッドと接続された導電性フィルムを具備することを特徴とする。

10

20

20

30

40

50

**【0039】**

前記ゲートライン及び前記共通ラインは、主導電層と、その主導電層の断線防止のための補助導電層を具備することを特徴とする。

**【0040】**

前記ゲートパッド及び前記共通パッドは、前記主導電層と前記補助導電層を具備して、前記補助導電層が露出した構造を持つことを特徴とする。

**【0041】**

前記ゲートパッド及び前記共通パッドは、前記補助導電層を具備することを特徴とする。

**【0042】**

前記主導電層は、低抵抗金属であるアルミニウム系金属、銅、モリブデン、クロム、タンゲステンの中から少なくとも一つの金属を含み、前記補助導電層は、チタンを含むことを特徴とする。

**【0043】**

前記データラインは、主導電層と、その主導電層の断線防止のための補助導電層を具備することを特徴とする。

**【0044】**

前記データパッドは、前記主導電層と前記補助導電層を具備して、前記補助導電層が露出した構造を有することを特徴とする。

**【0045】**

前記データパッドは、前記補助導電層を具備することを特徴とする。

**【0046】**

前記主導電層は、低抵抗金属であるアルミニウム系金属、銅、モリブデン、クロム、タンゲステンの中から少なくとも一つの金属を含み、前記補助導電層は、チタンを含むことを特徴とする。

**【0047】**

前記水平電界印加型液晶表示装置は、前記基板のエッティング防止のためのエッティング防止層をさらに具備することを特徴とする。

**【0048】**

前記エッティング防止層は、フッ酸系エッチャントに対して強い透明オキサイド系物質を

50

含むことを特徴とする。

【0049】

前記エッティング防止層は、 $TiO_2$  及び  $Al_2O_3$  の中からいずれかを含むことを特徴とする。

【0050】

前記薄膜トランジスタは、前記ゲートラインと接続されたゲート電極と、前記データラインと接続されたソース電極と。前記ソース電極と対向されるドレーン電極と、前記ゲート電極と前記ゲート絶縁膜を間に置いて重畳されて前記ソース電極及び前記ドレーン電極の間にチャンネル部を形成する半導体層とを具備することを特徴とする。

【0051】

前記ドレーン電極と前記画素電極は、同一な導電層で構成されたことを特徴とする。

10

【0052】

前記水平電界印加型液晶表示装置は、前記共通ラインの一部からなるストレージ下部電極と、前記ゲート絶縁膜上に前記ストレージ下部電極と重畳されるように形成されて、前記画素電極と同一な導電層で構成されたストレージ上部電極とを具備するストレージキャパシタをさらに具備することを特徴とする。

【0053】

前記半導体層は、前記データライン、前記ソース電極、前記ドレーン電極、前記画素電極、及び前記ストレージ上部電極に沿って前記ゲート絶縁膜上に形成されることを特徴とする。

【0054】

前記画素電極は、前記共通電極と並行するように形成されて前記共通電極と水平電界を成すフィンガー部と、前記フィンガー部と連結されて、前記ゲートラインと並行するように形成される水平部を含むことを特徴とする。

20

【0055】

前記半導体層は、少なくとも前記画素電極のフィンガー部と同一な幅を持つように形成されることを特徴とする。

【0056】

前記水平電界印加型液晶表示装置は、前記ゲートパッド、前記データパッド、前記共通パッド及び前記画素電極を露出させる保護膜をさらに具備することを特徴とする。

30

【0057】

前記目的を達成するために、本発明に係る水平電界印加型液晶表示装置の製造方法は、ゲートラインとデータラインの交差部に形成された薄膜トランジスタと、その薄膜トランジスタと接続された画素電極、前記画素電極と水平電界を形成する共通電極、その共通電極と接続された共通ラインを含み、前記ゲートラインに含まれる少なくとも一つの導電層で形成されたゲートパッド、前記データラインに含まれる少なくとも一つの導電層で形成されたデータパッド、前記共通ラインに含まれる少なくとも一つの導電層で形成された共通パッドが保護膜を通じて露出した構造を持つ薄膜トランジスタアレイ基板を用意する段階と、前記薄膜トランジスタアレイ基板と対向されられるカラーフィルターアレイ基板を用意する段階と、前記薄膜トランジスタアレイ基板と前記カラーフィルターアレイ基板を合着する段階と・前記露出したゲートパッド、データパッド、及び前記共通パッドに導電性フィルムを接続させる段階とを含むことを特徴とする。

40

【0058】

前記薄膜トランジスタアレイ基板を用意する段階は、基板上に前記ゲートライン、そのゲートラインと接続された前記薄膜トランジスタのゲート電極、そのゲートラインと平行な前記共通ライン、前記共通電極、前記ゲートパッド、及び前記共通パッドを含む第1導電パターン群を形成する段階と、前記第1導電パターン群が形成された前記基板上にゲート絶縁膜を形成する段階と、前記データライン、そのデータラインと接続された前記薄膜トランジスタのソース電極、そのソース電極と対向される前記薄膜トランジスタのドレーン電極、そのドレーン電極と接続されて前記共通電極と平行な画素電極、及び前記データパッドを含む第2導電パターン群と、前記薄膜トランジスタのチャンネルを含んで前記第

50

2導電パターン群に沿う半導体層を形成する段階と、前記半導体層及び前記第2導電パターン群が積層された前記ゲート絶縁膜上に前記ゲートパッド、前記データパッド、及び前記共通パッドを露出させる保護膜を形成する段階とを含むことを特徴とする。

【0059】

前記第1及び第2導電パターン群の中から少なくとも一つは、主導電層と、その主導電層の断線防止のための補助導電層の二層構造で形成されることを特徴とする。

【0060】

前記保護膜を形成する段階は、前記ゲートパッド及び前記共通パッドの補助導電層を露出させる段階を含むことを特徴とする。

【0061】

前記保護膜を形成する段階は、前記保護膜及び前記ゲート絶縁膜を貫くコンタクトホールを形成し、前記ゲートパッド及び前記共通パッドの補助導電層を露出させる段階を含むことを特徴とする。

【0062】

前記保護膜を形成する段階は、前記保護膜、前記ゲート絶縁膜、前記ゲートパッド及び前記共通パッドの主導電層を貫くコンタクトホールを形成し、前記ゲートパッド及び前記共通パッドの補助導電層を露出させる段階を含むことを特徴とする。

【0063】

前記保護膜を形成する段階は、前記データパッドの補助導電層を露出させる段階を含むことを特徴とする。

【0064】

前記保護膜を形成する段階は、前記保護膜を貫くコンタクトホールを形成し、前記データパッドの補助導電層を露出させる段階を含むことを特徴とする。

【0065】

前記保護膜を形成する段階は、前記保護膜と前記データパッドの主導電層を貫くコンタクトホールを形成し、前記データパッドの補助導電層を露出させる段階を含むことを特徴とする。

【0066】

前記主導電層は、低抵抗金属であるアルミニウム系金属、銅、モリブデン、クロム、タンゲステンの中から少なくとも一つの金属を含み、前記補助導電層は、チタンを含むことを特徴とする。

【0067】

前記第2導電パターン群を形成する段階は、前記共通ラインと前記ゲート絶縁膜を間に置いて重畳されるストレージ上部電極を形成する段階をさらに含むことを特徴とする。

【0068】

前記薄膜トランジスタアレイ基板を用意する段階は、基板を用意する段階と、前記基板上に前記エッチング防止層を形成する段階とをさらに含むことを特徴とする。

【0069】

前記エッチング防止層は、フッ酸系エッチャントに対して強い透明オキサイド系物質を含むことを特徴とする。

【0070】

前記エッチング防止層は、 $TiO_2$ 及び $Al_2O_3$ の中からいずれかを含むことを特徴とする。

【0071】

前記薄膜トランジスタアレイ基板を用意する段階は、基板上に前記ゲートライン、そのゲートラインと接続された前記薄膜トランジスタのゲート電極、そのゲートラインと平行な前記共通ライン、前記共通電極、前記ゲートパッド、及び前記共通パッドを含む第1導電パターン群を形成する段階と、前記第1導電パターン群が形成された前記基板上にゲート絶縁膜を形成する段階と、前記データライン、そのデータラインと接続された前記薄膜トランジスタのソース電極、そのソース電極と対向される前記薄膜トランジスタのドレン電極、そのドレン電極に含まれる少なくとも一つの導電層で形成されて、前記共通電

10

20

30

40

50

極と水平電界を成すフィンガー部を持つ画素電極、前記データパッドを含む第2導電パターン群と、前記薄膜トランジスタのチャンネル部を形成し、前記画素電極と重畠される半導体層を形成する段階と、前記半導体層及び第2導電パターン群を覆うように前記ゲート絶縁膜上に保護膜を形成する段階と、少なくとも前記画素電極のフィンガー部において前記画素電極と同一な幅を持つように前記半導体層をパターニングする段階とを含むことを特徴とする。

【0072】

前記保護膜を形成する段階は、前記保護膜を貫くコンタクトホールを形成し、前記データパッドの補助導電層を露出させることと同時に、前記保護膜及び前記ゲート絶縁膜を貫く貫通ホールを形成し、前記画素電極の補助導電層及び前記画素電極と重畠される半導体層を露出させる段階を含むことを特徴とする。

【0073】

前記保護膜を形成する段階は、前記保護膜と前記主導電層を貫くコンタクトホールを形成し、前記データパッドの補助導電層を露出させることと同時に、前記保護膜及び前記ゲート絶縁膜と前記主導電層を貫く貫通ホールを形成し、前記画素電極の補助導電層及び前記画素電極と重畠される半導体層を露出させる段階を含むことを特徴とする。

【0074】

前記半導体層をパターニングする段階は、前記画素電極をマスクとして前記半導体層を乾式エッチングする段階を含むことを特徴とする。

【発明の効果】

【0075】

本発明に係る水平電界印加型液晶表示装置及びその製造方法においては、マスク工程数を減らすために画素電極をドレーン電極と同一な金属で形成し、断線不良を防止するよう、パッドを強度及び耐食性の大きい金属が露出した構造を持ち、ACFを通じてTCPと接続させる。

【発明を実施するための最良の形態】

【0076】

上記目的外に本発明の他の目的及び特徴は添付した図面を参照した実施の形態に対する説明を通じて明らかになる。

【0077】

以下、本発明の実施の形態を添付した図4乃至図24を参照して詳しく説明することにする。

【0078】

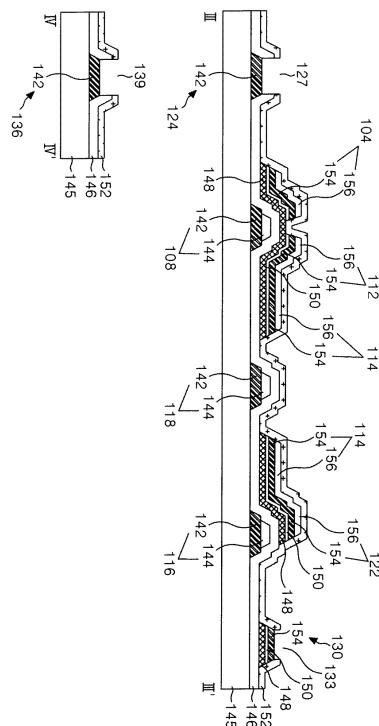

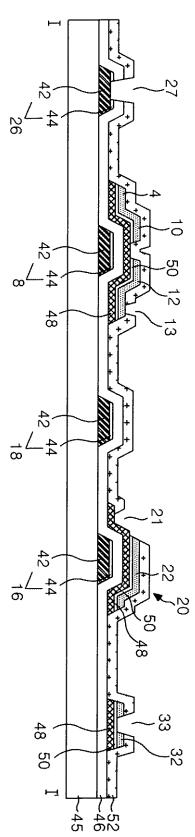

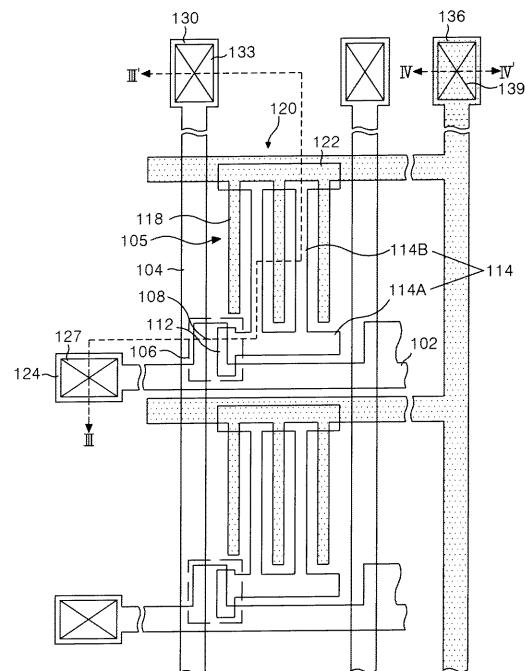

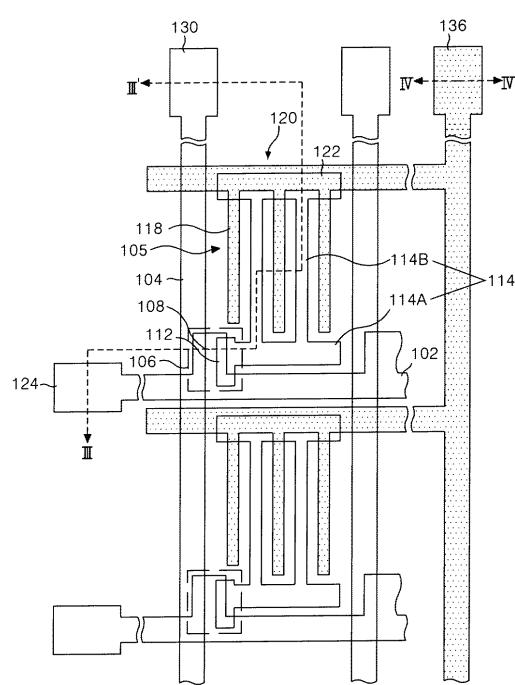

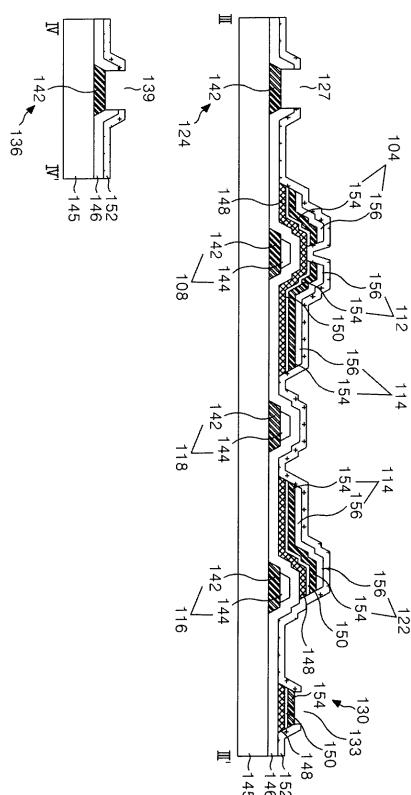

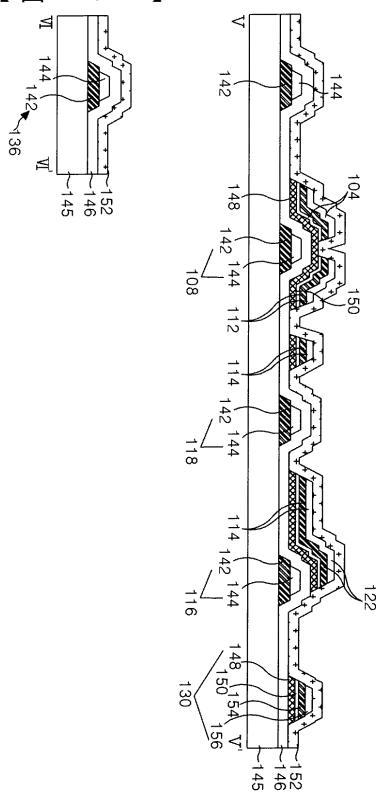

図4は本発明の第1の実施の形態に係る水平電界印加型液晶表示装置の薄膜トランジスタアレイ基板を示す平面図で、図5は図4に図示された薄膜トランジスタアレイ基板を線III-III'及びIV-IV'線に沿って切断して示す断面図である。

【0079】

図4及び図5に図示された薄膜トランジスタアレイ基板は、下部基板145上にゲート絶縁膜146を間に置いて交差するように形成されたゲートライン102及びデータライン104と、その交差部毎に形成された薄膜トランジスタ106と、その交差構造に用意された画素領域に水平電界を形成するように形成された画素電極114及び共通電極118と、共通電極118と接続された共通ライン116を具備する。そして、図4及び図5に図示された薄膜トランジスタアレイ基板は、ストレージ上部電極122と共にライン116の重畠部に形成されたストレージキャパシタ120と、ゲートライン102から延長されるゲートパッド124と、データライン104から延長されるデータパッド130と共に共通ライン116から延長される共通パッド136をさらに具備する。

【0080】

ゲート信号を供給するゲートライン102とデータ信号を供給するデータライン104は交差構造に形成されて画素領域105を定義する。

【0081】

10

20

30

40

50

液晶駆動のための基準電圧を供給する共通ライン 116 は画素領域 105 を間に置いてゲートライン 102 と並行するように形成される。

【0082】

薄膜トランジスタ 106 はゲートライン 102 のゲート信号に応答してデータライン 104 の画素信号が画素電極 114 に充電されて維持されるようにする。このため、薄膜トランジスタ 106 はゲートライン 102 に接続されたゲート電極 108 と、データライン 104 に含まれたソース電極と、画素電極 114 に接続されたドレーン電極 112 を具備する。また、薄膜トランジスタ 106 はゲート電極 108 とゲート絶縁膜 146 を間に置いて重畠されながら、ソース電極とドレーン電極 112 の間にチャンネルを形成する活性層 148 をさらに具備する。

10

【0083】

そして、活性層 148 はデータライン 104、データパッド 130、及びストレージ上部電極 122 とも重畠されるように形成される。このような活性層 148 上には、データライン 104、ドレーン電極 112、データパッド 130、及びストレージ上部電極 122 とオーミック接触のためのオーミック接触層 150 がさらに形成される。

【0084】

画素電極 114 は薄膜トランジスタ 106 のドレーン電極 112 と一体化されることと同時に、ストレージ上部電極 122 と一体化されて画素領域 105 に形成される。特に、画素電極 114 は、ドレーン電極 112 において隣接したゲートライン 102 と並行するように延長される水平部 114A と、水平部 114A から垂直方向に伸長されるフィンガーパー部 114B を具備する。

20

【0085】

共通電極 118 は共通ライン 116 と接続されて画素領域 105 に形成される。特に、共通電極 118 は画素領域 105 において画素電極 114 のフィンガーパー部 114B と並行するように形成される。

【0086】

これによって、薄膜トランジスタ 106 を通じて画素信号が供給される画素電極 114 と、共通ライン 116 を通じて基準電圧が供給される共通電極 118 との間には、水平電界が形成される。特に、画素電極 114 のフィンガーパー部 114B と共通電極 118 との間に水平電界が形成される。このような水平電界によって薄膜トランジスタアレイ基板とカラーフィルターアレイ基板との間で水平方向に配列された液晶分子が誘電異方性によって回転するようになる。そして、液晶分子の回転程度によって画素領域 105 を透過する光透過率が変わることで階調を具現するようになる。

30

【0087】

ストレージキャパシタ 120 は共通ライン 116 と、その共通ライン 116 とゲート絶縁膜 146、活性層 148、及びオーミック接触層 150 を間に置いて重畠されて、画素電極 114 と一体化されたストレージ上部電極 122 で構成される。このようなストレージキャパシタ 120 は、画素電極 114 に充電された画素信号が次の画素信号が充電されるまで安定的に維持されるようになる。

40

【0088】

ゲートライン 102 はゲートパッド 124 を通じてテープキャリアパッケージ (Tape Carrier Package; 以下、TCP という) に実装されたゲートドライバー (図示せず) と接続される。ゲートパッド 124 はゲートライン 102 から延長されて、ゲート絶縁膜 146 及び保護膜 152 を貫く第 1 コンタクトホール 127 を通じて露出する。このようなゲートパッド 124 はゲートライン 102 に含まれるチタン Ti、タングステン W などのような強度及び耐食性が相対的に大きい金属層が露出した構造を持つ。これによって、ゲートパッド 124 と TCP を附着する工程を繰り返す場合にもゲートパッド 124 の断線不良を防止することができるようになる。

【0089】

共通ライン 116 は共通パッド 136 に附着する TCP を通じて外部の基準電圧源 (図

50

示せず)から基準電圧を供給受けるようになる。共通パッド136は共通ライン116から延長されて、ゲート絶縁膜146及び保護膜152を貫く第3コンタクトホール139を通じて露出する。このような共通パッド136は、前記ゲートパッド124のように、チタンTi、タンゲステンWなどの強度及び耐食性が相対的に大きい金属層が露出した構造を持つ。これによって、共通パッド136とTCPを附着する工程を繰り返す場合にも共通パッド136の断線不良を防止することができるようになる。

【0090】

具体的には、ゲートライン102、ゲート電極108、共通ライン116、及び共通電極118は第1及び第2金属層142, 144が積層された二重金属層構造を持つようになる。これらの中から一つの金属層はチタンTi、タンゲステンWなどの強度及び耐食性が相対的に大きい金属からなる。そして、他の一つの金属層は一般的なゲート金属に利用されているアルミニウムAl系金属、モリブデンMo、銅Cuなどの低抵抗金属からなる。

【0091】

ここで、第1金属層142として強度及び耐食性が大きい金属を利用する場合、ゲートパッド124及び共通パッド138は、上部の第2金属層144は除去されて、下部の第1金属層142が露出した構造を持つようになる。一方、第2金属層144として強度及び耐食性が大きい金属を利用する場合、ゲートパッド124及び共通パッド138は上部の第2金属層144が露出した構造を持つようになる。

【0092】

データライン104はデータパッド130を通じてTCPに実装されたデータドライバ(図示せず)と接続される。データパッド130はデータライン104から延長されて、保護膜152を貫く第2コンタクトホール133を通じて露出する。このようなデータパッド130はデータライン104に含まれるチタンTi、タンゲステンWなどの強度及び耐食性が相対的に大きい金属層が露出した構造を持つ。これによって、データパッド130とTCPを附着する工程を繰り返す場合にもデータパッド130の断線不良を防止することができるようになる。

【0093】

具体的に、データライン104、ドレーン電極112、画素電極114、及びストレージ上部電極122は、第1及び第2金属層154, 156が積層された二重金属層構造を持つようになる。これらの中から一つの金属層はチタンTi、タンゲステンWなどの強度及び耐食性が相対的に大きい金属からなる。そして、他の一つの金属層は一般的なゲート金属に利用されているアルミニウムAl系金属、モリブデンMo、銅Cuなどの低抵抗金属からなる。

【0094】

ここで、第1金属層154として強度及び耐食性が大きい金属を利用する場合、データパッド130は、上部の第2金属層156は除去されて、下部の第1金属層154が露出した構造を持つようになる。一方、第2金属層156として強度及び耐食性が大きい金属を利用する場合、データパッド130は上部の第2金属層156が露出した構造を持つようになる。

【0095】

図6A及び図6Bは本発明の実施の形態に係る水平電界印加型薄膜トランジスタアレイ基板の製造方法の中、第1マスク工程を説明するための平面図及び断面図である。

【0096】

図6A及び図6Bに示すように、第1マスク工程で、下部基板145上にゲートライン102、ゲート電極108、ゲートパッド124、共通ライン116、共通電極118、共通パッド136を含む第1導電パターン群が形成される。

【0097】

詳細に説明すれば、下部基板145上にスパッタリング方法などの蒸着方法を通じて第1ゲート金属層142と第2ゲート金属層144が順次蒸着されることで二層構造のゲー

10

20

30

40

50

ト金属層が形成される。引き継いで、第1マスクを利用したフォトリソグラフィ工程とエッチング工程でゲート金属層がパターニングされることによりゲートライン102、ゲート電極108、ゲートパッド124、共通ライン116、共通電極118、共通パッド136を含む第1導電パターン群が形成される。ここで、第1及び第2ゲート金属層142, 144中から一つのゲート金属層はチタンTi、タンゲステンWなどの強度及び耐食性が相対的に大きい金属からなる、他の一つのゲート金属層はアルミニウムAl系金属、モリブデンMo、銅Cuなどの金属からなる。

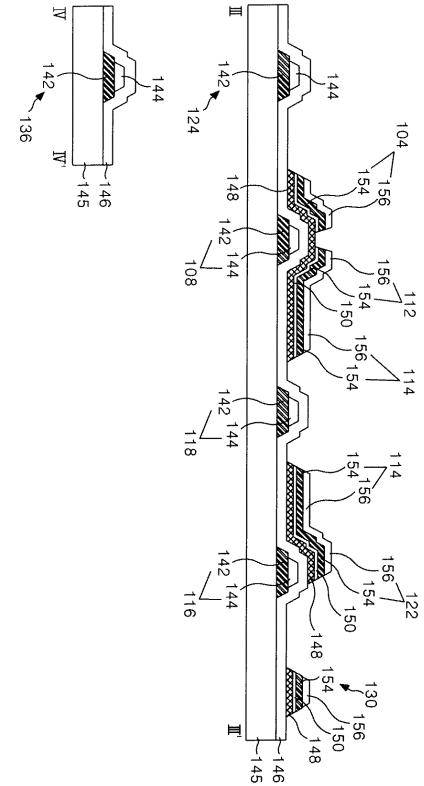

#### 【0098】

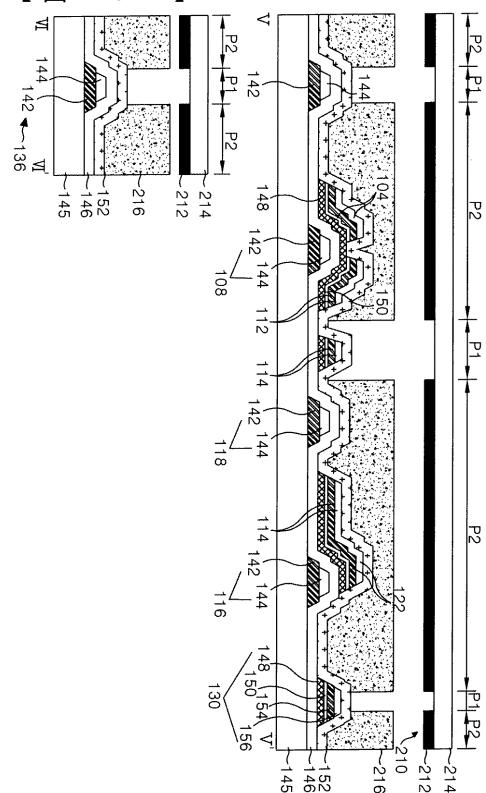

図7A及び図7Bは本発明の実施の形態に係る水平電界印加型薄膜トランジスタアレイ基板の製造方法の中、第2マスク工程を説明するための平面図及び断面図である。

10

#### 【0099】

まず、第1導電パターン群が形成された下部基板145上にPECVD、スパッタリングなどの蒸着方法を通じてゲート絶縁膜146が形成される。ゲート絶縁膜146の材料としては酸化シリコーンSiO<sub>x</sub>または窒化シリコーンSiN<sub>x</sub>などの無機絶縁物質が利用される。

#### 【0100】

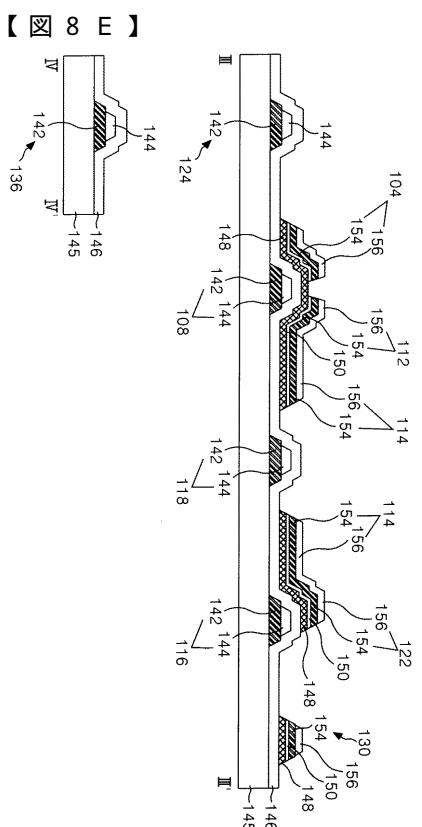

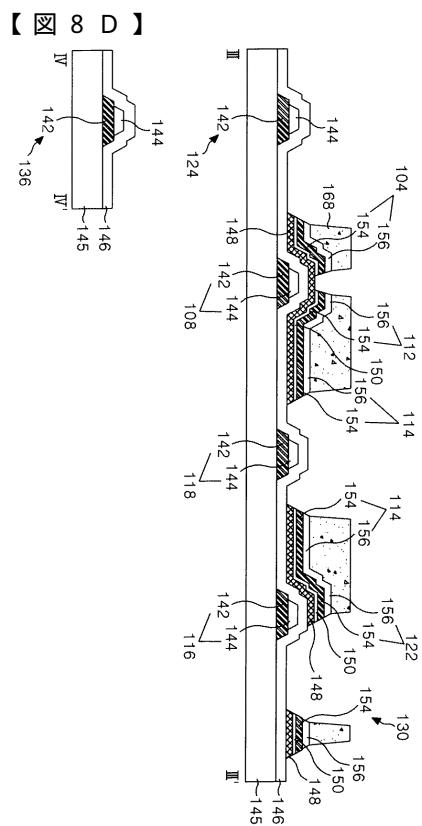

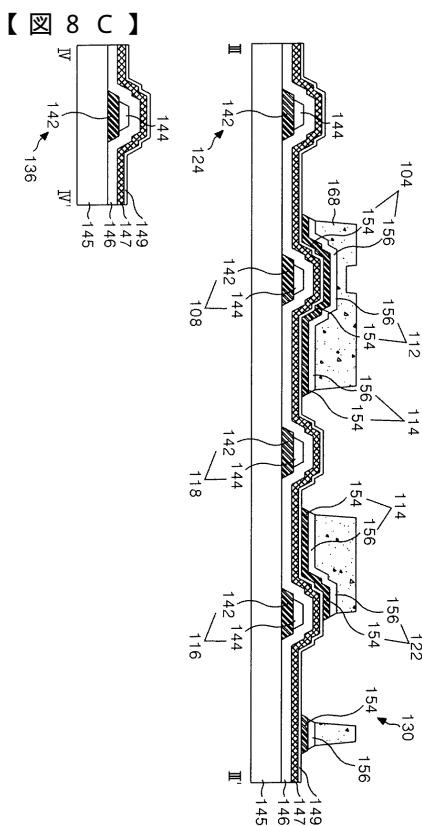

そして、図7A及び図7Bに示すように、第2マスク工程でゲート絶縁膜146上に積層された活性層148及びオーム接觸層150を含む半導体パターンと、データライン104、ドレーン電極112、画素電極114、データパッド130、ストレージ上部電極122を含む第2導電パターン群が形成される。このような第2マスク工程を図8A乃至図8Eを参照して詳しくすれば次の通りである。

#### 【0101】

図8Aに示すように、ゲート絶縁膜146上にPECVD、スパッタリングなどの蒸着方法を通じて非晶質シリコーン層147、n+非晶質シリコーン層149、及び第1及び第2ソース/ドレーン金属層154, 156が順次形成される。ここで、第1及び第2ソース/ドレーン金属層154, 156中、一つのソース/ドレーン金属層はチタンTi、タンゲステンWなどの強度及び耐食性が相対的に大きい金属からなる、他の一つのソース/ドレーン金属層はアルミニウムAl系金属、モリブデンMo、銅Cuなどの金属からなる。

#### 【0102】

次に、第2ソース/ドレーン金属層156上にフォトレジスト膜を形成した後、図8Bに示すように、部分露光の第2マスク160を利用したフォトリソグラフィ工程を利用して段差を持つフォトレジストパターン168が形成される。第2マスク160は透明な材質であるマスク基板162と、マスク基板162の遮断領域P2に形成された遮断部164と、マスク基板162の部分露光領域P3に形成された回折露光部166（または半透過部）を具備する。ここで、マスク基板162の露出した領域は露光領域P1になる。このような第2マスク160を利用したフォトレジスト膜を現象することで第2マスク160の遮断部164と回折露光部166（または半透過部）に対応して遮断領域P2と部分露光領域P3において段差を持つフォトレジストパターン168が形成される。具体的に、部分露光領域P3に形成されたフォトレジストパターン168は遮断領域P2に形成されたフォトレジストパターン168の第1高さh1より低い第2高さh2を持つようになる。

#### 【0103】

このようなフォトレジストパターン168を利用した湿式エッチング工程で第1及び第2ソース/ドレーン金属層154, 156がパターニングされることで、図8Cに示すように、データライン104、データライン104と接続されたドレーン電極112、画素電極114、ストレージ上部電極122、データパッド130を含む第2導電パターン群が形成される。

#### 【0104】

そして、フォトレジストパターン160を利用した乾式エッチング工程でn+非晶質シ

30

40

50

リコーン層 149 と非晶質シリコーン層 147 がパターニングされることで、図 8 D のように、オーミック接触層 150 と活性層 148 が第 2 導電パターン群に付いて形成される。引き継いで、酸素 O<sub>2</sub> プラズマを利用したアッシング (Ashing) 工程で部分露光領域 P 3 に第 2 高さ h 2 に形成されたフォトレジストパターン 168 は、図 8 D に示すように、除去されて、遮断領域 P 2 で第 1 高さ h 1 に形成されたフォトレジストパターン 168 は高さの低くなった状態になる。このようなフォトレジストパターン 168 を利用したエッチング工程で部分露光領域 P 3、すなわち薄膜トランジスタのチャンネル部に形成された第 1 及び第 2 ソース / ドレーン金属層 154, 156 が除去される。例えば、第 2 ソース / ドレーン金属層 156 としてモリブデン Mo が、第 1 ソース / ドレーン金属層 154 としてチタン Ti が利用された場合、第 2 ソース / ドレーン金属層 156 は乾式エッチング工程で、第 1 ソース / ドレーン金属層 154 は湿式エッチング工程でチャンネル部から除去される。反対に、第 2 ソース / ドレーン金属層 156 としてチタン Ti が、第 1 ソース / ドレーン金属層 154 としてモリブデン Mo が利用された場合、第 2 ソース / ドレーン金属層 156 は湿式エッチング工程で、第 1 ソース / ドレーン金属層 154 は乾式エッチング工程でチャンネル部から除去される。これによって、ドレーン電極 112 がソース電極を含むデータライン 104 から分離する。次に、フォトレジストパターン 168 を利用した乾式エッチング工程で薄膜トランジスタのチャンネル部においてオーミック接触層 150 が除去されることで活性層 148 が露出する。

10

## 【0105】

そして、図 8 E に示すように、第 2 導電パターン群上に残っていたフォトレジストパターン 168 がストリップ工程で除去される。

## 【0106】

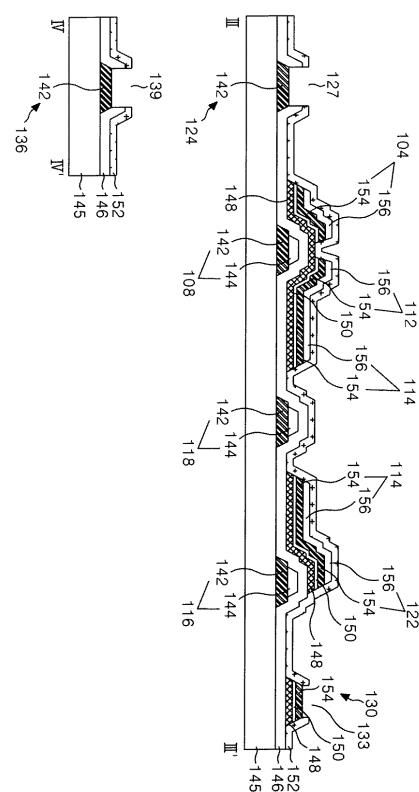

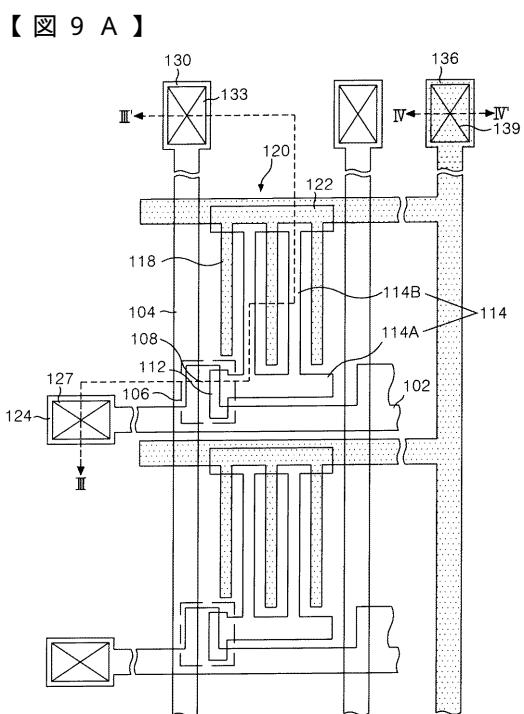

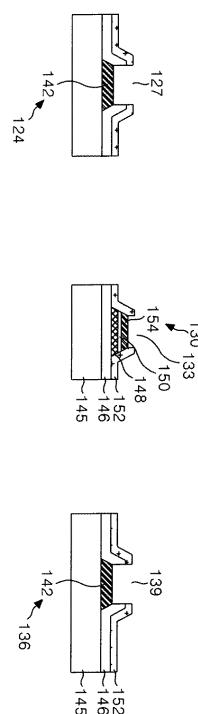

図 9 A 及び図 9 B は本発明の実施の形態に係る水平電界印加型薄膜トランジスタアレイ基板の製造方法の中、第 3 マスク工程を説明するための平面図及び断面図である。

## 【0107】

図 9 A 及び図 9 B に示すように第 3 マスク工程で前述した半導体パターン及びソース / ドレーン金属パターンが積層されたゲート絶縁膜 146 上に第 1 乃至第 3 コンタクトホール 127, 133, 139 を含む保護膜 152 が形成される。

## 【0108】

詳細に説明すれば、前記半導体パターンとソース / ドレーン金属パターンが積層されたゲート絶縁膜 146 上に PECVD などの蒸着方法で保護膜 152 が形成される。保護膜 152 の材料としてはゲート絶縁膜 146 のような無機絶縁物質や誘電常数が小さなアクリル (acryl) 系有機化合物、BCB または PFCB などの有機絶縁物質が利用される。引き継いで、保護膜 152 が第 3 マスクを利用したフォトリソグラフィ工程とエッチング工程でパターニングされることにより第 1 乃至第 3 コンタクトホールドル 127, 133, 139 が形成される。第 1 コンタクトホール 127 は保護膜 152 及びゲート絶縁膜 146 を貫いてゲートパッド 124 を露出させ、第 2 コンタクトホール 133 は保護膜 152 を貫いてデータパッド 130 を露出させ、第 3 コンタクトホール 139 は保護膜 152 及びゲート絶縁膜 146 を貫いて共通パッド 136 を露出させる。このように露出したゲートパッド 124、データパッド 130、及び共通パッド 136 は強度及び耐食性が大きい金属層が露出した構造を持つようになる。この場合、ゲートパッド 124、データパッド 130、及び共通パッド 136 は図 10 及び図 11 に示すように二つの構造を持つようになる。

30

40

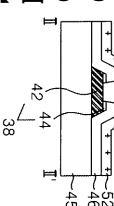

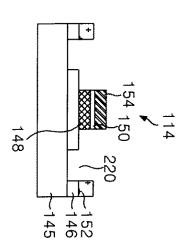

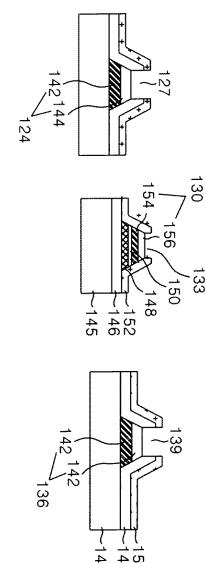

## 【0109】

例えば、下部の第 1 ゲート金属層 142 としてチタン Ti が、上部の第 2 ゲート金属層 144 としてモリブデン Mo が利用された場合、図 10 に示すようにゲートパッド 124 及び共通パッド 136 は下部の第 1 ゲート金属層 142 だけから構成される。これは第 1 及び第 3 コンタクトホール 127, 139 形成のためのエッチング工程で上部の第 2 ゲート金属層 144 が除去されるからである。

## 【0110】

50

反対に、下部の第1ゲート金属層142としてモリブデンMoが、第2ゲート金属層144としてチタンTiが利用された場合、図11に示すように、ゲートパッド124及び共通パッド136は、第1及び第2ゲート金属層142, 144が積層された二重金属層構造を持つようになる。そして、ゲートパッド124及び共通パッド136は、第1及び第3コンタクトホール127, 139によって上部の第2ゲート金属層144が露出した構造を持つようになる。

【0111】

また、下部の第1ソース／ドレーン金属層154としてチタンTiが、上部の第2ソース／ドレーン金属層156としてモリブデンMoが利用された場合、図10に示すように、データパッド130は下部の第1ソース／ドレーン金属層154だけで構成される。これは第2コンタクトホール133形成のためのエッチング工程で上部の第2ソース／ドレーン金属層156が除去されるからである。

【0112】

反対に、下部の第1ソース／ドレーン金属層154としてモリブデンMoが、第2ソース／ドレーン金属層156としてチタンTiが利用された場合、図11に示すように、データパッド130は、第1及び第2ソース／ドレーン金属層154, 156が積層された二重金属層構造を持つようになる。そして、データパッド130は第2コンタクトホール133によって上部の第2ソース／ドレーン金属層156が露出した構造を持つようになる。

【0113】

このように、本発明の第1の実施の形態に係る水平電界印加型薄膜トランジスタアレイ基板及びその製造方法は画素電極114をドレーン電極112と同一な金属で形成する。そして、ゲートパッド124、データパッド130、及び共通パッド136としては、TCPの反復的な付着工程でも断線不良を防止することができる強度及び耐食性が大きい金属を利用する。これによって、本発明は、透明導電膜が必要なくなるので、すなわち透明導電膜蒸着工程及びパターニング工程が必要なくなるので、一つのマスク工程を節減することができるようになる。換言すれば、本発明に係る水平電界印加型薄膜トランジスタアレイ基板は3マスク工程で形成されることができるようになる。

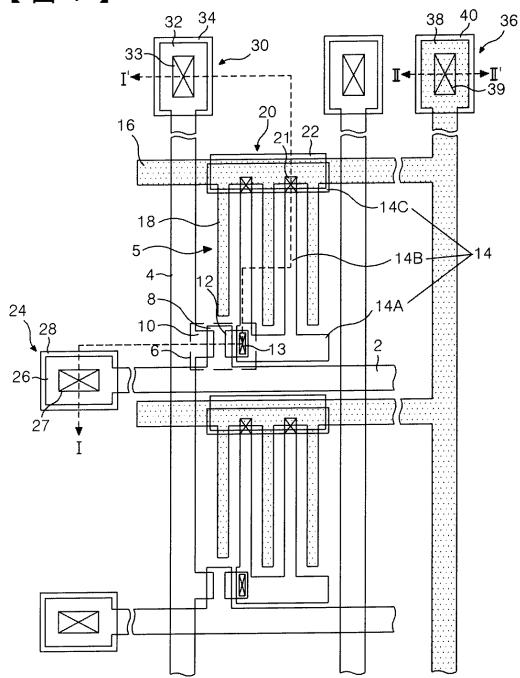

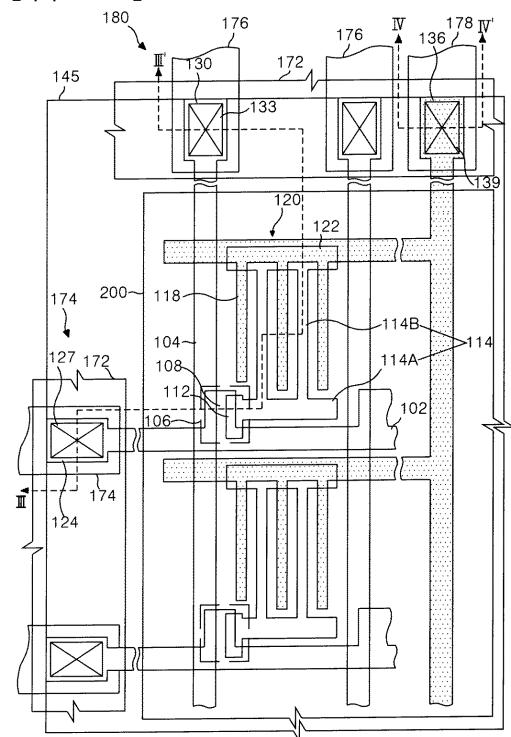

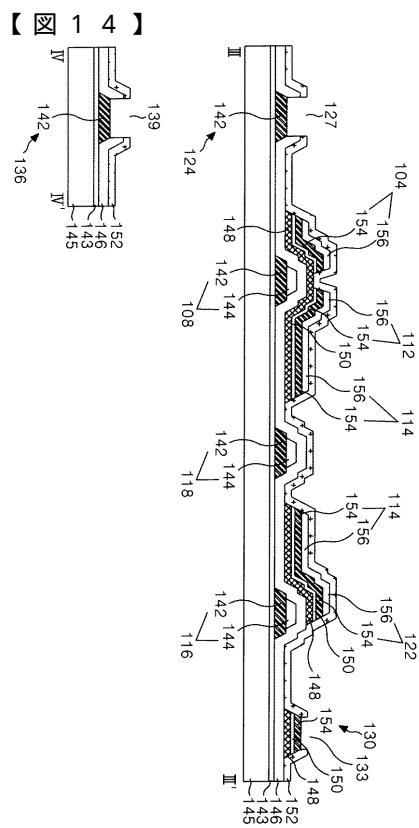

【0114】

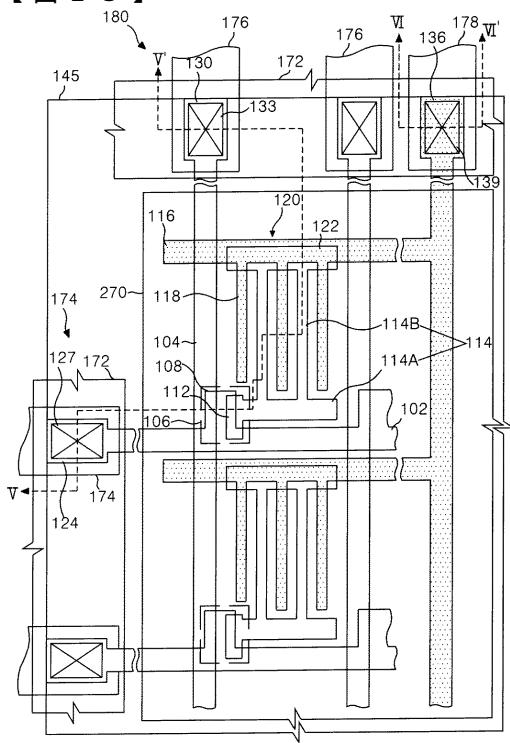

このように完成された薄膜トランジスタアレイ基板と、上部基板200上にカラーフィルターアレイが形成されたカラーフィルターアレイ基板202を用意する。二つのアレイ基板をシーリング材204を通じて相互合着させた後、液晶（図示せず）を注入して図12及び図13に示すように液晶パネルを製作するようになる。この場合、上部基板200は薄膜トランジスタアレイ基板において、ゲートパッド124、データパッド130、及び共通パッド136が形成されるパッド領域と重畳されないように合着される。

【0115】

引き継いで、薄膜トランジスタアレイ基板のパッド領域にドライブICが実装されたTCP170, 180を導電ボル184が含まれたACF(Anisotropic Conductive Film)182を利用して付着させるようになる。これによって、TCP170, 180に形成された出力パッド174, 176, 178はACF182の導電ボル184を通じてゲートパッド124、データパッド130、及び共通パッド136のそれぞれと電気的に接続される。具体的に、ゲートTCP170のベースフィルム172上に形成された第1TCPパッド174はゲートパッド124と、データTCP180のベースフィルム172上に形成された第2TCPパッド176はデータパッド130と、データTCP180のベースフィルム172上に形成された第3TCPパッド178は共通パッド136とACF182を通じて電気的に接続される。この場合、ゲートパッド124、データパッド130、及び共通パッド136は強度及び耐食性の大きい金属層が露出した構造を持っているのでTCP170, 180の付着工程を繰り返してもパッドの断線不良は防止される。

【0116】

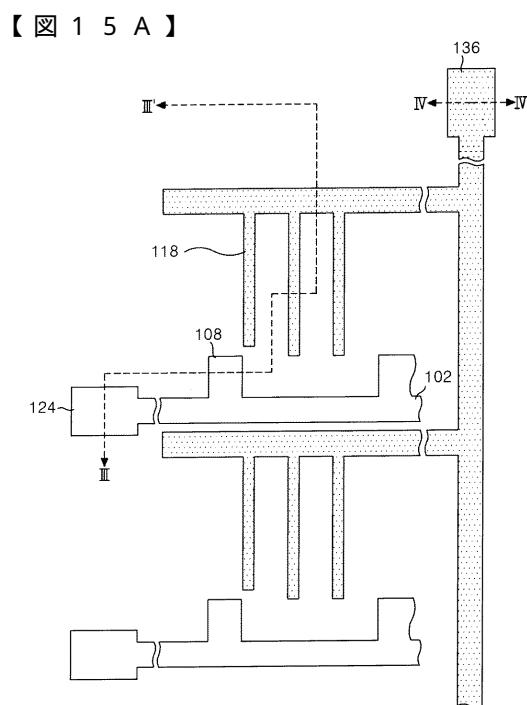

図14は本発明の第2の実施の形態に係る水平電界印加型液晶表示装置の薄膜トランジ

10

20

30

40

50

スタアレイ基板を示す断面図である。

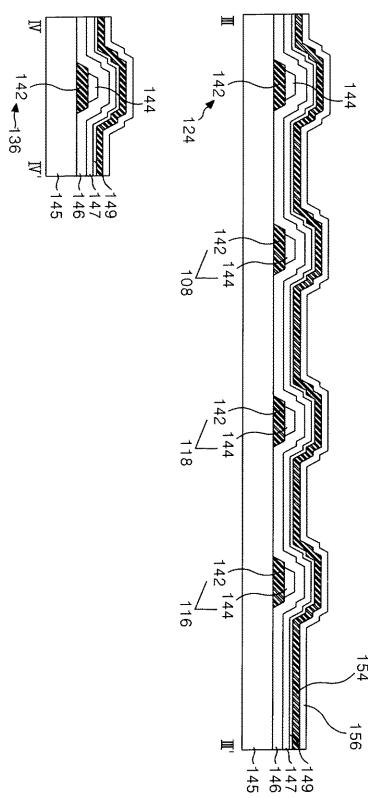

【0117】

図14に示す薄膜トランジスタアレイ基板は、第1ゲート金属層142または第2ゲート金属層144をエッティングし出すためのエッチャントから下部基板145を保護するためにエッティング防止層143をさらに具備することを除いては、図4及び図5に図示された薄膜トランジスタアレイ基板と同一な構成要素を具備する。これによって、同一な構成要素に対する詳細な説明は省略することにする。

【0118】

本発明の第2の実施の形態に係る薄膜トランジスタアレイ基板の第1ゲート金属層142または第2ゲート金属層144としては、チタンTi、タンゲステンWなどの強度及び耐食性が相対的に大きい金属を利用する。この場合、その金属層をパターニングするためのエッチャントは約0.5%程度のフッ酸HF系を含むようになる。このようなフッ酸HF系エッチャントによってガラス材質である下部基板145が過エッティングされることを防止するためにエッティング防止層143が下部基板145上に形成される。このエッティング防止層143はフッ酸HF系エッチャントに対して強いTiO<sub>2</sub>またはAl<sub>2</sub>O<sub>3</sub>などの透明オキサイド系物質からなるようになる。

【0119】

一方、本発明の第2の実施の形態に係る薄膜トランジスタ・基板の製造方法は、前述した本発明の第1の実施の形態に係る薄膜トランジスタ基板の製造方法と対比してエッティング防止層を形成する段階をさらに含むことで、第2及び第3マスク工程は、前述したのと同様なので省略することにする。

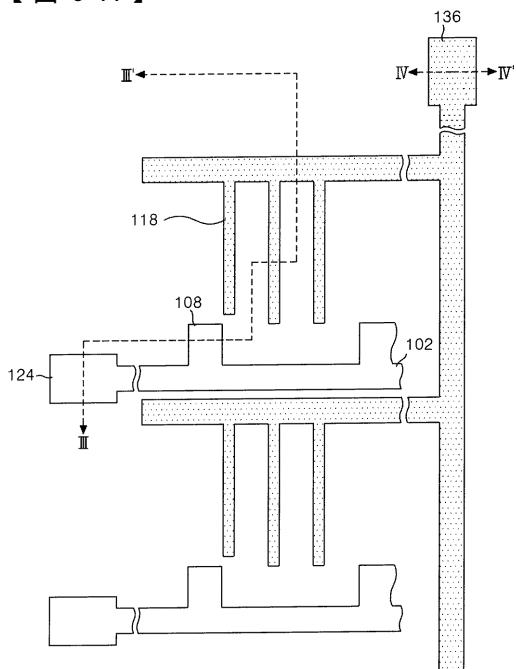

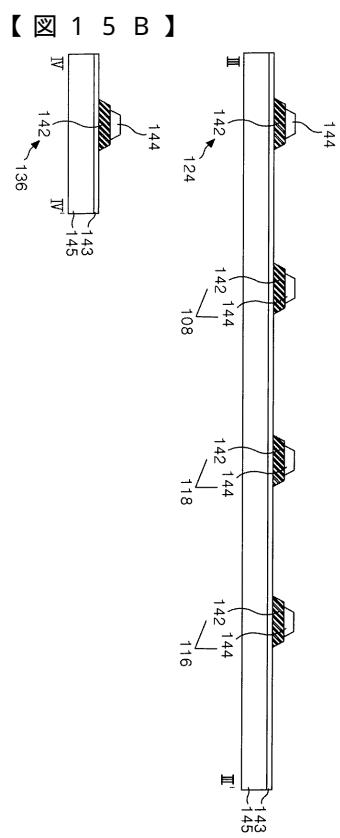

【0120】

図15A及び図15Bは本発明の第2の実施の形態に係る水平電界印加型薄膜トランジスタアレイ基板の製造方法の中、第1マスク工程を説明するための平面図及び断面図である。

【0121】

図15A及び図15Bに示すように、下部基板145上にエッティング防止層143と、第1マスク工程でエッティング防止層143上にゲートライン102、ゲート電極108、ゲートパッド124、共通ライン116、共通電極118、共通パッド136を含む第1導電パターン群が形成される。

【0122】

詳細に説明すれば、下部基板145上にスパッタリング方法などの蒸着方法を通じてエッティング防止層143が形成される。エッティング防止層143としてはフッ酸HF系エッチャントに対して強いTiO<sub>2</sub>またはAl<sub>2</sub>O<sub>3</sub>などの透明オキサイド系物質が利用される。

【0123】

引き継いで、エッティング防止層143が形成された下部基板145上にスパッタリング方法などの蒸着方法を通じて第1ゲート金属層142と第2ゲート金属層144が順次蒸着されることで二層構造のゲート金属層が形成される。引き継いで、第1マスクを利用したフォトリソグラフィ工程とエッティング工程でゲート金属層がパターニングされることによりゲートライン102、ゲート電極108、ゲートパッド124、共通ライン116、共通電極118、共通パッド136を含む第1導電パターン群が形成される。ここで、第1及び第2ゲート金属層142、144中、一つのゲート金属層はチタンTi、タンゲステンWなどの強度及び耐食性が相対的に大きい金属からなる、他の一つのゲート金属層はアルミニウムAl系金属、モリブデンMo、銅Cuなどの金属からなる。

【0124】

ここで、強度及び耐食性が相対的に大きい金属を利用したゲート金属層をパターニングするためにフッ酸HF系エッチャントを利用する場合、エッティング防止層143はそのフッ酸HF系エッチャントから下部基板145を保護するようになる。これによって、下部基板145がフッ酸HF系エッチャントによって過エッティングされることを防止すること

ができるようになる。

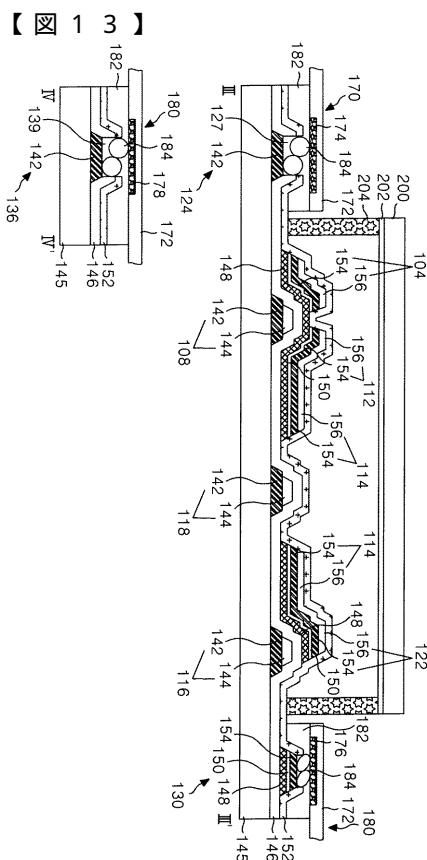

【0125】

一方、3マスク工程に完成された薄膜トランジスタアレイ基板と、他の工程でカラーフィルターアレイ基板202が形成された上部基板200を準備する。その後、図16及び図17に示すように、シーリング材204を通じて二つの基板を相互合着させた後、液晶(図示せず)を注入して液晶パネルを製作するようになる。この場合、上部基板200は、薄膜トランジスタアレイ基板においてゲートパッド124、データパッド130、及び共通パッド136が形成されるパッド領域と重畳されないように合着される。

【0126】

引き継いで、薄膜トランジスタアレイ基板のパッド領域にドライブICが実装されたTCP170, 180を導電ボル184が含まれたACF(Anisotropic Conductive Film)182を利用して付着させるようになる。これによって、TCP170, 180に形成された出力パッド174, 176, 178はACF182の導電ボル184を通じてゲートパッド124、データパッド130、及び共通パッド136のそれぞれと電気的に接続される。具体的に、ゲートTCP170のベースフィルム172上に形成された第1TCPパッド174はゲートパッド124と、データTCP180のベースフィルム172上に形成された第2TCPパッド176はデータパッド130と、データTCP180のベースフィルム172上に形成された第3TCPパッド178は共通パッド142とACF182を通じて電気的に接続される。この場合、ゲートパッド124、データパッド130、及び共通パッド136は、図10及び図11に示すように、強度及び耐食性の大きい金属層が露出した構造を持っているのでTCP170, 180の付着工程を繰り返してもパッドの断線不良は防止される。

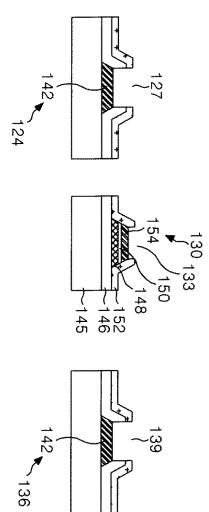

【0127】

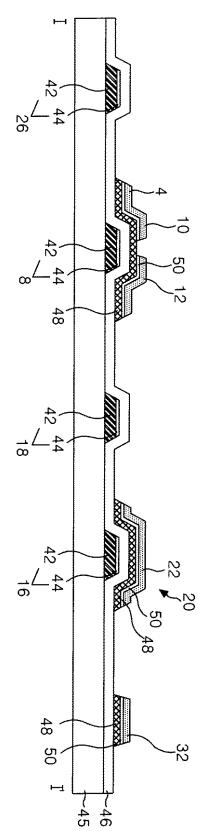

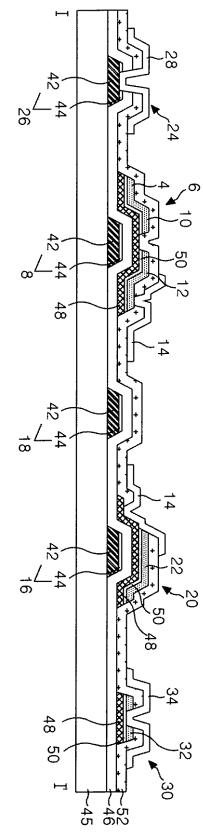

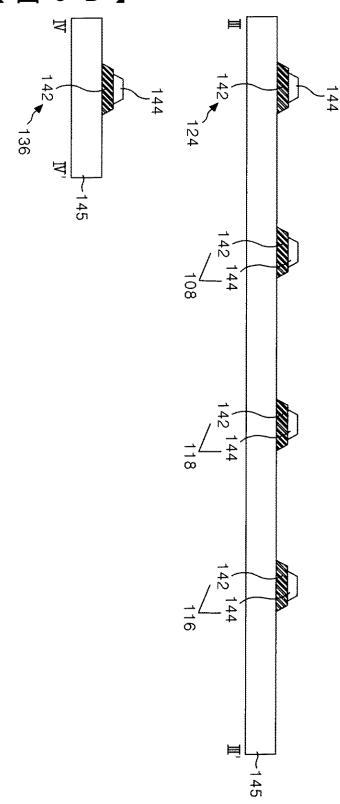

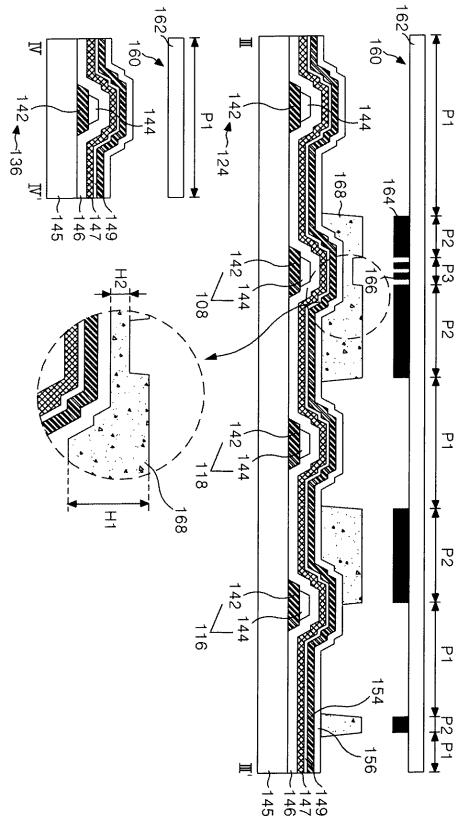

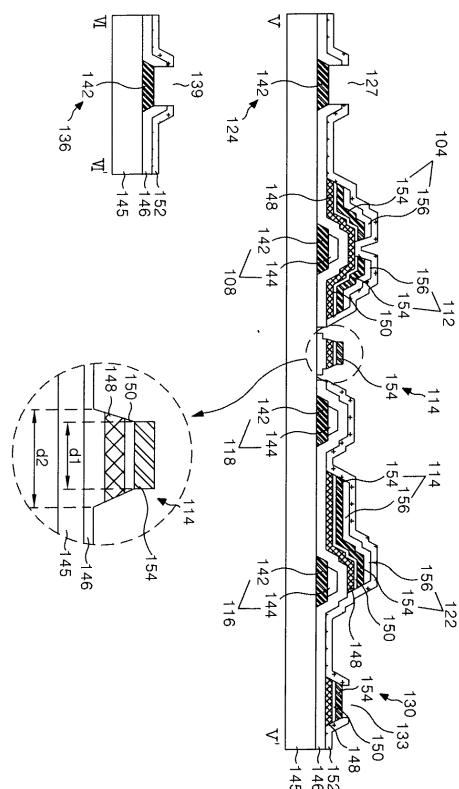

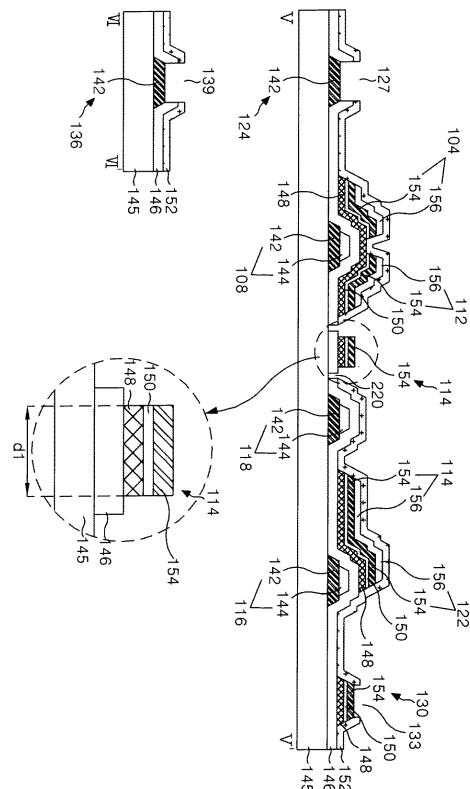

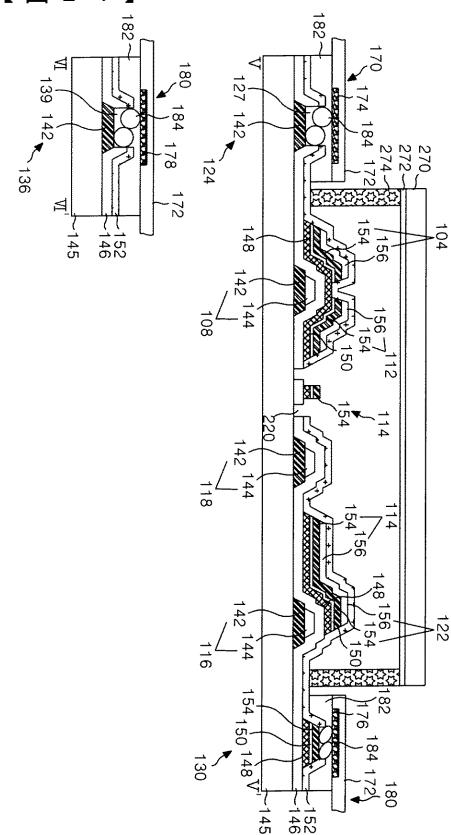

図18は本発明の第3の実施の形態に係る水平電界印加型薄膜トランジスタアレイ基板を示す平面図で、図19は図18で線V-V'、線VI-VI'に沿って切断した薄膜トランジスタアレイ基板を示す断面図である。

【0128】

図18及び図19に示す薄膜トランジスタアレイ基板は画素電極のフィンガー部と半導体層が同一な幅に形成されることを除いては、図4及び図5に図示された薄膜トランジスタアレイ基板と同一な構成要素を具備する。これによって、同一な構成要素に対する詳細な説明は省略することにする。

【0129】

本発明の第3の実施の形態に係る薄膜トランジスタアレイ基板の画素電極114はその画素電極114と重畳される活性層148及びオーミック接触層150を含む半導体パターンと同一な幅に形成される。特に、画素電極114のフィンガー部114Bと、そのフィンガー部と重畳される半導体パターン148, 150は同一な幅に形成される。これは画素電極のフィンガー部114B下部に位する半導体パターン148, 150がそのフィンガー部114Bより広い場合、その半導体パターン148, 150によって画素電極のフィンガー部114Bと共に電極118の間に用意された開口領域が縮むことを防止するためだ。

【0130】

一方、本発明の第3の実施の形態に係る薄膜トランジスタ基板の製造方法は前述した本発明の第1の実施の形態に係る薄膜トランジスタ基板の製造方法と対比して画素電極のフィンガー部と半導体パターンが重畳されるように画素電極をマスクとして半導体パターンをエッティングする段階をさらに含むもので、第1及び第2マスク工程は前述したのと同様なので省略することにする。

【0131】

図20A乃至図20Dは本発明の第3の実施の形態に係る水平電界印加型薄膜トランジスタアレイ基板の製造方法の中、第3マスク工程を説明するための平面図及び断面図である。

10

20

30

40

50

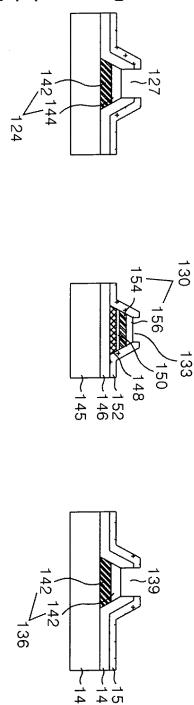

## 【0132】

図20Aに示すように半導体パターンとソース／ドレーン金属パターンが積層されたゲート絶縁膜146上にPECVDなどの蒸着方法で保護膜152が形成される。保護膜152の材料としては、ゲート絶縁膜146のような無機絶縁物質や誘電常数が小さなアクリル(acryl)系有機化合物、BCBまたはPFCBなどのような有機絶縁物質が利用される。引き継いで、保護膜152上にフォトレジスト膜が全面形成された後、図20Bに示すように、下部基板145上部に第3マスク210が整列される。第3マスク210は透明な材質であるマスク基板214と、マスク基板214の遮断領域P2に形成された遮断部212を具備する。ここで、マスク基板214の露出した領域は露光領域P1になる。このような第3マスク210を利用したフォトレジスト膜を露光及び現象することで第3マスク210の遮断部212と対応して遮断領域P2にフォトレジストパターン216が形成される。このようなフォトレジストパターン216を利用したエッチング工程で保護膜152がパターンングされることにより図20Cに示すように、第1乃至第3コンタクトホール127, 133, 139と貫通ホール220が形成される。

## 【0133】

第1コンタクトホール127は保護膜152及びゲート絶縁膜146を貫いてゲートパッド124を露出させ、第2コンタクトホール133は保護膜152を貫いてデータパッド130を露出させ、第3コンタクトホール139は保護膜152及びゲート絶縁膜146を貫いて共通パッド136を露出させる。このように露出したゲートパッド124、データパッド130、及び共通パッド136は強度及び耐食性の大きい金属層が露出した構造を持つようになる。

## 【0134】

貫通ホール220は保護膜152及びゲート絶縁膜146を貫いて第1幅d1を持つ画素電極114と、その画素電極114と重畠されて画素電極114より相対的に広い第2幅d2を持つ活性層148及びオーミック接触層150を含む半導体パターン及びゲート絶縁膜146を露出させる。この時、露出した半導体パターン148, 150の幅d2は例えば約6~6.5μmで、画素電極114の幅d1は約3~3.5μmである。

## 【0135】

引き継いで、露出した画素電極114をマスクで半導体パターン148, 150が乾式エッチングされることにより図20Dに示すように画素電極114と半導体パターン148, 150は等しい第1幅を持って互いに重畠される。例えば、重畠される画素電極114と半導体パターン148, 150は約3μmの幅を持つようになる。

## 【0136】

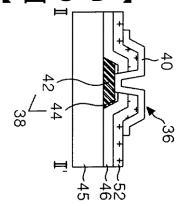

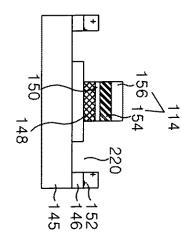

一方、第3マスク工程によって露出したゲートパッド124、データパッド130、共通パッド136及び画素電極114は図21及び図22に示すように二つの構造を持つようになる。

## 【0137】

例えば、下部の第1ゲート金属層142としてチタンTiが、上部の第2ゲート金属層144としてモリブデンMoが利用された場合、図21に示すように、ゲートパッド124及び共通パッド136は下部の第1ゲート金属層142だけで構成される。これは、第1及び第3コンタクトホール127, 139形成のためのエッチング工程で上部の第2ゲート金属層144が除去されるためである。

## 【0138】

反対に、下部の第1ゲート金属層142としてモリブデンMoが、第2ゲート金属層144としてチタンTiが利用された場合、図22に示すように、ゲートパッド124及び共通パッドは、第1及び第2ゲート金属層142, 144が積層された二重金属層構造を持つようになる。そして、ゲートパッド124及び共通パッド136は、第1及び第3コンタクトホール127, 139によって上部の第2ゲート金属層144が露出した構造を持つようになる。

## 【0139】

10

20

30

40

50

また、下部の第1ソース／ドレーン金属層154としてチタンTiが、上部の第2ソース／ドレーン金属層156としてモリブデンMoが利用された場合、図21に示すように、データパッド130及び画素電極114は下部の第1ソース／ドレーン金属層154だけで構成される。これは第2コンタクトホール133形成のためのエッチング工程で上部の第2ソース／ドレーン金属層156が除去されるためである。

#### 【0140】

反対に、下部の第1ソース／ドレーン金属層154としてモリブデンMoが、第2ソース／ドレーン金属層156としてチタンTiが利用された場合、図22に示すように、データパッド130及び画素電極114は、第1及び第2ソース／ドレーン金属層154, 156が積層された二重金属層構造を持つようになる。そして、データパッド130は、第2コンタクトホール133によって、上部の第2ソース／ドレーン金属層156が露出した構造を持つようになって、画素電極114は、貫通ホール220によって、上部の第2ソース／ドレーン金属層156が露出した構造を持つようになる。

#### 【0141】

このように、本発明の実施の形態に係る水平電界印加型薄膜トランジスタアレイ基板及びその製造方法は画素電極114をドレーン電極112と同一な金属で形成する。そして、画素電極114と半導体パターン148, 150が重畠されるように形成されることで、半導体パターン148, 150による開口率低下を防止することができるようになる。

#### 【0142】

また、ゲートパッド124、データパッド130、及び共通パッド136としては、TCPの反復的な付着工程でも断線不良を防止することができる強度及び耐食性が大きい金属を利用する。これによって、本発明は、透明導電膜が必要なくなるので、すなわち透明導電膜蒸着工程及びパターニング工程が必要なくなるので、一つのマスク工程を節減することができるようになる。換言すれば、本発明に係る水平電界印加型薄膜トランジスタアレイ基板は3マスク工程で形成されることができるようになる。

#### 【0143】

そして、図23及び図24に示すように、完成された薄膜トランジスタアレイ基板と、他の工程でカラーフィルターアレイ272が形成された上部基板270を準備する。その後、二つの基板をシーリング材274を通じて相互合着させた後、液晶（図示せず）を注入して液晶パネルを製作するようになる。この場合、上部基板270は、薄膜トランジスタアレイ基板においてゲートパッド124、データパッド130、及び共通パッド136が形成されるパッド領域と重畠されないように合着される。

#### 【0144】

引き継いで、薄膜トランジスタアレイ基板のパッド領域にドライブICが実装されたTCP170, 180を導電ボル184が含まれたACF (Anisotropic Conductive Film) 182を利用して付着させるようになる。これによって、TCP170, 180に形成された出力パッド174, 176, 178はACF182の導電ボル184を通じてゲートパッド124、データパッド130、及び共通パッド136それぞれと電気的に接続される。具体的に、ゲートTCP170のベースフィルム172上に形成された第1TCPパッド174はゲートパッド124と、データTCP180のベースフィルム172上に形成された第2TCPパッド176はデータパッド130と、データTCP180のベースフィルム172上に形成された第3TCPパッド178は共通パッド136とACF182を通じて電気的に接続される。この場合ゲートパッド124、データパッド130、及び共通パッド136は強度及び耐食性の大きい金属層が露出した構造を持っているので、TCP170, 180の付着工程を繰り返してもパッドの断線不良は防止される。

#### 【産業上の利用可能性】

#### 【0145】

上述したように、本発明に係る水平電界印加型液晶表示装置及びその製造方法は、画素電極をドレーン電極と同一な金属で形成し、パッドは、断線不良を防止するように、強度及び耐食性の大きい金属が露出した構造を持ち、ACFを通じてTCPと接続される。こ

10

20

30

40

50

れによって、本発明に係る水平電界印加型液晶表示装置及びその製造方法は、透明導電膜が必要なくなるので、すなわち透明導電膜蒸着工程及びパターニング工程が必要なくなるので、一つのマスク工程を節減することができるようになる。

#### 【0146】

また、本発明に係る水平電界印加型液晶表示装置及びその製造方法は、基板を保護するエッティング防止層を利用して強度及び耐食性が大きい金属層をパターニングするために利用されるフッ酸HF系エッチャントによって基板が損傷されることを防止することができるようになる。

#### 【0147】

また、本発明に係る水平電界印加型液晶表示装置及びその製造方法は、画素電極のフィンガー部とその下部に位する半導体パターンを重畳されるように形成する。これによって、本発明に係る水平電界印加型薄膜トランジスタアレイ基板及びその製造方法は、画素電極のフィンガー部の幅を持つ半導体パターンによって開口率が低下されることが防止される。

#### 【0148】

この結果、本発明に係る水平電界印加型液晶表示装置及びその製造方法は、3マスク工程で薄膜トランジスタアレイ基板を製造することができるようになるので、その薄膜トランジスタアレイ基板の構造及び工程を単純化して、製造原価を節減することができると同時に、製造収率を高めることができるようになる。

#### 【0149】

以上説明した内容を通じて当業者であれば本発明の技術思想を一脱しない範囲で多様な変更及び修正ができる。したがって、本発明の技術的範囲は明細書の詳細な説明に記載した内容に限定されるのではなく特許請求の範囲により決められなければならない。

#### 【図面の簡単な説明】

#### 【0150】

【図1】従来の水平電界印加型液晶表示装置の薄膜トランジスタアレイ基板を示す平面図である。

【図2】図1で線I-I'、線II-II'に沿って切断した薄膜トランジスタアレイ基板を示す断面図である。

【図3A】図2に図示された薄膜トランジスタアレイ基板の製造方法を段階的に示す断面図である。

【図3B】図2に図示された薄膜トランジスタアレイ基板の製造方法を段階的に示す断面図である。

【図3C】図2に図示された薄膜トランジスタアレイ基板の製造方法を段階的に示す断面図である。

【図3D】図2に図示された薄膜トランジスタアレイ基板の製造方法を段階的に示す断面図である。

【図4】本発明の第1の実施の形態に係る水平電界印加型液晶表示装置の中、薄膜トランジスタアレイ基板を示す平面図である。

【図5】図4で線III-III'、線IV-IV'に沿って切断した薄膜トランジスタアレイ基板を示す断面図である。

【図6A】本発明の第1の実施の形態に係る薄膜トランジスタアレイ基板の製造方法の中、第1マスク工程を説明するための平面図である。

【図6B】本発明の第1の実施の形態に係る薄膜トランジスタアレイ基板の製造方法の中、第1マスク工程を説明するための断面図である。

【図7A】本発明の第1の実施の形態に係る薄膜トランジスタアレイ基板の製造方法の中、第2マスク工程を説明するための平面図である。

【図7B】本発明の第1の実施の形態に係る薄膜トランジスタアレイ基板の製造方法の中、第2マスク工程を説明するための断面図である。

【図8A】本発明の第1の実施の形態に係る薄膜トランジスタアレイ基板の製造方法の中

10

20

30

40

50

、第2マスク工程を具体的に説明するための断面図である。

【図8B】本発明の第1の実施の形態に係る薄膜トランジスタアレイ基板の製造方法の中、第2マスク工程を具体的に説明するための断面図である。

【図8C】本発明の第1の実施の形態に係る薄膜トランジスタアレイ基板の製造方法の中、第2マスク工程を具体的に説明するための断面図である。

【図8D】本発明の第1の実施の形態に係る薄膜トランジスタアレイ基板の製造方法の中、第2マスク工程を具体的に説明するための断面図である。

【図8E】本発明の第1の実施の形態に係る薄膜トランジスタアレイ基板の製造方法の中、第2マスク工程を具体的に説明するための断面図である。

【図9A】本発明の第1の実施の形態に係る薄膜トランジスタアレイ基板の製造方法の中、第3マスク工程を説明するための平面図である。 10

【図9B】本発明の第1の実施の形態に係る薄膜トランジスタアレイ基板の製造方法の中、第3マスク工程を説明するための断面図である。

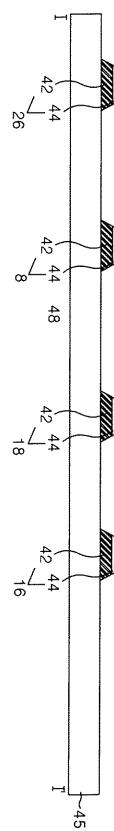

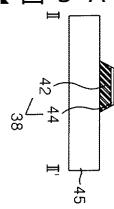

【図10】本発明の第1の実施の形態に係る薄膜トランジスタアレイ基板において第1構造を持つパッドを示す断面図である。

【図11】本発明の第1の実施の形態に係る薄膜トランジスタアレイ基板において第2構造を持つパッドを示す断面図である。

【図12】本発明の第1の実施の形態に係る液晶表示装置を示す平面図である。

【図13】図12に図示された液晶表示装置を示す断面図である。

【図14】本発明の第2の実施の形態に係る水平電界印加型液晶表示装置の中、薄膜トランジスタアレイ基板を示す断面図である。 20

【図15A】本発明の第2の実施の形態に係る薄膜トランジスタアレイ基板の製造方法の中、第1マスク工程を説明するための平面図である。

【図15B】本発明の第2の実施の形態に係る薄膜トランジスタアレイ基板の製造方法の中、第1マスク工程を説明するための断面図である。

【図16】本発明の第2の実施の形態に係る液晶表示装置を示す平面図である。

【図17】図16に図示された液晶表示装置を示す断面図である。

【図18】本発明の第3の実施の形態に係る水平電界印加型液晶表示装置の中、薄膜トランジスタアレイ基板を示す平面図である。

【図19】図18で線V-V'、線VI-VI'に沿って切断した薄膜トランジスタアレイ基板を示す断面図である。 30

【図20A】本発明の第3の実施の形態に係る薄膜トランジスタアレイ基板の製造方法の中、第3マスク工程を具体的に説明するための断面図である。

【図20B】本発明の第3の実施の形態に係る薄膜トランジスタアレイ基板の製造方法の中、第3マスク工程を具体的に説明するための断面図である。

【図20C】本発明の第3の実施の形態に係る薄膜トランジスタアレイ基板の製造方法の中、第3マスク工程を具体的に説明するための断面図である。

【図20D】本発明の第3の実施の形態に係る薄膜トランジスタアレイ基板の製造方法の中、第3マスク工程を具体的に説明するための断面図である。

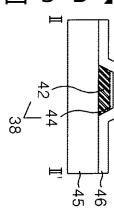

【図21】本発明の第3の実施の形態に係る薄膜トランジスタアレイ基板において第1構造を持つパッドと画素電極を示す断面図である。 40

【図22】本発明の第3の実施の形態に係る薄膜トランジスタアレイ基板において第2構造を持つパッドと画素電極を示す断面図である。

【図23】本発明の第3の実施の形態に係る液晶表示装置を示す平面図である。

【図24】図23に図示された液晶表示装置を示す断面図である。

【符号の説明】

【0151】

2、102 ゲートライン、4、104 データライン、6、106 薄膜トランジスタ、8、108 ゲート電極、10 ソース電極、12、112 ドレーン電極、13、27、33、39 コンタクトホール、14、114 画素電極、16、116 共通ラ 50

イン、18、118 共通電極、20、120 ストレージキャパシタ、22、122

ストレージ上部電極、24、124 ゲートパッド、26 ゲートパッド下部電極、28

ゲートパッド上部電極、30、130 データパッド、32 データパッド下部電極、

34 データパッド上部電極、36、136 共通パッド、38 共通パッド下部電極、

40 共通パッド上部電極、42、142 第1ゲート金属層、44、144 第2ゲー

ト金属層、45、145 基板、46、146 ゲート絶縁膜、48、148 活性層、

50、150 オーミック接触層、52、152 保護膜、147 非晶質シリコーン層

、140 n+ 非晶質シリコーン層、154 第1ソース/ドレーン金属層、156 第

2ソース/ドレーン金属層、127、133、139 コンタクトホール、160 第2

マスク、162 マスク基板、164 遮断部、166 回折露光部、168 フォトレ

ジストパターン、174 ゲートTCP、176 データTCP、172 ベースフィル

ム、174、176、178 TCPパッド、182 ACF、200 上部基板、20

2 カラーフィルターアレイ基板、204 シーリング材、143 エッチング防止層。

10

【図1】

【図2】

【図3 A】

【図3 B】

【図3 C】

【図3 D】

【 図 4 】

【 四 5 】

【図 6 A】

【 図 6 B 】

【 図 7 A 】

【 図 7 B 】

【図 8 A】

【 図 8 B

【 図 9 B 】

【 図 1 0 】

【 図 1 1 】

【 図 1 2 】

【 図 1 6 】

【 図 17 】

【 図 1 8 】

【 図 1 9 】

【図20A】

【 図 2 0 B 】

【図20c】

【 図 2 0 D 】

### 【図21】

【 図 2 3 】

【 図 2 2 】

【 図 2 4 】

---

フロントページの続き

(72)発明者 ピョン・チョル・アン

大韓民国、キョンギ - ド、アニヤン - シ、トンアン - ク、ピョンチョン - ドン 899-2、ファンチョン・アパートメント #203-903

(72)発明者 ピョン・ホ・リム

大韓民国、キョンサンプク - ド、クミ - シ、トラン - ドン、パク・マンション #102-103

F ターム(参考) 2H088 HA01 HA02 HA04 HA12 JA03 MA20

2H090 JA07 LA01

2H092 GA11 GA51 HA28 JA34 JA37 JA41 JA46 MA17 NA27 PA01

PA08 QA05

5C094 AA43 AA45 BA03 BA43 CA19 CA24

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 水平电场施加型液晶显示装置及其制造方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2004302466A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 公开(公告)日 | 2004-10-28 |

| 申请号            | JP2004093398                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 申请日     | 2004-03-26 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 申请(专利权)人(译)    | Eruji飞利浦杜迪股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| [标]发明人         | ピョン・チヨル・アン<br>ピョン・ホリム                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 发明人            | ピョン・チヨル・アン<br>ピョン・ホリム                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| IPC分类号         | G02F1/137 G02F1/1333 G02F1/1343 G02F1/1362 G09F9/30 G09F9/35                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| CPC分类号         | G02F1/13458 G02F1/134363 G02F1/136286 G02F2001/136231 G02F2001/13629                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| FI分类号          | G02F1/1343 G02F1/1333.505 G02F1/137 G09F9/30.338 G09F9/35 G02F1/1368                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| F-TERM分类号      | 2H088/HA01 2H088/HA02 2H088/HA04 2H088/HA12 2H088/JA03 2H088/MA20 2H090/JA07 2H090/LA01 2H092/GA11 2H092/GA51 2H092/HA28 2H092/JA34 2H092/JA37 2H092/JA41 2H092/JA46 2H092/MA17 2H092/NA27 2H092/PA01 2H092/PA08 2H092/QA05 5C094/AA43 5C094/AA45 5C094/BA03 5C094/BA43 5C094/CA19 5C094/CA24 2H092/GA14 2H190/JA07 2H190/LA01 2H192/AA24 2H192/BB02 2H192/BB72 2H192/BB86 2H192/CB05 2H192/CB44 2H192/CB46 2H192/CC32 2H192/CC72 2H192/EA76 2H192/FA64 2H192/FB46 2H192/GA41 2H192/HA47 2H192/HA64 |         |            |

| 代理人(译)         | 英年古河<br>Kajinami秩序                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 优先权            | 1020030019781 2003-03-29 KR<br>1020030019783 2003-03-29 KR<br>1020030021118 2003-04-03 KR                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

## 摘要(译)

种类：A1提供一种能够减少掩模工艺数量的薄膜晶体管阵列基板及其制造方法。一种成型形成在像素区域中的栅极线，公共线，数据线，薄膜晶体管，连接到公共线的公共电极连接到在像素区域中的薄膜晶体管和一个公共电极和一个水平电场在衬底上由包括在栅极线中的至少一个导电层形成的栅极焊盘，由包括在数据线中的至少一个导电层形成的数据焊盘，以及至少一个的导电层，一个栅极焊盘，彩色滤光器阵列的薄膜晶体管阵列基板的具有保护膜以暴露出数据焊盘和公共焊盘，在此期间，薄膜晶体管阵列基板和接合到填充液晶的形成公共焊盘1.一种薄膜晶体管阵列基板，包括：;而要继续的导电膜。点域5