## 【特許請求の範囲】

【請求項 1】 能動素子基板と、対向基板と、前記能動素子基板と前記対向基板との間に挟まれた状態で保持されている液晶層とからなる液晶表示装置であって、前記能動素子基板は、少なくともゲート電極、ドレイン電極、ソース電極を有する薄膜トランジスタと、表示すべき画素に対応した画素電極と、基準電位が与えられる共通電極と、データ線と、走査線と、共通電極配線とを備え、前記ゲート電極は前記走査線に、前記ドレイン電極は前記データ線に、前記ソース電極は前記画素電極に、前記共通電極は前記共通電極配線に、それぞれ電気的に接続されており、前記画素電極と前記共通電極の間に印加される前記能動素子基板の表面に略平行な電界により前記液晶層の分子軸を前記能動素子基板に平行な面内において回転させることにより表示を行う横電界方式のアクティブラチクス型液晶表示装置において、前記走査線を挟んで前記共通電極配線が形成されており、各共通電極配線毎に前記データ線と同一層の画素電位膜が層間膜を挟んで重畳されて表示状態を安定化させるための蓄積容量が形成されており、単位画素当たりにそれぞれ形成される、前段の走査線近傍の共通電極配線に重畳される画素電位膜と自段の走査線近傍の共通電極配線に重畳される画素電位膜は、透明電極からなる画素電極により相互に接続されていることを特徴とする横電界方式のアクティブラチクス型液晶表示装置。

【請求項 2】 能動素子基板と、対向基板と、前記能動素子基板と前記対向基板との間に挟まれた状態で保持されている液晶層とからなる液晶表示装置であって、前記能動素子基板は、少なくともゲート電極、ドレイン電極、ソース電極を有する薄膜トランジスタと、表示すべき画素に対応した画素電極と、基準電位が与えられる共通電極と、データ線と、走査線と、共通電極配線とを備え、前記ゲート電極は前記走査線に、前記ドレイン電極は前記データ線に、前記ソース電極は前記画素電極に、前記共通電極は前記共通電極配線に、それぞれ電気的に接続されており、前記画素電極と前記共通電極の間に印加される前記能動素子基板の表面に略平行な電界により前記液晶層の分子軸を前記能動素子基板に平行な面内において回転させることにより表示を行う横電界方式のアクティブラチクス型液晶表示装置において、前記走査線を挟んで前記共通電極配線が形成されており、各共通電極配線毎に前記データ線と同一層の画素電位膜が層間膜を挟んで重畳されて表示状態を安定化させるための蓄積容量が形成されており、単位画素当たりにそれぞれ形成される、前段の走査線近傍の共通電極配線に重畳される画素電位膜と自段の走査線近傍の共通電極配線に重畳される画素電位膜は、前記液晶層から最も遠い導電層で形成された接続電極により相互に接続されていることを特徴とする横電界方式のアクティブラチクス型液晶表示装置。

【請求項 3】 前記データ線と前記共通電極との層間に形成される層間絶縁膜が無機膜単層であることを特徴とする請求項 1 に記載の横電界方式のアクティブラチクス型液晶表示装置。

【請求項 4】 前記対向基板には、前記単位画素に対応する色層が形成されていることを特徴とする請求項 1 に記載の横電界方式のアクティブラチクス型液晶表示装置。

【請求項 5】 前記対向基板には、前記単位画素に対応する色層が形成されていないことを特徴とする請求項 1 に記載の横電界方式のアクティブラチクス型液晶表示装置。

【請求項 6】 前記接続電極は前記共通電極配線及び前記走査線と同一層に形成されていることを特徴とする請求項 2 に記載の横電界方式のアクティブラチクス型液晶表示装置。

【請求項 7】 前記共通電極配線と前記走査線は異なる層に形成されており、前記接続電極は前記共通電極配線と同一層に形成されていることを特徴とする請求項 2 に記載の横電界方式のアクティブラチクス型液晶表示装置。

【請求項 8】 前記単位画素当たりの 2 つの画素電位膜は、前記データ線の延伸方向と略平行な方向に離れて配置され、配置されたそれぞれの領域においてコンタクトホールを介して前記画素電極または接続電極に接続されていることを特徴とする請求項 1 ないし 7 のいずれかに記載の横電界方式のアクティブラチクス型液晶表示装置。

【請求項 9】 前記共通電極及び画素電極はそれぞれ透明電極から成り、前記データ線より前記液晶層に近い層上に形成されており、前記走査線近傍を除いて、前記データ線は絶縁膜を挟んで前記共通電極によって完全に覆われておらず、前記共通電極は各々の画素ごとにコンタクトホールを介して前記共通電極配線に接続されており、前記データ線が前記共通電極によって完全に覆われた領域においては、前記データ線に対向する位置の前記対向基板に配されたブラックマトリクスの幅は前記データ線を覆うように形成された前記共通電極の幅よりも小さい幅を有するように形成されており、前記データ線を覆う共通電極と、これに隣接する前記画素電極の間には平面上において遮光膜が存在しないように形成されていることを特徴とする請求項 1 ないし 8 のいずれかに記載の横電界方式のアクティブラチクス型液晶表示装置。

【請求項 10】 前記画素電極と前記共通電極は同一層に形成されることを特徴とする請求項 9 に記載の横電界方式のアクティブラチクス型液晶表示装置。

【請求項 11】 前記画素電極と共通電極は、絶縁膜を介して異なる層に形成されることを特徴とする請求項 9 に記載の横電界方式のアクティブラチクス型液晶表示装置。

【請求項12】 絶縁膜を介して異なる層に形成される前記画素電極と前記共通電極は、前記共通電極が前記液晶層に配向膜を介して接することを特徴とする請求項11に記載の横電界方式のアクティブマトリクス型液晶表示装置。

【請求項13】 前記共通電極は、前記走査線、データ線、共通電極配線の少なくとも一つに電気信号を入力する配線端子部を構成する導電材料と同一層に形成されることを特徴とする請求項1ないし12のいずれかに記載の横電界方式のアクティブマトリクス型液晶表示装置。

【請求項14】 前記画素電極と共通電極は、少なくとも下地の共通電極配線及びデータ線に乗り上げるもしくは乗り越える領域においては局所的に電極幅が太いことを特徴とする請求項13に記載の横電界方式のアクティブマトリクス型液晶表示装置。

【請求項15】 前記画素電極と共通電極の材料は、ITOもしくはIZOであることを特徴とする請求項1乃至6に記載の横電界方式のアクティブマトリクス型液晶表示装置。

#### 【発明の詳細な説明】

##### 【0001】

【発明の属する技術分野】 本発明は液晶表示装置、特に、横電界方式のアクティブマトリクス型液晶表示装置に関する。

##### 【0002】

【従来の技術】 薄膜電界効果型トランジスタ(Thin Film Transistor: 以下、TFTと記す)を画素のスイッチング素子として用いるアクティブマトリクス型液晶表示装置(以下、AMLCDと記す)は高品位の画質を有し、携帯型コンピュータの表示デバイスあるいは最近では省スペースのデスクトップコンピュータのモニターとして幅広く用いられている。AMLCDの種類には大きく区分して、配向した液晶分子の分子軸の方向(「ディレクタ」と呼ばれる)を基板に対して直交する面内において回転させ、表示を行う形式のものと、基板に対して平行な面内において回転させ、表示を行う形式のものがある。前者の代表例がTN(Twisted Nematic: ねじねマティック)モードの液晶表示装置であり、後者はIPS(In-Plane Switching)モード(横電界方式)の液晶表示装置と呼ばれる。IPSモードの液晶表示装置は、基本的には視点を動かしても液晶分子の短軸方向のみを見ていることになるため、液晶分子の「立ち方」の視野角に対する依存性がなく、TNモードの液晶表示装置よりも広い視野角を達成することができる。このため、IPSモードのLCDは、大型用途に用いられることが多い。

【0003】 一方で、従来のIPSモードのLCDは、液晶を挟持する2枚の透明基板のいずれか一方に、走査線及びデータ線のいずれかからなる不透明材料からなる液晶を駆動するための電極が形成されるため、これら電

極によって開口率が低くなり、これに伴い透過率が低いといった問題点を有している。そのため、透過率向上検討がなされてきた。高開口率化の手法の一つとして、特許第3123273号公報に開示された技術がある(以下、従来例1と呼ぶ)。従来例1においては、「信号配線の液晶層に面する部分の一部が絶縁物を介して導電体で覆われており、前記導電体が、前記液晶に対して主として基板面に平行な電界を印加する電極の一方であるソース電極あるいは共通電極と電気的に接続されている」ことが特徴である。このようにすることにより、共通電極で信号線の電界を遮蔽することができ、画素の有効表示領域を広げることができるので、画素の開口率ひいては光利用効率を高めることができる。また、特開平9-73101号公報において開示されている技術として、液晶を駆動する電極を透明材料化することで、光利用効率をさらに高めることができるとしている。

【0004】 ところで、AMLCDの場合、その動作モードに関わらず、TFTを介して誘電体である液晶に所望の電荷を書きこみ、書きこまれた電荷から生ずる電界によって、液晶配向を制御することで、外部光の透過強度を制御して表示動作させることが基本原理である。TFTを介して書きこまれた電荷は、次のタイミングで新たな電荷を書きこむまで(1フレーム内)は、書きこまれた電荷(すなわち電界)を保持することが理想であるが、液晶は誘電率異方性を有するため、電界に応じて液晶が回転し、TFTを介して書きこまれた電荷による電界の低下が発生する(以下、誘電緩和と呼ぶ)。この誘電緩和による電界低減は、液晶容量に対してある比率を有する蓄積容量を形成することで、TFTがオン状態になったときに書きこむ電荷量を増大させ、誘電緩和が発生しても蓄積容量に書きこんだ電荷を液晶容量に分散させることで抑制している。

【0005】 また、蓄積容量を設けることも考えられており、この蓄積容量は、TFTのゲートスイッチがオン状態からオフ状態に変化した際に発生する画素電圧低下(一般に、フィードスルーレベルV<sub>p</sub>と称する)抑制に対しても効果的があることから、フリッカ対策としても取り入れられている。このフィードスルーレベルが発生する原因是、TFTのゲート・ソース間の寄生容量C<sub>gs</sub>であり、ゲートパルスがオンになったときに液晶容量C<sub>1</sub>、蓄積容量C<sub>s</sub>に充電された各電荷が、ゲートパルスがオフになった瞬間に各々の容量に再分配されることに起因する。横方向電界駆動方式は、TN方式におけるカラーフィルター形成基板上の透明電極が存在しないため、ピクセル電極とコモン電極により発生した電気力線は色層内部を通過する。すなわち、横方向駆動方式におけるフィードスルーレベルV<sub>p</sub>は、色層容量C<sub>color</sub>の関数にもなる。フィードスルーレベルV<sub>p</sub>は次式で表される。

$$V_p = C_{gs} / (C_{gs} + C_{sc} + C_{lc} + C_{color}) \times$$

(V<sub>gon</sub> - V<sub>goff</sub>)

以上から、IPSモードのLCDにおいても、蓄積容量Cscを大きくすることはAM-LCD動作の上で必要である。

【0006】一方で、IPSモードのLCDにおける蓄積容量の付与は、固定電位の金属膜と画素電極との間に層間絶縁膜を挟んで形成するが、一般に蓄積容量は2つの手法で形成される。一つはコモンストレージ法であり、他方はゲートストレージ法である。後者は、前段の走査線と画素電極との間に蓄積容量を形成することを指すが、走査線と画素電極間の蓄積容量が走査線信号への負荷になることによって、ゲート線信号が信号遅延を引き起こし、パネル面内におけるパネル透過率バラツキとなりやすいため、一般に大型LCDにおいてはコモンストレージが好んで使用される。コモンストレージ法は、共通電極と画素電極との間に蓄積容量を形成手法であるが、IPSモードのLCDの場合、必然的に単位画素内に櫛歯状共通電極が配置されることから、共通電極に対する蓄積容量付与をしやすいこと、また走査線に対する負荷がないので走査線信号遅延も起こりにくいため、一般に大型LCDにおいてはコモンストレージが好んで使用される。

【0007】ここでLCDに形成される共通電極配線とデータ線は、大型LCDの場合に関しては、以下の理由により不透明材料から構成される。共通電極配線は共通電極電位遅延を防止するために、例えばクロム、チタン、モリブデン、タングステン、アルミなどの単層や、これらの金属の積層構造といった低抵抗配線材料を用いる必要がある。これらの配線材料は不透明材料であるため、共通電極配線が占める面積は開口部として機能せず、光透過に寄与しない。また、TFTの製造工程数の増加を避けて、走査線と同一工程・同一材料にて共通電極配線を形成する場合、走査線及び共通電極配線の配線抵抗を下げる目的及びTFTのバックチャネルを外光から保護する目的で、低抵抗かつ不透明の配線材料を使用する必要がある。この場合も共通電極配線が占める面積は開口部として機能せず、光透過に寄与しない。さらに、データ線についても走査線と同様に、配線抵抗を低減する目的で、低抵抗かつ不透明の配線材料を使用する必要がある。

【0008】また、別な問題として、データ線信号による電界を開口部の液晶に与えないようにするために、データ線を覆うように共通電極を形成すると、データ線と共通電極との間の寄生容量が大きくなり、データ線信号遅延が生じ易くなる。データ線信号遅延を防止するには、データ線と共通電極との間の寄生容量を小さくする必要があるが、そのためデータ線とデータ線をシールドする共通電極間に、低誘電率の層間膜を形成することにより、達成できる。そのため、LCDの表示を安定させるための大

(4) 6

きな蓄積容量は、データ線層とデータ線をシールドする共通電極層との間に形成することはできず、共通電極配線層とデータ線層との間に蓄積容量を形成する必要があった。この場合、蓄積容量を増大させるには、共通電極配線層とデータ線層との間の層間膜を薄膜化することも一つの手段であるが、配線同士の電気的短絡による歩留まり低下の確率が増大すること、TFTのスイッチ特性に影響を与えるというデメリットがあるため、TFTアレイとしては、走査線を挟んで2本の共通電極配線を形成して蓄積容量面積を大きくすることが最も効果的である。

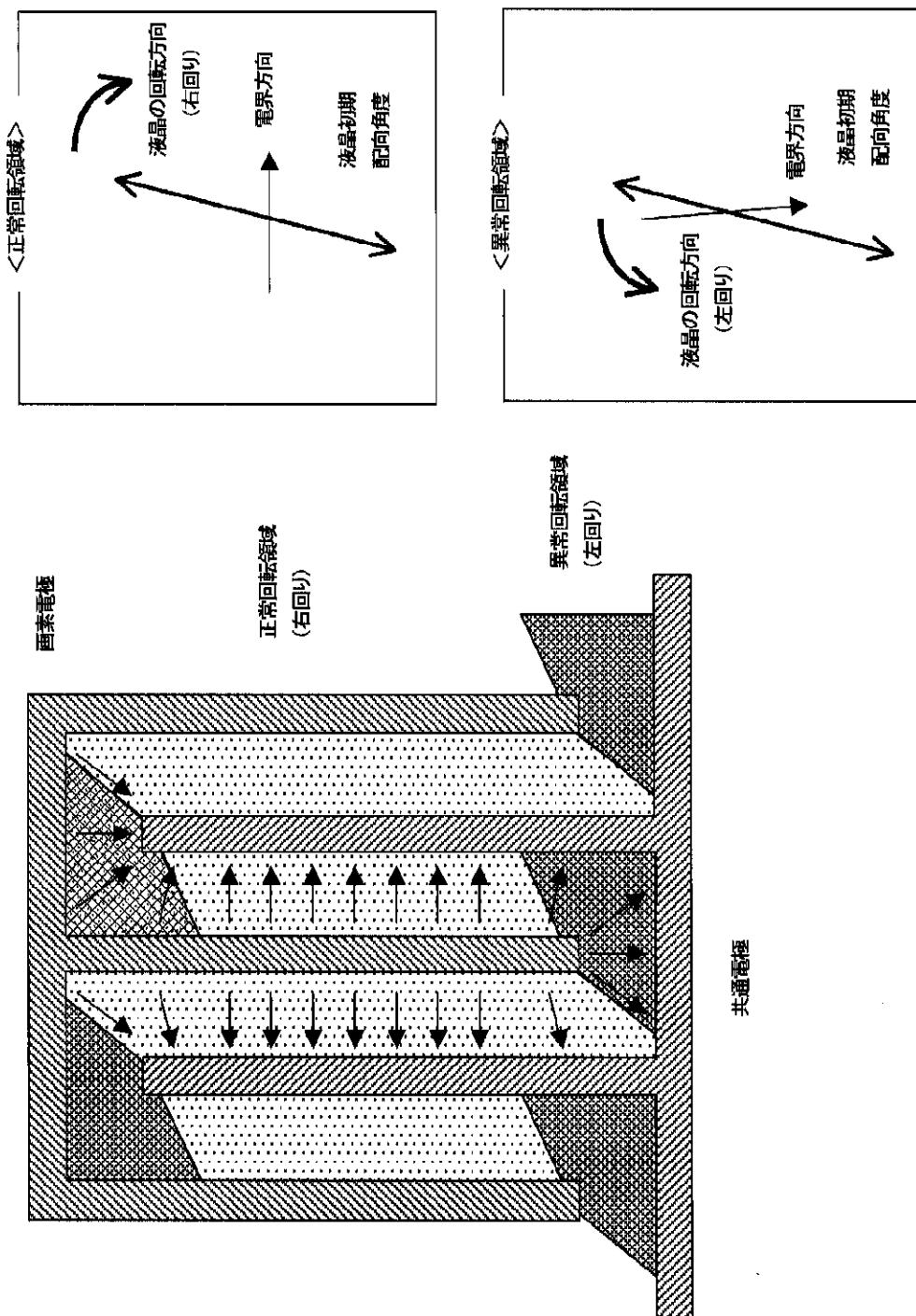

【0009】さらに別な問題として、IPS-LCDにおいては、図22に示すように、共通電極と画素電極に囲まれた縦長の領域をコラムと称するが、コラム終端においては、液晶に印加される電界方向は複雑になるため、所望の方向に回転する液晶領域と、所望の方向とは逆方向に回転する液晶領域の2つ液晶領域が形成される現象が生じやすい。また、所望の方向とは逆方向に回転する液晶領域は、正常に回転する液晶領域と比較して、強電界を印加しないと液晶が回転しないため、この逆方向に回転する液晶領域が発生している面積分はパネル透過率にあまり寄与できず、パネル透過率を下げてしまうという問題点があった。さらに、上記2つの領域の境界は電界強度に依存なく液晶は殆ど回転しないため、領域境界は単位画素内に発生する割合だけ、パネル透過率を低下させてしまっていたため、高透過率を有するIPSモードのLCDにおいては、単位画素内において所望の方向とは逆方向に回転する液晶領域を形成しない工夫が必要であった。

【0010】この液晶回転領域発生を防止する技術が特許第2973934号公報(以下、従来例3と呼ぶ)において開示されている。この従来例3で記載されている技術は、液晶を駆動するための電極(すなわち画素電極と共通電極)を張り出す/引っ込める凹凸構造として、液晶に印加する電界を制御するものである。

【0011】このように、コラム終端での複雑な電界方向を規定するため、及び走査線電位をシールドするため、走査線を共通電極配線で挟む(すなわち単位素子当たりに2本の共通電極配線を形成する)ことは、走査線信号の漏れ電界による液晶の配向乱れ及び液晶の逆回転を防止し、LCDとしての信頼性を向上させるために必要であった。このようなことから、共通電極配線を単位画素当たりに2本形成することで、LCDの表示を安定化する蓄積容量も単位画素当たりに少なくとも2ヶ所に形成することができるようになり、さらなる大きな蓄積容量をとることができる。ここで、単位画素内において蓄積容量が2箇所以上に分離されると、それぞれの部位が蓄積容量として機能するためには、蓄積容量のデータ線と同層の画素電位膜を共通配線に対して形成し、これらの画素電位膜をTFTを介して入力される画素電位と等

電位とする必要があった。

【0012】このような2箇所の蓄積容量を構成する画素電位膜を相互に電気接続して所定の電位に接続するために両画素電位膜を導電層の一部を利用して相互に接続する構成を採用すると、次のような問題が生じることが判明した。

【0013】第1は、2箇所の蓄積容量を構成する画素電位膜を相互に接続する電位膜がデータ線と同層の金属膜で形成され、この金属膜と画素電極が液晶セルのセル厚方向に重畠されると、これらが重畠されている領域においては、画素電極上の液晶が電界により回転しても、その部分はパネル透過率に寄与できないため、全体としてのパネル透過率が低下するという問題点があった。

【0014】第2は、液晶に印加する横電界は画素電極と画素電位膜が積層している領域においては、2つの画素電位膜をつなぐ金属膜と画素電極が異なる層から形成されるため、それぞれをパターン化する際の層間の重ねずれが生じた場合に、画素電極電位となっている面積が増加し、実効的な開口率を低下させ、透過率が下がるという問題点があった。

【0015】第3は、2つの画素電位膜をつなぐ金属膜が画素電極の下層に配置された櫛歯電極においては、電界が局所的に強くなり、単位素子内で電界強度がばらつくことで、全白表示をした際の輝度が低下するという問題点があった。

【0016】その他、透明材料で構成される画素電極及び共通電極の電極形状は、エッティングをする際に、下地金属（走査線層及びデータ線層）の段差により、局所的な電極断線が生じ、電極パターンに断線が生じることで、部分的に液晶に横電界が印加されない表示不良が発生することといった歩留まりを低下させる原因となっていた。

【0017】本発明はこのような問題点に鑑みてなされたものであり、更なる高透過率を有するIPS型液晶表示装置を製造し、かつその製造歩留まりを向上させることを目的とする。

#### 【0018】

【課題を解決するための手段】本発明は、画素電極と共通電極の間に印加される能動素子基板の表面に略平行な電界により液晶層の分子軸を能動素子基板に平行な面内において回転させることにより表示を行う横電界方式のアクティブマトリクス型液晶表示装置において、走査線を挟んで共通電極配線が形成されており、各共通電極配線毎にデータ線と同一層の画素電位膜が層間膜を挟んで重畠されて表示状態を安定化させるための蓄積容量が形成されており、単位画素当たりにそれぞれ形成される、前段の走査線近傍の共通電極配線に重畠される画素電位膜と自段の走査線近傍の共通電極配線に重畠される画素電位膜は、液晶層から最も遠い導電層で形成された接続電極により相互に接続されていることを特徴とする。

【0019】ここで、データ線と共通電極との層間に形成される層間絶縁膜が無機膜単層であることが好ましい。また、能動素子基板と液晶層を介して対向配置される対向基板には、単位画素に対応する色層が形成されており、あるいは形成されていない構成とする。

【0020】また、本発明は、画素電極と共通電極の間に印加される能動素子基板の表面に略平行な電界により液晶層の分子軸を能動素子基板に平行な面内において回転させることにより表示を行う横電界方式のアクティブマトリクス型液晶表示装置において、走査線を挟んで前記共通電極配線が形成されており、各共通電極配線毎にデータ線と同一層の画素電位膜が層間膜を挟んで重畠されて表示状態を安定化させるための蓄積容量が形成されており、単位画素当たりにそれぞれ形成される、前段の走査線近傍の共通電極配線に重畠される画素電位膜と自段の走査線近傍の共通電極配線に重畠される画素電位膜は、液晶層から最も遠い導電層で形成された接続電極により相互に接続されていることを特徴とする。

【0021】ここで、接続電極は共通電極配線及び走査線と同一層に形成される。あるいは、共通電極配線と走査線は異なる層に形成されており、接続電極は共通電極配線と同一層に形成される。

【0022】さらに、本発明は前記本発明の横電界方式のアクティブマトリクス型液晶表示装置において、共通電極及び画素電極はそれぞれ透明電極から成り、データ線より液晶層に近い層上に形成されており、走査線近傍を除いてデータ線は絶縁膜を挟んで共通電極によって完全に覆われておらず、共通電極は各々の画素ごとにコンタクトホールを介して共通電極配線に接続されており、データ線が共通電極によって完全に覆われた領域においては、データ線に対向する位置の対向基板に配されたブラックマトリクスの幅はデータ線を覆うように形成された共通電極の幅よりも小さい幅を有するように形成されており、データ線を覆う共通電極と、これに隣接する画素電極の間には平面上において遮光膜が存在しないように形成されていることが好ましい。

【0023】本発明によれば、特定の櫛歯間隔の液晶のみ強電界が印加されることによる白輝度低下を防止でき、高透過率を有する横電界方式のアクティブマトリクス型液晶表示装置を製造することができる。

【0024】なお、本発明においては次の形態とすることが好ましい。すなわち、画素電極と共通電極は同一層に形成される。あるいは画素電極と共通電極は、絶縁膜を介して異なる層に形成される。異なる層に形成することにより、液晶表示装置の製造に関して製造プロセスは増加するが、画素電極と共通電極の配置に関する自由度が上がり、更なる高透過率を有する横電界方式のアクティブマトリクス型液晶表示装置を製造することができる。

【0025】また、画素電極と共通電極は、共通電極が

前記液晶層に配向膜を介して接することにより、データ線とデータ線をシールドする共通電極との間の寄生容量を小さくでき、データ線信号遅延を防止できるため、高開口率でかつ更なる表示均一化を有する横電界方式のアクティブマトリクス型液晶表示装置を製造することができる。

【0026】さらに、共通電極は、走査線、データ線、共通電極配線の少なくとも一つに電気信号を入力する配線端子部を構成する導電材料と同一層に形成することにより、液晶表示装置の製造に関してプロセス増加無しに高透過率を有する横電界方式のアクティブマトリクス型液晶表示装置を製造することができる。

【0027】さらに、画素電極と共通電極は、少なくとも下地の共通電極配線及びデータ線に乗り上げるもしくは乗り越える領域においては局所的に電極幅が太い構成とすることにより、透明電極の局所的な断線を防止できるため、高透過率でかつ製造歩留まりの高い横電界方式のアクティブマトリクス型液晶表示装置を製造することができる。

【0028】また、画素電極と共通電極の材料を、ITOもしくはIZOとすることにより、配向膜を介して液晶駆動電極が液晶と接しても電気化学的に安定な材料を用いることができるため、画素電極と共通電極が透明となり、液晶を駆動する櫛歯電極の上層に位置する液晶を電界制御することで、高透過率を有する横電界方式のアクティブマトリクス型液晶表示装置を製造することができる。

#### 【0029】

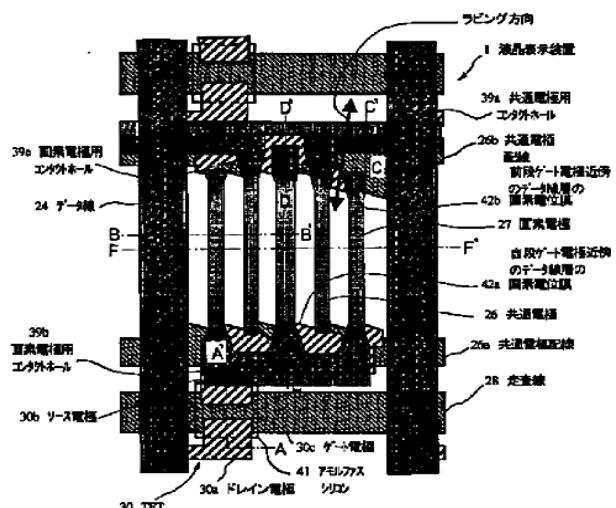

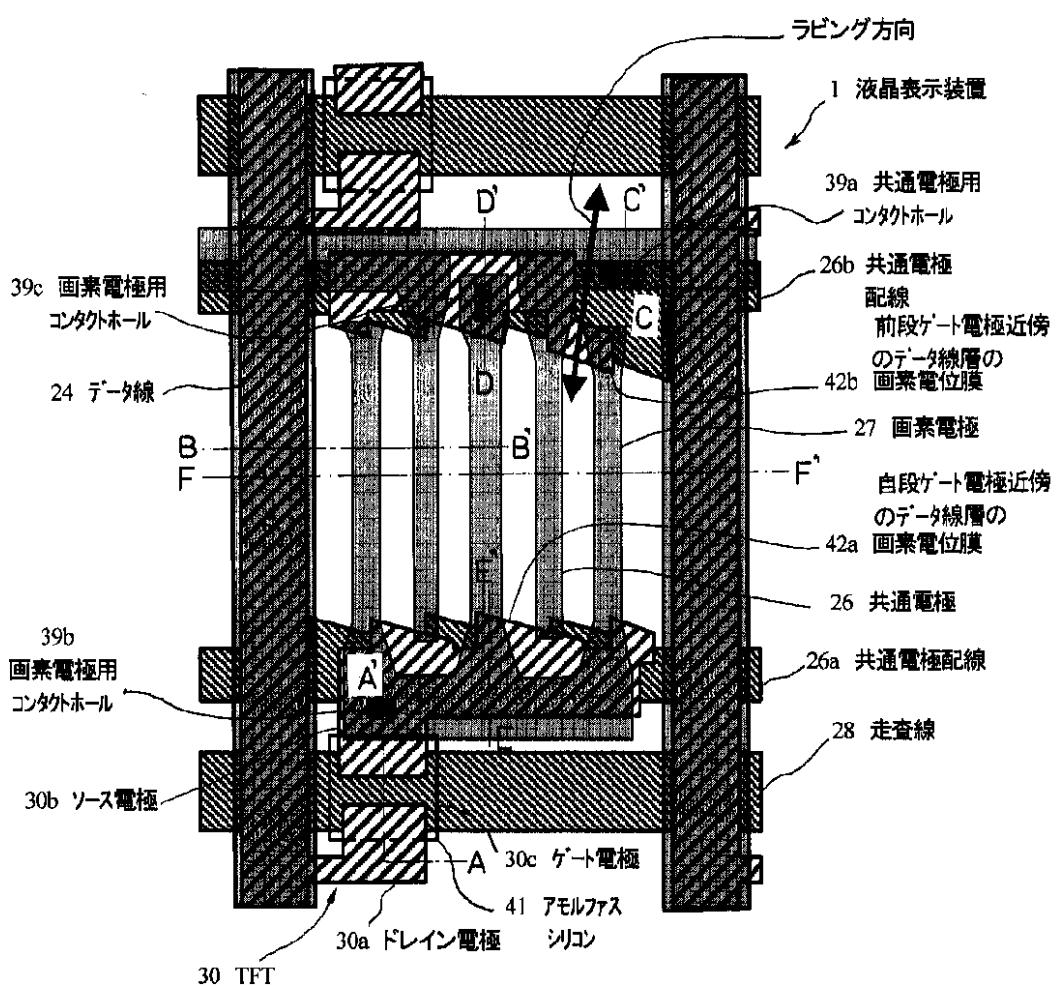

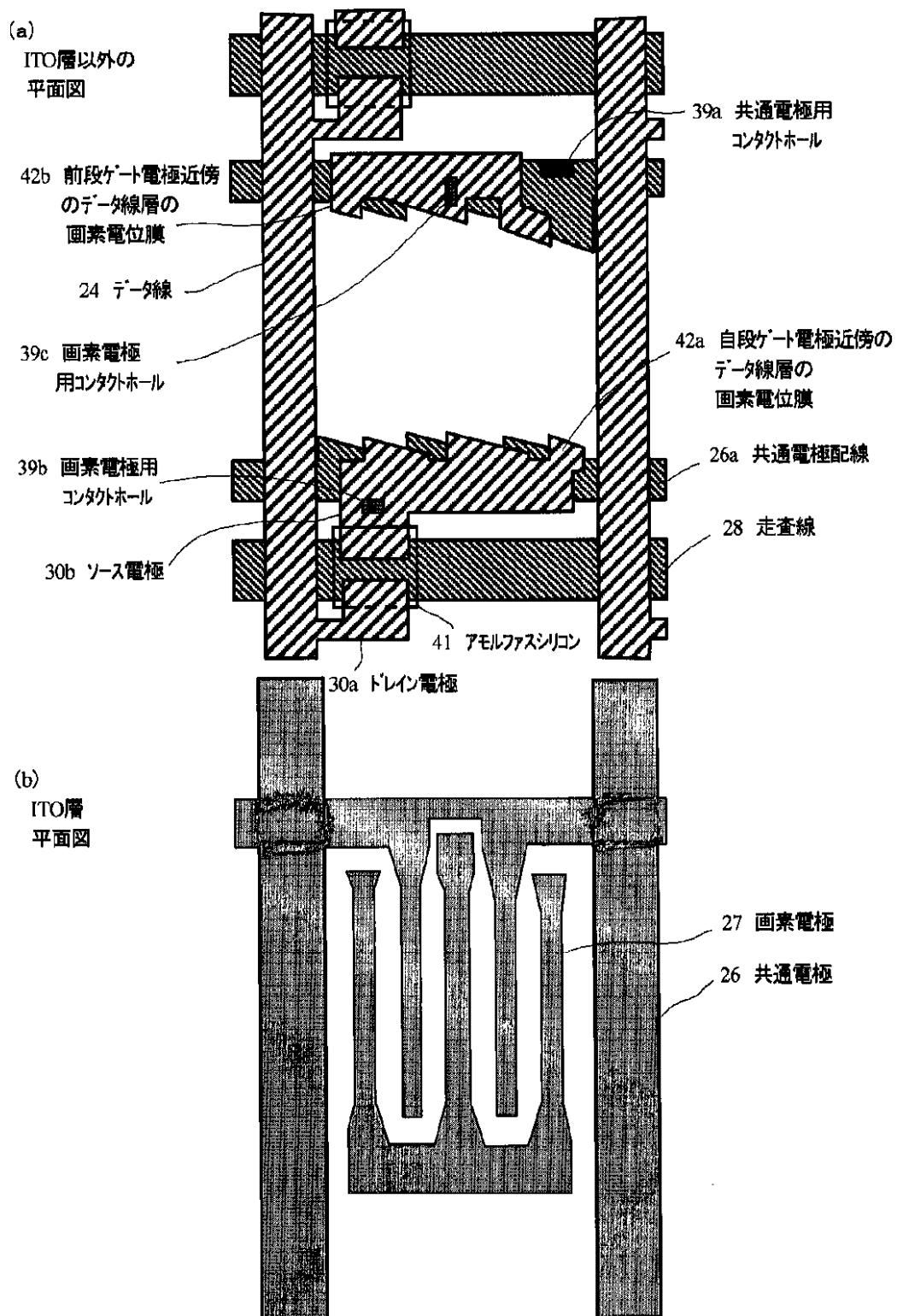

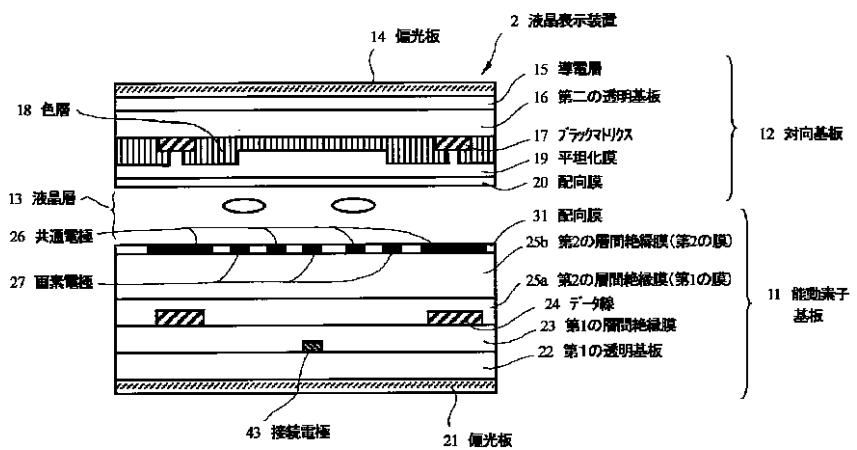

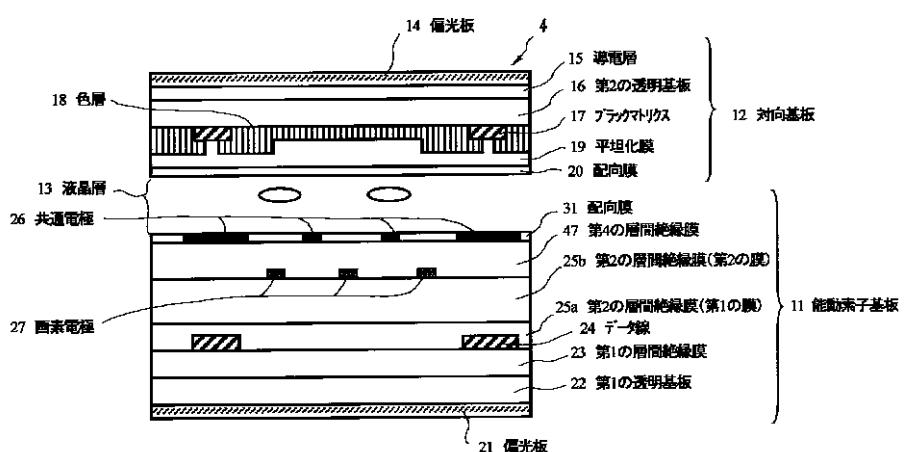

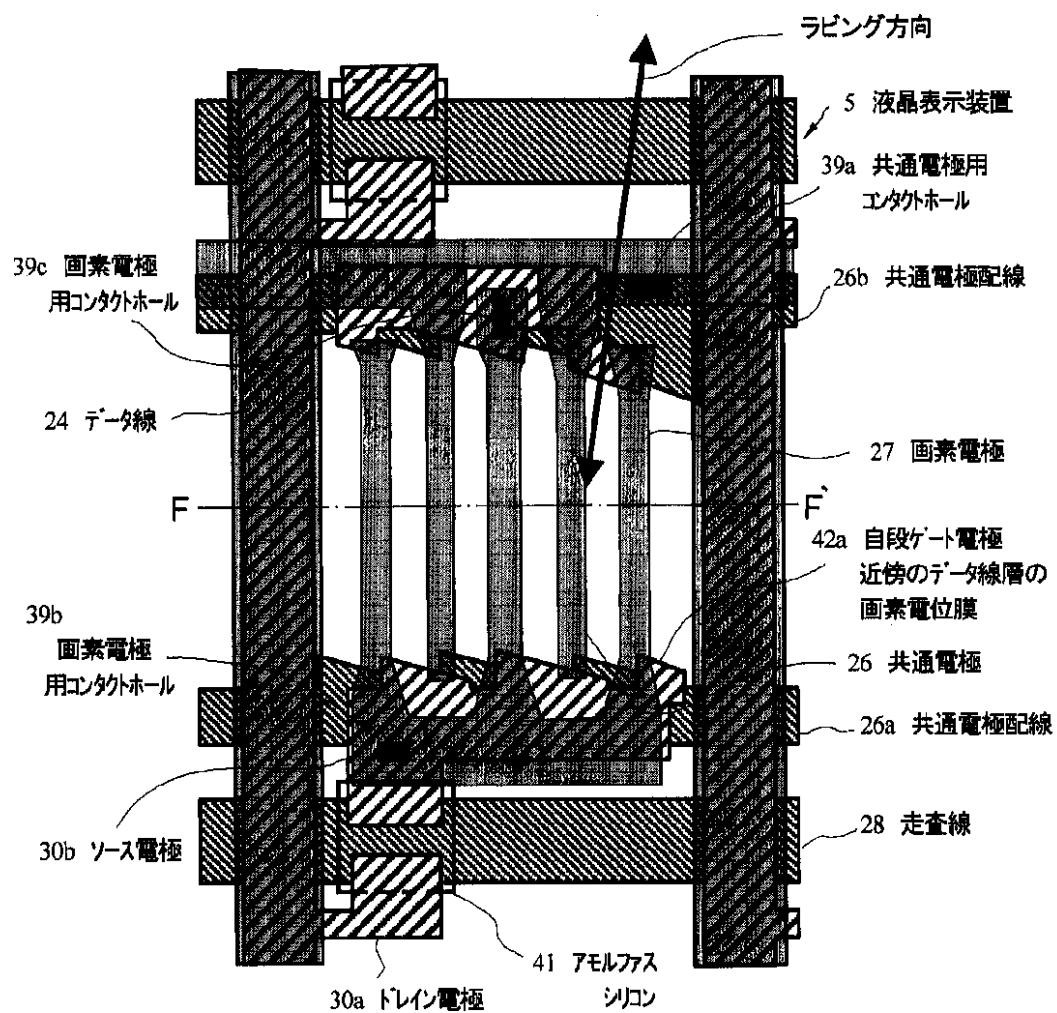

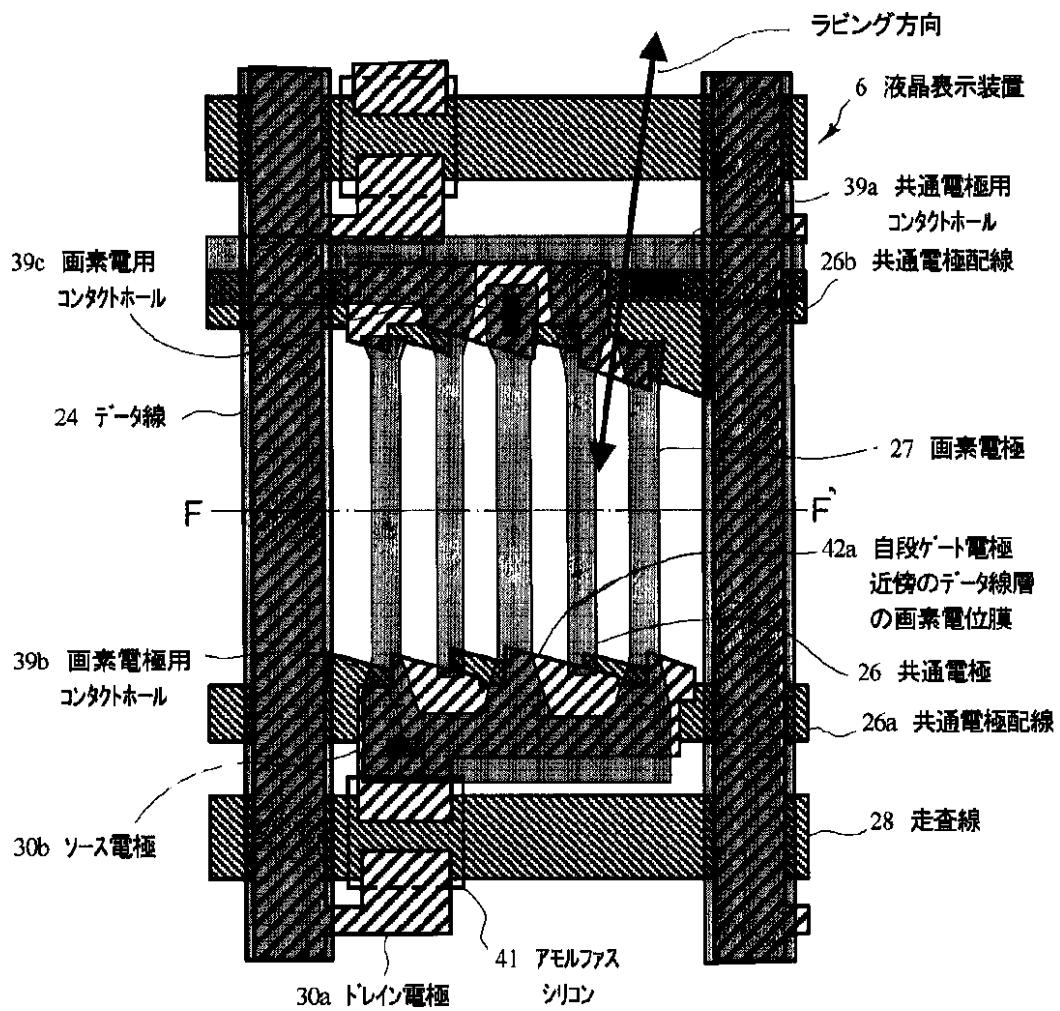

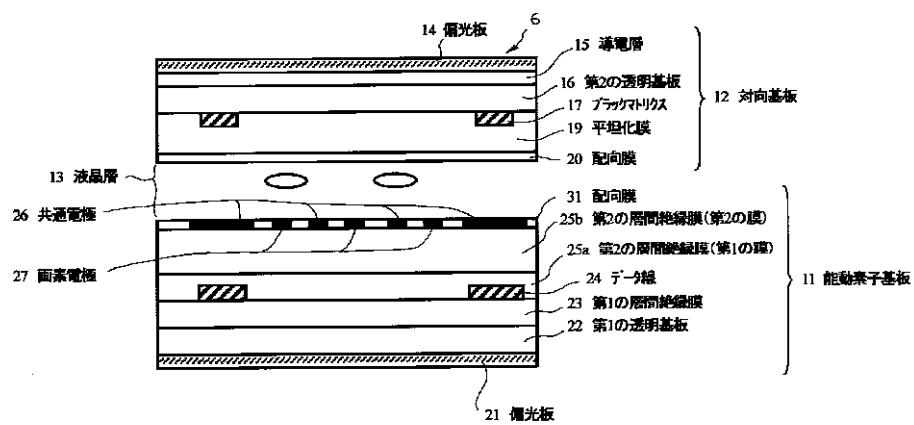

【発明の実施の形態】(第1の実施形態) 次に、本発明の実施形態を図面を参照して説明する。図1～図4に本発明の第1の実施形態に係る横電界方式のアクティブマトリクス型液晶表示装置を示す。図1は液晶表示装置1を構成する能動素子基板の平面図、図2は図1のF-F'線における箇所の液晶表示装置111の断面図である。これらの図において、液晶表示装置1は、能動素子基板11と、対向基板12と、前記能動素子基板11と対向基板12との間に挟まれた状態で保持されている液晶層13を備えている。また、前記能動素子基板11と対向基板12の各外側面にはそれぞれ偏光板14, 21を備えている。なお、本明細書では、前記能動素子基板11及び対向基板12において、液晶層13により近い層を上側、液晶層13からより遠い層を下側と称することにする。

【0030】前記対向基板12は、ガラス等の透明な絶縁性基板からなる第2の透明基板16の上面に複数の画素領域を区画するための遮光膜としてのブラックマトリクス17と、各画素領域に形成されるとともに、周辺部において前記ブラックマトリクス17に重なりあってい る色層18と、前記ブラックマトリクス17と色層18の上に形成された透明なオーバーコート層からなる平坦

化膜19から形成されている。前記色層18は、赤(R)、緑(G)及び青(B)の染料または顔料を含む樹脂膜からなっている。また、液晶表示パネル表面からの接触等による帯電が液晶層13へ電気的な影響を与えることを防止するために、前記第2の透明基板16の下面には、透明な導電層15が形成されている。

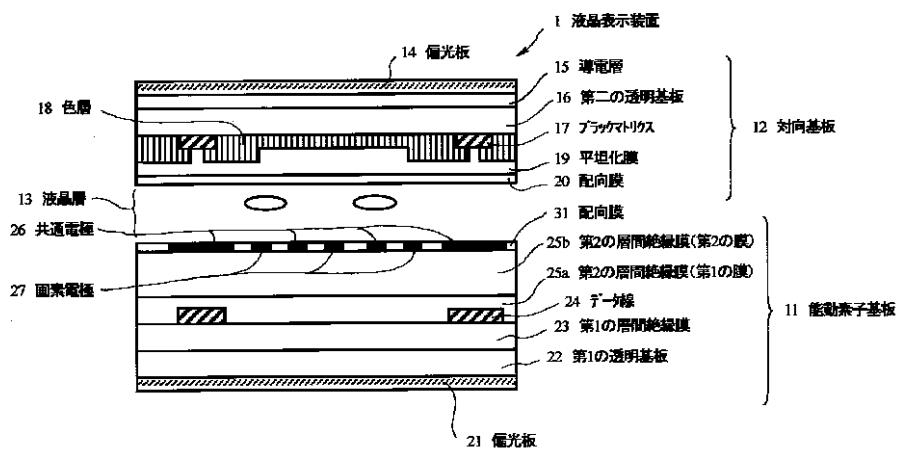

【0031】前記能動素子基板11は、同様な透明絶縁性基板からなる第1の透明基板22上に、第1の金属層により形成される走査線28、ゲート電極30c及び共通電極配線26a, 26bと、その上層に形成された第1の層間絶縁膜23と、前記第1の層間絶縁膜23の上層の前記ゲート電極を覆う領域に形成された島状の非晶質(アモルファス)シリコン膜41と、第2の金属層により形成されるデータ線24、薄膜トランジスタ(TFT:Thin Film Transistor)30のソース電極30b、及びドレイン電極30aと、この上に形成されて第2の層間絶縁膜25を構成する第1の絶縁膜25a及び第2の絶縁膜25bと、その上に透明電極材料により形成された共通電極26及び画素電極27とを有する。

【0032】さらに、前記能動素子基板11と対向基板12とは、それぞれの上面に配向膜31、配向膜20を配し、図1に示すように画素電極27および共通電極26の延伸方向から、10乃至30°程度の角度を傾けた所定の方向に液晶層13がホモジニアス配向するようにラビング処理がなされた後に、相互に対向配置される。この角度を液晶分子の初期配向方位と言う。そして、前記能動素子基板11と対向基板12とは、液晶層13の厚みを保持するためのスペーサー(図示せず)によって前記配向膜31, 20を所要間隙で対向した状態で、しかも周囲をシール(図示せず)で囲った状態で貼り合わされており、この囲まれた間隙内に液晶が密封状態に充填されて前記液晶層13が形成されている。

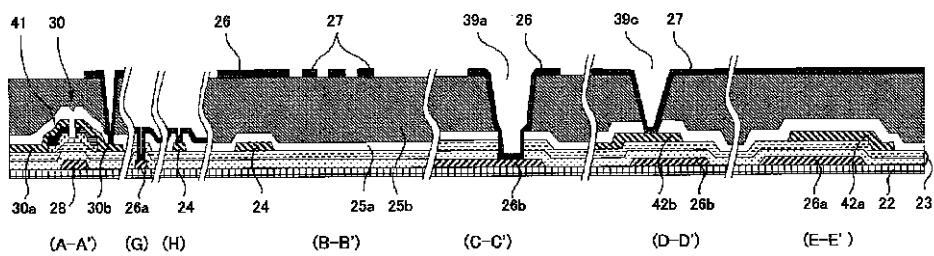

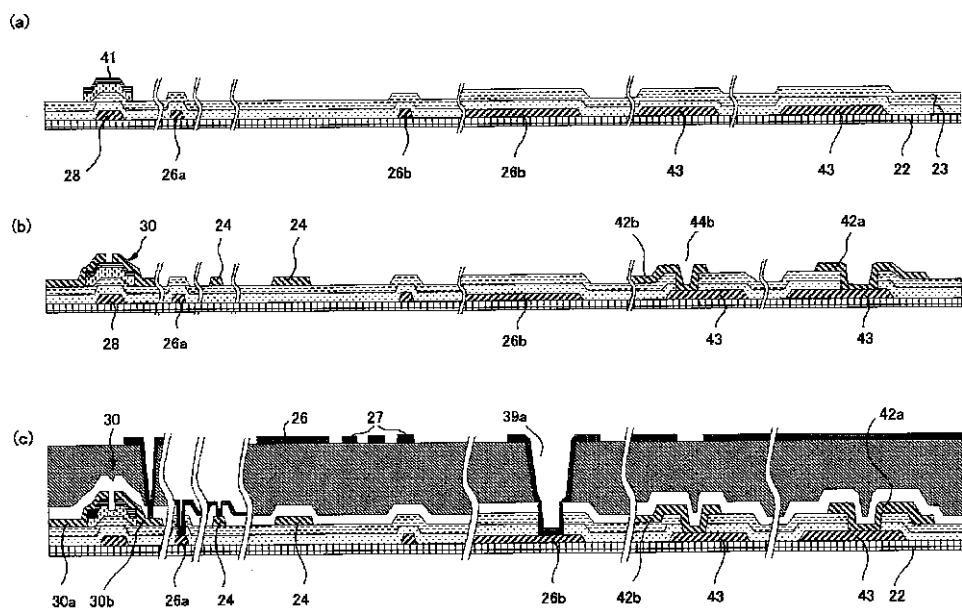

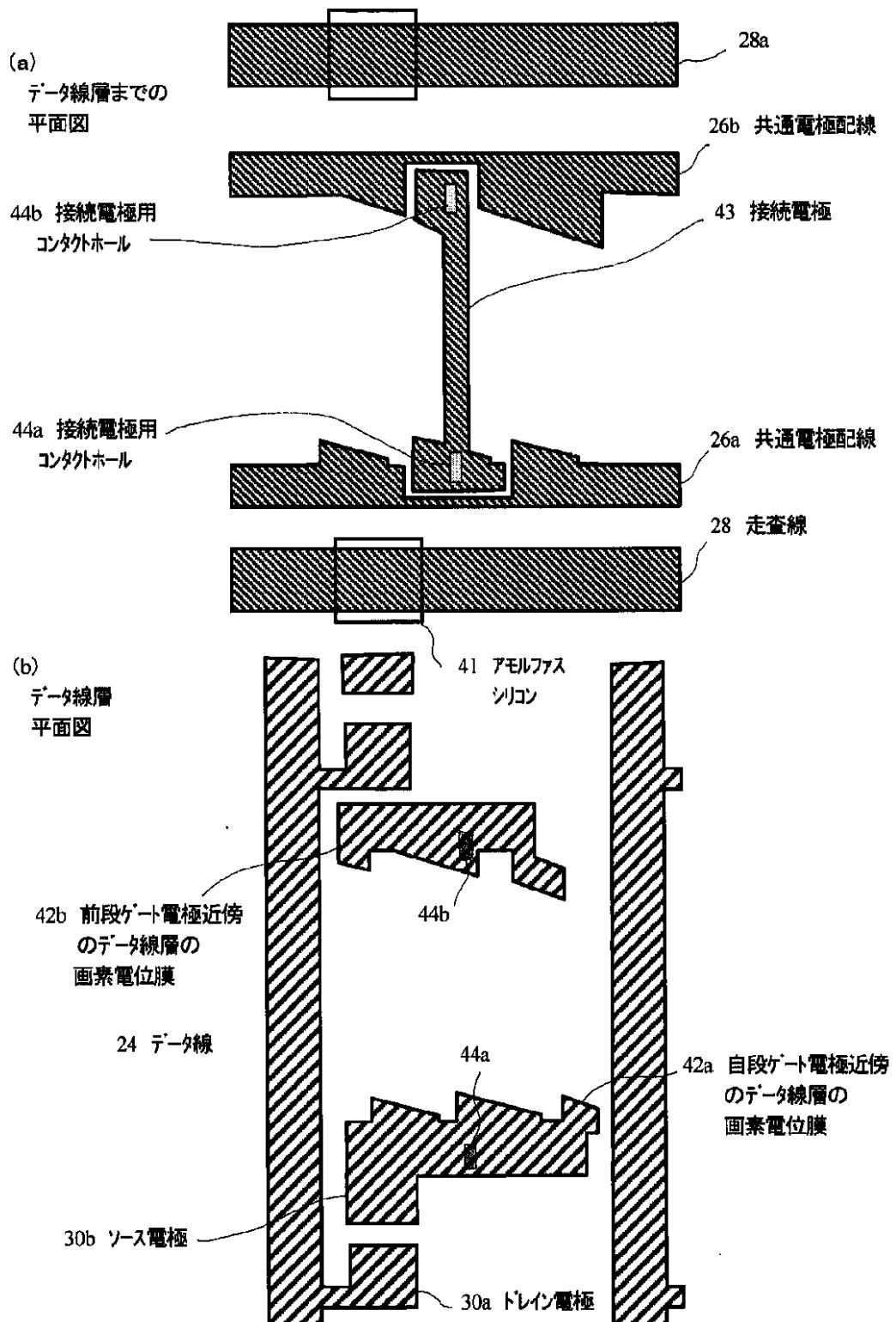

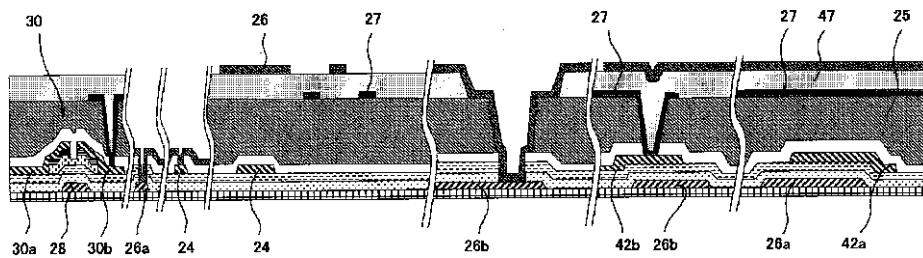

【0033】次に、前記能動素子基板11の構成について詳細に説明する。図3(a)は前記第1及び第2の金属層まで形成した時点での平面図、図3(b)は透明電極材料の層の平面図である。また、図4は図1のA-A'線～E-E'線の各断面図であり、前記TFT30(A-A')、単位画素領域の一部(B-B')、共通電極用コンタクトホール39a(C-C')、画素電極42bのコンタクトホール39c(D-D')、画素電極27の一部(E-E')、並びに図1～3には表れない共通電極配線の外部コンタクト部(G)とデータ線の外部コンタクト部の接続部(H)の各断面構造をそれぞれ示したものである。図3(a)に示すように、能動素子基板11の上面には、クロム等の低抵抗な金属材料からなる第1の金属層により、走査用信号が供給される走査線28と、図には表れない周辺部において基準電位が供給される共通電極配線26がX方向(図の左右方向)に延びるように形成されている。前記走査線28は画素領域のY方向(図の上下方向)単位ごとに配列さ

れ、共通電極配線26は走査線28をY方向に挟み込む形で配置されている。また、同様にクロム等の低抵抗な金属材料からなる第2の金属層により、データ信号が供給されるデータ線24が画素領域のX方向単位毎に配列される。また、この第2の金属層により、後述するよう にTFT30のドレイン電極30a及びソース電極30bが形成されるとともに、各画素領域内においてそれぞれ自段の走査線28とY方向に前段の画素の走査線に近接配置してそれぞれ2つの画素電位膜42a, 42bが形成されている。以下、前者を自段の画素電位膜、後者を前段の画素電位膜と称する。

【0034】前記TFT30は走査線28とデータ線24との交点の近傍に各画素に対応して設けられている。前記走査線の一部でゲート電極30cが形成されており、このゲート電極30cを覆う第1層間絶縁膜上にアイランド状にアモルファスシリコン41が形成され、その上に前記データ線24と同じ第2の金属層によってドレイン電極30aと、ソース電極30bとが形成されている。したがって、ゲート電極30cは走査線28と一緒に、ドレイン電極30aはデータ線24に電気的に接続される。また、ソース電極30bは前記2つの画素電位膜42a, 2bのうち、自段の走査線28に近接配置された側の画素電位膜42aと一緒に形成される。

【0035】前記第2の金属層の上には、第2の層間絶縁膜25が形成される。ここでは、図4に示すように、第2の層間絶縁膜25は下層の第1の絶縁膜25aと上層の第2の絶縁膜25bの積層構造として形成されている。なお、この第2の層間絶縁膜25はここでは1ないし2μmの膜厚を有しているが、無機膜または有機膜の何れかからなる単層膜として構成することができる。勿論、他の膜厚、膜材料で構成することも可能である。そして、前記第2の層間絶縁膜25の上に、図3(b)に示すように、ITO(Indium Tin Oxide)からなる透明電極材料によって共通電極26及び画素電極27が形成される。共通電極26はX方向及びY方向にマトリクスに近い形状に形成されており、前記共通電極配線とデータ線の上側に沿って配設される。特に、データ線24が走査線28と交差する領域及びその近傍の領域を除いて、データ線の上側ではデータ線24を完全に覆うように幅広に形成されている。なお、共通電極26と画素電極27に囲まれた縦長の領域をコラムと言い、各コラムに画素が対応している。また、各画素においては共通電極26と画素電極27は何れも櫛歯形状をなしており、各電極の櫛歯は何れもデータ線24と平行に延びているとともに、共通電極26と画素電極27の櫛歯が相互に噛み合うように、かつ両者の櫛歯が相互に隔置されるように配置されている。その上で、前記共通電極26は、共通電極用コンタクトホール39aを介して、画素毎に共通電極配線26a, 26bに接続される。また、画素電極27は前記自段の画素電位膜42a、すなわちTFT

10 T30のソース電極30bと前段の画素電位膜42bにそれぞれ画素電極用コンタクトホール39b, 39cを介して電気接続されている。なお、これらコンタクトホールの形状、配置は図示のものに限定されるものではない。

【0036】一方、対向基板12においては、図2に示したように、前記ブラックマトリクス17は、データ線24と平面上において重なり合う領域においては、隣の画素から漏れ出る光を遮光するために存在するため、前述のようにデータ線24を完全に覆っている共通電極26よりも幅狭にできており、共通電極26を透過する光を遮らないように構成されている。

【0037】以上の構成の横電界方式の本液晶表示装置1においては、走査線28を介して供給される走査用信号により選択され、かつ、データ線24を介して供給されるデータ信号が書き込まれた画素において、共通電極26と画素電極27との間で、前記第1及び第2の透明基板16, 22に平行な電界を生じさせ、この電界に従って液晶分子の配向方向を前記両透明基板16, 22と平行な平面内において回転させ、所定の表示が行われる。

【0038】そして、本液晶表示装置1においては、共通電極26及び画素電極27は透明材料からなるため、共通電極26が占める領域の分だけ透明領域が増えることになり、開口率の向上を図ることができる。また、第1の層間絶縁膜23の上には、データ線24とともに、共通電極配線に重畳する形で第2の金属層からなる画素電位膜42a, 42bが形成されているが、これら画素電位膜42a, 42bは、2つの目的で形成される。一つは液晶容量と電気的に並列接続される大きな蓄積容量を形成するため、もう一つは液晶が逆回転方向に回転することを防止する構造を形成するためである。第2の金属層からなる画素電位膜42a, 42bは単位画素当たりにデータ線24が延伸する方向に、少なくとも2ヶ所に分離されることになるが、自段のゲート電極30c近傍に形成される画素電位膜42aは、TFT30の第2の金属層からなるソース電極30bと一緒に化することで電位供給され、前段の走査線28a近傍の画素電位膜42bは、コンタクトホール39bを介して同電位となる画素電極27とコンタクトホール39cを介して接続されている。

【0039】このように透明材料からなる画素電極27を橋渡しとして少なくとも2ヶ所の画素電位膜42a, 42bを相互に接続することにより、画素の平面図上の上下両側にそれぞれ蓄積容量部を形成することができるため、蓄積容量を大きくとることができ表示を安定化することができる。また、単位画素当たりの少なくとも2ヶ所の蓄積容量部を透明材料からなる画素電極27により接続するため、画素電極での透過光を遮光することなく、コラム毎の電界強度が一定になるため、更なる高透

過率を有するIPS型液晶表示を製造することができる。なお、画素電位膜42a, 42b及び共通電極配線26a, 26bの縁部の形状を凹凸形状とすることで、液晶の逆回転方向の回転を防止することが可能になる。

【0040】ここで、共通電極26は前述したように、データ線24が走査線28と交差する領域及びその近傍の領域を除いてデータ線24を完全に覆うように形成されている。すなわち、データ線24の幅をL(D)、共通電極26の幅をL(COM)とすると、

$$L(COM) > L(D)$$

であり、かつ、データ線24の幅L(D)は共通電極26の幅L(COM)に含まれる。なお、データ線24が走査線28と交差する領域及びその近傍の領域は段差が大きいので、ショート防止のためにこの領域では、共通電極26はデータ線24を覆っていない。

【0041】以上のように、本液晶表示装置1においては、共通電極26がデータ線24を完全に覆っているため、データ線24の電界を共通電極26がシールドすることができる。このため、共通電極26がデータ線24を完全に覆っていない場合に、この部分とこれに隣接する画素電極27との間に電界が発生し、この部分で液晶は誤動作し、共通電極26と画素電極27との間の電位差で決まらない動きを行って縦クロストークの原因となるが、このような問題が解消できる。本液晶表示装置1においては、ほとんどの領域で共通電極26はデータ線24を完全に覆うように形成されているが、共通電極26はデータ線24の両側においてそれぞれ1.5μm以上の張り出し幅を有していることが好ましい。

【0042】さらに、縦クロストークの発生が抑制されることに伴い、データ線24からの漏れ電界に起因して発生する表示不良を防止するためのブラックマトリクス17の形成は不要となる。従って、ブラックマトリクス17はコントラストの改善のためにのみ形成すればよいこととなり、ブラックマトリクス17の幅を短縮することが可能である。ブラックマトリクス17の幅を小さくすることに伴い、本液晶表示装置1における開口率を大きくすることができる。

【0043】このように、データ線24上のブラックマトリクス17の幅は共通電極26の幅よりも小さく設定され、上方から見た場合の平面図上、データ線を覆う共通電極26とこれに隣接する位置にある画素電極27との間にはいかなる遮光膜も存在していない。また、ブラックマトリクス17はデータ線24よりも小さい幅を有しており、その全領域においてデータ線24と重なり合っている。すなわち、データ線24の幅をL(D)、ブラックマトリクス17の幅をL(BM)とすると、

$$L(D) > L(BM)$$

であり、かつ、平面図上、ブラックマトリクス17の幅L(BM)はデータ線24の幅L(D)に含まれる。

ブラックマトリクス17がデータ線24より小さい幅を

有することにより、データ線24を覆う透明な共通電極26のはみだし部分からの透過光を全て利用することができ、パネル透過率をさらに向上させることができる。因みに、本実施形態におけるブラックマトリクス17は6μmの幅を有しているが、この幅寸法は6μmに限定されるものではなく、6μm以上の任意の幅を有することが望ましい。6μm未満の場合、データ線24からの反射が大きくなるため、明るい使用環境では見えにくくなる。

10 【0044】ここで、対向基板12のブラックマトリクス17の幅が充分広い場合は、誤動作領域を観察者に対して遮光すればよいが、本実施形態のようにブラックマトリクス17がデータ線24を完全には覆っていない場合は、データ線24の下方に共通電極26に接続された遮光層を設け、バックライトからの光を遮光することによって、誤動作領域を観察者に対して遮光することができる。この遮光層が共通電極26に接続されていないと、電位的に不安定となり、画素電極27との間にDC電界を発生させてしまうか、もしくはクロストークなどの誤動作の原因と成り得る。具体的には、走査線28を形成する第1の金属層で共通電極配線26aに接続された遮光層を形成する。共通電極配線26a, 26bはコンタクトホール39aによって共通電極26と接続されているので、共通電極配線26a, 26bを遮光層にすることもできる。遮光層としては、例えばクロム、チタン、モリブデン、タンゲステン、アルミなどの単層や、これらの金属の積層構造を用いることができる。積層構造を用いることにより、さらに低抵抗化を図ることができる。

30 【0045】本液晶表示装置1における共通電極26は透明材料であるITOから形成されているため、前述のように本液晶表示装置1における透明領域が増大して開口率を高めることができるが、ITOのシート抵抗は100/程度と大きいという不利な点がある。しかしながら、共通電極26を画素ごとに共通電極配線26aまたは26bに接続して横方向に接続することで、共通電極26の配線全体の抵抗を下げ、かつ冗長性を持たせる効果がある。このように、共通電極26をITOで構成することにより、他の金属から構成する場合と比較して、本液晶表示装置1の信頼性を向上させることができる。

【0046】なお、共通電極26は本液晶表示装置1の端子を被覆する材料と同一材料から形成することができる。すなわち、図4のGに示す共通電極用コンタクト部のように端子を共通電極26のITOと同じ層で構成することができる。図4のHに示すデータ線端子、及び図には表れない走査線端子も同様に共通電極26のITOと同じ層で形成することができる。これにより、共通電極26は本液晶表示装置1の端子部と同じ工程で、かつ同じ材料で形成することが可能となり、ひいては、共

通電極26の形成のために工程数が増加することを防止することができる。

【0047】また、本液晶表示装置1においては、共通電極26と画素電極27とは何れも第2の層間絶縁膜25上に形成されている。このように、共通電極26と画素電極27とを同層上に形成することにより、共通電極26と画素電極27とを同一工程において、かつ、同一材料で形成することができるようになり、ひいては、製造効率を向上させることができる。

【0048】また、共通電極26とデータ線24との間に存在する第2の層間絶縁膜25の膜厚(d)と誘電率(ε)の除算d/εを十分大きくとることにより、データ線24と共通電極26との間の寄生容量を低減させることができる。

【0049】また、図1に示すように、透明材料からなる画素電極26と共通電極27は、少なくともこれより下層の共通電極配線層及びデータ線層に乗り上げるもしくは乗り越える領域においては、局所的に電極幅を太く形成している。これにより、透明電極の局所的な断線を防止できるため、高透過率でかつ製造歩留まりの高い横電界方式のアクティブマトリクス型液晶表示装置を製造することができる。

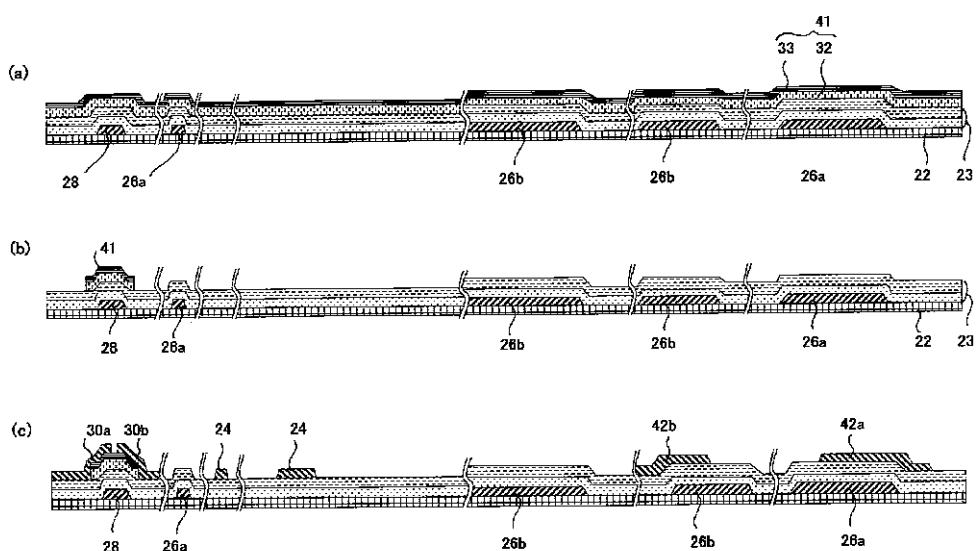

【0050】以上説明した第1の実施形態の液晶表示装置1の製造方法を図5～図6を参照して説明する。なお、これらの図で示される各断面部分は、図4に示した断面図と同じ箇所の断面部分である。先ず、図5(a)において、第1の透明基板22としてのガラス基板上に第1の金属層としてクロム層からなるゲート電極30c及び共通電極配線26a, 26bをフォトリソグラフィ及びドライエッティングによりパターニングし、形成する。次いで、ゲート電極30c及び共通電極配線26a, 26bを覆って、前記透明基板22上に酸化シリコン膜(SiO<sub>2</sub>)と窒化シリコン膜(SiNx)との積層膜から成る第1の層間絶縁膜23を一面に形成する。次いで、a(アモルファス)-Si膜32とn型不純物を高濃度に含むn<sup>+</sup>a-Si膜33の積層膜から成るアモルファシリコン41を第1の層間絶縁膜23の上に一面に形成する。次いで、図5(b)のように、前記アモルファシリコン膜32, 33をフォトリソグラフィ及びドライエッティングによりTFTの島状半導体層となるようにパターニングする。

【0051】次いで、図5(c)のように、前記透明絶縁性基板22上に第2の金属層としてクロム層を一面に堆積させ、このクロム層をフォトリソグラフィー及びドライエッティングによりパターニングし、第2の金属層でTFT30のドレイン電極30a、ソース電極30b、データ線24を形成する。この際に、蓄積容量として機能するように、単位画素当たりに少なくとも2箇所に分離して画素電位膜42a, 42bを形成する。これらの画素電位膜42a, 42bは共通電極配線26a及び2

6bに対してそれぞれ第1の層間絶縁膜23を挟みこむ形で重畳されてパターン形成される。また、2箇所の画素電位膜42a, 42bのうち、自段のゲート電極30c近傍に配置される画素電位膜42aは前記ソース電極30bと一体化されて形成され、前段のゲート電極30c近傍に配置される画素電位膜42bは孤立パターンとして形成される。

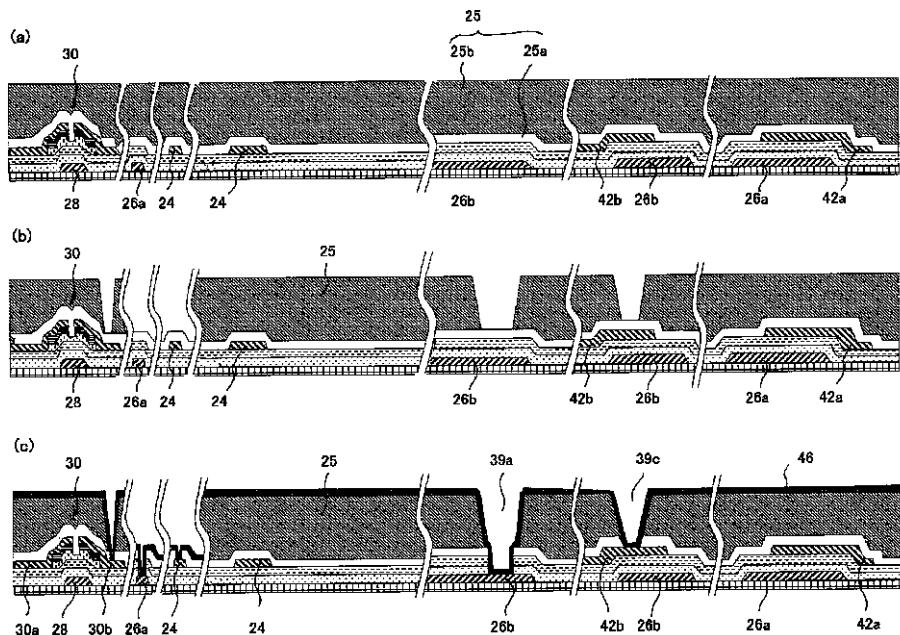

【0052】次いで、図6(a)のように、ドレイン電極30aとソース電極30bとの間の開口部において、アモルファシリコン41の途中まで、n<sup>+</sup>型a-Si膜33及びa-Si膜32をドレイン電極30a及びソース電極30bをマスクとしてエッティングし、TFT30のチャネルを形成する。次いで、無機膜としての窒化シリコン膜から成る第2の層間絶縁膜25の第1の絶縁膜25aを全面に堆積させる。次いで、その上有機膜としての感光性アクリル樹脂膜から成る第2の層間絶縁膜25の第2の絶縁膜25bを堆積させる。次いで、図6(b)のように、前記第2の絶縁膜25bの感光性アクリル樹脂膜を露光、現像、焼成し、自段のゲート電極30c近傍に配置されるソース電極30bの上方において、第1の層間絶縁膜23の窒化シリコン膜に到達する画素電極用コンタクトホール39b、前段のゲート電極近傍に配置されるコンタクトホール39cを形成し、同時に、共通電極配線26bの上方において、第1の層間絶縁膜23の窒化シリコン膜に到達する共通電極用コンタクトホール39aを形成する。

【0053】次いで、図6(c)のように、画素電極用コンタクトホール39b, 39c及び共通電極用コンタクトホール39aを介して、露出している第2の層間絶縁膜25の第1の絶縁膜25aの窒化シリコン膜をエッティングし、共通電極用コンタクトホール39aの場合には、さらに酸化シリコン膜と窒化シリコン膜との積層膜から成る第1の層間絶縁膜23をエッティングし、画素電極用コンタクトホール39b及び39c、共通電極用コンタクトホール39aをそれぞれソース電極30b及び画素電位膜42a, 42b、共通電極配線26aもしくは26bに到達させる。次いで、ITO46を全面に堆積させ、各コンタクトホール39a, 39b, 39cの内壁をITO46で覆うとともに、フォトリソグラフィ及びエッティングにより、単位素子の形成領域内において、ITO46からなる共通電極26及び画素電極27を形成する。このようにして形成された能動素子基板11は、透明材料からなる画素電極27により自段ゲート電極30c近傍の蓄積容量部と前段ゲート電極30d近傍の各画素電位膜42a, 42bが画素電極27を介して相互に接続され、これらにより2箇所において蓄積容量が構成されることになる。

【0054】対向基板12については、図示は省略するが、図2を参照すると、第2の透明基板としてのガラス基板16の所定の領域に対して遮光層17、色層18、

オーバーコート層19を所定のパターンに形成して作成した。また、ガラス基板16には手で液晶パネルを触った際に発生するチャージアップによる表示むらを防止するよう裏面にITOなどの透明導電膜15をスパッタして形成した。

【0055】このようにして得られた能動素子基板11と対向基板12を所定の間隔を持つようセル内スペーサ等(図示せず)で間隙を形成して、その中にネマティック液晶を封止して液晶層13を形成し、液晶パネルを構成した。液晶材料は誘電率異方性  $\gamma$  が正でその値が8(589nm, 20)、屈折率異方性  $n$  が0.075、液晶の比抵抗が $1.5 \times 10^{12} \cdot \text{cm}$ のネマティック液晶を使用した。液晶層の厚み(セルギャップ)は4.0μmとした。また、能動素子基板11及び対向基板12のそれぞれの表面にオフセット印刷等の手法にて配向膜31及び20を形成し、液晶分子を所定の方向に並ばせるようラビング方法にて櫛歯電極の短手方向に対して15°傾けて平行配向するように液晶分子を配向させた。さらに、両基板11, 12の外側面にはそれぞれ偏光板14, 21を配設した。

【0056】このようにして形成された液晶パネルについて、外部からの信号電圧により液晶の配向状態を変化させることで液晶パネルを透過する光の強さを制御し、液晶表示装置として階調表示を行なった。その際、画素電極27と共通電極26との間に電位差を与えない場合を黒表示とし、ガラス基板に対して概平行な電界を生むように、初期配向角度から約45°液晶が回転して透過光強度が最大になるよう電位差を与える場合に白表示として動作させた(ノーマリープラック方式)。このようにして得られた液晶パネルを液晶表示装置として駆動装置に組み込み表示を行い、高い透過率を有するIPS型液晶表示装置が確認できた。

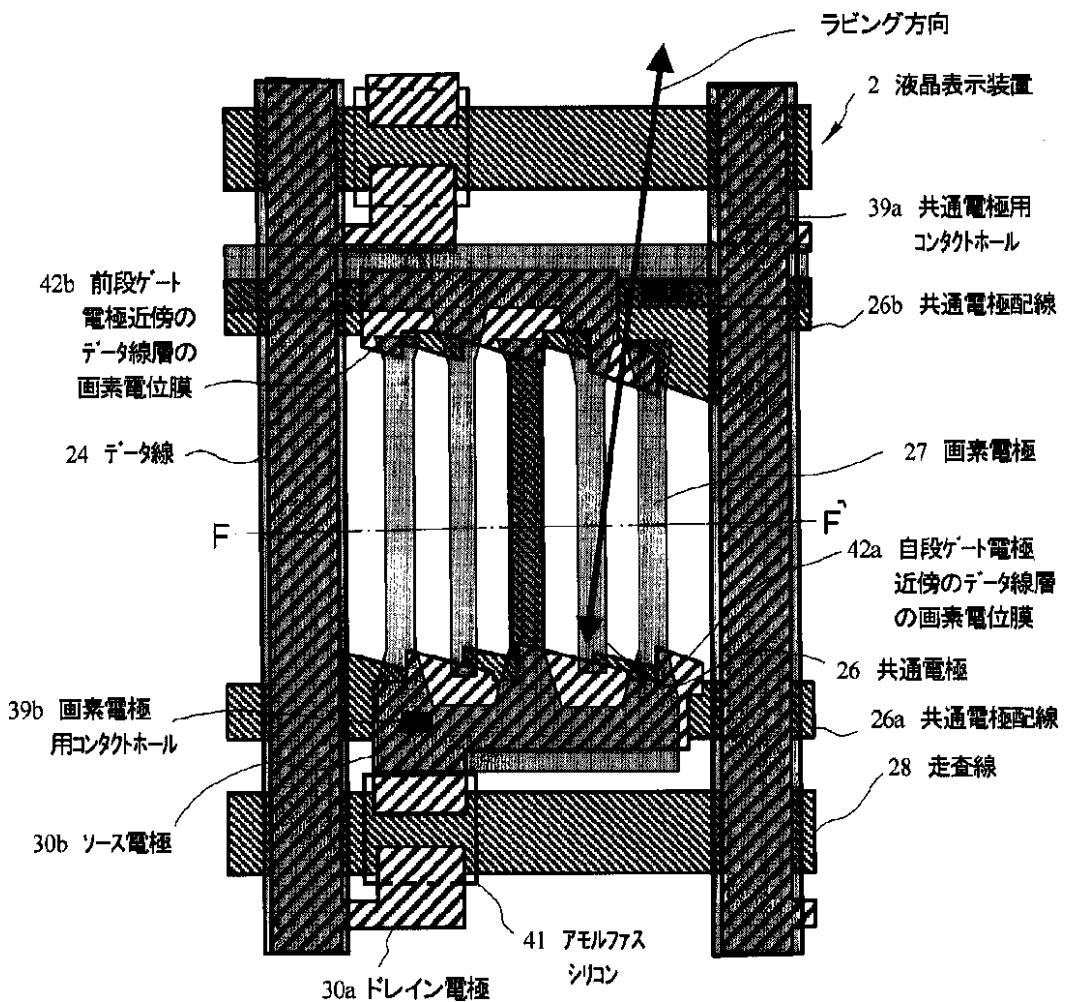

【0057】(第2の実施形態)図7は本発明の第2の実施形態にかかる能動素子基板の平面図、図8はそのF-F'線に沿う部分の液晶表示装置2の断面図、図9(a), (b)は下層の金属層と上層の金属層のレイアウト図である。なお、第1の実施形態と等価な部分には同一符号を付してある。以降の実施形態についても同様である。本実施形態は第1の実施形態と比較すると、能動素子基板11において、自段ゲート電極近傍の画素電位膜42aと前段ゲート電極近傍の画素電位膜42bを電気接続する構成が異なることを除けばその他は同一である。すなわち、前記第1の実施形態では、前記2つの画素電位膜42a, 42bを透明材料である画素電極27を橋渡しとして接続しているが、本実施形態ではコンタクトホール44a, 44bを介して不透明材料である走査線28と同一層の接続電極43で接続する。対向基板12については第1の実施形態と同じである。

【0058】その製造方法は、第10図の工程断面図を参照すると、第1の実施形態の図5(a)の工程で、ガ

ラス基板22上にクロム層からなるゲート電極30c及び共通電極配線26a, 26bをフォトリソグラフィ及びドライエッチングによりパターニングして形成するが、このとき同時に、図10(a)に示すように、画素領域のほぼ中央に共通電極配線26a, 26bと直交する方向に向けて接続電極43を形成する。この接続電極43の平面パターン形状は図9(a)に示す通りである。次いで、第1の実施形態の図5(b)から(c)までの工程と同様に、酸化シリコン膜と窒化シリコン膜との積層膜から成る第1の層間絶縁膜23を一面に形成し、さらにTFTのアモルファスシリコン41を島状半導体層となるように形成する。

【0059】次いで、図10(b)のように、自段のゲート電極30c近傍及び前段のゲート電極30d近傍において、酸化シリコン膜と窒化シリコン膜との積層膜から成る第1の層間絶縁膜23をエッチングし、図9(a)のように、接続電極用コンタクトホール44a, 44bを形成し、第1の金属層である接続電極43に到達させる。次いで、第2の金属層としてクロム層を一面に堆積させ、このクロム層をフォトリソグラフィ及びドライエッチングによりパターニングし、第2の金属層でTFT50のドレイン電極30a、ソース電極30b、データ線24を形成する。この際、自段のゲート電極30c近傍及び前段のゲート電極30d近傍においては、第1の金属層からなる接続電極43と第2の金属層からなるソース電極30bはコンタクトホール44a, 44b及び接続電極43を介して接続される。

【0060】次いで、図10(c)のように、ドレイン電極30aとソース電極30bとの間の開口部において、アモルファスシリコン膜の途中まで、 $n^+$ 型a-Si膜33及びa-Si膜32をドレイン電極30a及びソース電極30bをマスクとしてエッチングし、TFT50のチャネルを形成する。次いで、無機膜としての窒化シリコン膜から成る第2の層間絶縁膜25の第1の絶縁膜25aを全面に堆積させる。次いで、窒化シリコン膜から成る第2の層間絶縁膜25の第1の絶縁膜25aの上有機膜としての感光性アクリル樹脂膜から成る第2の層間絶縁膜25の第2の絶縁膜25bを堆積させる。次いで、第2の層間絶縁膜の第2の膜25bの感光性アクリル樹脂膜を露光、現像、焼成し、ソース電極30bの上方において、第1の層間絶縁膜23の窒化シリコン膜に到達する画素電極用コンタクトホール39bを形成し、同時に、共通電極配線26bの上方において、第1の層間絶縁膜23の窒化シリコン膜に到達する共通電極用コンタクトホール39aを形成する。

【0061】次いで、画素電極用コンタクトホール39b、共通電極用コンタクトホール39aを介して、露出している第2の層間絶縁膜25の第1の膜25aの窒化シリコン膜をエッチングし、共通電極用コンタクトホール39aの場合には、さらに酸化シリコン膜と窒化シリ

コン膜との積層膜から成る第1の層間絶縁膜23をエッチングし、画素電極用コンタクトホール39b、共通電極用コンタクトホール39aをそれぞれソース電極30b、共通電極配線26aもしくは26bに到達させる。次いで、ITO46を全面に堆積させ、各コンタクトホール39a、39bの内壁をITO46で覆うとともに、フォトリソグラフィー及びエッチングにより、単位素子の形成領域内において、ITO46からなる共通電極26及び画素電極27を形成する。

【0062】このようにして形成された能動素子基板1は、液晶層から不透明材料からなるゲート電極層からなる接続電極43により自段のゲート電極30c近傍の蓄積容量部と前段のゲート電極30d近傍の蓄積容量部を2つのコンタクトホール44a、44b及び接続電極43を介して接続することになる。

【0063】そして、得られた能動素子基板11と対向基板12の間に、第1の実施形態と同様な条件でネマティック液晶を封止して液晶層13を形成し、液晶パネルを構成した。そして、外部からの信号電圧により液晶の配向状態を変化させることで液晶パネルを透過する光の強さを制御し、液晶表示装置として階調表示を行なった。その際、画素電極27と共通電極26との間に電位差を与えない場合を黒表示とし、ガラス基板に対して概平行な電界を生むように、初期配向角度から略45°液晶が回転して透過光強度が最大になるよう電位差を与える場合に白表示として動作させた（ノーマリープラック方式）。このようにして得られた液晶パネルを液晶表示装置として駆動装置に組み込み表示を行い、高い透過率を有するIPS型液晶表示装置が確認できた。

【0064】特に、本実施形態では、前段のゲート電極30dの近傍に形成される画素電位膜42bへの電気的な接続は、液晶層13から最も離れた共通電極配線26a、26bと同じ層の接続電極43により行っているので、当該接続電極43は不透明材料であり、透明材料からなる画素電極での透過光を遮光することにはなるが、接続電極43は最も下層に形成されていて液晶層13から最も遠い導電層で構成されているため、当該接続電極43からの液晶への電界印加寄与は小さくなり、これによりコラム毎の電界強度のバラツキが小さくなり、高透過率を有するIPS型液晶表示装置を得ることが可能になる。

【0065】なお、この実施形態では、接続電極43を共通電極配線26a、26bと同じ層で形成しているが、共通電極配線26a、26bと走査線28が異なる層で形成される場合は、液晶層から最も遠い側の配線層で接続電極43を形成して、画素電位膜42a、42bの接続を行うようにすればよい。

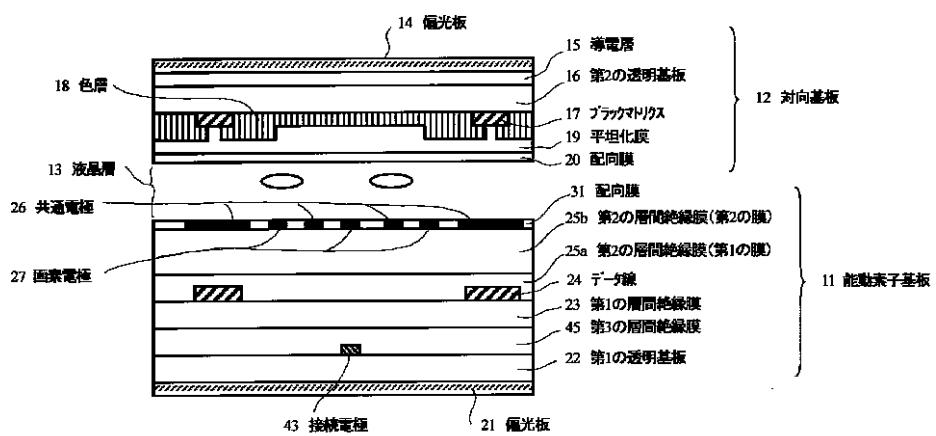

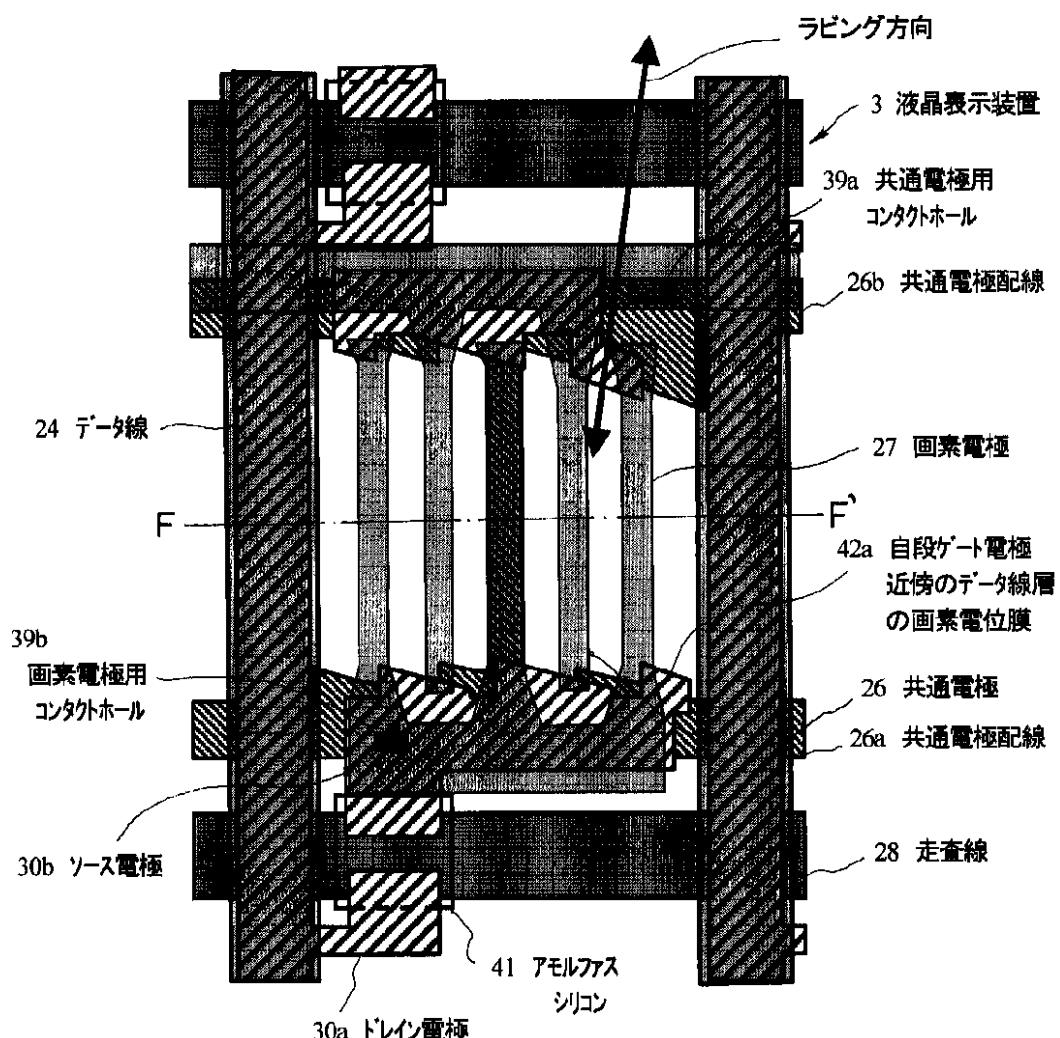

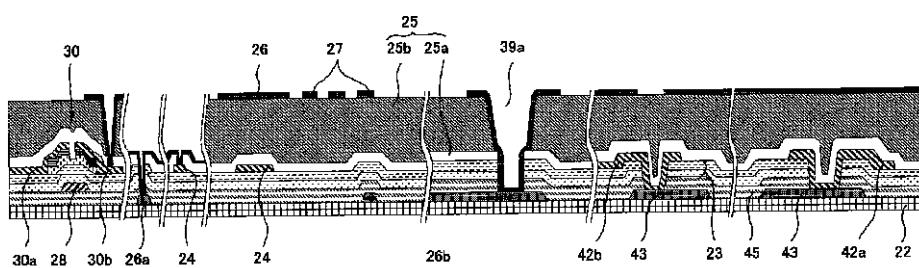

【0066】（第3の実施形態）図11は本発明の第3の実施形態にかかる能動素子基板の平面図、図12はそのF-F'線に沿う部分の液晶表示装置3の断面図、図50

13は下層の導電層と上層の導電層のレイアウト図である。本実施形態は第2の実施形態と比較すると、能動素子基板11において、第2の実施形態では2つの画素電位膜42a、42bを走査線及び共通電極配線を形成するための不透明材料である第1の金属層からなる接続電極43を橋渡しとして接続しているが、本実施形態は走査線と共に共通電極配線を互いに異なる層から形成し、共通電極配線と同一層で形成した接続電極により接続する。その他の構成及び対向基板12については第2の実施形態と同じである。

【0067】この実施形態の製造方法は、図14の断面図を参照すると、透明絶縁性基板22としてのガラス基板上にクロム層からなる共通電極配線26a、26b及び接続電極43をフォトリソグラフィ及びドライエッチングによりパターニングし、形成する。次いで、共通電極配線26a及び接続電極43を覆って、透明絶縁性基板22上に窒化シリコン膜から成る第3の層間絶縁膜45を一面に形成する。次いで、窒化シリコン膜から成る第3の層間絶縁膜45上に、第3の金属層としてクロム層からなる走査線28をフォトリソグラフィ及びドライエッチングによりパターニングし、形成する。次いで、走査線28を覆って、第3の層間絶縁膜45上に、前記各実施形態と同様に積層構造から成る第1の層間絶縁膜23を一面に形成する。

【0068】次いで、a-Si膜32とn<sup>+</sup>a-Si膜33の積層膜から成るアモルファスシリコン膜を第1の層間絶縁膜23の上に一面に形成する。次いで、アモルファスシリコン膜32、33をフォトリソグラフィ及びドライエッチングにより薄膜トランジスタの島状半導体層となるようにパターニングしアモルファスシリコン41を形成する。次いで、自段のゲート電極30c近傍及び近傍前段のゲート電極30d近傍において、第1の層間絶縁膜23及び第3の層間絶縁膜45を同時にエッチングし、接続電極用コンタクトホール44a、44bを形成し、接続電極43に到達させる。

【0069】次いで、クロム層を一面に堆積させ、このクロム層をフォトリソグラフィ及びドライエッチングによりパターニングし、TFT50のドレイン電極30a、ソース電極30b、データ線24、画素電位膜42a、42bを形成する。なお、ソース電極30bと画素電位膜42aは一体に形成する。この際、自段のゲート電極30c近傍及び前段のゲート電極30d近傍においては、接続電極43とソース電極30b（画素電位膜42a）と画素電位膜42bはそれぞれコンタクトホール44a、44b及び接続電極43を介して接続される。

【0070】以下、第2の実施形態と同様であり、ドレイン電極30aとソース電極30bとの間の開口部において、アモルファスシリコン膜の途中まで、n<sup>+</sup>型a-Si膜33及びa-Si膜32をドレイン電極30a及びソース電極30bをマスクとしてエッチングし、TFT

T 3 0 のチャネルを形成する。次いで、無機膜としての窒化シリコン膜から成る第2の層間絶縁膜2 5 の第1の絶縁膜2 5 a を全面に堆積させる。次いで、窒化シリコン膜から成る第2の層間絶縁膜2 5 の第1の絶縁膜2 5 a の上に有機膜としての感光性アクリル樹脂膜から成る第2の層間絶縁膜2 5 の第2の絶縁膜2 5 b を堆積させる。次いで、第2の層間絶縁膜の第2の膜2 5 b の感光性アクリル樹脂膜を露光、現像、焼成し、ソース電極3 0 b の上方において、第1の層間絶縁膜2 3 の窒化シリコン膜に到達する画素電極用コンタクトホール3 9 b を形成し、同時に、共通電極配線2 6 b の上方において、第1の層間絶縁膜2 3 の窒化シリコン膜に到達する共通電極用コンタクトホール3 9 a を形成する。

【0071】次いで、画素電極用コンタクトホール3 9 b 、共通電極用コンタクトホール3 9 a を介して、露出している第2の層間絶縁膜2 5 の第1の膜2 5 a の窒化シリコン膜をエッチングし、共通電極用コンタクトホール3 9 a の場合には、さらに酸化シリコン膜と窒化シリコン膜との積層膜から成る第1の層間絶縁膜2 3 をエッチングし、画素電極用コンタクトホール3 9 b 、共通電極用コンタクトホール3 9 a をそれぞれソース電極3 0 b 、共通電極配線2 6 a もしくは2 6 b に到達させる。次いで、ITO 4 6 を全面に堆積させ、各コンタクトホール3 9 a 、3 9 b の内壁をITO 4 6 で覆うとともに、フォトリソグラフィー及びエッチングにより、単位素子の形成領域内において、ITO 4 6 からなる共通電極2 6 及び画素電極2 7 を形成する。

【0072】このようにして形成された能動素子基板1 1 は、液晶層1 3 から最も遠い層である不透明材料の共通電極配線と同一層からなる接続電極4 3 により、自段のゲート電極3 0 c 近傍の画素電位膜と前段のゲート電極3 0 d 近傍の画素電位膜を2つのコンタクトホール4 4 a 、4 4 b 及び接続電極4 3 を介して接続することになる。

【0073】そして、得られた能動素子基板1 1 と対向基板1 2 の間に、第1の実施形態と同様な条件でネマティック液晶1 3 を封止して液晶パネルを構成した。そして、外部からの信号電圧により液晶の配向状態を変化させることで液晶パネルを透過する光の強さを制御し、液晶表示装置として階調表示を行なった。その際、画素電極2 7 と共通電極2 6 との間に電位差を与えない場合を黒表示とし、ガラス基板に対して概平行な電界を生むように、初期配向角度から約45° 液晶が回転して透過光強度が最大になるよう電位差を与える場合に白表示として動作させた（ノーマリーブラック方式）。このようにして得られた液晶パネルを液晶表示装置として駆動装置に組み込み表示を行い、高い透過率を有するIPS型液晶表示装置が確認できた。

【0074】本実施形態においては、前段のゲート電極3 0 d の近傍に形成される画素電位膜4 2 b への電気的

10

な接続は、液晶層1 3 から最も離れた共通電極配線2 6 a 、2 6 b と同じ層の接続電極4 3 により行っているので、当該接続電極4 3 は不透明材料であり、透明材料からなる画素電極での透過光を遮光することにはなるが、接続電極4 3 は最も下層に形成されていて液晶層1 3 から最も遠い配線層で構成されているため、当該接続電極4 3 からの液晶への電界印加寄与は小さくなり、これによりコラム毎の電界強度のバラツキが小さくなり、高透過率を有するIPS型液晶表示装置を得ることが可能になる。

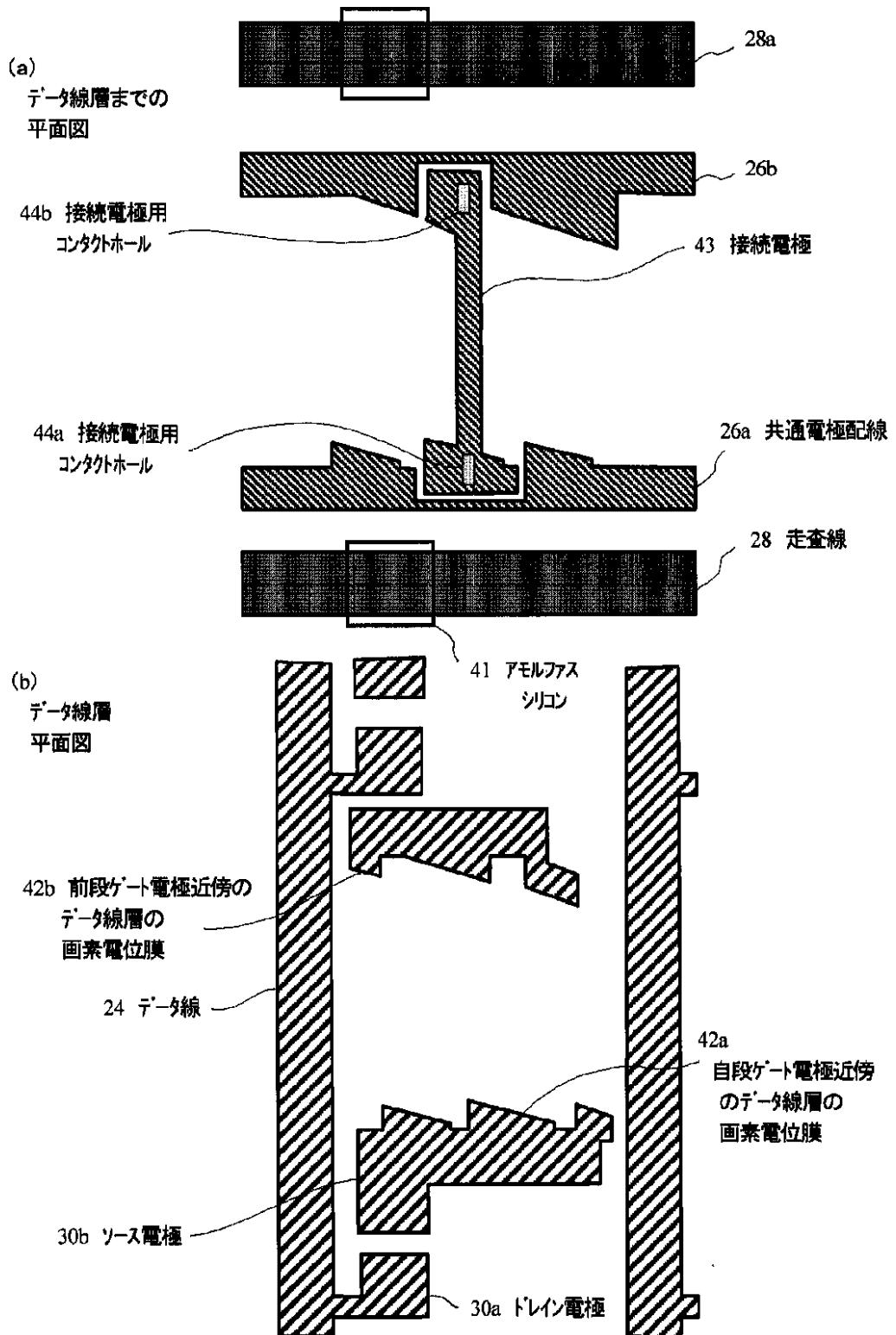

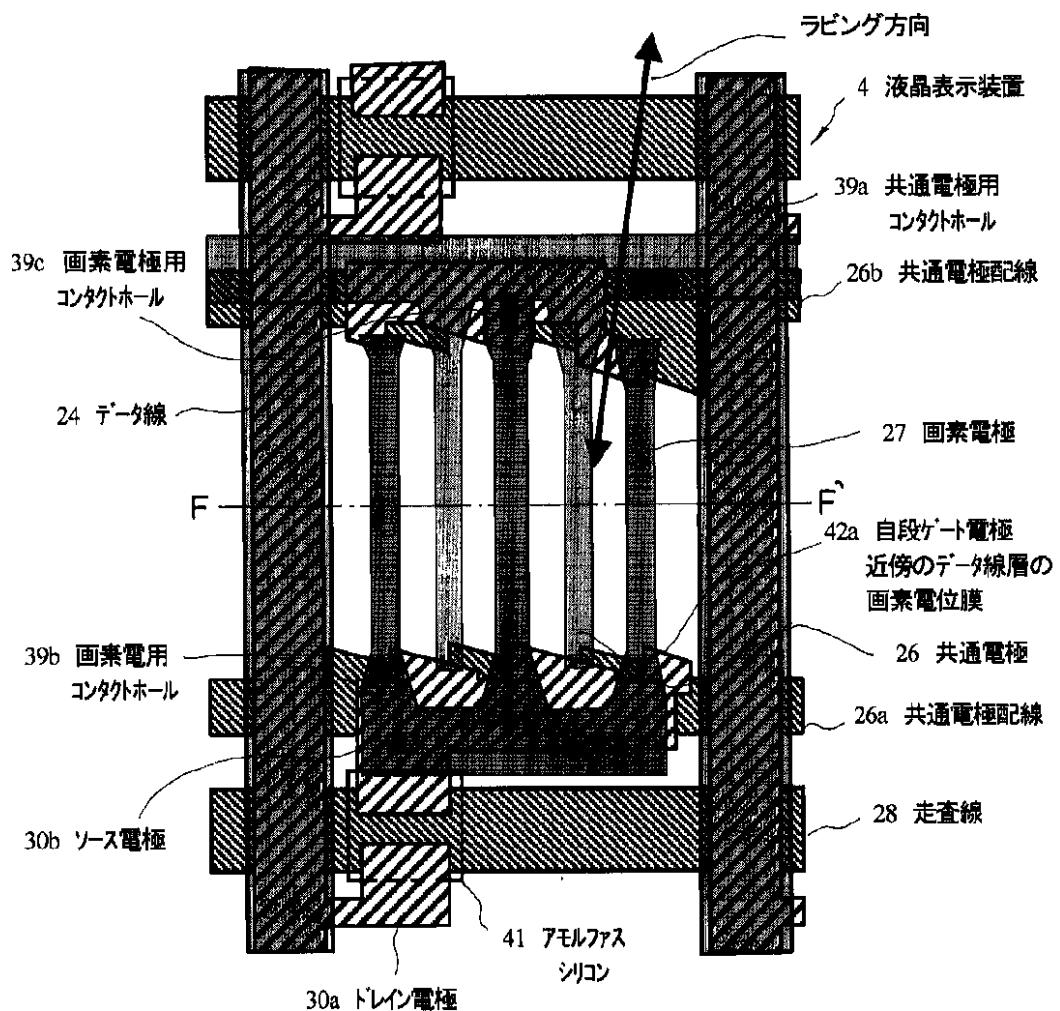

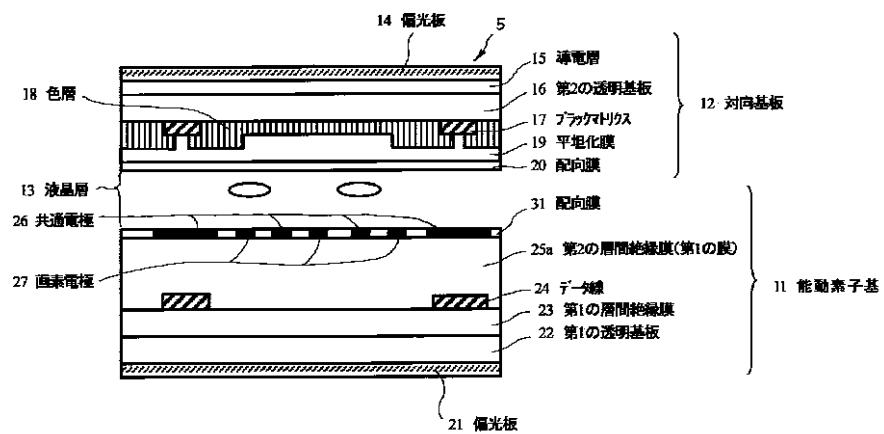

【0075】（第4の実施形態）図15は本発明の第4の実施形態にかかる能動素子基板の平面図、図16はそのF-F'線に沿う部分の液晶表示装置4の断面図である。本実施形態は第1の実施形態と比較すると、能動素子基板1 1 において、液晶を駆動するための透明電極である画素電極2 7 と共通電極2 6 が層間絶縁膜を介して異なる層に形成されていることを除けば、その他は同一である。すなわち、2つの蓄積容量を構成するための画素電位膜4 2 a 、4 2 b を透明電極である画素電極2 7 を橋渡しとして接続していることは第1の実施形態と同じである。ここで、画素電極2 7 は第2の層間絶縁膜の上に形成されているが、共通電極2 6 は画素電極の上に形成された第4の層間絶縁膜の上に形成されている。また、対向基板は第1の実施形態と同じである。

【0076】この第4の実施形態の液晶表示装置の製造方法では、第1の実施形態の製造方法を示す図5(a)から図6(b)までの工程は同じである。以降は、図17の断面図を併せて参照すると、第2の層間絶縁膜2 5 を形成した後、第2の層間絶縁膜の第2の絶縁膜2 5 b の感光性アクリル樹脂膜を露光、現像、焼成し、自段のゲート電極3 0 c 近傍に配置されるソース電極3 0 b の上方において、第1の層間絶縁膜2 3 の窒化シリコン膜に到達する画素電極用コンタクトホール3 9 b 、前段のゲート電極3 0 d 近傍に配置される共通電極用コンタクトホール3 9 c を形成し、同時に、共通電極配線2 6 b の上方において、第1の層間絶縁膜2 3 の窒化シリコン膜に到達する共通電極用コンタクトホール3 9 a を形成する。次いで、画素電極用コンタクトホール3 9 b 、3 9 c 及び共通電極用コンタクトホール3 9 a を介して、露出している第2の層間絶縁膜2 5 の第1の膜2 5 a の窒化シリコン膜をエッチングし、共通電極用コンタクトホール3 9 a の場合には、さらに酸化シリコン膜と窒化シリコン膜との積層膜から成る第1の層間絶縁膜2 3 をエッチングし、画素電極用コンタクトホール3 9 b 及び3 9 c 、共通電極用コンタクトホール3 9 c をそれぞれ画素電位膜4 2 a 及び4 2 b 、共通電極配線2 6 b に到達させる。

【0077】次いで、ITO 4 6 を全面に堆積させ、各コンタクトホール3 9 a 、3 9 b 、3 9 c の内壁をITO 4 6 で覆うとともに、フォトリソグラフィー及びエッ

50

チングにより、単位素子の形成領域内において、ITO 46 からなる画素電極 27 を形成する。次いで、前記透明絶縁性基板の上に、有機膜としての感光性アクリル樹脂からなる第4の層間絶縁膜 47 を堆積させる。次いで、第4の層間絶縁膜 47 を感光性アクリル樹脂膜を露光、現像、焼成し、コンタクトホール 39a を共通電極配線 26b に到達させる。さらに、ITO 46 を全面に堆積させ、各コンタクトホール 39a, 39b, 39c の内壁を ITO 46 で覆うとともに、フォトリソグラフィ及びエッチングにより、単位素子の形成領域内において、ITO 46 からなる共通電極 26 を形成する。このようにして形成された能動素子基板 11 は、透明材料からなる画素電極 27 により自段ゲート電極 30c 近傍の画素電位膜 42a と前段ゲート電極 30d 近傍の画素電位膜 42b を相互に電気接続することになる。

【0078】このようにして得られた能動素子基板 11 と対向基板 12 の間に、第1の実施形態と同様な条件でネマティック液晶 13 を封止して液晶パネルを構成した。そして、外部からの信号電圧により液晶の配向状態を変化させることで液晶パネルを透過する光の強さを制御し、液晶表示装置として階調表示を行なった。その際、画素電極 27 と共通電極 26 との間に電位差を与えない場合を黒表示とし、ガラス基板に対して概平行な電界を生むように、初期配向角度から約 45° 液晶が回転して透過光強度が最大になるよう電位差を与える場合に白表示として動作させた（ノーマリーブラック方式）。このようにして得られた液晶パネルを液晶表示装置として駆動装置に組み込み表示を行い、高い透過率を有するIPS型液晶表示装置が確認できた。

【0079】この実施形態のように、第4の層間絶縁膜 47 を介して共通電極 26 と画素電極 27 が互いに異なる層で形成する場合、LCDの製造コストは増加するが、電極設計の自由度が上昇するため、さらなる高透過率化を図ることができる。このように、共通電極 26 と画素電極 27 が互いに異なる層に形成される場合、LCDの表示の安定性及び信頼性の面からは、共通電極 26 を液晶層 13 に配置したほうが好ましい。

【0080】（第5の実施例）図18は本発明の第5の実施形態にかかる能動素子基板の平面図、図19はそのF-F'線に沿う部分の液晶表示装置5の断面図である。本実施形態は第1の実施形態と比較すると、能動素子基板 11 において、データ線 24 とその上層の共通電極 26 との層間に形成される第2の層間絶縁膜 25 が無機膜単層であることを除けば、その他は同一である。また、対向基板 12 についても同じである。

【0081】この第5の実施形態の製造方法は図5(a)～図6(c)に示した第1の実施形態の製造工程とほぼ同じであるが、図6(a)に示した第2の層間絶縁膜の製造工程においては、無機膜としての窒化シリコン膜から成る第2の層間絶縁膜 25 を全面に堆積させ

る。次いで、第1の実施形態と同様に、自段のゲート電極 30c 近傍に配置される第1の層間絶縁膜 23 の窒化シリコン膜に到達する画素電極用コンタクトホール 39b、前段のゲート電極 30d 近傍に配置されるコンタクトホール 39c を形成し、同時に、共通電極配線 26b の上方において、第1の層間絶縁膜 23 の窒化シリコン膜に到達する共通電極用コンタクトホール 39a を形成する。共通電極用コンタクトホールの場合には、さらに酸化シリコン膜と窒化シリコン膜との積層膜から成る第1の層間絶縁膜 23 をエッチングし、共通電極用コンタクトホール 39a を共通電極配線 26a もしくは 26b に到達させる。

【0082】以下、第1の実施形態と同じ工程により、第5の実施形態の能動素子基板 11 を製造する。このようにして形成された能動素子基板 11 は、透明材料からなる画素電極 27 により自段ゲート電極 30c 近傍の画素電位膜 42a と前段ゲート電極 30d 近傍の画素電位膜 42b を相互に電気接続することになる。

【0083】このようにして得られた能動素子基板 11 と対向基板 12 の間に、第1の実施形態と同様な条件でネマティック液晶を封止して液晶層 13 を形成し液晶パネルを構成した。そして、外部からの信号電圧により液晶の配向状態を変化させることで液晶パネルを透過する光の強さを制御し、液晶表示装置として階調表示を行なった。その際、画素電極 27 と共通電極 26 との間に電位差を与えない場合を黒表示とし、ガラス基板に対して概平行な電界を生むように、初期配向角度から約 45° 液晶が回転して透過光強度が最大になるよう電位差を与える場合に白表示として動作させた（ノーマリーブラック方式）。このようにして得られた液晶パネルを液晶表示装置として駆動装置に組み込み表示を行い、高い透過率を有するIPS型液晶表示装置が確認できた。

【0084】（第6の実施例）図20は本発明の第6の実施形態にかかる能動素子基板の平面図、図21はそのF-F'線に沿う部分の液晶表示装置6の断面図である。本実施形態は第1の実施形態と比較すると、能動素子基板 11 は同一であり、対向基板 12 の構成が異なっている。第6の実施形態では、対向基板 12 に色層が形成されていないことが第1の実施形態と相違している。

【0085】すなわち、第6の実施形態の対向基板 12 については、第2の透明基板としてのガラス基板 16 の所定の領域に対して遮光層 17、オーバーコート層 19 を所定のパターンに形成して作成した。また、ガラス基板 16 には手で液晶パネルを触った際に発生するチャージアップによる表示むらを防止するよう裏面にITOなどの透明導電膜 15 をスパッタして形成した。

【0086】この実施形態では、第1の実施形態と同様な能動素子基板 11 と、本実施形態の対向基板 12 の間に、第1の実施形態と同様な条件でネマティック液晶を封止して液晶層 13 を形成して液晶パネルを構成した。

そして、外部からの信号電圧により液晶の配向状態を変化させることで液晶パネルを透過する光の強さを制御し、液晶表示装置として階調表示を行なった。その際、画素電極27と共に電極26との間に電位差を与えない場合を黒表示とし、ガラス基板に対して概平行な電界を生むように、初期配向角度から約45°。液晶が回転して透過光強度が最大になるよう電位差を与える場合を白表示として動作させた(ノーマリーブラック方式)。このようにして得られた液晶パネルを液晶表示装置として駆動装置に組み込み表示を行い、高い透過率を有するIPS型液晶表示装置が確認できた。

【0087】なお、前記各実施形態においては共に透明材料からなる共通電極26と画素電極17は、高信頼性の観点から前記したITOに限られるものではなく、IZO(Indium Zn Oxide)からなる導電膜で構成してもよい。

【0088】以上のように、第1ないし第6の実施形態において、液晶駆動電極である共通電極と画素電極が直線型構造についてのみ詳細に記述してきたが、製造コストを上げること無く、表示ムラを防止した液晶表示装置を提供するという点に関しては、液晶駆動電極が折れ曲った、いわゆるマルチドメイン単位素子構造についても、共通電極配線に突起を設けると同様の効果を得ることができ。この場合、更なる視野角を拡大する利点があり、液晶表示装置として好ましい。

【0089】なお、上記の各実施形態の説明においては、本発明の特徴となる部分について主に説明し、本分野において通常の知識を有する者にとって既知の事項については特に詳述していないが、たとえ記載がなくてもこれらの事項は上記の者にとって類推可能な事項に属する。

#### 【0090】

【発明の効果】以上のように、本発明に係る液晶表示装置によれば、横電界方式のアクティブマトリクス型液晶表示装置の単位画素当たりにそれぞれ形成される、前段の走査線近傍の共通電極配線に重畠される画素電位膜と自段の走査線近傍の共通電極配線に重畠される画素電位膜はを透明電極からなる画素電極により相互に接続した構成とすることにより、あるいは、液晶層から最も遠い層に形成された接続電極により相互に接続した構成とすることにより、製造コストを上げることなく、開口率を向上させ、かつ製造歩留まりの高いIPSモードの液晶表示装置を提供することを達成することができる。

#### 【図面の簡単な説明】

【図1】本発明の第1の実施形態における能動素子基板の平面レイアウト図である。

【図2】図1のF-F'線に沿う液晶表示装置の断面図である。

【図3】第1の実施形態における下層の導電層のレイアウトとその上層のITO層のレイアウトをそれぞれ示す

平面図である。

【図4】図1のA-A'~E-E'線、及びコンタクト部分の各断面図である。

【図5】第1の実施形態の製造方法の工程断面図のその1である。

【図6】第1の実施形態の製造方法の工程断面図のその2である。

【図7】第2の実施形態における能動素子基板の平面レイアウト図である。

【図8】図7のF-F'線に沿う液晶表示装置の断面図である。

【図9】第2の実施形態における下層の導電層のレイアウトとその上層の導電層のレイアウトをそれぞれ示す平面図である。

【図10】第2の実施形態の製造方法の工程断面図である。

【図11】第3の実施形態における能動素子基板の平面レイアウト図である。

【図12】図11のF-F'線に沿う液晶表示装置の断面図である。

【図13】第3の実施形態における下層の導電層のレイアウトとその上層の導電層のレイアウトをそれぞれ示す平面図である。

【図14】第3の実施形態の各部の断面図である。

【図15】第4の実施形態における能動素子基板の平面レイアウト図である。

【図16】図15のF-F'線に沿う液晶表示装置の断面図である。

【図17】第4の実施形態の各部の断面図である。

【図18】第5の実施形態における能動素子基板の平面レイアウト図である。

【図19】図18のF-F'線に沿う液晶表示装置の断面図である。

【図20】第6の実施形態における能動素子基板の平面レイアウト図である。

【図21】図20のF-F'線に沿う液晶表示装置の断面図である。

【図22】液晶表示装置において逆方向に回転する液晶領域を説明するための図である。

#### 【符号の説明】

1~6 第1ないし第6の各実施形態の液晶表示装置

1.1 能動素子基板

1.2 対向基板

1.3 液晶層

1.4 偏光板

1.5 導電層

1.6 第2の透明基板

1.7 ブラックマトリクス

1.8 色層

1.9 オーバーコート層

20, 31 配向膜

21 偏光板

22 第1の透明基板

23 第1の層間絶縁膜

24 データ線

25 第2の層間絶縁膜

25a 第2の層間絶縁膜の第1の膜

25b 第2の層間絶縁膜の第2の膜

26 共通電極

26a, 26b 共通電極配線

27 画素電極

28 走査線

29 金属膜

29a 第1の金属層

29b 第2の金属層

30 薄膜トランジスタ(TFT)

30a ドレイン電極

30b ソース電極

\* 30c 自段のゲート電極

30d 前段のゲート電極

32 a-Si膜

33 n<sup>+</sup>a-Si膜

39a 共通電極用コンタクトホール

39b, 39c 画素電極用コンタクトホール

30d 前段のゲート電極

41 島状アモルファシリコン

42a 自段のゲート電極近傍のデータ線層の画素電位

10 膜

42b 前段のゲート電極近傍のデータ線層の画素電位

膜

43 接続電極

44a, 44b 接続電極用コンタクトホール

45 第3の層間絶縁膜

46 ITO

47 第4の層間絶縁膜

\*

【図1】

【図2】

【図4】

【図5】

【図3】

【図6】

【図7】

【図8】

【図10】

【図12】

【図9】

【図11】

【図14】

【図13】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

## フロントページの続き

F ターム(参考) 2H092 GA14 JA24 JA34 JA37 JA41

JA46 JB01 JB16 JB22 JB31

JB52 JB56 JB61 JB68 KA05

KB11 MA13 MA18 NA15 NA29

PA02 PA06 PA09

5C094 AA06 AA42 BA03 BA43 CA19

CA20 DA09 DB01 EA04 EB02

ED15

5F110 AA30 BB01 CC07 DD02 EE04

FF02 FF03 FF09 GG02 GG15

HK04 HK09 HK21 NN03 NN24

NN27 NN72 NN73

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)     | 面内开关型有源矩阵型液晶显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号     | <a href="#">JP2003207803A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2003-07-25 |

| 申请号         | JP2002003005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 申请日     | 2002-01-10 |

| 申请(专利权)人(译) | NEC公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| [标]发明人      | 松本公一<br>半貫貴久                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 发明人         | 松本 公一<br>半貫 貴久                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号      | G02F1/1368 G02F1/1343 G02F1/1362 G09F9/30 G09F9/35 H01L21/336 H01L29/786                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| CPC分类号      | G02F1/136213 G02F1/134363                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| FI分类号       | G02F1/1368 G09F9/30.338 G09F9/35 H01L29/78.612.C H01L29/78.612.Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| F-TERM分类号   | 2H092/GA14 2H092/JA24 2H092/JA34 2H092/JA37 2H092/JA41 2H092/JA46 2H092/JB01 2H092/JB16 2H092/JB22 2H092/JB31 2H092/JB52 2H092/JB56 2H092/JB61 2H092/JB68 2H092/KA05 2H092/KB11 2H092/MA13 2H092/MA18 2H092/NA15 2H092/NA29 2H092/PA02 2H092/PA06 2H092/PA09 5C094/AA06 5C094/AA42 5C094/BA03 5C094/BA43 5C094/CA19 5C094/CA20 5C094/DA09 5C094/DB01 5C094/EA04 5C094/EB02 5C094/ED15 5F110/AA30 5F110/BB01 5F110/CC07 5F110/DD02 5F110/EE04 5F110/FF02 5F110/FF03 5F110/FF09 5F110/GG02 5F110/GG15 5F110/HK04 5F110/HK09 5F110/HK21 5F110/NN03 5F110/NN24 5F110/NN27 5F110/NN72 5F110/NN73 2H092/JA42 2H092/JB23 2H192/AA24 2H192/BB03 2H192/BB66 2H192/BB73 2H192/BC35 2H192/BC51 2H192/CB05 2H192/CC04 2H192/CC42 2H192/DA32 2H192/DA42 2H192/DA65 2H192/DA74 2H192/EA03 2H192/EA17 2H192/EA22 2H192/EA43 2H192/EA67 2H192/EA72 2H192/FA65 2H192/GA03 2H192/GA06 2H192/GA41 2H192/HA33 2H192/JA33 |         |            |

| 代理人(译)      | 铃木昭雄                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 其他公开文献      | <a href="#">JP4047586B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 外部链接        | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

#### 摘要(译)

要解决的问题：提供一种在不增加制造成本的情况下具有提高的制造成品率的高透射率的IPS（水平电场型）液晶显示装置。在由像素电极27和由透明材料制成的公共电极26通过水平电场驱动的液晶显示装置中，两个公共电极布线26a，26b布置成在它们之间具有扫描线28，并且每个公共电极布线26a，在26b中，作为像素电极电势的像素电势膜42a和42b与夹在其间的层间绝缘膜重叠，以形成存储电容器部分。自身级的栅极附近的像素电位膜42a和前级的栅极附近的像素电位膜42b通过接触孔39b和39c由像素电极27连接，并且两个像素电位被该像素电极27桥接。采用将来自TFT 30的电势输入到膜42a和42b的配置。可以通过像素电位膜42a和42b来增加存储电容，同时防止开口率降低，并且可以获得具有高透射率的IPS的液晶显示装置。