(12) 实用新型专利

(10) 授权公告号 CN 202443728 U

(45) 授权公告日 2012. 09. 19

(21) 申请号 201220079453. 4

(22) 申请日 2012. 03. 05

(73) 专利权人 京东方科技股份有限公司

地址 100015 北京市朝阳区酒仙桥路 10 号

(72) 发明人 张玉婷

(74) 专利代理机构 北京路浩知识产权代理有限公司 11002

代理人 王莹

(51) Int. Cl.

G09G 3/36 (2006. 01)

G09G 3/20 (2006. 01)

权利要求书 2 页 说明书 6 页 附图 3 页

(54) 实用新型名称

移位寄存器、栅极驱动器及显示装置

(57) 摘要

本实用新型涉及显示器件技术领域, 提提供了一种移位寄存器、栅极驱动器及显示装置。本实用新型的移位寄存器包括: 上拉晶体管、下拉晶体管、输出晶体管和复位单元, 还包括: 用于对输出端放电的输出下拉单元, 分别连接当前下拉节点、相邻级下拉节点、低电压信号端和输出端, 在当前下拉节点或所述相邻级下拉节点为高电位时将所述输出端导通至所述低电压信号端; 以及控制晶体管, 其栅极与上拉节点相连, 漏极连接所述相邻级下拉节点, 源极连接低电压信号端。本实用新型通过输出下拉单元对当前输出后第奇数个和第偶数个时间单元内的噪声进行抑制, 有效防止了多输出现象的产生, 增强了 GOA 单元的稳定性, 保证了液晶面板显示效果。

1. 一种移位寄存器,所述移位寄存器包括 :

上拉晶体管,其漏极连接第一时钟信号端,栅极连接上拉节点,源极连接输出端;

第一电容,连接在所述上拉晶体管栅极和源极之间;

下拉晶体管,其源极连接所述上拉节点,栅极连接当前下拉节点,漏极连接低电压信号端;

输出晶体管,其栅极连接第二时钟信号端,源极连接输出端,漏极连接低电压信号端;

复位单元,分别连接复位信号端、上拉节点、输出端和低电压信号端;

其特征在于,所述移位寄存器还包括 :

对输出端放电的输出下拉单元,分别连接当前下拉节点、相邻级下拉节点、低电压信号端和输出端。

2. 根据权利要求 1 所述的移位寄存器,其特征在于,所述移位寄存器还包括 :

控制晶体管,其栅极与上拉节点相连,漏极连接所述相邻级下拉节点,源极连接低电压信号端。

3. 根据权利要求 1 所述的移位寄存器,其特征在于,所述移位寄存器还包括 :

控制上拉节点电位的上拉驱动单元,分别连接输入端、第二时钟信号端和上拉节点;以及

连接在第二时钟信号端、上拉节点和低电压信号端之间、控制当前下拉节点电位的下拉驱动单元。

4. 根据权利要求 1 所述的移位寄存器,其特征在于,所述输出下拉单元包括第一输出下拉晶体管和第二输出下拉晶体管,其中,

第一输出下拉晶体管,其栅极连接当前下拉节点,源极连接低电压信号端,漏极连接输出端;以及

第二输出下拉晶体管,其栅极连接所述相邻级下拉节点,源极连接低电压信号端,漏极连接输出端。

5. 根据权利要求 1 所述的移位寄存器,其特征在于,所述复位单元包括第一复位晶体管和第二复位晶体管,其中,

第一复位晶体管,其源极连接上拉节点,漏极连接低电压信号端,栅极连接复位信号端;

第二复位晶体管,其源极连接输出端,漏极连接低电压信号端,栅极连接复位信号端。

6. 根据权利要求 2 所述的移位寄存器,其特征在于,所述上拉驱动单元包括第一上拉驱动晶体管和第二上拉驱动晶体管,其中,

第一上拉驱动晶体管,其栅极和源极同时连接输入端,漏极连接上拉节点;

第二上拉驱动晶体管,源极连接输入端,漏极连接上拉节点,栅极连接第二时钟信号端;

所述下拉驱动单元包括第一至第四下拉驱动晶体管,其中,

第一下拉驱动晶体管,其源极连接第二时钟信号端,漏极连接当前下拉节点;

第二下拉驱动晶体管,其源极连接当前下拉节点,漏极连接低电压信号端,栅极连接上拉节点;

第三下拉驱动晶体管,其栅极和源极同时连接第二时钟信号端,漏极连接第一下拉驱动单元;

动晶体管的栅极；

第四下拉驱动晶体管，其源极连接第三下拉驱动晶体管的漏极，漏极连接低电压信号端，栅极连接上拉节点。

7. 一种栅极驱动器，其特征在于，所述栅极驱动器包括多个级联的如权利要求 1-6 任一项所述的移位寄存器。

8. 根据权利要求 7 所述的栅极驱动器，其特征在于，所述栅极驱动器的级联结构为：

每一级移位寄存器的第一时钟信号端和第二时钟信号端分别接两个反相的时钟信号；低电压信号端连接低电压信号；每一级的输入端连接上一级的输出端，以上一级的输出作为本级的输入；同时每一级的输出端还连接上一级的复位信号端，以本级的输出作为上一级的复位信号；此外，每一级的当前下拉节点连接到上一级或下一级的输出下拉单元。

9. 根据权利要求 8 所述的栅极驱动器，其特征在于，所述级联结构中：奇数级寄存器的第一时钟信号端与偶数级寄存器的第二时钟信号端连接第一时钟信号，奇数级寄存器的第二时钟信号端与偶数级寄存器的第一时钟信号端连接与第一时钟信号反相的第二时钟信号，第一级的输入端连接初始启动信号，最后一级复位信号由两个晶体管组成的复位端提供。

10. 一种显示装置，其特征在于，所述显示装置包括：如权利要求 7-9 中任一项所述的栅极驱动器。

## 移位寄存器、栅极驱动器及显示装置

### 技术领域

[0001] 本实用新型涉及显示器件技术领域,提供了一种移位寄存器、栅极驱动器及显示装置。

### 背景技术

[0002] 在 TFT-LCD (Thin Film Transistor-Liquid Crystal Display, 薄膜晶体管液晶显示) 类显示器中, 每一像素单元在阵列基板上有一 TFT 与之对应, 该 TFT 的栅极 (Gate) 连接至水平方向的扫描线 (又称行扫描线), 漏极 (Drain) 连接至垂直方向的数据线, 而源级 (Source) 则连接至像素电极。在显示器进行显示时, 如果在水平方向的某一行扫描线上施加足够的正电压, 通过 TFT 栅极的控制会使得该行所有的 TFT 打开, 此时该行 TFT 对应的像素电极会与垂直方向的数据线连通, 从而将数据线上传输的显示信号电压写入像素电极中, 进而控制该像素电极对应像素单元区域上的液晶达到不同的透光度, 实现对像素单元显示的灰度和 / 或色彩的控制。

[0003] 目前, TFT-LCD 面板的驱动电路主要是通过在面板外沿粘接 IC (Integrated Circuit, 集成电路) 来完成, 其 IC 制作一般使用的是 CMOS 制成的硅芯片。因为粘接的 IC 需要占用一定面积, 同时 IC 连接时的线路设计也要占用一定面积, 这种方式得到的面板集成度不高、面积较大, 不利于显示设备的小型化和超薄化。

[0004] 针对这一问题, 出现了 GOA (Gate Driver on Array, 阵列基板行驱动, 又称集成栅极驱动) 技术, 直接将 TFT-LCD 的栅极驱动电路 (Gate driver ICs) 制作在阵列基板上, 由此来代替在面板外沿粘接的、由硅芯片制作的驱动芯片。由于该技术可以将驱动电路直接做在阵列基板上, 面板周围无需再粘接 IC 和布线, 减少了面板的制作程序, 降低了产品成本, 同时提高了 TFT-LCD 面板的集成度, 使面板能更薄型化。现有技术中集成栅极驱动的寄存器实现方法有很多种, 可以包含多个晶体管和电容, 常用的有 12T1C (12 个 TFT 晶体管 1 个耦合电容的形式, 下同)、9T1C、13T1C 等等结构, 其移位脉冲的实现都至少要包含一组时钟信号、一个上拉晶体管、一个下拉晶体管和一个输出晶体管。

[0005] 由于集成栅极驱动的寄存器集成度较高, 对噪声比较敏感, 而现有的移位寄存器中由于 CLK 信号 (时钟信号) 或者 CLKB 信号 (时钟反相信号, 即时钟信号的反相信号) 产生的 PD (Pull Up, 下拉) 电压占空比仅为 50%, 一个下拉晶体管只能在一帧的一半时间内对输出噪声进行放电。如果当前一级移位寄存器电路的输出噪声不能有效地抑制, 就会作为下一级的输入产生输出, 这样噪声就被逐级放大。尤其是在高温工作一段时间后, 这个噪声就会更加明显, 甚至引起多个输出, 导致 TFT-LCD 显示紊乱。

### 实用新型内容

[0006] (一) 要解决的技术问题

[0007] 针对上述缺点, 本实用新型为了解决现有技术中移位寄存器在高温下会产生多输出的问题, 提供了一种移位寄存器、栅极驱动器及显示装置。

[0008] (二) 技术方案

[0009] 为解决上述问题,首先,本实用新型提供了一种移位寄存器,所述移位寄存器包括:上拉晶体管,其漏极连接第一时钟信号端,栅极连接上拉节点,源极连接输出端;

[0010] 第一电容,连接在所述上拉晶体管栅极和源极之间;

[0011] 下拉晶体管,其源极连接所述上拉节点,栅极连接当前下拉节点,漏极连接低电压信号端;

[0012] 输出晶体管,其栅极连接第二时钟信号端,源极连接输出端,漏极连接低电压信号端;

[0013] 复位单元,分别连接复位信号端、上拉节点、输出端和低电压信号端;

[0014] 其特征在于,所述移位寄存器还包括:

[0015] 对输出端放电的输出下拉单元,分别连接当前下拉节点、相邻级下拉节点、低电压信号端和输出端。

[0016] 优选地,所述移位寄存器还包括:控制晶体管,其栅极与上拉节点相连,漏极连接所述相邻级下拉节点,源极连接低电压信号端。

[0017] 优选地,所述移位寄存器还包括:控制上拉节点电位的上拉驱动单元,分别连接输入端、第二时钟信号端和上拉节点;以及

[0018] 连接在第二时钟信号端、上拉节点和低电压信号端之间、控制当前下拉节点电位的下拉驱动单元。

[0019] 优选地,所述输出下拉单元包括第一输出下拉晶体管和第二输出下拉晶体管,其中,

[0020] 第一输出下拉晶体管,其栅极连接当前下拉节点,源极连接低电压信号端,漏极连接输出端;以及

[0021] 第二输出下拉晶体管,其栅极连接所述相邻级下拉节点,源极连接低电压信号端,漏极连接输出端。

[0022] 优选地,所述复位单元包括第一复位晶体管和第二复位晶体管,其中,

[0023] 第一复位晶体管,其源极连接上拉节点,漏极连接低电压信号端,栅极连接复位信号端;

[0024] 第二复位晶体管,其源极连接输出端,漏极连接低电压信号端,栅极连接复位信号端。

[0025] 优选地,所述上拉驱动单元包括第一上拉驱动晶体管和第二上拉驱动晶体管,其中,

[0026] 第一上拉驱动晶体管,其栅极和源极同时连接输入端,漏极连接上拉节点;

[0027] 第二上拉驱动晶体管,源极连接输入端,漏极连接上拉节点,栅极连接第二时钟信号端;

[0028] 所述下拉驱动单元包括第一至第四下拉驱动晶体管,其中,

[0029] 第一下拉驱动晶体管,其源极连接第二时钟信号端,漏极连接当前下拉节点;

[0030] 第二下拉驱动晶体管,其源极连接当前下拉节点,漏极连接低电压信号端,栅极连接上拉节点;

[0031] 第三下拉驱动晶体管,其栅极和源极同时连接第二时钟信号端,漏极连接第一下

拉驱动晶体管的栅极；

[0032] 第四下拉驱动晶体管，其源极连接第三下拉驱动晶体管的漏极，漏极连接低电压信号端，栅极连接上拉节点。

[0033] 另一方面，本实用新型还同时提供一种栅极驱动器，所述栅极驱动器包括多个级联的如上所述的移位寄存器。

[0034] 优选地，所述栅极驱动器的级联结构为：每一级移位寄存器的第一时钟信号端和第二时钟信号端分别接两个反相的时钟信号；低电压信号端连接低电压信号；每一级的输入端连接上一级的输出端，以上一级的输出作为本级的输入；同时每一级的输出端还连接上一级的复位信号端，以本级的输出作为上一级的复位信号；此外，每一级的当前下拉节点连接到上一级或下一级的输出下拉单元。

[0035] 优选地，所述级联结构中：奇数级寄存器的第一时钟信号端与偶数级寄存器的第二时钟信号端连接第一时钟信号，奇数级寄存器的第二时钟信号端与偶数级寄存器的第一时钟信号端连接与第一时钟信号反相的第二时钟信号，第一级的输入端连接初始启动信号，最后一级复位信号由两个晶体管组成的复位端提供。

[0036] 最后，本实用新型还提供一种显示装置，所述显示装置包括：如上所述的栅极驱动器。

### [0037] (三) 有益效果

[0038] 本实用新型通过输出下拉单元对当前输出后第奇数个和第偶数个时间单元内的噪声进行抑制，有效防止了多输出现象的产生，增强了 GOA 单元的稳定性，保证了液晶面板显示效果。

## 附图说明

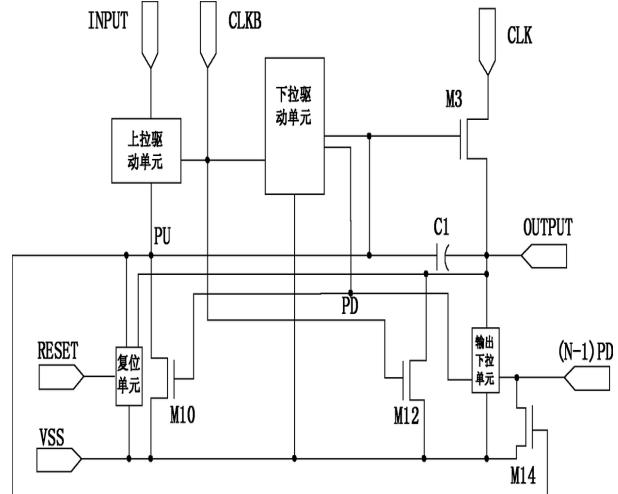

[0039] 图 1 为本实用新型中移位寄存器的电路结构图；

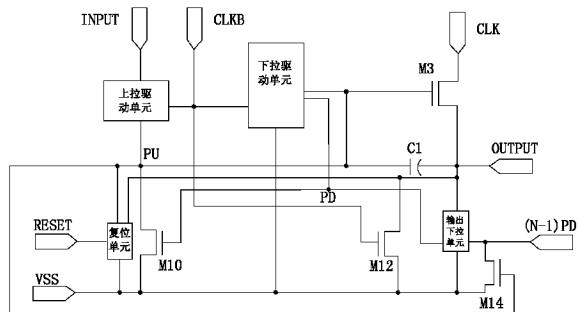

[0040] 图 2 为本实用新型的一个实施例中的移位寄存器电路结构图；

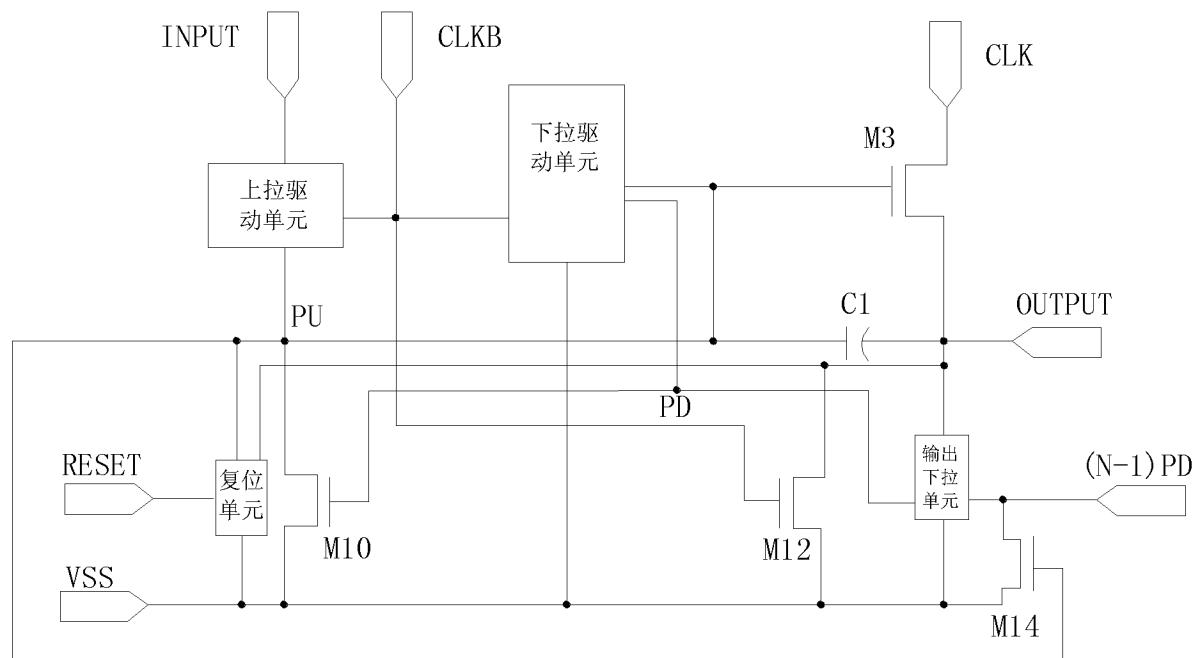

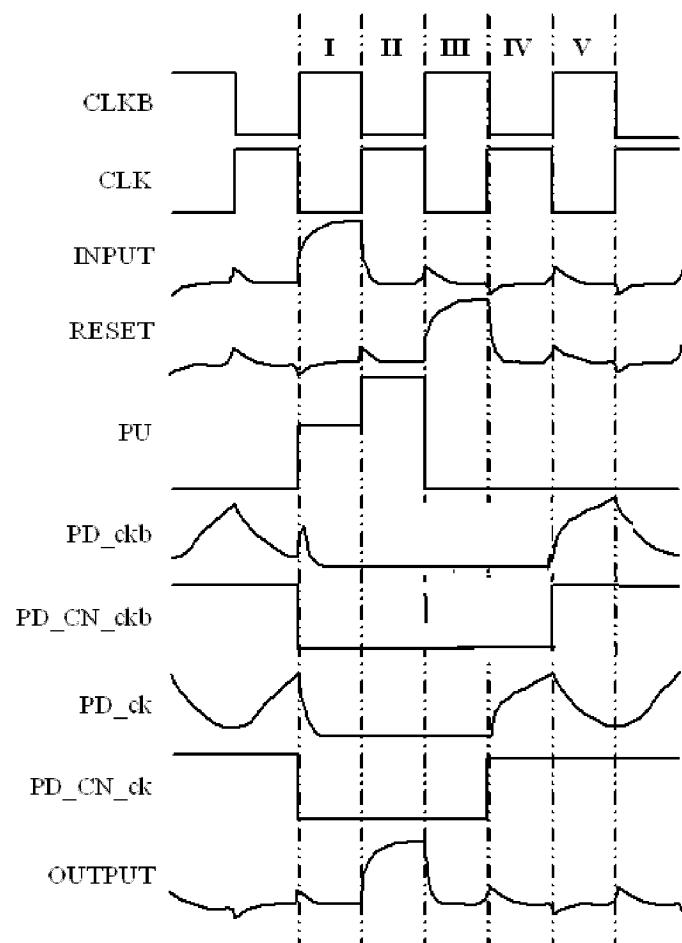

[0041] 图 3 为本实用新型中移位寄存器的电平信号逻辑时序图；

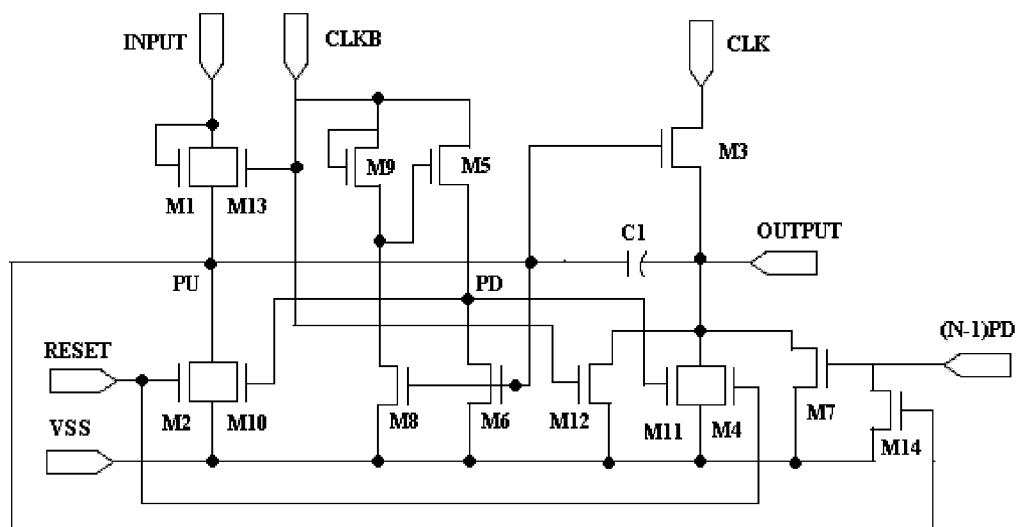

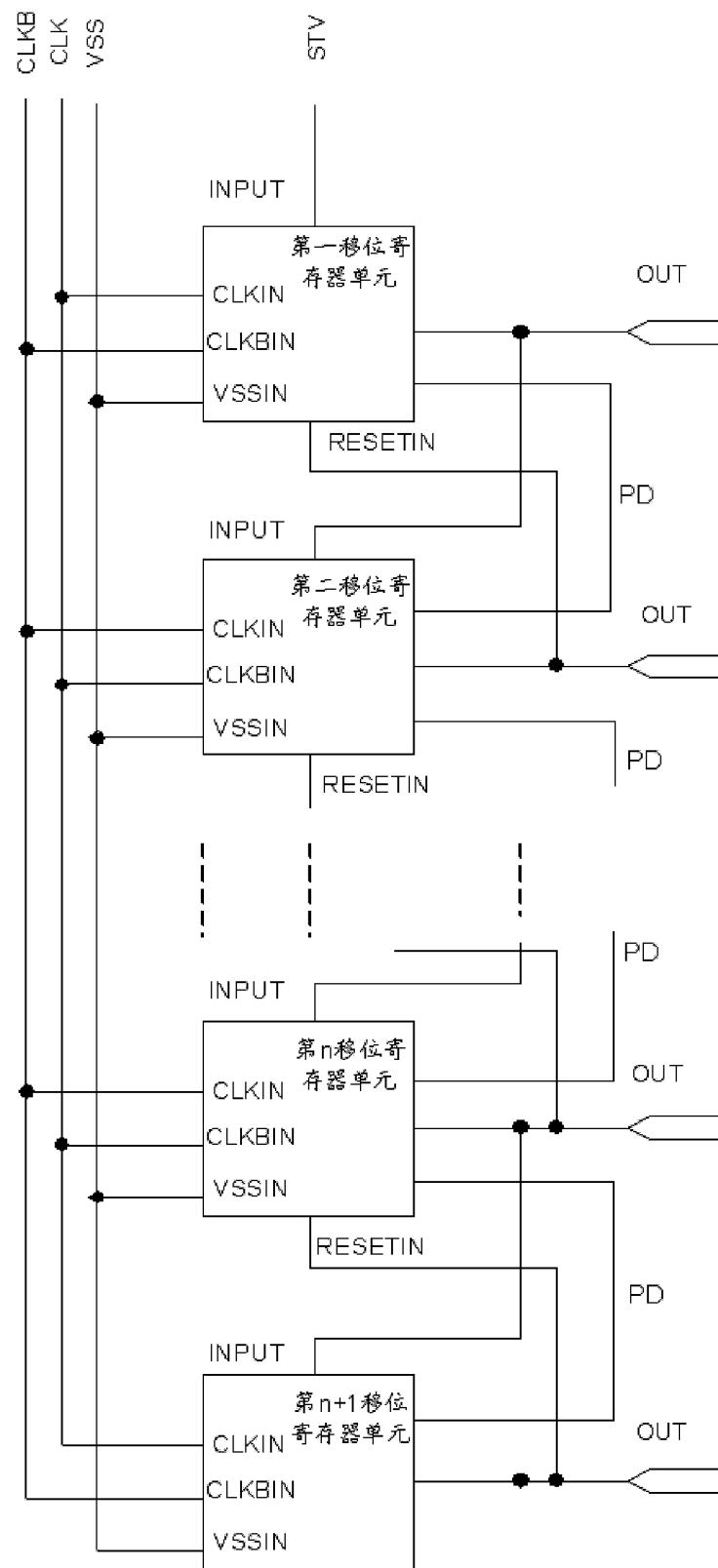

[0042] 图 4 为本实用新型中多个移位寄存器级联的栅极驱动器电路结构图。

## 具体实施方式

[0043] 下面将结合本实用新型实施例中的附图，对本实用新型实施例中的技术方案进行清楚、完整地描述，显然，所描述的实施例是本实用新型的一部分实施例，而不是全部的实施例。基于本实用新型中的实施例，本领域普通技术人员在没有做出创造性劳动的前提下所获得的所有其他实施例，都属于本实用新型保护的范围。

[0044] 在本实用新型的移位寄存器中，主要加入了输出下拉单元，用于分别对当前输出后第奇数个和第偶数个时间单元内的噪声抑制，使得其在高温下可以有效防止多输出的产生。

[0045] 具体地，本实用新型的移位寄存器中利用输出下拉单元对输出放电，这输出下拉单元分别接当前 PD(Pull Down, 下拉)点电压和相邻级下拉节点(即上一级或下一级移位寄存器电路的 PD 点)电压信号，实现奇偶时间单元内的放电。此外，本实用新型中同时设置相应的控制晶体管，令 PU(Pull Up, 上拉)电压作为其栅极输入，当 PU 点电位为高时，对

所述相邻级电路的 PD 电压进行放电,使相应输出下拉单元的控制电位为低。

[0046] 更进一步地,如图 1 所示,本实用新型的实施例中,移位寄存器包括输入端 INPUT、输出端 OUTPUT、复位信号端 RESET、第一时钟信号端 CLK、第二时钟信号端 CLKB(其中,第二时钟信号 CLKB 为第一时钟信号 CLK 的反相信号)、低电压信号端 VSS 以及一个相邻级下拉节点端(图 1 中以上一级下拉节点 (N-1)PD 为例进行说明);此外,移位寄存器内部还有几个特定控制电压点,分别记为上拉节点 PU、当前下拉节点 PD。具体的电路连接图详见图 1,移位寄存器包括:上拉晶体管 M3,其漏极连接第一时钟信号端 CLK,栅极连接上拉节点 PU,源极连接输出端 OUTPUT;第一电容 C1,连接在所述上拉晶体管 M3 栅极和源极之间;下拉晶体管 M10,其源极连接所述上拉节点 PU,栅极连接当前下拉节点 PD,漏极连接低电压信号端 VSS;输出晶体管 M12,其栅极连接第二时钟信号端 CLKB,源极连接输出端 OUTPUT,漏极连接低电压信号端 VSS;复位单元,分别连接复位信号端 RESET、上拉节点 PU、输出端 OUTPUT 和低电压信号端 VSS;以及,对输出端放电的输出下拉单元,分别连接当前下拉节点 PD、相邻级下拉节点 (N-1)PD、低电压信号端 VSS 和输出端 OUTPUT。

[0047] 此外,所述移位寄存器还可以进一步包括控制晶体管 M14,其栅极与上拉节点 PU 相连,漏极连接所述相邻级下拉节点 PD,源极连接低电压信号端 VSS。该控制晶体管 M14 可以在 PU 点电位为高时,对相邻级电路的 (N-1)PD 电压进行放电,使相应输出下拉单元的控制电位为低,从而可以更有效地控制输出下拉单元对输出的下拉效果。

[0048] 需要说明的是,图 1 中仅以上一级下拉节点 (N-1)PD 为例进行说明相邻级下拉节点,实际情况中由于栅极驱动器逐级驱动,与当前级相邻的上一级或下一级的驱动情况相同,因而图 1 中的上一级下拉节点 (N-1)PD 可等效替换为下一级下拉节点 (N+1)PD,其工作原理相同不再赘述。

[0049] 更优选地,本实用新型移位寄存器中的各晶体管及各元件单元可以采用 TFT(Thin Film Transistor, 薄膜晶体管)构成,下面通过图 2 的优选实施例进一步介绍本实用新型的各关键元件的信号连接方式。

[0050] 其中,TFT M11、TFT M7 为两个输出下拉晶体管,其共同组成输出下拉单元,第一输出下拉晶体管 TFT M11 由第二时钟信号控制,当 CLKB 高电位到来时,PD 点为高电平,TFT M11 管导通,对于 OUTPUT 进行下拉,将当前输出噪声放掉;第二输出下拉晶体管 TFTM7 由上一级的 PD 节点 (N-1)PD 控制,当前一级的 PD 点为高时,TFTM7 导通,将输出噪声放掉,避免出现多输出现象。TFT M11 的栅极与 PD 点相连,漏极连接 VSS,源极连接 OUTPUT;TFT M7 的栅极与 (N-1)PD 相连,漏极连接 VSS,源极连接 OUTPUT。

[0051] TFT M14 为输出下拉晶体管 TFT M7 的控制晶体管,在当前 PU 点为高电平时导通,将上一级的下拉节点 (N-1)PD 电压放掉而保证 TFTM7 的栅极电压输入为低,从而不影响正常的 Gate 信号输出。TFT M14 的栅极与上拉节点 PU 相连,源极连接 (N-1)PD,漏极连接 VSS。

[0052] 其余晶体管及电容 C1 的工作原理与现有的 12T1C 结构基本相同,简单介绍如下:TFT M3 为上拉晶体管,当 TFT M3 被上拉节点 PU 打开时,第一时钟信号端 CLK 输入的信号向输出端 OUTPUT 输出信号;TFT M2 以及 TFT M4 为两个复位晶体管,其共同组成复位单元,当由复位信号输入端 RESET 输入的复位信号(即下一级的输出信号)到来的时候,第一复位晶体管 TFT M2 和第二复位晶体管 TFT M4 打开,对于上拉节点 PU 和 OUTPUT 进行复位,将其信号进行下拉至关断电压;TFT M1、TFT M13 为两个上拉驱动晶体管,其共同组成上拉驱动

单元, 电容 C1 也用于上拉驱动, 信号输入端 INPUT 输入信号和第二时钟信号 CLKB 同相位, 当输入信号和第二时钟信号 CLKB 到来的时候, 第一上拉驱动晶体管 TFT M1 和第二上拉驱动晶体管 TFT M13 打开, 对 C1 的一个极板进行充电, 使得上拉节点 PU 为高电位, 并且使得第二上拉驱动晶体管 TFT M3 处于导通状态, 当下一时刻 CLK 输入的时钟高电平信号到来的时候, 由于自举效应 (bootstrapping), 使得上拉节点 PU (即为 TFT M3 的栅极) 电位变得更高, 从而产生了阈值电压补偿的效果; 下拉晶体管 TFT M10, 由节点 PD 控制, 当 PD 节点为高电位时, TFT M10 导通, 从而对上拉节点 PU 点进行下拉, 其可以放掉 CLK 由低变高时产生的耦合噪声; TFT M5、TFT M6、TFT M8、以及 TFT M9 为四个下拉驱动晶体管, 其共同组成下拉驱动单元, 主要控制节点 PD 电位的输出, 驱动下拉晶体管的工作; TFT M12 为输出晶体管, 在第二时钟信号端 CLKB 输入的第二时钟信号控制下形成移位寄存器的输出信号。

[0053] 下面进一步参考图 3 的电平信号示意图, 对本实用新型的图 2 中的移位寄存器的工作过程介绍如下:(说明, 在图 3 中, 由 CLKB 信号产生的下拉电压 PD 被定义为 PD\_ckb, 上一级电路由 CLK 信号产生的下拉电压 (N-1)PD 被定义为 PD\_ck。)

[0054] 第 I 阶段, INPUT 为高电平, RESET 为低电平, 则 PU 节点为高电平, 晶体管 M1、M3、M6、M8、M12 和 M14 导通; CLK 为低电平, PD\_ck 为低电平, CLKB 为高电平, 晶体管 M5 导通, 通过设置 M5/M6 沟道宽长比的比例, 使得 PD\_ckb 节点接近低电平; RESET 为低电平, 则晶体管 M2、M4 截止; 由于晶体管 M4、M10、M11 截止, M3 导通输出等于 CLK, CLK 为低电平所以输出为低电平。

[0055] 第 II 阶段, INPUT 变为低电平, RESET 仍为低电平, 则 PU 节点仍为高电平, 晶体管 M3、M6、M8、M14 仍导通, PD\_ck 为低电平; CLKB 变为低电平, 晶体管 M5 截止, 那么节点 PD\_ckb 仍为低电平; RESET 仍为低电平, 则晶体管 M2、M4 仍截止; CLK 变为高电平, M3 导通输出等于 CLK, CLK 为高电平所以输出变为高电平。

[0056] 第 III 阶段, INPUT 仍为低电平, 晶体管 M1 截止; RESET 变为高电平, 则晶体管 M2、M4 导通; 于是 PU 节点被放电至低电平, 晶体管 M3、M6、M8、M14 截止; CLKB 为高电平, 晶体管 M5 导通; CLK 为低电平, PD\_ck 为低电平, 则 M7 截止; 由于 M3 截止, 晶体管 M4 导通输出等于低电平 VSS, 所以输出变为低电平。

[0057] 第 IV 阶段, INPUT 仍为低电平, 晶体管 M1 截止; RESET 变为低电平, 则晶体管 M2、M4 截止; PU 节点仍为低电平, 则晶体管 M3、M6、M8、M14 仍截止; CLKB 为低电平, 晶体管 M5 截止, 那么节点 PD\_ckb 电平为低, 则晶体管 M10, M11 截止; CLK 变为高电平, 则 PD\_ck 节点变为高电平, M7 导通, 由于晶体管 M3、M4 截止, 所以输出保持低电平。

[0058] 第 V 阶段, INPUT 仍为低电平, 晶体管 M1 截止; RESET 仍为低电平, 则晶体管 M2、M4 截止; PU 节点仍为低电平, 晶体管 M3、M6、M8、M14 仍截止; CLKB 为高电平, 晶体管 M9 导通, 那么节点 PD\_ckb 电平由最低点逐渐升高, 则晶体管 M5 由关闭逐渐到最大导通(此时, 如果 PU 结点有噪声, 则可通过 M10 放掉; 如果输出有噪声, 则可通过 M11 放掉); CLK 为低电平, PD\_ck 为低电平, M7 截止; 由于晶体管 M3、M4 截止, 所以输出保持为低电平。

[0059] 在本实用新型中, 多个上述的移位寄存器级联构成液晶面板的栅极驱动器。具体地, 由 n+1 个移位寄存器级联成栅极驱动器的级联结构如图 4 所示: 每一级移位寄存器的第一时钟信号端 CLKIN 和第二时钟信号端 CLKBIN 分别接两个反相的时钟信号(第一时钟信号 CLK 和第二时钟信号 CLKB); 低电压信号端 VSSIN 连接低电压信号 VSS; 每一级的输入端

INPUT 连接上一级的输出端 OUT, 以上一级的输出作为本级的输入 ; 同时每一级的 OUT 端还连接上一级的复位信号端 RESETIN, 以本级的输出作为上一级的复位信号 ; 此外, 每一级的 PD 点连接到下一级为下一级的第二输出下拉晶体管提供控制信号 ( 如上所述 PD 点连接到相邻级即可, 因而也可连接到上一级的输出下拉单元 ) 。特别地, 奇数级寄存器的第一时钟信号端 CLKIN ( 在图 1-2 中对应为 M3 漏极连接的第一时钟信号端 CLK, 以下的端口对应与之类似 ) 与偶数级寄存器的第二时钟信号端 CLKBIN 接第一时钟信号 CLK, 奇数级寄存器的第二时钟信号端 CLKBIN 与偶数级寄存器的第一时钟信号端 CLKIN 接与第一时钟信号反相的第二时钟信号 CLKB ( 即第 1,3,5... 级的奇数级的时钟控制与第 2,4,6... 级的偶数级的时钟控制正好反相 ) ; 第一级的输入端接初始启动信号 STV, 最后一级复位信号由两个晶体管组成的复位端提供 ( 图 4 中未示出 ) 。通过这种级联的栅极驱动器, 液晶面板在各信号的驱动下依次打开每一行的扫描线并关闭其他行的扫描线, 从而仅驱动该行像素单元对应的 TFT 实现逐行扫描。

[0060] 优选地, 上述栅极驱动器集成在阵列基板上形成 GOA 单元。本实用新型还提供了一种显示装置, 该显示装置包括如上所说的栅极驱动器。所述显示装置可以为 : 液晶面板、电子纸、OLED 面板、液晶电视、液晶显示器、数码相框、手机、平板电脑等具有任何显示功能的产品或部件。

[0061] 在实用新型的每一级移位寄存器中, 当 CLK 信号由高变低时, 这时前一级的 PD 点为高, 将噪声放掉 ; 而 CLK 由低变高产生的耦合噪声仍是被当前的 PD 点高电压放掉 ; 所以 PU 点上非期望的电压波动在输出上的耦合噪声就被有效地抑制了。同时本实用新型中设置一个控制晶体管 M14 使得当前 PU 点为高电平时前一级 PD 点电压输入为低, 不影响正常的 Gate 信号输出。通过本实用新型的方式, 在不影响栅极驱动信号的正常输出的情况下, 可以有效地抑制输出噪声对下一级的影响, 从而避免了高温工作下出现的多输出现象, 保证了液晶显示效果。

[0062] 以上实施方式仅用于说明本实用新型, 而并非对本实用新型的限制, 有关技术领域的普通技术人员, 在不脱离本实用新型的精神和范围的情况下, 还可以做出各种变化和变型, 因此所有等同的技术方案也属于本实用新型的范畴, 本实用新型的专利保护范围应由权利要求限定。

图 1

图 2

图 3

图 4

|                |                                                             |                      |            |

|----------------|-------------------------------------------------------------|----------------------|------------|

| 专利名称(译)        | 移位寄存器、栅极驱动器及显示装置                                            |                      |            |

| 公开(公告)号        | <a href="#">CN202443728U</a>                                | 公开(公告)日              | 2012-09-19 |

| 申请号            | CN201220079453.4                                            | 申请日                  | 2012-03-05 |

| [标]申请(专利权)人(译) | 京东方科技股份有限公司                                                 |                      |            |

| 申请(专利权)人(译)    | 京东方科技股份有限公司                                                 |                      |            |

| 当前申请(专利权)人(译)  | 京东方科技股份有限公司                                                 |                      |            |

| [标]发明人         | 张玉婷                                                         |                      |            |

| 发明人            | 张玉婷                                                         |                      |            |

| IPC分类号         | G09G3/36 G09G3/20                                           |                      |            |

| CPC分类号         | G11C19/28 G09G3/3648 G09G3/3677 G09G2300/0408 G09G2310/0286 |                      |            |

| 代理人(译)         | 王莹                                                          |                      |            |

| 外部链接           | <a href="#">Espacenet</a>                                   | <a href="#">Sipo</a> |            |

## 摘要(译)

本实用新型涉及显示器件技术领域，提供了一种移位寄存器、栅极驱动器及显示装置。本实用新型的移位寄存器包括：上拉晶体管、下拉晶体管、输出晶体管和复位单元，还包括：用于对输出端放电的输出下拉单元，分别连接当前下拉节点、相邻级下拉节点、低电压信号端和输出端，在当前下拉节点或所述相邻级下拉节点为高电位时将所述输出端导通至所述低电压信号端；以及控制晶体管，其栅极与上拉节点相连，漏极连接所述相邻级下拉节点，源极连接低电压信号端。本实用新型通过输出下拉单元对当前输出后第奇数个和第偶数个时间单元内的噪声进行抑制，有效防止了多输出现象的产生，增强了GOA单元的稳定性，保证了液晶面板显示效果。