(12)发明专利申请

(10)申请公布号 CN 110322856 A

(43)申请公布日 2019.10.11

(21)申请号 201910648934.9

(22)申请日 2019.07.18

(71)申请人 深圳市华星光电半导体显示技术有限公司

地址 518132 广东省深圳市光明新区公明

街道塘明大道9-2号

(72)发明人 王珊 温亦谦

(74)专利代理机构 深圳翼盛智成知识产权事务所(普通合伙) 44300

代理人 黄威

(51)Int.Cl.

G09G 3/36(2006.01)

G02F 1/1362(2006.01)

权利要求书2页 说明书5页 附图4页

(54)发明名称

一种液晶显示面板及其驱动方法

(57)摘要

本发明公开了一种液晶显示面板及其驱动方法。该液晶显示面板包括：像素单元组，包括以矩阵方式排列的多个像素单元；扫描线，每条扫描线连接同一行至少两个像素单元；栅极驱动电路，与扫描线连接，用于在扫描线上提供栅极信号，以控制扫描线所连接的像素单元打开；数据线，分别连接不同列的至少一个像素单元；数据驱动电路，与数据线连接，用于给数据线提供数据信号，以对数据线所连接的且处于打开状态的像素单元进行充电；其中，数据驱动电路给多条数据线提供的数据信号沿着远离栅极驱动电路的方向依次延迟，使得液晶显示面板中多个像素单元打开的时间与充电的时间相匹配。通过上述方式，本发明能够提升液晶显示面板的均匀性，改善显示效果。

1. 一种液晶显示面板，其特征在于，包括：

像素单元组，包括多个像素单元，所述多个像素单元以矩阵方式排列；

多条扫描线，每条所述扫描线连接同一行至少两个所述像素单元；

栅极驱动电路，与所述多条扫描线连接，用于在所述扫描线上提供栅极信号，以控制所述扫描线所连接的所述像素单元打开；

多条数据线，所述多条数据线分别连接不同列的所述至少一个像素单元；

数据驱动电路，与所述多条数据线连接，用于给所述数据线提供数据信号，以对所述数据线所连接的且处于打开状态的所述像素单元进行充电；

其中，数据驱动电路给所述多条数据线提供的所述数据信号沿着远离所述栅极驱动电路的方向依次延迟，使得所述液晶显示面板中所述多个像素单元打开的时间与充电的时间相匹配。

2. 根据权利要求1所述的液晶显示面板，其特征在于，所述显示面板进一步包括：

多条监测线，每条所述监测线分别与同一行不同的像素单元连接，用于监测所连接的所述像素单元打开的时间；

栅极信号偏移检测电路，连接所述多条监测线，用于通过所述多条监测线监测到每个所述像素单元打开的时间，并计算出同一所述栅极线连接的至少两个所述像素单元的打开时间的时间差；

逻辑板，连接所述栅极信号偏移检测电路，并与所述数据驱动电路连接，用于将所述时间差发送给所述数据驱动电路，使得所述数据驱动电路根据所述时间差给所述多条数据线提供的所述数据信号沿着远离所述栅极驱动电路的方向依次延迟。

3. 根据权利要求2所述的液晶显示面板，其特征在于，

数据驱动电路向所述至少两个像素单元所在列对应的数据线提供的驱动信号延迟时间为所述时间差的绝对值。

4. 根据权利要求2所述的液晶显示面板，其特征在于，

所述像素单元的打开时间为所述像素单元栅极信号电压达到标准值的90%的时间。

5. 根据权利要求4所述的液晶显示面板，其特征在于，

所述标准值为所述栅极驱动电路的起始脉冲电压值。

6. 根据权利要求2所述的液晶显示面板，其特征在于，

所述逻辑板通过偏移所述数据驱动电路中的驱动信号来控制数据驱动电路给所述多条数据线提供的所述数据信号依次延迟。

7. 根据权利要求2所述的液晶显示面板，其特征在于，所述数据驱动电路包括多个数据驱动芯片，每个所述驱动芯片与一条所述数据线连接；

其中，所述驱动芯片用于提供所述驱动信号。

8. 根据权利要求7所述的液晶显示面板，其特征在于，

所述多个驱动芯片和所述逻辑板连接，根据所述逻辑板计算出的所述时间差依次延迟所述驱动信号。

9. 根据权利要求1所述的液晶显示面板，其特征在于，所述液晶显示面板进一步包括：

定时控制器，所述定时控制器连接所述栅极驱动电路和所述数据驱动电路，用于控制所述栅极驱动电路和所述数据驱动电路工作。

10. 一种液晶显示装置,其特征在于,包括权利要求1-9任一项所述的液晶显示面板。

## 一种液晶显示面板及其驱动方法

### 技术领域

[0001] 本发明涉及显示领域,特别是涉及一种液晶显示面板及其驱动方法。

### 背景技术

[0002] 随着显示行业的发展,对于面板的各种性能要求提高,对面板的分辨率要求也不断提升,面板的刷新频率提高,使得面板充电时间不断缩短,又由于面板制程工艺的影响,面板有较大的RC loading,导致gate打开时间不一致,进一步缩短充电时间。面板充电时间过短会造成充电不足,从而导致了面板显示效果与均匀性下降。

### 发明内容

[0003] 本发明主要解决的技术问题是提供一种液晶显示面板及其驱动方法,能够提升液晶显示面板的均匀性,改善显示效果。

[0004] 为解决上述技术问题,本发明采用的一个技术方案是:提供一种液晶显示面板,包括:像素单元组,包括多个像素单元,所述多个像素单元以矩阵方式排列;多条扫描线,每条所述扫描线连接同一行至少两个所述像素单元;栅极驱动电路,与所述多条扫描线连接,用于在所述扫描线上提供栅极信号,以控制所述扫描线所连接的所述像素单元打开;多条数据线,所述多条数据线分别连接不同列的所述多个像素单元;数据驱动电路,与所述多条数据线连接,用于给所述数据线提供数据信号,以对所述数据线所连接的且处于打开状态的所述像素单元进行充电;其中,数据驱动电路给所述多条数据线提供的所述数据信号依次延迟,使得所述液晶显示面板中所述多个像素单元打开的时间与充电的时间相匹配。

[0005] 其中,所述显示面板进一步包括:多条监测线,每条所述监测线分别与同一行不同的像素单元连接,用于监测每个所述像素单元打开的时间;逻辑板,所述逻辑板连接所述多条监测线并连接所述数据驱动电路,用于获取所述多条监测线监测到的每个所述像素单元打开的时间,并计算出距离所述栅极驱动电路最近的所述像素单元的打开时间与同一行中其他所述像素单元的打开时间之间的时间差;所述逻辑板与所述数据驱动电路连接,所述数据驱动电路根据所述时间差给所述多条数据线提供的所述数据信号依次延迟。

[0006] 其中,数据驱动电路给其他所述像素单元所在列对应的数据线提供的驱动信号比距离所述栅极驱动电路最近的所述像素单元所在列的数据线延迟所述时间差的绝对值。

[0007] 其中,所述像素单元的打开时间为所述像素单元栅极信号电压达到标准值的90%的时间。

[0008] 其中,所述标准值为所述栅极驱动电路的起始脉冲电压值。

[0009] 其中,所述逻辑板通过偏移所述数据驱动电路中所述驱动信号来控制数据驱动电路给所述多条数据线提供的所述数据信号依次延迟。

[0010] 其中,所述数据驱动电路包括多个数据驱动芯片,每个所述驱动芯片与一条所述数据线连接;所述驱动芯片提供的所述数据信号沿着远离所述栅极驱动电路方向依次延迟。

[0011] 其中，所述多个驱动芯片和所述逻辑板连接，根据所述逻辑板计算出的所述时间差依次延迟所提供的数据信号。

[0012] 其中，所述液晶显示面板进一步包括：定时控制器，所述定时控制器连接所述栅极驱动电路和所述数据驱动电路，用于控制所述栅极驱动电路和所述数据驱动电路工作。

[0013] 为解决上述技术问题，本发明采用的另一个技术方案是：提供一种液晶显示装置，包括如上所述的液晶显示面板。

[0014] 本发明的有益效果是：区别于现有技术的情况，本发明中液晶显示面板的数据驱动电路给多条数据线提供的所述数据信号沿着原理栅极驱动电路的方向依次延迟，使得所述液晶显示面板中所述多个像素单元打开的时间与充电的时间相匹配，使数据信号的充电时间充足，从而解决因栅极信号延迟导致数据信号充电不足，使面板发光不均匀的现象，改善面板的显示质量。

## 附图说明

[0015] 为了更清楚地说明本申请实施例中的技术方案，下面将对实施例描述中所需要使用的附图作简单地介绍，显而易见地，下面描述中的附图仅仅是本申请的一些实施例，对于本领域普通技术人员来讲，在不付出创造性劳动的前提下，还可以根据这些附图获得其他的附图。其中：

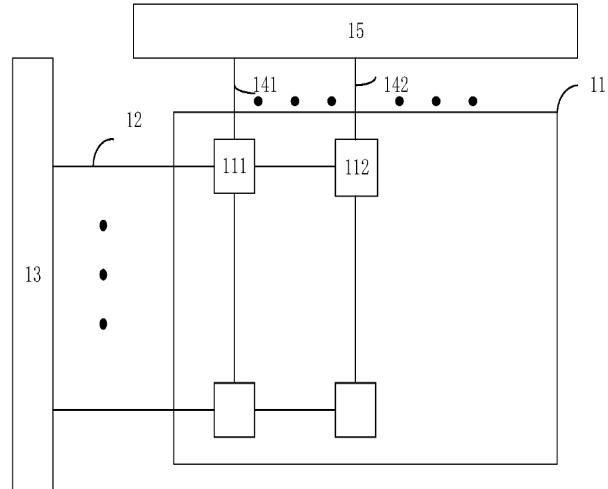

[0016] 图1是本申请提供的液晶显示面板的第一实施例的结构示意图；

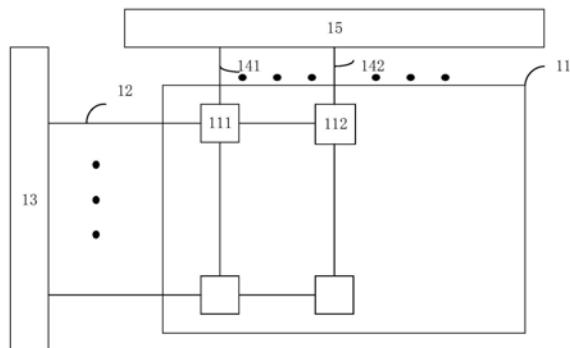

[0017] 图2是本申请提供的液晶显示面板的第二实施例的结构示意图；

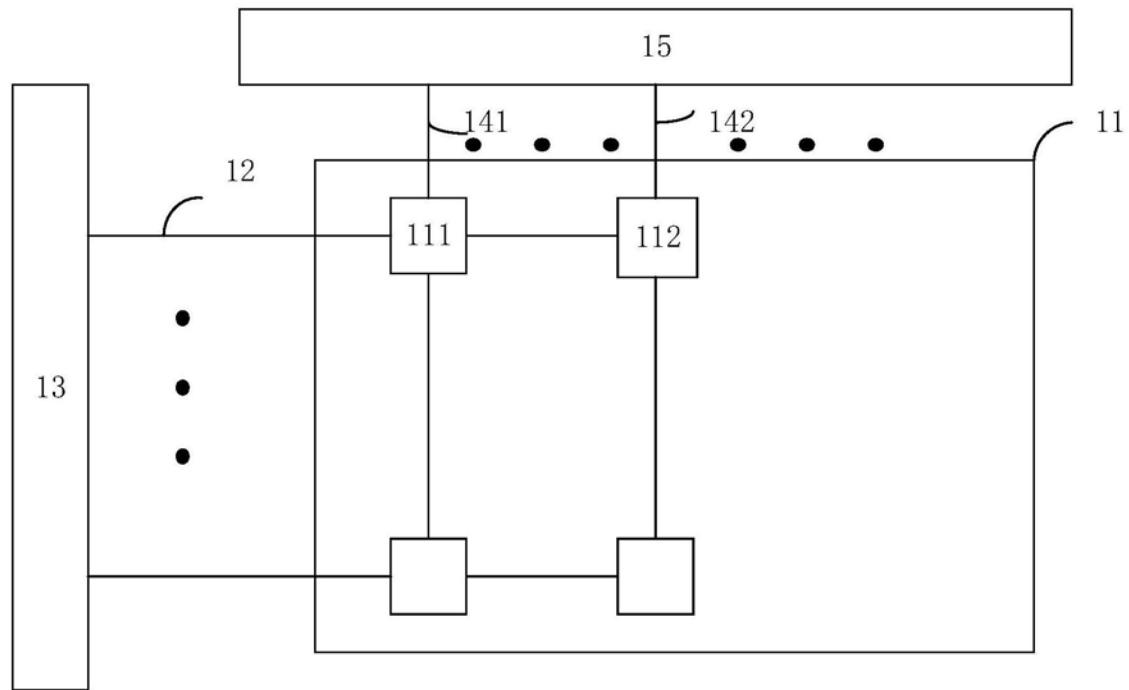

[0018] 图3是本申请提供的液晶显示面板的第三实施例的结构示意图；

[0019] 图4是本申请提供的经过逻辑板偏移后的液晶显示面板的各信号时序示意图；

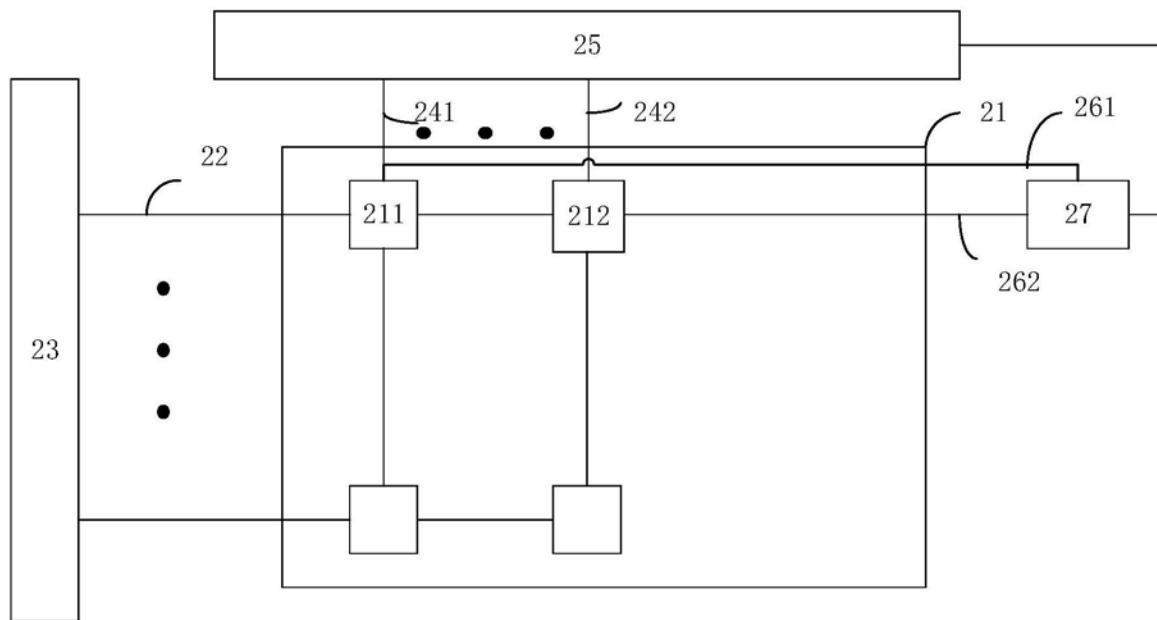

[0020] 图5是本申请提供的液晶显示面板的第四实施例的结构示意图；

[0021] 图6是本申请提供的液晶显示装置的一实施例的结构示意图

## 具体实施方式

[0022] 下面将结合本申请实施例中的附图，对本申请实施例中的技术方案进行清楚、完整地描述，显然，所描述的实施例仅仅是本申请一部分实施例，而不是全部实施例。基于本申请中的实施例，本领域普通技术人员在没有做出创造性的劳动前提下所获得的所有其他实施例，都属于本申请保护的范围。

[0023] 请参阅图1，图1是本申请提供的液晶显示面板的第一实施例的结构示意图。液晶显示面板10包括多个诸如像素单元111和像素单元112之类的像素单元组11、扫描线12、栅极驱动电路13、数据线141和142、数据驱动电路15。其中，该像素单元组11中的多个像素单元以矩阵方式排列。每条扫描线12连接同一行至少两个像素单元（例如，像素单元111和像素单元112）。栅极驱动电路13与扫描线12连接，用于在扫描线12上提供栅极信号，以控制扫描线12所连接的像素单元（例如，像素单元111或像素单元112）打开。数据线141和数据线142分别连接不同列的像素单元（例如，数据线141连接像素单元111，数据线142连接像素单元112）。数据驱动电路15与数据线141和142连接，用于给数据线141和142提供数据信号，以对数据线141和数据线142所连接的且处于打开状态的像素单元（即，像素单元111和像素单元112）进行充电。

[0024] 在液晶显示面板10的面积较大时,由于RC延迟等原因,距离栅极驱动电路13较近的像素单元111,接收到的栅极信号十分接近原始信号,而距离栅极驱动电路13较远的像素单元112接收到的栅极信号则是由低逐渐升高至标准值的信号,像素单元111比像素单元112更快处于打开状态。而像素电路111和像素单元112处于不同列,因此由不同的数据线(数据线141和数据线142)提供数据信号,数据驱动电路15给数据线141和数据线142提供的数据信号沿着远离栅极驱动电路13的方向依次延迟,即提供给数据线142的数据信号比提供给数据线141的数据信号延迟,这样像素单元112接收的数据信号比像素单元111接收数据信号延迟,由于像素单元112打开的时间比像素单元111延迟,因此像素单元112的打开时间与充电时间相匹配。这样数据信号的充电时间充足,有效解决了面板发光不均匀的现象,改善面板的显示质量。

[0025] 需要说明的是,在本实施场景中,仅列举了一条驱动线、两个像素单元和两条数据线,在其他实施场景中,可以设置更多的驱动线、像素单元和数据线。

[0026] 通过上述描述可知,在本实施例中数据驱动电路给多条数据线提供的数据信号沿着远离栅极驱动电路的方向依次延迟,使得液晶显示面板中多个像素单元打开的时间与充电的时间相匹配,使数据信号的充电时间充足,从而解决因栅极信号延迟导致数据信号充电不足,使面板发光不均匀的现象,改善面板的显示质量。

[0027] 请参阅图2,图2是本申请提供的液晶显示面板的第二实施例的结构示意图。液晶显示面板20包括多个诸如像素单元211和像素单元212之类的像素单元组21、扫描线22、栅极驱动电路23、数据线241和242、数据驱动电路25、监测线261和262、逻辑板27。

[0028] 其中,该像素单元组21中的多个像素单元以矩阵方式排列。每条扫描线22连接同一行至少两个像素单元(例如,像素单元211和像素单元212)。栅极驱动电路23与扫描线22连接,用于在扫描线22上提供栅极信号,以控制扫描线22所连接的像素单元(例如,像素单元211或像素单元212)打开。数据线241和数据线242分别连接不同列的像素单元(例如,数据线241连接像素单元211,数据线242连接像素单元212)。数据驱动电路25与数据线241和242接,用于给数据线241和242提供数据信号,以对数据线241和数据线242所连接的且处于打开状态的像素单元(即,像素单元211和像素单元212)进行充电。

[0029] 监测线261与像素单元211连接,监测线262与像素单元212连接,像素单元211和像素单元212位于同一行。监测线261和监测线262用于分别用于监测像素单元211和212的打开时间。在本实施场景中,像素单元的打开时间为像素单元栅极信号电压达到标准值的90%的时间。该标准值为栅极驱动电路23提供的起始脉冲(STV)的电压值。例如,像素单元211最靠近栅极驱动电路23,则像素单元211接收到的栅极信号瞬间到的STV的值,即像素单元211瞬间处于打开状态,将此时的时间记为0点,而像素单元212距离栅极驱动电路23较远,则接收到的栅极信号是由低逐渐升高的,因此,在一段时间t后,像素单元212接收到的栅极信号的电压达到STV的90%,即为,像素单元212在时间t时打开。在其他实施场景中,还可以设置其他的电压值作为判断像素单元打开的评判依据,例如STV的80%、或者STV的70%等。

[0030] 逻辑板27连接监测线261和监测线262,获取监测线261和监测线262通过像素单元211和212的打开时间,并根据获取到的像素单元211和212的打开时间计算出像素单元211和212的打开时间差。例如,在本实施场景中,时间差为t。逻辑板27与数据驱动电路25连接,

将计算出的时间差 $t$ 发送给数据驱动电路25，使得数据驱动电路根据该时间差 $t$ 控制给数据线241和数据线242提供的数据信号之间的延迟时间。即数据线242提供的数据信号比数据线241提供的数据信号延迟了 $t$ 。

[0031] 需要说明的是，在本实施场景中，仅列举了一条驱动线、两个像素单元、两条数据线、两条监测线和一个逻辑板，在其他实施场景中，可以设置更多的驱动线、像素单元、数据线、监测线和逻辑板。

[0032] 通过上述描述可知，在本实施例中通过监测线和逻辑板可以准确计算出像素单元打开的时间差，从而可以准确获取数据驱动电路给多条数据线提供的数据信号沿着远离栅极驱动电路的方向延迟的时间差，使得液晶显示面板中多个像素单元打开的时间与充电的时间相匹配，使数据信号的充电时间充足，从而解决因栅极信号延迟导致数据信号充电不足，使面板发光不均匀的现象，改善面板的显示质量。

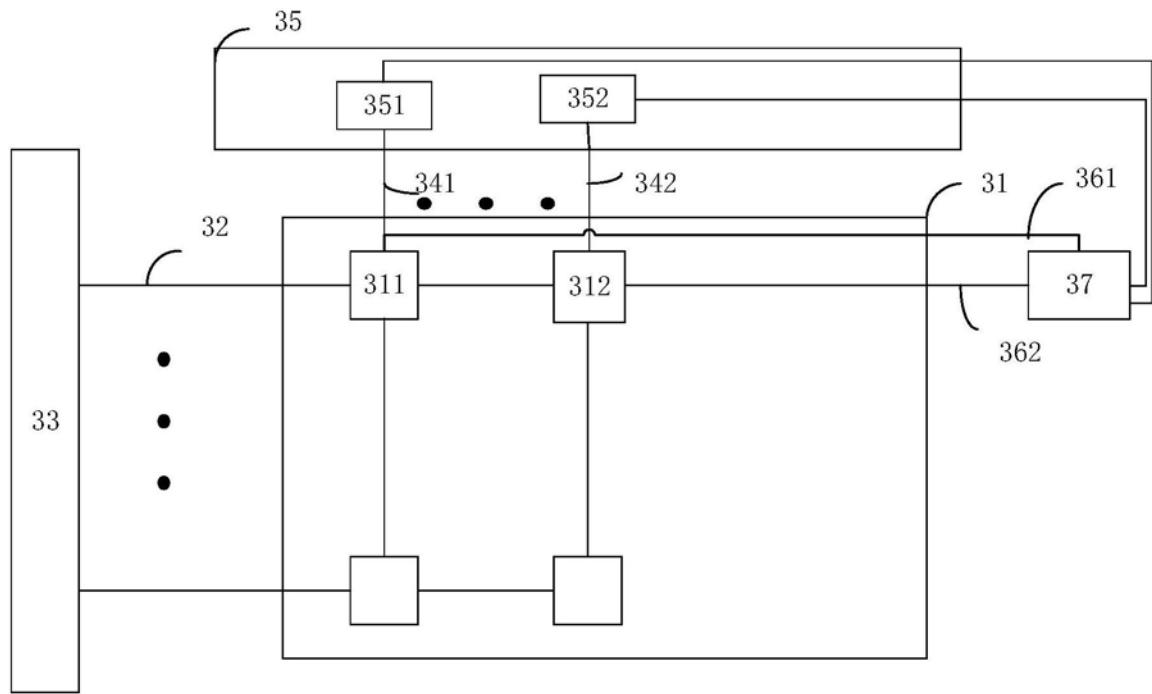

[0033] 请参阅图3，图3是本申请提供的液晶显示面板的第三实施例的结构示意图。液晶显示面板30包括多个诸如像素单元311和像素单元312之类的像素单元组31、扫描线32、栅极驱动电路33、数据线341和342、数据驱动电路35、监测线361和362、逻辑板37。像素单元311和像素单元312之类的像素单元组31、扫描线32、栅极驱动电路33、数据线341和342、数据驱动电路35、监测线361和362、逻辑板37与本申请提供的液晶显示面板的第二实施例中的像素单元211和像素单元212之类的像素单元组21、扫描线22、栅极驱动电路23、数据线241和242、数据驱动电路25、监测线261和262、逻辑板27的结构和连接关系一致，此处不再进行赘述。

[0034] 数据驱动电路35包括数据驱动芯片351和352，数据驱动芯片351和数据线341连接，数据驱动芯片352和数据线342连接。数据驱动芯片351和352还与逻辑板37连接。数据驱动芯片351提供给数据线341的数据信号比数据驱动芯片352提供给数据线342的数据信号延迟。在本实施场景中数据驱动芯片351和352为COF (Chip On Film, 覆晶薄膜) 芯片。

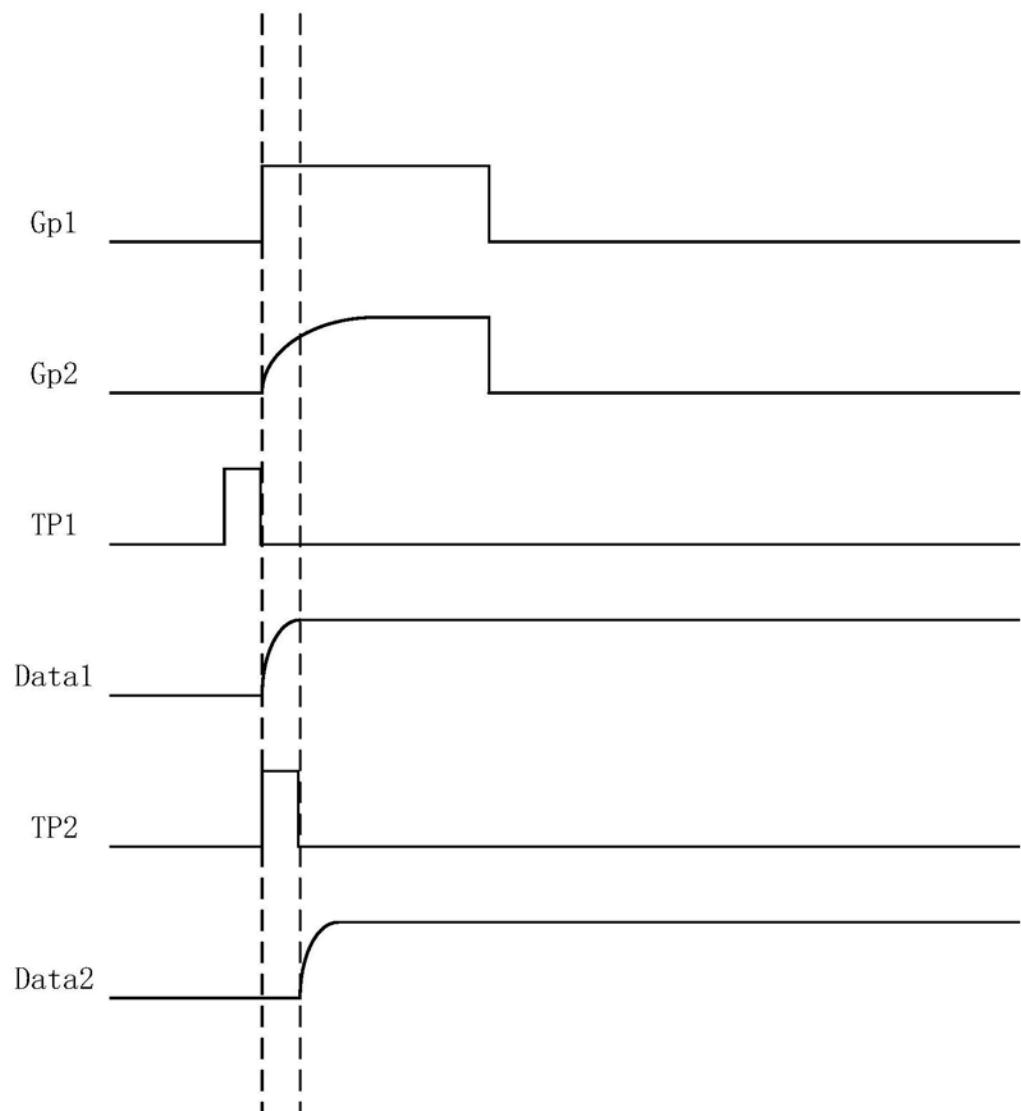

[0035] 在本实施场景中，逻辑板27通过偏移数据驱动电路25中由数据驱动芯片提供的数据信号(TP)来控制数据驱动电路给多条数据线提供的数据信号依次延迟。请结合参阅图4，图4是本申请提供经过逻辑板27偏移后的液晶显示面板30的各信号时序示意图。

[0036] 其中，Gp1是像素单元311接收到的栅极信号，Gp2是像素单元312接收到的栅极信号，TP1是数据驱动芯片351提供的驱动信号，TP2是数据驱动芯片352提供的驱动信号，Data1是数据驱动电路35通过数据线341向像素单元311提供的数据信号，Data2是数据驱动电路35通过数据线342向像素单元312提供的数据信号。

[0037] 根据图4可知，像素单元312比像素单元311的打开时间延迟了时间 $t$ ，则数据驱动芯片352提供的驱动信号比数据驱动芯片351提供的驱动信号延迟了时间 $t$ ，数据驱动电路35通过数据线342向像素单元312提供的数据信号比数据驱动电路35通过数据线341向像素单元311提供的数据信号延迟了时间 $t$ 。于是像素单元311和312打开的时间与充电的时间相匹配。

[0038] 通过上述描述可知，在本实施例中通过偏移数据驱动芯片提供的驱动信号来延迟数据驱动电路通过数据线向像素单元提供的数据信号，使得液晶显示面板中多个像素单元打开的时间与充电的时间相匹配，使数据信号的充电时间充足，从而解决因栅极信号延迟导致数据信号充电不足，使面板发光不均匀的现象，改善面板的显示质量。

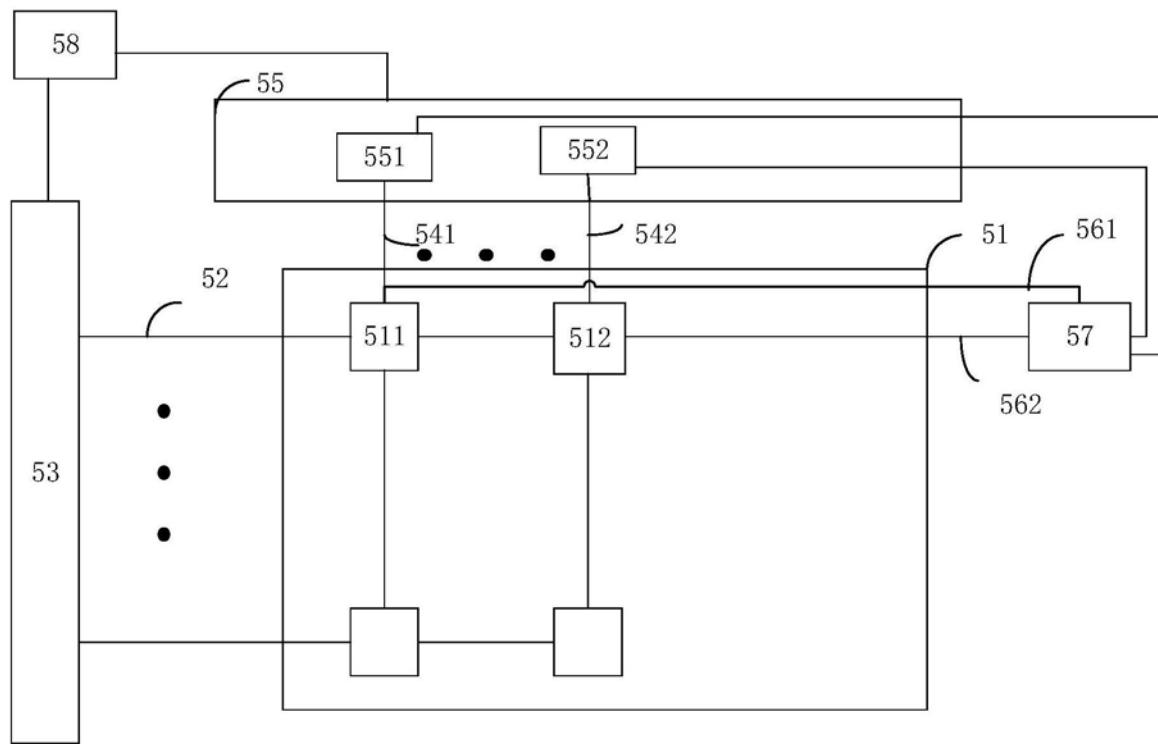

[0039] 请参阅图5，本申请提供的液晶显示面板的第三实施例的结构示意图。液晶显示面

板50包括多个诸如像素单元511和像素单元512之类的像素单元组51、扫描线52、栅极驱动电路53、数据线541和542、数据驱动电路55、监测线561和562、逻辑板57和定时控制器58，数据驱动电路55包括数据驱动芯片551和552，数据驱动芯片551和数据线541连接，数据驱动芯片552和数据线542连接。

[0040] 其中，像素单元511和像素单元512、扫描线52、栅极驱动电路53、数据线541和542、数据驱动电路55、监测线561和562、逻辑板57与本申请提供的液晶显示面板的第二实施例中的像素单元211和像素单元212之类的像素单元组21、扫描线22、栅极驱动电路23、数据线241和242、数据驱动电路25、监测线261和262、逻辑板27的结构和连接关系一致，此处不再进行赘述。

[0041] 定时控制器58连接栅极驱动电路53和数据驱动电路55，用于控制栅极驱动电路53和数据驱动电路55工作。定时控制器58向栅极驱动电路53和数据驱动电路55提供时钟信号，使得栅极驱动电路53和数据驱动电路55根据时钟信号驱动工作。

[0042] 通过上述描述可知，本实施例中通过定时控制器使得栅极驱动电路和数据驱动电路工作更加精准。

[0043] 请参阅图6，图6是本申请提供的液晶显示装置的一实施例的结构示意图。液晶显示装置60包括液晶显示面板61，液晶显示面板61为图1-图3以及图5任一幅所示的液晶显示面板。

[0044] 通过上述描述可知，本实施例通过采用上述内容所述的液晶显示面板，可以有效提升显示效果，改善用户体验。

[0045] 区别于现有技术，本申请数据驱动电路给多条数据线提供的所述数据信号沿着原理栅极驱动电路的方向依次延迟，使得所述液晶显示面板中所述多个像素单元打开的时间与充电的时间相匹配，使数据信号的充电时间充足，从而解决因栅极信号延迟导致数据信号充电不足，使面板发光不均匀的现象，改善面板的显示质量。

[0046] 以上所述仅为本发明的实施方式，并非因此限制本发明的专利范围，凡是利用本发明说明书及附图内容所作的等效结构或等效流程变换，或直接或间接运用在其他相关的技术领域，均同理包括在本发明的专利保护范围内。

图1

图2

图3

图4

图5

图6

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种液晶显示面板及其驱动方法                                 |         |            |

| 公开(公告)号        | <a href="#">CN110322856A</a>                   | 公开(公告)日 | 2019-10-11 |

| 申请号            | CN201910648934.9                               | 申请日     | 2019-07-18 |

| [标]申请(专利权)人(译) | 深圳市华星光电技术有限公司                                  |         |            |

| [标]发明人         | 王珊<br>温亦谦                                      |         |            |

| 发明人            | 王珊<br>温亦谦                                      |         |            |

| IPC分类号         | G09G3/36 G02F1/1362                            |         |            |

| CPC分类号         | G02F1/136286 G09G3/3674 G09G3/3685             |         |            |

| 代理人(译)         | 黄威                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

本发明公开了一种液晶显示面板及其驱动方法。该液晶显示面板包括：像素单元组，包括以矩阵方式排列的多个像素单元；扫描线，每条扫描线连接同一行至少两个像素单元；栅极驱动电路，与扫描线连接，用于在扫描线上提供栅极信号，以控制扫描线所连接的像素单元打开；数据线，分别连接不同列的至少一个像素单元；数据驱动电路，与数据线连接，用于给数据线提供数据信号，以对数据线所连接的且处于打开状态的像素单元进行充电；其中，数据驱动电路给多条数据线提供的数据信号沿着远离栅极驱动电路的方向依次延迟，使得液晶显示面板中多个像素单元打开的时间与充电的时间相匹配。通过上述方式，本发明能够提升液晶显示面板的均匀性，改善显示效果。