(12) 发明专利申请

(10) 申请公布号 CN 103680451 A

(43) 申请公布日 2014. 03. 26

(21) 申请号 201310700186. 7

(22) 申请日 2013. 12. 18

(71) 申请人 深圳市华星光电技术有限公司

地址 518132 广东省深圳市光明新区塘明大道 9—2 号

(72) 发明人 虞晓江 李长晔 赖梓杰

(74) 专利代理机构 深圳市德力知识产权代理事务所 44265

代理人 林才桂

(51) Int. Cl.

G09G 3/36 (2006. 01)

权利要求书2页 说明书5页 附图4页

(54) 发明名称

用于液晶显示的 GOA 电路及显示装置

(57) 摘要

本发明涉及用于液晶显示的 GOA 电路及显示装置。该 GOA 电路包括级联的多个 GOA 单元，第 n 级 GOA 单元包括上拉电路 (100)、下拉电路 (200)、下拉维持电路 (300)、上拉控制电路 (400) 及自举电容 (Cb)，工作时，分别输入第 n 级时钟信号 (CK(n))、第一和第二时钟信号 (LC1 和 LC2)，该第一时钟信号 (LC1) 和该第二时钟信号 (LC2) 的频率低于该第 n 级时钟信号 (CK(n))，并且该第一时钟信号 (LC1) 对第一电路点 (P) 的充电和第二时钟信号 (LC2) 对第二电路点 (K) 的充电交替进行。本发明还提供了相应的显示装置。本发明的 GOA 电路通过低频时钟信号和高频时钟信号来准确控制影响水平扫描线充电的栅极 Q(n) 的电压，保证 GOA 充电信号的稳定输出。

1. 一种用于液晶显示的 GOA 电路, 其特征在于, 包括级联的多个 GOA 单元, 按照第 n 级 GOA 单元控制对显示区域第 n 级水平扫描线 (G(n)) 充电, 该第 n 级 GOA 单元包括上拉电路 (100)、下拉电路 (200)、下拉维持电路 (300)、上拉控制电路 (400) 及自举电容 (Cb), 该上拉电路 (100)、下拉电路 (200)、下拉维持电路 (300) 及自举电容 (Cb) 分别与栅极信号点 (Q(n)) 和该第 n 级水平扫描线 (G(n)) 连接, 该上拉控制电路 (400) 与该栅极信号点 (Q(n)) 连接;

该下拉维持电路 (300) 包括:

第一薄膜晶体管 (T32), 其栅极连接第一电路点 (P), 漏极和源极分别连接该第 n 级水平扫描线 (G(n)) 和输入直流低电压 (VSS);

第二薄膜晶体管 (T33), 其栅极连接第二电路点 (K), 漏极和源极分别连接该第 n 级水平扫描线 (G(n)) 和输入直流低电压 (VSS);

第三薄膜晶体管 (T52), 其栅极连接该栅极信号点 (Q(n)), 漏极和源极分别连接该第一电路点 (P) 和输入该直流低电压 (VSS);

第四薄膜晶体管 (T62), 其栅极连接该栅极信号点 (Q(n)), 漏极和源极分别连接该第二电路点 (K) 和输入该直流低电压 (VSS);

第五薄膜晶体管 (T43), 其漏极和源极分别连接该栅极信号点 (Q(n)) 和该第 n 级水平扫描线 (G(n));

第六薄膜晶体管 (T42), 其漏极和源极分别输入第 n 级时钟信号 (CK(n)) 和连接该第五薄膜晶体管 (T43) 的栅极;

第七薄膜晶体管 (T72), 其栅极输入第一时钟信号 (LC1), 漏极和源极分别连接该第六薄膜晶体管 (T42) 的栅极和该第一电路点 (P);

第八薄膜晶体管 (T73), 其栅极输入第二时钟信号 (LC2), 漏极和源极分别连接该第六薄膜晶体管 (T42) 的栅极和该第二电路点 (K);

第九薄膜晶体管 (T12), 其栅极输入该第一时钟信号 (LC1), 漏极和源极分别输入该第一时钟信号 (LC1) 和连接该第六薄膜晶体管 (T42) 的栅极;

第十薄膜晶体管 (T13), 其栅极输入该第二时钟信号 (LC2), 漏极和源极分别输入该第二时钟信号 (LC2) 和连接该第六薄膜晶体管 (T42) 的栅极;

工作时, 该第一时钟信号 (LC1) 和该第二时钟信号 (LC2) 的频率低于该第 n 级时钟信号 (CK(n)), 并且该第一时钟信号 (LC1) 对该第一电路点 (P) 的充电和该第二时钟信号 (LC2) 对该第二电路点 (K) 的充电交替进行。

2. 如权利要求 1 所述的用于液晶显示的 GOA 电路, 其特征在于, 该上拉电路 (100) 包括: 第十一薄膜晶体管 (T21), 其栅极连接该栅极信号点 (Q(n)), 漏极和源极分别输入该第 n 级时钟信号 (CK(n)) 和连接该第 n 级水平扫描线 (G(n))。

3. 如权利要求 1 所述的用于液晶显示的 GOA 电路, 其特征在于, 该下拉电路 (200) 包括: 第十二薄膜晶体管 (T31), 其栅极连接第 n+2 级水平扫描线 (G(n+2)), 漏极和源极分别连接该第 n 级水平扫描线 (G(n)) 和输入该直流低电压 (VSS); 第十三薄膜晶体管 (T41), 其栅极连接该第 n+2 级水平扫描线 (G(n+2)), 漏极和源极分别连接该栅极信号点 (Q(n)) 和输入该直流低电压 (VSS)。

4. 如权利要求 1 所述的用于液晶显示的 GOA 电路, 其特征在于, 该上拉控制电路 (400)

包括：第十四薄膜晶体管(T11)，其栅极连接第n-2级水平扫描线(G(n-2))，漏极和源极分别连接该第n-2级水平扫描线(G(n-2))和该栅极信号点(Q(n))。

5. 如权利要求1所述的用于液晶显示的GOA电路，其特征在于，该第n级时钟信号的占空比为40%。

6. 如权利要求1所述的用于液晶显示的GOA电路，其特征在于，该第一时钟信号(LC1)通过公共的金属线输入所述级联的多个GOA单元。

7. 如权利要求1所述的用于液晶显示的GOA电路，其特征在于，该第二时钟信号(LC2)通过公共的金属线输入所述级联的多个GOA单元。

8. 如权利要求1所述的用于液晶显示的GOA电路，其特征在于，该直流低电压(VSS)通过公共的金属线输入所述级联的多个GOA单元。

9. 一种显示装置，其特征在于，包括如权利要求1所述的用于液晶显示的GOA电路。

## 用于液晶显示的 GOA 电路及显示装置

### 技术领域

[0001] 本发明涉及液晶显示技术领域,尤其涉及一种用于液晶显示的 GOA (Gate Driver on Array, 阵列基板行驱动) 电路及显示装置。

### 背景技术

[0002] 液晶显示器具有机身薄、省电、无辐射等众多优点,得到了广泛的应用。现有市场上的液晶显示器大部分为背光型液晶显示器,其包括液晶面板及背光模组(backlight module)。液晶面板的工作原理是在两片平行的玻璃基板当中放置液晶分子,并在两片玻璃基板上施加驱动电压来控制液晶分子的旋转方向,以将背光模组的光线折射出来产生画面。

[0003] 主动式液晶显示器中,每个像素具有一个薄膜晶体管(TFT),其栅极(Gate)连接至水平扫描线,漏极(Drain)连接至垂直方向的数据线,源极(Source)则连接至像素电极。在水平扫描线上施加足够的电压,会使得该条线上的所有 TFT 打开,此时该水平扫描线上的像素电极会与垂直方向的数据线连接,从而将数据线上的显示信号电压写入像素,控制不同液晶的透光度进而达到控制色彩的效果。目前主动式液晶显示面板水平扫描线的驱动主要由面板外接的 IC 来完成,外接的 IC 可以控制各级水平扫描线的逐级充电和放电。而 GOA 技术,即 Gate Driver on Array (阵列基板行驱动) 技术,可以运用液晶显示面板的原有制程将水平扫描线的驱动电路制作在显示区周围的基板上,使之能替代外接 IC 来完成水平扫描线的驱动。GOA 技术能减少外接 IC 的绑定(bonding) 工序,有机会提升产能并降低产品成本,而且可以使液晶显示面板更适合制作窄边框或无边框的显示产品。

[0004] 现有的 GOA 电路,通常包括级联的多个 GOA 单元,每一级 GOA 单元对应驱动一级水平扫描线。GOA 单元的主要结构包括上拉电路(Pull-up part),上拉控制电路(Pull-up control part),下传电路(Transfer Part),下拉电路(Key Pull-down Part)和下拉维持电路(Pull-down Holding Part),以及负责电位抬升的自举(Boast)电容。上拉电路主要负责将时钟信号(Clock)输出为栅极(Gate)信号;上拉控制电路负责控制上拉电路的打开时间,一般连接前面级 GOA 电路传递过来的下传信号或者 Gate 信号;下拉电路负责在第一时间将 Gate 拉低为低电位,即关闭 Gate 信号;下拉维持电路则负责将 Gate 输出信号和上拉电路的 Gate 信号(通常称为 Q 点)维持(Holding)在关闭状态(即负电位),通常有两个下拉维持模块交替作用;自举电容(C boast)则负责 Q 点的二次抬升,这样有利于上拉电路的 G(N) 输出。

[0005] GOA 电路的目的就是将集成电路输出的扫描波形通过电路操作的方式输出,使像素开关打开从而可以向氧化铟锡(ITO)电极输入数据信号。数据信号输入完后将数据信号内容保持住直到下一帧的开启。在电路操作过程中,因一条扫描电路打开过后在一帧剩余的时间里都是关闭的,扫描电路关闭(保持)时间比扫描时间长很多,对 GOA 电路中的薄膜晶体管稳定特定要求很高。为保证 GOA 电路充电信号的稳定输出,亟需 GOA 电路中影响水平扫描线充电的薄膜晶体管的栅极 Q(n) 的电压能够得到准确控制的解决方案。

## 发明内容

[0006] 因此,本发明的目的在于提供一种用于液晶显示的 GOA 电路,实现通过低频时钟信号和高频时钟信号来准确控制影响水平扫描线充电的薄膜晶体管的栅极 Q(n) 电压,从而保证 GOA 充电信号的稳定输出。

[0007] 本发明的另一目的在于提供一种应用上述 GOA 电路的液晶显示装置,实现通过低频时钟信号和高频时钟信号来准确控制影响水平扫描线充电的薄膜晶体管的栅极 Q(n) 电压,从而保证 GOA 充电信号的稳定输出。

[0008] 为实现上述目的,本发明提供了一种用于液晶显示的 GOA 电路,包括级联的多个 GOA 单元,按照第 n 级 GOA 单元控制对显示区域第 n 级水平扫描线充电,该第 n 级 GOA 单元包括上拉电路、下拉电路、下拉维持电路、上拉控制电路及自举电容,该上拉电路、下拉电路、下拉维持电路及自举电容分别与栅极信号点和该第 n 级水平扫描线连接,该上拉控制电路与该栅极信号点连接;

[0009] 该下拉维持电路包括:

[0010] 第一薄膜晶体管,其栅极连接第一电路点,漏极和源极分别连接该第 n 级水平扫描线和输入直流低电压;

[0011] 第二薄膜晶体管,其栅极连接第二电路点,漏极和源极分别连接该第 n 级水平扫描线和输入该直流低电压;

[0012] 第三薄膜晶体管,其栅极连接该栅极信号点,漏极和源极分别连接该第一电路点和输入该直流低电压;

[0013] 第四薄膜晶体管,其栅极连接该栅极信号点,漏极和源极分别连接该第二电路点和输入该直流低电压;

[0014] 第五薄膜晶体管,其漏极和源极分别连接该栅极信号点和该第 n 级水平扫描线;

[0015] 第六薄膜晶体管,其漏极和源极分别输入第 n 级时钟信号和连接该第五薄膜晶体管的栅极;

[0016] 第七薄膜晶体管,其栅极输入第一时钟信号,漏极和源极分别连接该第六薄膜晶体管的栅极和该第一电路点;

[0017] 第八薄膜晶体管,其栅极输入第二时钟信号,漏极和源极分别连接该第六薄膜晶体管的栅极和该第二电路点;

[0018] 第九薄膜晶体管,其栅极输入该第一时钟信号,漏极和源极分别输入该第一时钟信号和连接该第六薄膜晶体管的栅极;

[0019] 第十薄膜晶体管,其栅极输入该第二时钟信号,漏极和源极分别输入该第二时钟信号和连接该第六薄膜晶体管的栅极;

[0020] 工作时,该第一时钟信号和该第二时钟信号的频率低于该第 n 级时钟信号,并且该第一时钟信号对该第一电路点的充电和该第二时钟信号对该第二电路点的充电交替进行。

[0021] 其中,该上拉电路包括:第十一薄膜晶体管,其栅极连接该栅极信号点,漏极和源极分别输入该第 n 级时钟信号和连接该第 n 级水平扫描线。

[0022] 其中,该下拉电路包括:第十二薄膜晶体管,其栅极连接第 n+2 级水平扫描线,漏

极和源极分别连接该第 n 级水平扫描线和输入该直流低电压 ; 第十三薄膜晶体管, 其栅极连接该第 n+2 级水平扫描线, 漏极和源极分别连接该栅极信号点和输入该直流低电压。

[0023] 其中, 该上拉控制电路包括 : 第十四薄膜晶体管, 其栅极连接第 n-2 级水平扫描线, 漏极和源极分别连接该第 n-2 级水平扫描线和该栅极信号点。

[0024] 其中, 该第 n 级时钟信号的占空比为 40%。

[0025] 其中, 该第一时钟信号通过公共的金属线输入所述级联的多个 GOA 单元。

[0026] 其中, 该第二时钟信号通过公共的金属线输入所述级联的多个 GOA 单元。

[0027] 其中, 该直流低电压通过公共的金属线输入所述级联的多个 GOA 单元。

[0028] 本发明还提供了一种显示装置, 包括如上面所述的用于液晶显示的 GOA 电路。

[0029] 本发明的用于液晶显示的 GOA 电路及显示装置可以通过低频时钟信号和高频时钟信号来准确控制影响水平扫描线充电的薄膜晶体管栅极 Q(n) 在充电时期及非充电时期的电压, 保证 GOA 充电信号的稳定输出 ; 运用本发明的 GOA 电路可以制作低成本的窄边框或无边框的液晶显示装置。

## 附图说明

[0030] 下面结合附图, 通过对本发明的具体实施方式详细描述, 将使本发明的技术方案及其他有益效果显而易见。

[0031] 附图中,

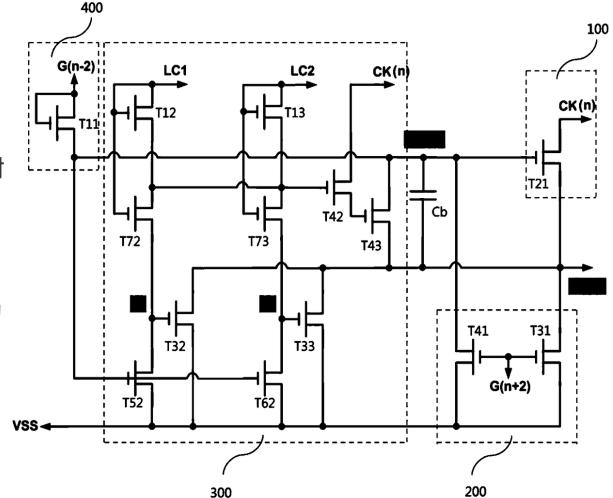

[0032] 图 1 为本发明用于液晶显示的 GOA 电路(单级)一实施例的电路图 ;

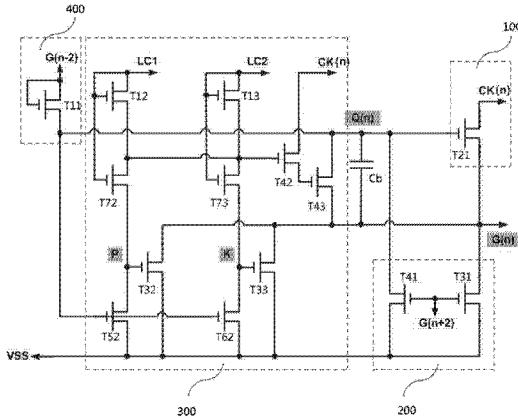

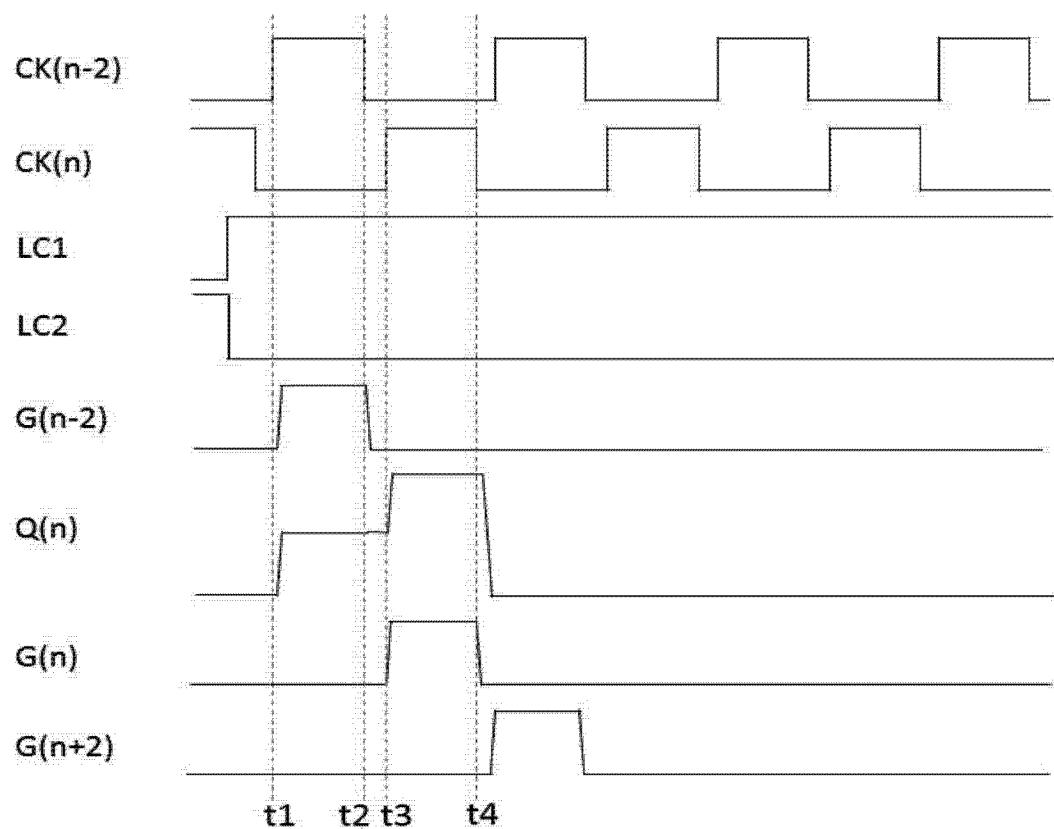

[0033] 图 2 为本发明用于液晶显示的 GOA 电路在常温时的输出波形示意图 ;

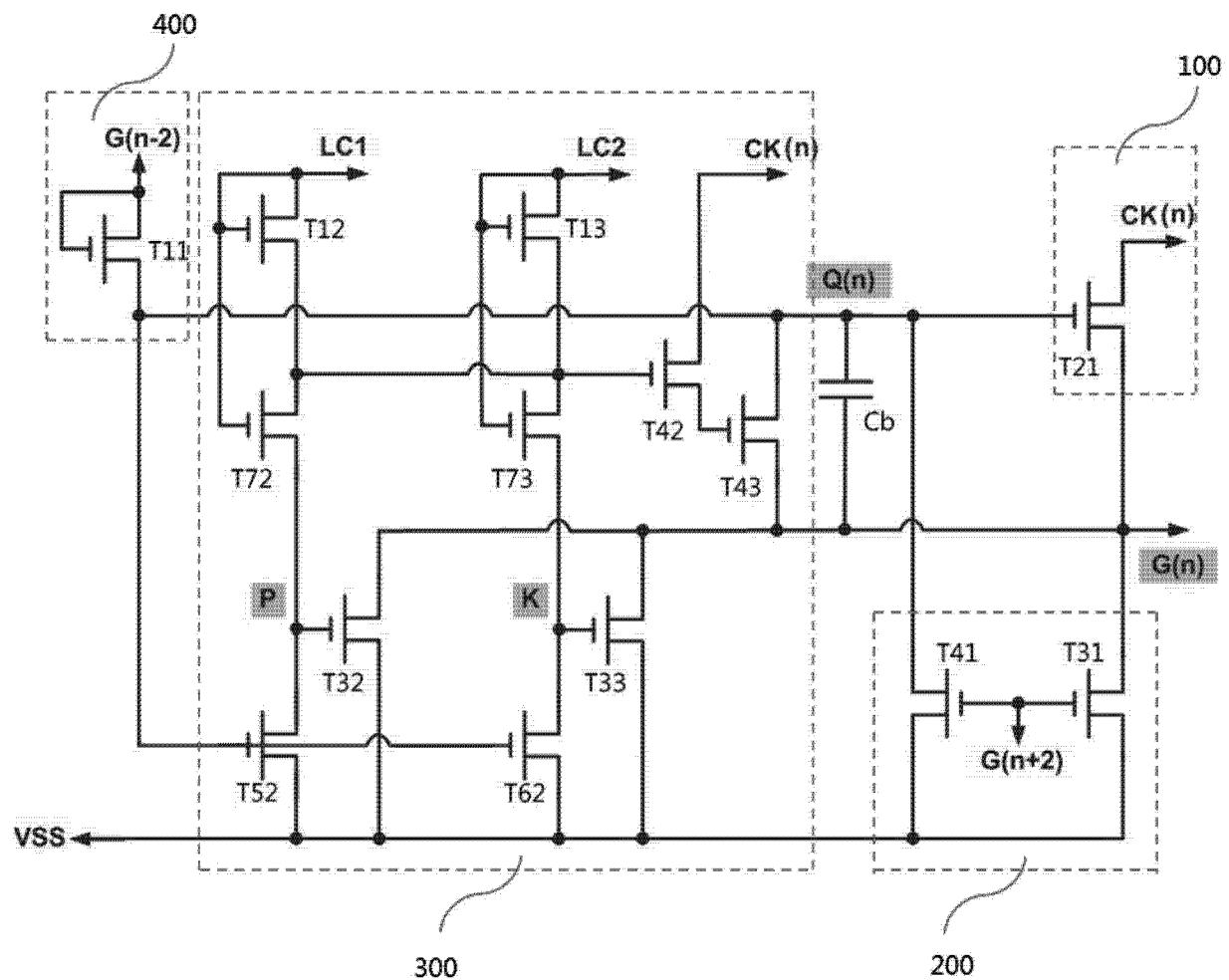

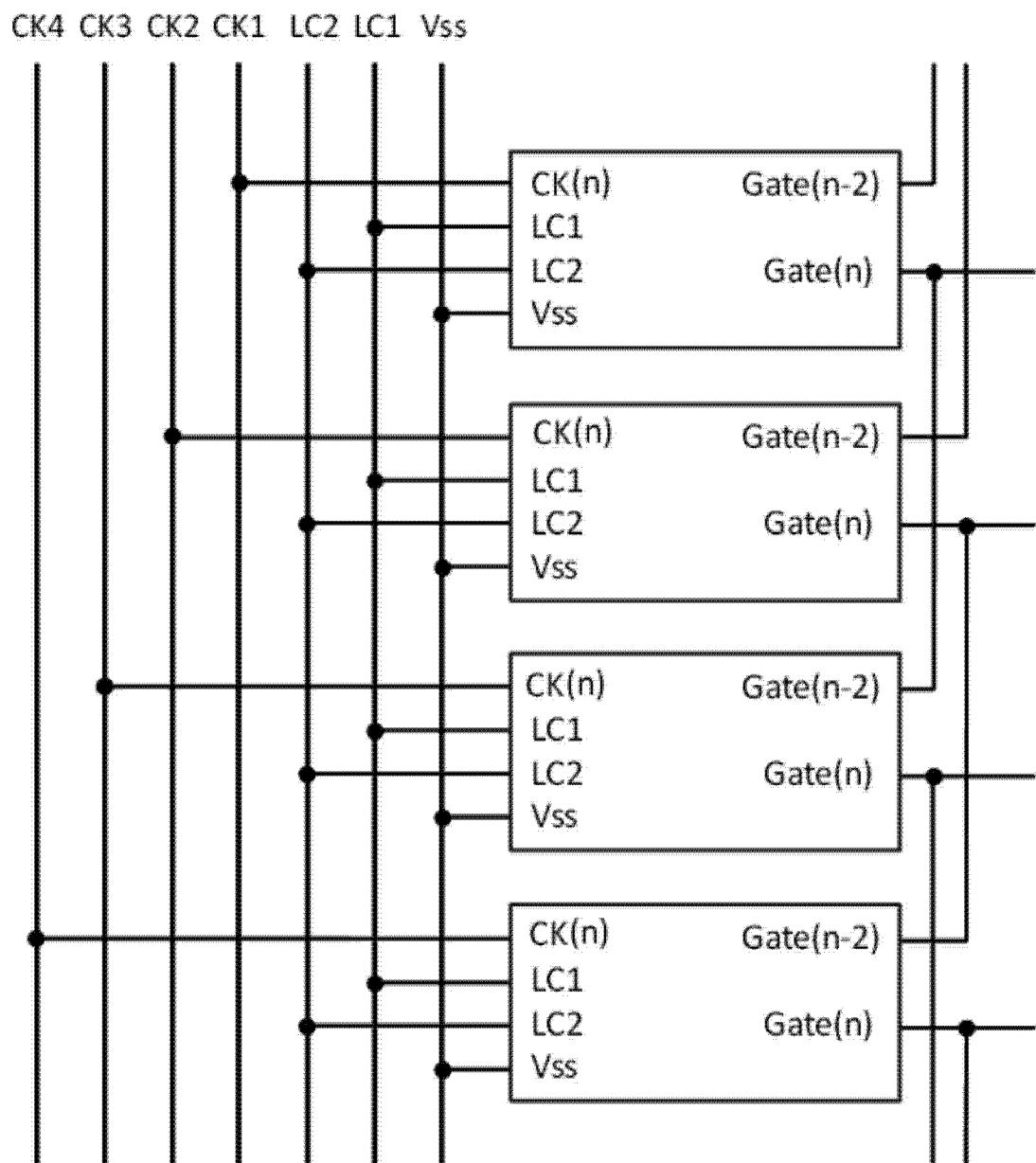

[0034] 图 3 为本发明用于液晶显示的 GOA 电路的多级架构示意图 ;

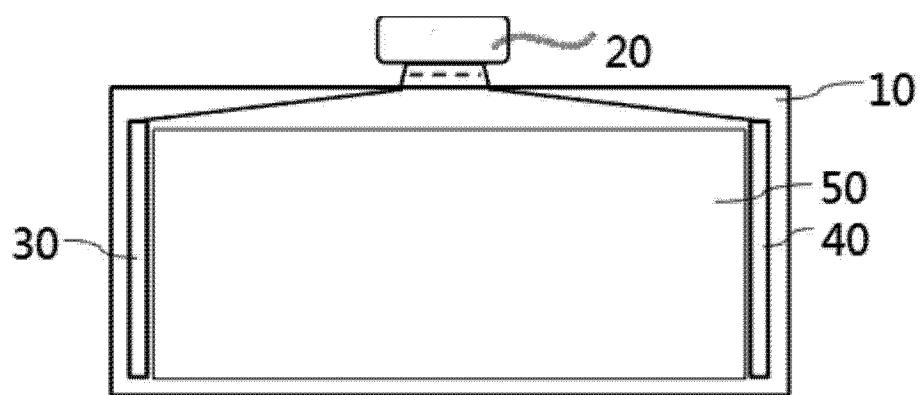

[0035] 图 4 为应用了本发明用于液晶显示的 GOA 电路的液晶显示装置的结构示意图。

## 具体实施方式

[0036] 参见图 1, 其为本发明用于液晶显示的 GOA 电路(单级)一实施例的电路图。本发明的 GOA 电路可以包括级联的多个 GOA 单元, 按照第 n 级 GOA 单元控制对显示区域第 n 级水平扫描线 G(n) 充电, 第 n 级 GOA 单元包括上拉电路 100、下拉电路 200、下拉维持电路 300、上拉控制电路 400 及自举电容 Cb, 该上拉电路 100、下拉电路 200、下拉维持电路 300 及自举电容 Cb 分别与栅极信号点 Q(n) 和第 n 级水平扫描线 G(n) 连接, 该上拉控制电路 400 与该栅极信号点 Q(n) 连接。

[0037] 上拉电路 100 包括直接控制给显示区域第 n 级水平扫描线 G(n) 进行充电的薄膜晶体管 T21, 其栅极连接该栅极信号点 Q(n), T21 的漏极和源极分别输入第 n 级高频时钟信号 CK(n) 和连接第 n 级水平扫描线 G(n), T21 栅极 Q(n) 的电位可直接影响 CK(n) 对 G(n) 充电。

[0038] 下拉电路 200 包含在 G(n) 充电结束时进行放电的一组薄膜晶体管, 包括对 G(n) 进行放电的 T31 和对 Q(n) 进行放电的 T41 ; T31 栅极连接第 n+2 级水平扫描线 G(n+2), 漏极和源极分别连接该第 n 级水平扫描线 G(n) 和输入该直流低电压 VSS ; T41 栅极连接该第 n+2 级水平扫描线 G(n+2), 漏极和源极分别连接栅极信号点 Q(n) 和输入直流低电压 VSS。

[0039] 上拉控制电路 400 包括薄膜晶体管 T11, 其栅极连接第 n-2 级水平扫描线 G(n-2),

漏极和源极分别连接第 n-2 级水平扫描线 G (n-2) 和栅极信号点 Q (n)。薄膜晶体管 T11 可以控制将第 n-2 级 GOA 信号传递给第 n 级 GOA 电路,使 GOA 电路可以逐级充放电。

[0040] Q(n) 和 G(n) 之间所连接的有自举功能的电容 Cb,可在 G(n) 电位提升时通过 Cb 的耦合效应使 Q(n) 电位提升,从而获得更高的 Q(n) 电位及更小的 GOA 充电信号的阻容延迟 (RC delay)。

[0041] 下拉维持电路(300)包括的一组薄膜晶体管可以在 GOA 电路非充电时期保持 G(n) 和 Q(n) 的低电位。薄膜晶体管 T32 栅极连接第一电路点 P,漏极和源极分别连接第 n 级水平扫描线 G (n) 和输入直流低电压 VSS ;薄膜晶体管 T33 栅极连接第二电路点 K,漏极和源极分别连接第 n 级水平扫描线 G(n) 和输入该直流低电压 VSS ;薄膜晶体管 T52 栅极连接该栅极信号点 Q (n),漏极和源极分别连接该第一电路点 P 和输入直流低电压 VSS ;薄膜晶体管 T62 栅极连接栅极信号点 Q (n),漏极和源极分别连接第二电路点 K 和直流低电压 VSS ;薄膜晶体管 T43 漏极和源极分别连接该栅极信号点 Q (n) 和第 n 级水平扫描线 G (n);薄膜晶体管 T42 漏极和源极分别输入第 n 级时钟信号 CK (n) 和薄膜晶体管 T43 的栅极 ;薄膜晶体管 T72 栅极输入第一时钟信号 LC1,漏极和源极分别连接薄膜晶体管 T42 的栅极和第一电路点 P ;薄膜晶体管 T73 栅极输入第二时钟信号 LC2,漏极和源极分别连接薄膜晶体管 T42 的栅极和第二电路点 K ;薄膜晶体管 T12 栅极输入第一时钟信号 LC1,漏极和源极分别输入第一时钟信号 LC1 和连接薄膜晶体管 T42 的栅极 ;薄膜晶体管 T13 栅极输入第二时钟信号 LC2,漏极和源极分别输入第二时钟信号 LC2 和连接薄膜晶体管 T42 的栅极 ;直流低电压 VSS 可以为接低电平或接地。工作时,输入第 n 级时钟信号 CK(n)、第一时钟信号 LC1 和第二时钟信号 LC2,第一时钟信号 LC1 和第二时钟信号 LC2 的频率低于第 n 级时钟信号 CK (n),并且第一时钟信号 LC1 对第一电路点 P 的充电和该第二时钟信号 LC2 对该第二电路点 K 的充电交替进行。

[0042] 电路的 P 点和 K 点交替受低频时钟信号 LC1 和 LC2 的充电而处于高电位,从而交替控制薄膜晶体管 T32 或 T33 的打开,以维持 G(n) 在非充电时期的低电位,并避免薄膜晶体管 T32 或 T33 长时间受栅极电压应力的影响。薄膜晶体管 T52 连接 P 点和输入直流低电压 VSS,薄膜晶体管 T62 连接 K 点和输入直流低电压 VSS, T52 和 T62 可在 Q(n) 处于高电位时打开而将 P 点、K 点电位拉低以关闭 T32 和 T33 使之不影响充电。在非充电时期,薄膜晶体管 T12&T72 或 T13&T73 会打开,P 点或 K 点会处于高电位,因此薄膜晶体管 T42 的栅极处于高电位,高频时钟信号 CK(n) 可周期性打开薄膜晶体管 T43 以维持 Q(n) 处于低电位。在充电时期, Q(n) 充至高电位后, T52 或 T62 打开, T42 的栅极电位被拉低而导致 T42 关闭, T43 也无法打开,因此 Q(n) 通过 T43 的漏电也得以减小, Q(n) 电压的稳定性得以提升。

[0043] 本发明的 GOA 电路可以通过低频时钟信号和高频时钟信号来准确控制影响水平扫描线充电的薄膜晶体管的栅极 Q(n) 在非充电时期及充电时期的电压,因此能保证 GOA 充电信号的稳定输出。具体来讲:1、在非充电时期,连接高频时钟信号 CK(n) 和薄膜晶体管 T43 的薄膜晶体管 T42 导通,高频时钟信号 CK(n) 可以周期性的打开薄膜晶体管 T43 以维持 Q(n) 处于低电位;2、在充电时期, Q(n) 被充至高电位后,薄膜晶体管 T42 和 T43 被关闭, Q(n) 通过 T43 的漏电得以降低。

[0044] 参见图 2,其为本发明用于液晶显示的 GOA 电路在常温时的输出波形示意图,其中高频时钟信号的占空比(duty ratio)为 40%。图 2 中, t1 ~ t3 为 G(n) 充电前的准备时间,

$t_3 \sim t_4$  为  $G(n)$  的充电时间,  $t_4$  后  $G(n)$  被放电。低频时钟信号  $LC1$  和  $LC2$  可以选择为频率相同, 相位相反。可结合图 1 来理解图 2,  $t_1$  时,  $CK(n-2)$  的电位开始抬升,  $G(n-2)$  的电位也跟着开始抬升, 薄膜晶体管  $T11$  打开给  $Q(n)$  充电。 $Q(n)$  电位抬升后, 可打开薄膜晶体管  $T52$  和  $T62$ , 从而关闭  $T32$ 、 $T42$ 、 $T33$  和  $T43$  使之不影响  $Q(n)$  和  $G(n)$  充电。 $t_2$  时,  $CK(n-2)$  的电位开始下降, 但薄膜晶体管  $T11$  的连接方式会阻止  $Q(n)$  的漏电,  $Q(n)$  电位基本保持不变。 $t_3$  时,  $CK(n)$  的电位开始抬升, 薄膜晶体管  $T21$  打开,  $Q(n)$  自举到更高电位并控制  $T21$  给  $G(n)$  充电。 $t_4$  时,  $CK(n)$  开始下降,  $Q(n)$  电位并未立即被拉低, 薄膜晶体管  $T21$  在  $t_4$  后的短时间内仍保持导通, 将  $G(n)$  电位拉低。这之后,  $G(n+2)$  电位抬升, 薄膜晶体管  $T31$  和  $T41$  打开, 确保  $G(n)$  和  $Q(n)$  被拉至低电位。 $T52$  和  $T62$  在  $Q(n)$  电位拉低后关闭,  $T32$ 、 $T33$ 、 $T42$ 、 $T43$  可正常打开, 以维持  $G(n)$  和  $Q(n)$  在非充电时期的低电位。综上所述, 本发明可以通过低频时钟信号和高频时钟信号来准确控制  $Q(n)$  电压, 能保证 GOA 充电信号的稳定输出。

[0045] 参见图 3, 其为本发明用于液晶显示的 GOA 电路的多级架构示意图。图 3 给出了本发明的 GOA 电路的一种多级架构, 用于传递低频时钟信号  $LC1$  和  $LC2$ 、直流低电压  $VSS$ 、以及  $CK1 \sim CK4$  的 4 个高频时钟信号的金属线放置于各级 GOA 电路(具体连接方法参见图 1)的外围。低频时钟信号  $LC1$ 、低频时钟信号  $LC2$  和直流低电压  $VSS$  分别可以通过各自的公共的金属线输入级联的多个 GOA 单元中。在此实施例中, 第  $n$  级 GOA 电路分别接受  $LC1$ 、 $LC2$ 、 $VSS$ 、 $CK1 \sim CK4$  中的 1 个  $CK$  信号、第  $n-2$  级 GOA 电路产生的  $G(n-2)$ 、第  $n+2$  级 GOA 电路产生的  $G(n+2)$ , 并产生  $G(n)$  信号。图 3 所示的各级 GOA 电路间的连接方法可保证 GOA 信号可以逐级传递, 使得各级水平扫描线可以被逐级充电和放电。对于首、末端级联的 GOA 单元可以采用输入激活信号的方式来代替缺少的  $G(n)$  信号输入。

[0046] 本发明的 GOA 电路可以运用液晶显示面板的原有制程将面板水平扫描线的驱动电路制作在显示区周围的基板上, 使之能替代外接 IC 来完成平板显示面板各级水平扫描线的驱动。本发明尤其适合制作窄边框或无边框的液晶显示产品。

[0047] 参见图 4, 其为应用了本发明用于液晶显示的 GOA 电路的液晶显示装置的结构示意图。图 4 中, 液晶显示装置具有显示基板 10, 显示基板 10 上方的驱动控制板 20 为显示基板 10 提供驱动和控制信号, 显示基板 10 左边区域 30 和右边区域 40 制作了 GOA 电路, 可从左边和右边两个方向驱动显示区域 50 的水平扫描线。GOA 电路接受驱动控制板 20 的输入信号并逐级产生水平扫描线的控制信号, 可以控制显示区域 50 中的像素逐行打开。

[0048] 综上所述, 本发明的用于液晶显示的 GOA 电路及显示装置可以通过低频时钟信号和高频时钟信号来准确控制影响水平扫描线充电的薄膜晶体管栅极  $Q(n)$  在充电时期及非充电时期的电压, 保证 GOA 充电信号的稳定输出; 运用本发明的 GOA 电路可以制作低成本的窄边框或无边框的液晶显示装置。

[0049] 以上所述, 对于本领域的普通技术人员来说, 可以根据本发明的技术方案和技术构思作出其他各种相应的改变和变形, 而所有这些改变和变形都应属于本发明后附的权利要求的保护范围。

图 1

图 2

图 3

图 4

|                |                                                                                                                                                                                   |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于液晶显示的GOA电路及显示装置                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">CN103680451A</a>                                                                                                                                                      | 公开(公告)日 | 2014-03-26 |

| 申请号            | CN201310700186.7                                                                                                                                                                  | 申请日     | 2013-12-18 |

| [标]申请(专利权)人(译) | 深圳市华星光电技术有限公司                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | 深圳市华星光电技术有限公司                                                                                                                                                                     |         |            |

| 当前申请(专利权)人(译)  | 深圳市华星光电技术有限公司                                                                                                                                                                     |         |            |

| [标]发明人         | 虞晓江<br>李长晔<br>赖梓杰                                                                                                                                                                 |         |            |

| 发明人            | 虞晓江<br>李长晔<br>赖梓杰                                                                                                                                                                 |         |            |

| IPC分类号         | G09G3/36                                                                                                                                                                          |         |            |

| CPC分类号         | G09G3/3674 G09G3/3677 G09G2310/0286 G11C19/28 G09G3/3607 G09G3/3648 G09G3/3688<br>G09G2300/0809 G09G2310/0248 G09G2310/027 G09G2320/0242 G09G2320/0252 G02F1/13306<br>G02F1/13454 |         |            |

| 其他公开文献         | CN103680451B                                                                                                                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                                                                                                    |         |            |

### 摘要(译)

本发明涉及用于液晶显示的GOA电路及显示装置。该GOA电路包括级联的多个GOA单元，第n级GOA单元包括上拉电路(100)、下拉电路(200)、下拉维持电路(300)、上拉控制电路(400)及自举电容(Cb)，工作时，分别输入第n级时钟信号(CK(n))、第一和第二时钟信号(LC1和LC2)，该第一时钟信号(LC1)和该第二时钟信号(LC2)的频率低于该第n级时钟信号(CK(n))，并且该第一时钟信号(LC1)对第一电路点(P)的充电和第二时钟信号(LC2)对第二电路点(K)的充电交替进行。本发明还提供了相应的显示装置。本发明的GOA电路通过低频时钟信号和高频时钟信号来准确控制影响水平扫描线充电的栅极Q(n)的电压，保证GOA充电信号的稳定输出。