(19) 中华人民共和国国家知识产权局

## (12) 发明专利申请

(10) 申请公布号 CN 103995406 A

(43) 申请公布日 2014.08.20

(21) 申请号 201310053564.7

(22) 申请日 2013.02.19

(71) 申请人 群创光电股份有限公司

地址 中国台湾新竹科学工业园区苗栗县竹南镇科学路 160 号

(72)发明人 陈建宏

(74) 专利代理机构 上海专利商标事务所有限公司 31100

代理人 陆嘉

(51) Int. Cl.

G02F 1/1362 (2006-01)

G02E 1/1368 (2006.01)

H011 29/786 (2006-01)

权利要求书1页 说明书5页 附图6页

(54) 发明名称

## 液晶面板

## (57) 摘要

一种液晶面板，包括液晶层、第一数据线、扫描线、像素电极及第一薄膜晶体管。液晶层包括高介电系数液晶材料，而像素电极驱动液晶层。第一薄膜晶体管包括第一电极及第二电极。第一电极耦接至像素电极，且具有至少两个第一分支电极。第二电极耦接至第一资料线，且具有至少一个第二分支电极。第一电极与扫描线的第一重迭面积大于第二电极与扫描线的第二重迭面积，且至少一个该第二分支电极会位在两个该第一分支电极之间。

1. 一种液晶面板,包括:

—液晶层,包括一高介电系数液晶材料;

—第一资料线;

—扫描线;

—像素电极,用以驱动该液晶层;以及

—第一薄膜晶体管,包括:

—第一电极,耦接至该像素电极,且具有至少两个第一分支电极;及

—第二电极,耦接至该第一资料线,且具有至少一个第二分支电极,该第一电极与该扫描线的第一重迭面积大于该第二电极与该扫描线的第二重迭面积,且至少一个该第二分支电极会位在两个该第一分支电极之间。

2. 如权利要求1所述的液晶面板,其特征在于,该第一电极与该扫描线形成一第一电容,且该第二电极与该扫描线形成一第二电容,该第一电容大于该第二电容。

3. 如权利要求1所述的液晶面板,其特征在于,该第一重迭面积与该第二重迭面积的比值大于1,且该第一重迭面积与该第二重迭面积的比值小于或等于4。

4. 如权利要求1所述的液晶面板,其特征在于,该高介电系数液晶材料的平均介电系数介于20至500之间。

5. 如权利要求1所述的液晶面板,其特征在于,该第一薄膜晶体管为非对称J型薄膜晶体管。

6. 如权利要求1所述的液晶面板,其特征在于,更包括一第二数据线及一第二薄膜晶体管,该第二薄膜晶体管包括:

—第三电极,耦接至该像素电极,且具有至少两个第三分支电极;及

—第四电极,耦接至该第二资料线,且具有至少一个第四分支电极,该第三电极与该扫描线的第三重迭面积大于该第四电极与该扫描线的第四重迭面积,且至少一个该第四分支电极会位在两个该第三分支电极之间。

7. 如权利要求6所述的液晶面板,其特征在于,该第三电极与该扫描线形成一第三电容,且该第四电极与该扫描线形成一第四电容,该第三电容大于该第四电容。

8. 如权利要求6所述的液晶面板,其特征在于,该第三重迭面积与该第四重迭面积的比值大于1,且该第三重迭面积与该第四重迭面积的比值小于或等于4。

9. 如权利要求6所述的液晶面板,其特征在于,该高介电系数液晶材料的平均介电系数介于20至500之间。

10. 如权利要求6所述的液晶面板,且特征在于,该第二薄膜晶体管为非对称J型薄膜晶体管。

## 液晶面板

### 技术领域

[0001] 本揭露是有关于一种显示面板,且特别是有关于一种液晶面板。

### 背景技术

[0002] 近年来,液晶显示器已经广泛应用于电子产品的显示屏幕。液晶显示器有许多不同的形式,包括扭转向列 (Twister Nematic, TN), 超扭曲向列 (Super Twisted Nematic, STN), 平面切换 (In-Plane Switching, IPS), 多区域垂直排列 (Multi-domain Vertical Alignment, MVA) 等。当施加电压时可以控制液晶分子的旋转方向,并调变光的偏振方向,进而影响光通过量而造成亮态及暗态的反差作为显示结果。

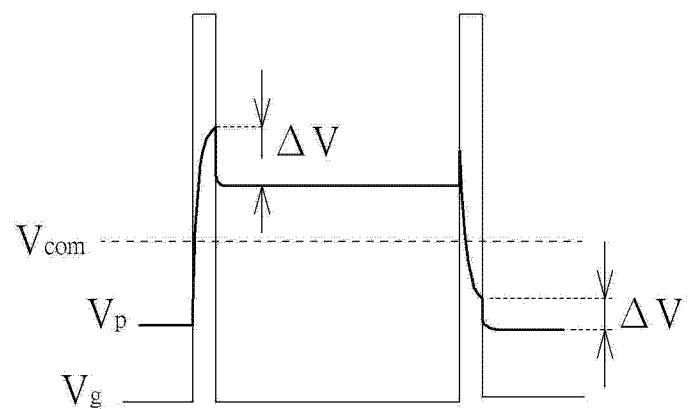

[0003] 请参照图 1,图 1 绘示为传统液晶显示器的扫描信号与像素电压的信号时序图。薄膜晶体管的漏极耦接至资料线,且薄膜晶体管的源极耦接至像素电极。薄膜晶体管关闭的瞬间,薄膜晶体管的栅极上的扫描信号  $V_g$  会造成薄膜晶体管的源极上的像素电压  $V_p$  下降一回踢电压 (kick-back)  $\Delta V$ 。这是因为当扫描信号  $V_g$  急速下降时,像素电压  $V_p$  也会由于薄膜晶体管的源极与栅极之间的寄生电容  $C_{gs}$  (parasitic capacitance) 所引起的耦合现象

(coupling phenomenon) 而下降。回踢电压  $\Delta V$  与  $\frac{C_{gs}}{C_{gs} + C_{LC} + C_{st}}$  成正比。其  $C_{LC}$  表示液晶

电容,  $C_{gs}$  表示在薄膜晶体管的源极与栅极间的寄生电容。

[0004] 为了避免回踢电压  $\Delta V$  太大造成画面闪烁 (Flicker) 或影像残留 (Image Sticking), 传统液晶显示器会尽量使寄生电容  $C_{gs}$  越小越好。因此传统薄膜晶体管的设计上,耦接至像素电极的源极的面积会小于薄膜晶体管的耦接至资料线的漏极的面积。但随着面板尺寸越大,像素数目越多,对数据线的负荷大为增加,而可能造成信号失真的问题。

### 发明内容

[0005] 本揭露有关于一种液晶面板,并提供一新薄膜晶体管设计,以降低数据线负担及信号失真的问题。

[0006] 根据本揭露,提出一种液晶面板。液晶面板包括液晶层、第一数据线、扫描线、像素电极及第一薄膜晶体管。液晶层包括高介电系数液晶材料,而像素电极驱动液晶层。第一薄膜晶体管包括第一电极及第二电极。第一电极耦接至像素电极,且具有至少两个第一分支电极。第二电极耦接至第一资料线,且具有至少一个第二分支电极。第一电极与扫描线的第一重迭面积大于第二电极与扫描线的第二重迭面积,且至少一个该第二分支电极会位在两个该第一分支电极之间。

[0007] 为了对本揭露的上述及其它方面有更佳的了解,下文特举实施例,并配合所附附图,作详细说明如下:

### 附图说明

[0008] 图 1 绘示为传统液晶显示器的扫描信号与像素电压的信号时序图。

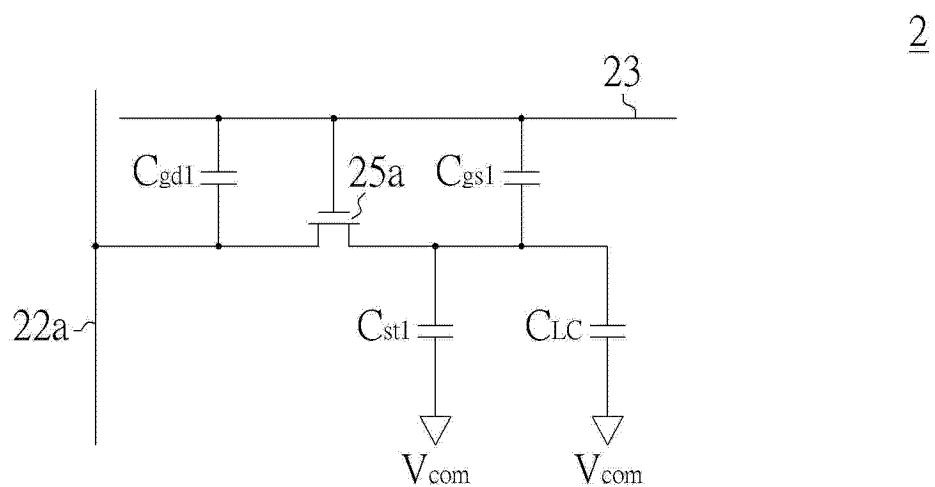

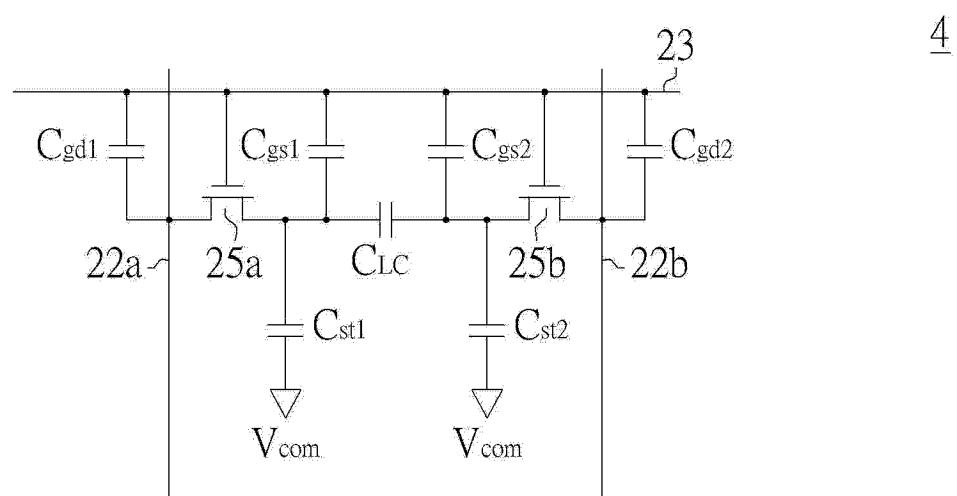

- [0009] 图 2 绘示为依照第一实施例的一种液晶面板的电路图。

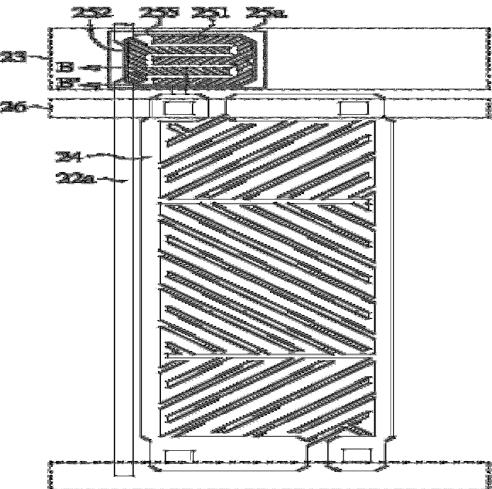

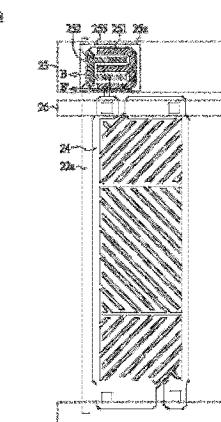

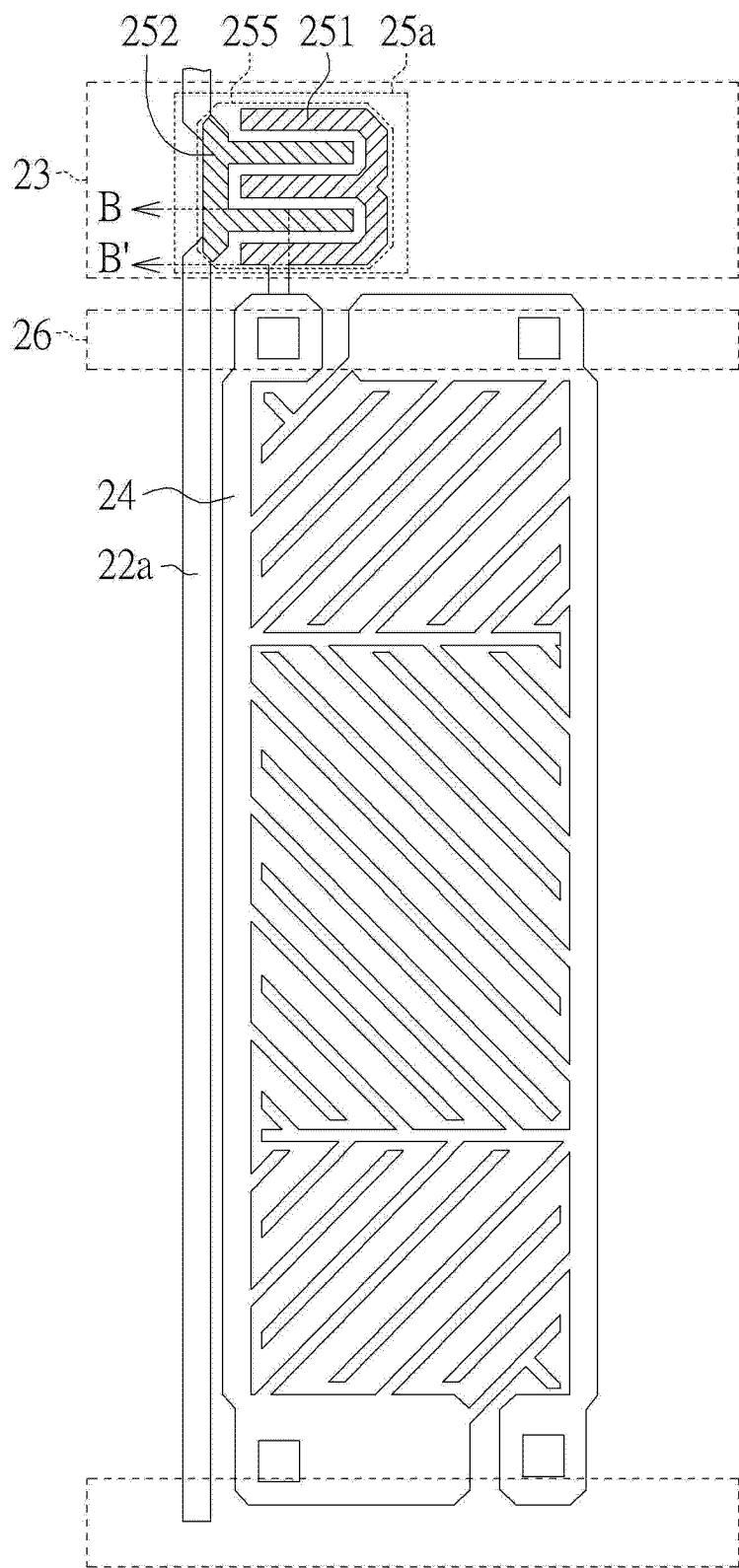

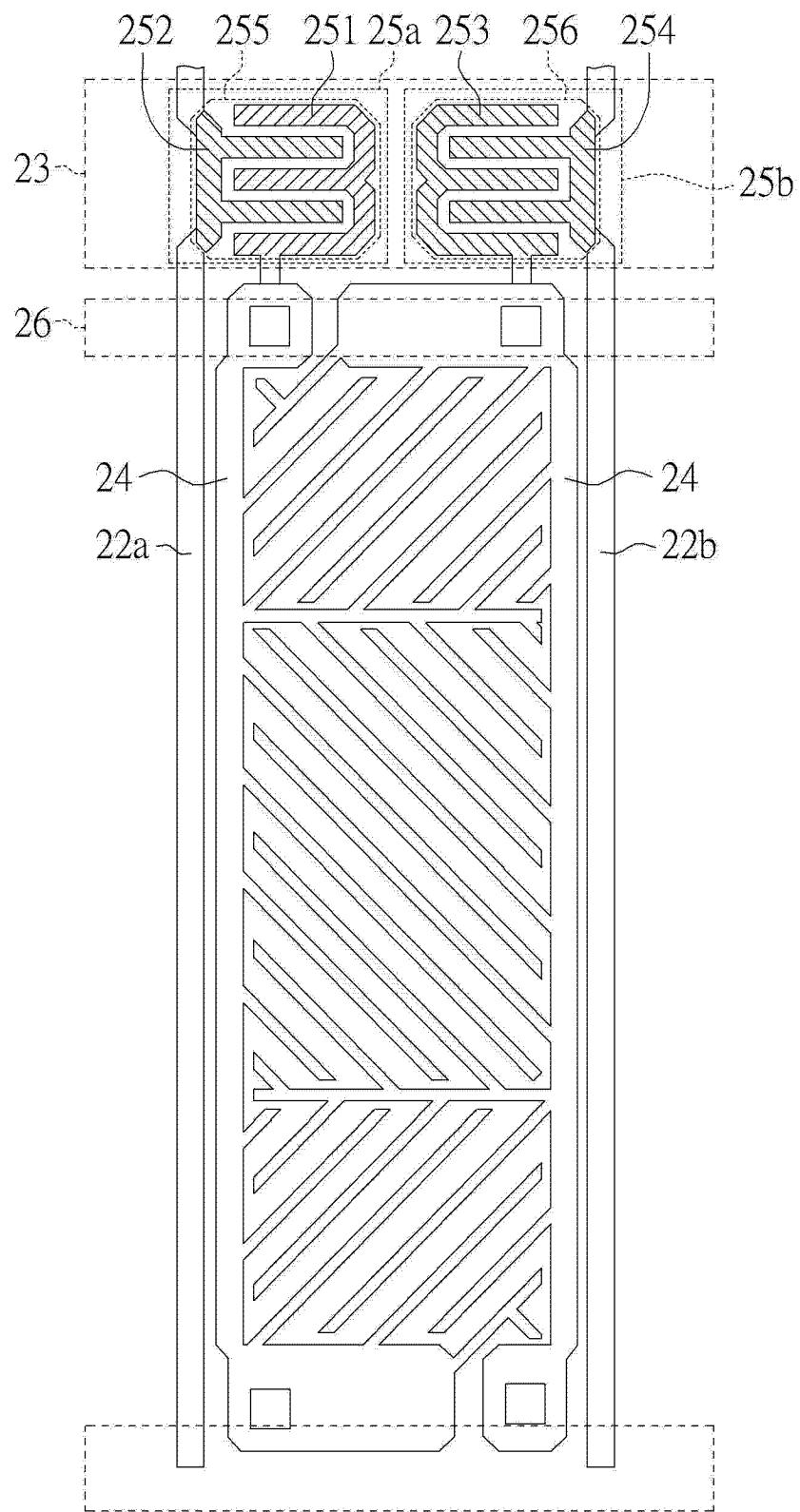

- [0010] 图 3 绘示为依照第一实施例的一种液晶面板的电路布局图。

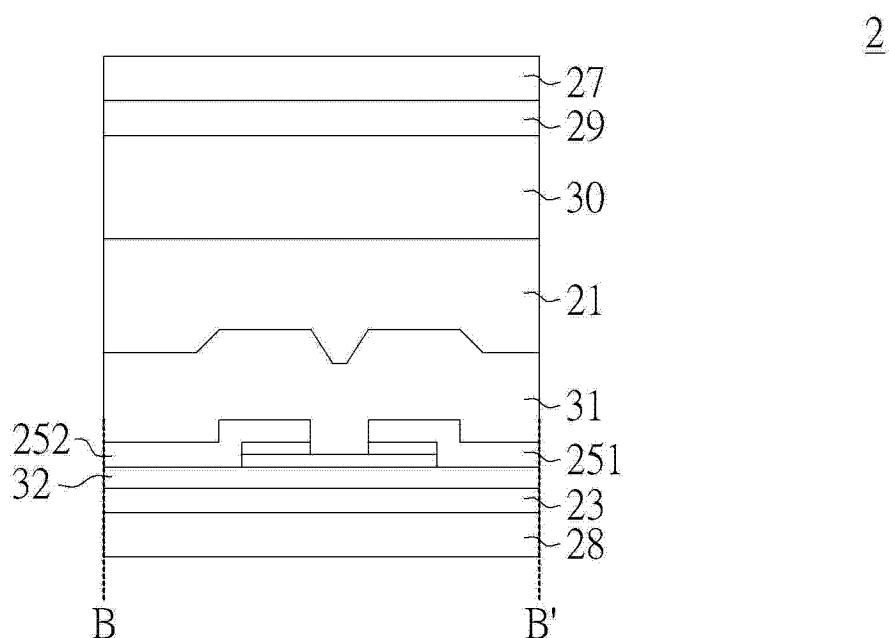

- [0011] 图 4 绘示为沿 BB' 剖面线的剖面图。

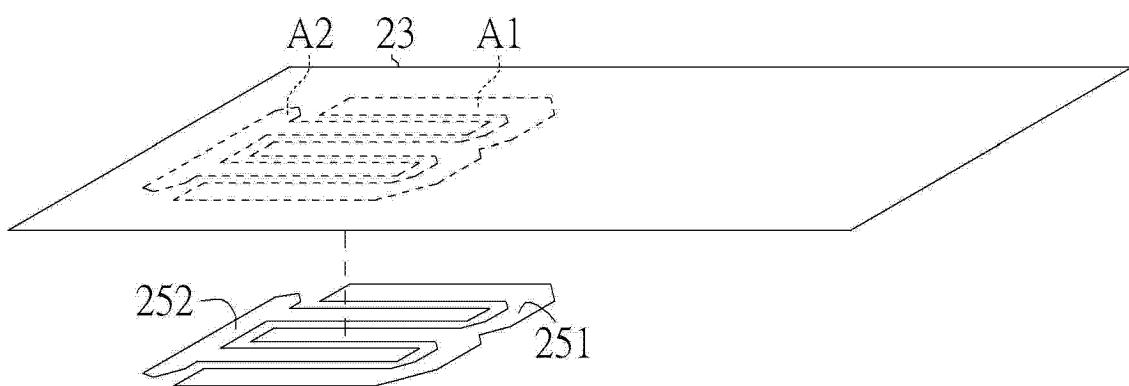

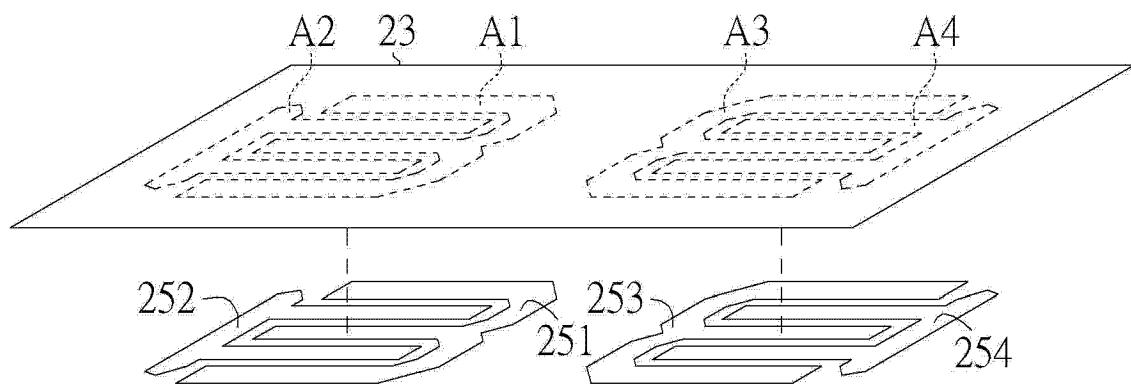

- [0012] 图 5 绘示为第一电极、第二电极与扫描线的侧视图。

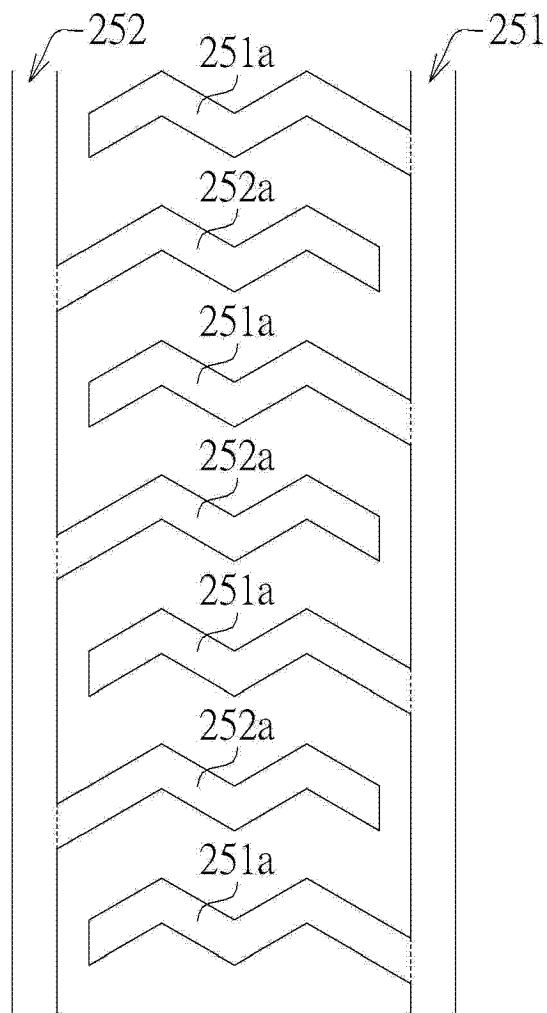

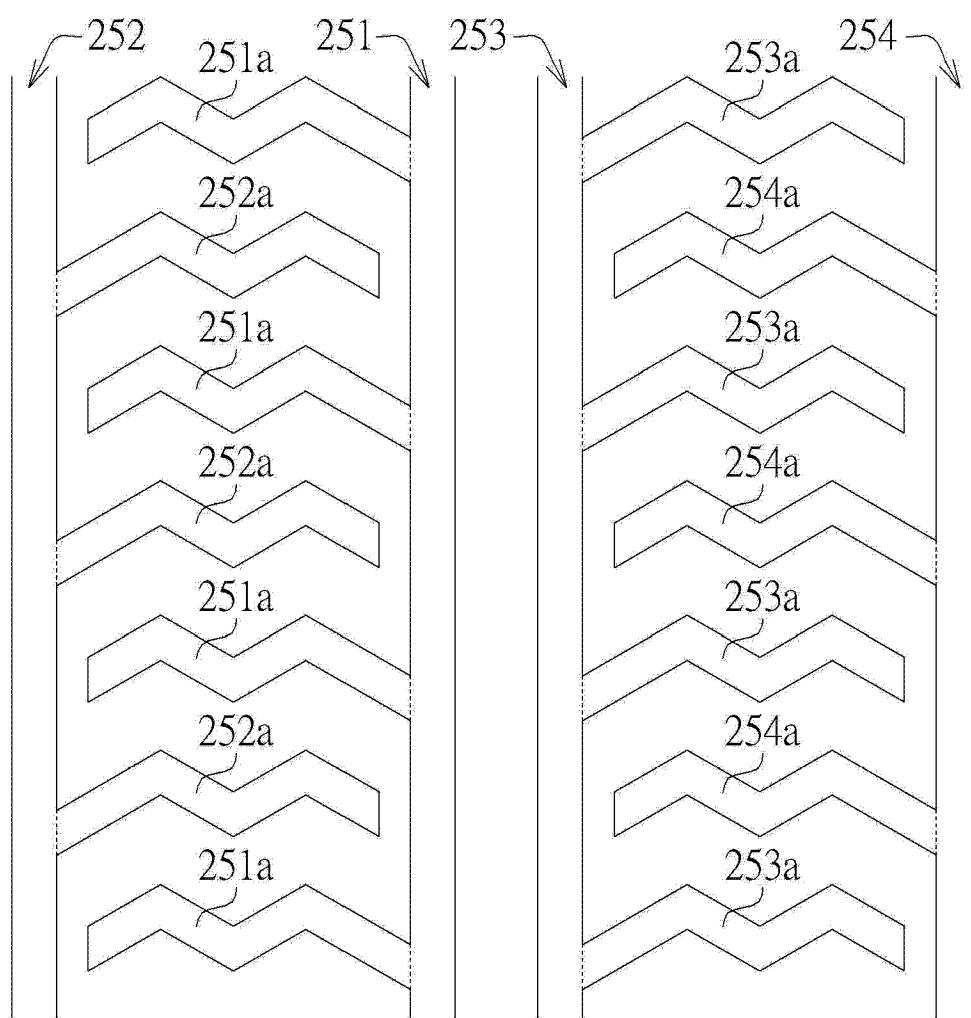

- [0013] 图 6 绘示为依照第一实施例的第一电极与第二电极的示意图。

- [0014] 图 7 为依照第二实施例的一种液晶面板的电路图。

- [0015] 图 8 绘示为依照第二实施例的一种液晶面板的电路布局图。

- [0016] 图 9 绘示为第一电极、第二电极、第三电极、第四电极与扫描线的侧视图。

- [0017] 图 10 绘示为依照第二实施例的第一电极、第二电极、第三电极及第四电极的示意图。

- [0018] 【主要组件符号说明】

- [0019] 2 : 液晶面板

- [0020] 21 : 液晶层

- [0021] 22a : 第一资料线

- [0022] 22b : 第二资料线

- [0023] 23 : 扫描线

- [0024] 24 : 像素电极

- [0025] 25a : 第一薄膜晶体管

- [0026] 25b : 第二薄膜晶体管

- [0027] 26 : 共同电极

- [0028] 27 : 第一玻璃基板

- [0029] 28 : 第二玻璃基板

- [0030] 29 : 黑色矩阵

- [0031] 30 : 彩色滤光片

- [0032] 31 : 绝缘层

- [0033] 32 : 栅极保护层

- [0034] 251 : 第一电极

- [0035] 251a : 第一分支电极

- [0036] 252 : 第二电极

- [0037] 252a : 第一分支电极

- [0038] 253 : 第三电极

- [0039] 253a : 第一分支电极

- [0040] 254 : 第四电极

- [0041] 254a : 第一分支电极

- [0042] 255、256 : 主动层

- [0043] BB' : 剖面线

- [0044]  $C_{LC}$  : 液晶电容

- [0045]  $C_{st1}$ 、 $C_{st2}$  : 储存电容

- [0046]  $C_{gs1}$  : 第一电容

- [0047]  $C_{gd1}$  : 第二电容

- [0048]  $C_{gs2}$  : 第三电容

- [0049]  $C_{gd2}$  : 第四电容

- [0050]  $V_g$  : 扫描信号

- [0051]  $V_p$  : 像素电压

- [0052]  $\Delta V$  : 回踢电压

- [0053]  $V_{com}$  : 共同电压

### 具体实施方式

- [0054] 第一实施例

[0055] 请同时参照图 2、图 3、图 4、图 5 及图 6, 图 2 绘示为依照第一实施例的一种液晶面板的电路图, 图 3 绘示为依照第一实施例的一种液晶面板的电路布局图, 图 4 绘示为沿 BB' 剖面线的剖面图, 图 5 绘示为第一电极、第二电极与扫描线的侧视图, 图 6 绘示为依照第一实施例的第一电极与第二电极的示意图。液晶面板 2 例如为平面切换式 (In-Plane Switching, IPS) 面板、垂直配向式 (Vertical Alignment, VA) 面板或平面搭垂直混合式面板, 平面切换式面板是利用横向电场来改变液晶分子的转向, 而垂直配向式面板是利用纵向电场来改变液晶分子的转向, 而混合式则是两者兼具。液晶面板 2 包括液晶层 21、第一数据线 22a、扫描线 23、像素电极 24、第一薄膜晶体管 25a 及共同电极 26。像素电极 24 用以驱动液晶层 21, 像素电极 24 可具有不同形状, 于此并不限制。且像素电极 24 可依不同设计而有不同的电位, 例如为由共同电极 26 提供的共同电位, 或例如为由不同的薄膜晶体管提供的不同电位。液晶层 21 包括高介电系数液晶材料。高介电系数液晶材料的平均介电系数介于 20 至 500 之间, 且高介电系数液晶材料例如为蓝相液晶或其它具有高极性官能基的液晶, 或例如加入高比例的旋性 (Chiral, 或称手性) 材料。液晶层 21 的等效电容在图 2 是以液晶电容  $C_{LC}$  表示。共同电极 26 被施加一共同电位  $V_{com}$ , 且像素电极 24 与共同电极 26 形成储存电容  $C_{st1}$ 。

[0056] 第一薄膜晶体管 25a 包括第一电极 251、第二电极 252 及主动层 255, 且第一电极 251 及第二电极 252 形成于主动层 255 上。第一薄膜晶体管例如为非晶硅 (Amorphous Silicon) 薄膜晶体管、低温多晶硅 (Low Temperature Poly-Silicon, LTPS) 薄膜晶体管或氧化铟镓锌 (Indium Gallium Zinc Oxide, IGZO) 薄膜晶体管, 第一薄膜晶体管 25a 例如为第一电极 251 与第二电极 252 的形状不对称的 J 型 (J-Type) 薄膜晶体管。第一电极 251 耦接至像素电极 24, 而第二电极 252 耦接至第一资料线 22a。第一电极 251 具有至少两个第一分支电极 251a。第二电极 252 具有至少一个第二分支电极 252a。第一分支电极 251a 沿第二电极 252 连续弯曲以形成一指叉状, 并包覆部份第二电极 252, 且至少一个该第二分支电极 252a 会位在两个该第一分支电极 251a 之间。需说明的是, 第一分支电极 251a 及第二分支电极 252a 的形状可以例如是矩形、L 形、圆弧形、半圆形、波浪状或其它形状, 在此并不特别局限。第一分支电极 251a 的个数不局限于 2 个, 第一电极 251 也可以包括两个以上的第一分支电极 251a。相似地, 第二分支电极 252a 的个数不局限于 1 个, 第二电极 252 也可以包括两个以上第二分支电极 252a, 但至少有一第二分支电极会位在两个第一分支电极之间。

[0057] 液晶面板 2 更进一步包括第一玻璃基板 27、第二玻璃基板 28、黑色矩阵 (Black Matrix, BM) 29、彩色滤光片 30、绝缘层 31 与栅极保护层 32。扫描线 23 形成于第二玻璃基板 28 上, 且绝缘层 31 形成于第一电极 251 及第二电极 252 上。栅极保护层 32 形成于扫描线 23 上。液晶层 21 形成于绝缘层 31 与彩色滤光片 30 之间, 且黑色矩阵 29 形成于彩色滤光片 30 与第一玻璃基板 27 之间。然实际应用并不局限于此, 于其它实施例中, 当背光模块是以色序法 (Color Sequence) 的方式提供背光至液晶面板 2, 则液晶面板 2 可不使用彩色滤光片 30。于其它实施例中, 彩色滤光片 30 可形成于第一玻璃基板 27 或第二玻璃基板 28。黑色矩阵 29 可形成于第一玻璃基板 27 或第二玻璃基板 28。

[0058] 请同时参照图 2、图 3、图 4 及图 5, 图 5 绘示为第一电极、第二电极与扫描线的侧视图。第一电极 251 与扫描线 23 形成第一电容  $C_{gs1}$ , 且第二电极 252 与扫描线 23 形成第二电容  $C_{gd1}$ 。第一电极 251 与扫描线 23 的第一重迭面积  $A1$  大于第二电极 252 与扫描线 23 的第二重迭面积  $A2$ 。由于第一重迭面积  $A1$  大于第二重迭面积  $A2$ , 因此第一电容  $C_{gs1}$  大于第二电容  $C_{gd1}$ 。其中, 第一重迭面积  $A1$  与第二重迭面积  $A2$  的比值为  $\frac{A1}{A2}$ , 且  $1 < \frac{A1}{A2} \leq 4$ 。

[0059] 于第一实施例中, 当第一重迭面积  $A1$  大于第二重迭面积  $A2$  时, 回踢电压  $\Delta V$  并不会随之增加。这是因为液晶层 21 是使用高介电系数液晶材料而变大。当液晶电容  $C_{lc}$  变大后, 已经可以平衡第一电容  $C_{gs1}$  的增加而使回踢电压  $\Delta V$  不增加。此外, 由于第二重迭面积  $A2$  小于第一重迭面积  $A1$ , 因此能让第二电容  $C_{gd1}$  比第一电容  $C_{gs1}$  小。如此一来, 于使用此实施例的薄膜晶体管设计, 可在维持相同薄膜晶体管的通道宽度与长度的比例下, 将能改善第一数据线 22a 及扫描线 23 上的上电阻电容延迟 (RC Delay) 效应, 以避免第一数据线 22a 上的信号失真。

#### [0060] 第二实施例

[0061] 请同时参照图 7、图 8 及图 10, 图 7 为依照第二实施例的一种液晶面板的电路图, 图 8 绘示为依照第二实施例的一种液晶面板的电路布局图, 图 10 绘示为依照第二实施例的第一电极、第二电极、第三电极及第四电极的示意图。第二实施例与第一实施例主要不同之处在于液晶面板 4 更包括第二数据线 22b 及第二薄膜晶体管 25b。第二薄膜晶体管 25b 例如为非晶硅 (Amorphous Silicon) 薄膜晶体管、低温多晶硅 (Low Temperature Poly-Silicon, LTPS) 薄膜晶体管或氧化铟镓锌 (Indium Gallium Zinc Oxide, IGZO) 薄膜晶体管。

[0062] 第二薄膜晶体管 25b 包括第三电极 253、第四电极 254 及主动层 256, 且第三电极 253 及第四电极 254 形成于主动层 256 上。第三电极 253 耦接至像素电极 24, 而第四电极 254 耦接至第二数据线 22b。第二薄膜晶体管 25b 例如为第三电极 253 与第四电极 254 的形状不对称的 J 型 (J-Type) 薄膜晶体管。第三电极 253 具有至少两个第三分支电极 253a。第四电极 254 具有至少一个第四分支电极 254a。第三分支电极 253a 沿第四电极 254 连续弯曲以形成一指叉状, 并包覆部份第四电极 254。需说明的是, 第三分支电极 253a 及第四分支电极 254a 的形状可以例如是矩形、L 形、圆弧形、半圆形、波浪状或其它形状, 在此并不特别局限。第三分支电极 253a 的个数不局限于 2 个, 第三电极 253 也可以包括两个以上的第三分支电极 253a。相似地, 第四分支电极 254a 的个数不局限于 1 个, 第四电极 254 也可以包括两个以上的第四分支电极 254a。

[0063] 请同时参照图 7、图 8 及图 9, 图 9 绘示为第一电极、第二电极、第三电极、第四电极与扫描线的侧视图。第三电极 253 与扫描线 23 形成第三电容  $C_{gs2}$ , 且第四电极 254 与扫描线 23 形成第四电容  $C_{gd2}$ 。第三电极 253 与扫描线 23 的第三重迭面积  $A3$  大于第四电极 254 与扫描线 23 的第二重迭面积  $A4$ 。由于第三重迭面积  $A3$  大于第四重迭面积  $A4$ , 因此第三电容  $C_{gs2}$  大于第四电容  $C_{gd2}$ 。其中, 第三重迭面积  $A3$  与第四重迭面积  $A4$  的比值为  $\frac{A3}{A4}$ , 且  $1 < \frac{A3}{A4} \leq 4$ 。此外, 由于第四重迭面积  $A4$  小于第三重迭面积  $A3$ , 因此能让第四电容  $C_{gd2}$  比第三电容  $C_{gs2}$  小。如此一来, 于使用此实施例的薄膜晶体管设计, 可在维持相同薄膜晶体管的通道宽度与长度的比例下, 将能改善第二数据线 22b 及扫描线 23 上的上电阻电容延迟 (RC Delay) 效应, 以避免第二数据线 22b 上的信号失真。

[0064] 综上所述, 虽然本揭露已以实施例揭露如上, 然其并非用以限定本揭露。本揭露所属技术领域中具有通常知识者, 在不脱离本揭露的精神和范围内, 当可作各种更动与润饰。因此, 本揭露的保护范围当视后附的权利要求所界定者为准。

图 1

图 2

2

图 3

图 4

图 5

图 6

图 7

4

图 8

图 9

图 10

|                |                                  |                      |            |

|----------------|----------------------------------|----------------------|------------|

| 专利名称(译)        | 液晶面板                             |                      |            |

| 公开(公告)号        | <a href="#">CN103995406A</a>     | 公开(公告)日              | 2014-08-20 |

| 申请号            | CN201310053564.7                 | 申请日                  | 2013-02-19 |

| [标]申请(专利权)人(译) | 群创光电股份有限公司                       |                      |            |

| 申请(专利权)人(译)    | 群创光电股份有限公司                       |                      |            |

| 当前申请(专利权)人(译)  | 群创光电股份有限公司                       |                      |            |

| [标]发明人         | 陈建宏                              |                      |            |

| 发明人            | 陈建宏                              |                      |            |

| IPC分类号         | G02F1/1362 G02F1/1368 H01L29/786 |                      |            |

| 代理人(译)         | 陆嘉                               |                      |            |

| 外部链接           | <a href="#">Espacenet</a>        | <a href="#">Sipo</a> |            |

### 摘要(译)

一种液晶面板，包括液晶层、第一数据线、扫描线、像素电极及第一薄膜晶体管。液晶层包括高介电系数液晶材料，而像素电极驱动液晶层。第一薄膜晶体管包括第一电极及第二电极。第一电极耦接至像素电极，且具有至少两个第一分支电极。第二电极耦接至第一资料线，且具有至少一个第二分支电极。第一电极与扫描线的第一重迭面积大于第二电极与扫描线的第二重迭面积，且至少一个该第二分支电极会位在两个该第一分支电极之间。