(12) 发明专利

(10) 授权公告号 CN 1987990 B

(45) 授权公告日 2011.02.09

(21) 申请号 200610169249.0

(56) 对比文件

(22) 申请日 2006.12.21

JP 2005121995 A, 2005.05.12, 全文.

(30) 优先权数据

JP 2005173418 A, 2005.06.30, 全文.

369758/2005 2005.12.22 JP

CN 1620628 A, 2005.05.25, 说明书第3页第12段, 第14页第3段、图1, 图4.

(73) 专利权人 株式会社日立显示器

审查员 刘畅

地址 日本千叶县

(72) 发明人 田中靖洋 勇广宣 饭田治久

菊池秀德 尾手幸秀

(74) 专利代理机构 北京市金杜律师事务所

11256

代理人 季向冈

(51) Int. Cl.

G09G 3/36 (2006.01)

G09G 5/02 (2006.01)

G09G 3/20 (2006.01)

G02F 1/133 (2006.01)

H04N 11/00 (2006.01)

H03K 19/0185 (2006.01)

权利要求书 2 页 说明书 18 页 附图 36 页

(54) 发明名称

显示装置

(57) 摘要

本发明提供一种显示装置,目的在于减小栅极线延伸方向的像素的TFT元件的写入时间的离差。在该显示装置中,包括按矩阵状配置了多条栅极线和多条漏极线的显示板、对各漏极线输出显示数据信号的数据驱动器,上述数据驱动器,具有内部控制信号生成电路,将上述多条漏极线划分为多个块,生成按每个块设定向各块的漏极线输出数据信号的时序的内部控制信号;以及寄存电路,记录了上述块的划分的设定、输出上述数据信号的时序的延迟方向和延迟宽度的设定、内部控制信号的上升沿和下降沿的设定。

1. 一种数据驱动器, 对显示板输出显示数据信号, 其特征在于, 包括:

- 数据锁存电路, 暂时保持显示数据;

- 第一锁存电路, 保持从上述数据锁存电路按时分方式传送来的显示数据直到其达到 1 水平同步期间;

- 第二锁存电路, 保持上述 1 水平同步期间的显示数据;

- 电平移位电路, 接收由上述第二锁存电路所保持的显示数据, 变换上述显示数据的信号电平;

- 译码电路, 生成与由上述电平移位电路变换后的显示数据的信号电平对应的模拟信号;

- 输出电路, 将由上述译码电路生成的模拟信号放大;

- 开关电路, 将由上述输出电路放大后的模拟信号输出至漏极线; 以及

- 水平同步信号延迟电路, 当从上述第二锁存电路向上述电平移位电路传送上述显示数据时, 将上述第二锁存电路保持的显示数据划分为多个块, 并使按每个块传送上述显示数据的时序延迟。

2. 根据权利要求 1 所述的数据驱动器, 其特征在于,

上述水平同步信号延迟电路, 随着从与上述第二锁存电路的中央附近对应的显示数据的块向端部的块变化而使传送上述显示数据的时序延迟。

3. 根据权利要求 1 所述的数据驱动器, 其特征在于,

上述第二锁存电路具有锁存电路和多路复用电路,

上述水平同步信号延迟电路具有上述锁存电路用的延迟电路和上述多路复用电路用的延迟电路。

4. 根据权利要求 3 所述的数据驱动器, 其特征在于,

上述水平同步信号延迟电路, 随着从与上述第二锁存电路的中央附近对应的显示数据的块向端部的块变化而使传送上述显示数据的时序延迟。

5. 根据权利要求 1 所述的数据驱动器, 其特征在于,

上述数据驱动器由连接在公用总线布线上的多个驱动 IC 构成, 上述各驱动 IC 包括:

- 内部控制信号生成电路, 生成用于设定上述水平同步信号延迟电路所延迟的时序的内部控制信号;

- 寄存电路, 记录有上述块的划分设定、使上述时序延迟的方向和延迟宽度的设定。

6. 根据权利要求 5 所述的数据驱动器, 其特征在于,

上述数据驱动器的上述各驱动 IC, 在存储于上述寄存电路中的寄存数据的读入结束后, 对外部输出载波信号。

7. 根据权利要求 5 所述的数据驱动器, 其特征在于,

上述数据驱动器的上述各驱动 IC, 被提供地址信息和存储在上述寄存电路中的寄存数据。

8. 根据权利要求 1 所述的数据驱动器, 其特征在于,

上述数据驱动器由连接在公用总线布线上的多个驱动 IC 构成, 上述各驱动 IC 包括:

- 内部控制信号生成电路, 生成用于设定将与上述多个块的每一个对应的显示数据信号输出至上述显示板的时序的内部控制信号; 和

寄存电路,记录有上述块的划分设定、输出上述显示数据信号的时序的延迟方向和延迟宽度的设定。

9. 根据权利要求 8 所述的数据驱动器,其特征在于,

上述数据驱动器的上述各驱动 IC,在存储于上述寄存电路中的寄存数据的读入结束后,对外部输出载波信号。

10. 根据权利要求 8 所述的数据驱动器,其特征在于,

上述数据驱动器的上述各驱动 IC,被提供地址信息和存储在上述寄存电路中的寄存数据。

## 显示装置

### 技术领域

[0001] 本发明涉及显示装置,尤其是涉及适用于液晶显示装置的有效技术。

### 背景技术

[0002] 以往,作为显示装置,有使用了液晶显示板的液晶显示装置。上述液晶显示板,是将液晶材料封入到一对基板之间的显示板。其中,在上述基板上,例如按矩阵状配置有多条栅极线和多条漏极线。而且,将由邻接的 2 条栅极线和邻接的 2 条漏极线所包围的区域作为 1 个像素区域,在各像素区域内配置有 TFT 元件和像素电极。

[0003] 当在上述液晶显示板上使图像或影像显示时,例如,对各漏极线预先输入显示数据信号、依次对各栅极线输入扫描信号。

[0004] 这时,输入到上述各漏极线的显示数据信号的生成和输入的时序,由时序控制器和数据驱动器(漏极驱动器)来执行。另外,输入到上述各栅极线的扫描信号的生成和输入的时序,由上述时序控制器和扫描驱动器(栅极驱动器)来执行。

[0005] 上述数据驱动器,例如,包括保持显示数据直到其达到 1 水平同步期间的锁存电路、变换上述显示数据的信号电平的电平移动器电路、基于变换了信号电平的显示数据生成模拟信号(灰度等级电压)的译码电路、将由上述译码电路生成的模拟信号放大的输出电路、以及将由上述输出电路放大后的模拟信号输出到漏极线的开关电路等(例如,参照专利文献 1)。

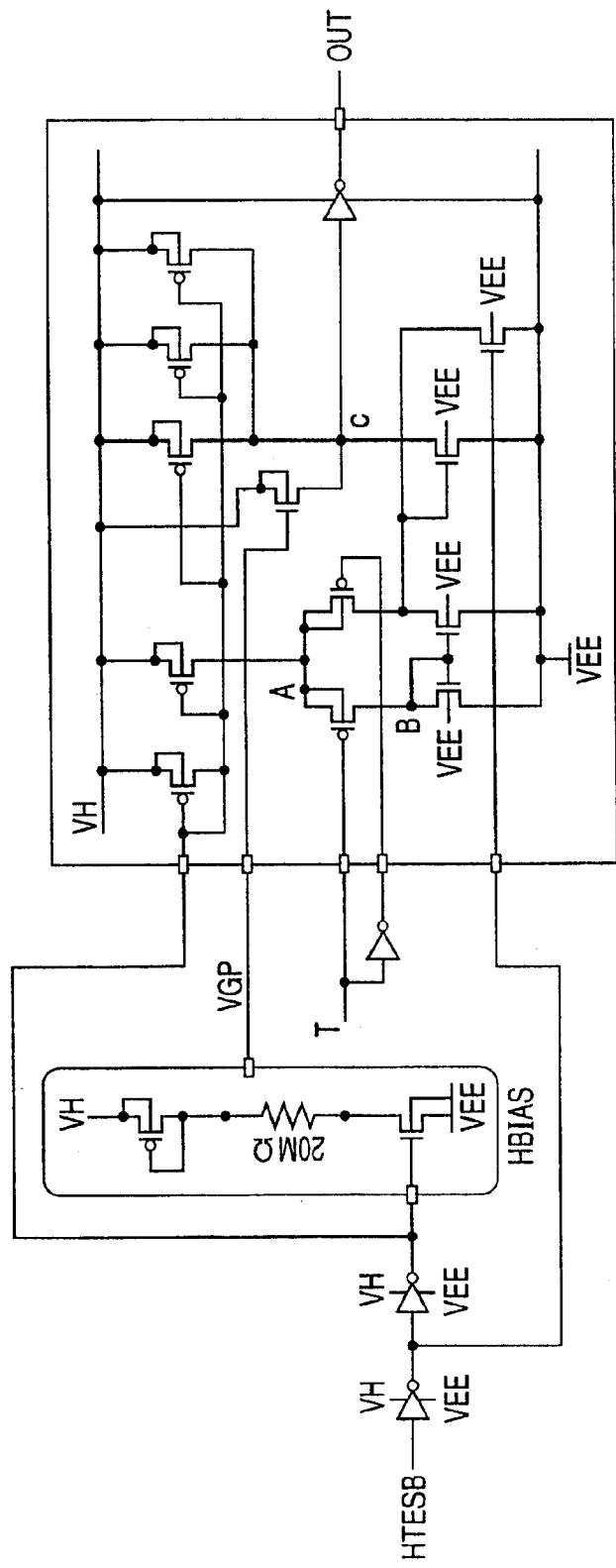

[0006] 上述电平移动器电路是电压变换电路,一般为低电压动作部和高电压动作部的 2 级结构。这时,上述高电压动作部,例如,形成为由 4 个或 6 个 MOS 晶体管构成的被称为交叉方式的电路结构(例如,参照专利文献 2)。

[0007] 另外,在上述液晶显示装置中,近年来,为提高动图像的画质,例如,提出了在显示数据之间插入黑显示的方法(例如,参照专利文献 3)。

[0008] [专利文献 1] 日本特开 2004-301946 号公报

[0009] [专利文献 2] 日本特开 2004-289329 号公报

[0010] [专利文献 3] 日本特开 2003-208599 号公报

[0011] 但是,本申请的发明人发现,在上述以往的液晶显示装置中,存在例如下述那样的问题。

[0012] (a) 当从上述数据驱动器向各漏极线输出显示数据信号时,以相同的时序输出到所有的漏极线。但是,在栅极线的靠近扫描信号输入端的像素和栅极线的远离扫描信号输入端的像素上,扫描信号的波形不同,因此,存在着在 TFT 元件的显示数据信号(灰度等级电压信号)的写入时间上产生离差这样的问题。

[0013] (b) 在上述数据驱动器中,在根据水平同步信号汇总地进行数据锁存的时刻产生瞬时电流。这时,存在着因瞬时电流引起的电源电压变动而使数据驱动器和显示装置的可靠性降低这样的问题。

[0014] (c) 在上述数据驱动器由多个驱动 IC 构成的情况下,存在着输出上述显示数据用

的扫描信号的栅极线和输出黑显示插入用的扫描信号的栅极线之间必须空出不小于芯片间距的间隔这样的问题。其原因是,无法对连接在同一个驱动 IC 上的 2 条栅极线进行使其中 1 条栅极线输出显示数据用的扫描信号、使另 1 条栅极线输出黑显示插入用的扫描信号这样的控制。因此,在将多个驱动 IC 串联连接时,存在着在显示数据用的栅极线和黑显示插入用的栅极线的间隔的设定上有一定的限度的问题。

[0015] (d) 在上述驱动器中,与移位寄存器的前级的逻辑电路的动作电压相比,提供给上述 TFT 元件的电压非常高,因而存在着无法用以往的电平移动器电路的 MOS 晶体管的尺寸进行动作的问题。而且,为使电平移动器电路动作,需要尺寸为以往的一倍以上的 MOS 晶体管,因而存在着使驱动 IC 变大的问题。

[0016] 具体地说明上述问题 (a),该问题 (a) 是由于输入到栅极线的扫描信号在输入端的附近为陡峭的波形、随着远离输入端而变为平缓的波形所产生的。在以往的数据驱动器中,由于是汇总地向各漏极线输出显示数据信号,所以写入时序设于栅极线的输入端的近端或远端中的任一者。因此,存在着在其中的一端会发生写入不充分的状况,使显示品质降低这样的问题。

[0017] 具体地说明上述问题 (b),在上述数据驱动器中,根据水平同步信号从锁存电路汇总输出的数据,同时驱动电平移动器电路,并选择译码电路的预定的灰度等级电压。这时,在高耐压系统(高电压动作部)的电源和地(GND)之间,将流过与输出数相当的电平移动器电路的电流,因此,如输出数增加,则瞬时电流与之相应地增大。因而电源电压的变动增大。这种问题,例如在汽车导航系统等的车载用液晶显示装置中尤为显著。

## 发明内容

[0018] 本发明的目的在于,提供一种在液晶显示装置中能够减小栅极线延伸方向的像素的 TFT 元件的写入时间的离差的技术。

[0019] 本发明的另一个目的在于,提供一种在液晶显示装置中能够减小在数据驱动器中产生的瞬时电流的峰值,能够使数据驱动器和显示装置的可靠性提高的技术。

[0020] 本发明的另一个目的在于,提供一种在液晶显示装置中能够将多个扫描驱动 IC 串联连接、且提高输出显示数据用的扫描信号的栅极线和输出黑显示插入用的扫描信号的栅极线的组合自由度的技术。

[0021] 本发明的另一个目的在于,提供一种在液晶显示装置中能够用以往的尺寸的 MOS 晶体管使电平移动器电路动作的技术。

[0022] 本发明的上述以及其他的优点和新的特征,将通过本说明书的记述和附图来得到明确。

[0023] 说明本申请所公开的发明的概要如下。

[0024] (1) 一种显示装置,包括按矩阵状配置了多条栅极线和多条漏极线的显示板、对各栅极线输出扫描信号的扫描驱动器、对各漏极线输出显示数据信号的数据驱动器、以及控制从上述扫描驱动器输出扫描信号的时序和从上述数据驱动器输出数据信号的时序的显示控制电路,所述显示装置的特征在于:上述数据驱动器,包括内部控制信号生成电路,将上述多条漏极线划分为多个块,基于来自上述显示控制电路的水平同步时钟信号生成按每个块设定向各块的漏极线输出数据信号的时序的内部控制信号;寄存电路,记录了上述块

的划分的设定、输出上述数据信号的时序的延迟方向和延迟宽度的设定、内部控制信号的上升沿和下降沿的设定,是一种具有按每个块输出上述数据信号的功能的显示装置。

[0025] (2) 在上述 (1) 的显示装置中,上述内部控制信号生成电路,从上述栅极线的靠近上述扫描信号的输入端的块到离得远的块,使输出上述数据信号的时序越来越延迟。

[0026] (3) 在上述 (1) 或 (2) 的显示装置中,上述数据驱动器,由连接在公用总线布线上的多个驱动 IC 构成,上述各驱动 IC,分别具有上述内部控制信号生成电路和寄存电路,上述显示控制电路,生成按每个上述驱动 IC 汇集了上述块的划分的设定、输出上述数据信号的时序的延迟方向和延迟宽度的设定、内部控制信号的上升沿和下降沿的设定的寄存数据,将其输出到各驱动 IC,上述各驱动 IC,基于所输入的寄存数据中的分配给自身的驱动 IC 的寄存数据,生成内部控制信号。

[0027] (4) 在上述 (3) 的显示装置中,上述各驱动 IC,具有对各自进行识别的地址信息,上述显示控制电路,生成包含上述地址信息的寄存数据,将其输出到各驱动 IC。

[0028] (5) 在上述 (3) 的显示装置中,上述各驱动 IC,在分配给自身的驱动 IC 的寄存数据的读入结束后,向下一级的驱动 IC 传送载波信号。

[0029] (6) 一种显示装置,包括按矩阵状配置了多条栅极线和多条漏极线的显示板、对各栅极线输出扫描信号的扫描驱动器、对各漏极线输出显示数据信号的数据驱动器、以及控制从上述扫描驱动器输出扫描信号的时序和从上述数据驱动器输出数据信号的时序的显示控制电路,该显示装置的特征在于:上述数据驱动器,包括暂时保持显示数据的数据锁存电路;保持从上述数据锁存电路按时分方式传送来的显示数据直到其达到 1 水平同步期间的第一锁存电路;保持上述 1 水平同步期间的显示数据的第二锁存电路;接收由上述第二锁存电路保持着的显示数据,变换上述显示数据的信号电平的电平移动器电路;生成与由上述电平移动器电路变换后的显示数据的信号电平对应的模拟信号的译码电路;将由上述译码电路生成的模拟信号放大的输出电路;将由上述输出电路放大后的模拟信号输出到漏极线的开关电路;以及从上述第二锁存电路向上述电平移动器电路传送上述显示数据时将上述多条漏极线划分为多个块,使对每个块传送上述显示数据的时序错开的水平同步信号延迟电路。

[0030] (7) 在上述 (6) 的显示装置中,上述第二锁存电路,具有锁存电路和多路复用电路,上述水平同步信号延迟电路,具有上述锁存电路用的延迟电路和上述多路复用电路用的延迟电路。

[0031] (8) 在上述 (6) 或 (7) 的显示装置中,上述水平同步信号延迟电路,随着从上述漏极线的配置方向的中央附近的块到端部的块,使传送上述显示数据的时序延迟。

[0032] (9) 一种显示装置,包括按矩阵状配置了多条栅极线和多条漏极线的显示板、对各栅极线输出扫描信号的扫描驱动器、对各漏极线输出显示数据信号的数据驱动器、以及控制从上述扫描驱动器输出扫描信号的时序和从上述数据驱动器输出数据信号的时序的显示控制电路,该显示装置的特征在于:上述扫描驱动器,由多个驱动 IC 构成,各驱动 IC,包括:显示数据控制用的第一移位寄存电路;黑插入数据用的第二移位寄存电路;选择上述第一移位寄存电路的输出或第二移位寄存电路的输出的任何一个的选择开关电路。

[0033] (10) 在上述 (9) 的显示装置中,上述扫描驱动器,具有接收上述第一移位寄存电路或第二移位寄存电路的输出并变换上述接收到的输出的信号电平的电平移动器电路,在

上述选择开关电路和上述移位寄存电路之间,具有将上述移位寄存电路的输出信号变换为具有3值的不同电压电平的输出信号的锁存电路。

[0034] (11) 在(9)或(10)的显示装置中,上述各驱动IC串联连接。

[0035] (12) 一种显示装置,包括按矩阵状配置了多条栅极线和多条漏极线的显示板、对各栅极线输出扫描信号的扫描驱动器、对各漏极线输出显示数据信号的数据驱动器、以及控制从上述扫描驱动器输出扫描信号的时序和从上述数据驱动器输出数据信号的时序的显示控制电路,所述显示装置的特征在于:上述扫描驱动器,具有变换从移位寄存电路输出的信号的信号电平的电平移动器电路,上述电平移动器电路,具有以低电压电源进行动作的第一电路部和以高电压电源进行动作的第二电路部,上述第一电路部,具有暂时保持所输入的信号的锁存电路,上述第二电路部,至少具有2个P沟道MOS晶体管和2个N沟道MOS晶体管,第一N沟道MOS晶体管,它的栅电极与上述第一电路部的第一输出端连接,它的漏电极与第一P沟道MOS晶体管的漏电极及第二P沟道MOS晶体管的栅电极连接,第二N沟道MOS晶体管,它的栅电极与上述第一电路部的第二输出端连接,它的漏电极与上述第二P沟道MOS晶体管的漏电极、上述第一P沟道MOS晶体管的栅电极连接。

[0036] (13) 在(12)的显示装置中,上述第一电路部,具有第三P沟道MOS晶体管、第三N沟道MOS晶体管、第四N沟道MOS晶体管、第五N沟道MOS晶体管,上述第三P沟道MOS晶体管的栅电极与基于上述移位寄存电路的输出端和第一允许信号的输入信号的输入端连接,上述第三N沟道MOS晶体管,它的栅电极与第二允许信号的输入端连接,它的漏电极通过上述第三P沟道MOS晶体管的漏电极和“非”门与上述第四N沟道MOS晶体管的栅电极连接,上述第四N沟道MOS晶体管的源电极,与上述第三P沟道MOS晶体管的漏电极连接,上述第五N沟道MOS晶体管,它的栅电极与第三允许信号的输入端连接,它的漏电极与上述第四N沟道MOS晶体管的漏电极连接,上述第一输出端,与上述第三P沟道MOS晶体管的漏电极连接,上述第二输出端,从上述第三P沟道MOS晶体管的漏电极和上述第四N沟道MOS晶体管的源电极的节点通过“非”门与后级连接。

[0037] (14) 在上述(13)的显示装置中,上述第二允许信号和上述第三允许信号,由差动放大电路生成。

[0038] 在本发明的显示装置中,为了减小对沿栅极线的延伸方向排列的各像素的TFT元件的写入时间的离差,使上述数据驱动器的结构和对数据驱动器输入的控制数据按上述方式(1)~方式(5)实施。即,如上述方式(1)所示,在上述数据驱动器中,生成上述内部控制信号,并按对每个块不同的时序输出显示数据信号。这时,向各块的漏极线输出显示数据信号的时序,例如,如上述方式(2)所示,使离栅极线的输入端远的块的输出时序延迟。按照这种方式,能够调整对靠近上述扫描信号的波形陡峭的输入端的像素的TFT元件的写入时间和对离输入端远的像素的TFT元件的写入时间。因此,可以防止因写入时间的离差而引起的显示品质的降低。

[0039] 另外,当上述数据驱动器由连接在公用总线布线上的多个驱动IC构成时,例如,如上述方式(3)所示,按每个驱动IC汇集内部控制信号的设定所需的寄存数据,输入到各驱动IC即可。这时,若上述各驱动IC具有地址信息,则上述寄存数据按上述方式(4)那样做成即可。另外,当不具备地址信息时,按上述方式(5)那样做成即可。

[0040] 另外,在本发明的显示装置中,为减小在数据驱动器中产生的瞬时电流的峰值并

提高数据驱动器和显示装置的可靠性,而使上述数据驱动器的结构按上述方式(6)~方式(8)实施。即,当从上述第二锁存电路向电平移动器电路传送显示数据时,划分为多个块并分多次传送。这时,第二锁存电路的结构,例如按上述方式(7)那样实施。而且,当按上述每个块传送显示数据时,例如,按上述方式(8)那样进行。按照这种方式,能够将驱动了电平移动器电路时产生的瞬时电流分散,由此能使峰值降低,因此,能够提高数据驱动器和显示装置的可靠性。

[0041] 另外,在本发明的显示装置中,为了将多个扫描驱动IC串联连接、且将黑显示插入用的扫描信号输出到任意的栅极线上,而使扫描驱动器的结构按上述方式(9)实施。按照这种方式,能够对与同一个驱动IC连接的不同的栅极线同时输出显示数据用的扫描信号和黑显示插入用的扫描信号。这时,若按照上述方式(10),则能够延长数据的取入时间,使显示画质进一步提高。另外,在构成如上述方式(9)和方式(10)那样的结构的情况下,能够如上述方式(11)那样将多个驱动IC串联连接。

[0042] 另外,在本发明的显示装置中,为了用以往的尺寸的MOS晶体管使电平移动器电路动作,使电平移动器电路的结构按上述方式(12)实施。这时,上述第一电路部的结构,例如,按上述方式(13)和方式(14)实施。这样,上述第一电路部的MOS晶体管能以最小的尺寸构成,并且不需要为进行反转而流过电流。因此,能够抑制消耗电流,不增大MOS晶体管的尺寸也能使电平移动器电路动作。

## 附图说明

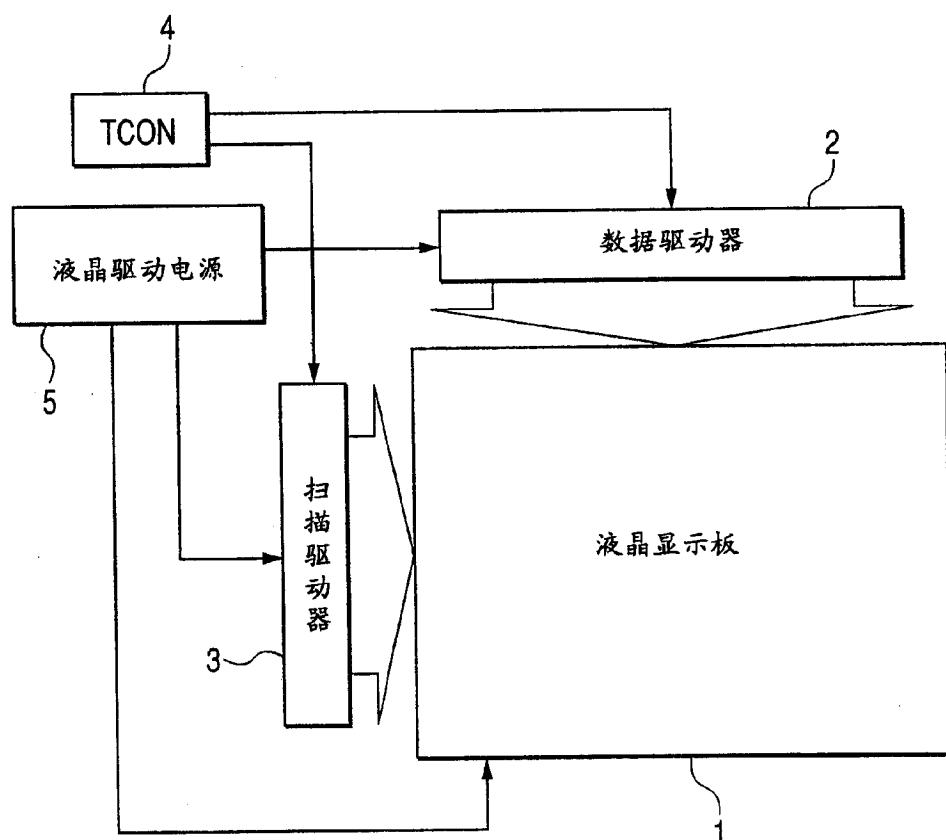

[0043] 图1是表示应用本发明的显示装置的概略结构的示意图,是表示液晶显示装置的结构例的框图。

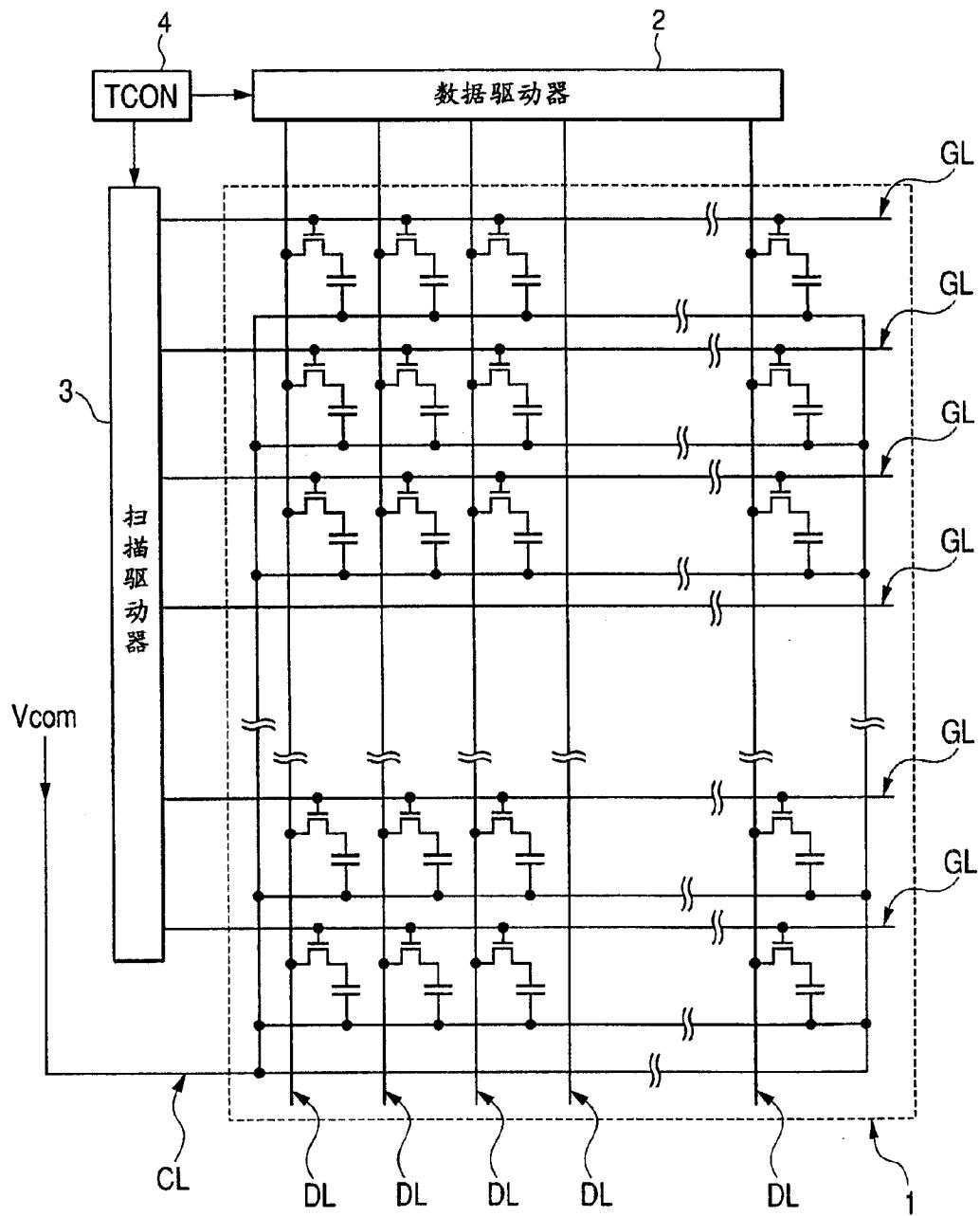

[0044] 图2是表示应用本发明的显示装置的概略结构的示意图,是表示液晶显示板的结构例的电路图。

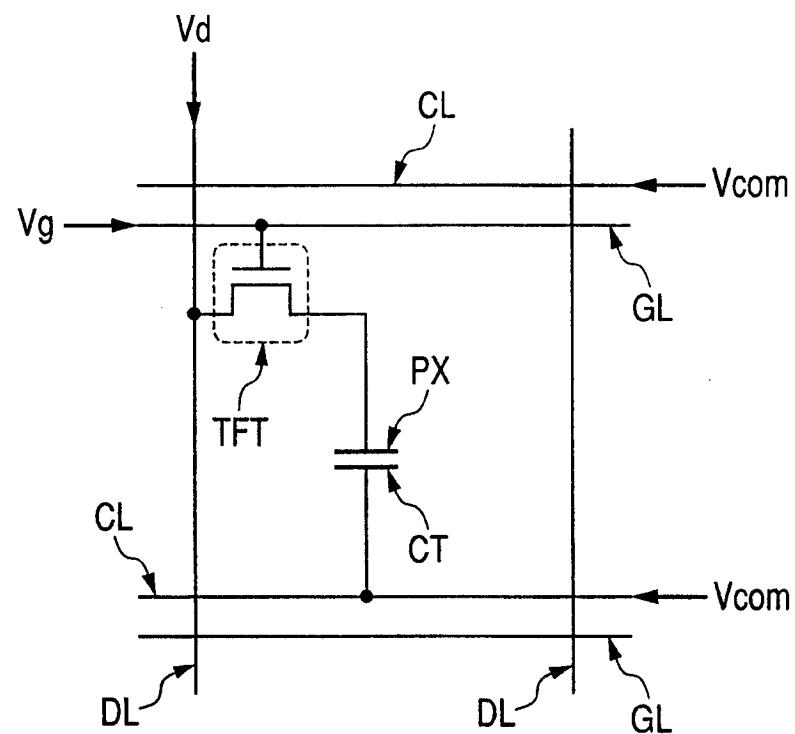

[0045] 图3是表示应用本发明的显示装置的概略结构的示意图,是说明1个像素的结构和动作的图。

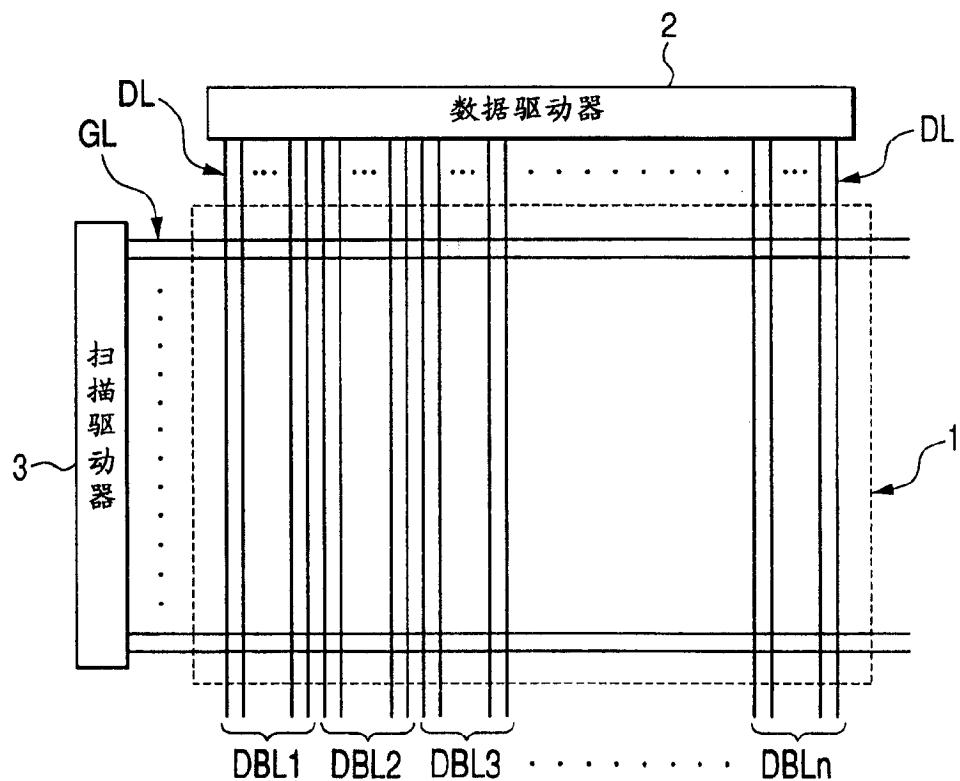

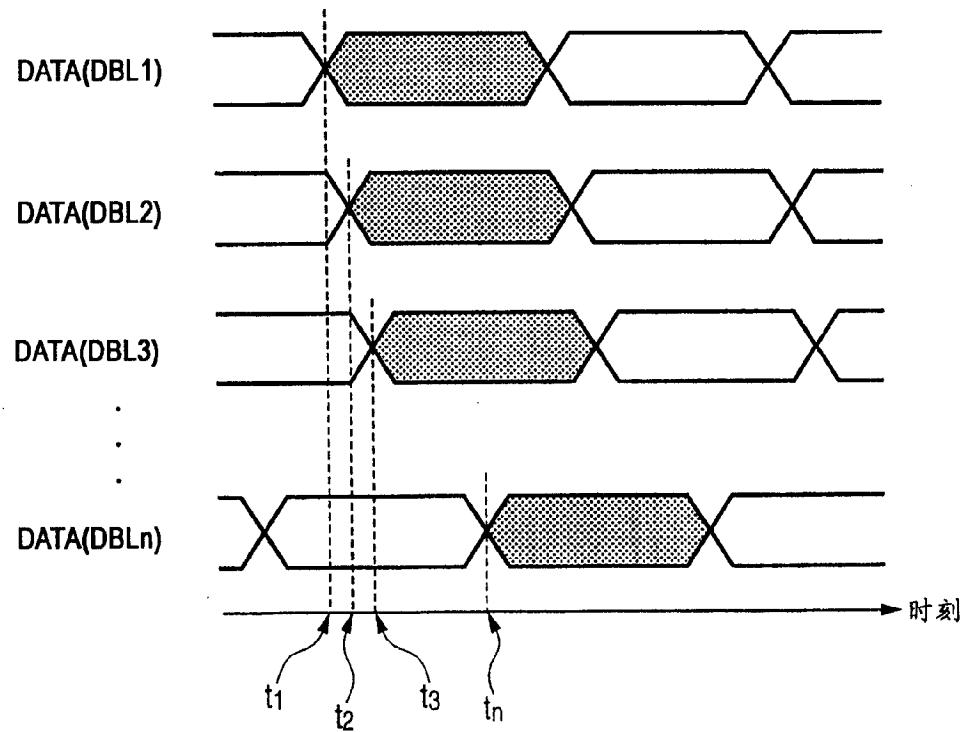

[0046] 图4是用于说明本发明的实施例1的液晶显示装置的动作原理的示意图,是说明漏极线的划分方法的图。

[0047] 图5是用于说明本发明的实施例1的液晶显示装置的动作原理的示意图,是说明显示数据的输出方法的图。

[0048] 图6是用于说明本发明的实施例1的液晶显示装置的动作原理的示意图,是说明延迟量的设定方法的图。

[0049] 图7是说明本实施例1的液晶显示装置中的数据驱动器的结构例和动作的示意图,是表示数据驱动器的结构例的框图。

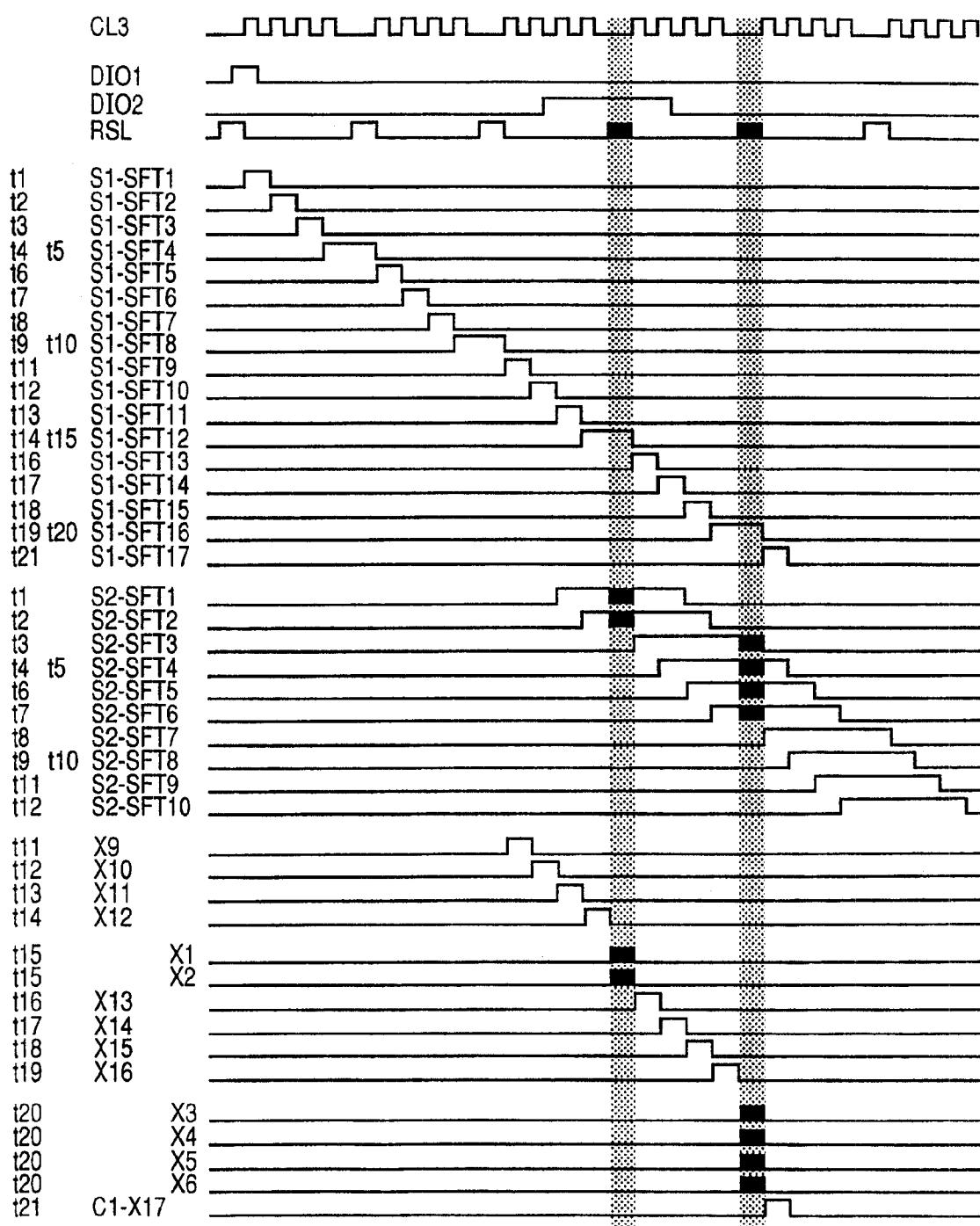

[0050] 图8是说明本实施例1的液晶显示装置中的数据驱动器的结构例和动作的示意图,是说明显示数据的输出时序的图。

[0051] 图9是说明本实施例1的液晶显示装置中的数据驱动器的结构例和动作的示意图,是说明内部控制信号的生成方法的图。

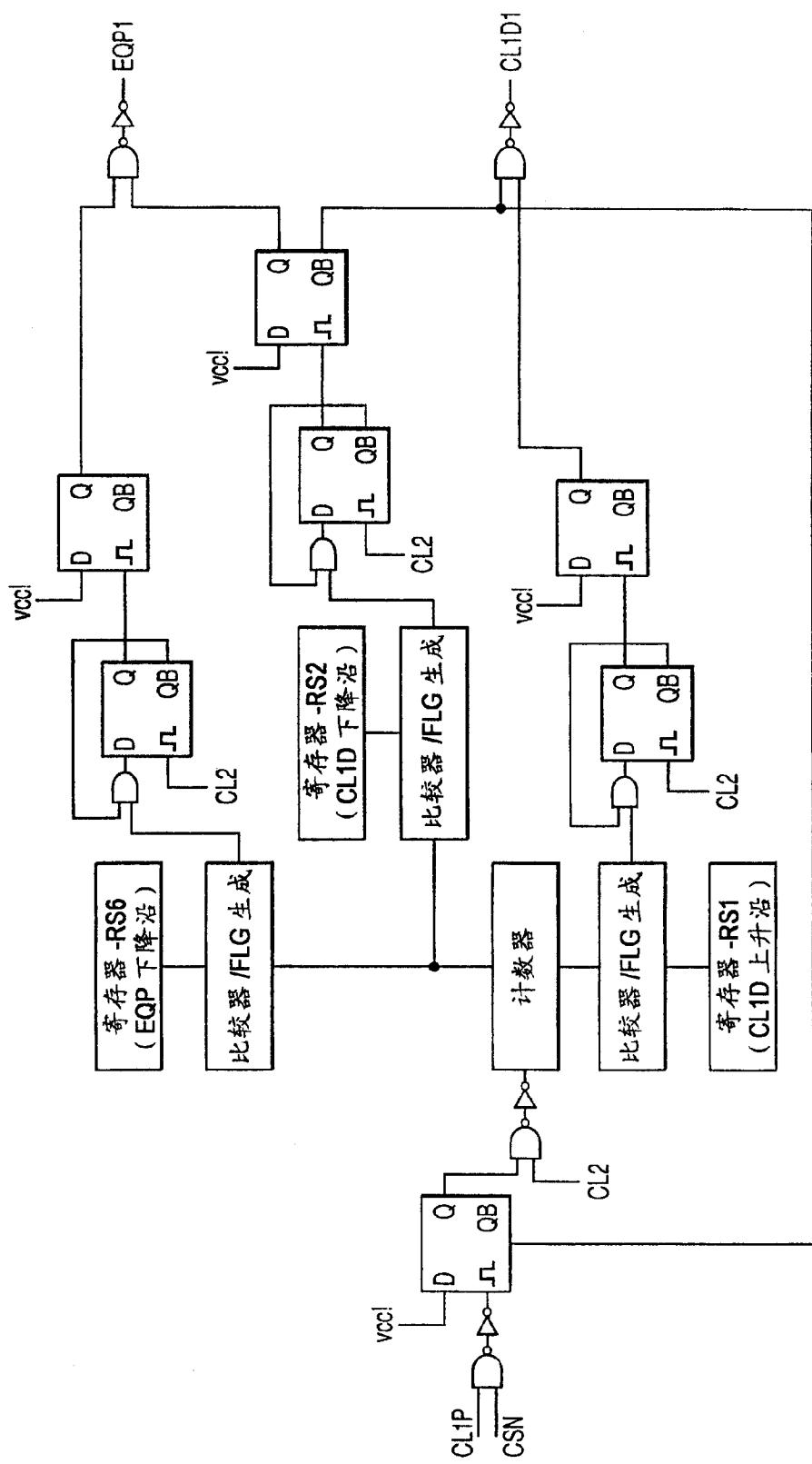

[0052] 图10是说明本实施例1的液晶显示装置中的数据驱动器的结构例和动作的示意图,是表示内部控制信号生成电路的初级的结构例的电路图。

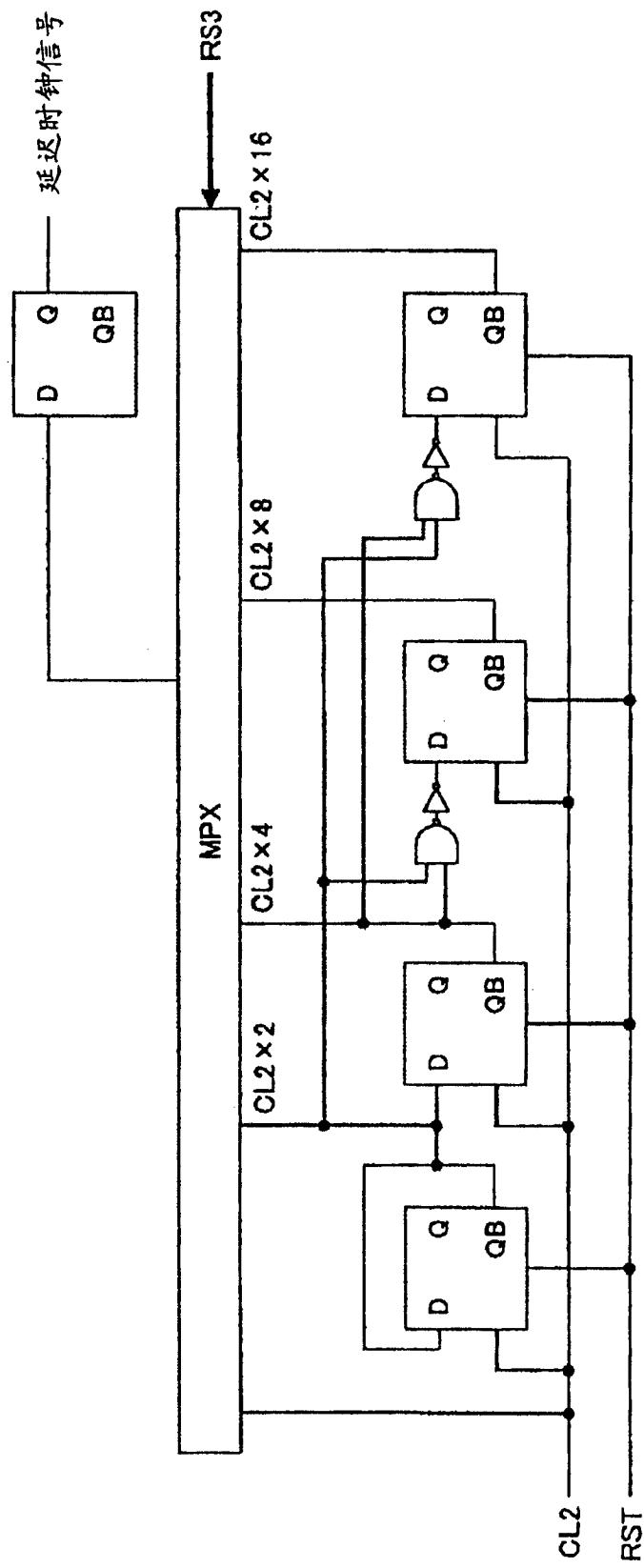

[0053] 图 11 是说明本实施例 1 的液晶显示装置中的数据驱动器的结构例和动作的示意图, 是表示内部控制信号生成电路的移位寄存器用时钟信号的结构例的电路图。

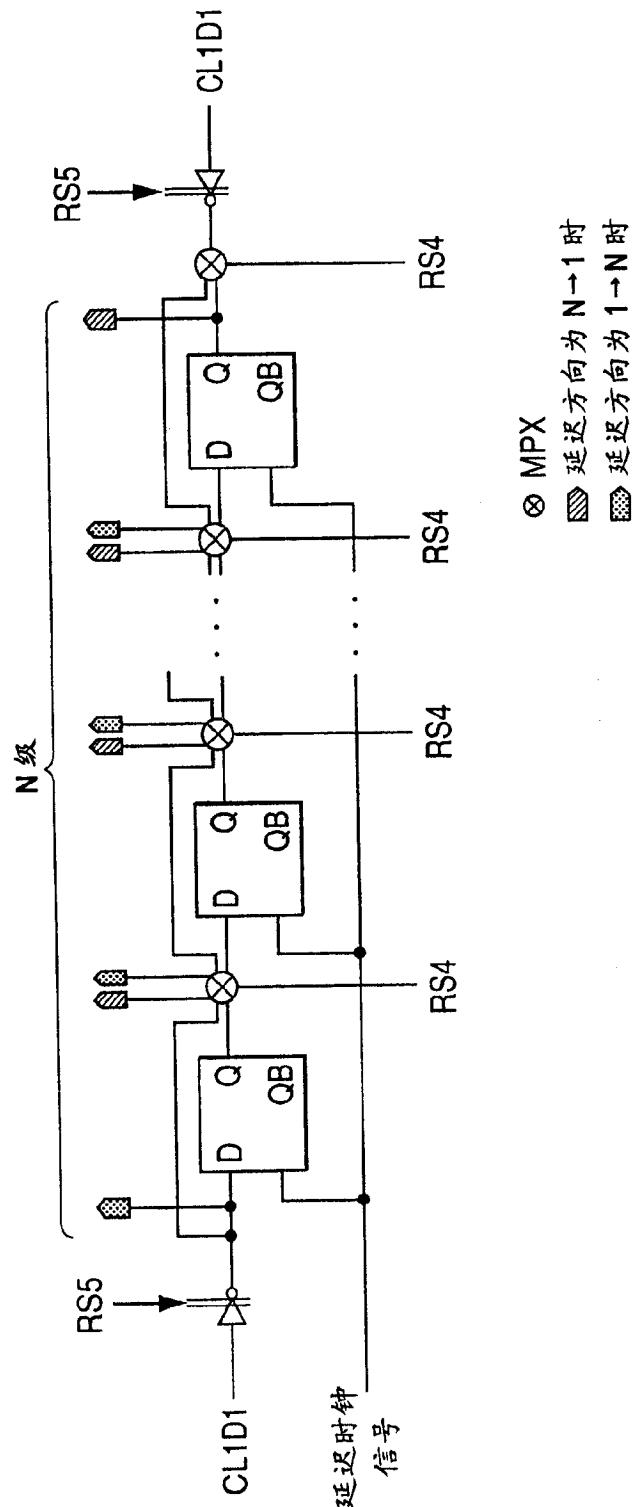

[0054] 图 12 是说明本实施例 1 的液晶显示装置中的数据驱动器的结构例和动作的示意图, 是表示内部控制信号生成电路的第 2 级以后的结构例的电路图。

[0055] 图 13 是说明本实施例 1 的液晶显示装置中的数据驱动器的结构例和动作的示意图, 是说明移位寄存器的输入方法的图。

[0056] 图 14 是说明本实施例 1 的液晶显示装置中的数据驱动器的结构例和动作的示意图, 是说明移位寄存器的输入方法的图。

[0057] 图 15 是说明本实施例 1 的液晶显示装置中的数据驱动器的结构例和动作的示意图, 是说明移位寄存器的输入例的图。

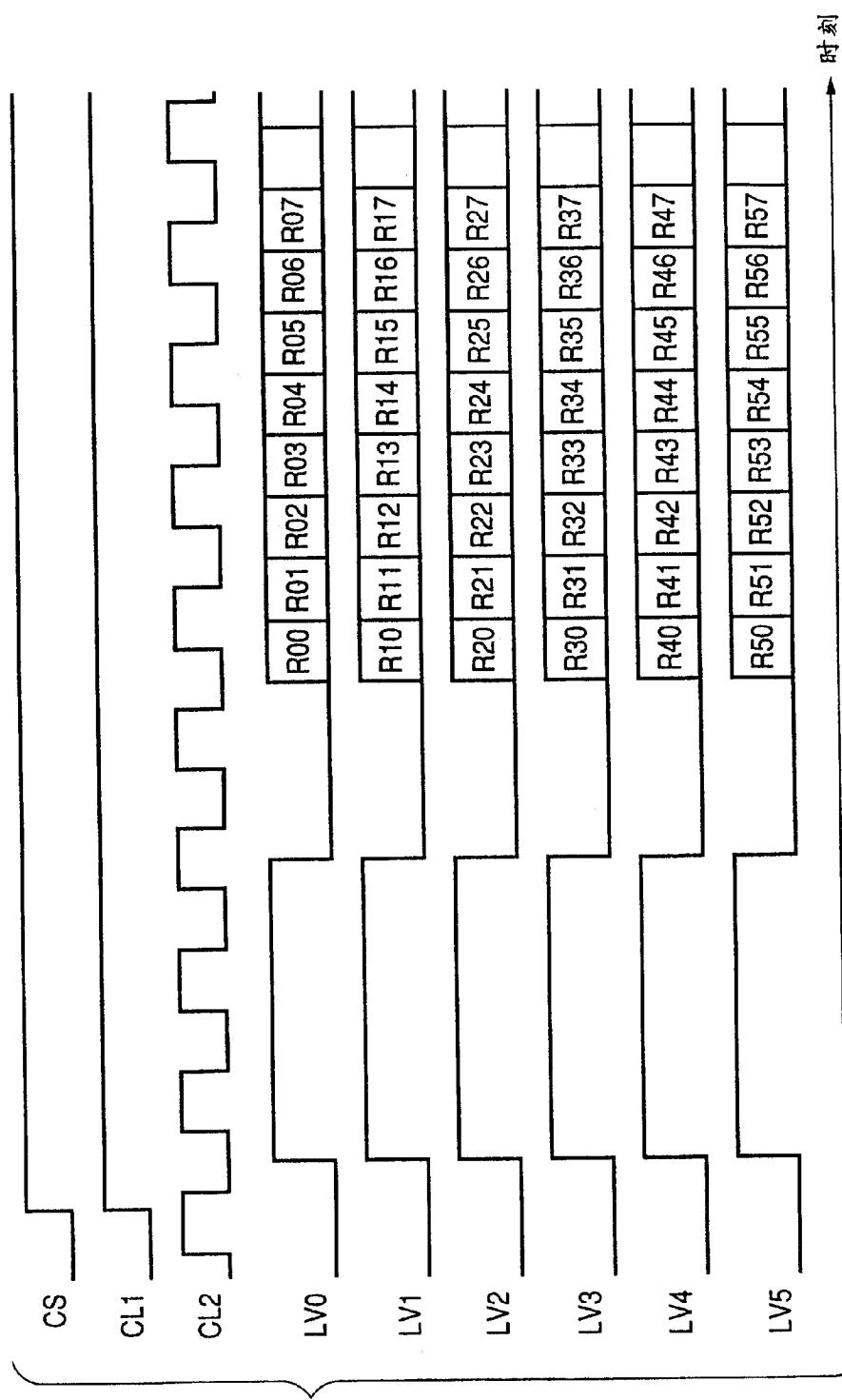

[0058] 图 16 是说明本实施例 1 的液晶显示装置中的数据驱动器的结构例和动作的示意图, 是说明移位寄存器的输入例的图。

[0059] 图 17 是说明本实施例 1 的液晶显示装置中的数据驱动器的结构例和动作的示意图, 是说明移位寄存器的输入例的图。

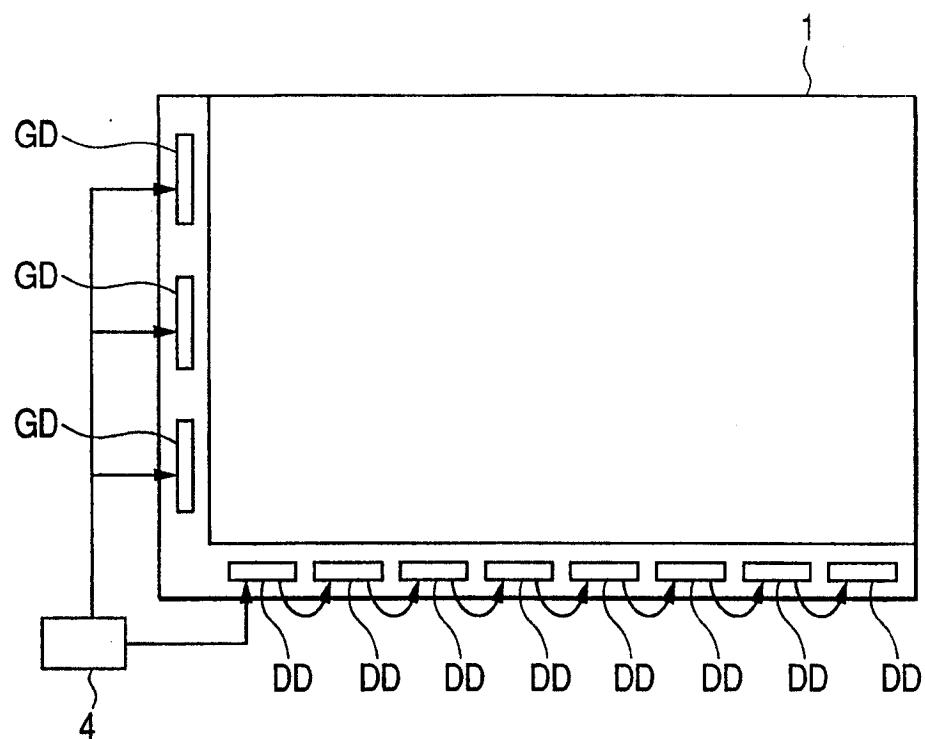

[0060] 图 18 是用于说明显示数据的传送方法的示意图, 是表示仅将扫描驱动器配置在一边时的传送方法的例子的图。

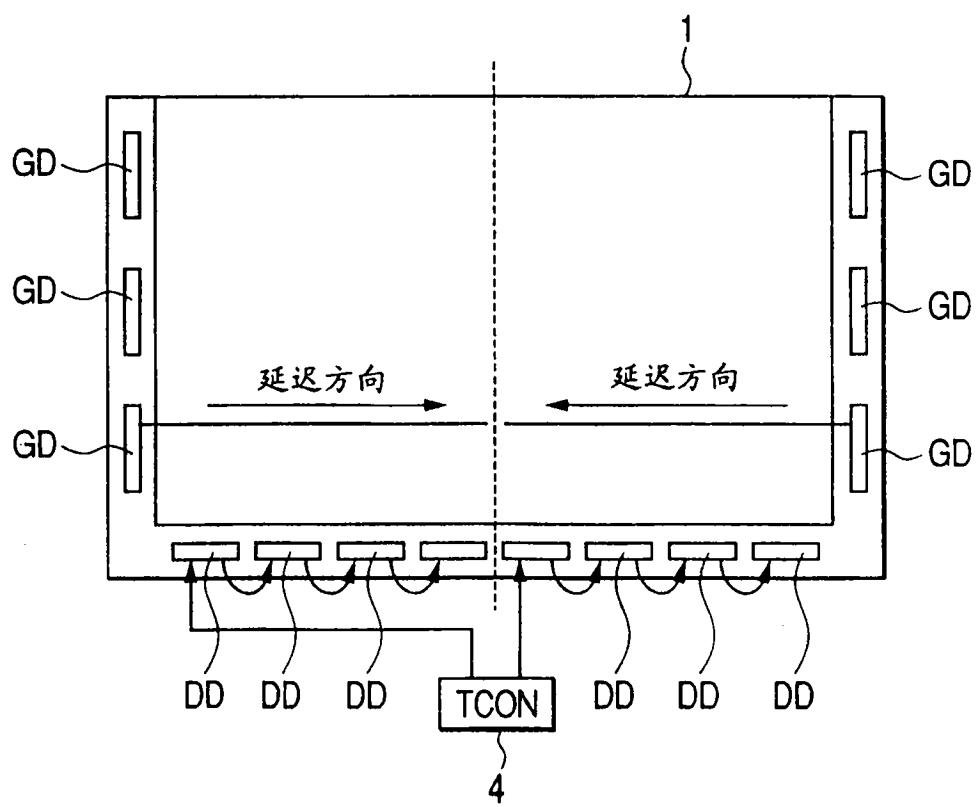

[0061] 图 19 是用于说明显示数据的传送方法的示意图, 是表示将扫描驱动器配置在相对的 2 边时的传送方法的例的图。

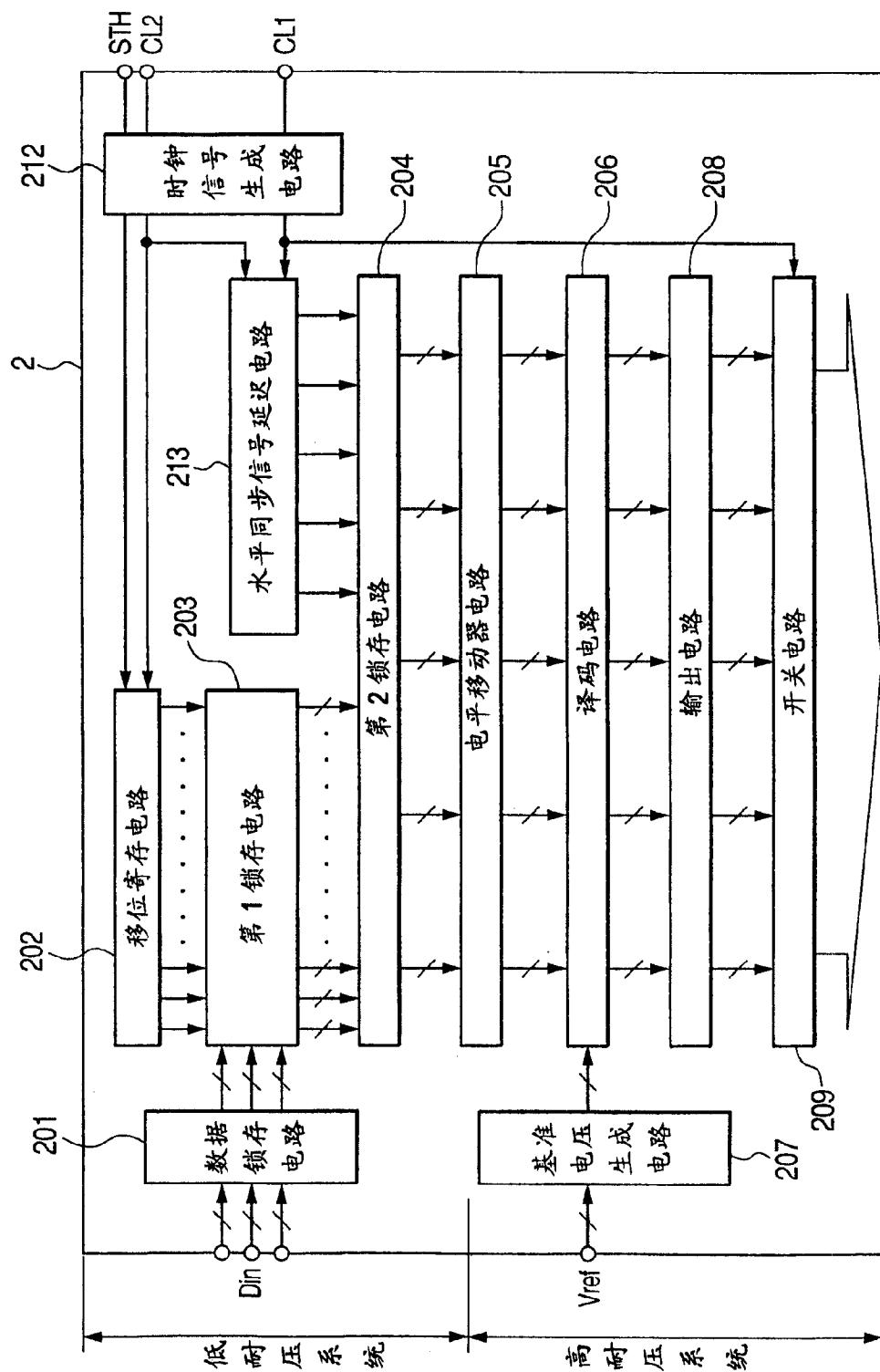

[0062] 图 20 是表示本发明的实施例 2 的显示装置的概略结构的示意图, 是表示数据驱动器的结构例的框图。

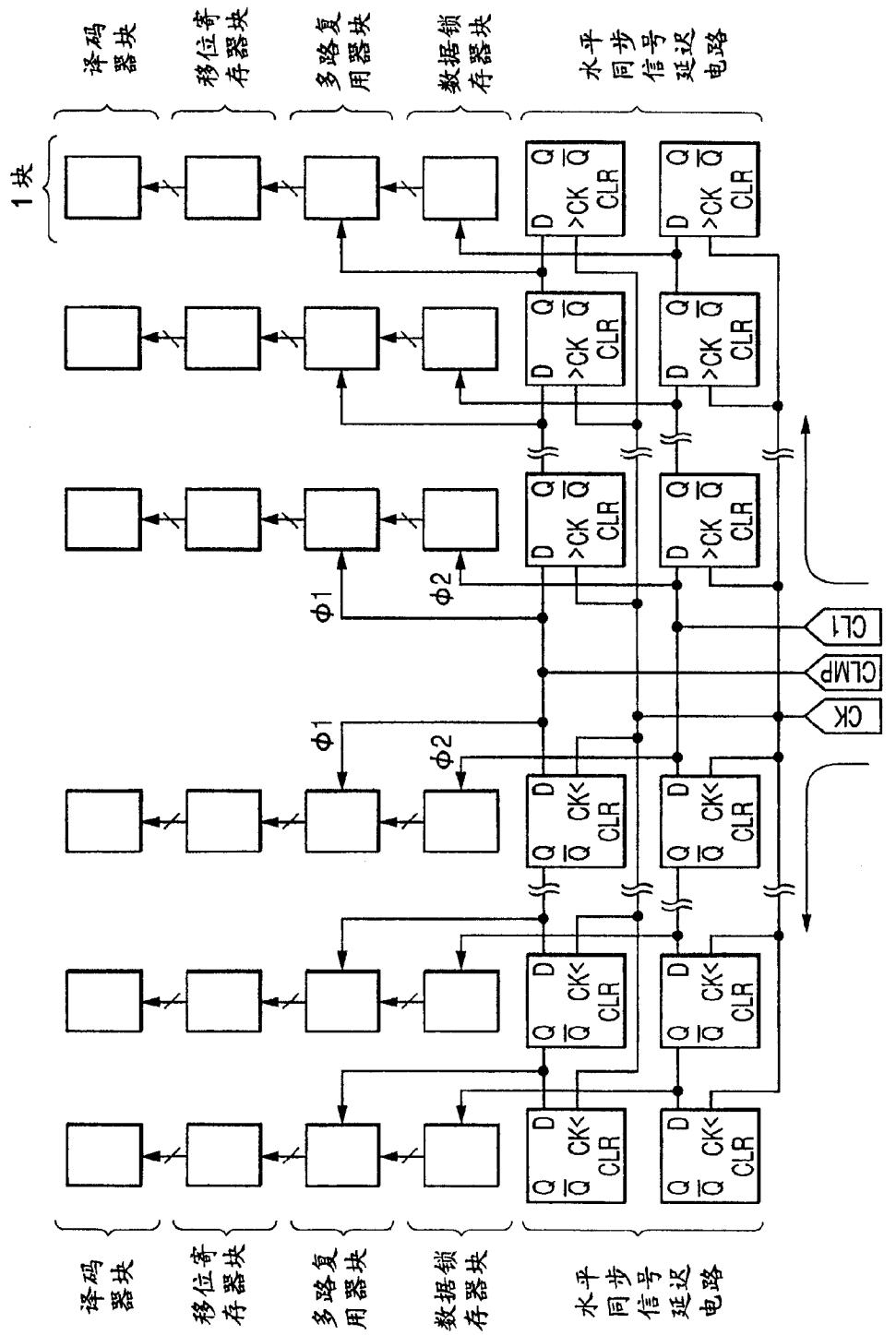

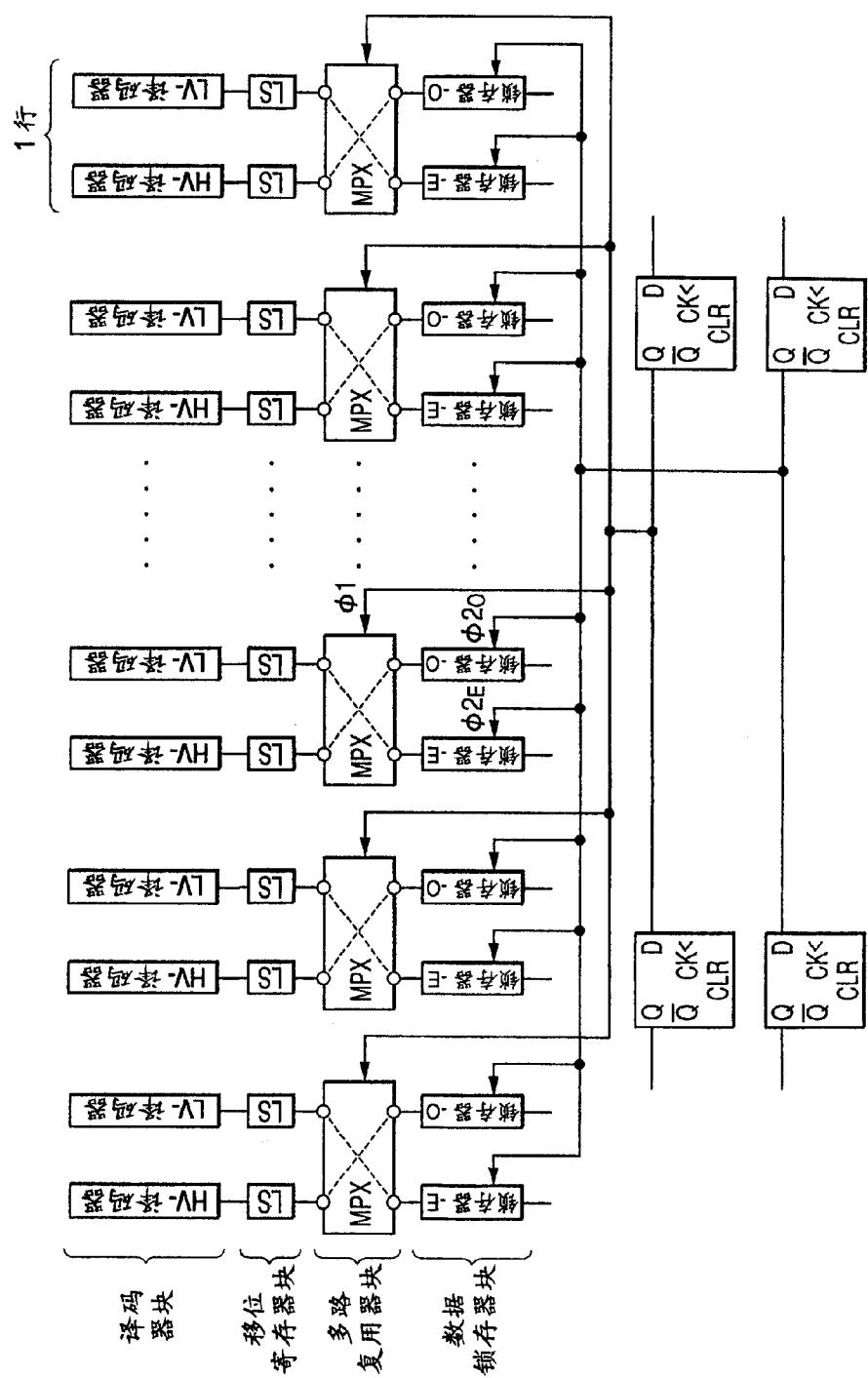

[0063] 图 21 是表示本发明的实施例 2 的显示装置的概略结构的示意图, 是表示从水平同步信号延迟电路到译码电路的结构例的电路框图。

[0064] 图 22 是表示本发明的实施例 2 的显示装置的概略结构的示意图, 是表示从水平同步信号延迟电路到译码电路的结构例的电路框图。

[0065] 图 23 是用于说明显示数据的取入的延迟方法的示意图。

[0066] 图 24 是表示本发明的实施例 3 的显示装置的概略结构的示意图, 是表示扫描驱动器的结构例的框图。

[0067] 图 25 是表示本发明的实施例 3 的显示装置的概略结构的示意图, 是表示移位寄存电路的结构例的电路框图。

[0068] 图 26 是表示本发明的实施例 3 的显示装置中的扫描信号的时序波形的示意图。

[0069] 图 27 是表示本发明的实施例 3 的扫描驱动器中的 3 值选择器电路的结构例的电路图。

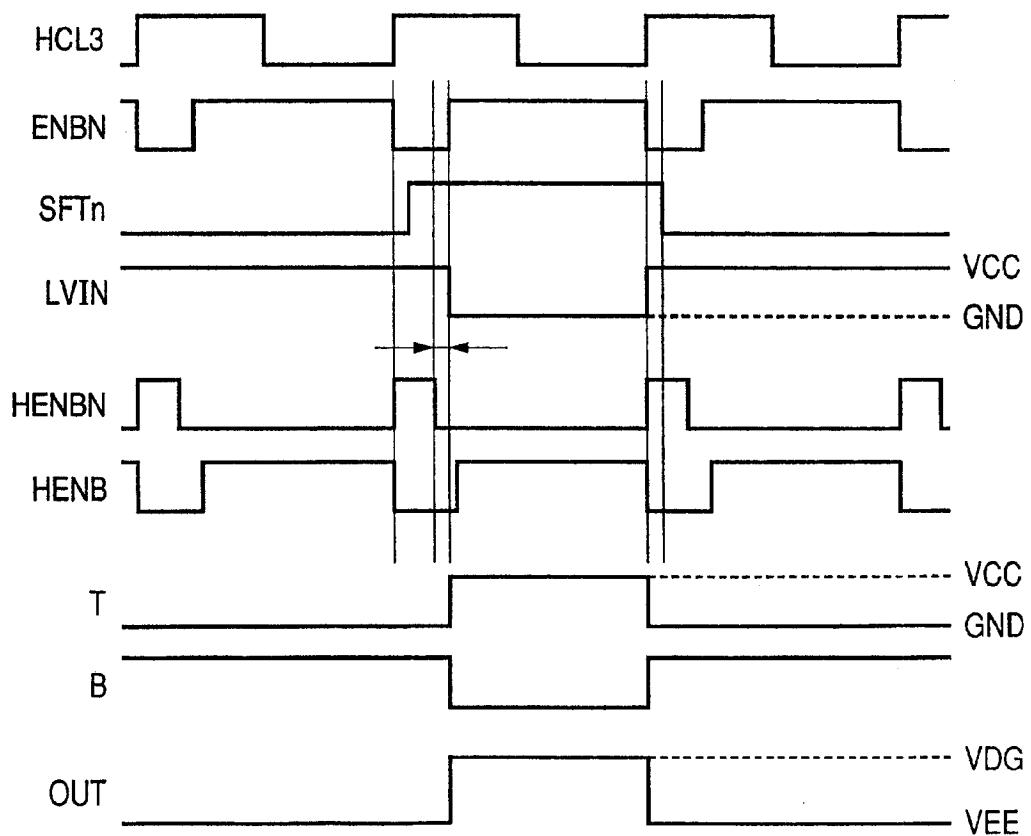

[0070] 图 28 是说明 3 值选择器电路的动作的波形图。

[0071] 图 29 是表示 3 值输出时的扫描信号的输出波形的图。

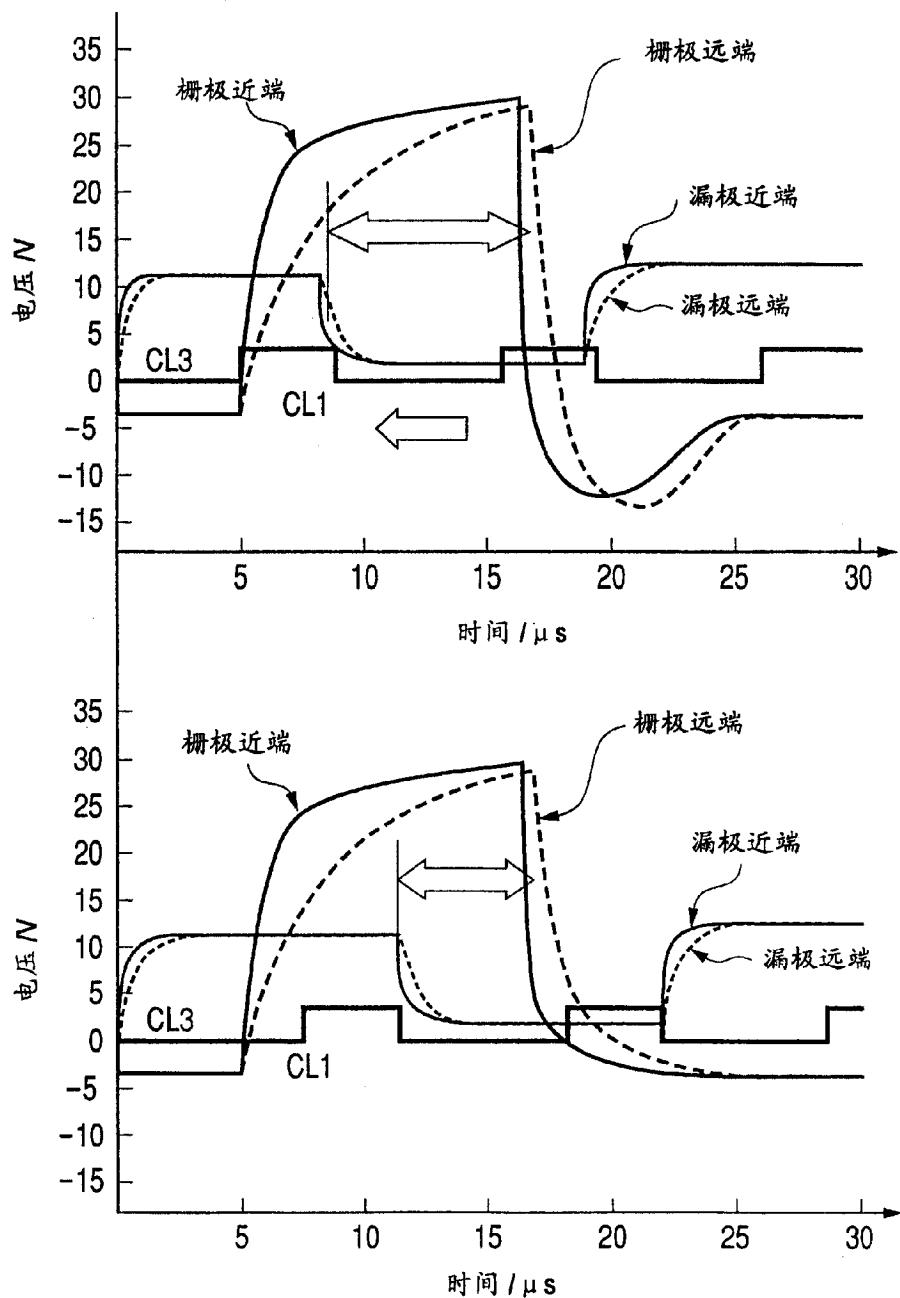

[0072] 图 30 是说明 3 值输出的作用效果的图。

[0073] 图 31 是表示移位寄存电路的结构例的图, 是示意地示出的电路图。

[0074] 图 32 是表示移位寄存电路的结构例的图, 是具体地示出图 31 的电路的电路图。

[0075] 图 33 是表示本发明的实施例 4 的显示装置的概略结构的示意图, 是表示扫描驱动器的结构例的框图。

[0076] 图 34 是表示本发明的实施例 4 的显示装置的概略结构的示意图, 是表示电平移动器电路的结构例的框图。

[0077] 图 35 是说明本发明的实施例 4 的电平移动器电路的动作的示意图。

[0078] 图 36 是表示用于与本发明的实施例 4 的电平移动器电路进行比较的以往的电平移动器电路的结构例的图。

[0079] 图 37 是表示图 36 中示出的电平移动器电路的动作的图。

[0080] 图 38 是表示生成高耐压的允许信号的差动电路的结构例的电路图。

[0081] 图 39 是说明本发明的实施例 4 的效果的示意图。

## 具体实施方式

[0082] 以下, 参照附图并与实施方式(实施例)一起详细说明本发明。

[0083] 此外, 在用于说明实施例的所有附图中, 具有相同功能的标以相同的标号, 其重复的说明从略。

[0084] 图 1 ~ 图 3 是表示应用本发明的显示装置的概略结构的示意图, 图 1 是表示液晶显示装置的结构例的框图, 图 2 是表示液晶显示板的结构的电路图, 图 3 是说明 1 个像素的结构和动作的图。

[0085] 应用本发明的显示装置, 例如, 如图 1 所示, 是具有液晶显示板 1、数据驱动器 2、扫描驱动器 3、时序控制器 4、以及液晶驱动电源 5 的液晶显示装置。

[0086] 上述液晶显示板 1, 例如, 如图 2 和图 3 所示, 按矩阵状配置有多条漏极线 DL 和多条栅极线 GL, 各漏极线 DL 与数据驱动器 2 连接, 各栅极线 GL 与扫描驱动器 3 连接。而且, 在液晶显示板 1 上, 由邻接的 2 条漏极线 DL 和邻接的 2 条栅极线 GL 所包围的区域为 1 个像素区域, 并在各像素区域内配置有 TFT 元件、像素电极 PX 和公用电极 CT。这时, TFT 元件的栅电极与上述邻接的 2 条栅极线 GL 中的一条栅极线 GL 连接, 漏电极与上述邻接的 2 条漏极线 DL 中的一条漏极线 DL 连接。而且, TFT 元件的源电极与像素电极 PX 连接。另外, 在像素电极 PX 和与公用信号线 CL 连接的公用电极 CT 之间形成电容元件。

[0087] 当由这种液晶显示板 1 显示图像时, 在从数据驱动器 2 向各漏极线 DL 输出显示数据信号的状态下, 从扫描驱动器 3 向各栅极线 GL 依次输出扫描信号。这时, 数据驱动器 2 和扫描驱动器 3 的各信号的输出的时序由时序控制器 4 控制。

[0088] [实施例 1]

[0089] 图 4 ~ 图 6 是用于说明本发明的实施例 1 的液晶显示装置的动作原理的示意图, 图 4 是说明漏极线的划分方法的图, 图 5 是说明显示数据的输出方法的图, 图 6 是说明延迟量的设定方法的图。

[0090] 本实施例 1 的液晶显示装置, 是以防止对上述液晶显示板 1 上沿栅极线 GL 的延伸方向排列的各像素的 TFT 元件写入数据的时间的离差的发生为目的的显示装置。在这种液晶显示装置中, 例如, 如图 4 所示, 将配置在液晶显示板 1 上的多条漏极线 DL 划分为多个块 DBL1 ~ DBLn。而且, 当从数据驱动器 2 向各漏极线 DL 输出显示数据信号(灰度等级电压信号)时, 例如图 5 所示, 使对各块 DBL1 ~ DBLn 输出的时序错开。这时, 具体地说, 如图 5 所示, 从栅极线 GL 的最靠近输入端(扫描驱动器 3)的块 DBL1 到离得最远的块 DBLn, 使输出的时序越来越延迟。

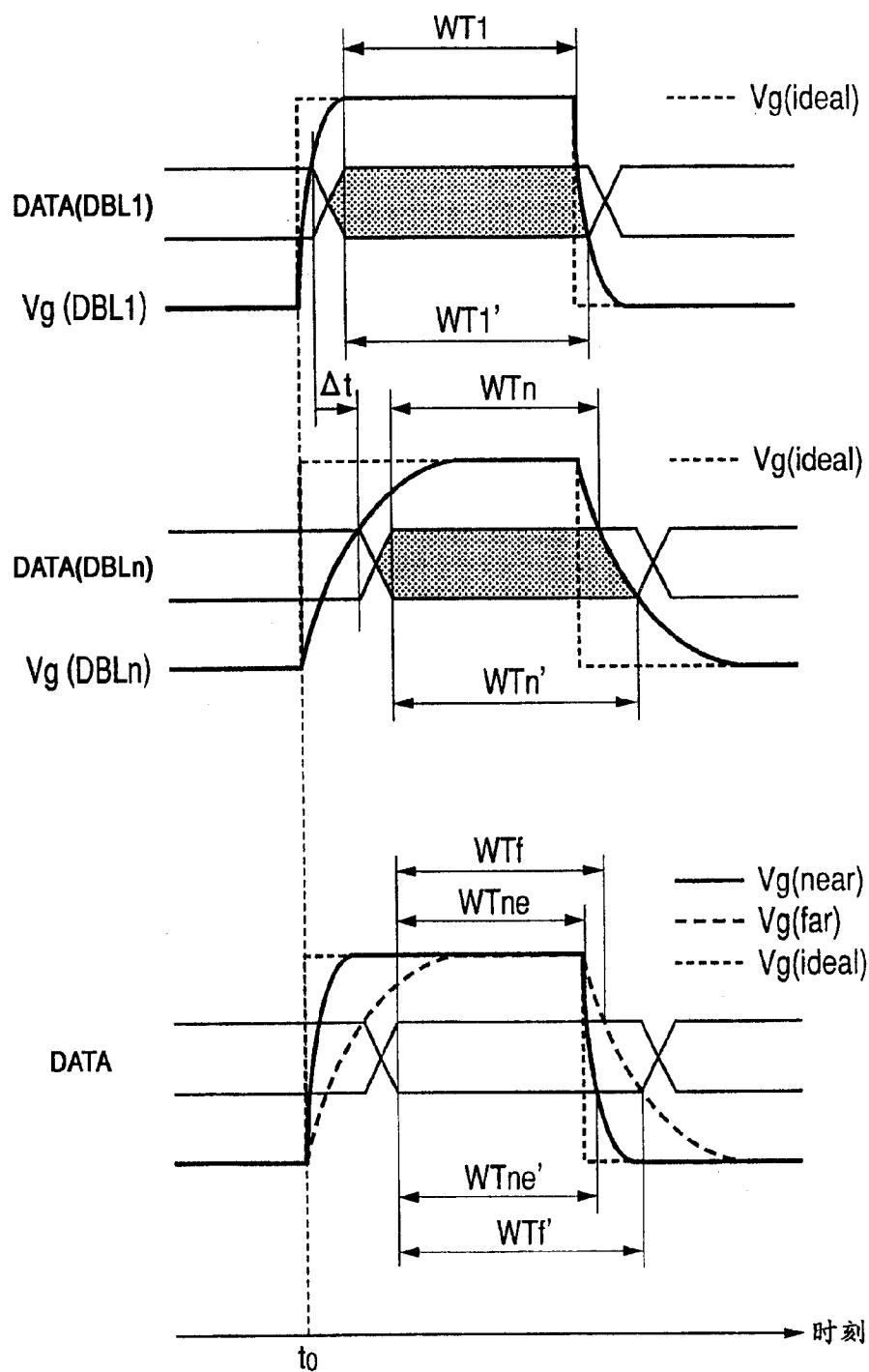

[0091] 另外,将显示数据信号的输出时序延迟时的延迟量(延迟时间),基于各块DBL2~DBLn内的栅极线GL的扫描信号的波形的平缓程度来设定。输入到栅极线GL的扫描信号的理想波形,例如,是像图6中用虚线示出的扫描信号的波形Vg(ideal)那样的矩形。但是,从扫描驱动器3向栅极线GL输出的扫描信号,在到达各块的区域之前波形变得平缓了。这时,离扫描驱动器3最近的块DBL1内的扫描信号的波形Vg(DBL1),如图6所示,上升沿陡峭、下降沿也陡峭。另一方面,离扫描驱动器3最远的块DBLn内的扫描信号的波形Vg(DBLn),如图6所示,上升沿平缓,下降沿也平缓。

[0092] 在以往的液晶显示装置中,如图6的下侧所示,对所有的漏极线以相同的时序输出显示数据信号DATA。另外,在液晶显示装置中,扫描信号和显示数据信号的时序,通常根据栅极远端的波形Vg(far)和显示数据信号DATA的最低电位的关系来决定,以免写入下一个显示数据信号。因此,像栅极近端的波形Vg(near)那样的上升沿和下降沿陡峭的区域上的写入时间WTne、WTne',比栅极远端的写入时间WTf、WTf'短。

[0093] 因此,在本实施例1的液晶显示装置中,对块DBL1,根据扫描信号的波形Vg(DBL1)和显示数据信号DATA(DBL1)的最低电位的关系确定显示数据信号DATA(DBL1)的输出时序。而且,对块DBLn,根据扫描信号的波形Vg(DBLn)和显示数据信号DATA(DBLn)的最低电位的关系确定显示数据信号DATA(DBLn)的输出时序。按照这种方式,例如,如图6所示,栅极近端的块DBL1的显示数据信号DATA(DBL1)的重写时刻与栅极远端的块DBLn的显示数据信号DATA(DBLn)的重写时刻产生 $\Delta t$ (秒)的时间差。就是说,能够通过将对栅极近端的块DBL1的显示数据信号的输出时序提早 $\Delta t$ (秒)而弥补在栅极近端的块DBL1内的写入时间的不足。由此,能够使栅极近端的块DBL1内的写入时间WT1、WT1'与栅极远端的块DBLn内的写入时间WTn、WTn'大致相等。此外,在图6中仅示出离扫描驱动器3最近的块DBL1和最远的块DBLn,但实际上为了使所有的块DBL1~DBLn内的显示数据的写入时间大致相等而设定输出时序。

[0094] 图7~图17是说明本实施例1的液晶显示装置中的数据驱动器的结构例和动作的示意图,图7是表示数据驱动器的结构例的框图,图8是说明显示数据的输出时序的图,图9是说明内部控制信号的生成方法的图,图10是表示内部控制信号生成电路的初级的结构例的电路图,图11是表示内部控制信号生成电路的移位寄存器用时钟信号的结构例的电路图,图12是表示内部控制信号生成电路的第2级以后的结构例的电路图,图13和图14是说明移位寄存器的输入方法的图,图15~图17是说明移位寄存器的输入例的图。

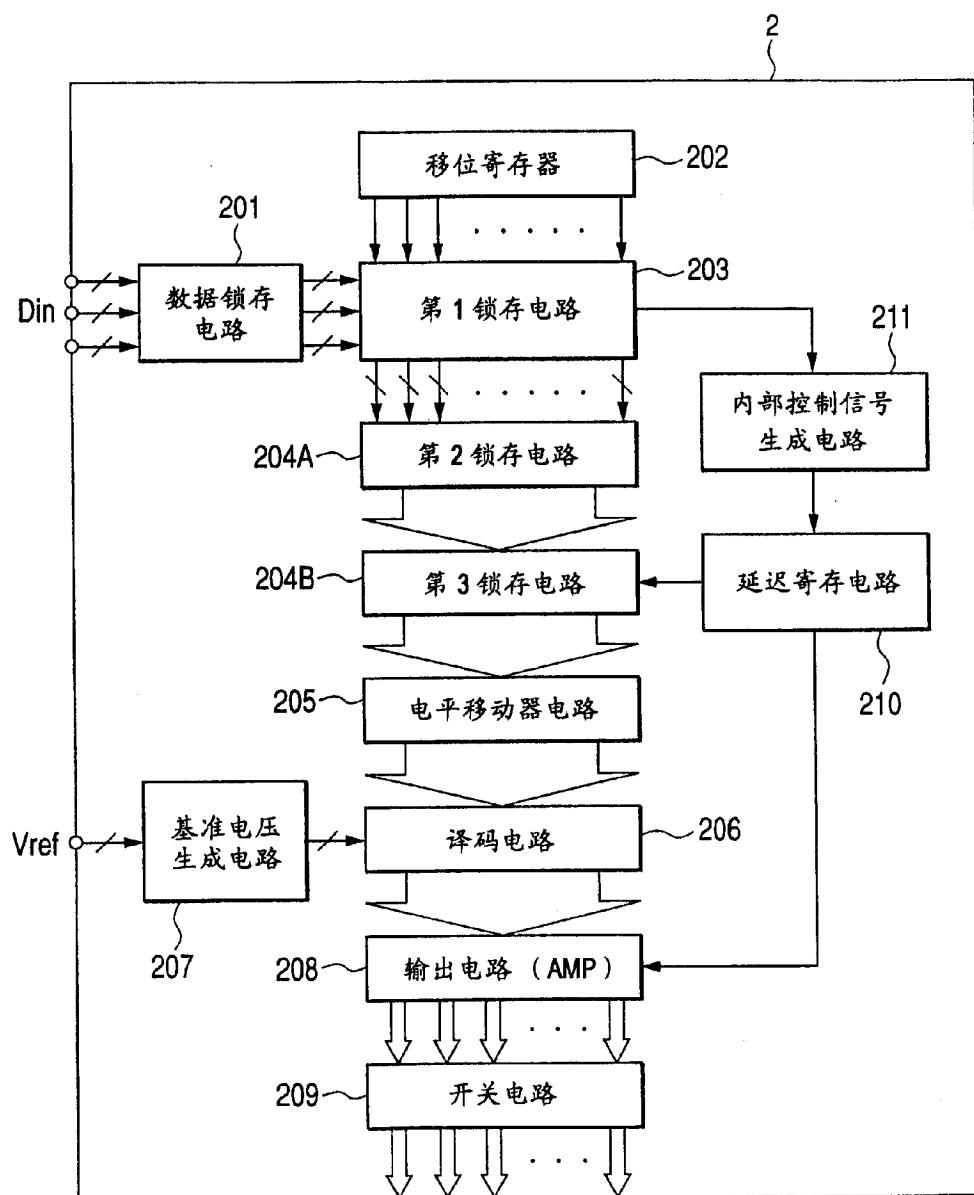

[0095] 在本实施例1的液晶显示装置中,在将从数据驱动器2向各块DBL1~DBLn的漏极线DL输出显示数据信号的时序错开(延迟)的情况下,例如,使数据驱动器2为如图7所示的结构。在图7所示的数据驱动器2的结构中,数据锁存电路201、移位寄存电路202、第1锁存电路203、第2锁存电路204A、第3锁存电路204B、电平移动器电路205、译码电路206、基准电压生成电路207、输出电路208、以及开关电路209的结构,是以往的数据驱动器也具备的结构。另外,在本实施例1的显示装置中,除上述各构成电路以外,还备有生成上述内部控制信号的内部控制信号生成电路210、预先存储用于内部控制信号的生成的设定的延迟寄存电路211。

[0096] 在数据驱动器2中,首先由数据锁存电路201暂时保持从外部输入的显示数据,并按时分方式传送到第1锁存电路203。第1锁存电路203,保持按时分方式传送来的显示数

据直到达到 1 水平同步期间。然后,只要达到 1 水平同步期间就传送到第 2 锁存电路 204A。第 2 锁存电路 204A,根据水平同步信号,将所保持的显示数据传送到第 3 锁存电路 204B,第 3 锁存电路 204B,根据来自内部控制信号生成电路 210 的内部控制信号,将显示数据传送到电平移动器电路 205。电平移动器电路 205,将接收到的显示数据的信号电平变换后传送到译码电路 206。译码电路 206,根据由基准电压生成电路 207 生成的基准电压和从电平移动器电路 205 接收到的显示数据,生成与显示数据的信号电平对应的灰度等级电压信号(模拟信号),将其传送到输出电路 208。

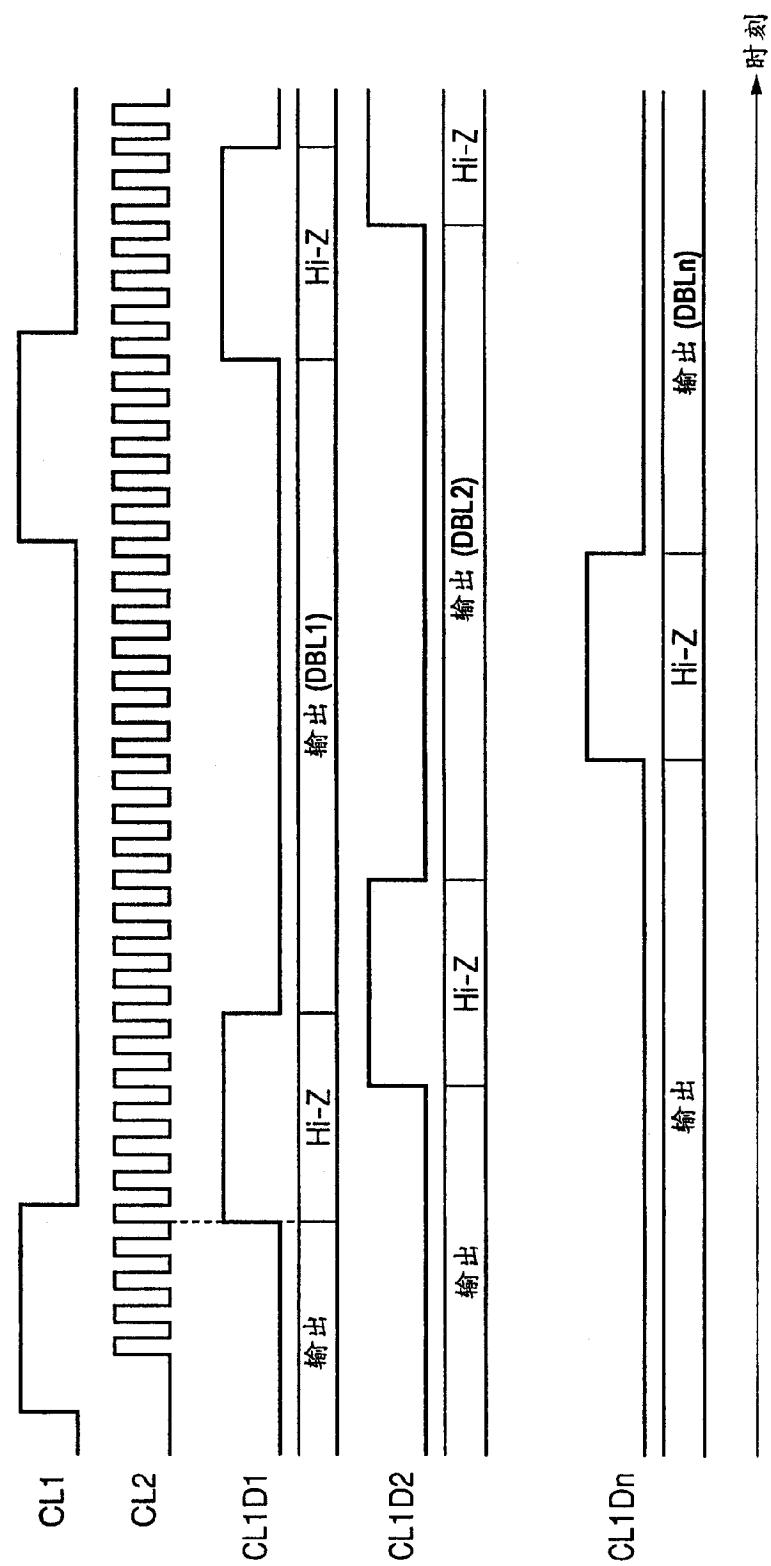

[0097] 另外,第 1 锁存电路 203,一边将显示数据传送到第 2 锁存电路 204A,一边将指示各块 DBL1 ~ DBLn 的输出时序的寄存数据传送到延迟寄存电路 211。延迟寄存电路 211,根据寄存数据将输出时序的设定所需的信息传送到内部控制信号生成电路 210。内部控制信号生成电路 210,根据接收到的信息生成内部控制信号,将其传送到第 3 锁存电路 204B 和输出电路 208。此时生成的内部控制信号,例如,如图 8 的 CL1D1 ~ CL1Dn 所示,是将各块 DBL1 ~ DBLn 的输出时序设定为使其与在数据驱动器 2 的内部生成的时钟信号 CL2 同步的信号。

[0098] 输出电路 208,将从译码电路 206 接收到的灰度等级电压信号放大,并根据内部控制信号以对每个块设定的时序将灰度等级电压信号传送到开关电路 209。然后,开关电路 209 按接收到的灰度等级电压信号顺序将这些灰度等级电压信号依次输出到漏极线 DL。

[0099] 当由内部控制信号生成电路 210 生成内部控制信号时,例如,如图 9 所示,需要内部控制信号 CL1D1 ~ CL15 的上升沿设定 RS1 及 CL1D1 和 EQ2 的下降沿设定 RS2、延迟宽度的设定 RS3、延迟块的划分的设定 RS4、所延迟的方向的设定 RS5、均衡信号 EQ 的设定。这时,内部控制信号的上升沿设定 RS1 和下降沿设定 RS2,例如,通过寄存器设定而用内部时钟信号 CL2 的计数值来设定。另外,延迟宽度的设定 RS3,由将内部时钟信号 CL2 分频后的移位寄存用时钟信号设定。延迟块的划分的设定 RS4,例如,相对于前级的内部时钟信号延迟时设定为“1”、不延迟时设定为“0”。在所延迟的方向的设定 RS5 中,设定从第 1 个块 DBL1 向第 N 个块 DBLn 延迟还是按其相反顺序延迟。

[0100] 这时,最初输出的块的内部控制信号 CL1D1 由计数电路生成、其余的内部控制信号 CL1D2 ~ CL1D5 由移位寄存器生成。

[0101] 生成上述最初输出的块的内部控制信号 CL1D1 和均衡信号 EQP1 的计数电路,例如,具有如图 10 所示的结构。在该计数电路中,利用触发电路、内部控制信号的上升沿设定 RS1 和下降沿设定 RS2、以及均衡信号的下降沿设定 RS6,根据由时序控制器所输入的水平同步时钟信号 CL1P 和内部时钟信号 CL2 等生成内部控制信号 CL1D1 和均衡信号 EQP1。

[0102] 另外,其余的内部控制信号,由移位寄存器用时钟信号电路和移位寄存电路基于由上述计数电路生成的内部控制信号 CL1D1 设定对该内部控制信号 CL1D1 延迟多少而生成。这时,移位寄存器用时钟信号电路,例如,具有如图 11 所示的结构。在该移位寄存器用时钟信号电路中,以内部时钟信号 CL2 的 1 个周期为基准,生成为其 2 倍、4 倍、8 倍、16 倍的延迟时钟信号。

[0103] 另外,上述移位寄存电路,例如,具有如图 12 所示的结构。在该移位寄存器中,根据由上述计数电路生成的内部控制信号 CL1D1、由上述移位寄存器用时钟信号电路生成的延迟时钟信号、延迟块的划分的设定 RS4 和所延迟的方向的设定 RS5,生成其余块的内部控制信号。

制信号 CL1D2 ~ CL1DN。

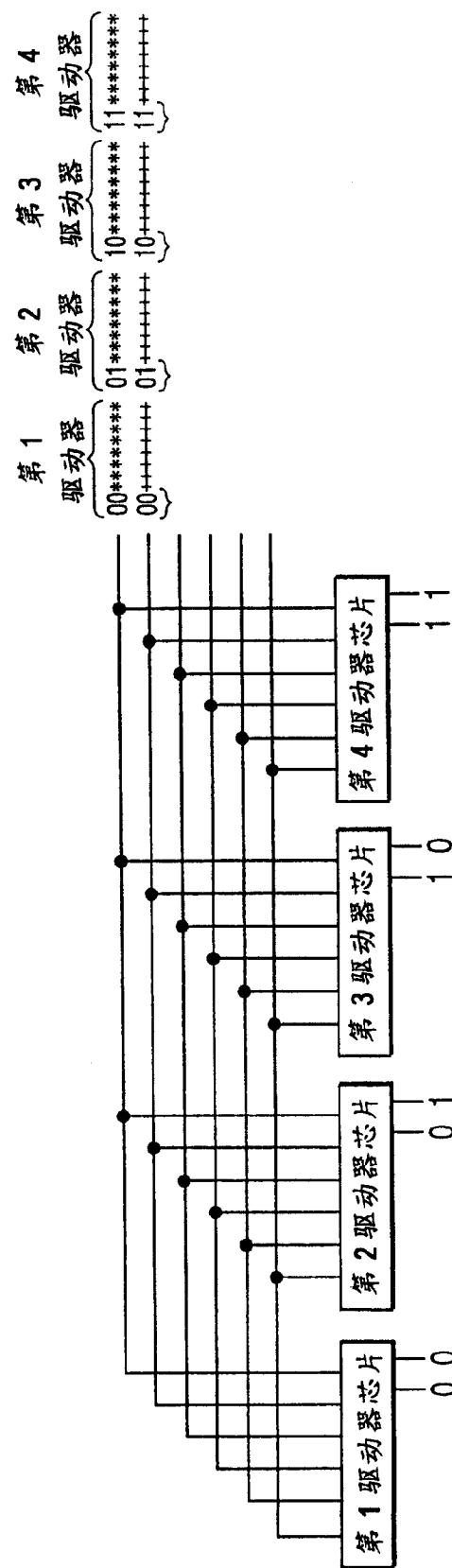

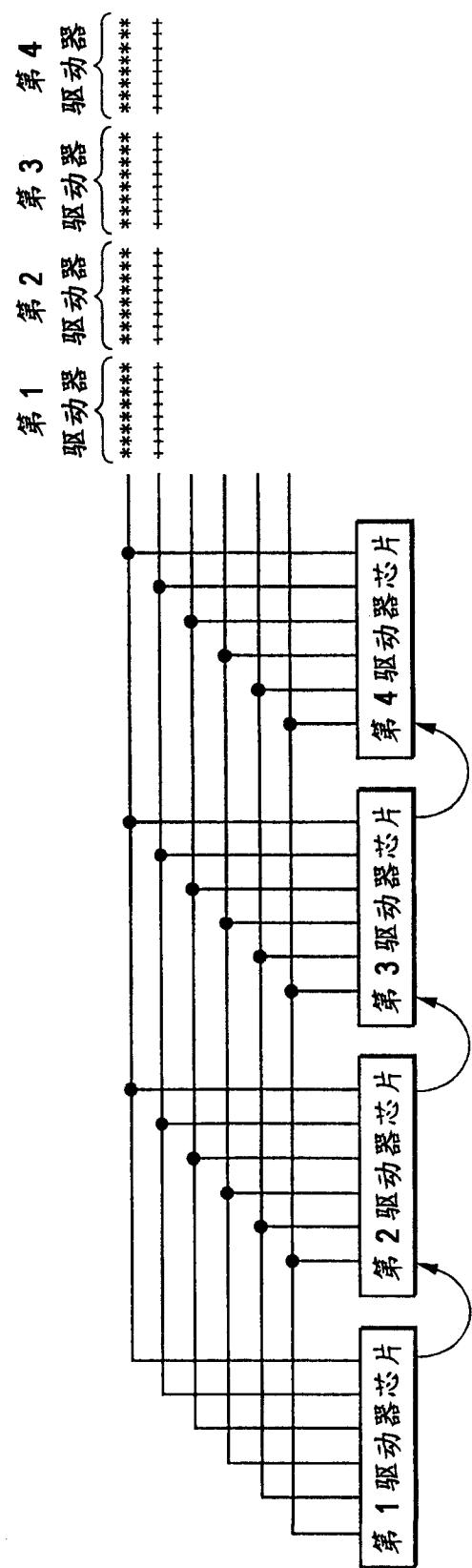

[0104] 上述数据驱动器,通常由多个驱动 IC(驱动器芯片)DD 构成,如图 13 和图 14 所示,各驱动 IC DD 由公用总线布线连接。这时,要传送到各驱动 IC DD 的数据汇总地传送到各布线上。因此,各驱动 ICDD,需要预先能够判别在接收到的数据中哪个部分是用于其自身的驱动 IC 的数据。这时,例如,如图 13 所示,如果在各驱动 IC DD 中具有用于识别的地址信息,则将地址信息附加在各驱动 IC DD 用的数据的起始进行发送。按照这种方式,各驱动 IC DD 能够读取附加了自身的地址信息的部分的数据作为所分配的数据。

[0105] 另外,当在各驱动 IC DD 中没有用于识别的地址信息时,预先指定从最初的 1 个数据起逐个地计数的第几个数据为各驱动 IC DD 的数据的输入开始数据,如图 14 所示,在各驱动 IC DD 读完分配给其自身的数据的时刻,向下一级驱动 IC 传送载波信号。

[0106] 以下,作为数据驱动器的输入接口的一例,用图 15 ~ 图 17 说明被称为 mini-LVDS 的接口时的显示数据的输入方法。

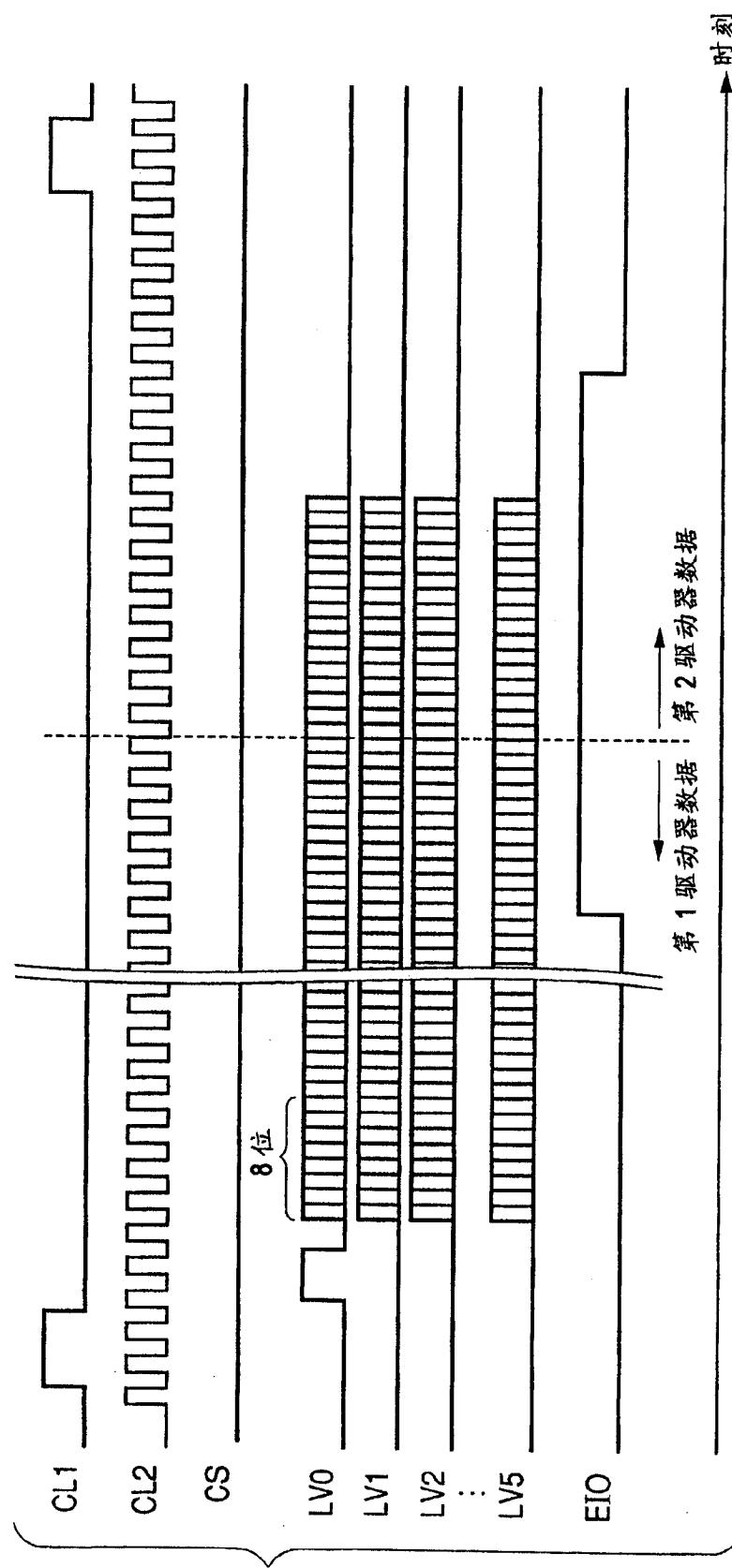

[0107] 在上述 mini-LVDS 接口中,通常,数据输入线(公用总线布线)为 6 条,显示数据如图 15 所示,以串行数据的方式从时序控制器 4 进行传送。这时,第 2 驱动器(driver),将来自第 1 驱动器(driver)的载波作为允许信号 EIO,开始取入数据。

[0108] 然后,例如图 16 所示,若将 CS 信号变为 H(高电平)这一情况作为寄存器设定模式,并将生成内部控制信号所需的寄存器设定用的值写入到数据的起始的 8 位(bit)的值中,则基于该值设定延迟寄存电路 211 的值。

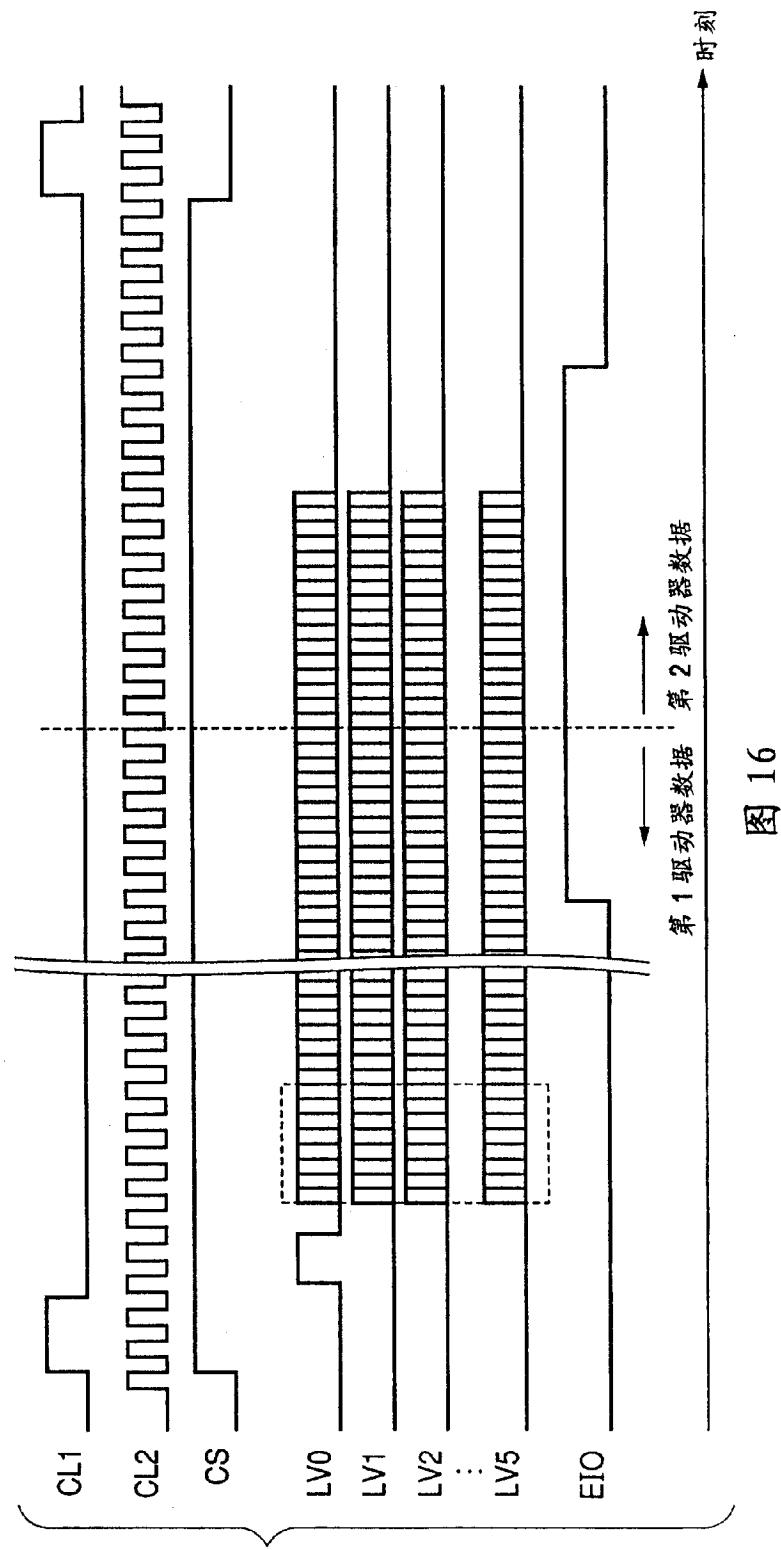

[0109] 当在显示数据的起始写入寄存器设定用的值时,例如,如图 17 所示,写入由数据线 LV0 传送的数据的起始的 8 位部分 R00 ~ R07、由数据线 LV1 传送的数据的开头的 8 位的 R10 ~ R17、由数据线 LV2 传送的数据的开头的 8 位的 R20 ~ R27、由数据线 LV3 传送的数据的起始的 8 位的 R30 ~ R37、由数据线 LV4 传送的数据的起始的 8 位的 R40 ~ R47、由数据线 LV5 传送的数据的起始的 8 位的 R50 ~ R57。这时,对于由数据线 LV0 传送的数据的起始的 8 位的 R00 ~ R07,例如,如下面的表 1 所示,写入设定延迟方向和延迟宽度的值。就是说,当延迟方向为从第 1 块到第 17 块时,例如,使由数据线 LV0 传送的数据位 R01 为“1”、数据位 R02 为“0”。另外,关于延迟宽度,只使与要设定的宽度对应的数据位为“1”、其余的数据位为“0”。

[0110] 【表 1】

[0111]

|   | 延迟方向设定 |      | 延迟宽度设定 |     |       |       |       |        |

|---|--------|------|--------|-----|-------|-------|-------|--------|

|   | R00    | R01  | R02    | R03 | R04   | R05   | R06   | R07    |

| — | —      | 1→17 | 17→1   | 无   | CL2/2 | CL2/4 | CL2/8 | CL2/16 |

[0112] 另外,对由数据线 LV1 传送的数据的起始的 8 位的 R10 ~ R17 和由数据线 LV2 传送的数据的起始的 8 位的 R20 ~ R27,例如,如下面的表 2 和表 3 所示,写入设定延迟块的划分、即使哪个块和块之间延迟的值。就是说,只使与要产生延迟的块之间对应的数据位为“1”、其余的数据位为“0”。

[0113] 【表 2】

[0114]

| 延迟块划分设定 (1) |         |         |         |         |         |         |         |

|-------------|---------|---------|---------|---------|---------|---------|---------|

| R10         | R11     | R12     | R13     | R14     | R15     | R16     | R17     |

| 9 - 10      | 10 - 11 | 11 - 12 | 12 - 13 | 13 - 14 | 14 - 15 | 15 - 16 | 16 - 17 |

[0115] 【表 3】

[0116]

| 延迟块划分设定 (2) |       |       |       |       |       |       |       |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| R20         | R21   | R22   | R23   | R24   | R25   | R26   | R27   |

| 1 - 2       | 2 - 3 | 3 - 4 | 4 - 5 | 5 - 6 | 6 - 7 | 7 - 8 | 8 - 9 |

[0117] 另外,对由数据线 LV3 传送的数据的起始的 8 位的 R30 ~ R37,例如,如下面的表 4-1 所示,写入设定内部控制(内部 CL1)信号的上升沿的值。该上升沿的设定,用时钟信号的 8 位计数值指定,并根据各数据位 R30 ~ R37 的值(“1”或“0”)的组合设定上升时间。这时,具体地说,例如,如下面的表 4-2 所示,根据取决于各数据位 R30 ~ R37 的值的 8 位计数值,将上升时间(延迟时钟脉冲数)设定为从 0 时钟脉冲(无延迟)到 255 时钟脉冲中的任何一个值。

[0118] 【表 4-1】

[0119]

| 内部 CL1 初始延迟上升沿设定 |     |     |     |     |     |     |     |

|------------------|-----|-----|-----|-----|-----|-----|-----|

| R30              | R31 | R32 | R33 | R34 | R35 | R36 | R37 |

| [0]              | [1] | [2] | [3] | [4] | [5] | [6] | [7] |

[0120] 【表 4-2】

[0121]

| 8 位计数值 | 延迟时钟脉冲数 |

|--------|---------|

| 8h' 00 | 0(无延迟)  |

| 8h' 01 | 1       |

| 8h' 02 | 2       |

| ·      | ·       |

| ·      | ·       |

| ·      | ·       |

|        |     |

|--------|-----|

| 8h' ff | 255 |

|--------|-----|

[0122] 另外,对由数据线 LV4 传送的数据的起始的 8 位的 R40 ~ R47,例如,如下面的表 5-1 所示,写入设定内部控制(内部 CL1)信号的下降沿的值。该下降沿的设定,也用时钟信号的 8 位计数值指定,并根据各数据位 R40 ~ R47 的值(“1”或“0”)的组合设定下降时间。这时,具体地说,例如,如下面表 5-2 所示,根据由各数据位 R40 ~ R47 的值确定的 8 位计数值,将下降时间(延迟时钟脉冲数)设定为从 0 时钟脉冲(无延迟)到 255 时钟脉冲中的任一个值。

[0123] 【表 5-1】

[0124]

| 内部 CL1 初始延迟下降沿设定 |     |     |     |     |     |     |     |

|------------------|-----|-----|-----|-----|-----|-----|-----|

| R40              | R41 | R42 | R43 | R44 | R45 | R46 | R47 |

| [0]              | [1] | [2] | [3] | [4] | [5] | [6] | [7] |

[0125] 【表 5-2】

[0126]

| 8 位计数值 | 延迟时钟脉冲数 |

|--------|---------|

| 8h' 00 | 0(无延迟)  |

| 8h' 01 | 1       |

| 8h' 02 | 2       |

| .      | .       |

| .      | .       |

| .      | .       |

| 8h' ff | 255     |

[0127] 另外,对由数据线 LV5 传送的数据的起始的 8 位的 R50 ~ R57,例如,如下面的表 6-1 所示,写入设定均衡信号的上升沿的值。该上升沿的设定,用时钟信号的 8 位计数值指定,并根据各数据位 R50 ~ R57 的值(“1”或“0”)的组合设定上升时间。这时,具体地说,例如,如下面的表 6-2 所示,根据取决于各数据位 R50 ~ R57 的值的 8 位计数值,将上升时间(延迟时钟脉冲数)设定为从 0 时钟脉冲(无延迟)到 8 时钟脉冲的任一个值。

[0128] 【表 6-1】

[0129]

| 均衡信号初始延迟上升沿设定 |     |     |     |     |     |     |     |

|---------------|-----|-----|-----|-----|-----|-----|-----|

| R50           | R51 | R52 | R53 | R54 | R55 | R56 | R57 |

| [0]           | [1] | [2] | [3] | [4] | [5] | [6] | [7] |

[0130] 【表 6-2】

[0131]

| 8 位计数值 | 延迟时钟脉冲数  |

|--------|----------|

| 8h' 00 | 0( 无延迟 ) |

| 8h' 01 | 1        |

| 8h' 02 | 2        |

| .      | .        |

| .      | .        |

| .      | .        |

| 8h' ff | 255      |

[0132] 图 18 和图 19 是用于说明显示数据的传送方法的示意图, 图 18 是表示仅将扫描驱动器配置在一边时的传送方法的例子的图, 图 19 是表示将扫描驱动器配置在相对的 2 边时的传送方法的例子的图。

[0133] 在本实施例 1 所述的显示数据信号的输出方法中, 不仅能够将各块的输出时序延迟, 而且还能够控制所延迟的方向。

[0134] 作为上述液晶显示板 1, 例如, 如图 18 所示, 一般是将扫描驱动器(驱动 IC GD)配置在显示板的一个边上。在这种液晶显示板的情况下, 如图 18 所示, 可以从离上述扫描驱动器最近的驱动 IC DD1 到最远的驱动 IC DD8 依次输入来自时序控制器 4 的显示数据和寄存数据, 并生成延迟宽度随着远离扫描驱动器而增大的内部控制信号。

[0135] 但是, 在上述液晶显示板 1 上, 例如, 如图 19 所示, 也可以将扫描驱动器的驱动 IC GD 配置在显示板的相对的 2 边。在这种液晶显示板的情况下, 如图 19 所示, 存在延迟方向彼此相反的 2 种栅极线。因此, 如果像本实施例 1 这样连延迟方向也能够控制, 则即使在如图 19 所示的液晶显示板的情况下, 也能够按照通过各块的栅极线的延迟方向延迟各块的显示数据的输出时序。

[0136] 如上所述, 按照本实施例 1 的液晶显示装置, 通过将漏极线划分为多个块并将对各块的显示数据的输出的时序错开(延迟), 能够调整沿栅极线的延伸方向排列的各像素的 TFT 元件的数据写入时间。因此, 能够防止因数据写入的不充分而引起的显示不均匀、显示品质的降低。

[0137] [ 实施例 2 ]

[0138] 图 20 ~ 图 22 是表示本发明的实施例 2 的显示装置的概略结构的示意图, 图 20 是表示数据驱动器的结构例的框图, 图 21 和图 22 是表示从水平同步信号延迟电路到译码电路为止的结构例的电路框图。

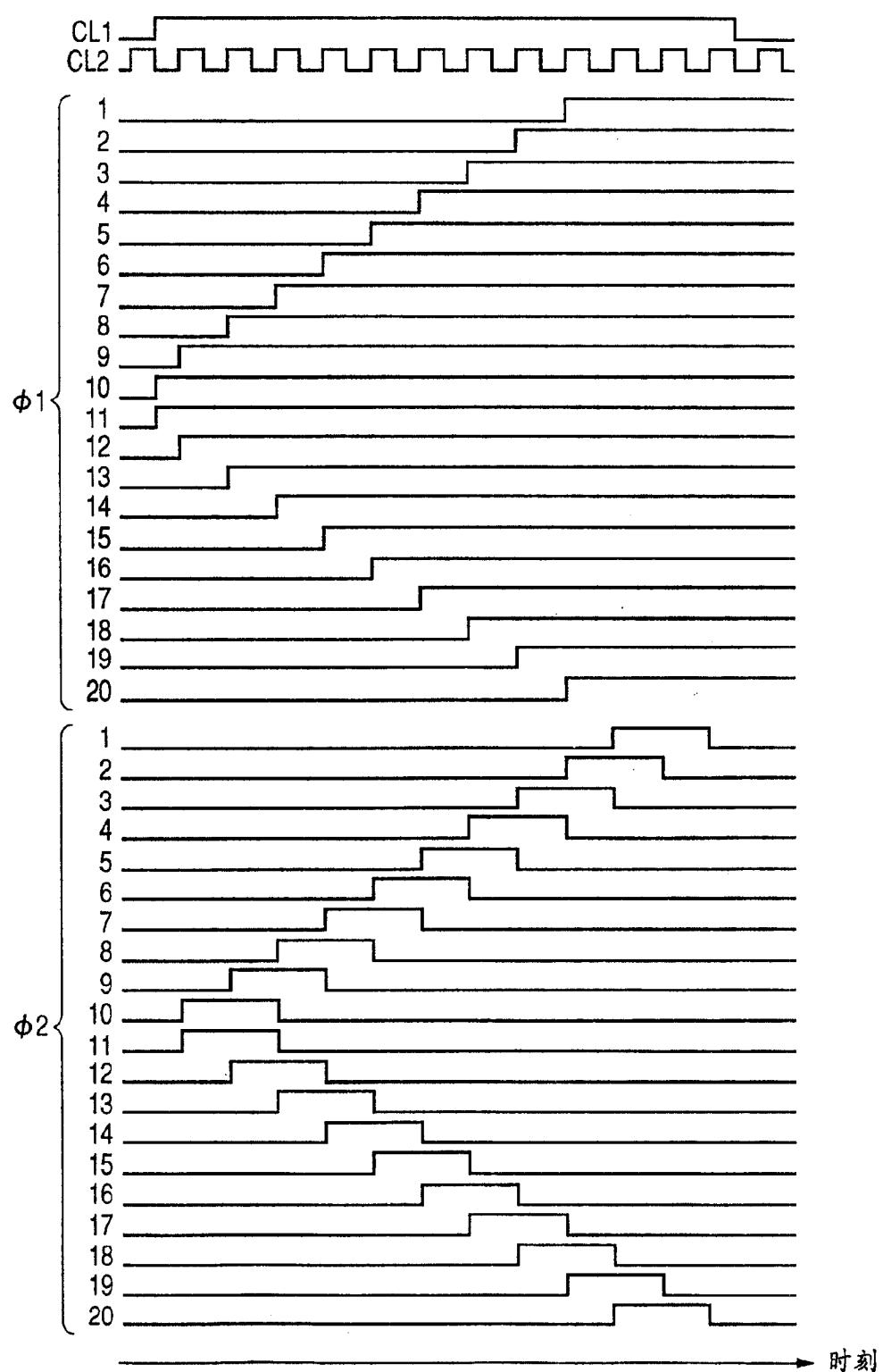

[0139] 本实施例 2 的液晶显示装置, 是以减小在数据驱动器中产生的瞬时电流的峰值并防止数据驱动器和显示装置的可靠性降低为目的的显示装置。在这种液晶显示装置中, 数据驱动器 2, 例如具有如图 20 所示的结构。在图 20 所示的数据驱动器 2 的结构中, 数据锁存电路 201、移位寄存电路 202、第 1 锁存电路 203、第 2 锁存电路 204、电平移动器电路 205、译码电路 206、基准电压生成电路 207、输出电路 208、开关电路 209、时钟信号生成电路 212 这样的结构, 是以往的数据驱动器也具备的结构。在本实施例 2 的显示装置中, 除上述各构成电路以外, 还备有水平同步信号延迟电路 213。

[0140] 水平同步信号延迟电路 213, 例如图 21 和图 22 所示, 由触发电路那样的时钟同步式的延迟电路构成。这时, 由第 2 锁存电路 204 所保持的将要输出到各漏极线的显示数据, 划分为几个块, 并以块为单位生成使水平同步信号延迟的延迟信号, 输入到第 2 锁存电路。这时, 显示数据例如划分为大约 10 个块到 20 个块。

[0141] 另外, 当数据驱动器 2 是与一般的点反转对应的驱动器时, 如图 22 所示, 作为使电平移动器电路动作的时序, 具有选择 HV 译码器 (Decoder) 或 LV 译码器 (Decoder) 的多路复用器, 所以该切换的时序也必须改变。因此, 在本实施例 2 中, 在水平同步信号延迟电路 213 内, 设有生成使上述多路复用脉冲延迟的延迟信号  $\Phi 1$  的系统和生成使上述第 2 锁存电路的数据锁存脉冲延迟的延迟信号  $\Phi 2$  的系统这 2 个系统的延迟电路。

[0142] 这时, 对于第 2 锁存电路 204 的各块, 输入由使水平同步信号 CL1 与时钟信号同步的延迟电路所生成的延迟信号  $\Phi 2$ 。因此, 第 2 锁存电路 204, 按照延迟信号  $\Phi 2$  的种类, 以块为单位分成多次地取入由第 1 锁存电路 203 所保持的 1 水平同步期间的显示数据。就是说, 通过分成多次地取入以往汇总取入的显示数据, 来减少同时驱动的电平移动器电路的数量。因此, 能够避免驱动电平移动器电路并由译码电路选择灰度等级电压时产生的瞬时电流的集中。其结果是, 能够降低瞬时电流的峰值, 并能减小电源电压的变动。因此, 能够提高数据驱动器 2 和显示装置的可靠性。

[0143] 图 23 是用于说明显示数据的取入的延迟方法的示意图。

[0144] 当使第 2 锁存电路 204 的显示数据的取入延迟时, 优选的是, 例如图 23 所示, 在划分后的块中从位于中心的块开始输出、随着趋向两端而延迟输出。在图 23 示出的例子中, 将第 2 锁存电路 204 划分为 20 个块, 从一端的块开始依次标以序号 1、2、3、… 20。这时, 从位于中心的第 10 块和第 11 块开始输出, 位于两端的第 1 块和第 20 块最后输出。按照这种方式, 例如, 当数据驱动器由多个驱动 IC 构成、各驱动 IC 具有如图 20 ~ 图 22 所示的结构时, 能够降低发生各驱动 IC 的块之间的不均的可能性。

[0145] 如上所述, 按照本实施例 2 的显示装置, 当由第 2 锁存电路 204 取入 1 水平同步期间的显示数据时, 通过划分为多个块进行取入, 能够避免驱动电平移动器电路时的瞬时电流的集中, 能够提高数据驱动器 2 和显示装置的可靠性。

[0146] 另外, 由于能够减小因瞬时电流引起的电源电压的变动, 能够排除旁路电容器等抑制变动的电路部件。因此, 本实施例 2 的结构, 优选的是, 例如应用于汽车导航系统之类的车载用液晶显示装置等。

[0147] 另外,在本实施例 2 中,说明了避免上述瞬时电流的集中的数据驱动器的结构和动作,但当然也可以将在上述实施例 1 中说明过的结构与本实施例 2 的结构进行组合。就是说,也可以设置水平同步信号延迟电路 213 并将电平移动器电路 204 的显示数据的取入分散而避免瞬时电流的集中,并按每个块延迟从数据驱动器输出的时序。此外,只要是块间的相位错开的结构,甚至例如只错开了半周期的结构,也能同样地进行动作。

[0148] [ 实施例 3 ]

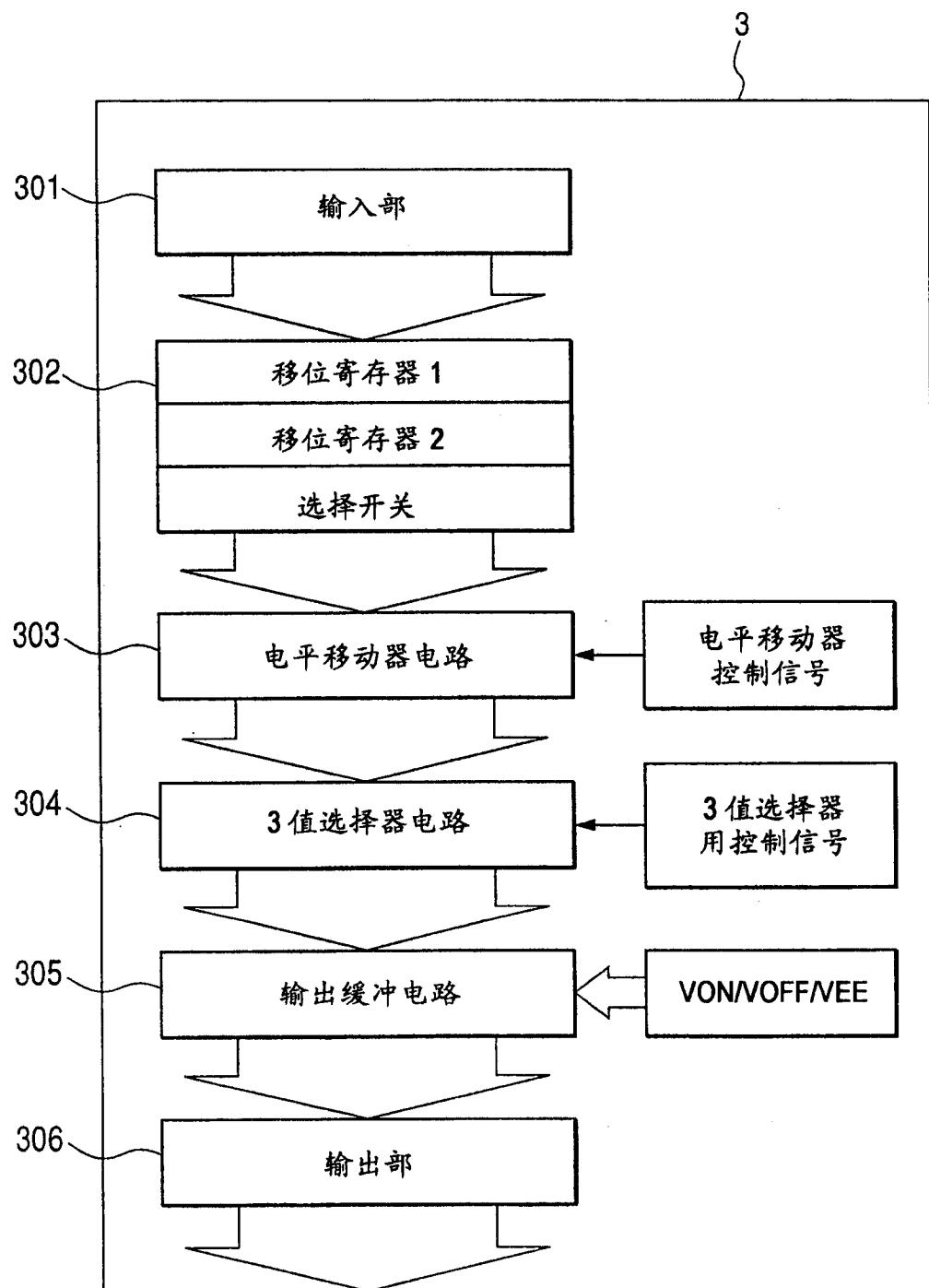

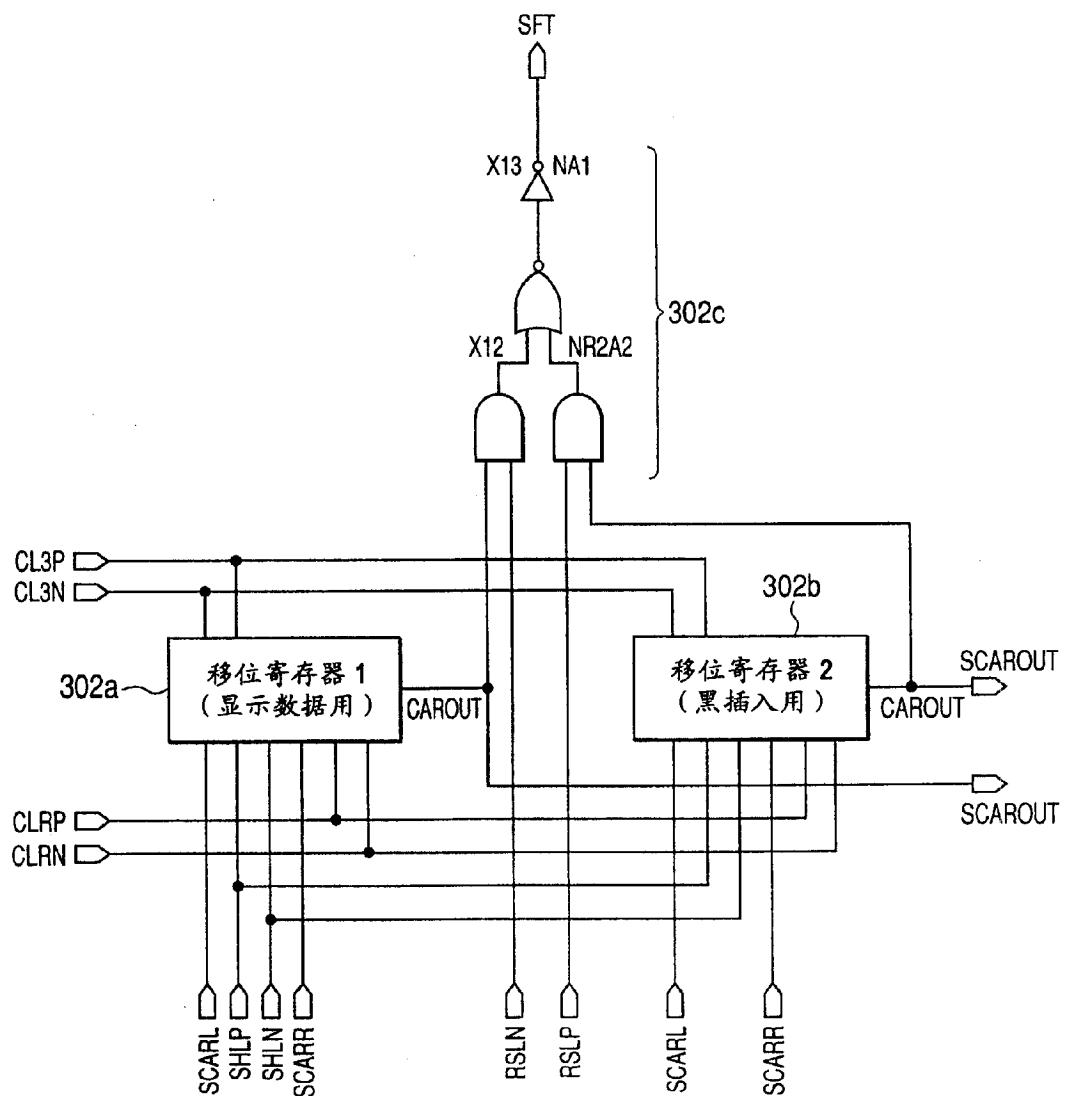

[0149] 图 24 和图 25 是表示本发明的实施例 3 的显示装置的概略结构的示意图,图 24 是表示扫描驱动器的结构例的框图,图 25 是表示移位寄存电路的结构例的电路框图。

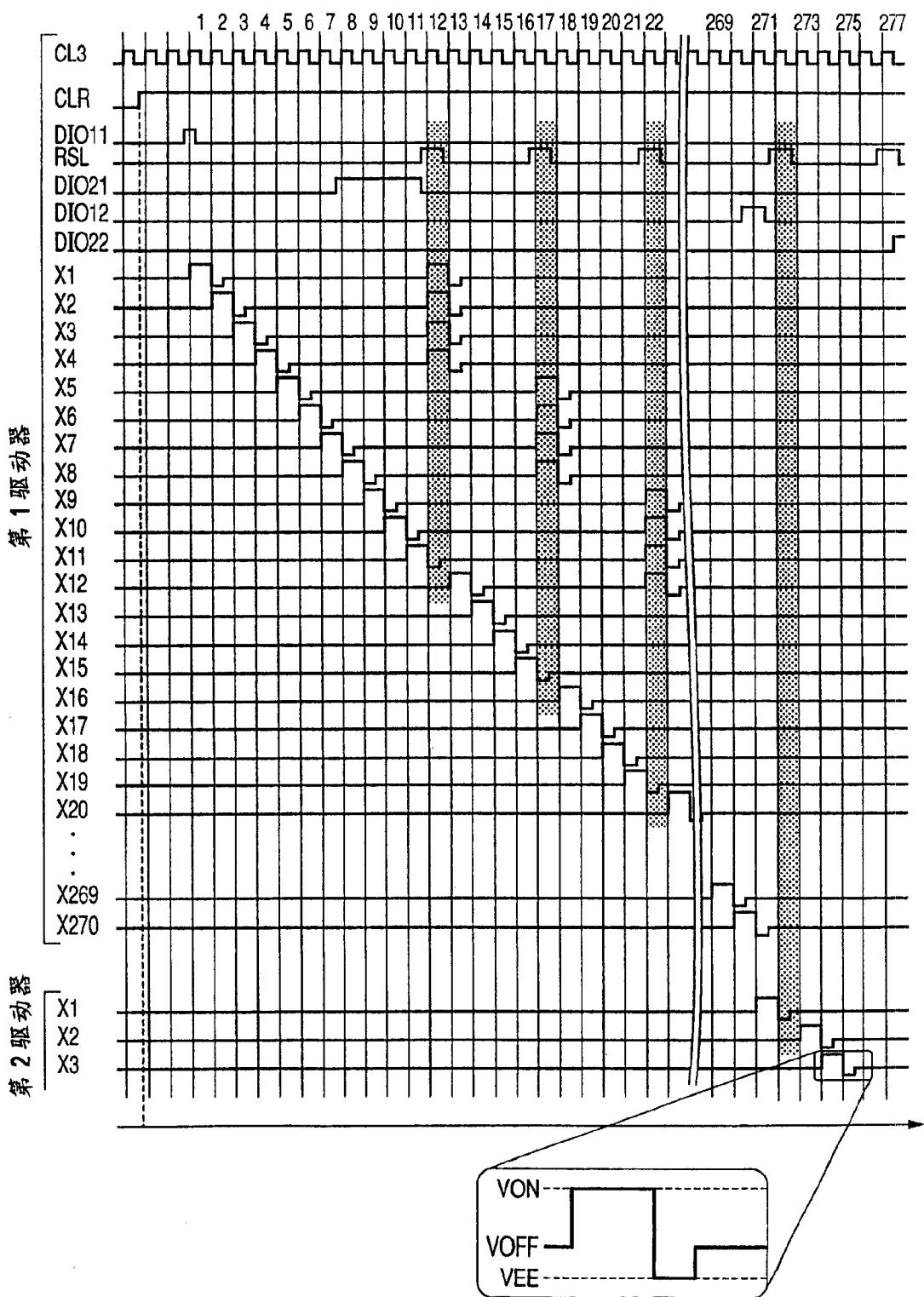

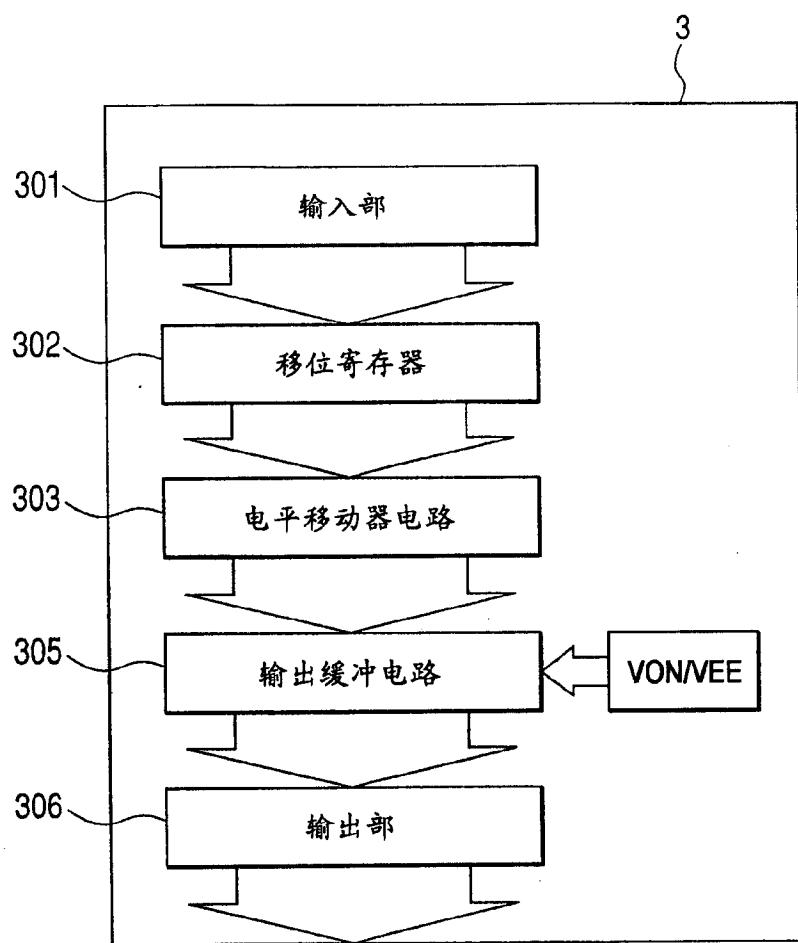

[0150] 本实施例 3 的液晶显示装置,是以当显示图像(影像)时在按一定的间隔插入黑显示的液晶显示装置中将多个扫描驱动 IC 串联连接、且提高输出显示数据用的扫描信号的栅极线和输出黑显示插入用的扫描信号的栅极线的组合自由度为目的的显示装置。在这种液晶显示装置中,扫描驱动器 3,例如,如图 24 所示,具有输入部 301、移位寄存部 302、电平移动器电路 303、3 值选择器电路 304、输出缓冲电路 305、以及输出部 306。其中,输入部 301、输出缓冲电路 305 及输出部 306,也可以是与以往的扫描驱动器 3 相同的结构。

[0151] 另外,上述移位寄存部 302,如图 24 和图 25 所示,具有第 1 移位寄存器(移位寄存器 1)302a、第 2 移位寄存器(移位寄存器 2)302b、以及将各移位寄存器 302a、302b 的输出的任一者输出到电平移动器电路 303 的选择开关 302c。这时,第 1 移位寄存器 302a 作为显示数据用的移位寄存器,第 2 移位寄存器 302b 作为黑显示插入用的第 2 移位寄存器。

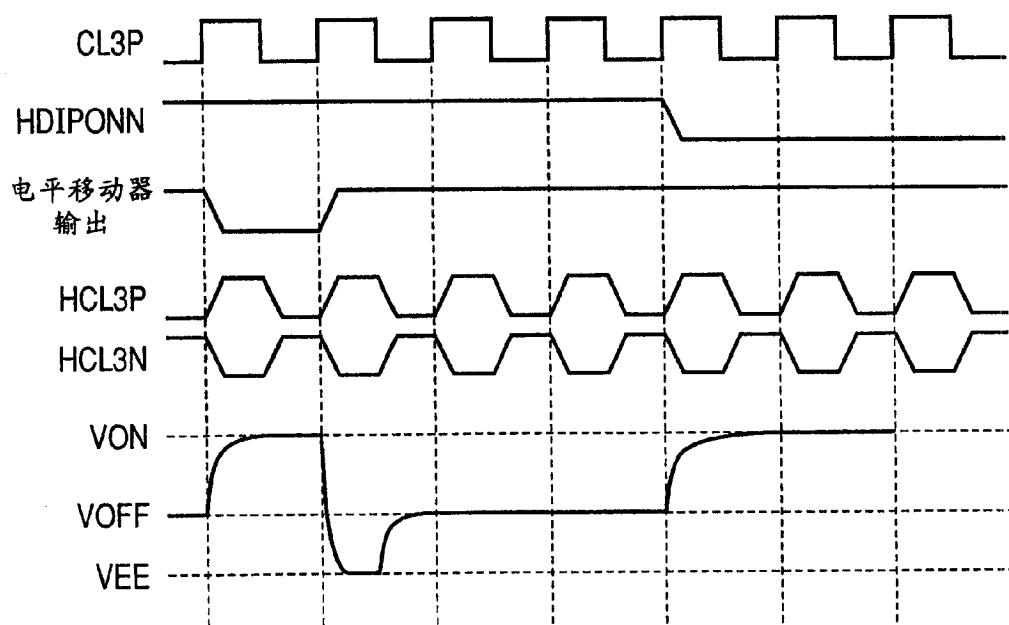

[0152] 图 26 是表示本实施例 3 的显示装置中的扫描信号的时序波形的示意图。

[0153] 本实施例 3 的显示装置的扫描驱动器 3,具有显示数据用的第 1 移位寄存器 302a 和黑显示插入用的第 2 移位寄存器 302b。这时,对各移位寄存器 302a、302b 输入各自独立的 DIO 信号,即,对第 1 移位寄存器 302a 输入第 1DIO 信号 DI01,对第 2 移位寄存器 302b 输入第 2DIO 信号 DI02。这时,第 2DIO 信号 DI02 由输入信号的时序控制。这时,各 DIO 信号 DI01、DI02 与输入到选择开关 302c 的选择信号 RSRL 的时序波形的关系,例如图 26 所示。

[0154] 在本实施例 3 的显示装置中,作为基于来自第 1 移位寄存器 302a 的输出的显示数据用的扫描信号,例如图 26 所示,在开始时刻 t1 ~ 时刻 t12 之间输出 S1-SFT1 ~ S1-SFT17。

[0155] 而作为基于来自第 2 移位寄存器 302b 的输出的黑显示插入用的扫描信号,例如图 26 所示,在开始时刻 t1 ~ 时刻 t12 之间输出 S2-SFT1 ~ S2-SFT10。

[0156] 这时,对各栅极线 GL 从端部起依次标以序号 X1 ~ XM,在时间 t11 ~ t21 之间输出扫描信号的栅极线的关系,如图 26 所示。例如,在输出黑显示插入用的扫描信号 S2-SFT1、S2-SFT2 的时刻,输出显示数据用的扫描信号 S1-SFT12。当像以往那样移位寄存器为 1 个时,若在同一芯片内出现这种状况,则在想要保留显示数据信号的像素、即与栅极线 GL(X12) 连接的像素内写入黑数据。而如本实施例 3 这样使移位寄存器为 2 个,就不会写入黑数据。

[0157] 在图 26 示出的例子中,在时刻 t14 或 t19,选择 S1 的寄存器输出,输出显示数据用的扫描信号。即,在与栅极线 GL(X12 或 X16) 连接的像素内写入显示数据。当如本实施例 3 这样使移位寄存器为 2 个时,在与 t14 或 t19 相同周期内的时刻 t15 或 t20,不选择 S1 的移位寄存器输出而是选择 S2 的移位寄存器输出,输出黑显示插入用的扫描信号。即,在与栅极线 GL(X1 ~ X2 或 X3 ~ X6) 连接的像素内写入黑显示数据。但是,这时,与在 t14 或

t19 输出显示数据用扫描信号的栅极线 GL(X12 或 X16) 连接的像素不会受到影响。因此,能够防止在想保留显示数据信号的像素、即与栅极线 GL(X12) 连接的像素内写入黑数据。因此,可以从同一芯片输出显示数据用的扫描信号和黑显示插入用的扫描信号。而且,由此,可以将多个芯片(驱动 IC)串联连接。

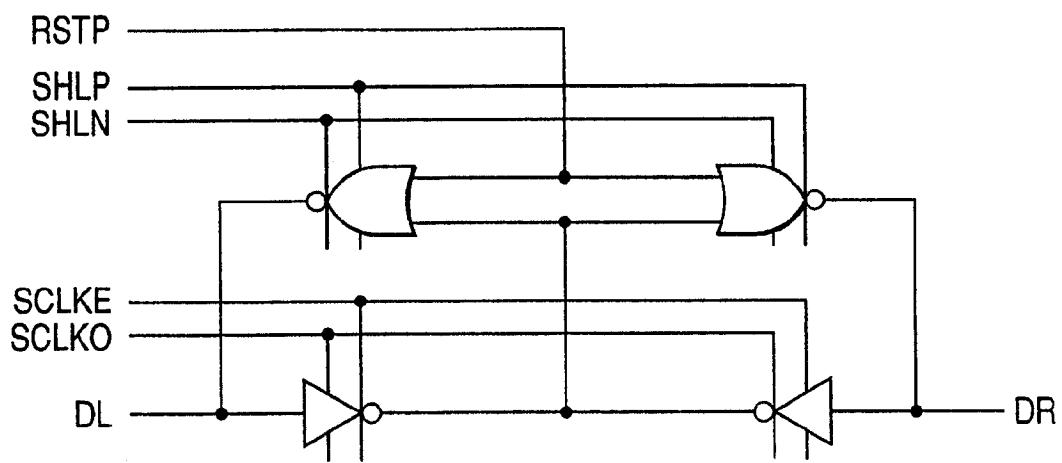

[0158] 图 27 是表示本实施例 3 的扫描驱动器中的 3 值选择器电路的结构例的电路图。图 28 是说明 3 值选择器电路的动作的波形图。图 29 是表示 3 值输出时的扫描信号的输出波形的图。

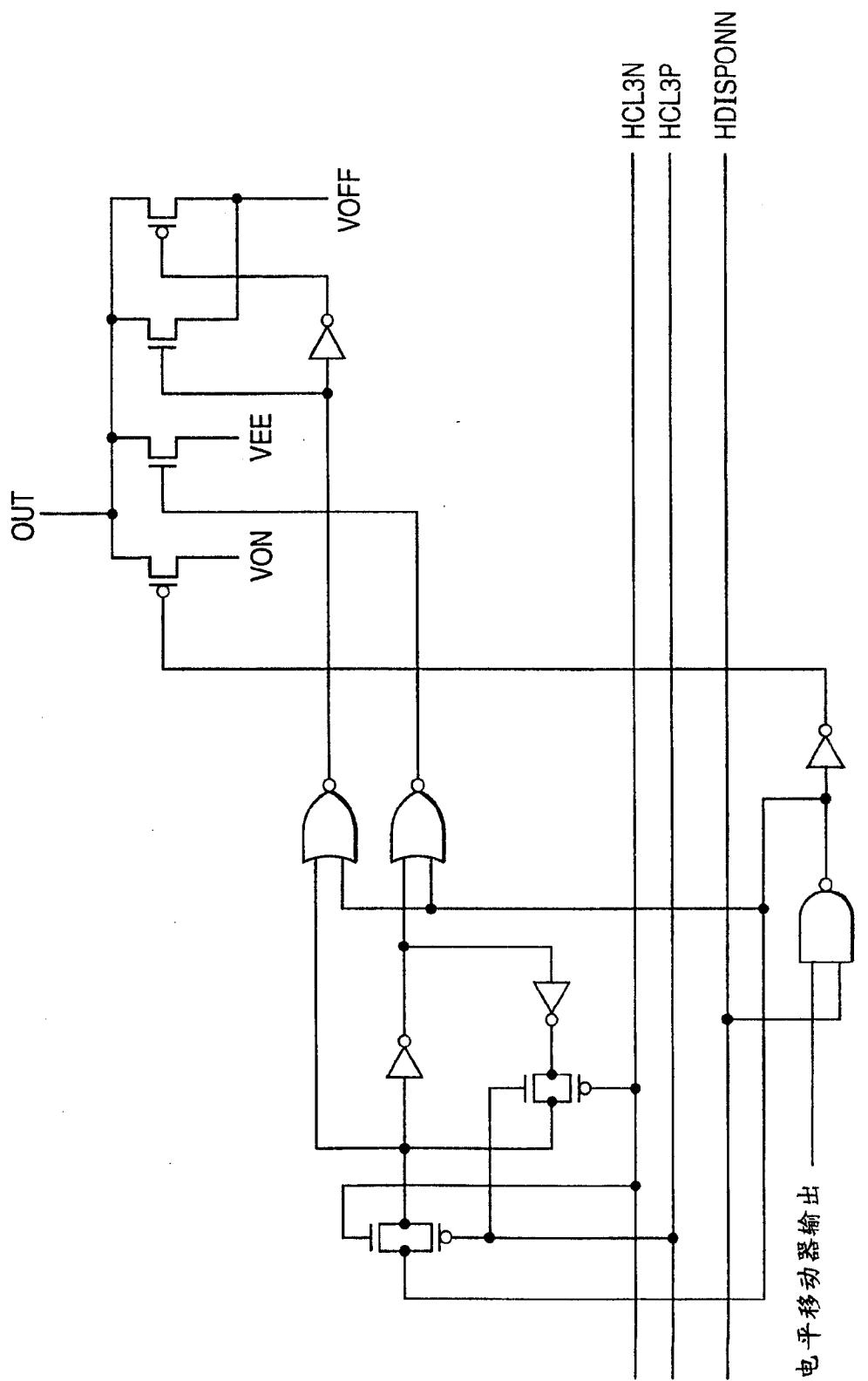

[0159] 在本实施例 3 的扫描驱动器中,由电平移动器电路 303 和 3 值选择器电路 304 进行 3 值输出。这时,3 值选择器电路 304,例如具有图 27 所示的结构。按照这种结构,例如图 28 所示,除设置显示电平 VON、非显示电平 VOFF 这 2 种电平以外,还可以设置非显示电平 VOFF 以下的第 3 电平 VEE。

[0160] 按照这种方式,实际上输出到各栅极线(X1、X2、...)的操作信号的波形,如图 28 所示。

[0161] 图 30 是说明 3 值输出的作用效果的图。此外,在图 30 中,上侧示出 3 值输出时的波形,下侧示出用于比较的以往的 2 值输出时的波形。

[0162] 当如本实施例 3 这样设置了显示电平 VON 和非显示电平 VOFF、以及非显示电平 VOFF 以下的第 3 电平 VEE 时,输入到栅极线的扫描信号的波形,如图 30 所示,当从显示电平 VON 下降,返回到非显示电平 VOFF 的过程中,将会出现一次这样的情况,即变成非显示电平 VOFF 以下的第 3 电平 VEE。这时,从显示电平 VON 的下降,比以往的 2 值输出时陡峭,这能够缩短下降时间。因此,能够延长数据的取入时间。

[0163] 对于像以往的扫描驱动器那样只有显示电平 VON 和非显示电平 VOFF 的 2 值的电路结构来说,进行 3 值输出就意味着电路规模的增加。而且,当一边独立地控制显示数据用的扫描信号和黑显示插入用的扫描信号一边进行 3 值输出时,不仅需要简单的逻辑电路的组合,而且需要对数据进行锁存。并且,还需要用高耐压系统(高电压动作系统)构成这种电平移动器之后的电路。因此,不仅电路规模变大,其结构也将变得复杂,驱动 IC 的芯片的尺寸增大。

[0164] 而如本实施例 3 所示,通过设置 2 个移位寄存电路 302a、302b 并选择其任一者的输出来进行 3 值输出,能够抑制电路规模的增大,能够抑制驱动 IC 的芯片尺寸的大型化。

[0165] 如上所述,按照本实施例 3 的液晶显示装置,通过由显示数据用的第一移位寄存器 302a、黑显示插入用的第二移位寄存器 302b、选择各移位寄存器的输出的任一者并传送到电平移动器电路 303 的选择开关 302c 来构成移位寄存部 302,可以从同一芯片输出显示数据用的扫描信号和黑显示插入用的扫描信号。由此,可以将多个芯片(驱动 IC)串联连接。

[0166] 另外,由电平移动器电路 303 和 3 值选择器电路 304 将扫描信号进行 3 值输出,能够延长各像素的 TFT 元件的数据取入时间,能够使显示画质提高。

[0167] 另外,在本实施例 3 的扫描驱动器中,对于黑显示插入用的数据,也可以将控制时序和输出数的信号输入到各芯片(驱动 IC),在芯片内用计数电路、锁存电路等生成黑显示插入用的数据并进行控制。

[0168] 另外,由于采用差动式电平移动器电路作为电平移动器电路 303,可以用小规模构成并提供由高耐压系统构成的锁存电路的控制信号电路。

[0169] 图 31 和图 32 是表示移位寄存电路的结构例的图, 图 31 是示意地示出的电路图, 图 32 是具体地示出图 31 的电路的电路图。

[0170] 在本实施例 3 的扫描驱动器中, 各移位寄存电路 302a、302b, 例如, 一般具有如图 31 和图 32 所示的结构。但是, 只要具有传送数据的功能, 并不限于这种结构, 也可以是其他的电路结构。

[0171] [实施例 4]

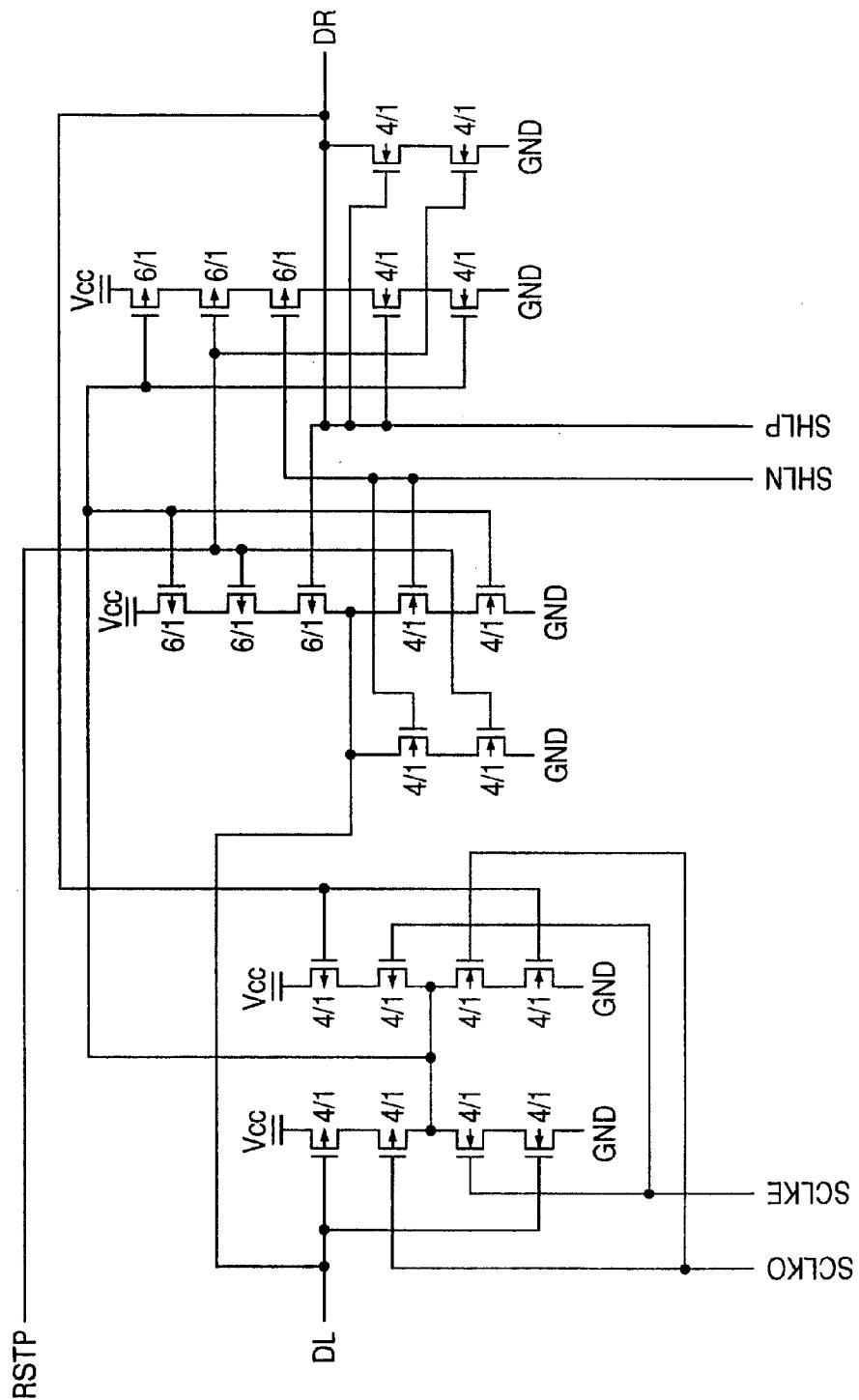

[0172] 图 33 和图 34 是表示本发明的实施例 4 的显示装置的概略结构的示意图, 图 33 是表示扫描驱动器的结构例的框图, 图 34 是表示电平移动器电路的结构例的框图。

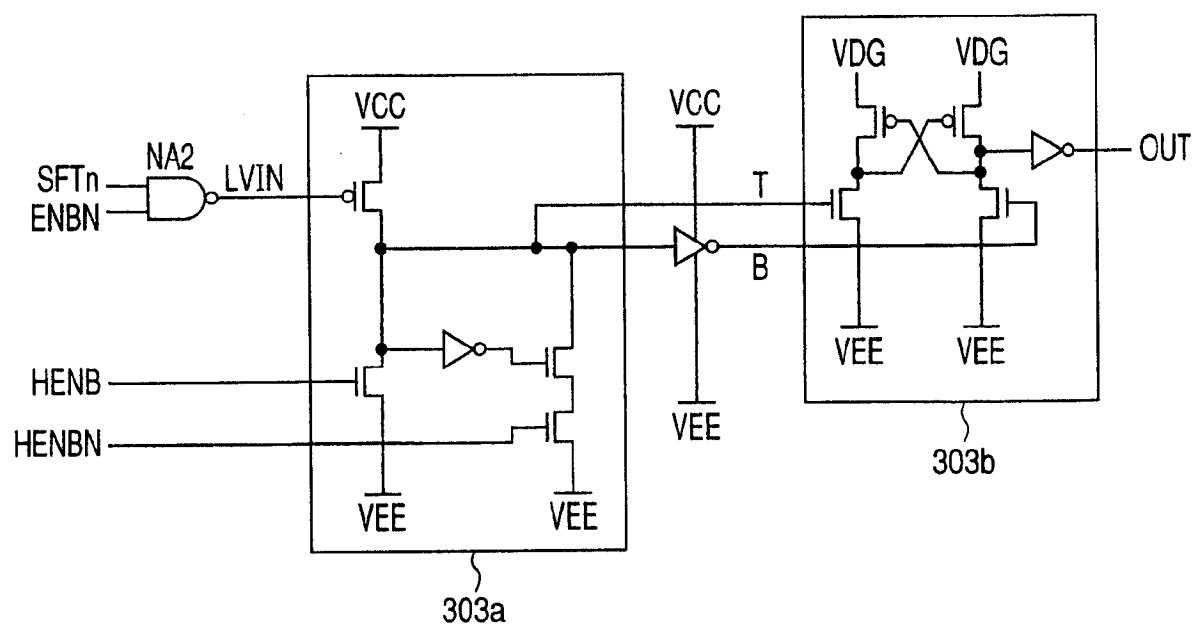

[0173] 本实施例 4 的液晶显示装置, 是目的在于用以往的尺寸的 MOS 晶体管使电平移动器电路动作的显示装置。在这种液晶显示装置中, 扫描驱动器 3, 例如, 具有如图 33 所示的结构。图 33 所示的结构, 示出排列了输出数的量的电路块和用于控制该块的信号的结构, 具有输入部 301、移位寄存部 302、电平移动器电路 303、输出缓冲电路 305、以及输出部 306。在本实施例 4 的扫描驱动器中, 移位寄存部 302, 也可以不是如上述实施例 3 所述的结构, 而是以往的一般的结构。

[0174] 另外, 电平移动器电路 303, 不需要进行上述实施例 3 那样的 3 值输出, 而可以做成为以往的 2 值输出的电路结构。在本实施例 4 中, 电平移动器电路 303, 如图 34 所示, 使初级为锁存方式的电路 303a, 第 2 级为以往的所谓交叉方式的电路 303b。

[0175] 这种结构的电平移动器电路 303, 在初级的锁存方式的电路 303a 中, 保持从 NAND(“与非”)门电路输入的信号 LVIN 的时钟信号 1 个周期量, 在输入下一个信号之前, 用 3 种允许信号 ENBN、HENB、HENBN 进行输入信号 LVIN 的控制和信号保持部分的清除 (reset)。

[0176] 图 35 是说明本实施例 4 的电平移动器电路的动作的示意图。

[0177] 在本实施例 4 的电平移动器电路 303 中, 如图 35 所示, 首先, 由第 1 允许信号 HENB 和第二允许信号 HENBN 进行保持部分的节点清除。接着, 由第三允许信号 ENBN 进行输入信号 LVIN 的取入。然后, 保持所取入的输入信号 LVIN 的时钟信号 1 个周期量, 之后, 在输入下一个周期的信号之前, 由第 1 允许信号 HENB 和第二允许信号 HENBN 进行保持部分的节点清除。

[0178] 当进行了这种动作时, 从初级的电路 303a 向第 2 级的电路 303b 传送的两个信号 T、B 如图 35 所示。因此, 经由第 2 级的电路 303b 输出的输出信号 OUT 如图 35 所示。

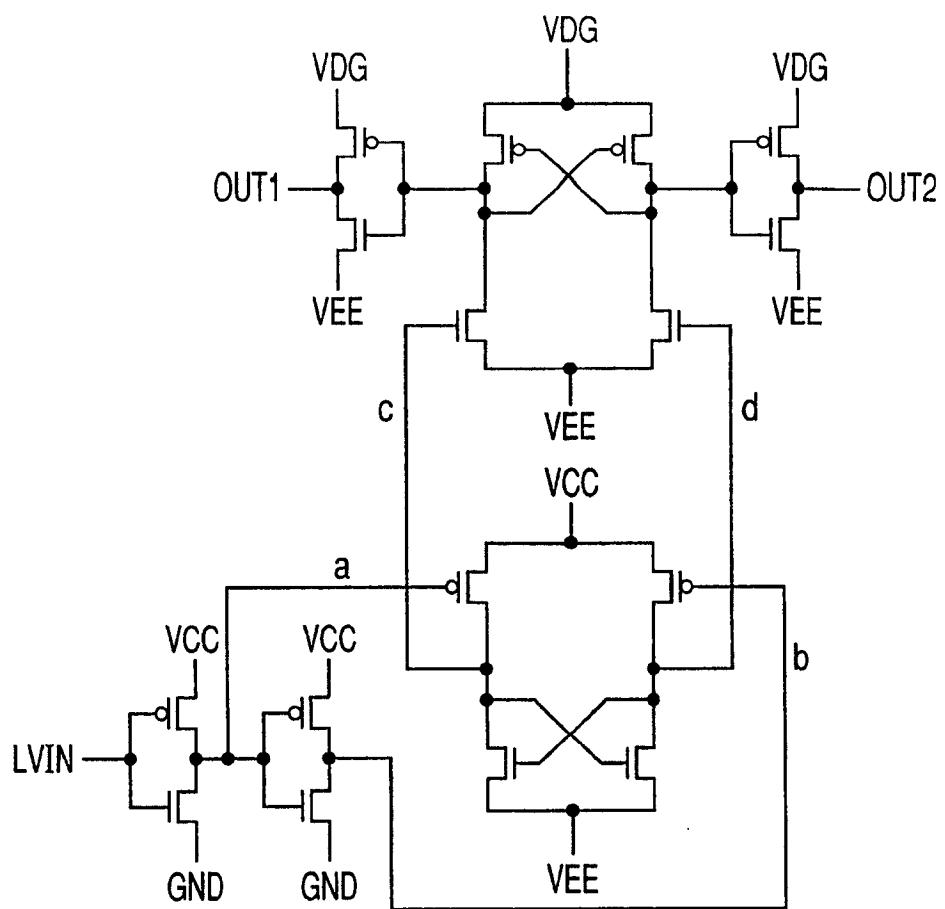

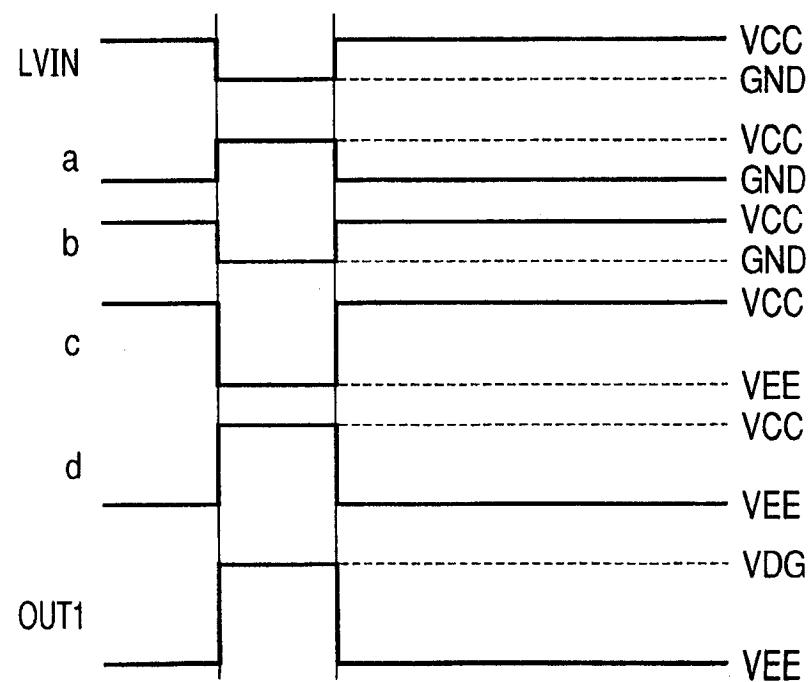

[0179] 图 36 是表示用于与本实施例 4 的电平移动器电路进行比较的以往的电平移动器电路的结构例的图。图 37 是表示图 36 中示出的电平移动器电路的动作的图。

[0180] 以往的电平移动器电路, 通常是使第 2 级的电路 303b 那样的交叉方式的电路为 2 级的结构。例如, 如图 36 所示, 从 2 个反相电路输出的输出信号 a、b 输入到初级的交叉方式的电路的 2 个 P 沟道 MOS 晶体管的各栅极, 并且, 将从 2 个 N 沟道 MOS 晶体管的漏极输出的输出信号 c、d 输入到第 2 级的交叉方式的电路的 2 个 N 沟道 MOS 晶体管的各栅极。然后, 从 2 个 P 沟道 MOS 晶体管将输出分别输入到反相电路, 最终取出 2 个输出信号 OUT1、OUT2。这时, 输入到电平移动器电路的信号 LVIN、反相电路的输出信号 a、b、初级的交叉方式的电路的输出信号 c、d、最终取出的 2 个输出信号 OUT1、OUT2, 例如图 37 所示。这时, 图 37 中的输入信号 LVIN 和最终的输出信号 OUT1 的关系, 与图 35 中的输入信号 LVIN 和输出信号 OUT 的关系一致。因此, 图 34 中示出的电平移动器电路, 具有与图 36 中示出的电平移动器

电路同样的功能。

[0181] 另外,当比较图 34 的电平移动器电路和图 36 中示出的电平移动器电路时,MOS 晶体管电路数相同。但是,图 34 中示出的电路结构不需要图 36 中示出的电平移动器所需的那么大的电流,因此能够减小每 1 个晶体管的尺寸。另外,通过使初级的电路从以往的交叉方式变为锁存方式的电路 303a,能够减小整个电平移动器电路的尺寸。

[0182] 但是,在锁存方式的电路 303a 中,作为第 1 允许信号 HENB 和第二允许信号 HENBN,必须输入高耐压信号。生成该第 1 允许信号 HENB 和第二允许信号 HENBN 的电路,也可以是交叉方式的电路,但是,采用差动方式的电路能够进一步减小芯片尺寸。

[0183] 图 38 是表示生成高耐压的允许信号的差动电路的结构例的电路图。

[0184] 为生成第 1 允许信号 HENB 和第二允许信号 HENBN,例如,采用如图 38 所示的差动放大电路。但是,在本实施例 4 中,不是用作放大小信号的放大器,而是用作电压变换电路。按照这种方式,可以生成和供给锁存方式的电路 303a 中所需的高耐压的允许信号 HENB、HENBN。

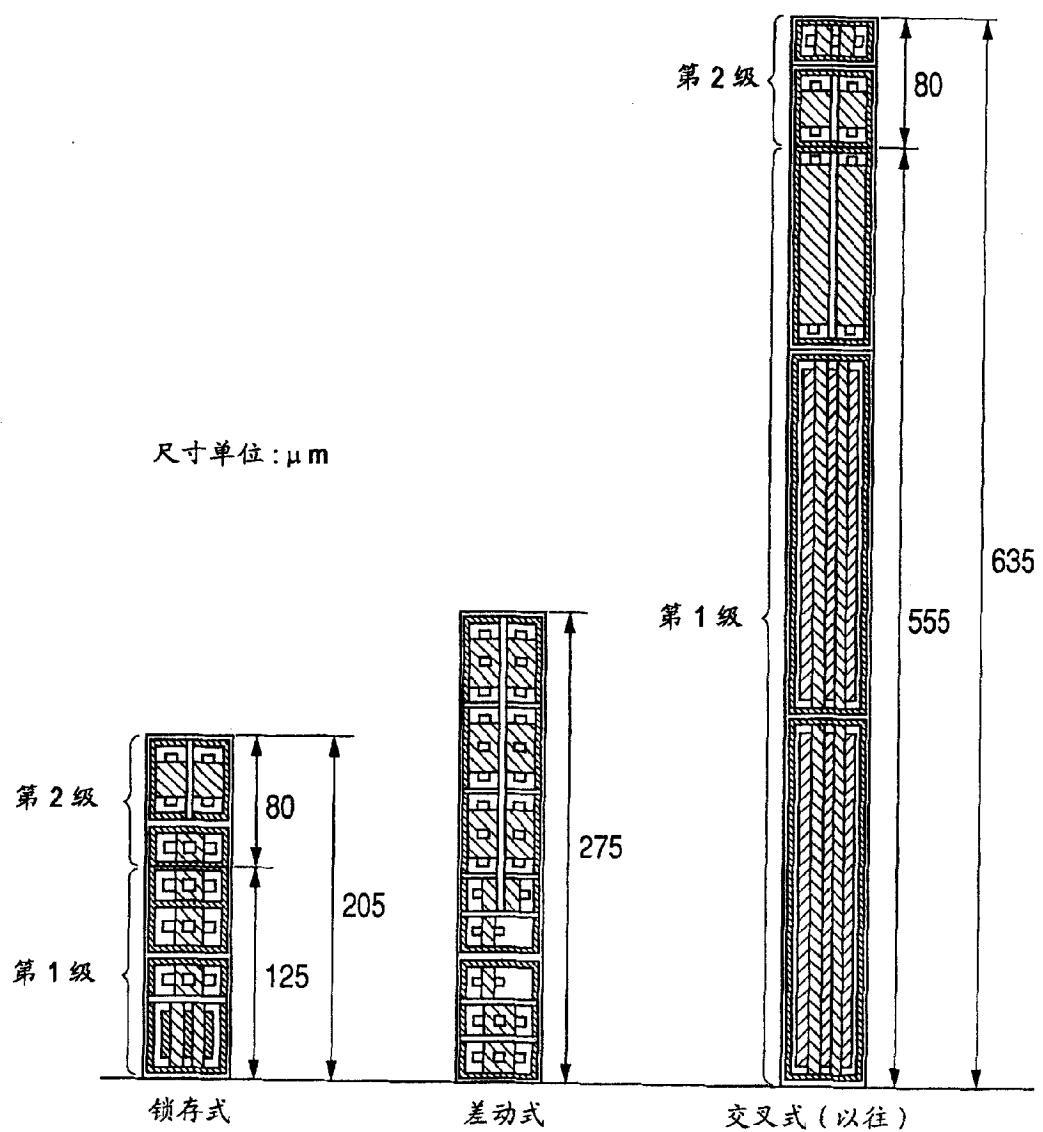

[0185] 图 39 是说明本实施例 4 的效果的示意图。在图 39 中,从左至右示出本实施例 4 的电平移动器电路的尺寸、差动放大电路的尺寸、以往的电平移动器电路的尺寸。

[0186] 以往的电平移动器电路,为增大所流过的电流而必须加大 MOS 晶体管的尺寸,因此,例如,如图 39 所示,增大了第 1 级(初级)的交叉方式的电路的面积。而在本实施例 4 的电平移动器电路中,无需流过用于使 MOS 晶体管反转的电流,因而能够减小第 1 级的锁存方式的电路 303a。然而,需要用于生成提供给锁存方式的电路 303a 的高耐压的允许信号 HENB、HENBN 的电压变换电路(差动放大电路)。

[0187] 但是,如图 39 所示,即使将本实施例 4 的电平移动器电路 303 的纵向尺寸(205 μm)和电压变换电路(差动放大电路)的纵向尺寸(275 μm)加起来也比以往的电平移动器电路的纵向尺寸(635 μm)小。

[0188] 如上所述,按照本实施例 4 的液晶显示装置,对于电平移动器电路 303 的结构,使其初级为锁存方式的电路 303a、第 2 级为交叉方式的电路 303b,因此能够减小芯片(驱动 IC)上的电平移动器电路 303 的面积。

[0189] 另外,在本实施例 4 中,使初级的电路为锁存方式的电路 303a,但只要是能够保持输入信号 LVIN 的电路结构,也可以是其他的电路。

[0190] 另外,在本实施例 4 中,初级为锁存方式的电路 303a、第 2 级为交叉方式的电路 303b,但并不限于此,例如,也可以使第 2 级为锁存方式的电路。

[0191] 另外,在本实施例 4 中,采用如图 38 所示的电压变换电路(差动放大电路)生成提供给初级的锁存方式的电路 303a 的高耐压的允许信号 HENB、HENBN,但并不限于此,例如,也可以从扫描驱动器的外部直接提供高耐压信号。

[0192] 另外,在本实施例 4 中,举出了在以往的结构的扫描驱动器中改变电平移动器电路 303 的结构的例,但也可以将在上述实施例 3 中说明过的结构与本结构组合。

[0193] 以上,根据实施例具体地说明了本发明,但是,本发明并不限于上述实施例,在不脱离其主旨的范围内,当然可以进行各种变更。

图 2

图 3

图 4

图 5

图 6

图 7

图 8

图 9

图 10

11

图 12

图 13

图 14

图 15

图 16

图 17

图 18

图 19

图 20

21

22

图 23

图 24

图 25

图 26

图 27

图 28

图 29

图 30

图 31

图 32

图 33

图 36

图 37

图 38

图 39

|                |                                                                                                               |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">CN1987990B</a>                                                                                    | 公开(公告)日 | 2011-02-09 |

| 申请号            | CN200610169249.0                                                                                              | 申请日     | 2006-12-21 |

| [标]申请(专利权)人(译) | 株式会社日立显示器                                                                                                     |         |            |

| 申请(专利权)人(译)    | 株式会社日立显示器                                                                                                     |         |            |

| 当前申请(专利权)人(译)  | 株式会社日立显示器                                                                                                     |         |            |

| [标]发明人         | 田中靖洋<br>勇广宣<br>饭田治久<br>菊池秀德<br>尾手幸秀                                                                           |         |            |

| 发明人            | 田中靖洋<br>勇广宣<br>饭田治久<br>菊池秀德<br>尾手幸秀                                                                           |         |            |

| IPC分类号         | G09G3/36 G09G5/02 G09G3/20 G02F1/133 H04N11/00 H03K19/0185                                                    |         |            |

| CPC分类号         | G09G2310/027 G09G2310/0289 G09G3/20 G09G3/3688 G09G5/001 G09G2310/08 G09G3/3677<br>G09G2310/061 G09G2310/0286 |         |            |

| 审查员(译)         | 刘畅                                                                                                            |         |            |

| 优先权            | 2005369758 2005-12-22 JP                                                                                      |         |            |

| 其他公开文献         | CN1987990A                                                                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                                |         |            |

## 摘要(译)

本发明提供一种显示装置，目的在于减小栅极线延伸方向的像素的TFT元件的写入时间的离差。在该显示装置中，包括按矩阵状配置了多条栅极线和多条漏极线的显示板、对各漏极线输出显示数据信号的数据驱动器，上述数据驱动器，具有内部控制信号生成电路，将上述多条漏极线划分为多个块，生成按每个块设定向各块的漏极线输出数据信号的时序的内部控制信号；以及寄存电路，记录了上述块的划分的设定、输出上述数据信号的时序的延迟方向和延迟宽度的设定、内部控制信号的上升沿和下降沿的设定。

|   | 延迟方向设定 |      | 延迟宽度设定 |       |       |       |        |     |

|---|--------|------|--------|-------|-------|-------|--------|-----|

|   | R00    | R01  | R02    | R03   | R04   | R05   | R06    | R07 |

| — | 1→17   | 17→1 | 无      | CL2/2 | CL2/4 | CL2/8 | CL2/16 |     |