[19] 中华人民共和国国家知识产权局

[51 ] Int. Cl.

## [12] 发明专利申请公布说明书

〔21〕申请号 200610100312.5

*G09G 3/36 (2006. 01 )*

*G09G 3/20 (2006. 01 )*

*G02F 1/133 (2006. 01 )*

[43] 公开日 2007 年 1 月 10 日

[11] 公开号 CN 1892798A

[22] 申请日 2006.6.30

[21] 申请号 200610100312.5

### [30] 优先权

[32] 2005. 6. 30 [33] KR [31] 10-2005-0058609

[71] 申请人 LG. 菲利浦 LCD 株式会社

地址 韩国首尔

[72] 发明人 张容豪 金彬 尹洙荣

[74] 专利代理机构 北京三友知识产权代理有限公司

代理人 李 辉

权利要求书 16 页 说明书 42 页 附图 15 页

[54] 发明名称

## 显示装置的驱动电路和显示装置的驱动方法

[57] 摘要

公开了一种显示装置的驱动电路和显示装置的驱动方法，其能够防止向液晶板的选通线提供的扫描脉冲发生畸变。该驱动电路包括：第1移位寄存器，用于分别向显示器中包括的多条选通线的一侧端顺序地提供多个第1扫描脉冲，以顺序地驱动所述多条选通线，该第1移位寄存器同时驱动所述多条选通线中的至少两条相邻选通线达预定时间段；和第2移位寄存器，用于分别向所述多条选通线的另一侧端顺序地提供多个第2扫描脉冲，以顺序地驱动所述多条选通线，该第2移位寄存器同时驱动所述多条选通线中的至少两条相邻选通线达预定时间段。

1、一种显示装置的驱动电路，包括：

第 1 移位寄存器，用于分别顺序地向显示器中包括的多条选通线的一侧端提供多个第 1 扫描脉冲，以顺序地驱动所述多条选通线，该第 1 移位寄存器同时驱动所述多条选通线中的至少两条相邻选通线达预定时间段；和

第 2 移位寄存器，用于分别顺序地向所述多条选通线的另一侧端提供多个第 2 扫描脉冲，以顺序地驱动所述多条选通线，该第 2 移位寄存器同时驱动所述多条选通线中的至少两条相邻选通线达预定时间段。

2、根据权利要求 1 所述的驱动电路，其中，用于驱动第  $n+1$  条选通线的第 1 扫描脉冲，在用于驱动第  $n$  条选通线的第 1 扫描脉冲保持在有效状态的预定时间段内，被提供到第  $n+1$  条选通线，在此 “ $n$ ” 是自然数。

3、根据权利要求 1 所述的驱动电路，其中，用于驱动第  $n+1$  条选通线的第 2 扫描脉冲，在用于驱动第  $n$  条选通线的第 2 扫描脉冲保持在有效状态的预定时间段内，被提供到第  $n+1$  条选通线，在此 “ $n$ ” 是自然数。

4、根据权利要求 1 所述的驱动电路，还包括：

定时控制器，用于向第 1 移位寄存器和第 2 移位寄存器中的每一个提供彼此之间都具有相位差的多个时钟脉冲。

5、根据权利要求 4 所述的驱动电路，其中，所述多个时钟脉冲顺序地输出，在相邻时间段中输出的时钟脉冲具有针对预定时间段同时发生的有效状态。

6、根据权利要求 5 所述的驱动电路，其中，所述多个时钟脉冲中的连续时钟脉冲同时保持在有效状态的预定时间段，具有与所述多个扫描脉冲中的连续扫描脉冲同时保持在有效状态的预定时间段相等的长度。

7、根据权利要求 1 所述的驱动电路，其中：

第 1 移位寄存器包括按一个方向排列的多个级，并且适于分别向所述多条选通线提供第 1 扫描脉冲；并且

第 2 移位寄存器包括按一个方向排列的多个级，并且适于分别向所

述多条选通线提供第 2 扫描脉冲。

8、根据权利要求 7 所述的驱动电路，其中，第 1 移位寄存器中包括的每一个级都响应于从设置在关注级上游的一个级输出的第 1 扫描脉冲而被使能，以输出一个相关联的第 1 扫描脉冲，并且响应于从设置在关注级下游的一个级输出的第 1 扫描脉冲而被禁能。

9、根据权利要求 8 所述的驱动电路，其中，第 1 移位寄存器中包括的所述多个级中的第  $n$  级响应于从第  $n-1$  级输出的第 1 扫描脉冲而被使能，以输出一个相关联的第 1 扫描脉冲，并且响应于从第  $n+2$  级输出的扫描脉冲而被禁能，在此 “ $n$ ” 是自然数。

10、根据权利要求 9 所述的驱动电路，其中：

第 1 移位寄存器中包括的所述多个级中的第 1 级响应于第 1 起始脉冲而被使能，该第 1 起始脉冲是从外部提供的；并且

第 1 移位寄存器中包括的所述多个级中的第 2 级响应于第 2 起始脉冲而被使能，该第 2 起始脉冲是从外部提供的。

11、根据权利要求 9 所述的驱动电路，其中：

第 1 移位寄存器还包括：

第 1 哑级，用于输出一扫描脉冲，以禁能第 1 移位寄存器中的所述多个级中的最后一级；和

第 2 哑级，用于输出一扫描脉冲，以禁能设置在所述最后一级直接上游的级。

12、根据权利要求 11 所述的驱动电路，其中，第 2 哑级响应于从第 1 哑级输出的扫描脉冲而被使能。

13、根据权利要求 7 所述的驱动电路，其中，第 1 移位寄存器中包括的每一个级都包括：

节点控制器，用于控制第 1 节点、第 2 节点以及第 3 节点的逻辑状态；和

输出单元，用于根据第 1 节点、第 2 节点以及第 3 节点的逻辑状态，输出一个相关联的扫描脉冲或一个断态电压，并且将该输出的扫描脉冲和断态电压提供到一条相关联的选通线、设置在关注级下游的一个级，

以及设置在关注级上游的一个级。

14、根据权利要求 13 所述的驱动电路，其中，第 1 移位寄存器中包括的所述多个级中的第 n 级的节点控制器包括：

第 1 开关器件，用于响应于起始脉冲和来自第 n-1 级的扫描脉冲中的一个，利用第 1 电压对第 1 节点进行充电；

第 2 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，利用第 2 电压对第 2 节点进行放电；

第 3 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，利用第 2 电压对第 3 节点进行放电；

第 4 开关器件，用于在第 4 开关器件导通时，利用逐帧交替改变极性的第 3 电压对第 2 节点进行充电，第 4 开关器件响应于第 3 电压导通或截止；

第 5 开关器件，用于在第 5 开关器件导通时，利用第 3 电压对第 3 节点进行放电，第 5 开关器件响应于第 3 电压导通或截止；

第 6 开关器件，用于在第 6 开关器件导通时，利用极性与第 3 电压的极性相反的第 4 电压对第 3 节点进行充电，第 6 开关器件响应于第 4 电压导通或截止；

第 7 开关器件，用于在第 7 开关器件导通时，利用第 2 电压对第 2 节点进行放电，第 7 开关器件响应于第 4 电压导通或截止；

第 8 开关器件，用于响应于充入第 1 节点中的第 1 电压，利用第 2 电压对第 2 节点进行放电；

第 9 开关器件，用于响应于充入第 1 节点中的第 1 电压，利用第 2 电压对第 3 节点进行放电；

第 10 开关器件，用于响应于充入第 2 节点中充电的第 3 电压，利用第 2 电压对第 1 节点进行放电；

第 11 开关器件，用于响应于充入第 3 节点中的第 4 电压，利用第 2 电压对第 1 节点进行放电；以及

第 12 开关器件，用于响应于来自第 n+2 级的所述扫描脉冲，利用第 2 电压对第 1 节点进行放电。

15、根据权利要求 14 所述的驱动电路，其中，第 1 移位寄存器中的第 n 级的输出单元包括：

第 13 开关器件，用于响应于充入第 1 节点中的第 1 电压，向与第 n 级相关联的选通线并且向第 n+1 级和第 n-2 级提供扫描脉冲；

第 14 开关器件，用于响应于充入第 2 节点中的第 3 电压，向所述相关联的选通线并且向第 n+1 级和第 n-2 级提供第 2 电压；以及

第 15 开关器件，用于响应于充入第 3 节点中的第 4 电压，向所述相关联的选通线并且向第 n+1 级和第 n-2 级提供第 2 电压。

16、根据权利要求 13 所述的驱动电路，其中，第 1 移位寄存器中包括的所述多个级中的第 n 级的节点控制器包括：

第 1 开关器件，用于响应于起始脉冲和来自第 n-1 级的扫描脉冲中的一个，利用第 1 电压对第 1 节点进行充电；

第 2 开关器件，用于响应于充入第 1 节点中的第 1 电压，利用第 2 电压对第 2 节点进行放电；

第 3 开关器件，用于响应于充入第 1 节点中的第 1 电压，利用第 2 电压对第 3 节点进行放电；

第 4 开关器件，用于在第 4 开关器件导通时，输出逐帧交替改变极性的第 3 电压，第 4 开关器件响应于第 3 电压导通或截止；

第 5 开关器件，用于响应于第 3 电压，利用从第 4 开关器件输出的第 3 电压对第 2 节点进行充电；

第 6 开关器件，用于响应于充入第 2 节点中的第 3 电压，利用第 2 电压对第 1 节点进行放电；

第 7 开关器件，用于响应于充入第 2 节点中的第 3 电压，利用第 2 电压对第 3 节点进行放电；

第 8 开关器件，用于响应于充入第 1 节点中的第 1 电压，向第 5 开关器件的栅极端子提供第 2 电压，以使第 5 开关器件截止；

第 9 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，向第 5 开关器件的栅极端子提供第 2 电压，以使第 5 开关器件截止；

第 10 开关器件，用于响应于来自第 n-1 级的起始脉冲中的一个，向第 5 开关器件的栅极端子提供第 2 电压，以使第 5 开关器件截止；

第 11 开关器件，用于在第 11 开关器件导通时，输出极性与第 3 电压的极性相反的第 4 电压，第 11 开关器件响应于第 4 电压导通或截止；

第 12 开关器件，用于响应于从第 11 开关器件输出的第 4 电压，利用第 4 电压对第 3 节点进行充电；

第 13 开关器件，用于响应于充入第 3 节点中的第 4 电压，利用第 2 电压对第 1 节点进行放电；

第 14 开关器件，用于响应于充入第 3 节点中的第 4 电压，利用第 2 电压对第 2 节点进行放电；

第 15 开关器件，用于响应于充入第 1 节点中的第 1 电压，向第 12 开关器件的栅极端子提供第 2 电压，以使第 12 开关器件截止；

第 16 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，向第 12 开关器件的栅极端子提供第 2 电压，以使第 12 开关器件截止；

第 17 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，向第 12 开关器件的栅极端子提供第 2 电压，以使第 12 开关器件截止；

第 18 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，利用第 2 电压对第 2 节点进行放电；

第 19 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，利用第 2 电压对第 3 节点进行放电；

第 20 开关器件，用于响应于来自第 n+2 级的扫描脉冲中的一个，利用第 2 电压对第 1 节点进行放电。

17、根据权利要求 16 所述的驱动电路，其中，第 1 移位寄存器中的第 n 级的输出单元包括：

第 21 开关器件，用于响应于充入第 1 节点中的第 1 电压，向与第 n 级相关联的选通线并且向第 n+1 级和第 n-2 级提供扫描脉冲；

第 22 开关器件，用于响应于充入第 2 节点中的第 3 电压，向所述相

关联的选通线并且向第  $n+1$  级和第  $n-2$  级提供第 2 电压；以及

第 23 开关器件，用于响应于充入第 3 节点中的第 4 电压，向所述相关联的选通线并且向第  $n+1$  级和第  $n-2$  级提供第 2 电压。

18、根据权利要求 7 所述的驱动电路，其中，第 1 移位寄存器中包括的每一个级都包括：

节点控制器，用于控制第 1 节点、第 2 节点、以及第 3 节点的逻辑状态；和

第 1 输出单元，用于根据第 1 节点、第 2 节点、以及第 3 节点的逻辑状态，输出相关联的扫描脉冲和断态电压中的一个，并且将该输出的扫描脉冲和断态电压中的一个提供到一条相关联的选通线；以及

第 2 输出单元，用于根据第 1 节点、第 2 节点、以及第 3 节点的逻辑状态，输出所述相关联的扫描脉冲和断态电压中的一个，并且将该输出的扫描脉冲和断态电压中的一个提供到设置在关注级下游的一个级，和设置在关注级上游的一个级。

19、根据权利要求 18 所述的驱动电路，其中，第 1 移位寄存器中包括的所述多个级中的第  $n$  级的节点控制器包括：

第 1 开关器件，用于响应于起始脉冲和来自第  $n-1$  级的扫描脉冲中的一个，利用第 1 电压对第 1 节点进行充电；

第 2 开关器件，用于响应于充入第 1 节点中的第 1 电压，利用第 2 电压对第 2 节点进行放电；

第 3 开关器件，用于响应于充入第 1 节点中的第 1 电压，利用第 2 电压对第 3 节点进行放电；

第 4 开关器件，用于在第 4 开关器件导通时，输出逐帧交替改变极性的第 3 电压，第 4 开关器件响应于第 3 电压导通或截止；

第 5 开关器件，用于响应于从第 4 开关器件输出的第 3 电压，利用该第 3 电压对第 2 节点进行充电；

第 6 开关器件，用于响应于充入第 2 节点中的第 3 电压，利用第 2 电压对第 1 节点进行放电；

第 7 开关器件，用于响应于充入第 2 节点中的第 3 电压，利用第 2

电压对第 3 节点进行放电；

第 8 开关器件，用于响应于充入第 1 节点中的第 1 电压，向第 5 开关器件的栅极端子提供第 2 电压，以使第 5 开关器件截止；

第 9 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，向第 5 开关器件的栅极端子提供第 2 电压，以使第 5 开关器件截止；

第 10 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，向第 5 开关器件的栅极端子提供第 2 电压，以使第 5 开关器件截止；

第 11 开关器件，用于在第 11 开关器件导通时，输出极性与第 3 电压的极性相反的第 4 电压，第 11 开关器件响应于第 4 电压导通或截止；

第 12 开关器件，用于响应于从第 11 开关器件输出的第 4 电压，利用第 4 电压对第 3 节点进行充电；

第 13 开关器件，用于响应于充入第 3 节点中的第 4 电压，利用第 2 电压对第 1 节点进行放电；

第 14 开关器件，用于响应于充入第 3 节点中的第 4 电压，利用第 2 电压对第 2 节点进行放电；

第 15 开关器件，用于响应于充入第 1 节点中的第 1 电压，向第 12 开关器件的栅极端子提供第 2 电压，以使第 12 开关器件截止；

第 16 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，向第 12 开关器件的栅极端子提供第 2 电压，以使第 12 开关器件截止；

第 17 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，向第 12 开关器件的栅极端子提供第 2 电压，以使第 12 开关器件截止；

第 18 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，利用第 2 电压对第 2 节点进行放电；

第 19 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，利用第 2 电压对第 3 节点进行放电；

第 20 开关器件，用于响应于来自第  $n+2$  级的扫描脉冲，利用第 2 电压对第 1 节点进行放电。

20、根据权利要求 19 所述的驱动电路，其中，第 1 移位寄存器中的第  $n$  级的第 1 输出单元包括：

第 21 开关器件，用于响应于充入第 1 节点中的第 1 电压，向与第  $n$  级相关联的选通线提供扫描脉冲；

第 22 开关器件，用于响应于充入第 2 节点中的第 3 电压，向所述选通线提供第 2 电压；以及

第 23 开关器件，用于响应于充入第 3 节点中的第 4 电压，向所述选通线提供第 2 电压。

21、根据权利要求 20 所述的驱动电路，其中，第 1 移位寄存器中的第  $n$  级的第 2 输出单元包括：

第 24 开关器件，用于响应于充入第 1 节点中的第 1 电压，向第  $n+1$  级和第  $n-2$  级提供扫描脉冲；

第 25 开关器件，用于响应于充入第 2 节点中的第 3 电压，向第  $n+1$  级和第  $n-2$  级提供第 2 电压；以及

第 26 开关器件，用于响应于充入第 3 节点中的第 4 电压，向第  $n+1$  级和第  $n-2$  级提供第 2 电压。

22、根据权利要求 7 所述的驱动电路，其中，第 2 移位寄存器中包括的每一个级都响应于从设置在关注级上游的一个级输出的第 2 扫描脉冲而被使能，以输出一个相关联的第 2 扫描脉冲，并且响应于从设置在关注级下游的一个级输出的第 2 扫描脉冲而被禁能。

23、根据权利要求 22 所述的驱动电路，其中，第 2 移位寄存器中包括的所述多个级中的第  $n$  级响应于从第  $n-1$  级输出的第 2 扫描脉冲而被使能，以输出一个相关联的第 2 扫描脉冲，并且响应于从第  $n+2$  级输出的扫描脉冲而被禁能，在此 “ $n$ ” 是自然数。

24、根据权利要求 23 所述的驱动电路，其中：

第 2 移位寄存器中包括的所述多个级中的第 1 级响应于第 1 起始脉冲而被使能，该第 1 起始脉冲是从外部提供的；并且

第 2 移位寄存器中包括的所述多个级中的第 2 级响应于第 2 起始脉冲而被使能，该第 2 起始脉冲是从外部提供的。

25、根据权利要求 23 所述的驱动电路，其中：

第 2 移位寄存器还包括：

第 1 哑级，用于输出一扫描脉冲，以禁能第 2 移位寄存器中的所述多个级中的最后一级；和

第 2 哑级，用于输出一扫描脉冲，以禁能设置在所述最后一级直接上游的级。

26、根据权利要求 27 所述的驱动电路，其中，第 2 哑级响应于从第 1 哑级输出的扫描脉冲而被使能。

27、根据权利要求 7 所述的驱动电路，其中，第 2 移位寄存器中包括的每一个级都包括：

节点控制器，用于控制第 1 节点、第 2 节点、以及第 3 节点的逻辑状态；和

输出单元，用于根据第 1 节点、第 2 节点、以及第 3 节点的逻辑状态，输出扫描脉冲和断态电压中的一个，并且将该输出的扫描脉冲和断态电压中的一个提供到所述选通线、所述设置在关注级下游的级，以及所述设置在关注级上游的级。

28、根据权利要求 27 所述的驱动电路，其中，第 2 移位寄存器包括的所述多个级中的第 n 级的节点控制器包括：

第 1 开关器件，用于响应于起始脉冲和来自第 n-1 级的扫描脉冲中的一个，利用第 1 电压对第 1 节点进行充电；

第 2 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，利用第 2 电压对第 2 节点进行放电；

第 3 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，利用第 2 电压对第 3 节点进行放电；

第 4 开关器件，用于在第 4 开关器件导通时，利用逐帧交替改变极性的第 3 电压对第 2 节点进行充电，第 4 开关器件响应于第 3 电压导通或截止；

第 5 开关器件，用于在第 5 开关器件导通时，利用第 2 电压对第 3 节点进行放电，第 5 开关器件响应于第 3 电压导通或截止；

第 6 开关器件，用于在第 6 开关器件导通时，利用极性与第 3 电压的极性相反的第 4 电压对第 3 节点进行充电，第 6 开关器件响应于第 4 电压导通或截止；

第 7 开关器件，用于在第 7 开关器件导通时，利用第 2 电压对第 2 节点进行放电，第 7 开关器件响应于第 4 电压导通或截止；

第 8 开关器件，用于响应于充入第 1 节点中的第 1 电压，利用第 2 电压对第 2 节点进行放电；

第 9 开关器件，用于响应于充入第 1 节点中的第 1 电压，利用第 2 电压对第 3 节点进行放电；

第 10 开关器件，用于响应于充入第 2 节点中的第 3 电压，利用第 2 电压对第 1 节点进行放电；

第 11 开关器件，用于响应于充入第 3 节点中的第 4 电压，利用第 2 电压对第 1 节点进行放电；以及

第 12 开关器件，用于响应于来自第  $n+2$  级的扫描脉冲，利用第 2 电压对第 1 节点进行放电。

29、根据权利要求 28 所述的驱动电路，其中，第 2 移位寄存器中的第  $n$  级的输出单元包括：

第 13 开关器件，用于响应于充入第 1 节点中的第 1 电压，向与第  $n$  级相关联的选通线并且向第  $n+1$  级和第  $n-2$  级提供扫描脉冲；

第 14 开关器件，用于响应于充入第 2 节点中的第 3 电压，向所述相关联的选通线并且向第  $n+1$  级和第  $n-2$  级提供第 2 电压；以及

第 15 开关器件，用于响应于充入第 3 节点中的第 4 电压，向所述相关联的选通线并且向第  $n+1$  级和第  $n-2$  级提供第 2 电压。

30、根据权利要求 27 所述的驱动电路，其中，第 2 移位寄存器包括的所述多个级中的第  $n$  级的节点控制器包括：

第 1 开关器件，用于响应于起始脉冲和来自第  $n-1$  级的扫描脉冲中的一个，利用第 1 电压对第 1 节点进行充电；

第 2 开关器件，用于响应于充入第 1 节点中的第 1 电压，利用第 2 电压对第 2 节点进行放电；

第 3 开关器件，用于响应于充入第 1 节点中的第 1 电压，利用第 2 电压对第 3 节点进行放电；

第 4 开关器件，用于在第 4 开关器件导通时，输出逐帧交替改变极性的第 3 电压，第 4 开关器件响应于第 3 电压导通或截止；

第 5 开关器件，用于响应于从第 4 开关器件输出的第 3 电压，利用该第 3 电压对第 2 节点进行充电；

第 6 开关器件，用于响应于充入第 2 节点中的第 3 电压，利用第 2 电压对第 1 节点进行放电；

第 7 开关器件，用于响应于充入第 2 节点中的第 3 电压，利用第 2 电压对第 3 节点进行放电；

第 8 开关器件，用于响应于充入第 1 节点中的第 1 电压，向第 5 开关器件的栅极端子提供第 2 电压，以使第 5 开关器件截止；

第 9 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，向第 5 开关器件的栅极端子提供第 2 电压，以使第 5 开关器件截止；

第 10 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，向第 5 开关器件的栅极端子提供第 2 电压，以使第 5 开关器件截止；

第 11 开关器件，用于在第 11 开关器件导通时，输出极性与第 3 电压的极性相反的第 4 电压，第 11 开关器件响应于第 4 电压导通或截止；

第 12 开关器件，用于响应于从第 11 开关器件输出的第 4 电压，利用该第 4 电压对第 3 节点进行充电；

第 13 开关器件，用于响应于充入第 3 节点中的第 4 电压，利用第 2 电压对第 1 节点进行放电；

第 14 开关器件，用于响应于充入第 3 节点中的第 4 电压，利用第 2 电压对第 2 节点进行放电；

第 15 开关器件，用于响应于充入第 1 节点中的第 1 电压，向第 12

开关器件的栅极端子提供第 2 电压，以使第 12 开关器件截止；

第 16 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，向第 12 开关器件的栅极端子提供第 2 电压，以使第 12 开关器件截止；

第 17 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，向第 12 开关器件的栅极端子提供第 2 电压，以使第 12 开关器件截止；

第 18 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，利用第 2 电压对第 2 节点进行放电；

第 19 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，利用第 2 电压对第 3 节点进行放电；以及

第 20 开关器件，用于响应于来自第 n+2 级的扫描脉冲，利用第 2 电压对第 1 节点进行放电。

31、根据权利要求 30 所述的驱动电路，其中，第 2 移位寄存器中的第 n 级的输出单元包括：

第 21 开关器件，用于响应于充入第 1 节点中的第 1 电压，向与第 n 级相关联的选通线并且向第 n+1 级和第 n-2 级提供扫描脉冲；

第 22 开关器件，用于响应于充入第 2 节点中的第 3 电压，向所述选通线并且向第 n+1 级和第 n-2 级提供第 2 电压；以及

第 23 开关器件，用于响应于充入第 3 节点中的第 4 电压，向所述选通线并且向第 n+1 级和第 n-2 级提供第 2 电压。

32、根据权利要求 7 所述的驱动电路，其中，第 2 移位寄存器中包括的每一个级都包括：

节点控制器，用于控制第 1 节点、第 2 节点、以及第 3 节点的逻辑状态；和

第 1 输出单元，用于根据第 1 节点、第 2 节点、以及第 3 节点的逻辑状态，输出扫描脉冲和断态电压中的一个，并且将该输出的扫描脉冲和断态电压中的一个提供到一条相关联的选通线；以及

第 2 输出单元，用于根据第 1 节点、第 2 节点、以及第 3 节点的逻辑状态，输出扫描脉冲和断态电压中的一个，并且将该输出的扫描脉冲和断态电压中的一个提供到一条相关联的选通线；以及

辑状态，输出扫描脉冲和断态电压中的一个，并且将该输出的扫描脉冲和断态电压中的一个提供到设置在关注级下游的一个级，和设置在关注级上游的一个级。

33、根据权利要求 32 所述的驱动电路，其中，第 2 移位寄存器中包括的所述多个级中的第 n 级的节点控制器包括：

第 1 开关器件，用于响应于起始脉冲和来自第 n-1 级的扫描脉冲中的一个，利用第 1 电压对第 1 节点进行充电；

第 2 开关器件，用于响应于充入第 1 节点中的第 1 电压，利用第 2 电压对第 2 节点进行放电；

第 3 开关器件，用于响应于充入第 1 节点中的第 1 电压，利用第 2 电压对第 3 节点进行放电；

第 4 开关器件，用于在第 4 开关器件导通时，输出逐帧交替改变极性的第 3 电压，第 4 开关器件响应于第 3 电压导通或截止；

第 5 开关器件，用于响应于从第 4 开关器件输出的第 3 电压，利用该第 3 电压对第 2 节点进行充电；

第 6 开关器件，用于响应于充入第 2 节点中的第 3 电压，利用第 2 电压对第 1 节点进行放电；

第 7 开关器件，用于响应于充入第 2 节点中的第 3 电压，利用第 2 电压对第 3 节点进行放电；

第 8 开关器件，用于响应于充入第 1 节点中的第 1 电压，向第 5 开关器件的栅极端子提供第 2 电压，以使第 5 开关器件截止；

第 9 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，向第 5 开关器件的栅极端子提供第 2 电压，以使第 5 开关器件截止；

第 10 开关器件，用于响应于所述起始脉冲和来自第 n-1 级的扫描脉冲中的一个，向第 5 开关器件的栅极端子提供第 2 电压，以使第 5 开关器件截止；

第 11 开关器件，用于在第 11 开关器件导通时，输出极性与第 3 电压的极性相反的第 4 电压，第 11 开关器件响应于第 4 电压导通或截止；

第 12 开关器件，用于响应于从第 11 开关器件输出的第 4 电压，利用该第 4 电压对第 3 节点进行充电；

第 13 开关器件，用于响应于充入第 3 节点中的第 4 电压，利用第 2 电压对第 1 节点进行放电；

第 14 开关器件，用于响应于充入第 3 节点中的第 4 电压，利用第 2 电压对第 2 节点进行放电；

第 15 开关器件，用于响应于充入第 1 节点中的第 1 电压，向第 12 开关器件的栅极端子提供第 2 电压，以使第 12 开关器件截止；

第 16 开关器件，用于响应于所述起始脉冲和来自第  $n-1$  级的扫描脉冲中的一个，向第 12 开关器件的栅极端子提供第 2 电压，以使第 12 开关器件截止；

第 17 开关器件，用于响应于所述起始脉冲和来自第  $n-1$  级的扫描脉冲中的一个，向第 12 开关器件的栅极端子提供第 2 电压，以使第 12 开关器件截止；

第 18 开关器件，用于响应于所述起始脉冲和来自第  $n-1$  级的扫描脉冲中的一个，利用第 2 电压对第 2 节点进行放电；

第 19 开关器件，用于响应于所述起始脉冲和来自第  $n-1$  级的扫描脉冲中的一个，利用第 2 电压对第 3 节点进行放电；

第 20 开关器件，用于响应于来自第  $n+2$  级的扫描脉冲，利用第 2 电压对第 1 节点进行放电。

34、根据权利要求 33 所述的驱动电路，其中，第 2 移位寄存器中的第  $n$  级的第 1 输出单元包括：

第 21 开关器件，用于响应于充入第 1 节点中的第 1 电压，向与第  $n$  级相关联的选通线提供扫描脉冲；

第 22 开关器件，用于响应于充入第 2 节点中的第 3 电压，向所述选通线提供第 2 电压；以及

第 23 开关器件，用于响应于充入第 3 节点中的第 4 电压，向所述选通线提供第 2 电压。

35、根据权利要求 34 所述的驱动电路，其中，第 2 移位寄存器中的

第 n 级的第 2 输出单元包括：

第 24 开关器件，用于响应于充入第 1 节点中的第 1 电压，向第 n+1 级和第 n-2 级提供扫描脉冲；

第 25 开关器件，用于响应于充入第 2 节点中的第 3 电压，向第 n+1 级和第 n-2 级提供第 2 电压；以及

第 26 开关器件，用于响应于充入第 3 节点中的第 4 电压，向第 n+1 级和第 n-2 级提供第 2 电压。

36、一种用于驱动显示装置的方法，包括以下步骤：

分别向显示器中包括的多条选通线的一侧端顺序地提供多个第 1 扫描脉冲，以顺序地驱动所述多条选通线，而且同时驱动所述多条选通线中的至少两条相邻选通线达预定时间段；和

分别向所述多条选通线的另一侧端顺序地提供多个第 2 扫描脉冲，以顺序地驱动所述多条选通线，而且同时驱动所述多条选通线中的至少两条相邻选通线达预定时间段。

37、根据权利要求 36 所述的用于驱动显示装置的方法，其中，用于驱动第 n+1 条选通线的第 1 扫描脉冲，在用于驱动第 n 条选通线的第 1 扫描脉冲保持在有效状态的预定时间段内，被提供到第 n 条选通线，在此“n”是自然数。

38、根据权利要求 36 所述的用于驱动显示装置的方法，其中，用于驱动第 n+1 条选通线的第 2 扫描脉冲，在用于驱动第 n 条选通线的第 2 扫描脉冲保持在有效状态的预定时间段内，被提供到第 n 条选通线，在此“n”是自然数。

39、根据权利要求 36 所述的用于驱动显示装置的方法，还包括以下步骤：

向第 1 移位寄存器和第 2 移位寄存器中的每一个提供彼此之间都具有相位差的多个时钟脉冲。

40、根据权利要求 39 所述的用于驱动显示装置的方法，其中，所述多个时钟脉冲顺序地输出，在相邻时间段中输出的多个时钟脉冲具有针对预定时间段同时发生的有效状态。

---

41、根据权利要求 40 所述的用于驱动显示装置的方法，其中，所述多个时钟脉冲中的连续时钟脉冲同时保持在有效状态的时间段，具有与所述多个扫描脉冲中的连续扫描脉冲同时保持在有效状态的时间段相等的长度。

---

## 显示装置的驱动电路和显示装置的驱动方法

### 技术领域

本发明涉及显示装置的驱动电路，更具体地说，涉及这样的显示装置的驱动电路，即，其能够顺序地输出脉冲宽度增大的多个扫描脉冲，而使所述多个扫描脉冲中的连续扫描脉冲相互交叠预定时间，由此防止扫描脉冲的畸变，本发明还涉及这种显示装置的驱动方法。

### 背景技术

典型地，液晶显示 (LCD) 装置通过利用电场使液晶透光来显示图像。为了实现该功能，这种 LCD 装置包括：具有按矩阵形式排列的多个像素区的 LCD 板，和用于驱动该 LCD 板的驱动电路。

在 LCD 板中，多条选通线和多条数据线被设置得相互交叉。LCD 板的像素区设置在由交叉的选通线和数据线限定的区域处。在液晶板中形成有多个像素电极和一个公共电极，以向每一个像素区施加电场。

每一个像素电极都经由充任开关器件的薄膜晶体管 (TFT) 的源电极和漏电极连接到多条数据线中的一条相关联的数据线。TFT 由经由相关联的选通线施加到该 TFT 的栅电极的扫描脉冲导通，以使得能够利用来自相关联的数据线的数据信号，对像素电极进行充电。

同时，所述驱动电路包括：用于驱动选通线的选通驱动器、用于驱动数据线的数据驱动器、用于为控制选通驱动器和数据驱动器而提供控制信号的定时控制器，以及用于提供 LCD 装置中使用的各种驱动电压的电源。

定时控制器控制选通驱动器和数据驱动器的驱动定时，并且向数据驱动器提供像素数据信号。电源对输入电压进行升压或降压，以生成诸如公共电压 VCOM、选通高压信号 VGH 以及选通低压信号 VGL 的驱动电压。选通驱动器向选通线顺序地提供扫描脉冲，使得能够逐行地顺序驱动 LCD

板的液晶单元。每当一条选通线被提供了扫描脉冲时，数据驱动器就向各数据线提供一像素电压信号。从而，LCD 装置根据向与每一液晶单元相关联的数据线施加的像素电压信号，利用在相关联的像素电极与公共电极之间施加的电场来控制该液晶单元的透光率，由此显示图像。

为了顺序地输出扫描脉冲，选通驱动器包括移位寄存器。下面将参照附图对其进行更详细的说明。

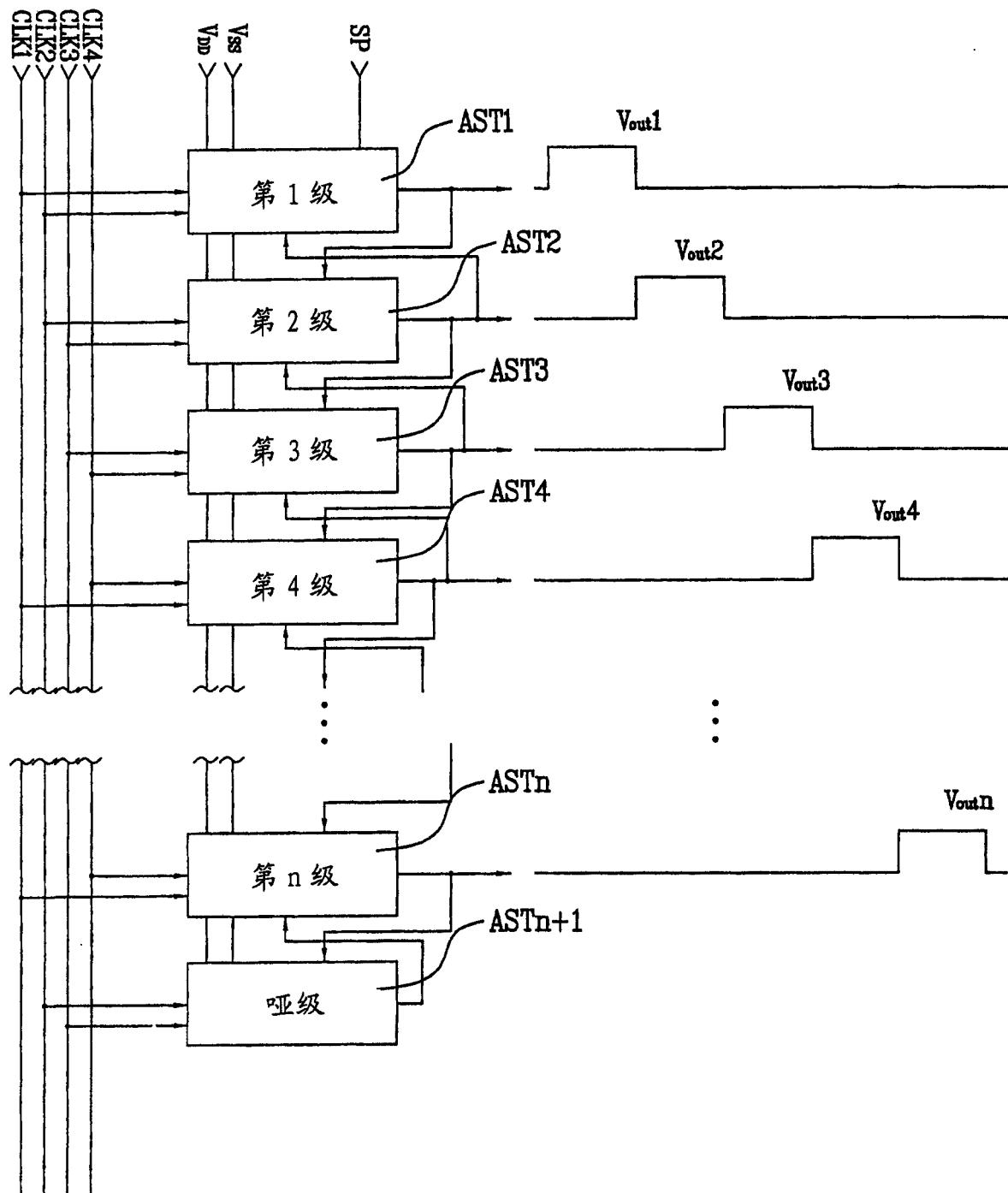

图 1 是例示常规移位寄存器的图。

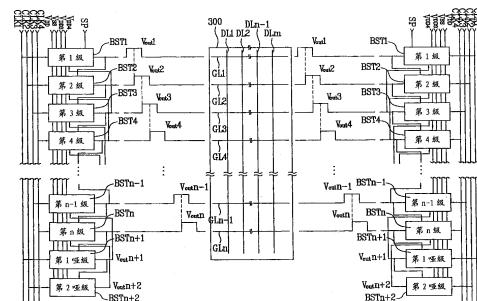

如图 1 所示，常规移位寄存器包括串联连接的  $n$  个级 AST1 到 ASTn 和一个哑级 ASTn+1。级 AST1 到 ASTn+1 分别输出扫描脉冲 Vout1 到 Voutn+1。即，从第 1 级 AST1 开始，而在哑级 ASTn+1 结束，从级 AST1 到 ASTn+1 按顺序方式输出扫描脉冲 Vout1 到 Voutn+1。除了哑级 ASTn+1 之外，从级 AST1 到 ASTn 输出的扫描脉冲 Vout1 到 Voutn 分别被顺序地提供给液晶板（未示出）的多条选通线，以使得顺序地扫描所述多条选通线。

具有上述结构的移位寄存器的级 AST1 到 ASTn+1 中的每一个都接收第 1 电压 VDD、第 2 电压 VSS，以及第 1 时钟脉冲 CLK1 到第 4 时钟脉冲 CLK4 中的两个时钟脉冲。第 1 时钟脉冲 CLK1 到第 4 时钟脉冲 CLK4 中的连续时钟脉冲相对于彼此具有相位差。第 1 电压 VDD 指正电压，而第 2 电压 VSS 指地电压。

设置在其余的级 AST2 到 ASTn+1 上游的第 1 级 AST1，除了接收第 1 电压 VDD、第 2 电压 VSS 以及两个时钟脉冲之外，还接收起始脉冲 SP。

然而，具有上述结构的常规移位寄存器存在一些问题。下面对其进行说明。

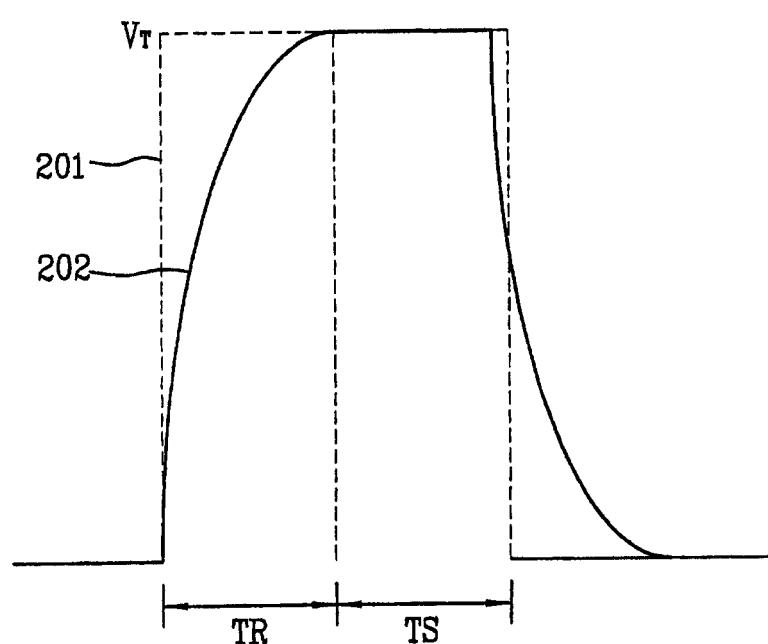

图 2 是例示理想扫描脉冲和畸变扫描脉冲的波形的波形图。

通常，在显示面积增大的 LCD 装置中，其多条选通线具有增加的长度。随着选通线的长度增加，选通线的电阻分量和电容分量也将增大。在这种情况下，向选通线提供的扫描脉冲可能因增大的电阻分量和电容分量而畸变。在图 2 中，标号“201”标示在假定相关联的选通线中没有电阻分量和电容分量的情况下理想扫描脉冲。另一方面，当扫描脉冲

因相关联的选通线的电阻分量和电容分量而畸变时，该扫描脉冲的上升时间 TR 增加，由此，使该扫描脉冲发生畸变。在图 2 中，标号“202”标示因相关联的选通线的电阻分量和电容分量而畸变的扫描脉冲。由于畸变扫描脉冲 202 与理想扫描脉冲 201 相比具有增加的上升时间 TR，所以该畸变扫描脉冲保持在目标电压 VT 的有效充电时间 TS 缩短了。当向相关联的 TFT 的栅电极施加如上所述具有畸变波形的扫描脉冲 202 时，该 TFT 的导通时间缩短了，由此缩短了通过导通的 TFT 从相关联的数据线提供的数据电压的切换时间。结果，经由导通的 TFT 的漏极/源极端子施加给相关联的像素电极的数据电压的波形发生了畸变。因而，存在数据电压未被充分充入像素电极中的问题。

### 发明内容

因此，本发明致力于提供一种显示装置的驱动电路和该显示装置的驱动方法，其基本上消除了因现有技术的局限和缺点而造成的一个或更多个问题。

本发明的一个目的是，提供一种显示装置的驱动电路，其能够顺序地输出脉冲宽度增大的多个扫描脉冲，而使所述多个扫描脉冲中的连续扫描脉冲相互交叠预定时间，以增加使扫描脉冲保持在目标电压的有效充电时间，由此防止扫描脉冲的畸变；还提供一种该显示装置的驱动方法。

本发明的其它优点、目的以及特征，将部分地在下面的描述中加以阐述，并且本领域普通技术人员在考察以下内容时将部分地明白，或者可以通过实施本发明而获知。通过在文字描述及其权利要求以及附图中具体指出的结构，可以认识到并实现本发明的目的和其它优点。

为了实现这些目的和其它优点，并且根据本发明的目的，如在此具体实现并广泛描述的，提供了一种显示装置的驱动电路，其包括：第 1 移位寄存器，用于分别向显示器中包括的多条选通线的一侧端顺序地提供第 1 扫描脉冲，以顺序地驱动所述多条选通线，第 1 移位寄存器同时驱动所述多条选通线中的至少两条相邻选通线达预定时间段；和第 2 移

位寄存器，用于分别向所述多条选通线的另一侧端顺序地提供第 2 扫描脉冲，以顺序地驱动所述多条选通线，第 2 移位寄存器同时驱动所述多条选通线中的至少两条相邻选通线达预定时间段。

在本发明的另一方面，提供了一种显示装置的驱动方法，其包括以下步骤：分别向显示器中包括的多条选通线的一侧端顺序地提供第 1 扫描脉冲，以顺序地驱动所述多条选通线，但同时驱动所述多条选通线中的至少两条相邻选通线达预定时间段；和分别向所述多条选通线的另一侧端顺序地提供第 2 扫描脉冲，以顺序地驱动所述多条选通线，但同时驱动所述多条选通线中的至少两条相邻选通线达预定时间段。

应当明白，本发明上面的一般描述和下面的详细描述都是示例性和解释性的，旨在提供对如权利要求所述的本发明的进一步阐释。

### 附图说明

附图被包括进来以提供对本发明的进一步理解，其被并入并构成本申请的一部分，例示了本发明的实施例，并与说明书一起用于解释本发明的原理。在附图中：

图 1 是例示常规移位寄存器的图；

图 2 是例示理想扫描脉冲和畸变扫描脉冲的波形的波形图；

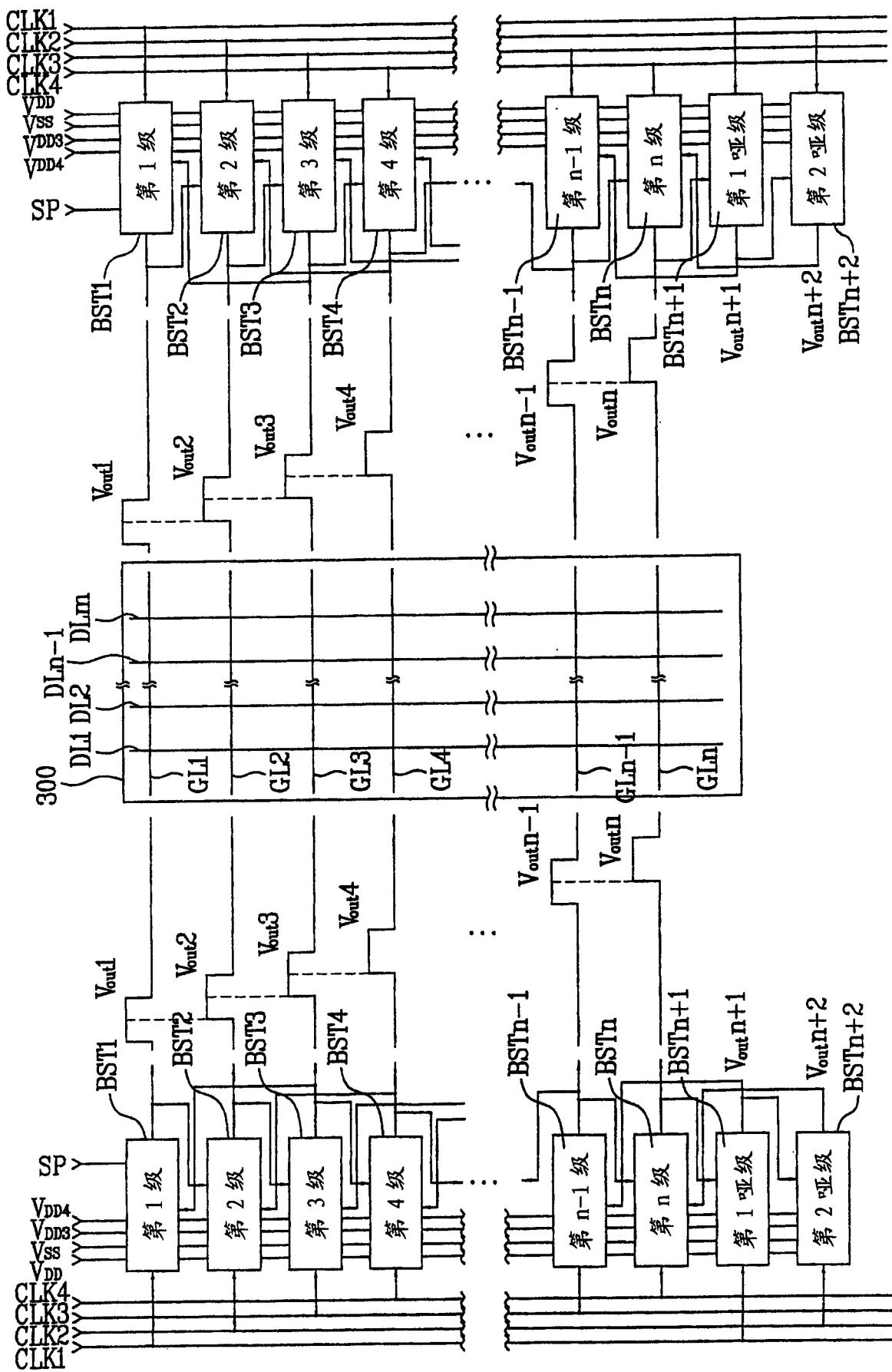

图 3 是例示根据本发明第一实施例的移位寄存器的结构的框图；

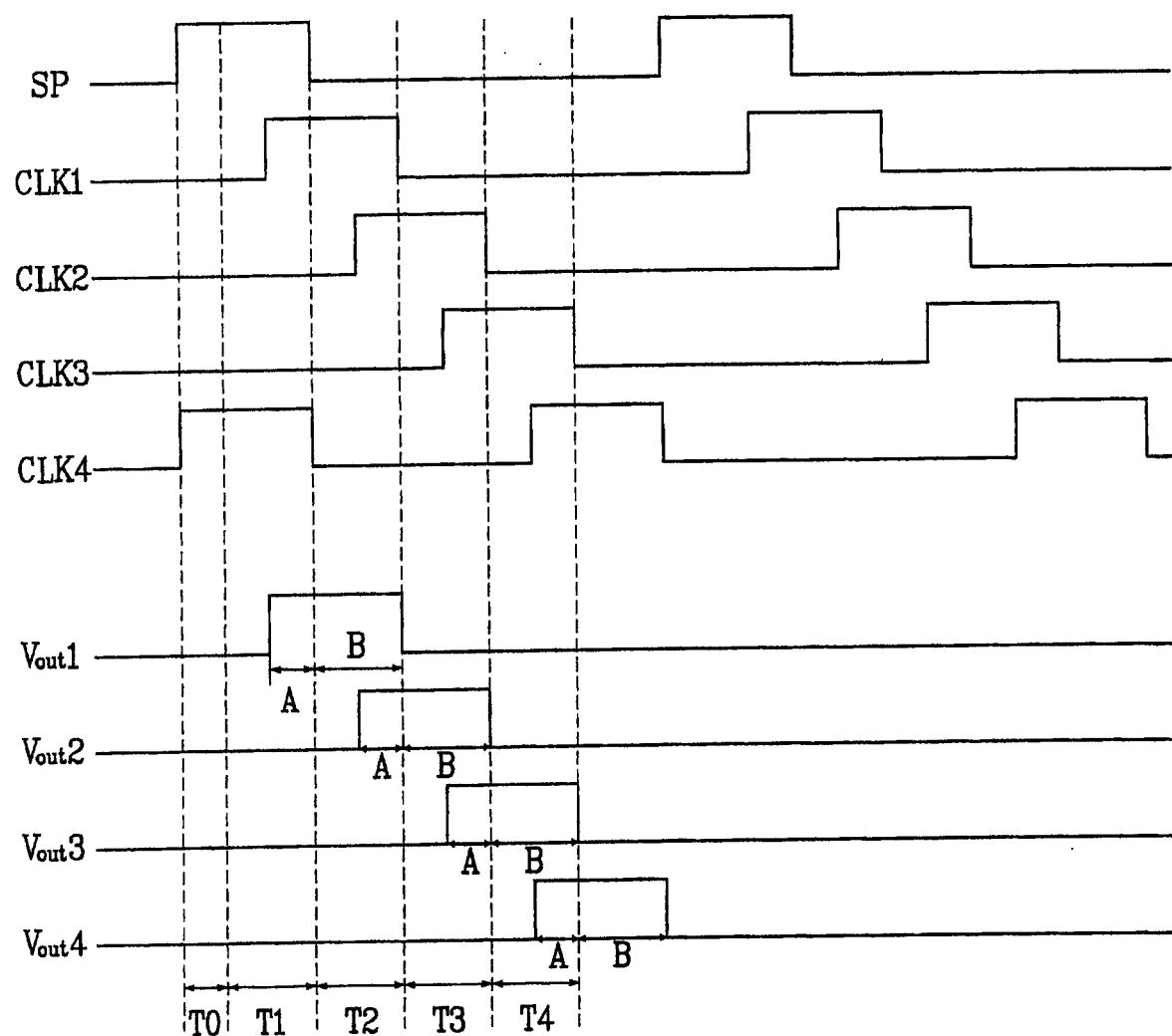

图 4 是第 1 到第 4 时钟脉冲和第 1 到第 4 扫描脉冲的时序图；

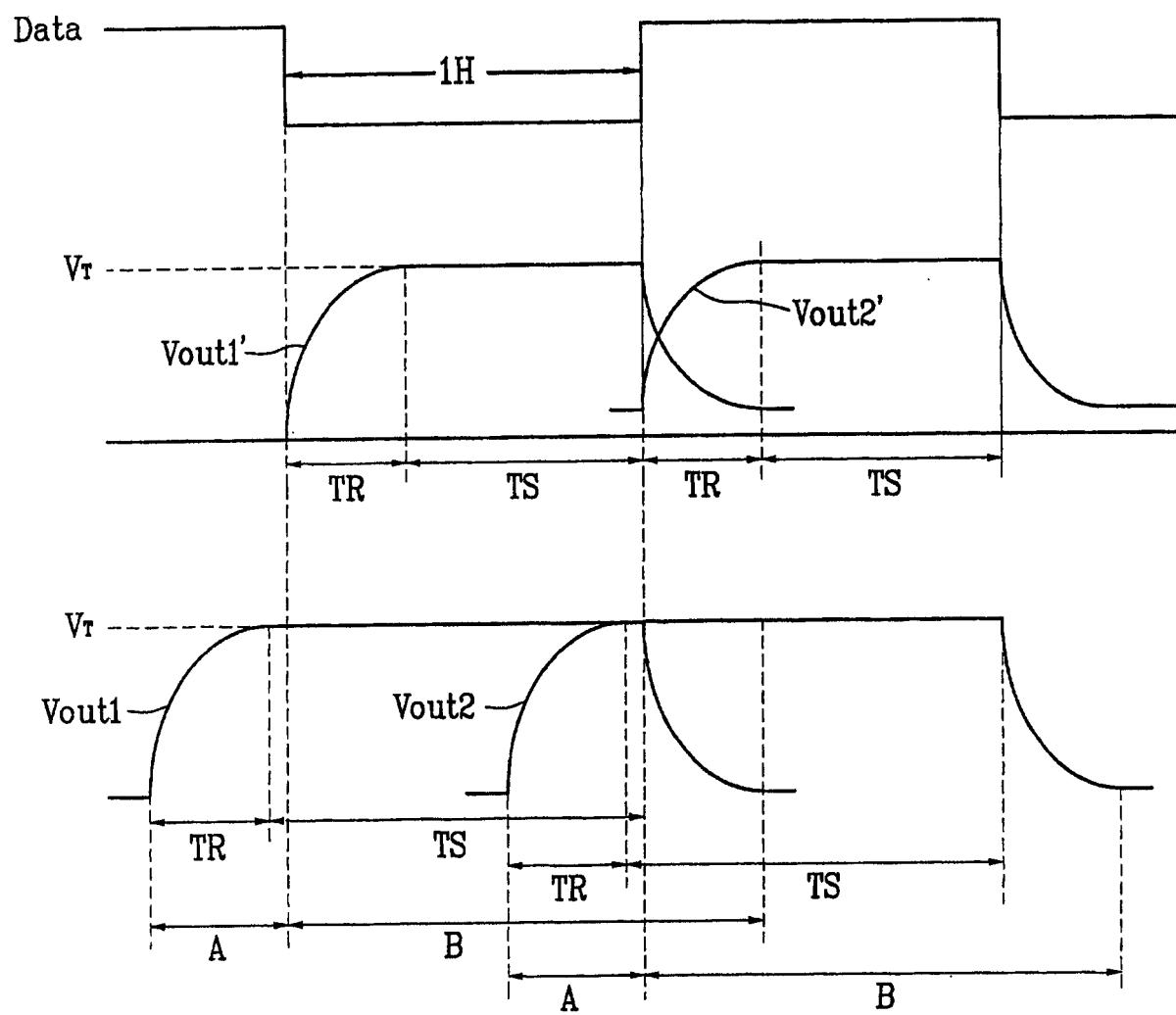

图 5 是说明根据本发明的扫描脉冲与常规扫描脉冲的对比的波形图；

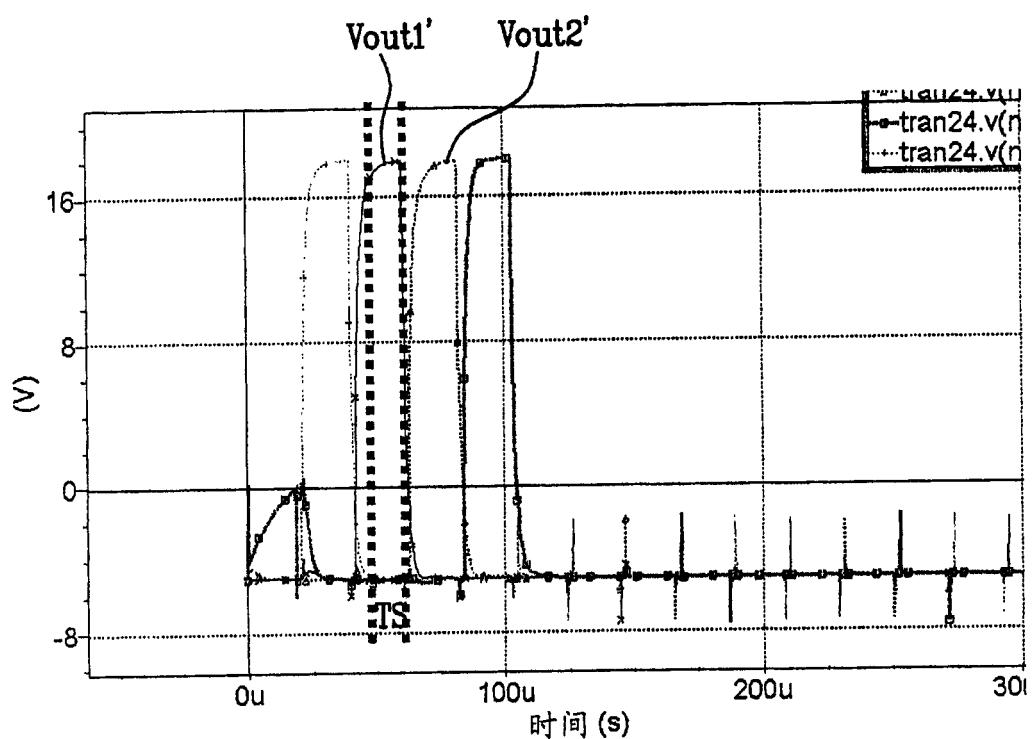

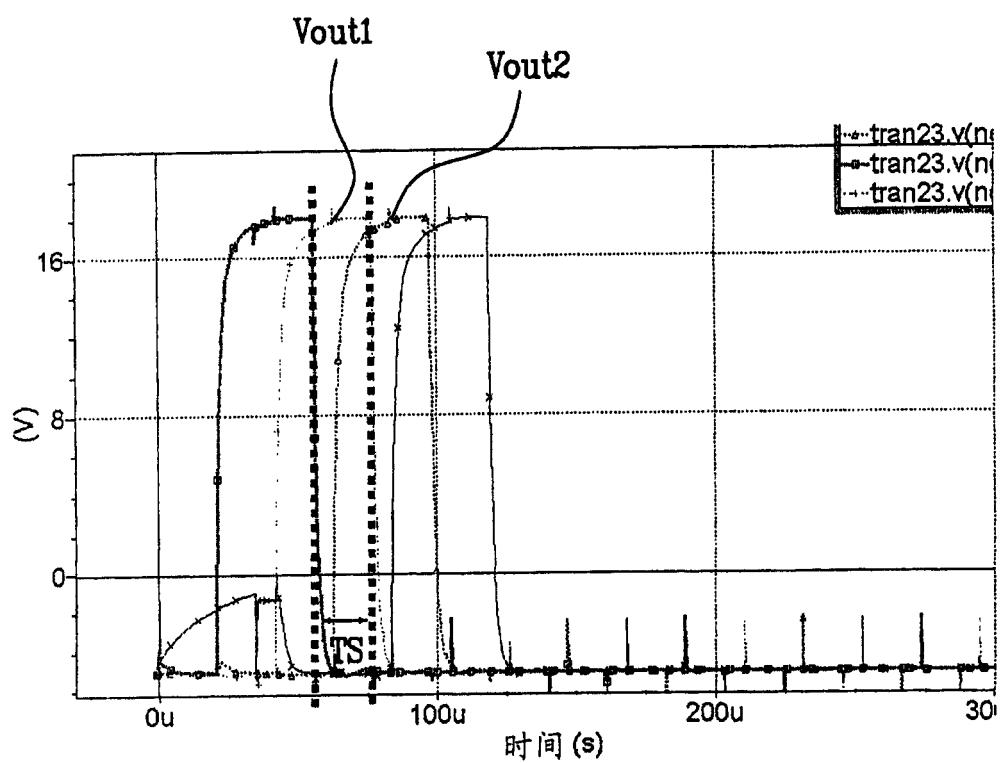

图 6A 和 6B 是分别例示根据本发明的扫描脉冲的仿真波形和常规扫描脉冲的仿真波形的波形图；

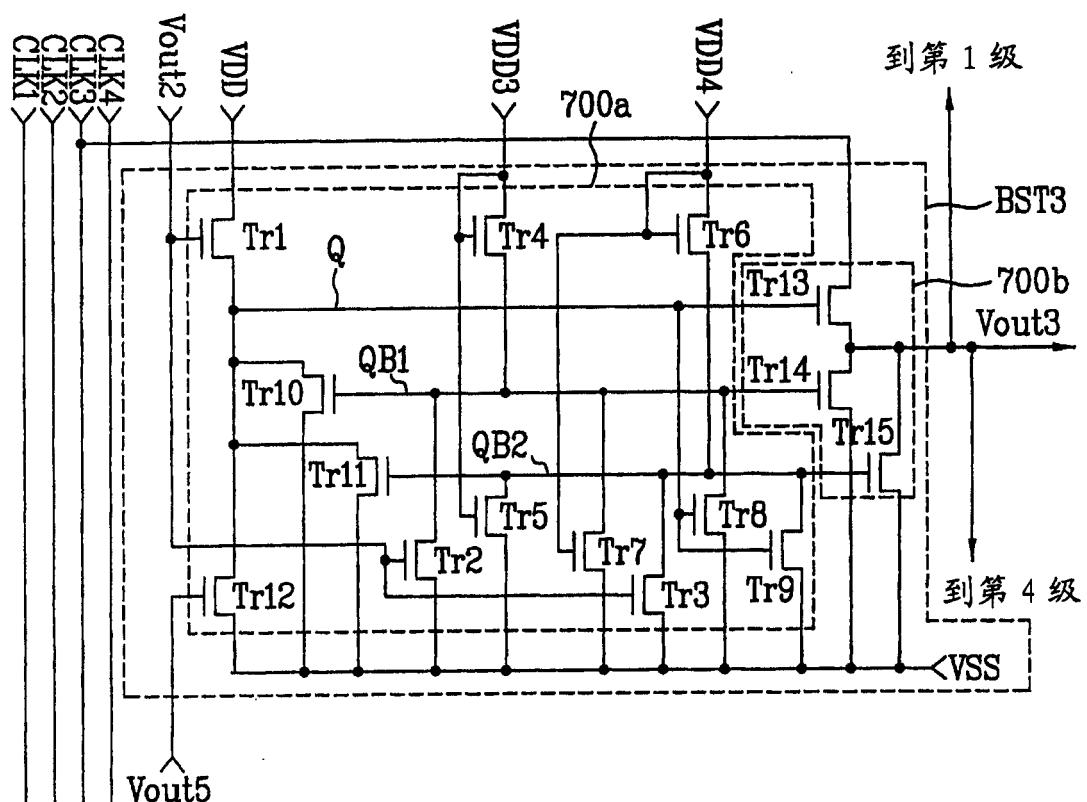

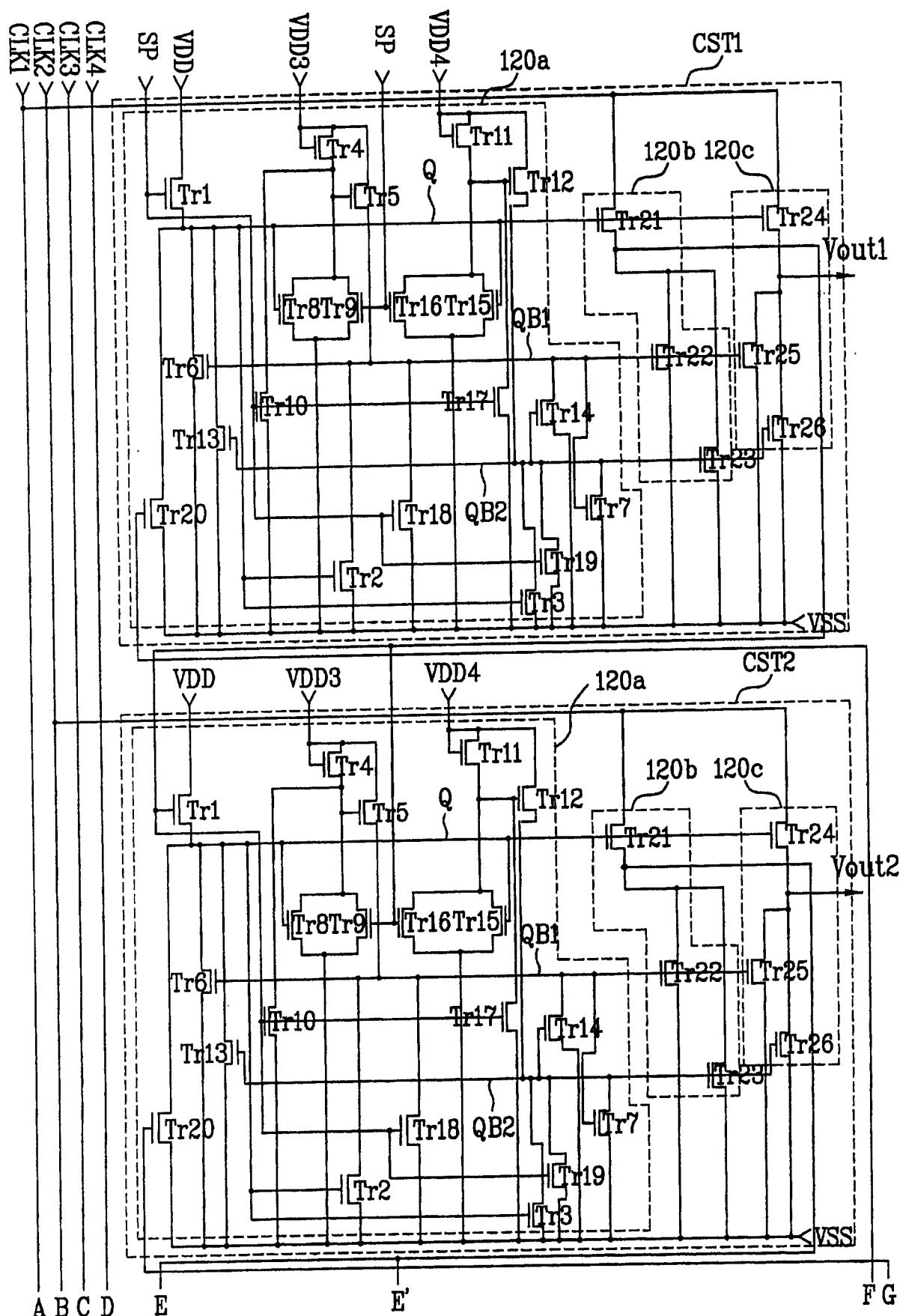

图 7 是例示在图 3 中示出的第 1 移位寄存器的第 3 级中包括的电路的电路图；

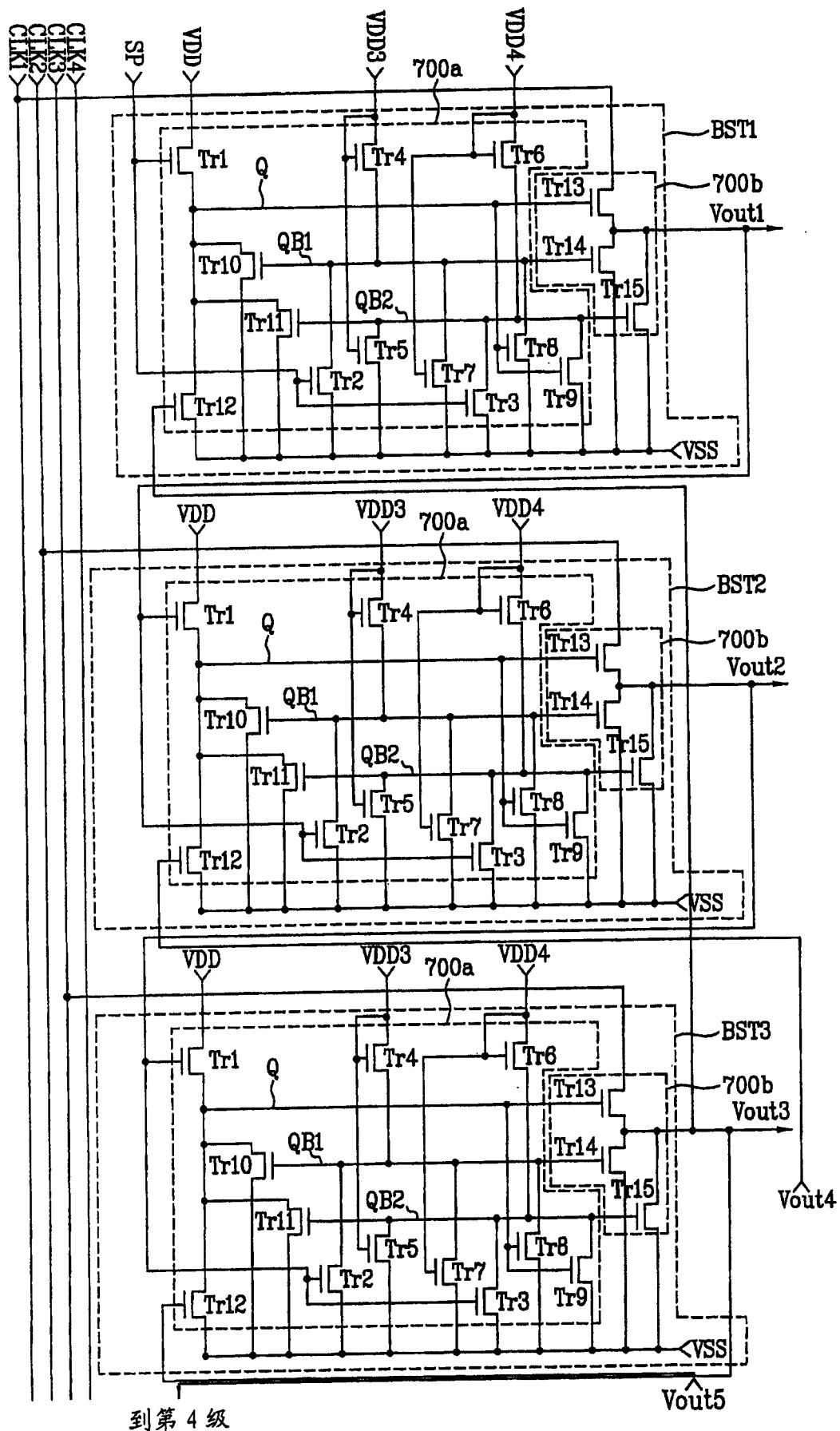

图 8 是例示第 1 移位寄存器的第 1 到第 3 级的电路图，其中的每一个级都具有图 7 中示出的电路结构；

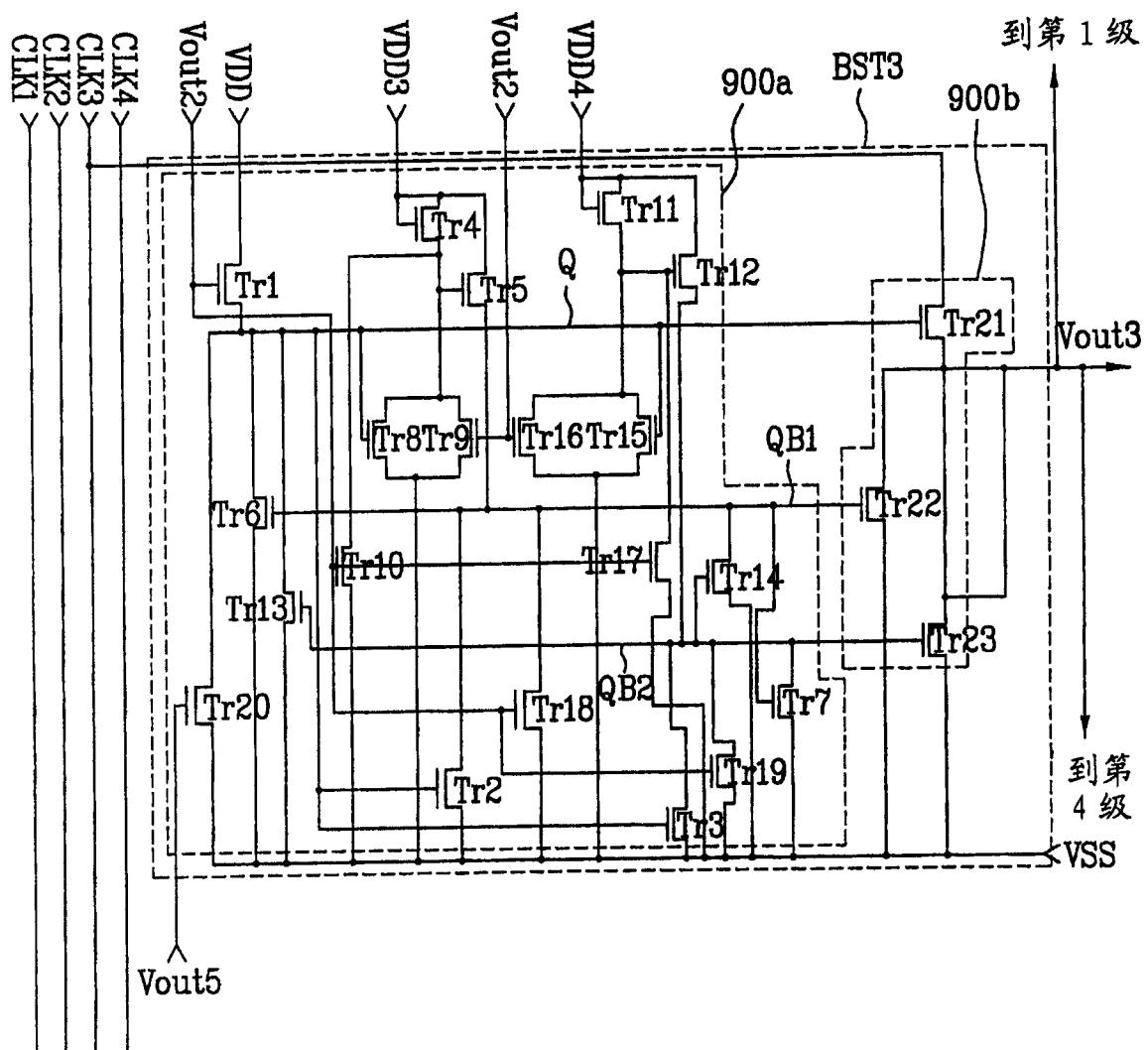

图 9 是例示在图 3 中示出的第 1 移位寄存器的第 3 级中包括的电路结构的电路图；

图 10A 和 10B 是例示第 1 移位寄存器的第 1 到第 3 级的电路图，其中的每一个级都具有图 9 中示出的电路结构；

图 11 是例示根据本发明第二实施例的移位寄存器的框图；

图 12 是例示在图 11 中示出的第 1 移位寄存器的第 3 级中包括的电路的电路图；以及

图 13A 和图 13B 是例示具有图 12 中示出的电路结构的第 1 移位寄存器的第 3 级的电路图。

### 具体实施方式

下面，详细说明本发明的优选实施例，附图中例示了其示例。尽可能地，所有图中都使用相同的标号来指代相同或相似的部分。

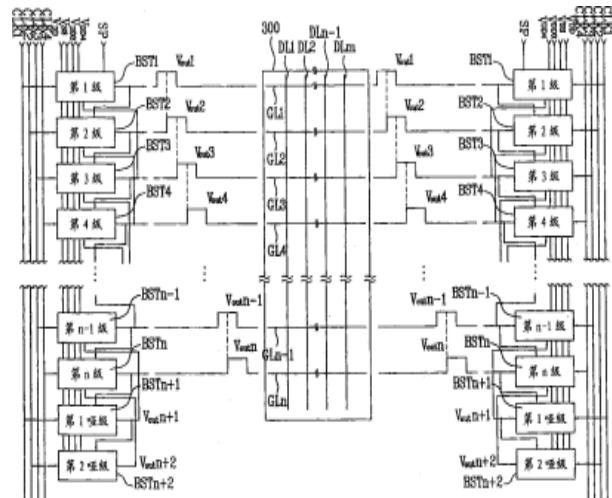

图 3 是例示根据本发明第一实施例的移位寄存器的结构的框图。

如图 3 所示，应用于 LCD 装置的根据本发明第一实施例的移位寄存器的特征在于，该移位寄存器响应于时钟脉冲 CLK1 到 CLK4 中的相关联的时钟脉冲和一起始脉冲，按顺序方式分别向 LCD 板 300 的选通线 GL1 到 GLn 输出多个扫描脉冲 Vout1 到 Voutn，同时增大所述多个扫描脉冲 Vout1 到 Voutn 中的每一个的脉冲宽度，使得所述多个扫描脉冲 Vout1 到 Voutn 中的连续扫描脉冲相互交叠预定时间。

该移位寄存器可以分成两个移位寄存器，即，第 1 移位寄存器 301a 和第 2 移位寄存器 301b。第 1 移位寄存器 301a 设置在 LCD 板 300 的左侧，向选通线 GL1 到 GLn 中的每一条的一端提供一扫描脉冲。第 2 移位寄存器 301b 设置在 LCD 板 300 的右侧，向选通线 GL1 到 GLn 中的每一条的另一端提供一扫描脉冲。

为了缩小显示装置的尺寸，优选的是，把第 1 移位寄存器 301a 和第 2 移位寄存器 301b 内建在 LCD 板 300 中。

LCD 板 300 包括：按一个方向平行延伸的多条选通线 GL1 到 GLn，和按垂直于选通线 GL1 到 GLn 的方向平行延伸的多条数据线 DL1 到 DLm。利用从数据驱动器输出的数据电压对数据线 DL1 到 DLm 中的每一条进行充电。在由选通线 GL1 到 GLn 中的一条相关联的选通线和数据线 DL1 到 DLm

中的一条相关联的数据线限定的每一个像素区处都形成有 TFT 和像素电极。具体地，TFT 形成在一区域附近，在该区域中，选通线 GL1 到 GLn 中的一条相关联的选通线和数据线 DL1 到 DLm 中的一条相关联的数据线相互交叉。TFT 响应于对选通线 GL1 到 GLn 中的一条相关联的选通线充入的扫描脉冲 Vout1 到 Voutn 中的一个相关联的扫描脉冲，切换对数据线 DL1 到 DLm 中的一条相关联的数据线充入的数据电压，以向相关联的像素电极施加数据电压。从而，在 LCD 板 300 上显示图像。

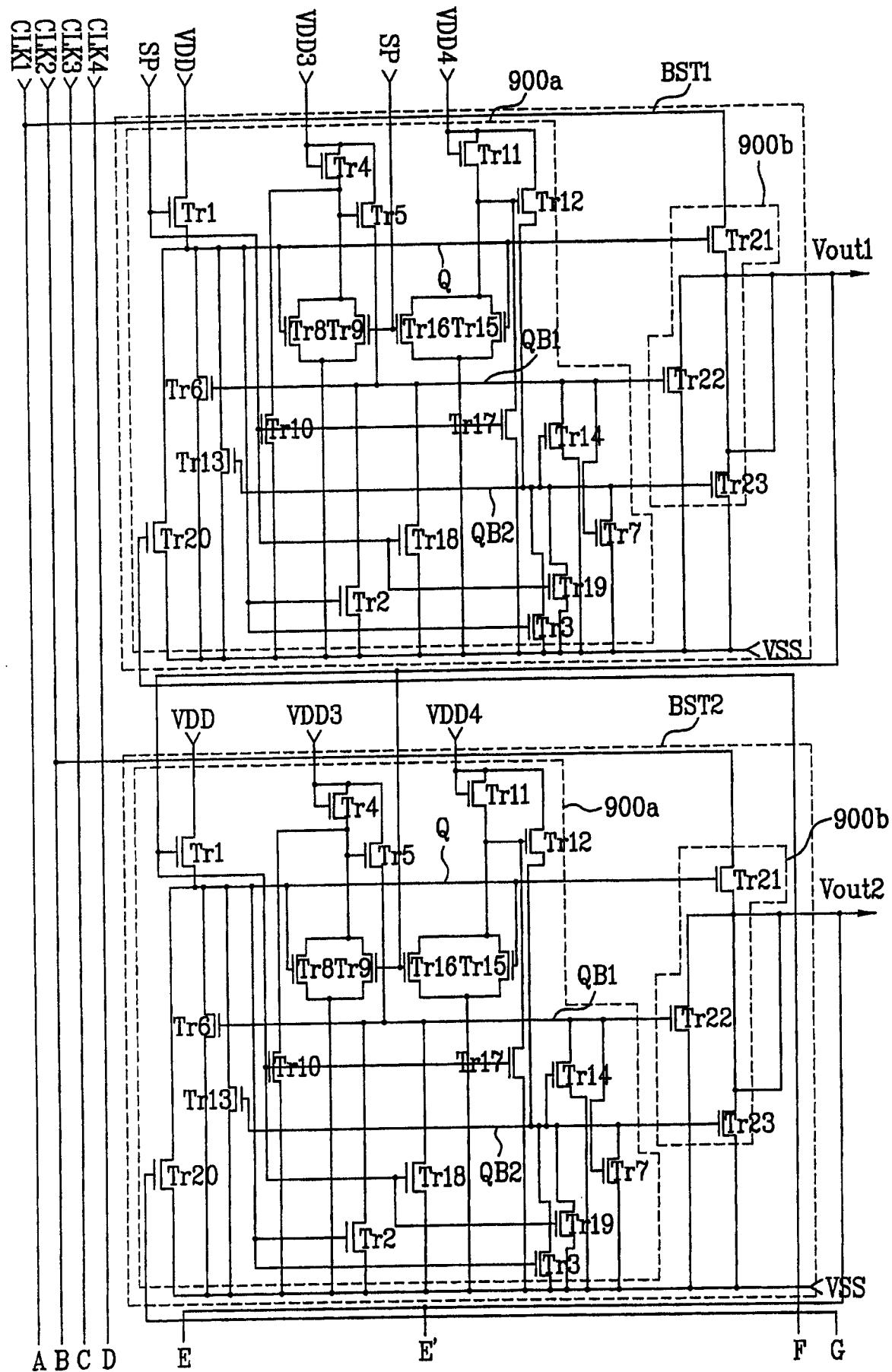

如图 3 所示，第 1 移位寄存器 301a 包括：串联连接的 n 个级 BST1 到 BSTn、第 1 哑级 BSTn+1，以及第 2 哑级 BSTn+2。级 BST1 到 BSTn+2 分别输出扫描脉冲 Vout1 到 Voutn+2。即，从第 1 级 BST1 开始，而在第 2 哑级 BSTn+2 结束，按顺序方式从级 BST1 到 BSTn+2 输出扫描脉冲 Vout1 到 Voutn+2。除了第 1 哑级 BSTn+1 和第 2 哑级 BSTn+2 之外，从级 BST1 到 BSTn 输出的扫描脉冲 Vout1 到 Voutn 分别被顺序提供给 LCD 板 300(未示出) 的选通线 GL1 到 GLn，以使得选通线 GL1 到 GLn 被顺序扫描。

第 2 移位寄存器 301b 具有与第 1 移位寄存器 301a 相同的结构。因此，从第 1 移位寄存器 301a 的级 BST1 到 BSTn+2 输出的扫描脉冲 Vout1 到 Voutn+2 分别与从第 2 移位寄存器 301b 中包括的级 BST1 到 BSTn+2 输出的扫描脉冲 Vout1 到 Voutn+2 相同。例如，从第 1 移位寄存器 301a 的第 1 级 BST1 输出的第 1 扫描脉冲 Vout1，和从第 2 移位寄存器 301b 的第 1 级 BST1 输出的第 1 扫描脉冲 Vout1 在同一时间点，被提供给第 1 选通线 GL1。从而，第 1 移位寄存器 301a 的级 BST1 到 BSTn+2 对应于第 2 移位寄存器 301b 的级 BST1 到 BSTn+2，使得它们分别输出相同的扫描脉冲 Vout1 到 Voutn+2。然而，第 1 移位寄存器 301a 中包括的级 BST1 到 BSTn 中的每一个都向选通线 GL1 到 GLn 中的一条相关联的选通线的一端施加扫描脉冲 Vout1 到 Voutn 中的一个相关联的扫描脉冲。而第 2 移位寄存器 301b 中包括的级 BST1 到 BSTn 中的每一个都向选通线 GL1 到 GLn 中的一条相关联的选通线的另一端施加扫描脉冲 Vout1 到 Voutn 中的一个相关联的扫描脉冲。

具有上述结构的第 1 移位寄存器 301a 的级 BST1 到 BSTn+2 中的每一

个都接收第 1 到第 4 电压 VDD、VSS、VDD3 和 VDD4，以及循环的而且连续时钟脉冲之间具有相位差的第 1 时钟脉冲 CLK1 到第 4 时钟脉冲 CLK4 中的一个时钟脉冲。第 1 电压 VDD 指具有正极性的 DC 电压，而第 2 电压 VSS 指具有负极性的电压。第 3 电压 VDD3 和第 4 电压 VDD4 中的每一个都是逐帧交替改变极性的 AC 电压。第 3 电压 VDD3 和第 4 电压 VDD4 在同一帧中具有不同的极性。

设置在第 1 移位寄存器 301a 中的其余级 BST2 到 BSTn 上游的第 1 级 BST1，除了接收第 1 到第 4 电压 VDD、VSS、VDD3 和 VDD4，以及第 1 时钟脉冲 CLK1 到第 4 时钟脉冲 CLK4 中的两个时钟脉冲之外，还接收一起始脉冲 SP。

如上所述，第 1 时钟脉冲 CLK1 到第 4 时钟脉冲 CLK4 在相对于彼此延迟相位之后输出。即，第 2 时钟脉冲 CLK2 在相对于第 1 时钟脉冲 CLK1 延迟相位之后输出。第 3 时钟脉冲 CLK3 在相对于第 2 时钟脉冲 CLK2 延迟相位之后输出。第 4 时钟脉冲 CLK4 在相对于第 3 时钟脉冲 CLK3 延迟相位之后输出。

向第 1 移位寄存器 301a 中的级 BST1 到 BSTn+1 中的最上游级（即，第 1 级 BST1）施加的起始脉冲 SP，被早于时钟脉冲 CLK1 到 CLK4 输出。而且，起始脉冲 SP 针对每一帧输出一次。即，对于每一帧，首先输出起始脉冲 SP，接着按循环方式顺序输出第 1 时钟脉冲 CLK1 到第 4 时钟脉冲 CLK4。即，顺序地输出一组第 1 时钟脉冲 CLK1 到第 4 时钟脉冲 CLK4，接着顺序地输出另一组第 1 时钟脉冲 CLK1 到第 4 时钟脉冲 CLK4。因此，在输出第 4 时钟脉冲 CLK4 时的时间点与输出第 2 时钟脉冲 CLK2 时的时间点之间的时段输出第 1 时钟脉冲 CLK1。第 4 时钟脉冲 CLK4 可以与起始脉冲 SP 同步输出。在这种情况下，第 4 时钟脉冲 CLK4 早于第 1 时钟脉冲 CLK1 到第 3 时钟脉冲 CLK3 输出。

同时，根据本发明，第 1 移位寄存器 301a 可以使用两个或更多个时钟脉冲。即，根据本发明，第 1 移位寄存器 301a 可以只使用第 1 时钟脉冲 CLK1 到第 4 时钟脉冲 CLK4 中的两个，例如，第 1 时钟脉冲 CLK1 和第 2 时钟脉冲 CLK2，或者可以仅使用第 1 时钟脉冲 CLK1 到第 4 时钟脉冲 CLK4

中的三个，例如，第 1 时钟脉冲 CLK1 到第 3 时钟脉冲 CLK3。另选地，根据本发明，第 1 移位寄存器 301a 可以使用顺序输出的至少五个时钟脉冲。

第 2 移位寄存器 301b 与第 1 移位寄存器 301a 具有相同的结构。

下面，详细说明具有上述结构的移位寄存器的操作。

因为第 1 移位寄存器 301a 和第 2 移位寄存器 301b 按相同方式操作，所以仅结合第 1 移位寄存器 301a 进行以下说明。

在首先将来自定时控制器的起始脉冲 SP 输入给第 1 级 BST1 时，第 1 级 BST1 响应于该起始脉冲 SP 而被使能。此后，被使能的第 1 级 BST1 从定时控制器接收第 1 时钟脉冲 CLK1，接着输出第 1 时钟脉冲 CLK1 作为第 1 扫描脉冲 Vout1。来自第 1 级 BST1 的第 1 扫描脉冲 Vout1 被提供给第 1 选通线 GL1 和第 2 级 BST2。响应于第 1 扫描脉冲 Vout1，第 2 级 BST2 被使能。此后，被使能的第 2 级 BST2 接收来自定时控制器的第 2 时钟脉冲 CLK2，接着输出第 2 时钟脉冲 CLK2 作为第 2 扫描脉冲 Vout2。来自第 2 级 BST2 的第 2 扫描脉冲 Vout2 被提供给第 2 选通线 GL2 和第 3 级 BST3。响应于第 2 扫描脉冲 Vout2，第 3 级 BST3 被使能。随后，被使能的第 3 级 BST3 接收来自定时控制器的第 3 时钟脉冲 CLK3，接着输出第 3 时钟脉冲 CLK3 作为第 3 扫描脉冲 Vout3。来自第 3 级 BST3 的第 3 扫描脉冲 Vout3 被提供给第 3 选通线 GL3、第 4 级 BST4 以及第 1 级 BST1。响应于第 3 扫描脉冲 Vout3，第 4 级 BST4 被使能。而且，第 1 级 BST1 响应于第 3 扫描脉冲 Vout3 向第 1 选通线 GL1 提供第 3 电压 VSS。此后，被使能的第 4 级 BST4 接收来自定时控制器的第 4 时钟脉冲 CLK4，接着输出第 4 时钟脉冲 CLK4 作为第 4 扫描脉冲 Vout4。来自第 4 级 BST4 的第 4 扫描脉冲 Vout4 被提供给第 4 选通线 GL4 和第 5 级 BST5。响应于第 4 扫描脉冲 Vout4，第 5 级 BST5 被使能。被使能的第 5 级 BST5 接收来自定时控制器的第 1 时钟脉冲 CLK1，接着输出第 1 时钟脉冲 CLK1 作为第 5 扫描脉冲 Vout5。来自第 5 级 BST5 的第 5 扫描脉冲 Vout5 被提供给第 5 选通线 GL5、第 6 级 BST6 以及第 3 级 BST3。响应于第 5 扫描脉冲 Vout5，第 6 级 BST6 被使能。而且，第 3 级 BST3 响应于第 5 扫描脉冲 Vout5 向第 3 选通线 GL3 提供第 2 电压 VSS。按这种方式，分别从第 6 级 BST6 到第 n 级 BSTn 顺序

地输出第 6 扫描脉冲  $V_{out6}$  到第  $n$  扫描脉冲  $V_{outn}$ 。第 6 扫描脉冲  $V_{out6}$  到第  $n$  扫描脉冲  $V_{outn}$  分别被顺序提供给第 6 选通线  $GL_6$  到第  $n$  选通线  $GL_n$ 。这些扫描脉冲具有使得这些扫描脉冲中的连续扫描脉冲相互交叠预定宽度的脉冲宽度。在这种情况下，第 1 级  $BST_{n+1}$  操作，以向第  $n-1$  级  $BST_{n-1}$  提供第  $n+1$  扫描脉冲  $V_{outn+1}$ ，而第 2 级  $BST_{n+2}$  操作，以向第  $n$  级  $BST_n$  提供第  $n+2$  扫描脉冲  $V_{outn+2}$ 。即，不向任何一条选通线提供从第 1 级  $BST_{n+1}$  和第 2 级  $BST_{n+2}$  输出的第  $n+1$  扫描脉冲  $V_{outn+1}$  和第  $n+2$  扫描脉冲  $V_{outn+2}$ 。第  $n+1$  扫描脉冲  $V_{outn+1}$  和第  $n+2$  扫描脉冲  $V_{outn+2}$  分别充任用于使能第  $n-1$  级  $BST_{n-1}$  和第  $n$  级  $BST_n$  以输出第 2 电压  $VSS$  的驱动输出。

从而，级  $BST_1$  到  $BST_n$  输出扫描脉冲  $V_{out1}$  到  $V_{outn}$ ，以分别向选通线  $GL_1$  到  $GL_n$  顺序提供扫描脉冲  $V_{out1}$  到  $V_{outn}$ 。同时，级  $BST_1$  到  $BST_n$  中的每一个都向下游级提供扫描脉冲  $V_{out1}$  到  $V_{outn}$  中的一个相关联的扫描脉冲，作为起始脉冲  $SP$ 。级  $BST_1$  到  $BST_n$  中的每一个都响应于从下游级输出的扫描脉冲向相关联的选通线提供第 2 电压  $VSS$ 。

第 2 移位寄存器  $301b$  与第 1 移位寄存器  $301a$  按相同的方式操作。然而，第 2 移位寄存器  $301b$  中包括的级  $BST_1$  到  $BST_n$  中的每一个都向选通线  $GL_1$  到  $GL_n$  中的一条相关联的选通线的另一端提供扫描脉冲  $V_{out1}$  到  $V_{outn}$  中的一个相关联的扫描脉冲，这与第 1 移位寄存器  $301a$  不同，在第 1 移位寄存器  $301a$  中，级  $BST_1$  到  $BST_n$  中的每一个都向选通线  $GL_1$  到  $GL_n$  中的一条相关联的选通线的一端提供扫描脉冲  $V_{out1}$  到  $V_{outn}$  中的一个相关联的扫描脉冲。

下面，对在第 1 移位寄存器  $301a$  和第 2 移位寄存器  $301b$  中的每一个中包括的级  $BST_1$  到  $BST_n$  中的每一个都不接收从第 1 下游级输出的扫描脉冲，而是接收从第 2 下游级输出的扫描脉冲的原因进行说明。在进行该说明之前，先对扫描脉冲  $V_{out1}$  到  $V_{outn+2}$  和第 1 时钟脉冲  $CLK_1$  到第 4 时钟脉冲  $CLK_4$  进行更详细说明。因为扫描脉冲  $V_{out1}$  到  $V_{outn}$  具有相同的波形，所以仅结合第 1 扫描脉冲  $V_{out1}$  到第 4 扫描脉冲  $V_{out4}$  进行以下说明。

图 4 是第 1 到第 4 时钟脉冲和第 1 到第 4 扫描脉冲的时序图。

如图 4 所示, 第 1 扫描脉冲  $V_{out1}$  到第 4 扫描脉冲  $V_{out4}$  中的每一个都具有可以分成预充电时段 A 和有效充电时段 B 的脉冲宽度。扫描脉冲  $V_{out1}$  到  $V_{out4}$  中的每一个的预充电时段 A 都与前一扫描脉冲的有效充电时段 B 在时间上交叠。而且, 扫描脉冲  $V_{out1}$  到  $V_{out4}$  中的每一个的有效充电时段 B 都与下一扫描脉冲的预充电时段 A 在时间上交叠。因此, 扫描脉冲  $V_{out1}$  到  $V_{out4}$  中的每一个都在前一扫描脉冲的有效充电时段 B 中就开始被输出, 而在受关注扫描脉冲 (即, 当前扫描脉冲) 的有效充电时段 B 中达到目标电压  $VT$ 。

即, 第 1 扫描脉冲  $V_{out1}$  在起始脉冲  $SP$  的与第 1 扫描脉冲  $V_{out1}$  的预充电时段 A 对应的一个时段中开始被输出, 而在第 1 扫描脉冲  $V_{out1}$  的有效充电时段 B 中保持为目标电压  $VT$ 。第 2 扫描脉冲  $V_{out2}$  在第 1 扫描脉冲  $V_{out1}$  的与第 2 扫描脉冲  $V_{out2}$  的预充电时段 A 对应的有效充电时段 B 中开始被输出, 而在第 2 扫描脉冲  $V_{out2}$  的有效充电时段 B 中保持为目标电压  $VT$ 。第 3 扫描脉冲  $V_{out3}$  在第 2 扫描脉冲  $V_{out2}$  的与第 3 扫描脉冲  $V_{out3}$  的预充电时段 A 对应的有效充电时段 B 中开始被输出, 而在第 3 扫描脉冲  $V_{out3}$  的有效充电时段 B 中保持为目标电压  $VT$ 。第 4 扫描脉冲  $V_{out4}$  在第 3 扫描脉冲  $V_{out3}$  的与第 4 扫描脉冲  $V_{out4}$  的预充电时段 A 对应的有效充电时段 B 中开始被输出, 而在第 4 扫描脉冲  $V_{out4}$  的有效充电时段 B 中保持为目标电压  $VT$ 。

从而, 扫描脉冲  $V_{out1}$  到  $V_{out4}$  中的每一个的脉冲宽度都大体上比常规扫描脉冲的脉冲宽度大了对应于预充电时段 A 的脉冲宽度。因此, 其优点在于, 接收扫描脉冲  $V_{out1}$  到  $V_{out4}$  的液晶板 300 的 TFT 的导通时间增加了。

同时, 因为扫描脉冲  $V_{out1}$  到  $V_{out4}$  中的每一个都与第 1 时钟脉冲  $CLK1$  到第 4 时钟脉冲  $CLK4$  中的一个相关联的时钟脉冲同步输出, 所以第 1 时钟脉冲  $CLK1$  到第 4 时钟脉冲  $CLK4$  中的连续时钟脉冲按与扫描脉冲  $V_{out1}$  到  $V_{out4}$  中的连续扫描脉冲相互交叠的时间相等的预定时间相互交叠。

因为第 1 时钟脉冲 CLK1 到第 4 时钟脉冲 CLK4 连续循环，同时在它们中的连续时钟脉冲之间保持预定相位差，所以第 1 时钟脉冲 CLK1 与第 4 时钟脉冲 CLK4 交叠。

下面将对照常规扫描脉冲来说明根据本发明的扫描脉冲。例如结合常规第 1 扫描脉冲  $V_{out1}'$  和第 2 扫描脉冲  $V_{out2}'$  和根据本发明的第 1 扫描脉冲  $V_{out1}$  和第 2 扫描脉冲  $V_{out2}$  进行以下说明。

图 5 是说明根据本发明的扫描脉冲与常规扫描脉冲的对比的波形图。图 6A 和 6B 是分别例示根据本发明的扫描脉冲的仿真波形和常规扫描脉冲的仿真波形的波形图。

当常规扫描脉冲  $V_{out1}'$  和  $V_{out2}'$  的波形因相关联的选通线的电阻分量和电容分量而畸变时，常规扫描脉冲  $V_{out1}'$  和  $V_{out2}'$  的上升时间  $TR$  增加了。结果，常规扫描脉冲  $V_{out1}'$  和  $V_{out2}'$  中的扫描脉冲保持为目标电压  $VT$  的有效充电时间  $TS$  缩短了。同时，数据电压  $Data$  在正极性与负极性之间周期性地改变极性，同时被施加给每一条数据线。在这种情况下，扫描脉冲的有效充电时间  $TS$  比数据电压  $Data$  保持为正极性状态或者保持为负极性状态的时间  $1H$  短。为此，数据电压  $Data$  不能被正常地施加给相关联的像素电极。

然而，根据本发明，第 1 扫描脉冲  $V_{out1}$  从起始脉冲  $SP$ （对应于第 1 扫描脉冲  $V_{out1}$  的预充电时段 A）的一个时段内的一时间点开始输出，并且在电压逐渐增大之后达到目标电压  $VT$ 。此后，第 1 扫描脉冲  $V_{out1}$  保持为目标电压  $VT$  达与第 1 扫描脉冲  $V_{out1}$  的有效充电时段 B 相对应的时间。即，第 1 扫描脉冲  $V_{out1}$  的上升时间  $TR$  不包括在与第 1 扫描脉冲  $V_{out1}$  的有效充电时段 B 相对应的时间内，而是包括在与第 1 扫描脉冲  $V_{out1}$  的预充电时段 A 相对应的时间内。因此，与第 1 扫描脉冲  $V_{out1}$  的有效充电时段 B 相对应的时间不因上升时间  $TR$  而减少。类似地，第 2 扫描脉冲  $V_{out2}$  从第 1 扫描脉冲  $V_{out1}$ （对应于第 2 扫描脉冲  $V_{out2}$  的预充电时段 A）的有效充电时段 B 内的一时间点开始输出，并且在电压逐渐增大之后达到目标电压  $VT$ 。此后，第 2 扫描脉冲  $V_{out2}$  保持为目标电压  $VT$  达与第 2 扫描脉冲  $V_{out2}$  的有效充电时段 B 相对应的时间。即，第 2 扫

描脉冲  $V_{out2}$  的上升时间  $TR$  不包括在与第 2 扫描脉冲  $V_{out2}$  的有效充电时段 B 相对应的时间内，而是包括在与第 2 扫描脉冲  $V_{out2}$  的预充电时段 A 相对应的时间内。因此，与第 2 扫描脉冲  $V_{out2}$  的有效充电时段 B 相对应的时间不因上升时间  $TR$  而减少。

从而，如图 6A 和 6B 所示，本发明的第 1 扫描脉冲  $V_{out1}$  和第 2 扫描脉冲  $V_{out2}$  的有效充电时间  $TS$  比常规第 1 扫描脉冲  $V_{out1}'$  和第 2 扫描脉冲  $V_{out2}'$  的有效充电时间  $TS$  长。因为根据本发明的第 1 扫描脉冲  $V_{out1}$  和第 2 扫描脉冲  $V_{out2}$  的有效充电时间  $TS$  比数据电压  $Data$  保持为正极性状态或者保持为负极性状态的时间  $1H$  长，所以数据电压  $Data$  可以被正常地传输给相关联的像素电极。

同时，因为根据本发明的扫描脉冲  $V_{out1}$  到  $V_{outn}$  中的连续扫描脉冲具有交叠脉冲宽度时段，所以在级  $BST1$  到  $BST_{n+2}$  中的每一个都接收来自下游级的扫描脉冲时可能产生问题。例如，如果把从第 2 级  $BST2$  输出的第 2 扫描脉冲  $V_{out2}$  输入到第 1 级  $BST1$  (与常规情况下相同)，则因为连续输出的第 1 扫描脉冲  $V_{out1}$  和第 2 扫描脉冲  $V_{out2}$  具有交叠脉冲宽度时段，所以输出第 1 扫描脉冲  $V_{out1}$  的第 1 级  $BST1$  在第 1 扫描脉冲  $V_{out1}$  的有效充电时段 B 内的某一时间点向第 1 选通线  $GL1$  提供第 2 电压  $VSS$ 。换句话说，在将第 1 扫描脉冲  $V_{out1}$  完整地施加到第 1 选通线  $GL1$  之前，第 1 级  $BST1$  在输出第 2 扫描脉冲  $V_{out2}$  时的时间点 (具体地，在第 2 扫描脉冲  $V_{out2}$  的预充电时段 A 内的某一时间点) 向第 1 选通线  $GL1$  提供第 2 电压  $VSS$ 。因此，第 1 级  $BST1$  可能输出不完整的扫描脉冲。在这种情况下，向每一条选通线都提供脉冲宽度与常规情况的脉冲宽度相同的扫描脉冲。结果，扫描脉冲可能畸变。为此，根据本发明的级  $BST1$  到  $BST_{n+2}$  中的每一个都不接收来自第 1 下游级的扫描脉冲，而是接收来自第 2 下游级的扫描脉冲。即，级  $BST1$  到  $BST_{n+2}$  中的每一个都接收没有与从受关注级输出的扫描脉冲交叠的时段的扫描脉冲。

下面，详细说明级  $BST1$  到  $BST_{n+2}$  中分别包括的电路，以及第 1 哑级  $BST_{n+1}$  和第 2 哑级  $BST_{n+2}$ 。因为第 1 移位寄存器 301a 和第 2 移位寄存器 301b 中包括的级  $BST1$  到  $BST_{n+2}$  具有相同的结构，所以仅结合例如

第 1 移位寄存器 301a 中包括的第 3 级 BST3 进行以下说明。

图 7 是例示在图 3 中示出的第 1 移位寄存器的第 3 级中包括的电路的电路图。

如图 7 所示，第 3 级 BST3 包括：节点控制器 700a，其控制针对第 1 节点 Q、第 2 节点 QB1 以及第 3 节点 QB2 的充电和放电操作；和输出单元 700b，其根据第 1 节点 Q、第 2 节点 QB1 以及第 3 节点 QB2 的充电/放电状态而导通，以选择性地输出扫描脉冲或第 2 电压 VSS。第 1 节点 Q、第 2 节点 QB1 以及第 3 节点 QB2 被选择性地充电或放电。具体地，当第 1 节点 Q 处于充电状态时，第 2 节点 QB1 和第 3 节点 QB2 都保持为放电状态。另一方面，当第 1 节点 Q 处于放电状态时，第 2 节点 QB1 和第 3 节点 QB2 中的一个保持为充电状态。即，当第 1 节点 Q 在奇数帧中处于放电状态时，第 2 节点 QB1 被充电，而第 3 节点 QB2 被放电。另一方面，当第 1 节点 Q 在偶数号帧中处于放电状态时，第 2 节点 QB1 被放电，而第 3 节点 QB2 被充电。之所以在第 1 节点 Q 处于放电状态时，分别向第 2 节点 QB1 和第 3 节点 QB2 施加具有相反极性并且逐帧交替改变极性的电压 VDD3 和 VDD4（充电和放电），是为了防止在其栅极端子处连接到第 2 节点 QB1 和第 3 节点 QB2 的开关器件的劣化。

第 3 级 BST3 的节点控制器 700a 包括第 1 NMOS 晶体管 Tr1 到第 12 NMOS 晶体管 Tr12。

第 1 NMOS 晶体管 Tr1 响应于来自设置在第 3 级 BST3 直接上游的级的扫描脉冲，利用第 1 电压 VDD 对第 1 节点 Q 进行充电。即，第 1 NMOS 晶体管 Tr1 响应于来自第 2 级 BST2 的第 2 扫描脉冲 Vout2，利用第 1 电压 VDD 对第 1 节点 Q 进行充电。为了执行该操作，第 1 NMOS 晶体管 Tr1 在其栅极端子处连接到第 2 级 BST2，在其源极端子处连接到用于传输第 1 电压 VDD 的电源线，而在其漏极端子处连接到第 1 节点 Q。

第 2 NMOS 晶体管 Tr2 响应于来自设置在第 3 级 BST3 直接上游的级的扫描脉冲，利用第 2 电压 VSS 对第 2 节点 QB1 进行放电。即，第 2 NMOS 晶体管 Tr2 响应于来自第 2 级 BST2 的第 2 扫描脉冲 Vout2，利用第 2 电压 VSS 对第 2 节点 QB1 进行放电。为了执行该操作，第 2 NMOS 晶体管 Tr2

在其栅极端子处连接到第 2 级 BST2，在其源极端子处连接到第 2 节点 QB1，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 3 NMOS 晶体管 Tr3 响应于来自设置在第 3 级 BST3 直接上游的级的扫描脉冲，利用第 2 电压 VSS 对第 3 节点 QB2 进行放电。即，第 3 NMOS 晶体管 Tr3 响应于来自第 2 级 BST2 的第 2 扫描脉冲 Vout2，利用第 2 电压 VSS 对第 3 节点 QB2 进行放电。为了执行该操作，第 3 NMOS 晶体管 Tr3 在其栅极端子处连接到第 2 级 BST2，在其源极端子处连接到第 3 节点 QB2，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 4 NMOS 晶体管 Tr4 响应于第 3 电压 VDD3 而导通或截止。在第 4 NMOS 晶体管 Tr4 的导通状态中，其利用第 3 电压 VDD3 对第 2 节点 QB1 进行充电。为了执行该操作，第 4 NMOS 晶体管 Tr4 在其栅极端子和源极端子处连接到用于传输第 3 电压 VDD3 的电源线，而在其漏极端子处连接到第 2 节点 QB1。第 3 电压 VDD3 是逐帧在正极性与负极性之间交替极性的 AC 电压。即，第 3 电压 VDD3 在奇数帧中具有正极性，而在偶数帧中具有负极性。

第 5 NMOS 晶体管 Tr5 响应于第 3 电压 VDD3，利用第 2 电压 VSS 对第 3 节点 QB2 进行放电。为了执行该操作，第 5 NMOS 晶体管 Tr5 在其栅极端子处连接到用于传输第 3 电压 VDD3 的电源线，在其源极端子处连接到第 3 节点 QB2，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 6 NMOS 晶体管 Tr6 响应于第 4 电压 VDD4 而导通或截止。在第 6 NMOS 晶体管 Tr6 的导通状态中，其利用第 4 电压 VDD4 对第 3 节点 QB2 进行充电。为了执行该操作，第 6 NMOS 晶体管 Tr6 在其栅极端子和源极端子处连接到用于传输第 4 电压 VDD4 的电源线，而在其漏极端子处连接到第 3 节点 QB2。第 4 电压 VDD4 是逐帧在正极性与负极性之间交替极性的 AC 电压。即，第 4 电压 VDD4 在奇数帧中具有负极性，而在偶数帧中具有正极性。

第 7 NMOS 晶体管 Tr7 响应于第 4 电压 VDD4，利用第 2 电压 VSS 对第 2 节点 QB1 进行放电。为了执行该操作，第 7 NMOS 晶体管 Tr7 在其栅极端子处连接到用于传输第 4 电压 VDD4 的电源线，在其源极端子处连接到

第 2 节点 QB1, 而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 8 NMOS 晶体管 Tr8 响应于充入第 1 节点 Q 中的第 1 电压 VDD, 利用第 2 电压 VSS 对第 2 节点 QB1 进行放电。为了执行该操作, 第 8 NMOS 晶体管 Tr8 在其栅极端子处连接到第 1 节点 Q, 在其源极端子处连接到第 2 节点 QB1, 而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 9 NMOS 晶体管 Tr9 响应于充入第 1 节点 Q 中的第 1 电压 VDD, 利用第 2 电压 VSS 对第 3 节点 QB2 进行放电。为了执行该操作, 第 9 NMOS 晶体管 Tr9 在其栅极端子处连接到第 1 节点 Q, 在其源极端子处连接到第 3 节点 QB2, 而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 10 NMOS 晶体管 Tr10 响应于充入第 2 节点 QB1 中的第 3 电压 VDD3, 利用第 2 电压 VSS 对第 1 节点 Q 进行放电。为了执行该操作, 第 10 NMOS 晶体管 Tr10 在其栅极端子处连接到第 2 节点 QB1, 在其源极端子处连接到第 1 节点 Q, 而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 11 NMOS 晶体管 Tr11 响应于充入第 3 节点 QB2 中的第 4 电压 VDD4, 利用第 2 电压 VSS 对第 1 节点 Q 进行放电。为了执行该操作, 第 11 NMOS 晶体管 Tr11 在其栅极端子处连接到第 3 节点 QB2, 在其源极端子处连接到第 1 节点 Q, 而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 12 NMOS 晶体管 Tr12 响应于来自设置在第 3 级 BST3 次下游的级的扫描脉冲, 利用第 2 电压 VSS 对第 1 节点 Q 进行放电。即, 第 12 NMOS 晶体管 Tr12 响应于来自第 5 级 BST5 的第 5 扫描脉冲 Vout5, 利用第 2 电压 VSS 对第 1 节点 Q 进行放电。为了执行该操作, 第 12 NMOS 晶体管 Tr12 在其栅极端子处连接到第 5 级 BST5 的输出单元, 在其源极端子处连接到第 1 节点 Q, 而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 3 级 BST3 的输出单元 700b 包括第 13 NMOS 晶体管 Tr13 到第 15 NMOS 晶体管 Tr15。

第 13 NMOS 晶体管 Tr13 响应于充入第 1 节点 Q 中的第 1 电压 VDD, 向相关联的选通线输出一时钟脉冲作为扫描脉冲。该扫描脉冲被提供给第 2 上游级和第 1 下游级。为了执行该操作, 第 13 NMOS 晶体管 Tr13 在其栅极端子处连接到第 1 节点 Q, 在其源极端子处连接到用于传输第 3 时

钟脉冲 CLK3 的时钟线,而在其漏极端子处连接到第 3 选通线、第 1 级 BST1 中的第 12 NMOS 晶体管 Tr12 的栅极端子、以及第 4 级 BST4 中的第 1 NMOS 晶体管 Tr1 到第 3 NMOS 晶体管 Tr3 的栅极端子。

第 14 NMOS 晶体管 Tr14 响应于充入第 2 节点 QB1 中的第 3 电压 VDD3, 向相关联的选通线输出第 2 电压 VSS。即, 第 14 NMOS 晶体管 Tr14 响应于充入第 2 节点 QB1 中的第 3 电压 VDD3, 向第 3 选通线提供第 2 电压 VSS。为了执行该操作, 第 14 NMOS 晶体管 Tr14 在其栅极端子处连接到第 2 节点 QB1, 在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线, 而在其源极端子处连接到第 3 选通线、第 1 级 BST1 中的第 12 NMOS 晶体管 Tr12 的栅极端子、以及第 4 级 BST4 中的第 1 NMOS 晶体管 Tr1 到第 3 NMOS 晶体管 Tr3 的栅极端子。

第 15 NMOS 晶体管 Tr15 响应于充入第 3 节点 QB2 中的第 4 电压 VDD4, 向相关联的选通线输出第 2 电压 VSS。即, 第 15 NMOS 晶体管 Tr15 响应于充入第 3 节点 QB2 中的第 4 电压 VDD4, 向第 3 选通线提供第 2 电压 VSS。为了执行该操作, 第 15 NMOS 晶体管 Tr15 在其栅极端子处连接到第 2 节点 QB1, 在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线, 而在其源极端子处连接到第 3 选通线、第 1 级 BST1 中的第 12 NMOS 晶体管 Tr12 的栅极端子, 以及第 4 级 BST4 中的第 1 NMOS 晶体管 Tr1 到第 3 NMOS 晶体管 Tr3 的栅极端子。

第 1 级 BST1 和第 2 级 BST2、第 4 级 BST4 到第 n 级 BSTn, 以及第 1 哑级 BSTn+1 和第 2 哑级 BSTn+2 都与第 3 级 BST3 具有相同的结构。

因为第 1 级 BST1 没有上游级, 所以第 1 级 BST1 的第 1 NMOS 晶体管 Tr1 到第 3 NMOS 晶体管 Tr3 都接收来自定时控制器的起始脉冲 SP。即, 第 1 级 BST1 的第 1 NMOS 晶体管 Tr1 响应于来自定时控制器的起始脉冲 SP, 利用第 1 电压 VDD 对第 1 级 BST1 的第 1 节点 Q 进行充电。

第 1 级 BST1 的第 2 NMOS 晶体管 Tr2 响应于来自定时控制器的起始脉冲 SP, 利用第 2 电压 VSS 对第 1 级 BST1 的第 2 节点 QB1 进行放电。第 1 级 BST1 的第 3 NMOS 晶体管 Tr3 响应于来自定时控制器的起始脉冲 SP, 利用第 2 电压 VSS 对第 1 级 BST1 的第 3 节点 QB2 进行放电。

在第 1 级 BST1 或第 2 级 BST2 次上游没有设置级。为此，第 1 级 BST1 向第 1 选通线和第 2 级 BST2 提供从其输出的第 1 扫描脉冲  $V_{out1}$ 。类似地，第 2 级 BST2 向第 2 选通线和第 3 级 BST3 提供从其输出的第 2 扫描脉冲  $V_{out2}$ 。

在第 2 哑级  $BST_{n+2}$  直接下游没有设置级。因此，第 2 哑级  $BST_{n+2}$  中的第 13 NMOS 晶体管  $Tr_{13}$  的源极端子、第 14 NMOS 晶体管  $Tr_{14}$  的漏极端子，以及第 15 NMOS 晶体管  $Tr_{15}$  的漏极端子都连接到第  $n$  级  $BST_n$  的第 12 NMOS 晶体管  $Tr_{12}$  的栅极端子。

第 2 移位寄存器 301b 的级  $BST_1$  到  $BST_{n+2}$  与第 1 移位寄存器 301a 的级  $BST_1$  到  $BST_{n+2}$  具有相同的结构。

下面将说明根据本发明的例示实施例的移位寄存器的操作。因为第 1 移位寄存器 301a 和第 2 移位寄存器 301b 按相同的方式操作，所以仅结合第 1 移位寄存器 301a 的操作进行以下说明。

图 8 是例示第 1 移位寄存器的第 1 级到第 3 级的电路图，其中的每一个级都具有图 7 中示出的电路结构。

在下面的描述中，假定在第 1 帧中，第 3 电压  $VDD3$  保持在正极性状态，而第 4 电压  $VDD4$  保持在负极性状态。还假定在第 2 帧中，第 3 电压  $VDD3$  保持在负极性状态，而第 4 电压  $VDD4$  保持在正极性状态。即，假定在奇数帧中，第 3 电压  $VDD3$  保持在正极性状态，而第 4 电压  $VDD4$  保持在负极性状态；而在偶数号帧中，第 3 电压  $VDD3$  保持在负极性状态，而第 4 电压  $VDD4$  保持在正极性状态。

首先，将一起始脉冲  $SP$  施加到第 1 NMOS 晶体管  $Tr_1$  到第 3 NMOS 晶体管  $Tr_3$  的栅极端子。结果，第 1 NMOS 晶体管  $Tr_1$  到第 3 NMOS 晶体管  $Tr_3$  导通。

接着，将第 1 电压  $VDD$  经由导通的第 1 NMOS 晶体管  $Tr_1$  提供给第 1 节点  $Q$ 。在利用第 1 电压  $VDD$  对第 1 节点  $Q$  进行充电时，第 8 NMOS 晶体管  $Tr_8$ 、第 9 NMOS 晶体管  $Tr_9$  以及第 13 NMOS 晶体管  $Tr_{13}$ （其中的每一个在其栅极端子处都连接到第 1 节点  $Q$ ）同时导通。因此，将第 2 电压  $VSS$  经由导通的第 8 NMOS 晶体管  $Tr_8$  和第 2 NMOS 晶体管  $Tr_2$  提供给第 2

节点 QB1。因而，第 2 节点 QB1 保持在放电状态。结果，第 10 NMOS 晶体管 Tr10 和第 14 NMOS 晶体管 Tr14（其中的每一个在其栅极端子处都连接到第 2 节点 QB1）截止。

将第 2 电压 VSS 经由导通的第 3 NMOS 晶体管 Tr3 和第 9 NMOS 晶体管 Tr9 提供到第 3 节点 QB2。在利用第 2 电压 VSS 对第 3 节点 QB2 进行放电时，第 11 NMOS 晶体管 Tr11 和第 15 NMOS 晶体管 Tr15（其中的每一个在其栅极端子处都连接到第 3 节点 QB2）截止。

在将第 3 电压 VDD3 施加到第 4 NMOS 晶体管 Tr4 的栅极端子时，第 4 NMOS 晶体管 Tr4 导通。因为第 3 电压 VDD3 在第 1 帧期间保持在正极性状态，所以第 4 NMOS 晶体管 Tr4 在第 1 帧期间保持在导通状态。将第 3 电压 VDD3 经由导通的第 4 NMOS 晶体管 Tr4 提供到第 2 节点 QB1。从而，第 2 电压 VSS 和第 3 电压 VDD3 被提供到第 2 节点 QB1。然而，因为提供第 2 电压 VSS 的晶体管的数目大于提供第 3 电压 VDD3 的晶体管的数目，所以第 2 节点 QB1 保持在第 2 电压 VSS。为此，第 2 节点 QB1 保持在放电状态。结果，第 10 NMOS 晶体管 Tr10 和第 14 NMOS 晶体管 Tr14（其中的每一个在其栅极端子处都连接到第 2 节点 QB1）截止。

还将第 3 电压 VDD3 提供到第 5 NMOS 晶体管 Tr5 的栅极端子。因此，第 5 NMOS 晶体管 Tr5 在第 1 帧期间保持在导通状态。将第 2 电压 VSS 经由导通的第 5 NMOS 晶体管 Tr5 提供到第 3 节点 QB2。从而，第 3 节点 QB2 由第 3 NMOS 晶体管 Tr3、第 5 NMOS 晶体管 Tr5 以及第 9 NMOS 晶体管 Tr9 保持在放电状态。因此，第 11 NMOS 晶体管 Tr11 和第 15 NMOS 晶体管 Tr15（其中的每一个在其栅极端子处都连接到第 3 节点 QB2）截止。

在将第 4 电压 VDD4 施加到第 6 NMOS 晶体管 Tr6 的栅极端子时，第 6 NMOS 晶体管 Tr6 截止。因为第 4 电压 VDD4 在第 1 帧期间保持在负极性状态，所以第 6 NMOS 晶体管 Tr6 在第 1 帧期间保持在截止状态。

还将第 4 电压 VDD4 提供到第 7 NMOS 晶体管 Tr7 的栅极端子。因此，第 7 NMOS 晶体管 Tr7 在第 1 帧期间保持在截止状态。

在利用第 1 电压 VDD 对第 1 级 BST1 的第 1 节点 Q 进行充电，并且利用第 2 电压 VSS 对第 2 节点 QB1 和第 3 节点 QB2 进行放电时，根据起始

脉冲 SP, 第 1 级 BST1 被使能。

当在上述状态中将第 1 时钟脉冲 CLK1 提供到第 1 级 BST1 的第 13 NMOS 晶体管 Tr13 时, 第 13 NMOS 晶体管 Tr13 输出该第 1 时钟脉冲 CLK1, 作为第 1 扫描脉冲 Vout1。在这种情况下, 因为第 1 时钟脉冲 CLK1 与起始脉冲 SP 交叠, 所以与起始脉冲 SP 相交叠地输出第 1 扫描脉冲 Vout1。

将第 1 扫描脉冲 Vout1 提供到第 1 选通线和第 2 级 BST2。即, 将来自第 1 级 BST1 的第 1 扫描脉冲 Vout1 提供到第 2 级 BST2 的第 1 NMOS 晶体管 Tr1、第 2 NMOS 晶体管 Tr2 以及第 3 NMOS 晶体管 Tr3。结果, 对第 2 级 BST2 的第 1 节点 Q 进行充电, 而对第 2 级 BST2 的第 2 节点 QB1 和第 3 节点 QB2 进行放电。即, 第 2 级 BST2 由第 1 扫描脉冲 Vout1 使能。换句话说, 类似于第 1 级 BST1 由起始脉冲 SP 使能, 第 2 级 BST2 由第 1 扫描脉冲 Vout1 使能。当在上述状态中将第 2 时钟脉冲 CLK2 提供到第 2 级 BST2 的第 13 NMOS 晶体管 Tr13 时, 第 13 NMOS 晶体管 Tr13 输出该第 2 时钟脉冲 CLK2, 作为第 2 扫描脉冲 Vout2。在这种情况下, 因为第 2 时钟脉冲 CLK2 与第 1 时钟脉冲 CLK1 交叠, 所以与第 1 扫描脉冲 Vout1 交叠地输出第 2 扫描脉冲 Vout2。

将第 2 扫描脉冲 Vout2 提供到第 2 选通线和第 3 级 BST3。即, 将来自第 2 级 BST2 的第 2 扫描脉冲 Vout2 提供到第 3 级 BST3 的第 1 NMOS 晶体管 Tr1、第 2 NMOS 晶体管 Tr2 以及第 3 NMOS 晶体管 Tr3。结果, 对第 3 级 BST3 的第 1 节点 Q 进行充电, 而对第 3 级 BST3 的第 2 节点 QB1 和第 3 节点 QB2 进行放电。即, 第 3 级 BST3 由第 2 扫描脉冲 Vout2 使能。换句话说, 类似于第 1 级 BST1 由起始脉冲 SP 使能, 第 3 级 BST3 由第 2 扫描脉冲 Vout2 使能。

当在上述状态中将第 3 时钟脉冲 CLK3 提供到第 3 级 BST3 的第 13 NMOS 晶体管 Tr13 时, 第 13 NMOS 晶体管 Tr13 输出该第 3 时钟脉冲 CLK3, 作为第 3 扫描脉冲 Vout3。在这种情况下, 因为第 3 时钟脉冲 CLK3 与第 2 时钟脉冲 CLK2 交叠, 所以与第 2 扫描脉冲 Vout2 交叠地输出第 3 扫描脉冲 Vout3。

将第 3 扫描脉冲 Vout3 提供到第 3 选通线和第 4 级 BST4。即, 将来

自第3级BST3的第3扫描脉冲Vout3提供到第4级BST4的第1NMOS晶体管Tr1、第2NMOS晶体管Tr2以及第3NMOS晶体管Tr3。结果，对第4级BST4的第1节点Q进行充电，而对第4级BST4的第2节点QB1和第3节点QB2进行放电。即，第4级BST4由第3扫描脉冲Vout3使能。换句话说，类似于第1级BST1由起始脉冲SP使能，第4级BST4由第3扫描脉冲Vout3使能。

当在上述状态中将第4时钟脉冲CLK4提供到第4级BST4的第13NMOS晶体管Tr13时，第13NMOS晶体管Tr13输出该第4时钟脉冲CLK4，作为第4扫描脉冲Vout4。在这种情况下，因为第4时钟脉冲CLK4与第3时钟脉冲CLK3交叠，所以与第3扫描脉冲Vout3交叠地输出第4扫描脉冲Vout4。

同时，还把从第3级BST3输出的第3扫描脉冲Vout3提供到第1级BST1的第12NMOS晶体管Tr12。即，将第3扫描脉冲Vout3提供到第1级BST1中的第12NMOS晶体管Tr12的栅极端子。结果，第1级BST1被禁能。

具体地，第3扫描脉冲Vout3使第1级BST1的第12NMOS晶体管Tr12导通。因此，将第2电压VSS经由导通的第12NMOS晶体管Tr12提供到第1级BST1的第1节点Q。从而，对第1级BST1的第1节点Q进行放电。结果，与第1级BST1的第1节点Q相连接的第8NMOS晶体管Tr8、第9NMOS晶体管Tr9以及第13NMOS晶体管Tr13截止。而且，随着起始脉冲SP过渡到低电平状态，接收到低电平起始脉冲SP的第1级BST1的第1NMOS晶体管Tr1、第2NMOS晶体管Tr2以及第3NMOS晶体管Tr3截止。

如上所述，因为第1级BST1的第2NMOS晶体管Tr2和第8NMOS晶体管Tr8处于截止状态，所以利用经由第4NMOS晶体管Tr4提供的第1电压VDD对第1级BST1的第2节点QB1进行充电。因此，第10NMOS晶体管Tr10和第14NMOS晶体管Tr14（其中的每一个在其栅极端子处都连接到第1级BST1的第2节点QB1）导通。结果，将第2电压VSS经由导通的第14NMOS晶体管Tr14提供到第1选通线。

还将第2电压VSS经由导通的第10NMOS晶体管Tr10提供到第1节

点 Q。结果，通过第 10 NMOS 晶体管 Tr10 和第 14 NMOS 晶体管 Tr14 对第 1 级 BST1 的第 1 节点 Q 进行放电。

从而，利用来自第 3 级 BST3 的第 3 扫描脉冲 Vout3，对第 1 级 BST1 的第 1 节点 Q 和第 3 节点 QB2 进行放电，而对第 1 级 BST1 的第 2 节点 QB1 进行充电。即，响应于来自第 3 级 BST3 的第 3 扫描脉冲 Vout3 而禁能第 1 级 BST1。禁能的第 1 级 BST1 经由第 1 级 BST1 中包括的第 14 NMOS 晶体管 Tr14 输出第 2 电压 VSS，以向第 1 选通线提供第 2 电压 VSS。

按上述方式，级 BST1 到 BSTn+2 中的每一个都由从第 1 上游级输出的扫描脉冲使能，而由从第 2 下游级输出的扫描脉冲禁能。

同时，在第 2 帧中，第 3 电压 VDD3 保持在负极性状态，而第 4 电压 VDD4 处于正极性状态。因此，当级 BST1 到 BSTn+2 中的每一个都被禁能时，对该级的第 2 节点 QB1 进行放电，而对该级的第 3 节点 QB2 进行充电。即，当级 BST1 到 BSTn+2 中的每一个都被禁能时，经由在其栅极端子连接到第 3 节点 QB2 的第 15 NMOS 晶体管 Tr15 输出第 2 电压 VSS。从而，第 2 节点 QB1 和第 3 节点 QB2 逐帧交替充电和放电，由此防止输出单元 700b 中包括的第 14 NMOS 晶体管 Tr14 和第 15 NMOS 晶体管 Tr15 劣化。

第 2 移位寄存器 301b 的级 BST1 到 BSTn+2 分别按与第 1 移位寄存器 301a 的级 BST1 到 BSTn+2 相同的方式操作。如果第 1 移位寄存器 301a 中的级 BST1 到 BSTn+2 中的每一个都向选通线 GL1 到 GLn 中的一条相关联的选通线的一端施加扫描脉冲 Vout1 到 Voutn 中的一个相关联的脉冲，则第 2 移位寄存器 301b 的级 BST1 到 BSTn+2 中的每一个都向选通线 GL1 到 GLn 中的一条相关联的选通线的另一端施加扫描脉冲 Vout1 到 Voutn 中的一个相关联的脉冲。

同时，第 1 移位寄存器 301a 和第 2 移位寄存器 301b 的级 BST1 到 BSTn+2 都可以具有下面的电路结构。

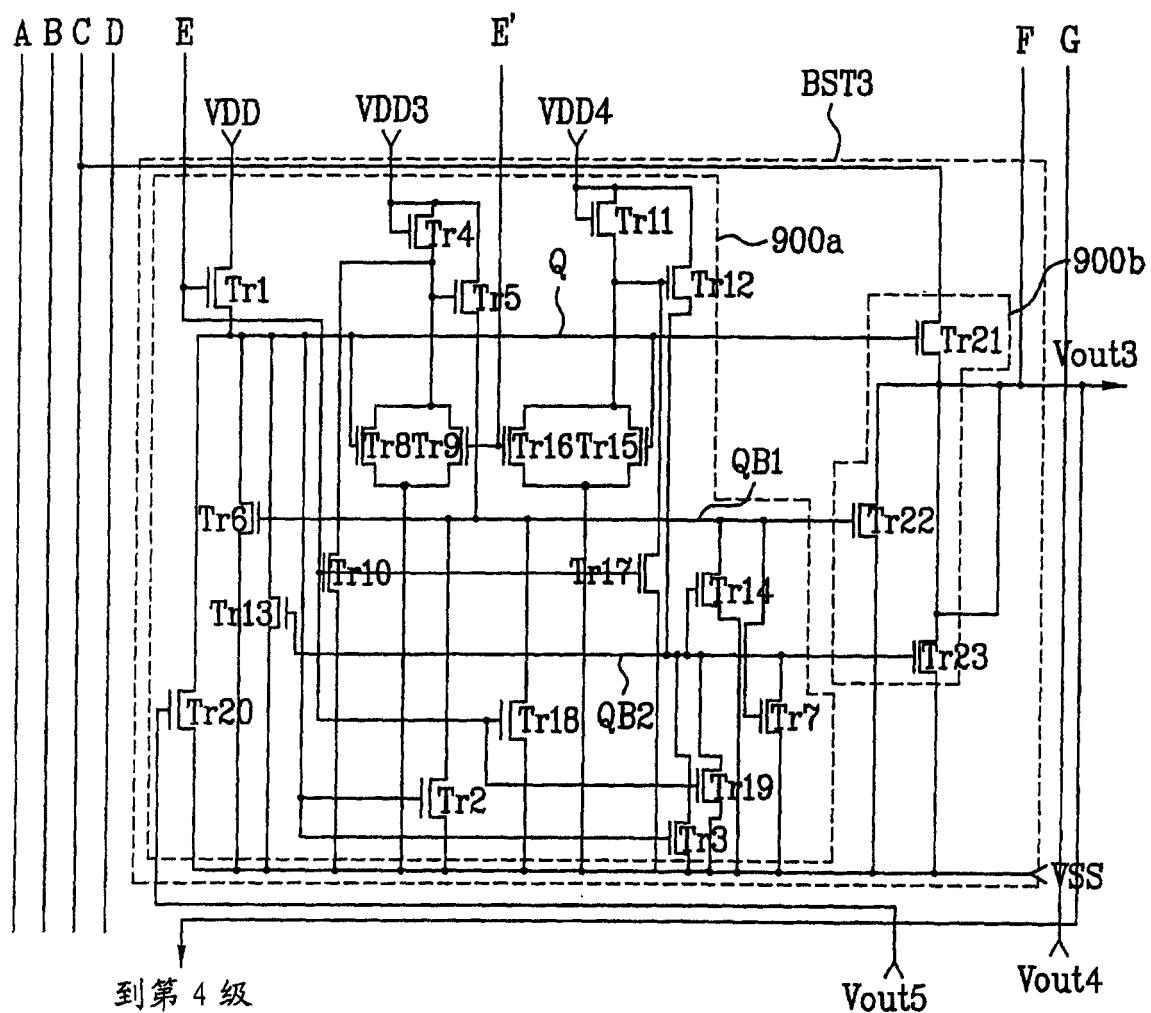

图 9 是例示图 3 中示出的第 1 移位寄存器的第 3 级中包括的电路结构的电路图。

如图 9 所示，由标号 900a 标示的第 3 级 BST3 的节点控制器包括第 1

NMOS 晶体管 Tr1 到第 20 NMOS 晶体管 Tr20。

第 1 NMOS 晶体管 Tr1 响应于来自设置在第 3 级 BST3 直接上游的级的扫描脉冲，利用第 1 电压 VDD 对第 1 节点 Q 进行充电。即，第 1 NMOS 晶体管 Tr1 响应于来自第 2 级 BST2 的第 2 扫描脉冲 Vout2，利用第 1 电压 VDD 对第 1 节点 Q 进行充电。为了执行该操作，第 1 NMOS 晶体管 Tr1 在其栅极端子处连接到第 2 级 BST2，在其源极端子处连接到用于传输第 1 电压 VDD 的电源线，而在其漏极端子处连接到第 1 节点 Q。

第 2 NMOS 晶体管 Tr2 响应于充入第 1 节点 Q 中的第 1 电压 VDD，利用第 2 电压 VSS 对第 2 节点 QB1 进行放电。为了执行该操作，第 2 NMOS 晶体管 Tr2 在其栅极端子处连接到第 1 节点 Q，在其源极端子处连接到第 2 节点 QB1，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 3 NMOS 晶体管 Tr3 响应于充入第 1 节点 Q 中的第 1 电压 VDD，利用第 2 电压 VSS 对第 3 节点 QB2 进行放电。为了执行该操作，第 3 NMOS 晶体管 Tr3 在其栅极端子处连接到第 1 节点 Q，在其源极端子处连接到第 3 节点 QB2，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 4 NMOS 晶体管 Tr4 响应于第 3 电压 VDD3 而导通或截止，其中每一个状态下都逐帧交替改变极性。在第 4 NMOS 晶体管 Tr4 的导通状态中，其输出第 3 电压 VDD3。为了执行该操作，第 4 NMOS 晶体管 Tr4 在其栅极端子和源极端子处连接到用于传输第 3 电压 VDD3 的电源线。

第 5 NMOS 晶体管 Tr5 响应于第 3 电压 VDD3，利用从第 4 NMOS 晶体管 Tr4 输出的第 3 电压 VDD3 对第 2 节点 QB1 进行充电。为了执行该操作，第 5 NMOS 晶体管 Tr5 在其栅极端子处连接到第 4 NMOS 晶体管 Tr4 的漏极端子，在其源极端子处连接到用于传输第 3 电压 VDD3 的电源线，而在其漏极端子处连接到第 2 节点 QB1。

第 6 NMOS 晶体管 Tr6 响应于充入第 2 节点 QB1 中的第 3 电压 VDD3，利用第 2 电压 VSS 对第 1 节点 Q 进行放电。为了执行该操作，第 6 NMOS 晶体管 Tr6 在其栅极端子处连接到第 2 节点 QB1，在其源极端子连接到第 1 节点 Q，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 7 NMOS 晶体管 Tr7 响应于充入第 2 节点 QB1 中的第 3 电压 VDD3，

利用第 2 电压 VSS 对第 3 节点 QB2 进行放电。为了执行该操作，第 7 NMOS 晶体管 Tr7 在其栅极端子处连接到第 2 节点 QB1，在其源极端子处连接到第 3 节点 QB2，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 8 NMOS 晶体管 Tr8 响应于充入第 1 节点 Q 中的第 1 电压 VDD，向第 5 NMOS 晶体管 Tr5 的栅极端子提供第 2 电压 VSS，以使第 5 NMOS 晶体管 Tr5 截止。为了执行该操作，第 8 NMOS 晶体管 Tr8 在其栅极端子处连接到第 1 节点 Q，在其源极端子处连接到第 5 NMOS 晶体管 Tr5 的栅极端子，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 9 NMOS 晶体管 Tr9 响应于来自第 1 上游级的扫描脉冲，向第 5 NMOS 晶体管 Tr5 的栅极端子提供第 2 电压 VSS，以使第 5 NMOS 晶体管 Tr5 截止。即，第 9 NMOS 晶体管 Tr9 响应于来自第 2 级 BST2 的扫描脉冲 Vout2，向第 5 NMOS 晶体管 Tr5 的栅极端子提供第 2 电压 VSS，以使第 5 NMOS 晶体管 Tr5 截止。为了执行该操作，第 9 NMOS 晶体管 Tr9 在其栅极端子处连接到第 2 级 BST2，在其源极端子处连接到第 5 NMOS 晶体管 Tr5 的栅极端子，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 10 NMOS 晶体管 Tr10 响应于来自第 1 上游级的扫描脉冲，向第 5 NMOS 晶体管 Tr5 的栅极端子提供第 2 电压 VSS，以使第 5 NMOS 晶体管 Tr5 截止。即，第 10 NMOS 晶体管 Tr10 响应于来自第 2 级 BST2 的扫描脉冲 Vout2，向第 5 NMOS 晶体管 Tr5 的栅极端子提供第 2 电压 VSS，以使第 5 NMOS 晶体管 Tr5 截止。为了执行该操作，第 10 NMOS 晶体管 Tr10 在其栅极端子处连接到第 2 级 BST2，在其源极端子处连接到第 5 NMOS 晶体管 Tr5 的栅极端子，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 11 NMOS 晶体管 Tr11 响应于逐帧交替改变极性的第 4 电压 VDD4 而导通或截止。在第 11 NMOS 晶体管 Tr11 的导通状态中，其输出第 4 电压 VDD4。为了执行该操作，第 11 NMOS 晶体管 Tr11 在其栅极端子和源极端子处连接到用于传输第 4 电压 VDD4 的电源线。第 4 电压 VDD4 的极性与第 3 电压 VDD3 的极性在每一帧中都相反。

第 12 NMOS 晶体管 Tr12 响应于第 4 电压 VDD4，利用从第 11 NMOS 晶

体管 Tr11 输出的第 4 电压 VDD4 对第 3 节点 QB2 进行充电。为了执行该操作，第 12 NMOS 晶体管 Tr12 在其栅极端子处连接到第 11 NMOS 晶体管 Tr11 的漏极端子，在其源极端子处连接到用于传输第 4 电压 VDD4 的电源线，而在其漏极端子处连接到第 3 节点 QB2。

第 13 NMOS 晶体管 Tr13 响应于充入第 3 节点 QB2 中的第 4 电压 VDD4，利用第 2 电压 VSS 对第 1 节点 Q 进行放电。为了执行该操作，第 13 NMOS 晶体管 Tr13 在其栅极端子处连接到第 3 节点 QB2，在其源极端子处连接到第 1 节点 Q，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 14 NMOS 晶体管 Tr14 响应于充入第 3 节点 QB2 中的第 4 电压 VDD4，利用第 2 电压 VSS 对第 2 节点 QB1 进行放电。为了执行该操作，第 14 NMOS 晶体管 Tr14 在其栅极端子处连接到第 3 节点 QB2，在其源极端子处连接到第 2 节点 QB1，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 15 NMOS 晶体管 Tr15 响应于充入第 1 节点 Q 中的第 1 电压 VDD，向第 12 NMOS 晶体管 Tr12 的栅极端子提供第 2 电压 VSS，以使第 12 NMOS 晶体管 Tr12 截止。为了执行该操作，第 15 NMOS 晶体管 Tr15 在其栅极端子处连接到第 1 节点 Q，在其源极端子处连接到第 12 NMOS 晶体管 Tr12 的栅极端子，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 16 NMOS 晶体管 Tr16 响应于来自第 1 上游级的扫描脉冲，向第 12 NMOS 晶体管 Tr12 的栅极端子提供第 2 电压 VSS，以使第 12 NMOS 晶体管 Tr12 截止。即，第 16 NMOS 晶体管 Tr16 响应于来自第 2 级 BST2 的第 2 扫描脉冲 Vout2，使第 12 NMOS 晶体管 Tr12 截止。为了执行该操作，第 16 NMOS 晶体管 Tr16 在其栅极端子处连接到第 2 级 BST2，在其源极端子处连接到第 12 NMOS 晶体管 Tr12 的栅极端子，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 17 NMOS 晶体管 Tr17 响应于来自第 1 上游级的扫描脉冲，向第 12 NMOS 晶体管 Tr12 的栅极端子提供第 2 电压 VSS，以使第 12 NMOS 晶体管 Tr12 截止。即，第 17 NMOS 晶体管 Tr17 响应于来自第 2 级 BST2 的第 2 扫描脉冲 Vout2，使第 12 NMOS 晶体管 Tr12 截止。为了执行该操作，第

17 NMOS 晶体管 Tr17 在其栅极端子处连接到第 2 级 BST2，在其源极端子处连接到第 12 NMOS 晶体管 Tr12 的栅极端子，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 18 NMOS 晶体管 Tr18 响应于来自第 1 上游级的扫描脉冲，利用第 2 电压 VSS 对第 2 节点 QB1 进行放电。即，第 18 NMOS 晶体管 Tr18 响应于来自第 2 级 BST2 的扫描脉冲 Vout2，利用第 2 电压 VSS 对第 2 节点 QB1 进行放电。为了执行该操作，第 18 NMOS 晶体管 Tr18 在其栅极端子处连接到第 2 级 BST2，在其源极端子处连接到第 2 节点 QB1，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 19 NMOS 晶体管 Tr19 响应于来自第 1 上游级的扫描脉冲，利用第 2 电压 VSS 对第 3 节点 QB2 进行放电。即，第 19 NMOS 晶体管 Tr19 响应于来自第 2 级 BST2 的扫描脉冲 Vout2，利用第 2 电压 VSS 对第 3 节点 QB2 进行放电。为了执行该操作，第 19 NMOS 晶体管 Tr19 在其栅极端子处连接到第 2 级 BST2，在其源极端子处连接到第 3 节点 QB2，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 20 NMOS 晶体管 Tr20 响应于来自设置在第 3 级 BST3 次下游的第 2 级的扫描脉冲，利用第 2 电压 VSS 对第 1 节点 Q 进行放电。即，第 20 NMOS 晶体管 Tr20 响应于来自第 5 级 BST5 的第 5 扫描脉冲 Vout5，利用第 2 电压 VSS 对第 1 节点 Q 进行放电。为了执行该操作，第 20 NMOS 晶体管 Tr20 在其栅极端子处连接到第 5 级 BST5 的输出单元，在其源极端子处连接到第 1 节点 Q，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

由标号 900b 标示的第 3 级 BST3 的输出单元包括第 21 NMOS 晶体管 Tr21 到第 23 NMOS 晶体管 Tr23。

第 21 NMOS 晶体管 Tr21 响应于充入第 1 节点 Q 中的第 1 电压 VDD，向相关联的选通线输出第 3 时钟脉冲 CLK3，作为扫描脉冲。第 3 扫描脉冲 Vout3 还被提供给第 2 上游级和第 1 下游级。为了执行该操作，第 21 NMOS 晶体管 Tr21 在其栅极端子处连接到第 1 节点 Q，在其源极端子处连接到用于传输第 3 时钟脉冲 CLK3 的时钟线，而在其漏极端子处连接到第 3 选通线、第 1 级 BST1 中的第 20 NMOS 晶体管 Tr20 的栅极端子，以及第

4 级 BST4 中的第 1 NMOS 晶体管 Tr1、第 9 NMOS 晶体管 Tr9、第 10 NMOS 晶体管 Tr10、第 16 NMOS 晶体管 Tr16、第 17 NMOS 晶体管 Tr17、第 18 NMOS 晶体管 Tr18，以及第 19 NMOS 晶体管 Tr19 的栅极端子。

第 22 NMOS 晶体管 Tr22 响应于充入第 2 节点 QB1 中的第 3 电压 VDD3，向相关联的选通线输出第 2 电压 VSS。即，第 22 NMOS 晶体管 Tr22 响应于充入第 2 节点 QB1 中的第 3 电压 VDD3，向第 3 选通线提供第 2 电压 VSS。为了执行该操作，第 22 NMOS 晶体管 Tr22 在其栅极端子处连接到第 2 节点 QB1，在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线，而在其源极端子处连接到第 3 选通线、第 1 级 BST1 中的第 20 NMOS 晶体管 Tr20 的栅极端子，以及第 4 级 BST4 中的第 1 NMOS 晶体管 Tr1、第 9 NMOS 晶体管 Tr9、第 10 NMOS 晶体管 Tr10、第 16 NMOS 晶体管 Tr16、第 17 NMOS 晶体管 Tr17、第 18 NMOS 晶体管 Tr18，以及第 19 NMOS 晶体管 Tr19 的栅极端子。

第 23 NMOS 晶体管 Tr23 响应于充入第 3 节点 QB2 中的第 4 电压 VDD4，向相关联的选通线输出第 2 电压 VSS。即，第 23 NMOS 晶体管 Tr23 响应于充入第 3 节点 QB2 中的第 4 电压 VDD4，向第 3 选通线提供第 2 电压 VSS。为了执行该操作，第 23 NMOS 晶体管 Tr23 在其栅极端子处连接到第 2 节点 QB1，在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线，而在其源极端子处连接到第 3 选通线、第 1 级 BST1 中的第 20 NMOS 晶体管 Tr20 的栅极端子，以及第 4 级 BST4 中的第 1 NMOS 晶体管 Tr1、第 9 NMOS 晶体管 Tr9、第 10 NMOS 晶体管 Tr10、第 16 NMOS 晶体管 Tr16、第 17 NMOS 晶体管 Tr17、第 18 NMOS 晶体管 Tr18，以及第 19 NMOS 晶体管 Tr19 的栅极端子。

第 1 级 BST1 和第 2 级 BST2、第 4 级 BST4 到第 n 级 BSTn，以及第 1 哑级 BSTn+1 和第 2 哑级 BSTn+2 都与第 3 级 BST3 具有相同的结构。

因为第 1 级 BST1 没有上游级，所以第 1 级 BST4 中的第 1 NMOS 晶体管 Tr1、第 9 NMOS 晶体管 Tr9、第 10 NMOS 晶体管 Tr10、第 16 NMOS 晶体管 Tr16、第 17 NMOS 晶体管 Tr17、第 18 NMOS 晶体管 Tr18 以及第 19 NMOS 晶体管 Tr19 都接收来自定时控制器的起始脉冲 SP。即，第 1 级 BST1 的

第 1 NMOS 晶体管 Tr1 响应于来自定时控制器的起始脉冲 SP, 利用第 1 电压 VDD 对第 1 级 BST1 的第 1 节点 Q 进行充电。

第 1 级 BST1 的第 9 NMOS 晶体管 Tr9 响应于来自定时控制器的起始脉冲 SP, 利用第 2 电压 VSS 对第 1 级 BST1 的第 2 节点 QB1 进行放电。

第 1 级 BST1 的第 10 NMOS 晶体管 Tr10 响应于来自定时控制器的起始脉冲 SP, 向第 4 NMOS 晶体管 Tr4 的栅极端子提供第 2 电压 VSS, 以使第 4 NMOS 晶体管 Tr4 截止。

第 1 级 BST1 的第 16 NMOS 晶体管 Tr16 响应于来自定时控制器的起始脉冲 SP, 向第 20 NMOS 晶体管 Tr12 的栅极端子提供第 2 电压 VSS, 以使第 20 NMOS 晶体管 Tr12 截止。

第 1 级 BST1 的第 17 NMOS 晶体管 Tr17 响应于来自定时控制器的起始脉冲 SP, 向第 20 NMOS 晶体管 Tr12 的栅极端子提供第 2 电压 VSS, 以使第 20 NMOS 晶体管 Tr12 截止。

第 1 级 BST1 的第 18 NMOS 晶体管 Tr18 响应于来自定时控制器的起始脉冲 SP, 利用第 2 电压 VSS 对第 2 节点 QB1 进行放电。

第 1 级 BST1 的第 19 NMOS 晶体管 Tr19 响应于来自定时控制器的起始脉冲 SP, 利用第 2 电压 VSS 对第 3 节点 QB2 进行放电。

在第 1 级 BST1 或第 2 级 BST2 次上游没有设置级。因此, 第 1 级 BST1 向第 1 选通线和第 2 级 BST2 提供从其输出的第 1 扫描脉冲 Vout1。类似地, 第 2 级 BST2 向第 2 选通线和第 3 级 BST3 提供从其输出的第 2 扫描脉冲 Vout2。

在第 2 哑级 BSTn+2 直接下游没有设置级。因此, 第 2 哑级 BSTn+2 中的第 21 NMOS 晶体管 Tr21 的源极端子、第 22 NMOS 晶体管 Tr22 的漏极端子以及第 23 NMOS 晶体管 Tr23 的漏极端子都连接到第 n 级 BSTn 的第 20 NMOS 晶体管 Tr20 的栅极端子。

第 2 移位寄存器 301b 的级 BST1 到 BSTn+2 与第 1 移位寄存器 301a 的级 BST1 到 BSTn+2 具有相同的结构。

下面, 说明根据本发明的例示实施例的移位寄存器的操作。

下面, 说明根据本发明第一实施例的移位寄存器的操作。

图 10A 和 10B 是例示第 1 移位寄存器的第 1 级到第 3 级的电路图，其中的每一个级都具有图 9 中示出的电路结构。

在以下说明中，假定在第 1 帧中，第 3 电压 VDD3 保持在正极性状态，而第 4 电压 VDD4 保持在负极性状态。还假定在第 2 帧中，第 3 电压 VDD3 保持在负极性状态，而第 4 电压 VDD4 保持在正极性状态。即，假定在奇数号帧中，第 3 电压 VDD3 保持在正极性状态，而第 4 电压 VDD4 保持在负极性状态；而在偶数号帧中，第 3 电压 VDD3 保持在负极性状态，而第 4 电压 VDD4 保持在正极性状态。

首先，将一起始脉冲 SP 施加到第 1 NMOS 晶体管 Tr1、第 9 NMOS 晶体管 Tr9、第 10 NMOS 晶体管 Tr10、第 16 NMOS 晶体管 Tr16、第 17 NMOS 晶体管 Tr17、第 18 NMOS 晶体管 Tr18 以及第 19 NMOS 晶体管 Tr19 的栅极端子。结果，第 1 NMOS 晶体管 Tr1、第 9 NMOS 晶体管 Tr9、第 10 NMOS 晶体管 Tr10、第 16 NMOS 晶体管 Tr16、第 17 NMOS 晶体管 Tr17、第 18 NMOS 晶体管 Tr18 以及第 19 NMOS 晶体管 Tr19 导通。

接着，将第 1 电压 VDD 经由导通的第 1 NMOS 晶体管 Tr1 提供到第 1 节点 Q。随着利用第 1 电压 VDD 对第 1 节点 Q 进行充电，第 2 NMOS 晶体管 Tr2、第 3 NMOS 晶体管 Tr3、第 8 NMOS 晶体管 Tr8、第 15 NMOS 晶体管 Tr15 以及第 21 NMOS 晶体管 Tr21（其中的每一个在其栅极端子处都连接到第 1 节点 Q）导通。

将第 2 电压 VSS 经由导通的第 2 NMOS 晶体管 Tr2 和第 8 NMOS 晶体管 Tr8 提供到第 2 节点 QB1。从而，对第 2 节点 QB1 进行放电。结果，第 6 NMOS 晶体管 Tr6、第 7 NMOS 晶体管 Tr7 以及第 22 NMOS 晶体管 Tr22（其中的每一个在其栅极端子处都连接到第 2 节点 QB1）截止。

还将第 2 电压 VSS 经由导通的第 3 NMOS 晶体管 Tr3 和第 19 NMOS 晶体管 Tr19 提供到第 3 节点 QB2。因此，对第 3 节点 QB2 进行放电。结果，第 13 NMOS 晶体管 Tr13、第 14 NMOS 晶体管 Tr14 以及第 23 NMOS 晶体管 Tr23（其中的每一个在其栅极端子处都连接到第 3 节点 QB2）截止。

还将第 2 电压 VSS 经由导通的第 8 NMOS 晶体管 Tr8、第 9 NMOS 晶体管 Tr9 以及第 10 NMOS 晶体管 Tr10 提供到第 5 NMOS 晶体管 Tr5 的栅极

端子。在第 3 电压 VDD3 具有正极性的第 1 帧期间，将第 3 电压 VDD3 经由第 3 电压 VDD3 保持在导通状态的第 4 NMOS 晶体管 Tr4 提供到第 5 NMOS 晶体管 Tr5 的栅极端子。从而，将第 2 电压 VSS 和第 3 电压 VDD3 都提供到第 5 NMOS 晶体管 Tr5 的栅极端子。然而，因为向第 5 NMOS 晶体管 Tr5 的栅极端子提供第 2 电压 VSS 的晶体管的数目大于向第 5 NMOS 晶体管 Tr5 的栅极端子提供第 3 电压 VDD3 的晶体管的数目，所以第 5 NMOS 晶体管 Tr5 的栅极端子保持在第 2 电压。结果，第 5 NMOS 晶体管 Tr5 截止。

将第 2 电压 VSS 经由导通的第 15 NMOS 晶体管 Tr15、第 16 NMOS 晶体管 Tr16 以及第 17 NMOS 晶体管 Tr17 施加到第 12 NMOS 晶体管 Tr12 的栅极端子。因此，使第 12 NMOS 晶体管 Tr12 截止。同时，第 11 NMOS 晶体管 Tr11 在第 1 帧期间由在第 1 帧期间保持在负极性状态的第 4 电压 VDD4 保持在截止状态。

因而，如上所述，利用第 1 电压 VDD 对第 1 级 BST1 的第 1 节点 Q 进行充电，而利用第 2 电压 VSS 对第 2 节点 QB1 和第 3 节点 QB2 进行放电。因此，第 1 级 BST1 被使能。

当在上述状态中将第 1 时钟脉冲 CLK1 提供到第 1 级 BST1 的第 21 NMOS 晶体管 Tr21 时，第 21 NMOS 晶体管 Tr21 输出该第 1 时钟脉冲 CLK1 作为第 1 扫描脉冲 Vout1。在这种情况下，因为第 1 时钟脉冲 CLK1 与起始脉冲 SP 交叠，所以与起始脉冲 SP 交叠地输出第 1 扫描脉冲 Vout1。

将第 1 扫描脉冲 Vout1 提供到第 1 选通线和第 2 级 BST2。即，将来自第 1 级 BST1 的第 1 扫描脉冲 Vout1 提供到第 2 级 BST2 的第 1 NMOS 晶体管 Tr1、第 9 NMOS 晶体管 Tr9、第 10 NMOS 晶体管 Tr10、第 16 NMOS 晶体管 Tr16、第 17 NMOS 晶体管 Tr17、第 18 NMOS 晶体管 Tr18 以及第 19 NMOS 晶体管 Tr19。结果，对第 2 级 BST2 的第 1 节点 Q 进行充电，而对第 2 级 BST2 的第 2 节点 QB1 和第 3 节点 QB2 进行放电。即，第 2 级 BST2 由第 1 扫描脉冲 Vout1 使能。换句话说，类似于第 1 级 BST1 由起始脉冲 SP 使能，第 2 级 BST2 由第 1 扫描脉冲 Vout1 使能。当在上述状态中将第 2 时钟脉冲 CLK2 提供到第 2 级 BST2 的第 21 NMOS 晶体管 Tr21 时，第 21

NMOS 晶体管 Tr21 输出第 2 时钟脉冲 CLK2，作为第 2 扫描脉冲 Vout2。在这种情况下，因为第 2 时钟脉冲 CLK2 与第 1 时钟脉冲 CLK1 交叠，所以与第 1 扫描脉冲 Vout1 交叠地输出第 2 扫描脉冲 Vout2。

将第 2 扫描脉冲 Vout2 提供到第 2 选通线和第 3 级 BST3。即，将来自第 2 级 BST2 的第 2 扫描脉冲 Vout2 提供到第 3 级 BST3 的第 1 NMOS 晶体管 Tr1、第 9 NMOS 晶体管 Tr9、第 10 NMOS 晶体管 Tr10、第 16 NMOS 晶体管 Tr16、第 17 NMOS 晶体管 Tr17、第 18 NMOS 晶体管 Tr18 以及第 19 NMOS 晶体管 Tr19。结果，对第 3 级 BST3 的第 1 节点 Q 进行充电，而对第 3 级 BST3 的第 2 节点 QB1 和第 3 节点 QB2 进行放电。即，第 3 级 BST3 由第 2 扫描脉冲 Vout2 使能。换句话说，类似于第 1 级 BST1 由起始脉冲 SP 使能，第 3 级 BST3 由第 2 扫描脉冲 Vout2 使能。

当在上述状态中将第 3 时钟脉冲 CLK3 提供到第 3 级 BST3 的第 21 NMOS 晶体管 Tr21 时，第 21 NMOS 晶体管 Tr21 输出第 3 时钟脉冲 CLK3，作为第 3 扫描脉冲 Vout3。在这种情况下，因为第 3 时钟脉冲 CLK3 与第 2 时钟脉冲 CLK2 交叠，所以与第 2 扫描脉冲 Vout2 交叠地输出第 3 扫描脉冲 Vout3。

将第 3 扫描脉冲 Vout3 提供到第 3 选通线和第 4 级 BST4。即，将来自第 3 级 BST3 的第 3 扫描脉冲 Vout3 提供到第 4 级 BST4 的第 1 NMOS 晶体管 Tr1、第 9 NMOS 晶体管 Tr9、第 10 NMOS 晶体管 Tr10、第 16 NMOS 晶体管 Tr16、第 17 NMOS 晶体管 Tr17、第 18 NMOS 晶体管 Tr18 以及第 19 NMOS 晶体管 Tr19。结果，对第 4 级 BST4 的第 1 节点 Q 进行充电，而对第 4 级 BST4 的第 2 节点 QB1 和第 3 节点 QB2 进行放电。即，第 4 级 BST4 由第 3 扫描脉冲 Vout3 使能。换句话说，类似于第 1 级 BST1 由起始脉冲 SP 使能，第 4 级 BST4 由第 3 扫描脉冲 Vout3 使能。

当在上述状态中将第 4 时钟脉冲 CLK4 提供到第 4 级 BST4 的第 21 NMOS 晶体管 Tr21 时，第 21 NMOS 晶体管 Tr21 输出第 4 时钟脉冲 CLK4，作为第 4 扫描脉冲 Vout4。在这种情况下，因为第 4 时钟脉冲 CLK4 与第 3 时钟脉冲 CLK3 交叠，所以与第 3 扫描脉冲 Vout3 交叠地输出第 4 扫描脉冲 Vout4。

同时, 还将从第 3 级 BST3 输出的第 3 扫描脉冲 Vout3 提供到第 1 级 BST1 的第 20 NMOS 晶体管 Tr20。即, 将第 3 扫描脉冲 Vout3 提供到第 1 级 BST1 中的第 20 NMOS 晶体管 Tr20 的栅极端子。结果, 第 1 级 BST1 被禁能。

具体地, 第 3 扫描脉冲 Vout3 使第 1 级 BST1 的第 20 NMOS 晶体管 Tr20 导通。因此, 将第 2 电压 VSS 经由导通的第 20 NMOS 晶体管 Tr20 提供到第 1 级 BST1 的第 1 节点 Q。从而, 对第 1 级 BST1 的第 1 节点 Q 进行放电。结果, 连接到第 1 级 BST1 的第 1 节点 Q 的第 2 NMOS 晶体管 Tr2、第 8 NMOS 晶体管 Tr8、第 15 NMOS 晶体管 Tr15 以及第 21 NMOS 晶体管 Tr21 截止。而且, 随着起始脉冲 SP 转变到低电平状态, 第 1 级 BST1 的接收到低电平起始脉冲 SP 的第 1 NMOS 晶体管 Tr1、第 9 NMOS 晶体管 Tr9、第 10 NMOS 晶体管 Tr10、第 16 NMOS 晶体管 Tr16、第 17 NMOS 晶体管 Tr17、第 18 NMOS 晶体管 Tr18 以及第 19 NMOS 晶体管 Tr19 截止。

当第 1 级 BST1 的第 9 NMOS 晶体管 Tr9 和第 10 NMOS 晶体管 Tr10 截止时, 可以不再向第 5 NMOS 晶体管 Tr5 的栅极端子提供第 2 电压 VSS。代替的是, 将第 3 电压 VDD3 经由第 4 NMOS 晶体管 Tr4 提供到第 1 级 BST1 中的第 5 NMOS 晶体管 Tr5 的栅极端子。结果, 第 5 NMOS 晶体管 Tr5 由第 3 电压 VDD3 导通。接着, 将第 3 电压 VDD3 经由导通的第 5 NMOS 晶体管 Tr5 提供到第 1 级 BST1 的第 2 节点 QB1。因此, 对第 1 级 BST1 的第 2 节点 QB1 进行充电。而且, 第 6 NMOS 晶体管 Tr6、第 7 NMOS 晶体管 Tr6 以及第 22 NMOS 晶体管 Tr22 (其中的每一个在其栅极端子处都连接到的第 1 级 BST1 的第 2 节点 QB1) 导通。

还将第 2 电压 VSS 经由导通的第 6 NMOS 晶体管 Tr6 提供到第 1 级 BST1 的第 1 节点 Q。结果, 第 1 级 BST1 的第 1 节点 Q 的放电速率增大。还将第 2 电压 VSS 经由导通的第 7 NMOS 晶体管 Tr7 提供到第 1 级 BST1 的第 3 节点 QB2。因此, 对第 3 节点 QB2 进行放电。结果, 第 13 NMOS 晶体管 Tr13、第 14 NMOS 晶体管 Tr13 以及第 23 NMOS 晶体管 Tr23 (其中的每一个在其栅极端子处都连接到第 3 节点 QB2) 截止。

因而, 利用来自第 3 级 BST3 的第 3 扫描脉冲 Vout3, 对第 1 级 BST1

的第 1 节点 Q 和第 3 节点 QB2 进行放电, 而对第 1 级 BST1 的第 2 节点 QB1 进行充电。即, 第 1 级 BST1 响应于来自第 3 级 BST3 的第 3 扫描脉冲 Vout3 而被禁能。禁能的第 1 级 BST1 经由第 1 级 BST1 中包括的第 22 NMOS 晶体管 Tr22 输出第 2 电压 VSS, 以向第 1 选通线提供第 2 电压 VSS。

在上述方式中, 级 BST1 到 BSTn+2 中的每一个都由从第 1 上游级输出的扫描脉冲使能, 而由从第 2 下游级输出的扫描脉冲禁能。

同时, 在第 2 帧中, 第 3 电压 VDD3 保持在负极性状态, 而第 4 电压 VDD4 处于正极性状态。因此, 当级 BST1 到 BSTn+2 中的每一个都被禁能时, 对级的第 2 节点 QB1 进行放电, 而对级的第 3 节点 QB2 进行充电。即, 当级 BST1 到 BSTn+2 中的每一个都被禁能时, 经由在其栅极端子连接到第 3 节点 QB2 的第 23 NMOS 晶体管 Tr23 输出第 2 电压 VSS。从而, 第 2 节点 QB1 和第 3 节点 QB2 逐帧交替地充电和放电, 由此防止输出单元 900b 中包括的第 22 晶体管 Tr22 和第 23 晶体管 Tr23 劣化。

第 2 移位寄存器 301b 的级 BST1 到 BSTn+2 分别按与第 1 移位寄存器 301a 的级 BST1 到 BSTn+2 相同的方式操作。然而, 第 1 移位寄存器 301a 中的级 BST1 到 BSTn+2 中的每一个都向选通线 GL1 到 GLn 中的一条相关联的选通线的一端施加扫描脉冲 Vout1 到 Voutn 中的一个相关联的扫描脉冲, 而第 2 移位寄存器 301b 中的级 BST1 到 BSTn+2 中的每一个都向选通线 GL1 到 GLn 中的一条相关联的选通线的另一端施加扫描脉冲 Vout1 到 Voutn 中的一个相关联的扫描脉冲。

下面将详细说明根据本发明第二实施例的移位寄存器。

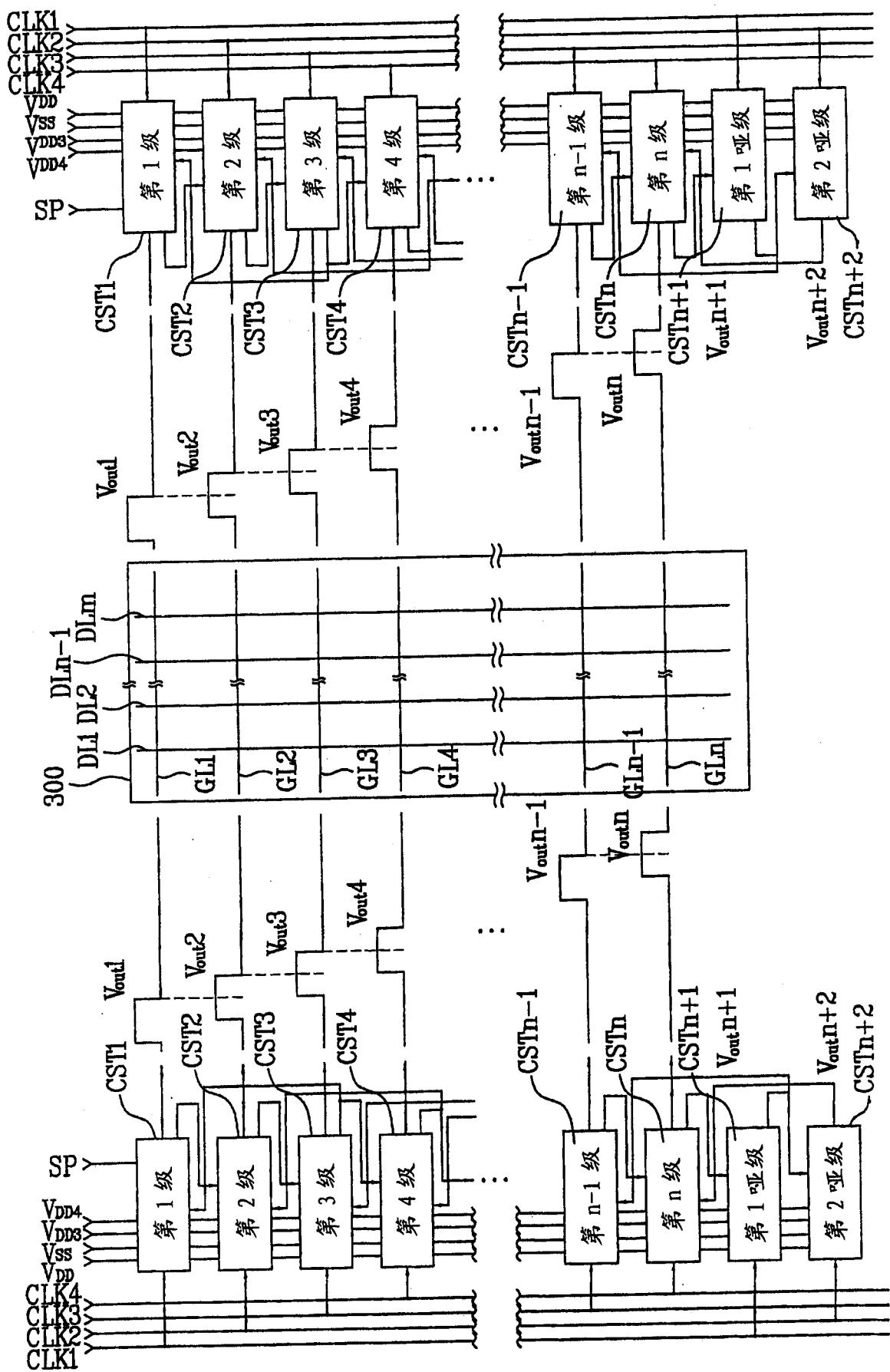

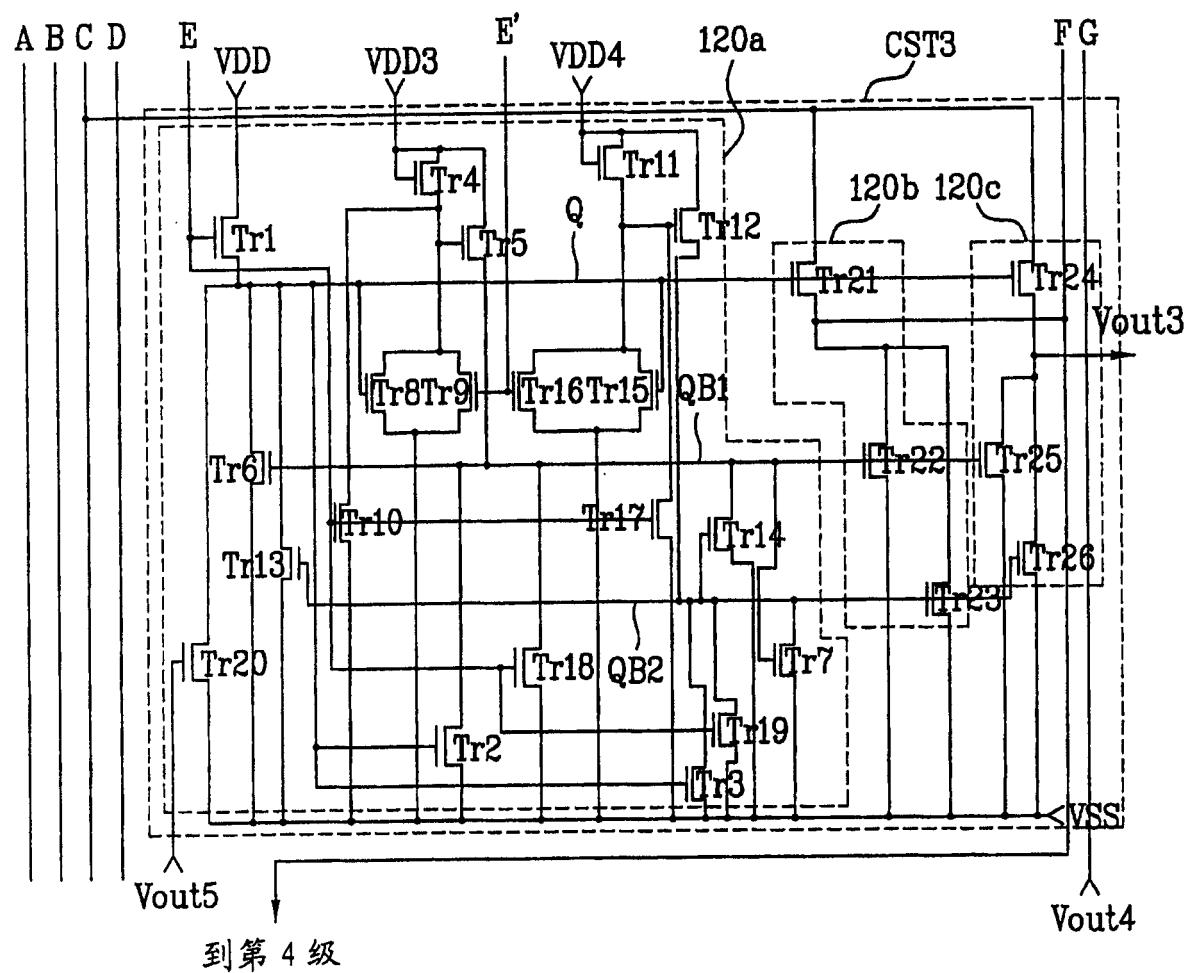

图 11 是例示根据本发明第二实施例的移位寄存器的框图。

如图 11 所示, 根据本发明第二实施例的移位寄存器包括第 1 移位寄存器 110a 和第 2 移位寄存器 110b。

如图 11 所示, 第 1 移位寄存器 110a 包括串联连接的 n 个级 CST1 到 CSTn、第 1 哑级 CSTn+1、以及第 2 哑级 CSTn+2。级 CST1 到 CSTn+2 分别输出多对扫描脉冲 Vout1 到 Voutn+2。即, 级 CST1 到 CSTn+2 中的每一个都同时输出一对扫描脉冲。而且, 从 CST1 到 CSTn+2 按顺序方式输出扫描脉冲 Vout1 到 Voutn+2。除了第 1 哑级 CSTn+1 和第 2 哑级 CSTn+2 之外,

从级 CST1 到 CSTn 输出的扫描脉冲 Vout1 到 Voutn 分别被顺序提供给 LCD 板 300 的选通线 GL1 到 GLn，以使得选通线 GL1 到 GLn 被顺序扫描。

即，首先，第 1 级 CST1 同时输出一对第 1 扫描脉冲 Vout1。随后，第 2 级 CST2 同时输出一对第 2 扫描脉冲 Vout2。接下来，第 3 级 CST3 同时输出一对第 3 扫描脉冲 Vout3。按这种方式，最后，第 n 级 CSTn 同时输出一对第 n 扫描脉冲 Voutn。在第 n 级 CSTn 同时输出一对第 n 扫描脉冲 Voutn 之后，第 1 哑级 CSTn+1 同时输出一对第 n+1 扫描脉冲 Voutn+1。第 n+1 扫描脉冲 Voutn+1 未被提供给任何一条选通线，而是被提供给第 n-1 级 CSTn-1。在第 1 哑级 CSTn+1 同时输出一对第 n+1 扫描脉冲 Voutn+1 之后，第 2 哑级 CSTn+2 同时输出一对第 n+2 扫描脉冲 Voutn+2。第 n+2 扫描脉冲 Voutn+2 未被提供给任何一条选通线，而被提供给第 n 级 CSTn。同时，从各级 CST1 到 CSTn+2 输出的扫描脉冲 Vout1 到 Voutn+2 的脉冲宽度使得扫描脉冲 Vout1 到 Voutn+2 中的连续扫描脉冲相互交叠预定宽度。

级 CST1 到 CSTn+2 中的每一个都具有两个输出端子（下面，称为第 1 输出端子和第 2 输出端子），以分别通过第 1 输出端子和第 2 输出端子同时输出两个扫描脉冲。换句话说，级 CST1 到 CSTn+2 中的每一个都通过其第 1 输出端子输出一个扫描脉冲，并且同时通过其第 2 输出端子输出另一个扫描脉冲。因而，从级 CST1 到 CSTn+2 中的每一个同时输出两个扫描脉冲。在这种情况下，从级 CST1 到 CSTn+2 的各第 1 输出端子输出的扫描脉冲 Vout1 到 Voutn+2 的脉冲宽度使得扫描脉冲 Vout1 到 Voutn+2 中的连续扫描脉冲相互交叠预定宽度。同样，从级 CST1 到 CSTn+2 的各第 2 输出端子输出的扫描脉冲 Vout1 到 Voutn+2 的脉冲宽度使得扫描脉冲 Vout1 到 Voutn+2 中的连续扫描脉冲相互交叠所述预定宽度。例如，从第 1 级 CST1 输出的两个第 1 扫描脉冲 Vout1 与从第 2 级 CST2 输出的两个第 2 扫描脉冲 Vout2 相互交叠所述预定宽度。

第 1 移位寄存器 110a 中包括的级 CST1 到 CSTn+2 中的每一个都向相关联的选通线提供其两个扫描脉冲中的一个扫描脉冲，并且向第 1 下游级和第 2 上游级提供另一个扫描脉冲。例如，输出两个第 3 扫描脉冲 Vout3

的第 3 级 CST3 向第 3 选通线提供一个第 3 扫描脉冲 Vout3，并且向第 4 级 CST4 和第 1 级 CST1 提供另一个第 3 扫描脉冲 Vout3。同时，第 2 哑级 CSTn+2 可以输出两个扫描脉冲，或者可以输出一个扫描脉冲。

具有上述结构的第 1 移位寄存器 110a 的级 CST1 到 CSTn+2 中的每一个都接收第 1 到第 4 电压 VDD、VSS、VDD3 以及 VDD4，和循环的而且其连续时钟脉冲之间具有相位差的第 1 时钟脉冲 CLK1 到第 4 时钟脉冲 CLK4 中的一个时钟脉冲。第 1 电压 VDD 指具有正极性的 DC 电压，而第 2 电压 VSS 指具有负极性的电压。第 3 电压 VDD3 和第 4 电压 VDD4 中的每一个都是逐帧交替改变极性的 AC 电压。第 3 电压 VDD3 和第 4 电压 VDD4 在同一帧具有不同的极性。

如上所述，第 1 时钟脉冲 CLK1 到第 4 时钟脉冲 CLK4 在相对于彼此相位延迟一个脉冲宽度之后被输出。即，第 2 时钟脉冲 CLK2 在相对于第 1 时钟脉冲 CLK1 相位延迟一个脉冲宽度之后被输出。第 3 时钟脉冲 CLK3 在相对于第 2 时钟脉冲 CLK2 相位延迟一个脉冲宽度之后被输出。第 4 时钟脉冲 CLK4 在相对于第 3 时钟脉冲 CLK3 相位延迟一个脉冲宽度之后被输出。按循环方式顺序输出第 1 时钟脉冲 CLK1 到第 4 时钟脉冲 CLK4。即，顺序输出一组第 1 时钟脉冲 CLK1 到第 4 时钟脉冲 CLK4，接着顺序输出另一组第 1 时钟脉冲 CLK1 到第 4 时钟脉冲 CLK4。因此，在输出第 4 时钟脉冲 CLK4 的时间点与输出第 2 时钟脉冲 CLK2 的时间点之间的时段期间输出第 1 时钟脉冲 CLK1。可以与起始脉冲 SP 同步输出第 4 时钟脉冲 CLK4。在这种情况下，第 4 时钟脉冲 CLK4 早于第 1 时钟脉冲 CLK1 到第 3 时钟脉冲 CLK3 输出。

同时，根据本发明，第 1 移位寄存器 110a 可以使用两个或更多个时钟脉冲。即，根据本发明，第 1 移位寄存器 110a 可以使用第 1 时钟脉冲 CLK1 到第 4 时钟脉冲 CLK4 中的仅两个，例如，第 1 时钟脉冲 CLK1 和第 2 时钟脉冲 CLK2，或者可以使用第 1 时钟脉冲 CLK1 到第 4 时钟脉冲 CLK4 中的仅三个，例如，第 1 时钟脉冲 CLK1 到第 3 时钟脉冲 CLK3。另选地，根据本发明，第 1 移位寄存器 110a 可以使用顺序输出的至少五个时钟脉冲。

第 2 移位寄存器 110b 与第 1 移位寄存器 110a 具有相同的结构。

下面对根据本发明第二实施例的移位寄存器中包括的多个级的结构进行更详细的说明。

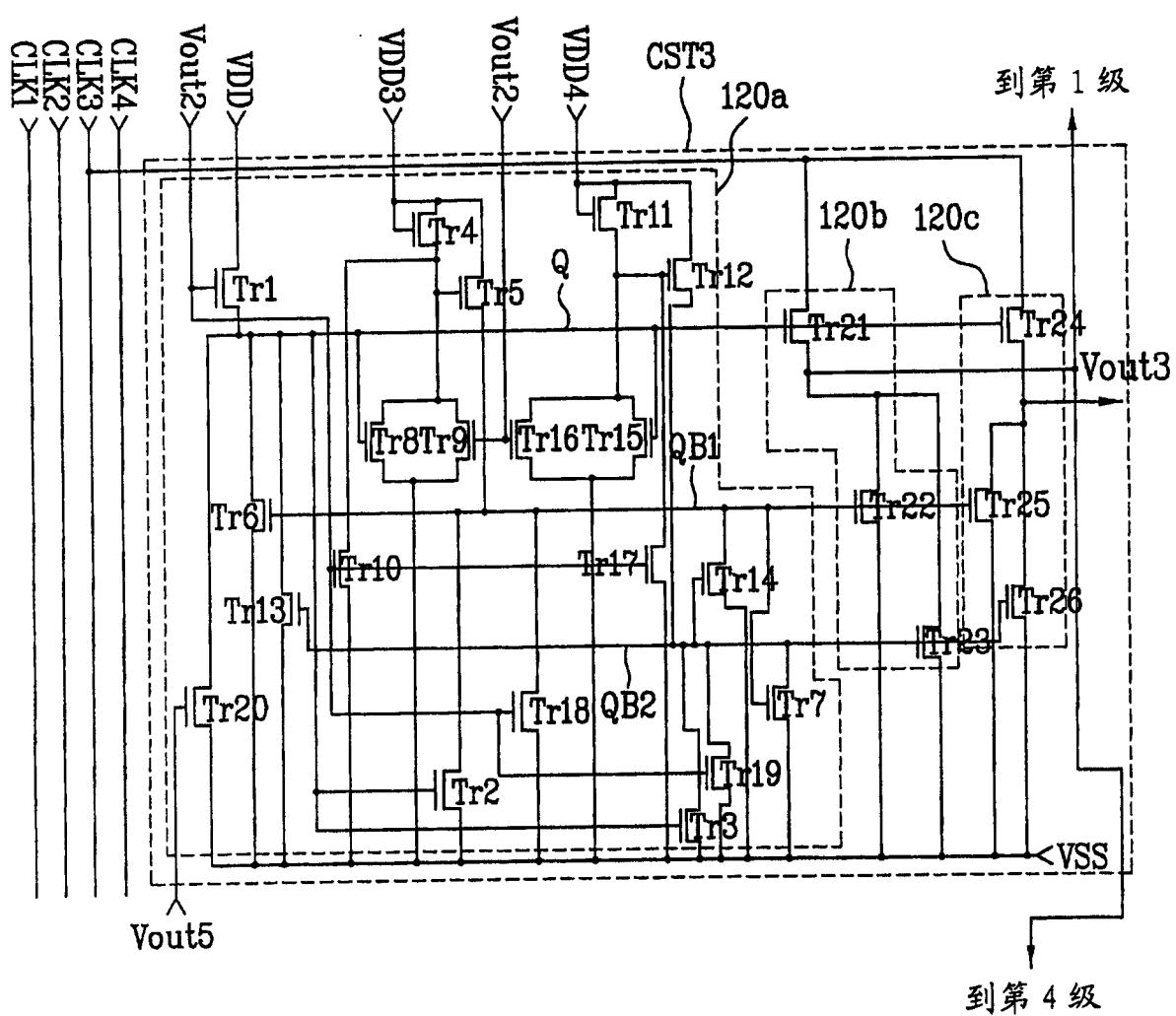

图 12 是例示图 11 中示出的第 1 移位寄存器的第 3 级中包括的电路的电路图。

如图 12 所示，第 3 级 CST3 包括：节点控制器 120a，其控制针对第 1 节点 Q、第 2 节点 QB1 以及第 3 节点 QB2 的充电操作和放电操作；和输出单元 120b 和 120c，其中的每一个都根据第 1 节点 Q、第 2 节点 QB1 以及第 3 节点 QB2 的充电/放电状态而导通，以选择性地输出一扫描脉冲或第 2 电压 VSS。第 1 节点 Q、第 2 节点 QB1 以及第 3 节点 QB2 选择性地充电或放电。具体地，当第 1 节点 Q 处于充电状态时，第 2 节点 QB1 和第 3 节点 QB2 都保持在放电状态。另一方面，当第 1 节点 Q 处于放电状态时，第 2 节点 QB1 和第 3 节点 QB2 中的一个保持在充电状态。即，当第 1 节点 Q 在奇数号帧中处于放电状态时，对第 2 节点 QB1 进行充电，而对第 3 节点 QB3 进行放电。另一方面，当第 1 节点 Q 在偶数号帧中处于放电状态时，对第 2 节点 QB1 进行放电，而对第 3 节点 QB2 进行充电。之所以在第 1 节点 Q 处于放电状态时，分别向第 2 节点 QB1 和第 3 节点 QB2 施加具有相反极性并且逐帧交替改变极性的电压 VDD3 和 VDD4（充电和放电），是为了防止在其栅极端子处连接第 2 节点 QB1 和第 3 节点 QB2 的开关器件的劣化。

第 3 级 CST3 的节点控制器 120a 包括第 1 NMOS 晶体管 Tr1 到第 20 NMOS 晶体管 Tr20。

第 1 NMOS 晶体管 Tr1 响应于来自设置在第 3 级 CST3 直接上游的级的扫描脉冲，利用第 1 电压 VDD 对第 1 节点 Q 进行充电。即，第 1 NMOS 晶体管 Tr1 响应于来自第 2 级 CST2 第 2 扫描脉冲 Vout2，利用第 1 电压 VDD 对第 1 节点 Q 进行充电。为了执行该操作，第 1 NMOS 晶体管 Tr1 在其栅极端子处连接到第 2 级 CST2，在其源极端子处连接到用于传输第 1 电压 VDD 的电源线，而在其漏极端子处连接到第 1 节点 Q。

第 2 NMOS 晶体管 Tr2 响应于充入第 1 节点中的第 1 电压 VDD，利用

第 2 电压 VSS 对第 2 节点 QB1 进行放电。为了执行该操作，第 2 NMOS 晶体管 Tr2 在其栅极端子处连接到第 1 节点 Q，在其源极端子处连接到第 2 节点 QB1，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 3 NMOS 晶体管 Tr3 响应于充入第 1 节点中的第 1 电压 VDD，利用第 2 电压 VSS 对第 3 节点 QB2 进行放电。为了执行该操作，第 3 NMOS 晶体管 Tr3 在其栅极端子处连接到第 1 节点 Q，在其源极端子处连接到第 3 节点 QB2，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 4 NMOS 晶体管 Tr4 响应于逐帧交替改变极性的第 3 电压 VDD3 而导通或截止。在第 4 NMOS 晶体管 Tr4 的导通状态中，其利用第 3 电压 VDD3 对第 2 节点 QB1 进行充电。为了执行该操作，第 4 NMOS 晶体管 Tr4 在其栅极端子和源极端子处连接到用于传输第 3 电压 VDD3 的电源线。

第 5 NMOS 晶体管 Tr5 响应于第 3 电压 VDD3，利用从第 4 NMOS 晶体管 Tr4 输出的第 3 电压 VDD3 对第 2 节点 QB1 进行充电。为了执行该操作，第 5 NMOS 晶体管 Tr5 在其栅极端子处连接到第 4 NMOS 晶体管 Tr4 的漏极端子，在其源极端子处连接到用于传输第 3 电压 VDD3 的电源线，而在其漏极端子处连接到第 2 节点 QB1。

第 6 NMOS 晶体管 Tr6 响应于充入第 2 节点 QB1 中的第 3 电压 VDD3，利用第 2 电压 VSS 对第 1 节点 Q 进行放电。为了执行该操作，第 6 NMOS 晶体管 Tr6 在其栅极端子处连接到第 2 节点 QB1，在其源极端子连接到第 1 节点 Q，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 7 NMOS 晶体管 Tr7 响应于充入第 2 节点 QB1 中的第 3 电压 VDD3，利用第 2 电压 VSS 对第 3 节点 QB2 进行放电。为了执行该操作，第 7 NMOS 晶体管 Tr7 在其栅极端子处连接到第 2 节点 QB1，在其源极端子处连接到第 3 节点 QB2，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 8 NMOS 晶体管 Tr8 响应于充入第 1 节点 Q 中的第 1 电压 VDD，向第 5 NMOS 晶体管 Tr5 的栅极端子提供第 2 电压 VSS，以使第 5 NMOS 晶体管 Tr5 截止。为了执行该操作，第 8 NMOS 晶体管 Tr8 在其栅极端子处连接到第 1 节点 Q，在其源极端子处连接到第 5 NMOS 晶体管 Tr5 的栅极端子，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 9 NMOS 晶体管 Tr9 响应于来自第 1 上游级的扫描脉冲, 向第 5 NMOS 晶体管 Tr5 的栅极端子提供第 2 电压 VSS, 以使第 5 NMOS 晶体管 Tr5 截止。即, 第 9 NMOS 晶体管 Tr9 响应于来自第 2 级 CST2 的扫描脉冲 Vout2, 向第 5 NMOS 晶体管 Tr5 的栅极端子提供第 2 电压 VSS, 以使第 5 NMOS 晶体管 Tr5 截止。为了执行该操作, 第 9 NMOS 晶体管 Tr9 在其栅极端子处连接到第 2 级 CST2, 在其源极端子处连接到第 5 NMOS 晶体管 Tr5 的栅极端子, 而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 10 NMOS 晶体管 Tr10 响应于来自第 1 上游级的扫描脉冲, 向第 5 NMOS 晶体管 Tr5 的栅极端子提供第 2 电压 VSS, 以使第 5 NMOS 晶体管 Tr5 截止。即, 第 10 NMOS 晶体管 Tr10 响应于来自第 2 级 CST2 的扫描脉冲 Vout2, 向第 5 NMOS 晶体管 Tr5 的栅极端子提供第 2 电压 VSS, 以使第 5 NMOS 晶体管 Tr5 截止。为了执行该操作, 第 10 NMOS 晶体管 Tr10 在其栅极端子处连接到第 2 级 CST2, 在其源极端子处连接到第 5 NMOS 晶体管 Tr5 的栅极端子, 而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 11 NMOS 晶体管 Tr11 响应于逐帧交替改变极性的第 4 电压 VDD4 而导通或截止。在第 11 NMOS 晶体管 Tr11 的导通状态中, 其输出第 4 电压 VDD4。为了执行该操作, 第 11 NMOS 晶体管 Tr11 在其栅极端子和源极端子处连接到用于传输第 4 电压 VDD4 的电源线。第 4 电压 VDD4 在每一帧中具有与第 3 电压 VDD3 的极性相反的极性。

第 12 NMOS 晶体管 Tr12 响应于第 4 电压 VDD4, 利用从第 11 NMOS 晶体管 Tr11 输出的第 4 电压 VDD4 对第 3 节点 QB2 进行充电。为了执行该操作, 第 12 NMOS 晶体管 Tr12 在其栅极端子处连接到第 11 NMOS 晶体管 Tr11 的漏极端子, 在其源极端子处连接到用于传输第 4 电压 VDD4 的电源线, 而在其漏极端子处连接到第 3 节点 QB2。

第 13 NMOS 晶体管 Tr13 响应于充入第 3 节点 QB2 中的第 4 电压 VDD4, 利用第 2 电压 VSS 对第 1 节点 Q 进行放电。为了执行该操作, 第 13 NMOS 晶体管 Tr13 在其栅极端子处连接到第 3 节点 QB2, 在其源极端子处连接到第 1 节点 Q, 而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 14 NMOS 晶体管 Tr14 响应于充入第 3 节点 QB2 中的第 4 电压 VDD4，利用第 2 电压 VSS 对第 2 节点 QB1 进行放电。为了执行该操作，第 14 NMOS 晶体管 Tr14 在其栅极端子处连接到第 3 节点 QB2，在其源极端子处连接到第 2 节点 QB1，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 15 NMOS 晶体管 Tr15 响应于充入第 1 节点 Q 中的第 1 电压 VDD，向第 12 NMOS 晶体管 Tr12 的栅极端子提供第 2 电压 VSS，以使第 12 NMOS 晶体管 Tr12 截止。为了执行该操作，第 15 NMOS 晶体管 Tr15 在其栅极端子处连接到第 1 节点 Q，在其源极端子处连接到第 12 NMOS 晶体管 Tr12 的栅极端子，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 16 NMOS 晶体管 Tr16 响应于来自第 1 上游级的扫描脉冲，向第 12 NMOS 晶体管 Tr12 的栅极端子提供第 2 电压 VSS，以使第 12 NMOS 晶体管 Tr12 截止。即，第 16 NMOS 晶体管 Tr16 响应于来自第 2 级 CST2 的第 2 扫描脉冲 Vout2，使第 12 NMOS 晶体管 Tr12 截止。为了执行该操作，第 16 NMOS 晶体管 Tr16 在其栅极端子处连接到第 2 级 CST2，在其源极端子处连接到第 12 NMOS 晶体管 Tr12 的栅极端子，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 17 NMOS 晶体管 Tr17 响应于来自第 1 上游级的扫描脉冲，向第 12 NMOS 晶体管 Tr12 的栅极端子提供第 2 电压 VSS，以使第 12 NMOS 晶体管 Tr12 截止。即，第 17 NMOS 晶体管 Tr17 响应于来自第 2 级 CST2 的第 2 扫描脉冲 Vout2，使第 12 NMOS 晶体管 Tr12 截止。为了执行该操作，第 17 NMOS 晶体管 Tr17 在其栅极端子处连接到第 2 级 CST2，在其源极端子处连接到第 12 NMOS 晶体管 Tr12 的栅极端子，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 18 NMOS 晶体管 Tr18 响应于来自第 1 上游级的扫描脉冲，利用第 2 电压 VSS 对第 2 节点 QB1 进行放电。即，第 18 NMOS 晶体管 Tr18 响应于来自第 2 级 CST2 的扫描脉冲 Vout2，利用第 2 电压 VSS 对第 2 节点 QB1 进行放电。为了执行该操作，第 18 NMOS 晶体管 Tr18 在其栅极端子处连接到第 2 级 CST2，在其源极端子处连接到第 2 节点 QB1，而在其漏极端

子处连接到用于传输第 2 电压 VSS 的电源线。

第 19 NMOS 晶体管 Tr19 响应于来自第 1 上游级的扫描脉冲，利用第 2 电压 VSS 对第 3 节点 QB2 进行放电。即，第 19 NMOS 晶体管 Tr19 响应于来自第 2 级 CST2 的扫描脉冲 Vout2，利用第 2 电压 VSS 对第 3 节点 QB2 进行放电。为了执行该操作，第 19 NMOS 晶体管 Tr19 在其栅极端子处连接到第 2 级 CST2，在其源极端子处连接到第 3 节点 QB2，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 20 NMOS 晶体管 Tr20 响应于来自设置在第 3 级 CST3 次下游的级的扫描脉冲，利用第 2 电压 VSS 对第 1 节点 Q 进行放电。即，第 20 NMOS 晶体管 Tr20 响应于来自第 5 级 CST5 的第 5 扫描脉冲 Vout5，利用第 2 电压 VSS 对第 1 节点 Q 进行放电。为了执行该操作，第 20 NMOS 晶体管 Tr20 在其栅极端子处连接到第 5 级 CST5，在其源极端子处连接到第 1 节点 Q，而在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线。

第 3 级 CST3 的第 1 输出单元 120b 包括第 21 NMOS 晶体管 Tr21 到第 23 NMOS 晶体管 Tr23。

第 21 NMOS 晶体管 Tr21 响应于充入第 1 节点 Q 中的第 1 电压 VDD，输出第 3 时钟脉冲 CLK3 作为扫描脉冲。第 3 扫描脉冲 Vout3 被提供给第 2 上游级和第 1 下游级。为了执行该操作，第 21 NMOS 晶体管 Tr21 在其栅极端子处连接到第 1 节点 Q，在其源极端子处连接到用于传输第 3 时钟脉冲 CLK3 的时钟线，而在其漏极端子处连接到第 1 级 CST1 中的第 20 NMOS 晶体管 Tr20 的栅极端子，和第 4 级 CST4 中的第 1 NMOS 晶体管 Tr1、第 9 NMOS 晶体管 Tr9、第 10 NMOS 晶体管 Tr10、第 16 NMOS 晶体管 Tr16、第 17 NMOS 晶体管 Tr17、第 18 NMOS 晶体管 Tr18 以及第 19 NMOS 晶体管 Tr19 的栅极端子。

第 22 NMOS 晶体管 Tr22 响应于充入第 2 节点 QB1 中的第 3 电压 VDD3，输出第 2 电压 VSS。来自第 22 NMOS 晶体管 Tr22 的第 2 电压 VSS 被提供给第 2 上游级和第 1 下游级。为了执行该操作，第 22 NMOS 晶体管 Tr22 在其栅极端子处连接到第 2 节点 QB1，在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线，而在其源极端子处连接到第 1 级 CST1 中的第 20 NMOS

晶体管 Tr20 的栅极端子, 和第 4 级 CST4 中的第 1 NMOS 晶体管 Tr1、第 9 NMOS 晶体管 Tr9、第 10 NMOS 晶体管 Tr10、第 16 NMOS 晶体管 Tr16、第 17 NMOS 晶体管 Tr17、第 18 NMOS 晶体管 Tr18 以及第 19 NMOS 晶体管 Tr19 的栅极端子。

第 23 NMOS 晶体管 Tr23 响应于充入第 3 节点 QB2 中的第 4 电压 VDD4, 输出第 2 电压 VSS。来自第 23 NMOS 晶体管 Tr23 的第 2 电压 VSS 被提供给第 2 上游级和第 1 下游级。为了执行该操作, 第 23 NMOS 晶体管 Tr23 在其栅极端子处连接到第 2 节点 QB1, 在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线, 而在其源极端子处连接到第 1 级 CST1 中的第 20 NMOS 晶体管 Tr20 的栅极端子, 和第 4 级 CST4 中的第 1 NMOS 晶体管 Tr1、第 9 NMOS 晶体管 Tr9、第 10 NMOS 晶体管 Tr10、第 16 NMOS 晶体管 Tr16、第 17 NMOS 晶体管 Tr17、第 18 NMOS 晶体管 Tr18 以及第 19 NMOS 晶体管 Tr19 的栅极端子。

第 3 级 CST3 的第 2 输出单元 120c 包括第 24 NMOS 晶体管 Tr24 到第 26 NMOS 晶体管 Tr26。

第 24 NMOS 晶体管 Tr24 响应于充入第 1 节点 Q 中的第 1 电压 VDD, 向第 3 选通线输出第 3 时钟脉冲 CLK3 作为第 3 扫描脉冲 Vout3。为了执行该操作, 第 24 NMOS 晶体管 Tr24 在其栅极端子处连接到第 1 节点 Q, 在其源极端子处连接到用于传输第 3 时钟脉冲 CLK3 的时钟线, 而在其漏极端子处连接到第 3 选通线。

第 25 NMOS 晶体管 Tr25 响应于充入第 2 节点 QB1 中的第 3 电压 VDD3, 向第 3 选通线输出第 2 电压 VSS。为了执行该操作, 第 25 NMOS 晶体管 Tr25 在其栅极端子处连接到第 2 节点 QB1, 在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线, 而在其源极端子处连接到第 3 选通线。

第 26 NMOS 晶体管 Tr26 响应于充入第 3 节点 QB2 中的第 4 电压 VDD4, 向第 3 选通线输出第 2 电压 VSS。为了执行该操作, 第 26 NMOS 晶体管 Tr26 在其栅极端子处连接到第 2 节点 QB1, 在其漏极端子处连接到用于传输第 2 电压 VSS 的电源线, 而在其源极端子处连接到第 3 选通线。

第 1 级 CST1 和第 2 级 CST2、第 4 级 CST4 到第 n 级 CSTn、以及第 1

哑级 CST<sub>n+1</sub> 和第 2 哑级 CST<sub>n+2</sub>，都与第 3 级 CST3 具有相同的结构。

可是，因为第 1 级 CST1 没有上游级，所以第 1 级 CST4 中的第 1 NMOS 晶体管 Tr1、第 9 NMOS 晶体管 Tr9、第 10 NMOS 晶体管 Tr10、第 16 NMOS 晶体管 Tr16、第 17 NMOS 晶体管 Tr17、第 18 NMOS 晶体管 Tr18 以及第 19 NMOS 晶体管 Tr19 接收来自定时控制器的起始脉冲 SP。即，第 1 级 CST1 的第 1 NMOS 晶体管 Tr1 响应于来自定时控制器的起始脉冲 SP，利用第 1 电压 VDD 对第 1 级 CST1 的第 1 节点 Q 进行充电。

第 1 级 CST1 的第 9 NMOS 晶体管 Tr9 响应于来自定时控制器的起始脉冲 SP，利用第 2 电压 VSS 对第 1 级 CST1 的第 2 节点 QB1 进行放电。

第 1 级 CST1 的第 10 NMOS 晶体管 Tr10 响应于来自定时控制器的起始脉冲 SP，向第 4 NMOS 晶体管 Tr4 的栅极端子提供第 2 电压 VSS，以使第 4 NMOS 晶体管 Tr4 截止。

第 1 级 CST1 的第 16 NMOS 晶体管 Tr16 响应于来自定时控制器的起始脉冲 SP，向第 20 NMOS 晶体管 Tr12 的栅极端子提供第 2 电压 VSS，以使第 20 NMOS 晶体管 Tr12 截止。

第 1 级 CST1 的第 17 NMOS 晶体管 Tr17 响应于来自定时控制器的起始脉冲 SP，向第 20 NMOS 晶体管 Tr12 的栅极端子提供第 2 电压 VSS，以使第 20 NMOS 晶体管 Tr12 截止。

第 1 级 CST1 的第 18 NMOS 晶体管 Tr18 响应于来自定时控制器的起始脉冲 SP，利用第 2 电压 VSS 对第 2 节点 QB1 进行放电。

第 1 级 CST1 的第 19 NMOS 晶体管 Tr19 响应于来自定时控制器的起始脉冲 SP，利用第 2 电压 VSS 对第 3 节点 QB2 进行放电。

在第 1 级 CST1 或第 2 级 CST2 次上游没有设置级。为此，第 1 级 CST1 向第 1 选通线和第 2 级 CST2 提供从其输出的第 1 扫描脉冲 Vout1。类似地，第 2 级 CST2 向第 2 选通线和第 3 级 CST3 提供从其输出的第 2 扫描脉冲 Vout2。

在第 2 哑级 CST<sub>n+2</sub> 的直接下游没有设置级。因此，第 2 哑级 CST<sub>n+2</sub> 中的第 21 NMOS 晶体管 Tr21 的源极端子、第 22 NMOS 晶体管 Tr22 的漏极端子，以及第 23 NMOS 晶体管 Tr23 的漏极端子，都连接到第 n 级 CST<sub>n</sub>

的第 20 NMOS 晶体管 Tr20 的栅极端子。

第 2 移位寄存器 110b 的级 CST1 到 CSTn+2 与第 1 移位寄存器 110a 的级 CST1 到 CSTn+2 具有相同的结构。

图 13A 和图 13B 是例示具有图 12 中示出的电路结构的第 1 移位寄存器的第 3 级的电路图。

根据本发明第二实施例的移位寄存器与图 9、10A 以及 10B 中示出的第一实施例的电路按相同的方式操作。然而，根据第二实施例的移位寄存器中的级 CST1 到 CSTn+2 中的每一个都输出两个扫描脉冲。来自每一个级的一个扫描脉冲被提供给第 1 下游级和第 2 上游级。来自每一个级的另一个扫描脉冲被提供给相关联的选通线。第 1 哑级 CSTn+1 和第 2 哑级 CSTn+2 中的每一个都可以输出一个扫描脉冲。

本领域技术人员应当明白，在不脱离本发明的精神或范围的情况下，可以对本发明进行各种修改和变型。因而，本发明将覆盖落入所附权利要求及其等同物的范围内的对本发明的各种修改和变型。

由上述说明可以明白，根据本发明的 LCD 装置的移位寄存器顺序地输出脉冲宽度增大的多个扫描脉冲，而使所述多个时钟脉冲中的连续扫描脉冲相互交叠预定时间。因此，可以增加扫描脉冲保持在目标电压的有效充电时间，从而防止该扫描脉冲的畸变。在这种情况下，即使所述扫描脉冲由选通线的电阻分量和电容分量畸变，也可以确保有充分的有效充电时间来将数据电压正常施加到像素电极。

图 1

现有技术

图 2

现有技术

图 3

图 4

图 5

图 6A

图 6B

图 7

图 8

图 9

图 10A

图 10B

图 13A

图 13B

|                |                                                  |         |            |

|----------------|--------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置的驱动电路和显示装置的驱动方法                              |         |            |

| 公开(公告)号        | <a href="#">CN1892798A</a>                       | 公开(公告)日 | 2007-01-10 |

| 申请号            | CN200610100312.5                                 | 申请日     | 2006-06-30 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                         |         |            |

| 申请(专利权)人(译)    | LG. 菲利浦LCD株式会社                                   |         |            |

| 当前申请(专利权)人(译)  | LG. 菲利浦LCD株式会社                                   |         |            |

| [标]发明人         | 张容豪<br>金彬<br>尹洙荣                                 |         |            |

| 发明人            | 张容豪<br>金彬<br>尹洙荣                                 |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                      |         |            |

| CPC分类号         | G11C19/28 G09G2310/0205 G09G3/3677 G09G2320/0223 |         |            |

| 代理人(译)         | 李辉                                               |         |            |

| 优先权            | 1020050058609 2005-06-30 KR                      |         |            |

| 其他公开文献         | CN1892798B                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>   |         |            |

#### 摘要(译)

公开了一种显示装置的驱动电路和显示装置的驱动方法，其能够防止向液晶板的选通线提供的扫描脉冲发生畸变。该驱动电路包括：第1移位寄存器，用于分别向显示器中包括的多条选通线的一侧端顺序地提供多个第1扫描脉冲，以顺序地驱动所述多条选通线，该第1移位寄存器同时驱动所述多条选通线中的至少两条相邻选通线达预定时间段；和第2移位寄存器，用于分别向所述多条选通线的另一侧端顺序地提供多个第2扫描脉冲，以顺序地驱动所述多条选通线，该第2移位寄存器同时驱动所述多条选通线中的至少两条相邻选通线达预定时间段。