[19] 中华人民共和国国家知识产权局

## [12] 发明专利申请公布说明书

[21] 申请号 200680052336.6

[51] Int. Cl.

G09G 3/36 (2006.01)

G09G 3/20 (2006.01)

G02F 1/133 (2006.01)

[43] 公开日 2008 年 12 月 31 日

[11] 公开号 CN 101336447A

[22] 申请日 2006.11.30

[21] 申请号 200680052336.6

[30] 优先权

[32] 2006.3.23 [33] JP [31] 081641/2006

[86] 国际申请 PCT/JP2006/323906 2006.11.30

[87] 国际公布 WO2007/108177 日 2007.9.27

[85] 进入国家阶段日期 2008.8.5

[71] 申请人 夏普株式会社

地址 日本大阪府

[72] 发明人 大河宽幸 村上祐一郎 辻野幸生

[74] 专利代理机构 上海专利商标事务所有限公司

代理人 侯颖媖

权利要求书 2 页 说明书 20 页 附图 12 页

[54] 发明名称

显示装置及其驱动方法

[57] 摘要

在液晶显示装置(1)中，源极驱动器(4)的移位寄存器用对置位输入端子的有源输入优先于对复位输入端子的有源输入的非同步型的RS触发器构成。在第2工作模式中，通过将第1和第2时钟信号与触发脉冲固定于高电平，进行从液晶面板(2)全部像素(PIX)的放电。

1. 一种显示装置，是由具备移位寄存器的驱动电路利用所述移位寄存器的输出信号驱动有源矩阵型的显示面板的显示装置，其特征在于，

所述移位寄存器所具有的串联连接的各级分别具备：作为用于数据保持的电路的、对置位输入端子的有源输入优先于对复位端子的有源输入的 RS 触发器，

所述移位寄存器执行第 1 工作模式以及第 2 工作模式，

所述第 1 工作模式根据与所述各级对应的定时信号，一边依次向后级传递输入到规定级的所述 RS 触发器的所述置位输入端子的规定的脉冲，一边由所述各级将所述输出信号作为脉冲从所述规定的级依次输出，

所述第 2 工作模式对初级的所述 RS 触发器的所述置位输入端子进行有源输入，使全部的所述输出信号共同成为有源信号。

2. 如权利要求 1 所述的显示装置，其特征在于，

具备用所述驱动电路构成的扫描信号线驱动电路，

所述扫描信号线驱动电路在所述第 1 工作模式中，用所述输出信号生成具有向各扫描信号线依次输出的脉冲的扫描信号，在所述第 2 工作模式中，用所述输出信号生成具有向全部扫描信号线共同输出的脉冲的信号。

3. 如权利要求 1 所述的显示装置，其特征在于，

具备用所述驱动电路构成的扫描信号线驱动电路以及数据信号线驱动电路，

所述扫描信号线驱动电路在所述第 1 工作模式中，用所述扫描信号线驱动电路的所述移位寄存器的所述输出信号，生成具有向各扫描信号线依次输出的脉冲的扫描信号，在所述第 2 工作模式中，用所述扫描信号线驱动电路的所述移位寄存器的所述输出信号，生成具有向全部扫描信号线共同输出的脉冲的信号，

所述数据信号线驱动电路在所述第 1 工作模式中，用所述数据信号线驱动电路的所述移位寄存器的所述输出信号，从视频信号线向各数据信号线依次提供数据信号，在所述第 2 工作模式中，用所述数据信号线驱动电路的所述移位寄存器的所述输出信号，从所述视频信号线向全部数据信号线共同提供公共电位。

4. 如权利要求 1 所述的显示装置，其特征在于，

具备用所述驱动电路构成的扫描信号线驱动电路以及数据信号线驱动电路，所述扫描信号线驱动电路在所述第1工作模式中，用所述扫描信号线驱动电路的所述移位寄存器的所述输出信号，生成具有向各扫描信号线依次输出的脉冲的扫描信号，在所述第2工作模式中，用所述扫描信号线驱动电路的所述移位寄存器的所述输出信号，生成具有向全部扫描信号线共同输出的脉冲的信号，

所述数据信号线驱动电路在所述第1工作模式中，用所述数据信号线驱动电路的所述移位寄存器的所述输出信号，从视频信号线向各数据信号线依次提供数据信号，在所述第2工作模式中，用所述数据信号线驱动电路的所述移位寄存器的所述输出信号，从所述视频信号线上断开全部数据信号线，同时使全部数据信号线相互导通。

5. 一种显示装置的驱动方法，是由具备移位寄存器的驱动电路利用所述移位寄存器的输出信号驱动有源矩阵型的显示面板的显示装置的驱动方法，所述移位寄存器所具有的串联连接的各级分别具备作为用于数据保持的电路的、对置位输入端子的有源输入优先于对复位端子的有源输入的RS触发器，其特征在于，

执行第1工作模式以及第2工作模式，

所述第1工作模式根据与所述各级对应的定时信号，一边依次向后级传递输入到规定级的所述RS触发器的所述置位输入端子的规定的脉冲，一边由所述各级将所述输出信号作为脉冲从所述规定的级依次输出，

所述第2工作模式对初级的所述RS触发器的所述置位输入端子进行有源输入，使全部的所述输出信号共同成为有源信号。

## 显示装置及其驱动方法

### 技术领域

本发明涉及有源矩阵型液晶显示装置等的，通过对像素进行充电以进行显示的显示装置。

### 背景技术

通过 TFT 对像素进行充电以进行显示的有源矩阵型液晶显示装置中，在进行交流驱动的情况下，在显示面板上，积蓄正极性电荷的像素与积蓄负极性电荷的像素为混合的。从而，在切断该液晶显示装置的电源时，对于对置电极的各像素电极的电位因电源切断瞬间之前积蓄正极性电荷的像素与积蓄负极性电荷的像素而不同，所以在液晶显示装置的驱动结束时，成为与数据信号线的电位之差较大的电位的极性的像素的电荷容易向数据信号线漏出。其结果是，有时候施加于像素上的电压会发生波动，画面上发生混乱。又，即使在电源接通时电源上升的过程中，而液晶显示装置的驱动电路的逻辑尚未确立的状态下，由于在视频信号线和对置电极上产生电位，像素上积蓄电荷，有时候画面上产生混乱。

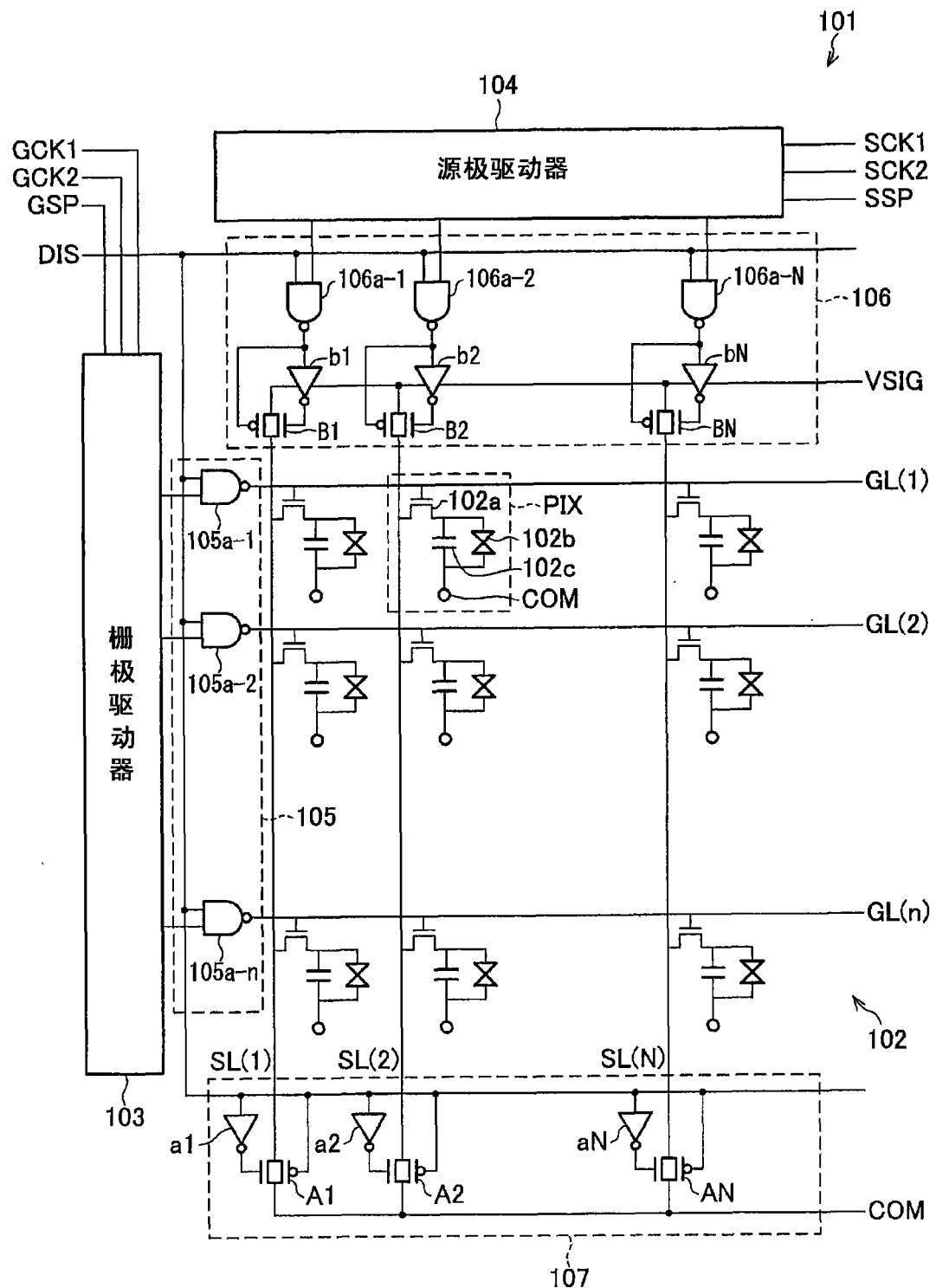

对于这样的问题，以往提出了如图 12 所示的结构（参照例如专利文献 1）。

图 12 所示的液晶显示装置 101 具备液晶面板 102、栅极驱动器 103、源极驱动器 104、扫描信号供给控制电路 105、数据信号供给控制电路 106、以及像素放电电路 107。

液晶面板 102 是有源矩阵型的显示面板，具备扫描信号线 GL(1)・GL(2)・…・GL(n)・…与数据信号线 SL(1)・SL(2)・…・SL(N)・…，而且互相垂直。而且，在其各交点上配置像素 PIX。像素 PIX 具备 TFT102a、液晶电容 102b、以及辅助电容 102c。TFT102a 的栅极端子连接于与该像素 PIX 对应的扫描信号线 GL。TFT102a 的一个源极/漏极端子连接于与该像素 PIX 对应的数据信号线 SL，另一源极/漏极端子连接于该像素 PIX 的像素电极。液晶电容 102b 与辅助电容 102c 相互并联连接于像素 PIX 的像素电极与对置电极

COM 之间。

栅极驱动器 103 根据从外部输入的时钟信号 GCK1 • GCK2 以及栅极触发脉冲 GSP，利用内部的移位寄存器以及逻辑电路，在各级生成信号，该信号用于生成输出到各扫描信号线 GL 的扫描信号。源极驱动器 104 根据从外部输入的时钟信号 SCK1 • SCK2 以及源极触发脉冲信号 SSP，利用内部的移位寄存器，在各级生成信号，该信号用于生成下述数据信号供给控制电路 106 具备的模拟开关 B 的控制信号。

扫描信号供给控制电路 105 是具备对栅极驱动器 103 生成的扫描信号与从外部输入的放电控制信号 DIS 进行 NAND 运算的 NAND 电路 105a—1 • 105a—2 • … • 105a—n • …，且依次与扫描信号线 GL (1) • GL (2) • … • GL (n) • … 对应的电路。

数据信号供给控制电路 106 是具备对源极驱动器 104 生成的信号与从外部输入的上述放电控制信号 DIS 进行 NAND 运算的 NAND 电路 106a—1 • 106a—2 • … • 106a—N • …，且依次与数据信号线 SL (1) • SL (2) • … • SL (N) • … 对应的电路。数据信号供给控制电路 106 具备将 NAND 电路 106a—1 • 106a—2 • … • 106a—N • … 生成的信号依次作为控制信号 CMOS 结构的模拟开关 B1 • B2 • … • BN • …。该模拟开关 B 的 p 道型 MOS 晶体管的栅极端子上，直接输入对应的 NAND 电路 106a 生成的信号，在 n 道型 MOS 晶体管的栅极端子上，NAND 电路 106a 生成的信号在逆变器 b (依次与 NAND 运算电路 106a—1 • 106a—2 • … • 106a—N • … 对应的逆变器 b1 • b2 • … • bN • …) 上经电平反转后输入。又，模拟开关 B1 • B2 • … • BN • … 依次与数据信号线 SL (1) • SL (2) • … • SL (N) • … 对应，实现数据信号线 SL 与视频信号线 VSIG 之间的导通和切断。

像素放电电路 107 具备 CMOS 的模拟开关 A1 • A2 • … • AN • …，且依次与数据信号线 SL (1) • SL (2) • … • SL (N) • … 对应。作为该模拟开关 A 的控制信号，使用上述放电控制信号 DIS。模拟开关 A 的 n 道型 MOS 晶体管的栅极上，放电控制信号 DIS 利用逆变器 a (依次对应于数据信号线 SL (1) • SL (2) • … • SL (N) • … 的逆变器 a1 • a2 • … • aN • …) 电平反转而输入，p 道型 MOS 晶体管的栅极上，直接输入放电控制信号 DIS。

在上述结构的液晶显示装置 101 中，通常工作时，放电控制信号 DIS 为高电平。这时，像素放电电路 107 的模拟开关 A1 • A2 • … • AN • … 共同为截止

(OFF) 状态，数据信号供给控制电路 106 的模拟开关 B1・B2・…・BN・…，由于源极驱动器 104 对应的级的输出信号为高电平时对应的 NAND 电路 106a 的输出信号为低电平，因此依次为导通 (ON) 状态。而且，栅极驱动器 103 从各级依次输出低电平信号，但是，NAND 电路 105a 在栅极驱动器 103 的对应的级的输出信号为低电平时，向对应的扫描信号线 GL 输出高电平的扫描信号。由此，对 TFT102a 为导通状态的像素 PIX，从视频信号线 VSIG 通过导通状态的模拟开关 B 利用视频信号进行充电，进行图像显示。

另一方面，在切断液晶显示装置 101 的电源时，或接通电源时，在其瞬间之前放电控制信号 DIS 为低电平。由此，数据信号供给控制电路 106 的 NAND 电路 106a-1・106a-2・…・106a-N・…的输出信号共同为高电平，所以模拟开关 B1・B2・…・BN・…共同为截止状态。又，像素放电电路 107 的模拟开关 A1・A2・…・AN・…共同为导通状态。而且，扫描信号供给控制电路 105 的 NAND 电路 105a-1・105a-2・…・105a-n・…的输出信号共同为高电平，因此各像素 PIX 的 TFT102a 共同为导通状态。

由此，各像素 PIX 的像素电极一侧连接于对置电极 COM，因此各像素 PIX 共同进行放电（也可以称为来自对置电极 COM 的充电）。从而，各像素 PIX 的液晶电容 102b 和辅助电容 102c 的施加电压为 0，可以防止液晶显示装置 101 电源切断时或电源接通时的画面的混乱。

专利文献 1：特开 2000-347627 号公报（2000 年 12 月 15 日公开）

专利文献 2：特开 2004-45785 号公报（2004 年 2 月 12 日公开）

### 发明内容

但是，在上述以往的液晶显示装置 101 的结构中，为防止在电源切断时或电源接通时画面的混乱，具备 NAND 电路 105a-1・105a-2・…・105a-n・… 以及 NAND 电路 106a-1・106a-2・…・106a-N・…，因此必须有这些电路的空间。从而，存在液晶显示装置的小型化和区域的有效利用受到限制的问题。

本发明是鉴于上述问题点而作出的，其目的在于，实现即使是防止电源切断时或电源接通时画面的混乱，也不会因利用防止画面混乱用的电路而妨碍小型化和区域的有效利用的显示装置及其驱动方法。

为了解决上述问题，本发明的显示装置，是具备移位寄存器的驱动电路利用上述移位寄存器的输出信号驱动有源矩阵型的显示面板的显示装置，其特征在

于，上述移位寄存器中，上述移位寄存器具有的串联连接的各级，作为数据保持用的电路，具备对置位输入端子的有源输入优先于对复位端子的有源输入的 RS 触发器；执行根据与上述各级对应的定时信号，一边依次向后级传递输入到规定级的上述 RS 触发器的上述置位输入端子的规定的脉冲，一边由上述各级将上述输出信号作为脉冲从上述规定的级依次输出的第 1 工作模式、以及对初级的上述 RS 触发器的上述置位输入端子进行有源输入，使全部上述输出信号共同为有源信号的第 2 工作模式。

如果采用上述发明，采用对置位输入端子的有源输入优先于对复位端子的有源输入的 RS 触发器，在第 1 工作模式中，通过脉冲的顺序输出可以进行显示装置通常的显示工作，同时在第 2 工作模式中，采用对置位输入端子的有源输入优先于对复位端子的有源输入的方式，能够进行有源输出信号的共同输出。如果在例如电源切断时使用第 2 工作模式，对于进行交流驱动的显示装置能够进行像素的放电，在像素之间进行正极性电荷与负极性电荷的相互抵消。又，如果在电源接通时使用第 2 工作模式，则对于任意显示装置能够在像素之间使电荷量一致。从而，利用第 2 工作模式，不用对应于驱动电路的各输出而设置 NAND 电路等多余的电路，就能够防止在电源切断时或电源接通时的画面混乱。

根据以上所述，具有如下效果，即能够实现一种显示装置，即使是防止电源切断时或电源接通时画面的混乱，也不会因利用防止画面混乱的电路而妨碍小型化和区域的有效利用。

为了解决上述问题，本发明的显示装置的驱动方法，是具备移位寄存器的驱动电路用上述移位寄存器的输出信号驱动有源矩阵型显示面板的显示装置的驱动方法，上述移位寄存器中串联连接的各级，作为数据保持用的电路，具备对置位输入端子的有源输入优先于对复位端子的有源输入的 RS 触发器，其特征在于，

执行根据与上述各级对应的定时信号，一边依次向后级传递输入到规定级的上述 RS 触发器的上述置位输入端子的规定的脉冲，一边由上述各级将上述输出信号作为脉冲从上述规定的级依次输出的第 1 工作模式、以及对初级的上述 RS 触发器的上述置位输入端子进行有源输入，使全部上述输出信号共同为有源信号的第 2 工作模式。

如果采用上述发明，使用对置位输入端子的有源输入优先于对复位端子的有源输入的 RS 触发器，在第 1 工作模式中，利用脉冲的依次输出可以进行显示

装置的通常的显示工作，同时在第 2 工作模式中，利用对置位输入端子的有源输入优先于对复位端子的有源输入的方法，能够进行有源输出信号的共同输出。如果在例如电源切断时采用第 2 工作模式，对于进行交流驱动的显示装置，能够实现从像素放电、在像素间的正极性电荷和负极性电荷相互抵消。又，如果在电源接通时采用第 2 工作模式，则对于任意显示装置能够在像素间使电荷量一致。从而，利用第 2 工作模式，不用对应于驱动电路的各输出设置 NAND 电路等多余的电路，就能够防止电源切断时或电源接通画面的混乱。

根据以上所述，具有以下效果，即能够实现即使是防止电源切断时或电源接通时画面的混乱，也不会因利用防止画面混乱用的电路而妨碍小型化和区域的有效利用的显示装置的驱动方法。

本发明的其他目的、特征以及优点根据以下所示应该可以充分了解。又，本发明的利益从参照附图的以下说明中应该可以清楚地了解到。

### 附图说明

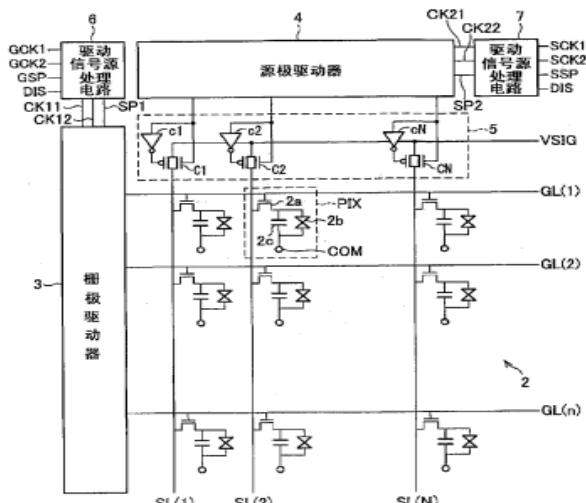

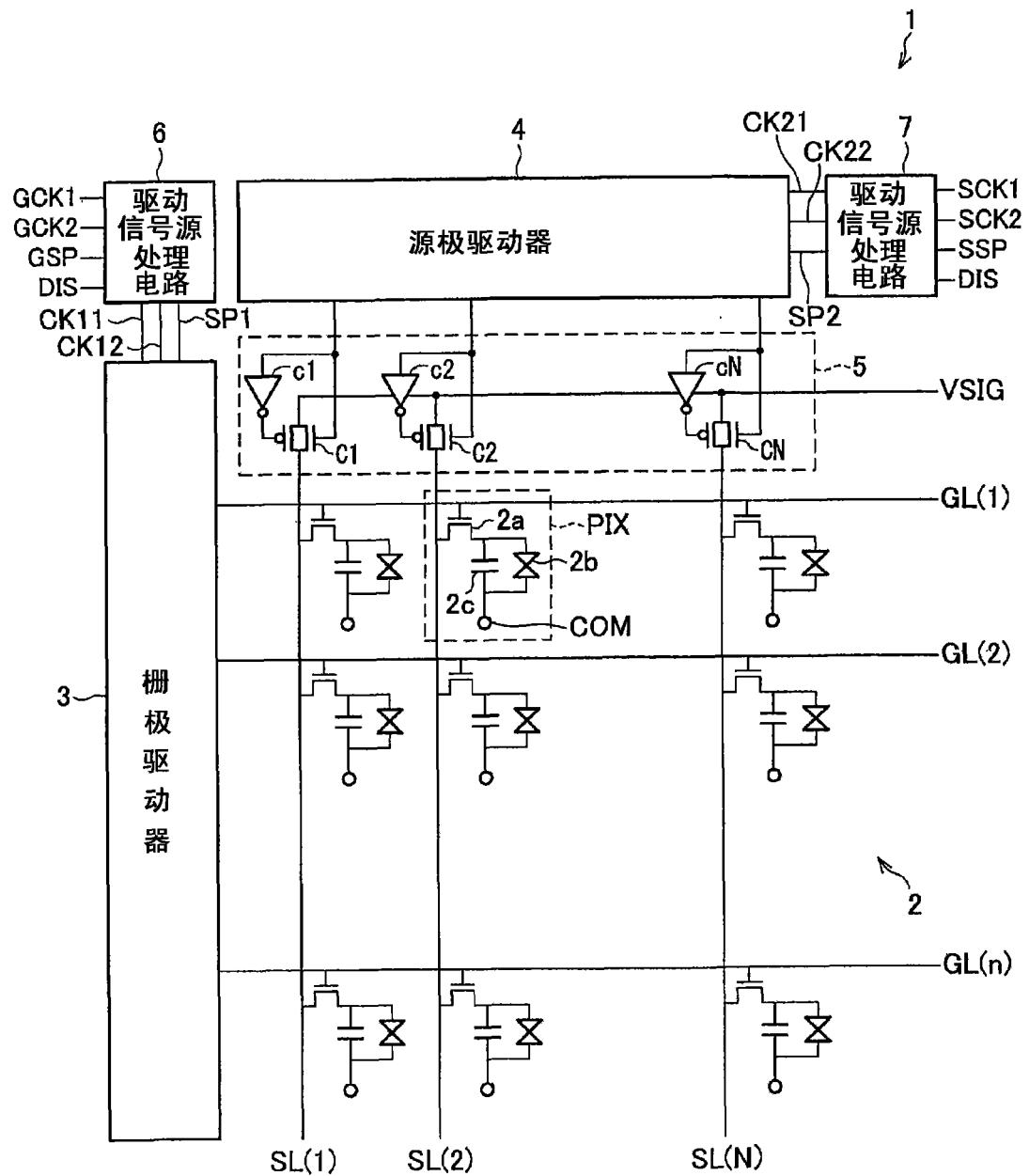

图 1 表示本发明的实施形态，是表示液晶显示装置的要部结构的电路方框图。

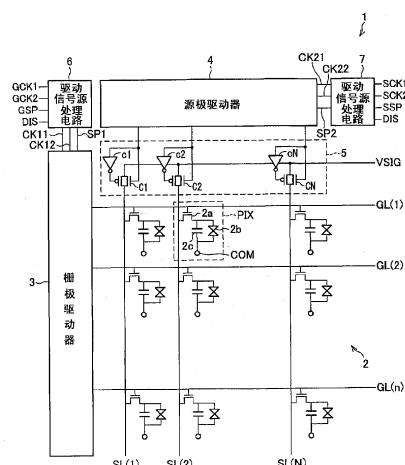

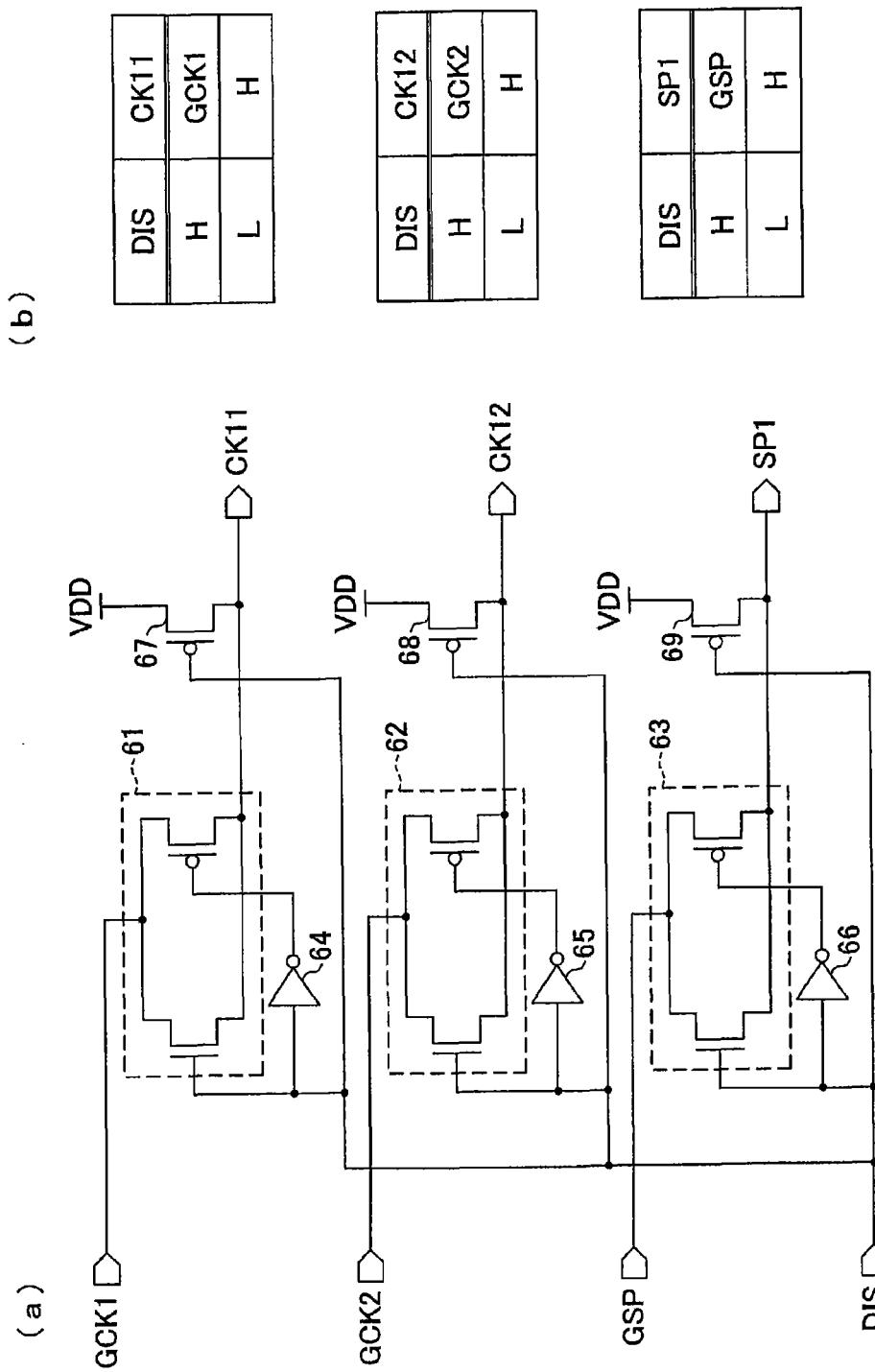

图 2 (a) 是表示图 1 的液晶显示装置具备的驱动信号源处理电路的结构的电路图，(b) 是 (a) 的真值表。

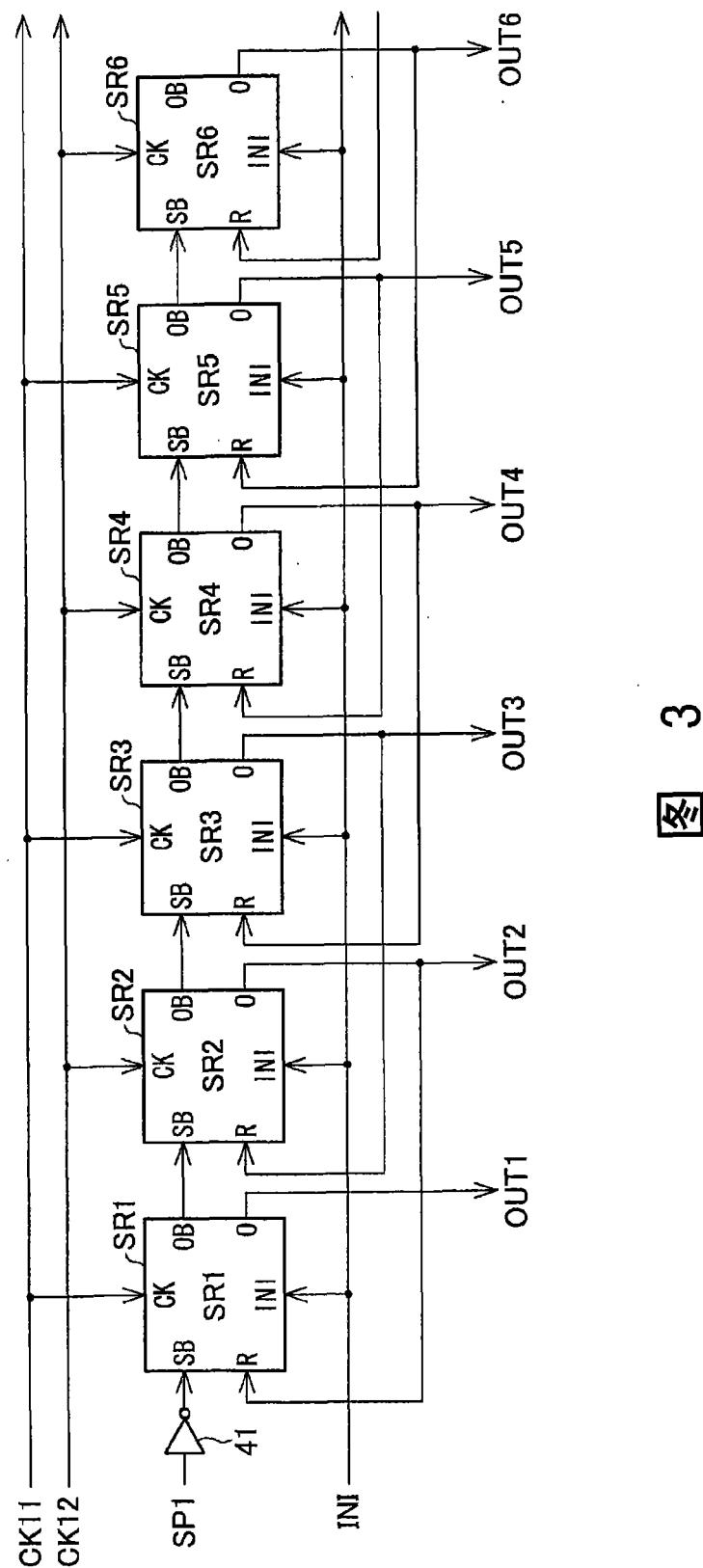

图 3 是表示图 1 的液晶显示装置具备的栅极驱动器的结构的电路方框图。

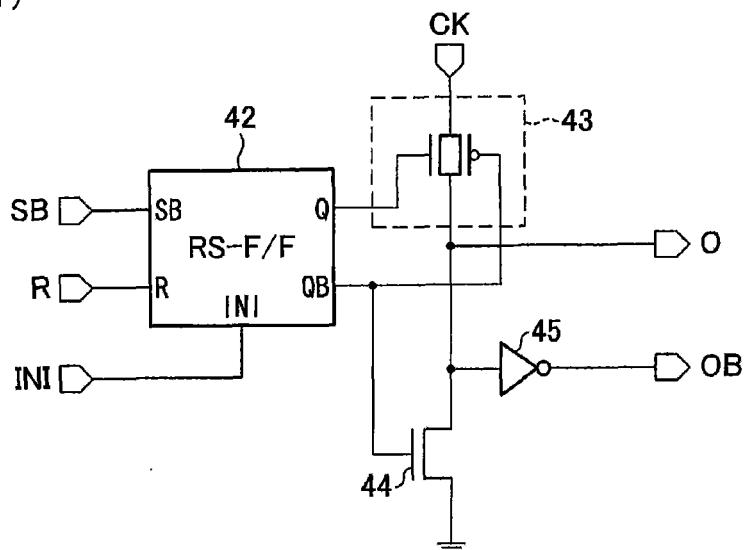

图 4 (a) 是表示图 3 (a) 的栅极驱动器具备的移位寄存器的各级的结构的电路方框图，(b) 是 (a) 的真值表。

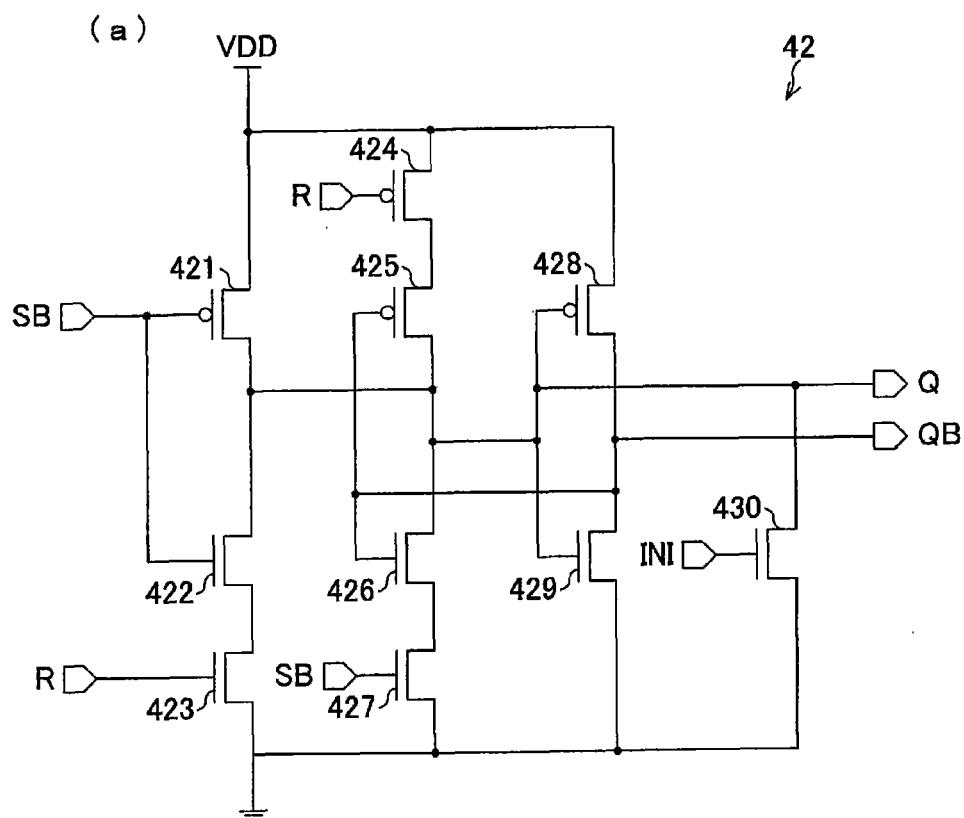

图 5 (a) 是表示图 4 (a) 的移位寄存器的各级具备的 RS 触发器的结构的电路图，(b) 是 (a) 的真值表。

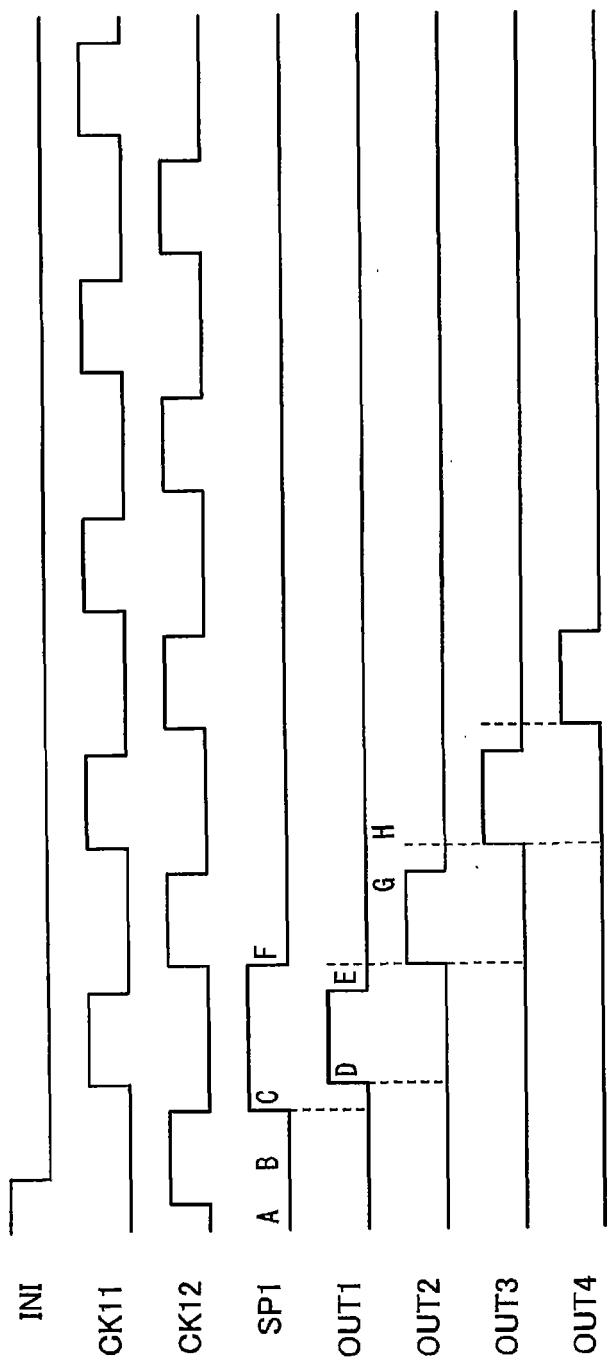

图 6 是表示图 3 的栅极驱动器的第 1 工作模式的工作的时序图。

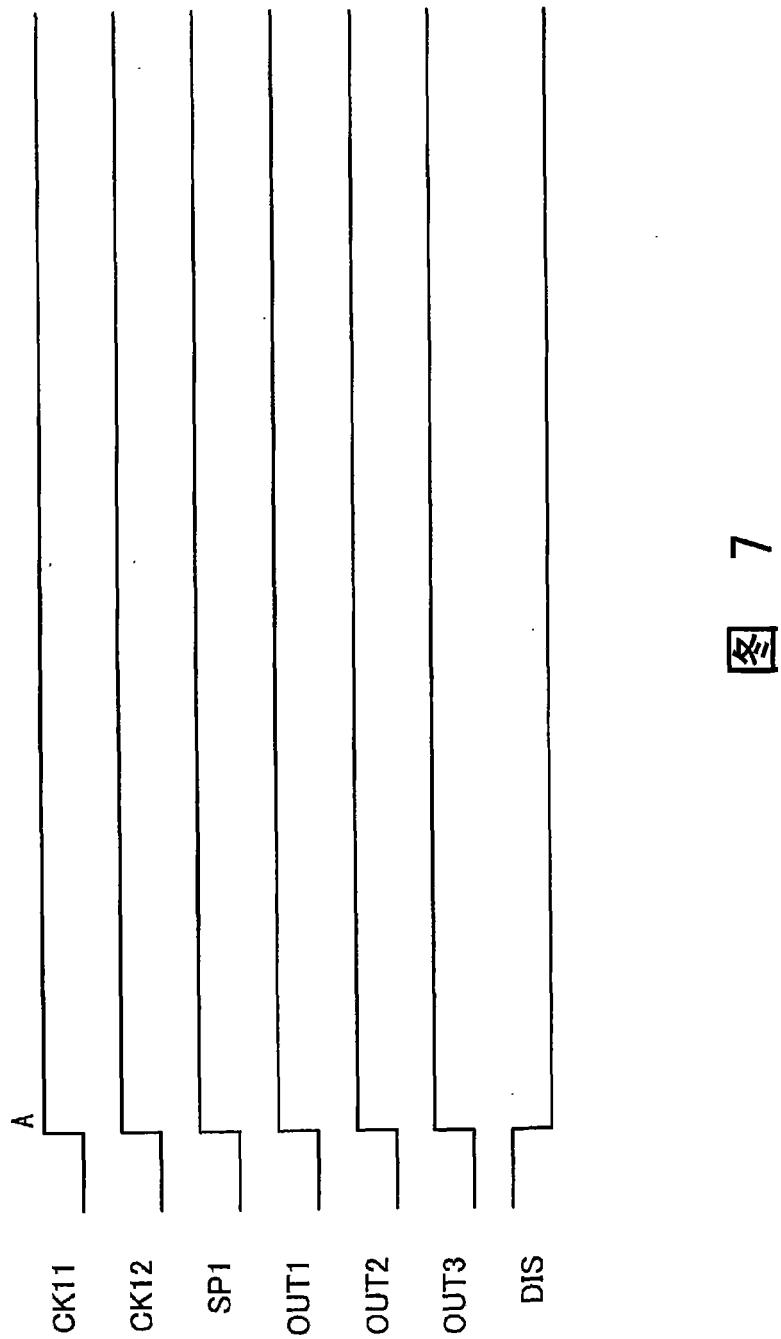

图 7 是表示图 3 的栅极驱动器的第 2 工作模式的工作的时序图。

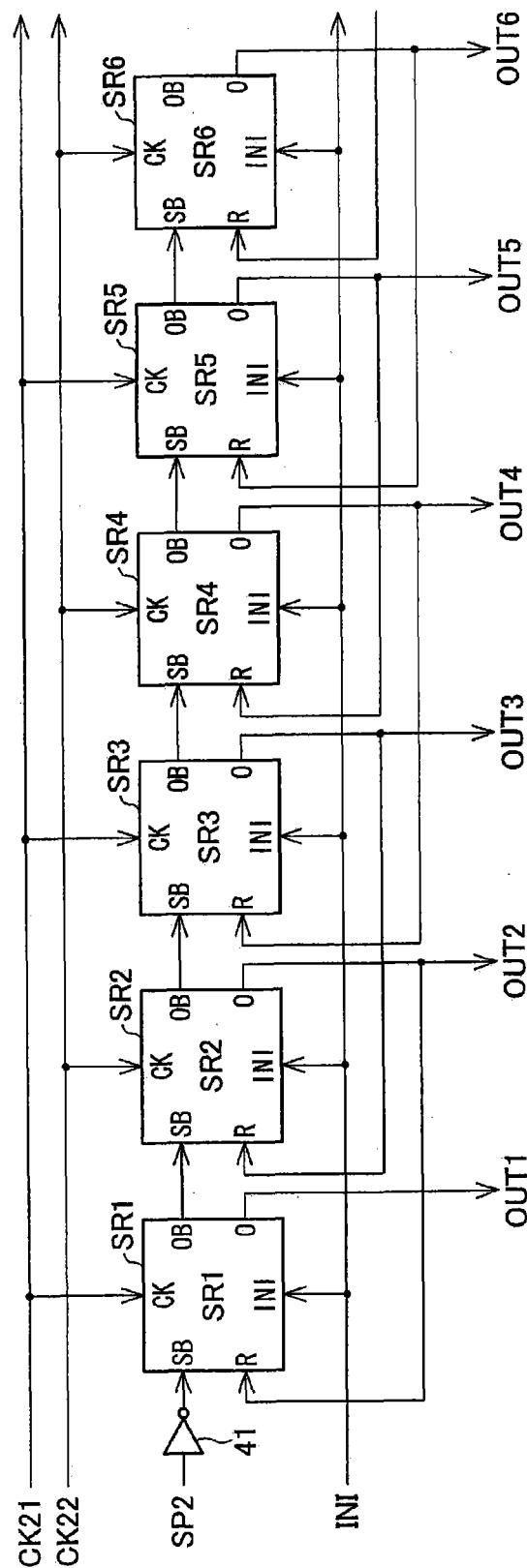

图 8 是表示图 1 的液晶显示装置具备的源极驱动器的结构的电路方框图。

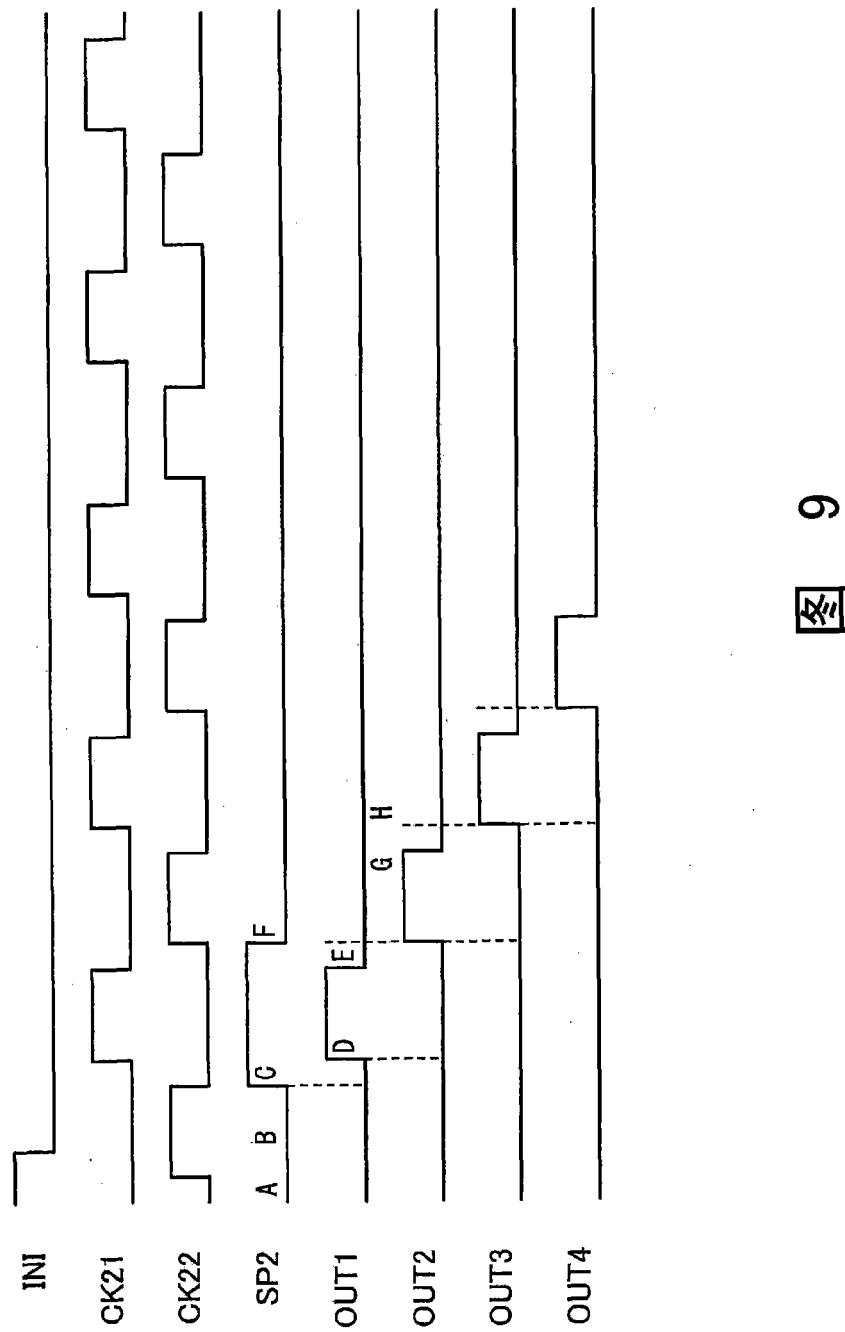

图 9 是表示图 8 的源极驱动器的第 1 工作模式的工作的时序图。

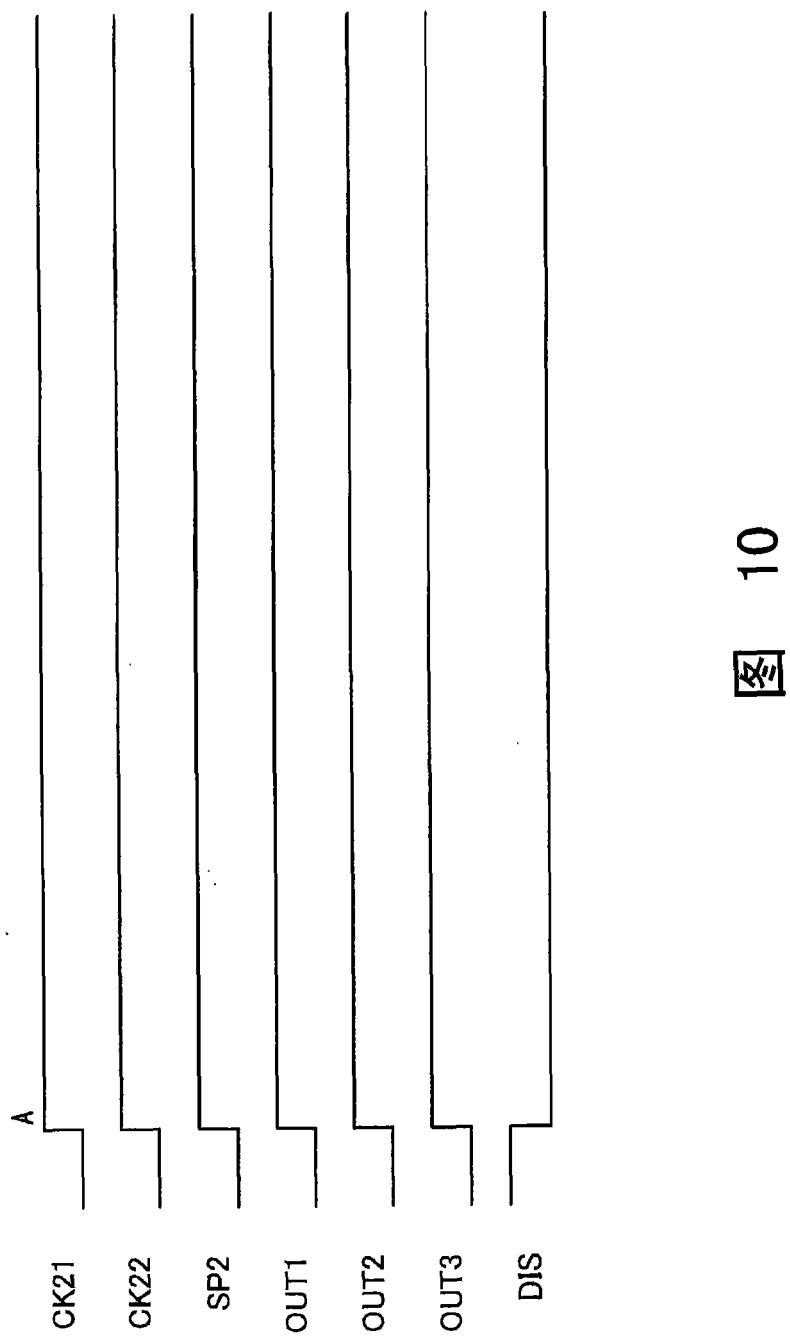

图 10 是表示图 8 的源极驱动器的第 2 工作模式的工作的时序图。

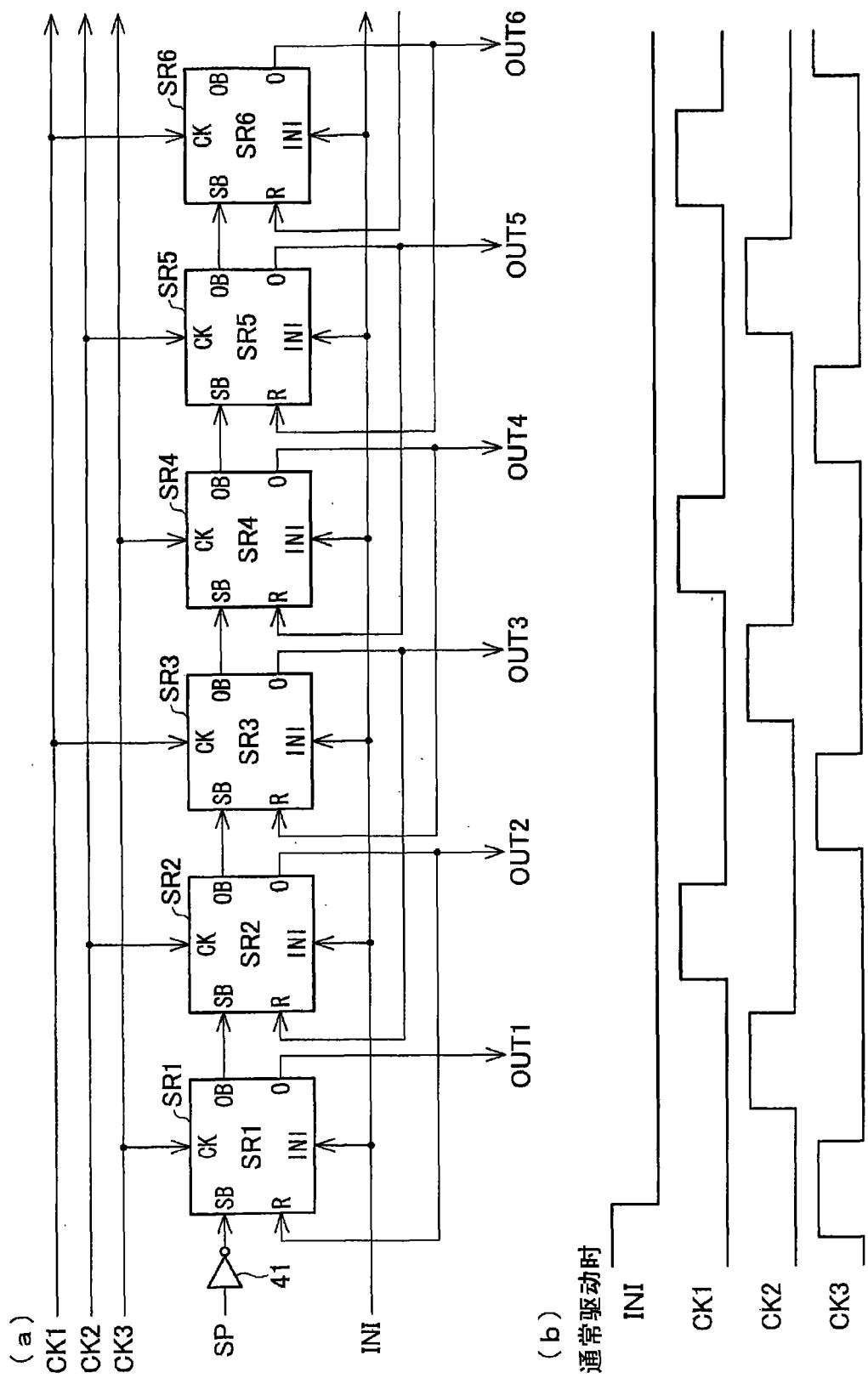

图 11 (a) 是表示驱动电路的变形例的结构的电路方框图，(b) 是 (a) 的电路方框图中使用的时钟信号的波形图。

图 12 表示以往的技术，是表示液晶显示装置的要部结构的电路方框图。

### 标号说明

- 1 液晶显示装置（显示装置）

- 2 液晶面板（显示面板）

- 3 栅极驱动器（扫描信号线驱动电路、驱动电路）

- 4 源极驱动器（数据信号线驱动电路、驱动电路）

### 具体实施方式

下面利用实施例和比较例更详细地说明本发明，但是，本发明不限于这些说明。

根据图1～图7对本发明的一实施形态的说明，如下所示。

图1中表示本实施形态的液晶显示装置（显示装置）1的结构。液晶显示装置1具备液晶面板2、栅极驱动器3、源极驱动器4、模拟开关电路5、以及驱动信号源处理电路6·7。还有，驱动信号源驱动电路6·7也以作为液晶面板2的一部分设置。

该液晶显示装置1对液晶显示面板2，利用使上下左右邻接的像素PIX之间电荷极性不同的点反转驱动，或使连接于邻接的扫描信号线的像素PIX之间电荷极性不同的扫描信号线反转驱动进行交流驱动。

液晶面板2是有源矩阵型的显示面板，具备扫描信号线GL(1)·GL(2)·…·GL(n)·…和数据信号线SL(1)·SL(2)·…·SL(N)·…，且互相垂直。而且在其各交点上配置像素PIX。像素PIX具备TFT2a、液晶电容2b、以及辅助电容2c。TFT2a的栅极端子连接于与该像素PIX对应的扫描信号线GL。TFT2a的一个源极/漏极端子连接于与该像素PIX对应的数据信号线SL，另一源极/漏极端子连接于该像素PIX的像素电极。液晶电容2b与辅助电容2c相互并联连接于像素PIX的像素电极与对置电极COM之间。

栅极驱动器（扫描信号线驱动电路）3根据从下述驱动信号源处理电路6输入的时钟信号CK11·CK12以及触发脉冲SP1，利用内部的移位寄存器，或利用对移位寄存器再追加逻辑电路的结构，在各级生成向各扫描信号线GL输出的扫描信号。时钟信号（定时信号）CK11和时钟信号（定时信号）CK12在液晶显示装置1的通常工作时，如图6所示，相互之间相位不同，是使电平变化周期性反复的2值周期信号。在这里表示的是时钟信号CK11和时钟信号CK12

相互之间在高电平期间不重叠的例子。又，时钟信号 CK11、CK12 在液晶显示装置 1 的电源切断瞬间之前，如图 7 所示，是均固定于有源电平（active level）（这里是高电平）的信号。触发脉冲 SP1 是液晶显示装置 1 的通常工作时，如图 6 所示，每一规定期间具有一个脉冲的信号，对于触发脉冲 SP1，该规定期间是一垂直期间。又，触发脉冲 SP1 在液晶显示装置 1 的电源切断瞬间之前，如图 7 所示，是固定于有源电平（在这里是高电平）的信号。

源极驱动器（数据信号线驱动电路）4 根据从下述驱动信号源处理电路 7 输入的时钟信号 CK21・SCK22 以及触发脉冲信号 SP2，利用内部的移位寄存器，在各级生成下述模拟开关电路 5 具备的模拟开关 C 的控制信号。

模拟开关电路 5 与源极驱动器 4 的各级输出一一对应，具备 CMOS 的模拟开关 C1・C2・…・CN・…。在各模拟开关 C 的 p 道型 MOS 晶体管的栅极上，源极驱动器 4 的对应的级的输出信号利用逆变器 c（逆变器 c1・c2・…・cN・…依次与模拟开关 C1・C2・…・CN・…对应）电平反转而输入，n 道型 MOS 晶体管的栅极上直接输入源极驱动器 4 的对应的级的输出信号。又，模拟开关 C1・C2・…・CN・…依次对应于数据信号线 SL(1)・SL(2)・…・SL(N)・…，进行在对应的数据信号线 SL 与视频信号线 VSIG 之间的接通和切断。对视频信号线 VSIG 提供数据信号，通过连接于导通的模拟开关的数据信号线 SL，写入利用扫描信号选择的像素 PIX。

驱动信号源处理电路 6 从由外部输入的时钟信号 GCK1 以及放电控制信号 DIS 生成时钟信号 CK11，又，从由外部输入的时钟信号 GCK2 以及上述放电控制信号 DIS 生成时钟信号 CK12，又从由外部输入的栅极触发脉冲 GSP 以及放电控制信号 DIS 生成触发脉冲 SP1，将生成的各信号输入栅极驱动器 3。放电控制信号 DIS 是在液晶显示装置 1 通常工作时被固定于高电平，在液晶显示装置 1 的电源切断时的瞬间之前，如图 7 所示，被固定于低电平的信号。

驱动信号源处理电路 7 根从由外部输出的时钟信号 SCK1 生成时钟信号 CK21，又从由外部输入的时钟信号 SCK2 生成时钟信号 CK22，又从由外部输入的源极触发脉冲 SSP 生成触发脉冲 SP2，将生成的各信号输入到源极驱动器 4。放电控制信号 DIS 是其他结构中使用的信号，在这里不做说明。

又，也可以将上述驱动信号源处理电路 6 与上述驱动信号源处理电路 7 汇集在一处配置。

图 2 (a) 中表示驱动信号源处理电路 6 的结构。

驱动信号源处理电路 6 具备 CMOS 模拟开关 61・62・63、逆变器 64・65・66、以及 p 道型 MOS 晶体管 67・68・69。

模拟开关 61 实施时钟信号 GCK1 的输入端子与时钟信号 CK11 的输出端子之间的导通和切断。模拟开关 62 实施时钟信号 GCK2 的输入端子与时钟信号 CK12 的输出端子之间的导通和切断。模拟开关 63 实施栅极触发脉冲 GSP 的输入端子与触发脉冲 SP1 的输出端子之间的导通和切断。模拟开关 61～63 各自的控制信号使用放电控制信号 DIS。模拟开关 61～63 的各 n 道型 MOS 晶体管的栅极上直接输入放电控制信号 DIS。分别在模拟开关 61 的 p 道型 MOS 晶体管的栅极上，输入用逆变器 64 将放电控制信号 DIS 电平反转的信号；又，在模拟开关 62 的 p 道型 MOS 晶体管的栅极输入用逆变器 65 将放电控制信号 DIS 电平反转的信号；在模拟开关 63 的 p 道型 MOS 晶体管的栅极输入用逆变器 66 将放电控制信号 DIS 电平反转的信号。

MOS 晶体管 67 的源极连接于电源 VDD，漏极连接于时钟信号 CK11 的输出端子。MOS 晶体管 68 的源极连接于电源 VDD，漏极连接于时钟信号 CK12 的输出端子。MOS 晶体管 69 的源极连接于电源 VDD，漏极连接于触发脉冲 SP1 的输出端子。

图 2 (b) 中，表示放电控制信号 DIS 为高电平时和低电平时，作为时钟信号 CK11、时钟信号 CK12、以及触发脉冲 SP1，记载将输出怎样的信号的真值表。在液晶显示装置 1 通常工作时，放电控制信号 DIS 为高电平，分别输出作为时钟信号 CK11 的时钟信号 GCK1，作为时钟信号 CK12 的时钟信号 GCK2，作为触发脉冲 SP1 的栅极触发脉冲 GSP。在液晶显示装置 1 电源切断瞬间之前，放电控制信号 DIS 为低电平，时钟信号 CK1、时钟信号 CK2、以及触发脉冲 SP1 全部为高电平。还有，模拟开关 61～63 也可以是具有电平移位功能的构件。

接着，图 3 中表示栅极驱动器 3 的结构。

栅极驱动器 3 由移位寄存器构成，具备逆变器 41 和移位寄存器级 SR1・SR2・…。移位寄存器级 SR1・SR2・…构成移位寄存器的各级，从初级开始，依次与 SR1・SR2・…串联连接。各移位寄存器级 SR 具备移位信号输入端子 SB、输出端子 O・OB、时钟信号输入端子 CK、复位输入端子 R、以及初始复位输入端子 INI。移位信号输入端子 SB 是下述 RS 触发器的低有源复位输入端子，复位输入端子 R 是该 RS 触发器的复位输入端子。时钟信号输入端子 CK，在奇数级的移位寄存器级 SR (SR1・SR3・… ) 中是输入从驱动信号源处

理电路 6 输出的时钟信号 CK11 的端子, 在偶数级的寄存器级 SR(SR2・SR4・… ) 中, 是输入从驱动信号源处理电路 6 输出的时钟信号 CK12 的端子。

各移位寄存器级 SR 在向移位信号输入端子 SB 输入低电平信号时, 将输入到时钟输入端子 CK 的信号从输出端子 O 作为输出信号 OUT(从初级开始依次为 OUT1・OUT2・… ) 输出, 将输入到时钟输入端子 CK 的信号的电平反转信号从输出端子 OB 输出。各输出信号 OUT 作为栅极驱动器 3 的输出信号, 即扫描信号向栅极信号线 GL 输出。从输出端子 OB 输出的信号输入到下一级的移位寄存器级 SR 的移位信号输入端子 SB。又, 向复位输入端子 R 输入从下一级的移位寄存器级 SR 的输出端子 O 输出的信号。

逆变器 41 设置于初级的移位寄存器级 SR1 之前, 生成从驱动信号源处理电路 6 输出的触发脉冲 SP1 的电平反转信号, 并输入到移位寄存器级 SR1 的 SB 端子上。

还有, 栅极驱动器 3 也可以采用将上述输出信号 OUT1・OUT2・… 再输入到逻辑电路生成扫描信号的结构。

接着, 图 4 (a) 中表示各移位寄存器级 SR 的结构。

移位寄存器级 SR 具备非同步型的 RS 触发器 42、CMOS 模拟开关 43、n 道型 MOS 晶体管 44、以及逆变器 45。

RS 触发器 42 是使用于移位寄存器级 SR 的数据保持的电路, 具备置位输入端子 SB、输出端子 Q・QB、复位输入端子 R、以及初始复位输入端子 INI。置位输入端子 SB 等于上述移位寄存器级 SR 的移位信号输入端子 SB。又, 复位输入端子 R、初始复位输入端子 INI 依次等于移位寄存器级 SR 的复位输入端子 R、初始复位输入端子 INI。还有, 所谓置位 (set) 是指使输出端子 Q 的信号为有源信号。

模拟开关 43 实施时钟信号输入端子 CK 与移位寄存器级 SR 的输出端子 O 以及逆变器 45 的输入端子之间的导通和切断。向模拟开关 43 的 n 道型 MOS 晶体管的栅极输入来自 RS 触发器 42 的输出端子 Q 的输出信号, 向 p 道型 MOS 晶体管的栅极端子输入来自 RS 触发器 42 的输出端子 QB 的输出信号。逆变器 45 的输出端子成为移位寄存器级 SR 的输出端子 OB。MOS 晶体管 44 的漏极端子连接于输出端子 O 以及逆变器 45 的输入端子, 源极连接于 GND。向 MOS 晶体管 44 的栅极端子输入来自 RS 触发器 42 的输出端子 QB 的输出信号。

图 4 (b) 中表示对于向移位信号输入端子 (置位输入端子) SB 输入的信号

以及向复位输入端子 R 输入的信号，来自输出端子 O・OB 的输出信号的真值表。

在 RS 触发器 42 中，形成对置位输入端子 SB 的有源信号的输入优先于对复位端子 R 的有源信号的输入的结构，如该表所示，如果向置位输入端子 SB 输入低电平，向复位输入端子 R 不仅在输入低电平时，在输入高电平时也分别从输入端子 Q 输出高电平，从输出端子 QB 输出低电平（参照下述图 5 (b)）。由此，分别从输出端子 O（表中  $O_n$ ）输出向时钟信号输入端子 CK 输入的信号，又从输出端子 OB（表中  $OB_n$ ）输出向时钟信号输入端子 CK 输入的信号的反转信号（表中记为 CKB）。

又，在置位输入端子 SB 上输入高电平、复位端子 R 上输入高电平时，分别从输出端子 Q 输出低电平，从输出端子 QB 输出高电平（参照下述图 5 (b)）。由此，分别从输出端子 O 输出低电平，从输出端子 OB 输出高电平。在置位输入端子 SB 上输入高电平、在复位端子 R 上输入低电平时，向输出端子 Q 原封不动地输出之前的输出端子 Q 的状态  $Q_{n-1}$ （参照下述图 5 (b)）。由此，作为第 1 状态，如果  $Q_{n-1}$  是低电平，则输出端子 O 的之前的状态  $O_{n-1}$  为低电平，分别从输出端子 O ( $O_n$ ) 输出低电平，从输出端子 OB ( $OB_n$ ) 输出高电平。又，作为第 2 状态，如果  $Q_{n-1}$  是高电平，则输出端子 O 的之前的状态  $O_{n-1}$  为输出向时钟信号输入端子 CK 输入信号的状态（表中 CK），分别从输出端子 O ( $O_n$ ) 输出向时钟信号输入端子 CK 的输入信号（表中 CK），从输出端子 OB ( $OB_n$ ) 输出向时钟信号输入端子 CK 的输入信号的反转信号（表中记为 CKB）。

还有，也可以将模拟开关 43 的位置作为使用移位寄存器和逻辑电路的电路，导出同样的逻辑。

接着，图 5 (a) 中表示 RS 触发器 42 的结构。

RS 触发器 42 具备 MOS 晶体管 421～430。MOS 晶体管 421・424・425・428 是 p 道型，MOS 晶体管 422・423・426・427・429・430 是 n 道型。

MOS 晶体管 421 的源极端子连接于电源 VDD，漏极端子连接于 MOS 晶体管 422 的漏极端子。MOS 晶体管 422 的源极端子连接于 MOS 晶体管 423 的漏极端子。MOS 晶体管 421・422 的栅极端子连接于置位输入端子 SB。MOS 晶体管 423 的源极端子连接于 GND。MOS 晶体管 423 的栅极端子连接于复位端子 R。

MOS 晶体管 424 的源极端子连接于电源 VDD，漏极端子连接于 MOS 晶体

管 425 的源极端子。MOS 晶体管 424 的栅极端子连接于复位端子 R。MOS 晶体管 425 的漏极端子连接于 MOS 晶体管 426 的漏极端子。MOS 晶体管 425 的栅极端子连接于 MOS 晶体管 426 的栅极端子。又，MOS 晶体管 421 的漏极端子与 MOS 晶体管 425 的漏极端子相互连接。MOS 晶体管 426 的源极端子连接于 MOS 晶体管 427 的漏极端子。MOS 晶体管 427 的源极端子连接于 GND。MOS 晶体管 427 的栅极端子连接于置位输入端子 SB。

MOS 晶体管 428 的源极端子连接于电源 VDD，漏极端子连接于 MOS 晶体管 429 的漏极端子。MOS 晶体管 429 的源极端子连接于 GND。MOS 晶体管 425 的漏极端子、MOS 晶体管 428 的栅极端子、MOS 晶体管 429 的栅极端子相互连接，其连接点连接于输出端子 Q。MOS 晶体管 425・426 的栅极端子和 MOS 晶体管 428 与 MOS 晶体管 429 的连接点，连接于输出端子 QB。MOS 晶体管 430 的漏极端子连接于输出端子 Q，源极端子连接于 GND。MOS 晶体管 430 的栅极端子连接于初始复位端子 INI。

图 5(b) 是对于向置位输入端子 SB 输入的信号以及向复位输入端子输入的信号，从输出端子 Q 输出的信号的真值表。该内容如图 4(b) 的说明上述，因此省略，但是从图 5(a) 可知，向置位输入端子 SB 的有源输入优先于向复位端子 R 的有源输入，是因为即使是向 MOS 晶体管 423 的栅极端子输入高电平，只要向 MOS 晶体管 421・422 的栅极端子输入低电平，MOS 晶体管 422 就形成截止状态，就不能向输出端子 Q 导出低电平。

接着，用图 6 和图 7 说明上述结构的液晶显示装置 1 的栅极驱动器的工作。图 6 是液晶显示装置 1 进行显示图像的工作、即通常工作时的时序图。将这时的液晶显示装置 1 的工作模式记为第 1 工作模式。图 7 是液晶显示装置 1 在电源切断瞬间之前的状态的时序图。将这时的液晶显示装置 1 的工作模式记为第 2 工作模式。与图 3 对应进行说明。

在图 6 中，在时刻 A，向初始复位端子 INI 输入的信号（以下记为信号 INI）设定为高电平，触发脉冲 SP1 设定为低电平，因此向移位寄存器级 SR1 的移位信号输入端子 SB 输入高电平，从输出端子 O 输出低电平，同时从输出端子 OB 输出高电平。同样地，向移位寄存器级 SR2 的移位信号输入端子 SB 输入高电平，信号 INI 为高电平，因此从移位寄存器级 SR2 的输出端子 O 输出低电平，同时从输出端子 OB 输出高电平。从而，全部输出信号 OUT1・OUT2・… 为低电平，进行栅极驱动器 3 的初始复位。

接着，在时刻 B，将信号 INI 设定为低电平，将触发脉冲 SP1 设定为低电平。这时，向移位寄存器级 SR1 的移位信号输入端子 SB 输入高电平，向复位端子 R 输入低电平，因此从输出端子 O 输出低电平，从输出端子 OB 输出高电平。由此，向移位寄存器级 SR2 的移位信号输入端子 SB 输入高电平，因此从移位寄存器级 SR2 的输出端子 O 输出低电平。从而，全部输出信号 OUT1 • OUT2 • ……保持低电平不变。

接着，在时刻 C 将触发脉冲 SP1 设定为高电平，向移位寄存器级 SR1 的移位信号输入端子 SB 输入低电平。由此，从移位寄存器级 SR1 的输出端子 O 输出时钟信号 CK11，从输出端子 OB 输出时钟信号 CK11 的电平反转信号。在时刻 C，时钟信号 CK11 为低电平，因此输出信号 OUT1 为低电平，从输出端子 OB 输出高电平。从而，全部输出信号 OUT1 • OUT2 • ……保持低电平不变。

接着，在时刻 D，触发脉冲 SP1 保持高电平，时钟信号 CK11 为高电平。由此，从移位寄存器级 SR1 的输出端子 O 输出高电平，从输出端子 OB 输出低电平。从而，向移位寄存器级 SR2 的移位信号输入端子 SB 输入低电平，从移位寄存器级 SR2 的输出端子 O 输出时钟信号 CK12，从输出端子 OB 输出时钟信号 CK12 的电平反转信号。在时刻 D，时钟信号 CK12 为低电平，因此从移位寄存器级 SR2 的输出端子 O 输出低电平，从输出端子 OB 输出高电平。从而，输出信号 OUT1 为高电平，其他的输出信号 OUT2 • OUT3 • ……为低电平。

接着，在时刻 E，触发脉冲 SP1 保持高电平，信号 CK11 为低电平，时钟信号 CK12 为高电平。由此，从移位寄存器级 SR1 的输出端子 O 输出低电平，从输出端子 OB 输出高电平。又，向移位寄存器级 SR2 的移位信号输入端子 SB 输入高电平，向复位端子 R 输入低电平，而输出端子 O 的状态  $O_{n-1}$ （时刻 E 瞬间之前的状态）为输出时钟信号 CK12 的状态，所以输出端子 O 的状态  $O_n$ （时刻 E 的状态）为输出时钟信号 CK12 的状态，输出端子 OB 的状态  $OB_n$ （时刻 E 的状态）为输出时钟信号 CK12 的电平反转信号的状态。从而，全部输出信号 OUT1 • OUT2 • ……为低电平。

接着，从时刻 D 开始到时钟信号 CK12 变为高电平的时刻 F 期间，触发脉冲 SP1 设定为从高电平到低电平。由此，向移位寄存器级 SR1 的移位信号输入端子 SB 输入高电平，向复位端子 R 输入低电平，移位寄存器级 SR1 的输出端子 O 的状态  $O_{n-1}$ （触发脉冲 SP1 变成低电平瞬间之前的状态）为输出时钟信号 CK11 的状态，所以输出端子 O 的状态  $O_n$ （触发脉冲 SP1 变成低电平时的状态）

为输出时钟信号 CK11 的状态，输出端子 OB 的状态  $OB_n$ （触发脉冲 SP1 变为低电平时的状态）为输出时钟信号 CK11 的电平反转信号的状态。在触发脉冲 SP1 变成低电平时，时钟信号 CK11 为低电平，因此从移位寄存器级 SR1 的输出端子 O 输出低电平，从输出端子 OB 输出高电平。从而移位寄存器级 SR2 维持持续地从输出端子 O 输出时钟信号 CK12，从输出端子 OB 输出时钟信号 CK12 的电平反转信号的状态，因此即使是在时刻 D 到时刻 F 期间，也从移位寄存器级 SR2 的输出端子 O 输出低电平，从输出端子 OB 输出高电平。这样，全部输出信号  $OUT1 \cdot OUT2 \cdot \dots$  保持为低电平。还有，触发脉冲 SP1 也可以与时刻 F 同时设定为低电平。

接着，在时刻 F，时钟信号 CK12 变成高电平。由于持续从移位寄存器级 SR2 的输出端子 O 输出时钟信号 CK12，从输出端子 OB 输出时钟信号 CK12 的电平反转信号的状态，所以从移位寄存器级 SR2 的输出端子 O 输出高电平，从输出端子 OB 输出低电平。由此，持续向移位寄存器级 SR1 的复位端子 R 输入高电平，但是由于持续向移位信号输入端子 SB 输入高电平，因此移位寄存器级 SR1 为复位状态，从输出端子 O 输出低电平，从输出端子 OB 输出高电平。又，向移位寄存器级 SR3 的移位信号输入端子 SB 输入低电平，因此从移位寄存器级 SR3 的输出端子 O 输出时钟信号 CK11，从输出端子 OB 输出时钟信号 CK11 的电平反转信号。在时刻 F，时钟信号 CK11 为低电平，因此从移位寄存器级 SR3 的输出端子 O 输出低电平，从输出端子 OB 输出高电平。从而，输出信号  $OUT2$  为高电平。其他输出信号  $OUT1 \cdot OUT3 \cdot OUT4 \cdot \dots$  为低电平。

接着，在时刻 G，时钟信号 CK12 为低电平。由于持续从移位寄存器级 SR2 的输出端子 O 输出时钟信号 CK12，同时从输出端子 OB 输出时钟信号 CK12 的电平反转信号的状态，因此从移位寄存器级 SR2 的输出端子 O 输出低电平，从输出端子 OB 输出高电平。又，向移位寄存器级 SR3 的移位信号输入端子 SB 输入高电平，向复位端子 R 输入低电平，但是，由于移位寄存器级 SR3 的输出端子 O 的状态  $O_{n-1}$ （时刻 G 瞬间之前的状态）为输出时钟信号 CK11 的状态，所以输出端子 O 的状态  $O_n$ （时刻 G 的状态）为输出时钟信号 CK11 的状态，输出端子 OB 的状态  $OB_n$ （时刻 G 的状态）为输出时钟信号 CK11 的电平反转信号的状态。在时刻 G 时钟信号 CK11 为低电平，因此从移位寄存器级 SR3 的输出端子 O 输出低电平，从输出端子 OB 输出高电平。从而全部输出信号  $OUT1 \cdot OUT2 \cdot \dots$  为低电平。

接着，在时刻 H，时钟信号 CK11 为高电平。由于持续从移位寄存器级 SR3 的输出端子 O 输出时钟信号 CK11，同时从输出端子 OB 输出时钟信号 CK11 的电平反转信号的状态，所以从移位寄存器级 SR3 的输出端子 O 输出高电平，从输出端子 OB 输出低电平。由此，向移位寄存器级 SR2 的复位端子 R 输入高电平，但是由于持续向移位寄存器级 SR2 的移位信号输入端子 SB 输入高电平，因此移位寄存器级 SR2 为复位状态，从输出端子 O 输出低电平，从输出端子 OB 输出高电平。从而，输出信号 OUT3 为高电平，其他输出信号 OUT1 · OUT2 · OUT4 · … 为低电平。

下面同样地，从输出信号 OUT1 开始依次输出高电平的输出信号 OUT。这些输出信号 OUT 相互不重叠，按照 GL (1) · GL (2) · … 的顺序，作为高电平的扫描信号提供给扫描信号线 GL。与被提供高电平扫描信号的扫描信号线 GL 连接的像素 PIX 的 TFT2a 共同导通，在该期间所提供的视频信号被写入像素电极。像素 PIX 利用与像素电极的电位和对置电极的电位之差相应的电压对液晶电容 2b 和辅助电容 2c 进行充电，以此进行图像显示。像素 PIX 中积蓄的电荷通过被扫描信号为低电平的 TFT2a 截止，而被保持到下一次充电。

还有，在本实施形态中，在第 1 工作模式，触发脉冲 SP1 · SP2 不一定要通过逆变器 41 输入到初级的移位寄存器级 SR1，也可以输入到第 2 级以后的移位寄存器级 SR 中的任何一级。也就是说，触发脉冲 SP1 · SP2 只要输入到规定级的移位寄存器级 SR 即可。这时，输出信号 OUT 从规定级向后级依次输出脉冲。

接着，用图 7 对液晶显示装置 1 在电源切断时的工作进行说明。

将液晶显示装置 1 的切断电源的指示提供给液晶显示装置 1，或在液晶显示装置 1 内发生时，在图 7 的作为规定时刻设定的时刻 A，设定放电控制信号 DIS 为低电平。由此，利用具有图 2 (a) 所示结构的驱动信号源处理电路 6 进行设定，使得时钟信号 CK11 · CK12 以及触发脉冲 SP1 全部固定于高电平。

由此，在图 3 中，向全部移位寄存器级 SR1 · SR2 · … 的移位信号输入端子 SB 输入低电平。从而，在图 7 中，栅极驱动器 3 的全部输出信号 OUT1 · OUT2 … 为高电平，由此，能够使全部像素 PIX 的 TFT2a 共同导通。又，栅极驱动器 3 形成在上述移位寄存器上还具备逻辑电路的结构时，通过移位寄存器的输出信号共同为高电平，由此，向全部逻辑电路进行相同的逻辑输入，因此可以使逻辑电路的全部输出信号为高电平。从而，即使在这种情况下，由于向全部扫描信号线 GL 输出高电平的扫描信号，所以能够使全部像素 PIX 的 TFT2a 共同导

通。

这里，如果在切断电源时预先将模拟开关 C1・C2・…全部切断，液晶显示装置 1 进行点反转驱动或扫描信号线反转驱动，因此可以在连接于同一数据信号线 SL 的像素 PIX 之间进行正负电荷的相互抵消。由此，在对置电极 COM 向无电压状态转移时，能够在全部像素 PIX 间大致一致地进行显示的同时，一边向终止状态转移。从而能够防止液晶显示装置 1 在电源切断时画面发生混乱。

如上所述，可以实现一种显示装置，即使是在电源切断时从像素进行放电，也就是即使防止在电源切断时画面的混乱，也不会因利用放电用的电路、也就是防止画面混乱用的电路而妨碍小型化和区域的有效利用。

接着，对液晶显示装置 1，进行相邻的数据信号线上连接的像素 PIX 之间电荷极性不同的数据信号线反转驱动的情况下结构进行说明。还有，该结构也可以使用于前面的点反转驱动和扫描信号线反转驱动。

用于进行数据信号线反转驱动的结构在图 1 中，源极驱动器 4 采用与栅极驱动器 3 相同的结构，驱动信号源处理电路 7 采用与驱动信号源处理电路 6 相同的结构。

如图 8 所示，源极驱动器 4 的结构，是在图 3 所示的栅极驱动器 3 的结构中，以时钟信号 CK11 的输入端子为时钟信号 CK21 的输入端子，以时钟信号 CK12 的输入端子为时钟信号 CK22 的输入端子，以触发脉冲 SP1 的输入端子为触发脉冲 SP2 的输入端子的结构。在这种情况下，图 8 的输出端子 OUT1・OUT2・…・OUTn・…依次成为模拟开关 C1・C2・…・Cn・…的控制信号。

驱动信号源处理电路 7 从由外部输入的时钟信号 SCK1 和放电控制信号 DIS 生成时钟信号 CK21，又，从由外部输入的时钟信号 SCK2 和放电控制信号 DIS 生成时钟信号 CK22，又，从由外部输入的源极触发脉冲 SSP 和放电控制信号 DIS 生成触发脉冲 SP2，将生成的各信号输入到源极驱动器 4。放电控制信号 DIS 与使用于驱动信号源处理电路 6 的放电控制信号相同。

又，在图 2(a) 中，如果分别将时钟信号 GCK1 置换为时钟信号 SCK1、将时钟信号 GCK2 置换为时钟信号 SCK2、将栅极触发脉冲 GSP 置换为源极触发脉冲 SSP、将时钟信号 CK11 置换为时钟信号 CK21、将时钟信号 CK12 置换为时钟信号 CK22、将触发脉冲 SP1 置换为触发脉冲 SP2，则形成驱动信号源处理电路 7 的结构。

图 9、图 10 是说明源极驱动器 4 的工作的时序图，依次在图 6、图 7 中，将时钟信号 CK11 置换为时钟信号 CK21，将时钟信号 CK12 置换为时钟信号 CK22，将触发脉冲 SP1 置换为触发脉冲 SP2。

时钟信号（定时信号）CK21 和时钟信号（定时信号）CK22 在液晶显示装置 1 进行通常工作时如图 9 所示，相互之间相位不同，是使电平变化周期性反复的二值周期信号。这里示出时钟信号 CK21 与时钟信号 CK22 相互在高电平期间不重叠的例子。又，时钟信号 CK21・CK22 在液晶显示装置 1 的电源切断的瞬间之前，如图 10 所示，是均固定于有源（active）电平（这里是高电平）的信号。触发脉冲 SP2 在液晶显示装置 1 的通常工作时如图 9 所示，是每一规定期间有一个脉冲的信号，对于触发脉冲 SP2，该规定期间为 1 垂直期间。又，触发脉冲 SP2 在液晶显示装置 1 电源切断瞬间之前如图 10 所示，固定于有源电平（这里是高电平）的信号。

图 9 和图 10 中所表示的源极驱动器 4 的工作与图 6 和图 7 中所表示的栅极驱动器 3 的工作相同。

液晶显示装置 1 的电源切断时，在时刻 A 源极驱动器 4 的全部输出信号 OUT1・OUT2 ……为高电平，由此，模拟开关电路 5 的全部模拟开关 C1・C2 ……共同导通。

从而，通过实施将视频信号线 VSIG 连接于对置电极 COM 的工作等，对视频信号线 VSIG 提供与对置电极 COM 相同的电位，可以使全部像素 PIX 将全部电荷放电。如果将视频信号线 VSIG 连接于对置电极 COM，在电源切断时，随着对置电极 COM 转移到 GND 等的无电压状态，像素电极的电位也追随对置电极 COM 的电位而变化。这样，在全部像素 PIX 中，使施加于液晶的电压为 0，因此，即使液晶面板是由交流驱动的，在像素 PIX 之间施加电压的波动也被消除，可以防止液晶显示装置 1 在电源切断时画面发生混乱。

如上所述，能够实现一种显示装置，即使是在电源切断时进行像素的放电，也不会因利用进行放电的电路而妨碍小型化和区域的有效利用。

又，在上述例子中，像素 PIX 进行放电时，对视频信号线 VSIG 提供对置电极 COM 的电位，但是并不限于此，也可以将对液晶施加阈值电压以下的电压（不影响显示的电压）那样的电位提供给视频信号线 VSIG。这样也能够使图像显示不能进行，因此能够防止液晶显示装置 1 在电源切断时画面发生混乱。

又，在图 10 中，源极驱动器 4 的输出信号共同为高电平，同时栅极驱动器

3 的输出信号共同为高电平。在这种情况下，液晶面板 2 即使是点反转驱动、扫描信号线反转驱动、数据信号线反转驱动等不管哪一种交流驱动，都能够实现使全部像素 PIX 的电荷状态一致的放电。

又，作为利用上述正负电荷的相互抵消的结构的另一个例子，也可以采用将视频信号线 VSIG 从数据信号线的供给目的地断开，同时使全部模拟开关 C1・C2・…导通的结构。这样也能够实现使全部像素 PIX 之间的正负电荷互相抵消，因此即使是点反转驱动、扫描信号线反转驱动、数据信号线反转驱动等不管哪一种交流驱动，都能够在对置电极 COM 向无电压状态转移时，一边在全部像素 PIX 之间实现一致的显示一边向终止状态转移。从而，能够防止液晶显示装置 1 在切断电源时画面发生混乱。

又，如上所述的防止在电源切断时画面发生混乱的结构，也可以作为防止在电源接通时画面发生混乱的结构使用。在电源接通瞬间，视频信号电位和对置电极电位、CS（辅助电容）电极电位也不稳定，因此在像素部上无意中积累了电荷。这是因为，在电源还没有确实升上来的情况下，由于电路的逻辑控制不能正常进行，从视频信号线会有不需要的电荷向像素流入，对置电极电位和 Cs 电极电位不稳定，因此对置电极与像素电极之间产生电位差（积蓄电荷）等原因造成的。而且，这种现象成为发生显示噪声的原因。作为这种现象的对策，在电源接通时使像素的开关元件导通，并在瞬间消除电荷的方法是有效的，如果是在瞬间消除电荷，作为显示人眼是看不见的。

作为其方法，例如在电源接通时，确定电源电压后立即使放电控制信号 DIS 为有源（active）信号，采用第 2 工作模式消除像素的电荷，其后，使放电控制信号 DIS 为非有源信号后，转移到通常显示这样的办法是有效的。又，在接通电源的同时，使放电控制信号 DIS 为有源信号，采用第 2 工作模式，电源上升，在面板内电路的逻辑确定之前，继续使该放电控制信号 DIS 为有源信号，在电源电压确定后使放电控制信号 DIS 为非有源信号，然后转移到通常工作这样的办法也是有效的。

如果是这些方法，栅极驱动器 3 根据有源的放电控制信号 DIS 向全部扫描信号线输出有源的输出信号时，在全部模拟开关 C1・C2・…为切断的情况下，连接于同一的数据信号线的像素之间电荷量平均化，在全部像素间使电荷量比较良好地一致；在全部模拟开关 C1・C2・…共同接通的情况下，全部像素之间电荷量平均化，且良好地使像素间电荷量一致。也就是说，对于任意显示装

置，可以在像素之间使电荷量一致。从而，即使是电源接通面板内的逻辑确定后的时间变长，也不会在显示上发生无意的显示，因此能够避免显示上不稳定的上升。由此，不用对应于驱动电路的各输出设置 NAND 电路等多余的电路，就能够防止在电源切断时或电源接通时发生的画面混乱。

由此，能够实现一种显示装置，即使是防止电源接通时的画面混乱也不会因利用防止画面混乱的电路而妨碍小型化和区域的有效利用。

在以上所述的全部结构中，信号的极性等是一个例子，当然，即使是反转逻辑也能够实现本发明。例如在输入时钟信号 GCK1・GCK2・SCK1・SCK2 的逻辑电路中，改变结构以导出必要的极性的输出是容易的。从而，同样考虑在液晶显示装置 1 电源切断时，也可以将各时钟信号 GCK1・GCK2・SCK1・SCK2 以及触发脉冲信号 SP1・SP2 全部固定于低电平进行像素 PIX 的放电。在这种情况下，只要相应于电源的切断使信号电平为低电平即可，因此可以在电源切断瞬间之前减少消耗的电力，同时用电源切断工作生成信号。

又，在液晶显示装置 1 电源切断时，不必使时钟信号 GCK1・GCK2・SCK1・SCK2 以及触发脉冲信号 SP1・SP2 完全相同的极性，只要为了进行使像素 PIX 之间电荷量一致的工作而采用有源信号即可。

又，也可以在液晶显示装置 1 中具备对数据信号线进行预备充电的预备充电电路或图 12 所示的放电电路 107，取代通过模拟开关电路 5 在电源切断时进行像素 PIX 的放电，而通过该预备充电电路或图 12 所示的放电电路 107 进行像素 PIX 的放电。

又，作为移位寄存器中具备的 RS 触发器的复位信号，可以使用任意信号。

又，在上述结构中，时钟信号（定时信号）为 2 相，但是时钟信号（定时信号）即使用 3 相以上也可以实施本发明。通常，定时信号只要是与移位寄存器的各级对应的信号即可。这些时钟信号的有源期间可以相互重叠也可以不重叠。又，在显示装置的第 1 工作模式中，只要是能够利用移位寄存器进行数据传送的信号，不管是怎样的定时信号都可以。

图 11(a) 表示使用 3 相的时钟信号（定时信号）CK1・CK2・CK3 的驱动线路的结构。这是在图 3 的结构中，向移位寄存器级 SR1・SR2・SR3・SR4・SR5 … 的时钟输入端子 CK 依次地，如时钟信号 CK3・CK2・CK1・CK3・CK2・… 那样按照一定的相位顺序，输入时钟信号。

图 11(b) 中表示时钟信号 CK1・CK2・CK3 的波形。时钟信号 CK1・CK2・CK3

是在液晶显示装置 1 进行通常工作时，相互之间相位不同，电平变化周期性反复的 2 值周期信号。这里，表示了时钟信号 CK1、时钟信号 CK2 与时钟信号 CK3 相互之间在高电平期间不重叠的例子。又，时钟信号 CK1、CK2、CK3 在液晶显示装置 1 电源切断瞬间之前，与图 7 和图 10 相同，全部固定于有源电平（例如高电平）。又，触发脉冲 SP 是与触发脉冲 SP1 或 SP2 相同的信号。

还有，本发明的显示装置具备使用上述驱动电路构成的扫描信号线驱动电路，上述扫描信号线驱动电路只要是，在上述第 1 工作模式中，使用上述输出信号生成具有向各扫描信号线依次输出的脉冲的扫描信号，在上述第 2 工作模式中，使用上述输出信号生成具有向全部扫描信号线共同输出的脉冲的信号的电路即可。

如果采用上述发明，在交流驱动的显示装置的电源切断时使用第 2 工作模式，就能够在同一数据信号线上连接的像素的正极性电荷与负极性电荷之间进行相互抵消。从而，在进行点反转驱动或扫描信号线反转驱动的显示装置中，具有如下效果，能够容易地实现即使是防止电源切断时画面的混乱，也不会因利用防止画面混乱用电路而妨碍小型化和区域的有效利用

又，如果将第 2 工作模式使用于任意显示装置的电源接通时，能够在；连接于同一数据信号线上的像素之间实施电荷量的平均化，使全部像素的电荷量比较良好地一致，从而，在任意显示装置中，具有如下效果，能够容易地实现即使是防止电源接通时画面的混乱，也不会因利用防止画面混乱用的电路而妨碍小型化和区域的有效利用。

又，本发明的显示装置也可以是，具备用上述驱动电路构成的扫描信号线驱动电路和数据信号线驱动电路，上述扫描信号线驱动电路在上述第 1 工作模式中，用上述扫描信号线驱动电路的上述移位寄存器的上述输出信号，生成具有向各扫描信号线依次输出的脉冲的扫描信号，在上述第 2 工作模式中，用上述扫描信号线驱动电路的上述移位寄存器的上述输出信号，生成具有向全部扫描信号线共同输出的脉冲的信号，上述数据信号线驱动电路，在上述第 1 的工作模式中，将上述数据信号线驱动电路的上述移位寄存器的上述输出信号用于从视频信号线向各数据信号线依次提供数据信号的工作，在上述第 2 工作模式中，将上述数据信号线驱动电路的上述移位寄存器的上述输出信号用于从上述视频信号线向全部数据信号线共同提供公共电位的工作。

如果采用上述发明，在第 2 工作模式中，从视频信号线向全部像素提供公共

电位，因此可以使全部像素施加的电压大致一致。从而在任意显示装置中，具有如下效果，能够容易地实现即使是防止电源切断时或电源接通时画面的混乱，也不会因利用防止画面混乱的电路而妨碍小型化和区域的有效利用这一目标的效果。

又，本发明的显示装置也可以是，具备使用上述驱动电路构成的扫描信号线驱动电路和数据信号线驱动电路，上述扫描信号线驱动电路在上述第1工作模式中，用上述扫描信号线驱动电路的上述移位寄存器的上述输出信号，生成具有向各扫描信号线依次输出的脉冲的扫描信号，在上述第2工作模式中，用上述扫描信号驱动电路的上述移位寄存器的上述输出信号，生成具有向全部扫描信号线共同输出的脉冲的信号，上述数据信号线驱动电路在上述第1工作模式中，将上述数据信号线驱动电路的上述移位寄存器的上述输出信号用于从视频信号线向各数据信号线依次提供数据信号的工作，在上述第2工作模式中，将上述数据信号线驱动电路的上述移位寄存器的上述输出信号用于将全部数据信号线从上述视频信号线断开，同时使全部数据信号线相互导通的工作。

如果采用上述本发明，在交流驱动的显示装置电源切断时使用第2工作模式，能够在全部像素间实施正极性的电荷与负极性的电荷的相互抵消。从而，在进行交流驱动的所有显示装置中，具有如下效果，能够容易地实现即使是防止电源切断时或电源接通时画面的混乱，也不会因利用防止画面混乱用的电路而妨碍小型化和区域的有效利用。

又，如果在任意显示装置接通电源时使用第2工作模式，则能够在全部像素间实施电荷量平均化。从而，对于任意显示装置，具有如下效果，能够容易地实现即使是防止电源接通时画面的混乱，也不会利用因防止画面混乱用的电路而妨碍小型化和区域的有效利用。

本发明并不限于上述实施形态，在权利要求中所示的范围内可以作种种变更。也就是说，在权利要求中所示的范围内将适当变更的技术方法进行组合而得到的实施形态也包含在本发明的技术范围内。例如，在本实施形态中，作为显示装置以液晶显示装置为例列举，但是并不限于此，本发明可以广泛使用于通过对像素进行充电以进行显示的显示装置。

### 工业上的实用性

本发明能够很好地使用于液晶显示装置。

图 1

图 2

冬 3

(a)

(b)

| SB | R | $O_{n-1}$ | $O_n$ | $OB_n$ |

|----|---|-----------|-------|--------|

| H  | H | -         | L     | H      |

| H  | L | L         | L     | H      |

| H  | L | CK        | CK    | CKB    |

| L  | H | -         | CK    | CKB    |

| L  | L | -         | CK    | CKB    |

图 4

(b)

| SB | R | Q         |

|----|---|-----------|

| H  | H | L         |

| H  | L | $Q_{n-1}$ |

| L  | H | H         |

| L  | L | H         |

图 5

图 6

图 8

图 9

图 11

图 12

|                |                                                                          |         |            |

|----------------|--------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置及其驱动方法                                                               |         |            |

| 公开(公告)号        | <a href="#">CN101336447A</a>                                             | 公开(公告)日 | 2008-12-31 |

| 申请号            | CN200680052336.6                                                         | 申请日     | 2006-11-30 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                   |         |            |

| 申请(专利权)人(译)    | 夏普株式会社                                                                   |         |            |

| 当前申请(专利权)人(译)  | 夏普株式会社                                                                   |         |            |

| [标]发明人         | 大河宽幸<br>村上祐一郎<br>辻野幸生                                                    |         |            |

| 发明人            | 大河宽幸<br>村上祐一郎<br>辻野幸生                                                    |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                              |         |            |

| CPC分类号         | G09G3/3688 G09G3/3677 G09G2310/0245 G09G2310/0286 G09G2330/027 G11C19/28 |         |            |

| 优先权            | 2006081641 2006-03-23 JP                                                 |         |            |

| 其他公开文献         | <a href="#">CN101336447B</a>                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">SIPO</a>                           |         |            |

#### 摘要(译)

在液晶显示装置(1)中，源极驱动器(4)的移位寄存器用对置位输入端子的有源输入优先于对复位输入端子的有源输入的非同步型的RS触发器构成。在第2工作模式中，通过将第1和第2时钟信号与触发脉冲固定于高电平，进行从液晶面板(2)全部像素(PIX)的放电。