## [12] 发明专利申请公开说明书

[21] 申请号 200410042671.0

[43] 公开日 2005 年 6 月 22 日

[11] 公开号 CN 1629925A

[22] 申请日 2004.5.31

[74] 专利代理机构 北京律诚同业知识产权代理有限公司

[21] 申请号 200410042671.0

代理人 徐金国 祁建国

[30] 优先权

[32] 2003.12.17 [33] KR [31] 10-2003-0092694

[71] 申请人 LG. 菲利浦 LCD 株式会社

地址 韩国汉城

[72] 发明人 张容豪 金彬 尹洙荣

权利要求书 5 页 说明书 18 页 附图 12 页

[54] 发明名称 液晶显示器的栅极驱动装置和方法

[57] 摘要

液晶显示器的一种栅极驱动装置包括一移位寄存器，提供给它的有相位彼此反转并各自具有半周期脉冲宽度的第一和第二半周期时钟信号，依次移相并各自具有一周期脉冲宽度的第一到第四一周期时钟信号，一起始脉冲，一高电平电源电压，和一低电平电源电压。移位寄存器响应起始脉冲及第一和第二半周期时钟信号产生半周期输出。移位寄存器还响应任何一个第一到第四一周期时钟信号从半周期输出结束时起按半周期延迟产生一周期输出。

1. 液晶显示器的一种栅极驱动装置包括：

5 移位寄存器，提供给它的有相位彼此反转的第一和第二半周期时钟信号，依次移相并各自具有一周期脉冲宽度的第一到第四一周期时钟信号，一起始脉冲，一高电平电源电压和一低电平电源电压，

移位寄存器响应起始脉冲及第一和第二半周期时钟信号产生半周期输出，并响应任何一个第一到第四一周期时钟信号从半周期输出结束时起按半周期延迟产生一周期输出。

10 2. 按照权利要求 1 的栅极驱动装置，其特征在于，移位寄存器包括用来产生半周期输出和一周期输出的多级，并且多级是按照级联结构连接的，对半周期输出和一周期输出依次移位。

15 3. 按照权利要求 1 的栅极驱动装置，其特征在于，任何一个第一和第二半周期时钟信号，任何一个第一到第四一周期时钟信号以及起始脉冲都是彼此同步的。

4. 液晶显示器的栅极驱动装置包括：

20 第一输入电路，它响应起始脉冲及相位彼此反转并各自具有半周期脉冲宽度的第一和第二半周期时钟信号的第二半周期时钟信号为第一充电控制节点充电，并响应第二半周期时钟信号和相位依次移位并各自具有一周期脉冲宽度的第一到第四时钟信号中的第四时钟信号对第一放电控制节点充电；以及

第一输出电路，它响应来自第一充电控制节点的控制信号和第一半周期时钟信号向输出节点输出一个半周期输出，并响应来自第一放电控制节点的控制信号使输出节点放电。

25 5. 按照权利要求 4 的栅极驱动装置，其特征在于，该栅极驱动装置还包括：

第二输入电路，它响应半周期输出和第二半周期时钟信号对第二充电控制节点充电，并响应第三时钟信号对第二放电控制节点充电；以及

30 第二输出电路，它响应来自第二充电控制节点的控制信号和第一时钟信号向输出节点输出一个从半周期输出结束时起按半周期延迟的一周期输出，

并响应来自第二放电控制节点的控制信号使输出节点放电。

6. 按照权利要求 5 的栅极驱动装置，其特征在于，多级中的各级都包括第一输入电路，第一输出电路，第二输入电路和第二输出电路。

7. 按照权利要求 6 的栅极驱动装置，其特征在于，起始脉冲被提供给多5 级中的第一级。

8. 按照权利要求 4 的栅极驱动装置，其特征在于，第二半周期时钟信号，第二时钟信号和起始脉冲都是彼此同步的。

9. 按照权利要求 4 的栅极驱动装置，其特征在于，第一输入电路包括一个反相器，它响应起始脉冲和第一半周期时钟信号从起始脉冲结束时起按半10 周期延迟对第一充电控制节点充电。

10. 按照权利要求 9 的栅极驱动装置，其特征在于，反相器包括：

第一晶体管，为其栅极和源极提供起始脉冲；

第二晶体管，为其栅极提供第二半周期时钟信号，并为源极提供高电平电源电压；以及

15 第三晶体管，其栅极连接到第一晶体管的漏极，源极连接到第二晶体管的漏极，而漏极连接到第一充电控制节点。

11. 按照权利要求 10 的栅极驱动装置，其特征在于，反相器还包括为起始脉冲充电的电容，向第三晶体管的栅极提供一个栅极电压。

12. 按照权利要求 10 的栅极驱动装置，其特征在于，第一输入电路包括：

20 第四晶体管，为其栅极提供第四时钟信号，为漏极提供低电平电源电压，而源极连接到第三晶体管的栅极；以及

第五晶体管，为其漏极提供低电平电源电压，栅极连接到第一放电控制节点，而源极连接到第一充电控制节点。

13. 按照权利要求 4 的栅极驱动装置，其特征在于，第一输入电路包括：

25 第六晶体管，为其栅极提供第四时钟信号，而为源极提供高电平电源电压；以及

第七晶体管，为其栅极提供第二半周期时钟信号，源极连接到第六晶体管的漏极，而漏极连接到第一放电控制节点。

14. 按照权利要求 4 的栅极驱动装置，其特征在于，第一输入电路包括：

30 第八晶体管，为其栅极提供起始脉冲，为漏极提供低电平电源电压，而

源极连接到第一放电控制节点；以及

第九晶体管，为其漏极提供低电平电源电压，栅极连接到输出节点，而源极连接到第一放电控制节点。

15. 按照权利要求 6 的栅极驱动装置，其特征在于，第一输出电路包括：

5 第十晶体管，为其源极提供第一半周期时钟信号，漏极连接到输出节点，而栅极连接到第一充电控制节点；

第十一晶体管，为其漏极提供低电平电源电压，源极连接到输出节点，而栅极连接到第一放电控制节点；以及

10 第十二晶体管，为其源极提供第一半周期时钟信号，栅极连接到第一充

电控制节点，而漏极连接到下一级的起始脉冲输入端子。

16. 按照权利要求 5 的栅极驱动装置，其特征在于，第二输入电路包括一个反相器，它响应半周期输出和第二半周期时钟信号从半周期输出结束时起按半周期延迟对第二充电控制节点充电。

17. 按照权利要求 16 的栅极驱动装置，其特征在于，反相器包括：

15 第十三晶体管，为其源极提供高电平电源电压，而栅极连接到输出节点；

第十四晶体管，为其源极提供高电平电源电压，并为栅极提供第二半周

期时钟信号；以及

第十五晶体管，其栅极连接到第十三晶体管的漏极，源极连接到第十四

晶体管的漏极，而漏极连接到第二充电控制节点。

20 18. 按照权利要求 17 的栅极驱动装置，其特征在于，反相器还包括为高

电平电源电压充电的电容，向第十五晶体管的栅极提供一个栅极电压。

19. 按照权利要求 17 的栅极驱动装置，其特征在于，第二输入电路包括：

第十六晶体管，为其栅极提供第一时钟信号，为漏极提供低电平电源电

压，而源极连接到第十三晶体管的漏极和第十五晶体管的栅极；以及

25 第十七晶体管，为其漏极提供低电平电源电压，栅极连接到第二放电控

制节点，而源极连接到第十五晶体管的漏极和第二充电控制节点。

20. 按照权利要求 5 的栅极驱动装置，其特征在于，第二输入电路包括：

第十八晶体管，为其栅极和源极提供第三时钟信号，而漏极连接到第二

放电控制节点；

30 第十九晶体管，为其漏极提供低电平电源电压，栅极连接到输出节点，

而源极连接到第二放电控制节点；以及

第二十晶体管，为其漏极提供低电平电源电压，栅极连接到第二充电控制节点，而源极连接到第二放电控制节点。

21. 按照权利要求 5 的栅极驱动装置，其特征在于，第二输出电路包括：

5 第二十一晶体管，为其源极提供第一时钟信号，栅极连接到第二充电控制节点，而漏极连接到输出节点；以及

第二十二晶体管，为其漏极提供低电平电源电压，栅极连接到第二放电控制节点，而源极连接到输出节点。

22. 液晶显示器的一种栅极驱动方法包括以下步骤：

10 接收相位彼此反转且各自具有半周期脉冲宽度的第一和第二半周期时钟信号，依次移相并各自具有一周期脉冲宽度的第一到第四一周期时钟信号，一起始脉冲，一高电平电源电压和一低电平电源电压；并且

15 响应起始脉冲及第一和第二半周期时钟信号产生一半周期输出，并响应任何一个第一到第四一周期时钟信号从半周期输出结束时起按半周期延迟产生一周期输出。

23. 按照权利要求 22 的驱动方法，其特征在于，任何一个第一和第二半周期时钟信号，任何一个第一到第四一周期时钟信号以及起始脉冲都是彼此同步的。

24. 液晶显示器的一种栅极驱动方法包括以下步骤：

20 响应起始脉冲及相位彼此反转并各自具有半周期脉冲宽度的第一和第二半周期时钟信号的第二半周期时钟信号为第一充电控制节点充电；

响应来自第一充电控制节点的控制信号和第一半周期时钟信号向输出节点输出一个半周期输出；

25 响应第二半周期时钟信号和相位依次移位并各自具有一周期脉冲宽度的第一到第四时钟信号中的第四时钟信号对第一放电控制节点充电；

响应来自第一放电控制节点的控制信号使输出节点放电；

响应半周期输出和第二半周期时钟信号对第二充电控制节点充电；

响应第三时钟信号对第二放电控制节点充电；

30 响应来自第二充电控制节点的控制信号和第一时钟信号向输出节点输出一个从半周期输出结束时起按半周期延迟的一周期输出；并

---

响应来自第二放电控制节点的控制信号使输出节点放电。

25. 按照权利要求 24 的栅极驱动方法，其特征在于，第一半周期时钟信号，第二时钟信号和起始脉冲都是彼此同步的。

## 液晶显示器的栅极驱动装置和方法

5 本申请要求享有 2003 年 12 月 17 日提出的第 92694/2003 号韩国专利申请的利益，其在此引用以作参考。

### 技术领域

10 本发明涉及到液晶显示器，具体涉及到液晶显示器的栅极驱动装置和方法。

### 背景技术

液晶显示器 (LCD) 用电场控制液晶的光透射比来显示图像。

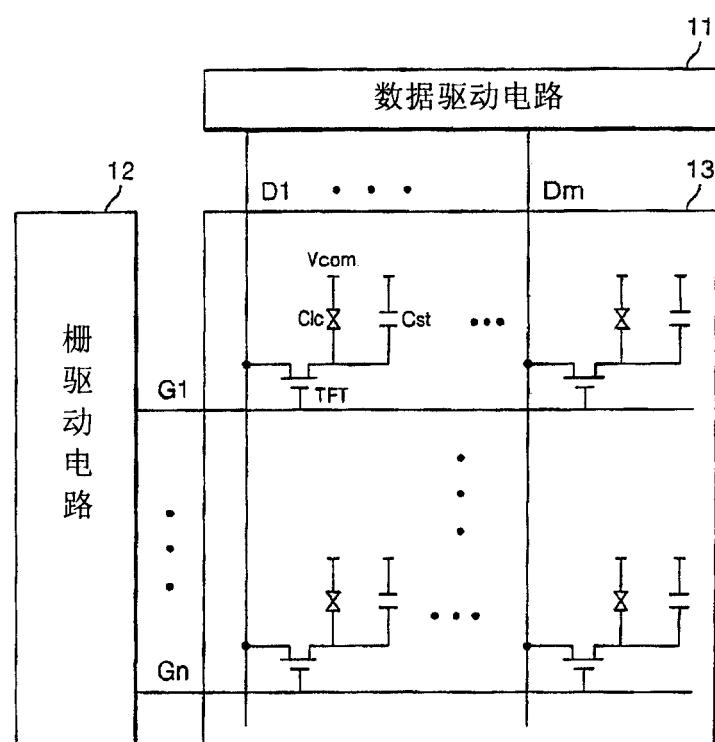

15 图 1 是按照现有技术的一种有源矩阵液晶显示器件的结构示意图。参见图 1，有源矩阵 LCD 包括一个液晶显示面板 13。LCD 面板 13 包括按矩阵布置的  $(m \times n)$  个液晶单元 C1c， $m$  条数据线 D1 到  $D_m$  和  $n$  条栅极线 G1 到  $G_n$  彼此交叉。TFT 被设置在数据线和栅极线的交叉点上。LCD 面板包括对液晶显示面板 13 的数据线 D1 到  $D_m$  提供数据的数据驱动电路 11。LCD13 还包括对栅极线 G1 到  $G_n$  提供扫描脉冲的栅极驱动电路 12。

20 液晶显示面板具有注入两个玻璃基板之间的液晶分子。彼此垂直交叉的数据线 D1 到  $D_m$  和栅极线 G1 到  $G_n$  被设置在液晶显示面板 13 的下玻璃基板上。设在数据线 D1 到  $D_m$  和栅极线 G1 到  $G_n$  之间各个交叉点上的 TFT 响应来自栅极线 G1 到  $G_n$  的扫描脉冲通过数据线 D1 到  $D_m$  向液晶单元 C1c 提供数据电压。为此要将 TFT 的栅极连接到栅极线 G1 到  $G_n$ ，同时，漏极要连接到数据线 D1 到  $D_m$ 。还要将 TFT 的源极连接到液晶单元 C1c 的像素电极。

25 液晶显示面板 13 的上玻璃基板设有黑色矩阵、滤色片和公共电极 (未表示)。具有一垂直光轴的偏振器被附着在液晶显示面板 13 的上、下玻璃基板上，并在其与液晶正切的内表面上设有用来形成自由倾斜角度液晶的一个对准薄膜。

30 液晶显示面板 13 的液晶单元 C1c 设有存储电容 Cst。存储电容 Cst 被设

置在液晶单元 Clc 的像素电极与前级栅极线之间或是液晶单元 Clc 的像素电极与公共电极线(未表示)之间，持续保持液晶单元 Clc 的电压。

数据驱动电路 11 包括多个数据驱动集成电路。各个数据驱动集成电路包括移位寄存器，锁存器，数-模转换器和输出缓冲器。数据驱动电路 11 锁存 5 一数字视频数据，并将数字视频数据变换成模拟灰度系数补偿电压后提供给数据线 D1 到 Dm。

栅极驱动电路 12 包括多个栅极驱动集成电路。各个栅极驱动集成电路包括一移位寄存器，用来依次移位每一水平周期的起始脉冲产生一扫描脉冲，一电平移位器，将移位寄存器的输出信号变换成适合用来驱动液晶单元 Clc 10 的摆动宽度，以及连接在电平移位器和栅极线 G1 到 Gn 之间的输出缓冲器。

栅极驱动电路 12 依次对栅极线 G1 到 Gn 施加扫描脉冲，为液晶显示面板 13 的一条水平线选择提供数据。

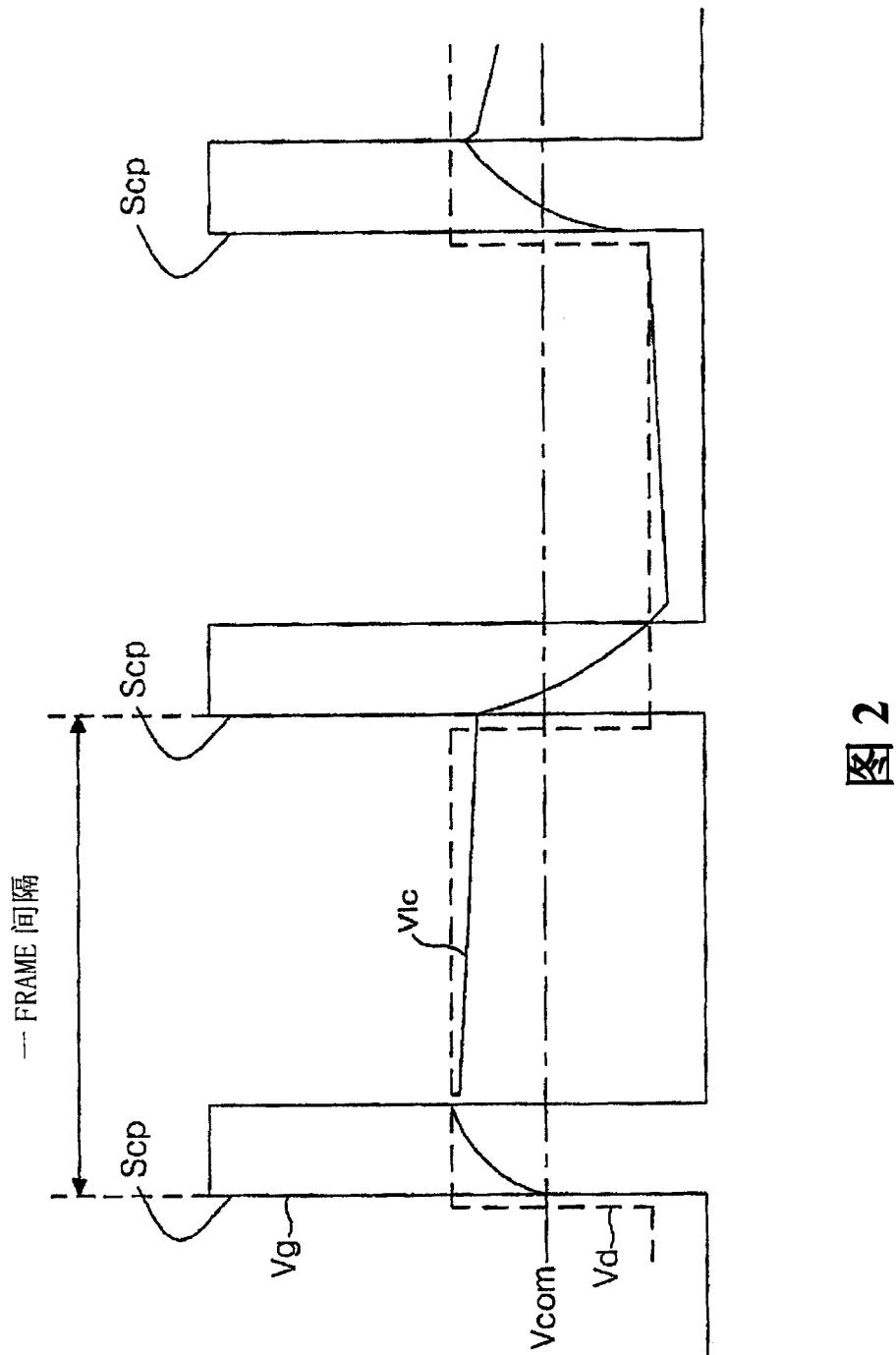

图 2 是按照现有技术提供给液晶显示面板的液晶单元的驱动信号和数据电压的波形图。

15 在图 2 中，‘Vd’ 代表由数据驱动电路 11 输出并且提供给数据线 D1 到 Dm 的数据电压。‘Vlc’ 代表液晶单元 Clc 充电和放电的数据电压。而 ‘Scp’ 代表一个水平周期内产生的扫描脉冲。‘Vcom’ 代表提供给液晶单元 Clc 的公共电极的公共电压。

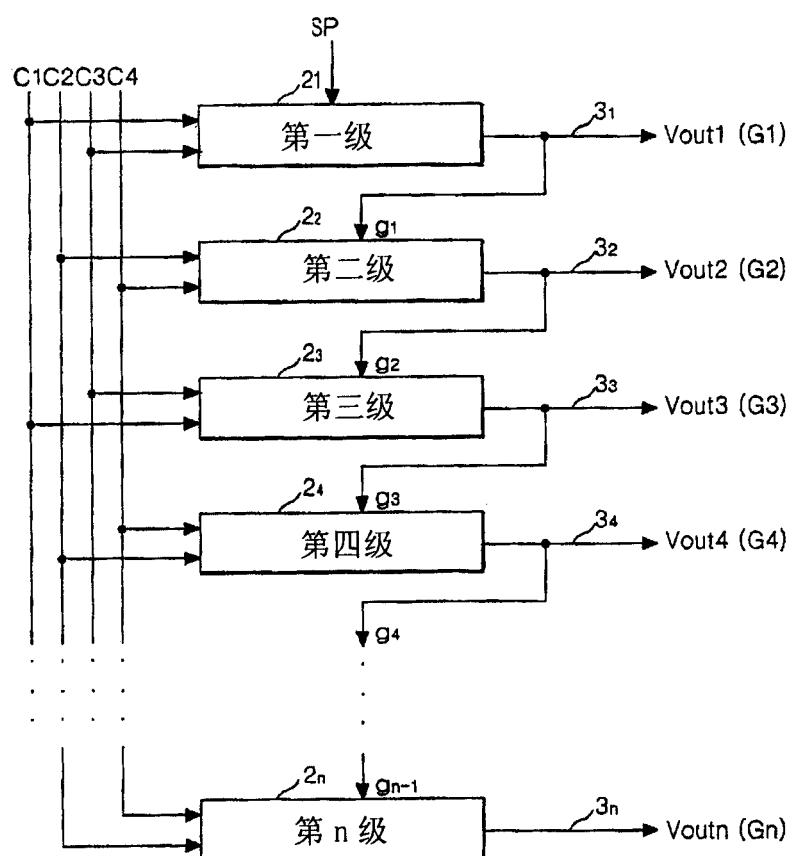

20 图 3 是按照现有技术的栅极驱动电路中移位寄存器的电路图。在图 3 中，移位寄存器包括级联的 n 级 31 到 3n。电平移位器和输出缓冲器(未表示)被设置在各级 31 到 3n 与栅极线 G1 到 Gn 之间。

25 在图 3 中所示的移位寄存器中，起始脉冲 SP 被输入到第一级 21。来自第 1 级到第 n-1 级的输出信号 g1 到 gn-1 作为起始脉冲被分别输入到第二到第 n 级。各级 21 到 2n 具有相同的电路结构，并响应四个时钟信号 C1 到 C4 中的两个时钟信号将起始脉冲 SP 或前级的输出信号 g1 到 gn-1 移位产生一个扫描脉冲。产生的扫描脉冲具有一个水平周期的脉冲宽度。

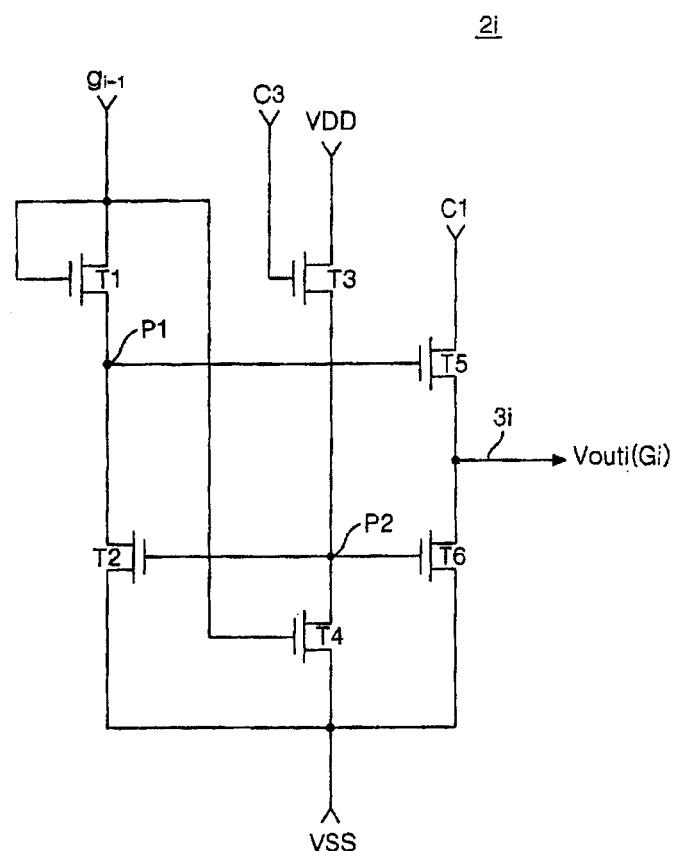

30 图 4 是现有技术的移位寄存器中级联电路结构的具体电路图。图 4 表示图 3 的移位寄存器中第 i 级 2i(i 是从 1 到 n 的整数)的具体电路结构。级 2i 包括用来对输出节点 3i 施加高逻辑电压的第五 NMOS 晶体管 T5，以及对输出节点 3i 施加低逻辑电压的第六 NMOS 晶体管 T6。

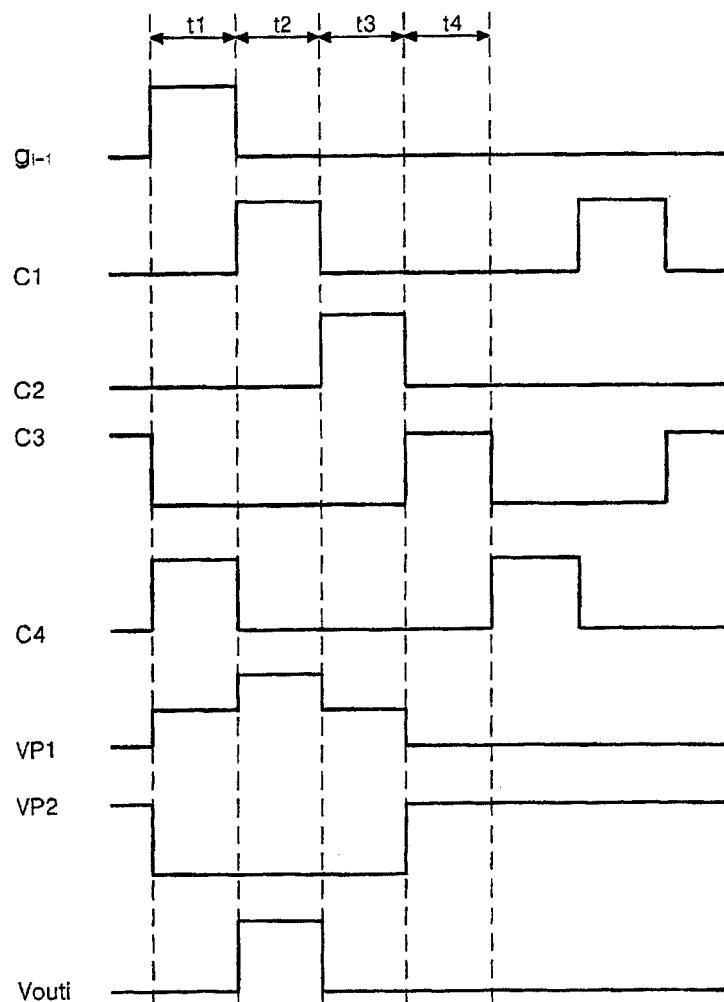

图 5 是按照现有技术的级联电路输入信号和控制节点及输出节点上的信号的波形图。以下要参照图 4 和图 5 描述第 2i 级的操作。

在一个时间间隔  $t_1$  内, 第一和第二时钟信号  $C_1$  和  $C_2$  保持在低逻辑电压。前级上具有高逻辑电压的起始脉冲  $SP$  或输出信号  $g_{i-1}$  被提供给第一和第四 NMOS 晶体管  $T_1$  和  $T_4$  的栅极电极使 NMOS 晶体管  $T_1$  和  $T_4$  导通。第一节点  $P_1$  上的电压  $VP_1$  上升到中间电压使第五 NMOS 晶体管  $T_5$  导通, 而输出节点  $3i$  上的电压  $V_{outi}$  维持在低逻辑电压, 因为第一时钟信号  $C_1$  是维持在低逻辑电压。第四 NMOS 晶体管  $T_4$  导通会降低第二节点  $P_2$  上的电压使第二和第六 NMOS 晶体管  $T_2$  和  $T_6$  关断, 从而切断第一节点  $P_1$  的放电路径。

在一个时间间隔  $t_2$  内, 第一时钟信号  $C_1$  翻转到高逻辑电压, 而起始脉冲  $SP$  和前级的输出信号  $g_{i-1}$  翻转到低逻辑电压。第一和第四 NMOS 晶体管  $T_1$  和  $T_4$  被关断。第一节点  $P_1$  上的电压  $VP_1$  被获得高逻辑电压第一时钟信号  $C_1$  的第五 NMOS 晶体管  $T_5$  的漏极和栅极之间寄生电容的充电电压抬升。这样, 电压  $VP_1$  就会上升到超过第五 NMOS 晶体管  $T_5$  的门限电压。换句话说, 由于自举效应, 第一节点  $P_1$  上的电压  $VP_1$  在时间间隔  $t_2$  内比时间间隔  $t_1$  内要高。因此, 第五 NMOS 晶体管  $T_5$  在时间间隔  $t_2$  内导通。输出节点  $3i$  上的电压  $V_{outi}$  受第五 NMOS 晶体管  $T_5$  导通而提供的第一时钟信号  $C_1$  电压的驱动, 使得电压  $V_{outi}$  翻转到高逻辑电压。

在一个时间间隔  $t_3$  内, 第一时钟信号  $C_1$  翻转到低逻辑电压。第五 NMOS 晶体管  $T_5$  维持导通状态。输出节点  $3i$  上的电压  $V_{outi}$  在第五 NMOS 晶体管  $T_5$  放电的过程中翻转到低逻辑电压。同时, 第一节点  $P_1$  上的电压  $VP_1$  下降到中间电压。

在一个时间间隔  $t_4$  内, 第三时钟信号  $C_3$  翻转到高逻辑电压。第三 NMOS 晶体管  $T_3$  响应第三时钟信号  $C_3$  被导通, 并通过第三 NMOS 晶体管  $T_3$  向第二节点  $P_2$  提供高电平电源电压  $VDD$ , 使第二节点  $P_2$  上的电压  $VP_2$  上升。第二节点  $P_2$  上上升的电压  $VP_2$  使第六 NMOS 晶体管  $T_6$  导通, 输出节点  $3i$  上的电压  $V_{outi}$  放电到地电压  $VSS$ 。同时, 电压  $VP_2$  使第二 NMOS 晶体管  $T_2$  导通, 第一节点  $P_1$  上的电压  $VP_1$  放电到地电压  $VSS$ 。

然而, 现有技术 LCD 存在的问题是设在液晶显示面板 13 上的许多数据线  $D_1$  到  $D_m$  和用来向数据线  $D_1$  到  $D_m$  提供数据电压的数据驱动电路 11 的许多驱

动集成电路会造成高制作成本。这一问题随着分辨率越来越高且液晶显示面板 13 越来越大而越发严重。

## 发明内容

5 对此，本发明提出了一种液晶显示器的栅极驱动装置和方法，能够基本上消除因现有技术的局限和缺点造成的这些问题。

本发明的目的是提供一种用来驱动液晶显示器的装置，它具有少量的数据线和数据驱动集成电路。

10 本发明的另一目的是提供一种驱动液晶显示器的方法，能够减少数据线和数据驱动集成电路。

本发明的其他特征和优点将在以下的描述中给出，根据该描述，它们的一部分将变得很明显，或者可以通过对本发明的实践学会。本发明的这些和其他优点将通过说明书及其权利要求书以及附图具体指出的结构实现和得到。为了实现这些和其他优点，根据本发明的目的，如所具体和概括描述的那样，按照本发明一方面的一种液晶显示器栅极驱动装置包括一移位寄存器，提供给它的有相位彼此反转并各自具有半周期脉冲宽度的第一和第二半周期时钟信号，依次移相并各自具有一周期脉冲宽度的第一到第四一周期时钟信号，一起始脉冲，一高电平电源电压和一低电平电源电压。移位寄存器响应起始脉冲及第一和第二半周期时钟信号产生半周期输出，并响应任何一个第一到第四一周期时钟信号从半周期输出结束时起按半周期延迟产生一周期输出。

在另一方面，液晶显示器的栅极驱动装置包括第一输入电路，它响应起始脉冲及相位彼此反转并各自具有半周期脉冲宽度的第一和第二半周期时钟信号的第二半周期时钟信号为第一充电控制节点充电，并响应第二半周期时钟信号和相位依次移位并各自具有一周期脉冲宽度的第一到第四时钟信号中的第四时钟信号对第一放电控制节点充电。栅极驱动装置进一步包括第一输出电路，它响应来自第一充电控制节点的控制信号和第一半周期时钟信号向输出节点输出一半周期输出，并响应来自第一放电控制节点的控制信号使输出节点放电。栅极驱动装置还包括第二输入电路，它响应半周期输出和第二半周期时钟信号对第二充电控制节点充电，并响应第三时钟信号对第二放电

控制节点充电。栅极驱动装置还包括第二输出电路，它响应来自第二充电控制节点的控制信号和第一时钟信号向输出节点输出一个从半周期输出结束时起按半周期延迟的一周期输出，并响应来自第二放电控制节点的控制信号使输出节点放电。

5 按照本发明再一方面的液晶显示器栅极驱动方法包括以下步骤，接收相位彼此反转且各自具有半周期脉冲宽度的第一和第二半周期时钟信号，依次移相并各自具有一周期脉冲宽度的第一到第四一周期时钟信号，一起始脉冲，一高电平电源电压和一低电平电源电压，并响应起始脉冲及第一和第二半周期时钟信号产生一半周期输出，并且响应任何一个第一到第四一周期时钟信号从半周期输出结束时起按半周期延迟产生一周期输出。

10 按照本发明又一方面的液晶显示器栅极驱动方法包括以下步骤，响应起始脉冲及相位彼此反转并各自具有半周期脉冲宽度的第一和第二半周期时钟信号的第二半周期时钟信号为第一充电控制节点充电，响应来自第一充电控制节点的控制信号和第一半周期时钟信号向输出节点输出一半周期输出，响应第二半周期时钟信号和相位依次移位并各自具有一周期脉冲宽度的第一到第四时钟信号中的第四时钟信号对第一放电控制节点充电，响应来自第一放电控制节点的控制信号使输出节点放电，响应半周期输出和第二半周期时钟信号对第二充电控制节点充电，响应第三时钟信号对第二放电控制节点充电，响应来自第二充电控制节点的控制信号和第一时钟信号向输出节点输出一个20 从半周期输出结束时起按半周期延迟的一周期输出，并响应来自第二放电控制节点的控制信号使输出节点放电。

应理解的是，前面总的描述和下面详细的描述是示例和解释性的，意欲用它们对所要求保护的本发明作进一步的解释。

## 25 附图说明

所包括用来提供对本发明进一步理解并且包括在内构成本说明书一部分的附图示出了本发明的各个实施例，它们连同文字描述一起用来解释本发明的原理。在附图中：

图 1 是按照现有技术的一种有源矩阵液晶显示器件的结构示意图；

30 图 2 是按照现有技术提供给液晶显示面板的液晶单元的驱动信号和数据

电压的波形图；

图 3 是按照现有技术的栅极驱动电路中移位寄存器的电路图；

图 4 是按照现有技术的移位寄存器级联电路结构的具体电路图；

图 5 是按照现有技术的级联电路输入信号和控制节点及输出节点上的信号的波形图；

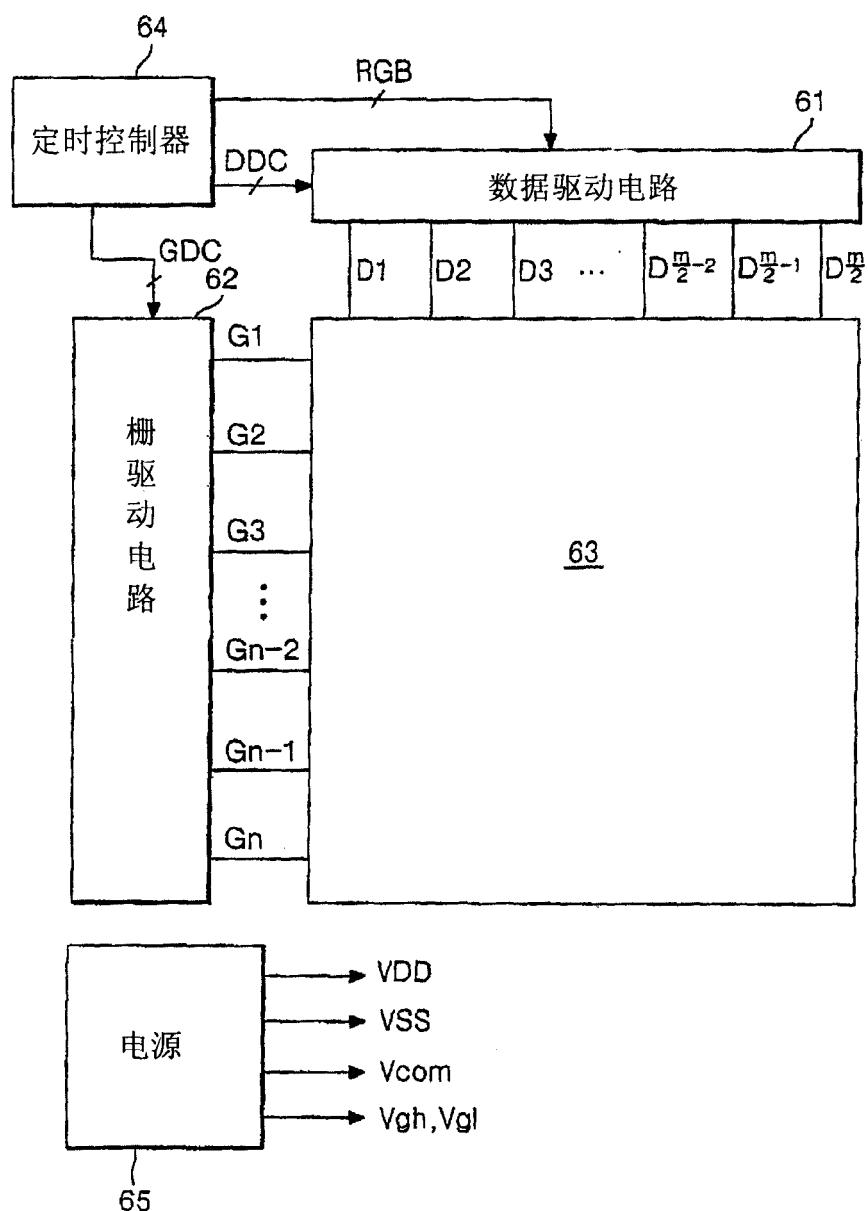

图 6 是按照本发明实施例的液晶显示器件结构的一例示意性框图；

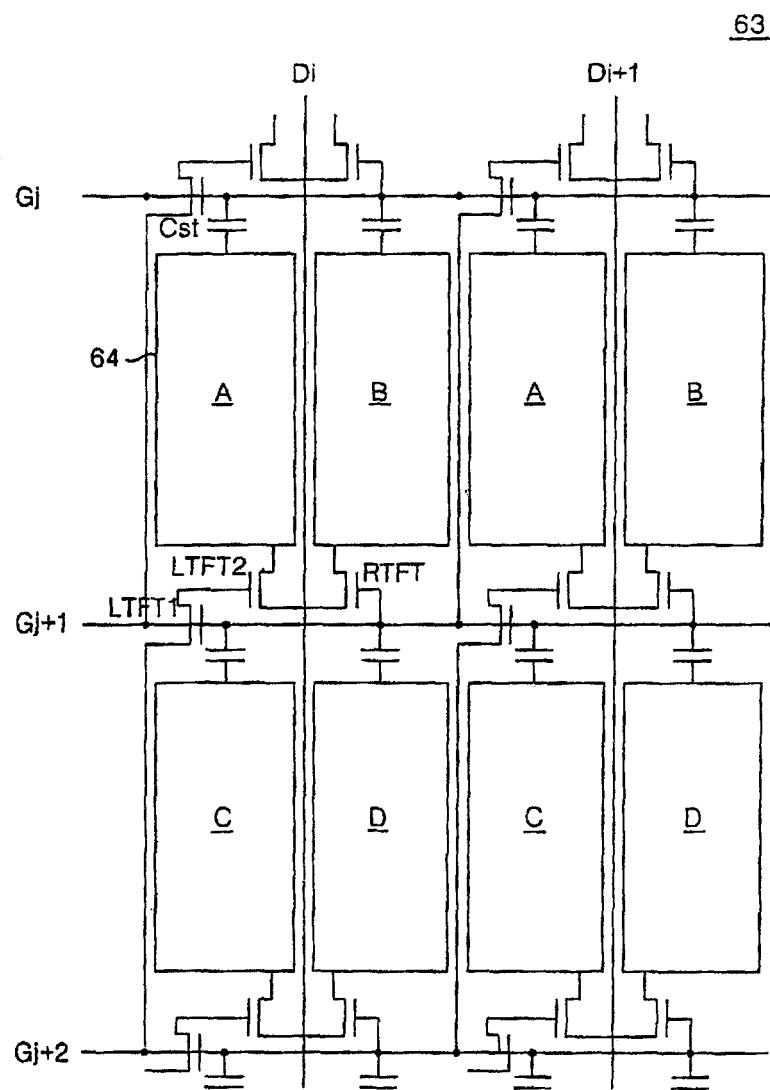

图 7 是按照本发明实施例的液晶显示面板中一部分象素单元的电路示意图；

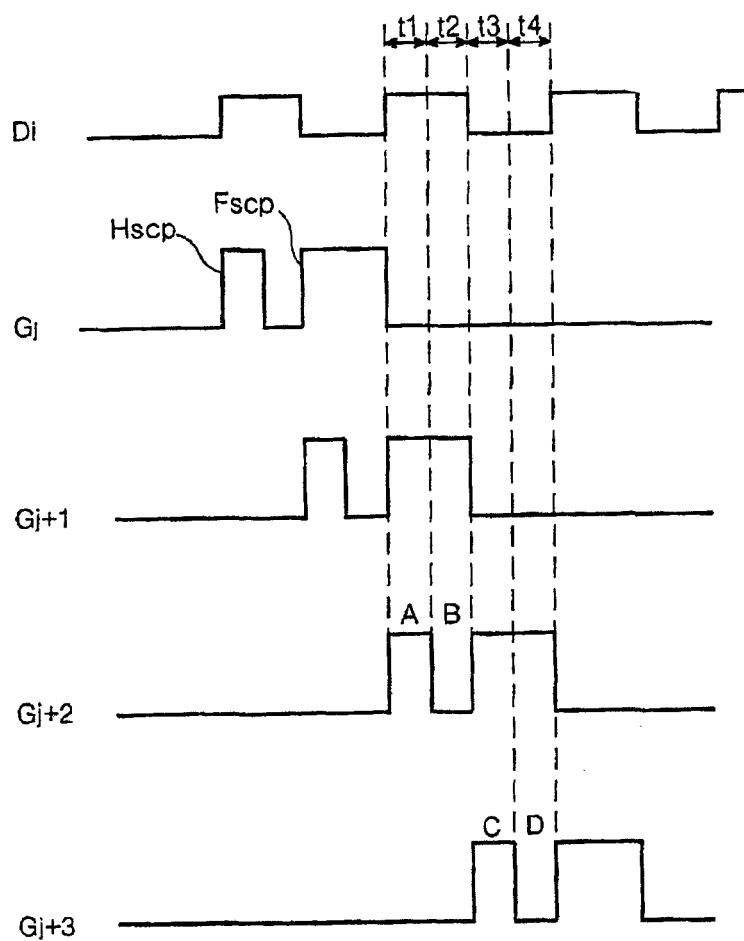

图 8 是按照本发明实施例的数据驱动电路的输出数据电压和栅极驱动电路的输出扫描脉冲的一例波形图；

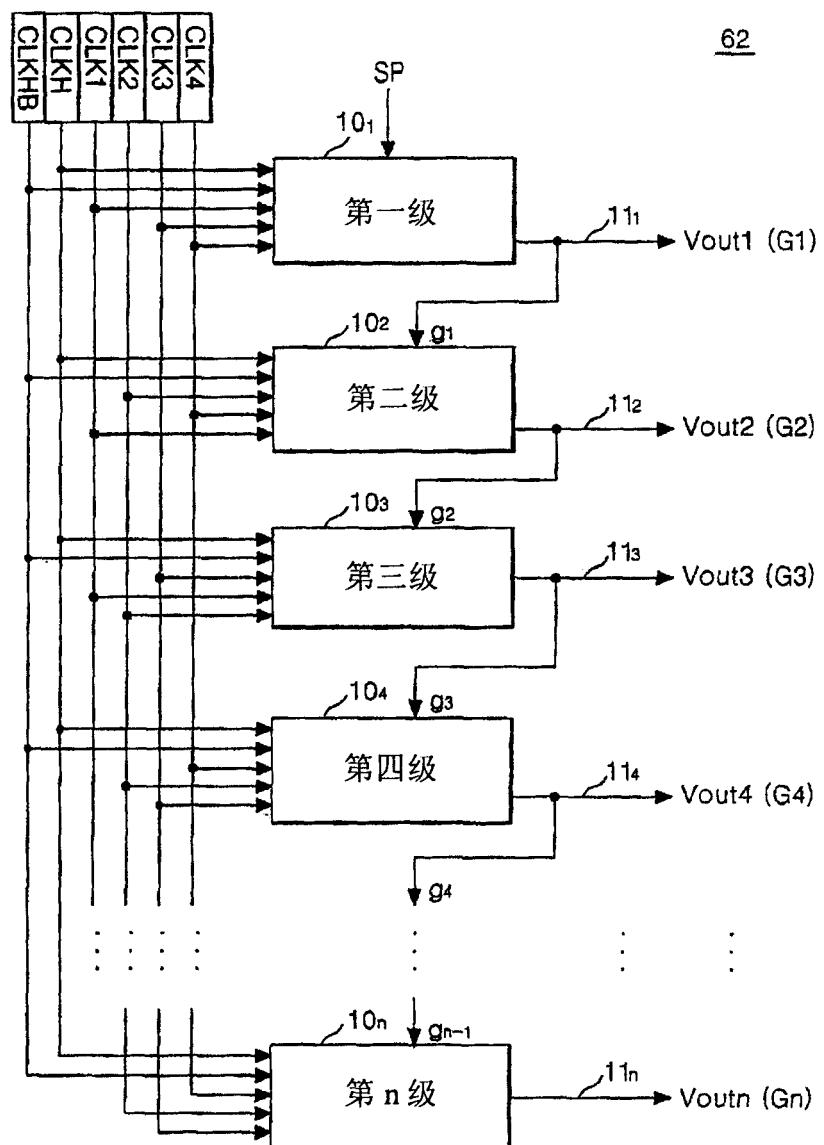

图 9 是按照本发明实施例的栅极驱动电路中一个移位寄存器的电路图；

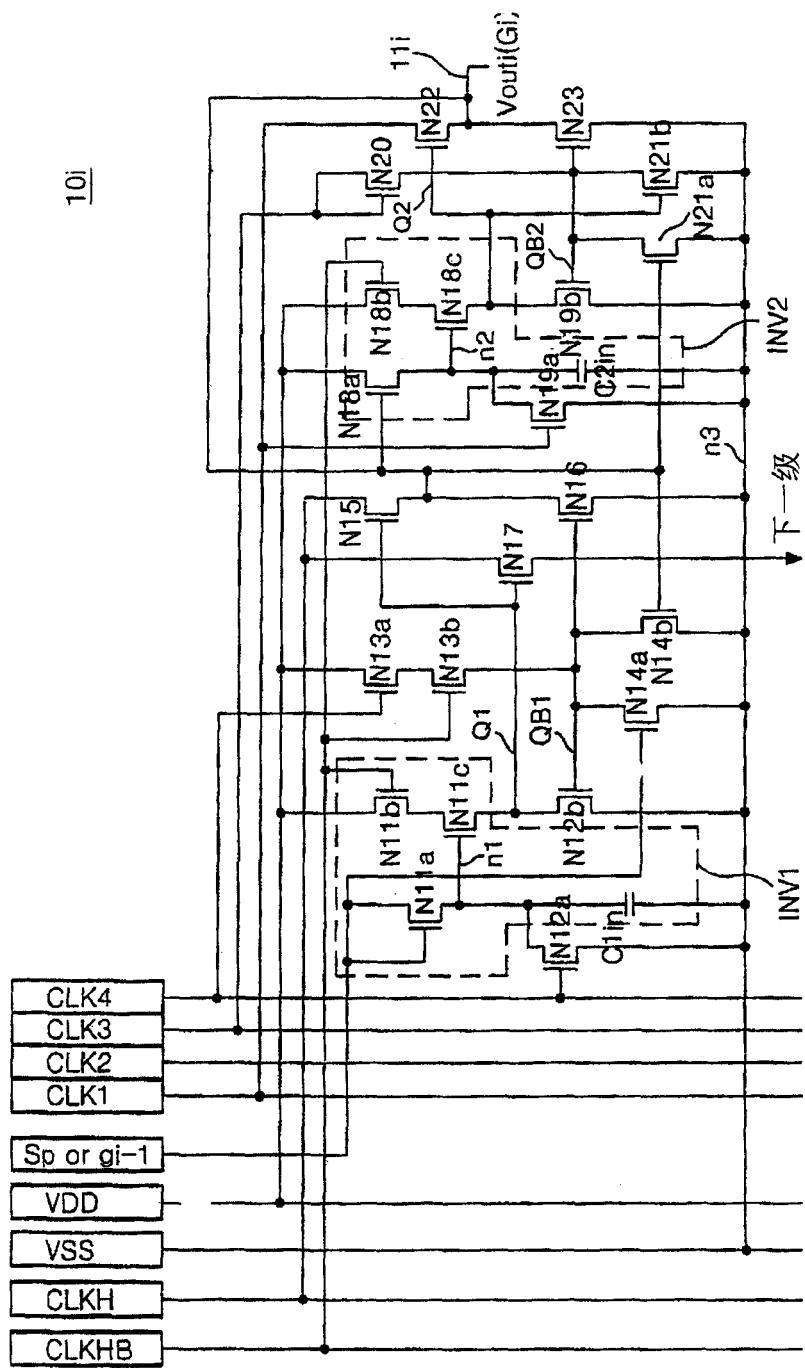

图 10 是按照本发明实施例的移位寄存器级联电路结构的一例具体电路图；

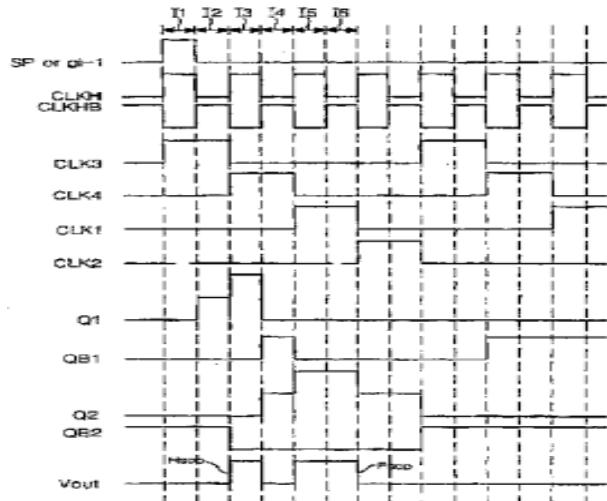

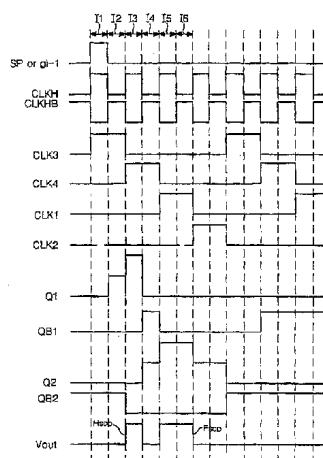

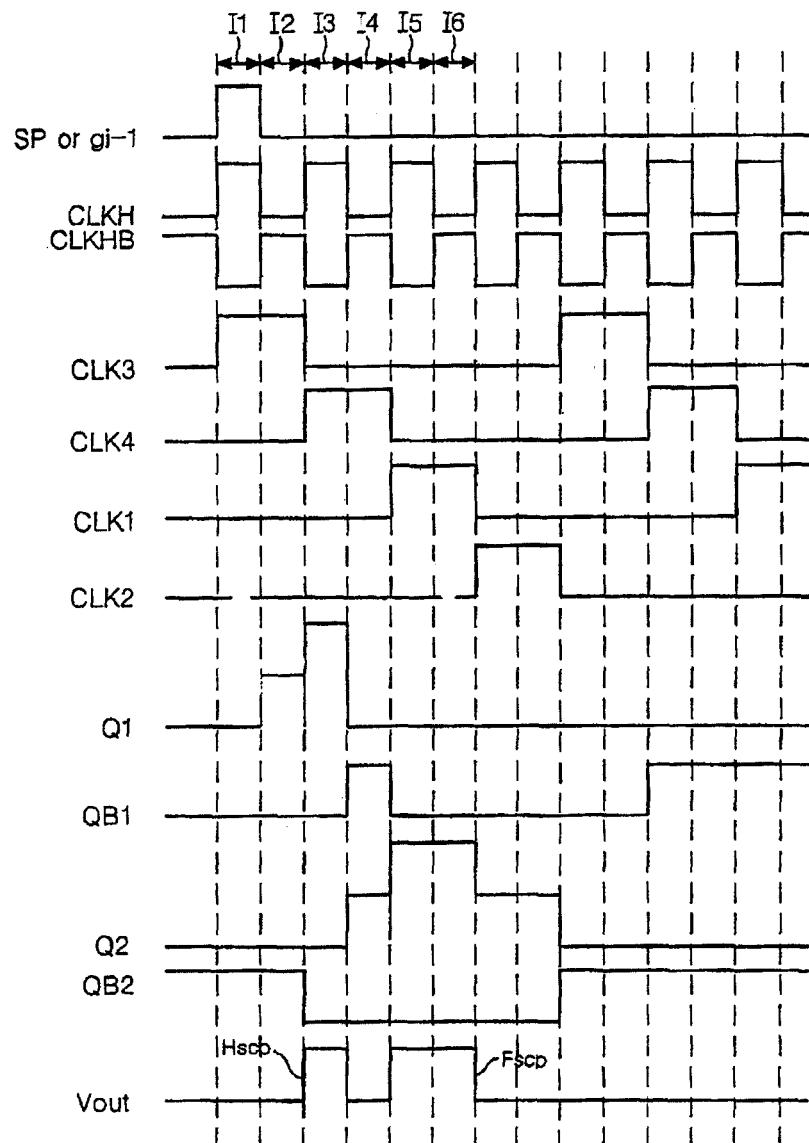

图 11 是按照本发明实施例的级联电路输入信号及控制节点和输出节点上的信号的一例波形图；以及

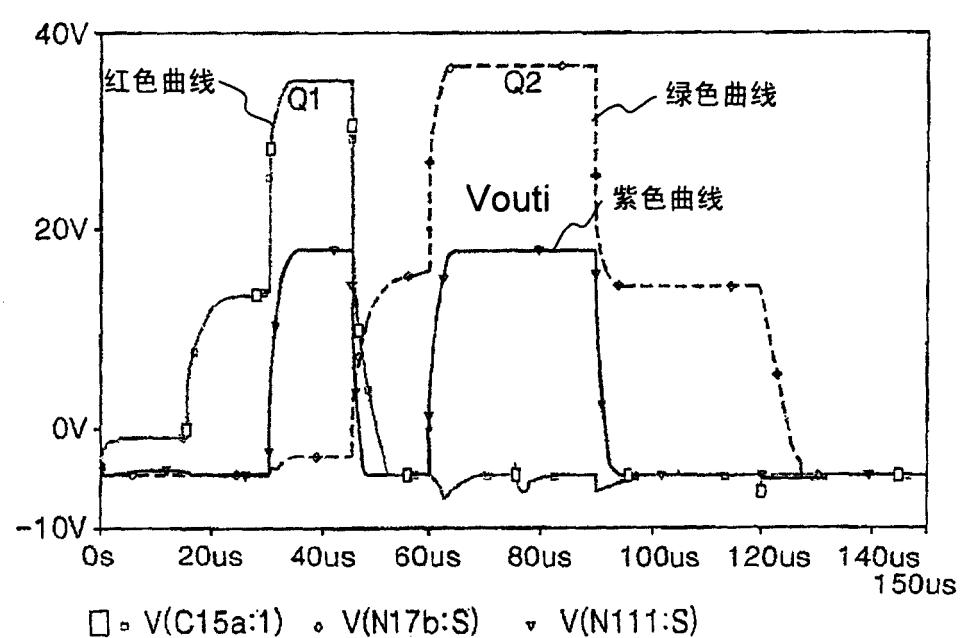

图 12 表示用来检验按照本发明实施例的移位寄存器的一种仿真结果。

### 具体实施方式

图 6 是按照本发明实施例的液晶显示器件结构的一例示意性框图。参见图 6, 按照本发明实施例的 LCD 包括液晶显示面板 63, 它具有按矩阵布置的( $m \times n$ )个液晶单元 Clc 和彼此交叉的  $m/2$  条数据线 D1 到  $Dm/2$  和  $n$  条栅极线 G1 到 Gn。LCD 还包括向液晶显示面板 63 的数据线 D1 到  $Dm/2$  提供数据的数据驱动电路 61。用栅极驱动电路 62 对栅极线 G1 到 Gn 提供扫描脉冲。用定时控制器 64 控制数据驱动电路 61 和栅极驱动电路 62。用一个电源 65 产生驱动液晶显示面板 63 所需的驱动电压。

图 7 是按照本发明实施例的液晶显示面板中一部分象素单元的电路示意图。液晶显示面板 63 具有注入两个玻璃基板之间的液晶分子。设在液晶显示面板 63 的下玻璃基板上的数据线 D1 到  $Dm/2$  和栅极线 G1 到 Gn 可以彼此垂直交叉。在数据线 D1 到  $Dm/2$  和栅极线 G1 到 Gn 之间的各个交叉点上可以设置 LCD 的第一左象素驱动 TFT(以下称为“LTFT1”), 第二左象素驱动

TFT(以下称为“LTFT2”), 和一个右像素驱动 TFT(以下称为“RTFT”), 用来为一个左像素和一个右像素分配来自同一数据线的数据电压。

LTFT1 响应来自第  $j$  条栅极线  $G_j$  的扫描脉冲将第  $(j+1)$  条栅极线  $G_{j+1}$ ( $j$  是小于  $n$  的整数)上的电压提供给 LTFT2 的栅极使 LTFT2 导通。为此, LTFT1 的漏极被连接到第  $(j+1)$  条栅极线  $G_{j+1}$ 。LTFT1 的栅极被连接到第  $j$  条栅极线  $G_j$ 。还要将 LTFT1 的源极连接到 LTFT2 的栅极, 用来驱动第  $i$  条数据线  $D_i$ ( $i$  是小于  $m/2$  的整数)的左液晶单元。

LTFT2 响应来自 LTFT1 的源极的控制电压形成或切断左液晶单元的像素电极 64 和第  $i$  条数据线  $D_i$  之间的电流路径。为此要将 LTFT2 的漏极电极连接到第  $i$  条数据线  $D_i$ , 而其源极电极连接到位于第  $i$  条数据线  $D_i$  左侧的液晶单元的像素电极 64。

RTFT 响应来自第  $j$  条栅极线  $G_j$  的扫描脉冲向第  $i$  条数据线  $D_i$  提供一个数据电压。为此要将 RTFT 的漏极电极连接到第  $i$  条数据线。RTFT 的栅极电极被连接到第  $j$  条栅极线  $G_j$ 。还要将 RTFT 的源极电极连接到位于第  $i$  条数据线  $D_i$  右侧的液晶单元的像素电极 64。

液晶显示面板 63 的各个液晶单元可以有一存储电容  $C_{st}$ 。存储电容  $C_{st}$  被设在液晶单元的像素电极和前级栅极线之间, 用来稳定保持液晶单元的电压。

液晶显示面板 63 的上玻璃基板上设有黑色矩阵, 滤色片和公共电极(未表示)。具有垂直光轴的偏振器被分别附着在液晶显示面板 63 的上、下玻璃基板上。并在其与液晶正切的内表面上设有用来形成自由倾斜角度液晶的一对准薄膜。

数据驱动电路 61 包括多个数据驱动集成电路。各个数据驱动集成电路包括移位寄存器, 锁存器, 数-模转换器和输出缓冲器。

数据驱动电路 61 在定时控制器 64 的控制下锁存一数字视频数据, 并将数字视频数据变换成模拟灰度系数补偿电压。这样, 数据驱动电路 61 就能向数据线  $D_1$  到  $D_{m/2}$  提供模拟灰度系数补偿电压。

数据驱动电路 61 能在一个水平周期内通过同一条数据线向位于数据线左侧和右侧的两个液晶单元提供不同的数据电压。为此, 数据驱动电路将一个水平周期划分成两个间隔, 每半周期向数据线  $D_1$  到  $D_{m/2}$  提供不同的数据

电压。

5 棚极驱动电路 62 包括多个棚极驱动集成电路。各个棚极驱动集成电路包括一个移位寄存器。移位寄存器连续产生半周期扫描脉冲和一周期扫描脉冲并且移位产生的扫描脉冲。半周期扫描脉冲的脉冲宽度等于一水平周期的一半(1/2)。一周期扫描脉冲的脉冲宽度是一个水平周期。半周期和一周期脉冲之间可以有一个水平周期的 1/2 延迟时间。

棚极驱动电路 62 还可以包括一电平移位器, 将移位寄存器的输出信号变换成适合用来驱动液晶单元的摆动宽度。棚极驱动电路还可以包括连接在电平移位器和棚极线 G1 到 Gn 之间的输出缓冲器。

10 棚极驱动电路 62 在定时控制器 64 的控制下向各条棚极线 G1 到 Gn 连续提供半周期扫描脉冲和一周期扫描脉冲, 棚极驱动电路 62 向棚极线 G1 到 Gn 依次提供扫描脉冲, 为液晶显示面板 63 的一条水平线选择提供数据。此时, 一周期扫描脉冲与提供给下一棚极线的半周期扫描脉冲重叠。

15 图 8 是按照本发明实施例的数据驱动电路的输出数据电压和棚极驱动电路的输出扫描脉冲的一例波形图。如图 8 所示, 为第 j 条棚极线 Gj 提供半周期扫描脉冲 HScp。在半周期延迟时间之后为第 j 条棚极线 Gj 提供一周期扫描脉冲 FScp。一周期扫描脉冲 FScp 的初始 1/2 脉冲宽度与提供给第(j+1)条棚极线 Gj+1 的半周期扫描脉冲 HScp 重叠。

20 定时控制器 64 能接收垂直/水平同步信号, 一时钟信号和一数据控制信号 DDC。定时控制器用时钟信号产生控制棚极驱动电路 62 的棚极控制信号 GDC。定时控制器用数据控制信号 DDC 控制数据驱动电路 61。定时控制器 64 对数字视频数据 RGB 采样, 然后经重新对准将对准的数据提供给数据驱动电路 61。

25 棚极控制信号 GDC 可以包括棚极起始脉冲 GSP, 棚极移位时钟信号 GSC, 和棚极输出使能信号 GOE。棚极移位时钟信号 GSC 被用来驱动移位寄存器。数据控制信号 DDC 可以包括源极起始脉冲 SSP, 源极移位时钟 SSC, 源极输出使能信号 SOC 和一个极性信号 POL。

30 电源 65 产生驱动液晶显示面板 63 所需的驱动电压。驱动电压包括高电平电源电压 VDD, 作为低电平电源电压的地电压 VSS, 公共电压 Vcom, 棚极高压 Vgh 和棚极低电压 Vgl。公共电压 Vcom 是提供给液晶单元的象素

电极对面的公共电极的电压。栅极高电压  $V_{gh}$  是扫描脉冲的高逻辑电压,被设置在高于 LTFT1, LTFT2 和 RTFT 的门限电压。栅极低电压  $V_{gl}$  是扫描脉冲的低逻辑电压, 被设置在 TFT 的关断电压。

以下要参照图 7 和图 8 来解释按照本发明实施例的 LCD 的操作。在时间间隔  $t_1$  内, 对第  $i$  条数据线  $D_i$  提供 A 象素电压, 同时对第  $(j+1)$  条栅极线  $G_{j+1}$  提供一周期扫描脉冲  $FScp$  使栅极被连接到第  $(j+1)$  条栅极线  $G_{j+1}$  的 LTFT1 导通。同时对第  $(j+1)$  条栅极线  $G_{j+1}$  提供半周期扫描脉冲  $HScp$ , 导通受通过 LTFT1 提供的栅极电压驱动的 LTFT2, 用 A 象素数据电压对 A 象素充电。进而, 在时间间隔  $t_1$  内, 栅极被连接到第  $(j+1)$  条栅极线  $G_{j+1}$  的 RTFT 被导通, 10 用 A 象素电压对 A 象素充电。

在时间间隔  $t_2$  内, 对第  $i$  条数据线  $D_i$  提供 B 象素数据电压, 同时对第  $(j+2)$  条栅极线  $G_{j+2}$  提供低于 TFT 门限电压的栅极低电压, 使栅极连接到第  $(j+1)$  条栅极线  $G_{j+1}$  的 LTFT1 关断。这样, A 象素维持在数据电压, 而 B 象素对通过 RTFT 提供的 B 象素数据电压充电。

15 按照本发明实施例的 LCD 借助于半周期扫描脉冲和一周期扫描脉冲按时分方式通过一条数据线向左/右液晶单元依次提供两个数据电压。这样, 本发明的实施例就能减少数据线的数量及其数据驱动集成电路的数量。

图 9 是按照本发明实施例的栅极驱动电路中一个移位寄存器的电路图。参见图 9, 按照本发明实施例的移位寄存器可以包括级联的  $n$  级  $101$  到  $10n$ 。20 在各级  $101$  到  $10n$  与栅极线  $G_1$  到  $G_n$  之间设有电平移位器和输出缓冲器(未表示)。

在图 9 所示的移位寄存器中, 起始脉冲  $SP$  被输入到第一级  $101$ 。前级的输出信号  $g_1$  到  $g_{n-1}$  分别被输入到第二到第  $n$  级  $102$  到  $10n$  作为起始脉冲。各级  $101$  到  $10n$  具有相同的电路结构, 并且产生一个半周期扫描脉冲  $HScp$  25 和一个一周期扫描脉冲  $FScp$ 。各级  $101$  到  $10n$  响应来自第一和第二半周期时钟信号  $CLKH$  和  $CLKHB$  及来自第一到第四时钟信号  $CLK1$  到  $CLK4$  的六个时钟信号, 产生扫描脉冲。 $CLKH$  和  $CLKHB$  各自具有的脉冲宽度相当于一个水平周期的一半( $1/2$ )。各个时钟信号  $CLK1$  到  $CLK4$  的脉冲宽度是一个水平周期。

30 第一和第二半周期时钟信号  $CLKH$  和  $CLKHB$  的相位如图 11 所示每  $1/2$

水平周期彼此反转一次。起始脉冲 SP 和第一和第二半周期时钟信号 CLKH 和 CLKHB 具有相同的脉冲宽度。第一到第四时钟信号 CLK1 到 CLK4 按每个水平周期依次移位。起始脉冲 SP, 第一半周期时钟信号 CLKH 和第三时钟信号 CLK3 是彼此同步的。

5 图 10 是按照本发明实施例的移位寄存器级联电路结构的一例具体电路图。图 10 具体表示移位寄存器中第 i 级 10i 的一例电路结构。级 10i 包括用来产生半周期扫描脉冲 HScp 的第一输入电路和第一输出电路, 和用来产生一周期扫描脉冲 FScp 的第二输入电路和第二输出电路。

参见图 10, 级 10i 的第一输入电路响应起始脉冲 SP 或前级的输出信号及 10 第一和第二半周期时钟信号 CLKH 和 CLKHB 对第一充电控制节点 Q1 充电。级 10i 的第一输入电路还响应第二半周期时钟信号 CLKHB 和第四时钟信号 CLK4 对第一放电控制节点 QB1 充电。第一输入电路包括第一 NMOS 晶体管 N11a, N11b 和 N11c, 第二 NMOS 晶体管 N12a 和 N12b, 第三 NMOS 晶体管 N13a 和 N13b, 第四 NMOS 晶体管 N14a 和 N14b, 以及第一反相器电容 C1in。

15 第一 NMOS 晶体管 N11a, N11b 和 N11c 以及第一反相器电容 C1in 构成第一反相器 INV1。第一反相器 INV1 在起始脉冲 SP 或前级输出信号 gi-1 之后的半周期对第一充电控制节点 Q1 充电。第一反相器 INV1 响应第二半周期时钟信号 CLKHB 和一个起始脉冲 SP 或前级的输出信号 gi-1 对第一充电控制节点 Q1 充电。

20 起始脉冲 SP 或前级的输出信号 gi-1 被提供给 NMOS 晶体管 N11a 的栅极和源极。NMOS 晶体管 N11a 的漏极被共同连接到 NMOS 晶体管 N11c 的栅极, NMOS 晶体管 N12a 的源极以及第一反相器电容 C1in。NMOS 晶体管 N11a 作为一个二极管, 在获得起始脉冲 SP 或前级的输出信号 gi-1 时向 NMOS 晶体管 N11c 的栅极和第一反相器电容 C1in 提供起始脉冲 SP 或前级的输出信号 25 gi-1。

为 NMOS 晶体管 N11b 的栅极提供第二半周期时钟信号 CLKHB, 同时为其源极提供高电平电源电压 VDD。NMOS 晶体管 N11b 的漏极被连接到 NMOS 晶体管 N11c 的源极。NMOS 晶体管 N11b 响应第二半周期时钟信号 CLKHB 为 NMOS 晶体管 N11c 的源极提供高电平电源电压 VDD。

30 起始脉冲 SP 或前级的输出信号 gi-1 通过 NMOS 晶体管 N11a 提供给

NMOS 晶体管 N11c 的栅极。NMOS 晶体管 N11c 的漏极被连接到第一充电控制节点 Q1。NMOS 晶体管 N11c 响应起始脉冲 SP 或前级的输出信号 gi-1 用通过 NMOS 晶体管 N11b 提供的高电平电源电压 VDD 对第一充电控制节点 Q1 充电。

5 第一反相器电容 C1in 充入通过 NMOS 晶体管 N11a 提供的起始脉冲 SP 或前级输出信号 gi-1, 在 NMOS 晶体管 N11b 关断时稳定保持 NMOS 晶体管 N11c 的栅极电压。

10 为 NMOS 晶体管 N12a 的栅极提供第四时钟信号 CLK4, 同时为其漏极提供地电压 VSS。NMOS 晶体管 N12a 的源极被连接到 NMOS 晶体管 N11a 的漏极, NMOS 晶体管 N11c 的栅极和第一反相器电容 C1in。NMOS 晶体管 N12a 响应第四时钟信号 CLK4 使 NMOS 晶体管 N11c 的栅极电压和第一反相器电容 C1in 的电压放电。

15 为 NMOS 晶体管 N12b 的漏极提供地电压 VSS。NMOS 晶体管 N12b 的栅极被连接到第一放电控制节点 QB1, 而其源极被连接到 NMOS 晶体管 N11c 的漏极和第一充电控制节点 Q1。在第一放电控制节点 QB1 被充电使第一充电控制节点 Q1 放电时, NMOS 晶体管 N12b 被导通。

20 为 NMOS 晶体管 N13a 的栅极提供第四时钟信号 CLK4, 同时为其源极提供高电平电源电压 VDD。NMOS 晶体管 N13a 的漏极被连接到 NMOS 晶体管 N13b 的源极。NMOS 晶体管 N13a 响应第四时钟信号 CLK4 为 NMOS 晶体管 N13b 的源极提供高电平电源电压 VDD。

为 NMOS 晶体管 N13b 的栅极提供第二半周期时钟信号 CLKHB。NMOS 晶体管 N13b 的漏极被连接到第一放电控制节点 QB1。NMOS 晶体管 N13b 响应第二半周期时钟信号 CLKHB 向第一放电控制节点 QB1 提供来自 NMOS 晶体管 N13a 的高电平电源电压 VDD, 对第一放电控制节点 QB1 充电。

25 为 NMOS 晶体管 N14a 的栅极提供起始脉冲 SP 或前级的输出信号 gi-1, 同时为其漏极提供地电压 VSS。NMOS 晶体管 N14a 的源极被连接到第一放电控制节点 QB1。NMOS 晶体管 N14a 响应起始脉冲 SP 或前级的输出信号 gi-1 使第一放电控制节点 QB1 放电。

30 为 NMOS 晶体管 N14b 的漏极提供地电压 VSS。NMOS 晶体管 N14b 的栅极被连接到输出节点 11i, 而其源极被连接到第一放电控制节点 QB1。NMOS

晶体管 N14b 响应输出节点 11i 上的输出电压  $V_{out}(i)$  使第一放电控制节点 QB1 放电。

仍然参见图 10, 级 10i 的第一输出电路响应第一充电控制节点 Q1 上的控制电压和第一半周期时钟信号 CLKH 产生半周期扫描脉冲 HScp 和下一级的起始脉冲。级 10i 的第一输出电路还响应第一放电控制节点 QB1 上的控制电压使输出节点 11i 上的电压放电。第一输出电路包括第五 NMOS 晶体管 N15, 第六 NMOS 晶体管 N16 和第七 NMOS 晶体管 N17。

为第五 NMOS 晶体管 N15 的栅极提供第一充电控制节点 Q1 上的电压, 同时为其源极提供第一半周期时钟信号 CLKH。第五 NMOS 晶体管 N15 的漏极被连接到输出节点 11i。第五 NMOS 晶体管 N15 作为缓冲器晶体管响应第一充电控制节点 Q1 上的控制电压通过输出节点 11i 输出半周期扫描脉冲 HScp。

为第六 NMOS 晶体管 N16 的栅极提供第一放电控制节点 QB1 上的电压, 同时为其漏极提供地电压 VSS。第六 NMOS 晶体管 N16 的源极被连接到输出节点 11i。第六 NMOS 晶体管 N16 响应第一放电控制节点 QB1 上的控制电压将输出节点 11i 上的电压保持在地电压 VSS。换句话说, 第六 NMOS 晶体管 N16 在第一半周期时钟信号 CLKH 期间随着输出电压的产生在输出节点 11i 与地电压节点 n3 之间构成一个电流路径, 将输出节点 11i 保持在关断状态。

为第七 NMOS 晶体管 N17 的栅极提供第一充电控制节点 Q1 上的电压, 同时为其源极提供第一半周期时钟信号 CLKH。第七 NMOS 晶体管 N17 的漏极被连接到下一级(未表示)的起始脉冲输入端子。第七 NMOS 晶体管 N17 响应第一充电控制节点 Q1 上的控制电压向下一级的起始脉冲输入端子提供第一半周期时钟信号 CLKH 作为下一级的起始脉冲 gi。

仍然参见图 10, 用来自第一输出电路的半周期扫描脉冲 HScp 驱动级 10i 的第二输入电路对第二充电控制节点 Q2 充电, 产生一周期扫描脉冲 FScp。第二输入电路包括第八 NMOS 晶体管 N18a, N18b 和 N18c, 第九 NMOS 晶体管 N19a 和 N19b, 第十 NMOS 晶体管 N20, 第十一 NMOS 晶体管 N21a 和 N21b, 以及第二反相器电容 C2in。

NMOS 晶体管 N18a, N18b 和 N18c 和第二反相器电容 C2in 构成第二反相器 INV2, 响应输出节点 11i 上的输出电压  $V_{out}(i)$  和第二半周期时钟信号

CLKHB 在输出电压 Vouti 之后延迟半周期对第二充电控制节点 Q2 充电。

5 为 NMOS 晶体管 N18a 的栅极提供输出电压 Vouti, 同时为其源极提供高电平电源电压 VDD。NMOS 晶体管 N18a 的漏极被共同连接到 NMOS 晶体管 N18c 的栅极, NMOS 晶体管 N19a 的源极和第二反相器电容 C2in。NMOS 晶体管 N18a 响应半周期扫描脉冲 Hscp 向 NMOS 晶体管 N18c 的栅极电极和第二反相器电容 C2in 提供高电平电源电压 VDD。

10 用第二半周期时钟信号 CLKHB 驱动 NMOS 晶体管 N18b 的栅极, 同时为其源极提供高电平电源电压 VDD。NMOS 晶体管 N18b 的漏极被连接到 NMOS 晶体管 N18c 的源极。NMOS 晶体管 N18b 响应第二半周期时钟信号 CLKHB 为 NMOS 晶体管 N18c 的源极提供高电平电源电压 VDD。

高电平电源电压通过 NMOS 晶体管 N18a 提供给 NMOS 晶体管 N18c 的栅极。NMOS 晶体管 N18c 的漏极在 NMOS 晶体管 N18a 导通期间响应高电平电源电压 VDD 用通过 NMOS 晶体管 N18b 提供的高电平电源电压 VDD 对第二充电控制节点 Q2 充电。

15 用通过 NMOS 晶体管 N18a 提供的高电平电源电压 VDD 对第二反相器电容 C2in 充电, 在 NMOS 晶体管 N18a 关断时保持 NMOS 晶体管 N18c 的栅极电压恒定。

20 用第一时钟信号 CLK1 驱动 NMOS 晶体管 N19a 的栅极, 同时为其漏极提供地电压 VSS。NMOS 晶体管 N19a 的源极被连接到 NMOS 晶体管 N18a 的漏极, NMOS 晶体管 N18c 的栅极和第二反相器电容 C2in。NMOS 晶体管 N19a 响应第一时钟信号 CLK1 使 NMOS 晶体管 N18c 的栅极电压和第二反相器电容 C2in 上的电压放电。

25 为 NMOS 晶体管 N19b 的漏极提供地电压 VSS。NMOS 晶体管 N19b 的栅极被连接到第二放电控制节点 QB2, 而其源极被连接到 NMOS 晶体管 N18c 的漏极和第二充电控制节点 Q2。NMOS 晶体管 N19b 在第二放电控制节点 QB2 被充电时导通, 使第二充电控制节点 Q2 放电。

30 用第三时钟信号 CLK3 驱动第十 NMOS 晶体管 N20 的栅极和源极。第十 NMOS 晶体管 N20 的漏极被连接到第二放电控制节点 QB2 和 NMOS 晶体管 N21b 的源极。NMOS 晶体管 N20 响应第三时钟信号 CLK3 对第二放电控制节点 QB2 充电。

5 为 NMOS 晶体管 N21a 的漏极提供地电压 VSS。NMOS 晶体管 N21a 的栅极被连接到输出节点 11i 和 NMOS 晶体管 N14b 的栅极，而其源极被连接到第二放电控制节点 QB2。NMOS 晶体管 N21b 在电压被充入输出节点 11i 对第二放电控制节点 QB2 充电时被导通，从而导通 NMOS 晶体管 N19b 和 NMOS 晶体管 N23。

为 NMOS 晶体管 N21b 的漏极提供地电压 VSS。NMOS 晶体管 N21b 的栅极被连接到第二充电控制节点 Q2，而其源极被连接到第二放电控制节点 QB2。NMOS 晶体管 N21b 在第二充电控制节点 Q2 被充电时导通，使第二放电控制节点 QB2 放电，并且关断 NMOS 晶体管 N19b 和 NMOS 晶体管 N23。

10 仍然参见图 10，级 10i 的第二输出电路响应第二充电控制节点 Q2 上的控制电压产生一周期扫描脉冲 FScp。级 10i 的第二输出电路还响应第二放电控制节点 QB2 上的控制电压使输出节点 11i 上的电压放电。第二输出电路包括第十二 NMOS 晶体管 N22 和第十三 NMOS 晶体管 N23。

15 为 NMOS 晶体管 N22 的栅极提供第二充电控制节点 Q2 上的电压，同时为其源极提供第一时钟信号 CLK1。NMOS 晶体管 N22 的漏极被连接到输出节点 11i。NMOS 晶体管 N22 作为缓冲器晶体管响应第二充电控制节点 Q2 上的控制电压通过输出节点 11i 输出一周期扫描脉冲 Fscp。

20 为 NMOS 晶体管 N23 的栅极提供第二放电控制节点 QB2 上的电压，同时为其漏极提供地电压 VSS。NMOS 晶体管 N23 的源极被连接到输出节点 11i。NMOS 晶体管 N23 响应第二放电控制节点 QB2 上的控制电压，在输出节点 11i 上产生一个输出电压之后将输出节点 11i 上的电压保持在地电压 Vss。进而，在第一时钟信号 CLK1 在产生输出电压之后变成低逻辑时，NMOS 晶体管 N23 在输出节点 11i 和地电压节点 n3 之间构成一个电流路径，使输出节点 11i 保持在关断状态。

25 图 11 是按照本发明实施例的级联电路输入信号及控制节点和输出节点上的信号的一例波形图。参见图 10 和图 11，在起始脉冲 SP 或前级输出信号 gi-1 具有高逻辑电压的时间间隔 I1 内，第一半周期时钟信号 CLKH 和第三时钟信号 CLK3 具有高逻辑电压，而第一，第二和第四时钟信号 CLK1,CLK2 和 CLK4 具有低逻辑电压。在时间间隔 I1 内，NMOS 晶体管 N11a 和 N11c 30 被起始脉冲 SP 或前级输出信号 gi-1 导通。起始脉冲 SP 或前级输出信号 gi-1

的电压被充入第一反相器电容 C1in。同时, NMOS 晶体管 N14a 响应通过 NMOS 晶体管 N11a 提供的起始脉冲 SP 或前级输出信号 gi-1 被导通, 将第一放电控制节点 QB1 上的电压保持在地电压 VSS。进而, 在时间间隔 I1 内, 第十 NMOS 晶体管 N20 响应第三时钟信号 CLK3 被导通, 对第二放电控制节点 QB2 充电。此时, NMOS 晶体管 N19a 和 N23 被导通, 将输出节点 11i 上的电压保持在地电压 VSS。

在时间间隔 I2 内, 第三时钟信号 CLK3 维持在高逻辑电压。第一半周期时钟信号 CLKH 和起始脉冲 SP 或前级输出信号 gi-1 被逆变成低逻辑电压。同样, 响应第二半周期时钟信号 CLKHB, NMOS 晶体管 N11a 和 N14 被关断, 10 而 NMOS 晶体管 N11b 被导通。

用通过被充入 NMOS 晶体管 N11b 和第一反相器电容 C1in 的电压而维持导通的 NMOS 晶体管 N11c 提供的高电平电源电压 VDD 对第一充电控制节点 Q1 充入中间电压。第二放电控制节点 QB2 保持地电压 VSS 是因为第三时钟信号 CLK3 具有高逻辑电压。

15 在时间间隔 I3 内, 第三时钟信号 CLK3 变成低逻辑电压, 而第四时钟信号 CLK4 变成高逻辑电压。同时, 第一和第二半周期时钟信号 CLKH 和 CLKHB 的相位彼此再次反转。第一充电控制节点 Q1 上的电压被第一半周期时钟信号 CLKH 充电提高到第七 NMOS 晶体管 N17 的栅极-源极寄生电压。因此, 第一充电控制节点 Q1 上的电压因自举效应比 NMOS 晶体管的门限电压要高。

20 第一半周期时钟信号 CLKH 作为起始脉冲通过第七 NMOS 晶体管 N17 被提供给下一级的起始脉冲输入端子。此时, 第五 NMOS 晶体管 N15 被第一半周期时钟信号 CLKH 导通, 允许第一半周期时钟信号 CLKH 作为半周期扫描脉冲 Hscp 通过输出节点 11i 输出。同时, 连接到输出节点 11i 的 NMOS 晶体管 N14b 和 N21a 被导通, 将第一放电控制节点 QB1 保持在地电压 VSS, 25 并使第二放电控制节点 QB2 放电到地电压 VSS。进而, 在时间间隔 I3 内, 随着 NMOS 晶体管 N18a 被输出节点 11i 上的半周期扫描脉冲 Hscp 导通, NMOS 晶体管 N18c 的栅极电压被充入第二反相器电容 C2in。

30 在时间间隔 I4 内, 第四时钟信号 CLK4 维持在高逻辑电压, 而第一和第二半周期时钟信号 CLKH 和 CLKHB 的相位彼此再次反转。此时, NMOS 晶体管 N13a 因第四时钟信号 CLK4 被维持导通。NMOS 晶体管 N13b 被第二半

周期时钟信号 CLKHB 导通。结果，第一放电控制节点 QB1 用高电平电源电压 VDD 充电，导通 NMOS 晶体管 N12b 和 N16，使第一充电控制节点 Q1 和输出节点 11i 放电。

在时间间隔 I4 内，第二充电控制节点 Q2 被通过 NMOS 晶体管 N18c 提供的高电平电源电压 VDD 充电。NMOS 晶体管 N18c 因充入 NMOS 晶体管 N18b 和第二反相器电容 C2in 的电压而维持导通。NMOS 晶体管 N18b 被第二半周期时钟信号 CLKHB 导通。这样，第二充电控制节点 Q2 就上升到中间电压。

在时间间隔 I5 内，第四时钟信号 CLK4 变成低逻辑电压，而第一时钟信号 CLK1 变成高逻辑电压。第一和第二半周期时钟信号 CLKH 和 CLKHB 的相位彼此再次反转。第二充电控制节点 Q2 上的电压被第一时钟信号 CLK1 充电提高到 NMOS 晶体管 N22 的栅极-源极寄生电压。具体地说，第二充电控制节点 Q2 上的电压因自举效应比 NMOS 晶体管的门限电压要高。第一时钟信号 CLK1 通过被第一时钟信号 CLK1 导通的 NMOS 晶体管 N22 提高输出节点 11i 上的电压。此时，一周期扫描脉冲 Fscp 通过输出节点 11i 输出。同时，连接到输出节点 11i 的 NMOS 晶体管 N14b 和 N21a 被导通，将第二放电控制节点 QB2 保持在地电压 VSS，并使第一放电控制节点 QB1 放电到地电压 VSS。

在时间间隔 I6 内，第一时钟信号 CLK1 维持在高逻辑值。第一和第二时钟信号 CLKH 和 CLKHB 的相位彼此再次反转。此时，第二充电控制节点 Q2 因第一时钟信号 CLK1 维持在自举状态，通过输出节点 11i 持续输出一周期扫描脉冲 Fscp。在周期 I6 内，由于输出节点 11i 维持在高逻辑电压，第一和第二放电控制节点 QB1 和 QB2 维持在地电压 VSS。

参见图 9—11，如果起始脉冲 SP 或移位寄存器的前级输出信号 gi-1 被输入到起始脉冲输入端子，第一充电控制节点 Q1 就在第一反相器 INV1 的半周期延迟之后被充电。具体地说，如果起始脉冲 SP 或前级输出信号 gi-1 被输入到起始脉冲输入端子，第一充电控制节点 Q1 就在第一反相器 INV1 的 NMOS 晶体管 N11c 导通时被导通，而第一半周期时钟信号 CLKH 被变成高逻辑电压。

如果第一半周期时钟信号 CLKH 在第一充电控制节点 Q1 的这种充电状态下被变成高逻辑电压，第五 NMOS 晶体管 N15 就会导通，通过输出节点

11i 输出一个半周期输出信号，由于自举不会有任何损失。此时，半周期输出信号被作为第二反相器 INV2 的起始脉冲，由 NMOS 晶体管 N17 启动对第二充电控制节点 Q2 和下一级的充电。

5 输出节点 11i 被连接到四个晶体管例如是 NMOS 晶体管 N15, N16, N22 和 N23。因此，在产生输出信号时，第一充电控制节点 Q1 之外的其余节点应保持在接地状态。其余节点包括第二充电控制节点 Q2，第一放电控制节点 QB1 和第二放电控制节点 QB2。如果还有其他任何控制节点被充电，输出电压就会因充电的节点而下降。

10 半周期输出使第二反相器 INV2 的 NMOS 晶体管 N18c 导通。第二充电控制节点 Q2 在再次提供第二半周期时钟信号 CLKHB 时被充电。同时，与第二半周期时钟信号 CLKHB 周期性重叠的第四时钟信号 CLK4 对第一放电控制节点 QB1 充电，从而使第一充电控制节点 Q1 放电。进而，如果提供第一时钟信号 CLK1，第二充电控制节点 Q2 的自举效应就会产生一个一周期输出。

15 在产生一周期输出之后，第三时钟信号 CLK3 对第二放电控制节点 QB2 充电，从而使第二充电控制节点 Q2 放电。第一放电控制节点 QB1 被第二半周期时钟信号 CLKHB 和第四时钟信号 CLK4 充电。同时，第一放电控制节点 QB1 和第二放电控制节点 QB2 如图 11 所示每四个周期被充电一次。

20 由移位寄存器产生的半周期扫描脉冲 Hscp 和一周期扫描脉冲 Fscp 被电平移位器(未表示)转换成在栅极高电压 Vgh 和栅极低电压 Vgl 之间具有一定的摆动宽度。然后通过输出缓冲器将扫描脉冲依次提供给栅极线 G1 到 Gn。

25 图 12 表示用来检验按照本发明实施例的移位寄存器的一种仿真结果。从图 12 中可见，按照本发明实施例的栅极驱动装置能够连续产生半周期扫描脉冲和一周期扫描脉冲，使得扫描脉冲之间具有一半周期延迟。在图 12 中，紫色曲线代表输出电压 Vouti，红色和绿色曲线分别代表第一和第二充电控制节点 Q1 和 Q2 上的电压。

30 如上所述，按照本发明，借助于相位彼此反转的两个半周期时钟信号和相位依次移位的四个时钟信号，先产生半周期输出，在反转延迟半周期之后再产生一个一周期输出。这样就能产生半周期扫描脉冲和一周期扫描脉冲，使得扫描脉冲之间具有半周期的延迟。由此，驱动系统的栅极驱动电路就能减少数据线的数量，同时还能减少数据驱动集成电路的数量。

---

显然，对本领域的那些人员来说，在不脱离本发明的精神或者范围的情况下，可以在本发明的液晶显示器栅极驱动装置和方法中进行各种修改和变换。因此，任何落在所附权利要求及其等同物的范围内的对于本发明的修改和变换都将属于本发明的保护范围。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8

图 9

图 10

图 11

|                |                                                          |         |            |

|----------------|----------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器的栅极驱动装置和方法                                          |         |            |

| 公开(公告)号        | <a href="#">CN1629925A</a>                               | 公开(公告)日 | 2005-06-22 |

| 申请号            | CN200410042671.0                                         | 申请日     | 2004-05-31 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                 |         |            |

| 申请(专利权)人(译)    | LG. 菲利浦LCD株式会社                                           |         |            |

| 当前申请(专利权)人(译)  | 乐金显示有限公司                                                 |         |            |

| [标]发明人         | 张容豪<br>金彬<br>尹洙荣                                         |         |            |

| 发明人            | 张容豪<br>金彬<br>尹洙荣                                         |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36 G11C19/00 G11C19/28          |         |            |

| CPC分类号         | G09G3/3688 G09G2310/02 G09G2310/0297 G11C19/00 G11C19/28 |         |            |

| 代理人(译)         | 徐金国                                                      |         |            |

| 优先权            | 1020030092694 2003-12-17 KR                              |         |            |

| 其他公开文献         | CN100369102C                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">SIPO</a>           |         |            |

#### 摘要(译)

液晶显示器的一种栅极驱动装置包括一移位寄存器，提供给它的有相位彼此反转并各自具有半周期脉冲宽度的第一和第二半周期时钟信号，依次移相并各自具有一周期脉冲宽度的第一到第四一周期时钟信号，一起始脉冲，一高电平电源电压，和一低电平电源电压。移位寄存器响应起始脉冲及第一和第二半周期时钟信号产生半周期输出。移位寄存器还响应任何一个第一到第四一周期时钟信号从半周期输出结束时起按半周期延迟产生一周期输出。