[19] 中华人民共和国国家知识产权局

[12] 发明专利说明书

专利号 ZL 200610009004.1

[51] Int. Cl.

G09G 3/36 (2006.01)

G09G 3/20 (2006.01)

G02F 1/133 (2006.01)

[45] 授权公告日 2010 年 3 月 24 日

[11] 授权公告号 CN 100595822C

[22] 申请日 2006.2.16

[21] 申请号 200610009004.1

[30] 优先权

[32] 2005.4.11 [33] KR [31] 29903/05

[73] 专利权人 三星电子株式会社

地址 韩国京畿道

[72] 发明人 金宇哲 李濬表 文胜煥 孙宣圭

[56] 参考文献

CN1534583A 2004.10.6

KR1020040070537A 2004.8.11

CN1480952A 2004.3.10

US20040217935A1 2004.11.4

KR20010007610A 2001.1.26

US20020140364A1 2002.10.3

KR20030080979A 2003.10.17

CN1209567A 1999.3.3

CN1573878A 2005.2.2

审查员 保蕴鉅

[74] 专利代理机构 北京市柳沈律师事务所

代理人 邱万奎 黄小临

权利要求书 4 页 说明书 10 页 附图 9 页

[54] 发明名称

用于显示设备的选通驱动设备及其显示设备

[57] 摘要

一种用于显示设备的选通驱动部分，该显示设备包括各自具有第一和第二子像素的多个像素，该选通驱动部分包括：第一移位寄存器，其响应于第一选通时钟信号而生成第一输出信号；第二移位寄存器，其响应于第二选通时钟信号而生成第二输出信号；电平转移器，其耦接到第一和第二移位寄存器，并放大第一和第二输出信号；以及输出缓冲器，其耦接到电平转移器，并生成第一和第二选通信号。与第一选通时钟信号同步生成第一选通信号，并与第二选通时钟信号同步生成第二选通信号。因而，可通过独立地驱动奇数和偶数子像素而改善第一和第二子像素的充电时间，并且，还可改善 LCD 设备的可视性。

400

1、一种用于显示设备的选通驱动部分，该显示设备包括各自具有第一和第二子像素的多个像素，该选通驱动部分包括：

第一移位寄存器，其响应于第一选通时钟信号而生成第一输出信号；

第二移位寄存器，其响应于第二选通时钟信号而生成第二输出信号；

电平转移器，其耦接到第一和第二移位寄存器，并放大第一和第二输出信号；以及

输出缓冲器，其耦接到电平转移器，并生成第一和第二选通信号，

其中每个像素内的第一和第二子像素分别接收第一和第二选通信号，

其中相邻像素的充电时间不重叠，而每个像素内的第一和第二子像素的充电时间重叠，

其中，在第一选通时钟信号的高电平期间的第一选通时钟信号的宽度与在第二选通时钟信号的高电平期间的第二选通时钟信号的宽度不同。

2、如权利要求 1 所述的选通驱动部分，其中与第一选通时钟信号同步生成第一选通信号，并且与第二选通时钟信号同步生成第二选通信号。

3、如权利要求 2 所述的选通驱动部分，其中第一选通时钟信号与第二选通时钟信号部分重叠。

4、如权利要求 3 所述的选通驱动部分，其中第一选通时钟信号比第二选通时钟信号超前  $1/4 H$ 。

5、如权利要求 3 所述的选通驱动部分，其中第二选通时钟信号比第一选通时钟信号超前  $1/4 H$ 。

6、如权利要求 3 所述的选通驱动部分，其中，第一和第二移位寄存器包括相互连续连接的多个级，并且，在第一和第二移位寄存器中的每个里面的第一级和最后级中的至少一个接收垂直同步开始信号。

7、一种用于显示设备的驱动设备，该显示设备包括各自具有第一和第二子像素的多个像素，该驱动设备包括：

多条第一选通线，其耦接到第一子像素，并传递第一选通信号；

多条第二选通线，其耦接到第二子像素，并传递第二选通信号；以及

选通驱动部分，其生成第一和第二选通信号，并包括：

第一移位寄存器，其响应于第一选通时钟信号而生成第一输出信

号；

第二移位寄存器，其响应于第二选通时钟信号而生成第二输出信号；

电平转移器，其分别耦接到第一和第二移位寄存器；以及

输出缓冲器，其耦接到电平转移器，

其中相邻像素的充电时间不重叠，而每个像素内的第一和第二子像素的

充电时间重叠，以及

其中，在第一选通时钟信号的高电平期间的第一选通时钟信号的宽度与

在第二选通时钟信号的高电平期间的第二选通时钟信号的宽度不同。

8、如权利要求 7 所述的驱动设备，其中，第一选通信号与第一选通时

钟信号同步，而第二选通信号与第二选通时钟信号同步。

9、如权利要求 8 所述的驱动设备，其中，第一选通时钟信号与第二选

通时钟信号部分重叠。

10、如权利要求 9 所述的驱动设备，其中，第一选通时钟信号比第二选

通时钟信号超前 1/4 H。

11、如权利要求 9 所述的驱动设备，其中，第二选通时钟信号比第一选

通时钟信号超前 1/4 H。

12、如权利要求 8 所述的驱动设备，其中，第一和第二移位寄存器包括

相互连续连接的多个级，并且，在第一和第二移位寄存器中的每个里面的第

一级和最后级中的至少一个接收垂直同步开始信号。

13、如权利要求 7 所述的驱动设备，其中，多条第一和第二选通线各自

具有与该驱动设备的第一侧相邻的第一末端、以及与该驱动设备的第二侧相

邻的第二末端，该选通驱动部分仅耦接到多条第一和第二选通线的第一末

端。

14、一种显示设备，包括：

多个主像素，各自包括第一和第二子像素，并以矩阵方式排列；

多条第一选通线，其耦接到第一子像素，并传递第一选通信号；

多条第二选通线，其耦接到第二子像素，并传递第二选通信号；

选通驱动部分，其生成第一和第二选通信号，并包括：

第一移位寄存器，其响应于第一选通时钟信号而生成第一输出信

号；

第二移位寄存器，其响应于第二选通时钟信号而生成第二输出信号；

电平转移器，其分别耦接到第一和第二移位寄存器；以及

输出缓冲器，其耦接到电平转移器，以及

信号控制器，其将控制信号施加到该选通驱动部分，

其中，相邻主像素的充电时间不重叠，而每个像素内的第一和第二子像素的充电时间重叠，以及

在第一选通时钟信号的高电平期间的第一选通时钟信号的宽度与在第二选通时钟信号的高电平期间的第二选通时钟信号的宽度不同。

15、如权利要求 14 所述的显示设备，还包括第一和第二液晶电容器，其分别与第一和第二子像素中的每个耦接，其中，不同时对第一和第二液晶电容器充电。

16、如权利要求 15 所述的显示设备，其中，后充电的子像素的充电时间与先充电的子像素的充电时间相比减小。

17、如权利要求 14 所述的显示设备，其中，第一和第二子像素接收不同的数据电压。

18、如权利要求 14 所述的显示设备，其中，第一选通信号与第一选通时钟信号同步，而第二选通信号与第二选通时钟信号同步。

19、如权利要求 18 所述的显示设备，其中，第一选通时钟信号与第二选通时钟信号部分重叠。

20、如权利要求 19 所述的显示设备，其中，第一选通时钟信号比第二选通时钟信号超前 1/4 H。

21、如权利要求 19 所述的显示设备，其中，第二选通时钟信号比第一选通时钟信号超前 1/4 H。

22、如权利要求 19 所述的显示设备，其中，第一和第二移位寄存器包括相互连续连接的多个级，并且，在第一和第二移位寄存器中的每个里面的每一级和最后级中的至少一个接收垂直同步开始信号。

23、如权利要求 14 所述的显示设备，其中，多条第一和第二选通线从该显示设备的第一侧延伸到该显示设备的第二侧，该选通驱动部分仅位于该显示设备的第一侧。

24、一种显示设备，包括：

多个主像素，其各自包括第一和第二子像素，并以矩阵方式排列；

多条第一选通线，其耦接到第一子像素，并传递第一选通信号；

多条第二选通线，其耦接到第二子像素，并传递第二选通信号；以及

选通驱动部分，其生成第一和第二选通信号，并包括：

第一移位寄存器，其响应于第一选通时钟信号而生成第一选通信号；以及

第二移位寄存器，其响应于第二选通时钟信号而生成第二选通信号，

其中，相邻主像素的充电时间不重叠，而每个各自的主像素内的第一和第二子像素的充电时间重叠，以及

在第一选通时钟信号的高电平期间的第一选通时钟信号的宽度与在第二选通时钟信号的高电平期间的第二选通时钟信号的宽度不同。

25、如权利要求 24 所述的显示设备，其中，第一和第二选通线各自包括与该显示设备的第一侧相邻的第一末端、以及与该显示设备的第二侧相邻的第二末端，该选通驱动部分仅耦接到第一和第二选通线中的每条的第一末端。

## 用于显示设备的选通驱动设备及其显示设备

### 技术领域

本发明涉及用于显示设备的选通 (gate) 驱动设备、以及具有该选通驱动设备的显示设备。更具体地，本发明涉及在显示设备中改进子像素的充电时间的选通驱动设备、以及具有该选通驱动设备的显示设备。

### 背景技术

近来，例如有机发光显示器 (“OLED”)、等离子显示面板 (“PDP”)、以及液晶显示器 (“LCD”) 设备的平板显示设备比阴极射线管 (“CRT”) 设备更迅速地发展着。在平板显示设备之中，广泛使用的 LCD 设备包括上显示基板和下显示基板，在其中形成电场生成电极 (例如，像素电极和公共电极)。此外，LCD 设备包括开关元件、显示信号线、以及生成用于导通和关断开关元件的选通控制信号的选通驱动部分。选通驱动部分包括能够将选通控制信号输出到选通线的移位寄存器、电平转移器 (level shifter)、以及输出缓冲器。移位寄存器包括一个接一个相互连接的多个级。每级依次生成每条选通线的输出，并将所生成的输出通过电平转移器和输出缓冲器而施加到选通线。

已更好地认可了 LCD 设备的垂直对齐模式，其中在无电压施加状态下，液晶分子相对于上和下显示基板而被垂直排列，这是由于其具有较大的对比度，并提供比其它类型的 LCD 设备更宽的基本视角。这里，基本视角表示具有 1 至 10 的对比率的视角、或灰度级中的亮度反转 (inversion) 的阈值角度。

在 LCD 设备的垂直对齐模式中，存在几种用来执行宽视角的方法(例如，形成电场生成电极的部分移除部分、以及形成电场生成电极上的突起 (protrusion) 的方法)。由于液晶分子的部分移除部分和突起控制朝向，可通过使用部分移除部分和该突起、沿几个方向重新排列液晶分子，而使视角变宽。

然而，LCD 设备的垂直对齐模式具有与前视属性相比会恶化侧视属性的缺点 (例如，具有较窄的视角)。举一个例子，提供有电场生成电极的部分移除部分的 LCD 设备的图案化垂直对齐模式会从正面至侧面而变得更亮。换句

话说，高灰度级的亮度具有基本上相同的电平，于是，存在显示出不良质量的图像的问题。

为解决以上问题，在将一个像素划分为两个子像素、并电容性耦接两个子像素之后，已建议了改变 LCD 设备的透射率的方法，其包括：将电压施加到一个子像素；通过在另一个子像素上的电容性耦接而产生压降；以及在子像素上具有不同电压。然而，当将选通电压施加到所述两个子像素时，上述选通驱动部分的每级在每一个水平时间生成选通电压（即，水平时刻表示处理一行像素的时间）。此时，同时导通所述两个子像素，由此，不会将不同的电压施加到所述两个子像素。尽管独立地驱动 LCD 设备的所述两个子像素（其中，在 LCD 设备的两端边缘上均形成选通驱动部分），但制造成本仍然提高，并且所占用的选通驱动部分的面积增大，由此增大了 LCD 设备的尺寸。

## 发明内容

本发明提供了用于改善显示设备内的子像素的充电时间的选通驱动部分。

本发明还提供了包括上述选通驱动部分的驱动设备。

本发明还提供了包括上述选通驱动部分的显示设备。

在本发明的示范实施例中，一种用于显示设备的选通驱动部分，该显示设备包括各自具有第一和第二子像素的多个像素，选通驱动部分包括：第一移位寄存器，其响应于第一选通时钟信号而生成第一输出信号；第二移位寄存器，其响应于第二选通时钟信号而生成第二输出信号；电平转移器，其耦接到第一和第二移位寄存器，并放大第一和第二输出信号；以及输出缓冲器，其耦接到电平转移器，并生成第一和第二选通信号。

在本发明的其它示范实施例中，一种用于显示设备的驱动设备，该显示设备包括各自具有第一和第二子像素的多个像素，该驱动设备包括：多条第一选通线，其耦接到第一子像素，并传递第一选通信号；多条第二选通线，其耦接到第二子像素，并传递第二选通信号；以及选通驱动部分，其生成第一和第二选通信号，并具有生成第一选通信号的第一移位寄存器、生成第二选通信号的第二移位寄存器、分别耦接到第一和第二移位寄存器的电平转移器、以及耦接到电平转移器的输出缓冲器。

在其它示范实施例中，一种显示设备包括：多个主像素，其各自包括第

一和第二子像素，并以矩阵方式排列；多条第一选通线，其耦接到第一子像素，并传递第一选通信号；多条第二选通线，其耦接到第二子像素，并传递第二选通信号；选通驱动部分，其生成第一和第二选通信号，并具有生成第一选通信号的第一移位寄存器、生成第二选通信号的第二移位寄存器、分别耦接到第一和第二移位寄存器的电平转移器、以及耦接到电平转移器的输出缓冲器；以及信号控制器，其将控制信号施加到选通驱动部分。

在其它示范实施例中，一种显示设备包括：多个主像素，其各自包括第一和第二子像素，并以矩阵方式排列；多条第一选通线，其耦接到第一子像素，并传递第一选通信号；多条第二选通线，其耦接到第二子像素，并传递第二选通信号；以及选通驱动部分，其生成第一和第二选通信号，并包括生成第一选通信号的第一移位寄存器、以及生成第二选通信号的第二移位寄存器。

#### 附图说明

通过参照附图来详细地描述本发明的实施例，本发明的以上及其它特征和优点将变得更为清楚，附图中：

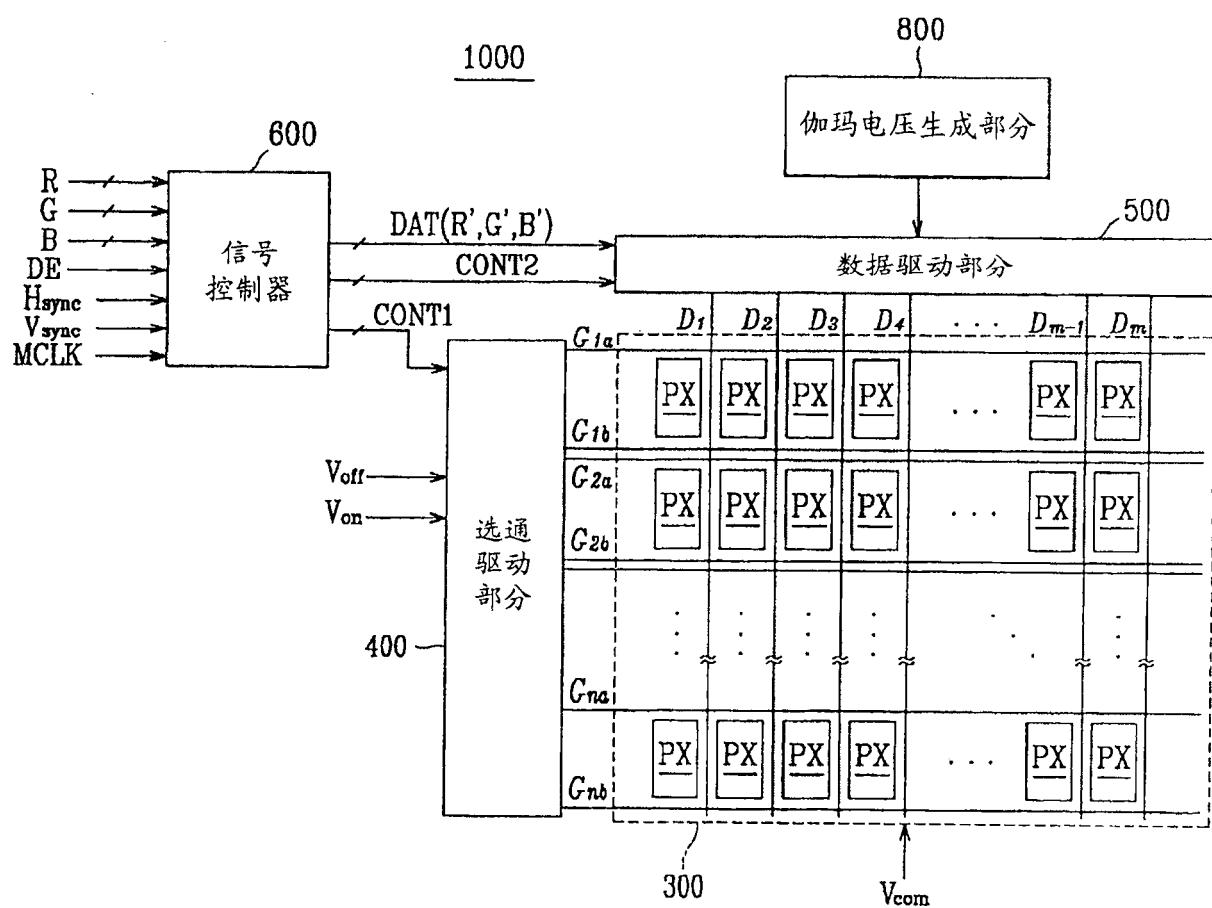

图 1 是根据本发明的液晶显示（“LCD”）设备的示范实施例的框图；

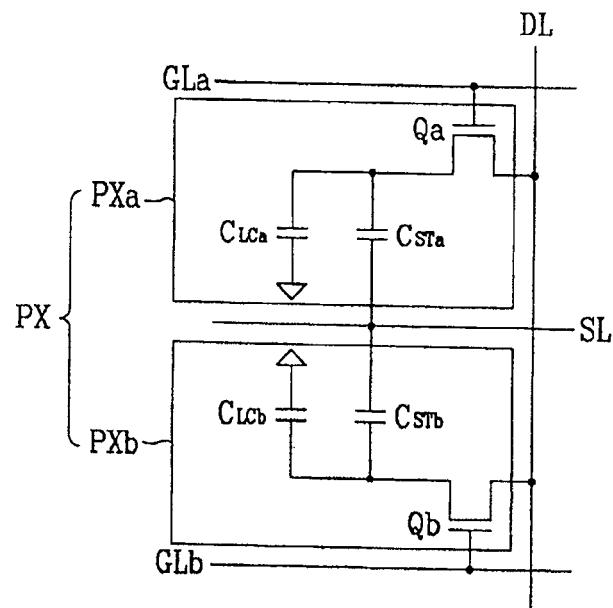

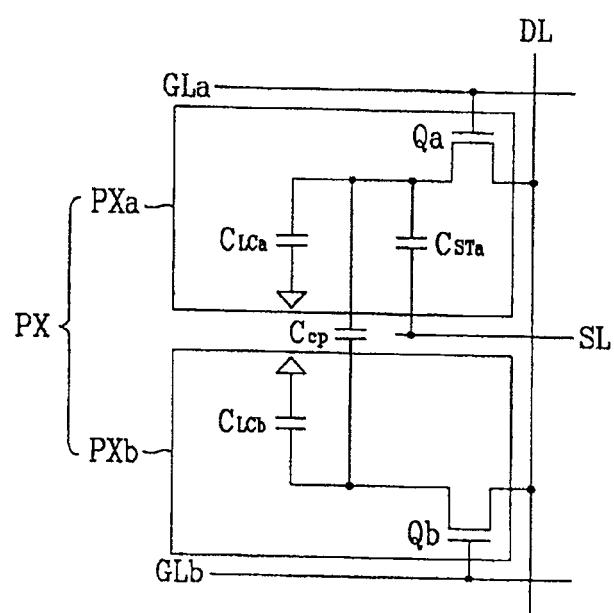

图 2A 和 2B 是根据本发明的 LCD 设备中的像素的示范实施例的等价电路图；

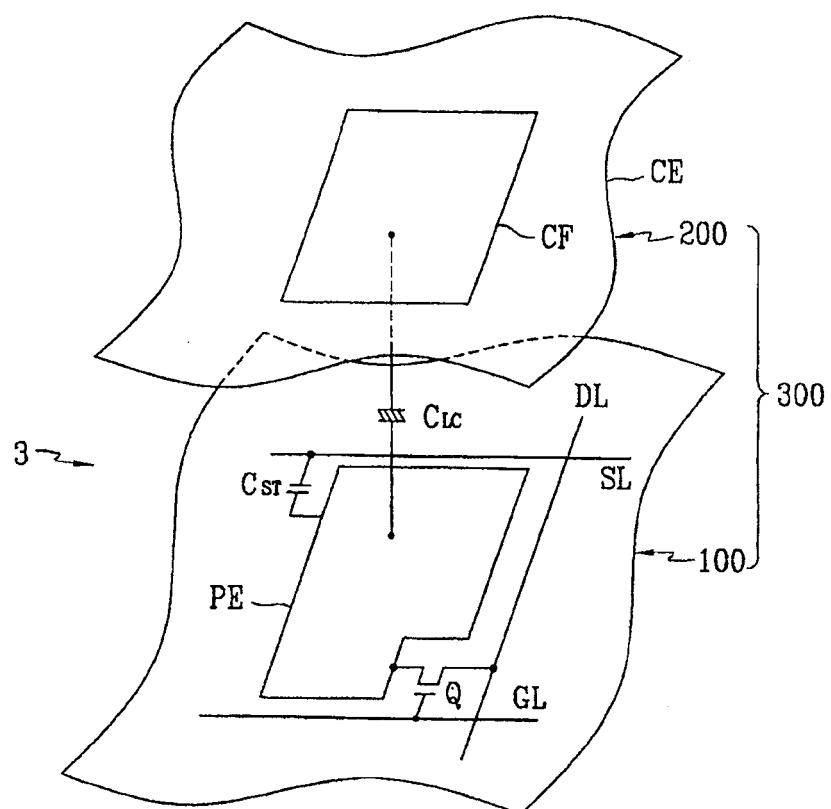

图 3 是根据本发明的 LCD 设备的一个子像素的示范实施例的等价电路图；

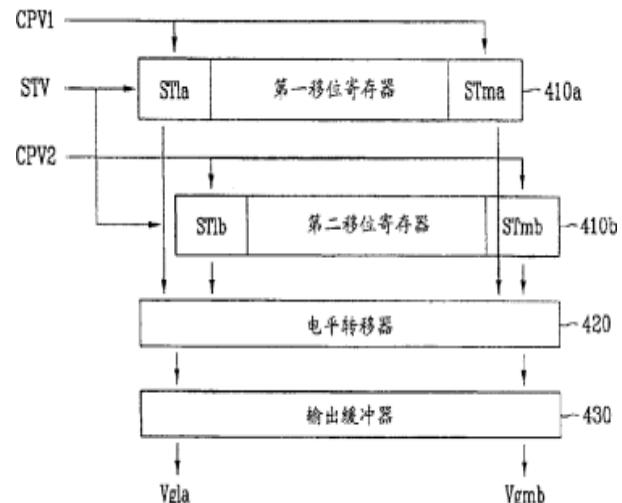

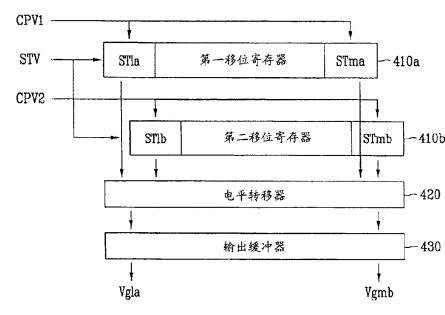

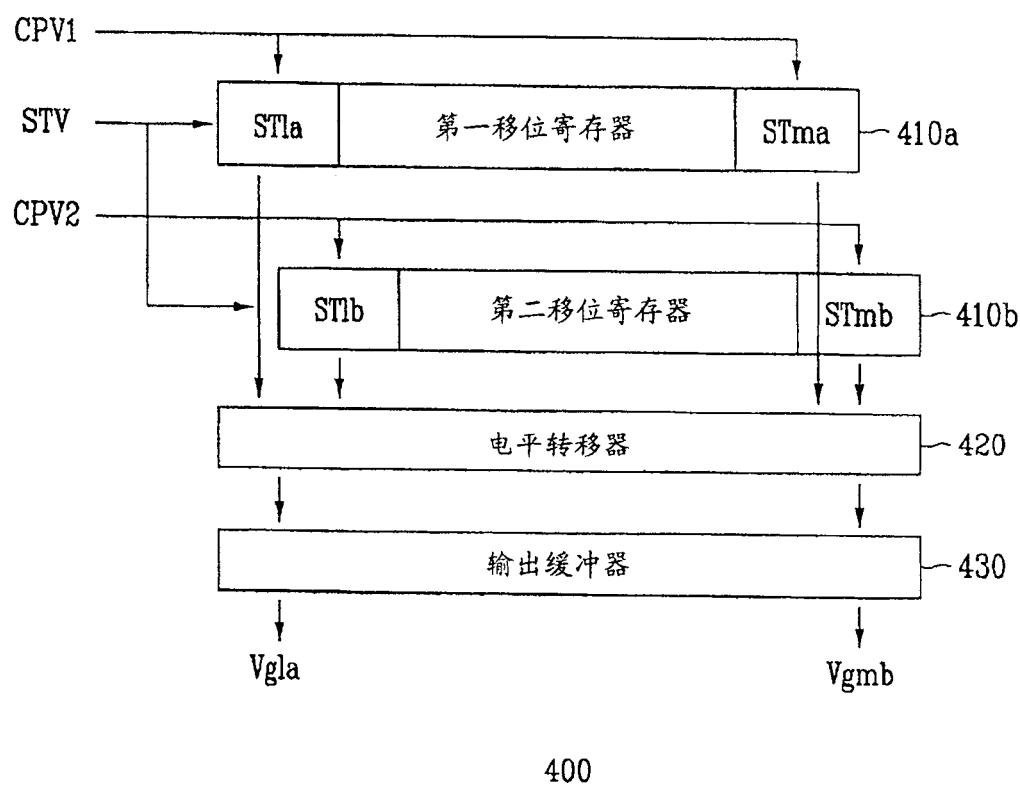

图 4 是根据本发明的选通驱动部分的示范实施例的框图；

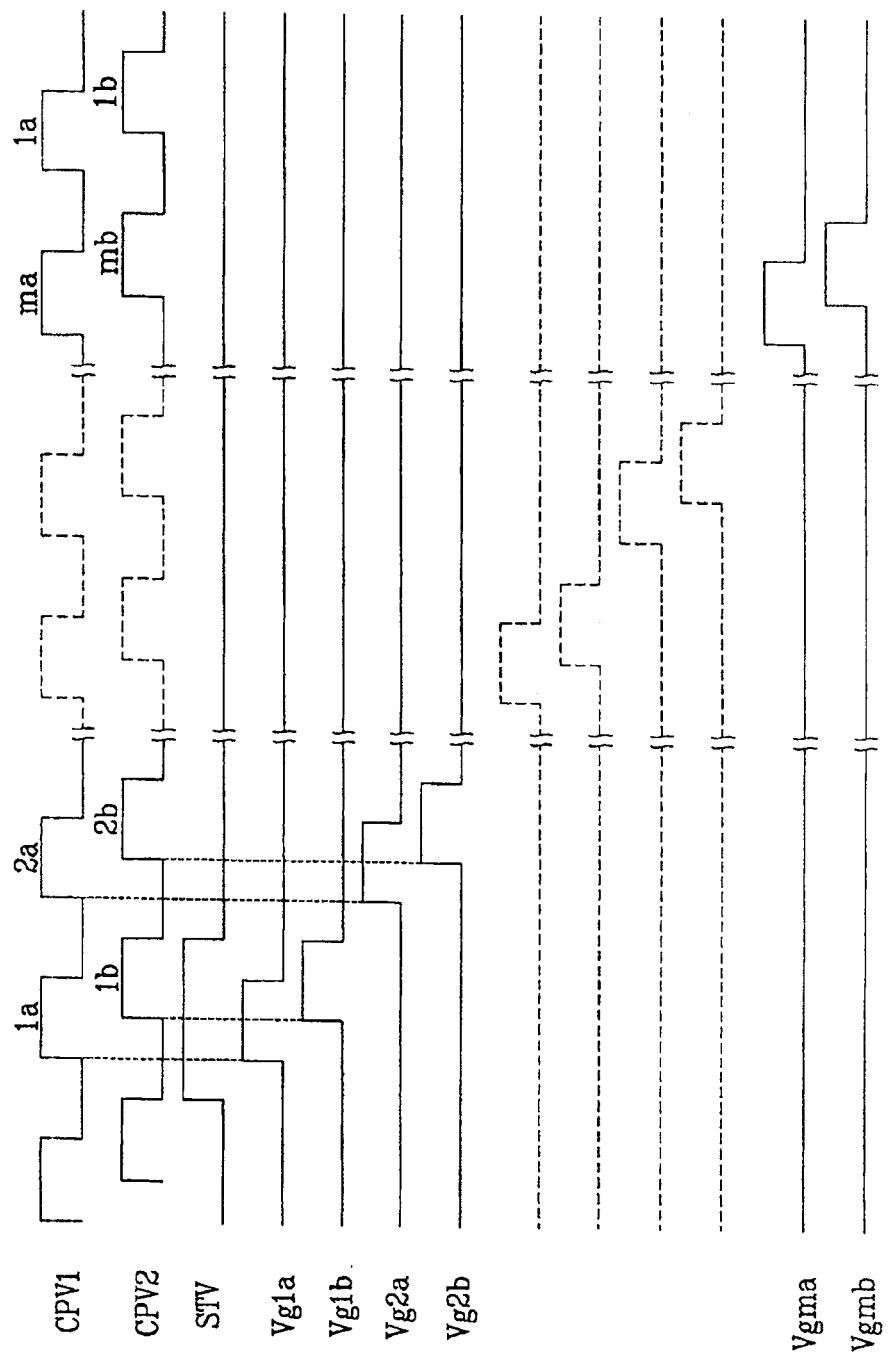

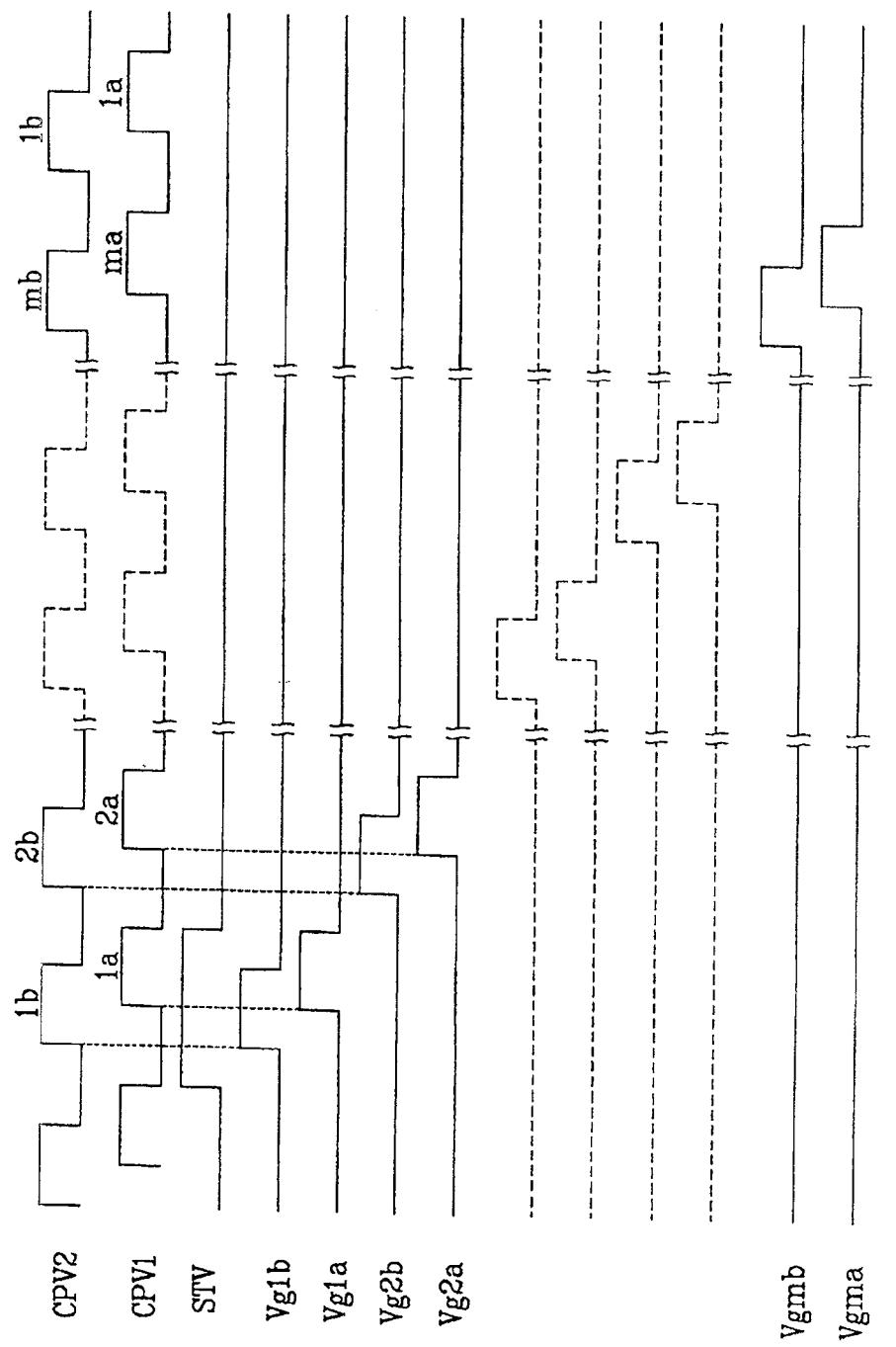

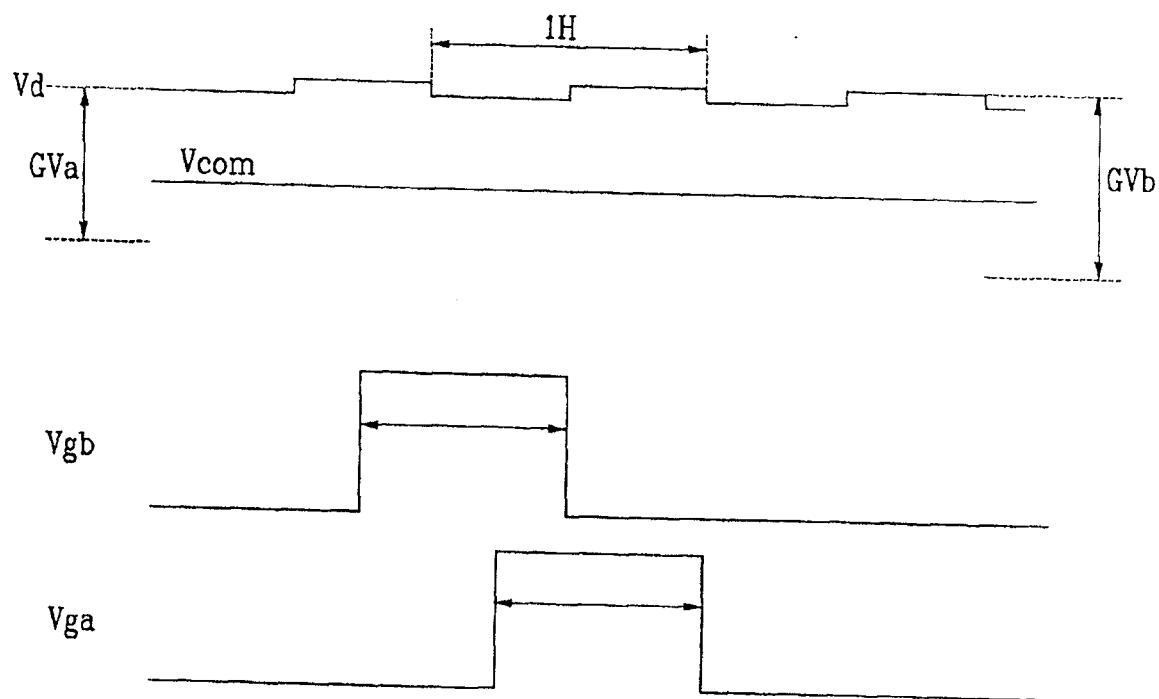

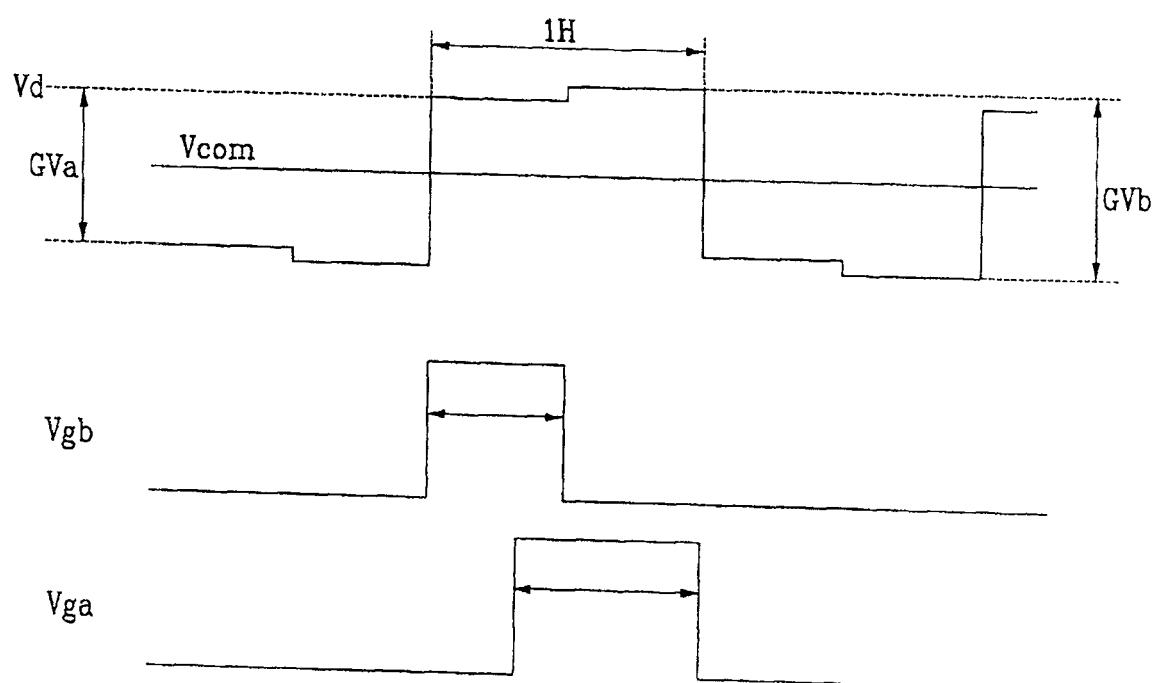

图 5A 和 5B 是图 4 中的示例选通驱动部分的信号波形；

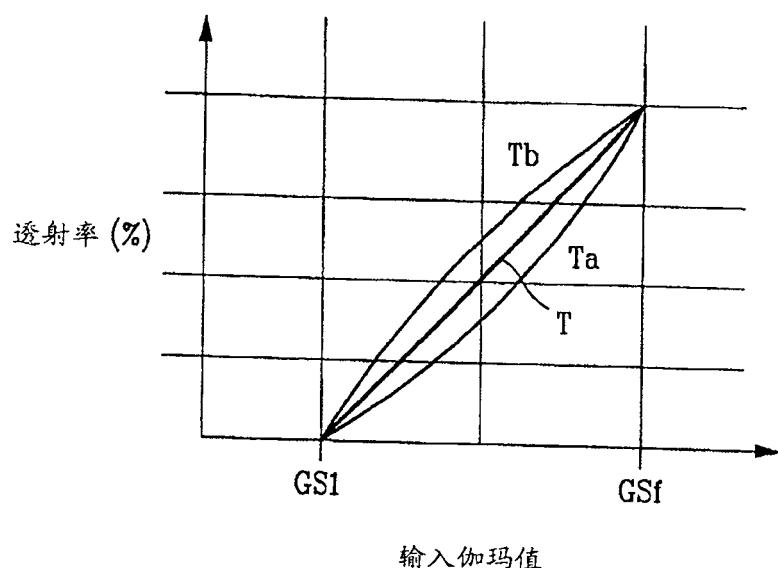

图 6 是示出根据本发明的 LCD 设备的示范实施例的伽玛曲线的图形；和

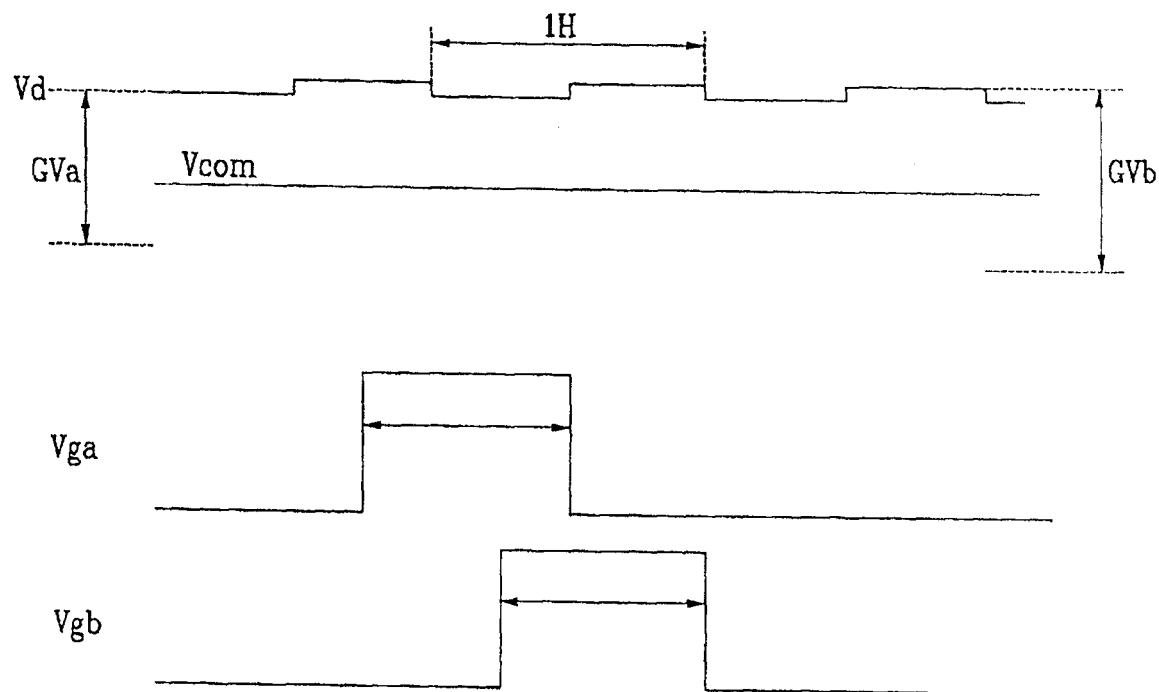

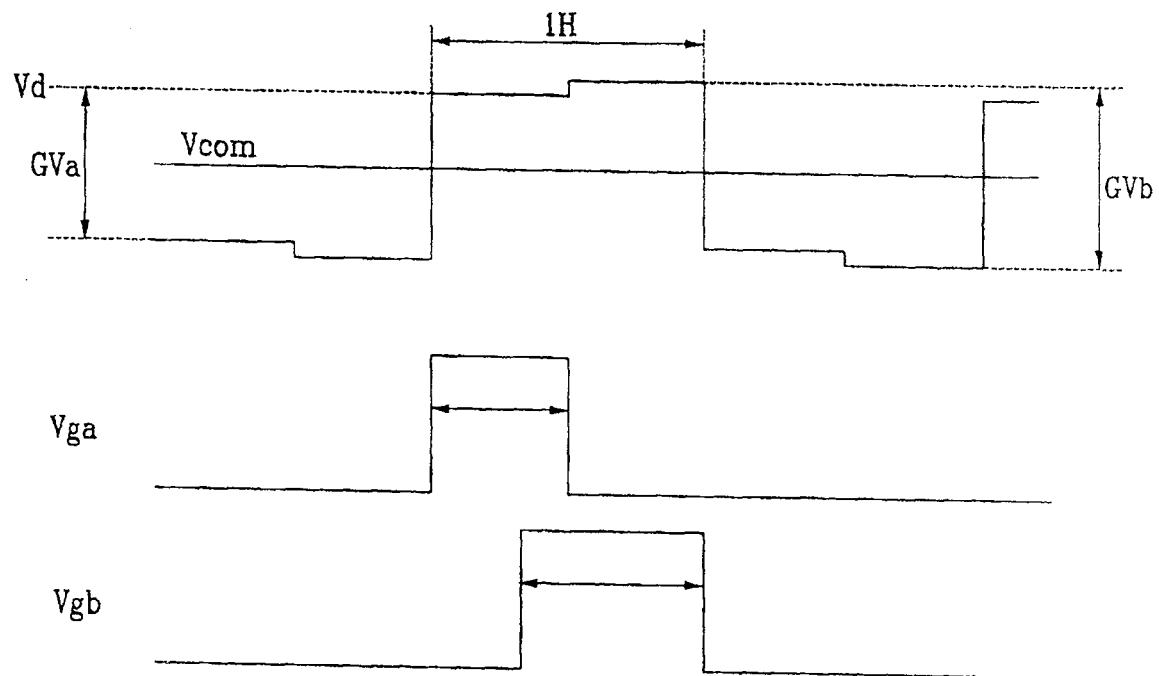

图 7A 至 8B 是示出根据本发明的 LCD 设备的示范实施例的信号波形的图形。

#### 具体实施方式

现在，将在下文中通过参照附图而更完整地描述本发明，附图中示出了本发明的示范实施例。然而，可以很多不同形式实现本发明，并且，不应将本发明限于这里阐述的实施例。

图 1 是根据本发明的液晶显示 (“LCD”) 设备的示范实施例的框图，图 2A 和 2B 是根据本发明的 LCD 设备中的像素的示范实施例的等价电路图，而图 3 是根据本发明的 LCD 设备的一个子像素的示范实施例的等价电路图。

转到图 1，LCD 设备 1000 包括薄膜晶体管 (“TFT”) 阵列面板 300、选通驱动部分 400、数据驱动部分 500、信号控制器 600、以及伽玛电压生成部分 800。选通和数据驱动部分 400 和 500 分别连接到 TFT 阵列面板 300。伽玛电压生成部分 800 连接到数据驱动部分 500，并还可连接到信号控制器 600。

TFT 阵列面板 300 具有信号线，其包括：延伸到选通驱动部分 400 的选通线 G1a、G1b、G2a、G2b、……、Gna 和 Gnb；以及延伸到数据驱动部分 500 的数据线 D1-Dm。TFT 阵列面板 300 还包括各自连接到信号线且以矩阵方式排列的像素 PX。选通线 G1a、G1b、G2a、G2b、……、Gna 和 Gnb 沿水平 (横向) 方向而彼此并行地形成，并且，数据线 D1-Dm 彼此平行、且与选通线 G1a、G1b、G2a、G2b、……、Gna 和 Gnb 基本垂直相交地形成。每个像素 PX 包括：开关元件 Q (在图 2A-3 中示出)，其连接到选通线 G1a、G1b、G2a、G2b、……、Gna 和 Gnb、以及数据线 D1-Dm；以及像素电路 (未示出)，其连接到开关元件 Q。开关元件 Q 可为 TFT。另外，开关元件 Q 可通过非晶硅 (“a-Si”) 而制成。

转到图 2A 和 2B，LCD 设备 1000 还包括：平行延伸到在图 2A 和 2B 中被表示为 GLa 和 GLb 的选通线的存储电极线 SL。如图 2A 所示，每个像素 PX 包括第一和第二子像素 PXa、PXb，并且，第一和第二子像素 PXa、PXb 各自包括：开关元件 Qa、Qb，其连接到对应的选通线 GLa、GLb、以及对应的数据线 DL；以及液晶电容器 C<sub>LCa</sub>、C<sub>LCb</sub>，其分别连接到开关元件 Qa、Qb；以及存储电容器 C<sub>STa</sub>、C<sub>STb</sub>，其连接到存储电极线 SL。可替换地，存储电容器 C<sub>STa</sub>、C<sub>STb</sub> 和存储电极线 SL 可根据需要而被省略。

如图 2B 所示，每个像素 PX 包括：第一和第二子像素 PXa、PXb；以及耦合电容器 C<sub>cp</sub>，其被置于第一和第二子像素 PXa、PXb 之间。第一和第二子像素 PXa、PXb 各自包括：开关元件 Qa、Qb，其连接到对应的选通线 GLa 和 GLb、以及对应的数据线 DL；以及液晶电容器 C<sub>LCa</sub>、C<sub>LCb</sub>，其分别连接到开关元件 Qa、Qb。第一和第二子像素 PXa、PXb 中的一个包括存储电容器 C<sub>STa</sub>，其被置于开关元件 Qa、Qb 中的一个和存储电极线 SL 之间。

转到图 3，例如，第一和第二子像素 PXa、PXb 的开关元件 Q 可以是形

成在下显示基板 100 上的 TFT。开关元件 Q 具有连接到选通线 GL 的控制端子、连接到数据线 DL 的输入端子、以及连接到液晶电容器  $C_{LC}$  和存储电容器  $C_{ST}$  的输出端子。

液晶电容器  $C_{LC}$  具有两个端子，所述两个端子具有下显示基板 100 的子像素电极 PE、以及上显示基板 200 的公共电极 CE，并且，被置于子像素电极 PE 和公共电极 CE 之间的液晶层 3 作为电介质而操作。子像素电极 PE 连接到开关元件 Q，并且，公共电极 CE 形成在上显示基板 200 的整个表面或基本上整个表面上，并接收公共电压  $V_{com}$ 。可替换地，公共电极 CE 可形成在下显示基板 100 上，并且，在此情况下，例如，子像素电极 PE 和公共电极 CE 中的至少一个可按照线形或条形而制造。

作为对液晶电容器  $C_{LC}$  的补充而操作的存储电容器  $C_{ST}$  具有绝缘体，其被置于形成在下显示基板 100 上的存储电极线 SL 和子像素电极 PE 之间。存储电极线 SL 接收期望电压，如公共电压  $V_{com}$ 。可替换地，通过作为绝缘体而布置子像素电极 PE、并与先前的选通线重叠，来形成存储电容器  $C_{ST}$ 。

同时，每个像素通过显示三种颜色（如基色）中的一种（即，空间划分）、或随着时间变化而依次显示三种颜色，而将期望的图像识别为三种颜色（例如，红、绿和蓝）的顺序和空间和。图 3 示出了：每个像素包括滤色器 CF，作为空间划分的例子，其指示上显示基板 200 的区域处的基色中的一种。可替换地，滤色器 CF 可形成在下显示基板 100 的子像素电极 PE 之上或之下。

回到图 1，选通驱动部分 400 包括选通驱动器（未示出），并且，选通驱动器连接到选通线 G1a、G1b、G2a、G2b、……、Gna 和 Gnb。选通驱动部分 400 将选通信号分别施加到选通线 G1a、G1b、G2a、G2b、……、Gna 和 Gnb。可替换地，选通驱动部分 400 可形成在下显示基板 100 上。

伽玛电压部分 800 具有正和负的伽玛电压的组，例如，正组伽玛电压具有比公共电压  $V_{com}$  高的电压，而负组伽玛电压具有比公共电压  $V_{com}$  低的电压。伽玛电压的正和负组的数目分别取决于 LCD 设备 1000 的分辨率。

数据驱动部分 500 包括数据驱动器（未示出），并且，数据驱动器连接到数据线 D1-Dm。数据驱动部分 500 通过从伽玛电压部分 800 选择特定伽玛电压，而将期望的图像信号施加到数据线 D1-Dm。选通和数据驱动器可通过将磁带载体包装（tape carrier package，“TCP”）附加到 TFT 面板组件 300 而形成，并可被安装在下显示基板 100 上，例如，玻璃上的芯片（chip on glass，

“COG”）。

信号控制器 600 生成控制和定时信号，并控制选通驱动部分 400 和数据驱动部分 500。

现在，将通过参照图 1 至 3 而更详细地描述 LCD 设备 1000 的操作。

转到图 1，信号控制器 600 从外部图形控制器（未示出）接收输入控制信号 Vsync、Hsync、Mclk、DE 以及输入图像信号 R、G、B，并且，关于输入控制信号 Vsync、Hsync、Mclk、DE 以及输入图像信号 R、G、B 而生成图像信号 R'、G'、B'、选通控制信号 CONT1、以及数据控制信号 CONT2。此外，信号控制器 600 将选通控制信号 CONT1 发送到选通驱动部分 400，并将数据控制信号 CONT2 发送到数据驱动部分 500。选通控制信号 CONT1 包括指示一帧的开始的垂直同步开始信号 STV、控制选通开信号(gate on signal)的输出定时的选通时钟信号 CPV、指示一条水平线的结束时刻的输出使能信号 OE 等。数据控制信号 CONT2 包括指示一条水平线的开始的水平同步开始信号 STH、指示数据电压的输出的 TP 或 LOAD、指示数据电压相对于公共电压 Vcom 而极性反向的 RVS 或 POL 等。

转到图 1-3，数据驱动部分 500 从信号控制器 600 接收图像信号 R'、G'、B'，并通过根据数据控制信号 CONT2 而选择与图像信号 R'、G'、B'相对应的伽玛电压，而输出数据电压。选通驱动部分 400 根据选通控制信号 CONT1 而将选通开信号施加到选通线 G1a、G1b、G2a、G2b、……、Gna 和 Gnb，并导通连接到选通线 G1a、G1b、G2a、G2b、……、Gna 和 Gnb 的开关元件 Qa、Qb。因而，将施加到数据线 D1-Dm 的数据电压通过被导通的开关元件 Qa、Qb 而施加到对应的子像素 PXa、PXb。

施加到第一和第二子像素 PXa、PXb 的数据电压、以及公共电压 Vcom 之间的差指示液晶电容器 C<sub>LCa</sub>、C<sub>LCb</sub> 的充电电压（即，像素电压）。液晶层 3 中的液晶分子的对齐方式根据像素电压的大小而变化，并且因而，通过液晶层 3 的光的偏振发生变化。这样的偏振变化表示通过附接到下和上显示基板 100、200 的一个或多个偏振器（未示出）而造成的光的透射率的变化。例如，可将第一偏振膜和第二偏振膜分别置于下和上显示基板 100、200 上。第一和第二偏振膜可根据液晶层 3 的对齐方向，而分别调节外部提供的光到下显示基板 100 和上显示基板 200 中的传送方向。第一和第二偏振膜可分别具有基本上彼此垂直的其第一和第二偏振轴。偏振器的其它排列也在这些实施例的

范围内。

现在，将通过参照图 4、5A 和 5B 来描述使用于将选通开信号施加到两个相邻选通线的时间周期重叠的操作。

图 4 是根据本发明的选通驱动部分 400 的示范实施例的框图，而图 5A 和 5B 是图 4 中的示例选通驱动部分 400 的信号波形。

转到图 4，选通驱动部分 400 包括：第一和第二移位寄存器 410a、410b；连接到第一和第二移位寄存器 410a、410b 的电平转移器 420；以及输出缓冲器 430。第一和第二移位寄存器 410a、410b 接收垂直同步开始信号 STV、以及第一和第二选通时钟信号 CPV1、CPV2。垂直同步开始信号 STV 以及第一和第二选通时钟信号 CPV1、CPV2 是从信号控制器 600 发送到选通驱动部分 400 的选通控制信号 CONT1 的一部分。第一和第二移位寄存器 410a、410b 中的每个分别包括多个级 ST1a、……、STma 和 ST1b、……、STmb。

电平转移器 420 将第一和第二移位寄存器 410a、410b 的输出放大到适于操作像素 PX 的开关元件 Q 的幅度，并将第一放大输出发送到输出缓冲器 430。输出缓冲器 430 考虑到由于信号延迟造成的选通电压的减小、而利用减小的电平来放大第一放大输出，并发送第二放大输出。假定选通线 GLa 表示奇数选通线 G1a、G2a、……、Gna，而选通线 GLb 表示偶数选通线 G1b、G2b、……、Gnb（参照图 2A 和 2B），第一移位寄存器 410a 生成用于操作连接到奇数选通线 G1a、G2a、……、Gna 的开关元件 Qa 的选通信号，而第二移位寄存器 410b 生成用于操作连接到偶数选通线 G1b、G2b、……、Gnb 的开关元件 Qb 的选通信号。

转到图 5A 和 5B，第一和第二选通时钟信号 CPV1、CPV2 具有一个水平周期 1H、以及 50% 的占空比，其中，占空比是脉冲持续时间对脉冲周期的比。通过 50% 或近似 50% 的占空比，第一和第二选通时钟信号 CPV1、CPV2 具有脉冲周期的一半的脉冲持续时间。图 5A 中的第一选通时钟信号 CPV1 比第二选通时钟信号 CPV2 超前 1/4H 或近似 1/4H，而图 5B 中的第二选通时钟信号 CPV2 比第一选通时钟信号 CPV1 超前 1/4H 或近似 1/4H。这里，由第一和第二移位寄存器 410a、410b、电平转移器 420、以及输出缓冲器 430 生成的选通电压是指在第一和第二移位寄存器 410a、410b 处生成的电压，并表示为“Vg”。Vga 是指施加到奇数选通线 G1a、G2a、……、Gna 的选通电压，而 Vgb 是指施加到偶数选通线 G1b、G2b、……、Gnb 的选通电压。

当将垂直同步开始信号 STV 施加到第一和第二移位寄存器 410a、410b 时，第一和第二移位寄存器 410a、410b 的第一级 ST1a、ST1b（在图 4 中示出）在垂直同步开始信号 STV 的高电平期间与第一和第二选通时钟信号 CPV1、CPV2 的上升沿同步，并分别输出选通信号 Vg1a、Vg1b。

第一移位寄存器 410a 的每个余下的级（未示出）接收先前级的输出，作为进位信号（而不是垂直同步开始信号 STV），与第一选通时钟信号 CPV1 同步，并将选通信号 Vg2a、…、Vgma 发送到奇数选通线 G2a、…、Gna。第二移位寄存器 410b 具有与第一移位寄存器 410a 相同的配置。换句话说，第二移位寄存器 410b 的每个余下的级通过接收先前级的输出作为进位信号、并与第二选通时钟信号 CPV2 同步，而将选通信号 Vg2b、…、Vgmb 发送到偶数选通线 G1b、G2b、…、Gnb。

转到图 2A 和 5A，由于第一选通时钟信号 CPV1 比第二选通时钟信号 CPV2 超前  $1/4H$ ，所以，连接到奇数选通线 GLa 的第一子像素 PXa 的液晶电容器  $C_{LCa}$  首先被充电，并且随后，连接到偶数选通线 GLb 的第二子像素 PXb 的液晶电容器  $C_{LCb}$  被充电。可替换地，如图 2B 和 5B 所示，连接到偶数选通线 GLb 的第二子像素 PXb 的液晶电容器  $C_{LCb}$  首先被充电，并且随后，连接到奇数选通线 GLa 的第一子像素 PXa 的液晶电容器  $C_{LCa}$  被充电。

转到图 5A 和 5B，奇数选通信号 Vg1a、Vg2a、…、Vgma 中的每个分别与偶数选通信号 Vg1b、Vg2b、…、Vgmb 中的每个重叠，但选通信号 Vg1a、Vg1b 不与选通信号 Vg2a、Vg2b 重叠。换句话说，选通信号 Vg1b 不与如图 5A 所示的选通信号 Vg2a 重叠，而选通信号 Vg1a 不与如图 5B 所示的选通信号 Vg2b 重叠。因而，各自连接到奇数和偶数选通线 GLa、GLb 的第一和第二子像素 PXa、PXb 分别在  $1H$  期间接收数据电压，并且由此，第一和第二子像素 PXa、PXb 的液晶电容器  $C_{LCa}$ 、 $C_{LCb}$  被充分地充电。

同时，例如，第二选通时钟信号 CPV2 具有 50% 的占空比，但不限于此。换句话说，可通过第二选通时钟信号 CPV2 的较大占空比（例如，但不限 75% 的占空比）而得到第一子像素 PXa 的较高充电率。

转到图 6，图 6 示出了伽玛曲线，其表示依赖于输入伽玛值的透射率，其中，GS1 是最低输入伽玛值，而 GSf 是最高输入伽玛值。伽玛电压的正和负组（参照图 1）分别具有第一和第二伽玛曲线 Ta、Tb。一个像素 PX 的第一和第二子像素 PXa、PXb 接收对第一和第二伽玛曲线 Ta、Tb 求和的第三伽

玛曲线 T 的特性。对于定义更好的参考伽玛值的参考伽玛曲线，前视图上的第三伽玛曲线 T 符合前视图上的参考伽玛曲线，而任一侧视图上的第三伽玛曲线 T 更接近地符合任一侧视图上的参考伽玛曲线。

现在，将通过参照图 7A 至 8B 而描述具有选通驱动部分 400 的 LCD 设备 1000 中的数据电压的类型。

图 7A 至 8B 示出了示出根据本发明的 LCD 设备的示范实施例的信号波形的图形，其中  $V_d$  是在一条数据线上流动的数据电压。图 7A 和 7B 示出了通过参照图 5A 而描述的第一选通时钟信号 CPV1 超前第二选通时钟信号 CPV2 的情况的数据电压，而图 8A 和 8B 示出了通过参照图 5B 而描述的第二选通时钟信号 CPV2 超前第一选通时钟信号 CPV1 的情况的数据电压。

在 LCD 设备 1000 的点反转 (dot-inversion) 驱动中，由于相邻像素  $P_X$  的极性不同，所以，接收相邻像素  $P_X$  的数据电压不会帮助减小充电时间。因而，如图 7A 和 8A 所示，相邻像素  $P_X$  的充电时间不重叠，但是子像素  $P_{Xa}$ 、 $P_{Xb}$  的充电时间重叠。如图 7A 和 8A 所示，由于第一和第二子像素  $P_{Xa}$ 、 $P_{Xb}$  的之后充电的子像素  $P_{Xa}$  或  $P_{Xb}$  的充电时间减小，所以，施加到之后充电的子像素  $P_{Xa}$  或  $P_{Xb}$  的数据电压  $GV_b$  变得大于施加到首先充电的子像素  $P_{Xb}$  或  $P_{Xa}$  的数据电压  $GV_a$ 。

同时，在 LCD 设备的列反转驱动中，由于沿垂直方向的相邻像素的极性相同，所以，通过施加相邻像素的数据电压而执行预充电。因而，如图 7B 和 8B 所示，所有子像素的充电时间可在大于期望时间的期间重叠。

此外，选通驱动部分 400 (向回参照图 1) 不能使第一和第二选通时钟信号 CPV1、CPV2 重叠，并且，这可能适用于当一个像素具有一个开关元件时的配置。可替换地，与选通驱动部分 400 不同，该选通驱动部分可将垂直同步开始信号 STV 分别施加到第一和第二移位寄存器的最后级，并且在此情况下，可从左至右而依次生成选通信号。换句话说，当将垂直同步开始信号 STV 分别施加到第一和第二移位寄存器的第一级时，从左至右而依次生成选通信号 (例如， $Vg1a$ 、 $Vg2a$ 、...、 $Vgma$ )。可替换地，当将垂直同步开始信号 STV 分别施加到第一和第二移位寄存器的最后级时，从右至左而依次生成选通信号 (例如， $Vgma$ 、...、 $Vg2a$ 、 $Vg1a$ )。

根据本发明的实施例，通过独立地驱动奇数和偶数子像素而改善子像素的充电时间，并且还可改善 LCD 设备的可视性。另外，可通过利用仅在下显

---

示基板的一个边缘上形成的选通驱动部分而驱动奇数和偶数选通线，而减小显示基板的尺寸。

在已描述了本发明的实施例及其优点之后，应注意，这里可做出各种改变、替换和变更，而不会背离如所附权利要求定义的本发明的精神和范围。此外，“第一”、“第二”等术语的使用不表示任何次序或重要性，而是使用术语“第一”、“第二”等来使元件相互区分。此外，术语“a, an(一个)”等的使用不表示量的限制，而是表示至少一个所引用项的存在。

此申请要求于2005年4月11日提交的韩国专利申请第2005-0029903号的优先权，并且，通过引用而将其全部内容合并于此。

图 1

图 2A

图 2B

图 3

图 4

图 5A

图 5B

图 6

图 7A

图 7B

图 8A

图 8B

|                |                                                   |         |            |

|----------------|---------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于显示设备的选通驱动设备及其显示设备                               |         |            |

| 公开(公告)号        | <a href="#">CN100595822C</a>                      | 公开(公告)日 | 2010-03-24 |

| 申请号            | CN200610009004.1                                  | 申请日     | 2006-02-16 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                          |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                          |         |            |

| 当前申请(专利权)人(译)  | 三星电子株式会社                                          |         |            |

| [标]发明人         | 金宇哲<br>李濬表<br>文胜煥<br>孙宣圭                          |         |            |

| 发明人            | 金宇哲<br>李濬表<br>文胜煥<br>孙宣圭                          |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                       |         |            |

| CPC分类号         | G09G2300/0439 G09G2310/0251 G09G3/3659 G09G3/3677 |         |            |

| 优先权            | 1020050029903 2005-04-11 KR                       |         |            |

| 其他公开文献         | CN1848226A                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">SIPO</a>    |         |            |

#### 摘要(译)

一种用于显示设备的选通驱动部分，该显示设备包括各自具有第一和第二子像素的多个像素，该选通驱动部分包括：第一移位寄存器，其响应于第一选通时钟信号而生成第一输出信号；第二移位寄存器，其响应于第二选通时钟信号而生成第二输出信号；电平转移器，其耦接到第一和第二移位寄存器，并放大第一和第二输出信号；以及输出缓冲器，其耦接到电平转移器，并生成第一和第二选通信号。与第一选通时钟信号同步生成第一选通信号，并与第二选通时钟信号同步生成第二选通信号。因而，可通过独立地驱动奇数和偶数子像素而改善第一和第二子像素的充电时间，并且，还可改善LCD设备的可视性。