[19] 中华人民共和国国家知识产权局

[12] 发明专利说明书

专利号 ZL 200410092118.8

[51] Int. Cl.

G09G 3/36 (2006.01)

G09G 5/18 (2006.01)

G09G 5/00 (2006.01)

G06F 3/14 (2006.01)

[45] 授权公告日 2008 年 11 月 5 日

[11] 授权公告号 CN 100430988C

[22] 申请日 2004.9.17

[21] 申请号 200410092118.8

[30] 优先权

[32] 2003.9.18 [33] US [31] 60/504060

[32] 2004.4.15 [33] US [31] 60/563120

[32] 2004.7.29 [33] US [31] 10/909103

[73] 专利权人 创世纪微芯片公司

地址 美国加利福尼亚州

[72] 发明人 O·科巴亚施

[56] 参考文献

US6356260B1 2002.3.12

CN1409290A 2003.4.9

US2003076282A1 2003.4.24

US2002089517A1 2002.7.11

WO9963513A2 1999.12.9

审查员 吕东

[74] 专利代理机构 中国专利代理(香港)有限公司

代理人 程天正 王勇

权利要求书 2 页 说明书 9 页 附图 7 页

[54] 发明名称

使用包传输驱动 LCD 屏板的驱动电路

[57] 摘要

公开了一种在数字显示设备中，通过包含在列驱动器中的相关数据锁存器来驱动选定的像素元的基于包的方法。对于一个视频帧中的每个帧行，直接以链路速率向列驱动器提供多个视频数据包，并且在一个行周期  $\tau$  内多个数据锁存器中的每一个都根据视频数据包输入了合适的视频数据。根据视频数据驱动选定的像素元。

1. 在数字显示设备中，一种通过包含在列驱动器中的相关的数据锁存器来驱动选定像素元的基于数据包的方法，包括：

(a) 以链路速率直接向列驱动器提供多个视频数据包；

(b) 根据视频数据包，在一行周期  $\tau$  内，向多个数据锁存器中的每一个输入合适的视频数据；

(c) 根据视频数据驱动选定的像素元；

(d) 对于一视频帧中的所有帧行重复 (a) - (c)。

2. 根据权利要求 1 所述的方法，进一步包括：

在通过链路耦合到数字显示设备的视频源产生一视频信号；

根据该视频信号形成一基于数据包的视频流；以及

通过链路以链路速率向数字显示设备发送基于数据包的视频流。

3. 根据权利要求 2 所述的方法，其中该数字显示设备包括一与该链路耦合的存储设备，用于在步骤 (a) 之前存储选定的视频数据包。

4. 根据权利要求 3 所述的方法，其中存储设备是一行缓冲器，用于存储至少与一帧行相容的视频数据包量。

5. 根据权利要求 1 所述的方法，其中每个视频数据包包括一包头和一包有效载荷，其中包头包括一包 ID，并且包有效载荷包括适于驱动一相应像素的视频数据。

6. 一种数字显示设备，包括：

多个像素元；

一用于以链路速率接收和分配视频数据包的接口；

多个数据锁存器，每个数据锁存器都用于从接口接收分配的视频数据包，存储与接收到的视频数据包相关的视频数据，并且根据存储的视频数据驱动选定的像素元。

7. 根据权利要求 6 所述的显示器，其中在与一视频帧中的一扫描行相应的行周期  $\tau$  内向选定的多个数据锁存器输入合适的视频数据。

8. 根据权利要求 7 所述的显示器，其中像素元以行和列排列。

9. 根据权利要求 8 所述的显示器，其中每列像素都与一列驱动器相连，从

---

而提供一显示信号。

10. 根据权利要求 9 所述的显示单元，其中每个列驱动单元包括多个数据锁存器的一子集。

11. 根据权利要求 10 所述的显示单元，其中视频数据包直接以链路速率发送到列驱动器。

12. 根据权利要求 11 所述的显示单元，其中多个扫描行乘以行周期小于或者等于一视频帧周期。

13. 根据权利要求 12 所述的显示器，其中显示器通过链路连接到一视频源，其中视频源形成了一基于数据包的视频流，并且将通过链路以链路速率将基于数据包的视频流传送到数字显示器。

14. 根据权利要求 13 所述的显示器，其中数字显示设备包括一与该链路耦合的存储设备，适用于存储选定的视频数据包。

15. 根据权利要求 14 所述的显示器，其中存储设备是一用于存储至少与一个帧行相容的视频数据包量的行缓冲器。

16. 根据权利要求 15 所述的显示器，其中每个视频数据包包括一包头和一包有效载荷，其中包头包括一包 ID，并且包有效载荷包括适于驱动一相应像素的视频数据。

## 使用包传输驱动 LCD 屏板的驱动电路

### 相关申请的交叉参考

本专利申请根据 35.U.S.C.119(e)要求(i)Kobayashi 于 2003 年 9 月 18 日提交的，题目为“数字/模拟视频互连及其使用方法”的美国临时专利申请 No.60/504,060 (代理卷号为 GENSP013P2) 以及 (ii) Kobayashi 于 2004 年 4 月 15 日提交的，题目为“使用包传输驱动 LCD 屏板的驱动电路”的美国临时专利申请 No.60/563, 120 (代理卷号为 GENSP112P) 的优先权，上述两篇文件在此全部引入并作为参考。本申请也涉及下面的共同待决的美国专利申请，它们也被在此引入以供参考：(i) 美国专利申请 No.10/726, 802 (代理卷号：GENSP014)，题目为“适配连接视频源和视频显示器的方法”，Kobayashi 为发明人；(ii) 美国专利申请 No.10/726,438(代理卷号：GENSP015)，题目为“多媒体数据包的高效传输的方法和装置”，Kobayashi 为发明人；(iii) 美国专利申请 No.10/726,440(代理卷号：GENSP105)，题目为“优化多媒体包传输速率的方法”，Kobayashi 为发明人；(iv) 美国专利申请 No.10/727/131(代理卷号 GENSP104)，题目为“使用辅助频道用于视频监视训练”，Kobayashi 为发明人；(v) 美国专利申请 No.10/726,350(代理卷号：GENSP106)，题目为“降低多媒体数据包开销的技术”，Kobayashi 为发明人；(vi) 美国专利申请 No.10/726,362(代理卷号：GENSP107)，题目为“具有周期性的状态检查的基于包的闭环视频显示接口”，Kobayashi 为发明人；(vii) 美国专利申请 No.10/726,895(代理卷号：GENSP108)，题目为“最小化数字视频系统中所需的缓冲器”，Kobayashi 为发明人；(viii) 美国专利申请 No.10/726,441(代理卷号：GENSP109)，题目为“用于提供独立于链路字符时钟的像素数据的视频接口”，Kobayashi 为发明人；(ix) 美国专利申请 No.10/726,934(代理卷号：GENSP110)，题目为“链路时钟速率和像素/音频时钟速率的列举方法”，Kobayashi 为发明人；以及 (x) 美国专利申请 No.10/726,794(代理卷号：GENSP013)，题目为“基于包的视频显示接口以及其使用方法”，Kobayashi 为发明人。

### 技术领域

本发明涉及显示设备。尤其是，本发明描述了一种使用驱动 LCD 屏板的驱动电路的方法和装置。

### 背景技术

在监视器和电视产品市场上，液晶显示器（LCD）已经开始代替基于阴极射线管（CRT）的监视器，这部分由于与基于 CRT 的技术相比，LCD 具有许多优点。这些优点包括尺寸更为小巧（与 CRT 相比减小了 60%），更低的能量消耗（50%），更轻的重量（比 CRT 轻 70%），没有电磁场，以及更长的使用寿命。

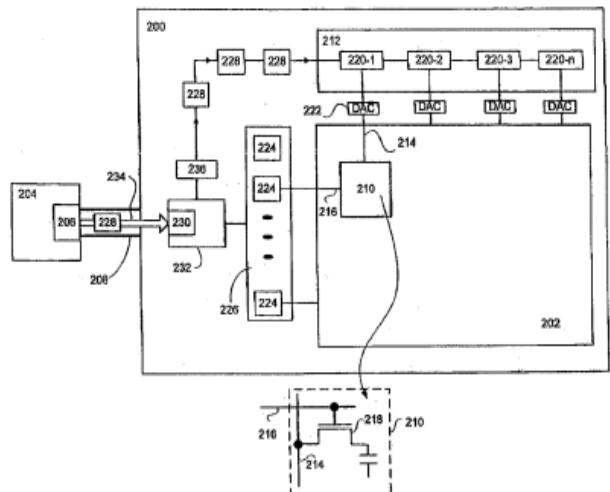

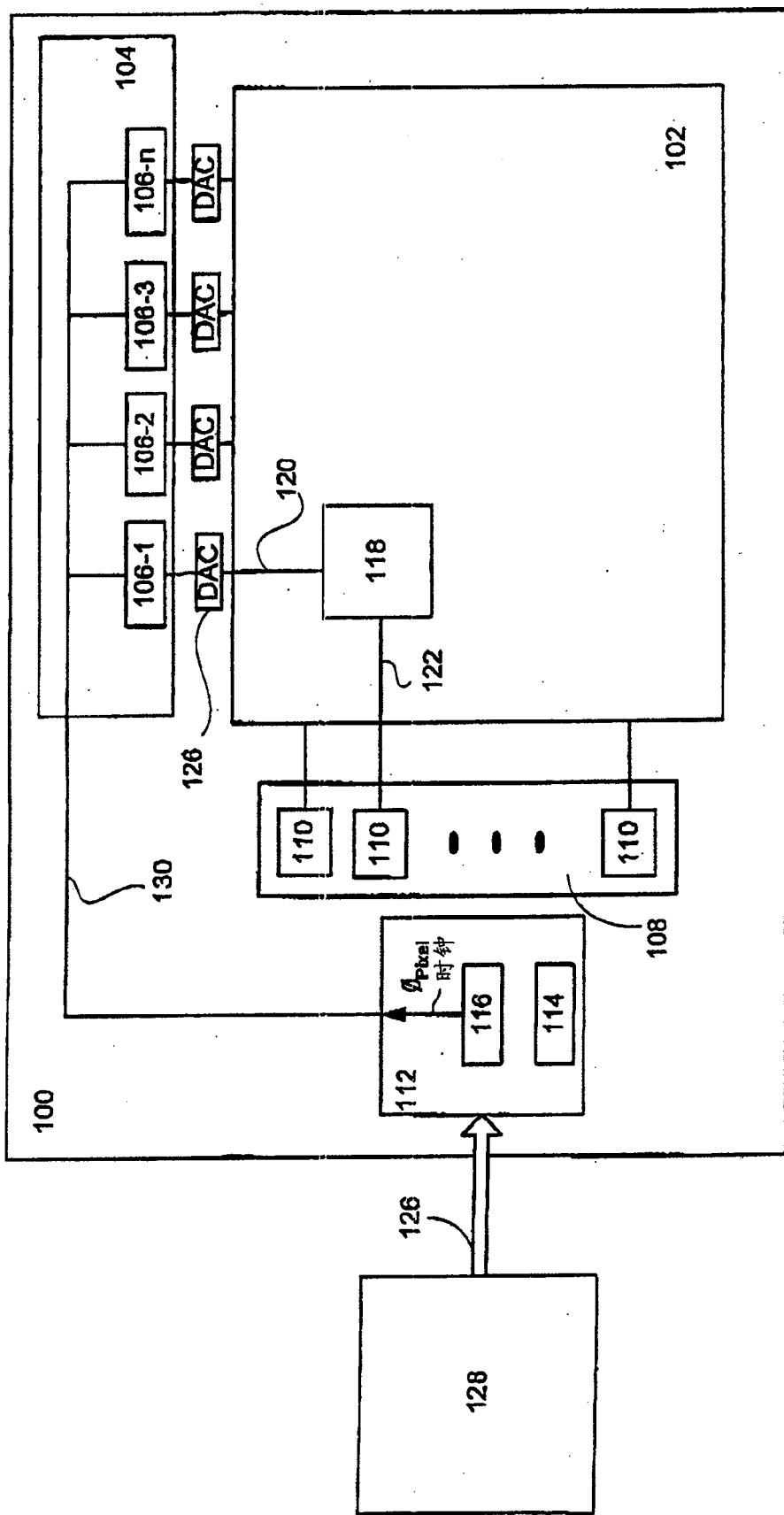

附图 1 是表明一个传统的有源矩阵液晶显示设备 100 的方框图，其包括一个液晶显示屏 102，一个包括几个适于存储图像数据的数据锁存器 106-1 到 106-n 的数据（或者列）驱动器 104，一个门驱动器 108，该门驱动电路包括门驱动逻辑电路 110，定时控制单元（也称为 TCON）112，以及一个包含在 TCON 当中或者与之耦合的适于存储图像数据的存储器 114。在一些情况下，存储器 114 呈现能够存储整个视频帧的帧存储器的形式，或者在其他情况下，存储器 114 呈现出能够存储一行视频数据的行缓冲器的形式。在上述任一情况下，图像数据以这种方式存储在存储器 114 当中，从而能够在一个被称为行周期  $\tau$  的时间周期内，每次传送一帧行到锁存器 106。如图所示，包含在或者耦合到 TCON112 的像素时钟产生单元 116 被用于把以链路时钟速率传送的视频数据转换成所需的像素时钟速率。

通常，TCON112 连接到一个视频源 128（例如一个个人计算机，电视或者其它类似设备），用于输出一个视频信号（在多数情况下，还有一个相关的音频信号）。在操作过程中，TCON112 通过多路总线 130 每次发送一个像素的视频数据，从而使其存储在一个被相应启动的数据锁存器 106 当中。例如，如果显示屏每行具有 1024 个像素，那么每行就具有 1024 个锁存器（应当注意在一个完整彩色显示的情况下，每个像素由 3 个子像素构成，红，绿，蓝，因此总共有  $1024 \times 3=3072$  个数据锁存器），每个数据锁存器都连接到多路数据总线 130。当视频数据加载到 TCON112 时，第一个锁存器就接收一个锁存器启动信号并且存储适当的像素数据，之后第二个锁存器接收锁存器启动信号并且存储合适的像素数据，并且这样继续直到所有的 3072 个锁存器都被启动，并且每次都存储合适的像素数据。这样，对于每个帧行，TCON112 必须在行周期  $\tau$

内向 3072 个数据锁存器中的一个合适的数据锁存器发送所有的像素数据。一旦一个特定的帧行的所有视频数据都被接收并被锁存，就可以使用视频数据驱动用于形成显示图像的包含在 LCD 阵列 102 中的多个图像源 118 中选定的图像源。

因此，为了使 TCON112 向正确的数据锁存器提供正确的像素数据，TCON112 必须在每个数据锁存器 106 之间提供一个握手启动信号，该信号必须从最左边的数据锁存器 106-1 向最右边的数据锁存器 106-n 传播，这样特定帧行的所有视频数据都能够在行周期  $\tau$  内被存储。由于即使最右侧的数据锁存器 106-n 必须由 TCON112 驱动，每行像素的数目要由 TCON112 能够充分驱动最右侧（距离最远）的数据锁存器 106-n 的能力所限制。耦合到大的多点总线 130 的元件的大数目（在 1024RGB 显示器的情况下是 3072）在保持信号完整性的方面对 TCON112 提出了严峻的挑战。由于信号的完整对于显示器 100 的正确操作至关紧要，由于一帧行的所有数据必须在通常为 20 微秒的一个行周期  $\tau$  内传送到所有的数据锁存器 106，通常数据率要被降低，因此严重限制了显示器 100 的分辨率。

一种解决该问题的方法是增加多路总线 130 的尺寸，不幸的是，这同时也增加了线路电容从而使得在总线上优化数据的传输非常困难。其他的方法（例如降低摆动差信号或者 RSDS）使用每个时钟具有两个像素的多路总线来代替一个多路总线和每时钟一个像素。尽管该方法降低了 TCON112 所需的驱动能力，但其也存在显著提高了 TCON 驱动电路的复杂度（以及加倍的插头数目）的不幸结果。例如，在 24 位彩色的情况下，RSDS 方法除了专用时钟线以外还需要 24 个传输线，这极大提高了 LCD 列驱动器 104 的复杂度。

因此需要一种驱动数字显示器的高速，大带宽的方法。

### 发明内容

提供了一种显示器结构，具体为适于和诸如液晶显示器（LCD）的数字显示器一起实施的方法，装置和系统，其独立于像素速率并且提供了一个高速，大带宽的数字显示平台。

公开了一种在一种数字显示设备中的，通过包含在列驱动器中的相关数据锁存器来驱动选定的像素元的基于包的方法。对于一个视频帧中的每个帧行，直接以链路速率向列驱动器提供多个视频数据包，并且多个数据锁存器中的每

一个都根据一个行周期  $\tau$  内的视频数据包输入了合适的视频数据。根据视频数据驱动选定的像素元。

在另一个实施例中，公开了一种数字显示设备，所述的数字显示设备包括多个像素元，一个用于以链路速率接收和分配视频数据包的接口，多个数据锁存器，每个数据锁存器都用于从接口接收一个分配的视频数据包，存储与接收到来的视频数据包相关的视频数据，并且根据存储的视频数据驱动选定的像素元。

在又一个实施例中，公开了一种用于在一个基于包的数字显示设备中，通过包含在列驱动器中的相关数据锁存器来驱动选定的像素元的计算机程序产品。所述的计算机程序产品包括用于以链路速率直接向列驱动器提供多个视频数据包的计算机代码，用于在一个行周期  $\tau$  内向多个数据锁存器中的每一个输入合适的视频数据的计算机代码，用于根据该视频数据驱动选定的像素元的计算机代码以及用于存储该计算机代码的计算机可读介质。

#### 附图说明

附图 1 是一个表明传统的有源矩阵液晶显示设备的例子的方框图。

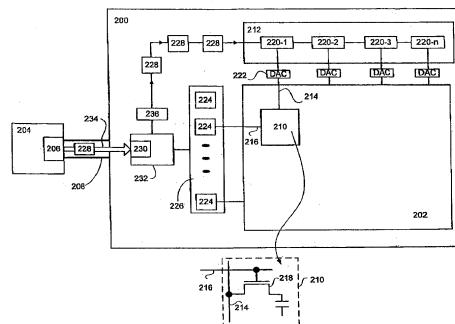

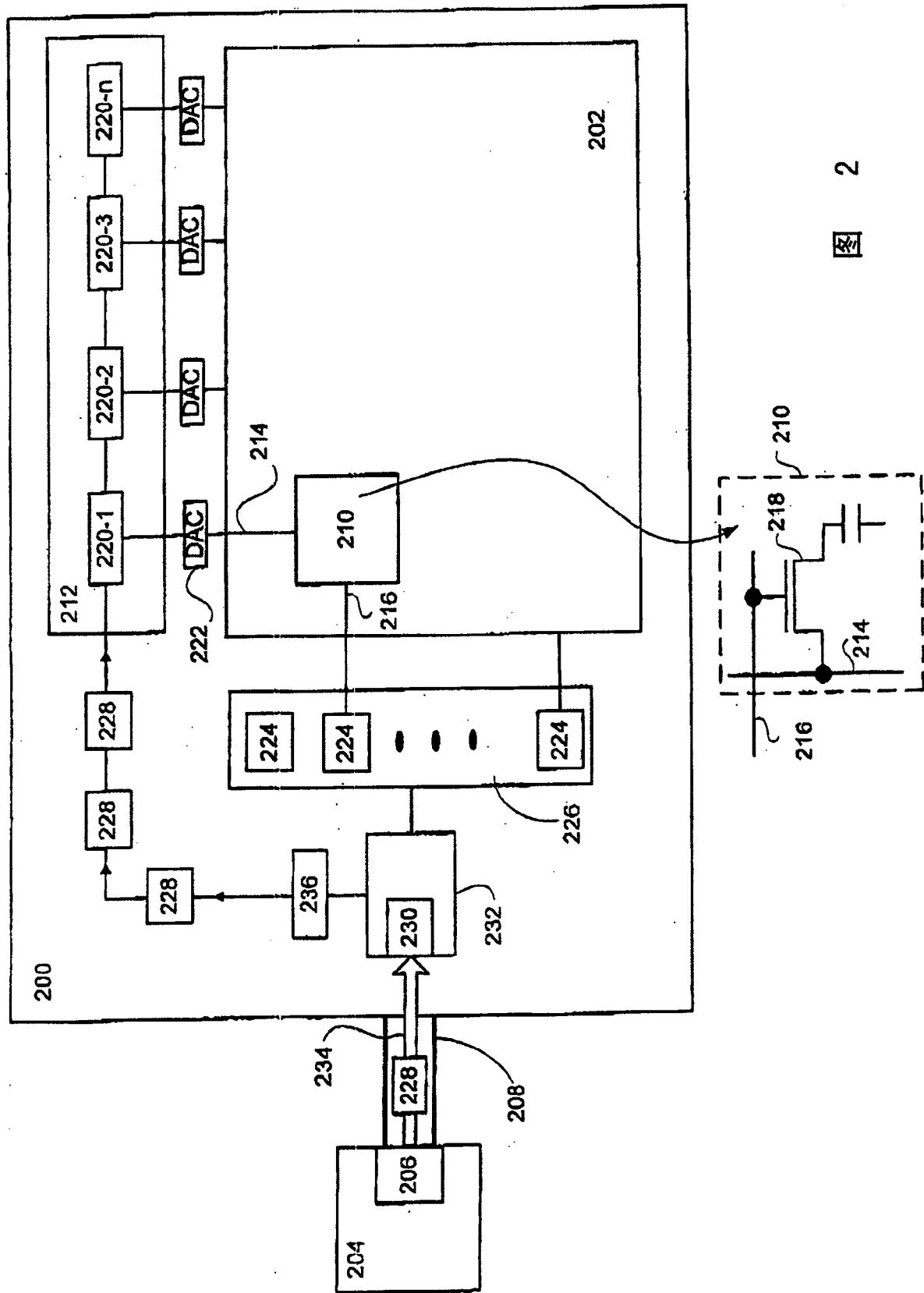

附图 2 表明了根据本发明的一个实施例的一个数字显示系统的例子。

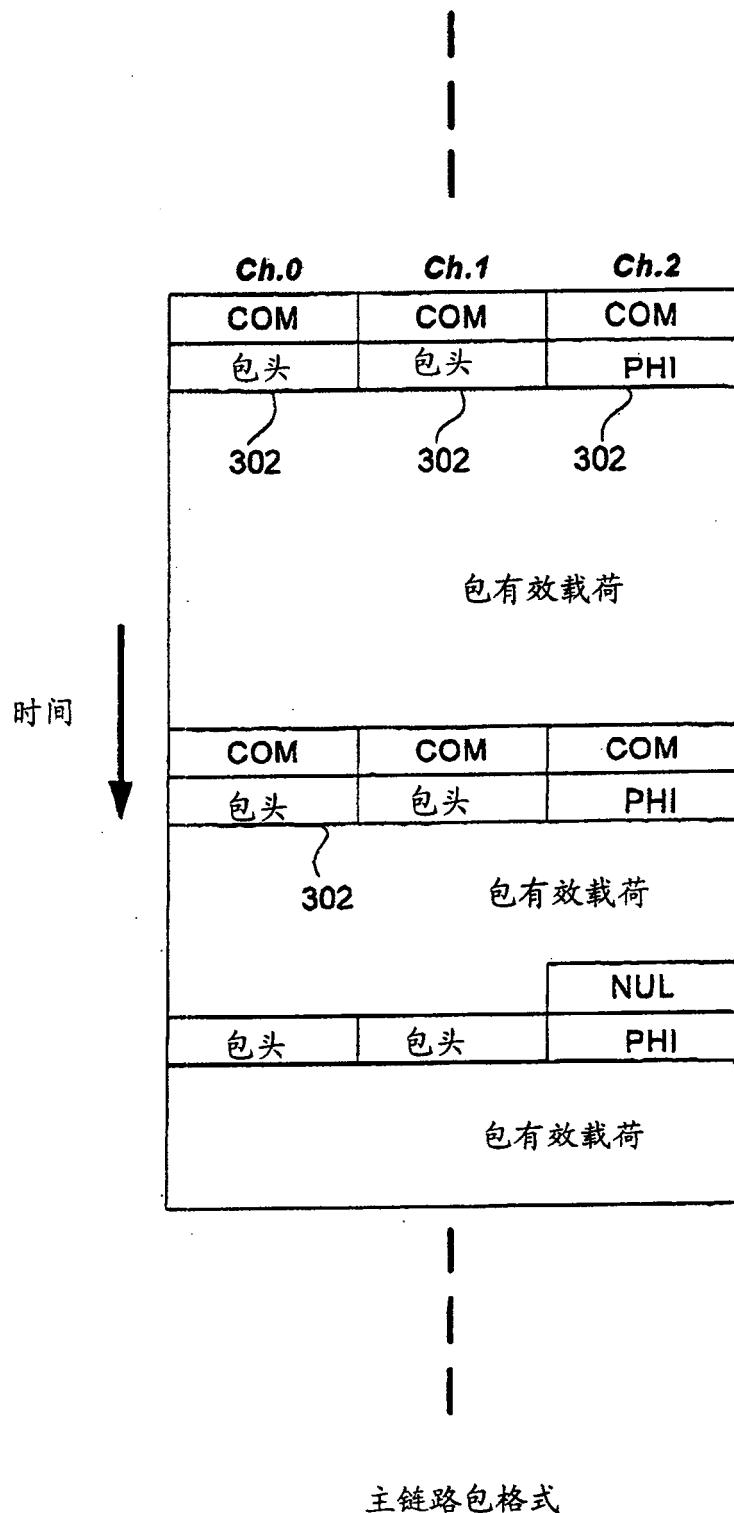

附图 3A 表明了根据本发明的一个实施例的典型的数据包。

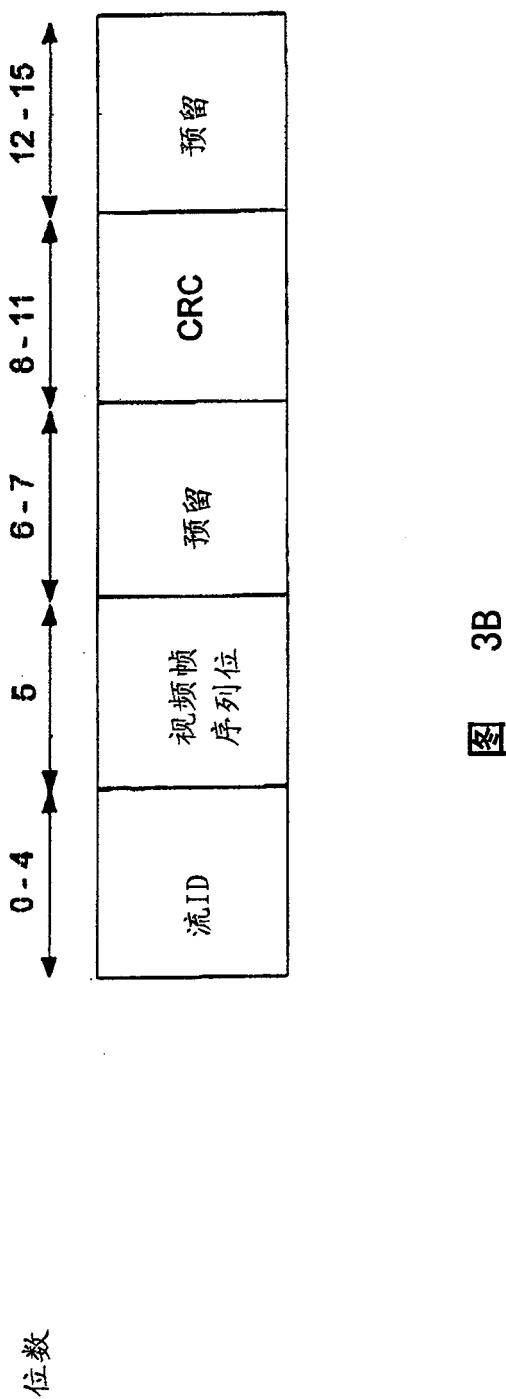

附图 3B 表明了附图 3A 所示的数据包的详细视图。

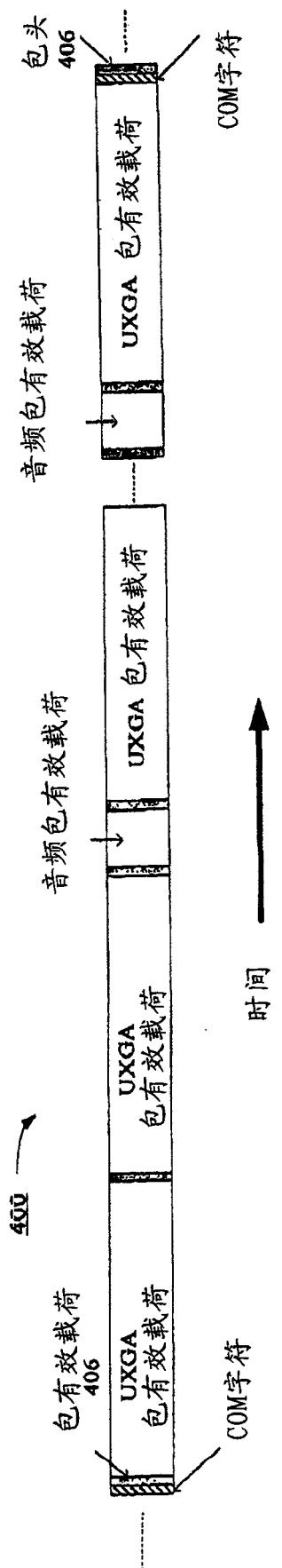

附图 4 是表明根据本发明的一个实施例在链路上传输数据流的高级框图。

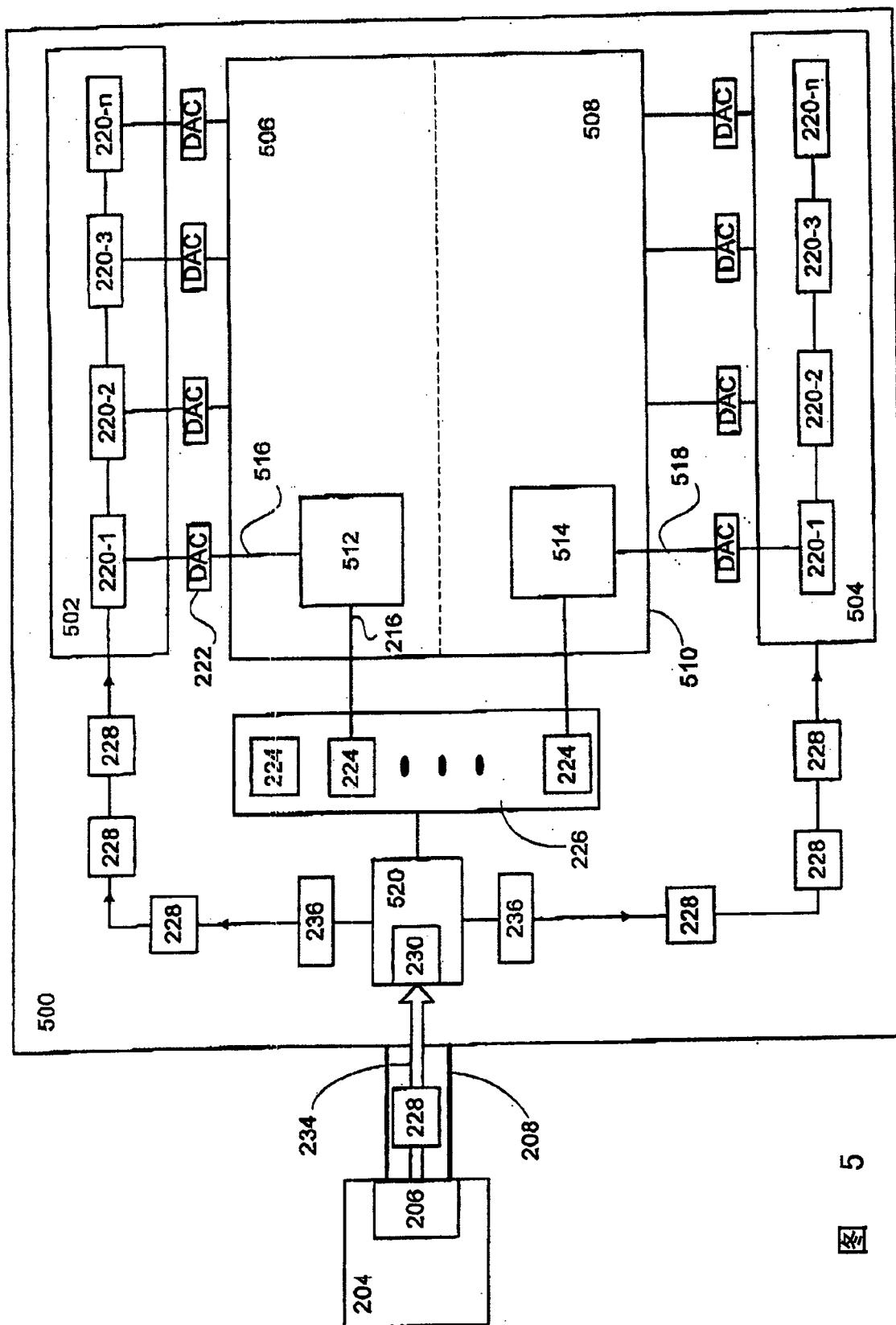

附图 5 表明了本发明的一个实施例。

附图 6 表明了能够用于执行本发明的一个系统。

#### 具体实施方式

现在将参照附图所示的本发明的特定实施例进行详细描述。尽管本发明是结合特定的实施例进行描述的，但是应该理解上述描述并不是将本发明局限于所述的实施例。相反，其期望覆盖包含在追加的权利要求所定义的本发明的精神和范围内的各种改变，变形和等价物。

为了使诸如 LCD 屏板的传统配置的数字显示设备显示图像，定时控制器必须从第一（通常为最左侧的数据锁存器）到最后（通常为最右侧的数据锁存器）传播视频数据（以象素时钟上的象素数据的形式），这样一个特定帧行的

所有视频数据就能够在一单个的行周期  $\tau$ （通常为 20 微秒）内被存储。由于即使最后的数据锁存器也必需由定时控制器驱动，每行的像素的数目由定时控制器能够在一个特定的行周期  $\tau$  内充分驱动最右侧（距离最远）的数据锁存器的能力所限制。随着显示器的分辨率的提高（在 1024RGB 显示器的情况下是 3072 个数据锁存器），定时控制器能够充分驱动一个与其耦合的多点总线（multidrop bus）的能力变得越来越困难，并且保持信号的完整性成为一个问题。由于信号的完整性对于显示器的正确操作来说至关重要，因此数据率被显著降低，由于一帧行的所有数据必须在通常为大约 20 微秒的一个行周期  $\tau$  内传送到所有的数据锁存器，因此这严重限制了显示器的分辨率。

一种解决该问题的方法是增加多点总线的尺寸，但是不幸的是，这同时也具有增加线路电容的效果，从而使得在总线上优化数据的传输非常困难。其他的方法（例如降低摇摆差信号，或者 RSDS）使用每时钟具有两个像素的多路总线来代替一个多点总线和每时钟一个像素。尽管这种方法降低了定时控制器的驱动要求，但是其也存在着增加了定时控制驱动电路的复杂性（以及加倍的插头数目）的不幸效果。例如，在 24 位彩色的情况下，RSDS 方法需要数据总线具有至少 24 个传输线以及一个专用的时钟线，因此极大的增加了 LCD 列驱动器的复杂度。

因此，一种基于包的显示结构被实现为适于和诸如液晶显示器（LCD）的数字显示器一起实施的方法，装置和系统，其使像素速率与行周期  $\tau$  分离，简化了列驱动电路，并提供了一个高速，大带宽的数字显示平台。该显示结构去除了传统的数字显示结构普遍使用的大的数据总线，而使用点对点“链环”结构。在该结构中，与显示器的本地水平行分辨率相容的多个数据锁存器彼此直接相连。这样，就能够以链路数据速率来传送和接收视频数据包，而不是象传统的显示结构所要求的那样以像素数据速率来传送和接收。

这样，由于不需要像素时钟再生（例如时基恢复），LCD 驱动电路的复杂度被极大的简化，并且由于数据包本身能够被编码从而提供必需的定时和在数据总线上分离数据线所提供的其他信号，数据总线的尺寸也被显著降低。此外，显示器的本地行分辨率（即水平像素的数目）能够显著增加而不会伴随增加驱动器复杂度或者总线尺寸，这是因为唯一的限制是必须在一行周期  $\tau$  内锁存一个特定的帧行的所有必需的视频数据。

现在根据典型的 LCD 屏板来描述本发明。但是应当理解诸如 LCD，等离子，基于 DLP 的任何数字固定像素显示器也能够适用，下面的描述不能被看作是限制本发明的范围或内容，应当注意本发明也适于与任何基于包的视频显示接口组合使用，例如在 Kobayashi 于 2003 年 12 月 3 日提交的题目为“基于包的视频显示接口及其使用方法”的美国待决的专利申请中有所描述，该文件在此结合作为参考。

因此，附图 2 表明了根据本发明的一个实施例的典型数字显示系统 200 的一个例子。该系统 200 包括一个通过数据链路 208 与一个具有一个图形引擎 206 的视频源 204 耦合的数字显示单元 202。应当注意视频源 204 可以包括数字图像源（即，静止或者数字视频源）和/或模拟图像（即静止或者模式视频）源。因此，视频源 204 提供多种具有任何数目和类型的已知格式的视频信号，例如复合视频，串行数字，并行数字，RGB，或者用户数字视频。视频信号可以是模拟视频信号，只要源 204 包括某种形式的模拟视频源，例如模拟电视机，照相机，模拟 VCR, DVD 播放器，可携式摄像机，激光盘播放器，TV 调谐器，机顶盒（利用卫星 DSS 或者有线信号）等。源 204 也可以包括数字图像源，例如一个数字电视机（DTV），数字照相机，等。数字视频信号可以是任何数目和类型的已知的数字格式，例如 SMPTE274M—1995(1920×1080 分辨率，逐行或者隔行扫描)，SMPTE296M-1997(1280×720 分辨率，逐行扫描)，以及标准 480 逐行扫描视频。

LCD 屏板 202 包括多个图像元 210（像素），它们以矩阵方式排列通过多个数据线 214 和多个门线 216 连接到一个数据驱动器 212。在所述的实施例中，这些图像元的形式是连接在数据线 214 和门线 216 之间的多个薄膜晶体管

(TFT) 218。在操作过程中，每个数据锁存器 220 通过数据线 214 将数字数据信号输出到相关的数字/模拟转换器 222 (DAC)。同时，包含在门驱动器 226 中的每个逻辑电路 224 中在与水平同步信号同步的定时向门线 216 依次输出一个预定的扫描信号。以这种方式，当预定的扫描信号被提供给门线 214 时，TFT 218 被打开从而通过数据线 214 的方式传送 DAC 222 所提供的模拟数据信号，最终驱动选定的图像元 210。

当图形引擎 206 包含在一个模式视频源中或者与之耦合时，图形引擎 206 数字化模拟数据以形成数字数据，然后数字数据被打包成多个数据包 228。在

所述的实施例中，每个数据包都以传输速率通过链路 208 传送到显示器 202，所述的传输速率是指独立于视频数据的本地流速率 LR。但是，应当注意链路 208 的带宽必须大于在链路 208 上传输的所有数据流的总带宽。但是，不论视频源或者显示器的类型如何，所有的视频数据都被数字化（如果需要），并且，在多数情况下，在通过链路 208 进行传输以前打包。但是，在某些情况下，使用包含在一个显示接口 232 中或者与之耦合的打包器 230，显示单元 202 本身将打包链路 208 上传输的任何未打包形式的视频和/或音频数据，因此显示器 202 可以与所有的视频源共同使用。

在所述的实施例中，链路 208 的速度或者链路速率可以配置成包括多个逻辑数据信道（未显示），其能够被调整从而补偿链路环境。例如，以 2.5Gbps 每信道，链路 208 能够在每个单一信道上支持 60Hz 的每像素 18 比特的彩色深度的 SXGA。应当注意信道数目的减少不仅降低了互连的成本，而且降低了能量消耗，这是诸如便携式设备等能量敏感型设备需要重点考虑（和期望）的问题。但是，通过将信道的数目增加到 4，链路 208 能够支持 60Hz 的、每像素 24 比特的彩色深度的 WQSXGA (3200×2048 图像分辨率)，或者 60Hz 的每像素 18 比特的彩色深度的 QSXGA (2560×2048)，而不需要进行数据压缩。即使在每信道 1.0Gbps 的最低速率的情况下，仅需要两个信道来支持一个未压缩的 HDTV (即，1080i 或者 720p) 数据流。

附图 3A 表明了一个典型的数据包 300，该数据包 300 包括一个 16 位的数据包头 302，其在附图 3B 中详细描述，其中 4-0 位是流 ID (SID)，位 5 是视频帧序列位，其是帧计数器的最低有效位，在视频帧的边界从“0”到“1”或者从“1”到“0”的开关变化(仅用于未压缩的视频流)。位 7 和位 6 是预留位，而位 8-10 是校验先前八位的误差的 4 位 CRC。

为了传送视频数据，视频源 204 形成了数据流 234，数据流包括多个数据包 228，数据被接收并且由显示器接口 230 处理。在所述的实施例中，数据包 228 被直接传送到包含在列驱动器 212 中的数据锁存器 220，这样用于显示视频帧的特定帧行 n 所使用的全部视频数据（像素数据的格式）在一行周期  $\tau$  内传送到数据锁存器 220。因此，一旦每个数据锁存器 220 具有存储于其中的适当的像素数据，数据驱动器 212 就驱动 LCD 阵列 202 中的合适的 TFT 218。

附图 4 表明了用于在链路 208 上传输的数据流 400 的高级框图，其中由多

一个视频数据包 402 和音频数据包 404 复用形成一个数据流 400。在该实施例中，视频数据包 402 与具有音频包 404（流 ID=2）格式的相关音频的 UXGA 图形  $1280 \times 720\text{p}$  的视频（流 ID=1）相容。在该实施例中，每个帧行由至少 1280 个像素（或者 3840 个子像素）构成，因此需要使用 3840 个数据锁存器以便在行周期  $\tau$  内存储视频数据的一个帧行。例如，在一个实施例中，当在显示器接口 230 接收到数据流 400 时，一组 3840 个数据包（由相应的包头 406 定义）被存储在既可以是帧缓冲器也可是行缓冲器的存储器 236 中。但是，也应当注意，如果需要严格的管道结构，存储器 236 能够被旁路或者没有存储器。在管道结构中，视频源 204 应当提供必须的控制信号并且适当地配置数据包。

回到所述的实施例，其包括一个存储器 236，一旦所有的 3840 个数据包都正确存储在存储器 236 中并被说明（account for），所存储的数据包就将被传送到 LCD 列控制器 212。然后数据包 228 以点对点（以后称为链环方式）的方式被传送到合适的数据锁存器 220，在此每个数据包都被解包从而使得适当的视频数据（或者音频数据）都能够在一个行周期  $\tau$  内存储到合适的数据锁存器中。这时，视频数据已经准备好在由相应的 DAC222 进行处理之后驱动位于显示器 202 中的合适的像素元 210。这样，向数据锁存器 220 提供合适的视频数据所需的行的数目能够低至 2，而传统的 LCD 驱动结构大约为 24。

附图 5 表明了本发明的一个实施例，其中一个数字显示单元 500 包括两个列驱动器 502 和 504，每个列驱动器都用于在分区显示器 510 的相应部分 506 和 508 中驱动像素。通过将显示器 510 分成部分 506 和 508，由于数据线 516 和 518 的长度降低，寄生电容也被相应降低，每个列驱动器 506 和 508 驱动相应的图像元 512 和 514（其可以包括例如以前描述的 TFT218）所需的电流显著减少。

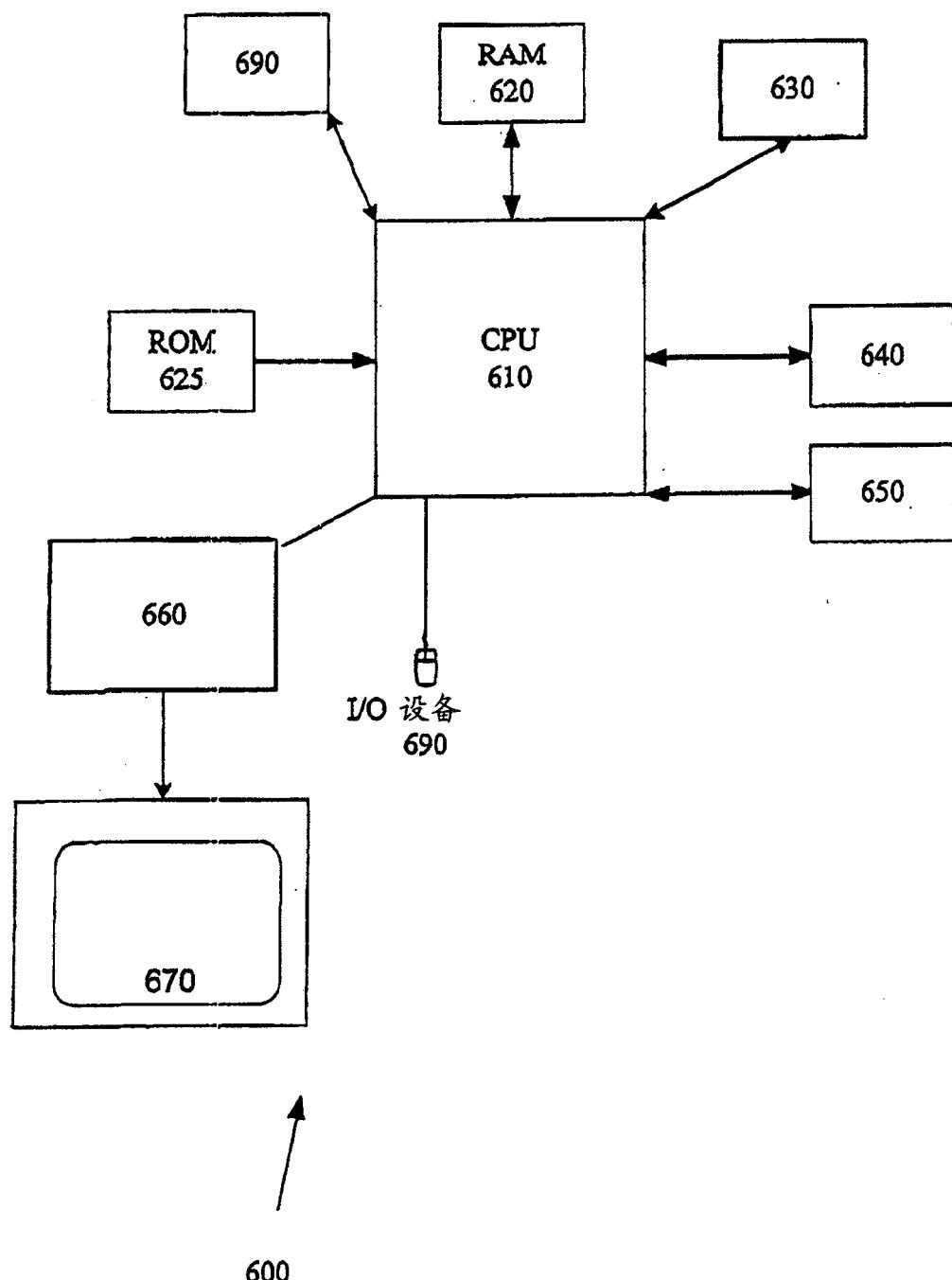

附图 6 表明了一个能够用于执行本发明的系统 600。系统 600 仅是一个可以实现本发明的图形系统的示例。系统 600 包括中央处理单元（CPU）610，随机访问存储器（RAM）620，只读存储器（ROM）625，一个或者多个外部设备 630，图形控制器 660，主存储设备 640 和 650，以及数字显示单元 670。CPU 610 也耦合到一个或者多个输入/输出设备 690。图形控制器 660 产生图像数据和相应的参考信号，并且将图像数据和参考信号提供给数字显示单元 670。根据例如从 CPU 610 或者从外部电路接收到的像素数据来产生图像数据。

---

尽管仅描述了本发明的几个实施例，但是应当理解本发明可以在不背离本发明的精神和范围内以多种其他的特定形式实现。目前的例子仅是为了示例，不是为了限制，并且本发明也并不局限于这里所给出的细节，可以在追加的权利要求的范围内以及其等价物的全部范围内进行改变。

尽管本发明是以优选实施例的方式进行描述的，但是在本发明的范围内存在各种替换、转换和等价物。应当注意存在多种替换方式来实现本发明的处理方法和装置。因此本发明期望被理解成包含落入到本发明的精神和范围内的所有替换、转换和等价物。

图 1

图 2

图 3A

图 4

图 5

图 6

|                |                                                                                                                                    |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 使用包传输驱动LCD屏板的驱动电路                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">CN100430988C</a>                                                                                                       | 公开(公告)日 | 2008-11-05 |

| 申请号            | CN200410092118.8                                                                                                                   | 申请日     | 2004-09-17 |

| [标]申请(专利权)人(译) | 创世纪微芯片公司                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 创世纪微芯片公司                                                                                                                           |         |            |

| 当前申请(专利权)人(译)  | 创世纪微芯片公司                                                                                                                           |         |            |

| [标]发明人         | O科巴亚施                                                                                                                              |         |            |

| 发明人            | O·科巴亚施                                                                                                                             |         |            |

| IPC分类号         | G09G3/36 G09G5/18 G09G5/00 G06F3/14 G02F1/133 G09G3/20 G09G3/28 H04N5/66                                                           |         |            |

| CPC分类号         | G09G2310/0281 G09G5/006 G09G3/20 G09G2310/027 G06F3/14 G09G3/3611 G09G2320/0223 G09G2310/0221 G09G2300/0426 G09G3/3666 G09G2370/08 |         |            |

| 代理人(译)         | 王勇                                                                                                                                 |         |            |

| 审查员(译)         | 吕东                                                                                                                                 |         |            |

| 优先权            | 60/504060 2003-09-18 US<br>60/563120 2004-04-15 US<br>10/909103 2004-07-29 US                                                      |         |            |

| 其他公开文献         | CN1604173A                                                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                                                     |         |            |

### 摘要(译)

公开了一种在数字显示设备中，通过包含在列驱动器中的相关数据锁存器来驱动选定的像素元的基于包的方法。对于一个视频帧中的每个帧行，直接以链路速率向列驱动器提供多个视频数据包，并且在一个行周期T内多个数据锁存器中的每一个都根据视频数据包输入了合适的视频数据。根据视频数据驱动选定的像素元。