[12] 发明专利申请公开说明书

「21」申请号 01119036.1

[43]公开日 2001年10月17日

[11]公开号 CN 1317779A

[22] 申请日 2001.4.11 [21] 申请号 01119036.1

[30] 优先权

[32]2000. 4. 11 [33]JP [31]109958/2000

[32]2001. 3. 29 [33]JP [31]96386/2001

[32]2001. 3. 29 [33]JP [31]96471/2001

[32]2001. 3. 29 [33]JP [31]96576/2001

[71] 申请人 三洋电机株式会社

地址 日本大阪府

[72]发明人 筒井雄介 北川诚 小林贡

上原久夫 藤冈诚

[74]专利代理机构 中国专利代理(香港)有限公司

代理人 刘宗杰 叶恺东

[54]发明名称 显示装置的驱动方法以及驱动电路

[57] 摘要

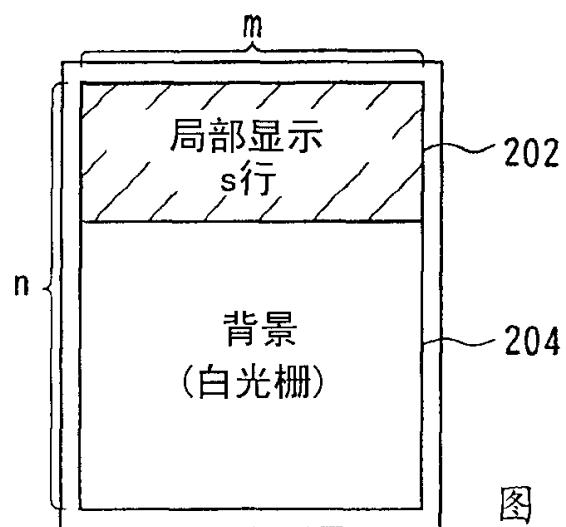

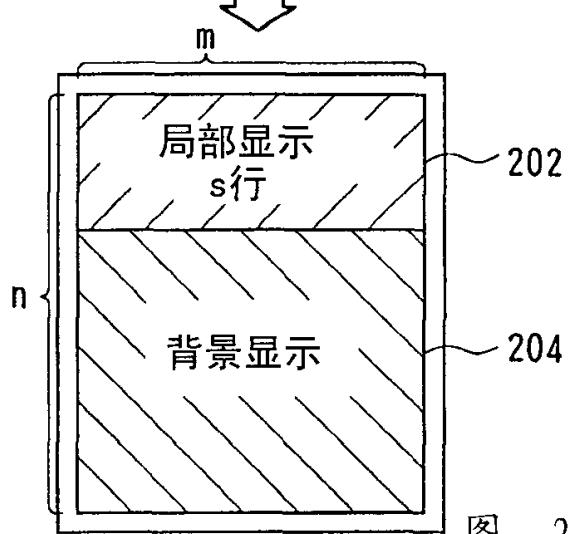

在具备 n 行 m 列矩阵的像素的液晶显示装置等的驱动时,在发出了局部显示命令的情况下,在 1 帧期间中,在 n 行 m 列矩阵内,在能够进行设定的 s 行 m 列的显示局部显示区(202)中顺序地选择各行写入预定的局部显示数据,在局部显示区(202)以外的背景区(204)中写入关断显示(白显示)数据等的预定背景数据。可靠地以背景显示数据把背景区的像素反转驱动。

## 权 利 要 求 书

---

1. 一种显示装置的驱动方法，该显示装置具备  $n$  行  $m$  列矩阵的多个像素，并且根据局部显示命令，在由任意的  $s$  行  $m$  列的像素组成的局部显示区进行所希望的局部显示，在上述  $n$  行  $m$  列的剩余的背景区显示背景，其特征在于：

在局部显示模式中，

在 1 帧期间中，

在上述  $s$  行  $m$  列的局部显示区的各个像素中写入上述局部显示数据，

而且，在上述背景区中的  $k$  行  $m$  列的像素中写入背景显示数据(其中， $n$ ， $m$ ， $s$  以及  $k$  全部是 1 以上的整数，而且  $s < n$ ， $k < n$ )。

2. 如权利要求 1 中所述的显示装置的驱动方法，其特征在于：

上述背景区中的上述  $k$  行  $m$  列的像素在每 1 帧使选择行移位。

3. 如权利要求 2 中所述的显示装置的驱动方法，其特征在于：

在上述背景区的各像素中，在总计  $(n - s) / k$  帧期间写入上述背景显示数据。

4. 如权利要求 2 中所述的显示装置的驱动方法，其特征在于：

在上述背景区的各像素中，在总计  $(n - s) / k$  帧期间写入背景显示数据，在下一个总计  $(n - s) / k$  帧期间，对于同一行的像素，写入使对于背景显示数据的基准电位极性反转了的背景显示数据。

5. 如权利要求 1 中所述的显示装置的驱动方法，其特征在于：

上述背景区中，对于在 1 帧期间中选择的行以外的行，禁止行选择动作。

6. 如权利要求 1 中所述的显示装置的驱动方法，其特征在于：

如果发出上述局部显示命令，则把比在 1 帧期间选择上述  $n$  行  $m$  列的所有像素进行通常显示时的单位时钟的像素时钟频率还低的像素时钟用作为单位时钟，

在上述局部显示区的所有像素中写入局部显示数据，在上述背景区中的上述  $k$  行  $m$  列的像素中写入背景显示数据。

7. 如权利要求 6 中所述的显示装置的驱动方法，其特征在于：

如果发出上述局部显示命令，并且检测到在上述背景区中，对于

上述  $k$  行  $m$  列像素以外的行的选择期间到来，则增大行选择脉冲的传输速度。

8. 如权利要求 1 中所述的显示装置的驱动方法，其特征在于：

5 在发出了上述局部显示命令以后，在上述  $n$  行  $m$  列矩阵的所有像素中写入了背景显示数据后，在上述  $s$  行  $m$  列的像素中顺序地写入局部显示数据，而且在上述  $k$  行  $m$  列的像素中写入背景显示数据。

9. 如权利要求 1 中所述的背景显示装置的驱动方法，其特征在于：

上述背景显示数据是关断显示数据或者任意的背景色数据。

10 10. 如权利要求 1 中所述的显示装置的驱动方法，其特征在于：该显示装置是液晶显示装置。

11. 一种显示装置的驱动方法，该显示装置具备  $n$  行  $m$  列矩阵的多个像素，并且根据局部显示命令，在任意  $s$  行  $m$  列矩阵的局部显示区进行局部显示，在剩余的区域中作为背景区进行背景显示，其特征在于：

在局部显示模式中，

在 1 帧期间中，

20 在上述局部显示区的各像素中顺序地写入预定的局部显示数据，同时在上述背景区内，在上述局部显示区最末行的下一个第  $(s + 1)$  行区域的像素和  $k$  行  $m$  列的像素中写入背景显示数据（其中， $n$ ， $m$ ， $s$  以及  $k$  全部是 1 以上的整数，而且  $s < n$ ， $k < n - s - 1$ ）。

12. 如权利要求 11 中所述的显示装置的驱动方法，其特征在于：上述背景区中的上述  $k$  行  $m$  列的像素在每 1 帧使选择行移位。

13. 如权利要求 12 中所述的显示装置的驱动方法，其特征在于：25 在上述背景区中的  $(n - s - 1)$  行  $m$  列矩阵的像素中，在总计  $(n - s - 1) / k$  帧期间写入背景显示数据。

14. 如权利要求 12 中所述的显示装置的驱动方法，其特征在于：

在上述背景区中的  $(n - s - 1)$  行  $m$  列矩阵的像素中，在总计  $(n - s - 1) / k$  帧期间写入背景显示数据，

30 在下一个总计  $(n - s - 1) / k$  帧期间，对于同一行的像素，写入对于背景显示数据的基准电位的极性反转了的背景显示数据。

15. 如权利要求 11 中所述的显示装置的驱动方法，其特征在于：

如果发出上述局部显示命令，则把比在 1 帧期间选择上述  $n$  行  $m$  列的所有像素进行通常显示时的单位时钟的像素时钟频率还低的像素时钟用作为单位时钟，

5 在上述局部显示区的所有像素中写入局部显示数据，在上述背景区中的上述第  $s+1$  行区域的像素和上述  $k$  行  $m$  列的像素中写入背景显示数据。

16. 如权利要求 11 中所述的显示装置的驱动方法，其特征在于：

在发出了上述局部显示命令后，在上述  $n$  行  $m$  列矩阵的全部像素中写入了背景显示数据以后，在上述  $s$  行  $m$  列的像素中顺序地写入局部显示数据，而且在上述第  $s+1$  行的像素和上述  $k$  行  $m$  列的像素中写入背景显示数据。

17. 如权利要求 11 中所述的显示装置的驱动方法，其特征在于：

如果检测出上述局部显示命令，则在下一个第 1 帧的期间中，

10 在上述  $s$  行  $m$  列的局部显示区的各个像素中顺序地写入预定的局部显示数据，

而且在上述背景区的所有像素中顺序地写入背景显示数据，

15 在上述第 1 帧后续的第 2 帧以后的各帧期间中，

在上述  $s$  行  $m$  列的局部显示区的各个像素中写入上述局部显示数据，

20 而且在上述背景之中的第  $s+1$  行区域的像素和上述  $k$  行  $m$  列的像素中写入背景显示数据。

18. 如权利要求 1 中所述的显示装置的驱动方法，其特征在于：

上述背景显示数据是关断显示数据或者任意的背景色数据。

19. 如权利要求 1 中所述的显示装置的驱动方法，其特征在于：

25 该显示装置是液晶显示装置。

20. 一种显示装置的驱动方法，该显示装置具备  $n$  行  $m$  列矩阵的多个像素，并且根据局部显示命令，在由任意的  $s$  行  $m$  列像素组成的局部显示区中进行所希望的局部显示，在上述  $n$  行  $m$  列的剩余的背景区中显示背景，其特征在于：

30 在检测出上述局部显示命令，从通常显示模式向局部显示模式转移的转移第 1 帧的期间中，

在上述  $s$  行  $m$  列的局部显示区的各个像素中顺序地写入预定的局

部显示数据，而且在上述背景区的各个像素中顺序地写入背景显示数据，

在上述转移第 1 帧后续的第 2 帧以后的各帧期间中，

5 在上述  $s$  行  $m$  列的局部显示区的各个像素中写入上述局部显示数据，而且，在上述背景区中的  $k$  行  $m$  列的像素中写入背景显示数据(其中， $n$ ， $m$ ， $s$  以及  $k$  全部是 1 以上的整数，而且满足  $s < n$ ， $k < n - s$ )。

21. 如权利要求 20 中所述的显示装置的驱动方法，其特征在于：

上述背景区中被选择的上述  $k$  行  $m$  列的像素在每 1 帧使被选择的行移位。

10 22. 如权利要求 21 中所述的显示装置的驱动方法，其特征在于：

上述转移第 2 帧以后，在上述背景区的所有像素中，总计  $(n - s)$   $k$  帧期间写入上述背景显示数据。

23. 如权利要求 21 中所述的显示装置的驱动方法，其特征在于：

上述转移第 2 帧以后，上述背景区中对于 1 帧期间中被选择的上述  $k$  行以外的行，禁止行选择动作。

24. 如权利要求 20 中所述的显示装置的驱动方法，其特征在于：

上述转移第 2 帧以后的各帧期间中，

把比在 1 帧期间中选择上述  $n$  行  $m$  列的所有像素进行通常显示时的单位时钟的像素时钟频率还低的像素时钟用作为单位时钟，

20 在上述局部显示区的所有像素中写入局部显示数据，在上述背景区中的上述  $k$  行  $m$  列的像素中写入背景显示数据。

25. 如权利要求 20 中所述的显示装置的驱动方法，其特征在于：

上述背景显示数据是关断显示数据或者任意的背景色数据。

26. 如权利要求 20 中所述的显示装置的驱动方法，其特征在于：

该显示装置是液晶显示装置。

27. 一种显示装置的驱动电路，该显示装置的  $n$  行  $m$  列矩阵的多个像素在每个行线进行选择并且从列线接受显示数据的供给进行显示，而且，如果发出局部显示命令，则在 1 帧期间中，选择上述  $n$  行  $m$  列矩阵内的  $s$  行  $m$  列的像素顺序地写入预定的局部显示数据，另外，在上述  $n$  行  $m$  列的剩余的背景区中的  $k$  行  $m$  列的像素中写入背景显示数据，其特征在于：

具备

发生对应于各行的选择期间的行时钟的行时钟生成单元；

在每一个帧计数行时钟的行时钟计数单元；

10 检测要写入上述局部显示数据的  $s$  行的到来时间的局部显示行检测单元；

5 检测在上述 1 帧期间中要写入背景显示数据的  $k$  行的到来时间的背景显示行检测单元；

10 如果由上述局部显示行检测单元或者上述背景行检测单元的某一个检测出显示行的到来，则发生允许在每 1 行驱动上述  $n$  行  $m$  列矩阵的行驱动器中的行驱动动作的驱动控制信号的驱动控制信号发生单元（其中，  $n$ ，  $m$ ，  $s$  以及  $k$  全部是 1 以上的整数，而且满足  $s < n$ ，  $k < n$ ）。

28. 如权利要求 27 中所述的显示装置的驱动电路，其特征在于：还具备计数帧数的帧计数单元，

15 上述背景显示行检测单元根据上述帧计数单元中的计数值，使要写入上述背景显示数据的行移位。

29. 如权利要求 27 中所述的显示装置的驱动电路，其特征在于：

还具备用于使对于显示数据的预定基准电压的极性在每个单位期间反转的极性反转信号生成单元，

20 上述背景区的各像素在由总计  $(n - s) / k$  帧期间构成的 1 个背景显示期间分别被选择一次，

上述极性反转信号生成单元检测下一个 1 个背景期间的到来并且使上述背景显示数据的极性反转。

30. 如权利要求 27 中所述的显示装置的驱动电路，其特征在于：

25 还具有把在 1 帧期间中选择上述  $n$  行  $m$  列的所有像素进行通常显示时的单位时钟分频的分频电路，

如果发出上述局部显示命令，则把来自上述分频电路的分频像素时钟用作为单位时钟，进行在 1 帧期间中向上述  $s$  行  $m$  列像素的上述局部显示数据的写入控制以及向上述  $k$  行  $m$  列像素的上述背景显示数据的写入控制。

30 31. 如权利要求 30 中所述的显示装置的驱动电路，其特征在于：

具备根据上述局部显示行检测单元以及上述背景显示行检测单元的显示行检测信号，

检测上述背景区中对于上述  $k$  行  $m$  列的像素以外的行的选择期间的到来，增大上述行时钟的频率的行时钟控制单元。

32. 如权利要求 27 中所述的显示装置的驱动电路，其特征在于：还具有

5 如果发出从通常显示模式向局部显示模式转移的命令，

则该命令的下一个 1 帧把向上述  $n$  行  $m$  列矩阵的所有像素的显示数据变更为背景显示数据

从其下一个帧开始，启动发生上述驱动控制信号发生单元中的上述驱动控制信号的模式切换时序控制单元。

10 33. 如权利要求 27 中所述的显示装置的驱动电路，其特征在于：上述背景显示数据是关断显示数据或者任意的背景色数据。

34. 如权利要求 27 中所述的显示装置的驱动电路，其特征在于：该显示装置是液晶显示装置。

15 35. 一种显示装置的驱动电路，该显示装置的  $n$  行  $m$  列矩阵的多个像素在每条行线被选择并且从列线接受显示数据的供给进行显示，而且，如果发出局部显示命令，则在 1 帧期间中，选择上述  $n$  行  $m$  列矩阵内的  $s$  行  $m$  列像素顺序地写入预定的局部显示数据，另外，选择上述  $n$  行  $m$  列的剩余的背景区中的第  $s+1$  行像素和  $k$  行  $m$  列像素写入背景显示数据，其特征在于：

20 具备

发生对应于各行的选择期间的行时钟的行时钟生成单元；

在每 1 帧计数行时钟的行时钟计数单元；

检测要写入上述局部显示数据的行的到来时间的局部显示行检测单元；

25 检测在上述 1 帧期间中要写入背景显示数据的第  $s+1$  行以及  $k$  行的到来时间的背景显示行检测单元；

30 如果由上述局部显示行检测单元或者上述背景行检测单元的某一个检测出显示行的到来，则发生允许在每 1 行驱动上述  $n$  行  $m$  列矩阵的行驱动器的行驱动动作的驱动控制信号的驱动控制信号发生单元（其中， $n$ ， $m$ ， $s$  以及  $k$  全部是 1 以上的整数，而且满足  $s < n$ ， $k < n - s - 1$ ）。

36. 如权利要求 35 中所述的显示装置的驱动电路，其特征在于：

还具备计数帧数的帧计数单元，

上述背景显示行检测单元根据上述帧计数单元的计数值，是要写入上述背景显示数据的行移位。

37. 如权利要求 35 中所述的显示装置的驱动电路，其特征在于：

5 还具备用于使对于显示数据的预定基准电压的极性在每个单位期间反转的极性反转信号生成单元，

上述背景区中的除去上述第  $s+1$  行以外的各像素在由总计  $(n-s-1)/k$  帧期间组成的 1 个背景显示期间分别被选为一次，

10 上述极性反转信号生成单元检测下一个 1 个背景显示期间的到来并且使上述背景显示数据的极性反转。

38. 如权利要求 35 中所述的显示装置的驱动电路，其特征在于：

还具有把在 1 帧期间中选择上述  $n$  行  $m$  列的所有像素进行通常显示时的单位时钟分频的分频电路，

15 如果发出上述局部显示命令，则把来自上述分频电路的分频像素时钟用作为单位时钟，进行在 1 帧期间中向上述  $s$  行  $m$  列像素的上述局部显示数据的写入控制以及向上述第  $s+1$  行区域的像素以及上述  $k$  行  $m$  列的像素的背景显示数据的写入控制。

39. 如权利要求 38 中所述的显示装置的驱动电路，其特征在于：

20 具备根据上述局部显示行检测单元以及上述背景显示行检测单元的显示行检测信号，

检测对于上述背景区中，上述第  $s+1$  行区域的像素以及上述  $k$  行  $m$  列像素以外的行的选择期间的到来，增大上述行时钟的频率的行时钟控制单元。

40. 如权利要求书 35 中所述的显示装置的驱动电路，其特征在

25 于：

上述背景显示数据是关断显示数据或者任意的背景色数据。

41. 如权利要求 35 中所述的显示装置的驱动电路，其特征在于：该显示装置制是液晶显示装置。

42. 一种显示装置的驱动电路，该显示装置的  $n$  行  $m$  列矩阵的多30 个像素在每条行线被选择并且从列线接受显示数据的供给进行显示，而且，在局部显示模式下，在 1 帧期间中，选择上述  $n$  行  $m$  列矩阵内的  $s$  行  $m$  列像素顺序地写入预定的局部显示数据，另外，选择上

述  $n$  行  $m$  列的剩余的背景区中的  $k$  行  $m$  列像素写入背景显示数据，其特征在于：

具备

发生对应于各行的选择期间的行时钟的行时钟生成单元；

5 检测要写入上述局部显示数据的行的到来时间的局部显示行检测单元；

检测上述背景区的起始行以及最末行的到来时间的背景区检测单元；

10 检测在局部显示模式中的 1 帧期间中，要写入背景显示数据的背景区中的  $k$  行的到来时间的背景显示行检测单元；

15 在通常显示模式向局部显示模式的转移第 1 帧中，在由上述局部显示行检测单元检测出显示行的到来期间，允许局部显示数据的输出，并且在上述背景区检测单元从上述背景区的起始行的到来检测出最末行的到来的期间，把输出显示数据设定为约定的背景显示数据的数据输出控制单元；

20 一旦成为向局部显示模式的转移第 2 帧以后，如果由上述局部显示行检测单元以及上述背景显示行检测单元的某一个检测出显示行的到来，则发生允许上述行控制器中的行驱动动作的驱动控制信号的驱动控制信号发生单元（其中， $n$ ， $m$ ， $s$  以及  $k$  全部是 1 以上的整数，而且满足  $s < n$ ， $k < n - s$ ）。

43. 如权利要求 42 中所述的显示装置的驱动电路，其特征在于：上述背景显示数据是关断显示数据或者任意的背景色数据。

44. 如权利要求 42 中所述的显示装置的驱动电路，其特征在于：该显示装置是液晶显示装置。

# 说 明 书

## 显示装置的驱动方法以及驱动电路

5 本发明涉及液晶显示装置等平面显示装置的驱动方法以及驱动电路，特别是涉及其局部显示。

以液晶显示装置或者有机 EL 显示装置等为代表的平面显示装置由于轻、薄而且低功耗，因此很适于作为便携电话等便携设备的显示装置，用在众多的便携设备中。

10 该显示装置已知有通过矩阵形排列的多个像素能够显示任意图形的矩阵型显示装置，显示时钟等固定图形的阶段型显示装置，还有在同一个显示面板内安装了该矩阵型和阶段型的显示装置等。

15 然而，在便携设备中，要求功耗进一步降低，在显示装置中也要求进一步低功耗化。于是，在现有技术中，已知在省电时，能够在画面内仅显示所需要的最小限度部分的所谓局部显示的显示装置。这样的局部显示，例如，由在液晶显示装置的显示区的一部分中设置用于电池余量，时刻显示等固定图形的显示区，以及在其它区域矩阵形配置多个像素，显示任意的图形的显示区构成，能够通过在省电时仅驱动固定图形显示区，显示固定图形等实现。

20 如上述那样，如果采用在同一个显示面板内，分别设置能够个别驱动的多个区域，驱动也分别进行控制的结构，则能够根据要求仅显示一部分区域。然而，即使在省电时，有时有希望在任意的位置进行显示或者显示任意图形的要求，而在单独控制预先分割的显示区的显示装置中不能够对应该要求。

25 另外，根据搭载显示装置的设备种类，由于省电时的显示内容、显示位置的要求不同，因此必须根据需要分别专门开发显示面板的构造、驱动电路。

30 如果是矩阵型的显示装置，则虽然能够在任意的位置进行任意的显示，然而在省电显示中，即使仅在一部分上显示图形的情况下，由于其它的区域也需要通常的驱动，因此并没有由局部显示所带来的降低功耗的效果。

为了解决上述问题，本发明的目的在于提供能够在任意位置局部显示任意图形的同时，能够根据需要降低局部显示时的功耗的显示装

置。

另外，其它的目的在于在任意的位置进行局部显示的显示装置中提高其背景区中的显示品质。

再一个目的是在从通常显示向局部显示的模式转移时平滑地进行画面的切换。

为了达到上述目的，本发明具有以下的特征。

首先，这是具备  $n$  行  $m$  列矩阵的多个像素，根据局部显示命令，在由任意的  $s$  行  $m$  列像素组成的局部显示区中进行所希望的局部显示，在上述  $n$  行  $m$  列的剩余的背景区中显示背景的显示装置的驱动方法，其特征在于，在局部显示模式下，在 1 帧期间中，在上述  $s$  行  $m$  列的局部显示区的各像素中，写入上述局部显示数据，而且，仅在上述背景区中的  $k$  行  $m$  列的像素中，写入背景显示数据。其中， $n$ ， $m$ ， $s$  以及  $k$  全部是 1 以上的整数，而且  $s < n$ ， $k < n$ 。

本发明的另一个特征是在上述驱动方法中，从上述背景区中选择的  $k$  行  $m$  列像素在每 1 帧使所选择的行移位。

本发明的其它特征是在上述驱动方法中，在上述背景区的所有像素中，在总计  $(n - s) / k$  帧期间写入上述背景显示数据。

本发明的其它特征是在上述背景区的所有像素中，在总计  $(n - s) / k$  帧期间写入上述背景显示数据，在下一个总计  $(n - s) / k$  帧期间，对于同一行的像素，写入使对于背景显示数据的基准电位反转了极性的背景显示数据。

本发明的其它特征是在上述驱动方法中，在上述背景区中，对于除去在 1 帧期间中选择的  $k$  行以外的行，禁止行选择动作。

本发明的驱动电路是显示装置的驱动电路，其中，该显示装置的  $n$  行  $m$  列矩阵的多个像素在每条行线被选择并且从列线接受显示数据的供给进行显示，而且，如果发出局部显示命令，则在 1 帧期间中，选择上述  $n$  行  $m$  列矩阵内的  $s$  行  $m$  列像素顺序地写入预定的局部显示数据，另外，选择上述  $n$  行  $m$  列的剩余的背景区中的  $k$  行  $m$  列像素写入背景显示数据，其特征在于具备发生对应于各行的选择期间的行时钟的行时钟生成单元；在每 1 帧计数行时钟的行时钟计数单元；检测要写入上述局部显示数据的  $s$  行的到来时序的局部显示行检测单元；检测上述 1 帧期间中要写入背景显示数据的  $k$  行的到来时序的背景显

示行检测单元；如果由上述局部显示行检测单元或者上述背景显示行检测单元的某一个检测出了显示行的到来则发生允许在每1行驱动上述n行m列矩阵的行驱动器的行驱动动作的驱动控制信号的驱动控制信号发生单元。其中，n，m，s以及k全部是1以上的整数，而且满足s < n，k < n。

本发明的其它特征是在上述驱动电路中，还具有计数帧数的帧计数单元，上述背景显示行检测单元根据上述帧计数单元的计数值，使要写入上述背景显示数据的行移位。

本发明的其它特征是上述驱动电路还具备在每个单位期间使对于显示数据的预定基准电压的极性反转的极性反转信号生成单元，上述n行m列矩阵的局部显示区以外的所有像素在由总计 $(n - s) / k$ 帧期间构成的1个背景显示期间，分别被选择1次，上述极性反转信号生成单元检测下一个1个背景显示期间的到来并且使上述背景显示数据的极性反转。

在采用以上的驱动方法、驱动电路并且具备液晶显示面板等显示面板的显示装置中，能够不变更面板自身的结构，在面板的任意位置进行局部显示。另外，对于不进行局部显示的背景区，通过在1帧期间中仅选择预定的k行能够根据需要谋求降低功耗。另外，在背景区中，在1帧期间中没有被选择的上述k行以外的区域，以预定周期写入背景显示数据。背景显示数据通常没有文字和符号等特别的信息，由于信息自身没有变化因此不需要频繁写入。另外，如果是这样的数据，则即使对各像素的写入周期加长到某种程度也不存在显示的恶化。另外，作为背景显示数据如果采用非标准显示数据则显示内容的恶化非常小。进而，在每个预定周期写入背景显示数据时，例如在液晶显示面板上通过进行有效显示数据的极性反转，能够可靠地防止由于加入直流成分而恶化的液晶等显示元件的恶化。

本发明的其它特征是在上述显示装置的驱动方法中，如果发出上述局部显示命令，则把比构成在1帧期间中选择上述n行m列的所有像素进行通常显示时的单位时钟的像素时钟频率还低的像素时钟用作为单位时钟，在1帧期间中在上述局部显示区的所有像素中写入局部显示数据，在上述背景区中的上述k行m列像素中写入背景显示数据。

本发明的其它特征是在上述显示装置的驱动方法中，如果发出上述局部显示命令，检测上述背景区中对于上述  $k$  行  $m$  列像素以外的行的选择期间的到来，则能够增大行检测脉冲的传输速度。

另外，本发明的显示装置的驱动电路的其它特征是在上述驱动电路中，还具有把在 1 帧期间中选择上述  $n$  行  $m$  列的所有像素写入显示数据进行通常显示时的单位时钟进行分频的分频电路，如果发出上述局部显示命令，则把来自上述分频电路的分频像素时钟用作为单位时钟，进行在 1 帧期间中对上述  $s$  行  $m$  列像素的上述局部显示数据的写入控制以及对于上述  $k$  行  $m$  列像素的上述背景显示数据的写入控制。

另外，本发明的驱动电路的其它特征是在上述驱动电路中，具备根据上述局部显示行检测单元以及上述背景显示行检测单元的显示行检测信号，检测上述背景区中对于上述  $k$  行  $m$  列像素以外的行的选择期间的到来，增大上述行时钟的频率的行时钟控制单元。

在这样的背景区中，在 1 帧期间中仅选择一部分线，不选择其它的线。另外，对于没有选择的总计  $(n - s - k)$  线，如果顺序地传输并送出到各行，则使进行行选择的行选择脉冲的传输速度增大。传输速度的增大，例如通过增加行时钟的频率实现。由此在局部显示模式时，可以减少 1 帧期间中选择的行，能够加长各行的选择时间。从而，能够降低其动作时钟，能够降低局部显示模式时的显示装置，特别是数字信号处理电路中的功耗。

另外，本发明的其它特征是如果由模式切换时序控制单元等发出从通常显示模式向局部显示模式的转移命令，则该命令的下一个帧把向上述  $n$  行  $m$  列矩阵的所有像素的显示数据变更为背景显示数据，从其下一个帧开始，启动上述驱动控制信号发生单元中的上述驱动控制信号的发生。

通过这样的控制，在发出局部显示命令以后，一旦在  $n$  行  $m$  列矩阵的所有像素中写入背景显示数据，则转移到局部显示模式，不会发生从背景区内没有长期被选择的像素中，逐渐丢失被写入的通常数据的现象。

如以上说明的那样，在本发明中，能够不变更液晶显示面板等显示面板的结构而在任意的位置进行局部显示。

另外，对于背景区，如果进行在 1 帧期间中仅选择一部分线，不

选择其它的线，使其动作时钟降低的控制，则能够降低局部显示模式时的显示装置，特别是数字信号处理电路中的功耗。

进而，在本发明中，对于背景区，以预定周期在全部区域中写入非标准显示数据等的预定背景数据。这样的背景区即使不与通常显示区以相同周期进行数据写入，也不会看到显示的恶化，另外，通过使显示数据反转使得在每个预定周期写入背景显示数据时反转驱动液晶，能够可靠地防止液晶等的恶化。

作为背景显示数据如果写入非标准显示数据，则在该背景区中，虽然与通常显示时相比较较长地设定数据写入周期，然而即使这样背景显示的长时变化也非常小，能够进行显示品质几乎不降低的显示。

另外，背景显示数据还能够采用任意的彩色数据，由此装置使用者能够选择所喜欢的背景色。

本发明的显示装置的驱动方法是具备  $n$  行  $m$  列矩阵的多个像素，根据局部显示命令，在任意的  $s$  行  $m$  列矩阵的局部显示区中进行局部显示，在其余的区域作为背景区进行背景显示的显示装置的驱动方法，其特征在于，在局部显示模式中，在 1 帧期间中，在上述局部显示区的各个像素上顺序地写入预定的局部显示数据，同时，在上述背景区，在上述局部显示区的最末行的下一个第  $s+1$  行区域的像素和  $k$  行  $m$  列像素中写入背景显示数据。其中， $n$ ， $m$ ， $s$  以及  $k$  全部是 1 以上的整数，而且  $s < n$ ， $k < n - s - 1$ 。

本发明的显示装置的驱动电路是在每个行线选择  $n$  行  $m$  列矩阵的多个像素并且从列线接受显示数据的供给进行显示，而且，如果发出局部显示命令，则在 1 帧期间中，选择上述  $n$  行  $m$  列矩阵内的  $s$  行  $m$  列的像素顺序地写入预定的局部显示数据，另外，选择上述  $n$  行  $m$  列的其余的背景区中的第  $s+1$  行的像素和  $k$  行  $m$  列的像素，写入背景显示数据的显示装置的驱动电路，其特征在于，具备发生对应于各行的选择期间的行时钟的行时钟生成单元；在每一个帧计数行时钟的行时钟计数单元；检测要写入上述局部显示数据的  $s$  行的到来时序的局部显示行检测单元；检测在上述帧期间要写入背景显示数据的第  $s+1$  行以及  $k$  行的到来时序的背景显示行检测单元；如果由上述局部显示行检测单元或者上述背景显示行检测单元的某一个检测出显示行的到来则发生允许在每 1 行驱动上述  $n$  行  $m$  列矩阵的行驱动器的行驱动

动作的驱动控制信号的驱动器控制信号发生单元。

另外，本发明中，在上述驱动方法或者驱动电路中，上述背景区中的上述  $k$  行  $m$  列像素在每 1 帧使选择行移位并进行选择。

本发明的其它特征是在上述驱动方法或者驱动电路中，在上述背景区中的  $(n - s - 1)$  行  $m$  列矩阵像素中，在总计  $(n - s - 1) / k$  帧期间写入上述背景显示数据。

本发明的其它特征是在上述驱动方法或者驱动电路中，在上述背景区中的  $(n - s - 1)$  行  $m$  列矩阵像素中，在总计  $(n - s - 1) / k$  帧期间写入上述背景显示数据，在下一个总计  $(n - s - 1) / k$  帧期间，对于同一行的像素，写入使对于背景显示数据的基准电位反转了极性的背景显示数据。

本发明的其它特征是在上述驱动方法或者驱动电路中，如果发出上述局部显示命令，则把比在 1 帧期间选择上述  $n$  行  $m$  列的所有像素进行通常显示时的单位时钟的像素时钟频率还低的像素时钟用作为单位时钟，在上述局部显示区的所有像素中写入局部显示数据，在上述背景显示区中的上述第  $s + 1$  行区域的像素和上述  $k$  行  $m$  列像素中写入背景显示数据。

本发明的其它特征是在上述驱动方法或者驱动电路中，在发出了上述局部显示命令以后，在下一个帧中，在上述  $n$  行  $m$  列矩阵的所有像素中写入背景显示数据以后，在上述  $s$  行  $m$  列的局部显示区的各个像素中顺序地写入预定的局部显示数据，而且在上述背景区的所有像素中，顺序地写入背景显示数据。而且，从该下一个帧开始在上述  $s$  行  $m$  列的像素中顺序地写入局部显示数据，而且在上述第  $s + 1$  行的像素和上述  $k$  行  $m$  列像素中写入背景显示数据。

如果采用以上的驱动方法、驱动电路，则在具备液晶显示面板等显示面板的显示装置中，能够不变更面板自身的结构，在面板的任意位置进行局部显示。而且，在没有进行局部显示的背景区，首先，对于连接在局部显示区最末行的背景区的起始行，与局部显示区相同在每帧写入背景显示数据。另一方面，背景区的其余像素在 1 帧期间仅在  $k$  行  $m$  列矩阵的像素中写入背景显示数据。

这样，由于按每帧选择位于背景显示区边界的背景区起始行，因此对于剩余的背景区尽管分别在数帧中仅被选择一次，然而在这些背

5 景区中，能够防止丢失局部显示区中的显示内容，防止引起交调失真等。另一方面，在除去背景区的上述起始行的区域，在一定期间中通过仅选择预定的  $k$  行，能够根据需要谋求降低功耗，通过设置在 1 帧期间区间中没有选择的行，能够把对于选择的行的驱动时间加长与其相

应的部分。

10 另外，背景显示数据通常由于没有文字或者符号等特别的信息，在信息自身中没有变化，因此不需要频繁地写入。进而，如果是这样的数据，则即使对各像素的写入期间加长到某种程度显示的恶化也很少。

15 10 如以上所说明的那样，如果依据本发明，则能够在任意的位置进行局部显示，另外，能够以很高的显示品质进行剩余的背景区中的背景显示。进而，在背景区中，由于把在 1 帧期间中与上述局部显示区一起被选择的区域取为背景区起始行和作为其余区域中的一部分的  $k$  行  $m$  列区域，因此在局部显示模式中通过把 1 帧期间中选择的行数比通常显示模式时减少，能够谋求降低功耗。

20 本发明的显示装置的驱动方法是具备  $n$  行  $m$  列矩阵的多个像素，根据局部显示命令，在由任意的  $s$  行  $m$  列像素组成局部显示区中进行所希望的局部显示，在上述  $n$  行  $m$  列的其余的背景区中显示背景显示装置的驱动方法，其特征在于，在检测出上述局部显示命令，从通常显示模式向局部显示模式转移时的转移第 1 帧的期间中，在上述  $s$  行  $m$  列的背景显示区的各个像素中顺序地写入预定的局部显示数据，而且在上述背景区的各个像素中顺序地写入背景显示数据。另外，在连接于上述转移第 1 帧的转移第 2 帧以后的各个帧期间中，在上述  $s$  行  $m$  列的局部显示区的各个像素中写入上述局部显示数据，而且，在上述背景区中的  $k$  行  $m$  列的像素中写入背景显示数据。其中， $n$ ， $m$ ， $s$  以及  $k$  全部为 1 以上的整数，而且满足  $s < n$ ， $k < n - s$ 。

30 本发明的显示装置的驱动电路是按照每条行线选择  $n$  行  $m$  列矩阵的多个像素而且从列线接受显示数据的供给进行显示，而且，在局部显示模式中，在 1 帧期间中，选择上述  $n$  行  $m$  列矩阵内的  $s$  行  $m$  列像素并且顺序地写入预定的局部显示数据，另外，选择上述  $n$  行  $m$  列的剩余的背景区中的  $k$  行  $m$  列像素并且顺序地写入背景显示数据的显示装置的驱动电路，其特征在于，具备发生对应于各行的选择期间的时

5 钟的行时钟生成单元；在每 1 帧计数行时钟的行时钟计数单元；检测要写入上述局部显示数据的  $s$  行的到来时序的局部显示行检测单元；检测上述背景区的起始行以及最终行的到来时序的背景区检测单元；检测在局部显示模式中的 1 帧期间要写入背景显示数据的背景区域中的  $k$  行的到来时序的背景显示行检测单元；在从通常显示模式向局部显示模式的转移第 1 帧中，由上述局部显示行检测单元检测显示行的到来的期间，允许局部显示数据的输出，在由上述背景区检测单元检测从上述背景区的起始行的到来至最终行的到来的期间，把输出显示数据设定为预定的背景显示数据的数据输出控制单元；如果成为向局部显示模式的转移第 2 帧以后，则发生由上述局部显示行检测单元以及上述背景显示行检测单元的某一个检测显示行的到来和允许上述行驱动器中的行驱动动作的驱动控制信号的驱动控制信号发生单元。

10 本发明的其它特征是在上述显示装置的驱动方法或者驱动电路中，上述转移第 2 帧以后，在上述背景区的所有像素中，在总计  $(n - s) / k$  帧期间写入上述背景显示数据。

15 进而，本发明的其它特征是在上述显示装置的驱动方法或者执行该方法的驱动电路中，在上述转移第 2 帧以后，在上述背景区中，对于在一定期间中选择的上述  $k$  行以外的行，禁止行选择动作。

20 如以上那样，在转移时的第 1 帧中，通过进行局部显示和对于背景区的全部区域的背景显示，局部显示区从通常显示直接切换到局部显示，在背景区中，从通常显示直接切换为背景显示。从而，能够从通常显示的画面平滑地向局部显示切换。从转移第 2 帧开始，背景区的 1 帧期间中各选择作为其一部分的  $k$  行  $m$  列矩阵区。这样，虽然能够谋求降低动作时钟，降低功耗，但在这些背景区中，多个帧中仅被选择一次。因此，有时没有同时清除通常显示时的数据，在背景区中渐渐清除通常显示的同时在背景显示中进行变化，这是一种不理想的状况。在本发明中，即使在全部画面上一起进行背景显示而没有清除通常显示数据，但由于在转移第 1 帧中对于所有像素分别写入称为局部或者背景显示数据的有意数据，因此在上述的背景区中，能够防止通常时的显示逐渐变化到背景显示状态的情况。

30 如以上所说明的那样，如果依据本发明，则能够在任意的位置进

行局部显示。另外，能够从通常显示平滑地进行向局部显示的转移。另外，在向局部显示模式的转移第 2 帧以后，在背景区中不残存前面的通常显示，能够以高品质进行背景显示。进而，在背景区中，由于把在 1 帧期间中选择的区域作为上述局部显示区和作为背景显示区中一部分的  $k$  行  $m$  列区域，因此在局部显示模式中，1 帧期间中选择的行数比通常显示模式时少，能够谋求降低功耗。

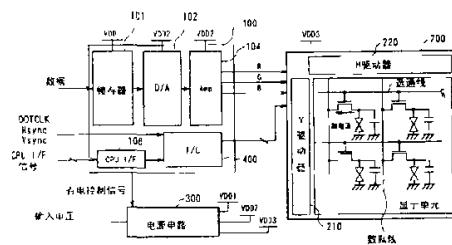

图 1 示出本发明的实施形态的显示装置的结构。

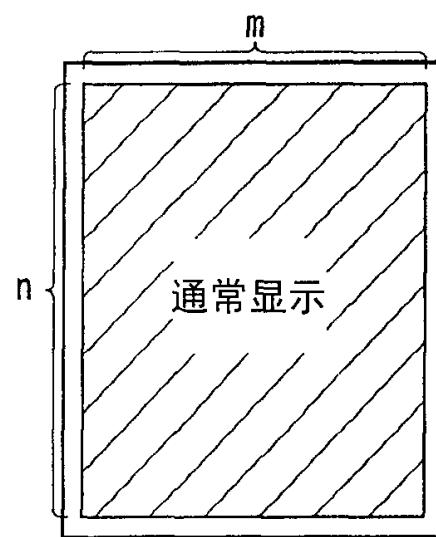

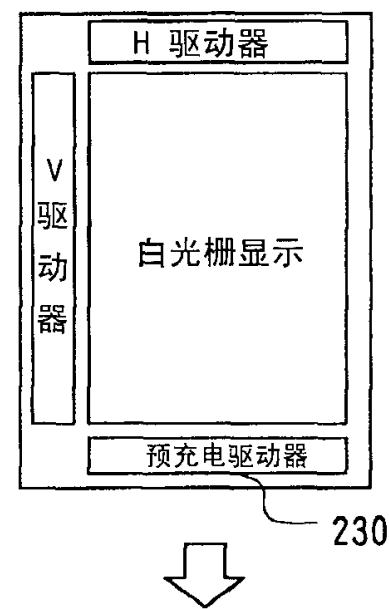

图 2 (a)，2 (b) 和 2 (c) 是说明本发明实施形态的显示装置的显示种类的概念图。

图 3 (a)，3 (b)，3 (c) 和 3 (d) 示出本发明实施形态的显示模式的切换动作以及切换动作时的显示状态。

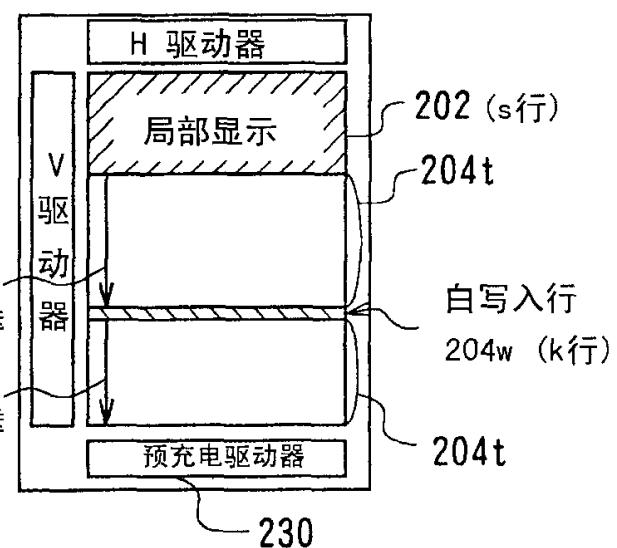

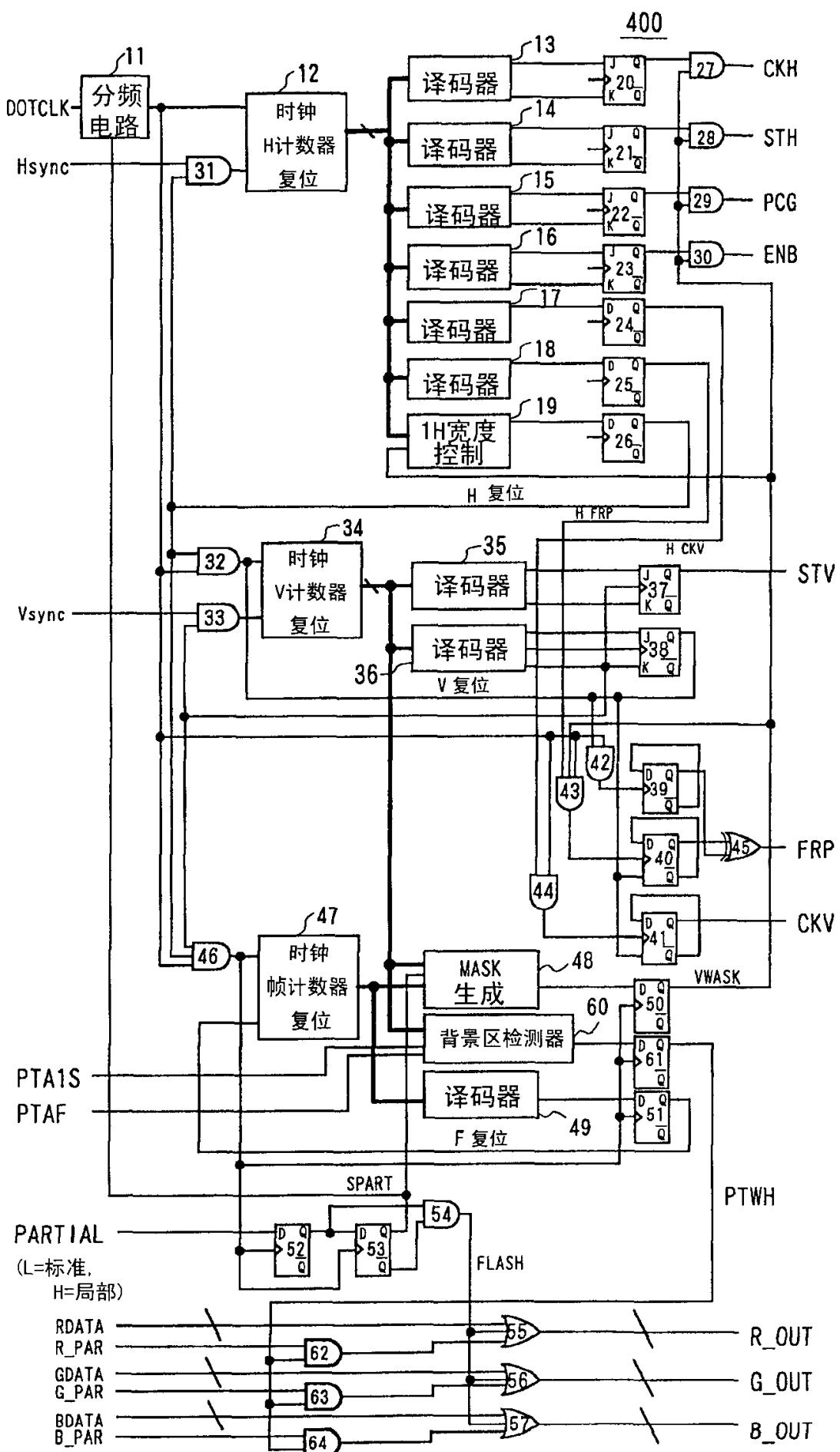

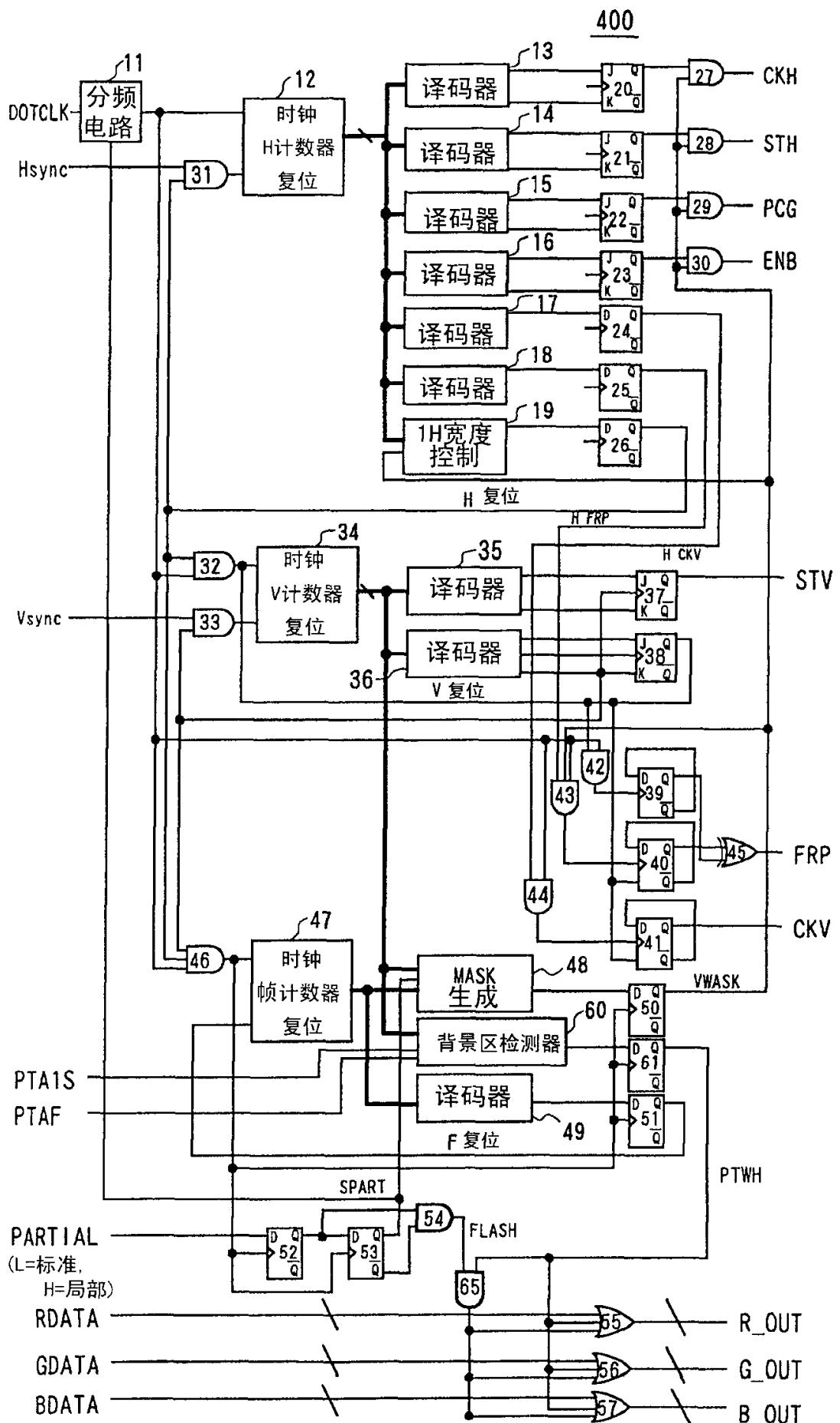

图 4 示出本发明实施形态的驱动电路的时序控制单元中的结构。

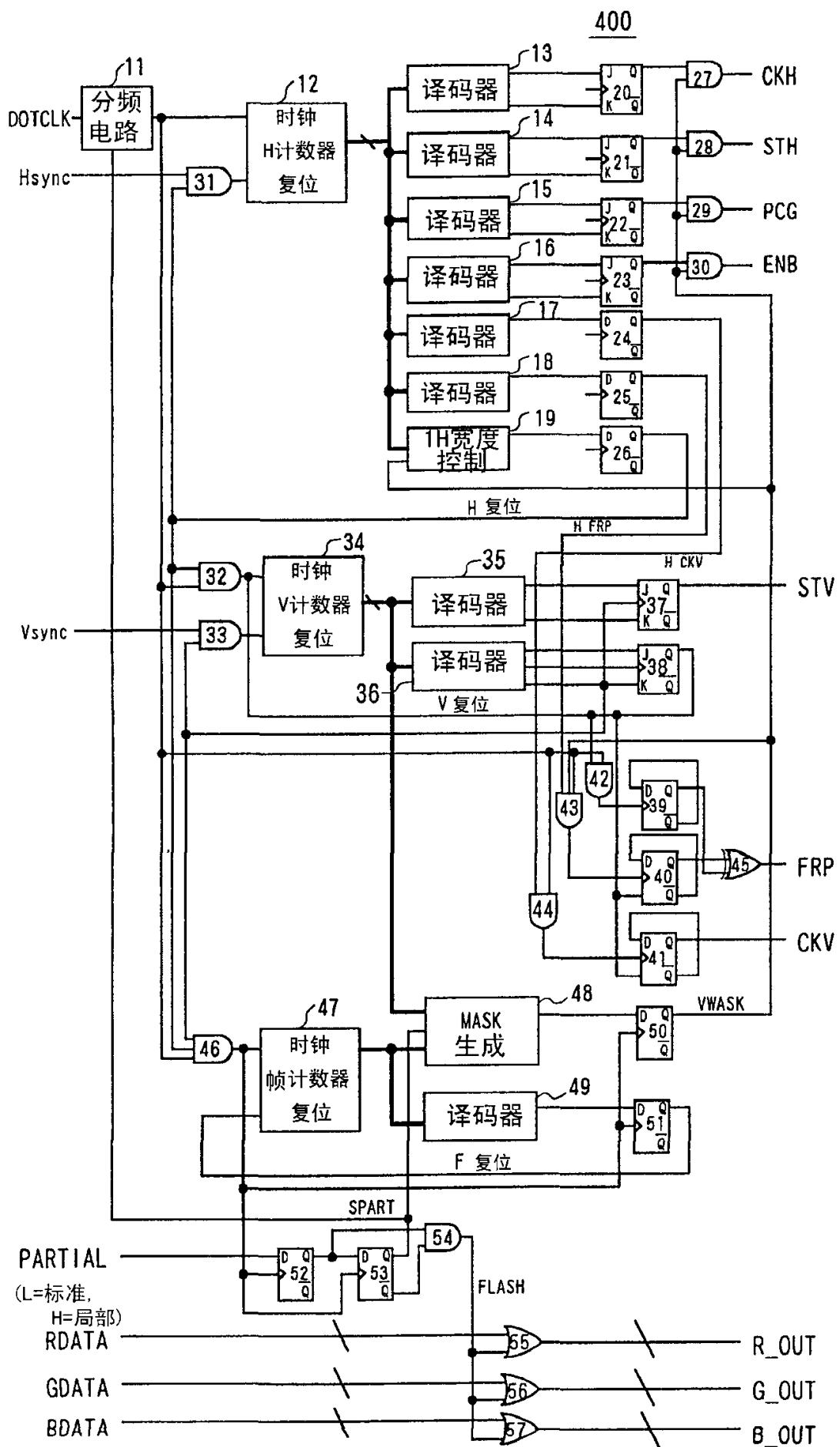

图 5 示出本发明实施形态的 LCD 面板的 V 驱动器的结构。

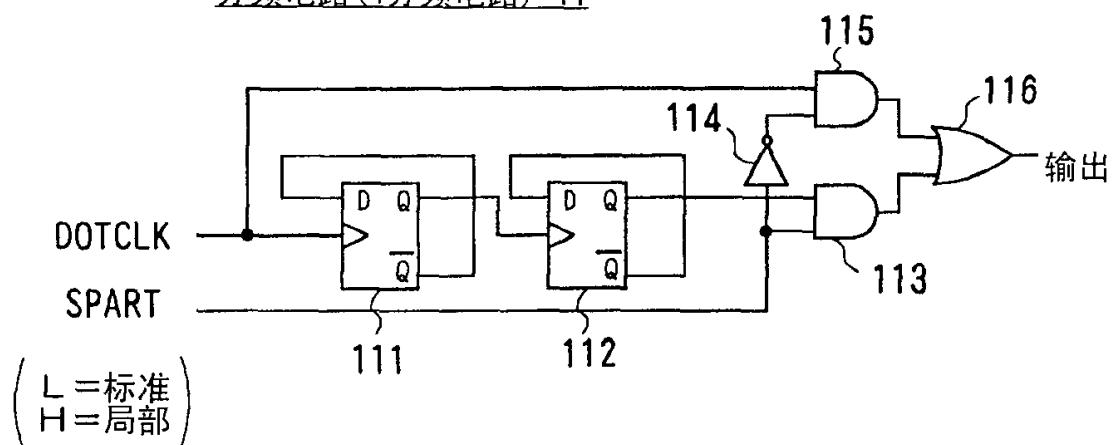

图 6 示出图 4 的分频电路 11 的结构。

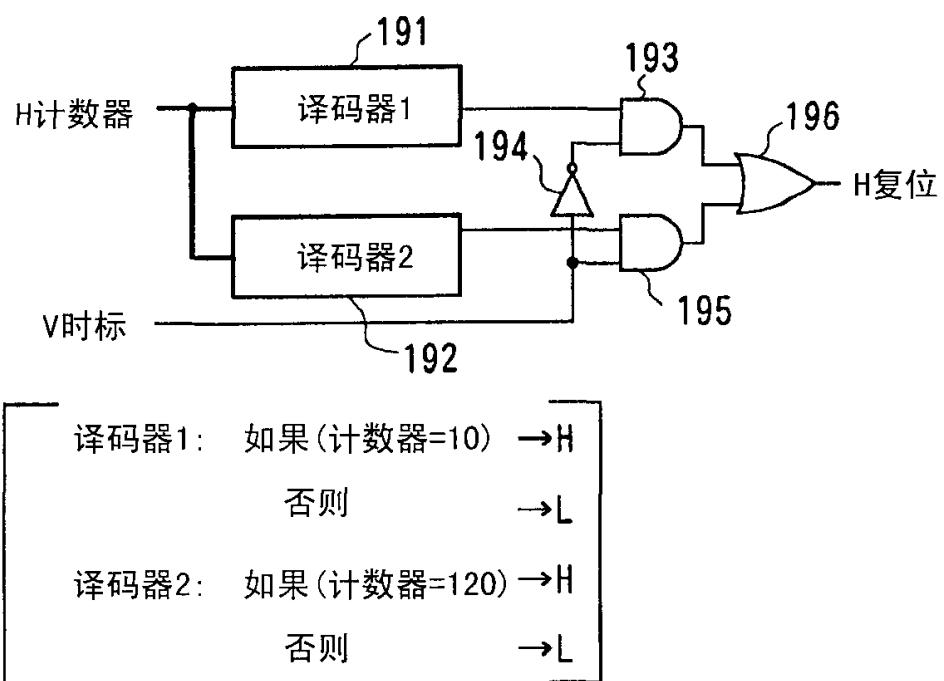

图 7 示出图 4 的 1H 宽度控制电路 19 的结构。

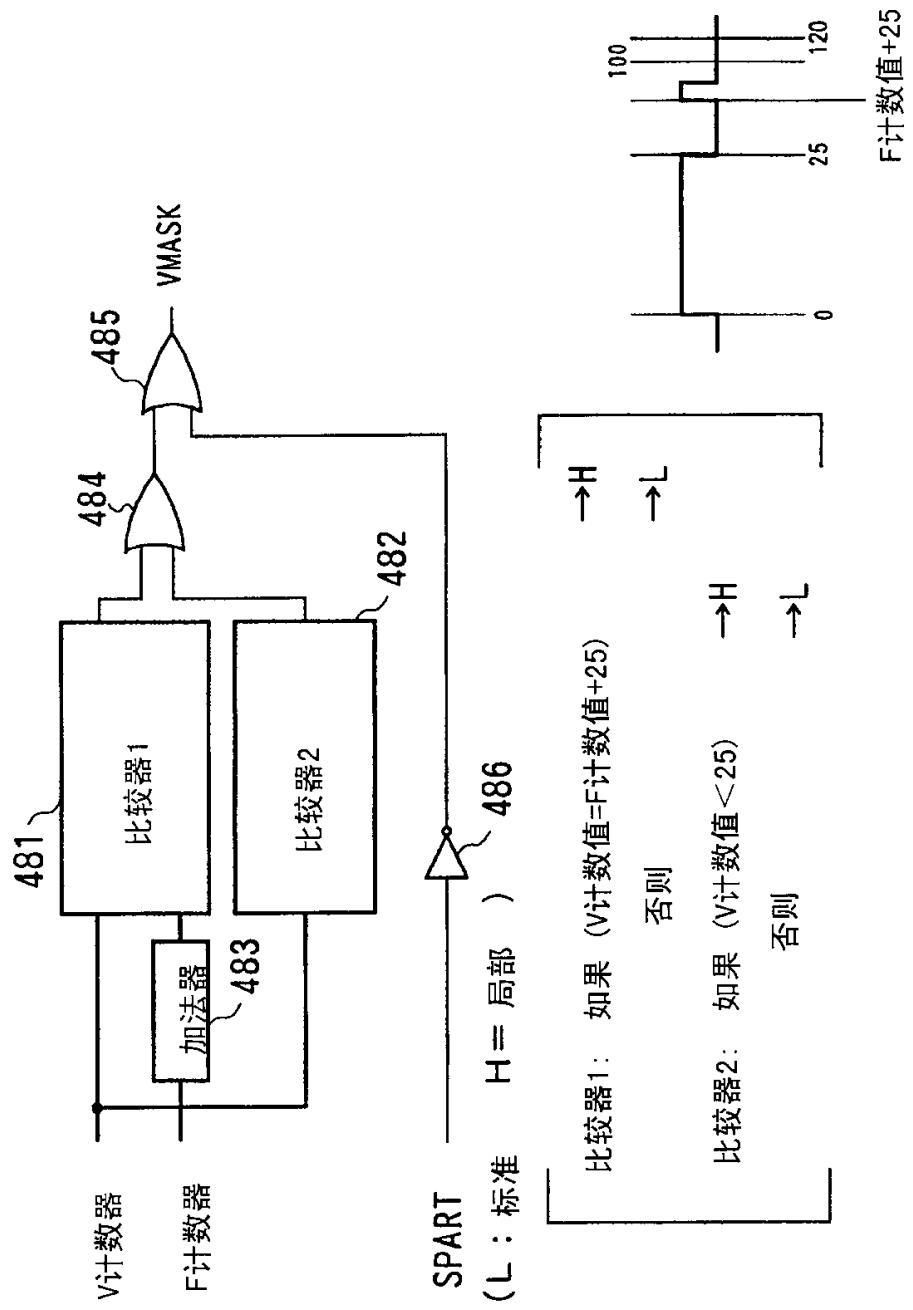

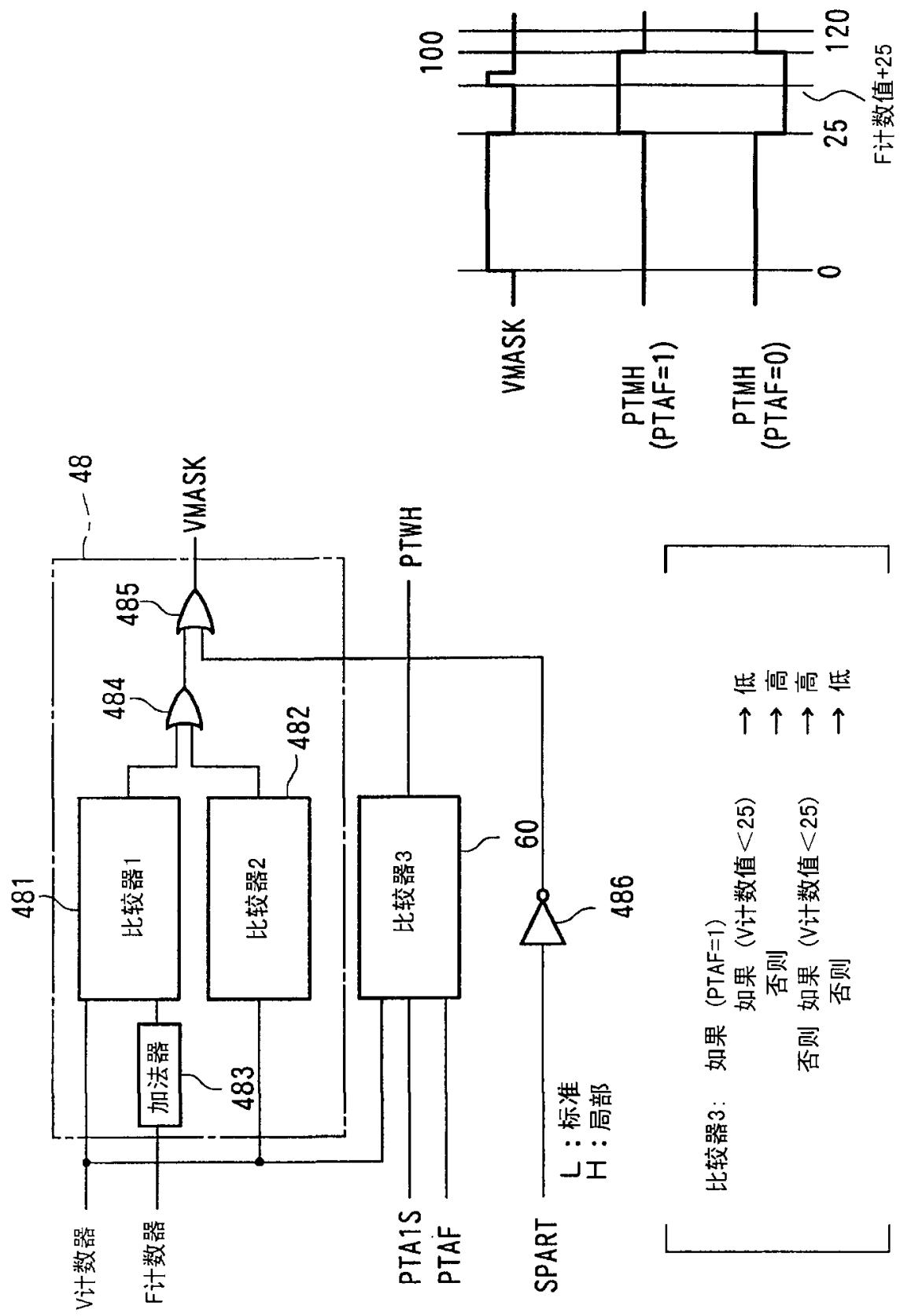

图 8 示出图 4 的 MASK 生成电路 48 的结构。

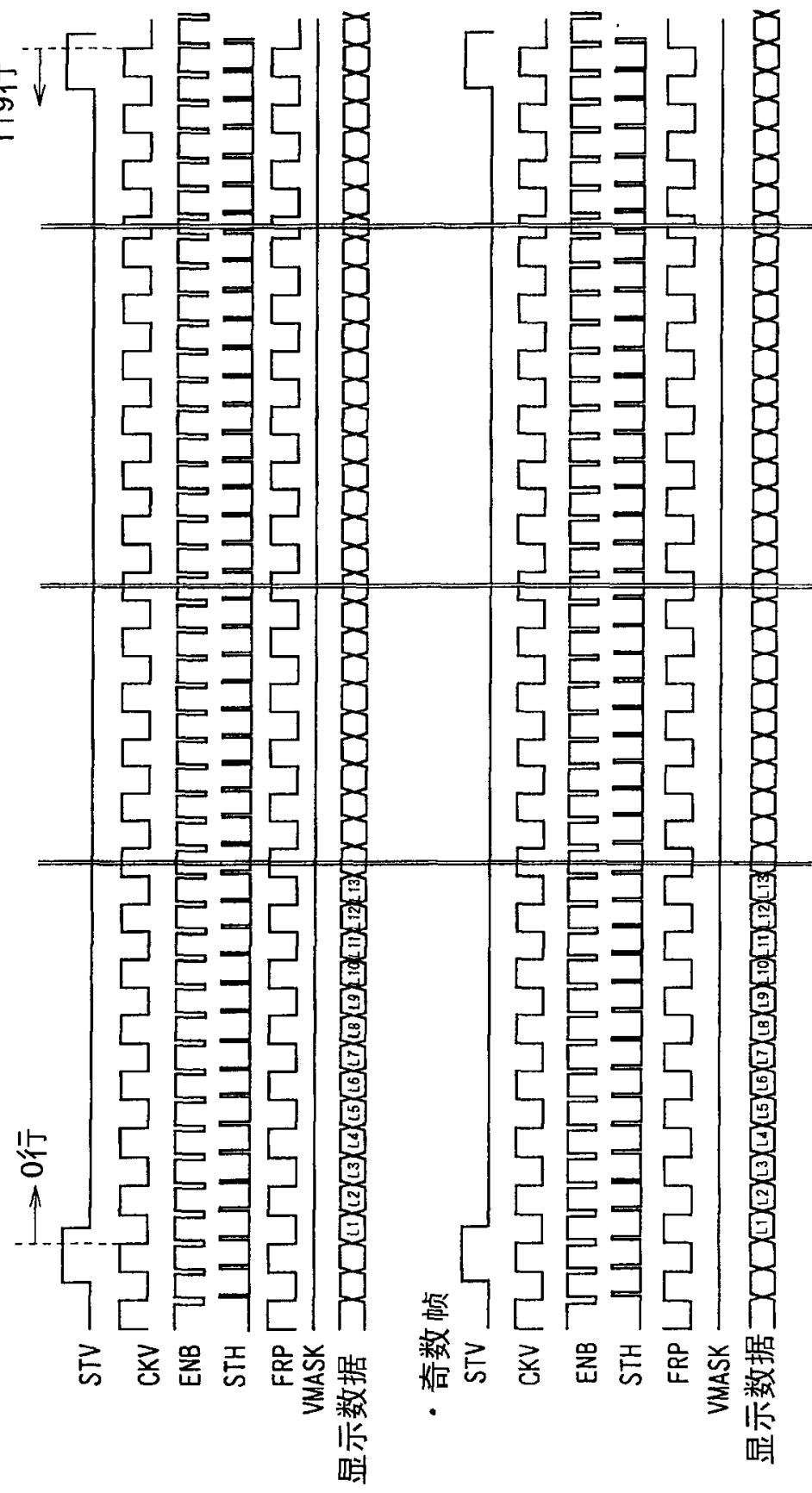

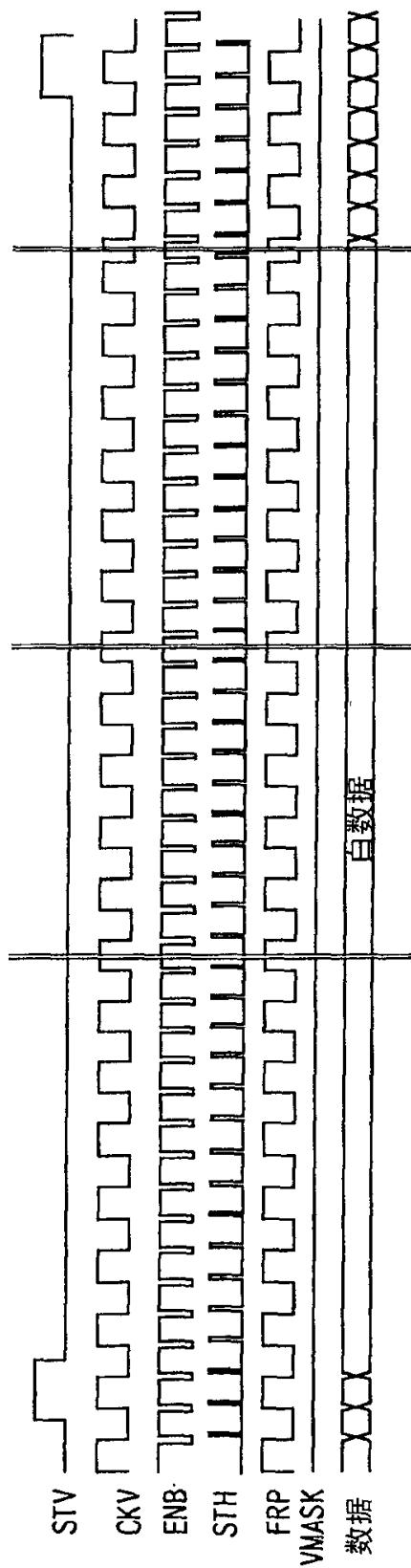

图 9 是示出本发明实施形态的通常显示时的动作的时序图。

图 10 是示出本发明实施形态的白光栅显示时的动作的时序图。

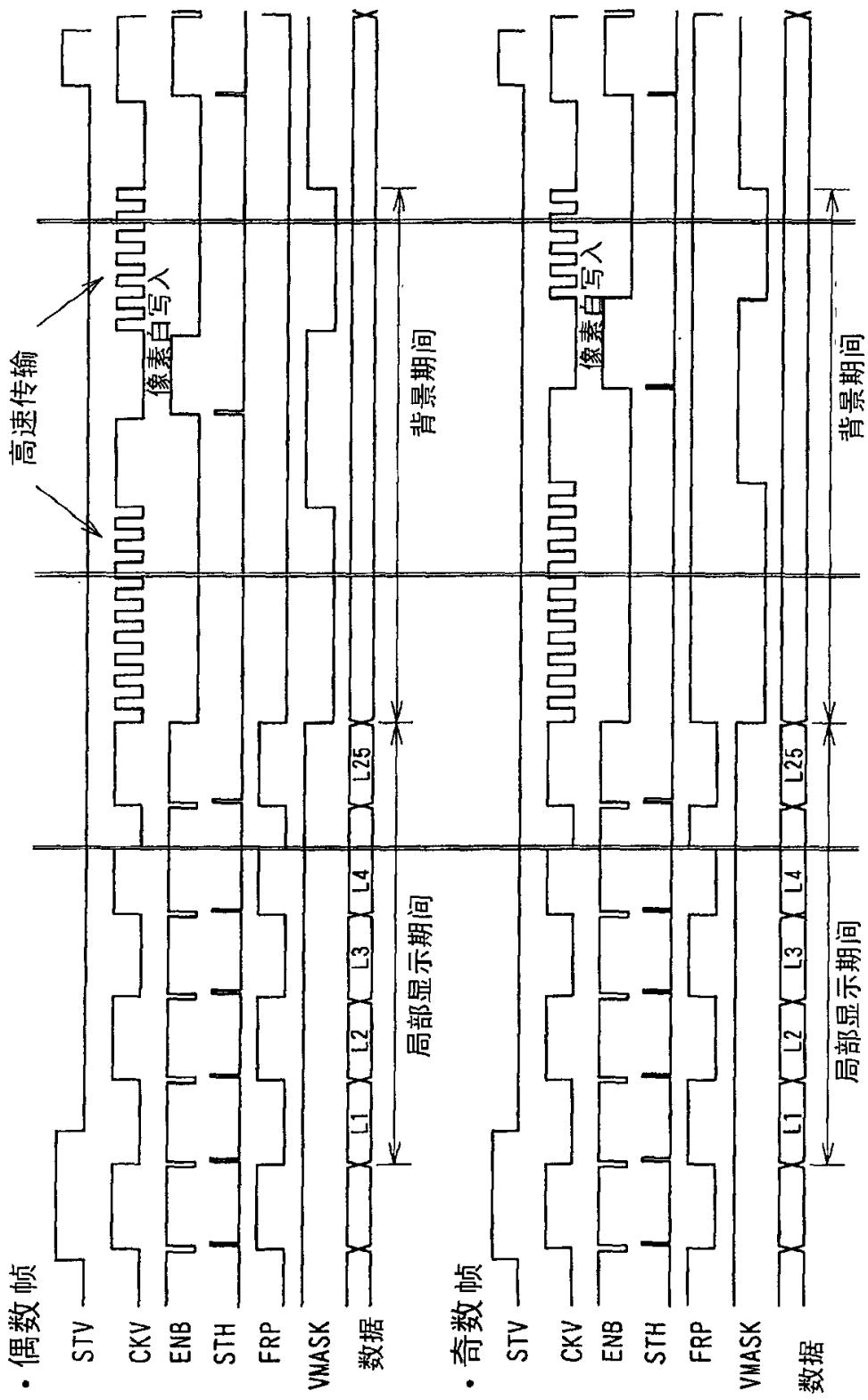

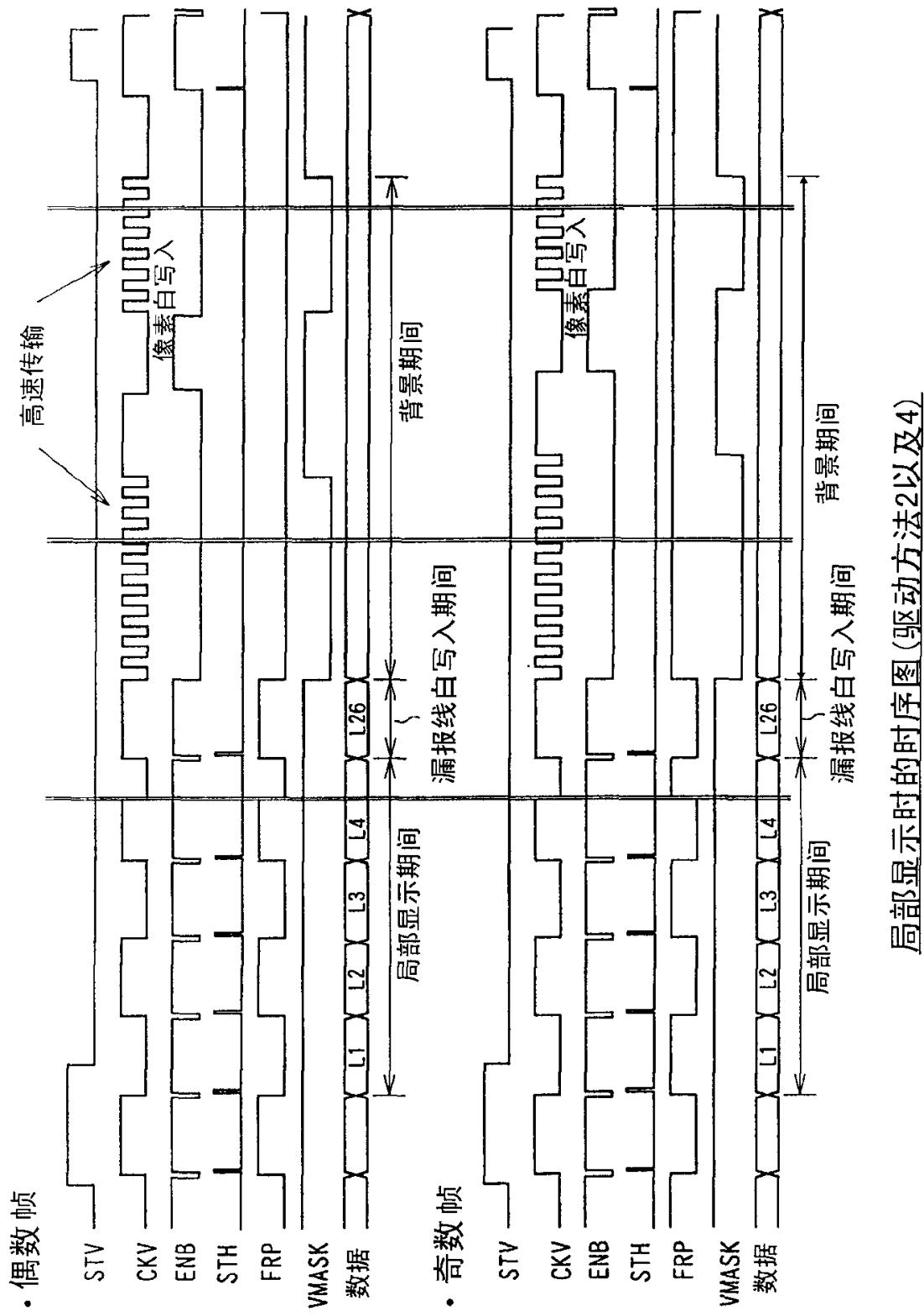

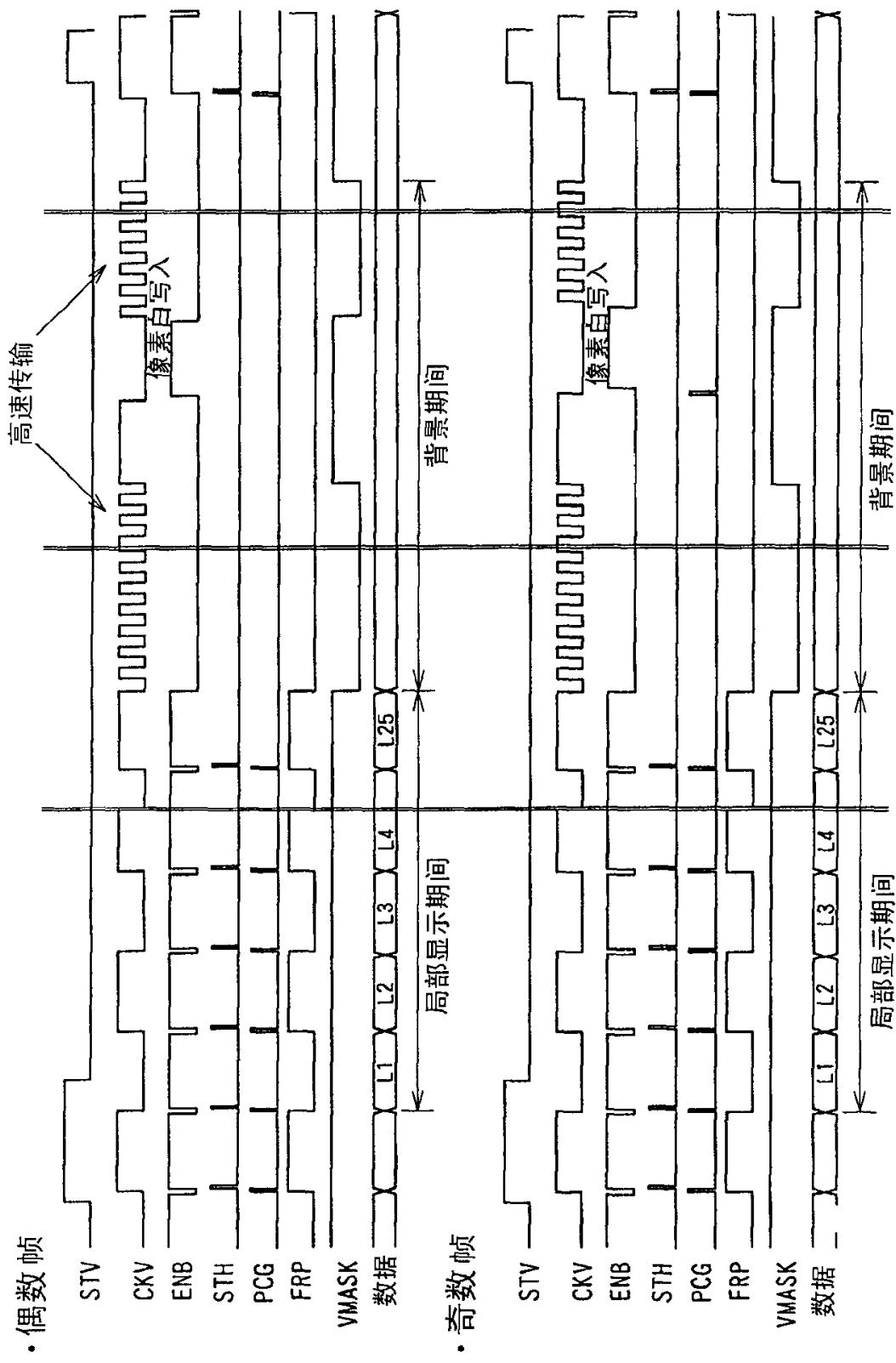

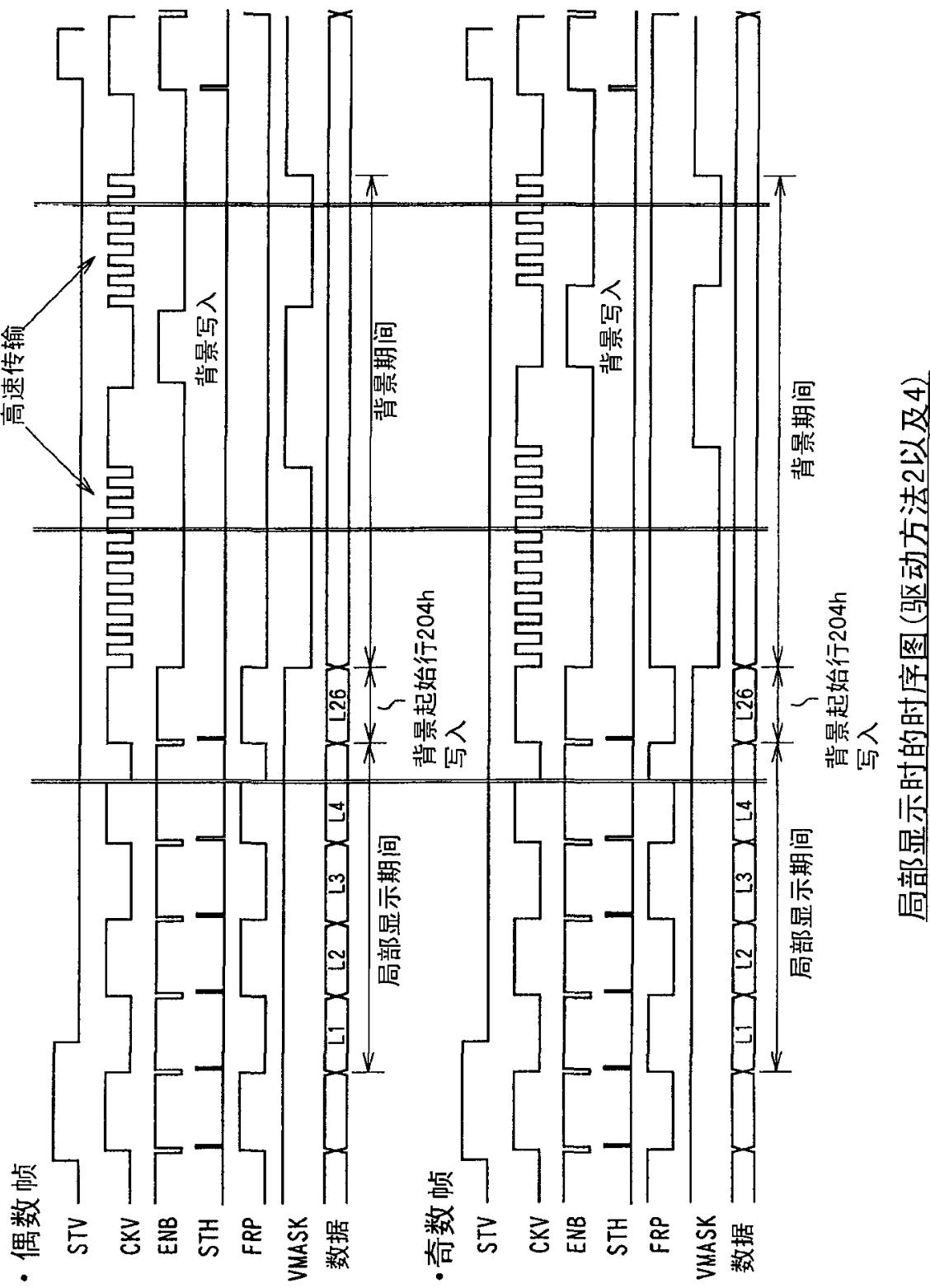

图 11 是示出执行本发明实施形态的驱动方法 1 以及方法 4 时的局部显示时的动作的时序图。

图 12 是示出执行本发明实施形态的驱动方法 1 时的局部显示时的动作的时序图。

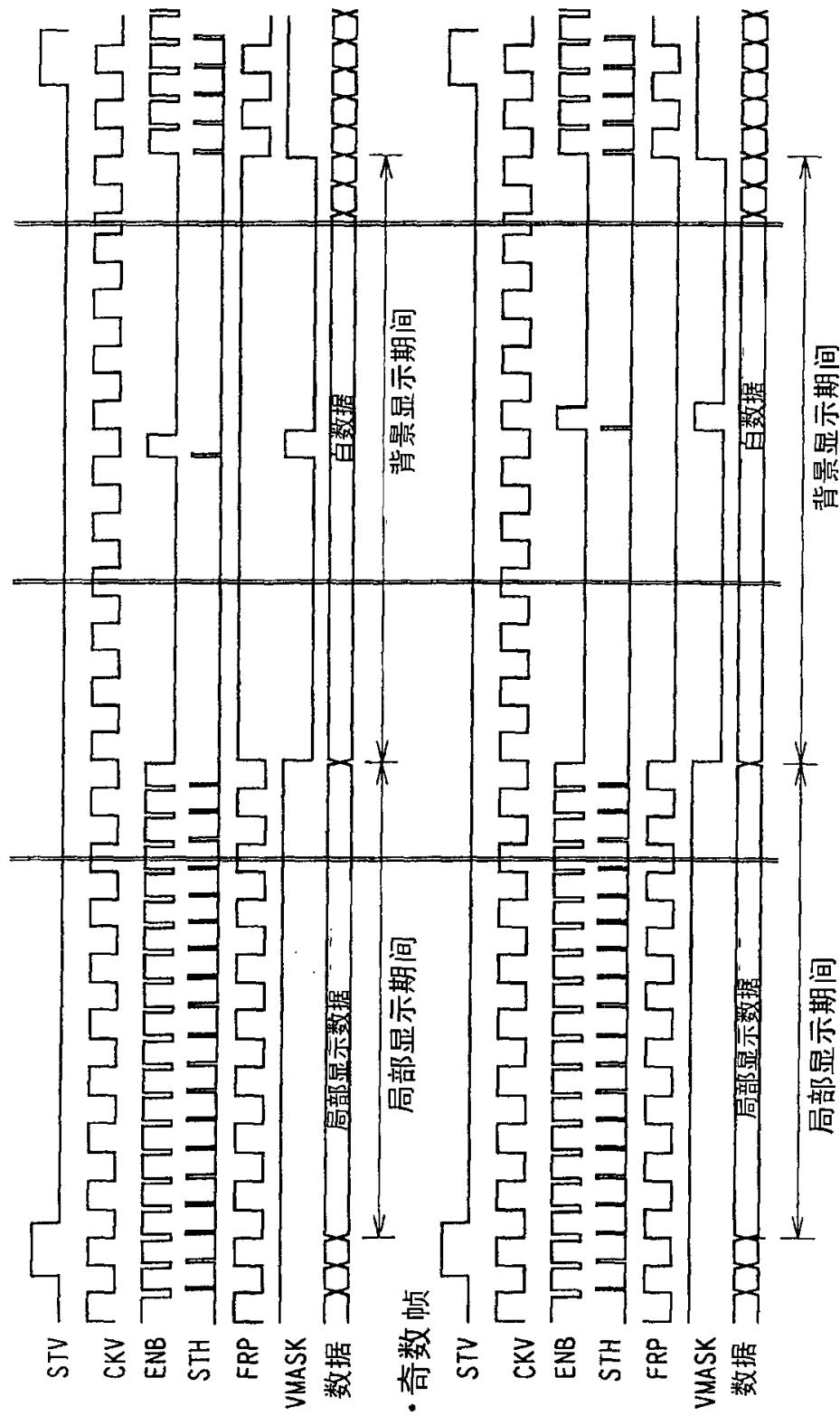

图 13 是示出执行本发明实施形态的驱动方法 2 时的局部显示时的动作的时序图。

图 14 是示出执行本发明实施形态的驱动方法 2 以及方法 4 时的局部显示时的动作的时序图。

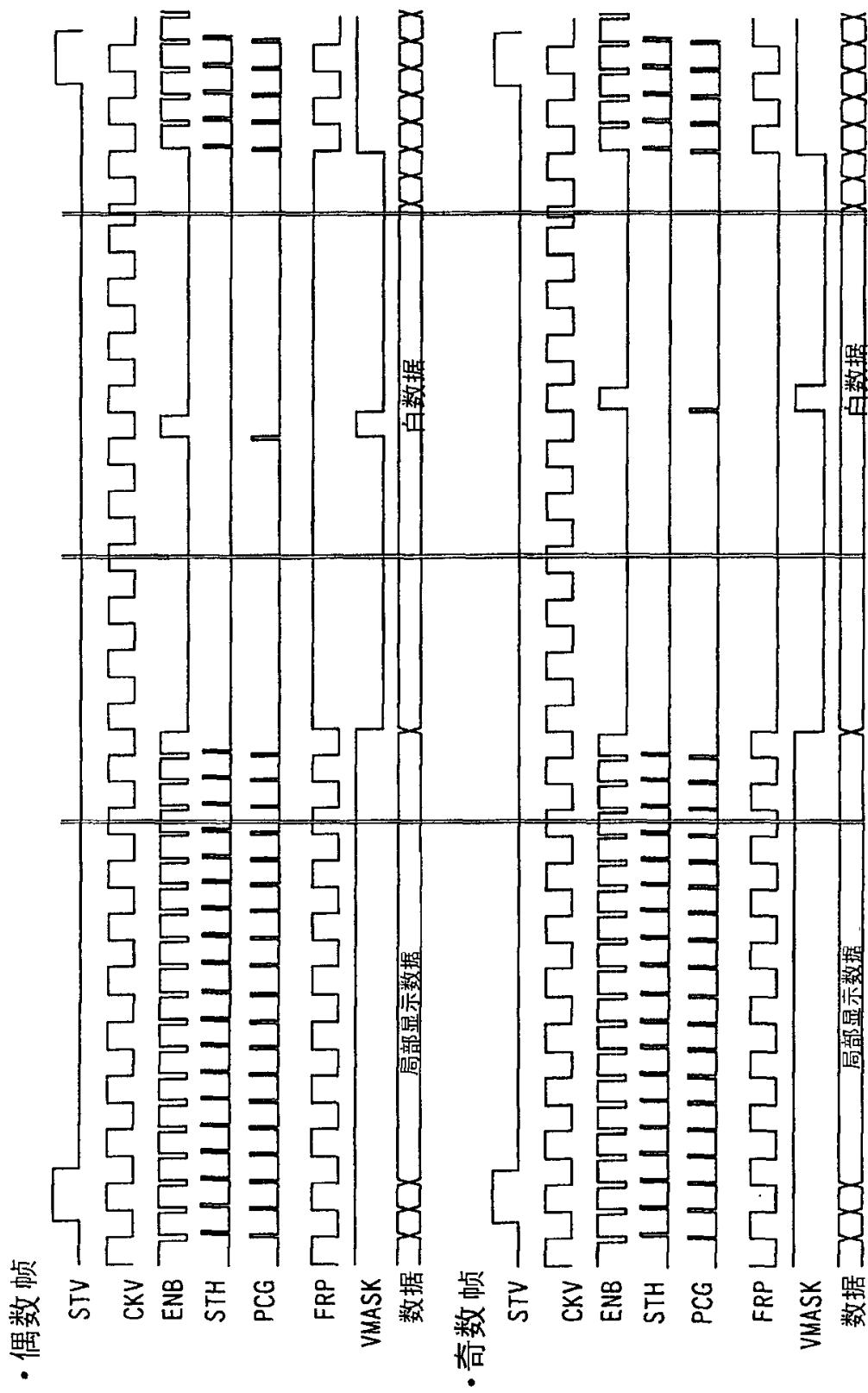

图 15 是示出执行本发明实施形态的驱动方法 3 时的局部显示时的动作的时序图。

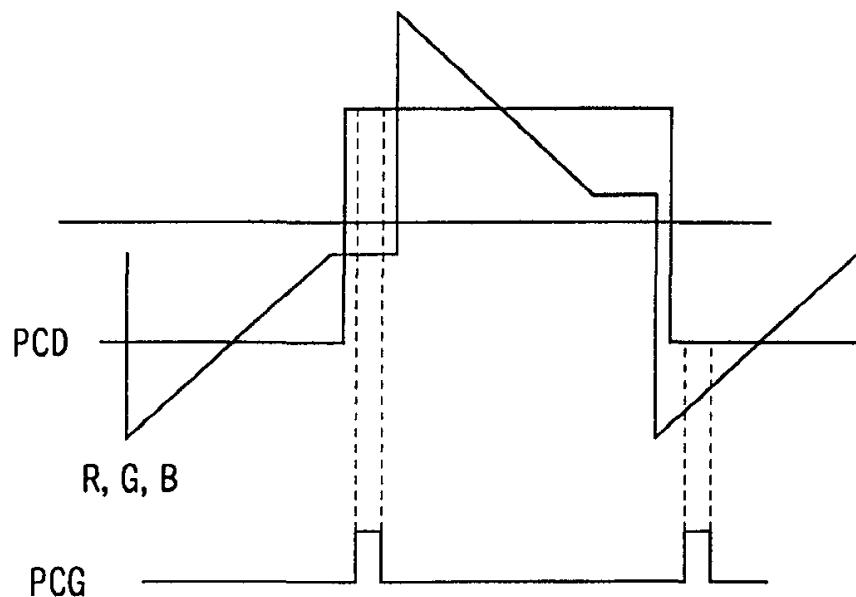

图 16 示出在本发明实施形态中使用的预充电波形。

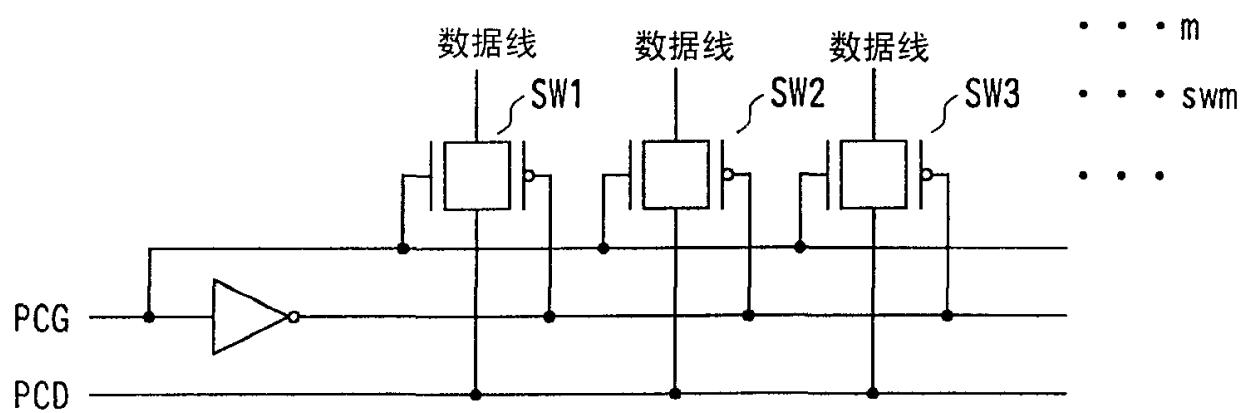

图 17 示出在本发明实施形态中使用的预充电驱动器 230 的结构。

图 18 是示出执行本发明实施形态的驱动方法 3 以及方法 4 时的局部显示时的动作的时序图。

图 19 示出本发明实施形态的驱动电路的时序控制单元中的结构。

5 图 20 说明本发明的图 19 中所示的背景区检测电路 60 的动作。

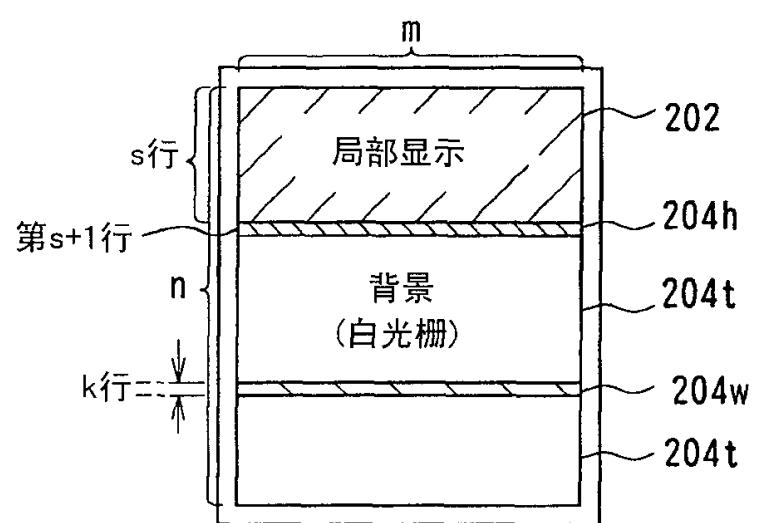

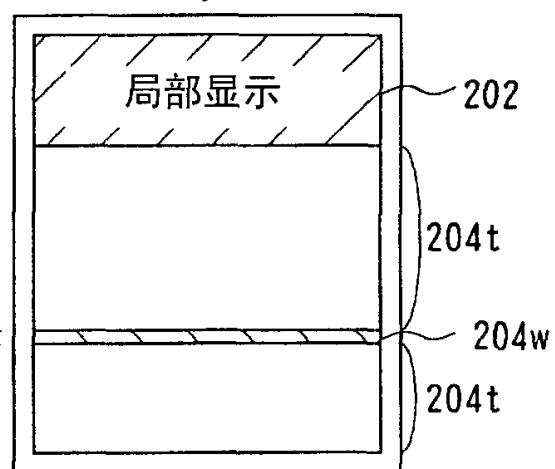

图 21 是说明本发明实施形态的显示装置的局部显示模式下的背景区选择方法的概念图。

图 22 示出为了执行图 21 所示的方法在时标生成电路 48 以及背景区检测电路 60 中所示的阈值以及这些电路的输出。

10 图 23 说明为了执行图 21 所示的方法来自时标生成电路 48 以及背景区检测电路 60 的输出波形。

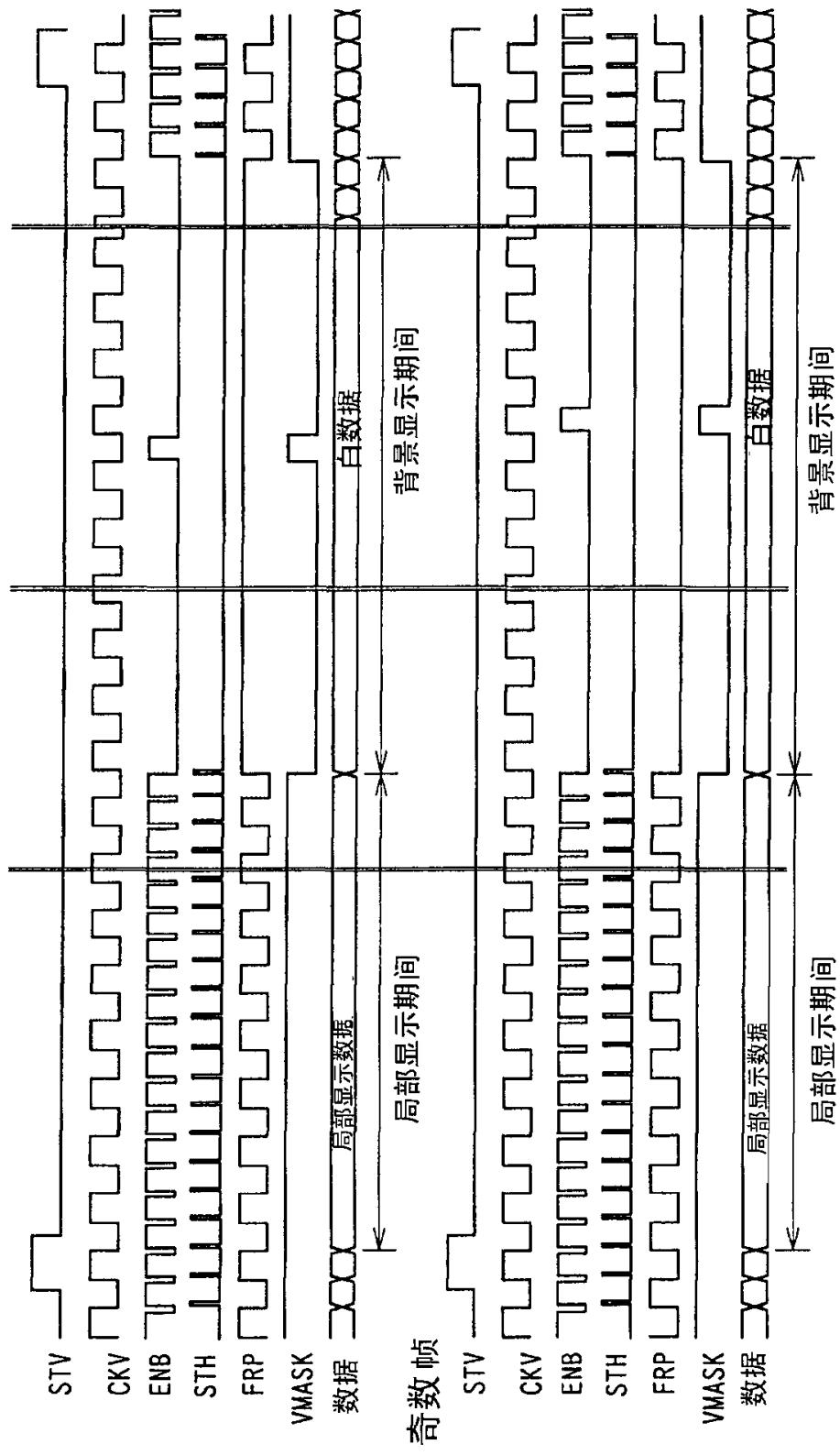

图 24 是示出采用了图 21 所示的方法时的动作例的时序图。

图 25 说明在本发明实施形态的显示装置中向局部显示时的转移时开始进行局部以及背景显示的顺序地的例子。

15 图 26 示出在本发明实施形态显示装置中向局部显示的转移时用于执行局部以及背景显示时的时序控制单元中的结构。

以下，使用附图说明本发明的理想实施形态（以下称为实施形态）。

## 20 基本结构

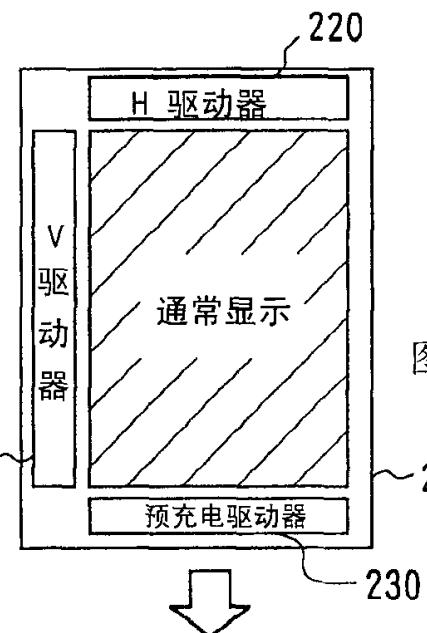

图 1 示出本发明的显示装置的概略结构。该显示装置例如是搭载在便携电话机中的 LCD 等平面显示装置，具备在一对基板中封入液晶构成的液晶显示（LCD）面板 200，驱动该 LCD 面板 200 的驱动电路 100，向驱动电路 100 以及 LCD 面板 200 供给必要的电源电压（例如 25 ADD1, ADD2, ADD3）的电源电路 300。

LCD 面板 200 是有源矩阵型的面板，该面板作为在各像素中的开关元件设置薄膜晶体管，由沿着行方向延伸的选通线控制该薄膜晶体管的导通·关断，经过该薄膜晶体管从沿着列方向延伸的数据线向各像素提供显示数据，由此能够进行每个像素的显示。另外，在面板的显示部分的周围，形成顺序地控制选通线的垂直方向驱动器（V 驱动器）210，以对应的时序向数据线供给显示数据的水平方向驱动器（H 驱动器）220。其中，该 V 驱动器 210 以及 H 驱动器 220 不限定于形

成在面板 200 上，有时也形成为 IC 化了的驱动电路 100 的一部分或者独立的电路。

驱动电路 100 具备锁存供给的 RGB 数字数据的锁存电路 101，把锁存数据变换为模拟数据的数字·模拟 (D/A) 变换电路 102，把被变换了的模拟数据进行放大作为 R、G、B 模拟显示数据供给到 LCD 面板 200 的 H 驱动器 220 的放大器 104。驱动电路 100 还具备从未图示的 CPU 接受命令，输出对应于命令的控制信号的 CPU 接口 (I/F) 电路 106，时序控制器 (T/C) 400。I/F 接口电路 106 接受从未图示的 CPU 发出的命令并且分析该命令，输出对应于命令的控制信号。从 CPU 发出的命令除去省电控制命令以外，是在显示面板上的显示位置的调整命令或者对比度调整命令。

T/C400 是根据点时钟 DOTCLK、水平同步信号 Hsync、垂直同步信号 Vsync 等时序信号，发生 LCD 面板 200 的 V 驱动器 210 或者 H 驱动器 220 的动作以及显示所需要的时序信号、控制信号的电路，如后述那样，在本实施形态中，能够进行任意位置的局部显示，而且，能够根据需要降低局部显示时的功耗。

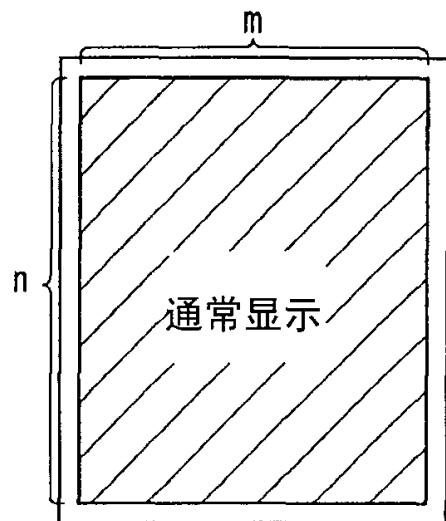

举例说明具备  $n$  行  $\times m$  列矩阵像素的 LCD 面板 200。在本实施形态中，在通常显示模式中，在 1 帧期间驱动所有的像素，通过顺序地选择各行，同时在  $m$  列的数据线上供给预定显示数据，在与各行对应的要素中写入显示数据，对于全部  $n$  行进行以上的动作，如图 2 (a) 所示，进行全面显示。

例如，如果根据来自 CPU 的省电命令转移到局部显示模式，则如图 2 (b) 所示，只有全部  $n$  行中任意的  $s$  行  $m$  列成为局部显示区 202，进行预定的局部显示，其它区域成为背景显示区域（背景区）204，进行背景显示（关断显示）。如果夹持液晶层设置的共同电极与像素电极之间的电压是 0V（关断时），则在显示白的标准白显示模式 LCD 的情况下，在上述背景区 204 显示相当于关断显示的白（进行白光栅显示）。

在本实施形态中，背景区 204 在局部显示期间并不是一直关断，如图 2 (c) 所示，在每个预定期间，顺序地选择每 1 行，在对应像素中写入白显示数据。白显示在标准白的情况下，原理上通过在电极之间不加入电压而实现，但实际上在共同电极与显示白的各像素电极之

间加入数伏特的电压。从而，把实际装置中的相当于关断显示的电压作为白显示数据经过像素晶体管写入到背景区 204 的各个像素电极中。

以画面是  $100 \text{ 行} \times 100 \text{ 列像素}$  ( $n, m = 100$ ) 矩阵的 LCD 的情况，

5 局部显示区 202 是  $25 (s = 25) \times 100$  的像素区，背景区 204 是  $75 \times 100$  的情况为例进行说明，在某 1 帧期间中，对于背景区 204 中预定的  $k$  行与局部显示区 202 同样地进行选择，在其中写入背景显示数据（背景区是白显示数据）。在下一个 1 帧期间中，选择背景区 204 内的其它行，写入白显示数据。

10 在上述例中背景区是 75 行，设定  $k = 1$  的情况，在背景区 204 中顺序地选择与 75 帧 ( $(n - s) / k$  帧) 对应一次的行 204w，写入白显示数据。从而，背景区 204 的各行在 75 帧以后至到被再次选择之前不被选择，维持写入的白显示。

15 另外，虽然背景区 204 在多个帧 ( $(n - s) / k$  帧) 期间在全部像素中写入白数据，但如果着眼于对其中的某行 204w，则在该任意帧 ( $(n - s) / k$  帧) 期间的下一个多个帧 ( $(n - s) / k$  帧) 期间，对于同一行，写入与前面的该任意帧 ( $(n - s) / k$  帧) 期间极性反转（以共同电极电压为基准的极性反转）了的白显示数据进行反转驱动。

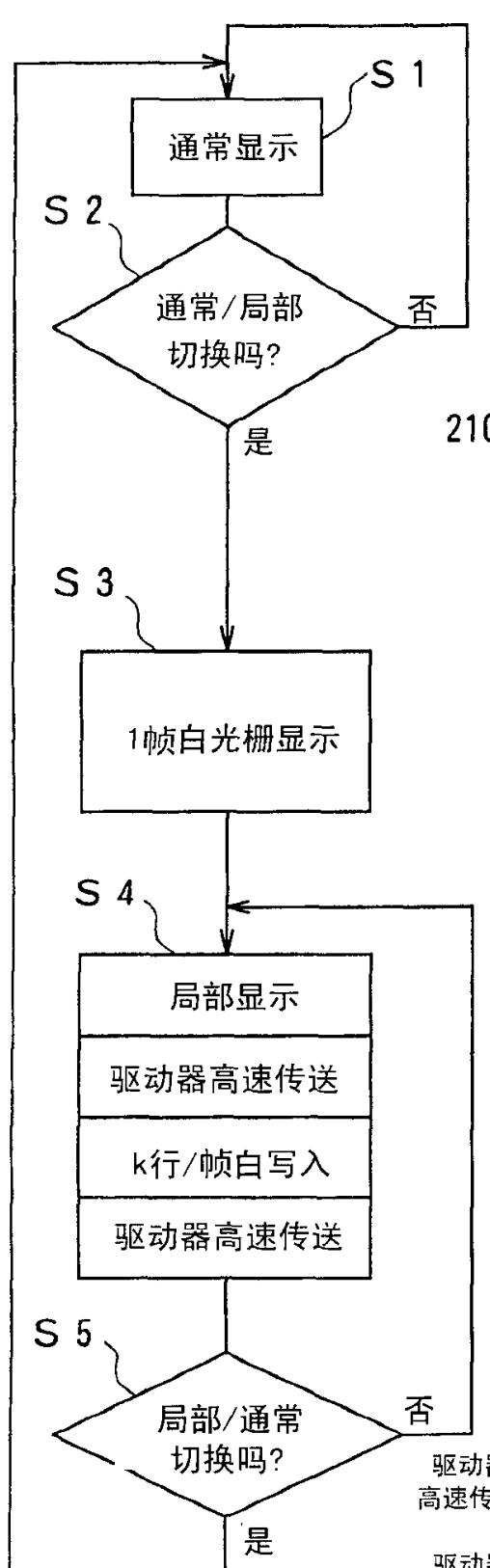

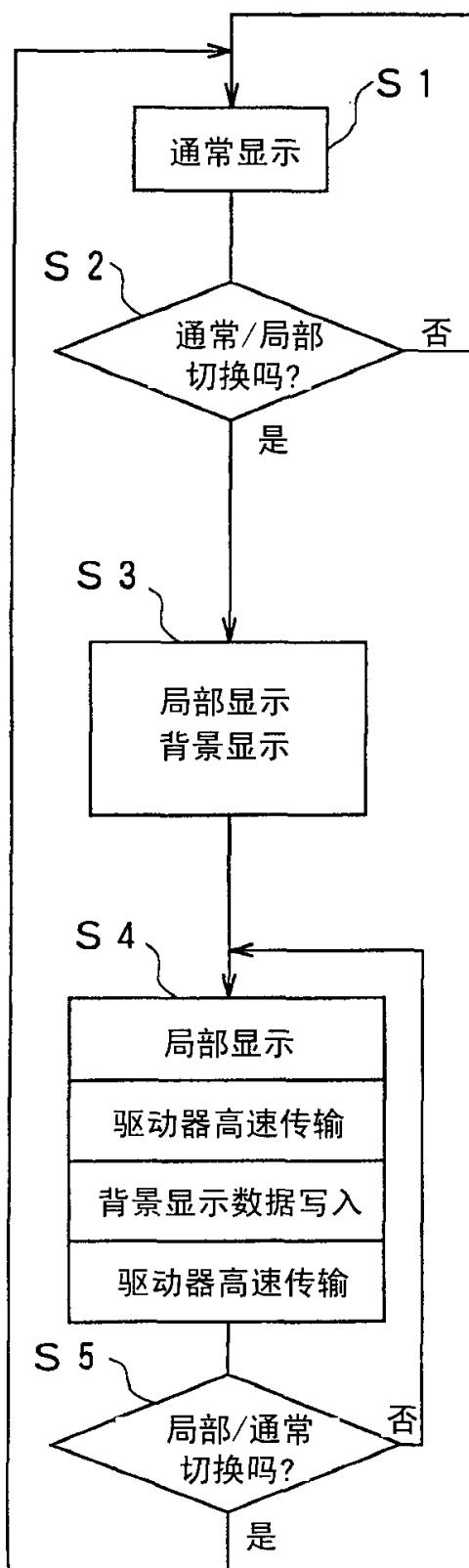

20 图 3 (a) ~ (d) 示出本实施形态的显示装置中从通常显示模式向局部显示模式转移时的动作。在图 1 的 I/F 电路 106 判断为是通常显示模式的情况下，如图 3 (a) 所示，LCD 面板 200 使用全部画面进行通常显示 (S1)。如果从 CPU 传输来局部显示控制命令，则 I/F 电路 106 分析该命令发生局部显示控制信号，切换为局部显示模式 (S2)。另外，在设置了开关等的情况下，也可以通过设备使用者切换这些开关，发生相同的局部控制信号，转移到局部显示模式。

25

装置切换为局部显示模式以后，可以直接进行上述那样的局部以及背景显示，而在本实施形态中，在从通常显示向局部显示转移时，暂时使整个画面关断。具体地讲，转移时的 1 帧，首先，如通常那样选择各像素写入白显示数据进行白光栅显示 (S3, 图 3 (b))。

30 进行这样的控制是为了防止切换到局部显示时，在背景区中通常显示时的显示逐渐地向关断显示状态变化。即，在从通常显示切换到局部显示时，在背景区 204 的像素中，写入着前面的通常帧的像素显

示数据。然而在背景区 204 中，如上述那样在每 1 帧都没有被选择。从而，即使设置在各像素中的像素晶体管被关断控制到选择选通线为止，但由于晶体管的 OFF 漏电流，像素显示数据逐渐地退出晶体管，向夹持液晶层而相对的共同电极的电位接近。即，背景区 204 中，从通常显示帧切换时，需要数秒逐渐地变化到关断显示（白光栅），这种缓慢的显示变化对于装置使用者来讲大多不理想。因此，在切换到局部显示之前，暂时在整个画面写入使得进行白光栅显示，由此在局部显示时，所有的像素从作为关断状态的白显示状态变化，能够减少局部显示时的背景区 204 中的显示恶化。另外，以下，作为 LCD 面板 200，只要没有特别提及，就是标准白显示型，所谓白显示实质上取为关断显示。

一旦进行了整个画面的白光栅显示以后，在 LCD 面板 200 中，进行图 3 (c) 那样的局部显示 (S4)。本实施形态中，LCD 面板 200 的局部显示通过图 1 的 T/C400 根据局部控制信号发生后述的控制信号、时序信号进行，在 LCD 面板 200 中也可以不具备用于对应局部显示的特殊结构而实现。

在局部显示模式下，局部显示区与通常显示相同，在 1 帧选择各行写入显示数据。以下参照图 3 (c) 说明本实施形态中的背景区 204 的驱动方法 1~4。后面参照图 9~图 15 以及图 18 说明由各驱动方法生成的具体的驱动波形的例子。

另外，从局部显示模式向通常显示模式的恢复，通过从 CPU 等发出通常显示控制命令，图 1 的 I/F 电路 106 分析该命令，根据其结果，发生通常显示控制信号或者停止输出局部显示控制信号等实现（图 3, S5）。

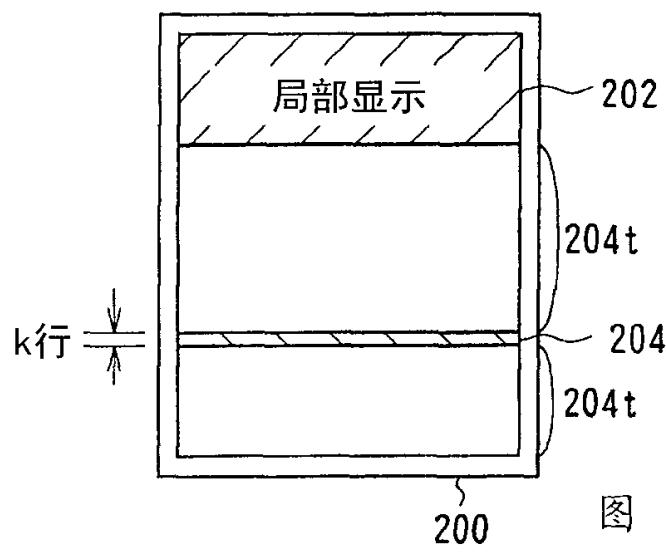

## 25 驱动方法 1

在方法 1 中，局部显示区 202 在 1 帧期间中，顺序地选择所有 s 行（选通线）写入预定的显示数据，背景区 204 中，在相同的 1 帧期间，仅选择区域 204 的 k 行写入白显示数据。即，在本驱动方法 1 中，在 1 帧期间中顺序地选择局部显示区 202 的所有 s 行和背景区 204 的 k 行总计 (s + k) 行，对于被选择的行，以预定的时序向 m 列的数据线发送显示数据，由此在对应的像素中顺序地写入对应的显示数据。

而且，在局部显示区 202 是 25 行，背景区 204 是 75 行，k = 1

的情况下，在 1 帧期间顺序地选择 26 行（25 行 + 1 行），背景区 204 的其它行 204t 根据图 1 的 T/C400 生成的信号中后述的作为控制信号的垂直控制信号（vmask）禁止选择。

5 在下一个帧中，局部显示区 202 再次选择所有的 s 行写入显示数据（其中，显示数据通过行反转，1 帧反转，极性在每 1 行，每 1 帧变化）。另外，背景区 204 中，选择与在前面的帧中写入了白显示数据的行不同的行，写入白显示数据。从而，在全部 100 行中如果局部显示区 202 的行数是 25，背景区 204 中相当于 1 帧的选择行数是 1，则如上述那样，局部显示区 202 在各个帧中全部区域 202 中写入显示数据，背景区 204 中，遍及 75 帧，在全部区域中写入白显示数据。

10 另外，在  $k = 1$ ，背景区 204 中，在下一个帧中选择与在上一个帧中选择了的 1 行邻接的 1 行的情况下，在邻接的行中写入相反极性的白显示数据进行行反转驱动。

15 进而，在多个  $((n - s) / k)$  帧期间（1 背景显示期间）（在上述例中是 75 帧），如果背景区 204 的所像素中写入了白显示数据，则在下一个  $(n - s) / k$  帧期间，在同一行中写入相反极性的显示数据。

另外，在背景区中，通过在每 1 行而且每一个背景画面把极性反转进行白显示，由此即使在背景区中也能够避免始终在液晶上加入直流电压成分，防止液晶的恶化。

20 在驱动方法 1 中，在局部显示模式下，反复进行以上的过程进行局部显示以及背景显示。

25 另外，驱动方法 1 中，也能够适用于点顺序驱动各像素的情况以及线顺序驱动各像素的情况。点顺序驱动的情况下，即使在某个局部显示区以及背景区的某一个，选择了对应的行（选通线）时，在数据线上顺序地发出显示数据，在线顺序驱动的情况下，在所有的数据线上一起发出要写入的显示数据。

## 驱动方法 2

30 在 1 帧期间中，选择局部显示区 202 的所有 s 行和背景区 204 的 k 行写入显示数据这一点与上述方法 1 相同，而在方法 2 中，在点顺序驱动（或者线顺序驱动）局部显示区 202 的所有 s 行的像素写入了显示数据以后，向全部数据线（m 列）上供给显示数据后，选择背景区 204 的 k 行。更具体地讲，对于局部显示区 202 结束了驱动以后，

在下一个 1 个水平扫描期间 (1H: 一个选通线选择期间)，在全部  $m$  条数据线上写入了白显示数据以后，选择背景区 204 的  $k$  行的选通线。由此被选择了选通线的像素晶体管导通，取入供给到数据线的白显示数据，对应的像素显示白。

5 在背景区 204 中选择并且写入了白显示数据行与上述方法 1 相同，在每一个帧变化，而且在前一个和下一个帧中背景区 204 的选择行邻接的情况下，在邻接的行中白显示数据的电压成为相互相反的极性。

10 对于背景区 204，在多个帧中在全部区域中写入白显示数据，在每一个背景画面在同一行中写入的白显示数据的电压极性反转这一点与上述方法 1 相同。

15 在上述驱动方法 1 中，在对于局部显示区 202 的行选择结束以后，H 驱动器 202 停止动作直到在同一个帧期间中被选择的背景区 204 中的行的选择期间到来。选择了对应的行以后，再次停止工作。与此不同，在本驱动方法 2 中，在对于局部显示区 202 的行选择结束以后，如果仅是后续的 1H 期间使驱动器 202 动作，在各个数据线中写入显示数据，则能够在其余背景区 204 的选择期间，使其动作停止。而且，这样的控制与上述的驱动方法 1 相同，能够通过 T/C400 中的最小限度的结构变更、添加而容易地实现。

### 20 驱动方法 3

在驱动方法 3 中，利用预充电控制信号在背景区 204 的  $k$  行中写入白显示数据。在有源矩阵型的 LCD 中，通常的情况下，在 1H 期间，选择对应的选通线使像素晶体管导通，经过像素晶体管在像素中写入这时加入到数据线中的显示数据，进行每个像素的显示。然而，行反转驱动方式的情况下，特别是，但每个 1H 中，由于加入到数据线的显示数据的极性反转，因此在 1H 切换以后，希望数据线的电压迅速而可靠的成为要进行显示的显示数据的电压。因此，进行预先把与在后续的 1H 写入数据线中的显示数据电压接近的电压写入到各数据线中的预充电。特别是，在薄膜晶体管的有源层使多晶硅的 p-SiTFTLCD 中，为了减轻 TFT 的动作负荷等目的，如图 3 那样，，把专用的预充电驱动器 230 与其它的驱动器 210、220 一起形成在 LCD 驱动器 200 上，进行预充电驱动。

在本实施形态的驱动方法 3 中，在背景区 204 中的背景显示方面也利用这种预充电所利用的预充电控制信号以及预充电数据。即，如果在某帧期间中成为背景区 204 的要选择行的选择时序时，如后所述，在图 1 的 T/C400 中，在其 1H 即将开始之前发生预充电控制信号 (PCG)，根据该控制信号在各数据线写入相当于白显示数据的预充电数据。另外，在局部显示区 202 中，根据预充电控制信号，在各数据线中即将选择任意的行之前，在其行中供给对应于要显示的局部显示数据电平的预定预充电数据。另外，该预定的预充电数据也可以与局部显示数据的电平无关，设定为预定的电平。

在背景区 204 中在每个帧中变更选择的行（选通线），在每行中使显示数据的极性反转，在每个背景画面使显示数据的极性反转这一点与上述方法 1 以及 2 相同。

如果利用预充电控制信号写入对于背景区 204 的  $k$  行的显示数据，则在背景显示期间中，不需要控制驱动器 220，能够在省电方面做出贡献。

#### 驱动方法 4

本实施形态中，方法 4 关于在 1 帧期间中背景区 204 所选择的  $k$  行的驱动方法按照上述方法 1~3 的任一个进行，在与设有选择的 ( $n - s - k$ ) 行的选择期间相当的期间，提高控制 1H 期间长度的脉冲（例如行时钟）的频率，在行驱动器（V 驱动器 210）内高速传输各行选脉冲。

通过进行这样的驱动，在 1 帧期间中显示的行数是  $s$  行 +  $k$  行的情况下，能够以比通常动作 ( $n$  行驱动) 时更低的频率驱动各行，能够降低功耗与动作频率有依存关系的数字处理系统中的电路内的功耗。

另外，在 1 帧期间中与在背景区 204 内设有选择的行相当的期间不使 V 驱动器 210 停止，而如果在 V 驱动器 210 内进行输出则不把选择各行的选择脉冲输出到该行而高速传输。从而，接着在作为目标的行上输出选择脉冲驱动该行时，不需要进行特别的脉冲输入输出动作，而能够直接在所需要的行（选通线）上输出选择脉冲。

这样，局部显示模式时，部分地增大用于 V 驱动器选择行的选择脉冲的传输频率，由此，能够降低显示装置总体的动作频率。由此，

能够不变更安装在 LCD 面板 200 内的驱动器等的设计，实现降低由于驱动频率较低而引起功耗，能够在省电模式下进行局部显示。

### 驱动电路

其次，说明实现上述驱动的本实施形态的驱动电路的结构例。图 5 4 示出图 1 的驱动电路 100 中的 T/C400 的结构，图 5 示出在本实施形态中安装在 LCD 面板 200 内的 V 驱动器 210 的结构。

在 T/C400 中供给点时钟 (DOTCLK)，水平同步信号 (Hsync)，垂直同步信号 (Vsync) 以及局部显示控制信号 (PARTIAL)，根据这些信号，生成水平时钟 (CKH)，水平启动脉冲 (STH)，预充电控制信号 (PCG)，选通线选择控制信号 (ENB)，垂直时钟 (CKV)，垂直启动脉冲 (STV)，极性反转控制信号 (FRP)，把这些信号供给到 LCD 面板 200 的 V 驱动器 210，H 驱动器 220。

H 计数器 12 把经过分频电路 11 供给的点时钟 (DOTCLK) 作为时钟并且计数该点时钟。而且 H 计数器 12 由于根据经过与门 31 在 1H 期间输出一次的水平同步信号 (Hsync) 和来自后述的 1H 宽度控制电路 19 的 H 复位信号 (Hreset) 把计数值进行复位，因此在每 1H 期间计数点时钟。

上述分频电路 11 是图 6 所示的结构，具备两级 F/F 111、112，与门 113、115，反相器 114 以及把点时钟和分频时钟选择输出的或门 116。而且，如驱动方法 4 那样，对于背景区 204 在 1 帧期间中仅选择了 k 行的情况下，把通常的点时钟 (DOTCLK) 分频，通过对于 H 计数器 12、后述的 V 计数器 34 以及帧计数器 47 供给该分频时钟，在局部显示模式时用于使电路的动作速度下降，降低功耗。

把 H 计数器 12 的点时钟计数值在译码器 13 中译码得到的脉冲信号经过触发器 (F/F) 20，与门 27，作为水平时钟 (CKH) 输出，供给到 LCD 面板 200 的 H 驱动器 220。

译码器 14 根据 H 计数器 12 的点时钟计数值发生决定各一个水平扫描期间中的启动时序的脉冲，该脉冲经过 F/F 21 以及与门 28 作为水平启动脉冲 (STH) 输出。

译码器 15 根据 H 计数器 12 的点时钟计数值，求一个水平期间即将在开始之前的时序并且生成脉冲信号。该脉冲信号经过 F/F 22 以及与门 29，作为用于在 1H 即将开始之前，使数据线的电压接近后续的

1H 期间的显示数据电压的预充电控制信号 (PCG) 输出。

译码器 16 根据 H 计数器 12 的点时钟计数器值，求控制各选通线的选择许可期间的时序，该时序经过 F/F 23 以及与门 30，作为选通线选择控制信号 (ENB) 输出。该控制信号 (ENB) 是在 1H 期间开始之前对于数据线所进行的上述预充电期间中，用于禁止选择选通线使像素晶体管导通在各像素上写入预充电数据的控制信号。选通线选择控制信号 (ENB) 供给到图 5 所示的 LCD 面板 200 的 V 驱动器 210。

图 5 所示的 V 驱动器 210 具有根据脉冲的选通线数 (n)，把后述的垂直时钟 (非反转 CKV, 反转 CKV) 作为时钟，顺序地把垂直启动脉冲 (STV) 移位的多级移位寄存器 251、252……，输出第 y 个和第 y + 1 个移位寄存器的逻辑积的与门 261、262……，对于选通线的各个最终输出门的 271、272……，上述选通线选择控制信号 (ENB) 供给到该最终输出门 271、272……的一个输入端子。而且，该控制信号 (ENB) 由于在 1H 期间即将开始之前的预充电期间中成为 L 电平，因此对于栅极选择信号的输出在控制信号 (ENB) 的 L 电平期间被禁止。

来自把在 H 计数器 12 中的点时钟计数值译码的译码器 17 的输出经过 F/F 24 供给到与门 44 的一个输入端。在该与门 44 的另一个输入端经过分频电路 11 供给点时钟 (DOTCLK)。在通常显示状态由于不用分频电路 11 进行分频，因此，门电路 44 的与输出几乎与点时钟相同，从把该输出作为时钟的 F/F 41 的 Q 端子得到每 1H 电平发生变化的信号，把该信号作为垂直时钟 (CKV) 输出到 LCD 面板 200 的 V 驱动器 210。

译码器 18 发生基于计数器 12 的点时钟计数值的脉冲信号，该脉冲信号经过 F/F 25 作为一个输入供给到与门 43，该与门 43 向输出用于在每 1H 时使显示数据反转的反转控制信号 (FRP) 的 F/F 40 供给时钟。

1H 宽度控制电路 19 发生在对应于各个选通线的一个选择期间的 1H 期间 1 次 H 复位信号 (Hreset)，并且与后述的与门 32 以及 V 计数器 34 一起起到行时钟生成单元的一部分的作用。另外，如在上述驱动方法 4 中说明的那样，在 T/C400 内，使成为 1H 期间、1V (1 帧)

期间的基准的 H 复位信号 (Hreset) 的输出时序提高, 对于在背景区中未被选择的行缩短数据处理期间。由此, 提高图 5 的 V 驱动器中的栅极选择脉冲的传输速度。

该 1H 宽度控制电路 19 是图 7 所示的结构, 具有例如在 H 计数值为高速复位设定值的「10」时输出 H 的译码器 191, H 计数值为通常复位设定值的「120」时输出 H 的译码器 192, 取这些计数器 191、192 的输出与后述的 V 时标信号 (VMASK) 的反转、非反转信号的与的门电路 193、195, 取 2 个与门的或的或门 196. 由于是背景区 204, 因此后述的 V 时标信号 (VMASK) 是 L 电平, 在没有进行该期间中的选择的期间, 通过反相器 194 反转时标信号供给到与门 193, 允许来自与门 193 的译码器 191 的输出。由此, 通常能够把计数值以  $m$  (例如  $m = 120$ , 其中这里  $m$  包括回扫期间) 输出的 H 复位脉冲 (Hreset) 输出到 H 计数器计数到 10 时。

V 计数器 34 把与门 32 的输出作为时钟接收, 根据与门 33 的输出复位。与门 32 中, 输入来自 1H 宽度控制电路 19 的 H 复位脉冲 (Hreset) 和经过分频电路 11 供给的点时钟 (DOTCLK), 该 V 计数器 34 计数在 1H 中成为一次 H 的脉冲, 在每个 1V 期间根据垂直同步信号 (Vsync) 把该计数值复位。

译码器 35 根据 V 计数器 34 中的计数值, 在一个垂直扫描期间 (1V), 经过 F/F 37 输出一次表示 1V 期间的启动的垂直启动脉冲 (STV)。

译码器 36 根据 V 计数器 34 中的计数值, 经过 F/F 38 输出该计数值成为对应于 LCD 面板 200 的线数 (选通线数 n) 的数值的 V 复位脉冲 (Vreset)。该 V 复位脉冲供给到 F/F 40 复位端子, 把在每个 1H 以及 1 帧使显示数据的极性反转了的反转脉冲 (FRT) 复位, 另外还供给到 F/F 41 的复位端子把上述的时钟 (CKV) 复位。进而, 该 V 复位脉冲供给到取与点时钟 (DOTCLK) 的逻辑积的与门 42, F/F 39 通过在时钟端子接受该门电路 42 的与输出进行动作, 可以从 F/F 39 得到在每一个帧反转的 Q 输出。

EXOR 门 45 取上述 F/F 39 以及 40 的输出的异或, 将其作为极性反转脉冲 (FRP) 输出到 LCD 面板 200 的 H 驱动器 20.

进而, 在本实施形态中, 如图 4 的下侧所记述的那样, 具备帧计

数器 47, 根据帧计数值生成并输出时标信号 (VMASK) 的时标生成电路 48 以及 F/F 50, 用于把帧计数值译码并且把帧计数器复位的译码器 49 以及 F/F 51.

5 帧计数器 47 计数取 V 复位 (Vreset)、H 复位 (Hreset) 以及点时钟的与的与门 46 的输出。由于在 1V 期间中可以从与门 46 得到一次即在 1 帧期间中得到一次成为 H 电平的输出, 因此帧计数器 47 通过计数该与输出计数帧数, 把结果输出到 MASK 生成电路 48 和译码器 49.

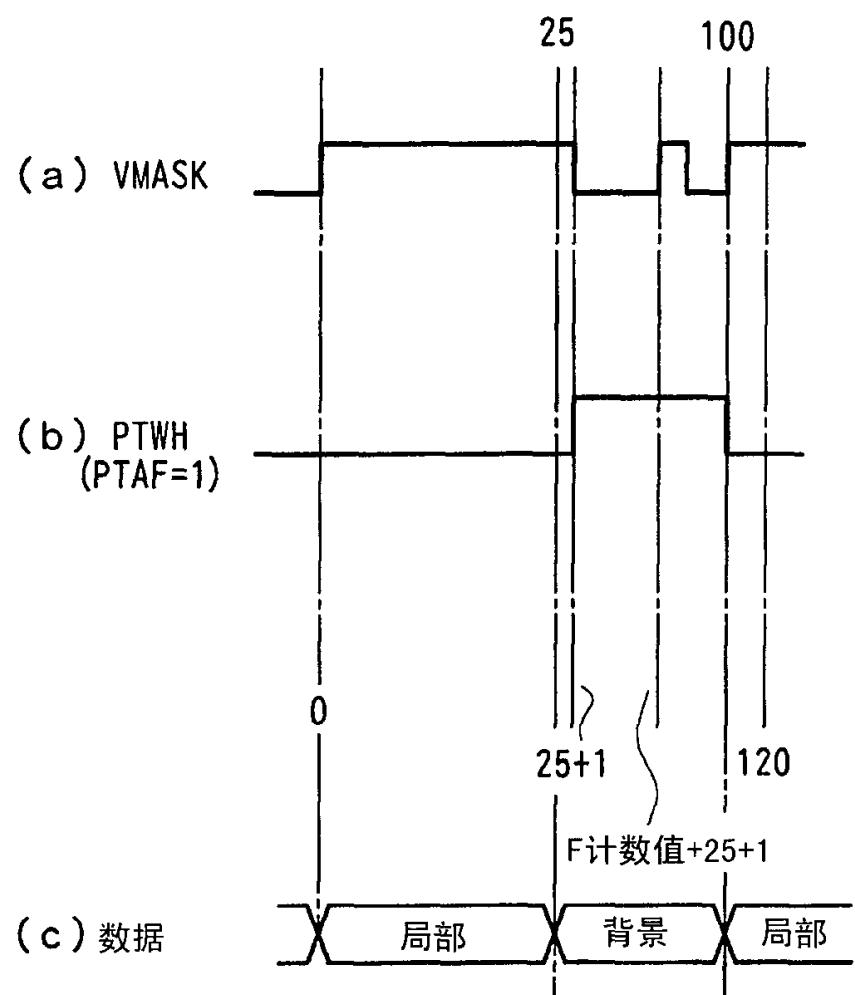

10 MASK 生成电路 48 是图 8 所示的结构, 具备相当于检测局部显示行的到来时序的局部显示行检测单元的比较器 482, 相当于检测在背景区内写入关断显示数据的行的到来的背景显示行检测单元的比较器 481 以及加法电路 483, 另外, 还具备或门 484 以及 485, 反相器 486。加法电路 483 在帧 (F) 计数值上加入可以任意设定的设定值, 例如「25」, 输出到比较器 481.

15 比较器 481 把来自 V 计数器 34 的计数值与 F 计数值 + 设定值「25」进行比较, 如果 V 计数值成为 F 计数值 + 设定值「25」则输出 H 电平, 在其它的值时输出 L 电平。另外, 比较器 482 如果 V 计数值小于根据作为目标局部显示位置而任意设定的值, 例如这里是「25」则输出 H 电平, 大于「25」则输出 L 电平。

20 由此, 从或门 484, 仅在 V 计数值为 0~24 的期间和 F 计数值 + 25 的期间输出 H 电平, 从或门 485 仅在后述的局部显示启动信号 (SPART) 是 H 电平 (局部显示模式) 时, 来自上述门电路 484 的输出作为 V 时标信号 (VMASK) 经过 F/F 50 输出。

25 另外, 在通常显示时, 由于启动信号 (SPART) 维持 L 电平, 因此经过反相器 486 在或门 485 中长时输入 H, 因而 V 时标信号 (VMASK) 维持 H 电平。

30 V 时标信号 (VMASK) 供给到与门 27~30 的一个输入端, 在 V 时标信号 (VMASK) 是 L 电平时, 禁止 H 时钟 (CKH), H 启动脉冲 (STH), 预充电控制信号 (PCG) 以及允许信号 (ENB) 的输出。另外, V 时标信号 (VMASK) 供给到 1H 宽度控制电路 19, 1H 宽度控制电路 19 如上述那样仅在该 V 时标信号 (VMASK) 是 L 电平时, 以 1H 期间 H 计数值成为 10 的时序, 输出 H 复位脉冲 (Hreset)。进而, 该 V 时标信号

(VMASK) 还供给到与门 43 的输入端, 在 V 时标信号 (VMASK) 是 L 电平时固定 F/F 40 的输出, 其结果在其期间固定极性反转信号 (FRP) 的电平。

在译码器 49 中根据背景区 204 的行数 (n - s) 和在局部显示时 5 在 1 帧期间中选择的背景区 204 的行数 k 设定  $\lceil (n - s) / k \rceil$ 。例如, 这里是  $n = 100$ ,  $s = 25$ ,  $k = 1$ , 设定「75」, 在 F 计数值是 75, 即局部显示时在第 75 帧输出脉冲。该脉冲经过 F/F 51 在帧计数器 47 中供给为 F 复位脉冲 (Freset), 帧计数器 47 在局部显示模式时, 在每个  $\lceil (n - s) / k \rceil$  帧 (75 帧) 把计数值复位。

10 F/F 52 在 D 端子从图 1 的 I/F 电路 106 接受成为局部显示模式而输出局部显示控制信号 (PARTIAL), 把取 V 复位 (Vreset), H 复位 (Hreset) 以及点时钟的与的与门 46 的输出作为时钟进行动作。由于从与门 36 供给在 1V 期间上升一次的脉冲信号, 因此 F/F 52 如果接收到局部显示控制信号则在下一个 1V 期间取入该信号从 Q 端子 15 输出。

20 来自 F/F 52 的输出供给到与门 54 的一个输入端和 F/F 53 的 D 端子。另外, F/F 53 作为时钟, 与上述 F/F 52 相同接受与门 46 的输出, 从 F/F 53 的 Q 端子输出在命令局部显示后经过了 1V 期间时成为 H 电平的局部显示启动信号 (SPART), 该启动信号 (SPART) 供给到上述时标生成电路 48 以及分频电路 11. 另外, F/F 53 的反转 Q 输出供给到与门 54 的另一个输入端。从而, 仅在成为 H 电平的下一个 1V 期间局部从与门 54 输出显示控制信号 (PARTIAL) 是 H 电平, 在其它期间维持 L 的闪速信号 (FLASH)。

25 上述闪速信号 (FLASH) 供给到或门 55、56、57 的一个输入端, 如果闪速信号 (FLASH) 成为 H, 则来自各个或门 55~57 的 R、G、B 数字输出全部成为 H 电平。

30 该 R、G、B 数字输出的所有 H 电平意味着白显示, 该 R、G、B 数字输出被输出到图 1 的闩锁电路 101 等数字处理电路, 经过 D/A 变换器电路 102、放大器 104, 作为用于白显示的 R、G、B 模拟显示信号供给到 LCD 面板 200 的 H 驱动器 220。

从而, 根据以上那样的结构, 如果局部显示控制信号成为 H, 则如图 3 所示, 首先, 在下一个 1 帧中, 成为全画面白显示 (白光栅显

示），从发出命令后经过了 1 帧时，从 F/F 53 输出局部显示启动信号（SPART），开始局部显示动作。

### 显示装置动作

其次，进一步参照图 9~11 说明根据上述结构实现的显示装置的动作时序。另外，图 9 示出通常显示动作时，图 10 示出全画面白显示时，图 11 示出采用了上述的驱动方法 1 以及方法 4 的局部显示时的时序。

### 通常显示

在通常显示时，由于局部显示控制信号（PARTIAL）维持 L 电平，因此 V 时标信号（VMASK）维持 H 电平。为此，在偶数帧、奇数帧中，1H 宽度控制电路 19 都根据数据线数输出 H 复位脉冲（Hreset），所以 1H 期间恒定，V 时钟（CKV）也恒定。另外，还不禁止 H 时钟（CKH），H 启动脉冲（STH），预充电控制信号（PCG），允许信号（ENB）的任一个而输出。

从而，如果在图 5 所示的 LCD 面板 200 的 V 驱动器 210 输出 V 启动脉冲（STV），则根据每个 1H 的 V 时钟（CKV）顺序地发生选择各个选通线的信号，在对应的选通线上允许信号（ENB）顺序地输出各个 H 电平的期间栅极选择信号。另外，LCD 面板 200 的 H 驱动器如果输出 H 启动脉冲（STH），则根据 H 时钟（CKH），在对应的数据线上顺序地输出要写入到由 V 驱动器 210 选择的选通线的各个像素上的显示数据。

这样由 V 驱动器 210 顺序地选择选通线，从 H 驱动器 220 相对应顺序地在数据线上输出显示数据，使连接在被选择的选通线上的像素晶体管 ON，经过数据线和像素晶体管在各像素上写入显示数据。而且，在各帧中反复进行这样的动作，进行任意的显示。

另外，显示数据通过极性反转控制信号（FRP）在每个 1H，即每个线反转，把其极性进行反转控制加入到各像素。另外，由于在偶数帧和奇数帧中该控制信号（FRP）都反转，因此对于同一行在每个帧维持极性反转了的显示数据。

### 白光栅显示

如上所述，如果从图 1 的 I/F 电路 106 等供给到 T/C400 的局部显示控制信号（PARTIAL）从 L 电平（通常显示）向 H 电平（局部显

示) 变化, 则从与门 54 输出仅在后续的 1V 期间成为 H 电平的闪速信号 (FLASH)。从而, 如图 10 所示, R、G、B 显示数据在 1V (1 帧) 期间全部成为白数据。在该白光栅显示时, 其它的时序信号由于与在图 9 中所说明的通常显示时相同没有变化, 因此 V 驱动器 210 与通常显示时相同如果输出 V 启动脉冲 (STV) 则顺序地选择选通线, 如果 H 驱动器 220 输出 H 启动脉冲 (STH), 则在各数据线上顺序地输出白数据。从而, 1 帧期间整个画面显示白。

#### 局部显示 (驱动方法 1 以及驱动方法 4)

图 11 示出由图 4 所示的结构实现的驱动方法的局部显示时的动作, 执行上述的驱动方法 1 和驱动方法 4。即, 在向预定位置的局部显示, 在剩余的背景区的白显示的基础上, 使 1 帧期间中的动作速度降低谋求减少驱动电路中的功耗。1 帧期间的工作速度的降低能够进行图 4 的 1H 宽度控制电路 19 的 V 驱动器的高速传输控制以及把分频电路 11 的分频信号作为点时钟 (DOTCLK) 使用。

如果局部显示控制信号 (PARTIAL) 变化到 H 电平, 则如上所述在最初的 1 帧中画面整体显示白, 如果成为下一个帧则局部显示启动信号 (SPART) 从 L 电平变化到 H 电平。从而, 在图 6 所示结构的分频电路 11 中, 禁止来自与门 115 的点时钟 (DOTCLK) 的输出, 这里, 由 F/F 111 以及 112 四分频了的点时钟 (以下称为分频点时钟) 经过与门 113 以及或门 116 输出。根据该四分频点时钟进行动作的电路其动作速度成为四分之一, 图 11 所示那样生成的控制信号 (CKH, CKV, ENB, FRP 等) 也成为 1/4 的频率。

另外, 在 MASK 生成电路 48 中, 由或门 485 选择来自比较器 482 以及比较器 481 的比较输出, 如图 8 那样, 设定对于比较器 482 以及加法电路 483 的设定值使得局部显示位置成为 1~25 线时, 输出 V 计数值为 0~24 期间和帧计数器值 + 25 期间成为 H 电平的 V 时标信号 (VMASK)。在从第 1 行顺序地选择选通线的 V 驱动器 210 中, 首先, 在进行局部显示的 1~25 线的期间, 供给根据 V 时标信号 (VMASK) 生成的允许信号 (ENB)。从而, 在该期间 (局部显示期间) V 驱动器 210 中允许 H 电平的允许信号 (ENB) 的输出, 允许对于各线 (行) 的选择脉冲的输出。由此, 除去根据上述四分频点时钟生成的通常时的 1/4 频率的 V 时钟 (CKV) 进行动作的点以外, V 驱动器 210 与通常显

示时相同，在允许信号（ENB）为 H 电平期间，在各个选通线上输出栅极选择脉冲。另外，在 H 驱动器 220 中，除去 H 时钟（CKH）以及 V 时钟（CKV）等是通常时的 1/4 频率的点以外，也与通常时相同，在 1H 期间中，顺序地输出写入到与由数据线选择的选通线对应的像素中的显示数据（局部显示数据）。

如果 V 计数值成为局部显示区以外则时标生成电路 48 把 V 时标信号（VMASK）置为 L。从而，在该 V 时标信号（VMASK）为 L 期间禁止由 V 驱动器 210 进行的选通线的选择，极性反转信号（FRP）的反转动作维持紧前面的状态。

另外，如果 V 时标信号（VMASK）成为 L 电平，则 1H 宽度控制电路 19 例如在图 7 中，在 H 计数值成为 10 的时刻输出通常 H 计数值成为 120 所输出的 H 复位脉冲（Hreset）。从而，H 复位脉冲（Hreset）的输出周期加快，H 计数器 12 中的计数处理加快，根据 H 计数值生成的来自 F/F 41 的 V 时钟（CKV）的周期如图 11 所示那样缩短。这里，如图 5 所示，在 LCD 面板 200 的 V 驱动器 210 中，由于移位寄存器 251……以该 V 时钟（CKV）作为移位时钟进行动作，因此通过加快 V 时钟（CKV），在其期间加快 V 驱动器 210 内的移位寄存器传输速度。

在背景显示期间，如果时标生成电路 48 的比较器 481 检测出要在背景区中选择的线，则如图 11 所示仅在该线选择期间把 V 时标信号（VMASK）置为 H 电平。由此，V 驱动器 210 在 V 时标信号（VMASK）为 H 电平期间，与局部显示期间相同，在对应选通线上输出选择信号。另外，H 驱动器 220 如果输出 H 启动脉冲（STH），则以由极性反转控制信号（FRP）决定的极性顺序地在数据线中写入所供给的白显示数据。从而，背景区 204 的预定的线在 1 帧期间中与局部显示区相同地进行选择，并在这里写入白显示数据。

在图 11 中，在接续于上级偶数帧的下级奇数帧中，局部显示期间中的动作除去极性反转控制信号（FRP）与偶数帧反转，在各像素中写入与偶数帧时相反极性的显示数据这一点以外相同。在背景显示期间，在奇数帧中，一旦成为 L 电平的 V 时标信号（VMASK）再次成为 H 电平的时序延迟 1H 期间。这是由于在图 8 的时标生成电路 48 中，F 计数值比前一个帧（偶数帧）多一个，选择在前一个帧中所选择的下一个线。另外，这时，由于极性反转控制信号（FRP）的电平与偶

数帧时相反，因从 H 驱动器 220 在数据线上输出与前一个帧相反极性的白显示数据，写入到对应于所选择的选通线的像素中。

通过反复进行以上的动作，如图 3 (c) 所示，在局部显示区 202 中，在每一个帧写入显示数据，另外在背景区 204 中，与未被选择的线（选通线）相当的期间（204t）在 V 驱动器 210 内进行高速传输，仅选择预定的线写入显示数据。而且，在背景区 204 中，在图 8 那样设定的情况下，在 75 帧中在整个区域写入白显示数据。进而，在下一个 75 帧中，由于极性反转控制信号（FRP）的电平与前一个 75 帧时相反，因此在同一个选通线中写入与 75 帧以前极性相反的白显示数据。

#### 局部显示（驱动方法 1）

其次，使用图 12 仅说明驱动方法 1 时的具体的动作时序。在驱动方法 1 中，如上所述在 V 驱动器 210 中不进行高速传输，如果使用图 4 的结构进行说明，则不进行分频电路 11 中的分频，而且在背景显示期间中，1H 宽度控制电路 19 不加快 H 复位脉冲的输出周期。在时序图中，与图 11 不同点在于，V 时钟（CKV）的周期与 V 时标信号（VNASK）的电平无关是恒定的，其它与在图 11 中说明过的局部显示动作以及背景显示动作相同。根据这样的驱动方法 1，如上述图 11 时那样，由于不改变局部显示模式时的驱动频率，因此不改变数字电路系统中的功耗，然而根据时标生成电路 48 中的设定（比较器 481, 482 以及加法电路 483），能够在任意的位置进行局部显示，另外，对于背景区，能够在 1 帧期间中选择任意数量的线写入白显示数据。

#### 局部显示（驱动方法 2）

其次，使用图 13 仅说明驱动方法 2 时的具体的动作时序。与图 12 的驱动方法 1 相同，不进行 V 驱动器 210 中的高速传输以及驱动频率的降低。与上述图 12 所示的驱动方法 1 的不同点在于，在图 13 中，在背景显示期间开始以后，在最初的 1H 期间输出 H 启动脉冲（STH），H 驱动器 220 根据该 H 启动脉冲在数据线中写入白显示数据。因此，V 时标信号（VMASK）在背景显示期间中成为 H 电平，V 驱动器 210 如果选择对应的选通线，则把已经写入到各个数据线中的白显示数据直接写入到对应的像素中。

#### 局部显示（驱动方法 2 以及 4）

5      图 14 示出把上述驱动方法 2 与驱动方法 4 组合的驱动方法下的具体动作时序。与上述图 13 不同点在于，与图 11 和图 12 的差异相同，首先，在局部显示模式时通过利用图 4 的分频电路 11 降低各电路的动作频率，图 14 中， CKV, ENB, FRP, VMASK, 显示数据等的周期比通常显示动作时长。另外，在背景显示期间在最初的 1H 中在数据线上写入了白显示数据以后，以及结束了背景区中要在 1 帧中选择的选通线的选择以后，通过利用图 4 的 1H 宽度控制电路 19 等，加快 V 复位脉冲 (Hreset) 的输出时序，最终提高成为 LCD 面板 200 的 V 驱动器 210 中的移位寄存器的数据传输时钟的 V 时钟 (CKV) 的频率。

10     因此，如图 14 所示 V 时标信号为 L 电平期间在 V 驱动器内进行栅极选择脉冲的高速传输。

### 局部显示 (驱动方法 3)

15     图 15 示出驱动方法 3 时的具体的动作时序。在该方法中也与上述图 12 所示的驱动方法 1 相同，不进行 V 驱动器 210 内的脉冲高速传输以及驱动频率的降低。在上述图 12 的方法中，在背景显示期间中，V 时标信号 (VMASK) 成为 H 电平时，根据 H 启动脉冲 (STH) H 驱动器 220 在数据线上写入白显示数据，而在图 15 的方法中，与通常显示相同，在 H 启动脉冲的紧前面发生预充电控制信号 (PCG)，由预充电电路在各个数据线上写入白显示数据。

20     这里，使用图 16 以及图 17 说明预充电波形以及能够安装在 LCD 面板 220 内的预充电驱动器 230 的结构。预充电驱动器 230 由根据预充电控制信号 (PCG) 和其反转信号导通电阻关断的 TFT 构成的开关 SW1, SW2 … … SW<sub>m</sub> 组成。这里，如图 16 所示，如果输出预充电控制信号 (PCG) 各个开关 SW1, … … 导通，则经过对应的开关 SW, 连接在预充电数据线上的第 1 个到第 <sub>m</sub> 个数据线上，分别加入预充电数据 (PCD)。该预充电数据 (PCD) 如图 16 所示，与在预充电控制信号 (PCG) 刚刚输出后而开始的 1H 期间中加入到数据线上的 R, G, B 显示数据的极性一致。而且，其电压电平设定为通常显示时的 R, G, B 显示数据的中间电压电平。

25

30     在背景显示期间中向数据线输出白显示数据，如果是白显示则 R, G, B 显示数据的中间电压电平都与白显示数据相同。从而，背景显示期间中，如果使该预充电驱动器 230 的开关 SW1 ~ SW<sub>m</sub> 导通，则

即使 H 驱动器 20 不进行动作，也能够在各个数据线上把预充电数据作为白显示数据供给到所选择的选通线的像素上。从而，减少 H 驱动器 220 的负荷，能够降低其功耗。

#### 局部显示（驱动方法 3 以及 4）

5 图 18 示出把驱动方法 3 和方法 4 组合起来时的具体的动作时序。与上述图 15 不同点在于，降低局部显示模式中的各个时序信号的频率，在背景显示期间的 V 时标信号（VMASK）为 L 电平期间，提高 V 时钟（CKV）的频率，在 V 驱动器内高速传输栅极选择信号。根据这样的驱动方法，能够不降低局部显示模式中的驱动频率降低引起的功耗，降低 H 驱动器的处理负荷。

#### 10 背景显示色

15 在上述基本结构中，说明了转移到局部显示模式后在背景区显示白数据（关断显示）的情况。然而，作为背景显示数据，不限定于关断显示数据，可以采用其它的背景显示色数据，在背景区显示其数据所显示的颜色。以下，说明把背景显示色取为预定颜色的情况。所采用的显示色例如是彩色显示装置中的红（R）、绿（G）或者蓝（B）的某一种。

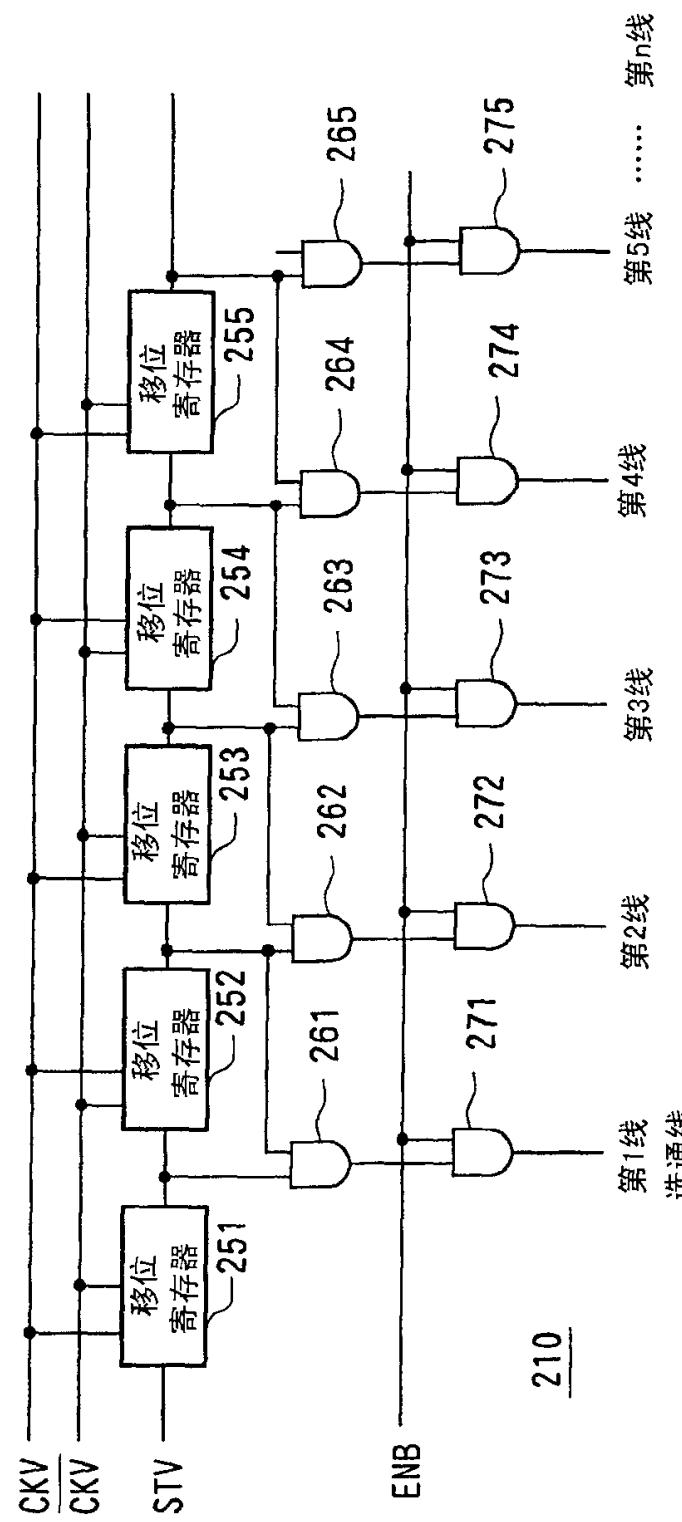

20 图 19 示出在局部显示时，用于在背景区显示关断显示以外的预定颜色的时序控制器 400 的结构例。图 20 概念性地说明该图 19 的背景区检测电路 60 的动作。在图 19 中，与上述图 4 相同的部分标注相同的符号并且省略说明。与图 4 不同点在于，图 19 的时序控制器 400 在图 4 的结构的基础上，采用检测局部显示时的背景区，在其背景显示期间允许预定颜色的数字信号的输出的结构，具备背景区检测电路 60，F/F 61，与门 62、63、64。

25 在背景区检测电路 60 中供给来自 V 计数器 34 的 V 计数值（行计数值），另外，从未图示的 CPU 经过图 1 的 CPU 接口部分 106 供给局部显示区的边界位置信息（PTAIS）以及表示局部显示区是位于该边界上方还是下方（例如如果是上方则为「H」，如果是下方则为「L」）的位置信息（PTAF），根据这些信息输出以下的背景区检测信号（PTWH）。例如位置信息 PTAF 如果是「H」，则意味着局部显示区位于边界位置（PTAIS）以上。由此，背景区检测电路 60 在 V 计数值表示上述 PTAIS 所显示的局部显示区的边界位置以上的行的期间输出

「L」，在 V 计数值表示边界位置以下的行的期间输出「H」的信号 PTWH。另外，如果位置信息 PTAF 是「L」，则在 V 计数值表示边界位置上方的行的期间输出「H」，表示边界位置下方的行的期间输出「L」的信号 PTWH。

5 这样，图 19 的背景区检测电路 60 仅在背景显示期间输出成为「H」的背景区检测信号（PTWH）。例如如图 20 所示，如果背景区取为第 25 行～100 行，则背景区检测电路 60 输出在 V 计数值成为 25 之前是「L」电平，在 25～100 的选择期间成为「H」的信号 PTWH。而且，以上那样的信号 PTWH 经过 F/F 61，供给到设置在 R、G、B 的 10 数字输出线的与门 62、63 以及 64 的一个输入端。

15 在与门 62、63 以及 64 的另一个输入端上，供给例如通过操作者或者 CPU 设定的背景色信号（R-PAR, G-PAR, B-PAR）。从而，如果在背景显示期间中检测信号称为「H」，则这时供给到与门 62、63 以及 64 的背景色显示信号经过或门 55、56 以及 57 作为背景显示数据输出。

20 这里，「白」在 R、G、B 输入数字数据（例如 6 比特）中，以「H: 1」表示 R、G、B 数据的所有比特，与此不同，例如单色的「蓝」R 以及 G 的所有比特以「L: 0」，B 以「H: 1」表示。从而，作为上述背景色，例如设定单色的「蓝」的情况下，在本实施形态中，R-PAR 以及 G-PAR 的所有比特是「L」，B-PAR 的所有比特是「H」，这样的数据作为局部显示模式下的背景区的显示数据供给到显示面板，在显示区显示单色的「蓝」。

25 另外，在采用了这样预定背景显示色的情况下，最好也如图 3 所说明的那样，在向局部显示模式的转移后的第 1 帧中，进行全画面显示（关断显示），从随后的第 2 帧开始进行局部显示和任意颜色的背景显示。进而，在向局部显示动作的转移的第 1 帧中进行的全画面显示不限定于上述全画面白色，也可以把全画面取为预定的背景色。例如，该显示色可以取为与上述那样在局部显示动作时作为背景色设定的颜色相同的颜色。这样如果把转移帧的全画面显示色取为与局部显示动作时的背景色相同的颜色，则能够避免向局部显示模式转移时使显示色的急剧变化。另外，能够用简单的电路结构把转移第 1 帧中的 30 全画面显示色取为关断显示颜色以外的颜色。

另外，如果是向局部显示模式的转移以后，从 CPU 在背景期间供给预定颜色的背景显示数据，则能够不改变在上述基本结构中说明过的图 4 那样的电路结构显示白以外的预定颜色的背景。

进而，也可以像后述那样，在转移第 1 帧中，不进行全画面白显示等背景显示，而进行局部显示和对于背景区的背景显示。

这里，对于以上说明的背景显示色，能够设定为导通显示色（例如在标准白的情况下是黑色）或者其它任意的中间色。根据设置在各个像素中的 TFT 的关断漏电流，对于背景区如果加长像素选择间隔则可能发生一些退色，其颜色产生变化。然而，在本发明中，背景区并不是以显示特别信息为目的，在这样区域中颜色的多少变化从显示品质观点出发也包含在允许的范围内。从而，在这种情况下，通过把背景区采用能够以任意颜色显示的结构，能够使操作者选择所希望的背景色。

另外，另一方面，如果像素 TFT 的关断漏电流很小，则即使把背景显示色设定为预定导通显示色或者中间色，也能够不改变颜色而长时间地在背景区显示其颜色。另外，R、G、B 某一种单色的背景显示表现为 R、G、B 的某一种是与白显示相同的关断显示数据，其余 2 色是导通显示数据，或者某一种颜色是导通显示数据，其余 2 色是关断显示数据表现。即，如果是 R、G、B 某一种单色的背景显示，则至少一种颜色与「关断显示」相等，能够与所希望中间色相比，减少由上述各像素 TFT 中的关断漏电流引起的退色的影响，局部显示模式中的背景显示色的变化很小。

### 背景区起始行

其次，参照图 21 说明用于谋求局部显示模式下提高背景显示品质的驱动方法。在该方法中，如上述那样，在向局部显示模式的转移第 1 帧中进行全画面关断显示的背景显示，然后，转移到局部显示模式。而且，从上述转移第 1 帧后续的第 2 帧开始，对于任意  $s$  行  $m$  列矩阵的局部显示区 202 写入局部显示数据，在上述局部显示区的最末行后续的背景显示起始行 204h(第  $s+1$  行)和  $k$  行  $m$  列矩阵区的 204w 中分别写入背景显示数据。即，背景显示区 204 中，对于背景显示区起始行 204h 进行每帧写入，对于  $k$  行  $m$  列矩阵 204w 与上述说明的相同在每 1 帧把位置移位后进行写入， $n$  行  $m$  列矩阵内除去局部显示区

202 和第  $s + 1$  行区 204h 以外的背景区的各个像素在  $(n - s - 1) / k$  帧写入一次背景显示数据。

通过采用这样的驱动方法，局部显示区 202 后续的背景区 204 的起始行在 1 帧一定写入一次关断显示数据等背景显示数据。从而，仅在多个帧期间选择的其它背景区 204 能够防止受到写入到局部显示区 202 的最末行的数据的影响而交调失真地显示。

其次，说明用于对这样的背景区的起始行 204h 写入每帧背景数据的具体的动作。另外，在以下的说明中，在作为起始行的第  $s + 1$  行区 204h 中，作为背景显示数据写入关断显示数据，在除去该区域 204h 的其它背景区 204 中，作为背景显示数据，显示 R、G、B 的单色显示等任意的颜色，以这样的情况为例，显示任意的颜色。这种情况下，在上述图 19 所示的时序控制器 400 中，能够通过变更时标生成电路 48 以及背景区检测电路 60 的设定进行对应。

即，这些电路 48 以及电路 60 的结构与上述图 22 相同，如图 22 所示，预先变更在比较器 1 (481)、比较器 2 (482) 以及比较器 3 (60) 中设定的值 (参照图 20)，生成图 23 所示波形的 (a) VMASK, (b) PTWH。

具体地讲，例如如果局部显示区 202 是  $n$  行  $m$  列矩阵的第 1 行 ~ 第 25 行，则把「 $25 + 1$ 」分别设置在比较器 1 以及 2 中。因此，首先，比较器 2 的输出一旦 V 计数值 (行数) 成为「 $25 + 1$ 」以上，则从「L」变化到「H」。而且，比较器 1 仅在从帧计数器 47 供给的 F 计数值成为「 $25 + 1$ 」时输出「H」，除此以外输出「L」。从而，在 SPART 信号是 H 的局部显示模式时，从或门 485 输出的 VMASK 信号如图 23(a) 所示，在 1 帧期间中，从第 1 行 ~  $25 + 1$  行期间，以及第 (F 计数值 +  $25 + 1$ ) 行期间成为「H」电平，信号成为「H」电平期间，对于面板与通常显示模式相同进行像素选择以及显示数据写入。另外，在图 23 的例中，显示数据在背景区期间的第  $25 + 1$  行到来时从局部显示数据切换到背景显示数据。从而，允许显示数据以第「 $25 + 1$ 」行的时序写入到各像素中，与局部显示区最末行的选择写入相接续，进行对于下一行的背景显示数据的选择写入。

另外，对于背景区检测电路 60 (比较器 3)，作为边界位置的起始值设定「 $25 + 1$ 」，在结束值中设定「100」。由此，在局部显示区

位于背景边界位置之前的情况下 ( $PTAF = 1$ )，如图 23 所示，输出如果  $V$  计数值成为「 $25 + 1$ 」以上则成为「H」电平，如果  $V$  计数值成为「 $100$ 」以上则成为「L」电平的背景检测信号 (PTWH)。该 PTWH 信号如图 19 所示，控制背景色数据 (R-PAR, G-PAR, B-PAR) 向各个 R、G、B 数据线的输出，如图 23 图 (b) 那样在背景期间中，除去与局部显示区的边界起始行区  $204h$  相当的期间以外的期间成为「H」电平，允许背景检测数据的输出。

从而，在背景区  $204$  中的  $k$  行  $m$  列矩阵区  $204w$  的选择期间中，由操作者或者 CPU 指定的任意的背景色数据写入该区  $204w$  并且进行显示。当然，对于  $k$  行  $m$  列矩阵区  $204w$  也可以写入关断显示数据，这种情况下，能够如上述那样，对于局部显示行数  $s$  仅把图 8 所示的 MASK 生成电路 48 中的比较器比较值设定为「 $s + 1$ 」进行对应。

图 24 示出对于以上那样的控制，进一步使用了上述的驱动方法 4 时的时序的一例，除去对于背景起始行  $204h$  的控制以外，进行与上述图 14 几乎相同动作。图 24 中，如已经对于驱动方法 4 以及图 14 说明过的那样，在背景区中，在与 1 帧期间中没有被选择的行（这里是「 $n - s - 1$ 」行）的选择期间相当的期间，提高控制  $1H$  期间长度的行时钟的频率。通过这样提高行时钟等的频率，能够使图 5 的  $V$  驱动器 201 内的各行选脉冲高速传输。从而，能够以比通常动作 ( $n$  行驱动) 时更低的频率驱动各行 ( $s$  行 + 1 行 +  $k$  行)，能够降低功耗依赖于动作频率的数字处理系统的电路中的功耗。当然，对于在 1 帧期间中没有被选择的背景区期间也可以不执行时钟的高速传输而采用其它的驱动方法 1、2 以及 3。

这里，写入到起始行区  $204h$  中的背景显示数据除去关断显示数据（标准白的情况下是白显示）以外，如上述那样也可以写入彩色显示时的 R、G、B 的任一种或者任意的颜色。其中，该背景显示数据通过采用与写入到其余背景区  $204$  中的数据相同的数据，能够防止只是起始行区  $204h$  醒目这样的问题。

另外，在  $n$  行  $m$  列画面内设定多个局部显示区 202 的情况下，最好对于各个局部显示区 202 最末行的下一行 ( $204h$ ) 写入每帧背景显示数据。另外，例如局部显示区 20 位于  $n$  行  $m$  列矩阵的中央或者后侧（图 21 中画面下侧）时，如果对于局部显示区 202 的起始行的前

一行也写入每帧背景显示数据，则能够防止该局部显示区 202 的起始行的显示数据对位于局部显示区 202 前面的行的背景区 204 带来恶劣影响，能够谋求进一步提高背景区的显示品质。如以上那样对于与局部显示区 202 邻接的行，通过写入每帧背景显示数据提高背景区 204 的显示品质。

#### 向局部显示模式的转移第 1 帧的显示

其次，说明在装置切换到局部显示模式时，转移第 1 帧中，不是进行全面画面背景显示而进行局部以及背景显示时的动作以及驱动电路的例子。

在上述图 3 所示的动作中，如果命令局部显示，则在转移第 1 帧中，进行全面画面背景显示，从随后的第 2 帧转移到局部显示。与此不同，通过转移后在第 1 帧中，在局部显示区进行局部显示，在背景区的全部区域进行背景显示，能够在转移时不出现全面画面瞬间消失的现象，而平滑地转移到局部显示。

图 25 示出这样的模式转移动作。在图 1 的 I/F 电路 106 判断为是通常显示模式时，如图 3 (a) 所示 LCD 面板 200 使用全面画进行通常显示 (S1)。如果从 CPU 等传输来局部显示控制命令，则图 1 的 I/F 电路 106 分析该命令，发生局部显示控制信号，切换到局部显示模式 (S2)。

如果装置切换到局部显示模式，则如图 25 (b) 所示，在局部显示区 202 中写入局部显示数据，另外对于背景区 204 的整个区域，写入关断显示数据或者所设定的任意色数据等背景显示数据 (S3)。

通过在转移时的 1 帧中这样进行局部显示和对于背景区 204 的整个区域的背景显示，如上述那样全面画不会一起成为背景显示，而能够从刚刚转移之后立即在局部显示区 202 中进行所希望的显示。另外，对于所有像素由于写入局部显示数据或者背景显示数据这样有意的数据，因此在切换到局部显示时，能够防止在多个帧中仅被选择一次的背景区中，通常显示时的显示逐渐向背景显示状态变化。

如图 25 (c) 所示，在转移第 2 帧以后，能够采用已经说明过的各种局部显示动作。即，如图 25 (c) 所示，在 1 帧期间中，选择由  $s$  行  $m$  列矩阵组成的局部显示区 202，背景区 204 中的  $k$  行  $m$  列矩阵区 204w，分别进行局部显示以及背景显示 (S4)。

另外，关于背景显示模式中的背景区 204 的驱动方法，能够采用上述的方法 1~4 的任一种或者把它们进行组合，作为一例，如图 25 (d) 的步骤 S4 所示，对于背景区的行列区 204W 以外的非选择行能够采用进行驱动器的高速传输等的驱动方法。另外，如同参照图 21 5 进一步说明的那样，还能够采用在与局部显示区的最末行邻近的背景起始区 204h 中，与局部显示区相同进行每帧选择，在这里写入背景显示数据的方法。

图 26 示出进行以上那样的转移动作的时序控制器 400 的一例。在该时序控制器 400 中与上述图 19 所示的结构相同部分标注相同的 10 符号并且省略说明。与图 19 不同点在于数字显示数据的输出控制部分的结构。具体地讲，在图 26 的时序控制器 400 中，具备取从背景区检测电路 60 经过 F/F 61 输出的背景检测信号 (PTWH) 与闪速信号 (FLASH) 的逻辑积的与门 65。或门 55、56、57 分别具备 3 个输入 15 端，在第 1 输入端供给对应的 R、G、B 数字信号，在第 2 输入端供给背景检测信号 (PTWH)，在剩余的第 3 输入端供给来自上述与门 65 的输出。

在这样的结构中，如果从把 CPU 等经过 CPU/F 电路供给的局部显示控制信号 (PARTIAL) 成为 H 电平，则经过 F/F 52、53 以及与门 20 54 输出的闪速信号 (FLASH) 在下一个 1 帧期间成为 H 电平，在其它期间成为 L 电平。另外，背景检测信号 (PTWH) 在背景区期间成为 H 电平。从而，从与门 65 在局部显示控制信号成为 H 电平的下 1 帧的背景区输出 H 电平，对于 R、G、B 数字数据的各比特设置的或门 55、56 以及 57 的输出全部成为 H 电平。R、G、B 数字输出 R-OUT、G- 25 OUT、B-OUT 的全部比特是 H 电平在这里意指白显示 (关断显示) 数据，根据这样的结构，在局部显示控制信号成为 H 电平的下一个 1 帧的背景期间在背景区写入关断显示数据。

另外，闪速信号 (FLASH) 从局部显示控制信号成为 H 电平后经过 1 帧期间，从第 2 帧开始再次成为 L 电平。从而，在第 2 帧以后，与门 65 的输出维持 L 电平。另一方面，由于背景检测信号 (PTWH) 30 如上所述如果成为背景期间则成为 H 电平，因此来自或门 55、56 以及 57 的输出在背景期间固定为 H 电平。从而，转移到局部显示模式后，从第 2 帧开始在各个背景显示期间中作为显示数据，这里在数据

线上供给白显示数据（关断显示数据）。

另外，在向局部显示模式的转移第 1 帧以及第 2 帧中在背景区中显示的数据当然不限定于由上述结构实现关断显示数据，也可以像上述那样采用 R、G、B 的某一种色数据或者任意的中间色数据。

5 另外，向局部显示模式转移后的第 2 帧以后的局部显示可以根据上述驱动方法 1~4 的某一种或者其组合进行。或者，也可以如上述那样，对于局部显示区最末行后续的背景区起始行（或者局部显示区的边界邻接行），采用进行每帧选择写入背景显示数据的方法。

# 说 明 书 图

图 1

图 2a

图 2b

图 2c

图 3d

图 3a

图 3b

图 3c

图 5

分频电路(4分频电路) 11

图 6

### 1H宽度控制电路 19

图 7

### MASK生成电路 48

• 偶数帧

通常显示时的时序图

自光栅显示时的时序图

图 10

• 偶数帧

局部显示时的时序图(驱动方法1)

图 12

• 偶数帧

局部显示时的时序图(驱动方法2)

图 13

### 局部显示时的时序图(驱动方法3)

图 16

预充电驱动器 230

图 17

局部显示时的时序图(驱动方法3以及4)

图 18

图 19

图 21

比较器1：如果  $(V_{计数值} = F_{计数值} + 25 + 1) \rightarrow$  高

否则  $\rightarrow$  低

比较器2：如果  $(V_{计数值} < 25 + 1) \rightarrow$  高

否则  $\rightarrow$  低

比较器3：如果  $(PTAF = 1)$

如果  $(V_{计数值} < 25 + 1) \rightarrow$  低

否则  $\rightarrow$  高

否则 如果  $(V_{计数值} < 25) \rightarrow$  高

否则  $\rightarrow$  低

图 22

图 23

图 24

图 25a

图 25b

图 25c

图 25d

冬

|                |                                                                                                              |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置的驱动方法以及驱动电路                                                                                              |         |            |

| 公开(公告)号        | <a href="#">CN1317779A</a>                                                                                   | 公开(公告)日 | 2001-10-17 |

| 申请号            | CN01119036.1                                                                                                 | 申请日     | 2001-04-11 |

| [标]申请(专利权)人(译) | 三洋电机株式会社                                                                                                     |         |            |

| 申请(专利权)人(译)    | 三洋电机株式会社                                                                                                     |         |            |

| 当前申请(专利权)人(译)  | 三洋电机株式会社                                                                                                     |         |            |

| [标]发明人         | 筒井雄介<br>北川诚<br>小林贡<br>上原久夫<br>藤冈诚                                                                            |         |            |

| 发明人            | 筒井雄介<br>北川诚<br>小林贡<br>上原久夫<br>藤冈诚                                                                            |         |            |

| IPC分类号         | G09G3/36 G09G5/02                                                                                            |         |            |

| CPC分类号         | G09G2310/04 G09G3/3677 G09G2320/043 G09G5/024 G09G3/3688 G09G2330/021 G09G3/3648<br>G09G2310/0248            |         |            |

| 代理人(译)         | 刘宗杰                                                                                                          |         |            |

| 优先权            | 2000109958 2000-04-11 JP<br>2001096386 2001-03-29 JP<br>2001096471 2001-03-29 JP<br>2001096576 2001-03-29 JP |         |            |

| 其他公开文献         | CN1183504C                                                                                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">SIPO</a>                                                               |         |            |

## 摘要(译)

在具备n行m列矩阵的像素的液晶显示装置等的驱动时，在发出了局部显示命令的情况下，在1帧期间中，在n行m列矩阵内，在能够进行设定的s行m列的显示局部显示区(202)中顺序地选择各行写入预定的局部显示数据，在局部显示区(202)以外的背景区(204)中写入关断显示(白显示)数据等的预定背景数据。可靠地以背景显示数据把背景区的像素反转驱动。