## [12] 发明专利说明书

[21] ZL 专利号 02107561.1

[45] 授权公告日 2005 年 6 月 1 日

[11] 授权公告号 CN 1204541C

[22] 申请日 2002.3.15 [21] 申请号 02107561.1

[74] 专利代理机构 中国国际贸易促进委员会专利

商标事务所

[30] 优先权

代理人 王以平

[32] 2001.3.15 [33] JP [31] 073289/2001

[71] 专利权人 株式会社日立制作所

地址 日本东京

共同专利权人 日立器件工程株式会社

[72] 发明人 饭田治久 竹本一八男 松本克巳

足立重雄

审查员 詹靖康

权利要求书 1 页 说明书 28 页 附图 20 页

[54] 发明名称 具有低压驱动电路的液晶显示器

[57] 摘要

本发明涉及具有低压驱动电路的液晶显示器，该液晶显示器具有夹在一对基板之间的液晶组分以及在一个第一基板上设置的多个像素。每个像素都经连接到其第一电极的开关元件而被提供视频信号，并设置电容。形成电容的两个电容形成电极中的一个连接到相应像素的第一电极，两个电容形成电极中的另一个被提供像素 - 电势控制信号。视频信号的极性相对于第一基准电压周期性地转换，而且，像素 - 电势控制信号在相对于第二基准电压为相同极性的两个电平之间变换，从而在像素的第一电极上的电压波动变得比视频信号的更大。

1. 一种液晶显示器，包括：

第一基板；

第二基板；

夹在所述第一基板和所述第二基板之间的液晶组分；

设置在所述第一基板上的多个象素，所述多个象素的每一个都包括开关元件、象素电极和电容；

与所述开关元件的控制端子连接的多条扫描信号线；

与所述多条扫描信号线连接的扫描信号线驱动电路；

与所述开关元件的第一电极连接的多条视频信号线；以及

与所述多条视频信号线连接的视频信号线驱动电路；

其特征在于：

多条象素-电势控制线连接于形成所述电容的两个电容形成电极中的一个电极；

象素-电势控制电路连接于所述多条象素-电势控制线；

形成所述电容的两个电容形成电极中的另一个电极连接于所述象素电极，

所述象素-电势控制电路具有移位寄存器电路和输出电路，所述移位寄存器电路向所述输出电路输出定时信号，所述输出电路向所述象素-电势控制信号线输出象素-电势控制信号，以及

所述扫描信号线电路设置于所述扫描信号线的一端一侧，所述象素-电势控制电路设置于所述扫描信号线的另一端一侧。

2. 如权利要求1所述的液晶显示器，其中所述第一基板由硅制成。

3. 如权利要求1所述的液晶显示器，还包括在所述多个象素电极的下面形成的光阻挡膜，其中所述光阻挡膜与所述多个象素电极之间的间隙重叠并且形成所述象素-电势控制信号线的一部分。

4. 如权利要求3所述的液晶显示器，其中所述第一基板由硅制成。

## 具有低压驱动电路的液晶显示器

### 技术领域

本发明涉及液晶显示器，并且更具体地涉及对向每个像素提供视频信号电压的电路有帮助的技术。

### 背景技术

近来，液晶显示器已广泛用于小型显示器、以及办公自动化设备的显示终端等中。一般而言，液晶显示器包括液晶显示板（也称为液晶显示元件或液晶单元），此液晶显示板包括一对绝缘基板以及夹在绝缘基板之间的液晶组分层（液晶层），其中至少一个绝缘基板由透明板、或透明塑料板等制成。

液晶显示器大致分为简单矩阵型和有源矩阵型。在简单矩阵型液晶显示器内，通过有选择性地向在液晶显示器板的两个绝缘基板上形成的像素成形电极施加电压，并随后改变与此像素对应的液晶组分的部分液晶分子的取向而形成图象元素（以下称作像素）。另一方面，在有源矩阵型液晶显示器内，液晶显示板设置信号线、扫描线、像素电极以及有源元件，其中每个有源元件都与在一个基板上形成的用于像素选择的一个像素电极联系，并且，通过选择与像素联系的有源元件并随后改变存在于连接到有源元件的像素电极和与像素电极相连的基准电压电极之间的液晶分子的取向而形成像素。

具有用于每个像素的有源元件（如薄膜晶体管）并切换有源元件的有源矩阵型液晶显示器广泛用作笔记本式个人计算机显示器等。在有源矩阵型液晶显示器中，所谓的驱动电路集成型液晶显示器已知具有在基板上制作的像素电极驱动电路，在基板上制作有像素电极。液晶显示器通过AC驱动工作，AC驱动周期性地转换施加到液晶层两端

的电压极性。AC 驱动的目的是防止液晶组分因在液晶层两端施加的 DC 电压而引起的降质。

对于在象素电极和基准电极之间施加电压的有源矩阵型液晶显示器，一种 AC 驱动方法是在基准电极施加固定电压并且向象素电极交替提供正极性和负极性信号电压。然而，在上述 AC 驱动方法中，驱动电路必须是能承受象素电极电压的最大正值和最大负值之间电压差的高压电路。用于薄膜晶体管的开或关控制的控制信号（扫描信号）也必须是高压。

近来，在液晶显示器内显示的灰度级的数量已经达到 64 或 256。还要求具有更大量象素的高分辨率液晶显示器。当要显示的灰度级的数量增加时，电路在规模上变大，并且当象素数量增加时，用于向各个象素提供信号的驱动电路在高速下工作，并且每个象素可占用的面积减少。另一方面，在高压电路内难以使它们的电路元件小型化，结果电路的规模变大。尤其是在小型液晶显示板内，即使在要求增加象素数量时，也难以在每个象素的有限面积内制作诸如高压有源元件的结构。进而，在具有被包含在液晶显示板内的驱动电路的驱动电路集成型液晶显示器中，由于驱动电路占据的面积增加而产生液晶显示板变大的问题。而且，在高压电路中还有这样的问题：由于它的电极和其它电极的面积增加，结果导致它们的电容性元件增加，使得难以在高速下操作驱动电路，并且还增加其功率消耗。

## 发明内容

本发明已致力于解决现有技术中的上述问题，并且提供一种能用低压驱动电路进行 AC 驱动而使液晶显示器高速工作、并且能减小象素尺寸和驱动电路规模的技术。

结合本文的描述和附图，本发明的上述目的和新颖特征将显而易见。

以下简单解释本发明的代表性实施例。

根据本发明的实施例，提供一种液晶显示器，包括：第一基板；第二基板；夹在所述第一基板和所述第二基板之间的液晶组分；设置在所述第一基板上的多个像素，所述多个像素的每一个都包括开关元件、像素电极和电容；与所述开关元件的控制端子连接的多条扫描信号线；与所述多条扫描信号线连接的扫描信号线驱动电路；与所述开关元件的第一电极连接的多条视频信号线；以及与所述多条视频信号线连接的视频信号线驱动电路；其特征在于：多条像素-电势控制线连接于形成所述电容的两个电容形成电极中的一个电极；像素-电势控制电路连接于所述多条像素-电势控制线；所述电容的两个电容形成电极中的另一个电极连接于所述像素电极，所述像素-电势控制电路具有移位寄存器电路和输出电路，所述移位寄存器电路向所述输出电路输出定时信号，所述输出电路向所述像素-电势控制信号线输出像素-电势控制信号，以及所述扫描信号线电路设置于所述扫描信号线的一端一侧，所述像素-电势控制电路设置于所述扫描信号线的另一端一侧。

根据本发明的另一实施例，提供一种液晶显示器，包括：第一基板；第二基板；夹在所述第一基板和所述第二基板之间的液晶组分；设置在所述第一基板上的多个像素，所述多个像素的每一个都包括开关元件、像素电极和电容；与所述开关元件的控制端子连接的多条扫描信号线；与所述多条扫描信号线连接的扫描信号线驱动电路；与所述开关元件的第一电极连接的多条视频信号线；以及与所述多条视频信号线连接的视频信号线驱动电路；其特征在于：在所述多个像素的下面形成有光阻挡膜；多条像素-电势控制线连接于形成所述电容的两个电容形成电极中的一个电极；像素-电势控制电路连接于所述多条像素-电势控制线；所述电容的两个电容形成电极中的另一个电极连接于所述像素电极，所述像素-电势控制电路具有移位寄存器电路和输出电路，所述移位寄存器电路向所述输出电路输出定时信号，所述输出电路向所述像素-电势控制信号线输出像素-电势控制信号，所述扫描信号线电路设置于所述扫描信号线的一端一侧，所述像素-电势控制电路设置于所述扫描信号线的另一端一侧。

设置于所述扫描信号线的另一端一侧，以及所述光阻挡膜与所述多个象素之间的间隙重叠并且形成所述象素-电势控制信号线的一部分。

### 附图说明

在所有附图中给相似的部件分配相同的参考号，在附图中：

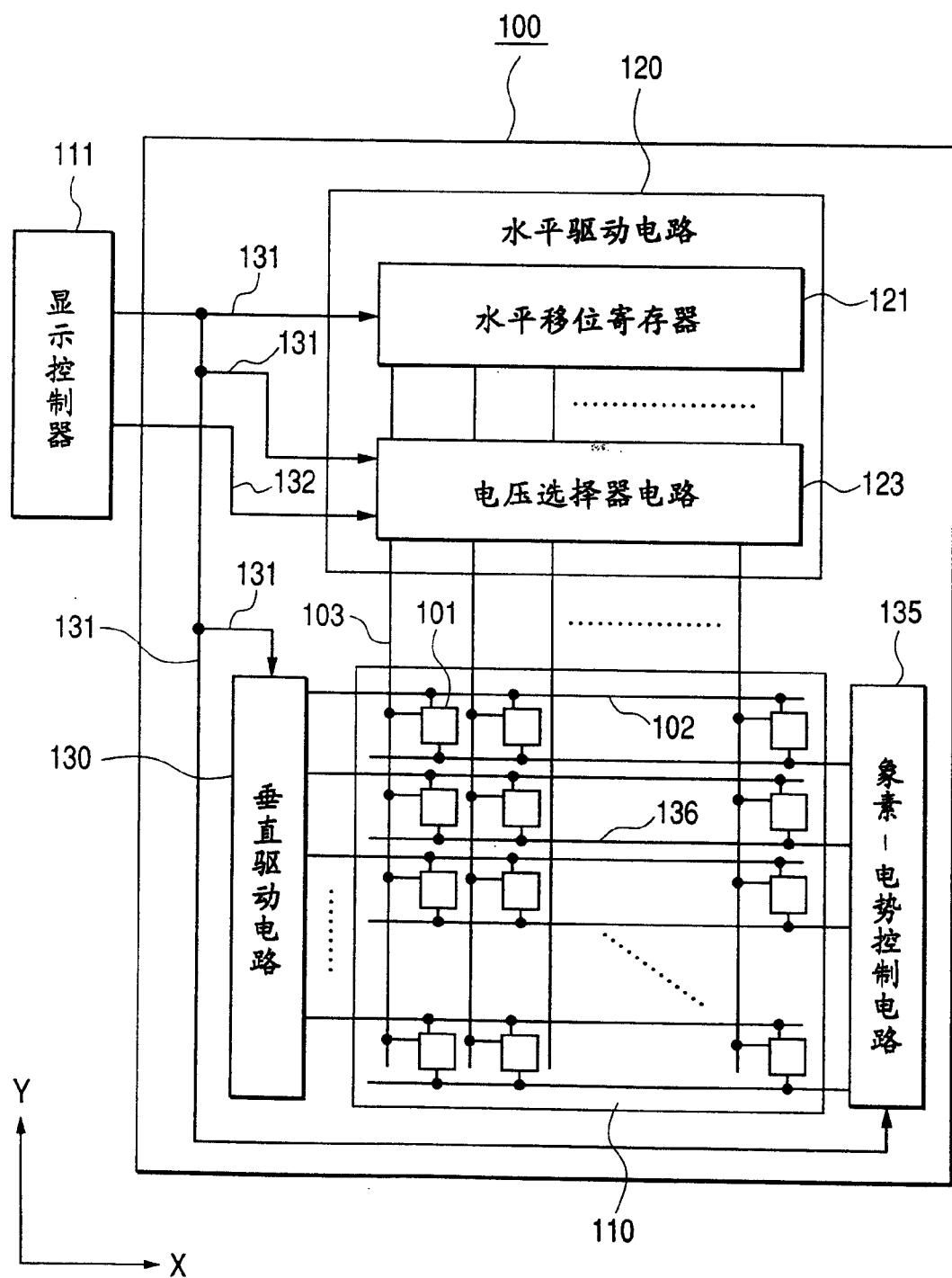

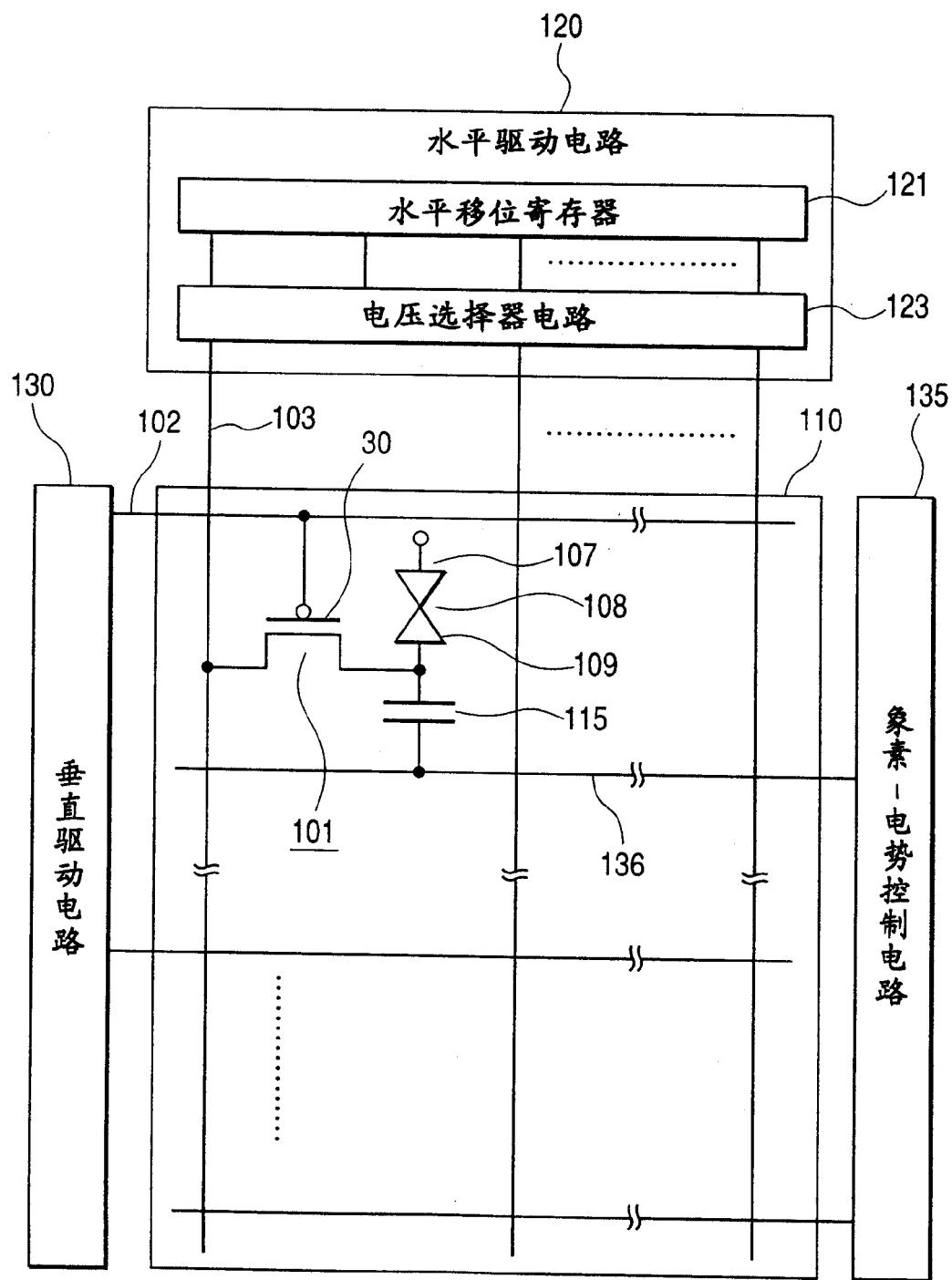

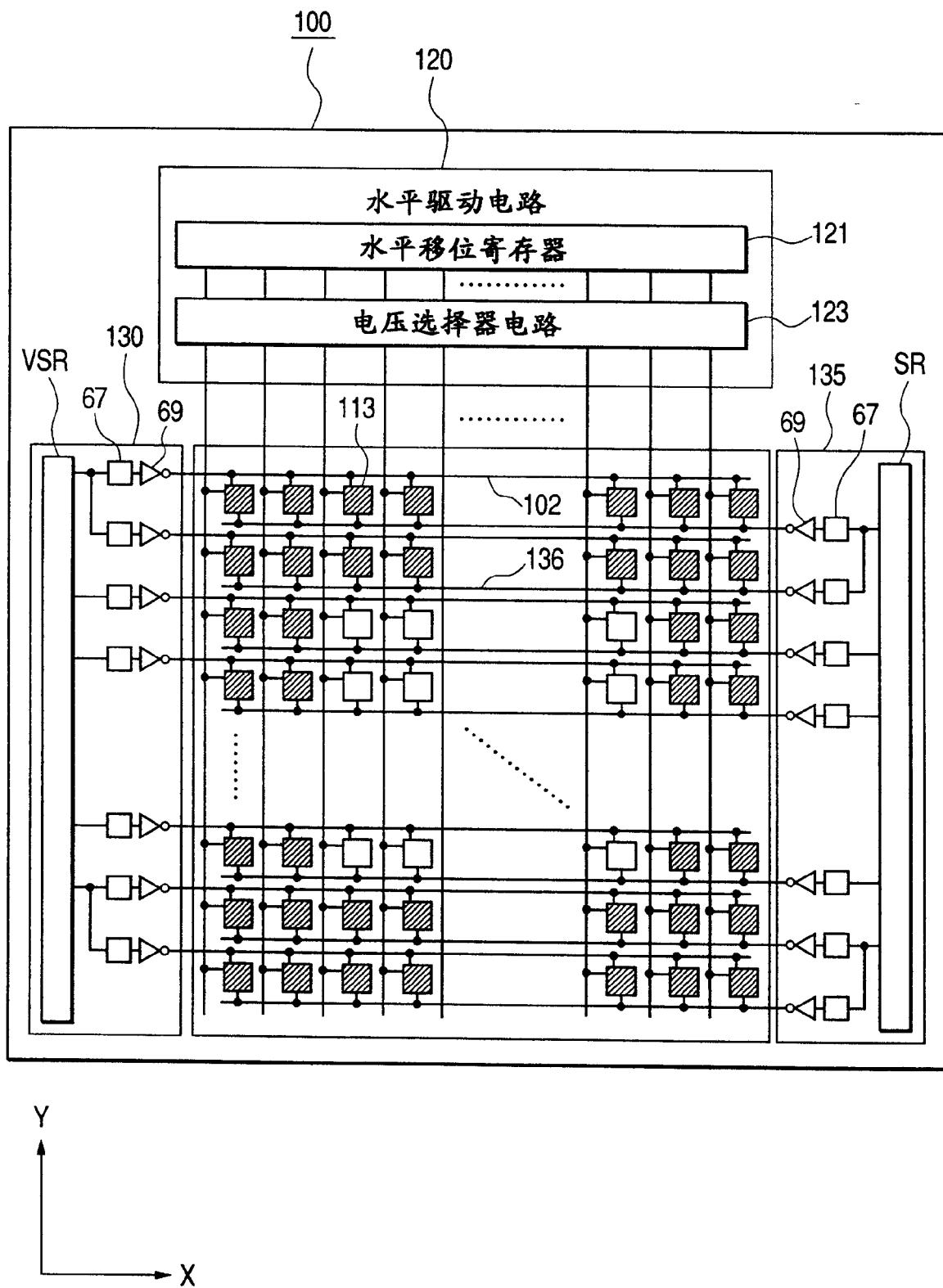

图 1 为用于说明根据本发明实施例的液晶显示器的大体结构的框图；

图 2 为示出根据本发明实施例的液晶显示板实例的框图；

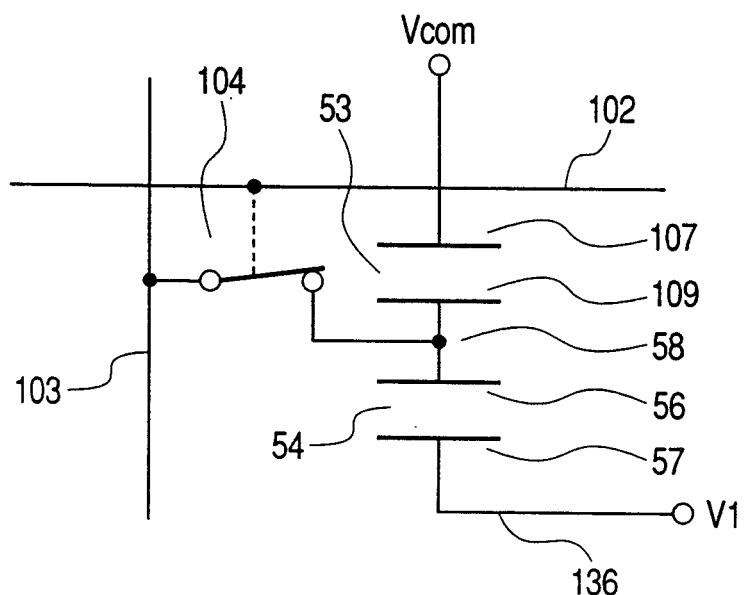

图 3A 和 3B 是用于解释象素电势控制方法的电路示意图；

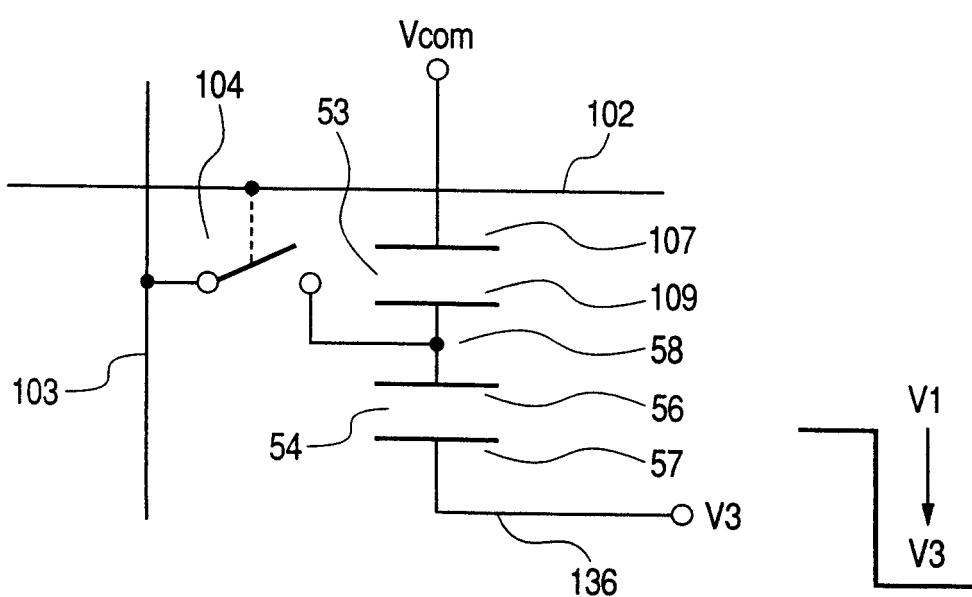

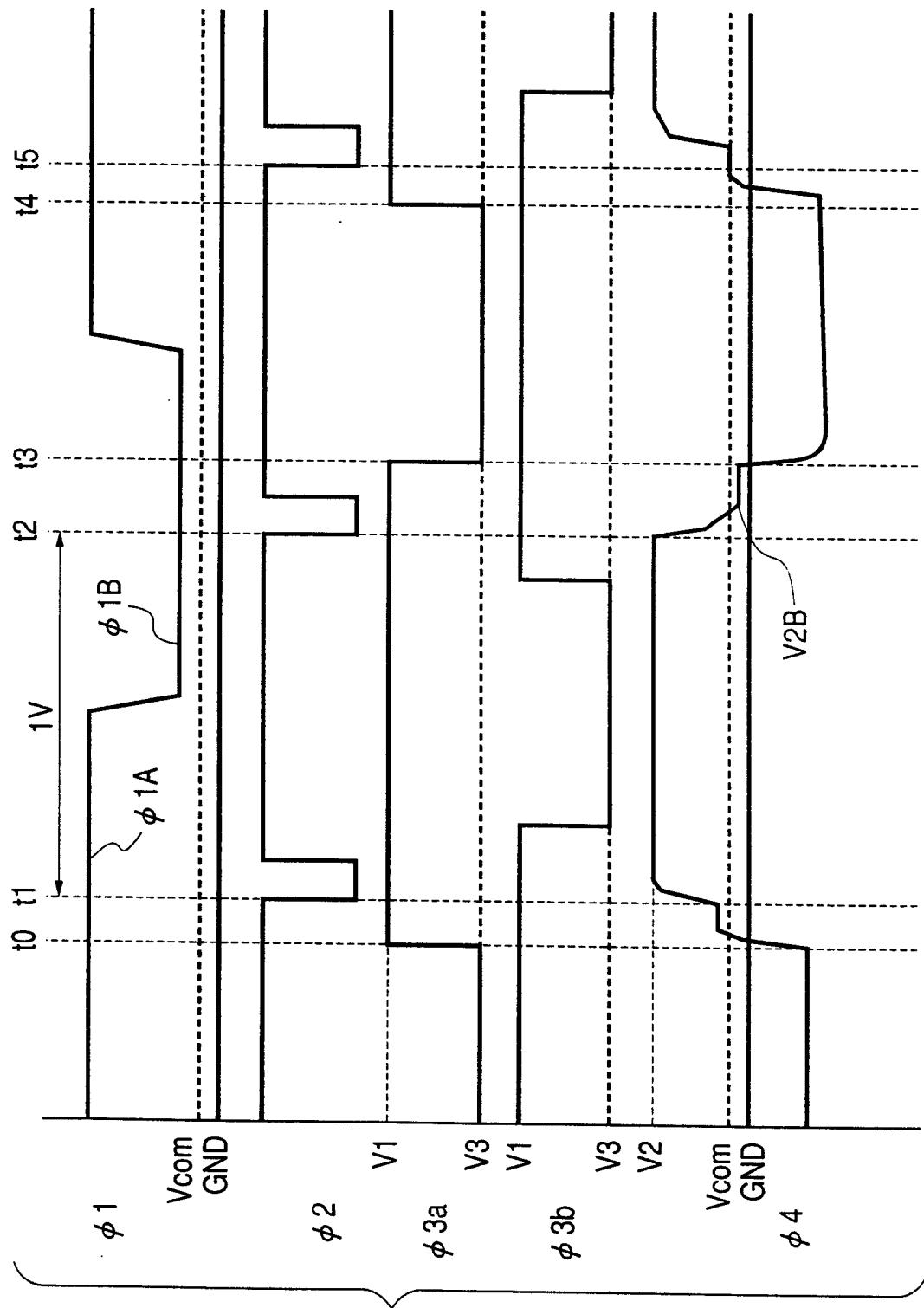

图 4 为用于解释图 2 所示液晶显示板的驱动方法的时间图；

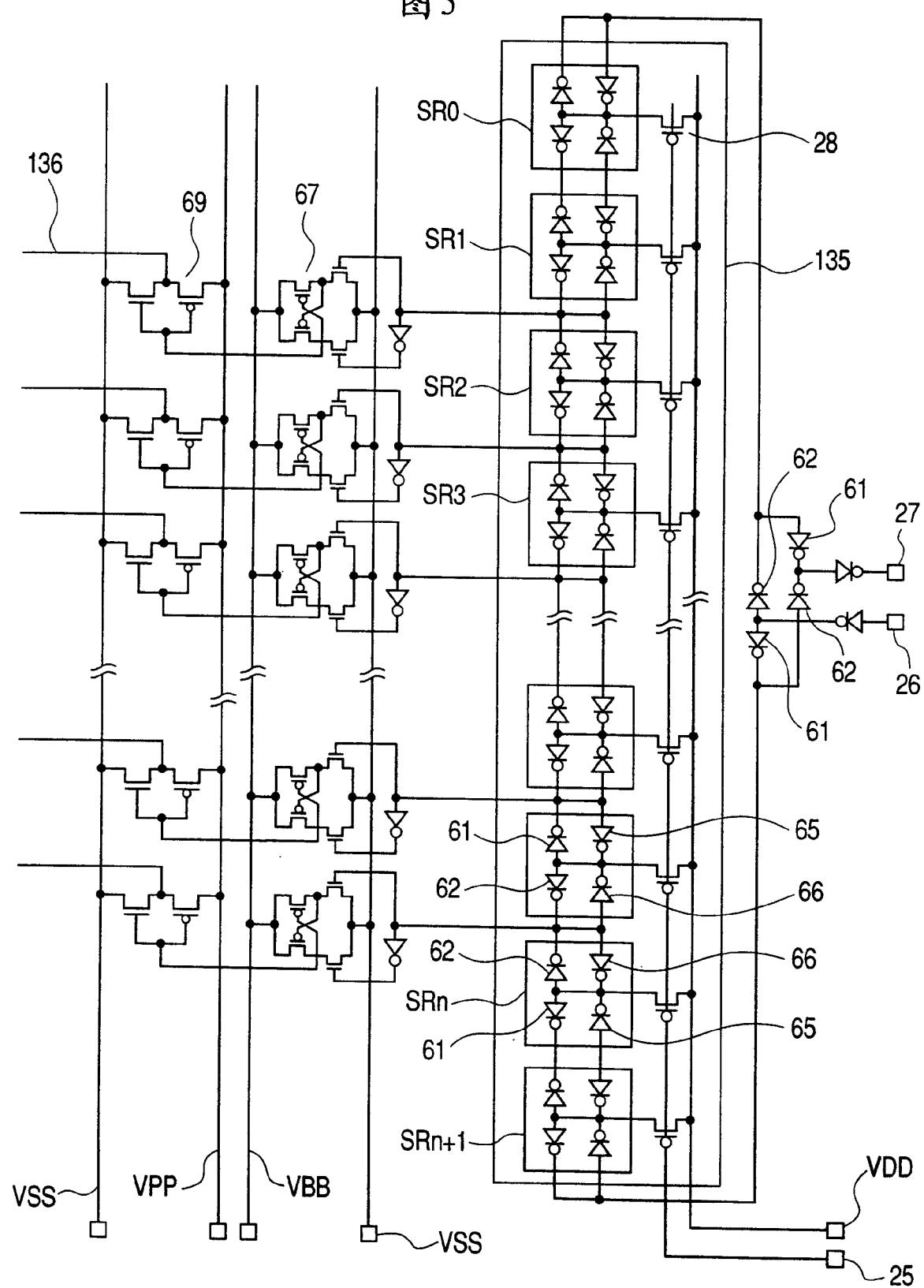

图 5 为用于说明象素-电势控制电路的电路示意图；

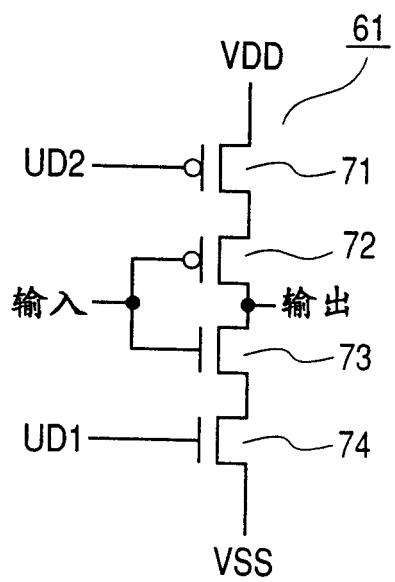

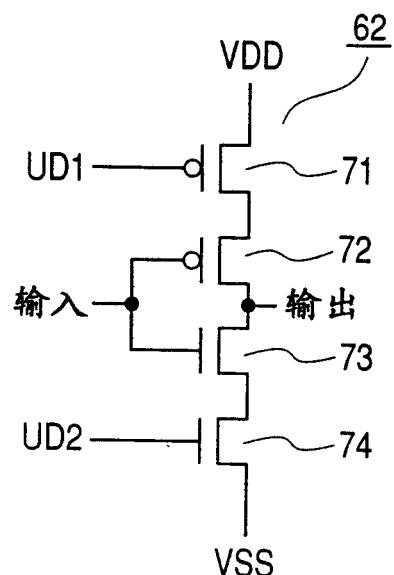

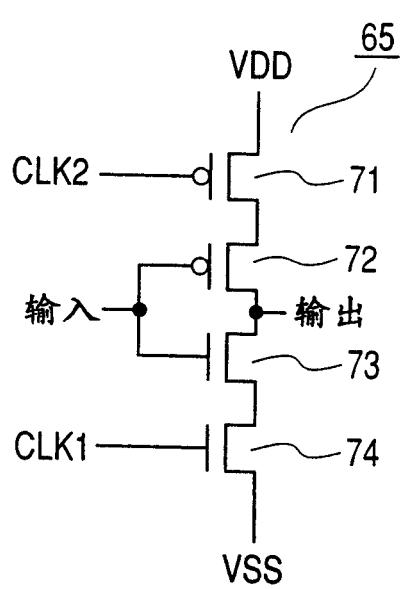

图 6A-6D 为用于说明在象素-电势控制电路中使用的时钟反相器的电路示意图；

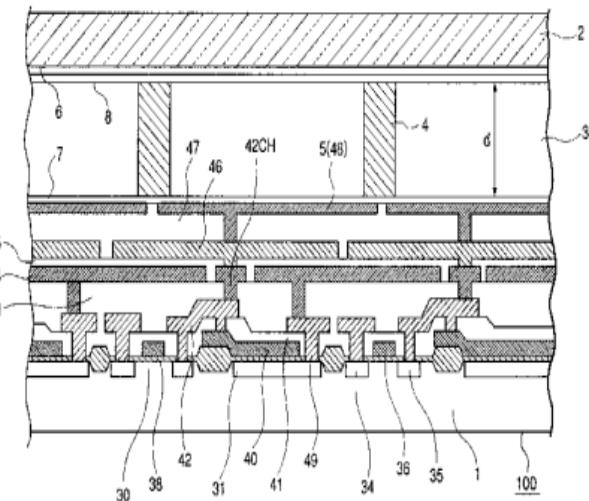

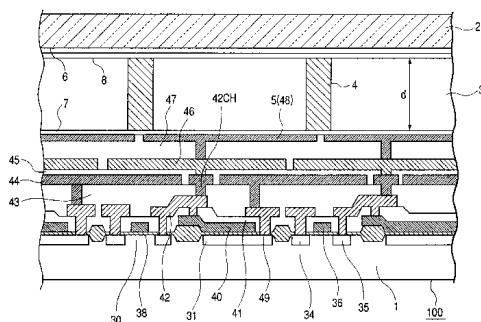

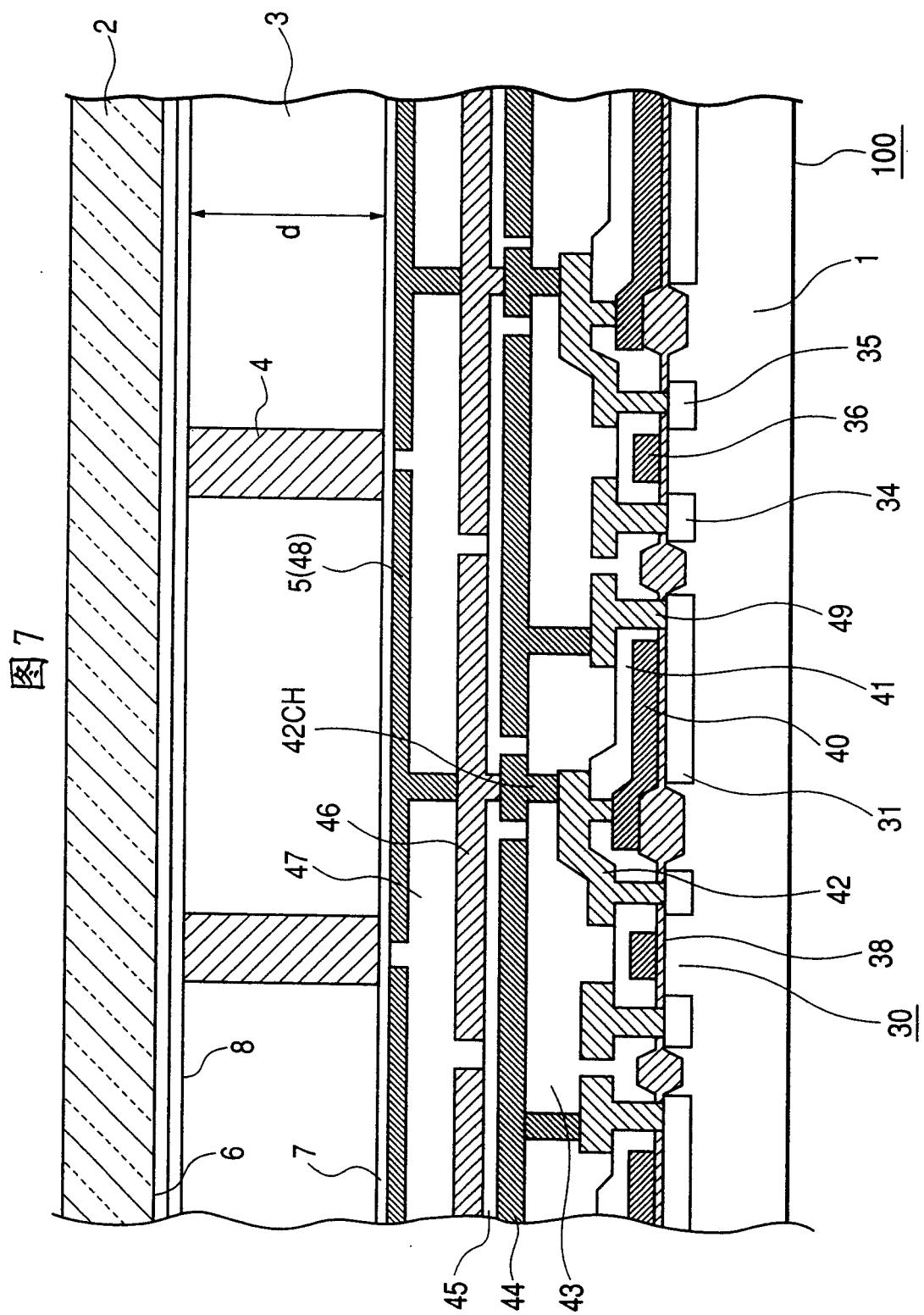

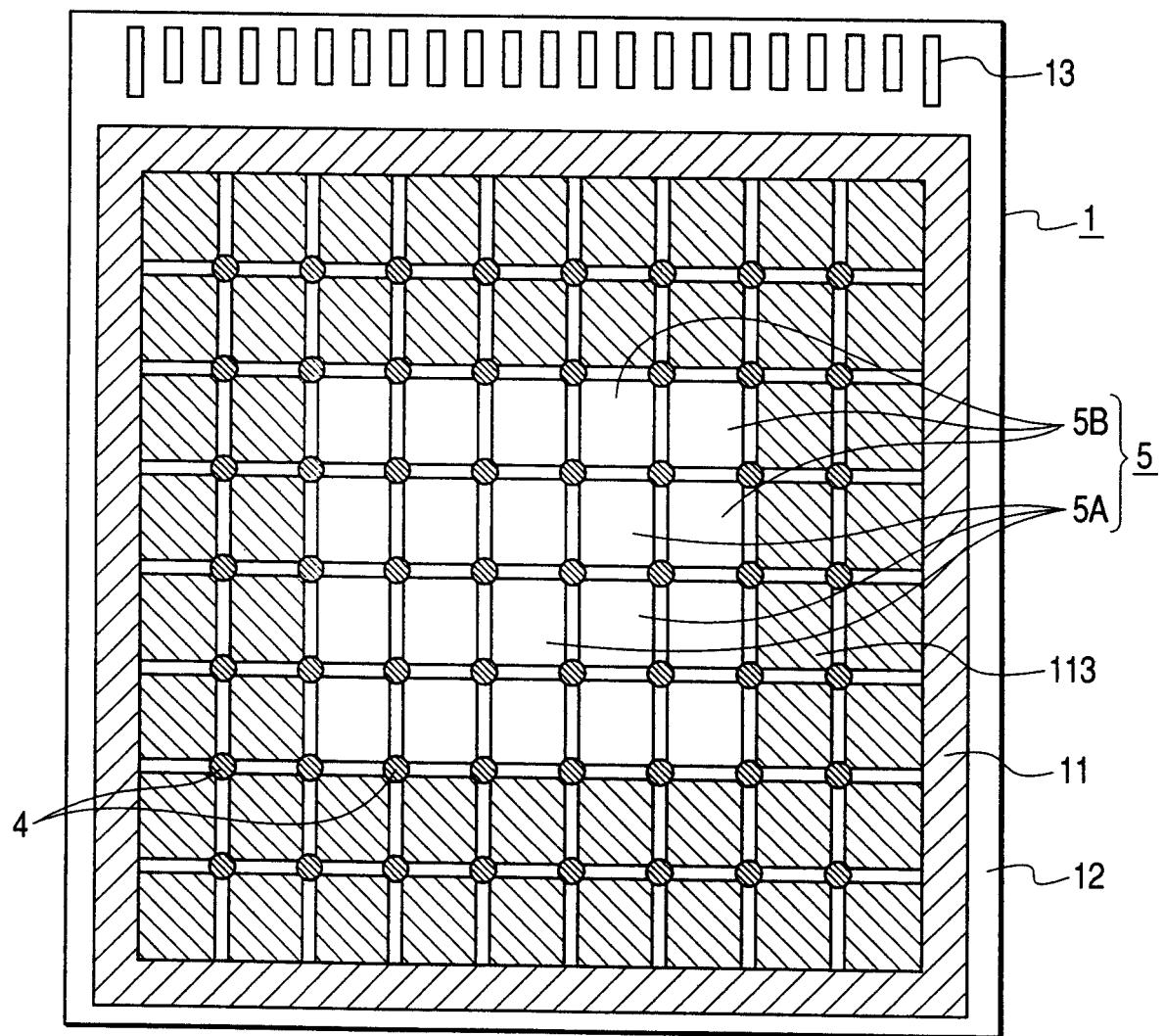

图 7 是在根据本发明实施例的液晶显示器中象素区的横截面示意图；

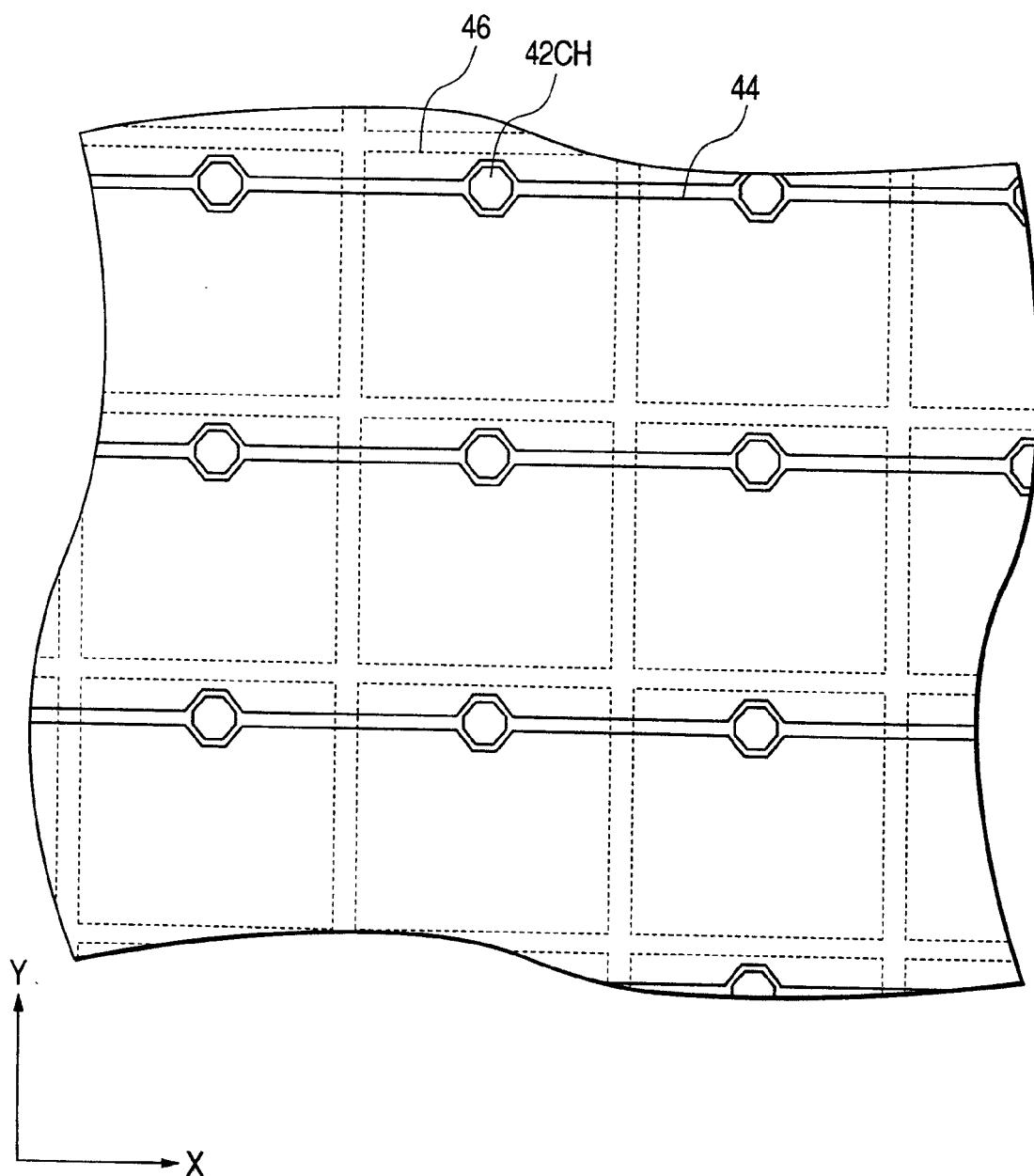

图 8 为通过使用光阻挡膜而形成的象素-电势控制线的配置的平面示意图；

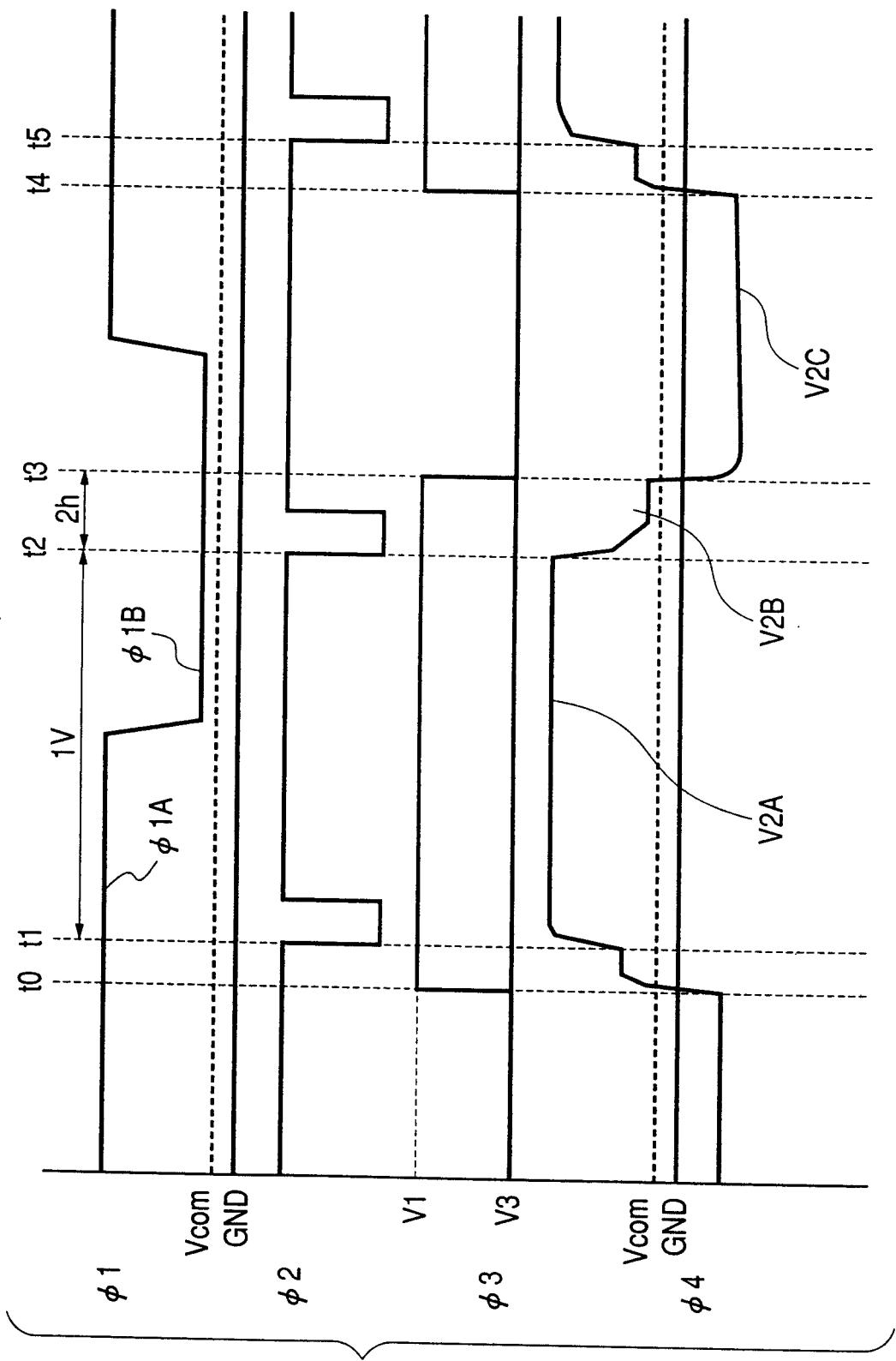

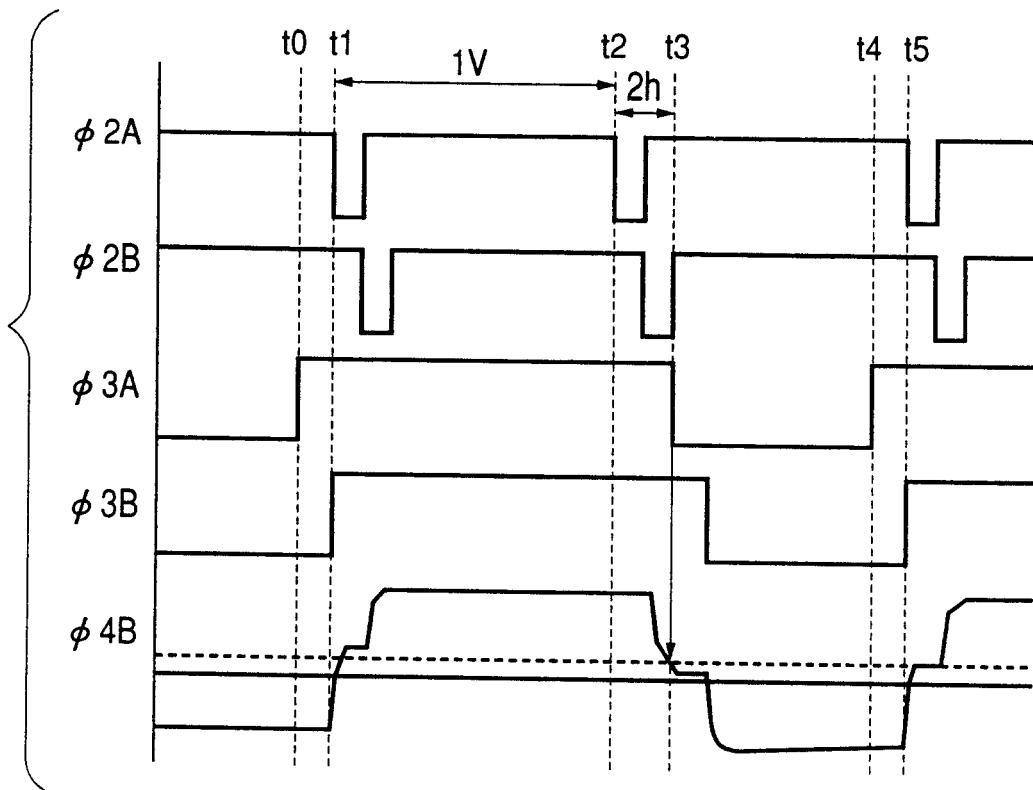

图 9A 和 9B 是说明根据本发明实施例的液晶显示器的驱动方法的时间图；

图 10A 是在根据本发明实施例的液晶显示器中构成输出电路的反相器电路的横截面视图，而图 10B 示出用于解释根据本发明实施例的液晶显示器的操作的时间图；

图 11 为根据本发明实施例的液晶显示器的平面示意图；

图 12 是说明根据本发明实施例的液晶显示器的驱动方法的时间图；

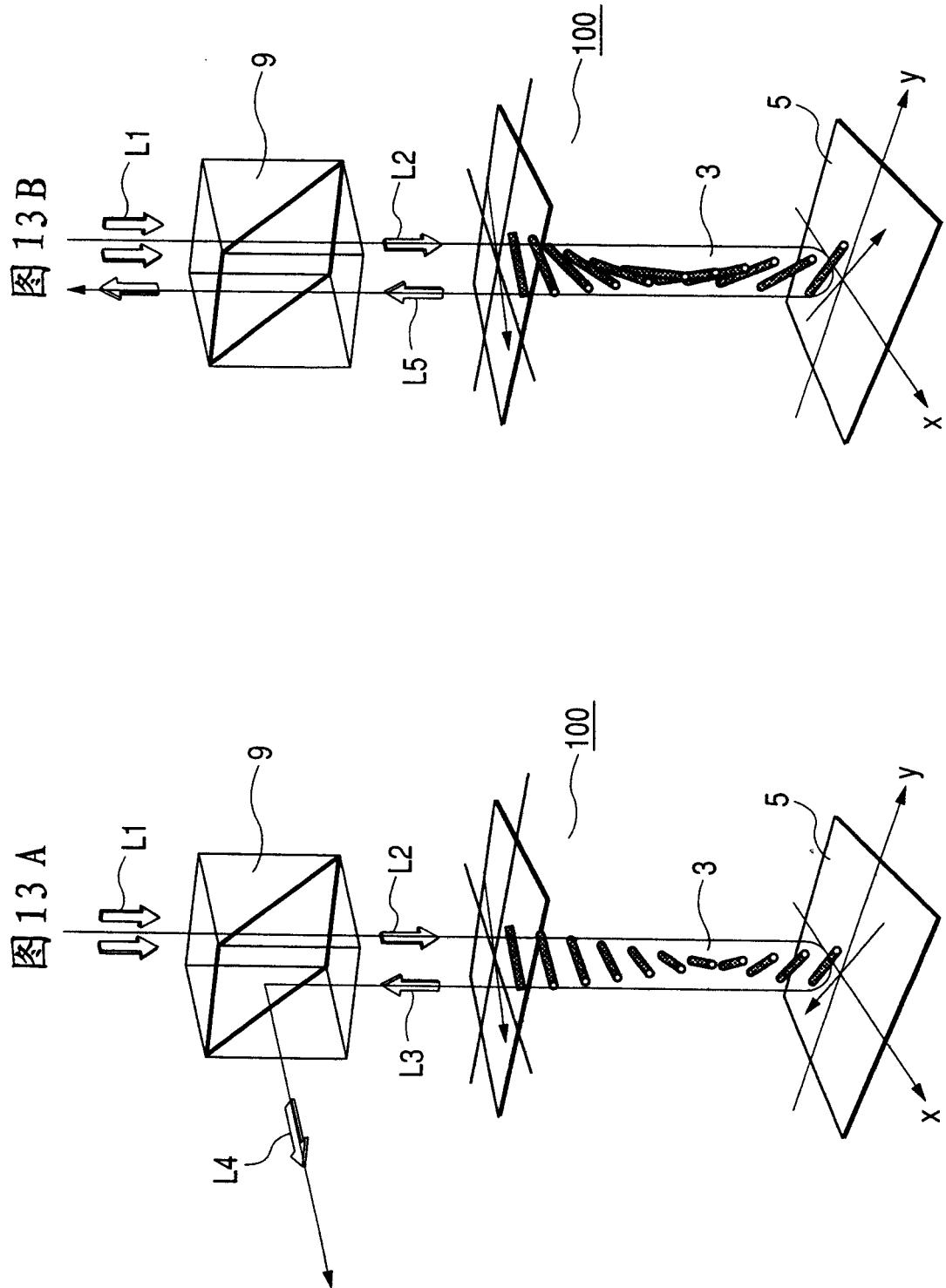

图 13A 和 13B 为根据本发明实施例的液晶显示器的透视图，用于解释该液晶显示器的操作；

图 14 为根据本发明实施例的液晶显示板的平面示意图；

图 15 为根据本发明实施例的液晶显示器的平面示意图；

图 16 是有源元件及其附近的横截面示意图，用于解释根据本发明实施例的液晶显示器；

图 17 是有源元件及其附近的横截面示意图，用于解释根据本发明实施例的液晶显示器；

图 18 为根据本发明实施例的液晶显示器的液晶显示板的示意性透视图；

图 19 为用于解释与根据本发明实施例的液晶显示器的液晶显示板的液晶板相连接的挠性印刷电路板的平面示意图；

图 20 是根据本发明实施例的液晶显示器的立体分解图；

图 21 是根据本发明实施例的液晶显示器的液晶显示板的液晶板的平面示意图。

### 具体实施方式

以下结合附图详细描述根据本发明的实施例。在所有用于解释本发明实施例的附图中，为功能相似的部件分配相同的参考号，并且不作重复解释。

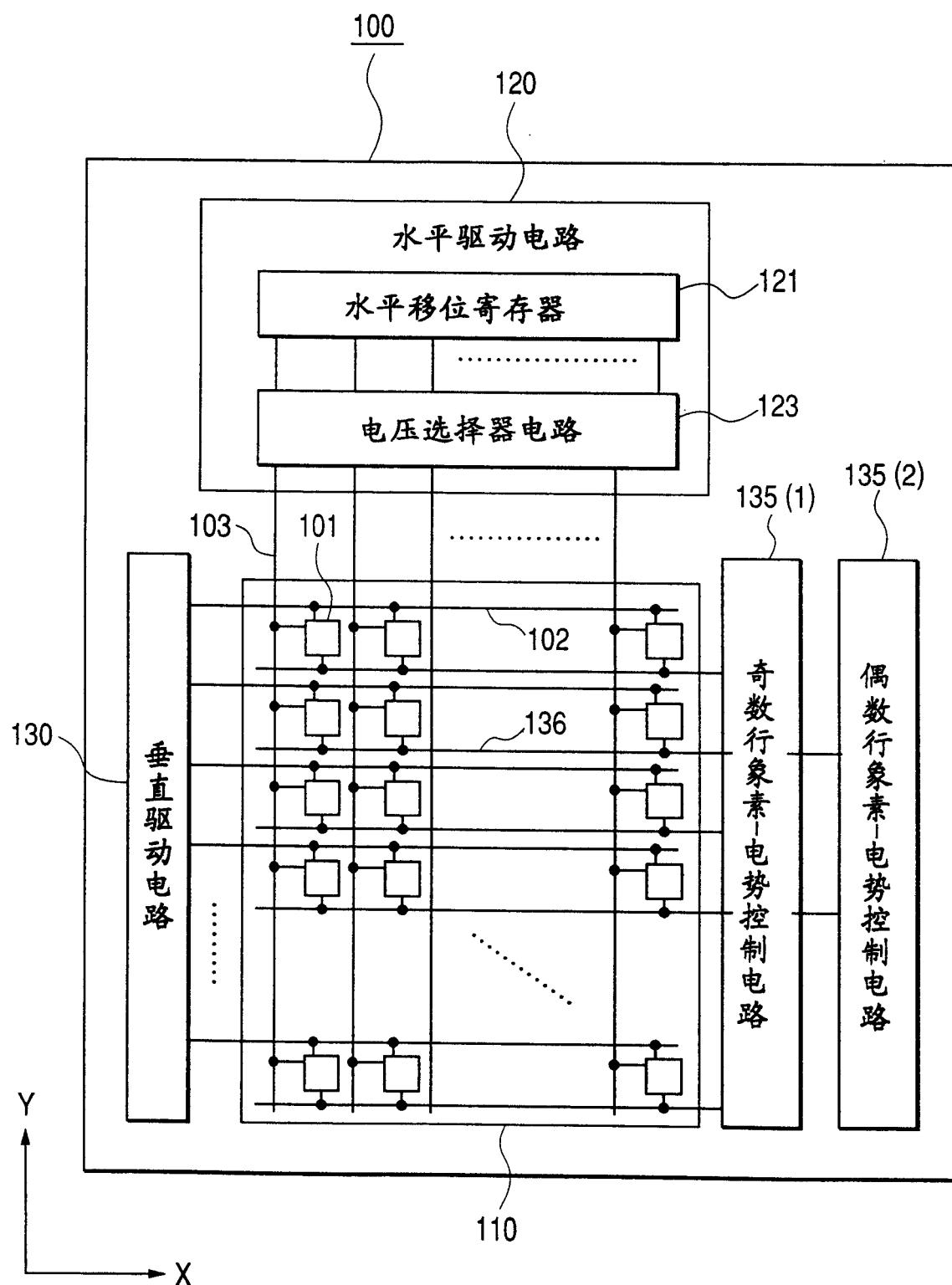

图 1 为用于说明根据本发明实施例的液晶显示器的大体结构的框图。本实施例的液晶显示器包括液晶显示板（液晶显示元件）100 和显示控制器 111。

液晶显示板 100 包括具有以矩阵形式排列的像素区 101 的显示区 110、水平驱动电路（视频信号线驱动电路）120、垂直驱动电路（扫描信号线驱动电路）130 以及像素-电势控制电路 135。在相同的基本板上布置显示区 110、水平驱动电路 120、垂直驱动电路 130 以及像素-电势控制电路 135。

显示控制器 111 基于外部传递的控制信号如时钟信号、显示定时

信号、水平同步信号、垂直同步信号，控制水平驱动电路 120、垂直驱动电路 130 和像素-电势控制电路 135。显示控制器 111 向水平驱动电路 120 提供将要在液晶显示板 100 上显示的显示数据。参考号 131 代表显示控制器 111 的控制信号线，而 132 是显示信号线。

多根视频信号线（也称作漏极信号线或垂直信号线）103 从水平驱动电路 120 沿垂直方向（图 1 的 Y 方向）延伸进显示区 110 中，并且它们在水平方向（图 1 中的 X 方向）上排列。多根扫描信号线（也称作栅极信号线或水平信号线）102 从垂直驱动电路 130 沿水平方向（图 1 中的 X 方向）延伸，并且它们在垂直方向（图 1 的 Y 方向）上排列。多根像素-电势控制线 136 从像素-电势控制电路 135 沿水平方向（X 方向）延伸，并且在垂直方向（Y 方向）上排列。

水平驱动电路 120 包括水平移位寄存器 121 和电压选择器电路 123。显示控制器 111 的控制信号线 131 和显示信号线 132 连接到水平移位寄存器 121 和电压选择器电路 123，用于提供控制信号和显示信号。在这提供数字形式和模拟形式两种显示数据。

为简单起见，图 1 省略掉到各个电路的电压馈送线，但应理解向各个电路应馈送必要的电源电压。

当显示控制器 111 在接收到外部提供的垂直同步信号之后立即接收第一显示定时信号时，显示控制器 111 通过控制信号线 131 向垂直驱动电路 130 输出开始脉冲。然后，显示控制器 111 基于水平同步脉冲向垂直驱动电路 130 输出具有水平扫描周期（下称为 1h）的移位时钟，以便顺序选择扫描信号线。垂直驱动电路 130 基于移位时钟选择扫描信号线 102，并向被选扫描信号线 102 提供扫描信号。也就是说，在图 1 中，垂直驱动电路 130 输出信号，以便从顶部到底部逐线选择扫描信号线 102，每根线选择时间为一个水平扫描周期 1h.

进而，当显示控制器 111 接收显示定时信号时，显示控制器 111 认可收到与显示起点相应的显示定时信号，并输出显示数据到水平驱

动电路 120。显示数据从显示控制器 111 顺序输出，水平移位寄存器 121 基于从显示控制器 111 传递的移位时钟输出定时信号。定时信号指电压选择器电路 123 选取提供给各个视频信号线 103 的显示数据的时间。

当显示信号为模拟形式时，电压选择器电路 123 从模拟信号中与定时信号同步地选取相应的电平作为显示数据（灰度电压），然后输出所选取的灰度电压到视频信号线 103 作为视频信号。另一方面，当显示数据为数字形式时，电压选择器电路 123 与定时信号同步地选取显示信号，然后根据显示信号（数字数据）选择（译码）灰度电压，随后输出灰度电压到视频信号线 103。输出到视频信号线 103 的灰度电压与垂直驱动电路 130 的扫描信号同步地写入到像素区 101 的像素电极中，作为视频信号。

像素-电势控制电路 135 根据显示控制器 111 的控制信号控制写入到像素电极中的视频信号电压。通过视频信号线 103 写入到像素电极中的灰度电压与反电极上的基准电压有一定的电压差。像素-电势控制电路 135 通过向像素区 101 提供控制信号而改变像素电极和反电极之间的电压差。下面解释像素-电势控制电路 135 的细节。

结合图 2 解释本发明实施例的液晶显示板 100 内的像素区 101。图 2 示出像素区 101 的等效电路。每个像素 101 都布置在显示区 110 内由两根相邻扫描信号线 102 和两根相邻视频信号线 103 所包围的区域内，并且像素 101 以矩阵形式排列。为了简单起见，在图 2 中只绘出一个像素区 101。每个像素区 101 都具有有源元件 30 和像素电极 109。像素电极 109 连接到像素电容 115。像素电容 115 的一个电极连接到像素电极 109，像素电容 115 的另一个电极连接到像素-电势控制线 136，而像素-电势控制线 136 又连接到像素-电势控制电路 135。在图 2 中，有源元件 30 示作 p-沟道型晶体管。

如上所述，垂直驱动电路 130 向扫描信号线 102 顺序输出扫描信

号，扫描信号用于有源元件 30 的开或关控制。向视频信号线 103 提供灰度电压作为视频信号，并且当有源元件 30 接通时，从视频信号线 103 向像素电极 109 提供灰度电压。反电极（公共电极）107 布置得面对像素电极 109，并且液晶层（未示出）置于像素电极 109 和反电极 107 之间。在图 2 所示的电路图中，示出因液晶层而形成的等效液晶电容 108，它连接在一个像素电极 109 和反电极 107 之间。通过在像素电极 109 和反电极 107 之间施加电压，随后改变液晶分子的取向并利用所获得的液晶层光学性质的改变而产生显示。

如上所述，对于驱动液晶显示器的方法，使用 AC 驱动以避免在液晶层两端施加 DC 电压。对于 AC 驱动，如果反电极 107 上的电压用作基准电压，电压选择器电路 123 输出相对基准电压为正、负极性的两个电压，作为灰度电压。

在该实施方式中，AC 驱动能够利用与基准电压相同极性的信号作为从电压选择器电路 123 向像素电极 109 提供的视频电压。

在以上实例中，首先，正极性电压写入到像素电极 109 中，随后，通过使用像素-电势控制电路 135 产生负极性电压。然而，可颠倒此关系。首先，负极性电压写入到像素电极 109 中，随后，可通过提高像素-电势控制电路 135 的像素-电势控制信号的电压而产生正极性电压。

以下结合图 3A 和 3B 解释改变像素电极 109 的电压的方法。在图 3A 和 3B 中，为了说明的目的，液晶电容 108 和像素电容 115 分别用第一电容器 53 和第二电容器 54 表示，有源元件 30 由开关 104 表示。参考号 56 代表连接到像素电极 109 的像素电容 115 的一个电极，而 57 是连接到像素-电势控制线 136 的像素电容 115 的另一个电极。像素电极 109 和电极 56 之间的结点用节点 58 表示。为了简单起见，假定可忽略其它寄生电容，第一电容器 53 和第二电容器 54 的电容分别为 CL 和 CC。

如图 3A 所示，首先，从外部向第二电容器 54 的电极 57 提供电

压 V1。随后，当用扫描信号接通开关 104 时，电压从视频信号线 103 提供到象素电极 109 和电极 56。在这，提供到节点 58 的电压假设为 V2。

然后，如图 3B 所示，在关断开关 104 时，施加到电极 57 以及象素-电势控制信号的电压从电压 V1 降低到电压 V3。由于储存在第一和第二电容器 53 和 54 内的电荷总量保持不变，因此节点 58 的电压改变为  $V2 - \{CC / (CL+CC)\} \times (V1-V3)$ 。

在此，如果第一电容器 53 的电容 CL 与第二电容器 54 的电容 CC 相比足够小，即当  $CL \ll CC$  时，那么  $CC / (CL+CC) \approx 1$ ，从而节点 58 的电压变成等于  $V2 - V1 + V3$ 。如果  $V2=0$  和  $V3=0$ ，节点 58 的电压变成等于  $(-V1)$ 。

通过使用以上解释的方法，首先从视频信号线 103 提供到象素电极 109 的电压被选择为相对于反电极 107 上的基准电压为正极性，随后通过控制施加到电极 57 上的电压即象素-电势控制信号可产生负极性信号。当以此方式产生负极性信号时，不必从电压选择器电路 123 提供负极性信号，由此可通过使用低压电路元件形成外围电路。

以下结合图 4 解释图 2 所示电路中的工作时间。在图 4 中“1V”指垂直扫描周期。 $\Phi 1$  代表提供到视频信号线 103 的灰度电压。 $\Phi 2$  为提供到扫描信号线 102 的扫描信号， $\Phi 3$  为提供到象素-电势控制信号线 136 的象素-电势控制信号（电压下降信号），而且  $\Phi 4$  为象素电极 109 的电势。如图 3A 和 3B 所示，象素-电势控制信号  $\Phi 3$  在电压 V3 和 V1 之间变动。

图 4 示出灰度电压  $\Phi 1$  由正极性电压输入信号  $\Phi 1A$  和负极性电压输入信号  $\Phi 1B$  组成的情况。正极性电压输入信号  $\Phi 1A$  施加到象素电极上，并保持不变。另一方面，负极性电压输入信号  $\Phi 1B$  首先施加到象素电极上，然后通过使用象素-电势控制信号  $\Phi 3$  转换成相对于基准电压为负极性的电压。在此实施例中，假设正极性电压输入信号  $\Phi 1A$

和负极性电压输入信号  $\Phi_{1B}$  相对于施加到反电极 107 的基准电压  $V_{com}$  都为正的。

在图 4 中，在从  $t_0$  到  $t_2$  的时间内，灰度电压  $\Phi_1$  是正极性电压输入信号  $\Phi_{1A}$ 。首先，在时间  $t_0$ ，像素-电势控制电路 135 输出电压  $V_1$  作为像素-电势控制信号  $\Phi_3$ ，然后，在时间  $t_1$  当扫描信号  $\Phi_2$  改变成与被选状态相应的低电平时，图 2 所示的 p 沟道型晶体管 30 导通，从而视频信号线 103 上的正极性电压输入信号  $\Phi_{1A}$  被写入像素电极 109 中。在图 4 中，写入到像素电极 109 中的信号由  $\Phi_4$  表示。在图 4 中，在时间  $t_1$  写入到像素电极 109 中的电压由  $V_{2A}$  表示。其次，当扫描信号  $\Phi_2$  改变成与非选择状态相应的高电平时，晶体管 30 关断，从而像素电极 109 从用于提供电压到其上的视频信号线 103 断开。液晶显示器基于写入到像素电极 109 中的电压  $V_{2A}$  显示灰度级。

以下解释从  $t_2$  到  $t_4$  的时间，此时灰度电压  $\Phi_1$  是负极性电压输入信号  $\Phi_{1B}$ 。在时间  $t_2$ ，输出扫描信号  $\Phi_2$ ，从而由  $\Phi_4$  表示的电压  $V_{2B}$  写入到像素电极 109 中。随后晶体管 30 关断，并且在时间  $t_3$ ，即在从时间  $t_2$  开始的  $2h$ （两个水平扫描周期）时间之后，提供到像素电容 115（见图 2）的电压从  $V_1$  下降到  $V_3$ ，如图 4 的像素-电势控制信号  $\Phi_3$  中所示。当像素-电势控制信号  $\Phi_3$  从  $V_1$  改变为  $V_3$  时，由于像素电容 115 用作耦合电容，因此像素电极 109 的电势可基于像素-电势控制信号  $\Phi_3$  的幅值下降一定的量。从而，在像素内产生相对于基准电压  $V_{com}$  为负极性的电压  $V_{2C}$ 。

当使用上述方法产生负极性信号时，外围电路可通过使用低压电路元件形成。从电压选择器电路 123 输出的信号是小幅值正极性信号，因此有可能把电压选择器电路 123 制作成低压电路。当电压选择器电路 123 在低压下工作时，由于其它外围电路如水平移位寄存器 121 和显示控制器 111 是低压电路，因此液晶显示器的整个电路可制作成低压电路。

图 5 示出像素-电势控制电路 135 的电路配置。参考符号

SR<sub>1</sub>-SR<sub>n+1</sub>（以下省略下标，除非它们应相互区别开）代表可向上和向下移位信号的双向移位寄存器。每个双向移位寄存器 SR 由时钟反相器 61、62、65 和 66 组成。参考号 67 表示电平移相器，而 69 为输出电路。诸如双向移位寄存器 SR 的电路用电源电压 VDD 工作。电平移相器 67 转换从双向移位寄存器 SR 输出的信号的电压电平。电平移相器 67 输出幅值在电源电压 VBB 和电源电压 VSS（接地电势）之间的信号，VBB 高于电源电压 VDD。向输出电路 69 施加电源电压 VPP 和电源电压 VSS，并且根据电平移相器 67 的信号输出电压 VPP 或 VSS 到像素-电势控制线 136。在结合图 4 解释的像素-电势控制信号 Φ3 中，电压 V1 和 V3 分别对应于电源电压 VPP 和电源电压 VSS。在图 5 中，输出电路 69 表示成由 p 沟道型和 n 沟道型晶体管组成的反相器。可以选择施加到 p 沟道型晶体管的电源电压 VPP 和施加到 n 沟道型晶体管的电源电压 VSS，以便它们可被输出作为像素-电势控制信号 Φ3。然而，由于其中制作有 p 沟道型晶体管的硅基板被施加以下解释的基板电压，因此电源电压 VPP 必须选择为对应于基板电压的适当值。参考号 26 为开始信号的输入端，用于向像素-电势控制电路 135 提供开始信号作为一个控制信号。在接收到开始信号之后，图 5 所示的双向移位寄存器 SR<sub>1</sub>-SR<sub>n+1</sub> 与外部提供的时钟信号同步地连续输出定时信号。电平移相器 67 根据定时信号输出电压 VSS 或 VBB，输出电路 69 根据电平移相器 67 的输出向像素-电势控制线 136 输出电压 VPP 或 VSS。可以通过向双向移位寄存器 SR 提供开始信号和时钟信号以便为图 4 所示像素-电势控制信号 Φ3 建立定时关系，而从像素-电势控制电路 135 输出具有所需定时关系的像素-电势控制信号 Φ3。参考号 25 指用于重置信号的输入端。

以下结合图 6A 和 6B 解释在双向移位寄存器 SR 内使用的时钟反相器 61 和 62。参考符号 UD1 和 UD2 分别代表第一和第二方向设置线。第一方向设置线 UD1 提供用于沿图 5 中从底部到顶部方向扫描的 H 电平，而第二方向设置线 UD2 提供用于沿图 5 中从顶部到底部方向扫描的 H 电平。为了清楚起见，省略图 5 中的接线，但第一和第二方向

设置线 UD1 和 UD2 连接到构成双向移位寄存器 SR 的时钟反相器 61 和 62.

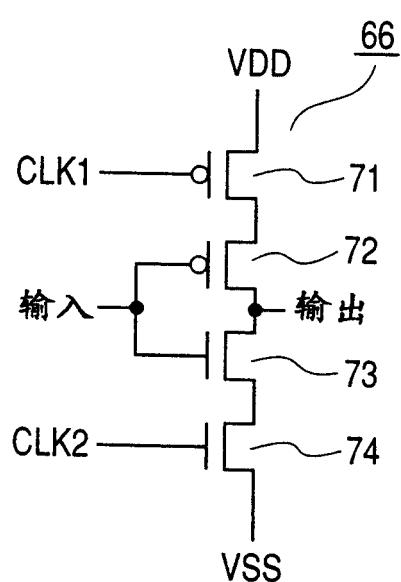

时钟反相器 61 由如图 6A 所示的 p 型晶体管 71、72 和 n 型晶体管 73、74 构成. p 型晶体管 71 连接到第二方向设置线 UD2, 而 n 型晶体管 74 连接到第一方向设置线 UD1. 当第一方向设置线 UD1 为 H 电平且第二方向设置线 UD2 为 L 电平时, 时钟反相器 61 用作反相器; 但当第二方向设置线 UD2 为 H 电平且第一方向设置线 UD1 为 L 电平时, 时钟反相器 61 用作高阻抗.

另一方面, 如图 6B 所示, 在时钟反相器 62 中, p 型晶体管 71 连接到第一方向设置线 UD1, 而 n 型晶体管 74 连接到第二方向设置线 UD2. 当第二方向设置线 UD2 为 H 电平时, 时钟反相器 62 用作反相器; 但当第一方向设置线 UD1 为 H 电平时, 时钟反相器 62 用作高阻抗.

图 6C 示出时钟反相器 65 的电路配置. 当时钟信号线 CLK1 为 H 电平且时钟信号线 CLK2 为 L 电平时, 时钟反相器 65 输出已被反相的输入; 当时钟信号线 CLK1 为 L 电平且时钟信号线 CLK2 为 H 电平时, 时钟反相器 65 用作高阻抗.

图 6D 示出时钟反相器 66 的电路配置. 当时钟信号线 CLK2 为 H 电平且时钟信号线 CLK1 为 L 电平时, 时钟反相器 66 输出已被反相的输入; 当时钟信号线 CLK2 为 L 电平且时钟信号线 CLK1 为 H 电平时, 时钟反相器 66 用作高阻抗. 为了清楚起见, 省略图 6A-6D 中时钟信号线 CLK1、CLK2 的连接, 但时钟信号线 CLK1 和 CLK2 连接到时钟反相器 65 和 66.

根据以上解释, 当双向移位寄存器由时钟反相器 61、62、65 和 66 形成时, 双向移位寄存器 SR 可连续输出定时信号. 如果象素-电势控制电路 135 由双向移位寄存器 SR 形成, 就可获得用于双向扫描的象素-电势控制信号  $\Phi_3$ . 由于垂直驱动电路 130 也由相似的双向移位寄存器组成, 因此根据本发明的液晶显示器能沿从顶部到底部和从底部到顶部的方向进行双向扫描. 由于具有此配置, 如果希望显示被反

相的图象时，就通过颠倒扫描方向，进行从显示屏的底部到顶部的扫描。当垂直驱动电路 130 设置成从底部到顶部扫描显示屏时，像素-电势控制电路 135 通过改变第一和第二方向设置线 UD1 和 UD2 的设置而同样设置成相应的底部-顶部扫描。水平移位寄存器 121 也由相似的双向移位寄存器组成。

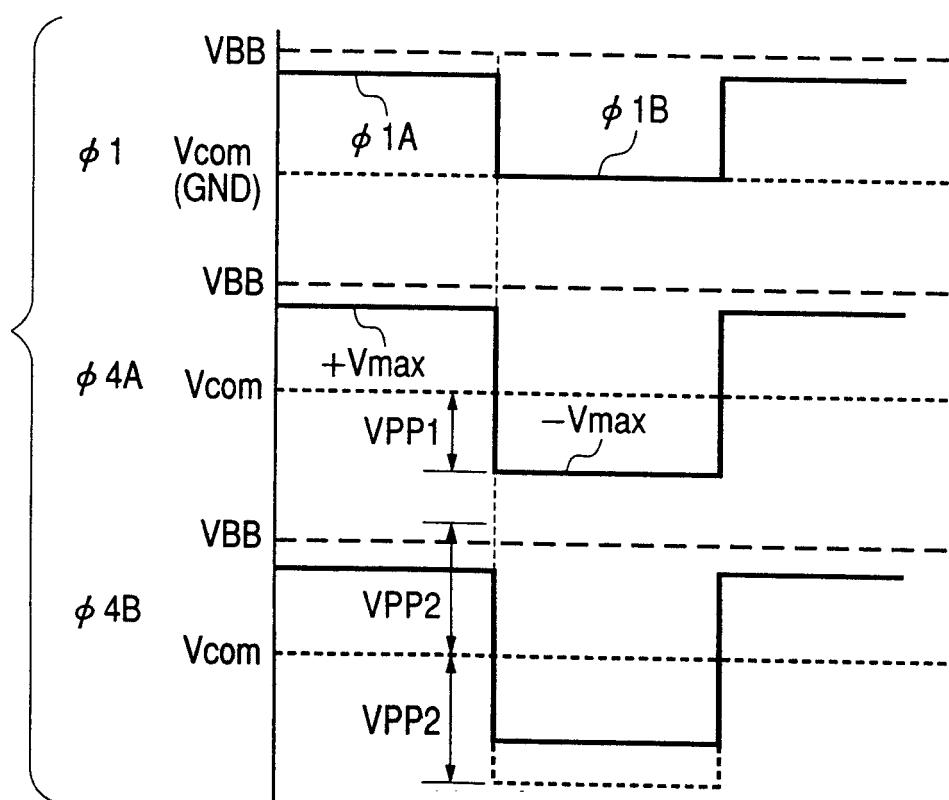

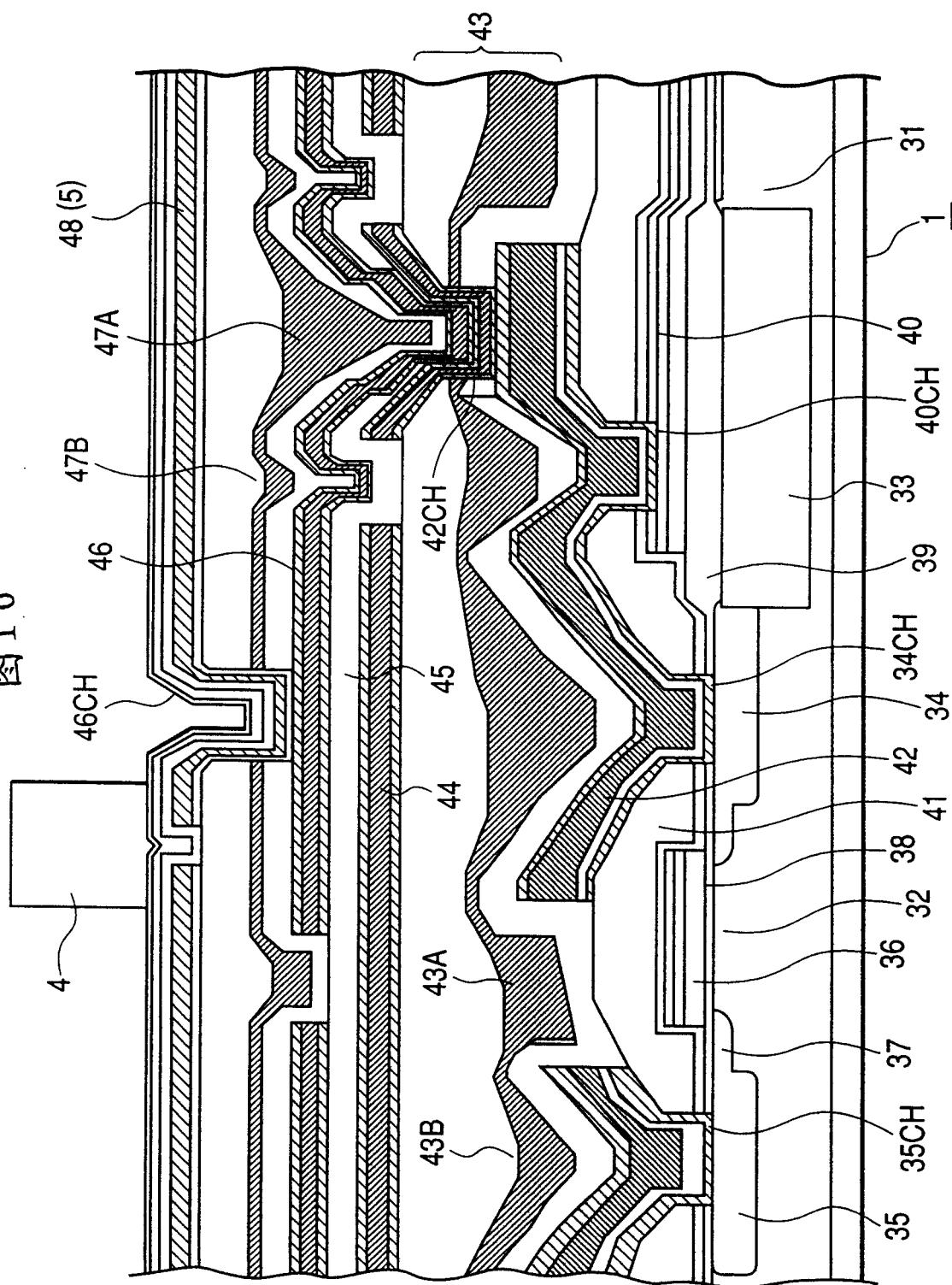

下面结合图 7 解释根据本发明的反射型液晶显示器的像素区。图 7 为根据本发明的反射型液晶显示器实施例的横截面示意图。在图 7 中，参考号 100 指液晶显示板，1 为用作驱动电路基板的第一基板，2 为用作透明基板的第二基板，3 为液晶组分，4 为隔板。隔板 4 在驱动电路基板 1 和透明基板 2 之间建立固定的单元间隙 d，驱动电路基板 1 和透明基板 2 之间夹着液晶组分 3。参考号 5 指在驱动电路基板 1 上形成的反射电极（像素电极），6 为用于与反射电极 5 一起在液晶组分 3 上施加电压的反电极，7 和 8 是用于对液晶组分 3 的液晶分子以特定方向取向的取向膜，而 30 为用于向反射电极 5 施加灰度电压的有源元件。参考号 34 指有源元件 30 的源极区域，35 为有源元件 30 的漏极区域，36 为有源元件 30 的栅极，38 为绝缘膜，31 和 40 分别为用于与它们之间的绝缘膜 38 形成像素电容的第一和第二电极。在图 7 中，第一和第二电极 31、40 示作用于形成像素电容的代表性电极，如果电连接到像素电极的其它导电层和连接到像素-电势控制线的其它导电层互相面对面，并且在它们之间有介电层，它们就可形成像素电容。

在图 7 中，参考号 41 是第一层间绝缘膜，42 为分别电连接漏极区域 35 和第二电极 40 的第一导电膜，43 为第二层间绝缘膜，44 为第一光阻挡膜，45 为第三层间绝缘膜，以及 46 为第二光阻挡膜。在第二和第三层间绝缘膜 43、45 内制作通孔 42CH，从而第一导电膜 42 与第二光阻挡膜 46 电连接在一起。参考号 47 为第四层间绝缘膜，而 48 为形成反射电极 5 的第二导电膜。灰度电压从有源元件的漏极区域 35 通过第一导电膜 42、通孔 42CH 和第二光阻挡膜 46 传递到反射电极 5。

在此实施例中的液晶显示器是反射型。大量的光（例如来自灯）投射到液晶显示板 100 中。光阻挡膜阻挡光进入驱动电路基板的半导体层。在反射型液晶显示器中，投射到液晶显示板 100 中的光从透明基板 2（在图 7 的顶部）进入，然后穿过液晶组分 3，随后被反射电极 5 反射回，接着再次穿过液晶组分 3 和透明基板 2，最后离开液晶显示板 100。然而，投射到液晶显示板 100 中的一部分光通过相邻反射电极 5 之间的间隙向驱动电路基板 1 泄漏。设置第一和第二光阻挡膜 44 和 46，以防止光进入有源元件 30。在此实施例中，第一和第二光阻挡膜 44 和 46 由导电膜制成，第二光阻挡膜 46 电连接到反射电极 5，并且向第一光阻挡膜 44 提供像素-电势控制信号以便光阻挡膜形成一部分像素电容。

顺便提到，如果向第一光阻挡膜 44 提供像素-电势控制信号，第一光阻挡膜 44 就可在被提供灰度电压的第二光阻挡膜 46 和形成视频信号线 103 的第一导电层 42 以及形成扫描信号线 102 的导电层（与栅极 36 在同一平面）之间用作电屏蔽层。这减小第一导电层 42 和栅极 36 之间、以及第二光阻挡膜 46 和反射电极 5 之间的寄生电容。如上所述，必需使像素电容 CC 比液晶电容 CL 足够大。如果第一光阻挡膜 44 被设置成电屏蔽，由于与液晶电容 LC 并联的寄生电容减小，因此对于获得上述关系是有效的。进而，有可能减小信号线产生的噪声量。

在反射型液晶显示元件中，当反射电极 5 在驱动电路基板 1 的液晶组分 3 一侧的表面上布置时，不透明基板如硅基板可用作驱动电路基板 1。此结构具有如下优点：有源元件 30 和接线可在反射电极 5 之下布置，从而形成像素的反射电极 5 的面积可以增加，因此可实现更高的孔径比。而且，此结构的优点还有：辐射从驱动电路基板 1 的背面投射进液晶显示板 100 的光所产生的热量。

下面解释通过使用光阻挡膜而形成部分像素电容。第一光阻挡膜 44 和第二光阻挡膜 46 互相面对面并且第三层间绝缘膜 45 置于它们之间，而且形成部分像素电容。参考号 49 指形成一部分像素-电势控制

线 136 的导电层. 第一电极 31 和第一光阻挡膜 44 被导电层 49 电连接. 导电层 49 可用于在象素-电势控制电路 135 和象素电容之间形成接线. 然而, 在此实施例中, 第一光阻挡膜 44 用于接线. 图 8 示出其中第一光阻挡膜 44 用作象素-电势控制线 136 的配置.

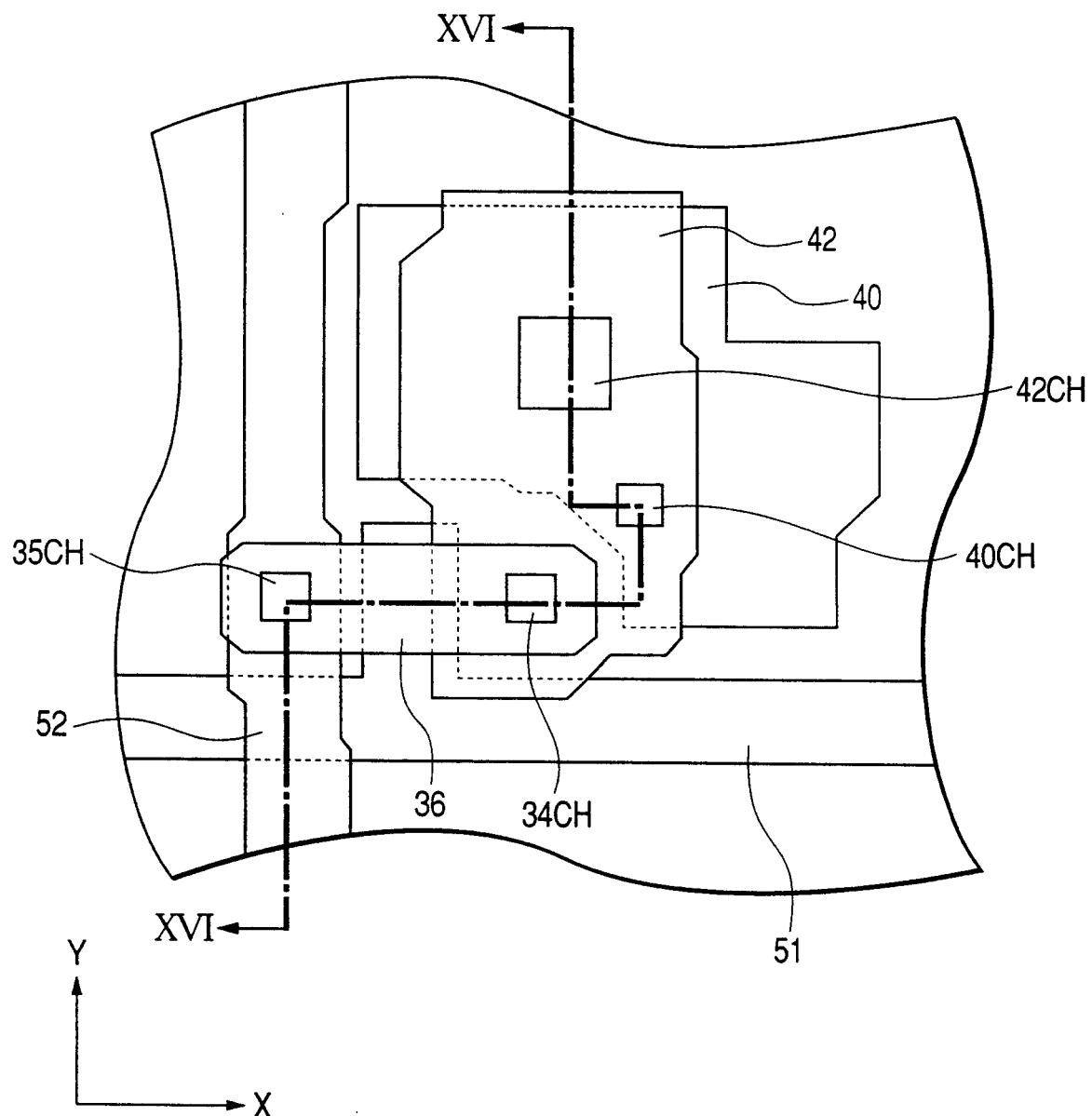

图 8 是示出第一光阻挡膜 44 排列的平面图. 参考号 46 表示第二光阻挡膜, 尽管它们位于第一光阻挡膜 44 之上, 但为了说明第二光阻挡膜的排列而用虚线表示. 参考号 42CH 指连接第一导电膜 42 和第二光阻挡膜 46 的通孔. 在图 8 中, 省略其它元件以避免使本图复杂. 第一光阻挡膜 44 用作象素-电势控制线 136, 因此它们被制作得沿图 8 中 X 方向连续延伸. 第一光阻挡膜 44 制作得覆盖整个显示区域以便用作光阻挡膜, 它们沿 X 方向 (与扫描信号线 102 平行的方向) 直线延伸, 在 Y 方向上依次排列, 并连接到象素-电势控制电路 135, 从而它们也用作象素-电势控制线 136. 第一光阻挡膜 44 布置得在尽可能大的区域内叠加在第二光阻挡膜 46 之上以便它们还用作象素电容的电极, 并且相邻的第一光阻挡膜 44 之间的间隙制作得尽可能小, 以减少光的泄漏.

当相邻的第一光阻挡膜 44 之间的间隙制作得如图 8 所示那么小时, 一行第一光阻挡膜 44 的局部位于与下一行第一光阻挡膜 44 相联系的一行第二光阻挡膜 46 之下. 如上所述, 根据本发明的液晶显示器能在两个方向上进行扫描. 当在双向扫描中利用象素-电势控制信号时, 出现两种情况: 一种是一行第一光阻挡膜 44 叠加在与下一行第一光阻挡膜 44 相联系的一行第二光阻挡膜 46 之上; 另一种情况是不发生上述重叠.

在图 8 所示的情况下, 当沿从图中的顶部到底部的方向进行扫描时, 一行第一光阻挡膜 44 的局部位于与即将扫描的下一行第一光阻挡膜 44 相联系的一行第二光阻挡膜 46 之下.

以下结合图 9A 和 9B 解释一行第一光阻挡膜 44 的局部和与将扫描的下一行第一光阻挡膜 44 相联系的一行第二光阻挡膜 46 之间的重叠所产生的问题和解决方案.

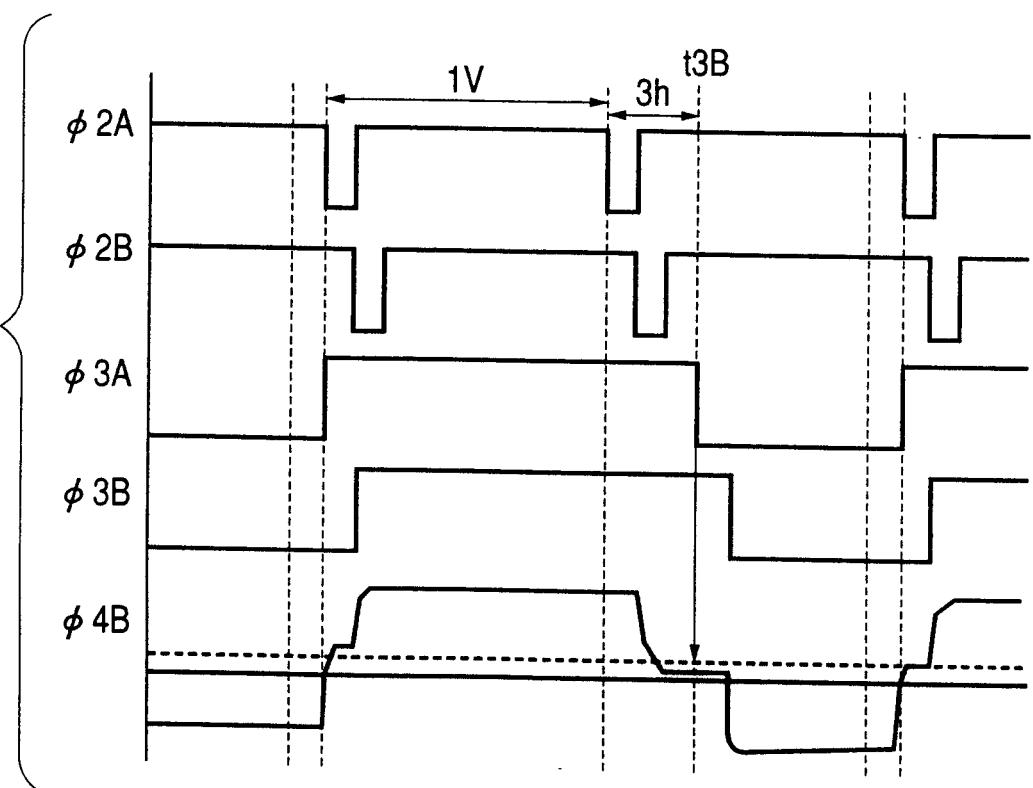

图 9A 示出用于解释此问题的时间图。在图 9A 中， $\Phi 2A$  是用于指定行 A 的扫描信号并被指定为用于行 A 的扫描信号，而 $\Phi 2B$  是用于下一行 B 的扫描信号并被指定为用于行 B 的扫描信号。下面解释从时间  $t_2$  到时间  $t_3$  的时段，在此时段中产生上述问题，而对于剩余时间的解释则将省略。

在图 9A 中，在扫描行 A 时，在时间  $t_3$ ，即在从  $t_2$  开始的 2h（两个水平扫描周期）时间之后，象素-电势控制信号 $\Phi 3A$  被改变。在从  $t_2$  开始的 1h 时间之后，扫描信号 $\Phi 2A$  的输出已停止，由行 A 扫描信号 $\Phi 2A$  驱动的有源元件 30 被关断，结果在行 A 中的象素电极 109 从视频信号线 103 断开。在时间  $t_3$ ，即在从  $t_2$  开始的 2h 时间之后，即使当考虑到因信号切换而引起的时间延迟时，行 A 中的有源元件 30 也为充分的 OFF（关断）状态。然而，在时间  $t_3$ ，用于行 B 的扫描信号 $\Phi 2B$  被改变。

由于在行 A 中的第一光阻挡膜 44 叠加在连接到行 B 中象素电极 109 的第二光阻挡膜 46 之上，在行 B 中的象素电极和行 A 中的象素-电势控制线之间形成电容。由于在时间  $t_3$  行 B 中的有源元件 30 被改变为关断状态，因此，这时行 B 中的象素电极 109 没有从视频信号线 103 充分断开。在时间  $t_3$ ，如果用于行 A 的象素-电势控制信号 $\Phi 3A$  被改变，行 A 电容性耦合到行 B 中的象素电极 109，放电电荷就在视频信号线 103 和象素电极 109 之间传输，因为它们相互之间没有充分断开。从而，行 A 的象素-电势控制信号 $\Phi 3A$  的改变对写入行 B 中象素电极 109 的电压 $\Phi 4B$  产生影响。在图 9A 和 9B 中的 $\Phi 3B$  代表用于行 B 的象素-电势控制信号。

如果单个液晶显示器在固定的扫描方向下操作，象素-电势控制信号 $\Phi 3A$  的改变所带来的影响就不是非常明显，因为该影响在整个显示区域是均匀的。然而，当通过叠加从三个独立的分别用于提供红、绿和蓝三原色的液晶显示器所提供的红、绿和蓝三种图象而产生彩色显示时，出现这样的情况，例如，由于它们的光学排列，三个液晶显示器中只有一个从底部到顶部扫描其显示区域，而三个液晶显示器中的

另外两个则从顶部到底部扫描它们的显示区域。与此情况类似，如果在多个液晶显示器中扫描方向不同，在液晶显示器中显示的质量就变得不均匀并且综合显示降质。

通过结合图 9B 解释解决上述问题的方法。在此方法中，在行 A 扫描信号  $\Phi_{2A}$  开始的  $3h$  时间延迟之后，输出行 A 象素-电势控制信号  $\Phi_{3A}$ 。此时，行 B 扫描信号  $\Phi_{2B}$  已经停止，因此行 B 中的有源元件 30 为充分的关断状态，从而，此种关系减少行 A 象素-电势控制信号  $\Phi_{3A}$  对写入行 B 中象素电极 109 的电压  $\Phi_{4B}$  的影响。在此情况下，使要写入的负极性电压输入信号的时间长度比正极性电压输入信号的时间长度短  $3h$  时间，但是，例如当扫描信号线 102 的数量超过 100 时，时间的缩短等于或小于 3%。在负极性电压输入信号和正极性电压输入信号之间的均方根值之差可由基准电压  $V_{com}$  等调节。

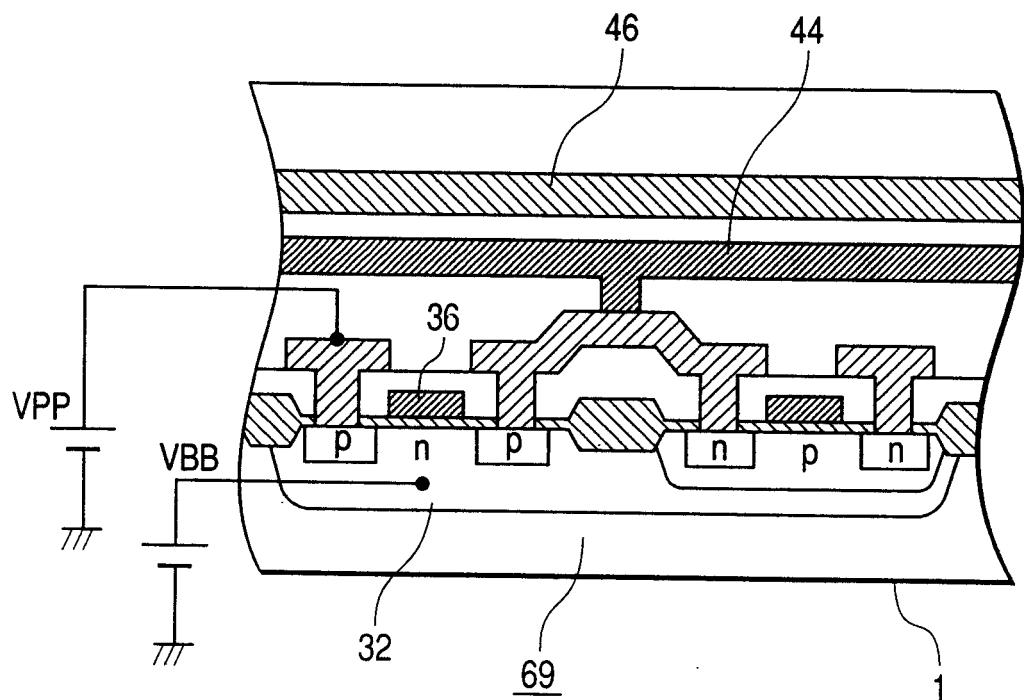

以下结合图 10A 和 10B 解释在施加到象素电容的电压  $V_{PP}$  和基板电势  $V_{BB}$  之间的关系。图 10A 是构成输出电路 69 的反相器电路的横截面视图。

在图 10A 中，参考号 32 指 p 沟道型晶体管的沟道区域，此 p 沟道型晶体管是通过在硅基板 1 中注入离子而制作的 n 型阱。硅基板 1 被施加基板电压  $V_{BB}$ ，并且 n 型阱 32 的电势为  $V_{BB}$ 。源极区域 34 和漏极区域 35 由通过在基板 1 中注入离子而制作的 p 型半导体层形成。当 p 沟道型晶体管 30 的栅极 36 被施加低于基板电压  $V_{BB}$  的电压时，在源极区域 34 和漏极区域 35 之间形成导电层。一般而言，由于不必提供绝缘区域，因此该结构得以简化，在相同硅基板上制作的晶体管被施加公共基板电势  $V_{BB}$ 。在根据本发明的液晶显示器中，在驱动电路区域和象素区中的晶体管在相同的硅基板 1 上制作。基于以上解释的原因，象素区中的晶体管也被施加上述基板电势  $V_{BB}$ 。

在图 10A 所示的反相器电路中，源极区域 34 被施加提供到象素电容的电压  $V_{PP}$ 。源极区域 34 由 p 型半导体层形成，并且，源极区域 34 和 n 型阱 32 形成 p-n 结。当源极区域 34 的电势被制作得高于 n 型阱 32 的时，产生如下问题：电流从源极区域 34 流入 n 型阱 32。鉴

于此问题，电压 VPP 选择得低于基板电压 VBB.

根据以上解释，在被象素-电势控制信号下降后的象素电极电压由  $V2-\{CC/(CL+CC)\} \times (VPP-VSS)$  表示，这里，V2 是写入象素电极的电压，CL 为液晶电容，CC 为象素电容，并且(VPP-VSS)是象素-电势控制信号的幅值。如果选择电压 VSS 为接地电势 GND，象素电极电压中的变化量就由电压 VPP、液晶电容 CL 和象素电容 CC 决定。

图 10B 示出  $CC/(CL+CC)$  和电压 VPP 之间的关系。为了简单起见，基准电压  $V_{com}$  采用接地电势 GND。下面解释这样的情况：在电压-关断状态时产生白色图象的普通白色类型液晶显示器中，灰度电压施加到象素电极以便产生黑色图象（灰度的最低程度）。图 10B 中的  $\Phi_1$  表示从电压选择器电路 123 写入到象素电极中的灰度电压。 $\Phi_{1A}$  是灰度电压  $\Phi_1$  的正极性电压输入信号，而  $\Phi_{1B}$  是灰度电压  $\Phi_1$  的负极性电压输入信号。为了形成黑色图象， $\Phi_{1A}$  和  $\Phi_{1B}$  选择得使基准电压  $V_{com}$  和写入到象素电极中的灰度电压之间的差值最大。

在图 10B 中，由于  $\Phi_{1A}$  是用于施加正极性电压的正极性电压输入信号，因此，通常取  $\Phi_{1A}$  为  $+V_{max}$  以便使其电压和基准电压  $V_{com}$  之间的差值最大。 $\Phi_{1B}$  取作  $V_{com}$  (GND)，并且开始  $\Phi_{1B}$  写入到象素电极中，随后通过使用象素电容而降低象素电极的电势。

图 10B 中的  $\Phi_{4A}$  和  $\Phi_{4B}$  分别表示在  $CC/(CL+CC)=1$  时的理想情况中和在  $CC/(CL+CC)<1$  时的非理想情况中的象素电极的电压。

首先，考虑理想情况。在象素电极的电压  $\Phi_{4A}$  为负值的过程中，由于开始电压  $V_{com}$  (GND) 写入象素电极中作为  $\Phi_{1B}$ ，因此，由于  $CC/(CL+CC)=1$  的关系，通过把象素电极电势降低象素-电势控制信号  $\Phi_3$  的幅值 VPP 而获得的最大负电压 ( $-V_{max}$ ) 变成 ( $-V_{max}$ ) = -VPP。

其次，考虑非理想情况。对于象素电极的电压  $\Phi_{4B}$  为负值的过程中，象素-电势控制信号  $\Phi_3$  的幅值 VPP2 必须选择得满足关系  $+V_{max} < VPP2$ ，因为  $CC/(CL+CC) < 1$ 。如上所述，必须满足关系  $VPP <$  基板电势 VBB 以及关系  $+V_{max} < VPP < VBB$ 。

在此实施例中，使用降低已写入的象素电极电压的方法以实现低

压电路，但是如果像素-电势控制信号 $\Phi 3$ 的幅值VPP非常高，基板电压VBB就变得太高并且最后电路将成为高压电路。因此，需要选择CL和CC的值以使 $CC/(CL+CC)$ 变得尽可能接近1，换而言之，满足 $CL \ll CC$ 。

在玻璃基板上制作薄膜晶体管的常规液晶显示器中，由于必需使像素电极的面积尽可能的大，即增加孔径比，因此可实现的 $CC/CL$ 之比最大为约1.0。在此实施例的液晶显示器中，驱动电路区域和像素区在相同的硅基板上制作，利用高电压作为基板电势VBB使得难以实现低压电路。

下面，结合图11和12解释行转换驱动方法的实施例。图11所示的液晶显示器100设置有奇数行像素-电势控制电路135(1)和偶数行像素-电势控制电路135(2)。在行转换驱动方法中，例如，当正极性灰度电压写入到奇数行像素电极中时，为了AC驱动，负极性灰度电压就写入到偶数行像素电极中。在行转换驱动方法中，电压极性每隔一行就颠倒一次，因此像素-电势控制信号的波形必须每隔一行就改变一次。从而，如图11所示，分别设置用于奇数行和偶数行的像素-电势控制电路135(1)、135(2)，用于交替输出如图12所示的两种像素-电势控制信号波形 $\Phi 3a$ 和 $\Phi 3b$ ，以便执行转换驱动。

以下解释反射型液晶显示器。对于一种反射型液晶显示元件，已知电控双折射模式。在电控双折射模式中，通过在把液晶组分夹在中间的反射电极和反电极之间施加电压而改变液晶组分的分子取向，从而改变液晶层的双折射。电控双折射模式通过把双折射的改变转换成光透射的改变而产生图象。

下面结合图13A和13B解释单偏振器扭曲向列(SPTN)模式，此模式是一种电控双折射模式。

参考号9代表把光源(未示出)的入射光L1分成两个偏振光的偏振束分离器，并且发射出两个偏振光中的线性偏振光L2。

在图13A和13B中，已穿过偏振束分离器9的光是p-偏振光，它进入液晶显示板100，但是，被偏振束分离器9反射的光也可进入液

晶显示板 100，此种光为 s-偏振光。

液晶组分 3 是具有正介电各向异性的向列液晶材料。液晶分子纵向轴的取向大约与驱动电路基板 1 和透明基板 2 的主表面平行，并且液晶分子在穿过液晶层时被取向膜 7、8 扭曲大约 90°。

图 13A 示出没有电压施加到液晶组分层 3 的情况。进入液晶显示板 100 的光 L2 因液晶组分 3 的双折射而被转换成椭圆形偏振光，然后在反射电极 5 上变为圆形偏振光。被反射电极 5 反射回的光再次穿过液晶组分 3，从而又一次变为椭圆形偏振光，然后当它离开液晶显示板 100 时再次变回到线性偏振光。出射的线性偏振光 L3 是 s-偏振光，其偏振方向相对于入射光 L2 的偏振方向旋转 90°，L3 再次进入偏振束分离器 9，被偏振束分离器 9 的内部界面反射，变为出射光 L4，L4 又投射到屏幕等上，产生显示。此种配置是所谓的普通白色（普通敞开）类型，当在液晶组分层 3 两端不施加电压时此种配置发射光。

图 13B 示出在液晶组分层 3 两端施加电压的情况。当电场施加到液晶组分层 3 时，液晶分子沿着电场方向对齐，因此不会出现液晶分子的双折射。结果，进入液晶显示板 100 的线性偏振光 L2 不经任何改变地被反射电极 5 反射，随后从液晶显示板 100 出射的光 L5 具有与入射光 L2 相同的偏振方向。出射光 L5 穿过偏振束分离器 9，返回到光源，从而没有光投射到屏幕上，在屏幕上产生黑色显示。

在单偏振器扭曲向列模式中，液晶分子的取向与基板的主表面平行，因此可使用取向液晶分子的一般方法，并且其制造工艺是极其稳定的。普通白色模式操作预防在低电压电平时产生有缺陷的显示。原因是，在普通白色模式中，当在液晶层两端施加高电压时提供暗点电平（黑色显示），而且在此状态中几乎所有的液晶分子沿电场的方向取向，此电场方向与基板的主表面正交，从而，暗点电平的显示不太依赖于有低电场施加到其上的液晶分子的取向的初始条件。人眼基于亮度比来察觉亮度的不均匀性，一般对亮度的对数敏感，从而对暗点电平的变化敏感。由于上述原因，普通白色模式的优点是防止因液晶分子取向的初始条件而引起亮度的不均匀性。

电控双折射模式要求在液晶显示板的基板之间有高度精确的单元间隙。电控双折射模式利用普通光线和异常光线在穿过液晶层时所产生的相位差，因此从液晶层透射的光强度取决于普通光线和异常光线之间的延迟 $\Delta n \cdot d$ ，在这， $\Delta n$  是双折射率， $d$  为由隔板 4 在透明基板 2 和驱动电路基板 1 之间建立的单元间隙。

在此实施例中，考虑到显示的不均匀性，单元间隙被控制在准确度为  $\pm 0.05 \mu\text{m}$ 。在反射型液晶显示板中，进入液晶层的光被反射电极反射，然后再次穿过液晶层，因此，如果反射型液晶显示板使用具有与在透射型液晶显示板中使用的液晶组分相同的双折射率 $\Delta n$  的液晶组分，反射型液晶显示板的单元间隙 $d$  就是透射型液晶显示板的一半。一般而言，透射型液晶显示板的单元间隙 $d$  在大约 5 微米到大约 6 微米的范围内，但在此实施例中单元间隙 $d$  选择为大约 2 微米。

在此实施例中，为了保证单元间隙的高准确度和比常规液晶显示板更小的单元间隙，在驱动电路基板 1 上制作柱状隔板以取代使用常规珠状分散方法。

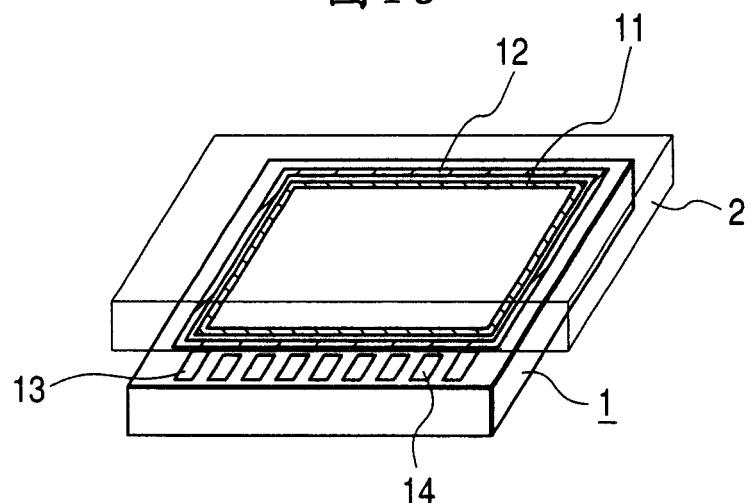

图 14 为用于解释布置在驱动电路基板 1 上的反射电极 5 和隔板 4 如何排列的液晶显示板的平面示意图。在驱动电路基板 1 的整个区域上以矩阵形式设置大量的隔板 4，用于在透明基板 2 和驱动电路基板 1 之间建立均匀的间隔。每个反射电极 5 确定像素，作为由液晶显示板形成的最小图象元素。为了简单起见，图 14 示出 5 列  $\times$  4 行的像素阵列，在最外面的列和行中的像素由参考号 5B 表示，在最外面的列和行以内的像素由参考号 5A 表示。

在图 14 中，5 列  $\times$  4 行的像素阵列形成显示区域，在其中通过液晶显示板形成显示。假像素 113 布置在显示区域周围，由与隔板 4 相同材料制成的外围边框 11 布置在假像素 113 周围，并且在驱动电路基板 1 上围绕外围边框 11 涂敷密封部件 12。参考号 13 指用于外部连接的接线端，此外部连接用于向液晶显示板 100 提供外部信号。

隔板 4 和外围边框 11 由树脂材料形成。例如，该树脂材料可以使用 JSR Corp. (日本东京) 制造的化学放大型负性光刻胶“BPR-113”

(商品名)。光刻胶材料用旋涂敷方法涂敷在其上形成有反射电极5的驱动电路基板1上，接着使用具有隔板4和外围边框11的形状图案的掩膜进行曝光，然后用去除剂显影，形成隔板4和外围边框11。

当隔板4和外围边框11使用光刻胶等材料制作时，通过控制材料涂层的厚度可控制隔板4和外围边框11的高度，从而能高精度地制作隔板4和外围边框11。通过掩膜图案可确定隔板4的位置，因此隔板4可准确定位在希望的位置上。

在液晶投影机内使用的液晶显示板中，如果一个隔板4位于像素上，就产生问题：隔板4的阴影在被投影的放大图象中是可见。通过用掩膜图案曝光和随后进行显影而制作隔板4，隔板4可定位在不使显示图象降质的位置上。

由于已同时制作隔板4和外围边框11，因此，通过首先在驱动电路基板1上滴少量的液晶组分3，接着在驱动电路基板1上重叠透明基板2从而在它们之间夹着液晶层，然后把透明基板2粘合到驱动电路基板1上，液晶组分3就可密封在驱动电路基板1和透明基板2之间。

当在驱动电路基板1和透明基板2中间插入液晶组分3之后组装完液晶显示板100时，液晶组分3保留在由外围边框11包围的区域内。

密封部件12涂敷在外围边框11的外侧，并把液晶组分3限制在液晶显示板100内。

如上所述，外围边框11使用图案掩膜而制作，因此，外围边框11以高位置准确度制作在驱动电路基板1上，从而可以高准确度地确定液晶组分3的边界。进而，外围边框11可以高准确度地确定密封部件12的边界。

密封部件12用于把驱动电路基板1和透明基板2固定在一起，而且还用于防止对液晶组分3有害的材料渗入其中。当涂敷流体密封部件12时，外围边框11用作对密封部件12的停止器。通过布置外围边框11作为对密封部件12的停止器，能极其精确地建立液晶组分3和密封部件12的边界，因而，可减少在显示区域和液晶显示板100外侧

之间的区域，导致围绕显示区域的外围边界减少。

假象素 113 布置在外围边框 11 和显示区域之间，用于使最外侧象素 5B 产生的显示质量与位于最外侧象素 5B 内的内部象素 5A 产生的显示质量相同。由于内部象素 5A 具有相邻象素，因此在内部象素 5A 和其相邻象素之间形成不希望有的电场，从而，所述内部象素 5A 产生的显示质量比没有其相邻象素时所产生的显示质量更差。

另一方面，假设连一个假象素 113 都不设置的情况，那么，在最外侧象素 5B 周围不产生使显示质量降低的不希望有的电场，结果，最外侧象素 5B 的显示质量比内部象素 5A 的更好。如果在一些象素之间存在显示质量的差异，在显示时就产生不均匀性。为了消除此问题，设置假象素 113，并与象素 5A 和 5B 一样施加信号电压，从而最外侧象素 5B 的显示质量与内部象素 5A 的相同。

进一步地，由于外围边框 11 制作得环绕显示区域，因此产生的问题是：在驱动电路基板 1 的表面上进行摩擦处理以把液晶组分 3 的液晶分子定位成特定方向时，外围边框 11 阻碍在外围边框 11 附近表面上的摩擦处理。在此实施例中，在驱动电路基板 1 上制作隔板 4 和外围边框 11 之后，在驱动电路基板 1 上涂敷液晶分子取向膜 7(见图 7)，随后，通过用布等摩擦液晶分子取向膜 7 而执行摩擦处理，以便被摩擦的取向膜 7 使液晶组分 3 的液晶分子定位成特定方向。

在摩擦处理中，因为外围边框 11 在驱动电路基板 1 的表面上形成，所以外围边框 11 附近的取向膜 7 因外围边框 11 形成的步骤而未被充分地摩擦，从而在外围边框 11 附近易于发生液晶分子取向的不一致性。为了使液晶组分 3 的液晶分子有缺陷的取向所导致的显示不均匀性不易觉察，在外围边框 11 的紧内侧制作一些不用于显示的象素，作为假象素 113。

然而，如果假象素 10 如象素 5A 和 5B 那样被提供信号，就产生这样的问题：由于在假象素 10 和透明基板 2 之间存在液晶组分 3，因此观察者也观察得到假象素 10 产生的显示。在普通白色型液晶显示板中，当在液晶组分 3 的层两端不施加电压时假象素 113 出现白点，因

而，显示区域的边界变得不确定并且显示质量下降。掩蔽假象素 113 是可以想象的，但难以在显示区域边界准确地制作光阻挡边框，因为象素之间只有几微米的间隔，因此，向假象素 113 施加一定的电压以使假象素 113 显示黑色图象，此黑色图象表现为围绕显示区域的黑色外围边框。

下面，结合图 15 解释驱动假象素 113 的方法。向假象素 113 施加电压以产生黑色显示，因此设置有假象素 113 的整个区域上都出现黑色。如果假象素 113 产生连续的大面积黑色显示，在象素置于显示区域中的情况下就不需制作互相分离开的假象素，但是可制作多个假象素电连接在一起。当考虑驱动所需的时间时，为假象素提供写时间是无用的。有可能通过集成多个假象素形成单个假象素，但是单个假象素的面积增加，结果其液晶电容变得太大。如上所述，如果液晶电容变大，此种增加降低通过使用象素电容而降低象素电极电势的效率。

考虑到以上情况，在此实施例中，与显示区域内的象素一样，假象素也制作得互相分离开。然而，如果在显示区域内写有效象素的情况下逐行执行写假象素，此种写操作就增加新增的多行假象素所需的时间长度，从而在显示区域内写有效象素的时间就减少这么多。

在高分辨率显示中，使用高速视频信号（高点状时钟信号），写象素所需的时间被进一步限制。考虑到这点，在写一幅图象的过程中为了节省写几行的时间，如图 15 所示，配置垂直驱动电路 130 的双向垂直移位寄存器 VSR，以便向多行串联的电平移相器 67 及其输出电路 69 同时提供定时信号，从而扫描信号同时输出到多个假象素行，而且，还配置象素-电势控制电路 135 的双向移位寄存器 SR，以便向多行串联的电平移相器 67 及其输出电路 69 同时提供定时信号，从而象素-电势控制信号同时输出到多个假象素行。

以下结合图 16 和 17 解释在驱动电路基板 1 上制作的有源元件 30 及其附近区域的配置。在图 7 中使用的相同参考号在图 16 和 17 中分配给相应的部件。图 17 为有源元件 30 及其附近区域的平面示意图，而图 16 为沿图 17 中 XVI-XVI 剖分的横截面视图。为了清晰起见，图

图 16 中部件之间的距离没有制作得与图 17 中的相应距离相等；图 17 用于示出扫描信号线 102、栅极 36、视频信号线 103、漏极区域 35、源极区域 34、用于形成像素电容的第二电极 40、第一导电层 42、接触孔 35CH、34CH、40CH 和 42CH 之间的位置关系，而对于其它的部件则省略掉。在图 16 中，参考号 1 代表用作驱动电路基板的硅基板，32 为通过使用离子注入而在驱动电路基板 1 内制作的半导体区域(p-型阱)，33 为沟道限制器，34 为在 p-型阱 32 内通过离子注入而制作得导电的漏极区域，35 为在 p-型阱 32 内通过离子注入而制作的源极区域，31 为在 p-型阱 32 内通过离子注入而制作得导电的像素电容的第一电极。顺便说一下，在此实施例中 p-沟道型晶体管用作有源元件 30，但也可代之以 n-沟道型晶体管。

在图 16 中，参考号 36 指栅极、37 为使栅极 36 边缘的电场减弱的抵消区域，38 为绝缘膜，39 为用于使晶体管相互之间电绝缘的场氧化膜，而 40 为用于与第一电极 31 一起形成像素电容的第二电极，第一电极 31 在硅基板 1 中制作并且绝缘膜 38 位于第一电极 31 和第二电极 40 之间。栅极 36 和第二电极 40 由位于绝缘膜 38 之上的导电膜和低电阻导电膜形成的双层膜制成。前一导电膜用于降低有源元件 30 的阈值电压。例如，双层膜可由两个多晶硅和硅化钨膜制成。参考号 41 是第一绝缘层间膜，而 42 为第一导电膜。第一导电膜 42 是由用于防止不完善接触的屏障金属膜及低电阻导电膜制成的多层膜。例如，由钨钛合金 (TiW) 和铝制成的溅镀多层金属膜可用作第一导电膜。

在图 17 中，参考号 102 代表扫描信号线。扫描信号线 102 沿图 17 中 X 方向延伸并在 Y 方向上排列，扫描信号线 102 被提供用于接通或关断有源元件 30 的扫描信号。扫描信号线 51 由与栅极 36 相同的双层膜形成。例如，由层叠的多晶硅和硅化钨膜制成的双层膜可用作扫描信号线 102。视频信号线 103 沿 Y 方向延伸并在 X 方向上排列，视频信号线 103 被提供用于写入反射电极 5 的视频信号。视频信号线 103 由与第一导电膜 42 相同的多层金属膜形成。例如，由钨钛合金 (TiW) 和铝制成的多层金属膜可用作视频信号线 103。

第一导电膜 42 通过接触孔 35CH 向漏极区域 35 提供视频信号，接触孔 35CH 在绝缘膜 38 和第一绝缘层间膜 41 内制作。当扫描信号提供到扫描信号线 102 时，有源元件 30 接通，并且视频信号从半导体区域（p-型阱）32 传递到源极区域 34，然后通过接触孔 34CH 传递到第一导电膜 42。随后，如图 16 所示，视频信号从第一导电膜 42 通过接触孔 40CH 传递到像素电容的第二电极 40，接着通过接触孔 42CH 传递到反射电极 5。接触孔 42CH 位于场氧化膜 39 之上。由于场氧化膜 39 的厚度大，因此场氧化膜 39 顶部表面的高度适于比其它元件更高。通过在场氧化膜 39 上布置接触孔 42CH，接触孔 42CH 可更靠近于上导电层，从而接触孔 42CH 处的电连接长度可缩短。

第二绝缘层间膜 43 使第二导电膜 44 与第一导电膜 42 绝缘。由平面膜 43A 和绝缘膜 43B 组成的两层形成第二绝缘层间膜 43，偏振膜 43A 用于填充凹槽和降低因下面的元件而引起的不平度，绝缘膜 43B 位于平面膜 43A 之上。平面膜 43A 通过涂敷 SOG（玻璃上自旋）而制作，而且绝缘膜 43B 是通过采用 TEOS（四乙基原硅酸盐）作为反应气体的 CVD 工艺制成的 SiO<sub>2</sub> 膜。在第二绝缘层间膜 43 涂敷到硅基板 1 上之后，用 CMP（化学机械抛光）工艺抛光而平面化。第一光阻挡膜 44 在平面化了的第二绝缘层间膜上制作。第一光阻挡膜 44 由与第一导电膜 42 相同的多层金属膜形成，此多层金属膜由钨钛（TiW）合金和铝制成。

如图 16 所示，第一光阻挡膜 44 覆盖在驱动电路基板 1 的几乎整个区域上，并且只在接触孔 42CH 处制作开孔。通过采用 TEOS（四乙基原硅酸盐）作为反应气体的 CVD 工艺在第一光阻挡膜 44 上制作第三绝缘层间膜 45。进而，第二光阻挡膜 46 在第三绝缘层间膜 45 上形成，并且由与第一导电膜 42 相同的多层金属膜形成，此多层金属膜由钨钛（TiW）合金和铝制成。第二光阻挡膜 46 经接触孔 42CH 连接到第一导电膜 42。在接触孔 42CH 中，形成第一光阻挡膜 44 的金属膜和形成第二光阻挡膜 46 的金属膜层叠在一起，用于电连接。

当第一光阻挡膜 44 和第二光阻挡膜 46 由导电膜制成时，由绝缘

(介电)膜制成的第三层间膜 45 置于它们之间，象素-电势控制信号施加到第一光阻挡膜 44 上，灰度电压施加到第二光阻挡膜 46 上，在第一光阻挡膜 44 和第二光阻挡膜 46 之间可形成象素电容。

考虑到第三绝缘层间膜 45 对灰度电压的耐压以及通过减小介电膜 45 的厚度而增大电容，希望第三绝缘层间膜 45 的厚度在 150nm-450nm 的范围内，并优选为约 300nm。

图 18 为其上叠加有透明基板 2 的驱动电路基板 1 的透视图。在驱动电路基板 1 周围形成的是外围边框 11，液晶组分 3 被限制在外围边框 11、驱动电路基板 1 和透明基板 2 所围成的空间内。密封部件 12 在层叠的驱动电路基板 1 和透明基板 2 之间围绕外围边框 11 的外侧涂敷。驱动电路基板 1 和透明基板 2 用密封部件 12 固定在一起，形成液晶显示板 100。参考号 13 代表用于外部连接的接线端。

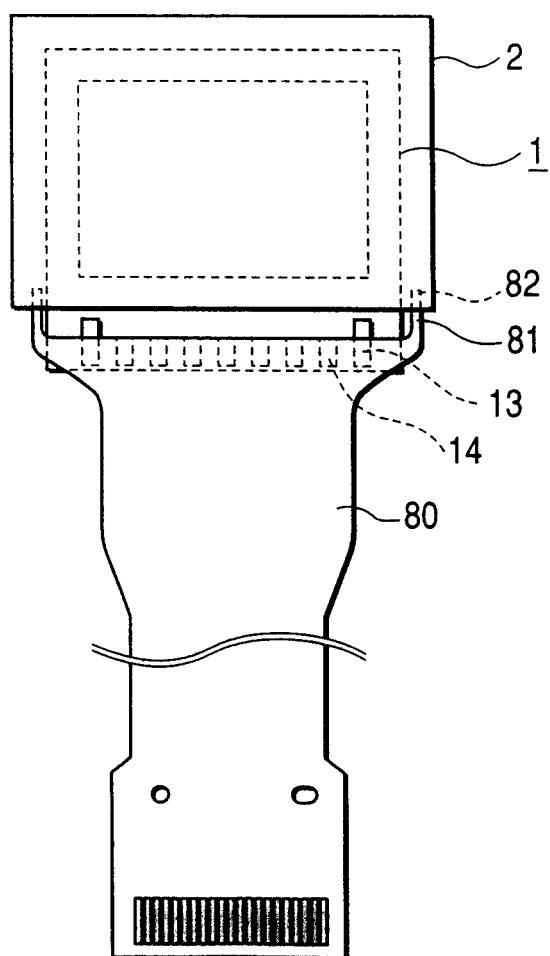

其次，如图 19 所示，用于向液晶显示板 100 提供外部信号的挠性印刷布线板 80 连接到接线端 13，以进行外部连接。在挠性印刷布线板 80 一端的相对侧上的两个最外侧接线端制作得比其余接线端更长，并连接到在透明基板 2 上形成的反电极 5，从而用作反电极接线端 81。挠性印刷布线板 80 以此方式连接到驱动电路基板 1 和透明基板 2。

一般而言，挠性印刷布线板只连接到位于驱动电路基板 1 上的用于外部连接的接线端，因此，挠性印刷布线板经驱动电路基板 1 接线到反电极 5。本发明此实施例中的透明基板 2 设置有准备连接到挠性印刷布线板 80 的连接部分 82，从而挠性印刷布线板 80 直接连接到反电极 5。通过在驱动电路基板 1 上叠加透明基板 2 形成液晶显示板 100。透明基板 2 在驱动电路基板 1 上叠加，从而透明基板 2 的外围部分延伸出驱动电路基板 1 的外缘并且设置连接部分 82，挠性印刷布线板 80 在连接部分 82 处连接到反电极 5。

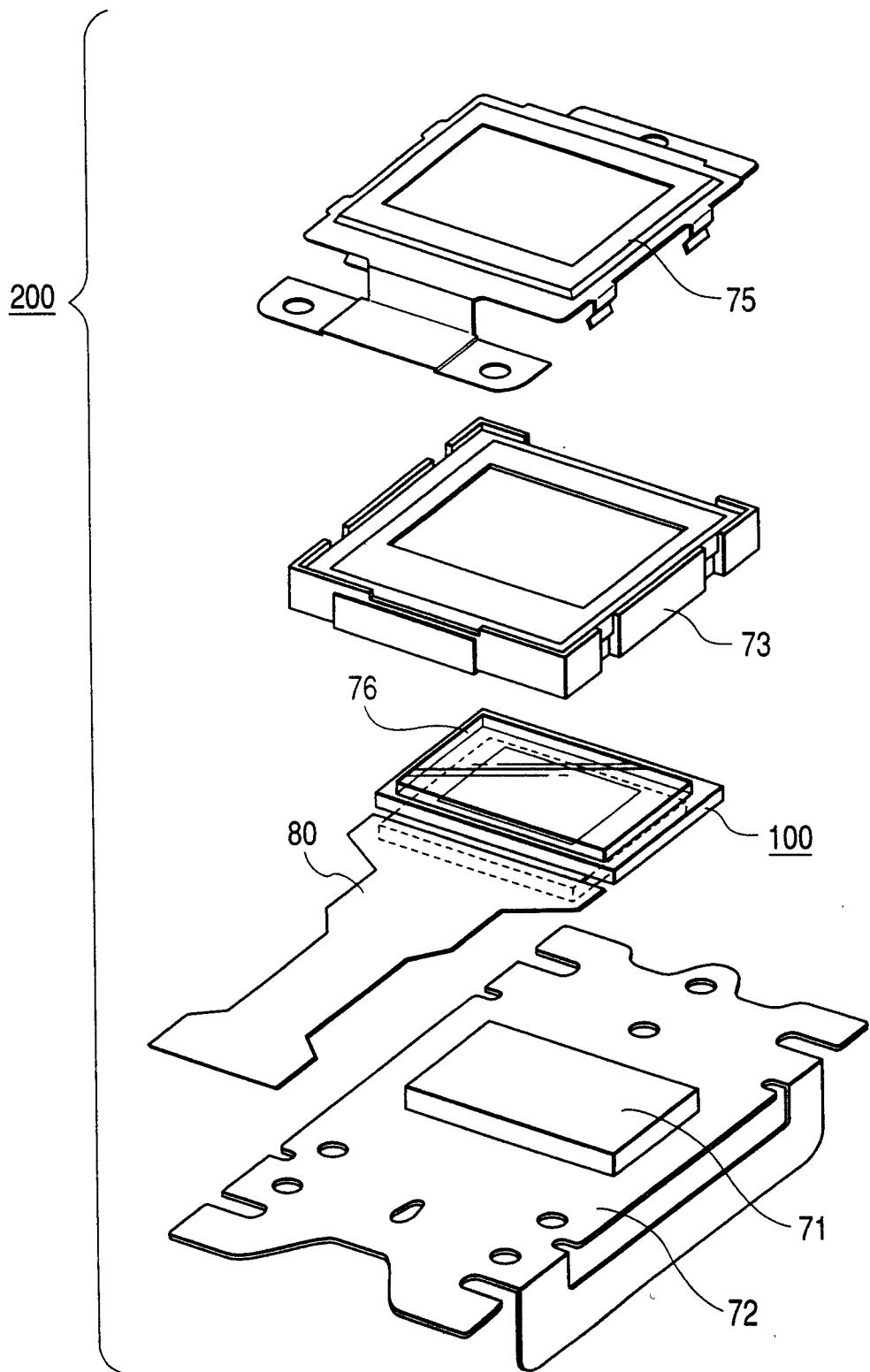

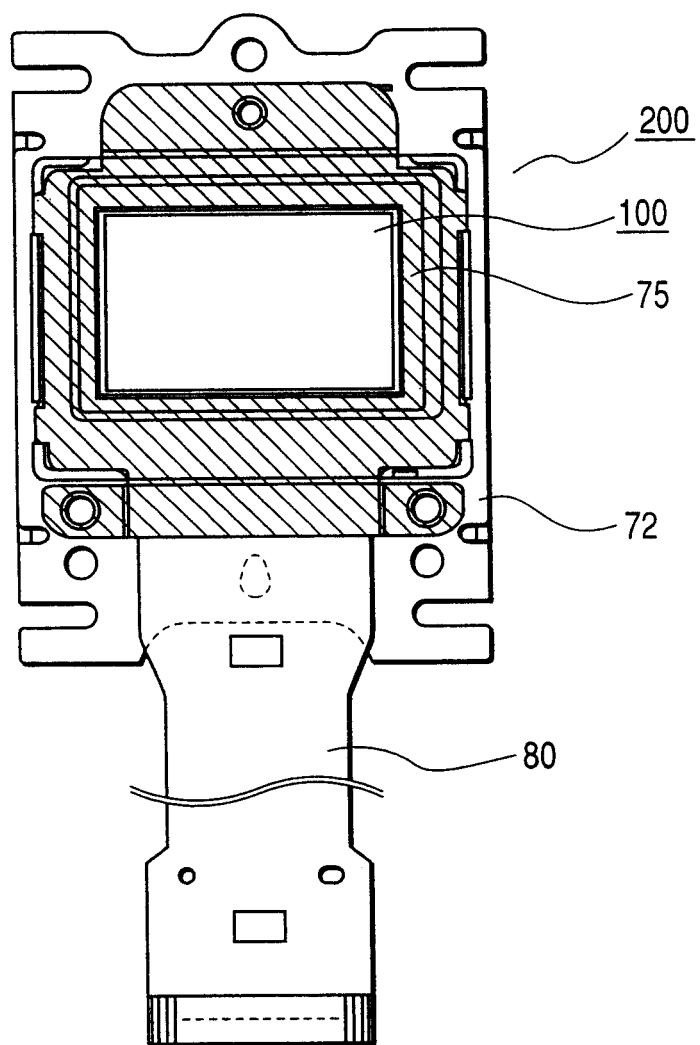

图 20 和 21 示出液晶显示器 200 的配置。图 20 是液晶显示器 200 的主要元件的立体分解图，而图 21 是液晶显示器 200 的平面视图。

如图 20 所示，挠性印刷布线板 80 连接到其上的液晶显示板 100 布置在散热板 72 上，并且在它们之间有垫片 71。垫片 71 是高度导热

的，而且填充散热板 72 和液晶显示板 100 之间的间隙，使得液晶显示板 100 的热量易于传导到散热板 72。参考号 73 指用粘附剂固定到散热板 72 上的模具。

如图 21 所示，挠性印刷布线板 80 在模具 73 和散热板 72 之间穿过，并从模具 73 引出。参考号 75 指光阻挡板，它防止光源的光进入液晶显示器 200 不希望的部分，并且 76 为确定液晶显示器 200 的显示区域的光阻挡边框。

本发明人的发明已基于本发明实施例进行了具体解释，但本发明并不局限于上述实施例，只要不偏离本发明的精神和范围，可作各种变化和变更。

通过在本文中公开的代表性实施例获得的优点概括如下：

当驱动电路包含在液晶显示元件中时，本发明通过使用低压电路有可能形成驱动电路，并且能减少驱动电路所占据的面积和每个象素所占据的面积，从而有可能实现电路的高速操作。进而，本发明能实现高分辨率的小型液晶显示元件。

图1

图2

图 3 A

图 3 B

图 4

图 5

图 6 A

图 6 B

图 6 C

图 6 D

图 8

图 9 A

图 9 B

图 10 A

图 10 B

图 11

图12

图 13 A

图 13 B

图 14

图 15

图 16

图 17

图 18

图 19

图 20

图 21

|                |                                                                                                        |         |            |

|----------------|--------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 具有低压驱动电路的液晶显示器                                                                                         |         |            |

| 公开(公告)号        | <a href="#">CN1204541C</a>                                                                             | 公开(公告)日 | 2005-06-01 |

| 申请号            | CN02107561.1                                                                                           | 申请日     | 2002-03-15 |

| [标]申请(专利权)人(译) | 株式会社日立制作所<br>株式会社日立显示器                                                                                 |         |            |

| 申请(专利权)人(译)    | 株式会社日立制作所<br>日立器件工程株式会社                                                                                |         |            |

| 当前申请(专利权)人(译)  | 株式会社日立制作所<br>日立器件工程株式会社                                                                                |         |            |

| [标]发明人         | 饭田治久<br>竹本一八男<br>松本克巳<br>足立重雄                                                                          |         |            |

| 发明人            | 饭田治久<br>竹本一八男<br>松本克巳<br>足立重雄                                                                          |         |            |

| IPC分类号         | G02F1/1333 G02F G02F1/13 G02F1/133 G02F1/1335 G02F1/1362 G02F1/1368 G09G G09G3/20<br>G09G3/36 G09G5/00 |         |            |

| CPC分类号         | G09G3/3655 G02F1/133308 G02F1/133512 G02F1/136213 G09G3/3614                                           |         |            |

| 优先权            | 2001073289 2001-03-15 JP                                                                               |         |            |

| 其他公开文献         | CN1375812A                                                                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                         |         |            |

### 摘要(译)

本发明涉及具有低压驱动电路的液晶显示器，该液晶显示器具有夹在一对基板之间的液晶组分以及在一个第一基板上设置的多个象素。每个象素都经连接到其第一电极的开关元件而被提供视频信号，并设置电容。形成电容的两个电容形成电极中的一个连接到相应象素的第一电极，两个电容形成电极中的另一个被提供象素-电势控制信号。视频信号的极性相对于第一基准电压周期性地转换，而且，象素-电势控制信号在相对于第二基准电压为相同极性的两个电平之间变换，从而在象素的第一电极上的电压波动变得比视频信号的更大。