(12) 发明专利申请

(10) 申请公布号 CN 102184719 A

(43) 申请公布日 2011.09.14

(21) 申请号 201110112231.8

(22) 申请日 2011.04.25

(30) 优先权数据

099144245 2010.12.16 TW

(71) 申请人 友达光电股份有限公司

地址 中国台湾新竹科学工业园区新竹市力

行二路 1 号

(72) 发明人 苏国彰 陈勇志 杨欲忠 林致颖

(74) 专利代理机构 北京律诚同业知识产权代理

有限公司 11006

代理人 梁挥 王颖

(51) Int. Cl.

G09G 3/36 (2006.01)

权利要求书 2 页 说明书 10 页 附图 12 页

(54) 发明名称

运用于电荷分享像素的整合面板型栅极驱动

电路

(57) 摘要

本发明公开一种运用于电荷分享像素的整合

面板型栅极驱动电路。液晶面板上的栅极驱动电

路中包括多个移位寄存器，每个移位寄存器皆可

以输出不互相重叠的主栅极驱动信号与子栅极驱

动信号，并且具有电路结构以及线路布局简单的

特征。

1. 一种栅极驱动电路，接收多个时钟脉冲信号，其特征在于，该栅极驱动电路包括多个移位寄存器，而一第 n 个移位寄存器包括：

—第一驱动晶体管，具有一栅极接收一第 n 控制信号，一漏极接收这些时钟脉冲信号中的一第一时钟脉冲信号，一源极输出一第 n 主栅极驱动信号；

—第二驱动晶体管，具有一栅极接收该第 n 控制信号，一漏极接收这些时钟脉冲信号中的一第二时钟脉冲信号，一源极输出一第 n 子栅极驱动信号；

—上拉单元，接收第 n 个移位寄存器前二级的一第 n-2 个移位寄存器输出的一第 n-2 控制信号以及一第 n-2 主栅极驱动信号，且该上拉单元接收这些时钟脉冲信号中的一第三时钟脉冲信号；其中，该上拉单元动作时，控制该第 n 控制信号开启该第一驱动晶体管以及该第二驱动晶体管；以及

一下拉单元，接收该第 n 控制信号与该第 n 主栅极驱动信号，该下拉单元在该上拉单元动作开始后的一预定时间周期动作，并控制该第 n 控制信号关闭该第一驱动晶体管以及该第二驱动晶体管；

其中，该第三时钟脉冲信号的相位超前该第一时钟脉冲信号，该第一时钟脉冲信号超前该第二时钟脉冲信号，且该第一时钟脉冲信号、该第二时钟脉冲信号与该第三时钟脉冲信号不重叠。

2. 根据权利要求 1 所述的栅极驱动电路，其特征在于，该第三时钟脉冲信号的相位超前该第一时钟脉冲信号 120 度，该第一时钟脉冲信号超前该第二时钟脉冲信号 120 度。

3. 根据权利要求 1 所述的栅极驱动电路，其特征在于，在该第一驱动晶体管与该第二驱动晶体管开启时，根据该第一时钟脉冲信号产生该第 n 主栅极驱动信号，根据该第二时钟脉冲信号产生该第 n 子栅极驱动信号。

4. 根据权利要求 1 所述的栅极驱动电路，其特征在于，在该第一驱动晶体管与该第二驱动晶体管关闭时，该下拉单元提供一最低电压电位至该第 n 主栅极驱动信号与该第 n 子栅极驱动信号。

5. 根据权利要求 1 所述的栅极驱动电路，其特征在于，该上拉单元包括：

—第三晶体管，具有一栅极接收该第 n-2 控制信号，一漏极接收该第三时钟脉冲信号；以及

—第四晶体管，具有一栅极连接至该第三晶体管源极，一漏极接收该第 n-2 主栅极驱动信号，一源极产生该第 n 控制信号。

6. 根据权利要求 5 所述的栅极驱动电路，其特征在于，当该第 n-2 控制信号开启该第三晶体管时，根据该第三时钟脉冲信号来开启该第四晶体管，进而使得该上拉单元根据该第 n-2 主栅极驱动信号来动作并开启该第一驱动晶体管与该第二驱动晶体管。

7. 一种栅极驱动电路，接收多个时钟脉冲信号，其特征在于，该栅极驱动电路包括多个移位寄存器，而一第 n 个移位寄存器包括：

—第一驱动晶体管，具有一栅极接收一第 n 控制信号，一漏极接收这些时钟脉冲信号中的一第一时钟脉冲信号，一源极输出一第 n 主栅极驱动信号；

—第二驱动晶体管，具有一栅极接收该第 n 控制信号，一漏极接收这些时钟脉冲信号中的一第二时钟脉冲信号，一源极输出一第 n 子栅极驱动信号；

—第一上拉单元，接收第 n 个移位寄存器前一级的一第 n-1 个移位寄存器输出的第一

n-1 控制信号以及一第 n-1 主栅极驱动信号,且该上拉单元接收这些时钟脉冲信号中的一第三时钟脉冲信号;其中,该第一上拉单元动作时,控制该第 n 控制信号开启该第一驱动晶体管以及该第二驱动晶体管;

一第二上拉单元,接收第 n 个移位寄存器后一级的一第 n+1 个移位寄存器输出的一第 n+1 控制信号以及一第 n+1 主栅极驱动信号,且该上拉单元接收这些时钟脉冲信号中的一第四时钟脉冲信号;其中,该第二上拉单元动作时,控制该第 n 控制信号开启该第一驱动晶体管以及该第二驱动晶体管;以及

一下拉单元,接收该第 n 控制信号与该第 n 主栅极驱动信号,该下拉单元在该上拉单元动作开始后的一预定时间周期动作,并控制该第 n 控制信号关闭该第一驱动晶体管以及该第二驱动晶体管;

其中,该第三时钟脉冲信号的相位超前该第一时钟脉冲信号,该第一时钟脉冲信号超前该第二时钟脉冲信号,该第四时钟脉冲信号的相位落后该第一时钟脉冲信号,且该第一时钟脉冲信号与该第二时钟脉冲信号不重叠。

8. 根据权利要求 7 所述的栅极驱动电路,其特征在于,该第三时钟脉冲信号的相位超前该第一时钟脉冲信号 60 度,该第一时钟脉冲信号超前该第二时钟脉冲信号 180 度,该第四时钟脉冲信号的相位落后该第一时钟脉冲信号 60 度。

9. 根据权利要求 7 所述的栅极驱动电路,其特征在于,在该第一驱动晶体管与该第二驱动晶体管开启时,根据该第一时钟脉冲信号产生该第 n 主栅极驱动信号,根据该第二时钟脉冲信号产生该第 n 子栅极驱动信号。

10. 根据权利要求 7 所述的栅极驱动电路,其特征在于,在该第一驱动晶体管与该第二驱动晶体管关闭时,该下拉单元提供一最低电压电位至该第 n 主栅极驱动信号与该第 n 子栅极驱动信号。

11. 根据权利要求 7 所述的栅极驱动电路,其特征在于,该第一上拉单元包括:

一第三晶体管,具有一栅极接收该第 n-1 控制信号,一漏极接收该第三时钟脉冲信号;以及

一第四晶体管,具有一栅极连接至该第三晶体管源极,一漏极接收该第 n-1 主栅极驱动信号,一源极产生该第 n 控制信号。

12. 根据权利要求 11 所述的栅极驱动电路,其特征在于,当该第 n-1 控制信号开启该第三晶体管时,根据该第三时钟脉冲信号来开启该第四晶体管,进而使得该第一上拉单元根据该第 n-1 主栅极驱动信号来动作并开启该第一驱动晶体管与该第二驱动晶体管。

13. 根据权利要求 7 所述的栅极驱动电路,其特征在于,该第二上拉单元包括:

一第五晶体管,具有一栅极接收该第 n+1 控制信号,一漏极接收该第四时钟脉冲信号;以及

一第六晶体管,具有一栅极连接至该第五晶体管源极,一漏极接收该第 n+1 主栅极驱动信号,一源极产生该第 n 控制信号。

14. 根据权利要求 13 所述的栅极驱动电路,其特征在于,当该第 n+1 控制信号开启该第五晶体管时,根据该第四时钟脉冲信号来开启该第六晶体管,进而使得该第二上拉单元根据该第 n+1 主栅极驱动信号来动作并开启该第一驱动晶体管与该第二驱动晶体管。

## 运用于电荷分享像素的整合面板型栅极驱动电路

### 技术领域

[0001] 本发明涉及一种栅极驱动电路，特别是关于一种运用于具有电荷分享像素 (charge sharing pixel) 的面板的整合型栅极驱动电路 (Gate driving circuit on array，以下简称 GOA)。

### 背景技术

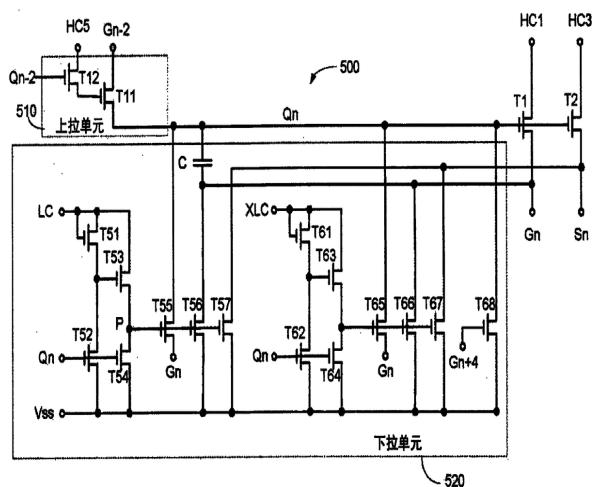

[0002] 请参照图 1A，其所绘示为公知液晶显示面板上单一电荷分享像素 (charge sharing pixel) 示意图。电荷分享像素 100 包括一主区域 (main area) 104 与一子区域 (sub area) 102。该电荷分享像素 100 包括三个三开关晶体管 Qd1 ~ Qd3、多个电容 C1 ~ C6。而一个电荷分享像素 100 需要连接至二条栅极线以及一条数据线，其中第一栅极线可接收主栅极驱动信号 (main gate driving signal) Gn，第二栅极线可接收子栅极驱动信号 (sub gate driving signal) Sn，数据线可接收数据信号 Dn。

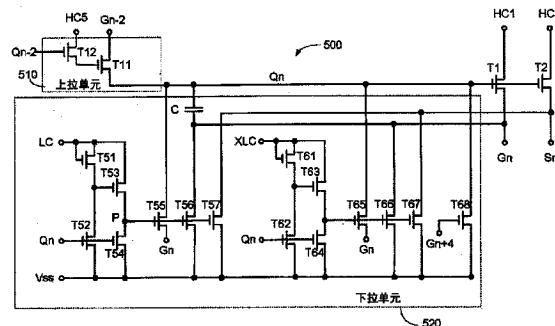

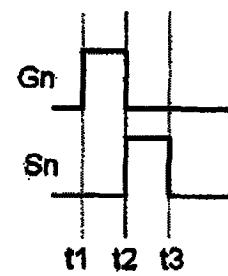

[0003] 请参照图 1B，其所绘示为电荷分享像素的动作信号示意图。在时间点 t1 与 t2 之间，主栅极驱动信号 Gn 产生一脉冲 (pulse)，此时第一开关晶体管 Qd1、第二开关晶体管 Qd2 开启 (turn on)，第三开关晶体管 Qd3 关闭 (turn off)，而数据线上的数据信号 Dn 储存在主区域 104 与子区域 102 中的电容 C1 ~ C6 内。

[0004] 在时间点 t2 与 t3 之间，子栅极驱动信号 Sn 产生一脉冲，此时第三开关晶体管 Qd3 开启，第一开关晶体管 Qd1、第二开关晶体管 Qd2 关闭，而子区域 102 中电容 C1 与 C2 上的电荷会经第三开关晶体管 Qd3 传递至主区域 104 的电容 C3 ~ C6 中。而上述的动作原理即为电荷分享像素 100 的动作原理。

[0005] 由上述说明可知，每个电荷分享像素 100 需要连接至二个栅极线，并且二个栅极线上的二个栅极驱动信号 Gn、Sn 的脉冲不可以互相重叠 (overlap)。以图 1B 为例，在任何的时间点上，主栅极驱动信号 Gn 与子栅极驱动信号 Sn 不可以同时为高电位，如此电荷分享像素 100 才可正常运作。

[0006] 为了要节省液晶显示面板的成本，一种整合面板型栅极驱动电路 (gate driver on array，简称 GOA) 已经被应用于液晶显示面板。也就是说，在此种 GOA 面板上直接制作一栅极驱动电路 (gate driving circuit)，因此可以节省外购栅极驱动电路的成本。

[0007] 请参照图 2A，其所绘示为公知 GOA 面板上的栅极驱动电路示意图。栅极驱动电路 200 包括多个移位寄存器 (shift register)。而所有的移位寄存器皆需接收多个不同相位的时钟脉冲信号 (例如相差 180 度的时钟脉冲信号 CK 以及反相时钟脉冲信号 XCK)。而图 2A 中仅利用三个移位寄存器 20n-1、20n、20n+1 来做说明。

[0008] 以第 n 级移位寄存器 20n 为例，其包括一上拉单元 (pull-up unit)、一下拉单元 (pull-down unit)、一驱动晶体管 (driving transistor) T1。一般来说，当第 n-1 级 (前一级) 移位寄存器 20n-1 输出低电位 (low level) 的第 n-1 个控制信号 Qn-1 以及第 n-1 个栅极驱动信号 Gn-1 时，第 n 级移位寄存器 20n 中的上拉单元不动作而下拉单元动作，并且控制第 n 个控制信号 Qn 维持在低电位，并且使得驱动晶体管 T1 为关闭状态进而使得第 n

个栅极驱动信号  $G_n$  维持在低电位。

[0009] 反之,当第  $n-1$  级(前一级)移位寄存器  $20n-1$  输出高电位(high level)的第  $n-1$  个控制信号  $Q_{n-1}$  以及第  $n-1$  个栅极驱动信号  $G_{n-1}$  时,第  $n$  级移位寄存器  $20n$  中的上拉单元动作而下拉单元不动作,并且控制第  $n$  个控制信号  $Q_n$  维持在高电位,并且使得驱动晶体管  $T_1$  为开启状态,而根据时钟脉冲信号( $CK$ 、 $XCK$ )的控制使得第  $n$  个栅极驱动信号  $G_n$  产生一个脉冲。

[0010] 利用上述原理,栅极驱动电路  $200$  中所有的移位寄存器可以逐级依序的产生栅极驱动信号至  $GOA$  面板。再者,上述栅极驱动电路  $200$  中移位寄存器由上而下的排列,所以栅极驱动信号由上而下逐级产生。当然,移位寄存器也可以由下而上的排列,使得栅极驱动信号由下而上逐级产生。

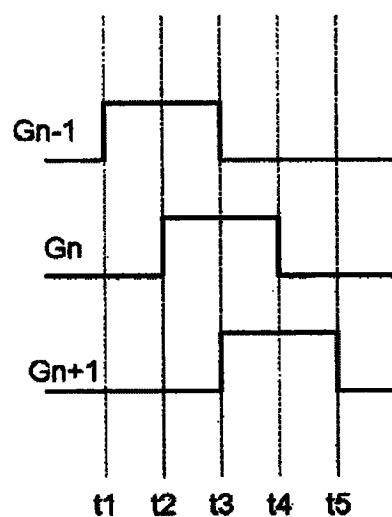

[0011] 再者,由于  $GOA$  面板上的栅极驱动电路  $200$  的驱动能力有限,因此栅极驱动信号之间需要彼此重叠。请参照图  $2B$ ,其所绘示为公知  $GOA$  面板上的栅极驱动电路所产生的栅极驱动信号示意图。在时间点  $t_1$  与  $t_3$  之间,第  $n-1$  个栅极驱动信号  $G_{n-1}$  产生一脉冲,  $t_2$  与  $t_4$  之间,第  $n$  个栅极驱动信号  $G_n$  产生一脉冲,  $t_3$  与  $t_5$  之间,第  $n+1$  个栅极驱动信号  $G_{n+1}$  产生一脉冲。

[0012] 在实际的运作上,  $t_1$  与  $t_2$  之间作为预充电的周期。也就是说,在液晶面板上接收到第  $n-1$  个栅极驱动信号  $G_{n-1}$  的所有像素在预充电周期尚无法接收到任何数据,这些像素必须等到  $t_2$  与  $t_3$  之间的数据周期才可由数据线上接收数据信号。而预充电周期与数据周期的时间相等。

[0013] 同理,  $t_2$  与  $t_3$  为第  $n$  个栅极驱动信号  $G_n$  的预充电的周期,  $t_3$  与  $t_4$  为第  $n$  个栅极驱动信号  $G_n$  的数据周期;  $t_3$  与  $t_4$  为第  $n+1$  个栅极驱动信号  $G_{n+1}$  的预充电的周期,  $t_4$  与  $t_5$  为第  $n+1$  个栅极驱动信号  $G_{n+1}$  的数据周期。

[0014] 上述的图  $2A$  与图  $2B$  的栅极驱动电路  $200$  及其栅极驱动信号应用于一般的像素。如果要应用于电荷分享像素时,则必须进一步考虑主栅极驱动信号与子栅极驱动信号之间不可以相互重叠的特征,并且更改栅极驱动电路  $200$  的相关设计。

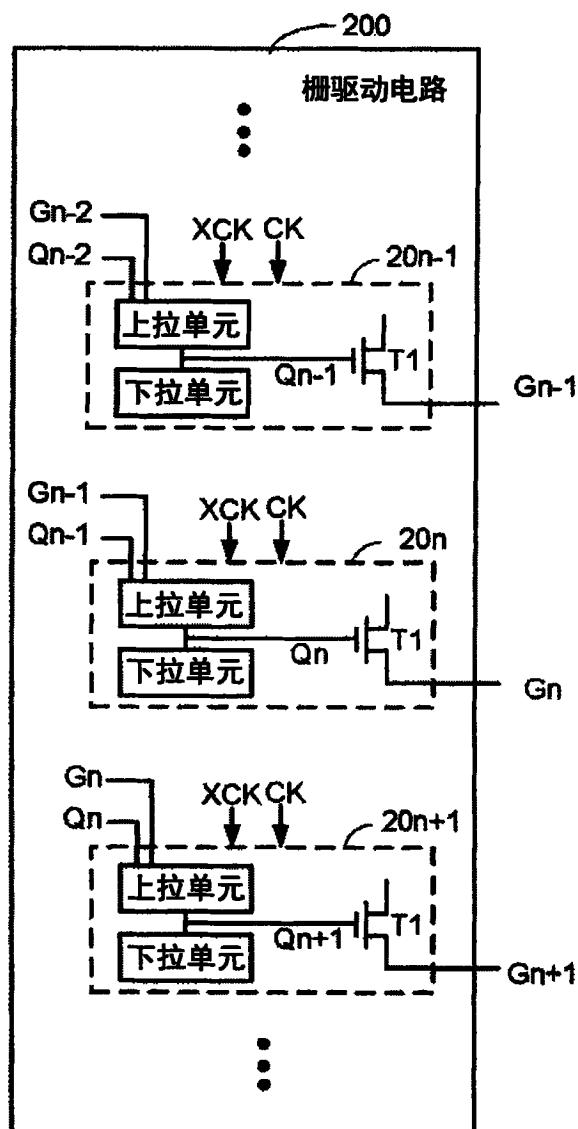

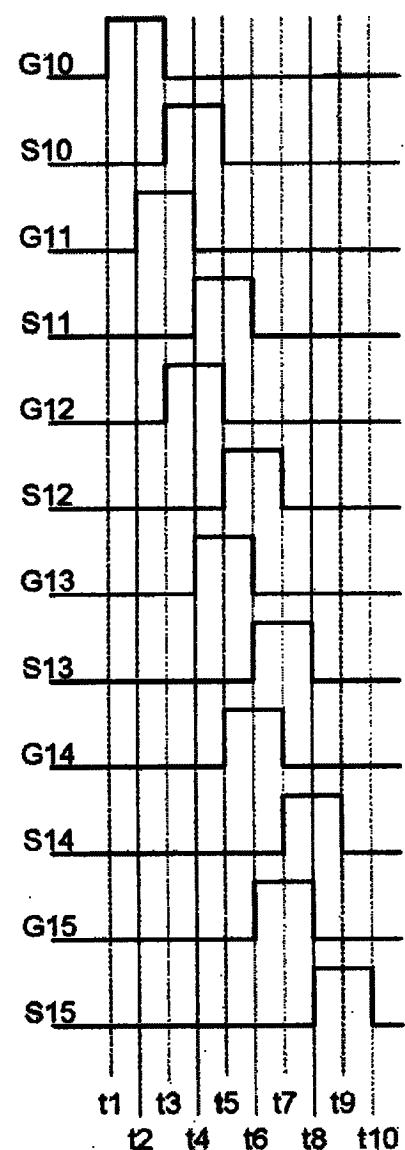

[0015] 请参照图  $3A$  与图  $3B$ ,其所绘示为公知  $GOA$  面板上运用于电荷分享像素的栅极驱动电路及其栅极驱动信号示意图。栅极驱动电路  $300$  中包括多个移位寄存器,而其动作原理如图  $2A$  所述,前一级的移位寄存器会控制次一级的移位寄存器产生栅极驱动信号,而其详细的运作情形则不再赘述。再者,图  $3A$  以第  $10$  至第  $15$  移位寄存器  $310 \sim 315$  来做说明,而其余的移位寄存器皆可利用相同的方式推得。

[0016] 很明显地,每个移位寄存器  $310 \sim 315$  皆可根据前一级移位寄存器的控制而产生一栅极驱动信号  $G_{10}、G_{11}、G_{12}、G_{13}、G_{14}、G_{15}$  来作为主栅极驱动信号。为了产生与主栅极驱动信号不相互重叠的子栅极驱动信号,公知栅极驱动电路  $300$  利用布线设计(layout trace)的方式将次二级移位寄存器所产生的主栅极驱动信号作为子栅极驱动信号。

[0017] 以第  $12$  移位寄存器  $312$  为例,其可产生第  $12$  主栅极驱动信号  $G_{12}$ ,而此第  $12$  主栅极驱动信号  $G_{12}$  也通过布线设计作为第  $10$  子栅极驱动信号  $S_{10}$ 。同理,第  $14$  主栅极驱动信号  $G_{14}$  利用布线设计而成为第  $12$  子栅极驱动信号  $S_{12}$ 。

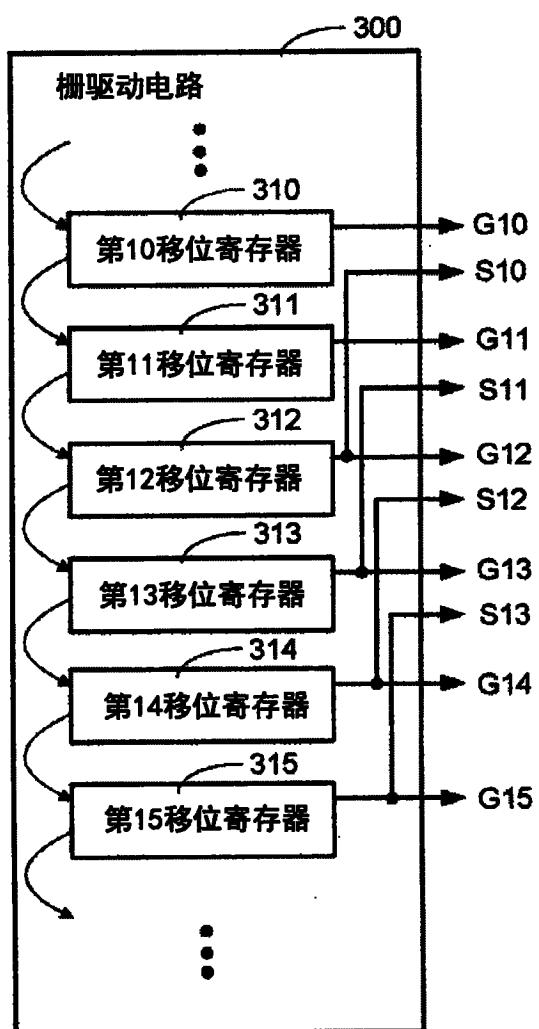

[0018] 因此,如图  $3B$  所示,时间点  $t_1$  至  $t_3$  为第  $10$  主栅极驱动信号  $G_{10}$  的脉冲,时间点  $t_3$  至  $t_5$  为第  $10$  子栅极驱动信号的脉冲  $S_{10}$ ;时间点  $t_2$  至  $t_4$  为第  $11$  主栅极驱动信号  $G_{11}$

的脉冲,时间点 t4 至 t6 为第 11 子栅极驱动信号 S11 的脉冲;时间点 t3 至 t5 为第 12 主栅极驱动信号 G12 的脉冲,时间点 t5 至 t7 为第 12 子栅极驱动信号 S12 的脉冲;时间点 t4 至 t6 为第 13 主栅极驱动信号 G13 的脉冲,时间点 t6 至 t8 为第 13 子栅极驱动信号 S13 的脉冲;时间点 t5 至 t7 为第 14 主栅极驱动信号 G14 的脉冲,时间点 t7 至 t9 为第 14 子栅极驱动信号 S14 的脉冲;时间点 t6 至 t8 为第 15 主栅极驱动信号 G15 的脉冲,时间点 t8 至 t10 为第 15 子栅极驱动信号 S15 的脉冲。

[0019] 然而,图 3A 的栅极驱动电路 300 中的移位寄存器具有相当多的跨线,因而使得 GOA 面板上的布线变的相当复杂。

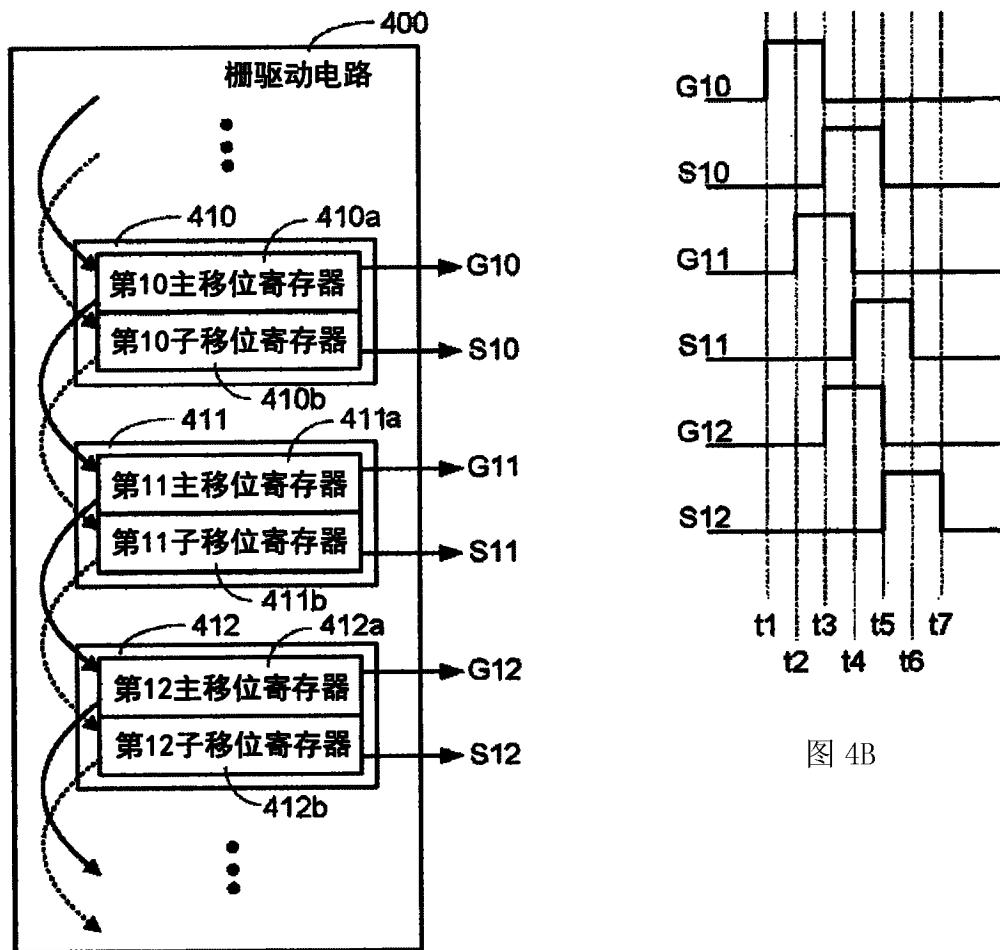

[0020] 请参照图 4A 与图 4B,其所绘示为公知 GOA 面板上运用于电荷分享像素的栅极驱动电路及其栅极驱动信号示意图。栅极驱动电路 400 中包括多个移位寄存器,而每个移位寄存器中皆包括一主移位寄存器与一子移位寄存器。

[0021] 图 4A 以第 10 至第 12 移位寄存器 410 ~ 412 来做说明,而其余的移位寄存器皆可利用相同的方式推得。其中,每个移位寄存器中的主移位寄存器受控于前一级移位寄存器中的主移位寄存器,并产生主栅极驱动信号;同理,每个移位寄存器中的子移位寄存器受控于前一级移位寄存器中的子移位寄存器,并产生子栅极驱动信号。再者,每个移位寄存器中的主移位寄存器与子移位寄存器之间并没有任何相互控制的关系。

[0022] 由图 4A 可知,第 10 主移位寄存器 410a,第 11 主移位寄存器 411a,第 12 主移位寄存器 412a 会依序产生第 10 主栅极驱动信号 G10、第 11 主栅极驱动信号 G11、第 12 主栅极驱动信号 G12。同理,第 10 子移位寄存器 410b,第 11 子移位寄存器 411b,第 12 子移位寄存器 412b 会依序产生第 10 子栅极驱动信号 S10、第 11 子栅极驱动信号 S11、第 12 子栅极驱动信号 S12。如此即可产生不互相重叠的主栅极控信号以及子栅极控信号。

[0023] 然而,主移位寄存器以及子移位寄存器的电路结构相同。因此图 4A 中,每一个移位寄存器的电路架构更复杂,并且占据更大的布局面积 (layout area)。

## 发明内容

[0024] 因此,本发明的目的在于提出一种运用于电荷分享像素的整合面板型栅极驱动电路。液晶面板上的栅极驱动电路中包括多个移位寄存器,每个移位寄存器皆可以输出不互相重叠的主栅极驱动信号与子栅极驱动信号,并且具有电路结构以及线路布局简单的特征。

[0025] 本发明提出一种栅极驱动电路,接收多个时钟脉冲信号,其中该栅极驱动电路包括多个移位寄存器,而一第 n 个移位寄存器包括:一第一驱动晶体管,具有一栅极接收一第 n 控制信号,一漏极接收这些时钟脉冲信号中的一第一时钟脉冲信号,一源极输出一第 n 主栅极驱动信号;一第二驱动晶体管,具有一栅极接收该第 n 控制信号,一漏极接收这些时钟脉冲信号中的一第二时钟脉冲信号,一源极输出一第 n 子栅极驱动信号;一上拉单元,接收第 n 个移位寄存器前二级的一第 n-2 个移位寄存器输出的一第 n-2 控制信号以及一第 n-2 主栅极驱动信号,且该上拉单元接收这些时钟脉冲信号中的一第三时钟脉冲信号;其中,该上拉单元动作时,控制该第 n 控制信号开启该第一驱动晶体管以及该第二驱动晶体管;以及,一下拉单元,接收该第 n 控制信号与该第 n 主栅极驱动信号,该下拉单元在该上拉单元动作开始后的一预定时间周期动作,并控制该第 n 控制信号关闭该第一驱动晶体管以及该

第二驱动晶体管；其中，该第三时钟脉冲信号的相位超前该第一时钟脉冲信号，该第一时钟脉冲信号超前该第二时钟脉冲信号，且该第一时钟脉冲信号、该第二时钟脉冲信号与该第三时钟脉冲信号不重叠。

[0026] 本发明更提出一种栅极驱动电路，接收多个时钟脉冲信号，其中该栅极驱动电路包括多个移位寄存器，而一第 n 个移位寄存器包括：一第一驱动晶体管，具有一栅极接收一第 n 控制信号，一漏极接收这些时钟脉冲信号中的一第一时钟脉冲信号，一源极输出一第 n 主栅极驱动信号；一第二驱动晶体管，具有一栅极接收该第 n 控制信号，一漏极接收这些时钟脉冲信号中的一第二时钟脉冲信号，一源极输出一第 n 子栅极驱动信号；一第一上拉单元，接收第 n 个移位寄存器前一级的一第 n-1 个移位寄存器输出的一第 n-1 控制信号以及一第 n-1 主栅极驱动信号，且该上拉单元接收这些时钟脉冲信号中的一第三时钟脉冲信号；其中，该第一上拉单元动作时，控制该第 n 控制信号开启该第一驱动晶体管以及该第二驱动晶体管；一第二上拉单元，接收第 n 个移位寄存器后一级的一第 n+1 个移位寄存器输出的一第 n+1 控制信号以及一第 n+1 主栅极驱动信号，且该上拉单元接收这些时钟脉冲信号中的一第四时钟脉冲信号；其中，该第二上拉单元动作时，控制该第 n 控制信号开启该第一驱动晶体管以及该第二驱动晶体管；以及一下拉单元，接收该第 n 控制信号与该第 n 主栅极驱动信号，该下拉单元在该上拉单元动作开始后的一预定时间周期动作，并控制该第 n 控制信号关闭该第一驱动晶体管以及该第二驱动晶体管；其中，该第三时钟脉冲信号的相位超前该第一时钟脉冲信号，该第一时钟脉冲信号超前该第二时钟脉冲信号，且该第一时钟脉冲信号、该第二时钟脉冲信号与该第三时钟脉冲信号不重叠。

[0027] 本发明的有益效果在于提出一种运用于电荷分享像素的整合面板型栅极驱动电路，GOA 面板上的栅极驱动电路中包括多个移位寄存器，每个移位寄存器可以输出不互相重叠的主栅极驱动信号与子栅极驱动信号，并且具有电路结构以及线路布局简单的特征。

[0028] 为让本发明的上述和其他目的、特征和优点能更明显易懂，下文特举较佳实施例，并配合所附附图，作详细说明如下。

## 附图说明

- [0029] 图 1A 所绘示为公知液晶显示面板上单一电荷分享像素示意图；

- [0030] 图 1B 所绘示为电荷分享像素的动作信号示意图；

- [0031] 图 2A 所绘示为公知 GOA 面板上的栅极驱动电路示意图；

- [0032] 图 2B 所绘示为公知 GOA 面板上的栅极驱动电路所产生的栅极驱动信号示意图；

- [0033] 图 3A 与图 3B 所绘示为公知 GOA 面板上运用于电荷分享像素的栅极驱动电路及其栅极驱动信号示意图；

- [0034] 图 4A 与图 4B 所绘示为公知 GOA 面板上运用于电荷分享像素的栅极驱动电路及其栅极驱动信号示意图；

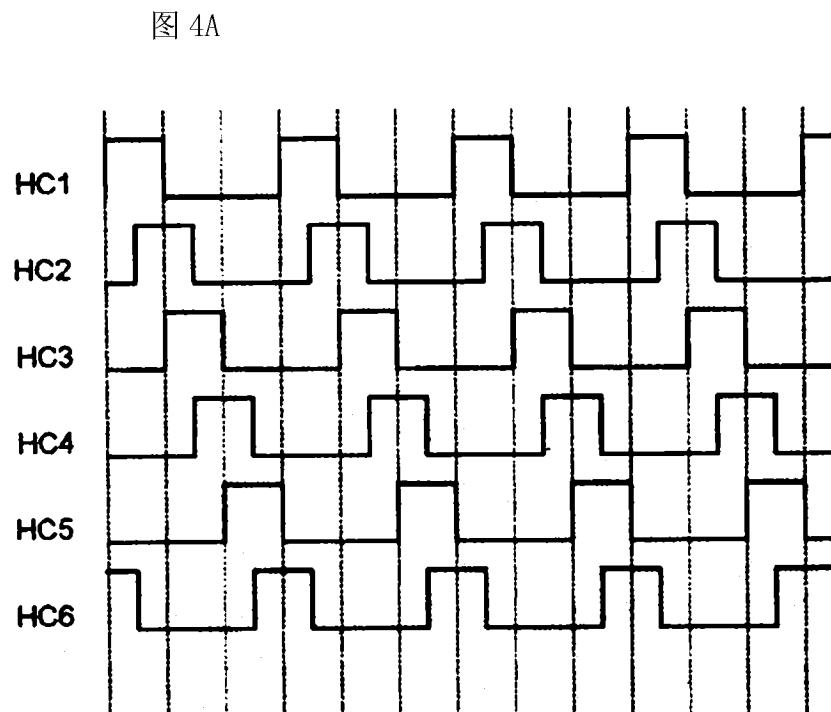

- [0035] 图 5 所示为 6 个时钟脉冲信号之间的相位关系；

- [0036] 图 6A 与图 6B 所绘示为本发明栅极驱动电路中的移位寄存器第一实施例及其相关信号示意图；

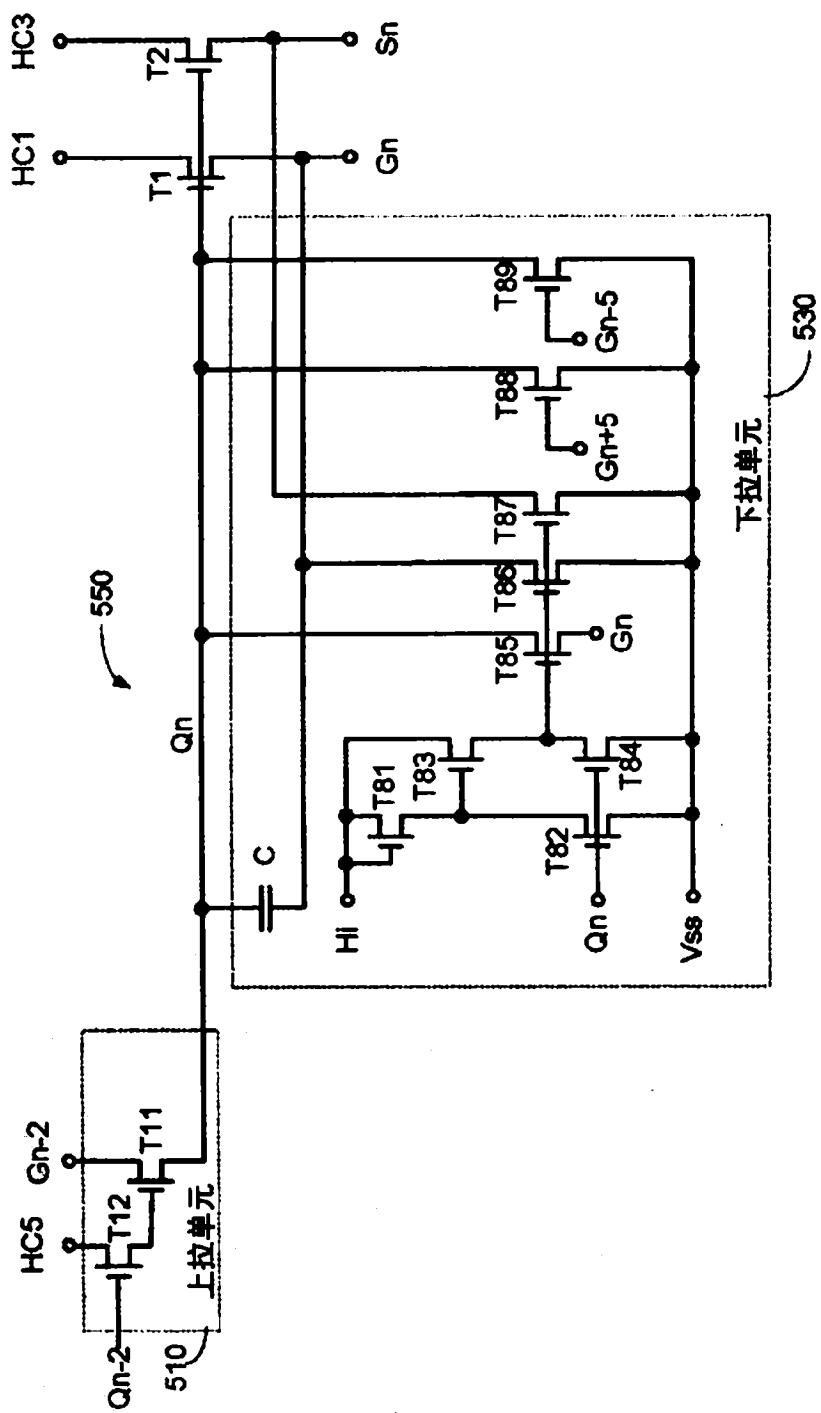

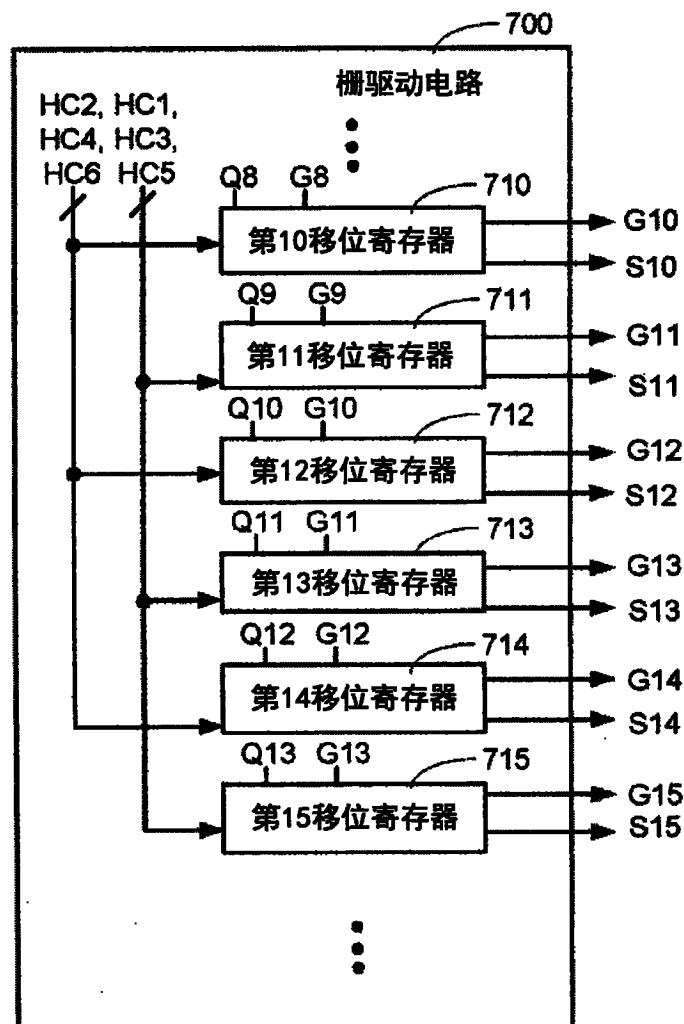

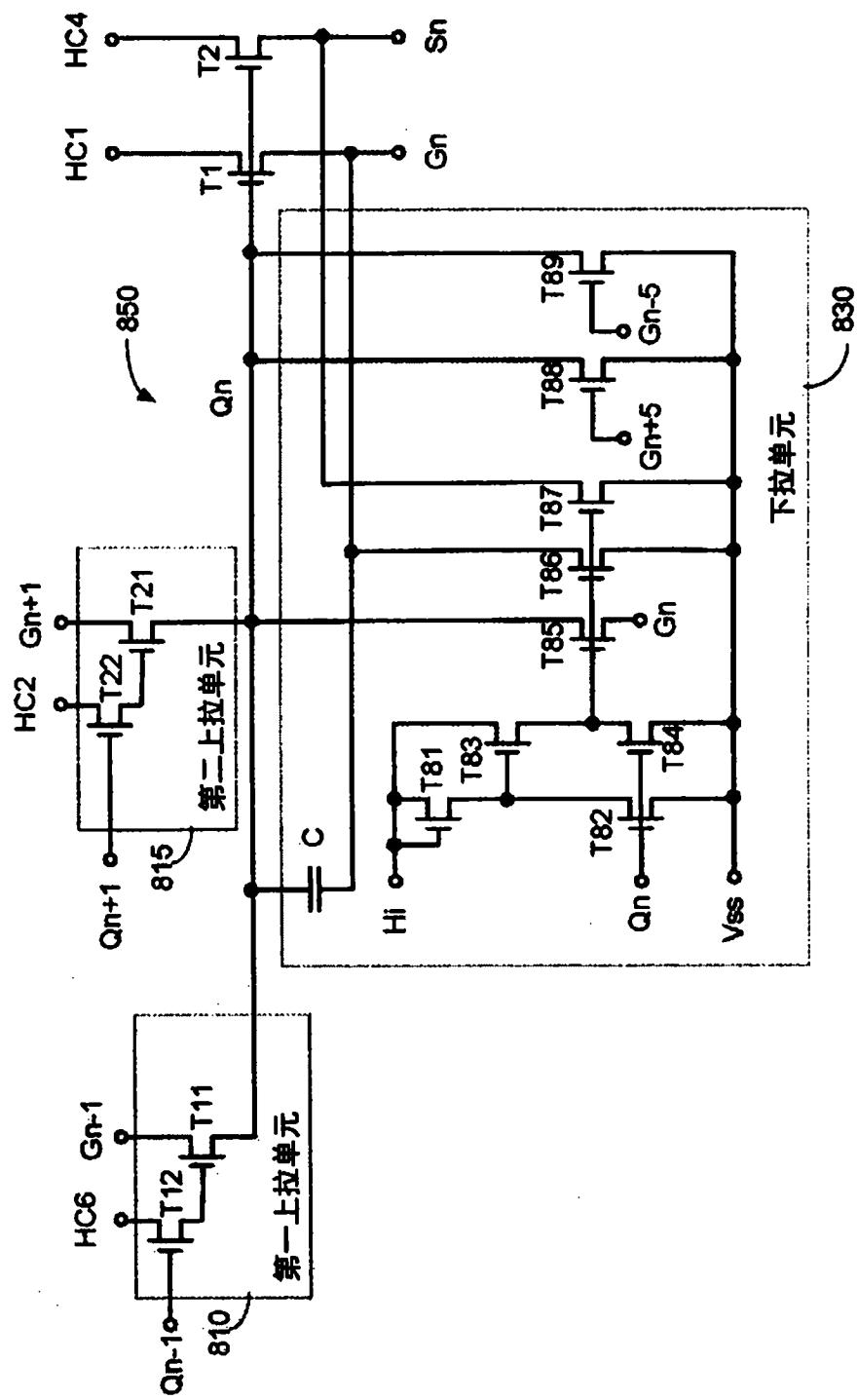

- [0037] 图 7 所绘示为本发明栅极驱动电路中的移位寄存器第二实施例；

- [0038] 图 8 所绘示为本发明第一实施例或第二实施例公开的移位寄存器所组成的栅极

驱动电路；

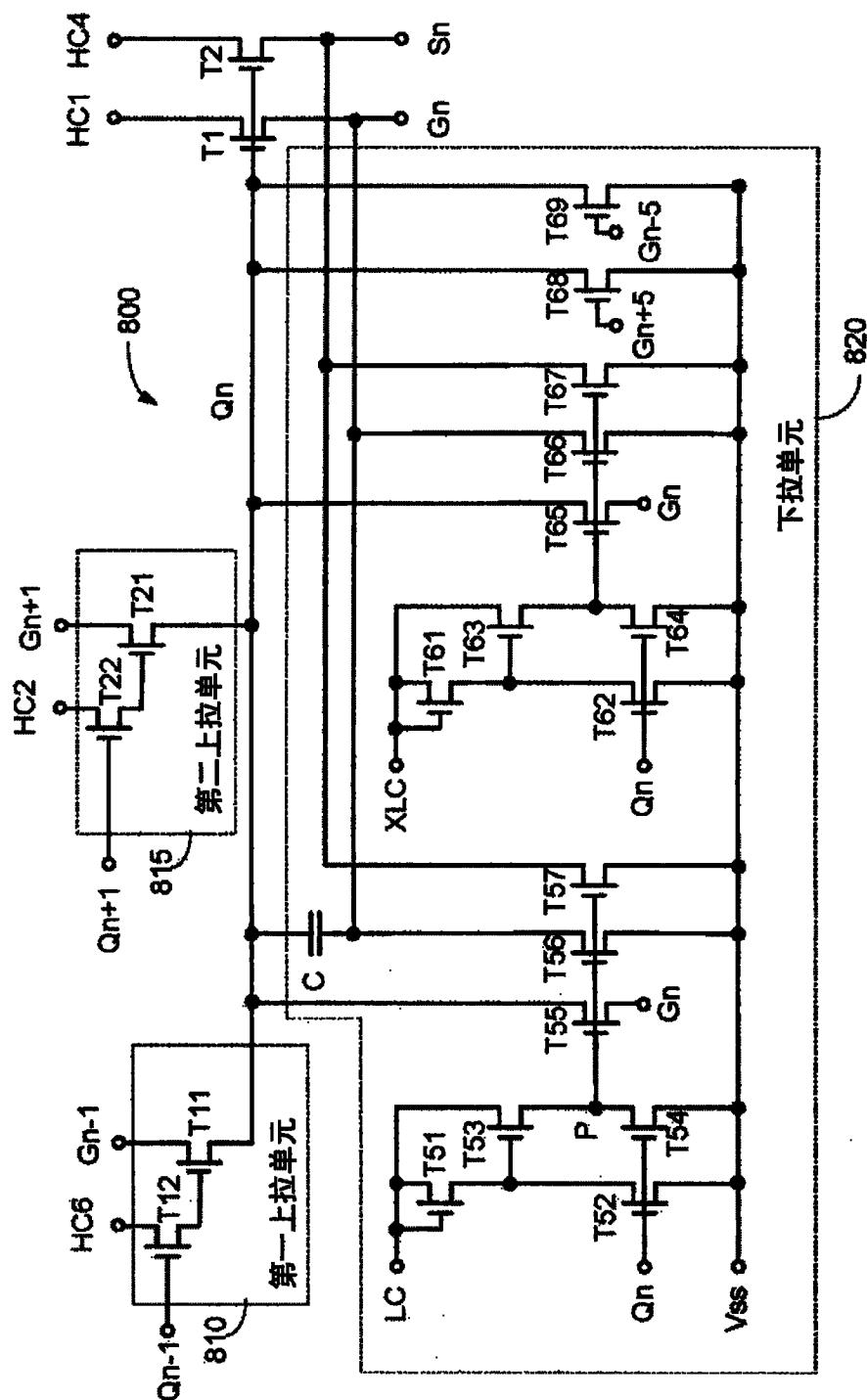

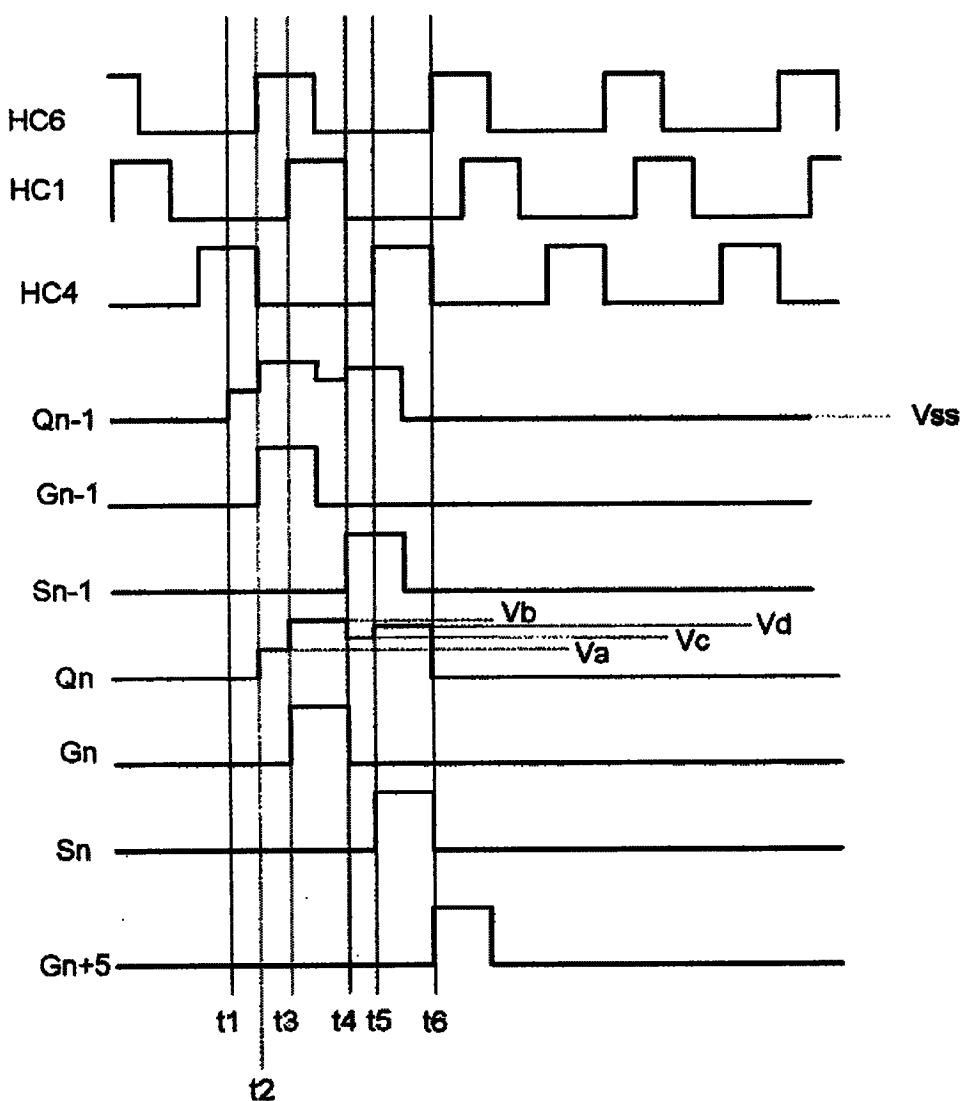

[0039] 图 9A 与图 9B 所绘示为本发明栅极驱动电路中的移位寄存器第三实施例及其相关信号示意图；

[0040] 图 10 所绘示为本发明栅极驱动电路中的移位寄存器第四实施例；

[0041] 图 11，其所绘示为本发明第三实施例或第四实施例公开的移位寄存器所组成的栅极驱动电路。

[0042] 其中，附图标记

|        |                    |                  |

|--------|--------------------|------------------|

| [0043] | 100 电荷分享像素         | 102 子区域          |

| [0044] | 104 主区域            | 200 栅极驱动电路       |

| [0045] | 20n-1 第 n-1 个移位寄存器 | 20n 第 n 个移位寄存器   |

| [0046] | 20n+1 第 n+1 个移位寄存器 | 300 栅极驱动电路       |

| [0047] | 310 第 10 移位寄存器     | 311 第 11 移位寄存器   |

| [0048] | 312 第 12 移位寄存器     | 313 第 13 移位寄存器   |

| [0049] | 314 第 14 移位寄存器     | 315 第 15 移位寄存器   |

| [0050] | 400 栅极驱动电路         | 410 第 10 移位寄存器   |

| [0051] | 410a 第 10 主移位寄存器   | 410b 第 10 子移位寄存器 |

| [0052] | 411 第 11 移位寄存器     | 411a 第 10 主移位寄存器 |

| [0053] | 410b 第 11 子移位寄存器   | 412 第 12 移位寄存器   |

| [0054] | 412a 第 12 主移位寄存器   | 412b 第 12 子移位寄存器 |

| [0055] | 500、550 第 n 个移位寄存器 | 510 上拉单元         |

| [0056] | 520、530 下拉单元       | 700 栅极驱动电路       |

| [0057] | 710 第 10 移位寄存器     | 711 第 11 移位寄存器   |

| [0058] | 712 第 12 移位寄存器     | 713 第 13 移位寄存器   |

| [0059] | 714 第 14 移位寄存器     | 715 第 15 移位寄存器   |

| [0060] | 800、850 第 n 个移位寄存器 | 810 第一上拉单元       |

| [0061] | 815 第二上拉单元         | 820、830 下拉单元     |

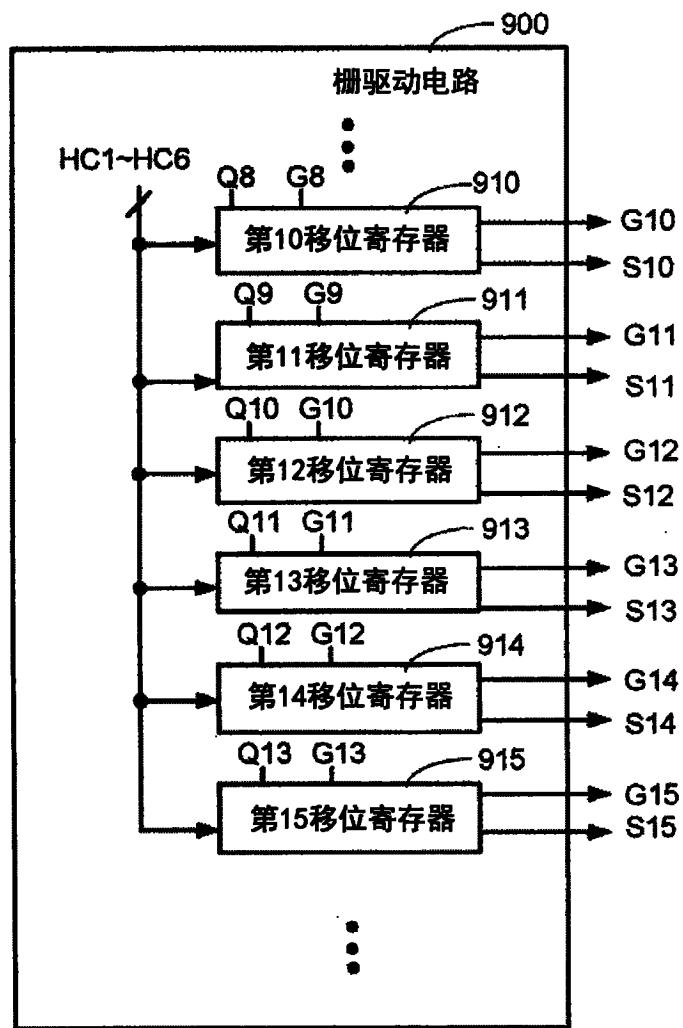

| [0062] | 900 栅极驱动电路         | 910 第 10 移位寄存器   |

| [0063] | 911 第 11 移位寄存器     | 912 第 12 移位寄存器   |

| [0064] | 913 第 13 移位寄存器     | 914 第 14 移位寄存器   |

| [0065] | 915 第 15 移位寄存器     |                  |

## 具体实施方式

[0066] 根据本发明的实施例，本发明提出一运用于电荷分享像素的整合面板型栅极驱动电路。在 GOA 面板上的栅极驱动电路中包括多个移位寄存器，每个移位寄存器可以输出不互相重叠的主栅极驱动信号与子栅极驱动信号。

[0067] 首先，本发明需要产生 6 个时钟脉冲信号，其占空比 (duty cycle) 皆为 1/3。再者，每个时钟脉冲信号之间的相位相差 60 度。此六个时钟脉冲信号依据相位先后次序命名为 HC1、HC2、HC3、HC4、HC5、HC6。如图 5 所示，即为 6 个时钟脉冲信号之间的相位关系。

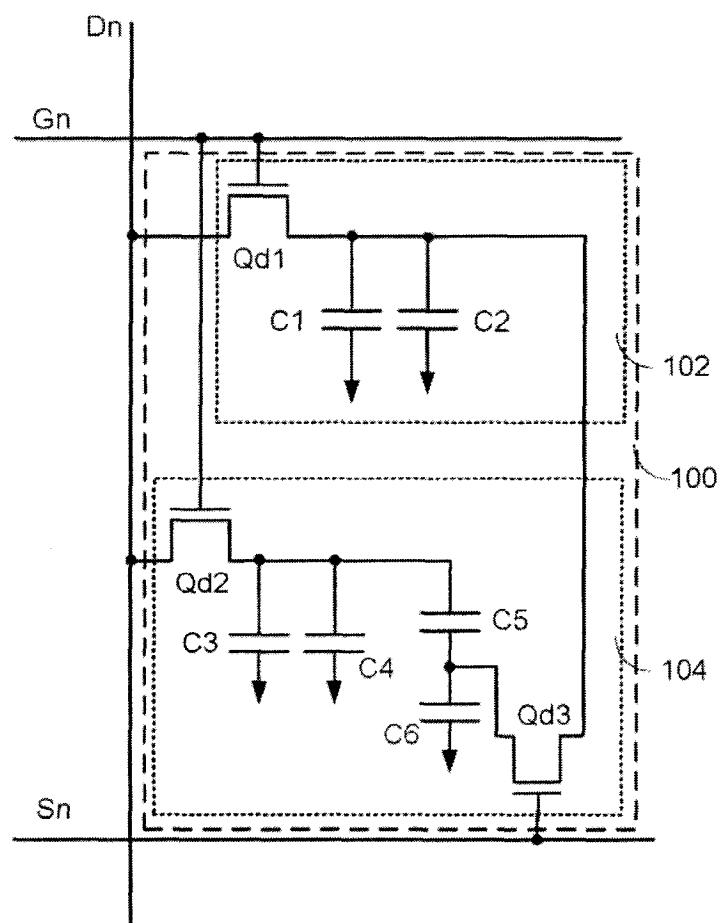

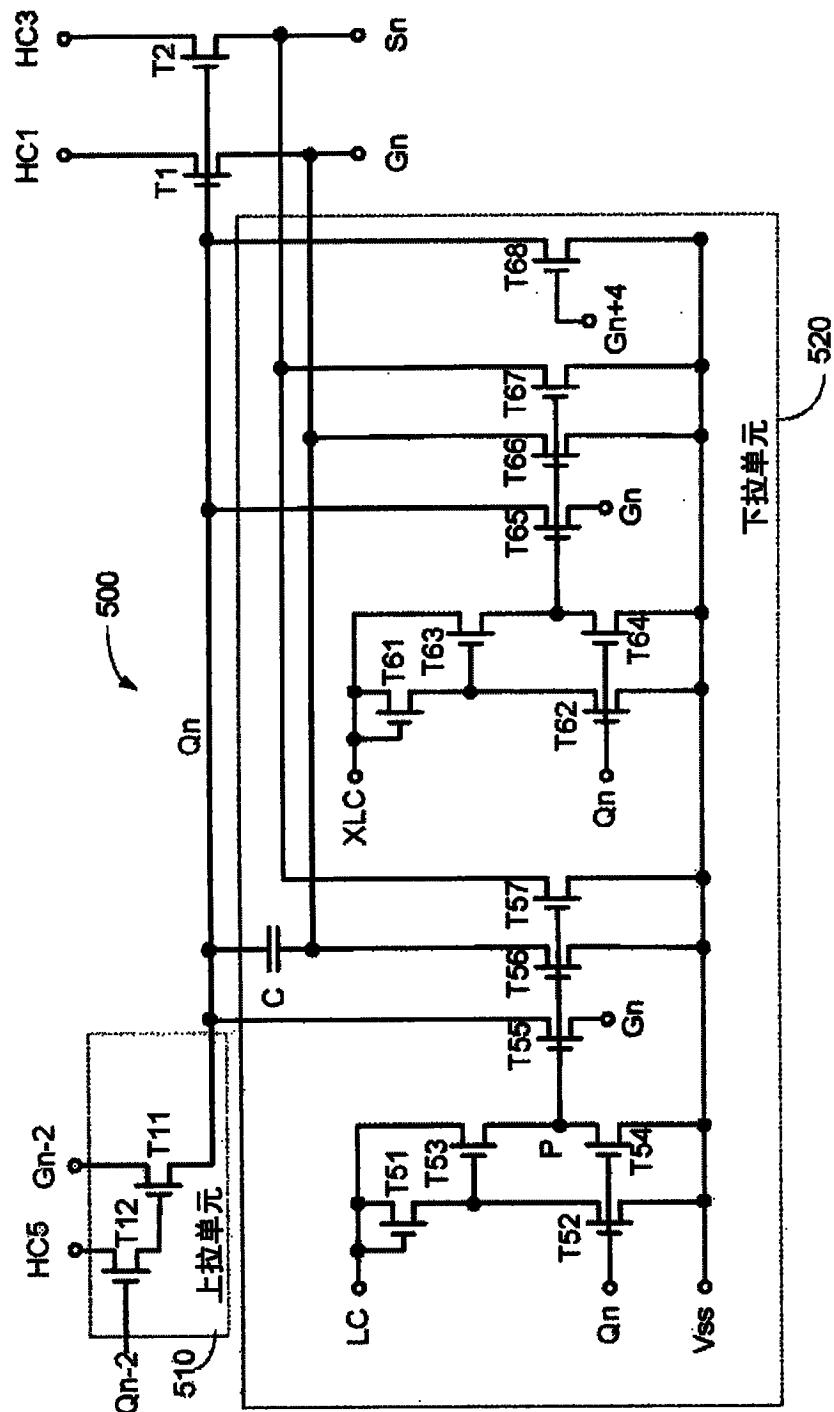

[0068] 请参照图 6A 与图 6B，其所绘示为本发明栅极驱动电路中的移位寄存器第一实施

例及其相关信号示意图。本发明第 n 个移位寄存器 500 包括一上拉单元 510、一下拉单元 520、一第一驱动晶体管 T1、与一第二驱动晶体管 T2。而第一驱动晶体管 T1 漏极接收 HC1 信号，源极产生 Gn 信号；第二驱动晶体管 T2 漏极接收 HC3 信号，源极产生 Sn 信号。

[0069] 上拉单元 510 包括晶体管 T12 与晶体管 T11，晶体管 T12 栅极接收 Qn-2 信号，漏极接收 HC5 信号；晶体管 T11 栅极连接至晶体管 T12 源极，漏极连接至 Gn-2 信号，源极产生 Qn 信号。上拉单元 510 接收前二级移位寄存器（第 n-2 个移位寄存器）所产生的第 n-2 个控制信号 Qn-2 与第 n-2 个主栅极驱动信号 Gn-2、以及 HC5 时钟脉冲信号。当上拉单元 510 动作时，可将第 n 个控制信号 Qn 上拉至第一电压电位 (first voltage level) 并且将开启第一驱动晶体管 T1 与第二驱动晶体管 T2。

[0070] 下拉单元 520 接收第 n 个控制信号 Qn，且在上拉单元 510 未动作时，下拉单元 520 将第 n 个控制信号 Qn 持续地保持在最低电压电位 (lowest voltage level)。而当上拉单元 510 动作时，则下拉单元 520 会在一预定时间周期 (predetermined time period) 之后将第 n 个控制信号 Qn 转换为最低电压电位并持续地保持在最低电压电位。

[0071] 如图 6A 所示，下拉单元 520 中的 LC 与 XLC 是一组互补的时钟脉冲信号，Vss 为最低电压电位。其中，当 Qn 维持在 Vss 时，晶体管 T52、T54、T62、T64 皆为关闭状态。在 LC 为高逻辑电位且 XLC 为低逻辑电位时，晶体管 T51、T53、T55、T56、T57 开启，下拉单元 520 中其他晶体管皆关闭，因此 Gn、Sn、Qn 皆为 Vss；同理，于 XLC 为高逻辑电位且 LC 为低逻辑电位时，晶体管 T61、T63、T65、T66、T67 开启，下拉单元 520 中其他晶体管皆关闭，因此 Gn、Sn、Qn 皆为 Vss。也就是说，当上拉单元 510 未动作时，Qn、Gn、Sn 皆会持续维持在 Vss。

[0072] 再者，当上拉单元 510 动作时，Qn 上升至第一电压电位时，此时晶体管 T52、T54、T62、T64 皆开启而晶体管 T55、T56、T57、T65、T66、T67 皆关闭。此时，再经过一预定时间之后，利用第 n+4 主栅极驱动信号 Gn+4 开启晶体管 T68 时，可以将 Qn 信号再次转换为 Vss。

[0073] 前面几段的描述介绍下拉单元 520 主要的功能，此下拉单元 520 也可以利用其他连接关系的晶体管达成相同的功能。后续的实施例中将会提出其他连接关系的下拉单元并且达成本发明的功效。

[0074] 如图 6B 所示，选择 6 个时钟脉冲信号中信号不相互重叠的 HC5、HC1、HC3，并且搭配第 n 个移位寄存器。因此，HC5、HC1、HC3 之间相位相差 120 度。

[0075] 请参考图 6A，上拉单元 510 接收前二级移位寄存器（第 n-2 个移位寄存器）所产生的第 n-2 个控制信号 Qn-2 与第 n-2 个主栅极驱动信号 Gn-2、以及相位最前面 HC5 时钟脉冲信号。

[0076] 在时间点 t1，Qn-2 信号由 Vss 变化至第一电压电位 Va，此时上拉单元 510 中的晶体管 T12 开启；而在时间点 t2，HC5 信号为高逻辑电位进而开启晶体管 T11 使得 Gn-2 信号传递至晶体管 T11 源极并产生 Qn 信号，而 Qn 信号即上升至第一电压电位 Va 并开启第一驱动晶体管 T1 以及第二驱动晶体管 T2。也就是说，在时间点 t2，上拉单元 510 开始动作，而下拉单元 520 停止动作。

[0077] 在时间点 t3，第一驱动晶体管 T1 以及第二驱动晶体管 T2 持续开启，由于 HC1 信号为高逻辑电位而 HC3 信号为低逻辑电位，因此 Gn 信号产生一脉冲，并且利用下拉单元 520 的电容 C 作为电荷泵 (charge pump) 使得 Qn 信号上升至第二高电位 Vb。

[0078] 当然，下拉单元 520 里的电容 C 也可以省略不需连接在 Qn 信号与 Gn 信号之间，而

此时  $Q_n$  信号维持在第一高电位  $V_a$ , 仍旧可以开启第一驱动晶体管 T1 以及第二驱动晶体管 T2。

[0079] 在时间点  $t_4$ , 第一驱动晶体管 T1 以及第二驱动晶体管 T2 持续开启, 由于  $HC1$  信号为低逻辑电位而  $HC3$  信号为高逻辑电位, 因此,  $S_n$  信号产生而  $G_n$  信号的脉冲停止, 而  $Q_n$  信号下降至第三高电位  $V_c$ 。

[0080] 在时间点  $t_5$ , 第  $n+4$  个主栅极驱动信号  $Q_{n+4}$  信号产生脉冲, 并进一步控制下拉单元 520 将  $Q_n$  信号下拉至  $V_{ss}$ , 并且结束第  $n$  个移位寄存器 500 的动作。因此, 预定时间周期即由时间点  $t_2$  至时间点  $t_5$ 。

[0081] 当然, 本发明也可以利用  $S_{n+4}$  信号、 $G_{n+5}$  信号、 $S_{n+5}$  信号、或者  $G_{n+6}$  信号来使得  $Q_n$  信号下拉至  $V_{ss}$ 。而预定时间周期也会跟着变化。

[0082] 由上述本发明的第一实施例可知, 每一个移位寄存器皆可产生不会互相重叠的主栅极驱动信号  $G_n$  以及子栅极驱动信号  $S_n$ 。

[0083] 如前面所述, 第一实施例中的下拉单元 520 也可以利用其他连接关系的晶体管达成相同的功能。如图 7 所示, 为本发明栅极驱动电路中的移位寄存器 550 第二实施例。与第一实施例的差异仅在于下拉单元 530, 而其他电路皆相同。

[0084] 下拉单元 530 中的  $V_{ss}$  为最低电压电位。其中, 当  $Q_n$  维持在  $V_{ss}$  时, 晶体管 T82、T84 为关闭状态。而由于晶体管 T81 连接至高逻辑电位 (Hi), 晶体管 T81、T83、T85、T86、T87 开启, 因此  $G_n$ 、 $S_n$ 、 $Q_n$  皆为  $V_{ss}$ 。也就是说, 当上拉单元 510 未动作时,  $Q_n$ 、 $G_n$ 、 $S_n$  皆会持续维持在  $V_{ss}$ 。

[0085] 再者, 当上拉单元 510 动作时,  $Q_n$  上升至第一电压电位时, 此时晶体管 T82、T84 开启而晶体管 T85、T86、T87 皆关闭。此时, 再经过一预定时间之后, 利用第  $n+5$  主栅极驱动信号  $G_{n+5}$  或者  $n-5$  主栅极驱动信号  $G_{n-5}$  开启晶体管 T88 或者晶体管 T89 时, 可以将  $Q_n$  信号再次转换为  $V_{ss}$ 。

[0086] 当然, 第二实施例中的其相关信号示意图与图 6B 相同, 不再赘述。

[0087] 请参照图 8, 其所绘示为本发明第一实施例或者第二实施例公开的移位寄存器所组成的栅极驱动电路。GOA 面板的栅极驱动电路 700 中以第 10 至第 15 移位寄存器 710 ~ 715 来做说明, 而其余的移位寄存器皆可利用相同的方式推得。

[0088] 很明显地, 每个移位寄存器 710 ~ 715 根据前二级移位寄存器的控制信号以及主栅极驱动信号并搭配适当地时钟脉冲信号组合而运作。以图 8 为例, 第 11 移位寄存器 711、第 13 移位寄存器 713、第 15 移位寄存器 715 接收 6 个时钟脉冲信号中的第一组时钟脉冲信号 ( $HC1$ 、 $HC3$ 、 $HC5$ )。第 10 移位寄存器 710、第 12 移位寄存器 712、第 14 移位寄存器 714 接收 6 个时钟脉冲信号中的第二组时钟脉冲信号 ( $HC2$ 、 $HC4$ 、 $HC6$ )。

[0089] 当然, 上述栅极驱动电路 700 中的移位寄存器由上而下的排列, 所以主栅极驱动信号以及子栅极驱动信号由上而下逐级产生。当然, 移位寄存器也可以由下而上的排列, 使得主栅极驱动信号以及子栅极驱动信号由下而上逐级产生。

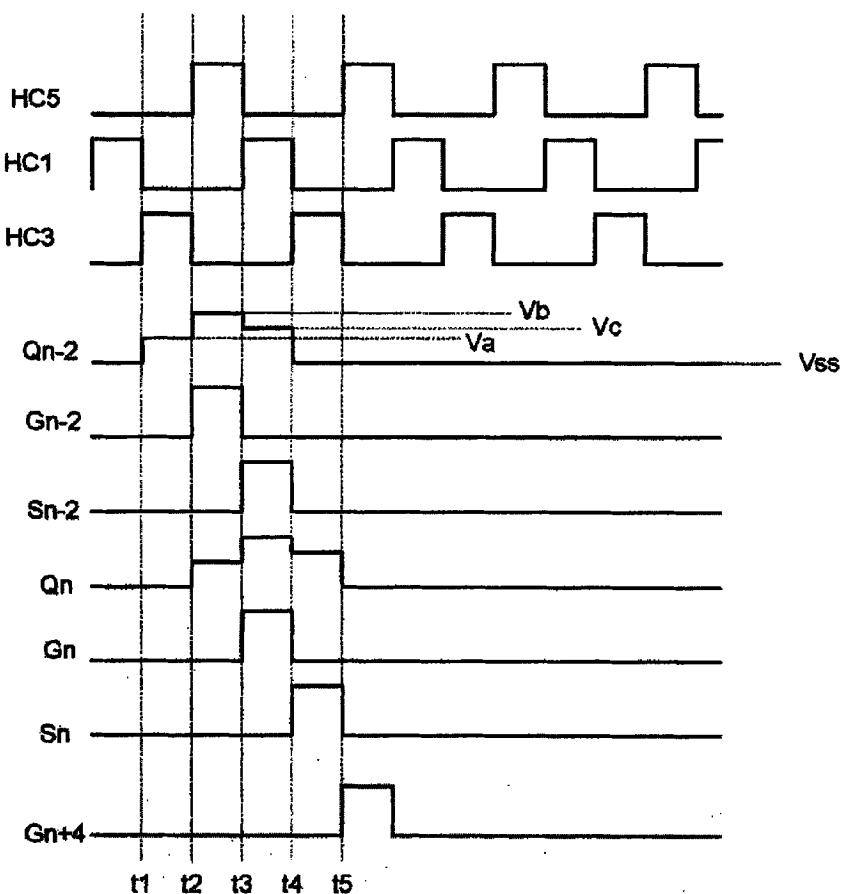

[0090] 请参照图 9A 与图 9B, 其所绘示为本发明栅极驱动电路中的移位寄存器第三实施例及其相关信号示意图。本发明第  $n$  个移位寄存器 800 可选择性地连接至前一级移位寄存器 (第  $n-1$  个移位寄存器) 或者后一级的移位寄存器 (第  $n+1$  个移位寄存器)。

[0091] 第  $n$  个移位寄存器 800 包括一第一上拉单元 810、第二上拉单元 815、一下拉单元

820、一第一驱动晶体管 T1、与一第二驱动晶体管 T2。而第一驱动晶体管 T1 漏极接收 HC1 信号,源极产生 Gn 信号;第二驱动晶体管 T2 漏极接收 HC4 信号,源极产生 Sn 信号。

[0092] 第一上拉单元 810 包括一晶体管 T12 与晶体管 T11,晶体管 T12 棚极接收 Qn-1 信号,漏极接收 HC6 信号;晶体管 T11 棚极连接至晶体管 T12 源极,漏极连接至 Gn-1 信号,源极产生 Qn 信号。第一上拉单元 810 接收前一级移位寄存器(第 n-1 个移位寄存器)所产生的第 n-1 个控制信号 Qn-1 与第 n-1 个主栅极驱动信号 Gn-1、以及 HC6 时钟脉冲信号。当第一上拉单元 810 动作时,可将第 n 个控制信号 Qn 上拉至一第一电压电位并且开启将第一驱动晶体管 T1 与第二驱动晶体管 T2。当第二实施例的第 n 个移位寄存器 800 仅使用第一上拉单元 810 时,连结而成的栅极驱动电路即为由上而下依序产生主栅极驱动信号与子栅极驱动信号。

[0093] 第二上拉单元 815 包括一晶体管 T22 与晶体管 T21,晶体管 T22 棚极接收 Qn+1 信号,漏极接收 HC2 信号;晶体管 T21 棚极连接至晶体管 T22 源极,漏极连接至 Gn+1 信号,源极产生 Qn 信号。第二上拉单元 815 接收后一级移位寄存器(第 n+1 个移位寄存器)所产生的第 n+1 个控制信号 Qn+1 与第 n+1 个主栅极驱动信号 Gn+1、以及 HC2 时钟脉冲信号。当第二上拉单元 815 动作时,可将第 n 个控制信号 Qn 上拉至一第一电压电位并且将开启第一驱动晶体管 T1 与第二驱动晶体管 T2。当第二实施例的第 n 个移位寄存器 800 仅使用第二上拉单元 815 时,连结而成的栅极驱动电路即为由下而上依序产生主栅极驱动信号与子栅极驱动信号。

[0094] 下拉单元 820 接收第 n 个控制信号 Qn,且在第一上拉单元 810 或者第二上拉单元 815 未动作时,下拉单元 820 将第 n 个控制信号 Qn 持续地保持在最低电压电位 (lowest voltage level)。而当第一上拉单元 810 或者第二上拉单元 815 动作时,则下拉单元 820 会在一预定时间周期 (predetermined time period) 之后将第 n 个控制信号 Qn 转换为最低电压电位并持续地保持在最低电压电位。

[0095] 如图 9A 所示,下拉单元 820 中的 LC 与 XLC 是一组互补的时钟脉冲信号,Vss 为最低电压电位。其中,当 Qn 维持在 Vss 时,晶体管 T52、T54、T62、T64 皆为关闭状态。在 LC 为高逻辑电位且 XLC 为低逻辑电位时,晶体管 T51、T53、T55、T56、T57 开启,下拉单元 820 中其他晶体管皆关闭,因此 Gn、Sn、Qn 皆为 Vss;同理,于 XLC 为高逻辑电位且 LC 为低逻辑电位时,晶体管 T61、T63、T65、T66、T67 开启,下拉单元 820 中其他晶体管皆关闭,因此 Gn、Sn、Qn 皆为 Vss。也就是说,当第一上拉单元 810 或者第二上拉单元 815 未动作时,Qn、Gn、Sn 皆会持续维持在 Vss。

[0096] 再者,当第一上拉单元 810 或者第二上拉单元 815 动作时,Qn 上升至第一电压电位时,此时晶体管 T52、T54、T62、T64 皆开启而晶体管 T55、T56、T57、T65、T66、T67 皆关闭。此时,再经过一预定时间之后,利用第 n+5 主栅极驱动信号 Gn+5 开启晶体管 T68,或者第 n-5 主栅极驱动信号 Gn-5 开启晶体管 T69 时,可以将 Qn 信号再次转换为 Vss。

[0097] 换句话说,利用第 n+5 主栅极驱动信号 Gn+5 开启晶体管 T68 时,则本发明的栅极驱动电路由上而下逐级产生栅极驱动信号以及子栅极驱动信号。反之,利用第 n-5 主栅极驱动信号 Gn-5 开启晶体管 T69 时,则本发明的栅极驱动电路由下而上逐级产生栅极驱动信号以及子栅极驱动信号。

[0098] 同理,图 9A 中的下拉单元 820 也可以利用其他连接关系的晶体管达成相同的功

能。

[0099] 请参照图 9B, 其为本发明由上而下依序产生主栅极驱动信号与子栅极驱动信号的信号示意图, 其使用第一上拉单元 810 连结而成的栅极驱动电路。

[0100] 如图 9B 所示, 选择 6 个时钟脉冲信号中的 HC6、HC2、HC1、HC4, 并且搭配第 n 个移位寄存器。其中, HC6 相位超前 HC1 有 60 度, HC1 相位超前 HC4 有 180 度, HC2 相位落后 HC1 有 60 度, 再者, HC1 与 HC4 信号不互相重叠。

[0101] 请同时参考图 9A 与图 9B, 第一上拉单元 810 接收前一级移位寄存器 (第 n-1 个移位寄存器) 所产生的第 n-1 个控制信号 Qn-1 与第 n-1 个主栅极驱动信号 Gn-1、以及相位最前面 HC6 时钟脉冲信号。

[0102] 在时间点 t1, 由于 HC5 信号 (未绘示), 使得 Qn-1 信号由 Vss 变化至第一电压电位 Va, 此时第一上拉单元 810 中的晶体管 T12 开启; 而在时间点 t2, HC6 信号为高逻辑电位进而开启晶体管 T11 使得 Gn-1 信号传递至晶体管 T11 源极并产生 Qn 信号, 而 Qn 信号即上升至第一电压电位 Va 并开启第一驱动晶体管 T1 以及第二驱动晶体管 T2。也就是说, 于时间点 t2, 第一上拉单元 810 开始动作, 而下拉单元 820 停止动作。

[0103] 于时间点 t3, 第一驱动晶体管 T1 以及第二驱动晶体管 T2 持续开启, 由于 HC1 信号为高逻辑电位而 HC4 信号为低逻辑电位, 因此 Gn 信号产生一脉冲, 并且利用下拉单元 820 的电容作为电荷泵 (charge pump) 使得 Qn 信号上升至第二高电位 Vb。

[0104] 在时间点 t4, 第一驱动晶体管 T1 以及第二驱动晶体管 T2 持续开启, 由于 HC1 信号为低逻辑电位而 HC4 信号为低逻辑电位, 因此 Gn 信号结束脉冲, 并且使得 Qn 信号下降至第三高电位 Vc。

[0105] 在时间点 t5, 第一驱动晶体管 T1 以及第二驱动晶体管 T2 持续开启, 由于 HC1 信号为低逻辑电位而 HC4 信号为高逻辑电位, 因此 Sn 信号产生一脉冲, 并且利用下拉单元 820 的电容作为电荷泵 (charge pump) 使得 Qn 信号上升至第四高电位 Vd。

[0106] 在时间点 t6, 第 n+5 个主栅极驱动信号 Gn+5 信号产生脉冲, 并进一步控制下拉单元 810 将 Qn 信号下拉至 Vss。同时, Sn 信号结束脉冲。而在时间点 t6 之后第 n 个移位寄存器 800 的动作结束。因此, 预定时间周期即由时间点 t2 至时间点 t6。

[0107] 当然, 本发明也可以利用 Sn+2 信号、Gn+6 信号、Sn+3 信号来使得 Qn 信号下拉至 Vss。而预定时间周期也会跟着变化。

[0108] 由上述本发明的第三实施例可知, 每一个移位寄存器皆可产生不会互相重叠的主栅极驱动信号 Gn 以及子栅极驱动信号 Sn。

[0109] 同理, 使用第二上拉单元 815 连结而成的栅极驱动电路并产生由下而上依序产生主栅极驱动信号与子栅极驱动信号, 也可以利用本发明的第三实施例来达成。也就是说, 选择 6 个时钟脉冲信号中的 HC1、HC5、HC6、HC3, 并且搭配图 9A 所示的移位寄存器 800。其中, HC5 相位超前 HC6 有 60 度, HC6 相位超前 HC3 有 180 度, HC1 相位落后 HC6 有 60 度, 且 HC3 与 HC6 信号不互相重叠。并且, 第一驱动晶体管 T1 漏极接收 HC6 信号; 第二驱动晶体管 T2 漏极接收 HC3 信号; 晶体管 T22 漏极接收 HC5 信号; 晶体管 T12 漏极接收 HC1 信号。其主要的动作原理与上述第一上拉单元 810 相同, 因此不再赘述。

[0110] 如前面所述, 第三实施例中的下拉单元 820 也可以利用其他连接关系的晶体管达成相同的功能。如图 10 所示, 为本发明栅极驱动电路中的移位寄存器 850 第四实施例。与

第三实施例的差异仅在于下拉单元 830，而其他电路皆相同。

[0111] 如图 10 所示，下拉单元 830 中的 Vss 为最低电压电位。其中，当 Qn 维持在 Vss 时，晶体管 T82、T84 为关闭状态。而由于晶体管 T81 连接至高逻辑电位 (Hi)，晶体管 T81、T83、T85、T86、T87 开启，因此 Gn、Sn、Qn 皆为 Vss。也就是说，当第一上拉单元 810 或者第二上拉单元 815 未动作时，Qn、Gn、Sn 皆会持续维持在 Vss。

[0112] 再者，当第一上拉单元 810 或者第二上拉单元 815 动作时，Qn 上升至第一电压电位时，此时晶体管 T82、T84 开启而晶体管 T85、T86、T87 皆关闭。此时，再经过一预定时间之后，利用第 n+5 主栅极驱动信号 Gn+5 或者 n-5 主栅极驱动信号 Gn-5 开启晶体管 T88 或者晶体管 T89 时，可以将 Qn 信号再次转换为 Vss。

[0113] 当然，第四实施例中的其相关信号示意图与图 9B 相同，不再赘述。

[0114] 请参照图 11，其所绘示为本发明第三实施例或第四实施例所公开的移位寄存器所组成的栅极驱动电路。GOA 面板的栅极驱动电路 900 中以第 10 至第 15 移位寄存器 910 ~ 915 来做说明，而其余的移位寄存器皆可利用相同的方式推得。

[0115] 很明显地，每个移位寄存器 910 ~ 915 根据前一级移位寄存器的控制信号以及主栅极驱动信号并搭配适当地选择 6 个时钟脉冲信号 (HC1 ~ HC6) 中不重叠的 3 个时钟脉冲信号而运作。

[0116] 因此，本发明的优点在于提出一种运用于电荷分享像素的整合面板型栅极驱动电路。GOA 面板上的栅极驱动电路中包括多个移位寄存器，每个移位寄存器可以输出不互相重叠的主栅极驱动信号与子栅极驱动信号，并且具有电路结构以及线路布局简单的特征。

[0117] 当然，本发明还可有其它多种实施例，在不背离本发明精神及其实质的情况下，熟悉本领域的技术人员当可根据本发明作出各种相应的改变和变形，但这些相应的改变和变形都应属于本发明所附的权利要求的保护范围。

图 1A

图 1B

图 3A

图 3B

图 5

图 6A

图 6B

图 7

图 8

图 9A

图 9B

图 10

图 11

|                |                                                            |         |            |

|----------------|------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 运用于电荷分享像素的整合面板型栅极驱动电路                                      |         |            |

| 公开(公告)号        | <a href="#">CN102184719A</a>                               | 公开(公告)日 | 2011-09-14 |

| 申请号            | CN201110112231.8                                           | 申请日     | 2011-04-25 |

| [标]申请(专利权)人(译) | 友达光电股份有限公司                                                 |         |            |

| 申请(专利权)人(译)    | 友达光电股份有限公司                                                 |         |            |

| 当前申请(专利权)人(译)  | 友达光电股份有限公司                                                 |         |            |

| [标]发明人         | 苏国彰<br>陈勇志<br>杨欲忠<br>林致颖                                   |         |            |

| 发明人            | 苏国彰<br>陈勇志<br>杨欲忠<br>林致颖                                   |         |            |

| IPC分类号         | G09G3/36                                                   |         |            |

| CPC分类号         | G09G3/3677 G09G2330/023 G09G2300/0447 G09G3/3659 G11C19/28 |         |            |

| 代理人(译)         | 王颖                                                         |         |            |

| 优先权            | 099144245 2010-12-16 TW                                    |         |            |

| 其他公开文献         | <a href="#">CN102184719B</a>                               |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>             |         |            |

### 摘要(译)

本发明公开一种运用于电荷分享像素的整合面板型栅极驱动电路。液晶面板上的栅极驱动电路中包括多个移位寄存器，每个移位寄存器皆可以输出不互相重叠的主栅极驱动信号与子栅极驱动信号，并且具有电路结构以及线路布局简单的特征。