## [12] 发明专利说明书

专利号 ZL 02140186.1

[45] 授权公告日 2009 年 10 月 14 日

[11] 授权公告号 CN 100550108C

[22] 申请日 2002.7.3 [21] 申请号 02140186.1

[30] 优先权

[32] 2001.7.6 [33] JP [31] 206987/2001

[73] 专利权人 日本电气株式会社

地址 日本东京

[72] 发明人 土 弘 内山义规

[56] 参考文献

CN1123121C 1999.6.9

审查员 许凌云

[74] 专利代理机构 中原信达知识产权代理有限责任公司

代理人 穆德骏

权利要求书 31 页 说明书 38 页 附图 25 页

## [54] 发明名称

驱动电路和液晶显示装置

## [57] 摘要

提供一种驱动电路，包括：工作范围达到高电位侧电源电位、低电位侧电源电位的第一、第二缓冲器电路 13、14，其输入端与将输入信号电压输入的一个输入端子共同连接，其输出端与输出端子共同连接；存储部 3，对于伽玛特性的标准时和调制时，存储并保持用于使第一和第二缓冲器电路能一起工作的范围内的输入信号电压所对应的基准数据；选择部 4，根据确定调制的调制信息，选择标准和与调制对应的基准数据并输出；和比较部 5，将输入的数据信号和所述选择部输出的基准数据进行比较。第一和第二缓冲器电路根据比较部 5 的比较结果信号和控制信号，控制其工作和停止。

1. 一种驱动电路，用于驱动输出负载，其特征在于，包括：

两个缓冲器电路，将输入端子共同连接到输入有输入信号电压的一个输入端子，将输出端子共同连接到一个输出端子中，其中，第一缓冲器电路具有高电位的工作范围，第二缓冲器电路具有低电位的工作范围，所述第一缓冲器电路和所述第二缓冲器电路具有可共同工作的范围；

存储部，存储并保持用于对所述第一缓冲器电路和第二缓冲器电路动作的切换进行选择的基准数据；

比较部，将输入的数据信号和所述基准数据进行比较；

控制装置，根据所述比较部的比较结果信号和控制信号，控制所述第一缓冲器电路和第二缓冲器电路在可工作的范围内工作和停止。

2. 根据权利要求 1 所述的驱动电路，其特征在于，所述基准数据与对应于能使所述第一缓冲器电路和第二缓冲器电路共同工作的范围内的电压的数据相对应。

3. 根据权利要求 1 所述的驱动电路，其特征在于，

在所述控制信号是表示动作的值时，所述比较部的比较结果信号表示在所述输入的数据为等于所述基准数据或者为比所述基准数据大的值的情况下，使所述第一缓冲器电路工作而使所述第二缓冲器电路停止；

在所述比较部的比较结果信号表示输入的数据为比所述基准数据小的值的情况下，所述第一缓冲器电路停止而所述第二缓冲器电路动作。

4. 根据权利要求 1 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括：

在低电位侧电源和所述输出端子间连接的构成源极跟随器的晶体管，

第一栅极偏压控制装置，输入输入信号电压，向所述构成源极跟随器的晶体管提供栅极偏置电压，和

对所述输出端子进行预充电的装置。

5. 根据权利要求 1 所述的驱动电路，其特征在于，

所述第二缓冲器电路包括：

在一个高电位侧电源和所述输出端子间连接的构成源极跟随器的晶体管，

第二栅极偏压控制装置，输入输入信号电压，向所述构成源极跟随器的晶体管提供栅极偏置电压，和

对所述输出端子进行预放电的装置。

6. 根据权利要求 1 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括：

在低电位侧电源和所述输出端子间连接的构成源极跟随器的第一晶体管；

第一栅极偏压控制装置，输入所述输入信号电压，向所述构成源极跟随器的晶体管提供栅极偏置电压；和

对所述输出端子进行预充电的装置，

所述第二缓冲器电路包括：

在高电位侧电源和所述输出端子间连接的构成源极跟随器的晶体管，

第二栅极偏压控制装置，输入输入信号电压，向所述构成源极跟随器的晶体管提供栅极偏置电压，和

对所述输出端子进行预放电的装置。

7. 根据权利要求 1 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括：

在所述输入端子和高电位侧电源间串联连接的第一电流源和第一开关；

源极与所述输入端子连接、栅极和漏极连接的第一导电型的第一 MOS 晶体管；

在所述第一 MOS 晶体管的漏极和低电位侧电源间串联连接的第二电流源和第二开关；

在所述输出端子和所述高电位侧电源间串联连接的第三电流源和第三开关；

源极与所述输出端子连接、栅极与所述第一 MOS 晶体管的栅极共同连接、漏极通过第四开关与低电位侧电源连接的第一导电型的第二 MOS 晶体管；

在所述输出端子和所述高电位侧电源之间，具有用于控制所述输出端子的充电的第五开关。

8. 根据权利要求 1 所述的驱动电路，其特征在于，

所述第二缓冲器电路包括：

在所述输入端子和低电位侧电源间串联连接的第四电流源和第六开关；

源极与所述输入端子连接、栅极和漏极连接的第二导电型的第三 MOS 晶体管；

在所述第三 MOS 晶体管的漏极和高电位侧电源间串联连接的第五电流源和第七开关；

在所述输出端子和所述低电位侧电源间串联连接的第六电流源和第八开关；

源极与所述输出端子连接、栅极与所述第三 MOS 晶体管的栅极共同连接、漏极通过第九开关与所述高电位侧电源连接的第二导电型的第四 MOS 晶体管；

在所述输出端子和所述高电位侧电源之间，具有用于控制所述输出端子的放电的第十开关。

9. 根据权利要求 1 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括：

在所述输入端子和高电位侧电源间串联连接的第一电流源和第一开关；

源极与所述输入端子连接、栅极和漏极连接的第一导电型的第一 MOS 晶体管；

在所述第一 MOS 晶体管的漏极和低电位侧电源间串联连接的第二电流源和第二开关；

在所述输出端子和所述高电位侧电源间串联连接的第三电流源和第三开关；

源极与所述输出端子连接、栅极与所述第一 MOS 晶体管的栅极共同连接、漏极通过第四开关与低电位侧电源连接的第一导电型的第二 MOS 晶体管，

在所述输出端子和所述高电位侧电源之间，具有用于控制所述输出端子的充电的第五开关，

所述第二缓冲器电路包括：

在所述输入端子和低电位侧电源间串联连接的第四电流源和第六开关；

源极与所述输入端子连接、栅极和漏极连接的第二导电型的第三 MOS 晶体管；

在所述第三 MOS 晶体管的漏极和高电位侧电源间串联连接的第五电流源和第七开关；

在所述输出端子和所述低电位侧电源间串联连接的第六电流源和第八开关；

源极与所述输出端子连接、栅极与所述第三 MOS 晶体管的栅极共同连接、漏极通过第九开关与所述高电位侧电源连接的第二导电型的第四 MOS 晶体管，

在所述输出端子和所述低电位侧电源之间，具有用于控制所述输出端子的放电的第十开关。

10. 根据权利要求 1 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括由差动放大电路构成的电压跟随器电路，具有由第二导电型的 MOS 晶体管对所构成的差动对，所述输入端子与同相输入端连接，所述输出端子与反相输入端连接。

11. 根据权利要求 10 所述的驱动电路，其特征在于，具有对所述输出端子预充电和预放电的装置。

12. 根据权利要求 1 所述的驱动电路，其特征在于，

所述第二缓冲器电路包括由差动放大电路构成的电压跟随器电路，具有第一导电型的 MOS 晶体管对所构成的差动对，所述输入端子与同相输入端连接，所述输出端子与反相输入端连接。

13. 根据权利要求 1 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括由差动放大电路构成的电压跟随器电路，具有由第二导电型的 MOS 晶体管对所构成的差动对，其所述输入端子与同相输入端连接，所述输出端子与反相输入端连接。

所述第二缓冲器电路包括由差动放大电路构成的电压跟随器电路，具有第一导电型的 MOS 晶体管对所构成的差动对，所述输入端子与同相输入端连接，所述输出端子与反相输入端连接。

14. 根据权利要求 1 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括

差动级，具有：

由第二导电型的 MOS 晶体管对所构成的差动对；

在所述差动对的输出和高电位侧电源间连接的负载电路；

驱动所述差动对的电流源；和

第一开关，它控制在所述电流源和低电位电源间电流通路的导通和截止，

MOS 晶体管，输入所述差动对的一个输出，其输出与所述输出

端子连接，

在所述输出端子和低电位侧电源连接的电流源以及开关，

所述差动对的 MOS 晶体管对的栅级与所述输入端子和所述输出端子连接。

15. 根据权利要求 14 所述的驱动电路，其特征在于，具有对所述输出端子预充电和预放电的装置。

16. 根据权利要求 1 所述的驱动电路，其特征在于，

所述第二缓冲器电路包括

差动级，具有：

由第一导电型的 MOS 晶体管对所构成的差动对；

在所述差动对的输出和高电位侧电源间连接的负载电路；

驱动所述差动对的电流源；和

控制所述电流源和所述高电位电源之间电流通路的导通和截止的开关，

MOS 晶体管，输入所述差动对的一个输出，其输出与所述输出端子连接，

在所述输出端子和高电位侧电源间连接的电流源以及开关，

所述差动对的 MOS 晶体管对的栅级与所述输入端子和所述输出端子连接。

17. 根据权利要求 1 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括

第一差动级，具有：

由第二导电型的第一和第二 MOS 晶体管对所构成的第一差动对；

在所述第一差动对的输出和低电位侧电源间连接的第一负载电路；

驱动所述第一差动对的第一电流源；和

第一开关，它控制在所述第一电流源和低电位电源间电流通路的导通和截止，

第三 MOS 晶体管，输入所述第一差动对的一个输出，其输出与所述输出端子连接，

在所述输出端子和高电位侧电源连接的第二电流源以及第二开关，

所述第一差动对的 MOS 晶体管对的栅级与所述输入端子和所述输出端子连接，

所述第二缓冲器电路包括

第二差动级，具有：

由第一导电型的第四和第五 MOS 晶体管对所构成的第二差动对；

在所述第二差动对的输出和低电位侧电源间连接的第二负载电路；

驱动所述第二差动对的第三电流源；和

第三开关，控制在所述第三电流源和高电位电源间电流通路的导通和截止，

第六 MOS 晶体管，输入所述第二差动对的一个输出，其输出与所述输出端子连接，

在所述输出端子和高电位侧电源间连接的第四电流源以及第四开关，

所述第二差动对的 MOS 晶体管对的栅级与所述输入端子和所述输出端子连接。

18. 根据权利要求 1 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括：

电压跟随器电路，由差动放大电路构成，具有

由第二导电型的 MOS 晶体管对所构成的差动对，其所述输入端子与同相输入端连接，所述输出端子与反相输入端连接；

连接在低电位侧电源和所述输出端子之间的构成源级跟随器的晶

体管；

第一栅极偏压控制装置，输入所述输入信号电压，向所述构成源极跟随器的晶体管提供栅极偏置电压。

19. 根据权利要求 18 所述的驱动电路，其特征在于，具有对所述输出端子预充电和预放电的装置。

20. 根据权利要求 1 所述的驱动电路，其特征在于，

所述第二缓冲器电路包括：

电压跟随器电路，由差动放大电路构成，具有

由第一导电型的 MOS 晶体管对所构成的差动对，其所述输入端子与同相输入端连接，所述输出端子与反相输入端连接；

连接在高电位侧电源和所述输出端子之间的构成源级跟随器的晶体管；

第二栅极偏压控制装置，输入所述输入信号电压，向所述构成源极跟随器的晶体管提供栅极偏置电压。

21. 根据权利要求 1 所述的驱动电路，其特征在于，包括

所述第一缓冲器电路包括：

第一电压跟随器电路，由差动放大电路构成，具有

由第二导电型的 MOS 晶体管对所构成的差动对，其所述输入端子与同相输入端连接，所述输出端子与反相输入端连接；

连接在低电位侧电源和所述输出端子之间的构成源级跟随器的晶体管；

第一栅极偏压控制装置，输入所述输入信号电压，向所述构成源极跟随器的晶体管提供栅极偏置电压，

所述第二缓冲器电路包括：

第二电压跟随器电路，由差动放大电路构成，具有

由第一导电型的 MOS 晶体管对所构成的差动对，其所述输入端子与同相输入端连接，所述输出端子与反相输入端连接；

连接在高电位侧电源和所述输出端子之间的构成源级跟随器的晶体管；

第二栅极偏压控制装置，输入所述输入信号电压，向所述构成源极跟随器的晶体管提供栅极偏置电压。

22. 根据权利要求 1 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括

差动级，具有：

由第二导电型的第一和第二 MOS 晶体管对所构成的差动对；

在所述差动对的输出和所述高电位侧电源之间连接的有源负载电路；

驱动所述差动对的第一电流源；和

第一开关，它控制在所述第一电流源和低电位电源间电流通路的导通和截止，

以及

第三 MOS 晶体管，输入所述差动对的一个输出，其输出与所述输出端子连接，

所述第一和第二 MOS 晶体管对的栅级与所述输入端子和所述输出端子连接，

在所述输入端子和高电位侧电源间串联连接的第二电流源和第二开关，

第一导电型的第四 MOS 晶体管，源极与所述输入端子连接，栅极和漏极连接，

在所述第四 MOS 晶体管的漏极和低电位侧电源间串联连接的第三电流源和第三开关，

在所述输出端子和所述高电位侧电源间串联连接的第四电流源和第四开关，

第一导电型的第五 MOS 晶体管，其源极与所述输出端子连接，栅极与所述第四 MOS 晶体管的栅极共同连接，漏极通过第五开关与低电位侧电源连接。

23. 根据权利要求 1 所述的驱动电路，其特征在于，

所述第二缓冲器电路包括

差动级，具有：

由第一导电型的第六和七 MOS 晶体管对所构成的差动对；

在所述差动对的输出和低电位侧电源间连接的有源负载电路；

驱动所述差动对的第五电流源；和

第六开关，它控制在所述第五电流源和高电位电源间电流通路的

导通和截止，

以及

第八 MOS 晶体管，输入所述差动对的输出，其输出与所述输出

端子连接，

所述第六和第七 MOS 晶体管对的栅级与所述输入端子和所述输

出端子连接，

在所述输入端子和低电位侧电源间串联连接的第六电流源和第七

开关，

第二导电型的第九 MOS 晶体管，源极与所述输入端子连接，栅

极和漏极连接，

在所述第九 MOS 晶体管的漏极和高电位侧电源间串联连接的第

七电流源和第八开关，

在所述输出端子和所述低电位侧电源间串联连接的第八电流源和

第九开关，

第一导电型第十 MOS 晶体管，其源极与所述输出端子连接，栅

极与所述第九 MOS 晶体管的栅极共同连接，漏极通过第十开关与高

电位侧电源连接。

24. 根据权利要求 1 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括

差动级，具有：

由第二导电型的第一和第二 MOS 晶体管对所构成的第一差动

对；

在所述第一差动对的输出和所述高电位侧电源间连接的有源负载电路；

驱动所述第一差动对的第一电流源； 和

第一开关，它控制在所述第一电流源和低电位电源间电流通路的导通和截止，

以及

第三 MOS 晶体管，输入所述第一差动对的一个输出，其输出与所述输出端子连接，

所述第一和第二 MOS 晶体管对的栅级与所述输入端子和所述输出端子连接，

在所述输入端子和高电位侧电源间串联连接的第二电流源和第二开关，

第一导电型的第四 MOS 晶体管，源极与所述输入端子连接，栅极和漏极连接，

在所述第四 MOS 晶体管的漏极和所述低电位侧电源间串联连接的第三电流源和第三开关，

在所述输出端子和所述高电位侧电源间串联连接的第四电流源和第四开关，

第一导电型第五 MOS 晶体管，其源极与所述输出端子连接，栅极与所述第四 MOS 晶体管的栅极共同连接，漏极通过第五开关与低电位侧电源连接，

所述第二缓冲器电路包括

差动级，具有：

由第一导电型的第六和七 MOS 晶体管对所构成的第二差动对；

在所述第二差动对的输出和所述低电位侧电源间连接的有源负载电路；

驱动所述第二差动对的第五电流源； 和

第六开关，它控制在所述第五电流源和高电位电源间电流通路的导通和截止，

以及

第八 MOS 晶体管，输入所述第二差动对的一个输出，其输出与所述输出端子连接，

所述第六和第七 MOS 晶体管对的栅级与所述输入端子和所述输出端子连接，

在所述输入端子和低电位侧电源间串联连接的第六电流源和第七开关，

第二导电型的第九 MOS 晶体管，源极与所述输入端子连接，栅极和漏极连接，

在所述第九 MOS 晶体管的漏极和高电位侧电源间串联连接的第七电流源和第八开关，

在所述输出端子和所述低电位侧电源间串联连接的第八电流源和第九开关，

第一导电型第十 MOS 晶体管，其源极与所述输出端子连接，栅极与所述第九 MOS 晶体管的栅极共同连接，漏极通过第十开关与高电位侧电源连接。

25. 一种液晶显示装置，其特征在于，在数据线的驱动中使用根据权利要求 1 所述的驱动电路。

26. 一种驱动电路，其特征在于，包括：

两个缓冲器电路，将输入端子共同连接到输入有输入信号电压的一个输入端子，将输出端子共同连接到一个输出端子中，其中，第一缓冲器电路的工作范围为高电位侧电源电位，第二缓冲器电路的工作范围为低电位侧电源电位，所述第一缓冲器电路和所述第二缓冲器电路具有可共同工作的范围；

存储部，用于保存第一、第二极性的基准数据，所述基准数据对应于输入的数字数据和信号电压之间的关系，对于根据预定的基准电压信号而确定特性的第一、第二极性的每一个极性，判断所述第一缓冲器电路和第二缓冲器电路动作的切换；

选择部，输入确定极性的极性信号，根据所述极性信号的值，选择所述第一、第二极性的基准数据中之一；

比较部，将输入的数字数据和从所述选择部输出的基准数据进行比较；

控制装置，根据所述比较部的比较结果信号和控制信号，控制所述第一缓冲器电路和第二缓冲器电路在可工作的范围内的工作和停止。

27. 根据权利要求 25 所述的驱动电路，其特征在于，所述第一极性和第二极性的基准数据对应于与在使所述第一缓冲器电路和第二缓冲器电路能够同时工作的范围内的电压对应的数据。

28. 一种驱动电路，其特征在于，包括：

两个缓冲器电路，将输入端子共同连接到输入有输入信号电压的一个输入端子，将输出端子共同连接到一个输出端子中，其中，第一缓冲器电路的工作范围达到高电位侧电源电位，第二缓冲器电路的工作范围达到低电位侧电源电位；

存储部，对于与灰度和信号电压相关的特性的标准状态以及调制时的状态，保存与所述第一缓冲器电路和第二缓冲器电路能够同时工作的范围内的输入信号电压对应的基准数据；

选择部，根据确定调制的调制信息，选择与标准或调制对应的基准数据并输出；

比较部，将输入的数据和从所述选择部输出的基准数据进行比较；

控制装置，根据所述比较部的比较结果信号和控制信号，控制所述第一缓冲器电路和第二缓冲器电路的工作和停止。

29. 根据权利要求 28 所述的驱动电路，其特征在于，

所述存储部保存与调制种类对应而规定的基准数据；

在所述选择部中，根据输入的调制信息，选择与调制种类对应的

---

基准数据输出。

30. 一种驱动电路，其特征在于，包括：

两个缓冲器电路，将输入端子共同连接到输入有输入信号电压的一个输入端子，将输出端子共同连接到一个输出端子中，其中，第一缓冲器电路的工作范围达到高电位侧电源电位，第二缓冲器电路的工作范围达到低电位侧电源电位；

第一存储部，用于分别对于与灰度和信号电压相关的特性的标准状态以及调制时的状态，保存与所述第一缓冲器电路和第二缓冲器电路能够同时工作的范围内的输入信号电压对应的正极性的基准数据；

第二存储部，用于分别对于与灰度和信号电压相关的特性的标准状态以及调制时的状态，保存与所述第一缓冲器电路和第二缓冲器电路能够同时工作的可驱动切换范围内的电压对应的负极性的基准数据；

选择部，根据确定极性的极性信号，选择所述第一、第二存储部之一，根据确定调制的调制信息，选择与标准或调制对应的基准数据并输出；

比较部，将输入的数据和从所述选择部输出的基准数据进行比较；

控制装置，根据所述比较部的比较结果信号和控制信号，控制所述第一缓冲器电路和第二缓冲器电路的工作和停止。

31. 根据权利要求 30 所述的驱动电路，其特征在于，

所述第一存储部保存与调制种类对应而规定的正极性基准数据；

所述第二存储部保存与调制种类对应而规定的负极性基准数据；

在所述选择部中，根据极性信号，选择所述第一、第二存储部之一，根据输入的调制信息，选择输出与调制种类对应的基准数据。

32. 根据权利要求 30 所述的驱动电路，其特征在于，所述极性信号作为表示液晶显示装置的相对电极的公共电位 (Vcom) 的反相驱

动中的极性的逻辑值。

33. 根据权利要求 30 所述的驱动电路，其特征在于，所述第一存储部、所述第二存储部、所述选择部的至少一个构成为与所述驱动电路的外部设置的所述驱动电路电连接。

34. 一种驱动电路，其特征在于，包括：

灰度电压发生装置，具有在第一、第二参考电压间串联连接的多个电阻，从各抽头生成灰度电压；

译码电路，输入数字信号，从所述灰度电压发生装置的输出电压选择对应的电压并输出；

多个根据权利要求 2 所述的驱动电路，将所述译码电路的输出输入，驱动输出负载；

对所述驱动电路的预定个数，至少有一个共用的所述第一和第二存储部、所述选择部。

35. 一种驱动电路，用于驱动输出负载，其特征在于，包括：

两个缓冲器电路，将输入端子共同连接到输入有输入信号电压的一个输入端子，将输出端子共同连接到一个输出端子中，其中，第一缓冲器电路至少具有高电位侧电源电位的工作范围，第二缓冲器电路至少具有低电位侧电源电位的工作范围；

基准电压发生装置，产生与能使所述第一缓冲器电路和第二缓冲器电路共同动作的电压范围对应的基准电压；

比较部，将从所述基准电压发生装置输出的基准电压和所述输入信号电压进行比较；

控制装置，根据所述比较部的比较结果信号和控制信号，控制所述第一缓冲器电路和第二缓冲器电路在能够工作的范围内工作和停止。

36. 根据权利要求 35 所述的驱动电路，其特征在于，

在所述控制信号是表示动作的值时，在所述比较部的比较结果信号表示所述输入的数据为等于所述基准数据或者为比所述基准数据大的值的情况下，使所述第一缓冲器电路工作而使所述第二缓冲器电路停止；

在所述比较部的比较结果信号表示所述输入的数据为比所述基准数据小的值的情况下，所述第一缓冲器电路停止，而所述第二缓冲器电路工作。

37. 根据权利要求 35 所述的驱动电路，其特征在于，所述比较器具有：

将所述输入信号电压和所述基准电压差动输入的差动放大电路；

通过开关与所述差动放大电路的输出连接的保持电路。

38. 根据权利要求 35 所述的驱动电路，其特征在于，

所述比较器具有：

将所述输入信号电压和所述基准电压差动输入的差动放大电路；

通过第一开关与所述差动放大电路的一个输出端连接的触发器电

路，

所述触发器具有：

输入端与所述第一开关连接的第一反相器；

输出端与所述第一开关的输出端连接的第二反相器；

在所述第二反相器的输出端和所述第一反相器的输入端之间连接

的第二开关，

将所述第二反相器的输出信号作为比较结果信号输出，

进行这样的控制，在所述差动放大电路动作时，所述第一开关为

导通状态，在接收所述差动放大电路的输出并锁存的情况下，为使所

述第一开关截止、而所述第二开关导通的状态。

39. 根据权利要求 35 所述的驱动电路，其特征在于，

所述比较器具有：

将所述输入信号电压和所述基准电压差动输入的差动放大电路；

和

触发器电路，

所述差动放大电路具有：

将所述输入信号电压和所述基准电压差动输入的差动对；

在驱动所述差动对的电流源的电源通路中插入的第一开关；

接收所述差动对的输出的输出级晶体管；

在所述输出级晶体管的电源通路中插入的第二开关；

所述触发器具有：

输入端通过第三开关与所述输出级晶体管的输出端连接的第一反相器；

输入端与所述第一反相器的输出端连接的第二反相器；

在所述第二反相器的输出端和所述第一反相器的输入端之间连接的第四开关，

所述第二反相器的输出端信号和/或所述第一反相器的输出端信号作为比较结果信号输出，

在所述差动放大电路工作时，所述第一、第二、第三开关全部为导通状态，

进行这样的控制，在触发器接收所述差动放大电路的输出而锁存时，所述第一开关、所述第二开关、所述第三开关截止，所述第四开关为导通状态。

40. 根据权利要求 35 所述的驱动电路，其特征在于，

所述比较器具有：

将所述输入信号电压和所述基准电压差动输入的差动放大电路；

和

触发器电路，

所述差动放大电路具有：

将所述输入信号电压和所述基准电压差动输入的差动对；

在驱动所述差动对的电流源的电源通路中插入的第一开关；

接收所述差动对的输出的输出级晶体管；

在所述输出级晶体管的电源通路中插入的第二开关；

所述触发器具有：

输入端通过第三开关与所述输出级晶体管的输出端连接的第一定时反相器；

输入端与所述第一定时反相器的输出端连接的第二定时反相器；

所述第二定时反相器的输出端和所述第一定时反相器的输入端连接，

所述第二定时反相器的输出端信号和/或所述第一定时反相器的输出端信号作为比较结果信号输出，

进行这样的控制，在所述差动放大电路动作时，所述第一、第二、第三开关全部为导通状态，在接收所述差动放大电路的输出而锁存时，所述第一开关、所述第二开关、所述第三开关截止。

41. 根据权利要求 35 所述的驱动电路，其特征在于，

所述比较器具有：

将所述输入信号电压和所述基准电压差动输入的差动放大电路；

和

触发器电路，

所述差动放大电路具有：

将所述输入信号电压和所述基准电压差动输入的差动对；

在驱动所述差动对的电流源的电源路径中插入的第一开关；

接收所述差动对的输出的输出级晶体管；

在所述输出级晶体管的电源通路中插入的第二开关；

所述触发器具有：

输入端通过第三开关与所述输出级晶体管的输出端连接的第一定时反相器，它具有在构成 CMOS 反相器的 P 沟道 MOS 晶体管的源极和所述高电位侧电源间连接的第四开关，和在构成所述 CMOS 反相器的 N 沟道 MOS 晶体管的源极和低电位侧电源间连接的第五开关；

输入端与所述第一定时反相器的输出端连接的第二定时反相器，

它具有在构成 CMOS 反相器的 P 沟道 MOS 晶体管的源极和所述高电位侧电源间连接的第六开关，和在构成所述 CMOS 反相器的 N 沟道 MOS 晶体管的源极和低电位侧电源间连接的第七开关；

所述第二定时反相器的输出端和所述第一定时反相器的输入端连接，

所述第二定时反相器的输出端信号或所述第一、第二定时反相器的输出端信号作为比较结果信号输出，

进行这样的控制，在所述差动放大电路工作时，所述第一、第二、第三开关全部为导通状态，在接收所述差动放大电路的输出而锁存时，所述第一开关、所述第二开关、所述第三开关截止，所述第四、第五、第六和第七开关为导通。

42. 根据权利要求 40 或 41 所述的驱动电路，其特征在于，所述第二定时反相器的输出端的负载电容的电容值比所述第一定时反相器的输出端的负载电容的电容值大。

43. 根据权利要求 35 所述的驱动电路，其特征在于，

所述基准电压发生装置具有在所述第一和第二参考电压之间连接的多个电阻和开关，在所述开关导通时，从所述电阻的连接点输出用所述第一、第二缓冲器电路工作范围的重叠规定的驱动切换范围内的电压。

44. 根据权利要求 35 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括：

在低电位侧电源和所述输出端子间连接的构成源极跟随器的晶体管；

第一偏压控制装置，将输入信号电压输入，向所述构成源极跟随器的晶体管提供栅极偏置电压；和

对所述输出端子预充电的装置。

45. 根据权利要求 35 所述的驱动电路，其特征在于，

所述第二缓冲器电路包括：

在高电位侧电源和所述输出端子间连接的构成源极跟随器的晶体管；

第二偏压控制装置，将输入信号电压输入，向所述构成源极跟随器的晶体管提供栅极偏置电压；和

对所述输出端子预放电的装置。

46. 根据权利要求 35 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括：

在低电位侧电源和所述输出端子间连接的构成源极跟随器的第一晶体管；

第一偏压控制装置，将输入信号电压输入，向所述构成源极跟随器的晶体管提供栅极偏置电压；和

对所述输出端子预充电的装置，

所述第二缓冲器电路包括：

在高电位侧电源和所述输出端子间连接的构成源极跟随器的第二晶体管；

第二偏压控制装置，将输入信号电压输入，向所述构成源极跟随器的晶体管提供栅极偏置电压；和

对所述输出端子预放电的装置。

47. 根据权利要求 35 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括：

在所述输入端子和高电位侧电源之间串连接的第一电流源和第一开关；

源极与所述输入端子连接、栅极和漏极连接的第一导电型的第一 MOS 晶体管；

在所述第一 MOS 晶体管的漏极和低电位侧电源间串联连接的第二电流源和第二开关；

在所述输出端子和所述高电位侧电源间串联连接的第三电流源和第三开关；

源极与所述输出端子连接、栅极与所述第一 MOS 晶体管的栅极共同连接、漏极通过第四开关与低电位侧电源连接的第一导电型的第二 MOS 晶体管，

在所述输出端子和所述高电位侧电源之间，具有用于控制所述输出端子的充电的第五开关。

48. 根据权利要求 35 所述的驱动电路，其特征在于，

所述第二缓冲器电路包括：

在所述输入端子和低电位侧电源间串联连接的第四电流源和第六开关；

源极与所述输入端子连接、栅极和漏极连接的第二导电型的第三 MOS 晶体管；

在所述第三 MOS 晶体管的漏极和高电位侧电源间串联连接的第五电流源和第七开关；

在所述输出端子和所述低电位侧电源间串联连接的第六电流源和第八开关；

源极与所述输出端子连接、栅极与所述第三 MOS 晶体管的栅极共同连接、漏极通过第九开关与所述高电位侧电源连接的第二导电型的第四 MOS 晶体管，

在所述输出端子和所述低电位侧电源之间，具有用于控制所述输出端子的放电的第十开关。

49. 根据权利要求 35 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括：

在所述输入端子和高电位侧电源之间串连接的第一电流源和第一开关；

源极与所述输入端子连接、栅极和漏极连接的第一导电型的第一 MOS 晶体管；

在所述第一 MOS 晶体管的漏极和低电位侧电源间串联连接的第二电流源和第二开关；

在所述输出端子和所述高电位侧电源间串联连接的第三电流源和第三开关；

源极与所述输出端子连接、栅极与所述第一 MOS 晶体管的栅极共同连接、漏极通过第四开关与低电位侧电源连接的第一导电型的第二 MOS 晶体管，

在所述输出端子和所述高电位侧电源之间，具有用于控制所述输出端子的充电的第五开关，

以及

所述第二缓冲器电路包括：

在所述输入端子和低电位侧电源间串联连接的第四电流源和第六开关；

源极与所述输入端子连接、栅极和漏极连接的第二导电型的第三 MOS 晶体管；

在所述第三 MOS 晶体管的漏极和高电位侧电源间串联连接的第五电流源和第七开关；

在所述输出端子和所述低电位侧电源间串联连接的第六电流源和第八开关；

源极与所述输出端子连接、栅极与所述第三 MOS 晶体管的栅极共同连接、漏极通过第九开关与所述高电位侧电源连接的第二导电型的第四 MOS 晶体管，

在所述输出端子和所述低电位侧电源之间，具有用于控制所述输出端子的放电的第十开关。

50. 根据权利要求 35 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括由差动放大电路构成的电压跟随器电路，具有由第二导电型的 MOS 晶体管对所构成的差动对，所述输入端子与同相输入端连接，所述输出端子与反相输入端连接。

51. 根据权利要求 35 所述的驱动电路，其特征在于，

所述第二缓冲器电路包括由差动放大电路构成的电压跟随器电

路，具有第一导电型的 MOS 晶体管对所构成的差动对，所述输入端

子与同相输入端连接，所述输出端子与反相输入端连接。

52. 根据权利要求 35 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括由差动放大电路构成的电压跟随器电

路，具有由第二导电型的 MOS 晶体管对所构成的差动对，其所述输

入端子与同相输入端连接，所述输出端子与反相输入端连接。

所述第二缓冲器电路包括由差动放大电路构成的电压跟随器电

路，具有第一导电型的 MOS 晶体管对所构成的差动对，所述输入端

子与同相输入端连接，所述输出端子与反相输入端连接。

53. 根据权利要求 51 所述的驱动电路，其特征在于，具有对所

述输出端子预充电和预放电的装置。

54. 根据权利要求 35 所述的驱动电路，

所述第一缓冲器电路包括

差动级，具有：

由第二导电型的 MOS 晶体管对所构成的差动对；

在所述差动对的输出和高电位侧电源间连接的负载电路；

驱动所述差动对的电流源；和

第一开关，它控制在所述电流源和低电位电源间电流通路的导通

和截止，

MOS 晶体管，输入所述差动对的一个输出，其输出与所述输出

端子连接，

在所述输出端子和低电位侧电源连接的电流源以及开关，

所述差动对的 MOS 晶体管对的栅级与所述输入端子和所述输出

端子连接。

55. 根据权利要求 35 所述的驱动电路，其特征在于，

所述第二缓冲器电路包括

差动级，具有：

由第一导电型的 MOS 晶体管对所构成的差动对；

在所述差动对的输出和低电位侧电源间连接的负载电路；

驱动所述差动对的电流源；和

控制所述电流源和所述高电位电源之间电流通路的导通和截止的开关，

MOS 晶体管，输入所述差动对的一个输出，其输出与所述输出端子连接，

在所述输出端子和高电位侧电源间连接的电流源以及开关，

所述差动对的 MOS 晶体管对的栅级与所述输入端子和所述输出端子连接。

56. 根据权利要求 35 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括

第一差动级，具有：

由第二导电型的第一和第二 MOS 晶体管对所构成的第一差动对；

在所述第一差动对的输出和高电位侧电源间连接的第一负载电路；

驱动所述第一差动对的第一电流源；和

第一开关，它控制在所述第一电流源和低电位电源间电流通路的导通和截止，

第三 MOS 晶体管，输入所述第一差动对的一个输出，其输出与所述输出端子连接，

在所述输出端子和高电位侧电源连接的第二电流源以及第二开关，

所述第一差动对的 MOS 晶体管对的栅级与所述输入端子和所述输出端子连接，

所述第二缓冲器电路包括

第二差动级，具有：

由第一导电型的第四和第五 MOS 晶体管对所构成的第二差动对；

在所述第二差动对的输出和低电位侧电源间连接的第二负载电路；

驱动所述第二差动对的第三电流源；和

第三开关，控制在所述第三电流源和高电位电源间电流通路的导通和截止，

第六 MOS 晶体管，输入所述第二差动对的一个输出，其输出与所述输出端子连接，

在所述输出端子和高电位侧电源间连接的第四电流源以及第四开关，

所述第二差动对的 MOS 晶体管对的栅级与所述输入端子和所述输出端子连接。

57. 根据权利要求 35 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括：

电压跟随器电路，由差动放大电路构成，具有

由第二导电型的 MOS 晶体管对所构成的差动对，其所述输入端子与同相输入端连接，所述输出端子与反相输入端连接；

连接在低电位侧电源和所述输出端子之间的构成源级跟随器的晶体管；

第一栅极偏压控制装置，输入所述输入信号电压，向所述构成源极跟随器的晶体管提供栅极偏置电压。

58. 根据权利要求 35 所述的驱动电路，其特征在于，

所述第二缓冲器电路包括：

电压跟随器电路，由差动放大电路构成，具有

由第一导电型的 MOS 晶体管对所构成的差动对，其所述输入端

子与同相输入端连接，所述输出端子与反相输入端连接；

连接在高电位侧电源和所述输出端子之间的构成源级跟随器的晶体管；

第二栅极偏压控制装置，输入所述输入信号电压，向所述构成源极跟随器的晶体管提供栅极偏置电压。

59. 根据权利要求 35 所述的驱动电路，其特征在于，包括

所述第一缓冲器电路包括：

第一电压跟随器电路，由差动放大电路构成，具有

由第二导电型的 MOS 晶体管对所构成的差动对，其所述输入端子与同相输入端连接，所述输出端子与反相输入端连接；

连接在低电位侧电源和所述输出端子之间的构成源级跟随器的晶体管；

第一栅极偏压控制装置，输入所述输入信号电压，向所述构成源极跟随器的晶体管提供栅极偏置电压，

所述第二缓冲器电路包括：

第二电压跟随器电路，由差动放大电路构成，具有

由第一导电型的 MOS 晶体管对所构成的差动对，其所述输入端子与同相输入端连接，所述输出端子与反相输入端连接；

连接在高电位侧电源和所述输出端子之间的构成源级跟随器的晶体管；

第二栅极偏压控制装置，输入所述输入信号电压，向所述构成源极跟随器的晶体管提供栅极偏置电压。

60. 根据权利要求 35 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括

差动级，具有：

由第二导电型的第一和第二 MOS 晶体管对所构成的差动对；

在所述差动对的输出和所述高电位侧电源之间连接的有源负载电

路；

驱动所述差动对的第一电流源；和

第一开关，它控制在所述第一电流源和低电位电源间电流通路的导通和截止，

以及

第三 MOS 晶体管，输入所述差动对的一个输出，其输出与所述输出端子连接，

所述第一和第二 MOS 晶体管对的栅级与所述输入端子和所述输出端子连接，

在所述输入端子和高电位侧电源间串联连接的第二电流源和第二开关，

第一导电型的第四 MOS 晶体管，源极与所述输入端子连接，栅极和漏极连接，

在所述第四 MOS 晶体管的漏极和低电位侧电源间串联连接的第三电流源和第三开关，

在所述输出端子和所述高电位侧电源间串联连接的第四电流源和第四开关，

第一导电型的第五 MOS 晶体管，其源极与所述输出端子连接，栅极与所述第四 MOS 晶体管的栅极共同连接，漏极通过第五开关与低电位侧电源连接。

61. 根据权利要求 35 所述的驱动电路，其特征在于，

所述第二缓冲器电路包括

差动级，具有：

由第一导电型的第六和七 MOS 晶体管对所构成的差动对；

在所述差动对的输出和低电位侧电源间连接的有源负载电路；

驱动所述差动对的第五电流源；和

第六开关，它控制在所述第五电流源和高电位电源间电流通路的导通和截止，

以及

第八 MOS 晶体管，输入所述差动对的输出，其输出与所述输出

端子连接，

所述第六和第七 MOS 晶体管对的栅级与所述输入端子和所述输出端子连接，

在所述输入端子和低电位侧电源间串联连接的第六电流源和第七开关，

第二导电型的第九 MOS 晶体管，源极与所述输入端子连接，栅极和漏极连接，

在所述第九 MOS 晶体管的漏极和高电位侧电源间串联连接的第七电流源和第八开关，

在所述输出端子和所述低电位侧电源间串联连接的第八电流源和第九开关，

第一导电型第十 MOS 晶体管，其源极与所述输出端子连接，栅极与所述第九 MOS 晶体管的栅极共同连接，漏极通过第十开关与高电位侧电源连接。

62. 根据权利要求 35 所述的驱动电路，其特征在于，

所述第一缓冲器电路包括

差动级，具有：

由第二导电型的第一和第二 MOS 晶体管对所构成的第一差动对；

在所述第一差动对的输出和所述高电位侧电源间连接的有源负载电路；

驱动所述第一差动对的第一电流源；和

第一开关，它控制在所述第一电流源和低电位电源间电流通路的导通和截止，

以及

第三 MOS 晶体管，输入所述第一差动对的一个输出，其输出与所述输出端子连接，

所述第一和第二 MOS 晶体管对的栅级与所述输入端子和所述输出端子连接，

在所述输入端子和高电位侧电源间串联连接的第二电流源和第二开关，

第一导电型的第四 MOS 晶体管，源极与所述输入端子连接，栅极和漏极连接，

在所述第四 MOS 晶体管的漏极和所述低电位侧电源间串联连接的第三电流源和第三开关，

在所述输出端子和所述高电位侧电源间串联连接的第四电流源和第四开关，

第一导电型第五 MOS 晶体管，其源极与所述输出端子连接，栅极与所述第四 MOS 晶体管的栅极共同连接，漏极通过第五开关与低电位侧电源连接，

所述第二缓冲器电路包括

差动级，具有：

由第一导电型的第六和七 MOS 晶体管对所构成的第二差动对；

在所述第二差动对的输出和所述低电位侧电源间连接的有源负载电路；

驱动所述第二差动对的第五电流源；和

第六开关，它控制在所述第五电流源和高电位电源间电流通路的导通和截止，

以及

第八 MOS 晶体管，输入所述第二差动对的一个输出，其输出与所述输出端子连接，

所述第六和第七 MOS 晶体管对的栅级与所述输入端子和所述输出端子连接，

在所述输入端子和低电位侧电源间串联连接的第六电流源和第七开关，

第二导电型的第九 MOS 晶体管，源极与所述输入端子连接，栅极和漏极连接，

在所述第九 MOS 晶体管的漏极和高电位侧电源间串联连接的第七电流源和第八开关，

在所述输出端子和所述低电位侧电源间串联连接的第八电流源和第九开关，

第一导电型第十 MOS 晶体管，其源极与所述输出端子连接，栅极与所述第九 MOS 晶体管的栅极共同连接，漏极通过第十开关与高电位侧电源连接。

63. 一种液晶显示装置，其特征在于，在数据线的驱动中使用根据权利要求 13 所述的驱动电路。

64. 一种驱动电路，其特征在于，包括：

两个缓冲器电路，将输入端子共同连接到输入有输入信号电压的一个输入端子，将输出端子共同连接到一个输出端子中，其中，第一缓冲器电路具有高电位侧电源电位的工作范围，第二缓冲器电路具有低电位侧电源电位的工作范围；

基准电压发生装置，产生与能使所述第一缓冲器电路和第二缓冲器电路共同动作的电压范围对应的基准电压；

比较部，将从所述基准电压发生装置输出的基准电压和输入信号电压进行比较；

第一逻辑电路，输入所述比较部的比较结果信号和控制信号，在所述控制信号为有效时，向所述第一缓冲器电路输出所述比较结果信号的逻辑运算结果；

第二逻辑电路，输入所述比较器的比较结果信号的反相信号和控制信号，在所述控制信号为有效时，向所述第二缓冲器电路输出所述比较结果信号的反相信号的逻辑运算结果。

65. 根据权利要求 63 所述的驱动电路，其特征在于，所述基准电压发生装置设置在所述驱动电路的外部。

66. 一种驱动电路，其特征在于，包括：

灰度电压发生装置，具有在第一、第二参考电压间串联连接的多

个电阻，从各抽头生成灰度电压；

译码电路，输入数字数据信号，从所述灰度电压发生装置的输出电压选择对应的电压并输出；

多个根据权利要求 13 所述的驱动电路，将所述译码电路的输出输入，驱动输出负载；

对所述驱动电路的预定个数，至少设有一个共用的所述基准电压发生装置。

## 驱动电路和液晶显示装置

### 发明的技术领域

本发明涉及驱动电路，更具体地，涉及适合于驱动电容性负载的驱动电路。

### 现有技术

以下是与本发明有关的技术的刊物，作为参考：

- (1) 文献 (H. Tsuchi, N. Ideda, H. Hayama, "A New Low Power TFT-LCD Driver for Portable Device," SID 00 DIGEST PP146~149)；

- (2) 特开 2000-338461 号公报。

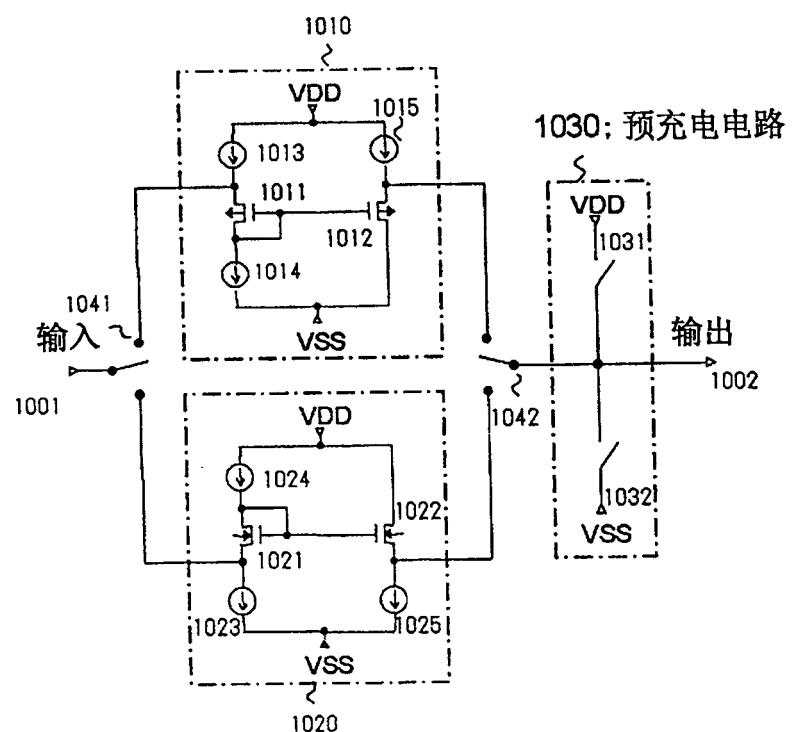

图 24 是表示液晶显示装置的图像数字数据的驱动电路构成的一例（参考文献（1）的图 1）

图 24 所示的缓冲器即使在单个模拟缓冲器不能全范围地输出的情况下，也可以切换两个模拟缓冲器电路（单个称为“缓冲器电路”），从而可以全范围地输出。所谓全范围输出是指在驱动电路的电源电压范围的几乎整个区域中的输出。参考图 24，第一缓冲器电路 1010 包括：第一切换开关 1041，其固定端与输入端子 1001 连接，并具有用于切换的第一和第二端子；第一恒流源 1013，串联连接在第一切换开关 1041 的用于切换的第一端子和高电位侧电源 VDD 之间；P 沟道 MOS 晶体管 1011，其源极与第一切换开关 1041 的第一端子连接、其栅极和漏极连接；第二恒流源 1014，连接在 P 沟道 MOS 晶体管 1011 的漏极和低电位侧电压源 VSS 之间；第二切换开关 1042，其固定端与输出端子 1002 连接，并具有用于切换的第一和第二端子；第三恒流源 1015，串联连接在第二切换开关 1042 的用于切换的第一端子和高电位侧电源 VDD 之间；P 沟道 MOS 晶体管 1012，其源极与第二切换

开关 1042 的第一端子连接、其栅极与 P 沟道 MOS 晶体管 1011 的栅极连接，其漏极与低电位侧电压源 VSS 连接。

第二缓冲器电路 1020 包括：第四恒流源 1023，串联连接在固定端与输入端子 1001 连接的第一切换开关 1041 的用于切换的第二端子和低电位侧电源 VSS 之间；N 沟道 MOS 晶体管 1021，其源极与第一开关 1041 的第二端子连接、其栅极和漏极连接；第五恒流源 1024，连接在 N 沟道 MOS 晶体管 1021 的漏极和高电位侧电源 VDD 之间；第六开关 1025，在其固定端与输出端子 1002 连接的第二切换开关 1042 的用于切换的第二端子和低电位侧电源 VSS 之间串联连接；N 沟道 MOS 晶体管 1022，其源极与第二切换开关 1042 的第二端子连接、其栅极与 N 沟道 MOS 晶体管 1021 的栅极连接，其漏极与高电位侧电源 VDD 连接。

此外，还具有预充放电电路 1030（预充电电路），它由输出端子 1002 和高电位侧电源 VDD 间的开关 1031、和在输出端子 1002 和低电位侧电源 VSS 间的开关 1032 构成，对输出端子 1002 进行预放电和预充电。

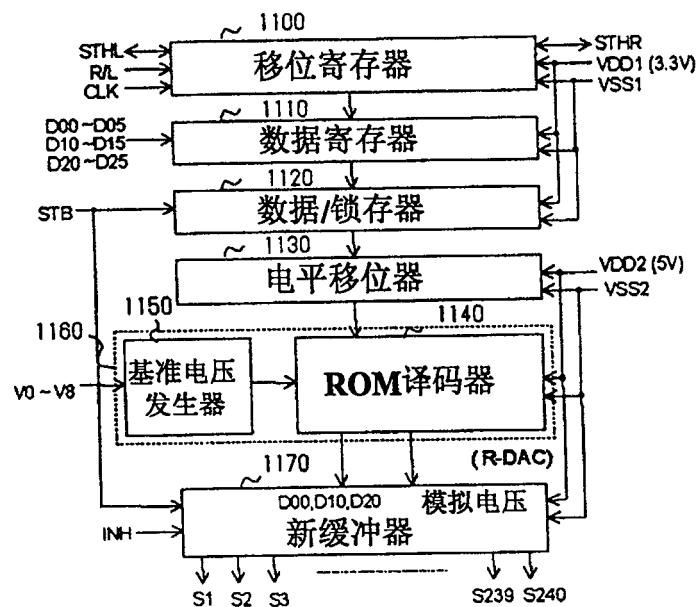

图 25 显示了 6 位数字数据驱动器的构成（参考文献（1）的图 3），包括：移位寄存器 1100、数据寄存器 1110、锁存器 1120、电平移位器 1130、R-DAC1160（基准电压发生电路 1150 和 ROM 译码器 1140）、新（New）缓冲器 1170。新缓冲器 1170 由图 24 所示的电路构成。模拟电压从 ROM 译码器 1140 提供给新缓冲器 1170。RGB 各 6 位的数据的高位各 1 比特（D00、D10、D20）从 ROM 译码器 1140 提供给新缓冲器 1170。根据该 1 比特，预充放电电路 1030 向数据线提供适当的电源电压（VDD，VSS），选择开关 1041、1042，选择缓冲器电路 1010 或电路 1020。

在图 24 所示的驱动电路适用于公共反相驱动方式（将相对的电

极  $V_{com}$  的电压反相的驱动方式) 的液晶显示驱动电路, 适合于在功率消耗低的例如移动电话等移动终端的液晶显示装置的驱动电路。此外, 通过使用全范围输出的驱动电路, 可以降低电源电压, 进一步使功率消耗降低。即, 图 24 的驱动电路是切换第一缓冲器电路 1010 和第二缓冲器电路 1020 以进行全范围输出的驱动电路。

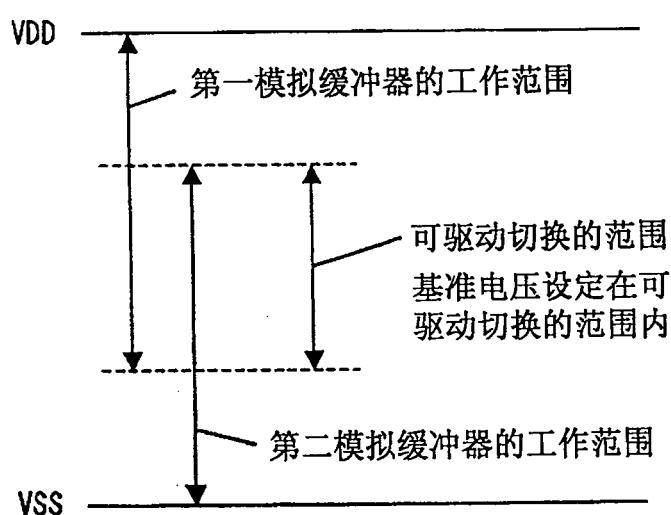

第一缓冲器电路 1010 和第二缓冲器电路 1020 分别由于晶体管的阈值电压  $V_{th}$  而存在工作范围的限制, 而第一缓冲器电路 1010 和第二缓冲器电路 1020 的切换必须在第一缓冲器电路 1010 和第二缓冲器电路 1020 共同工作的电压范围之内 ( $V_{lim1} \sim V_{lim2}$ ) 进行驱动切换。

在周围温度条件为一定的情况下, 可以对应于图像数字数据, 切换第一缓冲器电路 1010 和第二缓冲器电路 1020 来驱动。

以下, 为了理解本发明, 参考图 6, 对用于液晶显示面板的数据线驱动的使用图 24 所示驱动电路情况下第一缓冲器电路 1010 和第二缓冲器电路 1020 的切换进行说明。

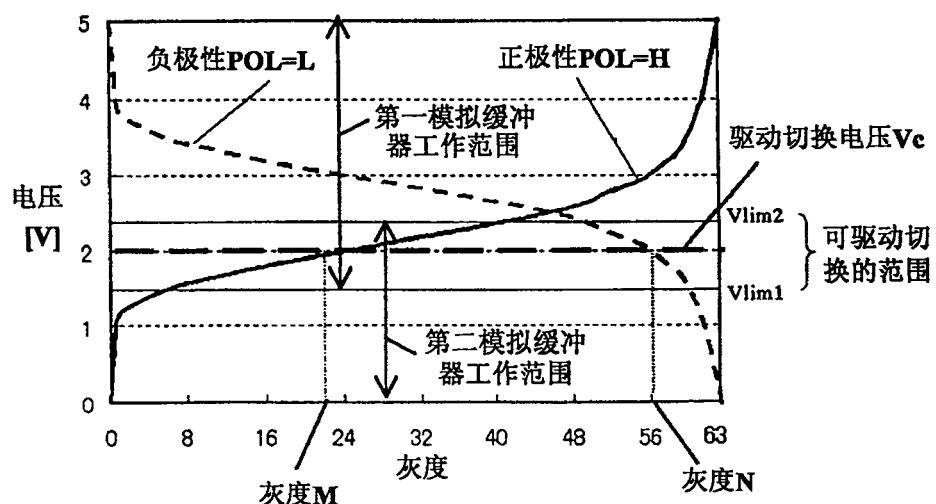

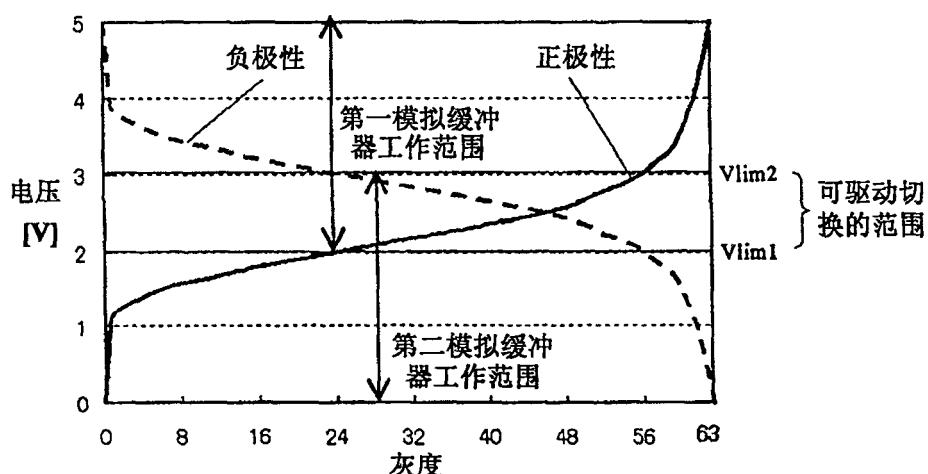

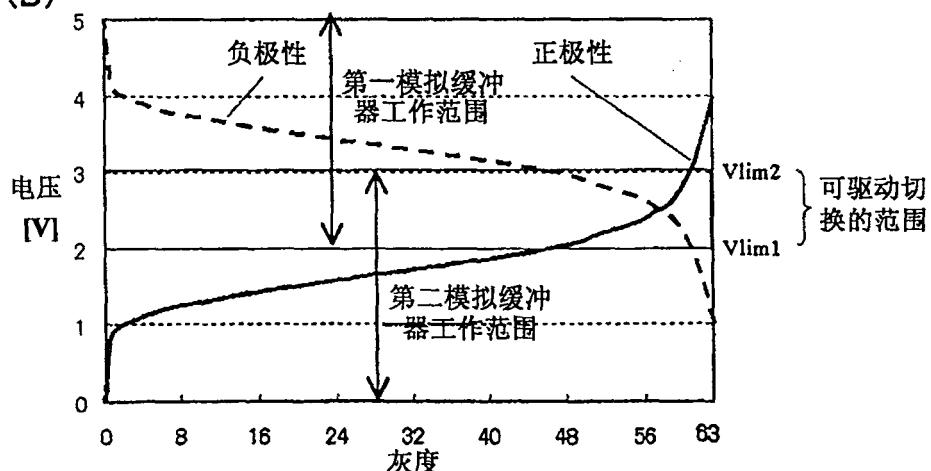

图 6 (A) 说明公共反相驱动 (将液晶显示装置的相对设置电极的电位  $V_{com}$  切换为高电位侧电源电压和低电位侧电源电压) 中液晶的伽玛特性 (灰度与信号电压) 以及驱动电路的工作范围 (标准)。在包括该图在内的以下同样的图中, 灰度和数字数据 1 对 1 地关联, 具有与极性对应的两个模拟电压。图 6 (B) 是说明公共反相驱动中液晶伽玛特性和驱动电路工作范围 (伽玛调制时) 的图。

第一模拟缓冲器 (与图 24 的缓冲器 1010 对应) 的工作范围为电压  $2V \sim 5V$  (灰度  $24 \sim 63$ ), 第二模拟缓冲器 (与图 24 的缓冲器 1020 对应) 的工作范围为电压  $0V \sim 3V$  (灰度  $24 \sim 63$ ), 可驱动切换的范围是  $2V \sim 3V$ , 例如在使用图像数字数据的高位 1 比特的灰度 32, 即使切换第一模拟缓冲器和第二模拟缓冲器的动作, 切换时电压 (与图

像数字数据对应的输入电压)为第一模拟缓冲器和第二模拟缓冲器能分别在正极性和负极性下共同工作的范围,因此可以输出与灰度对应的模拟电压。

因此,如图6(A)所示,在液晶的伽玛特性(灰度、电压特性)的情况下,通过图像数字数据的高位1比特而对32灰度图像分界,从而能够切换第一模拟缓冲器和第二模拟缓冲器。

但是,如图6(A)所示,在调节伽玛特性的条件下,在正极性特性(实线)中32灰度的电压为第一模拟缓冲器(与图24的缓冲器1010对应)的工作范围之外,负极性特性(虚线)中32灰度的电压为第二模拟缓冲器(与图24的缓冲器1020对应)的工作范围之外,不能在32灰度中切换。即,第一模拟缓冲器的工作范围为电压2V~5V(灰度48~63),第二缓冲器工作范围为电压0V~3V(灰度48~63)。在32灰度中切换第一和第二模拟缓冲器,在正极性中在灰度32~48间,即使输入与该灰度对应的图像数字信号,也不会输出与灰度对应的模拟电压,产生了所谓灰度的跳跃。尽管图6(B)中示出了在正极性和负极性中进行基本同样的伽玛特性的调节的情况,可以容易地理解,也能产生特性不同的调制。

在移动终端等中,为了能应对在宽的温度工作条件下的动作,通过对温度的伽玛特性的调节来保持显示质量,调节电源电压等而抑制功能消耗等,需要进行各种调节。在此情况下,存在不能根据图像数字数据(灰度数据)固定切换的问题。

## 发明概述

本发明要解决的问题是,提供具有两个缓冲器电路的驱动电路和配备有该驱动电路的液晶显示装置,其中,第一缓冲器电路具有至少高电位的工作范围,第二缓冲器电路具有至少低电位的工作范围。

本发明提供了解决上述问题的手段。根据其一个方面，在驱动输出负载的驱动电路中，包括：两个缓冲器电路，将输入端子共同连接到输入有输入信号电压的一个输入端子，将输出端子共同连接到一个输出端子中，其中，第一缓冲器电路至少具有高电位的工作范围，第二缓冲器电路至少具有低电位的工作范围；存储部，存储并保持用于对上述第一缓冲器电路和第二缓冲器电路动作的切换进行选择的、与在使上述第一缓冲器电路和第二缓冲器电路能一起动作的范围内的电压对应的基准数据；比较部，将输入的数据信号和基准数据进行比较，上述驱动电路根据上述比较部的比较结果信号和控制信号，控制上述第一缓冲器电路和第二缓冲器电路的工作和停止。

根据本发明的另一方面，包括两个缓冲器电路，将输入端子共同连接到输入有输入信号电压的一个输入端子，将输出端子共同连接到一个输出端子中，其中，第一缓冲器电路的工作范围为高电位侧电源电位，第二缓冲器电路的工作范围为低电位侧电源电位；还包括：存储部，与使上述缓冲器电路和第二缓冲器电路能一起动作的范围内的电压对应的能够驱动切换的范围内的电压对应，保存正极性和负极性的基准数据，该基准数据是，与输入的数字数据和信号电压的关系相对应，对于规定了来自低电位侧电源电位的特性的正极性和规定了来自高电位侧电源电位的特性的负极性，用于判断第一缓冲器电路和第二缓冲器电路动作的切换；选择部，输入确定极性的极性信号，根据上述极性信号的值，选择正极性或第二极性的基准数据；比较部，将输入的数字数据和从上述选择部输出的基准数据进行比较；上述第一缓冲器电路和第二缓冲器电路根据上述比较部的比较结果信号和控制信号，控制其工作和停止。

根据本发明的另一方面，本发明所涉及的驱动电路具有两个缓冲器电路，将输入端共同连接到输入有输入信号电压的一个输入端子，将输出端子共同连接到一个输出端子中，其中，第一缓冲器电路至少具有高电位侧电位的工作范围，第二缓冲器电路至少具有低电位侧电

位的工作范围；还具有：基准电压发生装置，产生与能使上述第一缓冲器电路和第二缓冲器电路共同动作的电压范围对应的基准电压；比较部，将从上述基准电压发生装置输出的基准电压和上述输入信号电压进行比较，上述第一缓冲器电路和第二缓冲器电路根据上述比较部的比较结果信号和控制信号，控制其动作和停止。

在本发明中，在上述控制信号指示动作的情况下，在上述比较部的比较结果信号表示上述输入的信号电压为等于或大于上述基准数据的值的情况下，使上述第一缓冲器电路动作而使上述第二缓冲器电路停止；在上述比较部的比较结果信号表示上述输入的信号电压为比上述基准数据小的值的情况下，使上述第一缓冲器电路停止而使上述第二缓冲器电路动作。

此外，根据其它方面，液晶显示装置包括灰度电压发生装置，具有在第一、第二参考电压间串联连接的多个电阻，从各抽头生成灰度电压；译码电路，输入数字信号，从上述灰度电压发生装置的输出电压选择对应的电压并输出，上述本发明所涉及的驱动电路将上述译码电路的输出输入，驱动作为输出负载的数据线。

#### 附图说明

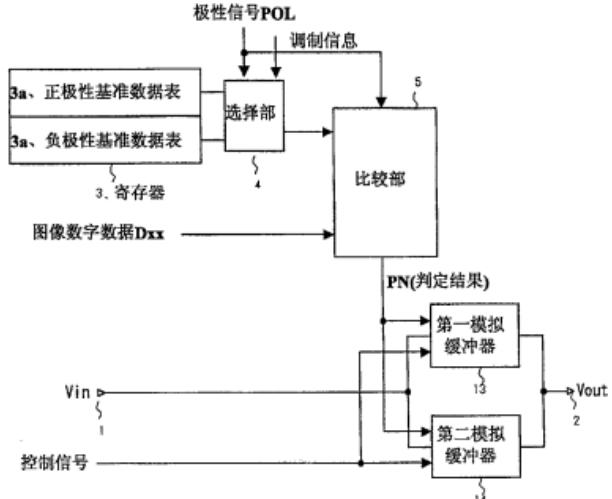

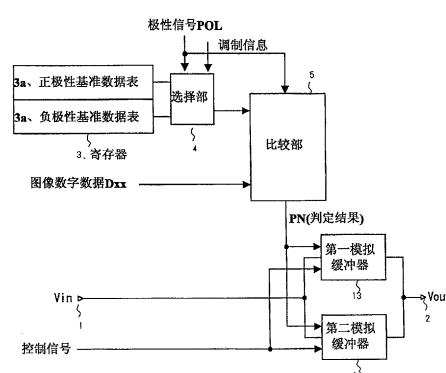

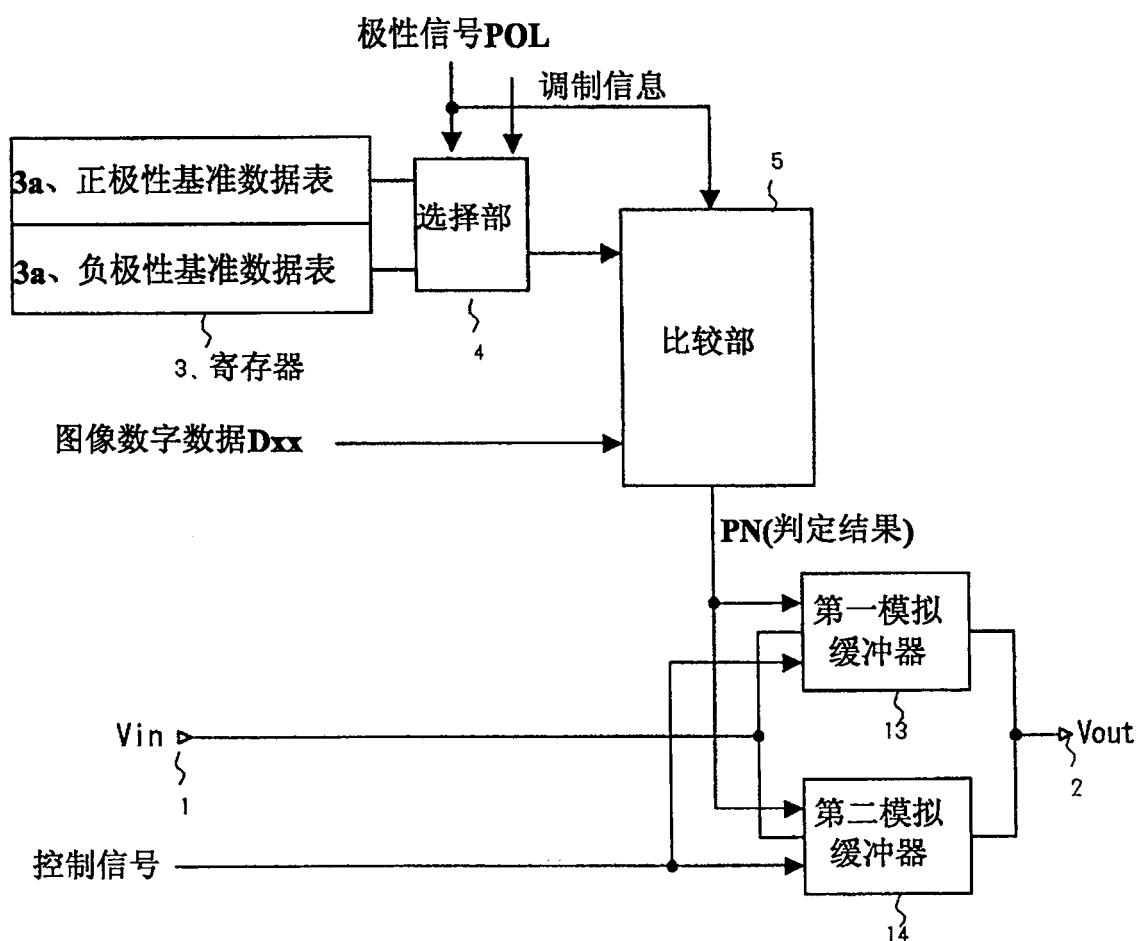

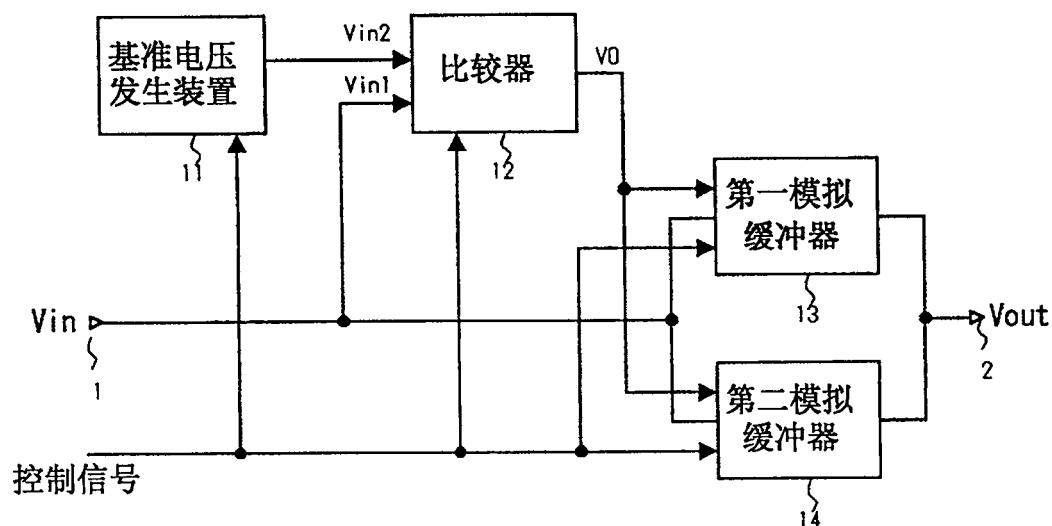

图 1 是表示本发明一实施例的驱动电路的结构的图。

图 2 是用于说明图 1 所示的本发明一实施例的驱动电路动作的图。

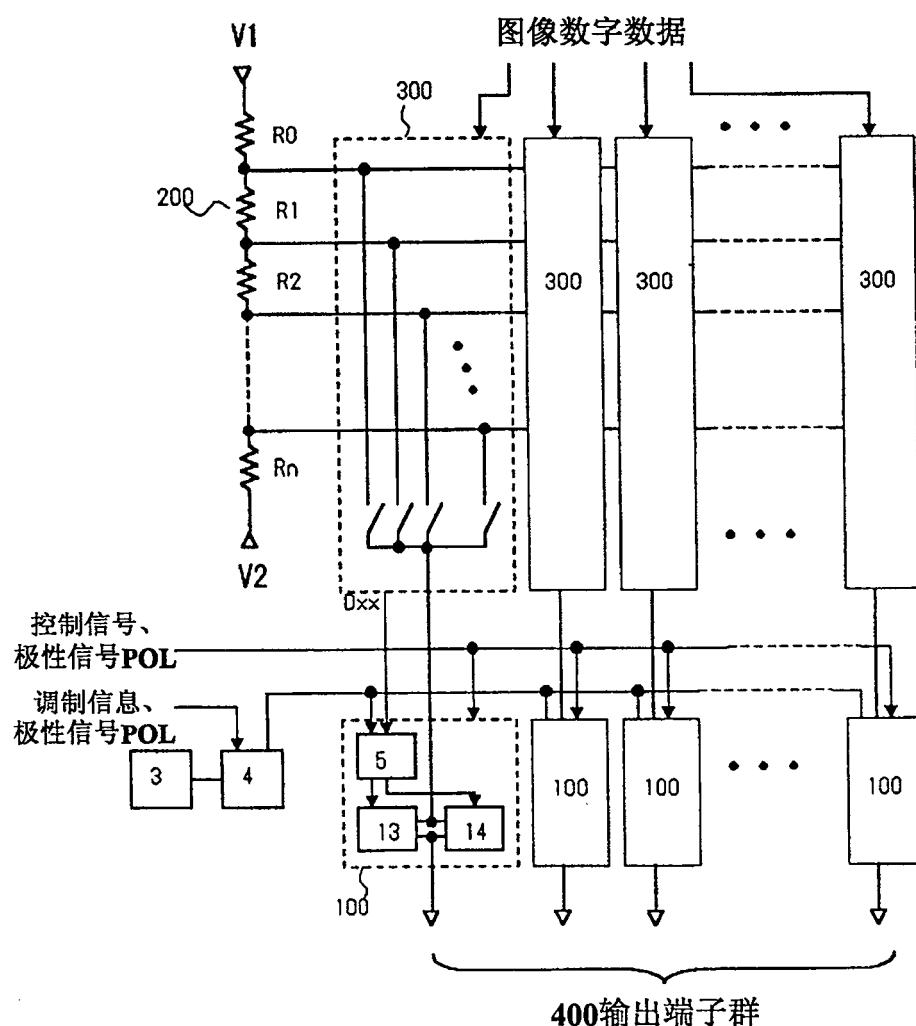

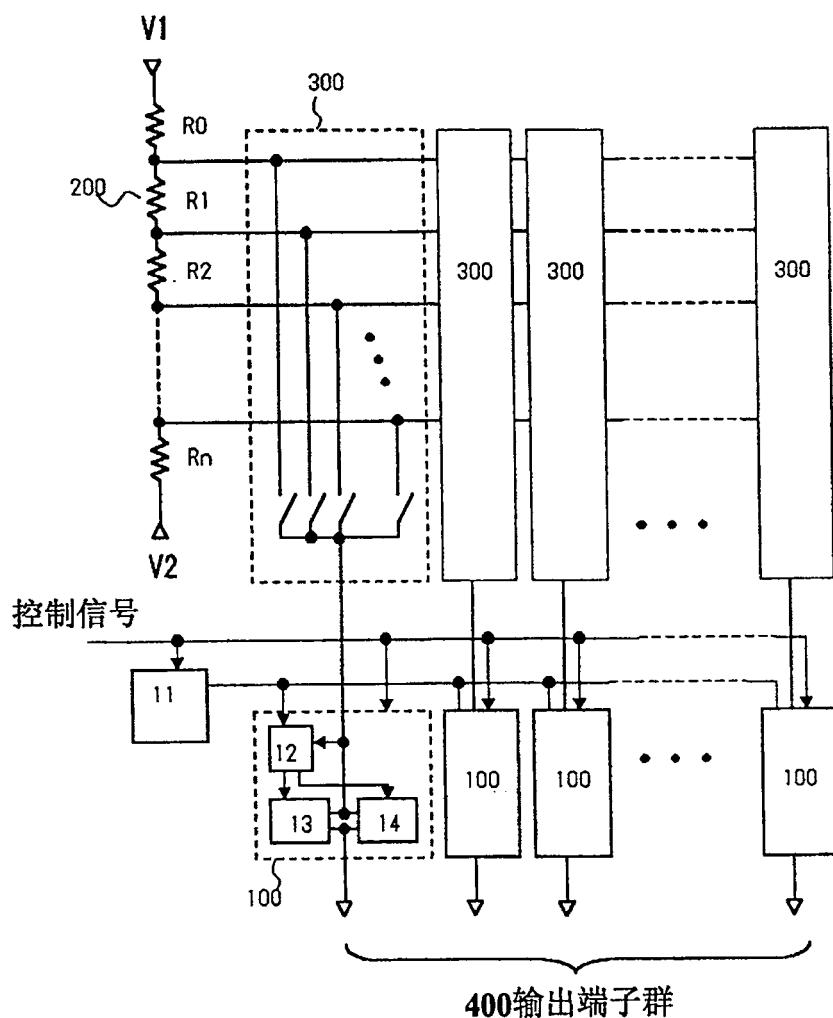

图 3 是表示具有多个图 1 所示的本发明一实施例的驱动电路的多输出驱动电路结构的图。

图 4 是用于说明本发明驱动电路中驱动切换电压的图。

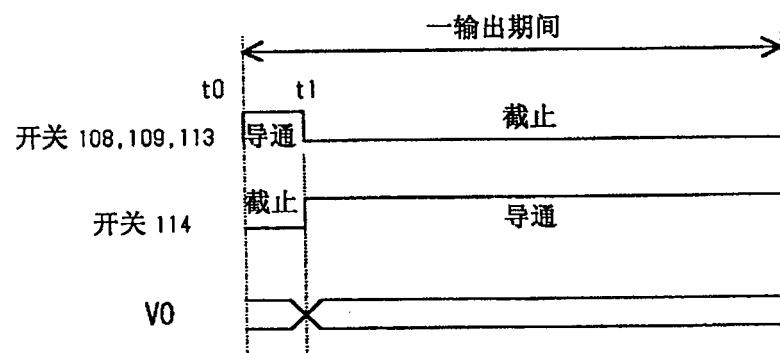

图 5 是用于说明本发明一实施例的驱动电路动作的时序图。

图 6 是说明作为比较例的以往驱动电路中驱动切换电压的图，

(A) 是公共反相驱动中液晶伽玛特性和驱动电路的工作范围(标准)

的示意图，(B) 是公共反相驱动中液晶伽玛特性和驱动电路的工作

范围（调制）的示意图。

图 7 是本发明的其它实施例的驱动电路的结构的示意图。

图 8 是用于说明图 7 所示的本发明另一实施例的驱动电路动作的图。

图 9 是表示具有多个图 7 所示的本发明另一实施例的驱动电路的多输出驱动电路结构的图。

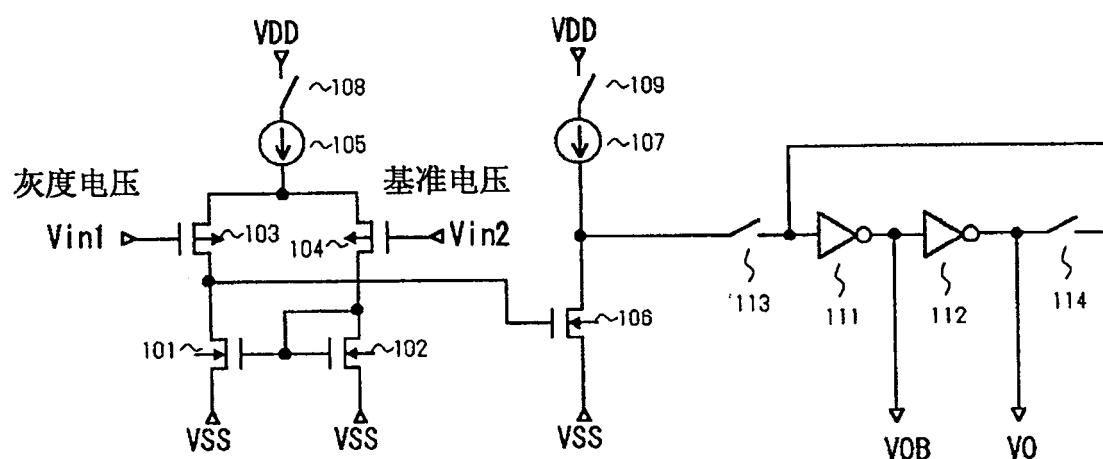

图 10 是表示图 7 所示的本发明另一实施例的驱动电路的比较器结构一例的图。

图 11 是说明图 10 所示的比较器动作的图。

图 12 是表示图 7 所示的本发明另一实施例的驱动电路的比较器结构一例的图。

图 13 是说明图 12 所示的比较器动作的图。

图 14 是表示图 12 所示的本发明另一实施例的驱动电路的比较器结构一例的图。

图 15 是说明图 14 所示的比较器动作的图。

图 16 (a) 是图 7 的本发明其它实施例的驱动电路结构例的示意图，(b) 是说明其动作的图。

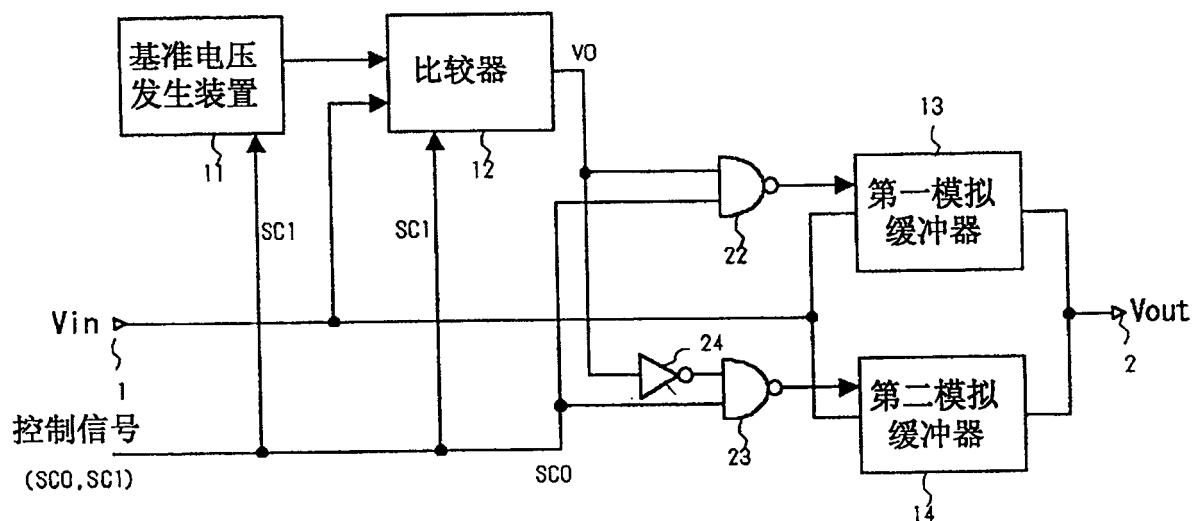

图 17 是表示图 1 所示的本发明一实施例的驱动电路中模拟缓冲器电路结构一例的图。

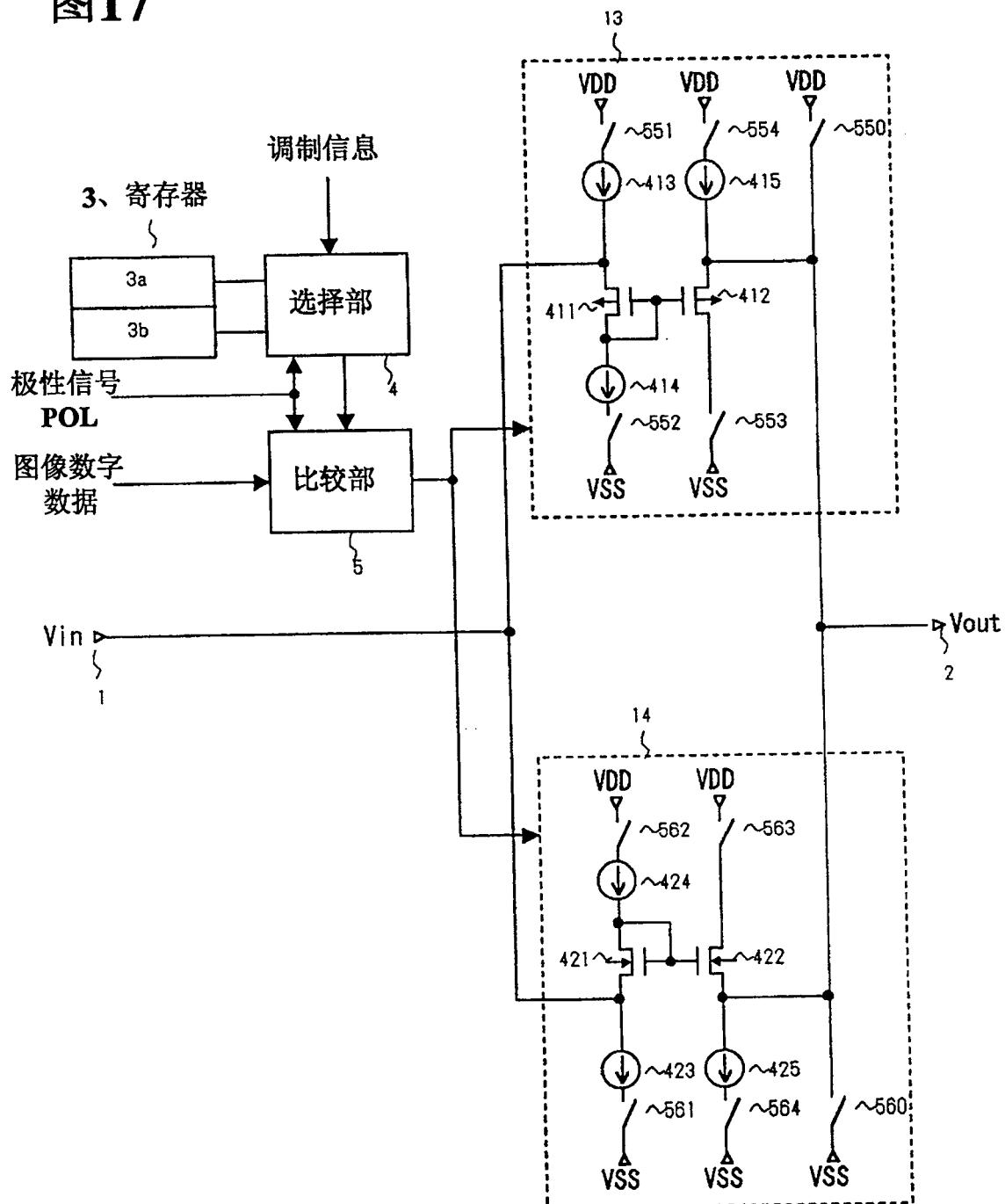

图 18 是表示图 7 所示的本发明另一实施例的驱动电路中模拟缓冲器电路结构一例的图。

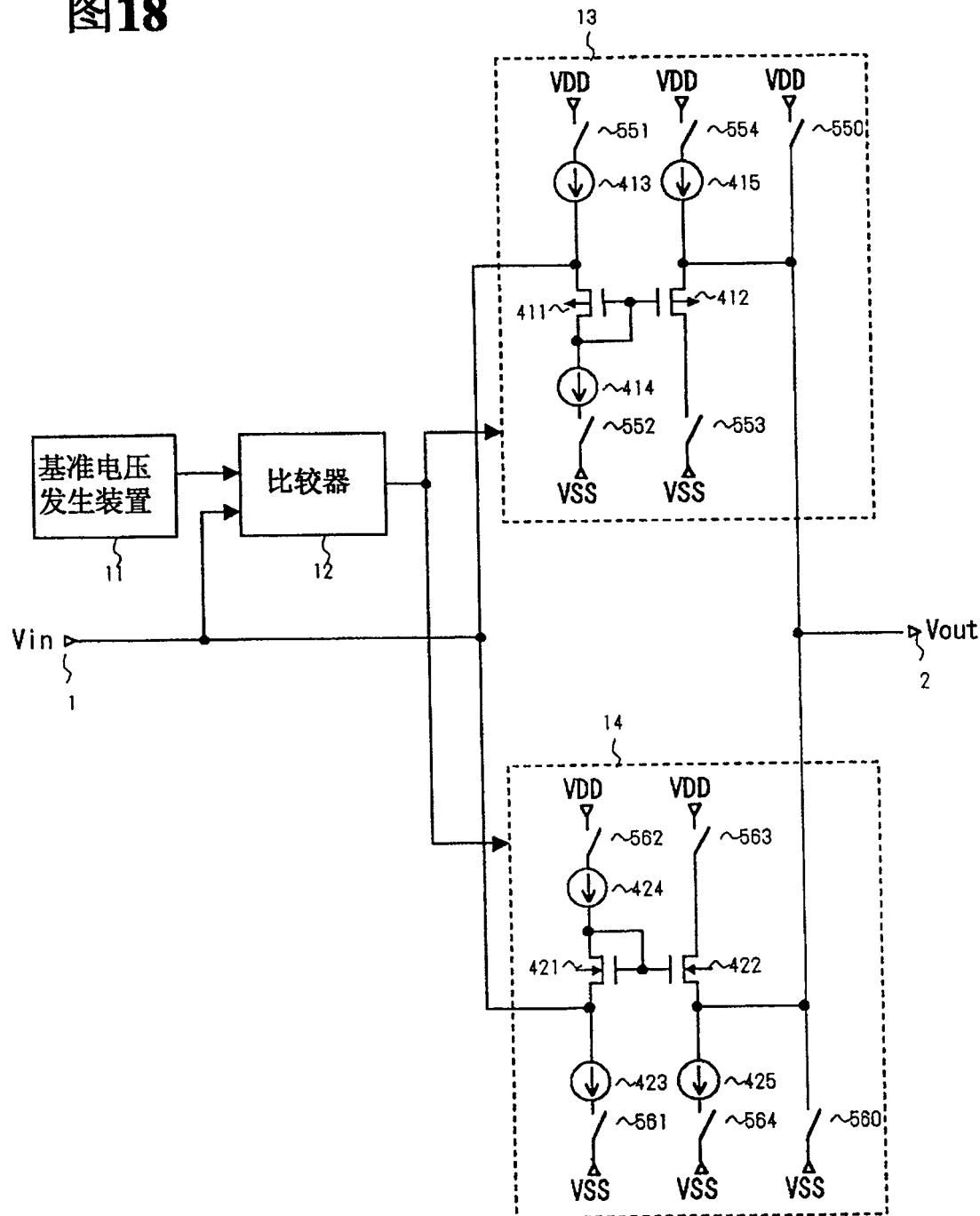

图 19 是表示图 1 所示的本发明一实施例的驱动电路中模拟缓冲器电路结构另一例的图。

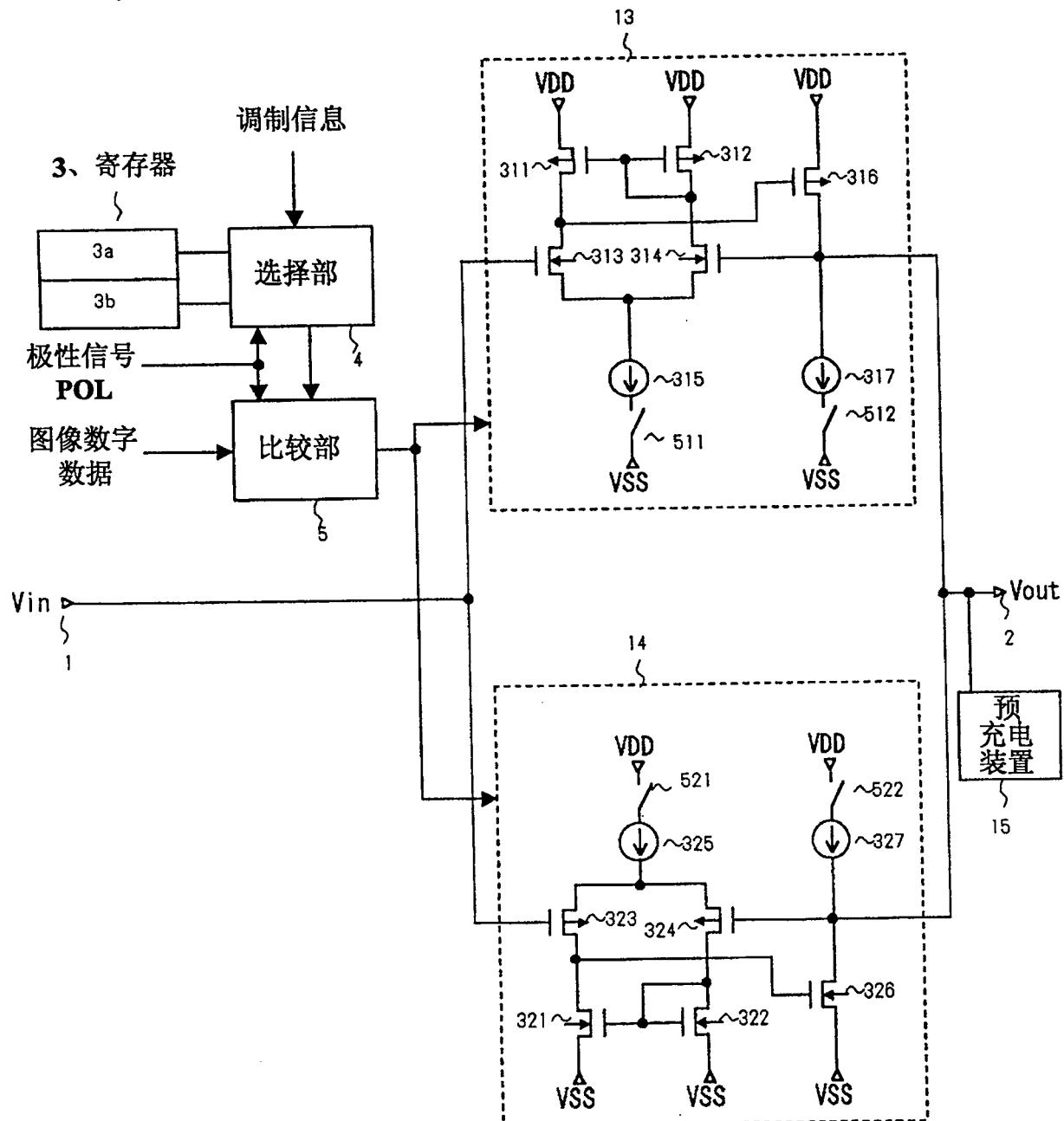

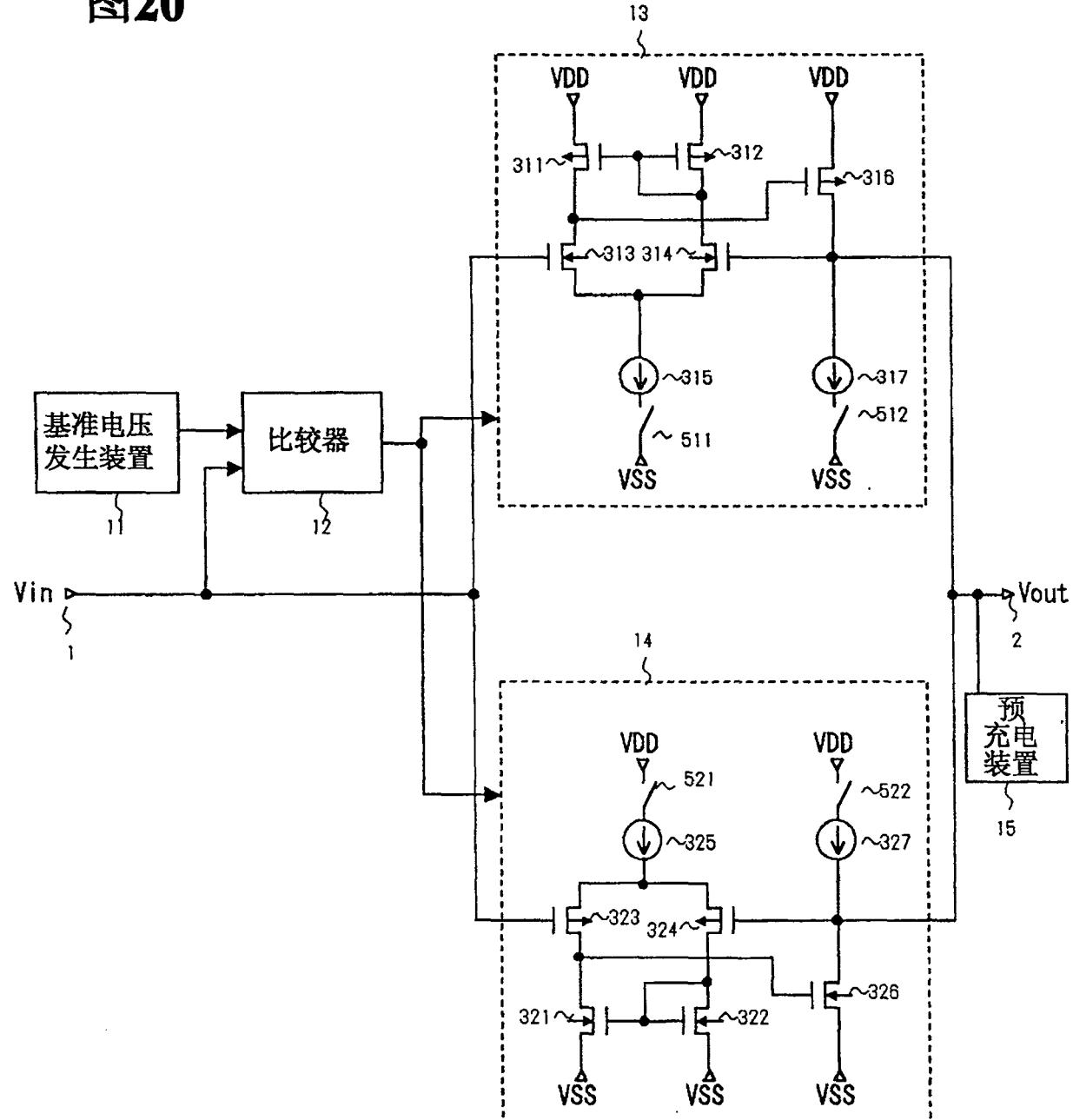

图 20 是表示图 7 所示的本发明另一实施例的驱动电路中模拟缓冲器电路结构另一例的图。

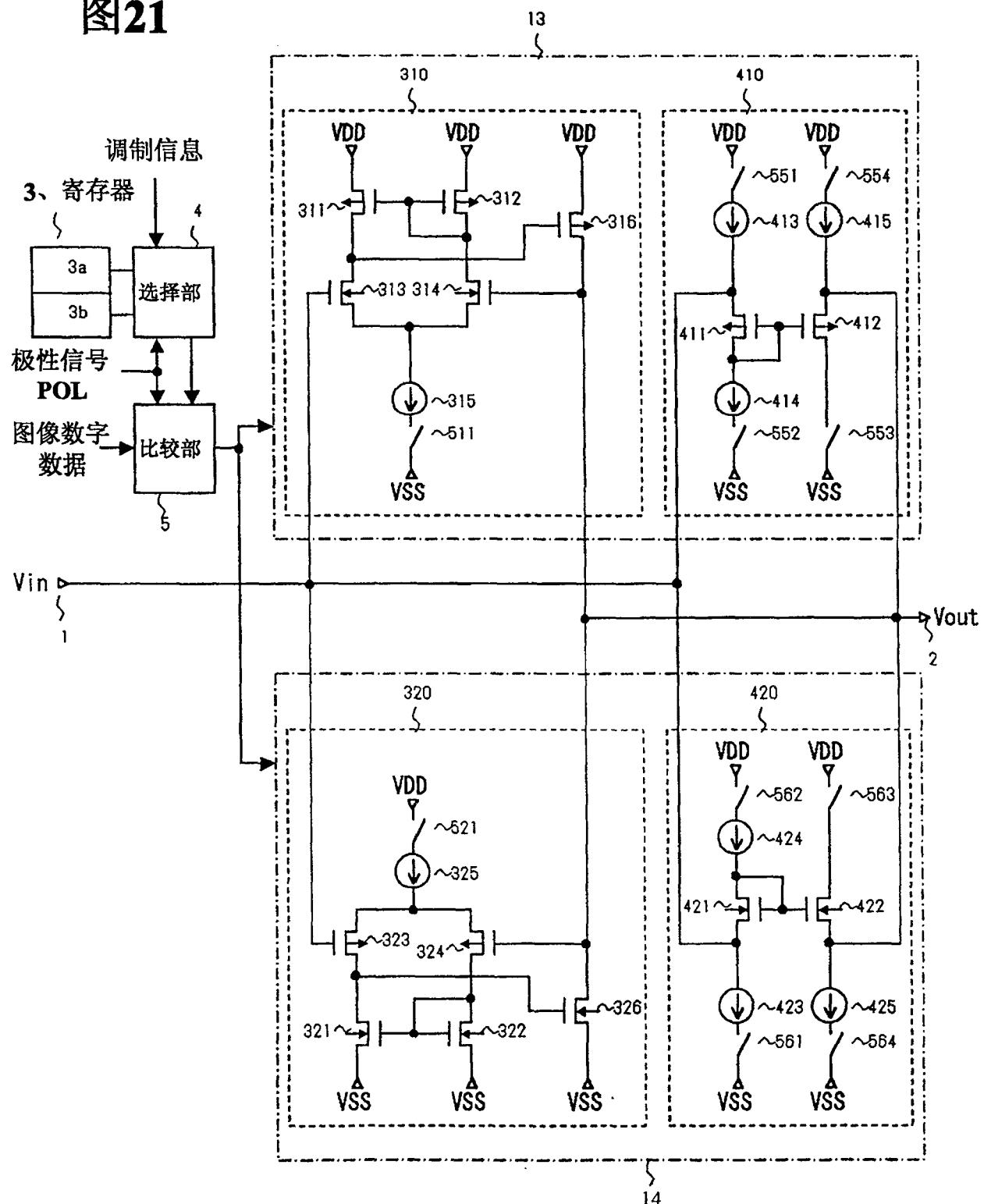

图 21 是表示图 1 所示的本发明一实施例的驱动电路中模拟缓冲器电路结构另一例的图。

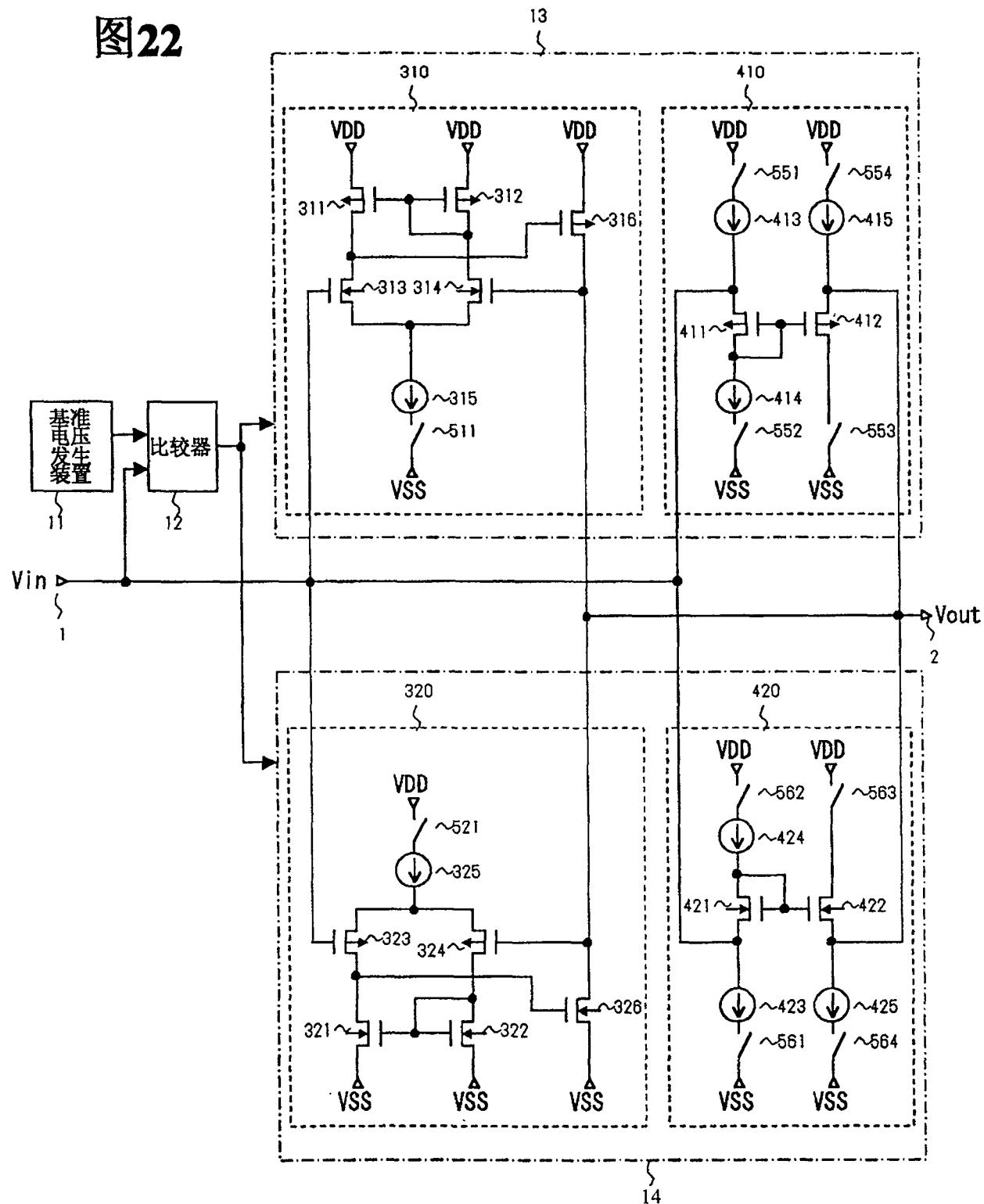

图 22 是表示图 7 所示的本发明另一实施例的驱动电路中模拟缓冲器电路结构另一例的图。

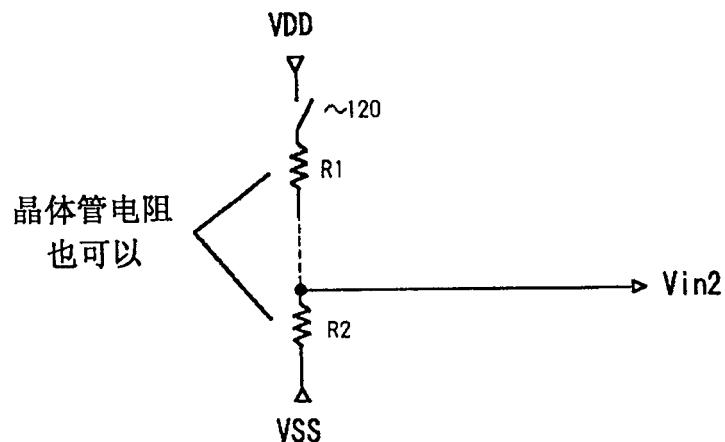

图 23 是表示图 7 所示的本发明另一实施例的驱动电路中基准电

压发生装置结构一例的图。

图 24 是文献 1(H. Tsuchi, N. Ideda, H. Hayama, “A New Low Power TFT-LCD Driver for Portable Device,” SID 00 DIGEST PP146~149) 中记载的缓冲器结构的示意图。

图 25 是文献 1 中记载的数字数据线驱动器结构的示意图。

### 发明的实施方式

下面对本发明实施方式进行说明。本发明的驱动电路即使在每个模拟缓冲器中不能全范围输出，但通过切换两个缓冲器也能够全范围地输出。在这种驱动电路中，即使对各种调制也能选择两个缓冲器最佳的一个而一直正常地驱动。即，将各种条件的调制分为多个步骤，在各调制的每个步骤中，设置将与切换的灰度对应的数字数据保存的表，以该表内的数据作为基准数据，与图像数字数据进行比较，根据比较结果，选择两个缓冲器中最佳的缓冲器。

对于各种条件的调制，以在两个缓冲器能够切换的范围内的电压作为基准电压，将所选择的灰度电压和基准电压进行比较，根据其大小选择两个缓冲器中最佳的缓冲器。

在本发明相关的驱动电路的一个实施方式中，在驱动电容负载等输出负载的驱动电路中，具有两个模拟缓冲器电路，其输入端与将输入信号电压 ( $V_{in}$ ) 输入的一个输入端子 (1) 共同连接，其输出端与输出端子 (2) 共同连接，其中，第一缓冲器电路 (13) 至少具有高电位的工作范围，第二缓冲器电路 (14) 至少具有低电位的工作范围。另外还增加了存储部，存储并保持用于使第一和第二缓冲器电路 (13、14) 能一起工作的范围内的电压所对应的基准数据，该基准数据是用于判断第一和第二缓冲器电路 (13、14) 切换的；和比较部 (5)，将输入的数据信号和基准数据进行比较。第一、第二缓冲器电路 (13、14) 根据比较部 (5) 的比较结果信号 (PN) 和控制信号，控制其工作和停止。

或者，在本发明的一个优选实施方式中，具有两个模拟缓冲器电路，其输入端与将输入信号电压输入的一个输入端子共同连接，其输出端与输出端子共同连接，其中，第一缓冲器电路（13）的工作范围达到高电位电源的电位，第二缓冲器电路（14）的工作范围达到低电位电源的电位。另外还附加了存储部（3），分别对应于与灰度和信号电压相关的特性的标准状态和调制时的状态，存储并保持用于使第一和第二缓冲器电路能一起工作的范围内的输入信号电压所对应的基准数据；选择部（4），根据确定调制的调制信息，选择标准和与调制对应的基准数据并输出；和比较部（5），将输入的数据信号和上述选择部输出的基准数据进行比较。上述第一和第二缓冲器电路根据比较部（5）的比较结果信号和控制信号，控制其工作和停止。

存储部（3）具有存储单元（3a、3b），其与使上述第一缓冲器电路和第二缓冲器电路能一起动作的能够驱动切换的范围内（参考图4）的电压对应，保存规定了来自低电位侧电源电位的特性的正极性和规定了来自高电位侧电源电位的特性的负极性的基准数据，该基准数据与输入的数字数据（图像数字数据）和信号电压的关系相对应，用于分别根据正极性和负极性来判断第一缓冲器电路和第二缓冲器电路动作的切换。

选择部（4）输入确定极性的极性信号（POL），根据上述极性信号的值选择正极性或负极性的基准数据。

存储单元（3a）优选分别对于与灰度和信号电压相关的标准时的伽码特性和调制时的伽码特性，对应于第一缓冲器电路和第二缓冲器电路能一起动作的范围内的输入信号电压，保存正极性的基准数据。

存储单元（3b）优选分别对于与灰度和信号电压相关的标准时的伽码特性和调制时的伽码特性，对应于第一缓冲器电路和第二缓冲器

电路能一起动作的范围内的输入信号电压，保存负极性的基准数据。

选择部（4）根据确定极性的极性信号（POL），选择存储单元（3a、3b）中之一，根据用于确定调制的调制信息，选择与标准或者与调制对应的基准数据。

也可以是，存储单元（3a）保存有多个相应于伽玛特性的调制种类而规定的正极性的基准数据，存储单元（3b）保存有多个相应于伽玛特性的调制种类而规定的负极性的基准数据。在选择部（4）中，根据极性信号，选择存储单元（3a、3b）中之一，根据调制信息，选择与调制种类对应的基准数据并输出。

在控制信号指示动作的情况下，在比较部（5）的比较结果信号表示上述输入数据为等于或大于上述基准数据的值的情况下，使第一缓冲器电路（13）动作而使上述第二缓冲器电路（14）停止；在比较部（5）的比较结果信号表示上述输入的数据为比上述基准数据小的值的情况下，使上述第一缓冲器电路（13）停止而使上述第二缓冲器电路（14）动作。

在本发明的实施方式中，极性信号（POL）是表示液晶显示装置的相对电极的公共电位（Vcom）反相驱动中极性的逻辑值。

在该实施方式中，存储部（3）和选择部（4）也可以设置在驱动电路的外部，和上述驱动电路有电连接。另外，存储部（3）可以是寄存器、ROM 或者可写入的 EEPROM 等非易失性半导体存储装置。

参考图 3，在该实施方式中，具有灰度发生装置（200），它具有在第一、第二参考电压间串联连接的多个电阻（R0、R1、...、Rn），并从各抽头生成灰度电压；以及输入数字数据信号并从上述灰度发生装置（200）的输出电压选择对应的电压来输出的译码电路（300）。

本发明的驱动电路输入来自译码电路（300）的输出，驱动输出负载。对应于多个的驱动电路，设置公共的存储部（3）、选择部（4）。驱动电路最好内置比较部（5）。

本发明在其它实施方式中，参考图 7，具有两个缓冲器电路，其输入端共同连接到将输入有输入信号电压  $V_{in}$  的一个输入端子（1），将输出端子共同连接到输出端子（2）中，其中，第一缓冲器电路（13）至少具有高电位侧电位的工作范围，第二缓冲器电路（14）至少具有低电位侧电位的工作范围；还具有：基准电压发生装置（11），产生与能使上述第一缓冲器电路（13）和第二缓冲器电路（14）共同动作的电压范围对应的基准电压  $V_{in2}$ ；比较部（12），将从上述基准电压发生装置（11）输出的基准电压  $V_{in2}$  和上述输入信号电压  $V_{in}$  ( $=V_{in1}$ ) 进行比较，第一缓冲器电路（13）和第二缓冲器电路（14）根据上述比较部（12）的比较结果信号（VO）和控制信号，控制其动作和停止。在控制信号指示动作的情况下，在比较部（12）的比较结果信号（VO）表示输入信号电压（ $V_{in}$ ）为基准电压以上的值的情况下，使第一缓冲器电路（13）动作而使上述第二缓冲器电路（14）停止；在比较部（12）的比较结果信号是表示输入信号电压（ $V_{in}$ ）比上述基准数据  $V_{in2}$  小的值的情况下，使上述第一缓冲器电路（13）停止而使上述第二缓冲器电路（14）动作。

在该实施方式中，可以构成为具有第一逻辑电路（图 16 的 22），它输入比较器（12）的比较结果信号（VO）和控制信号，在上述控制信号为有效时，将上述比较结果信号的逻辑运算结果输出到上述第一缓冲器电路；和第二逻辑电路（图 16 的 23），它输入比较器（12）的比较结果信号（VO）的反相信号和控制信号，在上述控制信号为有效时，将上述比较结果信号的反相信号的逻辑运算结果输出到上述第二缓冲器电路。

在该实施方式中，参考图 9，液晶显示装置具有灰度发生装置

(200)，它具有在第一、第二参考电压间串联连接的多个电阻( $R_0, R_1, \dots, R_n$ )，从各抽头生成灰度电压；输入数字数据信号并从上述灰度发生装置(200)的输出电压选择对应的电压来输出的译码电路(300)。本发明的驱动电路输入来自译码电路(300)的输出，驱动输出负载。对应于多个的驱动电路，设置共用的一个基准电压发生装置(11)。驱动电路最好内置比较器(12)。

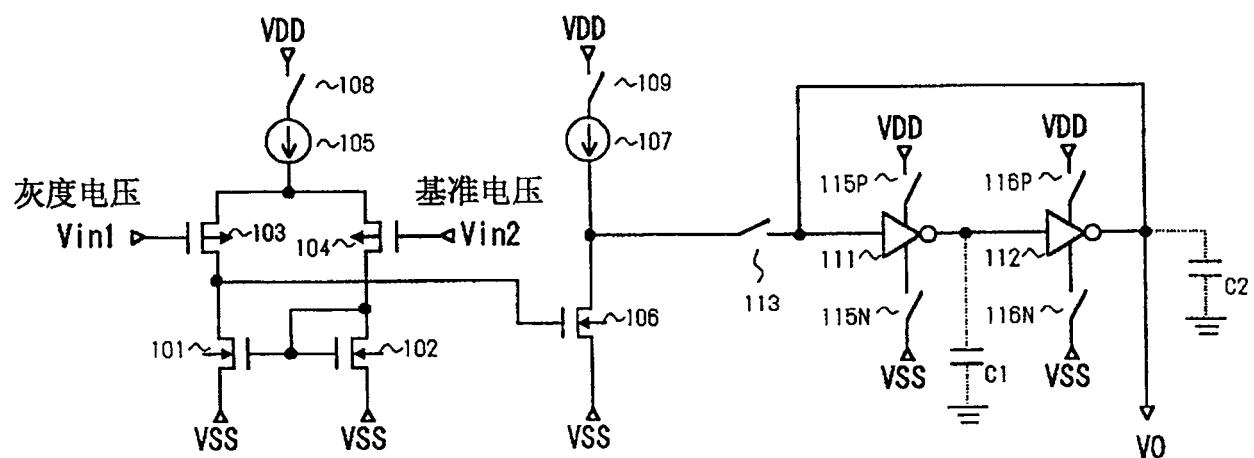

在该实施方式中，参考图10，比较器(12)具有差动放大电路，将输入信号电压 $V_{in}$ (= $V_{in1}$ )和基准电压 $V_{in2}$ 差动输入；保持电路，通过开关与差动放大电路的输出连接。保持电路由通过开关(113)与差动放大电路的一个输出端连接的触发器电路构成。触发器具有输入与开关(113)的输入端连接的第一反相器(111)、输入端与第一反相器的输出端连接的第二反相器(112)、在上述第二反相器的输出端和上述第一反相器的输入端之间连接的开关(114)。第二反相器(112)的信号作为比较结果信号(VO)输出，在差动放大电路动作时，开关(113)为导通状态，而在接受上述差动电路的输出并锁存时，开关(113)截止，开关(114)导通。

差动放大电路具有在驱动差动对的电流源(105)和电源间设置的开关(108)、以及在接收差动对的输出的输出级晶体管(106)的电源通路中插入的开关(109)。为了实现低消耗功率，只在比较动作时这些开关才导通。

进行这样的控制，差动放大电路在工作时，开关(108, 109, 113)为导通状态，在接收差动放大电路的输出并锁存时，开关(108, 109, 113)截止，开关(114)导通。

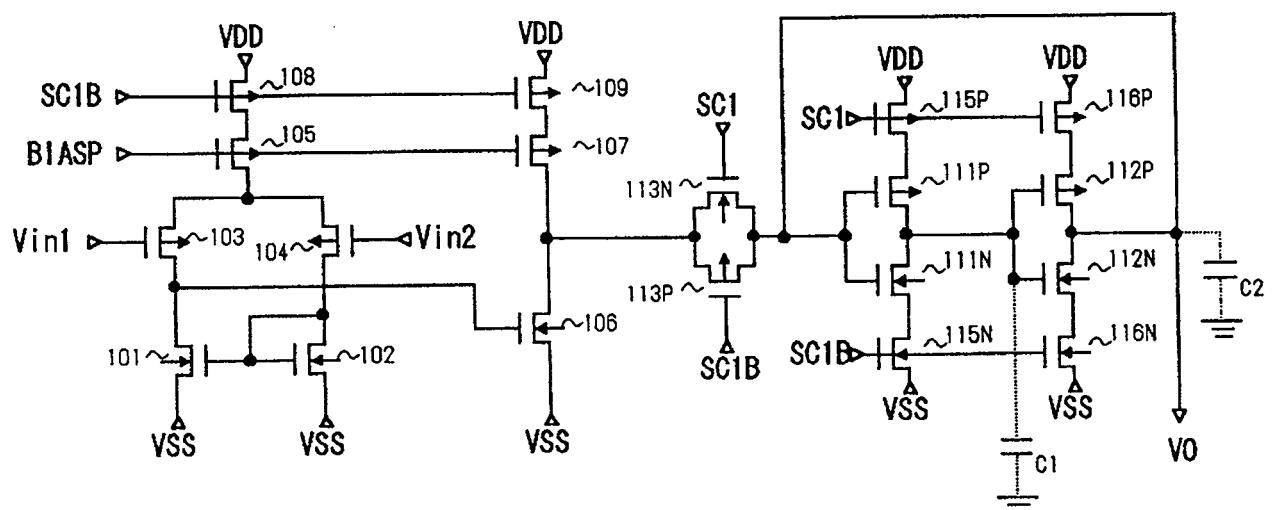

在该实施方式中，参考图12，比较器的触发器具有第一定时反相器(111)，通过开关(113)与差动放大电路的上述输出级晶体管的输出端连接；第二定时反相器(112)，其输入端与第一定时反相

器的输出端连接，第二定时反相器（112）的输出端与上述第一定时反相器（111）的输入端连接，第二定时反相器的输出端信号（VO）和/或上述第一定时反相器的输出端信号作为比较结果信号输出，进行如下的控制，在差动放大电路工作时，（108，109，113）全部导通，在接收上述差动放大电路的输出并锁存时，开关（108，109，113）截止。第二定时反相器（112）的输出端的负载电容（C2）的电容值比上述第一定时反相器（111）的输出端的负载电容（C2）的电容值大。

在该实施方式，参考图 17，18，第一缓冲器电路（13）具有构成源极跟随器的晶体管（412），其输出端子（2）与低电位侧电源（VSS）连接；第一栅偏压控制装置（晶体管 411、电流源 414、413、开关 551、552），将输入信号电压输入，向上述源极跟随器结构的晶体管（412）提供栅极偏置电压；以及对输出端子（2）充电的装置（550）。

第二缓冲器电路（14）具有构成源极跟随器的晶体管（422），其将输出端子（2）与高电位侧电源（VDD）连接；第二栅偏压控制装置（晶体管 421、电流源 424、423、开关 561、562），将输入信号电压输入，向上述源极跟随器结构的晶体管（422）提供栅极偏置电压；以及将输出端子（2）放电的装置（560）。

在该实施例中，参考图 19 和图 20，第一缓冲器电路（13）构成为第一电压跟随器电路，其由差动放大电路所构成，具有由 N 沟道 MOS 晶体管对（313，314）构成的差动对，输入端子（1）与其同相输入端连接、输出端子（2）与其反相输入端连接。第二缓冲器电路（14）构成为第二电压跟随器电路，其由差动放大电路所构成，具有由 P 沟道 MOS 晶体管对（323，324）构成的差动对，输入端子（1）与同相输入端连接、输出端子（2）与反相输入端连接。并具有将输出端子（2）充电和放电的装置（15）。

更详细地说，第一缓冲器电路（13）包括：差动级，具有由 N 沟道 MOS 晶体管对（313，314）构成的差动对，在上述差动对的输出和高电位电源间连接的负载电路（311，312）；驱动该差动对的电流源（315），将上述电流源和低电位电源间的电流通路导通和截止的第一开关（511）；输出级，具有 MOS 晶体管（316），输入上述差动对的输出，其输出与上述输出端子连接，以及在输出端子（2）与低电位侧电源间连接的电流源（317）和开关（512）。差动对的 MOS 晶体管对（313，314）的栅极与上述输入端子（1）和输出端子（2）连接。第二缓冲器电路（14）包括：差动级，具有由 P 沟道 MOS 晶体管对（323，324）构成的差动对，在上述差动对的输出和低电位电源间连接的负载电路（321，322），驱动上述差动对的电流源（325），控制上述电流源和高电位电源间的电流通路导通和截止的开关（521）；输出级，具有 MOS 晶体管（326），输入上述差动对的输出，其输出与上述输出端子连接，以及在输出端子（2）与低电位侧电源间连接的电流源（327）和开关（522）。上述差动对的 MOS 晶体管对（323，324）的栅极与上述输入端子（1）和上述输出端子（2）连接。

在该实施方式中，参考图 21 和图 22，第一缓冲器电路（13）包括：由差动放大电路构成的第一电压跟随器电路，具有由 N 沟道 MOS 晶体管对（313，314）构成的差动对，输入端子（1）与同相输入端连接，上述输出端子（2）与反相输入端连接；在低电位电源和输出端子间连接的源极跟随器结构的晶体管（412）；以及第一栅极偏压控制装置（晶体管 411，电流源 414，413，开关 551，552），将输入信号电压输入，向上述源极跟随器结构的晶体管提供栅极偏置电压。第二缓冲器电路（14）由第二电压跟随器电路构成，第二电压跟随器电路由差动放大电路构成，具有由 P 沟道 MOS 晶体管对（323，324）构成的差动对，上述输入端子与同相输入端连接，上述输出端子与反相输入端连接。该第二缓冲器电路（14）包括：在高电位电源和上述输出端子间连接的源极跟随器结构的晶体管（422）；以及第二栅极

偏压控制装置（晶体管 421，电流源 424，423，开关 561，562），将输入信号电压输入，向上述源极跟随器结构的晶体管提供栅极偏置电压。

在该实施方式中，基准电压发生装置（11）具有在第一、第二参考电压间连接的多个电阻元件（R1，R2），以及开关（120）。在开关（120）导通时，从电阻的连接点将以第一、第二缓冲器电路工作范围重叠来规定的驱动切换范围内的电压作为基准电压输出。作为多个电阻元件（R1，R2），可以使用二极管连接的晶体管。

### 实施例

为了详细说明上述的实施方式，下面参考附图详细说明本发明的实施例。图 1 是本发明的驱动电路一实施例的结构的示意图。参考图 1，该实施例的驱动电路包括：寄存器 3，它具有对在灰度和电压特性的每种调制中（当然也可以包括标准时），与切换第一、第二模拟缓冲器电路 13、14 的灰度对应的基准数据（正极性基准数据、负极性基准数据）进行保存的正极性基准数据表 3a、负极性基准数据表 3b；选择部 4，将正极性基准数据表 3a、负极性基准数据表 3b 的输出输入，根据极性信号 POL，选择其中之一，根据调制信息选择输出与调制对应的基准数据；比较部 5，将输入的图像数字数据与选择部 4 的输出进行比较；以及第一、第二模拟缓冲器电路 13、14，将比较部 5 的比较结果的输出和控制信号输入，控制动作和停止，输入端与输入端子 1 共同连接，输出端与输出端子 2 共同连接，进行正极性和负极性的驱动。正极性基准数据表 3a、负极性基准数据表 3b 的数据将图像数字数据和其比特宽度都用二进制来表示。比较器 5 由比较两个数字数据大小关系的公知数字比较器构成。输入端子 1 将与输入比较部 5 的图像数字数据所对应的模拟电压输入。

在任意的调制步骤中，由选择部 4 根据极性信号 POL，选择与调制步骤对应的基准数据（正极性、负极性），由比较部 5 对所选择的

基准数据和图像数字数据进行比较，与图像数字数据对应的灰度也根据切换灰度来判断低位和高位，根据从比较部 5 输出的判断信号 PN，选择第一、第二模拟缓冲器电路 13、14 中之一来驱动。控制信号进行第一、第二模拟缓冲器电路 13、14 的动作控制。极性信号 POL 在 Vcom 反相驱动控制中，Vcom 电压根据是低电位侧电位（正极驱动）还是高电位侧电位（负极驱动）而为 High （高）或 low （低）电平。

图 2 是图 1 的电路控制动作的示意图。在控制信号为低电平时，第一、第二模拟缓冲器电路 13、14 与比较部 5 的输出 PN 无关地停止动作（不激活）。在控制信号为高电平时，比较部 5 的输出 PN 为高电平时，第一模拟缓冲器电路 13 动作，第二模拟缓冲器电路 14 停止（不激活）。

在控制信号为高电平时，比较部 5 的输出 PN 为低电平时，第一模拟缓冲器电路 13 停止（不激活），第二模拟缓冲器电路 14 动作。

图 3 是本发明一实施例的驱动电路适用于多输出驱动电路的构成的示意图。该多输出驱动电路例如用于液晶显示装置的数据线的驱动中。参考图 3，该多输出驱动电路具有灰度电压发生装置 200，构成作为参考电压的例如电源 V1 和电源 V2 间串联连接的多个电阻元件 R0~Rn 的电阻串，从电阻串的抽头输出与极性对应的模拟电压。来自灰度电压发生装置 200 的灰度电压（模拟电压）输入到译码器 300，译码器 300 输入图像数字数据，选择输出与图像数字信号对应的灰度电压，输入到驱动电路 100 中。灰度电压发生装置 200 也可以将电源 V1 和电源 V2 分别作为固定电压，从两倍于灰度数的电阻串的抽头输出与极性对应的模拟电压，而且与将电源 V1 和电源 V2 极性反转同步地来将电位电平反转。从与灰度数相同数量的电阻串的抽头输出与极性对应的模拟电压。

驱动电路 100 由参考图 1 所说明的上述实施例的结构所构成，具

有第一、第二模拟缓冲器电路 13、14 和比较部 5，并在驱动电路 100 中具有公用的寄存器 3 和选择部 4。

图 4 是用于说明公共反相驱动中液晶伽玛特性和驱动电路工作范围一例的示意图。用实线表示正极性工作的伽玛特性（极性信号  $POL=H$ ）、用虚线表示负极性工作的伽玛特性（极性信号  $POL=L$ ），在寄存器 3 中存储正极性基准数据和负极性基准数据，以使驱动切换电压  $V_c$  在能驱动切换的范围  $V_{lim1}、V_{lim2}$  的范围内。即，根据该实施例，第一、第二模拟缓冲器电路 13、14 的切换对每种调制设置与能驱动切换的范围  $V_{lim1}、V_{lim2}$  内的电压  $V_c$  对应的基准数据。在图 4 的例子（作为标准状态）中，驱动切换电压  $V_c$  都为正极性和负极性，预先设定在每个极性中与电压  $V_c$  最接近的灰度 M、N（正极性为灰度 M，负极性为灰度 N）所对应的数字数据作为标准状态的基准数据。从而，输入的图像数字数据变为与基准数据相等或者比基准数据大的值时，第一模拟缓冲器电路 13 动作，在变为比基准数据小的值时，第二模拟缓冲器电路 14 动作。

另一方面，作为比较例，参考图 6 (A)、(B)，在 0~63 灰度中，例如在利用图像数字数据的高位 1 比特以灰度为 32 进行第一模拟缓冲器电路（对应于图 1 的缓冲器电路 13）和第二模拟缓冲器电路（对应于图 1 的缓冲器电路 14）的动作切换时，图 6 (A) 中，与灰度 32 对应的信号电压（输入的灰度电压）在第一、第二模拟缓冲器电路的能驱动切换的范围 ( $V_{lim1}、V_{lim2}$ ) 内能切换，但是在进行调制的图 6 (B) 中，与灰度 32 对应的信号电压在能驱动切换的范围 ( $V_{lim1}、V_{lim2}$ ) 外，在正极性中灰度 32~48 之间第一模拟缓冲器的输出电压固定为电压  $V_{lim1}$ ，在负极性中灰度 32~48 之间第二模拟缓冲器的输出电压固定为电压  $V_{lim2}$ 。即在灰度 32~48 之间，即使输入与该灰度对应的图像数字信号，也不输出与灰度对应的模拟电压，产生所谓的灰度跳跃。对此，根据本发明，以在能驱动切换的范围 ( $V_{lim1}、V_{lim2}$ ) 内的电压进行第一、第二模拟缓冲器的动作切换、

即进行每个调制时，对切换时的灰度数据进行可变的控制，从而不会产生灰度的跳跃。

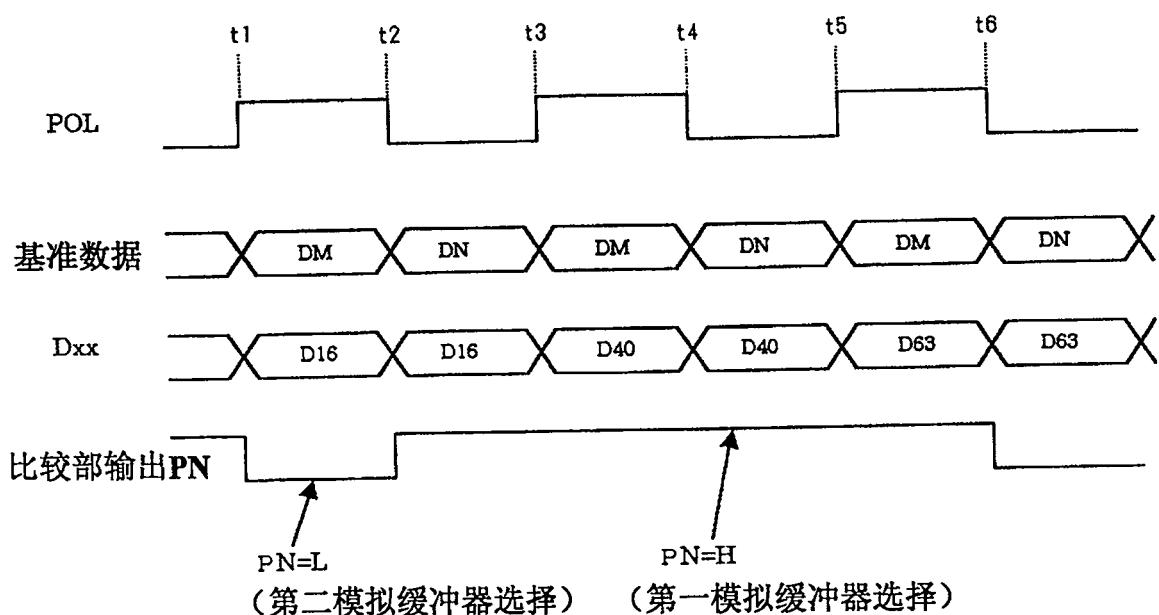

图 5 是表示具有图 4 的伽玛特性的调制步骤时的定时图。参考图 5，在时刻（定时） $t_1$  中，极性信号 POL 变为高电平时，基准数据变为正极性数据 DM（与灰度 M 对应的数据），与对应于灰度 16 的图像数字数据 D16 进行比较，比较部输出 PN 从高电平变为低电平，从第一模拟缓冲器电路 13 切换为第二模拟缓冲器电路 14，第二模拟缓冲器电路 14 动作。

在时刻  $t_2$ ，极性信号 POL 变为低电平时，基准数据变为负极性数据 DN（与灰度 N 对应的数据），与对应于灰度 16 的图像数字数据 D16 进行比较，比较部输出 PN 变为高电平，选择第一模拟缓冲器电路 13。

在时刻  $t_3$ ，极性信号 POL 变为高电平时，基准数据变为正极性数据（DM），与对应于灰度 40 的图像数字数据 D40 进行比较，比较部输出 PN 变为高电平，选择第一模拟缓冲器电路 13 动作。

在时刻  $t_4$ ，极性信号 POL 变为低电平时，基准数据变为负极性数据（DN），与对应于灰度 40 的图像数字数据 D40 进行比较，比较部输出 PN 变为高电平，选择第一模拟缓冲器电路 13 动作。

在时刻  $t_5$ ，极性信号 POL 变为高电平时，基准数据变为正极性数据（DM），与对应于灰度 63 的图像数字数据 D63 进行比较，比较部输出 PN 变为高电平，选择第一模拟缓冲器电路 13 动作。

在时刻  $t_6$ ，极性信号 POL 变为低电平时，基准数据变为负极性数据（DN），与对应于灰度 63 的图像数字数据 D63 进行比较，比较部输出 PN 变为低电平，选择第二模拟缓冲器电路 14 动作。

图 7 是本发明另一实施例的结构的示意图。参考图 7，它包括：基准电压发生装置 11，将基准电压发生装置 11 的输出与输入信号电压  $V_{in}(=V_{in1})$  比较的比较器 12，以及第一、第二模拟缓冲器电路 13，14。第一、第二模拟缓冲器电路 13，14 将比较器 12 的输出和控制信号输入，进行动作和停止的控制，其输入端与输入端子 1 共同连接，输出端与输出端子 2 共同连接，进行正极性和负极性的驱动。

基准电压发生装置 11 在每种调制步骤中，生成能切换驱动第一、第二模拟缓冲器电路 13，14 的基准电压  $V_c$ 。即，基准电压  $V_c$  设置在第一、第二模拟缓冲器电路 13，14 能一起工作的电压范围内。

在比较器 12 中，将根据图像数字数据选择的灰度电压  $V_{in}$  与基准电压  $V_c$  进行比较，根据其大小选择驱动第一、第二模拟缓冲器电路 13，14 中之一。控制信号控制着基准电压发生装置 11、比较器 12 和第一、第二模拟缓冲器电路 13，14 的动作，除必要时以外，停止动作。此外，比较器 12 的比较处理的延迟时间也可以是由延迟电路（图中未显示）将输入信号电压  $V_{in}$  进行延迟，提供给第一、第二模拟缓冲器电路 13，14 中。

图 8 是图 7 中结构的控制动作示意图。在控制信号为低电平时，第一、第二模拟缓冲器电路 13，14 的动作停止（不激活）。在控制信号为高电平时，第一模拟缓冲器电路 13 动作，第二模拟缓冲器电路 14 的动作停止（不激活）。

控制信号为高电平时，在比较器 12 的输出为低电平时，第二模拟缓冲器电路 14 动作，第一模拟缓冲器电路 13 停止（不激活）。

图 9 是图 7 所示的驱动电路适用于多输出驱动电路的图。多输出驱动电路例如在液晶显示装置的数据驱动线中使用。参考图 9，该多

输出驱动电路具有灰度电压发生装置 200，构成在作为参考电压的例如电源 V1 和电源 V2 间串联连接的多个电阻元件 R1~Rn 的电阻串，从电阻串的抽头输出与极性对应的模拟电压。来自灰度电压发生装置 200 的灰度电压（模拟电压）输入到译码器 300，译码器 300 输入图像数字数据，选择输出与图像数字信号对应的灰度数据，输入到驱动电路 100 中。灰度电压发生装置 200 也可以将电源 V1 和电源 V2 分别作为固定电压，从灰度数的两倍的电阻串的抽头输出与极性对应的模拟电压，而且与将电源 V1 和电源 V2 极性反转同步地来将电位电平反转。从与灰度数相同数量的电阻串的抽头中输出与极性相对应的模拟电压。

驱动电路 100 由参考图 7 所说明的上述实施例的结构所构成，具有第一、第二模拟缓冲器电路 13、14 和比较部 5，在驱动电路 100 中具有公用的基准电压发生装置 11。

图 10 是图 7 中所示的实施例中比较器 12 结构一例的示意图。参考图 10，该比较器 12 具有构成差动对的 P 沟道 MOS 晶体管 103、104，其源极连接在一起，并与恒流源 105 的一端连接。在 P 沟道 MOS 晶体管 103、104 的栅极，灰度电压（输入信号电压 Vin）和基准电压输入，P 沟道 MOS 晶体管 103、104 的漏极连接至构成电流镜电路的 N 沟道 MOS 晶体管 101、102（晶体管 102 为输入侧，晶体管 101 为输出侧）。恒流源 105 的另一端通过开关 108 与高电位电源 VDD 连接。

P 沟道 MOS 晶体管 103 的漏极与 N 沟道 MOS 晶体管 106 的栅极连接。N 沟道 MOS 晶体管 106 的源极与低电位侧电源 VSS 连接，漏极与恒流源 107 的一端连接。恒流源 107 的另一端通过开关 109 与高电位侧电源 VDD 连接。

N 沟道 MOS 晶体管 106 的漏极与开关 113 的一端连接，开关 113（传输开关）的另一端与由输入和输出相互连接的两个反相器所构成

的触发器连接。即，开关 113（传输开关）的另一端与反相器 111 的输入端连接，反相器 111 的输出端与反相器 112 的输入端连接，反相器 112 的输出端通过开关 114 与反相器 111 的输入端连接。反相器 111、112 的输出端取出输出 VOB、VO。

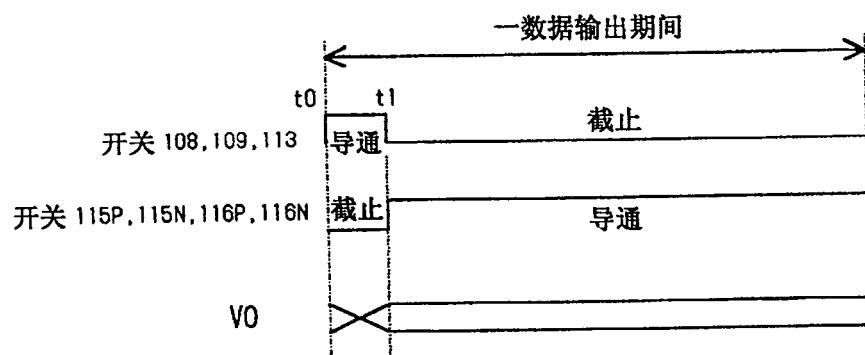

图 11 是用于说明图 10 中的电路结构的比较器 12 的动作的时序图。利用控制信号，在开关 108、109、113 导通、开关 114 截止时，差动放大电路激活，比较结果送至触发器。

下面对图 10 的比较器 12 的电路动作进行说明。首先，开关 108、109 和开关 113 导通，开关 114 截止，差动电路动作，进行灰度电压和基准电压的电压比较。灰度电压 Vin1 比基准电压 Vin2 低时，晶体管 103 比晶体管 104 流过更多的漏电流，N 沟道 MOS 晶体管 106 的栅极电压增大，晶体管 105 的漏极和恒流源 107 的连接点电位变为低电位电平。Vin1 比基准电压 Vin2 高时，晶体管 104 流过更多的漏电流，N 沟道 MOS 晶体管 106 的栅极电压减小，晶体管 105 的漏极和恒流源 107 的连接点电位变为高电位电平。差动电路的输出通过开关 113 输入至反相器 111（此时开关 114 截止）。

开关 113 截止（开关 108、109 也截止）、开关 114 导通、由两级反相器构成触发器，反相器 111 的输入数据（比较结果）被锁存，作为 VO 输出。

图 12 是本发明一实施例的比较器 12 的另一结构的图。该电路比图 10 的比较器的消耗功率低。

在图 12 中，差动电路的结构与图 11 所示的相同。在触发器中，在与反相器 111 的电源通路的高电位侧电源 VDD 之间设置开关 115P，在与低电位侧电源 VSS 之间设置开关 115N，在与反相器 112 的电源通路的高电位侧电源 VDD 之间设置开关 116P，在与低电位侧电源 VSS

之间设置开关 116N，去掉图 11 的开关 114。利用反相器 111 的输出的寄生电容 C1、反相器 112 的输出的寄生电容 C2 的累积电荷进行保存动作。电容 C2 比电容 C1 大。使通过反相器 111 对电容 C1 充放电的周期比通过反相器 112 对电容 C2 充放电的周期短，触发器稳定地工作。

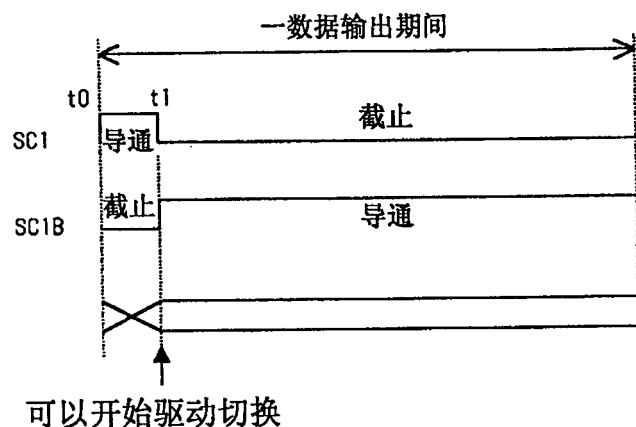

图 13 是说明图 12 中电路动作的时序图。在 1 输出期间的最初期间中，开关 108、109 和开关 113 导通，差动电路的比较结果输入至触发器的反相器 111 的输入端，在此期间，开关 115P、115N、116P、116N 截止。接着，开关 108、109 和开关 113 截止，开关 115P、115N、116P、116N 导通。触发器保存数据。

对于反相器 112 的负载电容 C2 和反相器 111 的负载电容 C1，通过使  $C_2 > C_1$ ，可以防止误动作。即，通过反相器 111 的输出负载的充电、放电的信号的上升、下降时间设定为比反相器 112 的短，触发器稳定地工作。

在开关 113 导通的时间点，差动比较电路的输出对电容 C2 充电或者放电，比较器的输出 V0 在开关 113 截止的时刻 t1 的前面发生值的变化。

图 12 的比较器在恒流源 105、107 控制的电流十分小的情况下，在开关 108、109、113 导通期间反相器 111 的输入电位变化缓慢时，由于开关 115P、115N、116P、116N 截止，因此不产生反相器 111、112 的贯通电流。从而如果反相器 111 的输入电位稳定为高或者低后，开关 108、109、113 截止，开关 115P、115N、116P、116N 导通，反相器 111、112 迅速动作，可以实现没有由于贯通电流造成的消耗功率损失的比较器动作，能实现低消耗功率。此外在图 12 中没有记载，在将比较器的输出 VO 输入的电路的电源通路中设置开关，可以进一步进行开关 115P、115N、116P、116N 的同步控制。另一方面，在图

10 的比较器中，在将恒流源 105、107 控制的电流抑制得十分小的情况下，反相器 111、112 的贯通电流导致的功率消耗损失增加，不能实现非常低的功率消耗。

图 14 是图 12 所示的电路结构的晶体管层的构成一例的示意图。参考图 14，图 12 的恒流源 105、107 由 P 沟道 MOS 晶体管构成，其栅极被提供有偏置电压 BIASP，图 12 的开关 108、109 由 P 沟道 MOS 晶体管构成，其栅极被提供有控制信号 SC1B (SC1 的反相信号)。

进一步参考图 14，图 12 的开关 113 由 CMOS 传输门构成，P 沟道 MOS 晶体管 113P 的栅极提供控制信号 SC1B，N 沟道 MOS 晶体管 113N 的栅极中提供有控制信号 SC1。开关 113 在控制信号 SC1 为高时导通。

反相器 111 由定时反相器构成，即由栅极连接在一起，漏极连接在一起的构成 CMOS (互补 MOS) 反相器的 P 沟道 MOS 晶体管 111P 和 N 沟道 MOS 晶体管 111N、源极与电源 VDD 连接，栅极与控制信号 SC1 连接，漏极与 P 沟道 MOS 晶体管 111P 的源极连接的 P 沟道 MOS 晶体管 115P、以及栅极与控制信号 SC1B 连接，漏极与 N 沟道 MOS 晶体管 111N 的源极连接的 N 沟道 MOS 晶体管 115N 构成。

反相器 112 由定时反相器构成，即由栅极连接在一起，漏极连接在一起的构成 CMOS 反相器的 P 沟道 MOS 晶体管 112P 和 N 沟道 MOS 晶体管 112N、源极与电源 VDD 连接，栅极与控制信号 SC1 连接，漏极与 P 沟道 MOS 晶体管 112P 的源极连接的 P 沟道 MOS 晶体管 116P、以及栅极与控制信号 SC1B 连接，漏极与 N 沟道 MOS 晶体管 112N 的源极连接的 N 沟道 MOS 晶体管 116N 构成。

图 15 是表示图 14 所示的比较器的定时动作的图。在一输出期间的最初期间 ( $t_0 \sim t_1$ ) 中，控制信号 SC1 为高电平 (导通) (SC1B 为

低电平），接着成为低电平（SC1B 为高电平）。利用控制信号 SC1 为高电平，使差动电路激活，开关 13 导通，反相器 11、12 为不激活状态，利用控制信号 SC1 为低电平，使开关 13 截止，反相器 11、12 激活。

图 16 是本发明另一实施例的结构的图。参考图 16 (a)，该电路具有基准电压发生装置 11，比较器 12，第一模拟缓冲器电路 13，第二模拟缓冲器电路 14，具有将比较器 12 的输出 VO 和控制信号 SC0 输入的 NAND 电路 22，和将比较器 12 的输出 VO 经反相器 24 反相后的信号和控制信号 SC0 输入的 NAND 电路 23，NAND 电路 22 和 NAND 电路 23 的输出作为控制信号提供给第一模拟缓冲器电路 13 和第二模拟缓冲器电路 14。

控制信号 SC1 是控制图 14 所示的比较器 12 的动作的信号。

图 16 (b) 是用于说明图 16 (a) 的动作的时序图。SC0 是控制信号，VO 是比较器 12 的输出。在 SC0 为低电平时，NAND 电路 22，23 的输出为高电平，SC0 为高电平时，NAND 电路 22 输出 VO 的反相信号，NAND 电路 23 输出 VO。

图 17 显示的是图 1 所示构成中模拟缓冲器电路 13、14 的构成的一例的示意图。参考图 17，第一模拟缓冲器电路 13 包括：在输入端子 1 和高电位电源 VDD 间串联连接的恒流源 413 和开关 551，源极与输入端子 1 连接、栅极和漏极连接的 P 沟道 MOS 晶体管 411，在 P 沟道 MOS 晶体管 411 的漏极和低电位电源 VSS 间串联连接的恒流源 414 和开关 552，在输出端子 2 和高电位电源 VDD 间串联连接的恒流源 415 和开关 554，源极与输出端子 2 连接、栅极和 P 沟道 MOS 晶体管 411 的栅极连接、漏极通过开关 553 与低电位电源 VSS 连接的 P 沟道 MOS 晶体管 412。在输出端子 2 和高电位电源 VDD 间与电流源 415 和开关 554 的串联电路并列地连接开关 550。

第二模拟缓冲器电路 14 包括：在输入端子 1 和低电位电源 VSS 间串联连接的恒流源 423 和开关 561，源极与输入端子 1 连接、栅极和漏极连接的 N 沟道 MOS 晶体管 421，在 N 沟道 MOS 晶体管 421 的漏极和高电位电源 VDD 间串联连接的恒流源 424 和开关 562，在输出端子 2 和低电位电源 VSS 间串联连接的恒流源 425 和开关 564，源极与输出端子 2 连接、栅极和 N 沟道 MOS 晶体管 421 的栅极连接、漏极通过开关 563 与高电位电源 VDD 连接的 N 沟道 MOS 晶体管 422。在输出端子 2 和低电位电源 VSS 间与电流源 425 和开关 564 的串联电路并列地连接开关 560。

以下说明第一模拟缓冲器电路 13 动作的一例。根据控制信号进行控制，开关 550 导通，开关 551、552、553、554 截止，接着开关 551、552 导通，然后开关 550 截止，开关 553、554 导通。

开关 551、552 导通，利用晶体管 411 的作用，晶体管 411、412 的公共的栅极电位 VG1 从输入信号电压 Vin 仅偏离晶体管 411 的栅极-源极间电压 Vgs1 的电压，

$$VG1=Vin+Vgs1 \quad (1)$$

栅极-源极电压 Vgs 用栅极对源极的电位表示。

此时，晶体管的漏极-源极电流 Ids 和栅极-源极间电压 Vgs 之间具有固有的 VI 特性，晶体管 411 的栅极-源极间电压 Vgs1 用晶体管 411 的 Ids-Vgs 特性和电流源 414 所控制的电流 I1 来确定。

在变为晶体管 411 的漏极-源极间电流 I1（电流源 414 的电流值）时的栅极-源极间电压为 Vgs1(I1)，晶体管 411 的栅极电压 VG1 稳定在：

$$VG1=Vin+Vgs1(I1) \quad (2)$$

将电压 VG1 加在晶体管 412 的栅极, 输出电压 Vout 仅从电压 VG1 偏离晶体管 412 的栅极-源极间电压 Vgs2 的电压:

$$Vout=VG1-Vgs2 \quad (3)$$

输出电压 Vout 稳定在等于晶体管 412 的漏极-源极间电流 I3 (电流源 415 的电流值) 的值。此时, 晶体管 42 的栅极-源极间电压 Vgs2 利用晶体管 412 的 Ids-Vgs 特性和电流 I3 而变为 Vgs2(I3), 输出电压 Vout 稳定在:

$$Vout=VG1-Vgs2 (I3) \quad (4)$$

从上式 (2) 和 (4) 可得到, 输入信号电压 Vin 为一定时的输出电压 Vout 变为:

$$Vout= Vin+Vgs1 (I1) -Vgs2 (I3) \quad (5)$$

此时, 输出电压范围从电源电压 VDD 和电源电压 VSS 的电压范围变为仅为至少在晶体管 412 的栅极-源极间电压 Vgs2 (I3) 的电压差的狭窄电压范围。其中通过控制电流源 414 和 415 的电流 I1 和 I3 而使晶体管 411、412 各处的栅极-源极间电压 Vgs1(I1)和 Vgs2(I3)变为相等, 则根据式 (5), 输出电压 Vout 变为与输入信号电压 Vin 相等的电压。此外, 即使晶体管的特性变动, 通过设定晶体管 411 和 412 的元件尺寸及电流 I1 和 I3 使 Vgs1(I1)-Vgs2(I3)不变, 晶体管的特性变动也不会发生波动, 能够输出高精度的电压。

具体地说, 将晶体管 411 和 412 的元件尺寸和电流 I1 和 I3 设定

为分别相等，或者使晶体管 411、412 的沟道长度一致，根据沟道的宽度比设定电流  $I_1$  和  $I_3$  等，可以形成晶体管阈值电压变动无波动的电压输出。另外，如果控制电流源 413 的电流  $I_2$  与电流源 414 的电流  $I_1$  相等，即使在提供输入信号电压  $V_{in}$  的外部电路的电流提供能力低的情况下，也可以使缓冲器电路容易地工作。此外，即使没有电流源 413，缓冲器电路也能工作，但是在此情况下提供输入信号电压  $V_{in}$  的外部电路需要充分的电流提供能力。

此外，在第一模拟缓冲器电路 13 的工作中，一输出期间的前半段通过开关 550 的控制将输出端子 2 充电至电压  $VDD$ ，从而对任意的输入信号电压  $V_{in}$  使晶体管 412 作为源极跟随器工作，输出端子 2 可以在上式（5）表示的电压下被快速地驱动。

另外，利用晶体管 412 的源极跟随器动作的电流提供能力在晶体管 412 的栅极-源极间电压降低接近阈值电压时，最少也具有电流  $I_3$  的电流提供能力。从而通过调节电流  $I_3$ ，可以改变缓冲器电路的驱动能力和消耗电流的变化。以上这样的缓冲器电路可以有简单的结构和高的驱动能力，通过考虑晶体管特性变动来设定晶体管 421、422 的元件尺寸及电流  $I_1$  和  $I_3$ ，晶体管的特性变动不会发生波动，可以实现高精度的电压输出。

以下说明第二模拟缓冲器电路 14 的动作的一例。根据控制信号，开关 560 导通，开关 561、562、563、564 导通，接着开关 561 和 562 导通，接着开关 560 截止，开关 563、564 导通。

开关 561 和 562 导通，利用开关 421 的作用，晶体管 421、422 的公共栅极电位  $VG2$  从输入信号电压  $V_{in}$  变为仅偏离晶体管 421 的栅极-源极间电压  $V_{gs3}$  的电压，表示为

$$VG2 = V_{in} + V_{gs3} \quad (1)$$

此时，晶体管在漏极-源极间电流  $I_{ds}$  和栅极-源极间电压  $V_{gs}$  之间具有固有 VI 特性，晶体管 421 的栅极-源极间电压  $V_{gs3}$  利用晶体管 421 的  $I_{ds}$ - $V_{gs}$  特性和电流  $I$  来确定。

晶体管 421 的漏极-源极间电流变为  $I_4$ （电流源 424 的电流值）时的栅极-源极间电压成为  $V_{gs3}(I_4)$  时，晶体管 421 的栅极电压  $VG_2$  稳定在：

$$VG_2 = Vin + V_{gs3}(I_4) \quad (2)'$$

向晶体管 422 的栅极电压施加电压  $VG_2$ ，输出电压  $V_{out}$  从  $VG_2$  仅偏离晶体管 422 的栅极-源极间电压  $V_{gs4}$ ，

$$V_{out} = VG_2 - V_{gs4} \quad (3)'$$

这样，输出电压  $V_{out}$  稳定在与晶体管 422 的漏极-源极间电流  $I_5$ （电流源 425 的电流值）相等之处。此时晶体管 422 的栅极-源极间电压  $V_{gs4}$  根据晶体管 422 的  $I_{ds}$ - $V_{gs}$  特性和电流  $I_5$  而变为  $V_{gs4}(I_5)$ ，输出电压  $V_{out}$  稳定在

$$V_{out} = VG_2 - V_{gs4}(I_5) \quad (4)'$$

根据上式(2)'和上式(4)', 输入信号电压  $Vin$  一定时输出电压  $V_{out}$  变为

$$V_{out} = Vin + V_{gs3}(I_4) - V_{gs4}(I_5) \quad (5)'$$

此时，输出电压范围从高电位电源电压  $VDD$  和低电位电源电压  $VSS$  的电压范围变为仅为至少在晶体管 422 的栅极-源极间电压  $V_{gs4}$

(I5) 的电压差的狭窄电压范围。其中通过控制电流源 424 和 425 的电流 I4 和 I5 而使晶体管 421、422 各自的栅极-源极间电压  $V_{gs3}(I4)$  和  $V_{gs4}(I5)$  变为相等，则根据式 (5)'，输出电压  $V_{out}$  变为与输入信号电压  $V_{in}$  相等的电压。此外，即使晶体管的特性变动，通过设定晶体管 421 和 422 的元件尺寸及电流 I4 和 I5 使  $V_{gs3}(I4)-V_{gs4}(I5)$  不变，晶体管的特性变动不会发生波动，能够输出高精度的电压。具体地说，将晶体管 421 和 422 的元件尺寸和电流 I4 和 I5 设定为分别相等，或者使晶体管 421、422 的沟道长度一致，根据沟道的宽度比设定电流 I4 和 I5 等，可以形成晶体管阈值电压变动无波动的电压输出。另外，如果控制电流源 423 的电流 I6 与电流源 424 的电流 I4 相等，即使在提供输入信号电压  $V_{in}$  的外部电路的电流提供能力低的情况下，也可以使缓冲器电路容易地工作。此外，即使没有电流源 423，缓冲器电路也能工作，但是在此情况下提供输入信号电压  $V_{in}$  的外部电路需要充分的电流提供能力。

此外，在第二模拟缓冲器电路 14 的工作中，在一输出期间的前半段，通过开关 560 的控制将输出端子 2 放电至电压 VSS，从而对任意的输入信号电压  $V_{in}$  使晶体管 422 作为源极跟随器工作，输出端子 2 可以在上式 (5)' 表示的电压下被快速地驱动。

另外，利用晶体管 422 的源极跟随器动作的电流提供能力在晶体管 422 的栅极-源极间电压降低接近阈值电压时，最少也具有电流 I5 的电流提供能力。从而通过调节电流 I5，可以改变缓冲器电路的驱动能力和消耗电流的变化。以上这样的缓冲器电路可以以简单的结构而具有高的驱动能力，通过考虑晶体管特性变动来设定晶体管 421、422 的元件尺寸及电流 I4 和 I5，晶体管的特性变动不会发生波动，可以实现高精度的电压输出。

图 18 是图 7 所示实施例中第一、第二模拟缓冲器电路 13、14 的构成的一例的图。与参考图 17 说明的内容相同的结构和动作的说明

将被省略。

图 19 是图 1 所示的实施例中第一、第二模拟缓冲器电路 13、14 结构一例的图。在该电路结构中，第一、第二模拟缓冲器电路 13、14 由使用差动放大电路的电压跟随器构成，具有对输出端子 2 进行预放电、预充电的预充放电装置 15。

参考图 19，第一模拟缓冲器电路 13 由差动级和输出级构成。差动级包括 P 沟道 MOS 晶体管 311、322 构成的电流镜电路、尺寸彼此相等的 N 沟道 MOS 晶体管构成的差动对 313、314、恒流源电路 315 以及开关 511。更详细地说，包括构成差动对的 N 沟道 MOS 晶体管 313、314，其源极共同连接，并与恒流源 315 的一端连接，栅级分别连接至输入端子 1 (Vin) 和输出端子 2 (Vout)；P 沟道 MOS 晶体管 311（成为电流镜电路的电流输出侧的晶体管），其源极与高电位侧电源 VDD 连接，其栅极与 P 沟道 MOS 晶体管 312 的栅极连接，其漏极与 N 沟道 MOS 晶体管 313 的漏极连接；P 沟道 MOS 晶体管 312（成为电流镜电路的电流输入侧的晶体管），其源极与高电位侧电源 VDD 连接，其栅极和漏极与连接的 N 沟道 MOS 晶体管 314 的漏极连接；以及在恒流源 315 的另一端与低电位侧电源 VSS 之间连接的开关 511。构成差动对的 N 沟道 MOS 晶体管 313、314 其尺寸相等。N 沟道 MOS 晶体管 313 的漏极作为输出端。

此外输出级包括：P 沟道 MOS 晶体管 316，其源极与输出端子 2 连接，其栅极输入差动电路的输出电压（N 沟道 MOS 晶体管 313 的漏极电压），其漏极与高电位侧电源 VDD 连接。还具有在输出端子 2 和低电位侧电源 VSS 间连接的电流源 317 和开关 512。另外，P 沟道 MOS 晶体管 316 也可以用漏极与升压电路连接的 N 沟道 MOS 晶体管来置换。另外也可以设置用于使差动电路的输出端和输出端子 2 之间的输出稳定的相位补偿电容。

开关 511、512 控制着控制端子与控制信号连接导通和截止，在开关截止时切断电流而使动作停止。各开关如果配置成切断电流，则也可以与图 19 配置不同。

第二模拟缓冲器电路 14 包括：N 沟道 MOS 晶体管 321、322 构成的电流镜电路、尺寸彼此相等的 P 沟道 MOS 晶体管构成的差动对 323、324、恒流源电路 325。更详细地说，包括构成差动对的 P 沟道 MOS 晶体管 323、324，其源极共同连接，并与恒流源 325 的一端连接，栅级分别连接至输入端子 1 (Vin) 和输出端子 2 (Vout)；N 沟道 MOS 晶体管 321（成为电流镜电路的电流输出侧的晶体管），其源极与低电位侧电源 VSS 连接，其栅极与 N 沟道 MOS 晶体管 322 的栅极连接，其漏极与 P 沟道 MOS 晶体管 323 的漏极连接；N 沟道 MOS 晶体管 322（成为电流镜电路的电流输入侧的晶体管），其源极与低电位侧电源 VSS 连接，其栅极和漏极连接并与 P 沟道 MOS 晶体管 324 的漏极连接；以及在恒流源 325 的另一端与高电位侧电源 VDD 之间连接的开关 521。构成差动对的 P 沟道 MOS 晶体管 323、324 其尺寸相等。P 沟道 MOS 晶体管 323 的漏极作为输出端。

此外，输出级包括：N 沟道 MOS 晶体管 326，其源极与输出端子 2 连接，其栅极输入差动电路的输出电压（P 沟道 MOS 晶体管 323 的漏极电压），其漏极与低电位侧电源 VSS 连接。还具有在输出端子 2 和高电位侧电源 VDD 间连接的电流源 327 和开关 522。另外，N 沟道 MOS 晶体管 326 也可以用漏极与降压电路连接的 P 沟道 MOS 晶体管来置换。另外也可以设置用于使差动电路的输出端和输出端子 2 之间的输出稳定的相位补偿电容。

开关 521 和 522 控制着控制端子与控制信号连接的导通和截止，在开关截止时切断电流而使动作停止。各开关如果配置成切断电流，则也可以与图 19 配置不同。

预充电装置 15 在低电位数据输出时对输出端子 2 预充电，在高电位数据输出时，对输出端子 2 预放电。优选地，如果预充电装置 15 的预充电电压和预放电电压被设置为在使第一模拟缓冲器电路 13 和第二模拟缓冲器电路 14 能一起工作的电压范围内设置的驱动切换电压  $V_c$  附近时，第一模拟缓冲器电路 13 由充电动作而进行驱动，第二模拟缓冲器电路 14 由放电动作而驱动，能够一起进行高速的动作。

图 20 是在图 7 的构成中，以第一、第二模拟缓冲器电路 13、14 如图 19 所示构成为例的图。第二模拟缓冲器电路 13、14 的构成和动作与参考图 19 说明的相同，因此省略其说明。

图 21 是表示在图 1 所示的实施例中第一、第二模拟缓冲器电路 13、14 为另外的构成例的情况。

参考图 21，第一模拟缓冲器电路 13 由如下部分构成：电压跟随器结构的差动放大电路 310，具有差动级和输出级；以及源极跟随器放电装置 410。第二模拟缓冲器电路 14 由如下部分构成：电压跟随器结构的差动放大电路 320，具有差动级和输出级；以及源极跟随器充电装置 420。

第一模拟缓冲器电路 13 的差动放大电路 310 由恒流源 315、开关 511、差动对 N 沟道 MOS 晶体管 313、314、电流镜电路 311 和 312、栅极接收差动级输出电压的 P 沟道 MOS 晶体管 316 构成。P 沟道 MOS 晶体管 316 的源极与高电位侧电源 VDD 连接，漏极与输出端子 2 连接。差动对的 N 沟道 MOS 晶体管 313、314 的栅极与输出端子 1 和输出端子 2 连接。该差动电路与图 19 的缓冲器电路的差动电路有基本相同的结构（但是没有进行放电作用的电流源 317 和开关 512）。

源极跟随器放电装置 410 包括：在输入端子 1 和高电位侧电源 VDD 间串联连接的恒流源 413 和开关 551；源极与输入端子 1 连接、

栅极与漏极连接的 P 沟道 MOS 晶体管 411；在 P 沟道 MOS 晶体管 411 的漏极与低电位侧电源 VSS 间串联连接的恒流源 414 和开关 552；在输出端子 2 与高电位侧电源 VDD 间串联连接的恒流源 415 和开关 554；源极与输出端子 2 连接、栅极与 P 沟道 MOS 晶体管 411 的栅极连接、漏极通过开关 553 与低电位电源 VSS 连接的 P 沟道 MOS 晶体管 412。

第二模拟缓冲器电路 14 的差动放大电路 320 由恒流源 325、开关 521、差动对 P 沟道 MOS 晶体管 323、324、电流镜电路 321 和 322、栅极接收差动级输出电压的 N 沟道 MOS 晶体管 326 构成。N 沟道 MOS 晶体管 326 的源极与高电位侧电源 VDD 连接，漏极与输出端子 2 连接。差动对的 P 沟道 MOS 晶体管 323、324 的栅极与输入端子 1 和输出端子 2 连接。该差动电路与图 19 的缓冲器电路的差动电路有基本相同的结构（但是没有进行充电作用的电流源 327 和开关 522）。

源极跟随器充电装置 420 包括：在输入端子 1 和低电位侧电源 VSS 间串联连接的恒流源 423 和开关 561；源极与输入端子 1 连接、栅极与漏极连接的 N 沟道 MOS 晶体管 421；在 N 沟道 MOS 晶体管 421 的漏极与高电位侧电源 VDD 间串联连接的恒流源 424 和开关 562；在输出端子 2 与低电位侧电源 VSS 间串联连接的恒流源 425 和开关 564；源极与输出端子 2 连接、栅极与 N 沟道 MOS 晶体管 421 的栅极连接、漏极通过开关 563 与高电位电源 VDD 连接的 N 沟道 MOS 晶体管 422。

在本实施例中，在电压跟随器电路（差动放大电路）中，通过将具有使输出电压稳定的作用的源极跟随器结构的电路进行组合，就不需要相位补偿装置（相位补偿电容），可以以低的消耗功率进行高速驱动。

第一模拟缓冲器电路 13 包括：具有电压跟随器结构的差动放大电路 310，它能够根据输入信号电压 Vin 和输出电压 Vout 二者的输入

而产生充电作用、从而使输出电压  $V_{out}$  升高；源极跟随器放电装置 410，与差动放大电路 310 相独立地动作，根据输入信号电压  $V_{in}$  和输出电压  $V_{out}$  的电压差，利用源极跟随动作产生放电作用。

差动放大电路 310 具有根据输入信号电压  $V_{in}$  和输出电压  $V_{out}$  的电压差来动作的差动级，以及根据差动级的输出产生放电作用的充电装置（晶体管 316）。差动放大电路 310 根据  $V_{in}$  和  $V_{out}$  的电压差动作，在输出电压  $V_{out}$  比电压  $V_{in}$  低的情况下，通过充电作用将输出电压  $V_{out}$  提高至电压  $V_{in}$ 。

差动放大电路 310 可以不设置相位补偿装置而能够高速动作，但是，在反馈型结构中由于电路元件的寄生电容，输出电压  $V_{out}$  的变化反映到充电作用中的响应略有一些延迟，产生过冲（过充电）。

另一方面，源极跟随器放电装置 410 具有相应于输入信号电压  $V_{in}$  和输出电压  $V_{out}$  的电压差的放电能力，输出电压  $V_{out}$  在比输入电压  $V_{in}$  高的情况下，利用晶体管 412 的源极跟随器动作的放电作用，可以将输出电压  $V_{out}$  下降至电压  $V_{in}$ 。

源极跟随器放电装置 410 在输入信号电压  $V_{in}$  和输出电压  $V_{out}$  的电压差大时放电能力高、而随着电压差变小放电能力也变小，因此利用放电作用使输出电压  $V_{out}$  的变化接近电压  $V_{in}$  也减缓了。因此，源极跟随器放电装置 410 在输出电压  $V_{out}$  快速地变化至电压  $V_{in}$  的同时，具有稳定在电压  $V_{in}$  的作用。

即，输出电压  $V_{out}$  在比输入电压  $V_{in}$  更低的情况下，输出电压  $V_{out}$  利用差动放大电路 310 高速地上升至电压  $V_{in}$ ，此时即使产生过冲（过充电），通过源极跟随器放电装置 410，也可以快速地下降至所需要的电压，从而稳定地输出。

另一方面，输出电压  $V_{out}$  在比所希望的电压高的情况下，差动放大电路 310 不工作，输出电压  $V_{out}$  利用源极跟随器放电装置 410，根据  $V_{in}$  和  $V_{out}$  的电压差，利用源极跟随器的放电作用而下降至所需要的电压，从而稳定地输出。

此外，电压跟随器结构的差动放大电路 310 由于不设置相位补偿电容，只有通过电路元件的寄生电容等而产生的略微的响应延迟，即使在产生过冲的情况下，也将其抑制在十分小的水平。因此，容易实现输出电压的稳定。而且由于不设置相位补偿电容，不需要用于将相位补偿电容充放电的电流，可以抑制电流消耗而实现低功率消耗。

这样，通过差动电路 310 和源极跟随器放电装置 410 的组合，在充电时可以进行高速充电并且使输出电压  $V_{out}$  快速地稳定在与输入信号电压  $V_{in}$  相等的电压。

第二模拟缓冲器电路 14 具有电压跟随器结构的差动放大电路 320，它能够根据输入信号电压  $V_{in}$  和输出电压  $V_{out}$  二者的输入而产生放电作用、从而使输出电压  $V_{out}$  降低；源极跟随器充电装置 420，与差动放大电路 320 相独立地动作，根据输入信号电压  $V_{in}$  和输出电压  $V_{out}$  的电压差，利用源极跟随器动作产生充电作用。

差动放大电路 320 具有根据输入信号电压  $V_{in}$  和输出电压  $V_{out}$  二者的电压差来动作的差动级，以及根据差动级的输出产生放电作用的放电装置（晶体管 326）。差动放大电路 320 根据  $V_{in}$  和  $V_{out}$  的电压差动作，在输出电压  $V_{out}$  比电压  $V_{in}$  高的情况下，通过放电作用将输出电压  $V_{out}$  降低至电压  $V_{in}$ 。

差动放大电路 320 可以不设置相位补偿装置而能够高速动作，但是，在反馈型结构中由于电路元件的寄生电容，输出电压  $V_{out}$  的变化反映到充电作用中的响应略有一些延迟，产生下冲（过放电）。

另一方面，源极跟随器充电装置 420 具有根据输入信号电压  $V_{in}$  和输出电压  $V_{out}$  二者的电压差来充电的能力，在输出电压  $V_{out}$  比输入信号电压  $V_{in}$  低的情况下，可以利用晶体管的源极跟随器动作产生的充电作用将输出电压  $V_{out}$  升高至电压  $V_{in}$ 。

源极跟随器充电装置 420 在输入信号电压  $V_{in}$  和输出电压  $V_{out}$  的电压差大时充电能力也强，在电压差小时充电能力也变小。因此，由充电作用所引起的输出电压  $V_{out}$  的变化在接近电压  $V_{in}$  时速度也放慢。所以，源极跟随器充电装置 420 在使输出电压  $V_{out}$  快速地接近电压  $V_{in}$  的同时，还具有稳定在电压  $V_{in}$  的作用。

即，在输出电压  $V_{out}$  比输入信号电压  $V_{in}$  高的情况下，输出电压  $V_{out}$  利用差动放大电路 320 以更快的速度下降至电压  $V_{in}$ 。此时即使产生下冲（过度放电），通过源极跟随器充电装置 420，也可以迅速地升高至所需要的电压，从而稳定地输出。

另一方面，在输出电压  $V_{out}$  比所希望的电压低的情况下，差动放大电路 320 不工作，输出电压  $V_{out}$  利用源极跟随器充电装置 420，根据  $V_{in}$  和  $V_{out}$  的电压差，利用源极跟随器的充电作用而升高至所需要的电压，从而稳定地输出。

此外，电压跟随器结构的差动放大电路 320 由于不设置相位补偿电容，只有通过电路元件的寄生电容等而产生的略微的响应延迟，即使在产生过冲的情况下，也将其抑制在十分小的水平。因此，容易实现输出电压的稳定。而且由于不设置相位补偿电容，不需要用于将相位补偿电容充放电的电流，可以抑制电流消耗而实现低功率消耗。

这样，通过差动电路 320 和源极跟随器充电装置 420 的组合，在放电时可以进行高速放电并且使输出电压  $V_{out}$  快速地稳定在与输入

信号电压  $V_{in}$  相等的电压。

此外，在图 21 的驱动电路中，可以设置预充电装置，在低电位数据输出时对输出端子 2 预充电，而在高电位数据输出时，对输出端子 2 预放电。预充电装置的预充电电压和预放电电压优选设置为在第一模拟缓冲器电路 13 和第二模拟缓冲器电路 14 能共同工作的电压范围内所设置的驱动切换电压  $V_c$  附近，这样第一模拟缓冲器电路 13 由差动放大电路 310 的充电动作驱动，第二模拟缓冲器电路 14 由差动放大电路 320 的放电动作驱动，能同时高速地动作。

图 22 显示了在图 7 的实施例中第一、第二模拟缓冲器电路 13、14 的结构如图 21 所示那样构成的情况。

图 23 (a) 是显示图 7 所示实施例中基准电压发生装置 11 的构成的示意图。在 VDD 和 VSS 间连接开关 120 和用于分压的电阻 R1、R2，分压值  $V_{in2}$  输出。该  $V_{in2}$  (基准电压) 如图 23 (b) 所示那样，为与第一、第二模拟缓冲器电路 13、14 的动作范围的重叠范围对应的可驱动切换的范围 (第一) 内的电压。电阻 R1、R2 当然也可以用三极管、二极管等有源元件构成。

另外，作为参考上面的附图说明的模拟缓冲器电路 13、14 的电路结构，当然可以将各实施例各自的电路组合使用。此外，作为本发明的驱动电路，并不仅适用于液晶显示装置的数据线驱动器。也就是说，高电位侧和低电位侧的两个缓冲器电路的切换在两个缓冲器电路共同工作的电压范围内确实地进行，实现了高精度的全范围电压输出，可适用于任何用途的高精度电压输出缓冲器电路。

虽然在上面说明了本发明的上述实施例，但是本发明并不限于这些实施例，本领域技术人员可以在权利要求的范围内对它们进行各种变形、修正。特别是在上述实施例中，关于两个极性的说明是以有源

---

矩阵型液晶显示装置的数据线驱动电路的优选例子来举例说明的，而在适用于不需要进行极性切换的有源矩阵型有机 EL 显示装置的数据线驱动电路等的情况下，也可以容易地用于两个极性中只有其中之一始终激活、另一方不激活的情况。而且可以去掉不激活的部分。

如以上说明的那样，在显示元件的特性的调制时等中，调制种类不会波动，能够始终在第一、第二模拟缓冲器电路动作的电压范围内进行切换，在有源矩阵型液晶显示装置的数据线驱动电路中使用的情况下，可以避免灰度跳跃等问题的发生。

图1

**图2**

| 控制信号       | L   | H  | H  |

|------------|-----|----|----|

| 比较部5输出(PN) | L或H | H  | L  |

| 第一模拟缓冲器    | 停止  | 动作 | 停止 |

| 第二模拟缓冲器    | 停止  | 停止 | 动作 |

图3

图4

**图5**

图6

(A)

公共反相驱动中液晶的伽玛特性和驱动电路的工作范围（标准）

(B)

公共反相驱动中液晶的伽玛特性和驱动电路的工作范围（伽玛调制时）

图7

**图8**

| 控制信号        | L     | H  | H  |

|-------------|-------|----|----|

| 比较器12输出(PN) | L 或 H | H  | L  |

| 第一模拟缓冲器     | 停止    | 动作 | 停止 |

| 第二模拟缓冲器     | 停止    | 停止 | 动作 |

**图9**

**图10**

图11

图12

\*  $C_1$ ,  $C_2$ : 寄生电容

通过设计为  $C_1 > C_2$ ,

可以防止误动作

图13

图14

\* C1, C2: 寄生电容

通过设计为 C1>C2,

可以防止误动作

图15

图16

(a)

(b)

| SC0        | L     | H | H |

|------------|-------|---|---|

| V0         | L 或 H | H | L |

| NAND22 的输出 | H     | L | H |

| NAND23 的输出 | H     | H | L |

图17

图18

图19

图20

图21

图22

**图23**

(A)

(B)

**图24**

图25

|               |                                                                           |         |            |

|---------------|---------------------------------------------------------------------------|---------|------------|

| 专利名称(译)       | 驱动电路和液晶显示装置                                                               |         |            |

| 公开(公告)号       | <a href="#">CN100550108C</a>                                              | 公开(公告)日 | 2009-10-14 |

| 申请号           | CN02140186.1                                                              | 申请日     | 2002-07-03 |

| 申请(专利权)人(译)   | 日本电气株式会社                                                                  |         |            |

| 当前申请(专利权)人(译) | 日本电气株式会社                                                                  |         |            |

| [标]发明人        | 土弘<br>内山义规                                                                |         |            |

| 发明人           | 土弘<br>内山义规                                                                |         |            |

| IPC分类号        | G09G3/36 G02F1/133 G09G3/20 H03K19/0175                                   |         |            |

| CPC分类号        | G09G2310/027 G09G2310/0291 G09G3/3614 G09G3/3696 G09G3/3688 G09G2310/0248 |         |            |

| 审查员(译)        | 许凌云                                                                       |         |            |

| 优先权           | 2001206987 2001-07-06 JP                                                  |         |            |

| 其他公开文献        | CN1396580A                                                                |         |            |

| 外部链接          | <a href="#">Espacenet</a> <a href="#">Sipo</a>                            |         |            |

#### 摘要(译)

提供一种驱动电路，包括：工作范围达到高电位侧电源电位、低电位侧电源电位的第一、第二缓冲器电路13、14，其输入端与将输入信号电压输入的一个输入端子共同连接，其输出端与输出端子共同连接；存储部3，对于伽玛特性的标准时和调制时，存储并保持用于使第一和第二缓冲器电路能一起工作的范围内的输入信号电压所对应的基准数据；选择部4，根据确定调制的调制信息，选择标准和与调制对应的基准数据并输出；和比较部5，将输入的数据信号和所述选择部输出的基准数据进行比较。第一和第二缓冲器电路根据比较部5的比较结果信号和控制信号，控制其工作和停止。