## (12) 发明专利

(10) 授权公告号 CN 102645773 B

(45) 授权公告日 2015.04.15

(21) 申请号 201210116918.3

(56) 对比文件

(22) 申请日 2007.11.16

CN 1870117 A, 2006.11.29,

(30) 优先权数据

CN 1892798 A, 2007.01.10,

10-2007-0041563 2007.04.27 KR

CN 1870117 A, 2006.11.29,

(62) 分案原申请数据

CN 1941208 A, 2007.04.04,

200710192711.3 2007.11.16

CN 1727972 A, 2006.02.01,

审查员 张贝

(73) 专利权人 三星显示有限公司

地址 韩国京畿道龙仁市

(72) 发明人 李奉俊 金景旭 金钟五 金圣万

李洪雨 金憲珍

(74) 专利代理机构 北京铭硕知识产权代理有限

公司 11286

代理人 韩芳

(51) Int. Cl.

G02F 1/133(2006.01)

G09G 3/36(2006.01)

权利要求书1页 说明书14页 附图8页

(54) 发明名称

栅极驱动电路和具有该栅极驱动电路的液晶显示器

(57) 摘要

本发明公开了一种栅极驱动电路和一种具有该栅极驱动电路的液晶显示器。该栅极驱动电路具有第一级,第一级包括:上拉驱动单元,从第二级接收第一进位信号并且分别在预先时间段期间、栅极活跃时间段期间、第一栅极不活跃时间段期间和第二栅极不活跃时间段期间向第一节点输出具有第一电压、第二电压、第三电压和第四电压的控制信号;上拉单元,接收控制信号并且在栅极活跃时间段期间向第二节点输出栅极导通信号;进位输出单元,接收控制信号并且在栅极活跃时间段期间向第三级输出第二进位信号;下拉单元,接收来自第二级的栅极导通信号并且在第二栅极不活跃时间段期间向第一节点输出具有第四电压电平的控制信号。

1. 一种液晶显示器,包括:

液晶面板,包括第一至第  $n$  棚极线和第一至第  $m$  数据线,其中,  $n$  是自然数,  $m$  是自然数;

棚极驱动电路,包括分别与第一至第  $n$  棚极线对应的第一至第  $n$  级以及不与任何棚极线对应的第  $n+1$  至第  $n+3$  级;

数据驱动电路,将数据电压提供到第一至第  $m$  数据线,

其中,第一至第  $n+3$  级顺序提供第一至第  $n+3$  棚极导通信号,

棚极驱动电路的第  $i$  级接收从棚极驱动电路的第  $i+3$  级输出的棚极导通信号并且向液晶面板的第一棚极线提供棚极截止信号,其中,  $1 \leq i \leq n$ 。

## 栅极驱动电路和具有该栅极驱动电路的液晶显示器

### 技术领域

[0001] 本发明涉及一种栅极驱动电路和一种具有该栅极驱动电路的液晶显示器,更具体地讲,本发明涉及一种减小了尺寸的栅极驱动电路和一种具有该栅极驱动电路的液晶显示器。

### 背景技术

[0002] 通常,液晶显示器包括液晶面板,液晶面板具有共电极显示面板、薄膜晶体管基底及设置在共电极显示面板和薄膜晶体管基底之间的液晶层。共电极显示面板具有形成在其上的共电极和滤色器,薄膜晶体管基底具有设置在其上的开关元件和像素电极。

[0003] 液晶面板还包括栅极线、数据线及连接到栅极线和数据线的像素。另外,薄膜晶体管和顺序向栅极线输出栅极信号的栅极驱动电路设置在液晶面板上。

[0004] 栅极驱动电路通常包括具有彼此级联的级的移位寄存器。更具体地讲,当前级向对应的栅极线提供栅极信号,并且控制前面的级和后面的级。

[0005] 每一级包括开关元件和电容器。开关元件向栅极线输出栅极信号,并且占用栅极驱动电路的尺寸的大约 20%。在液晶面板中,栅极驱动电路相对于其它组件占据大的空间,这使得难以减小液晶显示器的尺寸,从而难以增大生产余量和 / 或提高栅极驱动电路和具有该栅极驱动电路的液晶面板的生产效率。

### 发明内容

[0006] 在本发明的示例性实施例中,栅极驱动电路具有减小的尺寸。

[0007] 本发明的另一示例性实施例提供了一种具有减小了尺寸的栅极驱动电路的液晶显示器。

[0008] 本发明的示例性实施例不限于这里描述的实施例,本发明的其它示例性实施例对本领域技术人员来说将是清楚的。

[0009] 根据本发明示例性实施例的栅极驱动电路包括多个级。所述多个级中的至少第一级包括:第一节点;第二节点;上拉驱动单元,接收来自第二级的第一进位信号或者接收起始信号,并且将控制信号输出到第一节点。所述控制信号在预先时间段期间具有第一电压电平,在预先时间段之后并且接近预先时间段的栅极活跃时间段期间具有高于第一电压电平的第二电压电平,在栅极活跃时间段之后并且接近栅极活跃时间段的第一栅极不活跃时间段期间具有低于第二电压电平的第三电压电平,在第一栅极不活跃时间段之后并且接近第一栅极不活跃时间段的第二栅极不活跃时间段期间具有低于第三电压电平的第四电压电平。

[0010] 所述多个级中的至少第一级还包括:上拉单元,接收控制信号和时钟信号并且在栅极活跃时间段期间向第二节点输出栅极导通信号;进位输出单元,接收控制信号和时钟信号,并且在栅极活跃时间段期间向第三级输出第二进位信号;下拉单元,接收来自第二级的栅极导通信号,并且在第二栅极不活跃时间段期间向第一节点输出处于第四电压电平的

控制信号。

[0011] 上拉单元包括第一开关元件,第一开关元件响应控制信号向第二节点输出被时钟信号上拉的栅极导通信号。

[0012] 下拉单元包括将第一节点的电压电平下拉第二开关元件,并且下拉单元不包括将第二节点的电压电平下拉的第三开关元件;第二开关元件的宽长比在第一开关元件的宽长比的大约 1/20 至大约 1/10 的范围内。

[0013] 在可选示例性实施例中,下拉单元包括:第二开关元件,从第二级接收栅极导通信号并且下拉第一节点的电压电平;第三开关元件,从第二级接收栅极导通信号并且下拉第二节点的电压电平。第三开关元件的宽长比等于或小于第一开关元件的宽长比的大约 1/2。

[0014] 栅极驱动电路还可包括第一移位寄存器和第二移位寄存器,第一移位寄存器和第二移位寄存器中的每个具有分别与第一栅极线、第二栅极线、第三栅极线和第四栅极线对应的第一级、第二级、第三级和第四级。第一移位寄存器和第二移位寄存器中的每个的第一级、第二级、第三级和第四级分别向第一栅极线、第二栅极线、第三栅极线和第四栅极线顺序提供第一栅极导通信号、第二栅极导通信号、第三栅极导通信号和第四栅极导通信号。第一移位寄存器和第二移位寄存器中的每个的第一级接收从第一移位寄存器和第二移位寄存器中的每个的第四级输出的第四栅极导通信号,并且向第一栅极线输出第一栅极截止信号。

[0015] 另外,第一移位寄存器和第二移位寄存器中的每个的第一栅极导通信号包括预充电时间段和主充电时间段,第一移位寄存器和第二移位寄存器中的每个的第二栅极导通信号的施加时间比第一移位寄存器和第二移位寄存器中的每个的第一栅极导通信号的施加时间延迟预充电时间段。

[0016] 第一移位寄存器基本上沿着垂直方向布置,并且设置在其上设置有第一栅极线、第二栅极线、第三栅极线和第四栅极线的区域的第一侧;第二移位寄存器基本上沿着垂直方向布置,并且设置在其上设置有第一栅极线、第二栅极线、第三栅极线和第四栅极线的区域的相对第二侧。

[0017] 第一移位寄存器和第二移位寄存器被同时导通,第一移位寄存器和第二移位寄存器还可均包括第一哑级、第二哑级和第三哑级。

[0018] 在可选示例性实施例中,第一移位寄存器和第二移位寄存器被顺序导通。

[0019] 在又一可选示例性实施例中,栅极驱动电路可以包括:第一移位寄存器,具有与第一栅极线对应的第一级和与第三栅极线对应的第三级;第二移位寄存器,具有与第二栅极线对应的第二级和与第四栅极线对应的第四级。第一级、第二级、第三级和第四级分别向第一栅极线、第二栅极线、第三栅极线和第四栅极线顺序提供第一栅极导通信号、第二栅极导通信号、第三栅极导通信号和第四栅极导通信号。第一级接收从第四级输出的第四栅极导通信号并且将第一栅极截止信号输出到第一栅极线。第一移位寄存器基本上沿着垂直方向布置,并且设置在其上设置有第一栅极线、第二栅极线、第三栅极线和第四栅极线的区域的第一侧;第二移位寄存器基本上沿着垂直方向布置,并且设置在其上设置有第一栅极线、第二栅极线、第三栅极线和第四栅极线的区域的相对第二侧。第一移位寄存器和第二移位寄存器被顺序导通。

[0020] 根据本发明的另一示例性实施例,液晶显示器包括液晶面板。液晶面板包括第一

至第  $n$  棚极线（其中， $n$  是自然数）和第一至第  $m$  数据线（其中， $m$  是自然数）；棚极驱动电路，包括与第一至第  $n$  棚极线对应的第一至第  $n$  级以及不与第一至第  $n$  棚极线对应的第  $n+1$  至第  $n+3$  级；数据驱动电路，将数据电压提供到第一至第  $m$  数据线。在液晶显示器中，第一至第  $n+3$  级顺序提供第一至第  $n+3$  棚极导通信号，棚极驱动电路的第  $i$  级（其中， $1 \leq i \leq n$ ）接收从棚极驱动电路的第  $i+3$  级输出的棚极导通信号并且向液晶面板的第一棚极线提供棚极截止信号。

[0021] 根据本发明的又一可选示例性实施例，液晶显示器包括液晶面板。液晶面板包括：第一棚极线、第二棚极线、第三棚极线和第四棚极线；第一数据线、第二数据线、第三数据线和第四数据线；像素，设置在第一棚极线、第二棚极线、第三棚极线和第四棚极线中的对应的棚极线与第一数据线、第二数据线、第三数据线和第四数据线中的对应的数据线的交叉处。

[0022] 液晶显示器还包括：棚极驱动电路，具有设置在第一棚极线、第二棚极线、第三棚极线和第四棚极线中的每条的第一侧的第一移位寄存器以及设置在第一棚极线、第二棚极线、第三棚极线和第四棚极线中的每条的相对第二侧的第二移位寄存器；数据驱动电路，将数据电压提供到第一数据线、第二数据线、第三数据线和第四数据线。第一移位寄存器和第二移位寄存器均具有分别与第一棚极线、第二棚极线、第三棚极线和第四棚极线对应的第一级、第二级、第三级和第四级。

[0023] 在液晶显示器中，第一移位寄存器和第二移位寄存器中的每个的第一级、第二级、第三级和第四级分别向第一棚极线、第二棚极线、第三棚极线和第四棚极线顺序提供第一棚极导通信号、第二棚极导通信号、第三棚极导通信号和第四棚极导通信号，第一移位寄存器和第二移位寄存器中的每个的第一级接收从第一移位寄存器和第二移位寄存器中的每个的第四级输出的第四棚极导通信号，并且向第一棚极线输出第一棚极截止信号。

[0024] 第一移位寄存器和第二移位寄存器被同时导通，或者在可选示例性实施例中，第一移位寄存器和第二移位寄存器可以被顺序导通。

[0025] 根据本发明的又一可选示例性实施例，液晶显示器包括：液晶面板，液晶面板包括第一至第  $n$  棚极线（其中， $n$  是自然数）和第一至第  $m$  数据线（其中， $m$  是自然数）；棚极驱动电路，具有多个级；数据驱动电路，将数据电压提供到第一至第  $m$  数据线。多个级中的至少第一级包括：第一节点和第二节点；上拉驱动单元，接收第二级的第一进位信号或者起始信号，并且向第一节点输出控制信号。控制信号在预先时间段期间具有第一电压电平，在预先时间段之后并且接近预先时间段的棚极活跃时间段期间具有高于第一电压电平的第二电压电平，在棚极活跃时间段之后并且接近棚极活跃时间段的第一棚极不活跃时间段期间具有低于第二电压电平的第三电压电平，在第一棚极不活跃时间段之后并且接近第一棚极不活跃时间段的第二棚极不活跃时间段期间，具有低于第三电压电平的第四电压电平。多个级中的至少第一级还包括：上拉单元，接收控制信号和时钟信号并且在棚极活跃时间段期间向第二节点输出棚极导通信号；进位输出单元，接收控制信号和时钟信号，并且在棚极活跃时间段期间向第三级输出第二进位信号；下拉单元，接收来自第二级的棚极导通信号，并且在第二棚极不活跃时间段期间向第一节点输出处于第四电压电平的控制信号。

[0026] 上拉单元包括第一开关元件，第一开关元件响应控制信号向第二节点输出被时钟信号上拉的棚极导通信号。

[0027] 下拉单元包括将第一节点的电压电平下拉的第二开关元件，并且不包括将第二节点的电压电平下拉的第三开关元件；第二开关元件的宽长比在第一开关元件的宽长比的大约 1/20 至大约 1/10 的范围内。

[0028] 在可选的示例性实施例中，下拉单元包括：第二开关元件，从第二级接收栅极导通信号并且下拉第一节点的电压电平；第三开关元件，从第二级接收栅极导通信号并且下拉第二节点的电压电平。第三开关元件的宽长比等于或小于第一开关元件的宽长比的大约 1/2。

## 附图说明

[0029] 通过参照附图对本发明示例性实施例进行的更详细的描述，本发明的以上和其它方面、特征及优点将变得更容易清楚，在附图中：

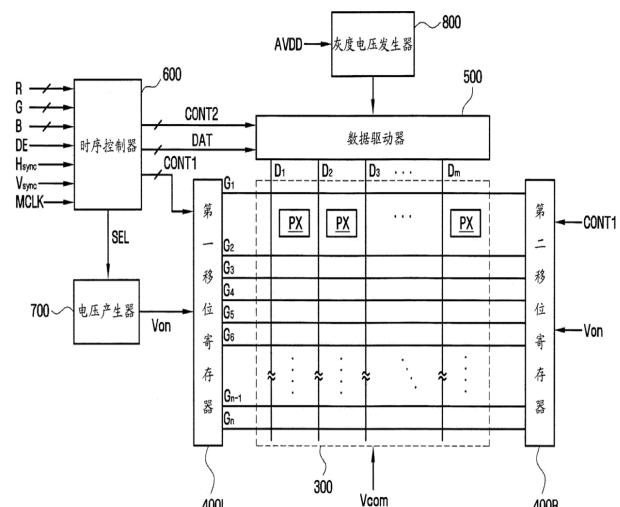

[0030] 图 1 是根据本发明示例性实施例的液晶显示器的框图；

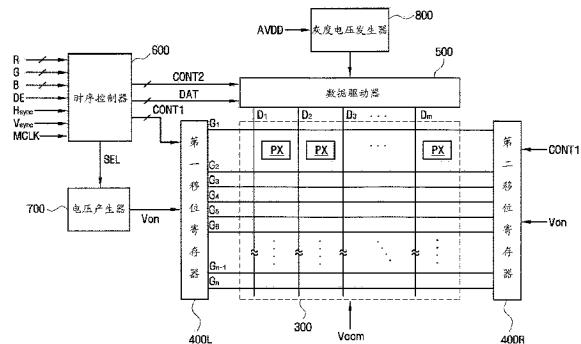

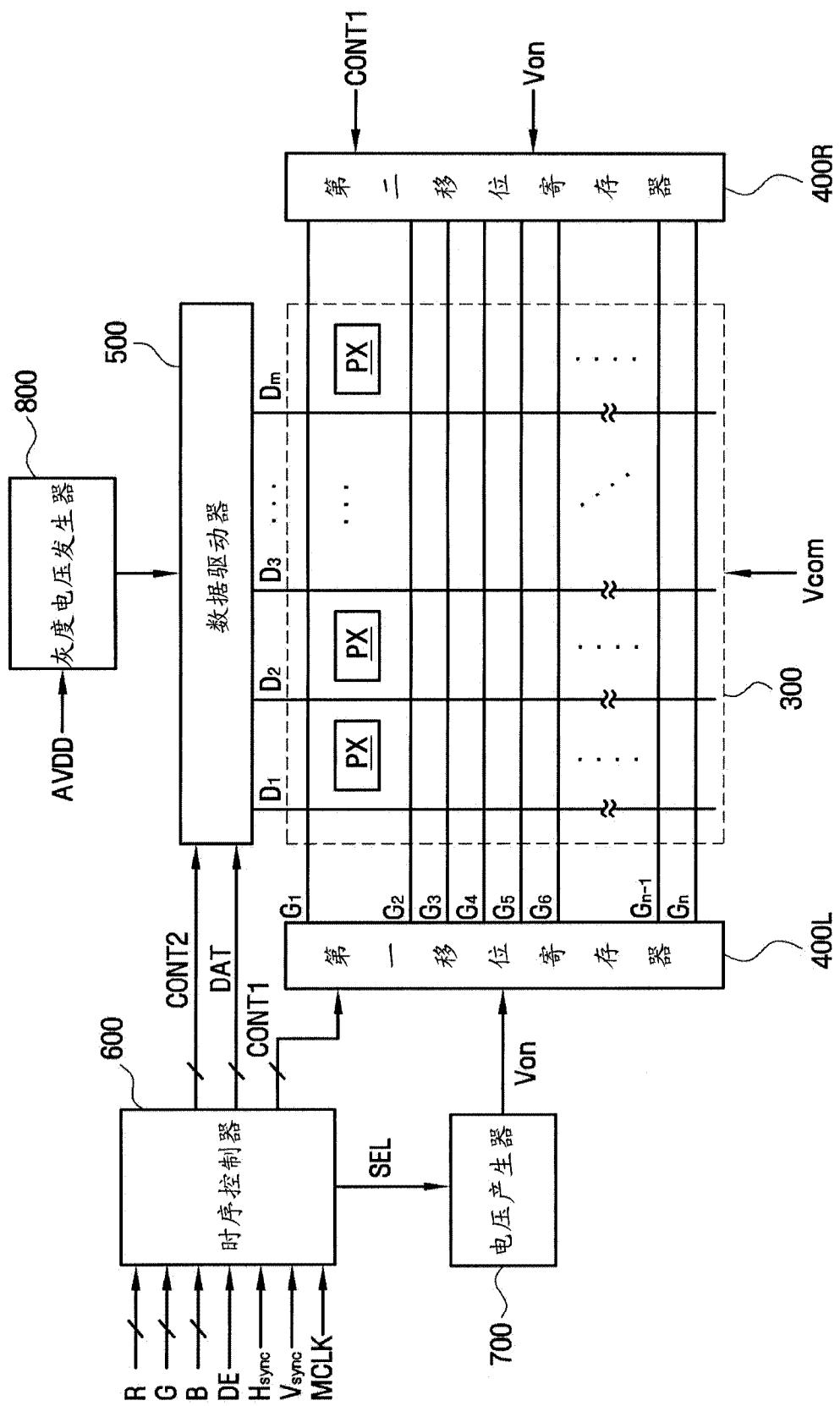

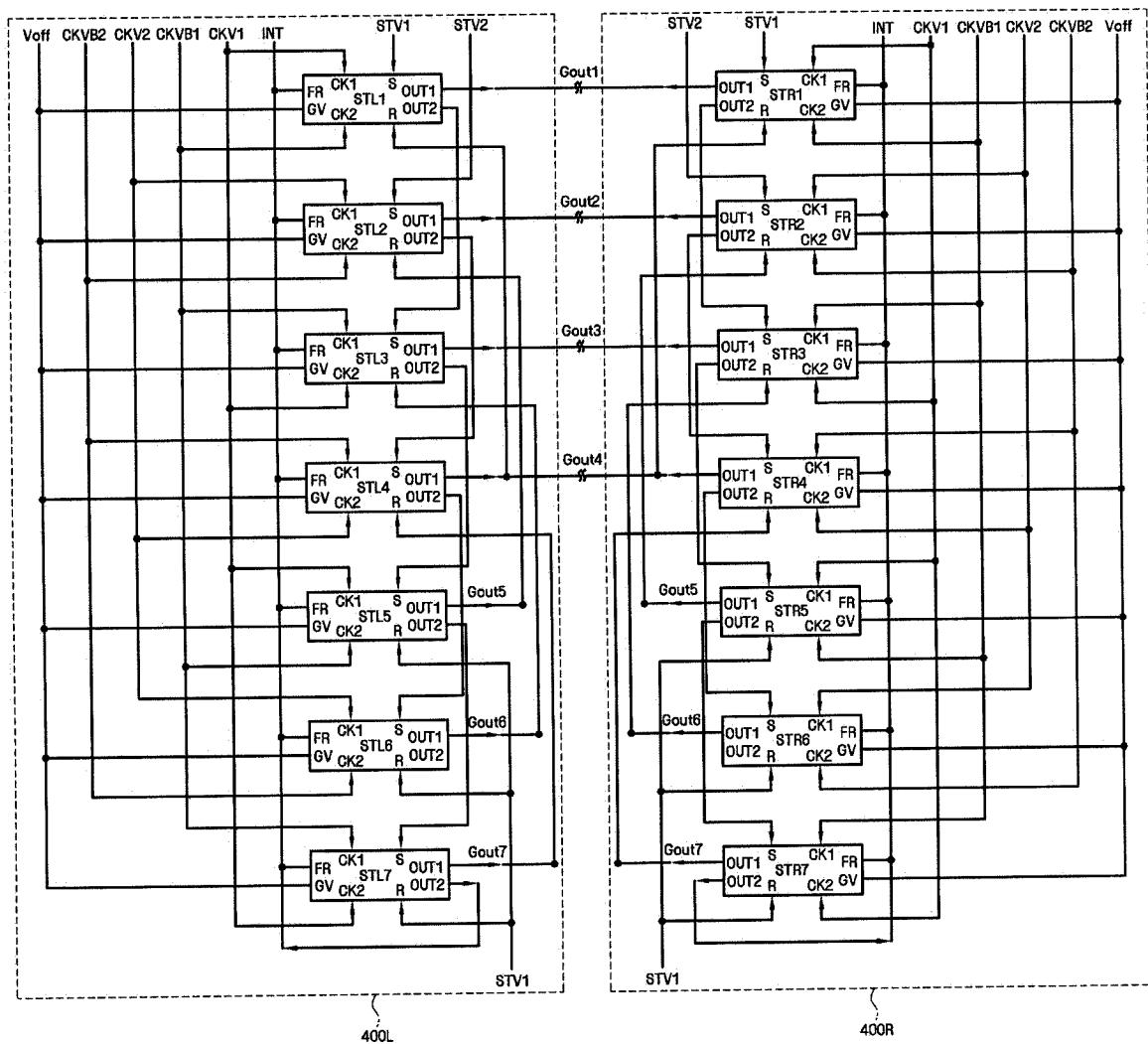

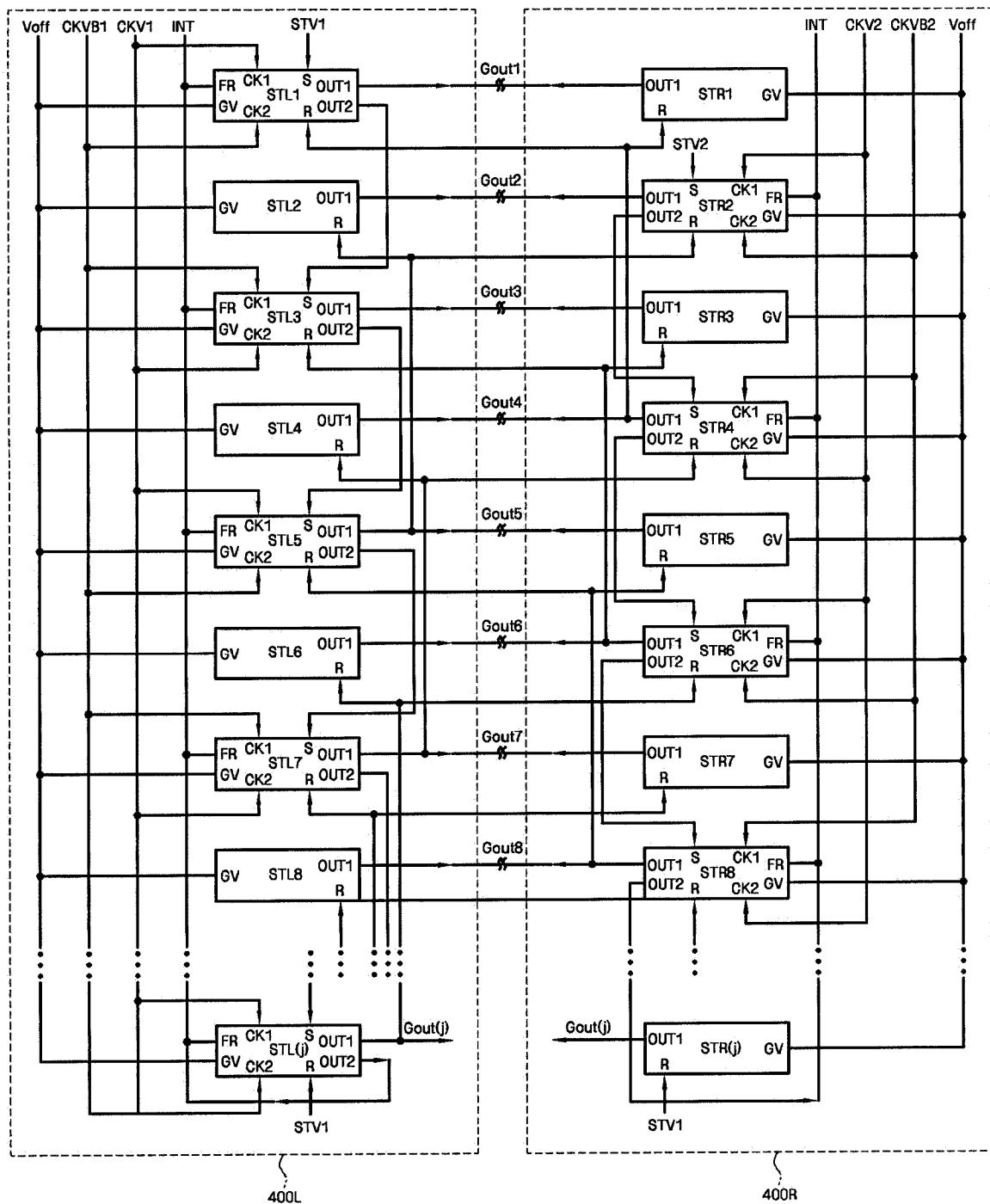

[0031] 图 2 和图 3 是根据本发明示例性实施例的栅极驱动电路的移位寄存器的框图；

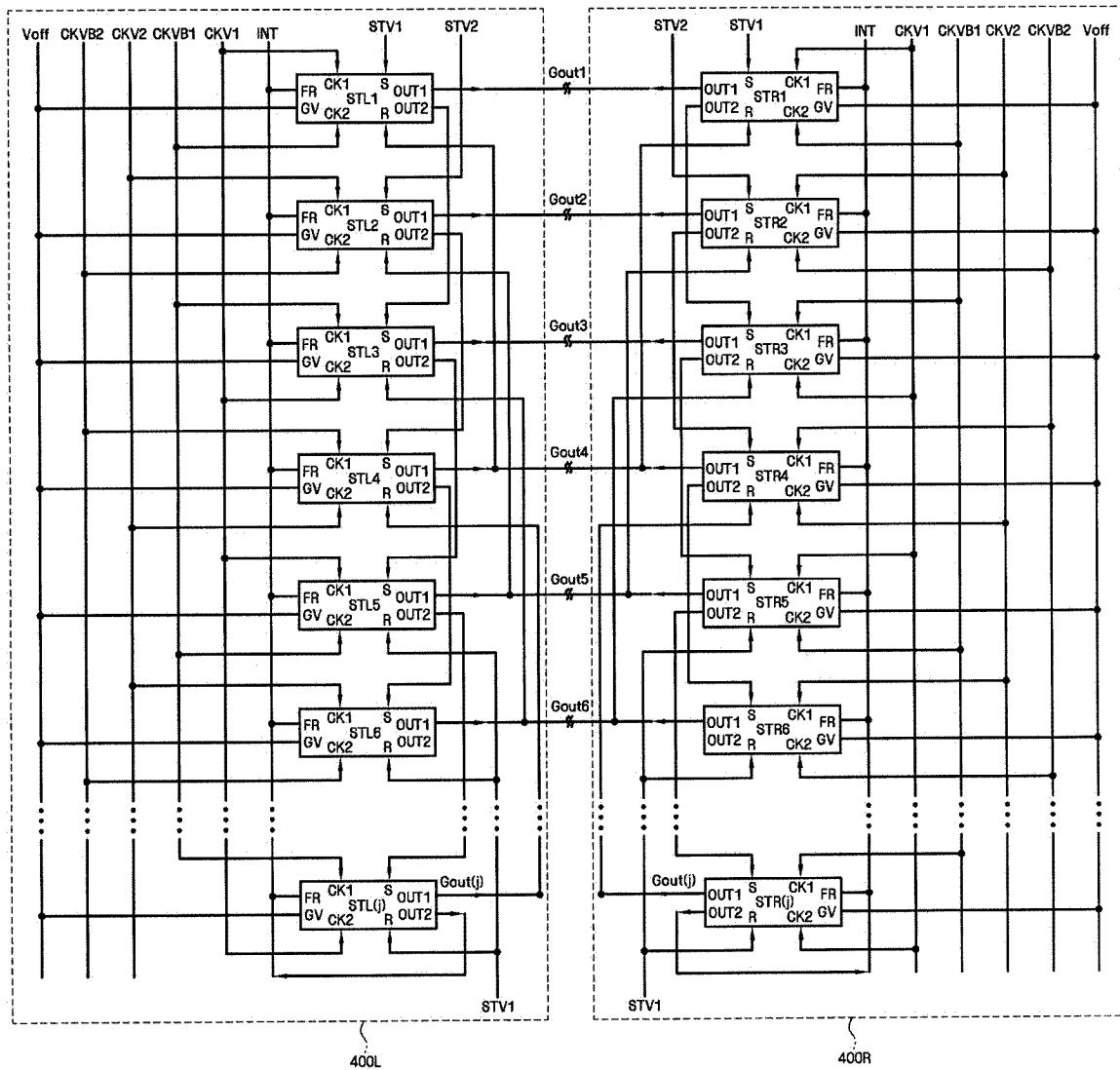

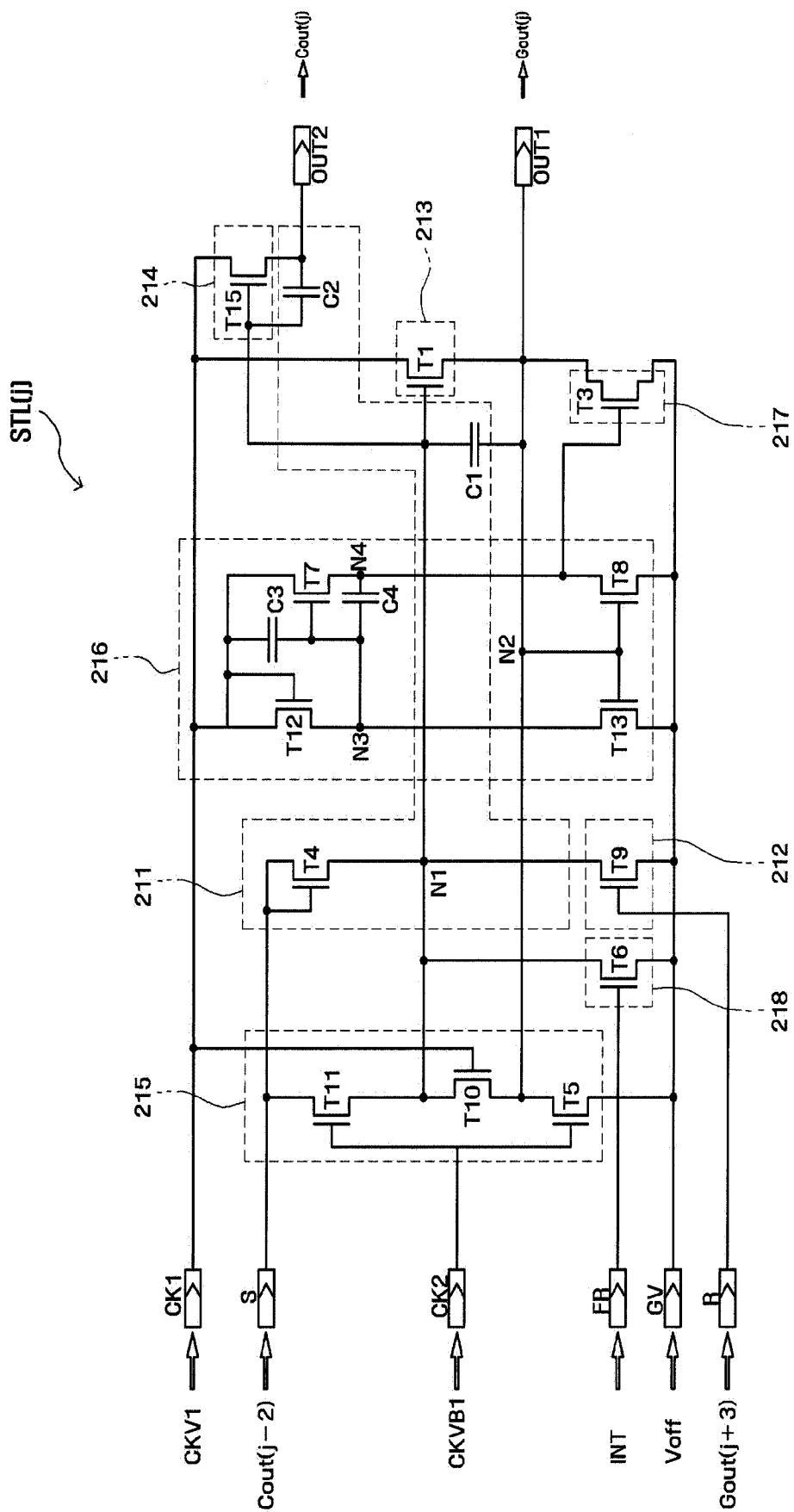

[0032] 图 4 是图 2 中的根据本发明示例性实施例的移位寄存器的级的内部电路结构的示意性电路图；

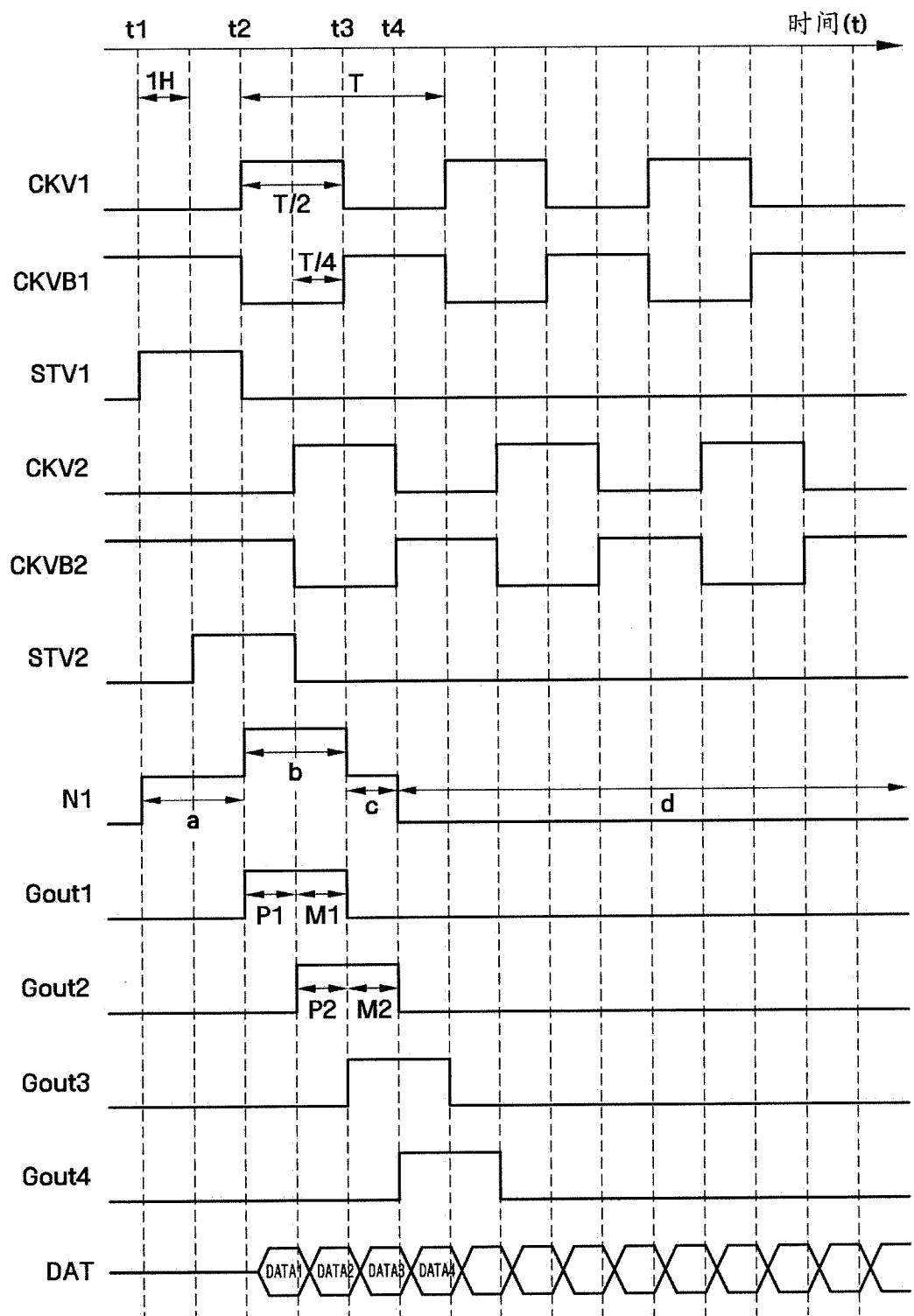

[0033] 图 5 是示出了图 4 中的根据本发明示例性实施例的移位寄存器的级的操作的信号波形时序图；

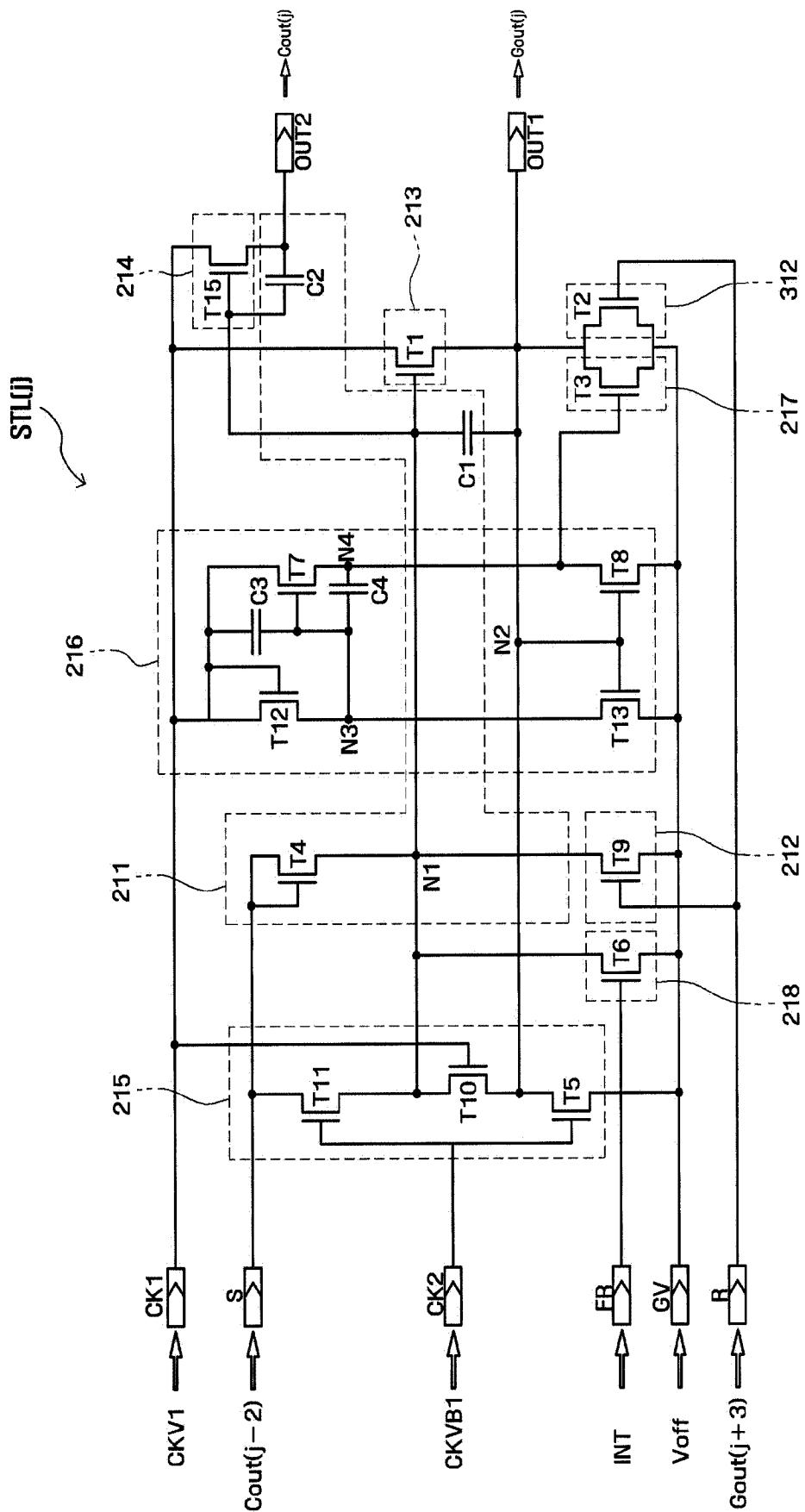

[0034] 图 6 是根据本发明可选示例性实施例的移位寄存器的级的内部电路结构的示意性电路图；

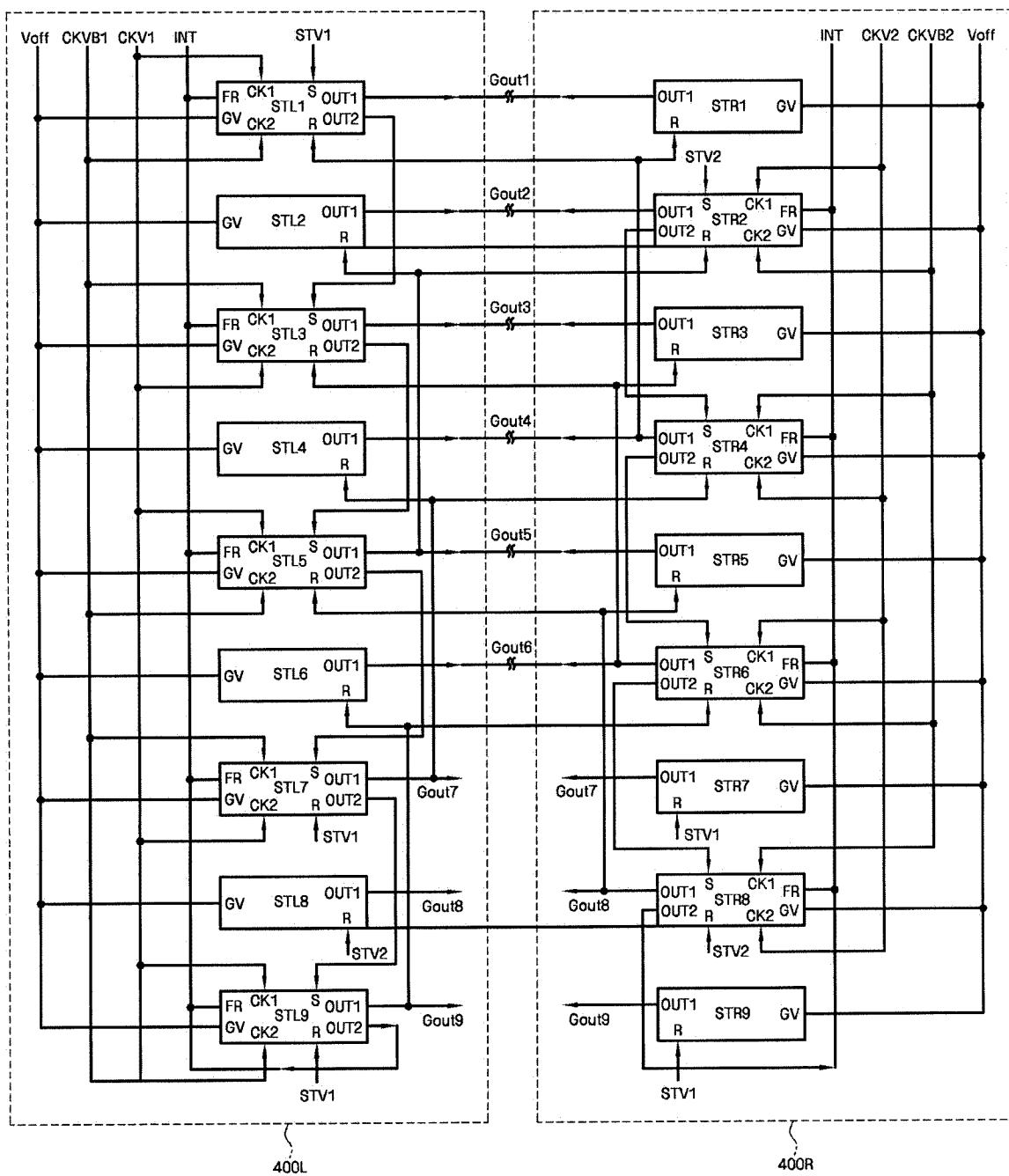

[0035] 图 7 和图 8 是根据本发明可选示例性实施例的栅极驱动电路的移位寄存器的框图。

## 具体实施方式

[0036] 现在，在下文中将参照附图来更充分地描述本发明，附图中示出了本发明的示例性实施例。然而，本发明可以以许多不同的形式实施，而不应该被理解为限于这里提出的实施例。相反，提供这些实施例使得本公开将是彻底和完全的，并且将把本发明的范围充分传达给本领域技术人员。相同的标号始终表示相同的元件。

[0037] 应该理解，当元件被称作“在另一元件上”时，该元件可以直接在另一元件上，或者可以在这两个元件之间存在中间元件。相反，当元件被称作“直接在另一元件上”时，不存在中间元件。如这里使用的，术语“和 / 或”包括相关列出项中的一个或多个的任意组合和所有组合。

[0038] 应该理解，尽管这里可以使用术语“第一”、“第二”、“第三”等来描述不同的元件、组件、区域、层和 / 或部分，但是这些元件、组件、区域、层和 / 或部分不应该受这些术语限制。这些术语仅用来将一个元件、组件、区域、层或部分与其它元件、组件、区域、层或部分区分开。因此，在不脱离本发明教导的情况下，下面讨论的第一元件、组件、区域、层或部分可以被定义为第二元件、组件、区域、层或部分。

[0039] 这里使用的技术术语仅是出于描述具体实施例的目的，并不意图成为本发明的限制。如这里使用的，除非上下文另外清楚地指出，否则单数形式也意图包括复数形式。还应该理解，当在本说明书中使用术语“包括”或“包含”时，说明存在所述特征、区域、整体、步

骤、操作、元件和 / 或组件,但是不排除存在或添加一个或多个其它特征、区域、整体、步骤、操作、元件、组件和 / 或它们的组。

[0040] 此外,这里可以使用相对术语例如,“下面”或“底部”和“上面”或“顶部”来描述如图中所示的一个元件与其它元件的关系。应该理解,相对术语意图包括除了图中描述的方位之外的装置的不同方位。例如,如果一幅图中的装置被翻转,则被描述为“在其它元件下侧”的元件随后将被定位为“在所述其它元件上侧”。因此,根据图中的具体方位,示例性术语“下面”可以包括“上面”和“下面”两个方位。类似地,如果一幅图中的装置被翻转,则被描述为“在其它元件下面”或“在其它元件下方”的元件随后将被定位为“在所述其它元件上面”。因此,示例性术语“在……下面”或“在……下方”可以包括上下两个方位。

[0041] 除非另外定义,否则这里使用的所有术语(包括技术术语和科学术语)具有与本发明所属领域的普通技术人员所通常理解的意思相同的意思。还应该理解,术语(例如,通用字典中定义的术语)应该被解释为具有与它们在相关领域和本公开的环境中的意思一致的意思,并且除非这里明确定义,否则将不被解释为理想的或过度正式的意思。

[0042] 这里,参照作为本发明理想实施例的示意性图示的剖视图来描述本发明的示例性实施例。这样,将预料到例如由制造技术和 / 或公差引起的图示的形状的变化。因此,本发明的实施例不应该被理解为限于这里示出的区域的具体形状,而是包括例如由制造引起的形状的偏差。例如,被示出或被描述为平坦的区域通常可具有粗糙和 / 或非线性的特征。此外,示出的锐角可以被倒圆。因此,图中示出的区域在本质上是示意性的,并且它们的形状不意图示出区域的精确形状,并且不意图限制本发明的范围。

[0043] 现在,将参照附图来更详细地描述本发明,在附图中示出了本发明的示例性实施例。

[0044] 图 1 是根据本发明示例性实施例的液晶显示器的框图。

[0045] 如图 1 中所示,根据本发明示例性实施例的液晶显示器包括液晶面板 300、连接到液晶面板 300 的第一移位寄存器 400L 和第二移位寄存器 400R、数据驱动器 500、连接到数据驱动器 500 的灰度电压发生器 800、控制例如上述组件(但不限于上述组件)的时序控制器 600 及电压发生器 700。

[0046] 如图 1 中所示,液晶面板 300 包括多条显示信号线 G<sub>1</sub> 至 G<sub>n</sub>、D<sub>1</sub> 至 D<sub>m</sub>(m、n 为自然数)以及连接到多条显示信号线 G<sub>1</sub> 至 G<sub>n</sub>、D<sub>1</sub> 至 D<sub>m</sub> 并且基本按照矩阵图案布置的多个单位像素 PX。

[0047] 多条显示信号线 G<sub>1</sub> 至 G<sub>n</sub>、D<sub>1</sub> 至 D<sub>m</sub> 包括传输栅极信号的多条栅极线 G<sub>1</sub> 至 G<sub>n</sub> 和传输数据信号的多条数据线 D<sub>1</sub> 至 D<sub>m</sub>。多条栅极线 G<sub>1</sub> 至 G<sub>n</sub> 中的单条栅极线基本上沿着第一行方向延伸并且基本上彼此平行,多条数据线 D<sub>1</sub> 至 D<sub>m</sub> 中的单条数据线基本上沿着第二列方向延伸并且基本上彼此平行。

[0048] 多个单位像素 PX 中的每个单位像素 PX 包括连接到对应的栅极线和对应的数据线的开关元件(未示出)、连接到开关元件的液晶电容器(未示出)及存储电容器(未示出)。在可选示例性实施例中,可以省略存储电容器。

[0049] 为了显示彩色图像,每个单位像素 PX 可以显示原色中的一种颜色例如,红色、绿色和蓝色中的一种颜色。在这种情况下,在与各个单位像素 PX 的像素电极对应的区域内设置红色滤色器、绿色滤色器和蓝色滤色器(未示出)。在示例性实施例中,滤色器设置在第

二显示面板（未示出）上的对应区域，但是例如在可选示例性实施例中，滤色器可以设置在第一显示面板（未示出）的单位像素 PX 的像素电极的上方或下方，但不限于此。

[0050] 在液晶面板 300 的第一显示面板（未示出）和第二显示面板（未示出）中的至少一个的外表面上安装使光偏振的偏振器（未示出）。

[0051] 灰度电压发生器 800 接收电源电压 AVDD 并且产生第一灰度电压组和第二灰度电压组，第一灰度电压组和第二灰度电压组中的每个均与单位像素 PX 的期望透射率有关。例如，第一灰度电压组相对于共电压 Vcom 可以具有正值，第二灰度电压组相对于共电压 Vcom 可以具有负值，但不限于此。另外，在根据本发明示例性实施例的液晶显示器的反转驱动（inversion driving）期间，可以通过数据驱动器 500 对液晶面板交替地施加正值灰度电压和负值灰度电压。

[0052] 如图 1 中所示，第一移位寄存器 400L 和第二移位寄存器 400R 沿着第一方向（例如，基本水平的纵向方向）设置在液晶面板 300 的相对的侧，并且连接到多条栅极线 G<sub>1</sub> 至 G<sub>n</sub>。第一移位寄存器 400L 和第二移位寄存器 400R 通过多条栅极线 G<sub>1</sub> 至 G<sub>n</sub> 向开关元件（未示出）提供栅极信号。

[0053] 数据驱动器 500 连接到液晶面板 300 的多条数据线 D<sub>1</sub> 至 D<sub>m</sub>，根据由灰度电压发生器 800 提供的第一灰度电压组和第二灰度电压组产生多个灰度电压，从多个灰度电压中选择产生的灰度电压，并将选择的产生的灰度电压提供到单位像素 PX 作为数据信号。通常，数据驱动器 500 包括多个集成电路，但不限于此。

[0054] 时序控制器 600 产生控制第一移位寄存器 400L、第二移位寄存器 400R、数据驱动器 500 和电压发生器 700 的操作的控制信号，并且将控制信号提供到上述组件。

[0055] 例如，电压发生器 700 产生多个驱动电压例如第一时钟信号 CKV1（图 2）、第二时钟信号 CKV2（图 2）和共电压 Vcom，但不限于此。

[0056] 现在，将参照图 1 来进一步详细地描述液晶显示器的操作。

[0057] 时序控制器 600 从外部图形控制器（未示出）分别接收红色输入图像信号 R、绿色输入图像信号 G 和蓝色输入图像信号 B 以及分别用于显示红色输入图像信号 R、绿色输入图像信号 G 和蓝色输入图像信号 B 的输入控制信号。例如，下面的信号可以用作输入控制信号，但不限于此，这些信号为垂直同步信号 V<sub>sync</sub>、水平同步信号 H<sub>sync</sub>、主时钟信号 MCLK 和数据使能信号 DE。时序控制器 600 产生例如栅极控制信号 CONT1 和数据控制信号 CONT2，并且根据液晶面板 300 的操作条件和输入控制信号分别处理红色输入图像信号 R、绿色输入图像信号 G 和蓝色输入图像信号 B，以产生图像数据信号 DAT。时序控制器 600 向第一移位寄存器 400L 和第二移位寄存器 400R 传输栅极控制信号 CONT1，向数据驱动器 500 传输数据控制信号 CONT2 和图像数据信号 DAT，向电压发生器 700 传输电压选择信号 SEL。

[0058] 栅极控制信号 CONT1 包括：第一起始信号 STV1（图 2）和第二起始信号 STV2（图 2），开始栅极导通信号 Von（未示出）的输出；输出使能信号 OE（未示出），限定栅极导通信号 Von 的宽度。

[0059] 数据控制信号 CONT2 包括：水平同步起始信号 STH（未示出），开始向数据驱动器 500 输入图像数据信号 DAT；数据加载信号 TP（未示出），使数据信号（未示出）被传输到多条数据线 D<sub>1</sub> 至 D<sub>m</sub> 中的数据线；数据时钟信号 HCLK（未示出）；反转信号 RVS（未示出），将数据电压的极性反转。在示例性实施例中，数据电压的极性相对于共电压 Vcom 被反转。

[0060] 数据驱动器 500 响应来自时序控制器 600 的数据控制信号 CONT2 接收与给定行的单位像素 PX 对应的图像数据信号 DAT, 从多个灰度电压中选择与该图像数据信号 DAT 对应的合适的灰度电压, 从而将该图像数据信号 DAT 转换为对应的数据电压。

[0061] 第一移位寄存器 400L 和第二移位寄存器 400R 响应栅极控制信号 CONT1 向多条栅极线  $G_1$  至  $G_n$  提供栅极导通信号 Von, 以导通连接到多条栅极线  $G_1$  至  $G_n$  中的对应的单条栅极线的对应的开关元件 (未示出)。

[0062] 当向多条栅极线  $G_1$  至  $G_n$  中的对应的栅极线提供栅极导通信号 Von 并且连接到对应的栅极线的对应的开关元件处于导通状态时, 例如, 在一个水平时间段 (1H), 数据驱动器 500 向多条数据线  $D_1$  至  $D_m$  中的对应的数据线提供数据电压。通过处于导通状态的开关元件将提供到多条数据线  $D_1$  至  $D_m$  中的对应的数据线的数据电压施加到对应的单位像素 PX。

[0063] 液晶面板 300 的液晶层 (未示出) 中的液晶分子的取向根据单位像素 PX 的像素电极和共电极 (未示出) 之间产生的电场的变化而变化, 这引起穿过液晶层的光的偏振发生变化。光的偏振的变化引起穿过偏振器 (未示出) 的光的透射率发生变化, 从而显示一行期望的图像。

[0064] 按照类似的方式, 对多条栅极线  $G_1$  至  $G_n$  中的每条栅极线顺序施加栅极导通信号 Von, 使得在一帧期间对每行单位像素 PX 施加数据电压, 从而显示一帧期望的图像。当显示完一帧时, 开始显示随后的帧。在示例性实施例中, 控制对数据驱动器 500 施加的反转信号 RVS (未示出) 的状态, 使得对每个单位像素 PX 施加的数据电压的极性与在前一帧中对每个单位像素 PX 施加的数据电压的极性相反 (帧反转)。在可选示例性实施例中, 在同一帧中, 对一条数据线施加的数据电压的极性可以根据反转信号 RVS 被反转 (行反转), 或者对像素行施加的数据电压的极性可以彼此不同 (点反转)。

[0065] 现在, 将参照图 2 至图 5 来进一步详细地描述根据本发明示例性实施例的栅极驱动电路中使用的第一移位寄存器 400L 和第二移位寄存器 400R。

[0066] 图 2 和图 3 是根据本发明示例性实施例的栅极驱动电路中的移位寄存器的框图, 图 4 是图 2 中的根据本发明示例性实施例的移位寄存器的级的示意性电路图, 图 5 是示出了图 4 中的根据本发明示例性实施例的移位寄存器的级的操作的信号波形时序图。

[0067] 返回参照图 1 和图 2, 第一移位寄存器 400L 连接到多条栅极线  $G_1$  至  $G_n$  中的每条栅极线的第一端, 第二移位寄存器 400R 连接到多条栅极线  $G_1$  至  $G_n$  中的每条栅极线的第二相对端。在根据本发明示例性实施例的操作中, 第一移位寄存器 400L 和第二移位寄存器 400R 被同时导通, 从而从第一移位寄存器 400L 和第二移位寄存器 400R 输出的栅极信号  $Gout1$ 、 $Gout2$ 、...、 $Gout(j)$  被同时提供给多条栅极线  $G_1$  至  $G_n$  中的对应的栅极线。

[0068] 参照图 2, 第一移位寄存器 400L 包括顺序输出栅极信号  $Gout1$ 、 $Gout2$ 、...、 $Gout(j)$  的多个左边的级  $STL1$ 、 $STL2$ 、...、 $STL(j)$ , 第二移位寄存器 400R 包括也顺序输出栅极信号  $Gout1$ 、 $Gout2$ 、...、 $Gout(j)$  的多个右边的级  $STR1$ 、 $STR2$ 、...、 $STR(j)$ 。

[0069] 多个左边的级  $STL1$ 、 $STL2$ 、...、 $STL(j)$  中的奇数的左边的级  $STL1$ 、 $STL3$  和  $STL5$  彼此级联, 多个左边的级  $STL1$ 、 $STL2$ 、...、 $STL(j)$  中的偶数的左边的级  $STL2$ 、 $STL4$  和  $STL6$  彼此级联。类似地, 多个右边的级  $STR1$ 、 $STR2$ 、...、 $STR(j)$  中的奇数的右边的级  $STR1$ 、 $STR3$  和  $STR5$  彼此级联, 多个右边的级  $STR1$ 、 $STR2$ 、...、 $STR(j)$  中的偶数的右边的级  $STR2$ 、 $STR4$  和  $STR6$  彼此级联。

[0070] 在本发明的示例性实施例中,第一移位寄存器 400L 和第二移位寄存器 400R 具有基本相同的结构。因此,下面将仅进一步详细地描述第一移位寄存器 400L,将省略关于第二移位寄存器 400R 的重复的描述。

[0071] 参照图 2,多个左边的级 STL1、STL2、...、STL(j) 中的每个级包括第一时钟端 CK1、第二时钟端 CK2、设置端 S、复位端 R、电源电压端 GV、帧复位端 FR、栅极输出端 OUT1 和进位输出端 (carry output terminal) OUT2。

[0072] 如图 2 中所示,在对奇数的左边的级 STL1 施加第一起始信号 STV1 的同时,向奇数的左边的级 STL1、STL3 和 STL5 提供第一时钟信号 CKV1、第一反相时钟信号 CKVB1 和栅极截止信号 Voff。在向偶数的左边的级 STL2 提供第二起始信号 STV2 的同时,向偶数的左边的级 STL2、STL4 和 STL6 提供第二时钟信号 CKV2、第二反相时钟信号 CKVB2 和栅极截止信号 Voff。

[0073] 第一反相时钟信号 CKVB1 的相位相对于第一时钟信号 CKV1 的相位被反相,第二反相时钟信号 CKVB2 的相位相对于第二时钟信号 CKV2 的相位被反相。另外,第二时钟信号 CKV2 比第一时钟信号 CKV1 延迟第一时钟信号 CKV1 的一个周期 (T) 的四分之一 (T/4),第二反相时钟信号 CKVB2 比第一反相时钟信号 CKVB1 延迟第一反相时钟信号 CKVB1 的一个周期 (T) 的四分之一 (T/4),如图 5 中所示。

[0074] 代替前面的级的进位信号,第一起始信号 STV1 输入到第一个左边的级 STL1 的设置端 S,第二起始信号 STV2 输入到第二个左边的级 STL2 的设置端 S,如图 2 中所示。第二起始信号 STV2 比第一起始信号 STV1 延迟一个周期 (T) 的四分之一 (T/4),如图 5 中所示。

[0075] 类似地,代替用于最后一级 STL(j) 的栅极信号,第一起始信号 STV1 输入到最后的级 STL(j) 的复位端 R,如图 2 中所示。

[0076] 仍然参照图 2,在左边的第三个左边的级 STL3 中,例如,分别向第三个左边的级 STL3 的设置端 S 和复位端 R 输入前面的级 (例如,第一个左边的级 STL1) 的进位信号和后面的级 (例如,第六个左边的级 STL6) 的栅极信号 Gout6,并且分别对第三个左边的级 STL3 的第一时钟端 CK1 和第二时钟端 CK2 输入第一反相时钟信号 CKVB1 和第一时钟信号 CKV1。另外,向第三个左边的级 STL3 的电源电压端 GV 输入栅极截止信号 Voff,向第三个左边的级 STL3 的帧复位端 FR 输入初始信号 INT。最后,栅极输出端 OUT1 输出栅极信号 Gout3,进位输出端 OUT2 输出提供到第五个左边的级 STL5 的设置端 S 的进位信号。

[0077] 向多个左边的级 STL1、STL2、...、STL(j) 中的每个左边的级的帧复位端 FR 提供最后一个左边的级 STL(j) 的进位信号作为初始信号 INT。

[0078] 出于解释的目的,图 3 中示出了具有七个级 (例如, j = 7) 的移位寄存器的框图,但是本发明的可选示例性实施例不限于此。

[0079] 参照图 1 和图 3,左边的级 STL1、STL2、STL3 和 STL4 分别向栅极线 G<sub>1</sub>、G<sub>2</sub>、G<sub>3</sub> 和 G<sub>4</sub> 提供栅极信号 Gout1、Gout2、Gout3 和 Gout4。左边的哑级 (dummy left stage) STL5、STL6 和 STL7 分别输出提供到左边的级 STL2、STL3 和 STL4 的栅极信号 Gout5、Gout6 和 Gout7。

[0080] 另外,左边的级 STL4 的栅极信号 Gout4 输入到左边的级 STL1 的复位端 R、左边的级 STL6 的栅极信号 Gout6 输入到左边的级 STL3 的复位端 R。左边的级 STL5 的栅极信号 Gout5 输入到左边的级 STL2 的复位端 R,左边的级 STL7 的栅极信号 Gout7 输入到左边的级 STL4 的复位端 R。因此,偶数的左边的级 STL4 和 STL6 的栅极信号分别输入到奇数的左边

的级 STL1 和 STL3 的复位端 R, 奇数的左边的级 STL5 和 STL7 的栅极信号分别输入到偶数的左边的级 STL2 和 STL4 的复位端 R。因此, 在本发明的示例性实施例中, 可以调节每个级的复位时间。

[0081] 现在, 将参照图 4 来进一步详细地描述第一移位寄存器 400L 和第二移位寄存器 400R 中的每一级的内部电路。

[0082] 如上所述, 第一移位寄存器 400L 和第二移位寄存器 400R 具有基本上相同的结构。因此, 将仅进一步详细地描述第一移位寄存器 400L, 下面将省略对第二移位寄存器 400R 的重复描述。

[0083] 参照图 4, 每个级 (例如, 级 STL(j)) 包括上拉 (pull-up) 驱动单元 211、下拉 (pull-down) 单元 212、上拉单元 213、进位输出单元 214、波纹防止单元 215、开关单元 216、保持 (holding) 单元 217 和复位单元 218。

[0084] 上拉驱动单元 211 包括开关元件 T4、第一电容器 C1 和第二电容器 C2。开关元件 T4 的栅极和源极均连接到设置端 S, 开关元件 T4 的漏极连接到第一节点 N1。第一电容器 C1 连接在第一节点 N1 和第二节点 N2 之间, 第二电容器 C2 连接在第一节点 N1 和进位输出端 OUT2 之间。

[0085] 下拉单元 212 包括开关元件 T9, 开关元件 T9 具有连接到复位端 R 的栅极、连接到电源电压端 GV 的源极和连接到第一节点 N1 的漏极。

[0086] 上拉单元 213 包括开关元件 T1, 开关元件 T1 具有连接到第一节点 N1 的栅极、连接到第一时钟端 CK1 的源极和连接到栅极输出端 OUT1 并连接至第二节点 N2 的漏极。在操作中, 上拉单元 213 向栅极输出端 OUT1 输出被通过第一时钟端 CK1 提供的第一时钟信号 CKV1 上拉到栅极导通信号 Von 的栅极信号 Gout(j)。

[0087] 在本发明的示例性实施例中, 开关元件 T9 的宽长比 (aspect ratio) 可以在开关元件 T1 的宽长比的大约 1/20 至大约 1/10 的范围内。

[0088] 进位输出单元 214 包括开关元件 T15, 开关元件 T15 具有连接到第一节点 N1 的栅极、连接到第一时钟端 CK1 的源极和连接到进位输出端 OUT2 的漏极。在操作中, 进位输出单元 214 向进位输出端 OUT2 输出被通过第一时钟端 CK1 提供的时钟信号 CKV1 上拉的进位信号 Cout(j)。

[0089] 波纹防止单元 215 包括串联连接在设置端 S 和电源电压端 GV 之间的开关元件 T11、T10 和 T5。更具体地讲, 开关元件 T11 具有连接到第二时钟端 CK2 的栅极、连接到设置端 S 的源极和连接到第一节点 N1 的漏极。开关元件 T10 具有连接到第一时钟端 CK1 的栅极、连接到第二节点 N2 的源极和连接到第一节点 N1 的漏极。开关元件 T5 具有连接到第二时钟端 CK2 的栅极、连接到电源电压端 GV 的源极和连接到第二节点 N2 的漏极。

[0090] 开关元件 T10 响应第一时钟信号 CKV1 将来自第二节点 N2 的信号提供到第一节点 N1, 以防止从栅极输出端 OUT1 输出的栅极信号 Gout(j) 的波纹。开关元件 T11 响应通过第二时钟端 CK2 提供的第一反相时钟信号 CKVB1 向第一节点 N1 提供来自不同级的进位信号 (例如, 前面的级的进位信号 Cout(j-2)), 以进一步防止从栅极输出端 OUT1 输出的栅极信号 Gout(j) 的波纹。另外, 开关元件 T5 响应通过第二时钟端 CK2 提供的第一反相时钟信号 CKVB1 向第二节点 N2 提供栅极截止信号 Voff, 以防止从栅极输出端 OUT1 输出的栅极信号 Gout(j) 的波纹。

[0091] 开关单元 216 包括开关元件 T12、T7、T13 和 T8、第三电容器 C3 和第四电容器 C4，并且将保持单元 217 的开关元件 T3 导通或截止。

[0092] 更具体地讲，开关元件 T12 具有连接到第一时钟端 CK1 的栅极和源极以及连接到第三节点 N3 的漏极。开关元件 T7 具有连接到第三节点 N3 的栅极、连接到第一时钟端 CK1 的源极和连接到第四节点 N4 的漏极。第三电容器 C3 连接在第一时钟端 CK1 和第三节点 N3 之间，第四电容器 C4 连接在第三节点 N3 和第四节点 N4 之间。开关元件 T13 和 T8 具有均连接到第二节点 N2 的栅极、均连接到电源电压端 GV 的源极和分别连接到第三节点 N3 和第四节点 N4 的漏极。

[0093] 当开关元件 T12 和 T7 响应第一时钟信号 CKV1 导通时，第一时钟信号 CKV1 提供到第三节点 N3 和第四节点 N4，从栅极输出端 OUT1 输出高电平栅极信号 Gout(j)，例如，栅极导通信号 Von。接着，开关元件 T13 和 T8 导通，第三节点 N3 和第四节点 N4 的电压电平降低为低电平，例如，降低为栅极截止信号 Voff。因此，保持单元 217 的开关元件 T3 被保持在截止状态。

[0094] 接着，当从栅极输出端 OUT1 输出低电平栅极信号 Gout(j) 例如栅极截止信号 Voff 时，开关元件 T13 和 T8 均被截止。随后，响应时钟信号 CKV1，开关元件 T12 和 T7 被导通，高电平的第一时钟信号 CKV1 被提供到第四节点 N4，开关元件 T3 向栅极输出端 OUT1 输出栅极截止信号 Voff 作为栅极信号 Gout(j)。因此，从栅极输出端 OUT1 输出栅极截止信号 Voff。

[0095] 保持单元 217 经过第四节点 N4 连接到开关单元 216，并且包括开关元件 T3，开关元件 T3 具有连接到第四节点 N4 的栅极、连接到电源电压端 GV 的源极和连接到栅极输出端 OUT1 (例如，节点 N2) 的漏极。

[0096] 复位单元 218 经过第一节点 N1 连接到上拉驱动单元 211，并且包括开关元件 T6，开关元件 T6 具有连接到帧复位端 FR 的栅极、连接到电源电压端 GV 的源极和连接到第一节点 N1 的漏极。开关元件 T6 响应前面的级的前面的进位信号 Cout(j-2) 将通过设置端输入的噪声放电至栅极截止信号 Voff。因此，栅极截止信号 Voff 被输出到第一节点 N1，开关元件 T1 和 T15 被截止，以将栅极输出端 OUT1 和进位输出端 OUT2 复位。

[0097] 现在，将参照图 4 和图 5 来进一步详细地描述第一移位寄存器 400L 和第二移位寄存器 400R 中的每一级的内部电路的操作。

[0098] 如图 5 中所示，提供到第一栅极线 G<sub>1</sub> 的栅极信号 Gout1 包括预充电时间段 P1 和主充电时间段 M1，提供到第二栅极线 G<sub>2</sub> 的栅极信号 Gout2 比栅极信号 Gout1 延迟预充电时间段 P1。

[0099] 参照图 4 和图 5，当在时间 t1 上拉驱动单元 211 的开关元件 T4 响应第一起始信号 STV1 (图 2 和图 3) 或者不同级的进位信号 (例如，Cout(j-2)，图 4) 而被导通时，第一电容器 C1 和第二电容器 C2 被充电。因此，第一节点 N1 在保持 2H 的预先时间段 “a” 期间具有第一电压电平，直到时间 t2。

[0100] 在时间 t2，上拉驱动单元 211 的开关元件 T4 被截止，从而第一节点 N1 被浮置，处于高电平的第一时钟信号 CKV1 被提供到第一时钟端 CK1，上拉单元 213 的开关元件 T1 和进位输出单元 214 的开关元件 T15 导通。因此，提供到第一时钟端 CK1 的时钟信号 CKV1 分别从栅极输出端 OUT1 和进位输出端 OUT2 输出作为栅极信号 Gout(j) 和进位信号 Cout(j)。此时，开关元件 T1 导通，第一节点 N1 在保持 2H 的栅极活跃时间段 (gate active period) “b”

期间具有比第一电压电平高的第二电压电平。

[0101] 在时间  $t_3$ , 开关元件  $T_1$  仍然处于导通状态, 提供到第一时钟端  $CK_1$  的时钟信号  $CKV_1$  从栅极输出端  $OUT_1$  输出作为栅极信号  $Gout(j)$ 。此时, 第一节点  $N_1$  在保持  $1H$  的第一栅极不活跃时间段 (gate inactive period) “c”期间具有低于第二电压电平的第三电压电平。第一栅极不活跃时间段“c”是后面级的栅极信号  $Gout(j+3)$  输入到下拉单元  $212$  的开关元件  $T_9$  的栅极之前的时间段。

[0102] 在时间  $t_4$ , 开关元件  $T_9$  响应施加到开关元件  $T_9$  的栅极的后面级的栅极信号  $Gout(j+3)$  而被导通, 第一节点  $N_1$  在第二栅极不活跃时间段“d”期间具有低于第三电压电平的第四电压电平, 例如, 第四电压电平基本上等于栅极截止信号  $V_{off}$  的电平。此时, 通过导通的开关元件  $T_9$ , 存储在第一电容器  $C_1$  和第二电容器  $C_2$  中的电荷被放电至栅极截止信号  $V_{off}$ 。

[0103] 如上所述, 根据本发明的示例性实施例, 将后面级的栅极信号  $Gout(j+3)$  提供到第  $j$  级 (例如,  $STL(j)$ ) 的复位端  $R$ , 从而在开关元件  $T_1$  向第二节点输出栅极截止信号的第一栅极不活跃时间段期间, 级  $STL(j)$  的第一节点具有恒定的电压电平。因此, 开关元件  $T_9$  作为单个的开关元件, 通过去除任何附加的开关元件 (否则这些开关元件将占据栅极驱动电路的另外的面积) 来有效地减少液晶面板中栅极驱动电路的面积。

[0104] 图 6 是根据本发明可选示例性实施例的移位寄存器的级的内部电路结构的示意性电路图。

[0105] 参照图 6, 每个级 (例如, 级  $STL(j)$ ) 包括上拉驱动单元  $211$ 、下拉单元  $212$ 、补充下拉单元  $312$ 、上拉单元  $213$ 、进位输出单元  $214$ 、波纹防止单元  $215$ 、开关单元  $216$ 、保持单元  $217$  和复位单元  $218$ 。

[0106] 除了补充下拉单元  $312$  之外, 在下文中参照图 6 进一步详细描述的根据本发明可选示例性实施例的级  $STL(j)$  与如上参照图 4 描述的示例性实施例的级  $STL(j)$  基本相同。因此, 相同或相似的组件在图 4 和图 6 中具有相同的标号, 下面将省略对相同或相似组件的任何重复描述。

[0107] 补充下拉单元  $312$  包括开关元件  $T_2$ , 开关元件  $T_2$  具有连接到复位端  $R$  以从后面的级  $STL(j+3)$  接收栅极信号  $Gout(j+3)$  的栅极、连接到电源电压端  $GV$  的源极和连接到栅极输出端  $OUT_1$  (例如, 节点  $N_2$ ) 的漏极。

[0108] 开关元件  $T_2$  的宽长比可以小于或者等于上拉单元  $213$  的开关元件  $T_1$  的宽长比的大约  $1/2$ 。

[0109] 现在, 将参照图 5 和图 6 来进一步详细地描述根据可选示例性实施例的具有补充下拉单元  $312$  的级  $STL(j)$  的操作。

[0110] 参照图 5 和图 6, 当在时间  $t_1$ , 上拉驱动单元  $211$  的开关元件  $T_4$  响应第一起始信号  $STV_1$  (图 2 和图 3) 或者前面的级的进位信号 (例如,  $Cout(j-2)$ , 图 6) 而被导通时, 第一电容器  $C_1$  和第二电容器  $C_2$  被充电。因此, 第一节点  $N_1$  在保持  $2H$  的预先时间段“a”(例如, 直到时间  $t_2$ ) 期间具有第一电压电平。

[0111] 在时间  $t_2$ , 上拉驱动单元  $211$  的开关元件  $T_4$  被截止, 从而第一节点  $N_1$  被浮置, 处于高电平的第一时钟信号  $CKV_1$  被提供到第一时钟端  $CK_1$ , 上拉单元  $213$  的开关元件  $T_1$  和进位输出单元  $214$  的开关元件  $T_{15}$  导通。因此, 提供到第一时钟端  $CK_1$  的时钟信号  $CKV_1$  分别

从栅极输出端 OUT1 和进位输出端 OUT2 输出作为栅极信号 Gout(j) 和进位信号 Cout(j)。此时,开关元件 T1 被导通,在保持 2H 的栅极活跃时间段“b”期间,第一节点 N1 具有高于第一电压电平的第二电压电平。

[0112] 在时间 t3,开关元件 T1 仍然处于导通状态,提供到第一时钟端 CK1 的时钟信号 CKV1 从栅极输出端 OUT1 输出作为栅极信号 Gout(j)。此时,第一节点 N1 在保持 1H 的第一栅极不活跃时间段“c”期间具有低于第二电压电平的第三电压电平。第一栅极不活跃时间段“c”是后面级的栅极信号 Gout(j+3) 输入到下拉单元 212 的开关元件 T9 的栅极和补充下拉单元 312 的开关元件 T2 的栅极之前的时间段。

[0113] 在时间 t4,下拉单元 212 的开关元件 T9 响应后面级的栅极信号 Gout(j+3) 而被导通,从而第一节点 N1 在第二栅极不活跃时间段“d”期间具有低于第三电压电平的第四电压电平(例如,等于栅极截止信号 Voff 的电平的电平)。另外,在时间 t4,补充下拉单元 312 的开关元件 T2 响应后面级的栅极信号 Gout(j+3) 而被导通,从而在第二栅极不活跃时间段“d”期间,第二节点 N2 具有低于第三电压电平的第四电压电平(例如,等于栅极截止信号 Voff 的电平的电压电平)。因此,通过下拉单元 212 的开关元件 T9 和补充下拉单元 312 的开关元件 T2,存储在第一电容器 C1 和第二电容器 C2 中的电荷被放电至栅极截止信号 Voff。

[0114] 如上所述,根据本发明的可选示例性实施例,通过减小开关元件 T2 的尺寸以使其具有小于或者等于开关元件 T1 的宽长比的大约 1/2 的宽长比,来有效地减小液晶面板中栅极驱动电路的面积。因此有效地提高栅极驱动电路的产率,结果基本上提高了具有该栅极驱动电路的液晶显示器的生产效率并降低了其生产成本。

[0115] 图 7 和图 8 是根据本发明可选示例性实施例的栅极驱动电路的移位寄存器的框图。

[0116] 参照图 1 和图 7,第一移位寄存器 400L 连接到多条栅极线 G<sub>1</sub> 至 G<sub>n</sub> 中的每条栅极线的第一端,第二移位寄存器 400R 连接到多条栅极线 G<sub>1</sub> 至 G<sub>n</sub> 中的每条栅极线的第二相对端。第一移位寄存器 400L 和第二移位寄存器 400R 被交替地导通。例如,从第一移位寄存器 400L 输出提供到第一栅极线 G<sub>1</sub> 的栅极信号 Gout1,接着从第二移位寄存器 400R 输出提供到第二栅极线 G<sub>2</sub> 的栅极信号 Gout2。

[0117] 如图 5 中所示,提供到第一栅极线 G<sub>1</sub> 的栅极信号 Gout1 包括预充电时间段 P1 和主充电时间段 M1,提供到第二栅极线 G<sub>2</sub> 的栅极信号 Gout2 比栅极信号 Gout1 延迟预充电时间段 P1。

[0118] 第一移位寄存器 400L 包括顺序输出奇数栅极信号的多个左边的级 STL1、STL2、...、STL(j),第二移位寄存器 400R 包括顺序输出偶数栅极信号的多个右边的级 STR1、STR2、...、STR(j)。具有多个左边的级 STL1、STL2、...、STL(j) 的对应的左边的级和具有多个右边的级 STR1、STR2、...、STR(j) 的对应的右边的级分别彼此级联。

[0119] 参照图 7,多个奇数的左边的级 STL1、STL3、STL5 和 STL7 及多个偶数的右边的级 STR2、STR4、STR6 和 STR8 均具有第一时钟端 CK1、第二时钟端 CK2、设置端 S、复位端 R、电源电压端 GV、帧复位端 FR、栅极输出端 OUT1 和进位输出端 OUT2。

[0120] 相反,多个偶数的左边的级 STL2、STL4、STL6 和 STL8 及多个奇数的右边的级 STR1、STR3、STR5 和 STR7 均具有电源电压端 GV、复位端 R 和栅极输出端 OUT1。

[0121] 如图 7 中所示,在将第一起始信号 STV1 施加到奇数的左边的级 STL1 的同时,将第一时钟信号 CKV1、第一反相时钟信号 CKVB1 和栅极截止信号 Voff 提供到多个奇数的左边的级 STL1、STL3、STL5 和 STL7 中的每个级。在将第二起始信号 STV2 提供到偶数的右边的级 STR2 的同时,将第二时钟信号 CKV2、第二反相时钟信号 CKVB2 和栅极截止信号 Voff 提供到多个偶数的右边的级 STR2、STR4、STR6 和 STR8 中的每个级。

[0122] 第一反相时钟信号 CKVB1 的相位相对于第一时钟信号 CKV1 的相位被反相,第二反相时钟信号 CKVB2 的相位相对于第二时钟信号 CKV2 的相位被反相。另外,第二时钟信号 CKV2 比第一时钟信号 CKV1 延迟第一时钟信号 CKV1 的一个周期 (T) 的四分之一 (T/4),并且第二反相时钟信号 CKVB2 比第一反相时钟信号 CKVB1 延迟第一反相时钟信号 CKVB1 的一个周期 (T) 的四分之一 (T/4)。

[0123] 代替前面级的进位信号,第一起始信号 STV1 被输入到第一个左边的级 STL1 的设置端 S,第二起始信号 STV2 被输入到第二个右边的级 STR2 的设置端 S。第二起始信号 STV2 比第一起始信号 STV1 延迟一个周期 (T) 的四分之一 (T/4)。

[0124] 将第一起始信号 STV1 输入到最后一个左边的级 STL(j) 和最后一个右边的级 STR(j) 的复位端 R。

[0125] 在多个奇数的左边的级 STL1、STL3、STL5 和 STL7 中的每个级 (例如,第三个左边的级 STL3) 中,例如,分别将前面的左边的级 STL1 的进位信号和后面的右边的级 STR6 的栅极信号 Gout6 输入到第三个左边的级 STL3 的设置端 S 和复位端 R,并且将第一反相时钟信号 CKVB1 和第一时钟信号 CKV1 分别输入到第三个左边的级 STL3 的第一时钟端 CK1 和第二时钟端 CK2。另外,将栅极截止信号 Voff 输入到第三个左边的级 STL3 的电源电压端 GV,将初始信号 INT 输入到第三个左边的级 STL3 的帧复位端 FR。栅极输出端 OUT1 输出栅极信号 Gout3,进位输出端 OUT2 输出进位信号 Cout3。

[0126] 后面的右边的级 STR6 的栅极信号 Gout6 同时被输入到第三个左边的级 STL3 的复位端 R 和第三个右边的级 STR3 的复位端 R。

[0127] 最后,最后一级 STL(j) 的进位信号 Cout(j) 提供到多个级 STL1、STL2、...、STL(j) 中的每一奇数级作为初始信号 INT。

[0128] 出于解释的目的,图 8 中示出了具有九个级 (例如, j = 9) 的移位寄存器的框图,但是本发明的可选示例性实施例不限于此。

[0129] 参照图 1 和图 8,在左边的哑级 STL7、STL8、STL9 和右边的哑级 STR7、STR8、STR9 向左边的第四个级 STL4 和右边的第四个级 STR4、左边的第五个级 STL5 和右边的第五个级 STR5、左边的第六个级 STL6 和右边的第六个级 STR6 分别提供栅极信号 Gout7 至 Gout9 时,奇数的左边的级 STL1、STL3 和 STL5、偶数的右边的级 STR2、STR4 和 STR6 向六条栅极线 G<sub>1</sub> 至 G<sub>6</sub> 提供栅极信号 Gout1 至 Gout6。

[0130] 右边的级 STR4 的栅极信号 Gout4 输入到左边的级 STL1 的复位端 R 和右边的级 STR1 的复位端 R。右边的级 STR6 的栅极信号 Gout6 输入到左边的级 STL3 的复位端 R 和右边的级 STR3 的复位端 R。

[0131] 左边的级 STL5 的栅极信号 Gout5 输入到右边的级 STR2 的复位端 R 和左边的级 STL2 的复位端 R。左边的级 STL7 的栅极信号 Gout7 输入到右边的级 STR4 的复位端 R 和左边的级 STL4 的复位端 R。因此,在可选示例性实施例中,可以通过改变连接到对应的复位端

R 的级来调节每个级的复位时间。

[0132] 参照图 7 和图 8, 第一移位寄存器 400L 的多个奇数的左边的级和第二移位寄存器 400R 的多个偶数的右边的级的结构与上面参照图 1 至图 6 更详细描述的结构基本相同。因此, 多个奇数的左边的级和多个偶数的右边的级可以包括与如图 4 和图 6 中所示的电路相同的电路, 因此这里将省略对相同电路的任何重复描述。

[0133] 与前面的上述本发明的可选示例性实施例相同或相似的优点和 / 或益处由参照图 7 和图 8 描述的示例性实施例产生。

[0134] 如上面更详细的描述, 在根据本发明示例性实施例的栅极驱动电路和包括该栅极驱动电路的液晶显示器中, 可以减小在栅极驱动电路中的晶体管的宽长比, 从而有效地减小栅极驱动电路的尺寸, 并且提供了改进的生产余量, 在生产效率方面有所提高并且降低了栅极驱动电路和具有该栅极驱动电路的液晶面板的生产成本。

[0135] 本发明不应该被理解为限于这里提出的示例性实施例。相反, 提供这些示例性实施例, 使得本公开将是彻底和完全的, 并且将把本发明的构思充分传达给本领域技术人员。

[0136] 尽管已经参照本发明的示例性实施例具体示出和描述了本发明, 但是本领域普通技术人员应该理解, 在不脱离由权利要求限定的本发明的精神或范围的情况下, 可以对此进行形式和细节上的各种改变。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8

|                |                                                              |         |            |

|----------------|--------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 栅极驱动电路和具有该栅极驱动电路的液晶显示器                                       |         |            |

| 公开(公告)号        | <a href="#">CN102645773B</a>                                 | 公开(公告)日 | 2015-04-15 |

| 申请号            | CN201210116918.3                                             | 申请日     | 2007-11-16 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                     |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                     |         |            |

| 当前申请(专利权)人(译)  | 三星显示有限公司                                                     |         |            |

| [标]发明人         | 李奉俊<br>金景旭<br>金钟五<br>金圣万<br>李洪雨<br>金燦珍                       |         |            |

| 发明人            | 李奉俊<br>金景旭<br>金钟五<br>金圣万<br>李洪雨<br>金燦珍                       |         |            |

| IPC分类号         | G02F1/133 G09G3/36                                           |         |            |

| CPC分类号         | G09G2310/0286 G09G2340/145 G09G3/3677 G11C19/184 G02F1/13454 |         |            |

| 代理人(译)         | 韩芳                                                           |         |            |

| 审查员(译)         | 张贝                                                           |         |            |

| 优先权            | 1020070041563 2007-04-27 KR                                  |         |            |

| 其他公开文献         | CN102645773A                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">SIPO</a>               |         |            |

### 摘要(译)

本发明公开了一种栅极驱动电路和一种具有该栅极驱动电路的液晶显示器。该栅极驱动电路具有第一级，第一级包括：上拉驱动单元，从第二级接收第一进位信号并且分别在预先时间段期间、栅极活跃时间段期间、第一栅极不活跃时间段期间和第二栅极不活跃时间段期间向第一节点输出具有第一电压、第二电压、第三电压和第四电压的控制信号；上拉单元，接收控制信号并且在栅极活跃时间段期间向第二节点输出栅极导通信号；进位输出单元，接收控制信号并且在栅极活跃时间段期间向第三级输出第二进位信号；下拉单元，接收来自第二级的栅极导通信号并且在第二栅极不活跃时间段期间向第一节点输出具有第四电压电平的控制信号。