[19] 中华人民共和国国家知识产权局

[51] Int. Cl.

G09G 3/20 (2006.01)

G09G 3/36 (2006.01)

## [12] 发明专利申请公布说明书

[21] 申请号 200610152801.5

[43] 公开日 2007 年 4 月 25 日

[11] 公开号 CN 1953007A

[22] 申请日 2006.10.18

[74] 专利代理机构 北京康信知识产权代理有限责任

[21] 申请号 200610152801.5

公司

[30] 优先权

代理人 李 伟

[32] 2005.10.18 [33] KR [31] 10-2005-0098210

[71] 申请人 三星电子株式会社

地址 韩国京畿道

[72] 发明人 朴宇一 金大燮

权利要求书 6 页 说明书 14 页 附图 6 页

[54] 发明名称

平板显示器及其驱动方法

[57] 摘要

在平板显示器中，显示面板包括数据线、栅极线、和电连接到数据线和栅极线的像素，并且定时控制器输出控制信号和图像数据信号。数据驱动器响应于控制信号的一部分和图像数据信号来驱动数据线，以及栅极驱动器响应于控制信号的不同部分来驱动栅极线。控制电路控制数据驱动器，使得数据线在电源导通开始之后维持复位状态达预定时间。因此，平板显示器可以防止在液晶面板上显示错误的图像。

1. 一种平板显示器，包括：

定时控制器，用于输出图像数据信号；

数据驱动器，用于响应于控制信号和所述图像数据信号来驱动数据线；以及

控制电路，用于产生所述控制信号，其中所述控制信号表示所述显示器的电源状态，以及所述数据驱动器用于在所述控制信号表示所述显示器的电源导通状态开始之后，驱动所述数据线处于复位状态达预定时间。

2. 根据权利要求 1 所述的平板显示器，其中，所述定时控制器还用于输出行锁存信号，以表示通过所述数据驱动器的所述数据线的驱动定时。

3. 根据权利要求 2 所述的平板显示器，其中，所述控制电路用于接收外部电源电压和所述行锁存信号，以及在所述预定时间之后，所述控制信号具有与所述行锁存信号相同的波形。

4. 根据权利要求 2 所述的平板显示器，其中，所述控制电路还包括：

延迟电路，用于延迟外部电源电压，以传送延迟的外部电源电压；

脉冲发生器，用于接收所述外部电源电压和来自所述延迟电路的所述延迟的外部电源电压，并还用于产生脉冲信号；以及

---

逻辑电路，用于根据所述行锁存信号和所述脉冲信号来输出所述控制信号。

5. 根据权利要求 1 所述的平板显示器，还包括：

显示像素，包括具有栅极的晶体管，响应于施加到所述栅极的足够的栅极导通电压，所述晶体管被设置为导通状态，其中，响应于施加到所述栅极的足够的栅极截止电压，所述晶体管被设置为截止状态；以及

栅极驱动器，用于驱动与所述栅极通信的栅极线，其中，所述预定时间被选择为约等于或大于开始所述电源导通状态的时间和使用足够的栅极截止电压使所述栅极驱动器驱动所述栅极之间的时间。

6. 一种平板显示器，包括：

定时控制器，用于输出第一行锁存信号和图像数据信号；

数据驱动器，用于响应于第二行锁存信号和所述图像数据信号来驱动数据线；以及

控制电路，用于接收所述第一行锁存信号，并且还用于在所述显示器的电源导通之后接收外部电源电压，所述控制电路还用于产生所述第二行锁存信号，其中，所述显示器用于在所述显示器的所述电源导通之后，将所述数据线维持在复位状态达预定时间。

7. 根据权利要求 6 所述的平板显示器，其中，所述控制电路还包括：

延迟电路，用于延迟所述外部电源电压，并传送延迟的外部电源电压；

脉冲发生器，用于接收所述外部电源电压和所述延迟的外部电源电压，并用于产生脉冲信号；以及

逻辑电路，用于根据所述第一行锁存信号和所述脉冲信号，输出所述第二行锁存信号。

8. 根据权利要求 6 所述的平板显示器，其中，所述数据驱动器包括：

锁存电路，用于响应于所述第二行锁存信号，锁存来自所述定时控制器的所述图像数据信号；以及

输出驱动电路，用于接收来自所述锁存电路的所述图像数据信号并响应于所述第二行锁存信号来驱动所述数据线。

9. 根据权利要求 8 所述的平板显示器，其中，所述控制电路用于输出所述第二行锁存信号，使得在所述显示器的所述电源导通之后，所述锁存电路的输出维持所述复位状态达所述预定时间。

10. 一种平板显示器，包括：

显示面板，具有数据线、栅极线、和电连接到所述数据线和所述栅极线的像素；

定时控制器，用于输出控制信号和图像数据信号；

数据驱动器，用于响应于所述控制信号的一部分和所述图像数据信号来驱动所述数据线；

栅极驱动器，用于响应于所述控制信号的不同部分来驱动所述栅极线；以及

控制电路，用于控制所述数据驱动器，以使所述数据线在所述显示器的电源导通状态开始之后的预定时间内不被所述图像数据信号驱动。

11. 根据权利要求 10 所述的平板显示器，其中，来自所述定时控制器的所述控制信号包括第一行锁存信号，其表示将所述图像数据信号施加到所述数据线的定时。

12. 根据权利要求 10 所述的平板显示器，其中，所述控制电路用于输出第二行锁存信号，以控制所述数据驱动器。

13. 根据权利要求 10 所述的平板显示器，其中，所述控制电路在所述显示器的所述电源导通状态开始之后，输出具有预定电平的第二行锁存信号达所述预定时间。

14. 根据权利要求 13 所述的平板显示器，其中，所述控制电路用于在所述显示器的所述电源导通状态开始后的所述预定时间之后，输出来自所述定时控制器的第一行锁存信号作为所述第二行锁存信号。

15. 根据权利要求 14 所述的平板显示器，其中，所述控制电路包括：

延迟电路，用于延迟外部电源电压并传送延迟的外部电源电压；

脉冲发生器，用于接收所述外部电源电压和来自所述延迟电路的所述延迟的外部电源电压，以产生脉冲信号；以及

逻辑电路，用于接收来自所述脉冲发生器的所述脉冲信号和来自所述定时控制器的所述第一行锁存信号，以及输出所述第二行锁存信号。

16. 根据权利要求 15 所述的平板显示器，其中，所述逻辑电路包括“或”门。

17. 根据权利要求 16 所述的平板显示器，其中，所述控制电路包括：

第一电阻器，具有用于接收所述外部电源电压的第一端；

电容器，电连接在所述第一电阻器的第二端和接地之间；

第二电阻器，具有用于接收所述外部电源电压的第一端；

晶体管，具有电连接到所述第一电阻器的所述第二端的栅极以及电连接在所述第二电阻器的第二端和所述接地之间的电流通路；

第一二极管，具有电连接到所述第二电阻器的所述第二端的输入端和输出端；以及

第二二极管，具有用于接收来自所述定时控制器的所述第一行锁存信号的输入端和输出端，

其中，所述第一和第二二极管的所述输出端彼此共同地连接，以及将所述控制电路配置成工作时从所述第一和所述第二二极管的所述输出端输出所述第二行锁存信号。

18. 根据权利要求 11 所述的平板显示器，其中，所述数据驱动器包括：

移位寄存器，用于响应于水平起始信号使时钟信号移位；

数据寄存器，用于响应于来自所述移位寄存器的所述时钟信号，存储来自所述定时控制器的所述图像数据信号；

锁存器，用于响应于来自所述控制电路的所述第二行锁存信号，将所述存储的图像数据信号锁存在所述数据寄存器中；

数/模转换器，用于将来自所述锁存器的所述图像数据信号转换为模拟图像信号；以及

输出缓冲器，用于响应于所述第一行锁存信号，将来自所述数/模转换器的所述模拟图像信号输出到所述数据线。

19. 一种平板显示器的驱动方法，所述平板显示器具有响应于图像数据信号来驱动数据线的数据驱动器，所述方法包括：

开启所述显示器的电源；以及

将所述数据驱动器复位达预定时间。

20. 根据权利要求 19 所述的方法，其中，所述预定时间是使所述显示器通电的时间和驱动所述栅极线至足以使连接到所述栅极线的一个或多个晶体管截止的栅极截止电压的时间之间的时

间。

21. 一种平板显示器的驱动方法，所述平板显示器具有响应于图像数据信号来驱动数据线的数据驱动器，所述方法包括：

施加电源电压；

延迟所述电源电压；

响应于所述电源电压和所述延迟的电源电压，产生脉冲信号，所述脉冲信号具有预定时间的脉冲宽度；以及

向所述数据驱动器提供所述脉冲信号，以使所述数据线复位达所述预定时间。

22. 根据权利要求 21 所述的方法，其中，所述脉冲信号是行锁存信号。

## 平板显示器及其驱动方法

### 相关申请的交叉参考

本申请要求于 2005 年 10 月 18 日提交的韩国专利申请第 2005 - 98210 号的优先权，其全部内容结合于此作为参考。

### 技术领域

本发明涉及一种平板显示器。更具体地，本发明涉及一种具有改进的显示质量的平板显示器及其驱动方法。

### 背景技术

近年来，平板显示器被广泛使用。因为其优点，例如重量轻，明显减少的厚度等，平板显示器被广泛地用作电子装置的用户接口。根据在其上显示图像的面板的类型，平板显示器被分成有机发光二极管 (OLED) 显示器、液晶显示器 (LCD)、场致发射显示器 (FED)、真空荧光显示器 (VFD)、等离子体显示面板 (PDP) 等。

包括在 LCD 中的液晶显示面板包括以矩阵配置的多个像素，其中像素包括用作开关装置的薄膜晶体管。每个像素通过薄膜晶体管来选择性地接收对应于图像信号的数据电压。LCD 还包括栅极驱动器，其将栅极导通电压施加到栅极线；数据驱动器，其将图像信号施加到数据线；以及控制电路，其控制栅极驱动器和数据驱动器。

栅极线提供使薄膜晶体管导通的栅极导通电压或使薄膜晶体管截止的栅极截止电压。例如，当通电时，直流/直流 (DC/DC) 转

换器输出大约-13 伏的栅极截止电压。然而，需要预定的时间间隔，直到栅极截止电压稳定在大约-13 伏。在栅极截止电压充分稳定在大约-13 伏之前，薄膜晶体管维持在轻微导通状态，直到栅极截止电压达到大约-6 伏。结果是，数据线具有随机电压电平，使得对应于数据线的随机电压电平的错误图像显示在 LCD 的液晶显示面板上。如上所述的错误图像被连续地显示在显示面板上大约 60 毫秒，直到由控制电路输出有效的像素数据信号。

当响应于通电时所具有的彼此相等的特定电压电平的数据信号，驱动电连接到数据驱动器的多个集成电路中的一些集成电路的数据线时，错误图像可能会被突出显示。

因此，当前系统在通电之后，通常不允许数据线具有特定电压电平，直到栅极截止电压足够稳定。

## 发明内容

本发明提供了一种具有改进的显示质量的平板显示器。

本发明还提供了一种适用于制造上述平板显示器的方法。

在本发明的一个方面，平板显示器包括定时控制器、数据驱动器、和控制电路。定时控制器输出图像数据信号，以及数据驱动器响应于控制信号和图像数据信号来驱动数据线。控制电路产生控制信号，从而在开始电源导通状态之后，将数据线维持在复位状态达预定时间。

定时控制器还输出行锁存信号，以指示通过数据驱动器的数据线的驱动定时。

控制电路接收外部电源电压和行锁存信号。控制信号在经过预定时间之后，具有与行锁存信号相同的波形。

控制电路还包括延迟电路，用于延迟外部电源电压；脉冲发生器，用于接收外部电源电压和由延迟电路延迟的外部电源电压，以产生脉冲信号；以及逻辑电路，基于行锁存信号和脉冲信号，输出控制信号。

平板显示器还包括栅极驱动器，用于驱动与一个或多个晶体管通信的栅极线。控制电路产生控制信号，使得在电源导通状态开始之后，使数据线维持在复位状态，直到栅极驱动器使用足够的栅极截至电压驱动栅极线。

在本发明的另一方面，平板显示器包括定时控制器、数据驱动器、和控制电路。定时控制器输出第一行锁存信号和图像数据信号。数据驱动器响应于第二行锁存信号和图像数据信号驱动数据线。控制电路接收外部电源电压和第一行锁存信号，并产生第二行锁存信号，从而在开始显示器的电源导通状态之后，使数据线维持在复位状态达预定时间。

控制电路还包括延迟电路、脉冲发生器、和逻辑电路。延迟电路延迟外部电源电压。脉冲发生器接收外部电源电压和由延迟电路延迟的外部电源电压，以产生脉冲信号。逻辑电路基于第一行锁存信号和脉冲信号，输出第二行锁存信号。

数据驱动器包括锁存电路，响应于第二行锁存信号，锁存来自定时控制器的图像数据信号；以及输出驱动电路，接收来自锁存电路的图像数据信号并响应于第二行锁存信号驱动数据线。

控制电路输出第二行锁存信号，从而在开始电源导通状态之后，使锁存电路的输出维持复位状态达预定时间。

在本发明的另一实施例中，平板显示器包括显示面板、定时控制器、数据驱动器、栅极驱动器、和控制电路。显示面板具有数据线、栅极线、和电连接到数据线和栅极线的像素。定时控制器输出控制信号和图像数据信号。数据驱动器响应于控制信号的一部分和图像数据信号来驱动数据线。栅极驱动器响应于控制信号的不同部分来驱动栅极线。控制电路控制数据驱动器，以使在开始电源导通状态之后预定时间内数据线不被图像数据信号驱动。

来自定时控制器的控制信号包括第一行锁存信号，其表示将图像数据信号施加于数据线的定时。

控制电路输出第二行锁存信号，以控制数据驱动器。

控制电路在开始电源导通状态之后，输出具有预定电平的第二行锁存信号达预定时间。

控制电路在通电并经过预定时间之后，输出来自定时控制器的第一行锁存信号作为第二行锁存信号。

控制电路包括延迟电路、脉冲发生器、和逻辑电路。延迟电路延迟外部电源电压。脉冲发生器接收外部电源电压和由延迟电路延迟的外部电源电压，以产生脉冲信号。逻辑电路接收来自脉冲发生器的脉冲信号和来自定时控制器的第一行锁存信号，以输出第二行锁存信号。

控制电路包括：第一电阻器、电容器、第二电阻器、晶体管、第一二极管、和第二二极管。第一电容器具有施加有外部电源电压的第一端。电容器电连接在第一电阻器的第二端和接地之间。第二电阻器具有施加有外部电源电压的第一端。晶体管具有电连接到第一电阻器的第二端的栅极以及电连接在第二电阻器的第二端和接地之间的电流通路。第一二极管具有输出端和电连接到第二电阻器

的第二端的输入端。第二二极管具有输出端和施加有来自定时控制器的第一行锁存信号的输入端。第一和第二二极管的输出端彼此共同地连接，并且从第一和第二二极管的输出端输出第二行锁存信号。

数据驱动器包括移位寄存器、数据寄存器、锁存器、数/模转换器以及输出缓冲器。移位寄存器响应于水平起始信号，使时钟信号移位。数据寄存器响应于来自移位寄存器的时钟信号，存储来自定时控制器的图像数据信号。锁存器响应于来自控制电路的第二行锁存信号，将所存储的图像数据信号锁存在数据寄存器中。数/模转换器将来自锁存器的图像数据信号转换为模拟图像信号。输出缓冲器响应于第一行锁存信号，将来自数/模转换器的模拟图像信号输出到数据线。

在本发明的另一方面，如下提供了一种平板显示器的驱动方法，其中，平板显示器具有响应于图像数据信号来驱动数据线的数据驱动器。当开启平板显示器的电源时，将数据驱动器复位达预定时间。预定时间是等于或大于将栅极线驱动到足够的栅极截止电压所用时间的时间间隔。

在本发明的另一方面，如下提供了一种平板显示器的驱动方法，其中，平板显示器具有响应于图像数据信号来驱动数据线的数据驱动器。

当向数据驱动器施加电源电压时，电源电压被延迟。响应于电源电压和延迟的电源电压，产生脉冲信号，并且使数据线复位达等于脉冲信号宽度的时间。脉冲信号是行锁存信号。

根据如上所述，在将数据驱动电压施加于数据驱动电路之前并且在开始电源导通状态之后，控制数据驱动电路中的锁存电路的行

锁存信号被设置为高电平。因此，尽管将数据驱动电压施加于数据驱动电路，也不从锁存电路输出数据驱动信号。

### 附图说明

通过以下参考附图的详细描述，本发明的上述和其它优点将变得更明显，在附图中：

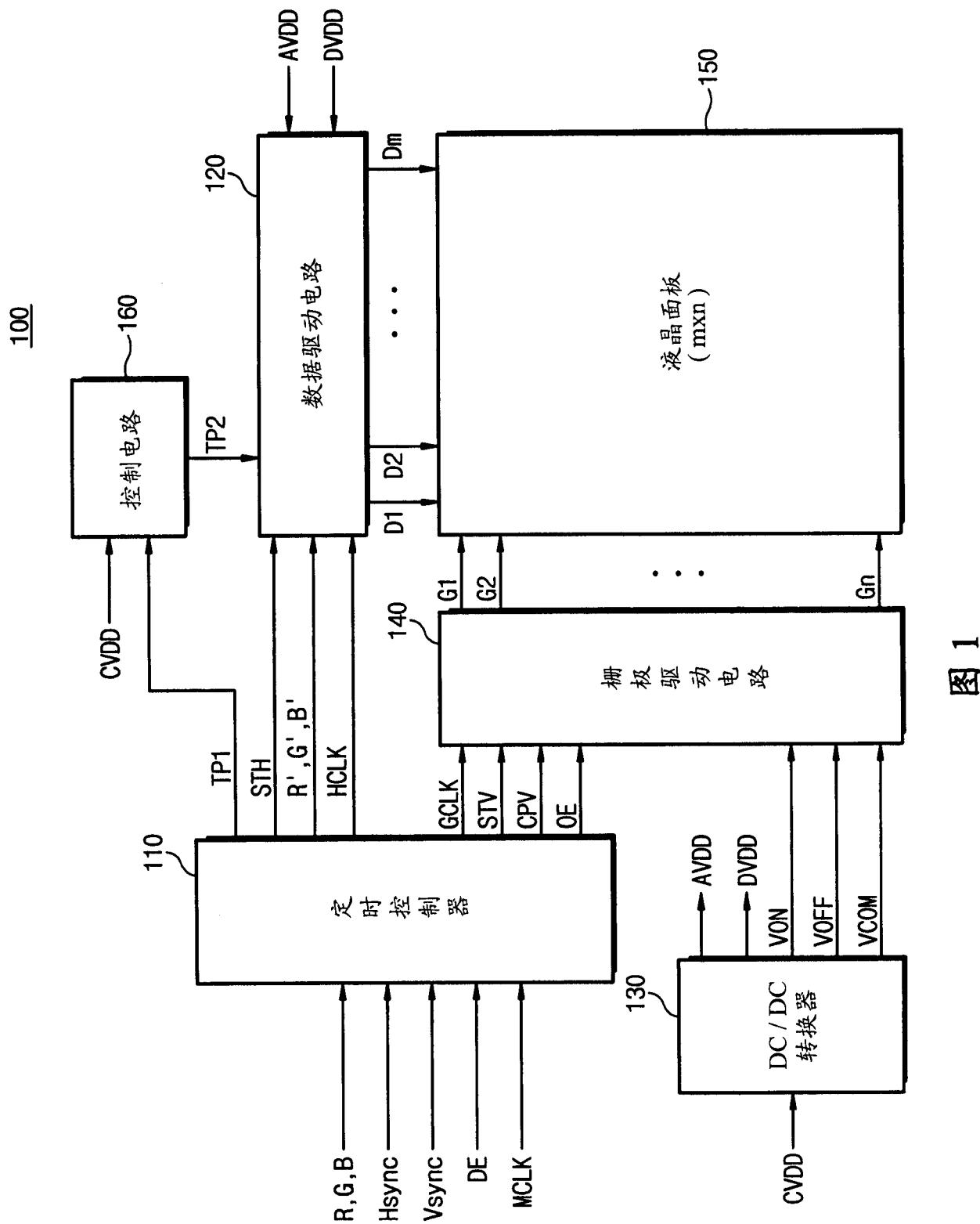

图 1 是示出根据本发明示例性实施例的作为一种平板显示器的实例的液晶显示器的框图；

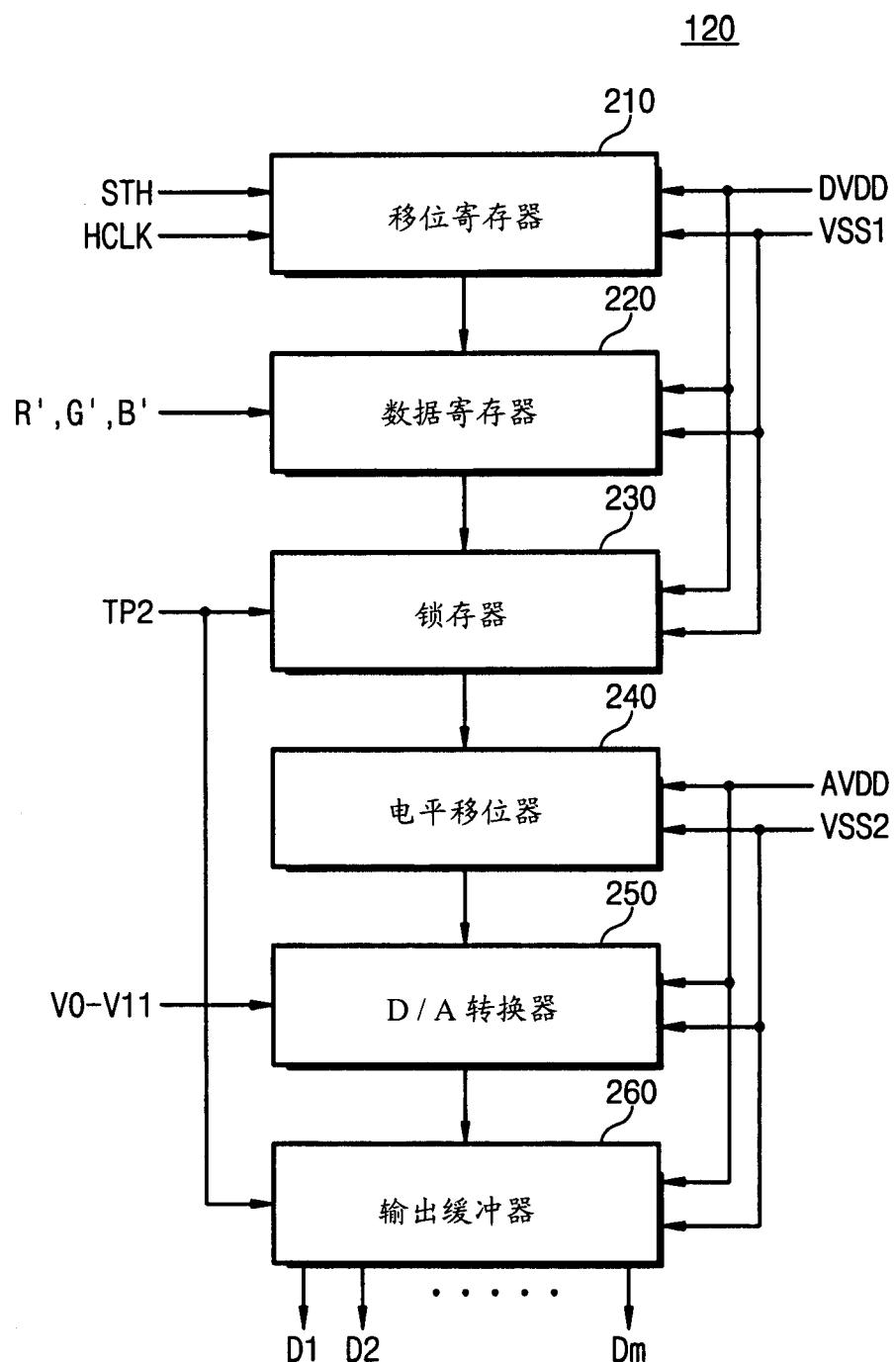

图 2 是详细地示出图 1 的显示器可以使用的数据驱动电路的实施例的框图；

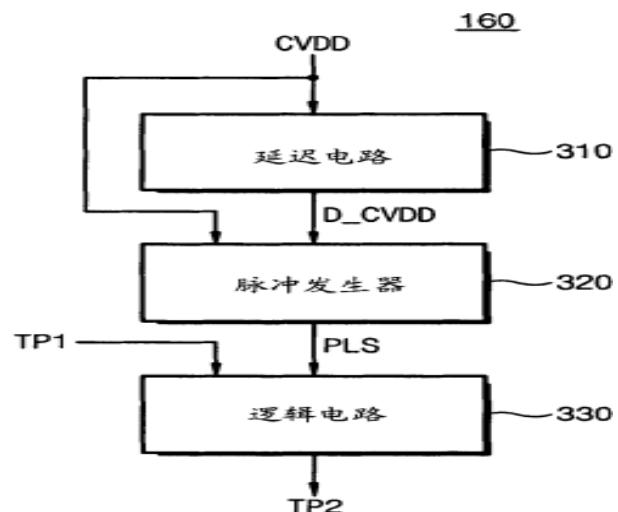

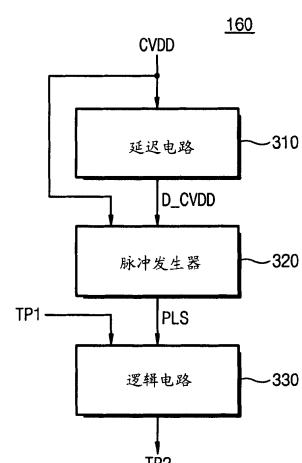

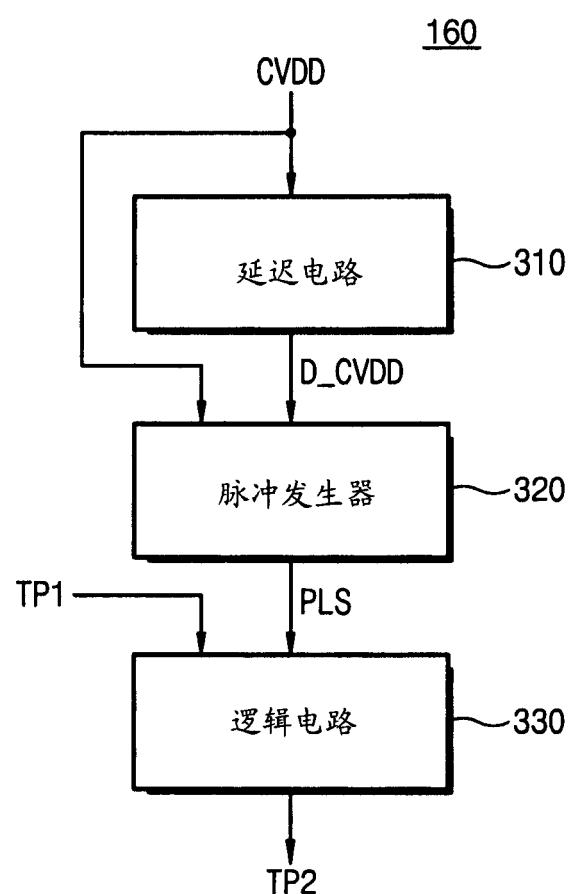

图 3 是示出图 1 的显示器可以使用的控制电路的实施例的框图；

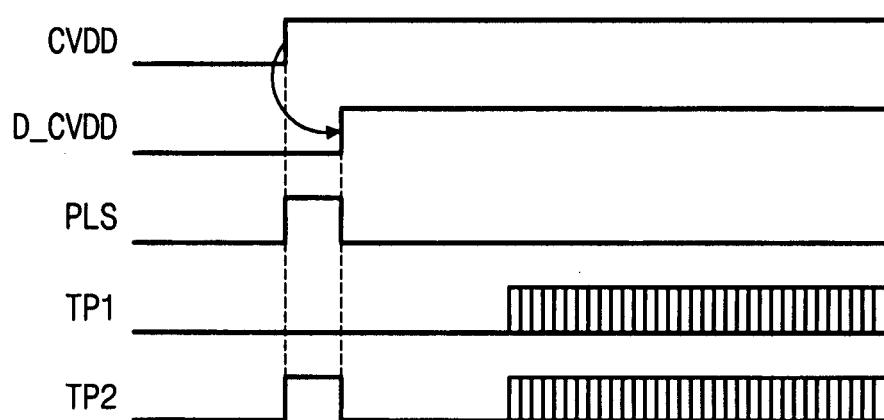

图 4 是用于图 3 中所示的控制电路的信号的时序图；

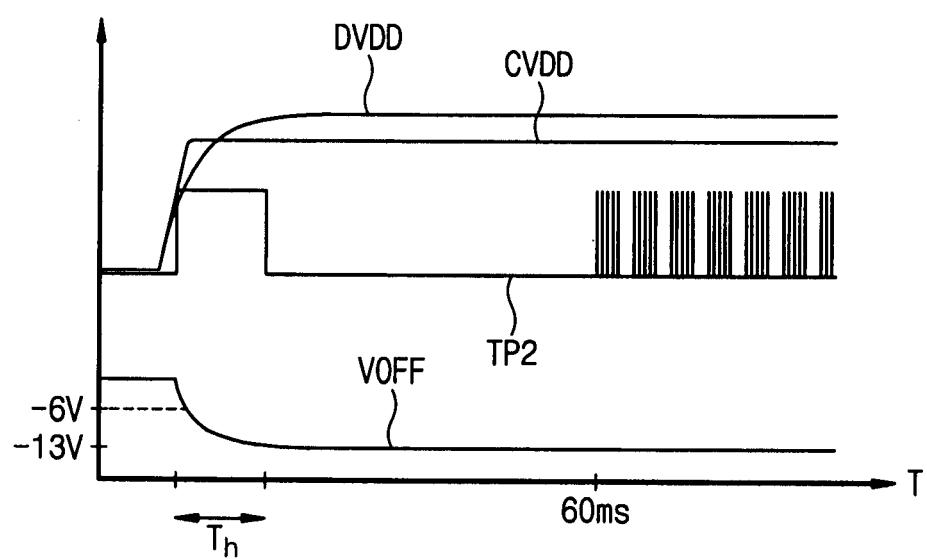

图 5 是示出栅极截止电压和第二行锁存信号之间的关系的视图；以及

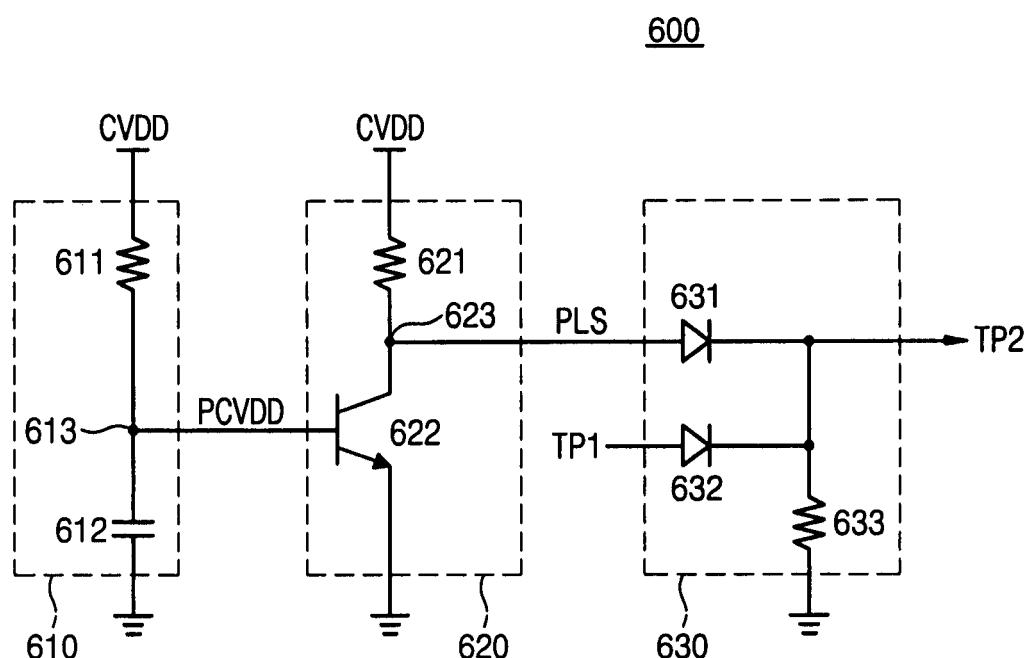

图 6 是示出根据本发明另一实施例的控制电路的电路图。

### 具体实施方式

应当理解，当元件或层被指出“位于”、“连接到”、“耦合到”另一个元件或层上时，该元件可直接位于、连接到、或耦合到另一个元件或层上，或者也可在其间存在插入的元件或层。相反地，当元件或层被指出“直接位于”、“直接连接到”、“直接耦合到”另一个元件或层上时，是指不存在插入的元件或层。通篇中相同的标号

表示相同的元件。正如在此所应用的，术语“和/或”包括任何的以及所有的一个或多个相关所列术语的结合。

应当理解，尽管在此可能使用术语第一、第二等来描述不同的元件、部件、区域、层、和/或部分，但是这些元件、部件、区域、层、和/或部分并不局限于这些术语。这些术语仅用于将一个元件、部件、区域、层、或部分与另一个区域、层、或部分相区分。因此，在不背离本发明宗旨的情况下，下文所述的第一元件、组件、区域、层、或部分可以称为第二元件、组件、区域、层、或部分。被描述为“第一”的元件并不意味着需要存在“第二”或其它元件。

为了便于说明，在此可能使用诸如“在...之下”、“在...下面”、“下面的”、“在...上面”、以及“上面的”等的空间关系术语，以描述如图中所示的一个元件或机构与另一元件或机构的关系。应当理解，除图中所示的方位之外，空间关系术语将包括使用或操作中的装置的各种不同的方位。例如，如果翻转图中所示的装置，则被描述为在其他元件或机构“下面”或“之下”的元件将被定位为在其他元件或机构的“上面”。因此，示例性术语“在...下面”包括在上面和在下面的方位。装置可以以其它方式定位（旋转 90 度或其他方位），并且通过在此使用的空间关系描述符进行相应地解释。

此使用的术语仅用于描述特定实施例而不是限制本发明的目的。正如在此使用的，单数形式的“一个”、“这个”也包括复数形式，除非文中有其它明确指示。应当进一步理解，当在本说明书中使用术语“包括”和/或“包含”时，是指存在所声称的特征、整数、步骤、操作、元件、和/或部件，但是并不排除还存在或添加一个或多个其它的特征、整数、步骤、操作、元件、部件、和/或其组合。

除非特别限定，在此所采用的所有的术语（包括技术和科技术语）具有与本发明所属领域的普通技术人员通常所理解的意思相同的解释。而该术语的进一步理解，例如，字典中通常采用的限定意思应该被解释为与相关技术上下文中的意思相一致，并且除非在此进行特别限定，其不应被解释为理想的或者过于正式的解释。

以下，将参考附图详细描述本发明的实施例。

图 1 是根据本发明的示例性实施例的作为一种平板显示器的液晶显示器 100 的框图。

参考图 1，液晶显示器 100 包括定时控制器 110、数据驱动电路 120、直流/直流 (DC/DC) 转换器 130、栅极驱动电路 140、液晶面板 150、以及控制电路 160。

液晶面板 150 包括多条栅极线 G1-Gn、多条与栅极线 G1-Gn 交叉以形成多个像素的数据线 D1-Dm、以及分别形成在多个像素区中的多个像素。像素以矩阵形状排列。每个像素均包括薄膜晶体管、液晶电容器（未示出）、以及存储电容器（未示出）。

薄膜晶体管包括栅电极，电连接到栅极线；数据电极，电连接到数据线；以及漏电极，电连接到液晶电容器。当通过栅极驱动电路 140 顺序选择栅极线 G1-Gn，并且以脉冲形状将栅极导通电压 VON 施加到所选择的栅极线时，连接到所选择的栅极线的薄膜晶体管被导通，并且数据驱动电路 120 将具有像素信息的电压（对应于所关联像素的期望图像部分的电压）施加于所关联的数据线。具有像素信息的电压通过由栅极导通电压 VON 导通的薄膜晶体管施加于液晶电容器和存储电容器。结果，液晶电容器和存储电容器被充电，并在液晶面板 150 上显示预定的图像部分。

定时控制器 **110** 接收来自外部图像源的垂直同步信号 Vsync、水平同步信号 Hsync、数据使能信号 DE、时钟信号 MCLK、和像素信号 RGB。在格式化像素数据 RGB 之后，定时控制器 **110** 输出用于液晶面板 **150** 的像素数据信号 R'、G'、B'。定时控制器 **110** 还将水平起始信号 STH 和时钟信号 HLCK 施加到数据驱动电路 **120**，并将第一行锁存信号 TP1 施加到控制电路 **160**。

此外，定时控制器 **110** 响应于水平同步信号 Hsync、垂直同步信号 Vsync 以及数据使能信号 DE，将垂直起始信号 STV、栅极时钟信号 CPV、和输出使能信号 OE 施加到栅极驱动电路 **140**。

控制电路 **160** 接收外部电源电压 CVDD 和来自定时控制器 **110** 的第一行锁存信号 TP1，以输出第二行锁存信号 TP2。

响应于第二行锁存信号 TP2 以及来自定时控制器 **110** 的像素数据信号 R'、G'、B'、水平起始信号 STH、和时钟信号 HCLK，数据驱动电路 **120** 输出信号以驱动数据线 D1-Dm。在一些实施例中，数据驱动电路 **120** 被设置成具有多个集成电路。

栅极驱动电路 **140** 响应于从定时控制器 **110** 施加的信号，顺序地扫描液晶面板 **150** 的栅极线 G1-Gn。在此，栅极驱动电路 **140** 的扫描操作意味着栅极驱动电路 **140** 顺序地将栅极导通电压施加到栅极线，使得连接到被施加有栅极导通电压的栅极线的像素处于数据可写状态。例如，对于包括液晶电容器的像素，将足够的栅极导通电压施加到与其相关的栅极线导致相关数据线电压（对于像素的期望图像部分）和液晶电容器之间的电气通信。

DC/DC 转换器 **130** 响应于外部电源电压 CVDD，产生用于驱动液晶显示器 **100** 的数据驱动电压 DVDD 和 AVDD、栅极导通电压 VON、栅极截止电压 VOFF、以及共电极电压 VCOM。

图 2 是详细地示出图 1 的数据驱动电路 120 的实施例的框图。

参考图 2, 数据驱动电路 120 包括移位寄存器 210, 产生采样信号; 数据寄存器 220, 响应于采样信号将像素数据 R'、G'、B'存储在其中; 锁存器 230, 锁存由数据寄存器 220 提供的像素数据 R'、G'、B'; 电平移位器 240, 增加来自锁存器 230 的像素数据的幅值; 数/模 (D/A) 转换器 250, 将从电平移位器 240 输出的像素数据转换为模拟信号; 以及输出缓冲器 260。

移位寄存器 210 响应于时钟信号 HCLK, 使来自定时控制器 110 的水平起始信号 STH 顺序地移位, 以输出经移位的水平起始信号作为采样信号。

数据寄存器 220 响应于来自移位寄存器 210 的采样信号, 对来自定时控制器 110 的像素数据 R'、G'、B' 进行采样, 并将采样的像素数据 R'、G'、B' 存储于此。数据寄存器 220 具有对应于通过将水平方向上的像素的数量与各个像素数据的位数相乘所得到的值的大小。锁存器 230 锁存来自数据寄存器 220 的像素数据 R'、G'、B', 并响应于来自控制电路 160 的第二行锁存信号 TP2, 输出锁存的像素数据 R'、G'、B'。

电平移位器 240 执行电位移运算, 以增加从锁存器 230 输出的像素数据 R'、G'、B' 的电压摆动宽度 (voltage swing width)。D/A 转换器 250 将来自电平移位器 240 的像素数据转换为具有灰度级电压 V0-V11 的模拟像素数据信号。输出缓冲器 260 存储从 D/A 转换器 250 输出的模拟像素数据信号, 并响应于液晶面板 150 的第二行锁存信号 TP2, 将具有所存储的模拟像素数据信号提供给数据线 D1-Dm。例如, 锁存器 230 在第二行锁存信号 TP2 的上升沿时, 将来自数据寄存器 220 的像素数据 R'、G'、B' 输出到电平移位器 240,

并在第二行锁存信号 TP2 的下降沿时，输出缓冲器 260 将来自 D/A 转换器 250 的模拟像素数据信号提供给数据线 D1-Dm。

当在开启电源之后，开始将数据驱动电压 DVDD 施加到数据驱动电路 120 时，移位寄存器 210、数据寄存器 220、和锁存器 230 被驱动，但是在输入第二行锁存信号 TP2 之前，锁存器 230 维持在不定状态。当将来自 DC/DC 转换器 130 的数据驱动电压 AVDD 施加到数据驱动电路 120 时，将从锁存器 230 输出的像素数据信号通过电平移位器 240、D/A 转换器 250 和输出缓冲器 260 施加到数据线 D1-Dm。在栅极截止电压 VOFF 低于足以使薄膜晶体管截止的电平之前，薄膜晶体管维持在轻微导通状态。结果，通过薄膜晶体管将施加到数据线 D1-Dm 的像素数据信号传送到液晶电容器，从而在液晶面板 150 上显示错误的图像。

为了防止在液晶面板 150 上显示错误的图像，在开启电源之后，至少到栅极截止电压低于足以使薄膜晶体管截止之前，电平控制电路 160 输出高电平的第二行锁存信号 TP2，以复位锁存器 230 的输出。因此，数据驱动电路 120 可以被维持在复位状态，而第二行锁存信号 TP2 被维持在高电平。

图 3 是示出图 1 的控制电路的框图。

参考图 3，控制电路 160 包括延迟电路 310、脉冲发生器 320、和逻辑电路 330。延迟电路 310 将外部电源电压 CVDD 延迟预定的时间，以输出信号 D\_CVDD。脉冲发生器 320 接收信号 D\_CVDD 和外部电源电压 CVDD，并输出脉冲信号 PLS。逻辑电路 330 接收来自定时控制器 110 的第一行锁存信号 TP1 以及来自脉冲发生器 320 的脉冲信号 PLS，以输出第二行锁存信号 TP2。在本发明的示例性实施例中，逻辑电路 330 可以为逻辑运算电路（其可以包括一

个或多个逻辑门)。例如, 逻辑电路 **330** 可以包括逻辑“或”运算电路。

图 4 是图 3 中所示的控制电路 **160** 的实施例的信号的时序图。图 5 是示出栅极截止电压 **VOFF** 和第二行锁存信号 **TP2** 之间的关系的视图。

参考图 4 和图 5, 在将外部电源电压 **CVDD** 施加到液晶显示器 **100** 之后, 第二行锁存信号 **TP2** 维持在高电平达预定时间 **T<sub>h</sub>**。第二行锁存信号 **TP2** 的高电平周期 **T<sub>h</sub>** 对应于延迟电路 **310** 的延迟时间, 并且基本上与在栅极截止电压 **VOFF** 低于足以使薄膜晶体管截止的电平之前所经过的时间相等。在一些实施例中, 第二行锁存信号 **TP2** 的高电平周期 **T<sub>h</sub>** 大约为 5 毫秒或更多。

因为在将数据驱动电压 **DVDD** 和 **AVDD** 施加到数据驱动电路 **120** 之前, 将第二行锁存信号 **TP2** 设置为高电平, 所以在将数据驱动电压 **DVDD** 和 **AVDD** 施加到数据驱动电路 **120** 之前, 将如图 2 所示的锁存器 **230** 和输出缓冲器 **260** 的输出复位。因此, 数据线 **D1-Dm** 未被驱动, 直到栅极截止信号低于足以使薄膜晶体管截止的电平, 从而防止在开启液晶显示器 **100** 时在液晶面板 **150** 上显示错误的图像。如图 4 所示, 在经过由延迟电路 **320** 所产生的延迟时间之后, 第二行锁存信号 **TP2** 显示出与来自定时控制器 **110** 的第一行锁存信号 **TP1** 相同的波形。

图 6 是示出了根据本发明另一示例性实施例的控制电路 **600** 的电路图。

参考图 6, 控制电路 **600** 包括延迟电路 **610**、脉冲发生电路 **620**、和输出电路 **630**。延迟电路 **600** 包括连接在外部电源电压 **CVDD** 和节点 **613** 之间的第一电阻器 **611**, 并且还包括连接到节点 **613** 和接

地的电容器 612。节点 613 处的电压在图 6 中被称作 PCVDD。脉冲发生电路 620 包括第二电阻器 621，该第二电阻器具有施加有外部电源电压 CVDD 的第一端。第二电阻器 621 的第二端和晶体管 622 的第一端通过节点 623 连接。晶体管 622 的第二端接地，而晶体管 622 的栅极连接到节点 613。

输出电路 630 包括第一二极管 631，该第一二极管具有连接到第二电阻器 621 和晶体管 622 之间的节点 623 的输入端以及从其输出第二行锁存信号 TP2 的输出端。节点 623 处的电压在图 6 中被称作 PLS。输出电路 630 还包括第二二极管 632，该第二二极管具有施加有第一行锁存信号 TP1 的输入端以及与第一二极管 631 的输出端和第三电阻器 633 共同连接的输出端。第三电阻器 633 连接在第一和第二二极管 631 和 632 的输出端与接地之间。从第一和第二二极管 631 和 632 的输出端输出第二行锁存信号 TP2。

以下，将详细描述图 6 中所示的控制单元的操作。

在将外部电源电压施加到液晶显示器 100 之后，外部电源电压 CVDD 通过第二电阻器 621 和第一二极管 631 作为第二行锁存信号 TP2 被输出，同时晶体管 622 截止。在经过由第一电阻器 611 的电阻和电容器 612 的电容决定的时间之后，晶体管 622 的栅极处的电压 PCVDD 从其初始值改变为基本上等于 CVDD 的电压。在预定时间（也取决于第一电阻器 611 的电阻和电容器 612 的电容）之后，当通过第一电阻器 611 和电容器 612 使晶体管 622 导通时，节点 623 处的电压 PLS 接近接地，并且二极管 631 截止。随后，通过第二二极管 632 的输出端输出来自定时控制器 110 的第一行锁存信号 TP1（即，信号 TP1 根据其值使二极管 632 导通和截止）。因此，在开启电源之后，经过由第一电阻器 611 和电容器 612 所产生的预定时间（延迟时间），第二行锁存信号 TP2 具有与来自定时控制器 110 的第一行锁存信号 TP1 相同的波形。

根据以上描述，在开始显示器的电源导通状态时，在将数据驱动电压施加到数据驱动电路之前，控制数据驱动电路中的锁存的行锁存信号被设置为高电平。因此，虽然将数据驱动电压施加到数据驱动电路，但是锁存并没有输出数据信号。结果，因为直到经过预定时间才驱动数据线，所以液晶显示器可以防止在液晶面板上显示错误的图像，其中，预定时间约等于或大于使栅极截止电压低于足以将薄膜晶体管截止的电平的时间。

尽管描述了本发明的示例性实施例，但是应该理解本发明不局限于这些示例性实施例，在由权利要求所限定的本发明的精神和范围内，本领域的技术人员可以做出各种改变和修改。

1

图 2

图 3

图 4

图 5

图 6

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 平板显示器及其驱动方法                                    |         |            |

| 公开(公告)号        | <a href="#">CN1953007A</a>                     | 公开(公告)日 | 2007-04-25 |

| 申请号            | CN200610152801.5                               | 申请日     | 2006-10-18 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                       |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                       |         |            |

| 当前申请(专利权)人(译)  | 三星电子株式会社                                       |         |            |

| [标]发明人         | 朴宇一<br>金大燮                                     |         |            |

| 发明人            | 朴宇一<br>金大燮                                     |         |            |

| IPC分类号         | G09G3/20 G09G3/36                              |         |            |

| CPC分类号         | G09G2310/0245 G09G3/3611 G09G3/3685            |         |            |

| 代理人(译)         | 李伟                                             |         |            |

| 优先权            | 1020050098210 2005-10-18 KR                    |         |            |

| 其他公开文献         | CN1953007B                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

#### 摘要(译)

在平板显示器中，显示面板包括数据线、栅极线、和电连接到数据线和栅极线的像素，并且定时控制器输出控制信号和图像数据信号。数据驱动器响应于控制信号的一部分和图像数据信号来驱动数据线，以及栅极驱动器响应于控制信号的不同部分来驱动栅极线。控制电路控制数据驱动器，使得数据线在电源导通开始之后维持复位状态达预定时间。因此，平板显示器可以防止在液晶面板上显示错误的图像。