[12] 发明专利申请公开说明书

〔21〕申请号 01124355.4

[43]公开日 2002年2月13日

[11]公开号 CN 1335534A

[22] 申请日 2001.7.27 [21] 申请号 01124355.4

[30] 优先权

[32]2000. 7. 27 [33]KR [31]43508/2000

[71] 申请人 三星电子株式会社

地址 韩国京畿道

[72]发明人 金东奎 金相洙 李相郁

[74]专利代理机构 柳沈知识产权律师事务所

代理人 陶风波

权利要求书3页 说明书9页 附图页数10页

〔54〕发明名称 液晶显示器

[57] 摘要

一种液晶显示器包括绝缘基板、成型在该基板上以确定像素区或总体上确定显示区的栅和数据线。栅信号互连线成型在基板的角落部分显示区以外以传送栅极电信号，并配置有栅信号互连线和连接在栅信号互连线两端的第一和第二栅信号互连延迟器。栅绝缘层和保护层进一步成型在该基板上，并配置有显露第一和第二栅信号互连延迟器的第一和第二接触孔。栅和数据信号传送膜附着在该基板上，并配置有第一和第二栅信号引线以及第一和第二栅信号线路。第一和第二栅信号引线通过第一和第二接触孔与第一和第二栅信号互连延迟器相连。第一或第二栅信号引线至少在引线长度方向上完全覆盖第一或第二接触孔。

# 权 利 要 求 书

## 1. 一种液晶显示器，包括：

5 绝缘基板，具有：多个栅线；交叉在栅线上以确定象素区的多个数据线；栅信号互连线系统，具有栅信号互连线以及连接在栅信号互连线两端以延迟栅极电信号到栅线的第一和第二栅信号互连延迟器；以及带有显露第一和第二栅信号互连延迟器的第一和第二接触孔的绝缘层；

10 栅信号传送膜，它附着在基板上，且每一个均在其上安装有栅驱动集成电路以接收栅极电信号并将栅信号发送至栅线，每个栅晶体管膜具有第一栅信号线路，以及通过第一接触孔与第一栅信号互连延迟器连接的第一栅信号引线；以及

信号传送膜，它附着在基板上，具有第二栅信号线路和通过第二接触孔与第二栅信号互连延迟器相连的第二栅信号引线；

15 其中，第一或第二栅信号引线至少在引线的长度方向上完全覆盖第一或第二接触孔。

2. 如权利要求 1 所述的液晶显示器，其特征在于，还包括成型在象素区绝缘层上的象素电极；

20 3. 如权利要求 2 所述的液晶显示器，其特征在于，还包括第一和第二辅助栅信号互连延迟器，它成型在与象素电极相同的平面上同时覆盖了第一和第二接触孔，第一和第二辅助栅信号互连延迟器分别位于第一和第二栅信号互连延迟器之间和第一和第二栅信号引线之间。

4. 如权利要求 1 所述的液晶显示器，其特征在于，所述绝缘层包括覆盖栅线的栅绝缘层和覆盖位于栅绝缘层之上的数据线的保护层。

25 5. 如权利要求 1 所述的液晶显示器，其特征在于，所述第一或第二栅信号引线在长度方向上完全覆盖每个接触孔的至少一侧。

6. 如权利要求 4 所述的液晶显示器，其特征在于，所述栅信号互连线系统成型在与栅线相同的平面上，且第一和第二接触孔成型在栅绝缘层和保护层上。

30 7. 如权利要求 4 所述的液晶显示器，其特征在于，所述栅信号互连线系统成型在与数据线相同的平面上，且第一和第二接触孔仅成型在保护层上。

8. 如权利要求 3 所述的液晶显示器，其特征在于，所述栅信号互连线系统包括成型在与栅线相同平面上的第一栅信号互连线，以及成型在与数据线相同平面上的第二栅信号互连线。

5 9. 如权利要求 8 所述的液晶显示器，其特征在于，所述第一和第二栅信号互连线经由第一和第二辅助栅信号互连延迟器而相互连接。

10. 如权利要求 1 所述的液晶显示器，其特征在于，所述信号传送膜是数据信号膜，每个膜均安装在数据驱动集成电路上以接收数据电信号和发送数据信号给数据线。

10 11. 如权利要求 10 所述的液晶显示器，其特征在于，还包括连接在数据传送膜上以发送栅电信号和数据电信号给栅驱动集成电路和数据驱动集成电路的印刷电路板。

12. 一种液晶显示器，包括：

15 具有一系列栅线的绝缘基板、交叉覆盖栅线以确定象素区的多个数据线、具有栅信号互连线和成型在该栅信号互连线两端的第一及第二栅信号互连延迟器的栅信号互连线系统、以及具有显露第一和第二栅信号互连延迟器的第一和第二接触孔的绝缘层；

其中，第一和第二栅信号互连延迟器成型在与数据线相同的平面上。

13. 如权利要求 12 所述的液晶显示器，其特征在于，还包括成型在象素区绝缘层上的象素电极。

20 14. 如权利要求 13 所述的液晶显示器，其特征在于，还包括成型在与象素电极相同的平面上且同时覆盖了第一和第二接触孔的第一和第二辅助栅信号互连延迟器，分别位于第一和第二栅信号互连延迟器与第一和第二栅信号引线之间的第一和第二辅助栅信号互连延迟器。

25 15. 如权利要求 12 所述的液晶显示器，其特征在于，所述绝缘层包括覆盖栅线的栅绝缘层和包括在栅绝缘层之上的数据线的保护层。

16. 如权利要求 12 所述的液晶显示器，其特征在于，还包括栅信号传送膜，它附着在基板上，同时每个膜安装了栅驱动集成电路以接收栅电信号并发送栅信号给栅线，每个栅信号传送膜具有第一栅信号线路和通过第一接触孔而连接在第一栅信号互连延迟器上的第一栅信号引线。

30 17. 如权利要求 12 所述的液晶显示器，其特征在于，还包括数据信号传送膜，它附着在基板上，同时每个膜安装了数据驱动集成电路以接收数

据电信号并发送数据信号给数据线，数据信号传送膜具有第二栅信号线路和通过第二接触孔而连接在第二栅信号互连延迟器上的第二栅信号引线。

# 说 明 书

---

## 液晶显示器

5

### 技术领域

本发明涉及液晶显示器和制造该液晶显示器的方法，更具体地，涉及表现出优良性能特征的液晶显示器。

10

液晶显示器是当前最广泛使用的平板显示器中的一种。基本地，这种液晶显示器有两块具有产生电场的电极的玻璃基板、夹在基板间的液晶层、以及从外部贴附在基板上的极化板。当向电极施加电压时，液晶分子重排而控制光传播。

15

基板中的一个设置有用于切换施加在电极上的电压的薄膜晶体管(TFT)

阵列。

20

TFT 阵列基板具有多个分别沿水平和垂直取向的栅线(gate lines)和数据线(date lines)。数据线交叉在栅线的上方，从而确定了象素区，且象素电极成型在象素区上。TFT 控制通过数据线传送来的图象信号，该信号与通过栅线传送来的扫描信号一致，并发送图象信号给象素电极。显示区域可以通过被连接线环绕的一组象素区描绘出来。多个栅延迟器(pad)和数据延迟器成型在 TFT 阵列基板上显示区的外部，并连接在栅线和数据线上。栅延迟器和数据延迟器直接连接到外部驱动集成电路上(IC)，以接收来自外部的扫描信号和图象信号，并传送这些信号至相关信号线。

25

栅印刷电路板和数据印刷电路板设置在 TFT 阵列基板的外部以传送相关信号到其上。数据信号传送薄膜将 TFT 阵列基板和数据印刷电路板连接起来，且数据驱动 IC 安装在数据信号传送薄膜上以将电信号转变为数据信号，并将数据信号发送给数据延迟器和数据线。此外，栅信号传送薄膜将 TFT 阵列基板和栅印刷电路板连接起来，栅驱动 IC 安装在栅信号传送薄膜上以将电信号转变成栅信号，并将栅信号发送给栅延迟器和数据线。

30

栅信号延迟器和数据信号延迟器与栅延迟器和数据延迟器一一对应地排列成行，并通过使用各向异性导电膜(ACF)的热压工艺连接其上。

同时，栅印刷电路板可以略去。此时，数据印刷电路板产生栅信号，并发送该信号给栅信号传送膜。传送栅信号的栅信号线路成型在连接在数据印刷电路板上的数据信号传送薄膜上。栅信号互连线线路成型在 TFT 阵列基板上以将栅信号传送薄膜的栅信号线与栅信号线路连接起来。栅信号线路和栅信号互连线彼此相连以从数据印刷电路板上接收栅信号，并将该信号传送至栅驱动 IC。

然而，在上述结构中，为了获取良好接触特性，连接栅信号线和栅信号线路的栅信号互连线的所有衰减部分处不应当发生腐蚀，且应当以稳定的方式进行使用 ACF 的热压工艺。

10

### 发明内容

本发明的一个目的是提供具有良好接触特性的液晶显示器。

本发明的另一个目的是提供一种液晶显示器，在该液晶显示器上，栅信号互连延迟器被栅信号和数据信号传送薄膜的引线所覆盖，或接触部位15 的阶梯差异被最小化。

这些及其它目的可以通过具有绝缘基板的液晶显示器达到。该基板覆盖有多个栅线，以及多个交叉在栅线上确定出象素区的数据线。栅信号互连线系统成型在基板上。栅信号互连线系统设置有栅信号互连线，以及第一和第二栅信号互连延迟器，该延迟器连接到栅信号互连线两端以延迟到20 栅线的栅极电信号。绝缘层成型在基板上且带有显露第一和第二栅信号互连延迟器的第一和第二接触孔。栅信号传送膜附着在基板上，且每一个均在其上安装有栅驱动集成电路以接收栅极电信号并将栅信号发送至栅线。每个栅晶体管膜具有第一栅信号线路，以及通过第一接触孔与第一栅信号互连延迟器连接的第一栅信号引线。数据信号传送膜附着在基板上，具有25 第二栅信号线路和通过第二接触孔与第二栅信号互连延迟器相连的第二栅信号引线。第一或第二栅信号引线至少在引线的长度方向上完全覆盖了第一或第二接触孔。

液晶显示器还包括印刷电路板，该印刷电路板连接至数据信号传送膜以发送栅电信号和数据电信号给栅驱动集成电路和数据驱动集成电路。

30 象素电极成型在象素区域的绝缘层上。第一和第二辅助栅信号互连延迟器成型在与象素电极相同的平面上，同时覆盖了第一和第二接触孔。第

一和第二辅助栅信号互连延迟器分别位于第一和第二栅信号互连延迟器与第一和第二栅信号引线之间。

绝缘层与覆盖在栅线上的栅绝缘层，以及覆盖在栅绝缘层之上的数据线上的保护层一同成型。第一或第二栅信号引线在长度方向上完全覆盖每个接触孔的至少一侧。栅信号互连线系统可以成型在与栅线或数据线相同的平面上，且设置有与该栅线位于同一平面的第一栅信号互连线，和与该数据线位于同一平面的第二栅信号互连线。第一和第二栅信号互连线通过第一和第二辅助栅信号互连延迟器而互相连接。

10

#### 附图说明

本发明的更完全的说明及其许多伴随的优点，将通过参照随后的结合附图的详细说明而更好地被理解，附图中相同的附图标记表明相同或相似的组件，其中：

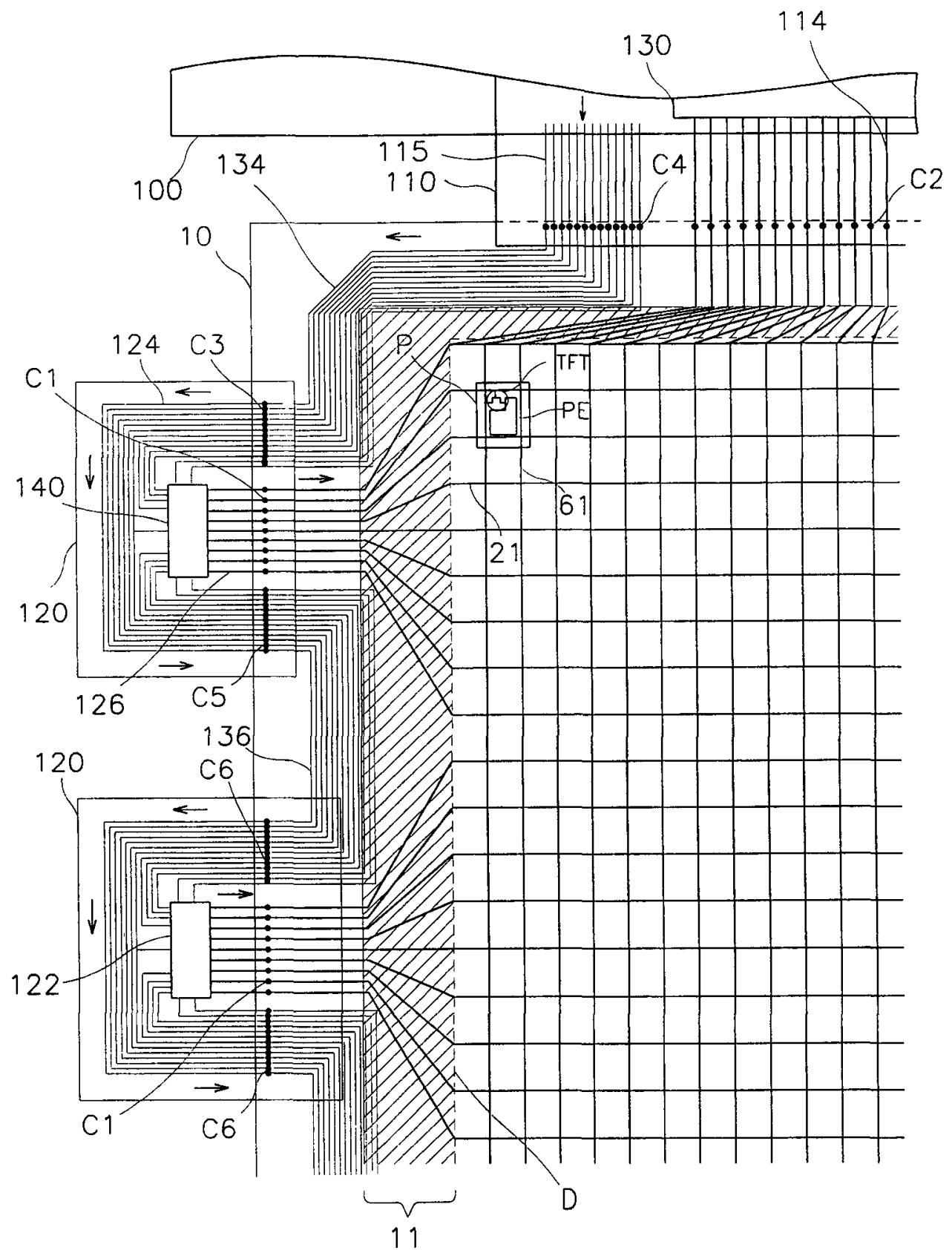

15 图 1 是本发明第一优选实施例的液晶显示器的 TFT 阵列基板的平面图；

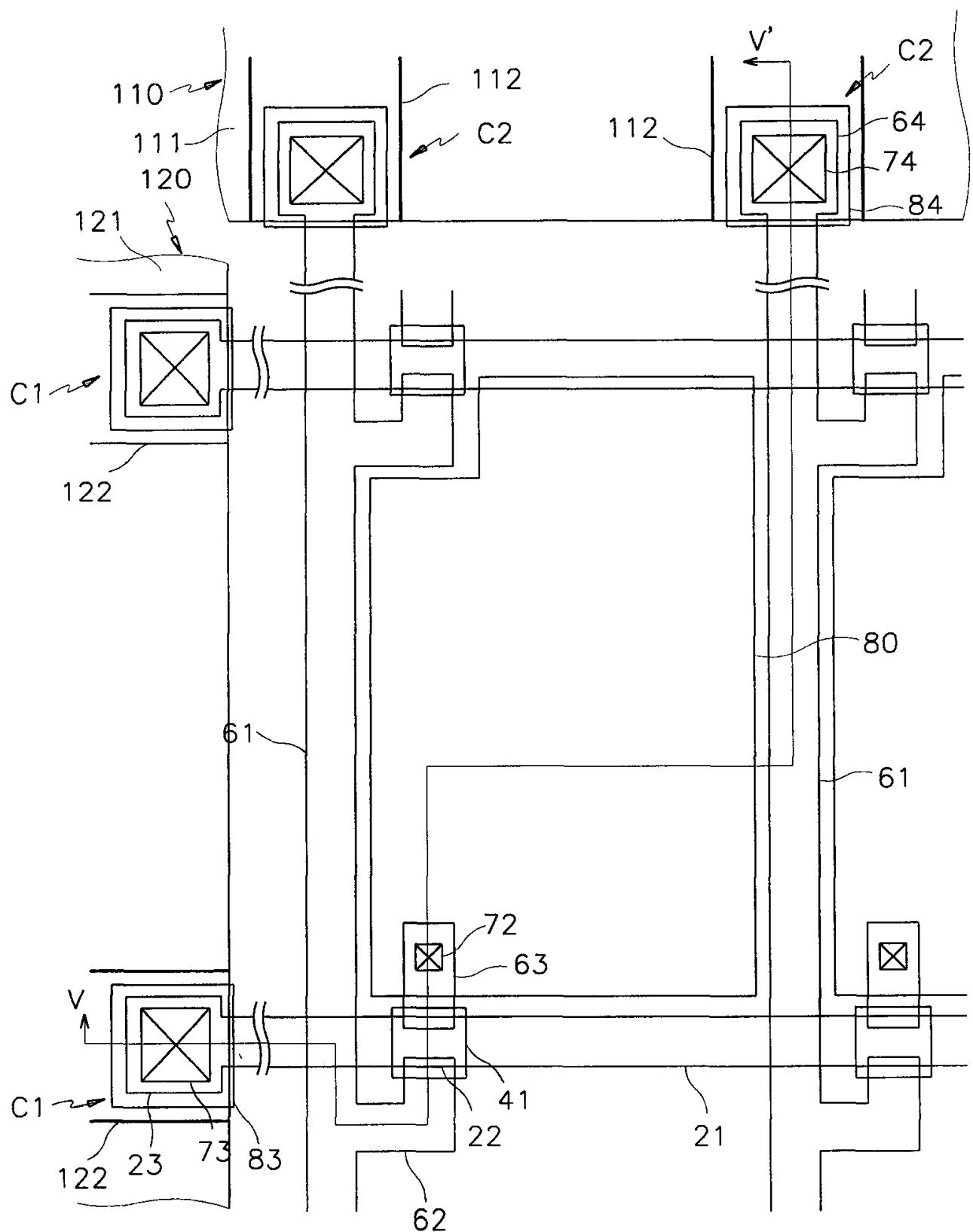

图 2 是图 1 所示 TFT 阵列基板的局部放大图，其中示出了像素区和延迟区；

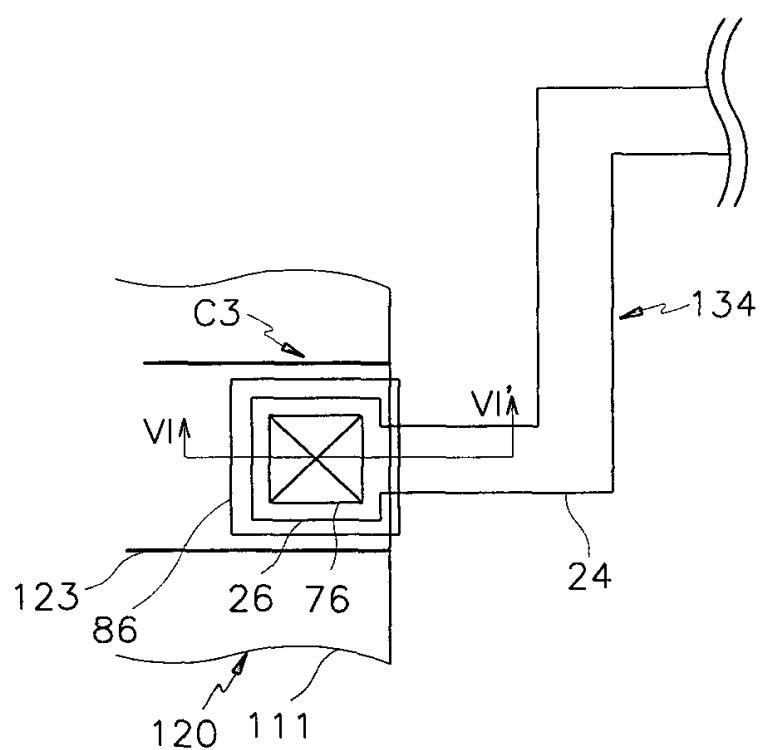

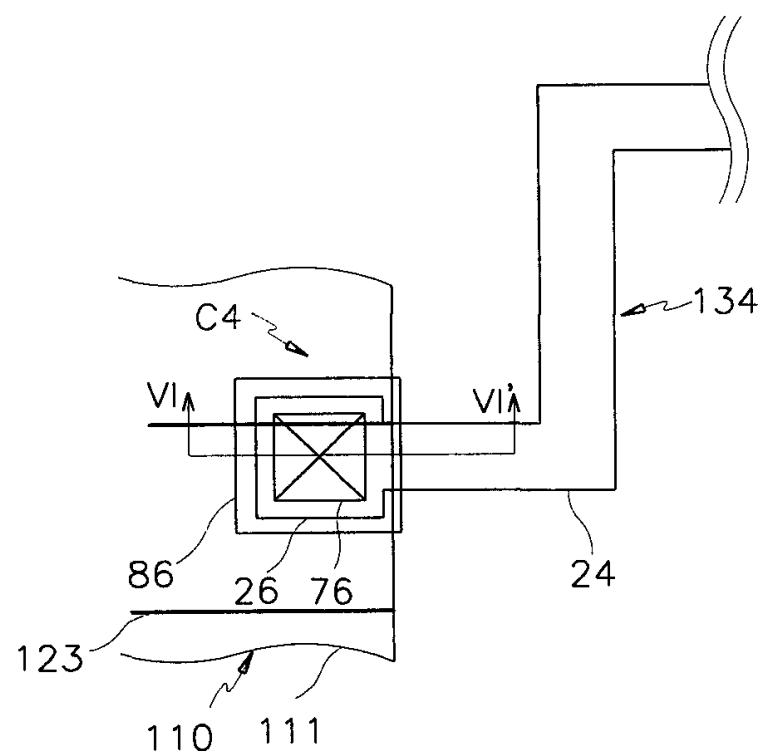

图 3 和图 4 是图 1 所示 TFT 阵列基板的局部放大图，其中明确示出了栅信号线路结构和接触或延迟器部分；

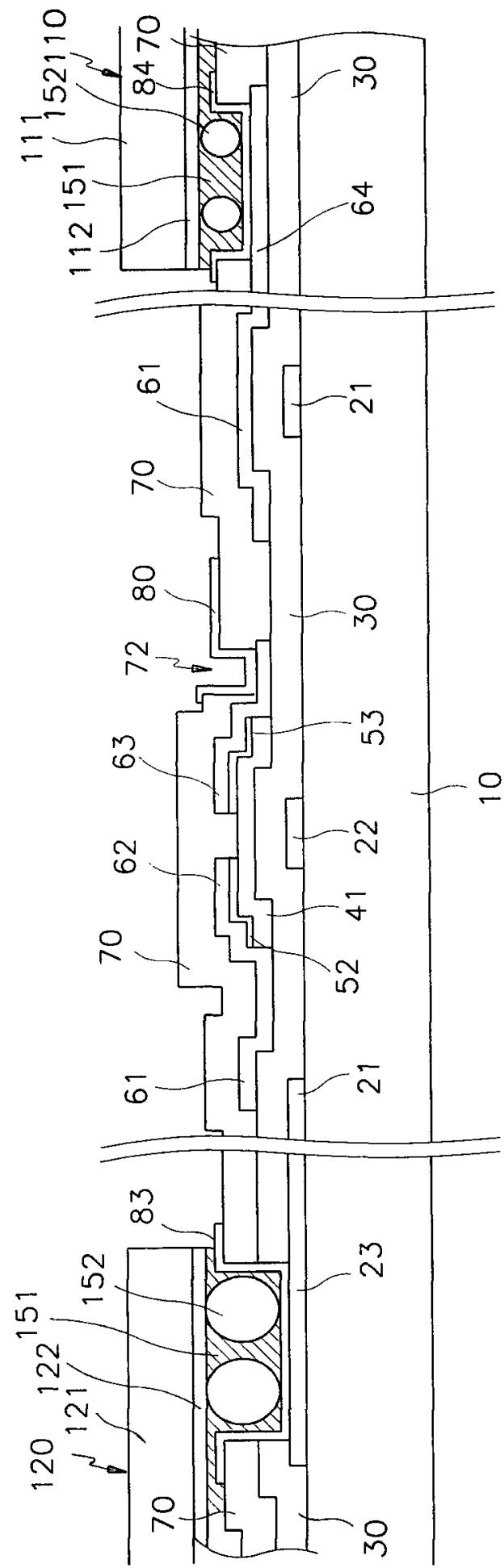

20 图 5 是沿图 2 中 V-V' 线的 TFT 阵列基板的剖视图；

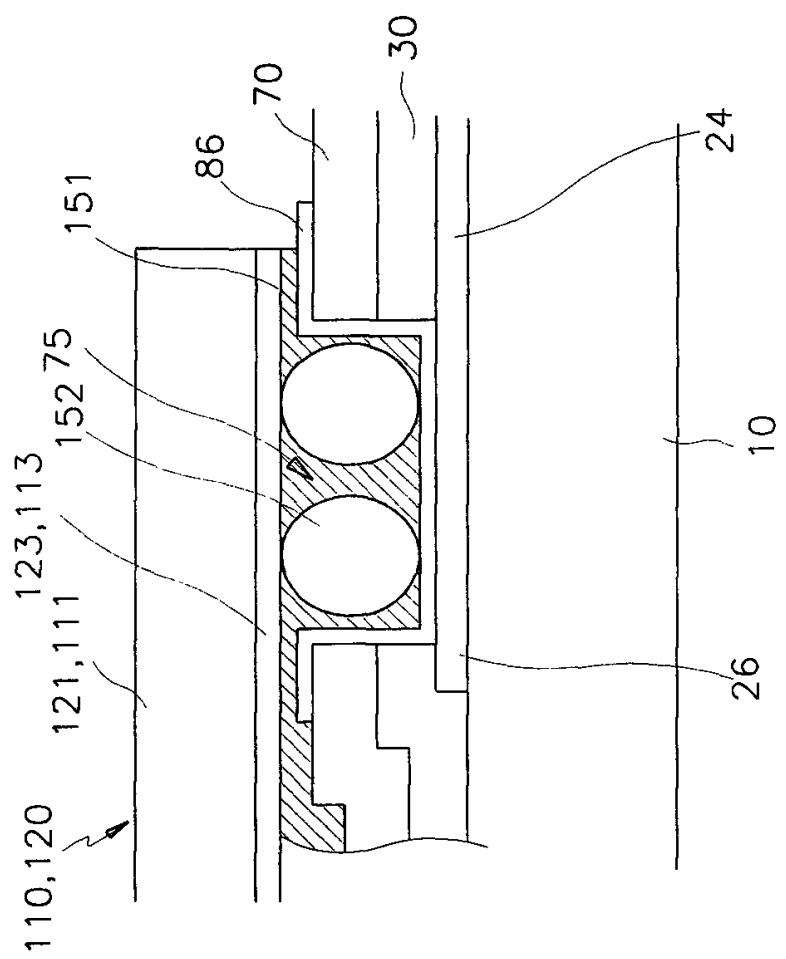

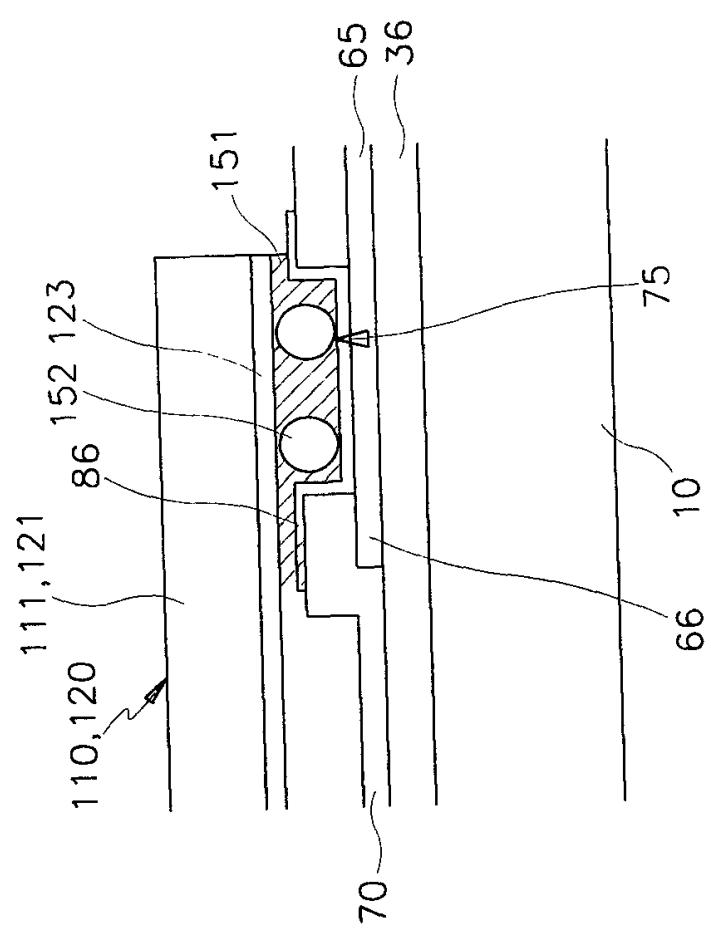

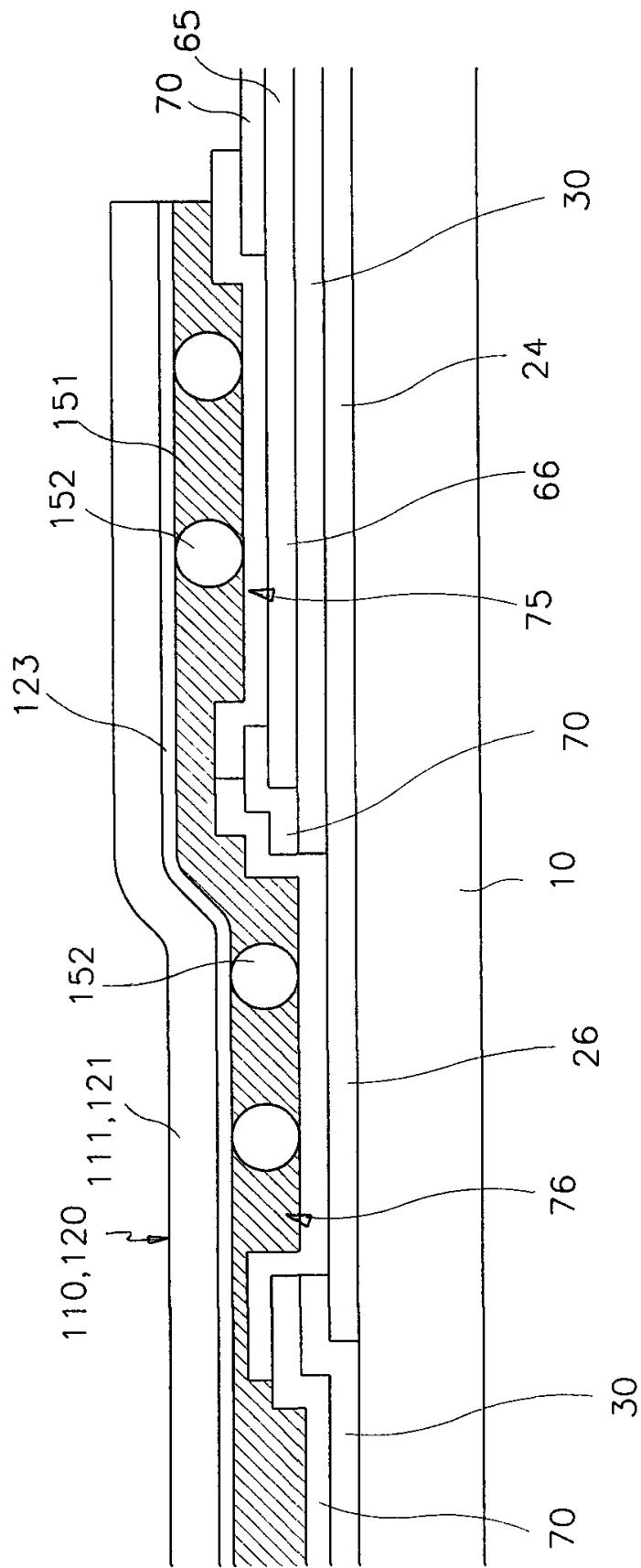

图 6 是沿图 3 或图 4 的 VI-VI' 线的 TFT 阵列基板的剖视图；

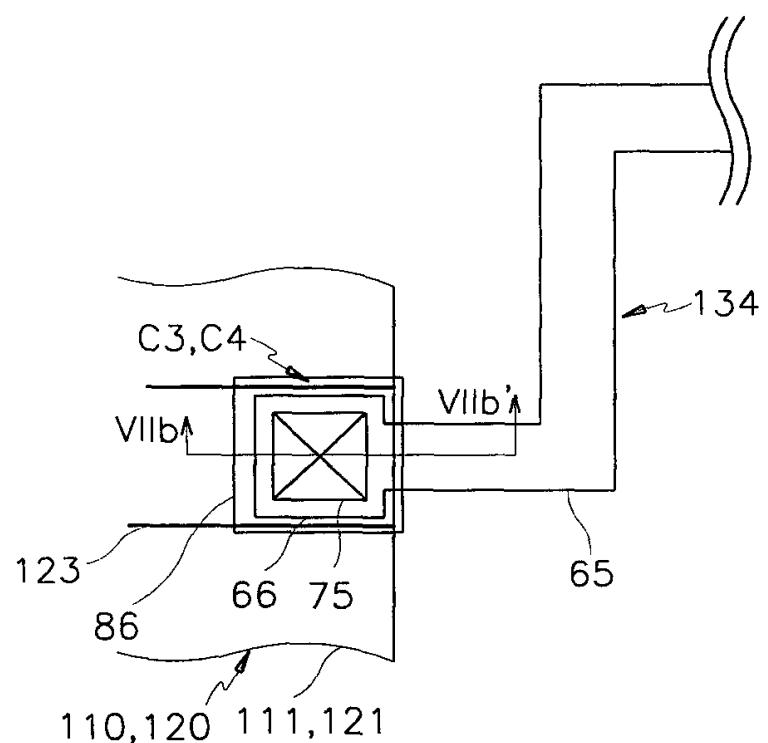

图 7A 和图 7B 是用于根据第二优选实施例的液晶显示器的 TFT 阵列基板的平面图，其中示出了栅信号互连线；以及

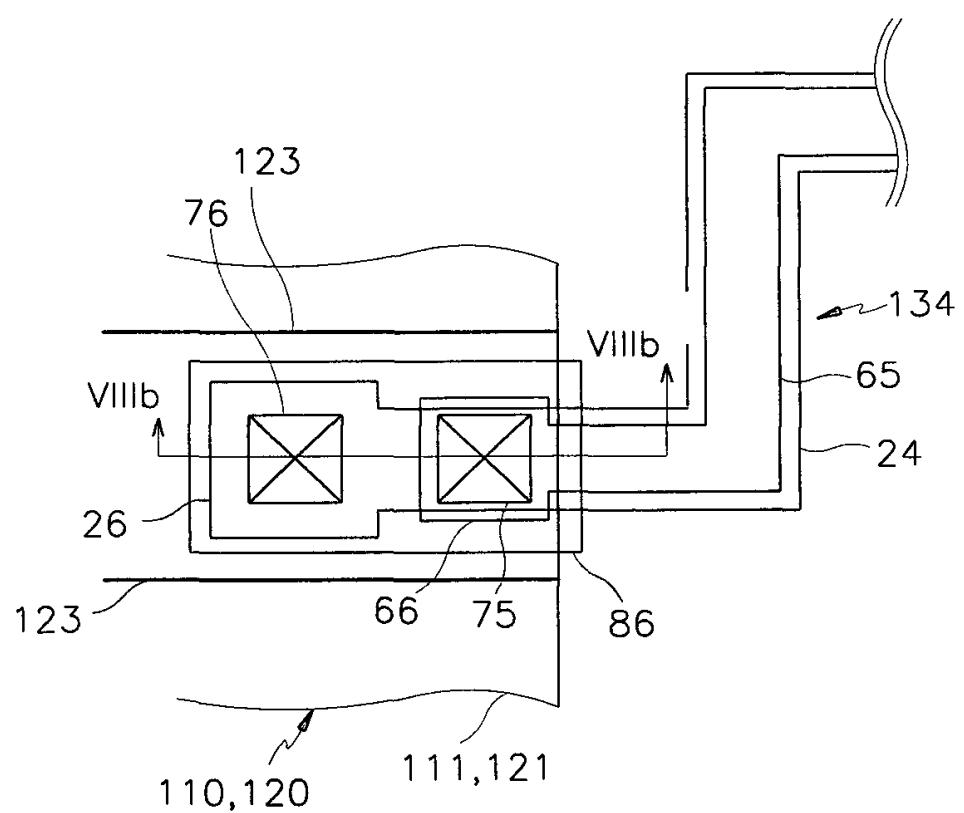

25 图 8A 和图 8B 是第三优选实施例的用于液晶显示器的 TFT 阵列基板的平面图，其中示出了栅信号互连线。

#### 具体实施方式

本发明的优选实施例将参照附图得以说明。

30 图 1 示意性示出了本发明第一优选实施例的用于液晶显示器的 TFT 阵列基板。

如图 1 所示，多个栅线 21 在水平方向上成型在绝缘基板 10 上，而多

个数据线 61 具有垂直的方向并与栅线 21 电绝缘。

数据线 61 交叉在栅线 21 的上方，因而确定了象素区 P，而象素区 P 集中形成了显示区 D。薄膜晶体管 TFT 成型在每个象素区 P 上，并与栅线 21 和数据线 61 相连。象素电极 PE 也设置在每个象素区上，并被连接到 TFT 上。黑色基体 11 成型在基板 10 上显示区域 D 之外，以防止光泄露。

印刷电路板 100 在垂直方向上位于基板 10 的外侧，以输出栅电信号和数据电信号以驱动装置。印刷电路板 100 和基板 10 通过数据信号传送膜 110 相互电连接。数据驱动 IC 130 安装在每个数据信号传送膜 110 上以提供图象信号。数据信号传送膜 110 也具有多个数据信号线 114，以及多个第一栅信号线路 115。数据信号线 114 连接到数据线 61 上的接触部分 C2 上，以延迟来自数据驱动 IC 130 上的图象信号到数据线 61。

在垂直方向上，多个栅信号传送膜 120 排列在基板 10 的左侧并在垂直方向上电连接在其上。栅驱动 IC 140 安装在每个栅信号传送膜 120 上，以发送扫描信号或栅信号。每个栅信号传送膜 120 也包括有多个第二栅信号线路 124 和连接在栅线 21 的连接部或接触部 C1 上以延迟发送自栅驱动 IC 140 的栅信号到栅线 21 上的栅信号线 126。

栅信号互连线 134 排列在基板 10 的左顶角部上显示区 D 之外。栅信号互连线 134 将数据信号传送膜 110 上的第一栅信号线路 115 和栅信号传送膜 120 上的第二栅信号线路 124 在接触部分 C4 和 C3 相连。

第三栅信号线路 136 成型在基板 10 的左侧显示区 D 之外。第三栅信号线路 136 在接触部分或延迟器部分 C5 和 C6 处连接近邻的栅信号传送膜 120 上的第二栅信号线路 124。

基板 10 和该多个信号线或线路 114、115、61、134、124、126 和 136 在延迟器部分或接触部分 C1 到 C6 具有延迟器，且通过使用各向异性导电膜的延迟器而相互连接。

在上述结构的液晶显示器中，发送自印刷电路板 100 的栅极电信号经由第一栅信号线路 115 而被传送至栅信号互连线 134。该栅极电信号于是经由第二栅信号线路 124 而被发送至栅驱动 IC 140，或传送至第三栅信号线路 136。然后，栅极电信号在栅驱动 IC 140 处被部分转变成栅信号，且栅信号通过栅信号线 126 发送给栅线 21。这就是，该发送自印刷电路板 100 的栅极电信号经由第一到第三栅信号线路 115、124 和 136 和栅信号互连线

路 134 而被部分地发送给栅线 21。

同时，除了数据信号传送薄膜 110 外，还可以设置分离的信号传送膜以将印刷电路板 100 连接到基板 10 上。在此结构中，第一栅信号线路 115 将成型在分离的信号传送膜上。

5 现在，将参照图 2 至图 6 对第一优选实施例的 TFT 阵列基板的主结构进行详细描述。

图 2 是图 1 所示 TFT 阵列基板的局部放大图，其中明确示出了像素区 P 和延迟器部分 C1 和 C2。图 3 和图 4 是图 1 所示 TFT 阵列基板的局部放大图，其中明确示出了栅信号线路结构和接触部分或延迟器部分 C3 和 C4。10 图 5 是沿图 2 中 V-V' 线截取的 TFT 阵列基板的剖视图，而图 6 是沿图 3 或图 4 中 VI-VI' 线截取的 TFT 阵列基板的剖视图。因为接触部 C3 和 C4 具有同样的结构，所以只有一个接触部显示在图 6 中。

像素区 P、接触部分 C1 至 C4 和栅信号互连线 134 将首先说明，而不对第三栅信号线路 136 和接触部分 C5 和 C6 详细说明，因为它们具有与 15 栅信号互连线 134 和接触部分 C3 和 C4 一样的结构。

如图 2 所示，栅线系统成型在绝缘基板 10 上，位于与栅信号互连线 134 相同的平面，用金属或导电材料如 Al 或 Al 合金、Mo 或 MoW 合金、Cr 和 Ta 等制造。

20 栅线系统包括多个栅线 21、栅线 21 的栅极 22 部分和栅延迟器 23，栅延迟器 23 连接在栅线 21 的端部以接收来自外部的扫描信号并将其传送至栅线 21。每条栅信号互连线 134 具有栅信号互连线 24 和栅信号互连延迟器 26，栅信号互连延迟器 26 连接在栅信号互连线 24 两端。

25 栅线系统和栅信号互连线 134 可以具有单层结构或多层结构。在双层结构的情形下，一层用具有低电阻的材料制成，而另一层用与其它材料具有良好接触特性的材料制成。例如，双层结构可以用铬基层和铝合金基层，或钼或钼基层和铝基层制造。

栅绝缘层 30 用氮化硅成型在基板 10 上，并覆盖住栅线系统和栅信号互连线 134。

30 半导体图案 41 用非晶硅成型在栅绝缘层 30 上且位于每个栅极 22 上方。在栅极 22 周围，欧姆接触图案 52 和 53 用掺诸如磷的 n 型杂质的非晶硅成型在半导体图案 41 上，且相互隔离。

数据线系统成型在欧姆接触图案 52 和 53，以及栅绝缘层 30 上，它用金属或导电材料，诸如 Al 或 Al 合金、Mo 或 MoW 合金、Cr 和 Ta 等制造。

数据线系统包括多个数据线 61、从数据线 61 上分枝出来的源电极 62、与源电极 62 分离的漏极 63(栅极 21 位于此二者之间)，以及连接到数据线 5 61 上以接收来自外部的图象信号并将它们传送至数据线 61 的数据延迟器 64。

数据线系统可以具有单层结构或多层结构。在双层结构的情形下，一层用具有低电阻的材料制成，而另一层用与其它材料具有良好接触特性的材料制成。

10 每个 TFT 形成有栅极 22、半导体图案 41 及源极 62 和漏极 63。

保护层 70 成型在数据线系统和通过数据线系统暴露出来的栅绝缘层 30 上，它用氮化硅或有机绝缘材料制造。保护层 70 在接触部分 C1 具有显露与栅绝缘层 30 在一起的栅延迟器 23 的接触孔 73，在接触部分 C2 具有显露数据延迟器 64 的接触孔 74，以及在象素区 P 显露漏极 63 的接触孔 72。15 此外，保护层 70 在接触部分 C3 和 C4 还具有显露与栅绝缘层 30 在一起的栅信号互连延迟器 26 的接触孔 76。

象素电极 80、辅助栅延迟器 83、辅助数据延迟器 84 和辅助栅信号互连延迟器 86 成型在保护层 70 上，它用诸如铟锡氧化物(ITO)或铟锌氧化物(IZO)的透明导电材料制成。

20 象素电极 80 通过接触孔 72 连接在漏极 63 上以接收图象信号。辅助栅和数据延迟器 83 和 84 通过接触孔 73 和 74 连接到栅和数据延迟器 64 上以保护它们，并提高其对外电路的附着力。

辅助栅信号互连延迟器 86 通过接触孔 76 与栅信号互连延迟器 26 相连。

25 同时，栅信号传送膜 120 具有覆盖有绝缘树脂层 121 的栅信号引线 122。每个栅信号引线 122 通过具有导电颗粒 152 和粘结剂 151 的各向异性导电膜而物理 - 电连接至辅助栅延迟器 83 上。栅信号引线 122 在长度方向和宽度方向上完全覆盖了接触孔 73。栅信号引线 122 可以完全覆盖、也可以不完全覆盖接触孔 73 或辅助栅延迟器 83。

30 数据信号传送膜 110 具有覆盖有绝缘树脂层 111 的数据信号引线 112。数据信号引线 122 通过具有导电颗粒 152 和粘结剂 151 的各向异性导电膜

而物理 - 电连接至辅助数据延迟器 84 上。数据信号引线 112 可以完全覆盖、也可以不完全覆盖接触孔 74 或辅助栅延迟器 84。

在位于接触部分 C3 和 C4 的栅信号传送膜 110 和数据信号传送膜 120 里，栅信号互连引线 123 成型在绝缘树脂层 111 和 121 下面。栅信号互连引线 123 经由具有导电颗粒 152 和粘结剂 151 的各向异性导电膜而连接至辅助栅信号互连延迟器 86 上，因而将第一栅信号线路 115 和第二栅信号线路 124 电连接。栅信号互连引线 123 在长度方向和宽度方向上完全覆盖保护层 70 的接触孔 76 和栅绝缘层 30。如图 4 所示，栅信号互连引线 123 至少覆盖接触孔 76 或辅助栅信号延迟器 86 的一个长度方向侧。栅信号互连引线 123 可以完全覆盖、也可以不完全覆盖辅助栅信号延迟器 86。

在上述结构中，栅信号互连引线 123 或栅信号传送膜 110 和数据信号传送膜 120 的各向异性导电膜完全覆盖辅助栅信号互连延迟器 86 上的接触孔 76，于是腐蚀不会在延迟器部分 C3 和 C4 发生，而在这些部位附着可被加强。

为了进一步提高接触部分 C3 和 C4 处的接触特性，可以控制的是接触孔 86 处的阶梯差异应当被最小化。为了此目的，栅信号互连线 134 的互连线可以在与数据线系统相同的平面成型。

图 7A 和图 7B 示出了本发明第二优选实施例的 TFT 阵列基板的线路结构。

在该优选实施例中，TFT 阵列基板的其它组件和结构与涉及第一优选实施例的那些组件和结构是一样的，不同之处是，栅信号互连线 134 中的栅信号互连线 65 和栅信号互连延迟器 66 设置在与栅线系统相同的平面上位于栅绝缘层 30 上，且显露栅信号互连延迟器 66 的接触孔 75 仅成型在保护层 70 上。接触孔 75 优选地成型为小于栅信号互连延迟器 66。

图 8A 和图 8B 示出了本发明第三优选实施例的 TFT 阵列基板的线路结构。在该优选实施例中，除了下述特征以外，TFT 阵列基板的其它组件和结构与那些涉及第一优选实施例的组件和结构相同。

如图 8A 和图 8B 所示，每个栅信号互连线 134 具有双结构的栅信号互连线 24 和 65，它们具有分别与栅线系统和数据线系统位于同一平面的栅信号互连延迟器 26 和 66。栅绝缘层 30 和保护层 70 共同拥有显露栅信号互连延迟器 26 的接触孔 76，保护层 70 仅具有显露栅信号互连延迟器 66 的接

触孔 75。辅助栅信号互连延迟器 86 通过接触孔 75 和 76 连接至栅信号互连延迟器 26 和 66 上，因而电物理互连栅信号互连线 24 和 65。在该结构中，由阶梯差异导致的接触失效被减少，同时弥补了栅信号互连线 24 和 65 的短路并最小化线路电阻。重叠的栅信号互连延迟器 66 可以延伸至下面的栅信号互连延迟器 66。此时，可以获得前述效果，并且还可以防止湿气被引入延迟器部分 C3 和 C4 中。

基于该双结构延迟器 26 和 66 的延迟器部分 C3 和 C4 的增强可以以同样的方式应用到其它延迟器部分 C1、C2、C5 和 C6 上。图 7A 到图 8B 所示的结构可以选择性地应用到该多个栅信号互连线 134 上。

现在，将参照图 2 到图 8B 对一种 TFT 阵列基板的制造方法进行说明。

导电层成型在绝缘基板 10 上，并被构图以形成栅线系统 21、22 和 23，以及栅信号互连线系统 24 和 26。然后，栅绝缘层 30、非晶硅基层和掺杂非晶硅基层顺序沉积在基板 10 上。非晶硅基层和掺杂非晶硅基层被构图因而在每个栅极 22 上形成半导体图案 41 和欧姆接触图案 51。此时，在栅信号互连线 24 上方，半导体图案可以留下。然后，导电层被沉积，且被构图以形成数据线系统 61 至 64。此时，如图 7A 至图 8B 所示，栅信号互连线系统 65 和 66 可以一起成型在与数据线系统 61 至 64 相同的平面上。暴露在源极 62 和漏极 63 之间的欧姆接触图案 51 的部分被除去，因而将其分隔成两个图案 52 和 53，同时显露半导体图案 41。保护层 70 沉积在基板 10 上，并被构图以形成接触孔 72 至 76。然后，沉积透明导电材料，并构图以形成像素电极 80、辅助栅延迟器 83、辅助数据延迟器 84 和辅助栅信号互连延迟器 86。

尽管半导体图案 41 和数据线系统 61 至 64 通过不同的工艺步骤成型，但是它们可以通过一个刻蚀过程成型。在该工艺中，在光传输中部分变异的掩模被用于形成具有不同厚度的光致抗蚀剂(photoresist)图案。使用上述掩模作为刻蚀掩模，半导体层 41 和数据线系统 61 至 64 被一起构图。在构图工艺中，中等厚度的光致抗蚀剂图案设置在位于源极 62 和漏极 63 之间的沟道部分上方，而具有大厚度的光致抗蚀剂图案设置在数据线系统 61 至 64 成型的区域上方。在得到的结构中，欧姆接触图案和半导体图案成型在数据线系统 61 至 64 和栅信号互连线系统 65 和 66 之下。欧姆接触图案 52 和 53 沿数据线系统 61 至 64 和栅信号互连线系统 65 和 66 的形状成型。半

导体图案 41 也沿数据线系统 61 至 64 和栅信号互连线系统 65 和 66 的形状成型，除了源极 62 和漏极 63 之间的沟道部分以外。

如上所述，接触部分由引线覆盖，且接触部分的阶梯差异被最小化。栅信号互连线系统设置成具有双线结构。这防止了线路线的短路并保持无 5 湿气状态，因而获得了良好接触特性。

尽管本发明参照优选实施例进行了描述，但本领域的技术人员将意识到，在不脱离所附权利要求所提出的精神和范围的情况下，可以对其进行各种改造和替换。

# 说 明 书 附 图

图 1

图 2

图 3

图 4

图 5

图 6

图 7a

图 7b

图 8a

图 8b

|                |                                                                         |         |            |

|----------------|-------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                                                   |         |            |

| 公开(公告)号        | <a href="#">CN1335534A</a>                                              | 公开(公告)日 | 2002-02-13 |

| 申请号            | CN01124355.4                                                            | 申请日     | 2001-07-27 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                |         |            |

| 当前申请(专利权)人(译)  | 三星电子株式会社                                                                |         |            |

| [标]发明人         | 金东奎<br>金相洙<br>李相郁                                                       |         |            |

| 发明人            | 金东奎<br>金相洙<br>李相郁                                                       |         |            |

| IPC分类号         | G02F1/1333 G02F1/13 G02F1/1343 G02F1/1345 G02F1/136 G02F1/1362 G09F9/30 |         |            |

| CPC分类号         | G02F1/13452 G02F1/136286 G02F1/13458 G02F1/1345                         |         |            |

| 优先权            | 1020000043508 2000-07-27 KR                                             |         |            |

| 其他公开文献         | CN1200311C                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">SIPO</a>                          |         |            |

## 摘要(译)

一种液晶显示器包括绝缘基板、成型在该基板上以确定像素区或总体上确定显示区的栅和数据线。栅信号互连线成型在基板的角落部分显示区以外以传送栅极电信号，并配置有栅信号互连线和连接在栅信号互连线两端的第一和第二栅信号互连延迟器。栅绝缘层和保护层进一步成型在该基板上，并配置有显露第一和第二栅信号互连延迟器的第一和第二接触孔。栅和数据信号传送膜附着在该基板上，并配置有第一和第二栅信号引线以及第一和第二栅信号线路。第一和第二栅信号引线通过第一和第二接触孔与第一和第二栅信号互连延迟器相连。第一或第二栅信号引线至少在引线长度方向上完全覆盖第一或第二接触孔。