## [12] 发明专利说明书

专利号 ZL 02120490. X

[45] 授权公告日 2006 年 10 月 18 日

[11] 授权公告号 CN 1280665C

[22] 申请日 2002.5.21 [21] 申请号 02120490. X

[30] 优先权

[32] 2001.5.29 [33] KR [31] P-2001-29811

[71] 专利权人 LG. 菲利浦 LCD 株式会社

地址 韩国首尔

[72] 发明人 蔡基成 李载钧 黄龙燮

审查员 韩 旭

[74] 专利代理机构 北京律诚同业知识产权代理有限公司

代理人 徐金国 陈 红

权利要求书 5 页 说明书 18 页 附图 20 页

## [54] 发明名称

液晶显示装置的阵列衬底及其制造方法

## [57] 摘要

本发明公开了一种液晶显示装置的阵列衬底和该阵列衬底的制造方法。所述阵列衬底包括衬底，在衬底上沿第一方向设置的栅极线，平行于栅极线且与栅极线彼此相隔一定距离的公用线，其中公用线用与栅极线相同的材料制作。所述阵列衬底还包括处于栅极线和公用线上的栅极绝缘层，处于栅极绝缘层上的半导体层，和用透明导电材料制成的像素电极，所述像素电极包括漏极区段。漏极区段与半导体层重叠而且透明材料的源极与漏极区段彼此相隔一定距离。钝化层包括处于像素电极和源极之上的第一接触孔和开口部分，其中第一接触孔暴露源极而开口部分暴露像素电极。在钝化层上沿第二方向设置数据线，数据线通过第一接触孔与源极相连并与栅极线交叉。

1. 一种液晶显示装置的阵列衬底，包括：

一衬底；

5 一在衬底上沿第一方向设置的栅极线；

一平行于栅极线且与栅极线彼此相隔一定距离的公用线，所述公用线用与栅极线相同的材料制作；

一处于栅极线和公用线上的栅极绝缘层；

一处于栅极绝缘层上的半导体层；

10 一用透明导电材料制成的像素电极，所述像素电极包括漏极区段，所述漏极区段与半导体层重叠；

一与漏极区段彼此相隔一定距离且用透明导电材料制成的源极；

一在像素电极和源极之上带有第一接触孔和开口部分的钝化层，其中第一接触孔暴露源极而开口部分暴露像素电极；和

15 一在钝化层上沿第二方向设置的数据线，数据线通过第一接触孔与源极相连并与栅极线交叉。

2. 根据权利要求 1 所述的阵列衬底，其中半导体层包括非晶硅有源层、掺杂非晶硅的欧姆接触层和钛或铬的金属层，并且在源极和漏极区段之间暴露出一部分有源层。

20 3. 根据权利要求 1 所述的阵列衬底，进一步包括处于栅极线端部的栅极连接件和栅极垫片，

栅极连接件用与数据线相同的材料制成而且与栅极线和栅极垫片重叠，

栅极线通过栅极绝缘层和钝化层上的第二接触孔与栅极连接件相连，

25 和

栅极垫片用与象素电极相同的材料制成并且通过钝化层上的第三接触孔与栅极连接件相连。

4. 根据权利要求 3 所述的阵列衬底，其中栅极连接件比栅极垫片宽。

5. 根据权利要求 1 所述的阵列衬底，进一步包括处于数据线端部的数

5 据垫片，数据垫片与数据线重叠并且用与象素电极相同的材料制成，而且通过第四接触孔与数据线相连。

6. 根据权利要求 5 所述的阵列衬底，其中重叠的数据线比数据垫片宽。

7. 根据权利要求 1 所述的阵列衬底，其中所述象素电极与栅极线重叠。

8. 根据权利要求 1 所述的阵列衬底，其中第一接触孔设置在数据线之

10 下。

9. 根据权利要求 1 所述的阵列衬底，其中透明材料是氧化铟锡。

10. 根据权利要求 1 所述的阵列衬底，其中钝化层用丙烯酸树脂制成。

11. 根据权利要求 1 所述的阵列衬底，其中还包括：

所述衬底上的公用电极，并且所述公用线与公用电极接触。

15 12. 一种液晶显示装置的阵列衬底，包括：

一衬底；

一在衬底上沿第一方向设置的栅极线，所述栅极线包括存储电极；

一处于栅极线上的栅极绝缘层；

一处于栅极绝缘层上的半导体层；

20 一用透明导电材料制成的象素电极，象素电极上带有漏极区段，漏极区段与半导体层重叠，而象素电极与栅极线重叠；

一用透明导电材料制成且与漏极区段彼此相隔一定距离的源极；

一带有第一接触孔和开口部分的钝化层，其中第一接触孔暴露源极而开口部分暴露象素电极；和

25 一在钝化层上沿第二方向设置的数据线，数据线通过第一接触孔与源

极相连并与栅极线交叉。

13. 根据权利要求 12 所述的阵列衬底，其中半导体层包括非晶硅有源层、掺杂非晶硅的欧姆接触层和钛或铬的金属层，并且在源极和漏极区段之间暴露出一部分有源层。

5 14. 根据权利要求 12 所述的阵列衬底，进一步包括处于栅极线端部的栅极连接件和栅极垫片，

栅极连接件用与数据线相同的材料制成而且与栅极线和栅极垫片重叠，

栅极线通过栅极绝缘层和钝化层上的第二接触孔与栅极连接件相连，

10 和

栅极垫片用与像素电极相同的材料制作并且通过钝化层上的第三接触孔与栅极连接件相连。

15. 根据权利要求 14 所述的阵列衬底，其中栅极连接件比栅极垫片宽。

16. 根据权利要求 12 所述的阵列衬底，进一步包括处于数据线端部的数据垫片，数据垫片与数据线重叠并且用与像素电极相同的材料制成，而且通过第四接触孔与数据线相连。

17. 根据权利要求 16 所述的阵列衬底，其中重叠的数据线比数据垫片宽。

18. 根据权利要求 12 所述的阵列衬底，其中所述像素电极与栅极线重叠。

19. 根据权利要求 12 所述的阵列衬底，其中第一接触孔设置在数据线之下。

20. 根据权利要求 12 所述的阵列衬底，其中透明材料是氧化铟锡。

21. 根据权利要求 12 所述的阵列衬底，其中钝化层用丙烯酸树脂制成。

25 22. 一种制造液晶显示装置阵列衬底的方法，包括：

在衬底上形成沿第一方向设置的栅极线和平行于栅极线的公用线，其中栅极线和公用线彼此相隔一定距离；

在栅极线和公用线上形成栅极绝缘层；

在栅极绝缘层上形成半导体层；

5 形成透明导电材料的源极和像素电极，所述像素电极包括漏极区段，漏极区段与半导体层重叠而源极与漏极区段彼此相隔一定距离；

形成带有第一接触孔和开口部分的钝化层，其中第一接触孔暴露源极，开口部分暴露像素电极；和

10 形成在钝化层上沿第二方向设置的数据线，所述数据线通过第一接触孔与源极相连并与栅极线交叉。

23. 根据权利要求 22 所述的方法，其中通过按顺序形成非晶硅有源层、掺杂非晶硅的欧姆接触层和钛或铬的金属层而完成半导体层的制作，而且在源极和漏极区段之间暴露出一部分有源层。

24. 根据权利要求 22 所述的方法，进一步包括在栅极线的端部形成栅极连接件和栅极垫片，

15 栅极连接件用与数据线相同的材料制成而且与栅极线和栅极垫片重叠，

栅极线通过栅极绝缘层和钝化层上的第二接触孔与栅极连接件相连，和

20 栅极垫片用与像素电极相同的材料制成并且通过钝化层上的第三接触孔与栅极连接件相连。

25. 根据权利要求 24 所述的方法，其中栅极连接件比栅极垫片宽。

26. 根据权利要求 22 所述的方法，进一步包括在数据线的端部形成数据垫片，数据垫片与数据线重叠并且用与像素电极相同的材料制成，而且通过第四接触孔与数据线相连。

27. 根据权利要求 26 所述的方法，其中重叠的数据线比数据垫片宽。

28. 根据权利要求 22 所述的方法，其中所述像素电极与栅极线重叠。

29. 根据权利要求 22 所述的方法，其中第一接触孔设置在数据线之下。

30. 根据权利要求 22 所述的方法，其中透明材料是氧化铟锡。

5 31. 根据权利要求 22 所述的方法，其中钝化层用丙烯酸树脂制成。

32. 根据权利要求 22 所述的方法，其中还包括：

在所述衬底上形成公用电极；并且所述公用线与该公用电极接触。

33. 一种制造液晶显示装置阵列衬底的方法，包括：

在衬底上形成沿第一方向设置的栅极线，所述栅极线包括存储电极；

10 在栅极线上形成栅极绝缘层；

在栅极绝缘层上形成半导体层；

形成透明导电材料的源极和像素电极，所述像素电极包括漏极区段，

源极与漏极区段彼此相隔一定距离，漏极区段与半导体层重叠而像素电极与栅极线重叠；

15 形成带有第一接触孔和开口部分的钝化层，其中第一接触孔暴露源极，

开口部分暴露像素电极；和

在钝化层上形成沿第二方向设置的数据线，所述数据线通过第一接触孔与源极相连并与栅极线交叉。

## 液晶显示装置的阵列衬底及其制造方法

5 按照 35U.S.C.§119 (a) 的规定，本非临时申请要求 2001 年 5 月 29 日

在韩国申请的第 2001-29811 号专利申请的优先权，该申请的全部内容在

本申请中以引用的形式加以结合。

### 技术领域

10 本发明涉及一种液晶显示装置，更确切地说，涉及一种具有高存储电

容量和高孔径比的阵列衬底及其制造方法。

### 背景技术

15 传统的液晶显示 (LCD) 装置利用的是液晶分子的光学各向异性和偏

振特性。液晶分子具有明确的成一条直线的取向序，这使得液晶分子为细

长形状。通过向液晶分子施加电场可以控制液晶分子的准直方向。换句话说

说，当改变电场的准直方向时，液晶分子的准直方向也发生变化。由于校

准的液晶分子具有光学各向异性而使入射光朝着液晶分子的取向方向折

射，由此可以显示多个图象。

20 不同类型的公知 LCDs，有源阵列 LCDs (AM-LCD) 由于其在显示

运动图象时具有高分辨率和优越性而成为广泛研究和开发的课题，这些

LCD 由薄膜晶体管和排列成阵列形式的像素电极构成。

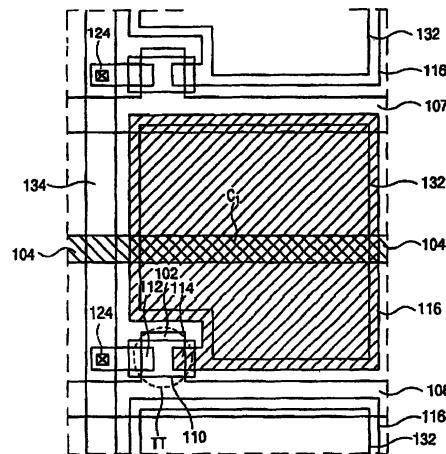

图 1 是局部地表示背景技术中 LCD 装置液晶显示板的示意性剖面图。

在图 1 中，液晶板 20 包括称作滤色器衬底的上衬底 2，和称作阵列衬底的

25 下衬底 1。上衬底 2 和下衬底 1 按照彼此相互面对和隔开一定距离设置，而

且在上下衬底之间设有液晶层 10。在上衬底 2 的内表面上以重叠的形式形成防止光漏的黑底 9 和选择性透光的滤色片 8。在黑底 9 和滤色片 8 上形成向液晶层 10 施加电压的公用电极 12。另一方面，在下衬底 1 的上部形成与上衬底 2 的公用电极 12 一起向液晶层 10 施加电压的像素电极 14。在下衬底 1 上形成控制施加在像素电极 14 上电压开关的薄膜晶体管 (TFT) “T”。

用于一个框区(for one frame)的保持施加到液晶层 10 上的电压的存储电容器 “Cst” 形成在设有像素电极 14 的像素区上。存储电容器 “Cst”的类型可以分成前栅极型和公用型。在前栅极型中，像素电极和前栅极线形成重叠区，而且该重叠区作为存储电容器使用。在公用型中，在像素区形成公用线而在公用线和像素电极之间形成存储电容器。前栅极型的优点在于其孔径比和产量，而公用型的优点在于其显示质量。

最近，由于对 LCD 装置的研究主要集中在高清晰度和高显示质量上，所以正在研究复杂的前栅极型和公用型的存储电容器。

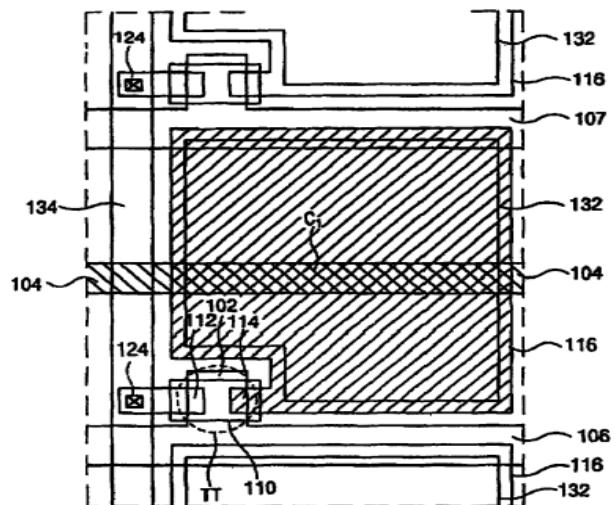

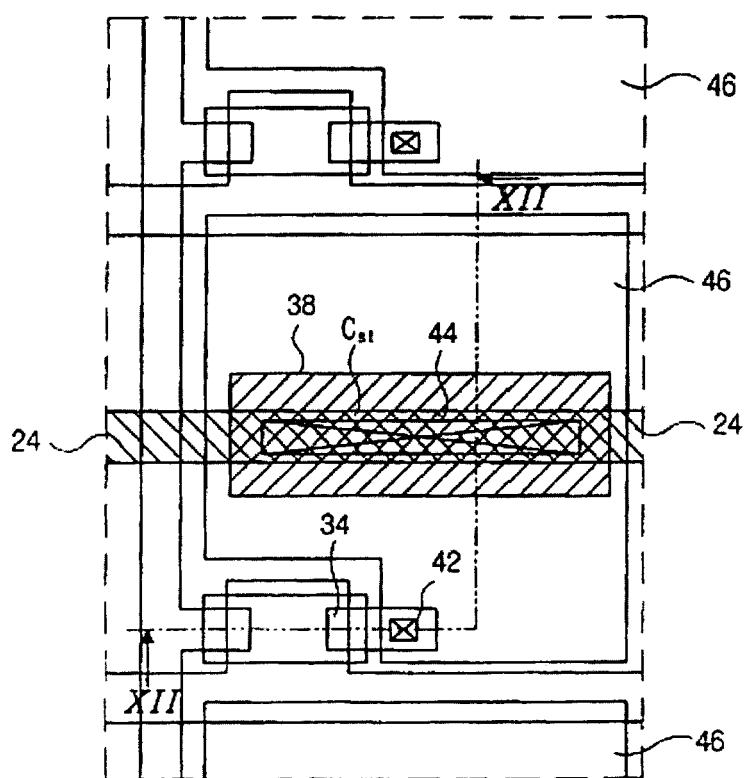

图 2 是局部地表示背景技术中具有公用型存储电容器的 LCD 装置的阵列衬底示意性平面图。在图 2 中，沿行的方向形成带有栅极 22 的栅极线 26 而与栅极线 26 相隔一定距离且与之平行地形成公用线 24。在栅极 22 上形成半导体层 30。与半导体层 30 重叠设置的源极 32 和漏极 34 彼此间相隔一定距离。沿列的方向形成与源极 32 相连的数据线 36，该数据线与栅极线 26 和公用线 24 交叉。像素电极 46 形成在由栅极线 26 和数据线 36 确定的像素区内而且存储电极 38 也形成在像素区内。

存储电极 38 用与数据线 36 相同的材料制作并以其第一面积设置在公用线 24 上。TFT 包括栅极 22、半导体层 30 和源极及漏极 32 和 34。像素电极 46 通过第一接触孔 42 与漏极 34 相连而通过第二接触孔 44 与存储电极 38 相连。栅极绝缘层设置在公用线和存储电极 24 和 38 之间，而钝化层设置在存储电极和像素电极 38 和 46 之间。钝化层包括第一和第二接触孔

42 和 44, 且可[s1]防止来自外部的对 TFT 的损坏。

在上述结构中, 存储电容器“Cst”形成在公用线 24 和存储电极 38 之间以及公用线 24 和像素电极 46 之间。电容量由下面的关系确定:

$$C = \epsilon A / d$$

5 其中 C 是电容量,  $\epsilon$  是所设介电材料的介电常数, A 是电容器的电极面积, d 是电容器的电极之间的距离。

由于栅极绝缘层比钝化层薄, 所以公用线 24 和存储电极 38 之间的电容量大于公用线 24 和像素电极 46 之间的电容量。因此, 存储电容量因添加了存储电极 38 而增加。然而, 由于存储电极 38 是用与数据线 36 相同的 10 不透明金属材料制造的, 所以添加不透明存储电极 38 会导致孔径比降低。

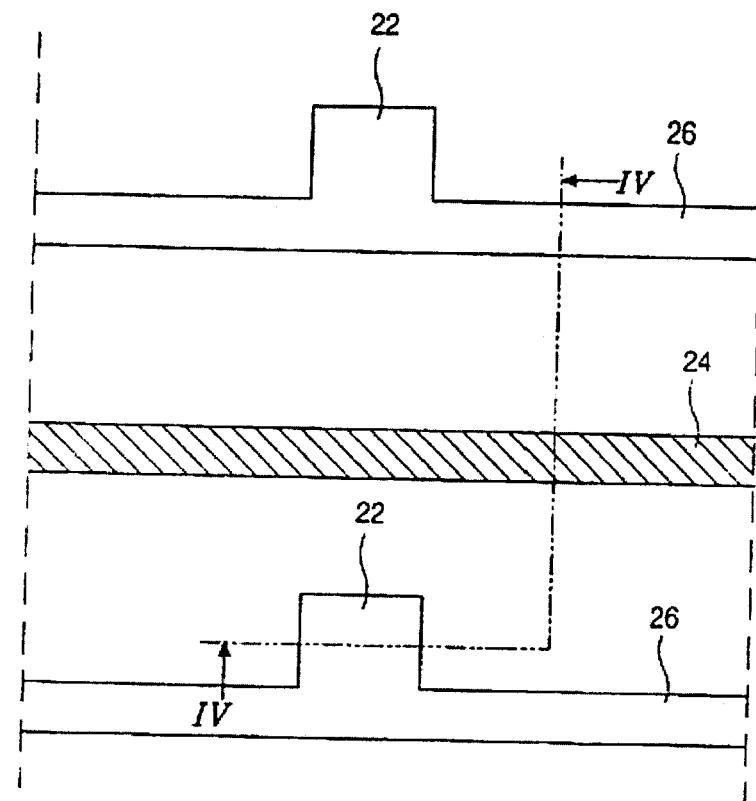

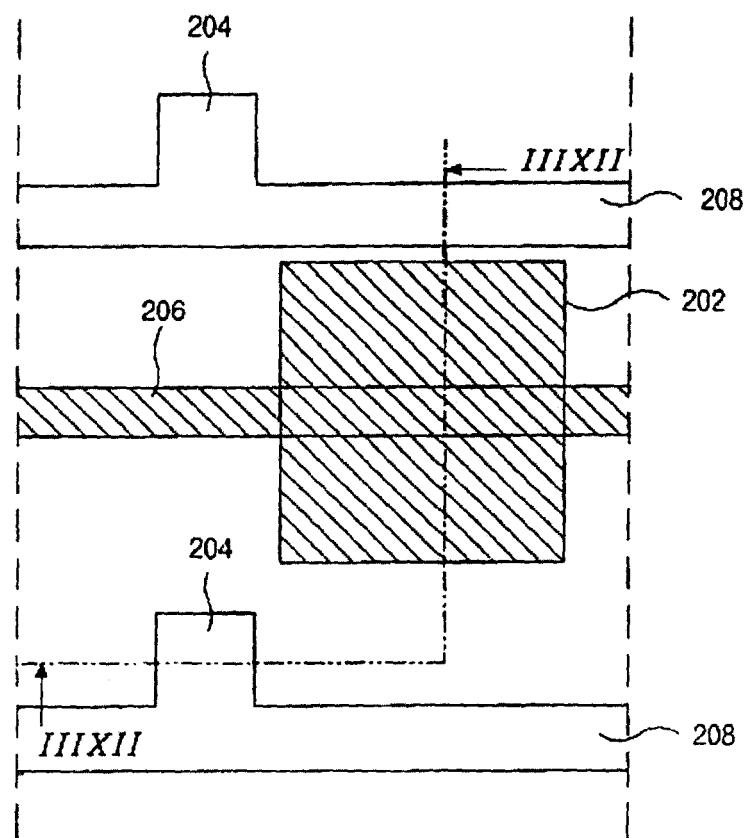

图 3 至 12 是表示背景技术中的 LCD 装置中阵列底制作过程的示意性平面图和示意性剖面图。在这些工序中, 通过反复进行沉积、光刻和蚀刻来制成阵列底。图 3 是表示背景技术中的 LCD 装置中阵列底制作过程的示意性平面图。图 4 是表示背景技术的 LCD 装置中阵列底制作过程的示意性剖面图。在图 3 和图 4 中, 在衬底 1 上沿行的方向形成带有栅极 22 的栅极线 26 和公用线 24。公用线 24 与栅极线 26 平行并与栅极线 26 隔开一定距离。主要用含有铝 (Al) 的双金属层作为栅极线 26 和公用线 24。 15

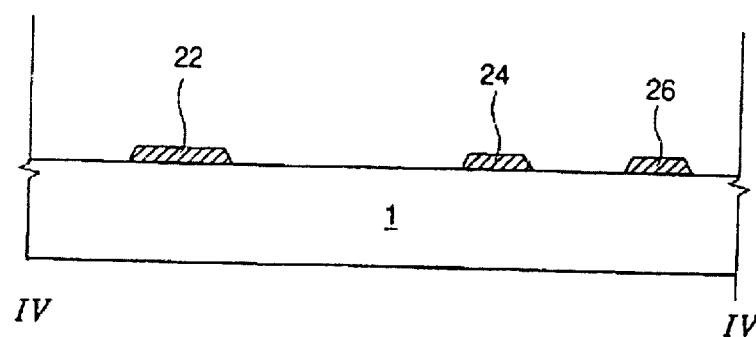

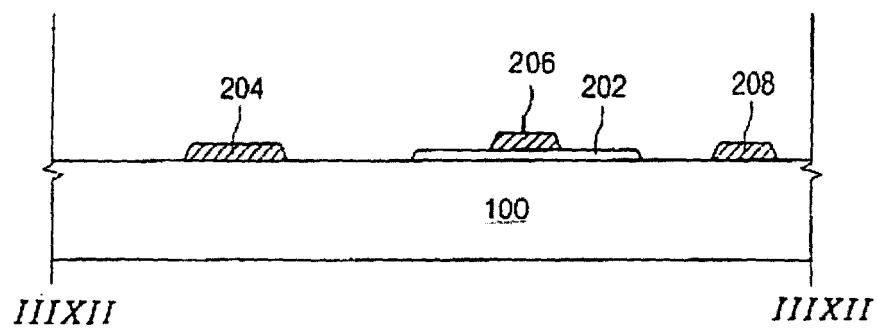

图 5 是表示背景技术的 LCD 装置中阵列底制作过程的示意性平面图。图 6 是表示背景技术的 LCD 装置中阵列底制作过程的示意性剖面图。 20 在图 5 和图 6 中, 当在带有栅极线 26 和公用线 24 的衬底 1 的整个表面上形成栅极绝缘层 28 之后, 在栅极 22 之上的栅极绝缘层 28 上按序形成非晶硅 (a-Si) 有源层 30a 和掺杂了非晶硅 (掺杂的 a-Si) 的欧姆接触层 30b 从而制得半导体层 30。由于离子掺杂过程增加了欧姆接触层 30b 的载流子迁移率, 所以欧姆接触层 30b 可以减小有源层 30a 和下一金属层之间的接触 25 电阻。

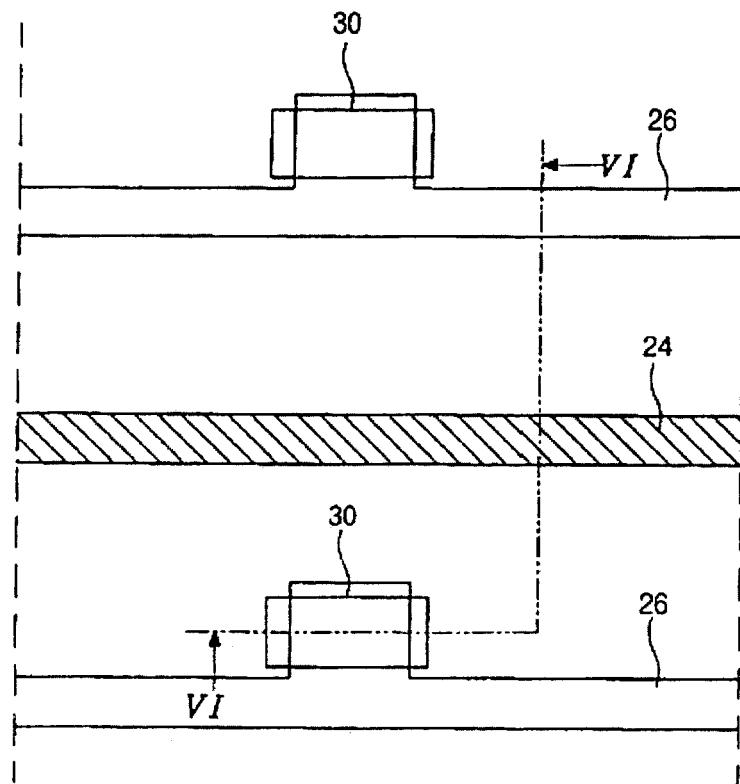

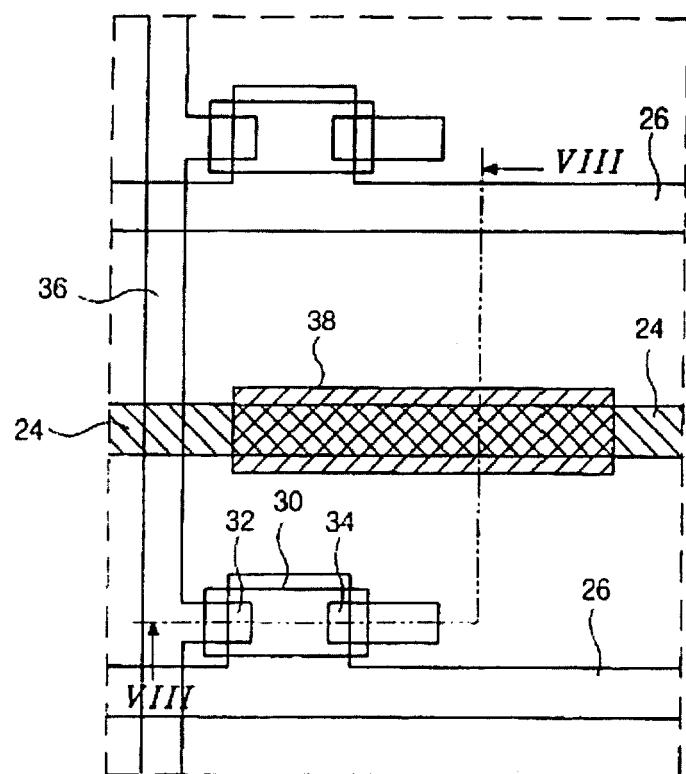

图 7 是表示背景技术的 LCD 装置中阵列衬底制作过程的示意性平面图。图 8 是表示背景技术的 LCD 装置中阵列衬底制作过程的示意性平面剖示图。在图 7 和图 8 中，在具有半导体层 30 的衬底上形成带有源极 32 的数据线 36、与源极 32 彼此隔开一定距离的漏极 34 和存储电极 38。与栅极线 26 和公用线 24 交叉的数据线 36 沿列的方向设置。与公用线 24 重叠的存储电极 38 设置在像素区内。主要用耐化学的金属例如钼 (Mo) 作为数据线 36、漏极 34 或存储电极 38。在制作源极 32 和漏极 34 的过程中，除去源极 32 和漏极 34 之间的欧姆接触层，从而通过暴露有源层 30a 来形成沟道 ch。

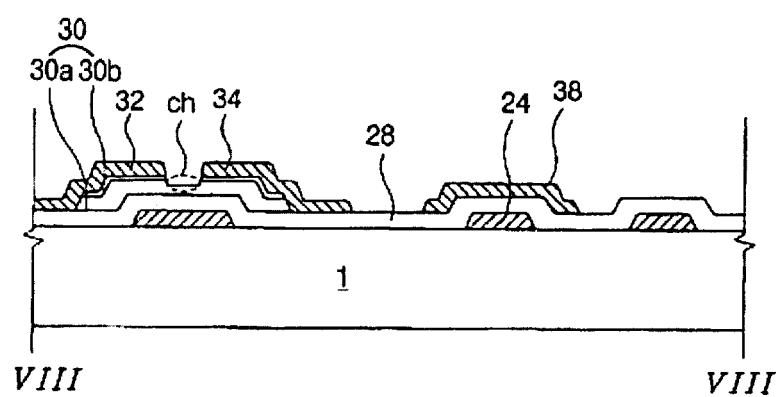

图 9 是表示背景技术的 LCD 装置中阵列衬底制作过程的示意性平面图。图 10 是表示背景技术的 LCD 装置中阵列衬底制作过程的示意性剖面图。在图 9 和图 10 中，在衬底的整个表面上形成带有第一接触孔 42 和第二接触孔 44 的钝化层 40。第一和第二接触孔 42 和 44 分别暴露漏极 34 和存储电极 38。

图 11 是表示背景技术的 LCD 装置中阵列衬底制作过程的示意性平面剖示图。图 12 是表示背景技术的 LCD 装置中阵列衬底制作过程的示意图。在图 11 和图 12 中，在钝化层 40 上形成像素电极 46，该像素电极通过第一和第二接触孔 42 和 44 分别与漏极 34 和存储电极 38 相连。像素电极 46 用例如氧化铟锡 (ITO) 或氧化铟锌 (IZO) 等透明导电材料制成。

通过第二接触孔 44 与像素电极 46 相连的存储电极 38 与公用线 24 一起形成存储电容器 “Cst”。由于公用线 24 和存储电极 38 之间的距离大于公用线 24 和像素电极 46 之间的距离，所以存储电容量变大。然而，由于用不透明金属制成的存储电极 38 的区域 “A” 会降低孔径比，所以很难增加孔径比和存储电容量。

## 发明内容

本发明克服了与背景技术中有关的一些缺点，并获得了背景技术未能实现的其它优点。

本发明的目的是提供一种液晶显示装置，该装置基本上克服了背景技术存在的上述一个或多个问题。

本发明的另一个目的是提供一种液晶显示装置的阵列衬底，该衬底具有高孔径比和高存储电容量。

本发明的再一个目的是提供一种制造液晶显示装置阵列衬底的方法，所述衬底具有高孔径比和高存储电容量。

本发明的这些和其他方面是通过液晶显示装置的阵列衬底实现的，所述阵列衬底包括：衬底；在衬底上沿第一方向设置的栅极线；平行于栅极线且与栅极线彼此相隔一定距离的公用线，所述公用线用与栅极线相同的材料制作；处于栅极线和公用线上的栅极绝缘层；处于栅极绝缘层上的半导体层；用透明导电材料制成的像素电极，所述像素电极包括漏极区段，所述漏极区段与半导体层重叠；与漏极区段彼此相隔一定距离且用透明导电材料制成的源极；在像素电极和源极之上带有第一接触孔和开口部分的钝化层，其中第一接触孔暴露源极而开口部分暴露像素电极；和在钝化层上沿第二方向设置的数据线，数据线通过第一接触孔与源极相连并与栅极线交叉。

本发明的这些和其他方面进一步由液晶显示装置的阵列衬底实现，所述阵列衬底包括：衬底；衬底上的公用电极；在衬底上沿第一方向设置的栅极线；平行于栅极线且与栅极线彼此隔开一定距离的公用线；公用线由与栅极线相同的材料制成且与公用电极接触；处于栅极线和公用线上的栅极绝缘层；处于栅极绝缘层上的半导体层；用透明导电材料制成的像素电极，像素电极上带有漏极区段，漏极区段与半导体层重叠；用透明导电材

料制成且与漏极区段彼此相隔一定距离的源极；带有第一接触孔和开口部分的钝化层，其中第一接触孔暴露源极而开口部分暴露像素电极；和在钝化层上沿第二方向设置的数据线，数据线通过第一接触孔与源极相连并与栅极线交叉。

5 本发明的这些和其他方面进一步由液晶显示装置的阵列衬底实现，所述阵列衬底包括：衬底；在衬底上沿第一方向设置的栅极线，所述栅极线包括存储电极；处于栅极线上的栅极绝缘层；处于栅极绝缘层上的半导体层；用透明导电材料制成的像素电极，像素电极上带有漏极区段，漏极区段与半导体层重叠，而像素电极与栅极线重叠；用透明导电材料制成且与

10 漏极区段彼此相隔一定距离的源极；带有第一接触孔和开口部分的钝化层，其中第一接触孔暴露源极而开口部分暴露像素电极；和在钝化层上沿第二方向设置的数据线，数据线通过第一接触孔与源极相连并与栅极线交叉。

本发明的这些和其他方面进一步由制造液晶显示装置阵列衬底的方法实现，所述方法包括：在衬底上形成沿第一方向设置的栅极线和平行于栅

15 极线设置的公用线，其中栅极线和公用线彼此相隔一定距离；在栅极线和公用线上形成栅极绝缘层；在栅极绝缘层上形成半导体层；形成透明导电材料的源极和像素电极，所述像素电极包括漏极区段，漏极区段与半导体层重叠而源极与漏极区段彼此相隔一定距离；形成带有第一接触孔和开口部分的钝化层，其中第一接触孔暴露源极，开口部分暴露像素电极；和在

20 钝化层上形成沿第二方向设置的数据线，所述数据线通过第一接触孔与源极相连并与栅极线交叉。

本发明的这些和其他方面进一步由制造液晶显示装置阵列衬底的方法实现，所述方法包括：在衬底上形成公用电极；形成沿第一方向设置的栅极线和平行于栅极线的公用线，其中公用线和栅极线彼此相隔一定距离，

25 并与公用电极相接触；在栅极线和公用线上形成栅极绝缘层；在栅极绝缘

层上形成半导体层；形成透明导电材料的源极和像素电极，所述像素电极包括漏极区段，漏极区段与半导体层重叠而源极与漏极区段彼此相隔一定距离；形成带有第一接触孔和开口部分的钝化层，其中第一接触孔暴露源极，开口部分暴露像素电极；和在钝化层上形成沿第二方向设置的数据线，

5 所述数据线通过第一接触孔与源极相连并与栅极线交叉。

本发明的这些和其他方面进一步由制造液晶显示装置阵列衬底的方法实现，所述方法包括：在衬底上形成沿第一方向设置的栅极线，所述栅极线包括存储电极；在栅极线上形成栅极绝缘层；在栅极绝缘层上形成半导体层；形成透明导电材料的源极和像素电极，所述像素电极包括漏极区段，

10 源极与漏极区段彼此相隔一定距离，漏极区段与半导体层重叠而像素电极与栅极线重叠；形成带有第一接触孔和开口部分的钝化层，其中第一接触孔暴露源极，开口部分暴露像素电极；和在钝化层上形成沿第二方向设置的数据线，所述数据线通过第一接触孔与源极相连并与栅极线交叉。

通过下面给出的详细说明将使发明在其它方面的应用得到明显体现。

15 然而，很显然，由于在本发明的构思和范围内进行各种变化和改进对于熟悉本领域的技术人员来说是显而易见的，所以，在展现本发明优选实施例的同时所给出的详细说明和特定实例仅是解释性的。

### 附图说明

20 通过下面给出的仅起解释作用的详细说明和附图将有助于更完整地理解本发明，但这些解释并不构成对本发明的限制，其中：

图 1 是局部性表示背景技术中 LCD 液晶板的示意性剖面图；

图 2 是局部性表示具有公用型存储电容器的背景技术中 LCD 阵列衬底的示意性平面图；

25 图 3 是表示背景技术中制作 LCD 装置阵列衬底过程的示意性平面图；

图 4 是表示背景技术中制作 LCD 装置阵列衬底过程的示意性剖面图；

图 5 是表示背景技术中制作 LCD 装置阵列衬底过程的示意性平面图；

图 6 是表示背景技术中制作 LCD 装置阵列衬底过程的示意性剖面图；

图 7 是表示背景技术中制作 LCD 装置阵列衬底过程的示意性平面图；

5 图 8 是表示背景技术中制作 LCD 装置阵列衬底过程的示意性平面剖示图；

图 9 是表示背景技术中制作 LCD 装置阵列衬底过程的示意性平面图；

图 10 是表示背景技术中制作 LCD 装置阵列衬底过程的示意性剖面图；

10 图 11 是表示背景技术中制作 LCD 装置阵列衬底过程的示意性平面剖示图；

图 12 是表示背景技术中制作 LCD 装置阵列衬底过程的示意图；

图 13 是按照本发明第一实施例所述 LCD 装置中阵列衬底的示意性平面图；

15 图 14 是表示按照本发明第一实施例所述 LCD 装置中阵列衬底制造过程的示意性平面图；

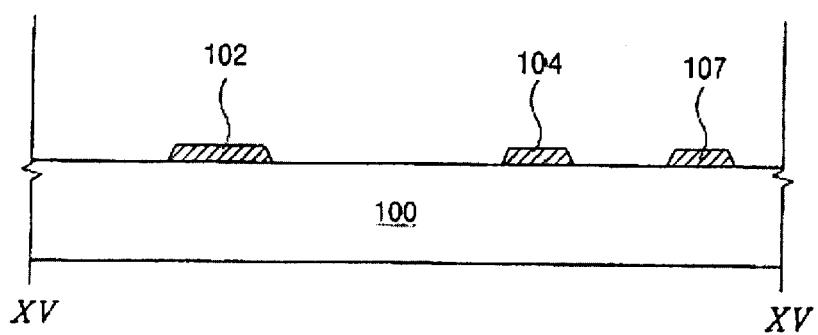

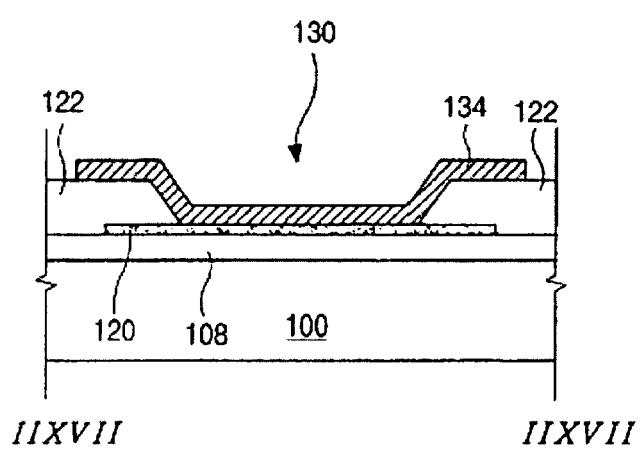

图 15 是表示按照本发明第一实施例所述 LCD 装置中阵列衬底制造过程的示意性剖面图；

图 16 是表示按照本发明第一实施例所述 LCD 装置中阵列衬底制造过程的示意性平面图；

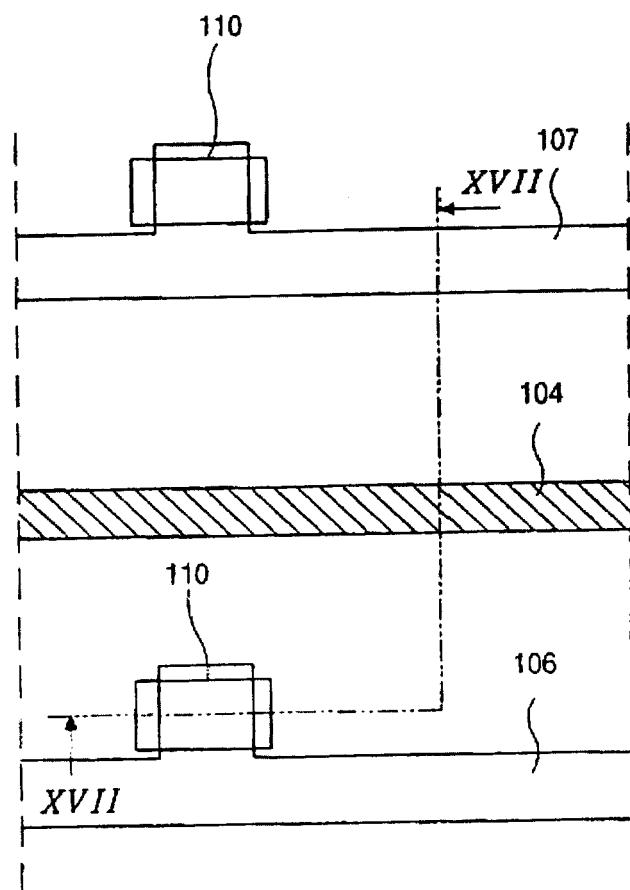

20 图 17 是表示按照本发明第一实施例所述 LCD 装置中阵列衬底制造过程的示意性剖面图；

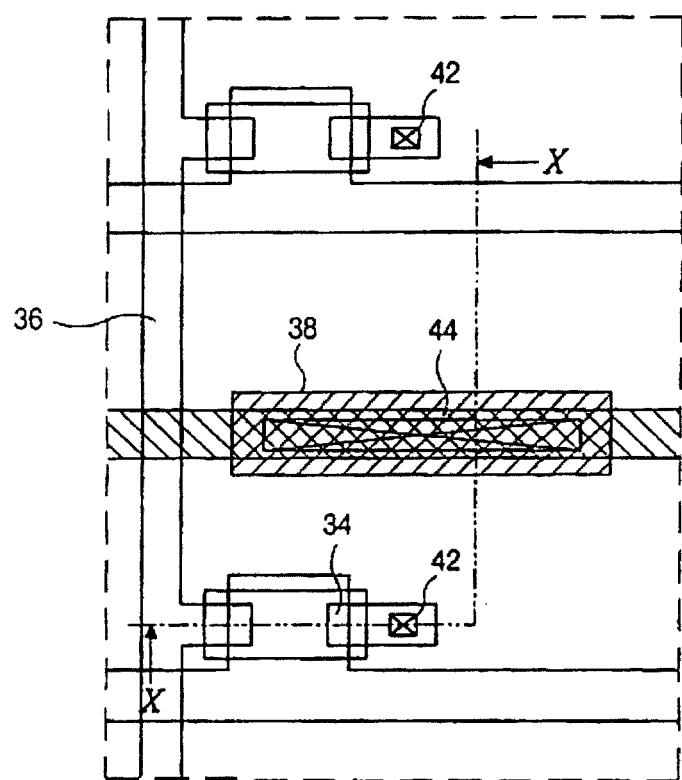

图 18 是表示按照本发明第一实施例所述 LCD 装置中阵列衬底制造过程的示意性平面图；

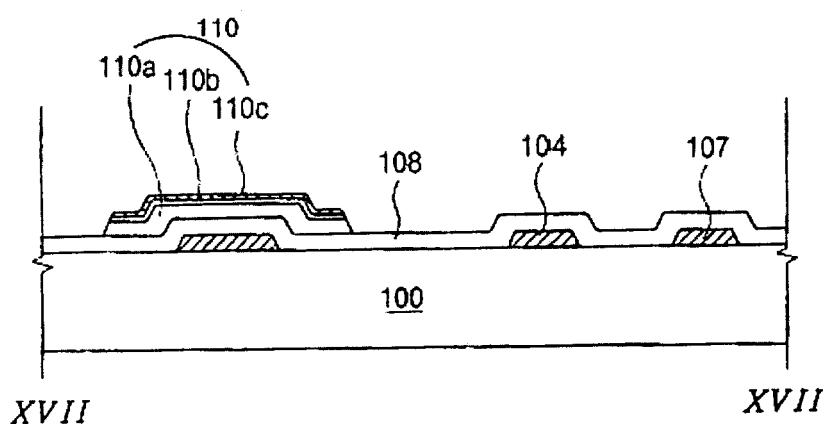

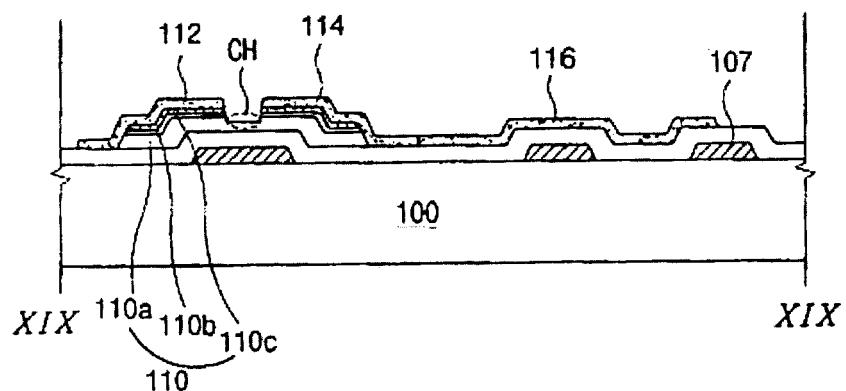

25 图 19 是表示按照本发明第一实施例所述 LCD 装置中阵列衬底制造过程的示意性剖面图；

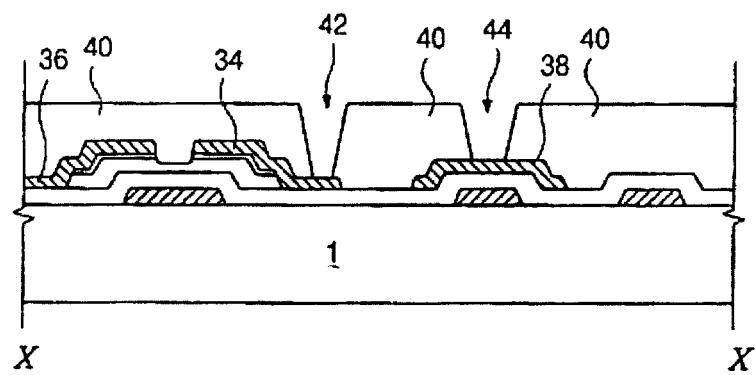

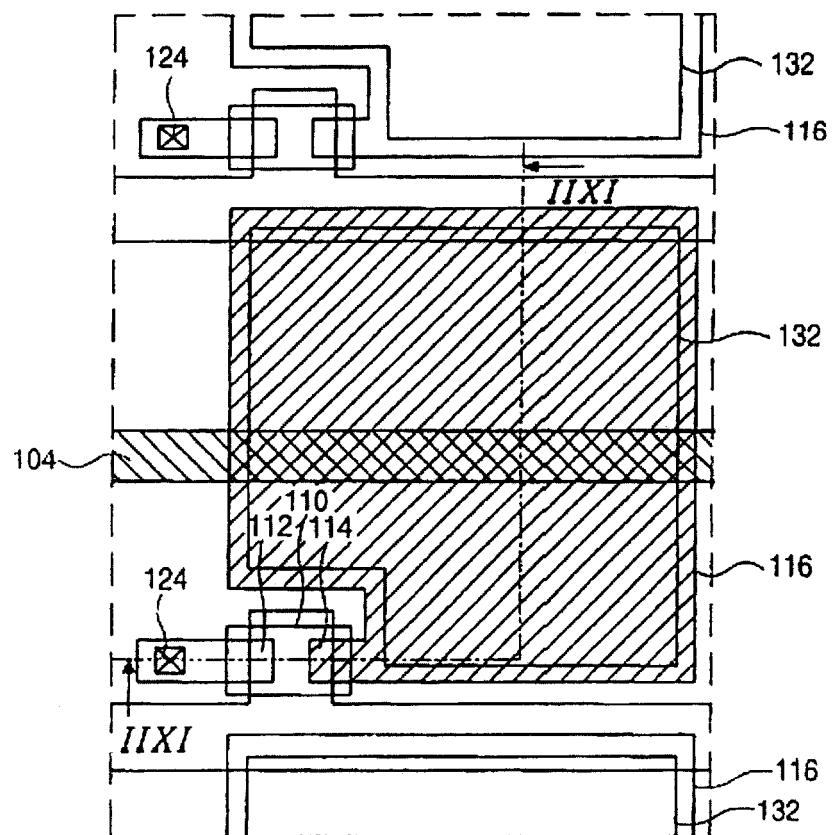

图 20 是表示按照本发明第一实施例所述 LCD 装置中阵列衬底制造过程的示意性平面图；

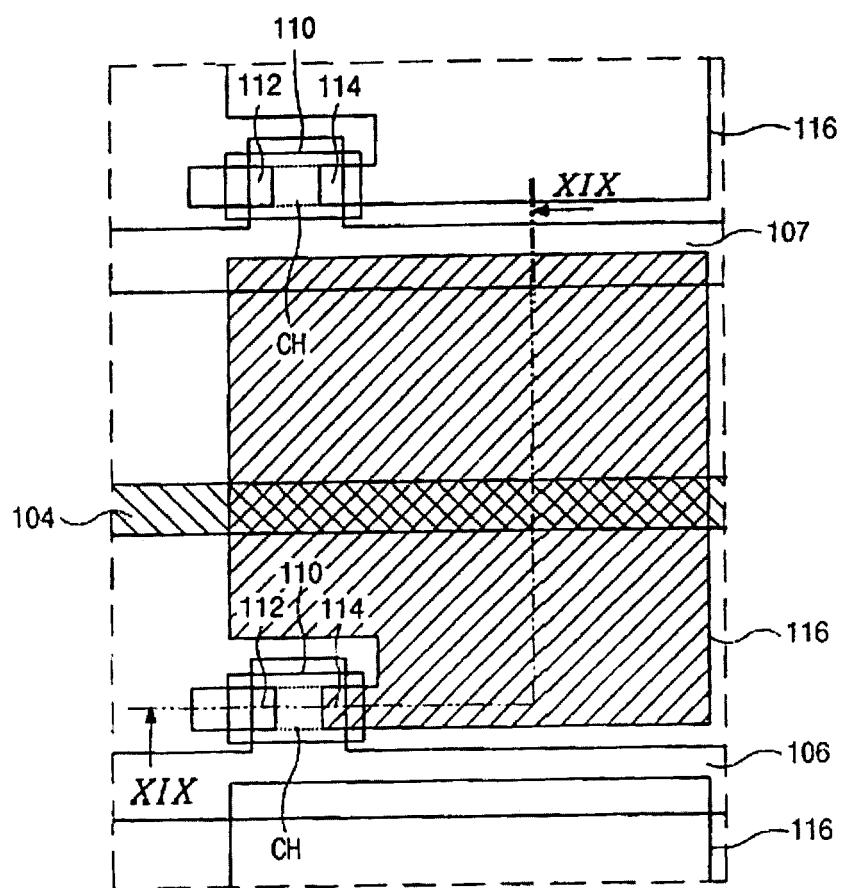

图 21 是表示按照本发明第一实施例所述 LCD 装置中阵列衬底制造过程的示意性剖面图；

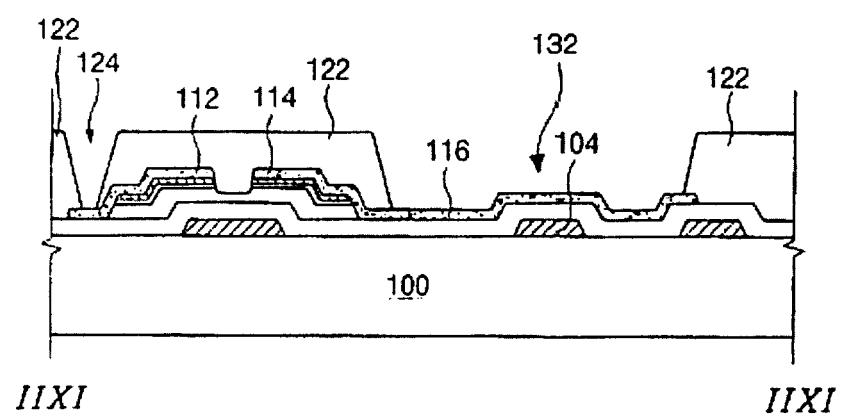

5 图 22 是表示按照本发明第一实施例所述 LCD 装置中阵列衬底制造过程的示意性平面图；

图 23 是表示按照本发明第一实施例所述 LCD 装置中阵列衬底制造过程的示意性剖面图；

10 图 24 是按照本发明第一实施例所述 LCD 装置中阵列衬底上栅极垫片的示意性平面图；

图 25 是按照本发明第一实施例所述 LCD 装置中阵列衬底上栅极垫片的示意性剖面图；

图 26 是按照本发明第一实施例所述 LCD 装置中阵列衬底上数据垫片的示意性平面图；

15 图 27 是按照本发明第一实施例所述 LCD 装置中阵列衬底上数据垫片的示意性剖面图；

图 28 是按照本发明第二实施例所述 LCD 装置中阵列衬底的示意性平面图；

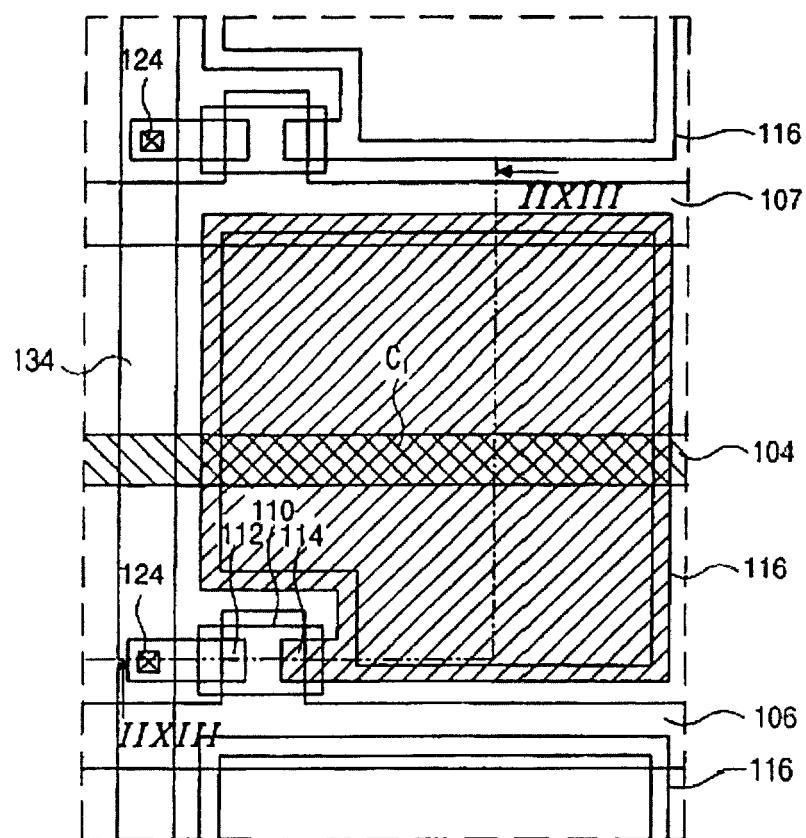

20 图 29 是表示按照本发明第二实施例所述 LCD 装置中阵列衬底制造过程的示意性平面图；

图 30 是表示按照本发明第二实施例所述 LCD 装置中阵列衬底制造过程的示意性剖面图；

图 31 是表示按照本发明第二实施例所述 LCD 装置中阵列衬底制造过程的示意性平面图；

25 图 32 是表示按照本发明第二实施例所述 LCD 装置中阵列衬底制造过

程的示意性剖面图；

图 33 是表示按照本发明第二实施例所述 LCD 装置中阵列衬底制造过程的示意性平面图；

图 34 是表示按照本发明第二实施例所述 LCD 装置中阵列衬底制造过

程的示意性剖面图；

图 35 是表示按照本发明第二实施例所述 LCD 装置中阵列衬底制造过

程的示意性平面图；

图 36 是表示按照本发明第二实施例所述 LCD 装置中阵列衬底制造过

程的示意性剖面图；

图 37 是按照本发明第三实施例所述 LCD 装置中阵列衬底的示意性平

面图；

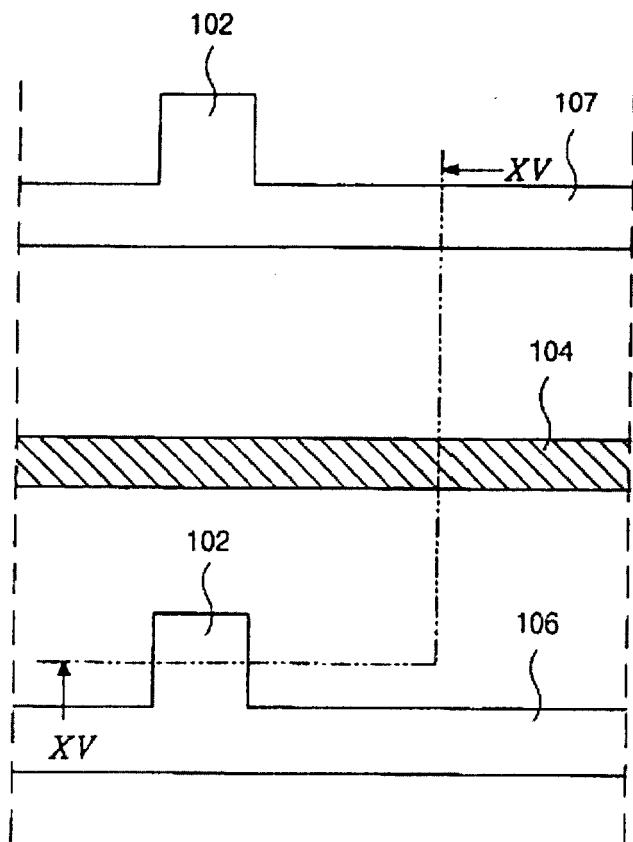

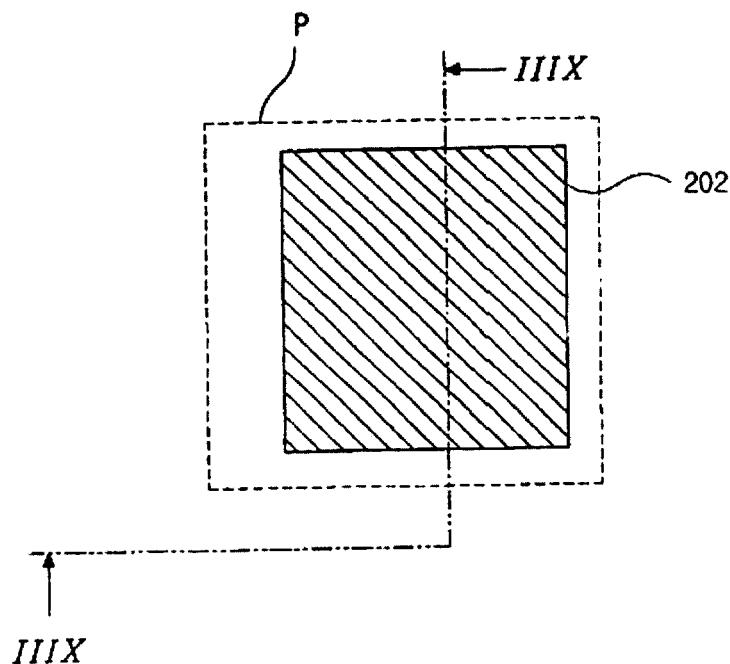

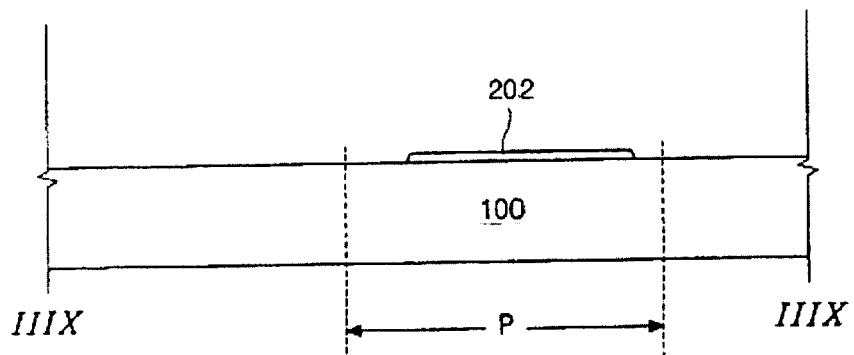

图 38 是沿图 37 中线“III XVIII—III XVIII”截取的剖面图。

## 具体实施方式

下面将参照附图说明本发明。在下面所述的本发明的优选实施例中，

用透明导电材料制作源极、漏极和像素电极，并在形成钝化层之后形成数

据线。

### 第一实施例

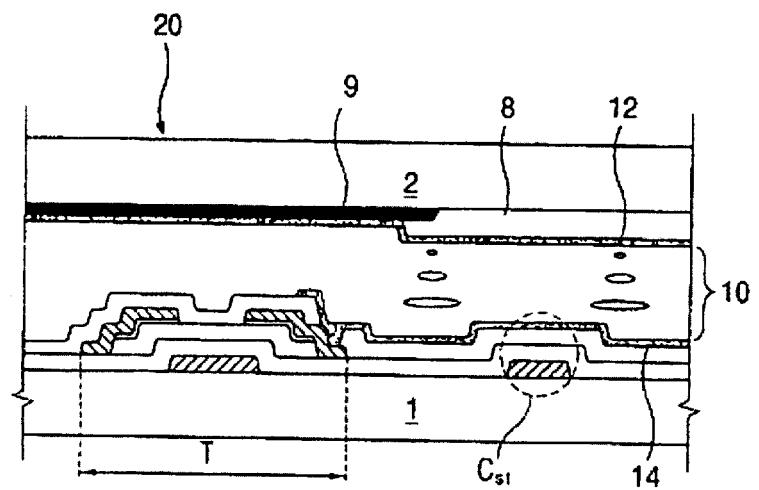

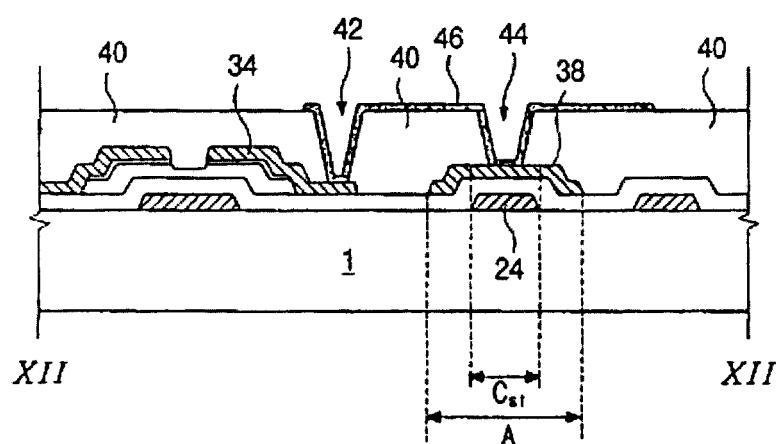

图 13 是按照本发明第一实施例所述 LCD 装置中阵列衬底的示意性平

面图。在图 13 中，沿行的方向形成带有栅极 102 的栅极线 106，与栅极线

106 平行的公用线 104 与栅极线 106 相隔一定距离。公用线 104 用与栅极线

106 相同的材料制作。在栅极 102 上形成半导体层 110。与半导体层 110 重

叠的源极 112 和漏极区段 114 彼此相隔一定距离。在由栅极线 106 和数据

线 134 确定的像素区上形成包含漏极区段 114 的像素电极 116。数据线 134

沿列的方向形成并与栅极线和公用线 106 和 104 相交。

带有第一接触孔 124 和开口部分 132 的钝化层（未示出）插设在源极和像素电极 112 和 116 以及数据线 134 之间。数据线 134 通过第一接触孔与源极 112 相连。开口部分 132 暴露像素电极 116 以防止液晶层的电场减弱。

源极和像素电极 112 和 116 以及漏极区段 114 由例如氧化铟锡 (ITO)、氧化铟锌 (IZO)、和氧化铟锡锌 (ITZO) 等透明导电材料制成；然而，优选使用 ITO，这是因为其与外部电路的金属有理想的接触特性。但是，由于透明材料与半导体材料的接触特性不理想，所以，在半导体层 110 上设置钛 (Ti) 或铬 (Cr) 等制成的缓冲接触层，从而使透明导电材料和半导体之间的接触电阻达到最小。像素电极 116 与前栅极线 107 重叠以便增加孔径比。

在第一实施例中，存储电容器“C1”形成在公用线 104 和像素电极 116 之间，而且在其之间仅插设了比钝化层薄的栅极绝缘层。因此，可以在没有另外的不透明金属存储电极的情况下，便可得到足够的存储电容量并且提高了孔径比。

第一实施例的 TFT “TT” 与传统的 TFT “T”（见图 2）不同。第一实施例的 TFT “TT” 在半导体层 110 上设有缓冲接触层而且源极 112 和漏极区段 114 由透明导电材料制成。此外，漏极区段 114 和像素电极 116 形成为一个图形而且源极 112 通过第一接触孔 124 与数据线 134 相连。

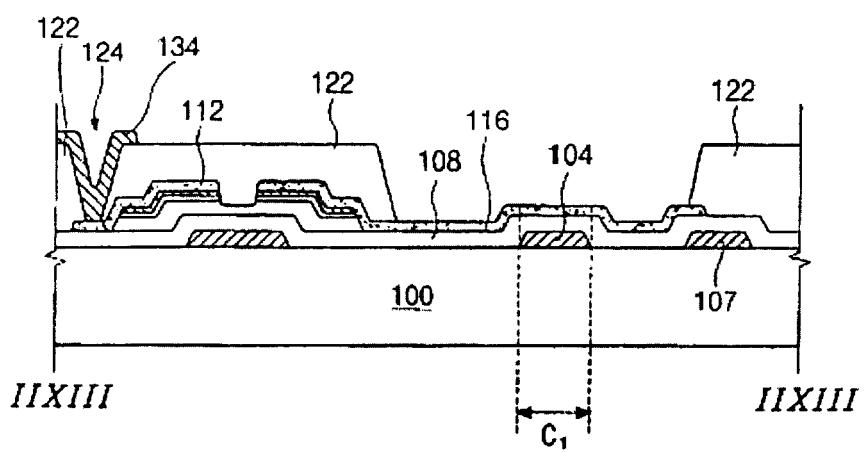

图 14—图 23 是表示按照本发明第一实施例所述 LCD 装置中阵列衬底制造过程的示意性平面图和示意性剖面图。图 14 是表示按照本发明第一实施例所述 LCD 装置中阵列衬底制造过程的示意性平面图。图 15 是表示按照本发明第一实施例所述 LCD 装置中阵列衬底制造过程的示意性剖面图。

在图 14 和图 15 中，在衬底 100 上沿行的方向形成具有栅极 102 的栅极线

106 和共用线 104。平行于栅极线 106 的公用线 104 与栅极线 106 相隔一定距离。可以用钕化铝和钼 (AlNd/Mo) 的双金属层作为栅极线和公用线 106 和 104。

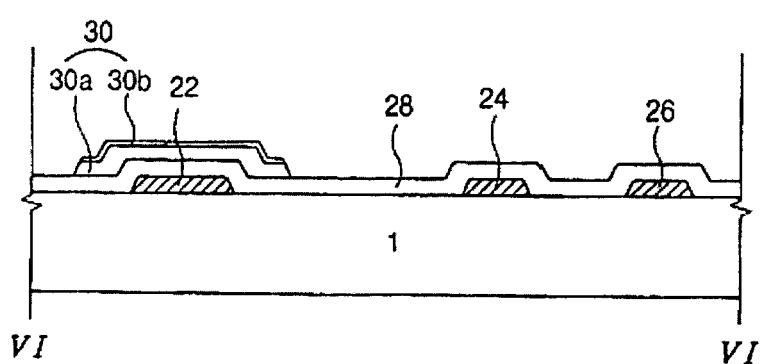

图 16 是表示按照本发明第一实施例所述 LCD 装置中阵列衬底制造过 5 程的示意性平面图。图 17 是表示按照本发明第一实施例所述 LCD 装置中阵列衬底制造过程的示意性剖面图；

在图 16 和图 17 中，首先在具有栅极线和公用线 106 和 104 衬底的整个表面上形成栅极绝缘层 108。接着，在栅极 102 上方的栅极绝缘层 108 上按序形成非晶硅 (a-Si) 有源层 110a、掺杂非晶硅 (掺杂的 a-Si) 的欧姆接触层 110b、和钛 (Ti) 或铬 (Cr) 的缓冲接触层 110c，从而形成带有附加缓冲层的半导体层 110。 10

在该制作过程中，当在 PECVD (等离子体增强的化学汽相沉积) 设备中按顺序在带有栅极线和公用线 106 和 104 的衬底 100 上沉积氮化硅 (SiNx) 膜、a-Si 膜和掺杂的 a-Si 膜之后，在溅射设备中将 Ti 和 Mo 之一 15 沉积在衬底 100 的整个表面上。然后，通过分别蚀刻 a-Si 膜、掺杂的 a-Si 膜、和 Ti 或 Mo 膜形成有源层 110a、欧姆接触层 110b、和缓冲接触层 110c。采用缓冲接触层 110c 可提高欧姆接触层 110b 和透明导电材料的漏极区段 114 之间的接触特性。

图 18 是表示按照本发明第一实施例所述 LCD 装置中阵列衬底制造过 20 程的示意性平面图。图 19 是表示按照本发明第一实施例所述 LCD 装置中阵列衬底制造过程的示意性剖面图。在图 18 和图 19 中，在设有半导体层 110 的衬底上形成透明材料 (优选为 ITO) 的源电极 112 和像素电极 116，所述半导体层 110 上带有附加的缓冲层。像素电极 116 包括漏极区段 114。源极 112 和漏极区段 114 彼此隔开一定距离。此外，为了增加孔径比，像素电极 116 叠压前栅极性 107。在这一制造过程中，在源极 112 和漏极区段 25 114 之间的接触特性。

114 之间蚀刻缓冲接触层和欧姆接触层 100c 和 100b 以便暴露有源层 110a 和形成 TFT 的沟道“CH”。

图 20 是表示按照本发明第一实施例所述 LCD 装置中阵列衬底制造过程的示意性平面图。图 21 是表示按照本发明第一实施例所述 LCD 装置中 5 阵列衬底制造过程的示意性剖面图。在图 20 和图 21 中，在衬底的整个表面上形成带有第一接触孔 124 和开口部分 132 的钝化层 122。第一接触孔 124 和开口部分 132 分别暴露源极 112 和像素电极 116。当将电压施加到像素电极 116 上时，产生的电场将驱动液晶层。由于钝化层 122 会削弱驱动液晶层的电场，所以应除去像素电极 116 上的钝化层 122。在优选实施例中 10 用例如丙烯酸树脂等绝缘材料制作钝化层 122。

图 22 是表示按照本发明第一实施例所述 LCD 装置中阵列衬底制造过程的示意性平面图。图 23 是表示按照本发明第一实施例所述 LCD 装置中阵列衬底制造过程的示意性剖面图。在图 22 和图 23 中，在钝化层 122 上 15 形成通过第一接触孔 124 与源极 112 相连接的数据线 134。与栅极线和公用线 106 和 104 交叉的数据线 134 沿列的方向设置。数据线 134 可以使用耐化学剂的金属，例如钼 (Mo)、镍 (Ni)、铬 (Cr) 和钨 (W)。

在第一实施例中，存储电容器“C1”形成在公用线 104 和像素电极 116 之间而且在其之间仅插设栅极绝缘层 108。因此，不需要附设存储电极 38 (见图 2)，而且可以在不降低孔径比的情况下形成具有足够电容量的存储 20 电容器。

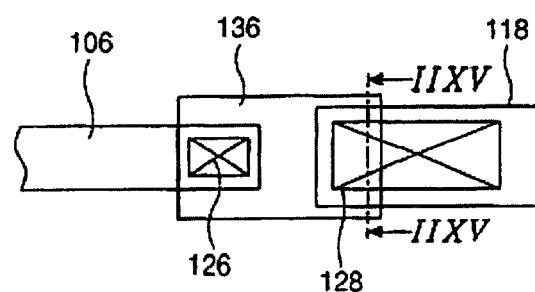

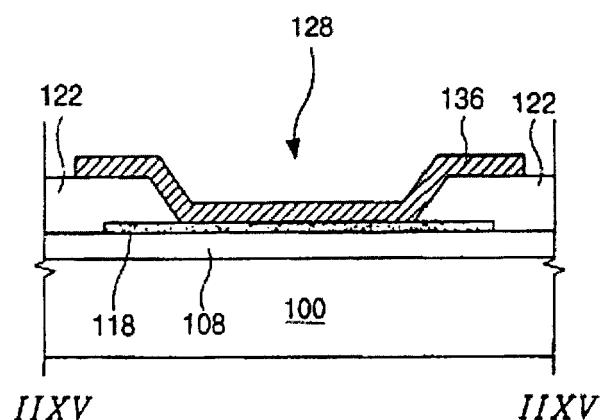

另一方面，为了将阵列衬底与外部电路相连，在栅极线和数据线的端部分别形成栅极垫片和数据垫片。图 24 是按照本发明第一实施例所述 LCD 装置中阵列衬底上栅极垫片的示意性平面图。图 25 是按照本发明第一实施例所述 LCD 装置中阵列衬底上栅极垫片的示意性剖面图。

25 在图 24 和图 25 中，栅极垫片 118 形成在与栅极线 106 和栅极连接件

136 的端部相隔一定距离的位置上, 所述栅极连接件 136 与栅极线 106 叠置。栅极连接件 136 通过第二接触孔 126 和第三接触孔 128 分别与栅极线 106 和栅极垫片 118 相连接。栅极垫片 118 用与像素电极 116 (见图 18) 相同的材料, 例如透明导电材料制作而栅极连接件 136 用与数据线 134 (见图 22) 相同的材料制作。由于通常将透明材料用作垫片的材料, 所以可在没有附加工序的情况下用透明材料制作栅极垫片。然而, 优选使栅极连接件 136 比栅极垫片 118 更宽一些以便保持稳定的连接。

图 26 是按照本发明第一实施例所述 LCD 装置中阵列衬底上数据垫片的示意性平面图。图 27 是按照本发明第一实施例所述 LCD 装置中阵列衬底上数据垫片的示意性剖面图。在图 26 和 27 中, 在数据线 134 的一端上形成与数据线 134 叠置的数据垫片 120。由于数据垫片 120 是在制作栅极垫片 118 (见图 24) 的过程中形成的, 所以要在形成数据垫 120 后形成数据线 134。与栅极垫片 118 (见图 24) 相同, 优选使数据线 134 的端部比数据垫片 120 宽以便确保稳定连接。数据线 134 通过第四接触孔 130 与数据垫片 120 相连接。在上述按照本发明第一实施例所述的制作过程中, 不需要任何附加工序便可形成栅极垫片和数据垫片。

## 第二实施例

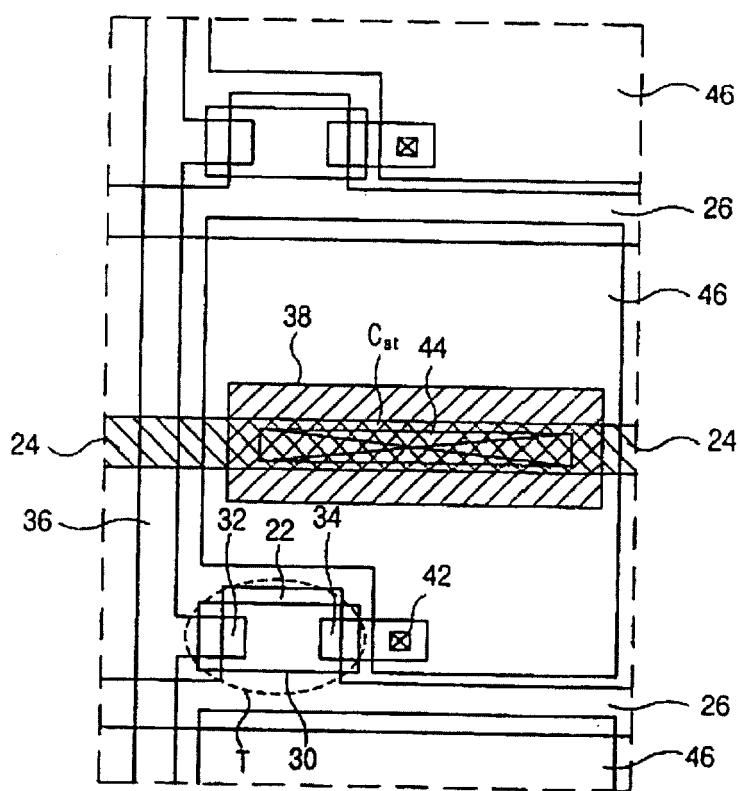

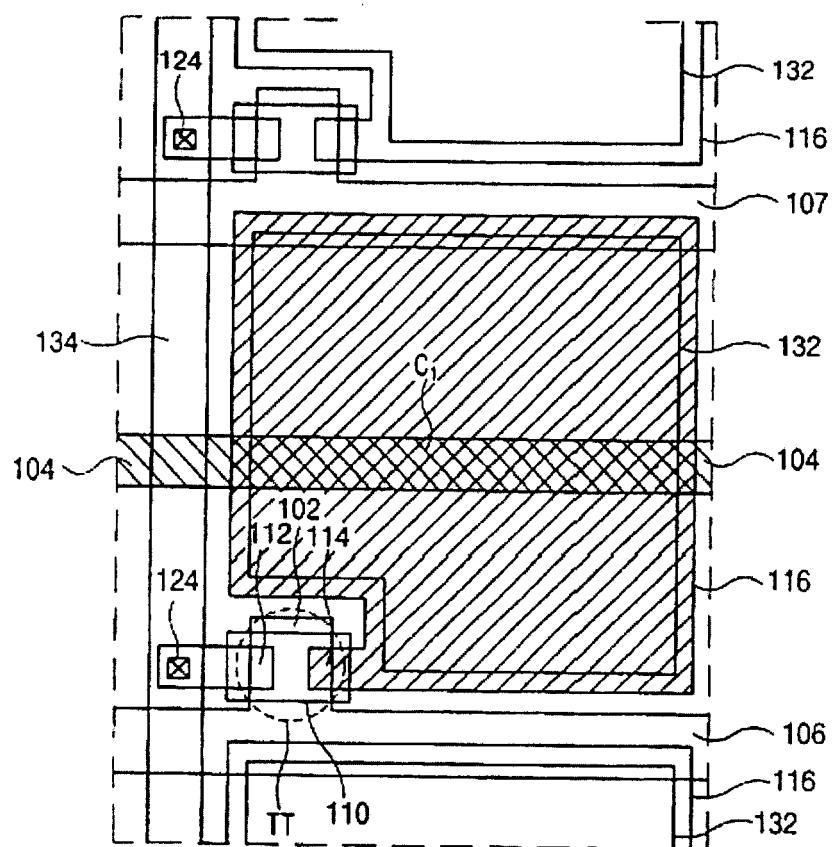

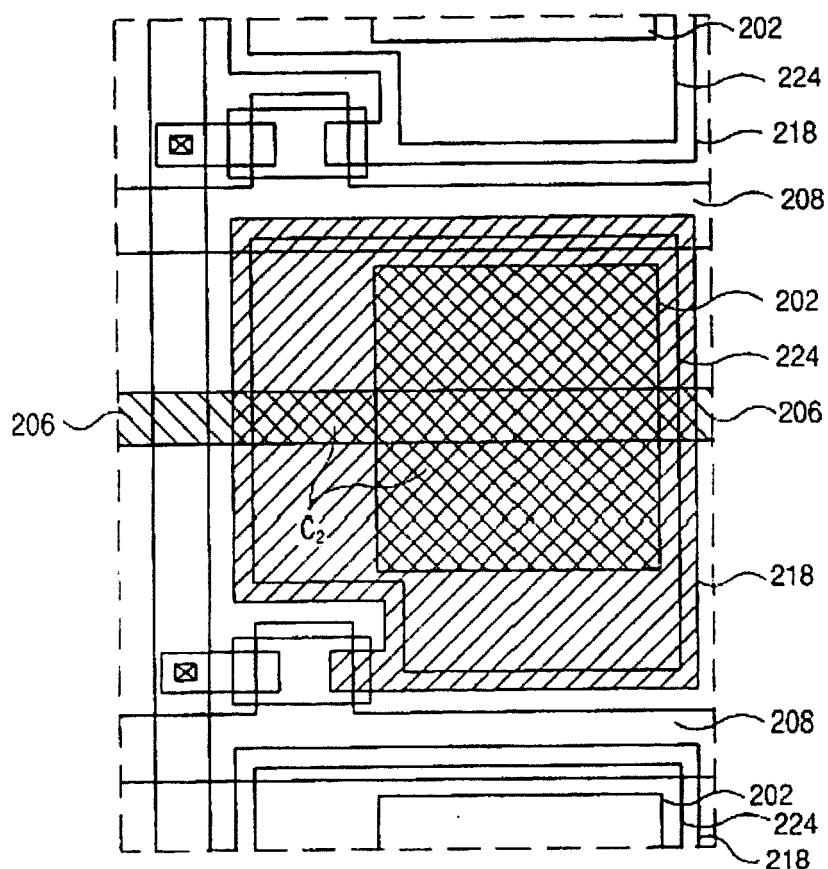

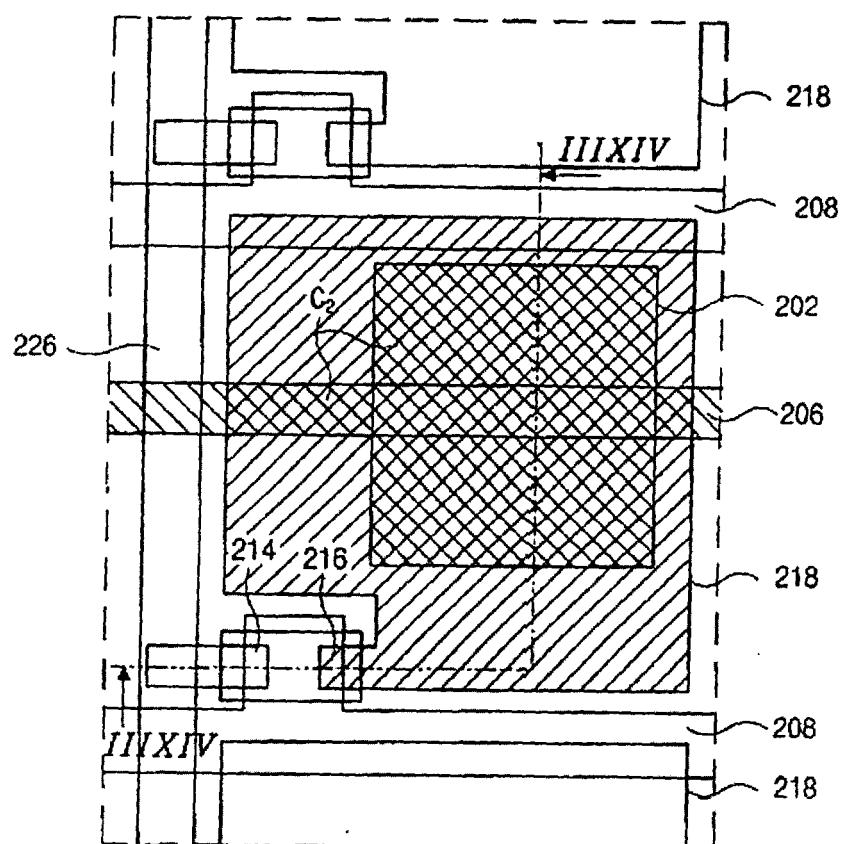

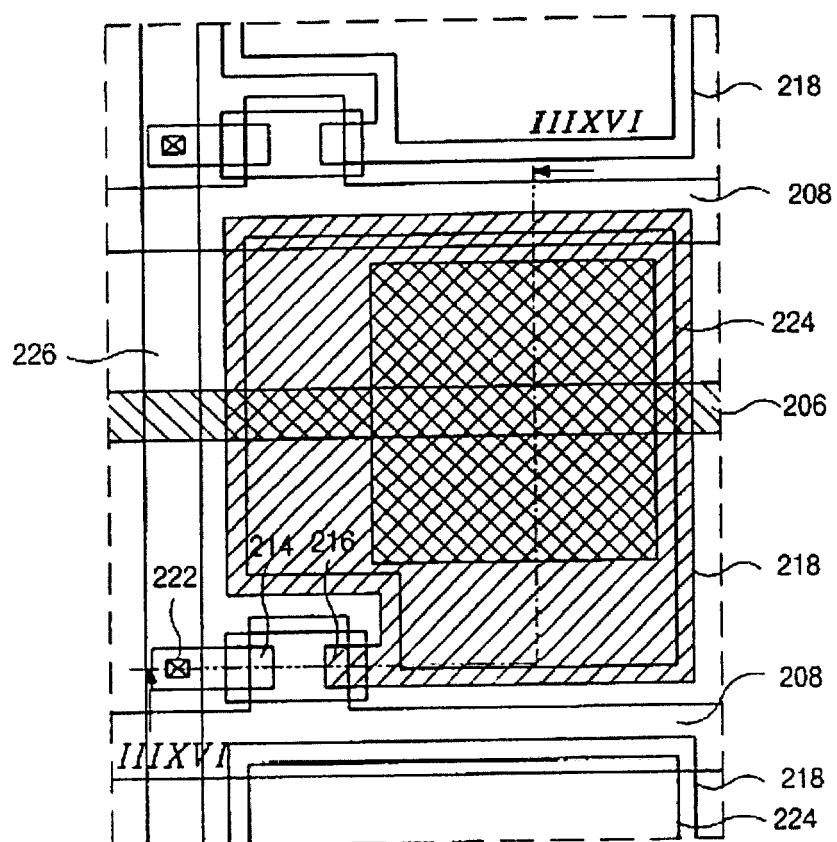

图 29—36 是表示按照本发明第二实施例所述 LCD 装置中阵列衬底制作过程的示意图。图 28 是按照本发明第二实施例所述 LCD 装置中阵列衬底的示意性平面图。在图 28 中, 在公用电极 202 和像素电极 218 之间以及在公用电极 206 和像素电极 218 之间形成存储电容器 “C2”。在形成电容器的电极之间插设栅极绝缘层。公用线 202 用透明导电材料制作并与公用线 206 接触。公用线 206 平行于栅极线 208 并与栅极线 208 相隔一定距离。透明导电材料的像素电极 218 设置在像素区内并与前栅极线 209 重叠。

钝化层包括暴露像素电极 218 的开口部分 224。用与上述第一实施例相同或相类似的工序形成第二实施例的 TFT、栅极和数据线、以及栅极和数据垫片。在第二实施例中，由于将透明导电材料的公用电极作为存储电容器的一个电极使用，所以可在不降低孔径比的情况下得到足够的存储电容量。

5

图 29 是表示按照本发明第二实施例所述 LCD 装置中阵列衬底制造过程的示意性平面图。图 30 是表示按照本发明第二实施例所述 LCD 装置中阵列衬底制造过程的示意性剖面图。在图 29 和图 30 中，在像素区内的衬底 100 上形成透明导电材料例如 ITO 等制成的公用电极 202。由于公用电极是透明的，所以公用电极 202 的面积可以扩大到得到所需的存储电容量。

10

图 31 是表示按照本发明第二实施例所述 LCD 装置中阵列衬底制造过程的示意性平面图。图 32 是表示按照本发明第二实施例所述 LCD 装置中阵列衬底制造过程的示意性剖面图。在图 31 和图 32 中，沿着衬底 100 上行的方向形成带有栅极 204 的栅极线 208 和公用线 206，所述衬底 100 上设有公用电极 202。平行于栅极线 208 的公用线 206 与栅极线 208 相隔一定距离并与公用电极 202 相接触。因此，公用线 206 的公用电压可以施加到公用电极 202 上。

15

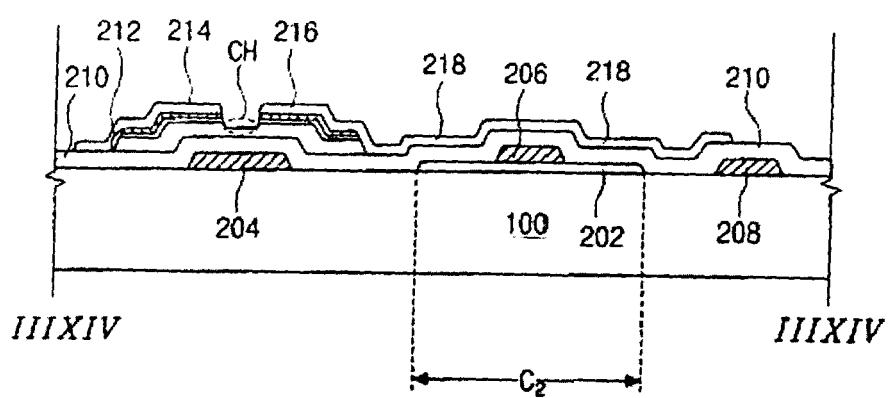

图 33 是表示按照本发明第二实施例所述 LCD 装置中阵列衬底制造过程的示意性平面图。图 34 是表示按照本发明第二实施例所述 LCD 装置中阵列衬底制造过程的示意性剖面图。在图 33 和图 34 中，在带有栅极线 208 和公用线 206 的衬底 100 的整个表面上形成栅极绝缘层 210。接着，在栅极绝缘层 210 上形成带有 Ti 或 Mo 缓冲接触层的半导体层 212。随后，在带有半导体层 212 的衬底上形成透明材料的源电极 214 和像素电极 218，所述半导体层 212 上带有缓冲接触层。

20

25 像素电极 218 包括漏电极区段 216 而且源电极 214 与漏电极区段 216

相隔一定距离。在该制作过程中，通过与所述第一实施例相同的工序形成栅极绝缘层 210、半导体层 212 和沟道“CH”。

图 35 是表示按照本发明第二实施例所述 LCD 装置中阵列衬底制造过程的示意性平面图。图 36 是表示按照本发明第二实施例所述 LCD 装置中阵列衬底制造过程的示意性剖面图。在图 35 和图 36 中，在衬底的整个表面上形成具有第一接触孔 222 和开口部分 224 的钝化层 220。然后，在钝化层 220 上形成通过第一接触孔 222 与源极 214 相连的数据线 226。沿列的方向设置与栅极线 208 和公用线 206 交叉的数据线 226。

在第二实施例中，由于公用电极 202 由透明导电材料制成，所以增大公用电极 202 的面积不会降低孔径比。因此，公用电极 202 和象素电极 218 之间的存储电容器“C2”具有更大的电容量。因此，在不降低存储电容量的情况下得到了具有高孔径比的阵列衬底。对于栅极垫片和数据垫片来说，可以在第二实施例中使用与第一实施例相同的结构。

### 15 第三实施例

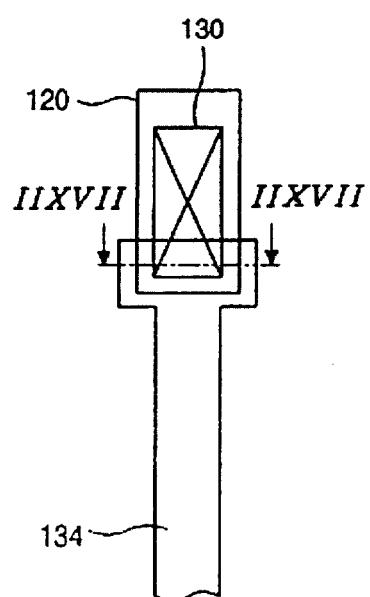

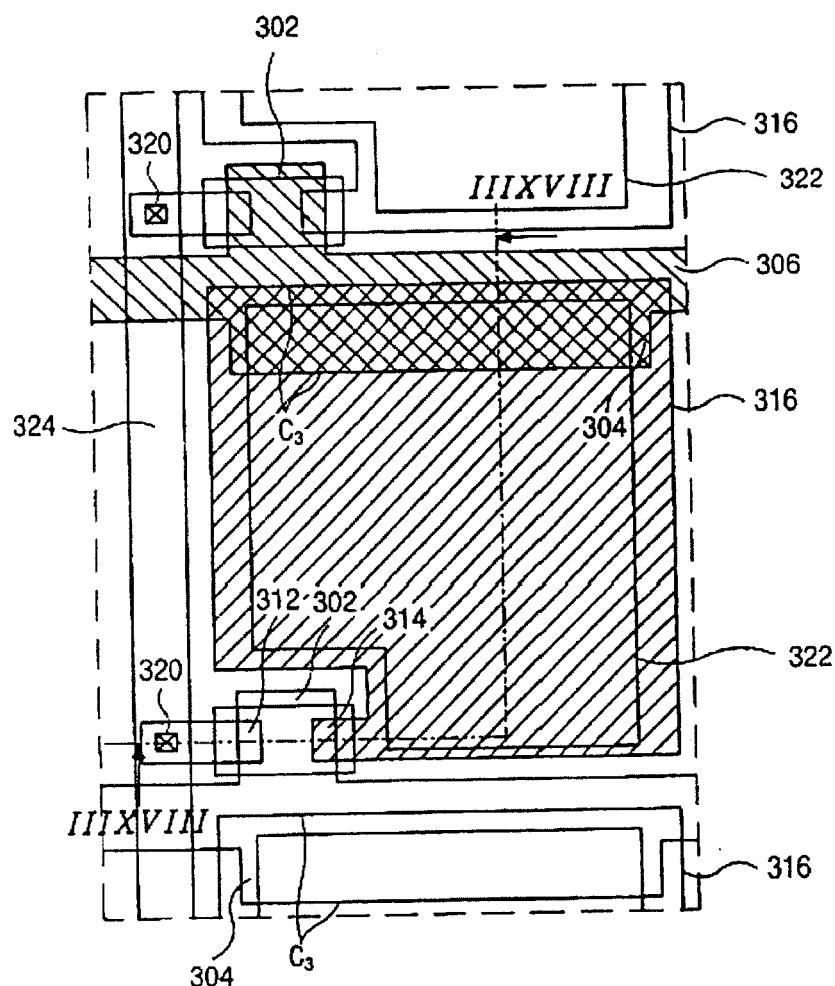

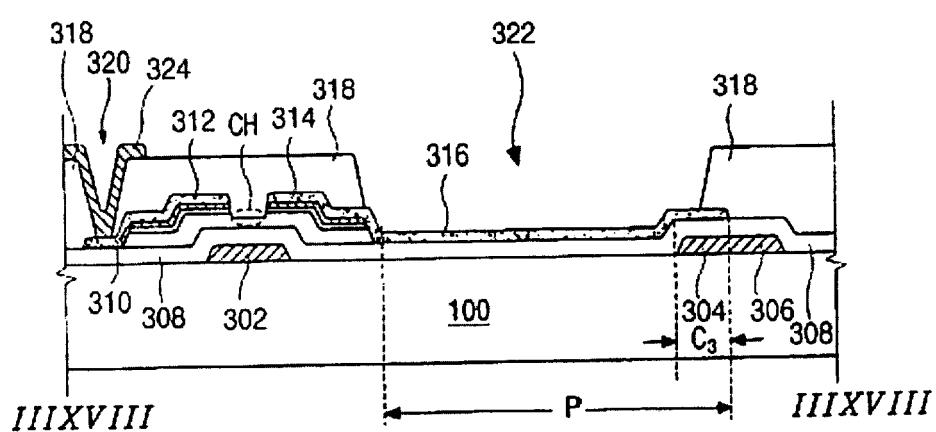

图 37 是按照本发明第三实施例所述 LCD 装置中阵列衬底的示意性平面图。在图 37 中，沿行的方向形成具有栅极 302 和存储电极 304 的栅极线 306。包含漏极区段 314 的象素电极 316 与存储电极 304 重叠。源极 312 与漏极区段 314 相隔一定距离。沿列的方向形成数据线 324 而且数据线通过第一接触孔 320 与源极 312 相连。钝化层上设有暴露象素电极 316 的开口部分 322。

在第三实施例中，在存储电极 304 和象素电极 316 之间形成存储电容器“C3”而且在电极之间插设栅极绝缘层。由于不使用不透明公用线，所以与使用公用型存储电容器的情况相比可以提高孔径比。此外，由于在存储电极和象素电极之间仅插设栅极绝缘层，所以与传统的前栅极存储电容

器相比，能够提高存储电容量。

图 38 是沿图 37 中线“IIIXVIII—IIIXVIII”截取的剖面图。在图 38 中，在衬底 100 上形成具有栅极 302 和存储电极 304 的栅极线 306。当在衬底 100 的整个表面上形成栅极绝缘层 308 之后，在绝缘层上形成带有 Ti 或 Mo 5 缓冲接触层的半导体层 310。然后，在具有半导体层 310 的衬底 100 上形成透明导电材料的源电极 312 和像素电极 316，所述半导体层 310 上带有缓冲接触层。像素电极 316 包括漏极区段 314 而且与半导体层 310 重叠的源极 312 与漏极区段 314 相隔一定距离。在源极 312 和漏极区段 314 的制作过程中，10 在源极 312 和漏极区段 314 之间形成沟道“CH”。

在衬底 100 的整个表面上形成具有第一接触孔 320 和开口部分 322 的钝化层 318。第一接触孔 320 和开口部分 322 分别暴露源极 312 和像素电极 316。最后，在钝化层 318 上形成通过第一接触孔 320 与源电极 312 相连的数据线 324。沿行和列的方向分别形成栅极线 306 和数据线 324。此外，对于栅极线和数据线端部的栅极垫片和数据垫片而言，在第三实施例中使用 15 与第一实施例相同的结构。

在第三实施例中，存储电极 304 从栅极线 306 延伸到像素电极区“P”，而且在存储电极 304 和像素电极 316 之间形成存储电容器“C3”，电极之间插设栅极绝缘层 308。由于不使用不透明公用线，所以与公用型存储电容器的情况相比，可以提高孔径比。此外，由于在存储电极和像素电极之间仅 20 插设栅极绝缘层，所以与传统的前栅极型相比，可以提高存储电容量。

因此，在按照本发明所述的公用型阵列衬底中，公用电极是在形成栅极线的过程中同时形成的，而像素电极是在形成源极和漏极区段的过程中同时形成的。由于在公用线的像素电极之间仅插设例如比钝化层薄的栅极绝缘层，所以在不降低孔径比的情况下可以提高存储电容量。

25 另一方面，把与公用线接触的透明导电材料的公用电极作为存储电容

器的一个电极使用，可以提高存储电容量。在按照本发明所述前栅极型的阵列衬底中，由于在前栅极线的存储电极和像素电极之间仅插设栅极绝缘层，所以与传统前栅极型阵列衬底相比更能提高存储电容量而且与传统公用型阵列衬底相比更能在不降低存储电容量的情况下提高孔径比。

5 对于熟悉本领域的技术人员来说，很显然，在不脱离本发明的构思或范围的情况下可以对按照本发明所述阵列衬底和其制造方法做出各种改进和变型。因此，本发明意在覆盖这些落入后面的权利要求及其等同物范围内的改进和变型。

很显然，在此所述的发明可以用很多方式加以改变。然而不能认为这

10 些改变脱离了本发明的构思和范围，而是应当确定，所有这些对于熟悉本领域的技术人员来说是显而易见的改进都包含在下述权利要求的范围内。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8

图 9

图 10

图 11

图 12

图 13

图 14

图 15

图 16

图 17

图 18

图 19

图 20

图 21

图 22

图 23

图 24

图 25

图 26

图 27

图 28

图 29

图 30

图 31

图 32

图 33

图 34

图 35

图 36

图 37

图 38

|                |                                                                  |         |            |

|----------------|------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置的阵列衬底及其制造方法                                                |         |            |

| 公开(公告)号        | <a href="#">CN1280665C</a>                                       | 公开(公告)日 | 2006-10-18 |

| 申请号            | CN02120490.X                                                     | 申请日     | 2002-05-21 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                         |         |            |

| 申请(专利权)人(译)    | LG. 菲利浦LCD株式会社                                                   |         |            |

| 当前申请(专利权)人(译)  | LG. 菲利浦LCD株式会社                                                   |         |            |

| [标]发明人         | 蔡基成<br>李载钧<br>黄龙燮                                                |         |            |

| 发明人            | 蔡基成<br>李载钧<br>黄龙燮                                                |         |            |

| IPC分类号         | G02F1/136 G02F1/1333 G02F1/1343 G02F1/1362 G02F1/1368 H01L29/786 |         |            |

| CPC分类号         | G02F1/13458 G02F1/1362 G02F1/136213                              |         |            |

| 代理人(译)         | 徐金国<br>陈红                                                        |         |            |

| 优先权            | 1020010029811 2001-05-29 KR                                      |         |            |

| 其他公开文献         | CN1388405A                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                   |         |            |

#### 摘要(译)

本发明公开了一种液晶显示装置的阵列衬底和该阵列衬底的制造方法。所述阵列衬底包括衬底，在衬底上沿第一方向设置的栅极线，平行于栅极线且与栅极线彼此相隔一定距离的公用线，其中公用线用与栅极线相同的材料制作。所述阵列衬底还包括处于栅极线和公用线上的栅极绝缘层，处于栅极绝缘层上的半导体层，和用透明导电材料制成的象素电极，所述象素电极包括漏极区段。漏极区段与半导体层重叠而且透明材料的源极与漏极区段彼此相隔一定距离。钝化层包括处于象素电极和源极之上的第一接触孔和开口部分，其中第一接触孔暴露源极而开口部分暴露象素电极。在钝化层上沿第二方向设置数据线，数据线通过第一接触孔与源极相连并与栅极线交叉。