## (12) 发明专利申请

(10) 申请公布号 CN 101763831 A

(43) 申请公布日 2010. 06. 30

(21) 申请号 200910168523. 6

(22) 申请日 2009. 08. 21

## (30) 优先权数据

10-2008-0132466 2008. 12. 23 KR

(71) 申请人 乐金显示有限公司

地址 韩国首尔

(72) 发明人 赵舜东 姜弼盛 朴万奎 姜正浩

郑良锡 高勤雨 曹畅训 金贤喆(74) 专利代理机构 北京律诚同业知识产权代理

有限公司 11006

代理人 徐金国

(51) Int. Cl.

G09G 3/36 (2006. 01)

G09G 3/20 (2006. 01)

权利要求书 4 页 说明书 23 页 附图 29 页

## (54) 发明名称

液晶显示器及其驱动方法

## (57) 摘要

公开了一种液晶显示器及其驱动方法。该液晶显示器包括：时序控制器，N个源极驱动集成电路（IC），其中N是等于或者大于2的整数；N对数据总线，其每一对数据总线按照点对点的方式使时序控制器与N个源极驱动IC的每一个相连；锁定检查线，用于使N个源极驱动IC的第一源极驱动IC与时序控制器相连并且使N个源极驱动IC彼此级联；以及反馈锁定检查线，用于使N个源极驱动IC的最后源极驱动IC与时序控制器相连。时序控制器的输出电压的摆动宽度与在时序控制器与N个源极驱动IC之间的距离成比例地增大。

1. 一种液晶显示器,包括 :

时序控制器 ;

N 个源极驱动集成电路 (IC),其中 N 是等于或者大于 2 的整数 ;

N 对数据总线,其每一对数据总线按照点对点的方式使时序控制器与 N 个源极驱动 IC 的每一个相连 ;

锁定检查线,使所述 N 个源极驱动 IC 的第一源极驱动 IC 与所述时序控制器相连并且使所述 N 个源极驱动 IC 彼此级联;以及

反馈锁定检查线,使所述 N 个源极驱动 IC 的最后源极驱动 IC 与所述时序控制器相连,

其中所述时序控制器通过所述 N 对数据总线的每一对数据总线将前导信号串行传输到所述 N 个源极驱动 IC 的每一个,在所述前导信号中顺序排列有具有高逻辑电平的多个位、然后顺序排列有具有低逻辑电平的多个位;所述时序控制器通过所述锁定检查线将锁定信号传输到所述第一源极驱动 IC,该锁定信号表示从所述 N 个源极驱动 IC 的每一个输出的内部时钟脉冲的相位被锁定;所述时序控制器通过所述反馈锁定检查线接收来自所述最后源极驱动 IC 的锁定信号的反馈信号,并且通过所述 N 对数据总线的每一对数据总线将至少一个源极控制包串行传输到所述 N 个源极驱动 IC 的每一个,所述至少一个源极控制包用于对从所述 N 个源极驱动 IC 的每一个输出的数据电压进行控制,

其中包括所述前导信号、锁定信号、以及源极控制包的时序控制器的输出电压的摆动宽度与在所述时序控制器与所述 N 个源极驱动 IC 之间的距离成比例地增大。

2. 根据权利要求 1 所述的液晶显示器,其中在所述时序控制器串行传输了所述源极控制包之后,所述时序控制器通过所述 N 对数据总线的每一对数据总线将至少一个 RGB 数据包串行传输到所述 N 个源极驱动 IC 的每一个,

其中提供给所述 N 个源极驱动 IC 的 RGB 数据包的电压的摆动宽度与在所述时序控制器与所述 N 个源极驱动 IC 之间的距离成比例地增大。

3. 根据权利要求 2 所述的液晶显示器,其中所述 RGB 数据包依次包括时钟位、第一 RGB 数据位、内部数据使能时钟位、以及第二 RGB 数据位。

4. 根据权利要求 3 所述的液晶显示器,其中所述 N 个源极驱动 IC 的每一个从所述前导信号恢复出第一参考时钟,用以输出该第一参考时钟以及第一内部时钟脉冲,该第一内部时钟脉冲的相位被锁定,

其中如果从所述 N 个源极驱动 IC 输出的第一内部时钟脉冲的相位被锁定,那么所述最后源极驱动 IC 通过所述反馈锁定检查线将所述锁定信号的反馈信号传输到所述时序控制器,然后所述 N 个源极驱动 IC 中的每一个从所述源极控制包恢复出源极控制数据,

其中所述 N 个源极驱动 IC 的每一个从包含在所述 RGB 数据包之内的时钟位恢复出第二参考时钟,根据该第二参考时钟以及第二内部时钟脉冲来对包含在所述 RGB 数据包之内的 RGB 数据进行采样,并且根据该源极控制数据将所述 RGB 数据转换成正或负数据电压用以输出该正 / 负数据电压,其中该第二内部时钟脉冲的相位被锁定。

5. 根据权利要求 4 所述的液晶显示器,其中该源极控制数据包括 :

极性控制信号,用于确定从所述 N 个源极驱动 IC 的每一个输出并提供给液晶显示器面板的数据线的正 / 负数据电压的极性;以及

源极输出使能信号,用于对从所述 N 个源极驱动 IC 的每一个输出的正 / 负数据的输出

时序进行控制。

6. 根据权利要求 5 所述的液晶显示器，其中该源极控制数据包括：

该源极输出使能信号的激活信息；

该源极输出使能信号的脉冲宽度信息；以及

该极性控制信号的激活信息。

7. 根据权利要求 6 所述的液晶显示器，其中根据该源极输出使能信号的脉冲宽度信息，通过将该源极控制包和所述 RGB 数据包中的一个的长度乘以“i”来确定该源极输出使能信号的脉冲宽度，其中 i 是自然数。

8. 根据权利要求 5 所述的液晶显示器，其中所述 N 个源极驱动 IC 的每一个依次输出第一正数据电压、第二正数据电压、第一负数据电压、以及第二负数据电压，

其中该源极输出使能信号包括用于对该第一正数据电压和第一负数据电压的每一个的输出时序进行控制的第一脉冲以及用于对该第二正数据电压和第二负数据电压的每一个的输出时序进行控制的第二脉冲，

其中该第二脉冲的宽度大于该第一脉冲的宽度。

9. 根据权利要求 4 所述的液晶显示器，其中所述 RGB 数据包包括待在该液晶显示器面板的奇数行上显示的第一 RGB 数据包以及待在该液晶显示器面板的偶数行上显示的第二 RGB 数据包，

其中该第一 RGB 数据包中的 RGB 数据排列顺序与该第二 RGB 数据包中的 RGB 数据排列顺序不同。

10. 根据权利要求 9 所述的液晶显示器，其中该第一 RGB 数据包依次包括第一像素的 R 数据、该第一像素的 G 数据、以及该第一像素的 B 数据，

其中该第二 RGB 数据包依次包括第二像素的 B 数据、第三像素的 R 数据、以及该第三像素的 G 数据。

11. 根据权利要求 10 所述的液晶显示器，其中该第一 RGB 数据包还包括排列在该第一像素的 R 数据之前的时钟位以及排列在该第一像素的第一 G 数据与该第一像素的第二 G 数据之间的内部数据使能时钟位，

其中该第二 RGB 数据包还包括排列在该第二像素的 R 数据之前的时钟位以及排列在该第三像素的第一 R 数据与该第三像素的第二 R 数据之间的内部数据使能时钟位。

12. 根据权利要求 11 所述的液晶显示器，其中根据该源极输出使能信号的脉冲宽度信息，所述 N 个源极驱动 IC 的每一个通过将该源极控制包与 RGB 数据包中的一个的长度乘以“i”来调节该源极输出使能信号的脉冲宽度，其中 i 是自然数。

13. 根据权利要求 11 所述的液晶显示器，其中该时序控制器通过所述 N 对数据总线的每一对数据总线将用于对从所述 N 个源极驱动 IC 的每一个输出的数据电压进行控制的至少一个第二源极控制包串行传输到所述 N 个源极驱动 IC 的每一个，

其中该第二源极控制包包括用于确定所述 N 个源极驱动 IC 的每一个的输出缓冲器的放大比率的 PWRC1/2 选择信息、用于确定所述 N 个源极驱动 IC 的每一个的充电共享电压的输出的 MODE 选择信息、用于确定该源极输出使能信号的接收路径的 SOE\_EN 选择信息、用于确定该极性控制信号的接收路径的 PACK\_EN 选择信息、用于确定所述 N 个源极驱动 IC 的输出通道数目的 CHMODE 选择信息、向所述 N 个源极驱动 IC 的每一个给予芯片标识码以对所

述 N 个源极驱动 IC 进行单独控制的 CID1/2 选择信息、以及用于确定从所述 N 个源极驱动 IC 输出的正 / 负数据电压的水平极性周期的 H\_2DOT 选择信息中的至少之一。

14. 根据权利要求 2 所述的液晶显示器，其中在该时序控制器接收到该锁定信号的反馈信号与预定测试模式使能信号中的至少一个之后，该时序控制器通过所述 N 对数据总线的每一对数据总线将该源极控制包和 RGB 数据包串行传输到所述 N 个源极驱动 IC 的每一个。

15. 根据权利要求 1 所述的液晶显示器，还包括使该时序控制器与所述 N 个源极驱动 IC 并联的一对控制线，

其中该时序控制器通过这对控制线将用于单独标识所述 N 个源极驱动 IC 的芯片标识码以及用于控制所述 N 个源极驱动 IC 的每一个的功能的控制数据传送到所述 N 个源极驱动 IC。

16. 一种液晶显示器的驱动方法，该液晶显示器包括时序控制器和 N 个源极驱动集成电路 (IC)，其中 N 是等于或大于 2 的整数，该方法包括：

从该时序控制器产生前导信号，在该前导信号中顺序排列有具有高逻辑电平的多个位、然后顺序排列有具有低逻辑电平的多个位；

通过按照点对点方式使该时序控制器与所述 N 个源极驱动 IC 相连的 N 对数据总线的每一对数据总线，将该前导信号串行传输到所述 N 个源极驱动 IC 的每一个；

从该时序控制器产生用于表示从所述 N 个源极驱动 IC 的每一个输出的内部时钟脉冲的相位被锁定的锁定信号；

通过使所述 N 个源极驱动 IC 的第一源极驱动 IC 与该时序控制器相连并且使所述 N 个源极驱动 IC 彼此级联的锁定检查线，将该锁定信号传输到该第一源极驱动 IC；

从所述 N 个源极驱动 IC 的最后源极驱动 IC 产生该锁定信号的反馈信号；

通过使该最后源极驱动 IC 与该时序控制器相连的反馈锁定检查线将该锁定信号的反馈信号传输到该时序控制器；

从该时序控制器产生用于对从所述 N 个源极驱动 IC 的每一个输出的数据电压进行控制的至少一个源极控制包；以及

通过所述 N 对数据总线的每一对数据总线将该源极控制包串行传输到所述 N 个源极驱动 IC 的每一个，

其中包括所述前导信号、锁定信号、以及源极控制包的该时序控制器的输出电压的摆动宽度与在该时序控制器与所述 N 个源极驱动 IC 之间的距离成比例地增加。

17. 根据权利要求 16 所述的方法，还包括：

在串行传输该源极控制包之后，从该时序控制器产生至少一个 RGB 数据包；以及

通过所述 N 对数据总线的每一对数据总线将该 RGB 数据包串行传输到所述 N 个源极驱动 IC 的每一个。

18. 根据权利要求 17 所述的方法，还包括：

在所述 N 个源极驱动 IC 的每一个内部从该前导信号恢复出第一参考时钟，用以从所述 N 个源极驱动 IC 的每一个输出第一参考时钟和第一内部时钟脉冲，该第一内部时钟脉冲的相位被锁定；

如果从所述 N 个源极驱动 IC 输出的第一内部时钟脉冲的相位被锁定，那么通过该反馈

锁定检查线将该最后源极驱动 IC 产生的锁定信号的反馈信号传输到该时序控制器；

在所述 N 个源极驱动 IC 的每一个的内部从该源极控制包恢复出源极控制数据；

在所述 N 个源极驱动 IC 的每一个的内部从包含在所述 RGB 数据包之内的时钟位恢复出第二参考时钟，用以从所述 N 个源极驱动 IC 的每一个输出该第二参考时钟以及第二内部时钟脉冲，该第二内部时钟脉冲的相位被锁定；

根据该第二内部时钟脉冲对包含在该 RGB 数据包之内的 RGB 数据进行采样；以及

在所述 N 个源极驱动 IC 的每一个的内部根据该源极控制数据将该 RGB 数据转换成正或负数据电压，用以输出所述正 / 负数据电压。

19. 根据权利要求 18 所述的方法，其中该 RGB 数据包包括待在液晶显示器面板的奇数行上显示的第一 RGB 数据包以及待在该液晶显示器面板的偶数行上显示的第二 RGB 数据包，

其中该第一 RGB 数据包依次包括第一像素的 R 数据、该第一像素的 G 数据、以及该第一像素的 B 数据，

其中该第二 RGB 数据包依次包括第二像素的 B 数据、第三像素的 R 数据、以及该第三像素的 G 数据。

20. 根据权利要求 19 所述的方法，其中该第一 RGB 数据包还包括排列在该第一像素的 R 数据之前的时钟位以及排列在该第一像素的第一 G 数据与该第一像素的第二 G 数据之间的内部数据使能时钟位，

其中该第二 RGB 数据包还包括排列在该第二像素的 R 数据之前的时钟位以及排列在该第三像素的第一 R 数据与该第三像素的第二 R 数据之间的内部数据使能时钟位。

## 液晶显示器及其驱动方法

[0001] 本申请要求 2008 年 12 月 23 日申请的韩国专利申请 No. 10-2008-0132466 的优先权，在此为了所有的目的并入本文中，就如同在此完全阐述一样。

### 技术领域

[0002] 本发明的实施方式涉及一种液晶显示器及其驱动方法。

### 背景技术

[0003] 有源矩阵型液晶显示器利用薄膜晶体管 (TFT) 作为开关元件来显示移动图片。有源矩阵型液晶显示器由于具有薄外观，因此已在电视机以及诸如办公设备和计算机这样的便携式设备的显示设备中实施。相应地，阴极射线管 (CRT) 正快速地被有源矩阵型液晶显示器替代。

[0004] 液晶显示器包括用于向液晶显示器面板的数据线提供数据电压的多个源极驱动集成电路 (IC)、用于向液晶显示器面板的栅极线顺序提供栅极脉冲 (即扫描脉冲) 的多个栅极驱动 IC、以及用于对源极驱动 IC 和栅极驱动 IC 进行控制的时序控制器。在液晶显示器中，通过接口将数字视频数据输入到时序控制器。

[0005] 时序控制器通过诸如微型低压差分信号 (LVDS) 接口这样的接口将数字视频数据、用于对数字视频数据进行采样的时钟、用于对源极驱动 IC 的操作进行控制的控制信号等等提供给源极驱动 IC。源极驱动 IC 对从时序控制器串行输入的数字视频数据进行反串行化以输出并行数据，并且此后利用伽玛补偿电压将该并行数据转换成模拟数据电压以将该模拟数据电压提供给数据线。

[0006] 时序控制器利用共同地将时钟和数字视频数据应用到源极驱动 IC 这样的多点 (multi-drop) 方式将必要信号提供给源极驱动 IC。因为源极驱动 IC 彼此级联，因此源极驱动 IC 对数字视频数据进行顺序采样并且此后同时输出与 1 条线相对应的数据电压。在这种数据传输方法中，在时序控制器与源极驱动 IC 之间必需具备诸如 R、G、B 数据传输线、用于对源极驱动 IC 的输出和源极驱动 IC 的极性变化的操作时序进行控制的控制线、以及时钟传输线之类的多条线。因为微型 LVDS 接口是采用以相位彼此不同的一对差分信号的形式对数字视频数据和时钟的每一个进行传输的方式，因此时序控制器与源极驱动 IC 之间至少需要 14 条数据传输线来同时传输奇数数据和偶数数据。相应地，由于需要在位于时序控制器与源极驱动 IC 之间的印刷电路板 (PCB) 上形成很多条数据传输线，因此很难降低数据传输线的数目。

[0007] 此外，在液晶显示器中，根据时序控制器与源极驱动 IC 之间的距离可能会引起输入到源极驱动 IC 的信号的延迟量偏差以及信号的压降量偏差。

### 发明内容

[0008] 本发明的实施方式提供了一种可对输入到源极驱动集成电路 (IC) 的信号的延迟量的偏差和信号的压降量的偏差进行补偿的液晶显示器及其驱动方法。

[0009] 在一个方面中，提供一种液晶显示器，包括：时序控制器；N个源极驱动集成电路（IC），其中N是等于或者大于2的整数；N对数据总线，其每一对数据总线按照点对点的方式使时序控制器与N个源极驱动IC的每一个相连；锁定检查线，使所述N个源极驱动IC的第一源极驱动IC与所述时序控制器相连并且使所述N个源极驱动IC彼此级联；以及反馈锁定检查线，使所述N个源极驱动IC的最后源极驱动IC与所述时序控制器相连。其中所述时序控制器通过所述N对数据总线的每一对数据总线将前导信号串行传输到所述N个源极驱动IC的每一个，在所述前导信号中顺序排列有具有高逻辑电平的多个位、然后顺序排列有具有低逻辑电平的多个位；所述时序控制器通过所述锁定检查线将锁定信号传输到所述第一源极驱动IC，该锁定信号表示从所述N个源极驱动IC的每一个输出的内部时钟脉冲的相位被锁定；所述时序控制器通过所述反馈锁定检查线接收来自所述最后源极驱动IC的锁定信号的反馈信号，并且通过所述N对数据总线的每一对数据总线将至少一个源极控制包串行传输到所述N个源极驱动IC的每一个，所述至少一个源极控制包用于对从所述N个源极驱动IC的每一个输出的数据电压进行控制。其中包括所述前导信号、锁定信号、以及源极控制包的时序控制器的输出电压的摆动宽度与在所述时序控制器与所述N个源极驱动IC之间的距离成比例地增大。

[0010] 在所述时序控制器串行传输了所述源极控制包之后，所述时序控制器通过所述N对数据总线的每一对数据总线将至少一个RGB数据包串行传输到所述N个源极驱动IC的每一个。其中提供给所述N个源极驱动IC的RGB数据包的电压的摆动宽度与在所述时序控制器与所述N个源极驱动IC之间的距离成比例地增大。

[0011] 所述RGB数据包依次包括时钟位、第一RGB数据位、内部数据使能时钟位、以及第二RGB数据位。

[0012] 所述N个源极驱动IC的每一个从所述前导信号恢复出第一参考时钟，用以输出该第一参考时钟以及第一内部时钟脉冲，该第一内部时钟脉冲的相位被锁定。其中如果从所述N个源极驱动IC输出的第一内部时钟脉冲的相位被锁定，那么所述最后源极驱动IC通过所述反馈锁定检查线将所述锁定信号的反馈信号传输到所述时序控制器，然后所述N个源极驱动IC中的每一个从所述源极控制包恢复出源极控制数据。其中所述N个源极驱动IC的每一个从包含在所述RGB数据包之内的时钟位恢复出第二参考时钟，根据该第二参考时钟以及第二内部时钟脉冲来对包含在所述RGB数据包之内的RGB数据进行采样，并且根据该源极控制数据将所述RGB数据转换成正或负数据电压用以输出该正/负数据电压，其中该第二内部时钟脉冲的相位被锁定。

[0013] 该源极控制数据包括：极性控制信号，用于确定从所述N个源极驱动IC的每一个输出并提供给液晶显示器面板的数据线的正/负数据电压的极性；以及源极输出使能信号，用于对从所述N个源极驱动IC的每一个输出的正/负数据的输出时序进行控制。

[0014] 该源极控制数据包括：该源极输出使能信号的激活信息；该源极输出使能信号的脉冲宽度信息；以及该极性控制信号的激活信息。

[0015] 根据该源极输出使能信号的脉冲宽度信息，通过将该源极控制包和所述RGB数据包中的一个的长度乘以“i”来确定该源极输出使能信号的脉冲宽度，其中i是自然数。

[0016] 所述N个源极驱动IC的每一个依次输出第一正数据电压、第二正数据电压、第一负数据电压、以及第二负数据电压。其中该源极输出使能信号包括用于对该第一正数据电

压和第一负数据电压的每一个的输出时序进行控制的第一脉冲以及用于对该第二正数据电压和第二负数据电压的每一个的输出时序进行控制的第二脉冲。其中该第二脉冲的宽度大于该第一脉冲的宽度。

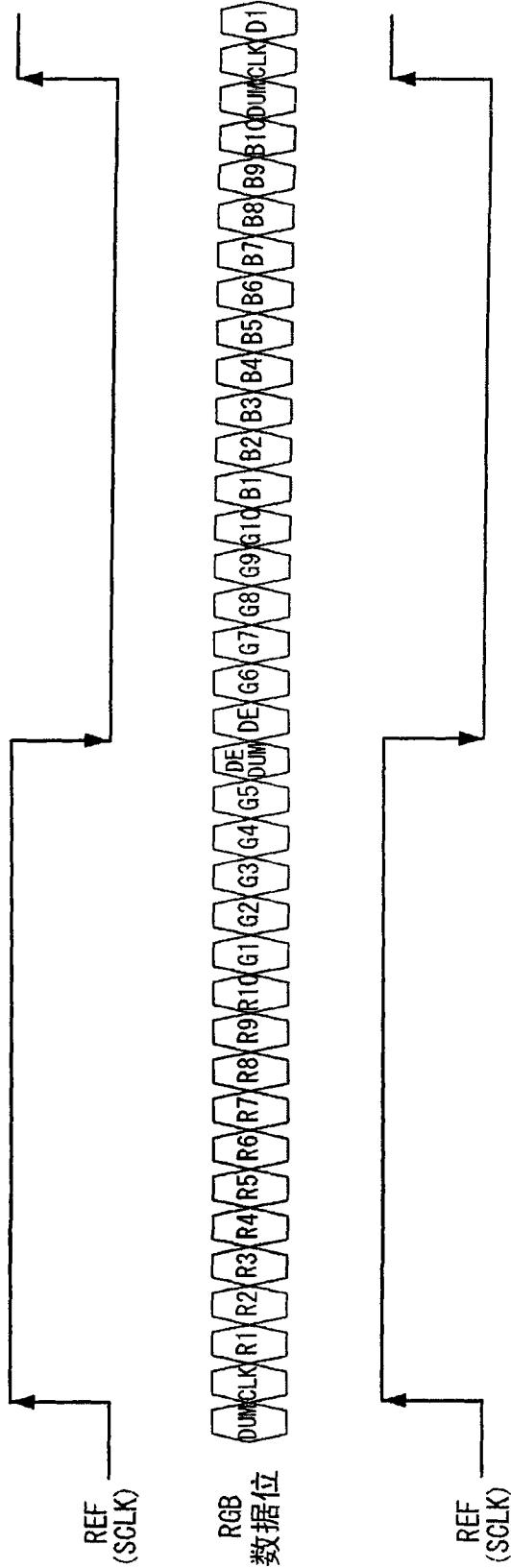

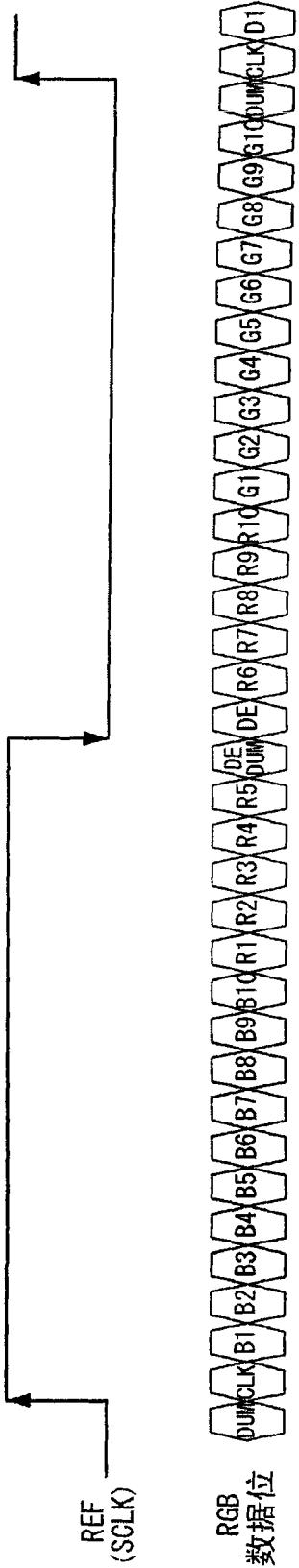

[0017] 所述 RGB 数据包包括待在该液晶显示器面板的奇数行上显示的第一 RGB 数据包以及待在该液晶显示器面板的偶数行上显示的第二 RGB 数据包，其中该第一 RGB 数据包中的 RGB 数据排列顺序与该第二 RGB 数据包中的 RGB 数据排列顺序不同。

[0018] 该第一 RGB 数据包依次包括第一像素的 R 数据、该第一像素的 G 数据、以及该第一像素的 B 数据，其中该第二 RGB 数据包依次包括第二像素的 B 数据、第三像素的 R 数据、以及该第三像素的 G 数据。

[0019] 该第一 RGB 数据包还包括排列在该第一像素的 R 数据之前的时钟位以及排列在该第一像素的第一 G 数据与该第一像素的第二 G 数据之间的内部数据使能时钟位，其中该第二 RGB 数据包还包括排列在该第二像素的 R 数据之前的时钟位以及排列在该第三像素的第一 R 数据与该第三像素的第二 R 数据之间的内部数据使能时钟位。

[0020] 根据该源极输出使能信号的脉冲宽度信息，所述 N 个源极驱动 IC 的每一个通过将该源极控制包与 RGB 数据包中的一个的长度乘以“i”来调节该源极输出使能信号的脉冲宽度，其中 i 是自然数。

[0021] 该时序控制器通过所述 N 对数据总线的每一对数据总线将用于对从所述 N 个源极驱动 IC 的每一个输出的数据电压进行控制的至少一个第二源极控制包串行传输到所述 N 个源极驱动 IC 的每一个。其中该第二源极控制包包括用于确定所述 N 个源极驱动 IC 的每一个的输出缓冲器的放大比率的 PWRC1/2 选择信息、用于确定所述 N 个源极驱动 IC 的每一个的充电共享电压的输出的 MODE 选择信息、用于确定该源极输出使能信号的接收路径的 SOE\_EN 选择信息、用于确定该极性控制信号的接收路径的 PACK\_EN 选择信息、用于确定所述 N 个源极驱动 IC 的输出通道数目的 CHMODE 选择信息、向所述 N 个源极驱动 IC 的每一个给予芯片标识码以对所述 N 个源极驱动 IC 进行单独控制的 CID1/2 选择信息、以及用于确定从所述 N 个源极驱动 IC 输出的正 / 负数据电压的水平极性周期的 H\_2DOT 选择信息中的至少之一。

[0022] 在该时序控制器接收到该锁定信号的反馈信号与预定测试模式使能信号中的至少一个之后，该时序控制器通过所述 N 对数据总线的每一对数据总线将该源极控制包和 RGB 数据包串行传输到所述 N 个源极驱动 IC 的每一个。

[0023] 本发明的液晶显示器还包括使该时序控制器与所述 N 个源极驱动 IC 并联的一对控制线，其中该时序控制器通过这对控制线将用于单独标识所述 N 个源极驱动 IC 的芯片标识码以及用于控制所述 N 个源极驱动 IC 的每一个的功能的控制数据传送到所述 N 个源极驱动 IC。

[0024] 根据另一方面，本发明还提供一种液晶显示器的驱动方法，该液晶显示器包括时序控制器和 N 个源极驱动集成电路 (IC)，其中 N 是等于或大于 2 的整数，该方法包括：从该时序控制器产生前导信号，在该前导信号中顺序排列有具有高逻辑电平的多个位、然后顺序排列有具有低逻辑电平的多个位；通过按照点对点方式使该时序控制器与所述 N 个源极驱动 IC 相连的 N 对数据总线的每一对数据总线，将该前导信号串行传输到所述 N 个源极驱动 IC 的每一个；从该时序控制器产生用于表示从所述 N 个源极驱动 IC 的每一个输出的内

部时钟脉冲的相位被锁定的锁定信号；通过使所述 N 个源极驱动 IC 的第一源极驱动 IC 与该时序控制器相连并且使所述 N 个源极驱动 IC 彼此级联的锁定检查线，将该锁定信号传输到该第一源极驱动 IC；从所述 N 个源极驱动 IC 的最后源极驱动 IC 产生该锁定信号的反馈信号；通过使该最后源极驱动 IC 与该时序控制器相连的反馈锁定检查线将该锁定信号的反馈信号传输到该时序控制器；从该时序控制器产生用于对从所述 N 个源极驱动 IC 的每一个输出的数据电压进行控制的至少一个源极控制包；以及通过所述 N 对数据总线的每一对数据总线将该源极控制包串行传输到所述 N 个源极驱动 IC 的每一个。其中包括所述前导信号、锁定信号、以及源极控制包的该时序控制器的输出电压的摆动宽度与在该时序控制器与所述 N 个源极驱动 IC 之间的距离成比例地增加。

[0025] 从在下文中所给出的详细说明可显而易见地得知本发明进一步可应用的范围。然而，应清楚的是通过说明仅给出了详细说明和具体示例，然而仅是以举例的方式提出，而并非对本发明范围的限制。所述领域普通技术人员从详细的说明书中可显而易见地得知在本发明的精神和范围之内的各种变化和修改。

## 附图说明

[0026] 附图包含在本申请中以构成本申请的一部分，用以对本发明提供进一步的理解。附图例示了本发明的实施方式，并与说明书一起用于解释本发明的原理。在附图中：

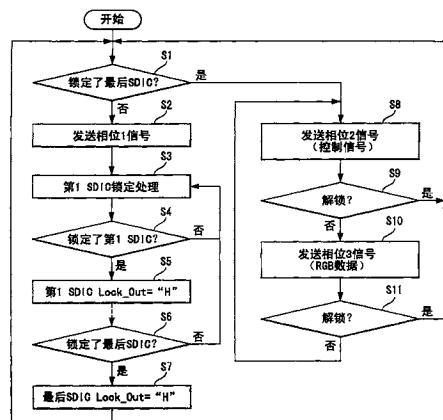

- [0027] 图 1 是例示了根据本发明实施方式的液晶显示器的框图；

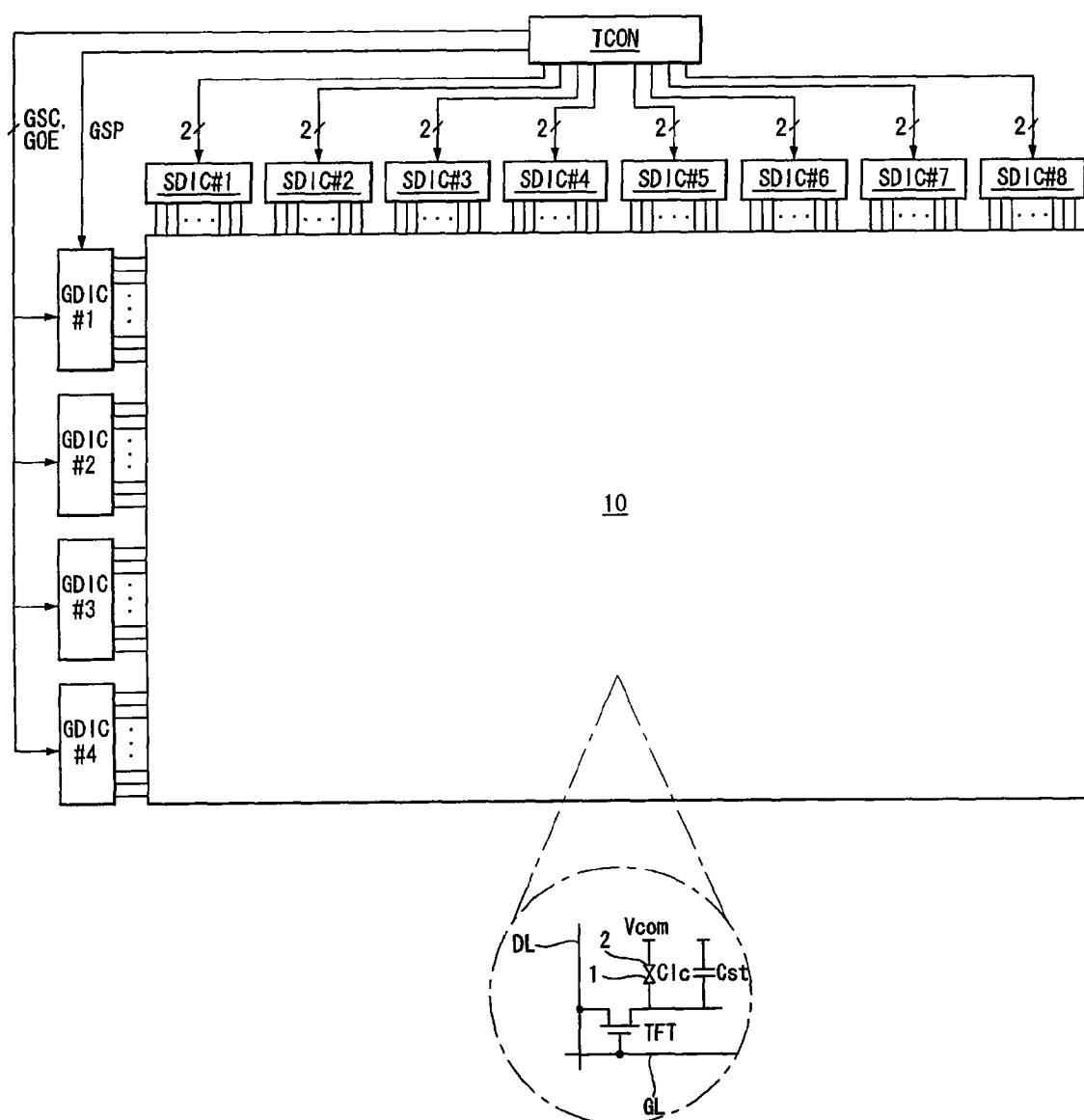

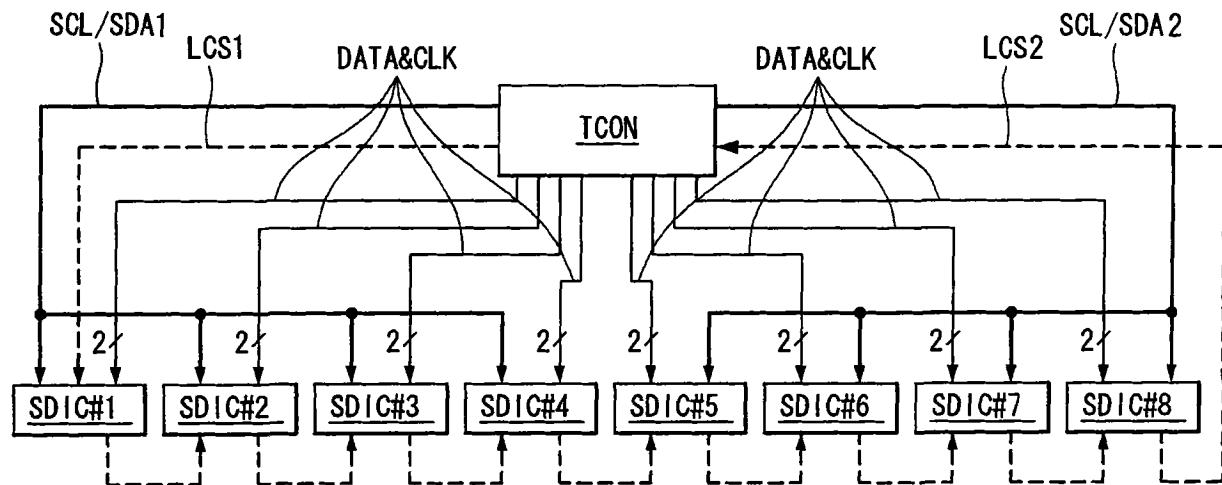

- [0028] 图 2 例示了时序控制器与源极驱动集成电路 (IC) 之间的线；

- [0029] 图 3 和 4 是对源极驱动 IC 的配置进行例示的框图；

- [0030] 图 5 是对栅极驱动 IC 的配置进行例示的框图；

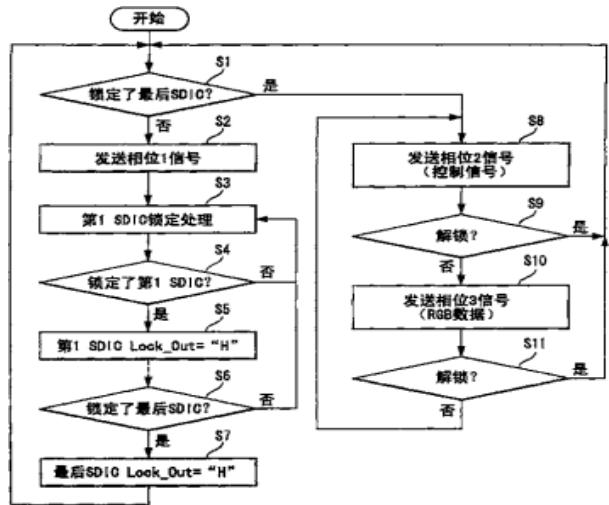

- [0031] 图 6 是按阶段例示了时序控制器与源极驱动 IC 之间的信号传输处理的流程图；

- [0032] 图 7 是对时钟分离和数据采样单元进行例示的框图；

- [0033] 图 8 例示了可使源极驱动 IC 执行调试操作的串行通信控制路径以及芯片标识码的实例；

- [0034] 图 9 是对锁相环 (PLL) 进行例示的框图；

- [0035] 图 10 是对时序控制器所产生的相位 1 信号进行例示的波形图；

- [0036] 图 11 是对时序控制器所产生的相位 2 信号进行例示的波形图；

- [0037] 图 12 和 13 是对时序控制器所产生的相位 3 信号进行例示的波形图；

- [0038] 图 14 例示了源极控制包和 RGB 数据包的数据映射表的实例；

- [0039] 图 15 例示了伪源极控制包、实际源极控制包、以及最后伪源极控制包的数据映射表的实例；

- [0040] 图 16 例示了实际源极控制包的第一实施例；

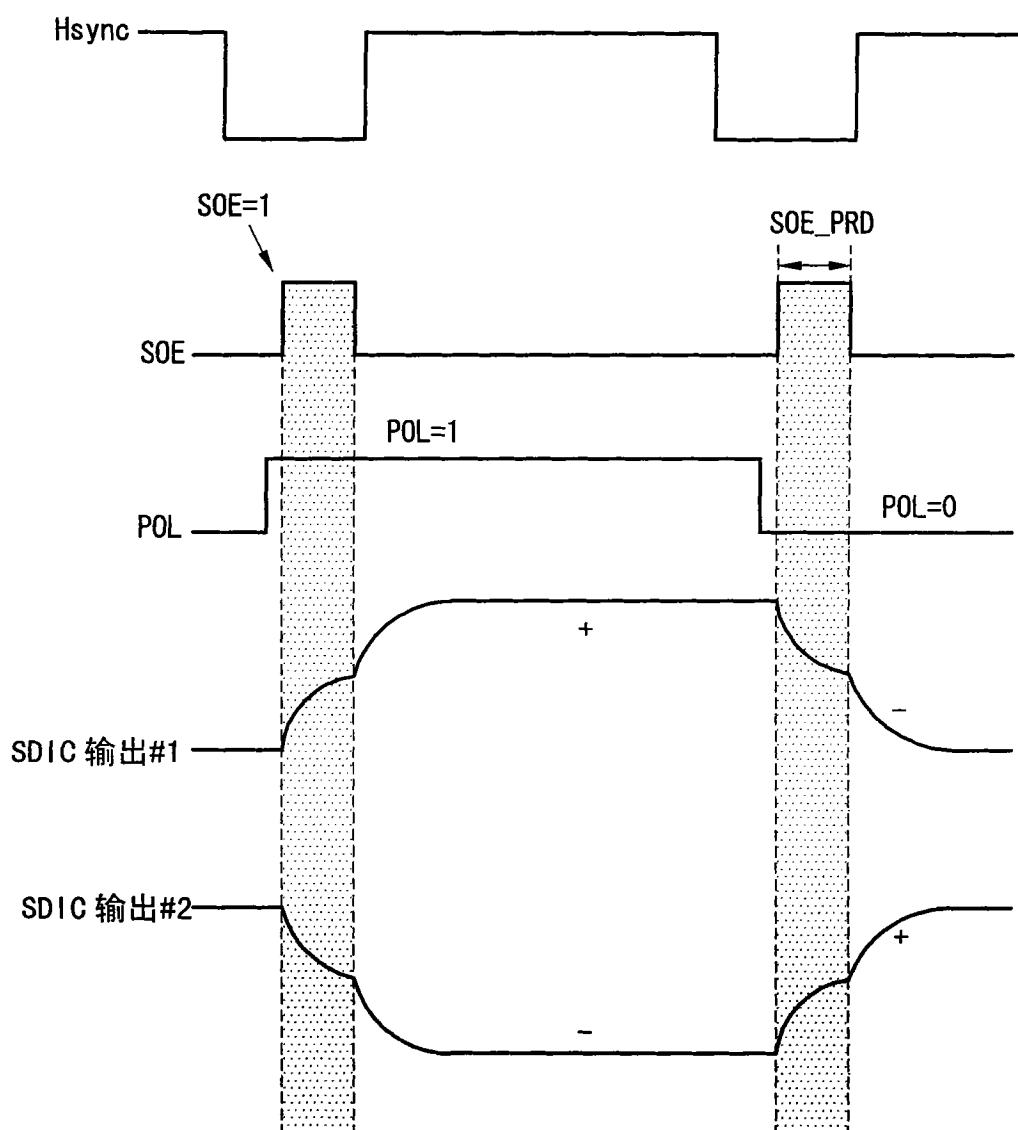

- [0041] 图 17 是对图 16 的实际源极控制包中的源极输出相关控制数据所控制的源极输出使能信号以及极性相关控制数据所控制的极性控制信号进行例示的波形图；

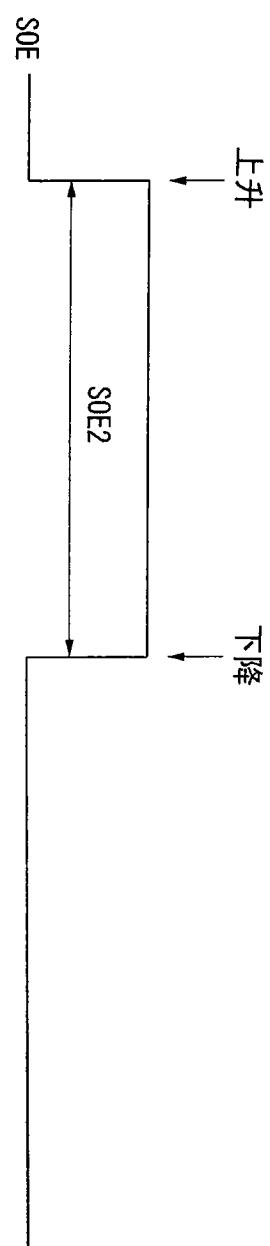

- [0042] 图 18 例示了根据实际源极控制包的 SOE\_PRD 所确定的源极输出使能信号的脉冲宽度；

- [0043] 图 19 是对源极输出使能信号的脉冲宽度根据实际源极控制包的 SOE\_PRD 的变化进行例示的波形图；

- [0044] 图 20 例示了实际源极控制包的第二实施例；

- [0045] 图 21 是对图 20 的实际源极控制包中的源极输出相关控制数据和极性相关控制数据所控制的源极输出使能信号和极性控制信号进行例示的波形图；

- [0046] 图 22A 至 22C 例示了根据实际源极控制包的源极输出相关控制数据所控制的源极输出使能信号的脉冲宽度；

- [0047] 图 23 是对按照垂直 2 点反相方式的液晶元件的充电不均匀性进行例示的波形；

- [0048] 图 24 是通过对源极输出使能信号的脉冲宽度的调节来补偿液晶元件的充电不均匀性的实例进行例示的波形；

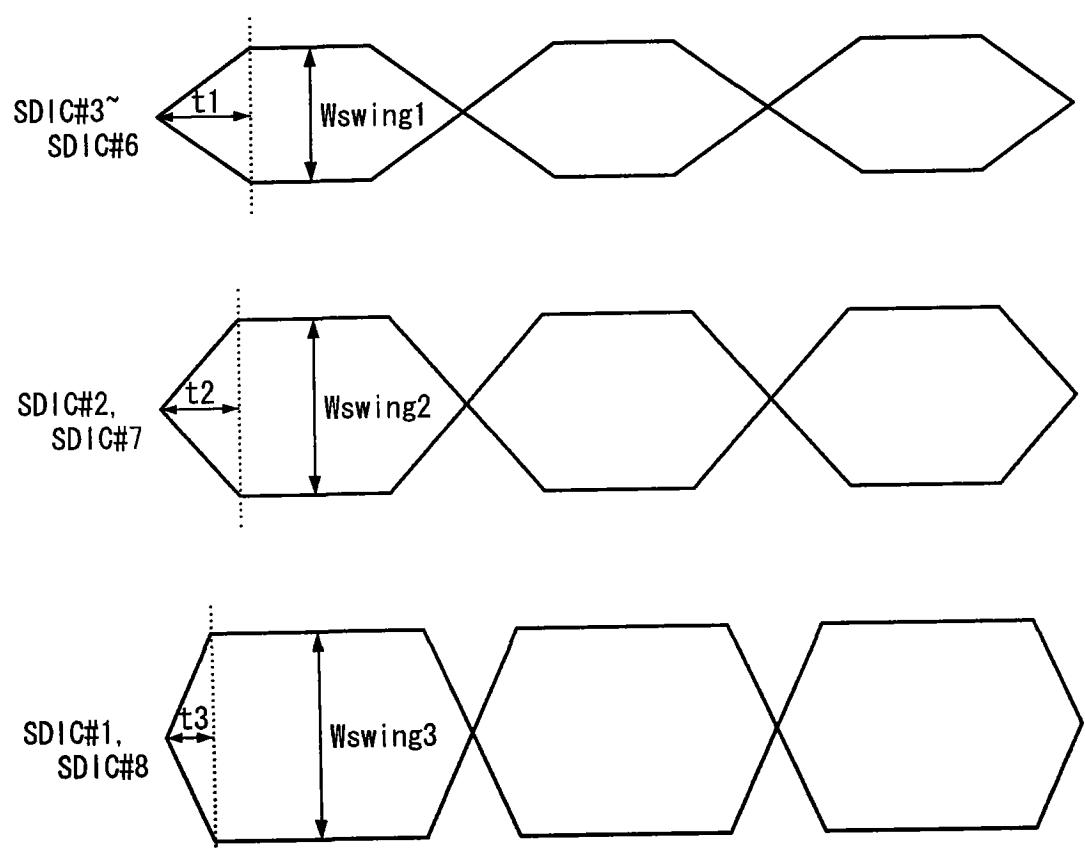

- [0049] 图 25 是对摆动宽度根据时序控制器与源极驱动 IC 之间的距离的变化进行例示的波形；

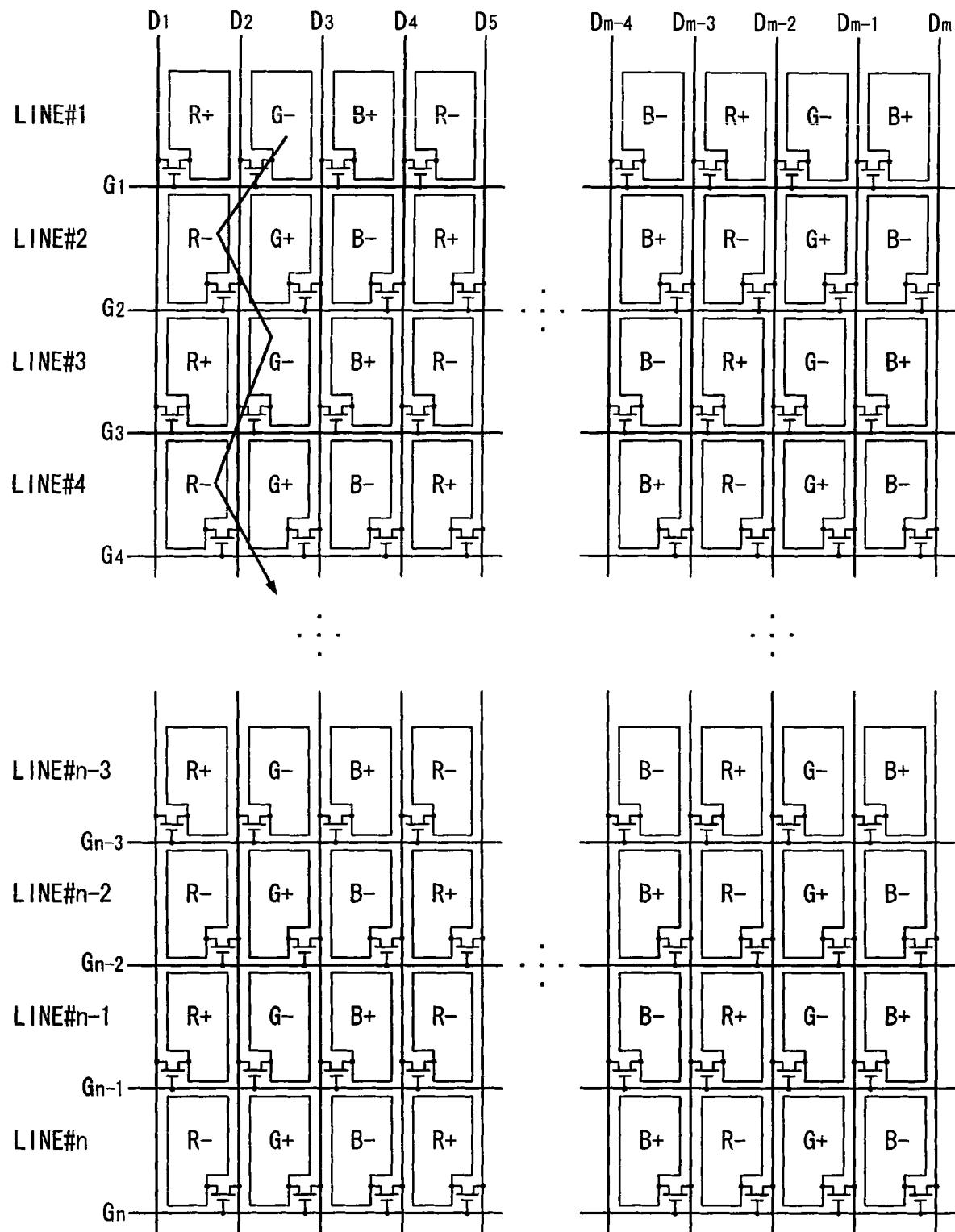

- [0050] 图 26 例示了像素阵列的实例；

- [0051] 图 27A 和 27B 例示了传输到像素阵列的 RGB 数据包；

- [0052] 图 28 是对时钟分离和数据采样单元的输出进行例示的波形图；

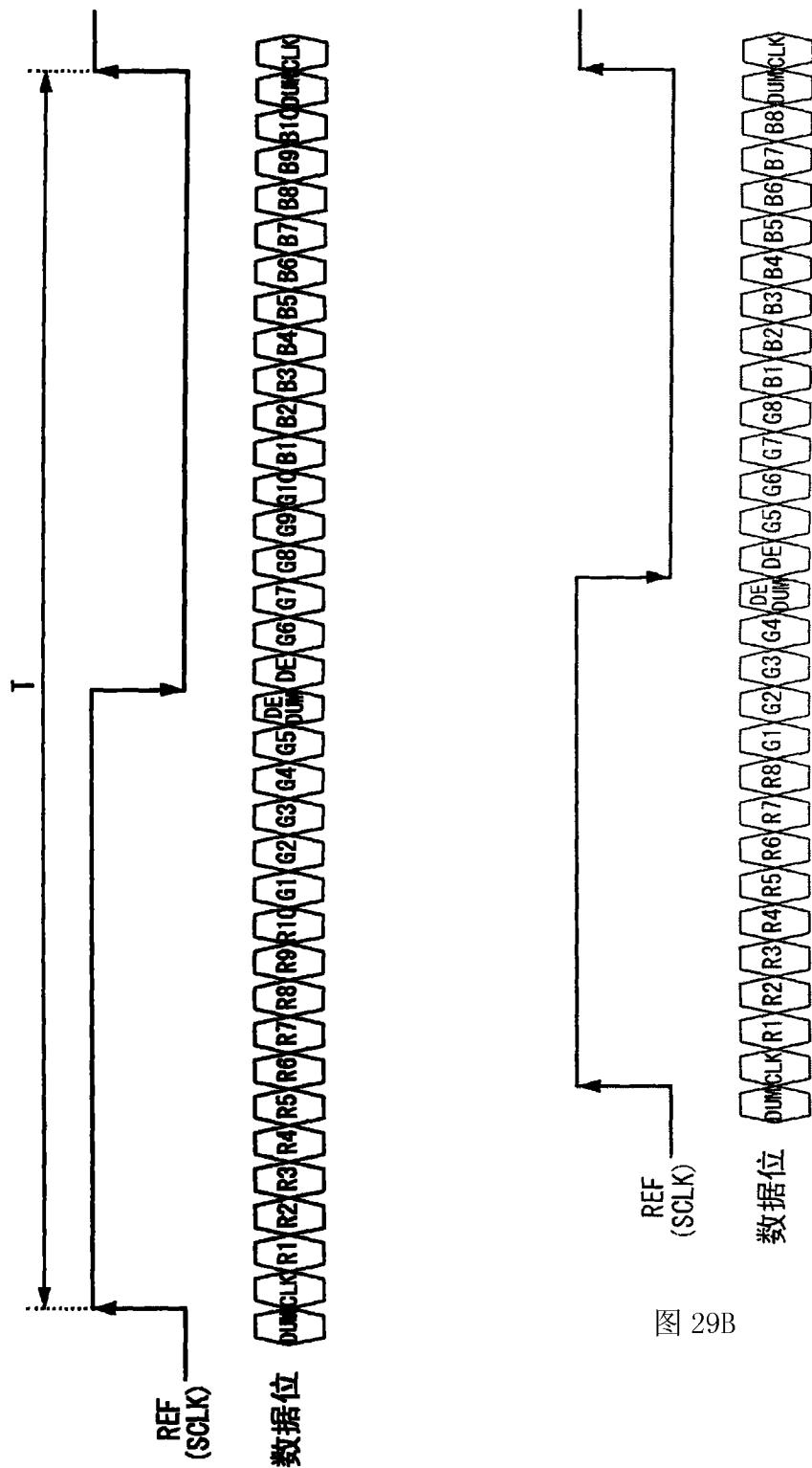

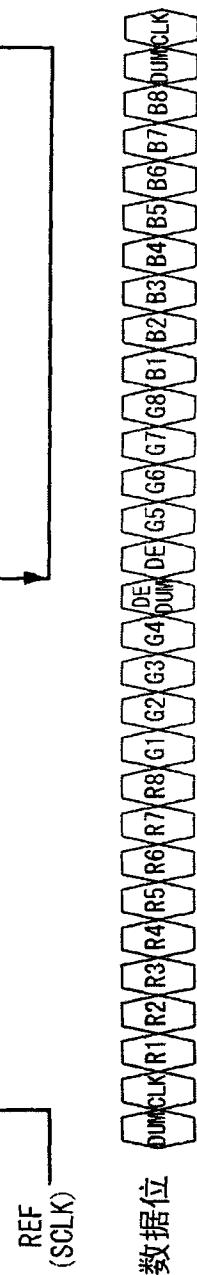

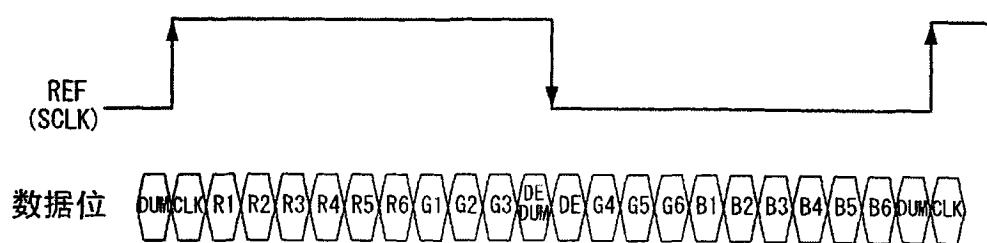

- [0053] 图 29A 至 29D 是例示了根据 RGB 数据包的比特率的变化来对 RGB 数据包进行长度转换的横截面图；

- [0054] 图 30 和 31 是对根据本发明另一实施方式的相位 1 信号进行例示的波形图；以及

- [0055] 图 32 例示了根据本发明实施方式的用于测试模式的液晶显示器的附加配置。

## 具体实施方式

- [0056] 现在参照附图详细描述本发明的实施方式。

- [0057] 如图 1 所示，根据本发明实施方式的液晶显示器包括液晶显示器面板 10、时序控制器 TCON、多个源极驱动集成电路 (IC) SDIC#1 至 SDIC#8、以及多个栅极驱动 IC GDIC#1 至 GDIC#4。

- [0058] 液晶显示器面板 10 包括上玻璃基板、下玻璃基板、以及位于上下玻璃基板之间的液晶层。液晶显示器面板 10 包括以矩阵形式排列在 m 条数据线 DL 与 n 条栅极线 GL 的每个交叉处的  $m \times n$  个液晶单元 C1c。

- [0059] 在液晶显示器面板 10 的下玻璃基板上形成包括有数据线 DL、栅极线 GL、多个薄膜晶体管 (TFT)、存储电容器 Cst 等等的像素阵列。由通过 TFT 接收数据电压的像素电极 1 与接收公共电压 Vcom 的公共电极 2 之间的电场来驱动每个液晶单元 C1c。在每个 TFT 中，栅极与栅极线 GL 相连，源极与数据线 DL 相连，并且漏极与液晶单元 C1c 的像素电极 1 相连。当通过栅极线 GL 提供了栅极脉冲时 TFT 导通，并且因此将通过数据线 DL 所接收到的正或负模拟视频数据电压提供给液晶单元 C1c 的像素电极 1。

- [0060] 在液晶显示器面板 10 的上玻璃基板上形成了黑矩阵、滤色器、公共电极 2 等等。

- [0061] 按照诸如扭曲向列 (TN) 模式和垂直对准 (VA) 模式之类的垂直电驱动方式在上玻璃基板上形成公共电极 2。按照诸如面内切换 (IPS) 模式和边缘场切换 (FFS) 模式之类的水平电驱动方式在下玻璃基板上形成公共电极 2 和像素电极 1。

- [0062] 液晶显示器面板 10 的上下玻璃基板分别附有偏振板。在上下玻璃基板上分别形成用于设置预倾角的取向层。在上下玻璃基板之间形成间隔体以保持液晶单元 C1c 的单元间隙恒定。

[0063] 根据本发明实施方式的液晶显示器可以具体体现为任何液晶模式，包括 TN、VA、IPS、FFS 模式。此外，根据本发明实施方式的液晶显示器可以实施为任何类型的液晶显示器，包括背光液晶显示器、透反射式液晶显示器、以及反射式液晶显示器。

[0064] 时序控制器 TCON 通过诸如低压差分信号 (LVDS) 接口和最小化跳变差分信号 (TMDS) 接口之类的接口接收诸如垂直和水平同步信号 Vsync 和 Hsync、外部数据使能信号 DE、以及点时钟 CLK 之类的外部时序信号，以产生用于对源极驱动 IC SDIC#1 至 SDIC#8 的操作时序和栅极驱动 IC GDIC#1 至 GDIC#4 的操作时序进行控制的时序控制信号。时序控制信号包括用于对栅极驱动 IC GDIC#1 至 GDIC#4 的操作时序进行控制的栅极时序控制信号以及用于对源极驱动 IC SDIC#1 至 SDIC#8 的操作时序进行控制的源极时序控制信号。

[0065] 时序控制器 TCON 按照点对点方式与源极驱动 IC SDIC#1 至 SDIC#8 相连。时序控制器 TCON 通过多对数据总线的每一对将用于对源极驱动 IC SDIC#1 至 SDIC#8 进行初始化的前导信号、包括源极时序控制信号的源极控制数据、时钟、RGB 数字视频数据等等传输到源极驱动 IC SDIC#1 至 SDIC#8 的每一个。例如，源极控制数据包括源极输出使能信号的激活信息；源极输出使能信号的脉冲宽度信息；以及极性控制信号的激活信息。

[0066] 栅极时序控制信号包括栅极起始脉冲 GSP、栅极移位时钟 GSC、栅极输出使能信号 GOE 等等。将栅极起始脉冲 GSP 施加到第一栅极驱动 IC GDIC#1 以表明扫描操作的扫描起始时间，从而第一栅极驱动 IC GDIC#1 产生第一栅极脉冲。栅极移位时钟 GSC 是用于使栅极起始脉冲 GSP 移位的时钟。栅极驱动 IC GDIC#1 至 GDIC#4 的每一个的移位寄存器在栅极移位时钟 GSC 的上升沿移位栅极起始脉冲 GSP。第二至第四栅极驱动 IC GDIC#2 至 GDIC#4 接收第一栅极驱动 IC GDIC#1 的进位信号作为栅极起始脉冲，从而开始操作。栅极输出使能信号 GOE 对栅极驱动 IC GDIC#1 至 GDIC#4 的输出时序进行控制。栅极驱动 IC GDIC#1 至 GDIC#4 在栅极输出使能信号 GOE 的低逻辑电平状态（即，从紧接在当前脉冲的下降沿之后至紧接在下一脉冲的上升沿之前的时间段期间）输出栅极脉冲。栅极输出使能信号 GOE 的 1 个周期大约是 1 个水平时段。

[0067] 在前导信号的传输时间与 RGB 数字视频数据的传输时间之间的预定时间间隔，通过数据总线对将源极时序控制信号传输到源极驱动 IC SDIC#1 至 SDIC#8。源极时序控制信号包括极性相关控制数据、源极输出相关控制数据等等。极性相关控制数据包括用于对在源极驱动 IC SDIC#1 至 SDIC#8 内部所产生的脉冲形式的极性控制信号 POL 进行控制的控制信息。响应极性控制信号 POL，源极驱动 IC SDIC#1 至 SDIC#8 每一个的数模转换器 (DAC) 将 RGB 数字视频数据转换成正或负模拟视频数据电压。源极输出相关控制数据包括用于对在源极驱动 IC SDIC#1 至 SDIC#8 内部所产生的脉冲形式的源极输出使能信号 SOE 进行控制的控制信息。源极输出使能信号 SOE 对来自源极驱动 IC SDIC#1 至 SDIC#8 的正 / 负模拟视频数据电压的输出时序进行控制。

[0068] 响应栅极时序控制信号，栅极驱动 IC GDIC#1 至 GDIC#4 的每一个顺序地将栅极脉冲提供给栅极线 GL。

[0069] 根据通过数据总线对从时序控制器 TCON 传输的前导信号，源极驱动 IC SDIC#1 至 SDIC#8 的每一个锁定从嵌入在源极驱动 IC SDIC#1 至 SDIC#8 每一个之内的时钟分离和数据采样单元输出的内部时钟脉冲的频率和相位。此后，源极驱动 IC SDIC#1 至 SDIC#8 的每一个从通过数据总线对作为数字比特流而输入的源极控制包恢复出时钟，以产生串行时

钟。随后,源极驱动 IC SDIC#1 至 SDIC#8 的每一个对极性相关控制数据和源极输出相关控制数据进行采样。源极驱动 IC SDIC#1 至 SDIC#8 的每一个利用极性相关控制数据和源极输出相关控制数据输出极性控制信号 POL 和源极输出使能信号 SOE。

[0070] 在源极驱动 IC SDIC#1 至 SDIC#8 的每一个从通过数据总线对作为数字比特流而输入的源极控制包恢复出时钟从而恢复极性控制信号 POL 和源极输出使能信号 SOE 之后,源极驱动 IC SDI C#1 至 SDIC#8 的每一个从通过数据总线对作为数字比特流而输入的 RGB 数据包恢复出时钟,以产生用于数据采样的串行时钟。此外,源极驱动 IC SDIC#1 至 SDIC#8 的每一个根据该串行时钟对串行输入的 RGB 数字视频数据进行采样。源极驱动 IC SDIC#1 至 SDIC#8 的每一个对顺序采样的 RGB 数字视频数据进行反串行化以输出 RGB 并行数据。此后,源极驱动 IC SDIC#1 至 SDIC#8 的每一个响应极性控制信号 POL 将 RGB 并行数据转换成正 / 负模拟视频数据电压,以响应源极输出使能信号 SOE 而将正 / 负模拟视频数据电压提供给数据线 DL。

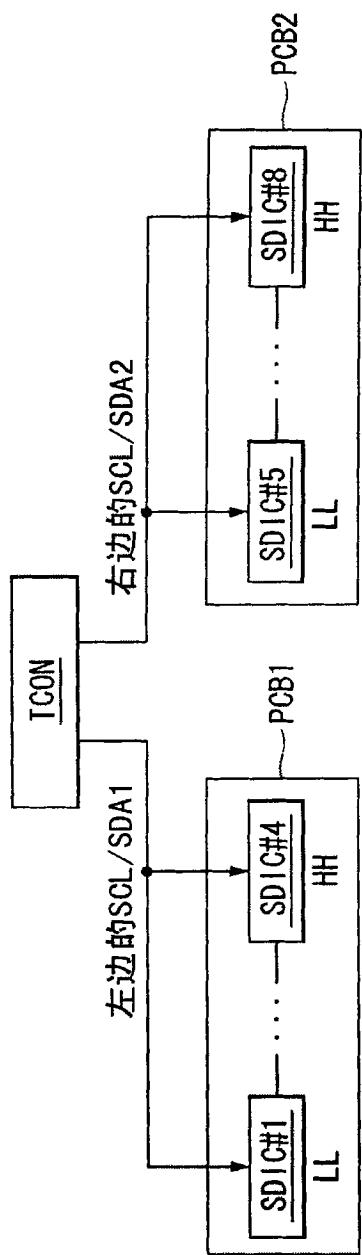

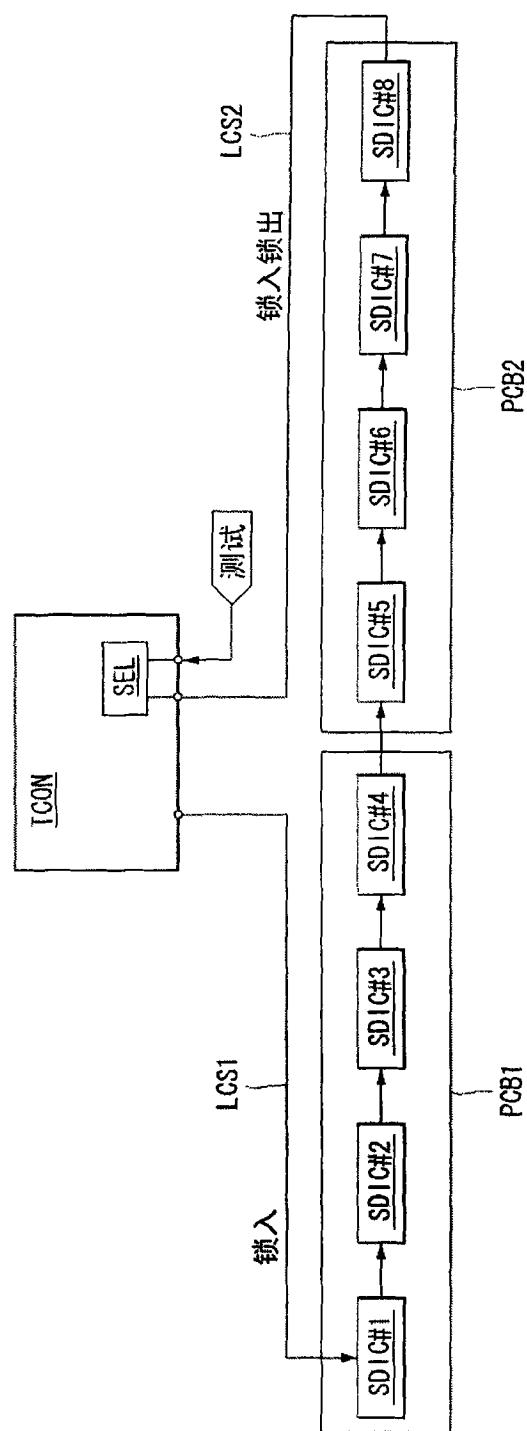

[0071] 图 2 例示了时序控制器 TCON 与源极驱动 IC SDIC#1 至 SDIC#8 之间的线。

[0072] 如图 2 所示,在时序控制器 TCON 与源极驱动 IC SDIC#1 至 SDIC#8 之间形成了多对数据总线 DATA&CLK、第一和第二对控制线 SCL/SDA1 和 SCL/SDA2、锁定检查线 LCS1 和 LCS2 等等。

[0073] 时序控制器 TCON 通过每对数据总线 DATA & CLK 将前导信号、源极控制包、以及 RGB 数据包顺序地传输到源极驱动 IC SDIC#1 至 SDIC#8 的每一个。源极控制包是包括时钟位、极性相关控制数据位、源极输出相关控制数据位等等的比特流。RGB 数据包是包括时钟位、内部数据使能时钟位、RGB 数据位等等的比特流。每对数据总线 DATA & CLK 使时序控制器 TCON 与源极驱动 IC SDIC#1 至 SDIC#8 的每一个串联。也就是说,按照点对点的方式时序控制器 TCON 与源极驱动 IC SDIC#1 至 SDIC#8 相连。源极驱动 IC SDIC#1 至 SDIC#8 的每一个恢复出通过数据总线对 DATA&CLK 输入的时钟。因此,在相邻源极驱动 IC SDIC#1 至 SDIC#8 之间不需要用于传输时钟进位和 RGB 视频数据的线。

[0074] 时序控制器 TCON 通过控制线对 SCL/SDA1 和 SCL/SDA2 将源极驱动 ICSDIC#1 至 SDIC#8 每一个的芯片标识码 CID 以及用于控制源极驱动 IC SDIC#1 至 SDIC#8 的每一个的功能的芯片单独控制数据传输到源极驱动 IC SDIC#1 至 SDIC#8 的每一个。控制线对 SCL/SDA1 和 SCL/SDA2 共同地连接在时序控制器 TCON 与源极驱动 IC SDIC#1 至 SDIC#8 之间。更具体地说,如图 8 所示,如果将源极驱动 IC SDIC#1 至 SDIC#8 分成两组并且这两组分别与印刷电路板 (PCB) PCB1 和 PCB2 相连,那么左边的第一对控制线 SCL/SDA1 使时序控制器 TCON 与第一至第四源极驱动 IC SDIC#1 至 SDIC#4 并联,并且右边的第二对控制线 SCL/SDA2 使时序控制器 TCON 与第五至第八源极驱动 ICSDIC#5 至 SDIC#8 并联。

[0075] 时序控制器 TCON 通过锁定检查线 LCS 1 将锁定信号 LOCK 提供给第一源极驱动 IC SDIC#1,所述锁定信号 LOCK 用于确认是否稳定地锁定了从源极驱动 IC SDIC#1 至 SDIC#8 的每一个的时钟分离和数据采样单元输出的内部时钟脉冲的相位和频率。源极驱动 IC SDIC#1 至 SDIC#8 通过锁定检查线 LCS1 彼此级联。如果锁定了从第一源极驱动 IC SDIC#1 输出的内部时钟脉冲的频率和相位,那么第一源极驱动 IC SDIC#1 将高逻辑电平的锁定信号 LOCK 传输到第二源极驱动 IC SDIC#2。接下来,在锁定了从第二源极驱动 IC SDIC#2 输出的内部时钟脉冲的频率和相位之后,第二源极驱动 IC SDIC#2 将高逻辑电平的锁定信号

LOCK 传输到第三源极驱动 IC SDIC#3。顺序执行上述锁定操作，并且最终，在锁定了从最后源极驱动 IC SDIC#8 输出的内部时钟脉冲的频率和相位之后，最后源极驱动 IC SDIC#8 通过反馈锁定检查线 LCS2 将高逻辑电平的锁定信号 LOCK 反馈输入到时序控制器 TCON。只有在时序控制器 TCON 接收到锁定信号 LOCK 的反馈信号之后，时序控制器 TCON 才将 RGB 数据包传输到源极驱动 IC SDIC#1 至 SDIC#8。

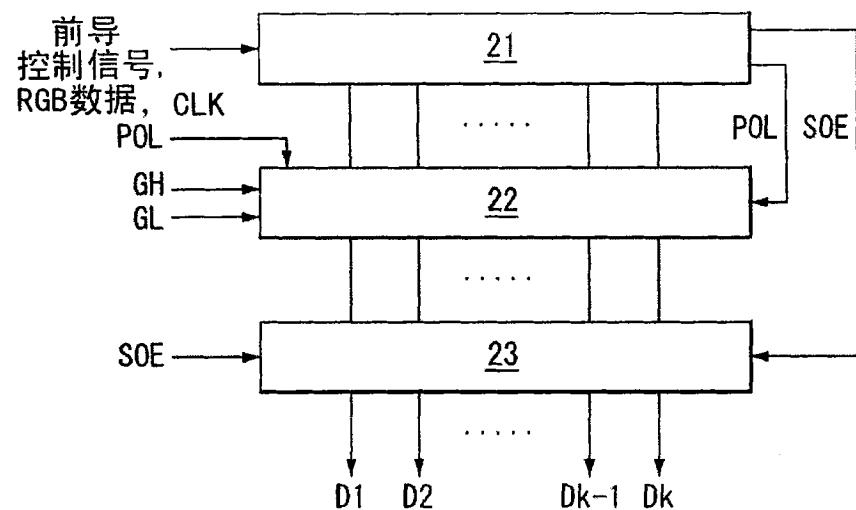

[0076] 图 3 是对源极驱动 IC SDIC#1 至 SDIC#8 的配置进行例示的框图。

[0077] 如图 3 所示，源极驱动 IC SDIC#1 至 SDIC#8 的每一个将正 / 负模拟视频数据电压提供给 k 条数据线 D1 至 Dk (其中 k 是小于 m 的正整数)。源极驱动 IC SDIC#1 至 SDIC#8 的每一个包括时钟分离和数据采样单元 21、数模转换器 (DAC) 22、输出电路 23 等等。

[0078] 在相位 1，时钟分离和数据采样单元 21 根据通过数据总线对 DATA&CLK 以低频输入的前导信号来锁定内部时钟脉冲的相位和频率。随后，在相位 2，时钟分离和数据采样单元 21 从通过数据总线对 DATA&CLK 作为比特流而输入的源极控制包恢复出参考时钟，并且从参考时钟分离出极性相关控制数据从而根据极性相关控制数据恢复出极性控制信号 POL。此外，时钟分离和数据采样单元 21 从源极控制包分离出源极输出相关控制数据，以根据该源极输出相关控制数据恢复出源极输出使能信号 SOE。

[0079] 随后，在相位 3，时钟分离和数据采样单元 21 从通过数据总线对 DATA&CLK 而输入的 RGB 数据包分离出时钟以恢复参考时钟。此外，时钟分离和数据采样单元 21 根据该参考时钟产生用于对 RGB 数字视频数据位的每一个进行采样的串行时钟信号。为此，时钟分离和数据采样单元 21 包括可输出具有稳定相位和稳定频率的内部时钟脉冲的锁相电路。锁相电路的实例包括锁相环 (PLL) 和延迟锁相环 (DLL)。在实施方式中，随后将描述利用 PLL 电路作为锁相电路的实例。在实施方式中，时钟分离和数据采样单元 21 可包括 DLL 以及 PLL。图 7 至 9 例示了具体体现使用 PLL 的时钟分离和数据采样单元 21 的实例。然而，也可使用 DLL 具体体现时钟分离和数据采样单元 21。

[0080] 时钟分离和数据采样单元 21 根据串行时钟对通过数据总线对 DATA&CLK 串行输入的每个 RGB 数据位进行采样和锁存，并且此后同时输出锁存的 RGB 数据。也就是说，时钟分离和数据采样单元 21 将串行数据转换成 RGB 并行数据。

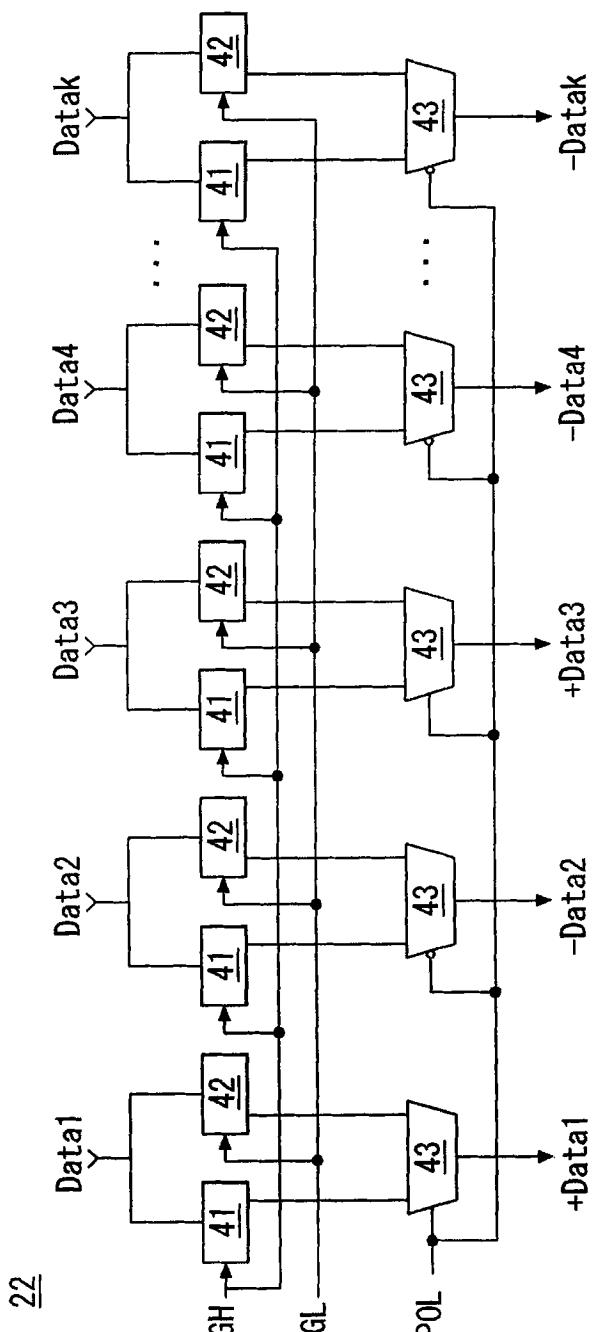

[0081] DAC 22 响应极性控制信号 POL 将来自时钟分离和数据采样单元 21 的 RGB 数字视频数据转换成正伽玛补偿电压 GH 或负伽玛补偿电压 GL，并且此后将正伽玛补偿电压 GH 或负伽玛补偿电压 GL 转换成正或负模拟视频数据电压。对于上述操作而言，如图 4 所示，DAC 22 包括用于接收正伽玛补偿电压 GH 的 P 解码器 (PDEC) 41、用于接收负伽玛补偿电压 GL 的 N 解码器 (NDEC) 42、以及用于响应极性控制信号 POL 而选择 P 解码器 41 的输出和 N 解码器 42 的输出的多路复用器 43。P 解码器 41 对从时钟分离和数据采样单元 21 输入的 RGB 数字视频数据进行解码以输出与 RGB 数字视频数据的灰度相对应的正伽玛补偿电压 GH。N 解码器 42 对从时钟分离和数据采样单元 21 输入的 RGB 数字视频数据进行解码以输出与 RGB 数字视频数据的灰度相对应的负伽玛补偿电压 GL。多路复用器 43 响应极性控制信号 POL 而交替地选择正伽玛补偿电压 GH 和负伽玛补偿电压 GL，并且输出正或负模拟视频数据电压作为所选的正或负伽玛补偿电压 GH 或 GL。

[0082] 输出电路 23 在源极输出使能信号 SOE 的高逻辑电平时段期间通过输出缓冲器将充电共享电压或公共电压 Vcom 提供给数据线 D1 至 Dk。输出电路 23 在源极输出使能信号

SOE 的低逻辑电平时段期间通过输出缓冲器将正 / 负模拟视频数据电压提供给数据线 D1 至 D<sub>k</sub>。当用于接收正模拟视频数据电压的数据线和用于接收负模拟视频数据电压的数据线短路时产生充电共享电压。充电共享电压具有正模拟视频数据电压与负模拟视频数据电压之间的平均电压电平。

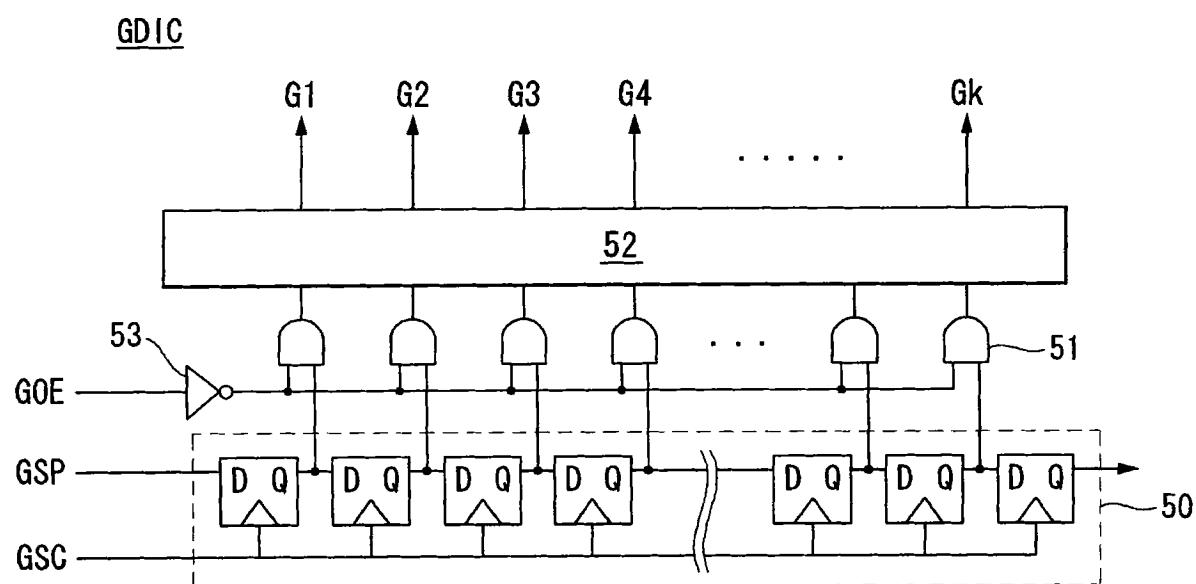

[0083] 图 5 是对栅极驱动 IC GDIC#1 至 GDIC#4 的配置进行例示的框图。

[0084] 如图 5 所示, 栅极驱动 IC GDIC#1 至 GDIC#4 的每一个包括移位寄存器 50、电平移位器 52、连接在移位寄存器 50 与电平移位器 52 之间的多个与 (AND) 门 51、以及用于使栅极输出使能信号 GOE 反相的反相器 53。

[0085] 移位寄存器 50 包括多个级联的 D 触发器, 并且利用级联的 D 触发器响应栅极移位时钟 GSC 而使栅极起始脉冲 GSP 顺序地移位。每个 AND 门 51 对移位寄存器 50 的输出信号和栅极输出使能信号 GOE 的反相信号执行 AND 操作以获得输出。反相器 53 使栅极输出使能信号 GOE 反相并且将栅极输出使能信号 GOE 的反相信号提供给 AND 门 51。因此, 当栅极输出使能信号 GOE 处于低逻辑电平状态时栅极驱动 IC GDIC#1 至 GDIC#4 的每一个输出栅极脉冲。

[0086] 电平移位器 52 使 AND 门 51 的输出电压的摆动宽度偏移到适于驱动液晶显示器面板 10 的像素阵列中的 TFT 的摆动宽度。顺序地将电平移位器 52 的输出信号提供给栅极线 G1 至 G<sub>k</sub>。

[0087] 移位寄存器 50 与像素阵列的 TFT 一起可直接形成于液晶显示器面板 10 的玻璃基板上。在这种情况下, 电平移位器 52 可以不形成在液晶显示器面板 10 的玻璃基板上, 而可以与时序控制器 TCON、伽玛电压产生电路等等一起形成在控制板或源极 PCB 上。

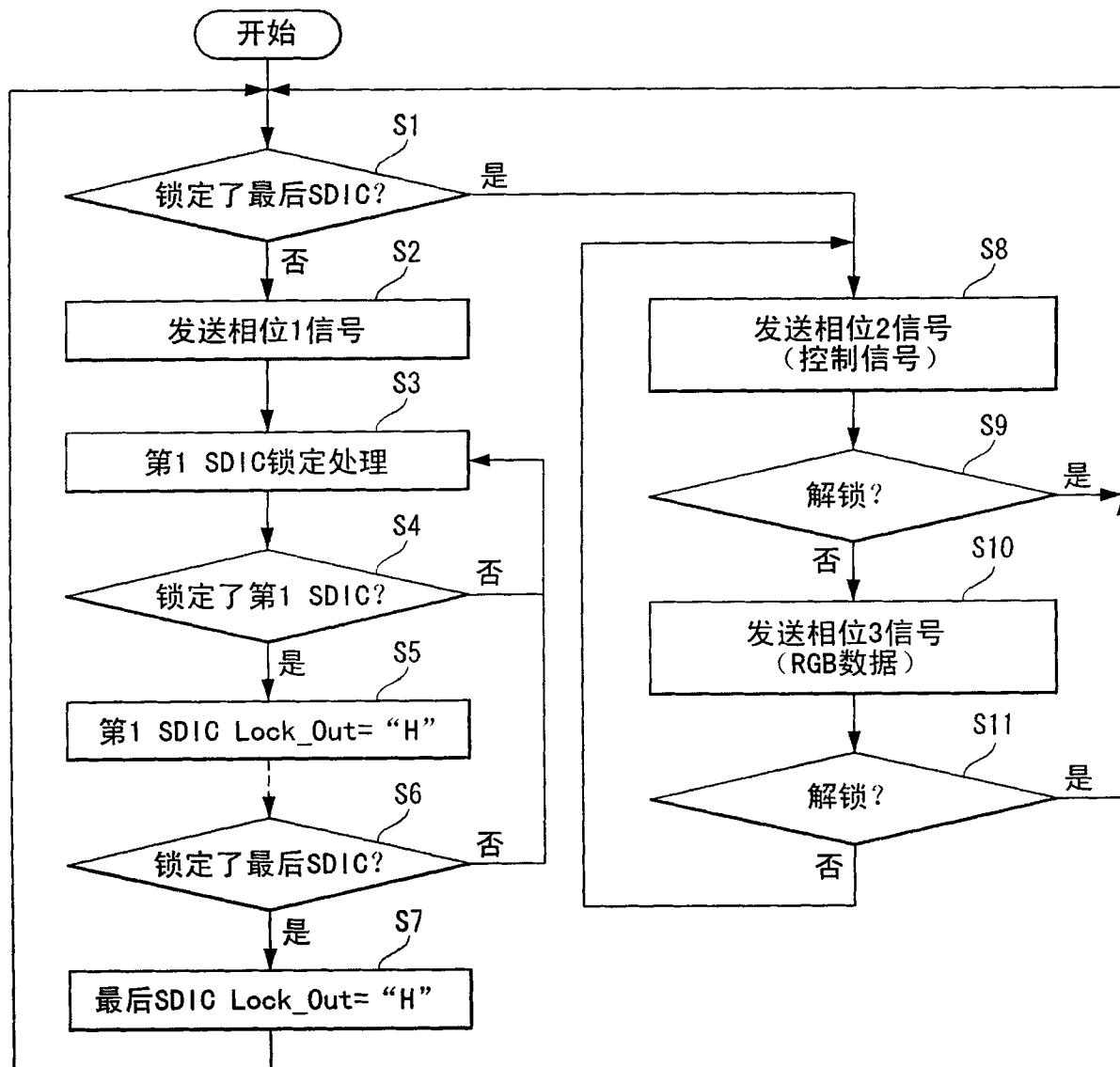

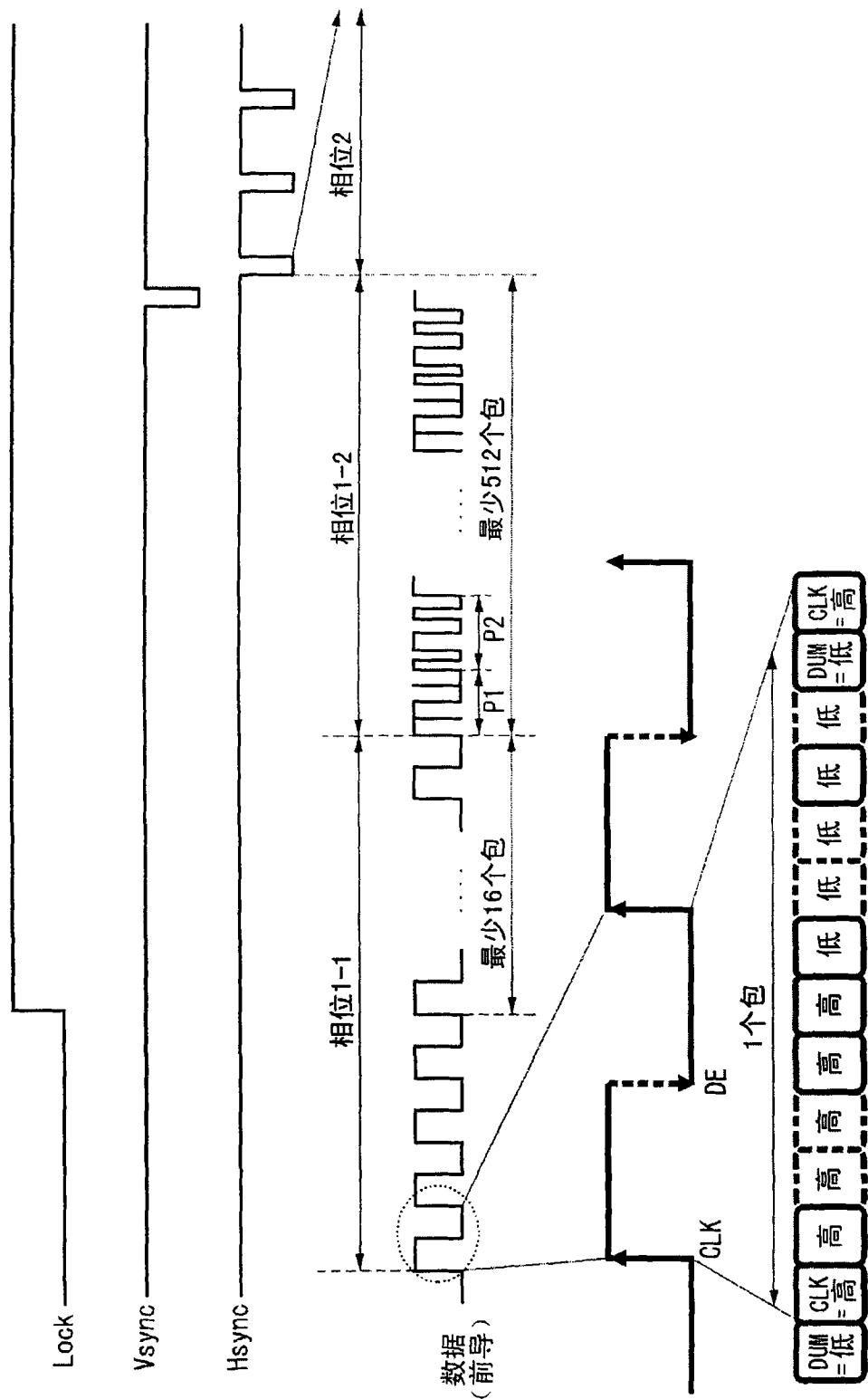

[0088] 图 6 是按阶段对时序控制器 TCON 与源极驱动 IC SDIC#1 至 SDIC#8 之间的信号传输处理进行例示的流程图。

[0089] 如图 6 所示, 如果将电源施加到液晶显示器上, 那么在步骤 S1 和 S2 中时序控制器 TCON 通过每对数据总线 DATA&CLK 将相位 1 信号提供给源极驱动 IC SDIC#1 至 SDIC#8 的每一个。相位 1 信号包括低频的前导信号以及提供给第一源极驱动 IC SDIC#1 的锁定信号。

[0090] 在步骤 S3 至 S5 中, 第一源极驱动 IC SDIC#1 的时钟分离和数据采样单元 21 将前导信号恢复成 PLL 参考时钟, 并且当锁定了 PLL 参考时钟的相位以及从第一源极驱动 IC SDIC#1 的 PLL 输出的内部时钟脉冲的相位时, 将高逻辑电平的锁定信号传输到第二源极驱动 IC SDIC#2。随后, 当顺序地稳定锁定了从第二至第八源极驱动 IC SDIC#2 至 SDIC#8 的时钟分离和数据采样单元 21 输出的内部时钟脉冲时, 在步骤 S6 和 S7 中第八源极驱动集成电路 SDIC#8 将高逻辑电平的锁定信号反馈输入到时序控制器 TCON。

[0091] 如果时序控制器 TCON 接收到来自第八源极驱动 IC SDIC#8 的高逻辑电平的锁定信号, 那么时序控制器 TCON 确定: 从所有 SDIC#1 至 SDIC#8 的每一个的时钟分离和数据采样单元 21 输出的内部时钟脉冲的相位和频率已被稳定锁定。因此, 在步骤 S8 中时序控制器 TCON 按照点对点方式通过数据总线对 DATA&CLK 将相位 2 信号提供给源极驱动 IC SDIC#1 至 SDIC#8。相位 2 信号包括含有极性相关控制数据位和源极输出相关控制数据位的多个源极控制包。

[0092] 继相位 2 信号之后, 在步骤 S10 中时序控制器 TCON 按照点对点方式将相位 3 信号提供给源极驱动 IC SDIC#1 至 SDIC#8。相位 3 信号包括在 1 个水平时段期间液晶显示器面

板 10 的 1 行上的液晶单元将被充电的多个 RGB 数据包。

[0093] 在相位 2 信号或相位 3 信号的输出传输处理期间, 可对源极驱动 IC SDIC#1 至 SDIC#8 的每一个的时钟分离和数据采样单元 21 的 PLL 输出进行解锁。也就是说, 可对从时钟分离和数据采样单元 21 的 PLL 输出的内部时钟脉冲的相位和频率进行解锁。更具体地说, 当时序控制器 TCON 接收到在低逻辑电平反相的锁定信号的反馈信号时, 在步骤 S9 和 S11 中, 时序控制器 TCON 确定: 从时钟分离和数据采样单元 21 的 PLL 输出的内部时钟脉冲被解锁。因此, 时序控制器 TCON 将相位 1 信号传输到源极驱动 IC SDIC#1 至 SDIC#8。随后, 在锁定了从源极驱动 IC SDIC#1 至 SDIC#8 的每一个的 PLL 输出的内部时钟脉冲的相位和频率之后, 时序控制器 TCON 再次起始执行对相位 2 信号和相位 3 信号的输出传输处理。

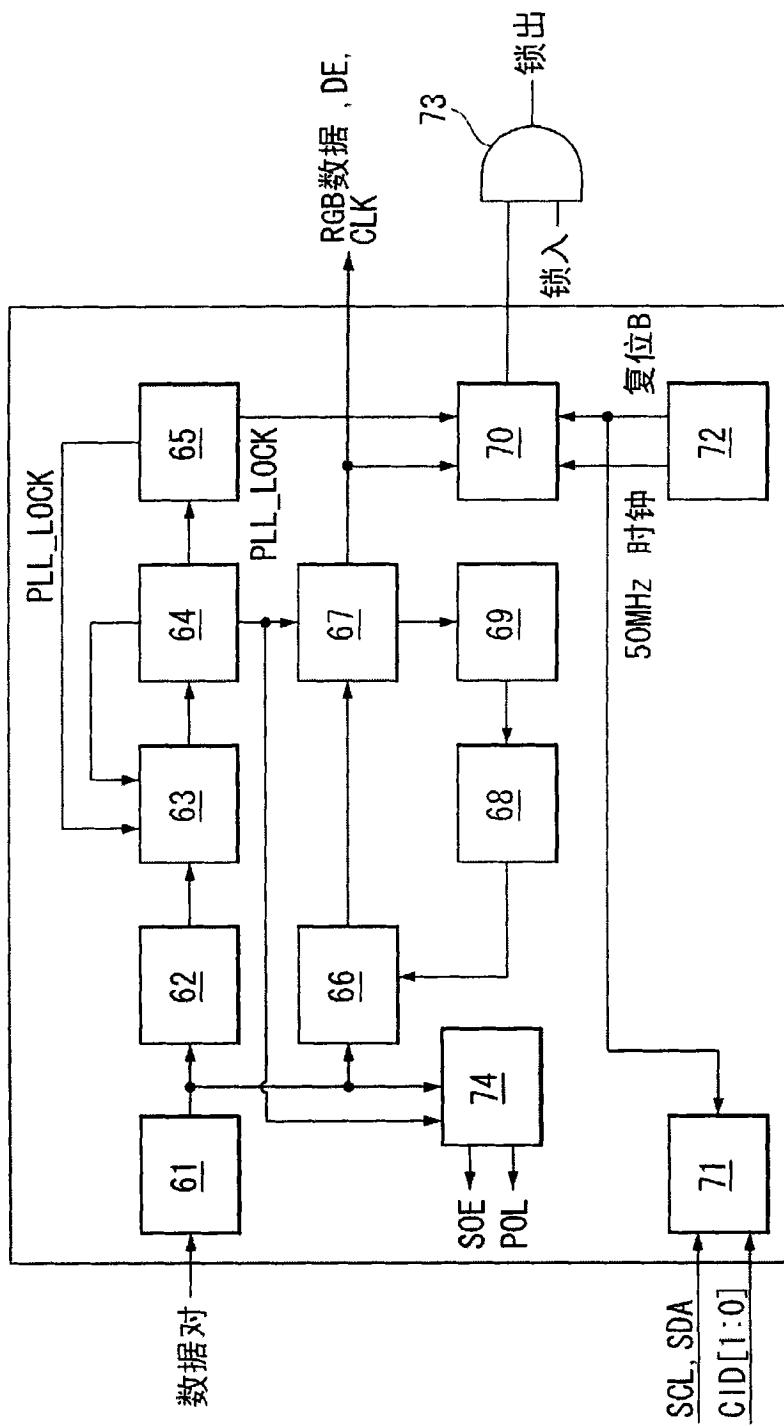

[0094] 图 7 是对源极驱动 IC SDIC#1 至 SDIC#8 每一个的时钟分离和数据采样单元 21 进行例示的框图。

[0095] 如图 7 所示, 时钟分离和数据采样单元 21 包括片上终结器 (on-die terminator, ODT) 61、模拟延迟副本 (ADR) 62、时钟分离器 63、PLL 64、PLL 锁定检测器 65、可调模拟延迟器 66、反串行器 67、数字滤波器 68、相位检测器 69、锁定检测器 70、I<sup>2</sup>C 控制器 71、加电复位 (power-on reset, POR) 72、AND 门 73、以及 SOE&POL 恢复单元 74。

[0096] ODT 61 包括嵌入在 ODT 61 内部的端接电阻, 以通过除去混入在通过数据总线对 DATA&CLK 所接收到的前导信号、源极控制包、以及 RGB 数据包中的噪声来提高信号完整性。此外, ODT 61 包括嵌入在 ODT 61 内部的接收缓冲器和均衡器以对输入差分信号进行放大并且将放大的差分信号转换成数字数据。ADR 62 使从 ODT 61 所接收到的 RGB 数据和时钟延迟了可调模拟延迟器 66 的延迟值, 以使时钟路径的延迟值等于数据路径的延迟值。

[0097] 时钟分离器 63 从 ODT 61 所恢复的源极控制包和 RGB 数据包分离出时钟位, 以将时钟位恢复成 PLL 64 的参考时钟。所述时钟位包括时钟位、伪时钟位、内部数据使能时钟位等等。PLL 64 产生用于对源极控制包的位和 RGB 数据包的位进行采样的时钟。如果 RGB 数据包包括 10 位 RGB 数据并且在 10 位 RGB 数据之间分配了 4 位时钟, 那么 PLL 64 对每 1 个 RGB 数据包产生 34 个内部时钟脉冲。PLL 锁定检测器 65 依照预定数据率来检查从 PLL 64 输出的每一个内部时钟脉冲的相位和频率以检测是否锁定了内部时钟脉冲。

[0098] 可调模拟延迟器 66 对从 ODT 61 所接收到的 RGB 数字数据与经由相位检测器 69 和数字滤波器 68 反馈输入的恢复时钟之间的微小相位差进行补偿, 以便在时钟中心采样数据。反串行器 67 包括嵌入在反串行器 67 内部的多个触发器, 以对基于从 PLL 64 串行输出的内部串行时钟脉冲而串行输入的 RGB 数字视频数据位进行采样和锁存。此后, 反串行器 67 同时输出锁存的 RGB 数字视频从而输出 RGB 并行数据。

[0099] 数字滤波器 68 和相位检测器 69 接收所采样的 RGB 数字视频数据并且确定可调模拟延迟器 66 的延迟值。锁定检测器 70 将反串行器 67 所恢复的 RGB 并行数据与 PLL 锁定检测器 65 的输出 PLL\_LOCK 进行比较以检查 RGB 并行数据的数据使能时钟的误差量。如果误差量等于或大于预定值, 那么物理接口 (PHY) 电路通过对从 PLL 64 输出的内部时钟脉冲进行解锁再次完整地操作。当对 PLL 64 输出的内部时钟脉冲被解锁时, 锁定检测器 70 产生低逻辑电平的输出。另一方面, 当锁定了从 PLL 64 输出的内部时钟脉冲时, 锁定检测器 70 产生高逻辑电平的输出。AND 门 73 将从时序控制器 TCON 所接收到的锁定信号“Lock In (锁入)”或者在先前阶段由源极驱动 IC SDIC#1 至 SDIC#7 所传输的锁定信号“Lock In”与锁

定检测器 70 的输出执行 AND 操作。此后,当锁定信号“Lock In”和锁定检测器 70 的输出处于高逻辑电平状态时,AND 门 73 输出高逻辑电平的锁定信号“Lock Out(锁出)”。在下一阶段中将高逻辑电平的锁定信号“Lock Out”传输到源极驱动 IC SDIC#2 至 SDIC#8,并且最后源极驱动 IC SDIC#8 将锁定信号“Lock Out”输入到时序控制器 TCON。

[0100] POR 72 根据先前设置的功率序列产生用于使时钟分离和数据采样单元 21 初始化的复位信号即复位 B(RESETB) 并且产生大约 50MHz 的时钟以将该时钟提供给包括上述电路的数字电路。

[0101] I<sup>2</sup>C 控制器 71 利用通过控制线对 SCL/SDA 作为串行数据而输入的芯片标识码 CID 以及芯片单独控制数据来对每个上述电路块的操作进行控制。如图 8 所示将每一个具有不同逻辑电平的芯片标识码 CID 分别赋予给源极驱动 ICSDIC#1 至 SDIC#8,以便可对源极驱动 IC SDIC#1 至 SDIC#8 进行单独控制。I<sup>2</sup>C 控制器 71 可根据通过控制线对 SCL/SDA 的串行数据总线 SDA 从时序控制器 TCON 输入的芯片单独控制数据,执行 PLL 断电、ODT 61 的缓冲器断电、ODT 61 的 EQ On/Off 操作、对 PLL 64 的充电冲击电流的控制、对 PLL 64 的 VCO 范围手动选择的控制、使 PLL 锁定信号完成 I<sup>2</sup>C 通信的操作、对模拟延迟控制值的调节、使锁定检测器 70 禁用、改变数字滤波器 68 的系数、改变数字滤波器 68 的系数的函数、物理接口 (PHY)\_RESETB 信号完成 I<sup>2</sup>C 通信的操作、使当前源极驱动 IC SDIC#1 至 SDIC#8 的复位信号代替先前源极驱动 IC SDIC#1 至 SDIC#7 的锁定信号的操作、设置输入图像的垂直分辨率、存储与数据使能时钟跳变有关的用于对物理接口 (PHY)\_RESETB 信号的产生原因进行分析的历史等等。

[0102] SOE&POL 恢复单元 74 响应从 PLL 64 输出的内部时钟脉冲而对来自 ODT61 的源极控制包的极性相关控制数据进行采样,以产生高逻辑电平(或低逻辑电平)的极性控制信号 POL。此后,SOE&POL 恢复单元 74 每个水平时段使极性控制信号 POL 的逻辑电平反相(其中“i”是自然数)。SOE&POL 恢复单元 74 响应从 PLL 64 输出的内部时钟脉冲而对来自 ODT 61 的源极控制包的源极输出相关控制数据进行采样。此后,SOE&POL 恢复单元 74 利用在图 16 至 22C 中所例示的方法,根据源极输出相关控制数据产生源极输出使能信号 SOE,并且对源极输出使能信号 SOE 的脉冲宽度进行调节,例如根据源极输出使能信号的脉冲宽度信息,通过将源极控制包和 RGB 数据包中的一个的长度乘以“i”来确定该源极输出使能信号的脉冲宽度,其中 i 是自然数。

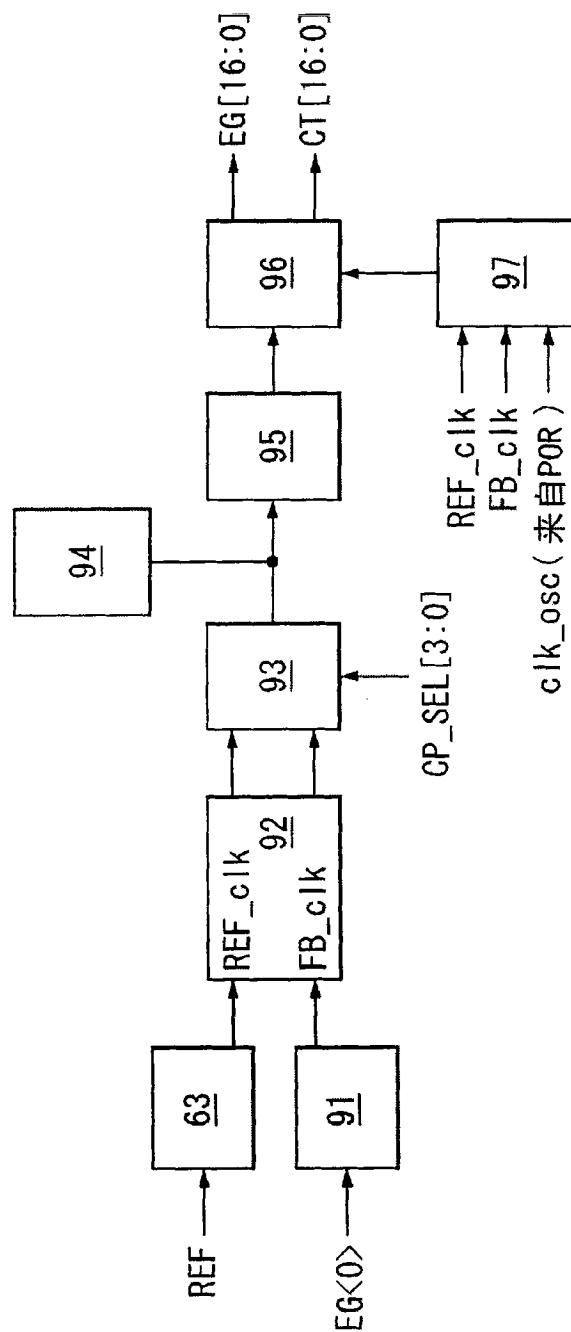

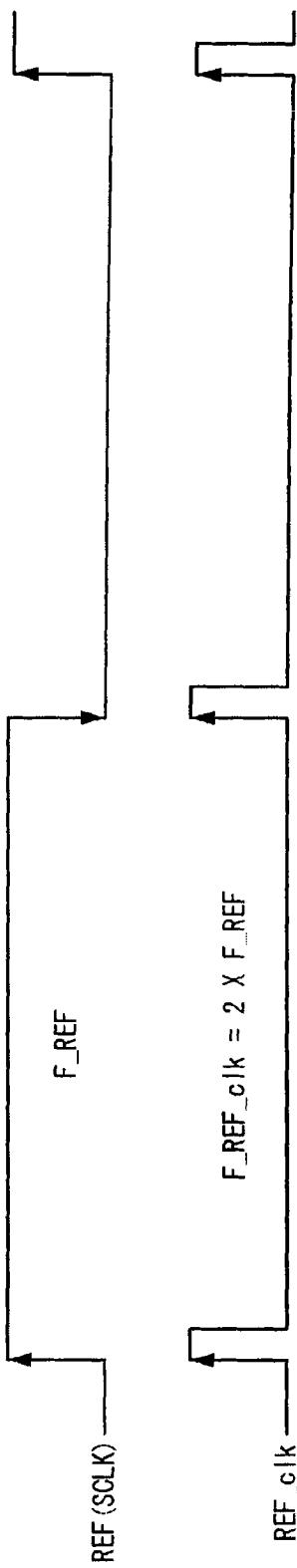

[0103] 图 9 是对 PLL 64 进行例示的框图。

[0104] 如图 9 所示,PLL 64 包括相位比较器 92、电荷泵 93、环路滤波器 94、脉冲电压转换器 95、压控振荡器 (VCO) 96、以及数字控制器 97。

[0105] 相位比较器 92 将从时钟分离器 63 所接收到的参考时钟 REF\_clk 的相位与从时钟分离器副本 (CSR) 91 所接收到的反馈边沿时钟 FB\_clk 的相位进行比较。相位比较器 92 具有与作为比较结果的参考时钟 REF\_clk 与反馈边沿时钟 FB\_clk 之间的相位差相对应的脉冲宽度。当参考时钟 REF\_clk 的相位早于反馈边沿时钟 FB\_clk 的相位时,相位比较器 92 输出正脉冲。另一方面,当参考时钟 REF\_clk 的相位晚于反馈边沿时钟 FB\_clk 的相位时,相位比较器 92 输出负脉冲。

[0106] 电荷泵 93 根据相位比较器 92 的输出脉冲的宽度和极性对提供给环路滤波器 94 的电荷量进行控制。环路滤波器 94 根据电荷泵 93 所控制的电荷量使电荷积聚或放电并且

除去输入到脉冲电压转换器 95 的时钟中的包括谐波分量的高频噪声。

[0107] 脉冲电压转换器 95 将从环路滤波器 94 所接收到的脉冲转换成 VCO 96 的控制电压并且根据从环路滤波器 94 所接收到的脉冲的宽度和极性对 VCO 96 的控制电压的电平进行控制。当 1 个 RGB 数据包的比特流包括 10 位 RGB 数据和 4 时钟位时, VCO 96 对每 1 个 RGB 数据包产生 34 个边沿时钟和 34 个中心时钟。此外, VCO 96 根据来自脉冲电压转换器 95 的控制电压并且根据来自数字控制器 97 的控制数据对时钟的相位延迟量进行控制。

[0108] 从 VCO 96 输出的第一边沿时钟 EG[0] 是反馈边沿时钟并且将其输入到时钟分离器副本 91。反馈边沿时钟 EG[0] 具有与 VCO 96 的输出频率的 1/34 相对应的频率。数字控制器 97 接收来自时钟分离器 63 的参考时钟 REF\_clk 并且接收来自时钟分离器副本 91 的反馈边沿时钟 FB\_clk, 并对参考时钟 REF\_clk 的相位与反馈边沿时钟 FB\_clk 的相位进行比较。此外, 数字控制器 97 对作为比较结果获得的相位差与来自 POR 72 的 50MHz 时钟信号 clk\_osc 的相位进行比较。数字控制器 97 根据相位差的比较结果对 VCO 96 的输出延迟量进行控制以选择 VCO 96 的振荡区域。

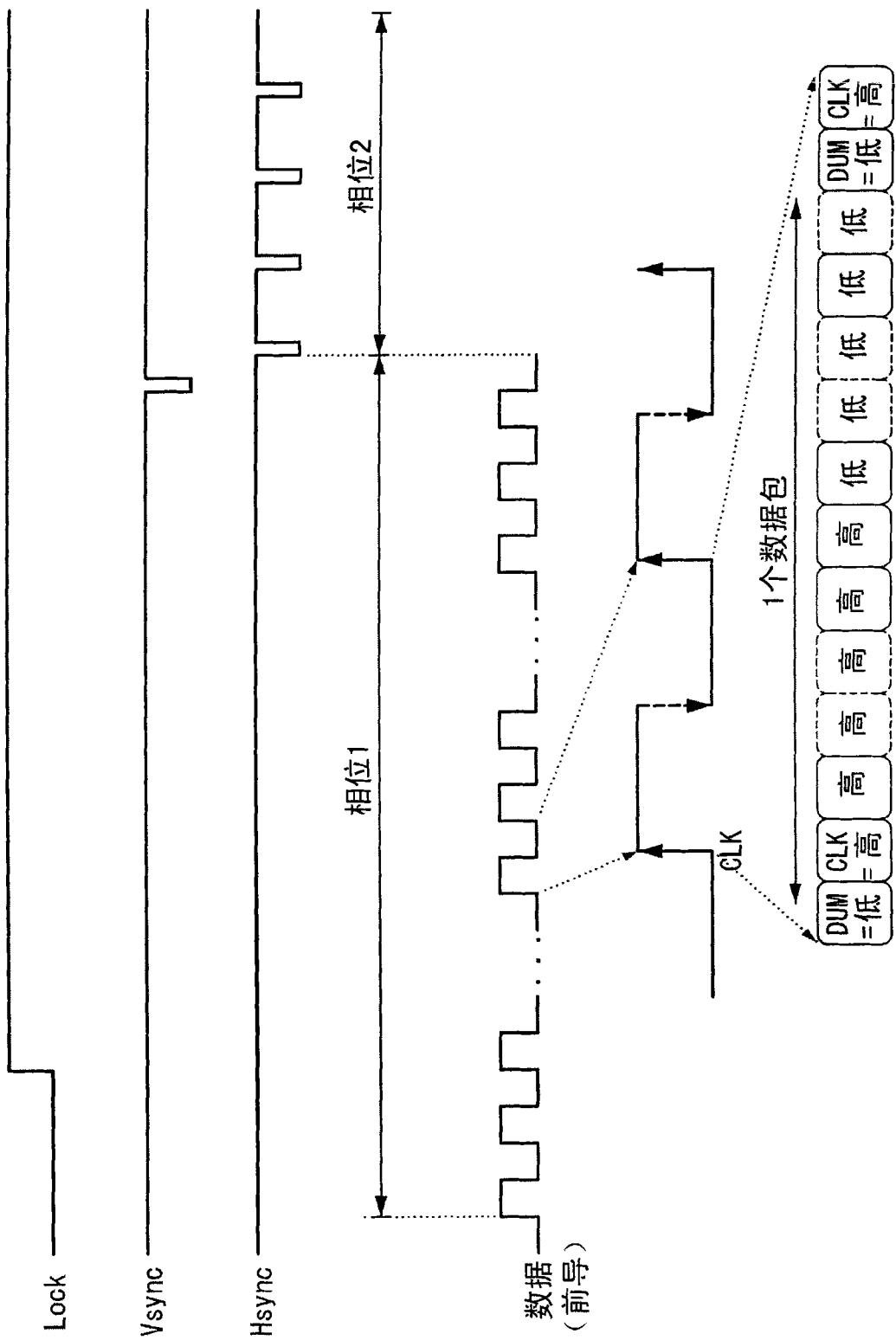

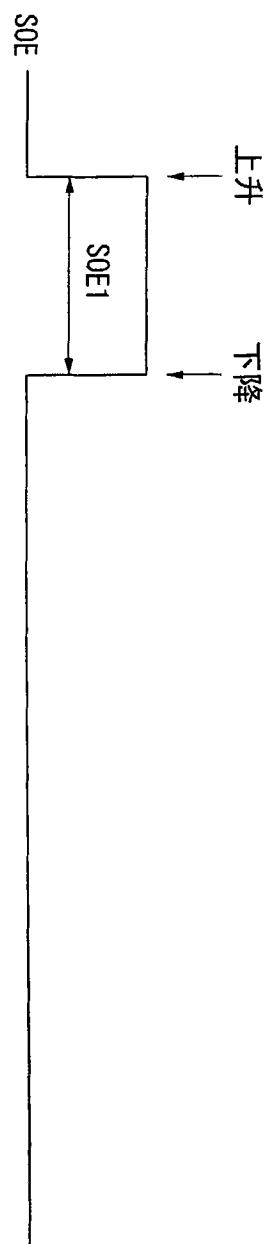

[0109] 图 10 是对时序控制器 TCON 在相位 1 产生的信号进行例示的波形图。

[0110] 如图 10 所示, 在相位 1, 时序控制器 TCON 产生锁定信号和低频的前导信号。在低频的前导信号中, 依次排列了具有高逻辑电平的多个位, 然后依次排列了具有低逻辑电平的多个位。当 1 个 RGB 数据包的比特流包括 10 位 RGB 数据和 4 时钟位时, 前导信号的频率与从时钟分离和数据采样单元 21 的 PLL64 输出的内部时钟脉冲的频率的 1/34 相一致。与高逻辑电平的前导信号的位同步地, 时钟分离和数据采样单元 21 的时钟分离器 63 使参考时钟 REF\_clk 跳变成高逻辑电平; 并且与低逻辑电平的前导信号的位同步地, 时钟分离和数据采样单元 21 的时钟分离器 63 使参考时钟 REF\_clk 跳变成低逻辑电平。

[0111] 源极驱动 IC SDIC#1 至 SDIC#8 每一个的时钟分离和数据采样单元 21 反复地执行对根据前导信号所产生的参考时钟 REF\_clk 的相位与反馈边沿时钟 FB\_clk 的相位进行比较并且锁定内部时钟脉冲的操作。如果稳定地锁定了内部时钟脉冲, 那么在下一阶段中将锁定信号传输到源极驱动 IC SDIC#1 至 SDIC#8。

[0112] 在液晶显示器的初始加电阶段中, 时序控制器 TCON 接收来自最后源极驱动 IC SDIC#8 的锁定信号以确认锁定了从时钟分离和数据采样单元 21 串行输出的内部时钟脉冲的相位和频率。此后, 时序控制器 TCON 在垂直同步信号 Vsync 的空白时段期间输出相位 2 信号。

[0113] 图 11 是对时序控制器 TCON 在相位 2 所产生的信号进行例示的波形图。

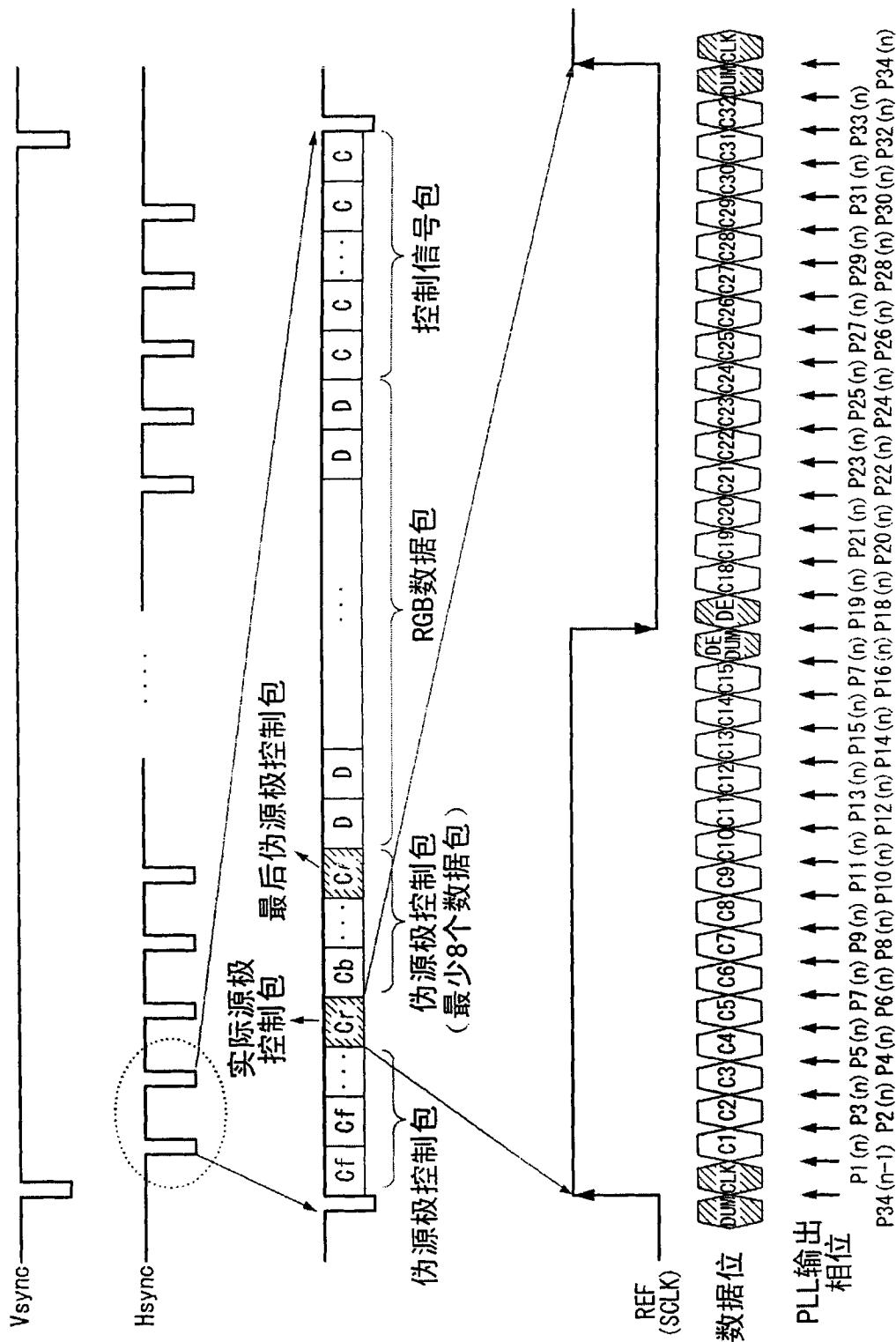

[0114] 如图 11 所示, 在相位 2, 在水平同步信号 Hsync 的 1 个周期(即 1 个水平时段)中, 时序控制器 TCON 在不存在数据的空白时段期间通过数据总线对 DATA&CLK 依次将多个前伪源极控制包 Cf、至少一个实际源极控制包 Cr、多个后伪源极控制包 Cb 和 C1 传输到源极驱动 IC SDIC#1 至 SDIC#8 的每一个。

[0115] 在实际源极控制包 Cr 之前依次将多个前伪源极控制包 Cf 传输到源极驱动 IC SDIC#1 至 SDIC#8, 以便时钟分离和数据采样单元 21 稳定地接收实际源极控制包 Cr。实际源极控制包 Cr 包括用于对源极驱动 IC SDIC#1 至 SDIC#8 的极性反转操作和数据输出进行控制的极性相关控制数据位和源极输出相关控制数据位。在实际源极控制包 Cr 之后依次将多个后伪源极控制包 Cb 和 C1 传输到源极驱动 IC SDIC#1 至 SDIC#8, 以便时钟分离和数

据采样单元 21 执行对实际源极控制包 Cr 的接收确认操作并且稳定地接收相位 3 信号。将表示在后伪源极控制包 Cb 和 C1 的最后伪源极控制包 C1 之后传输相位 3 信号的位值分配给最后伪源极控制包 C1。因为源极驱动 IC SDIC#1 至 SDIC#8 读取最后伪源极控制包 C1 的位值并且因此可预先知道在最后伪源极控制包 C1 之后输入的 RGB 数据包, 因此源极驱动 IC SDIC#1 至 SDIC#8 可稳定地执行 RGB 数据采样操作。

[0116] 通过如图 15 的数据映射表中所示的预定位值可彼此区分前伪源极控制包 Cf、实际源极控制包 Cr、以及后伪源极控制包 Cb 和 C1。因此, 时钟分离和数据采样单元 21 的 SOE&POL 恢复单元 74 通过预定位值来彼此区分源极控制包 Cf、Cr、Cb、以及 C1。因此, SOE&POL 恢复单元 74 可区分实际源极控制包 Cr 的极性相关控制数据与源极输出相关控制数据。

[0117] 源极驱动 IC SDIC#1 至 SDIC#8 每一个的时钟分离和数据采样单元 21 从源极控制包 Cf、Cr、Cb、以及 C1 分离出时钟以恢复参考时钟, 并且对参考时钟的相位与高频的内部时钟脉冲的相位进行比较以串行输出用于对极性相关控制数据位和源极输出相关控制数据位进行采样的内部时钟脉冲。此外, 时钟分离和数据采样单元 21 根据所采样的极性相关控制数据产生极性控制信号 POL 并且根据所采样的源极输出相关控制数据产生源极输出使能信号 SOE。

[0118] 如图 11 所示, 在 1 个水平时段期间在多个源极控制包 Cf、Cr、Cb、以及 C1 之后传输 RGB 数据包, 此后可在 RGB 数据包之后附加地传输多个源极控制包。在 RGB 数据包之后所附加传输的源极控制包可包括至少一个实际源极控制包和多个伪源极控制包, 并且实际源极控制包可影响下一水平时段的 RGB 数据包。

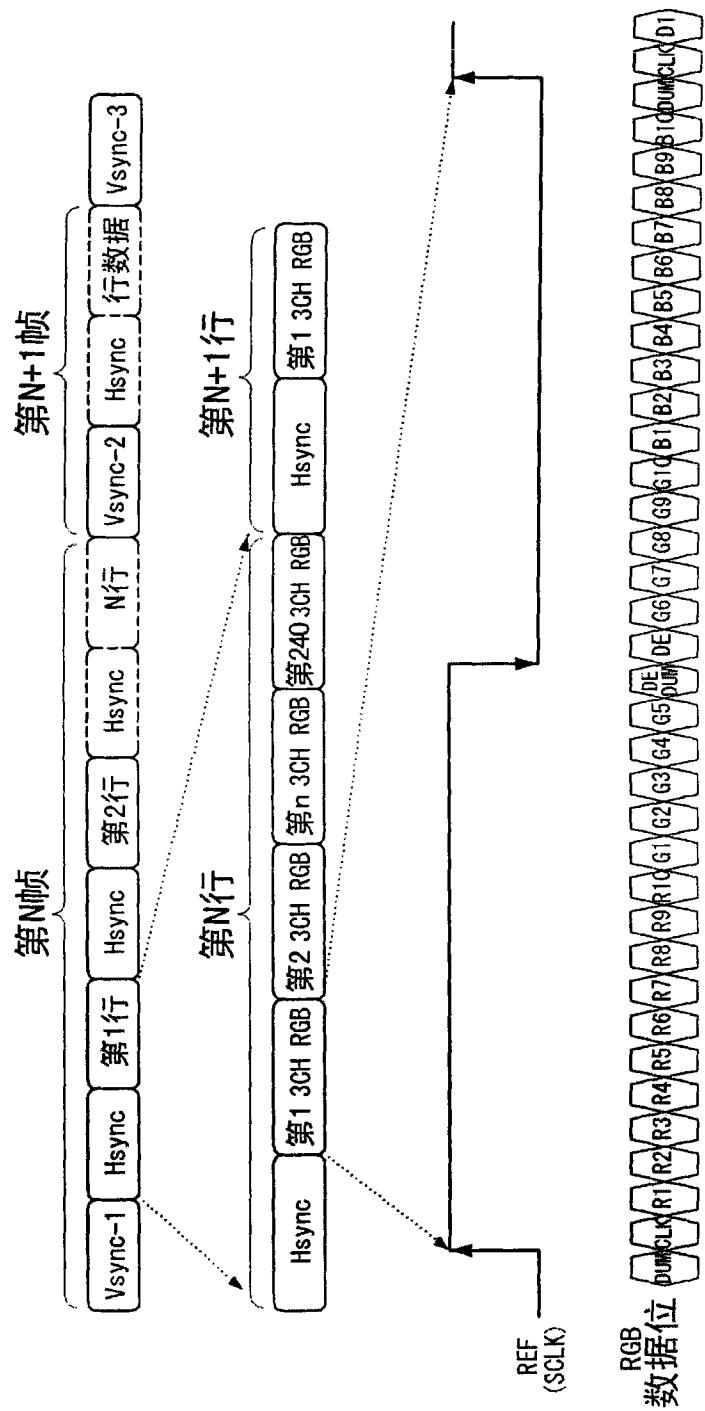

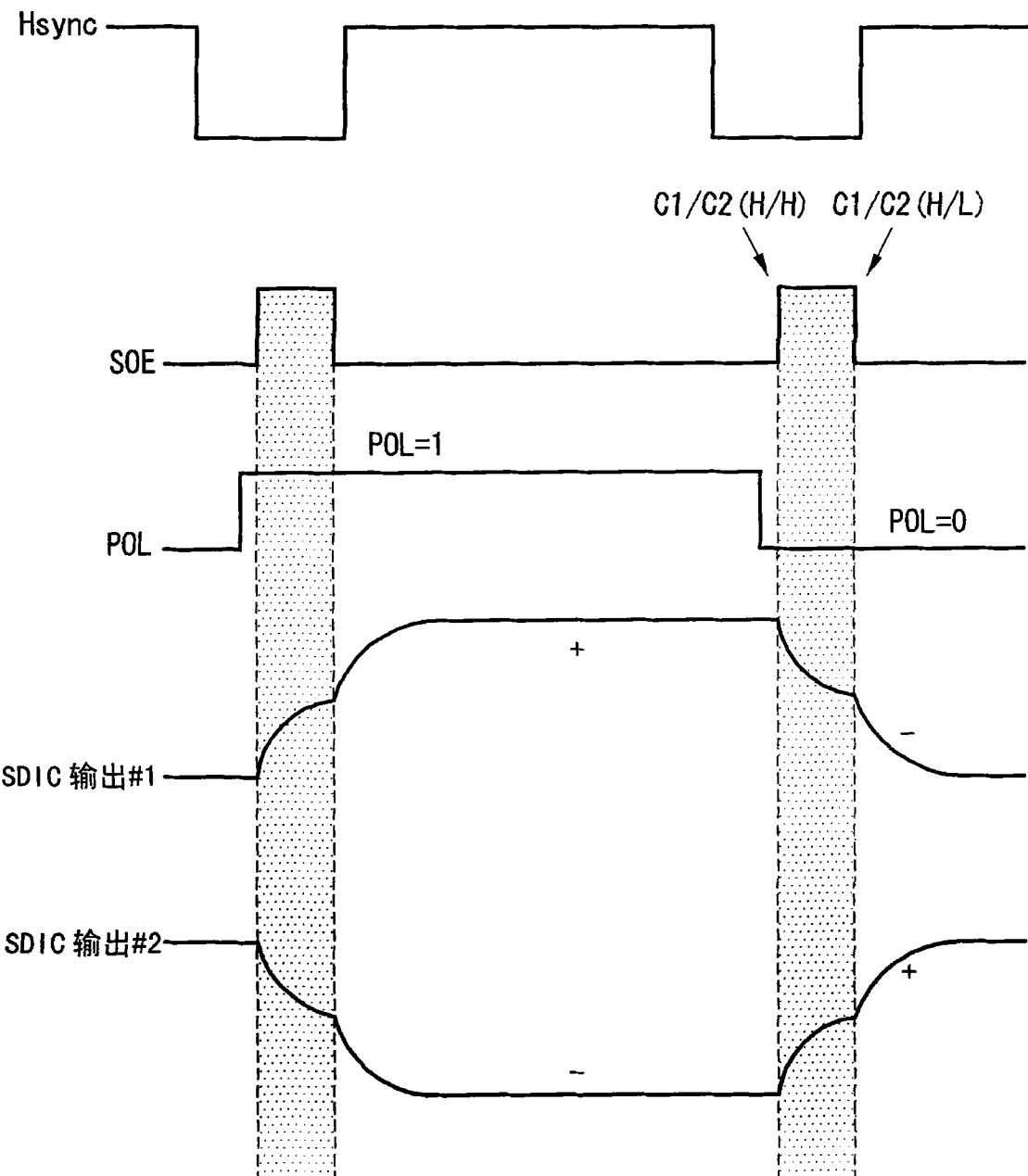

[0119] 图 12 和 13 是对时序控制器 TCON 在相位 3 所产生的信号进行例示的波形图。

[0120] 如图 12 和 13 所示, 继相位 2 信号之后, 时序控制器 TCON 在 1 个水平时段期间通过数据总线对 DATA&CLK 将相位 3 信号 (即在液晶显示器的 1 行上待显示的多个 RGB 数据包) 传输到源极驱动 IC SDIC#1 至 SDIC#8 的每一个。

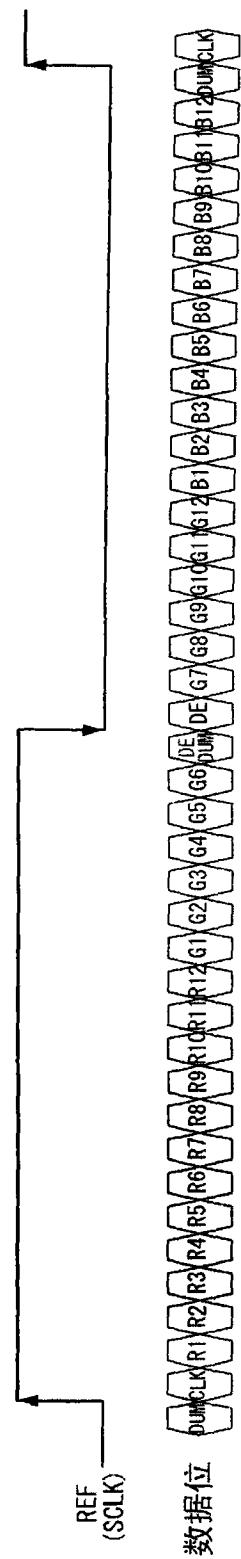

[0121] 更具体地说, 时钟分离和数据采样单元 21 从 RGB 数据包分离出时钟 CLK 和内部数据使能时钟 DE 以恢复出参考时钟。此后, 时钟分离和数据采样单元 21 对参考时钟的相位与高频的内部时钟脉冲的相位进行比较, 以串行输出用于对每个 RGB 数字视频数据位进行采样的内部时钟脉冲。如果 1 个 RGB 数据包的比特流包括 10 位 RGB 数据和 4 个时钟位, 那么依次将低逻辑电平的伪时钟 DUM 的位、高逻辑电平的时钟 CLK 的位、位 R1 至 R10、位 G1 至 G5、低逻辑电平的伪数据使能时钟 DE DUM 的位、高逻辑电平的内部数据使能时钟 DE 的位、位 G6 至 G10、以及位 B1 至 B10 分配给 1 个 RGB 数据包。时钟分离和数据采样单元 21 对时钟 CLK 和内部数据使能时钟 DE 进行检测, 并且因此确定在时钟 CLK 和内部数据使能时钟 DE 之后串行输入的数据作为 RGB 数字视频数据。此外, 时钟分离和数据采样单元 21 根据采样时钟对 RGB 数字视频数据进行采样。

[0122] 时钟分离和数据采样单元 21 将相位 1 信号和相位 2 信号每一个中的伪数据使能时钟 DE DUM 和数据使能时钟 DE 的位值设置为, 与相位 3 信号中的伪数据使能时钟 DE DUM 和数据使能时钟 DE 的位值不同的位值。因此, 时钟分离和数据采样单元 21 读取相位 3 中的伪数据使能时钟 DE DUM 和数据使能时钟 DE 的位值以对相位 3 中 (而不是相位 1 和相位 2 中) 的 RGB 数据进行采样。

[0123] 时钟分离和数据采样单元 21 的时钟分离器 63 产生其上升沿与时钟 CLK 和内部数据使能时钟 DE 相同步的参考时钟 REF\_clk。因为响应内部数据使能时钟 DE 而使参考时钟 REF\_clk 再次跳变,因此相位 3 中的参考时钟 REF\_clk 的频率可能是在相位 1 和相位 2 中所恢复的参考时钟 REF 的频率的两倍。如上所述,如果时钟分离和数据采样单元 21 的参考时钟 REF\_clk 的频率增加了,那么可进一步稳定 PLL 64 的输出,因为 PLL 64 的 VCO 之内的操作阶段 (stage) 数目减少了。更具体地说,如果 PLL 64 的参考时钟 REF\_clk 响应内部数据使能时钟 DE 而在 RGB 数据包的中间跳变以使 PLL 64 的参考时钟 REF\_clk 的频率增大为两倍,那么 PLL 64 的 VCO 之内的操作阶段数目可减少 1/2。如果内部数据使能时钟 DE 不使用参考时钟 REF\_clk 作为跳变时钟,那么 34 个 VCO 阶段是必需的。另一方面,如果内部数据使能时钟 DE 使用参考时钟 REF\_elk 作为跳变时钟,那么 17 个 VCO 阶段是必需的。如果 PLL 64 中的 VCO 阶段数目增加了,那么由多个 VCO 阶段中的增大宽度的乘积来表示由处理、电压、以及温度 PVT 的变化所引起的结果。因此,由于这种外部改变可释放对 PLL 64 的锁定。因此,本发明的实施方式除了使用时钟 CLK 之外还使用内部数据使能时钟 DE 作为跳变时钟并因此可使 PLL 的参考时钟 REF\_clk 的频率增大。由此,可提高对 PLL 64 的锁定可靠性。

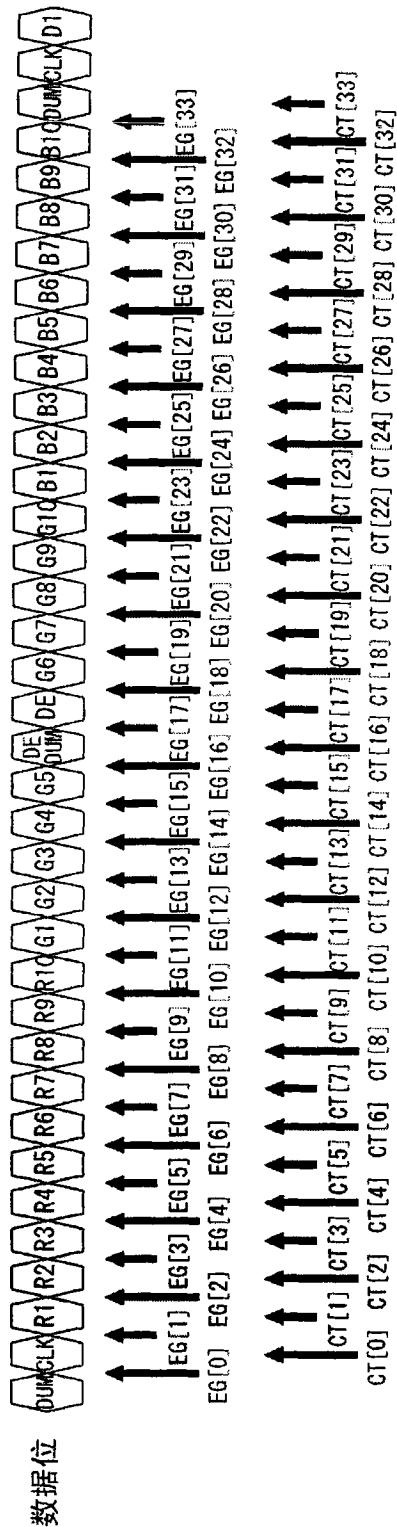

[0124] 通过彼此不同地设置预定位值可区分 RGB 数据包与源极控制包 Cf、Cr、Cb、以及 C1。图 14 例示了在相位 2 所产生的源极控制包 Cf、Cr、Cb、C1 以及在相位 3 所产生的 RGB 数据包的数据映射表。然而,根据本发明实施方式的数据映射表并不局限于图 14 所示的数据映射表,根据图 14 所示的数据映射表可作出各种变化。

[0125] 如图 14 所示,如果 R 数据、G 数据、以及 B 数据的每一个是 10 位数据,那么 RGB 数据包包括总共 34 位。更具体地说,RGB 数据包包括 1 位时钟、10 位 R 数据 [0:9]、5 位 G 数据 [0:4]、1 位伪使能时钟 DE\_DUM、1 位数据使能时钟 DE、5 位 G 数据 [5:9]、以及 10 位 B 数据 [0:9]。源极控制包 Cf、Cr、以及 Cb 具有等于 RGB 数据包的数据长度的数据长度(即 34 位)。更具体地说,源极控制包 Cf、Cr、以及 Cb 的每一个包括 1 位时钟、代替 R 数据 [0:9] 和 G 数据 [0:4] 的 15 位第一控制数据、1 位伪数据使能时钟 DE\_DUM、1 位数据使能时钟 DE、以及代替 G 数据 [5:9] 和 B 数据 [0:9] 的 15 位第二控制数据。通过彼此不同地设置伪数据使能时钟 DE\_DUM 的位值和数据使能时钟 DE 的位值可彼此区分 RGB 数据包与源极控制包 Cf、Cr、以及 Cb。

[0126] 通过图 14 的第一控制数据和第二控制数据所确定的预定位可彼此区分伪源极控制包 Cf、Cb、C1 与实际源极控制包 Cr。图 15 例示了源极控制包的数据映射表的实例。然而,根据本发明实施方式的数据映射表并不局限于图 15 所示的数据映射表,根据图 15 所示的数据映射表可做出各种变化。

[0127] 图 15 例示了源极控制包 Cf、Cr、Cb、以及 C1 的数据映射表。

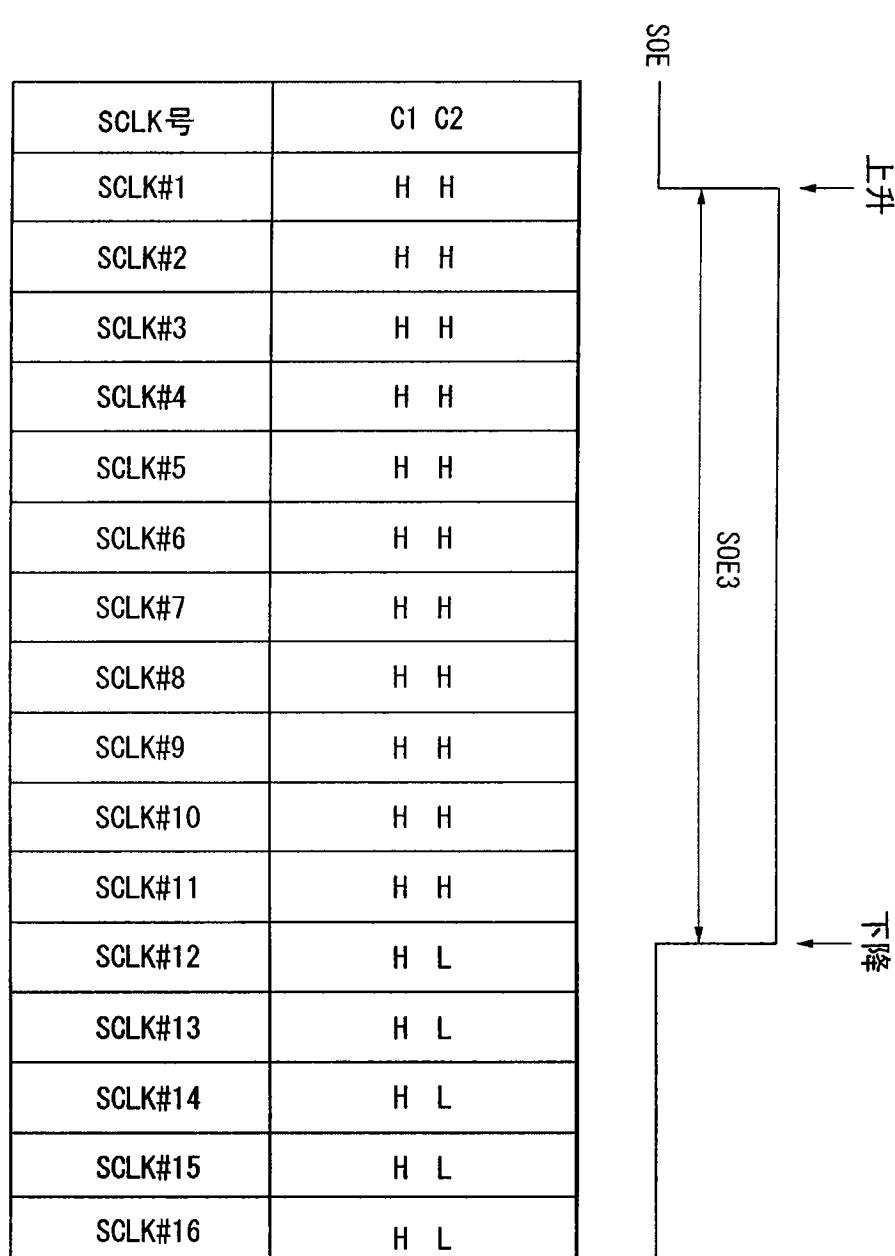

[0128] 如图 15 所示,在伪源极控制包 Cf、Cb、以及 C1 中,将高逻辑电平 H、低逻辑电平 L、低逻辑电平 L、以及低逻辑电平 L 分别分配给 4 位 C0 至 C3。另一方面,在实际源极控制包 Cr 中,将高逻辑电平 H、高逻辑电平 H、高逻辑电平 H、以及低逻辑电平 L 分别分配给 4 位 C0 至 C3。因此,通过 C1 和 C2 的位值可区分伪源极控制包 Cf、Cb、以及 C1 与实际源极控制包 Cr。

[0129] 通过 2 位 C16 和 C17 将表示对 RGB 数据包的传输的最后伪源极控制包 C1 与伪源

极控制包 Cf 和 Cb 区分开来。源极驱动 IC SDIC#1 至 SDIC#8 每一个的时钟分离和数据采样单元 21 读取最后伪源极控制包 C1 的 2 位 C16 和 C17 并且因此可预测在最后伪源极控制包 C1 之后待输入的 RGB 数据包。更具体地说,对伪源极控制包 Cf、Cb、C1 的每一个以及实际源极控制包 Cr 编码第一标识信息 C1 和 C2 以及第二标识信息 C16 和 C17。将对实际源极控制包 Cr 所编码的第一标识信息 C1 和 C2 的逻辑电平设置成与对伪源极控制包 Cf、Cb、C1 的每一个所编码的第一标识信息 C1 和 C2 的逻辑电平不同。此外,将对最后伪源极控制包 C1 所编码的第二标识信息 C16 和 C17 的逻辑电平设置成与对源极控制包 Cf、Cb、Cr 的每一个所编码的第二标识信息 C16 和 C17 的逻辑电平不同。源极驱动 IC SDIC#1 至 SDIC#8 的每一个可根据第一标识信息 C1 和 C2 的逻辑电平来确认是否输入了实际源极控制包 Cr 并且根据第二标识信息 C16 和 C17 的逻辑电平可预测 RGB 数据包的输入。

[0130] 在实际源极控制包 Cr 中,可按照图 16 或 20 中所例示的形式对极性相关控制数据和源极输出相关控制数据进行编码。

[0131] 图 16 是对实际源极控制包 Cr 的第一实施例进行例示的数据映射表。

[0132] 如图 16 所示,源极输出相关控制数据包括实际源极控制包 Cr 的位 C2 的“ SOE” 以及位 C4 与 C11 之间的 SOE\_PRD[3:0],并且极性相关控制数据包括实际源极控制包 Cr 的位 C14 的“ POL”。

[0133] 如图 17 所示,如果 SOE&POL 恢复单元 74 检测到实际源极控制包 Cr 的位 C2,那么 SOE&POL 恢复单元 74 在先前确定的上升时间产生源极输出使能信号 SOE 的脉冲。此外, SOE&POL 恢复单元 74 对实际源极控制包 Cr 的位 C5、C7、C9、以及 C11 中的 SOE\_PRD[3:0] 进行检测以将在图 12 和 13 中所例示的恢复的参考时钟 REF(SCLK) 添加到 SOE\_PRD[3:0] 的计数值上。因此,SOE&POL 恢复单元 74 确定源极输出使能信号 SOE 的下降时间。其结果是, SOE&POL 恢复单元 74 产生在先前确定的上升时间与 SOE\_PRD[3:0] 所确定的下降时间之间的预定时段保持高逻辑电平、并且在除了上述预定时段之外的时段保持低逻辑电平的源极输出使能信号 SOE。

[0134] 此外,如图 17 所示, SOE&POL 恢复单元 74 对实际源极控制包 Cr 的位 C14 进行检测以产生极性控制信号 POL。此后,在 SOE&POL 恢复单元 74 在“ i” 个水平时段期间保持极性控制信号 POL 在相同逻辑电平之后, SOE&POL 恢复单元 74 使极性控制信号 POL 反相。例如, SOE&POL 恢复单元 74 对实际源极控制包 Cr 的位 C14 进行检测以产生极性控制信号 POL 并且在 1 个或 2 个水平时段期间保持极性控制信号 POL 在高逻辑电平。此后, SOE&POL 恢复单元 74 使极性控制信号 POL 反相以在 1 个或 2 个水平时段期间保持极性控制信号 POL 在低逻辑电平。换句话说, SOE&POL 恢复单元 74 每隔 1 个或 2 个水平时段使极性控制信号 POL 的逻辑电平反相。

[0135] 图 18 例示了根据实际源极控制包 Cr 的 SOE\_PRD[3:0] 所确定的源极输出使能信号 SOE 的脉冲宽度。

[0136] 如图 18 所示,根据实际源极控制包 Cr 的 SOE\_PRD[3:0] 来确定源极输出使能信号 SOE 的脉冲宽度。更具体地说,当 SOE\_PRD[3:0] 的位值是“ 0000(或 LLLL)” 时源极输出使能信号 SOE 可具有最小脉冲宽度。当 SOE\_PRD[3:0] 的位值是“ 1111(或 HHHH)” 时源极输出使能信号 SOE 可具有最大脉冲宽度。源极输出使能信号 SOE 的脉冲宽度的最佳值可根据液晶显示器的型号而变。这是因为液晶单元的最佳数据的电荷量可根据诸如分辨率和反相

方式这样的面板属性而改变，并且也是由若干原因确定的。因此，需要改变源极输出使能信号 SOE 的脉冲宽度以便对液晶单元的数据充电时间进行控制。

[0137] 通过对时钟分离和数据采样单元 21 根据 SOE\_PRD[3:0] 所恢复的串行时钟 SCLK 的周期进行计数可对源极输出使能信号 SOE 的脉冲宽度进行控制。串行时钟 SCLK 的 1 个周期基本上等于 1 个源极控制包或 1 个 RGB 数据包的时间。在以 120Hz 的帧频所驱动的 FHD(全高清) 液晶显示器的情况下，串行时钟 SCLK 的 1 个周期大约是 27.2ns。在以 60Hz 的帧频所驱动的 FHD(全高清) 液晶显示器的情况下，串行时钟 SCLK 的 1 个周期大约是 55.2ns。因此，如图 18 和 19 所示，在 120Hz FHD 液晶显示器中，如果 SOE\_PRD[3:0] 的位值是“0000”，那么源极输出使能信号 SOE 的脉冲宽度降低为下述值：SCLK×4 = 27.2ns×4 = 108.8ns。此外，如果 SOE\_PRD[3:0] 的位值是“1111”，那么源极输出使能信号 SOE 的脉冲宽度增大到下述值：SCLK×64 = 27.2ns×64 = 1740.8ns。

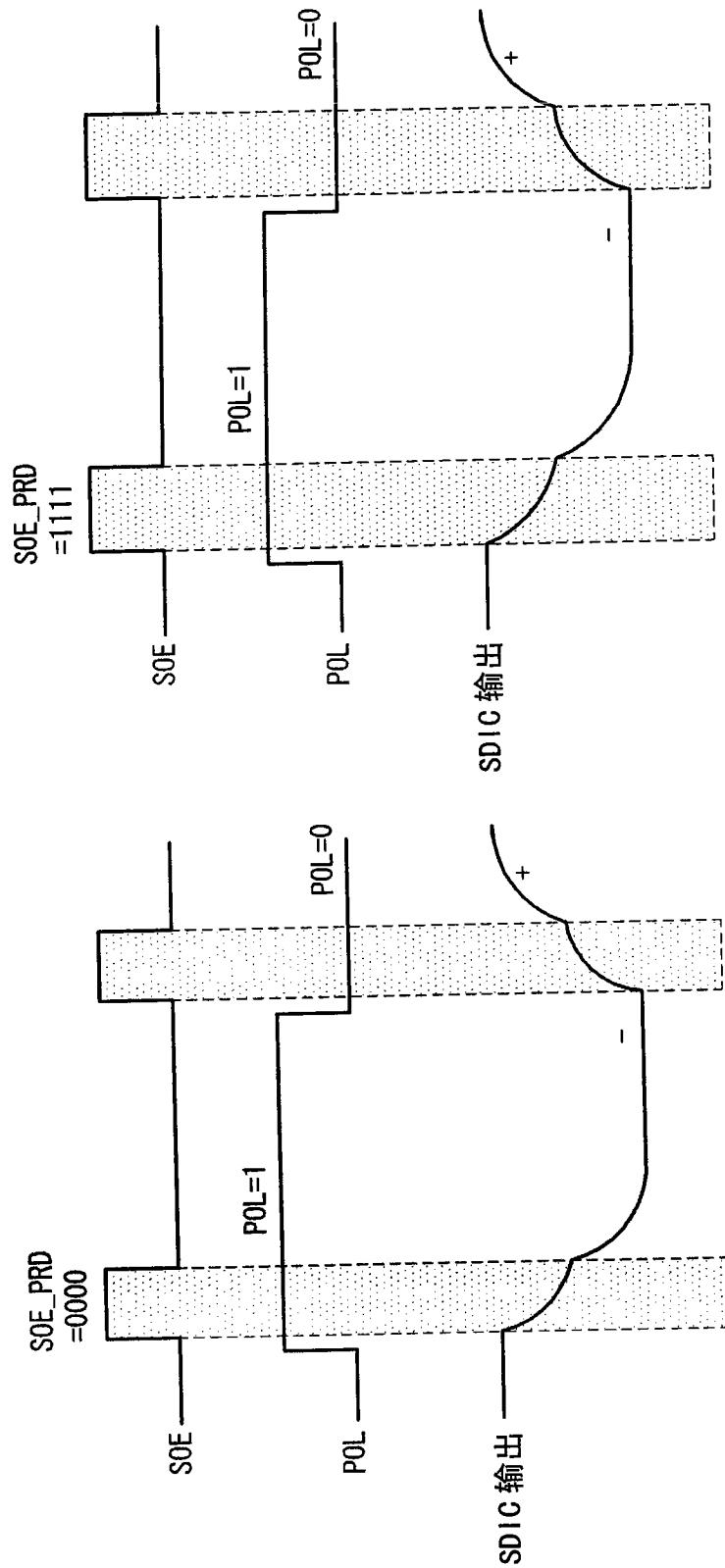

[0138] 图 20 是对实际源极控制包 Cr 的第二实施例进行例示的数据映射表。图 21 是对实际源极控制包 Cr 的第二实施例中的根据位 C1 和 C2 所控制的源极输出使能信号 SOE 以及根据位 C13 和 C14 所控制的极性控制信号 POL 进行例示的波形图。

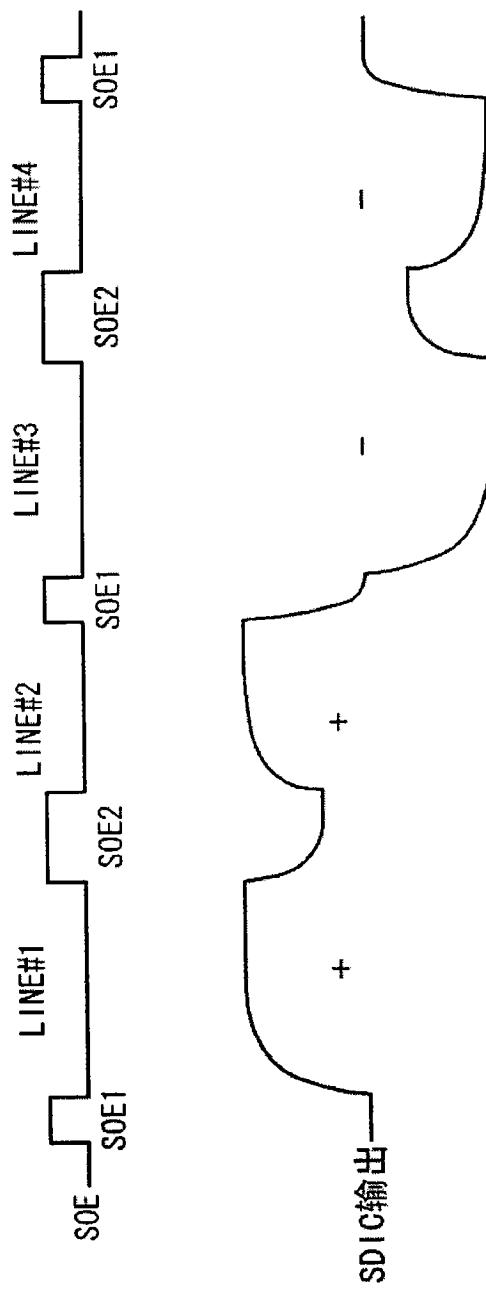

[0139] 如图 20 和 21 所示，实际源极控制包 Cr 包括位 C1 和 C2 的“SOE”以及位 C13 和 C14 的“POL”。

[0140] 当 SOE&POL 恢复单元 74 检测到具有第一逻辑值 (H/H) 的实际源极控制包 Cr 的位 C1 和 C2 时，SOE&POL 恢复单元 74 产生高逻辑电平的源极输出使能信号 SOE 并且在预定时段保持源极输出使能信号 SOE 在高逻辑电平。此后，SOE&POL 恢复单元 74 读取另一实际源极控制包 Cr 的位 C1 和 C2。当将另一实际源极控制包 Cr 的位 C1 和 C2 检测为第二逻辑值 (H/L) 时，SOE&POL 恢复单元 74 使源极输出使能信号 SOE 的逻辑电平反相为低逻辑电平。因此，根据实际源极控制包 Cr 的位 C1 和 C2 可自动调节源极输出使能信号 SOE 的脉冲宽度。根据图 22A 至 22C 中所例示的源极控制包的长度可对源极输出使能信号 SOE 的脉冲宽度进行调节。

[0141] 在图 22A 中所例示的实例中，第一实际源极控制包 Cr 的位 C1 和 C2 可包括源极输出使能信号 SOE 的上升时间信息 HH，并且第四实际源极控制包 Cr 的位 C1 和 C2 可包括源极输出使能信号 SOE 的下降时间信息 HL。SOE&POL 恢复单元 74 响应第一恢复时钟 SCLK#1 而产生高逻辑电平的源极输出使能信号 SOE 并且在从第一恢复时钟 SCLK#1 的产生时间点至紧接在产生第四恢复时钟 SCLK#4 之前的预定时段保持源极输出使能信号 SOE 在高逻辑电平。此后，当 SOE&POL 恢复单元 74 响应第四恢复时钟 SCLK#4 而检测到下降时间信息 HL 时，SOE&POL 恢复单元 74 使源极输出使能信号 SOE 的逻辑电平反相为低逻辑电平。因此，SOE&POL 恢复单元 74 可恢复具有与 (4× 源极控制包长度或 RGB 数据包长度) 相对应的脉冲宽度的源极输出使能信号 SOE。

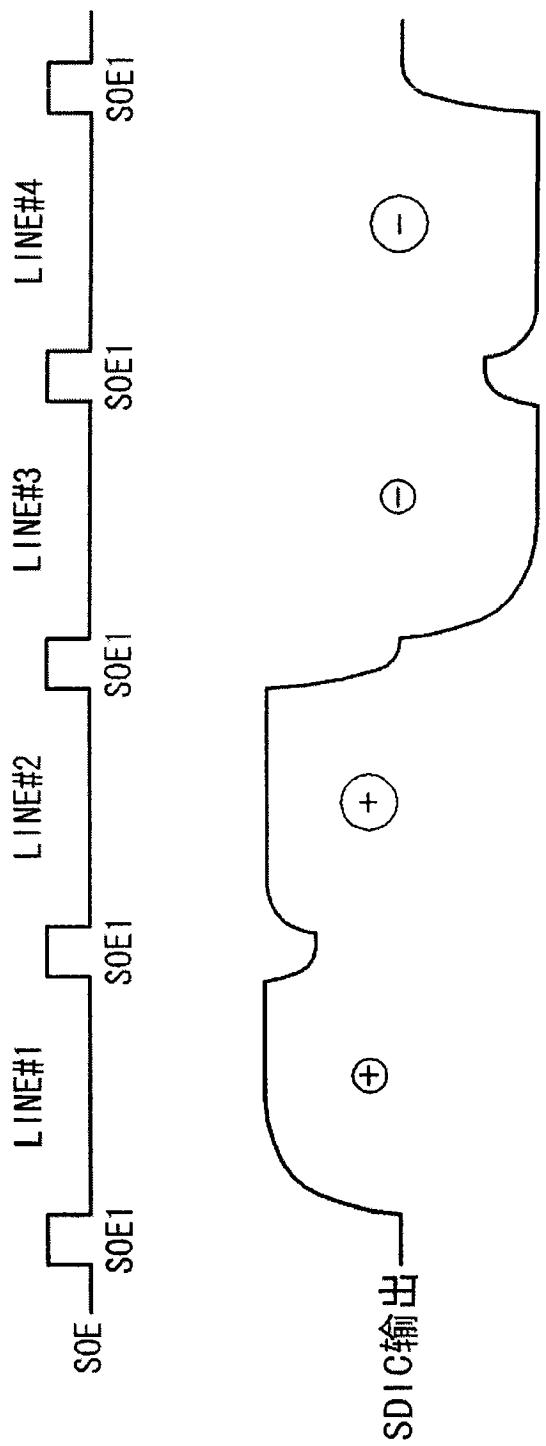

[0142] 在图 22B 中所例示的实例中，第一实际源极控制包 Cr 的位 C1 和 C2 可包括源极输出使能信号 SOE 的上升时间信息 HH，并且第八实际源极控制包 Cr 的位 C1 和 C2 可包括源极输出使能信号 SOE 的下降时间信息 HL。SOE&POL 恢复单元 74 响应第一恢复时钟 SCLK#1 而产生高逻辑电平的源极输出使能信号 SOE 并且在从第一恢复时钟 SCLK#1 的产生时间点至紧接在产生第八恢复时钟 SCLK#8 之前的预定时段保持源极输出使能信号 SOE 在高逻辑电平。此后，当 SOE&POL 恢复单元 74 响应第八恢复时钟 SCLK#8 而检测到下降时间信息 HL 时，

时, SOE&POL 恢复单元 74 使源极输出使能信号 SOE 的逻辑电平反相为低逻辑电平。因此, SOE&POL 恢复单元 74 可恢复具有与 (8× 源极控制包长度或 RGB 数据包长度) 相对应的脉冲宽度的源极输出使能信号 SOE。

[0143] 在图 22C 中所例示的实例中, 第一实际源极控制包 Cr 的位 C1 和 C2 可包括源极输出使能信号 SOE 的上升时间信息 HH, 并且第十二实际源极控制包 Cr 的位 C1 和 C2 可包括源极输出使能信号 SOE 的下降时间信息 HL。SOE&POL 恢复单元 74 响应第一恢复时钟 SCLK#1 而产生高逻辑电平的源极输出使能信号 SOE 并且在从第一恢复时钟 SCLK#1 的产生时间点至紧接在产生第十二恢复时钟 SCLK#12 之前的预定时段保持源极输出使能信号 SOE 在高逻辑电平。此后, 当 SOE&POL 恢复单元 74 响应第十二恢复时钟 SCLK#12 而检测到下降时间信息 HL 时, SOE&POL 恢复单元 74 使源极输出使能信号 SOE 的逻辑电平反相为低逻辑电平。因此, SOE&POL 恢复单元 74 可恢复具有与 (12× 源极控制包长度或 RGB 数据包长度) 相对应的脉冲宽度的源极输出使能信号 SOE。

[0144] 如图 20 所示, SOE&POL 恢复单元 74 对实际源极控制包 Cr 的位 C13 和 C14 进行检测以产生极性控制信号 POL。此后, 在 SOE&POL 恢复单元 74 在“i”个水平时段期间保持极性控制信号 POL 在相同逻辑电平之后, SOE&POL 恢复单元 74 使极性控制信号 POL 反相。例如, SOE&POL 恢复单元 74 对实际源极控制包 Cr 的位 C13 和 C14 进行检测以产生极性控制信号 POL 并且在 1 个或 2 个水平时段期间保持极性控制信号 POL 在高逻辑电平。此后, SOE&POL 恢复单元 74 使极性控制信号 POL 反相以在 1 个或 2 个水平时段期间保持极性控制信号 POL 在低逻辑电平。换句话说, SOE&POL 恢复单元 74 可每隔 1 个或 2 个水平时段使极性控制信号 POL 的逻辑电平反相。

[0145] 利用对图 16 至 22C 中所例示的源极输出使能信号 SOE 的脉冲宽度进行调节的方法可解决很可能按照 N 点反相方式 (其中 N 是等于或大于 2 的整数) 所产生的液晶单元的数据电压的充电量不均匀。图 23 例示了当按照垂直 2 点反相方式而使源极输出使能信号 SOE 的脉冲宽度 SOE1 均匀时所产生的数据电压的充电量的不均匀性。按照垂直 2 反相方式, 将正数据电压提供给第一和第二行 LINE#1 和 LINE#2 的液晶单元, 并且此后将负数据电压提供给第三和第四行 LINE#3 和 LINE#4 的液晶单元。按照垂直 2 点反相方式, 源极驱动 ICSDIC#1 至 SDIC#8 的每一个在 2 个水平时段期间依次输出正数据电压, 并且此后在这 2 个水平时段之后的 2 个水平时段期间依次输出负数据电压。在通过充电到负数据电压的数据线将第一行 LINE#1 的液晶单元充电到正数据电压的同时, 通过充电到正数据电压的数据线将第二行 LINE#2 的液晶单元充电到正数据电压。因此, 即使源极驱动 IC SDIC#1 至 SDIC#8 输出相同电压电平的正数据电压, 第二行 LINE#2 的液晶单元的正数据电压的充电量也大于第一行 LINE#1 的液晶单元的正数据电压的充电量。此外, 即使源极驱动 IC SDIC#1 至 SDIC#8 输出相同电压电平的负数据电压, 第四行 LINE#4 的液晶单元的负数据电压的充电量也大于第三行 LINE#3 的液晶单元的负数据电压的充电量。因此, 按照垂直 2 点反相方式会引起行之间的亮度差。

[0146] 根据本发明另一实施方式的液晶显示器对图 24 中所例示的源极输出使能信号 SOE 的脉冲宽度进行调节, 以便减少在相对长时间所充电的液晶单元的输出时间。源极驱动 IC SDIC#1 至 SDIC#8 的每一个在从具有相对窄脉冲宽度的第一源极输出使能信号 SOE1 的下降沿至具有相对宽脉冲宽度的第二源极输出使能信号 SOE2 的上升沿的时间段输出第一

正或负数据电压。此后,源极驱动 IC SDIC#1 至 SDIC#8 的每一个在第二源极输出使能信号 SOE2 的高逻辑电平时段期间输出公共电压或充电共享电压。此外,源极驱动 IC SDIC#1 至 SDIC#8 的每一个在从第二源极输出使能信号 SOE2 的下降沿至下一第一源极输出使能信号 SOE1 的上升沿的时间段输出第二正或负数据电压。因此,因为第二正 / 负数据电压的输出时间短于第一正 / 负数据电压的输出时间,那么补偿了行之间的数据电压的充电量的不均匀。

[0147] 在根据本发明实施方式的液晶显示器中,数据总线对 DATA&CLK 用于按照点对点方式使时序控制器 TCON 与源极驱动 IC SDIC#1 至 SDIC#8 相连,并且数据总线 DATA&CLK 的长度根据时序控制器 TCON 与源极驱动 IC SDIC#1 至 SDIC#8 之间的距离而变。在图 2 中,因为时序控制器 TCON 与第四源极驱动 IC SDIC#4 之间的距离较短,因此用于使时序控制器 TCON 与第四源极驱动 IC SDIC#4 相连的数据总线对 DATA&CLK 的长度较短。相反地,在图 2 中,因为时序控制器 TCON 与第一源极驱动 IC SDIC#1 之间的距离较长,因此用于使时序控制器 TCON 与第一源极驱动 IC SDIC#1 相连的数据总线对 DATA&CLK 的长度较长。当数据总线对 DATA&CLK 的长度增大时,RC 延迟量和压降量增大。其结果是,提供给第一源极驱动 IC SDIC#1 的相位 1 至 3 信号中的 RC 延迟量和压降量大于提供给第四源极驱动 IC SDIC#4 的相位 1 至 3 信号中的 RC 延迟量和压降量。

[0148] 如图 25 所示,根据本发明另一实施方式的液晶显示器使通过数据总线对 DATA&CLK 而提供的信号的电压与时序控制器 TCON 与源极驱动 IC SDIC#1 至 SDIC#8 之间的距离成比例地增大。时序控制器 TCON 可使待传输到第三至第六源极驱动 IC SDIC#3 至 SDIC#6 的信号的摆动宽度 Wswing1 较窄并且可使待传输到第一和第八源极驱动 IC SDIC#1 和 SDIC#8 的信号的摆动宽度 Wswing3 较宽。此外,时序控制器 TCON 可使待传输到第二和第七源极驱动 IC SDIC#2 和 SDIC#7 的信号的摆动宽度 Wswing2 大于摆动宽度 Wswing1 并且小于摆动宽度 Wswing3。由于上述摆动宽度控制,待传输到第一和第八源极驱动 IC SDIC#1 和 SDIC#8 的信号的偏斜率相关时间 t3 短于待传输到其他源极驱动 IC SDIC#2 至 SDIC#7 的信号的偏斜率相关时间 t1 和 t2。此外,待传输到第二和第七源极驱动 IC SDIC#2 和 SDIC#7 的信号的偏斜率相关时间 t2 短于待传输到第三至第六源极驱动 IC SDIC#3 至 SDIC#6 的信号的偏斜率相关时间 t1。其结果是,根据本发明另一实施方式的液晶显示器可对传输到第一和第八源极驱动 IC SDIC#1 和 SDIC#8 的信号的延迟和压降进行补偿。

[0149] 从时序控制器 TCON 传输到源极驱动 IC SDIC#1 至 SDIC#8 的 RGB 数据包的格式可根据液晶显示器面板 10 的像素阵列的结构而变化。

[0150] 图 26 是对液晶显示器面板 10 的像素阵列的示范性结构进行例示的等效电路图。

[0151] 如图 26 所示,液晶显示器面板 10 的像素阵列具有从列方向来看 TFT 锯齿形(或“Z”字型)地连接在左右数据线之间的结构。

[0152] 用于对奇数行 LINE#1 和 LINE#3 的液晶单元进行驱动的 TFT 连接到奇数栅极线 G1、G3、...、Gn-1 与数据线 D1 至 Dm-1 的交叉处,并且将来自第 i 条数据线 Di 的数据电压提供给奇数行 LINE#1 和 LINE#3 的像素电极 1。用于对偶数行 LINE#2 和 LINE#4 的液晶单元进行驱动的 TFT 连接到偶数栅极线 G2、G4、...、Gn 与数据线 D2 至 Dm 的交叉处,并且将来自第 (i+1) 条数据线 D(i+1) 的数据电压提供给偶数行 LINE#2 和 LINE#4 的像素电极 1。如果液晶显示器面板 10 是根据图 26 中所例示的像素阵列结构实现的,那么在 1 帧时段期

间源极驱动 IC SDIC#1 至 SDIC#8 的每一个将相同极性的数据电压提供给数据线 D1 至 D<sub>m</sub> 并且还将相反极性的数据电压提供给相邻数据线。因为将相同极性的数据电压输出到源极驱动 IC SDIC#1 至 SDIC#8 的每一个的输出通道,因此可降低源极驱动 IC SDIC#1 至 SDIC#8 的功耗。此外,因为相反极性的数据电压在垂直与水平相邻液晶单元之间充电,因此液晶显示器面板 10 可显示在行之间没有闪烁和亮度差的图像。

[0153] 为了将数据电压提供给图 26 所示的像素阵列,从时序 - 控制器 TCON 传输到源极驱动 IC SDIC#1 至 SDIC#8 的偶数行 LINE#2、LINE#4、...、LINE#n 的 RGB 数据包必须具有与从时序控制器 TCON 传输到源极驱动 IC SDIC#1 至 SDIC#8 的奇数行 LINE#1、LINE#3、...、LINE#(n-1) 的 RGB 数据包不同的格式。在图 27A 中所例示的奇数行 LINE#1、LINE#3、...、LINE#(n-1) 的 RGB 数据包的格式基本上等于在图 12 和 13 中所例示的 RGB 数据包的格式。当将数据写入到偶数行 LINE#2、LINE#4、...、LINE#n 的像素上时,第一数据线 D1 是与 TFT 和液晶单元不相连的伪数据线并且其他数据线 D2 至 D<sub>m</sub> 通过 1TFT 与液晶单元相连。如图 27B 所示,待写入到偶数行 LINE#2、LINE#4、...、LINE#n 的像素上的 1 个 RGB 数据包依次包括伪时钟 DUM、时钟 CLK、先前像素 B1 至 B10 的 10 位 B 数据、5 位 R 数据 R1 至 R5、伪数据使能时钟 DEDUM、数据使能时钟 DE、5 位 R 数据 R6 至 R10、以及 10 位 G 数据 G1 至 G10。

[0154] 图 28 是对在 R 数据、G 数据、以及 B 数据的每一个是 10 位数据时时钟分离和数据采样单元 21 的输出进行例示的波形图。

[0155] 在根据本发明实施方式的液晶显示器及其驱动方法中,RGB 数据包和控制数据包并不局限于在图 10 至 16 中所例示的数据长度,可根据在图 29A 至 29D 中所例示的输入图像的比特率来对它们的长度进行转换。

[0156] 当 R 数据、G 数据、以及 B 数据的每一个是 10 位数据时,如图 29A 所示,时序控制器 TCON 产生 1 个源极控制包或 1 个 RGB 数据包作为 T 小时的比特流,所述比特流包括 DUM、CLK、R1 至 R10、G1 至 G5、DE DUM、DE、G6 至 G10、以及 B1 至 B10。源极驱动 IC SDIC#1 至 SDIC#8 的每一个的时钟分离和数据采样单元 21 基于从时序控制器 TCON 所接收到的 1 个源极控制 /RGB 数据包产生 34 个边沿时钟和 34 个中心时钟,并且依照这些中心时钟对源极控制位或 RGB 数据位进行采样。

[0157] 当 R 数据、G 数据、以及 B 数据的每一个是 8 位数据时,如图 29B 所示,时序控制器 TCON 产生 1 个源极控制包 /RGB 数据包作为  $T \times (28/34)$  小时的比特流,所述比特流包括 DUM、CLK、R1 至 R8、G1 至 G4、DE DUM、DE、G5 至 G8、以及 B1 至 B8。源极驱动 IC SDIC#1 至 SDIC#8 的每一个的时钟分离和数据采样单元 21 基于从时序控制器 TCON 所接收到的 1 个源极控制 /RGB 数据包产生 28 个边沿时钟和 28 个中心时钟,并且依照这些中心时钟对源极控制位或 RGB 数据位进行采样。

[0158] 当 R 数据、G 数据、以及 B 数据的每一个是 6 位数据时,如图 29C 所示,时序控制器 TCON 产生 1 个源极控制 /RGB 数据包作为  $T \times (22/34)$  小时的比特流,所述比特流包括 DUM、CLK、R1 至 R6、G1 至 G3、DE DUM、DE、G4 至 G6、以及 B1 至 B6。源极驱动 IC SDIC#1 至 SDIC#8 的每一个的时钟分离和数据采样单元 21 基于从时序控制器 TCON 所接收到的 1 个源极控制 /RGB 数据包产生 22 个边沿时钟和 22 个中心时钟,并且依照这些中心时钟对源极控制位或 RGB 数据位进行采样。

[0159] 当 R 数据、G 数据、以及 B 数据的每一个是 12 位数据时,如图 29D 所示,时序控制

器 TCON 产生 1 个源极控制 /RGB 数据包作为  $T \times (40/34)$  小时的比特流，所述比特流包括 DUM、CLK、R1 至 R12、G1 至 G6、DE DUM、DE、G7 至 G12、以及 B1 至 B12。源极驱动 IC SDIC#1 至 SDIC#8 的每一个的时钟分离和数据采样单元 21 基于从时序控制器 TCON 所接收到的 1 个源极控制 /RGB 数据包产生 40 个边沿时钟和 40 个中心时钟，并且依照这些中心时钟对源极控制位或 RGB 数据位进行采样。

[0160] 时序控制器 TCON 确定输入数据的比特率并且可自动转换如图 29A 至 29D 中所例示的源极控制 /RGB 数据包的长度。

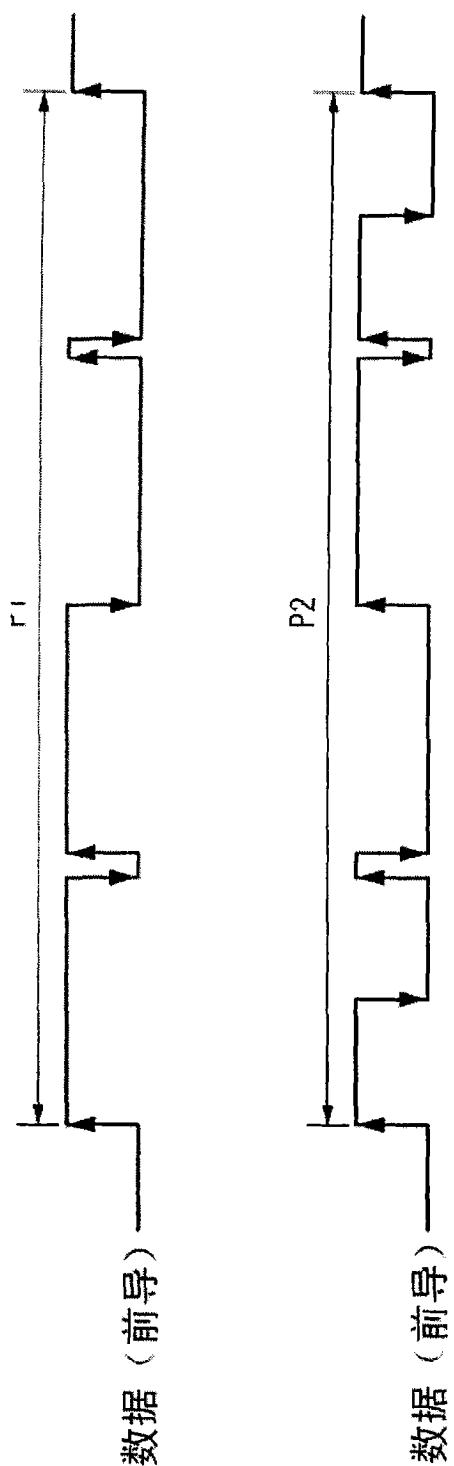

[0161] 根据本发明另一实施方式的液晶显示器产生包括分别具有不同脉冲宽度和不同周期的多个脉冲组的前导信号作为相位 1 信号，并且因此可更安全地锁定从时钟分离和数据采样单元 21 的 PLL 输出的内部时钟脉冲的相位和频率。

[0162] 图 30 和 31 是对根据本发明另一实施方式的相位 1 信号进行例示的波形图。

[0163] 如图 30 和 31 所示，相位 1 信号包括相位 1-1 信号和相位 1-2 信号。相位 1-1 信号是按照与上述前导信号相同的方式将其 1 个周期设置为与 1 个源极控制 /RGB 数据包相同时间的信号。相位 1-2 信号的频率大于相位 1-1 信号的频率，并且相位 1-2 信号的周期等于或小于相位 1-1 信号的周期的  $1/2$ 。相位 1-2 信号可具有交替产生下述两个脉冲组 P1 和 P2 的波形，所述这两个脉冲组 P1 和 P2 的分别具有不同相位和不同频率。第一脉冲组 P1 的频率等于或大于按照相位 1-1 信号的形式所产生的脉冲行的频率的两倍，并且第二脉冲组 P2 的频率等于或大于第一脉冲组 P1 的频率的两倍。如图 30 和 31 所示，虽然时钟分离和数据采样单元 21 的 PLL 64 对其频率大于相位 1-1 信号的频率并且相位有规律变化的脉冲进行跟踪，但是与图 10 中所例示的低频前导信号相比，时钟分离和数据采样单元 21 可更稳定且更快速地锁定内部时钟脉冲的相位和频率。

[0164] 当客户需要对 LCD 模块的操作进行改进时，LCD 模块制造商可向源极驱动 IC SDIC#1 至 SDIC#8 提供各个选项以便客户可对 LCD 模块的具体操作进行直接控制。为此，在现有技术中，只要需要，制造商就要向源极驱动 IC SDIC#1 至 SDIC#8 提供多个可选插脚并且使上拉电阻器或下拉电阻器与源极驱动 IC SDIC#1 至 SDIC#8 的可选插脚相连。此外，在现有技术中，通过将电源电压 Vcc 或接地电平电压 GND 施加到 LCD 模块上来对源极驱动 IC SDIC#1 至 SDIC#8 的可选操作进行控制。然而，在现有技术中，由于多个可选插脚而使源极驱动 IC SDIC#1 至 SDIC#8 的芯片大小增大了，并且还由于上拉 / 下拉电阻器与可选插脚和线路相连而使 PCB 大小增大了。

[0165] 根据本发明另一实施方式的液晶显示器通过在相位 2 的预定时段期间添加用于对源极驱动 IC SDIC#1 至 SDIC#8 的各种操作进行控制的信号可进一步减小源极驱动 IC SDIC#1 至 SDIC#8 的芯片大小和 PCB 的大小。为此，根据本发明实施方式的液晶显示器产生诸如 PWRC1/2、MODE、SOE\_EN、PACK\_EN、CHMODE、CID1/2、H\_2DOT 这样的用于对源极驱动 IC SDIC#1 至 SDIC#8 的各个操作进行控制的控制选择信息作为独立的源极控制包。可将包括控制选择信息的源极控制包插入到相位 2 的预定时段中并且可通过数据总线对将其传输到源极驱动 IC SDIC#1 至 SDIC#8。

[0166] 如以下表格 1 中所示的，PWRC1/2 是用于确定源极驱动 IC SDIC#1 至 SDIC#8 的输出缓冲器的放大率以选择源极驱动 IC SDIC#1 至 SDIC#8 的功率能力的选择信息。

[0167] [ 表格 1 ]

[0168]

|                   |        |

|-------------------|--------|

| PWRC1/2 = 11 (HH) | 高功率模式  |

| PWRC1/2 = 10 (HL) | 正常功率模式 |

| PWRC1/2 = 01 (LH) | 低功率模式  |

| PWRC1/2 = 00 (LL) | 超低功率模式 |

[0169] 如以下表格 2 中所示的, MODE 是用于在源极输出使能信号 SOE 的高逻辑电平时段期间确定充电共享电压的输出是使能还是禁用的选择信息。

[0170] [ 表格 2 ]

[0171]

|              |                        |

|--------------|------------------------|

| MODE = 1 (H) | Hi_Z 模式操作 ( 充电共享输出禁用 ) |

| MODE = 0 (L) | 充电共享模式操作 ( 充电共享输出使能 )  |

[0172] 如以下表格 3 中所示的, SOE\_EN 是用于确定是以嵌入到 RGB 数字视频数据中的形式还是通过与源极驱动 IC SDIC#1 至 SDIC#8 相分离的线来接收源极输出使能信号 SOE 的选择信息。

[0173] [ 表格 3 ]

|                | PACK_EN = 0 (L) | PACK_EN = 1 (H) |

|----------------|-----------------|-----------------|

| SOE_EN = 0 (L) | 禁止              | 使用内部 SOE        |

| SOE_EN = 1 (H) | 使用外部 SOE        |                 |

[0175] 如以下表格 4 中所示的, PACK\_EN 是用于确定是以嵌入到 RGB 数字视频数据中的形式还是通过与源极驱动 IC SDIC#1 至 SDIC#8 相分离的线来接收要传输到栅极驱动 IC GDIC#1 至 GDIC#4 的极性控制信号 POL 和栅极起始脉冲 GSP 的选择信息。

[0176] [ 表格 4 ]

[0177]

|                 |                        |

|-----------------|------------------------|

| PACK_EN = 1 (H) | 使能控制包                  |

| PACK_EN = 0 (L) | 禁用控制包 ( 忽略 SOE_EN 的值 ) |

[0178] 如以下表格 5 中所示的, CHMODE 是用于依照液晶显示器的分辨率来确定源极驱动 IC SDIC#1 至 SDIC#8 的输出通道数目的选择信息。

[0179] [ 表格 5 ]

[0180]

|                |                             |

|----------------|-----------------------------|

| CHMODE = 1 (H) | 690Ch. 输出 (691 ~ 720Ch. 禁用) |

| CHMODE = 0 (L) | 720Ch. 输出                   |

[0181] 如以下表格 6 中所示的, CID1/2 是赋予芯片标识码 CID 给源极驱动 ICSDIC#1 至 SDIC#8 每一个以对源极驱动 IC SDIC#1 至 SDIC#8 进行单独控制的选择信息。根据源极驱动 IC 的数目可对 CID1/2 的比特率进行调节。此外, 如上所述, 利用时序控制器 TCON 和控制线对 SCL/SDA 而通过 I<sup>2</sup>C 通信对源极驱动 IC SDIC#1 至 SDIC#8 进行单独控制。LCD 模块制造商在使用选择信息 CID1/2 的控制方法与使用通过 I<sup>2</sup>C 通信的控制方法中进行选择。

[0182] [ 表格 6]

[0183]

|                  |            |

|------------------|------------|

| CID1/2 = 00 (LL) | 分配给 SDIC#1 |

| CID1/2 = 01 (LH) | 分配给 SDIC#2 |

| CID1/2 = 10 (HL) | 分配给 SDIC#3 |

| CID1/2 = 11 (HH) | 分配给 SDIC#4 |

[0184] 如以下表格 7 中所示的, H\_2DOT 是用于对从源极驱动 IC SDIC#1 至 SDIC#8 输出的正 / 负模拟视频数据电压的水平极性周期进行控制的选择信息。例如, 如果 H\_2DOT 的位值是“1 (H)”, 那么源极驱动 IC SDIC#1 至 SDIC#8 按照水平 2 点反相方式来对数据电压的极性进行控制。按照水平 2 点反相方式, 源极驱动 IC SDIC#1 至 SDIC#8 将相同极性的数据电压输出到两条相邻数据线。也就是说, 按照水平 2 点反相方式每隔两条相邻数据线使数据电压的极性反转。因此, 如下控制对水平相邻液晶单元充电的数据电压的极性: “ -++-, . . . , +--+ ( 或者 +--+, . . . , -+- ) ”。此外, 如果 H\_2DOT 的位值是“0 (L)”, 那么源极驱动 IC SDIC#1 至 SDIC#8 按照水平 1 点反相方式来对数据电压的极性进行控制。按照水平 1 点反相方式, 源极驱动 IC SDIC#1 至 SDIC#8 每隔 1 条数据线使提供给相邻数据线的数据电压的极性反转。因此, 如下控制对水平相邻液晶单元充电的数据电压的极性: “ -+-+, . . . , +-+ ( 或者 +-+, . . . , -+- ) ”。

[0185] [ 表格 7]

[0186]

|                |            |

|----------------|------------|

| H_2DOT = 1 (H) | 水平 2 点反相使能 |

| H_2DOT = 0 (L) | 水平 2 点反相禁用 |

[0187] 在本发明的实施方式中, 时序控制器 TCON 必须接收来自最后源极驱动 ICSDIC#8 的高逻辑电平的反馈锁定信号, 以便时序控制器 TCON 继续相位 2。更具体地说, 如果所有源极驱动 IC SDIC#1 至 SDIC#8 的 PLL 锁定操作未完成, 那么时序控制器 TCON 仅重复产生相位 1 的前导信号, 并且源极驱动 ICSDIC#1 至 SDIC#8 不输出数据电压。因此, 如果时序控制器 TCON 没有接收到反馈锁定信号, 那么无法确认源极驱动 IC SDIC#1 至 SDIC#8 的各个驱动状态。然而, 需要确认源极驱动 IC SDIC#1 至 SDIC#8 当中有缺陷的源极驱动 IC, 并且还

需要确认源极驱动 IC SDIC#1 至 SDIC#8 每一个的驱动状态。

[0188] 根据本发明另一实施方式的液晶显示器提供了测试模式并且在该测试模式下将反馈锁定信号输入到时序控制器 TCON 以促使源极驱动 IC SDIC#1 至 SDIC#8 输出数据电压，以便确认源极驱动 IC SDIC#1 至 SDIC#8 的各个驱动状态。为此，在根据本发明实施方式的液晶显示器中，如图 32 所示，将选择单元 SEL 附加地安装到时序控制器 TCON 内部或外部。

[0189] 更具体地说，选择单元 SEL 的第一输入端与反馈锁定检查线 LCS2 相连，并且选择单元 SEL 的第二输入端与测试模式使能信号 TEST 的输入端相连。选择单元 SEL 可被实施为用于输出反馈锁定信号“Lock Out”与测试模式使能信号 TEST 中的至少一个的或 (OR) 门。即使没有将高逻辑电平的反馈锁定信号“Lock Out”输入到时序控制器 TCON，如果输入了高逻辑电平的测试模式使能信号 TEST，选择单元 SEL 也将高逻辑电平的测试模式使能信号 TEST 输入到时序控制器 TCON 的数据传输模块。因此，即使在测试模式下时序控制器 TCON 未接收到反馈锁定信号，时序控制器 TCON 也继续图 6 的步骤 S8 以将相位 2 信号和相位 3 信号传输到源极驱动 IC SDIC#1 至 SDIC#8。在测试模式下时序控制器 TCON 将从内部存储器所提取的测试数据编码为相位 3 的 RGB 数据包并且将所编码的测试数据传输到源极驱动 IC SDIC#1 至 SDIC#8。操作者在测试模式下观看在液晶显示器面板上所显示的测试数据的图像并且可确认源极驱动 IC SDIC#1 至 SDIC#8 的各个驱动状态以及在源极驱动 IC SDIC#1 至 SDIC#8 当中是否存在有缺陷的源极驱动 IC。

[0190] 如上所述，在根据本发明实施方式的液晶显示器及其驱动方法中，用于数据采样的时钟产生电路嵌入到每个源极驱动 IC 内部，并且通过数据总线对将源极控制包和 RGB 数据包传输到每个源极驱动 IC。因此，可减少时序控制器与源极驱动 IC 之间所需的数据传输线的数目。此外，因为传输到源极驱动 IC 的信号的摆动宽度是与时序控制器与源极驱动 IC 之间的距离成比例地增加，因此可补偿输入到源极驱动 IC 的信号的延迟量的偏差以及信号的压降量的偏差。

[0191] 此外，在根据本发明实施方式的液晶显示器及其驱动方法中，控制线连接在时序控制器与源极驱动 IC 之间，并且时序控制器通过控制线将芯片标识码和控制数据传输到源极驱动 IC。因此，可对源极驱动 IC 进行单独控制并且因此可独立执行调试操作。

[0192] 本说明书中对“一个实施方式”、“示范性实施方式”、“实例”等等的任何参考意味着结合该实施方式所描述的具体特点、结构、或者特性包含在本发明的至少一个实施方式中。在说明书不同地方出现的这种短语不是必定都指同一实施方式。此外，当结合任何实施方式对具体特点、结构、或者特性进行描述时，应当认为它在所属领域普通技术人员的视界范围以内结合其它实施方式也可能会起到这种特点、结构、或者特性的作用。

[0193] 虽然已参考多个示范性实施方式对实施方式进行了描述，但是应清楚的是所属领域普通技术人员可设计出属于本发明原理范围之内的许多其它修改和实施方式。更具体地，可对在说明书、附图、以及所附权利要求范围之内的部件和 / 或目标组合排列的布置做出各种改变和修改。除了对部件和 / 或排列的改变和修改之外，不脱离本发明的精神的条件下其他替代方式也落入本发明的范围之内。

图 1

图 2

SDIC

图 3

图 4

图 5

图 6

21

图 7

图 8

图 9

图 10

图 11

图 12

图 13

| 数据位 | CLK | D1~D10        | D11~D15     | DE_DUM | DE   | D16~D20        | D21~D30     |

|-----|-----|---------------|-------------|--------|------|----------------|-------------|

| 格式  | 时钟  | R_data[0:9]   | G_data[0:4] | 伪      | 数据使能 | G_data[5:9]    | B_data[0:9] |

|     | 时钟  | 控制数据 (C1~C15) |             | 伪      | 数据使能 | 控制数据 (C18~C32) |             |

图 14

| 项             | C0  | C1  | C2  | C3  | C12~C11 | C12 | C13~C14 | C15 | C16 | C17 | C18~C32 |

|---------------|-----|-----|-----|-----|---------|-----|---------|-----|-----|-----|---------|

| 伪源极控制包 Cf, Cb | H   | L   | L   | L   | 已分配     | L   | 已分配     | H   | H   | L   |         |

| 实际源极控制包 Cr    | H   | (H) | L   | L   | 已分配     | L   | 已分配     | H   | H   | L   |         |

| 最后伪源极控制包 C1   | H   | L   | L   | L   | 已分配     | L   | 已分配     | H   | (L) | (H) |         |

| 控制信号映射        | CLK | SOE | SOE | PRD |         | POL |         |     | DE  |     |         |

图 15

| 位置             |         | 项            | 描述           |

|----------------|---------|--------------|--------------|

| CLK            | C0      |              | -            |

| R0             | C1      | DUM_SOE      | SOE的伪信号      |

| R1             | C2      | SOE          | 频闪输出使能       |

| R2             | C3      | 保留           | -            |

| R3             | C4      | DUM_SOE_PRD0 | SOE_PRD0的伪信号 |

| R4             | C5      | SOE_PRD0     | 控制SOE时段      |

| R5             | C6      | DUM_SOE_PRD1 | SOE_PRD1的伪信号 |

| R6             | C7      | SOE_PRD1     | 控制SOE时段      |

| R7             | C8      | DUM_SOE_PRD2 | SOE_PRD2的伪信号 |

| R8             | C9      | SOE_PRD2     | 控制SOE时段      |

| R9             | C10     | DUM_SOE_PRD3 | SOE_PRD3的伪信号 |

| G0             | C11     | SOE_PRD3     | 控制SOE时段      |

| G1             | C12     | 保留           | -            |

| G2             | C13     | DUM_POL      | POL的伪信号      |

| G3             | C14     | POL          | 频闪极性控制       |

| G4             | C15     | 保留           | -            |

| DE_DUM         | C16     | DUM_DE       | -            |

| DE             | C17     | 数据使能         | 控制/RGB信号选择   |

| G4~G9<br>B0~B9 | C18~C32 | 保留           | -            |

图 16

图 17

| SOE_PRD<3:0> | SOE高时段    |

|--------------|-----------|

| 0000         | SCLK x 4  |

| 0001         | SCLK x 8  |

| 0010         | SCLK x 12 |

| 0011         | SCLK x 16 |

| 0100         | SCLK x 20 |

| 0101         | SCLK x 24 |

| 0110         | SCLK x 28 |

| 0111         | SCLK x 32 |

| 1000         | SCLK x 36 |

| 1001         | SCLK x 40 |

| 1010         | SCLK x 44 |

| 1011         | SCLK x 48 |

| 1100         | SCLK x 52 |

| 1101         | SCLK x 56 |

| 1110         | SCLK x 60 |

| 1111         | SCLK x 64 |

图 18

图 19

|     | C0  | C1  | C2 | C3 | C4~C11 | C12 | C13~C14 | C15 | C16 | C17 | C18~C32 |

|-----|-----|-----|----|----|--------|-----|---------|-----|-----|-----|---------|

| 控制包 | H   | 保留  | L  | 保留 | L      | 已分配 | H       | 保留  |     |     |         |

|     | CLK | SOE |    |    |        | POL |         | DE  |     |     |         |

图 20

图 21

| SCLK号   | C1 C2 |

|---------|-------|

| SCLK#1  | H H   |

| SCLK#2  | H H   |

| SCLK#3  | H H   |

| SCLK#4  | H L   |

| SCLK#5  | H L   |

| SCLK#6  | H L   |

| SCLK#7  | H L   |

| SCLK#8  | H L   |

| SCLK#9  | H L   |

| SCLK#10 | H L   |

| SCLK#11 | H L   |

| SCLK#12 | H L   |

| SCLK#13 | H L   |

| SCLK#14 | H L   |

| SCLK#15 | H L   |

| SCLK#16 | H L   |

图 22A

| SCLK号   | C1 C2 |

|---------|-------|

| SCLK#1  | H H   |

| SCLK#2  | H H   |

| SCLK#3  | H H   |

| SCLK#4  | H H   |

| SCLK#5  | H H   |

| SCLK#6  | H H   |

| SCLK#7  | H H   |

| SCLK#8  | H L   |

| SCLK#9  | H L   |

| SCLK#10 | H L   |

| SCLK#11 | H L   |

| SCLK#12 | H L   |

| SCLK#13 | H L   |

| SCLK#14 | H L   |

| SCLK#15 | H L   |

| SCLK#16 | H L   |

图 22B

图 22C

图 25

图 26

图 27A

图 27B

图 28

图 29A

图 29B

图 29C

图 29D

图 30

图 31

图 32

|                |                                                                                                                          |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器及其驱动方法                                                                                                              |         |            |

| 公开(公告)号        | <a href="#">CN101763831A</a>                                                                                             | 公开(公告)日 | 2010-06-30 |

| 申请号            | CN200910168523.6                                                                                                         | 申请日     | 2009-08-21 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                 |         |            |

| 申请(专利权)人(译)    | 乐金显示有限公司                                                                                                                 |         |            |

| 当前申请(专利权)人(译)  | 乐金显示有限公司                                                                                                                 |         |            |

| [标]发明人         | 赵舜东<br>姜弼盛<br>朴万奎<br>姜正浩<br>郑良锡<br>高勤雨<br>曹畅训<br>金贤喆                                                                     |         |            |

| 发明人            | 赵舜东<br>姜弼盛<br>朴万奎<br>姜正浩<br>郑良锡<br>高勤雨<br>曹畅训<br>金贤喆                                                                     |         |            |

| IPC分类号         | G09G3/36 G09G3/20                                                                                                        |         |            |

| CPC分类号         | G09G3/3614 G02F2201/52 G09G2310/0289 G09G2330/12 G09G3/3666 G09G2370/10 G09G3/006<br>G09G3/3688 G09G3/2096 G09G2310/0297 |         |            |

| 代理人(译)         | 徐金国                                                                                                                      |         |            |

| 优先权            | 1020080132466 2008-12-23 KR                                                                                              |         |            |

| 其他公开文献         | <a href="#">CN101763831B</a>                                                                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                                           |         |            |

**摘要(译)**

公开了一种液晶显示器及其驱动方法。该液晶显示器包括：时序控制器；N个源极驱动集成电路(IC)，其中N是等于或者大于2的整数；N对数据总线，其每一对数据总线按照点对点的方式使时序控制器与N个源极驱动IC的每一个相连；锁定检查线，用于使N个源极驱动IC的第一源极驱动IC与时序控制器相连并且使N个源极驱动IC彼此级联；以及反馈锁定检查线，用于使N个源极驱动IC的最后源极驱动IC与时序控制器相连。时序控制器的输出电压的摆动宽度与在时序控制器与N个源极驱动IC之间的距离成比例地增大。