(12) 发明专利申请

(10) 申请公布号 CN 102629444 A

(43) 申请公布日 2012. 08. 08

(21) 申请号 201110241400. 8

(22) 申请日 2011. 08. 22

(71) 申请人 北京京东方光电科技有限公司

地址 100176 北京市大兴区经济技术开发区

西环中路 8 号

(72) 发明人 陈希

(74) 专利代理机构 北京同达信恒知识产权代理

有限公司 11291

代理人 李娟

(51) Int. Cl.

G09G 3/20 (2006. 01)

G09G 3/36 (2006. 01)

权利要求书 2 页 说明书 7 页 附图 6 页

(54) 发明名称

栅极集成驱动电路、移位寄存器及显示屏

(57) 摘要

本发明实施例涉及液晶显示技术领域，特别涉及一种栅极集成驱动电路、移位寄存器及显示屏，该栅极集成驱动电路包括：第一薄膜晶体管 TFT、第二 TFT、第三 TFT、第四 TFT、电容和下拉模块，该下拉模块，连接在第一时钟信号输入端、第二时钟信号输入端、第一节点和输出端之间，并与低电平信号端连接，用于在所述本行栅极集成驱动电路的非工作时间内维持所述第一节点和输出端为低电平。这样，通过将栅极集成驱动电路中输入端和复位端的功能设计为对称实现，使得栅极集成驱动电路可以实现双向扫描，而且并未改变节点的充放电特性，确保了电路的信赖性和稳定性。

1. 一种栅极集成驱动电路,其特征在于,包括:

第一薄膜场效应晶体管 TFT,其栅极链接所述本行栅极集成驱动电路的输入端,漏极连接电源电压 VDD,源极连接作为上拉节点的第一节点;

第二 TFT,其栅极链接所述本行栅极集成驱动电路的复位端,源极连接公共连接电压 VSS,漏极连接所述第一节点;

第三 TFT,其栅极连接所述第一节点,漏极连接第一时钟信号输入端,源极连接输出端;

第四 TFT,其栅极连接第二时钟信号输入端,漏极连接输出端,源极连接低电压信号端;

电容,其连接在所述第一节点和输出端之间;

下拉模块,连接在第一时钟信号输入端、第二时钟信号输入端、第一节点和输出端之间,并与低电平信号端连接,用于在所述本行栅极集成驱动电路的非工作时间内维持所述第一节点和输出端为低电平。

2. 如权利要求 1 所述的栅极集成驱动电路,其特征在于,所述下拉模块包括:

第五 TFT,其漏极连接第二时钟信号输入端,源极与作为下拉节点的第二节点连接;

第六 TFT,其漏极连接所述第二节点,栅极连接所述第一节点,源极连接低电压信号端;

第七 TFT,其栅极和漏极一起连接第二时钟信号输入端,源极连接所述第五 TFT 的栅极;

第八 TFT,其漏极连接所述第七 TFT 的源极,栅极连接所述第一节点,源极连接低电压信号端;

第九 TFT,其漏极连接所述第一节点,栅极连接所述第二节点,源极连接低电压信号端;

第十 TFT,其漏极连接所述输出端,栅极连接所述第二节点,源极连接低电压信号端。

3. 如权利要求 1 所述的栅极集成驱动电路,其特征在于,所述栅极集成驱动电路位于奇数行时,其第一时钟信号输入端连接第一时钟信号线、第二时钟信号输入端连接第二时钟信号线;

所述栅极集成驱动电路位于偶数行时,其第二时钟信号输入端连接第一时钟信号线、第一时钟信号输入端连接第二时钟信号线。

4. 如权利要求 3 所述的栅极集成驱动电路,其特征在于,启动正向扫描时,所述 VDD 提供恒定高电平,对所述栅极集成驱动电路的输入端输入高电平脉冲信号,通过所述第一 TFT 的漏极对所述第一节点充电;

第一时钟信号输入端接收第一时钟信号线提供的高电平时钟信号,通过所述第三 TFT 控制所述输出端输出高电平;

所述第六 TFT 导通,将所述第二节点的电压拉低至低电压信号端的电压;

所述 VSS 提供恒定低电平,所述第二 TFT 栅极连接的所述复位端为高电平,对所述第一节点放电;

第二时钟信号输入端接收第二时钟信号线提供的高电平时钟信号,通过所述第四 TFT 对所述输出端放电;通过所述第五 TFT 对所述第二节点充电,控制第九 TFT 对所述第一节点

放电,控制所述第十 TFT 对输出端放电;通过所述第七 TFT、第八 TFT 对所述第一节点放电。

5. 如权利要求 3 所述的栅极集成驱动电路,其特征在于,启动正向扫描时,所述 VDD 提供恒定高电平,对栅极集成驱动电路的输入端输入高电平脉冲信号,通过所述第一 TFT 的漏极对所述第一节点充电;

第一时钟信号输入端接收第二时钟信号线提供的高电平时钟信号,通过所述第三 TFT 控制所述输出端输出高电平;

所述第六 TFT 导通,将所述第二节点的电压拉低至低电压信号端的电压;

所述 VSS 提供恒定低电平,所述第二 TFT 栅极连接的所述复位端为高电平,对所述第一节点放电;

第二时钟信号输入端接收第一时钟信号线提供的高电平时钟信号,通过所述第四 TFT 对所述输出端放电;通过所述第五 TFT 对所述第二节点充电,控制第九 TFT 对所述第一节点放电,控制所述第十 TFT 对输出端放电;通过所述第七 TFT、第八 TFT 对所述第一节点放电。

6. 如权利要求 3 所述的栅极集成驱动电路,其特征在于,启动反向扫描时,所述 VDD 提供恒定低电平,对栅极集成驱动电路的复位端输入高电平脉冲信号,通过所述第二 TFT 的源极对所述第一节点充电;

第一时钟信号输入端接收第一时钟信号线提供的高电平时钟信号,通过所述第三 TFT 控制所述输出端输出高电平;所述第六 TFT 导通,将所述第二节点的电压拉低至低电压信号端的电压;

所述 VSS 提供恒定高电平,所述第一 TFT 栅极连接的所述输入端为高电平,对所述第一节点放电;

第二时钟信号输入端接收第二时钟信号线提供的高电平时钟信号,通过所述第四 TFT 对所述输出端放电;通过所述第五 TFT 对所述第二节点充电,控制第九 TFT 对所述第一节点放电,控制所述第十 TFT 对输出端放电;通过所述第七 TFT、第八 TFT 对所述第一节点放电。

7. 如权利要求 3 所述的栅极集成驱动电路,其特征在于,启动反向扫描时,所述 VDD 提供恒定低电平,对栅极集成驱动电路的复位端输入高电平脉冲信号,通过所述第二 TFT 的源极对所述第一节点充电;

第一时钟信号输入端接收第二时钟信号线提供的高电平时钟信号,通过所述第三 TFT 控制所述输出端输出高电平;所述第六 TFT 导通,将所述第二节点的电压拉低至低电压信号端的电压;

所述 VSS 提供恒定高电平,所述第一 TFT 栅极连接的所述输入端为高电平,对所述第一节点放电;

第二时钟信号输入端接收第一时钟信号线提供的高电平时钟信号,通过所述第四 TFT 对所述输出端放电;通过所述第五 TFT 对所述第二节点充电,控制第九 TFT 对所述第一节点放电,控制所述第十 TFT 对输出端放电;通过所述第七 TFT、第八 TFT 对所述第一节点放电。

8. 一种移位寄存器,其特征在于,包括:多个如权利要求 1-7 中任一所述的栅极集成驱动电路,本行栅极集成驱动电路的输入端连接上一行栅极集成驱动电路的输出端,输出端连接下一行栅极集成驱动电路的输入端,复位端连接下一行栅极集成驱动电路的输出端。

9. 一种显示屏,其特征在于,包括:如权利要求 8 所述的移位寄存器和阵列基板;

所述移位寄存器的信号输出端连接所述阵列基板的栅线。

## 栅极集成驱动电路、移位寄存器及显示屏

### 技术领域

[0001] 本发明涉及液晶显示技术领域，特别涉及一种栅极集成驱动电路、移位寄存器及显示屏。

### 背景技术

[0002] GOA(Gate Drive on Array, 栅极集成驱动)，是指将 LCD(Liquid Crystal Display, 液晶显示)面板的栅极驱动集成在玻璃基板上。然后 GOA 电路与阵列基板的栅线连接，作为移位寄存器控制栅线信号。将相比传统的 COF(Chip On Film, 覆晶薄膜)和 COG(Chip On Glass, 直接绑定玻璃上)工艺，GOA 技术不仅节省了成本。

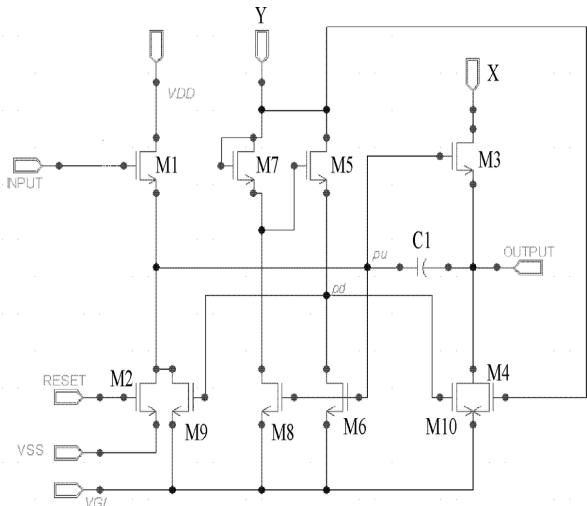

[0003] 但是，现有技术中 GOA 面板扫描方向只能是单一方向，如从上至下进行扫描或者从下至上进行扫描，如图 1 所示，为现有技术中一种单向扫描的 GOA 电路，其工作原理为：输入端 INPUT 信号为高电平时，TFT(Thin Film Transistor, 薄膜场效应晶体管)M1 开启，对 PU 节点充电；当时钟信号 CLK 为高电平时，M3 导通、输出端 OUTPUT 输出 CLK 的脉冲信号；同时通过电容 C1 的 Bootstrapping 作用将 PU 节点进一步拉高；之后复位端 RESET 为高电平，将 TFT M2 和 M4 打开，对 PU 节点和 OUTPUT 放电；接下来，通过时钟信号 CLKB 控制 PD 节点，对 PU 节点和 OUTPUT 进行放电，保证了在该行非工作时间内不会有发生噪声。当使用这样的面板与系统端搭配使用时，由于不同系统端的 IC 存在差异 (IC 向上或者向下)，有时需要再通过调试软件来使图像倒转，造成了很多不便。

### 发明内容

[0004] 本发明实施例提供的一种栅极集成驱动电路、移位寄存器及显示屏，可以实现 GOA 电路的双向扫描，并确保栅极集成驱动电路的稳定性。

[0005] 本发明实施例提供的一种栅极集成驱动电路，包括：

[0006] 第一薄膜场效应晶体管 TFT，其栅极连接所述本行栅极集成驱动电路的输入端，漏极连接电源电压 VDD，源极连接作为上拉节点的第一节点；

[0007] 第二 TFT，其栅极连接所述本行栅极集成驱动电路的复位端，源极连接公共连接电压 VSS，漏极连接所述第一节点；

[0008] 第三 TFT，其栅极连接所述第一节点，漏极连接第一时钟信号输入端，源极连接输出端；

[0009] 第四 TFT，其栅极连接第二时钟信号输入端，漏极连接输出端，源极连接低电压信号端；

[0010] 电容，其连接在所述第一节点和输出端之间；

[0011] 下拉模块，连接在第一时钟信号输入端、第二时钟信号输入端、第一节点和输出端之间，并与低电平信号端连接，用于在所述本行栅极集成驱动电路的非工作时间内维持所述第一节点和输出端为低电平。

[0012] 本发明实施例提供了一种移位寄存器，包括多个上述栅极集成驱动电路，本行栅

极集成驱动电路的输入端连接上一行栅极集成驱动电路的输出端，输出端连接下一行栅极集成驱动电路的输入端，复位端连接下一行栅极集成驱动电路的输出端。

[0013] 本发明实施例提供了一种显示屏，包括：上述移位寄存器和阵列基板；

[0014] 所述移位寄存器的信号输出端连接所述阵列基板的栅线。

[0015] 本发明实施例提供的栅极集成驱动电路、移位寄存器及显示屏，通过将栅极集成驱动电路中输入端和复位端的功能设计为对称实现，使得栅极集成驱动电路可以实现双向扫描，而且并未改变节点的充放电特性，确保了电路的信赖性和稳定性。

## 附图说明

[0016] 图 1 为现有技术中 GOA 电路的示意图；

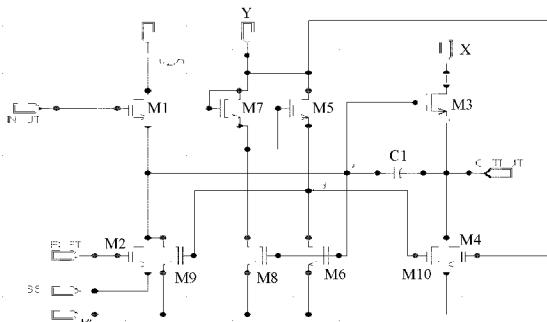

[0017] 图 2 为本发明实施例中栅极集成驱动电路的结构示意图；

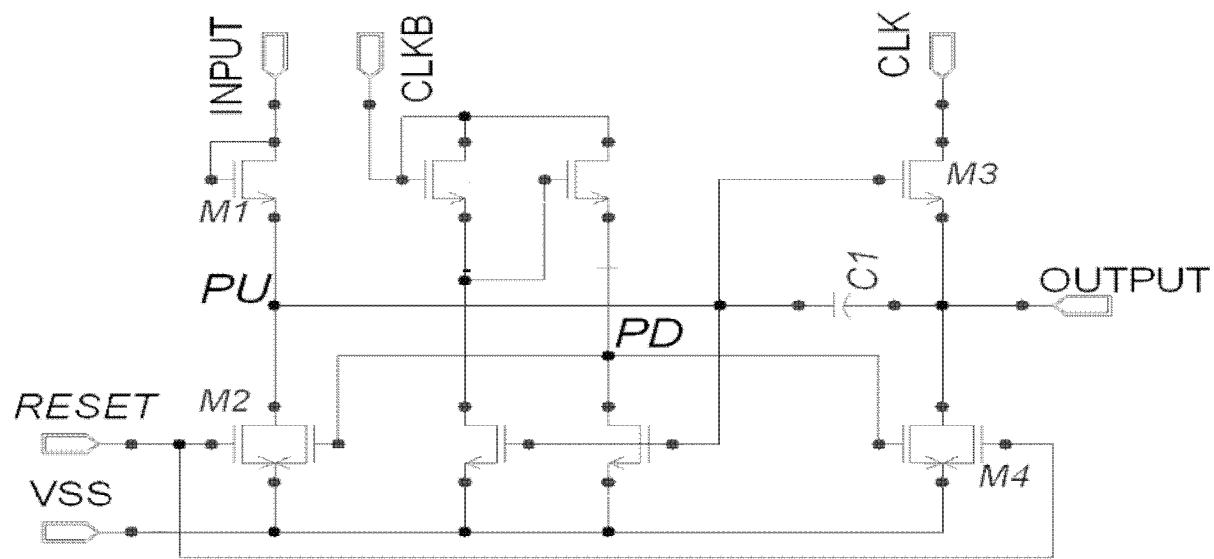

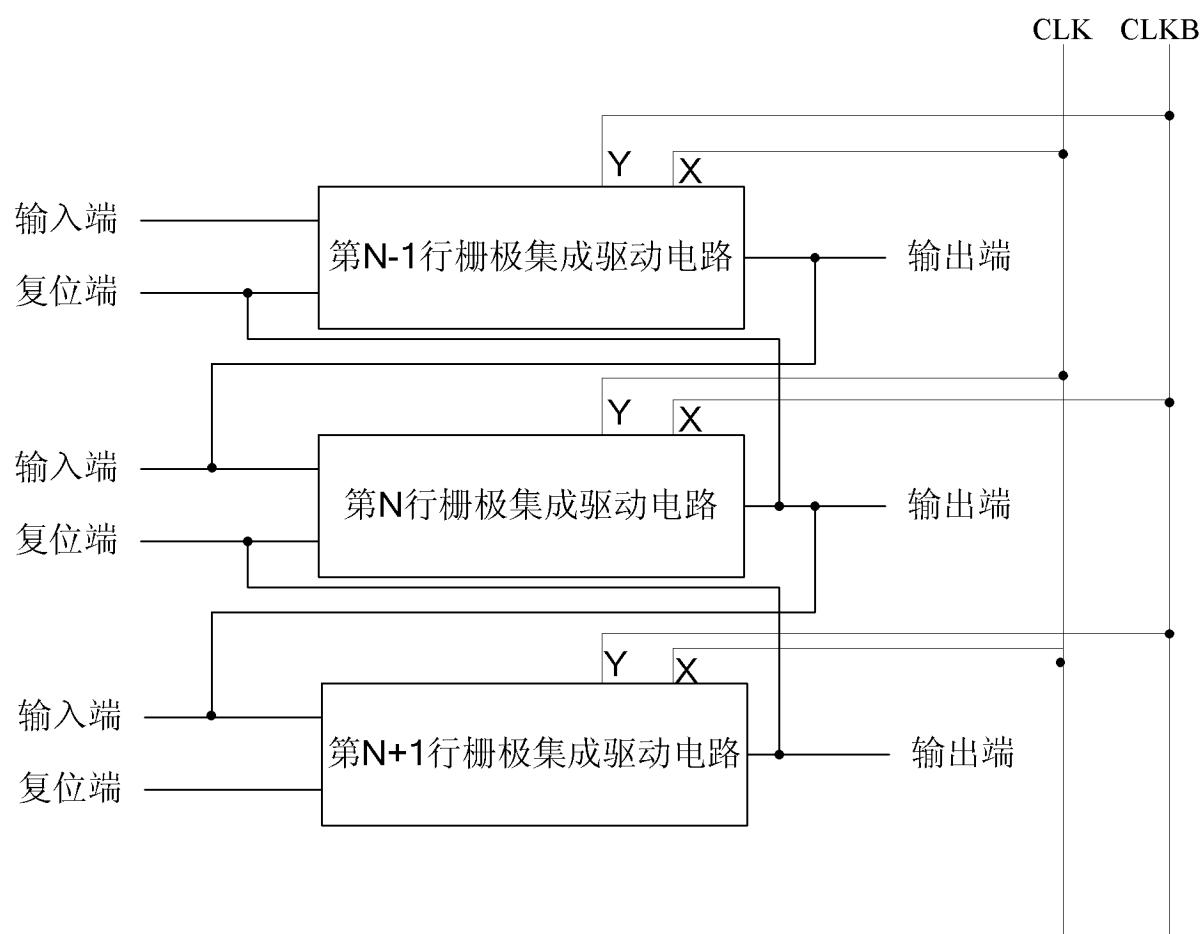

[0018] 图 3 为本发明另一实施例中移位寄存器的结构示意图；

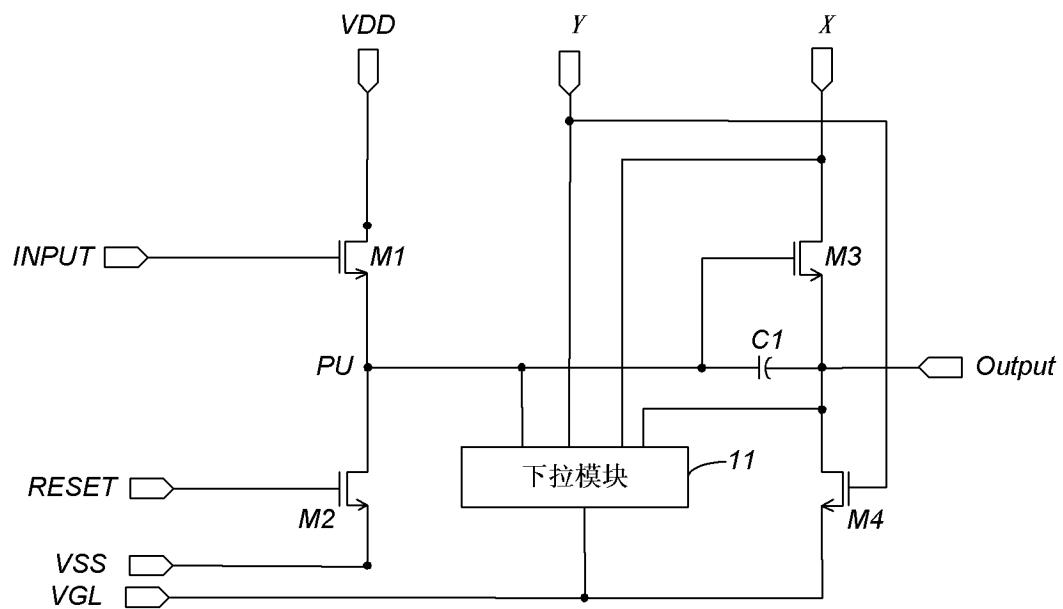

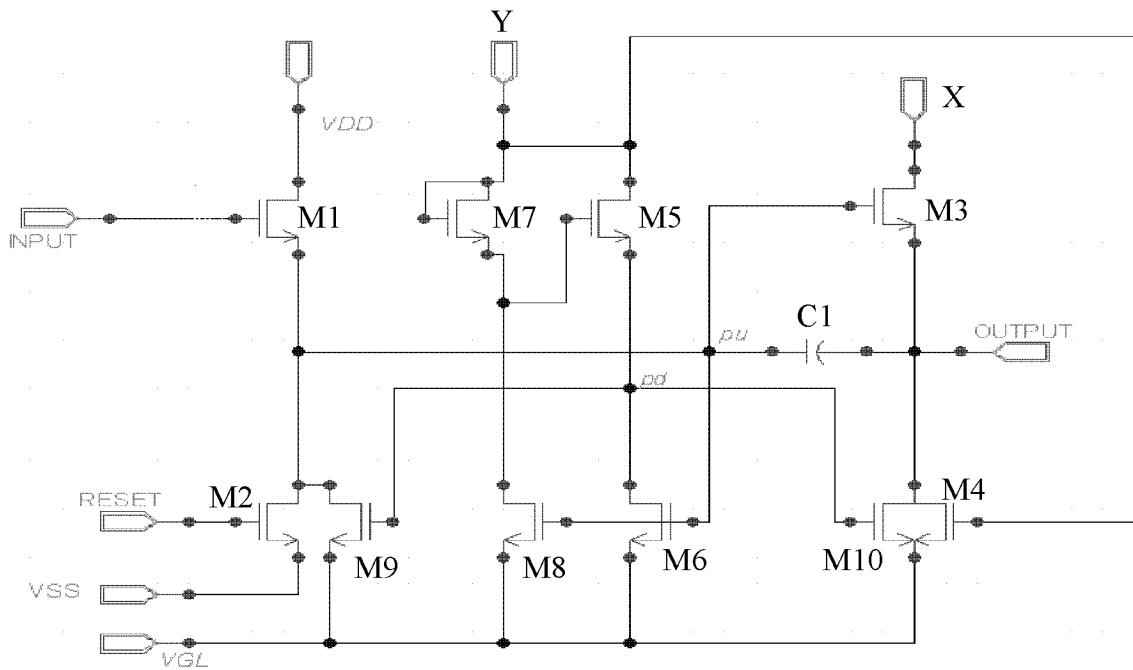

[0019] 图 4 为本发明实施例中本行栅极集成驱动电路的具体结构示意图；

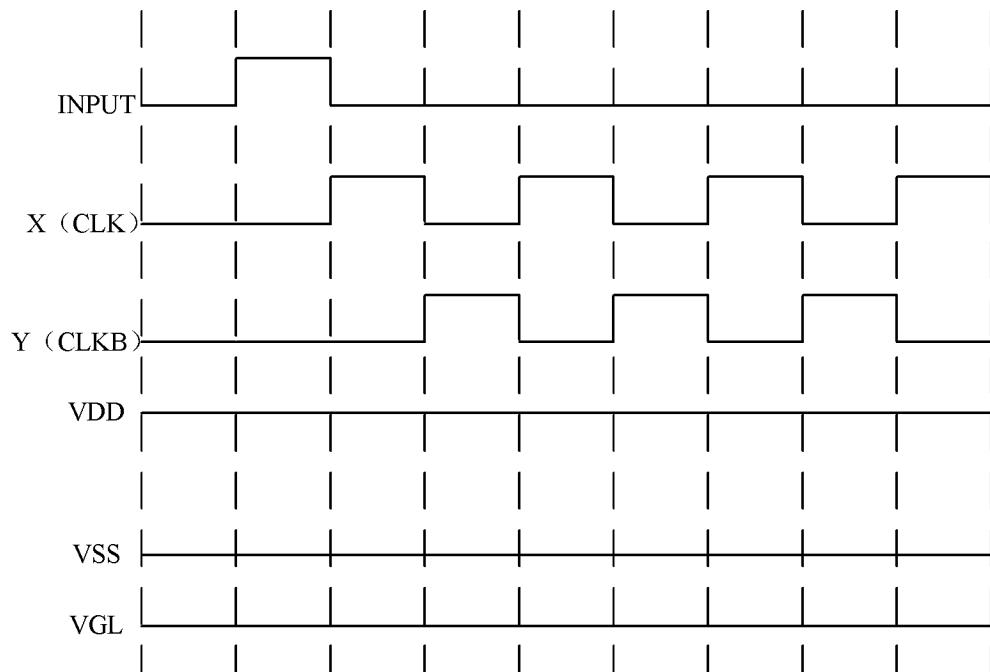

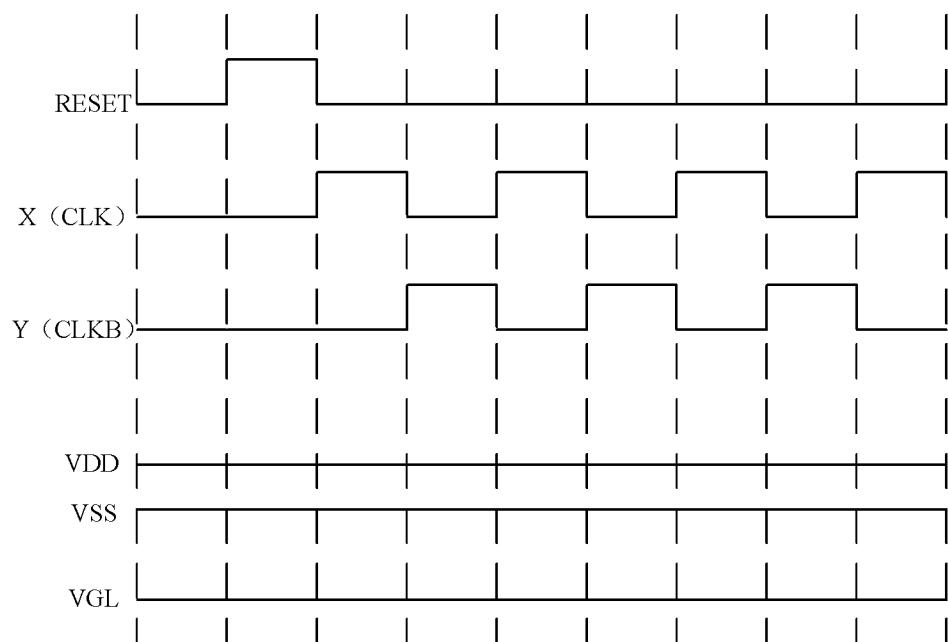

[0020] 图 5 为本发明实施例中本行栅极集成驱动电路为奇数行、正向扫描时各个端点的电压时序图；

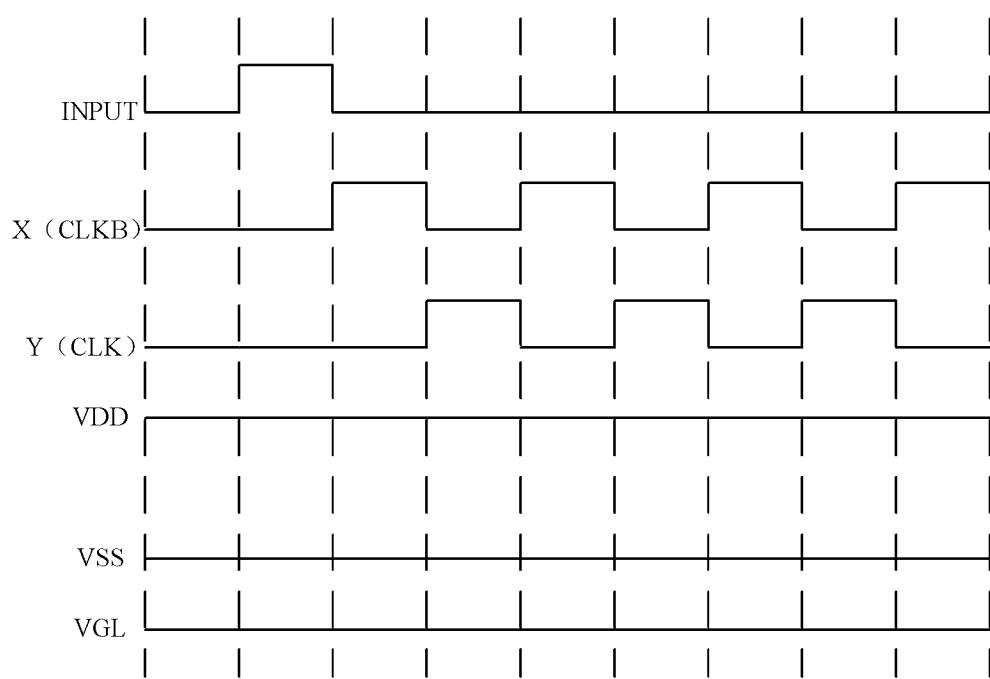

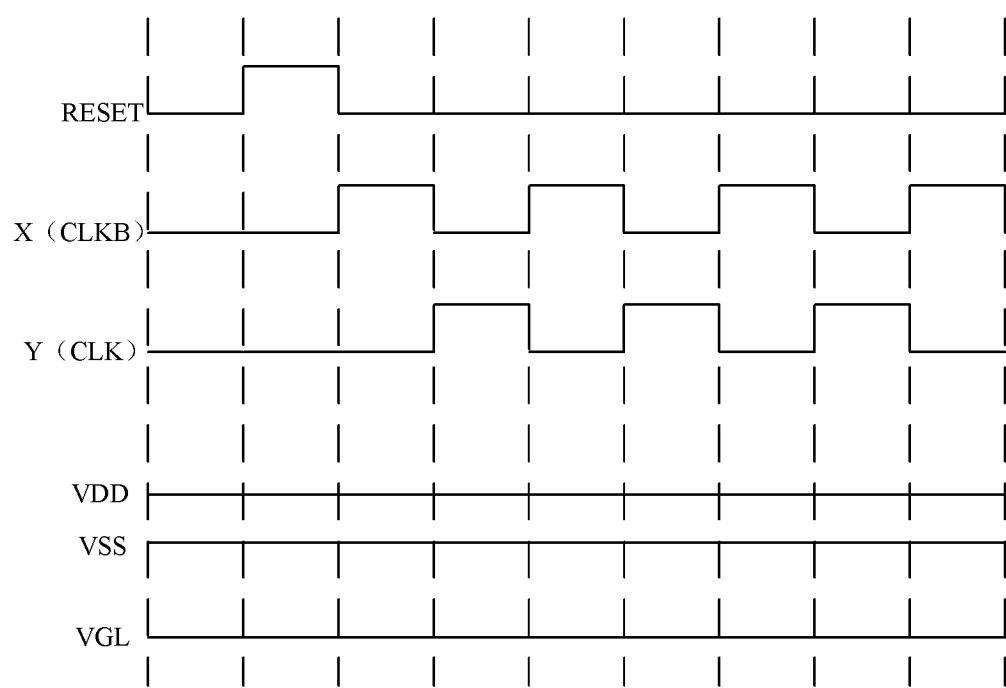

[0021] 图 6 为本发明实施例中本行栅极集成驱动电路为偶数行、正向扫描时各个端点的电压时序图；

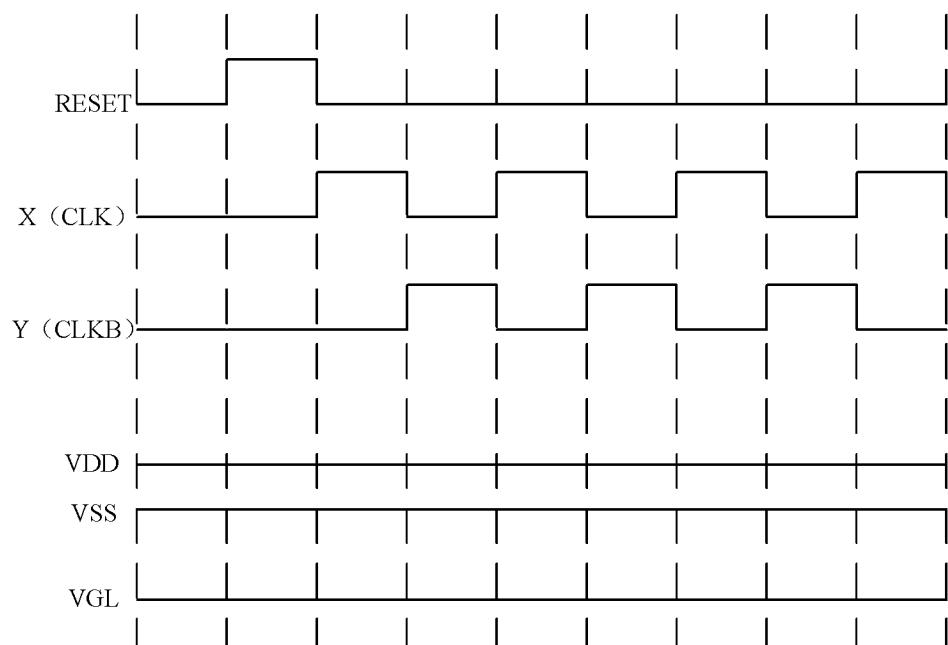

[0022] 图 7 为本发明实施例中移位寄存器中栅极集成驱动电路的总行数为奇数、本行栅极集成驱动电路为奇数行、反向扫描时各个端点的电压时序图；

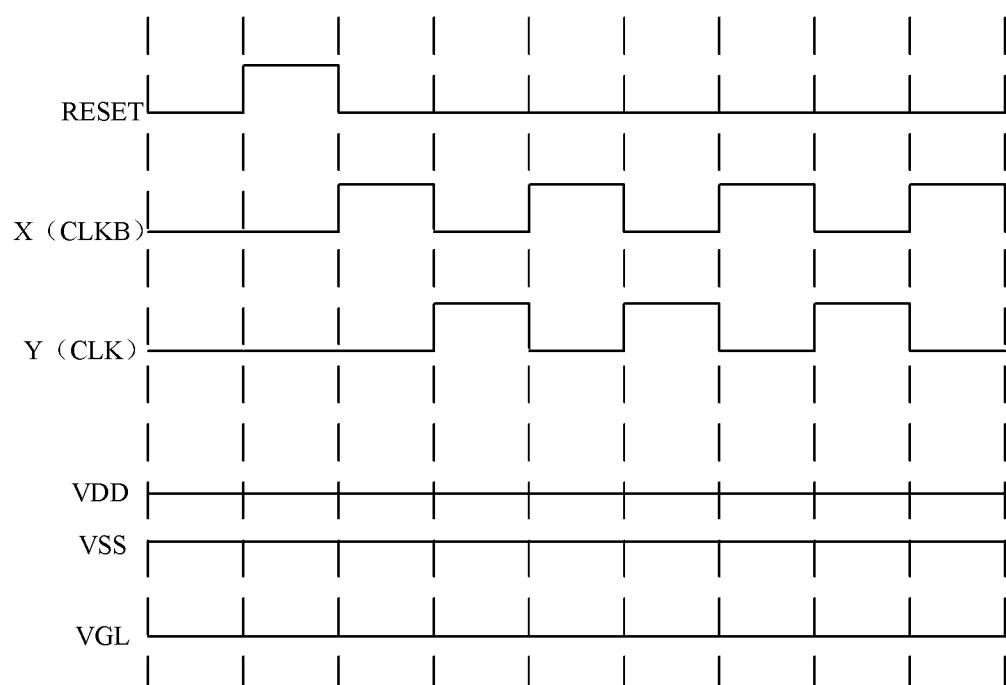

[0023] 图 8 为本发明实施例中移位寄存器中栅极集成驱动电路的总行数为奇数、本行栅极集成驱动电路为偶数行、反向扫描时各个端点的电压时序图；

[0024] 图 9 为本发明实施例中移位寄存器中栅极集成驱动电路的总行数为偶数、本行栅极集成驱动电路为奇数行、反向扫描时各个端点的电压时序图；

[0025] 图 10 为本发明实施例中移位寄存器中栅极集成驱动电路的总行数为偶数、本行栅极集成驱动电路为偶数行、反向扫描时各个端点的电压时序图。

## 具体实施方式

[0026] 下面结合说明书附图对本发明实施例作进一步详细描述。

[0027] 本发明实施例提供了一种多行栅极集成驱动电路，如图 2 所示，本行栅极集成驱动电路包括：

[0028] 第一薄膜场效应晶体管 TFT M1，其栅极链接所述本行栅极集成驱动电路的输入端 INPUT，漏极连接电源电压 VDD，源极连接作为上拉节点的第一节点 PU；

[0029] 第二 TFT M2，其栅极链接所述本行栅极集成驱动电路的复位端 RESET，源极连接公共连接电压 VSS，漏极连接所述第一节点 PU；

[0030] 第三 TFT M3，其栅极连接所述第一节点 PU，漏极连接第一时钟信号输入端 X，源极连接输出端 OUTPUT；

[0031] 第四 TFT M4，其栅极连接第二时钟信号输入端 Y，漏极连接输出端 OUTPUT，源极连接低电压信号端 VGL；

[0032] 电容 C1，其连接在所述第一节点 PU 和输出端 OUTPUT 之间；

[0033] 下拉模块 11，连接在第一时钟信号输入端 X、第二时钟信号输入端 Y、第一节点 PU 和输出端 OUTPUT 之间，并与低电平信号端 VGL 连接，用于在所述本行栅极集成驱动电路的非工作时间内维持所述第一节点 PU 和输出端 OUTPUT 为低电平。

[0034] 其中，该下拉模块 11 包括：

[0035] 第五 TFT，其漏极连接第二时钟信号输入端，源极与作为下拉节点的第二节点连接；

[0036] 第六 TFT，其漏极连接所述第二节点，栅极连接所述第一节点，源极连接低电压信号端；

[0037] 第七 TFT，其栅极和漏极一起连接第二时钟信号输入端，源极连接所述第五 TFT 的栅极；

[0038] 第八 TFT，其漏极连接所述第七 TFT 的源极，栅极连接所述第一节点，源极连接低电压信号端；

[0039] 第九 TFT，其漏极连接所述第一节点，栅极连接所述第二节点，源极连接低电压信号端；

[0040] 第十 TFT，其漏极连接所述输出端，栅极连接所述第二节点，源极连接低电压信号端。

[0041] 较佳的，栅极集成驱动电路位于奇数行时，其第一时钟信号输入端 X 连接第一时钟信号线如 CLK、第二时钟信号输入端 Y 连接第二时钟信号线如 CLB；栅极集成驱动电路位于偶数行时，其第二时钟信号输入端 Y 连接第一时钟信号线、第一时钟信号输入端 X 连接第二时钟信号线，其中 N 为偶数。

[0042] 使用上述多行栅极集成驱动电路，可以进行双向扫描，包括如下几种情况：

[0043] (1) 正向扫描，即从第一行扫描到最后一行，且本行栅极集成驱动电路为奇数行；

[0044] 启动正向扫描时，VDD 提供恒定高电平，对栅极集成驱动电路的输入端输入高电平脉冲信号，通过第一 TFT 的漏极对第一节点充电；第一时钟信号输入端接收第一时钟信号线提供的高电平时钟信号，通过所述第三 TFT 控制所述输出端输出高电平；所述第六 TFT 导通，将所述第二节点的电压拉低至低电压信号端的电压；所述 VSS 提供恒定低电平，所述第二 TFT 栅极连接的所述复位端为高电平，对所述第一节点放电；第二时钟信号输入端接收第二时钟信号线提供的高电平时钟信号，通过所述第四 TFT 对所述输出端放电；通过所述第五 TFT 对所述第二节点充电，控制第九 TFT 对所述第一节点放电，控制所述第十 TFT 对输出端放电；通过所述第七 TFT、第八 TFT 对所述第一节点放电。

[0045] (2) 正向扫描，即从第一行扫描到最后一行，且本行栅极集成驱动电路为偶数行；

[0046] 启动正向扫描时，VDD 提供恒定高电平，对栅极集成驱动电路的输入端输入高电平脉冲信号，通过所述第一 TFT 的漏极对所述第一节点充电；第一时钟信号输入端接收第二时钟信号线提供的高电平时钟信号，通过所述第三 TFT 控制所述输出端输出高电平；所述第六 TFT 导通，将所述第二节点的电压拉低至低电压信号端的电压；所述 VSS 提供恒定低电平，所述第二 TFT 栅极连接的所述复位端为高电平，对所述第一节点放电；第二时钟信号输入端接收第一时钟信号线提供的高电平时钟信号，通过所述第四 TFT 对所述输出端放电；通过所述第五 TFT 对所述第二节点充电，控制第九 TFT 对所述第一节点放电，控制所述第十 TFT 对输出端放电；通过所述第七 TFT、第八 TFT 对所述第一节点放电。

[0047] (3) 反向扫描,即从最后一行扫描到第一行,且多行栅极集成驱动电路的总行数为奇数、本行栅极集成驱动电路为奇数行;

[0048] 启动反向扫描时,VDD 提供恒定低电平,对栅极集成驱动电路的复位端输入高电平脉冲信号,通过所述第二 TFT 的源极对所述第一节点充电;第一时钟信号输入端接收第一时钟信号线提供的高电平时钟信号,通过所述第三 TFT 控制所述输出端输出高电平;所述第六 TFT 导通,将所述第二节点的电压拉低至低电压信号端的电压;所述 VSS 提供恒定高电平,所述第一 TFT 栅极连接的所述输入端为高电平,对所述第一节点放电;第二时钟信号输入端接收第二时钟信号线提供的高电平时钟信号,通过所述第四 TFT 对所述输出端放电;通过所述第五 TFT 对所述第二节点充电,控制第九 TFT 对所述第一节点放电,控制所述第十 TFT 对输出端放电;通过所述第七 TFT、第八 TFT 对所述第一节点放电。

[0049] (4) 反向扫描,即从最后一行扫描到第一行,且栅极集成驱动电路的总行数为奇数、本行栅极集成驱动电路为偶数行;

[0050] 启动反向扫描时,VDD 提供恒定低电平,对栅极集成驱动电路的复位端输入高电平脉冲信号,通过所述第二 TFT 的源极对所述第一节点充电;第一时钟信号输入端接收第二时钟信号线提供的高电平时钟信号,通过所述第三 TFT 控制所述输出端输出高电平;所述第六 TFT 导通,将所述第二节点的电压拉低至低电压信号端的电压;所述 VSS 提供恒定高电平,所述第一 TFT 栅极连接的所述输入端为高电平,对所述第一节点放电;第二时钟信号输入端接收第一时钟信号线提供的高电平时钟信号,通过所述第四 TFT 对所述输出端放电;通过所述第五 TFT 对所述第二节点充电,控制第九 TFT 对所述第一节点放电,控制所述第十 TFT 对输出端放电;通过所述第七 TFT、第八 TFT 对所述第一节点放电。

[0051] (5) 反向扫描,即从最后一行扫描到第一行,且栅极集成驱动电路的总行数为偶数、本行栅极集成驱动电路为奇数行;

[0052] 启动反向扫描时,VDD 提供恒定低电平,对栅极集成驱动电路的复位端输入高电平脉冲信号,通过所述第二 TFT 的源极对第一节点充电;第一时钟信号输入端接收第一时钟信号线提供的高电平时钟信号,通过所述第三 TFT 控制所述输出端输出高电平;所述第六 TFT 导通,将所述第二节点的电压拉低至低电压信号端的电压;所述 VSS 提供恒定高电平,所述第一 TFT 栅极连接的所述输入端为高电平,对所述第一节点放电;第二时钟信号输入端接收第二时钟信号线提供的高电平时钟信号,通过所述第四 TFT 对所述输出端放电;通过所述第五 TFT 对所述第二节点充电,控制第九 TFT 对所述第一节点放电,控制所述第十 TFT 对输出端放电;通过所述第七 TFT、第八 TFT 对所述第一节点放电。

[0053] (6) 反向扫描,即从最后一行扫描到第一行,且栅极集成驱动电路的总行数为偶数、本行栅极集成驱动电路为偶数行;

[0054] 启动反向扫描时,VDD 提供恒定低电平,对栅极集成驱动电路的复位端输入高电平脉冲信号,通过所述第二 TFT 的源极对所述第一节点充电;第一时钟信号输入端接收第二时钟信号线提供的高电平时钟信号,通过所述第三 TFT 控制所述输出端输出高电平;所述第六 TFT 导通,将所述第二节点的电压拉低至低电压信号端的电压;所述 VSS 提供恒定高电平,所述第一 TFT 栅极连接的所述输入端为高电平,对所述第一节点放电;第二时钟信号输入端接收第一时钟信号线提供的高电平时钟信号,通过所述第四 TFT 对所述输出端放电;通过所述第五 TFT 对所述第二节点充电,控制第九 TFT 对所述第一节点放电,控制所述第十

TFT 对输出端放电；通过所述第七 TFT、第八 TFT 对所述第一节点放电。

[0055] 较佳的，上述低电压信号端，用于为本行栅极集成驱动电路提供恒定低电平。

[0056] 通过上述描述，可以看出，本发明提供的栅极集成驱动电路，通过将栅极集成驱动电路中输入端和复位端的功能设计为对称现实，使得栅极集成驱动电路可以实现双向扫描，而且并未改变节点的充放电特性，确保了电路的信赖性和稳定性。

[0057] 基于同一构想，本发明实施例提供了一种移位寄存器，包括多个上述栅极集成驱动电路，如图 3 所示，本行栅极集成驱动电路的输入端连接上一行栅极集成驱动电路的输出端，输出端连接下一行栅极集成驱动电路的输入端，复位端连接下一行栅极集成驱动电路的输出端。栅极集成驱动电路位于奇数行时，其第一时钟信号输入端 X 连接第一时钟信号线如 CLK、第二时钟信号输入端 Y 连接第二时钟信号线如 CLKB；栅极集成驱动电路位于偶数行时，其第二时钟信号输入端 Y 连接第一时钟信号线、第一时钟信号输入端 X 连接第二时钟信号线，其中 N 为偶数。

[0058] 下面通过具体实施例对本发明提供的移位寄存器中的栅极集成驱动电路进行详细描述，以 10T1C 为例，如图 4 所示，第一薄膜场效应晶体管 TFT M1，其栅极链接本行栅极集成驱动电路的输入端 INPUT，漏极连接电源电压 VDD，源极连接作为上拉节点的第一节点 PU；第二 TFT M2，其栅极链接本行栅极集成驱动电路的复位端 RESET，源极连接公共连接电压 VSS，漏极连接第一节点 PU；第三 TFT M3，其栅极连接第一节点 PU，漏极连接第一时钟信号输入端 X，源极连接输出端 OUTPUT；第四 TFT M4，其栅极连接第二时钟信号输入端 Y，漏极连接输出端 OUTPUT，源极连接低电压信号端 VGL；电容 C1，其连接在第一节点 PU 和输出端 OUTPUT 之间；第五 TFT，其漏极连接第二时钟信号输入端 Y，源极与作为下拉节点的第二节点 PD 连接；第六 TFT M6，其漏极连接第二节点 PD，栅极连接第一节点 PU，源极连接低电压信号端 VGL；第七 TFT M7，其栅极和漏极一起连接第二时钟信号输入端 Y，源极连接第五 TFT M5 的栅极；第八 TFT M8，其漏极连接第七 TFT M7 的源极，栅极连接第一节点 PU，源极连接低电压信号端 VGL；第九 TFT M9，其漏极连接第一节点 PU，栅极连接第二节点 PD，源极连接低电压信号端 VGL；第十 TFT M10，其漏极连接输出端 OUTPUT，栅极连接第二节点 PD，源极连接低电压信号端 VGL。其中，TFT M3 的漏极为第一时钟信号输入端 X，TFT M5 的漏极为第二时钟信号输入端 Y。本行为奇数行时，第一时钟信号输入端 X 连接第一时钟信号线 CLK，第二时钟信号输入端 Y 连接第二时钟信号线 CLKB。本行为偶数行时，第一时钟信号输入端 X 连接第二时钟信号线 CLKB，第二时钟信号输入端 Y 连接第一时钟信号线 CLK。

[0059] 如图 5 所示，为本行栅极集成驱动电路在移位寄存器中为奇数行、正向扫描时各个输入信号端点的电压时序图，可见进行正向扫描（从第一行到最后一行）时，VDD 提供恒定高电压，VSS 提供恒定低电压，在输入端 INPUT 输入高电平脉冲信号，使得 M1 导通，进而对电压控制母线 PU 节点充电；然后第一时钟信号输入端 X 输入第一时钟信号线 CLK 提供的高电平时钟信号，使得 M3 导通，控制输出端 OUTPUT 输出高电平，同时电容 C1 储蓄的电荷转移到 PU 节点处，进一步提高 PU 节点处的电压。同时，PU 节点电压升高使得 M6 导通，进而将第二节点 PD 的电压拉低至低电压信号端 VGL 的电压。然后，复位端 RESET 为高电平，使得 M2 导通，对 PU 节点进行放电；同时第二时钟信号输入端 Y 输入第二时钟信号线 CLKB 提供的高电平时钟信号，使得 M4 导通，对输出端 OUTPUT 进行放电；而且使得 M5 导通，对 PD 节点充电，进而控制 PD 节点对应的下拉 M9 对 PU 节点进行放电，控制 PD 节点对应的下拉 TFT

M10 对输出端 OUTPUT 进行放电。并通过 M7、M8 对所述第一节点 PU 放电。

[0060] 如图 6 所示,为本行栅极集成驱动电路在移位寄存器中为偶数行、正向扫描时各个端点的电压时序图,可见进行正向扫描(从第一行到最后一行)时,VDD 提供恒定高电压,VSS 提供恒定低电压,在输入端 INPUT 输入高电平脉冲信号,使得 M1 导通,进而对 PU 节点充电;然后第一时钟信号输入端 X 输入第二时钟信号线 CLKB 提供的高电平时钟信号,使得 M3 导通,此时输出端 OUTPUT 输出高电平,同时电容 C1 储蓄的电荷转移到 PU 节点处,进一步提高 PU 节点处的电压。同时,PU 节点电压升高使得 M6 导通,进而将第二节点 PD 的电压拉低至低电压信号端 VGL 的电压。然后,复位端 RESET 为高电平,使得 M2 导通,对 PU 节点进行放电;同时第二时钟信号输入端 Y 输入第一时钟信号线 CLK 提供的高电平时钟信号,使得 M4 导通,对输出端 OUTPUT 进行放电;而且使得 M5 导通,对 PD 节点充电,进而控制 PD 节点对应的下拉 TFT M9 对 PU 节点进行放电,控制 PD 节点对应的下拉 M10 对输出端 OUTPUT 进行放电。并通过 M7、M8 对所述第一节点 PU 放电。

[0061] 如图 7 所示,为在移位寄存器中栅极集成驱动电路的总行数为奇数、本行栅极集成驱动电路为奇数行、反向扫描时各个输入信号端点的电压时序图,可见进行反向扫描(从最后一行到第一行)时,VDD 提供恒定低电压,VSS 提供恒定高电压,在复位端 RESET 输入高电平脉冲信号,使得 M2 导通,进而对 PU 节点充电;然后第一时钟信号输入端 X 输入第一时钟信号线 CLK 提供的高电平时钟信号,使得 M3 导通,此时输出端 OUTPUT 输出高电平,同时电容 C1 储蓄的电荷转移到 PU 节点处,进一步提高 PU 节点处的电压。同时,PU 节点电压升高使得 M6 导通,进而将第二节点 PD 的电压拉低至低电压信号端 VGL 的电压。然后,输入端 INPUT 为高电平,使得 M1 导通,对 PU 节点进行放电;同时第二时钟信号输入端 Y 输入第二时钟信号线 CLKB 提供的高电平时钟信号,使得 M4 导通,对输出端 OUTPUT 进行放电;而且使得 M5 导通,对 PD 节点充电,进而控制 PD 节点对应的下拉 M9 对 PU 节点进行放电,控制 PD 节点对应的 M10 对输出端 OUTPUT 进行放电。并通过 M7、M8 对所述第一节点 PU 放电。

[0062] 如图 8 所示,为多行在移位寄存器中栅极集成驱动电路的总行数为奇数、本行栅极集成驱动电路为偶数行、反向扫描时各个输入信号端点的电压时序图,可见进行反向扫描(从最后一行到第一行)时,VDD 提供恒定低电压,VSS 提供恒定高电压,在复位端 RESET 输入高电平脉冲信号,使得 M2 导通,进而对 PU 节点充电;然后第一时钟信号输入端 X 输入第二时钟信号线 CLKB 提供的高电平时钟信号,使得 M3 导通,此时输出端 OUTPUT 输出高电平,同时电容 C1 储蓄的电荷转移到 PU 节点处,进一步提高 PU 节点处的电压。同时,PU 节点电压升高使得 M6 导通,进而将第二节点 PD 的电压拉低至低电压信号端 VGL 的电压。然后,输入端 INPUT 为高电平,使得 M1 导通,对 PU 节点进行放电;同时第二时钟信号输入端 Y 输入第一时钟信号线 CLK 提供的高电平时钟信号,使得 M4 导通,对输出端 OUTPUT 进行放电;而且使得 M5 导通,对 PD 节点充电,进而控制 PD 节点对应的 M9 对 PU 节点进行放电,控制 PD 节点对应的 M10 对输出端 OUTPUT 进行放电。并通过 M7、M8 对所述第一节点 PU 放电。

[0063] 如图 9 所示,为在移位寄存器中栅极集成驱动电路的总行数为偶数、本行栅极集成驱动电路为奇数行、反向扫描时各个输入信号端点的电压时序图,可见进行反向扫描(从最后一行到第一行)时,VDD 提供恒定低电压,VSS 提供恒定高电压,在复位端 RESET 输入高电平脉冲信号,使得 M2 导通,进而对 PU 节点充电;然后第一时钟信号输入端 X 输入第一时钟信号线 CLK 提供的高电平时钟信号,使得 M3 导通,此时输出端 OUTPUT 输出高电平,

同时电容 C1 储蓄的电荷转移到 PU 节点处,进一步提高 PU 节点处的电压。同时,PU 节点电压升高使得 M6 导通,进而将第二节点 PD 的电压拉低至低电压信号端 VGL 的电压。然后,输入端 INPUT 为高电平,使得 M1 导通,对 PU 节点进行放电;同时第二时钟信号输入端 Y 输入第二时钟信号线 CLKB 提供的高电平时钟信号,使得 M4 导通,对输出端 OUTPUT 进行放电;而且使得 M5 导通,对 PD 节点充电,进而控制 PD 节点对应的 M9 对 PU 节点进行放电,控制 PD 节点对应的 M10 对输出端 OUTPUT 进行放电。并通过 M7、M8 对所述第一节点 PU 放电。

[0064] 如图 10 所示,为在移位寄存器中栅极集成驱动电路的总行数为偶数、本行栅极集成驱动电路为偶数行、反向扫描时各个输入信号端点的电压时序图,可见进行反向扫描(从最后一行到第一行)时,VDD 提供恒定低电压,VSS 提供恒定高电压,在复位端输入高电平脉冲信号,使得 M2 导通,进而对 PU 节点充电;然后第一时钟信号输入端输入第二时钟信号线 CLKB 提供的高电平时钟信号,使得 M3 导通,此时输出端输出高电平,同时电容 C1 储蓄的电荷转移到 PU 节点处,进一步提高 PU 节点处的电压。同时,PU 节点电压升高使得 M6 导通,进而将第二节点 PD 的电压拉低至低电压信号端 VGL 的电压。然后,输入端为高电平,使得 M1 导通,对 PU 节点进行放电;同时第二时钟信号输入端输入第一时钟信号线 CLK 提供的高电平时钟信号,使得 M4 导通,对输出端 OUTPUT 进行放电;而且使得 M5 导通,对 PD 节点充电,进而控制 PD 节点对应的 M9 对 PU 节点进行放电,控制 PD 节点对应的 M10 对输出端 OUTPUT 进行放电。并通过 M7、M8 对所述第一节点 PU 放电。

[0065] 通过上述描述,可以看出,本发明提供的栅极集成驱动电路,通过将栅极集成驱动电路中输入端和复位端的功能设计为对称现实,使得栅极集成驱动电路可以实现双向扫描,而且并未改变节点的充放电特性,确保了电路的信赖性和稳定性。

[0066] 基于同一构想,本发明实施例提供了一种显示屏,包括:上述移位寄存器和阵列基板;所述移位寄存器的信号输出端连接所述阵列基板的栅线。

[0067] 通过上述描述,可以看出,本发明实施例提供的栅极集成驱动电路、移位寄存器及显示屏,通过将栅极集成驱动电路中输入端和复位端的功能设计为对称现实,使得栅极集成驱动电路可以实现双向扫描,而且并未改变节点的充放电特性,确保了电路的信赖性和稳定性。

[0068] 显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8

图 9

图 10

|                |                                                                                      |         |            |

|----------------|--------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 栅极集成驱动电路、移位寄存器及显示屏                                                                   |         |            |

| 公开(公告)号        | <a href="#">CN102629444A</a>                                                         | 公开(公告)日 | 2012-08-08 |

| 申请号            | CN201110241400.8                                                                     | 申请日     | 2011-08-22 |

| [标]申请(专利权)人(译) | 北京京东方光电科技有限公司                                                                        |         |            |

| 申请(专利权)人(译)    | 北京京东方光电科技有限公司                                                                        |         |            |

| 当前申请(专利权)人(译)  | 北京京东方光电科技有限公司                                                                        |         |            |

| [标]发明人         | 陈希                                                                                   |         |            |

| 发明人            | 陈希                                                                                   |         |            |

| IPC分类号         | G09G3/20 G09G3/36                                                                    |         |            |

| CPC分类号         | G09G3/3674 G11C19/28 H03K5/153 G09G2310/0286 G09G2310/08 G09G2300/0408 G09G2310/0283 |         |            |

| 代理人(译)         | 李娟                                                                                   |         |            |

| 其他公开文献         | <a href="#">CN102629444B</a>                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                       |         |            |

### 摘要(译)

本发明实施例涉及液晶显示技术领域，特别涉及一种栅极集成驱动电路、移位寄存器及显示屏，该栅极集成驱动电路包括：第一薄膜晶体管TFT、第二TFT、第三TFT、第四TFT、电容和下拉模块，该下拉模块，连接在第一时钟信号输入端、第二时钟信号输入端、第一节点和输出端之间，并与低电平信号端连接，用于在所述本行栅极集成驱动电路的非工作时间内维持所述第一节点和输出端为低电平。这样，通过将栅极集成驱动电路中输入端和复位端的功能设计为对称实现，使得栅极集成驱动电路可以实现双向扫描，而且并未改变节点的充放电特性，确保了电路的信赖性和稳定性。