[19] 中华人民共和国国家知识产权局

[51] Int. Cl.

G09G 3/36 (2006.01)

## [12] 发明专利申请公布说明书

[21] 申请号 200810000319.9

[43] 公开日 2008 年 6 月 18 日

[11] 公开号 CN 101202026A

[22] 申请日 2003.8.26

[74] 专利代理机构 北京康信知识产权代理有限责任公司

代理人 章社昊 尚志峰

[21] 申请号 200810000319.9

分案原申请号 03818729.9

[30] 优先权

[32] 2002.8.30 [33] KR [31] 10-2002-0052020

[71] 申请人 三星电子株式会社

地址 韩国京畿道

[72] 发明人 文胜焕

权利要求书 4 页 说明书 28 页 附图 20 页

[54] 发明名称

液晶显示装置

[57] 摘要

本发明披露了一种具有改良显示特性的液晶显示装置。时钟发生器将第一时钟信号和第二时钟信号施加于栅极驱动器，以控制栅极驱动信号的脉冲宽度。在运行下一阶段之前，在当前阶段将与多条栅极线的第一端部连接的放电晶体管放电。这些栅极线包括第一栅极驱动器、以及在第一栅极驱动器以异常状态运行时用于运行这些栅极线的第二栅极驱动器。因此，液晶显示装置可以高速运行，并且可以防止栅极驱动信号被延迟。

1. 一种液晶显示装置，包括：

液晶面板，包括沿第一方向延伸的多条栅极线、沿第二方向延伸的多条数据线、具有与所述栅极线连接的第一电极和与所述数据线连接的第二电极的开关装置、以及与所述开关装置的第三电极连接的像素电极；

栅极驱动器，与所述栅极线连接，用于向所述栅极线依次施加栅极驱动信号；

数据驱动器，与所述数据线连接，用于向所述数据线施加数据驱动信号；以及

放电器，用于响应施加于下一条栅极线的第一栅极驱动信号，放电施加于当前栅极线的第二栅极驱动信号。

2. 根据权利要求 1 所述的液晶显示装置，其中，所述放电器包括晶体管，将所述晶体管的第一电极与所述当前栅极线连接且将第二电极与放电电压输入端连接，用于响应所述第一栅极驱动信号放电所述第二栅极驱动信号。

3. 根据权利要求 1 中所述的液晶显示装置，其中所述栅极驱动器接收第一时钟信号和与所述第一时钟信号具有相反相位的第二时钟信号，并且所述第一时钟信号及所述第二时钟信号分别在第一周期确定所述栅极驱动信号的电平且在第二周期进行充电或放电。

4. 根据权利要求 3 所述的液晶显示装置，其中，所述第一时钟信号包括在所述第一周期的第一电压和在所述第二周期的第一极性，而所述第二时钟信号包括在所述第一周期的具有与所述

---

第一电压相反相位的第二电压和在所述第二周期的具有与第一极性相反相位的第二极性，所述第一时钟信号和所述第二时钟信号分别在所述第二周期具有一斜度。

5. 一种液晶显示装置，包括：

液晶面板，包括沿第一方向延伸的多条栅极线、沿与所述第一方向垂直的第二方向延伸的多条数据线、具有与所述栅极线连接的第一电极和与所述数据线连接的第二电极的开关装置、以及与所述开关装置的第三电极连接的像素电极；

第一栅极驱动器，与所述栅极线的第一端部连接，用于向所述栅极线顺次施加栅极驱动信号；

第二栅极驱动器，与所述栅极线的第二端部连接，用于当所述第一栅极驱动器处于异常状态时向所述栅极线顺次施加所述栅极驱动信号；

数据驱动器，与所述数据线连接，用于向所述数据线施加数据驱动信号；

第一放电器，用于当运行所述第一栅极驱动器时响应施加于下一条栅极线的第一栅极驱动信号，放电施加于当前栅极线的第二栅极驱动信号；以及

第二放电器，用于当运行所述第二栅极驱动器时响应所述第二栅极驱动信号，放电所述第二栅极驱动信号。

6. 根据权利要求 5 所述的液晶显示装置，还包括与所述第一栅极驱动器连接的外部连接端，其中所述外部连接端包括：

第一输入端，用于接收开始信号；

第二输入端，用于接收第一时钟信号；

第三输入端，用于接收具有与第一时钟信号相反相位的第二时钟信号；

第四输入端，用于接收第一电源电压；以及

第五输入端，用于接收第二电源电压。

7. 根据权利要求6所述的液晶显示装置，其中，所述第一时钟信号及所述第二时钟信号分别在第一周期确定所述栅极驱动信号的电平，而在第二周期进行充电或放电。

8. 根据权利要求5所述的液晶显示装置，还包括与所述第二栅极驱动器连接的外部连接端，其中所述外部连接端包括：

第一输入端，用于接收开始信号；

第二输入端，用于选择性接收第一时钟信号和第一电源电压；

第三输入端，用于选择性接收具有与第一时钟信号相反相位的第二时钟信号和第二电源电压；

第四输入端，用于选择性接收所述第一电源电压和所述第二电源电压；以及

第五输入端，用于接收所述第二电源电压。

9. 根据权利要求8所述的液晶显示装置，其中，所述第一时钟信号和所述第二时钟信号包括用于确定所述栅极驱动信号的电平的第一周期，以及分别用于充电或放电所述第一时钟信号和所述第二时钟信号的第二周期。

-

10. 根据权利要求 5 所述的液晶显示装置，其中，所述第一放电器包括第一晶体管，将所述第一晶体管的第一电极与所述当前栅极线连接且将第二电极与放电电压输入端连接，用于响应所述第一栅极驱动信号放电所述第二栅极驱动信号。

11. 根据权利要求 5 中所述的液晶显示装置，其中，所述第二放电器包括第二晶体管，将所述第二晶体管的第一电极与所述当前栅极线连接且将第二电极与放电电压输入端连接，用于响应所述第一栅极驱动信号放电所述第二栅极驱动信号。

## 液晶显示装置

本申请是分案申请，其原案申请的申请号为03818729.9，申请日为2003年8月26日，发明名称为“液晶显示装置”。

### 技术领域

本发明涉及一种 LCD (液晶显示) 装置，更具体地，涉及一种具有改良显示特性的液晶显示装置。

### 背景技术

通常，液晶显示 (LCD) 装置包含两个基片，每个均包括设置在其内表面上的电极、以及置于两个基片之间的液晶层。在液晶显示装置中，将电压施加于电极以重新排列液晶分子并控制通过液晶层透射的光量，从而获得所需要的图像。

目前，薄膜晶体管显示器 (TFT-LCD) 是液晶显示器最通用的类型。将多个电极设置在两个基片的每个基片上并且将薄膜晶体管 (TFT) 用于开关提供给各电极的电源。通常将薄膜晶体管设置在两个基片的一侧上。一般而言，将其中将薄膜晶体管分别设置在单元像素区域中的液晶显示器分为非晶硅类型 TFT-LCD (非晶硅 TFT-LCD) 和多晶硅类型 TFT-LCD (多晶硅 TFT-LCD)。

与非晶硅 TFT-LCD 装置相比，多晶硅 TFT-LCD 装置具有较低功率消耗和较低廉价格的优点，但是其缺点在于其制造工艺复杂。因此，多晶硅 TFT-LCD 装置主要用于诸如移动电话这样的小型液

晶显示器，而非晶硅 TFT-LCD 装置由于其可容易地用于大屏幕和高的生产率，可其用于笔记本式个人电脑（PC）、液晶显示监测器、高分辨率（HD）电视等等这样的大型显示器。

最近，大量的研究和开发成果已经集中在减小用于非晶硅 TFT-LCD 装置的组装方法的步骤数，其通过数据驱动电路和栅极驱动电路与像素阵列一起同时形成在玻璃基片上实现，该组装方法类似于多晶硅 TFT-LCD 装置的组装方法。其它研究焦点范围包括用于提高运行速度和液晶显示器分辨率的方法，如通过在移动时间周期内运行 TFT-LCD 装置的更多信号线。

## 发明内容

本发明的实施例提供了一种可以进行高速运行的液晶显示器。

本发明的另一实施例提供了一种可以防止栅极驱动信号被延迟的液晶显示器。

本发明的再一个实施例提供了一种具有冗余功能且可以防止栅极驱动信号被延迟的液晶显示器。

在本发明的一个方面中，液晶显示装置包括：定时控制器，用于响应外部信号输出图像信号、第一定时信号、第二定时信号、及时钟发生控制信号；时钟发生器，用于产生第一时钟信号和具有与第一时钟信号不同相位的第二时钟信号，用于在第一周期控制第一时钟信号和第二时钟信号以确定栅极驱动信号的电压电平，以及用于在第二周期控制要进行充电或放电的第一时钟信号和第二时钟信号；栅极驱动器，用于响应第一定时信号、第一时钟信号、及第二时钟信号顺次输出栅极驱动信号；数据驱动器，用于响应第二定时信号输出图像信号；以及液晶面板，包括用于接收图像信号的多

---

条数据线、用于接收栅极驱动信号的多条栅极线、以及用于响应栅极驱动信号输出图像信号与数据线和栅极线连接的开关装置。

在另一方面中，液晶显示器包括：液晶面板，包括沿第一方向延伸的多条栅极线、沿第二方向延伸的多条数据线、具有与栅极线连接的第一电极和与数据线连接的第二电极的开关装置、以及与开关装置的第三电极连接的像素电极；栅极驱动器，与栅极线连接，用于向栅极线顺次施加栅极驱动信号；数据驱动器，与数据线连接，用于向数据线施加数据驱动信号；以及放电器，用于响应施加于下一个栅极线的第一栅极驱动信号，放电施加于当前栅极线的第二栅极驱动信号。

在再一个方面中，液晶显示器包括：液晶面板，包括沿第一方向延伸的多条栅极线、沿与第一方向垂直的第二方向延伸的多条数据线、具有与栅极线连接的第一电极和与数据线连接的第二电极的开关装置、以及与开关装置的第三电极连接的像素电极；第一栅极驱动器，与栅极线的第一端部连接，用于向栅极线顺次施加栅极驱动信号；第二栅极驱动器，与栅极线的第二端部连接，用于当第一栅极驱动器处于异常状态时向栅极线顺次施加栅极驱动信号；数据驱动器，与数据线连接，用于向数据线施加数据驱动信号；第一放电器，用于当运行第一栅极驱动器时响应施加于下一个栅极线的第一栅极驱动信号，放电施加于当前栅极线的第二栅极驱动信号；以及第二放电器，用于当运行第二栅极驱动器时响应第二栅极驱动信号，放电第二栅极驱动信号。

根据实施例的液晶显示器，这种液晶显示装置可以高速运行，这是由于第一时钟信号和第二时钟信号分别具有用于确定栅极驱动信号的电压电平的第一周期以及用充电或放电第一时钟信号和第二时钟信号的第二周期。

而且，在运行下一阶段之前与多条栅极线连接的第一端部放电晶体管在当前阶段放电，从而防止栅极驱动信号被延迟。

此外，栅极线包括第一栅极驱动器、及当第一栅极驱动器处于异常状态时用于运行栅极线的第二栅极驱动器。因此，尽管第一栅极驱动器运行异常，液晶显示装置由于第二栅极驱动器而可以正常运行。

## 附图说明

通过参照附图进行以下详细描述，本发明的上述及其它优点将变得更加显而易见，其中：

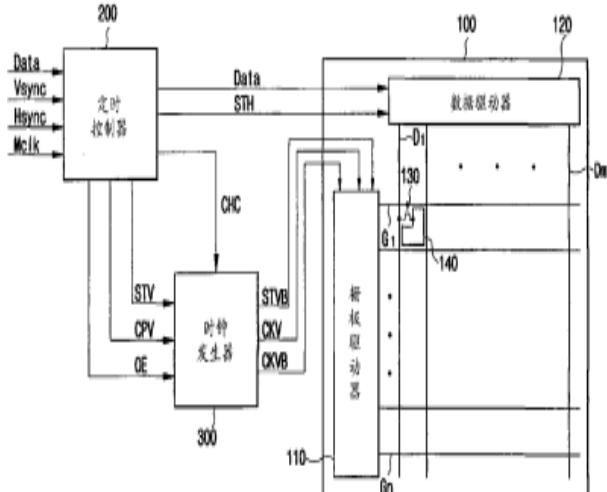

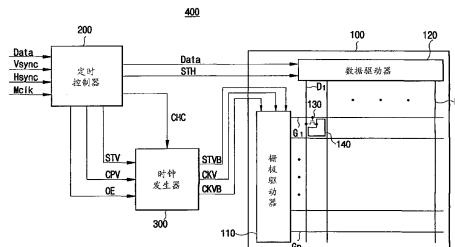

图 1 是根据本发明一具体实施例的液晶显示装置方框图；

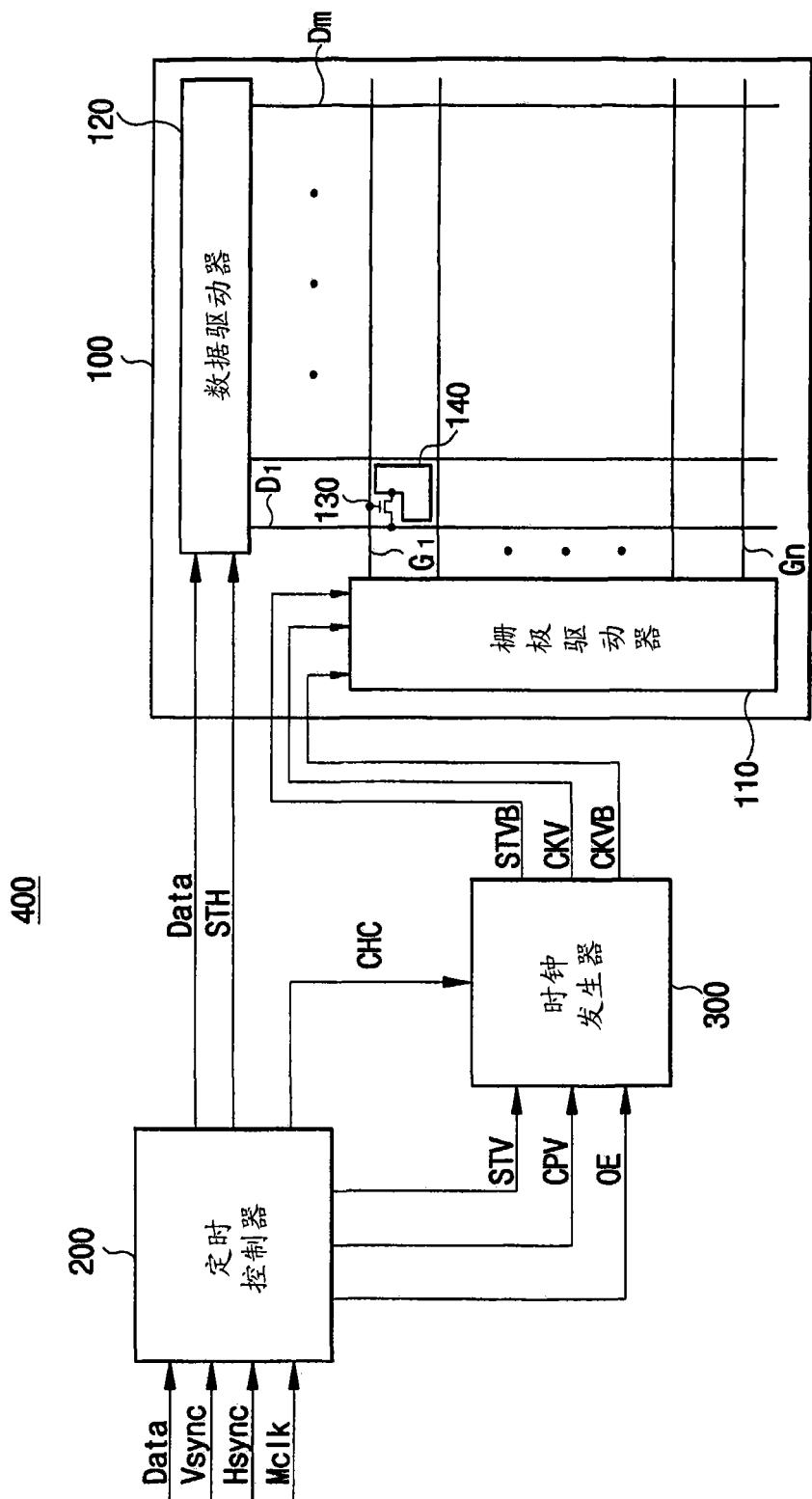

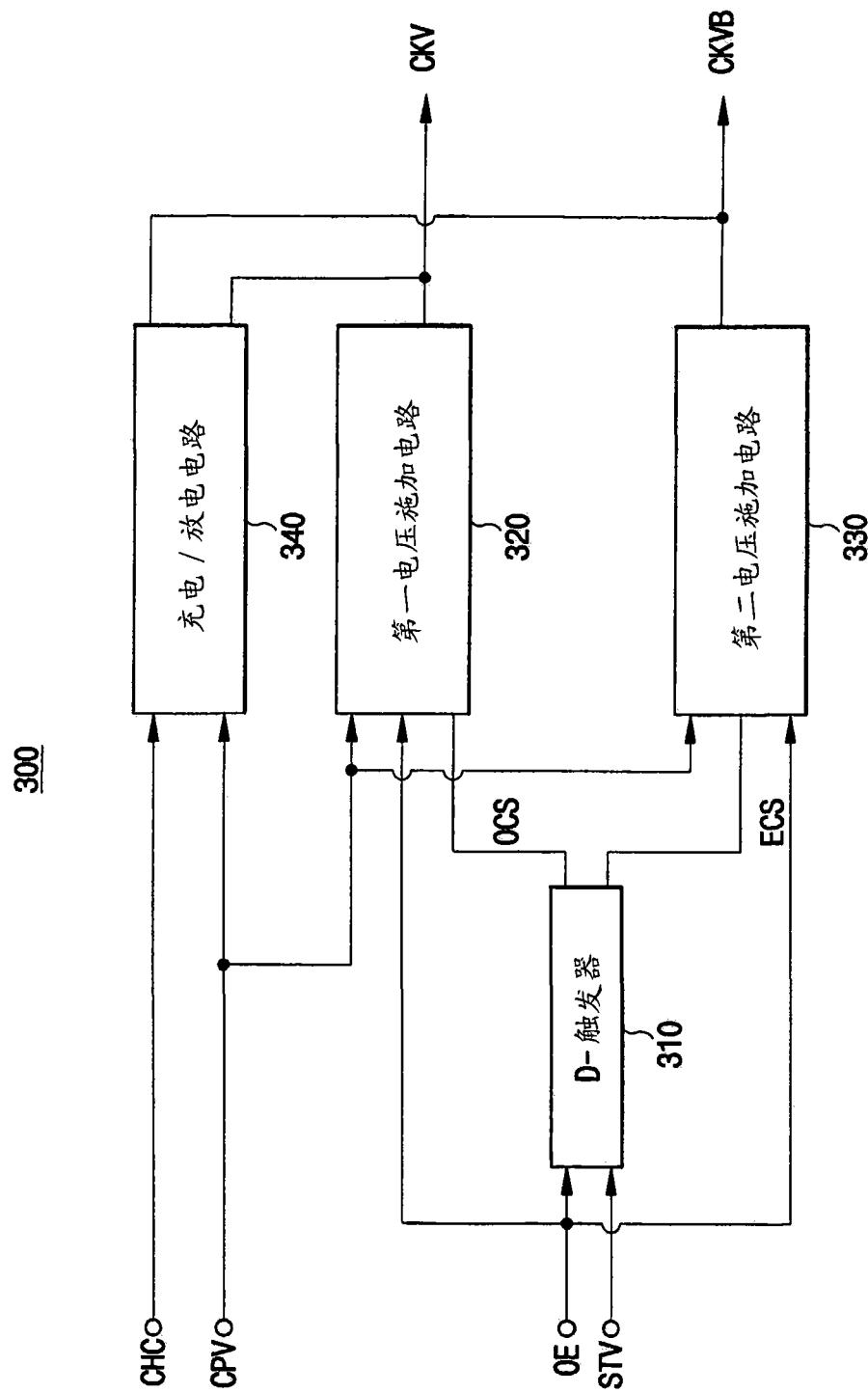

图 2 是示出图 1 所示的时钟发生器方框图；

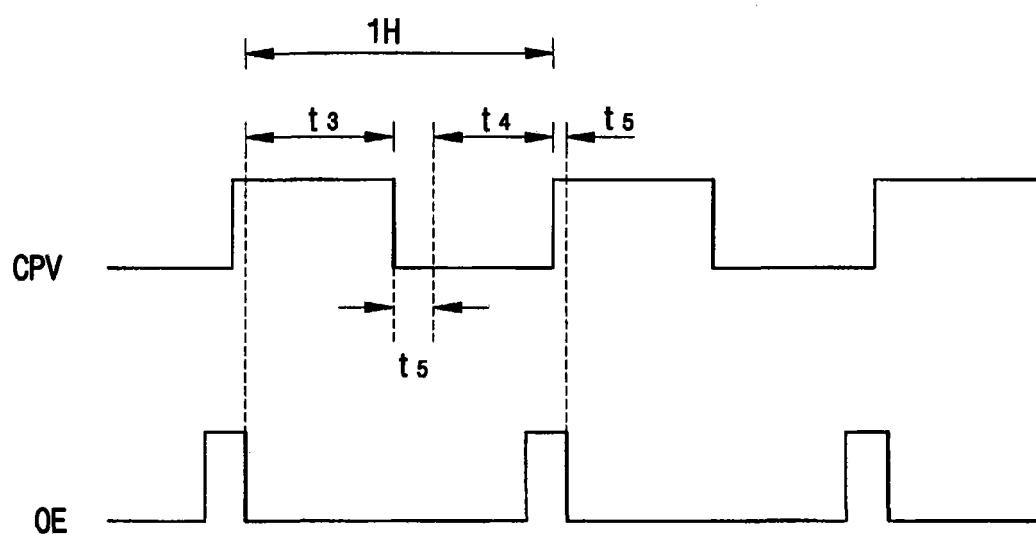

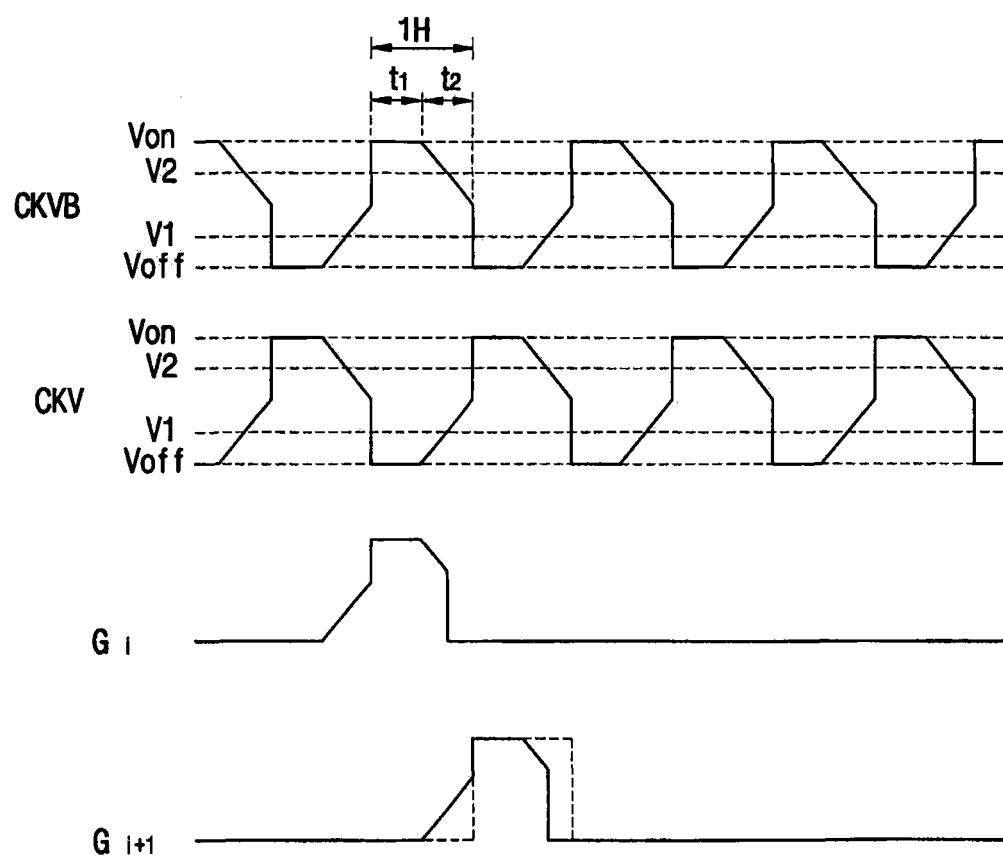

图 3 是图 2 所示的相应元件的定时图；

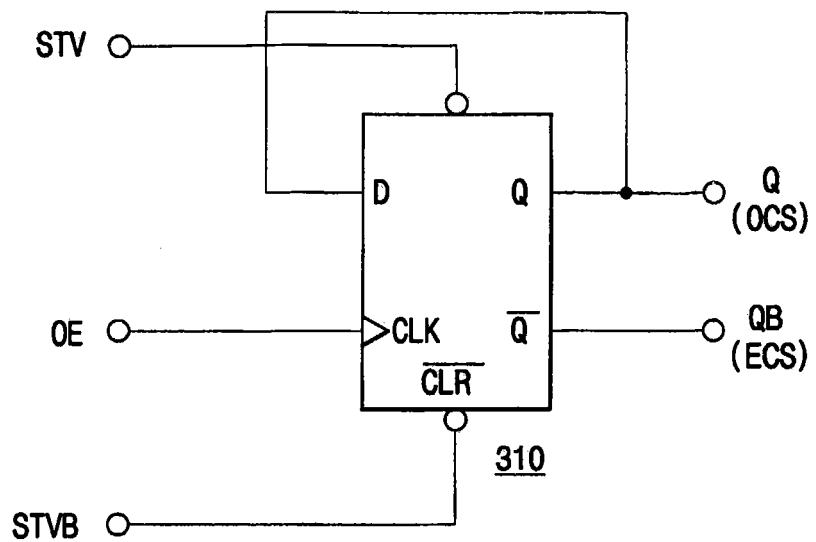

图 4 是图 2 所示的 D-触发器电路图；

图 5 是图 4 所示的 D-触发器定时图；

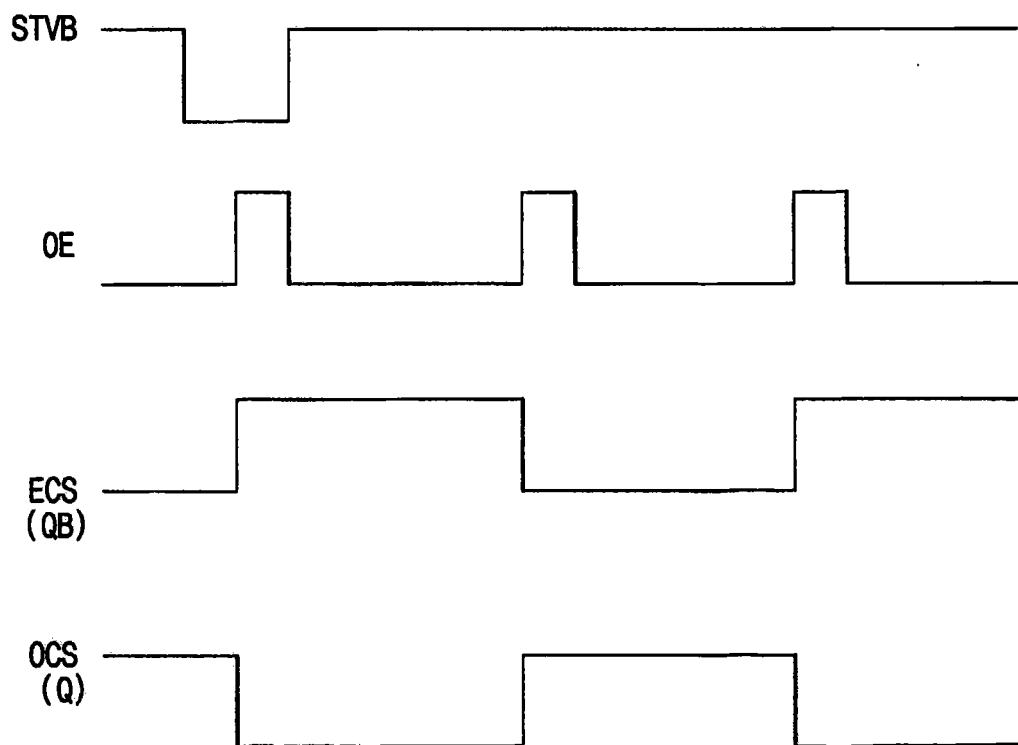

图 6 是示出图 2 所示的第一电压施加电路的电路图；

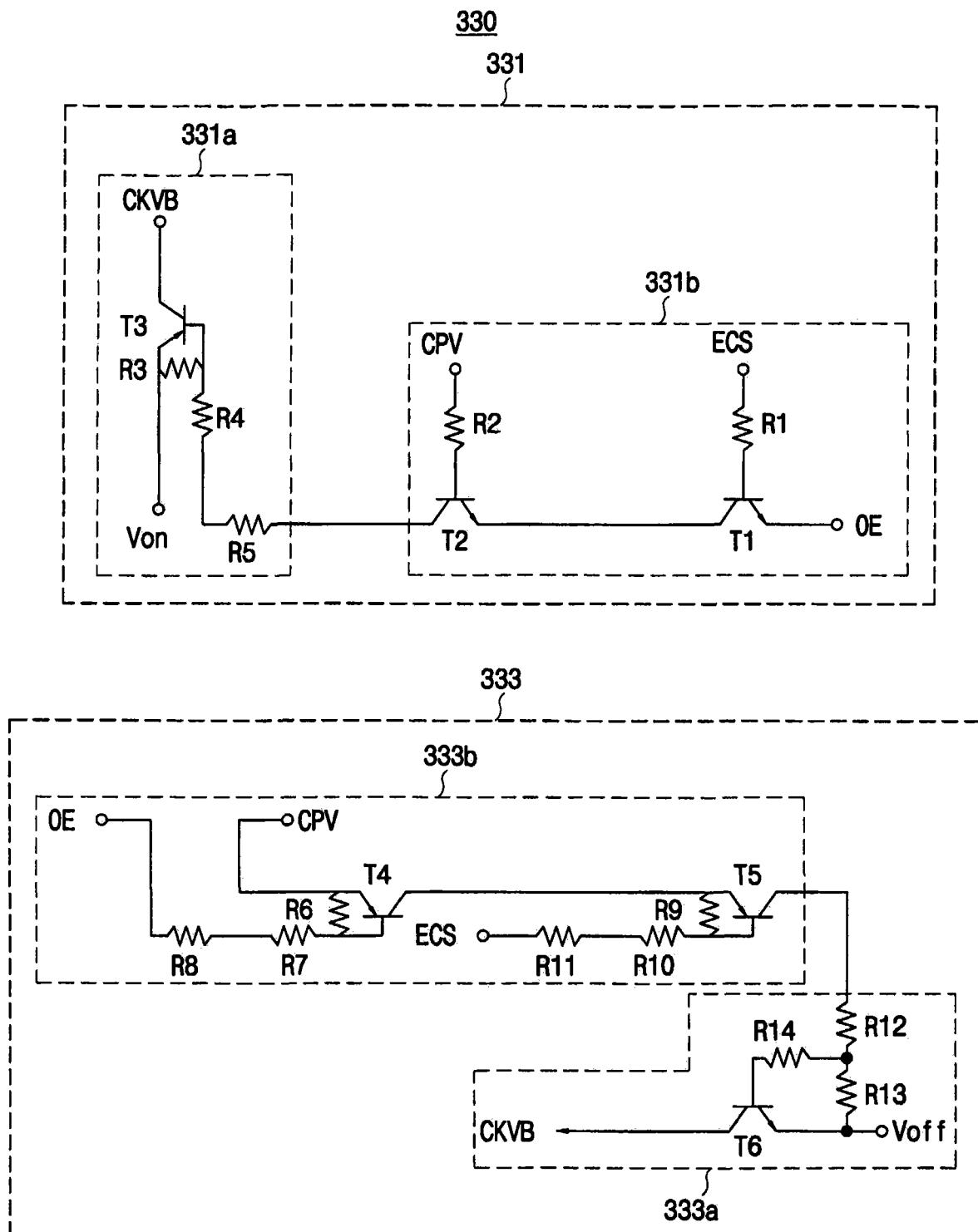

图 7 是示出图 2 所示的第二电压施加电路的电路图；

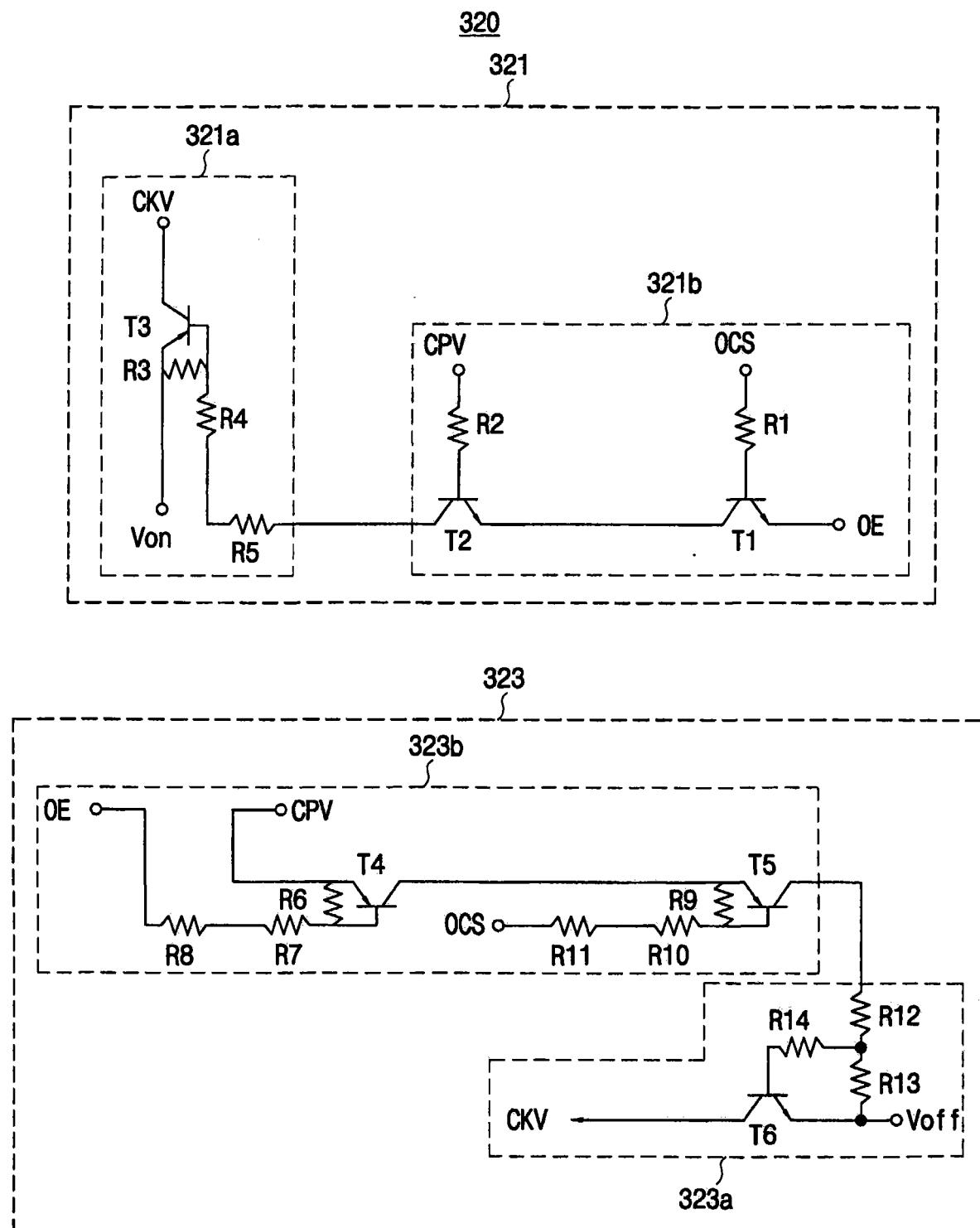

图 8 是示出图 2 所示的充电/放电电路的电路图；

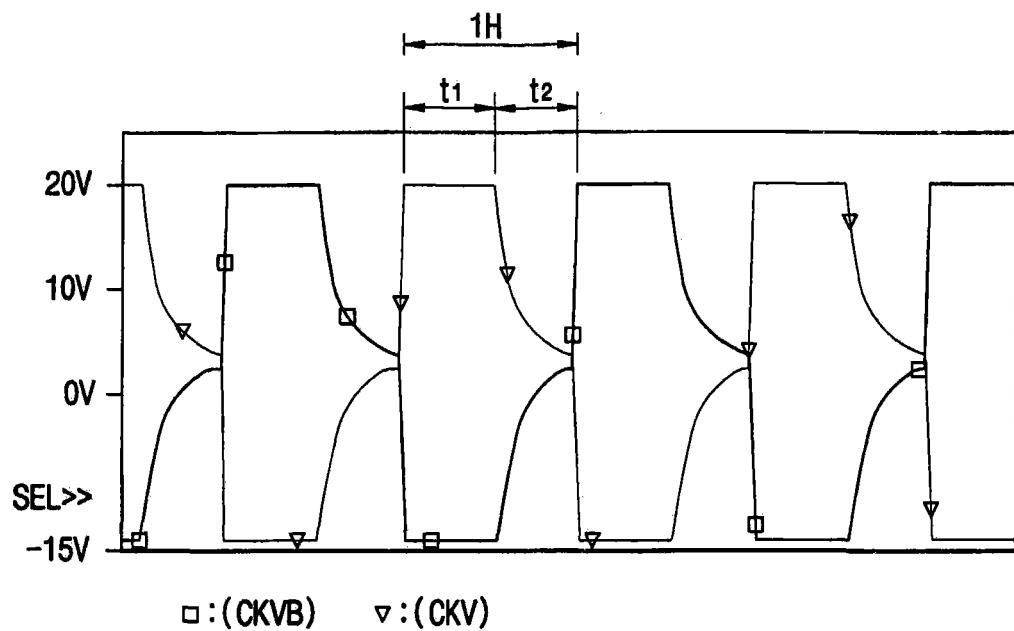

图 9 是来自图 2 所示的时钟发生器的第一时钟信号及第二时钟信号的波形；

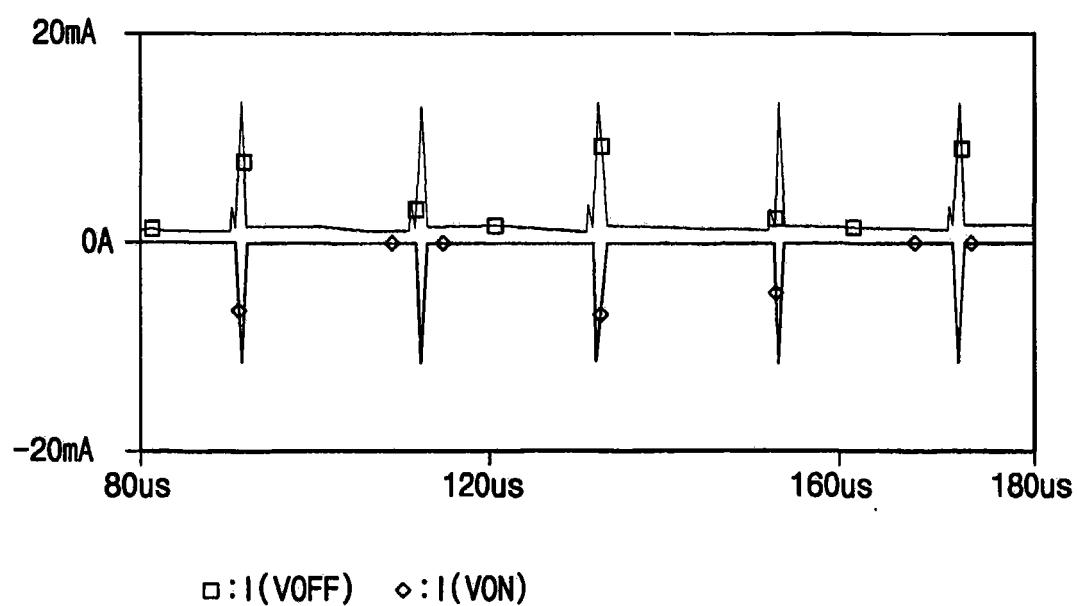

图 10 是用于输出来自图 2 所示的时钟发生器的第一时钟信号及第二时钟信号所需电流的波形；

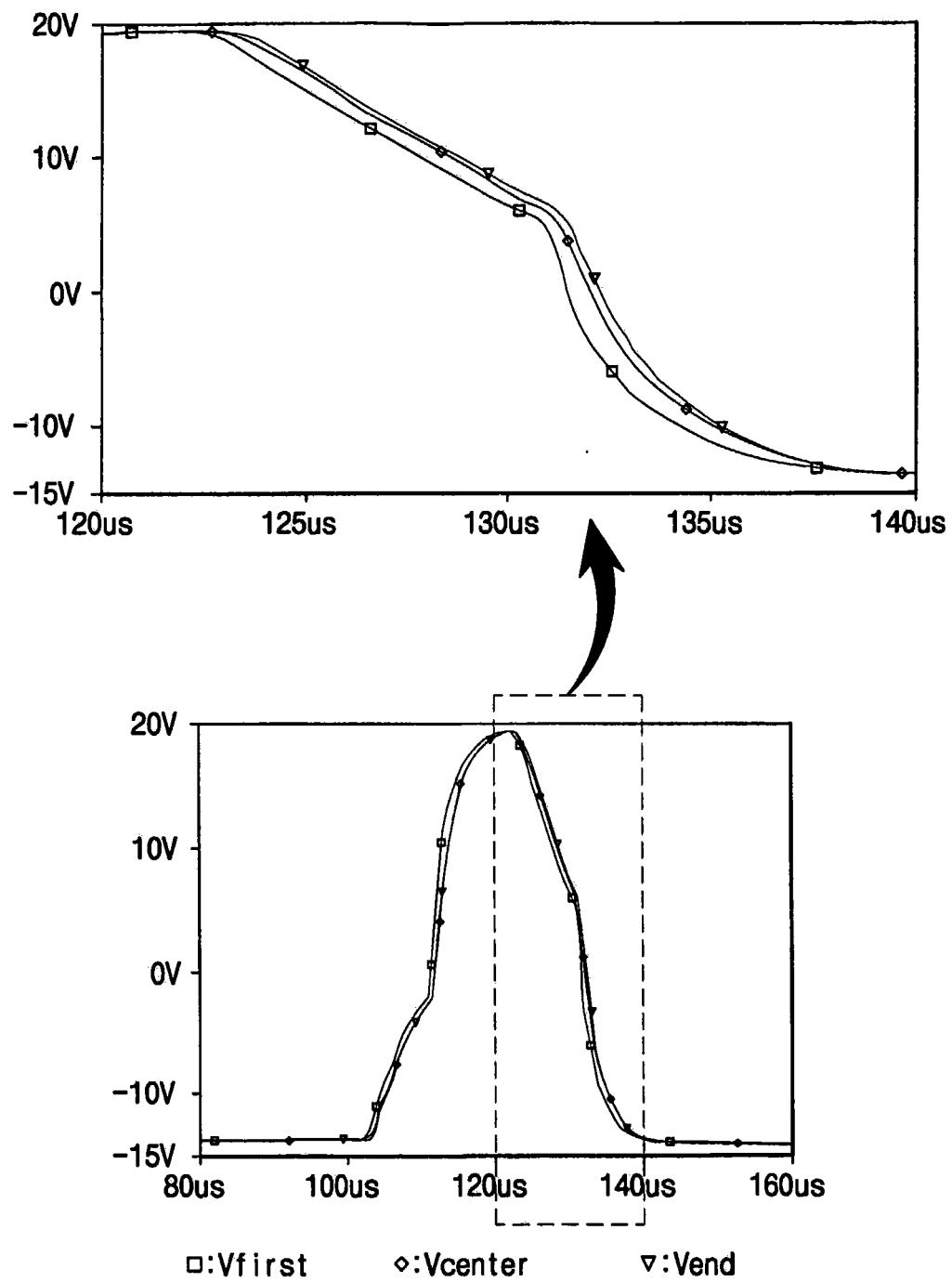

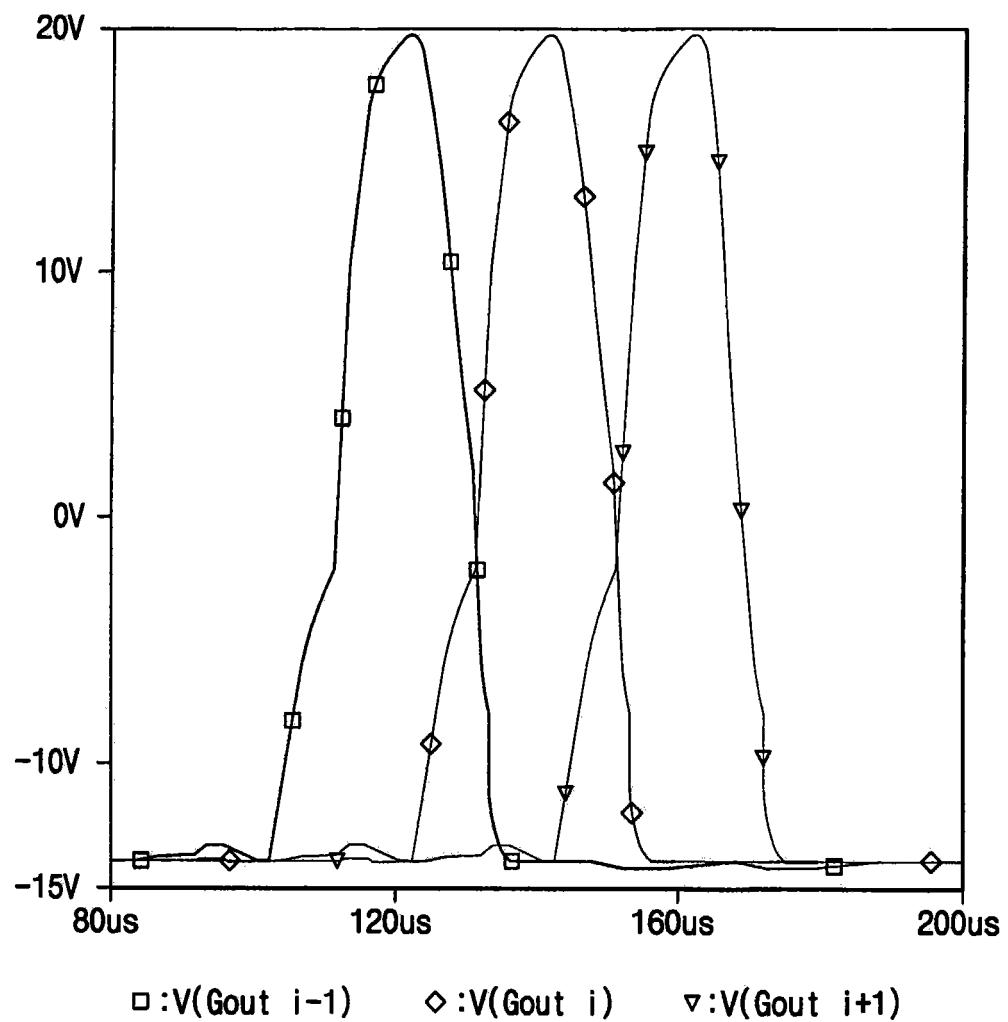

图 11 是根据第一时钟信号及第二时钟信号在相应阶段模拟的输出波形图；

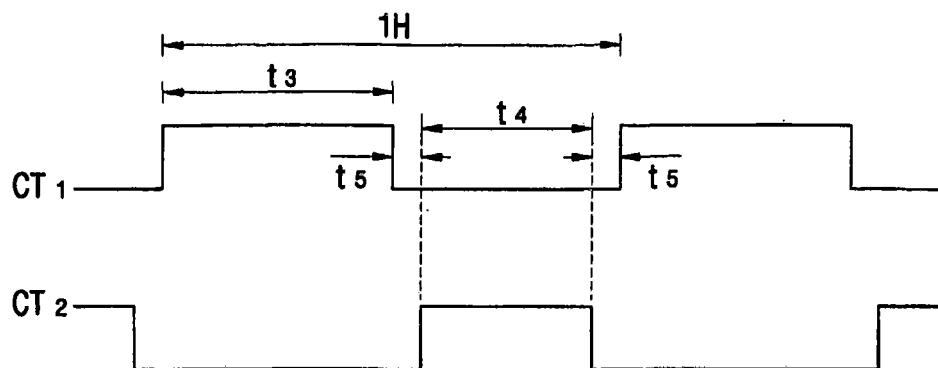

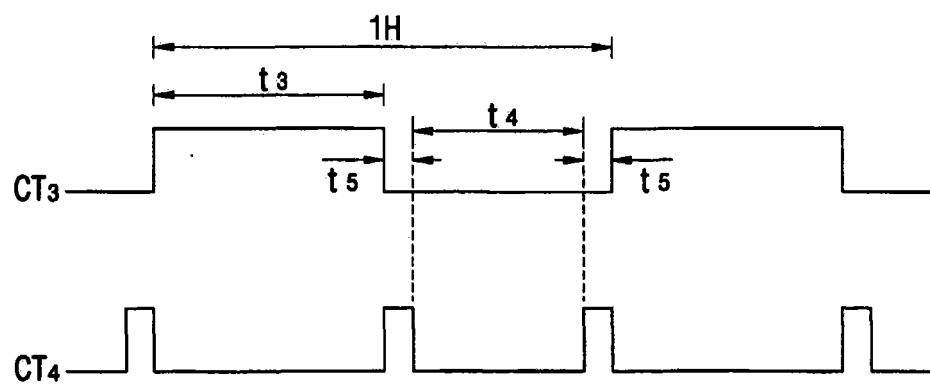

图 12 及图 13 是根据本发明另一具体实施例的时钟发生控制信号的波形；

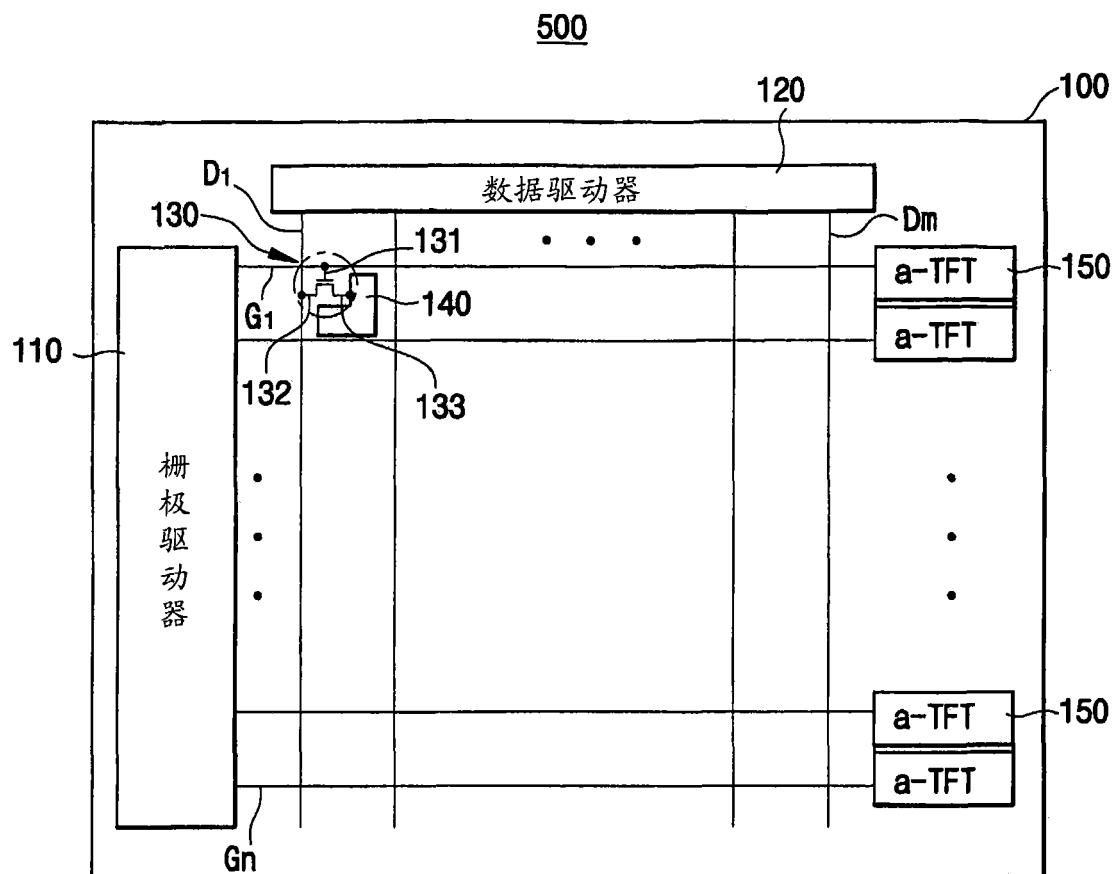

图 14 是示出根据本发明另一具体实施例的液晶显示装置示意图；

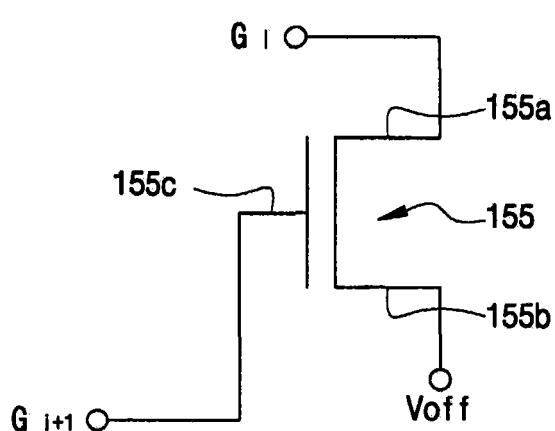

图 15 是示出图 14 所示的放电器示意图；

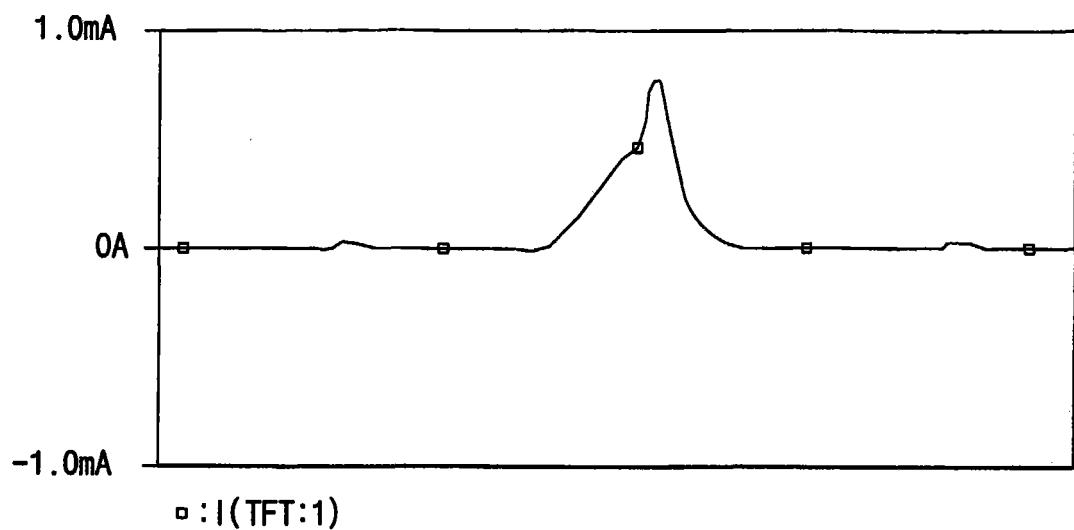

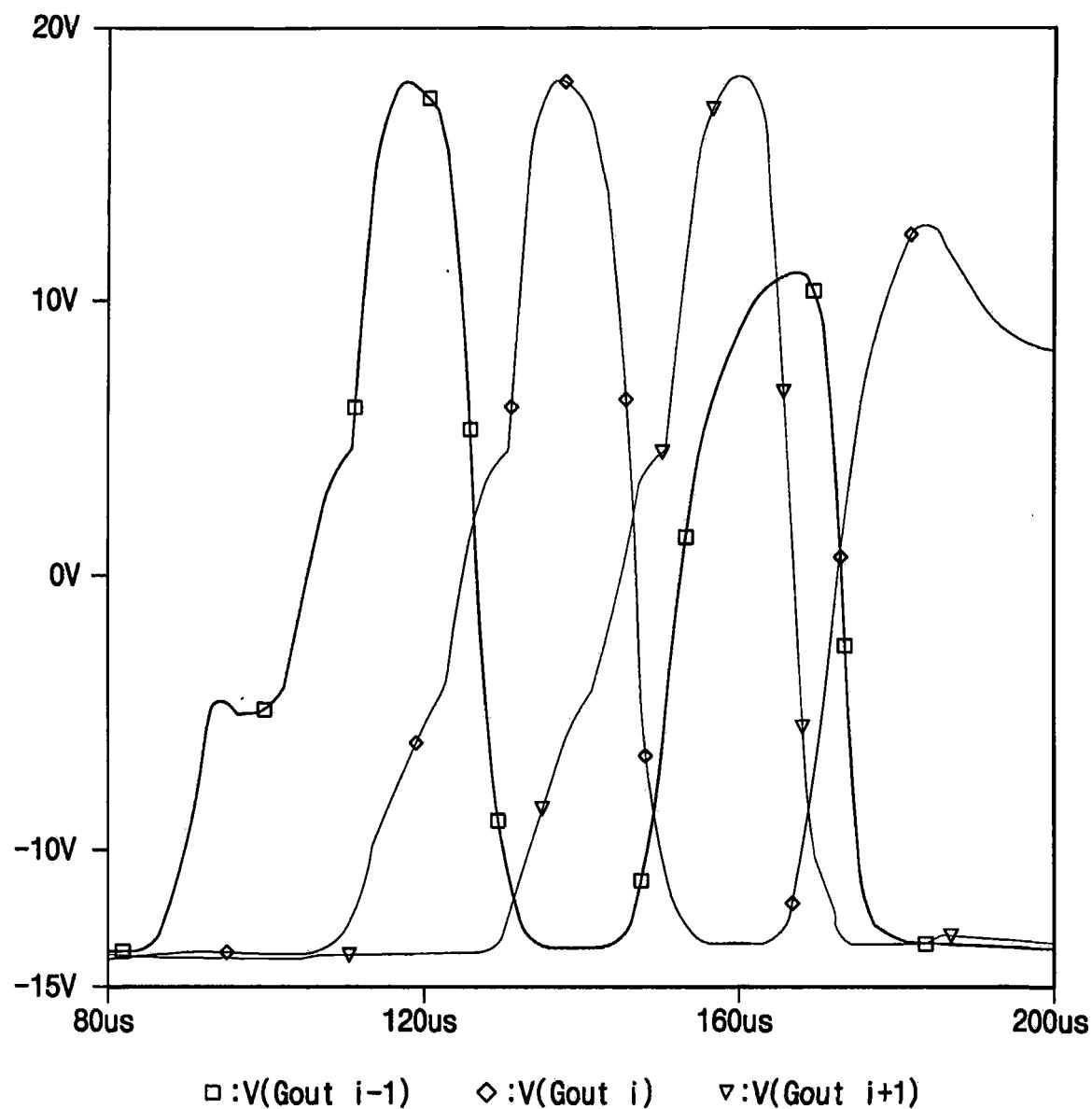

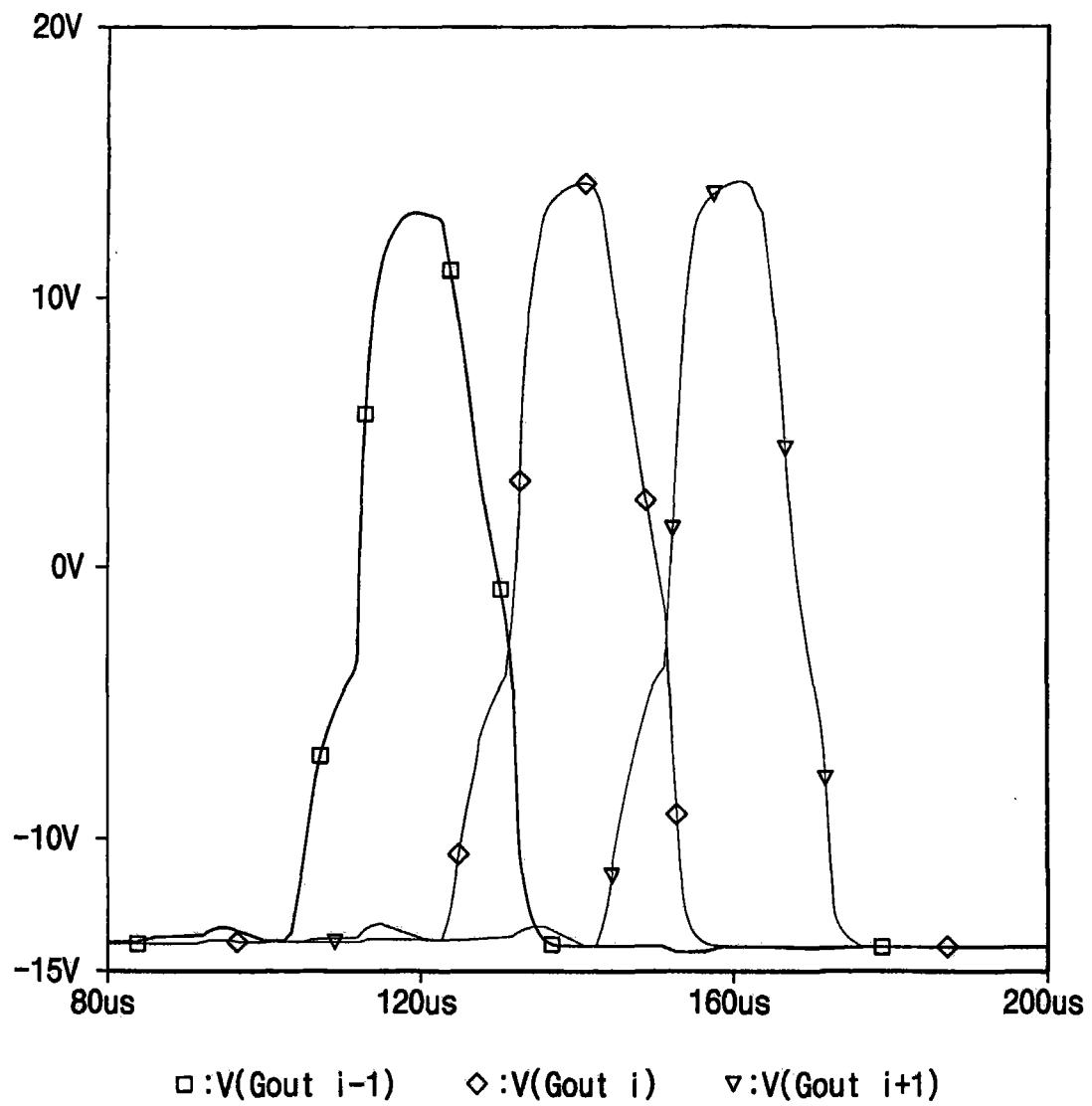

图 16 是在图 15 所示的放电器的模拟波形；

图 17 是图 14 所示的液晶显示器的栅极驱动信号波形；

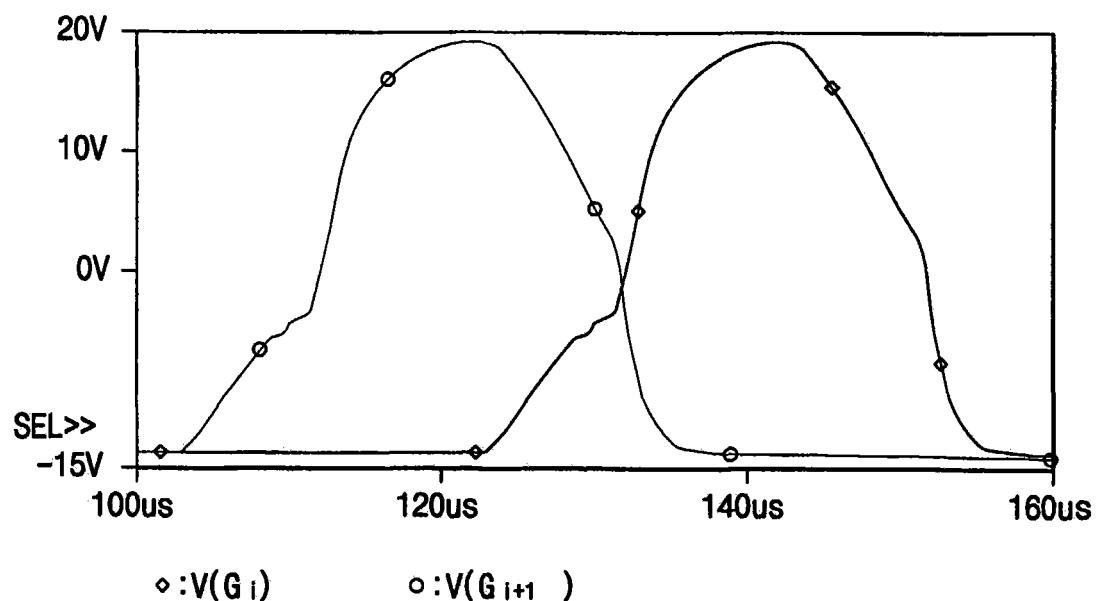

图 18 是传统栅极驱动信号的波形；

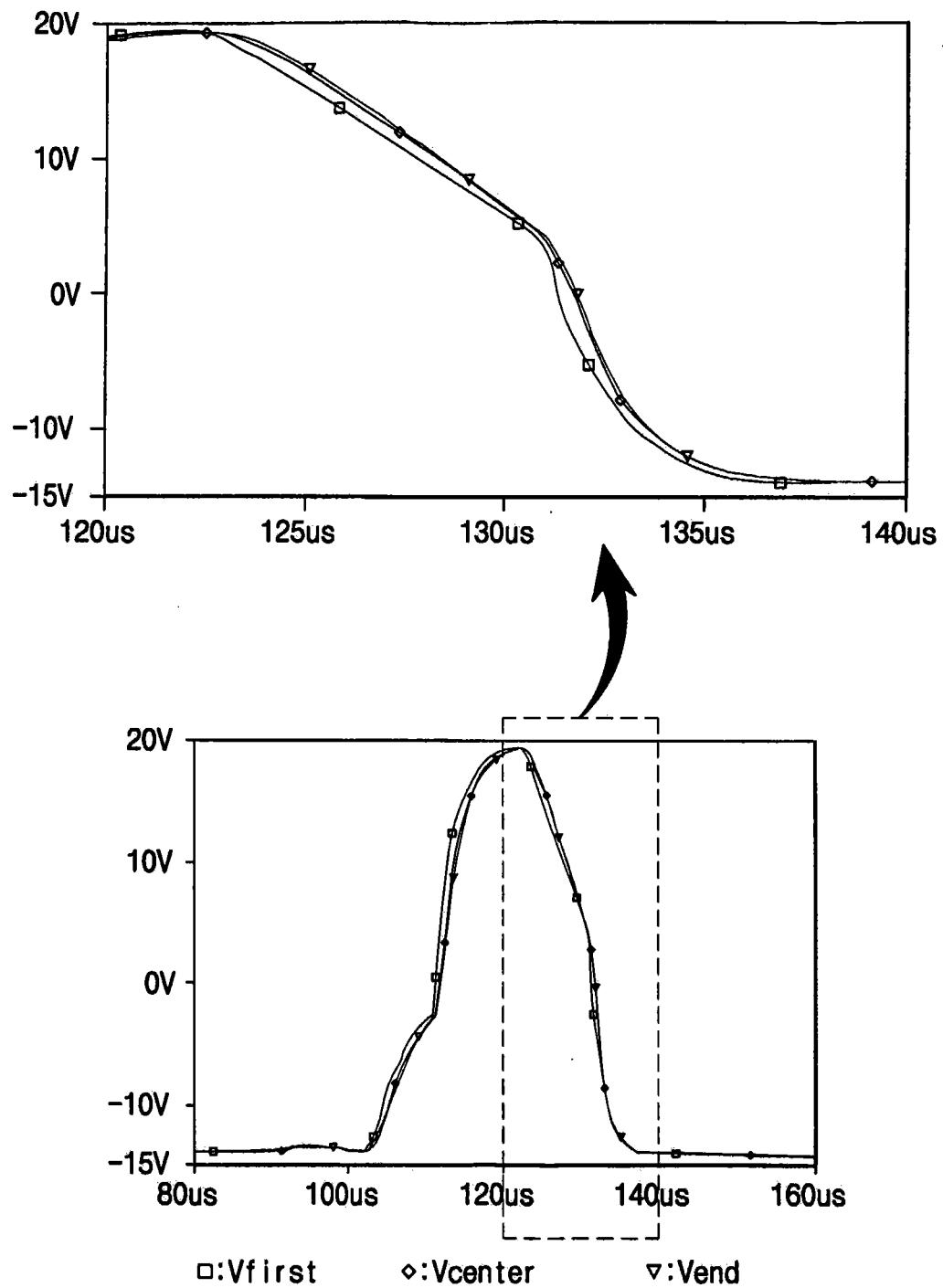

图 19 是根据图 14 所示的根据本发明具体实施例的栅极驱动信号波形；

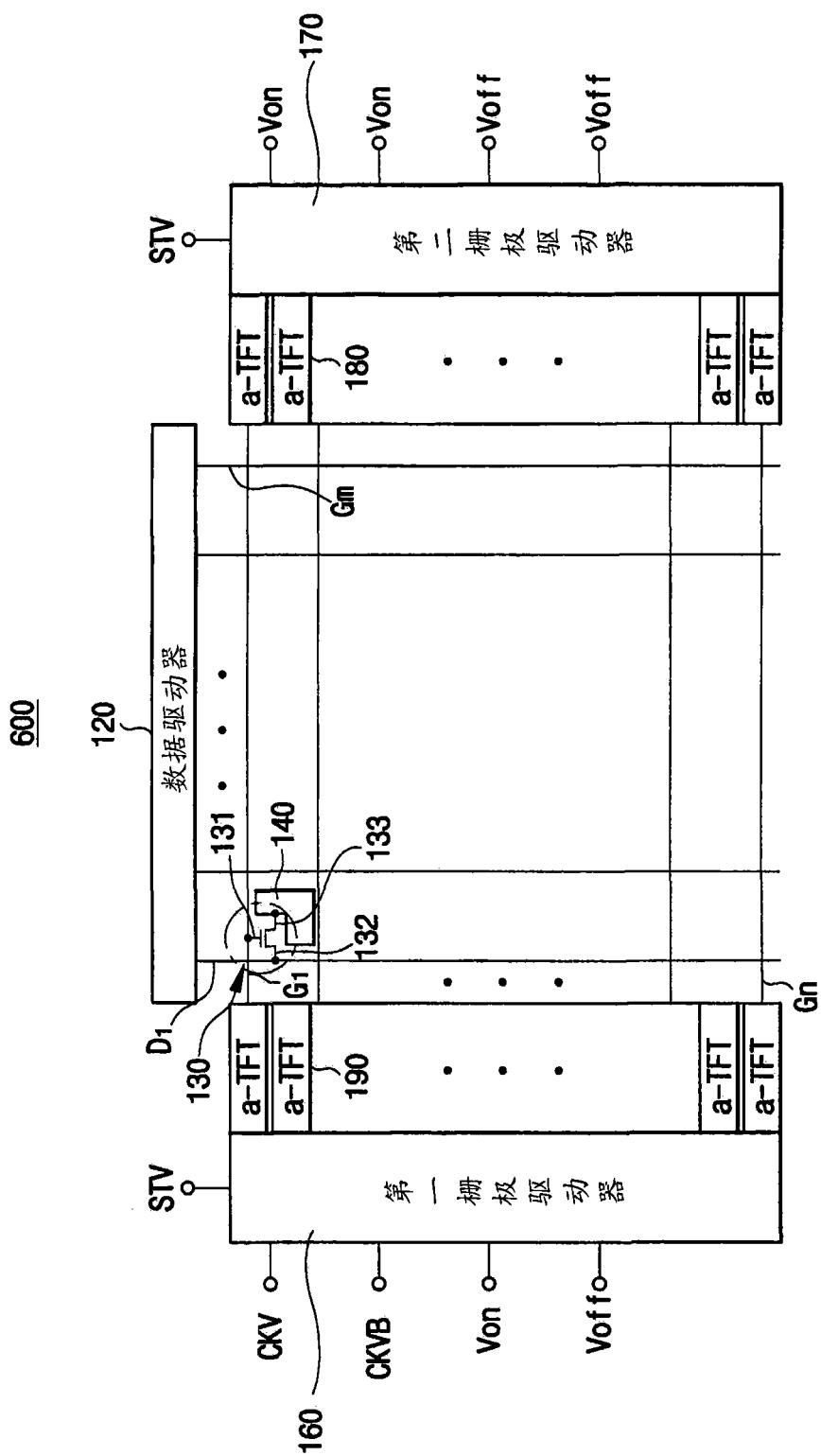

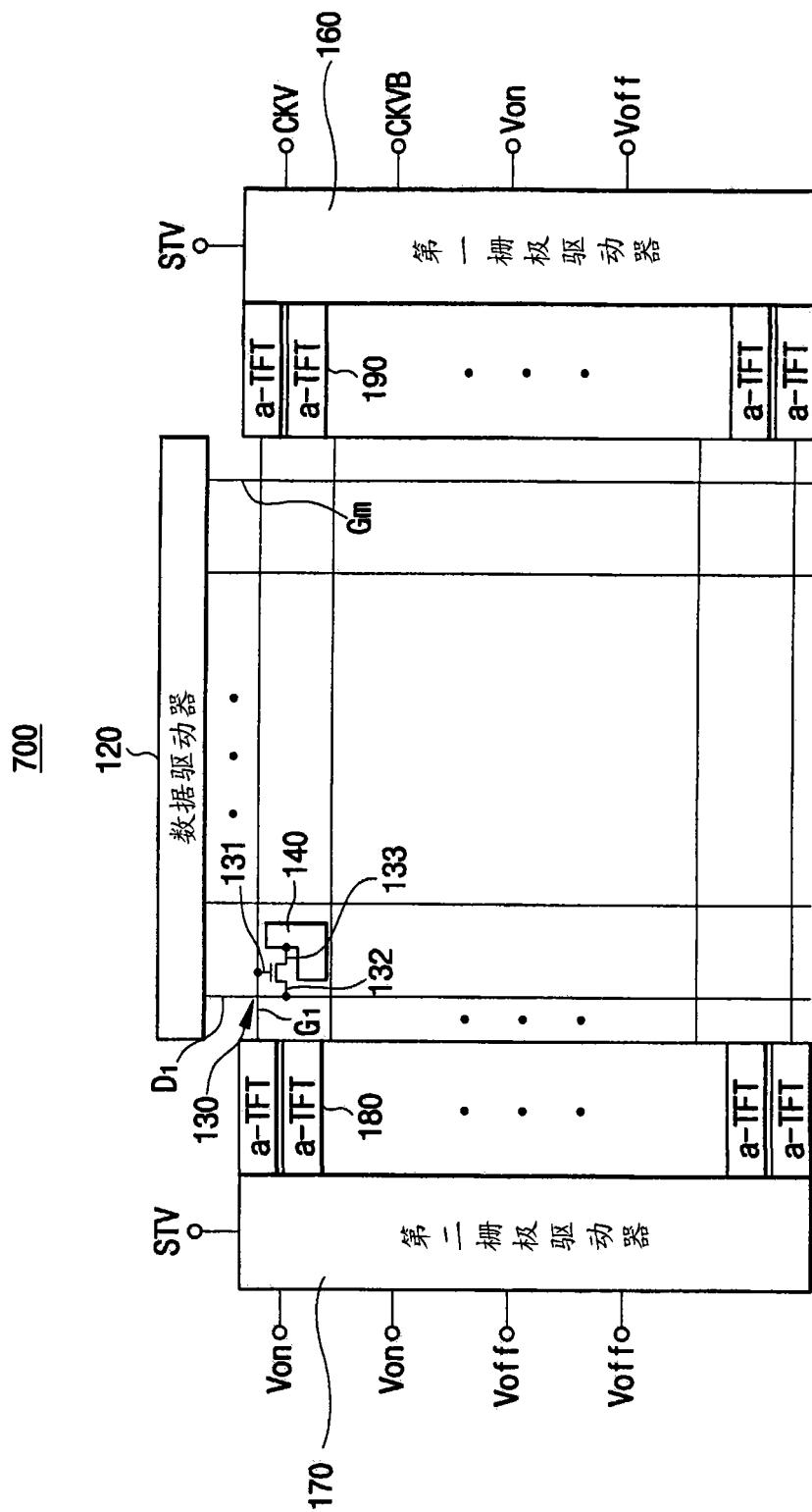

图 20 及图 21 是示出根据本发明其它具体实施例的液晶显示装置的示意图；

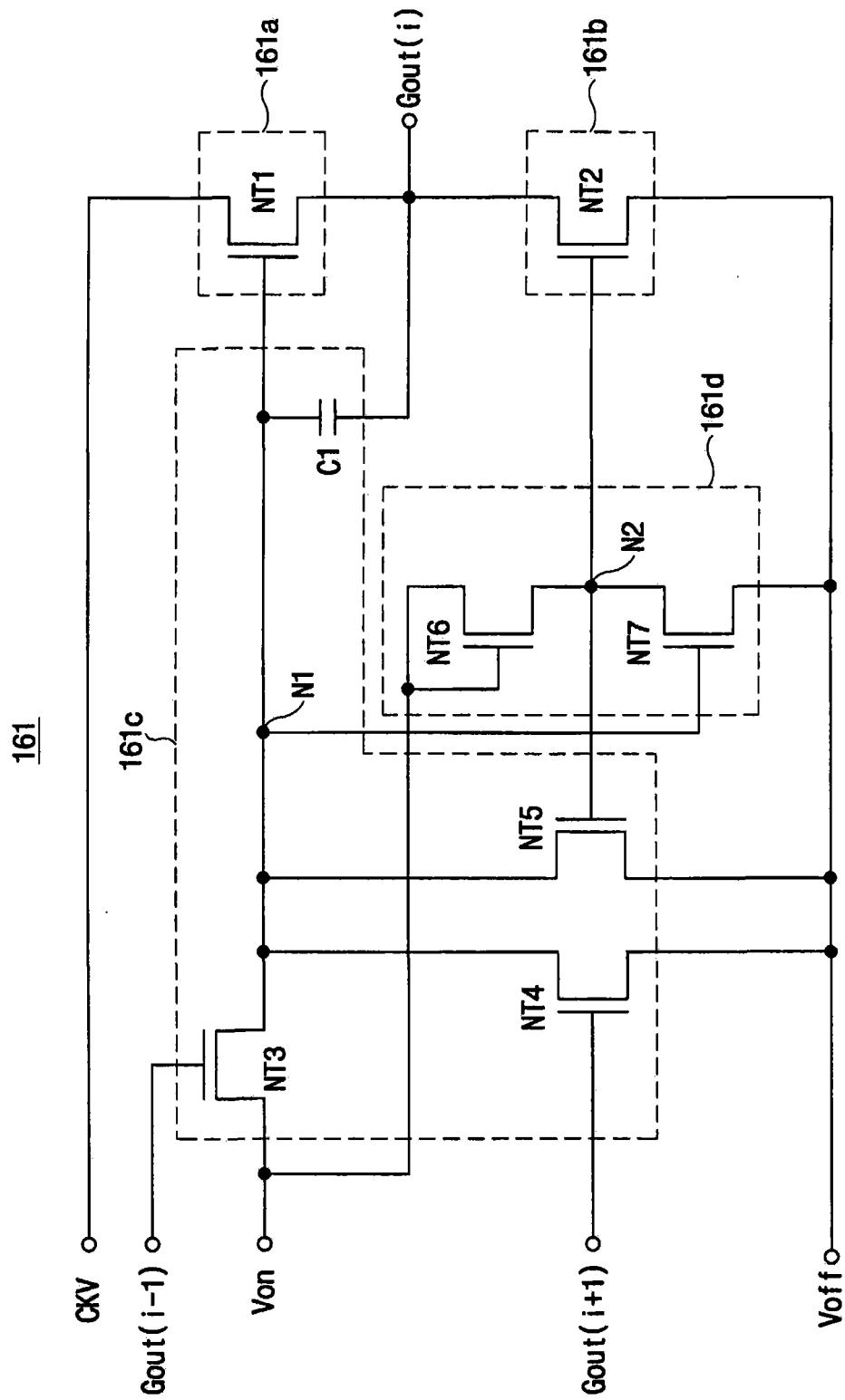

图 22 是示出图 20 所示的第一栅极驱动器电路图；

图 23 是从图 22 所示的第一栅极驱动器输出的波形；

图 24 是示出在向图 20 所示的第二栅极驱动器的第一电源电压输入端施加第一电源电压时第一栅极驱动器的输出信号的波形；以及

图 25 是示出在向图 20 所示的第二栅极驱动器的第一时钟信号及第二时钟信号输入端施加第二电源电压时第一栅极驱动器的输出信号的波形。

### 具体实施方式

图 1 是根据本发明一具体实施例的液晶显示装置方框图。

参照图 1，液晶显示装置 400 包括在其上设置栅极驱动器 110 和数据驱动器 120 的液晶面板 100、响应外部信号控制液晶面板 100 的定时控制器 200、以及用于产生施加于栅极驱动器 110 的第一和第二时钟信号 CKV 和 CKVB 的时钟发生器 300。

定时控制器 200 产生定时信号以控制栅极驱动器 110 和数据驱动器 120。定时控制器 200 响应由外部装置提供的 H-sync (水平同步) 信号将水平开始信号 STH 施于数据驱动器 120。数据驱动器 120 响应来自定时控制器 200 的水平开始信号 STH 将由定时控制器 200 提供的图像信号转换成模拟图像数据并将模拟图像数据提供给数据线。定时控制器 200 响应由外部装置提供的 V-sync (垂直同步) 信号将第一垂直开始信号 STV 施于时钟发生器 300。

定时控制器 200 向时钟发生器 300 施加用于确定栅极驱动信号的周期的栅极时钟信号 CPV、用于允许栅极驱动信号的允许信号 OE、以及用于控制第一时钟信号及第二时钟信号 CKV 和 CKVB 的充电或放电的充电/放电控制信号 CHC。

液晶面板 **100** 包括沿第一方向延伸的多条栅极线 G1~Gn、沿与第一方向垂直的第二方向延伸的多条数据线 D1~Dm、与栅极线 G1~Gn 和数据线 D1~Dm 连接的 TFT **130**、以及与 TFT **130** 连接的像素电极 **140**。

液晶显示器 **100** 包括用于向栅极线 G1~Gn 上顺次施加栅极驱动信号的栅极驱动器 **110** 和向数据线 D1~Dm 施加数据信号的数据驱动器 **120**。液晶面板 **100** 还包括 TFT 基片、滤色器基片、以及置于 TFT 基片和滤色器基片之间的液晶层。将栅极线 G1~Gn、数据线 D1~Dm、TFT **130**、以及像素电极 **140** 设置在 TFT 基片上。

数据驱动器 **120** 响应水平开始信号 STH 生成施加于液晶面板 **100** 的相应像素的数据信号。由数据驱动器 **120** 生成的数据信号是用于充电相应像素的充电电压。

栅极驱动器 **110** 包括移位寄存器，在该移位寄存器中，将多个阶段（stage）接连地彼此连接并将栅极线 G1~Gn 分别与多个阶段连接。因此，多个阶段依次向栅极线 G1~Gn 输出栅极驱动信号。即，响应具有与第一垂直开始信号相反相位的第二垂直开始信号 STVB 向栅极线 G1~Gn 依次施加具有高电平周期的栅极驱动信号，以控制施加于相应像素的数据信号。栅极信号包括足以驱动与栅极线 G1~Gn 连接的 TFT **130** 的电压电平。若响应栅极信号运行 TFT **130**，则数据信号通过 TFT **130** 施加到像素电极 **140** 以充电液晶层。

时钟发生器 **300** 响应栅极时钟信号 CPV 及允许信号 OE，输出具有相反相位的第一及第二时钟信号 CKV、CKVB。将第一时钟信号 CKV 施加到栅极驱动器 **110** 的奇数阶段，而将第二时钟信号 CKVB 施加到栅极驱动器 **110** 的偶数阶段。

时钟发生器 300 包括第一及第二电压施加电路（未示出）和充电/放电电路（未示出）。第一及第二电压施加电路产生具有预定电压的第一时钟信号及第二时钟信号 CKV 和 CKVB 以响应栅极时钟信号 CPV、允许信号 OE、和第一垂直开始信号 STV 确定栅极驱动信号的电平。充电/放电电路响应栅极时钟信号 CPV 和充电/放电 CHC，控制要进行充电或放电的第一时钟信号及第二时钟信号 CKV 和 CKVB。时钟发生器 300 输出第二垂直信号 STVB 到栅极驱动器 110 以顺次将来自栅极驱动器 110 的第一垂直开始信号 STV 施加于栅极线 G1~Gn。

因此，第一时钟信号 CKV 和第二时钟信号 CKVB 在第一周期具有预定电压，并且在第二周期进行充电或放电。通过控制第一时钟信号 CKV 和第二时钟信号 CKVB，栅极驱动信号的脉冲宽度减小，从而栅极驱动器 110 可以进行高速运行。

而且，时钟发生器 300 可以使用栅极时钟信号 CPV 及允许信号 OE，而无需施于时钟发生器 300 的另外控制信号，以产生第一时钟信号及第二时钟信号 CKV 和 CKVB。

图 2 是示出图 1 所示的时钟发生器方框图，图 3 是图 2 所示的相应元件的定时图。

参照图 2，时钟发生器 300 包括用于输出第一时钟允许信号 OCS（奇数时钟脉冲）和第二时钟允许信号 ECS（偶数时钟脉冲）的 D-触发器 310、用于响应第一时钟允许信号 OCS 输出第一定时 CKV 的第一电压施加电路 320、用于响应第二时钟允许信号 ECS 输出第二时钟信号 CKVB 的第二电压施加电路 330、以及用于充电或放电第一时钟信号 CKV 和第二时钟信号 CKVB 的充电/放电电路 340。

D-触发器 310 接收垂直开始信号 STV 并与允许信号 OE 同步，以分别通过第一接线端 QB 和第二接线端 Q 输出第一时钟允许信号 ECS 和第二时钟允许信号 OCS。该允许信号 OE 通过栅极信号的时间延迟来延迟来自栅极驱动器 110 的输出。即，当在第一周期 1H 延迟栅极驱动信号时允许信号 OE 具有高电平。

第一电压施加电路 320 响应栅极时钟信号 CPV、允许信号 OE、及第一时钟允许信号 OCS 输出在第一周期具有预定电压的第一时钟信号 CKV。第二电压施加电路 330 响应栅极时钟信号 CPV、允许信号 OE、及第一时钟允许信号 ECS 输出在第一周期维持预定电压的第二时钟信号 CKVB。充电/放电电路 340 接收栅极时钟信号 CPV，并且在关闭第一电压施加电路及第二电压施加电路 320 和 330 时充电/放电第一时钟信号及第二时钟信号 CKV、CKVB。

如图 3 所示，栅极时钟信号 CPV 具有第一周期 1H 且允许信号 OE 在第一周期 1H 产生，以及当栅极驱动信号被延迟时具有预定负载的高电平。

在栅极时钟信号 CPV 具有高电平且允许信号 OE 具有低电平的第三周期 t3，运行第一及第二电压施加电路 320、330。在栅极时钟信号 CPV 具有低电平且允许信号 OE 具有低电平或高电平的第四周期 t4，运行充电/放电电路 340。在位于第三周期与第四周期 t3、t4 之间的第五周期，第一及第二电压施加电路 320、330 和充电/放电电路 340 均处于操纵失灵状态。在第五周期，栅极时钟信号 CPV 和允许信号 OE 分别具有低电平或高电平。

下面，将详细地描述时钟发生器 300。

图 4 是图 2 所示的 D-触发器电路图，而图 5 是图 4 所示的 D-触发器定时图。

参照图 4 和图 5, 若响应具有与第一垂直开始信号 STV 相反相位的第二垂直开始信号 STVB 清除 D-触发器 310, 则由 D-触发器 310 的第一接线端 QB 输出的第二时钟允许信号 ECS 具有高电平。即, D-触发器 310 接收第一垂直开始信号 STV 并响应通过其时钟接线端 CLK 输入的允许信号 OE 输出作为一个周期具有两个高电平 (2H) 的第一时钟允许信号 OCS 和第二时钟允许信号 ECS。第一时钟允许信号 OCS 允许第一电压施加电路 320 输出施加于栅极驱动器 110 的奇数阶段的第一时钟信号 CKV, 而第二时钟允许信号 ECS 允许第二电压施加电路 330 输出施加于栅极驱动器 110 的偶数阶段的第二时钟信号 CKVB。

图 6 是示出图 2 所示的第一电压施加电路的电路图, 而图 7 是示出图 2 所示的第二电压施加电路的电路图。

参照图 6, 第一电压施加电路 320 包括用于响应具有高电平的第一时钟允许信号 OCS 将第一电源电压 Von 提供给第一时钟信号 CKV 的第一电源电压供给部 321、以及用于响应具有低电平的第一时钟允许信号 OCS 将第二电源电压 Voff 提供给第一时钟信号 CKV 的第二电源电压供给部 323。

第一电源电压供给部 321 包括接通电压发生器 321a 和用于控制接通电压发生器 321a 运行的第一控制器 321b。

第一控制器 321b 包括第一晶体管 T1、第二晶体管 T2、第一电阻器 R1、及第二电阻器 R2。

第一晶体管 T1 包括与用于允许信号 OE 的接线端连接的发射极以及与第二晶体管 T2 的发射极连接的集电极。将第一电阻器 R1 连接于第一晶体管 T1 的基极和用于第一时钟允许信号 OCS 的接线端之间。第二晶体管 T2 包括与接通电压发生器 321a 连接的集电极。

将第二电阻器 R2 连接于第二晶体管 T2 的基极和用于栅极时钟信号 CPV 的接线端之间。

因此，第一晶体管 T1 响应第一时钟允许信号 OCS 和允许信号 OE 之间的电压差被接通，而第二晶体管 T2 响应由第一晶体管 T1 提供的允许信号 OE 和栅极时钟信号 CPV 之间的电压差被接通，从而控制接通电压 (on-voltage) 发生部 321a 的运行。

接通电压发生部 321a 包括第三晶体管 T3、第三电阻器 R3、第四电阻器 R4、第五电阻器 R5。

第三晶体管 T3 包括与用于第一电源电压 Von 的接线端连接的发射极和与第一时钟信号 CKV 连接的集电极。将第三电阻器 R3 连接于第三晶体管 T3 的发射极和基极之间。将第四电阻器 R4 和第五电阻器 R5 串联连接于第三晶体管 T3 的基极和第二晶体管 T2 的集电极之间。因此，第三晶体管 T3 通过接线端输出第一时钟信号 CKV。

第二电源电压供给部 323 包括切断电压 (off-voltage) 发生器 323a 和用于控制切断电压发生器 323a 的第二控制器 323b。

第二控制器 323b 包括第四晶体管 T4、第五晶体管 T5、和第六至第十一电阻器 R6~R11。

第四晶体管 T4 包括与用于栅极时钟信号 CPV 的接线端连接的发射极和与第五晶体管 T5 连接的集电极。将第六电阻器 R6 连接于第四晶体管 T4 的发射极和基极之间。将第七电阻器 R7 和第八电阻器 R8 串联连接于第三晶体管 T4 的基极和用于允许信号 OE 的接线端之间。第五晶体管 T5 包括与切断电压发生器 323a 连接的集电极。将第九电阻器 R9 连接于第五晶体管 T5 的发射极和基极之间。将第

十电阻器 R10 和第十一电阻器 R11 串联连接于第五晶体管 T5 的基极和用于第一时钟允许信号 OCS 的接线端之间。

第四晶体管 T4 响应栅极钟信号 CPV 和允许信号 OE 之间的电压差输出栅极钟信号 CPV，而第五晶体管 T5 响应由第四晶体管 T4 输出的栅极时钟信号 CPV 和第一时钟允许信号 OCS 之间的电压差输出栅极时钟信号 CPV。将由第五晶体管 T5 输出的栅极时钟信号 CPV 提供给切断电压发生器 323a。

切断电压发生器 323a 包括第六晶体管 T6、第十二电阻器 R12、第十三电阻器 R13、和第十四电阻器 R14。

第六晶体管 T6 包括与用于第二电源电压 Voff 的接线端连接的发射极和与第一时钟信号 CKV 连接的集电极。将第十二电阻器 R12 连接于第五晶体管 T5 的集电极和并联的第十三和第十四电阻器 R13、R14 的第一接线端之间，将第十三电阻器 R13 与第六晶体管 T6 的发射极连接并将第十四电阻器 R14 与第六晶体管 T6 的基极连接。因此，若将第六晶体管 T6 响应由第二控制器 323b 输出的栅极时钟信号 CPV 被接通，则第二电源电压 Voff 通过用于第一时钟信号 CKV 的接线端被输出。

在图 6 中，第一至第六晶体管 T1、T2、T3、T4、T5、和 T6 是双极性结型晶体管。

参照图 7，第二电压施加电路 330 包括用于响应具有高电平的第二时钟允许信号 ECS 向第二时钟信号 CKVB 提供第一电源电压 Von 的第一电源电压供给部 331 以及用于响应具有低电平的第二时钟允许信号 ECS 向第二时钟信号 CKVB 提供第二电源电压 Voff 的第二电源电压供给部 333。

第一电源电压供给部 331 包括接通电压发生部 331a 和用于控制接通电压发生部 331a 运行的第一控制器 331b。

第一控制器 331b 包括第一晶体管 T1、第二晶体管 T2、第一电阻器 R1、和第二电阻器 R2。

第一晶体管 T1 包括与用于允许信号 OE 的接线端连接的发射极以及与第二晶体管 T2 的发射极连接的集电极。将第一电阻器 R1 连接于第一晶体管 T1 的基极和用于第二时钟允许信号 ECS 的接线端之间。第二晶体管 T2 包括与接通电压发生器 321a 连接的集电极。将第二电阻器 R2 连接于第二晶体管 T2 的基极和用于栅极时钟信号 CPV 的接线端之间。

因此，第一晶体管 T1 响应第二时钟允许信号 ECS 和允许信号 OE 之间的电压差被接通，而第二晶体管 T2 响应由第一晶体管 T1 提供的允许信号 OE 和栅极时钟信号 CPV 之间的电压差被接通，从而控制接通电压发生部 331a 的运行。

接通电压发生部 331a 包括第三晶体管 T3、第三电阻器 R3、第四电阻器 R4、和第五电阻器 R5。

第三晶体管 T3 包括与用于第一电源电压 Von 的接线端连接的发射极和与第二时钟信号 CKVB 连接的集电极。将第三电阻器 R3 连接于第三晶体管 T3 的发射极和基极之间。将第四电阻器 R4 和第五电阻器 R5 串联连接于第三晶体管 T3 的基极和第二晶体管 T2 的集电极之间。因此，第三晶体管 T3 通过接线端输出第二时钟信号 CKVB。

第二电源电压供给部 333 包括切断电压发生器 333a 和用于控制切断电压发生器 323a 的第二控制器 333b。

---

第二控制器 333b 包括第四晶体管 T4、第五晶体管 T5、和第六至第十一电阻器 R6~R11。

第四晶体管 T4 包括与用于栅极时钟信号 CPV 的接线端连接的发射极和与第五晶体管 T5 连接的集电极。将第六电阻器 R6 连接于第四晶体管 T4 的发射极和基极之间。将第七电阻器 R7 和第八电阻器 R8 串联连接于第三晶体管 T4 的基极和用于允许信号 OE 的接线端之间。第五晶体管 T5 包括与切断电压发生器 333a 连接的集电极。将第九电阻器 R9 连接于第五晶体管 T5 的发射极和基极之间。将第十电阻器 R10 和第十一电阻器 R11 串联连接于第五晶体管 T5 的基极和用于第二时钟允许信号 ECS 的接线端之间。

第四晶体管 T4 响应栅极钟信号 CPV 和允许信号 OE 之间的电压差输出栅极钟信号 CPV，而第五晶体管 T5 响应由第四晶体管 T4 输出的栅极时钟信号 CPV 和第二时钟允许信号 ECS 之间的电压差输出栅极时钟信号 CPV。将由第五晶体管 T5 输出的栅极时钟信号 CPV 提供给切断电压发生器 333a。

切断电压发生器 333a 包括第六晶体管 T6、第十二电阻器 R12、第十三电阻器 R13、和第十四电阻器 R14。

第六晶体管 T6 包括与用于第二电源电压 Voff 的接线端连接的发射极和与第二时钟信号 CKVB 连接的集电极。将第十二电阻器 R12 连接于第五晶体管 T5 的集电极和并联的第十三和第十四电阻器 R13、R14 的第一接线端之间，将第十三电阻器 R13 与第六晶体管 T6 的发射极连接并将第十四电阻器 R14 与第六晶体管 T6 的基极连接。因此，若将第六晶体管 T6 响应由第二控制器 333b 输出的栅极时钟信号 CPV 被接通，则第二电源电压 Voff 通过用于第二时钟信号 CKVB 的接线端被输出。

在图 7 中，第一至第六晶体管 T1、T2、T3、T4、T5、和 T6 是双极性结型晶体管。

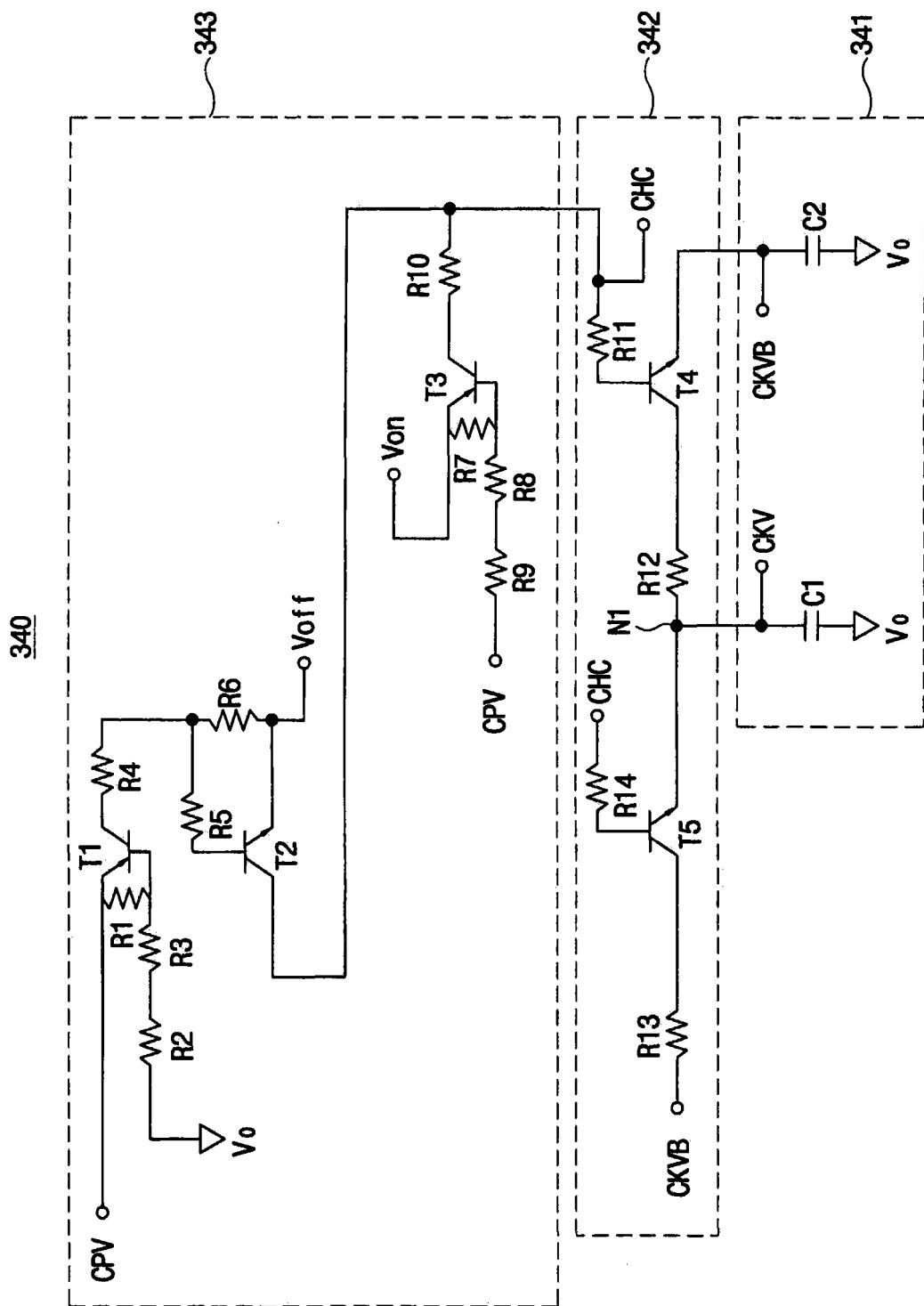

图 8 是示出图 2 所示的充电/放电电路的电路图。

参照图 8，充电/放电电路 340 包括用于充电/放电第一及第二时钟信号 CKV、CKVB 的充电器 341、用于驱动充电器 341 的充电驱动器 342、和用于控制充电驱动器 342 的充电控制器 343。

充电控制器 343 包括第一至第三晶体管 T1~T3、和第一至第十电阻器 R1~R10。

第一晶体管 T1 包括与用于栅极时钟信号 CPV 的接线端连接的发射极以及与第四电阻器 R4 的第一接线端连接的集电极。将第二电阻器 R1 和第三电阻器 R3 连接于串联的第一晶体管 T1 和接地端  $V_0$  的基极之间。将第四电阻器 R4 与并联的第五电阻器 R5 和第六电阻器 R6 连接。将第五电阻器 R5 与第二晶体管 T2 的基极连接，并将第六电阻器 R6 与第二晶体管 T2 的发射极连接。

第三晶体管 T3 包括与用于第一电源电压  $V_{on}$  的接线端连接的发射极和通过第十电阻器 R10 与第二晶体管 T2 连接的集电极。将第七电阻器 R7 连接于第三晶体管 T3 的发射极和基极之间。将第八电阻器 R8 和第九电阻器 R9 串联连接于第三晶体管 T3 的基极和用于栅极时钟信号 CPV 的接线端之间。

充电驱动器 342 包括第四晶体管 T4、第五晶体管 T5、和第十一至第十四电阻器 R11~R14。

第四晶体管 T4 包括与用于第二时钟信号 CKVB 的接线端连接的发射极和通过第十二电阻器 R12 与用于第一时钟信号 CKV 的接线端连接的集电极。将第十一电阻器 R11 连接于第四晶体管 T4 的

基极和用于充电/放电控制信号 CHC 的接线端之间。第五晶体管 T5 包括与第十二电阻器 R12 连接的发射极和通过第十三电阻器 R13 与用于第二时钟信号 CKVB 的接线端连接的集电极。将第十四电阻器 R14 连接于第五晶体管 T5 的基极和用于充电/放电控制信号 CHC 的接线端之间。

充电器 341 包括连接于用于第一时钟信号 CKV 和接地端  $V_0$  的接线端之间的第一电容器 C1 和连接于用于第二时钟信号 CKVB 和接地端  $V_0$  的接线端之间的第二电容器 C2。

因此，若将第一及第二电压施加电路 320、330 的第三及第六晶体管 T3、T6 关闭并且栅极时钟信号 CPV 具有低电平，则运行充电/放电电路 340。即，若栅极时钟信号 CPV 具有低电平，则关闭充电控制器 343 的第一晶体管 T1 和第二晶体管 T2。通过响应栅极时钟信号 CPV 和第一电源电压 Von 接通的第三晶体管 T3，将第一电源电压 Von 施加到充电驱动器 342。

因此，响应第一电源电压 Von 和充电/放电控制信号 CHC 接通充电驱动器 342 的第四晶体管 T4 以充电第二电容 C2。通过用于第二时钟信号 CKVB 的接线端将充电到第二电容 C2 的充电电压输出。将第一电容器 C1 进行放电并通过用于第一时钟信号 CKV 的接线端将放电电压输出。

响应充电/放电控制信号 CHC 接通充电驱动器 342 的第五晶体管 T5 并且在第一结点 N1 处提高电势。因此，将第一电容器 C1 进行充电并通过用于第一时钟信号 CKV 的接线端将充电电压输出。将第二电容器 C2 进行放电并通过用于第二时钟信号 CKVB 的接线端将放电电压输出。

若将第一及第二电压施加电路 320、330 关闭且栅极时钟信号 CPV 具有低电平，则将第一及第二时钟信号 CKV、CKVB 进行充电或放电。

当第一及第二电压施加电路 320、330 不运行时，与第三晶体管 T3 的集电极连接的第十电阻器 R10 延迟要施加于充电驱动器 342 的第一电源电压 Von 以驱动充电/放电电路 340。因此，可以防止第一电压施加电路 320、第二电源施加电路 330、和充电/放电电路 340 在第五周期内一起运行。

图 9 是来自图 2 所示的时钟发生器的第一时钟信号及第二时钟信号的模拟波形，而图 10 是用于输出来自图 2 所示的时钟发生器的第一时钟信号及第二时钟信号所需电流的模拟波形。在图 9 和图 10 中，第一电源电压 Von 和第二电源电压 Voff 分别为 20 伏特和 14 伏特。

参照图 9 及图 10，第一时钟信号 CKV 在第一周期 t1 具有第一电源电压 Von 且在第二周期 t2 具有一定斜度的第一极性。第二时钟信号 CKVB 在第一周期 t1 具有与第一时钟信号 CKV 相反相位的第二电源电压 Voff 且在第二周期 t2 具有与第一极性相反的一定斜度的第二极性。

第一时钟信号和第二时钟信号 CKV、CKVB 分别具有作为 1H 的第一周期和第二周期 t1、t2，并且在第二周期 t2 将具有彼此相反相位的第一时钟信号 CKV 和第二时钟信号 CKVB 进行充电或放电。这样，由于将时钟发生器 300 减少约一半的传统波形，因此可将时钟发生器 300 的功率消耗降低。

将功率消耗 (P) 定义为以下方程式：

$$P \propto f \Delta V_2 C \quad (1)$$

若电压转换减小，则时钟发生器 **300** 的功率消耗（P）可以减小约四分之一，这是因为功率消耗（P）与电压转换的平方成比例。即，用于产生第一时钟信号和第二时钟信号 CKV、CKVB 的时钟发生器 **300** 的功率消耗（P）可以减小。

图 11 是根据第一时钟信号及第二时钟信号在相应阶段模拟的输出波形图。

参照图 11，在第二时钟信号 CKVB 的上升边缘处，从第 i 阶段输出第 i 个栅极驱动信号。当从第 i+1 个阶段输出的第 i+1 个栅极驱动信号到达电压 V1 时，将第 i 个栅极驱动信号进行放电。因此，可将在高电平处维持的第 i 个栅极驱动信号时间量减小。

若栅极驱动器 **110** 接收第一及第二时钟信号 CKV、CKVB，可以调整栅极驱动信号的脉冲宽度，并且可将液晶显示器 **400** 以高速运行。

在图 1 至图 11 中，将栅极时钟信号 CPV 和允许信号 OE 作为用于控制第一及第二电压施加电路 **320**、**330** 和充电/放电电路 **340** 的时钟发生控制信号进行描述。然而，时钟发生控制信号并不局限于列举的具体实施例。

图 12 和图 13 是根据本发明另一具体实施例的时钟发生控制信号的波形。

参照图 12，时钟发生控制信号包括具有 1H 周期的第一控制信号 CT1 和具有部分与第一控制信号 CT1 相反相位及 1H 周期的第二控制信号 CT2。第一及第二控制信号 CT1、CT2 控制第一及第二电压施加电路 **320**、**330** 和充电/放电电路 **340** 的运行。

具体而言，在第一控制信号 CT1 具有高电平且第二控制信号 CT2 具有低电平的第三周期 t3，运行第一及第二电压施加电路 320、330。在第一控制信号 CT1 具有低电平且第二控制信号 CT2 具有高电平的第四周期 t4，运行充电/放电电路 340。而且，在第一控制信号 CT1 和第二控制信号 CT2 具有低电平的第五周期 t5，不运行第一及第二电压施加电路 320、330 和充电/放电电路 340。提供的第五周期 t5 位于第三周期 t3 及第四周期 t4 之间。因此，可以防止第一电压施加电路 320、第二电压施加电路 330、和充电/放电电路 340 同时运行。

如图 13 所示，时钟发生控制信号包括分别具有 1H 周期的第三控制信号 CT3 和第四控制信号 CT4。若第三控制信号 CT3 具有低电平，则第四控制信号 CT4 产生高电平。第三控制信号 CT3 和第四控制信号 CT4 控制第一及第二电压施加电路 320、330 和充电/放电电路 340 的运行。

具体而言，在第三控制信号 CT3 具有高电平且第四控制信号 CT4 具有低电平的第三周期 t3，运行第一及第二电压施加电路 320、330。在第三控制信号 CT3 具有低电平且第四控制信号 CT4 具有高电平的第四周期 t4，运行充电/放电电路 340。而且，在第三控制信号 CT3 和第四控制信号 CT4 具有低电平的第五周期 t5，不运行第一及第二电压施加电路 320、330 和充电/放电电路 340。提供的第五周期 t5 位于第三周期 t3 及第四周期 t4 之间。因此，可以防止第一电压施加电路 320、第二电压施加电路 330、和充电/放电电路 340 同时运行。

图 14 是示出根据本发明另一具体实施例的液晶显示装置示意图，图 15 是示出图 14 所示的放电器示意图，图 16 是在图 15 所示的放电器的模拟波形，而图 17 是图 14 所示的液晶显示器的栅极驱动信号波形。

---

参照图 14，液晶显示装置 **500** 包括设置有栅极驱动器 **110**、数据驱动器 **120**、及放电器 **150** 的液晶面板 **100**。

液晶面板 **500** 包括沿第一方向延伸的多条栅极线 **G1-Gn**、沿与第一方向垂直的第二方向延伸的多条数据线 **D1-Dm**、具有与栅极线 **G1-Gn** 连接的第一电极 **131** 和与数据线 **D1-Dm** 连接的第二电极 **132** 的 TFT **130**、以及与 TFT **130** 的第三电极 **133** 连接的像素电极 **140**。TFT **130** 通过第二电极 **132** 接收数据信号并且响应施加于第一电极 **131** 的栅极驱动信号向像素电极 **140** 提供该数据信号。

与栅极线 **G1-Gn** 的第一端部连接的栅极驱动器 **110** 向栅极线 **G1-Gn** 依次施加栅极驱动信号。与数据线 **D1-Dm** 连接的数据驱动器 **120** 向数据线 **D1-Dm** 施加数据信号。

将放电器 **150** 分别与栅极线 **G1-Gn** 的第二端部连接。如图 15 所示，放电器 **150** 响应施加于下一个栅极线 **Gi+1** 的第一栅极驱动信号放电施加于当前栅极线 **Gi** 的第二栅极驱动信号，从而第二栅极驱动信号具有第二电源电压 **Voff**。“i”是大于“1”且小于“n”的自然数。

放电器 **150** 包括具有与当前栅极线 **Gi** 连接的第一电极 **155a**、与用于第二电源电压输入端 **Voff** 的接线端连接的第二电极 **155b**、以及与下一个栅极线 **Gi+1** 连接的第三电极 **155c** 的放电晶体管 **155**。

也就是说，若第一栅极驱动信号的电压电平大于放电晶体管 **155** 的阈值电压，则放电晶体管 **155** 放电第二栅极驱动信号到第二电源电压 **Voff**。

如图 16 及图 17 所示，若第一栅极驱动信号增加到大于放电晶体管 **155** 的阈值电压，则放电晶体管 **155** 放电第二栅极驱动信号到第二电源电压 **Voff**。因此，放电晶体管 **155** 在上拉第一栅极驱动信

号之前充分放电第二栅极驱动信号，从而可以防止第二栅极驱动信号被延迟。

图 18 是传统栅极驱动信号的波形，而图 19 是根据图 14 所示的根据本发明具体实施例的栅极驱动信号波形。在图 18 及图 19 中，将向位于与栅极线 G1-Gn 的栅极线 G1 连接的多个开关装置之间的第一开关装置施加的第一栅极驱动信号 Vfirst、向位于与栅极线 G1-Gn 的栅极线 G1 连接的多个开关装置之间的中心开关装置施加的第二栅极驱动信号 Vcenter、以及向位于与栅极线 G1-Gn 的栅极线 G1 连接的多个开关装置之间的最后一个开关装置施加的第三栅极驱动信号 Vend 进行描述。

参照图 18，第一、第二、第三栅极驱动信号 Vfirst、Vcenter、Vend 在约  $140\mu s$  处被完全放电，并且每个分别在不同时间达到第二电源电压 Voff。

参照图 19，第一、第二、第三栅极驱动信号 Vfirst、Vcenter、Vend 在约  $136\mu s$  处被完全放电。因此，比较与如图 8 所示的传统第一、第二、第三栅极驱动信号 Vfirst、Vcenter、Vend 的延迟时间，本发明实施例的第一、第二、第三栅极驱动信号 Vfirst、Vcenter、Vend 的延迟时间可以缩短约  $4\mu s$ 。而且，由于第一、第二、第三栅极驱动信号 Vfirst、Vcenter、Vend 同时达到第二电源电压 Voff，从而改善了第一、第二、第三栅极驱动信号 Vfirst、Vcenter、Vend 的延迟特性。

图 20 及图 21 是示出根据本发明另一实施例的液晶显示装置的示意图。

参照图 20，液晶显示装置 **600** 包括第一栅极驱动器 **160**、第二栅极驱动器 **170**、数据驱动器 **120**、第一放电器 **180**、及第二放电器 **190**。

在液晶面板 **600** 包括沿第一方向延伸的多条栅极线 **G1-Gn**、沿与第一方向垂直的第二方向延伸的多条数据线 **D1-Dm**、具有与栅极线 **G1-Gn** 连接的第一电极 **131** 和与数据线 **D1-Dm** 连接的第二电极 **132** 的 TFT **130**、以及与 TFT **130** 的第三电极 **133** 连接的像素电极 **140**。TFT **130** 通过第二电极 **132** 接收数据信号并且响应施加于其第一电极 **131** 的栅极驱动信号向像素电极 **140** 提供该数据信号。

与栅极线 **G1-Gn** 的第一端部连接的第一栅极驱动器 **160** 向栅极线 **G1-Gn** 依次施加栅极驱动信号。若将栅极驱动信号施加于栅极线 **G1-Gn**，则与数据线 **D1-Dm** 连接的数据驱动器 **120** 向数据线 **D1-Dm** 施加数据信号。

若第一栅极驱动器 **160** 处于异常运行状态，则与栅极线 **G1-Gn** 的第二端部连接的第二栅极驱动器 **170** 向栅极线 **G1-Gn** 依次施加栅极驱动信号。因此，尽管第一栅极驱动器 **160** 处于异常运行，当第二栅极驱动器 **170** 处于正常状态时，液晶显示装置 **600** 也可以正常状态运行。

第一及第二栅极驱动器 **160**、**170** 分别包括彼此接连地连接的多个阶段的移位寄存器。移位寄存器的相应阶段具有相同的结构。

如图 20 所示，第一栅极驱动器 **160** 包括用于接收来自外部装置的诸如第一垂直开始信号 **STV**、第一时钟信号 **CKV**、第二时钟信号 **CKVB**、第一电源电压 **Von**、及第二电源电压 **Voff** 这样的信号的五个输入端。

第二栅极驱动器 **170** 还包括五个输入端。当第一栅极驱动器 **160** 处于正常状态运行时，第二栅极驱动器 **170** 接收第一垂直开始信号 STV、第一电源电压 Von、和第二电源电压 Voff。即，第二栅极驱动器 **170** 接收替代第一时钟信号 CKV 和第二时钟信号 CKVB 的第一电源电压 Von 以及替代用于第一电源电压 Von 的第二电源电压 Voff。因此，当第一栅极驱动器 **160** 处于正常状态运行时第二栅极驱动器 **170** 维持偏压状态。

然而，若第一栅极驱动器 **160** 处于异常状态运行，则第二栅极驱动器 **170** 接收第一时钟信号 CKV，第二时钟信号 CKVB、和第一电源电压 Von，以便可以向栅极线 G1-Gn 输出栅极驱动信号。

为了防止栅极驱动信号被延迟，若运行第一栅极驱动器 **160**，则将第一放电器 **180** 与栅极线 G1-Gn 的第二端部连接。若运行第二栅极驱动器 **170**，则将第二放电器 **190** 与栅极线 G1-Gn 的第一端部连接以防止栅极驱动信号被延迟。

第一放电器 **180** 包括具有与当前栅极线的第一端部连接的第一电极、与用于第二电源电压 Voff 的接线端连接的第二电极、以及与下一栅极线的第一端部连接的第三电极的第一放电晶体管。因此，第一放电晶体管响应从第一栅极驱动器 **160** 施加到下一栅极线的第一栅极驱动信号运行，以放电施加于当前栅极线的第二栅极驱动信号为第二电源电压 Voff。

第二放电器 **190** 包括具有与当前栅极线的第二端部连接的第一电极、与用于第二电源电压 Voff 的接线端连接的第二电极、以及与下一栅极线的第二端部连接的第三电极的第二放电晶体管。因此，第二放电晶体管响应从第二栅极驱动器 **170** 施加到下一栅极线的第一栅极驱动信号运行，以放电施加于当前栅极线的第二栅极驱动信号为第二电源电压 Voff。

在图 20 中，分别邻接栅极线 G1-Gn 的第一端部和第二端部设置第一栅极驱动器和第二栅极驱动器 **160、170**。然而，分别可以邻接栅极线 G1-Gn 的第二端部和第一端部设置第一栅极驱动器和第二栅极驱动器 **160、170**。

在图 21 中，在液晶显示装置 **700** 中，将第二栅极驱动器 **170**与栅极线 G1-Gn 的第一端部连接，而将第一栅极驱动器 **160** 与栅极线 G1-Gn 的第二端部连接。当第一栅极驱动器 **160** 处于异常状态运行时，运行第二栅极驱动器 **170**。

图 22 是示出图 20 所示的第一栅极驱动器电路图，而图 23 是图 22 所示的第一栅极驱动器的输出波形。第一栅极驱动器 **160** 具有彼此接连地连接的多个阶段的移位寄存器。移位寄存器的相应阶段具有相同的结构。

参照图 22，移位寄存器的每个阶段 **161** 包括上拉 (pull-up) 部 **161a**、下拉 (pill-down) 部 **161b**、上拉驱动部 **161c**、及下拉驱动部 **161d**。

上拉部 **161a** 包括第一 NMOS 晶体管 NT1，其中将漏极与时钟信号输入端 CKV 连接，将栅极与第一结点 N1 连接、以及将源极与当前阶段的输出端 Gout(i)连接。

下拉部 **161b** 包括第二 NMOS 晶体管 NT2，其中将漏极与输出端 Gout(i)连接，将栅极与第二结点 N2 连接，并且将源极与第二电源电压 Voff 连接。

上拉驱动部 **161c** 包括电容器 C1 和第三至第五 NMOS 晶体管 NT3~NT5。将电容器 C1 连接于第一结点 N1 和输出端 Gout(i)之间。第三 NMOS 晶体管 NT13 包括与第一电源电压 Von 连接的漏极、与接线端 Gout(i-1)连接的栅极、以及与第一结点 N1 连接的源极。第

四 NMOS 晶体管 NT4 包括与第一结点 N1 连接的漏极、与下一个阶段的输出端 Gout(i+1)连接的栅极、以及与第二电源电压 Voff 连接的源极。第五 NMOS 晶体管 NT5 包括与第一结点 N1 连接的漏极、与第二结点 N2 连接的栅极、以及与第二电源电压 Voff 连接的源极。

下拉驱动部 **161d** 包括第六及第七 NMOS 晶体管 NT6、NT7。第六 NMOS 晶体管 NT6 包括共同与第一电源电压 Von 连接的漏极和栅极以及与第二结点 N2 连接的源极。第七 NMOS 晶体管 NT7 包括与第二结点 N2 连接的漏极、第一结点 N1 连接的栅极、以及与第二电源电压 Voff 连接的源极。第六 NMOS 晶体管 NT6 与第七 NMOS 晶体管 NT7 的尺寸比率为 16:1。

若施加第一时钟信号和第二时钟信号 CKV、CKVB 及第一垂直开始信号 STV，则每个阶段依次输出栅极驱动信号。也就是说，每个阶段响应前一个阶段的输出信号，每个阶段通过输出端 Gout(i) 输出作为栅极驱动信号的高电平周期的第一时钟信号 CKV。

当在输出端 Gout(i) 处产生第一时钟信号 CKV 的高电平周期时，在电容器 C1 处引导（bootstrapped）输出电压，从而第一 NMOS 晶体管 NT11 的栅极电压上升为接通电压 VDD 以上。因此，第一 NMOS 晶体管 NT1 维持完全接通状态。这时，第三 NMOS 晶体管 NT3 与第五 NMOS 晶体管 NT5 的尺寸比率为 2:1。因此，即使响应第一垂直开始信号 STV 接通第五 NMOS 晶体管 NT5，第一 NMOS 晶体管 NT1 也转换到接通状态。

在下拉驱动部 **161d** 中，由于将第七 NMOS 晶体管 NT7 关闭且第二结点 N2 的电势上升为第一电源电压 Von，因此接通第二 NMOS 晶体管 NT2。这样，由输出端 Gout(i) 输出的栅极驱动信号电压保持第二电源电压 Voff。这时，将第二结点 N2 的电势降到第二电源电

压  $V_{off}$ , 这是因为第七 NMOS 晶体管 NT7 响应由前一阶段的输出端  $Gout(i-1)$  输出的栅极驱动信号被接通。

即使接通第六 NMOS 晶体管 NT6, 由于第七 NMOS 晶体管 NT7 的尺寸比第六 NMOS 晶体管 NT6 的尺寸大 16 倍, 因此第二结点 N2 维持第二电源电压  $V_{off}$ 。因此, 将第二 NMOS 晶体管 NT2 从接通状态转换到关闭状态。

若将由当前阶段的输出端  $Gout(i)$  输出的栅极驱动信号的电势降到第二电源电压  $V_{off}$ , 则关闭第七 NMOS 晶体管 NT7。因为第二结点 N2 通过第六 NMOS 晶体管 NT6 接收第一电源电压  $V_{on}$ , 所以第二结点 N2 的电势从第二电源电压  $V_{off}$  上升到第一电源电压  $V_{on}$ 。当接通第五 NMOS 晶体管 NT5 同时提高第二结点 N2 的电势, 将充入电容器 C1 的电压放电以关闭第一 NMOS 晶体管 NT1。

响应由具有接通电压的下一阶段的端输出端  $Gout(i+1)$  输出的栅极驱动信号的电压电平, 接通第四 NMOS 晶体管 NT4。这时, 由于第四 NMOS 晶体管 NT4 的尺寸大于第五 NMOS 晶体管 NT5 的尺寸 2 倍, 因此第一结点 N1 的电势迅速降低到第二电源电压  $V_{off}$  同时仅接通第五 NMOS 晶体管 NT5。因此, 第一 NMOS 晶体管 NT1 被关闭且第二 NMOS 晶体管 NT2 被接通, 所以由当前阶段的输出端  $Gout(i)$  输出的栅极驱动信号从第一电源电压  $V_{on}$  降到第二电源电压  $V_{off}$ 。

尽管响应降到第二电源电压  $V_{off}$  的由下一阶段的输出端  $Gout(i+1)$  输出的栅极驱动信号关闭第四 NMOS 晶体管 NT4, 但是第二结点 N2 通过第六 NMOS 晶体管 NT6 保持第一电源电压  $V_{on}$  且第一结点 N1 通过第五 NMOS 晶体管 NT5 保持第二电源电压  $V_{off}$ 。因此, 第二结点 N2 的电势可以保持第一电源电压并防止第二 NMOS 晶体管 NT2 被关闭。

图 24 是示出在向图 20 所示的第二栅极驱动器的第一电源电压输入端施加第一电源电压时第一栅极驱动器的输出信号的波形，而图 25 是示出在向图 20 所示的第二栅极驱动器的第一时钟信号及第二时钟信号输入端施加第二电源电压时第一栅极驱动器的输出信号的波形。

参照图 24，若将第一电源电压  $V_{on}$  施加于用于第二栅极驱动器 170 的第一电源电压  $V_{on}$  的输入端，则将来自第一栅极驱动器 160 的相应阶段的输出波形以异常波形输出。结果，液晶显示装置的显示特性变差。

如图 25 所示，若将第二电源电压  $V_{off}$  施加于用于第二栅极驱动器 170 的第一和第二时钟信号 CKV 和 CKVB 的输入端，则降低来自第一栅极驱动器 160 的相应阶段的输出波形的电压电平。结果，第一栅极驱动器 160 的功率消耗提高。

因此，用于第二栅极驱动器 170 的第一和第二时钟信号 CKV 和 CKVB 的输入端接收第一电源电压  $V_{on}$ ，并且当第一栅极驱动器 160 以正常状态运行时，用于第二栅极驱动器 170 的第一电源电压  $V_{on}$  的输入端接收第二电源电压  $V_{off}$ 。

根据液晶显示装置，时钟发生器分别产生具有可确定栅极驱动信号的电压电平的第一周期以及可充电或放电第一和第二时钟信号的第二周期的第一和第二时钟信号，并且将第一和第二时钟信号施加于栅极驱动器以控制栅极驱动信号的脉冲宽度。因此，通常栅极驱动器可以驱动对应 1H 帧的栅极线，从而改善液晶显示装置的显示特性。

---

而且，由于栅极线具有与其第一端部连接的放电晶体管，在运行下一个阶段之前可将当前阶段进行放电，从而防止栅极驱动信号被延迟。

此外，栅极线包括与其第一端部连接的第一栅极驱动器以及与其第二端部连接的第二栅极驱动器。当第一栅极驱动器以异常状态运行时，第二栅极驱动器一般正常运行。因此，即使第一栅极驱动器运行异常，液晶显示装置也由于第二栅极驱动器而可以正常状态运行。

以上所述仅为本发明的优选实施例而已，并不用于限制本发明，对于本领域的技术人员来说，本发明可以有各种更改和变化。凡在本发明的精神和原则之内，所作的任何修改、等同替换、改进等，均应包含在本发明的保护范围之内。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8

图 9

图 10

图 11

图 12

图 13

图 14

150

图 15

图 16

图 17

图 18

图 19

图 20

图 21

图 22

图 23

图 24

图 25

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置                                         |         |            |

| 公开(公告)号        | <a href="#">CN101202026A</a>                   | 公开(公告)日 | 2008-06-18 |

| 申请号            | CN200810000319.9                               | 申请日     | 2003-08-26 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                       |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                       |         |            |

| 当前申请(专利权)人(译)  | 三星电子株式会社                                       |         |            |

| [标]发明人         | 文胜煥                                            |         |            |

| 发明人            | 文胜煥                                            |         |            |

| IPC分类号         | G09G3/36 G02F1/133                             |         |            |

| CPC分类号         | G09G2330/08 G09G3/3677                         |         |            |

| 优先权            | 1020020052020 2002-08-30 KR                    |         |            |

| 其他公开文献         | <a href="#">CN101202026B</a>                   |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

本发明披露了一种具有改良显示特性的液晶显示装置。时钟发生器将第一时钟信号和第二时钟信号施加于栅极驱动器，以控制栅极驱动信号的脉冲宽度。在运行下一阶段之前，在当前阶段将与多条栅极线的第一端部连接的放电晶体管放电。这些栅极线包括第一栅极驱动器、以及在第一栅极驱动器以异常状态运行时用于运行这些栅极线的第二栅极驱动器。因此，液晶显示装置可以高速运行，并且可以防止栅极驱动信号被延迟。