[19] 中华人民共和国国家知识产权局

[12] 发明专利申请公布说明书

[21] 申请号 200710085560.1

[51] Int. Cl.

G02F 1/1362 (2006.01)

G02F 1/133 (2006.01)

H03K 19/017 (2006.01)

[43] 公开日 2007 年 8 月 29 日

[11] 公开号 CN 101025535A

[22] 申请日 2003.12.18

[21] 申请号 200710085560.1

分案原申请号 200380107645.5

[30] 优先权

[32] 2002.12.25 [33] JP [31] 375002/2002

[71] 申请人 株式会社半导体能源研究所

地址 日本神奈川县厚木市

[72] 发明人 木村肇

[74] 专利代理机构 中国专利代理(香港)有限公司

代理人 浦柏明 刘宗杰

权利要求书 4 页 说明书 36 页 附图 36 页

[54] 发明名称

液晶显示装置

[57] 摘要

本发明的目的是提供一种数字电路，它具有：有被供给电源电位(VDD、VSS)的第1晶体管(32、33)的开关电路(31)；以及连接在被施加输入信号的输入端(IN)与第1晶体管的控制端子(栅)之间的校正电路(34、36)，并具有：连接在上述控制端子与输入端之间的电容(C2、C3)；被设置在该电容与上述控制端子之间的节点(N5、N6)与电源电位之间的、与第1晶体管有大致相同的阈值的被连接成二极管的第2晶体管(35、37)；以及与第2晶体管串联连接的开关(SW2、SW3)。

1. 一种液晶显示装置，其特征在于，

具有：第1晶体管、第2晶体管、第3晶体管和电容元件，

所述第1晶体管中，源极或者漏极之一与栅极电连接，

所述第1晶体管和所述第3晶体管串联地电连接在第1布线和所述第2晶体管的栅极之间，

所述电容元件的一对端子中的一个与第1端子电连接，

所述第2晶体管的栅极与所述电容元件的一对端子中的另一个电连接，

所述第2晶体管的源极或者漏极之一与第2端子电连接，另一个与所述第1布线电连接。

2. 一种液晶显示装置，其特征在于，

具有：第1晶体管、第2晶体管、第3晶体管、第4晶体管和电容元件，

所述第1晶体管中，源极或者漏极之一与栅极电连接，

所述第1晶体管和所述第3晶体管串联地电连接在第1布线和所述第2晶体管的栅极之间，

所述电容元件的一对端子中的一个与第1端子电连接，

所述第2晶体管的栅极与所述电容元件的一对端子中的另一个电连接，

所述第2晶体管的源极或者漏极之一与第2端子电连接，另一个与所述第1布线电连接，

所述第4晶体管的源极或者漏极之一与所述第2晶体管的栅极电连接，另一个与第2布线电连接。

3. 一种液晶显示装置，其特征在于，

具有：第1晶体管、第2晶体管、第3晶体管、第4晶体管和电容元件，

所述第1晶体管中，源极或者漏极之一与栅极电连接，

所述第4晶体管中，源极或者漏极之一与栅极电连接，

所述第1晶体管和所述第3晶体管串联地电连接在第1布线和所述第2晶体管的栅极之间，

所述第1晶体管的栅极与所述第4晶体管的源极或者漏极的另一

个电连接，

所述电容元件的一对端子中的一个与第 1 端子电连接，

所述第 2 晶体管的栅极与所述电容元件的一对端子中的另一个电连接，

所述第 2 晶体管的源极或者漏极之一与第 2 端子电连接，另一个与所述第 1 布线电连接。

4. 如权利要求 3 记载的液晶显示装置，其特征在于，所述第 1 晶体管和所述第 4 晶体管为相同极性。

5. 如权利要求 1 记载的液晶显示装置，其特征在于，所述第 1 晶体管、所述第 2 晶体管以及所述第 3 晶体管为薄膜晶体管。

6. 如权利要求 2 或 3 记载的液晶显示装置，其特征在于，所述第 1 晶体管、所述第 2 晶体管、所述第 3 晶体管以及所述第 4 晶体管为薄膜晶体管。

7. 如权利要求 1 至 3 的任意一项记载的液晶显示装置，其特征在于，所述第 1 晶体管和所述第 2 晶体管为相同极性。

8. 一种液晶显示装置，其特征在于，

具有：第 1 N 型晶体管、第 1 P 型晶体管、第 2 N 型晶体管、第 2 P 型晶体管、第 3 N 型晶体管、第 3 P 型晶体管、第 1 电容元件和第 2 电容元件，

所述第 1 N 型晶体管中，源极或者漏极之一与栅极电连接，

所述第 1 N 型晶体管和所述第 3 N 型晶体管串联地电连接在第 1 布线和所述第 2 N 型晶体管的栅极之间，

所述第 1 电容元件的一对端子中的一个与第 1 端子电连接，

所述第 2 N 型晶体管的栅极与所述第 1 电容元件的一对端子中的另一个电连接，

所述第 2 N 型晶体管的源极或者漏极之一与第 2 端子电连接，另一个与所述第 1 布线电连接，

所述第 1 P 型晶体管中，源极或者漏极之一与栅极电连接，

所述第 1 P 型晶体管和所述第 3 P 型晶体管串联地电连接在第 2 布线和所述第 2 P 型晶体管的栅极之间，

所述第 2 电容元件的一对端子中的一个与所述第 1 端子电连接，

所述第 2 P 型晶体管的栅极与所述第 2 电容元件的一对端子中的

另一个电连接，

所述第2P型晶体管的源极或者漏极之一与所述第2端子电连接，另一个与所述第2布线电连接。

9. 一种液晶显示装置，其特征在于，

具有：第1N型晶体管、第1P型晶体管、第2N型晶体管、第2P型晶体管、第3N型晶体管、第3P型晶体管、第4N型晶体管、第4P型晶体管、第1电容元件和第2电容元件，

所述第1N型晶体管中，源极或者漏极之一与栅极电连接，

所述第1N型晶体管和所述第3N型晶体管串联地电连接在第1布线和所述第2N型晶体管的栅极之间，

所述第1电容元件的一对端子中的一个与第1端子电连接，

所述第2N型晶体管的栅极与所述第1电容元件的一对端子中的另一个电连接，

所述第2N型晶体管的源极或者漏极之一与第2端子电连接，另一个与所述第1布线电连接，

所述第4P型晶体管的源极或者漏极之一与所述第2N型晶体管的栅极电连接，另一个与第2布线电连接，

所述第1P型晶体管中，源极或者漏极之一与栅极电连接，

所述第1P型晶体管和所述第3P型晶体管串联地电连接在第3布线和所述第2P型晶体管的栅极之间，

所述第2电容元件的一对端子中的一个与所述第1端子电连接，

所述第2P型晶体管的栅极与所述第2电容元件的一对端子中的另一个电连接，

所述第2P型晶体管的源极或者漏极之一与所述第2端子电连接，另一个与所述第3布线电连接，

所述第4N型晶体管的源极或者漏极之一与所述第2P型晶体管的栅极电连接，另一个与第4布线电连接。

10. 如权利要求8记载的液晶显示装置，其特征在于，所述第1N型晶体管、所述第2N型晶体管、所述第3N型晶体管、所述第1P型晶体管、所述第2P型晶体管以及所述第3P型晶体管是薄膜晶体管。

11. 如权利要求9记载的液晶显示装置，其特征在于，所述第1N

---

型晶体管、所述第 2 N 型晶体管、所述第 3 N 型晶体管、所述第 4 N 型晶体管、所述第 1 P 型晶体管、所述第 2 P 型晶体管、所述第 3 P 型晶体管以及所述第 4 P 型晶体管是薄膜晶体管。

12. 如权利要求 1 至 3 的任意一项记载的液晶显示装置，其特征在于，所述电容元件是 MOS 电容。

13. 如权利要求 8 或 9 记载的液晶显示装置，其特征在于，所述第 1 电容元件和所述第 2 电容元件是 MOS 电容。

---

## 液晶显示装置

本申请是下述申请的分案申请：

发明名称：配备了校正电路的数字电路及具有该数字电路的电子装置

国际申请日：2003年12月18日

申请号：200380107645.5

### 技术领域

本发明涉及使用了晶体管的数字电路。特别是，在输入信号的振幅小于电源电压的情况下及相对于所使用的晶体管的阈值电压，电源电压不充分大的情况下，涉及用于校正输入信号的 DC 电平、实现恰当的电路工作的配备了校正电路的数字电路。

### 背景技术

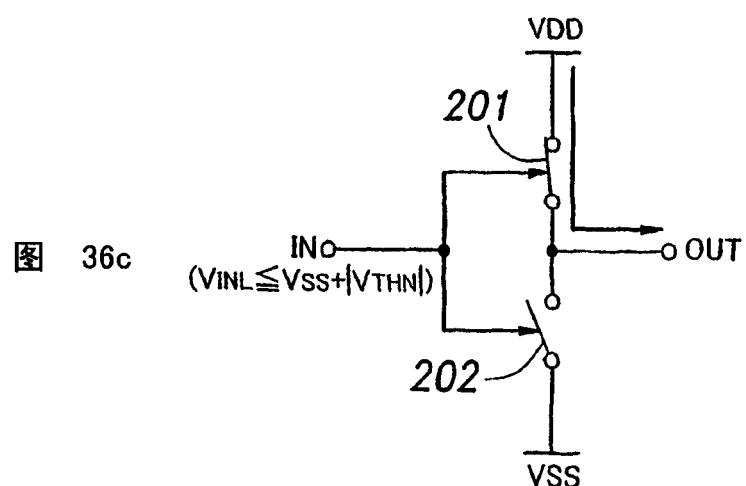

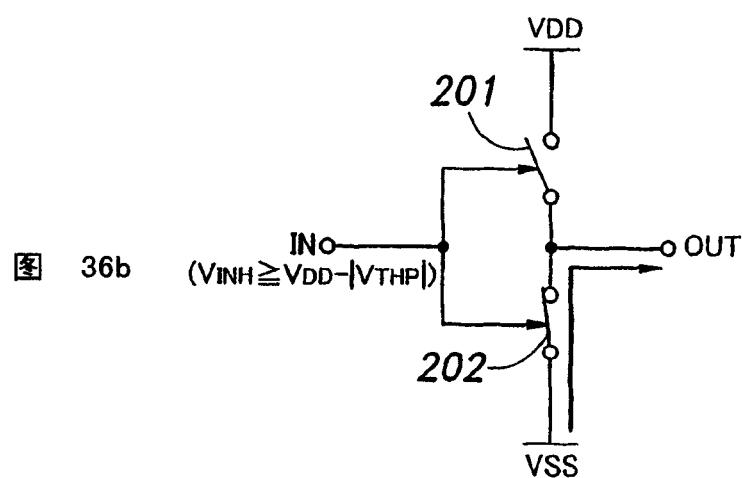

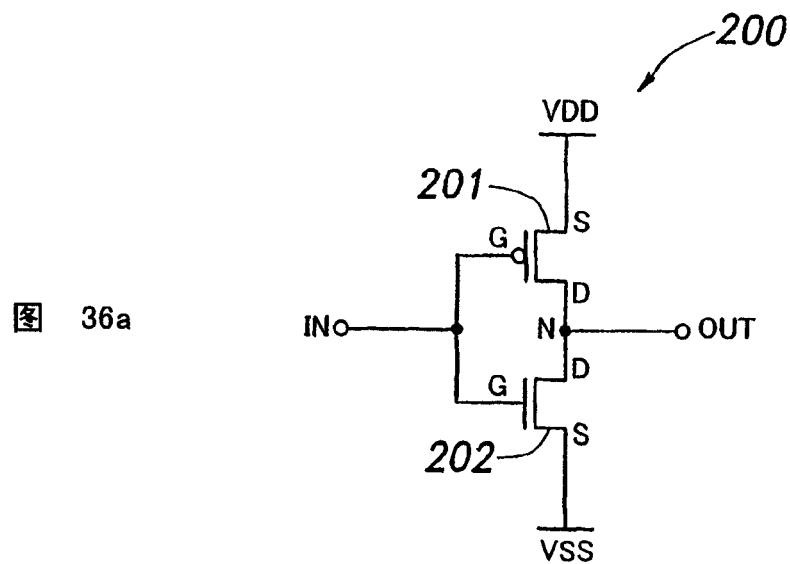

以往，一直广泛使用采用了双极晶体管及场效应晶体管（FET）的倒相电路。在图 36a 中，示出采用了 MOSFET 作为晶体管的现有的 CMOS 倒相电路的典型的例子。该 CMOS 倒相电路 200 具有被串联连接在高电平电源电位 VDD 与低电平电源电位 VSS 之间的有阈值电压  $V_{THP}$  的 P 型 MOSFET201 和有阈值电压  $V_{THN}$  的 N 型 MOSFET202（通常， $V_{THP}$  为负， $V_{THN}$  为正）。P 型 MOSFET201 的源与高电平电源电位 VDD 连接，N 型 MOSFET201 的源与低电平电源电位 VSS 连接。两 MOSFET201、202 的漏相互连接，其连接点 N（节点）与输出端 OUT 连接。另外，这些 MOSFET201、202 的栅与施加其振幅在高电平输入电位  $V_{INH}$  与低电平输入电位  $V_{INL}$  之间的输入信号的输入端 IN 连接。再有，在本说明书中，除非特别说明，电路元件的“连接”就意味着“电连接”。

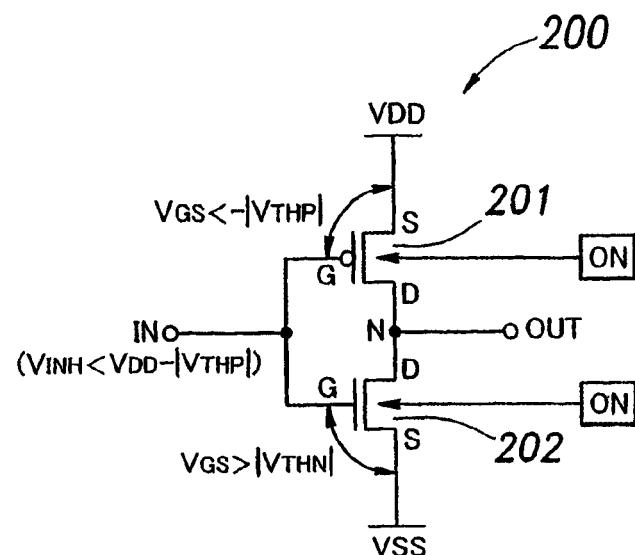

在图 36b 和图 36c 中示出了具有这样的结构的 CMOS 倒相电路 200 的通常的工作。再有，在图 36b 和 36c 中，为了表示 MOSFET201、202 的通/断状态，用开关的符号表示这些 MOSFET201、202。如图 36b 所示，如果向输入端 IN 输入等于或高于从高电平电源电位 VDD 减去 P 型 MOSFET 的阈值电压的绝对值  $|V_{THP}|$  后的值的高电平输入电位  $V_{INH}$ ，则 P 型 MOSFET201 关断，N 型 MOSFET202 导通，向输出端 OUT 供给大致等于低电平电源电位 VSS 的电位作为输出信号。另外，如图 36c 所

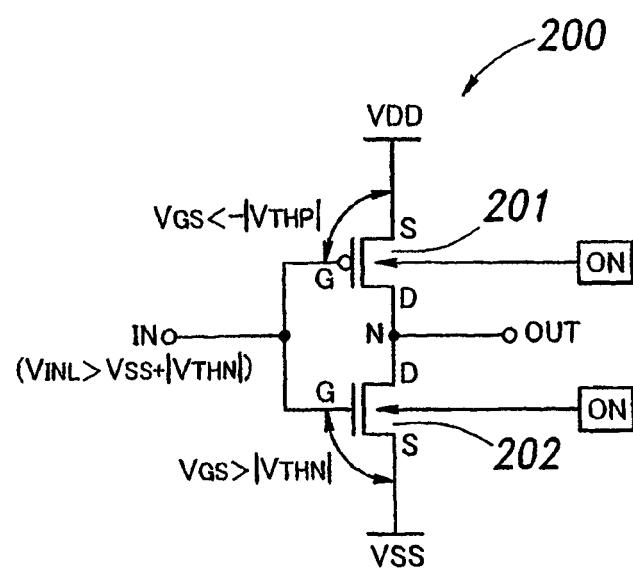

示，如果向输入端 IN 输入等于或低于将 N 型 MOSFET 的阈值电压的绝对值  $|V_{THN}|$  加上低电平电源电位 VSS 后的值的低电平输入电位  $V_{INL}$ ，则 P 型 MOSFET201 导通，N 型 MOSFET202 关断，向输出端 OUT 供给大致等于高电平电源电位 VDD 的电位作为输出信号。

但是，在例如从工作电压低的 IC 等供给输入信号的情况下，可发生以下问题。如图 37a 所示，在加到输入端 IN 的高电平输入电位  $V_{INH}$  低于从高电平电源电位 VDD 减去 P 型 MOSFET201 的阈值电压的绝对值  $|V_{THP}|$  后的值的情况下，在 P 型 MOSFET201 中，栅·源间电压  $V_{GS}$  (= 栅电位  $V_G$ -源电位  $V_S$ )  $< -|V_{THP}|$ ，不使 P 型 MOSFET201 关断，其结果是，两 MOSFET201、202 均为导通状态，向输出端 OUT 输出按 P 型 MOSFET201 与 N 型 MOSFET202 的导通状态电阻分压后的电位，不输出低电平电源电位 VSS。同样，在加到输入端 IN 的低电平输入电位  $V_{INL}$  高于 N 型 MOSFET202 的阈值电压的绝对值  $|V_{THN}|$  加上低电平电源电位 VSS 后的值的情况下，不使 N 型 MOSFET202 关断，两 MOSFET201、202 均为导通状态，不向输出端 OUT 输出高电平电源电位 VDD。这样，在输入电位  $V_{INH}$ 、 $V_{INL}$  与电源电位 VDD、VSS 之间的电平变得不同，确实不使倒相电路 200 的 MOSFET201、202 通·断，输出得不到所希望的值的情况下，产生无法驱动倒相电路 200 的后级的电路，或者这样的电路的工作变得不可靠的问题。另外，因为两 MOSFET201、202 同时导通，流过短路电流，故产生功耗增大的问题。

为了解决上述那样的问题，提出了在具有第 1 输入用倒相器和第 2 输出用倒相器的电平移位电路中，利用电容和偏置单元来变换从第 1 倒相器向第 2 倒相器输入的信号的 DC 电平（特开平 9-172367 号公报）。但是，在该电路中，因为连接在构成第 2 倒相器的各晶体管的栅与第 1 倒相器的输出之间 DC 电平变换用电容利用偏置单元总是与高电平电源电位或低电平电源电位连接，可产生这些电容的充放电对电路的动态特性给予恶劣影响（即招致电路工作速度的降低），或者与这些电容的充放电相伴的功耗增大至无法忽视的程度这样的问题。另外，在晶体管的阈值电压有分散性的情况下，使各电容的静电电容与对应的晶体管一致是困难的，因此，还可产生 DC 电平变换用电容的两端的电压与对应的晶体管的阈值电压不匹配，无法准确地进行晶体管的通·断这样的问题。

另外，在图 36a 所示的倒相电路 200 中，在例如为抑制功耗而电源电压（VDD-VSS）小、电源电压相对于 MOSFET201、202 的阈值电压的绝对值不充分大的情况下，往往产生即使施加到输入端 IN 的输入信号的振幅与电源电压相同，还无法向 MOSFET201、202 流过充分的电流进行高速驱动这样的问题。这是因为对流过 MOSFET 的电流有贡献的不是栅·源间电压  $V_{GS}$ ，而是  $V_{GS}-V_{TH}$  的缘故。例如，在图 36a 的倒相电路 200 中，假定  $VDD=3.3V$ ,  $VSS=0V$  (地), P 型 MOSFET201 的阈值电压  $V_{THP}=-2V$ , N 型 MOSFET202 的阈值电压  $V_{THN}=3V$ , 高电平输入电位  $V_{INH}=VDD=3.3V$ , 低电平输入电位  $V_{INL}=VSS=0$ 。在向输入端 IN 施加低电平输入电位  $V_{INL}$  的情况下，在 P 型 MOSFET201 中， $V_{GS}-V_{THP}=-3.3-(-2)=-1.3V$ , P 型 MOSFET201 导通，在 N 型 MOSFET202 中， $V_{GS}-V_{THP}=0-3=-3V$ , N 型 MOSFET202 关断。此时，由于 P 型 MOSFET202 的阈值电压 (-2V) 的绝对值相对于电源电压 (即输入信号的振幅) 充分地小，可将  $V_{GS}-V_{THP}$  的绝对值取得较大 (1.3V)，问题不会发生。另一方面，在向输入端 IN 施加高电平输入电位  $V_{INH}$  的情况下，在 P 型 MOSFET201 中， $V_{GS}-V_{THP}=0-(-2)=2V$ , P 型 MOSFET201 关断，在 N 型 MOSFET202 中， $V_{GS}-V_{THP}=3.3-3=0.3V$ , N 型 MOSFET202 导通，但由于  $V_{GS}-V_{THP}$  非常小，小至 0.3V，流过的电流变小，无法使 N 型 MOSFET202 高速地工作 (导通)。不言而喻，如果增高电源电压和输入信号的振幅，则可使高速工作成为可能，但功耗也增大了。

## 发明内容

本发明就是为了解决上述那样的现有技术的问题的发明，本发明的主要目的在于，提供具有使用了晶体管的开关电路的数字电路，即根据电源电压、输入信号的振幅、晶体管的阈值电压的关系适当地校正输入信号，可实现最佳的电路工作的数字电路。

本发明的第 2 目的在于，提供具有使用了晶体管的开关电路的数字电路，即使在输入信号的振幅小于电源电压（高电平电源电位与低电平电源电位之差）的情况下，也可提供能可靠地使晶体管通断的数字电路。

本发明的第 3 目的在于，提供具有使用了晶体管的开关电路的数字电路，即使在输入信号的振幅小于电源电压的情况下，也可提供不

使动态特性恶化、能可靠地使晶体管通断的数字电路。

本发明的第 4 目的在于，提供具有使用了晶体管的开关电路的数字电路，即使在输入信号的振幅小于电源电压的情况下，也可提供对与开关电路中所包含的晶体管的控制端子连接了的 DC 电平变换用电容充电到对应晶体管的与阈值电压对应的恰当的值、能使晶体管可靠地工作的数字电路。

本发明的第 5 目的在于，提供具有使用了晶体管的开关电路的数字电路，即使在电源电压相对于晶体管的阈值电压的绝对值不充分大的情况下，也可提供能让充分的电流流入晶体管使之高速工作的数字电路。

为了达到上述目的，根据本发明，提供一种数字电路，它是具有连接在输入端与输出端之间的开关电路，该开关电路具备第 1 端子、第 2 端子和控制端子，包含可通过改变控制端子对第 1 端子的电位来控制通/断的第 1 晶体管，对第 1 晶体管的第 1 端子，至少在通常工作中施加第 1 电源电位，第 1 晶体管的通/断状态可对上述输出端上的信号产生影响的数字电路，其特征在于：在通常工作中，振幅在用于关断第 1 晶体管的第 1 输入电位与用于接通第 1 晶体管的第 2 输入电位之间的输入信号被施加于输入端，该数字电路具有连接在输入端与第 1 晶体管的控制端子之间的校正电路，该校正电路具有：a) 一个端子与输入端连接，另一端子与第 1 晶体管的控制端子连接的电容；以及 b) 在通常工作之前的设定工作中，具有用于确定设定蓄积在电容中的电荷使电容两端的电压达到规定的值用的导电路径的至少 1 个开关，在通常工作中，至少 1 个开关的状态以保存电容两端的电压的方式被设定。

按照这样的结构，在通常工作之前的设定工作中，根据电源电压、输入信号的振幅、第 1 晶体管的阈值电压等，恰当地设定电容两端的电压，从而可在通常工作中校正输入信号的 DC 电平，实现最佳的电路工作。在通常工作中，由于进行了开关的设定以便保持所设定的电容的两端的电压（或电荷），故不担心电容对数字电路的动态特性产生恶劣影响（即，使工作速度降低）。直捷地说，因为电容与晶体管的寄生电容串联连接，使总电容降低，故可对动态特性的提高作出贡献。进而，由于没有必要频繁地进行设定工作，故伴随设定工作的功

耗也仅用少许即可。

理想情况是，校正电路是具备第1端子、第2端子和控制端子，可通过改变控制端子对第1端子的电位来控制通/断的具有与第1晶体管相同的导电类型并且具有大致相同的阈值电压的第2晶体管，还具有该第2晶体管的第1端子与第1电源电位连接、该第2晶体管的第2端子与控制端子相互连接并且被连接在上述电容与第1晶体管的控制端子之间的节点上的第2晶体管，至少1个开关包含与第2晶体管串联连接的第1开关，在通常工作中，第1开关是关断的。

典型情况是，第1和第2晶体管由TFT构成，第1和第2晶体管的第1端子、第2端子和控制端子分别由源、漏和栅构成。作为电源电位供给高电源电位和低电源电位，当输入信号的振幅在高电平输入电位与低电平输入电位时，例如第1晶体管为P型MOSFET的情况下，可假定第1电源电位为高电平电源电位，第1输入电位为高电平输入电位。另外，当第1晶体管例如为N型MOSFET的情况下，可假定第1电源电位为低电平电源电位，第1输入电位为低电平输入电位。

按照本发明的一个最佳实施形态，即使在输入信号的振幅小于电源电压的情况下，为了可靠地使第1晶体管通断，也要进行设定工作。即，在设定工作中，在第1开关为导通的状态下，在第2晶体管关断之前向电容的一个端子施加大致等于第1输入电位的电位。此处，如第2晶体管关断，则意味着基本上关断，不一定必须完全关断（即流过第2晶体管的电流完全为零），只要流过第2晶体管的电流变为充分的小即可。这样，在设定工作中，通过第2端子与控制端子相互连接了的（即连接成二极管的）第2晶体管，向连接在第1晶体管的控制端子与输入端之间的电容在第2晶体管关断之前或者在电流值变得非常小之前流过电流，以此可将电容充电成电容两端的电压成为反映了第1电源电位与第1输入电位之差和第1晶体管的阈值电压的恰当的电压。由此，在通常工作中，将充电后的电容的电压与输入信号相加，施加在第1晶体管的控制端子上，从而使第1晶体管可靠地通断成为可能。之所以能将第1晶体管的阈值电压反映为电容的电压，是因为第1晶体管的阈值电压与第2晶体管的阈值电压大体相等的缘故。再有，虽然希望第1晶体管与第2晶体管的阈值电压相等，但即便稍许不同，只要在设定工作中能将输入信号校正用的电容恰当地充

电、使数字电路正常地工作即可。另外，在将 FET 用作晶体管的情况下，阈值电压虽然以 N 型为正，P 型为负的情况居多，但阈值电压即使是除此以外的值，应用本发明也是可能的。

另外，最佳情况是，将整流元件与第 2 晶体管并联连接，而且使其正向成为与上述第 2 晶体管的正向相反的方向。由此，即使在将连接成二极管的第 1 晶体管反向偏置那样的电荷例如因噪声等而蓄积在电容内的情况下，在设定工作中使第 1 开关导通时，通过整流元件流过电流成为可能，可使电容两端的电压收敛成恰当的值。整流元件可以是例如由与第 2 晶体管相同导电类型的被连接成二极管的晶体管构成的整流元件。

另外，电容与第 1 晶体管的控制端子之间的节点经另一开关与不同于第 1 电源电位的电位连接，在设定工作之前通过使另一开关导通，可使节点的电位成为规定的电位。此处，规定的电位是，使节点的电位成为规定的电位后，在使另一开关关断的状态下所进行的设定工作中，在使第 1 开关导通时利用第 1 电源电位与规定的电位的电位差使第 2 晶体管导通那样的电位。通过这样做，例如即使在因噪声等而以不希望的方式使电荷滞留在电容内的情况下，在设定工作之前，通过将电容与第 1 晶体管的控制端子之间的节点的电位定为恰当的值，能可靠地进行设定工作，使电容两端的电压收敛成第 1 电源电位与第 1 输入电位之差和与第 1 晶体管的阈值电压对应的恰当的值。如将上述另一电位设定为与第 1 电源电位不同的第 2 电源电位，则由于能容易地提供另一电位，因而是合适的。

此外，电容的一个端子在经第 2 开关与输入端连接的同时，经第 3 开关与大致等于第 1 输入电位的电位连接，在通常工作中，第 2 开关是导通，第 1 和第 3 开关是关断的，在设定工作中，第 2 开关是关断，第 1 和第 3 开关是导通的。通过这样做，无需控制输入电位，仅通过转换开关就能容易地进行设定工作。另外，例如即使在具有极性不同的 2 个晶体管作为第 1 晶体管的情况下，这些晶体管的设定工作也可同时进行。

按照本发明的另一优选实施例，例如即使在电源电压低、电源电压相对于晶体管的阈值电压的绝对值不成分大的情况下，也有充分的电流流过晶体管，为了使高速工作进行，提供可进行设定工作的数字

电路。在这样的数字电路中，电容与第 1 晶体管的控制端子之间的节点经第 2 开关与规定的电位连接。设定工作包含第 1 设定工作和第 2 设定工作，在第 1 设定工作中，在使第 2 开关导通的同时，向输入端施加第 1 输入电位，对电容充电，在第 2 设定工作中，通过向输入端施加第 1 输入电位，又使第 2 开关关断并且使第 1 开关导通，通过第 2 晶体管使电容放电。通过了第 2 晶体管的电容的放电在流过第 2 晶体管的电流基本上为零之前，即电容两端的电压成为大致等于第 2 晶体管的阈值电压之前进行。再有，上述规定的电位是第 2 设定工作中使第 1 开关导通时使第 2 晶体管导通那样的电位，例如可以是与第 1 电源电位不同的第 2 电源电位。另外，典型情况是，第 1 输入电位等于第 1 电源电位，第 2 输入电位等于第 2 电源电位。

如上所述，通过设定电容两端的电压，在通常工作中，在第 1 输入电位被施加到输入端时，第 1 晶体管的控制端子与第 1 端子的电位差变得等于第 1 晶体管的阈值电压，第 1 晶体管关断，在施加了第 2 输入电位时，电容两端的电压被重叠在第 2 输入电位上，以促进第 1 晶体管的导通，有足够的电流流到第 1 晶体管中，使之高速工作成为可能。

另外，电容的一个端子在经第 3 开关与输入端连接的同时，经第 4 开关与大致等于第 1 输入电位的电位连接，在通常工作中，第 3 开关是导通，第 1、第 2 和第 4 开关是关断的，在第 1 设定工作中，第 2 和第 4 开关是导通，第 3 开关是关断的，在第 2 设定工作中，第 2 和第 3 开关是关断，第 1 和第 4 开关是导通的。通过这样做，无需控制输入电位，仅通过转换开关就能容易地进行设定工作。另外，例如即使在具有极性不同的 2 个晶体管作为第 1 晶体管的情况下，这些晶体管的设定工作也可同时进行。

开关电路可以取倒相电路、钟控倒相电路、NAND 及 NOR 之类的逻辑电路，或者电平移位电路及传输门等各种形态。在倒相电路的情况下，可以是使用了晶体管和电阻的倒相电路，也可以是将使用相同极性的晶体管的一方连接成二极管使之作为电阻工作，或者还可以是使用了极性不同的 2 个 MOSFET 的 CMOS 倒相器。在钟控倒相电路的情况下，设置校正电路的晶体管无论是构成倒相器主体的晶体管，还是时钟信号同步用的晶体管，或者是这两者的晶体管均可。

上述开关（与连接成二极管的第2晶体管串联连接的第1开关等）无论是电开关还是机械开关，可控制电流的流动的任何一种开关均可。是晶体管也可，是二极管也可，是将它们组合在一起的逻辑电路也可。如果开关是由MOSFET等半导体元件构成的开关，则由于可用半导体工艺形成数字电路整体，从而是合适的。再有，在开关由晶体管构成的情况下，由于仅仅用作开关，故对晶体管的导电类型不特别加以限制。但是，在关断电流少的一方是所希望的情况下，希望采用关断电流少的一方的极性的晶体管。作为关断电流少的晶体管，有设置LDD区的晶体管等。另外，在作为开关工作的晶体管的源端子的电位接近于低电位侧电源（Vss、Vgnd、0V等）的状态下进行工作的情况下，希望采用n沟道型，反之，在源端子的电位接近于高电位侧电源（Vdd等）的状态下进行工作的情况下，希望采用p沟道型。为什么呢？这是因为可增大栅·源间电压的绝对值，作为开关可容易地工作的缘故。再有，也可采用n沟道型和p沟道型两者形成CMOS型的开关。

另外，为了防止因噪声等而以不希望的方式滞留在电容内的电荷在设定工作中产生恶劣影响，也可连接与电容并联的另一开关。通过在设定工作之前使该开关导通，可使滞留在电容内的电荷放电。

采用具有使用了上述那样的晶体管的开关电路的数字电路，可最佳地实现以集成电路及半导体显示装置为代表的各种半导体装置（或电子装置）。对这样的半导体装置来说，例如有将液晶显示装置、有机EL显示发光元件配备在各像素中的自发光型显示装置、DMD（数字微镜器件）、PDP（等离子体显示面板）、FED（场发射显示器）等，本发明的数字电路可用于这些驱动电路等中。通过将本发明的数字电路应用于使用玻璃基板而形成的半导体装置中，即使不用升压电路控制从IC输入的信号的振幅也可，从而可使半导体装置小型化，抑制装置本身的成本。

本发明的特征、目的和作用效果可通过参照附图来说明优选实施例而变得更加明白。

#### 附图说明

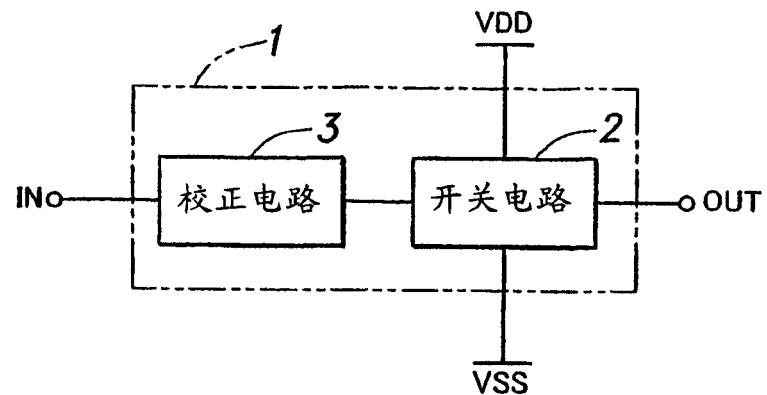

图1是表示本发明的概略结构的方框图。

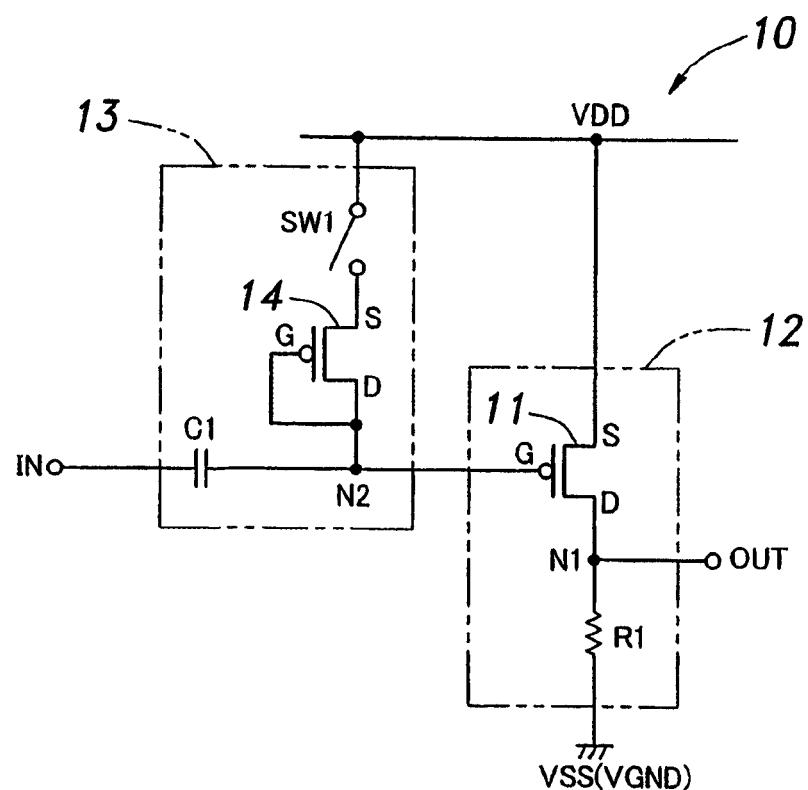

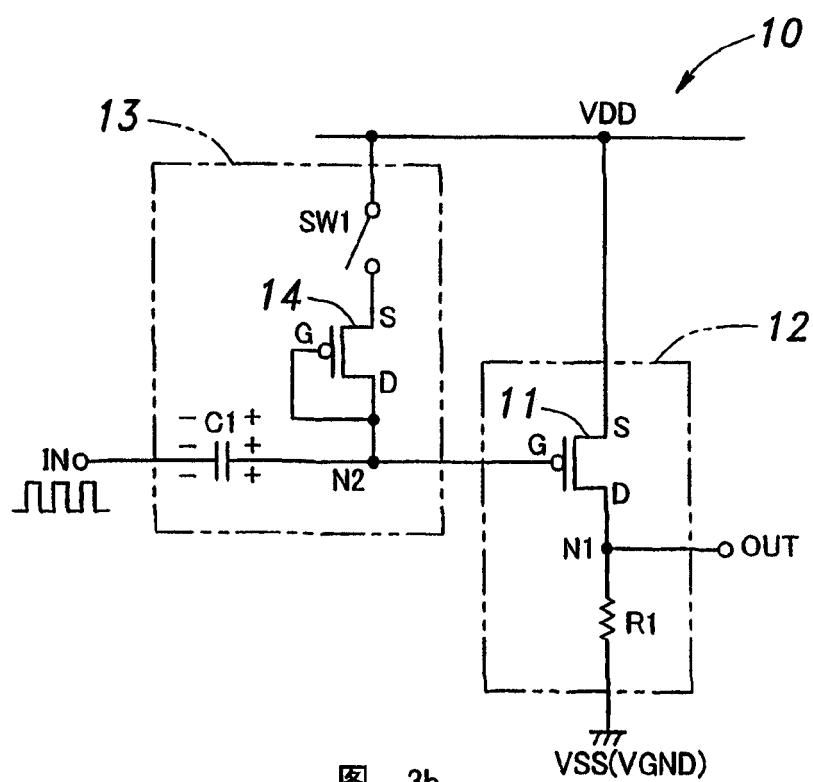

图 2 是表示基于本发明的数字电路的一个实施例的电路图。

图 3a 表示图 2 所示的数字电路的设定工作，图 3b 表示通常工作。

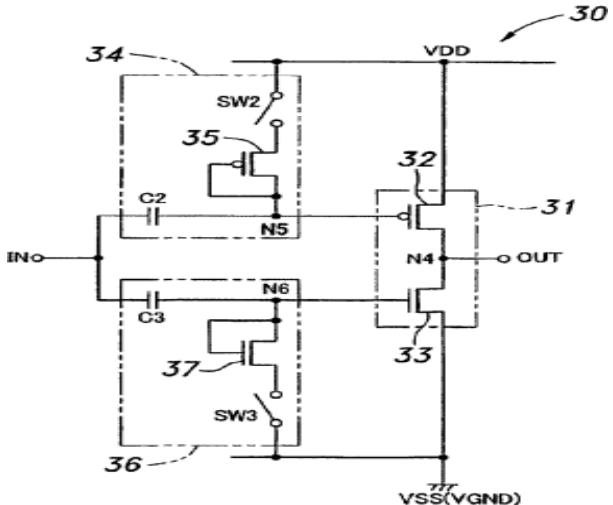

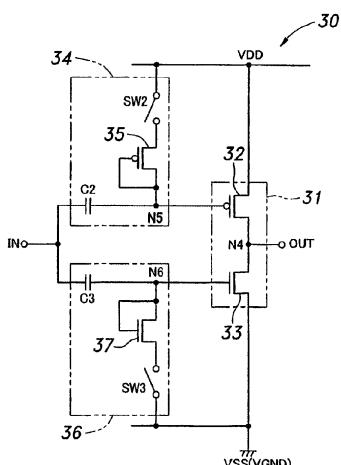

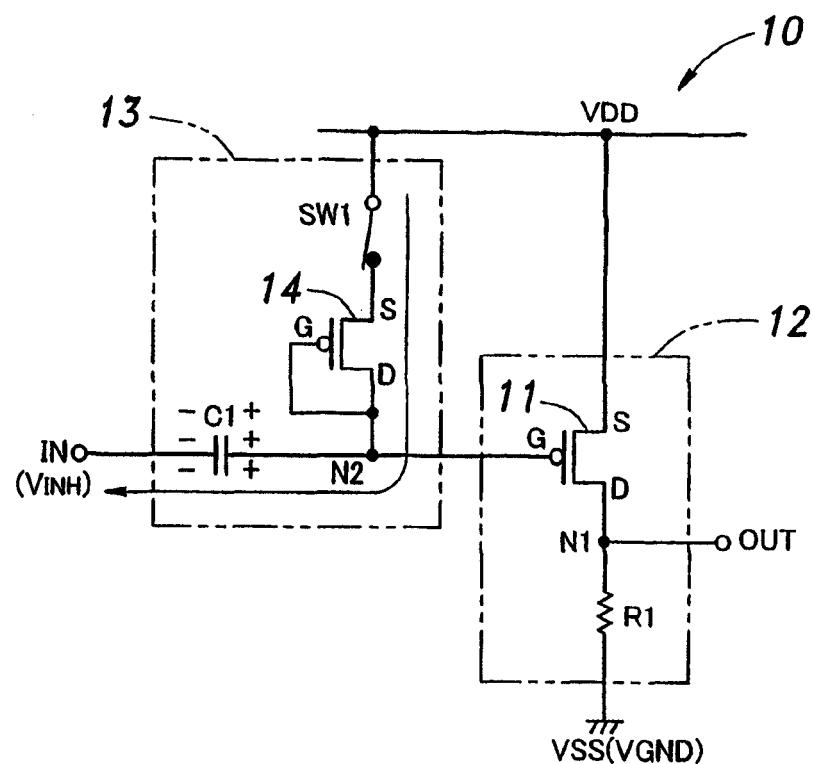

图 4 是表示基于本发明的数字电路的另一实施例的电路图。

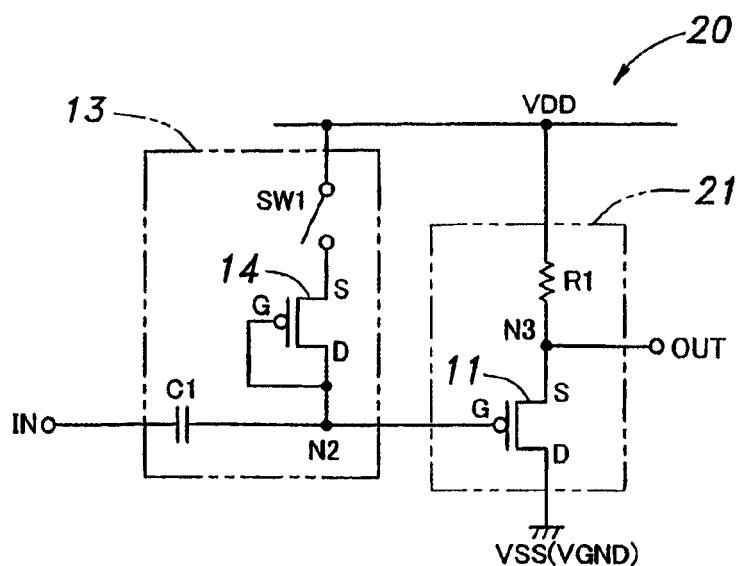

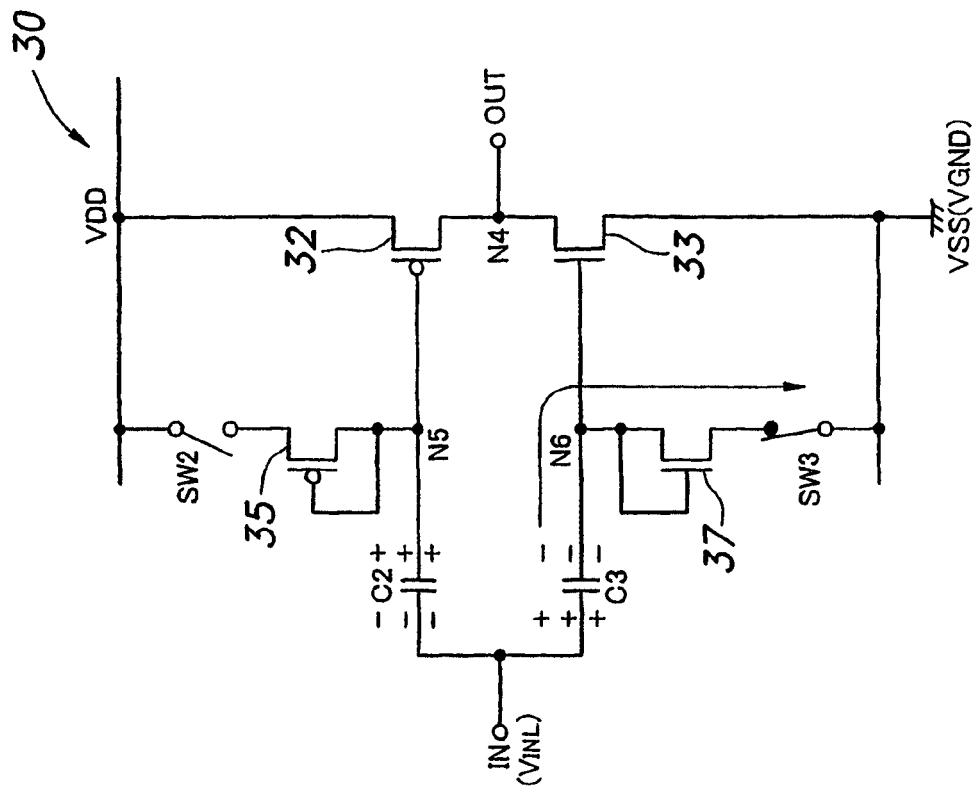

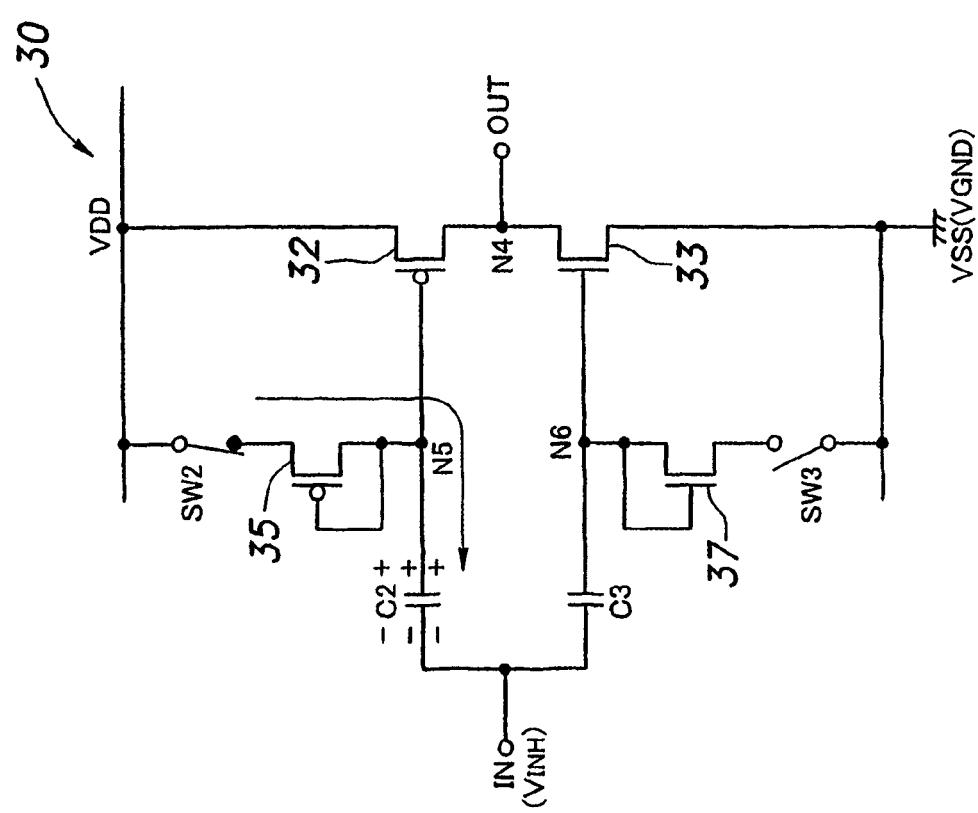

图 5 是表示将本发明应用于 CMOS 倒相电路而形成的基于本发明的数字电路的另一实施例的电路图。

图 6a 和图 6b 表示图 5 所示的数字电路的设定工作

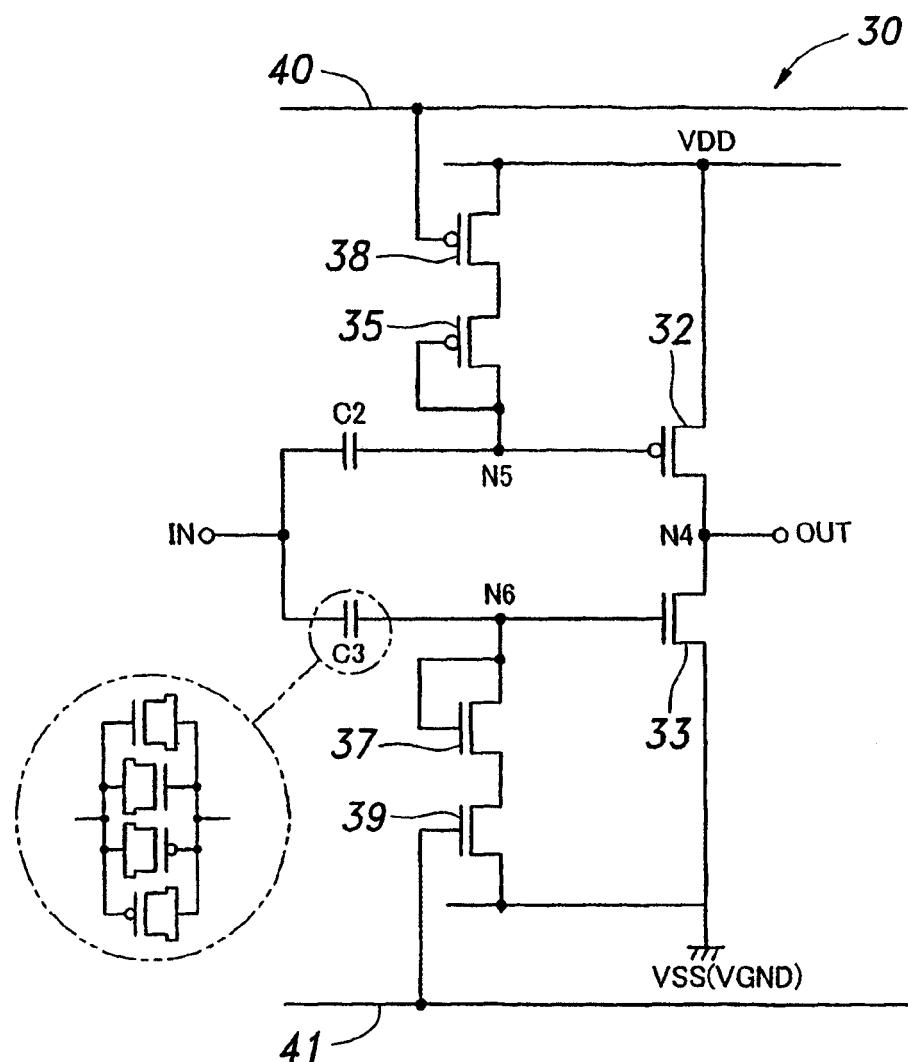

图 7 是表示分别用 P 型 MOSFET38、N 型 MOSFET39 实现了图 5 所示的开关 SW2、SW3 的数字电路的电路图。

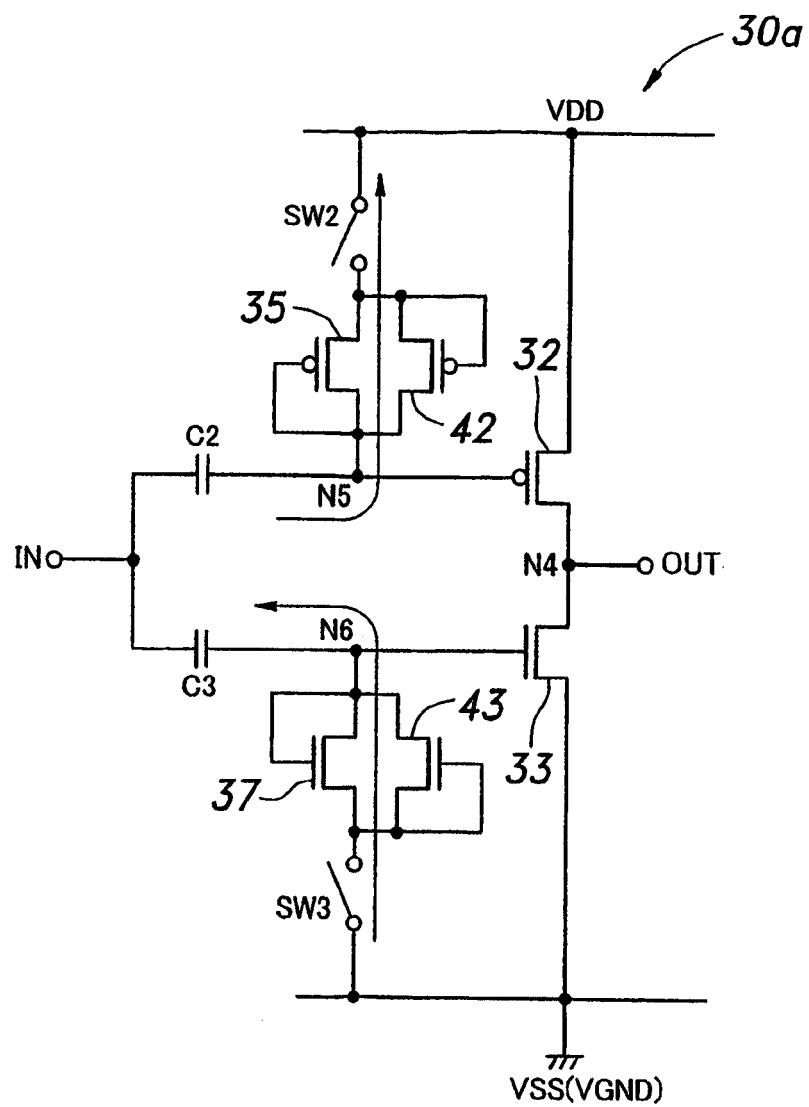

图 8 是表示图 5 所示的数字电路的变形实施例的电路图。

图 9 是表示图 5 所示的数字电路的另一变形实施例的电路图。

图 10 是表示图 5 所示的数字电路的又一变形实施例的电路图。

图 11a 和图 11b 表示图 10 所示的数字电路中的初始化工作。

图 12 是表示作为 MOSFET 实现了图 10 所示的开关的数字电路的电路图。

图 13 是表示图 5 所示的数字电路的又一变形实施例的电路图。

图 14 是表示应用了本发明的钟控倒相电路的一个实施例的电路图。

图 15 是表示图 14 所示的钟控倒相电路的变形实施例的电路图。

图 16 是表示图 14 所示的基于本发明的钟控倒相电路的另一变形实施例的电路图。

图 17 是示意地表示在液晶显示器等中所使用的有源矩阵装置的驱动电路的主要部分，同时表示驱动电路的移位寄存器中的典型的单位电路的图。

图 18 是表示将本发明应用于图 17 所示的移位寄存器的单位电路中的左侧的钟控倒相器的实施例的电路图。

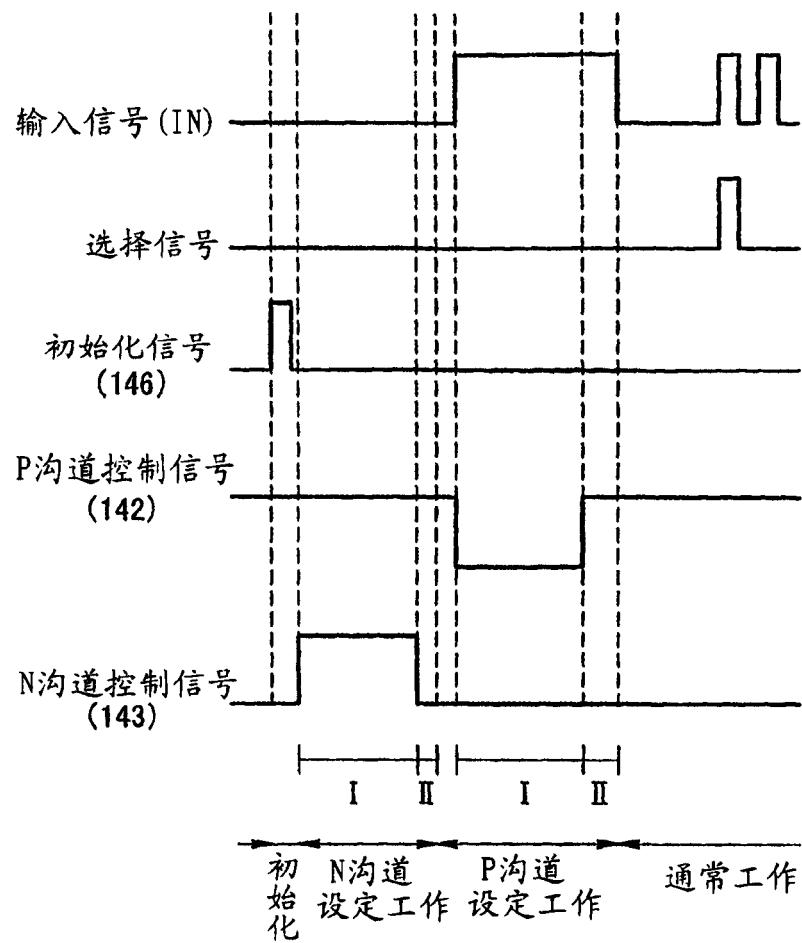

图 19 是表示图 18 所示的包含钟控倒相电路的移位寄存器的初始化、设定工作和通常工作中的各部的信号（电位）的时序图。

图 20 是表示图 18 所示的实施例的变形实施例的电路图。

图 21 是表示图 20 所示的包含钟控倒相电路的移位寄存器的初始化、设定工作和通常工作中的各部的信号（电位）的时序图。

图 22 是表示图 18 所示的钟控倒相器的另一实施例的电路图。

图 23 是表示图 17 所示的第 1 闩锁电路中的典型的单位电路的电

路图。

图 24 是表示将本发明应用于图 23 所示的第 1 闩锁电路的钟控倒相器的实施例的电路图。

图 25 是表示图 24 所示的钟控倒相器的初始化工作、设定工作和通常工作中的各部的信号（电位）的时序图。

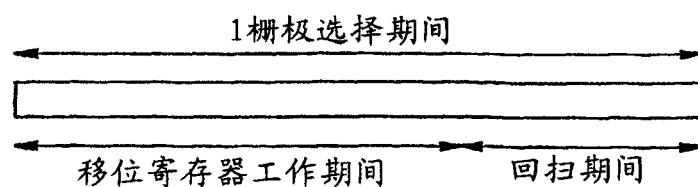

图 26a 示意性地表示回扫期间，图 26b 示意性地表示驱动停止期间。

图 27 是表示将本发明应用于构成 NAND 电路的晶体管的实施例的电路图。

图 28 是表示将本发明应用于构成 NOR 电路的晶体管的实施例的电路图。

图 29 是表示基于本发明的数字电路的又一变形实施例的电路图。

图 30a 和图 30b 表示图 29 所示的数字电路的设定工作。

图 31a 和图 31b 表示图 29 所示的数字电路的设定工作。

图 32a 和图 32b 表示图 29 所示的数字电路的通常工作。

图 33 是表示基于本发明的数字电路的又一变形实施例的电路图。

图 34a 和图 34b 表示图 33 所示的数字电路的设定工作。

图 35 是表示图 33 所示的数字电路的通常工作的电路图。

图 36a 是表示现有的 CMOS 倒相电路的典型的例子的电路图，图 36b 和图 36c 表示图 36a 所示的 CMOS 倒相电路的通常的工作。

图 37a 和图 37b 是说明图 36 所示的 CMOS 倒相电路的问题的图。

图 38a~图 38h 是应用了本发明的电子装置的图。

### 具体实施方式

以下，参照附图说明本发明的优选实施例。

图 1 是表示基于本发明的数字电路的概略结构的方框图。如图所示，基于本发明的数字电路 1 具有开关电路 2 和校正电路 3，该开关电路 2 具有连接在输入端 IN 与输出端 OUT 之间、根据施加于输入端的输入信号的值在输出端输出不同的信号（例如高电平电源电位 VDD 或低电平电源电位 VSS）的 MOSFET 等的晶体管，该校正电路 3 被连接在输入端 IN 与开关电路 2 之间。

图 2 是表示基于本发明的数字电路的一个实施例的电路图。该数

字电路 10 作为开关电路，具有由 1 个 P 型 MOSFET11 和电阻 R1 构成的倒相电路 12。P 型 MOSFET11 具有阈值电压  $V_{THP}$ ，其源与高电平电源电位 VDD 连接，其漏经电阻 R1 与低电平电源电位 VSS(例如地电位  $V_{GND}$ ) 连接。作为 P 型 MOSFET11 的控制端子而工作的栅与施加振幅在高电平输入电位  $V_{INH}$  与低电平输入电位  $V_{INL}$  之间的输入信号的输入端 IN 连接，漏与电阻 R1 之间的节点 N1 与输出端 OUT 连接。

在 P 型 MOSFET11 的栅与输入端 IN 之间连接校正电路 13。该校正电路 13 具有被连接在 P 型 MOSFET11 的栅与输入端 IN 之间的电容 C1、具有与 P 型 MOSFET11 相同的 P 型并且具有大致相同的阈值电压  $V_{THP}$  的设定工作用的 P 型 MOSFET14 和开关 SW1。P 型 MOSFET14 的漏被连接在电容 C1 与 P 型 MOSFET11 的栅之间的节点 N2 上，其源经开关 SW1 与高电平电源电位 VDD 连接。开关 SW1 可以被设置在 P 型 MOSFET14 的漏与节点 N2 之间，也可以与 P 型 MOSFET14 串联连接。此外，P 型 MOSFET14 的栅与漏连接，成为所谓的“二极管连接”。由此，P 型 MOSFET14 的栅·源间电压  $V_{GS}$  变得等于源·漏间电压  $V_{DS}$ 。

以下说明如此构成了的数字电路 10 的工作。再有，为了说明，在本实施例中，假定施加于输入端 IN 的输入信号的高电平输入电位  $V_{INH}$  比从高电平电源电位 VDD 减去阈值电压的绝对值  $|V_{THP}|$  后的差值低（即，在现有电路中，输入信号为高电平输入电位  $V_{INH}$  时 P 型 MOSFET11 不会关断那样的值），低电平输入电位  $V_{INL}$  等于地电位  $V_{GND}$ （即，为使 P 型 MOSFET11 导通的充分低的值）。

首先，在设定工作中，如图 3a 所示，使开关导通，在该状态下，向输入端 IN 施加高电平输入电位  $V_{INH}$ 。由此，如图中的箭头所示，通过 P 型 MOSFET14 流过电流，电容 C1 被充电。如具有充分的时间，则电容 C1 两端的电压上升，由此，P 型 MOSFET11 的栅·源间电压  $V_{GS}$  的绝对值减小，最终，P 型 MOSFET14 关断，电流停止。此时，电容 C1 两端的电压为  $VDD - V_{INH} - |V_{THP}|$ 。

这样，在设定工作中，在恰当地对电容 C1 充电后，在通常工作中，如图 3b 所示，使开关 SW1 关断，向输入端 IN 施加其振幅在高电平输入电位  $V_{INH}$  与低电平输入电位  $V_{INL}$  之间的输入信号。此时，因为开关 SW1 变为关断，保存蓄积在电容 C1 内的电荷，电容 C1 两端的电压保持恒定。从而，在向输入端 IN 施加了高电平输入电位  $V_{INH}$  的情况

下，电容 C1 两端的电压  $V_{DD} - V_{INH} - |V_{THP}|$  与此值相加，得到 P 型 MOSFET11 的栅电位为  $V_{DD} - |V_{THP}|$ ，栅·源间电压  $V_{GS} = -|V_{THP}|$ ，从而能可靠地使 P 型 MOSFET11 关断，没有漏泄电流。由此，在输出端 OUT 输出地电位  $V_{GND}$ 。再有，设定工作在 P 型 MOSFET14 变得完全关断之前（即，流过 P 型 MOSFET14 的电流完全变为零之前）无需进行。即使只有微少电流流过 P 型 MOSFET14，只要电容 C1 在通常工作中被充分地充电至可恰当地校正输入信号的程度（即，只要 P 型 MOSFET14 基本上被关断），即使在该时刻结束设定工作，在实际工作方面也没有问题。

另一方面，在向输入端 IN 施加了低电平输入电位  $V_{INL}$  的情况下，P 型 MOSFET11 的栅电位低于向输入端 IN 施加了高电平输入电位  $V_{INH}$  时，得到  $V_{GS} = -|V_{THP}| - (V_{INH} - V_{INL})$ ，从而， $V_{GS} < -|V_{THP}|$ ，P 型 MOSFET11 成为导通状态，输出端 OUT 的电位大致为高电平电源电位 VDD。再有，在电容 C1 相对于 P 型 MOSFET11 的栅电容不是充分大的情况下，输入电压 ( $V_{INH}, V_{INL}$ ) 被电容 C1 和栅电容分压，就没有充分的电压施加在 P 型 MOSFET11 的栅上。因而，电容 C1 的大小希望在考虑到连接电容 C1 的 P 型 MOSFET11 等的晶体管的栅电容后确定。例如，希望假定电容 C1 为 P 型 MOSFET11 的栅电容的 5 倍以上的大小。

这样，在上述的实施例中，即使在高电平输入电位  $V_{INH}$  低于作为第 1 电源电位的高电平电源电位 VDD 的情况下，对连接在构成倒相电路 12 的 P 型 MOSFET11 的栅与输入端 IN 之间的电容 C1 在设定工作中通过具有与 P 型 MOSFET11 大致相同的阈值电压并且被连接成二极管的设定工作用 P 型 MOSFET14 预先充电至恰当的电压，从而能使 P 型 MOSFET11 可靠地关断。按照本发明，由于无需另行设置升压装置，故对成本削减及装置的小型化作出贡献。另外，即使在向玻璃基板上形成了的数字电路输入来自 IC 的信号的情况下，也不用升压电路，可直接向数字电路输入信号。再有，在上述实施例中，即使在高电平输入电位  $V_{INH}$  等于或大于高电平电源电位 VDD 的情况下，在设定工作中正因为没有对电容 C1 充电，故通常工作变为正常是可能的。

在将这样的多个数字电路 10 用于例如液晶显示器或有机 EL 显示器的驱动装置的情况下，往往包含构成各倒相电路 12 的多个 P 型 MOSFET11，例如因杂质浓度或沟道部分的结晶状态等不同致使这些阈值电压产生分散性。但是，按照本发明，通过使与各 P 型 MOSFET11

对应的校正电路 13 中所包含的被连接成二极管的 P 型 MOSFET14 的阈值电压与构成倒相电路 12 的 P 型 MOSFET11 大致相同，可对校正电路 13 中所包含的 DC 电平变换用电容 C1 充电，以供给与对应的 P 型 MOSFET11 的阈值电压一致的恰当的电压。这样，假定构成倒相电路 12 的 P 型 MOSFET11 与设定工作用 P 型 MOSFET14 的阈值电压大致相同，在实际的半导体电路中，可通过将这些 MOSFET11、14 相互接近地设置，使之不产生杂质浓度差等来实现。另外，在包含通过激光照射使沟道部分结晶的制造工序的情况下，如果利用相同脉冲的激光束点使 P 型 MOSFET11 和 P 型 MOSFET14 的沟道部分结晶，则由于可使阈值电压成为更接近的值，从而是所希望的。再有，为了使大致相等的阈值电压容易实现，最好使 P 型 MOSFET11、14 的沟道长度 L 及沟道宽度 W 等尺寸大致相同，但如果阈值电压大致相同，则也可以使 P 型 MOSFET11 与 P 型 MOSFET14 的尺寸不同。例如，为了抑制布局面积，可减小 P 型 MOSFET14 的沟道长度 L 及/或沟道宽度 W。或者，也可增大 P 型 MOSFET14 的沟道宽度 W，使之能在较短时间内进行设定工作。

另外，在上述实施例中，由于在通常工作中与连接成二极管的 P 型 MOSFET14 串联连接了的开关 SW1 成为关断状态，故在设定工作中蓄积在校正电路 13 的电容 C1 内的电荷被保存，不担心在通常工作中电容 C1 对数字电路 10 的动态特性产生恶劣影响（即，使工作速度降低）。直接地说，因为电容 C1 与 P 型 MOSFET11 的栅与漏或源之间所形成的寄生电容串联连接，使总电容降低，故可对动态特性的提高作出贡献。设定工作只要在蓄积在电容 C1 内的电荷漏泄，无法确保正常的工作之前进行即可，从而，由于也没有必要频繁地进行设定工作，故伴随设定工作的功耗也仅用少许即可。在与本数字电路 10 的输入侧连接的电路中，由于可降低工作电压（电源电压或信号电压），从这一点看，也对抑制功耗作出贡献。

图 4 是表示包含使用了 1 个 P 型 MOSFET 作为开关电路的电平移位电路的基于本发明的数字电路的另一实施例的电路图。在本图中，对与图 2 相同的部分标以相同的符号而省略其详细的说明。图 4 的数字电路 20 具有与图 2 所示的数字电路大致相同的结构，但 P 型 MOSFET11 的漏与作为低电平电源电位 VSS 的地电位  $V_{GND}$  连接，其源经电阻 R1 与高电平电源电位 VDD 连接，输出端 OUT 被连接在 P 型 MOSFET11

的源与电阻之间的节点 N3 上，由此形成电平移位电路 21 作为开关电路，在这一点上两图的数字电路是不同的。其说明予以省略，但在本实施例中，通过进行与上述实施例同样的设定工作，预先对电容 C1 恰当地充电，在通常工作中使 P 型 MOSFET11 可靠地通/断而没有误动作是可能的。在本例中，如果向输入端 IN 施加高电平输入电位  $V_{INH}$ ，则 P 型 MOSFET11 关断，在输出端 OUT 输出高电平电源电位 VDD，如果施加低电平输入电位  $V_{INL}$ ，则 P 型 MOSFET11 导通，在输出端 OUT 输出低电平电源电位 VSS。这样，可考虑根据晶体管的通/断状态对输出端 OUT 供给不同的信号那样的各种各样状态的开关电路，但要理解，为了可靠地进行开关电路中所包含的晶体管的通/断，将本发明应用于这些电路是可能的。

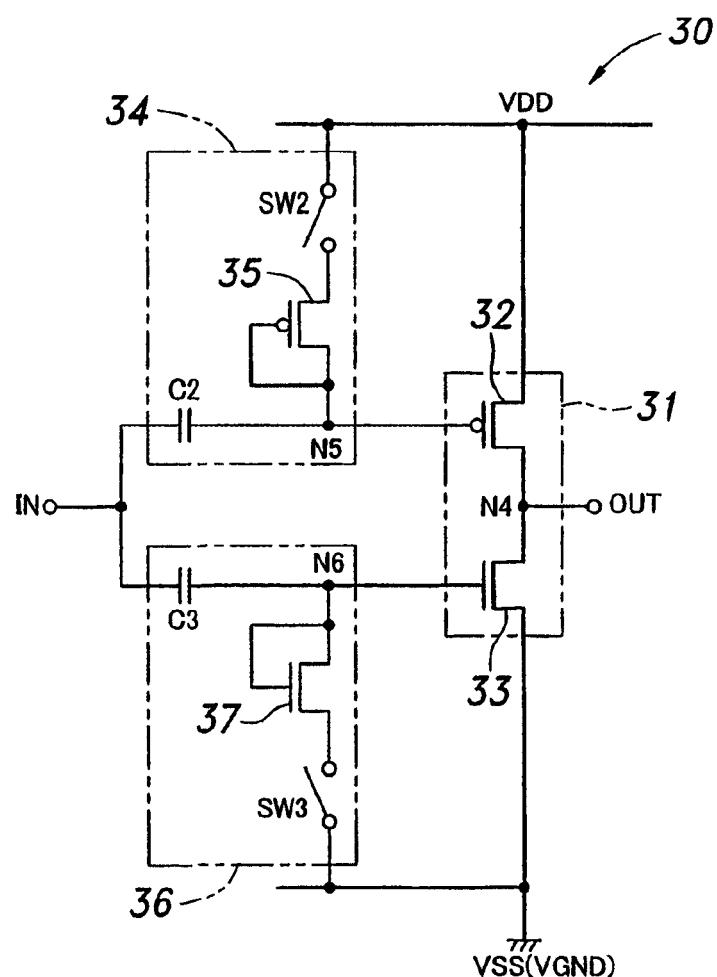

图 5 是表示基于本发明的数字电路的又一实施例，将本发明应用于 CMOS 倒相电路的例子的电路图。该数字电路 30 具有 CMOS 倒相电路 31 作为开关电路。CMOS 倒相电路 31 与以往一样，具有串联连接在作为电源电位的高电平电源电位 VDD 与低电平电源电位 VSS 之间的、阈值电压为  $V_{THP}$  的 P 型 MOSFET32 和阈值电压为  $V_{THN}$  的 N 型 MOSFET33。P 型 MOSFET32 的源与高电平电源电位 VDD 连接，N 型 MOSFET33 的源与低电平电源电位 VSS（在本例中，为地电位  $V_{GND}$ ）连接。两 MOSFET32、33 的漏互相连接，其连接点（节点）N4 与输出端 OUT 连接。另外，这些 MOSFET32、33 的栅共同连接在施加其振幅在高电平输入电位  $V_{INH}$  与低电平输入电位  $V_{INL}$  之间的输入信号的输入端 IN 上。

基于本发明，校正电路 34 被连接在 P 型 MOSFET32 的栅与输入端 IN 之间。该校正电路 34 与图 2 所示的实施例的校正电路 13 一样，具有被连接在 P 型 MOSFET32 的栅与输入端 IN 之间的电容 C2、具有与 P 型 MOSFET32 相同的导电类型并且具有大致相同的阈值电压  $V_{THP}$  的设定工作用的 P 型 MOSFET35 和开关 SW2。P 型 MOSFET35 的漏被连接在电容 C2 与 P 型 MOSFET32 的栅之间的节点 N5 上，其源经开关 SW2 与高电平电源电位 VDD 连接。此外，P 型 MOSFET35 的栅与漏连接，形成二极管连接。再有，开关 SW2 与图 2 的情况一样，只要与 P 型 MOSFET35 串联连接即可。

另外，校正电路 36 被连接在 N 型 MOSFET33 的栅与输入端 IN 之间。该校正电路 36 具有被连接在 N 型 MOSFET33 的栅与输入端 IN 之

间的电容 C3、具有与 N 型 MOSFET33 相同的导电类型并且具有大致相同的阈值电压  $V_{THN}$  的设定工作用的 N 型 MOSFET37 和开关 SW3。N 型 MOSFET37 的漏被连接在电容 C3 与 N 型 MOSFET33 的栅之间的节点 N6 上，其源经开关 SW3 与低电平电源电位 VSS 连接。此外，N 型 MOSFET37 的栅与漏连接，形成二极管连接。再有，开关 SW3 被设置在 N 型 MOSFET37 与节点 N6 之间即可。

以下参照图 6 说明如此构成了的数字电路 30 的工作。再有，为了说明，假定施加于输入端 IN 的输入信号的高电平输入电位  $V_{INH}$  比从 VDD 减去 P 型 MOSFET32 的阈值电压的绝对值  $|V_{THP}|$  后的差值低，低电平输入电位  $V_{INL}$  比将 N 型 MOSFET33 的阈值电压的绝对值  $|V_{THN}|$  与低电平电源电位 VSS ( $V_{GND}$ ) 相加后的值高。

如图 6a 所示，在使开关 SW2 导通、使开关 SW3 关断的状态下，如果向输入端 IN 施加高电平输入电位  $V_{INH}$ ，则在箭头所示的方向，通过连接成二极管的 P 型 MOSFET35 流过电流，与 P 型 MOSFET32 的栅连接的电容 C2 被充电，当电容 C2 两端的电压变为  $VDD - V_{INH} - |V_{THP}|$  时，P 型 MOSFET35 关断，电流停止 (P 沟道设定工作)。接着，如图 6b 所示，在使开关 SW2 关断、使开关 SW3 导通的状态下，如果向输入端 IN 施加低电平输入电位  $V_{INL}$ ，则在箭头所示的方向，通过连接成二极管的 N 型 MOSFET37 流过电流，与 N 型 MOSFET33 的栅连接的电容 C3 被充电，当电容 C3 两端的电压变为  $VSS - V_{INL} + |V_{THN}|$  时，N 型 MOSFET37 关断，电流停止 (N 沟道设定工作)。

这样，在设定工作中，在恰当地对电容 C2、C3 充电后，在通常工作中，使开关 SW2、SW3 一并关断，向输入端 IN 施加其振幅在高电平输入电位  $V_{INH}$  与低电平输入电位  $V_{INL}$  之间的脉冲输入信号。此时，因为开关 SW2、SW3 变为关断，保存蓄积在电容 C2、C3 内的电荷，电容 C2、C3 两端的电压保持恒定。在向输入端 IN 施加了高电平输入电位  $V_{INH}$  的情况下，得到 P 型 MOSFET32 的栅电位为  $VDD - |V_{THP}|$ ，栅·源间电压  $V_{GS} = -|V_{THP}|$ ，从而能可靠地使 P 型 MOSFET32 关断。此时，由于 N 型 MOSFET33 成为导通状态，在输出端 OUT 输出低电平电源电位 VSS (地电位  $V_{GND}$ )。另一方面，在向输入端 IN 施加了低电平输入电位  $V_{INL}$  的情况下，得到 N 型 MOSFET33 的栅电位为  $VSS + |V_{THN}|$ ，栅·源间电压  $V_{GS} = |V_{THN}|$ ，从而能使 N 型 MOSFET33 关断。此时，由于 P 型 MOSFET32

成为导通状态，在输出端 OUT 输出高电平电源电位 VDD。再有，设定工作即使不在 P 型 MOSFET35、N 型 MOSFET37 变得完全关断之前进行，在流过这些 MOSFET35、37 的电流变得充分地小的时刻（即，在 MOSFET35、37 基本上关断了的时刻）结束亦可。另外，在上述实施例中，在 P 型 MOSFET35 的设定工作后再进行 N 型 MOSFET37 的设定工作，但不限定于此顺序，不言而喻，先进行 N 型 MOSFET137 的设定工作亦可。

这样，即使在将本发明应用于构成 CMOS 倒相电路 31 的一对 P 型 MOSFET32 和 N 型 MOSFET33 的情况，在高电平输入电位  $V_{INH}$  比高电平电源电位 VDD 低，低电平输入电位  $V_{INL}$  比低电平电源电位 VSS 高的情况下，对连接在 P 型 MOSFET32 和 N 型 MOSFET33 的栅与输入端 IN 之间的电容 C2、C3 充电至与在设定工作中 MOSFET32、33 阈值电压和输入电位  $V_{INH}$ 、 $V_{INL}$  与电源电位 VDD、VSS 之差一致的恰当的电压，能可靠地使 P 型和 N 型 MOSFET32、33 通/断，实现正确的电路工作。

图 7 是表示分别用 P 型 MOSFET38、N 型 MOSFET39 实现了图 5 所示的开关 SW2、SW3 的数字电路 30 的电路图。再有，在本图中，对与图 5 相同的部分标以相同的符号。P 型 MOSFET38 的栅和 N 型 MOSFET39 的栅分别与 P 沟道控制信号线 40、N 沟道控制信号线 41 连接。在 P 沟道设定工作中，通过使这些控制信号线 40、41 的电位与例如低电平电源电位 VSS 相等并将低电平电源电位 VSS 加到 P 型 MOSFET38 和 N 型 MOSFET39 的栅上，在使 P 型 MOSFET38 成为导通状态的同时使 N 型 MOSFET39 成为关断状态，进而将高电平输入电位  $V_{INH}$  加到输入端 IN 上。在 N 沟道设定工作中，使控制信号线 40、41 的电位与例如高电平电源电位 VDD 相等并将高电平电源电位加到 P 型 MOSFET38 和 N 型 MOSFET39 的栅上，在使 P 型 MOSFET38 成为关断状态的同时使 N 型 MOSFET39 成为导通状态，将低电平输入电位  $V_{INL}$  加到输入端 IN 上。通过这些设定工作，如参照图 6a、6b 所作的说明那样，恰当地进行电荷对电容 C2、C3 的蓄积。在通常工作中，使 P 沟道控制信号线 40 的电位与高电平电源电位 VDD 相等，使 N 沟道控制信号线 41 的电位与低电平电源电位 VSS，使 P 型 MOSFET38 和 N 型 MOSFET39 两者皆为关断状态。

再有，如图 7 中作为放大图所示，电容 C2、C3 可用在 1 个或多

个 MOSFET 的栅与源和/或漏之间所形成的电容形成。再有，在连接作为电容用的 MOSFET 时，可在已充电时使 MOSFET 导通那样的（即形成沟道那样的）方向连接。例如，在用 1 个 P 型 MOSFET 连结的电容 C2 时，可将栅侧端子与输入端 IN 连接，将源/漏侧端子与 P 型 MOSFET32 的栅连接。另外，作为电容用的 MOSFET 的导电类型无论是 N 型还是 P 型，哪一种均可，但希望是阈值电压接近于 0 的一方。

在上述数字电路 30 中，虽然作为在设定工作前电容 C2、C3 上未蓄积电荷的情况进行了说明，但往往例如通过噪声等在电容 C2、C3 上蓄积电荷。通过这样的电荷，在设定工作之前，例如在要对电容 C2、C3 以图 6b 所示的极性充电至过大的情况下，在设定工作中即使使开关 SW2、SW3 导通，也不会使连接成二极管的 MOSFET35、37 导通，蓄积在电容 C2、C3 上的电荷（从而，电容 C2、C3 两端的电压）维持不变，往往无法使电容 C2、C3 两端的电压（或 MOSFET35、37 的栅电位）收敛于恰当的值。因此，在如此不希望的电荷蓄积在电容 C2、C3 上的情况下，希望采取措施将电容 C2、C3 两端的电压设定在恰当的值。

图 8 是表示图 5 所示的数字电路 30 的变形实施例的电路图，在本图中，对与图 5 相同的部分标以相同的符号而省略其详细的说明。在该数字电路 30a 中，与被连接成二极管的 P 型 MOSFET35 并联且以其正向为与 P 型 MOSFET35 的正向相反的方向的方式连接被连接成二极管的另一 P 型 MOSFET42。同样，与被连接成二极管的 N 型 MOSFET37 并联且反向连接被连接成二极管的另一 N 型 MOSFET43。由此，例如由于在设定工作前噪声等的影响，将被连接成二极管的 P 型和 N 型 MOSFET35、37 反向偏置而得到的电荷蓄积在电容 C2、C3 上的情况下，在设定工作中使开关 SW2、SW3 导通时可如图 8 中箭头所示那样流过电流，可使电容 C2、C3 两端的电压收敛在大致恰当的值。在被连接成二极管的 MOSFET42、43 的阈值电压分别等于 MOSFET32、33 的阈值电压  $V_{THP}$ 、 $V_{THN}$  的情况下，P 型 MOSFET32 的栅电位（即节点 N5 的电位）收敛于  $VDD + |V_{THP}|$ ，N 型 MOSFET33 的栅电位（即节点 N6 的电位）收敛于  $VSS + |V_{THN}|$ 。也可以用二极管等另外的整流元件来代替被连接成二极管的 MOSFET42、43。再有，与 P 型 MOSFET35 并联连接的被连接成二极管的 MOSFET42 也可以是 N 型。另外，与 N 型 MOSFET37 并联连接的被连接成二极管的 MOSFET43 也可以是 P 型。

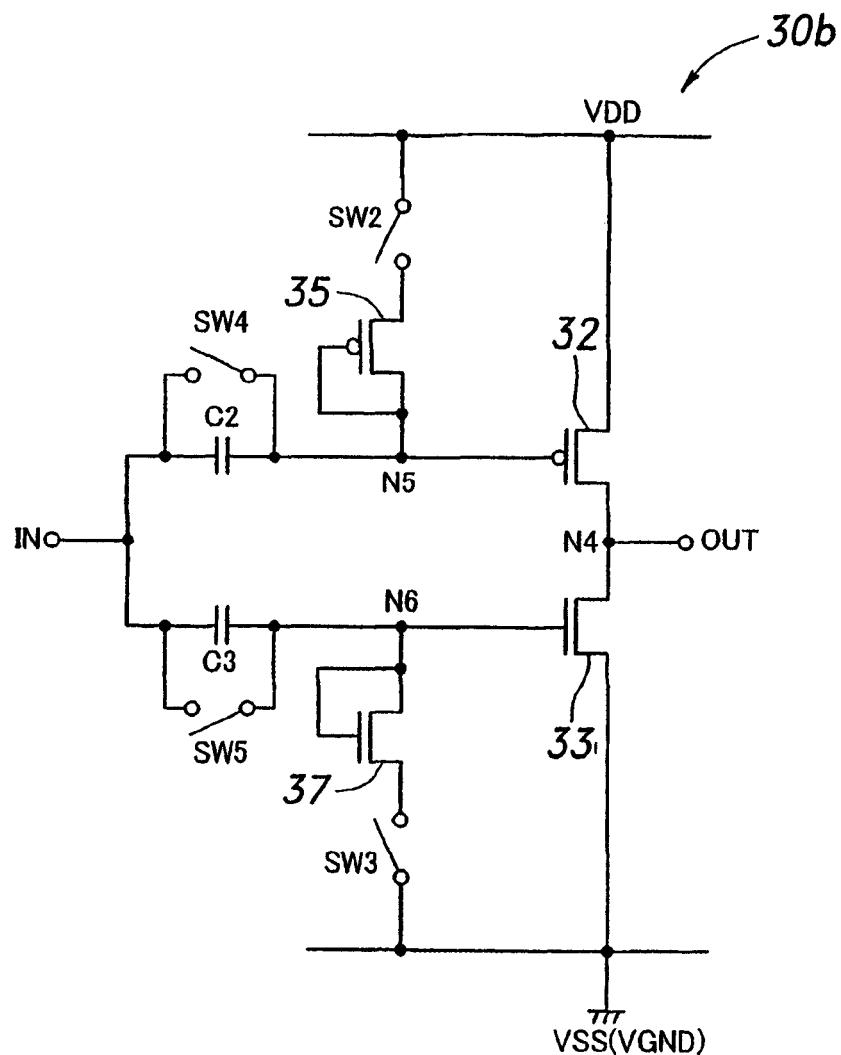

图 9 是表示图 5 所示的数字电路 30 的另一变形实施例的电路图，在本图中，对与图 5 相同的部分标以相同的符号而省略其详细的说明。在该数字电路 30b 中，分别设置开关 SW4、SW5 与电容 C2、C3 并联。由此，即使例如由于噪声等的影响而有不希望的电荷蓄积在电容 C2、C3 上，在设定工作前可使开关 SW4、SW5 导通，使电容 C2、C3 放电。从而，在设定工作中使开关 SW2、SW3 导通时，被连接成二极管的 MOSFET35、37 可靠地导通，电容 C2、C3 被恰当地充电。

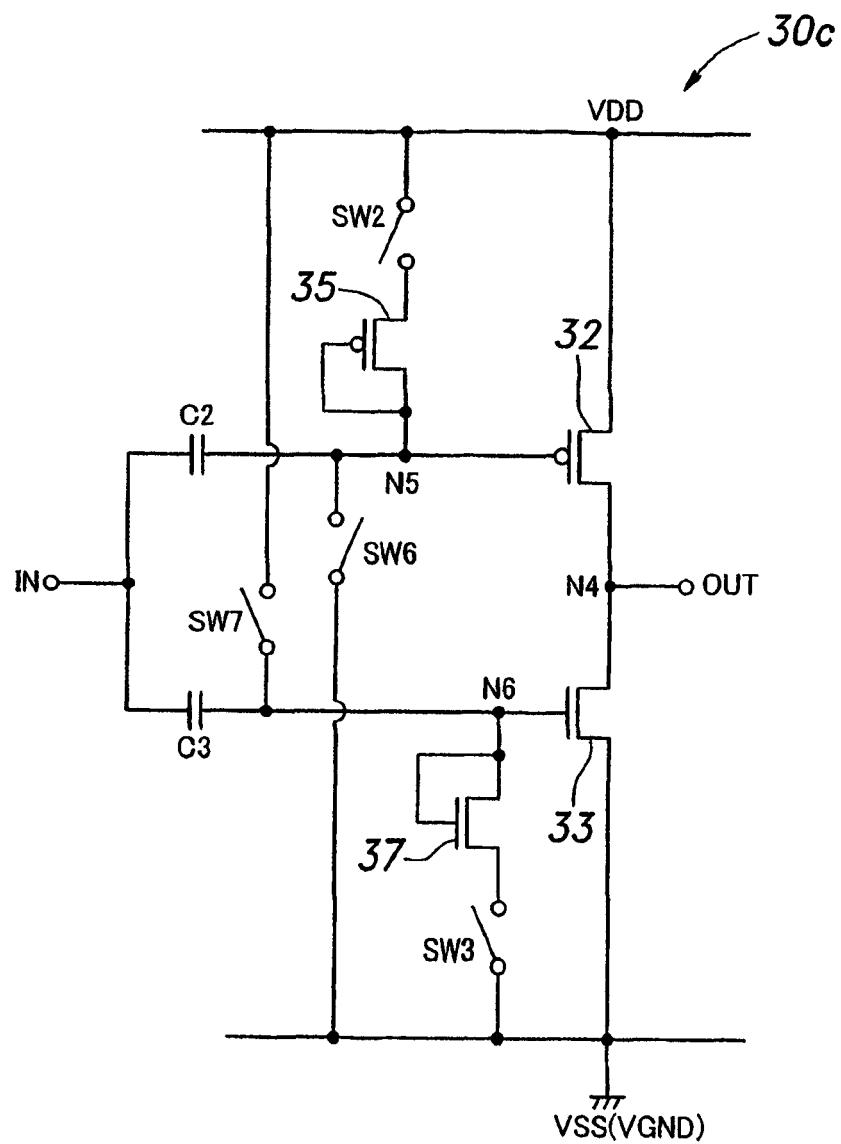

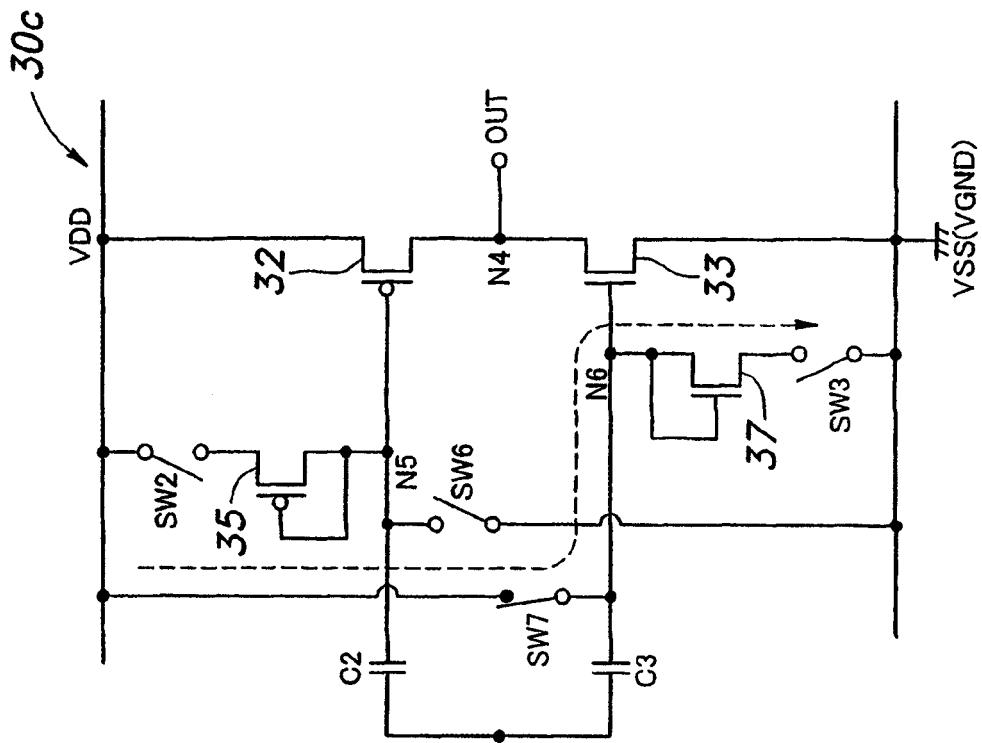

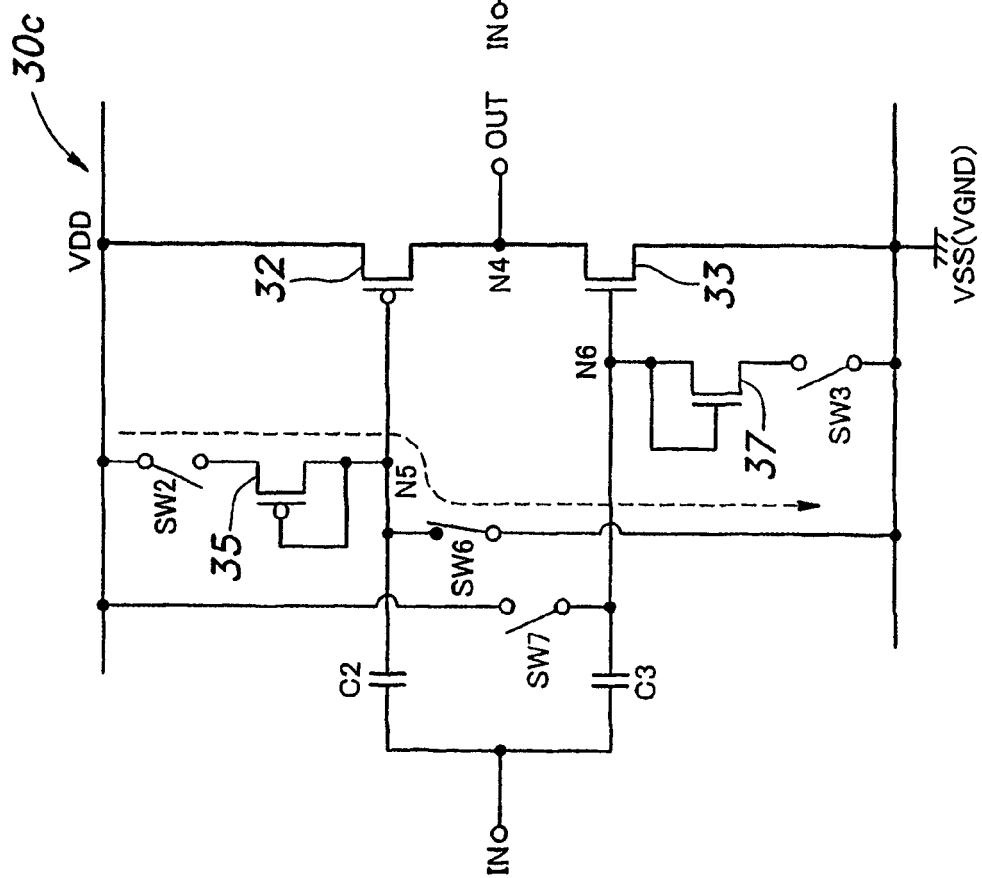

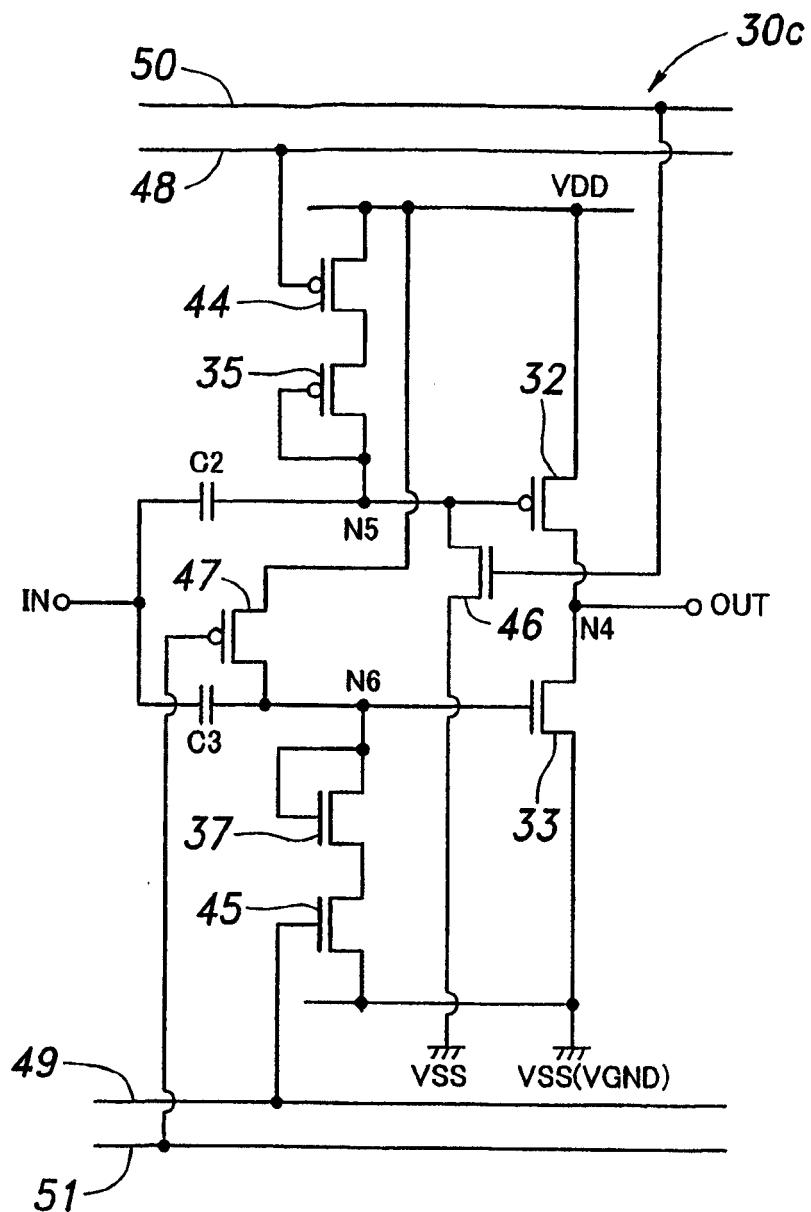

图 10 是表示图 5 所示的数字电路 30 的又一变形实施例的电路图，在本图中，对与图 5 相同的部分标以相同的符号而省略其详细的说明。在该数字电路 30c 中，P 型 MOSFET32 的栅与电容 C2 之间的节点 N5 经开关 SW6 与低电平电源电位 VSS 连接，N 型 MOSFET33 的栅与电容 C3 之间的节点 N6 经开关 SW7 与高电平电源电位 VDD 连接。

如图 11a 所示，在与 P 型 MOSFET32 的栅连接的电容 C2 的设定工作（P 沟道设定工作）之前的初始化工作中，如果使开关 SW6 导通，则例如通过噪声等使不需要的电荷滞留在电容 C2 上，即使以不希望的方式增高 P 型 MOSFET32 的栅与电容 C2 之间的节点 N5 的电位，也可使节点 N5 的电位大致下降到低电平电源电位 VSS。此时，最好使输入端 IN 的电位为高电平电源电位，但为低电平电源电位亦可。另外，开关 SW2 既可以是导通状态，又可以是关断状态，但在导通状态下，如图中的虚线箭头所示，流过电流，由于难以使节点 N5 的电位下降至充分低的电位，故更希望是成为关断状态的一方。

同样，如图 11b 所示，在与 N 型 MOSFET33 的栅连接的电容 C3 的设定工作（N 沟道设定工作）之前的初始化工作中，如果使开关 SW7 导通，则例如通过噪声等使不需要的电荷滞留在电容 C3 上，即使以不希望的方式降低 N 型 MOSFET33 的栅与电容 C3 之间的节点 N6 的电位，也可使节点 N6 的电位大致提高到高电平电源电位 VDD。此时，最好使输入端 IN 的电位为低电平输入电位，但为高电平输入电位亦可。另外，开关 SW3 既可以是导通状态，又可以是关断状态，但在导通状态下，如图中的虚线箭头所示，流过电流，由于难以使节点 N6 的电位提高至充分高的电位，故更希望是成为关断状态的一方。

在设定工作中，使开关 SW6、SW7 关断，如参照图 6a 和图 6b 所作的说明那样，使开关 SW2 或 SW3 导通。通过上述那样的初始化工作，

在设定工作之前使节点 N5、N6 的电位成为恰当的值，从而在设定工作中使开关 SW2、SW3 导通时，可将被连接成二极管的 MOSFET35、37 正向偏置，使之可靠地导通，通过这些 MOSFET35、37 流过电流，对电容 C2、C3 恰当地充电。再有，在图 10 和 11 的实施例中，在初始化工作中将节点 N5 连接到低电平电源电位 VSS，将节点 N6 连接到高电平电源电位 VDD，但在初始化工作后的设定工作中，只要将被连接成二极管的 MOSFET35、37 正向偏置，使之导通，则与电源电位以外的其它电位连接亦可。但是，如果用电源电位，则可容易地确保这样的电位，因而是理想的。另外，在上述实施例中，虽然分别进行 P 沟道初始化工作和 N 沟道初始化工作，但通过使开关 SW6、SW7 同时导通，也可一次进行这两种初始化工作。

图 12 是表示作为 MOSFET44、45、46、47 实现了图 10 所示的开关 SW2、SW3、SW6、SW7 的数字电路 30c 的电路图。MOSFET44 是

P 型 MOSFET，其栅与 P 沟道控制信号线 48 连接。MOSFET45 是 N 型 MOSFET，其栅与 N 沟道控制信号线 49 连接。MOSFET46 是 N 型 MOSFET，其栅与 P 沟道初始化信号线 50 连接。而且，MOSFET47 是

P 型 MOSFET，其栅与 N 沟道初始化信号线 51 连接。通过恰当地控制控制信号线 48、49 和初始化信号线 50、51 的电位，可恰当地使 MOSFET44~47 通断，使上述那样的初始化、设定、通常工作得以进行。

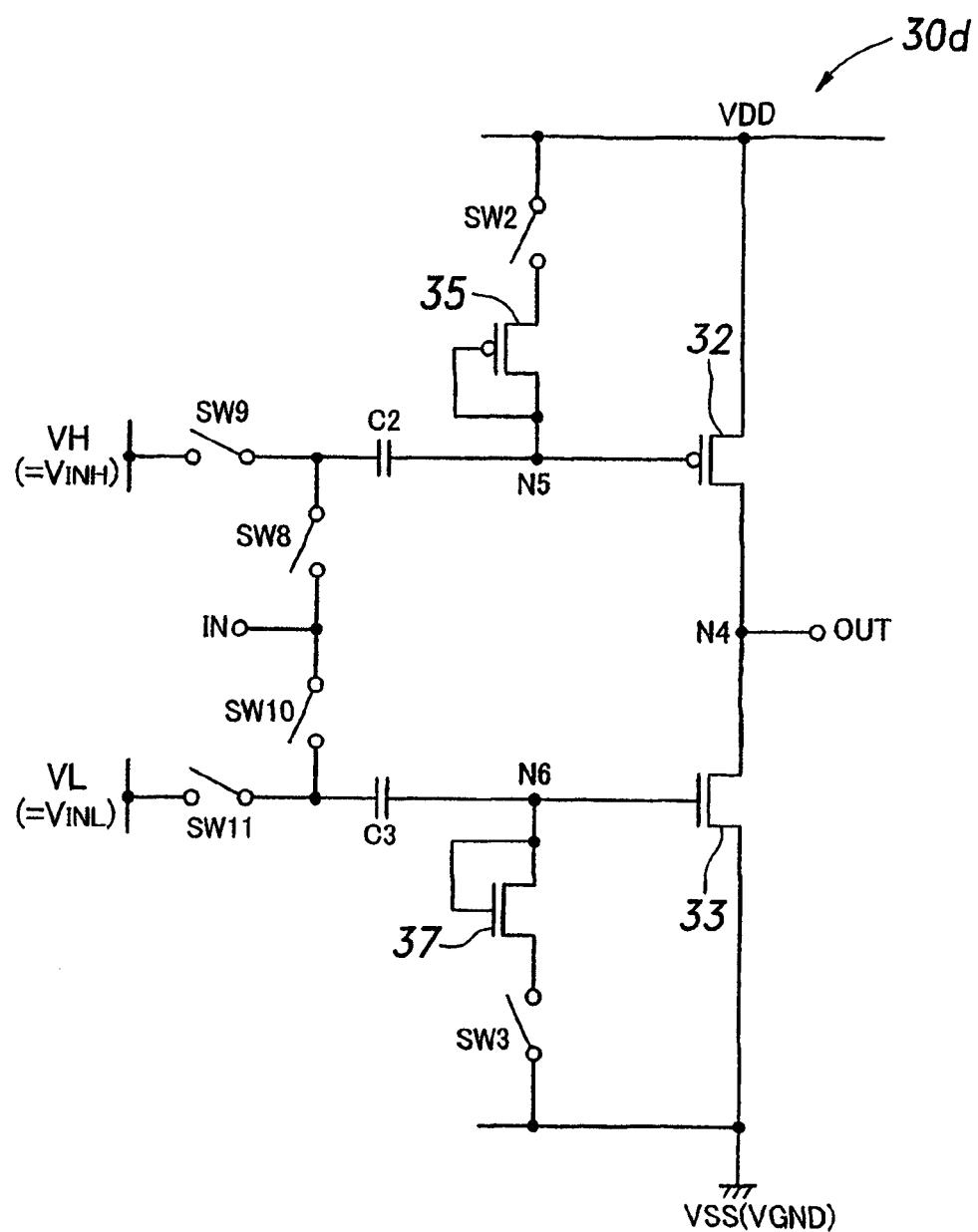

图 13 是表示图 5 所示的数字电路 30 的又一变形实施例的电路图。在本图中，对与图 5 所示的部分相同的部分标以相同的符号而省略其详细的说明。在该数字电路 30d 中，在与电容 C2 的与 P 型 MOSFET32 的栅连接的端子相反一侧的端子经开关 SW8 与输入端 IN 连接的同时，经开关 SW9 与通常工作中加到输入端 IN 的输入信号的与高电平输入电位  $V_{INH}$  大致相同的电位  $V_H$  连接。同样，在与电容 C3 的与 N 型 MOSFET33 的栅连接的端子相反一侧的端子经开关 SW10 与输入端 IN 连接的同时，经开关 SW11 与通常工作中加到输入端 IN 的输入信号的与低电平输入电位  $V_{INL}$  大致相同的电位  $V_L$  连接。

在本实施例中，通过使开关 SW2、SW3、SW9、SW11 导通，使开关 SW8、SW10 关断，可同时进行电容 C2、C3 的设定工作，而且与输入端 IN 的电位无关。在通常工作中，使开关 SW2、SW3、SW9、SW11 关断，使开关 SW8、SW10 导通，向输入端 IN 施加其振幅在高电平/低电平输

入电位  $V_{INH}$ 、 $V_{INL}$  之间的输入信号。

可是，可知在 CMOS 倒相器中，通过将 MOSFET 与构成倒相器的 P 型和 N 型 MOSFET 串联连接，用时钟信号（或相位与之相反的时钟补信号等的同步信号）使这些 MOSFET 通/断，使倒相器的输出与时钟信号等的同步信号同步。将这样的倒相器称为钟控倒相器。将本发明应用于在钟控倒相器中与构成 CMOS 倒相器的 P 型和 N 型 MOSFET 串联连接了的时钟信号同步用 MOSFET 是可能的，在图 14 上示出了这样的实施例。

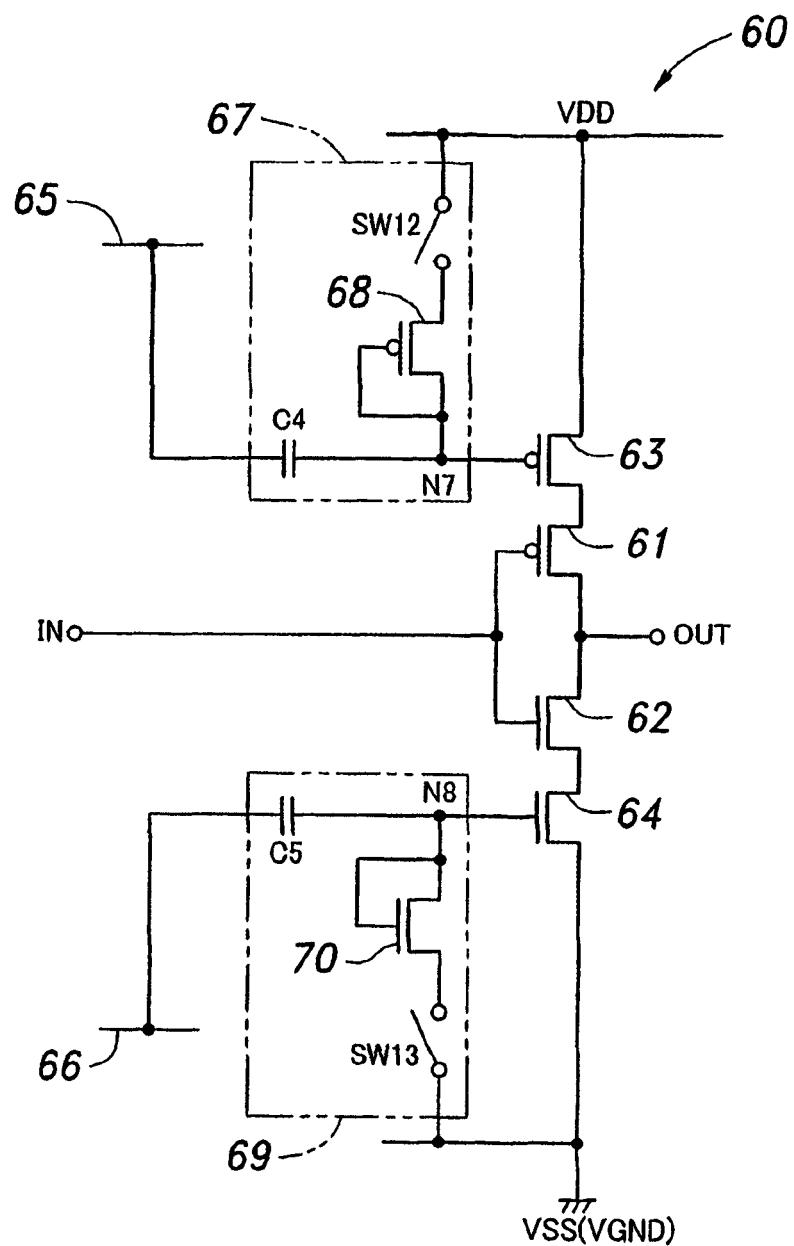

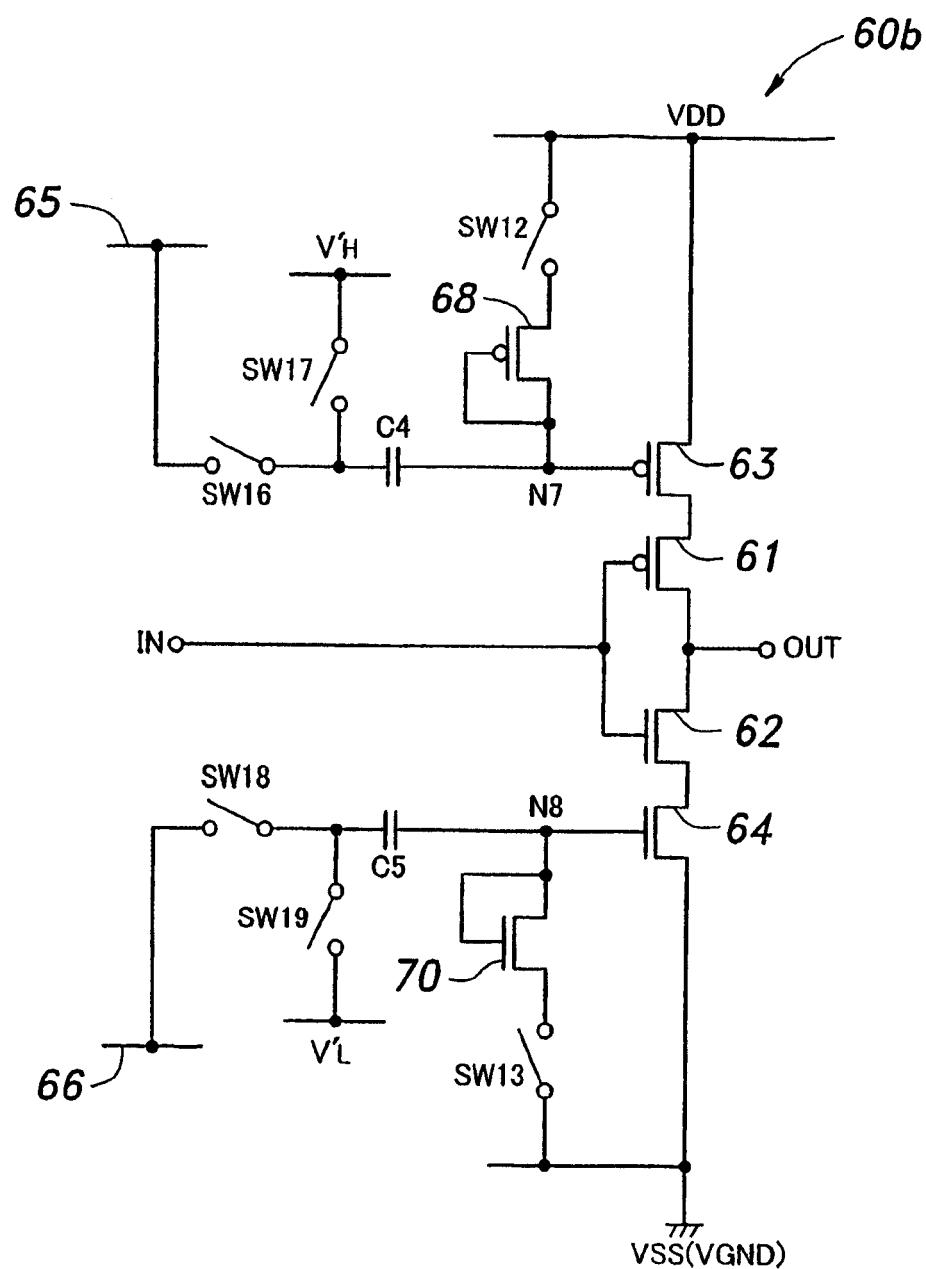

图 14 所示的钟控倒相电路（数字电路）60 具有构成 CMOS 倒相器的 P 型和 N 型 MOSFET61、62，这些 MOSFET61、62 的栅与输入端 IN 连接，输出端 OUT 与共同的漏连接。另外，P 型 MOSFET61 的源经时钟同步用的 P 型 MOSFET63 与高电平电源电位 VDD 连接，N 型 MOSFET62 的源经时钟同步用的 N 型 MOSFET64 与低电平电源电位 VSS（在本例中为地电位  $V_{GND}$ ）连接。P 型 MOSFET63 的栅与供给时钟补信号的时钟补信号线 65 连接，N 型 MOSFET64 的栅与供给时钟信号的时钟信号线 66 连接。假定时钟信号和时钟补信号的振幅在低于高电平电源电位 VDD 的高电平电位  $V_{CH}$  与高于低电平电源电位 VSS 的低电平电位  $V_{CL}$  之间。再有，在本实施例中假定施加到输入端 IN 的输入信号的振幅在高电平电源电位 VDD 与低电平电源电位 VSS 之间，但在输入信号的振幅小的情况下，与上述实施例一样，对构成倒相器的 MOSFET61、62 设置校正电路是可能的。再有，P 型 MOSFET61 可以连接在 P 型 MOSFET63 与电源电位 VDD 之间，或者 N 型 MOSFET62 可以连接在 N 型 MOSFET64 与电源电位 VSS 之间。

基于本发明，校正电路 67 被连接在 P 型 MOSFET63 的栅与时钟补信号线 65 之间。该校正电路 67 具有被连接在 P 型 MOSFET63 的栅与时钟补信号线 65 之间的电容 C4、其阈值电压与 P 型 MOSFET63 大致相同的被连接成二极管的 P 型 MOSFET68 和 SW12，P 型 MOSFET68 的漏被连接在电容 C4 与 P 型 MOSFET63 的栅之间的节点 N7 上，其源经开关 SW12 与高电平电源电位 VDD 连接。

同样，校正电路 69 被连接在 N 型 MOSFET64 的栅与时钟信号线 66 之间。该校正电路 69 具有被连接在 N 型 MOSFET64 的栅与时钟信号线 66 之间的电容 C5、其阈值电压与 N 型 MOSFET64 大致相同的被连接成

二极管的 N 型 MOSFET70 和 SW13，N 型 MOSFET70 的漏被连接在电容 C5 与 N 型 MOSFET64 的栅之间的节点 N8 上，其源经开关 SW13 与低电平电源电位 VSS 连接。

再有，在本实施例中，时钟信号、时钟补信号在从成为对象的 MOSFET63、64 看的情况下，可以说是本发明中的输入信号。另外，可以说由 P 型 MOSFET63 和校正电路 67 或者由 N 型 MOSFET64 和校正电路 69 形成本发明的数字电路，此时，可将 P 型 MOSFET63 和 N 型 MOSFET64 的漏视作输出端。

在设定工作中，首先，在使开关 SW12 和开关 SW13 一起导通的状态下，施加高电平电位  $V_{CH}$  作为时钟补信号（此时，时钟信号为低电平电位  $V_{CL}$ ）。由于高电平电位  $V_{CH}$  低于高电平电源电位 VDD，被连接成二极管的 P 型 MOSFET68 处于正向偏置，成为导通状态，流过电流，对电容 C4 充电。电流一直流过，直至为使 P 型 MOSFET68 关断而电容 C4 两端的电压变得充分大为止。另外，此时，由于施加高于低电平电源电位 VSS 的低电平电位  $V_{CL}$  作为时钟信号，故被连接成二极管的 N 型 MOSFET70 处于正向偏置而导通，流过电流，对电容 C5 充电。如果电容 C5 两端的电压变得充分地大，则 N 型 MOSFET70 关断，电流停止。这样，在本实施例中，可同时进行 2 个校正电路 67、69 内的电容 C4、C5 的设定工作。

在通常工作中，使开关 SW12、SW13 两者一并关断，施加时钟信号、时钟补信号和输入信号。此时，由于电容 C4、C5 被充电至与 P 型 MOSFET63、N 型 MOSFET64 的阈值电压匹配的适度的电压，时钟信号、时钟补信号被加到恰当地偏置的 P 型 MOSFET63 和 N 型 MOSFET64 的栅上，故能可靠地使 P 型 MOSFET63 和 N 型 MOSFET64 通·断，进行与输出信号的时钟信号的同步。

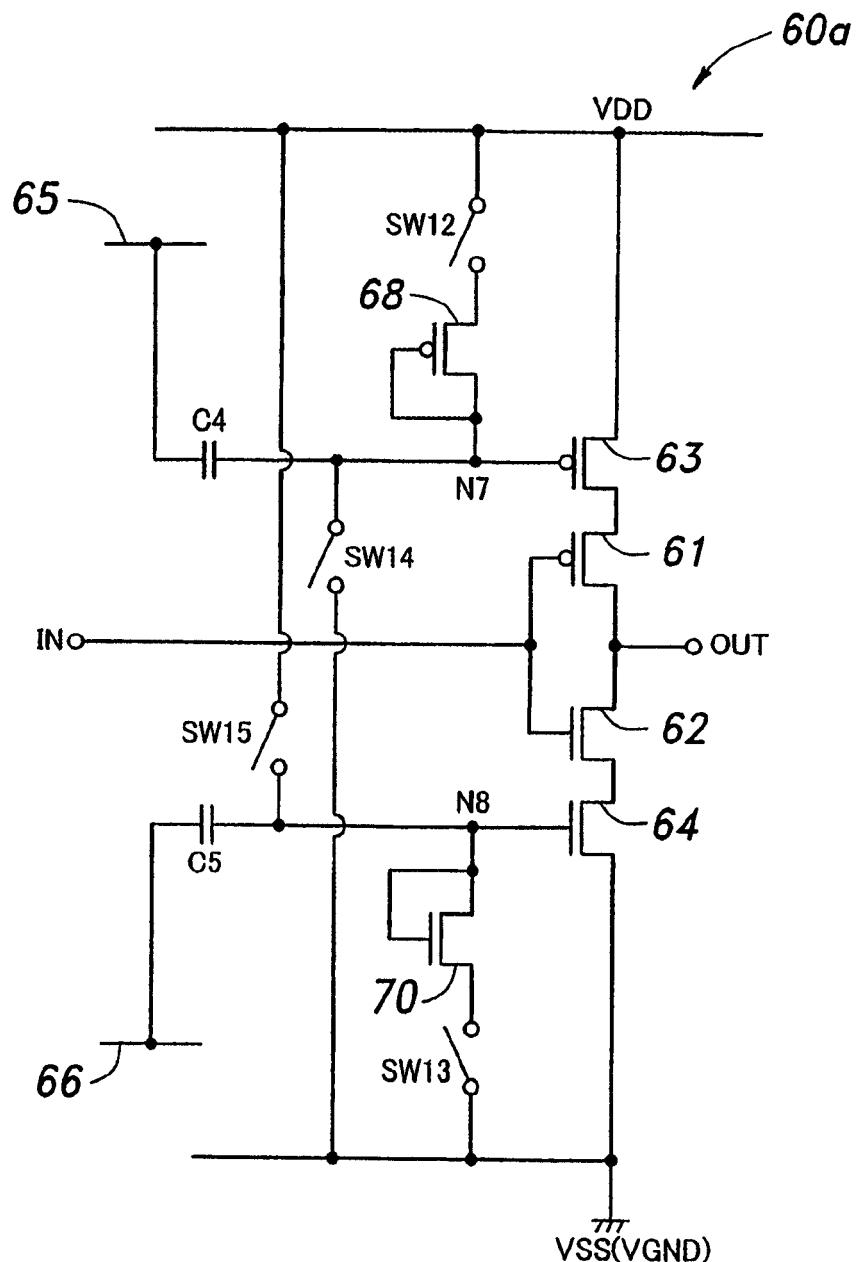

图 15 是表示图 14 所示的钟控倒相电路 60 的变形实施例的电路图。在本图中，对与图 14 相同的部分标以相同的符号而省略其详细的说明。图 15 的钟控倒相电路 60a 与图 10 的实施例一样，具有将与电容 C4、C5 对应的 MOSFET63、64 的栅之间的节点 N7、N8 有选择地与低电平电源电位 VSS 和高电平电源电位 VDD 连接用的开关 SW14、SW15。由此，在设定工作之前，通过使开关 SW14、SW15 导通，可将校正用电容 C4、C5 初始化，即使因噪声等而使不希望的电荷蓄积在

电容 C4、C5 上，MOSFET68、70 也不会由此受到恶劣影响。

图 16 是表示图 14 所示的基于本发明的钟控倒相电路 60 的另一变形实施例的电路图。在本图中，对与图 14 相同的部分标以相同的符号而省略其详细的说明。图 16 的钟控倒相电路 60b 与图 13 的实施例一样，在与电容 C4 的与 P 型 MOSFET63 的栅连接的端子相反一侧的端子经开关 SW16 与 5 连接的同时，经开关 SW17 连接到与时钟补信号的高电平电位  $V_{CH}$  大致相同的电位  $V'_{H}$  上。同样，在与电容 C5 的与 N 型 MOSFET64 的栅连接的端子相反一侧的端子经开关 SW18 与时钟信号线 66 连接的同时，经开关 SW19 连接到与时钟信号的低电平电位  $V_{CL}$  大致相同的电位  $V'_{L}$  上。

在本实施例中，通过使开关 SW12、SW13、SW17、SW19 为导通，使开关 SW16、SW18 为关断的状态，可同时进行电容 C4、C5 的设定工作，而且与时钟信号或时钟补信号的电位无关。在通常工作中，在使开关 SW12、SW13、SW17、SW19 关断，使开关 SW16、SW18 导通的状态下，在时钟信号和时钟补信号通过电容 C4、C5 加到 P 型 MOSFET63、N 型 MOSFET64 的栅上的同时，向输入端 IN 施加其振幅在高电平输入电位  $V_{INH}$  与低电平输入电位  $V_{INL}$  之间的输入信号。

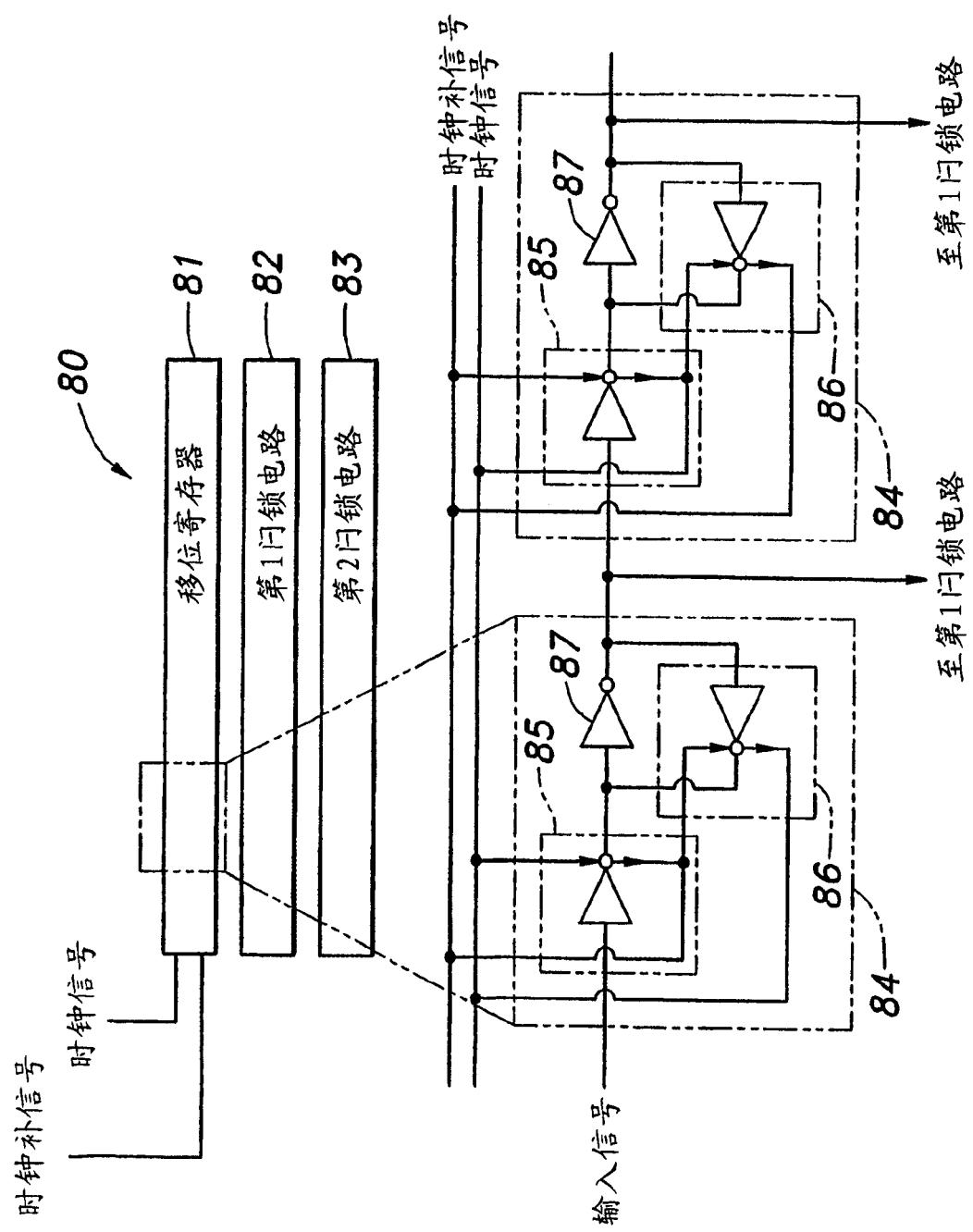

图 17 示意地表示例如在液晶显示器及有机 EL 显示器等中所使用的有源矩阵装置的驱动电路的主要部分，同时表示驱动电路的移位寄存器中的典型的单位电路。驱动电路 80 具有与时钟信号和时钟补信号同步地依次输出选择信号用的移位寄存器 81、基于来自移位寄存器 81 的选择信号以闩锁视频信号的第 1 闩锁电路 82 和闩锁从第 1 闩锁电路 82 传送来的数据的第 2 闩锁电路 83。移位寄存器 81 有多个单位电路 84，各单位电路 84 有 2 个钟控倒相器 85、86 和 1 个倒相器 87，例如在时钟信号为高电平电位  $V_{CH}$  时取入输入信号（此时输出信号可变化），在时钟信号为低电平时以保持输出信号的方式进行工作。在 1 个单位电路 84 和邻接的单位电路 84 中，由于时钟信号与时钟补信号为反相，故在某单位电路 84 中在取入输入信号时，邻接的单位电路 84 保持输出信号，在某单位电路 84 中在保持输出信号时，在邻接的单位电路 84 中进行输入信号的取入。这样的移位寄存器 81 的结构和工作在本领域中已为人们所熟知。假定施加于移位寄存器 81 的钟控倒相器 85、86 的时钟信号（或时钟补信号）的振幅比电源电压（高电

平电源电位 VDD-低电平电源电位 VSS) 小。此时，最好采取使这些钟控倒相器 85、86 无误动作地可靠关断的措施。通过将本发明应用于这些钟控倒相器 85、86，可恰当地达到这样的目的而不至降低工作速度。

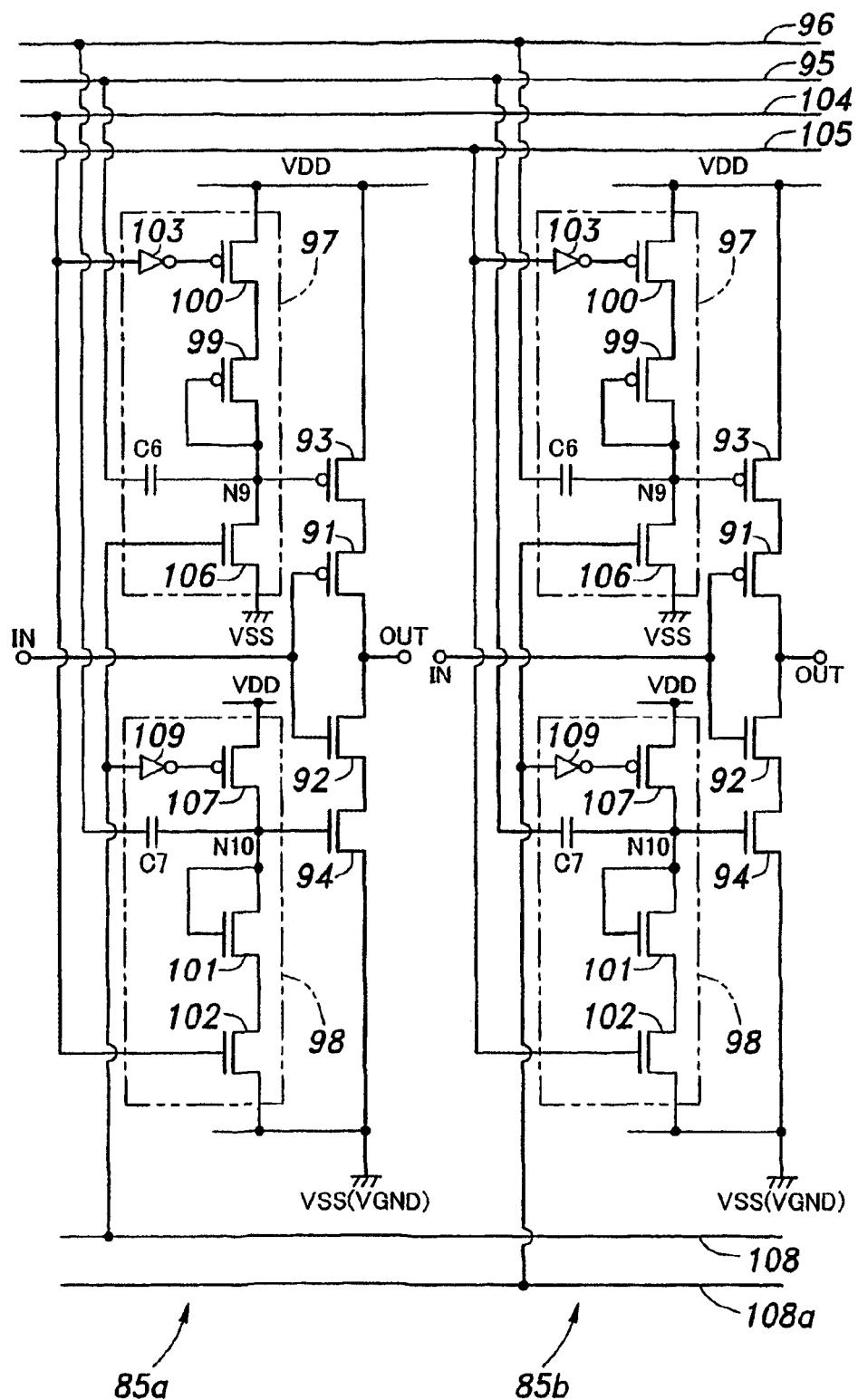

图 18 是表示将本发明应用于图 17 所示的移位寄存器 81 的单位电路 84 中的左侧的钟控倒相器 85 的实施例的电路图。在本图中，另一钟控倒相器 86 和倒相器 87 省略了图示。

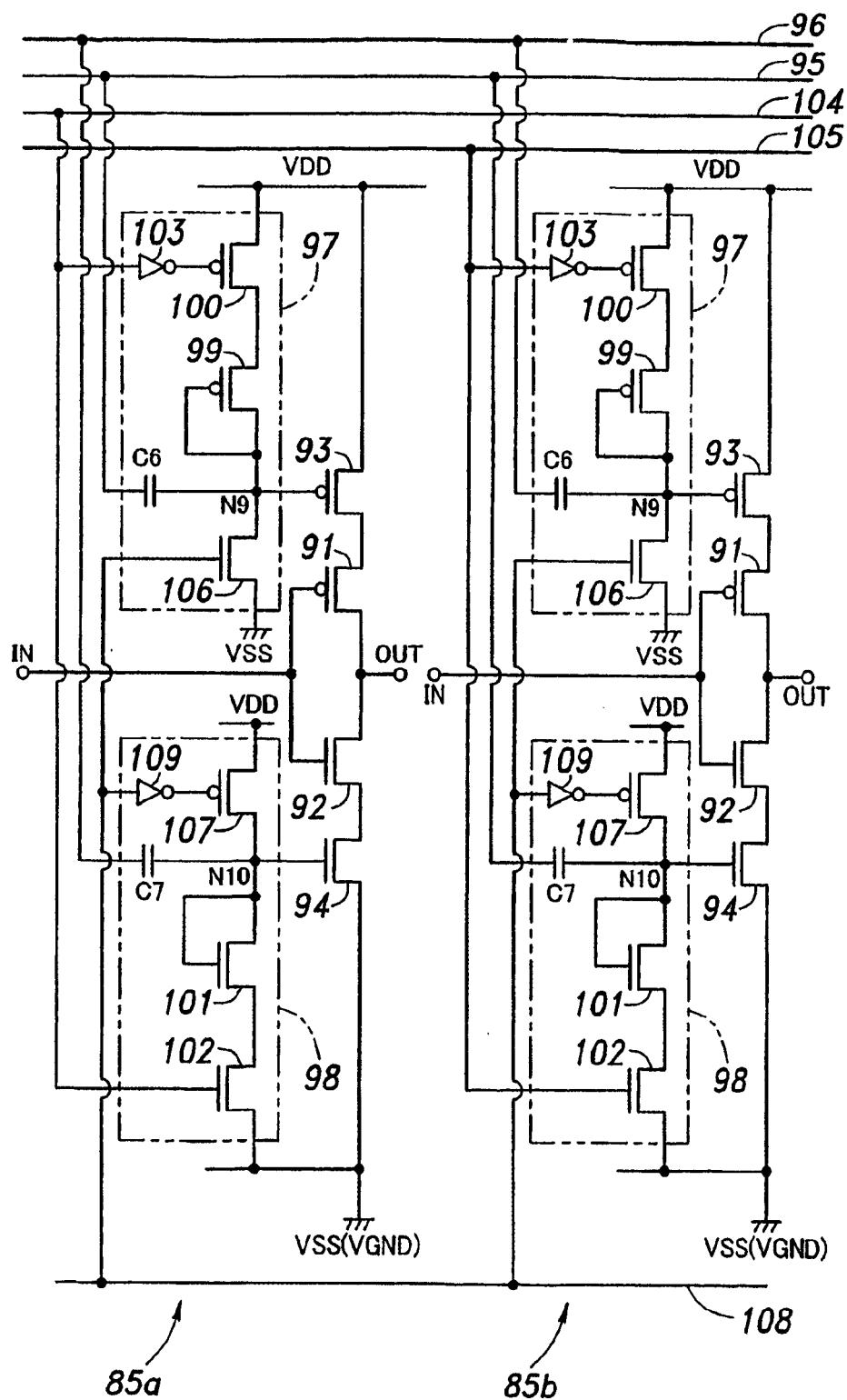

图 18 的左侧的钟控倒相器 85a (与图 17 中的左侧的单位电路 84 内的钟控倒相器 85 相对应) 具有为了构成 CMOS 倒相器而彼此的漏被连接、串联连接了的 P 型 MOSFET91 和 N 型 MOSFET92，P 型 MOSFET91 经时钟同步用 P 型 MOSFET93 与高电平电源电位 VDD 连接，N 型 MOSFET92 经时钟同步用 N 型 MOSFET94 与低电平电源电位 VSS (例如  $V_{GND}$ ) 连接。

P 型 MOSFET93 的栅经校正电路 97 与时钟补信号线 95 连接，N 型 MOSFET94 的栅经校正电路 98 与时钟信号线 96 连接。校正电路 97 具有被连接在 P 型 MOSFET93 的栅与时钟补信号线 95 之间的电容 C6、其阈值电压与 P 型 MOSFET93 大致相同的被连接成二极管的 P 型 MOSFET99 和有选择地进行设定工作用的作为开关而工作的 P 型 MOSFET100，P 型 MOSFET99 和 P 型 MOSFET100 被串联连接在电容 C6 与 P 型 MOSFET93 的栅之间的节点 N9 与高电平电源电位 VDD 之间。同样，校正电路 98 具有被连接在 N 型 MOSFET94 的栅与时钟信号线 96 之间的电容 C7、其阈值电压与 N 型 MOSFET94 大致相同的被连接成二极管的 N 型 MOSFET101 和有选择地进行设定工作用的作为开关而工作的 N 型 MOSFET102，N 型 MOSFET101 和 N 型 MOSFET102 被串联连接在电容 C7 与 N 型 MOSFET94 的栅之间的节点 N10 与低电平电源电位 VSS 之间。P 型 MOSFET100 的栅经倒相器 103 与第 1 控制信号线 104 连接，N 型 MOSFET102 的栅直接与第 1 控制信号线 104 连接。

此外，电容 C6 与 P 型 MOSFET93 的栅之间的节点 N9 经 N 型 MOSFET106 与低电平电源电位 VSS 连接，电容 C7 与 N 型 MOSFET94 的栅之间的节点 N10 经 P 型 MOSFET107 与高电平电源电位 VDD 连接，通过有选择地使 N 型 MOSFET106 和 P 型 MOSFET107 通断，可将电容 C6、C7 初始化。N 型 MOSFET106 的栅直接与初始化信号线 108 连接，P 型 MOSFET107 的栅经倒相器 109 与初始化信号线 108 连接，向这些

MOSFET106、107 的栅输入极性相反的信号。

图 18 的右侧的钟控倒相器 85b（与图 17 中的右侧的单位电路 84 内的钟控倒相器 85 相对应）具有与左侧的钟控倒相器 85a 相同的结构，但其不同点在于：P 型 MOSFET93 的栅经电容 C6 与时钟信号线 96 连接，N 型 MOSFET94 的栅经电容 C7 与时钟补信号线 95 连接，P 型 MOSFET100 和 N 型 MOSFET102 的栅与第 2 控制信号线 105 连接。再有，在图 18 中，虽然仅示出 2 个钟控倒相器 85a、85b，但要理解，在实际电路中，它们被交互配置多个。

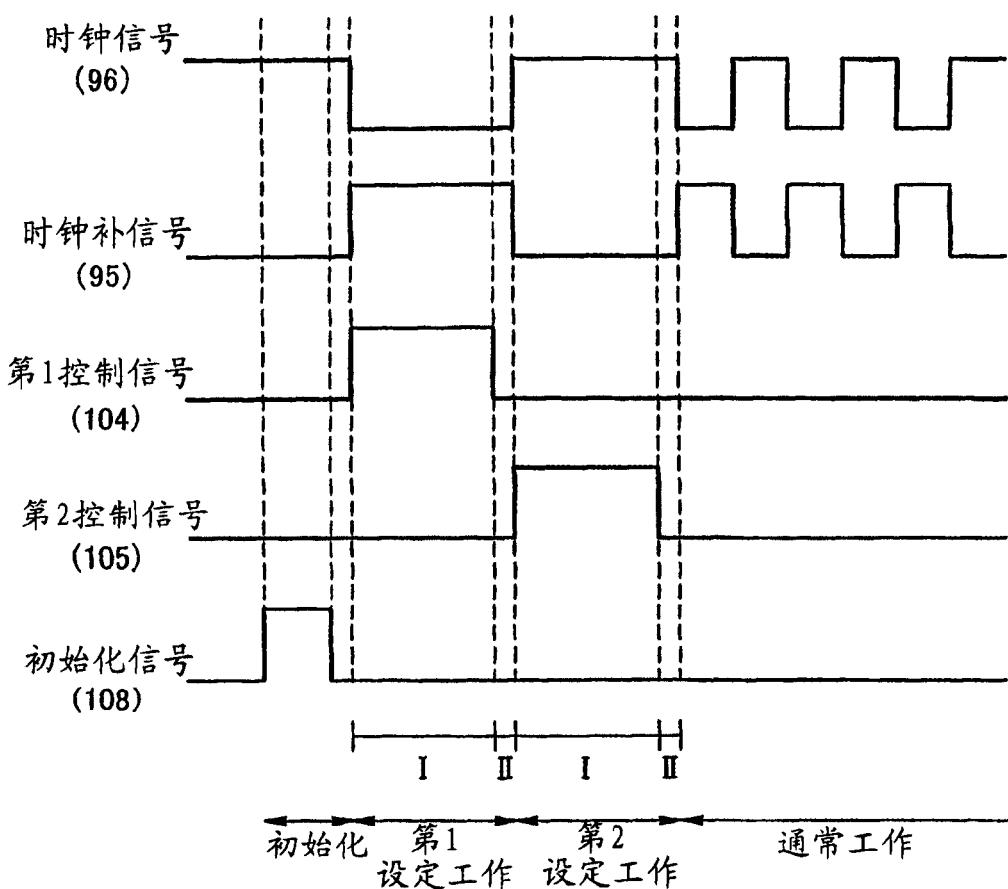

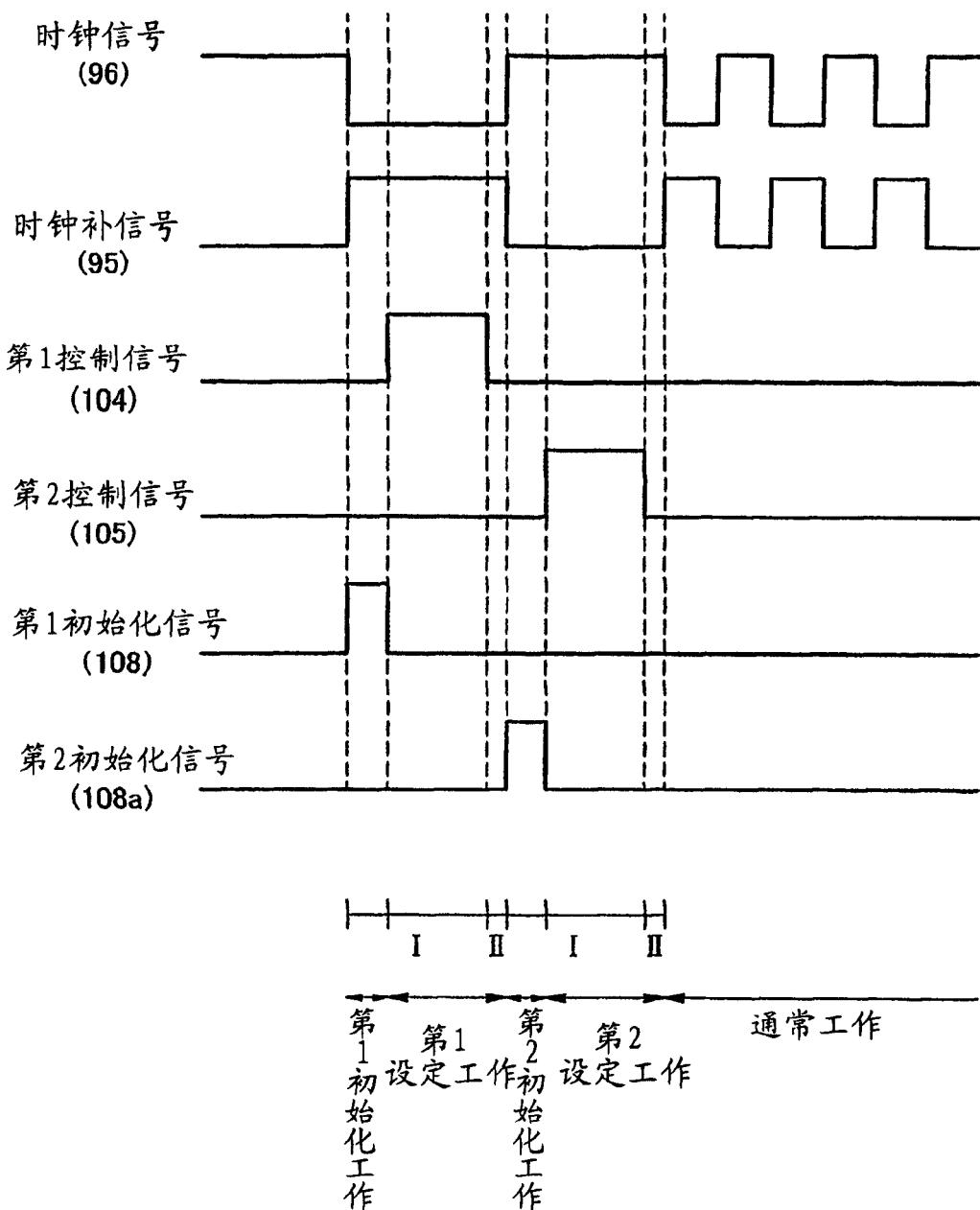

图 19 的时序图示出了如此构成了的移位寄存器 81 的钟控倒相器 85a、85b 的初始化、设定工作和通常工作中的各部的合适的信号（电位）变化。

在初始化工作中，在时钟信号线 96 的电位为高电平，时钟补信号线 95 的电位为低电平，而且第 1 控制信号线 104 和第 2 控制信号线 105 的电位为低电平的状态下，初始化信号线 108 的电位为高电平。由此，各钟控倒相器 85a、85b 的 N 型 MOSFET106 和 P 型 MOSFET107 成为导通状态，进行校正电路 97、98 内的电容 C6、C7 的初始化。如果初始化信号线 108 的电位成为低电平，则初始化工作结束，再有，在本实施例中，由于初始化工作对左侧和右侧钟控倒相器 85a、85b 同时进行，故在初始化工作中，在一个（在本例中为右侧）钟控倒相器 85b 中，在向与 P 型 MOSFET93 的栅连接的电容 C6 施加高电平电位  $V_{CH}$  的同时，可向与 N 型 MOSFET94 的栅连接的电容 C7 施加低电平电位  $V_{CL}$ ，但在另一（在本例中为左侧）钟控倒相器 85a 中，向与 P 型 MOSFET93 的栅连接的电容 C6 施加低电平电位  $V_{CL}$ ，向与 N 型 MOSFET94 的栅连接的电容 C7 施加高电平电位  $V_{CH}$ 。

设定工作由对图 18 的左侧的钟控倒相器 85a 的电容 C6、C7 进行电荷蓄积的第 1 设定工作和对图 18 的右侧的钟控倒相器 85b 的电容 C6、C7 进行电荷蓄积的第 2 设定工作构成。在第 1 设定工作中，在阶段 I，第 1 控制信号线 104 和时钟补信号线 95 的电位为高电平，第 2 控制信号线 105 和时钟信号线 96 的电位为低电平。由此，在左侧的钟控倒相器 85a 中，P 型 MOSFET100 和 N 型 MOSFET102 成为导通，进行电容 C6、C7 的设定工作，电容 C6、C7 被恰当地充电。在右侧的钟控倒相器 85b 中，由于 P 型 MOSFET100 和 N 型 MOSFET102 为关断状态，

故不进行设定工作。在阶段Ⅱ，由于第1控制信号线104的电位为低电平，MOSFET100和102成为关断，故左侧的钟控倒相器85a中的设定工作结束。

接着，在第2设定工作中，在阶段Ⅰ，在第2控制信号线105和时钟信号线96的电位为高电平的同时，时钟补信号线95的电位为低电平。由此，右侧的钟控倒相器85b的P型MOSFET100和N型MOSFET102成为导通，进行电容C6、C7的设定工作。在阶段Ⅱ中，第2控制信号线105的电位为低电平，右侧的钟控倒相器85b中的设定工作结束。而且，在通常工作中，在第1和第2控制信号线104、105的电位保持为低电平，保存了蓄积于各钟控倒相器85a、85b的电容C6、C7内的电荷的状态下，对时钟信号线和时钟补信号线95、96供给时钟信号。

图20是表示图18所示的包含钟控倒相器85a、85b的移位寄存器81的变形实施例的电路图。在本图中，对与图18相同的部位标出了相同的符号。在图20的实施例中，与图18的实施例的不同点在于：除了初始化信号线108（称为第1初始化信号线）外，还设置第2初始化信号线108a，右侧的钟控倒相器85b的初始化用MOSFET106、107的栅与第2初始化信号线108a连接，独立地进行左侧的钟控倒相器85a与右侧的钟控倒相器85b中的初始化工作。

图21是表示图20的实施例中的初始化、设定工作和通常工作中的各部的合适信号（电位）变化的时序图。如图所示，在本实施例中，在向图20的左侧的钟控倒相器85a的电容C6、C7进行电荷的蓄积的第1设定工作前进行第1初始化工作，在向右侧的钟控倒相器85b的电容C6、C7进行电荷的蓄积的第2设定工作前进行第2初始化工作。

在第1初始化工作中，在时钟信号线96的电位为低电平，时钟补信号线95的电位为高电平，而且第1控制信号线104和第2控制信号线105的电位为低电平的状态下，第1初始化信号线108的电位为高电平。由此，钟控倒相器85a的N型MOSFET106和P型MOSFET107成为导通状态，进行校正电路97、98内的电容C6、C7的初始化。由于参照图19说明了第1设定工作，故在此处省略其说明。

在第2初始化工作中，在时钟信号线96的电位为高电平，时钟补信号线95的电位为低电平，而且第1控制信号线104和第2控制

信号线 105 的电位为低电平的状态下，第 2 初始化信号线 108a 的电位为高电平。由此，钟控倒相器 85b 的 N 型 MOSFET106 和 P 型 MOSFET107 成为导通状态，进行校正电路 97、98 内的电容 C6、C7 的初始化。由于参照图 19 说明了第 2 设定工作，故在此处省略其说明。

在上述实施例中，由于初始化工作被分为第 1 初始化工作和第 2 初始化工作这两者，故在各初始化工作中，可恰当地控制时钟信号线 96 和时钟补信号线 95 的电位，对与 P 型 MOSFET93 的栅连接的电容 C6 施加高电平电位  $V_{CH}$ ，对与 N 型 MOSFET94 的栅连接的电容 C7 施加低电平电位  $V_{CL}$ 。

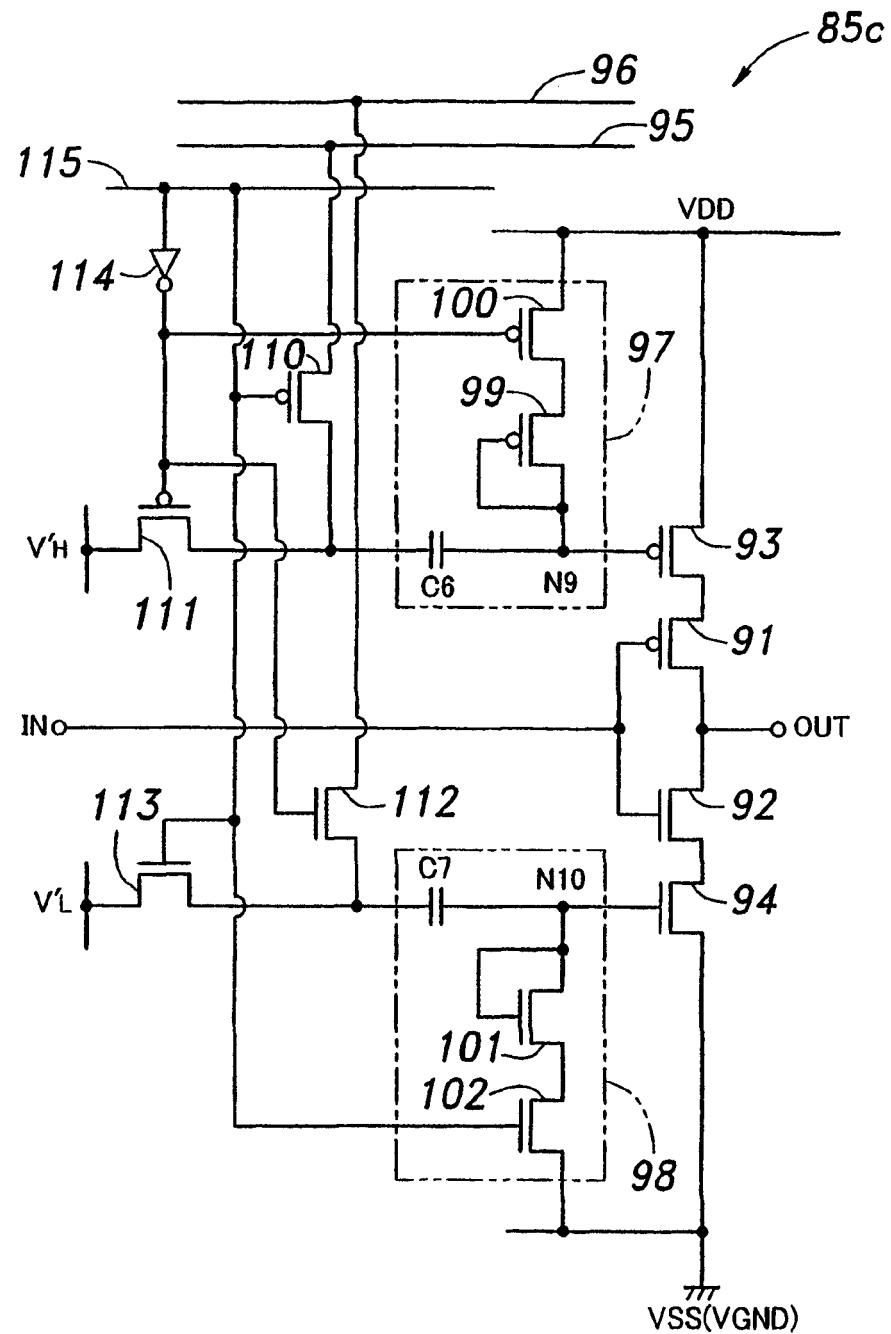

图 22 是表示图 18 所示的钟控倒相器 85a (85b) 的另一实施例的电路图。在本图中，对与图 18 相同的部分标以相同的符号而省略其详细的说明。在该钟控倒相器 85c 中，在与电容 C6 的与 P 型 MOSFET93 的栅连接的端子相反一侧的端子经 P 型 MOSFET110 与时钟补信号线 95 连接的同时，经 P 型 MOSFET111 与时钟补信号的与高电平电位  $V_{CH}$  大致相同的电位  $V_H'$  连接。同样，在与电容 C7 的与 N 型 MOSFET94 的栅连接的端子相反一侧的端子经 N 型 MOSFET112 与时钟信号线 96 连接的同时，经 N 型 MOSFET113 与时钟信号的与低电平电位  $V_{CL}$  大致相同的电位  $V_L'$  连接。MOSFET100、111 和 112 的栅经倒相器 114 与控制信号线 115 连接，MOSFET102、110 和 113 的栅直接与控制信号线 115 连接。由此，如果控制信号线 115 的电位为高电平，则 MOSFET100、111、102 和 113 为导通状态，MOSFET110、112 为关断状态，进行向电容 C6 和 C7 的电荷的蓄积（设定工作）。另一方面，在控制信号线 115 的电位为低电平的情况下，MOSFET100、111、102 和 113 为关断状态，MOSFET110、112 为导通状态，时钟补信号和时钟信号经充了电的电容 C6、C7 被供给 P 型 MOSFET93 和 N 型 MOSFET94 的栅。这样，图 22 的实施例可以说是用 MOSFET100、102、110~113 实现了图 16 所示的钟控倒相电路 60b 的开关 SW12、SW13、SW16~SW19 的实施例。再有，本实施例没有图 18 所示那样的电容 C6、C7 初始用的 MOSFET106、107，但如有需要也可以设置，这是不言而喻的。

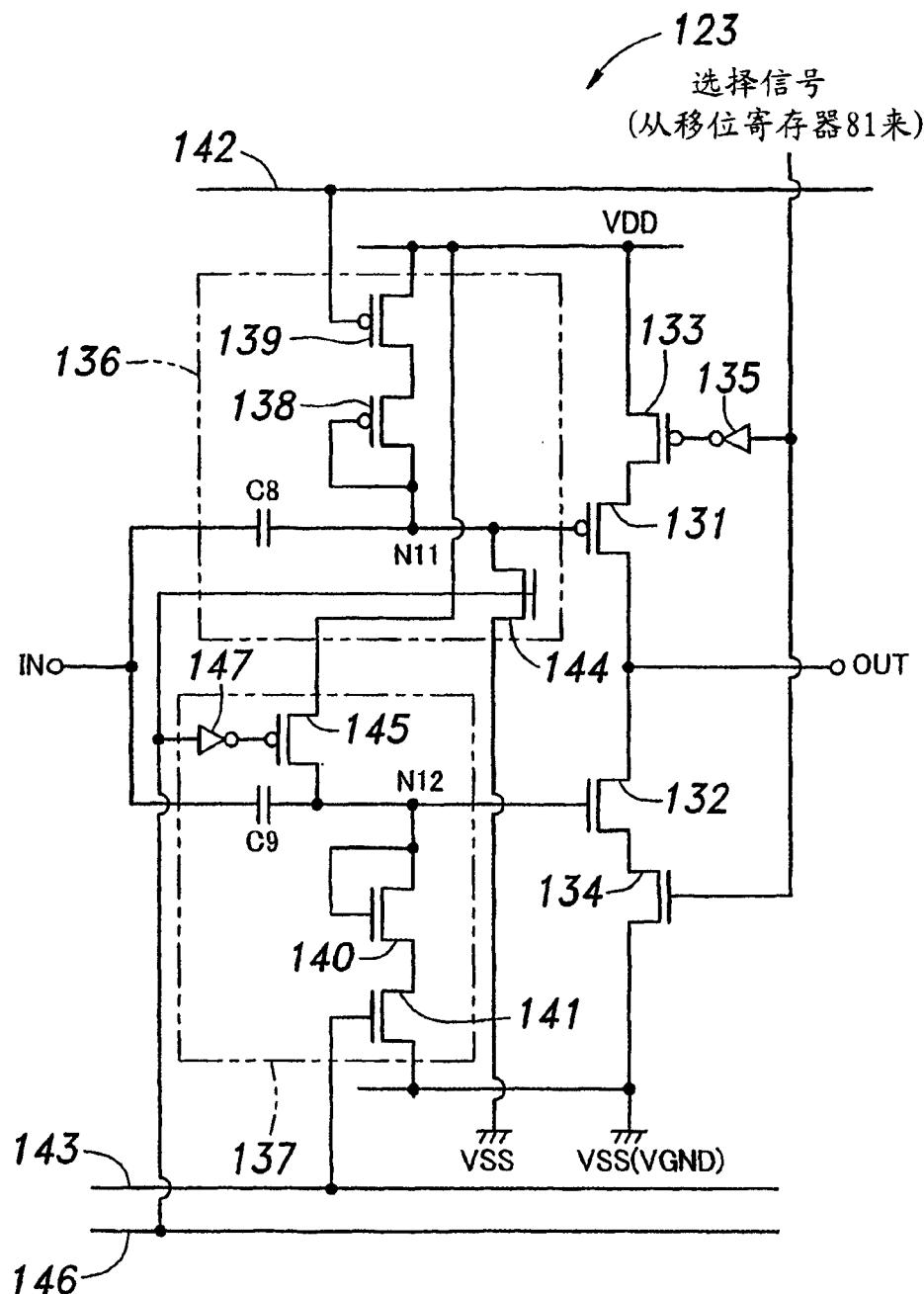

图 23 是表示图 17 所示的第 1 闩锁电路 82 中的典型的单位电路的电路图。该单位电路 120 有 2 个倒相器 121、122 和 2 个钟控倒相器 123、124，响应于来自移位寄存器 81 的选择信号，起闩锁数字化

了的视频信号的作用。在视频信号的高电平电位低于高电平电源电位 VDD 的情况和/或视频信号的低电平电位高于低电平电源电位 VSS 的情况下，可将本发明应用于被供给视频信号作为输入信号的钟控倒相器 123。

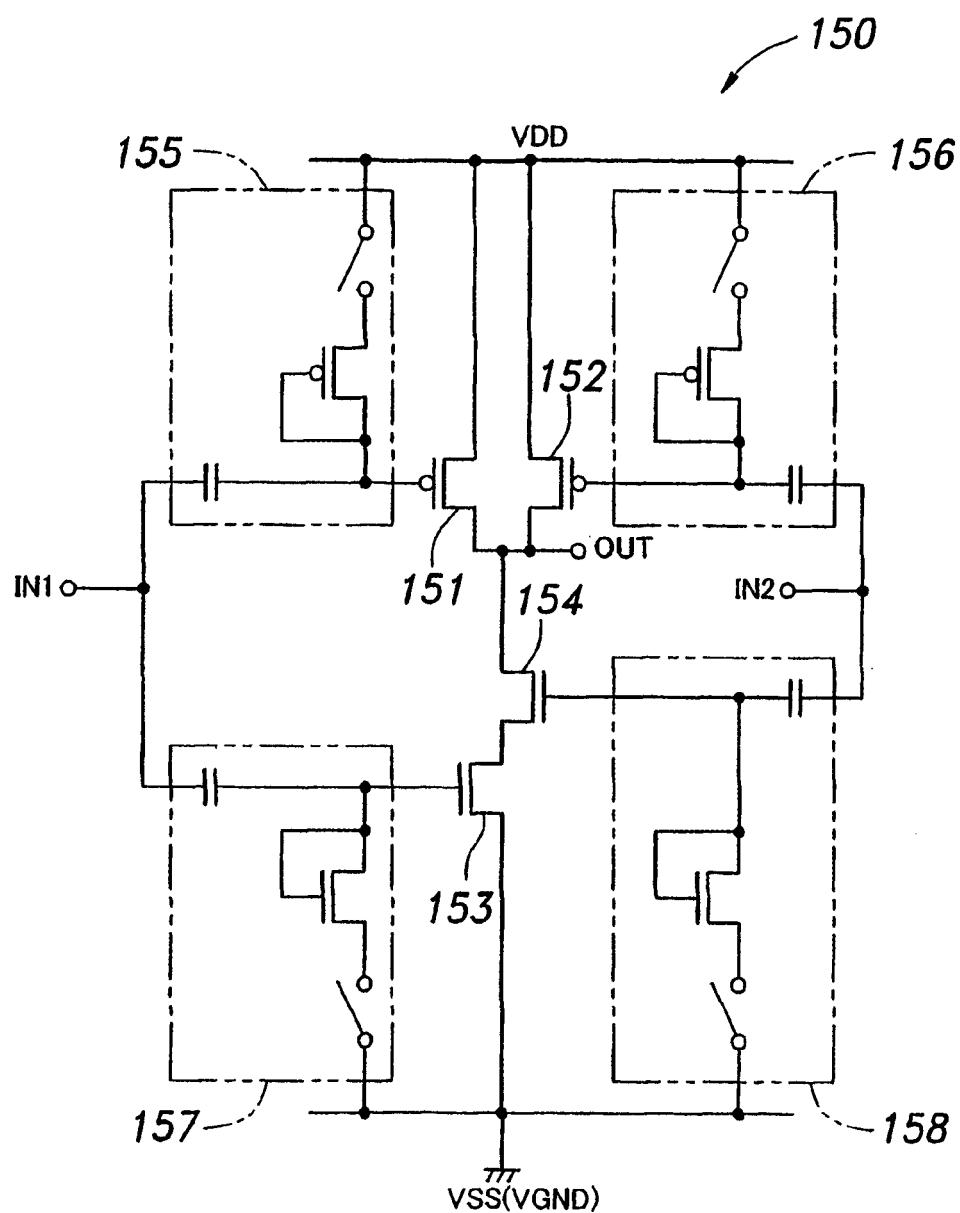

图 24 是表示将本发明应用于图 23 所示的第 1 闩锁电路 32 的钟控倒相器 123 的实施例的电路图。在图 22 中，虽然示出了将校正电路用于时钟信号同步用 MOSFET 的钟控倒相器 85c，但在图 24 中，却示出了将校正电路用于被输入输入信号的 MOSFET 的钟控倒相器。该钟控倒相器 123 具有为了构成 CMOS 倒相器其漏均与输出端 OUT 连接、串联连接了的 P 型 MOSFET131 和 N 型 MOSFET132，这些 MOSFET131、132 的栅均与被输入视频信号作为输入信号输入端 IN 连接。P 型 MOSFET131 的源经 P 型 MOSFET133 与高电平电源电位 VDD 连接，N 型 MOSFET132 的源经 N 型 MOSFET134 与低电平电源电位 VSS（在本例中为  $V_{GND}$ ）连接。虽然对 P 型 MOSFET133 和 N 型 MOSFET134 的栅输入来自移位寄存器的选择信号，但由于在 P 型 MOSFET133 的栅处设置倒相器 135，故被输入到这些 MOSFET133、134 的信号的极性变得相反。

在 P 型 MOSFET131 和 N 型 MOSFET132 的栅与输入端 IN 之间分别连接校正电路 136、137。校正电路 136 具有被连接在 P 型 MOSFET131 的栅与输入端 IN 之间的电容 C8、其阈值电压与 P 型 MOSFET131 大致相同的被连接成二极管的 P 型 MOSFET138 和有选择地进行设定工作用的起开关作用的 P 型 MOSFET139，P 型 MOSFET138 和 P 型 MOSFET139 被串联连接在电容 C8 与 P 型 MOSFET131 的栅之间的节点 N11 与高电平电源电位 VDD 之间。同样，校正电路 137 具有被连接在 N 型 MOSFET132 的栅与输入端 IN 之间的电容 C9、其阈值电压与 N 型 MOSFET132 大致相同的被连接成二极管的 N 型 MOSFET140 和有选择地进行设定工作用的起开关作用的 N 型 MOSFET141，N 型 MOSFET140 和 N 型 MOSFET141 被串联连接在电容 C9 与 N 型 MOSFET132 的栅之间的节点 N12 与低电平电源电位 VSS 之间。在本实施例中，P 型 MOSFET139 的栅与 P 沟道控制信号线 142 连接，N 型 MOSFET141 的栅与 N 沟道控制信号线 143 连接，但如图 16、图 22 所示，在 P 型 MOSFET 和 N 型 MOSFET 中平行地进行设定工作的情况下，与图 18 所示的实施例一样，通过在 P 型 MOSFET139 的栅和 N 型 MOSFET141 的栅中的某一个栅处设置倒相器，

也可以只用共同的 1 条控制信号线。

此外，电容 C8 与 P 型 MOSFET131 的栅之间的节点 N11 经 N 型 MOSFET144 与低电平电源电位 VSS 连接，电容 C9 与 N 型 MOSFET132 的栅之间的节点 N12 经 P 型 MOSFET145 与高电平电源电位 VDD 连接。N 型 MOSFET144 直接与初始化信号线 146 连接，P 型 MOSFET145 的栅经倒相器 147 与初始化信号线 146 连接，对这些 MOSFET144、145 的栅输入相位相反的信号。再有，如图 12 所示，也可分别配置初始化信号线。

图 25 的时序图示出了如此构成了的闩锁电路的钟控倒相器 123 的初始化、设定工作和通常工作中的各部的合适信号（电位）变化。如图所示，按初始化工作、N 沟道设定工作（电容 C9 的设定工作）、P 沟道设定工作（电容 C8 的设定工作）和通常工作的顺序执行，N 沟道设定工作和 P 沟道设定工作各自由 2 个阶段构成。不言而喻，即使变换 N 沟道设定工作和 P 沟道设定工作的顺序亦可。

在初始化工作中，在输入信号（视频信号）、选择信号、N 沟道控制信号（143）为低电平，P 沟道控制信号（142）为高电平的状态下，初始化信号（146）为高电平。由于 P 沟道控制信号为高电平，N 沟道控制信号为低电平，故 P 型 MOSFET139 和 N 型 MOSFET141 为关断状态。如果初始化信号为高电平，则 MOSFET144、145 导通，进行电容 C8、C9 的初始化（即，节点 N11 的电位下降至低电平电源电位 VSS，节点 N12 的电位上升至高电平电源电位 VDD）。如果初始化信号为低电平，则初始化工作结束。

在向与 N 沟道 MOSFET132 的栅连接的电容 C9 进行电荷的蓄积的 N 沟道设定工作中，在阶段 I，视频信号（IN）仍为低电平，N 沟道控制信号（143）为高电平。由此，N 型 MOSFET141 导通，电流从输入端 IN 流向低电平电源电位 VSS，进行电容 C9 的充电。N 沟道控制信号对于电容 C9 两端的电压成为适当的值、N 型 MOSFET141 成为关断状态有充分的时间保持高电平。在阶段 II，N 沟道控制信号变为低电平，N 沟道设定工作结束。

在向与 P 沟道 MOSFET131 的栅连接的电容 C8 进行电荷的蓄积的 P 沟道设定工作中，在阶段 I，在视频信号（IN）为高电平的同时，P 沟道控制信号（142）为低电平。由此，P 型 MOSFET139 导通，电流从

高电平电源电位 VDD 流向输入端 IN，进行电容 C8 的充电。在 P 沟道控制信号对于电容 C8 两端的电压成为适当的值、P 型 MOSFET139 成为关断状态有充分的时间保持低电平后，在阶段Ⅱ，返回到高电平。而且，如果视频信号为低电平，则通常工作可以开始。如图所示，在通常工作中，在 P 沟道控制信号为高电平，N 沟道控制信号为低电平的状态下，施加视频信号和选择信号。这样，具有如图 5、图 7 那样电容与输入端直接连结的类型和如图 13、图 16 那样电容经开关连结的类型。通过将这 2 种类型组合在一起，可构成各种各样的电路。而且，可针对各电路的结构，适当地变更设定工作的时序。

在基于上述本发明的各种实施例中，在进行了校正电路中所包含的电容的设定工作后，由于被连接在电容与电源电位（VDD 或 VSS）之间的开关成为关断状态，在原理上保存了蓄积于电容内的电荷，但实际上由于有微少的漏泄电流，最好以恰当的间隔进行设定工作。例如，在将本发明应用于液晶显示器的有源矩阵电路的移位寄存器中的晶体管的情况下，在所输入的视频信号的回扫期间，由于移位寄存器不工作，故在该期间可进行设定工作（参照图 26a）。

另外，已知在 1 帧期间内，通过有选择地组合多个不同的发光期间 E1、E2、E3、...，使各像素的处于 1 帧内的发光状态的总的期间变化而得到灰度的时间灰度方式的显示器（例如，在 4 位的情况下，假设最小的发光期间为 E1 时，通过假设  $E2=2 \times E1$ 、 $E3=4 \times E1$ 、 $E4=8 \times E1$ ，将 E1~E4 组合在一起，可得到 16 级灰度）。在这样的时间灰度方式的显示器中，例如就各像素进行了表示对发光期间 E3 是否进行发光的信息向存储器写入后，像在开始对发光期间 E4 的同样的写入之前的期间及在结束了表示对发光期间 E4 是否进行发光的信息向存储器写入后那样，存在驱动电路不工作的期间（参照图 26b）。在这样的驱动电路的停止期间，进行上述校正电路的设定工作也是可能的。再有，设定工作无需对全部的校正电路同时进行，也可对每个校正电路按不同的时序进行。另外，在图 17 及图 18 所示那样的移位寄存器中，信号依次移动并传送。从而，应用数级前的信号也可进行本级的校正电路的设定工作。

本发明也可用于 NAND 电路、NOR 电路及传输门等那样的逻辑电路。图 27 例如是将本发明应用于构成 NAND 电路的晶体管的实施例的电路

图，图 28 是将本发明应用于构成 NOR 电路的晶体管的实施例的电路图。

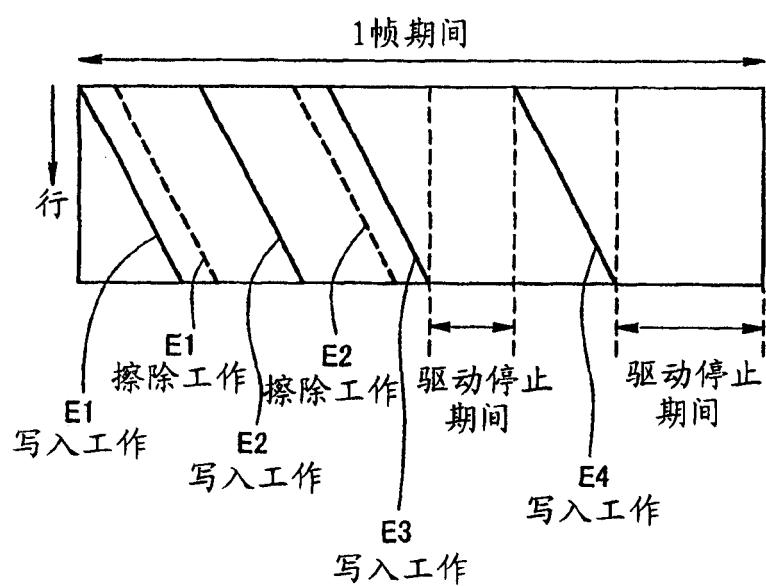

图 27 所示的数字电路 150 具有 2 个并联连接了的 P 型 MOSFET151、152 和 2 个串联连接了的 N 型 MOSFET153、154，利用这 4 个 MOSFET151~154 形成 NAND 电路。如要详细叙述，则是 P 型 MOSFET151 和 N 型 MOSFET153 的栅与第 1 输入端 IN1 连接，P 型 MOSFET152 和 N 型 MOSFET154 的栅与第 2 输入端 IN2 连接。另外，P 型 MOSFET151、152 的源均与高电平电源电位 VDD 连接，其漏在均与 N 型 MOSFET154 的漏连接的同时，也与输出端 OUT 连接。N 型 MOSFET154 的源与 N 型 MOSFET153 的漏连接，N 型 MOSFET153 的源与低电平电源电位 VSS（在本例中，为地电位  $V_{GND}$ ）连接。这样的 NAND 电路在本领域内为人们所熟知。

基于本发明，对 MOSFET151~154 分别设置校正电路 155~158。与上述实施例一样，各校正电路 155~158 具有被连接在对应的 MOSFET 的栅上的电容、有与对应的 MOSFET 相同的极性并且大致相同的阈值电压的被连接成二极管的 MOSFET 和与被连接成二极管的 MOSFET 串联连接的开关。这样的校正电路 155~158 的工作和作用效果由于与对上述实施例所作的说明相同，故省略其说明。

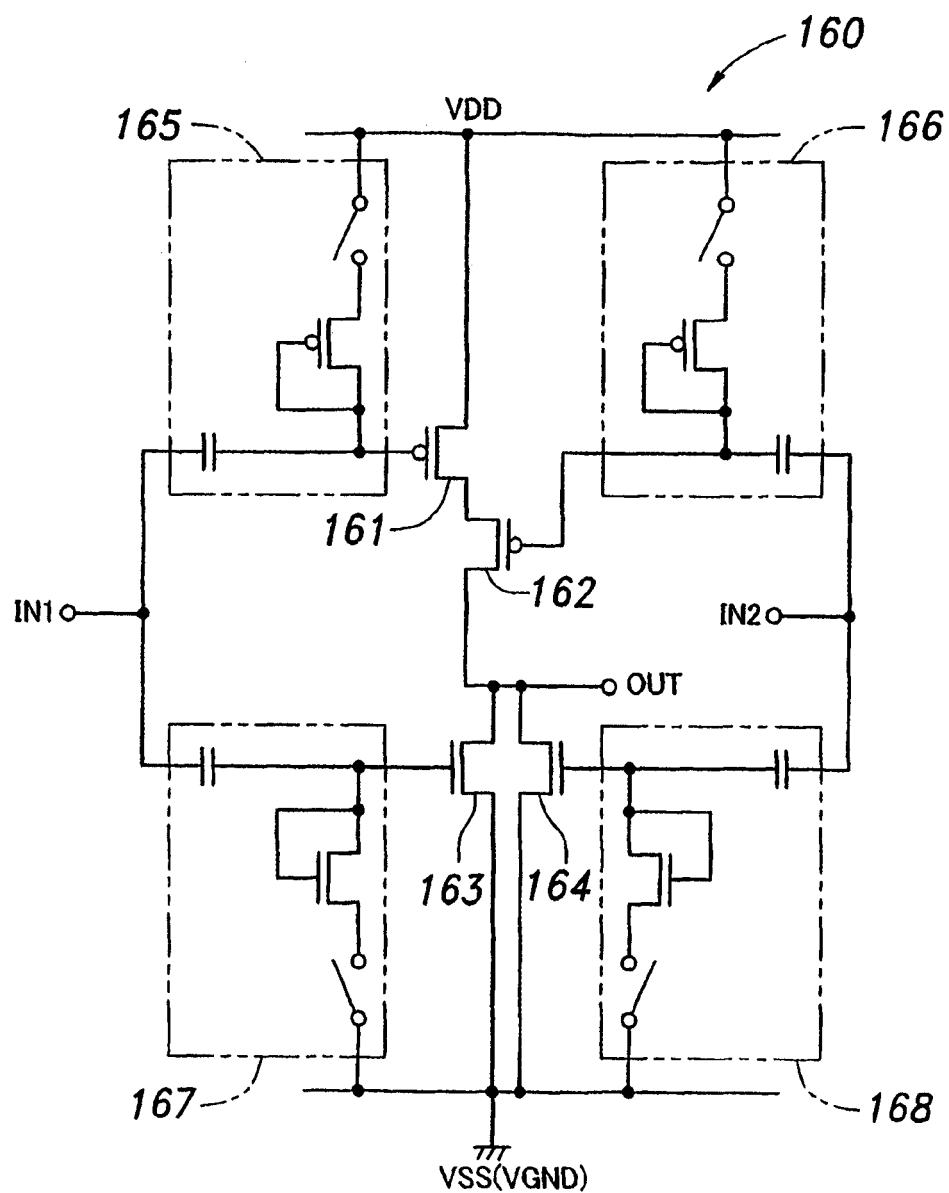

图 28 所示的数字电路 160 具有 2 个串联连接了的 P 型 MOSFET161、162 和 2 个并联连接了的 N 型 MOSFET163、164，利用这 4 个 MOSFET161~164 形成 NOR 电路。如要详细叙述，则是 P 型 MOSFET161 和 N 型 MOSFET163 的栅与第 1 输入端 IN1 连接，P 型 MOSFET162 和 N 型 MOSFET164 的栅与第 2 输入端 IN2 连接。另外，P 型 MOSFET161 的源与高电平电源电位 VDD 连接，其漏与 P 型 MOSFET162 的源连接。P 型 MOSFET162 的漏在与 N 型 MOSFET163、164 的漏连接的同时，也与输出端 OUT 连接。而且，N 型 MOSFET163、164 的源均与低电平电源电位 VSS（在本例中，为地电位  $V_{GND}$ ）连接。这样的 NOR 电路在本领域内为人们所熟知。

基于本发明，对 MOSFET161~164 分别设置校正电路 165~168。与上述实施例一样，各校正电路 165~168 具有被连接在对应的 MOSFET 的栅上的电容、有与对应的 MOSFET 相同的极性并且大致相同的阈值电压的被连接成二极管的 MOSFET 和与被连接成二极管的 MOSFET 串联

连接的开关。这样的校正电路 165~168 的工作和作用效果由于与对上述实施例所作的说明相同，故省略其说明。

在上述情况中，在输入信号的振幅小于电源电压（高电平电源电位与低电平电源电位之差）的情况下，虽然也就具有能可靠地使晶体管通断的、使用了晶体管的开关电路的数字电路的优选实施例进行了说明，但上述实施例通过恰当地变更设定工作，在电源电压相对于晶体管的阈值电压的绝对值不充分大的情况下，也可与希望提高晶体管的工作速度的情况相对应。在图 29 中，示出了可进行那样的设定工作的数字电路的另一变形实施例。再有，在本实施例中，对与图 5 的实施例相同的部位标以相同的符号而省略其详细的说明。

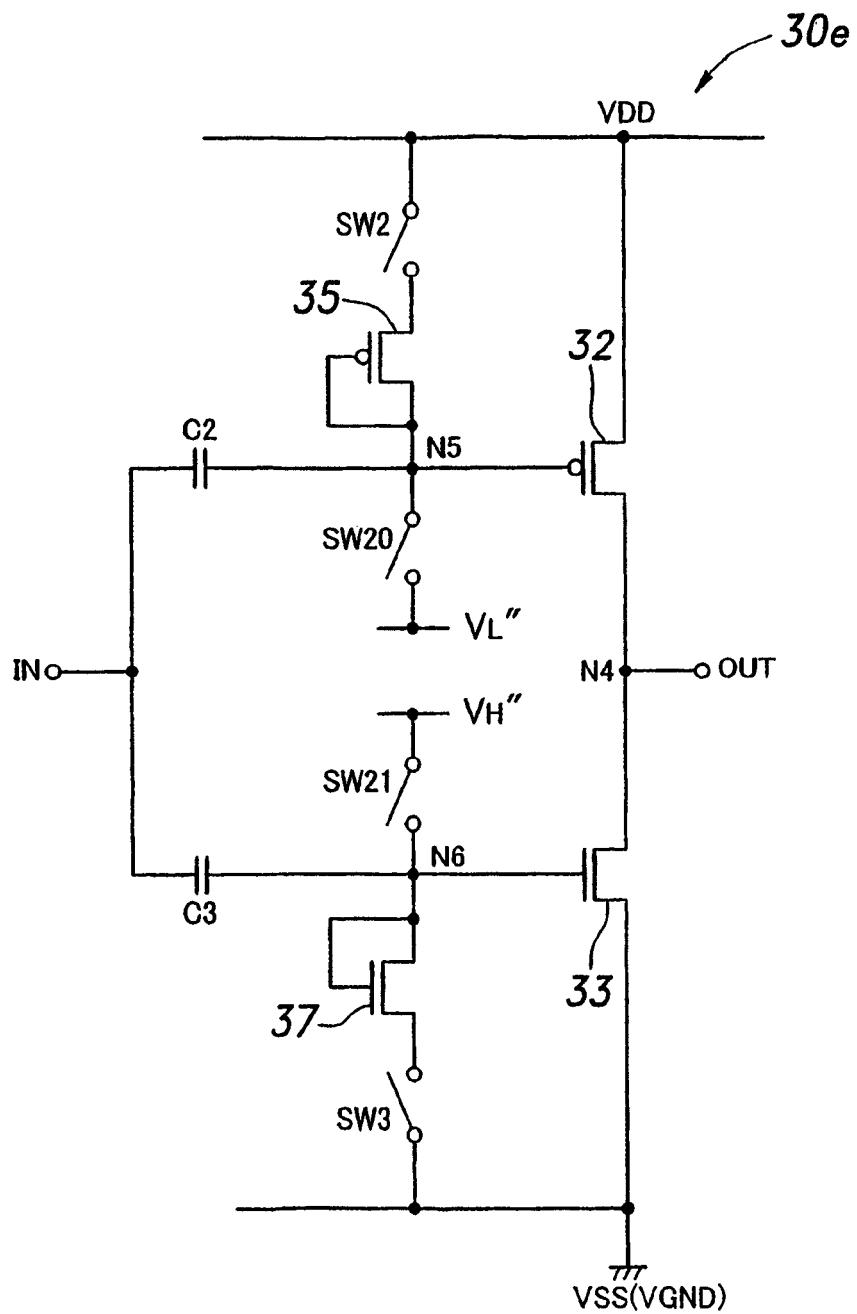

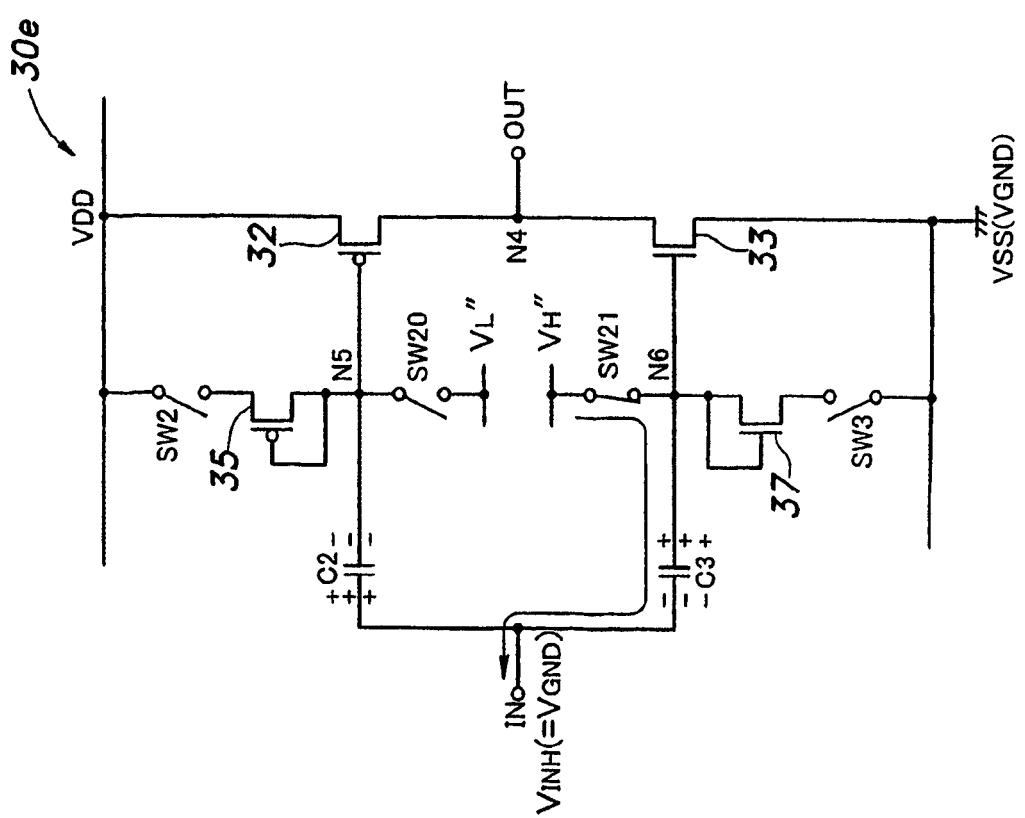

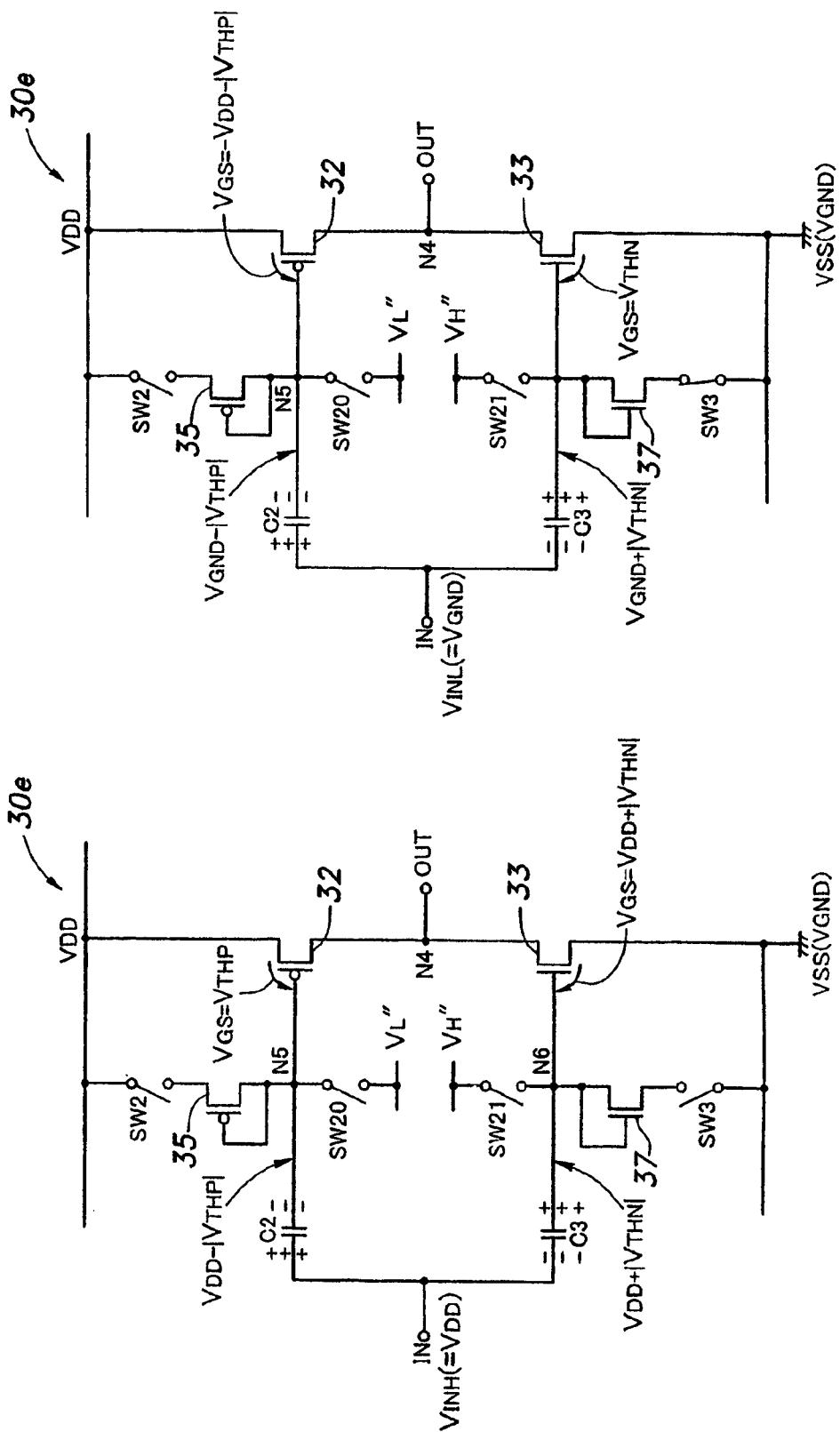

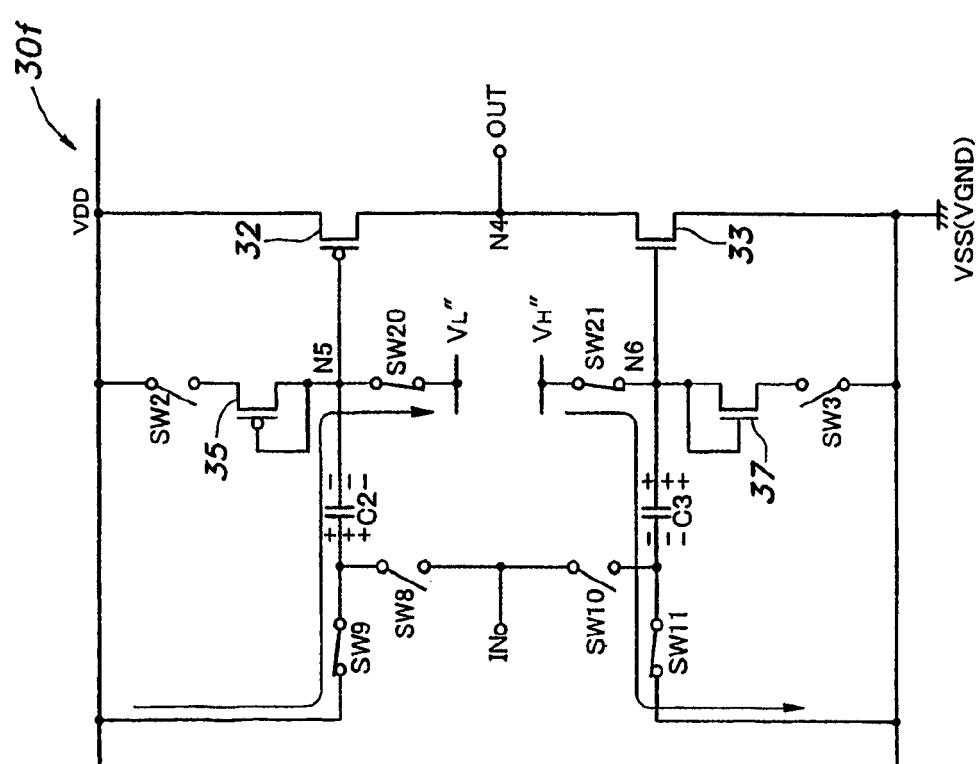

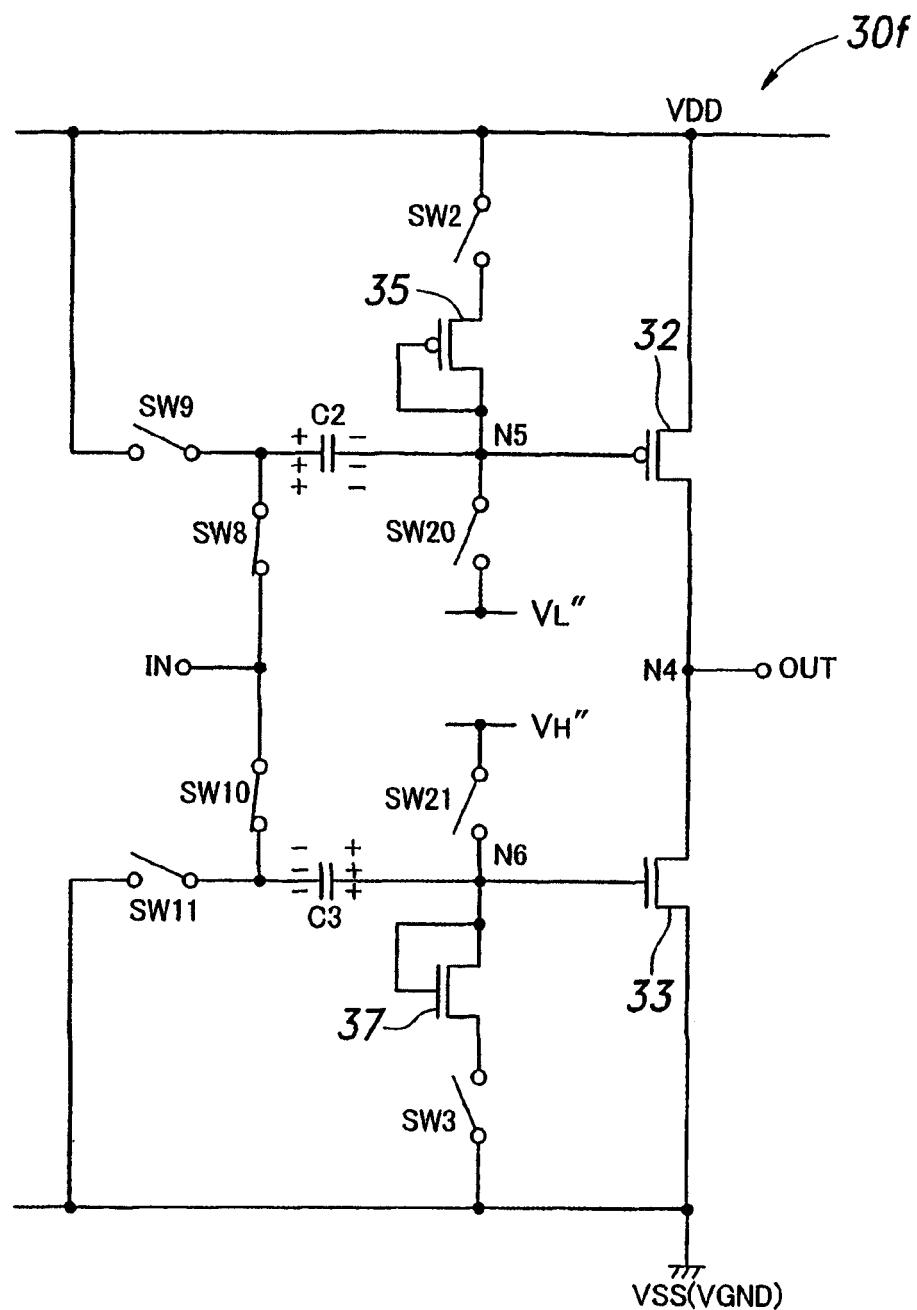

在图 29 的数字电路（倒相电路）30e 中，P 型 MOSFET32 的栅与电容 C2 之间的节点 N5 经开关 SW20 与低电平电位  $V_L''$  连接，N 型 MOSFET33 的栅与电容 C3 之间的节点 N6 经开关 SW21 与高电平电位  $V_H''$  连接。低电平电位  $V_L''$  可等于低电平电源电位 VSS。另外，高电平电位  $V_H''$  例如可等于高电平电源电位 VDD，但此时数字电路 30e 变得与数字电路 30c 相同。

以下说明如此构成的数字电路 30e 的设定和通常工作。此处，假定低电平输入电位  $V_{INL}$  等于低电平电源电位 VSS（在本例中，为  $V_{GND}$ ），高电平输入电位  $V_{INH}$  等于高电平电源电位 VDD。

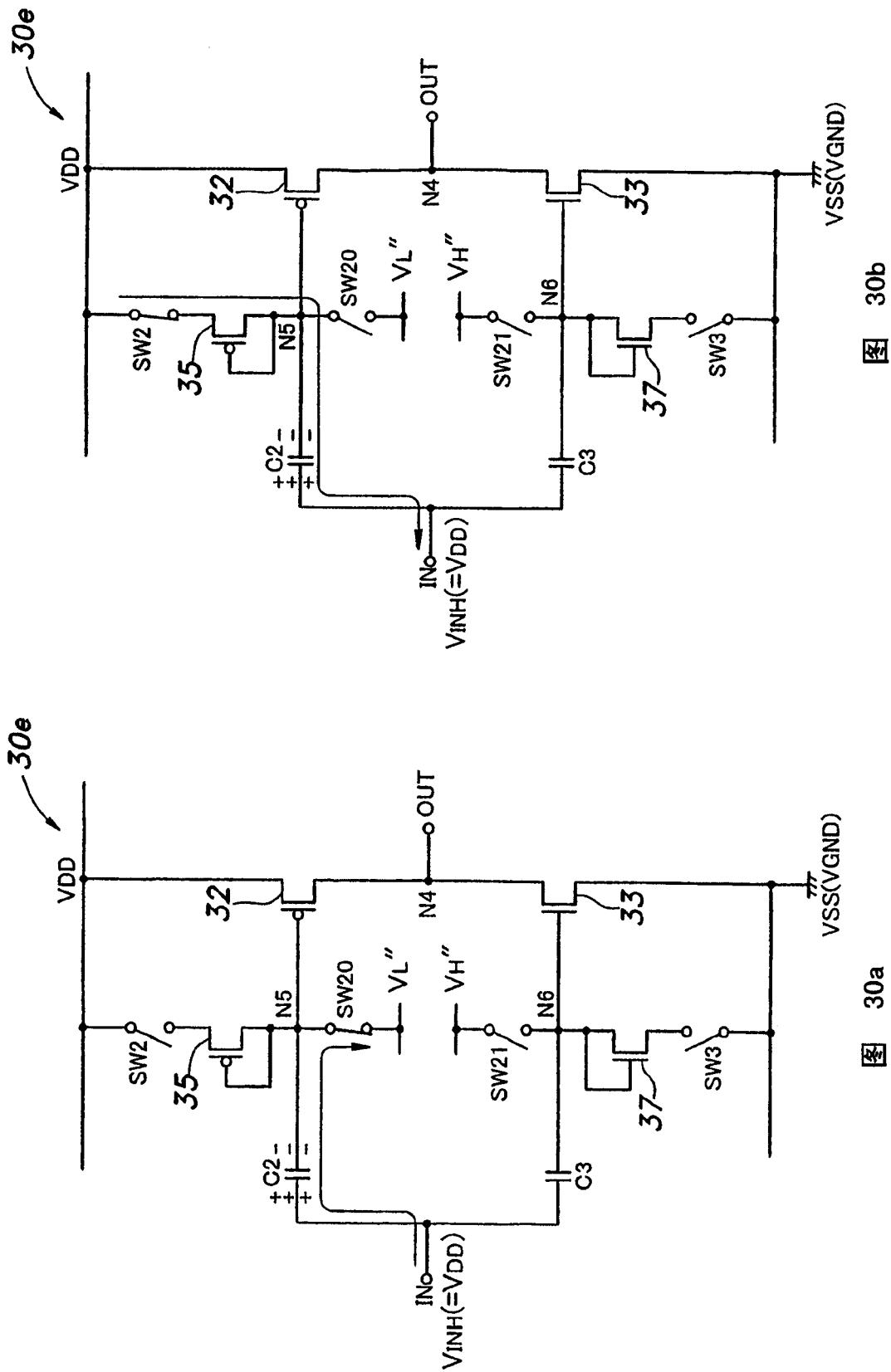

如图 30a 所示，在对电容 C2 的第 1 设定工作中，在开关 SW2、SW3 和 SW21 为关断的状态下，如果使 SW20 导通，向输入端 IN 施加高电平输入电位  $V_{INH}$ ，则在图的箭头方向流过电流，电容 C2 在输入端 IN 侧为高、P 型 MOSFET32 的栅侧为低的方向被充电。接着，如图 30b 所示，在第 2 设定工作中，在仍然向输入端 IN 施加了高电平输入电位  $V_{INH}$  时，如果使开关 SW20 关断、使开关 SW2 导通，则电容 C2 放电，在图中如箭头所示流过电流，在电容 C2 两端的电压等于 P 型 MOSFET35 的阈值电压  $V_{THP}$  时电流停止。再有，在第 1 设定工作中，也可使开关 SW2 导通。另外，低电平电位  $V_L''$  只要是在第 1 设定工作中能以大于 P 型 MOSFET35 的（即 P 型 MOSFET32 的）阈值电压  $V_{THP}$  的电压对电容 C2 充电那样的值即可，可以不一定等于 VSS。也可将第 1 设定工作称为初始化工作。

同样，如图 31a 所示，在对电容 C3 的第 1 设定工作中，在开关 SW2、

SW3 和 SW20 为关断的状态下，如果使 SW21 导通，向输入端 IN 施加低电平输入电位  $V_{INL}$ ，则在图的箭头方向流过电流，电容 C3 在输入端 IN 侧为低、N 型 MOSFET33 的栅侧为高的方向被充电。接着，在第 2 设定工作中，在仍然向输入端 IN 施加了低电平输入电位  $V_{INL}$  时，如果使开关 SW21 关断、使开关 SW3 导通，则电容 C3 放电，在图 31b 中如箭头所示流过电流，在电容 C3 两端的电压等于 N 型 MOSFET37 的阈值电压  $V_{THN}$  时电流停止。再有，在第 1 设定工作中，也可使开关 SW3 导通。另外，高电平电位  $V_H''$  只要是在第 1 设定工作中能以大于 N 型 MOSFET37 的（即 N 型 MOSFET33 的）阈值电压  $V_{THN}$  的电压对电容 C3 充电那样的值即可，可以不一定等于 VDD。

这样，在对电容 C2、C3 充电后，在通常工作中，使开关 SW2、SW3、SW20 和 SW21 关断，向输入端 IN 施加其振幅在高电平输入电位  $V_{INH}$  与低电平输入电位  $V_{INL}$  之间的输入信号。在施加了高电平输入电位  $V_{INH}$  时，如图 32a 所示，P 型 MOSFET32 的栅电位为  $V_{INH}-|V_{THP}|=VDD-|V_{THP}|$ ，从而，P 型 MOSFET32 的栅·源间电压  $V_{GS}=-|V_{THP}|$ ，P 型 MOSFET32 关断。另一方面，N 型 MOSFET33 的栅电位为  $V_{INH}+|V_{THN}|=VDD+|V_{THN}|$ ，从而，从 N 型 MOSFET33 的栅·源间电压  $V_{GS}$  减去了  $V_{THN}$  后的差值电压等于 VDD，可确保 N 型 MOSFET33 中流过大电流、使之高速导通所需的充分的电压。

同样地，在向输入端 IN 施加了低电平输入电位  $V_{INL}$  时，如图 32b 所示，N 型 MOSFET33 的栅电位为  $V_{INL}+|V_{THN}|=V_{GND}+|V_{THN}|$ ，从而，N 型 MOSFET33 的栅·源间电压  $V_{GS}=|V_{THN}|$ ，N 型 MOSFET33 关断。另一方面，P 型 MOSFET32 的栅电位为  $V_{INL}-|V_{THP}|=V_{GND}-|V_{THP}|$ ，从而，从 P 型 MOSFET32 的栅·源间电压  $V_{GS}$  减去了  $V_{THP}$  后的差值电压等于 -VDD，可确保 P 型 MOSFET32 中流过大电流、使之高速导通所需的充分的电压（绝对值）。

这样，在参照图 29~图 32 说明过的实施例中，在设定工作中，为了提高对应的 MOSFET32、33 的导通工作速度而校正输入信号的 DC 电平，以此对校正电路的电容 C2、C3 充电是可能的。从而，可减小电源电压以谋求降低功耗，而不降低电路的工作速度。再有，在上述说明中，虽然假定了低电平输入电位  $V_{INL}$  等于低电平电源电位 VSS（在本例中，为  $V_{GND}$ ），高电平输入电位  $V_{INH}$  等于高电平电源电位 VDD，但本发明却不限定于此。在上述电路中，一般来说，设定工作后的电容 C2 的电压的绝对值为  $|V_{THP}|-(VDD-V_{INH})$ ，设定工作后的电容 C3 的电

压的绝对值为  $|V_{THN}| - (V_{INL} - VSS)$ ，可以理解为，在关断状态下，无论是 P 型 MOSFET32、N 型 MOSFET33 中的任何一个在  $V_{GS}$ =阈值电压的极限状态下均关断，在导通状态下， $|V_{GS}| = |$  阈值电压  $| + V_{INH} - V_{INL}$ 。

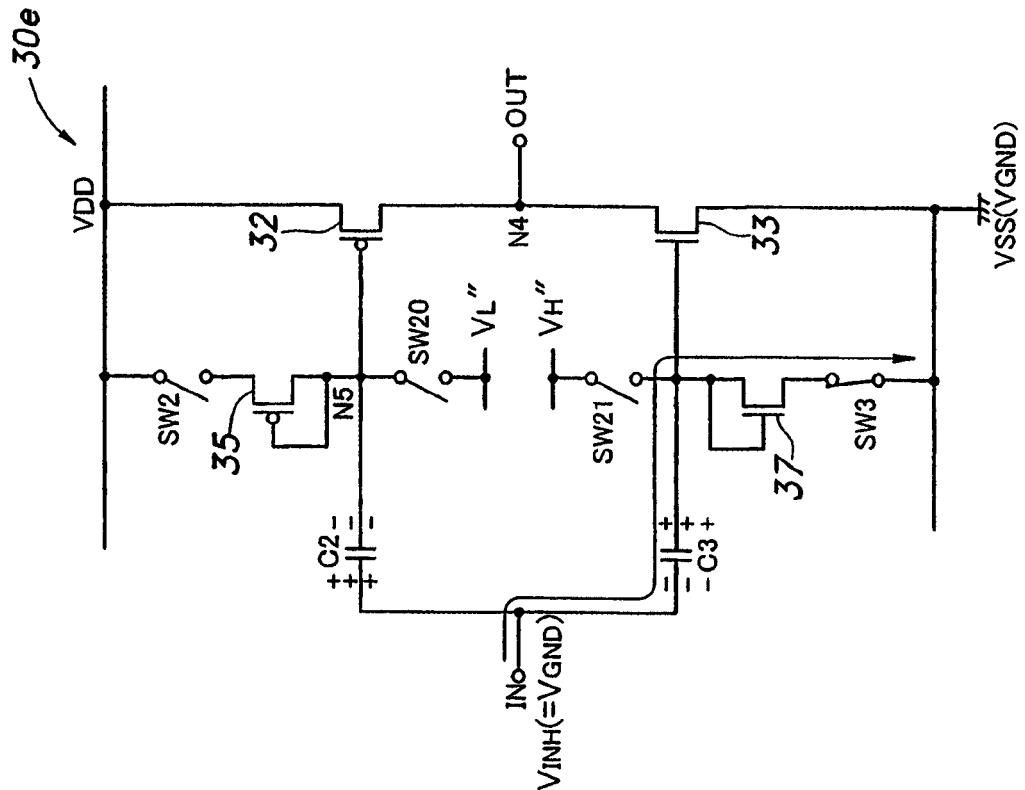

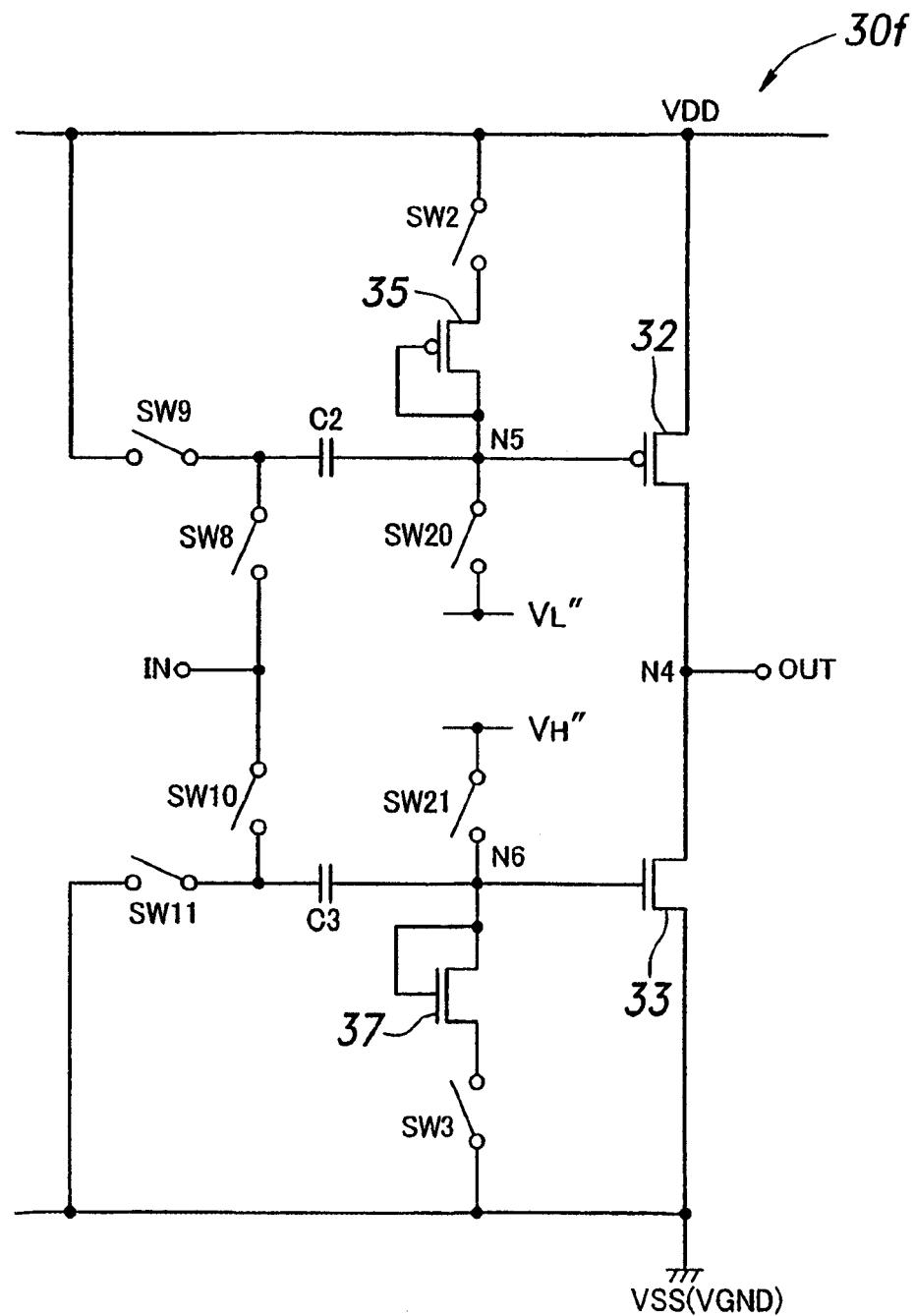

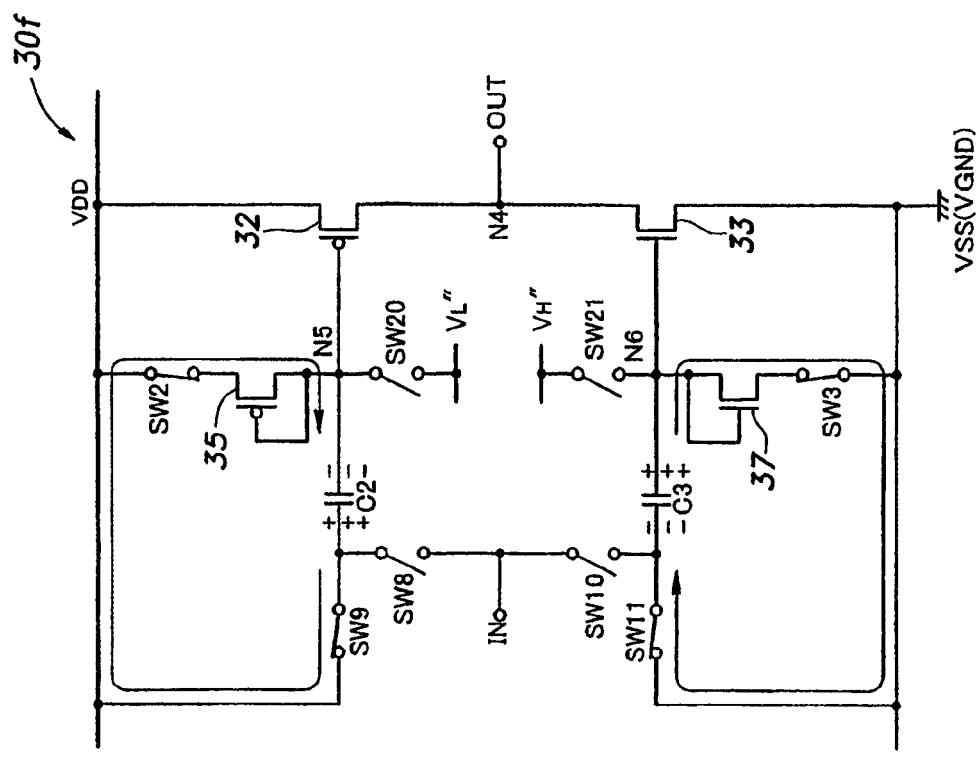

在图 29 的数字电路 30e 中，改变施加于输入端 IN 的输入信号的电位，分别进行了与 P 型 MOSFET32 的栅连接的电容 C2 和与 N 型 MOSFET33 的栅连接的电容 C3 的设定工作，但最好同时进行这两者。图 33 示出了这样的数字电路。再有，在本实施例中，应用了图 13 所示的数字电路 30d，在本图中，对与图 13 和图 29 所示的部位相同的部位标以相同的符号而省略其详细的说明。

在图 33 的数字电路 30f 中，在与电容 C2 的与 P 型 MOSFET32 的栅连接的端子相反一侧的端子经开关 SW8 与输入端 IN 连接的同时，经开关 SW9 与高电平电源电位 VDD 连接。同样，在与电容 C3 的与 N 型 MOSFET33 的栅连接的端子相反一侧的端子经开关 SW10 与输入端 IN 连接的同时，经开关 SW11 与低电平电源电位 VSS 连接。

以下说明如此构成的数字电路 30f 的设定和通常工作。此处，也与对数字电路 30e 的工作所作的说明同样地，假定低电平输入电位  $V_{INL}$  等于低电平电源电位 VSS（在本例中，为  $V_{GND}$ ），高电平输入电位  $V_{INH}$  等于高电平电源电位 VDD。

如图 34a 所示，在第 1 设定工作中，使开关 SW2、SW3、SW8 和 SW10 关断，使开关 SW9、SW11、SW20 导通。于是，电流在图的箭头方向流过，电容 C2 在输入端 IN 侧为高、P 型 MOSFET32 的栅侧为低的方向被充电，电容 C3 在输入端 IN 侧为低、N 型 MOSFET33 的栅侧为高的方向被充电。也可将第 1 设定工作称为初始化工作。

如图 34b 所示，在第 2 设定工作中，使开关 SW2、SW3、SW9 和 SW11 导通，使开关 SW8、SW10、SW20 和 SW21 关断。由此，电容 C2、C3 放电，电流在图中用箭头所示的方向流过，在电容 C2 两端的电压等于 P 型 MOSFET35 的阈值电压、电容 C3 两端的电压等于 N 型 MOSFET37 的阈值电压时各自的电流停止。

在电容 C2、C3 的设定结束后，在通常工作中，如图 35 所示，使开关 SW2、SW3、SW9、SW11、SW20 和 SW21 关断，使开关 SW8 和 SW10 导通，向输入端 IN 施加输入信号。此时的 MOSFET32、33 中的工作由于与图 32a、图 32b 中所作的说明相同，故在此处省略其说明。再有，

在本实施例中，由于假定低电平输入电位  $V_{INL}$  等于低电平电源电位 VSS，高电平输入电位  $V_{INH}$  等于高电平电源电位 VDD，故假定电容 C2、C3 分别经 SW9、SW11 与高电平电源电位 VDD、低电平电源电位 VSS 连接，若非如此，则电容 C2、C3 可分别经 SW9、SW11 与大致等于高电平输入电位  $V_{INH}$  的电位、大致等于低电平输入电位  $V_{INL}$  的电位连接。

以上，基于实施例详细说明了本发明，但这些实施例始终是示例性的，本发明不受这些实施例限定。不用说，如为专业人员，则在不背离由权利要求的范围确定的本发明的技术思想的前提下，可进行各种变形或变更。

例如，在上述实施例中，假定低电平电源电位 VSS 为地电位  $V_{GND}$ ，假定高电平电源电位 VDD 为高于  $V_{GND}$  的电位，但例如像假定高电平电源电位 VDD 为地电位  $V_{GND}$ ，假定低电平电源电位 VSS 为低于地电位  $V_{GND}$  的电位那样，假定为其它的电位亦可。另外，在上述实施例中，作为晶体管虽然对 MOSFET 作了说明，但使用双极晶体管及其它类型的 FET 等另外的晶体管也是可以的。晶体管也可以是用任何结构、材料、制造方法制作的产品。既可以用通常的单晶基板，又可以用 SOI（绝缘体上的硅）基板。另外，既可以是使用了无定形硅或多晶硅等的薄膜晶体管（TFT），又可以是使用了有机半导体的晶体管，还可以是使用了碳纳米管的晶体管。另外，晶体管也可以在玻璃基板、石英基板、塑料基板或其它的基板上形成。

如以上说明过的那样，基于本发明的数字电路具有：有供给电源电位的 MOSFET 等的第 1 晶体管的开关电路；以及连接在施加输入信号的输入端与第 1 晶体管的控制端子（栅）之间的校正电路，该校正电路具有：a) 连接在第 1 晶体管的控制端子与输入端之间的电容；以及 b) 在通常工作之前的设定工作中，用于设定蓄积于电容内的电荷使得电容两端的电压为规定的值的确定导电路径用的至少 1 个开关，在通常工作中，设定至少 1 个开关的状态，以保存电容两端的电压。由此，在输入电位电平与电源电位电平有差异（例如，高电平输入电位低于高电平电源电位）、如没有校正电路则开关电路工作不正常的情况下，或者，电源电压相对于晶体管的阈值电压不充分大（例如电源电压为 3.3V，晶体管的阈值电压为 3V）、晶体管难以进行高速工作的情况下，通过在设定工作中恰当地设定电容两端的电压，在通

常工作中使该设定了的电压（或电荷）得以保持，可恰当地校正输入信号的 DC 电平，实现恰当的电路工作。在通常工作中，由于保持了电容的电荷，故不担心电容对数字电路的动态特性产生恶劣影响（即，使工作速度降低）。直接地说，由于电容与晶体管的寄生电容串联连接，使总电容减少，故对动态特性的提高作出贡献。此外，由于无需频繁地进行设定工作，故伴随设定工作的功耗仅为少许即可。理想情况是，为了使电容的电压可反映对应的晶体管的阈值电压，校正电路具有设置在电容与第 1 晶体管的控制端子之间的节点与电源电位之间的、其阈值电压与第 1 晶体管大致相同的被连接成二极管的第 2 晶体管和与被连接成二极管的第 2 晶体管串联连接的开关。

作为可应用本发明的电子装置，可举出台式、床头或壁挂式显示器、摄像机、数码相机、护目镜式显示器（头戴显示器）、导航系统、音响再生装置（汽车音响、声音合成等）、笔记本式个人计算机、游戏机、便携式信息终端（便携式计算机、移动电话、便携式游戏机或电子书籍等）、配备了记录媒体的图像再生装置（具体地说，配备了能使记录于数字通用盘（DVD）等的记录媒体中的影像或静止图像再生并显示这些图像的显示器的装置）等。这些电子装置的具体例子示于图 38a~图 38h。

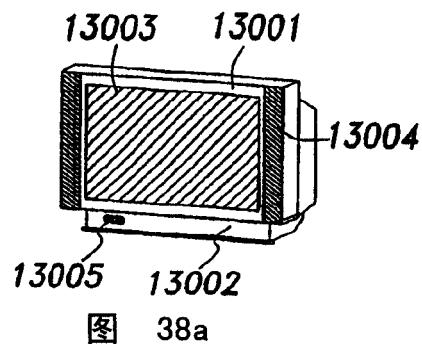

图 38a 是台式、床头或壁挂式显示器，包含机壳 13001、支撑台 13002、显示部 13003、扬声器部 13004、视频输入端子 13005 等。本发明可用于构成显示部 13003 的电路。这样的显示器可用作个人计算机用、TV 广播接收用、广告显示用等任意的信息显示用显示装置。

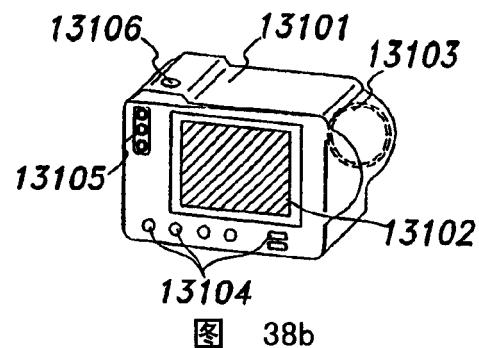

图 38b 是数码相机，包含主体 13101、显示部 13102、显像部 13103、操作键 13104、外部连接端口 13105、快门 13106 等。本发明可用于构成显示部 13102 的电路。

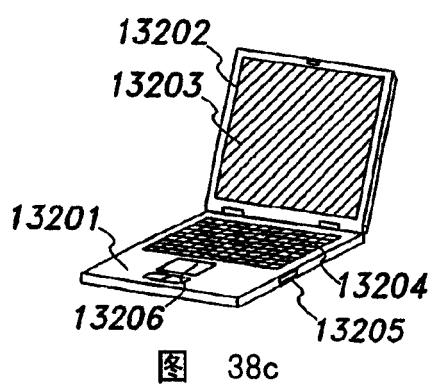

图 38c 是笔记本式个人计算机，包含主体 13201、机壳 13202、显示部 13203、键盘 13204、外部连接端口 13205、指示鼠标 13206 等。本发明可用于构成显示部 13203 的电路。

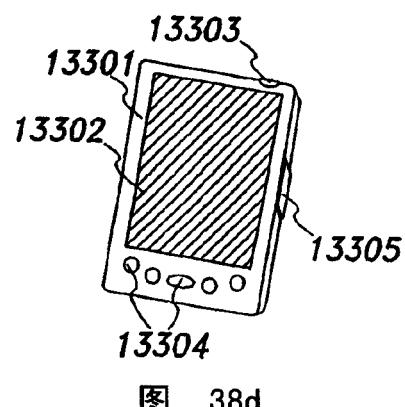

图 38d 是便携式计算机，包含主体 13301、显示部 13302、开关 13303、操作键 13304、红外线端口 13305 等。本发明可用于构成显示部 13302 的电路。

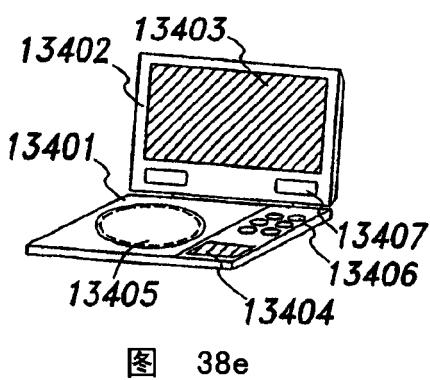

图 38e 是配备了记录媒体的便携式图像再生装置（具体地说，是

DVD 再生装置), 包含主体 13401、机壳 13402、第 1 显示部 13403、第 2 显示部 13404、记录媒体 (DVD 等) 读入部 13405、操作键 13406、扬声器部 13407 等。第 1 显示部 13403 主要显示图像信息, 第 2 显示部 13404 主要显示文字信息, 而本发明可用于构成第 1 和第 2 显示部 13403、13404 的电路。再有, 家庭用游戏机等也被包含在配备了记录媒体的图像再生装置中。

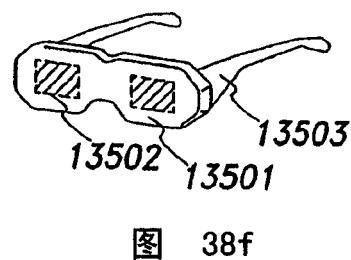

图 38f 是护目镜式显示器 (头戴显示器), 包含主体 13501、显示部 13502、键盘 13204、臂部 13503 等。本发明可用于构成显示部 13502 的电路。

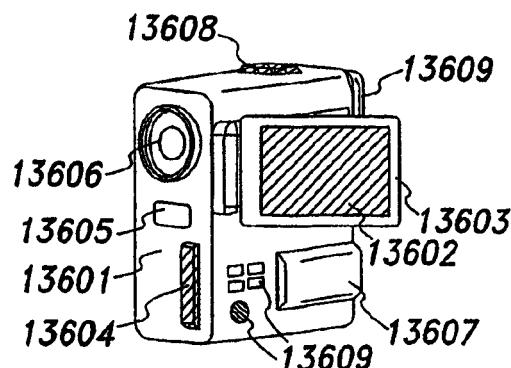

图 38g 是摄像机, 包含主体 13601、显示部 13602、机壳 13603、外部连接端口 13604、遥控接收部 13605、显像部 13606、电池 13607、声音输入部 13608、操作键 13609 等。本发明可用于构成显示部 13602 的电路。

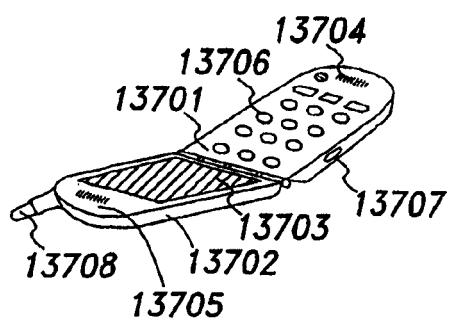

图 38h 是移动电话, 包含主体 13701、机壳 13702、显示部 13703、声音输入部 13704、声音输出部 13705、操作键 13706、外部连接端口 13707、天线 13708 等。本发明可用于构成显示部 13703 的电路。

上述那样的电子装置的显示部例如可以是在各像素中使用了 LED 或有机 EL 等发光元件的自发光型, 或者, 也可以是像液晶显示器那样使用了背光等另外的光源的类型, 但在自发光型的情况下, 可以是无需背光、比液晶显示器薄的显示部。

另外, 上述电子装置多显示通过因特网或 CATV (电缆电视) 等的电子通信线路而交换的信息, 特别是显示动态图像信息的机会正日益增多。在显示部为自发光型的情况下, 由于有机 EL 等的发光材料的响应速度比液晶快得多, 故很适合于这样的动态图像显示。在未来, 如果发光材料的发光亮度增高, 则也可用于用透镜等放大投影包含所输出的图像信息的正面式或背面式的投影仪。

在自发光型的显示部中, 由于发光的部分消耗电力, 故希望以竭力减少发光部分的方式来显示信息。从而, 便携式信息终端, 特别是在移动电话或音响再生装置之类的以文字信息为主的显示部是自发光型的情况下, 希望以非发光部分为背景、用发光部分形成文字信息的方式进行驱动。

如上所述, 本发明的应用范围极广, 可用于所有领域的电子装置。

图 2

图 4

图 5

图 6b

图 6a

图 7

图 8

图 9

图 10

图 11b

图 11a

图 12

图 13

图 14

图 15

图 16

图 17

图 18

图 19

图 20

图 21

图 22

图 24

图 25

图 26a

图 26b

图 27

图 28

图 29

图 30a

图 30b

图 31b

图 31a

图 33

图 34b

图 34a

图 35

图 37a

图 37b

|                |                                                                                                                           |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">CN101025535A</a>                                                                                              | 公开(公告)日 | 2007-08-29 |

| 申请号            | CN200710085560.1                                                                                                          | 申请日     | 2003-12-18 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                                                              |         |            |

| 申请(专利权)人(译)    | 株式会社半导体能源研究所                                                                                                              |         |            |

| 当前申请(专利权)人(译)  | 株式会社半导体能源研究所                                                                                                              |         |            |

| [标]发明人         | 木村肇                                                                                                                       |         |            |

| 发明人            | 木村肇                                                                                                                       |         |            |

| IPC分类号         | G02F1/1362 G02F1/133 H03K19/017                                                                                           |         |            |

| CPC分类号         | H01L27/0629 G02F1/1368 H03K19/01728 H01L27/1255 H03K19/018521 Y10T307/74 Y10T307/747<br>G02F1/136213 G11C19/28 H01L27/124 |         |            |

| 代理人(译)         | 刘宗杰                                                                                                                       |         |            |

| 优先权            | 2002375002 2002-12-25 JP                                                                                                  |         |            |

| 其他公开文献         | <a href="#">CN100538486C</a>                                                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                                            |         |            |

#### 摘要(译)

本发明的目的是提供一种数字电路，它具有：有被供给电源电位(VDD、VSS)的第1晶体管(32、33)的开关电路(31)；以及连接在被施加输入信号的输入端(IN)与第1晶体管的控制端子(栅)之间的校正电路(34、36)，并具有：连接在上述控制端子与输入端之间的电容(C2、C3)；被设置在该电容与上述控制端子之间的节点(N5、N6)与电源电位之间的、与第1晶体管有大致相同的阈值的被连接成二极管的第2晶体管(35、37)；以及与第2晶体管串联连接的开关(SW2、SW3)。