[19] 中华人民共和国国家知识产权局

[51] Int. Cl.

G02F 1/133 (2006.01)

G09G 3/36 (2006.01)

## [12] 发明专利说明书

专利号 ZL 200410100118.8

[45] 授权公告日 2008 年 10 月 22 日

[11] 授权公告号 CN 100428004C

[22] 申请日 2004.12.8

CN1412736 A 2003.4.23

[21] 申请号 200410100118.8

EP1069457 A1 2001.1.17

[30] 优先权

审查员 周永恒

[32] 2003.12.11 [33] KR [31] 10-2003-0090301

[74] 专利代理机构 北京三友知识产权代理有限公司

[32] 2004.4.28 [33] KR [31] 10-2004-0029611

司

[32] 2004.4.28 [33] KR [31] 10-2004-0029612

代理人 李 辉

[73] 专利权人 乐金显示有限公司

地址 韩国首尔

[72] 发明人 姜信浩 宋鸿声 洪镇铁

权利要求书 10 页 说明书 28 页 附图 18 页

[56] 参考文献

CN1405745 A 2003.3.26

US5440304 A 1995.8.8

US5886679 A 1999.3.23

CN1180418 A 1998.4.29

US5363424 A 1994.11.8

[54] 发明名称

液晶显示器件

[57] 摘要

液晶显示器件。一种具有数据驱动集成电路的显示器，包括：具有至少两个区并且包括第一输出通道和第 N 输出通道的 N 个输出通道，其中 N 是整数；包括 M 个数据输出通道的数据输出通道组，其中 M 是小于 N 的整数，所述 M 个数据输出通道根据显示器的期望分辨率向对应数量的数据线提供像素数据，其中 (N - M) 个输出通道未被提供像素数据，并且所述 (N - M) 个输出通道位于所述第一输出通道与所述第 N 输出通道之间；以及，通道选择器，用于选择所述 M 个数据输出通道。

1、一种具有多个数据驱动集成电路的显示器，所述多个数据驱动集成电路中的每一个包括：

N 个输出通道，包括第 1 输出通道和第 N 输出通道，其中 N 是整数；

数据输出通道组，具有至少两个组并且包括 M 个数据输出通道，其中 M 是小于 N 的整数，所述 M 个数据输出通道根据通过所述多个数据驱动集成电路设置的所述显示器的期望分辨率向对应数量的数据线提供像素数据，其中 (N-M) 个输出通道位于所述数据输出通道组中的所述至少两个组之间，并且未被提供像素数据， $(N-M) \geq 0$ ；以及

通道选择器，用于选择所述 M 个数据输出通道，

其中，全部所述多个数据驱动集成电路的 N 值和 M 值都是相同的，并且其中，通过所述多个数据驱动集成电路设置的所述显示器的所述期望分辨率是根据至少四个分辨率中的一个选择的。

2、根据权利要求 1 所述的显示器，其中，所述数据输出通道的数量是可编程的。

3、根据权利要求 1 所述的显示器，其还包括：

选择信号发生器，用于生成并且提供通道选择信号，以选择所述 M 个数据输出通道；以及

定时控制器，用于控制所述数据驱动集成电路并且向所述 M 个数据输出通道提供像素数据。

4、根据权利要求 3 所述的显示器，其中，所述选择信号发生器包括第一选择端子和第二选择端子，所述第一选择端子和所述第二选择端子中的每一个都与第一电压源和第二电压源中的一个相连接，以生成并且提供通道选择信号。

5、根据权利要求 3 所述的显示器，其中，所述数据驱动集成电路包括：

N 个移位寄存器，用于响应于来自定时控制器的控制信号，生成用于对像素数据进行移位的抽样信号，其中 N 是整数；

锁存单元，用于响应于来自所述 N 个移位寄存器的所述抽样信号对像素数据进行锁存；

数模转换器，用于将来自所述锁存单元的像素数据转换为模拟像素数据；以及

缓冲输出部，用于对来自所述数模转换器的像素数据进行缓冲，以将所述像素数据提供给与所述 M 个数据输出通道对应的所述多条数据线。

6、根据权利要求 3 所述的显示器，其中，所述第一选择端子和第二选择端子生成第一逻辑值和第二逻辑值以确定所述 M 个数据输出通道，以使得：

当所述逻辑值是第二逻辑值时，选择 I 个数据输出通道，其中 I 是小于 N 的正整数；以及

当所述逻辑值是第一逻辑值时，选择 J 个数据输出通道，其中 J 是小于 I 的正整数。

7、根据权利要求 3 所述的显示器，其中，所述第一选择端子和第二选择端子生成第一逻辑值至第四逻辑值以确定所述 M 个数据输出通道，以使得：

当所述逻辑值是第四逻辑值时，选择 I 个数据输出通道，其中 I 是小于 N 的正整数；

当所述逻辑值是第三逻辑值时，选择 J 个数据输出通道，其中 J 是小于 I 的正整数；

当所述逻辑值是第二逻辑值时，选择 K 个数据输出通道，其中 K 是小于 J 的正整数；以及

当所述逻辑值是第一逻辑值时，选择 L 个数据输出通道，其中 L 是小于 K 的正整数。

8、根据权利要求 7 所述的显示器，其中，所述数据输出通道组包括第 1 输出通道至第 I 数据输出通道、第 1 输出通道至第 J 数据输出通道、第 1 输出通道至第 K 数据输出通道、以及第 1 输出通道到第 L 数据输出通道中的任何一个。

9、根据权利要求 3 所述的显示器，其中，所述选择信号发生器基于以下条件中的至少一个来生成所述通道选择信号：所述数据线的数量、与期望的显示器分辨率对应的所述数据驱动集成电路的数量、安装有所述数据驱动集成电路的带载封装的宽度、以及位于所述定时控制器与所述数据驱动集成电路之间的数据传输线的数量。

10、根据权利要求 4 所述的显示器，其中，所述选择信号发生器包括与所述第一选择端子和所述第二选择端子相连接的开关装置。

11、根据权利要求 4 所述的显示器，其中，所述选择信号发生器包括与所述第一选择端子和所述第二选择端子相连接的双列直插式切换器。

12、根据权利要求 1 所述的显示器，其中，所述 (N-M) 个数据输出通道是哑通道。

13、根据权利要求 12 所述的显示器，其中，所述多个哑通道被浮置。

14、根据权利要求 12 所述的显示器，其中，所述多个哑通道被设置为恒定电压。

15、根据权利要求 1 所述的显示器，其中，所述数据输出通道组的所述至少两个组具有相同数量的数据输出通道。

16、一种显示器的包括与多条数据线相连接的多个可编程数据驱动集成电路的数据驱动器，所述多个可编程数据驱动集成电路中的每一个包括：

N 个输出通道，包括第一输出通道和第 N 输出通道，其中 N 是整数；

数据输出通道组，具有至少两个组并且包括 M 个数据输出通道，其中 M 是小于 N 的整数，所述 M 个数据输出通道根据通过所述多个数据驱动集成电路设置的所述显示器的期望分辨率向对应数量的数据线提供像素数据，其中 (N-M) 个输出通道未被提供像素数据， $(N-M) > 0$ ，并且所述 (N-M) 个输出通道位于所述第一输出通道与所述第 N 输出通道之间；以及

通道选择器，用于选择所述 M 个数据输出通道，

其中，全部所述多个数据驱动集成电路的 N 值和 M 值都是相同的，

并且其中，通过所述多个数据驱动集成电路设置的所述显示器的所述期望分辨率是根据至少四个分辨率中的一个选择的。

17、根据权利要求 16 所述的数据驱动器，其还包括：

选择信号发生器，用于生成通道选择信号以选择所述 M 个数据输出通道。

18、根据权利要求 17 所述的数据驱动器，其中，所述通道选择器根据所述通道选择信号改变所述数据输出通道组内的多个数据输出通道。

19、根据权利要求 17 所述的数据驱动器，其中，所述选择信号发生器基于以下条件中的至少一个来生成所述通道选择信号：所述数据线的数量、所述可编程数据驱动集成电路的数量、安装有所述可编程数据驱动集成电路的带载封装的宽度、以及所述像素数据的输入线的数量。

20、根据权利要求 17 所述的数据驱动器，其中，所述通道选择器生成第一逻辑值和第二逻辑值，以使得：

当所述逻辑值是第二逻辑值时，选择 I 个数据输出通道，其中 I 是小于 N 的正整数；以及

当所述逻辑值是第一逻辑值时，选择 J 个数据输出通道，其中 J 是小于 I 的正整数。

21、根据权利要求 17 所述的数据驱动器，其中，所述通道选择器生成第一逻辑值至第四逻辑值，以使得：

当所述逻辑值是第四逻辑值时，选择 I 个数据输出通道，其中 I 是小于 N 的正整数；

当所述逻辑值是第三逻辑值时，选择 J 个数据输出通道，其中 J 是小于 I 的正整数；

当所述逻辑值是第二逻辑值时，选择 K 个数据输出通道，其中 K 是小于 J 的正整数；以及

当所述逻辑值是第一逻辑值时，选择 L 个数据输出通道，其中 L 是小于 K 的正整数。

22、根据权利要求 21 所述的数据驱动器，其中，所述数据输出通道组包括第 1 输出通道至第 I 数据输出通道、第 1 输出通道至第 J 数据输出

---

通道、第 1 输出通道至第 K 数据输出通道以及第 1 输出通道至第 L 数据输出通道中的任何一个。

23、根据权利要求 16 所述的数据驱动器，其中，所述 (N-M) 个输出通道位于所述数据输出通道组的所述至少两个组之间。

24、根据权利要求 16 所述的数据驱动器，其中，所述数据输出通道组的所述至少两个组具有相同数量的数据输出通道。

25、根据权利要求 16 所述的数据驱动器，其中，所述 (N-M) 个输出通道被浮置。

26、根据权利要求 16 所述的数据驱动器，其中，所述 (N-M) 个输出通道被设置为恒定电压。

27、根据权利要求 17 所述的数据驱动器，其中，所述选择信号发生器包括分别与第一电压源和第二电压源相连接以生成所述通道选择信号的第一选择端子和第二选择端子。

28、根据权利要求 17 所述的数据驱动器，其中，所述选择信号发生器包括用于生成所述通道选择信号的开关。

29、根据权利要求 17 所述的数据驱动器，其中，所述选择信号发生器包括用于生成所述通道选择信号的双列直插式切换器。

30、根据权利要求 16 所述的数据驱动器，其还包括：

N 个移位寄存器，用于响应于控制信号生成用于对像素数据进行移位的抽样信号，其中 N 是整数；

锁存单元，用于响应于来自所述 N 个移位寄存器的所述抽样信号对像素数据进行锁存；

数模转换器，用于将来自所述锁存单元的像素数据转换为模拟像素数据；以及

缓冲输出单元，用于对来自所述数模转换器的像素数据进行缓冲，以将所述像素数据提供给与所述 M 个数据输出通道对应的多条数据线。

31、一种包括多个数据驱动集成电路的数据驱动器，所述多个数据驱动集成电路中的每一个包括：

N 个输出通道，包括第一输出通道组、第二输出通道组和第三输出

通道组，所述第二输出通道组是多个未被提供像素数据的哑输出通道，其中 N 是整数，其中，全部所述多个数据驱动集成电路的 N 值都是相同的，并且其中，通过所述多个数据驱动集成电路设置的所述显示器的期望分辨率是根据至少四个分辨率中的一个选择的；以及

通道选择器，用于选择与具有期望分辨率的显示器的多条数据线对应的所述第一输出通道组和所述第三输出通道组，以提供像素数据，所述通道选择器能够选择所述第一输出通道组、所述第二输出通道组和所述第三输出通道组中的任何一个作为哑输出通道，

其中，所述第二输出通道组位于所述第一输出通道组与所述第三输出通道组之间。

32、根据权利要求 31 所述的数据驱动器，其中，所述第二输出通道组包括第 1 至第 N 输出通道中的第一输出通道。

33、根据权利要求 31 所述的数据驱动器，其中，所述第二输出通道组包括第 1 至第 N 输出通道中的第 N/2 输出通道。

34、根据权利要求 31 所述的数据驱动器，其中，所述第二输出通道组包括第 1 至第 N 输出通道中的第 N 输出通道。

35、根据权利要求 31 所述的数据驱动器，其还包括选择信号发生器，该选择信号发生器生成用于选择所述多个输出通道的通道选择信号。

36、根据权利要求 31 所述的数据驱动器，其还包括：

N 个移位寄存器，生成用于对像素数据进行移位的抽样信号，其中 N 是整数；

锁存单元，用于响应于所述抽样信号对像素数据进行锁存；

数模转换器，用于将来自所述锁存单元的像素数据转换为模拟像素数据；以及

缓冲输出单元，用于对来自所述数模转换器的像素数据进行缓冲，以将所述像素数据提供给与第 1 输出通道组和第 3 输出通道组对应的所述多条数据线。

37、根据权利要求 35 所述的数据驱动器，其中，所述选择信号发生器基于以下条件中的至少一个来生成所述通道选择信号：所述数据线的

数量、与显示器的期望分辨率对应的所述数据驱动集成电路的数量、安装有所述数据驱动集成电路的带载封装的宽度、以及所述像素数据的输入线的数量。

38、根据权利要求 35 所述的数据驱动器，其中，所述选择信号发生器包括分别与第一电压源和第二电压源相连接以生成通道选择信号的第一选择端子和第二选择端子。

39、根据权利要求 31 所述的数据驱动器，其中，所述第一数据输出通道组和所述第二数据输出通道组具有相同数量的输出通道。

40、根据权利要求 31 所述的数据驱动器，其中，所述第 1 输出通道组包括所述 N 个输出通道的第 1 输出通道至所述 N 个输出通道的第 I<sub>1</sub>、第 I<sub>2</sub> 和第 I<sub>3</sub> 输出通道中的一个，其中 I<sub>1</sub> 是大于 1 的整数，I<sub>2</sub> 是大于 I<sub>1</sub> 的整数，I<sub>3</sub> 是大于 I<sub>2</sub> 并且小于 N 的整数，其中 N 是所述输出通道的总数。

41、根据权利要求 40 所述的数据驱动器，其中，所述第二数据输出通道组包括第 J<sub>1</sub>、第 J<sub>2</sub> 以及第 J<sub>3</sub> 输出通道中的一个至第 N 输出通道，其中 J<sub>1</sub> 是大于 I<sub>3</sub> 的整数，J<sub>2</sub> 是大于 J<sub>1</sub> 的整数，J<sub>3</sub> 是大于 J<sub>2</sub> 并且小于 N 的整数。

42、根据权利要求 41 所述的数据驱动器，其中，第(I<sub>1</sub>+1)至第(J<sub>3</sub>-1)输出通道、第(I<sub>2</sub>+1)至第(J<sub>2</sub>-1)输出通道、以及第(I<sub>3</sub>+1)至第(J<sub>1</sub>-1)输出通道中的任何一组是哑输出通道组。

43、根据权利要求 42 所述的数据驱动器，其中，所述哑输出通道组被浮置。

44、根据权利要求 35 所述的数据驱动器，其中，所述哑输出通道组被设置为恒定电压。

45、根据权利要求 35 所述的数据驱动器，其中，所述选择信号发生器包括用于生成所述通道选择信号的开关。

46、根据权利要求 35 所述的数据驱动器，其中，所述选择信号发生器包括用于生成所述通道选择信号的双列直插式切换器。

47、根据权利要求 31 所述的数据驱动器，其中，所述输出通道的数量是可编程的。

48、一种包括多个可编程数据驱动集成电路的数据驱动器，所述多个可编程数据驱动集成电路中的每一个包括：

移位寄存器部，具有将启动脉冲移位为顺序抽样信号的 N 个移位寄存器，其中 N 是正整数；

输出通道单元，包括第一输出通道组和第二输出通道组，以及位于所述第一输出通道组与所述第二输出通道组之间并且未被提供像素数据的哑输出通道组，其中，全部所述多个数据驱动集成电路的 N 值都是相同的，并且其中，通过所述多个数据驱动集成电路设置的所述显示器的期望分辨率是根据至少四个分辨率中的一个选择的；

第一选择器，用于选择来自与所述第一输出通道组对应的 N 个移位寄存器的第一移位寄存器组的输出信号，并且选择与所述第一输出通道组中的第一多条数据线相连接的第一数据输出通道组；以及

第二选择器，用于将来自所述第一选择器的输出信号提供给与所述第二输出通道组对应的第二移位寄存器组，并且选择与所述第二输出通道组中的第二多条数据线相连接的第二数据输出通道组。

49、根据权利要求 48 所述的数据驱动器，其还包括选择信号发生器，该选择信号发生器用于生成用于选择所述第一数据输出通道组和所述第二数据输出通道组的通道选择信号。

50、根据权利要求 49 所述的数据驱动器，其中，所述选择信号发生器基于以下条件中的至少一个来生成所述通道选择信号：所述数据线的数量、所述可编程数据驱动集成电路的数量、安装有所述可编程数据驱动集成电路的带载封装的宽度、以及所述像素数据的输入线的数量。

51、根据权利要求 49 所述的数据驱动器，其中，所述选择信号发生器包括与第一电压源和第二电压源相连接以生成所述通道选择信号的选择端子。

52、根据权利要求 49 所述的数据驱动器，其中，所述选择信号发生器包括用于生成所述通道选择信号的选择开关。

53、根据权利要求 49 所述的数据驱动器，其中，所述选择信号发生器包括用于生成所述通道选择信号的双列直插式切换器。

54、根据权利要求 48 所述的数据驱动器，其中，所述第一输出通道组和所述第二输出通道组具有相同数量的输出通道。

55、根据权利要求 48 所述的数据驱动器，其中，所述第一选择器包括第一多路复用器，该第一多路复用器用于响应于所述通道选择信号，选择所述 N 个移位寄存器的第 I1 移位寄存器、所述 N 个移位寄存器的第 I2 移位寄存器、以及所述 N 个移位寄存器的第 I3 移位寄存器的输出信号中的一个，其中 I1 是大于 1 的正整数，I2 是大于 I1 的正整数，I3 是大于 I2 并小于 N 的正整数。

56、根据权利要求 55 所述的数据驱动器，其中，所述第二选择器包括：

多路分解器，用于响应于所述通道选择信号，生成来自所述第一多路复用器的输出信号；

第二多路复用器，用于响应于所述通道选择信号，从所述多路分解器的输出信号和所述 N 个移位寄存器的第 (J1-1) 移位寄存器的输出信号中选择一个，以将该信号提供给第 J1 移位寄存器，其中 J1 是大于 I3 的正整数；

第三多路复用器，用于响应于所述通道选择信号，从所述多路分解器的输出信号和所述 N 个移位寄存器的第 (J2-1) 移位寄存器的输出信号中选择一个，以将该信号提供给第 J2 移位寄存器，其中 J2 是大于 J1 的正整数；以及

第四多路复用器，用于响应于所述通道选择信号，从所述多路分解器的输出信号和所述 N 个移位寄存器的第 (J3-1) 移位寄存器的输出信号中选择一个，以将该信号提供给第 J3 移位寄存器，其中 J3 是大于 J2 并且小于 N 的正整数。

57、根据权利要求 56 所述的数据驱动器，其中，所述通道选择器从第一数据输出通道组中的第 1 至第 I1 数据输出通道、第 1 至第 I2 数据输出通道、以及第 1 至第 I3 数据输出通道中选择一组，作为第一数据输出通道组，其中 I1 是大于 1 的整数，I2 是大于 I1 的整数，I3 是大于 I2 且小于 N 的整数。

58、根据权利要求 57 所述的数据驱动器，其中，所述通道选择器响应于所述通道选择信号，从所述输出通道组中的第 J1 至第 N 数据输出通道、第 J2 至第 N 数据输出通道、以及第 J3 至第 N 数据输出通道中选择一组，作为第二数据输出通道组，其中 J1 是大于 I3 的正整数，J2 是大于 J1 的正整数，J3 是大于 J2 且小于 N 的正整数。

59、根据权利要求 58 所述的数据驱动器，其中，第 (I1+1) 至第 (J3-1) 输出通道、第 (I2+1) 至第 (J2-1) 输出通道、以及第 (I3+1) 至第 (J1-1) 输出通道中的任何一组是哑输出通道组。

60、根据权利要求 59 所述的数据驱动器，其中，所述多个哑输出通道被设置为恒定电压。

61、根据权利要求 59 所述的数据驱动器，其中，所述多个哑输出通道被浮置。

62、一种用于驱动显示器中的包括多个可编程数据驱动集成电路的数据驱动器的方法，该方法包括如下步骤：

确定显示器的期望分辨率；

针对所述多个可编程数据驱动集成电路中的每一个，确定包括第一输出通道和第 N 输出通道的 N 个输出通道，其中 N 是正整数；

针对所述多个可编程数据驱动集成电路中的每一个，选择具有至少两个区并且包括 M 个数据输出通道的数据输出通道组，其中 M 是小于 N 的整数；

根据所述显示器的期望分辨率将来自所述 M 个数据输出通道的像素数据提供给对应数量的数据线；其中 (N-M) 个输出通道未被提供像素数据， $(N-M) > 0$ ，并且所述 (N-M) 个输出通道位于所述第一输出通道与所述第 N 输出通道之间，

其中，全部所述多个数据驱动集成电路的 N 值都是相同的，并且其中，通过所述多个数据驱动集成电路设置的所述显示器的期望分辨率是根据至少四个分辨率中的一个选择的。

## 液晶显示器件

### 技术领域

本发明涉及液晶显示器件。更具体地，本发明涉及一种液晶显示器件，其提高了液晶显示器件的工作效率并且降低了制造成本。

### 背景技术

通常，液晶显示器（LCD）使用电场来控制液晶的透光率，以显示图像。

为此，如图 1 所示，LCD 包括液晶显示板 2，其具有：以矩阵形式排列的多个液晶单元；选通驱动器 6，用于驱动液晶显示板 2 的选通线 GL<sub>1</sub> 至 GL<sub>n</sub>；数据驱动器 4，用于驱动液晶显示板 2 的数据线 DL<sub>1</sub> 至 DL<sub>m</sub>；以及定时控制器 8，用于控制选通驱动器 6 和数据驱动器 4。

液晶显示板 2 包括：设置在选通线 GL<sub>1</sub> 至 GL<sub>n</sub> 和数据线 DL<sub>1</sub> 至 DL<sub>m</sub> 的各交叉处的薄膜晶体管 TFT、以及与薄膜晶体管 TFT 相连接的液晶单元 7。当向薄膜晶体管 TFT 提供扫描信号（例如，来自选通线 GL 的选通高压 VGH）时，薄膜晶体管 TFT 导通，以将来自数据线 DL 的像素信号施加给液晶单元 7。此外，当向薄膜晶体管 TFT 提供来自选通线 GL 的选通低压 VGL 时，薄膜晶体管 TFT 截止，以保持充入液晶单元 7 中的像素信号。

可以将液晶单元 7 等效地表示为液晶电容器（liquid crystal capacitor）。液晶单元 7 包括与公共电极和薄膜晶体管相连的像素电极，在该像素电极与公共电极和薄膜晶体管之间具有液晶。此外，液晶单元 7 包括存储电容器，其保持所充入的像素信号的信号电平，直到充入下一像素信号。将存储电容器设置在像素电极与前级选通线之间。这种液晶单元 7 根据通过薄膜晶体管 TFT 充入的像素信号来改变具有介电各向异性的液晶的配向状态，以控制透光率，从而实现灰度级。

定时控制器 8 利用从视频卡（未示出）提供的同步信号 V 和 H，来产生选通控制信号（即，选通启动脉冲（GSP）、选通移位时钟（GSC）和选通输出使能（GOE））以及数据控制信号（即，源启动脉冲（SSP）、源移位时钟（SSC）、源输出使能（SOE）以及极性控制（POL））。将选通控制信号（即，GSP、GSC 和 GOE）施加到选通驱动器 6 以控制选通驱动器 6，而将数据控制信号（即，SSP、SSC、SOE 和 POL）施加到数据驱动器 4 以控制数据驱动器 4。此外，定时控制器 8 对红色（R）、绿色（G）和蓝色（B）像素数据 VD 进行排列，并且将这些数据提供给数据驱动器 4。

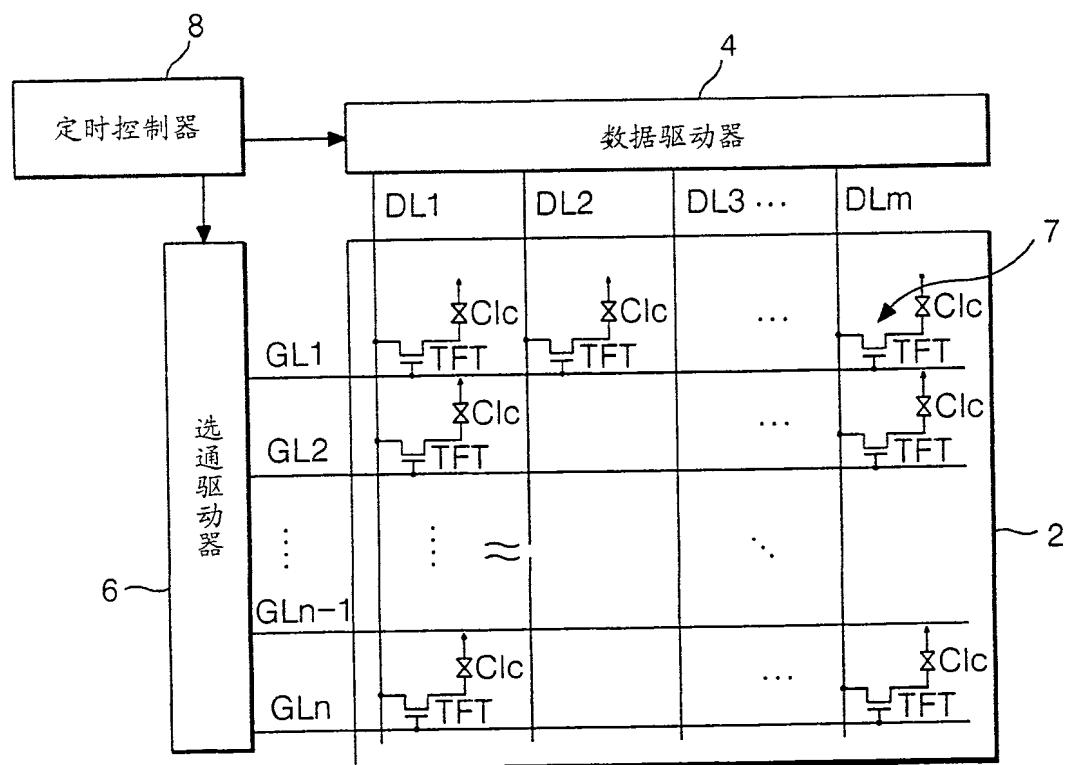

选通驱动器 6 顺序地驱动选通线 GL<sub>1</sub> 至 GL<sub>n</sub>。为此，选通驱动器 6 包括多个选通集成电路（IC）10，如图 2A 所示。在定时控制器 8 的控制下，选通 IC 10 顺序地驱动与其相连接的选通线 GL<sub>1</sub> 至 GL<sub>n</sub>。具体地，选通 IC 10 响应于来自定时控制器 8 的选通控制信号（即 GSP、GSC 和 GOE）顺序地向选通线 GL<sub>1</sub> 至 GL<sub>n</sub> 施加选通高压 VGH。

选通驱动器 6 响应于选通移位时钟 GSC 对选通启动脉冲 GSP 进行移位，以生成移位脉冲。然后，选通驱动器 6 响应于移位脉冲在每个水平周期将选通高压 VGH 施加给对应的选通线 GL。对于各水平周期使移位脉冲逐行移位，并且选通 IC 10 中的任何一个将选通高压 VGH 施加给对应的选通线 GL，以与移位脉冲相对应。在未将选通高压 VGH 提供给选通线 GL<sub>1</sub> 至 GL<sub>n</sub> 时的剩余时间间隔内选通 IC 提供选通低压 VGL。

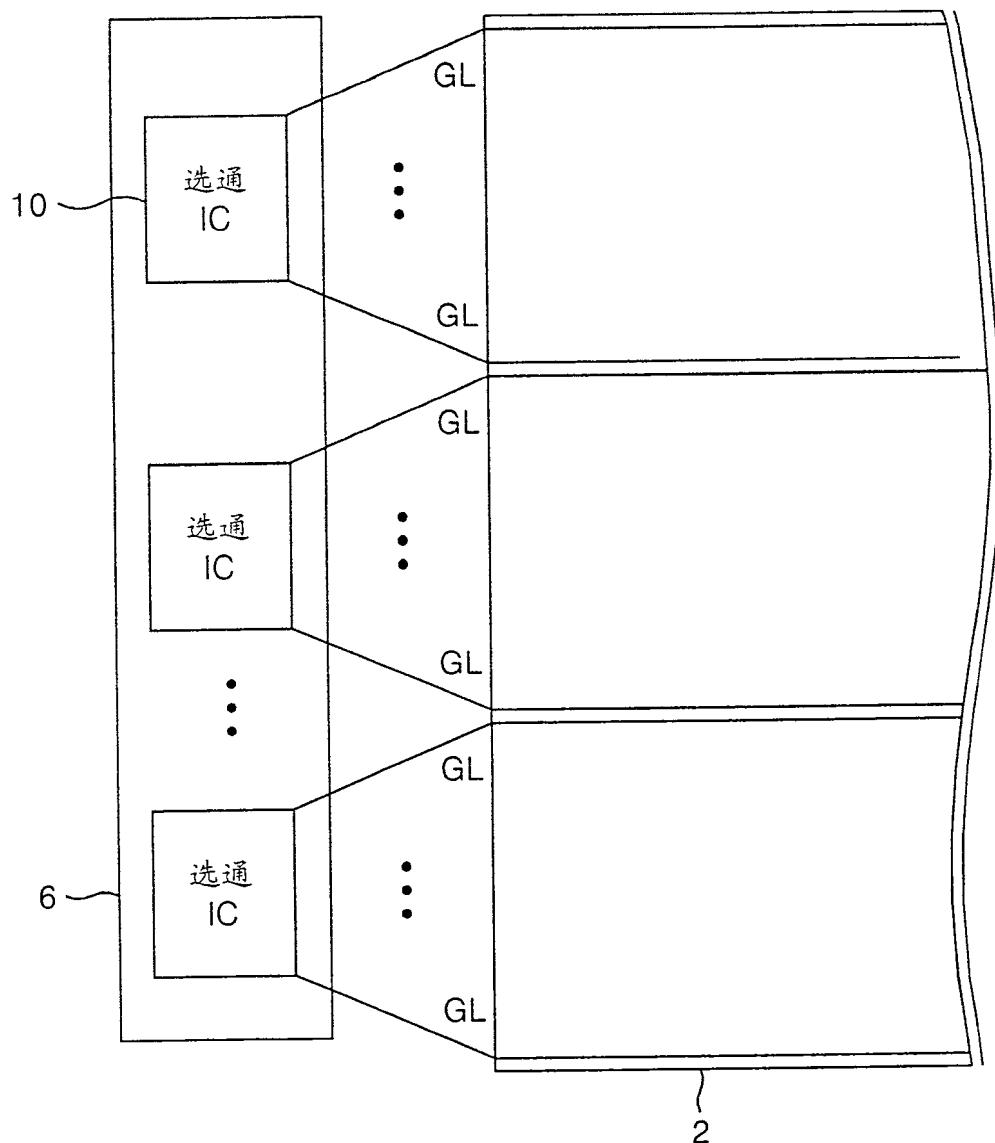

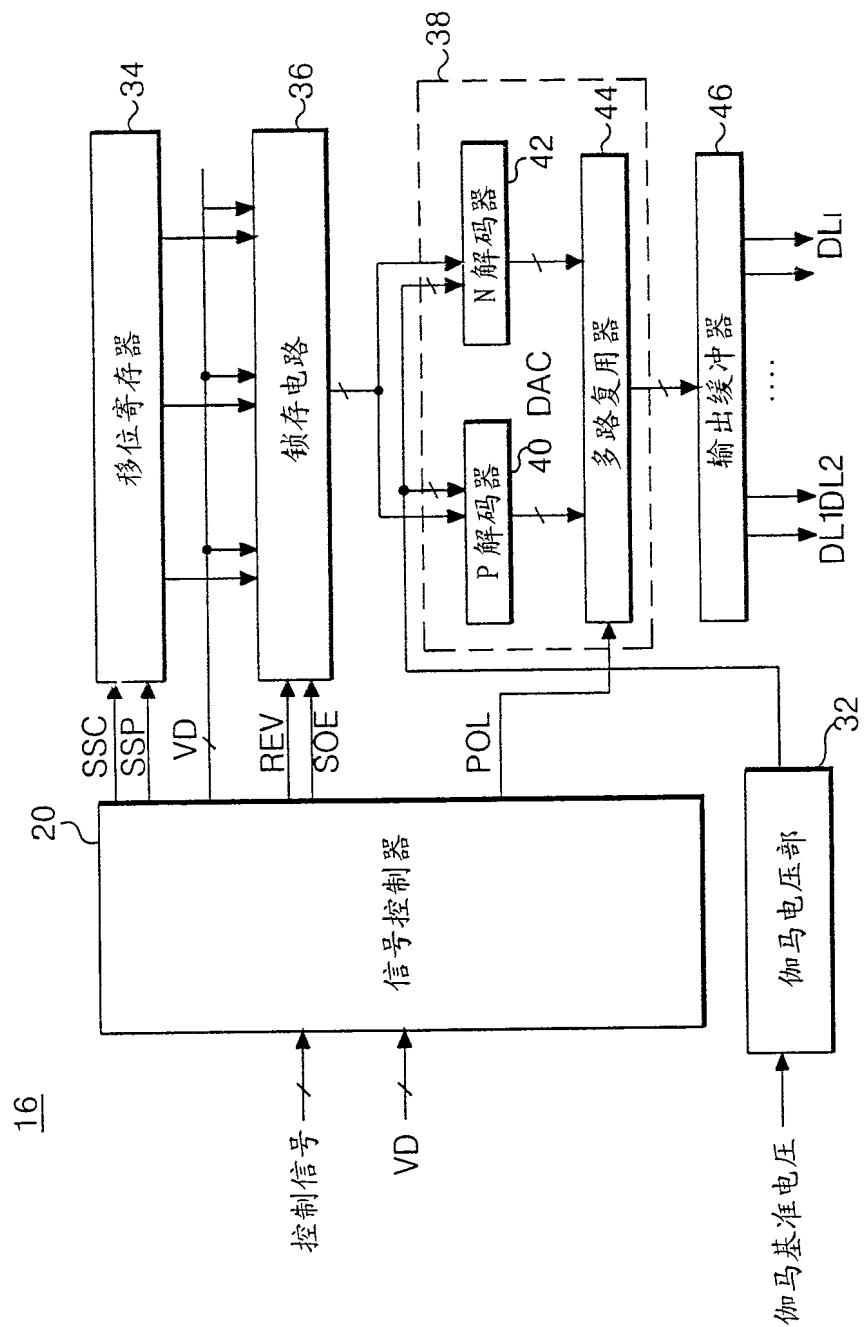

在各水平周期，数据驱动器 4 将用于各行的像素信号施加给数据线 DL<sub>1</sub> 至 DL<sub>m</sub>。数据驱动器 4 包括多个数据 IC 16，如图 2B 所示。数据 IC 16 响应于来自定时控制器 8 的数据控制信号（即，SSP、SSC、SOE 和 POL）向数据线 DL<sub>1</sub> 至 DL<sub>m</sub> 施加像素信号。数据 IC 16 利用来自伽马电压发生器（未示出）的伽马电压，将来自定时控制器 8 的像素数据 VD 转换为模拟像素信号，以将其输出。

数据 IC 16 响应于源移位时钟 SSC 对源启动脉冲 SSP 进行移位，以生成抽样信号。然后，数据 IC 16 响应于该抽样信号将用于特定单元的像素数据 VD 顺序锁存。之后，数据 IC 16 将锁存的一行像素数据 VD 转换

为模拟像素信号，并且在源输出使能信号 SOE 的使能区间，将所述信号施加给数据线 DL<sub>1</sub> 至 DL<sub>m</sub>。数据 IC 16 响应于极性控制信号 POL 将像素数据 VD 转换为正像素信号或负像素信号。

如图 3 所示，各个数据 IC 16 包括：移位寄存器部 34，用于顺序提供抽样信号；锁存器部 36，用于响应于抽样信号顺序锁存像素数据 VD，以同时输出这些信号；数模转换器（DAC）38，用于将来自锁存器部 36 的像素数据 VD 转换为像素电压信号；以及输出缓冲器部 46，用于对来自 DAC 38 的像素电压信号进行缓冲，以将其输出。此外，数据 IC 16 包括：信号控制器 20，用于将来自定时控制器 8 的各种控制信号（即，SSP、SSC、SOE、REV 和 POL 等等）和像素数据 VD 进行连接；以及伽马电压部 32，用于提供 DAC 38 所需的正伽马电压和负伽马电压。

信号控制器 20 对来自定时控制器 8 的各种控制信号（即，SSP、SSC、SOE、REV 和 POL 等等）和像素数据 VD 进行控制，以使其被输出到对应的元件。

伽马电压部 32 针对各灰度级将从伽马基准电压发生器（未示出）输入的多个伽马基准电压进行细分，以将其输出。

包括在移位寄存器部 34 中的多个移位寄存器响应于源抽样时钟信号 SSC，对来自信号控制器 20 的源启动脉冲顺序进行移位，以将其作为抽样信号输出。

锁存器部 36 响应于来自移位寄存器部 34 的抽样信号为特定单元对来自信号控制器 20 的像素数据 VD 顺序进行抽样，以将其锁存。锁存器部 36 包括 i 个（其中 i 是整数）锁存器，以锁存 i 个像素数据 VD，并且每个锁存器都具有与像素数据 VD 的位数相对应的大小。具体地，定时控制器 8 将像素数据 VD 分成偶像素数据 VD<sub>even</sub> 和奇像素数据 VD<sub>odd</sub> 以减小传输频率，并通过各传输线同时输出这些数据。偶像素数据 VD<sub>even</sub> 和奇像素数据 VD<sub>odd</sub> 中的每一个都包括红色（R）、绿色（G）和蓝色（B）像素数据。因此，锁存器部 36 为各个抽样信号同时锁存通过信号控制器 20 提供的偶像素数据 VD<sub>even</sub> 和奇像素数据 VD<sub>odd</sub>。然后，锁存器部 36 响应于来自信号控制器 20 的源输出使能信号 SOE 同时输出 i 个锁存的像素

数据 VD。

锁存器部 36 响应于数据反相 (inversion) 选择信号 REV 还原进行了调制以减少转换位数的像素数据 VD，以将其输出。定时控制器 8 通过使用基准值来调制像素数据 VD，使得转换位数变为最少，以确定是否应将这些位反相。由于从 LOW 转变为 HIGH 或者由 HIGH 转变为 LOW 的位数最少，从而使得数据传输时的电磁干扰 (EMI) 最小。

DAC 38 将来自锁存器部 36 的像素数据 VD 同时转换为正像素电压信号和负像素电压信号。DAC 38 包括：共同连接到锁存器部 36 的正 (P) 解码部 40 和负 (N) 解码部 42；以及多路复用器 (MUX) 部 44，用于对 P 解码部 40 和 N 解码部 42 的输出信号进行选择。

包括在 P 解码部 40 中的 n 个 P 解码器使用来自伽马电压部 32 的正伽马电压，将从锁存器部 36 同时输入的 n 个像素数据转换为正像素电压信号。包括在 N 解码部 42 中的 i 个 N 解码器使用来自伽马电压部 32 的负伽马电压，将从锁存器部 36 同时输入的 i 个像素数据转换为负像素电压信号。包括在多路复用器部 44 中的 i 个多路复用器响应于来自信号控制器 20 的极性控制信号 POL，选择性地输出来自 P 解码器 40 的正像素电压信号或者来自 N 解码器 42 的负像素电压信号。

包括在输出缓冲器部 46 中的 i 个输出缓冲器包括串联连接到相应的 i 条数据线 DL1 至 DLi 的多个电压跟随器等。这种输出缓冲器 46 对来自 DAC 38 的像素电压信号进行缓冲，以将这信号提供给数据线 DL1 至 DLi。

这种现有技术的 LCD 根据液晶显示板 2 的分辨率来区分包括在数据驱动器 4 中的数据 IC 16 的输出通道。这是由于对于液晶显示板 2 的每种分辨率，数据 IC 16 会有某些通道连接到数据线 DL。因此，会出现以下问题：对于液晶显示板 2 的每种分辨率类型需要使用不同数量的具有不同输出通道的数据 IC 16。这使工作效率下降并且增加了制造成本。

更具体地，对于具有 3072 条数据线 DL 的分辨率为扩展图形阵列 (eXtended Graphics Array) (XGA) 级（即 1024×3）的液晶显示器，需要 4 个数据 IC 16，每个数据 IC 16 都具有 768 个数据输出通道。对于具有 4200 条数据线 DL 的分辨率为高级扩展图形适配器+ (Super eXtended

Graphics Adapter+) (SXGA+) 级 (即, 1400×3) 的液晶显示器, 需要 6 个数据 IC 16, 每个数据 IC 16 都具有 702 个数据输出通道。将剩余的 12 个数据输出通道当作哑线 (dummy line)。另外, 具有 3840 条数据线 DL 的分辨率为宽扩展图形阵列 (Wide eXtended Graphics Array) (WXGA) 级 (即, 1280×3) 的液晶显示器, 需要 6 个数据 IC 16, 每个数据 IC 16 都具有 642 个数据输出通道。在此情况下, 将剩余的 12 个数据输出通道当作哑线。如上所述, 对于液晶显示板 2 的各分辨率必须使用具有特定数量的数据输出通道的不同的数据 IC 16。因此, 现有技术的液晶显示器具有降低工作效率并且增加制造成本的缺点。

### 发明内容

因此, 本发明致力于一种液晶显示 (LCD) 器件, 其提高了 LCD 的工作效率并且降低了制造成本。

本发明的一个优点在于提供了一种液晶显示器件, 其能够基于液晶显示板的分辨率来控制数据集成电路的输出通道。

本发明的其他特征和优点将在以下说明中加以阐述, 部分地通过该说明变得明了, 或者通过对本发明的实践而获知。通过文字说明及其权利要求以及附图中所具体指出的结构, 可实现并获得本发明的这些和其它优点。

为了实现这些和其他优点并且根据本发明的目的, 如所具体实施和广泛描述的那样, 根据本发明一个实施例的显示器包括: N 个数据输出通道 (N 为整数), 包括第 1 数据输出通道和第 N 数据输出通道; 数据输出通道组, 包括 M 个数据输出通道 (其中 M 为小于或者等于 N 的整数), 所述 M 个数据输出通道根据显示器的期望分辨率来向对应数量的数据线提供像素数据, 其中 (N-M) 个数据输出通道未被提供像素数据, 并且所述 (N-M) 个数据输出通道位于第 1 数据输出通道与第 N 数据输出通道之间; 以及, 通道选择器, 对 M 个数据输出通道进行选择。

在本发明的另一实施例中, 一种用于连接显示器的多条数据线的数据驱动集成电路, 包括: N 个数据输出通道 (其中 N 是整数), 包括第 1

数据输出通道和第 N 数据输出通道；数据输出通道组，包括 M 个数据输出通道（其中 M 为小于或者等于 N 的整数），所述 M 个数据输出通道根据显示器的期望分辨率向对应数量的数据线提供像素数据，其中 (N-M) 个数据输出通道未被提供像素数据，并且所述 (N-M) 个数据输出通道位于第 1 数据输出通道与第 N 数据输出通道之间；以及，通道选择器，对 M 个数据输出通道进行选择。

在本发明的又一实施例中，一种数据驱动集成电路，包括：多个输出通道，这多个输出通道包括第一输出通道组、第二输出通道组和第三输出通道组，所述第二输出通道组是不接收像素数据的哑输出通道；以及，通道选择器，用于对应于具有期望分辨率的显示器的多条数据线来选择第一数据输出通道组和第三数据输出通道组，该通道选择器能够选择所述第一数据输出通道组、第二数据输出通道组和第三数据输出通道组中的任何一组，作为哑输出通道，其中所述第二输出通道组位于所述第一输出通道组与所述第三输出通道组之间。

应该理解，上述概括说明和以下具体说明都是示例性和说明性的，旨在为如权利要求所述的本发明的提供进一步解释。

#### 附图说明

所包括的附图用于提供对于本发明的进一步理解，被并入说明书并构成本说明书的一部分，其示出了本发明的实施例，并与文字说明一起用于解释本发明的原理。附图中：

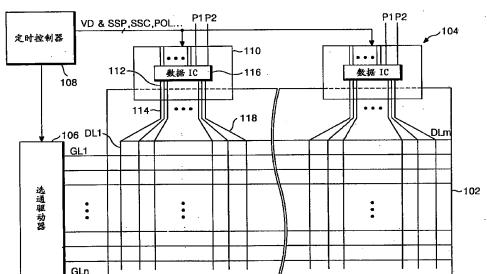

图 1 是表示现有技术的液晶显示器的电路框图；

图 2A 示出了包括在现有技术的选通驱动器中的选通集成电路；

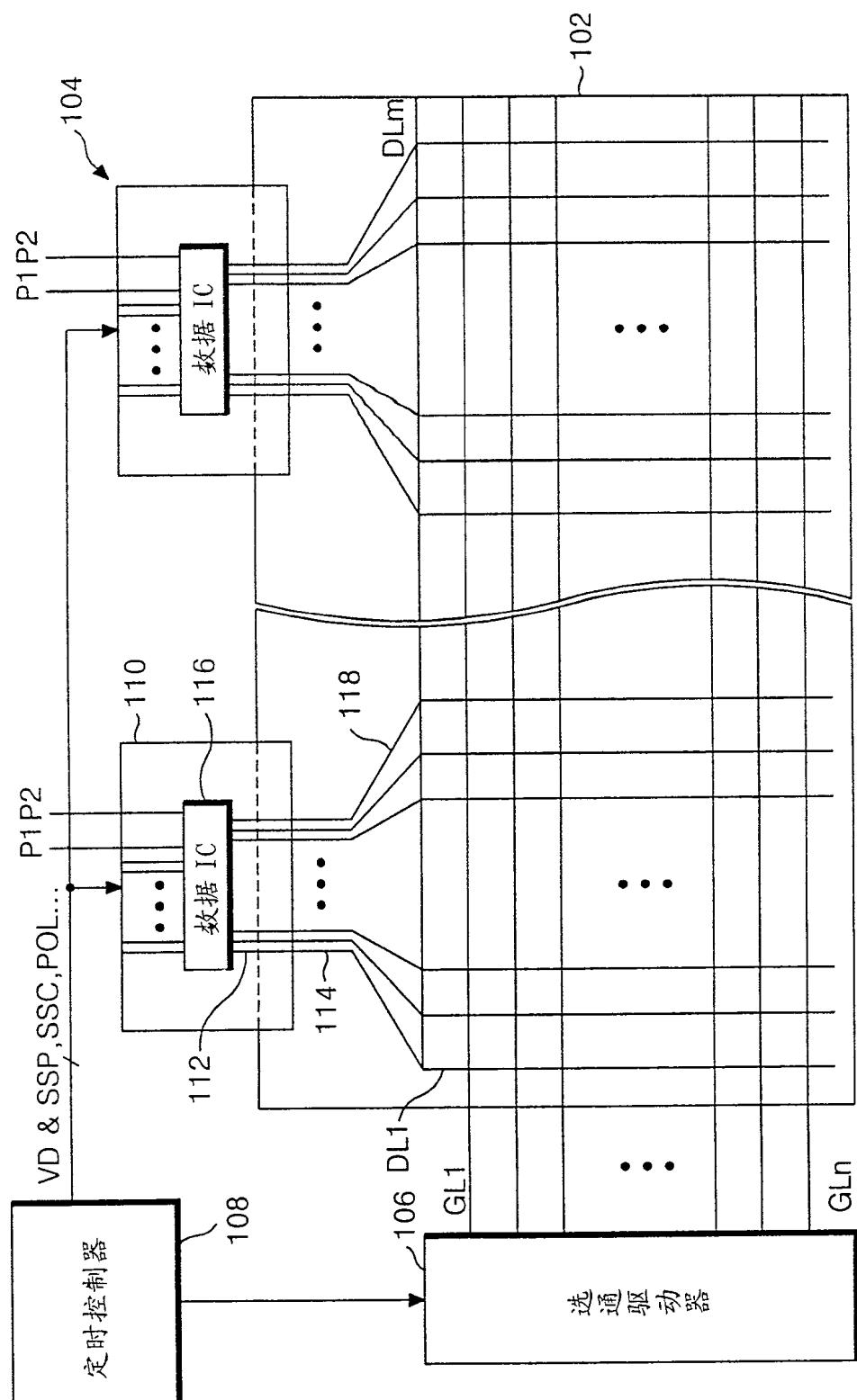

图 2B 示出了包括在现有技术的数据驱动器中的数据集成电路；

图 3 是表示图 2B 中的数据集成电路的内部结构的框图；

图 4 是表示根据本发明第一实施例的液晶显示器的电路框图；

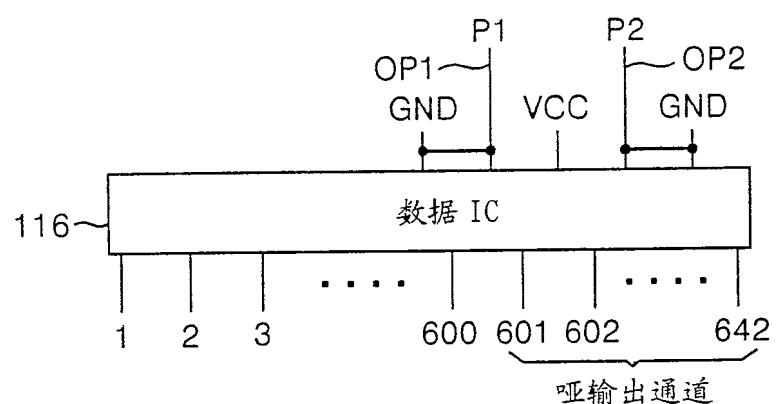

图 5 示出了根据图 4 中所示的第一和第二输出选择信号而设置为具有 600 个数据输出通道的数据集成电路；

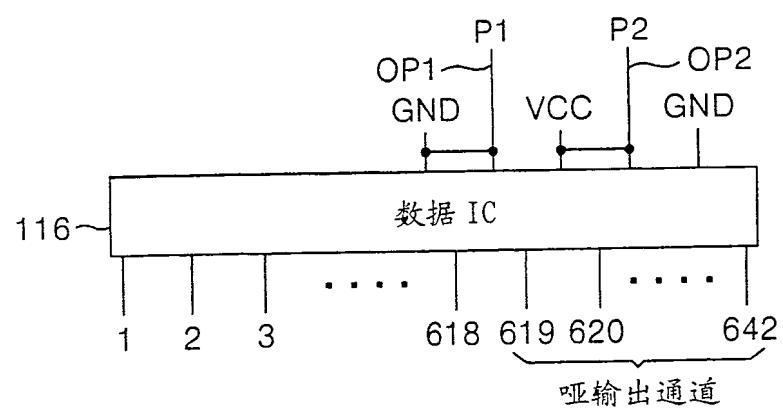

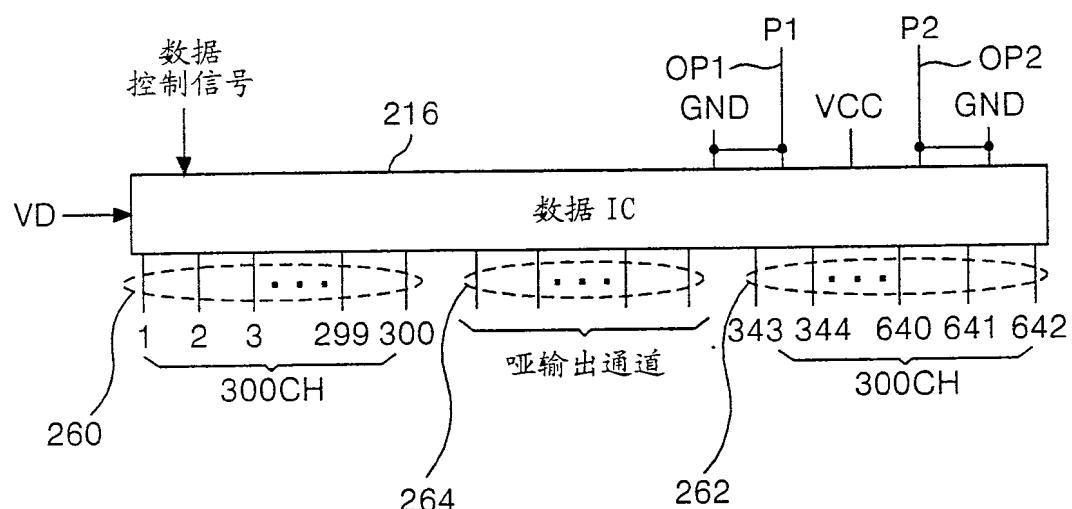

图 6 示出了根据图 4 中所示的第一和第二输出选择信号而设置为具

有 618 个数据输出通道的数据集成电路；

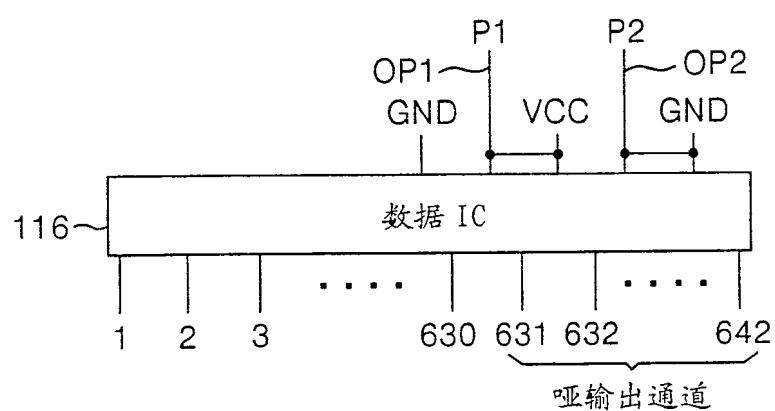

图 7 示出了根据图 4 中所示的第一和第二输出选择信号而设置为具有 630 个数据输出通道的数据集成电路；

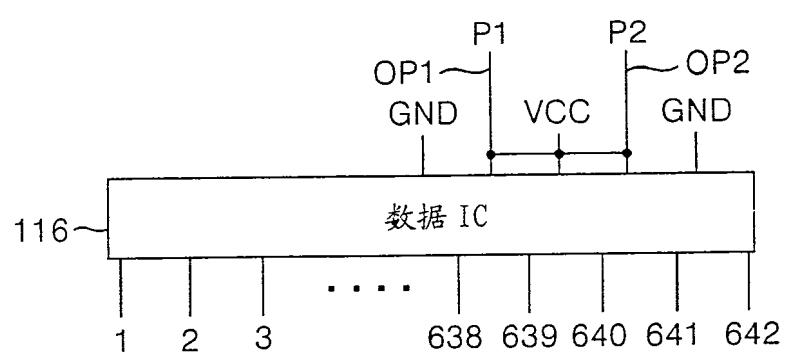

图 8 示出了根据图 4 中所示的第一和第二输出选择信号而设置为具有 642 个数据输出通道的数据集成电路；

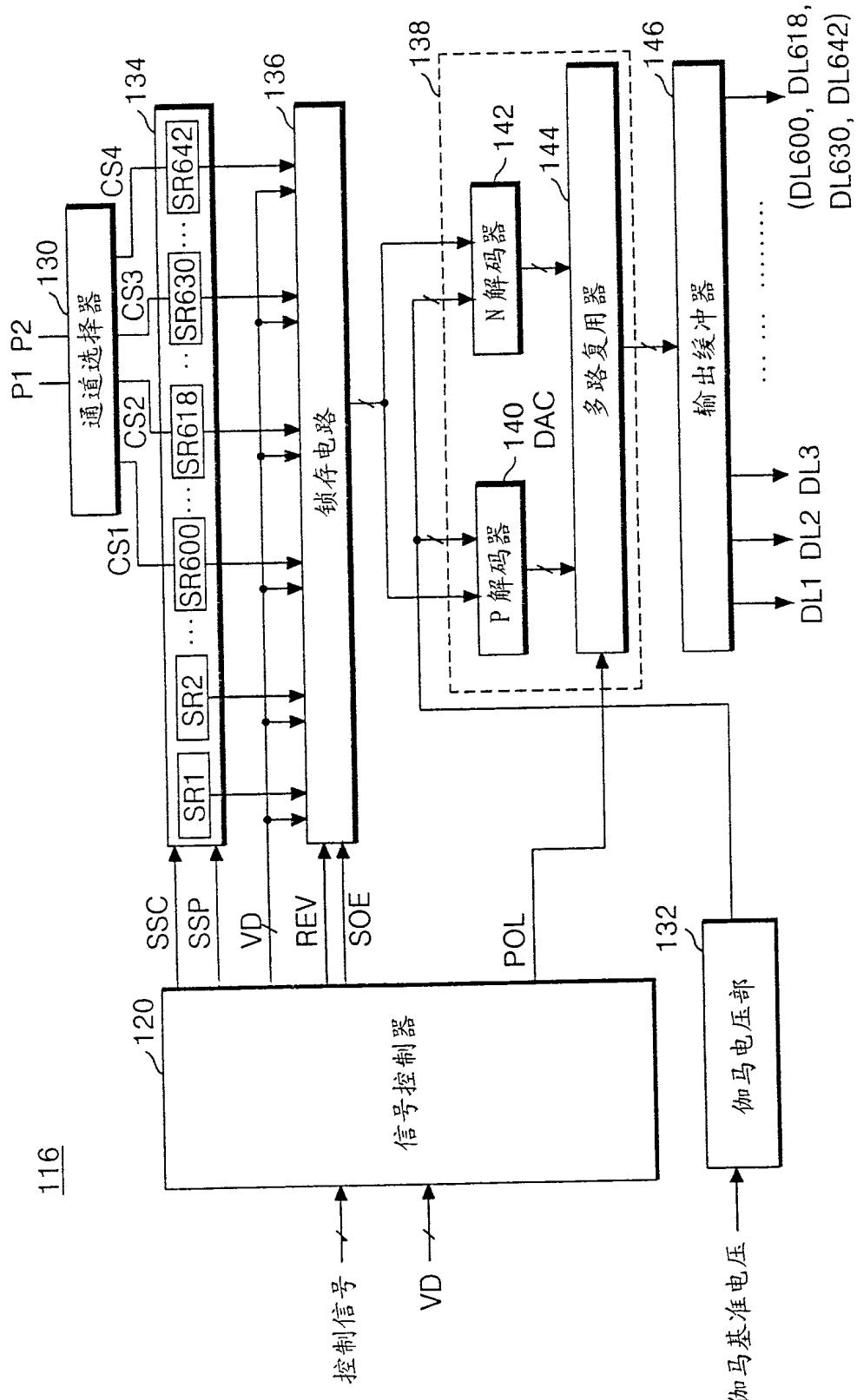

图 9 是表示图 4 中的数据集成电路的内部结构的框图；

图 10 是表示根据本发明第二实施例的液晶显示器的电路框图。

图 11 示出了根据图 10 中所示的第一和第二输出选择信号而设置为具有 600 个数据输出通道的数据集成电路；

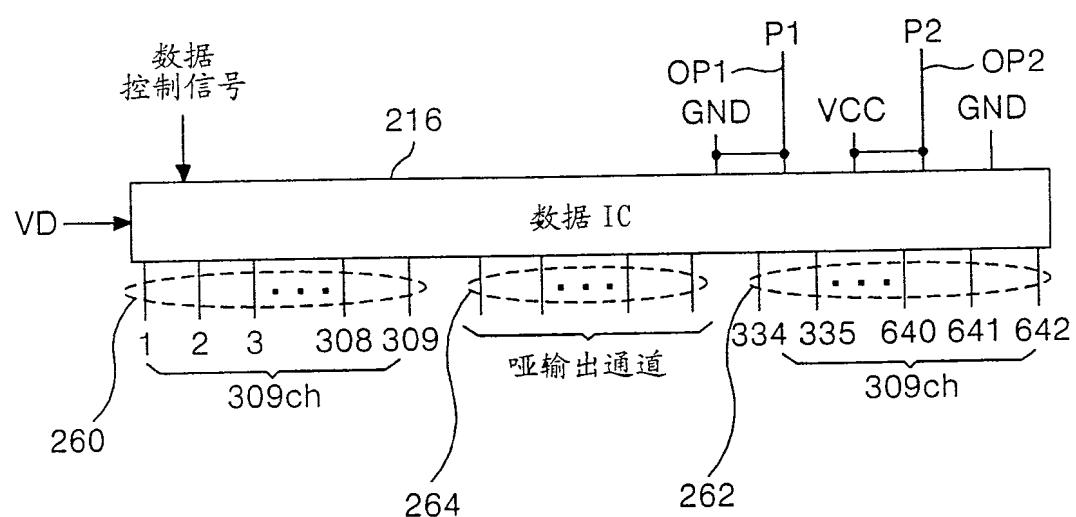

图 12 示出了根据图 10 中所示的第一和第二输出选择信号而设置为具有 618 个数据输出通道的数据集成电路；

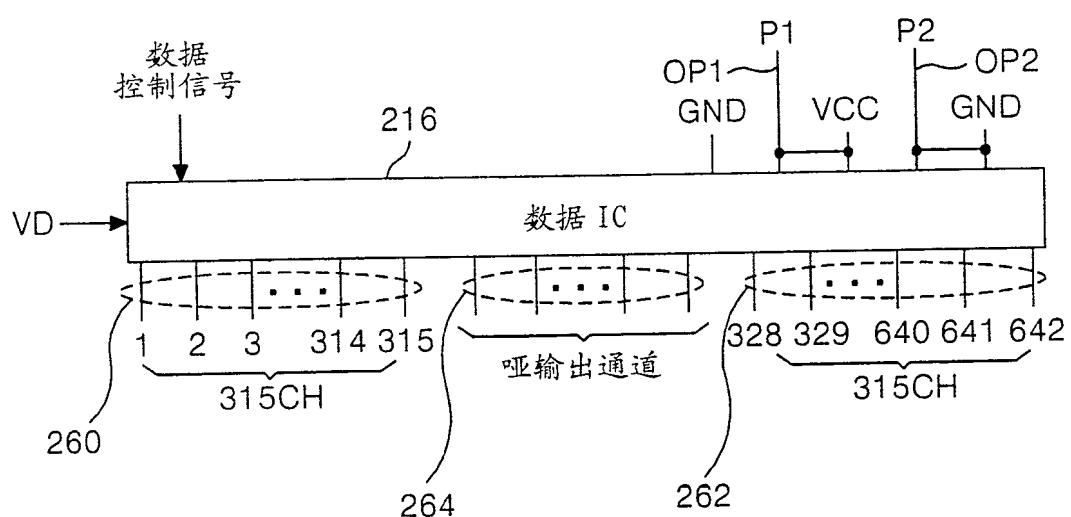

图 13 示出了根据图 10 中所示的第一和第二输出选择信号而设置为具有 630 个数据输出通道的数据集成电路；

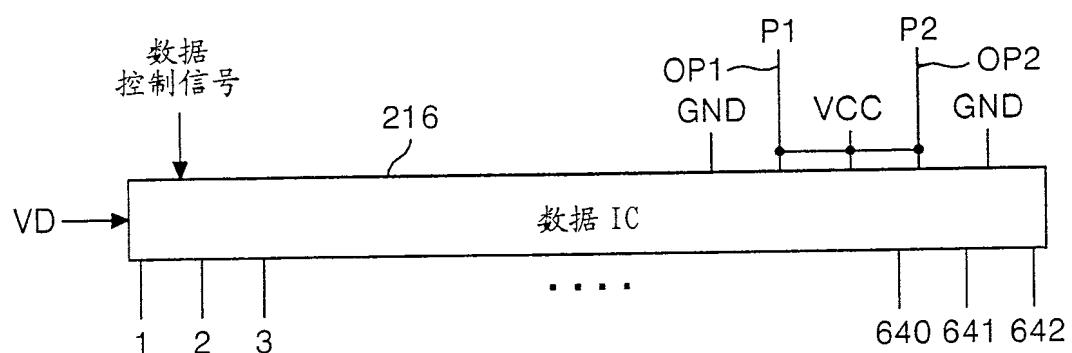

图 14 示出了根据图 10 中所示的第一和第二输出选择信号而设置为具有 642 个数据输出通道的数据集成电路；

图 15 示出了用于生成图 10 所示的第一和第二通道输出选择信号的开关装置；

图 16 示出了用于生成图 10 所示的第一和第二通道输出选择信号的双列直插式切换器；以及

图 17 是表示根据本发明第三实施例的数据集成电路中的通道选择器和移位寄存器部分的框图。

### 具体实施方式

下面详细说明优选的实施例，其示例示出在附图中。

图 4 示意性示出了根据本发明第一实施例的液晶显示器（LCD）。

在图 4 中，LCD 包括：液晶显示板 102，具有以矩阵形式排列的多个液晶单元；选通驱动器 106，用于驱动液晶显示板 102 的选通线 GL1 至 GLn；数据驱动器 104，用于驱动液晶显示板 102 的数据线 DL1 至 DLm；以及定时控制器 108，用于控制选通驱动器 106 和数据驱动器 104。

液晶显示板 102 包括：薄膜晶体管 TFT，设置在选通 GL1 至 GLn 与数据线 DL1 至 DLm 的各交叉部分处；以及，液晶单元（未示出），与所述薄膜晶体管 TFT 相连接。当向薄膜晶体管 TFT 提供扫描信号（即，来自选通线 GL 的选通高压 VGH）时，使得薄膜晶体管 TFT 导通，以将来自数据线 DL 的像素信号提供给液晶单元。此外，当向薄膜晶体管 TFT 提供来自选通线 GL 的选通低压 VGL 时，使得薄膜晶体管 TFT 截止。在液晶单元中保持所充入的像素信号。

可以将液晶单元等效地表示为液晶电容器。液晶单元包括与公共电极和薄膜晶体管相连接的像素电极，并且在像素电极与公共电极和薄膜晶体管之间具有液晶。此外，液晶单元包括存储电容器，其用于保持所充入的像素信号，直到充入下一像素信号。将该存储电容器设置在像素电极与前级选通线之间。这种液晶单元 7 根据通过薄膜晶体管 TFT 而充入的像素信号改变具有介电各向异性的液晶的配向状态，以控制透光率并实现灰度级。

定时控制器 108 使用从视频卡（未示出）提供的同步信号 V 和 H，来生成选通控制信号（即：选通启动脉冲（GSP）、选通移位时钟（GSC）和选通输出使能（GOE））以及数据控制信号（即：源启动脉冲（SSP）、源移位时钟（SSC）、源输出使能（SOE）以及极性控制（POL））。将选通控制信号（即 GSP、GSC 和 GOE）提供给选通驱动器 106，以控制选通驱动器 106，而将数据控制信号（即 SSP、SSC、SOE 和 POL）提供给数据驱动器 104，以控制数据驱动器 104。此外，定时控制器 108 对像素数据 VD 进行排列，并且将所述数据提供给数据驱动器 104。

选通驱动器 106 顺序地驱动选通线 GL1 至 GLn。选通驱动器 106 包括多个选通集成电路（IC）（未示出）。在定时控制器 108 的控制下，选通 IC 顺序地驱动与其相连的选通线 GL1 至 GLn。选通 IC 响应于来自定时控制器 108 的选通控制信号（即 GSP、GSC 和 GOE）将选通高压 VGH 顺序地提供给选通线 GL1 至 GLn。

具体地，选通驱动器 106 响应于选通移位时钟 GSC 对选通启动脉冲 GSP 进行移位，以生成移位脉冲。然后，选通驱动器 106 响应于该移位

脉冲在每个水平周期将选通高压 VGH 提供给对应的选通线 GL。换言之，在每个水平周期将移位脉冲逐行移位，并且多个选通 IC 中的任何一个根据该移位脉冲，将选通高压 VGH 提供给对应的选通线 GL。在此情况下，选通 IC 对剩余选通线施加选通低压 VGL。

在每个水平周期，数据驱动器 104 一次一行地将像素信号提供给数据线 DL1 至 DLm。数据驱动器 104 包括多个数据 IC 116。可以将各数据 IC 116 安装在数据带载封装 (tape carrier package) (TCP) 110 中。这些数据 IC 116 通过数据 TCP 焊盘 112、数据焊盘 114 以及线路 (link) 118 电连接到数据线 DL1 至 DLm。数据 IC 116 响应于来自定时控制器 108 的数据控制信号 (即 SSP、SSC、SOE 和 POL) 将像素信号提供给数据线 DL1 至 DLm。数据 IC 116 使用来自伽马电压发生器 (未示出) 的伽马电压，将来自定时控制器 108 的像素数据 VD 转换为模拟像素信号。

具体地，数据 IC 116 响应于源移位时钟 SSC 将源启动脉冲 SSP 移位，以生成抽样信号。然后，数据 IC 116 响应于该抽样信号为特定单元对像素数据 VD 顺序地进行锁存。之后，数据 IC 116 将所锁存的用于各行的像素数据 VD 转换为模拟像素信号，并且在源输出使能信号 SOE 的使能区间将所述模拟数据施加给数据线 DL1 至 DLm。数据 IC 116 响应于极性控制信号 POL 将像素数据 VD 转换为正像素信号或负像素信号。

同时，根据本发明第一实施例的 LCD 的各数据 IC 116 响应于从其外部输入的第一通道选择信号 P1 和第二通道选择信号 P2，改变用于将像素信号施加给各数据线 DL1 至 DLm 的输出通道。各数据 IC 116 例如包括被提供了第一通道选择信号 P1 和第二通道选择信号 P2 的第一选项引脚 (option pin) OP1 和第二选项引脚 OP2。

将第一选项引脚 OP1 和第二选项引脚 OP2 中的每一个选择性地连接到电压源 VCC 和地电压源 GND，以具有 2 位的二进制逻辑值。由此，通过第一选项引脚 OP1 和第二选项引脚 OP2 施加给数据 IC 116 的第一通道选择信号 P1 和第二通道选择信号 P2 具有的值为 ‘00’、‘01’、‘10’ 以及 ‘11’。

因此，各数据 IC 116 使用通过第一选项引脚 OP1 和第二选项引脚

OP2 而施加的第一通道选择信号 P1 和第二通道选择信号 P2，根据液晶显示板 102 的分辨率类型而预先设置输出通道的数量。

在下表中说明了根据基于液晶显示板 102 的分辨率的数据 IC 116 的多个输出通道的数据 IC 116 的数量：

表 1

| 分辨率    | 像素数量 |      | 根据数据 IC 的多个输出通道的数据 IC 的数量 |       |       |       |

|--------|------|------|---------------------------|-------|-------|-------|

|        | 数据线  | 选通线  | 600CH                     | 618CH | 630CH | 642CH |

| XGA    | 3072 | 768  | 5.12                      | 4.97  | 4.88  | 4.79  |

| SXGA+  | 4200 | 1050 | 7.00                      | 6.80  | 6.67  | 6.54  |

| UXGA   | 4800 | 1200 | 8.00                      | 7.77  | 7.62  | 7.48  |

| WXGA   | 3840 | 800  | 6.40                      | 6.21  | 6.10  | 5.98  |

| WSXGA- | 4320 | 900  | 7.20                      | 6.99  | 6.86  | 6.73  |

| WSXGA  | 5040 | 1050 | 8.40                      | 8.16  | 8.00  | 7.85  |

| WUXGA  | 5760 | 1200 | 9.60                      | 9.32  | 9.14  | 8.97  |

在表 1 中，可由 4 个通道来表示所有的分辨率。特别地，分辨率为 XGA 级的液晶显示板 102 需要 5 个数据 IC 116，其中每个数据 IC 116 具有 618 个数据输出通道。将剩余的 18 的数据输出通道当作哑线。分辨率为 SXGA+ 级的液晶显示板 102 需要 7 个数据 IC 116，其中每个数据 IC 116 具有 600 个数据输出通道。分辨率为超扩展图形适配器 (Ultra eXtended Graphics Adapter) (UXGA) 级的液晶显示板 102 需要 8 个数据 IC 116，其中每个数据 IC 116 具有 600 个数据输出通道。分辨率为 WXGA 级的液晶显示板 102 需要 6 个数据 IC 116，其中每个数据 IC 116 具有 642 个数据输出通道。分辨率为宽幅高级扩展图形适配器- (Wide aspect Super eXtended Graphics Adapter-) (WSXGA-) 级的液晶显示板 102 需要 7 个数据 IC 116，其中每个数据 IC 116 具有 618 个数据输出通道。分辨率为宽幅高级扩展图形适配器 (WSXGA) 级的液晶显示板 102 需要 8 个数据 IC 116，其中每个数据 IC 116 具有 630 个数据输出通道。分辨率为宽幅超扩展图形适配器 (Wide aspect Ultra eXtended Graphics Adapter)

(WUXGA) 级的液晶显示板 102 需要 9 个数据 IC 116，其中每个数据 IC 116 具有 642 个数据输出通道。

根据本发明第一实施例的 LCD 响应于第一通道选择信号 P1 和第二通道选择信号 P2，将数据 IC 116 的数据输出通道的数量设为 600 个通道、618 个通道、630 个通道和 642 个通道中的任何一种，从而表示出液晶显示板 102 的所有分辨率。例如，可以响应于例如来自第一选项引脚 OP1 和第二选项引脚 OP2 的第一选择信号 P1 和第二选择信号 P2，使根据本发明第一实施例的 LCD 的数据 IC 116 具有 642 个数据输出通道，并且设置数据 IC 116 的有效输出通道数量，从而使得可以将该数据 IC 116 兼容地用于液晶显示板 102 的所有分辨率类型。

可以将根据本发明第一实施例的 LCD 的数据 IC 116 制造为具有 642 个数据输出通道。当通过将第一选项引脚 OP1 和第二选项引脚 OP2 中的每一个都连接到地电压源 GND 从而使提供给数据 IC 116 的第一通道选择信号 P1 和第二通道选择信号 P2 的值为‘00’时，如图 5 所示，数据 IC 116 仅通过可用的 642 个数据输出通道中的第 1 数据输出通道至第 600 数据输出通道来输出像素电压信号。在此情况下，第 601 输出通道至第 642 输出通道成为哑输出通道。另一方面，当通过将第一选项引脚 OP1 连接到地电压源 GND、并将第二选项引脚 OP2 连接到电压源 VCC 而使提供给数据 IC 116 的第一通道选择信号 P1 和第二通道选择信号 P2 的值为‘01’时，如图 6 所示，数据 IC 116 仅通过可用的 642 个数据输出通道中的第 1 数据输出通道至第 618 数据输出通道来输出像素电压信号。在此情况下，第 619 输出通道至第 642 输出通道成为哑输出通道。

当通过将第一选项引脚 OP1 连接到电压源 VCC、并将第二选项引脚 OP2 连接到地电压源 GND 而使提供给数据 IC 116 的第一通道选择信号 P1 和第二通道选择信号 P2 的值为‘10’时，如图 7 所示，数据 IC 116 仅通过可用的 642 个数据输出通道中的第 1 数据输出通道至第 630 数据输出通道来输出像素电压信号。第 631 输出通道至第 642 输出通道成为哑输出通道。最后，当通过将第一选项引脚 OP1 和第二选项引脚 OP2 中的每一个都连接到电压源 VCC 而使提供给数据 IC 116 的第一通道选择信号 P1 和第二通

道选择信号 P2 的值为 ‘11’ 时，如图 8 所示，数据 IC 116 通过第 1 数据输出通道至第 642 数据输出通道来输出像素电压信号。

如图 9 所示，根据本发明第一实施例的 LCD 的数据 IC 116 包括：通道选择器 130，用于响应于施加给例如第一选项引脚 OP1 和第二选项引脚 OP2 的第一通道选择信号 P1 和第二通道选择信号 P2 来设置数据 IC 116 的输出通道；移位寄存器部 134，用于顺序地施加抽样信号；锁存器部 136，用于响应于来自移位寄存器部 134 的抽样信号顺序地锁存像素数据 VD，以同时输出所述数据；数模转换器（DAC）138，用于将来自锁存器部 136 的像素数据 VD 转换为像素电压信号；以及，输出缓冲器部 146，用于对来自 DAC 138 的像素电压信号进行缓冲，并且将其输出给数据线。

数据 IC 116 还包括：信号控制器 120，用于连接来自定时控制器 108 的各种控制信号和像素数据 VD；以及，伽马电压部 132，用于提供 DAC 138 所需的正伽马电压和负伽马电压。

信号控制器 120 控制来自定时控制器 108 的各种控制信号（即 SSP、SSC、SOE、REV 和 POL 等）和像素数据 VD，以将其输出给对应的元件。

伽马电压部 132 针对各灰度级将从伽马基准电压发生器（未示出）输入的多个伽马基准电压进行细分。

通道选择器 130 响应于第一通道选择信号 P1 和第二通道选择信号 P2，通过第一选项引脚 OP1 和第二选项引脚 OP2 将第一通道控制信号 CS1 至第四通道控制信号 CS4 提供给移位寄存器部 134。换言之，通道选择器 130 生成与值为 ‘00’ 的第一通道选择信号 P1 和第二通道选择信号 P2 对应的第一通道控制信号 CS1、与值为 ‘01’ 的第一通道选择信号 P1 和第二通道选择信号 P2 对应的第二通道控制信号 CS2、与值为 ‘10’ 的第一通道选择信号 P1 和第二通道选择信号 P2 对应的第三通道控制信号 CS3、以及与值为 ‘11’ 的第一通道选择信号 P1 和第二通道选择信号 P2 对应的第四通道控制信号 CS4。

包括在移位寄存器部 134 中的多个移位寄存器响应于源抽样时钟信

号 SSC 将来自信号控制器 120 的源启动脉冲 SSP 顺序地进行移位，并且输出抽样信号。在此示例中，移位寄存器部 134 由 642 个移位寄存器 SR1 至 SR642 构成。

这种移位寄存器部 134 响应于来自通道选择器 130 的第一通道控制信号 CS1 至第四通道控制信号 CS4 将第 600 移位寄存器 SR600、第 618 移位寄存器 SR618、第 630 移位寄存器 SR630 以及第 642 移位寄存器 SR642 的输出信号提供给下一级数据 IC 116。

更具体地，当从通道选择器 130 提供第一通道控制信号 CS1 时，移位寄存器部 134 通过使用第 1 移位寄存器 SR1 至第 600 移位寄存器 SR600，响应于源抽样时钟信号 SSC 将来自信号控制器 120 的源启动脉冲 SSP 顺序地进行移位，并且将其输出为抽样信号。在此情况下，将第 600 移位寄存器 SR600 的输出信号（即进位信号）提供给下一级数据 IC 116 的第 1 移位寄存器 SR1，以进行菊链连接。因此，第 601 移位寄存器 SR601 至第 642 移位寄存器 SR642 不输出抽样信号。如果以双向方式来驱动这些移位寄存器，则可以通过使用哑处理而不使用 42 个中间通道来更有利地使用这些移位寄存器。

当从通道选择器 130 提供第二通道控制信号 CS2 时，移位寄存器部 134 通过使用第 1 移位寄存器 SR1 至第 618 移位寄存器 SR618，响应于源抽样时钟信号 SSC 将来自信号控制器 120 的源启动脉冲 SSP 顺序地进行移位，并且将其输出为抽样信号。在此情况下，将第 618 移位寄存器 SR618 的输出信号（即进位信号）提供给下一级数据 IC 116 的第 1 移位寄存器 SR1。因此，第 619 移位寄存器 SR619 至第 642 移位寄存器 SR642 不输出抽样信号。如果以双向方式来驱动这些移位寄存器，则可以通过使用哑处理而不使用 42 个中间通道来更有利地使用这些移位寄存器。

当从通道选择器 130 提供第三通道控制信号 CS3 时，移位寄存器部 134 通过使用第 1 移位寄存器 SR1 至第 630 移位寄存器 SR630，响应于源抽样时钟信号 SSC 将来自信号控制器 120 的源启动脉冲 SSP 顺序地进行移位，并且将其输出为抽样信号。在此情况下，将第 630 移位寄存器 SR630 的输出信号（即进位信号）提供给下一级数据 IC 116 的第 1 移位

寄存器 SR1。因此，第 631 移位寄存器 SR631 至第 642 移位寄存器 SR642 不输出抽样信号。其中，如果以双向方式来驱动这些移位寄存器，则可以通过使用哑处理而不使用 12 个中间通道来更有利地使用这些移位寄存器。

当从通道选择器 130 提供第四通道控制信号 CS4 时，移位寄存器部 134 通过使用第 1 移位寄存器 SR1 至第 642 移位寄存器 SR642，响应于源抽样时钟信号 SSC 将来自信号控制器 120 的源启动脉冲 SSP 顺序地进行移位，并且将其输出为抽样信号。在此情况下，将第 642 移位寄存器 SR642 的输出信号（即进位信号）提供给下一级数据 IC 116 的第 1 移位寄存器 SR1。

锁存器部 136 响应于来自移位寄存器部 134 的抽样信号为特定单元对来自信号控制器 120 的像素数据 VD 顺序地进行抽样，以将其锁存。为此，锁存器部 136 包括最多 642 个锁存器，以锁存 642 个像素数据 VD，并且各锁存器具有与像素数据 VD 的位数对应的大小。具体地，定时控制器 108 将像素数据 VD 分成偶像素数据  $VD_{even}$  和奇像素数据  $VD_{odd}$ ，以减小传输频率，并通过各传输线同时输出这些数据。偶像素数据  $VD_{even}$  和奇像素数据  $VD_{odd}$  中的每一个都包括红色 (R)、绿色 (G) 和蓝色 (B) 像素数据。

锁存器部 136 对于各个抽样信号同时锁存通过信号控制器 120 提供的偶像素数据  $VD_{even}$  和奇像素数据  $VD_{odd}$ 。然后，锁存器部 136 响应于来自信号控制器 120 的源输出使能信号 SOE，通过所选数量个输出通道（600、618、630 或者 642 个数据输出通道）同时输出像素数据 VD。锁存器部 136 响应于数据反相选择信号 REV 还原进行了调制以减少转换位数的像素数据 VD。这是因为，定时控制器 108 对像素数据 VD（其中转换的位数超过基准值）进行调制，以使得减小转变位数，从而使数据传输时的电磁干扰 (EMI) 最小。

DAC 138 将来自锁存器部 136 的像素数据 VD 同时转换为正像素电压信号和负像素电压信号。DAC 138 包括：共同连接到锁存器部 136 的正 (P) 解码部 140 和负 (N) 解码部 142；以及多路复用器 (MUX) 部

144，用于对 P 解码部 140 和 N 解码部 142 的输出信号进行选择。

包括在 P 解码部 140 中的 n 个 P 解码器使用来自伽马电压部 132 的正伽马电压，将从锁存器部 136 同时输入的 n 个像素数据转换为正像素电压信号。包括在 N 解码部 142 中的 i 个 N 解码器使用来自伽马电压部 132 的负伽马电压，将从锁存器部 136 同时输入的 i 个像素数据转换为负像素电压信号。在该示例中，包括在多路复用器部 144 中的最多 642 个多路复用器响应于来自信号控制器 120 的极性控制信号 POL，选择性地输出来自 P 解码器 140 的正像素电压信号或者来自 N 解码器 142 的负像素电压信号。

包括在输出缓冲器部 146 中的最多 642 个输出缓冲器包括串联连接到相应的 642 条数据线 DL1 至 DL642 的多个电压跟随器等。这些输出缓冲器 146 对来自 DAC 138 的像素电压信号进行缓冲，以将这些信号提供给数据线 DL1 至 DL642。

在根据本发明第一实施例的 LCD 中，如以上表 1 所示，对于分辨率为 SXGA+ 级或 UXGA 级的液晶显示板 102 使用具有 600 个数据输出通道的数据 IC 116；对于分辨率为 XGA 级或者 WSXGA- 级的液晶显示板 102 使用具有 618 个数据输出通道的数据 IC 116；对于分辨率为 WSXGA 级的液晶显示板 102 使用具有 630 个数据输出通道的数据 IC 116；对于分辨率为 WXGA 级或 WUXGA 级的液晶显示板 102 使用具有 642 个数据输出通道的数据 IC 116。

同时，在根据本发明第一实施例的 LCD 中，液晶显示板 102 的 TCP 焊盘 112、数据焊盘 114 以及线路 118 与响应于第一通道选择信号 P1 和第二通道选择信号 P2 而变化的数据 IC 116 的输出通道相对应。

根据本发明第一实施例的 LCD 通过使用施加给第一选项引脚 OP1 和第二选项引脚 OP2 的第一选择信号 P1 和第二选择信号 P2，如以上表 1 所示地，根据液晶显示板 102 的分辨率来设置数据 IC 116 的数据输出通道的数量，从而仅使用一种类型的数据 IC 116 来构成多个分辨率。因此，根据本发明的第一实施例的 LCD 提高了 LCD 器件的工作效率并且降低了制造成本。

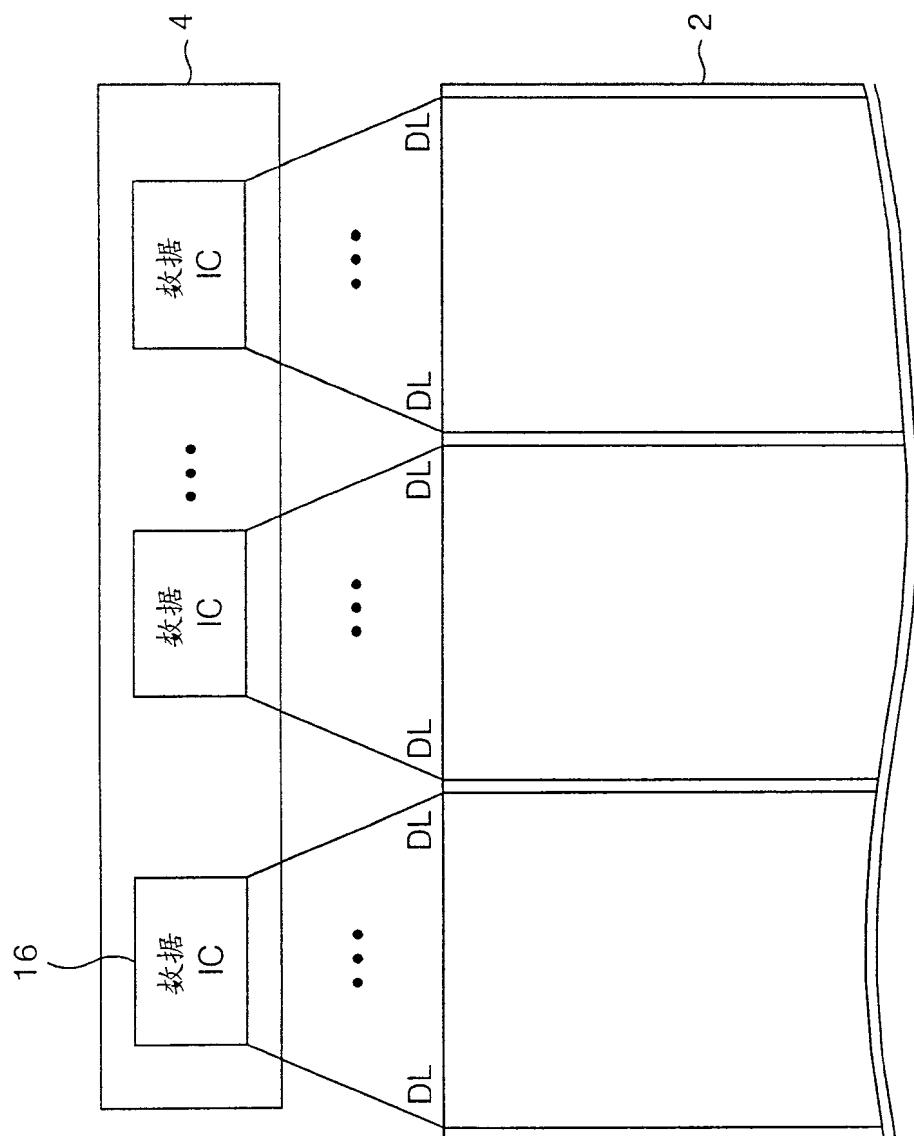

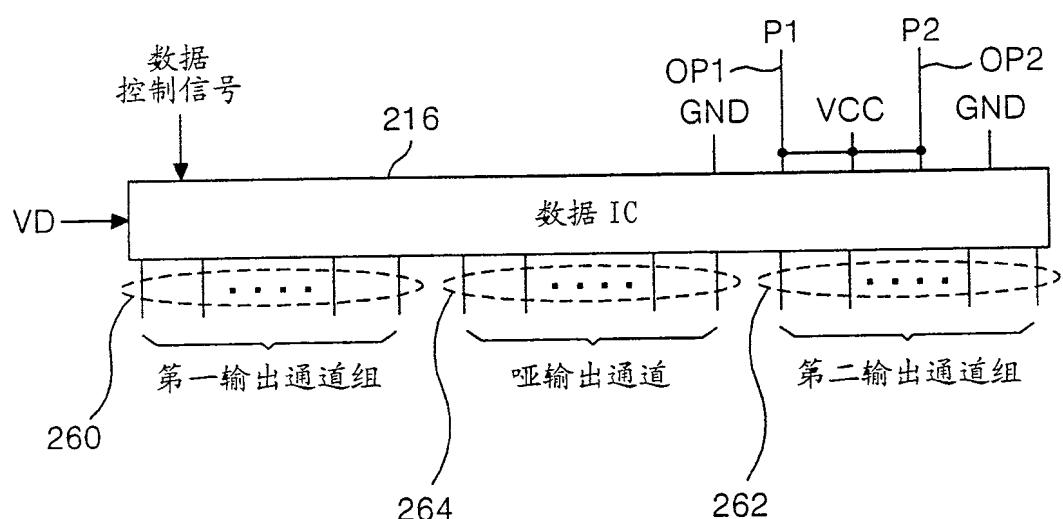

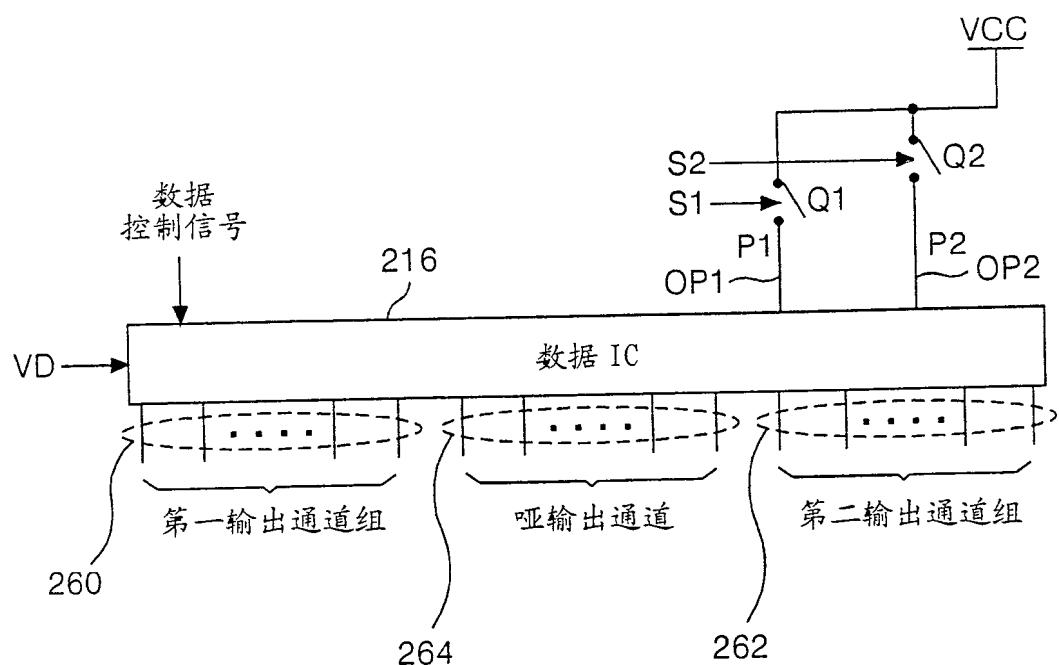

图 10 是表示根据本发明第二实施例的液晶显示器中的数据 IC 的结构的框图。

在图 10 中，除了数据 IC 216 以外，根据本发明第二实施例的 LCD 具有与根据本发明第一实施例的 LCD 相同的元件。因此，在根据本发明第二实施例的 LCD 中，将结合图 10 和图 4 说明数据 IC 216，并且将省略对相同元件的说明。其中，图 4 中所示的数据 IC 的标号为“116”。

在根据本发明第二实施例的 LCD 中，数据 IC 216 包括：第一数据输出通道组 260 和第二数据输出通道组 262，用于将数据提供给数据线 DL1 至 DLm；以及，哑输出通道组 264，设置在第一数据输出通道组 260 和第二数据输出通道组 262 之间。

数据 IC 216 还包括第一选项引脚 OP1 和第二选项引脚 OP2，对第一选项引脚 OP1 和第二选项引脚 OP2 提供第一通道选择信号 P1 和第二通道选择信号 P2，以确定是否输出了通过哑数据输出通道组 264 根据数据线 DL1 至 DLm 的数量而提供给数据线 DL1 至 DLm 的像素数据。

将第一选项引脚 OP1 和第二选项引脚 OP2 中的每一个选择性地连接到电压源 VCC 和地电压源 GND，以具有 2 位的二进制逻辑值。因此，通过第一选项引脚 OP1 和第二选项引脚 OP2 而提供给数据 IC 216 的第一通道选择信号 P1 和第二通道选择信号 P2 可以具有值‘00’、‘01’、‘10’以及‘11’。

因此，各数据 IC 216 使用通过第一选项引脚 OP1 和第二选项引脚 OP2 而提供的第一通道选择信号 P1 和第二通道选择信号 P2，根据液晶显示板 102 的期望分辨率而预先设置输出通道。

如以上表 1 中所示，根据数据 IC 216 的数据输出通道的数据 IC 216 的数量是基于液晶显示板 102 的分辨率的。

因此，根据本发明第二实施例的 LCD 可以响应于第一通道选择信号 P1 和第二通道选择信号 P2 将数据 IC 216 的数据输出通道设置为例如 600 个通道、618 个通道、630 个通道以及 642 个通道中的任何一个，从而构成液晶显示板 102 的多个分辨率。换言之，可以将根据本发明第二实施例的 LCD 的数据 IC 216 设置为具有 642 个数据输出通道，这 642 个数据

输出通道是响应于来自第一选项引脚 OP1 和第二选项引脚 OP2 的第一通道选择信号 P1 和第二通道选择信号 P2 而设置的，从而使得可以将数据 IC 216 兼容地用于液晶显示板 102 的所有分辨率。此外，在根据第二实施例的 LCD 中，根据位于数据 IC 216 的多个数据输出通道的中间部分处的输出通道的确定情况，来设置数据 IC 216 的哑数据输出通道组 264。换言之，数据 IC 216 的第一数据输出通道组 260 和第二数据输出通道组 262 具有相同的数据输出通道，它们之间具有哑数据输出通道组 264。因此，根据本发明第二实施例的 LCD 使数据 IC 216 的第一数据输出通道组 260 和第二数据输出通道组 262 的数据输出通道相等，由此降低了输出像素数据时的电磁干涉。

例如可以将根据本发明第二实施例的 LCD 的数据 IC 216 制造为具有 642 个数据输出通道。

当通过将第一选项引脚 OP1 和第二选项引脚 OP2 中的每一个都连接到地电压源 GND 从而使提供给数据 IC 216 的第一通道选择信号 P1 和第二通道选择信号 P2 的值为 ‘00’ 时，如图 11 所示，数据 IC 216 通过第一数据输出通道组 260（具有可用的 642 个数据输出通道中的第 1 输出通道至第 300 输出通道）和第二数据输出通道组 262（具有可用的第 343 输出通道至第 642 输出通道）来输出像素信号。哑数据输出通道组 264 具有被视为哑线的第 301 输出通道至第 342 输出通道。

在图 12 中，当通过将第一选项引脚 OP1 连接到地电压源 GND、并将第二选项引脚 OP2 连接到电压源 VCC 从而使提供给数据 IC 216 的第一通道选择信号 P1 和第二通道选择信号 P2 的值为 ‘01’ 时，数据 IC 216 通过第一数据输出通道组 260（具有 642 个数据输出通道中的第 1 输出通道至第 309 输出通道）和第二数据输出通道组 262（具有第 334 输出通道至第 642 输出通道）来输出像素信号，如图 12 所示。哑数据输出通道组 264 具有被视为哑线的第 310 输出通道至第 333 输出通道。

在图 13 中，当通过将第一选项引脚 OP1 连接到电压源 VCC、并将第二选项引脚 OP2 连接到地电压源 GND 从而使提供给数据 IC 216 的第一通道选择信号 P1 和第二通道选择信号 P2 的值为 ‘10’ 时，数据 IC 216

通过第一数据输出通道组 260(具有 642 个数据输出通道中的第 1 输出通道至第 315 输出通道)和第二数据输出通道组 262(具有可用的第 328 数据输出通道至第 642 数据输出通道)来输出像素信号, 如图 13 所示。因而, 哑数据输出通道组 264 包括被视为哑线的第 316 输出通道至第 327 输出通道。

最后, 在图 14 中, 当通过将第一选项引脚 OP1 和第二选项引脚 OP2 的每一个都连接到电压源 VCC 从而使提供给数据 IC 216 的第一通道选择信号 P1 和第二通道选择信号 P2 的值为 ‘11’ 时, 数据 IC 216 通过第一数据输出通道组 260、哑数据输出通道组 264 和第二数据输出通道组 262(即通过第 1 输出通道至第 642 输出通道)输出像素数据, 如图 14 所示。

为此, 与图 9 类似, 根据本发明第二实施例的 LCD 的数据 IC 216 包括: 通道选择器 130, 用于响应于施加给第一选项引脚 OP1 和第二选项引脚 OP2 的第一通道选择信号 P1 和第二通道选择信号 P2 来设置数据 IC 216 的输出通道; 移位寄存器部 134, 用于顺序地施加抽样信号; 锁存器部 136, 用于响应于抽样信号顺序地锁存像素数据 VD, 以同时输出该数据; 数模转换器 (DAC) 138, 用于将来自锁存器部 136 的像素数据 VD 转换为像素电压信号; 以及, 输出缓冲器部 146, 用于对来自 DAC 138 的像素电压信号进行缓冲。

数据 IC 216 还包括: 信号控制器 120, 用于连接来自定时控制器 108 的各种控制信号和像素数据 VD; 以及伽马电压部 132, 用于提供 DAC 138 所需的正伽马电压和负伽马电压。

由于包括通道选择器 130、移位寄存器部 134、锁存器部 136、DAC 138、输出缓冲器部 146、信号控制器 120 以及伽马电压部的数据 IC 216 与根据本发明第一实施例的 LCD 的数据 IC 116 相同, 因此将采用上述说明来代替对于相同元件的说明。

如上所述, 根据本发明第二实施例的 LCD 响应于施加给第一选项引脚 OP1 和第二选项引脚 OP2 的第一通道选择信号 P1 和第二通道选择信号 P2, 如以上表 1 所示, 基于液晶显示板 102 的分辨率来设置数据 IC 216 的输出通道, 从而仅利用一种数据 IC 216 就表示了所有的分辨率。因此,

根据本发明第二实施例的 LCD 提高了 LCD 的工作效率并且降低了制造成本。

在另一实施例中，如图 15 所示，通过对第一开关 Q1 和第二开关 Q2 的选择性开关来生成分别施加给本发明第一实施例和第二实施例的数据 IC 116 和数据 IC 216 的第一选项引脚 OP1 和第二选项引脚 OP2 的第一通道选择信号 P1 和第二通道选择信号 P2。

第一开关 Q1 连接在电压源 VCC 与第一选项引脚 OP1 之间，而第二开关 Q2 连接在电压源 VCC 与第二选项引脚 OP2 之间。分别通过来自计时控制器 108 的开关信号 S1 和 S2 来开关第一开关 Q1 和第二开关 Q2，或者分别通过基于液晶显示板 102 的分辨率类型而设置的开关信号 S1 和 S2 来对第一开关 Q1 和第二开关 Q2 进行开关。

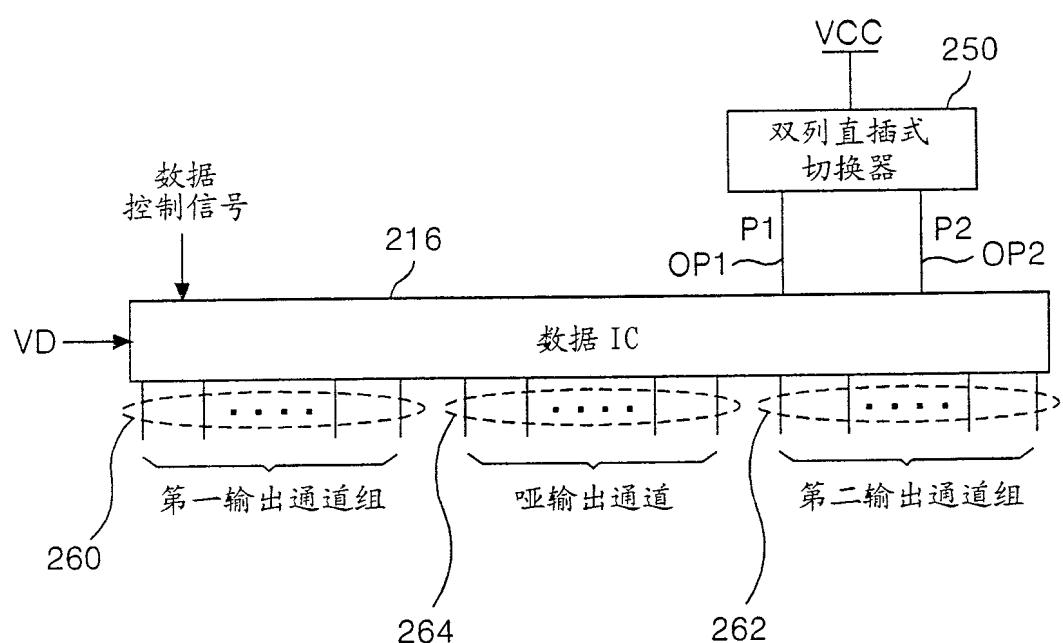

此外，如图 16 所示，还可以通过连接到电压源 VCC 同时连接到对应的第一选项引脚 OP1 和第二选项引脚 OP2 的双列直插式切换器 250 的切换操作，来生成施加给根据本发明的第一和第二实施例的数据 IC 116 和数据 IC 216 的第一选项引脚 OP1 和第二选项引脚 OP2 的第一通道选择信号 P1 和第二通道选择信号 P2。

系统工程师可以根据液晶显示板 102 的分辨率来预设双列直插式切换器 250，以生成第一通道选择信号和第二通道选择信号，从而分别将这些信号施加给第一选项引脚 OP1 和第二选项引脚 OP2。

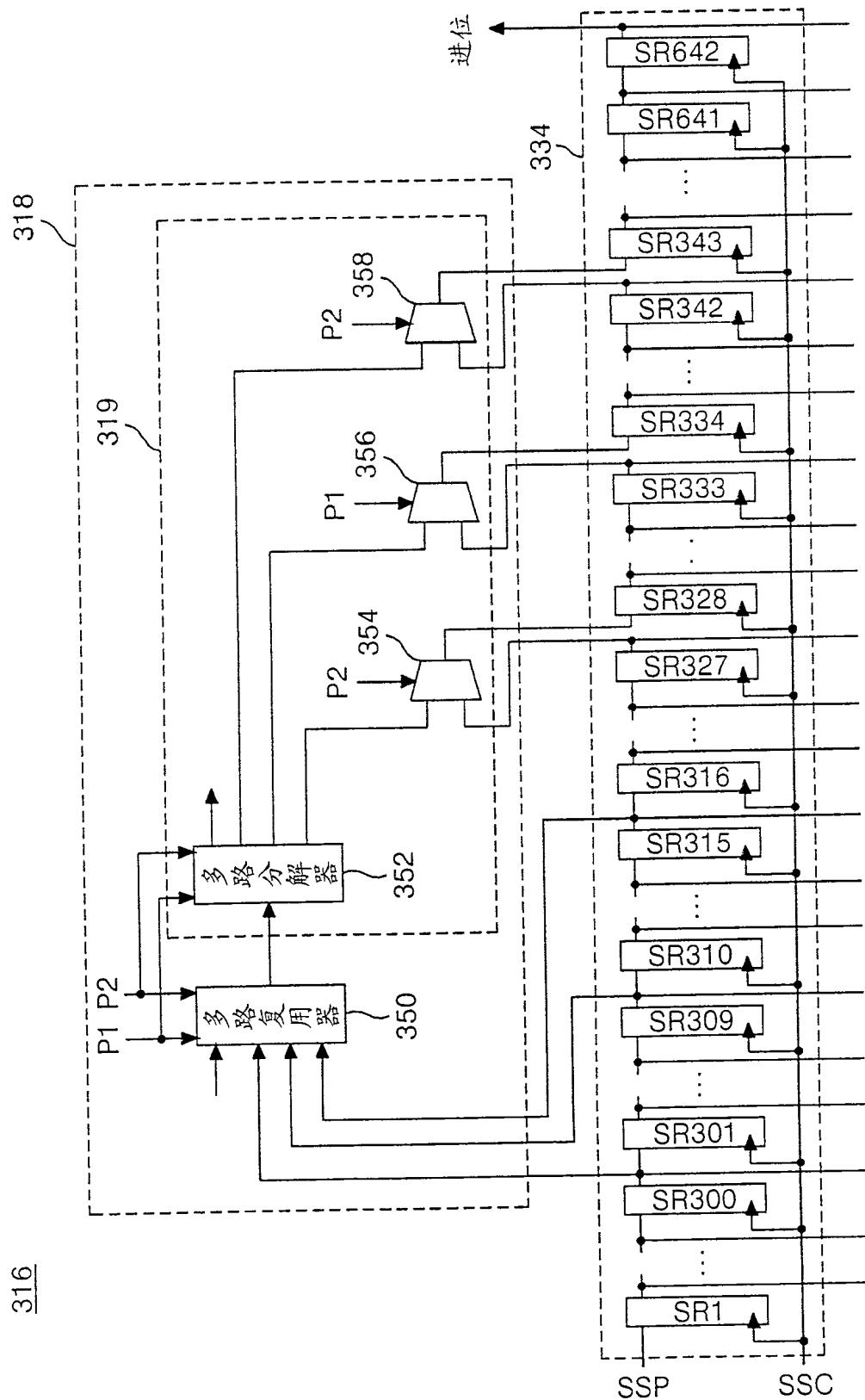

图 17 是表示根据本发明第三实施例的液晶显示板中的数据 IC 的结构的框图。

在图 17 中，除了数据 IC 316 以外，根据本发明第三实施例的 LCD 具有与根据本发明的第一实施例的 LCD 相同的元件。因此，在根据本发明第三实施例的 LCD 中，仅结合图 17 和图 4 说明数据 IC 316，省略对其他元件的说明。其中，图 4 中所示的数据 IC 的标号“116”将由图 17 中所示的标号“316”代替。

在根据本发明第三实施例的 LCD 中，数据 IC 316 包括：第一数据输出通道组 360 和第二数据输出通道组 362，用于向数据线 DL1 至 DLm 施加数据；以及，哑输出通道组 364，设置在第一数据输出通道组 360 与第

二数据输出通道组 362 之间。

这种数据 IC 316 还包括第一选项引脚和第二选项引脚，例如 OP1 和 OP2，对其提供第一通道选择信号 P1 和第二通道选择信号 P2，以确定是否输出了根据数据线 DL1 至 DLm 的数量通过哑数据输出通道组 364 提供给数据线 DL1 至 DLm 的像素数据。

将第一选项引脚 OP1 和第二选项引脚 OP2 中的每一个选择性连接到电压源 VCC 和地电压源 GND，以具有 2 位的二进制逻辑值。因此，通过第一选项引脚 OP1 和第二选项引脚 OP2 而提供给数据 IC 316 的第一通道选择信号 P1 和第二通道选择信号 P2 可以具有值 ‘00’、‘01’、‘10’ 以及 ‘11’。

因此，各数据 IC 316 响应于通过第一选项引脚 OP1 和第二选项引脚 OP2 而施加的第一通道选择信号 P1 和第二通道选择信号 P2，根据液晶显示板 102 的分辨率预先设置输出通道。

根据基于液晶显示板 102 的分辨率类型的数据 IC 316 的数据输出通道的数据 IC 316 的数量如以上的表 1 中所示。

因此，根据本发明第三实施例的 LCD 响应于第一通道选择信号 P1 和第二通道选择信号 P2，将数据 IC 316 的输出通道例如设置为 600 个通道、618 个通道、630 个通道以及 642 个通道中的任何一种，从而构成液晶显示板 102 的多个分辨率类型。换言之，根据本发明第三实施例的 LCD 的数据 IC 316 可以具有 642 个数据输出通道。数据 IC 316 的输出通道是响应于来自第一选项引脚 OP1 和第二选项引脚 OP2 的第一通道选择信号 P1 和第二通道选择信号 P2 而设置的，从而使得可以将 LCD 板兼容地用于液晶显示板 102 的所有分辨率类型。此外，根据本发明第三实施例的 LCD 将数据 IC 316 的哑数据输出通道组 364 设置在数据 IC 316 的多个数据输出通道的中间部分处。换言之，数据 IC 316 的第一数据输出通道组 360 和第二数据输出通道组 362 具有相同数量的输出通道，它们之间具有哑输出通道组 364。因此，根据本发明第三实施例的 LCD 使得数据 IC 316 的第一数据输出通道组 360 和第二数据输出通道组 362 的输出通道相等，由此降低了输出像素数据时的电磁干涉。

具体地，可以将根据本发明第三实施例的 LCD 的数据 IC 316 制造为具有 642 个数据输出通道。

当通过将第一选项引脚 OP1 和第二选项引脚 OP2 中的每一个都连接到地电压源 GND 使得提供给数据 IC 316 的第一通道选择信号 P1 和第二通道选择信号 P2 的值为 ‘00’ 时，与图 11 相似，数据 IC 316 通过第一数据输出通道组 360（具有 642 个数据输出通道中的第 1 输出通道至第 300 输出通道）和第二数据输出通道组 362（具有第 343 输出通道至第 642 输出通道）来输出像素信号。在此情况下，哑数据输出通道组 364 包括被视为哑线的第 301 输出通道至第 342 输出通道。

当通过将第一选项引脚 OP1 连接到地电压源 GND、并将第二选项引脚 OP2 连接到电压源 VCC 从而使提供给数据 IC 316 的第一通道选择信号 P1 和第二通道选择信号 P2 的值为 ‘01’ 时，与图 12 相似，数据 IC 316 通过第一数据输出通道组 360（具有 642 个数据输出通道中的第 1 输出通道至第 309 输出通道）和第二数据输出通道组 362（具有第 334 输出通道至第 642 输出通道）来输出像素信号。在此情况下，哑数据输出通道组 364 包括被视为哑线的第 310 输出通道至第 333 输出通道。

同时，当通过将第一选项引脚 OP1 连接到电压源 VCC、并将第二选项引脚 OP2 连接到地电压源 GND 从而使提供给数据 IC 316 的第一通道选择信号 P1 和第二通道选择信号 P2 的值为 ‘10’ 时，与图 13 相似，数据 IC 316 通过第一数据输出通道组 360（具有 642 个数据输出通道的第 1 输出通道至第 315 输出通道）和第二数据输出通道组 362（具有第 328 输出通道至第 642 输出通道）来输出像素信号。在此情况下，哑数据输出通道组 364 包括被视为哑线的第 316 输出通道至第 327 输出通道。

最后，与图 14 相似，当通过将第一选项引脚 OP1 和第二选项引脚 OP2 中的每一个都连接到电压源 VCC 从而使提供给数据 IC 316 的第一通道选择信号 P1 和第二通道选择信号 P2 的值为 ‘11’ 时，数据 IC 316 通过第一数据输出通道组 360、哑数据输出通道组 364 和第二输出通道组 362（即通过第 1 数据输出通道至第 642 数据输出通道）来输出像素数据。

为此，如图 17 所示，根据本发明第三实施例的 LCD 的数据 IC 316

包括：通道选择器 318，用于响应于施加给第一选项引脚 OP1 和第二选项引脚 OP2 的第一通道选择信号 P1 和第二通道选择信号 P2 来设置数据 IC 316 的输出通道；移位寄存器部 334，用于提供顺序的抽样信号；锁存器部（未示出），用于响应于抽样信号顺序地锁存像素数据 VD，以将这些数据同时输出；数模转换器（DAC）（未示出），用于将来自锁存器部的像素数据 VD 转换为像素电压信号；以及，输出缓冲器部（未示出），用于对来自 DAC 的像素电压信号进行缓冲。

数据 IC 316 还包括：信号控制器（未示出），用于连接来自定时控制器 108 的各种控制信号和像素数据 VD；以及，伽马电压部（未示出），用于提供 DAC 所需的正伽马电压和负伽马电压。

由于除了通道选择器 318 和移位寄存器部 334 以外，包括锁存器部、DAC、输出缓冲器部、信号控制器以及伽马电压部的数据 IC 316 与根据本发明第一实施例的 LCD 的数据 IC 116 相同，因此将采用上述说明来代替对于相同元件的说明。

在根据本发明第三实施例的 LCD 的数据 IC 316 中，数据 IC 316 的移位寄存器部 334 包括 N 个移位寄存器 SR1 至 SRn。包括在移位寄存器部 334 中的多个移位寄存器响应于源抽样时钟信号 SSC 对来自信号控制器的源启动脉冲 SSP 顺序地进行移位，以将这些信号作为抽样信号输出。将移位寄存器部 334 的第 N 移位寄存器 SRn 的输出信号（进位信号）施加到下一级数据 IC 316 的第 1 移位寄存器 SR1。在此情况下，假定移位寄存器部 334 包括 642 个移位寄存器 SR1 至 SR642 来对其进行说明。

通道选择器 318 包括：第一多路复用器 350，用于响应于第一通道选择信号 P1 和第二通道选择信号 P2，选择性地输出第 I1 移位寄存器 SRI1（其中 I1 是大于 1 的整数）的输出信号、第 I2 移位寄存器 SRI2（其中 I2 是大于 I1 的整数）的输出信号、以及第 I3 移位寄存器 SRI3（其中 I3 是大于 I2 并且小于 N 的整数）的输出信号中的一个；多路分解器 352，用于响应于第一通道选择信号 P1 和第二通道选择信号 P2，将第一多路复用器 350 的输出信号施加到第 J1 移位寄存器 SRJ1（其中 J1 是大于 I3 的整数）、第 J2 移位寄存器 SRJ2（其中 J2 是大于 J1 的整数）、以及第 J3

移位寄存器 SRJ3 (其中 J3 是大于 J2 并且小于 N 的整数) 中的一个; 第二多路复用器 354, 用于响应于第二通道选择信号 P2, 将第 (J1-1) 移位寄存器 SRJ1-1 的输出信号和多路分解器 352 的输出信号中的一个施加到第 J1 移位寄存器 SRJ1; 第三多路复用器 356, 用于响应于第一通道选择信号 P1, 将第 (J2-1) 移位寄存器 SRJ2-1 的输出信号和多路分解器 352 的输出信号中的一个施加到第 J2 移位寄存器 SRJ2; 以及, 第四多路复用器 358, 用于响应于第二通道选择信号 P2, 将第 (J3-1) 移位寄存器 SRJ3-1 的输出信号和多路分解器 352 的输出信号中的任一个施加到第 J3 移位寄存器 SRJ3。以下, I1 应指第 300 移位寄存器 SR300; I2 应指第 309 移位寄存器 SR309; 并且 I3 应指第 315 移位寄存器 SR315。此外, J1 应指第 328 移位寄存器 SR328; J2 应指第 334 移位寄存器 SR334; 并且 J3 应指第 343 移位寄存器 SR343。其中, 第一多路复用器 350 成为第一选择器, 多路分解器 352 和第二至第四多路复用器 354、356 以及 358 成为第二选择器 319。

当第一通道选择信号 P1 和第二通道选择信号 P2 的逻辑值为“00”时, 第一多路复用器 350 选择第 300 移位寄存器 SR300 的输出信号, 并且将其施加给多路分解器 352。当第一通道选择信号 P1 和第二通道选择信号 P2 的逻辑值为“01”时, 第一多路复用器 350 选择第 309 移位寄存器 SR309 的输出信号, 并且将其施加给多路分解器 352。当第一通道选择信号 P1 和第二通道选择信号 P2 的逻辑值为“10”时, 第一多路复用器 350 选择第 315 移位寄存器 SR315 的输出信号, 并且将其施加给多路分解器 352。当第一通道选择信号 P1 和第二通道选择信号 P2 的逻辑值为“11”时, 第一多路复用器 350 和多路分解器 352 是不必要的。

当第一通道选择信号 P1 和第二通道选择信号 P2 的逻辑值为“00”时, 多路分解器 352 将第一多路复用器 350 的输出信号施加给第四多路复用器 358。当第一通道选择信号 P1 和第二通道选择信号 P2 的逻辑值为“01”时, 多路分解器 352 将第一多路复用器 350 的输出信号施加给第三多路复用器 356。当第一通道选择信号 P1 和第二通道选择信号 P2 的逻辑值为“10”时, 多路分解器 352 将第一多路复用器 350 的输出信号施

加给第二多路复用器 354。另一方面，当第一通道选择信号 P1 和第二通道选择信号 P2 的值为“11”时，多路分解器 352 是不必要的。

当第二通道选择信号 P2 的逻辑值为‘0’时，第二多路复用器 354 将多路分解器 352 的输出信号提供给第 328 移位寄存器 SR328。当第二通道选择信号 P2 的逻辑值为‘1’时，第二多路复用器 354 将第 327 移位寄存器 SR327 的输出信号提供给第 328 移位寄存器 SR328。

当第一通道选择信号 P1 的逻辑值为‘0’时，第三多路复用器 356 将多路分解器 352 的输出信号提供给第 334 移位寄存器 SR334。当第一通道选择信号 P1 的逻辑值为‘1’时，第三多路复用器 356 将第 333 移位寄存器 SR332 的输出信号提供给第 334 移位寄存器 SR334。

当第二通道选择信号 P2 的逻辑值为‘0’时，第四多路复用器 358 将多路分解器 352 的输出信号提供给第 343 移位寄存器 SR343。当第二通道选择信号 P2 的逻辑值为‘1’时，第四多路复用器 358 将第 342 移位寄存器 SR342 的输出信号提供给第 343 移位寄存器 SR343。

以下将对通道选择器 318 和移位寄存器部 343 根据第一通道选择信号 P1 和第二通道选择信号 P2 的操作进行说明。

首先，如图 11 所示，当选择数据 IC 216 的输出通道中的第 1 至第 300 输出通道作为第一数据输出通道组 260，选择第 301 至第 342 输出通道作为哑输出通道组 264，并且选择第 343 至 642 输出通道作为第二输出通道组 262 时，对数据 IC 316 的通道选择器 318 提供逻辑值为“00”的第一通道选择信号 P1 和第二通道选择信号 P2。由此，移位寄存器部 334 通过使用第 1 移位寄存器 SR1 至第 600 移位寄存器 SR600，响应于源抽样时钟信号 SSC 对源启动脉冲 SSP 顺序地进行移位，从而将其输出为抽样信号。这时，通过第一多路复用器 350、多路分解器 352 以及第四多路复用器 358 将第 300 移位寄存器 SR300 的输出信号提供给第 343 移位寄存器 SR343。此外，将第 642 移位寄存器 SR642 的输出信号提供给下一级数据 IC 316 的第 1 移位寄存器 SR1。因此，第 1 移位寄存器 SR1 至第 300 移位寄存器 SR300、以及第 343 移位寄存器 SR343 至第 642 移位寄存器 SR642 向锁存器部施加抽样信号。这时，第 301 移位寄存器 SR301

至第 342 移位寄存器 SR342 也确实向锁存器部施加抽样信号。

接下来，如图 12 所示，当选择数据 IC 216 的输出通道的第 1 输出通道至第 309 输出通道作为第一通道组 260，选择第 310 输出通道至第 333 输出通道作为哑输出通道组 264，并且选择第 334 输出通道至第 642 输出通道作为第二输出通道组 262 时，对数据 IC 316 的通道选择器 318 提供逻辑值为“01”的第一通道选择信号 P1 和第二通道选择信号 P2。由此，移位寄存器部 334 通过使用第 1 移位寄存器 SR1 至第 600 移位寄存器 SR600，响应于源抽样时钟信号 SSC 对源启动脉冲 SSP 信号顺序地进行移位，从而将它们输出为抽样信号。这时，通过第一多路复用器 350、多路分解器 352 以及第三多路复用器 356 将第 309 移位寄存器 SR309 的输出信号提供给第 334 移位寄存器 SR334。此外，将第 642 移位寄存器 SR642 的输出信号提供给下一级数据 IC 316 的第 1 移位寄存器 SR1。因此，第 1 移位寄存器 SR1 至第 309 移位寄存器 SR309、以及第 334 移位寄存器 SR334 至第 642 移位寄存器 SR642 向锁存器部施加抽样信号。这时，第 310 移位寄存器 SR310 至第 333 移位寄存器 SR333 也确实向锁存器部施加抽样信号。

随后，如图 13 所示，当选择数据 IC 216 的输出通道的第 1 输出通道至第 315 输出通道作为第一输出通道组 260，选择第 316 数据输出通道至第 327 通道作为哑输出通道组 264，并且选择第 328 输出通道至第 642 输出通道作为第二输出通道组 262 时，对数据 IC 316 的通道选择器 138 提供了逻辑值为“10”的第一通道选择信号 P1 和第二通道选择信号 P2。由此，移位寄存器部 334 通过使用第 1 移位寄存器 SR1 至第 600 移位寄存器 SR600，响应于源抽样时钟信号 SSC 对源启动脉冲 SSP 信号顺序地进行移位，从而将它们输出为抽样信号。这时，通过第一多路复用器 350、多路分解器 352 以及第二多路复用器 354 将第 315 移位寄存器 SR315 的输出信号提供给第 328 移位寄存器 SR328。此外，将第 642 移位寄存器 SR642 的输出信号（即进位信号）提供给下一级数据 IC 316 的第 1 移位寄存器 SR1。因此，第 1 移位寄存器 SR1 至第 315 移位寄存器 SR315、以及第 328 移位寄存器 SR328 至第 642 移位寄存器 SR642 向锁存器部施

加抽样信号。第 316 移位寄存器 SR316 至第 327 移位寄存器 SR327 也确实向锁存器部施加抽样信号。

因此，如图 14 所示，当选择数据 IC 216 的输出通道的第 1 输出通道至第 321 输出通道作为第一输出通道组 260，并且选择第 322 数据输出通道至第 642 通道作为第二数据输出通道组 262 时，对数据 IC 316 的通道选择器 318 提供逻辑值为“11”的第一通道选择信号 P1 和第二通道选择信号 P2。由此，移位寄存器部 334 通过使用第 1 移位寄存器 SR1 至第 642 移位寄存器 SR642，响应于源抽样时钟信号 SSC 对源启动脉冲 SSP 信号顺序地进行移位，从而将它们输出为抽样信号。在逻辑值为“11”时，第一多路复用器 350 和多路分解器 352 是不必要的。此外，将第 327 移位寄存器 SR327 的输出信号通过第二多路复用器 354 提供给第 328 移位寄存器 SR328；将第 333 移位寄存器 SR333 的输出信号通过第三多路复用器 356 提供给第 334 移位寄存器 SR334；将第 342 移位寄存器 SR342 的输出信号通过第四多路复用器 358 提供给第 343 移位寄存器 SR343。因此，移位寄存器部 334 的第 1 移位寄存器 SR1 至第 642 移位寄存器 SR642 中的每一个都向锁存器部施加抽样信号。其中，将第 642 移位寄存器 SR642 的输出信号提供给下一级数据 IC 216 的第 1 移位寄存器 SR1。

按照根据本发明第一实施例的 LCD 的数据 IC 116 的操作，这种根据本发明第三实施例的 LCD 的数据 IC 316 通过使用来自移位寄存器部 334 的抽样信号，将来自定时控制器 108 的数据 VD 转换为像素数据，从而通过第一输出通道组 260、第二输出通道组 262 以及哑输出通道组 264 的一部分，将它们提供给液晶显示板 102 的多条数据线 DL。

如上所述，根据本发明第三实施例的 LCD 响应于提供给第一选项引脚 OP1 和第二选项引脚 OP2 的第一通道选择信号 P1 和第二通道选择信号 P2，如以上表 1 所示，根据液晶显示板 102 的期望分辨率来设置数据 IC 316 的数据输出通道，从而仅使用一种数据 IC 316 就构成多个分辨率类型。因此根据本发明第三实施例的 LCD 提高了工作效率并且降低了制造成本。

另选地，在根据本发明的第三实施例的 LCD 中，如图 15 所示，可

以通过选择性地开关第一开关 Q1 和第二开关 Q2 来生成施加给数据 IC 316 的第一选项引脚 OP1 和第二选项引脚 OP2 的第一通道选择信号 P1 和第二通道选择信号 P2。对于第一开关 Q1 和第二开关 Q2 的说明与对根据本发明第二实施例的 LCD 的上述说明相同。

此外，在根据本发明第三实施例的 LCD 中，如图 16 所示，可以由连接到电压源 VCC 并同时连接到各第一选项引脚 OP1 和第二选项引脚 OP2 的双列直插式切换器 250 的切换操作来生成施加给数据 IC 316 的第一选项引脚 OP1 和第二选项引脚 OP2 的第一通道选择信号 P1 和第二通道选择信号 P2。对于双列直插式切换器 250 的说明与根据本发明第二实施例的 LCD 的上述说明相同。

如上所述的根据本发明第一实施例至第三实施例的 LCD 不限于仅响应于第一通道选择信号 P1 和第二通道选择信号 P2 而改变数据 IC 116、216 和 316 的输出通道（每个数据 IC 具有 642 个通道），而是可应用于具有 642 个输出通道或者小于或大于 642 个数据通道的数据 IC 116、216 和 316。

此外，响应于第一通道选择信号 P1 和第二通道选择信号 P2 而设置的数据 IC 116、216 和 316 的输出通道不仅限于 600、618、630 以及 642 个数据输出通道，而可以适用于其他的情况。换言之，基于以下条件中的至少一个来确定响应于第一通道选择信号 P1 和第二通道选择信号 P2 而设置的数据 IC 116、216 和 316 的输出通道：即，液晶显示板 102 的分辨率类型、数据 IC 的数量、数据 TCP 的宽度、以及在定时控制器 108 与数据 IC 116、216 和 316 之间用于将像素数据从定时控制器 108 施加到数据 IC 116、216 和 316 的数据传输线的数量。因此，响应于第一通道选择信号 P1 和第二通道选择信号 P2 而设置的数据 IC 116、216 和 316 的输出通道的数量可以是 600、618、624、630、642、645、684、696、702 或者 720 等。

此外，用于设置数据 IC 116、216 和 316 的输出通道的通道选择信号 P1 和 P2 也不限于 2 位二进制逻辑值，而可以是具有两位或者更多位的二进制逻辑值。

可以将根据本发明第一至第三实施例的 LCD 的数据 IC 用于包括上述 LCD 的平板显示器件。

如上所述，根据本发明的 LCD 使用通道选择信号来根据液晶显示板的分辨率类型改变数据集成电路的通道，从而构成液晶显示板的多个分辨率类型。

此外，根据本发明的 LCD 包括数据集成电路，其具有设置在用于向数据线提供数据的第一数据输出通道组与第二数据输出通道组之间的哑数据输出通道组，并且该 LCD 使用通道选择信号来根据液晶显示板的分辨率类型改变数据集成电路的通道，从而通过使用一种类型的数据集成电路来驱动液晶显示板的所有分辨率。

因此，根据本发明的 LCD 可以兼容地使用数据集成电路，而不依赖于液晶显示板的分辨率类型，从而可以减少数据集成电路的数量。结果，根据本发明的 LCD 提高了工作效率并且降低了制造成本。

对于本领域技术人员，很明显可以在不脱离本发明的精神和范围的情况下对本发明进行各种修改和变型。因此，只要这些修改和变型落入如所附权利要求及其等同物的范围之内，本发明就涵盖这些修改和变型。

本申请要求于 2003 年 12 月 11 日提交的韩国专利申请 No. P2003-90301 以及于 2004 年 4 月 28 日提交的韩国专利申请 No. P2004-29611 和 No. P2004-29612 的优先权，通过引用将其并入本文，如同在本文中进行了充分地阐述。

图 1

现有技术

图 2A

现有技术

图 2B

现有技术

图 3 现有技术

图 4

图 5

图 6

图 7

图 8

图 9

图 10

图 11

图 12

图 13

图 14

图 15

图 16

图 17

|                |                                                                                           |         |            |

|----------------|-------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器件                                                                                    |         |            |

| 公开(公告)号        | <a href="#">CN100428004C</a>                                                              | 公开(公告)日 | 2008-10-22 |

| 申请号            | CN200410100118.8                                                                          | 申请日     | 2004-12-08 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                  |         |            |

| 申请(专利权)人(译)    | LG. 菲利浦LCD株式会社                                                                            |         |            |

| 当前申请(专利权)人(译)  | 乐金显示有限公司                                                                                  |         |            |

| [标]发明人         | 姜信浩<br>宋鸿声<br>洪镇铁                                                                         |         |            |

| 发明人            | 姜信浩<br>宋鸿声<br>洪镇铁                                                                         |         |            |

| IPC分类号         | G02F1/133 G09G3/36 G02F1/136 G09F9/35 G09G3/20 G09G3/32                                   |         |            |

| CPC分类号         | G09G3/3688 G09G2310/027 G09G3/20 G09G2340/0421 G09G2300/0426 G02F1/136 G09G3/32           |         |            |

| 代理人(译)         | 李辉                                                                                        |         |            |

| 审查员(译)         | 周永恒                                                                                       |         |            |

| 优先权            | 1020030090301 2003-12-11 KR<br>1020040029611 2004-04-28 KR<br>1020040029612 2004-04-28 KR |         |            |

| 其他公开文献         | CN1627142A                                                                                |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                            |         |            |

**摘要(译)**

液晶显示器件。一种具有数据驱动集成电路的显示器，包括：具有至少两个区并且包括第一输出通道和第N输出通道的N个输出通道，其中N是整数；包括M个数据输出通道的数据输出通道组，其中M是小于N的整数，所述M个数据输出通道根据显示器的期望分辨率向对应数量的数据线提供像素数据，其中(N-M)个输出通道未被提供像素数据，并且所述(N-M)个输出通道位于所述第一输出通道与所述第N输出通道之间；以及，通道选择器，用于选择所述M个数据输出通道。

| 分辨率    | 像素数量 |      | 根据数据 IC 的多个输出通道的数据 IC 的数量 |       |       |       |

|--------|------|------|---------------------------|-------|-------|-------|

|        | 数据线  | 选通线  | 600CH                     | 618CH | 630CH | 642CH |

| XGA    | 3072 | 768  | 5.12                      | 4.97  | 4.88  | 4.79  |

| SXGA+  | 4200 | 1050 | 7.00                      | 6.80  | 6.67  | 6.54  |

| UXGA   | 4800 | 1200 | 8.00                      | 7.77  | 7.62  | 7.48  |

| WXGA   | 3840 | 800  | 6.40                      | 6.21  | 6.10  | 5.98  |

| WSXGA- | 4320 | 900  | 7.20                      | 6.99  | 6.86  | 6.73  |

| WSXGA  | 5040 | 1050 | 8.40                      | 8.16  | 8.00  | 7.85  |

| WUXGA  | 5760 | 1200 | 9.60                      | 9.32  | 9.14  | 8.97  |