[19] 中华人民共和国国家知识产权局

## [12] 发明专利申请公开说明书

[21] 申请号 200510082262.8

[43] 公开日 2006 年 3 月 29 日

[51] Int. Cl.

G09G 3/36 (2006.01)

G09G 3/20 (2006.01)

G02F 1/133 (2006.01)

[22] 申请日 2005.6.30

[21] 申请号 200510082262.8

[30] 优先权

[32] 2004.9.23 [33] KR [31] 10 - 2004 - 0076457

[71] 申请人 LG 菲利浦 LCD 株式会社

地址 韩国首尔

[72] 发明人 金彬文秀焕尹洙荣

[74] 专利代理机构 北京三友知识产权代理有限公司

代理人 黄纶伟

权利要求书 3 页 说明书 11 页 附图 9 页

[54] 发明名称

液晶显示器件及其驱动方法

[57] 摘要

在此公开了一种液晶显示器件，其中使用双向内部选通驱动电路使得数据线的数量减半，以及一种驱动这种液晶显示器件的方法。该液晶显示器件在下基板上包括具有多个像素的像素阵列。像素被设置为使两个彼此水平相邻的像素成对地共享一个数据线。第一和第二选通驱动电路容纳在下基板的左侧和右侧，使其在像素阵列的左侧和右侧独立地工作。第一选通驱动电路由第一至第 n 奇数移位寄存器构成，第二选通驱动电路由第一至第 n 偶数移位寄存器构成。

1. 一种液晶显示器件，包括：

5 基板，其包括多个数据线、多个接收选通信号的选通线、第一组多

个像素、第二组多个像素，以及像素阵列，该像素阵列包括从第一组多

个像素和第二组多个像素中选出的多个像素，这些像素在基板上布置成

多个行和多个列，使得彼此相邻的两个像素成对地共享从多个数据线中

选出的一个数据线；

10 第一选通驱动电路，其包括输出第一选通信号的第一至第 n 移位寄

存器；以及

第二选通驱动电路，其包括输出第二选通信号的第一至第 n 移位寄

存器，

其中第一选通驱动电路和第二选通驱动电路布置在基板上，并且彼

此独立地工作。

15 2. 如权利要求 1 所述的液晶显示器件，其中第一节点是 Q 节点。

3. 如权利要求 1 所述的液晶显示器件，其中，共享一个数据线的相

邻像素包括一个从第一组多个像素中选出的像素和一个从第二组多个像

素中选出的像素，并且驱动从第一组多个像素中选出的像素的选通线和

驱动从第二组多个像素中选出的像素的选通线被分别布置在多个像素行

20 之间。

4. 如权利要求 3 所述的液晶显示器件，其中像素阵列中包含的各个

像素与向其提供数据信号的开关元件相连，该开关元件的漏极连接到数

据线，并且其源极与各个像素电极相连。

25 5. 如权利要求 1 所述的液晶显示器件，其中数据线的数量是水平排

列的像素的数量的一半。

6. 如权利要求 1 所述的液晶显示器件，其中第一选通驱动电路的第一

至第 n 移位寄存器被设置为将选通信号输出给从多个选通线中选出的

选通线，所述被选出的选通线驱动从第一组多个像素中选出的像素。

7. 如权利要求 1 所述的液晶显示器件，其中第二选通驱动电路的第

一至第 n 移位寄存器被设置为将选通信号输出给从多个选通线中选出的选通线，所述被选出的选通线驱动从第二组多个像素中选出的像素。

8. 如权利要求 1 所述的液晶显示器件，其中各个移位寄存器包括：

第一开关，其源极连接到第一节点，并且其栅极和漏极共同连接到 5 前一个移位寄存器的输出信号；

第二开关，其栅极连接到前一级的输出信号，漏极连接到第二节点，并且源极连接到第一电源电压；

第三开关，其栅极连接到第一节点，漏极连接到第二节点，并且源极连接到第一电源电压；

10 第四开关，其栅极连接到第一节点，漏极与第一和第二时钟信号中的一个相连，并且源极连接到本级的输出信号；

第五开关，其栅极与第三和第四时钟信号中的一个相连，漏极连接到第二电源电压，并且源极连接到第二节点；

15 第六开关，其栅极连接到第二节点，漏极连接到第一节点，并且源极连接到第一电源电压；

第七开关，其栅极连接到下一级的输出信号，漏极连接到第一节点，并且源极连接到第一电源电压；以及

第八开关，其栅极连接到第二节点，漏极连接到本级的输出信号，并且源极连接到第一电源电压。

20 9. 如权利要求 8 所述的液晶显示器件，其中移位寄存器的各个晶体管是非晶硅晶体管。

10. 一种液晶显示器件，包括：

排列在基板上的像素阵列，包括多个数据线、多个选通线、第一组多个像素和第二组多个像素；

25 第一选通驱动电路，其包括第一至第 n 移位寄存器；

第二选通驱动电路，其包括第一至第 n 移位寄存器，

其中第一选通驱动电路和第二选通驱动电路独立地工作，使得第一选通驱动电路驱动第一组多个像素，第二选通驱动电路驱动第二组多个像素。

11. 如权利要求 10 所述的液晶显示器件，其中像素阵列的各个元素是一对像素，它们共享多个数据线中的一个，一个像素从第一组多个像素中选出，另一个像素从第二组多个像素中选出。

12. 如权利要求 11 所述的液晶显示器件，其中从第一组多个像素中

5 选出的一个像素与从第一组多个像素中选出的另一个像素不相邻。

13. 如权利要求 11 所述的液晶显示器件，其中从第二组多个像素中选出的一个像素与从第二组多个像素中选出的另一个像素不相邻。

14. 一种驱动液晶显示器件的方法，包括：

连接第一选通驱动电路，该电路包括从第一级到第 n 级级联设置的

10 多级移位寄存器，使用第一电压源、第二电压源、前一级移位寄存器的输出信号、下一级移位寄存器的输出信号、以及多个时钟信号中的两个，通过输出信号线顺序地输出输出信号；

连接第二选通驱动电路，该电路包括从第一级到第 n 级级联设置的

15 多级移位寄存器，使用第一电压源、第二电压源、前一级移位寄存器的输出信号、下一级移位寄存器的输出信号、以及多个时钟信号中的两个，通过输出信号线顺序地输出输出信号；

连接基板，该基板包括多个数据线、多个接收选通信号的选通线、第一组多个像素、第二组多个像素、以及像素阵列，该像素阵列包括从第一组多个像素中选出的多个像素和从第二组多个像素中选出的多个像素；

20 用第一选通驱动电路中包含的移位寄存器顺序输出的信号驱动从第一组多个像素中选出的至少一个像素阵列像素；

等待一预定时间；以及

用第二选通驱动电路中包含的移位寄存器顺序输出的信号驱动从第二组多个像素中选出的至少一个像素阵列像素。

25 15. 如权利要求 14 所述的驱动液晶显示器件的方法，其中所述的预定时间是大约四分之一周期。

16. 如权利要求 14 所述的驱动液晶显示器件的方法，其中第一选通驱动电路和第二选通驱动电路输出的各个信号具有大约二分之一周期的持续时间。

---

## 液晶显示器件及其驱动方法

### 5 技术领域

本发明涉及液晶显示器件，更具体地，涉及使用双向内部选通驱动电路 (bi-directional internal gate drive circuit) 的可以减少数据线数量的液晶显示器件。

### 10 背景技术

近年来已努力地研究平板显示器件，如液晶显示器 (LCD)、等离子显示板 (PDP)、电致发光显示器 (ELD)、真空荧光显示器 (VFD) 等等。一些类型的平板显示器件正实际用于各种显示设备。

由于 LCD 的特性和卓越的图像质量、轻、薄、功耗低的优点，其已经作为阴极射线管 (CRT) 的替代品用在移动图像显示器中。正在开发 LCD 的各种应用，不仅涉及诸如膝上型电脑监视器的移动图像显示设备，还涉及接收和显示广播信号的电视监视器。

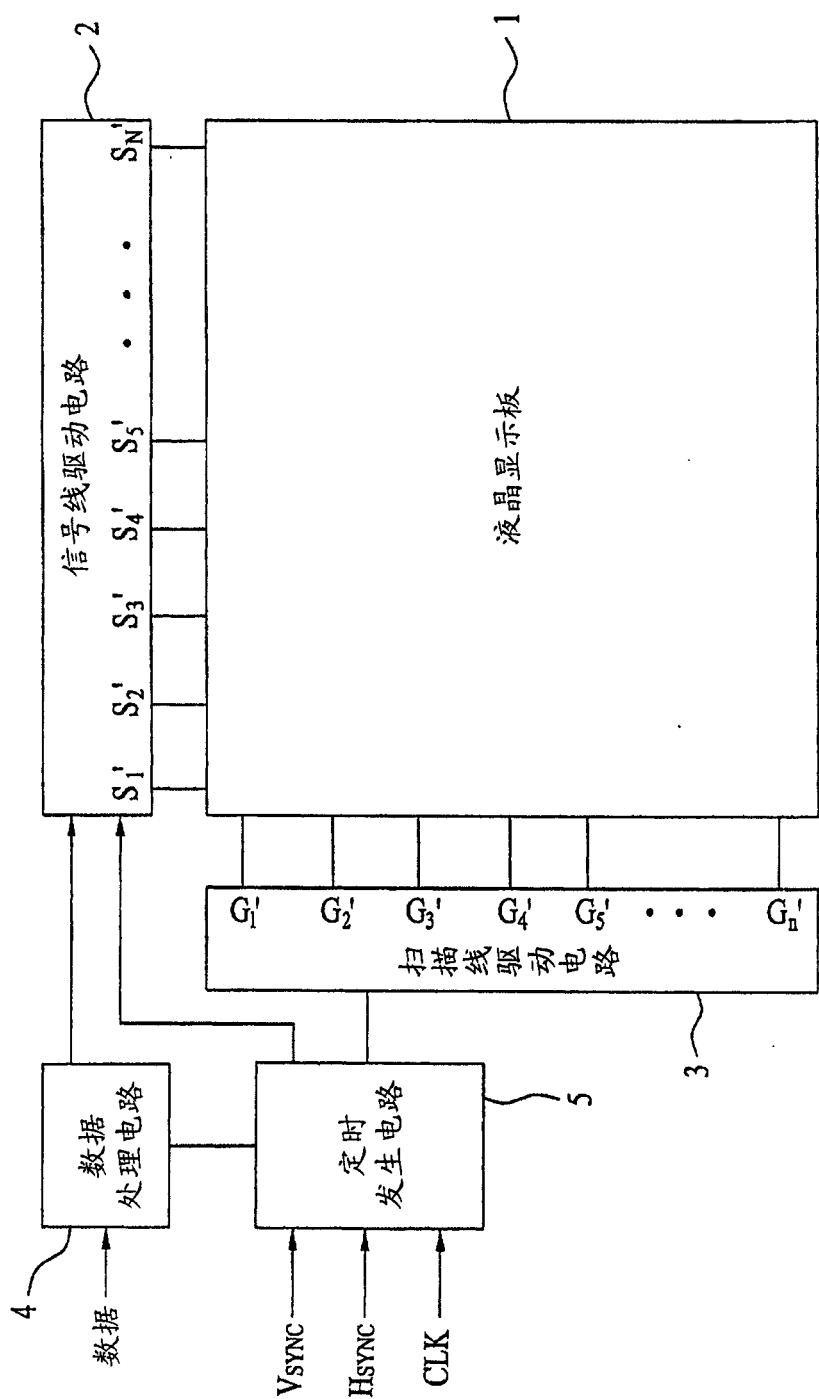

图 1 是示出一般的有源矩阵液晶显示 (LCD) 器件的框图。如图 1 中所示，一般的有源矩阵 LCD 包括用于显示图像的液晶显示板 1。在液晶显示板 1 的垂直和水平端部，分别有信号线驱动电路 2 和扫描线驱动电路 3，用于驱动液晶显示板 1。用于控制信号线驱动电路 2 和扫描线驱动电路 3 的控制信号由定时发生电路 5 产生。由外部输入的点时钟 (dot clock) (CLK)、水平同步信号 (Hsync) 和垂直同步信号 (Vsync) 产生各种控制信号。此外，根据 LCD 板和信号线驱动电路 2 的输入端之间的接口类型，可能需要执行数据处理以根据指派的命令安排数据。为此，可提供数据处理电路 4，它也通过定时发生电路 5 进行控制。通常，将数据处理电路 4 和定时发生电路 5 开发成 ASIC (专用集成电路) 这样的集成形式。

上述一般液晶显示器件通常包括用于显示图像信号的液晶显示板和用于从外部源向液晶显示板施加驱动信号的驱动电路。

尽管未在图 1 中示出，液晶显示板 1 包括两个透明的基板（玻璃基板），它们彼此接合使得这两个透明基板之间具有一定的间隙。液晶层位于该间隙内。在两个透明基板的一个中形成有以一定的均匀间距排列的多个选通线 G<sub>1</sub>, G<sub>2</sub>, G<sub>3</sub>, …, G<sub>n</sub>, 垂直于选通线以一定的均匀间距排列的多个数据线 S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub>, …, S<sub>n</sub>, 形成在阵列像素区中的多个像素电极（像素区行列布置，由选通线和数据线限定），以及多个薄膜晶体管（TFT）。这些 TFT 可以位于选通线和数据线的交叉处，用于根据选通线信号将数据线信号施加给像素电极。滤色层、公共电极（VCOM）和黑底层位于另一个透明基板中。

当顺序地对各个选通线施加接通信号时，数据信号被施加到于该选通线对应的像素电极上。被施加信号的像素显示出图像。

在上述结构的 TFT LCD 器件中，TFT 用作接通和切断该器件内的像素的开关元件。导通和截止 TFT 使得相应的像素接通或切断。

在一般的 TFT 液晶显示器件中，构成像素的单元以阵列的形式排列，像素行列布置。各个单元由开关 TFT、液晶单元和存储电容（CSTG）构成。TFT 的源极按列连接在一起构成数据线 S<sub>1</sub> 至 S<sub>n</sub>，数据线在接点 S<sub>1</sub>', S<sub>2</sub>', …, S<sub>n</sub>' 处与源极驱动器相连。TFT 的栅极按行连接在一起构成选通线 G<sub>1</sub> 至 G<sub>M</sub>，选通线在接点 G<sub>1</sub>', G<sub>2</sub>', …, G<sub>n</sub>' 处与选通驱动器相连。这样，在显示器件中实现了 N×M 分辨率（例如，SVGA (800×600), XGA (1024×768), UXGA (1600×1200)）。

源极驱动器也称作数据驱动器、列驱动器或信号线驱动电路，而选通驱动器也称作行驱动器、扫描驱动器或扫描线驱动电路。以下将源极驱动器称作“信号线驱动电路”，而将选通驱动器称作“扫描线驱动电路”。

液晶单元的一侧通过像素电极与 TFT 的漏极相连，另一侧与公共电极相连。像素电极由透明导电的氧化铟锡（ITO）构成。当对 TFT 的栅极施加接通信号时，信号电压通过信号线驱动电路施加给液晶单元，并且公共电极（也由 ITO 构成）将公共电压（VCOM）施加给液晶单元。存储电容（CSTG）用来将施加给像素电极（像素 ITO）的信号电压保持一段时间。这些存储电容（CSTG）还通过充放电改变液晶单元的排列状态以控

制各个像素的透光率。存储电容 (CSTG) 的一侧可与单独的电极或栅极连接。存储电容与栅极连接的结构称作栅上存储 (storage-on-gate) 结构。

近来，使用 TFT 的 LCD 器件已用作膝上型电脑的显示器，因此希望降低 5 成本。实现低价 LCD 器件的一个方法是降低材料的成本。此外，降低驱动液晶显示板的信号线的驱动器集成电路 (IC) 的成本可以使整个 LCD 器件的生产成本降低。因为信号线驱动器 IC 复杂的运算功能和所需的大量驱动器 IC，信号线驱动器 IC 占 LCD 器件的材料成本的大部分。例如，如果一个驱动器 IC 提供 240 个输出，一个 SVGA 板需要 10 个驱动器 IC。在日本专利申请公开第 3-38689, 5-265045 和 6-148680 号中，已经提出减少驱动器 IC 的数量。所有这些方法都试图通过允许在液晶显示板 10 中相邻的像素共享信号线而将信号驱动器 IC 的数量减半。

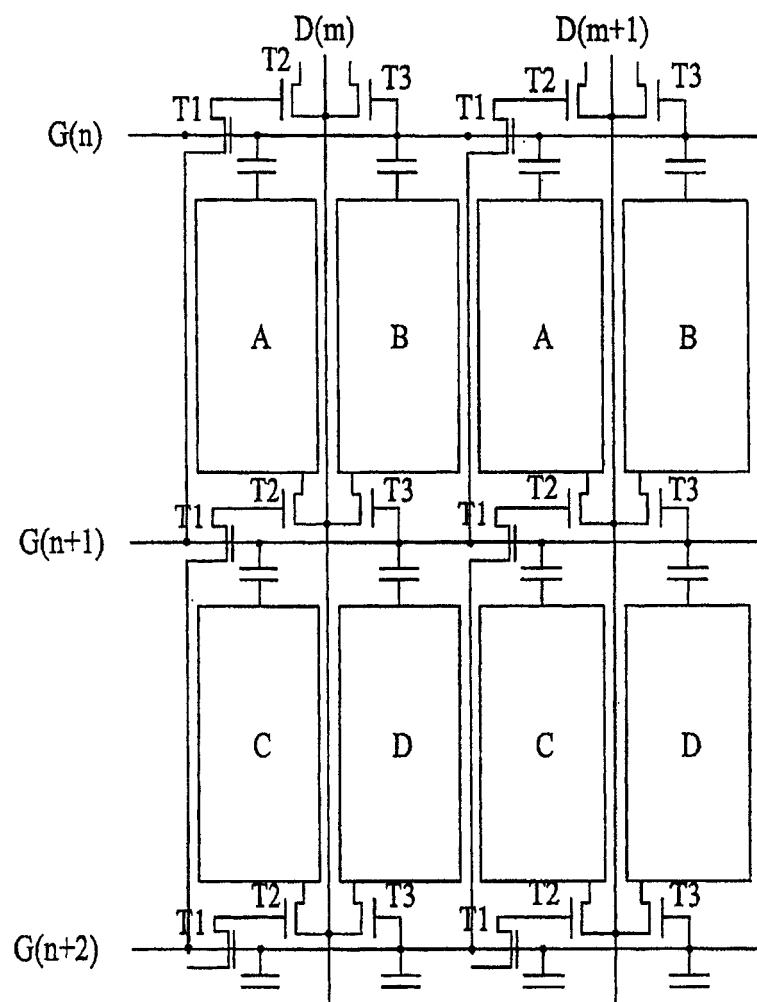

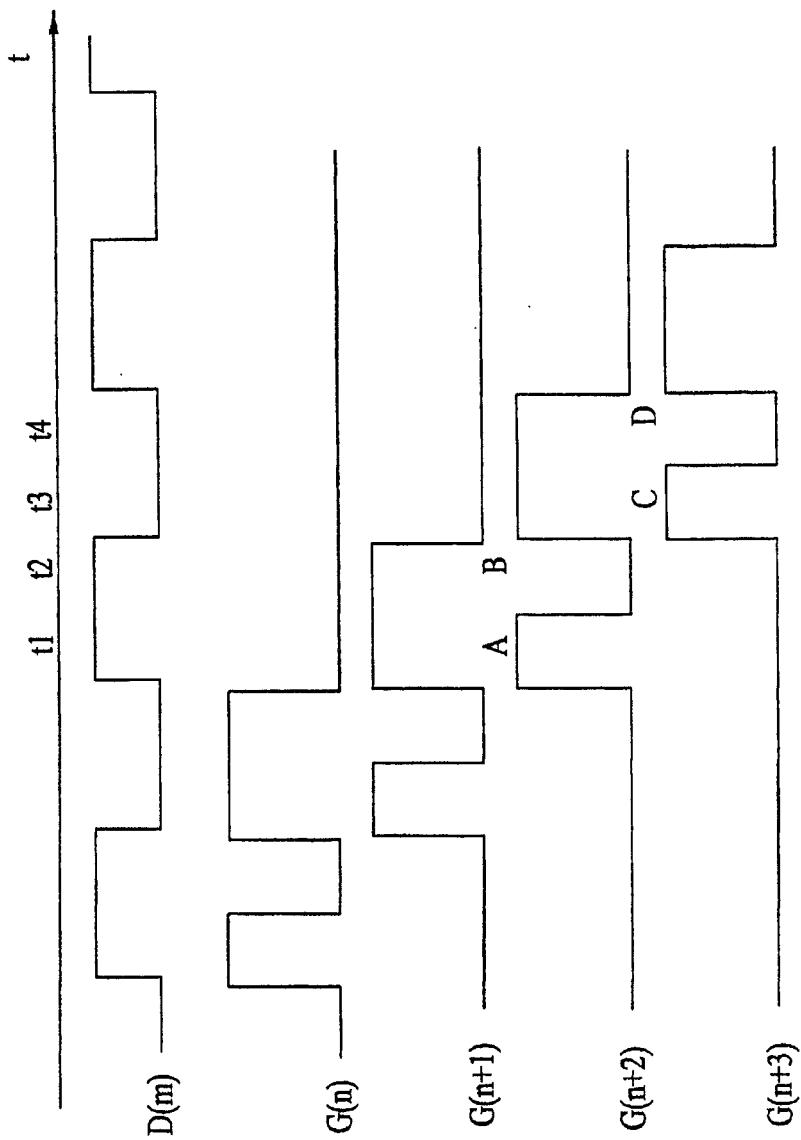

图 2 示出了采用传统技术将传统 LCD 器件中使用的信号驱动器的数量减半的电路的一部分。图 3 示出了图 2 的 LCD 电路的工作波形。

如图 2 中所示，传统 LCD 器件包括：在一个方向上排列的多个选通 15 线；与一个数据线相连的两个相邻像素的对（第一和第二像素 (A, B) (C, D)）；第一晶体管 T1，其接收来自各个选通线的导通或截止该晶体管的信号；第二晶体管 T2，其接收下一个选通线的导通或截止晶体管 T2 的信号，这样当晶体管 T1 和 T2 都导通时，通过数据线传送的数据信号被传送到 20 第一像素；第三晶体管 T3，其接收来自选通线的导通或截止晶体管 T3 的信号，这样当晶体管 T3 导通时，通过数据线传送的数据信号被传送到第二像素；以及连接在前一个选通线和各个像素之间的存储电容  $C_{st}$ 。

以上结构是通过一个数据线驱动两个相邻像素的数据线共享 (DLS) 25 驱动结构。在使用上述 DLS 驱动结构的 LCD 器件中，用一个数据线为两个相邻的像素提供数据信号，从而使数据驱动器 IC 的数量减半。

DLS 驱动需要与传统波形不同的波形。如图 3 中所示，使用一种在一个周期的输出波形之前有半周期输出波形的选通波形。施加给一个选通线的波形由两个波形构成，前一个波形的周期是后一个波形的周期的一半。

现在将参照图形说明上述 LCD 器件的工作原理。如图 2 和 3 所示，在选通信号被顺序提供给选通线  $G(n)$ ,  $G(n+1)$ ,  $G(n+2)$  的情况下，在 t1 部分，如果提供给选通线  $G(n+1)$  一个周期的“高”信号，并提供给选通线  $G(n+2)$  半个周期的“高”信号，第一和第三晶体管 T1 和 T3 接收到选通线  $G(n+1)$  的信号并导通。由于第一晶体管 T1 导通，第二晶体管 T2 接收到选通线  $G(n+2)$  的信号并导通。这样，数据信号通过数据线  $D(m)$ ,  $D(m+1)$ ,  $D(m+2)$  等被同时提供给第一像素 A 和第二像素 B。

在半个周期之后的 t2 部分，由于选通线  $G(n+2)$  处于低信号，因此晶体管 T2 截止，而第一和第三晶体管 T1 和 T3 保持导通。这样，第一像素 A 保持已经提供的数据信号，而第二像素 B 可以接收另一个数据信号。这样，使用一个数据线，可以为两个相邻的像素顺序地提供两个不同的数据信号。

如上所述，使用具有半个周期的下一选通线信号，可以选择性地将数据信号施加给两个彼此相邻的不同像素。与一般的一个数据线对应一个像素的数据驱动方法相比，这种驱动方法可以将数据线的数量减半，从而使数据驱动器 IC 的数量减半成为可能。

然而，这种数据线共享 (DLS) 方法的应用需要单独的选通驱动器 IC，该选通驱动器 IC 可以接连输出半周期波形和一个周期波形，而不是通常的波形。因此，虽然数据线的数量减半，但必须提供单独的选通驱动器 IC，因此限制了成本的降低。

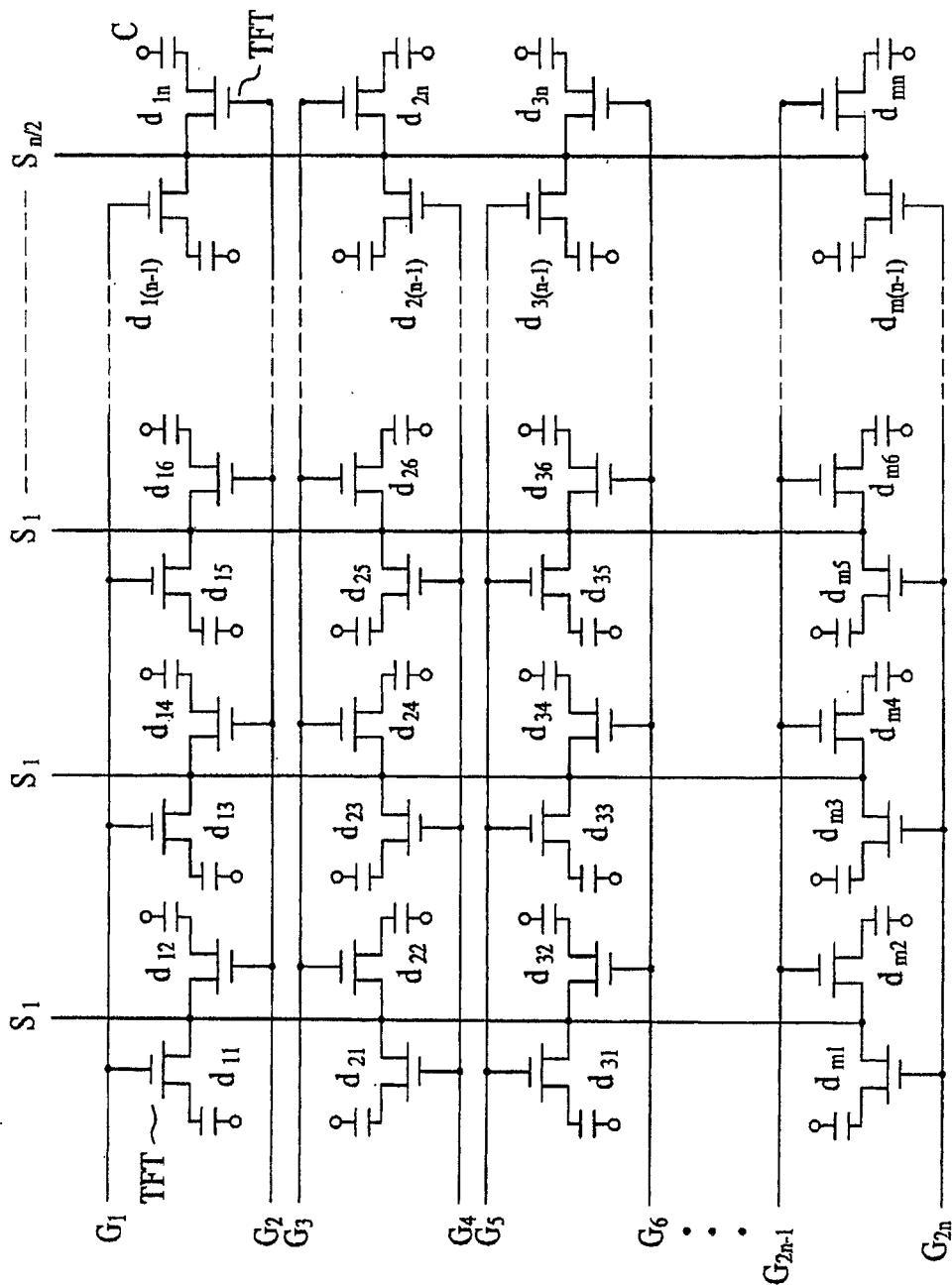

图 4 和 5 分别示出了利用第二种传统技术将传统 LCD 器件中使用的信号驱动器的数量减半的电路及其工作波形图。如图 4 中所示，液晶显示板包括  $n \times m$  阵列的像素电极，其中  $n$  和  $m$  是不小于 2 的整数。沿着水平方向（或行方向）的两个相邻的奇数像素和偶数像素共享一个数据线，数据线沿垂直方向延伸。TFT（与各个像素相连的开关元件）的漏极与共享的数据线 ( $S_1, S_2, \dots, S_{n/2}$ ) 相连。数据线的数量是水平排列的像素的数量的一半（例如， $n/2$ ）。

为了说明而非限定，被称为奇数 TFT ( $d_{m1}, d_{m3}, d_{m5}, \dots, d_{m(n-1)}$ ) 和偶数 TFT ( $d_{m2}, d_{m4}, d_{m6}, \dots, d_{mn}$ ) 的两个相邻 TFT 的栅极分别与两个不同的

选通线 ( $G_1, G_2, \dots, G_{2n}$ ) 相连，这两个选通线被指定给在水平方向延伸的一个水平显示线。选通线的数量是垂直排列的像素的数量的两倍（例如， $2m$ ）。

然而根据上述结构，在奇数显示线 ( $m=1, 3, 5$  等) 中，水平方向上 5 奇数像素的 TFT 的栅极与奇数选通线相连，水平方向上偶数像素的 TFT 的栅极与偶数选通线相连。此外，在偶数显示线 ( $m=2, 4, 6$  等) 中，水平方向上奇数像素的 TFT 的栅极与偶数选通线相连，水平方向上偶数像素的 TFT 的栅极与奇数选通线相连。至于任意一个水平延伸的被分配了 10 多个（例如，两个）选通线的显示线，水平方向奇数 TFT 的栅极与两个选通线之一相连，水平方向偶数 TFT 的栅极与另一个选通线相连。在与上述显示线相邻的显示线中，TFT 栅极与选通线的连接方式与前一个显示线相反。换言之，在 TFT 栅极与选通线的连接方面，奇数显示线与偶数显示线彼此相反。

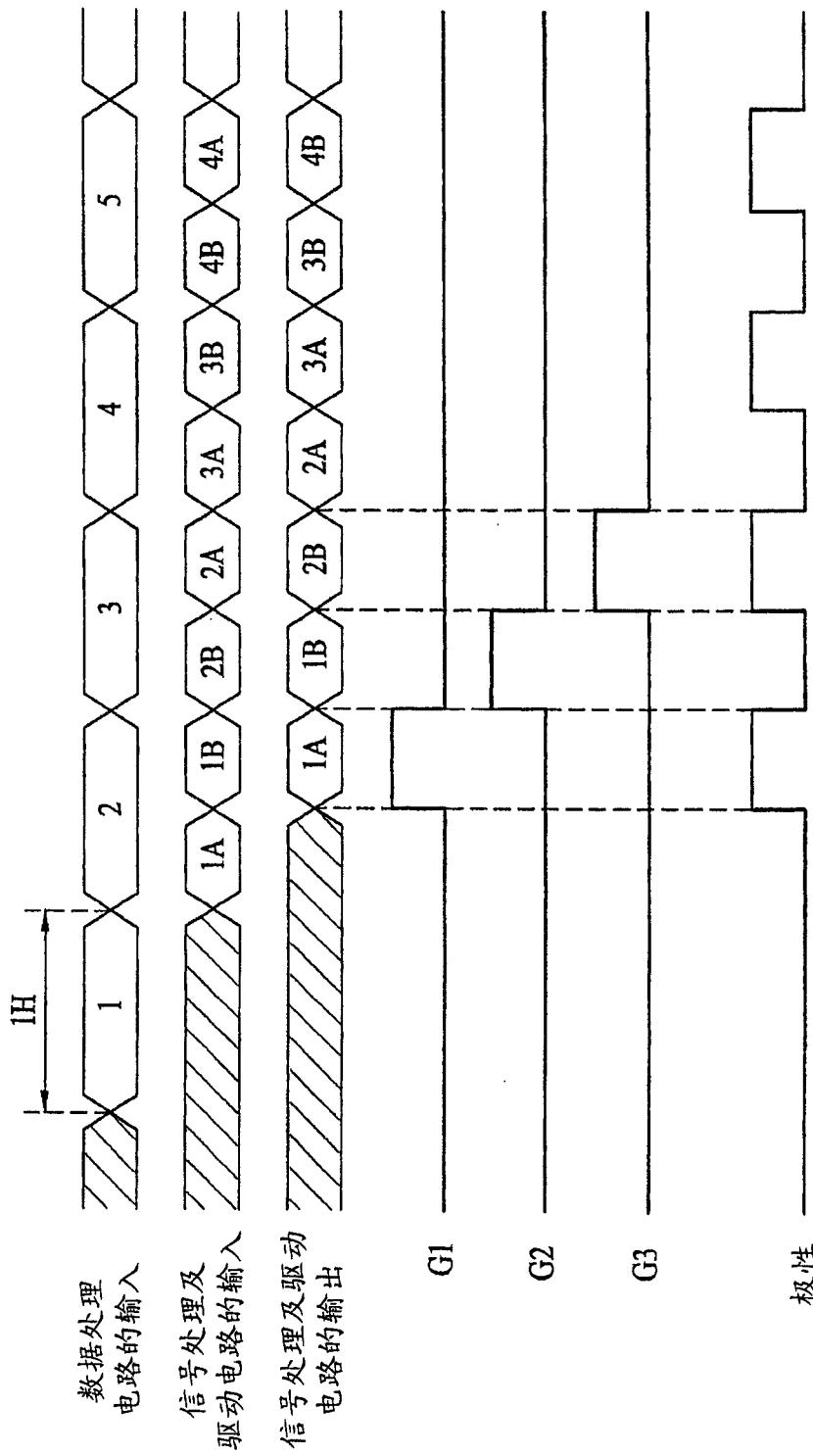

图 5 示出了图 4 的 LCD 电路的工作波形。数据处理电路（未示出） 15 接收连续输入的数据，所接收数据的一行部分被写入形成在数据处理电路中的行存储器中。根据显示板的 TFT、数据线和选通线之间的连接关系，将数据划分为分别与一个水平周期（1H）的第一半和第二半对应的两个部分。

在第一行显示线 ( $m=1$ ) 中，将第一半数据输出给奇数数据线  $S_1, S_3, 20 S_5, \dots$ ，形成图形 A。将第二半数据输出给偶数数据线  $S_2, S_4, S_6, \dots$ ，形成图形 B。

在第二行显示线 ( $m=2$ ) 中，将第一半数据输出给奇数数据线  $S_1, S_3, S_5, \dots$ ，但是形成图形 B，并且将第二半数据输出给偶数数据线  $S_2, S_4, S_6, \dots$ ，但是形成图形 A。从第三行显示线直到第  $m$  行显示线，重复上述 25 第一和第二行显示线的数据输出模式。以这种方式，如果将数据输出到数据线，选通线将 TFT 导通电压顺序施加给相应的选通线  $G_1, G_2, G_3, \dots$ ，这样将预期的数据写入预期的像素。

观察数据线  $S_1$ ，如果从第一选通线  $G_1$  开始顺序地接通选通线，则数据被顺序写入像素  $d_{11}(A), d_{12}(B), d_{22}(B), d_{21}(A), \dots$ 。这里，A 和 B

分别表示图形 A 和 B。

从信号线驱动电路的相邻输出端输出的信号彼此极性相反。考虑到针对每一个输出切换极性，在完成一帧写入时，屏幕上的极性在水平方向上以两个像素的间隔交替，而在垂直方向上以一个像素的间隔交替。

5 这与所有的相邻像素都具有相反极性的点反转驱动 (dot inversion driving) 稍有不同。在一个像素对由两个相邻像素构成的意义上，认为它们具有相反的极性，从而由于正负极性之间的差别减轻了屏幕的闪烁。

在上述传统的 LCD 器件中，驱动各个显示线中的奇数像素和偶数像

素涉及到了两个选通线。于是，由于通过两个选通线驱动一个显示线，

10 LCD 器件需要两倍于使用一个选通线的 LCD 器件的选通线。因此，为了在一帧期间驱动加倍后的所有选通线，一个像素的充电时间从  $1H$  减少到  $H/2$ ，因此不易达到各个像素的有效充电时间。

## 发明内容

15 一种液晶显示器器件，以及一种驱动液晶显示器器件的方法，提供了双

向内部选通驱动电路，其减少了数据线的数量，而不减少有效像素充电

时间。该液晶显示器器件的一半可由一个选通驱动电路驱动，而该液晶显

示器件的另一半可由另一个独立于第一选通驱动电路工作的选通驱动电

路驱动。

20 在研究了以下的附图和详细说明之后，本领域技术人员将清楚地理

解本发明的其他系统、方法、特征和优点。所有这些附加的系统、方法、

特征涵盖在本说明书中，处于本发明的范围之内，并由所附的权利要求

保护。

## 25 附图说明

参照下面的附图和说明可以更好地理解本发明。图中的部件无需按

比例，重点在于解释本发明的原理。而且，在图中，在不同的图之间相

似的标号指示对应的部分。

图 1 是示出一般 LCD 器件的框图；

图 2 是利用传统技术将传统 LCD 器件中使用的信号驱动器的数量减半的电路的一部分；

图 3 示出了图 2 的 LCD 器件的工作波形；

图 4 是利用第二种传统技术将传统 LCD 器件中使用的信号驱动器的

5 数量减半的另一电路的一部分；

图 5 示出了图 4 的 LCD 器件的工作波形；

图 6 是示出液晶显示器结构的框图；

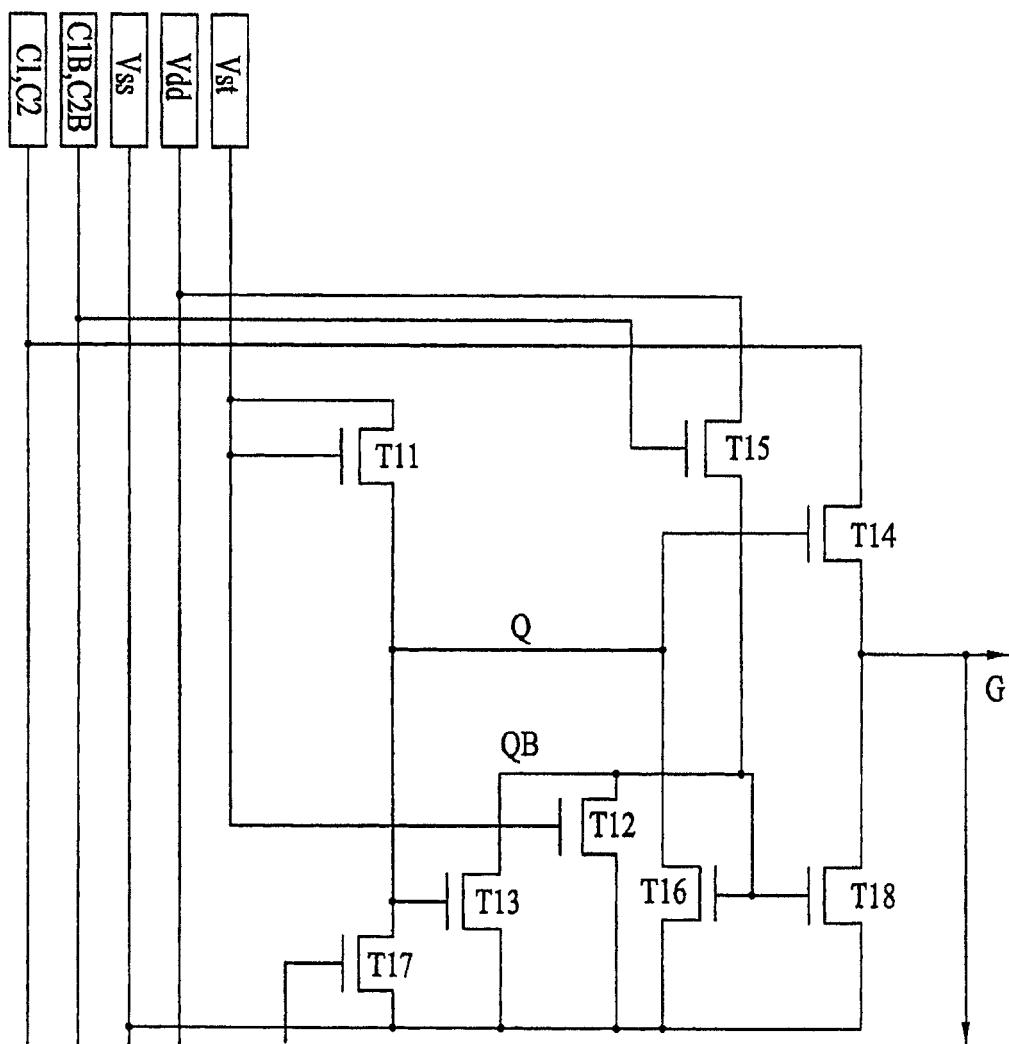

图 7 是图 6 中各个移位寄存器的电路图；

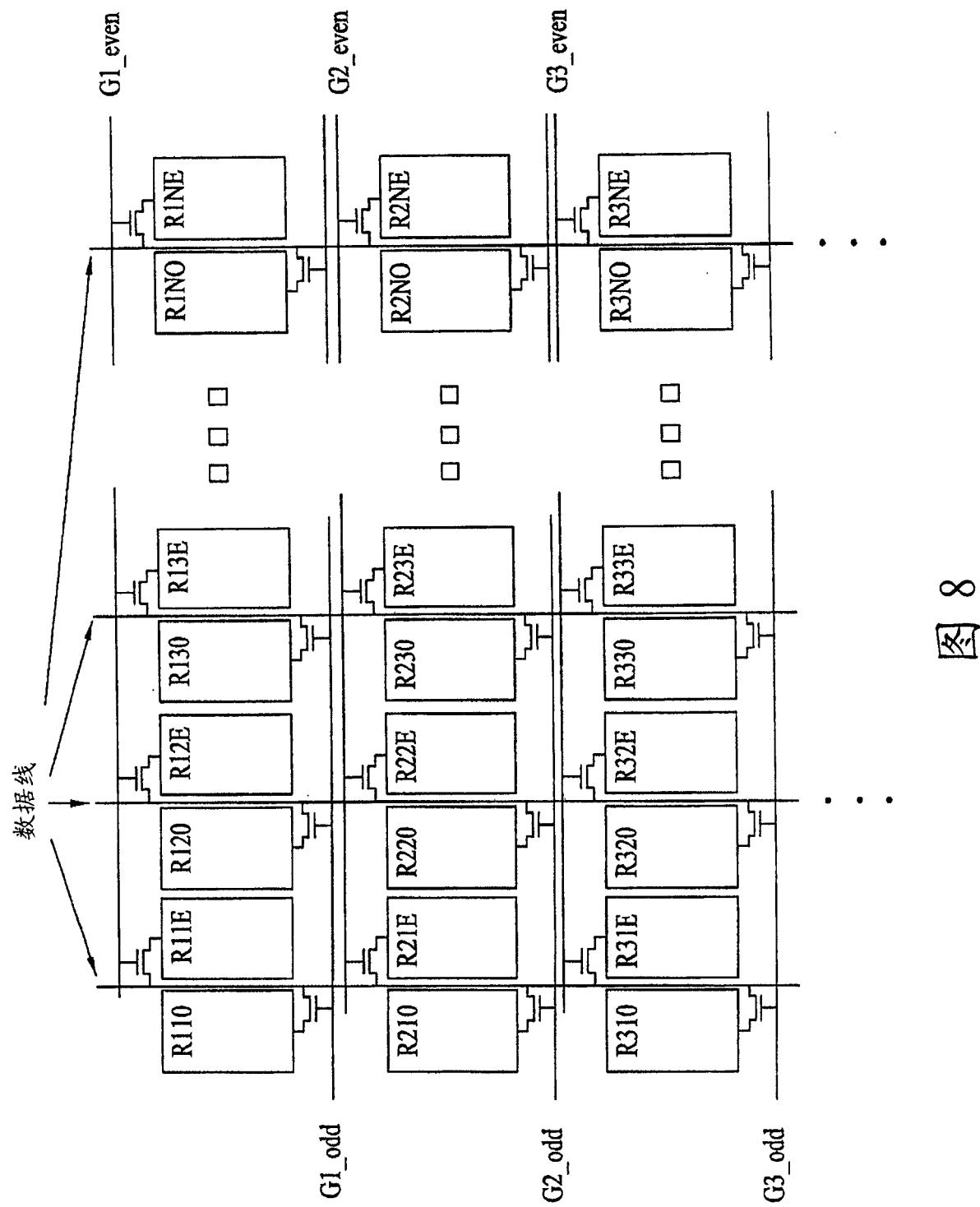

图 8 是示出图 6 中的像素阵列结构的框图；

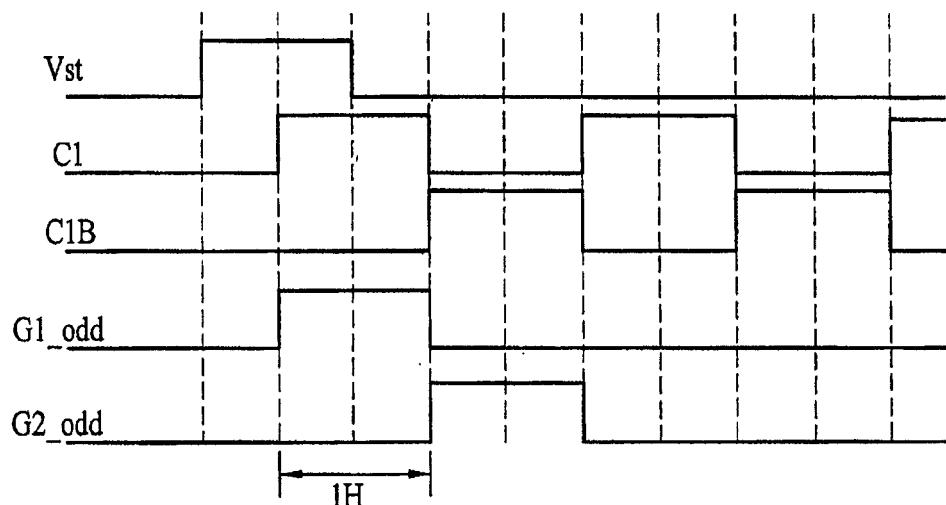

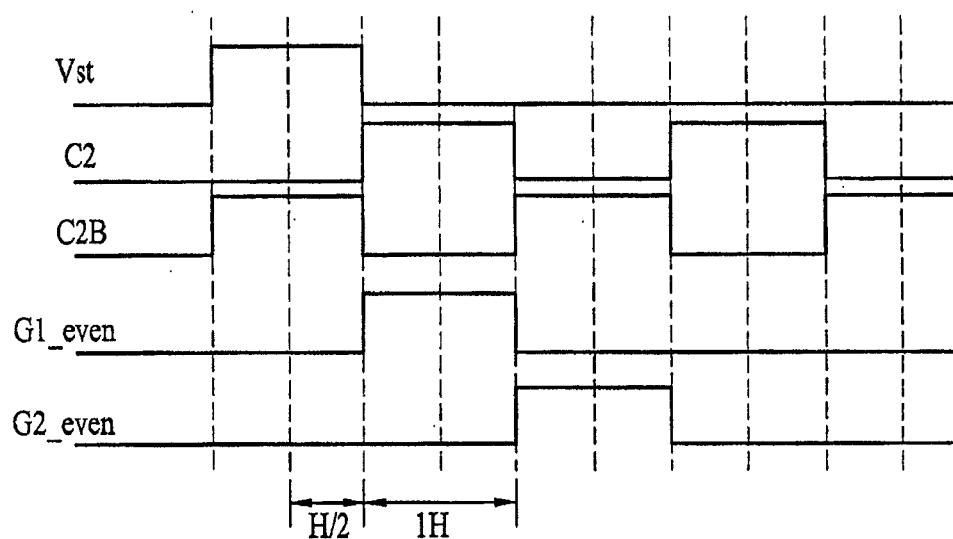

10 图 9A 和 9B 是根据本发明的执行选通驱动的双向内部选通驱动电路

的时序图。

### 具体实施方式

15 液晶显示器件可以通过使用彼此独立工作的第一选通驱动电路和第

二选通驱动电路驱动一个或更多像素。通过用一个选通驱动电路驱动某

些像素，并用另一个选通驱动电路驱动其他像素，可以无需提高选通驱

动速度而驱动像素。

20 此外，通过结合第一选通驱动电路和第二选通驱动电路实现 DLS 技

术，可以将选通线的数量减半而无需任何用于执行选通驱动的外部驱动

IC，并且不会缩短有效像素充电时间。

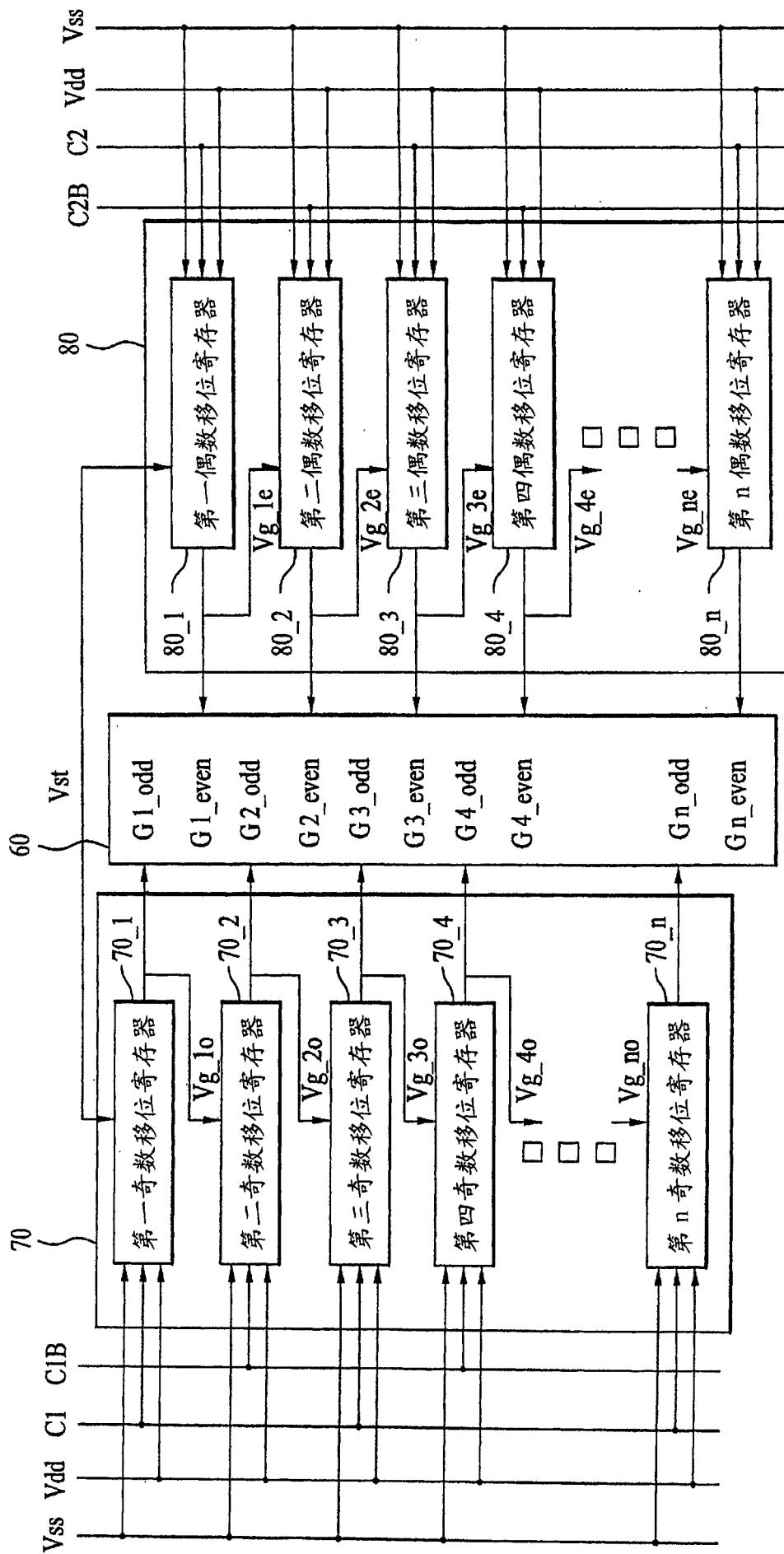

图 6 是示出液晶显示器的结构的框图。图 7 是图 6 中的各个移位寄

存器的电路图，图 8 是示出图 6 所示的按行列布置的像素阵列的结构的

框图。

25 液晶显示 (LCD) 器件可包括容纳在基板的第一部分内的选通驱动电

路，该选通驱动电路可位于基板的一侧部分上，以及容纳在基板的第二

部分内的选通驱动电路，该选通驱动电路可位于基板的另一侧部分。该

液晶显示器件可实现数据线共享 (DLS) 技术。如图 6 中所示，该 LCD 器

件可包括像素阵列 60，以及位于像素阵列 60 不同侧的第一选通驱动电路

70 和第二选通驱动电路 80。为了说明而非限定，第一驱动电路 70 可位

于像素阵列 60 的左侧，而第二驱动电路 80 可位于像素阵列 60 的右侧。

如图 8 中所示，像素阵列 60 以如下方式设置：从第一组多个像素中选出的像素和从第二组多个像素中选出的像素彼此相邻布置，以构成共享一个数据线的像素对。为了说明而非限定，从第一组多个像素中选出的像素将称为奇数像素，而从第二组多个像素中选出的像素将称为偶数像素。此外，为了说明而非限定，彼此相邻布置的像素可以在水平方向（或行方向）上排列，被共享的数据线垂直地位于两相邻的像素之间。应理解可以有其他结构。在各个像素线的水平行之间可以布置与第一选通驱动电路相连的选通线和与第二选通驱动电路相连的选通线。为了说明而非限制，与第一选通驱动电路相连的选通线可称为奇数选通线，而与第二选通驱动电路相连的选通线可称为偶数选通线（例如，G1\_odd 和 G2\_even，G2\_odd 和 G3\_even，等等）。

在各个像素上连接有用于提供数据信号的开关元件（TFT）。开关元件（TFT）的漏极与数据线相连，而源极与各个像素电极相连。各个开关元件（TFT）与一个像素相连。与水平奇数像素相连的 TFT 可与奇数选通线相连，而与水平偶数像素相连的 TFT 可与偶数选通线相连。每组选通线可被分配给一个水平显示线。于是，选通线两倍于垂直排列的像素（例如，R110，R11E，R120，R12E，等等）。

此外，一对水平相邻像素可共享一个垂直（列）数据线。因此数据线的数量是水平排列的像素数量的一半。

第一驱动电路 70 和第二驱动电路 80 可位于像素阵列 60 的左侧和右侧，并被设置为对像素阵列 60 中的奇数像素和偶数像素独立地提供选通驱动信号。

给第一选通驱动电路 70 提供扫描启动信号 Vst，两相时钟信号 C1 和 C1B，以及 VDD 和 VSS 信号。给第二选通驱动电路 80 提供扫描启动信号 Vst，两相时钟信号 C2 和 C2B，以及 VDD 和 VSS 信号。

第一和第二选通驱动电路 70 和 80 可被容纳在下基板中，位于像素阵列 60 左侧和右侧。第一和第二选通驱动电路 70 和 80 分别包括第一至第 n 奇数移位寄存器 70\_1~70\_n，和第一至第 n 偶数移位寄存器 80\_1~

80\_n。组成各个选通驱动电路的各个移位寄存器可包括非晶硅晶体管。

第一至第 n 奇数移位寄存器 70\_1~70\_n 将选通信号输出给像素阵列 60 的奇数选通线，并且接收扫描启动信号 Vst 或前一个移位寄存器的输出信号、两相时钟信号 C1 和 C1B，以及 VDD 和 VSS 信号。第一奇数移位寄存器 70\_1 被设置为接收扫描启动信号 Vst。第二至第 n 奇数移位寄存器 70\_2~70\_n 被设置为顺序地接收前一个移位寄存器的输出信号。

第一至第 n 偶数移位寄存器 80\_1~80\_n 将选通信号输出给像素阵列 60 的偶数选通线，并且接收扫描启动信号 Vst 或前一个移位寄存器的输出信号、两相时钟信号 C2 和 C2B，以及 VDD 和 VSS 信号。第一偶数移位寄存器 80\_1 被设置为接收扫描启动信号 Vst。第二至第 n 偶数移位寄存器 80\_2~80\_n 被设置为顺序接收前一个移位寄存器的输出信号。

第一至第 n 奇数移位寄存器和偶数移位寄存器中的每一个包括第一至第八晶体管 T11~T18，如图 7 所示，并且分别包括上拉 (pull-up) 驱动器，下拉 (pull-down) 驱动器，上拉部分和下拉部分。第一至第八晶体管 T11~T18 中的每一个可以是非晶硅晶体管。

上拉驱动器包括：第一晶体管 T11，其栅极和漏极共同连接到扫描启动信号 Vst，并且源极连接到 Q 节点；第二晶体管 T12，其栅极连接到 Vst 信号，漏极连接到 QB 节点，并且源极连接到地电压端 VSS；以及第三晶体管 T13，其栅极连接到 Q 节点，漏极连接到 QB 节点，并且源极连接到地电压端 VSS。

上拉部分包括第四晶体管 T14，其栅极连接到 Q 节点，漏极与第一时钟信号 C1 或第二时钟信号 C2 中的一个相连，并且源极连接到栅极输出信号端 G。

下拉驱动器包括：第五晶体管 T15，其栅极与第三时钟信号 C1B 或第四时钟信号 C2B 中的一个相连，漏极连接到 Vdd 端，并且源极连接到 QB 节点；第六晶体管 T16，其栅极连接到 QB 节点，漏极连接到 Q 节点，并且源极连接到地电压端 Vss；以及第七晶体管 T17，其栅极连接到下一级的输出信号，漏极连接到 Q 节点，并且源极连接到地电压端 Vss。

下拉部分包括第八晶体管 T18，其栅极连接到 QB 节点，漏极连接到

选通输出信号端 G，并且源极连接到地电压终端 Vss。

图 7 示出了组成第一和第二驱动电路 70 和 80 的各个移位寄存器的电路结构，但是可以使用各种其他电路结构。

将说明根据本发明的实施例的液晶显示器件的驱动方法。图 9A 和 9B 5 是双向内部选通驱动电路的时序图，用来驱动图 6 的 LCD 器件中使用的图 7 的移位寄存器级。

在图 8 所示 LCD 显示器中，排列在像素的水平线之间的奇数和偶数 10 选通线分别被第一和第二选通驱动电路 70 和 80 顺序地驱动。第一和第二选通驱动电路 70 和 80 以独立的方式分别驱动奇数像素和偶数像素。

为了说明而非限定，根据第一奇数移位寄存器 70\_1 的输出信号驱动 15 第一行的奇数像素，然后通过第一偶数移位寄存器 80\_1 的输出信号驱动第一行的偶数像素。然后分别驱动两个选通驱动电路的其他选通线。

如图 9A 和 9B 所示，根据第二时钟信号 C2 的上升沿，第一时钟信号 20 C1 落后于时钟信号 C2 一预定的时间。类似地，根据第四时钟信号 C2B 的上升沿，第三时钟信号 C1B 落后于时钟信号 C2B 一预定的时间。时钟信号 C1 和 C1B 被输入到选通驱动电路 70，而时钟信号 C2 和 C2B 被输入到选通驱动电路 80。各个时钟信号 C1, C1B, C2, 和 C2B 处于高信号的时间长度可以是 H/2，并且产生具有时间长度 H/2 的选通输出信号 (G1\_odd, 25 G1\_even), (G2\_odd, G2\_even), ~, (GN\_odd, GN\_even)。第一选通驱动电路 70 接收 Vst 或前一级的输出信号，以及 C1, C1B, Vdd 和 Vss 信号。第二选通驱动电路 80 通过 Vst 或前一级的输出信号，以及 C2, C2B, Vdd 和 Vss 信号而工作。

为了说明而非限定，当来自第一选通驱动电路 70 的信号 G1\_odd 被 25 输入像素阵列 60 中的第一奇数选通线时，与第一水平线的奇数像素 R110, R120, ~, R1NO 相连的开关元件 (TFT) 导通。于是，数据信号通过导通的开关元件 (TFT) 被写入奇数像素 R110, R120, ~, R1NO。经过一段时间 H/2 之后，当来自第二选通驱动电路 80 的信号 G1\_even 被输入像素阵列 60 中的第一偶数选通线时，与第一水平线的偶数像素 R11E, R12E, ~, R1NE 相连的开关元件 (TFT) 导通。于是，数据信号通过导通的开关元件

(TFT) 被写入偶数像素 R11E, R12E, ~, R1NE。以这种方式，将数据写入像素阵列的各个像素。

如果像素阵列 60 是被独立工作、且分别位于像素阵列 60 的左侧和右侧的第一选通驱动电路 70 和第二选通驱动电路 80 所驱动，那么 DLS

5 驱动并不提高选通驱动电路的驱动速度。

更具体地，对于 DLS 模式，常规地，由于选通线的数量加倍，因此为了在一帧期间驱动栅极，选通驱动速度必须加倍。在下基板中的移位寄存器由非晶硅晶体管构成的情况下，这种驱动速度的提高导致难以驱动那些移位寄存器。

10 液晶显示器件可以实现 DLS 驱动而不提高选通驱动速度，因为 DLS 驱动是由位于下基板的左侧和右侧的独立工作的第一选通驱动电路 70 和第二选通驱动电路 80 所执行。如图 9A 和 9B 所示，各个驱动电路的输出可以在工作期间交叠，因此由于驱动电路的加长了的波形，容易达到有效像素充电时间。在此，可以在 50% 以内调节上述交叠时间。

15 在上述结构中，选通驱动电路可以嵌入到任何两相或更多相的驱动电路中。

虽然已经描述了本发明的多种实施例，但对于本领域普通技术人员来说，很显然在本发明的范围之内可以有更多的实施例和实施方式。相应地，本发明的范围仅由所附的权利要求及其等价物限定。

20

本申请要求 2004 年 9 月 23 日提交的韩国专利申请第 P2004-76457 号的优先权，在此以引用的方式并入该申请，如同在此完整地阐述一样。

图 2

现有技术

图 3

现有技术

图 4

现有技术

图 5

现有技术

图 7

图 9A

图 9B

|                |                                                                           |         |            |

|----------------|---------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器件及其驱动方法                                                              |         |            |

| 公开(公告)号        | <a href="#">CN1753072A</a>                                                | 公开(公告)日 | 2006-03-29 |

| 申请号            | CN200510082262.8                                                          | 申请日     | 2005-06-30 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                  |         |            |

| 申请(专利权)人(译)    | LG. 菲利浦LCD株式会社                                                            |         |            |

| 当前申请(专利权)人(译)  | LG. 菲利浦LCD株式会社                                                            |         |            |

| [标]发明人         | 金彬<br>文秀焕<br>尹洙荣                                                          |         |            |

| 发明人            | 金彬<br>文秀焕<br>尹洙荣                                                          |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                               |         |            |

| CPC分类号         | G11C19/28 G09G2300/0408 G09G2310/0205 G09G3/3677 G11C19/184 G09G2300/0426 |         |            |

| 优先权            | 1020040076457 2004-09-23 KR                                               |         |            |

| 其他公开文献         | CN100447852C                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                            |         |            |

### 摘要(译)

在此公开了一种液晶显示器件，其中使用双向内部选通驱动电路使得数据线的数量减半，以及一种驱动这种液晶显示器件的方法。该液晶显示器件在下基板上包括具有多个像素的像素阵列。像素被设置为使两个彼此水平相邻的像素成对地共享一个数据线。第一和第二选通驱动电路容纳在下基板的左侧和右侧，使其在像素阵列的左侧和右侧独立地工作。第一选通驱动电路由第一至第n奇数移位寄存器构成，第二选通驱动电路由第一至第n偶数移位寄存器构成。