## [12] 发明专利申请公开说明书

[21] 申请号 03820007.4

[43] 公开日 2005 年 10 月 5 日

[11] 公开号 CN 1679170A

[22] 申请日 2003.7.23 [21] 申请号 03820007.4

[30] 优先权

[32] 2002.8.30 [33] JP [31] 255568/2002

[86] 国际申请 PCT/JP2003/009361 2003.7.23

[87] 国际公布 WO2004/023561 英 2004.3.18

[85] 进入国家阶段日期 2005.2.23

[71] 申请人 夏普株式会社

地址 日本大阪府

[72] 发明人 藤井晓义 中林敬哉

[74] 专利代理机构 中科专利商标代理有限责任公司

代理人 陈瑞丰

权利要求书 6 页 说明书 26 页 附图 17 页

[54] 发明名称 薄膜晶体管、液晶显示设备及其制备方法

[57] 摘要

本发明的薄膜晶体管的制备方法包括步骤：(i)通过施加电极原料的微滴形成其中形成有源极和漏极的电极形成区域，(ii)施加电极原料的微滴到远离半导体层的形成区域的滴落位置之上，并施加电极原料的微滴于电极形成区域中，以及(iii)在电极形成区域中形成源极和漏极。通过采用这种设置，在通过施加电极原料的微滴形成源极和漏极中，可以确定地避免每一电极之间通道部分上溅射微滴的粘附。

1. 一种薄膜晶体管，其包括：(i) 半导体层，其通过栅绝缘层面向

5 棚极，(ii) 源极和漏极，其与半导体层电连接，以及 (iii) 源极和漏极之

间的通道部分，其中：

通过施加电极原料的微滴形成源极和漏极，并具有在远离半导体层的

形成区域之外的分叉部分处的分支部分，分支部分包括多个分支电极，其

至少一部分在半导体层的形成区域中，交替地设置源极的分支电极和漏极

10 的分支电极。

2. 如权利要求 1 所述的薄膜晶体管，其中：

基于通过施加微滴以施加微滴于滴落位置之上来用于形成分支电极

部分，如此设置作为微滴施加于其上的滴落位置的分叉部分的位置，从而

使微滴施加于通道部分之上。

15 3. 如权利要求 1 所述的薄膜晶体管，其中：

每个分支电极具有在半导体层的形成区域内部彼此平行的平行部分，

在平行部分和分叉部分之间每一分支电极是线性的。

4. 如权利要求 1 所述的薄膜晶体管，其中：

源极和漏极的至少一个具有朝半导体层的形成区域逐渐变宽的部分。

20 5. 如权利要求 4 所述的薄膜晶体管，其中：

源极和漏极具有分别靠近半导体层的末端；并且逐渐变得较宽的部分

位于分叉部分的一个和末端的一个之间。

6. 如权利要求 1 所述的薄膜晶体管，其中：

通道部分具有不长于分支电极部分的长度的宽度。

25 7. 如权利要求 1 所述的薄膜晶体管，其中：

如此设置源极的分支电极或漏极的分支电极，以使当分支电极从分叉

部分朝通道部分延伸时，分支电极的每一相邻对之间的间隙变宽。

8. 如权利要求 7 所述的薄膜晶体管，其中：

半导体层具有基本上的圆形图案，其直径大于位于通道部分上的栅极

30 的宽度部分。

9. 如权利要求1所述的薄膜晶体管，其中：

半导体层具有基本上的圆形图案，其直径大于位于通道部分上的栅极的宽度部分；以及

5 每一分支电极的末端在栅极的宽度部分内部，但不会超出栅极的宽度部分。

10. 一种薄膜晶体管，其包括：(i) 半导体层，其通过栅绝缘层面向栅极，(ii) 源极和漏极，其与半导体层电连接，以及(iii) 源极和漏极之间的通道部分，其中：

源极通过源过渡部分与源线相连，并且漏极通过漏过渡部分与漏线相10 连；以及

源过渡部分和漏过渡部分位于半导体层的形成区域之外；以及

源过渡部分从源线朝半导体层的形成区域逐渐变宽，和/或漏过渡部分从漏线朝半导体层的形成区域逐渐变宽。

11. 一种薄膜晶体管，其包括：

15 位于线性栅极线上的基本上的圆形半导体层，半导体层部分覆盖线性栅极线，并在线性栅极线之间夹有栅绝缘层；

在半导体层上的源极和漏极；

源极和漏极之间的通道部分；

源极通过源过渡部分与源线相连，并且漏极通过漏过渡部分与漏线连20 接；以及

源过渡部分和漏过渡部分位于半导体层的形成区域之外。

12. 一种液晶显示设备，其包括薄膜晶体管，其中：

该薄膜晶体管包括 (i) 半导体层，其通过栅绝缘层面向栅极，(ii) 源极和漏极，其与半导体层电连接，以及 (iii) 源极和漏极之间的通道部分，

通过施加电极原料的微滴形成源极和漏极，并具有在其离开半导体层的形成区域的分叉部分处的分支部分，所述分支部分包括多个分支电极，其至少一部分在半导体层的形成区域中，源极的所述分支电极和漏极的所述分支电极交替地设置。

30 13. 一种液晶显示设备，其包括薄膜晶体管，该薄膜晶体管包括 (i)

半导体层，其通过栅绝缘层面向栅极，(ii) 源极和漏极，其与半导体层电连接，以及 (iii) 源极和漏极之间的通道部分，其中：

源极通过源过渡部分与源线相连，并且漏极通过漏过渡部分与漏线相连；以及

5 源过渡部分和漏过渡部分位于半导体层的形成区域之外；以及

源过渡部分从源线朝半导体层的形成区域逐渐变宽，和/或漏过渡部分从漏线朝半导体层的形成区域逐渐变宽。

14. 一种液晶显示设备，其包括薄膜晶体管，其中：

所述薄膜晶体管包括：

10 位于线性栅极线上的基本上圆形半导体层，半导体层部分覆盖线性栅极线，并且在线性栅极线之间夹有栅绝缘层；

在半导体层上的源极和漏极；

源极和漏极之间的通道部分；

源极通过源过渡部分与源线相连，并且漏极通过漏过渡部分与漏线相

15 连；以及

源过渡部分和漏过渡部分位于半导体层的形成区域之外。

15. 一种薄膜晶体管的制备方法，其中所述薄膜晶体管包括 (i) 栅极上的半导体层，(ii) 半导体层和栅极之间的栅绝缘层，(iii) 半导体层上的源极和漏极，以及 (iv) 源极和漏极之间的通道部分，该制备方法包括步骤：

在形成半导体层步骤之后，进行预处理，以形成其中形成有源极和漏极的电极形成区域；以及

施加电极原料的微滴到位于电极形成区域中的滴落位置上，从而在电极形成区域中分别形成源极和漏极，滴落位置离开半导体层的形成区域。

25 16. 如权利要求 15 所述的制备方法，其中预处理步骤包括步骤：

在栅绝缘层和半导体层上，沿着电极形成区域的边界，形成线导引；以及

湿润在其上不形成导引线的栅绝缘层和半导体层的那些部分，并且对导引线进行去湿。

30 17. 如权利要求 15 所述的制备方法，其中预处理步骤包括步骤：

在绝缘层和半导体层上形成：(i) 依据需求图案湿润作为源/漏线形成区域的湿润区域，以及 (ii) 依据需求图案去湿作为非-源/漏线形成区域的去湿区域。

18. 如权利要求 15 所述的制备方法，其中：

5 在预处理步骤中，如此形成电极形成区域，以使源极和漏极的至少一个具有在其离开半导体层的形成区域的分叉部分处的分支部分，所述分支部分包括在半导体层上的多个分支电极，第一电极的所述分支电极夹着第二电极，其中第一电极是源极和漏极的至少一个，并且第二电极是另一个；以及

10 在施加微滴的步骤中，分别对应于分叉部分的位置是电极原料的微滴施加于其上的滴落位置。

19. 如权利要求 15 所述的制备方法，其中：

基于包括在滴落位置上的公差，如此设置滴落位置，以使微滴不施加于通道部分之上。

15 20. 如权利要求 15 所述的制备方法，其中：

基于包括在滴落位置上的公差，如此设置滴落位置，以使溅射微滴不粘附于通道部分之上。

21. 如权利要求 18 所述的制备方法，其中：

如此形成每个分支电极，以具有在半导体层上彼此平行的平行部分，

20 在平行部分和分叉部分之间每个分支电极是线性的。

22. 如权利要求 15 所述的制备方法，其中：

在预处理步骤中，如此形成电极形成区域，以使源极和/或漏极具有朝半导体层的形成区域逐渐变宽的部分，以及

25 在施加微滴的步骤中，将电极原料的微滴施加于位于来自部分逐渐变宽的位置中的滴落位置之上。

23. 如权利要求 15 所述的制备方法，其中：

在预处理步骤中，如此形成电极形成区域，以使在其中栅极存在的区域中，分别朝半导体层的形成区域延伸的源极和漏极的部分平行于其中栅极延伸的方向。

30 24. 如权利要求 15 所述的制备方法，其中：

在预处理步骤中，如此形成电极形成区域，以使源极的分支电极或漏极的分支电极具有分支电极的每一相邻对之间的间隙，当分支电极从分叉部分朝通道部分延伸时，所述间隙变宽。

25. 如权利要求 15 所述的制备方法，其中：

5 在预处理步骤中，形成电极形成区域，以使 (i) 源极通过源过渡部分与源线相连，并且漏极通过漏过渡部分与漏线相连，源过渡部分和漏过渡部分位于半导体层的形成区域之外；以及 (ii) 源过渡部分朝与此相连的源线变得较窄，和/或漏过渡部分朝与此相连的漏线变得较窄；以及

10 在施加微滴的步骤中，电极原料的微滴施加于作为滴落位置的源过渡部分和漏过渡部分之上。

26. 如权利要求 15 所述的制备方法，其中：

在预处理步骤中，形成电极形成区域，以使 (i) 源极和漏极形成于半导体层之上，其是基本上的圆形并位于线性栅极线之上，半导体层部分覆盖线性栅极线，并且在线性栅极线之间夹有栅绝缘层，以及 (ii) 源极通过源过渡部分与源线相连，并且漏极通过漏过渡部分与漏线相连，源过渡部分和漏过渡部分位于半导体层的形成区域之外；以及

在施加微滴的步骤中，电极原料的微滴施加于作为滴落位置的源过渡部分和漏过渡部分之上。

27. 如权利要求 15 所述的制备方法，其中：

20 施加于滴落位置的一个之上的微滴的直径大于源极或漏极的宽度。

28. 如权利要求 18 所述的制备方法，其中：

包括在分支电极部分中的分支电极的宽度与施加于滴落位置的一个之上的微滴的直径之间的比基本上是一到二。

29. 一种液晶显示设备的制备方法，其包括薄膜晶体管的制备方法，

25 其中：

所述薄膜晶体管包括 (i) 栅极上的半导体层，(ii) 半导体层和栅极之间的栅绝缘层，(iii) 半导体层上的源极和漏极，以及 (iv) 源极和漏极之间的通道部分，所述薄膜晶体管的制备方法包括步骤：

30 在形成半导体层步骤之后，进行预处理，以形成其中形成有源极和漏极的电极形成区域；以及

---

施加电极原料的微滴到位于电极形成区域中的滴落位置上, 从而在电极形成区域中分别形成源极和漏极, 所述滴落位置远离半导体层的形成区域。

## 薄膜晶体管、液晶显示设备及其制备方法

5

### 技术领域

本发明涉及一种薄膜晶体管的制造方法，以及一种液晶显示设备的制备方法。

### 10 背景技术

近年来提出了一种通过喷墨方法，而不是通过照相平版术形成布线的技术。在此技术中，例如日本未审查专利申请 Tokoukaihei, No. 11-204529 (于 1999 年 7 月 30 日公开)，基片具有对形成线的原料具有亲和力的亲和区，以及对形成线的原料不具有亲和力的非亲和区。通过墨水喷射方法将形成线的原料的微滴施加 (粘合) 到基片的亲和区上 (在下文中，术语“施加”包括“滴落”和“喷射”的含义)。

在此说明的是，此日本未审查专利申请 Tokoukaihei, No. 11-204529 对应于美国专利申请 No. 2003/0003231A1。

此外，未审查的日本专利申请 Tokukai, No. 2000-353594 (于 2000 年 12 月 19 日公开) 给出了通过墨水喷射方法类似地形成线的技术，其中在线形成区域的两侧形成触排，从而避免线的原料溢出线形成区域，触排的上部部分具有对液体的非亲和性 (去湿特性)，而线形成区域具有湿润特性。

需要指出，未审查的日本专利申请 Tokukai, No. 2000-353594 对应于欧洲专利申请 No. EP0989778A1。

此外，在 SID 01 文摘，第 40-43 页，6.1 中给出的特约论文：“通过高分辨率喷墨印刷方法制造的全聚合体薄膜晶体管 (All-polymer Thin Film Transistors Fabricated by High-Resolution Ink-jet Printing)”(作者为 Takeo KAWASE 等) 中，其公开了通过利用墨水喷射方法、仅通过利用有机原料形成 TFT 的技术。

在该技术中，通过照相平版印刷、在 TFT 的通道部分中形成由聚酰亚胺制成的条带之后，通过利用墨水喷射印刷机将由传导性聚合体制成的电极的原料（电极原料）印刷于通道部分的两侧上。由于由聚酰亚胺制成的条带具有去湿特性，没有电极原料覆盖条带，源和漏极分别形成于通道部分的两侧之上。

5 下面说明本发明所要解决的问题。

当在薄膜晶体管的制备中采用通过墨水喷射法形成线等的技术，相比其中利用照相平版印刷的情况，减少了需要掩模的数量，并且这样减少了制备处理中步骤的数量。此外，由于用于形成线等的大规模处理设备不再是必须的，降低了设备的成本。这些导致了成本降低。

10 因此，在薄膜晶体管的制备中，由于通过使用该技术给出的优点，采用通过墨水喷射法形成线等的技术是有利的。

然而，在其中形成源或漏极的区域中，通过滴落（施加）电极的原料、仅利用墨水喷射法以形成薄膜晶体管的源或漏极的情况下，存在喷射中溅射的微滴（溅射微滴）可以粘附于薄膜晶体管中的通道部分之上并残留于其上的可能性。

在这种情况下，由于粘附于通道部分之上的溅射微滴，在源和漏极之间可以出现泄漏，或者在处理  $n^+$  层中溅射微滴可以作为掩模，从而残留  $n^+$  层，因此允许漏电流流动于源和漏极之间，故不能获得需求的 TFT 特性。

20

## 发明内容

本发明用于解决上面的问题，其主要目的在于提供具有其中电极原料的溅射微滴将不粘附于薄膜晶体管的通道部分的电极设置的薄膜晶体管和该薄膜晶体管的制备方法。

25 为了解决上面的目的，本发明的薄膜晶体管设置有 (i) 半导体层，其通过栅绝缘层面向栅极，(ii) 源极和漏极，其与半导体层电连接，以及 (iii) 源极和漏极之间的通道部分，其中通过施加电极原料的微滴形成源极和漏极，并具有在其离开半导体层的形成区域的分叉部分处的分支部分，所述分支部分包括多个分支电极，其至少一部分在半导体层的形成区域中，源极的分支电极和漏极的分支电极交替地设置。

通过采用上面的设置,在形成具有分支电极部分的源极和漏极的情况下,其中源极和漏极的分支电极部分的分叉部分离开半导体层的形成区域(其中存在半导体层的区域),它可能具有在离开半导体层的形成区域的分叉部分处的滴落位置。

5 通过采用上面的设置,在形成源极和漏极中,可能避免电极之间通道部分上溅射微滴的粘附。因此,可能避免由于溅射微滴作为掩模、残留剩余的n+层、源和漏极之间的漏电流而不能获得需求的TFT特性。

此外,在交替设置的分支电极的每一个之间形成宽的通道部分。这样,对于其中电荷转移是大的,比如其中驱动大量像素的情况的情况,该设置

10 是有效的。

如此设置本发明的液晶显示设备,以包括本发明的薄膜晶体管。

一种本发明的薄膜晶体管的制备方法,薄膜晶体管包括(i)栅极上的半导体层,(ii)半导体层和栅极之间的栅绝缘层,(iii)半导体层上的源极和漏极,以及(iv)源极和漏极之间的通道部分,该制备方法包括步骤:

15 在形成半导体层步骤之后,进行预处理,以形成其中形成源极和漏极的电极形成区域;以及施加电极原料的微滴于位于电极形成区域中的滴落位置之上,从而在电极形成区域中分别形成源极和漏极,所述滴落位置远离半导体层的形成区域。

通过采用上面的设置,其中通过施加微滴于位于电极形成区域中和离开半导体层的形成区域的滴落位置之上形成源极和漏极,可能避免电极之间通道部分上溅射微滴的粘附。因此,可能避免由于溅射微滴作为掩模、残留剩余的n+层、源和漏极之间的漏电流而不能获得需求的TFT特性。

20

本发明的液晶显示设备的制备方法包括本发明的薄膜晶体管的制备方法。

25 为了更完全地理解本发明的特征和优点,结合附图的以对本发明进行详细说明。

## 附图说明

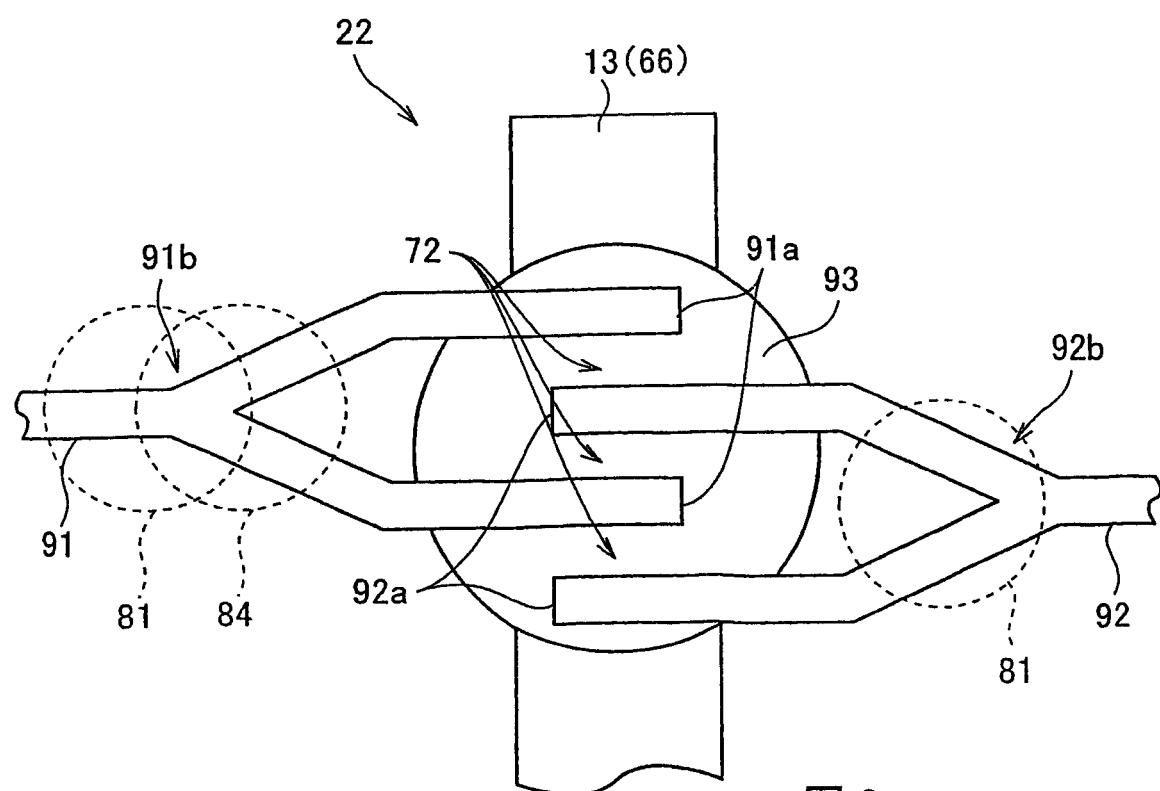

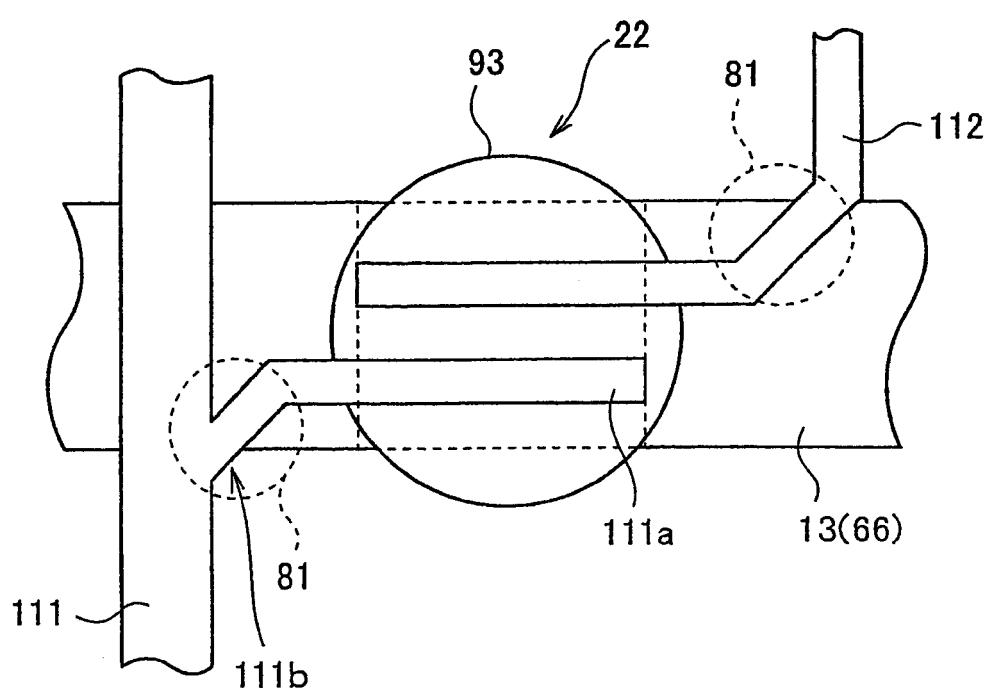

图1是说明了本发明的实施例的TFT阵列基片的TFT部分的设置的平面图。

30

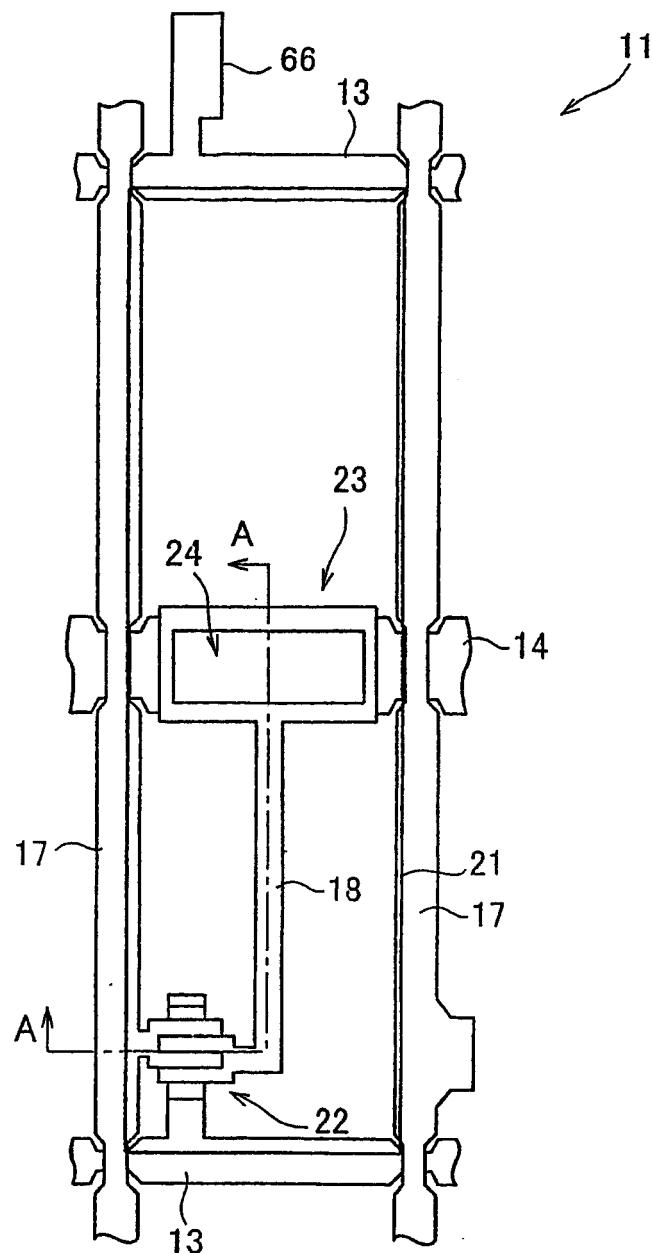

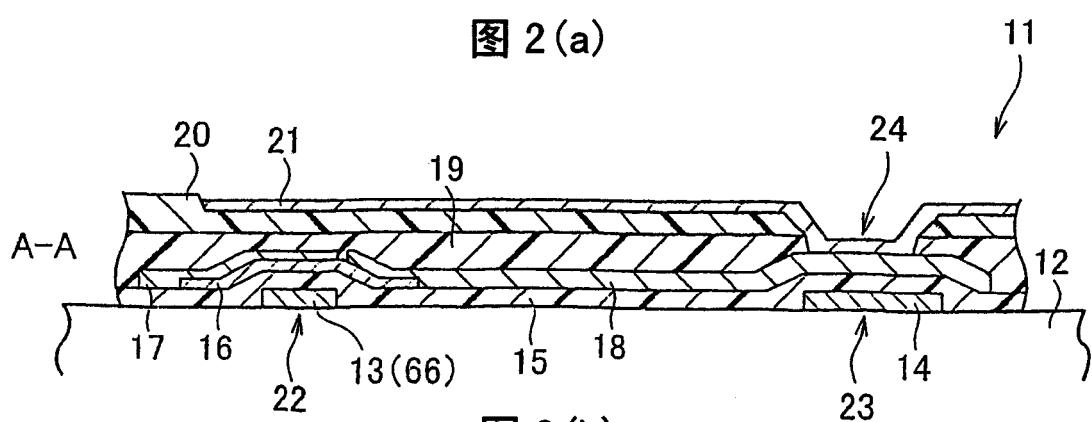

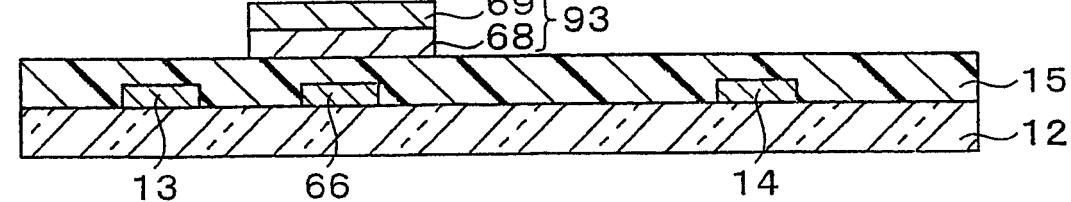

图 2 (a) 是示意性说明了本发明的实施例的液晶显示设备中的 TFT 阵列基片中像素设置的平面图, 同时, 图 2 (b) 是沿着图 2 (a) 的线 A-A 截取的横截面图。

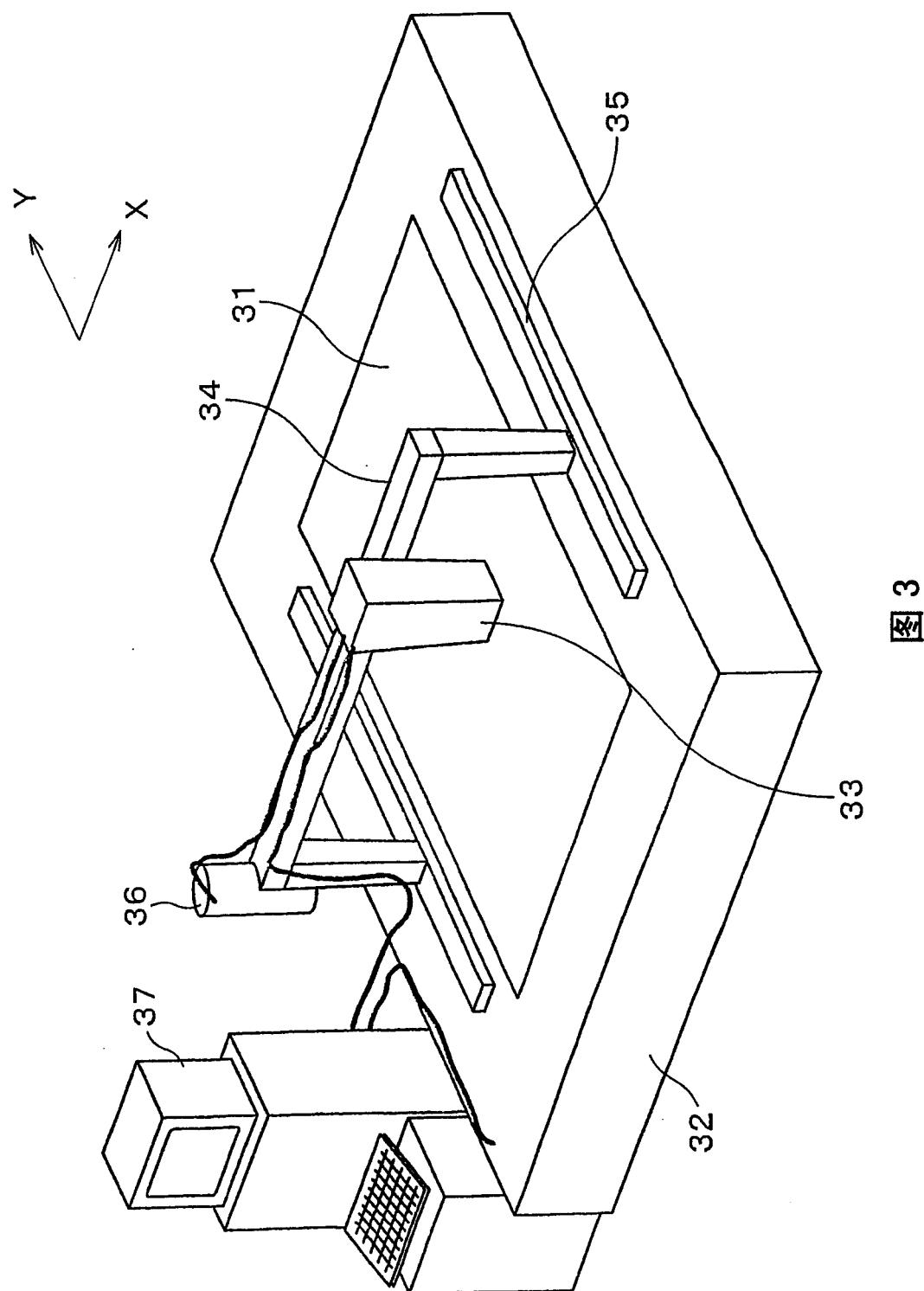

图 3 是说明了用于制备本发明的实施例的液晶显示设备的墨水喷射 5 方法的图案形成设备的示意性透视图。

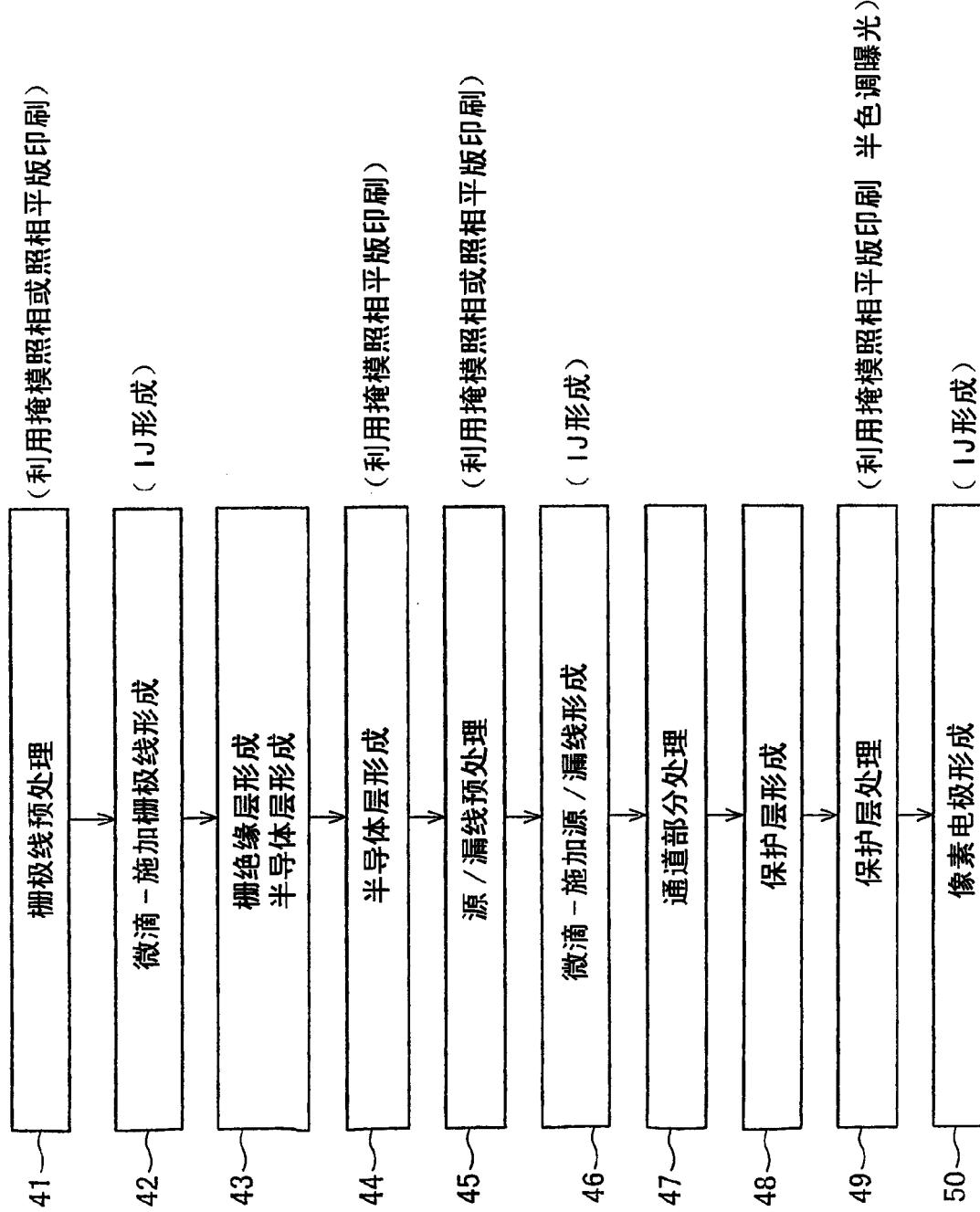

图 4 是说明了在图 2 (a) 和 2 (b) 中示出的 TFT 阵列基片的制备步骤的流程图。

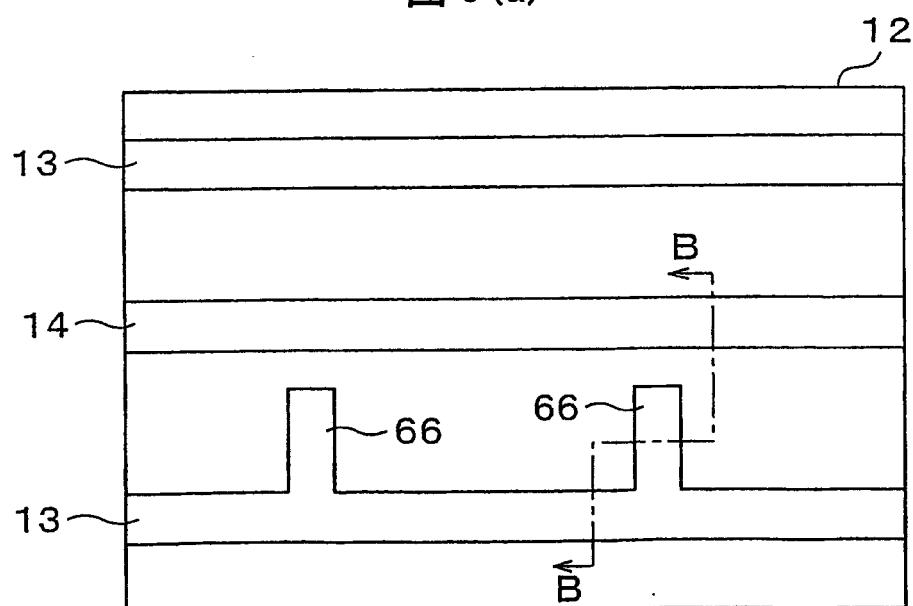

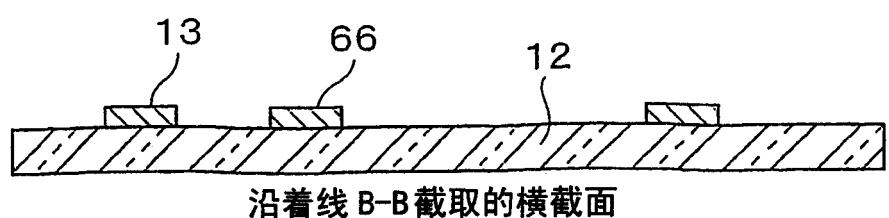

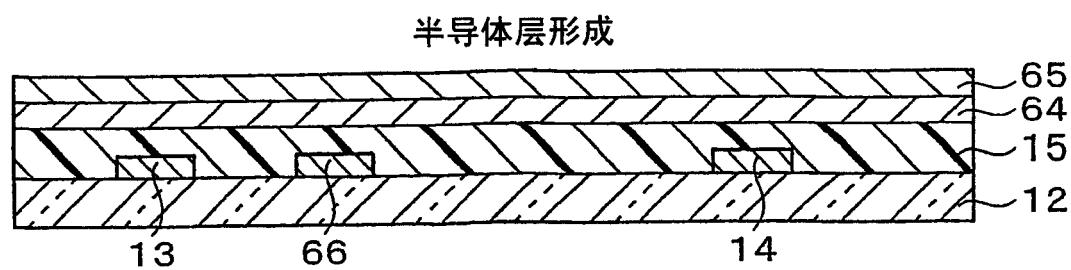

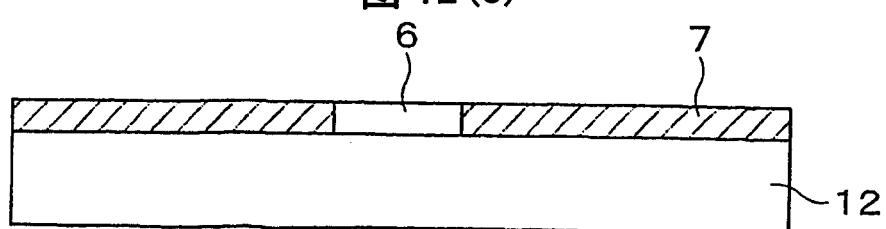

图 5 (a) 是 TFT 阵列基片的平面图, 该平面图说明了在图 3 中示出的栅极预处理步骤。图 5 (b) 是 TFT 阵列基片的平面图, 该平面图说明了在图 3 中示出的微滴-施加栅极线形成步骤的平面图。此外, 图 5 (c) 10 是沿着图 5 (b) 的线 B-B 截取的横截面图。

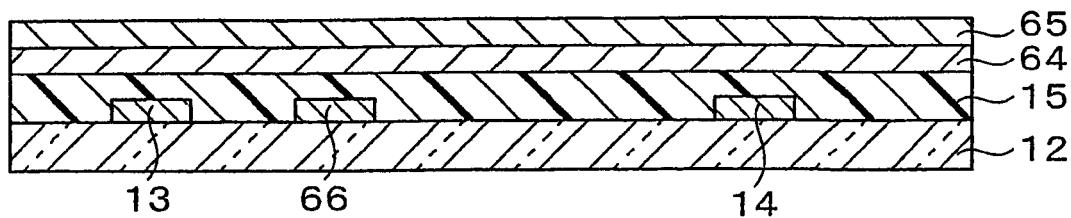

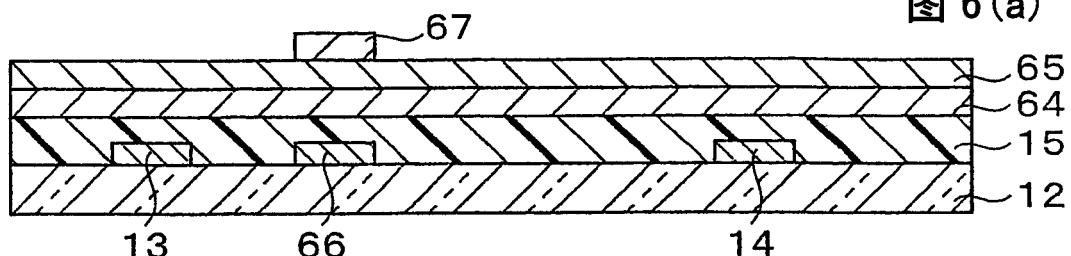

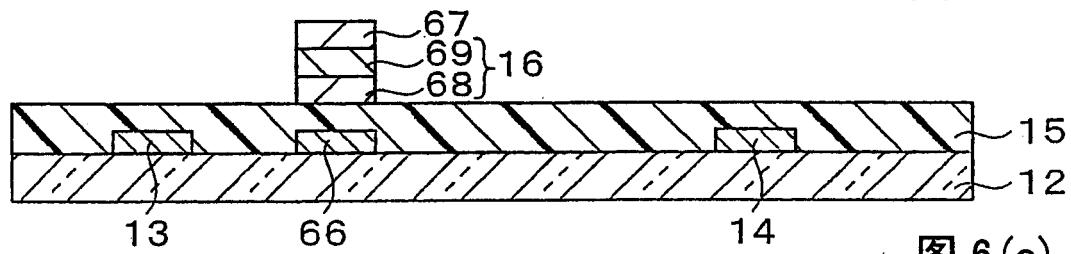

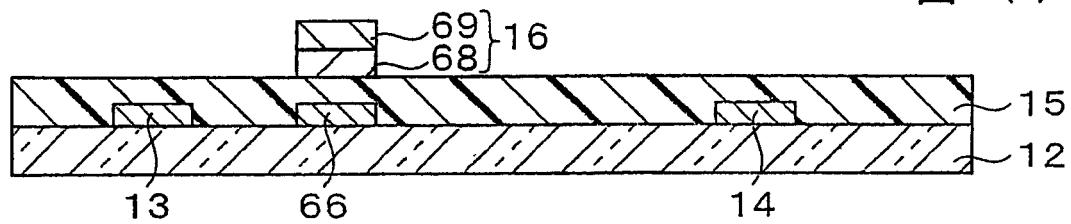

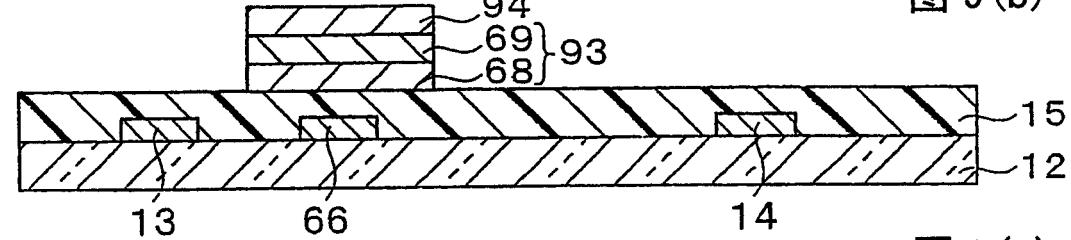

图 6 (a) 到 6 (c) 是对应于图 5 (b) 的线 B-B 截取的横截面的部分 15 的横截面图。图 6 (a) 说明了在图 4 中示出的栅绝缘层形成/半导体层形成步骤。图 6 (b) 说明了在图 4 中示出的半导体层形成步骤中形成栅绝缘层和半导体层的步骤之后完成照相平版印刷步骤之后的状态。图 6 (c) 说明了蚀刻半导体层形成步骤中的 a-Si 薄膜形成层和 n+ 薄膜形成层的步骤。图 6 (d) 是沿着图 6 (e) 的线 C-C 截取的横截面图。图 6 (d) 说明了去除半导体层形成步骤中的抗蚀层的步骤。图 6 (e) 是已被半导体层形成步骤处理的 TFT 阵列基片的平面图。

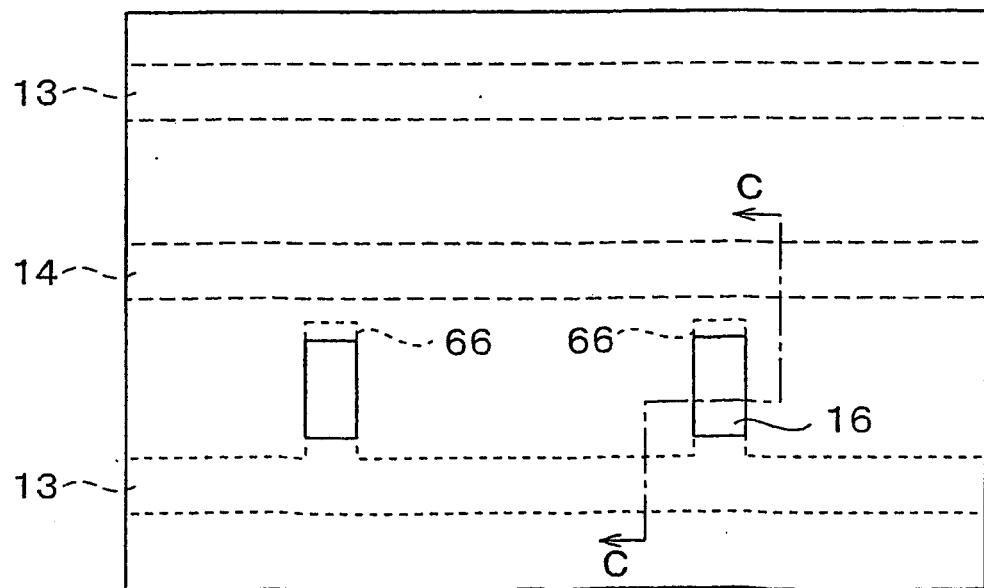

图 7 是示出了在图 1 中示出的 TFT 部分的部分的尺寸的平面图, 并且 20 相对于需求的滴落位置的公差范围需求。

图 8 是说明了本发明的另一实施例的 TFT 阵列基片的 TFT 部分的设置的平面图。

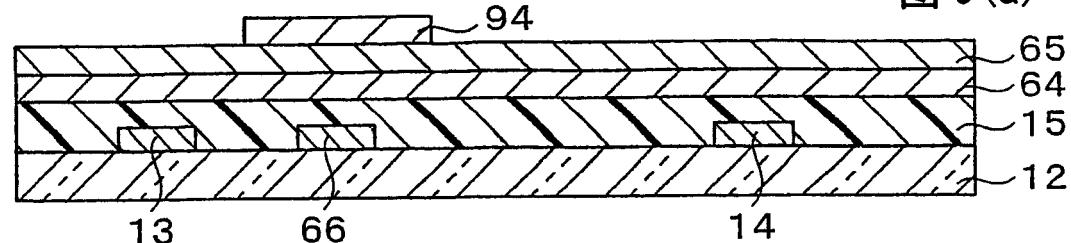

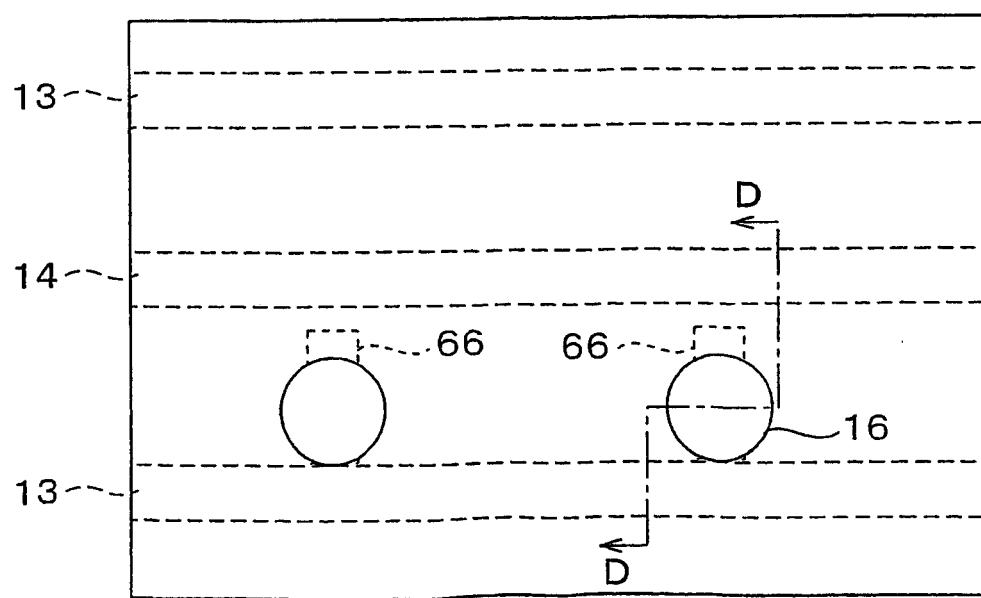

图 9 (a) 到 9 (c) 是对应于图 5 (b) 的线 B-B 截取的横截面的部分 25 的横截面图。图 9 (a) 说明了在图 4 中示出的栅绝缘层形成/半导体层形成步骤, 其用于其中 TFT 阵列基片具有在图 8 中示出的 TFT 部分的情况。图 9 (b) 说明了在图 4 中示出的半导体层形成步骤中形成栅绝缘层和半导体层的步骤之后完成照相平版印刷步骤之后的状态。图 9 (c) 说明了蚀刻半导体层形成步骤中的 a-Si 薄膜形成层和 n+ 薄膜形成层的步骤。图 30 9 (d) 是沿着图 9 (e) 的线 D-D 截取的横截面图, 且图 9 (d) 说明了去

除半导体层形成步骤中的抗蚀层的步骤。图 9 (e) 是已被半导体层形成步骤处理的 TFT 阵列基片的平面图。

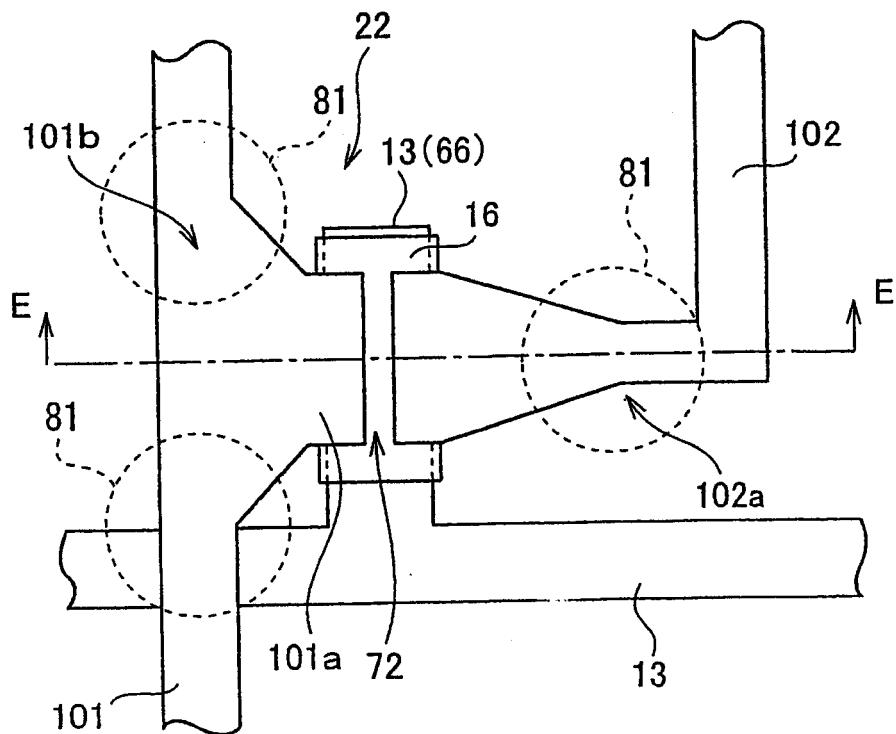

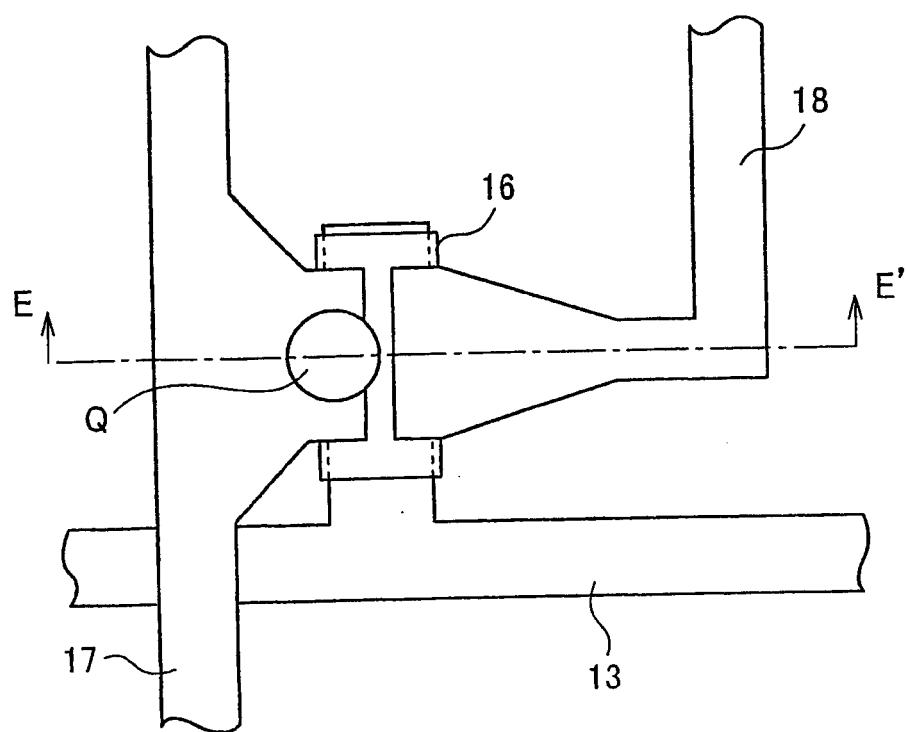

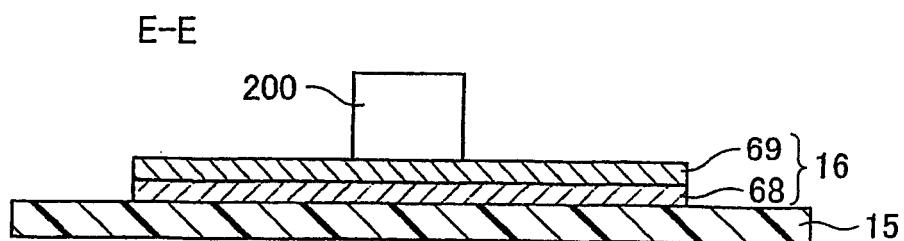

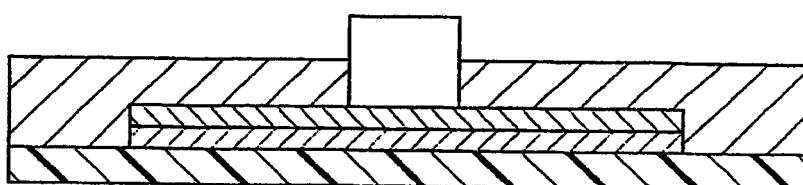

图 10 (a) 是说明了本发明的另一实施例的 TFT 阵列基片的 TFT 部分的设置的平面图。图 10 (b) 是对应于图 10 (a) 的线 E-E 截取的横截面 5 部分的横截面图，图 10 (b) 示出了在形成源极和漏极之前的部分。

图 11 是说明了本发明的又一实施例的 TFT 阵列基片的 TFT 部分的设置的平面图。

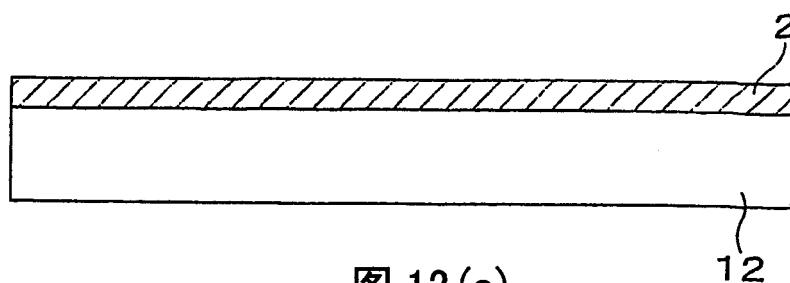

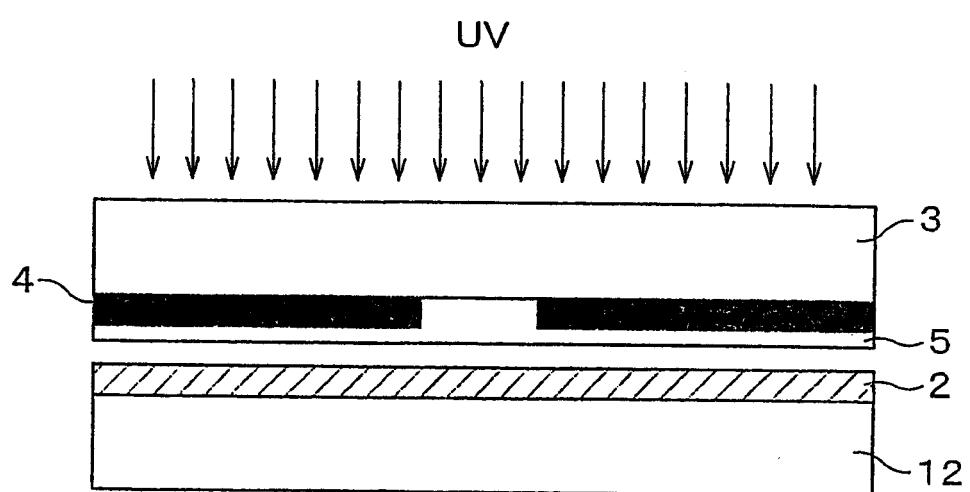

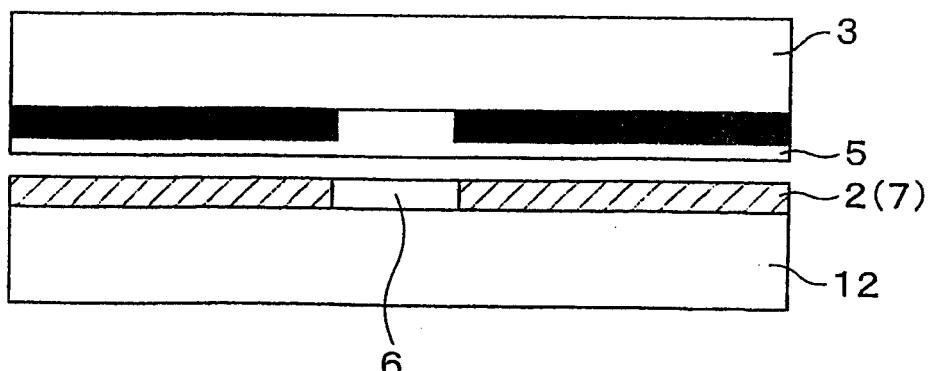

图 12 (a) 到 12 (d) 是说明了通过利用光催化剂、通过基片的湿润处理，在去湿区域中形成湿润图案的步骤的说明图。

图 13 是示出了其中电极原料的溅射微滴残留于源极的通道部分之上的环境的平面图。

图 14 (a) 到 14 (d) 是说明了 TFT 部分的通道部分的制备处理中的步骤的示意性横截面图。图 14 (e) 到图 14 (g) 是沿着图 13 的线 E-E' 获得的示意性横截面图，其说明了通道部分的制备处理中的步骤，其用于 15 其中电极原料的溅射微滴残留于通道部分之上的情况。

图 15 是说明了其中电极原料的溅射微滴残留并覆盖源极和漏极之间的通道部分的情况的平面图。

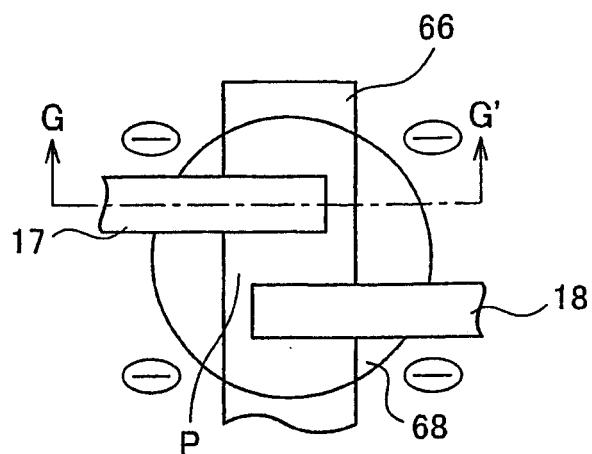

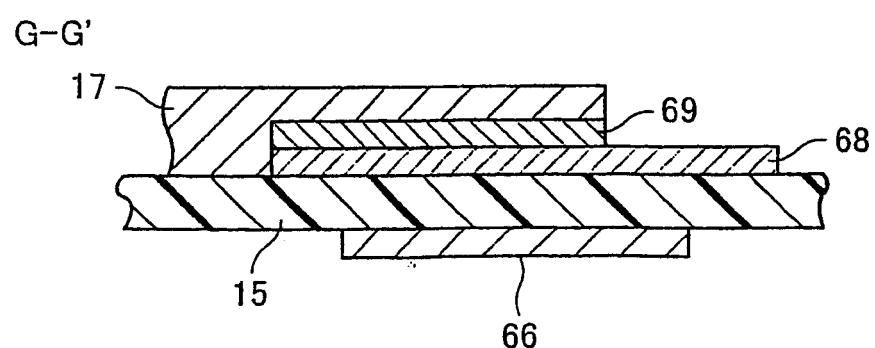

图 16 (a) 是说明了在半导体层的形状突出于 TFT 部分的栅极区域之外的情况下，在源极和漏极之间几乎不出现漏电流的设置的平面图。图 20 16 (b) 是沿着图 16 (a) 的线 G-G' 截取的横截面图。

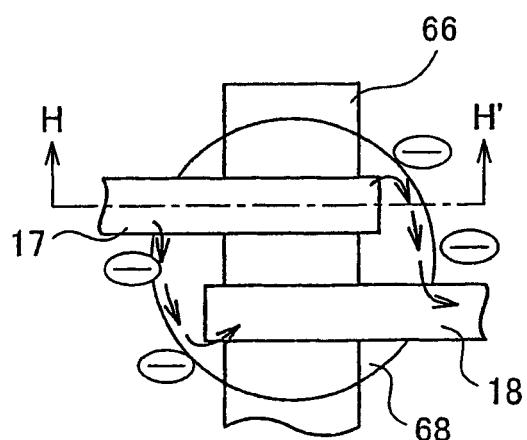

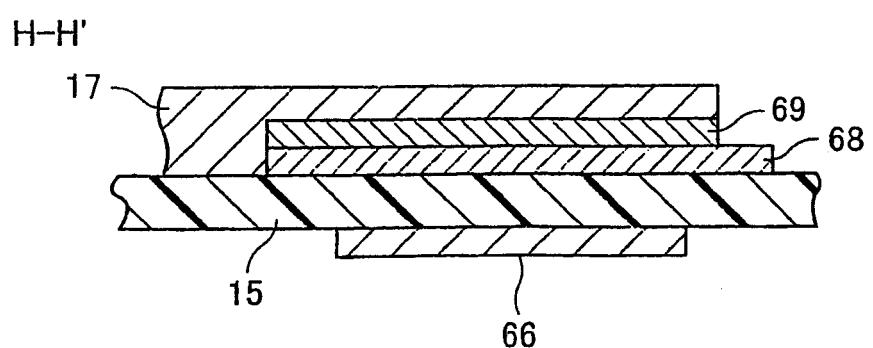

图 17 (a) 是说明了在半导体层的形状突出于 TFT 部分的栅极区域之外的情况下，在源极和漏极之间容易出现漏电流的设置的平面图。图 17 (b) 是沿着图 17 (a) 的线 H-H' 截取的横截面图。

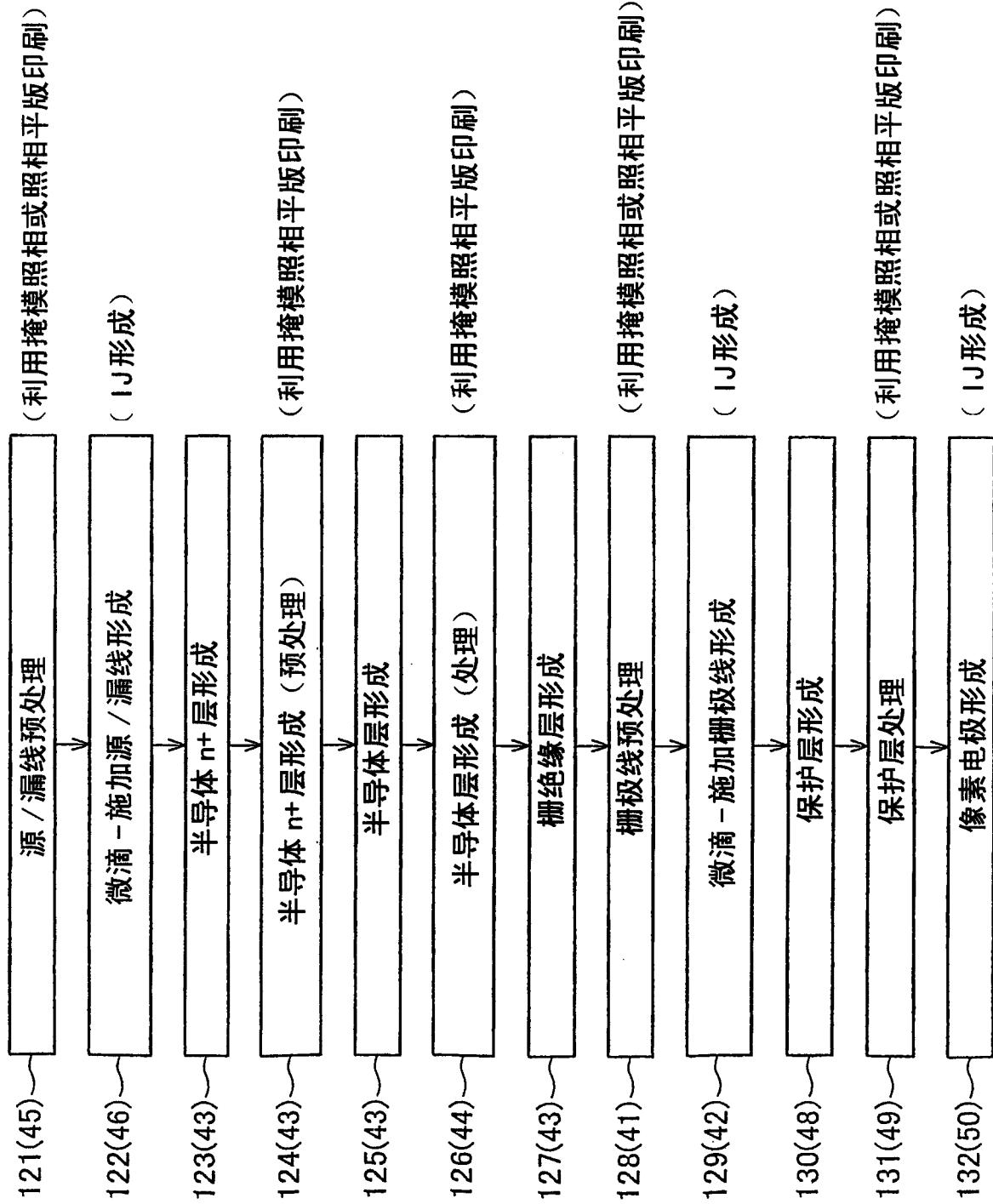

图 18 是示出了具有上部栅结构的 TFT 阵列基片的制备步骤的流程图。

25

## 具体实施方式

### [第一实施例]

参照附图，下面说明本发明的实施例。

30 本发明的实施例的液晶显示设备配备有在图 2 (a) 中示出的像素。

需要指出，图 2 (a) 是示意性说明了液晶显示设备的 TFT 阵列基片中像素的设置的平面图。此外，在图 2 (b) 中说明了沿着图 2 (a) 的线 A-A 截取的横截面图。

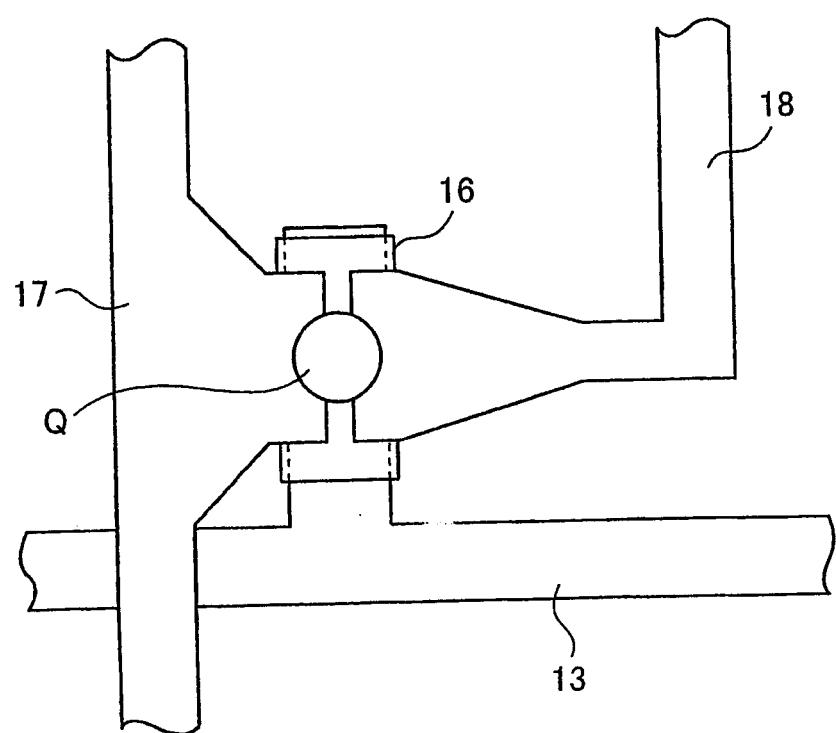

如图 2 (a) 和图 2 (b) 所示，在基片 11 的 TFT 阵列中，在玻璃基片 12 上以矩阵配备栅极 13 (栅极线) 和源极 17 (源线)。分别在邻近栅极 13 (栅极线) 之间，配备电容电极 14 (存储电容线)。

如图 2 (b) 所示，在 TFT 部分 22 的位置和存储电容部分 23 的位置之间，TFT 阵列基片 11 在玻璃基片 12 上配备一个栅极 13 和一个存储电容电极 14。

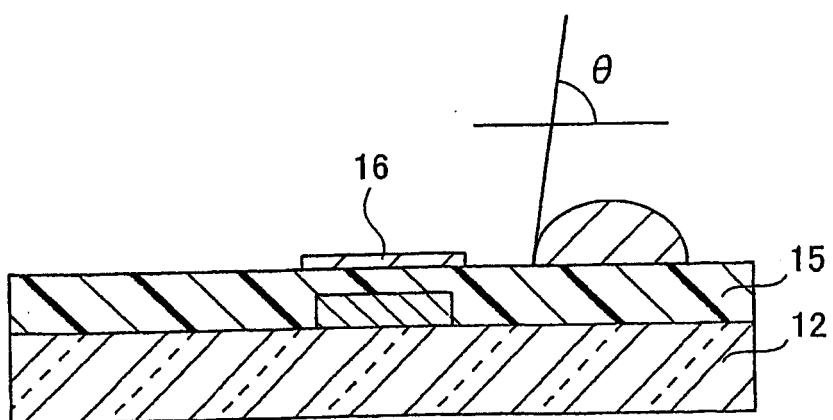

形成于栅极 13 之上的是包括 a-Si 层的半导体层 16。栅绝缘层 15 夹于栅极 13 和半导体层 16 之间。在半导体层 16 上形成源极 17 和漏极 18 的每一末端部分 (末端)。在存储电容电极 14 之上的位置上形成漏极 18 的每一另一末端，该位置和存储电容电极 14 夹着栅绝缘层 15。在该位置形成接触孔 24。在源极 17 和漏极 18 上形成保护层 19。在保护层 19 上，以该次序形成光敏丙烯酸树脂层 20 和像素电极 21。

TFT 部分 22 的设置被称为底部栅结构。本发明不局限于该底部栅结构，其也可以应用于上部栅结构，其中在半导体层 16 之上形成栅极 13，从而使栅绝缘层 15 夹于半导体层 16 和栅极 13 之间。

因此，在本发明的 TFT 部分 22 中形成半导体层 16，其通过栅绝缘层 15 面向栅极 13，并形成与半导体层 16 电连接的源极 17 和漏极 18。

在该实施例中，通过使用用于喷射或浇注形成层的原料的图案形成设备，例如通过墨水喷射方法制备 TFT 阵列基片 11。如图 3 所示，图案形成设备配备有台子 32、墨水喷射头 33、X 方向驱动部分 34 和 Y 方向驱动部分 35。台子 32 用于在其上放置基片 31 (对应于玻璃基片 12)。墨水喷射头 33 是用于喷射于台子 32 上的基片 31 之上的微滴喷射装置，例如包含线原料的可流动墨水 (微滴或可流动的原料)。X 方向驱动部分 34 和 Y 方向驱动部分 35 分别以 X 方向和 Y 方向移动墨水喷射头 33。

需要指出，X 和 Y 方向分别是平行于基片 31 的平面上的两维 X-Y 坐标的 X 轴和 Y 轴的方向。

此外，图案形成设备配备有墨水供给系统 36 和控制单元 37。墨水供

给系统 36 供给墨水至墨水喷射头 33，而控制单元 37 执行各种控制，比如墨水喷射头 33 的喷射控制、X 方向驱动部分 34 和 Y 方向驱动部分 35 的驱动控制等控制。控制单元 37 输出滴落位置信息至 X 和 Y 方向驱动部分 34 和 35，并输出喷射信息至墨水喷射头 33 的头部驱动器（未示出）。

5 因此，与 X 和 Y 方向驱动部分 34 和 35 的运动联合操作墨水喷射头 33，并以目标量供给微滴至基片 31 上的目标位置（滴落位置）之上。

墨水喷射头 33 可以采用其中使用压电调节器的压电方法，其中在头部中配备加热器的鼓泡方法或其它方法。通过控制向该处施加的电压可以控制从墨水喷射头 33 喷射的墨水量。可以以简便滴落微滴的方法的装置 10 或能够供给微滴的任何装置代替微滴喷射装置。

下面是液晶显示设备的 TFT 阵列基片 11 的制备方法。

在该实施例中，如图 4 所示，TFT 阵列基片 11 的制备方法包括栅极预处理步骤 41、微滴-施加栅极线形成步骤 42、栅绝缘层形成/半导体层形成步骤 43、半导体层形成步骤 44、源/漏线预处理步骤 45、微滴-施加源/漏线形成步骤 46、通道部分处理步骤 47、保护层形成步骤 48、保护层处理步骤 49 和像素电极形成步骤 50。

#### [栅极预处理步骤 41]

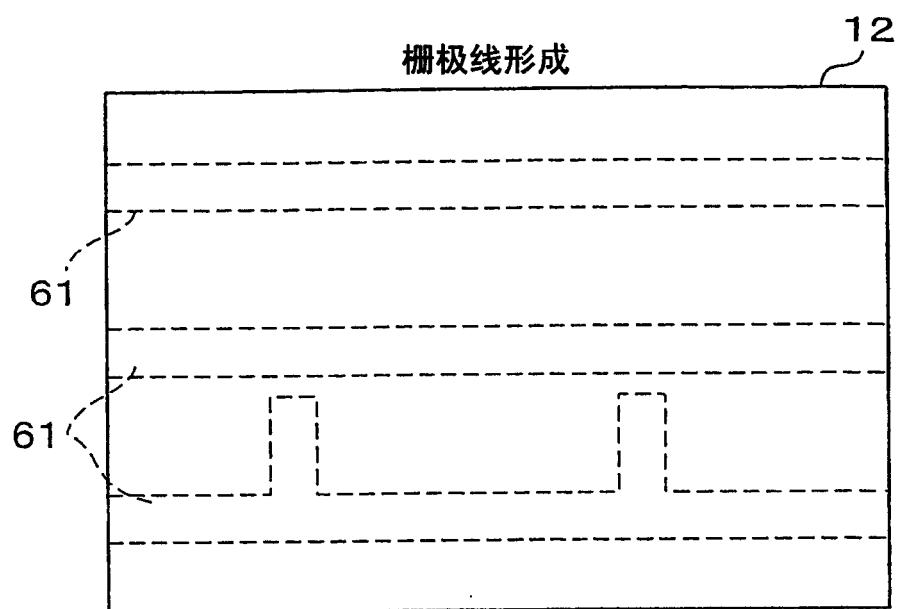

在栅极预处理步骤 41 中，实施用于微滴-施加栅极线形成步骤 42 的 20 预处理。在栅极预处理步骤 41 之后的微滴-施加栅极线形成步骤 42 中，通过使用图案形成设备、通过滴落液体线原料形成栅极线。为此，在栅极预处理步骤 41 中，当通过图案形成设备喷射（滴落）液体线原料至栅极线形成区域 61（在图 5（a）中示出）之上时，实施处理以准备获得液体线原料的更合适的应用。需要指出，图 5（a）是在 TFT 阵列基片 11 中配 25 备的玻璃基片 12 的平面图。

概略地讲，该步骤包括下面的步骤：第一步骤是对基片（玻璃基片 12）的一部分给出的湿润/去湿步骤、关于液体线原料的湿润或去湿特性，从而构图亲水区域（湿润区域）作为栅极线形成区域 61 和不易被水占湿的区域（去湿区域）作为非-栅极线形成区域；第二步骤是沿着每一栅极 30 线形成区域 61 的边界形成用于控制液体线原料的流动的导引的步骤。

如此前所述，通过利用氧化钛、通过光催化作用的湿润/去湿处理是典型的例子。如随后所述，通过使用抗蚀原料、通过照相平版印刷形成导引，从而对导引或基片的表面给出湿润特性或去湿特性，可以实施以等离子区中的 CF4 和 O2 气体对导引或基片的表面进行曝光的步骤。在形成线 5 之后去除抗蚀原料。

于此，如下实施使用氧化钛的光催化作用。在 TFT 阵列基片 11 的玻璃基片 12 上施加为非-离子类型含氟化合物的异丙醇和 ZONYL FSN (产品名称：由 E.I. du Pont de Nemours and Co. 获得) 的混合物 (去湿原料)。然而，通过旋转-涂敷施加其中分散二氧化钛微粒的乙醇和原料 (二氧化 10 钛微粒分散原料) 的混合物至用于栅极线的图案的掩膜之上，从而形成光催化层。在这之后以 150°C 烘焙这样制备的玻璃基片。然后，利用其上的掩膜，以 UV 光曝光玻璃基片 12。通过使用 70Mw/cm2 的强度中 356nm 的紫外线光实施 2 分钟的曝光。

参照图 12 (a) 至 12 (d)，下面给出更详细的说明。如图 12 (a) 所示，通过使用旋转涂敷方法等，将去湿原料施加于玻璃 12 之上。通过干燥玻璃基片 12 形成湿润层 2。需要指出，硅烷耦合介质可被用作去湿原料。 15

下面，如图 12 (b) 所示，通过其中预先形成由铬等组成的掩膜图案 4 和由氧化钛等构成光催化层 5 的光掩膜 3，在上面提到的曝光环境中实 20 施 UV 曝光。

结果，如图 12 (c) 和 12 (d) 所示，提高了受 UV 曝光支配的仅仅一部分的湿润特性。因此，形成对应于栅极线形成区域 61 的湿润图案 6。

#### [微滴-施加栅极线形成步骤 42]

25 在图 5 (b) 和 5 (c) 中说明微滴-施加栅极线形成步骤 42。图 5 (b) 是在栅极 13 和邻近其的栅极 13 之间形成存储电容电极 14 之后玻璃基片 12 的平面图。图 5 (c) 是沿着图 5 (b) 的线 B-B 截取的横截面图。

需要指出，如图 5 (b) 所示，确定栅极 13 的一部分朝与确定栅极 13 邻接的存储电容电极 14 突出。如图 1 和图 2 (a) 所示，该部分最后将变 30 成 TFT-部分栅极 66。然而，为了容易说明，省略在图 5 中示出的栅极 13

的上部一个的 TFT 部分栅极 66。

在微滴-施加栅极线形成步骤 42 中, 如图 5 (b) 和 5 (c) 所示, 通过使用图案形成设备, 将线原料施加 (施加其微滴) 于玻璃基片 12 上的栅极线形成区域 61 之上。作为线原料, 使用的是其中以 Ag 微粒涂敷有 5 机薄膜的原料, 以作为分散于有机溶剂中的表面涂敷层。设置线的宽度基本上为 50 $\mu\text{m}$ , 并且从墨水喷射头 33 喷射的线原料的量是 80pl。

从墨水喷射头 33 喷射线原料于湿润表面 (将受湿润/去湿处理置的表面) 之上, 然后线原料在栅极线形成区域 61 之上和之中流动和延伸。因此, 将喷射线原料于栅极线形成区域 61 之上的喷射间隔设置为大约 10 500 $\mu\text{m}$ 。在操作之后, 以 350 $^{\circ}\text{C}$  对玻璃基片 12 进行一个小时的烘焙, 因此形成栅极 13 和辅助电容电极 14。

将用于烘焙的温度设置为 350 $^{\circ}\text{C}$  是由于在下面的半导体层形成步骤 44 中施加大约 300 $^{\circ}\text{C}$  的处理温度。因此, 烘焙温度不局限于该温度。例如, 在其中形成有机半导体的情况下, 可将退火温度设置为 100 $^{\circ}\text{C}$  至 200 $^{\circ}\text{C}$  的 15 温度。在这种情况下, 可将烘焙温度设置为 200 $^{\circ}\text{C}$  至 250 $^{\circ}\text{C}$  的较低温度。

此外, 作为线原料, 可能使用有机溶剂中的微粒或糊原料。微粒或糊原料可以单独由一种金属或由除了 Ag 之外的比如 Ag-Pd、Ag-Au、Ag-Cu、Cu、Cu-Ni 等的合金组成。此外, 至于线原料, 依据必须的烘焙温度, 通过控制包含在有机溶剂中的有机原料或保护微粒的表面涂层的离解温度, 20 可能获得需求的阻抗值和表面条件。需要指出, 离解温度是蒸发表面涂层和有机溶剂时的温度。

#### [栅绝缘层形成/半导体层形成步骤 43]

在图 6 (a) 中说明栅绝缘层形成/半导体层形成步骤 43。

在栅绝缘层形成/半导体层形成步骤 43 中, 通过在已受微滴-施加栅极线形成步骤 42 处理的玻璃基片 12 上的 CVD 顺序和连续地形成栅绝缘层 15、a-Si 薄膜形成层 64 和 n+ 薄膜形成层 65。通过 CVD (化学汽相形成) 方法形成 a-Si 薄膜形成层 64。栅绝缘层 15、a-Si 薄膜形成层 64 和 n+ 薄膜形成层 65 的厚度分别是 0.3 $\mu\text{m}$ 、0.15 $\mu\text{m}$  和 0.05 $\mu\text{m}$ , 并且不需损坏真空 30 环境 (即, 维持真空环境) 就可形成 (沉积) 这些层。以 300 $^{\circ}\text{C}$  的温度实

施层形成（沉积）。

#### [半导体层形成步骤 44]

在图 6 (b) 至 6 (e) 中说明半导体层形成步骤 44。图 6 (e) 是说明

5 了已被半导体层形成步骤 44 处理的玻璃基片 12 的平面图。图 6 (d) 是

沿着图 6 (e) 的线 C-C 获得的透视图。图 6 (b) 至 6 (c) 是沿着和图 6

(d) 相同的线获得的垂直横截面图，其说明了在半导体层形成步骤 44 中

的每一步骤。

如图 6 (b) 所示，在半导体层形成步骤 44 中，将抗蚀原料施加于 n+

10 薄膜形成层 65 之上，然后通过照相平版印刷步骤和蚀刻步骤处理抗蚀原料，从而形成具有半导体层 16 的形状的树脂层 67。

下面，如图 6 (c) 所示，通过使用气体（例如 SF<sub>6</sub>+HCl），在 n+ 薄

膜形成层 65 和 a-Si 薄膜形成层 64 上实施干蚀刻，从而形成 n+ 薄膜 69 和

a-Si 层 68。之后，如图 5 (d) 所示，以有机溶剂清洗玻璃基片 12，从而

15 去皮和去除抗蚀层 67。

#### [源/漏线预处理步骤 45]

在源/漏线预处理步骤 45 中，沿着其中分别形成在图 1 中示出的源极

17 和漏极 18 的区域（源极形成区域/漏极形成区域）的轮廓形成线导引。

在此，以矩阵设置对应于的源线和漏线的源极 17 和漏极 18，并且以

20 同一时间形成位于 TFT 部分 22 之上的源极 17 和漏极 18。这样，源极/漏极形成区域包括源线和漏线的形成区域。

线导引由光致抗蚀剂原料制成。具体地，将光致抗蚀剂施加于已被半

导体形成步骤 44 处理的玻璃基片 12 之上。然后，预烘焙玻璃基片。在这

之后，利用光掩膜曝光玻璃基片，从而显影。下面，通过实施后烘焙形成

25 线导引。这样形成的线导引具有大约 10 $\mu$ m 的宽度。通过线导引形成的沟

槽的宽度（线形成区域的宽度）是大约 10 $\mu$ m。

需要注意，通过使用氧等离子体使 SiNx 表面（栅绝缘层 15 的上表面）

经受湿润处理，从而使线原料很好地依据通过图案形成设备在其上施加的

线原料之下的表面。其间，通过在等离子体中流动 CF<sub>4</sub> 使线导引经受去湿

30 处理。

湿润/去湿处理基本上等同于在日本专利:Tokukai, No. 2000-353594 (欧洲专利申请 EPO 989778A1) 中给出的湿润/去湿处理。由于以 F (氟) 修改光致抗蚀剂原料 (有机树脂) 的表面层, 线导引给出去湿特性。可以使用 CF6 气体取代 CF4 气体。

5 此外, 取代形成线导引, 利用用于栅极的形成的光催化作用的湿润/去湿处理可以适于依据线电极图案形成区域实施湿润和去湿 (从而形成湿润区域作为源极/漏线形成区域和去湿区域作为非-源极/漏线形成区域)。

#### [微滴-施加源/漏线形成步骤 46]

10 在微滴-施加源/漏线形成步骤 46 中, 通过图案形成设备施加线原料 (施加其微滴) 于通过利用线导引这样形成的源极/漏极形成区域之上。由此, 形成源极 17 和漏极 18。于此, 将从墨水喷射头 33 喷射出的线原料的量设置为 2pl。此外, Ag 微粒被用作线原料。将形成层的厚度设置为 0.3μm。此外, 将烘焙温度设置为 200° C。在烘焙之后, 通过使用有机溶剂去除线导引。

15 需要指出, 线原料可以和用于栅极 13 的原料相同。然而, 由于以大约 300° C 的温度形成 a-Si 层, 必须以不高于 300° C 的温度实施烘焙。

#### [通道部分处理步骤 47]

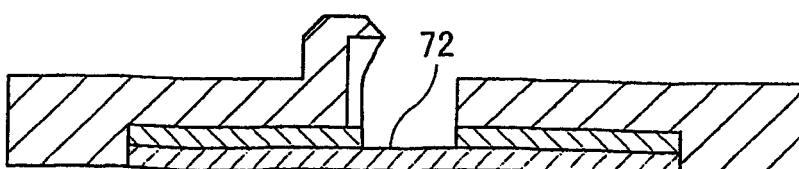

20 于此, 处理 TFT 的通道部分 72。首先, 通过利用有机溶剂去除线导引。可替代地, 通过灰化去除用于通道部分 72 的线导引。下面, 通过灰化或激光氧化氧化 n+层 69, 从而赋予 n+层 69 绝缘。

#### [保护层形成步骤 48、保护层处理步骤 49]

25 在保护层形成步骤 48 和保护层处理步骤 49 中, 首先, 通过已被经过处理直至形成源极和漏极的玻璃基片 12 上的 CVD 形成为保护层 19 的 SiO<sub>2</sub> 层 (见图 29 (b))。下面, 将为光敏丙烯酸树脂层 20 的丙烯酸树脂施加于 SiO<sub>2</sub> 层之上, 从而在树脂层上形成像素电极形成图案和电极处理图案。

30 如此形成图案以使掩膜具有 (i) 来自显影后被去除其中整个树脂层

的部分和 (ii) 来自关于在显影后被去除厚度的其中树脂层的垂直上半部分的部分。后者是用于其中透射率为大约 50% 的半色调的曝光。

具体地说，蚀刻保护层 19 和光敏丙烯树脂层 20，以去除来自其中在接触孔 24 中形成末端表面的部分的整个抗蚀层，从而减小在其中形成像素电极 21 的部分中的树脂层的厚度。在该部分中抗蚀层厚度减小的结果，赋予抗蚀层的厚度为这样施加的抗蚀层的厚度的一半，从而使环绕光敏丙烯树脂层 20 的像素电极形成图案的部分变成如图 2 (b) 所示的导引。

下面，通过使用抗蚀层作为掩膜，通过干蚀刻去除位于末端部分处的保护层 19 和光敏丙烯树脂层 20。

10

#### [像素电极形成步骤 50]

在像素电极上形成光敏丙烯树脂层 20 的图案，通过使用图案形成设备施加为像素电极原料的 ITO 微粒原料。其后，以 200℃的温度烘焙被这样处理的玻璃基片 12，从而形成像素电极 21。以这种方式，获得 TFT 像素基片 11。

如上面所述，依据该 TFT 阵列基片 11 的制备方法减少掩膜的数量，相比较于其中不采用利用墨水喷射方法的图案形成设备的传统制备方法，可以明显减少照相平版印刷步骤和多个真空层形成设备。这使投资设备的成本大大减小。

20

需要注意，通过如上面所述的制备步骤可能制备包括具有底部栅结构的 TFT 部分 22 的 TFT 阵列基片 11。然而，如图 18 的流程中所示，改变制备步骤以用于制备包括具有上部栅结构的 TFT 部分 22 的 TFT 阵列基片 11。

25

在图 18 中示出的步骤 121 至 132 分别与分别对应于其的步骤 41 至 50 的附图标号相关。

在上部栅结构的制备步骤中，在源极 17 和漏极 18 的形成和半导体层 16 的形成之后，实施栅极 13 的形成。然而，根据实施内容，步骤 121 至 132 基本上与分别对应于其的步骤 41 和 50 相同。

30

然而，将栅绝缘层形成/半导体层形成步骤 43 分成半导体 n+ 层形成步骤 123、半导体 n+ 层形成（处理）步骤 124、半导体层（a-Si 层）形成步

### 骤 125、半导体层形成步骤（处理）126 和栅绝缘层形成步骤 127。

如半导体层 16 形成的说明中所述，在半导体 n+ 层形成（处理）步骤 124 和半导体层形成步骤（处理）126 的每一个中，可以实现干蚀刻，其中使用形成于照相平版印刷步骤和蚀刻步骤中的抗蚀材料作为掩膜。

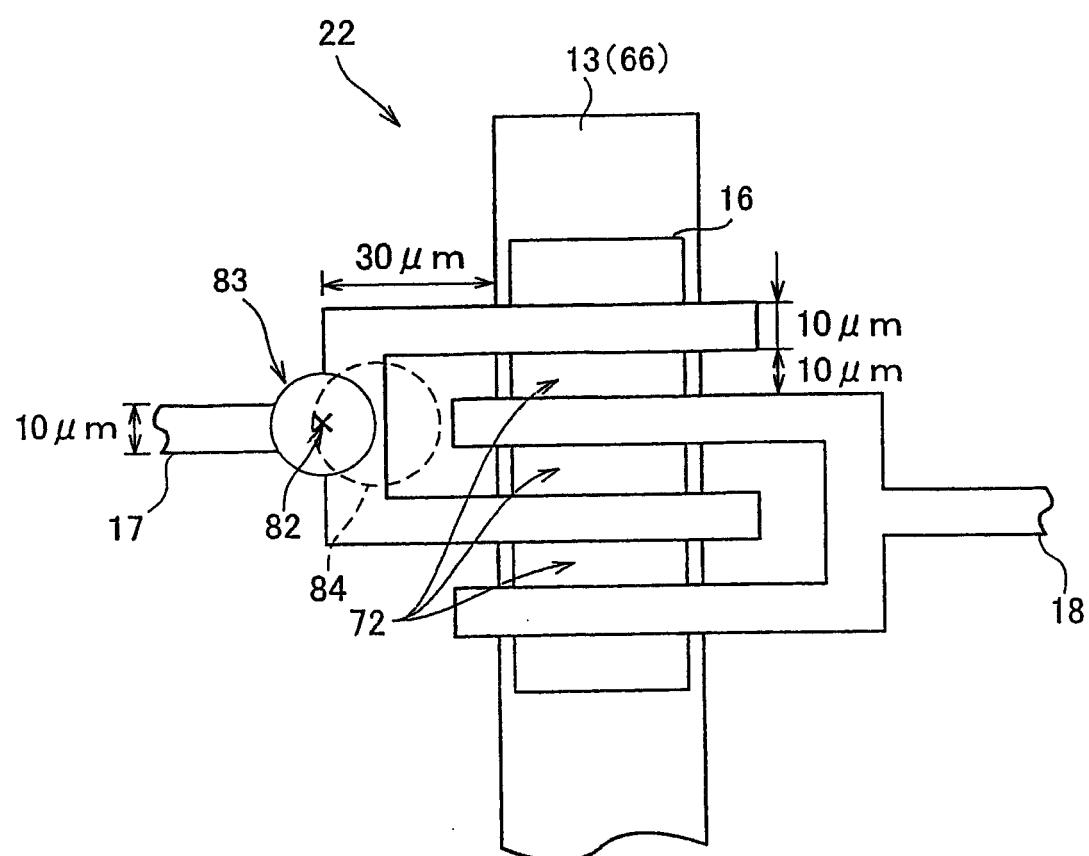

5 下面，进一步描述形成 TFT 部分 22 中的源极 17 和漏极 18 的方法。

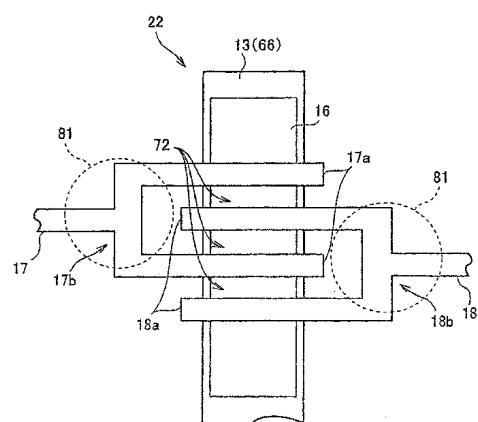

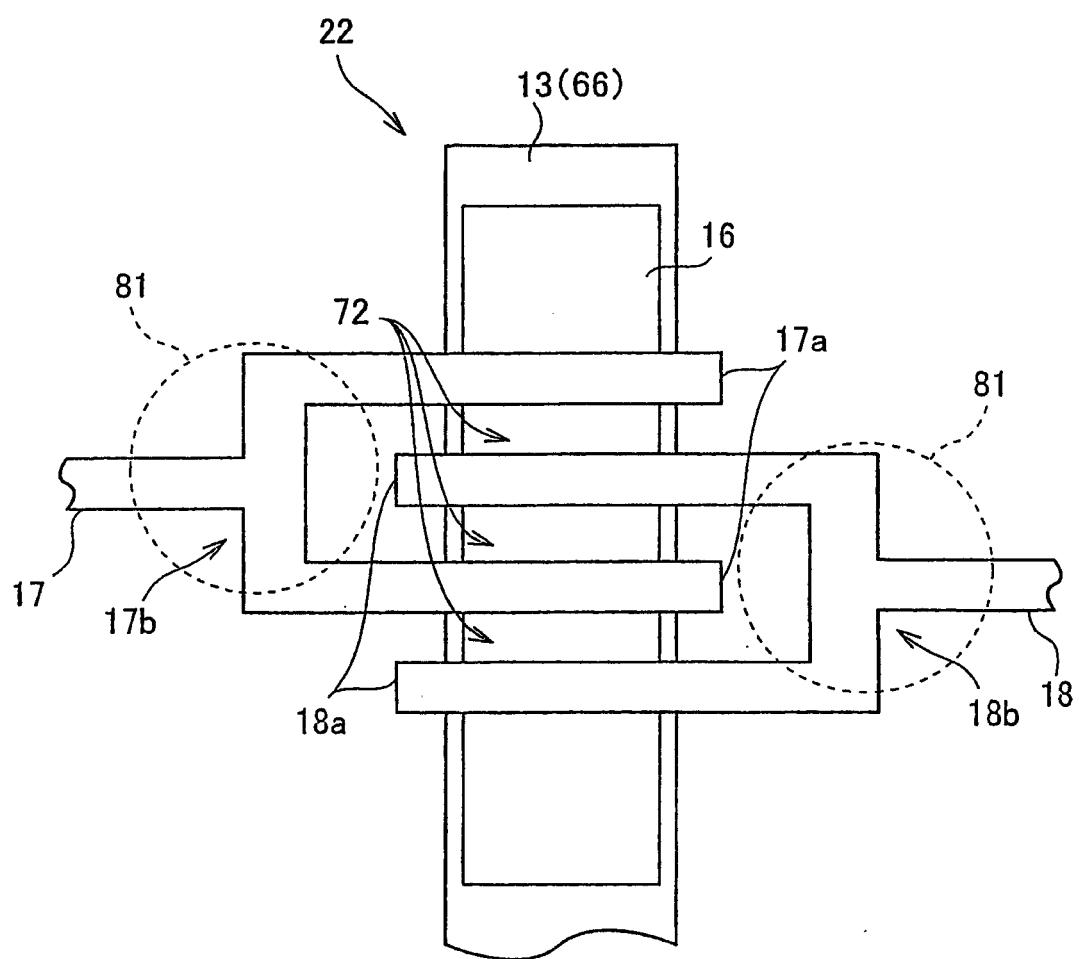

如图 1 和图 2 (a)，如此形成源极 17 和漏极 18，从而与 TFT 部分 22 中的多个分支（分支电极）。换句话说，源极 17 和漏极 18 分别具有具有多个分支电极的分支部分（17a 或 18a）。具体地，源极 17 配备有分支电极部分 17a，而漏极 18 配备有分支电极部分 18b。交替地设置源极 17 的分支电极部分 17a 的分支电极和漏极 18 的分支电极部分 18b 的分支电极。分支电极部分 17a 和 18a 的相邻分支电极之间的间隙是通道部分 72。例如，分支电极部分 17a 和 18b 的分支电极具有 10 $\mu\text{m}$  的宽度。例如，通道部分 72 具有 10 $\mu\text{m}$  的宽度（分支电极部分 17a 和 18b 之间的距离）。

10 15 在其中通过滴落来自图案形成设备的电极原料形成 TFT 部分 22 的源极 17 和漏极 18 的情况下，将线原料的微滴施加于每一电极之上，或在多个线上施加线原料的微滴。

20 于此，线通常具有几 $\mu\text{m}$  的宽度。为了实现具有几 $\mu\text{m}$  的直径的微滴，对于图案形成设备必须喷射大大小于 1pl 的量。然而，实现微滴的这种直径是困难的。此外，即使实现了微滴的这种直径，考虑到需要的时间和墨水喷射头 33 的寿命，在液体面板中滴落阴性微滴至 2 至 3 百万的 TFT 部分 22 之上也是困难的。因此，滴落（施加）具有大于几 $\mu\text{m}$  的直径的微滴。

在这种情况下，如果将微滴直接施加于通道部分 72 的电极（分支电极部分 17a 和 18b 的分支电极）之上，微滴会飞溅，从而使线原料粘附于 25 通道部分 72 之上，或残留线原料。

在线原料保持于通道部分 72 之上的情况下，残留线原料充当蚀刻通道部分 72 的 n+ 层 69 中的掩膜，从而留下 n+ 层 69。这引起源极 17 和漏极 18 之间的泄漏。

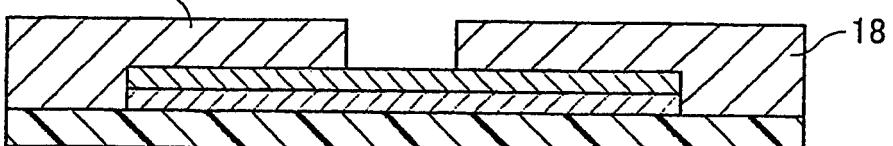

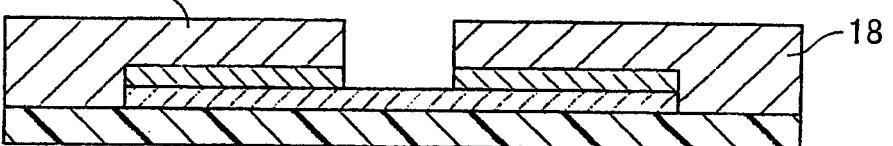

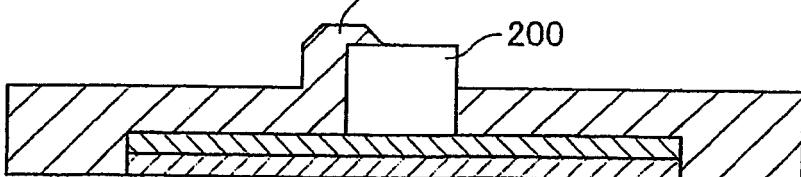

30 下面说明通道部分 72 的制备，从而说明泄露的原因。图 14 (a) 是沿着图 13 的线 E-E' 截取的横截面图，其说明了在形成源极和漏极之前的

情况。于此，在形成由 a-Si 层 68 和 n+层 69 组成的半导体层 16 之后紧接着形成导引 200。导引 200 用于分离在通道部分 72 上的源极 17 和漏极 18。

需要指出，在该横截面中，仅仅省略在栅绝缘层 15 之上的部分和栅极 66，其中半导体层 16 形成于栅绝缘层 15 中。

图 14 (b) 说明了施加源极 17 和漏极 18 的原料和实施烘焙之后的接下来的情况。图 14 (c) 示出了通过使用有机溶剂、或通过灰化去除导引 200 之后的下面情况。在该环境中，n+层 69 依然存在于半导体层 16 之上。如果这样残留 n+层 69，由于 n+层具有载体，源极 17 和漏极 18 上电压的施加容易引起电流。

因此，必须去除 n+层 69。对于去除 n+层 69，利用比如 SF<sub>6</sub>+HCl 的气体进行干蚀刻。然而，替代 n+层 69 的去除，通过灰化或激光氧化可将 n+层 69 转化成非导体。

图 14 (d) 说明了在去除 n+层 69 之后的情况。以这种方式，完成通道部分 72 的制备。

于此，在电极源原料保持于通道部分 72 的导引 200 之上的情况下，不能充分实现 n+层 69 的去除或将 n+层 69 的转化成非导体。

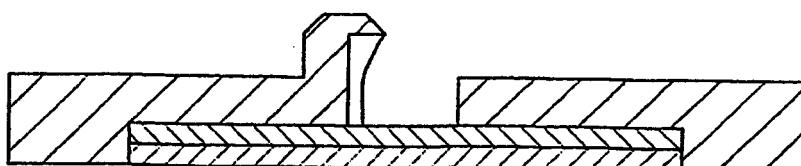

例如，图 13 示出了其中电极原料残留于与源极 17 相关联的侧面上的通道部分 72 的一部分上的情况。图 14 (e) 说明了沿着线 E-E' 截取的横截面。如图 14 (e) 所示，如果电极原料的残余 (Q) 残留于导引 200 之上，如图 14 (f) 所示，就存在残余 (Q) 充当去除导引 200 的步骤中的掩膜的可能性，从而残留导引 200 的一部分。这可以类似地出现于利用有机溶剂的处理的情况中或出现于通过灰化剥除的情况中。

如图 14 (f) 所示，如果导引 200 的一部分保持于通道部分 72 之上，在其中如图 14 (g) 所示去除 n+层 69 的的下一步骤中存在残余 (Q) (不能充分去除其中存在残余 (Q) 的区域中的 n+层 69 的一部分) 的区域中不能完全地去除 n+层 69。类似地，在通过灰化或激光氧化将 n+层 69 转化成非导体的步骤中，不能充分地将其中存在残余 (Q) 的区域中的 n+层 69 的一部分的部分转化成非导体。

如上面所述，残余 (Q) 引起 n+层 69 残留于通道部分 72 之上。因此，

如图 15 所示, 如果残余 (Q) 桥接源极 17 和漏极 18, 漏电流流动于源和漏极 17 和 18 之间。当然, 在该部分中, 残留 n+层 69。这样, 即使在用于完成 n+层 69 的处理之后去除残余 (Q), 电流也通过 n+层 69 流动于源和漏极 17 和 18 之间。因此, 在于源和漏极 17 和 18 之间引起泄漏。

5 如上面所述, 在形成于源和漏极 17 和 18 中避免形成残余 (Q) 是重要的。

因此, 在其中在 TFT 部分 22 中形成源和漏极 17 和 18 的情况中, 线原料的微滴被滴进其中形成源和漏极 17 和 18 的区域的部分中, 但避免了其中形成通道部分 72 (半导体层 16) 的部分。具体地说, 在源极 17 和漏极 18 具有如果上面所述的分支电极 17a 和 18a 的情况下, 分别对应于分 10 叉部分 17b 和 18b 的位置是滴落位置 81 (在其上滴落微滴)。

此外, 考虑图案形成设备如何精确地施加 (滴落) 微滴 (应用精确度) 设置滴落位置 81。在滴落位置 81 中, 分别定位分叉位置 17b 和 18b。

基于 (i) 墨水喷射头 33 的制备误差, (ii) 粘附于头部喷嘴之上的 15 微滴的量, (iii) 微滴在量上的均匀性, (iv) 通过 X-方向驱动部件 34 和 Y-方向驱动部件 35 重复墨水喷射头 33 的驱动荷定位的精确度, (v) 墨水喷射头 33 的热膨胀, (vi) 喷射中墨水喷射头 33 的移动速度和 (vii) 类似的因素, 设定图案形成设备的应用精确度, 也就是从作为目标的滴落 20 位置至精确施加微滴的位置的偏移长度。此外, 在其中一个喷嘴喷射出微滴, 同时不移动喷嘴的情况下, 例如以  $\pm 3 \mu\text{m}$  至  $\pm 5 \mu\text{m}$  的精确度实施通过图案形成设备微滴的施加 (滴落)。在多喷嘴的情况下, 例如, 在不移动多喷嘴的同时, 以  $\pm 10 \mu\text{m}$  至  $\pm 15 \mu\text{m}$  的精确度通过图案形成设备实现微滴的施加。

在该实施例中, 考虑从一个微滴形成多个线和从具有大于电极的宽度 25 的微滴形成具有  $10 \mu\text{m}$  的宽度的电极, 以及墨水喷射头 33 的头部寿命和操作时间有多长, 将微滴的量设置为 4pl。当微滴具有该量, 滴落中 (当微滴冲击玻璃基片 12 的表面) 微滴的直径是大约  $20 \mu\text{m}$ 。因此, (i) 分支电极部分 17a 和 18a 的宽度和 (ii) 滴落中微滴的直径之间的比率大致 30 优选是 1: 2。

此外, 考虑那些环境, 如图 7 所示, 滴落位置 81 位于分别距离半导

体层 16 (a-Si 层) 的边缘  $30 \mu\text{m}$  的位置中。需要指出，在图 7 中，标号 82 表示滴落位置 81 的滴落中心，并且标号 83 表示滴落中心公差范围，其在从滴落位置 82 为  $15 \mu\text{m}$  的范围内。标号 84 示出了用于其中以在通过从滴落位置 81 (滴落中心 82) 朝通道部分 72 为  $15 \mu\text{m}$  的距离 (偏移) 5 的位置中施加微滴的情况的滴落位置 (具有  $20 \mu\text{m}$  的微滴直径)。

如上所述，通过由在从通道部分 72 设定距离的滴落位置 81 中施加 (滴落) 微滴形成源极 17 和漏极 18，线原料的溅射微滴将粘附于 TFT 上，即通道部分 72。从而，避免了源极 17 和漏极 18 之间的泄漏。因此，在其中通过滴落线原料的微滴形成源极 17 和漏极 18 的情况下，可能获得稳定的 10 TFT 特性。

#### [第二实施例]

参照附图，下面说明本发明的另一实施例。

在该实施例中，如图 8 所示设置 TFT 阵列基片 11 的 TFT 部分 22 (见 15 图 2)。取代如上面所述的源极 17 和漏极 18，TFT 部分 22 配备源极 91 和漏极 92。此外，取代半导体层 16 的半导体层 93 具有基本上的圆形形状，其类似施加的微滴的形状 (滴落)。

如源极 17 和漏极 18，源极 91 和漏极 92 分别配备分支电极部分 91a 和 92a。例如，分支电极部分 91a 和 92a 在分叉部分 91b 和 92b 处分别分 20 叉成两个分支 (具有两个分支电极)。需要指出，可以任意设置分支 (分支电极) 的个数。

如迄今为止之所述，在图 1 示出的设置中，从分叉部分 17b 和 18b 平行于沿着 TFT-部分栅极 66 从栅极 13 突出的方向 (分别与两个方向相对)，首先延伸源极 17 的分支电极部分 17a 的分支电极和漏极 18 的分支 25 电极部分 18a 的分支电极。然后，在 TFT-部分栅极 66 之上，以垂直于沿着 TFT-部分栅极 66 突出方向的方向延伸分支电极部分 17a 和 18a 的分支电极。

另一方面，在图 8 示出的设置中，以倾斜方向 (两个方向) 延伸源极 91 的分支电极部分 91a 的分支电极和漏极 92 的分支电极部分 92a 的分支 30 电极，从而扩宽分支电极 91a 的分支电极之间的间隙，并扩宽分支电极

92a 的分支电极之间的间隙。然后，在 TFT-部分栅极 66 之上，以垂直于沿着 TFT-部分栅极 66 突出方向的方向延伸分支电极部分 91a 和 92a 的分支电极。

换句话说，分支电极部分 91a 和 92a 具有彼此平行的平行部分，并且 5 在半导体层 93 上，在平行部分和分支部分（91b 或 92b）之间分支电极部分 91a 和 92a 的分支电极是线性的。

此外，如上面所述，在该实施例中，半导体层 93 是类似于施加的微滴形状的基本上的圆形形状。下面说明这种情况的 TFT 阵列基片 11 的制备方法。

10 从栅极处理步骤 41 至栅绝缘层形成/半导体层形成步骤 43（见图 9 (a)）和在半导体层形成步骤 44 之后的源/漏线预处理步骤 45 至像素电极形成步骤 50，该制备方法与在第一实施例中说明的方法相同。半导体层形成步骤 44 如下实施。

15 在图 9 (b) 至图 9 (e) 中说明半导体层形成步骤 44。图 9 (e) 是说明了已被半导体层形成步骤 44 处理的玻璃基片 12 的平面图。图 9 (d) 是沿着图 9 (e) 的线 D-D 截取的横截面图，如图 9 (d)，图 9 (b) 和图 9 (c) 是沿着图 9 (e) 的线 D-D 获得的垂直横截面图。

20 如图 9 (b) 所示，在半导体层形成步骤 44 中，通过图案形成设备，将作为抗蚀原料施加热可固化树脂至位于从栅极 13 分叉的 TFT-部分栅极（分支电极部分）66 之上的 n+ 薄膜形成层 65，从而粘附热可固化树脂于其上。以这种方式形成的抗蚀层 94 是用于处理的图案。例如，喷射 10pl 的抗蚀原料的微滴。因此，在 TFT-部分栅极 66 之上的预定位置处形成的是具有圆形形状的图案，该圆形形状具有大约 30 μm 的直径。以 150°C 的温度烘焙这样制备的基片。用于抗蚀层 94 的热可固化树脂使用的是通过 25 Tokyo Ohka Kogyo Co. Ltd 获得的抗蚀 TEF 系列中的树脂。在粘性调节之后使用抗蚀 TEF 系列中的树脂，从而适合于墨水喷射。

需要指出，除了热可固化树脂之外，UV（超紫外）树脂或光敏树脂可被用作抗蚀层 94 的原料。然而，如果抗蚀层 94 是透明的，这种透明抗蚀 94 将允许对其中形成层等进行检查，同时抗蚀层 94 是透明的不是必须的。30 此外，抗蚀层 94 优选具有相对于干蚀刻中温度的热阻、相对于用于干蚀

刻气体的气体阻抗，并具有关于被蚀刻的原料的蚀刻选择性。

下面，如图 9 (c) 所示，通过使用气体（例如 SF<sub>6</sub>+HCl），干蚀刻 n<sup>+</sup> 薄膜形成层 65 和 a-Si 薄膜形成层 64，从而形成 n<sup>+</sup> 层（薄膜）69 和 a-Si 层（薄膜）68。其后，以有机溶剂清洗玻璃基片，从而如如图 9 (d) 所示剥除和去除抗蚀层 94。

如上面所述，在半导体层形成步骤 44 中，由 n<sup>+</sup> 层 69 和 a-Si 层 68 组成的半导体层 93 的形状是从图案形成设备喷射的树脂的图案（抗蚀层 94 的图案）的映像。因此，以圆形图案或由曲线组成的准圆形图案形成半导体层 93，就象当从墨水喷射头 33 施加（滴落）微滴于玻璃基片 12 之上时构形抗蚀层 94 的原料的微滴。

需要指出，如上面所述，在半导体层 93 具有半导体层 93 在 TFT- 部分栅极 66 的区域之外这种形状的情况下，必须没有分支电极部分 91a 和 92a 的分支电极的末端在 TFT- 部分栅极 66 的区域（形成区域）之外。（其中存在 TFT- 部分栅极 66 的区域）（换句话说，末端在 TFT 栅极 66 的内部）。

在图 8 中，不象在图 7 中示出的 TFT- 部分栅极 66 和半导体层 96，半导体层 93 具有延伸于 TFT- 部分栅极 66 的边缘之上的这种形状。由于该原因，分支电极部分 91a 和 92a 的末端（分支电极部分 91a 和 92a 的分支电极的末端）优选在 TFT- 部分栅极 66 边缘表面线的内部，也就是说，在 TFT- 部分栅极 66 上。这是因为如果源和漏极 17 和 18 延伸于 TFT- 部分栅极 66 之外，漏电流增加和 TFT 特性恶化。

在下面，参照图 16 (a)、16 (b)、17 (a) 和 17 (b)，说明在微滴- 施加源/漏线形成步骤 46 所示中出现漏电流的机理。

图 16 (a) 是在其中源极 17 在 TFT- 部分栅极 66 的边缘的线的内部、并在 TFT- 部分栅极 66 之上的情况中的 TFT 部分的平面图。图 16 (b) 是沿着图 16 (a) 的线 G-G' 截取的横截面图。另一方面，图 17 (a) 是在其中源极 17 延伸于 TFT- 部分栅极 66 的边缘的线之外，也就是延伸于 TFT- 部分栅极 66 之外的情况中的 TFT 部分的平面图。图 17 (b) 是沿着图 17 (a) 线 H-H' 截取的横截面图。

需要指出，图 16 (a) 和 17 (a) 说明了其中在 TFT- 部分栅极 66 上施加负电势的情况。如图 16 (b) 和 17 (b) 所示，在 TFT- 部分栅极 66

面向 a-Si 层 68，栅绝缘层 15 夹在其之间。于此，n+层 69 是导引载体进入 a-Si 层 68 的层，并且是掺杂磷 (P) 等的层，其具有过剩电子。

在图 16 (a)、16 (b)、17 (a) 和 17 (b) 中的 TFT 中，当例如-4V 的电压被施加于 TFT-部分栅极 66 之上时，测量源和漏极 17 和 18 之间的漏电流。结果，在其中源和漏极 17 和 18 在 TFT-部分栅极 66 之上的情况下漏电流是大约 1pA。另一方面，在其中源和漏极 17 和 18 延伸于 TFT-部分栅极 66 之外的情况下，漏电流增加至 20 pA 到 30 PA。

这证明如果源和漏极 17 和 18 向外延伸就会恶化 TFT 特性，此外，如下说明该结果的原因。首先，说明其中在 TFT-部分栅极 66 上施加负电势的情况。在 TFT-部分栅极 66 具有负电势的情况下，由于负电荷之间的排斥，从 TFT-部分栅极 66 漂移作为载体的电子。因此，电子存在于半导体区域周围，并且非常少的电子存在于 TFT-部分栅极 66 上的 a-Si 层 68 中。由于该原因，TFT 处于 OFF 状态。

即使电子试图流动于源和漏极 17 和 18 之间，电子将通过 TFT-部分栅极 66 的部分 (P)，其中施加负电势。负电荷之间的排斥将不允许电子通过 TFT-部分栅极 66。可以认为由于该原因，漏电流是小的。

另一方面，在图 17(a)的情况下，由于源和漏极 17 和 18 延伸于 TFT-部分栅极 66 的外部边缘之上，即使 TFT-部分栅极 66 具有负电势，电子不需通过 TFT-部分栅极 66 的部分 (P)，其中施加负电势，但其能够沿着 a-Si 层 68 的外部圆周移动。可以认为由于该原因，漏电流是容易流动的。

如从上面说明中所理解的，源和漏极 17 和 18 优选在 TFT-部分栅极 66 的外部边缘内部 (即，在 TFT-部分栅极 66 上)。下面是其中将负电势施加于 TFT-部分栅极 66 之上的情况的说明。在其中 TFT-部分栅极 66 具有负电势的情况下，通过 TFT-部分栅极 66 的电势牵引 n+层 69 的电子，并且载体存在于通道部分中。因此，电流容易地流动于源和漏极 17 和 18 之间，从而 TFT 处于 ON 状态。例如，当横越 TFT-部分栅极 66 施加 10V 的电压时，大约  $1\mu A$  的电流流动于源和漏极 17 和 18 之间。于此，在源和漏极之间施加的电压是 10V。当 TFT 是 ON，电子试图以最短距离流进源和漏极 17 和 18 之间。因此，在 TFT-部分栅极 66 的外部边缘之上源和漏极 17 和 18 的延伸不产生影响。

此外，即使通过施加（滴落/喷射）来自于此的墨水喷射头 33 的微滴实现抗蚀层 94 的形成，通过滴落多滴微滴也可以实现形成。然而，需要指出，如果以极度的精度、以尺寸已经不受限制地减小的极小微滴，通过喷射实现抗蚀层 94 的形成，它需要长时间形成半导体层 93，并且由于微 5 滴（多滴微滴）个数的增加会缩短墨水喷射头 33 的寿命。

在每一步骤中使用形成具有通过以最合适量的微滴和尽可能少的投射次数（喷射次数）施加微滴实现的需求区域的层（薄膜）的墨水喷射头 33 是重要的。通过执行如此的微滴的施加，可能最大化时间的次数，以在其寿命中使用墨水喷射头 33，从而保持设备的花费最低。

10 此外，半导体层形成步骤 44 具有这种重要特征：不需用于其中墨水喷射头 33 喷射出的微滴滴落于之上的表面的特殊处理。如果微滴滴落于其上的表面是极端可湿的，表面需要构图。此外，喷射至表面上的微滴将是展开的，从而形成不确定的形状，由此不能形成层。然而，在 a-Si 形成层 64（其表面）上，存在由 Si 形成的大量末端。由于此原因，a-Si 形成层 64 的表面基本上是去湿的。这样，a-Si 形成层 64 上的微滴具有大至一定程度的接触角度，并具有准圆形形状。因此，不必特定地处理基片（a-Si 形成层 64）。

20 此外，有下述大的可能性，具有短分子长度的基片试图粘附于已经被烘焙、气体处理（干-蚀刻）等类似处理的基片的表面之上。这样，即使不是 a-Si 的半导体，例如使用的有机半导体，在许多情况中存在这样喷射出具有大至一定程度的接触角度的微滴。

通常，半导体层的构图需要掩膜和照相平版印刷步骤。另一方面，在半导体层形成步骤 44 中，从墨水喷射头 33 施加微滴，从而直接拖动被掩膜的图案（抗蚀层 94）。这样，需要掩膜的掩膜和照相平版印刷步骤不再是必须的。这大大地降低了成本。

需要指出，为了形成类似施加的微滴的形状的半导体层 93，可能采用一种方法，其中除了利用其中通过滴落微滴形成抗蚀层 94、以及通过使用这样形成的抗蚀层 94 作为掩膜形成半导体层 93 的上面描述的方法，通过利用图案形成设备直接施加（滴落）半导体层 93 的原料。作为在这 30 种情况中的半导体原料，可以使用比如聚乙烯咔唑（polyvinylcarbazole）

(PVK) 和聚亚苯基亚乙烯基 (polyphenylene vinylene) (PPV) 的有机半导体原料。

如上所述,如此形成功支电极部分 91a 和 92a, 以使分支电极部分 91a 和 92a 的部分以关于沿着 TFT 部分栅极 66 突起的方向的倾斜方向延伸, 5 该部分分别与分叉部分 91b 和 92b 相连。(换句话说, 该部分分别在 (i) 分叉部分 91b 和 92b 和分支电极部分 91a 和 92a 的平行部分之间)。主要由于下面的原因如此形成功支电极部分 91a 和 92a。

以类似于施加微滴的形状的形状这样形成的半导体层 93 可以变得大于半导体层 16。在这种情况下, 为了避免通道部分 72 上飞溅微滴的粘附, 10 相比较于如图 1 所示的设置, 在滴落位置 81 中的分叉部分 91b 和 92b 将位于从其中存在 TFT 部分栅极 66 更远的距离。另一方面, 在对应于分叉部分 91b 和 92b (滴落位置 81) 的位置中施加的电极原料必须展开至分支电极部分 91a 和 92a 的分支电极的末端。通过形成功支电极部分 91a 和 92a, 以使与分叉部分 91b 和 92b 相连的部分是倾斜的, 可能以从 TFT 部分栅极 66 更远的距离定位分叉部分 91b 和 92b, 同时避免分支电极部分 15 91a 和 92b 在分叉部分 91b 和 92b 和末端之间较长。

此外, 即使在其中将来自图案形成设备的微滴施加至从作为目标的滴落位置 81 向通道部分 72 偏移的位置 (滴落位置 84) 之上的情况下, 由于分支电极部分 91a 和 92b 的部分是倾斜的, 该部分与分叉部分 91b 和 20 92b 相连, 例如, 在施加微滴处的位置中分支电极部分 91a 之间的间隙比在图 1 中示出的分支电极部分 17a 的分支电极之间的间隙狭窄。结果, 相比在图 1 中示出的设置, 容易滴落微滴于分支电极部分 91a 和 92a 之上。这允许关于将电极原料作为目标处的滴落位置 81 的更宽的公差。

### 25 [第三实施例]

参照图 10 (a) 和 10 (b), 下面说明本发明的另一实施例。

在该实施例中, TFT 阵列基片 11 的 TFT 部分 22 具有如图 10 (a) 所示的设置。TFT 部分 22 配备有取代源极 17 和漏极 18 的源极 101 和漏极 102, 并且例如上面所述的半导体层 16。可以以如第一实施例中相同的方法制备 TFT 阵列基片 11。 30

源极 101 具有下面的形状：分支电极部分 101a 延伸于半导体层 16 之上，与分叉部分 101b 相连的部分具有大的区域（更宽）。（当分支电极部分 101a 变得更接近于分叉部分 101b，分支电极部分 101a 变得更宽。）换句话说，分支电极部分 101a 从源极 101 以梯形形状突出，并且梯形形状的底部是分叉部分 101b。

为了具有这种设置，源极 101 从其中分支电极部分 101a 分叉的部分处逐渐变得宽阔，从而朝着连接至源极 101 的分支电极部分 101a 的两侧变宽。换句话说，分支电极部分 101a 的宽度从梯形形状的两个底部角度（分支电极部分 101a 的两侧）向其上部侧面部分逐渐变得狭窄，其突出于 10 半导体层 16 之上。进一步换句话说，其中两个底部角度部分被称作通过源极 101 的主线（源线）与连接 TFT 部分 22 的源极 101 的部分相连的源过渡部分，每个源过渡部分的宽度从源线朝着半导体层 16 的形成区域（其中半导体层 16 存在的区域）逐渐变得宽阔。

因此，在具有这种设置的源极 101 中，上面所述的滴落部分 81 位于 15 源极 101 的部分（两个源过渡部分）中，分别位于分叉部分 101b 的部分来自分叉的分支电极部分 101a，以此电极原料的微滴施加于其中通道部分 72（半导体层 16）存在的区域之外。

另一方面，漏极 102 从通道部分 72 附近朝通道部分 72 逐渐变宽。换 20 句话说，假设将附近称作漏过渡部分，通过其漏极 102 的线（漏线）与较接近 TFT 部分 22 的漏极 102 的部分相连，漏过渡部分的宽度从漏线朝半导体层 16 的形成区域逐渐变宽。然后，电极宽度加宽开始部分 102a（也就是漏过渡部分）是滴落位置 81。

在这种设置中，通过在上面所述的源/漏线预处理步骤 45 中 (i) 形成具有象山形状的导引或 (ii) 湿润/去湿处理，来制备电极原料滴落于 25 其上的电极形成区域。然后，在电极形成区域中，在图 10 (b) 中示出的接触角度  $\theta$  引起电极原料被朝其中电极形成区域变宽的方向拖曳，并且以该方向流动（自然地）。因此，即使在滴落位置 81 设置于其中通道部分 72（半导体层 16）存在的区域（形成区域）之外的情况下，也容易赋予这样施加的电极原料到达通道部分 72 的延伸末端。这样，线原料的应用 30（滴落）使可能在 TFT 部分 22 中确定地形成源极 101 和漏极 102。

在其中通过如上面所述的图案形成设备、通过施加微滴形成比如电极等的线的情况下，通过控制线的宽度（线形成区域的宽度）可能控制施加微滴的流动方向。

需要指出，在该第三实施例中，所述是其中 TFT 由通道部分 72 组成 5 的设置。然而，不必说，在第一和第二实施例和随后描述的第四实施例中所述的 TFT 中的电极部分中可以修改线的宽度。

#### [第四实施例]

参照图 11，下面说明本发明的另一实施例。

10 在该实施例中，TFT 阵列基片 11 的 TFT 部分 22 具有图 11 中示出的设置。TFT 部分 22 配备有取代源极 17 和漏极 18 的源极 111 和漏极 112，以及例如上面所述的半导体层 93。半导体层 93 具有基本上的圆形形状和将栅绝缘层 15（见图 9（a）至（e））夹于其之间的上面形成的线性栅极线（栅极 13 的干线）。通过如在第二实施例的相同方法可以制备 TFT 阵列 15 基片 11。

在图 1 至图 8 示出的每一设置中，在 TFT 部分 22 中形成多个电极，并形成分支电极部分 17a 和 18a 或分支电极部分 91a 和 92a，从而形成宽通道部分 72。在其中电荷转移是大的的情况下，这种设置是有效的，例如，在其中大量像素被驱动的情况下。此外，该设置具有这种优点：可以 20 不费力地获得稳定的特性，（i）即使在 TFT-部分栅极 66 的图案从源极 17 或 91（分支电极部分 17a 或 91a）和源极 18 或 92（分支电极部分 18b 或 92b）的图案以其中 TFT-部分栅极 99 延伸的方向移动，以及（ii）特别是在图 1 中示出的设置中，即使在 TFT-部分栅极 66 的图案从源极 17 或 91（分支电极部分 17a 或 91a）和源极 18 或 92（分支电极部分 18b 或 92b） 25 的图案以垂直于其中 TFT-部分栅极 99 延伸方向的方向进一步偏移。

在图 11 示出的该实施例的设置中，从源极 111 分叉并延伸于半导体层 93 之上（上面）的分支电极 111a 和较接近于通道部分 72 的漏极 112 的部分设置在其中 TFT-部分栅极延伸的方向，并且设置在其中 TFT 栅极 66 存在的区域内部。

30 换句话说，从交叉栅极线的源线、并沿着栅极线延伸分支电极部分

111a 的分支电极，从而延伸于半导体层 93 之上。反之，从垂直于其中栅极线延伸的方向延伸的漏线延伸漏极 112，从而沿着栅极线延伸于半导体层 93 之上。需要指出，在分支电极部分 111a 从源线分叉处的部分被称作源过渡部分，反之，在漏极 112 从漏线分叉处的部分被称作漏过渡部分。

5 在该设置中，TFT 部分 22 相对小。这对于高孔径比的实现是有利的。

在上面的设置中，在通道部分 72（半导体层 93）之外（远离）的滴落位置 81 位于对应于关于源极 111 的分支电极部分 111a 的分叉部分 111b 的位置（即，源过渡部分）。此外，关于漏极 112，滴落位置 81 位于漏极 112 朝通道部分 72 弯曲处的位置（即，漏过渡部分）中。由于这种设置，

10 可能避免通道部分 72 与从图案形成设备施加的电极原料的溅射微滴的粘附。

这样说明本发明，明显可以以多种途径变化相同的方式。这种变化不能被认为脱离本发明的精神和范围，并且对本领域的熟练技术人员来说是明显的，所有此类变更将包括在下面权利要求的范围内。

15 需要指出，基于通过施加微滴，施加微滴于滴落位置之上，以用于形成分支电极部分中的公差，可以如此设置薄膜晶体管，以使如此设置作为微滴施加于其上的滴落位置的分叉部分的位置，从而使微滴施加于通道部分之上。

该设置进一步确保避免在通过施加电极原料的微滴形成源极和漏极

20 中的每个电极之间、通道部分上的溅射微滴的粘附。

可以如此设置薄膜晶体管，以使每个分支电极具有在半导体层上彼此平行的平行部分，每个分支电极在平行部分和分叉部分之间是线性的。

由于上面的设置，可能确定地定位距离通道部分较远的分叉部分，从而避免每个电极之间通道部分上溅射微滴的粘附，同时避免了从分叉部分

25 至其末端分支电极的长的长度。

可以如此设置薄膜晶体管，以使源极和漏极的至少一个具有朝半导体层的形成区域逐渐变宽的部分。

该设置使它较容易用于施加的微滴，以以其中电极变宽的方向流动。这样，这允许滴落位置被定位于与通道部分较远的位置，并确保从滴落位

30 置朝半导体层的形成区域电极原料的流动。

可以如此设置薄膜晶体管的制备方法，以在预处理步骤中，如此形成电极形成区域，使源极和漏极的至少一个具有在其远离半导体层的形成区域的分叉部分处的分支部分，分支部分包括在半导体层上的多个分支电极，第一电极的分支电极夹着第二电极，其中第一电极是源极和漏极的至少一个，并且第二电极是另一个，并且在施加微滴的步骤中，分别对应于分叉部分的位置是电极原料的微滴施加于其上的滴落位置。

通过该设置，由于电极原料的微滴施加于分支电极部分的分叉部分之上，通过以少量的时间施加微滴，可能合适地形成源极和/或漏极的分支电极部分。

10 基于包括在滴落位置中的公差，可以如此设置薄膜晶体管的制备方法，以如此设置滴落位置，从而使微滴不施加于通道部分之上。

该设置进一步确保避免在通过施加电极原料、形成源极和漏极中的每个电极之间、通道部分上的溅射微滴的粘附。

15 可以如此设置薄膜晶体管的制备方法，以如此形成每个分支电极，以使每个分支电极具有在半导体层上彼此平行的平行部分，每个分支电极在平行部分和分叉部分之间是线性的。

通过采用上述设置，可能确定地定位距离通道部分较远的分叉部分，从而避免每个电极之间通道部分上溅射微滴的粘附，同时，避免了从分叉部分至其末端分支电极的长的长度。

20 可以如此设置薄膜晶体管的制备方法，以在预处理步骤中，如此形成电极形成区域，使源极和/或漏极具有朝半导体层的形成区域逐渐变宽的部分，并且在施加微滴的步骤中，将电极原料的微滴施加至位于从逐渐变宽的部分的位置中的滴落位置之上。

25 通过采用上面的设置，以其中电极形成区域是较宽的方向拖动施加于电极形成区域之上的微滴，并沿着该方向流动。这样，即使在其中滴落位置位于半导体层的形成区域之外的情况下，它变得较容易用于这样施加的电极原料，以达到源极和漏极的末端，所述末端较接近于通道部分。该设置确保通过电极原料的微滴的施加来形成（滴落/喷射）源极和漏极。

30 可以如此设置薄膜晶体管的制备方法，以在预处理步骤中，如此形成电极形成区域，以在其中栅极存在的区域中，分别朝半导体层的形成区域

延伸的源极和漏极的部分平行于其中栅极延伸的方向。

通过采用上面的设置，可能小型化薄膜晶体管。这样，例如在配备薄膜晶体管的液晶显示设备中，可能实现高孔径比。

尽管通过利用实施例和用于实施的最佳模式中的举例已经具体说明 5 了本发明，本领域的普通技术人员可以理解，该实施例和举例仅仅是说明本发明的那些技术特征，而不是用于限制本发明。不能仅以实施例和举例说明本发明，可对其在本发明的精神和下面叙述的权利要求的范围内部以其他方式进行修改。

本发明能够提供其中电极原料的溅射微滴不粘附于薄膜晶体管的通 10 道部分之上的电极设置的薄膜晶体管及其制备方法。

图 1

图 2(a)

图 2(b)

图 4

图 5(a)

图 5(b)

图 5(c)

## 半导体层形成

图 6(a)

图 6(b)

图 6(c)

图 6(d)

沿着线 C-C 截取的横截面

图 6(e)

图 7

图 8

图 9(a)

图 9(b)

图 9(c)

图 9(d)

沿着线 C-C 截取的横截面

图 9(e)

图 10(a)

沿着线 E-E 截取的横截面

图 10(b)

图 11

图 12(a)

图 12(b)

图 12(c)

图 12(d)

图 13

图 14(a)

图 14(b)

图 14(c)

图 14(d)

图 14(e)

图 14(f)

图 14(g)

图 15

图 16(a)

图 16(b)

图 17(a)

图 17(b)

图 18

|                |                                                                             |         |            |

|----------------|-----------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 薄膜晶体管、液晶显示设备及其制备方法                                                          |         |            |

| 公开(公告)号        | <a href="#">CN1679170A</a>                                                  | 公开(公告)日 | 2005-10-05 |

| 申请号            | CN03820007.4                                                                | 申请日     | 2003-07-23 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                      |         |            |

| 申请(专利权)人(译)    | 夏普株式会社                                                                      |         |            |

| 当前申请(专利权)人(译)  | 夏普株式会社                                                                      |         |            |

| [标]发明人         | 藤井晓义<br>中林敬哉                                                                |         |            |

| 发明人            | 藤井晓义<br>中林敬哉                                                                |         |            |

| IPC分类号         | G02F1/1368 G09F9/30 H01L21/288 H01L21/3205 H01L21/336 H01L29/417 H01L29/786 |         |            |

| CPC分类号         | G02F1/1368 H01L29/41758 H01L29/66765 H01L29/41733                           |         |            |

| 代理人(译)         | 陈瑞丰                                                                         |         |            |

| 优先权            | 2002255568 2002-08-30 JP                                                    |         |            |

| 其他公开文献         | CN100444404C                                                                |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                              |         |            |

#### 摘要(译)

本发明的薄膜晶体管的制备方法包括步骤：(i)通过施加电极原料的微滴形成其中形成有源极和漏极的电极形成区域，(ii)施加电极原料的微滴到远离半导体层的形成区域的滴落位置之上，并施加电极原料的微滴于电极形成区域中，以及(iii)在电极形成区域中形成源极和漏极。通过采用这种设置，在通过施加电极原料的微滴形成源极和漏极中，可以确定地避免每一电极之间通道部分上溅射微滴的粘附。