[19] 中华人民共和国国家知识产权局

[ 51 ] Int. Cl<sup>7</sup>

G02F 1/136

[12] 发明专利申请公开说明书

[21] 申请号 03109827.4

[43] 公开日 2003 年 10 月 29 日

[11] 公开号 CN 1452002A

[22] 申请日 2003.4.11 [21] 申请号 03109827.4

[30] 优先权

[32] 2002. 4. 16 [33] KR [31] P - 2002 - 20724

[71] 申请人 LG. 菲利浦 LCD 株式会社

地址 韩国汉城

〔72〕发明人 林柄昊

[74] 专利代理机构 北京律诚同业知识产权代理有限公司

代理人 徐金国 梁 挥

权利要求书 2 页 说明书 9 页 附图 27 页

## [54] 发明名称 液晶显示装置阵列基板的制造方法

[57] 摘要

一种液晶显示装置阵列基板的制造方法包括以下步骤：在一基板上形成一选通线、一选通垫和一栅极；在该选通线、栅极和选通垫上形成一栅极绝缘层；在该栅极绝缘层上形成一有源层；在该有源层上形成一欧姆接触层；在该欧姆接触层上形成一数据线、一数据垫以及源极和漏极；在源极和漏极上形成一像素电极，该像素电极接触漏极；在包括该像素电极的基板上形成第一钝化层；在第一钝化层上形成第二钝化层，第二钝化层暴露选通垫和数据垫之上的第一钝化层；以及对第二钝化层所暴露的第一钝化层制作图案，以暴露选通垫和数据垫。

1. 一种液晶显示装置阵列基板的制造方法，包括：

在一基板上形成一选通线、一选通垫和一栅极；

5 在该选通线、栅极和选通垫上形成一选通绝缘层；

在该选通绝缘层上形成一有源层；

在该有源层上形成一欧姆接触层；

在该欧姆接触层上形成一数据线、一数据垫以及源极和漏极；

在源极和漏极上形成一像素电极，该像素电极接触漏极；

10 在包括该像素电极的基板上形成第一钝化层；

在该第一钝化层上形成第二钝化层，该第二钝化层暴露选通垫和数据垫之上的第一钝化层；以及

对第二钝化层所暴露的第一钝化层制作图案，以暴露该选通垫和数据垫。

15 2. 根据权利要求 1 的方法，其中用一印刷法形成第二钝化层。

3. 根据权利要求 2 的方法，其中第二钝化层由聚酰亚胺制成。

4. 根据权利要求 3 的方法，还包括摩擦第二钝化层的步骤。

5. 根据权利要求 1 的方法，其中第一钝化层由诸如氮化硅(SiNx)和二氧化硅(SiO<sub>2</sub>)之类的无机绝缘材料制成。

20 6. 根据权利要求 5 的方法，其中在约 300 摄氏度的温度下形成第一钝化层。

7. 根据权利要求 5 的方法，其中第一钝化层的厚度在约 500 Å 到 1000 Å 的范围内。

25 8. 根据权利要求 1 的方法，其中通过一光刻过程实现以下步骤：在选通绝缘层上形成有源层；形成欧姆接触层；形成数据线、数据垫以及源极和漏极。

9. 根据权利要求 8 的方法，其中光刻过程采用一掩模，该掩模包括一透光部分、一挡光部分和一半透光部分。

10. 根据权利要求 9 的方法，其中该半透光部分包括狭缝。

11. 根据权利要求 9 的方法，其中光刻过程包括形成一光阻图案的步骤，该图案具有第一厚度和比第一厚度薄的第二厚度。

12. 根据权利要求 11 的方法，其中该光阻图案的第一厚度对应于掩模的挡光部分，而该光阻图案的第二厚度对应于半透光部分。

- 5 13. 根据权利要求 11 的方法，其中该光阻图案是一正类型，该正类型对曝光的部分显影并将该部分去除。

14. 根据权利要求 1 的方法，其中该有源层具有与数据线、源极、漏极和除源极与漏极之间那部分之外的数据垫相同的形状。

- 10 15. 根据权利要求 1 的方法，其中欧姆接触层具有与数据线、源极、漏极和数据垫相同的形状。

16. 根据权利要求 1 的方法，其中形成一像素电极的步骤包括：形成一选通垫端和一数据垫端，该选通垫端接触选通垫，该数据垫端接触数据垫。

17. 根据权利要求 1 的方法，其中形成数据线、数据垫以及源极和漏极的步骤包括形成一金属图案，该金属图案与选通线交叠且接触像素电极。

- 15 18. 根据权利要求 1 的方法，其中选通线、栅极和选通垫由一含铝的双层制成。

19. 根据权利要求 1 的方法，其中数据线、数据垫以及源极和漏极包括铬、钼、钨和钽中之一。

- 20 20. 根据权利要求 1 的方法，其中用一干刻法实现形成数据线、数据垫以及源极和漏极的步骤，并且实现形成欧姆接触层的步骤。

21. 根据权利要求 20 的方法，其中数据线、数据垫以及源极和漏极由钼制成。

22. 根据权利要求 1 的方法，其中用一湿刻法实现形成数据线、数据垫以及源极和漏极的步骤；用一干刻法实现形成欧姆接触层的步骤。

- 25 23. 根据权利要求 22 的方法，其中数据线、数据垫以及源极和漏极由铬制成。

## 液晶显示装置阵列基板的制造方法

5 本申请要求享有 2002 年 4 月 16 日于韩国提出的第 2002-20724 号韩国

专利申请的权益，其在此全部引用以作参考。

### 技术领域

10 本发明涉及一种液晶显示(LCD)装置，尤其涉及一种液晶显示装置阵列基

板的制造方法。

### 背景技术

15 通常，液晶显示(LCD)装置包括两个间隔开且彼此面对的基板和一液晶

层，该液晶层插在两基板之间。每一个基板包括一个电极，而每一个基板的

各个电极也彼此面对。每一个电极上施加有电压，在电极间感应出一个电

场。通过改变电场的强度或方向来改变液晶分子的取向(alignment)。LCD

装置通过改变根据液晶分子的取向而变化的光透射率来显示图像。

下文将参照附图更详细地描述一种传统的 LCD 装置。

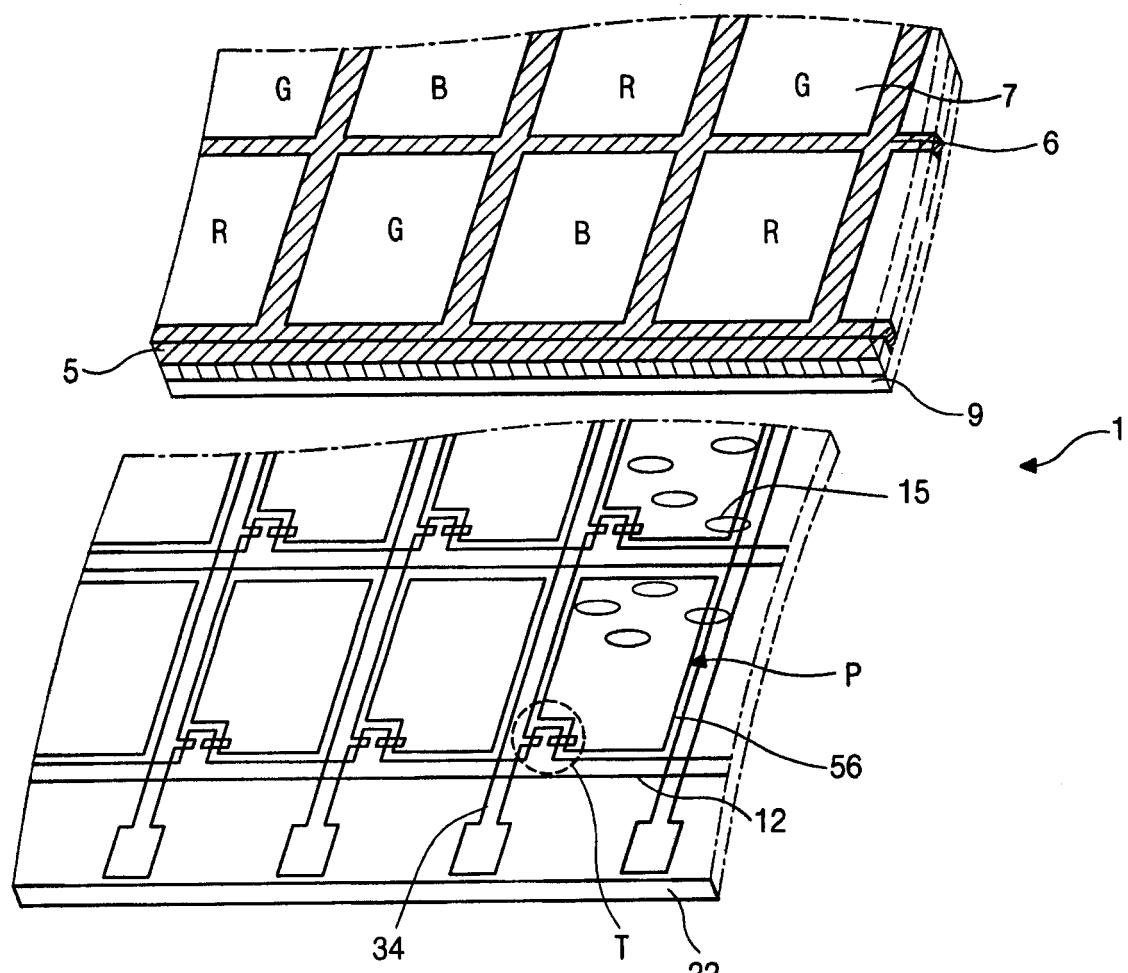

20 图 1 是示出一传统 LCD 装置的分解透视图。该传统的 LCD 装置 1 具有上

基板 5 和下基板 22，它们彼此间隔开且相互面对，该 LCD 装置 1 还具有插入

在上基板 5 与下基板 22 之间的液晶 15。

25 上基板 5 在其内侧上连续包括一黑色矩阵 6、一滤色器层 7 和一公共电

极 9。黑色矩阵 6 有一开口。滤色器层 7 对应于黑色矩阵 6 的这个开口，且

包括三个红(R)、绿(G)、蓝(B)分滤色器。公共电极 9 形成于滤色器 7

上且是透明的。

下基板 22 的内表面上形成有选通线(gate line) 12 和数据线 34。选

通线 12 和数据线 34 彼此交叉，限定一像素区 P。一作为开关元件的薄膜晶

体管 T 形成于选通线 12 与数据线 34 交叉之处。薄膜晶体管 T 由一栅极、一

源极和一漏极构成，它以矩阵形式排列。一接至该薄膜晶体管 T 的像素电极

56 形成于象素区 P 内。该象素电极 56 对应于分滤色器，由一种诸如铟锡氧化物之类透光性能较好的透明导电材料制成。包括以矩阵形式排列的薄膜晶体管 T 和象素电极 56 的下基板 22 一般可以称为阵列基板。

5 一扫描脉冲通过选通线 12 施加至薄膜晶体管 T 的栅极，而一数据信号通过数据线 34 施加至薄膜晶体管 T 的源极。

LCD 装置因液晶的光电效应而受到驱动。液晶是具有自发极化 (spontaneous polarization) 性质的介电各向异性材料。当施加电压时，液晶通过自发极化形成偶极子，因而由电场排列液晶分子。由根据液晶的取向而变化的液晶光学特性而产生光调制。通过控制因光调制导致的透光率，

10 产生 LCD 装置的图像。

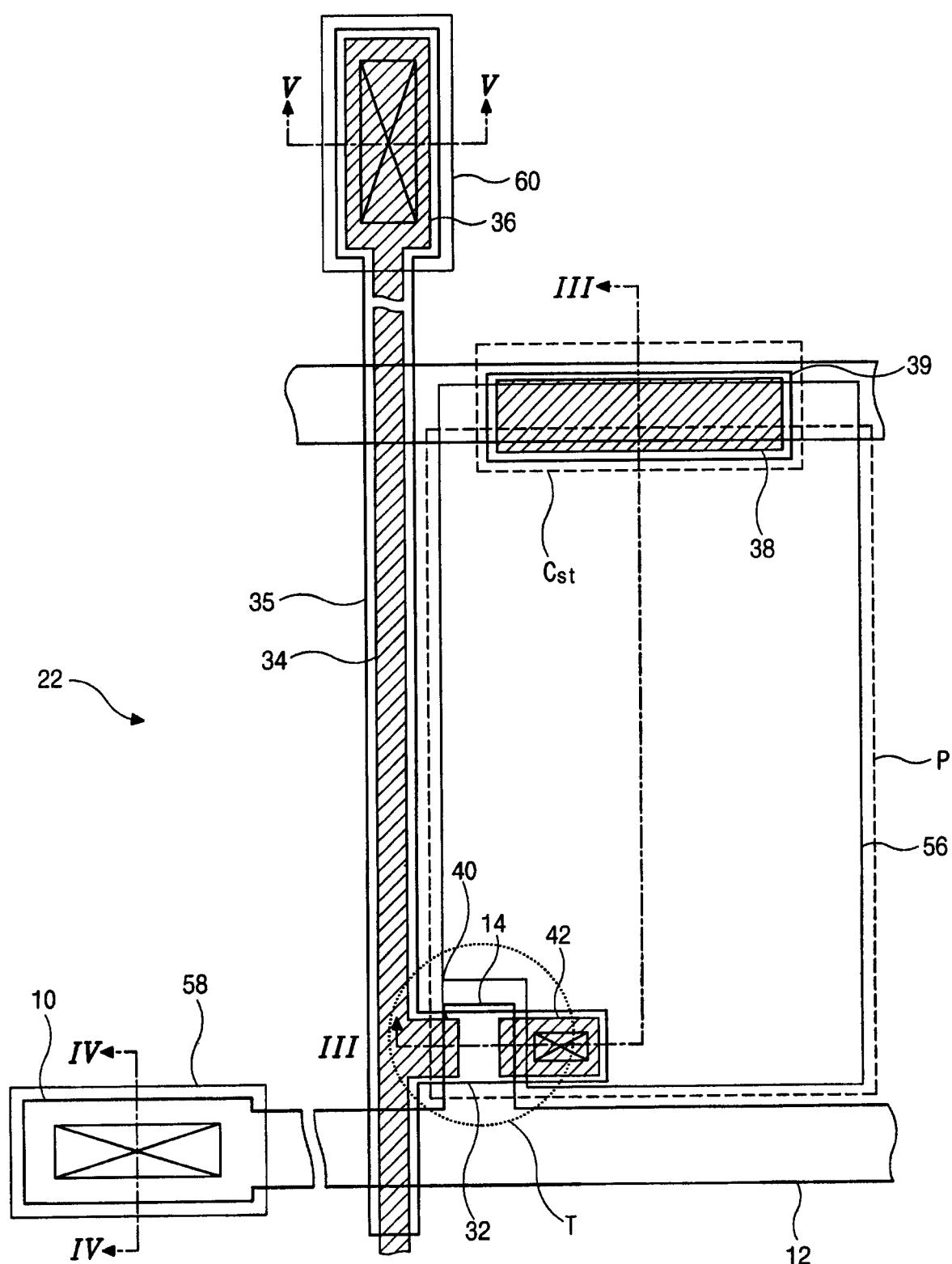

图 2 是一种根据已有技术 LCD 装置的阵列基板平面图。在图 2 中，选通线 12 和数据线 34 彼此交叉，限定一象素区 P，并且在选通线 12 与数据线 34 的交叉之处形成一作为开关元件的薄膜晶体管 T。选通垫 10 形成于选通线 12 的一端，数据垫 36 形成于数据线 34 的一端。形状为岛形且由一种透明导电

15 材料制成的选通垫端 58 和数据垫端 60 分别与选通垫 10 和数据垫 36 交叠。

薄膜晶体管 T 由栅极 14、源极 40 和漏极 42 构成，栅极 14 接至选通线 12 并且接收扫描信号，源极 40 接至数据线 34 并且接收数据信号，漏极 42 与源极 40 间隔开。薄膜晶体管 T 还包括一有源层 32，有源层 32 在栅极 14 与源极 40 和漏极 42 之间。一岛形金属图案 38 与选通线 12 交叠。

20 一象素电极 56 形成于象素区 P 中并且接至漏极 42。象素电极 56 还接至金属图案 38。选通线 12 和金属图案 38 分别起第一存储电容电极和第二存储电容电极的作用，它们和选通线 12 与金属图案 38 之间设置的一选通绝缘层（图中未示）形成一存储电容 Cst。

25 虽然图中未示，但是一欧姆接触层形成于有源层 32 与源极 40 和漏极 42 之间。有源层 32 由非晶硅制成，欧姆接触层由一种掺杂非晶硅制成。包括非晶硅和掺杂非晶硅的第一图案 35 和第二图案 39 分别形成于数据线 34 和金属图案 38 之下。

用四个掩模制作图 2 的阵列基板。

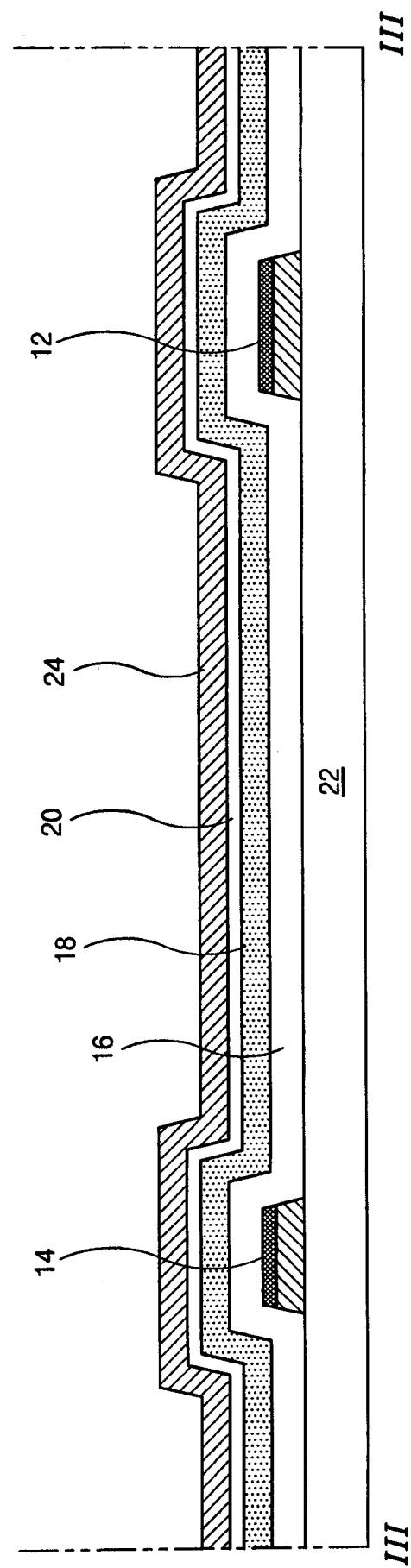

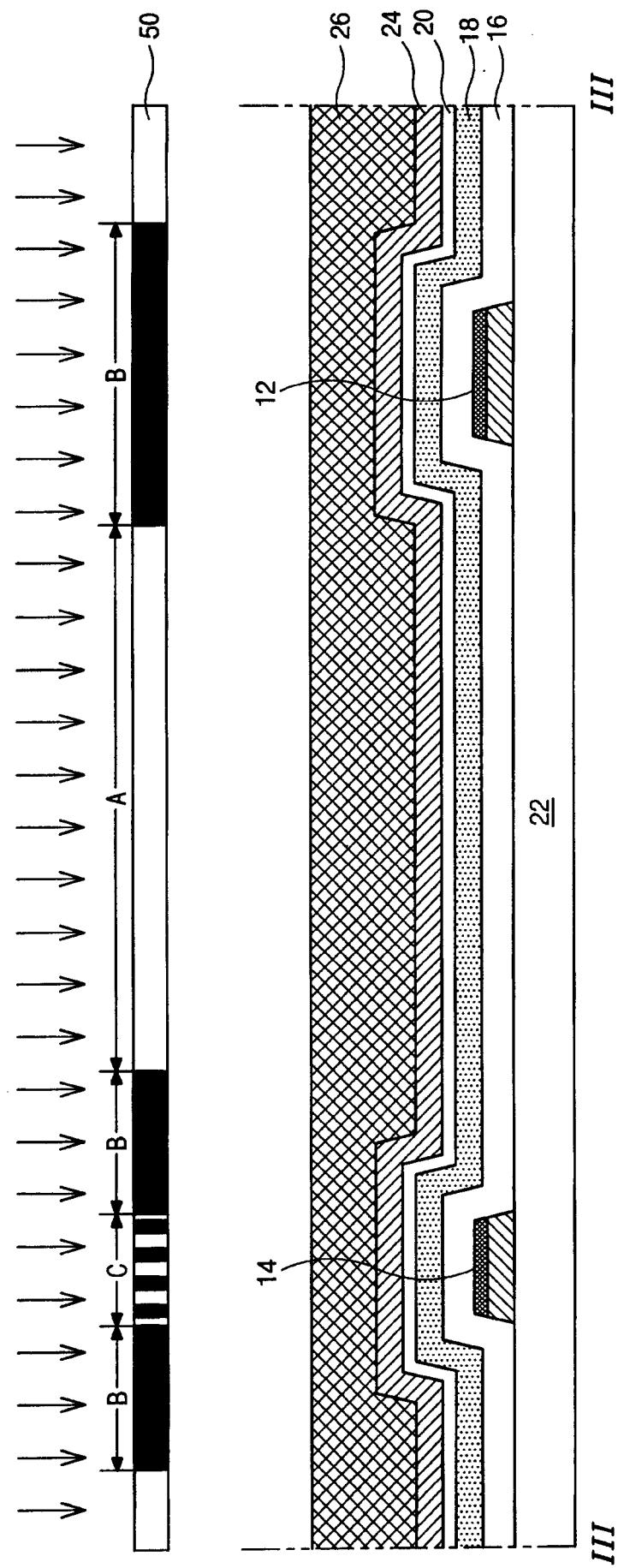

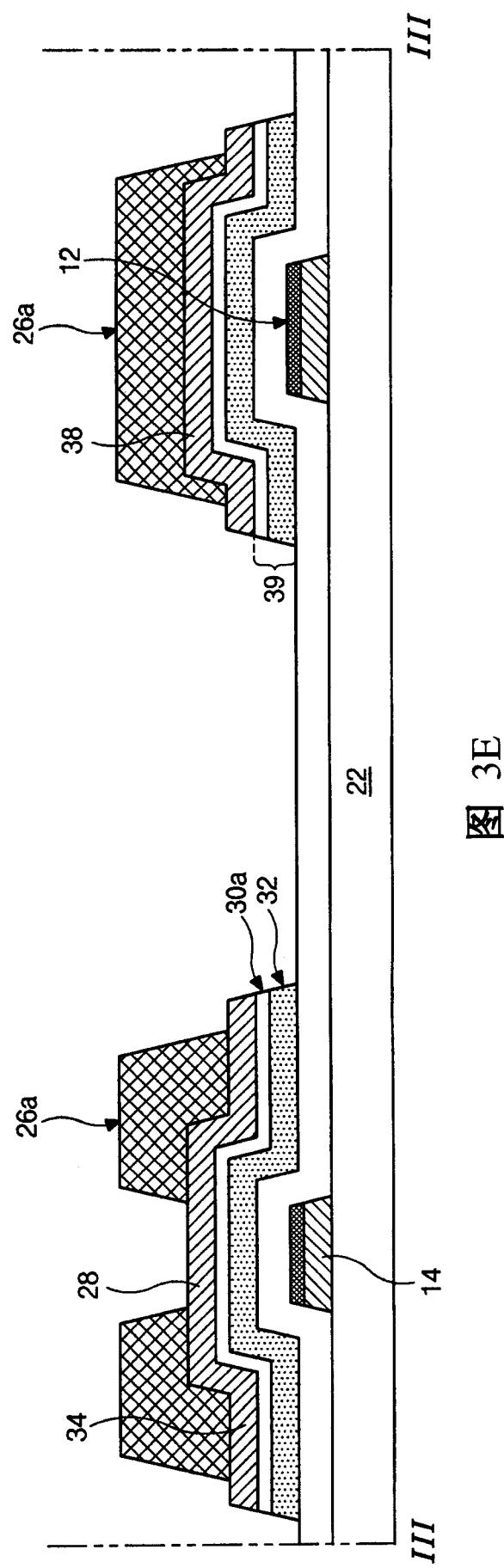

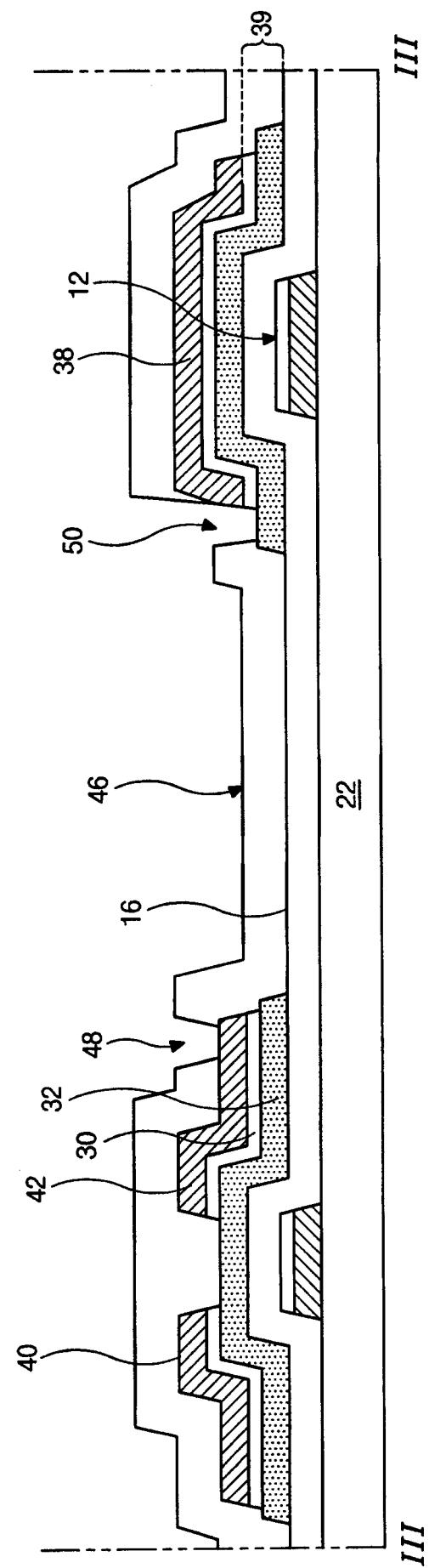

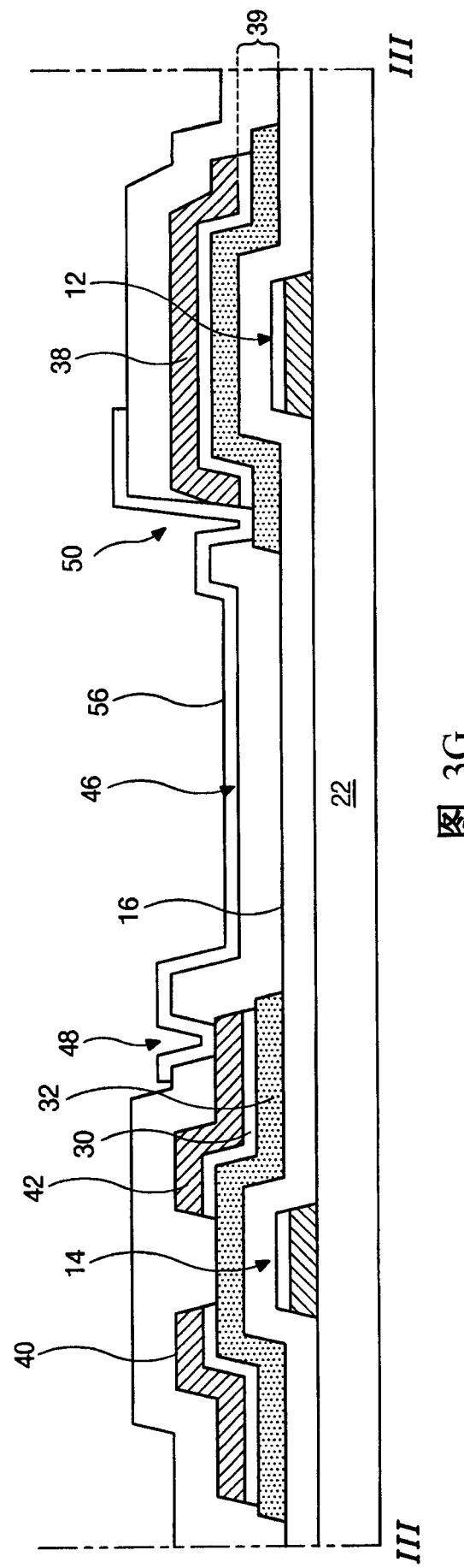

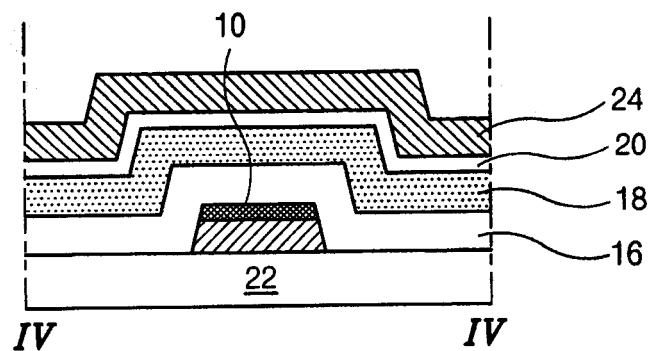

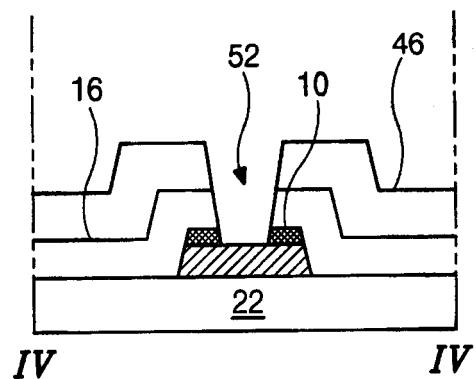

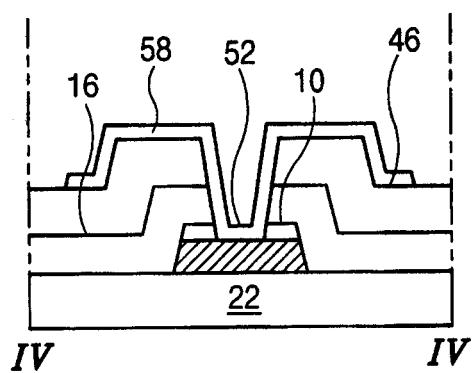

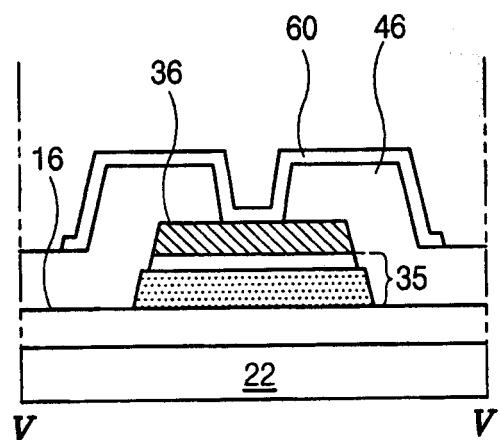

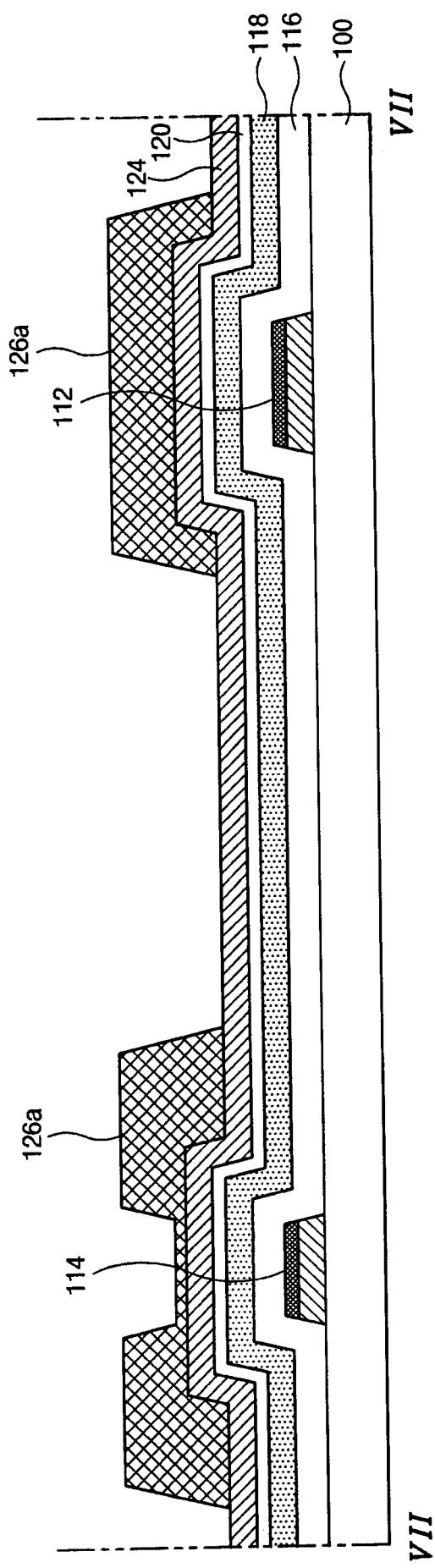

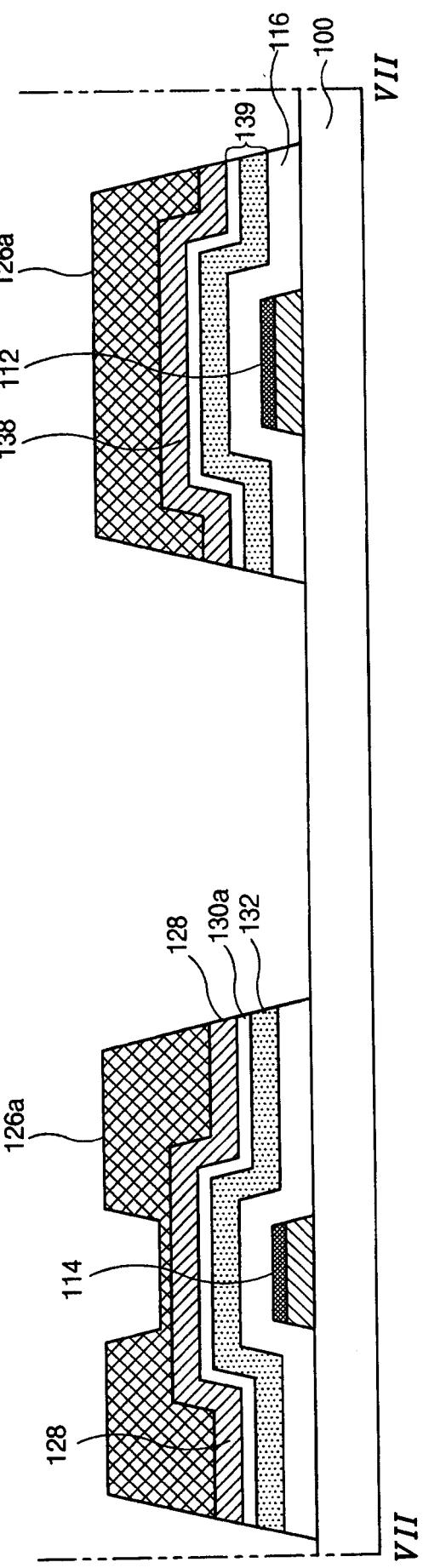

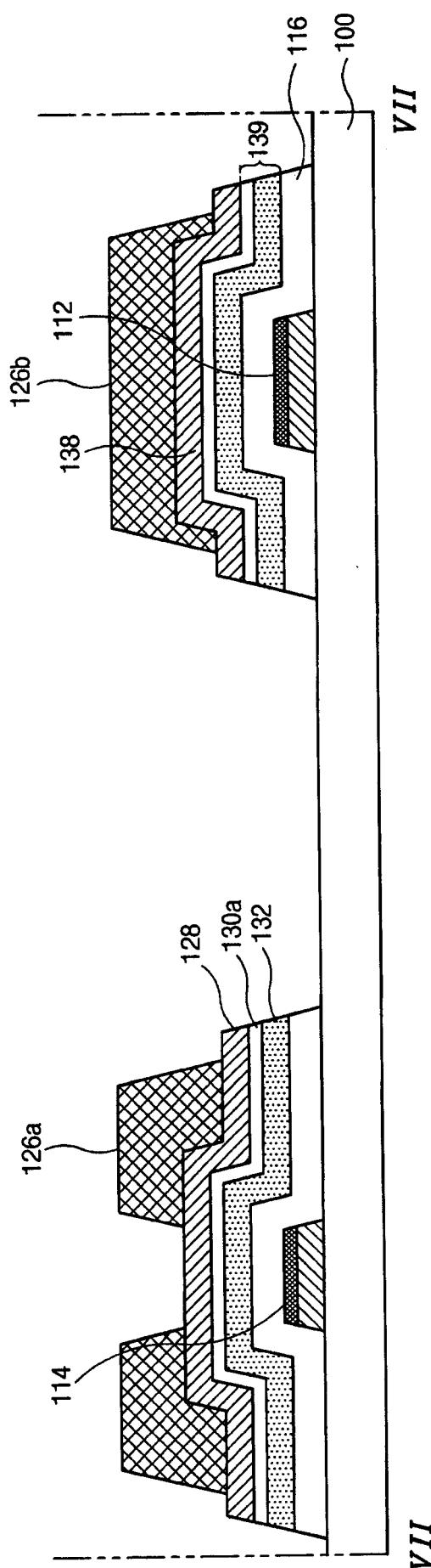

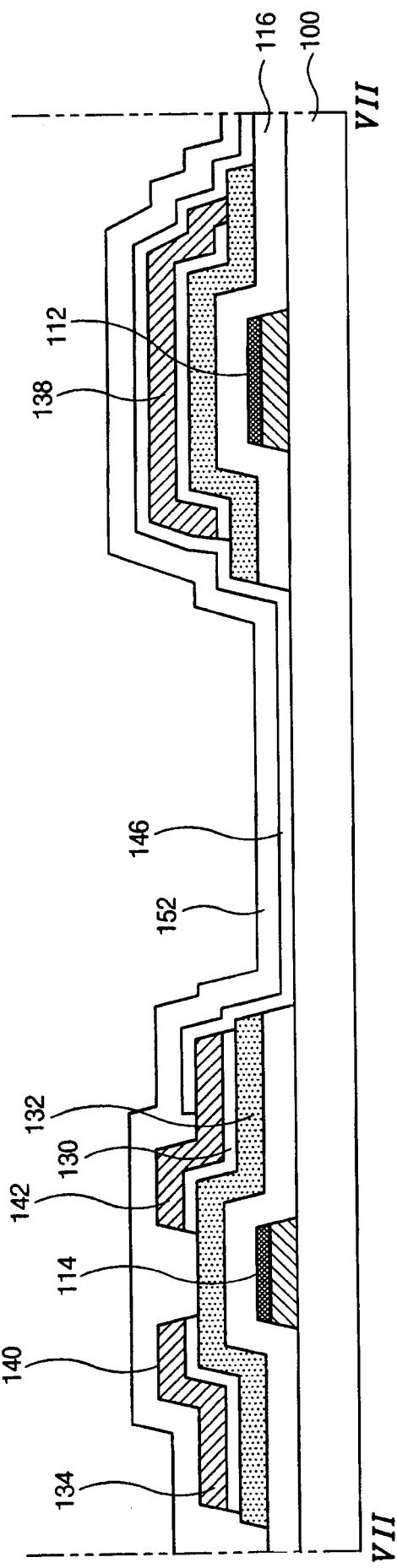

图 3A 至 3G、图 4A 至 4G 和图 5A 至 5G 示出了采用四个掩模的阵列基板制造过程，它们分别对应于沿图 2 中的线 III-III、IV-IV 和 V-V 所取的剖面图。

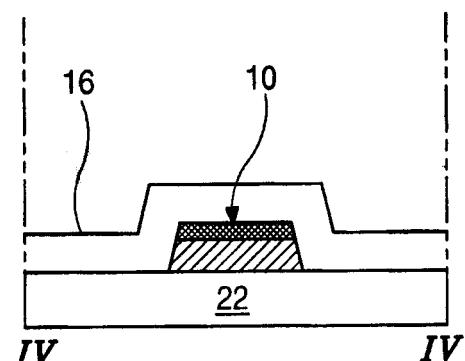

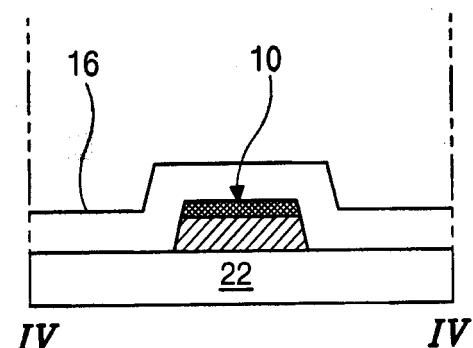

如图 3A、4A 和 5A 所示，通过淀积第一金属层，并且经第一光刻过程用 5 第一掩模对第一金属层制作图案，将一选通线 12、一栅极 14 和一选通垫 10 形成于一透明绝缘基板 22 上。选通线 12、栅极 14 和选通垫 10 由一种金属材料制成，如铝(Al)、铝合金、钼(Mo)、钨(W)和铬(Cr)。由铝或铝合金制成的选通线 12、栅极 14 和选通垫 10 可以由一含钼或铬的双层形成。

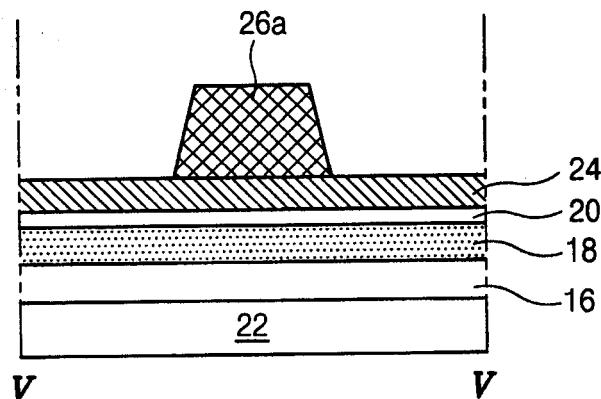

接着，随后在其上包括有选通线 12、栅极 14 和选通垫 10 的基板 22 上 10 淀积一选通绝缘层 16、一非晶硅层 18、一掺杂非晶硅层 20 和第二金属层 24。选通绝缘层 16 由一种无机绝缘材料制成，如氮化硅(SiNx)和二氧化硅(SiO<sub>2</sub>)，而第二金属材料 24 由铬、钼、钨和钽(Ta)中之一形成。

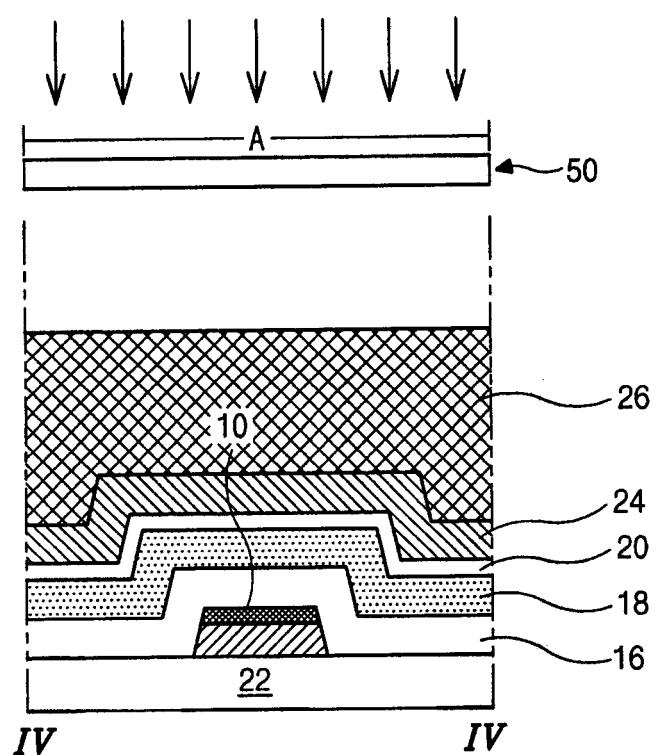

如图 3B、4B 和 5B 所示，通过涂敷光刻胶，在第二金属层 24 上形成一光 15 阻层 26。有一透光部分 A、一挡光部分 B 和一半透光部分 C 的第二掩模 50 设置在光阻层 26 之上，二者间隔开。半透光部分 C 对应于栅极 14。光阻层 26 是一正类型，曝光部分受到显影和去除。随后，将光阻层 26 曝光。对于半透光部分 C 的光阻层 26 其曝光量少于对于透光部分 A 的光阻层 26 的曝光量。

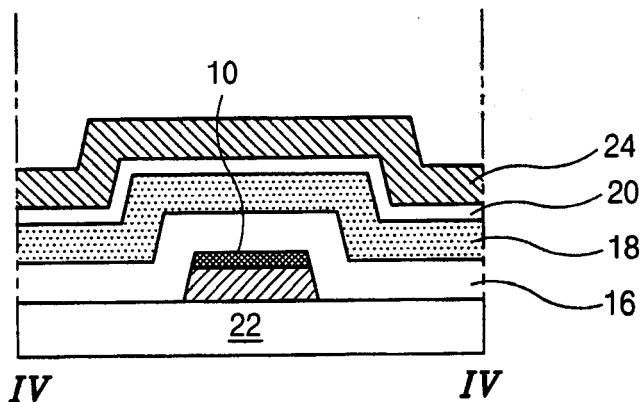

如图 3C、4C 和 5C 所示，图 3B、4B 和 5B 的已曝光光阻层 26 受到显影， 20 形成一光阻图案 26a。光阻图案 26a 具有不同的厚度。光阻图案 26a 的第一厚度对应于图 3B、4B 和 5B 中的挡光部分 B，而光阻图案 26a 的第二厚度对应于图 3B、4B 和 5B 中的半透光部分 C，第二厚度比第一厚度小。

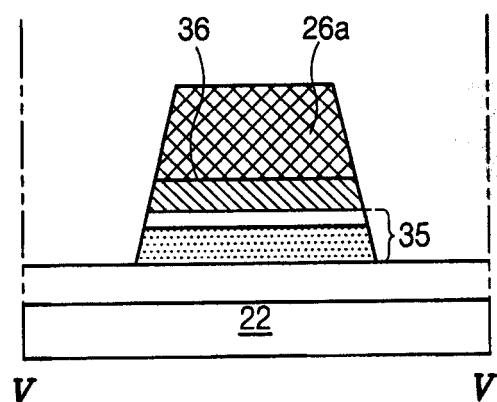

如图 3D、4D 和 5D 所示，去除图 3C、4C 和 5C 中被光阻图案 26a 所暴露的第二金属层 24、掺杂非晶硅层 20 和非晶硅层 18。这样，形成图 2 的源极 25 和漏极图案 28、数据线 34，还形成一数据垫 36、一掺杂非晶硅图案 30a 和一有源层 32。用一湿刻法蚀刻图 3C、4C 和 5C 中的第二金属层 24，而用一干刻法对图 3C、4C 和 5C 中的掺杂非晶硅层 20 和非晶硅层 18 制作图案。源极和漏极图案 28 形成于栅极 14 之上，并且接至图 2 中垂直延伸的数据线 34。该掺杂非晶硅图案 30a 和有源层 32 具有与源极和漏极图案 28 以及数据线 34 30 相同的形状。

这时，还在选通线 12 之上形成一岛形金属图案 38。形成包括非晶硅层和掺杂非晶硅层的第一图案 35 和第二图案 39。第一图案 35 位于数据线（图中未示）和数据垫 36 之下，而第二图案 39 位于金属图案 38 之下。

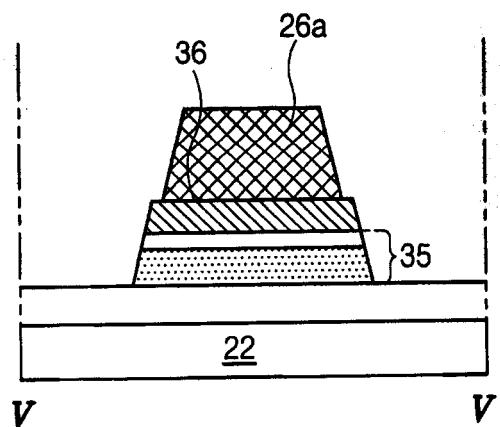

接着，如图 3E、4E 和 5E 所示，通过灰化过程去除光阻图案 26a 的第二厚度，这样，露出源极和漏极图案 28。这里，还部分去除第一厚度的光阻图案 26a，光阻图案 26a 的第一厚度变得更薄。另外，去除光阻图案 26a 的边缘，露出金属图案 28、36 和 38。

如图 3F、4F 和 5F 所示，蚀刻图 3E 中光阻图案 26a 所露出的图 3E 中的源极和漏极图案 28 和掺杂非晶硅图案 30a。这样，形成源极 40 和漏极 42 以及欧姆接触层 30，露出有源层 32。源极 40 与漏极 42 之间所露出的有源层 32 变成薄膜晶体管的一个沟道。源极 40 和漏极 42 彼此间隔开。源极 40 与漏极 42 之间的一个区域对应于图 3B 中第二掩模 50 的半透光部分 C。如果图 3E 中的源极和漏极图案 28 由钼 (Mo) 形成，那么可以利用干刻法同时去除图 3E 中的源极和漏极图案 28 以及掺杂非晶硅图案 30a。但是，如果源极和漏极图案 28 由铬 (Cr) 形成，那么用湿刻法蚀刻源极和漏极图案 28，然后用干刻法去除掺杂非晶硅图案 30a。

如上所述，通过第二光刻过程，利用图 3B、4B 和 5B 中的第二掩模，形成源极 40 和漏极 42、数据线 34、数据垫 36、金属图案 38、欧姆接触层 30 和有源层 32。

接着，去除光阻图案 26a，通过涂敷一种透明有机材料，或者淀积一种无机材料，在数据线 34、源极 40 和漏极 42、数据垫 36 以及金属图案 38 上形成一钝化层 46，这种透明有机材料例如是苯环丁烯 (BCB) 和丙烯酸树脂，这种无机材料例如是氮化硅 ( $\text{SiN}_x$ ) 和二氧化硅 ( $\text{SiO}_2$ )。通过第三光刻过程，利用第三掩模，对钝化层 46 连同栅极 16 一起制作图案，形成一漏极接触孔 48、一存储接触孔 50、一选通垫接触孔 52 和一数据垫接触孔 54。漏极接触孔 48、存储接触孔 50、选通垫接触孔 52 和数据垫接触孔 54 分别露出漏极 42、金属图案 38、选通垫 10 和数据垫 36。这里，存储接触孔 50 露出金属图案 38 的侧壁。

如图 3G、4G 和 5G 所示，通过淀积一种透明导电材料如铟锡氧化物 (ITO) 和铟锌氧化物 (IZO)，并且经第四光刻过程用第四掩模对该透明导电材料制作

图案，在钝化层 46 上形成一像素电极 56、一选通垫端 58 和一数据垫端 60。

像素电极 56 不仅通过漏极接触孔 48 接至漏极 42，还通过存储接触孔 50 接至金属图案 38。选通垫端 58 和数据垫端 60 分别接至选通垫 10 和数据垫 36。

5 如上所述，通过光刻过程，利用一掩模，制造阵列基板。该光刻过程包括几个步骤：清洁、涂敷一光阻层，通过一掩模曝光，对该光阻层进行显影和蚀刻。因此，通过减少光刻过程的数目，可以缩短制作时间，降低制作成本，还可以减少失误。

## 10 发明内容

因此，本发明涉及一种液晶显示装置阵列基板的制造方法，它基本上避免了因已有技术的局限和缺点带来的一个或多个问题。

本发明的一个优点在于提供一种液晶显示装置阵列基板的制造方法，它因缩短了各过程且降低了成本而提高了产量。

15 本发明的其他特征和优点将在以下的描述中列出，根据该描述，它们一部分将变得很明显，或者可以通过对本发明的实践来学会。通过所写的说明书及其权利要求书以及附图中特别指出的结构，能够实现和达到本发明的这些目的和其他优点。

为了实现这些和其他优点，根据本发明的目的，如所具体和概括描述的那样，一种液晶显示装置阵列基板的制造方法包括以下步骤：在一基板上形成一选通线、一选通垫和一栅极；在该选通线、栅极和选通垫上形成一栅极绝缘层；在该栅极绝缘层上形成一有源层；在该有源层上形成一欧姆接触层；在该欧姆接触层上形成一数据线、一数据垫以及源极和漏极；在源极和漏极上形成一像素电极，该像素电极接触漏极；在包括该像素电极的基板上形成第一钝化层；在第一钝化层上形成第二钝化层，第二钝化层暴露选通垫和数据垫之上的第一钝化层；以及对第二钝化层所暴露的第一钝化层制作图案，以暴露选通垫和数据垫。

应理解的是，前面总的描述和以下详细的描述是示例性和解释性的，意欲用它们提供对所要求保护的本发明的进一步解释。

## 附图说明

所包括用来提供对本发明进一步理解并且包括在内构成说明书一部分的附图示出了本发明的实施例，它们连同文字部分一起用来解释本发明的原理。

5       这些附图中：

图 1 是一分解透视图，它示出一种传统的液晶显示（LCD）装置；

图 2 是一种根据已有技术 LCD 装置阵列基板的平面图；

图 3A 至 3G、图 4A 至 4G 和图 5A 至 5G 是示出一种根据已有技术阵列基板制造方法的剖面图；

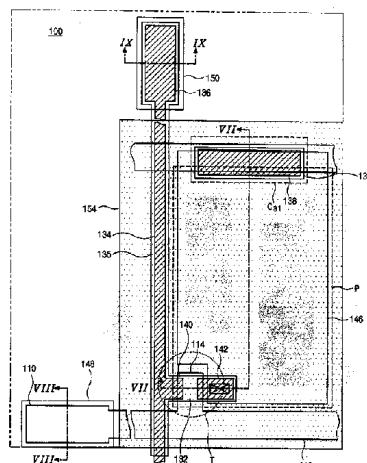

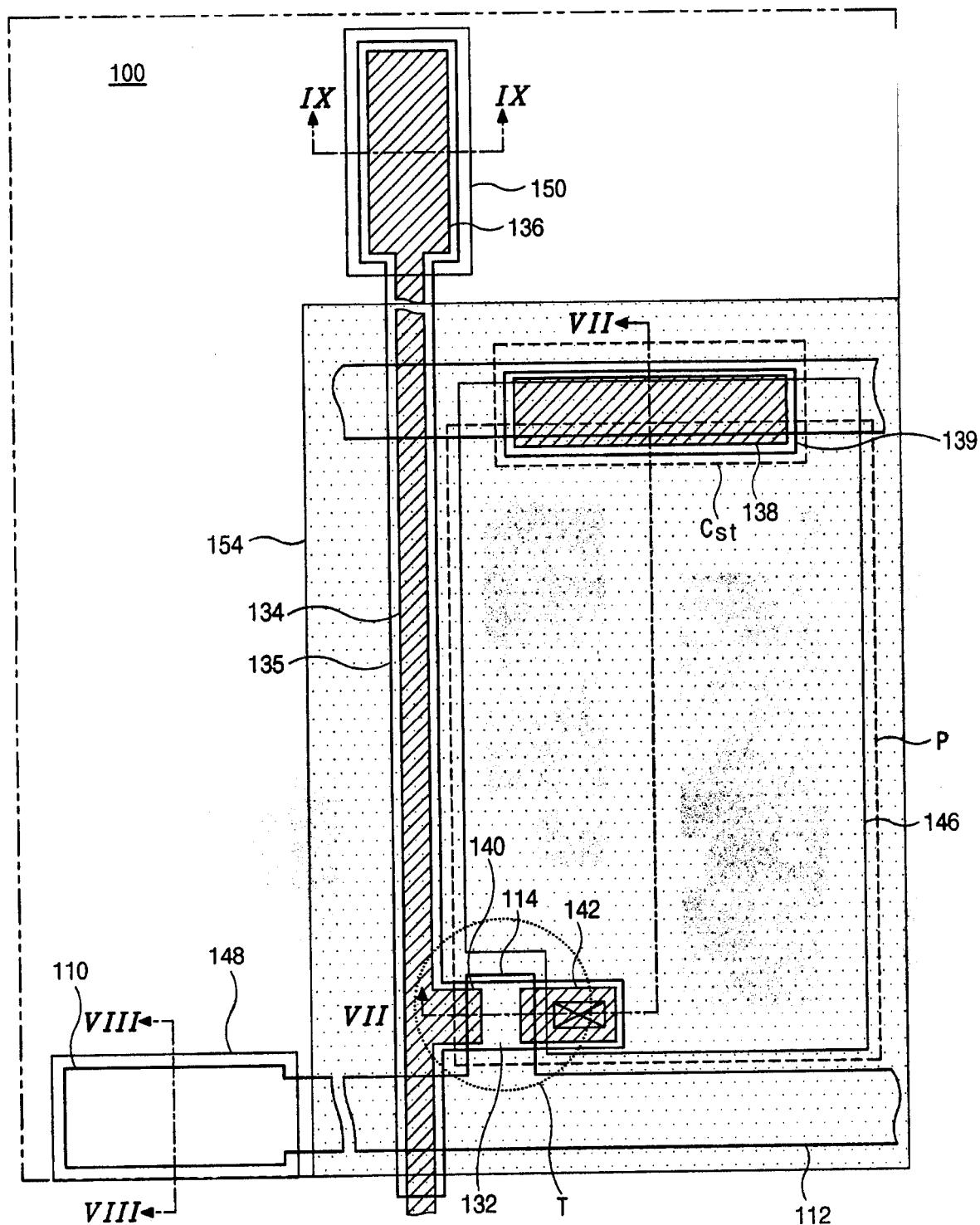

10      图 6 是根据本发明一个实施例液晶显示（LCD）装置一阵列基板的平面图；

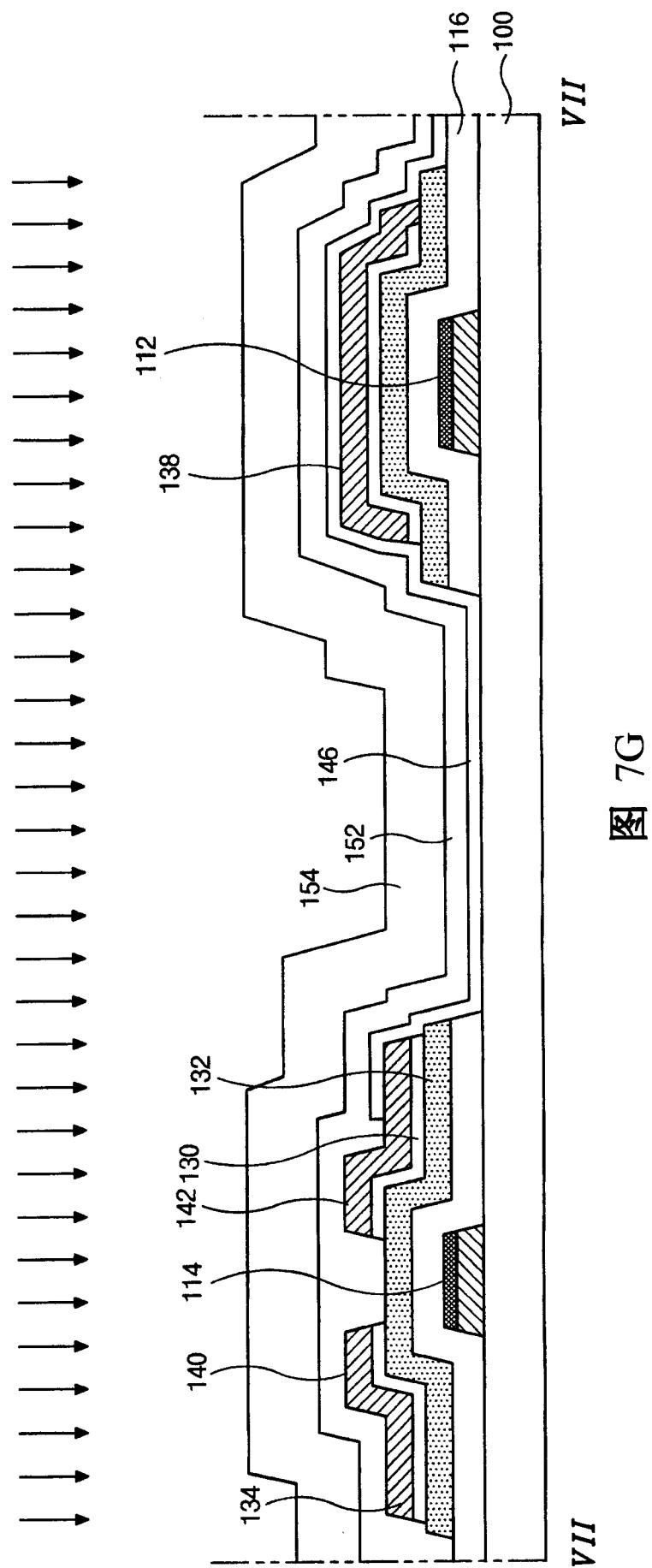

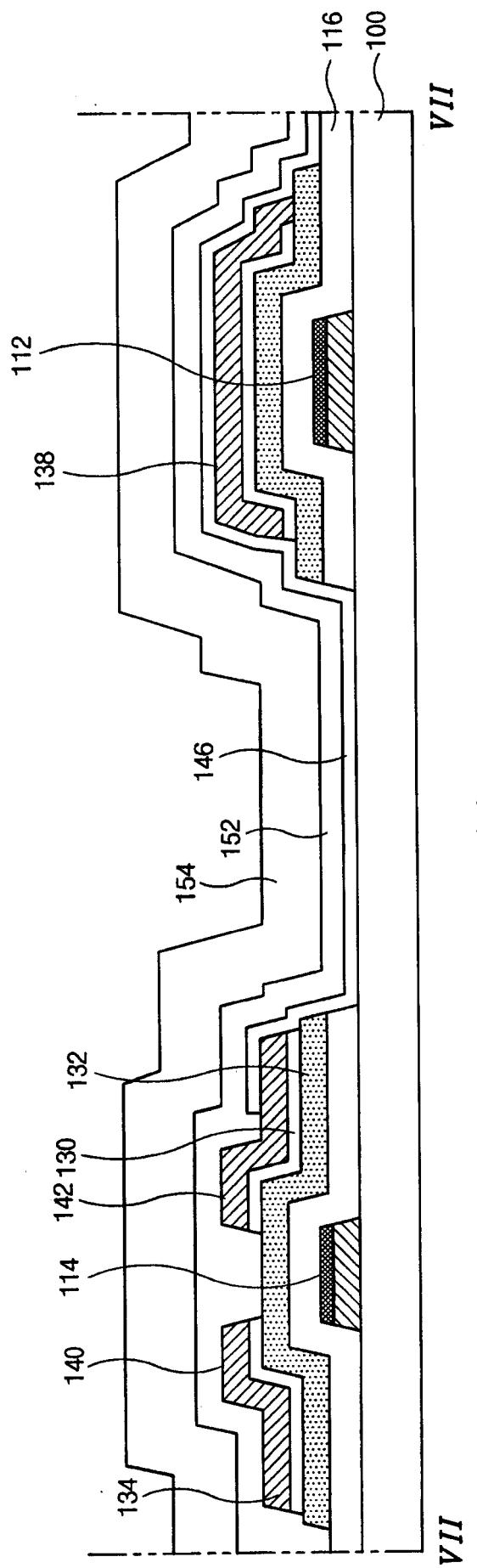

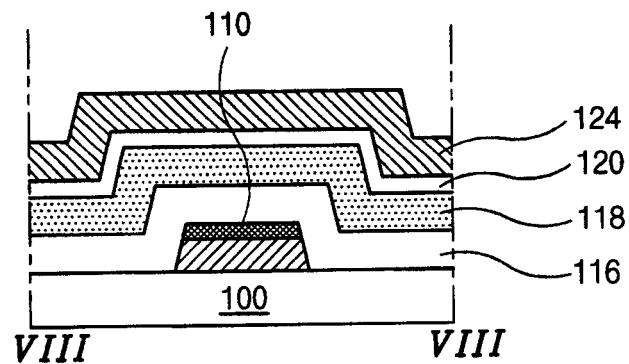

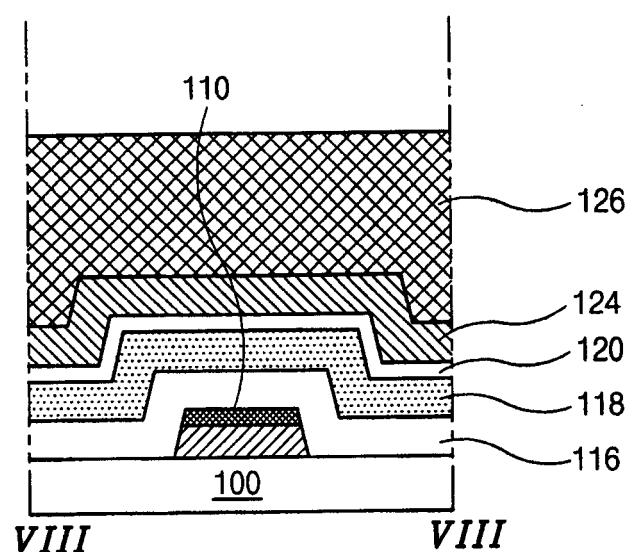

图 7A 至 7H、图 8A 至 8H 和图 9A 至 9H 是示出相应于本发明的一种阵列基板制造过程的剖面图。

## 15      具体实施方案

现在详细描述本发明的图示实施例，它们示于附图中。

图 6 是根据本发明一个实施例液晶显示（LCD）装置一阵列基板的平面图。

如图 6 所示，一选通线 112 和一数据线 134 形成于一透明绝缘基板 100 上。选通线 112 和数据线 134 彼此交叉，限定一像素区 P，一作为开关元件的薄膜晶体管 T 形成于选通线 112 与数据线 134 交叉之处。一选通垫 110 形成于选通线 112 一端，而一数据垫 136 形成于数据线 134 一端。形状为岛形且由一种透明导电材料制成的一选通垫端 158 和一数据垫端 160 分别与选通垫 110 和数据垫 136 交叠。

25      薄膜晶体管 T 由栅极 114、源极 140 和漏极 142 构成，栅极 114 接至选通线 112 并且接收扫描信号，源极 140 接至数据线 134 并且接收数据信号，漏极 142 与源极 140 间隔开。薄膜晶体管 T 还包括一有源层 132，有源层 132 在栅极 114 与源极 140 和漏极 142 之间。一金属材料 138 与选通线 112 交叠。该金属材料 128 可以用与数据线 134 相同的材料制成。

一像素电极 146 形成于像素区 P 内。该像素电极 146 借助侧面接触连接到漏极 142 和金属图案 138 上。选通线 112 和金属图案 138 分别起第一存储电容电极和第二存储电容电极的作用，它们和选通线 112 与金属图案 138 之间设置的一选通绝缘层（图中未示）形成一存储电容 Cst。

5 一透明有机层 154 形成于除选通垫 110 和数据垫 136 之外的一个区域内。

虽然图中未示，但是一欧姆接触层形成于有源层 132 与源极 140 和漏极 142 之间。有源层 132 由非晶硅制成，欧姆接触层由一种掺杂非晶硅制成。包括非晶硅和掺杂非晶硅的第一图案 135 和第二图案 139 分别形成于数据线 10 134 和金属图案 138 之下。

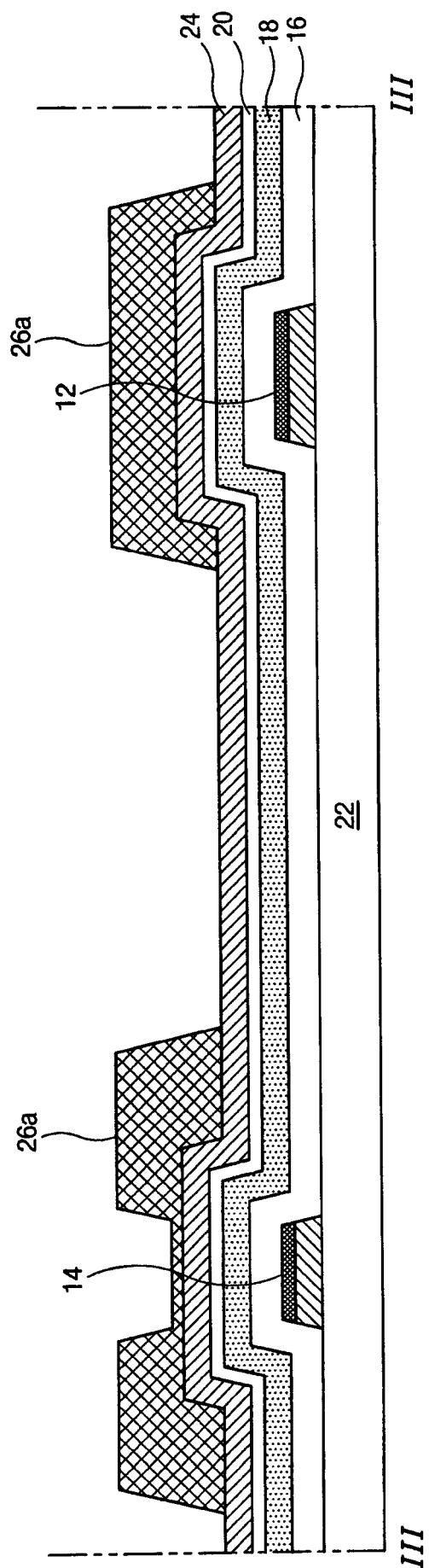

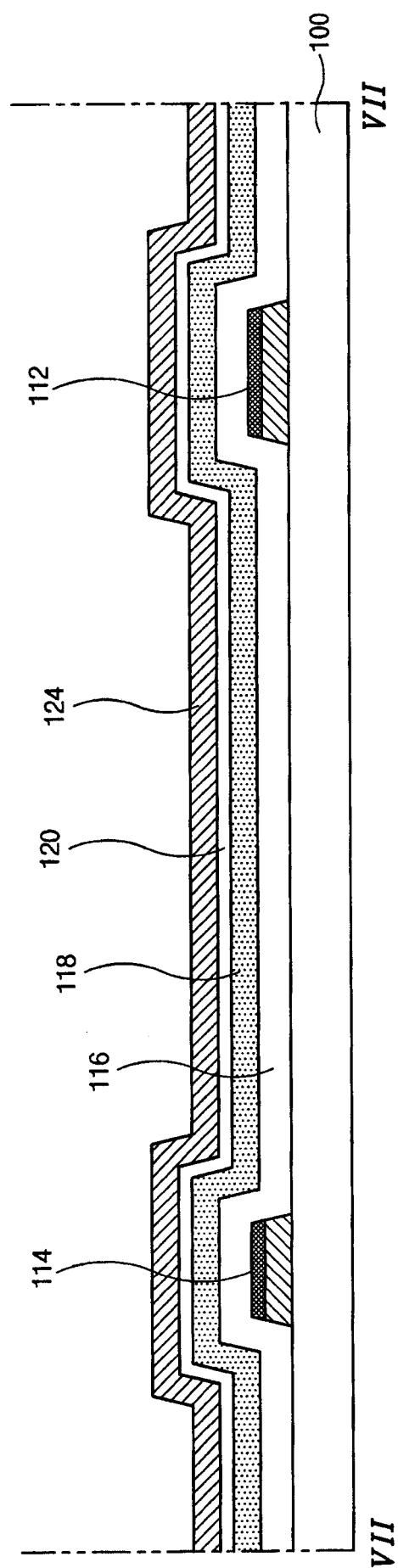

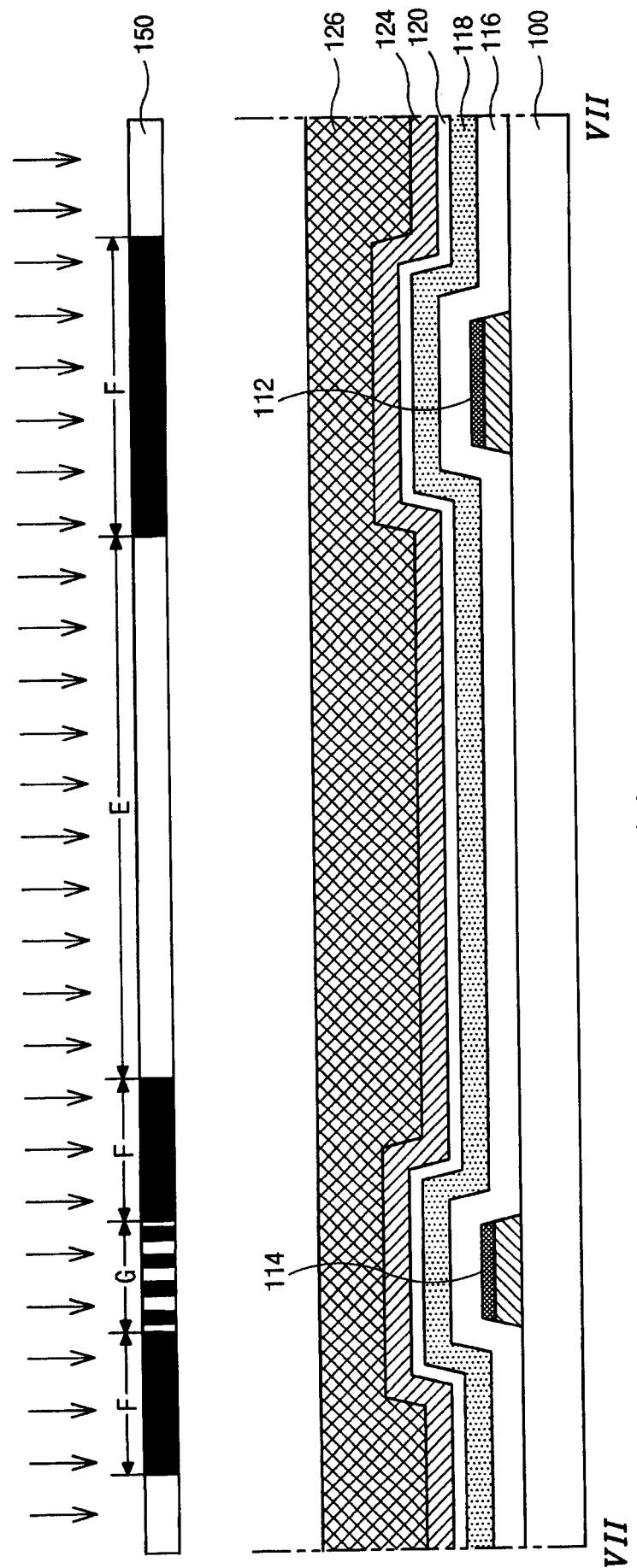

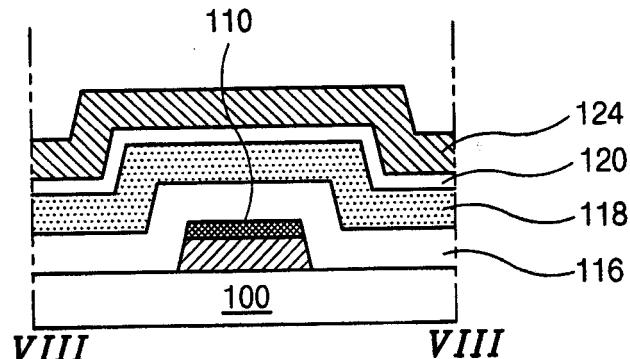

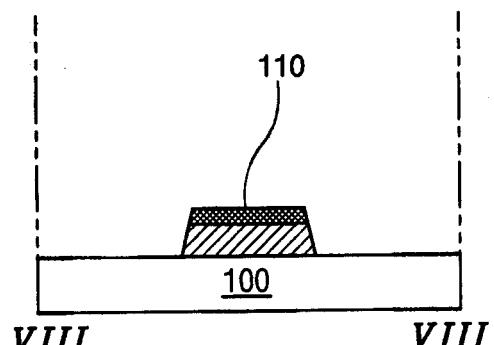

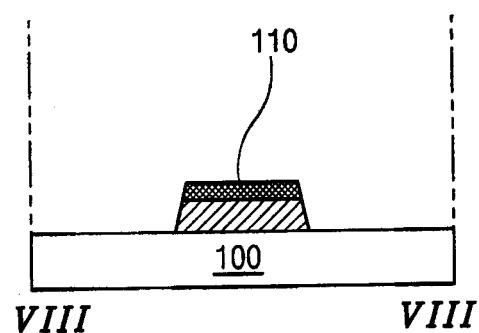

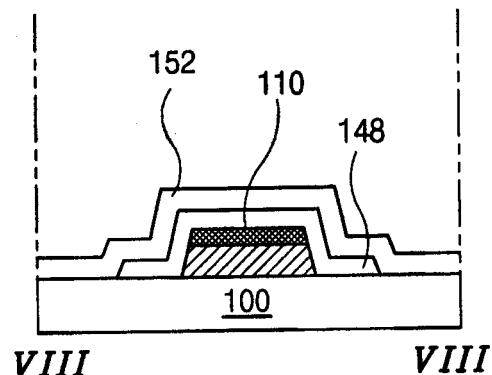

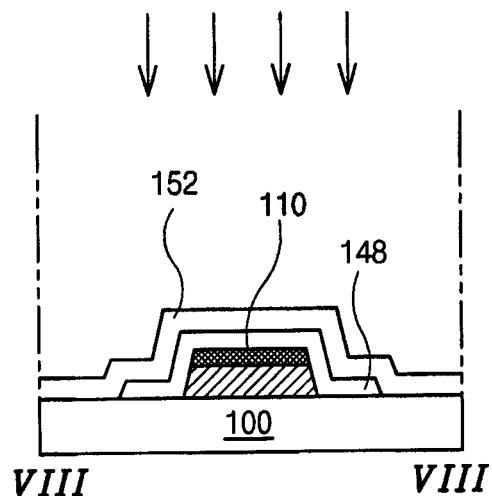

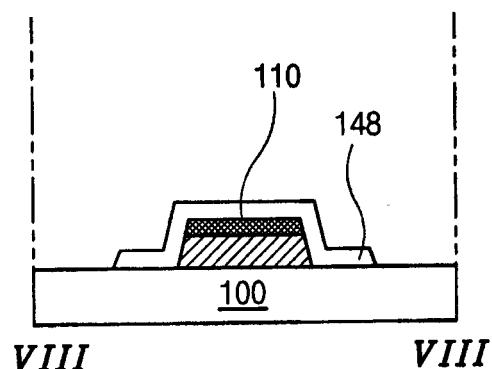

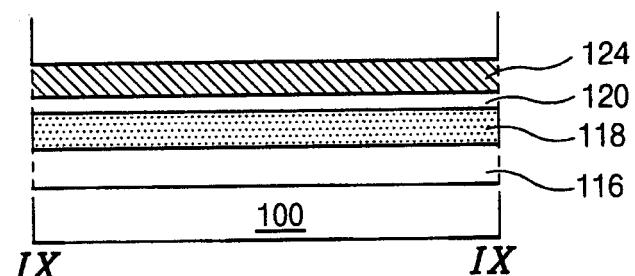

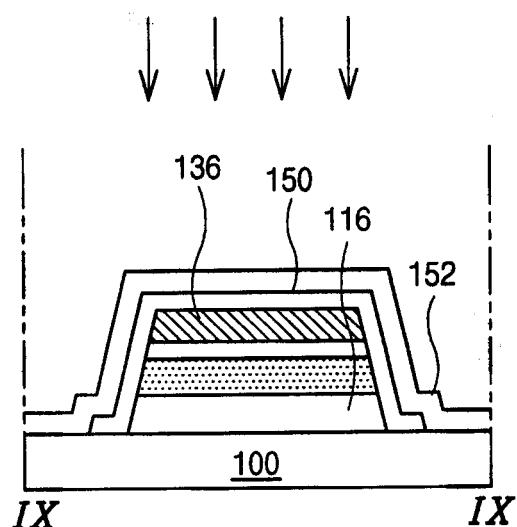

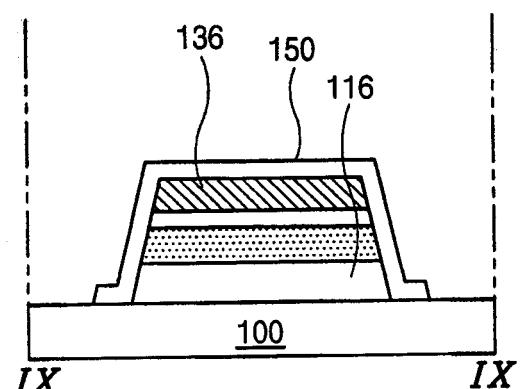

图 7A 至 7H、图 8A 至 8H 和图 9A 至 9H 示出了相应于本发明的一种阵列基板的制造方法，它们分别是沿图 6 中的线 VII-VII、VIII-VIII 和 IX-IX 所取的剖面图。

首先，如图 7A、8A 和 9A 所示，通过淀积第一金属层，并且经第一光刻过程用第一掩模对第一金属层制作图案，将一选通线 112、一栅极 114 和一选通垫 110 形成于一透明绝缘基板 100 上。栅极 114 从选通线 112 上伸出，选通垫 110 位于选通线 112 的一端上。为了防止 RC 延迟，具有较低电阻率的铝 (Al) 普遍用作栅极材料。但是，纯铝易被酸腐蚀，可能会在下面的过程中于高温下因小丘的存在而导致线存在瑕疵。因此，可以采用一种铝合金或者含铝和其他金属材料的双层结构。

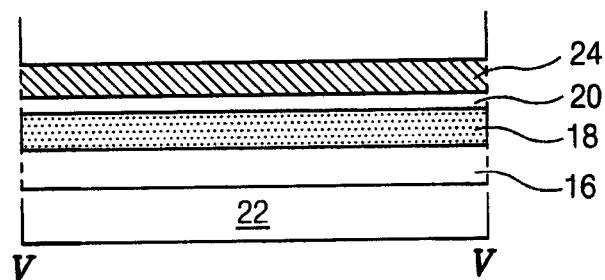

接着，随后在其上包括有选通线 112、栅极 114 和选通垫 110 的基板 100 上淀积一选通绝缘层 116、一非晶硅层 118、一掺杂非晶硅层 120 和第二金属层 124。选通绝缘层 116 由一种无机绝缘材料制成，如氮化硅 (SiNx) 和二氧化硅 (SiO<sub>2</sub>)。选通绝缘层 116 也可以由一种有机绝缘材料制成，如苯环丁烯 (BCB) 和丙烯酸树脂。第二金属层 124 由铬、钼、钨和钽 (Ta) 中之一制成。

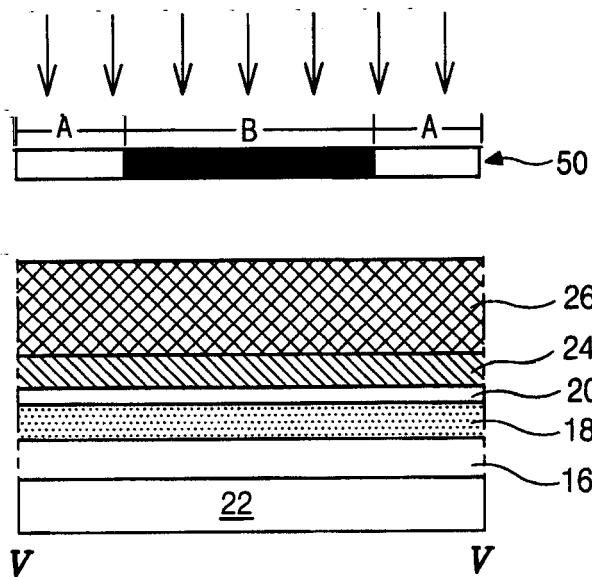

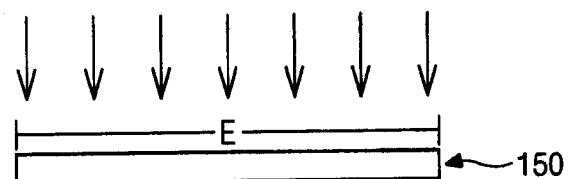

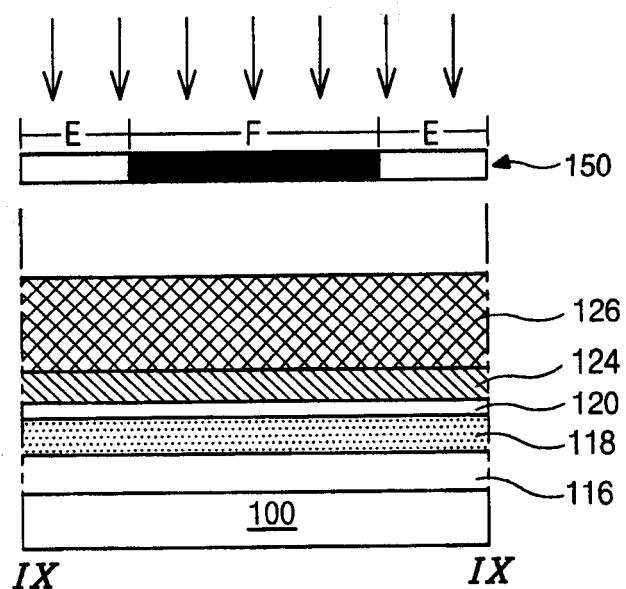

如图 7B、8B 和 9B 所示，通过涂敷光刻胶，在第二金属层 124 上形成一光阻层 126。有一透光部分 E、一挡光部分 F 和一半透光部分 G 的第二掩模 150 设置在光阻层 126 之上，二者间隔开。半透光部分 G 可以包括狭缝，对应于一薄膜晶体管的一个沟道。光阻层 126 可以是一正类型，因而曝光部分

受到显影和去除。随后，将光阻层 126 曝光，对应于半透光部分 G 的光阻层 126 其曝光量少于对应于透光部分 E 的光阻层 126 的曝光量。

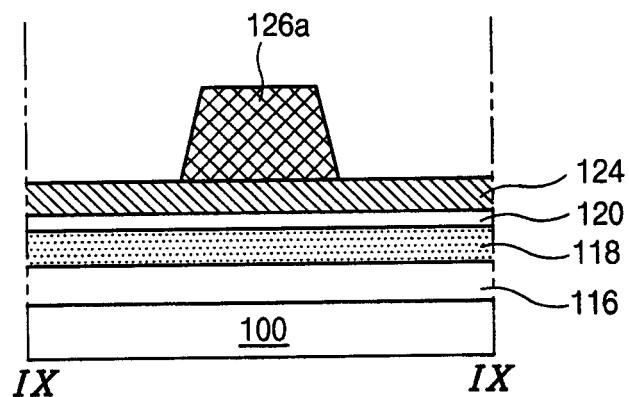

接着，如图 7C、8C 和 9C 所示，图 7B、8B 和 9B 的光阻层 126 受到显影，形成一具有不同厚度的光阻图案 126a。光阻图案 126a 的第一厚度对应于图 7B、8B 和 9B 中的挡光部分 F，而光阻图案 126a 的第二厚度对应于图 7B 中的半透光部分 G，第二厚度比第一厚度小。

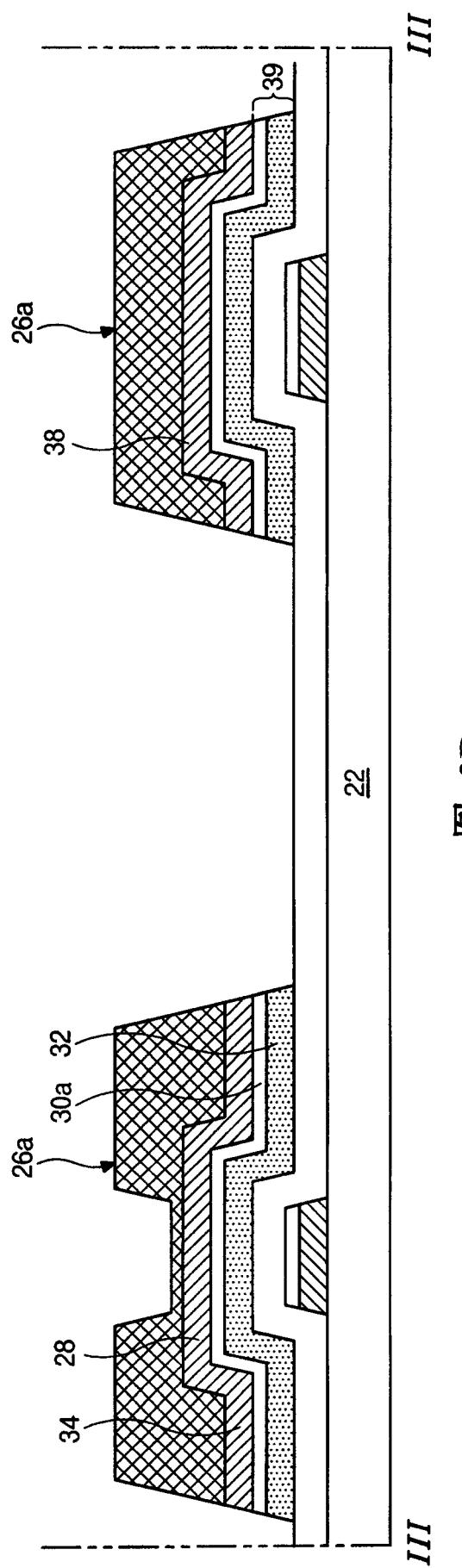

如图 7D、8D 和 9D 所示，去除图 7C、8C 和 9C 中被光阻图案 126a 所暴露的第二金属层 124、掺杂非晶硅层 120 和非晶硅层 118。这样，形成图 6 的源极和漏极图案 128、数据线 134，还形成一数据垫 136、一掺杂非晶硅图案 130a 和一有源层 132。用一湿刻法蚀刻图 7C、8C 和 9C 中的第二金属层 124，而用一干刻法对图 7C、8C 和 9C 中的掺杂非晶硅层 120 和非晶硅层 118 制作图案。源极和漏极图案 128 形成于栅极 114 之上，并且接至图 6 中垂直延伸的数据线 134。该掺杂非晶硅图案 130a 和有源层 132 具有与源极和漏极图案 128 以及数据线 134 相同的形状。这时，还在选通线 112 之上形成一岛形金属图案 138。形成包括非晶硅层和掺杂非晶硅层的第一图案 135 和第二图案 139。第一图案 135 位于数据线（图中未示）和数据垫 136 之下，而第二图案 139 位于金属图案 138 之下。这里，还可以蚀刻栅极绝缘层 116，可以露出基板 110 和栅极垫 110。

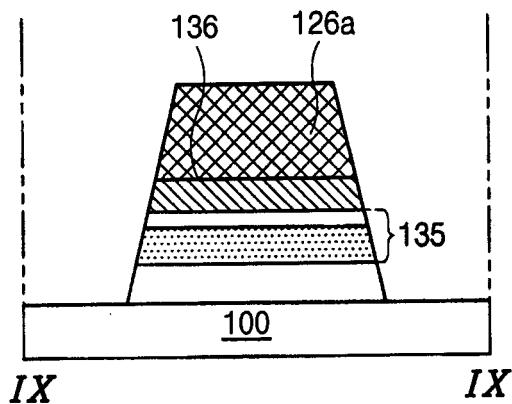

接着，如图 7E、8E 和 9E 所示，通过一灰化过程去除光阻图案 126a 的第二厚度，这样，露出源极和漏极图案 128。这里，还部分去除光阻图案 126a 的第一厚度，光阻图案 126a 的第一厚度变得更薄。另外，去除光阻图案 126a 的边缘，露出金属图案 128、136 和 138。

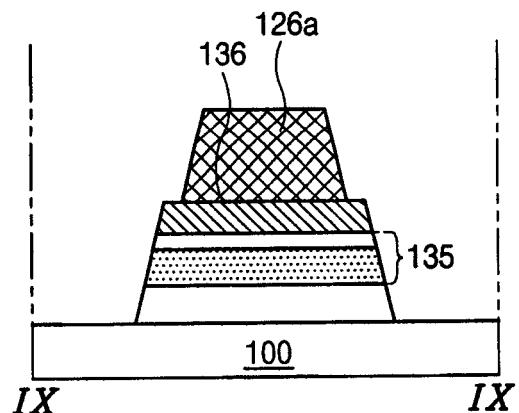

如图 7F、8F 和 9F 所示，蚀刻图 7E 中光阻图案 126a 所露出的图 7E 中的源极和漏极图案 128 和掺杂非晶硅图案 130a。这样，形成源极 140 和漏极 142 以及欧姆接触层 130，露出有源层 132。源极 140 与漏极 142 之间所露出的有源层 132 变成薄膜晶体管的一个沟道，并且对应于图 7B 中第二掩模 150 的半透光部分 G。源极 140 和漏极 142 彼此间隔开。如果图 7E 中的源极和漏极图案 128 由钼（Mo）形成，那么可以利用干刻法同时去除图 3E 中的源极和漏极图案 28 以及掺杂非晶硅图案 30a。但是，如果源极和漏极图案 28 由铬

(Cr) 形成，那么用湿刻法蚀刻源极和漏极图案 28，然后用干刻法去除掺杂非晶硅图案 30a。

如上所述，通过第二掩膜过程，利用图 7B、8B 和 9B 中的第二掩模，形成源极 140 和漏极 142、数据线 134、数据垫 136、金属图案 138、欧姆接触层 130 和有源层 132。

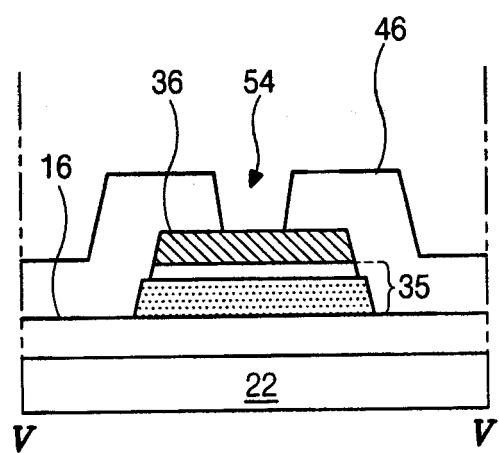

接着，去除光阻图案 126a，通过淀积一种透明导电材料如铟锡氧化物(ITO)和铟锌氧化物(IZO)，并且经第三光刻过程用第三掩模对该透明导电材料制作图案，在包括源极 140 和漏极 142 的基板 100 上形成一像素电极 146、一选通垫端 148 和一数据垫端 150。像素电极 146 借助侧面接触，不仅接至漏极 142，还接至金属图案 138。选通垫端 148 和数据垫端 150 分别接至选通垫 110 和数据垫 136。

通过在约 300 摄氏度的温度下淀积诸如氮化硅(SiNx)和二氧化硅(SiO<sub>2</sub>)之类的一种无机材料，在像素电极 146、选通垫端 148 和数据垫端 150 上形成第一钝化层 152，第一钝化层 152 的厚度在约 500 Å 至大约 1000 Å 的范围内。在接触有源层方面，无机绝缘材料的第一钝化层 152 比有机绝缘材料的要好。这时，像素电极 146、选通垫端 148 和数据垫端 150 从非晶相变为晶相。

如图 7G、8G 和 9G 所示，通过印刷一种透明有机材料，在除选通垫 110 和数据垫 136 之外的第一钝化层 152 上形成第二钝化层 154。该透明有机材料可以例如由聚酰亚胺制成。随后，干刻第二钝化层 156 露出的第一钝化层 154。

然后，如图 7H、8H 和 9H 所示，露出选通垫端 148 和数据垫端 150。通过摩擦第二钝化层 154 的表面，可以将第二钝化层 154 用作一取向层。

这样，利用三个掩模制造本发明的阵列基板。因此，根据本发明的阵列基板的制造方法减少了处理过程，降低了成本，提高了产量。

对于本领域的那些技术人员来说很明显的是，在不脱离本发明实质或范围的情况下，可以在本发明的制造和应用方面作各种修改和变换。因此，倘若本发明的这些修改和变换落在所附权利要求书及其等同物的范围内，那么意欲使本发明覆盖这些修改和变换。

图 1

图 2

图 3A

图 3B

图 3C

图 3D

图 3E

图 3E

图 3G

图 4A

图 4B

图 4C

图 4D

图 4E

图 4F

图 4G

图 5A

图 5B

图 5C

图 5D

图 5E

图 5F

图 5G

图 6

图 7A

图 7B

图 7C

图 7D

图 7E

图 7F

图 7G

图 7H

图 8A

图 8B

图 8C

图 8D

图 8E

图 8F

图 8G

图 8H

图 9A

图 9B

图 9C

图 9D

图 9E

图 9F

图 9G

图 9H

专利名称(译) 液晶显示装置阵列基板的制造方法

|                |                                                                                                        |         |            |

|----------------|--------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | <a href="#">CN1452002A</a>                                                                             | 公开(公告)日 | 2003-10-29 |

| 申请号            | CN03109827.4                                                                                           | 申请日     | 2003-04-11 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                               |         |            |

| 申请(专利权)人(译)    | LG. 菲利浦LCD株式会社                                                                                         |         |            |

| 当前申请(专利权)人(译)  | 乐金显示有限公司                                                                                               |         |            |

| [标]发明人         | 林柄昊                                                                                                    |         |            |

| 发明人            | 林柄昊                                                                                                    |         |            |

| IPC分类号         | G02F1/1368 G02F1/1333 G02F1/1362 G09F9/00 G09F9/30 H01L21/336 H01L29/786 G02F1/136 G03F7/00 G02F11/343 |         |            |

| CPC分类号         | G02F1/13458 G02F1/1362 G02F1/136227 G02F2001/136236                                                    |         |            |

| 代理人(译)         | 徐金国                                                                                                    |         |            |

| 优先权            | 1020020020724 2002-04-16 KR                                                                            |         |            |

| 其他公开文献         | CN100383646C                                                                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                         |         |            |

### 摘要(译)

一种液晶显示装置阵列基板的制造方法包括以下步骤：在一基板上形成一选通线、一选通垫和一栅极；在该选通线、栅极和选通垫上形成一栅极绝缘层；在该栅极绝缘层上形成一有源层；在该有源层上形成一欧姆接触层；在该欧姆接触层上形成一数据线、一数据垫以及源极和漏极；在源极和漏极上形成一像素电极，该像素电极接触漏极；在包括该像素电极的基板上形成第一钝化层；在第一钝化层上形成第二钝化层，第二钝化层暴露选通垫和数据垫之上的第一钝化层；以及对第二钝化层所暴露的第一钝化层制作图案，以暴露选通垫和数据垫。