[45] 授权公告日 2009 年 8 月 12 日

[11] 授权公告号 CN 100527211C

[22] 申请日 2003.1.15

[21] 申请号 200610103143.0

分案原申请号 03103303.2

[30] 优先权

[32] 2002.1.16 [33] JP [31] 007336/2002

[73] 专利权人 株式会社日立制作所

地址 日本东京

[72] 发明人 上田史朗

[56] 参考文献

US4845473 1989.7.4

US5604511A 1997.2.18

US6307532B1 2001.10.23

审查员 索子繁

[74] 专利代理机构 中国国际贸易促进委员会专利

商标事务所

代理人 王永刚

权利要求书 2 页 说明书 22 页 附图 15 页

[54] 发明名称

具有改进的预充电电路的液晶显示设备

[57] 摘要

一种液晶显示设备，包括驱动器电路，用来在水平扫描期开始阶段输出充电电压，接下来输出对应显示数据的灰阶电压至视频信号线。液晶显示设备的驱动方法为：每隔扫描线中的 N 线，其中  $N \geq 2$ ，反转像素电极上的灰阶电压相对于公共电极上的公共电压的极性；并使充电电压的第一充电时间不同于上述充电电压的第二充电时间，第一充电时间对应灰阶电压的极性反转之后立即被扫描的多个扫描线中 N 线的第一线，第二充电时间对应紧随第一线之后立即被扫描的上述 N 线的第二线。

1. 一种液晶显示设备，包括：

液晶层，

多个像素，

对所述多个像素共用设置的公共电极，

电连接于所述多个像素的多个视频信号线，

与所述多个视频信号线交叉排列、电连接于所述多个像素的多个扫描线，

驱动器电路，对于所述多个视频信号线，在一个水平扫描期的开始阶段输出某个值的充电电压，接下来输出对应于视频信号的灰阶电压，其中

所述多个扫描线中的扫描线按照第1、第2、第3、第4扫描线的顺序连续排列，

所述多个像素中的第1、第2、第3、第4个像素分别与第1、第2、第3、第4扫描线电连接，

当以施加于所述公共电极的电压作为基准来考虑提供给所述多个像素的信号极性时，

将提供给所述第1、第2像素的信号的极性反转后的极性信号提供给所述第3、第4像素，

将输出所述充电电压给所述第3像素的第1充电时间设定为比输出所述充电电压给所述第4像素的第2充电时间长。

2. 根据权利要求1所述的液晶显示设备，其中

所述充电电压大于将从所述驱动器电路输出的最大灰阶电压与最小灰阶电压平均以后的值。

3. 根据权利要求1所述的液晶显示设备，其中

随着所述像素的位置远离所述驱动器电路，逐渐增加输出所述充电电压的持续时间。

4. 一种液晶显示设备，包括：

液晶层，

多个像素，

对所述多个像素共用设置的公共电极，

电连接于所述多个像素的多个视频信号线，

与所述多个视频信号线交叉排列、电连接于所述多个像素的多个扫描线，

驱动器电路，对于所述多个视频信号线，在一个水平扫描期的开始阶段输出某个值的充电电压，接下来输出对应于视频信号的灰阶电压，

显示控制装置，用于向该驱动器电路输出充电控制时钟，其中所述多个扫描线中的扫描线按照第1、第2、第3、第4扫描线的顺序连续排列，

所述多个像素中的第1、第2、第3、第4个像素分别与第1、第2、第3、第4扫描线电连接，

当以施加于所述公共电极的电压作为基准来考虑提供给所述多个像素的信号极性时，

将提供给所述第1、第2像素的信号的极性反转后的极性信号提供给所述第3、第4像素，

在第1期间输出所述充电电压给所述第3像素，

在第2期间输出所述充电电压给所述第4像素，

通过充电控制时钟将所述第1期间设定为长于所述第2期间。

5. 根据权利要求4所述的液晶显示设备，其中

所述充电电压大于将从所述驱动器电路输出的最大灰阶电压与最小灰阶电压平均以后的值。

6. 根据权利要求4所述的液晶显示设备，其中

随着所述像素的位置远离所述驱动器电路，逐渐增加输出所述充电电压的持续时间。

## 具有改进的预充电电路的液晶显示设备

本申请是申请日为2003年1月15日、申请号为03103303.2、发明名称为“具有改进的预充电电路的液晶显示设备及其驱动方法”的发明专利申请的分案申请。

### 技术领域

本发明涉及液晶显示设备和驱动液晶显示设备的方法，更具体地说，涉及适合诸如N线反转(N-line-inversion)驱动方法之类的驱动方法的技术，N线反转驱动方法中每隔N条扫描线应用于像素的灰阶电压的极性被反转。

### 背景技术

有源矩阵型显示器被广泛用作笔记本个人电脑等设备（下文简称为个人电脑）的显示器，在有源矩阵型显示器中，提供有源元件（例如，薄膜晶体管）至每个像素并打开或关闭。

在有源矩阵型液晶显示设备中，人们比较熟悉的是TFT型液晶模块，它包括使用薄膜晶体管（TFT）作为有源元件的液晶显示面板，配置在液晶显示面板长边的漏驱动器（drain driver），配置在液晶显示面板短边的栅驱动器，和配置在液晶显示面板背面的接口部件。

我们知道在这种液晶显示模块中，应用预充电电压至液晶显示面板中的漏信号线，以在水平扫描期（下文称为预充电期）的开始阶段，在预定的期间内把漏信号线充电至预充电电压。

举例说来，这样的技术在日本公开号为Hei 11-85107（1999年3月30日公开）的专利中被说明。

### 发明内容

通常，如果沿液晶层应用相同电压（直流电压）较长一段时间，液晶模块的倾角被调整，结果导致液晶层表现图像保留（image retention）现象，因此，液晶层的寿命缩短。

为了阻止上述现象的发生，在液晶显示模块中，每隔固定的一段

时间，沿液晶层应用电压的极性被反转。相对于应用于公共电极的公共电压，应用于像素电极的灰阶电压每隔固定的一段时间在正极和负极之间切换。

人们知道沿液晶层应用交流电压的两种驱动方法，一种是相对于固定公共电极电压对称 (symmetrical-about-fixed-common-electrode-voltage) 的驱动方法，另一种是公共电极电压反转的驱动方法。

公共电极电压反转驱动方法使公共电极上的公共电压和像素电极上的灰阶电压两者其中之一极性为正，另一个的极性为负，反之亦然。

相对于固定公共电极电压对称的驱动方法保持应用于公共电极上的公共电压固定不变，相对于应用于公共电极上的公共电压，在正极性和负极性之间切换应用于像素电极上的灰阶电压。在这种驱动方法的例子中，人们熟悉的是点反转驱动方法和 n 线 (例如两线) 反转驱动方法。

在本说明书中，相对于应用于通常与像素电压相关的公共电极上的电压，定义应用于像素电极上的灰阶电压的极性。

图 16A 和 16B 是用来帮助解释在采用点反转驱动方法作为液晶显示模块驱动方法的情况下，施加于漏驱动器的漏信号线的灰阶电压 (即应用于像素电极的灰阶电压) 极性的图表。

如图 16A 所示，在点反转驱动方法中，例如，在奇数帧中，相对于应用于公共电极上的公共电压 ( $V_{com}$ )，奇数扫描线中的奇数漏信号线被施加来自漏驱动器的负极性灰阶电压 (图 16A 以实心圆表示)，相对于应用于公共电极上的公共电压 ( $V_{com}$ )，奇数扫描线中的偶数漏信号线被施加来自漏驱动器的正极性灰阶电压 (图 16A 以空心圆表示)。反之，偶数扫描线中的奇数漏信号线被施加来自漏驱动器的正极性灰阶电压，偶数扫描线中的偶数漏信号线被施加来自漏驱动器的负极性灰阶电压。

每个扫描线上的电压的极性在连续的帧上被反转。如图 16B 所示，在偶数帧中，奇数扫描线中的奇数漏信号线被施加来自漏驱动器的正极性灰阶电压 (图 16B 以空心圆表示)，奇数扫描线中的偶数漏信号线被施加来自漏驱动器的负极性灰阶电压 (图 16B 以实心圆表示)。反之，

偶数扫描线中的奇数漏信号线被施加来自漏驱动器的负极性灰阶电压，偶数扫描线中的偶数漏信号线被施加来自漏驱动器的正极性灰阶电压。

在点反转驱动方法中，应用相反极性的电压至相邻的漏信号线，因此，流经相邻栅电极的电流互相抵消，这使得降低能耗成为可能。

最小化显示质量的降低也是可能的，由于流入公共电极的电流很小，因此由电流引起的电压降很小，公共电极上的电压很稳定。

但是，在个人电脑含有采用点反转驱动方法的液晶显示模块的情况下，会有液晶显示面板上某种显示图案发生闪烁的问题，因此当极性反转的定时和显示图案（例如，Windows（注册商标）的结束图案）之间存在特定关系时显示质量降低。

这个问题可以通过采用 N 线反转（例如，两扫描线反转）驱动方法解决，这种方法中每隔 N 条扫描线从漏驱动器施加于漏信号线的灰阶电压的极性被反转。

但是，在使用 N 扫描线反转（例如，两扫描线反转）驱动方法的情况下，会有如图 17 所示的每隔 N 个扫描线出现伪水平线的问题，因此，液晶显示面板上的显示质量严重降低，例如，当具有相同灰阶水平和相同颜色的图案显示于整个显示区时。

随着液晶显示模块之类的液晶显示设备对更大尺寸液晶面板的市场需求，要求液晶面板增加分辨率，从而能够显示 1024x768 像素的 XGA（扩展图形阵列）显示模式，1280x1024 像素的 SXGA（高级扩展图形阵列）显示模式，和 1600x1200 像素的 UXGA（超级扩展图形阵列）显示模式。

因此，随着在垂直扫描期中水平扫描线数量的增加，用来写每个水平线的时间减少，于是，漏驱动器的输出延迟时间（tDD）导致严重的问题。

具体说来，当漏驱动器的输出延迟时间（tDD）相对用来写每个水平扫描线的时间的比值增加时，像素写电压变得不足，这导致液晶显示面板上显示质量的明显降低。

因此，传统的液晶显示模块如此设置，在预充电期间施加预充电

电压至漏信号线，以把漏信号线充电至预充电电压。

但是，即使在预充电期间施加预充电电压至漏信号线，在远离漏驱动器的漏信号线远端部分，预充电电压也不能达到所需的预充电电压。

因此，位置远离漏驱动器的像素的写电压变得不足，可以想到液晶显示面板上所显示图像的显示质量大大降低。

本发明就是为了解决现有技术的问题而提出的，本发明的一个目的是提供液晶显示设备和它的驱动方法中的技术，此技术在灰阶电压的极性每隔  $N$  ( $N \geq 2$ ) 条扫描线被反转的情况下，能够阻止显示区域中伪水平线的产生，从而提高所显示图像的显示质量。

本发明的另一目的是提供液晶显示设备和它的驱动方法中的技术，与传统的技术相比，此技术能够降低靠近漏驱动器的视频信号线近端部分在预充电期间的充电电压和远离漏驱动器的视频信号线远端部分在预充电期间的充电电压之间的电压差。

将通过下面的说明书和附图解释本发明的上述目的和新特征。

本发明的代表性结构如下：

按照本发明的实施方式，提供驱动液晶显示设备的方法，上述液晶显示设备包括液晶层，以矩阵形状排列的多个像素，上述多个像素每个都装备有像素电极，以在上述液晶层中上述像素电极和通常与上述多个像素相关的公共电极之间产生电场，连接至上述多个像素的多个视频信号线，与上述多个视频信号线交叉排列并连接至上述多个像素的多个扫描线，和驱动器电路，它在水平扫描期开始阶段输出充电电压，接下来输出对应显示数据的灰阶电压至上述多个视频信号线，上述方法包括：每隔上述多个扫描线中的  $N$  条线，其中  $N \geq 2$ ，反转上述灰阶电压相对于上述公共电极上的公共电压的极性；上述充电电压的第一充电时间，它对应上述灰阶电压的极性反转之后立即被扫描的上述多个扫描线中  $N$  条线的第一线，不同于上述充电电压的第二充电时间，第二充电时间对应紧随上述第一线之后立即被扫描的上述  $N$  条线的第二线。

按照本发明的另一实施方式，提供驱动液晶显示设备的方法，上

述液晶显示设备包括液晶层，以矩阵形状排列的多个像素，上述多个像素每个都装备有像素电极，以在上述液晶层中上述像素电极和通常与上述多个像素相关的公共电极之间产生电场，连接至上述多个像素的多个视频信号线，与上述多个视频信号线交叉排列并连接至上述多个像素的多个扫描线，和驱动器电路，它在水平扫描期开始阶段输出充电电压，接下来输出对应显示数据的灰阶电压至上述多个视频信号线，上述方法包括随上述驱动器电路至上述多个扫描线中的被扫描线的距离，而改变上述充电电压的充电时间。

按照本发明的另一实施方式，提供驱动液晶显示设备的方法，上述液晶显示设备包括液晶层，以矩阵形状排列的多个像素，上述多个像素每个都装备有像素电极，以在上述液晶层中上述像素电极和通常与上述多个像素相关的公共电极之间产生电场，连接至上述多个像素的多个视频信号线，与上述多个视频信号线交叉排列并连接至上述多个像素的多个扫描线，驱动器电路，它在水平扫描期开始阶段输出充电电压，接下来输出对应显示数据的灰阶电压至上述多个视频信号线，和显示控制设备，它用来输出控制上述液晶层交流驱动的交流驱动信号，并输出充电控制时钟至上述驱动器电路，上述方法包括：每隔上述多个扫描线中的  $N$  条线，其中  $N \geq 2$ ，基于上述交流驱动信号，反转上述灰阶电压相对于上述公共电极上的公共电压的极性；随时间改变上述充电控制时钟的第一级持续时间，以使上述充电电压的第一充电时间，它对应上述灰阶电压的极性反转之后立即被扫描的上述多个扫描线中  $N$  条线的第一线，不同于上述充电电压的第二充电时间，第二充电时间对应紧随上述第一线之后立即被扫描的上述  $N$  条线的第二线。

按照本发明的另一实施方式，提供驱动液晶显示设备的方法，上述液晶显示设备包括液晶层，以矩阵形状排列的多个像素，上述多个像素每个都装备有像素电极，以在上述液晶层中上述像素电极和通常与上述多个像素相关的公共电极之间产生电场，连接至上述多个像素的多个视频信号线，与上述多个视频信号线交叉排列并连接至上述多个像素的多个扫描线，驱动器电路，它在水平扫描期开始阶段输出充电电压，接

下来输出对应显示数据的灰阶电压至上述多个视频信号线，和显示控制设备，它用来输出充电控制时钟至上述驱动器电路，上述方法包括：随时间改变上述充电控制时钟的第一级持续时间，以使上述充电电压的充电时间随上述驱动器电路至上述多个扫描线中的被扫描线的距离而改变。

按照本发明的另一实施方式，提供液晶显示设备，它包括：液晶层；以矩阵形状排列的多个像素，上述多个像素每个都装备有像素电极，以在上述液晶层中上述像素电极和通常与上述多个像素相关的公共电极之间产生电场；连接至上述多个像素的多个视频信号线；与上述多个视频信号线交叉排列并连接至上述多个像素的多个扫描线；驱动器电路，它在水平扫描期开始阶段输出充电电压，接下来输出对应显示数据的灰阶电压至上述多个视频信号线；和显示控制设备，它用来输出控制上述液晶层交流驱动的交流驱动信号，并输出充电控制时钟至上述驱动器电路，其中上述显示控制设备装备有脉冲持续时间改变电路，它用来改变上述充电控制时钟的第一级持续时间，上述驱动器电路包括：极性反转电路，它用来每隔上述多个扫描线中的  $N$  条线，其中  $N \geq 2$ ，基于上述交流驱动信号，反转上述灰阶电压相对于上述公共电极上的公共电压的极性，和充电时间控制电路，它用来基于上述充电控制时钟上述第一级的上述持续时间，控制上述充电电压的充电时间，以使上述充电电压的第一充电时间，它对应上述灰阶电压的极性反转之后立即被扫描的上述多个扫描线中  $N$  条线的第一线，不同于上述充电电压的第二充电时间，第二充电时间对应紧随上述第一线之后立即被扫描的上述  $N$  条线的第二线。

按照本发明的另一实施方式，提供液晶显示设备，它包括：液晶层；以矩阵形状排列的多个像素，上述多个像素每个都装备有像素电极，以在上述液晶层中上述像素电极和通常与上述多个像素相关的公共电极之间产生电场；连接至上述多个像素的多个视频信号线；与上述多个视频信号线交叉排列并连接至上述多个像素的多个扫描线；驱动器电路，它在水平扫描期开始阶段输出充电电压，接下来输出对应显示数据的灰阶电压至上述多个视频信号线；和显示控制设备，它用来输出充电控制

时钟，其中上述显示控制设备包括脉冲持续时间改变电路，它用来改变上述充电控制时钟的第一级持续时间，上述驱动器电路包括充电时间控制电路，它用来基于上述充电控制时钟上述第一级的上述持续时间，改变上述充电电压的充电时间，以使上述充电电压的上述充电时间随上述驱动器电路至上述多个扫描线中的被扫描线的距离而改变。

### 附图说明

附图中，所有图表中同样的标号代表同样的元件，其中：

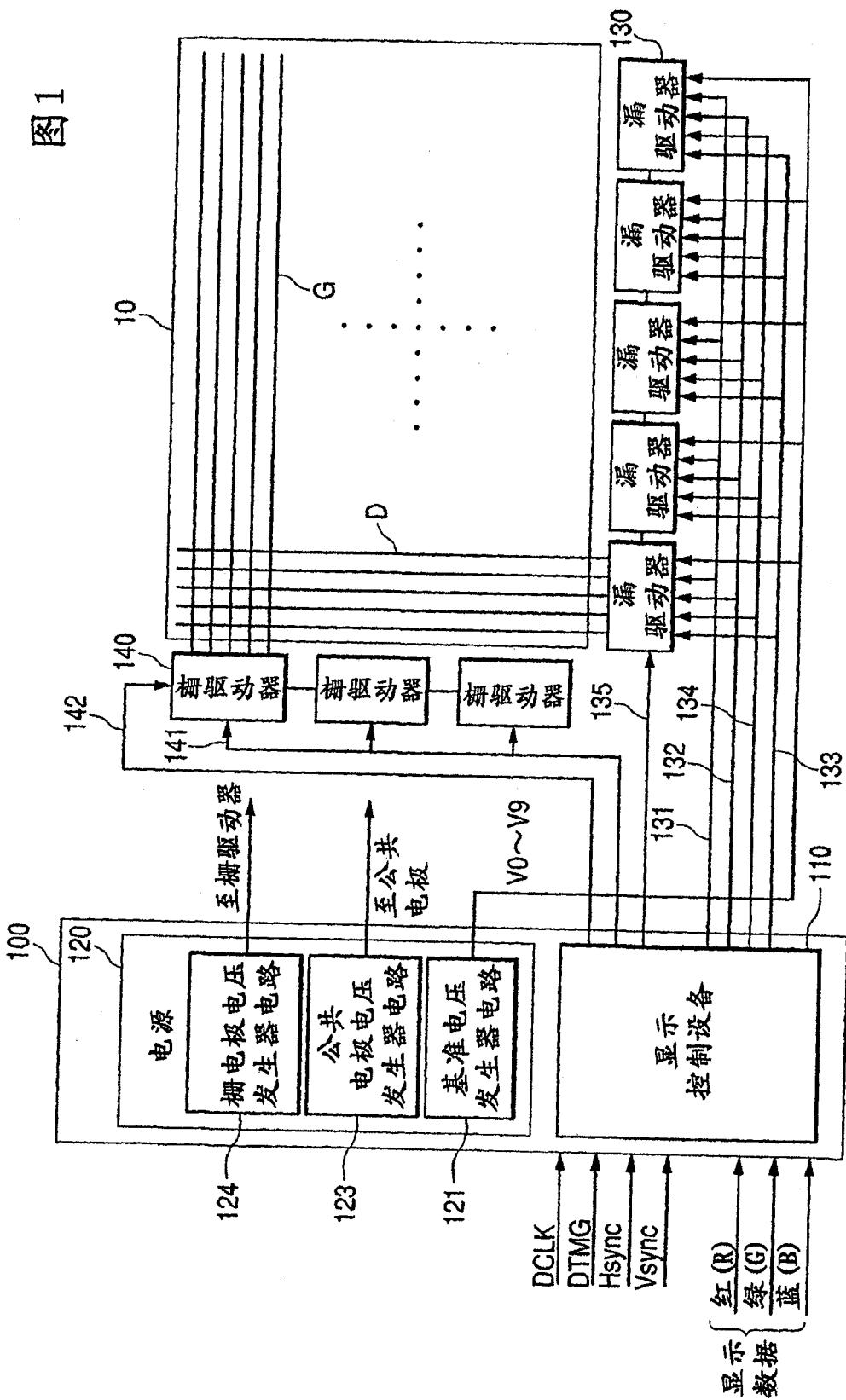

图 1 是表示本发明适用的液晶显示模块的示意构造框图；

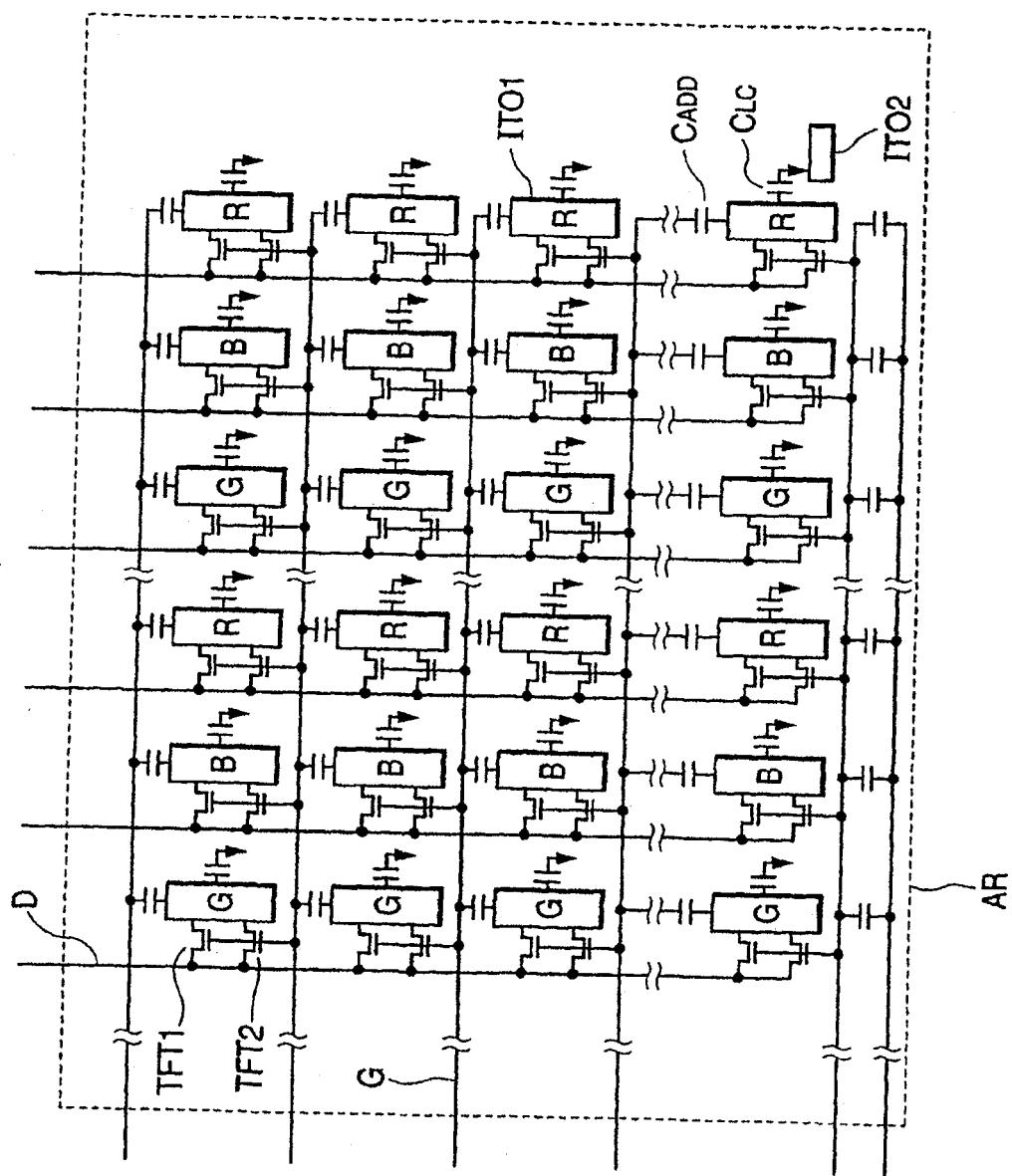

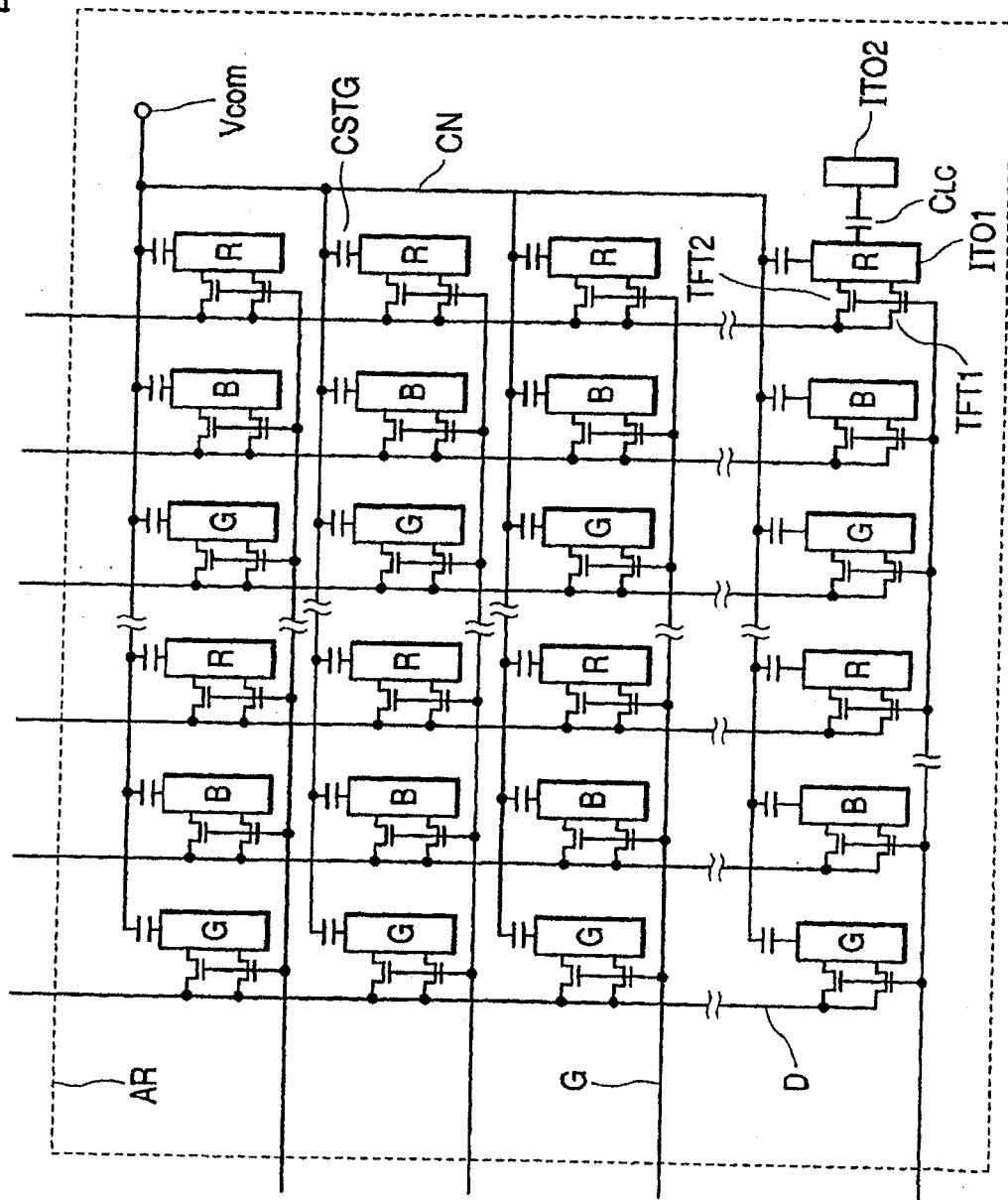

图 2 表示图 1 所示液晶显示面板实例的等效电路；

图 3 表示图 1 所示液晶显示面板另一实例等效电路；

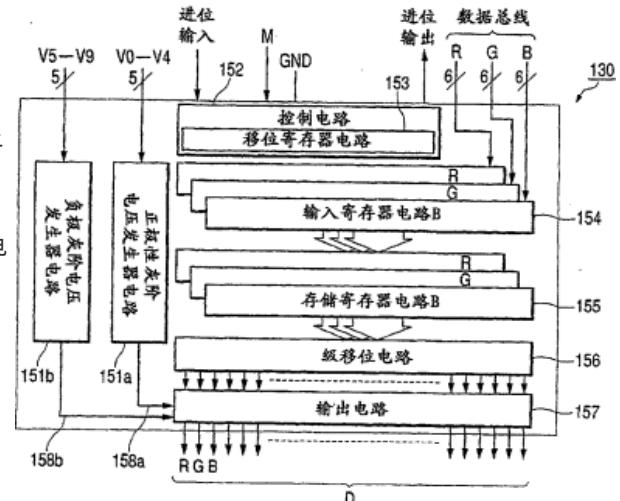

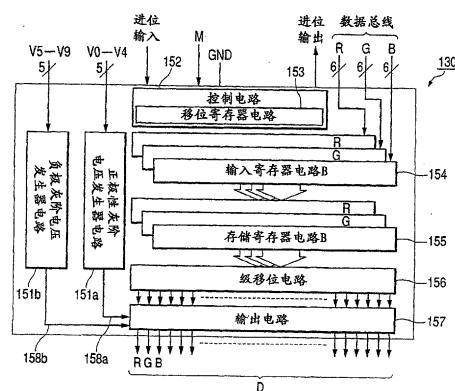

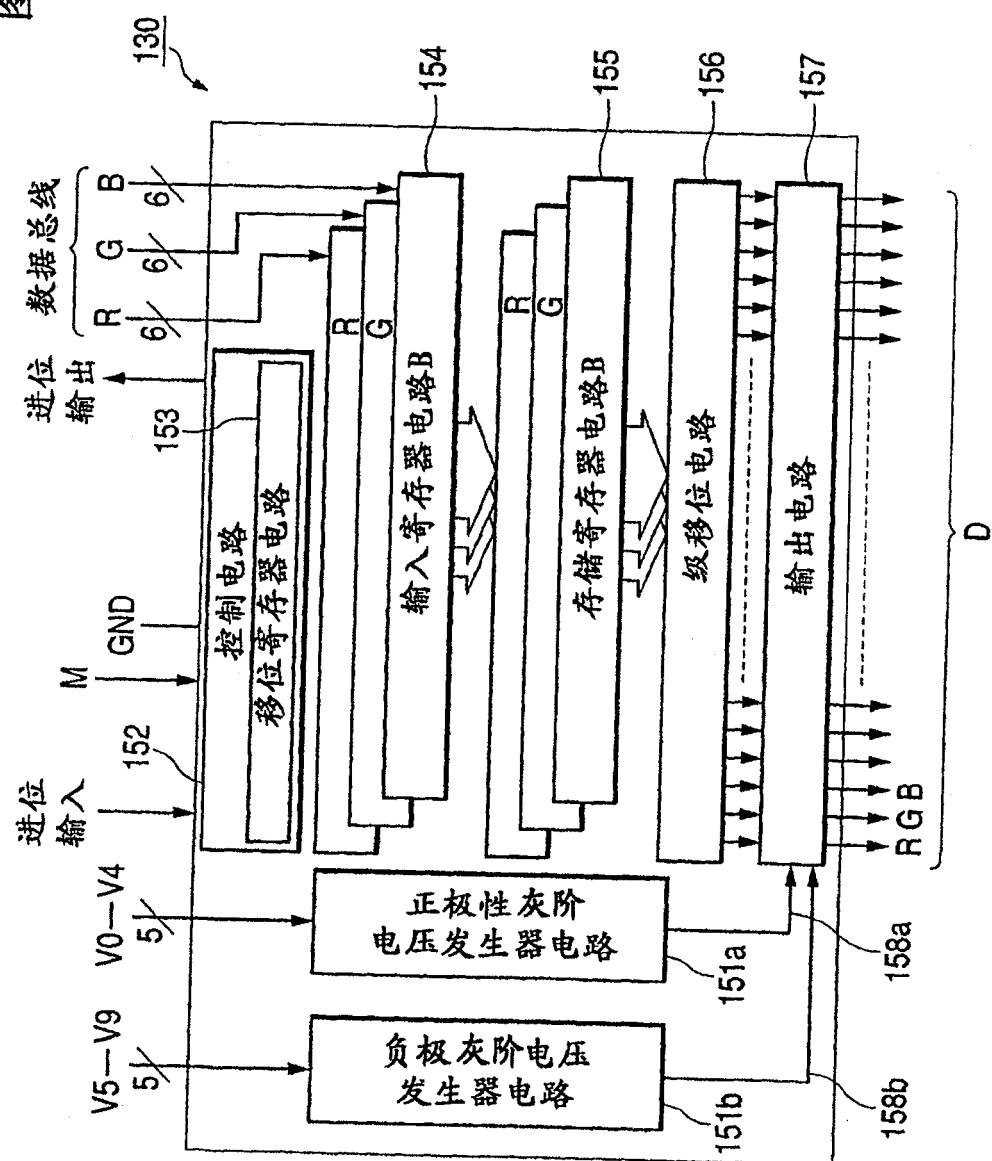

图 4 是表示图 1 所示漏驱动器的示意构造框图；

图 5 是解释图 4 所示漏驱动器的构造的框图，它以其输出电路为中心；

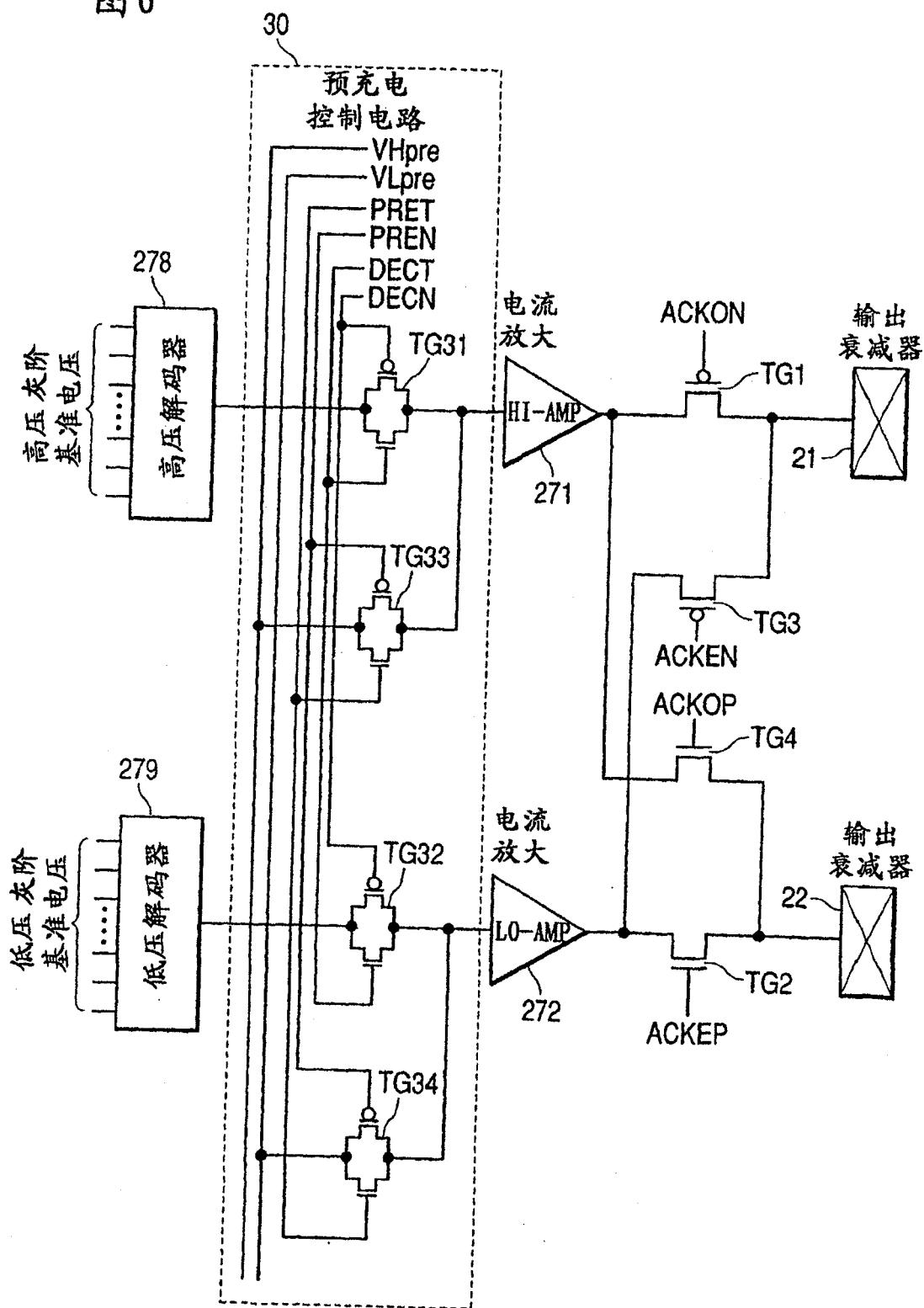

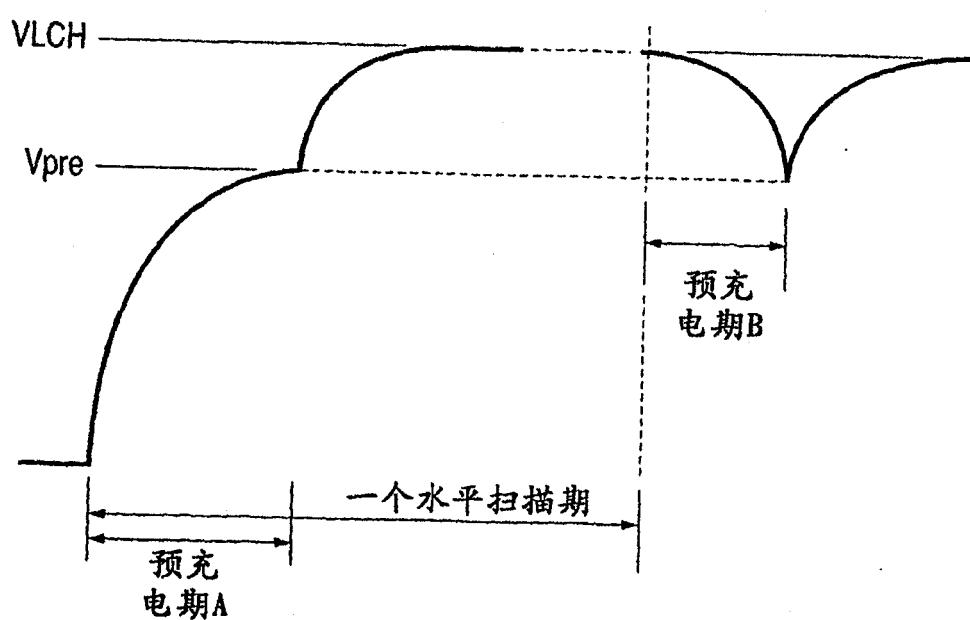

图 6 是解释图 5 所示预充电电路操作的简图；

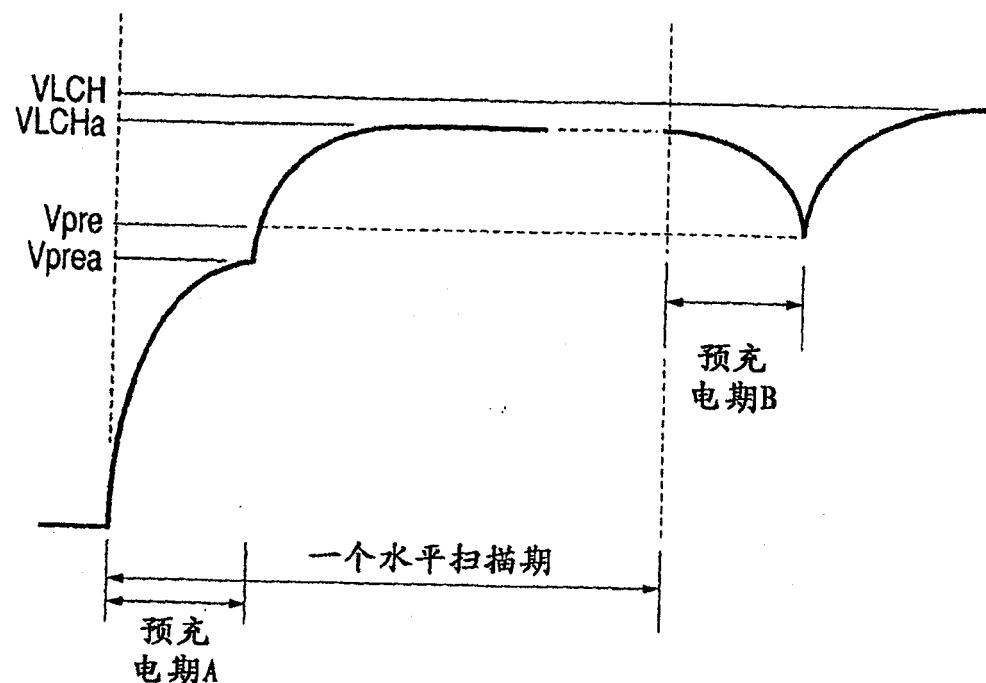

图 7 是解释图 1 所示液晶显示面板的漏信号线 (D) 电压波形的简图；

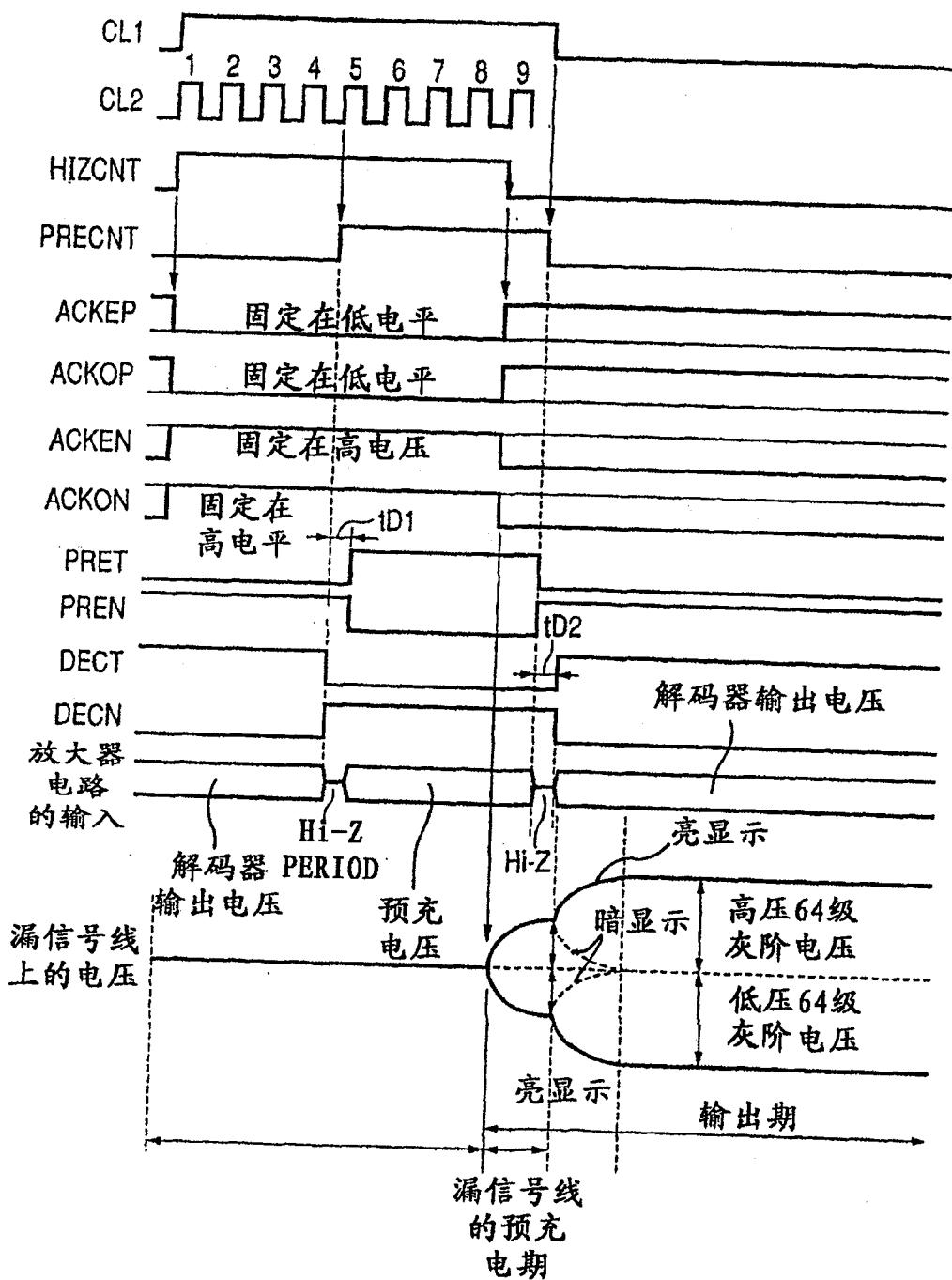

图 8 表示解释图 6 所示预充电电路操作的脉冲波形图实例；

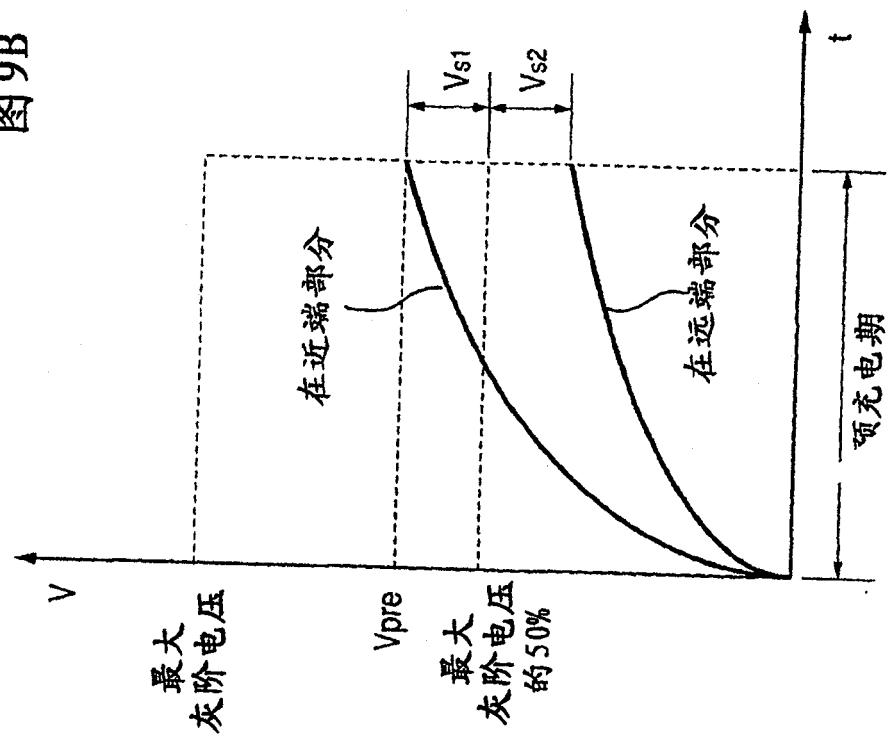

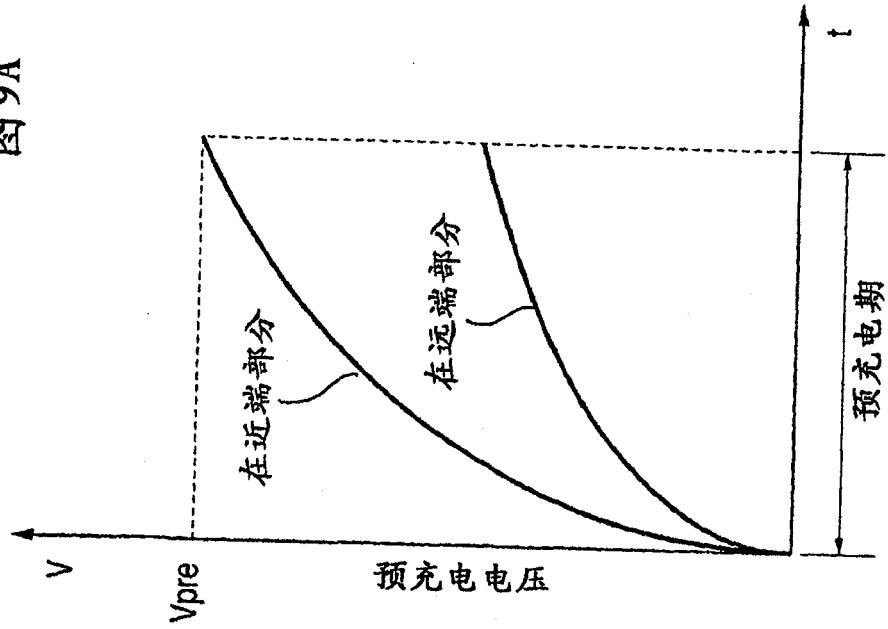

图 9A 和 9B 解释在预充电期间靠近漏驱动器的漏信号线 (D) 近端部分的充电电压和远离漏驱动器的漏信号线 (D) 远端部分的充电电压的电压变化；

图 10A 和 10B 解释在使用两线反转驱动方法驱动液晶显示模块的情况下由漏驱动器施加至漏信号线 (D) 的灰阶电压的极性；

图 11 解释在使用两线反转驱动方法驱动液晶显示模块的情况下显示图像中伪水平线的产生原因；

图 12 解释按照本发明的驱动方法的概要；

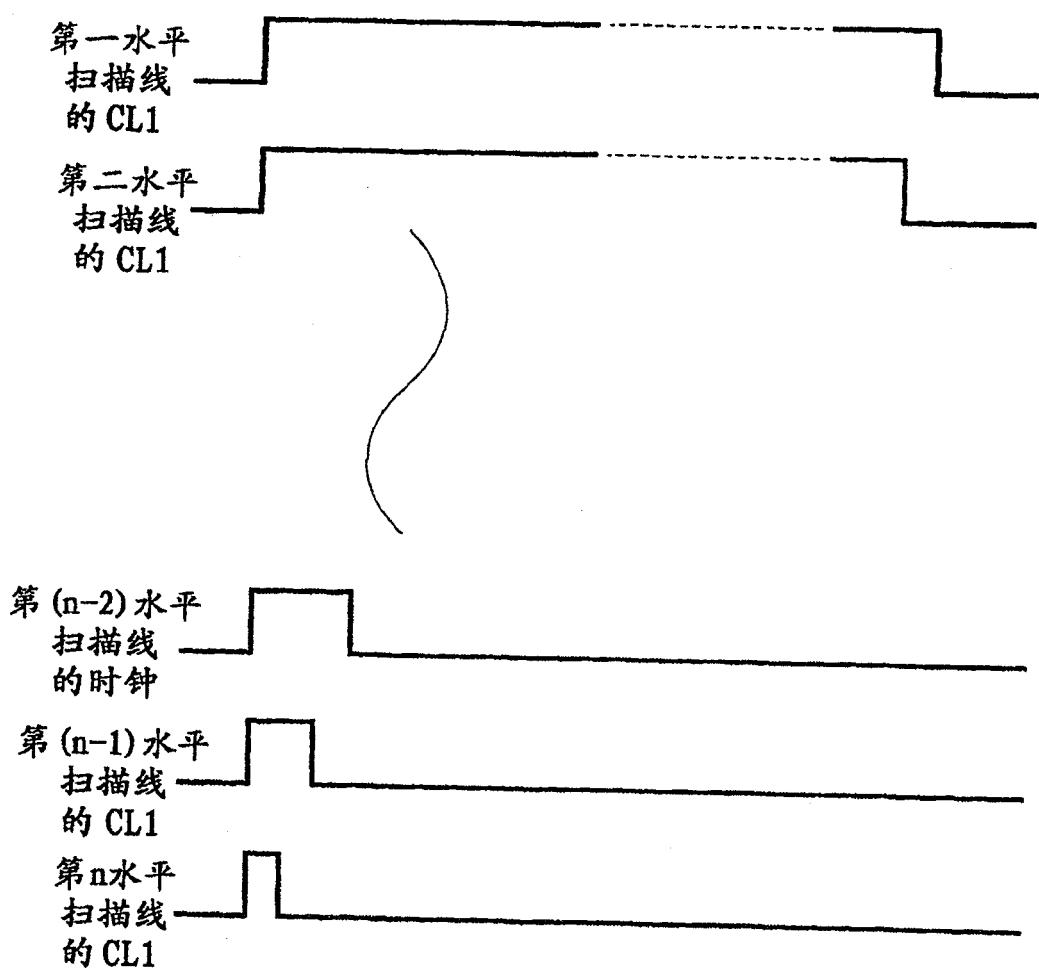

图 13 解释按照本发明的实施方式中每个扫描线的时钟脉冲 (CL1) 的 H 水平期；

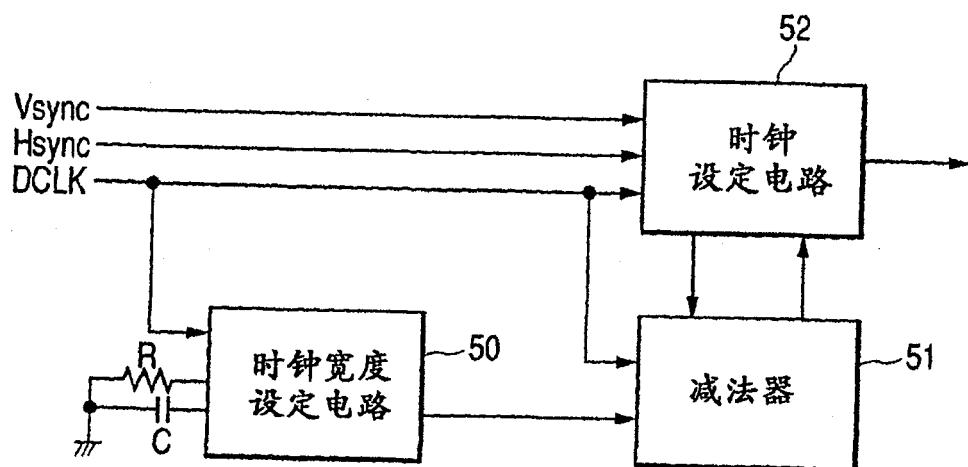

图 14 是表示按照本发明的实施方式中的时钟 (CL1) 发生器电路

的框图；

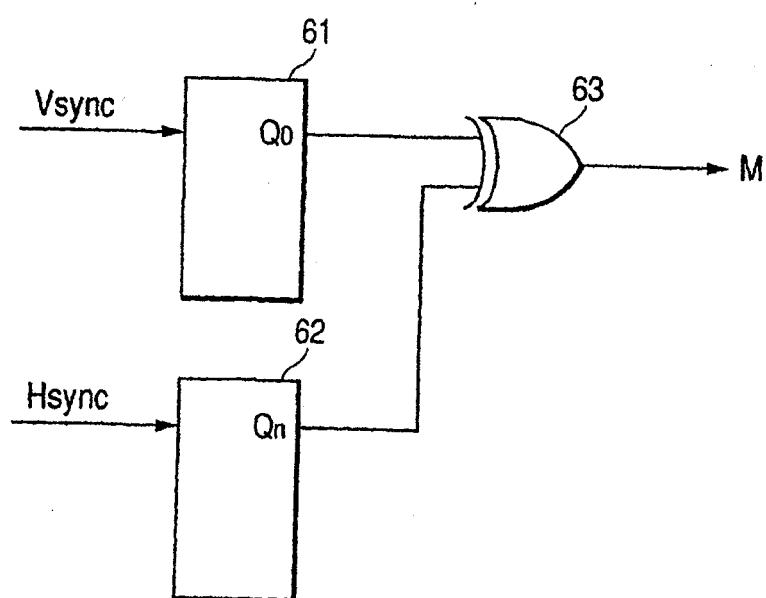

图 15 是表示按照本发明的实施方式的液晶显示模块中，用以产生交流驱动信号 (M) 的电路构造的电路图；

图 16A 和 16B 解释在使用点反转驱动方法驱动液晶显示模块的情况下由漏驱动器施加至漏信号线 (D) 的灰阶电压的极性；

图 17 是表示在使用两线反转驱动方法的情况下在液晶显示面板上的 N 扫描线间隙之间产生伪水平线的示意图。

### 具体实施方式

现在将参照附图详细描述本发明的优选实施方式。

在用来解释实施方式的参考图中，具有相同功能的元件被赋予相同的标号，并将省去解释的重复。

本发明适用的 TFT 型液晶显示模块的基本构造

图 1 是表示本发明适用的液晶显示模块的示意构造框图。

在图 1 所示的液晶显示模块中，漏驱动器 130 配置在液晶显示面板 10 的长边，栅驱动器 140 配置在液晶显示面板 10 的短边。漏驱动器 130 和栅驱动器 140 直接安装在液晶显示面板 10 的玻璃衬底(例如，TFT 安装衬底，下文称作 TFT 衬底)的外围部分。接口部件 100 安装在接口板上，这个接口板安装在液晶显示面板 10 的背面上。

图 1 所示液晶显示面板 10 的构造

图 2 表示图 1 所示液晶显示面板 10 实例等效电路。如图 2 所示，液晶显示面板 10 含有多个以矩阵形状排列的像素。每个像素装置在被两个相邻漏信号线 (D) 和两个相邻栅信号线 (G) 包围的区域内。

每个像素含有薄膜晶体管 (TFT1, TFT2)。每个像素的薄膜晶体管 (TFT1, TFT2) 的源电极被连接至像素电极 (IT01)。在像素电极 (IT01) 和公共电极 (IT02) 之间提供液晶层，因此由液晶层形成等效液晶电容 (CLC)，它举例说明为连接在像素电极 (IT01) 和公共电极 (IT02) 之间。另外，存储电容 (CADD) 连接在薄膜晶体管 (TFT1, TFT2) 的源电极和上述栅信号线 (G) 之间。

图 3 表示图 1 所示液晶显示面板 10 的另一实例等效电路。

在图 2 所示的例子中，在上述扫描线的栅信号线 (G) 和源电极之间形成存储电容 (CADD)，但是在图 3 示例的等效电路中，在公共信号线 (COM) 和源电极之间形成附加电容 (CSTG)。

本发明对图 2 和图 3 所示的两种液晶显示面板都分别适用。在图 2 所示的液晶显示面板 10 中，应用于上述栅信号线 (G) 之上的脉冲通过存储电容被导入像素电极 (IT01)，而在图 3 所示的液晶显示面板 10 中，脉冲不会导入像素电极，因此可以获得更好的显示质量。

图 2 和图 3 表示垂直电场型（所谓的扭转向列型）液晶显示面板的等效电路。在图 2 和图 3 中，标符 AR 代表显示区。图 2 和图 3 是与实际几何排列一致的电路图。

在垂直电场型液晶显示设备中，通过沿夹在形成于一对反向透光衬底内表面上的一对反向透光电极之间的液晶材料层应用的垂直电场，控制每个像素的光透射。每个像素分别通过在两个反向透光衬底内表面上制作的两个电极形成。为了说明设备构造和操作的目的，1975 年 11 月 Fergason 公布的美国第 3,918,796 号专利以引用方式包含在本文中。

在图 2 和图 3 所示的液晶显示面板 10 中，沿一列排列的所有像素的薄膜晶体管 (TFT1, TFT2) 输出电极被连接至相同的漏信号线 (D)。每个漏信号线 (D) 被连接至漏驱动器 130 (见图 1)，漏驱动器 130 施加灰阶电压至排列在同一列的液晶像素。

沿同一行排列的所有像素的薄膜晶体管 (TFT1, TFT2) 栅电极被连接至相同的栅信号线 (G)，每个栅信号线 (G) 被连接至栅驱动器 140，栅驱动器 140 在水平扫描期间施加扫描驱动电压 (正或负偏压) 至以相应行排列第每个像素的薄膜晶体管 (TFT1, TFT2) 栅电极。

### 图 1 所示的接口部件 100 的构造及其操作概要

图 1 所示的显示控制设备 110 由大规模集成电路 (LSI) 制成，它基于显示控制信号，例如外部时钟信号 (DCLK)，显示定时信号 (DTMG)，水平同步信号 (Hsync)，垂直同步信号 (Vsync) 和由计算机主机发出的显示数据 (红，绿，蓝信号)，控制和驱动漏驱动器 130 和栅驱动器

140。

一旦接收显示定时信号 (DTMG)，显示控制设备 110 判断它为显示开始位置，并通过信号线 135 输出开始脉冲 (显示数据接收开始信号) 至第一漏驱动器 130，并接着通过显示数据总线 133 输出接收到的对应一行像素的显示数据至漏驱动器 130。此时显示控制设备 110 通过信号线 131 输出显示数据锁存器时钟 (CL2) (下文简称为时钟 (CL2)) 至每个漏驱动器 130 的数据锁存器电路 (未显示)，时钟 (CL2) 作为锁存显示数据的显示控制信号。

由计算机主机发出的显示信号，以红 (R)，绿 (G) 和蓝 (B) 显示数据三个一组的形式传送，例如，在特定的时间内，各显示数据对于一个像素包含六位。

第一漏驱动器 130 中数据锁存器电路的锁存操作，通过输入第一漏驱动器 130 的开始脉冲控制。第一漏驱动器 130 中数据锁存器电路的锁存操作完成之后，从第一漏驱动器 130 输出开始脉冲至第二漏驱动器 130，第二漏驱动器 130 中数据锁存器电路的锁存操作通过开始脉冲控制。以相同的方式连续，控制后续的漏驱动器 130 中数据锁存器电路的锁存操作，以使显示数据被正确地写入数据锁存器电路。

当显示定时信号 (DTMG) 的输入完成时，或在显示定时信号 (DTMG) 输入之后的特定时间，显示控制设备判断对应水平扫描线的显示数据的输入已经完成，接下来显示控制设备 110 通过信号线 132，施加输出定时控制时钟 (CL1) (下文简称为时钟 (CL1)) 至相应的漏驱动器 130，时钟 (CL1) 作为显示控制信号，用来把对应存储在漏驱动器 130 的数据锁存器电路中的显示数据的灰阶电压，输出至液晶显示面板 10 的漏信号线 (D)。

当显示控制设备 110 在垂直同步信号 (Vsnc) 输入之后含有第一显示定时信号 (DTMG) 时，显示控制设备 110 判断第一显示定时信号 (DTMG) 为第一显示线时间，并通过信号线 142 输出帧开始命令信号 (FLM) 至一个栅驱动器 140。

基于水平同步 (Hsync)，显示控制设备 110 通过信号线 141 输出

时钟 (CL3) 至栅驱动器 140, 时钟 (CL3) 作为具有等于水平扫描期的重复期的移位时钟, 以使栅驱动器 140 在水平扫描期连续地应用正偏压至液晶显示面板 10 的相应栅信号线 (G)。鉴于此, 连接至液晶显示面板 10 的每个栅信号线 (G) 的多个薄膜晶体管 (TFT1, TFT2) 在水平扫描期间具有导电性。上述操作组液晶显示面板 10 上显示图像。

#### 图 1 所示电源电路 120 的构造

图 1 所示电源电路 120 包括灰阶基准电压发生器电路 121, 公共电极电压 (计数电极) 发生器电路 123 和栅电极电压发生器电路 124。灰阶基准电压发生器电路 121 由串联电阻电压分配器电路制成, 并输出 10 级灰阶基准电压 (V0 至 V9)。这些灰阶基准电压 (V0 至 V9) 被施加至相应的漏驱动器 130。交流驱动信号 (交流驱动的定时信号, M) 也从显示控制设备 110 通过信号线 134 被施加至每个漏驱动器 130。公共电极电压发生器电路 123 产生公共电压 (Vcom), 并应用于公共电极 (IT02), 栅电极电压发生器电路 124 产生驱动电压 (正和负偏压), 并应用于薄膜晶体管 (TFT1, TFT2) 的栅电极。

#### 图 1 所示漏驱动器 130 的构造

图 4 是表示图 1 所示漏驱动器的示意构造框图。每个漏驱动器 130 由大规模集成电路 (LSI) 组成。

图 4 中, 正极性灰阶电压发生器电路 151a 基于由灰阶基准电压发生器电路 121 (见图 1) 施加的正极性 5 级灰阶基准电压 (V0 至 V4), 产生正极性 64 级灰阶电压, 并通过电压总线 158a 输出正极性 64 级灰阶电压至输出电路 157。负极性灰阶电压发生器电路 151b 基于由灰阶基准电压发生器电路 121 (见图 1) 施加的负极性 5 级灰阶基准电压 (V5 至 V9), 产生负极性 64 级灰阶电压, 并通过电压总线 158b 输出负极性 64 级灰阶电压至输出电路 157。

漏驱动器 130 的控制电路 152 中的移位寄存器电路 153 基于由显示控制设备 110 (见图 1) 施加的时钟 (CL2), 产生用于输入寄存器电路 154 的数据接收信号, 并输出数据接收信号至输入寄存器电路 154。输入寄存器电路 154 基于由移位寄存器电路 153 输出的数据接收信号,

锁存每种颜色包含六位的数据，它在数目上等于漏驱动器 130 的输出端数目，与由显示控制设备 110 输入的时钟 (CL2) 同步。

一旦接收来自显示控制设备 110 的时钟 (CL1)，存储寄存器电路 155 把存储在输入寄存器电路 154 中的显示数据锁存器存在存储寄存器电路 155 中。存储寄存器电路 155 接收的显示数据通过级移位电路 156 被输入至输出电路 157。

输出电路 157 从正极性 64 级灰阶电压和负极性 64 级灰阶电压中，选择对应显示数据的灰阶电压，并输出所选灰阶电压至相应的漏信号线 (D)。

图 5 是解释图 4 所示漏驱动器 130 的构造的框图，它以输出电路 157 的构造为中心。

图 5 中，标号 153 代表图 4 所示的控制电路 152 中的移位寄存器电路，标号 156 代表图 4 所示的级移位电路。数据锁存器电路 265 代表图 4 所示的输入寄存器电路 154 和存储寄存器电路 155。另外，解码器部件 (灰阶电压选择器电路) 261，放大器偶电路 263，和切换放大器偶电路 263 输出的切换部件 (2) 264，组成图 4 所示的输出电路 157。

切换部件 (1) 262 和切换部件 (2) 264 基于交流驱动信号 (M) 控制。标符 D1 至 D6 分别代表第一至第六漏信号线 (D)。

在图 5 所示的漏驱动器 130 中，通过切换部件 (1) 262 改变输入数据锁存器电路 265 (更具体地说，图 4 所示的输入寄存器 154) 的数据接收信号，相同颜色的显示数据被输入相同颜色的相邻数据锁存器电路 265。

下文解释解码部件 261 和放大器偶电路 263。下面将解释预充电控制电路 (下文简称预充电电路) 30。

解码器部件 261 包括高压解码器电路 278 和低压解码器电路 279。高压解码器电路 278 从由灰阶电压发生器电路 151a 通过电压总线 158a 施加的正极性 64 级灰阶电压中，选择对应由相应数据锁存器电路 265 (更具体地说，如图 4 所示的存储寄存器 155) 施加的显示数据的正极性灰阶电压。电压解码器电路 279 从由灰阶电压发生器电路 151b 通过

电压总线 158b 输出的负极性 64 级灰阶电压中，选择对应由相应数据锁存器电路 265 施加的显示数据的负极性灰阶电压。

一对高压解码器电路 278 和电压解码器电路 279 被提供至一对相邻的数据锁存器电路 265。放大器偶电路 263 包括高压放大器电路 271 和低压放大器电路 272。高压放大器电路 271 接收高压解码器电路 278 中产生的正极性灰阶电压，电流放大正极性灰阶电压，并把它输出。低压放大器电路 272 接收低压解码器电路 279 中产生的负极性灰阶电压，电流放大负极性灰阶电压，并把它输出。

在点反转驱动方法中，应用于两个相邻漏信号线 D1, D4 的，举例来说分别用来显示相同颜色的灰阶电压的极性，互相相反。放大器偶电路 263 的高压放大器电路 271 和低压放大器电路 272 的排列顺序为：高压放大器电路 271 → 低压放大器电路 272 → 高压放大器电路 271 → 低压放大器电路 272。

起初，通过切换部件 (1) 262，改变输入数据锁存器电路 265 的数据接收信号，输入相邻漏信号线 D1, D4，举例来说分别用来显示相同颜色的两个显示数据其中之一，例如漏信号线 D1 的数据，被输入图 5 所示连接至高压放大器电路 271 的数据锁存器电路 265 中的 D1/D4 数据锁存器，另一漏信号线 D4 的数据，被输入图 5 所示连接至低压放大器电路 272 的数据锁存器电路 265 中的 D4/D1 数据锁存器，此时切换部件 (2) 264 设定为高压放大器电路 271 的输出被施加至漏信号线 D1，而低压放大器电路 272 的输出被施加至漏信号线 D4。

接下来，通过改变切换部件 (1) 262，以使漏信号线 D1 的数据，被输入连接至低压放大器电路 272 的数据锁存器电路 265 中的 D4/D1 数据锁存器，漏信号线 D4 的数据被输入连接至高压放大器电路 271 的数据锁存器电路 265 中的 D1/D4 数据锁存器，此时切换部件 (2) 264 设定为低压放大器电路 272 的输出被施加至漏信号线 D1，而高压放大器电路 271 的输出被施加至漏信号线 D4。

根据上述构造，第一漏信号线 D1 和第四漏信号线 D4 被分别施加相反极性的灰阶电压，并施加至第一和第四漏信号线的灰阶电压的极性

被定期反转。

### 预充电电路 30 的操作

图 6 解释图 5 所示预充电电路 30 的操作。

图 6 仅显示高压解码器电路 278, 低压解码器电路 279, 高压放大器电路 271 和低压放大器电路 272。图 6 仅显示输出系统, 它包括用以相同颜色的两个相邻漏信号线 (D), 例如第一漏信号线 (D1) 和第四漏信号线 (D4)。

如图 6 所示, 传送门电路 (TG1 至 TG4) 构成图 5 所示的切换部件 (2) 264 的一部分。输出衰减器 (21, 22) 表示例如分别连接至第一漏信号线 (D1) 和第四漏信号线 (D4) 的半导体芯片 (漏驱动器) 的输出衰减器。

预充电电路 30 被提供在高压解码器电路 278 和高压放大器电路 271 之间, 并在低压解码器电路 279 和低压放大器电路 272 之间。

预充电电路 30 包括连接至高压解码器电路 278 和高压放大器电路 271 之间的传送电路 (TG31), 和连接至低压解码器电路 279 和低压放大器电路 272 之间传送门 (TG32)。这些传送门电路 (TG31, TG32) 通过控制信号 (DECT, DECN) 控制, 在预充电期间, 高压解码器电路 278 和低压解码器电路 279 分别与高压放大器电路 271 和低压放大器电路 272 分离。预充电电路 30 还包括传送门电路 (TG33, TG34)。

这些传送门电路 (TG33, TG34) 通过控制信号 (PRET, PREN) 控制, 在预充电期间, 为应用正极性灰阶电压, 预充电电路施加预充电电压 (下文称为高压预充电电压, 例如任意正极性灰阶电压) (VHpre) 至高压放大器电路, 为应用负极性灰阶电压, 预充电电路也施加预充电电压 (下文称为低压预充电电压, 例如任意负极性灰阶电压) (VLpre) 至低压放大器电路 272。图 7 表示图 1 所示液晶显示面板 10 的漏信号线 (D) 的电压波形。

在图 1 所示的液晶显示模块中, 在预充电期间, 高压解码器电路 278 和低压解码器电路 279 分别与高压放大器电路 271 和低压放大器电路 272 分离, 而高压放大器电路 271 和低压放大器电路 272 分别被施加

高压预充电电压 (VHpre) 和低压预充电电压 (VLpre)。因此，漏信号线 (D) 被提前充电至高压预充电电压 (VHpre) 和低压预充电电压 (VLpre)。

漏信号线 (D) 通过高压放大器电路 271 和低压放大器电路 272 的预充电操作，与高压解码器电路 278 和低压解码器电路 279 的解码操作同时执行。

预充电期结束之后，高压放大器电路 271 和低压放大器电路 272 分别跟踪高压解码器电路 278 和低压解码器电路 279 的输出，并分别施加对应显示数据的灰阶电压 (VLCH, VLCL) 至漏信号线 (D)。

这样，在预充电期，通过为漏信号线 (D) 充高压预充电电压 (VHpre) 或低压预充电电压 (VLpre)，漏信号线 (D) 的电压可以在预充电期结束之后迅速跟踪对应显示数据的灰阶电压。

图 8 表示图 6 所示预充电电路 30 的示例定时图。图 8 所示的控制信号 (HIZCNT) 用来产生控制信号 (ACKON, ACKEP, ACKEN, ACKOP)，以应用至传送门电路 (TG1 至 TG4) 的栅电极。当时钟 (CL1) 处于高电平 (下文简称 H 电平) 期间，在等于八倍时钟 (CL2) 的重复周期的时间间隙内，控制信号 (HIZCNT) 处于高电平。当从一个扫描线转换到下一个时，高压放大器电路 271 和低压放大器电路 272 都变得不稳定。当需要在扫描线之间转换时，控制信号 (HIZCNT) 被用来防止相应的放大器电路 (271, 272) 输出它们的输出至相应的漏信号线 (D)。

在控制信号 (HIZCNT) 处于 H 电平的时间间隙内，控制信号 (ACKEP, ACKOP) 被转换至低电平 (下文简称 L 电平)，而控制信号 (ACKON, ACKEN) 被转换至 H 电平。因此，所有的传送门电路 (TG1 至 TG4) 被关闭。

图 8 所示的控制信号 (PRECNT) 用来产生控制信号 (PRET, PREN, DECT, DECN)，以应用至传送门电路 (TG31 至 TG34) 的栅电极。控制信号 (HIZCNT) 的上升沿之后，在等于 4 倍时钟 (CL2) 的重复周期的时间内，控制信号 (PRECNT) 被转换至 H 电平，在时钟 (CL1) 的下降沿时被转换至 L 电平。

在控制信号 (PREN) 从 H 电平转换至 L 电平之前，控制信号 (DECT)

从 H 电平转换为 L 电平。在控制信号 (PRET) 从 L 电平转换至 H 电平之前, 控制信号 (DECN) 从 L 电平转变为 H 电平。因此, 首先, 传送门 (TG31, TG32) 被关闭, 接着, 时间 (tD1) 之后, 传送门 (TG33, TG34) 被打开。

在控制信号 (DECT) 从 L 电平转换至 H 电平之前, 控制信号 (PREN) 从 L 电平转换为 H 电平。在控制信号 (DECN) 从 H 电平转换至 L 电平之前, 控制信号 (PRET) 从 H 电平转变为 L 电平。因此, 首先, 传送门 (TG33, TG34) 被关闭, 接着, 时间 (tD2) 之后, 传送门 (TG31, TG32) 被打开。

如图 8 所示, 预充电期表示为从控制信号 (HIZCNT) 的下降沿至控制信号 (DECT) 上升沿之间, 但实际上预充电电压应用至漏信号线 (D) 的时间是从控制信号 (HIZCNT) 的下降沿至控制信号 (PRET) 下降沿。

#### 图 6 所示预充电电路的电压值

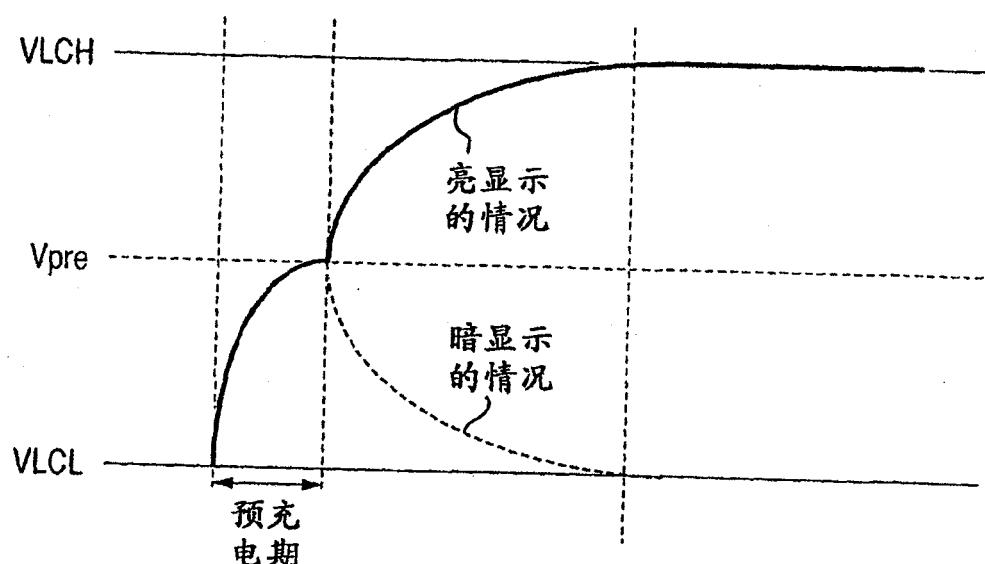

图 9A 解释在预充电期间靠近漏驱动器 130 的漏信号线 (D) 近端部分和远离漏驱动器的漏信号线 (D) 远端部分的电压变化。

如图 9A 所示, 在预充电期间, 当在漏信号线 (D) 上应用预充电电压 (高压预充电电压 (VHpre), 或低压预充电电压 (VLpre)) 时, 靠近漏驱动器 130 的漏信号线 (D) 近端部分的电压变化不同于最远离漏驱动器 130 的漏信号线 (D) 远端部分。通常, 正极性灰阶电压的中值是高压预充电电压 (VHpre) 的优选值。

但是, 如图 9A 所示, 在正极性灰阶电压的中值被采用为高压预充电电压 (VHpre) 的情况下, 最远离漏驱动器 130 的漏信号线 (D) 远端部分的电压并没有达到正极性灰阶电压的中值。

因此, 如图 9B 所示, 选择高压预充电电压 (VHpre), 以使靠近漏驱动器 130 的漏信号线近端部分的预充电电压与正极性灰阶电压的中值之间的电压差的绝对值 (Vs1), 等于最远离漏驱动器 130 的漏信号线远端部分的预充电电压与正极性灰阶电压的中值之间的电压差的绝对值 (Vs2), 即  $Vs1 = Vs2$ 。也就是说, 图 6 所示的高压预充电电压 (VHpre)

从正极性灰阶电压的中值至灰阶电压最大值之间的区间选择电压值。同样，图 6 所示的低压预充电电压 (VLpre) 从负极性灰阶电压的中值至灰阶电压最大负值之间的区间选择电压值。

### 本发明概要

本实施方式所示的液晶显示模块使用两线反转驱动方法。

图 10A 和 10B 解释在使用两线反转驱动方法驱动液晶显示模块的情况下，由漏驱动器 130 施加至漏信号线 (D) 的灰阶电压 (即施加至像素电极的灰阶电压) 的极性。图 10A 和 10B 中，正极性灰阶电压以空心圆表示，负极性灰阶电压以实心圆表示。

两线反转驱动方法与对照图 16A 和 16B 解释的点反转驱动方法相似，除了从漏驱动器 130 施加至漏信号线 (D) 的灰阶电压的极性每隔两扫描线被反转，因此这里省略了对其的详细解释。

例如，当使用两线反转驱动方法，具有相同灰阶级跨越几个扫描线的图形显示在液晶显示面板 10 上时，漏驱动器 130 输出灰阶电压至漏信号线 (D)，灰阶电压的极性每隔两个扫描线被反转。

下面参照图 11 解释当使用两线反转驱动方法时，为什么产生上述伪水平线的原因。

现在考虑从漏驱动器 130 施加至漏信号线 (D) 的灰阶电压的极性由负转变为正的情况。

在这种情况下，漏信号线 (D) 上的灰阶电压在极性反转之前，极性为负，极性反转之后，灰阶电压的极性变为正，但是，由于漏信号线 (D) 可以看作分布常数线，漏信号线上的灰阶电压不能从负极性立即转变为正极性，因而，漏信号线上的电压在一定的时间延迟之后，从负极性灰阶电压转变为正极性灰阶电压。

因此，即使预充电电压 (Vpre) 在图 11 所示的预充电期 A 之间应用至漏信号线 (D)，漏信号线 (D) 也将被充电至低于预充电电压 (Vpre) 的电压 Vprea，因此即使灰阶电压 VLCH 在预充电期之后被应用至漏信号线 (D)，漏信号线 (D) 上的电压也将是低于灰阶电压 VLCH 的电压 VLCHa。接下来考虑扫描线，例如，图 10A 中的线 4，在电压极性反转之后紧随

的扫描线，如图 10A 中的线 3。从漏驱动器 130 施加至漏信号线 (D) 的线 4 的灰阶电压极性，与施加至漏信号线的线 3 的灰阶电压极性相同。因此，在图 11 所示预充电期 B 之间，预充电电压 (Vpre) 的应用把漏信号线 (D) 充电至预充电电压 (Vpre)。此后，当应用灰阶电压 VLCH 至漏信号线 (D) 时，漏信号线 (D) 被充电至灰阶电压 VLCH。

上述的现象在漏驱动器 130 把漏信号线 (D) 的灰阶电压的极性由正转换为负时发生。

因此，即使扫描线线 4 上的像素计划显示与扫描线线 3 上的像素相同灰阶级时，写入极性反转之后扫描线线 4 上的像素的电压不同于写入扫描线线 3 上的像素的电压，两者具有图 11 所示的电压差 (VLCH-VLCHa)，因此，在两个扫描线之间产生上述伪水平线。

当液晶显示面板 10 的分辨率增加为 1280x1024 的 SXGA 显示模式，1600x1200 的 UXGA 显示模式等情况下，伪水平线变得明显。

如上所述，伪水平线的产生，是由写入极性反转之后扫描线（例如线 3）上的像素的电压，与写入上述扫描线（线 3）极性反转之后紧随扫描线（线 3）的扫描线（例如线 4）上的像素的电压之间的压差。

在本发明中，如图 12 所示，极性反转之后扫描线（例如，图 10A 所示的线 3）的预充电期 A 不同于极性反转之后紧随扫描线（线 3）的扫描线（例如，图 10A 所示的线 4）的预充电期 B。在这种构造中，写入极性反转之后扫描线（线 3）上的像素的电压，等于写入极性反转之后紧随扫描线（线 3）的扫描线（线 4）上的像素的电压。

也就是说，极性反转之后扫描线（线 3）的预充电期 A，要长于极性反转之后紧随扫描线（线 3）的扫描线（线 4）的预充电期 B。这种构造使把漏信号线 (D) 分别在图 12 所示的预充电期 A 和预充电期 B 充电至预充电电压 (Vpre) 成为可能，因此，写入极性反转之后扫描线（线 3）上的像素的电压，等于写入极性反转之后紧随扫描线（线 3）的扫描线（线 4）上的像素的电压。

另外，最远离漏驱动器 130 的扫描线的时钟 (CL1) 的高 (H) 电平期选择为最长，随着扫描线接近漏驱动器 130，扫描线的时钟 (CL1)

的高 (H) 电平期逐渐变短, 以使扫描线的预充电期随漏驱动器 130 至扫描线的距离增加而变长。通过在漏信号线 (D) 上应用上述构造的预充电电压, 靠近漏驱动器 130 的漏信号线 (D) 近端部分的充电电压, 等于最远离漏驱动器 130 的漏信号线 (D) 远端部分的充电电压。

按照本发明的实施方式中液晶显示模块的特征

在按照本发明的实施方式中, 为了使极性反转之后扫描线的预充电期 A, 长于极性反转之后紧随此扫描线的扫描线的预充电期 B, 预充电期 A 的时钟 (CL1) H 电平期要长于预充电期 B 的时钟 (CL1) H 电平期。

如参照图 8 的解释, 在预充电电压应用于漏信号线 (D) 的实际周期是从控制信号 (HIZCNT) 的下降沿至控制信号 (PRET) 下降沿的时间段。控制信号 (PRET) 下降沿在时间上与时钟 (CL1) 的下降沿一致。因此, 通过加长时钟 (CL1) 的高电位期, 预充电电压应用至漏信号线 (D) 上的时间, 如图 8 所示可以增加预充电期。这样, 本发明使不改变漏驱动器 130 的构造而加长预充电期成为可能。

如图 13 所示, 灰阶电压在相应扫描线的像素上的应用中, 最远离漏驱动器 130 的扫描线 (图 13 中表示为第一 (顶) 扫描线, 同时参见图 1) 的时钟 (CL1) H 电位期最长, 随着扫描线接近漏驱动器 130, 相应扫描信号线的时钟 (CL1) 的高 (H) 电平期逐渐变短。也就是说, 随着漏驱动器 130 至相应扫描线的距离增大, 相应扫描线的预充电期变短。因此, 通过在漏信号线 (D) 上应用上述预充电电压, 使靠近漏驱动器 130 的漏信号线近端部分的充电电压, 等于最远离漏驱动器 130 的漏信号线远端部分的充电电压。

下文解释用来改变时钟 (CL1) H 电平期的显示控制设备 110 的构造。

图 14 是本实施方式中的时钟 (CL1) 发生器电路的框图。

在本实施方式的 CL1 H 电平宽度设定电路 50 中, 设定外部时钟 (DCLK) 的时钟脉冲的数目 (下文称作时钟脉冲最大数目), 以使时钟脉冲最大数目符合时钟 (CL1) 的 H 电平最大宽度 (图 13 所示第一 (顶) 扫描线需要的时钟 (CL1) 的 H 电平宽度)。在 CL1 H 电平宽度设定电路

50 中，调整包含寄存器 R 和电容 C 作为其振荡器元件的振荡回路，以使其振荡频率符合上述时钟脉冲最大数目。减法器 51 从时钟脉冲最大数目中减去分配给每个扫描线的外部时钟 (DCLK) 的时钟脉冲的数目。CL1 设定电路 52 从减法器 51 中读出减法运算之后的剩余数，当外部时钟 (DCLK) 的时钟脉冲的计数值达到减法运算之后的时钟脉冲剩余数时，CL1 设定电路 52 把时钟 (CL1) 的 H 电平转换为低 (L) 电平。这种操作产生具有如图 13 所示相应 H 电平宽度的时钟 (CL1)。

下文解释在实施方式中交流驱动信号 (M)

图 15 是在本实施方式中，用以产生交流驱动信号 (M) 的电路构造的电路图。图 15 所示的电路被提供至显示控制设备 110 中。

如图 15 所示，计数器 61 为垂直同步信号 (Vsync) 的脉冲计数，并施加其 Q0 输出至专用 OR 电路 63。计数器 61 的 Q0 输出分别施加于垂直同步信号 (Vsync) 的每个脉冲的 H 电平和 L 电平信号。

计数器 62 的 Qn 输出被输入专用 OR 电路 63，而专用 OR 电路的输出作为交流驱动信号 (M) 提供。

如上所述，在本实施方式中，极性反转之后扫描线的预充电期 A，长于极性反转之后紧随此扫描线的扫描线的预充电期 B，因此应用于极性反转之后扫描线上的像素的电压，等于应用于极性反转之后紧随此扫描线的扫描线上的像素的电压，因此，上述伪水平线的产生被防止。

另外，最远离漏驱动器 130 的扫描线的时钟 (CL1) 的 H 电平期最长，随着相应扫描线至漏驱动器 130 的距离减小，扫描线的时钟 (CL1) 的高 (H) 电平期逐渐变短，以使相应扫描线的预充电期随相应扫描线至漏驱动器 130 的距离增加而变长，因此，靠近漏驱动器 130 的漏信号线 (D) 近端部分的充电电压，等于最远离漏驱动器 130 的漏信号线 (D) 远端部分的充电电压。这防止液晶显示面板上显示质量的严重下降，它是由于用以写入最远离漏驱动器 130 的漏信号线远端部分的像素的电压级不足而引起的。

另外，在本实施方式中，高压预充电电压 (VHpre) 可以选择正极性灰阶电压的中值，低压预充电电压 (VLpre) 可以选择负极性灰阶电

压的中值。

但是，高压预充电电压 (VHpre) 可以选择为位于正极性灰阶电压的中值至灰阶电压最大值之间的区间的电压值，低压预充电电压 (VLpre) 可以选择为位于负极性灰阶电压的中值至灰阶电压最大负值之间的区间的电压值。这种构造进一步保证最远离漏驱动器 130 的漏信号线 (D) 远端部分的充电电压，等于靠近漏驱动器 130 的漏信号线 (D) 近端部分的充电电压。

上述说明解释了本发明应用于垂直电场型液晶显示面板的实施方式。但是，本发明并不限于此，它可以应用于水平电场型液晶显示面板。

在水平电场型（通常称为面内转换（IPS）型）液晶显示设备中，每个像素的光传送通过应用与夹在一对反向透光衬底之间的液晶材料层平行的水平电场控制。每个像素通过两个形成于反向透光衬底内表面上的电极形成。为了说明设备构造和操作的目的，1997年1月28日Kondo等人公布的美国第5,598,285号专利以引用形式包含在本文中。

在图2或图3所示的垂直电场型液晶显示面板中，在与TFT衬底相对的衬底上提供公共电极 (IT02)。另一方面，在水平电场型液晶显示面板中，提供反电极 (CT) 和反电极信号线 (CL)，以在TFT衬底的反电极上应用公共电压 (Vcom)。通过液晶层形成的等效液晶成形电容 (Cpix) 被连接在像素电极 (PX) 和反电极 (CT) 之间。存储电容 (Cstg) 也在像素电极 (PX) 和反电极 (CT) 之间形成。

基于按照本发明的优选实施方式，已经具体地解释了本发明人的发明，但本发明不限于上述优选实施方式，它们是说明性的而不是限制性的，可以在不偏离本发明领域和精神的条件下，对其进行各种修改。

本具体实施方式中公开的代表性本发明提供的优点，可以简单解释如下。

(1) 在灰阶电压的极性每隔  $N$  ( $N > 2$ ) 条扫描线被反转的情况下，本发明能够阻止显示屏幕上伪水平线的产生，从而改善显示屏幕上的显示质量。

(2) 与传统技术相比，在预充电期间，本发明能够降低靠近漏驱

---

动器的漏信号线近端部分的充电电压和最远离漏驱动器的漏信号线远端部分的充电电压之间的差别，从而改善显示屏幕上的显示质量。

图 2

图 3

图4

5

图 6

图 7

图 8

图 9B

图 9A

图 10A

### 奇数帧

图 10B

偶数帧

图 11

图 12

图13

图 14

图 15

图 16A

奇数帧

100

图 16B

偶數帧

1

图 17

|                |                                                                                         |         |            |

|----------------|-----------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 具有改进的预充电路的液晶显示设备                                                                        |         |            |

| 公开(公告)号        | <a href="#">CN100527211C</a>                                                            | 公开(公告)日 | 2009-08-12 |

| 申请号            | CN200610103143.0                                                                        | 申请日     | 2003-01-15 |

| [标]申请(专利权)人(译) | 株式会社日立制作所                                                                               |         |            |

| 申请(专利权)人(译)    | 株式会社日立制作所                                                                               |         |            |

| 当前申请(专利权)人(译)  | 株式会社日立制作所                                                                               |         |            |

| [标]发明人         | 上田史朗                                                                                    |         |            |

| 发明人            | 上田史朗                                                                                    |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                             |         |            |

| CPC分类号         | G09G2310/027 G09G3/3659 G09G2310/0297 G09G2320/0223 G09G3/3688 G09G3/3614 G09G2310/0248 |         |            |

| 代理人(译)         | 王永刚                                                                                     |         |            |

| 优先权            | 2002007336 2002-01-16 JP                                                                |         |            |

| 其他公开文献         | CN1892801A                                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                          |         |            |

### 摘要(译)

一种液晶显示设备，包括驱动器电路，用来在水平扫描期开始阶段输出充电电压，接下来输出对应显示数据的灰阶电压至视频信号线。液晶显示设备的驱动方法为：每隔扫描线中的N线，其中N≥2，反转像素电极上的灰阶电压相对于公共电极上的公共电压的极性；并使充电电压的第一充电时间不同于上述充电电压的第二充电时间，第一充电时间对应灰阶电压的极性反转之后立即被扫描的多个扫描线中N线的第一线，第二充电时间对应紧随第一线之后立即被扫描的上述N线的第二线。