[19] 中华人民共和国国家知识产权局

[12] 发明专利说明书

专利号 ZL 200810006339.7

[51] Int. Cl.

G02F 1/1362 (2006.01)

G02F 1/1343 (2006.01)

H01L 27/12 (2006.01)

[45] 授权公告日 2010 年 2 月 24 日

[11] 授权公告号 CN 100592183C

[22] 申请日 2008.2.26

[21] 申请号 200810006339.7

[30] 优先权

[32] 2007.2.27 [33] JP [31] 2007-046534

[73] 专利权人 索尼株式会社

地址 日本东京

[72] 发明人 田中大直 野口幸治 金谷康弘

中岛大贵 野津大辅 猪野益充

[56] 参考文献

CN1837907A 2006.9.27

US20010046027A1 2001.11.29

CN101008750A 2007.8.1

审查员 钟 宇

[74] 专利代理机构 北京康信知识产权代理有限公司

代理人 余 刚 吴孟秋

权利要求书 3 页 说明书 24 页 附图 14 页

[54] 发明名称

液晶显示装置和显示设备

[57] 摘要

本发明提供了一种液晶显示装置和显示设备，其中，该液晶显示装置包括介于第一基板和第二基板之间的液晶层，并且在第一基板侧上具有用于向所述液晶层施加电场的共电极和像素电极，该液晶显示装置包括：多条扫描线和多条信号线；驱动元件；第一绝缘膜；共电极；第二绝缘膜；以及像素电极，其中，共电极覆盖第一绝缘膜上除接触孔的形成区域外的像素区域、以及扫描线和信号线中的至少一条。

1. 一种液晶显示装置，包括介于第一基板和第二基板之间的液晶层，并且在第一基板侧上具有用于向所述液晶层施加电场的共电极和像素电极，所述液晶显示装置包括：

多条扫描线和多条信号线，被配置为以矩形形式设置在所述第一基板上；

驱动元件，被配置为设置在所述扫描线和所述信号线之间的交叉点处；

第一绝缘膜，被配置为设置在所述第一基板上并覆盖所述驱动元件；

共电极，被配置为设置在所述第一绝缘膜上；

第二绝缘膜，被配置为设置在所述第一绝缘膜上并覆盖所述共电极；以及

像素电极，被配置为设置在像素区域内的所述第二绝缘膜上并且具有多个狭缝，所述像素电极经由设置在所述第二绝缘膜和所述第一绝缘膜中的接触孔连接至所述驱动元件，其中，

所述共电极覆盖在所述第一绝缘膜上除所述接触孔的形成区域外的所述像素区域、以及所述扫描线和所述信号线中的至少一条，

所述共电极连接至由具有比所述共电极的电阻值低的电阻值的材料构成的共电位线，以及

所述共电位线在平面图中与所述信号线或所述扫描线重叠。

2. 根据权利要求 1 所述的液晶显示装置，其中，

所述共电极被设置在所述第一绝缘膜上除所述接触孔的所述形成区域外的整个显示区域上。

3. 根据权利要求 1 所述的液晶显示装置，其中，

所述第一绝缘膜由旋涂玻璃膜或有机绝缘膜形成。

4. 根据权利要求 1 所述的液晶显示装置，其中，

所述像素电极的所述多个狭缝平行于所述信号线设置。

5. 根据权利要求 1 所述的液晶显示装置，其中

所述像素电极经过配置，使所述像素电极在信号线侧上的端部和最接近所述信号线的狭缝之间的电极部分的宽度不同于其它狭缝间的电极部分的宽度。

6. 一种包括液晶显示装置的显示设备，所述液晶显示装置包括介于第一基板和第二基板之间的液晶层，并且在第一基板侧上具有用于向所述液晶层施加电场的共电极和像素电极，所述显示设备通过使用由所述液晶显示装置调制的光来显示影像，所述显示设备包括：

多条扫描线和多条信号线，被配置为以矩形形式设置在所述第一基板上；

驱动元件，被配置为设置在所述扫描线和所述信号线之间的交叉点处；

第一绝缘膜，被配置为设置在所述第一基板上并覆盖所述驱动元件；

共电极，被配置为设置在所述第一绝缘膜上；

---

第二绝缘膜，被配置为设置在所述第一绝缘膜上并覆盖所述共电极；以及

像素电极，被配置为设置在像素区域内的所述第二绝缘膜上并且具有多个狭缝，所述像素电极经由设置在所述第二绝缘膜和所述第一绝缘膜中的接触孔连接至所述驱动元件，其中，

所述共电极覆盖在所述第一绝缘膜上除所述接触孔的形成区域外的所述像素区域、以及所述扫描线和所述信号线中的至少一条，

所述共电极连接至由具有比所述共电极的电阻值低的电阻值的材料构成的共电位线，以及

所述共电位线在平面图中与所述信号线或所述扫描线重叠。

## 液晶显示装置和显示设备

### 相关申请的交叉引用

本发明包含于 2007 年 2 月 27 日向日本专利局提交的日本专利申请 JP 2007-046534 的主题，其全部内容结合于此作为参考。

### 技术领域

本发明涉及一种液晶显示装置和显示设备，更具体地，涉及一种边缘场切换 (FFS) 模式（也称为板内切换 (IPS) 支持模式）的液晶显示装置以及包括该液晶显示装置的显示设备。

### 背景技术

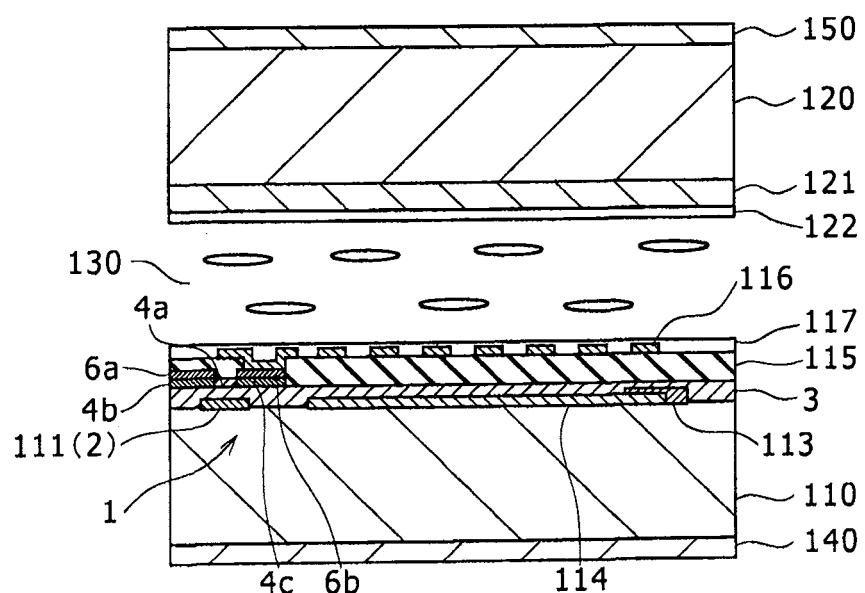

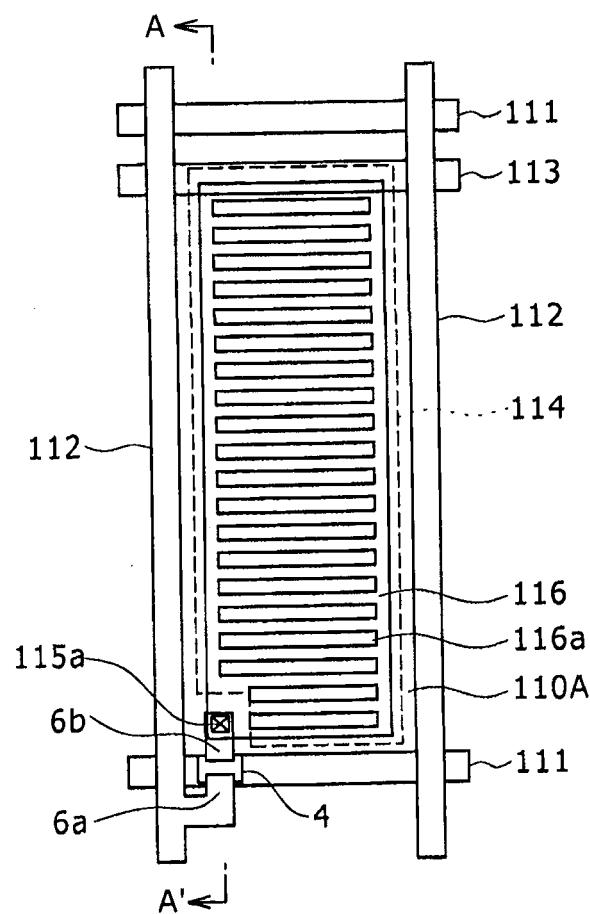

在 FFS 模式的液晶显示装置中，用于向液晶层施加基本上与基板表面平行的横向电场的共电极和像素电极被设置同一基板侧上，并且通过该横向电场驱动液晶元件用于显示图像。以下将参考图 14 描述现有技术的 FFS 模式的液晶显示装置。图 14A 的截面图是沿图 14B 中的线 A-A' 得到的。

该附图中所示的液晶显示装置是透射的。该液晶显示装置包括液晶面板，液晶面板由第一基板 110、面向第一基板 110 的元件形成表面设置的第二基板 120、以及介于这些第一基板 110 和第二基板 120 之间的液晶层 130 形成。而且，在该液晶面板中，偏光镜 140 和 150 分别紧密接触第一基板 110 和第二基板 120 的外表面设置。

---

在第一基板 110 上的偏光镜 140 的更外侧，设置用作用于透射显示的光源的背光（未示出）。

第一基板 110 由诸如玻璃的透明基板形成。在其面向液晶层 130 的表面上，以矩阵形式排列多条扫描线 111 和多条信号线 112。在条扫描线 111 和信号线 112 的每个交叉点处，设置用于驱动各个像素的由薄膜晶体管（TFT）形成的驱动元件。被扫描线 111 和信号线 112 所包围的区域用作像素区域 110A。

在扫描线 111 和用于相邻像素的下一扫描线 111 之间，平行于这些扫描线 111、接近用于相邻像素的扫描线 111 设置共电位线 113。此外，在同一平面，在除 TFT 1 的形成区域外的像素区域 110A 中设置共电极 114，以此方式使共电极 114 的端部与共电位线 113 重叠。共电极 114 与扫描线 111 设置在相同的平面上，因此，共电极 114 的排列受限于扫描线 111。

TFT 1 的栅电极 2 由扫描线 111 的一部分形成。在第一基板 110 上，设置栅极绝缘膜 3 以覆盖扫描线 111、共电位线 113、和共电极 114。此外，在覆盖栅电极 2 的栅极绝缘膜 3 上图样化形成半导体层 4。

半导体层 4 直接位于栅电极 2 之上的一部分用作沟道层 4a。在沟道层 4a 的两个侧面上，设置含有 n 型杂质的源极区 4b 和漏极区 4c。在源极区 4b 上，源电极 6a 经设置连接至源极区 4b，并且源电极 6a 连接至信号线 112。在漏极区 4c 上，漏电极 6b 经设置连接至漏极区 4c。以此方式形成了 TFT 1。

在栅极绝缘膜 3 上，设置层间绝缘膜 115 以覆盖 TFT 1。在该层间绝缘膜 115 中，设置了连接到 TFT1 的漏极 6b 的接触孔 115a。在层间绝缘膜 115 上，设置通过接触孔 115a 连接至 TFT1 并具有多

个狭缝的像素电极 116。这些狭缝 116a 与扫描线 111 平行。此外，在层间绝缘膜 115 之上设置对准层 117，并且对准层 117 覆盖像素电极 116。

由于这种结构，在共电极 114 和像素电极 116 的电极部分的端部之间产生电场，其中，这些电极部分夹着狭缝 116a。因此，向液晶层 130 施加基本上平行于基板表面的横向电场。

第二基板 120 也由诸如玻璃基板的透明基板形成。在面向液晶层 130 的表面上，顺序设置分别用于红色 (R)、绿色 (G)、和蓝色 (B) 的各种颜色的滤色片 121、以及对准层 122。

在具有上述结构的液晶显示装置中，扫描线 111 和共电极 114 位于第一基板 110 的同一平面上，因此共电极 114 的形成区域受扫描线 111 的限制。这会导致孔径比 (aperture ratio) 低和透光率低的问题。

为了解决这些问题，已报道了液晶显示装置的一个实施例，这种液晶显示装置是通过在以上通过使用图 14 所述的液晶显示装置的结构中，将具有狭缝 116a 的像素电极 116 设置在栅极绝缘膜 3 上以及将共电极 114 设置在层间绝缘膜 115 上而得到的（例如，参看第 3742837 号日本专利（专利文献 1））。

此外，也已报道了以下的实施例，其中，在以上通过使用图 14 所述的液晶显示装置中，共电极 114 被设置在栅极绝缘膜 3 上（例如，参看第 3740514 号日本专利和第 3742836 号日本专利（专利文献 2 和 3））。

然而，在专利文献 1 所述的液晶显示装置中，尽管对共电极 114 的配置没有任何限制，但是由于具有狭缝 116a 的像素电极 116 并没

有接近液晶层 130 设置，所以很难施加与基板表面平行的电场。因此，不能控制液晶层 130，并因此本身就很难进行液晶显示。

而且，在专利文献 2 和 3 描述的液晶显示装置中，共电极 114 的配置受到信号线 112 的限制，因此很难维持高孔径比。

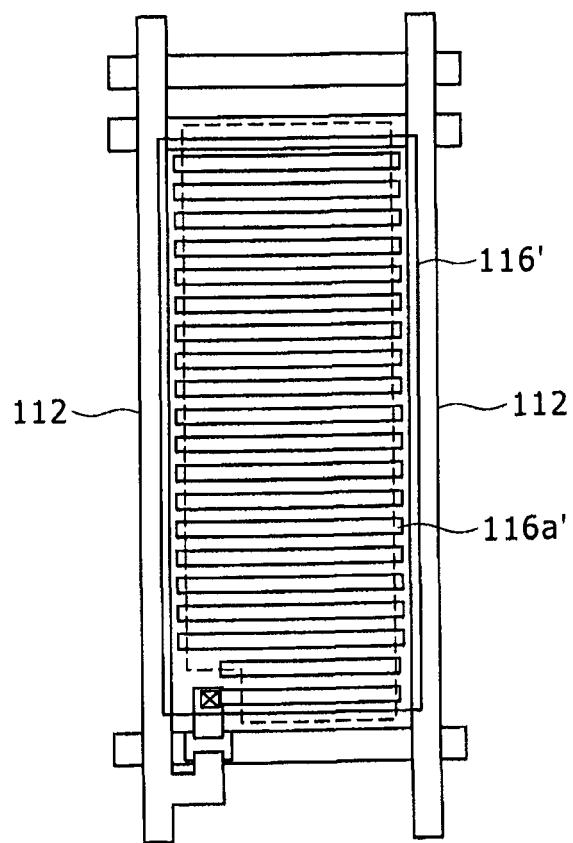

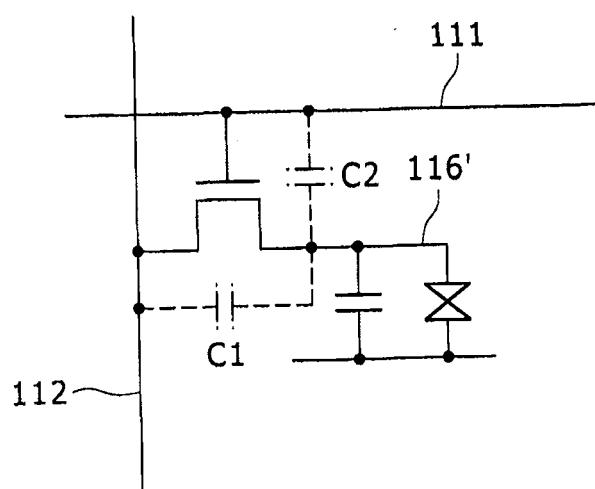

为了解决这些问题，如图 15A 的平面图所示，经形成在信号线侧具有比共电极 114 更大尺寸的像素电极 116' 经过设置与信号线 112 重叠。然而，在此结构中，如图 15B 的电路图所示，在信号线 112 和像素电极 116' 之间生成寄生电容 C1 和 C2，这会导致垂直的色度亮度干扰 (crosstalk)。

## 发明内容

本发明需要提供一种可以提高孔径比并抑制寄生电容的液晶显示装置，以及包括该液晶显示装置的显示设备。

根据本发明的实施例，提供了一种液晶显示装置，其包括介于第一基板和第二基板之间的液晶层，并且在第一基板侧上具有用于向液晶层施加电场的共电极和像素电极。该液晶显示装置包括被配置为以矩阵形式设置在第一基板上的多条扫描线和多条信号线、被配置为设置在扫描线和信号线之间的交叉点处的驱动元件、以及被配置为设置在第一基板上并且盖驱动元件的第一绝缘膜。此外，该液晶显示装置还包括被配置为设置在第一绝缘膜上的共电极、被配置为设置在第一绝缘膜上并覆盖共电极的第二绝缘膜、以及被配置为设置在像素区域内的在第二绝缘膜上并且具有多个狭缝的像素电极。像素电极经由设置在第二绝缘膜和第一绝缘膜中的接触孔连接至驱动元件。共电极覆盖第一绝缘膜上除接触孔的形成区域外的像素区域、以及扫描线和信号线中的至少一条。

根据本发明的另一个实施例，提供了包括液晶显示装置的显示设备，该液晶显示装置包括介于第一基板和第二基板之间的液晶层，并且在第一基板侧上具有用于向液晶层施加电场的共电极和像素电极。该显示设备通过使用由液晶显示装置调制的光显示影像(video)。该显示设备包括被配置为以矩阵形式设置在第一基板上的多条扫描线和多条信号线、被配置为设置在扫描线和信号线之间的交叉点处的驱动元件、以及被配置为设置在第一基板上并且盖驱动元件的第一绝缘膜。此外，该液晶设备还包括被配置为设置在第一绝缘膜上的共电极、被配置为设置在第一绝缘膜上并覆盖共电极的第二绝缘膜、以及被配置为设置在像素区域内的在第二绝缘膜上并且具有多个狭缝的像素电极。像素电极经由设置在第二绝缘膜和第一绝缘膜中的接触孔连接至驱动元件。共电极覆盖第一绝缘膜上除接触孔的形成区域外的像素区域、以及扫描线和信号线中的至少一条。

在这种液晶显示装置和显示设备中，共电极被设置在覆盖信号线和扫描线的第一绝缘膜上，从而共电极不仅覆盖除接触孔的形成区域外的像素区域，并且还覆盖扫描线和信号线中的至少一条。这个特征使得有效像素区域增大，并且可以提高孔径比。此外，由于提供了覆盖扫描线和信号线中的至少一条的共电极，所以抑制了在扫描线和像素电极之间或者信号线和像素电极之间的寄生电容。

如上所述，根据本发明实施例的液晶显示装置和显示设备，可以提高孔径比。因此，增强了光的透射，并且提高了液晶显示装置的对比度。此外，由于抑制了在扫描线和像素电极之间或者信号线和像素电极之间的寄生电容，所以可以防止像素中出现信号干扰。因此，稳定了所保持的像素电位，并且既不会出现垂直色度亮度干扰，也不会出现水平色度亮度干扰，这可以提高液晶显示装置的图像质量。

此外，由于来自信号线、扫描线以及像素电极的电场，根据本发明实施例的液晶显示装置以及包括该液晶显示装置的显示设备没有在由例如晶体管形成的驱动元件的半导体层中生成反向沟道。因此，可以防止由于寄生的反向沟道所引起的不稳定运行。

## 附图说明

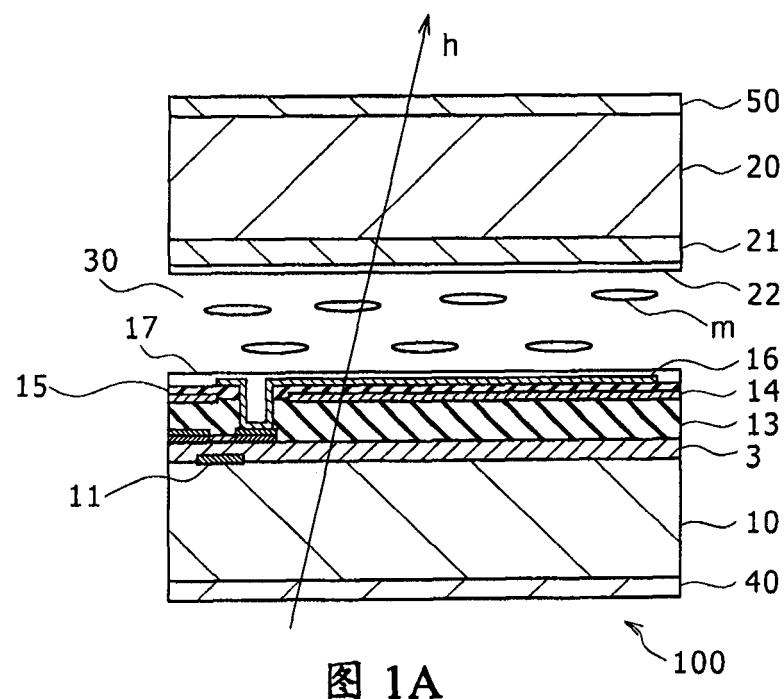

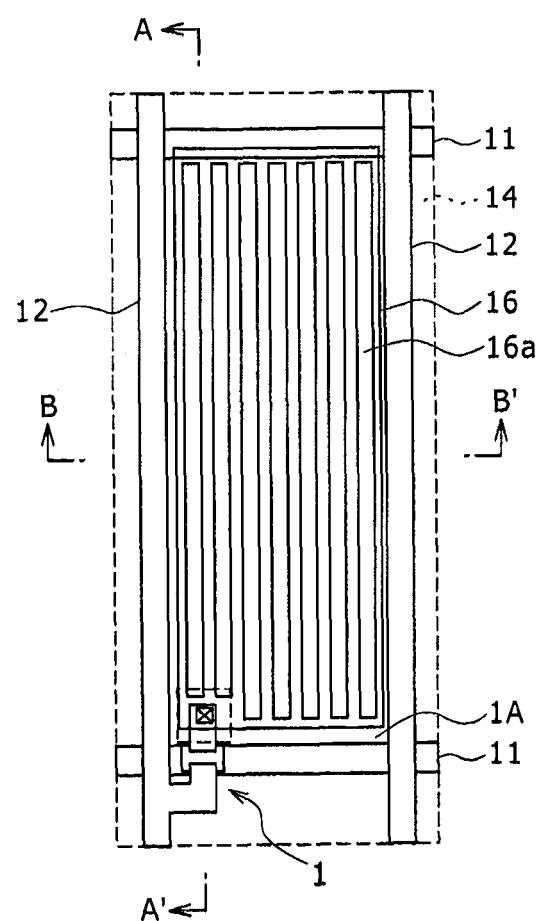

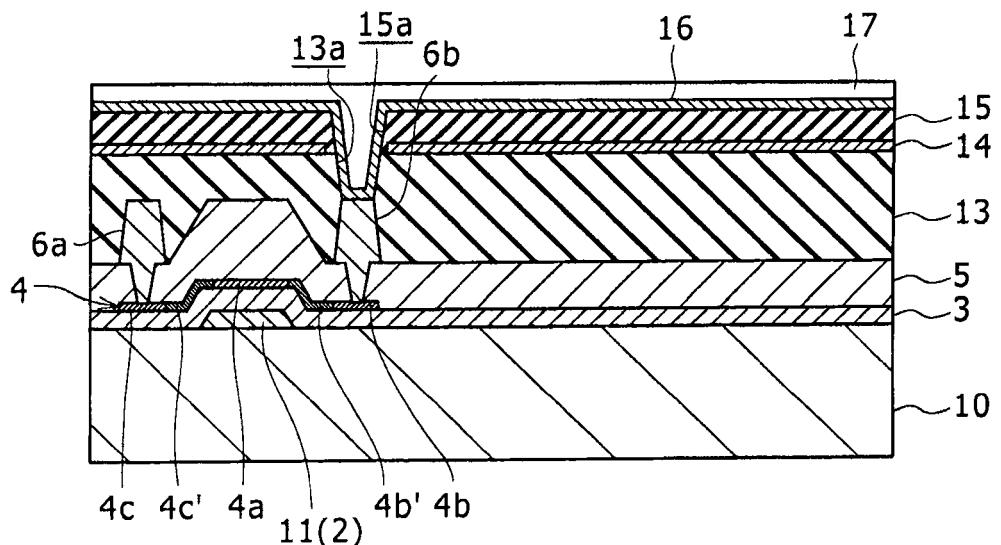

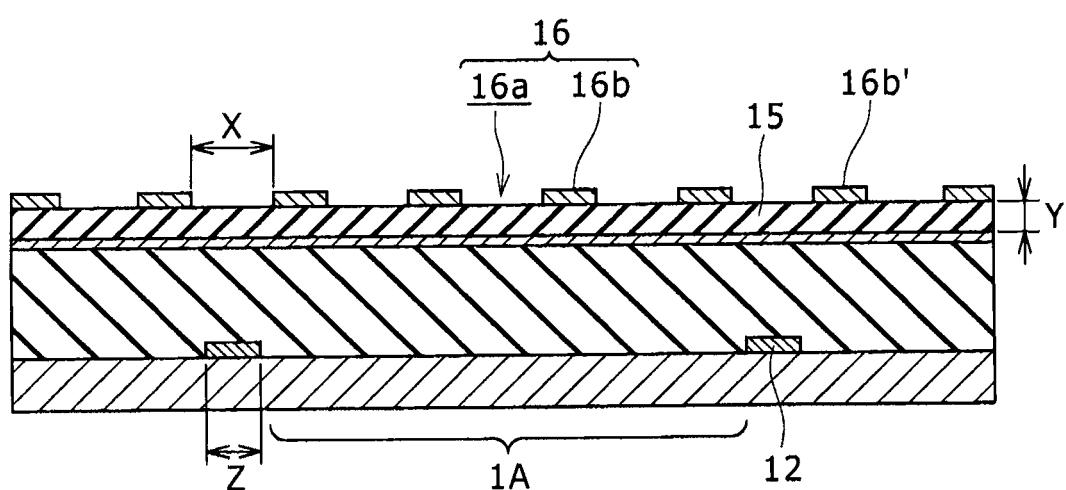

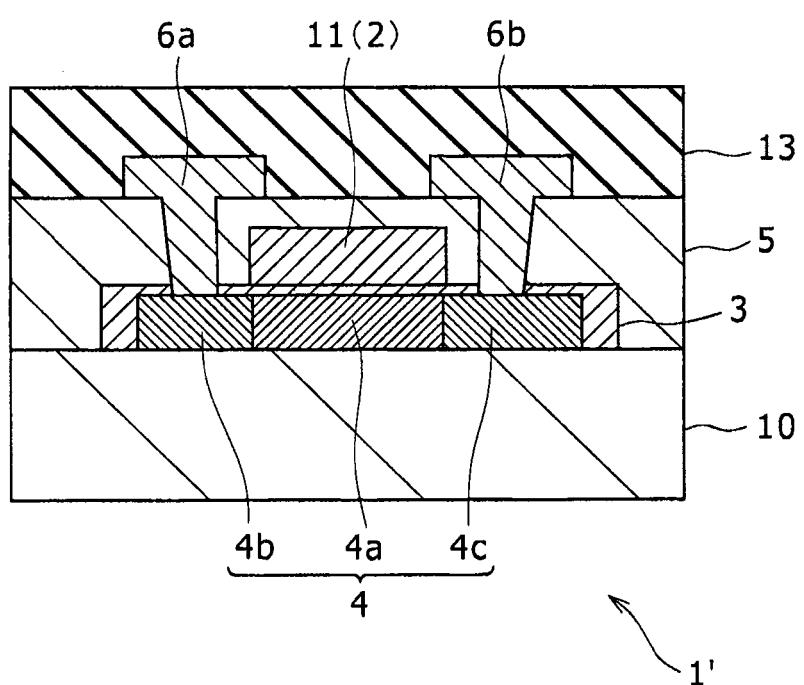

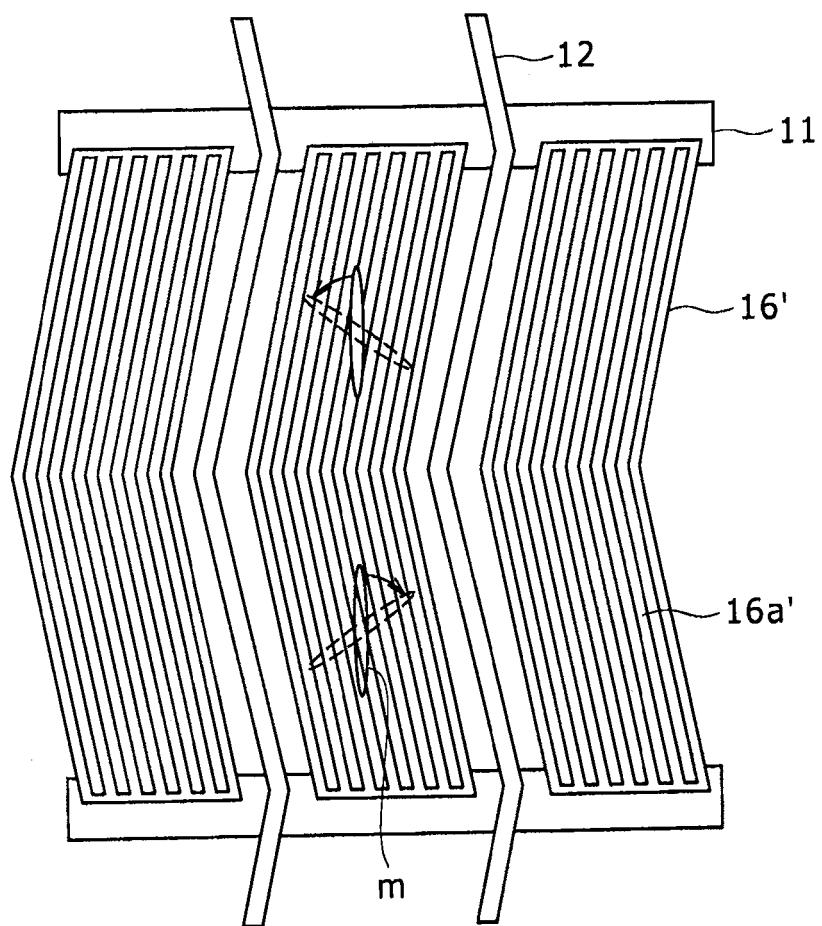

图 1A 和图 1B 是分别示出了根据本发明实施例的液晶显示装置的结构的截面图和平面图；

图 2A 和图 2B 是示出了根据本发明实施例的液晶显示装置的第一基板的主要部分的沿图 1B 中的线 A-A' 的放大截面图；

图 3A 和图 3B 是分别示出了在根据本发明实施例的液晶显示装置中不设置共电位线的情况、和设置共电位线的情况的示意图；

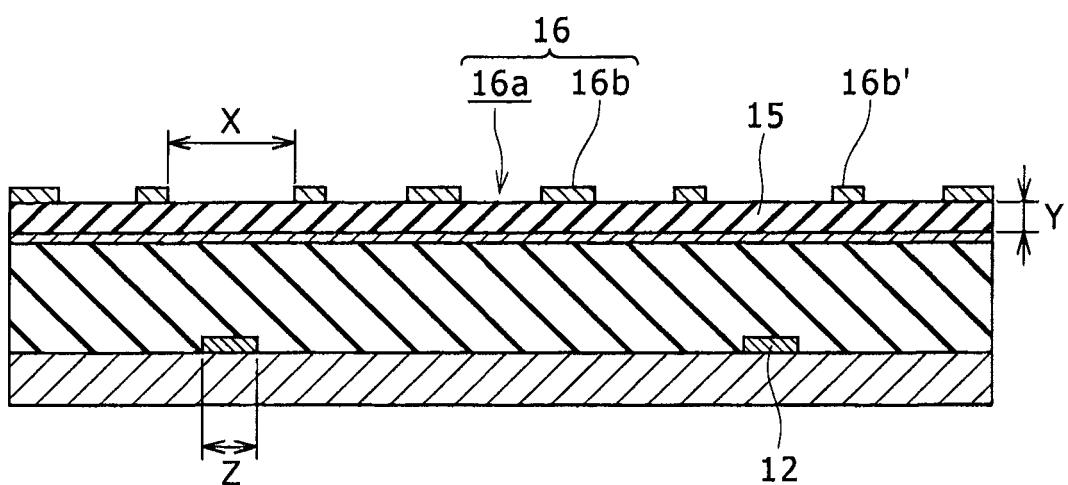

图 4 是示出了根据本发明实施例的液晶显示装置的第一基板的主要部分的沿图 1B 中的线 B-B' 的放大截面图；

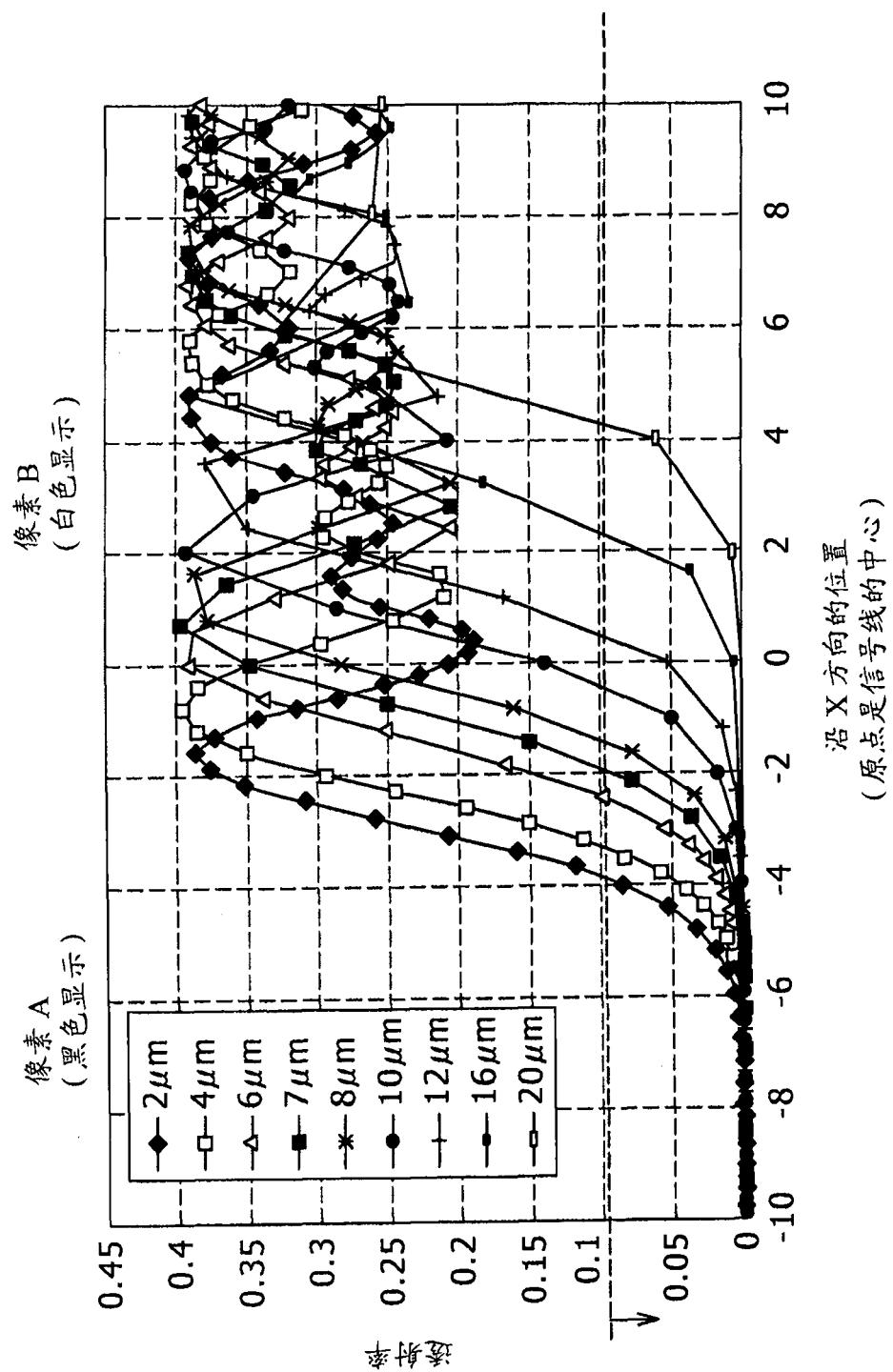

图 5 是示出了根据本发明实施例的使用相邻像素的像素电极之间距离的改变所测量的漏光 (light leakage) 的曲线图；

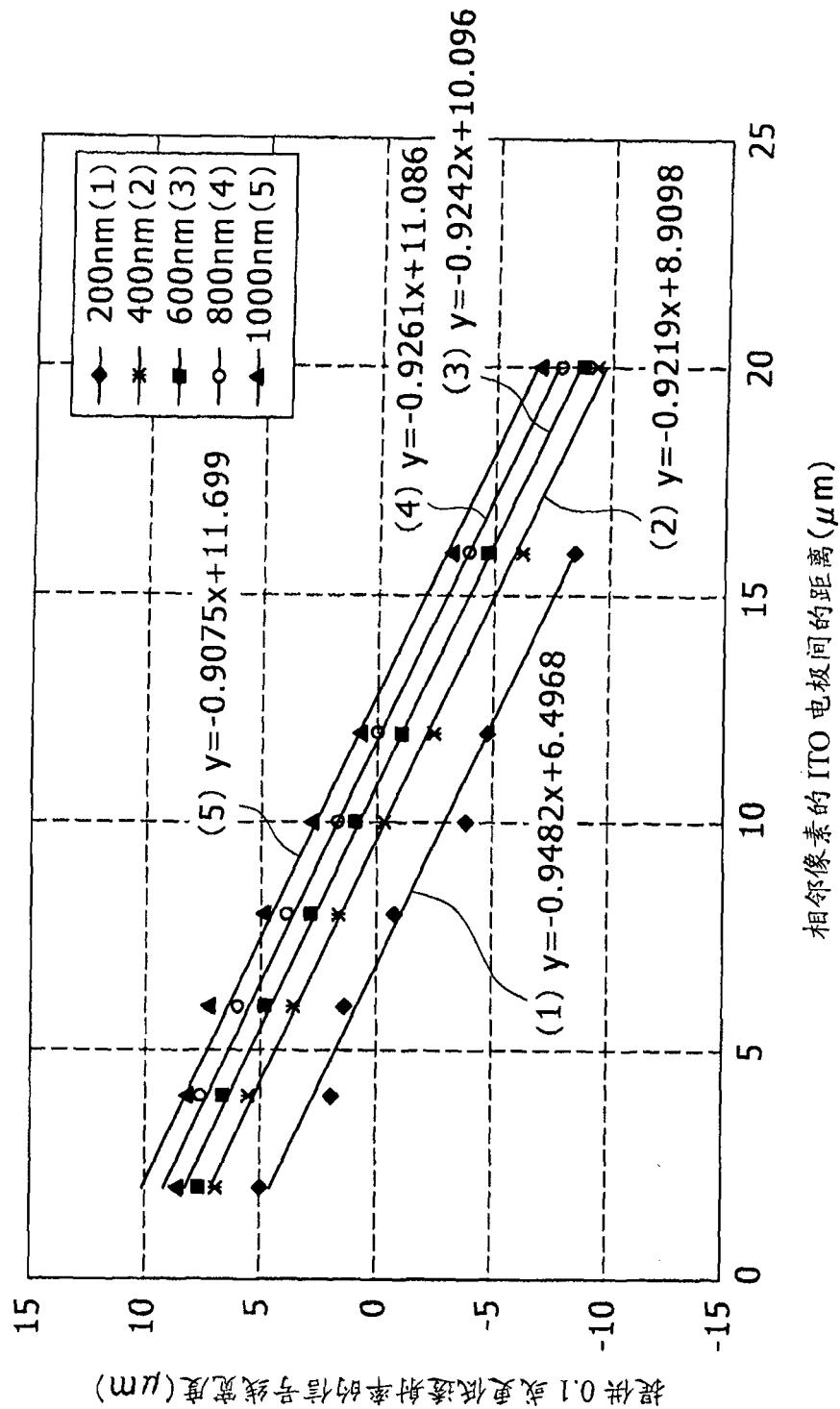

图 6 是示出了根据本发明实施例的在与相邻像素的像素电极之间距离的改变相关联的信号线宽度和第二绝缘膜的厚度之间关系的曲线图；

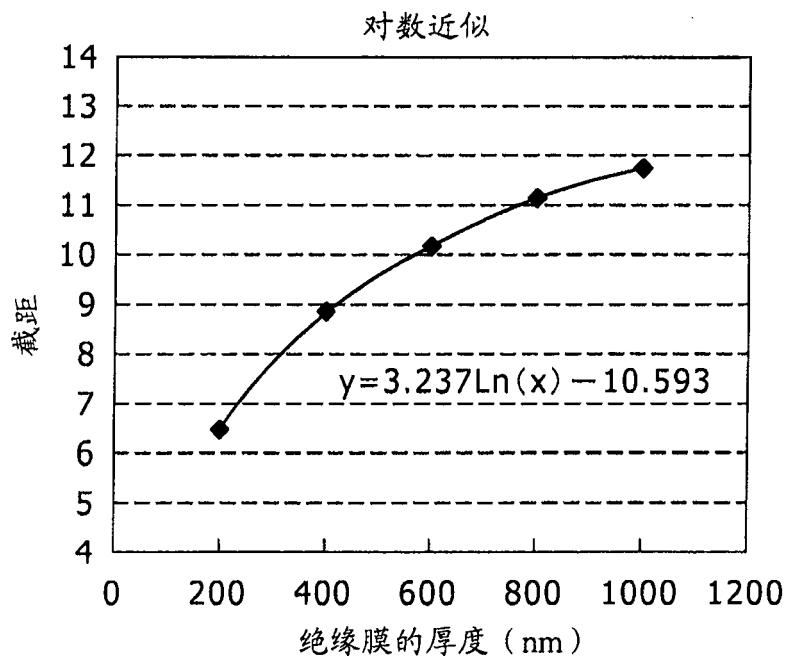

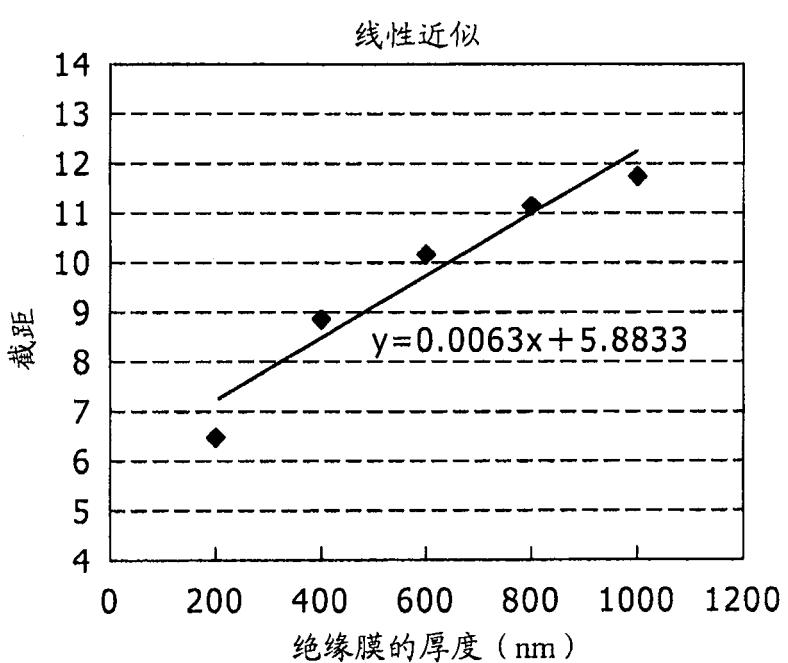

图 7A 和图 7B 是分别示出了根据本发明实施例的分别与 y 截距相关的对数近似 (log approximation) 和线性近似的曲线图，y 截距是用于表示与作为变量的像素电极间的距离相关联的信号线宽度的线性函数的术语，并且 y 截距取决于第二绝缘膜的膜厚度；

图 8 是示出了根据本发明实施例的液晶显示装置的第一基板的主要部分的沿图 1B 中的线 B-B' 的放大截面图；

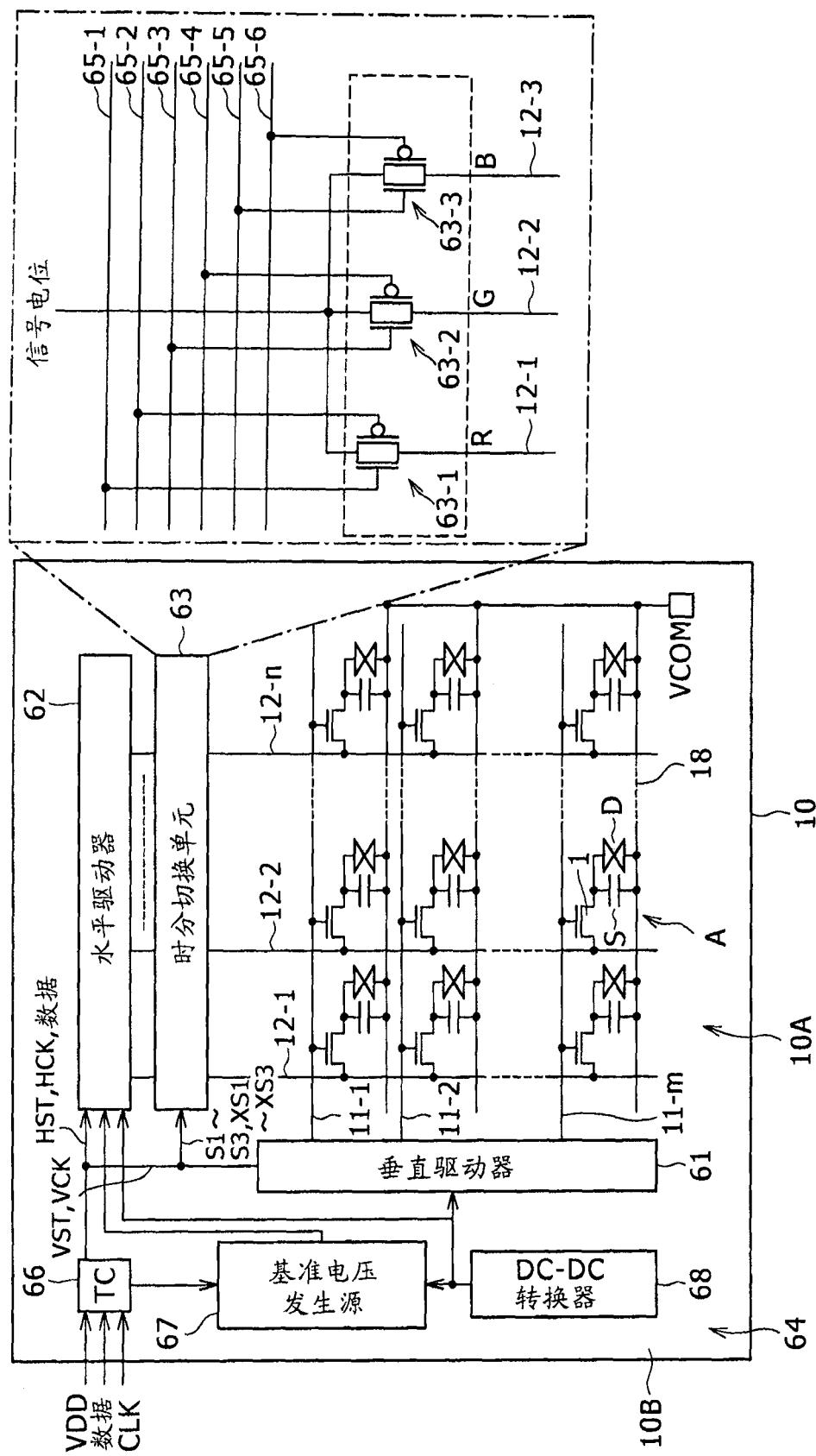

图 9 是示出了根据本发明实施例的电路图；

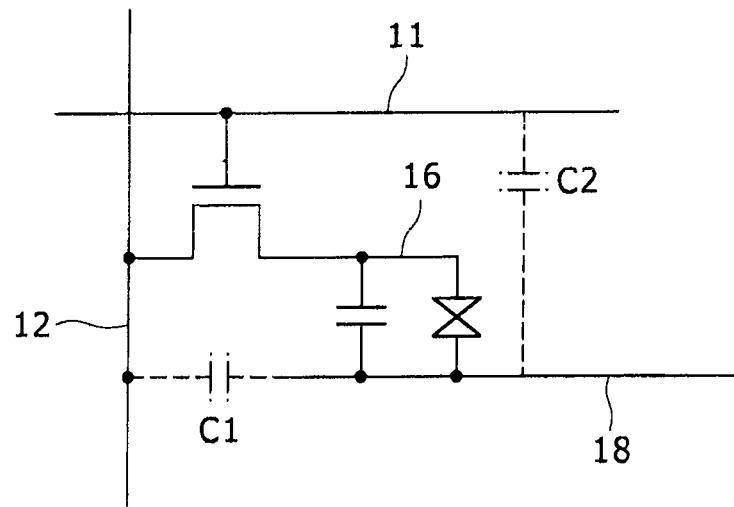

图 10 是示出了根据本发明实施例的一个像素的电路图；

图 11 是示出了根据本发明实施例的另一个晶体管的结构图；

图 12 是示出了根据本发明实施例的变型实例 1 的平面图；

图 13 是示出了根据本发明实施例的变型实例 2 的平面图；

图 14A 和图 14B 是分别用于阐述现有技术的液晶显示装置的结构的截面图和平面图；

图 15A 和图 15B 是分别示出了现有技术的液晶显示装置的问题的平面图和电路图。

## 具体实施方式

以下将详细描述本发明实施例。

### <第一实施例>

图 1A 是示出了 FFS 模式的透射型液晶显示装置的截面图，以及图 1B 是其平面图。图 1A 是沿图 1B 中的线 A-A' 得到的。

液晶显示装置 100 包括液晶面板，该液晶面板由第一基板 10、面向第一基板 10 的元件形成表面设置的第二基板 20、和介于第一基板 10 和第二基板 20 之间的液晶层 30 形成。液晶层 30 由向列型液晶构成。在该液晶面板中，设置偏光镜 40 和 50，使用粘合剂作

为中间物（未示出），使偏光镜 40 和 50 分别紧密接触第一基板 10 和第二基板 20 的外表面。所设置的这些偏光镜 40 和 50 处于为正交偏光镜状态（crossed-Nicols state）。在第一基板 10 上的偏光镜 40 的更外侧，设置用作用于进行透射显示的光源的背光（未示出）。

除第一基板 10 外，该结构是一个很一般的结构。例如，作为显示侧基板的第二基板 20 由诸如玻璃基板的透明基板形成。在其面向液晶层 30 的表面上，顺序设置分别用于红色（R）、绿色（G）和蓝色（B）的滤色片 21 以及对准层 22。

另一方面，作为背侧基板的第一基板 10 具有特有结构，因此，以下将对其进行详细描述。

第一基板 10 由诸如玻璃基板的透明基板形成。在其面向液晶层 30 的表面上，以矩阵形式设置多条扫描线 11 和多条信号线 12。作为扫描线 11 和信号线 12 的材料，可以使用以下材料中的任意种：铝（Al）、钼（Mo）、铬（Cr）、钨（W）、钛（Ti）、铅（Pb）、任意这些材料的复合层（例如，Ti/Al）、以及金属化合物层（MoSi、AlSi）。在本实例中，例如，这两种线都由铝（Al）构成。然而，扫描线 11 和信号线 12 可以由不同材料构成。

在扫描线 11 和信号线 12 之间的每个交叉点处，设置用于驱动各个像素的由底栅型 TFT 1 形成的驱动元件。被扫描线 11 和信号线 12 包围的区域用作像素区域 1A。在本实例中，例如，平面图中，此像素区域 1A 具有矩形形状，该矩形形状具有沿信号线 12 延伸的较长边，和沿扫描线 11 延伸的较短边。

如图 2A（沿线 A-A'的主要部分的放大截面图）所示，TFT 1 的栅电极 2 由扫描线 11 的一部分形成。在第一基板 10 上形成栅极

绝缘膜 3，并且栅极绝缘膜 3 覆盖包括栅电极 2 的扫描线 11。此外，在覆盖栅电极 2 的栅极绝缘膜 3 上图样化形成半导体层 4。

例如，半导体层 4 由不定形硅 (a-Si)、多晶硅 (poly-Si)、或单晶硅构成。其在栅电极 2 正上方的部分用作沟道层 4a。例如，在沟道层 4a 的两侧上，设置含有 n 型杂质的源极区 4b 和漏极区 4c。此外，在沟道层 4a 与源和漏极区 4b 和 4c 之间，设置杂质浓度低于源和漏极区 4b 和 4c 的杂质浓度的 LDD 区域 4b' 和 4c'。

在栅极绝缘膜 3 上，设置绝缘层 5 以覆盖半导体层 4。将源电极 6a 和漏电极 6b 经由接触孔连接至源和漏极区 4b 和 4c，接触孔被设置在绝缘层 5 中，从而能够到达源和漏极区 4b 和 4c。源电极 6a 由与信号线 12 相同的层形成。

在绝缘层 5 上，设置第一绝缘膜 13 以覆盖源和漏电极 6a 和 6b。在接下来的步骤中，将以约 200°C 到 400°C 的高温，在第一绝缘膜 13 上沉积第二绝缘膜。因此，优选地，第一绝缘膜 13 具有耐热性。此外，由于将在第一绝缘膜 13 上形成共电极，所以优选地，第一绝缘膜 13 具有高平面性。此外，为了抑制寄生电容，优选地，第一绝缘膜 13 具有高的透射性、低的膜应力、和低的相对介电常数。作为具有这样特性的第一绝缘膜 13，例如，尤其优选地，使用旋涂玻璃 (spin-on-glass, SOG) 膜。第一绝缘膜 13 的厚度对扫描线 11、信号线 12、和将在接下来的步骤中形成在第一绝缘膜 13 上的共电极的负载电容具有很大的影响：教大的厚度得到教小的负载电容。因此，在与液晶显示装置的驱动特性相关的容许范围内，例如，第一绝缘膜 13 优选地具有约 0.5 μm ~ 4.0 μm 范围的膜厚度。

代替 SOG 薄膜，还可以将诸如通过化学汽相沉积 (CVD) 沉积的氧化硅 (SiO<sub>2</sub>) 或氮化硅 (SiN) 的无机绝缘膜用作第一绝缘膜 13。可选地，可以使用有机绝缘膜。然而，比使用由 CVD 沉积

的无机绝缘膜更优选地，使用有机绝缘膜作为第一绝缘膜 13，这是因为有机绝缘膜具有更高的平面性和更低的相对介电常数，并且可以通过涂覆的方法轻易进行沉积。对于有机绝缘膜，使用非感光树脂或者感光树脂。非感光树脂的实例包括丙烯酸树脂、聚酯、氯乙烯、聚碳酸酯、聚丙烯、聚乙烯、三乙酸酯、和聚酰亚胺。感光树脂的实例包括丙烯酸树脂、聚酰亚胺、和由 Sumitomo Bakelite Co., Ltd. 生产的 Sumiresin Excel CRC-8300。在表 1 中示出了有机绝缘膜的材料的性质。

表 1-1

|                                    | 聚酯<br>PET  | 氯乙烯<br>PVC | 聚碳酸<br>酯 PC | 聚丙烯 PP    | 聚乙烯 PE   |

|------------------------------------|------------|------------|-------------|-----------|----------|

| 厚度(μm)                             | 25         | 25         | 25          | 25        | 25       |

| 密度(g/cm <sup>2</sup> )             | 1.40       | 1.40       | 1.20        | 0.91      | 0.92     |

| 抗张强度(Mpa)                          | 176        | 98         | 98          | 186       | 20       |

| 延伸率(%)                             | 120        | 50         | 140         | 110       | 400      |

| 边缘撕裂强度(Kg)                         | 23         | 8          | 10          | 15        | 2        |

| 透湿性<br>(g/m <sup>2</sup> ·24hr)    | 21         | 35         | 60          | 8         | 20       |

| 透氧性<br>(cc/m <sup>2</sup> ·hr·atm) | 3          | 6          | 300         | 100       | 250      |

| 吸水率(%)                             | 0.3        | 0.05       | 0.2         | 0.01      | 0.02     |

| 热膨胀系数<br>(ppm/°C)                  | 90         | 118        | 70          | 110       | 170      |

| 湿膨胀系数<br>(ppm/%RH)                 | -          | -          | -           | -         | -        |

| 击穿电压(KV/mm)                        | 130        | 80         | 1200        | 120       | 80       |

| 体积电阻率(Ω·cm)                        | 1.0E+17    | 1.0E+15    | 1.0E+17     | 1.0E+16   | 1.0E+17  |

| 介电常数                               | 3.2        | 3.0        | 3.0         | 2.1       | 2.3      |

| 介质损耗角正切                            | 0.002      | 0.01       | 0.002       | 0.003     | 0.0005   |

| 熔点(°C)                             | 258        | 180        | 240         | 170       | 135      |

| 脆化温度                               | -70<br>150 | -45        | -100<br>130 | -40       | -60      |

| 适用温度                               | -70<br>150 | -20 ~ 80   | -100<br>130 | -50 ~ 120 | -50 ~ 75 |

表 1-2

|                                    | 三乙酸<br>酯 TAC | 聚酰亚胺 1<br>*1 | 聚酰亚胺 2<br>*2 | 聚酰亚胺 3<br>*3 | CRC-8300<br>Sumitomo<br>Bakelite |

|------------------------------------|--------------|--------------|--------------|--------------|----------------------------------|

| 厚度(μm)                             | 25           | 25           | 25           | 12           | 12                               |

| 密度(g/cm <sup>2</sup> )             | 1.30         | 1.43         | -            | -            | -                                |

| 抗张强度(Mpa)                          | 118          | 274          | 140 ~ 350    | 120          | 120                              |

| 延伸率(%)                             | 30           | 9            | 57 ~ 150     | 42           | 65                               |

| 边缘撕裂强度<br>(Kg)                     | 3            | 17           | -            | -            | -                                |

| 透湿性<br>(g/m <sup>2</sup> ·24hr)    | 700          | 4            | -            | 150          | 300                              |

| 透氧性<br>(cc/m <sup>2</sup> ·hr·atm) | 110          | 9.3          | -            | -            | -                                |

| 吸水率(%)                             | 4.4          | 1.3          | 1.0 ~ 2.9    | 1.9          | 0.3                              |

| 热膨胀系数<br>(ppm/°C)                  | -            | 54           | 16 ~ 60      | 43           | 47                               |

| 湿膨胀系数<br>(ppm/%RH)                 | -            | -            | 16 ~ 24      | -            | -                                |

| 击穿电压<br>(KV/mm)                    | 60           | 140          | 60 ~ 400     | 260          | 260                              |

| 体积电阻率<br>(Ω·cm)                    | 1.0E+15      | 1.0E+17      | 1.0E+15      | 3.5E+16      | 1.0E+16                          |

| 介电常数                               | 3.5          | 3.3          | -            | 3.5          | 2.9                              |

| 介质损耗角正切                            | 0.02         | 0.001        | -            | -            | -                                |

| 熔点(°C)                             | 290          | -            | -            | -            | -                                |

| 脆化温度                               | -            | -            | -            | -            | -                                |

| 适用温度                               | ~ 120        | -            | -            | -            | -                                |

\*1... 非感光性, PI(Literature)

\*2... 非感光性, Du Pont-Toray

\*3... 非感光性, Sumitomo Bakelite

作为本实施例的特性, 共电极 14 被设置在第一绝缘膜 13 上, 从而覆盖除用于连接后述的像素电极和 TFT 1 的接触孔的形成区域外的像素区域 1A、以及扫描线 11 和信号线 12 中的至少一条。由

于此特性，由于用共电极 14 覆盖扫描线 11 和信号线 12 中的至少一条，所以可以增大有效像素区域并且可以提高孔径比。例如，此共电极 14 由氧化铟锡 (ITO) 或氧化铟锌 (IZO) 膜的透明电极膜形成。

在本实例中，共电极 14 被设置在除接触孔的形成区域外的整个显示区域上。在此情况下，从连接至显示区域外侧的 Vcom 端的金属互连线 (metal interconnect) 向共电极 14 提供电位，因此可以进一步提高孔径比。共电极 14 与接触孔分离，从而能够防止后述设置在接触孔中的像素电极对共电极形成短路。

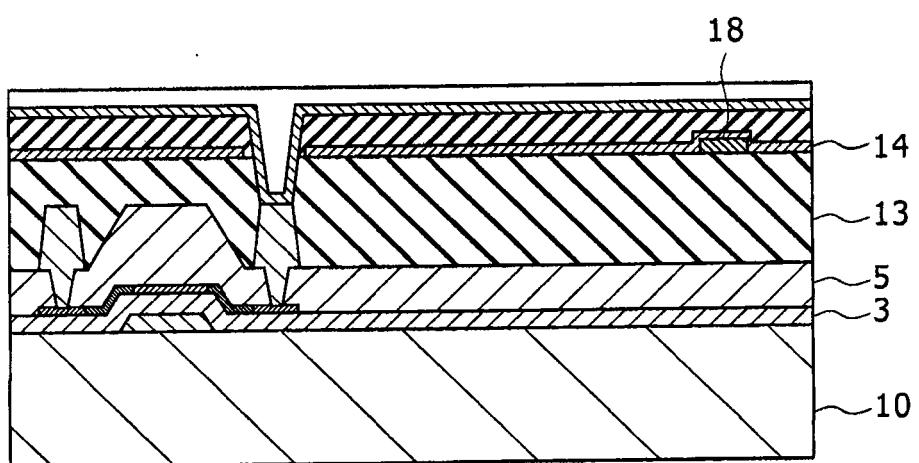

尽管在本实施例中，从连接至显示区域外侧的 Vcom 端的金属互连线向共电极 14 提供电位，但是图 2B 所示的结构也是可行的。具体地，在此结构中，在第一绝缘膜 13 上平行于扫描线 11 设置由具有低于共电极 14 的电阻值的材料构成的多条共电位线 18。共电位线 18 连接至共电极 14。例如，通过使用 Al、Mo、Ti、Pb、W、Cr 中的任意种、任意这些金属的复合层 (例如、Ti/Al)、以及金属化合物层 (MoSi, AlSi) 形成共电位线 18。在本实例中，与扫描线 11 和信号线 12 类似，例如，共电位线 18 由 Al 构成。然而，扫描线 11、信号线 12、和共电位线 18 可以由不同材料构成。

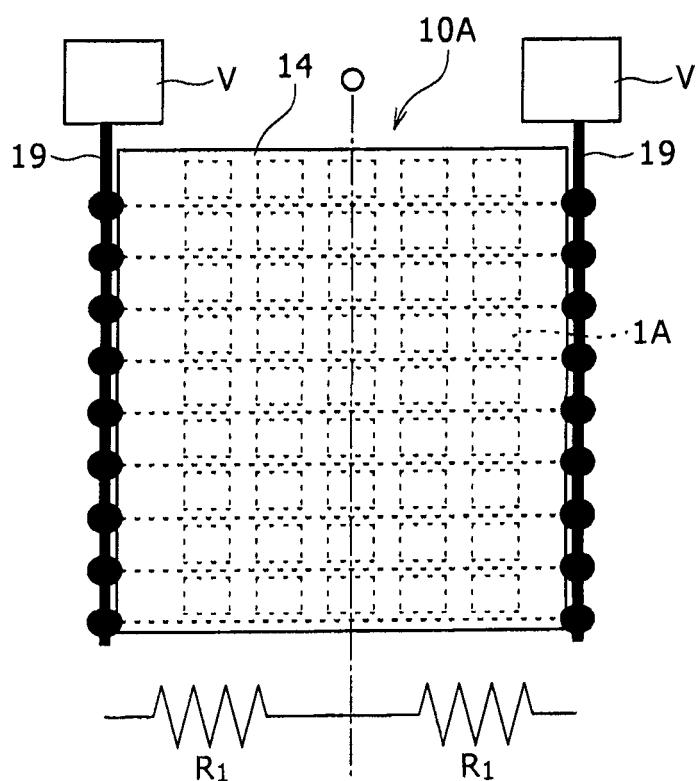

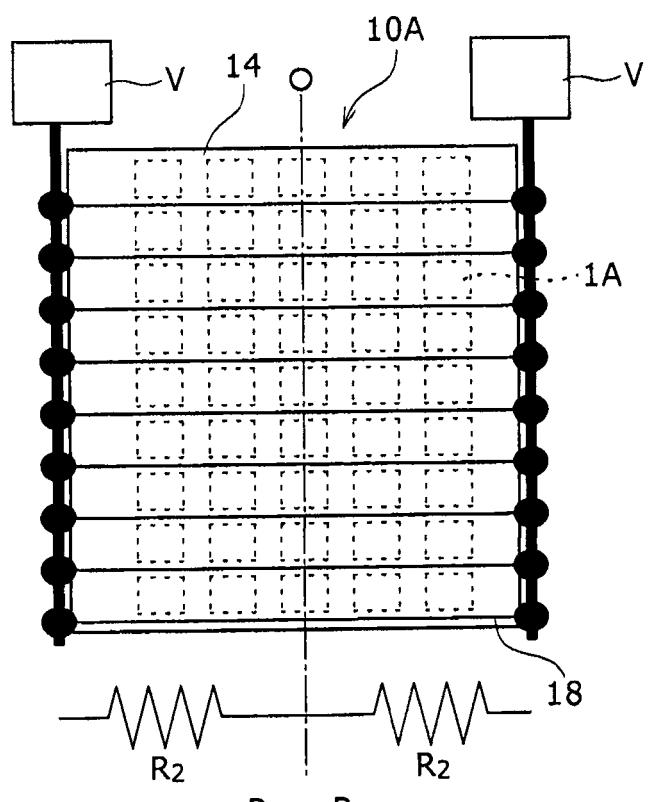

图 3A 是示出了没有设置共电位线的情况的示意图，以及图 3B 是示出了设置有共电位线的情况的示意图。这些图用来对这些情况间的电阻值进行比较。在图 3 的这些实例中，连接至 Vcom 端 V 的金属互连线 19 并列在配置有像素区域 1A 的显示区域 10A 的两侧，并且从这些金属互连线 19 向设置在除接触孔的形成区域外的整个显示区域 10A 上的共电极 14 提供电位。由此，从两条金属互连线 19 向显示区域 10A 的中心 O 提供电位。

在图 3A 的情况下，没有设置共电位线并因此从设置在显示区域 **10A** 外侧的金属互连线 **19** 直接向 ITO 构成的共电极 **14** 提供电位，共电极 **14** 在从显示区域 **10A** 的端部到中心 **O** 的范围内的电阻  $R_1$  很高，因为 ITO 的电阻为  $10 \Omega/\text{um}^2 \sim 200 \Omega/\text{um}^2$ 。因此，在从显示区域 **10A** 的端部向中心 **O** 提供电位中出现时滞 (time lag)，这将导致亮度在液晶面板的显示区域 **10A** 中的各处不同。相反，在图 3B 的情况下，为每个像素行设置了多条共电位线 **18**，共电极 **14** 在从显示区域 **10A** 的端部到中心 **O** 的范围内的电阻  $R_2$  低于电阻  $R_1$ ，这是因为共电位线 **18** 的金属材料具有比用于共电极 **14** 的 ITO 更低的电阻：例如，Al 和 Mo 的电阻分别为  $0.05 \Omega/\text{um}^2$  和  $0.5 \Omega/\text{um}^2$ 。因此，可以防止从显示区域 **10A** 的端部向中心 **O** 提供的电位中出现时滞，从而可以抑制亮度在显示区域 **10A** 中的各处不同。

优选地，共电位线 **18** 与扫描线 **11** 或者信号线 **12** 重叠，因为这种结构能够所设置的共电位线 **18** 不会对孔径比起反作用。

尽管在图 3 的实施例中，在显示区域 **10A** 的两侧上设置两个金属互连线 **19**，但另一种在显示区域 **10A** 的一侧上仅设置一个金属互连线 **19** 的结构也是可行的。然而，优选地，在显示区域 **10A** 的两侧上设置两个金属互连线 **19**，因为可以减小共电极 **14** 从显示区域 **10A** 的端部到其中心的范围内的电阻。

尽管在本实例中共电位线 **18** 被设置在第一绝缘膜 **13** 和共电极 **14** 之间，但是只要连接至共电极 **14**，可以将共电位线 **18** 设置在绝缘层 **5**、栅极绝缘膜 **3**、和第一基板 **10** 中的任一个上。

再次参照图 2A，在共电极 **14** 上，设置由例如通过 CVD 沉积的  $\text{SiO}_2$  或  $\text{SiN}$  薄膜的无机绝缘膜形成的第二绝缘膜 **15**。使用通过 CVD 沉积的作为第二绝缘膜 **15** 的无机绝缘膜提供了防止预烧 (burn-in) 和提高成品率等优点。代替无机绝缘膜，还可以由 SOG

薄膜或有机绝缘膜形成第二绝缘膜 15。作为有机绝缘膜的材料，可以使用预上述用于第一绝缘膜 13 的材料相同的任意材料。

在表 2 中示出了第一绝缘膜 13 和第二绝缘膜 15 之间的组合。

表 2

|      | 第一绝缘膜     | 第二绝缘膜     |

|------|-----------|-----------|

| 体系 1 | SOG       | CVD-无机绝缘膜 |

| 体系 2 | 有机绝缘膜     | CVD-无机绝缘膜 |

| 体系 3 | CVD-无机绝缘膜 | CVD-无机绝缘膜 |

| 体系 4 | SOG       | SOG       |

| 体系 5 | 有机绝缘膜     | SOG       |

| 体系 6 | CVD-无机绝缘膜 | SOG       |

| 体系 7 | SOG       | 有机绝缘膜     |

| 体系 8 | 有机绝缘膜     | 有机绝缘膜     |

| 体系 9 | CVD-无机绝缘膜 | 有机绝缘膜     |

虽然如表 2 所示第一绝缘膜 13 和第二绝缘膜 15 之间存在各种组合，但是优选的是体系 1 和体系 2 的组合，其中，如上所述，SOG 膜或者有机绝缘膜用作第一绝缘膜 13，而将通过 CVD 沉积沉积的无机绝缘膜（表 2 中的“CVD-无机绝缘膜”）用作第二绝缘膜 15。

在第二绝缘膜 15 和第一绝缘膜 13 中，设置到达漏电极 6b 的接触孔 15a 和 13a 以彼此互通，即，在平面图中相互重叠。在第二绝缘膜 15 上，设置像素电极 16 以经由接触孔 15a 和 13a 连接至漏电极 6b。

因为接触孔 15a 和 13a 在平面图中相互重叠，所以优选地，通过使用一个蚀刻掩膜的一次蚀刻形成这些孔。尽管本实施例还可以应用于接触孔 15a 和 13a 在平面图中并不相互重叠的情况，但是优选地，这些孔相互重叠，因为这样的结构提供更高的孔径比。

对准层 17 被设置在第二绝缘膜 15 上并覆盖像素电极 16。如图 1B 所示，像素电极 16 具有平行于信号线 12 设置的多个狭缝 16a。

当因此平行于信号线 12 设置像素电极 16 的多个狭缝 16a 时，与以上图 14 所述的现有技术相同，与平行于扫描线 11 设置多个狭缝的情况相比，增大了有效像素区域。这是由于以下原因。具体地，当狭缝平行于扫描线 11 时，接近信号线 12 的狭缝的短边附近的区域将不用作有效像素区域，因为液晶分子 m 的取向受到限定这些短边的电极部分的约束。相反，当平行于信号线 12 设置狭缝 16a 时，甚至包括像素电极 16 在信号线侧上的端部也可以用作有效像素区域。同样，在这种情况下，像素电极 16 在狭缝 16a 的短边附近的区域也不用作有效像素区域。然而，如果这个区域与扫描线 11 重叠，那么可以顺利确保高孔径比。

参照图 4，其是在图 1B 中沿线 B-B' 的截面图，用于驱动像素的驱动电压受到狭缝 16a 在像素电极 16 的中心部分的宽度、电极部分 16b 在狭缝 16a 间的宽度、以及第二绝缘膜 15 的厚度的限定。如果相邻像素的像素电极 16 间的距离 X 过小，从相邻像素会出现漏光。因此，优选地，使像素电极 16 彼此分隔预定距离或更远的距离。为了控制相邻像素的像素电极 16 间的距离 X，存在于像素电极 16 在信号线侧上的端部和最接近信号线 12 的狭缝 16a 间的电极部分 16b' 的宽度经过调节不同于电极部分 16b 除这个电极部分 16b' 外的宽度。

图 5 是示出了通过测量从彼此相邻的白色显示像素 B 到黑色显示像素 A 的漏光而得到的曲线图。在曲线图的纵坐标上绘制漏光作为透射率。通过使像素 A 和 B 的像素电极 16 间的距离 X 变为 2、4、6、7、8、10、12、16、和 20  $\mu\text{m}$  执行测量。如该图所示，证明相邻像素的像素电极 16 间的较小距离 X 会导致更高程度的漏光。由

Al 构成的信号线 12 用作光屏蔽体。因此，可以通过增加信号线 12 的线宽度 Z 防止漏光。

通过模拟研究信号线 12 的优选宽度。对于这个模拟，黑色显示像素 A 中 0.1 或更低的透射率用作了在像素 A 中无法视觉识别漏光的状态的标准。图 6 是示出了作为模拟结果得到的提供了透射率为 0.1 或更低的黑色显示像素 A 的信号线 12 的宽度 Z 的曲线图。在曲线图中，在横坐标上绘制相邻像素的像素电极 16 间的距离 X。通过使第二绝缘膜 15 的厚度 Y 变为 200、400、600、800、和 1000 nm 进行模拟。如该曲线图所示，发现通过线性函数表示信号线的宽度 Z(y)，线性函数的变量是像素电极 16 间的距离 X，并且与第二绝缘膜 15 的厚度无关，该函数的斜率几乎为常数。此外，发现函数的 y 截距取决于第二绝缘膜 15 的厚度，并且较大的第二绝缘膜 15 的厚度需要用作光屏蔽体的信号线的宽度更大。

如下归纳了线性函数的表达式。具体地，作为归纳表达式的斜率，采用作为对于第二绝缘膜 15 的不同厚度得到的模拟结果的五个表达式的斜率的平均值。通过使用近似等式获得归纳表达式的截距。图 7A 和图 7B 是分别示出了关于截距的对数近似和线性近似的曲线图。

基于归纳表达式，当采用对数 (log) 近似时，通过表达式 (1) 表示信号线 12 的优选宽度 Z，而当采用线性近似时，通过表达式 (2) 表示信号线 12 的优选宽度 Z。

$$Z \geq -0.92558X + 3.237\ln(Y) - 10.593 \quad \dots \text{表达式 (1)}$$

$$Z \geq -0.92558X + 0.0063Y + 5.8833 \quad \dots \text{表达式 (2)}$$

相邻像素的像素电极间的距离 X、第二绝缘膜的膜厚度 Y、和光屏蔽体的线宽 Z 经过设置以满足这两个表达式中的一个。更具体地，当基于更精确的对数近似的表达式 (1) 设置各个值时，可以确保抑制漏光。

然而，在本实施例中，光屏蔽体的功能通过信号线 12 实现，并且基于液晶显示装置的设计限定信号线 12 的宽度和第二绝缘膜 15 的厚度 Y。然而，较小的宽度 Z 提供较高的孔径比。因此，通过将宽度 Z 设为最小值，相邻像素的像素电极间的距离 X 经过设置以满足表达式 (1) 或表达式 (2)。此外，如图 8 所示，像素电极 16 最接近信号线 12 的电极部分 16b' 的宽度经过设置小于另一电极部分 16b 的宽度，从而调节相邻像素的像素电极间的距离 X。

尽管在本实施例中信号线 12 还用作光屏蔽体，可以在信号线 12 下设置并不电连接至任何电极的光屏蔽体。

再次参照图 1，以下将描述液晶显示装置 100 的操作。当不施加任何电场时，液晶层 30 中的液晶分子 m 经过取向以不会产生任何相位差。因此，从背光发出并穿过偏光镜 40 的光 h 被偏光镜 50 吸收，其中，相对于偏光镜 40，以正交偏光镜状态设置偏光镜 50，从而显示黑色。

另一方面，当施加电场时，由于光穿过液晶层 30，液晶分子 m 的排列使其出现  $\lambda/2$  的相位差。因此，作为穿过液晶层 30 的结果，从背光发出并穿过偏光镜 40 的光 h 转变为由  $\lambda/2$  的相位差产生的 90° 旋转线性偏光。因此，光穿过偏光镜 50，从而显示白色。

图 9 是液晶显示装置 100 的电路图。在液晶显示装置 100 的第一基板 10 上，限定显示区域 10A 和外围区域 10B。该电路对应于

如上图 3A 和图 3B 所述的将用于提供电位的金属互连线 19 仅安置在显示区域 10A 外部的一侧的外围区域 10B 的情况。

显示区域 10A 作为像素阵列部而形成，其中，以矩阵形式设置多条扫描线 11 和多条信号线 12，并且在扫描线 11 和信号线 12 的每个交叉点处设置一个像素 A。

此外，在外围区域 10B 中安放以下单元：逐行顺序选择在显示区域 10A 中的各个像素 A 的垂直驱动器 61；将像素信号逐行写入各个像素 A 的水平驱动器 62；用于进行时分驱动的时分切换单元 63；以及控制垂直和水平驱动器 61 和 62 以及时分切换单元 63 的控制系统 64。

每个像素 A 均包括 TFT 1、显示元件 D、和辅助电容器 S。TFT 1 的栅电极连接至扫描线 11-1 ~ 11-m 中之一，以及 TFT 1 的源电极 6a 连接至信号线 12-1 ~ 12-n 中之一。显示元件 D 的像素电极 16 连接至 TFT 1 的漏电极 6b。辅助电容器 S 的一个电极连接至 TFT 1 的漏电极 6b。在具有该结构的每个像素 A 中，显示元件 D 的共电极以及辅助电容器 S 的另一个电极连接至共电位线 18。对共电位线 18，提供与水平同步信号同步的预定 DC 电压或矩形波形电压作为共电位 VCOM。

该液晶显示装置 100 是通过时分驱动方法驱动的。在时分驱动方法中，以使彼此相邻的多条信号线 12 作为一个单元（部件）的方式划分显示区域 10A，并且以时序（time-series）方式从水平驱动器 62 的各个输出端输出将被提供给一个分割部件中的多条信号线 12 的信号电压。此外，对许多信号线 12 提供时分切换单元 63 作为一个单元，并且通过时分切换单元 63 以时分方式采样从水平驱动器 62 输出的时序信号电压，接下来将这些电压顺序提供给多条信号线。

时分切换单元 **63** 由用于以时分方式采样从水平驱动器 **62** 输出的时序信号电压的模拟开关（传输开关）形成。以下将描述时分切换单元 **63** 的具体配置实例。为水平驱动器 **62** 的各个输出设置一个时分切换单元 **63**。本实例对应于对红色 (R)、绿色 (G) 和蓝色 (B) 的三种颜色执行三重时分驱动 (tripartite-time-division manner) 的情况。

该时分切换单元 **63** 由每个均具有通过并联连接 PchMOS 晶体管和 NchMOS 晶体管得到的 CMOS 配置的模拟开关 **63-1**、**63-2**、和 **63-3** 形成。尽管在本实施例中采用具有 CMOS 配置的开关作为模拟开关 **63-1**、**63-2**、和 **63-3**，但也可能使用具有 PMOS 或者 NMOS 配置的开关。

在该时分切换单元 **63** 中，三个模拟开关 **63-1**、**63-2**、和 **63-3** 的各个输入端连接在一起，而其每个输出端分别连接至三条信号线 **12-1**、**12-2** 和 **12-3** 的各个端部。对这些模拟开关 **63-1**、**63-2**、和 **63-3** 的各个输入端，提供以时序方式从水平驱动器 **62** 输出的信号电位。

如果本实施例的共电极 **14** 还被设置在模拟开关 **63-1**、**63-2** 和 **63-3** 上，那么每个均由具有底栅结构的 TFT **1** 形成的模拟开关 **63-1**、**63-2** 和 **63-3** 可以消除由于来自附近的栅极选择信号以及每个邻近的信号线 **12-1**、**12-2**、和 **12-3** 的寄生电容带来的电位变化的影响。显然，当所形成模拟开关 **63-1**、**63-2** 和 **63-3** 具有顶栅结构时，也得到同样的优点。

两条控制线连接至一个模拟开关；提供总共六条控制线 **65-1** ~ **65-6**。模拟开关 **63-1** 的两个控制输入端（例如，CMOS 晶体管的各个栅极）连接至控制线 **65-1** 和 **65-2**。模拟开关 **63-2** 的两个控制输入端连接至控制线 **65-3** 和 **65-4**。模拟开关 **63-3** 的两个控制输入端连接至控制线 **65-5** 和 **65-6**。

对六条控制线 **65-1 ~ 65-6**，从后述的定时控制器 (TC) **66** 提供用于顺序选择三个模拟开关 **63-1**、**63-2**、和 **63-3** 的栅极选择信号 **S1 ~ S3** 和 **XS1 ~ XS3**。栅极选择信号 **XS1** 到 **XS3** 是栅极选择信号 **S1 ~ S3** 的反转信号。

同步于从水平驱动器 **62** 输出的时序信号电位，栅极选择信号 **S1 ~ S3** 和 **XS1 ~ XS3**，依次打开三个模拟开关 **63-1**、**63-2**、和 **63-3**。因而，在 **1H** 时间内，模拟开关 **63-1**、**63-2** 和 **63-3** 以三重时分方式取样从水平驱动器 **62** 输出的时序信号电位，然后将信号电位分别提供给对应信号线 **12-1**、**12-2**、和 **12-3**。

控制垂直驱动器 **61**、水平驱动器 **62**、和时分切换单元 **63** 的控制系统 **64** 包括定时控制器 (TC) **66**、基准电压发生源 **67**、和 DC-DC 转换器 **68** 等。这些电路与垂直驱动器 **61**、水平驱动器 **62** 以及时分切换单元 **63** 一起被安装在第一基板上的外围区域 **10B** 中。

对该控制系统 **64** 中的定时控制器 **66**，经由 TCP (未示出) 输入来自外部电源单元 (未示出) 的电源电压 **VDD**、来自外部 CPU (未示出) 的数字图像数据、以及来自外部时钟发生器 (未示出) 的时钟 **CLK**。

图 10 是示出了本实施例的液晶显示装置中的每个像素 **A** 的电路图。如图 10 所示，由于共电极 **14** 被设置在除接触孔的形成区域外的整个显示区域 **10A** 上，所以分别在信号线 **12** 和像素电极 **16** 间、以及扫描线 **11** 和像素电极 **16** 间产生的寄生电容 **C1** 和 **C2** 耦连至共电极 **14**，从而抑制了对像素电位的影响。

在这种液晶显示装置和包括其的显示设备中，共电极 **14** 被设置在第一绝缘膜 **13** 上，以不仅覆盖除接触孔 **13a** 和 **15a** 的形成区域外的像素区域 **1A** 并且还覆盖扫描线 **11** 和信号线 **12** 中的至少一

条。该特征可以增大有效像素区域，并且可以提高孔径比。因此，可以提高透光率，并且可以提高对比度。

此外，由于所提供的共电极 14 覆盖扫描线 11 和信号线 12 中的至少一条，因此抑制了信号线 12 和像素电极 16 间或者扫描线 11 和像素电极 16 间的寄生电容。更具体地，在本实施例的液晶显示装置中，除接触孔 13a 和 15a 的形成区域外的整个显示区域 10A 被共电极 14 覆盖。该特征可以确保防止像素中出现信号干扰。因此，稳定所保持的像素电位，并且既不会出现垂直色度亮度干扰，也不会出现水平色度亮度干扰，从而提高了液晶显示装置的图像质量。

此外，由于来自于信号线 11、扫描线 12、和像素电极 16 的电场，本实施例的液晶显示装置以及包括其的显示设备不会在对半导体层 4 采用 a-Si、多晶-Si、或者单晶硅的底栅极 TFT 1 的半导体层 4 中生成反向沟道。因此，可以防止由于寄生反向沟道带来的不稳定操作。显然，也提供了与顶栅型 TFT 同样的优点。

当如图 11 所示，TFT 1 为顶栅型晶体管时，在第一基板 10 上图样化形成 a-Si、多晶-Si 或者单晶硅构成的半导体层 4。在该半导体层 4 上，使用栅极绝缘膜 3 作为中间物图样化形成沿一个方向延伸并且具有作为栅电极 2 的一部分的扫描线 11。在这种情况下，使用栅电极 2 作为注入掩膜离子注入 n 型杂质。因此，直接位于栅电极 2 下方的半导体层 4 用作沟道层 4a，并且在沟道层 4a 的两侧上的半导体层 4 用作源极区 4b 和漏极区 4c。此外，绝缘层 5 被设置在栅电极 2 和栅极绝缘膜 3 上，并且源和漏极区 4b 和 4c 经由设置在绝缘层 5 中的接触孔 5a 和 5b 连接至源和漏电极 6a 和 6b。此外，第一绝缘膜 13 经过设置覆盖源和漏电极 6a 和 6b。

<变型实例 1>

在上述第一实施例中，像素电极 16 具有矩形形状，并且作为实例提供矩形狭缝 16a。可选地，可以使用图 12 的平面图所示的多域结构。具体地，在图 12 的结构中，像素电极 16' 具有通过在平面图中使矩形电压在纵向侧的中心弯曲得到的形状，即，通过将矩形电极弯曲成“V 字型”得到的形状。在这种情况下，像素电极 16' 的狭缝 16a' 也展开成为“V 字型”以匹配像素电极 16' 的外侧形状。在该结构中，具有不同电场方向的两个域存在于像素区域 1A 中。因此，像素区域 1A 中的液晶分子 m 的取向方向数也是二，从而可以大大改善视角特性。在图 12 的结构中，信号线 12 被设置成 Z 字型，从而匹配像素电极 16' 的弯曲。

如下设计展开成“V 字型”的狭缝 16a' 的具体形状。具体地，如果当施加电场时，在上述两个具有不同电场方向的域中，将液晶分子 m 的纵轴的排列方向设定为 90°，则相对于液晶分子 m 的纵轴将狭缝 16a' 的纵向角度设为等于或大于 45° 并小于 90°，并且优选地设为等于或大于 65° 并等于或小于 89°。

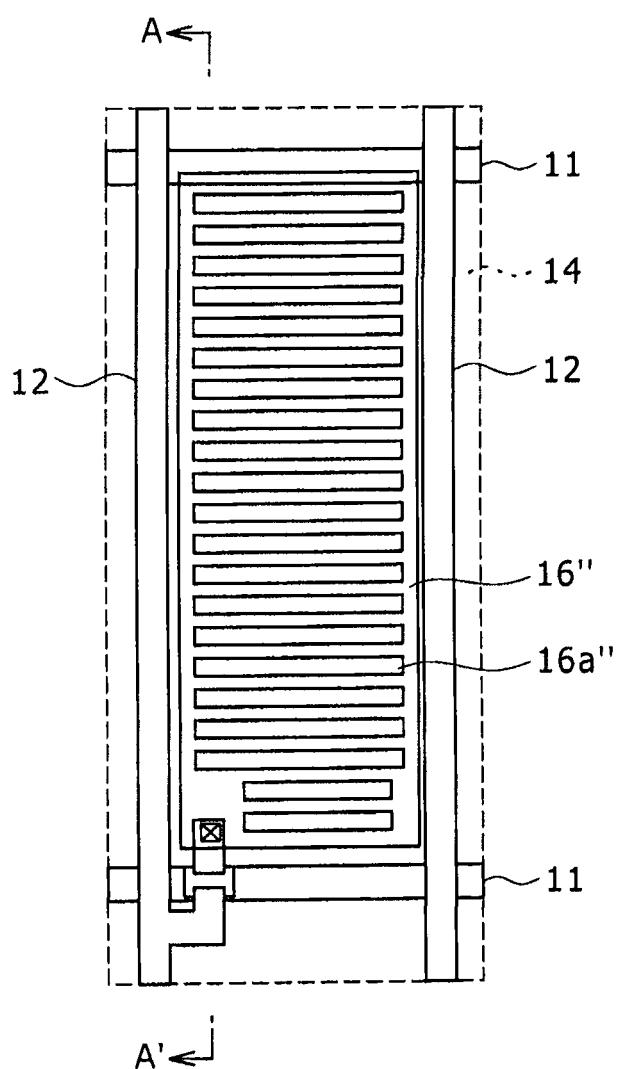

#### <变型实例 2>

如图 13 的平面图所示，可以基本上平行于扫描线 11 设置像素电极 16”的许多狭缝 16a”。“主要地平行”意味着狭缝 16a”相对于扫描线 11 具有 0° 到约 45° 范围内的倾斜。同样，在该结构中，由于共电极 14 被设置在除接触孔 13a 和 15a 的形成区域外的整个显示区域 10A 上，所以提高了孔径比，并且抑制了信号线 12 和像素电极 16”间以及扫描线 11 和像素电极 16”间的寄生电容。然而，如以上第一实施例所述，优选地，因为得到了更高的孔径比，所以平行于信号线 12 设置像素电极 16 的狭缝 16a。

即使在这样的液晶显示装置中，由于孔径比的增大，提高了透光率，并且可以提高对比度。此外，因为抑制了扫描线和像素电极

间或者信号线和像素电极间的寄生电容，所以可以防止像素中的信号干扰。因此，稳定了所保持的像素电位，并且既不会出现垂直色度亮度干扰，也不会出现水平色度亮度干扰，从而提高了液晶显示装置的图像质量。

同样，对于变型实例 2 的结构，如图 2B 所述设置连接至共电极 14 的共电位。此外，可以应用变型实例 1 所述的多域结构。

将上述实施例以及变型实例作为实施例应用于透射型液晶显示装置。然而，本发明的实施例并不限于此，而可以应用于反射型或具有反射区和透射区的半透明型的 FFS 模式液晶显示装置。

## 实施例

以下将具体描述实例的各个具体实施例。

### <实施例 1>

制造液晶显示装置，其中，类似于关于第一实施例的图 1 所述的结构，共电极 14 被设置在第一绝缘膜 13 上除接触孔的形成区域外的整个显示区域上，并且平行于信号线 12 设置像素电极 16 的多个狭缝。

### <实施例 2>

制造液晶显示装置，其中，类似于关于变型实例 2 的图 13 所述的结构，共电极 14 被设置在第一绝缘膜 13 上除接触孔的形成区域外的整个显示区域上，并且平行于扫描线 11 设置像素电极 16” 的多个狭缝 16a”。

### <比较实例 1>

作为关于实施例 1 和实施例 2 的比较实例, 制造液晶显示装置, 其中, 类似于关于现有技术的图 14 所述的结构, 共电极 114 被设置在第一基板 110 上除 TFT 1 的形成区域外的整个像素区域上, 并且平行于扫描线 111 设置像素电极 116 的多个狭缝 116a。

测量并相互比较实施例 1 和 2 以及比较实例 1 的液晶显示装置的孔径比和相对透射率。相对透射率表示了当将入射光的比率限定为 100% 时提取的光的比率, 并且该比率与孔径比成比例。在表 3 中示出了测量结果。

表 3

|         | 孔径比 (%) | 相对透射率 (%) |

|---------|---------|-----------|

| 实例 1    | 132     | 7.0       |

| 实例 2    | 120     | 6.4       |

| 比较实施例 1 | 100     | 5.3       |

如表 3 所示, 确定了实施例 1 和实施例 2 的液晶显示装置的孔径比高于比较实例 1 的液晶显示装置的孔径比: 当将比较实例 1 的孔径比限定为 100% 时, 执行的实例 1 和 2 的孔径比分别为 132% 和 120%。此外, 比较实例 1 的相对透射率为 5.3%, 而实例 1 和实例 2 的相对透射率分别为 7.0% 和 6.4%。因此, 确定随着孔径比的增大, 相对透射率也增大。

本领域的技术人员应理解, 根据设计要求和其他因素, 可以有多种修改、组合、再组合和改进, 均应包含在本发明的权利要求或等同物的范围之内。

图 1A

图 1B

图 2A

图 2B

图 3A

图 3B

图 4

图 5

图 6

图 7A

图 7B

图 8

图 10

图 11

图 12

图 13

图 14A

图 14B

图 15A

图 15B

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置和显示设备                                    |         |            |

| 公开(公告)号        | <a href="#">CN100592183C</a>                   | 公开(公告)日 | 2010-02-24 |

| 申请号            | CN200810006339.7                               | 申请日     | 2008-02-26 |

| [标]申请(专利权)人(译) | 索尼公司                                           |         |            |

| 申请(专利权)人(译)    | 索尼株式会社                                         |         |            |

| 当前申请(专利权)人(译)  | 索尼株式会社                                         |         |            |

| [标]发明人         | 田中大直<br>野口幸治<br>金谷康弘<br>中岛大贵<br>野津大辅<br>猪野益充   |         |            |

| 发明人            | 田中大直<br>野口幸治<br>金谷康弘<br>中岛大贵<br>野津大辅<br>猪野益充   |         |            |

| IPC分类号         | G02F1/1362 G02F1/1343 H01L27/12                |         |            |

| CPC分类号         | G02F1/136213 G02F2201/40 G02F1/134363          |         |            |

| 代理人(译)         | 余刚                                             |         |            |

| 审查员(译)         | 钟宇                                             |         |            |

| 优先权            | 2007046534 2007-02-27 JP                       |         |            |

| 其他公开文献         | CN101256324A                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

本发明提供了一种液晶显示装置和显示设备，其中，该液晶显示装置包括介于第一基板和第二基板之间的液晶层，并且在第一基板侧上具有用于向所述液晶层施加电场的共电极和像素电极，该液晶显示装置包括：多条扫描线和多条信号线；驱动元件；第一绝缘膜；共电极；第二绝缘膜；以及像素电极，其中，共电极覆盖第一绝缘膜上除接触孔的形成区域外的像素区域、以及扫描线和信号线中的至少一条。