## [12] 发明专利说明书

专利号 ZL 200410028272.9

[45] 授权公告日 2007 年 10 月 24 日

[11] 授权公告号 CN 100345179C

[22] 申请日 2004.3.10

审查员 刘士奎

[21] 申请号 200410028272.9

[74] 专利代理机构 中原信达知识产权代理有限公司

[30] 优先权

代理人 穆德骏 陆弋

[32] 2003.3.10 [33] JP [31] 062766/2003

[73] 专利权人 恩益禧电子股份有限公司

地址 日本神奈川

[72] 发明人 中井大三郎 桥本义春

[56] 参考文献

CN1375814A 2002.10.23

CN1348167A 2002.5.8

US2002027551A1 2002.3.7

US5477234A 1995.12.19

US2002105492A1 2002.8.8

CN1143417A 1997.2.19

CN1052565A 1991.6.26

权利要求书 5 页 说明书 24 页 附图 26 页

## [54] 发明名称

用于液晶显示器的驱动电路和驱动方法

## [57] 摘要

一种显示设备的驱动电路，其中多条扫描线与多条数据线相同垂直，在所述驱动电路中，第一数据锁存电路(103)响应水平信号锁存用于每条线的图像数据。解码电路(104)对锁存的图像数据进行解码。等级电压选择电路(105)基于解码的图像数据，选择电压线以将多条数据线的每条与任何电压线连接。数据确定电路(107)基于选择的电压线产生数据确定信号，从而多个等级放大器的每个基于确定信号可选地设定为无效状态。等级放大器电路(111)包括多个等级放大器，每个等级放大器当处于有效状态时放大对应的等级电压之一，并且当处于无效状态时不放大对应的等级电压，放大的等级电压在对应的电压线之一上输出。输出电路(106)基于电压线上放大的等级电压驱动多条数据线。

1. 一种用于液晶显示器的驱动电路，包括排列成行列矩阵的多条扫描线与多条数据线，所述驱动电路包括：

数据锁存电路，响应于水平信号，用于锁存对应于所述多条数据线的图像数据；

解码电路，用于对所述锁存的图像数据进行解码；

等级电压选择电路，基于所述解码的图像数据，用于选择要连接到所述多条数据线的多条等级电压线的至少一条；以及

数据确定电路，基于所述多条等级电压线的所述选择的至少一条，用于产生确定信号，使得基于所述确定信号，多个等级放大器分组为至少一个有效等级放大器和除所述至少一个有效等级放大器的无效等级放大器，从而驱动所述多条等级电压线的所述至少一条以及随后驱动所述多条数据线。

2. 如权利要求1所述的驱动电路，还包括：

等级放大器电路，其包括所述多个等级放大器，每个等级放大器仅当激活时放大对应的等级电压之一，所述放大的等级电压输出到所述多条等级电压线的至少一条；以及

输出电路，基于所述多条等级电压线的所述放大的等级电压，用于驱动所述多条数据线；以及

偏压控制电路，基于来自所述数据确定电路的所述确定信号，用于将所述多个等级放大器的每个设定为所述有效状态和无效状态之一。

3. 如权利要求1所述的驱动电路，还包括：

帧存储器，用于存储一帧图像数据，其中所述锁存电路响应于锁存信号锁存一行图像数据，并随后将所述一行图像数据输出到所述解码电路。

4. 如权利要求3所述的驱动电路，还包括：

数据切换电路，当所述输入图像数据为静止图像数据时，所述数据切换电路将输入的图像数据输出到所述帧存储器，并且当所述输入图像数据为视频图像数据时，所述数据切换电路将所述输入的图像数据输出到所述锁存电路。

5. 如权利要求1所述的驱动电路，还包括：

等级电压产生电路，用于产生多个等级电压；以及

极性切换电路，提供在所述等级电压产生电路与所述等级放大器电路之间，以响应于极性信号从所述等级电压产生电路产生的所述多个电压中选择等级电压。

6. 如权利要求1至5任一个所述的驱动电路，其中所述数据确定电路响应于所述水平信号进行操作。

7. 如权利要求1至5任一个所述的驱动电路，其中所述数据确定电路响应于所述水平信号与所述极性信号进行操作。

8. 如权利要求1到5任一个所述的驱动电路，其中所述等级电压选择电路包括：

多个等级选择开关，基于所述解码的图像数据，用于选择所述多条等级电压线之一；以及

多个第一开关，用于允许所有所述多条等级电压线、和用于提供彼此不同的电压的电压电源的一个之间的连接，

所述输出电路包括：

多个第二开关，用于允许所述多条等级电压线的所述选择的一条和其它所述电压电源之间的连接；以及

多个第三开关，用于允许所述多条等级电压线的至少一条和所述多条数据线之间的连接，以及

所述数据确定电路基于所述多条等级电压线上的电压，产生所述

确定信号。

9. 如权利要求 8 所述的驱动电路，还包括：

命令控制电路，当存储在所述帧存储器中的像素数据数目超过所述显示设备的像素数目时，用于将所述多个第二开关的至少一个和相应的至少一个第三开关设置为断开状态。

10. 如权利要求 8 所述的驱动电路，其中所述等级电压选择电路还包括：

多个第四开关，用于允许所有所述多条等级电压线和用于提供彼此不同的电压的电压电源的一个之间的连接，以及

所述输出电路还包括：

多个第五开关，用于允许所述多条等级电压线的所述选择的一条和其它所述电压电源之间的连接。

11. 如权利要求 10 所述的驱动电路，还包括：

命令控制电路，当所述帧存储器的像素数目大于显示设备的像素数目时，所述命令控制电路总是将不和显示设备的所述多条数据线连接的所述第三开关与第五开关设定为断开状态。

12. 如权利要求 1 到 5 任一个所述的驱动电路，其中，当所述帧存储器的像素数目大于显示设备的像素数目时，在不存在对应于所述图像数据的所述多条扫描线周期期间，所述等级电压选择电路将所述多个等级放大器设定为所述无效状态。

13. 如权利要求 1 到 5 任一个所述的驱动电路，其中所述数据确定电路包括：

计数器，其用于对由所述等级电压选择电路选择的等级电压进行计数，以及

所述数据确定电路基于所述计数器的计数值，改变每个所述多个

---

等级放大器处于所述有效状态的周期，使得随着所述计数值变小，所述周期变短。

14. 如权利要求 1 至 5 任一个所述的驱动电路，其中每个所述多个等级放大器包括恒定电流源和输出级，以及

当所述等级放大器处于所述无效状态时，所述数据确定电路将所述恒定电流源的电流值设置为 0，并且将所述输出级设置为高阻抗状态。

15. 如权利要求 1 到 5 任一个所述的驱动电路，其中所述等级放大器电路包括：

第一组等级放大器，其每个具有 N 沟道晶体管作为差分输入晶体管；以及

第二组等级放大器，其每个具有 P 沟道晶体管作为差分输入晶体管。

16. 一种使用驱动电路来驱动液晶显示设备的方法，其中所述显示设备包括排列成行列矩阵的多条扫描线和多条数据线，并且所述驱动电路包括：

等级电压选择电路，基于图像数据，用于选择多条等级电压线的至少一条；和

数据确定电路，用于激活用于驱动等级电压线的多个等级放大器的至少一个，

所述方法包括：

(a) 基于图像数据，选择所述多条等级电压线的至少一条；

(b) 将所有所述多条等级电压线连接到具有第一电压的第一电源，然后将所述多条等级电压线的所述选择的至少一条连接到具有不同于所述第一电压的第二电压的第二电源；以及

(c) 仅激活所述多个等级放大器中的至少一个，该至少一个等级放大器对应于所述多条等级电压线的所述选择的至少一条。

17. 如权利要求 16 的方法，在步骤（a）和（b）之间进一步包括：

（d）从所述多个等级放大器断开所有所述多条等级电压线，并同时将所有所述多个等级放大器设置为无效状态。

18. 如权利要求 17 的方法，其中在步骤（d）中，所有所述多条等级电压线从所述多条数据线和所述所有所述多个等级放大器断开。

19. 如权利要求 16 至 18 任一个所述的方法，在步骤（b）和（c）之间进一步包括：

（e）生成用于区别所述多条等级电压线的所述选择的至少一条和其余所述多条等级电压线的确定信号。

20. 如权利要求 16 至 18 任一个所述的方法，在步骤（c）之后进一步包括：

（f）使得所述激活的至少一个等级放大器驱动所述多条数据线。

## 用于液晶显示器的驱动电路和驱动方法

### 技术领域

本发明涉及具有帧存储器的显示设备的驱动电路。

### 背景技术

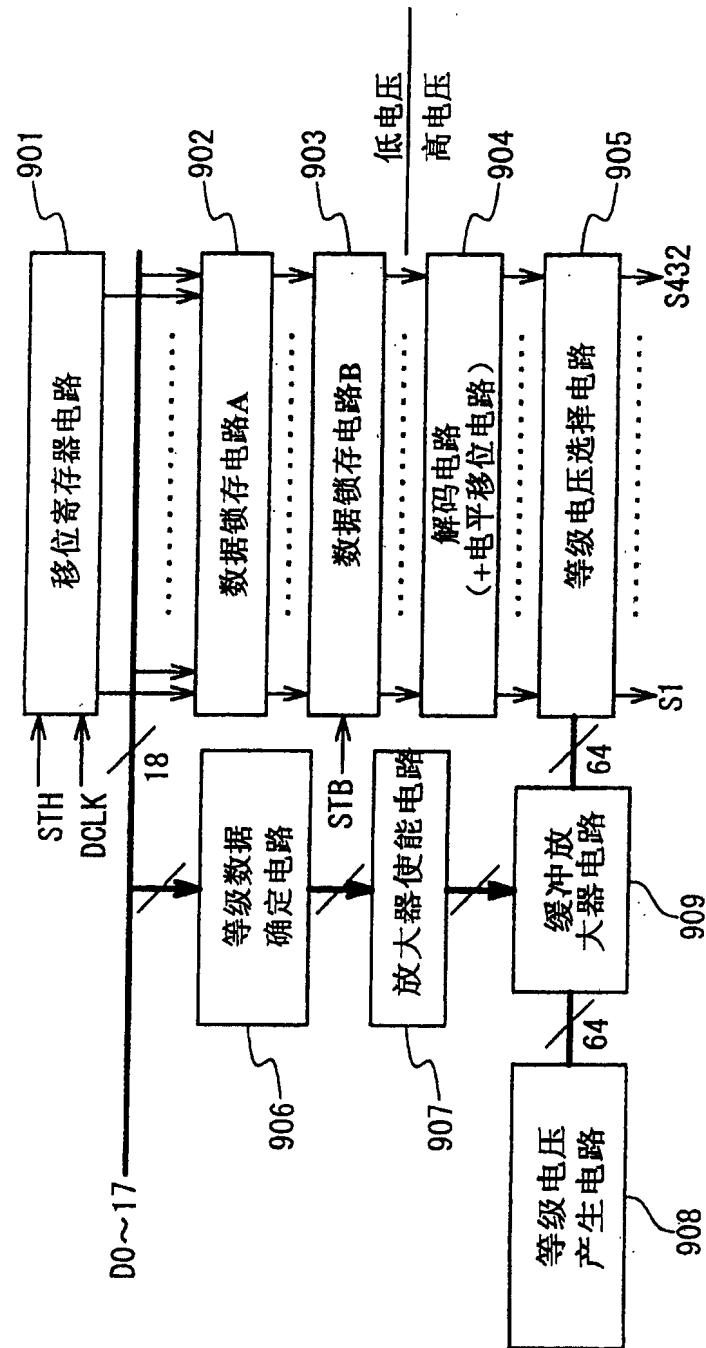

图 1 示出了诸如便携式电话的液晶显示之类的显示设备的数据线驱动电路的例子，其中多条扫描线与多条数据线呈网格状排列。当提供水平开始信号 STH 时，移位寄存器电路 901 产生与信号 DCLK 同步的采样信号。图像数据 D0-17 锁存在与采样信号顺序同步的数据锁存电路 A 902 中，并且锁存的图像数据每次响应水平信号 STB 锁存在数据锁存电路 B 903 中。锁存在数据锁存电路 B 903 中的图像数据被解码电路 904 解码。等级电压选择电路 905 与解码电路 904 连接，并且根据解码的图像数据选择等级开关。等级电压产生电路 908 具有多个串联连接的电阻，并且产生多个符合用作显示设备的等级电压的电压。缓冲放大器 909 通过使用电压跟随电路，转换由等级电压产生电路 908 产生的电压，并且缓冲放大器 909 通过等级电压选择电路 905，驱动显示设备的数据线。

因为用于驱动诸如液晶显示器之类的显示设备的电压通常高于用于诸如移位寄存器电路与数据锁存电路之类的逻辑电路部分的电压，所以驱动电路需要包括电平移位电路。此时，考虑到图像数据的位数与功率消耗的减少，在解码电路以前或以后，提供电平移位电路。例如，当图像数据是 6 位 ( $2^6=64$  等级) 且电平移位电路相对于解码电路放置在下游（当从数据流方向观察电路组件时）时，[数据锁存电路 B]、[解码电路 (64x6-输入与非)]、和[64 电平移位电路]以这种顺序排列，使得驱动电路具有 64 个电平移位电路。另一方面，如果电平移位电路相对于解码电路排列在上游，并且电路以[数据锁存电路 B]、

[电平移位电路(6)]和[解码电路]的顺序排列，使得驱动电路仅仅具有6个电平移位电路。因为大瞬态电流流过电平移位电路，所以考虑到降低功率消耗，以这种方式嵌入移动电话的显示设备最好被设计为包括尽可能少数目的电平移位电路。因此，当图像数据大于等于4位时，通常在相对于解码电路的上游放置电平移位电路。

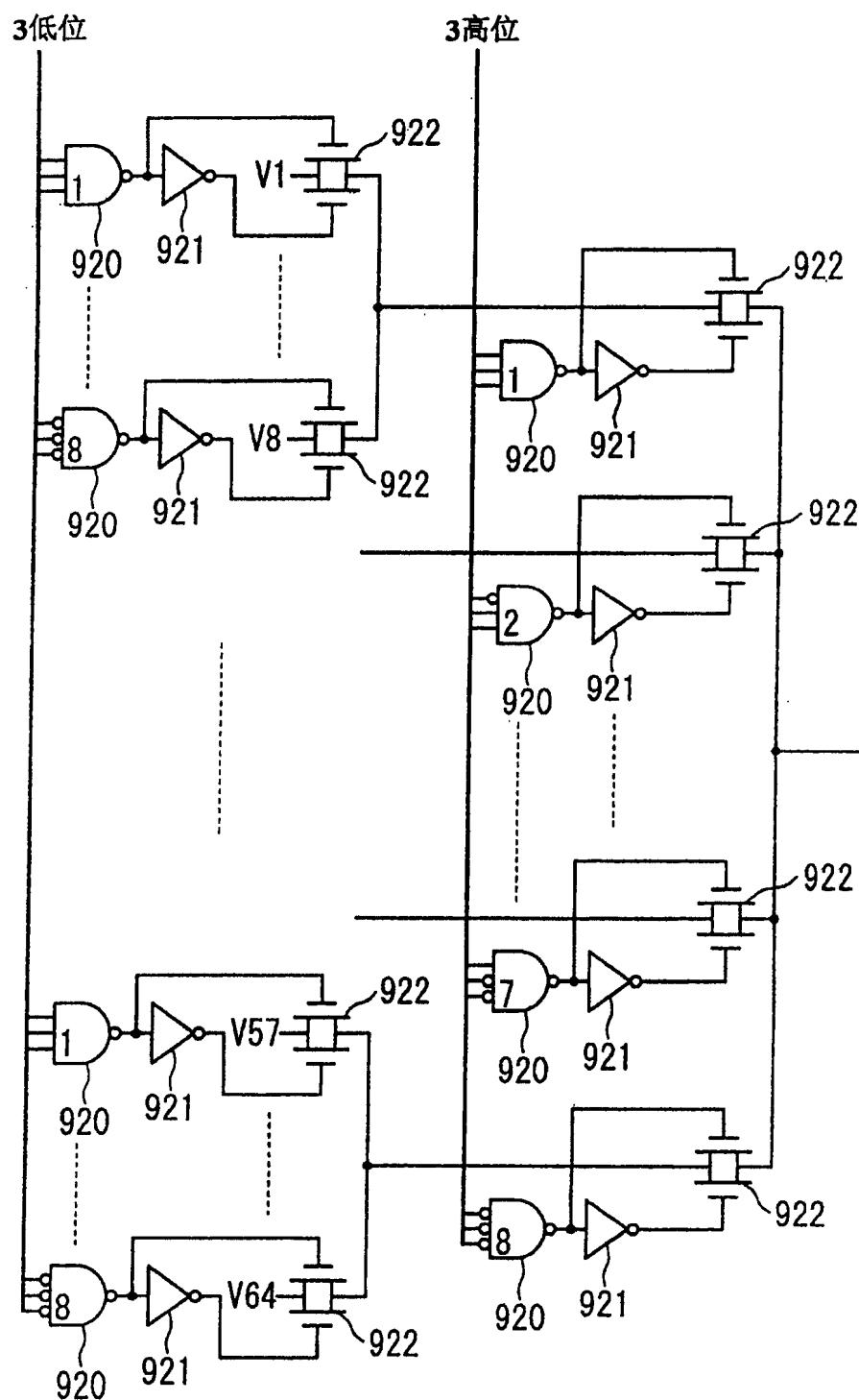

然而，当以此方式相对于解码电路的上游放置电平移位电路时，相对于电平移位电路的下游放置的电路必需被制造带有高电压持续时间。因此，出现新的问题，即驱动电路的规模变得很大。为了解决此问题，如图2所示，可考虑：图像数据的位被划分为三个高位与三个低位，以使解码电路的电路规模变小。也就是说，64个等级开关922基于三个高位控制，并且分别与等级电压V1到V64连接。从64个等级当中基于三个低位选择八个等级，并且基于三个高位，从八个等级当中进一步选择一个等级。解码电路由(64+8)个3输入NAND电路920组成。

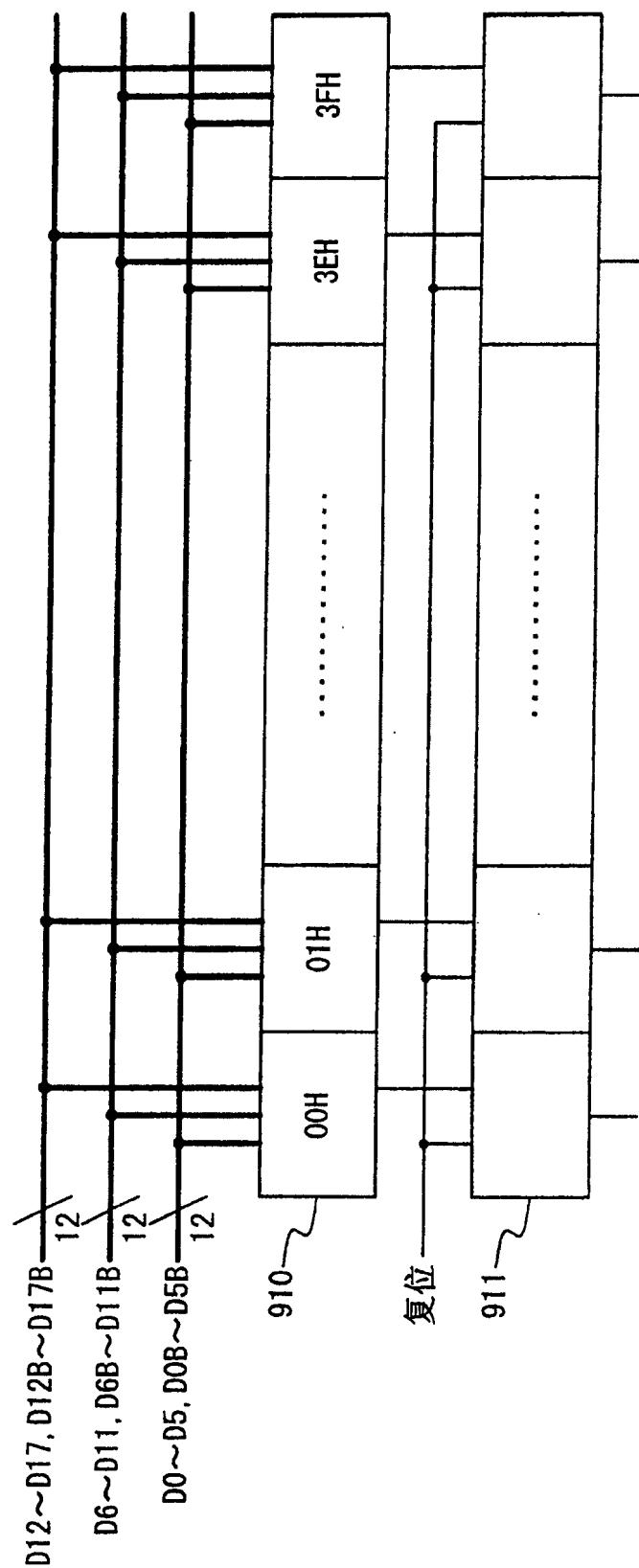

减少驱动电路的功率消耗的方法的一个例子是已公知公开于日本专利申请未决(JP-P2002-108301A)的技术。在此传统的例子中，图像数据D0-D17被确定，并且通过放大器使能电路，减少了没有使用的缓冲放大器(电压跟随电路)的功率消耗。图像数据与时钟信号DCLK同步提供。图3示出了当减少功率消耗的技术应用于图1中示出的等级数据确定电路906时的细节。等级数据确定电路906由解码电路910组成，解码电路910包括：三个6输入NAND(与非)电路、一个3输入NAND电路和连接解码电路的RS锁存器电路911。使用三个6输入NAND电路的原因在于图像数据以像素为单位传递，并且图像数据具有彩色显示中代表红色、绿色与蓝色的6位宽度。当数据在两个像素的单元传递时，七个(=6+1)6输入NAND电路是必需的。因为液晶显示设备不是能够发光的设备并且驱动电压同样与要显示的色彩无关，所以64个解码电路910与64个RS锁存器电路911是必需的。包括再图24中示出的解码电路中的00H与3FH意味着：图像数据由

000000=00H 和 111111=3FH（在下文中，在十六进制表示中，加入 H）表示。

配置等级数据确定电路 906，使得图像数据总线 D0-D17 连接到解码电路 910，并且确定电路 906 执行与时钟信号 DCLK 同步的确定。例如，即使在一个水平周期期间只有一个 00H 作为图像数据输入到电路 906 时，数据 00H 设置在 RS 锁存器电路中，并且对应 00H 的缓冲放大器通过放大器使能电路设定为使能状态。如果在一个水平周期期间那里没有输入 00H，则对应 00H 的缓冲放大器设定为禁用状态，使得减少缓冲放大器中消耗的电流量。此确定在每个水平周期执行，并且预定信号在每个水平周期提供以初始化包含在 RS 锁存器电路中的数据。这样，确定图像数据值与时钟信号 DCLK 相同步，以将对应于等级的缓冲放大器设定为禁用状态，试图减少消耗电流，其中对应于等级的缓冲放大器在相应的水平周期中不被使用。

在此技术中，图像数据通常锁存在与来自 CPU 的信号同步的行存储器（数据锁存电路 A 与数据锁存电路 B）中。并且，图像数据的确定与来自 CPU 的信号同步执行。然而，便携式电话在许多场合下显示静止图像，因此，它被设置为使得数据驱动电路部分包括帧存储器，并且仅当帧图像改变时 CPU 才发送数据，从而降低功耗。为此，用于控制驱动电路的控制信号与来自 CPU 的信号被同步。换句话说，只有当图像改变时，才提供时钟信号与图像数据。然而，为了显示此图像，必须以与来自 CPU 的信号异步的恒定周期驱动图像数据。响应于具有恒定周期的锁存器信号，图像数据立刻全部从帧存储器传递到行存储器。因此，需要立刻确定存储在行存储器中的全部图像数据。然而，传统的技术不能提供用于立刻确定存储在行存储器中的全部图像数据的方法。

结合上述描述，液晶显示的驱动电路公开于日本专利申请未决 (JP-P2001-272655A)。在此传统的例子中，通过使用 A/D 转换器，

基于  $n$  位数字数据信号，从用于  $2^n$  个等级的等级电压到从正极与负极到公共电压中选择一个作为液晶显示面板的数据线的驱动电压。通过能够输出上升波形与下降波形的电压跟随连接的运算放大器，增加了的驱动能力，并且从输出终端输出等级电压。当此输出的极性每隔预定周期改变时，输出终端连接公共电压。运算放大器的输入设定为用于下一个极性的等级电压，其中在从输出终端连接到公共电压时到用于下一个极性的下一个等级电压被 D/A 转换器选择期间，通过运算放大器流动的电流变得最小。

并且，液晶显示的驱动设备公开于日本专利申请未决 (JP-P2001-343944A)。在此传统的例子中，通过用于数据线的每次扫描在正极性与负极性之间可选地切换的 D/A 转换器，对应液晶显示面板的数据线的  $k$  位数据信号被转换成所需的  $2^k$  个等级电压之一。等级电压的驱动能力通过电压跟随输出电路增加，并且等级电压被输出到数据线。逻辑处理应用于用来第  $n$  次扫描的数据信号与用来第  $(n+1)$  次扫描的数据信号，并且  $(n+1)$  次扫描中的电压跟随输出电路的通过比率根据逻辑处理结果改变。

并且，液晶显示的驱动电路公开于日本专利申请未决 (JP-P2002-215108A)。在此传统的例子中，数字视频图像数据作为其本身输出或者基于用于每个水平同步周期或垂直同步周期反相的极性信号在反相以后输出。一组用于正极的等级电压与一组用于负极的等级电压被预定以符合液晶显示中正应用电压的透射率特性和负应用电压的透射率特性，并且基于极性信号从上述组中选择一个。基于数字视频图像数据或反相的数字视频图像数据，在选择的组的等级电压当中选择一个，并且选择的等级电压应用于相应的数据电极。

并且，一种驱动电路公开于日本专利申请未决 (JP-P2002-366106A)。在此传统的例子中，实施扫描线反相驱动，以将通过电光物质与像素电极相反的计数电极的扫描周期中的电压电平设定为不同

于以前扫描周期中的电压电平。在第 M 扫描周期中，计数电极的电压电平被设定为第一电压电平与第二电压电平的一个。在紧次于第 M 扫描周期的虚拟扫描周期中，计数电极的电压电平被设定为第一与第二电压电平的另一个。在虚拟扫描周期以后的第一扫描周期中，计数电极的电压电平被设定为第一与第二电压电平的一个电压电平。

## 发明内容

因此，本发明的一个目的是提供一种显示设备的驱动电路，其中减少驱动电路的功率消耗是可能的。

本发明的另一个目的是提供一种显示设备的驱动电路，其中通过使用上一行中的图像数据的等级，能够减少驱动电路的功率消耗。

本发明的另一个目的是提供一种显示设备的驱动电路，其中驱动电路具有帧存储器，并且除了静止图像显示以外，当显示视频图像时，能够减少驱动电路的功率消耗。

在本发明的一个方面，其中多条扫描线与多条数据线相互垂直的显示设备的驱动电路包括：第一数据锁存电路，其响应水平信号锁存用于每条线的图像数据；解码电路，其对锁存的图像数据进行解码；以及等级电压选择电路，其基于解码的图像数据，选择电压线以将多条数据线的每条与任何电压线连接。驱动电路还包括：数据确定电路，其基于选择的电压线产生数据确定信号，从而多个等级放大器的每个基于该确定信号可选地设定为无效状态；等级放大器电路，其可包括多个等级放大器，每个等级放大器当处于有效状态时放大对应的等级电压之一，并且当处于无效状态时不放大对应的等级电压，放大的等级电压在对应的电压线之一上输出；以及输出电路，其基于电压线上放大的等级电压驱动多条数据线。

这时，驱动电路还可包括偏压控制电路，其基于来自数据确定电

---

路的确定信号，将多个等级放大器的每个设定为有效状态或无效状态。

并且，驱动电路还可包括：帧存储器，其存储一帧图像数据；以及第二锁存电路，其响应锁存信号锁存一行图像数据，以输出到第一锁存电路。在此情况下，驱动电路还可包括数据切换电路，当输入图像数据为视频图像数据时，该数据切换电路将输入图像数据输出到帧存储器，并且当输入图像数据为静止图像数据时，该数据切换电路将输入图像数据输出到第二锁存电路。

并且，驱动电路还可包括：等级电压产生电路，其产生多个电压；以及极性切换电路，其在等级电压产生电路与等级放大器电路之间提供，以响应极性信号从等级电压产生电路产生的多个电压中选择等级电压。在此情况下，数据确定电路可响应水平信号或响应水平信号与极性信号进行操作。

并且，等级电压选择电路可包括：多个等级选择开关，其基于解码的图像数据，选择用于多条数据线的每条的电压线之一；以及第一开关，其用于多个等级选择开关的每个，以将多个等级选择开关的每个输入终端与较高电压或较低电压功率连接。并且，输出电路可包括：第二开关，其用于多个等级选择开关的每个，以将多个等级选择开关的每个输出终端与较低电压或较高电压连接；以及第三开关，其用于多个等级选择开关的每个，以在多个等级选择开关的每个输出终端与输出电路之间切换。此时，数据确定电路基于每条电压线的电压，产生确定信号。在此情况下，驱动电路还可包括命令控制电路，当帧锁存器的像素的数目大于显示设备的像素的数目时，该命令控制电路通常将与显示设备的多条数据线断开的第三开关设定为断开状态。

并且，等级电压选择电路可包括：多个等级选择开关，其基于解码的图像数据，选择用于多条数据线的每条的电压线之一；第一开关，

其用于多个等级选择开关的每个以将多个等级选择开关的每个输入终端与较高电压连接；以及第二开关，其用于多个等级选择开关的每个，以将多个等级选择开关的每个输入终端与较低电压连接。并且，输出电路可包括：第三开关，其用于多个等级选择开关的每个，以将多个等级选择开关的每个输出终端与较低电压连接；第四开关，其用于多个等级选择开关的每个，以将多个等级选择开关的每个输出终端与较高电压连接；以及第五开关（206），其用于多个等级选择开关的每个，以在多个等级选择开关的每个输出终端与输出电路之间切换。此时，数据确定电路基于多个等级选择开关的每个输出电压，产生确定信号。在此情况下，驱动电路还可包括命令控制电路，当帧锁存器的像素的数目大于显示设备的像素的数目时，该命令控制电路通常将和显示设备的多条数据线断开的第三开关与第五开关设定为断开状态。

并且，驱动电路还可包括：等级电压选择电路，当帧锁存器的像素的数目大于显示设备的像素的数目时，对应图像数据在不存在多条扫描线期间，该等级电压选择电路将多个等级放大器设定为无效状态。

并且，数据确定电路可包括计数器，其用于计算由等级电压选择电路选择的等级电压。数据确定电路可改变一周期，在该周期期间，多个等级放大器的每个基于计数器的计数值处于有效状态，从而当该计数值减少时，该周期变短。

并且，多个等级放大器的每个还可包括恒定电流源，以及输出级。数据确定电路当等级放大器处于无效状态时将恒定电流源的电流值设定为0，并且将输出级设定为高阻抗状态。

并且，等级放大器电路可包括第一组等级放大器，其中的每个等级放大器具有作为差动输入晶体管的N沟道晶体管；以及第二组等级放大器，其中的每个等级放大器具有作为差动输入晶体管的P沟道晶

体管。

## 附图说明

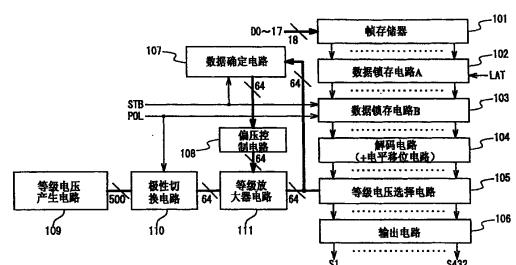

- 图 1 是传统显示设备的数据线驱动电路的框图；

图 2 是传统显示设备中解码电路与等级电压选择电路的框图；

图 3 是传统显示设备中确定电路的框图；

图 4 是应用本发明的显示设备的结构的框图；

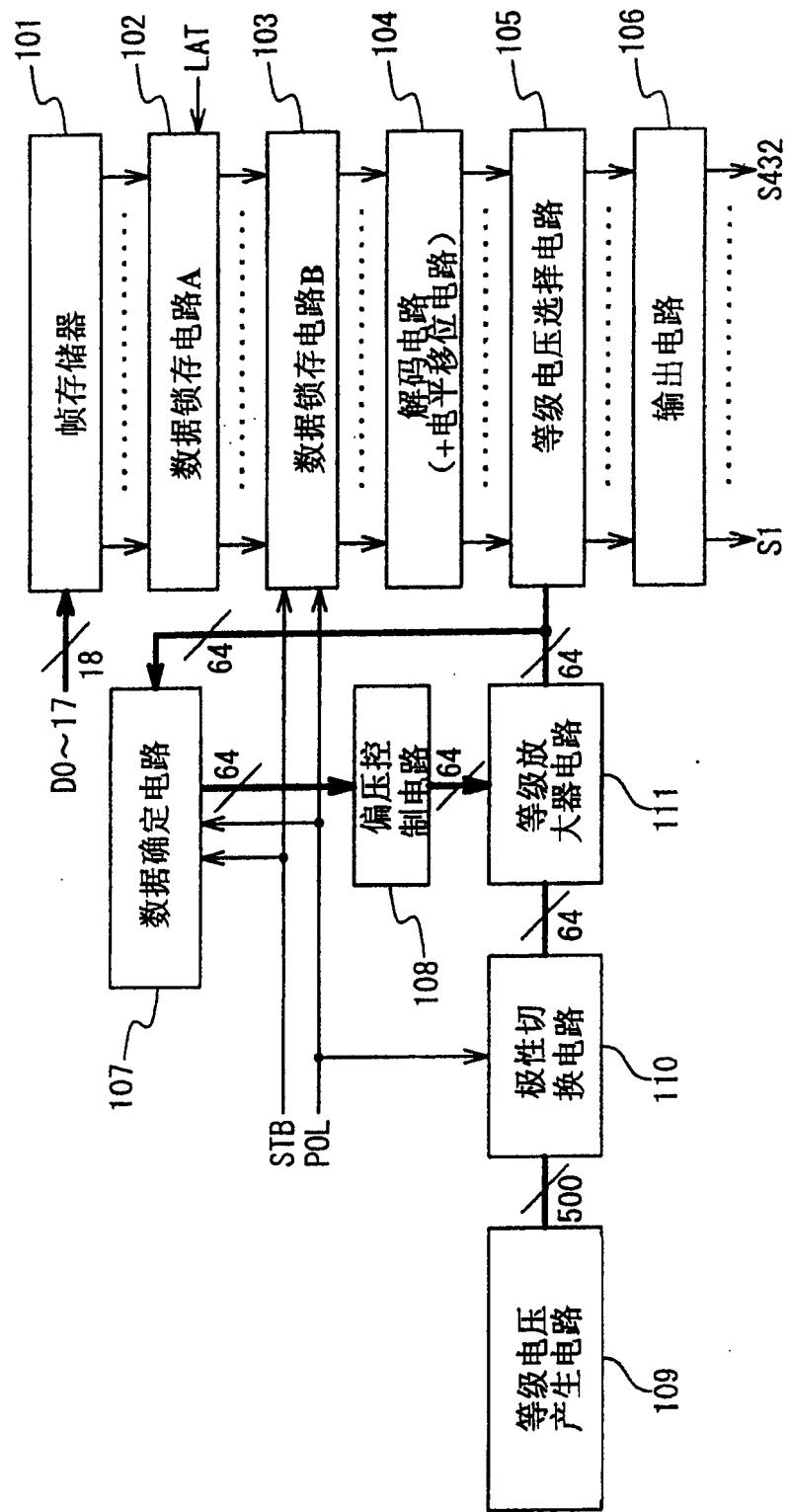

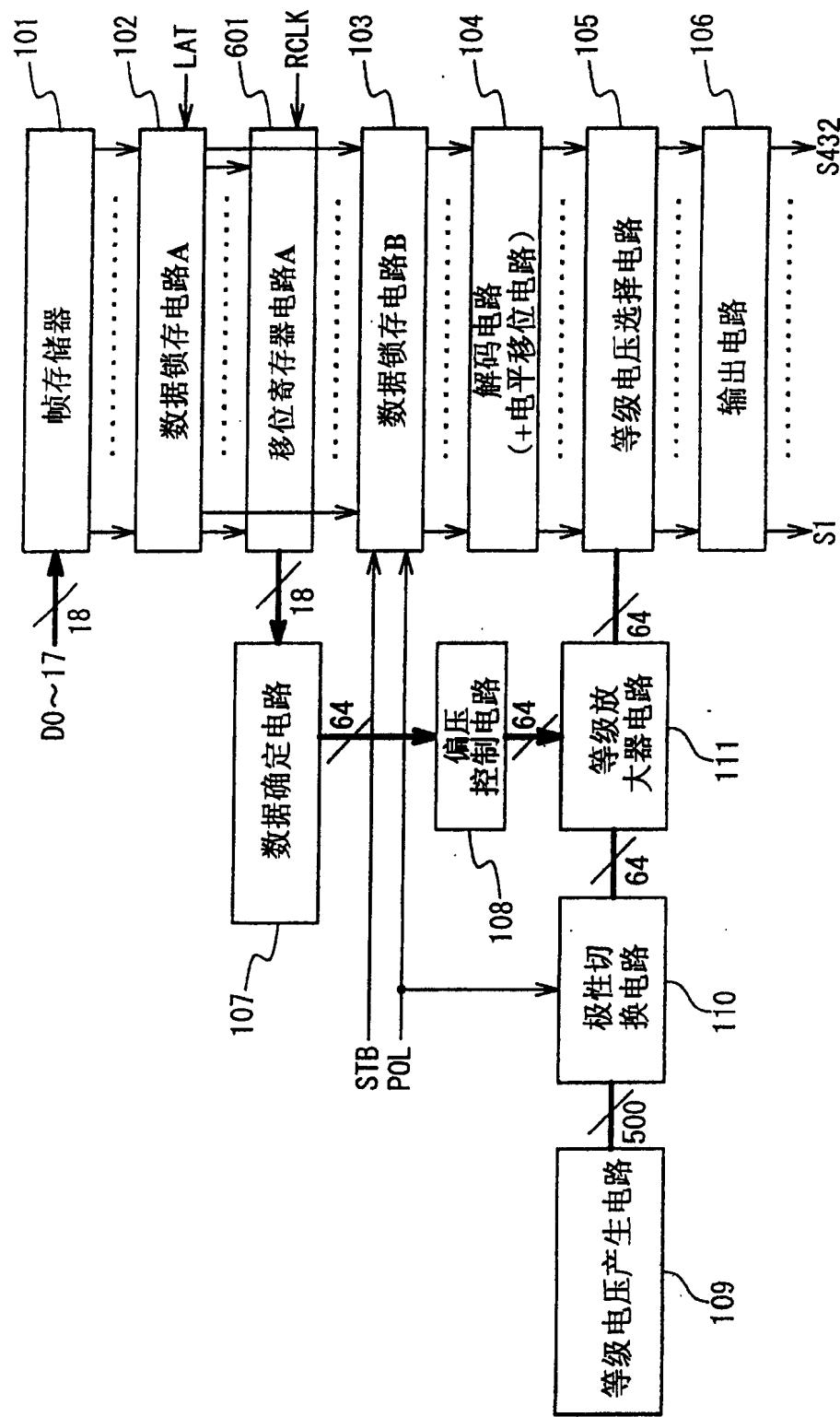

图 5 是示出了根据本发明第一实施例的数据线驱动电路的框图；

图 6A 是示出了第一实施例中图像数据与用于正极性与负极性的输出电压之间关系的图；

图 6B 是示出了第一实施例中图像数据与用于正极性与负极性的输出电压之间关系的图；

图 6C 是示出了第一实施例中等级放大器与用于正极性与负极性的输出电压之间关系的图；

图 6D 是示出了第一实施例中图像数据与等级之间关系的图；

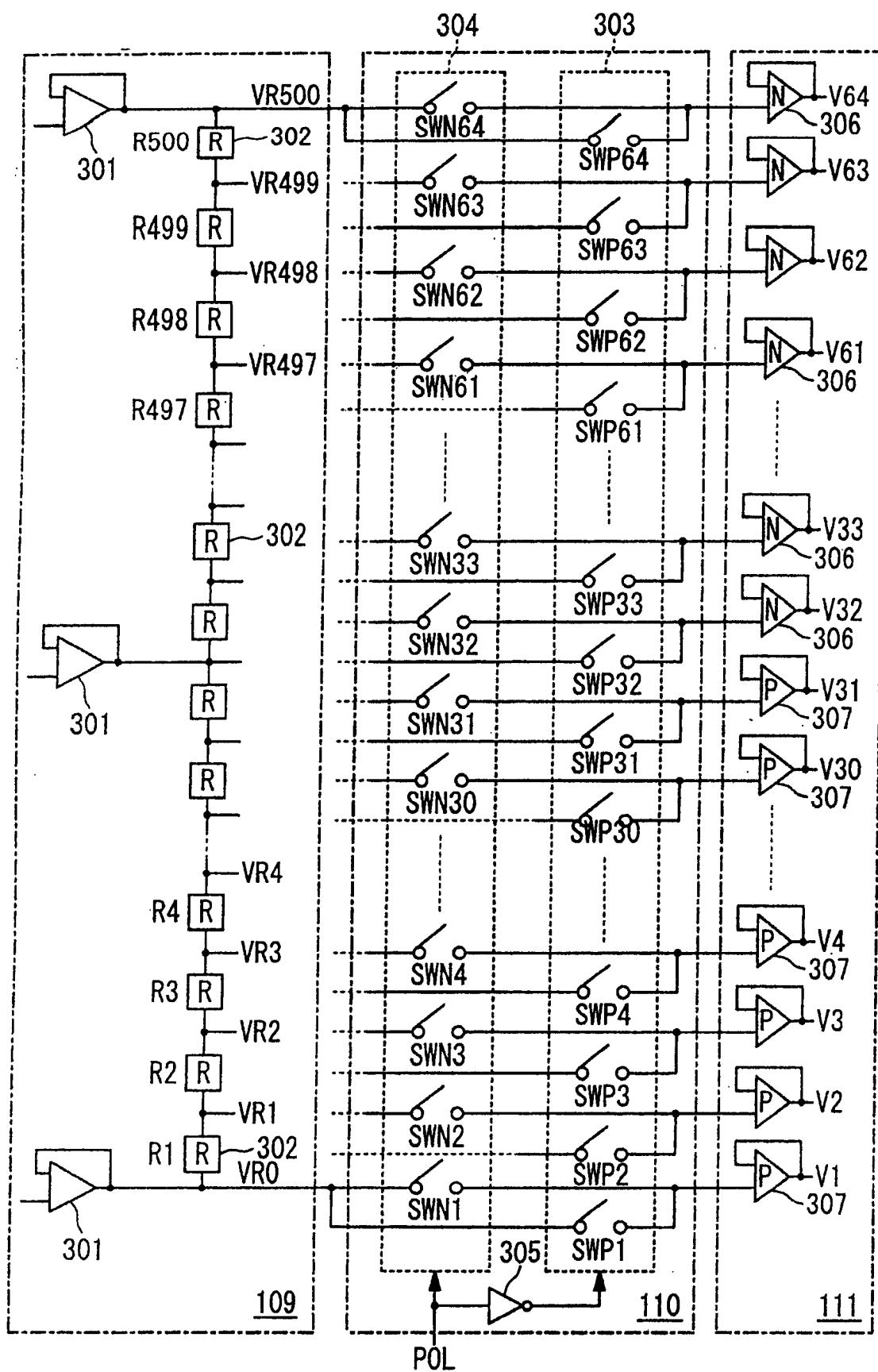

图 7 是示出了第一实施例中等级电压产生电路与等级放大器电路的结构的图；

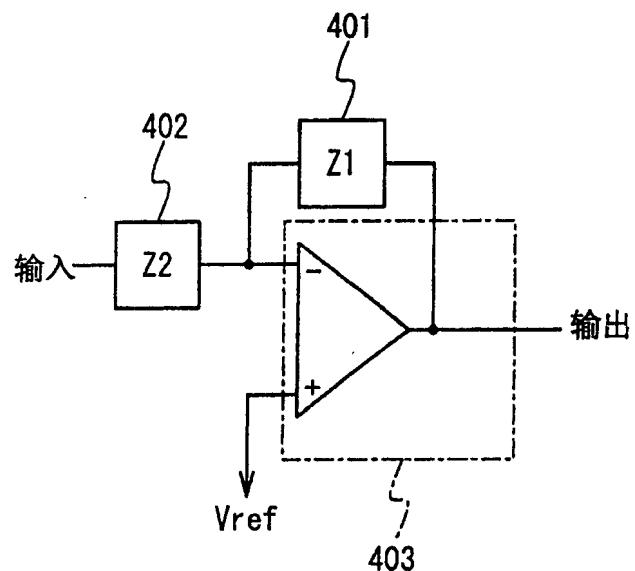

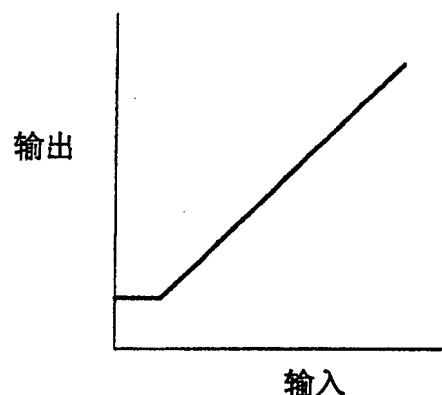

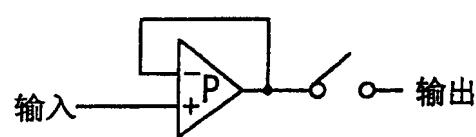

图 8A 是示出了等级放大器电路中采用大于 1 的增益的等级放大器的等价电路的电路图；

图 8B 是等级放大器的输入/输出特性曲线的图；

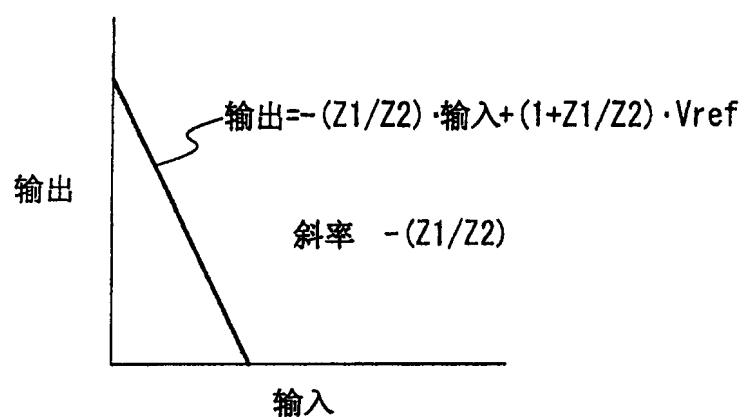

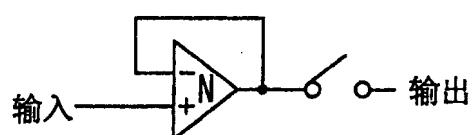

图 9A 是示出了第一等级放大器的电路图；

图 9B 是示出了第一等级放大器的输入/输出特性曲线的图；

图 9C 是示出了第一等级放大器的等价电路的图；

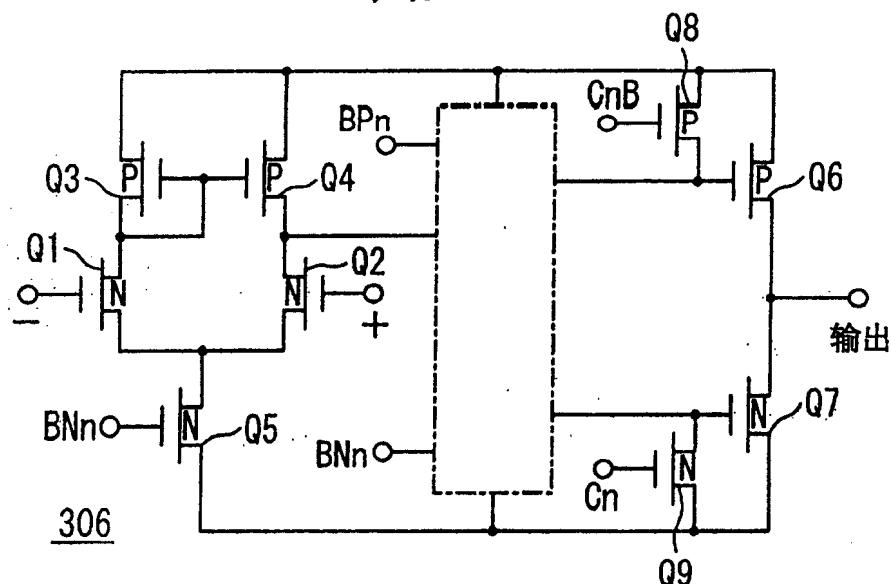

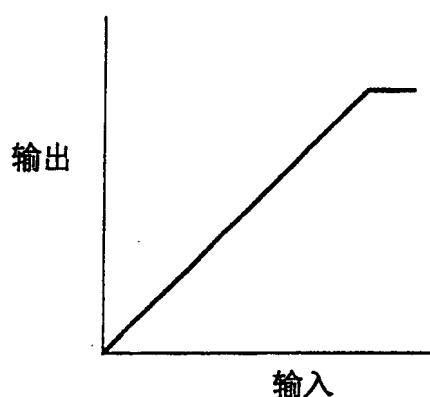

图 10A 是示出了第二等级放大器的电路图；

图 10B 是示出了第二等级放大器的输入/输出特性曲线的图；

图 10C 是示出了第二等级放大器的等价电路的图；

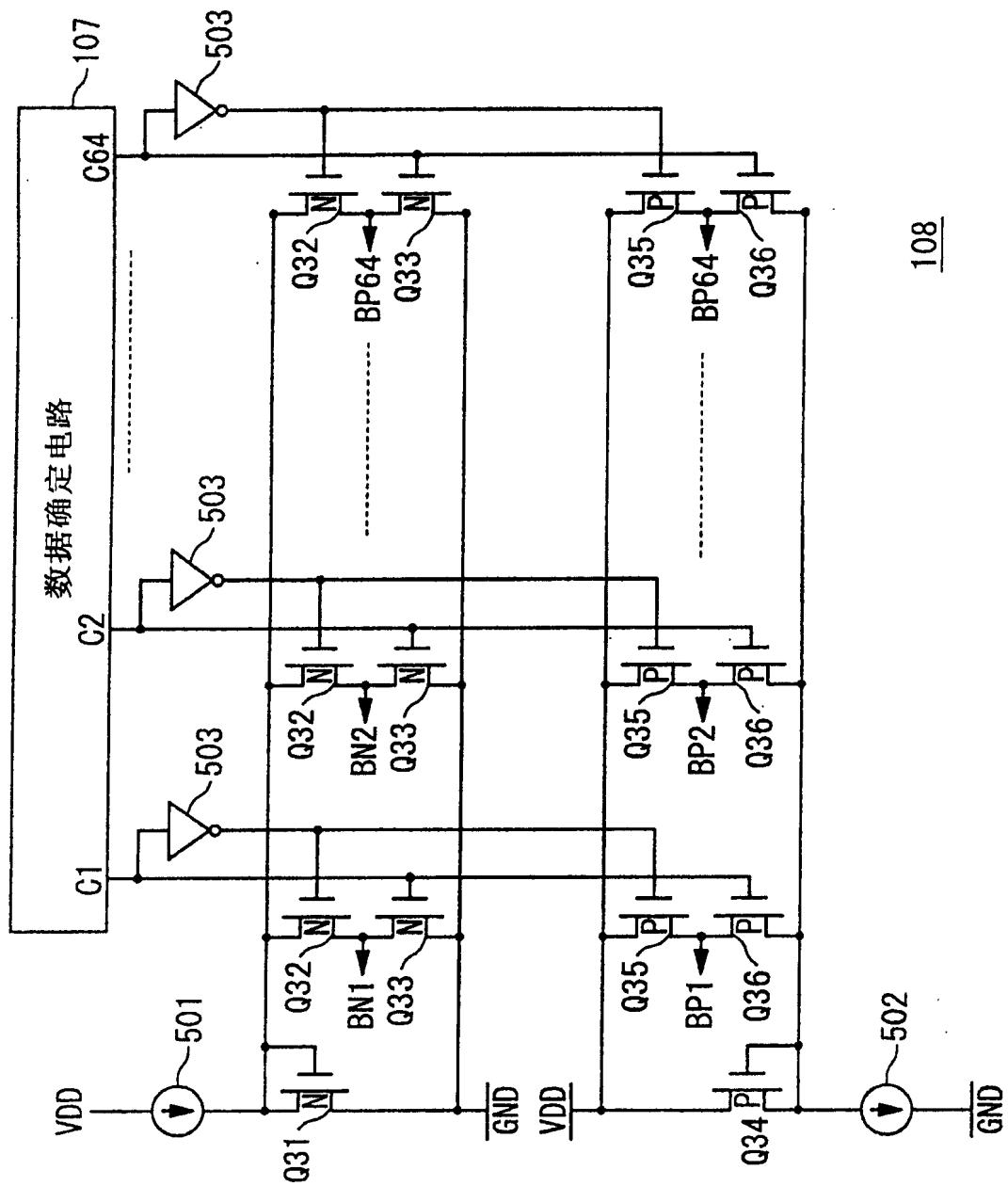

图 11 是示出了偏压电流控制电路的电路图；

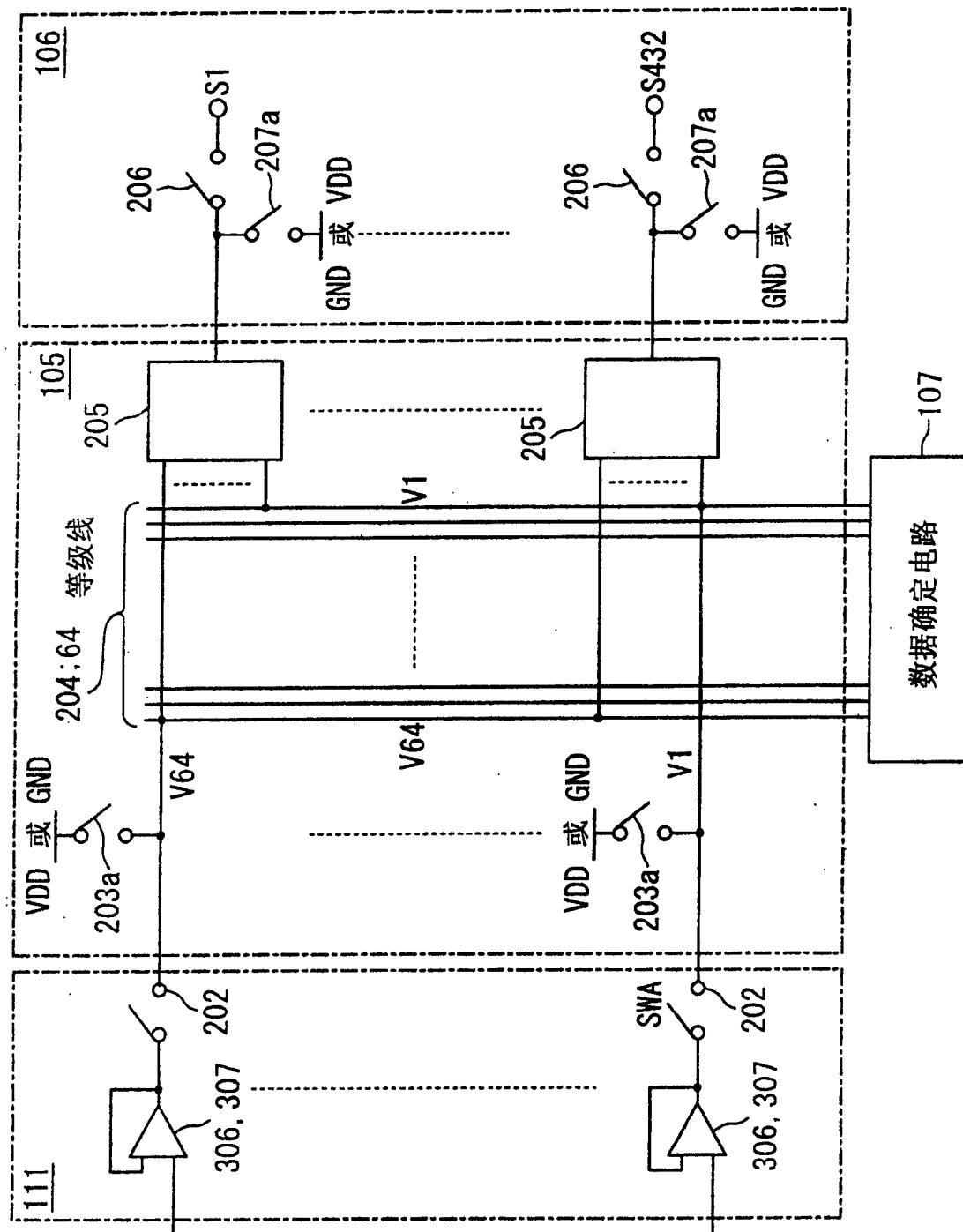

图 12 是根据本发明第一实施例的数据确定电路的框图；

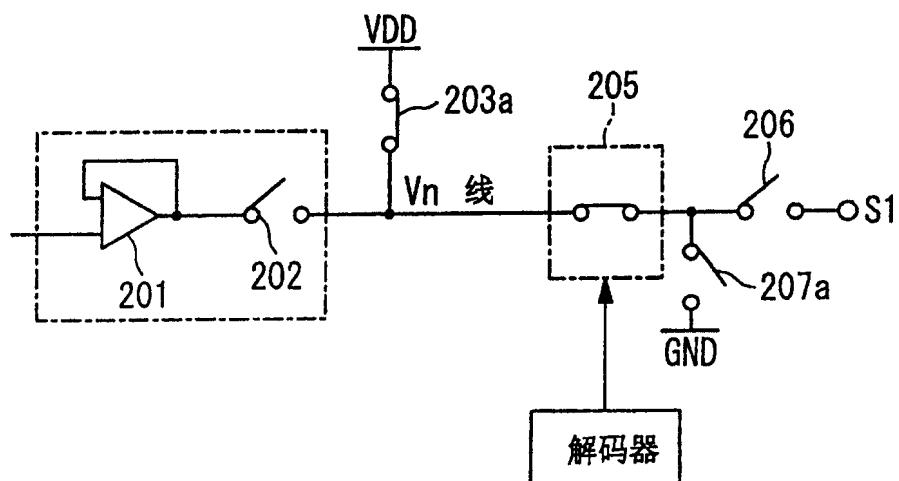

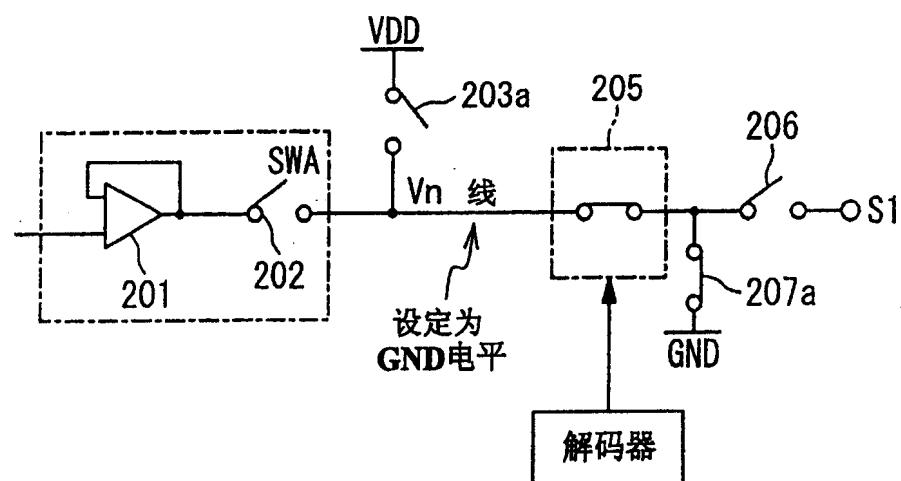

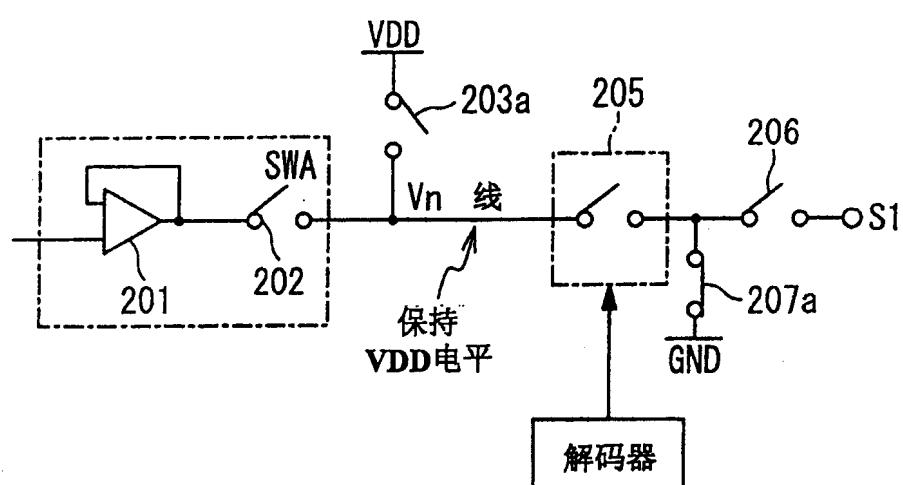

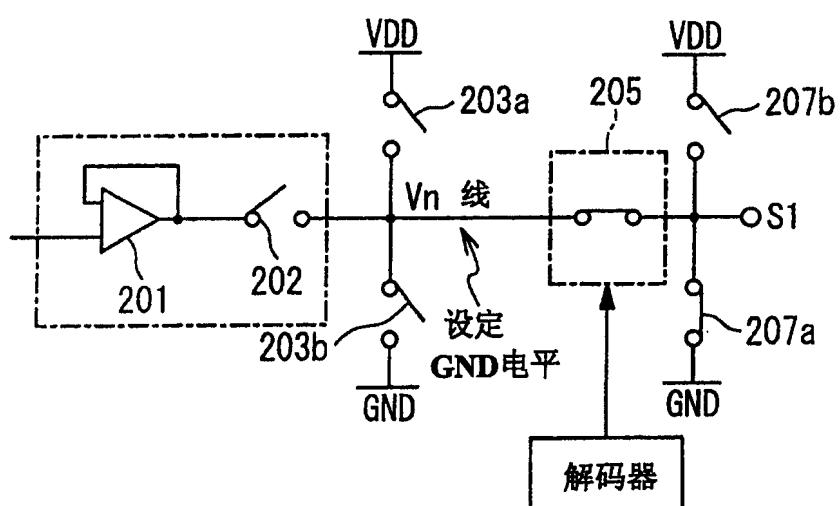

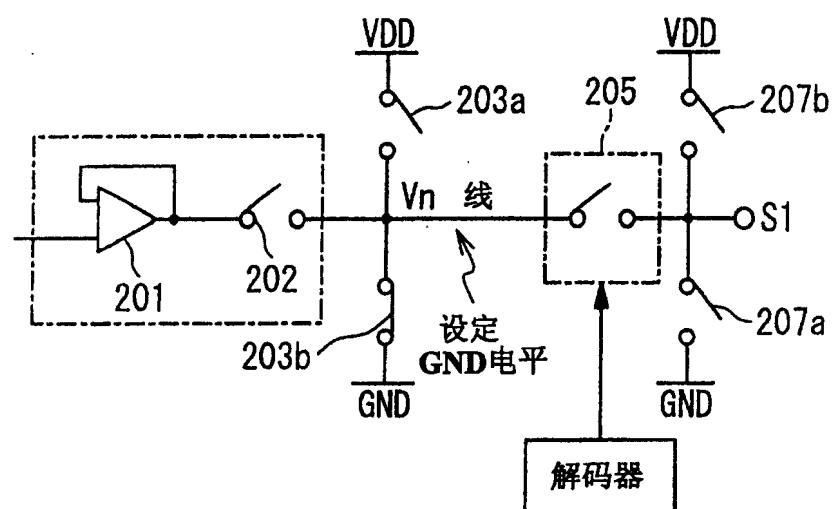

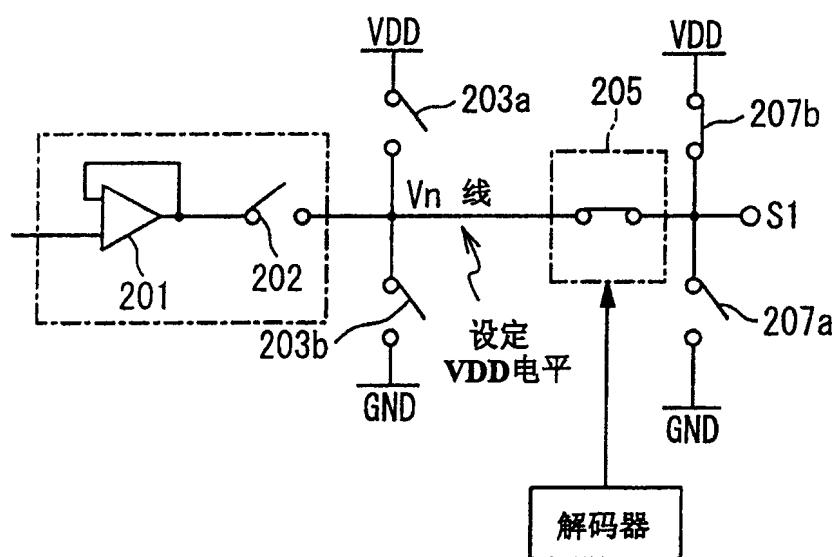

图 13A 到 13D 是示出了第一实施例中数据确定的开关状态的电路图；

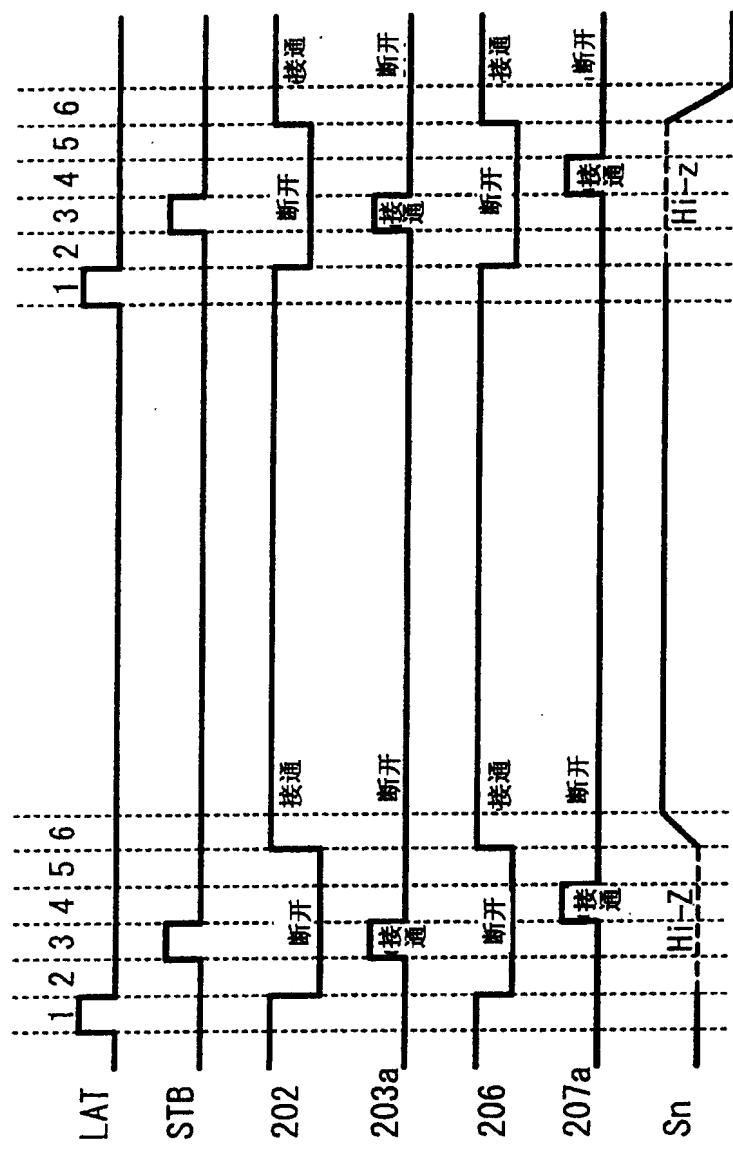

图 14A 到 14G 是第一实施例的显示设备中数据确定的时间图表；

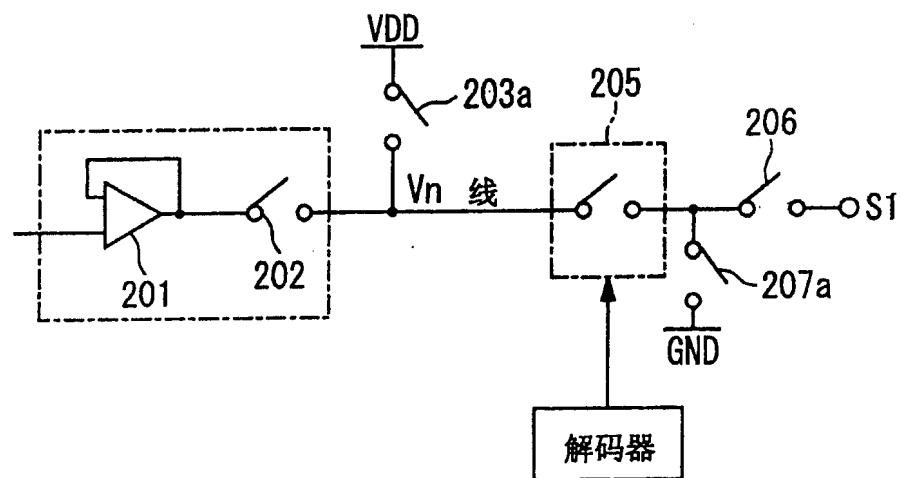

图 15 是根据本发明第二实施例的驱动电路的框图；

图 16 是第二实施例中数据确定电路的框图；

图 17A 到 17J 是第二实施例中数据确定的时序图；

图 18A 到 18D 是示出了第二实施例中数据确定的开关状态的图；

图 19 是根据本发明第三实施例的数据线驱动电路的框图；

图 20 是第三实施例中数据确定电路的框图；

图 21 A 到 21B 是示出了当等级放大器电路设定为有效状态时的时间图；

图 22 是根据本发明第四实施例的数据确定电路的框图；

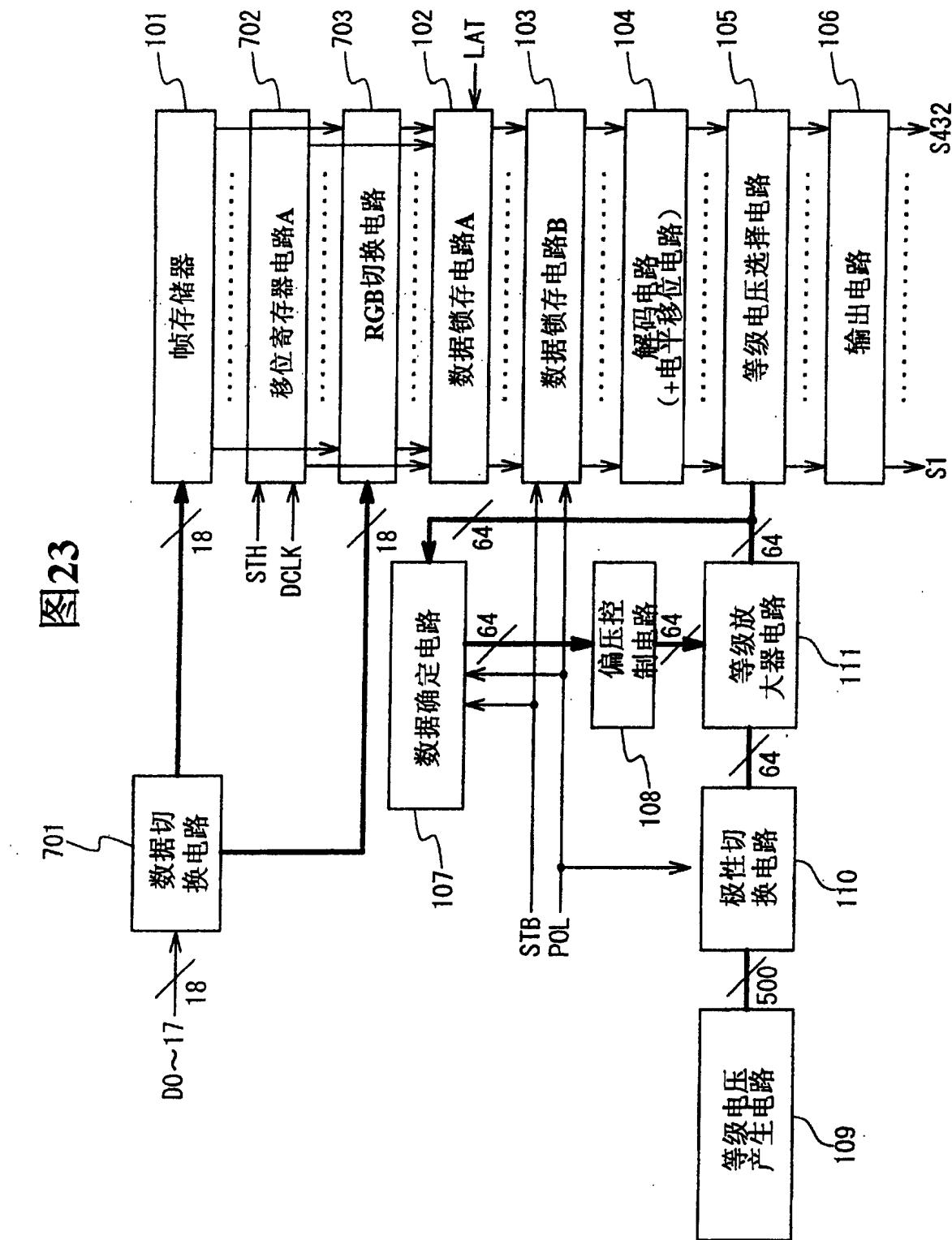

图 23 是根据本发明第五实施例的驱动电路的框图；

图 24A 到 24B 是示出了接口电路与图像数据输入系统的框图。

## 具体实施方式

在下文中，显示设备的驱动电路将参照附图详细描述。

### (第一实施例)

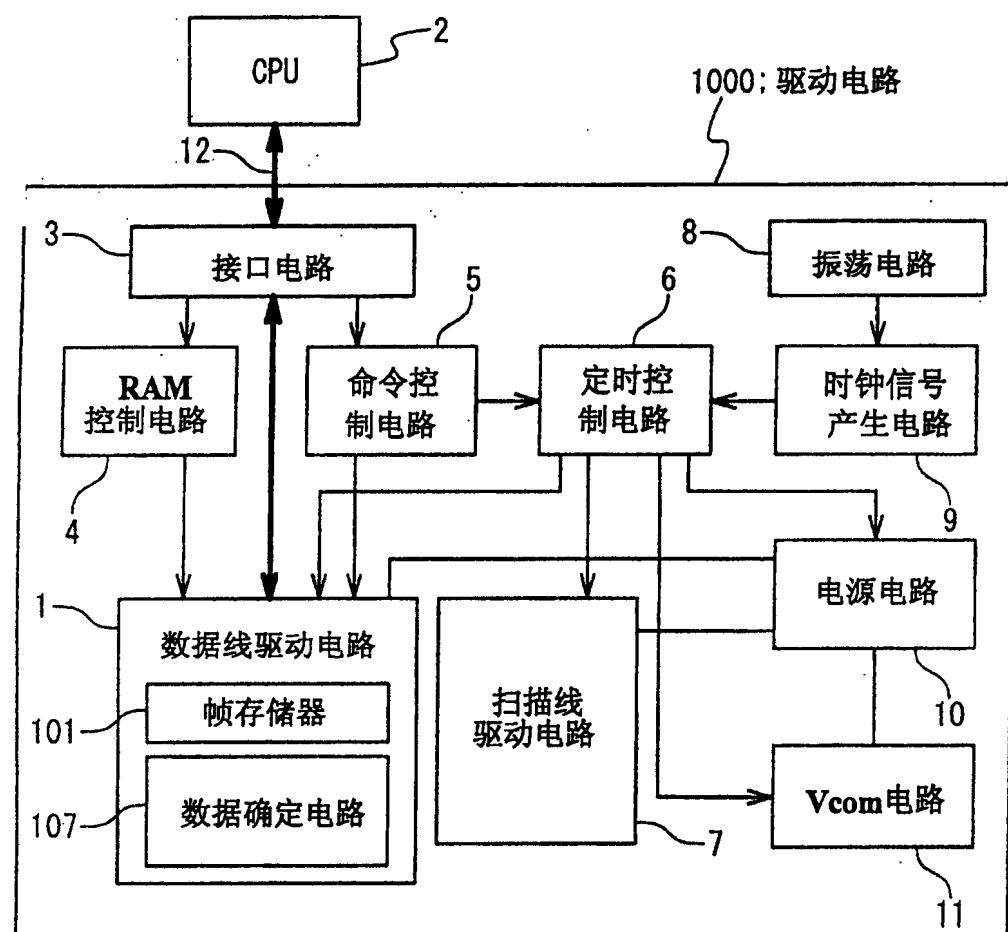

图 4 是示出了显示设备的结构的框图，例如应用本发明的液晶显示设备。用于便携式电话等的显示设备 1000 连接到 CPU2，并且响应来自 CPU2 的信号 12 显示图像。尽管没有在图中示出，显示设备 1000 也包含显示单元，其中多条扫描线与多条数据线以行和列的矩阵来排列。而且，显示设备 1000 包括数据线驱动电路 1、接口电路 3、RAM 控制电路 4、命令控制电路 5、定时控制电路 6、扫描线驱动电路 7、振荡电路 8、定时产生电路 9、电源电路 10 与 Vcom 电路 11。

数据线驱动电路 1 驱动显示单元的数据线，并且包含随后描述的帧存储器 101 与数据确定电路 107。接口电路 3 与 CPU2 连接以进行接口。RAM 控制电路 4 与接口电路 3 和驱动电路 1 连接。RAM 控制电路 4 控制帧存储器 101 的写地址等。命令控制电路 5 与接口电路 3、驱动电路 1 与定时控制电路 6 连接。命令控制电路 5 输入驱动显示单

元所需的数据，比如伽马电路中的设定数据以及驱动频率、驱动电压与通过接口电路 3 来自 CPU2 的帧存储器 101 的像素的数目，并且命令控制电路 5 保持 EEPROM（没有示出）中写入的数据。命令控制电路 5 控制驱动电路 1 与定时控制电路 6。

振荡电路 8 产生与 CPU2 提供的信号同步的时钟信号 RCLK。定时产生电路 9 基于振荡电路 8 提供的时钟信号产生信号，比如垂直信号 VS、水平信号 STB 与驱动显示单元所必需的极性信号 POL。定时控制电路 6 产生定时信号以控制显示单元的驱动定时，并且驱动定时提供给数据线驱动电路 1、扫描线驱动电路 7、电源电路 10 与 Vcom 电路 11。电源电路 10 响应来自定时控制电路的驱动定时而产生用于显示设备 1000 的电压，并且提供给各种部件，比如驱动电路 1、扫描线驱动电路 7 与 Vcom 电路 11。使用的电压由电源电路 10 产生以驱动显示单元的数据线、扫描线与公共电极。使用电压根据来自定时控制电路的驱动定时，Vcom 电路 11 驱动公共电极。扫描线驱动电路 7 响应驱动定时驱动扫描线。

应当注意：上述电路不总是必需在相同的基底或电路板上形成。电源电路 10、扫描线驱动电路 7 与 Vcom 电路 11 可在另一基底或板上形成。并且，部分或整个电路可在玻璃基底上制造。

并且，应当注意：诸如振荡电路 8 与接口电路 3 之类的用于逻辑电路部分的电源线如图 4 所示。并且，尽管除了用于图像数据与命令数据的数据信号 D0 到 D17 以外，从 CPU 提供的信号 12 还包括芯片部件信号、写信号、读信号、数据/命令部件信号与恢复信号等，全部信号也共同地如信号 12 所示。

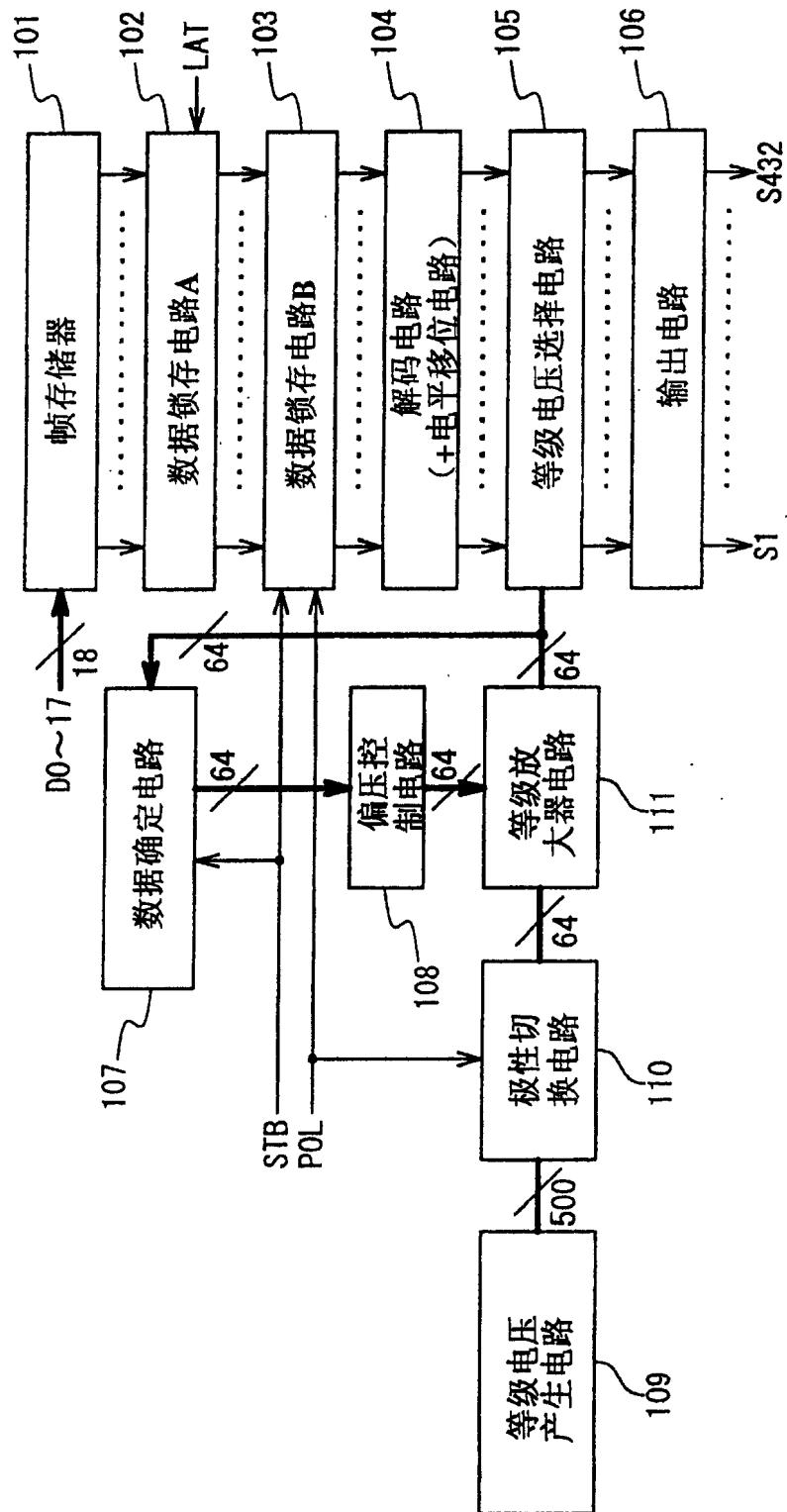

其次，包含帧存储器 101 的数据线驱动电路 1 将参照图 5 描述。帧存储器 101 能够存储一帧的图像数据，并且从 CPU2 提供的静止的图像数据被写入在帧存储器 101 中。用于存储在帧存储器 101 中的一

行图像数据响应来自定时控制电路 6 的锁存信号 LAT 一次被传送到数据锁存电路 A102。当从 CPU2 提供的写信号与锁存器信号在定时上重叠时，从 CPU2 写入到帧存储器 101 的写指令以更高的优先权实施。锁存在数据锁存电路 A102 中的图像数据响应水平信号 STB 与极性信号 POL 立即传送到并通过数据锁存电路 B103 锁存，并且保持电流水平周期。

锁存在数据锁存电路 B103 中的图像数据通过解码电路 104 解码，其包括用于电平移位电路的 NAND 电路。等级电压产生电路 109 产生多个电压。提供极性切换电路 110，从而要从电路 110 输出的某个电压响应于极性信号 POL 而在一组正伽马电压与一组负伽马电压之间切换，以作为等级电压输出。等级放大器 111 包含多个等级放大器，其放大来自极性切换电路 110 的等级电压，并且放大的等级电压提供到等级电压选择电路 105。等级电压选择电路 105a 包含多个等级选择开关。根据来自解码电路的解码的图像数据激活等级选择开关。对应激活的等级选择切换的放大的等级电压输出到输出电路 106，并且用作驱动数据线。

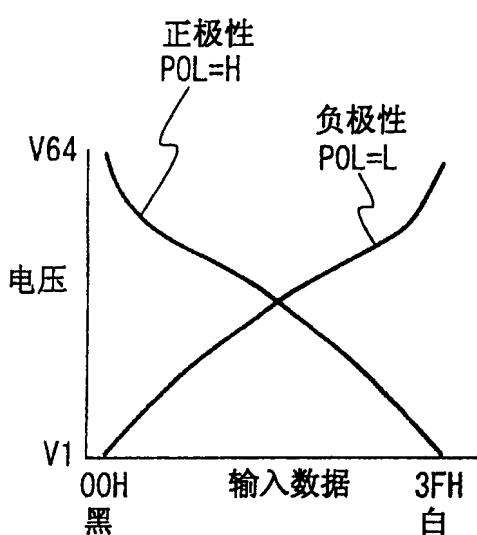

数据确定电路 107 从对应于当前水平周期的激活的等级选择开关的放大等级电压中产生用于当前水平周期的确定信号。偏压控制电路 108 在当前水平周期期间，基于确定信号，控制等级放大器电路 111 的等级放大器。

更特别地，等级电压产生电路 109 包含多个电阻串联连接其中的电阻串电路。等级电压产生电路 109 使用电阻串电路产生多个电压以使得电压满足显示单元的伽马特性。液晶显示设备为了防止液晶的退化通常需要交替地驱动。为此，正电压与负电压交替地应用于液晶显示设备的公共电极，并且要施加的电压极性以预定周期改变。因为如图 6A 到 6D 示出的电压特性所示，代表相同光强的正极性等级电压与负极性等级电压相互略微不同，所以提供了极性切换电路 110 以使得

等级电压在正伽马电压与负伽马电压之间切换。等级电压产生电路 109 和极性切换电路 110 构成了电压产生装置。来自极性切换电路 110 的多个等级电压被等级放大器电路 111 的多个等级放大器 111 分别放大，并且提供到等级电压选择电路 105。

这时，在移动电话的显示单元的情况下，当显示诸如照片之类的静止图像时，CPU 不需要经常传递图像数据，并且仅当图像改变时，才传递图像数据。这样，因为来自 CPU2 的图像数据 12 是否输入到驱动电路是随机的，所以驱动电路系统中使用的信号必需与来自 CPU2 的信号 12 异步。为此，驱动电路系统中使用的时钟信号由振荡电路 8 产生，其包括电容与电阻。时钟产生电路 9 基于来自振荡电路 8 的时钟信号，产生诸如水平信号 STB、垂直信号 VS、锁存器信号 LAT 与电极信号 POL 之类驱动显示单元所必需的信号。

图 7 示出了等级电压产生电路 109、极性切换电路 110 与等级放大器电路 111 的结构。这时，等级电压产生电路 109 包含具有相同电阻值的电阻 R1 到 R500 与输入缓冲器 301。电阻 R1 到 R500 串联连接，并且输入缓冲器 301 连接在一些电阻的连接节点之间。从单个连接节点能够得到单个电压。例如，假设在电阻 R500 的连接节点处的电压 VR500 为 5V，并且在电阻 R0 的连接节点处的电压 VR0 为 0 V。在此情况下，相邻连接节点之间的电压差值为 10mV (=5 V/500)，并且在第 n 个连接节点处的电压 VR 为  $n \times 10mV$ 。

极性切换电路 110 包括切换单元 303 和切换单元 304，切换单元 303 具有用于提供正电压的 64 个开关，切换单元 304 具有用于提供负电压的 64 个开关。极性切换电路 110 连接从等级电压产生电路 109 产生的 500 个电压当中挑选的 64 个预定的电压与每个切换单元 303 与 304 的输入端子，以使得 64 个预定电压满足液晶的伽马特性。在极性切换电路 110 中操作，使得当极性信号 POL 为 “H” 时，接通切换单元 303 的开关 SWN1 到 SWN64，并且断开切换单元 304 的开关

SWP1 到 SWP64。类似的，当极性信号 POL 为“L”，则断开切换单元 303 的开关 SWP1 到 SWP64，并且接通切换单元 304 的开关 SWP1 到 SWP64。将 64 个选择的电压提供到等级放大器电路 111。

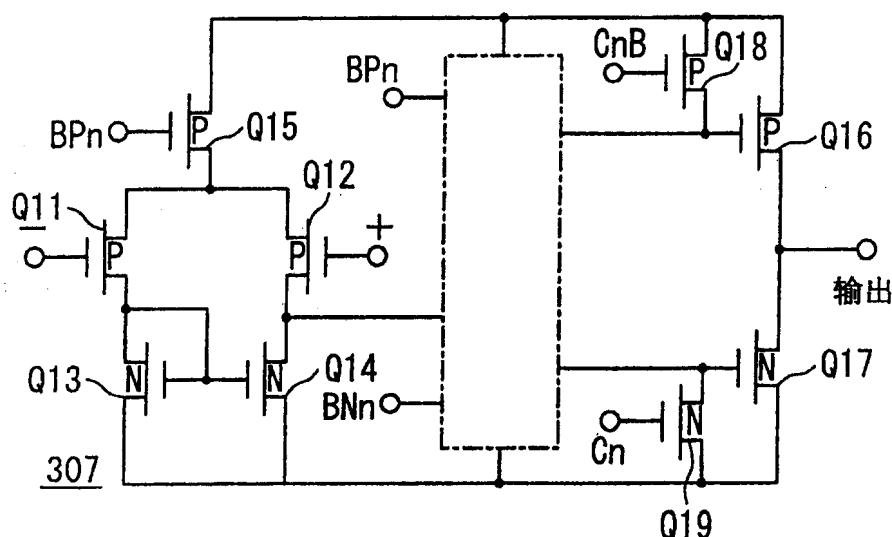

等级放大器电路 111 可包括多个等级放大器，并且当图像数据为 6 位时，可包括 64 ( $=2^6$ ) 个等级放大器。每个等级放大器可为电压跟随型（具有增益为 1）。然而，等级放大器 111 不必为电压跟随型。在此例子中，如图 8A 与 8B 所示，每个等级放大器由具有负载 401 与 402 的运算放大器 403 组成，并且每个等级放大器具有大于一的增益。并且，等级放大器划分成一组等级放大器 306 与一组等级放大器 307。等级放大器 306 具有图 9A 中示出的电路结构与图 9B 中示出的输入-输出特性曲线。图 9C 示出了等级放大器 306 的等价电路。如图 9A 所示，N 沟道晶体管 Q1 与 Q2 用作等级放大器 306 中差动级的输入晶体管。等级放大器 307 具有图 10A 中示出的电路结构与图 10B 中示出的输入-输出特性曲线。图 10C 示出了等级放大器 307 的等价电路。如图 10A 所示，P 沟道晶体管 Q11 与 Q12 用作等级放大器 307 的差动级的输入晶体管。如果差动级处的输入晶体管为 N 沟道类型，则如图 9B 示出的输入-输出特性曲线所示，在较高电压一端上能够保证动态范围。并且，如果差动级的输入晶体管为 P 沟道型，则如图 10B 示出的输入-输出特性曲线所示，在低电压一端上能够保证动态范围。因此，使用两种类型的放大器，能够形成低功率消耗的等级放大器电路 111。如上所述，一般而言，当图像数据为 m 位时，等级放大器电路 111 包含  $2^m$  个等级放大器，并且这些  $2^m$  个等级放大器由 k (k 为大于 0 的整数) 个 N 沟道等级放大器 306 与  $2^m-k$  个 P 沟道等级放大器 307 组成。

提供了图 5 中示出的偏压控制电路 108，以控制由每个等级放大器 306 与 307 的恒定电流源提供的电流。如图 11 所示，偏压控制电路 108 包括：恒定电流源 501；N 沟道晶体管 Q31 与在 N 沟道一端上的 64 组 N 沟道晶体管 Q32 和 Q33 及恒定电流源 502；P 沟道晶体管 Q34 与在 P 沟道一端 64 组 P 沟道晶体管 Q35 与 Q36；以及 64 个反相

器 503。来自数据确定电路的 64 个确定信号的每个连接 N 沟道晶体管 Q33 的栅极与 P 沟道晶体管 Q36 的栅极。被反相器 503 反相的 64 个确定信号的每个连接 N 沟道晶体管 Q32 的栅极与 P 沟道晶体管 Q35 的栅极。这样，偏压控制电路 108 基于来自数据确定电路 107 的确定信号，在每个等级放大器 306 与 307 中单独控制 64 个恒定电流源的每个的电流值。偏压控制电路 108 具有作为 N 沟道晶体管 Q32 与 33 之间节点的偏压终端 BN<sub>n</sub> ( $n=1, 2, \dots, 64$ )，并且偏压控制电路 108 具有 P 沟道晶体管 Q35 与 Q36 之间的偏压终端 BP<sub>n</sub> ( $n=1, 2, \dots, 64$ )。偏压终端 BN<sub>n</sub> 与每个等级放大器 306 的恒定电流源晶体管 Q5 的栅极连接，并且偏压终端 BP<sub>n</sub> 与每个等级放大器 307 的恒定电流源晶体管 Q15 的栅极连接。当来自数据确定电路 107 的确定信号 C<sub>n</sub> ( $n=1, 2, \dots, 64$ ) 为“H”时，终端 BN<sub>n</sub> 的电压为 GND，并且终端 BP<sub>n</sub> 的电压在偏压控制电路 108 中为 VDD，使得单独的放大器为无效。当确定信号 C<sub>n</sub> ( $n=1, 2, \dots, 64$ ) 为“L”时，终端 BN<sub>n</sub> 的电压设定为预定电压 N，并且终端 BP<sub>n</sub> 的电压设定为预定电压 P。这样，预定量的电流通过每个等级放大器 306 与 307 的恒定电流源流动，使得放大器为有效。

如图 9A 与 10A 所示，每个等级放大器 306 与 307 的输出级包括 P 沟道晶体管 (Q6 或 Q16) 与 N 沟道晶体管 (Q7 或 Q17)。为了将每个等级放大器 306 与 307 设定为无效状态，从数据确定电路 107 提供到偏压控制电路 108 的确定信号 C<sub>n</sub> 设定为“H”，并且信号 C<sub>nB</sub> 设定为“L”(C<sub>nB</sub> 表示确定信号 C<sub>n</sub> 的反相信号)。在此状态中，晶体管 Q8 接通从而晶体管 Q6 的栅极电压变为 VDD，导致晶体管 Q6 断开。并且，晶体管 Q9 接通从而晶体管 Q7 的栅极电压变为 GND，导致晶体管 Q7 断开。因此，输出级的输出变为高阻抗状态。并且，恒定电流源 Q5 的栅极电压 BN<sub>n</sub> 变为 GND，并且恒定电流源 Q5 的电流值变为 0。因此，N 沟道等级放大器 306 变为无效状态。以同样方式，晶体管 Q18 接通从而晶体管 Q16 的栅极电压变为 VDD，导致 Q16 断开。并且，晶体管 Q19 接通，从而晶体管 Q17 的栅极电压变为 GND，导致晶体管 Q17 断开。因此，输出级的输出变为高阻抗状态。恒定电流

源 Q15 的栅极电压 BPn 变为 VDD，从而恒定电流源 Q15 的电流值变为 0，并且 P 沟道等级放大器变为无效状态。这样，等级放大器能够基于确定信号设定为无效状态。

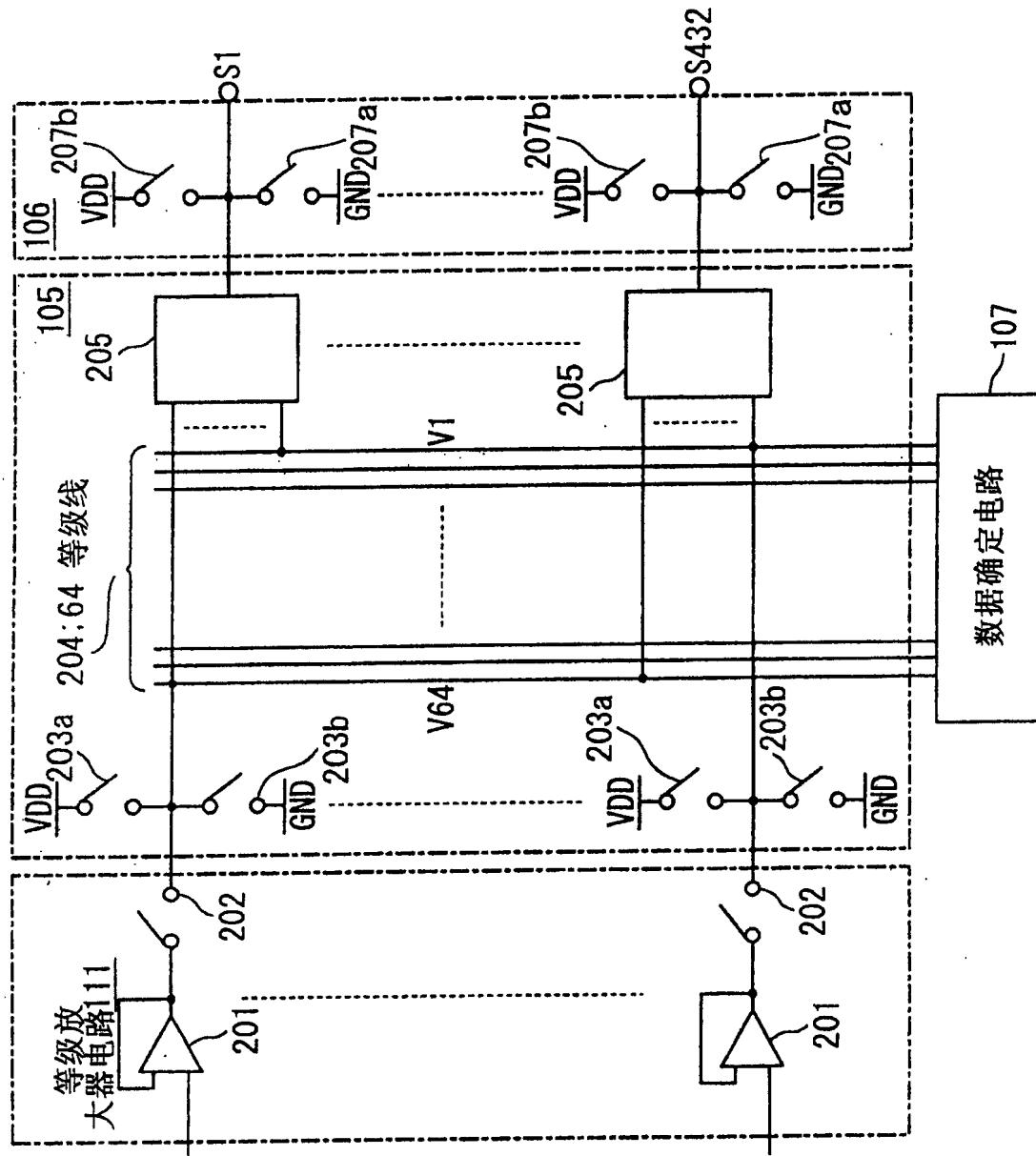

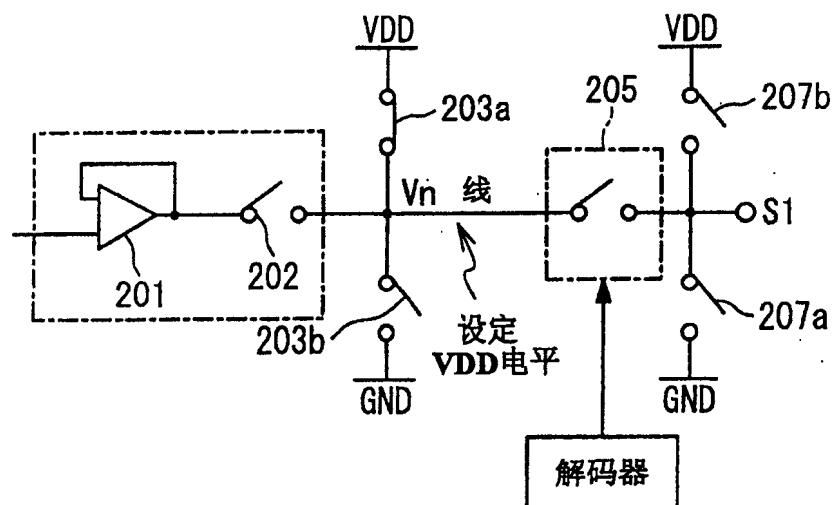

图 12 示出了等级放大器电路 111、等级电压选择电路 105 与输出电路 106。等级放大器电路 111 包括多个等级放大器。如图 9C 与 10C 的等价电路所示，多个开关 202 的每个为等级放大器的一部分。等级电压选择电路 105 由 64 条等级线 204、开关 203a 与等级选择开关 205 组成。等级线 204 连接等级放大器电路 111 中的图 9A 与 10A 的等级放大器 306 与 307 的输出终端 202。开关 203a 连接相应的等级线 204。每个等级选择开关 205 包括 64 个模拟开关，并且与等级线 204 连接。并且，等级线 204 与数据确定电路 107a 连接。输出电路 106 由开关 206 与开关 207a 组成。本领域的普通技术人员应该懂得，本驱动电路可以设置为再等级电压选择电路 105 中包括开关 207a，而不是在输出电路 106 中。在显示单元的数据线与等级选择开关 205 的输出之间提供开关 206。在等级选择开关 205 的输出与 GND 或 VDD 的电压之间提供开关 207a。在该实施例中，所有开关 203a 与 VDD 连接，并且所有开关 207a 与 GND 连接，或者所有开关 203a 与 GND 连接，并且所有开关 207a 与 VDD 连接。如果开关 203a 和所有开关 207a 与相同的电源电压连接，则无法检测出在每个等级线 204 上的电势变化。

这时，数据确定电路 107 结合解码电路 104、等级电压选择电路 105 与输出电路 106，执行数据确定。

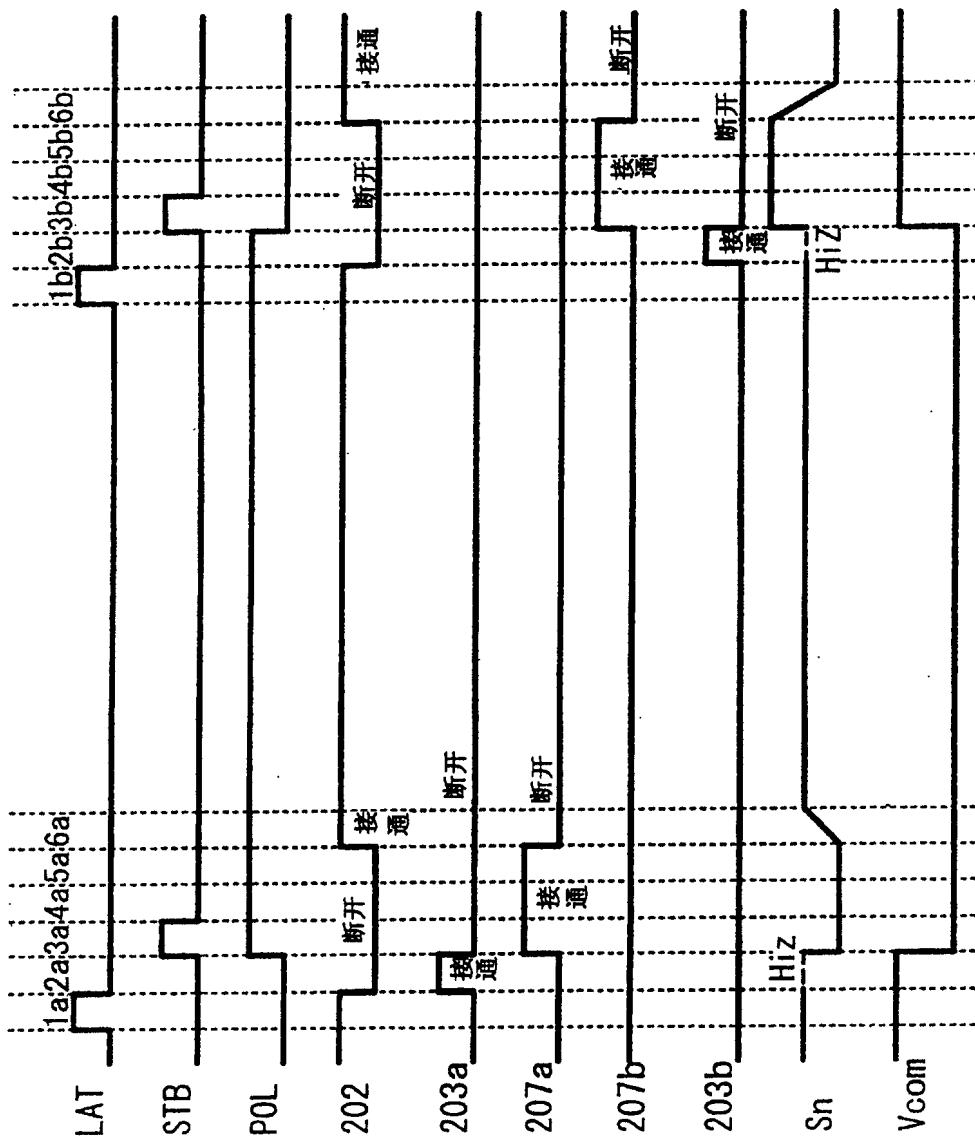

此数据确定操作将参照图 13A 到 13D 的操作状态图与图 14A 到 14G 的时序图描述。为了简化，如图 13A 到 13D 所示，假定仅接通等级选择开关 205，以使得可选的等级线 Vn 和数据线 S1 之间连接。如上所述，实质上，等级选择开关 205 由 64 个模拟开关组成，并且有 64 条等级线。

在图 14A 到 14G 中的时间 t1 处，响应于锁存信号 LAT，从帧存储器 101 读取的图像数据被传递到并锁存在数据锁存电路 A102。其次，上述确定信号 Cn 响应于来自定时控制电路 6 的定时信号全部设定为“高”，而不管图 14A 到 14G 中时间 t2 处的图像数据。结果，全部开关 202 断开，并且全部等级放大器 201 设定为无效状态。图 13A 示出了在此状态下开关的状态。开关 206 设定为断开状态的原因是防止在数据确定过程期间显示单元的数据线被相应的等级线的电压所驱动。在图 14A 到 14G 中的时间 t3 处，响应于水平信号 STB，图像数据从数据锁存电路 A102 传递到数据锁存电路 B103，并且锁存其中。解码电路 104 解码数据锁存电路 B103 中的图像数据。开关 203a 响应于来自定时控制电路 6 的定时信号接通，以将所有等级线 204 预充电或上拉到电源电压 VDD。此时，等级选择开关 205 的一个基于由解码电路 104 解码的图像数据，响应于来自定时控制电路 6 的定时信号接通。图 13B 示出了开关的状态。在图 14A 到 14G 中的时间 t4 处，响应于来自定时控制电路 6 的定时信号，所有的开关 203a 断开，并且然后所有的开关 207a 接通。结果，只有对应于接通的等级选择开关 205 的等级线 204 被设置为 GND 电平，并且对应于断开的等级选择开关 205 的等级线 204 保持 VDD 电平。图 13C 与图 13D 示出了开关如何操作。数据确定电路 107 包括锁存电路（没有示出），并且在图 14A 到图 14G 的时间 t4 处，当等级线 204 保持 VDD 电平时，锁存 64 等级线 204 的每个的电压电平为“1”，当等级线 204 保持 GND 电平时，锁存 64 等级线 204 的每个的电压电平为“0”。为了防止由于由例如在图像数据确定期间来自 CPU2 的信号产生的噪声的数据确定电路 107 的故障，每个等级线连接了一电容，尽管没有示出。

其次，在图 14A 到 14G 中的时间 t5 处，所有开关 207a 响应于来自定时控制电路 6 的定时信号断开。数据确定电路 107 基于锁存的电压电平产生确定信号，并且驱动偏压控制电路 108。偏压控制电路 108 产生信号 BN1 到 BN64 与 BP1 到 BP64。这样，在图 14A 到 14G 中的时间 t6 处，根据来自偏压控制电路 108 的信号 BN1 到 BN64 与 BP1

到 BP64，等级放大器 201 保持无效状态或者改变为有效状态。然后，开关 202 基于来自数据确定电路 107 的确定信号可选地接通。而且，开关 206 响应来自定时控制电路 6 的时间信号接通。这样，等级电压仅从有效状态下的等级放大器施加到数据线。

如上所述，同时确定 64 个值 00H 到 3FH 中的哪个对应于每个数据线是可能的。这样，确定了一水平行（或扫描行）的图像数据，并且基于确定的图像数据，没必要的等级放大器转换到无效状态，使得等级放大器电路在低功率下操作，并进一步允许采用低功率驱动显示单元。例如，当假定等级放大器消耗大约  $10\mu\text{A}$  时，如果驱动电压 5V，则在全部单色显示中，最多能够减少  $3.15\text{mW}$  ( $=10\mu\text{A} \times 5\text{V} \times 63$ ) 的功率消耗。并且，因为通过相同的解码电路得到确定图像数据的解码功能与选择等级电压的解码功能，所以数据确定电路 107 可由锁存电路（没有示出）组成，导致电路规模的减少。

并且，当制造显示单元的驱动电路以将帧存储器 101 包含在半导体集成电路中时，存在下列情况：显示单元的像素数目与帧存储器的像素数目不同。当帧存储器的像素数目大于显示单元的像素数目时，例如，在显示单元中的 120x160 像素与帧存储器中 144x176 像素的情况下，从 CPU2 中没有提供用于 72 (=24x3) 条未连接的数据线的图像数据。因此，在对应于这些未连接的数据线的区域中，帧存储器 101 具有随机数据，并且在数据确定的情况下，此区域必须设定为无效。为了使该区域无效，没有与数据线连接的开关 206 通常基于来自命令控制电路 5 的指令断开。并且，因为 16 条扫描线没有连接，所以基于来自命令控制电路 5 的指令，响应于来自定时控制电路 6 的定时信号，在对应未连接的扫描线期间，数据线驱动电路 1 的等级放大器设定为无效状态。这样，能够减少功率消耗。

#### （第二实施例）

图 15 是根据本发明第二实施例，数据线驱动电路 1 的框图，并

且图 16 示出了包括用于数据确定的数据确定电路 107 的电路结构。第二实施例不同于第一实施例在于一部分电路结构。在第一实施例中，与数据线连接的开关 206 设定为断开状态，并且在数据确定的例子中，没有任何电压应用于数据线。然而，在第二实施例中，GND 或 VDD 的电压应用于数据确定的例子。为此目的，如图 16 所示，连接等级线 204 的开关 203a 和连接等级选择开关 205 的输出的开关 207a 在第一实施例与第二实施例之间是相同的。并且，连接等级线 204 的开关 203b 和连接等级选择开关 205 的开关 207b 加入到第二实施例中。开关 203a 连接 VDD，并且开关 207a 连接 GND，并且开关 203b 连接 GND 以及开关 207b 连接 VDD。

其次，将描述第二实施例的操作。图 17A 到图 17J 示出了操作的时间图。并且，对应这些图 13A 到图 13D 的操作状态在图 18A 到图 18D 中示出。在操作中第二实施例与第一实施例的区别在于当确定图像数据时，输出电路不在高阻抗状态下，并且根据极性信号 POL，输出电压。在图 17A 到图 17J 的时间 t1a 与 t1b 处，存储在帧存储器 101 中的图像数据被读取，并且传递到数据锁存电路 A102 中，并且响应锁存信号 LAT 锁存在数据锁存电路 A102 中。其次，在图 17A 到图 17J 的时间 t2a 处，上述确定信号 Cn 响应于来自时间控制电路 6 的时间信号全部设定为“H”，而不管图像数据。结果，断开开关 202，并且全部等级放大器 201 设定为无效状态。并且，响应于来自定时控制电路 6 的定时信号，断开等级选择开关 205，而不管等级数据。并且，响应于来自定时控制电路 6 的定时信号，接通开关 203a，并且将等级线预充电到电压 VDD（图 18A）。

在图 17A 到图 17J 的时间 t2b 处，响应于来自定时控制电路 6 的定时信号，极性信号 POL 反相，并且开关 203b 接通以及等级线预充电到电压 GND（图 18C）。

在图 17A 到图 17J 的时间 t3a 处，图像数据响应于水平信号 STB

从数据锁存电路 A102 传递到数据锁存电路 B103，并且锁存在数据锁存电路 B103 中。然后，解码电路 104 对锁存在数据锁存电路 103 中的图像数据进行解码。响应于来自定时控制电路 6 的定时信号，断开开关 203a，并且响应于来自定时控制电路 6 的定时信号，根据由解码电路 104 解码的图像数据可选地接通等级选择开关 205。而且，响应来自定时控制电路 6 的定时信号接通开关 207a。这样，数据线固定在 GND 上。在此情况下，当接通等级选择开关 205 时，等级线设定为电压 GND。对应断开状态中的等级选择开关 205 的等级线保持电压 VDD。对应开关 205 的等级线的电压电平锁存在数据确定电路 107（图 18B）的锁存电路（没有示出）中。

在图 17A 到图 17J 中的时间 t3b 处，响应于来自定时控制电路 6 的定时信号，极性信号 POL 反相，开关 203b 断开，并且开关 207b 接通。结果，数据线固定在电压 VDD 上。对应于根据图像数据设定为接通状态的等级选择开关 205 的等级线 204 被设定为电压 VDD（图 18D）。对应于断开状态中的等级选择开关 205 的等级导线 204 保持电压 GND。在图 17A 到图 17J 的时间 3a 与 3b 处，64 条等级线 204 的电压电平应当在电压 VDD 的情况下由数据确定电路 107 的锁存电路锁存为“1”，在电压 GND 的情况下锁存为“0”。如上所述，除了锁存电路以外，根据极性信号 POL 用于确定将图像数据反相的电路（没有示出）为数据确定电路 107 所必需。

其次，在图 17A 到图 17J 中的时间 t6a 处，响应于来自定时控制电路 6 的定时信号，开关 207b 断开。数据确定电路 107 基于锁存的电压电平，产生确定信号，并且驱动偏压控制电路 108。偏压控制电路 108 产生信号 BN1 到 BN64 与 BP1 到 BP64。这样，在图 17A 到图 17J 中的时间 t6a 处，基于来自偏压控制电路 108 的信号 BN1 到 BN64 与 BP1 到 BP64，等级放大器 201 保持无效状态或者设定为有效状态。并且，开关 202 基于来自数据确定电路 107 的确定信号可选地接通。而且，开关 206 响应于来自定时控制电路 6 的时间信号接通。这样，

等级电压仅从有效状态下的等级放大器施加到数据线。

类似地，在图 17A 到图 17J 中的时间 t6b 处，开关 207b 断开，并且响应来自偏压控制电路 108 的信号基于数据确定电路 107 的确定结果，等级放大器 201 保持无效状态或者设定为有效状态。根据图像数据确定的等级电压能够应用于数据线。

在第一实施例中，在数据确定期间，连接数据线的开关设定为高阻抗。然而，在第二实施例中，根据 Vcom 电路 11 的操作，数据线固定在 VDD 或 GND 上。这用于防止：当 Vcom 反相时，在串音的影响下数据线被反相，从而高于耐压特性的电压没有应用于驱动电路系统。并且，在第一实施例中的开关 206 可加入到第二实施例。

### （第三实施例）

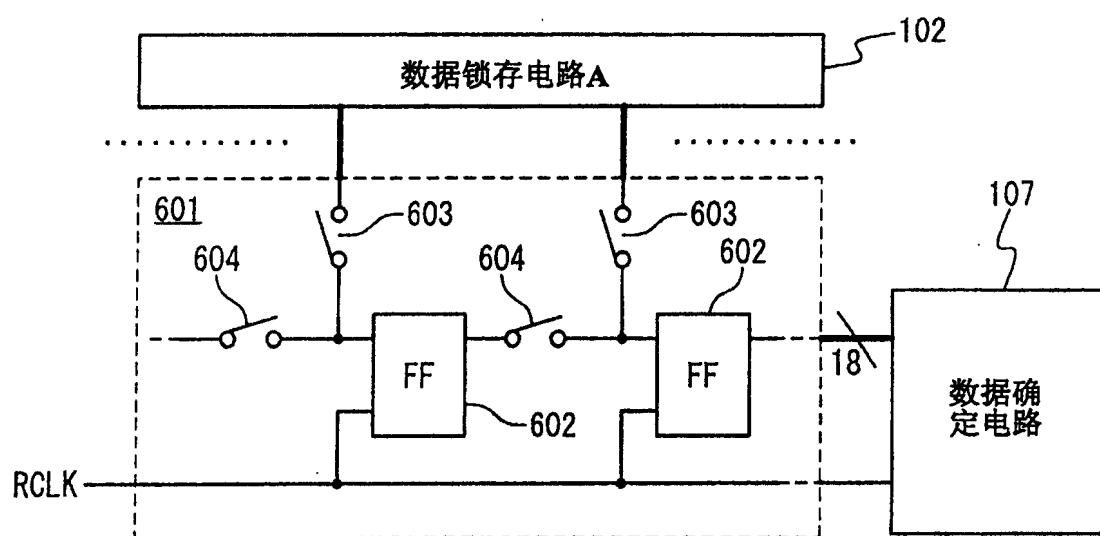

图 19 示出了根据本发明第三实施例的数据线驱动电路 1 的框图。在此实施例中，与图 1 中示出的传统结构比较，移位寄存器电路 A601 的位置不同。在传统的例子中，在数据锁存电路 A 902 的前级提供移位寄存器电路 901，并且移位寄存器电路 901 具有产生采样信号的功能，从而图像数据顺序锁存在数据锁存电路 A 902 中。然而，在此实施例中，在数据锁存电路 A102 的后级中提供移位寄存器电路 A601，并且移位寄存器电路 A601 具有下列功能：将在数据锁存电路 A102 中锁存的图像数据与时钟信号 RCLK 同步顺序传递到数据确定电路 107。

并且，图 20 示出了数据确定部分。移位寄存器电路 A601 包括两个触发器 602 和用于每位数据的开关 603 与 604。尽管没有在图中示出，数据确定电路 107 也包括三个 6 输入 NAND、一个 3 输入 NAND 与锁存电路。

其次，将描述操作。存储在帧存储器 101 中的图像数据与锁存信

号 LAT 同步采用线存储功能传递到数据锁存电路 A102，锁存信号 LAT 与 CPU2 的信号 12 异步。通过在数据锁存电路 A102 的后级中提供的移位寄存器电路 A601，在数据锁存电路 A102 中锁存的图像数据与时钟信号 RCLK 同步顺序传递到数据确定电路 107，时钟信号 RCLK 与 CPU2 的信号 12 异步。当一行图像数据确定时停止时钟信号 RCLK，并且数据确定结束。其次，图像数据响应于水平信号 STB 传递到数据锁存电路 B103，根据图像数据选择等级选择开关 205，并且驱动显示单元的数据线。当数据线的驱动结束并且提供下一个锁存信号 LAT 时，由数据确定电路 107 确定的图像数据复位，并且开始下一行的数据确定。

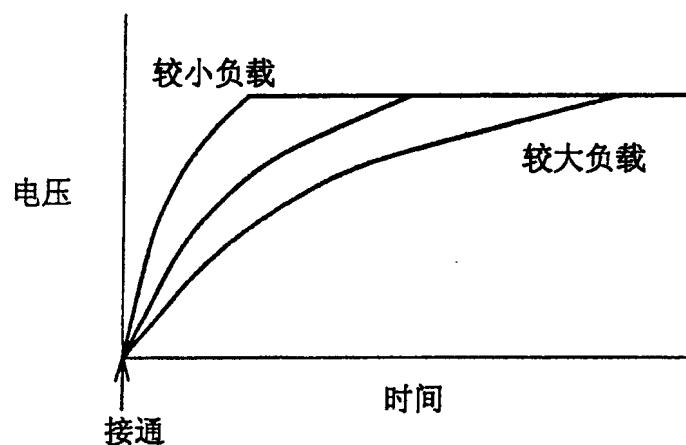

并且，如果计数器（没有示出）加入到数据确定电路 107，则确定每个等级使用多少条数据线是可能的。如图 21A 与图 21B 所示，根据此计数值，通过提供改变驱动时间的功能，能够得到低功率消耗驱动。例如，如果全部数据线具有相同的数据，则在有效状态中等级放大器仅为一，并且等级放大器的负载变得很大，导致大的输出延迟。然而，当存在两种或多种数据时，在有效状态中等级放大器的数目为两个或多个。在此情况下，因为负载被分配，并且等级放大器的电容负载变小，所以功率消耗变大，但输出延迟变小。结果，在短的有效时间中驱动等级放大器是可能的。特别地，当右半显示屏为白色并且左半显示屏为黑色时，两个等级放大器处于有效状态。然而，与整个屏幕是相同颜色的情况比较，因为等级放大器的电容性负载变成一半，所以输出延迟时间变短。以相同的方式，与整个屏幕显示为黑色或白色情况比较，当在相同时间中进行 64 彩色显示时，等级放大器的功率消耗变为 64 倍。然而，根据图像数据的种类，通过改变等级放大器的有效时间，减少大量功率消耗是可能的。

#### （第四实施例）

在第一实施例中，数据确定电路 107 仅在数据为“1”的情况下具有激活等级放大器 201 的功能，并且仅在数据为“0”的情况下具

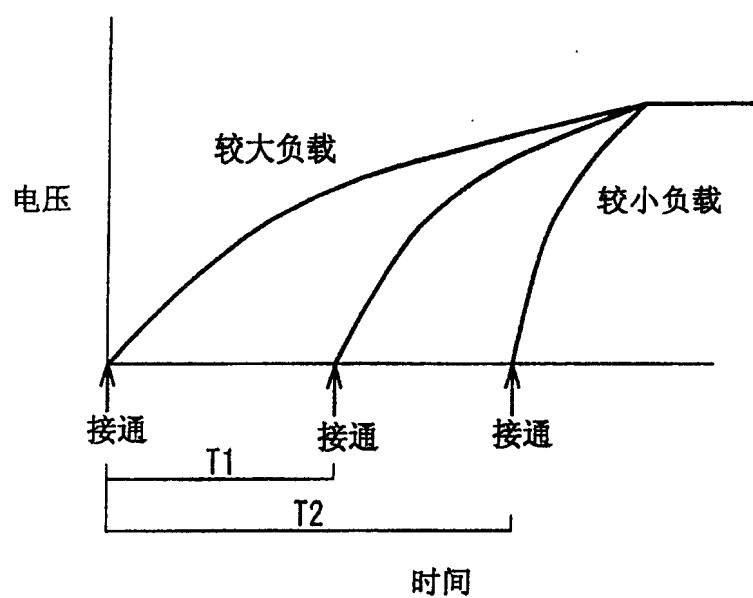

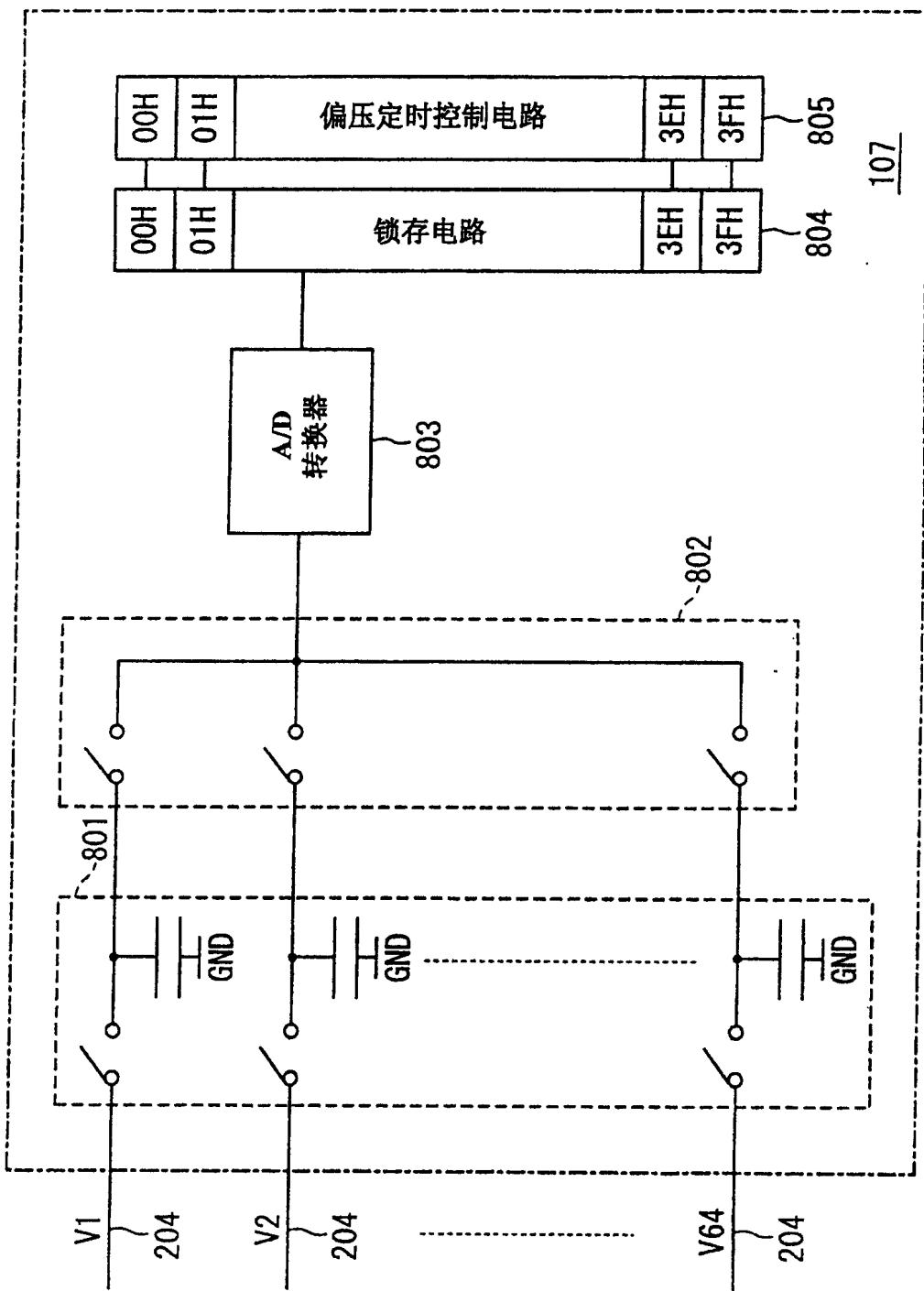

有去激活等级放大器 201 的功能，这是由于通过锁存电路（没有示出）保持的数据为二进制数据 0 或 1。然而，在第四实施例中，通过将恒定电流源功能分配到图 12 的开关 207a 并且将 A/D 转换功能分配到数据确定电路 107，而且通过使用多位确定数据以将时间数据加入到确定信号，从而改变有效时间周期是可能的。图 22 示出了具有 A/D 转换功能的数据确定电路 107 的细节。提供一个 A/D 转换电路 803 是足够的，并且为每条等级线提供采样保持电路 801，以具有开关与电容。A/D 转换电路 803 通过切换电路 802 在等级线之间顺序切换，以测量连接的等级线的电压。测量的电压在锁存电路 804 中锁存。类似于第三实施例，偏压定时控制电路 805 根据锁存电路 804 中锁存的数据的数目，改变等级放大器 201 的有效时间周期。这样，能够减少功率消耗。

更特别地，如果图 12 中开关 207a 的恒定电流值为  $0.1\mu\text{A}$ ，则当 432 条数据线用作相同的数据时， $43.2\mu\text{A}$  的电流流动。因为  $dt=C$ （电容量  $C$ ） $\times V$ （电压）/ $I$ （电流），所以如果采样保持电路 803 的电容量为  $10\text{pF}$ ，则电荷以  $1.16\mu\text{s}$  的时间损失 ( $dt=10\text{pF} \times 5\text{V}/43.2\mu\text{A}$ )。当 144 条数据线用作相同的数据时，在  $1.16\mu\text{s}$  以后电压变为大约  $2/3$ 。这样，如果用于数据确定的时间周期预先设定，并且在时间周期中的电压改变由 A/D 转换电路检测，则近似地检测每个等级的数据的数目是可能的。为了将恒定电流功能提供给开关 207a，调节每个开关的晶体管的栅极电压是足够的。

#### （第五实施例）

图 23 示出了根据本发明第五实施例的数据线驱动电路 1 的框图。第五实施例不同于第一实施例在于：能够选择在帧存储器中存储图像数据的模式和不存储图像数据的模式。在便携式电话中，在许多场合下显示静止图像，但有时显示视频图像。当显示视频图像时，当视频图像数据写入到帧存储器 101 时，消耗的功率变大。为此，最好将视频图像数据直接传递到数据锁存电路 A102 作为行存储器，而不用在

显示视频图像的情况下在帧存储器 101 中写入视频图像数据。因为在视频图像显示的情况下，视频图像数据能够与来自 CPU2 的信号 12 同步提供，所以为此目的提供移位寄存器电路 702。并且，提供数据切换电路 701 与 RGB 切换电路 703 以根据静止图像显示或视频图像显示，将图像数据传递到帧存储器 101 或者数据锁存电路 A102。

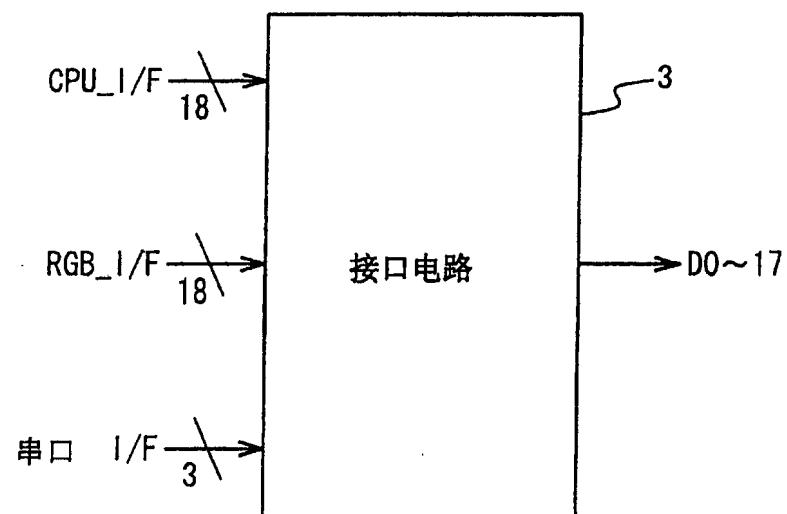

如图 24A 所示，在数据切换电路 701 中，输入由接口电路 3 切换。在视频图像显示中，通过数据切换电路 701 与 RGB 切换电路 703，将视频图像数据直接传递到数据锁存电路 A102。在静止图像显示中，图像数据通过数据切换电路 701 传递到帧存储器 101。数据移位寄存器电路 702 在静止图像显示中停止操作。在数据锁存电路 A102 以后电路的操作与第一实施例中的操作相同。数据切换电路 701 与移位寄存器电路 702 可加入到图 19 示出的第三实施例的结构。如图 24B 所示，存在下列情况：当图像数据从 CPU2 提供时，信号线根据静止图像数据或视频图像数据不同。模式 1 与模式 4 主要用于视频图像显示的场合，并且模式 2 与模式 3 主要用于静止图像的情况。切换由接口电路 3 实现。

本发明的第一到第五实施例描述如上。然而，在本发明中，在第一到第五实施例中描述的结构能够适当地结合。

如上所述，根据本发明，在具有帧存储器的数据端驱动电路中，因为等级放大器根据图像数据为有效或无效，所以能够减少功率消耗。并且，当来自帧存储器的图像数据象第一实施例一样共同地确定时，减少数据确定电路的电路元件的数目是可能的。特别地，在 NAND 电路象传统的例子一样用作数据确定电路的情况下，64 个 6 输入 NAND 必需用于每条数据线，并且需要 768 个晶体管。然而，在本发明中，使用最初已提供的解码电路，并且新的元件为连接等级线的多个开关和连接数据线的输出电路的开关。因此，能够大量减少必需的元件的数目。在第三实施例中，移位寄存器电路必需将图像数据传递到数据

确定电路，并且移位寄存器电路的数目为每条数据线最少 288( $=16 \times 18$  位)。然而，仍然可得到电路规模的减少。通过将计数器功能加入到数据确定电路，并且根据图像数据的数据数目，通过控制等级放大器的有效时间周期，能够得到低功率消耗驱动。

**图1 现有技术**

**图2 现有技术**

图3 现有技术

图4

图5

图6A

| 输入数据   | 正极性<br>(POL=H) |       | 负极性<br>(POL=L) |       |

|--------|----------------|-------|----------------|-------|

|        | 内部数据           | Sn 输出 | 内部数据           | Sn 输出 |

| 000000 | 000000         | V64   | 111111         | V1    |

| 000001 | 000001         | V63   | 111110         | V2    |

| 000010 | 000010         | V62   | 111101         | V3    |

| ⋮      | ⋮              | ⋮     | ⋮              | ⋮     |

| ⋮      | ⋮              | ⋮     | ⋮              | ⋮     |

| 111101 | 111101         | V3    | 000010         | V62   |

| 111110 | 111110         | V2    | 000001         | V63   |

| 111111 | 111111         | V1    | 000000         | V64   |

图6C

图6B

| 等级<br>放大器 | 正极性       | 负极性       |

|-----------|-----------|-----------|

| $V_n$     | $VR_x(V)$ | $VR_x(V)$ |

| 1         | 0.000     | 0.000     |

| 2         | 0.330     | 0.050     |

| 3         | 0.430     | 0.150     |

| 4         | 0.540     | 0.200     |

| ⋮         | ⋮         | ⋮         |

| 29        | 2.000     | 2.250     |

| 30        | 2.100     | 2.340     |

| 31        | 2.190     | 2.430     |

| 32        | 2.320     | 2.520     |

| 33        | 2.410     | 2.610     |

| ⋮         | ⋮         | ⋮         |

| 61        | 4.330     | 4.350     |

| 62        | 4.520     | 4.490     |

| 63        | 4.710     | 4.700     |

| 64        | 5.000     | 5.000     |

图6D

|     |     |     |     |     |     |     |     |    |    |     |     |    |    |    |    |     |    |

|-----|-----|-----|-----|-----|-----|-----|-----|----|----|-----|-----|----|----|----|----|-----|----|

| D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7  | D6  | D5 | D4 | D3 | D2 | D1  | D0 |

| B5  | B4  | B3  | B2  | B1  | B0  | G5  | G4  | G3 | G2 | G1  | G0  | R5 | R4 | R3 | R2 | R1  | R0 |

| MSB |     |     |     | LSB | MSB |     |     |    |    | LSB | MSB |    |    |    |    | LSB |    |

图7

图8A

图8B

图9A

图9B

图9C

**图10A****图10B****图10C**

图11

12

**图13A****图13B**

图13C

图13D

图14A

图14B

图14C

图14D

图14E

图14F

图14G

图15

图 16

图 17A

图 17B

图 17C

图 17D

图 17E

图 17F

图 17G

图 17H

图 17I

图 17J

**图18A****图18B**

**图18C****图18D**

图 19

**图20**

**图21A****图21B**

图22

图23

图24A

图24B

| 图像数据输入类型 |                    |

|----------|--------------------|

| 模式1      | CPU_I/F            |

| 模式2      | RGB_I/F+SERIAL_I/F |

| 模式3      | CPU_I/F+RGB_I/F    |

| 模式4      | 串口 I/F             |

|                |                                                             |         |            |

|----------------|-------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于液晶显示器的驱动电路和驱动方法                                           |         |            |

| 公开(公告)号        | <a href="#">CN100345179C</a>                                | 公开(公告)日 | 2007-10-24 |

| 申请号            | CN200410028272.9                                            | 申请日     | 2004-03-10 |

| [标]申请(专利权)人(译) | NEC电子股份有限公司                                                 |         |            |

| 申请(专利权)人(译)    | 恩益禧电子股份有限公司                                                 |         |            |

| 当前申请(专利权)人(译)  | 恩益禧电子股份有限公司                                                 |         |            |

| [标]发明人         | 中井大三郎<br>桥本义春                                               |         |            |

| 发明人            | 中井大三郎<br>桥本义春                                               |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20 G09G5/10 H04N5/66               |         |            |

| CPC分类号         | G09G2320/0276 G09G3/3614 G09G3/3696 G09G3/3688 G09G2330/021 |         |            |

| 优先权            | 2003062766 2003-03-10 JP                                    |         |            |

| 其他公开文献         | CN1530918A                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>              |         |            |

#### 摘要(译)

一种显示设备的驱动电路，其中多条扫描线与多条数据线相同垂直，在所述驱动电路中，第一数据锁存电路(103)响应水平信号锁存用于每条线的图像数据。解码电路(104)对锁存的图像数据进行解码。等级电压选择电路(105)基于解码的图像数据，选择电压线以将多条数据线的每条与任何电压线连接。数据确定电路(107)基于选择的电压线产生数据确定信号，从而多个等级放大器的每个基于确定信号可选地设定为无效状态。等级放大器电路(111)包括多个等级放大器，每个等级放大器当处于有效状态时放大对应的等级电压之一，并且当处于无效状态时不放大对应的等级电压，放大的等级电压在对应的电压线之一上输出。输出电路(106)基于电压线上放大的等级电压驱动多条数据线。