## (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 101916020 B (45) 授权公告日 2012.05.02

(21)申请号 201010247342.5

(22)申请日 2003.06.28

(30) 优先权数据 0036979/02 2002.06.28 KR

(62) 分案原申请数据 03158843.3 2003.06.28

(73) 专利权人 三星电子株式会社 地址 韩国京畿道

(72) 发明人 宋长根

(74) **专利代理机构** 北京市柳沈律师事务所 11105

代理人 张波

(51) Int. CI.

*G02F* 1/1362 (2006.01) *G02F* 1/1333 (2006.01)

(56)对比文件

WO 9408331 A, 1994.04.14, 全文.

US 6069600 A, 2000. 05. 30, 全文. CN 1270383 A, 2000. 10. 18, 全文. JP 2001330852 A, 2001. 11. 30, 全文.

审查员 张帆

权利要求书 2 页 说明书 7 页 附图 6 页

### (54) 发明名称

液晶显示器

#### (57) 摘要

本发明公开一种液晶显示器,其包括:第一基板;多个像素,至少一个所述像素分别包括设置在所述第一基板上位于同一层的第一像素电极和第二像素电极;面对所述第一基板的第二基板;以及置于所述第一基板和所述第二基板之间的液晶层,其中,所述第一像素电极和所述第二像素电极每一个上的液晶层被分割成多个畴,且施加给所述第一像素电极的电压不同于施加给所述第二像素电极的电压,其中,在俯视的情况下,所述畴的液晶分子的方向向多条第一信号线倾斜。

CN 101916020 B

1. 一种液晶显示器,包括:

第一基板:

多个像素,至少一个所述像素分别包括设置在所述第一基板上位于同一层的第一像素 电极和第二像素电极;

面对所述第一基板的第二基板;以及

置于所述第一基板和所述第二基板之间的液晶层,

其中,所述第一像素电极和所述第二像素电极每一个上的液晶层被分割成多个畴,且 施加给所述第一像素电极的电压不同于施加给所述第二像素电极的电压,

其中,所述第一像素电极和所述第二像素电极每一个上的所述液晶层的畴包括第一方向畴和第二方向畴,所述第一和第二方向畴中的液晶分子的平均定向器相对于多条第一信号线成约 0-90°的预定角度。

- 2. 如权利要求 1 所述的液晶显示器,其中所述第一像素电极通过第一薄膜晶体管电连接至所述第一信号线中的一条,且所述第二像素电极通过第二薄膜晶体管电连接至所述第一信号线中的所述一条。

- 3. 如权利要求 1 所述的液晶显示器,其中所述第一像素电极和所述第二像素电极彼此 电绝缘。

- 4. 如权利要求1所述的液晶显示器,还包括:

多条第二信号线,

其中在两条相邻的第一信号线之间设置至少一条第二信号线。

- 5. 如权利要求 4 所述的液晶显示器,其中所述第二信号线与所述第一像素电极和所述 第二像素电极中的至少一个容性耦合。

- 6. 如权利要求 5 所述的液晶显示器,其中所述第二信号线与相邻像素的第一像素电极和第二像素电极中的至少一个容性耦合。

- 7. 如权利要求 6 所述的液晶显示器,其中所述第二像素电极被第二信号线的一部分重叠,第二信号线的所述部分与该第二信号线的重叠所述第一像素电极的部分不同。

- 8. 如权利要求1所述的液晶显示器,其中所述液晶层的所述畴由畴分割部件定义。

- 9. 如权利要求8所述的液晶显示器,其中所述畴分割部件形成在所述第一基板上。

- 10. 如权利要求 9 所述的液晶显示器,其中所述畴分割部件是所述第一像素电极上的 多个切口。

- 11. 如权利要求 8 所述的液晶显示器,其中所述第一像素电极与所述第二像素电极的面积比为 1 至 4。

- 12. 如权利要求 8 所述的液晶显示器,其中所述第一像素电极和所述第二像素电极的阈值电压之间的差在 0. 4 至 1V 的范围。

- 13. 如权利要求 11 或 12 所述的液晶显示器,其中在没有电场的情况下,畴的液晶分子的主轴基本上垂直于所述第一基板和所述第二基板的表面。

- 14. 如权利要求 13 所述的液晶显示器,其中所述畴分割部件是所述第一像素电极上的多个切口。

- 15. 如权利要求 1 所述的液晶显示器,其中所述第一像素电极和所述第二像素电极每一个上的所述液晶层被分割成四个畴。

- 16. 如权利要求 1 所述的液晶显示器,其中所述第一像素电极的面积不同于所述第二像素电极的面积。

- 17. 如权利要求 1 或 16 所述的液晶显示器,其中所述第一像素电极的边界的形状不同于所述第二像素电极的边界的形状。

- 18. 如权利要求 17 所述的液晶显示器,其中所述第一像素电极和所述第二像素电极的边界在形状上是多边形。

# 液晶显示器

[0001] 本申请是申请日为 2003 年 6 月 28 日且题为"液晶显示器及其薄膜晶体管阵列面板"的第 200810130505. 4 号发明专利申请的分案申请。

### 技术领域

[0002] 本发明涉及液晶显示器,特别涉及用于液晶显示器的面板。

### 背景技术

[0003] 通常,液晶显示器 (LCD) 包括液晶 (LC) 面板组件,该面板组件包括设有两种场发生电极如像素电极和公共电极的两个面板、以及间插在其间具有介电各向异性的 LC 层。场发生电极之间的电压差的变化,即由电极产生的电场的强度的变化改变了透过 LCD 的光的透射率,因此通过控制电极之间的电压差获得所希望的图像。

[0004] 然而,LCD 具有视角窄的关键性缺陷。为了克服这种问题,已经研制了用于增宽视角的各种技术,其中,在像素电极和公共电极上形成切口或突起的同时将 LC 分子垂直于上和下面板排列的技术是最有希望的增宽视角的技术。

[0005] 设置在各个像素电极和公共电极上的切口产生弥散场(fringe field),该弥散场控制了LC分子的倾斜方向,由此增宽视角。

[0006] 设置在各个像素电极和公共电极上的突起使电场变形,并且由于变形的电场而控制了 LC 分子的倾斜方向,由此增宽视角。

[0007] 或者,在下面板的像素电极上设置切口,而在上面板的公共电极上设置突起。由切口和突起产生的弥散场控制 LC 分子的倾斜方向,由此形成多个畴(multiple domain)。

[0008] 多畴 LCD 具有在所有方向的高达 80° 或更大的非常优异的基于对比度的视角或基于灰度反转的视角。基于对比度的视角(contrast-based viewing angle)定义为显示1:10 的对比率的视角,而基于灰度反转的视角(gray inversion-based viewing angle)由灰度间亮度反转的限制角表示。然而,多畴 LCD 显示出侧向伽马(gamma)曲线变形,即正面伽马曲线和侧向伽马曲线互相不一致使得与甚至扭转向列(TN)模式 LCD 相比都呈现为变坏的左和右可视度。例如,具有用于隔开各个畴的切口的图案化垂直配向(PVA)模式的 LCD 随着进入侧向侧边而变得更亮并且颜色偏向白色。在严重的情况下,消除了明亮灰度之间的差异,因此图像变得很密集。然而,由于 LCD 近年来已经用于多媒体目的以显示静止或运动图像,所以越来越多地提高可见度成为关键问题。

#### 发明内容

[0009] 提供一种液晶显示器,包括:第一绝缘基板;形成在第一绝缘基板上的第一和第二信号线;形成在第一绝缘基板上并与第一和第二信号线交叉的第三信号线;连接到第一和第三信号线的第一薄膜晶体管;连接到第二和第三信号线的第二薄膜晶体管;连接到第一薄膜晶体管的第一像素电极;连接到第二薄膜晶体管的第二像素电极;面对第一绝缘基板的第二绝缘基板;形成在第二绝缘基板上的公共电极;置于第一和第二绝缘基板之间并

包括在第一像素电极上的第一液晶区和在第二像素电极上的第二液晶区的液晶层;以及形成在第一和第二绝缘基板的至少一个上用于分别将第一和第二液晶区分割成多个畴的畴分割部件,其中第一和第二液晶区的每个的畴包括第一方向畴和第二方向畴,第一和第二方向畴中的液晶分子的平均定向器关于第一或第二信号线成约 0-90°的预定角度,第一像素电极和第二像素容性耦合。

[0010] 优选第一像素电极占第一和第二像素电极的总面积的约 50-80%,并在激励第一薄膜晶体管之后激励第二薄膜晶体管。

[0011] 第一像素电极的阈值电压优选比第二像素电极的阈值电压低约 0.4-1.0V。

[0012] 该液晶显示器还可以包括形成在第一基板上的存储电极线,该存储电极线沿着第一和第二像素电极形成存储电容器。

[0013] 第一和第二方向畴中的液晶分子的平均定向器优选关于第一或第二信号线成约 45°角。

[0014] 优选,该液晶显示器还包括置于第一基板的外表面上并且偏振轴平行于第一或第二信号线的第一偏振板、以及置于第二基板的外表面上并且偏振轴与第一偏振板的偏振轴交叉的第二偏振板。

[0015] 提供一种薄膜晶体管阵列面板,包括:绝缘基板;形成在该基板上的第一和第二栅极线;形成在第一和第二栅极线上的栅极绝缘层;形成在栅极绝缘层上的半导体层;至少形成在半导体层上并与栅极线相交的数据线;至少形成在半导体层上并位于第一栅极线和数据线之间的相交部位附近的第一和第二漏极;至少形成在半导体层上并位于第二栅极线和数据线之间的相交部位附近的第三和第四漏极;形成在栅极绝缘层上的耦合电极;形成在数据线、第一到第四漏极和耦合电极上并具有露出第一到第四漏极和耦合电极的多个接触孔的钝化层;形成在钝化层上并连接到第一漏极和耦合电极的第一像素电极;形成在钝化层上并连接到第二漏极的第二像素电极;形成在钝化层上并连接到第三漏极的第三像素电极;和形成在钝化层上并连接到第四漏极上而且部分地与耦合电极重叠的第四像素电极,其中第一和第四像素电极的至少之一具有倾斜切口。

[0016] 提供一种液晶显示器,包括:第一绝缘基板;形成在第一基板上的第一和第二栅极线;形成在第一和第二栅极线上的栅极绝缘层;形成在栅极绝缘层上的半导体层;至少形成在半导体层上并与栅极线交叉的数据线;至少形成在半导体层上并位于第一栅极线和第二栅极线之间的交叉部位附近的第一和第二漏极;至少形成在半导体层上并位于第二栅极线和数据线之间的相交部位附近的第三和第四漏极;形成在栅极绝缘层上的耦合电极;形成在数据线、第一到第四漏极和耦合电极上并具有露出第一到第四漏极和耦合电极的多个接触孔的钝化层;形成在钝化层上并连接到第一漏极和耦合电极的第一像素电极;形成在钝化层上并连接到第二漏极的第三像素电极;和形成在钝化层上并连接到第四漏极而且部分地与耦合电极重叠的第四像素电极;面对第一绝缘基板的第二绝缘基板;形成在第二绝缘基板上的公共电极;置于第一和第二绝缘基板之间的液晶层;以及形成在第一和第二绝缘基板的至少一个上并将液晶层分割成多个畴的畴分割部件,其中该畴的两个长边与栅极线或数据线基本上成约45°角。

[0017] 优选地,第一像素电极占第一和第四像素电极的总面积的约50-80%,并且在给第一像素电极输送电压之后给第四像素电极输送电压。

[0018] 第一像素电极的阈值电压优选比第四像素电极的阈值电压低约 0.4-1.0V。

[0019] 根据本发明的一个方面,提供一种液晶显示器,其包括:第一基板;多个像素,至少一个所述像素分别包括设置在所述第一基板上位于同一层的第一像素电极和第二像素电极;面对所述第一基板的第二基板;以及置于所述第一基板和所述第二基板之间的液晶层,其中,所述第一像素电极和所述第二像素电极每一个上的液晶层被分割成多个畴,且施加给所述第一像素电极的电压不同于施加给所述第二像素电极的电压,其中,第一和第二像素电极每一个上的液晶层的畴包括第一和第二方向畴,第一和第二方向畴中的液晶分子的平均定向器相对于多条第一信号线成约0-90°的预定角度。

[0020] 附图说明

[0021] 通过参照附图详细地介绍本发明的优选实施例使本发明的上述和其它优点更显而易见,附图中:

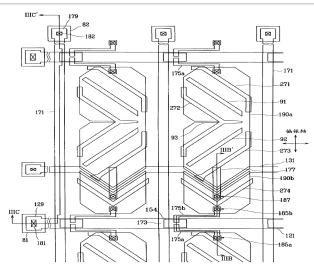

[0022] 图 1 是根据本发明一实施例的 LCD 的电路图;

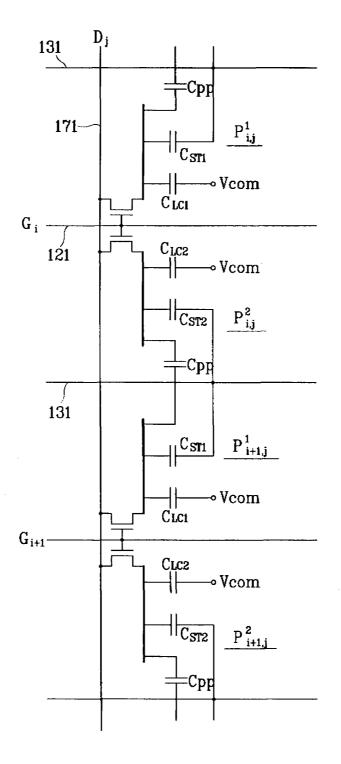

[0023] 图 2 是根据本发明实施例的 LCD 的布局图;

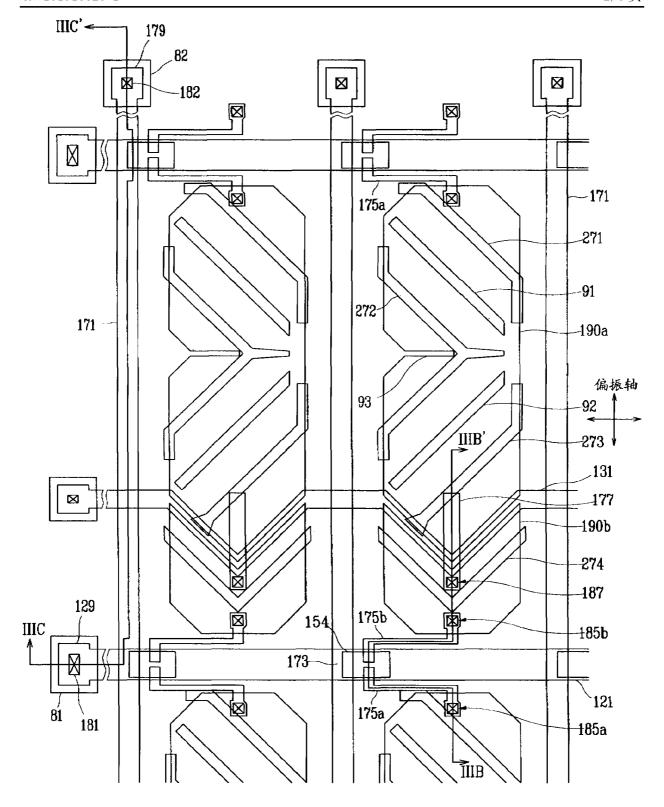

[0024] 图 3A 是沿着线 IIIB-IIIB′截取的图 2 所示的 LC 面板组件的剖视图;

[0025] 图 3B 是图 3A 中所示的 TFT 阵列面板的剖视图,该图是除了滤色器阵列面板和偏振膜之外的图 3A 中所示 LC 面板组件的一部分:

[0026] 图 3C 是沿着线 IIIC-IIIC' 截取的图 2 中所示的 TFT 阵列面板的剖视图;

[0027] 图 4 是表示作为电压偏移和畴比率 (domain ratio) 的函数的可见度的变形的曲线;

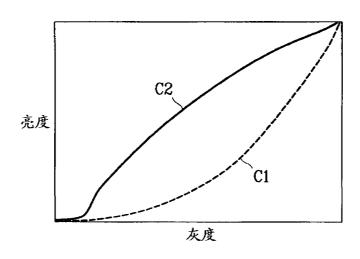

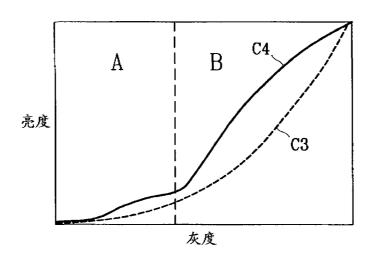

[0028] 图 5 是表示传统图案化垂直配向 (PVA) LCD (patterned-vertically-aligned LCD) 的正视和侧视伽马曲线的曲线图:

[0029] 图 6 是表示根据本发明一实施例的 LCD 的正视和侧视伽马曲线的曲线图;

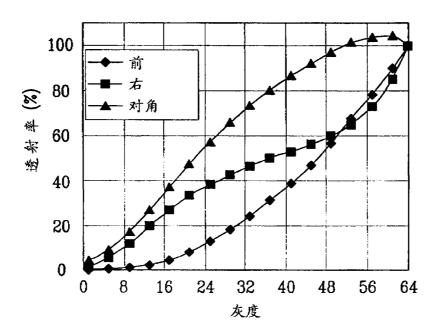

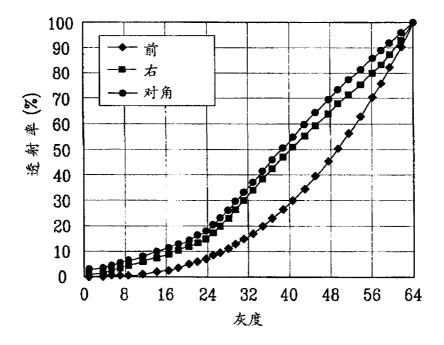

[0030] 图 7 表示常规 PVA 模式 LCD 的实测伽马曲线;以及

[0031] 图 8 表示根据本发明一实施例的 LCD 的实测伽马曲线。

[0032] 具体实施方式

[0033] 下面参照附图更全面地介绍本发明,其中附图中示出了本发明的优选实施例。然而,本发明可以以很多不同的形式实施,并不限于这里所述的实施例。

[0034] 在附图中,为清楚起见放大了层、膜和区域的厚度。相同的标记始终表示相同的部件。应该理解,当如层、膜、区域或基板的元件被称为"在另一元件上"时,它可以直接位于该另一元件上或其间可置入其它元件。相反,当元件被称为"直接位于另一元件上"时,指的是没有中间元件。

[0035] 下面参照附图详细地介绍根据本发明实施例的 LCD。

[0036] 图 1 是根据本发明实施例的 LCD 的像素的等效电路图。

[0037] 参见图 1,根据一实施例的 LCD 包括多个显示信号线  $G_i$ 、 $D_j$  和 131、以及与之连接并基本上排列成矩阵的多个像素。

[0038] 该显示信号线  $G_i$  和  $D_j$  包括输送栅极信号(称为扫描信号)的多个栅极线  $G_i$  和输送数据信号的多个数据线  $D_j$ 。栅极线  $G_i$  基本上在行方向延伸并大致互相平行,数据线  $D_j$  基本上在列方向延伸并大致互相平行。

[0039] 显示信号线 131 还包括位于栅极线  $G_i$  之间以及像素之间并被施以公共电压  $V_{com}$  的

多个存储电极线 131。

[0040] 每个像素  $P_{i,j}$  ( $i=1,2,\ldots,n$ ;  $j=1,2,\ldots,m$ ) 包括一对子像素  $P_{i,j}$  和  $P_{i,j}$  ,每个子像素  $P_{i,j}$  可以  $P_{i,j}$  包括连接到成对的一条栅极线  $P_{i,j}$  和一条数据线  $P_{i,j}$  也的开关元件  $P_{i,j}$  即  $P_{i,j}$  包括连接到成对的一条栅极线  $P_{i,j}$  和一条数据线  $P_{i,j}$  也的开关元件  $P_{i,j}$  即  $P_{i,j}$  包括连接到成对的一条栅极线  $P_{i,j}$  和一条数据线  $P_{i,j}$  和  $P_{i,j}$  和

[0041] 列方向上的两个相邻像素由耦合电容器  $C_{PP}$  容性耦合。例如,像素  $P_{i,j}$  的上部子像素  $P_{i,j}$  与上部像素  $P_{i-1,j}$  的下部子像素  $P_{i,j}$  容性耦合,像素  $P_{i,j}$  的下部子像素  $P_{i,j}$  与下部像素  $P_{i+1,j}$  的上部子像素  $P_{i+1,j}$  容性耦合。

[0042] 开关元件 Q1 或 Q2 具有三个端子:连接到栅极线  $G_1$ - $G_n$ 之一的控制端子;连接到数据线  $D_0$ - $D_m$ 之一的输入端子;和连接到 LC 电容器  $C_{LC1}$  或  $C_{LC2}$ 、存储电容器  $C_{ST1}$  或  $C_{ST2}$ 、以及耦合电容器  $C_{PP}$  的输出端子。

[0043] LC 电容器  $C_{LC1}$  或  $C_{LC2}$  连接在开关元件 Q1 或 Q2 和公共电压 Vcom 之间。存储电容器  $C_{ST1}$  或  $C_{ST2}$  连接在开关元件 Q1 或 Q2 和存储电极线 131 之间。

[0044] 现在参照图 2 至 3C 详细介绍根据本发明实施例的用于 LCD 的 LC 面板组件。

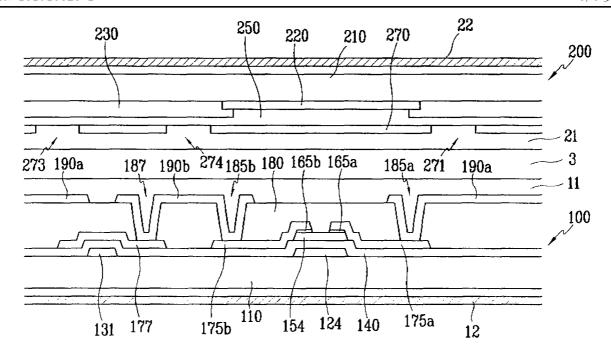

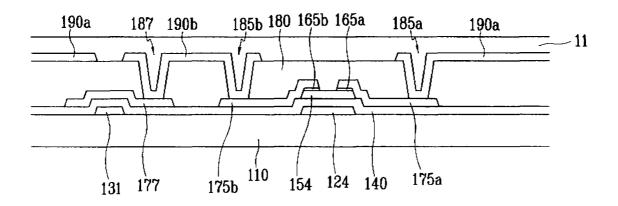

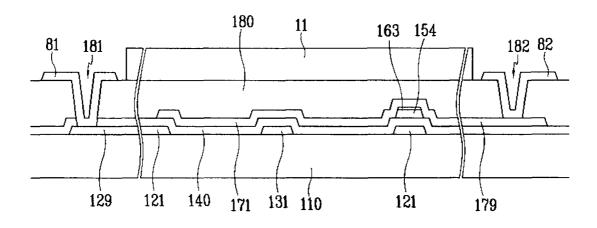

[0045] 图 2 是根据本发明实施例的 LC 面板组件的布局图,图 3A 是沿着线 IIIB-IIIB'截取的图 2 中所示的 LC 面板组件的剖视图,图 3B 是图 3A 中所示的 TFT 阵列面板的剖视图,该图是图 3A 所示 LC 面板组件的除了滤色器阵 列面板和偏振膜之外的部分。图 3C 是沿着线 IIIC-IIIC'截取的图 2 中所示的 TFT 阵列面板的剖视图。

[0046] 参见图 3A,根据本实施例的 LC 面板组件包括 TFT 阵列面板 100、面对 TFT 阵列面板 100 的滤色器阵列面板 200、和置于其间的 LC 层 3。

[0047] 参见图 2 至 3C, TFT 阵列面板 100 包括多个栅极线 121 和多个存储电极线 131,它们都形成在优选由透明玻璃制成的绝缘基板 110 上。每个栅极线 121 基本上在行方向延伸并包括多个栅极电极 124。存储电极线 131 基本上在行方向延伸并部分地弯曲。

[0048] 栅极绝缘层 140 形成在栅极线 121 和存储电极线 131 上,并且多个半导体岛 154 形成在栅极绝缘层 140 上,与栅极电极 124 相对。每个半导体岛 154 优选由非晶硅("a-Si")制成并形成 TFT 的沟道。在半导体岛 154 上形成优选由用 N型杂质如磷(P)重掺杂的 a-Si制成的多个欧姆接触部 163、165a 和 165b。

[0049] 在欧姆接触部 163、165a 和 165b 以及栅极绝缘层 140 上形成多个数据线 171、多对漏极 175a 和 175b 以及多个耦合电极 177。

[0050] 每个数据线 171 基本上在列方向延伸并包括多个源极电极 173,每个源极电极 173 与关于栅极电极 124 分开的一对漏极电极 175a 和 175b 相对设置。

[0051] 每对漏极电极 175a 和 175b 关于栅极线 124 在相反方向延伸。

[0052] 每个耦合电极 177 在列方向延伸并跨过存储电极线 131。

[0053] 半导体岛 154 的位于源极电极 173 和漏极电极 175a 和 175b 之间的部分暴露出来,并且欧姆接触部 163、165a 和 165b 只设置在半导体岛 154 与数据线 171 和漏极 175a 和 175b 之间。

[0054] 钝化层 180 形成在数据线 171、漏极电极 175a 和 175b、以及耦合电极 177 上。钝化层 180 具有露出漏极电极 175a 和 175b 的端部的多个接触孔 185a 和 185b、以及露出耦合电极 177 的端部的多个接触孔 187。钝化层 180 还具有露出数据线 171 的端部 179 的多个接触孔 182,并且钝化层 180 和栅极绝缘层 140 具有露出栅极线 121 的端部 129 的多个接触

孔 181。

[0055] 多对像素电极 190a 和 190b 以及多个辅助接触部 (contact assistant) 81 和 92 形成在钝化层 180 上。像素电极 190a 和 190b 以及辅助接触部 81 和 92 优选由透明导电材料如氧化铟锡 (ITO) 和氧化铟锌 (IZO) 或反光材料 (reflective material) 制成。

[0056] 每对像素电极 190a 和 190b 包括分别通过接触孔 185a 和 185b 连接到漏极 175a 和 175b 的下部像素电极 190a 和上部像素电极 190b。上部电极 190b 通过接触孔 187 连接 到耦合电极 177,下部电极 190a 与耦合电极 177 交叠,使得上部像素的下部像素电极 190a 和下部像素的上部像素电极 190b 容性耦合。此外,上部像素的下部像素电极 190a 和下部像素的上部像素电极 190b 跨过存储电极线 131 相对设置并与存储电极线 131 交叠,以形成多个存储电容器。像素电极 190a 和 190b 跨过存储电极线 131 相对的边缘弯曲以形成 V 字形,并且像素电极 190a 的 V 字形边缘是凸出的,而像素电极 190b 的 V 字形边缘是凹进的。

[0057] 每个下部像素电极 190a 具有上、下和中间线形切口 91-93。中间切口 93 位于列方向的中部并从左向右进入像素电极 190a,由此将像素电极 190a 分割成上和下部分。上切口 91 和下切口 92 分别倾斜地在上和下部分中延伸,并关于中间切口 93 对称地设置。

[0058] 辅助接触部 81 和 82 分别通过接触孔 181 和 182 连接到栅极线 121 和数据线 171 的露出的端部 129 和 179,并且用于保护露出的端部 129 和 179,但这是可选的。

[0059] 配向层 11 涂敷在 TFT 阵列面板 100 的除了辅助接触部 81 和 82 以外的整个表面上。

[0060] 一个栅极电极 124、一个源极电极 173、一对漏极电极 175a 和 175b 以及一个半导体岛 154 形成分别连接像素电极 190a 和 190b 的一对 TFT。

[0061] 参见图 2 和 3A,滤色器阵列面板 200 包括形成在优选由透明玻璃形成的绝缘基板 210 上的黑矩阵 220。黑矩阵 220 限定多个窗口,在窗口中形成多个红、绿和蓝色滤色器 230。在滤色器上形成保护层,并在其上形成公共电极 270。公共电极 270 优选由透明导电材料如 ITO 和 IZO 制成,并具有多组四个线形切口 271-274。切口 271-274 中的三个切口 271-273 与下部像素电极 190a 交叠并与切口 91-93 一起将像素电极 190a 分成多个子区域。具有 V 字形状的切口 274 与上部电极 190b 交叠,以便将上部像素电极 190b 平分 (bisect)成两个子区域。在滤色器阵列面板 200 的整个表面上涂敷配向层 (alignment layer) 21。

[0062] 由切口 91-93 和 271-273 限定的每个子区域大致具有四边形形状,其两 条长边与栅极线 121 和数据线 171 形成约 45 度角。由上部像素电极 190b 和切口 274 的边缘限定的子区域具有由两个四边形组合而成的 V 形。

[0063] 一对偏振板 12 和 22 分别附着在面板 100 和 200 的外表面上。偏振板 12 和 22 的偏振轴交叉并且基本上平行于栅极线 121 或数据线 171。

[0064] LC 层 3 的分子排列成使得在没有电场的情况下它们的主轴基本上垂直于面板 100和 200的表面。

[0065] 再参见图 1,施加给像素的数据电压和公共电压  $V_{com}$ 之间的差表示为 LC 电容器  $C_{LC1}$  或  $C_{LC2}$  的充电电压,即像素电压。 LC 分子的取向取决于像素电压的幅度,并且该取向确定了通过 LC 电容器  $C_{LC1}$  或  $C_{LC2}$  的光的偏振。偏振板 11 和 21 将光的偏振化转变为光的透射率。

[0066] 同时,假设用于像素  $P_{up}$  的数据电压和公共电压  $V_{com}$  之间的差为  $d_{up}$ ,且在像素  $P_{up}$  的上部和下部子像素  $P_{up}^1$  和  $P_{up}^2$  的 LC 电容器  $C_{LC1}$  和  $C_{LC2}$  中充电的像素电压分别是  $V(P_{up}^1)$  和

$V(P^2_{up})$ 。此外,我们假设像素  $P_{up}$  的下部子像素  $P^2_{up}$  和像素  $P_{down}$  的上部子像素  $P^1_{down}$  通过耦合电容器  $C_{pp}$  耦合,并且用于像素  $P_{down}$  的数据电压和公共电压  $V_{com}$  之间的差为  $d_{down}$ 。此外,在给像素  $P_{up}$  输送数据电压之后,给像素  $P_{down}$  输送数据电压。则满足下列关系式:

[0067]

$$V(P_{up}^1) = d_{up}; \pi$$

(1)

[0068]

$$V(P_{up}^2) = d_{up} + \frac{C_{pp}}{C_{LC2} + C_{ST2} + C_{pp}} \cdot (d_{down} - d'_{down})$$

(2)

[0069] 在等式 1 和 2 中, $C_{LC2}$  和  $C_{ST2}$  是下部子像素  $P^2_{up}$  的 LC 电容器和存储电容器的电容, $C_{pp}$  是耦合电容器的电容,并且  $d'_{down}$  是施加于在先帧中的子像素  $P^1_{down}$  的数据电压和公共电压  $V_{com}$  之间的差。为便于说明,忽略了数据线  $D_i$  的导线电阻和信号延迟。

[0070] 在等式 2 中,如果由于  $d_{up}$  和  $d_{down}$  具有相同极性而使  $d_{down}$  和  $d'_{down}$  具有相反的极性,像素  $P_{down}$  显示与像素  $P_{up}$  相同的灰度,并且显示的图像是静止图像,则  $d_{up} = d_{down}$  =  $-d'_{down}$ , 且等式 2 变为:

$$[0071] V(P_{up}^2) = d_{up} + \frac{2d_{up}C_{PP}}{C_{LC2} + C_{ST2} + C_{PP}} = \frac{C_{LC2} + C_{ST2} + 3C_{PP}}{C_{LC2} + C_{ST2} + C_{PP}} d_{up} = T_1 d_{up}, \quad (3)$$

[0072]

$$\sharp +, T_1 = \frac{C_{LC2} + C_{ST2} + 3C_{PP}}{C_{LC2} + C_{ST2} + C_{PP}} > 1.$$

[0073] 相反,如果  $d_{up}$  和  $d_{down}$  具有相反极性,像素  $P_{down}$  显示与像素  $P_{up}$  相同 的灰度,并且显示的图像是静止图像,则等式 2 变为:

[0074]

$$V(P_{up}^{2}) = d_{up} - \frac{2d_{up}C_{PP}}{C_{LC2} + C_{ST2} + C_{PP}} = \frac{C_{LC2} + C_{ST2} - C_{PP}}{C_{LC2} + C_{ST2} + C_{PP}} d_{up} = T_{2}d_{up}, \quad (4)$$

[0075]

$$\sharp +, T_2 = \frac{C_{LC2} + C_{ST2} - C_{PP}}{C_{LC2} + C_{ST2} + C_{PP}} < 1.$$

[0076] 根据等式 3 和 4,如果像素  $P_{up}$  的下部子像素  $P_{up}^2$  与像素  $P_{down}$  的上部子像素  $P_{down}^1$  容性耦合,则在施加于两个子像素  $P_{up}^2$  和  $P_{down}^1$  的数据电压的极性相同时,用比在像素  $P_{up}$  的上部子像素  $P_{up}^1$  中充电的电压高的电压给像素  $P_{up}$  的下部子像素  $P_{up}^2$  充电,当极性相反时则反之。

[0077] 像素包括两个开关元件和两个 LC 电容器并且相邻像素通过耦合电容器容性耦合的这种像素结构防止了底部观察时灰度的倒置,并提高了所有方向上的可见度。

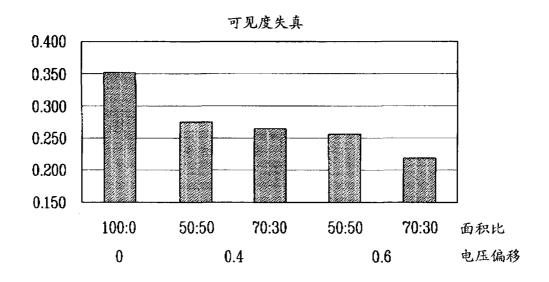

[0078] 图 4 是表示作为像素电极的电压偏移和面积比的函数的可见度失真 (distortion in the visibility) 的曲线。

[0079] 图 4 中所示的垂直轴表示量化可见度失真的值,并且水平轴表示对于 0、0.4V 和 0.6V 电压偏移的下部和上部像素电极 190a 和 190b 之间的面积比 (areal ratio)。

[0080] 在 0.1-0.2 范围内的可见度失真意味着可见度特别优异,其等价于阴极射线管 (CRT)的水平,而在 0.2-0.25 范围内的可见度失真意味着可见度很优异。在 0.25-0.3 范围内的可见度失真意味着可见度优异,并且在 0.3-0.35 范围内的可见度失真意味着可见度良好。然而,小于约 0.35 的可见度失真意味着可见度差,这将导致不良的显示质量。

[0081] 从图 4 中可知, 当下部像素电极与上部像素电极的面积比在 50 : 50 到 80 : 20 范

围内时,且当电压偏移在接近于阈值电压  $V_{th}$  的 0. 4-1. 0V 范围内时,可获得优异的可见度。即,下部像素电极优选设计成比上部像素电极大。然而,当下部像素电极等于或大于 80%时,由于回扫电压 (kickback voltage) 或其它因素而可能产生各种问题,如闪烁现象。此外,当下部像素电极的阈值电压  $V_{th}$  比上部像素电极的阈值电压  $V_{th}$  优 0. 4-1. 0V 时,提高了可见度。下部和上部像素电极之间的用于更高灰度的电压差可以更大。

[0082] 然后,下面参照图 5 和 6 说明根据本发明的 LCD 的可见度提高的原因。

[0083] 图 5 是表示分别对于传统图案化垂直配向 (PVA) LCD 的正向观察和 侧向观察的伽马曲线 C1 和 C2 的曲线图,图 6 是表示分别对于根据本发明实施例的 LCD 的正向观察 (front view) 和侧向观察 (lateral view) 的伽马曲线 C3 和 C4 的曲线图。

[0084] 如图 5 所示,对于一个像素具有一个像素电极的传统 PVALCD 的侧向伽马曲线 C2 与正向伽马曲线 C1 相比大大地向上变形。

[0085] 然而,根据本发明的实施例,当建立数据电压使得施加于下部子像素的像素电压低于通常的数据电压时,对于低一些的灰度,下部子像素的电压可保持低于阈值电压 $V_{th}$ 。相应地,下部子像素可保持在黑色状态,而上部子像素呈现透射状态,如图 6 中的附图标记 A所示。然而,由于上部像素电极的面积小,因此总亮度小于传统 LCD 的总亮度。对于等于或大于预定值的灰度(由附图标记 B所示),下部子像素的电压超过阈值电压  $V_{th}$ ,因此下部子像素也对总亮度起作用。因此,取决于灰度增加的亮度的增加增大了。因而,如图 6 所示,伽马曲线的失真变小。

[0086] 图 7 示出了传统 PVA 模式 LCD 的实测的伽马曲线,图 8 表示根据本发明实施例的 LCD 的实测伽马曲线。

[0087] 比较图 7 和 8 所示的伽马曲线,可知根据本发明实施例的 LCD 的所有方向的伽马曲线失真小于传统 LCD 的所有方向的伽马曲线失真。

[0088] 如上所述,一个像素配置两个像素电极和两个 TFT,并且相邻两个像素的两个像素电极容性耦合,由此提高了所有方向的可见度。此外,由于进行区域分割使得液晶分子的平均定向器 (average director)与栅极线或数据线成 45 度角,所以可以使用具有平行于栅极线或数据线的偏振轴的偏振板。因而,可以降低制造偏振板的成本。

[0089] 虽然前面已经详细说明了本发明的优选实施例,但是应该清楚理解,对本领域普通技术人员显然的、对此处所教导的基本发明原理的诸多改变和/或修改仍为所附权利要求所限定的本发明的精神和范围所涵盖。

图 1

图 2

图 3A

图 3B

图 3C

图 4

图 5

图 6

图 7

图 8

| 专利名称(译)        | 液晶显示器                                                                                                                                                                                                     |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | CN101916020B                                                                                                                                                                                              | 公开(公告)日 | 2012-05-02 |

| 申请号            | CN201010247342.5                                                                                                                                                                                          | 申请日     | 2003-06-28 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                  |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                  |         |            |

| 当前申请(专利权)人(译)  | 三星电子株式会社                                                                                                                                                                                                  |         |            |

| [标]发明人         | 宋长根                                                                                                                                                                                                       |         |            |

| 发明人            | 宋长根                                                                                                                                                                                                       |         |            |

| IPC分类号         | G02F1/1362 G02F1/1333 G02F1/1368 G02F1/1343                                                                                                                                                               |         |            |

| CPC分类号         | G02F2001/134318 G02F1/13439 G02F1/13624 G02F1/136213 G02F1/133707 G02F1/133345 G02F1 /133514 G02F1/133528 G02F1/134309 G02F1/136286 G02F1/1368 G02F2001/133531 G02F2001 /134345 G02F2201/121 G02F2201/123 |         |            |

| 代理人(译)         | 张波                                                                                                                                                                                                        |         |            |

| 审查员(译)         | 张帆                                                                                                                                                                                                        |         |            |

| 优先权            | 1020020036979 2002-06-28 KR                                                                                                                                                                               |         |            |

| 其他公开文献         | CN101916020A                                                                                                                                                                                              |         |            |

| 外部链接           | Espacenet SIPO                                                                                                                                                                                            |         |            |

### 摘要(译)

本发明公开一种液晶显示器,其包括:第一基板;多个像素,至少一个 所述像素分别包括设置在所述第一基板上位于同一层的第一像素电极和 第二像素电极;面对所述第一基板的第二基板;以及置于所述第一基板 和所述第二基板之间的液晶层,其中,所述第一像素电极和所述第二像 素电极每一个上的液晶层被分割成多个畴,且施加给所述第一像素电极 的电压不同于施加给所述第二像素电极的电压,其中,在俯视的情况 下,所述畴的液晶分子的方向向多条第一信号线倾斜。