# [19] 中华人民共和国国家知识产权局

# [12] 发明专利说明书

专利号 ZL 200510052507.2

[51] Int. Cl.

G02F 1/136 (2006.01)

G02F 1/133 (2006.01)

H01L 29/786 (2006.01)

G09G 3/36 (2006.01)

[45] 授权公告日 2008 年 8 月 13 日

[11] 授权公告号 CN 100410789C

「22] 申请日 2005.2.28

[21] 申请号 200510052507.2

[30] 优先权

[32] 2004. 7.28 [33] JP [31] 2004 – 220263

[73] 专利权人 富士通株式会社

地址 日本神奈川县

共同专利权人 友达光电股份有限公司

[72] 发明人 镰田豪 笹林贵 上田一也

吉田秀史

[56] 参考文献

US2001/0033354A 2001.10.25

US6400427B1 2002.6.4

JP10 - 213812A 1998. 8. 11

CN1470924A 2004.1.28

CN1129035A 1996. 8. 14

CN1460880A 2003.12.10

审查员 安 蕾

[74] 专利代理机构 隆天国际知识产权代理有限公

司

代理人 张龙哺 张浴月

权利要求书1页 说明书31页 附图37页

#### [54] 发明名称

液晶显示器及其防止影像残留的方法

#### [57] 摘要

本发明提供一种液晶显示器及其防止影像残留的方法。 其中,直接连接至薄膜晶体管的子像素电极,位子电容性耦接至控制电极的浮置子像素电极与栅极总线之间,以防止电荷从栅极总线注入到该浮置子像素电极。 此外,电连接至辅助电容总线的屏蔽图案形成在辅助子像素电极和数据总线之间。该屏蔽图案避免电荷从数据总线注入到该浮置子像素电极。

1. 一种液晶显示器, 其特征在于包括:

第一和第二基板,彼此相对设置:

液晶,密封在该第一和第二基板之间;

栅极总线和数据总线,形成在该第一基板上;

薄膜晶体管,连接至该栅极总线和该数据总线:

多个子像素电极,形成在由该栅极总线和该数据总线所限定的像素区域中;以及

控制电极,电容性耦接至该多个子像素电极中的至少一个,并且通过该薄膜晶体管从该数据总线施加显示电压到该控制电极,

其中,该液晶显示器包括屏蔽构件,用以电屏蔽在该电容性耦接至该控制电极的子像素电极与该栅极总线和该数据总线中的至少一个之间的连接, 以及

其中,该屏蔽构件是该多个子像素电极中连接至该薄膜晶体管的一个。

2. 根据权利要求1所述的液晶显示器,

其中,用作该屏蔽构件的该子像素电极围绕该电容性耦接至该控制电极的子像素电极。

3. 根据权利要求1所述的液晶显示器,还包括:

辅助电容总线,保持恒定电势,并且电容性耦接至该控制电极以构成辅助电容。

4. 根据权利要求 3 所述的液晶显示器,

其中,该屏蔽构件电连接至该辅助电容总线。

5. 根据权利要求 4 所述的液晶显示器,

其中, 该屏蔽构件与所述子像素电极形成在同一层上。

6. 根据权利要求 3 所述的液晶显示器,

其中,该多个子像素电极中连接至该薄膜晶体管的两个,位于该电容性耦接至该控制电极的子像素电极和该栅极总线之间,以作为该屏蔽构件,以及

电连接至该辅助电容总线的屏蔽构件,位于该电容性耦接至该控制电极的子像素电极和该数据总线之间。

# 液晶显示器及其防止影像残留的方法

# 技术领域

本发明涉及一种在一个像素区域中包含多个子像素电极的液晶显示器 及其防止影像残留(image sticking)的方法。更特别地,本发明涉及这样一 种液晶显示器,其中至少一个液晶子像素电极与控制电极电容性耦接,显示 电压被施加至该控制电极,以及防止这种液晶显示器的影像残留的方法。

## 背景技术

与阴极射线管(CRT)相比,液晶显示器具有薄、轻以及低电压驱动性能和低功耗的优点。因此,液晶显示器被用于各种电子设备中,包括电视、笔记本个人计算机(PC)、台式 PCs,个人数字助理(PDA)、移动电话等等。特别是有源矩阵液晶显示器,其设置有薄膜晶体管(TFT)作为各个像素(子像素)的开关元件,表现出几乎比得上因高驱动性能产生的 CRT 那样优异的显示特性。因此,有源矩阵液晶显示器现今已用于传统上应用 CRT 的各种领域,如台式 PC 和电视。

通常,液晶显示器包括两个基板和密封在这些基板之间的液晶。在一个基板上为各个像素形成像素电极、TFT等。同时,在另一个基板上形成与像素电极相对的彩色滤光片以及各个像素共用的公共电极。彩色滤光片包括红(R)、绿(G)和蓝(B)三种,这些颜色中的一种颜色的彩色滤光片被设置在每个像素处。彼此相邻设置的红(R)、绿(G)和蓝(B)三种像素共同构成一个像素。在本说明书中,包含形成像素电极和TFT的基板以后称为TFT基板,而与TFT基板相对设置的基板以后称为相对基板。此外,通过把液晶密封在TFT基板和相对基板之间所形成的结构以后称为液晶面板。

通常,扭曲向列(TN)液晶显示器已被广泛应用,其构成为在两个基板之间密封水平排列型液晶(具有正介电常数各向异性的液晶)并使液晶分子扭曲排列。然而,扭曲向列液晶显示器具有视角特性差的缺点,即从斜向观看屏幕时对比度与色调(color tone)会显著改变。因此,

具有良好视角特性的多域垂直排列(MVA)液晶显示器已经被研发出来并投入实际应用中。

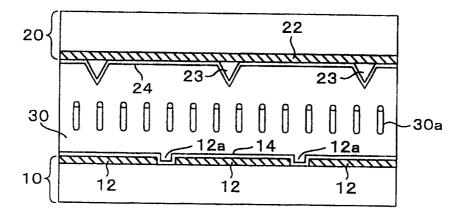

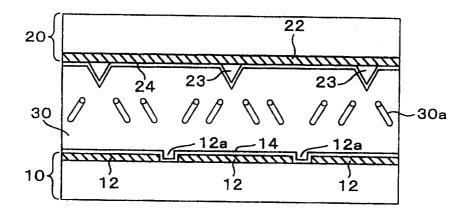

图 1A 和 1B 是显示 MVA 液晶显示器实例的示意剖面图。TFT 基板 10 和相对基板 20 夹着衬垫 (未示出)的同时彼此相对设置,并且垂直排列型液晶 (具有负介电常数各向异性的液晶)密封在这些基板 10 和 20 之间。TFT 基板 10 上的像素电极 12 设置有缝隙 (slit) 12a,用作域调节结构,以在施加电压时确定液晶分子倾斜的方向。像素电极 12 的表面覆盖例如由聚酰亚胺制成的垂直配向膜 (alignment film) 14。

在相对基板 20 的公共电极 22 下方形成多个丘状的突起 23,作为域调节结构。如图 1A 所示,这些突起 23 设置在相对于基板 10 上的缝隙 12a 沿斜向偏移的位置处。公共电极 22 和突起 23 的表面上也覆盖例如由聚酰亚胺制成的垂直配向膜 24。

偏光板(未示出)分别置于 TFT 基板 10 之下和相对基板 20 之上。放置这些偏光板是为了设置相互正交的吸收轴。

在具有上述结构的 MVA 液晶显示器中, 当像素电极 12 和公共电极 22 之间没有施加电压时, 大多数液晶分子 30a 垂直于基板的表面排列。但是, 在突起 23 附近的液晶分子 30a 垂至于突起 23 的倾斜表面排列。在这种情况下, 从 TFT 基板 10 的底部经偏光板进入到液晶层的光被传输通过液晶层, 而不改变偏振的方向, 然后被相对基板 20 上的其他偏光板屏蔽。简而言之, 在这种情况下获得了黑屏。

当在像素电极 12 和公共电极 22 之间施加给定电压时,由于电场的影响液晶分子 30a 倾斜于基板表面排列。在这种情况下,如图 1B 所示,在每个缝隙 12a 或每个突起 23 的两侧的液晶分子 30a 的倾斜方向不同。以这种方式,获得所谓的排列划分(或多区域)。当如图 1B 所示液晶分子 30a 倾斜于基板表面排列时,从 TFT 基板 10 的底部经偏光板进入到液晶层的光改变了偏振方向,并被传输通过相对基板 20 之上的偏光板。传输通过偏光板的光的量取决于施加在像素电极 12 和公共电极 22 之间的电压。

在 MVA 液晶显示器中,如图 1B 所示,由于在施加电压时每个缝隙 12a 或每个突起 23 的两侧的液晶分子 30a 的倾斜方向不同。因而,在倾斜方向上的光的泄漏得到抑制,而获得优秀的视角特性。

尽管以上实例解释了突起和缝隙构成域调节结构的情况,但是也存在基板表面上的凹陷(沟槽)用作域调节结构的情况。此外,尽管图 1A 和 1B 描述了 TFT 基板 10 和相对基板 20 上都形成域调节结构的实例,也可以仅在 TFT 基板 10 和相对基板 20 其中之一上形成域调节结构。

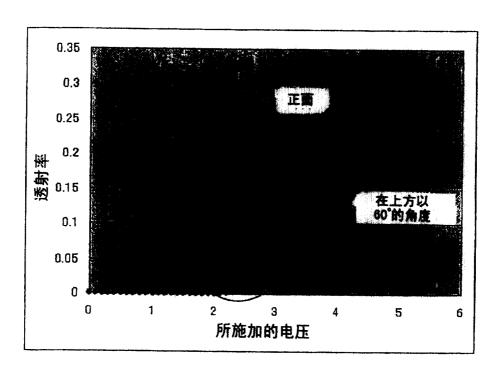

顺便提及,传统 MVA 液晶显示器导致从斜向观看时屏幕看起来略微发白的现象。图 2 示出了从正面观看屏幕时的透射率一所施加的电压(T-V)特性和从上方 60°角观看屏幕时的 T-V 特性,其中横轴表示施加的电压(V),纵轴表示透射率。如图 2 所示,当施加略微高于阈值电压的电压(图中被圆环围绕的区域)时,从斜向观看屏幕时的透射率高于从正面观看屏幕时的透射率。相反,当施加的电压增加到一定水平时,从斜向观看屏幕时的透射率变为低于从正面观看屏幕时的透射率。因此,从斜向观看屏幕时,红色像素、绿色像素和蓝色像素之间在亮度上的差异减小,从而,出现如前述的发白(whiter)屏幕的现象。这种现象称为淡化(wash out)。淡化不仅会出现在MVA 液晶显示器中,而且会出现在 TN 液晶显示器中。

美国专利 No.4840460 的说明书中公开了一种把一个像素划分成多个子像素并使子像素电容性耦接的技术。在这种液晶显示器中,取决于各个子像素之间的电容比来划分电势。因此,可以对各个子像素施加不同的电压量。因此,就 T-V 特性而言,一个像素呈现出包括具有不同阈值的多个区域。当就 T-V 特性而言一个像素包括具有不同阈值的多个区域时,可以抑制从斜向观看屏幕时的透射率高于从正面观看屏幕时的透射率的现象,由此,抑制发白屏幕(淡化)的现象。上述通过把一个像素分成多个电容性耦接的子像素来改善显示特性的方法就是所谓的运用电容性耦接半色调灰度(halftone gray scale,HT)方法。注意在美国专利 No.4840460 中公开的液晶显示器是 TN液晶显示器。

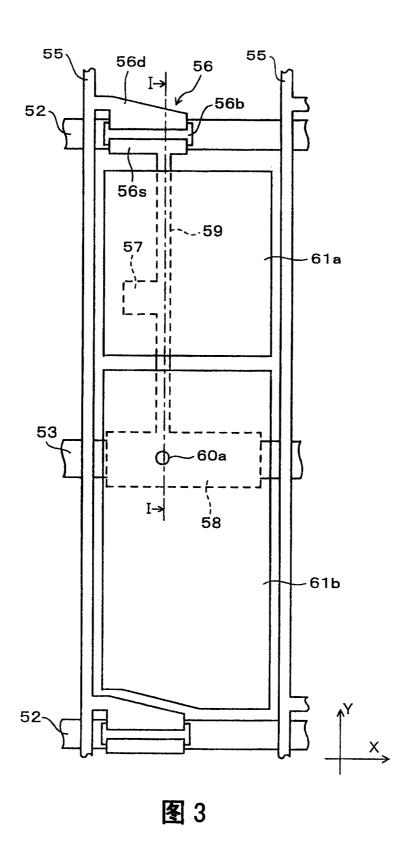

图 3 是配置为实现运用电容性耦接的 HT 方法的液晶显示器中的 TFT 基板的实例的平面图,以及图 4 是沿图 3 中的 I-I 线截取的剖面图。

在构成 TFT 基板的基础的玻璃基板 51 上,形成多条沿水平方向(X 方向)延伸的栅极总线 52 和多条沿垂直方向(Y 方向)延伸的数据总线(漏极总线)55。由栅极总线 52 和数据总线 55 限定的矩形区域构成每个像素区域。同时,在玻璃基板 51 上,形成辅助电容总线 53,其平行于栅极总线 52

设置并穿过各个像素区域的中心。

在每条栅极总线 52 和每条数据总线 55 之间的空间以及每条辅助电容总线 53 和每条数据总线 55 之间的空间,形成第一绝缘膜 54。通过利用该第一绝缘膜 54,栅极总线 52 和数据总线 55 之间以及辅助电容总线 53 和数据总线 55 之间分别电绝缘。

在每个像素区域中形成薄膜晶体管(TFT)56、控制电极57、辅助电容电极58以及子像素电极61a和61b。如图3所示,TFT56使用部分栅极总线52作为栅极电极。此外,如图4所示,构成TFT56有源层的半导体膜56a形成在栅极总线52上方,以及沟道保护膜56b形成在此半导体膜56a上。

TFT56 的漏极电极 56d 连接至数据总线 55, 而源极电极 56s 设置在与漏极电极 56d 相对的位置处,同时把栅极总线 52 夹在中间。此外,辅助电容电极 58 形成在与辅助电容总线 53 相对的位置处,同时把第一绝缘膜 54 夹在中间。此外,如图 3 所示,控制电极 57 通过导线 59 电连接至源极电极 56s 和辅助电容电极 58。

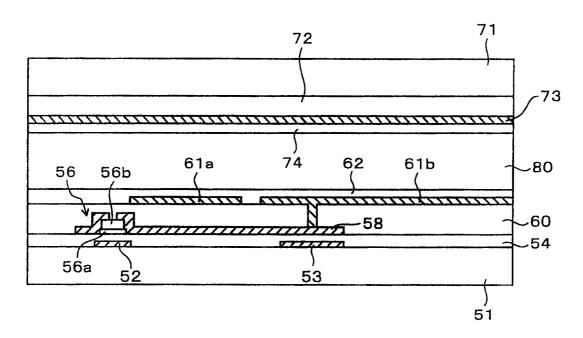

数据总线 55、TFT 56、控制电极 57、辅助电容电极 58 和导线 59 覆盖有第二绝缘膜 60,并且子像素电极 61a 和 61b 形成在第二绝缘膜 60 上。子像素电极 61a 电容性耦接至控制电极 57,同时把第二绝缘膜 60 夹在中间。同时,子像素电极 61b 通过接触孔 60a 电连接至辅助电容电极 58,该接触孔 60a 形成在第二绝缘膜 60 上。子像素电极 61a 和 61b 的表面覆盖有配向膜 62。

同时,如图 4 所示,相对基板包括:形成在构成基础的玻璃基板 71 的一个表面上(图 4 的下侧)的彩色滤光片 72,在彩色滤光片 72 上形成的公共电极 73,以及覆盖公共电极 73 表面的配向膜 74。

TFT 基板和相对基板彼此相对设置,同时中间夹着衬垫(未示出)。然后,液晶 80 被密封在 TFT 基板和相对基板之间。

在透射式液晶显示器的情况下,子像素电极 61a 和 61b 是由透明导电材料例如铟锡氧化物 (ITO) 制成。另一方面,在反射式液晶显示器的情况下,子像素电极 61a 和 61b 由高反射材料例如铝制成。

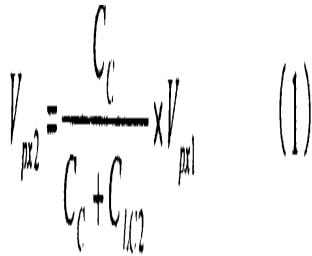

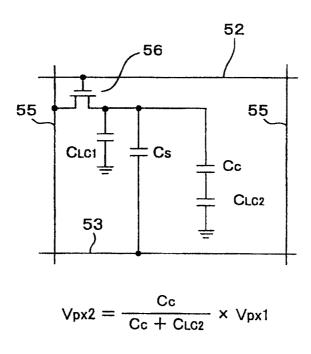

图 5 是示出包括上述 TFT 基板的液晶显示器中一个像素的等效电路图。 在图 5 中, 附图标记 C<sub>LC1</sub> 表示由子像素电极 61b 和公共电极 73 构成的电容, 附图标记 C<sub>S</sub>表示由辅助电容电极 58 和辅助电容总线 53 构成的电容, 附图 标记  $C_{C}$ 表示由子像素电极 61a 和控制电极 57 构成的电容,以及附图标记  $C_{LC2}$  表示由子像素电极 61a 和公共电极 73 构成的电容。如图 5 所示,电压被子像素电极 61a 和公共电极 73 之间形成的电容  $C_{LC2}$  和控制电容  $C_{C}$  分担。因此,当施加至子像素电极 61b 上的电压为  $V_{px1}$  时,则施加至子像素电极 61a 上的电压  $V_{px2}$  通过以下公式(1)算出:

$$V_{px2} = \frac{C_C}{C_C + C_{1C2}} \times V_{px1}$$

(1)

尽管实际电压比( $V_{px2}/V_{px1}$ )对于液晶显示器的显示特性而言为设计的项目,但是电压比在近似从 0.6-0.8 的范围内被视为理想的。

通过电容性耦接被施加显示电压的子像素电极例如子像素电极 61a,以下被称为浮置子像素电极。同时,通过低电阻导体(例如导线)电连接至 TFT 的子像素电极例如子像素电极 61b,以下被称为直接连接至 TFT 的子像素电极。

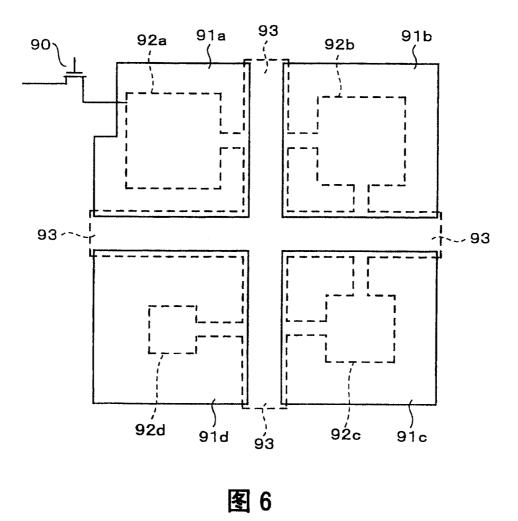

如图 6 所示,日本专利 No.3076938 的说明书(等同于日本待审专利公开 No.5(1993)-66412)中公开了一种 TN 液晶显示器,其中,像素电极被分成多个(在图 6 中为四个)子像素电极 91a 至 91d,以及控制电极 92a 至 92d 通过绝缘膜分别设置在子像素电极 91a 至 91d 之下。在这种液晶显示器中,显示电压通过 TFT 90 被施加至控制电极 92a-92d。由于各个控制电极 92a-92d 的尺寸互不相同,要施加在子像素电极 91a-91d 上的电压也互不相同。因此,可以获得 HT 方法所可以产生的效果,也就是抑制淡化的效果。这里,为了避免光从任意子像素电极 91a 至 91d 之间的空间泄漏,另一个控制电极 93 也设置在任意子像素电极 91a 至 91d 之间的空间中。

然而,本发明的发明人已经进行了实验和研究,并发现包括上述传统浮置子像素电极的液晶显示器由于影像残留(image sticking)而导致显示特性的退化。

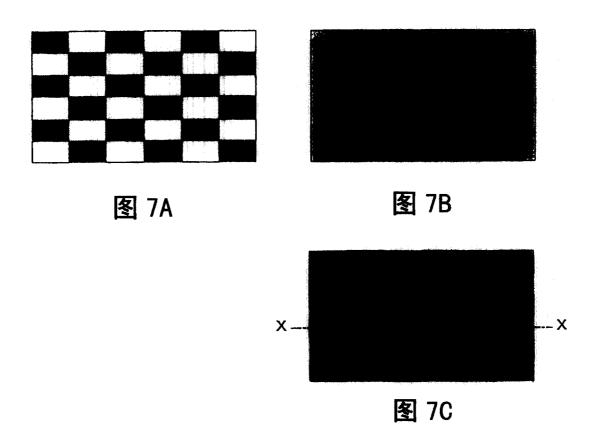

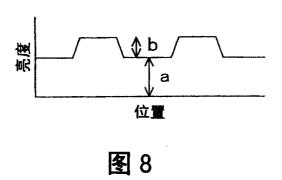

图 7A 至图 7C 和图 8 是显示测量图像阻延程度的测试方法的示意图。首先,如图 7A 所示的黑白检测图案持续在液晶显示器上显示一定期间。之后,在整个液晶显示器的屏幕上显示如图 7B 所示的半色调图案。在这种情况下,当屏幕上出现影像残留时,检测图案明显变暗,如图 7C 所示。在从检测图案显示切换到半色调显示之后,沿图 7C 中的 X-X 线测量亮度。然后,假设

在黑暗部分出的亮度为"a",而在黑暗部分和明亮部分之间的亮度差为"b",如图 8 所示,计算由 100×b/(a+b) 定义的影像残留比。

根据上述方法来测量不包括浮置子像素电极的液晶显示器的影像残留比,以及包括浮置子像素电极的液晶显示器的影像残留比。结果不包括浮置子像素电极的液晶显示器的影像残留比等于或小于 5%。相反,包括浮置子像素电极的液晶显示器的影像残留比等于或大于 10%。

# 发明内容

考虑以上问题,本发明的目的是提供一种运用电容性耦接的 HT 方法来 抑制淡化的液晶显示器,其能够防止影像残留的发生,并且提供一种防止影像残留的方法。

上述问题通过一种液晶显示器可得到解决,该液晶显示器包括:第一和第二基板,彼此相对设置;液晶,密封在该第一和第二基板之间;栅极总线和数据总线,形成在该第一基板上;薄膜晶体管,连接至该栅极总线和该数据总线所限定的像素区域中;以及控制电极,电容性耦接至所述多个子像素电极中的至少一个,并且通过该薄膜晶体管从该数据总线施加显示电压到该控制电极。这里,该液晶显示器包括屏蔽构件,用以电屏蔽电容性耦接至该控制电极的该子像素电极与至少该栅极总线和该数据总线中至少一个之间的连接,该屏蔽构件是多个子像素电极中连接至薄膜晶体管的一个。

在本发明中,电容性耦接至该控制电极的该子像素电极与至少该栅极总 线和该数据总线中任一个之间的连接,例如被连接至辅助电容总线的屏蔽构 件电屏蔽,该辅助电容总线保持恒定的电势。以这种方式,通过使用屏蔽构 件屏蔽电容性耦接至该控制电极的子像素电极,可以避免电荷从栅极总线或 从数据总线注入到子像素电极。结果,可防止影像残留。

直接连接至 TFT 的子像素也可用作屏蔽构件。例如,通过在电容性耦接 至控制电极的子像素电极与栅极总线之间,设置直接连接至 TFT 的子像素电 极,可以避免电荷从栅极总线注入到电容性耦接至控制电极的子像素电极。

上述问题通过一种防止液晶显示器上影像残留的方法可得到解决,该液晶显示器包括:第一和第二基板,彼此相对设置:液晶,密封在该第一和第

二基板之间;栅极总线和数据总线,形成在该第一基板上;薄膜晶体管,连接至该栅极总线和该数据总线;多个子像素电极,形成在由该栅极总线和该数据总线所限定的像素区域中;控制电极,电容性耦接至所述多个子像素电极中的至少一个,并且通过该薄膜晶体管从该数据总线施加显示电压到该控制电极;以及公共电极,形成在该第二基板上,并且与该第一基板上的多个子像素电极相对。这里,假设相对于该公共电极的电势该数据总线的中心电势为 $V_{gdc}$ ,电容性耦接至该控制电极的子像素电极与该数据总线之间的电阻为 $R_D$ ,以及电容性耦接至该控制电极的子像素电极与该栅极总线之间的电阻为 $R_G$ ,该方法包括设置电容性耦接至该控制电极的子像素电极的位置和形状以满足 $V_{ddc}$ - $V_{gdc}$ × $R_D/R_G$ 近似等于零的步骤。

为了保持 TFT 处于关状态,在一个帧期间的多数时间内施加负电压到栅极总线。同时,为了通过电压补偿反馈,正直流电压与数据总线上流动的信号选加。因此,可以通过设置子像素电极(电容性耦接至控制电极的子像素电极)的位置和形状来防止影像残留,以使得在数据总线上流动的信号的直流电压成分(即相对于公共电极的电势数据总线的中心电势)的影响和在栅极总线上流动的信号的直流电压成分(即相对于公共电极的电势栅极总线的中心电势)的影响相互抵消,即满足  $V_{ddc}$ - $V_{edc}$ × $R_D/R_G$ 近似等于零。

上述问题通过一种液晶显示器可得到解决,该液晶显示器包括:第一和第二基板,彼此相对设置;液晶,密封在该第一和第二基板之间;栅极总线和数据总线,形成在该第一基板上;薄膜晶体管,连接至该栅极总线和该数据总线所限定的像素区域中;控制电极,电容性耦接至所述多个子像素电极中的至少一个,并且通过该薄膜晶体管从该数据总线施加显示电压到该控制电极;以及公共电极,形成在该第二基板上,并且与该第一基板上的多个子像素电极相对。这里,电容性耦接至该控制电极的子像素通过电阻电连接至与该薄膜晶体管连接的子像素电极。

在本发明中,电容性耦接至控制电极的子像素电极(浮置子像素电极),通过例如由多晶硅制成的高电阻电阻连接至直接连接至薄膜晶体管的子像素电极。以这种方式,降低浮置子像素电极和控制电极之间的电阻值,并且

降低保持在液晶层中的直流电压,由此,防止影像残留的发生。但是,如果电阻的电阻值太低,则电流会在浮置子像素电极和直接连接至 TFT 的子像素电极之间流动,从而电势差降低。由此,防止淡化的效果会下降。

上述问题通过一种液晶显示器可得到解决,该液晶显示器包括:第一和第二基板,彼此相对设置;液晶,密封在该第一和第二基板之间;栅极总线和数据总线,形成在该第一基板上;薄膜晶体管,连接至该栅极总线和该数据总线:多个子像素电极,形成在由该栅极总线和该数据总线:多个子像素电极,形成在由该栅极总线和该数据总线流力。全个子像素电极,电容性耦接至所述多个子像素电极中的至少一个,并且通过该薄膜晶体管从该数据总线施加显示电压到该控制电极;以及辅助电容总线,保持恒定的电势,并与该控制电极的支控制电极。这里,该液晶显示器包括被与该薄膜晶体管连接的栅极总线不同的栅极总线上流动的信号驱动的开关元件,该开关元件设置在电容性耦接至该控制电极的子像素电极与连接至该薄膜晶体管的子像素电极之间的位置中的任一位置处。

在本发明中,开关元件位于浮置子像素电极与辅助电容总线之间或者位于浮置子像素电极与直接连接至薄膜晶体管的子像素电极之间,并且开关元件被与连接至薄膜晶体管的栅极总线不同的栅极总线上流动的信号驱动。以这种方式,在给定计时浮置子像素电极中充入的电荷,会在辅助电容总线上或者直接连接至 TFT 的子像素电极上流动,由此防止影像残留的发生。

上述问题通过一种防止液晶显示器上影像残留的方法可得到解决,该液晶显示器包括:第一和第二基板,彼此相对设置;液晶,密封在该第一和第二基板之间;栅极总线和数据总线,形成在该第一基板上;薄膜晶体管,连接至该栅极总线和该数据总线;多个子像素电极,形成在由该栅极总线和该数据总线所限定的像素区域中;控制电极,电容性耦接至所述多个子像素电极中的至少一个,并且通过该薄膜晶体管从该数据总线施加显示电压到该控制电极;辅助电容总线,保持恒定的电势,并与该控制电极一起构成辅助电容;以及公共电极,形成在该第二基板上,并且与该第一基板上的多个子像素电极相对。这里,该方法包括形成与一电容并联的第二辅助电容的步骤,该电容是电容性耦接至该控制电极的子像素电极和该公共电极之间的电容。

在白色显示部分和黑色像素部分之间浮置子像素电极出现电势差的原因之一是液晶电容的变化。由此,在本发明中,与液晶电容并联形成第二辅助电容,以降低液晶电容的变化带来的影响。

通常,辅助电容总线保持与公共电极相同的电势或相对于公共电极保持 恒定的电势。因此,例如,当在浮置子像素电极与辅助电容总线之间形成辅 助电容电极并且该辅助电容电极连接至该浮置子像素电极时,相当于形成与 液晶电容并联的第二辅助电容。以这种方式,可以避免影像残留的发生。

## 附图说明

图 1A 和图 1B 是显示 MVA 液晶显示器的实例的示意剖面图。

图 2 为示出当从正面观看液晶显示器的屏幕时透射率-所施加的电压 (T-V) 特性和当从上方 60°角观看该屏幕时的 T-V 特性的坐标图;

图 3 是配置为实现运用电容性耦接的 HT 方法的液晶显示器中 TFT 基板的实例的平面图。

图 4 是沿图 3 中的 I-I 线截取的剖面图。

图 5 是图 3 所示的液晶显示器中一个像素的等效电路图。

图 6 是在日本专利 No.3076938 的说明书中公开的液晶显示器的平面图。

图 7A 至图 7C 是显示测量图像阻延程度的测试方法的示意图(No.1)。

图 8 是显示测量图像阻延程度的测试方法的示意图(No.2)。

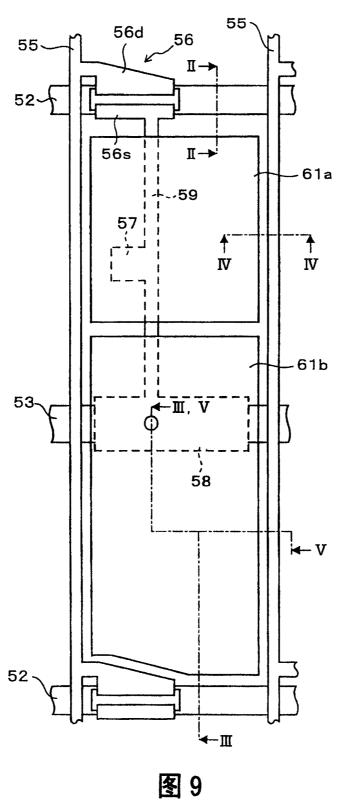

图 9 是显示包括浮置子像素电极的液晶显示器中一个像素的平面图。

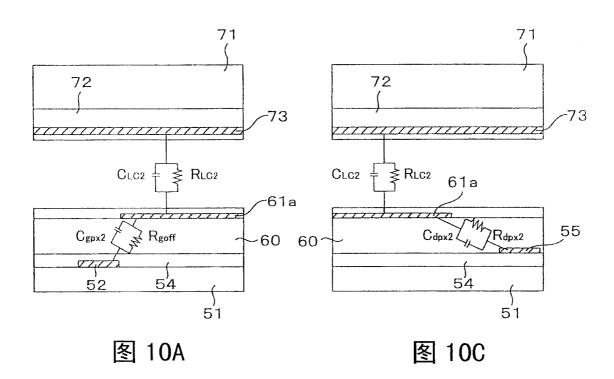

图 10A 是沿图 9 中的 II-II 线截取的示意剖面图,图 10B 是沿图 9 中的 III-III 线截取的示意剖面图,图 10C 是沿图 9 中的 IV-IV 线截取的示意剖面图,图 10D 是沿图 9 中的 V-V 线截取的示意剖面图。

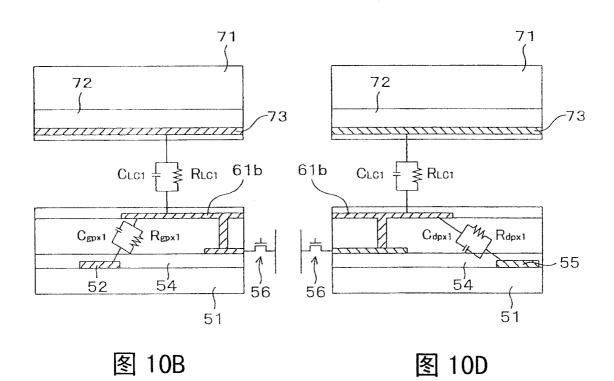

图 11 是包括浮置子像素电极的子像素电极的等效电路图。

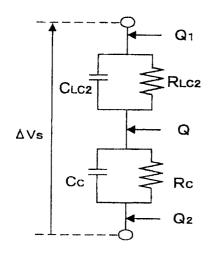

图 12 为示出当施加显示电压到液晶层时(当液晶打开时) $\Delta V_s$  和  $\Delta V_{LC2}$  之间的关系,以及当没有施加显示电压到液晶层时(当液晶关闭时) $\Delta V_s$  和  $\Delta V_{LC2}$  之间的关系的坐标图。

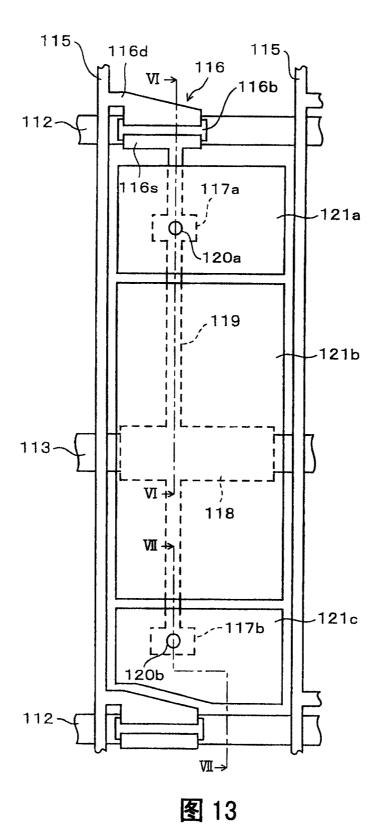

图 13 是显示根据本发明第一实施例的液晶显示器的平面图。

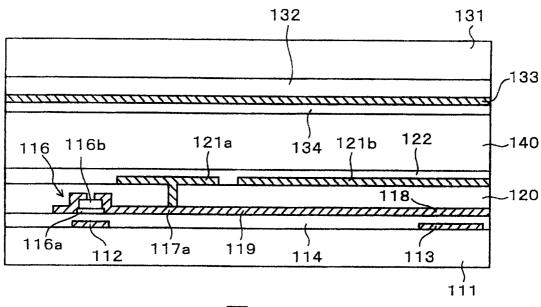

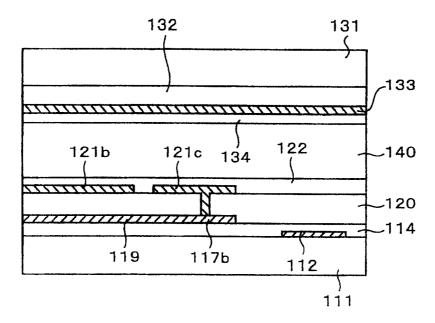

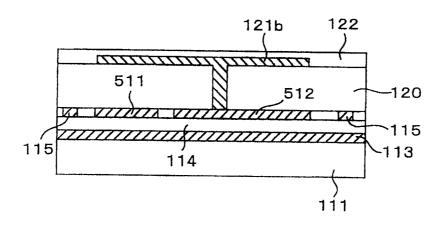

图 14A 是沿图 13 中的VI-VI线截取的剖面图,图 14B 是沿图 13 中的VII-VII线截取的剖面图。

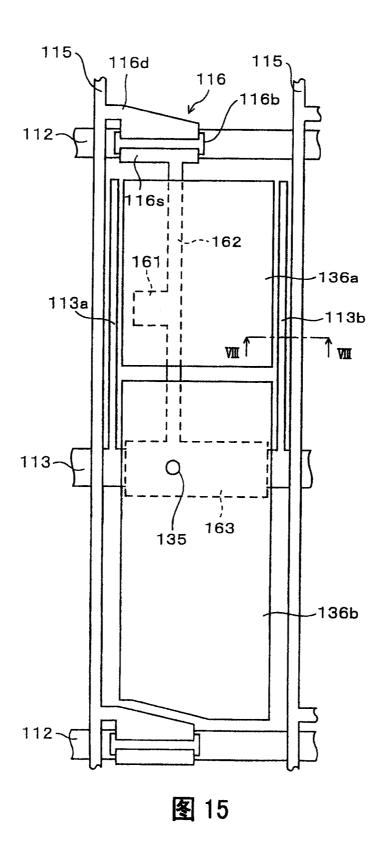

- 图 15 是显示根据第一实施例的第一修改实例的液晶显示器的平面图。

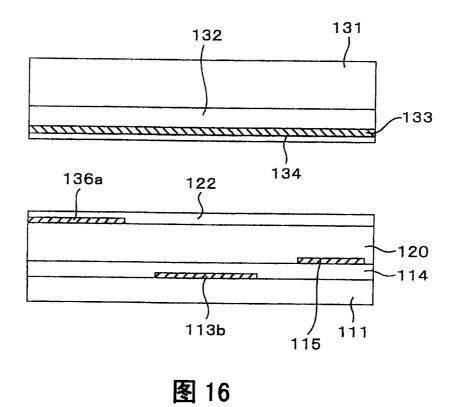

- 图 16 是沿图 15 中的/III-/IIIX线截取的剖面图。

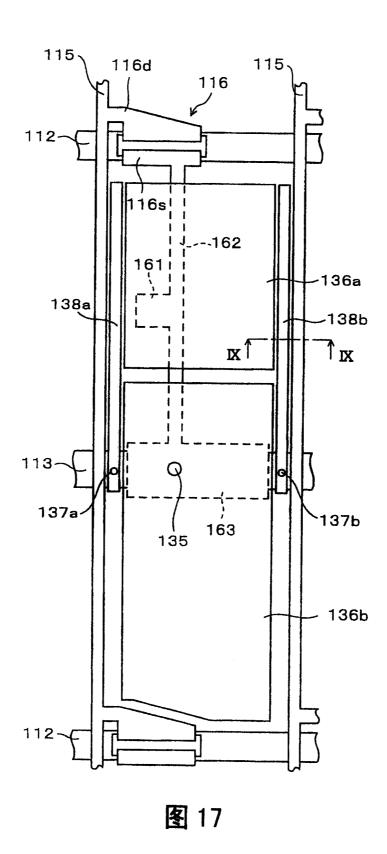

- 图 17 是显示根据第一实施例的第二修改实例的液晶显示器的平面图。

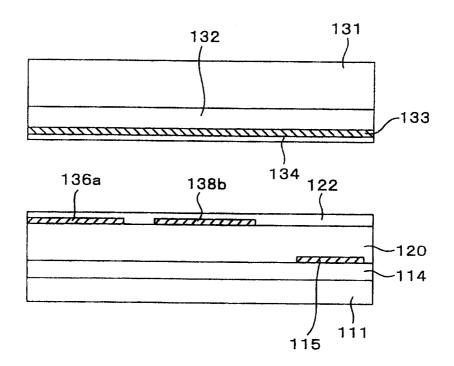

- 图 18 是沿图 17 中的IX-IX线截取的剖面图。

- 图 19 是显示根据第一实施例的第三修改实例的液晶显示器的平面图。

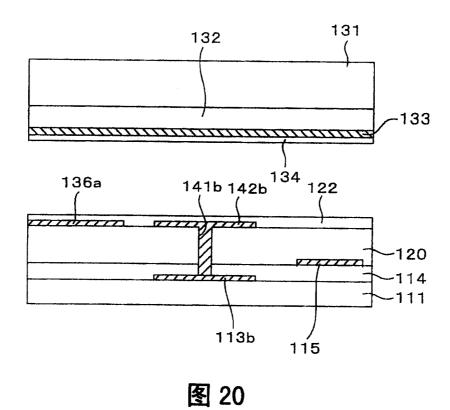

- 图 20 是沿图 19 中的 X-X 线截取的剖面图。

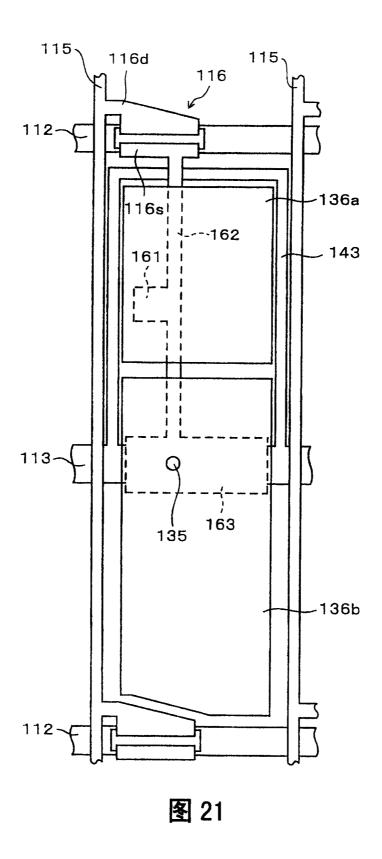

- 图 21 是显示根据第一实施例的第四修改实例的液晶显示器的平面图。

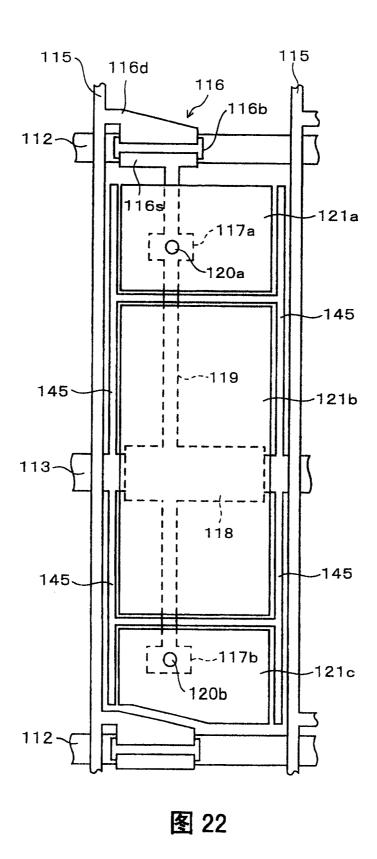

- 图 22 是显示根据第一实施例的第五修改实例的液晶显示器的平面图。

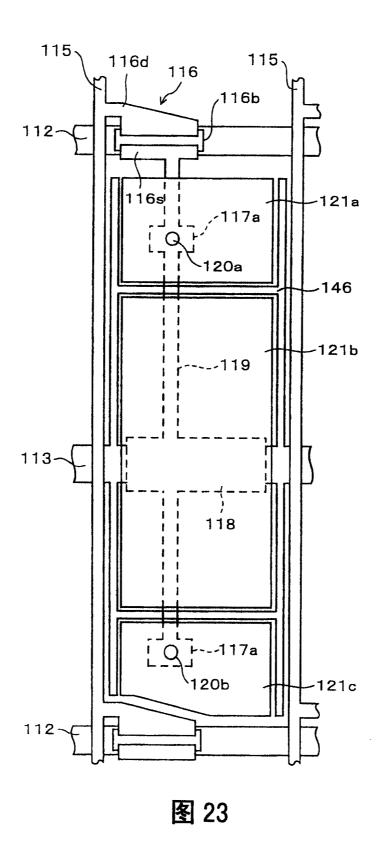

- 图 23 是显示根据第一实施例的第六修改实例的液晶显示器的平面图。

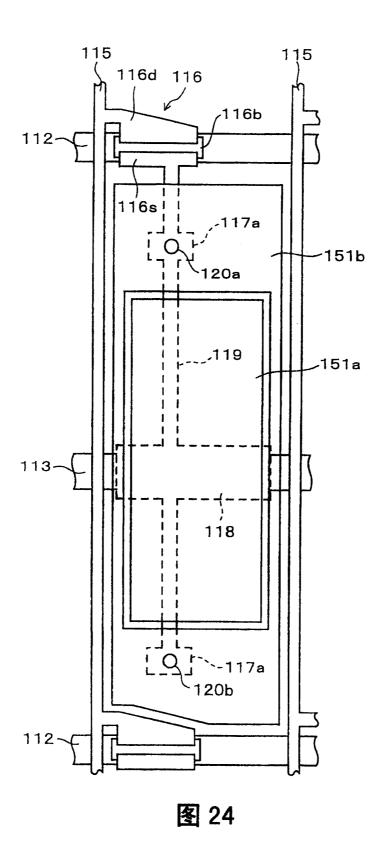

- 图 24 是显示根据第一实施例的第七修改实例的液晶显示器的平面图。

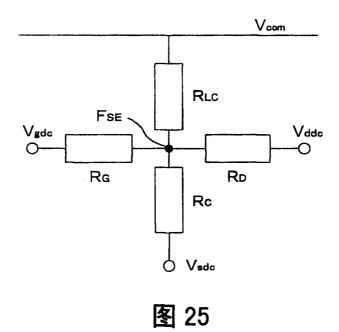

- 图 25 是示出本发明第二实施例的原理的示意图。

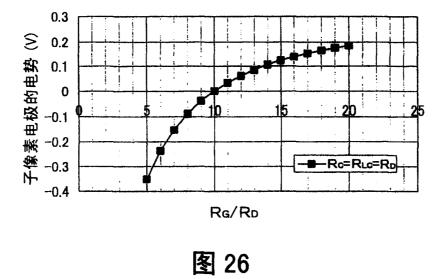

- 图 26 是显示  $R_G/R_D$  和浮置子像素电极的最终获得的电势之间的关系的示意图。

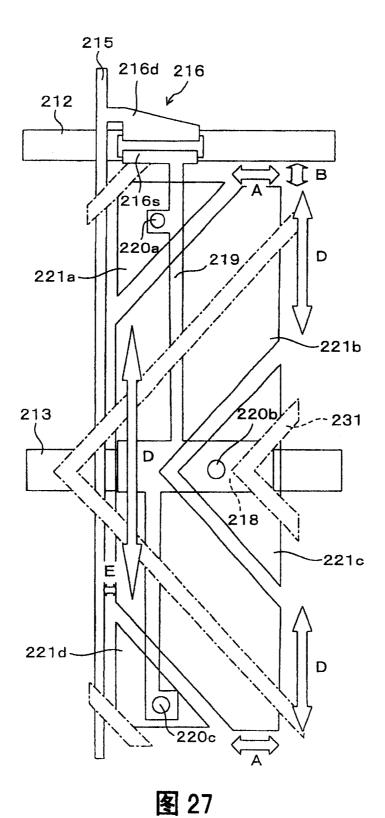

- 图 27 是显示液晶显示器的像素部分的示意平面图,示出了调节浮置子像素电极和栅极总线之间的电阻以及浮置子像素电极和数据总线之间的电阻的方法。

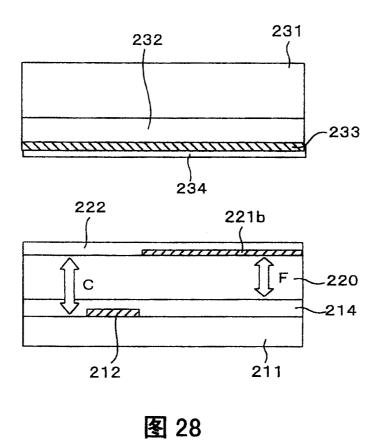

- 图 28 是显示图 27 的像素的示意剖面图。

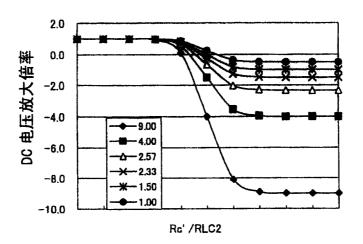

- 图 29 是示出影像残留电压对控制电极和浮置子像素电极之间的电阻  $R_C$ 上以及在浮置子像素电极和公共电极之间的电阻  $R_{LC2}$ 的依赖性 (DC 电压的放大倍率)的计算结果的示意图。

- 图 30 是图 29 所示的结果的表格。

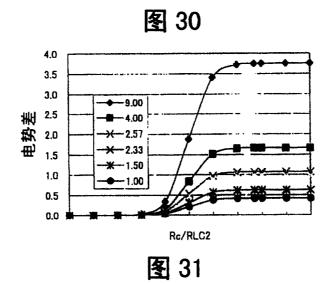

- 图 31 是显示 R<sub>c</sub>/R<sub>LC2</sub> 与子像素电极在白色显示部分和黑色显示部分处的电势差之间的关系的坐标图。

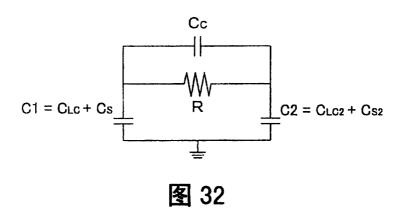

- 图 32 是显示浮置子像素电极和直接连接至 TFT 的子像素的等效电路图。

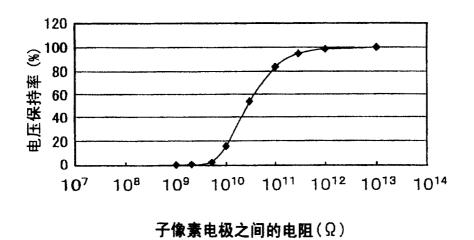

- 图 33 是显示位于浮置子像素电极和直接连接至 TFT 的子像素之间的电阻 R 和在一个帧期间中电压保持率之间的关系的坐标图。

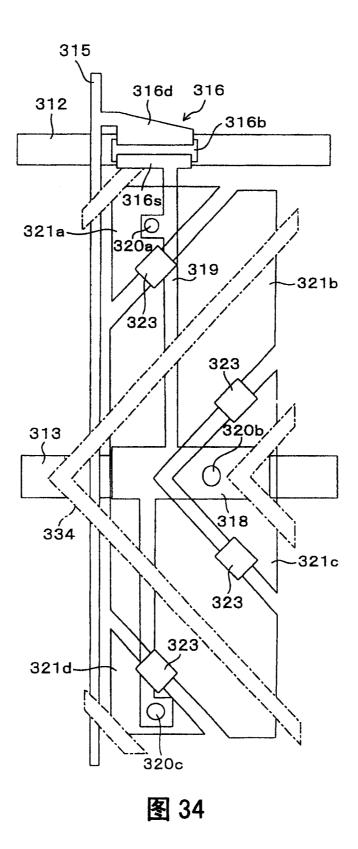

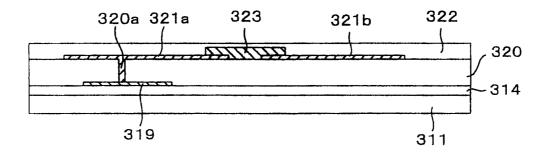

- 图 34 是根据本发明第三实施例的液晶显示器中 TFT 基板的平面图。

- 图 35 是图 34 所示的 TFT 基板的剖面图。

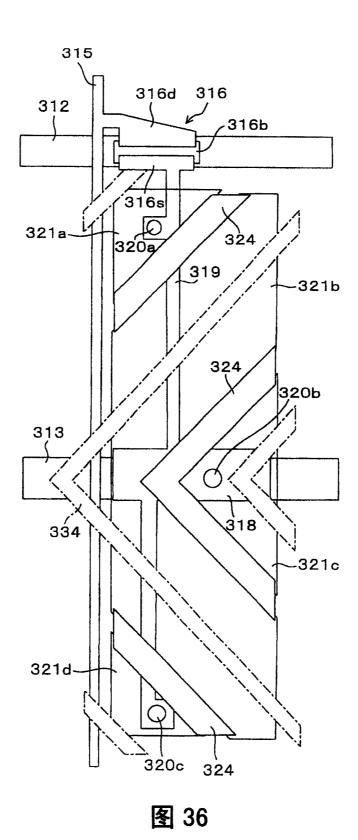

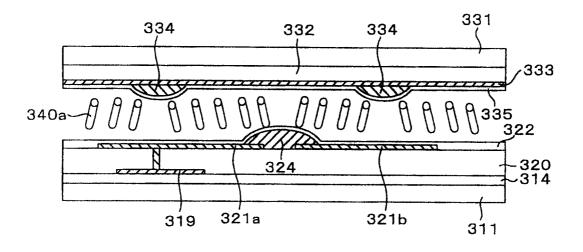

- 图 36 是显示根据第三实施例的第一修改实例的液晶显示器的平面图。

- 图 37 是显示图 36 的液晶显示器的剖面图。

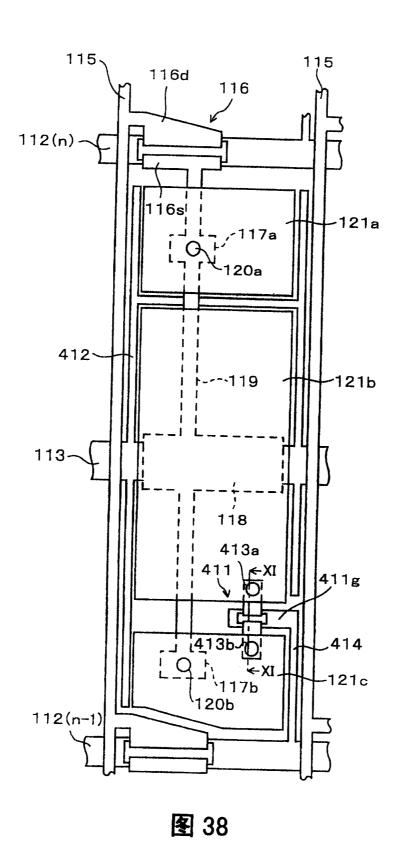

- 图 38 是显示根据本发明的第四实施例的液晶显示器的平面图。

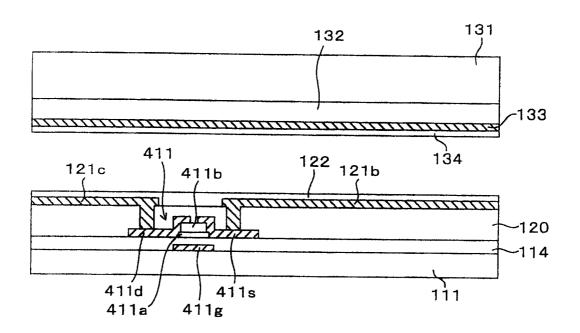

- 图 39 是沿图 38 中的XI-XI线截取的剖面图。

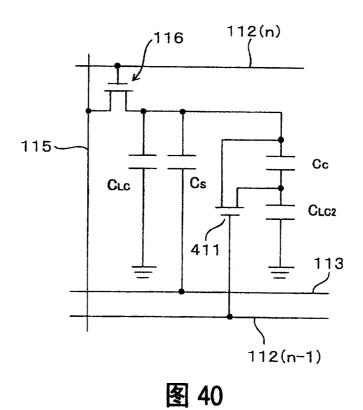

- 图 40 是显示根据第四实施例的液晶显示器中一个像素的等效电路图。

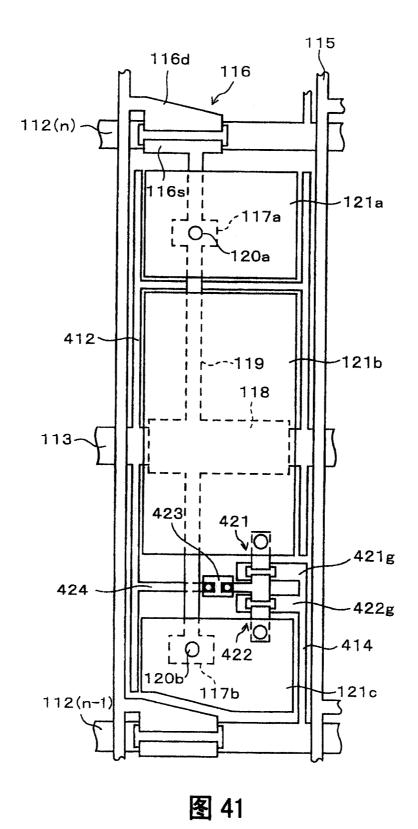

- 图 41 是显示根据第四实施例的第一修改实例的液晶显示器的平面图。

- 图 42 是显示根据第四实施例的第一修改实例的液晶显示器中一个像素的等效电路图。

- 图 43 是显示本发明第五实施例的原理的像素的电路图。

- 图 44 是显示  $R_{C}/R_{LC2}$  和浮置子像素电极在白色显示部分和黑色显示部分的电势差之间的关系的坐标图。

- 图 45 是显示根据第五实施例的液晶显示器的平面图。

- 图 46 是沿图 45 中的XII-XII线截取的剖面图。

# 具体实施方式

下面,进一步详细描述本发明。

通常,液晶显示器上的影像残留可归因于栅极总线、数据总线等上流动的信号中直流电压成分的存在,而结果是液晶层在白色显示模式和黑色显示模式之间 CR 值(液晶电容值和液晶电阻值)的变化。下面,描述在包含浮置子像素电极的液晶显示器中发生影像残留的原因。

图 9 是显示在包含浮置子像素电极的液晶显示器中一个像素的平面图。同时,图 10A 是沿图 9 中的 II-II 线截取的示意剖面图,图 10B 是沿图 9 中的 III-III 线截取的示意剖面图,图 10C 是沿图 9 中的 IV-IV线截取的示意剖面图,图 10D 是沿图 9 中的 V-V线截取的示意剖面图。

在图 9 所示的液晶显示器中,可以认为  $C_{LC2}$  和  $R_{LC2}$  并联连接在子像素电极(浮置子像素电极)61a 和公共电极 73 之间,如图 10A 所示。这里,附图标记  $C_{LC2}$ 表示子像素电极 61a 和公共电极 73 之间的电容,而附图标记  $R_{LC2}$ 表示子像素电极 61a 和公共电极 73 之间的电阻。

此外,也可以认为  $C_{gpx2}$  和  $R_{goff}$  并联连接在子像素电极 61a 和栅极总线 52 之间。这里,附图标记  $C_{gpx2}$  表示子像素电极 61a 和栅极总线 52 之间的电容,而附图标记  $R_{goff}$  表示子像素电极 61a 和栅极总线 52 之间的电阻。

同时,也可以认为 CLC1 和 RLC1 并联连接在子像素电极(直接连接至薄膜

晶体管(TFT)56 的子像素电极)61b 和公共电极 73 之间,如图 10B 所示。这里,附图标记  $C_{LC1}$  表示子像素电极 61b 和公共电极 73 之间的电容, $R_{LC1}$  表示子像素电极 61b 和公共电极 73 之间的电阻。

此外,也可以认为  $C_{gpx1}$  和  $R_{gpx1}$  并联连接在子像素电极 61b 和栅极总线 52 之间。这里,附图标记  $C_{gpx1}$  表示子像素电极 61b 和栅极总线 52 之间的电容,而附图标记  $R_{gpx1}$  表示子像素电极 61b 和栅极总线 52 之间的电阻。

为了保持 TFT 56 在一个场期间内的大部分时间处于关闭状态,比公共电极 73 的电势低-12V 的直流电压(Vgoff)施加至栅极总线 52。对应此直流电压的电荷通过电容 Cpgx2 和电阻 Rgoff 积累在子像素电极 61a 和 61b 中。但是,在每个场内,TFT 56 正常地为打开一次,而使子像素电极 61b 电连接至数据总线 55。因此,在 TFT 56 关闭期间内充入子像素电极 61b 的电荷将向数据总线 55 流动,从而直流电压成分将不再保留在子像素电极 61b 上。相反,即使 TFT 56 打开,充入子像素电极 61a 的电荷仍保持在其中。因此,直流电压成分会保留在子像素电极 61a 中。

如图 10C 所示,可以认为  $C_{dpx2}$ 和  $R_{dpx2}$ 并联连接在子像素电极 61a 和数据总线 55 之间。这里附图标记  $C_{dpx2}$ 表示子像素电极 61a 和数据总线 55 之间的电容,而附图标记  $R_{dpx2}$ 表示子像素电极 61a 和数据总线 55 之间的电阻。

此外,如图 10D 所示,也可以认为  $C_{dpx1}$  和  $R_{dpx1}$  并联连接在子像素电极 61b 和数据总线 55 之间。这里,附图标记  $C_{dpx1}$  表示子像素电极 61b 和数据总线 55 之间的电容,而附图标记  $R_{dpx1}$  表示子像素电极 61b 和数据总线 55 之间的电阻。

为了通过电压补偿反馈,比公共电极 73 的电势高约  $1 \le 2V$  的直流电压与数据总线 55 上的显示信号(交变电流信号)相迭加。对应此直流电压的电荷也通过电容  $C_{dpx2}$  和电阻  $R_{dpx2}$  积累在子像素电极 61a 中。

但是,如上所述,在每个场内 TFT 56 被打开一次,而使子像素电极 61b 电连接至数据总线 55。因此,在 TFT 56 关闭期间内充入子像素电极 61b 的电荷将在 TFT 56 打开时向数据总线 55 流动。因此,直流电压成分将不再保留在子像素电极 61b 上。相反,即使 TFT 56 被打开,充入子像素电极 61a 的电荷将依旧保留在其中。因此,直流电压成分将仍然保留在子像素电极 61a 中。

如上所述,在直接连接至 TFT56 的子像素电极 61b 上几乎看不到直流电压成分的积累的同时,电荷充入浮置子像素电极 61a,从而直流电压成分保留在其中。

接下来,描述充入浮置子像素电极上的电荷和影像残留之间的关系。

图 11 为显示包括浮置子像素电极的子像素电极的等效电路图,这里,控制电极和公共电极之间的直流电压成分被定义为  $\Delta Vs$ ,浮置子像素电极中的电荷量被定义为 Q,公共电极中的电荷量被定义为 Q1,以及控制电极中的电荷量被定义为 Q2。在暂态结束之后,通过以下公式(2a)至(2c)计算处于定态的 Q1、Q2 和 Q 值:

$$Q1 = \frac{R_{LC2}}{R_{LC2} + R_C} \times \Delta Vs \times C_{LC2}$$

(2a)

$$Q2 = \frac{R_C}{R_{LC2} + R_C} \times \Delta Vs \times C_C$$

(2b)

$$Q = Q2 - Q1$$

$$= \frac{-((R_{LC2} \times C_{LC2}) - (R_C \times C_C))}{R_{LC2} + R_C} \times \Delta Vs$$

(2c)

即使去除直流电压成分  $\Delta V_s$ ,在以下公式(3)中所示的  $\Delta V_{LC2}$  将仍保留液晶层中:

$$\Delta V_{LC2} = -Q/Q_{LC2} = \frac{((R_{LC2} \times C_{LC2}) - (R_C \times C_C)}{(R_{LC2} + R_C) \times C_{LC2}} \times \Delta Vs$$

(3)

假设子像素电极的面积是 S而单元厚度为 d,液晶电容  $C_{LC2}$  可表示为  $C_{LC2}$   $=\epsilon$  (S/d)。这里, $\epsilon$  为液晶的介电常数。由于液晶分子垂直于基板表面排列时的介电常数与液晶分子水平排列时的介电常数不同,因此在显示检测图案的白色部分的像素和显示检测图案的黑色部分的像素之间液晶电容值会不同。因此,在这些像素之间,施加至液晶层的直流电压成分  $\Delta V_{LC2}$  值也不同。当检测图案显示切换到半色调显示时,保留在液晶层中的直流电压成分不会立即改变。因此,显示白色的像素和显示黑色的像素具有不同的待施加至液晶层的电压。因此,显示白色的像素的光透射率与显示黑色的像素的光透射率不同,由此引起影像残留。这里,由于上述原因出现的影像残留在与这一时间常数相对应的周期内下降,该时间常数是子像素电极和控制电极或

者公共电极之间的时间常数。但为了提高显示质量,有必要尽可能减少影像 残留。

图 12 是示出当施加显示电压到液晶层时(当液晶打开时) $\Delta V_{LC2}$  之间的关系,以及当没有施加显示电压到液晶层时(当液晶关闭时) $\Delta V_{S}$  和  $\Delta V_{LC2}$  之间的关系的坐标图,其中,横轴表示控制电极和公共电极之间的直流电压成分  $\Delta V_{S}$  ,而纵轴表示保留在液晶层中的直流电压成分  $\Delta V_{LC2}$ 。这里,应该注意,图 12 中的数字是基于具有图 9 所示结构的液晶显示器计算得到的,在该结构中,像素间距设置为 125 $\mu m$ ,电容性耦接至控制电极 57 的子像素电极 61a 和电连接至 TFT 56 的子像素电极 61b 之间的面积比设置为 3 至 7,以及在施加至子像素电极(浮置子像素电极)61a 的显示电压和施加至子像素电极(直接连接至 TFT 的子像素电极)61b 的显示电压的比率设置为 0.72。

从图 12 可明显看出,高于控制电极和公共电极之间的直流电压成分 ΔVs 几倍的电压被施加在液晶层。因此,即使降低控制电极和公共电极之间的直流电压成分 ΔVs,也会限制抑制影像残留的效果。

本发明的发明人认为为防止影像残留,很必要应用任一以下对策。

- (1)通过在这种总线和浮置子像素电极之间的电屏蔽,来抑制在浮置子像素电极上电荷的积累,该总线(例如栅极总线或数据总线)允许包含直流电压成分的信号在其上流动。

- (2)在栅极总线上流动的信号包含的直流电压成分具有与在数据总线上流动的信号包含的直流电压成分相反的偏振。因此,浮置子像素电极和栅极总线之间的电阻以及浮置子像素电极和数据总线之间的电阻被优化,从而这两个直流电压成分的影响可彼此消除。

- (3)当浮置子像素电极和控制电极之间的电阻降低时,保留在液晶层中的直流电压成分也降低。然而,如果浮置子像素电极和控制电极之间的电阻大幅降低时,可以获得抑制淡化的效果。因此,浮置子像素电极和控制电极之间的电阻被优化,以避免引起淡化或影像残留。

- (4)在浮置子像素电极上积累的电荷以固定频率被释放到数据总线、 辅助电容总线等。

- (5) 形成与浮置子像素电极和公共电极之间的电容(液晶电容)并联

辅助电容,以降低液晶电容变化的影响。

下面,描述使用上述对策的本发明优选实施例的液晶显示器。

(第一实施例)

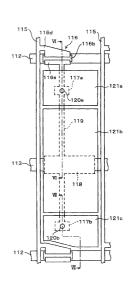

图 13 是显示根据本发明第一实施例的液晶显示器的平面图。同时,图 14A 是沿图 13 中的VII-VI线截取的剖面图,图 14B 是沿图 13 中的VII-VII线截取的剖面图。

在构成 TFT 基板的基础的玻璃基板 111 上,形成多条沿水平方向(X方向)延伸的栅极总线 112 和多条沿垂直方向(Y方向)延伸的数据总线 115。由栅极总线 112 和数据总线 115 限定的矩形区域构成像素区域。同时,在玻璃基板 111 上,形成辅助电容总线 113,其与栅极总线 112 平行设置并穿过各个像素区域的中心。

在每条栅极总线 112 和每条数据总线 115 之间的空间以及每条辅助电容总线 113 和每条数据总线 115 之间的空间形成由绝缘材料例如 SiN 或 SiO<sub>2</sub>制成的第一绝缘膜 114。通过利用该第一绝缘膜 114,栅极总线 112 和数据总线 115 之间以及辅助电容总线 113 和数据总线 115 之间分别电绝缘。

在每个像素区域中形成 TFT 116、连接电极 117a 和 117b、控制电极 118、及由透明材料例如 ITO 制成的子像素电极 121a 至 121c。控制电极 118 与辅助电容总线 113 和第一绝缘膜 114 一起构成辅助电容电极。如图 13 所示,TFT 116 使用部分栅极总线 112 作为栅极电极。此外,如图 14A 所示,构成TFT 116 有源层的半导体膜 116a 形成在栅极总线 112 上方,以及沟道保护膜116b 形成在此半导体膜 116a 上。

TFT 116 的漏极电极 116d 连接至数据总线 115,源极电极 116s 设置在此位置,在那里,源极电极 116s 与漏极电极 116d 相对,同时把栅极总线 112 夹在中间。此外,控制电极 118 形成在此位置,在那里,控制电极 118 与辅助电容总线 113 相对,同时把第一绝缘膜 114 夹在中间。连接电极 117a 设置在子像素电极 121a 的下面,而连接电极 117b 设置在子像素电极 121c 的下面。连接电极 117a 和 117b 以及控制电极 118 通过导线 119 连接至源极电极 116s。

数据总线 115、TFT 116、连接电极 117a 和 117b、控制电极 118、和导线 119 覆盖有由 SiN、绝缘树脂等制成的第二绝缘膜 120。此外,子像素电

极 121a 至 121c 形成在此第二绝缘膜 120 上。如图 13 所示,子像素电极 (浮置子像素电极) 121b 设置在像素区域的中心处,并且电容性耦接至控制电极 118。同时,子像素电极 121a 设置在子像素电极 121b 和其上方的栅极总线 112 之间,并且子像素电极 121c 设置在子像素电极 121b 和其下方的栅极总线 112 之间。这些子像素电极 121a 和 121c 通过接触孔 120a 和 120b、连接电极 117a 和 117b 以及导线 119 电连接至 TFT 116 的源极电极 116s。此外,子像素电极 121a 至 121c 的表面覆盖有例如由聚酰亚胺制成的配向膜 122。

这里,例如依照光刻方法,通过图案化 Cr 膜或 Al-Ti 层叠膜而同时形成 栅极总线 112 和辅助电容总线 113。同时,例如依照光刻方法,通过图案化 Ti-Al-Ti 层叠膜而同时形成数据总线 115、源极电极 116s、漏极电极 116d 以及控制电极 118。

同时,如图 14A 和图 14B 所示,相对基板包括形成在构成基础的玻璃基板 131 的一个表面(在图 14A 和图 14B 中是下侧)上的彩色滤光片 132,在 彩色滤光片 132 的表面上形成的公共电极 133 以及覆盖公共电极 133 表面的配向膜 134。例如,公共电极 133 由透明导电材料如 ITO 制成,配向膜 134 由聚酰亚胺制成。

TFT基板和相对基板在设置有配向膜的表面向内放置的同时彼此相对设置,并且在中间夹着间隔层的同时结合在一起。然后,液晶 140 被密封在 TFT 基板和相对基板之间。

在具有上述结构的第一实施例的液晶显示器中,子像素电极 121a 和 121c 电连接至 TFT 116,并且由此在 TFT 116 打开时连接至数据总线 115。因此,即使在 TFT 116 关闭期间,由于栅极总线 112 上流动信号的直流电压成分而在子像素电极 121a 和 121b 中积累电荷,在 TFT 116 打开期间电荷会流向数据总线 115,由此避免了电荷的积累。因此,在这些子像素电极 121a 和 121b 中不会出现影像残留。

同时,电容性耦接至控制电极 118 的子像素电极 (浮置子像素电极) 121b 远离栅极总线 112,并且子像素电极 121a 和 121c 介于子像素电极 121b 和栅极总线 112 之间。因此,由于在栅极总线 112 上流动的信号的直流电压成分而在浮置子像素电极 121b 上积累的电荷非常少。以这种方式,可以避免影像残留的出现并获得最佳的显示品质。

#### (第一修改实例)

图 15 是显示根据第一实施例的第一修改实例的液晶显示器的平面图, 而图 16 是沿图 15 中的WI-VII线截取的剖面图。就图 15 和图 16 来说,与图 13、图 14A 和图 14B 中所示相同的部件由相同的附图标记表示,并且省略其详细描述。

在图 15 和图 16 所示的第一修改实例的液晶显示器中,在一个像素中设置两个子像素电极 136a 和 136b。此外,控制电极 161 设置在子像素电极 136a 之下,同时把第二绝缘膜 120 夹在中间,以及子像素电极 136a 电容性耦接至控制电极 161。

辅助电容电极 163 设置在辅助电容总线 113 之上,并且此辅助电容电极 163 通过接触孔 135 电连接至子像素电极 136b。同时,辅助电容电极 163 和 控制电极 161 通过导线 162 电连接至 TFT 116 的源极电极 116s。

此外,从辅助电容总线 113 延伸出来的屏蔽图案 113a 和 113b 设置在子像素电极 136a 和数据总线 115 之间。辅助电容总线 113 保持与公共电极 133 的电势相同的电势,或者保持相对于公共电极 133 的电势恒定的电势。

在此第一修改实例的液晶显示器中,保持与辅助电容总线 113 的电势相同的电势的屏蔽图案 113a 和 113b 设置在浮置子像素电极 136a 和数据总线 115 之间。因此,由于任一个数据总线 115 上流动的信号的直流电压成分引起的在浮置子像素电极 136a 中电荷的积累得到抑制。以这种方式,这种液晶显示器可发挥出抑制影像残留的效果。

# (第二修改实例)

图 17 是显示根据第一实施例的第二修改实例的液晶显示器的平面图,而图 18 是沿图 17 中的IX-IX线截取的剖面图。就图 17 和图 18 而言,与图 15 和图 16 中所示相同的部件由相同的附图标记表示,并且省略其详细描述。

在图 17 和图 18 所示的第二修改实例的液晶显示器中,与子像素电极 136a 形成在同一层上的屏蔽图案 138a 和 138b,设置在浮置子像素电极 136a 和数据总线 115 之间。这些屏蔽图案 138a 和 138b 通过分别在第一和第二绝缘膜 114 和 120 上形成的接触孔 137a 和 137b 电连接至辅助电容总线 113。 类似于第一修改实例的液晶显示器,辅助电容总线 113 保持与公共电极 133 的电势相同的电势,或者保持相对于公共电极 133 的电势恒定的电势。

在图 15 和图 16 所示的第一修改实例的液晶显示器中,屏蔽图案 113a 和 113b 形成在比数据总线 115 和子像素电极 136a 更低的层上。相反,在第二修改实例的液晶显示器中,屏蔽图案 138a 和 138b 与子像素电极 136a 形成在同一层上。因此,在第二修改实例的液晶显示器中,第一绝缘膜 114 的电阻成分不存在了。因此,第二修改实例的液晶显示器比第一修改实例的液晶显示器具有更大的保护子像素电极 136a 不受数据总线 115 影响的效果。以这种方式,第二修改实例的液晶显示器能够比第一修改实例的液晶显示器更可靠地避免影像残留。

#### (第三修改实例)

图 19 是显示根据第一实施例的第三修改实例的液晶显示器的平面图, 而图 20 是沿图 19 中的 X-X线截取的剖面图。就图 19 和图 20 而言,与图 15 和图 16 中所示相同的部件由相同的附图标记表示,并且省略其详细描述。

在图 19 和图 20 所示的第三修改实例的液晶显示器中,从辅助电容总线 113 的延伸出来的屏蔽图案 113a 和 113b 以及与子像素电极 136a 形成在同一层的屏蔽图案 142a 和 142b,设置在浮置子像素电极 136a 和数据总线 115 之间。屏蔽图案 142a 和 142b 通过分别在第一和第二绝缘膜 114 和 120 上形成的接触孔 141a 和 141b 电连接至屏蔽图案 113a 和 113b。

在第三修改实例的液晶显示器中,同样,屏蔽图案 113a、113b、142a 和 142b 形成在浮置子像素电极 136a 和数据总线 115 之间。因此,可以抑制由于任一个数据总线 115 上流动的信号的直流电压成分引起的在浮置子像素电极 136a 中电荷的积累,由此避免影像残留。

# (第四修改实例)

图 21 是显示根据第一实施例的第四修改实例的液晶显示器的平面图。 就图 21 来说,与图 15 中所示相同的部件由相同的附图标记表示,并且省略其详细描述。

在图 21 中所示的第四修改实例的液晶显示器中,屏蔽图案 143 围绕浮置子像素电极 136a,该屏蔽图案 143 与辅助电容总线 113 形成在同一层上并连接至辅助电容总线 113。

在第四修改实例的液晶显示器中,不仅可以屏蔽包含在任一个数据总线 115 上流动的信号中的直流电压成分,而且可以屏蔽包含在任一个栅极总线 112 上流动的信号中的直流电压成分。以这种方式,此液晶显示器可比第一修改实例的液晶显示器更可靠地发挥抑制影像残留的效果。

## (第五修改实例)

图 22 是显示根据第一实施例的第五修改实例的液晶显示器的平面图。 就图 22 来说,与图 13 中所示相同的部件由相同的附图标记表示,并且省略 其详细描述。

在图 22 所示的液晶显示器中,子像素电极 121a 和 121c 位于浮置子像素电极 121b 和栅极总线 112 之间,如在图 22 的上侧和下侧所示出的。这些子像素电极 121a 和 121c 经接触孔 120a 和 121b 通过导线 119 电连接至 TFT 116。同时,在图 22 的右侧和左侧,分别从辅助电容总线 113 延伸出来的屏蔽图案 145 位于浮置子像素电极 121b 和数据总线 115 之间。

在第五修改实例的液晶显示器中,通过子像素电极 121a 和 121c 以及屏蔽图案 145,来屏蔽浮置子像素电极 121b 不受栅极总线 112 和数据总线 115 的影响。由此,此液晶显示器可以发挥抑制由于任意栅极总线 112 和任意数据总线 115 上流动的信号的直流电压成分引起的电荷积累的效果,由此有效地避免影像残留。

此外,在第五修改实例的液晶显示器中,屏蔽图案 145 也位于电连接至 TFT 116 的子像素电极 121a 和 121c 以及数据总线 115 之间。由此,该液晶显示器也具有抑制由于任一数据总线 115 上流动的信号中包含的直流电压成分引起的在子像素电极 121a 和 121c 中电荷的积累。

# (第六修改实例)

图 23 是显示根据第一实施例的第六修改实例的液晶显示器的平面图。 就图 23 来说,与图 22 中所示相同的部件由相同的附图标记表示,并且省略 其详细描述。

在图 23 所示的第六修改实例的液晶显示器中,与辅助电容总线 113 形成在同一层上并且连接至辅助电容总线 113 的屏蔽图案 146,也位于浮置子像素电极 121b 与直接连接至 TFT 116 的子像素电极 121a 和 121c 之间。在第六修改实例的液晶显示器中,也可以抑制由于任意栅极总线 112 和数据总线 115 上流动的信号的直流电压成分引起的电荷积累,从而有效地避免影像残留。

#### (第七修改实例)

图 24 是显示根据第一实施例的第七修改实例的液晶显示器的平面图。 就图 24 来说,与图 13 中所示相同的部件由相同的附图标记表示,并且省略 其详细描述。

在图 24 所示的第七修改实例的液晶显示器中,子像素电极 151b 围绕浮置子像素电极 151a。该子像素电极 151b 通过接触孔 120a 和 120b 以及导线 119 电连接至 TFT 116 的源极电极 116s。

在第七修改实例的液晶显示器中,同样,浮置子像素电极 151a 被屏蔽 免于栅极总线 112 和数据总线 115 的影响。由此,该液晶显示器可发挥抑制 由于任意栅极总线 112 和数据总线 115 上流动的信号的直流电压成分引起的 电荷存储的效果,由此有效地避免影像残留。

## (第二实施例)

下面, 描述本发明的第二实施例。

图 25 是示出本发明第二实施例的原理的示意图。图 25 示出了包括浮置子像素电极 F<sub>SE</sub>、公共电极、控制电极、栅极总线和数据总线的等效电路图。

如图 25 所示,可以认为: 电阻  $R_G$ 存在于浮置子像素电极  $F_{SE}$ 和栅极总线之间,电阻  $R_D$ 存在于浮置子像素电极  $F_{SE}$ 和数据总线之间,电阻  $R_C$ 存在于浮置子像素电极  $F_{SE}$ 和控制电极之间,以及电阻(液晶电阻) $R_{LC}$ 存在于浮置子像素电极  $F_{SE}$ 和公共电极之间。这里,控制电极的电势定义为  $V_{sdc}$ ,公共电极的电势定义为  $V_{com}$ ,在栅极总线上流动的信号的直流电压成分(中心电势)定义为  $V_{gdc}$ ,以及在数据总线上流动的信号的直流电压成分(中心电势)定义为  $V_{ddc}$ 。

如上所述,比公共电极的电势低大约-12V 的直流电压被施加至栅极总线以关闭 TFT。同时,比公共电极的电势高大约+2V 的直流电压选加到数据总线上的显示信号上,以通过电压补偿反馈。与施加至在数据总线上流动的信号的直流电压成分相比,施加至在栅极总线上流动的信号的直流电压成分具有相反的极性。由此,通过将  $V_{ddc}$ 、 $V_{gdc}$ 、 $R_G$ 和  $R_D$ 的值设定为满足以下公式(4),可以防止由于栅极总线和数据总线的直流电压成分引起的浮置子像素电极中电荷的积累的效果,并且最终防止影像残留的发生。

$$V_{ddc} \times R_{G} - V_{gdc} \times R_{D} = 0 \tag{4}$$

通过电势差和电阻,来确定栅极总线上流动的信号的直流电压成分的影响量级和数据总线上流动的信号的直流电压成分的影响量级。然而,电势差  $V_{ddc}$  和  $V_{gdc}$  也和 TFT 的性能等相关,并且具有较小的调节自由度。相反,电阻  $R_G$  和  $R_D$  通过浮置子像素电极的尺寸、形状和位置,绝缘膜的厚度等来确定,并且具有较大的调节自由度。因此,在本实施例中,调节浮置子像素电极和栅极总线之间的电阻  $R_G$  和浮置子像素电极和数据总线之间的电阻  $R_D$ ,以消除在栅极总线上流动的信号的直流电压成分的影响和在数据总线上流动的信号的直流电压成分的影响。

图 26 是显示横轴上表示的浮置子像素电极的  $R_G/R_D$  和纵轴上表示的浮置子像素电极最终获得的电势之间的关系的坐标图。但是,应该注意,在图 26 中,电阻  $R_C$ 、 $R_{LC}$  和  $R_D$  被设置为相等( $R_C=R_{LC}=R_D$ )。此外, $V_{com}$  和  $V_{sdc}$  被设置为 0V, $V_{gdc}$  被设置为-11.28V,以及  $V_{ddc}$  被设置为+1.13V。在这种情况下,如从图 26 可清楚看出,可以消除栅极总线上流动的信号的直流电压成分的影响和在数据总线上流动的信号的直流电压成分的影响,并且在电阻  $R_G$  的值被设置为电阻  $R_D$  的十倍大小( $R_G/R_D=10$ )时,可防止影像残留的发生。

图 27 是液晶显示器的像素部分的平面图,示出了调节浮置子像素电极和栅极总线之间的电阻以及浮置子像素电极和数据总线之间的电阻的方法。同时,图 28 是显示图 27 的像素的剖面示意图。

在图 27 和图 28 所示的液晶显示器中,由栅极总线 212 和数据总线 215 限定的每个像素区域包含 TFT 216、四个子像素电极 221a-221d 以及控制电极 218。

控制电极 218 通过导线 219 电连接至 TFT 216 的源极电极 216s。同时,子像素电极 221a 和 221d 通过接触孔 220a 和 220c 及导线 219 电连接至 TFT 216 的源极电极。此外,子像素电极 221c 通过接触孔 220b、控制电极 218 以及导线 219 电连接至 TFT 216 的源极电极。另一方面,子像素电极 (浮置子像素电极) 221b 通过第二绝缘膜 220 电容性耦接至控制电极 218。

如图 28 所示, 栅极总线 212 和辅助电容总线 213 形成在玻璃基板 211 上并且覆盖有第一绝缘膜 214。数据总线 215、源极电极 216s、漏极电极 216d、 控制电极 218、以及导线 219 形成在第一绝缘膜 214 上。数据总线 215、源 极电极 216s、漏极电极 216d、控制电极 218、以及导线 219 覆盖有第二绝缘膜 220,以及子像素电极 221a-221d 形成在第二绝缘膜 220 上。这些子像素电极 221a-221d 被缝隙划分开,沿着栅极总线 212 和辅助总线 213 之上弯曲的 Z 字形线形成该缝隙。

在图 27 中,连线 (chain line) 231 显示出形成在相对基板侧的丘状突起的位置(域调节结构)。

在该液晶显示器中,当栅极总线 212 和浮置子像素电极 221b 相面对的部分的长度(图 27 中由箭头 A 表示的部分)增加时,电阻  $R_G$  值减少,而当上述长度减少时,电阻  $R_G$  值增加。而且,此外,当栅极总线 212 和浮置子像素电极 221b 之间的距离(图 27 中由箭头 B 表示的部分)增加时,电阻  $R_G$  值增加,而当上述距离减少时,电阻  $R_G$  值减少。此外,当第一绝缘膜 214 和第二绝缘膜 220 的总厚度(图 28 中由箭头 C 表示的部分)增加时,电阻  $R_G$  值增加,而当上述厚度减少时,电阻  $R_G$  值减少。

同时,当数据总线 215 和浮置子像素电极 221b 相面对的部分的长度(图 27 中由箭头 D 表示的部分)增加时,电阻  $R_D$  值减少,而当上述长度减少时,电阻  $R_D$  值增加。此外,当数据总线 215 和浮置子像素电极 221b 之间的距离(图 27 中由箭头 E 表示的部分)增加时,电阻  $R_D$  值增加,而当上述距离减少时电阻  $R_D$  值减少。此外,当第二绝缘膜 220 的厚度(图 28 中由箭头 F 表示的部分)增加时电阻  $R_D$  值增加,而当上述厚度减少时,电阻  $R_D$  值减少。

在第二实施例中,通过调节上述参数,消除包含在栅极总线 212 上流动的信号中的直流电压成分的影响和包含在数据总线 215 上流动的信号中的直流电压成分的影响。以这种方式,可以避免影像残留并获得良好的显示特性。

(第三实施例)

下面,描述本发明的第三实施例。

通过修改上述公式(3)获得以下公式(5):

$$\Delta V_{LC2} = \frac{((R_{LC2} \times C_{LC2}) - (R_C \times C_C))}{(R_{LC2} + R_C) \times C_{LC2}} \times \Delta V_S$$

$$= \frac{(1 - (R_C / R_{LC2} \times C_C / C_{LC2}))}{(1 + R_C / R_{LC2})} \times \Delta V_S$$

(5)

在此公式(5)中,设置在控制电极和浮置子像素电极之间的电容 $C_C$ 与

设置在浮置子像素电极和公共电极之间的电容  $C_{LC2}$ 之间的比率  $C_{C}/C_{LC2}$ 为指定值,该指定值通过响应直接连接至 TFT 的子像素电极上的电压和浮置子像素电极上的电压之间的电压比来确定。

图 29 示出了当设置  $C_C/C_{LC2}$  为恒定值( $C_C/C_{LC2}$ =1.0-9.0)时,影像残留电压对控制电极和浮置子像素电极之间的电阻  $R_C$  与浮置子像素电极和公共电极之间的电阻  $R_{LC2}$ 的依赖性的计算结果,其中,横轴表示  $R_C$  和  $R_{LC2}$ 之间的比率,而纵轴表示直流电压的放大倍率。同时,图 30 为显示图 29 所示结果的表格。

在图 3 和图 4 所示的液晶显示器的情况下,液晶的特定电阻比 TFT 绝缘膜的特定电阻低 2 位(digits)或更多。由此, $R_{\rm C}/R_{\rm LC2}$ 值接近  $10^3$ 。在这种情况下,如从图 29 和图 30 明显看出,直流电压的放大倍率近似等于  $C_{\rm C}/C_{\rm LC2}$ 。在电容性耦接的 HT 方法中,浮置子像素电极和直接连接至 TFT 的子像素电极之间的电压比设置在约 0.9-0.6 范围内。由此,直流电压的放大倍率最大达到接近 9,并且易于发生影像残留。

同时,图 31 显示通过降低控制电极和浮置子像素电极之间的  $R_C$  可以显著降低浮置子像素电极上的电压。图 31 是表示在横轴表示的  $R_C/R_{LC2}$  与纵轴表示的子像素电极在白色显示部分和黑色显示部分处的电势差之间的关系的坐标图。计算中假设  $C_{LCON}/C_{LCOFF}$  值等于 1.5。

图 32 是显示浮置子像素电极和直接连接至 TFT 的子像素的等效电路图。这里,附图标记 C1 表示包含在直接连接至 TFT 的子像素电极中的电容  $(C1=C_{LC}+C_s)$ ,附图标记 C2 表示包含在浮置子像素电极中的电容 $(C2=C_{LC2}+C_{S2})$ ,附图标记 Cc 表示位于浮置子像素电极和直接连接至 TFT 的子像素之间的电容,以及附图标记 R 表示位于浮置子像素电极和直接连接至 TFT 的子像素之间的电阻。在这种情况下,通过以下公式(6)可获得在时间 t 浮置子像素电极上的电压  $V_C$ (t):

$V_C(t)=V_C(0)\times \exp-(t/((Cse+C_C)\times R)) \qquad (6)$

这里, Cse 为 C1 和 C2 的串联电容(Cse=(1/((1/C1)-(1/C2)))。

图 33 是显示在由横轴表示的位于浮置子像素电极和直接连接至 TFT 的子像素之间的电阻 R 和由纵轴表示的在一个帧期间(t=16.6ms)中电压保持率之间的关系的坐标图。这里,假设液晶显示器具有如图 3 和图 4 所示的结

构。计算中,像素间距设置为 125μm, 浮置子像素电极和直接连接至 TFT 的子像素电极之间的面积比设置为 3-7, 以及施加至浮置子像素电极的显示电压和施加至直接连接至 TFT 的子像素电极的显示电压之间的比率设置为 0.72。

从图 33 可明显看出,当浮置子像素电极和直接连接至 TFT 的子像素电极之间的电阻等于或大于 10<sup>11</sup>Ω 时,电压保持率将维持在约 90%或之上。如果电压保持率降到低于 50%,则由于不均匀电阻引起的电势差变化达到最大。由此,根据显示稳定性,优选设置电压保持率等于或大于 50%。

如上所述,通过将位于浮置子像素电极和直接连接至 TFT 的子像素电极之间的电阻 R 设置为满足  $R_C$ 等于或小于  $R_{LC2}$ 的 100 倍,及在一个帧期间内电压保持率等于或大于 50%,来获得防止影像残留的效果。

图 34 是采用上述配置的第三实施例的液晶显示器中的 TFT 基板的平面图。同时,图 35 是图 34 所示的 TFT 基板的剖面图。

如图 34 所示,在 TFT 基板上形成多条沿水平方向延伸的栅极总线 312 (在图 34 中仅示出了一条栅极总线)以及多条沿垂直方向延伸的数据总线 315 (在图 34 中仅示出了一条数据总线)。由栅极总线 312 和数据总线 315 限定的每个矩形区域构成一个像素区域。同时,在 TFT 基板上,穿过像素区域的辅助电容总线 313 形成为平行于栅极总线 312。如在下文中所述,在每条栅极总线 312 和每条数据总线 315 之间的空间以及每条辅助电容总线 313 和每条数据总线 315 之间的空间形成第一绝缘膜 314。通过利用该第一绝缘膜 314,栅极总线 312 与数据总线 315 之间以及辅助电容总线 313 与数据总线 315 之间分别电绝缘。

在每个像素区域中形成 TFT 316、控制电极 318 以及四个子像素电极 321a-321d。通过导线 319, TFT 316 的漏极电极 316d 连接至数据总线 315, 而其源极电极 316s 连接至控制电极 318。

子像素电极 321a-321d 被沿着栅极总线 312 和辅助总线 313 之上弯曲的 Z 字形线形成的缝隙划分开。此外,子像素电极 321a 和 321d 通过接触孔 321a 和 321c 以及导线 319 电连接至源极电极 316s。子像素电极 321c 通过接触孔 320b 电连接至控制电极 318。另一方面,子像素电极 (浮置子像素电极) 321b 通过下文中描述的第二绝缘膜 320 电容性耦接至控制电极 318。此外,这些

子像素电极 321a-321d 通过连接部分 323 相互电连接,该连接部分 323 是由高电阻导电材料制成。这里,控制电极 318 也用作辅助电容电极并与辅助电容总线 313 和第一绝缘膜 314 一起构成辅助电容。

下面,参照图 35 描述 TFT 基板的层结构。

在构成 TFT 基板的基础的玻璃基板 311 上,形成栅极总线 312 和辅助电容总线 313。例如,按照光刻方法,通过图案化 Cr 膜或 Al-Ti 层叠膜,来同时形成栅极总线 312 和辅助电容总线 313。

此外,由绝缘材料例如 SiN 和 SiO<sub>2</sub>制成的第一绝缘膜 314 形成在玻璃基板 311 之上,并且栅极总线 312 和辅助电容总线 313 被该绝缘膜 314 覆盖。

数据总线 315、TFT 316 的源极电极 316s 和漏极电极 316d、控制电极 318 以及导线 319 形成在第一绝缘膜 314 上。例如,按照光刻方法,通过图案化 Ti-Al-Ti 层叠膜,来同时形成数据总线 315、源极电极 316s 和漏极电极 316d、控制电极 318 以及导线 319。

如图 34 所示, TFT 316 利用部分栅极总线 312 作为栅极电极。此外, 在栅极电极上, 形成构成有源层的半导体膜(未示出)和沟道保护模 316b。源极电极 316s 和漏极电极 316d 彼此相对设置, 同时夹着栅极总线 312。

数据总线 315、源极电极 316s 和漏极电极 316d、控制电极 318 以及导线 319 被第二绝缘膜 320 覆盖,该第二绝缘膜 320 例如由 SiN 或绝缘树脂制成。子像素电极 321a-321d 形成在该第二绝缘膜 320 之上。这些子像素电极 321a-321d 是由透明导电材料例如 ITO 制成。子像素电极 321a 和 321d 分别通过在第二绝缘膜 320 上形成的接触孔 320a 和 320c 电连接至导线 319,子像素电极 321c 通过接触孔 320b 电连接至控制电极 318。此外,子像素电极 321b 通过第二绝缘膜 320 电容性耦接至控制电极 318。

子像素电极 321a-321d 通过连接部分 323 相互电连接,该连接部分 323 由高电阻导电材料制成。此外,例如由聚酰亚胺制成的配向膜 322 形成在子像素电极 321a-321d 和连接部分 323 之上。

连接部分 323 例如由掺杂非晶硅制成。如上所述,浮置子像素电极 321b 和直接连接至 TFT316 的子像素电极 321a、321c 和 321d 之间的电阻设置为等于或小于浮置子像素电极 321b 和公共电极之间的电阻的 100 倍,并且在一个帧期间内的电压保持率设置为等于或大于 50%。

用于连接部分 323 的材料不仅限于上述非晶硅,并且也可以使用例如有机导电材料形成连接部分 323。但作为连接部分 323 的材料,优选使用具有适当范围内的电阻值并且不会污染液晶的材料。此外,也要求该材料具有对形成配向膜工艺的抵抗性。例如,优选几乎不溶于溶剂并具有高耐热性的材料。

在图 34 中,连线 331 显示出形成在相对基板侧上的丘状的突起的位置(域调节结构)。

在本实施例的液晶显示器中,浮置子像素电极 321b 通过高电阻连接部分 323 电连接至直接连接至 TFT 316 的子像素电极 321a、321c 和 321d。此外,将浮置子像素电极 321b 和直接连接至 TFT 316 的子像素电极 321a、321c 和 321d 之间的电阻设置为等于或小于浮置子像素电极 321b 和公共电极之间的电阻的 100 倍,并且在一个帧期间内的电压保持率设置为等于或大于 50%。由此,可以抑制淡化并避免影像残留的发生。以此方式,可以获得良好的显示品质。

#### (第一修改实例)

图 36 是显示根据第三实施例的第一修改实例的液晶显示器的平面图,而图 37 是显示图 36 的液晶显示器的剖面图。就图 36 和图 37 来说,与图 34 和图 35 中所示相同的部件由相同的附图标记表示,并且省略其详细描述。

在第一修改实例的液晶显示器中,用于电连接浮置子像素电极 321b 和直接连接至 TFT 316 的子像素电极 321a、321c 和 321d 的连接部分 324,沿用于划分子像素电极 321a-321d 的缝隙形成为丘状。连接部分 324 是由高电阻导电材料例如掺杂的非晶硅制成。子像素电极 321a-321d 和连接部分 324 的表面覆盖有配向膜 322。

另一方面,在构成相对基板的基础的玻璃基板 331 的一个表面 (在图 37 中为下侧)上形成彩色滤光片 332 和公共电极 333,并且在公共电极 333 上 (在图 37 中为下侧)形成丘状的域调节突起 334。公共电极 333 和突起 334 的表面覆盖有配向膜 335。类似于连接部分 324,采用介电材料或高电阻导电材料形成突起 334。

在该液晶显示器中,通过使用在 TFT 基板侧形成的丘状连接部分 324 和 在相对基板上侧形成的丘状的突起 334,可以获得多区域,如图 37 所示。即,

施加电压时,在每个连接部分 324 两侧或者在每个突起 334 的两侧的液晶分子 340a 的倾斜方向不同。以这种方式,可以防止斜向漏光。

在这种液晶显示器中,同样,浮置子像素电极 321b 通过例如由非晶硅制成的高电阻连接部分 324, 电连接至直接连接至 TFT 316 的子像素电极 321a、321c 和 321d。此外,浮置子像素电极 321b 和控制电极 318 之间的电阻 R 设置为等于或小于浮置子像素电极 321b 和公共电极之间的电阻的 100倍,并且在一个帧期间内的电压保持率设置为等于或大于 50%。由此,可以抑制淡化并避免影像残留的发生。以这种方式,可以获得良好的显示品质。

这里,如果构成域调节突起的连接部分 324 具有低电阻,则整个连接部分 324 被设置为与子像素电极 321a-321d 的电势相同的电势。由此,会出现从连接部分 324 到基板的表面垂直的电力线,从而无法获得多区域。然而,在上述实例中,连接部分 324 是由高阻导电材料制成。由此,可以沿预定方向排列液晶分子。

#### (第四实施例)

图 38 是显示根据本发明第四实施例的液晶显示器的平面图,而图 39 是沿图 38 中的XI-XI线截取的剖面图。就图 38 和图 39 来说,与图 13、图 14A 和图 14B 中所示相同的部件由相同的附图标记表示,并且省略其详细描述。

在本实施例中,由栅极总线 112 和数据总线 115 限定的每个像素区域包括三个子像素电极 121a-121c。子像素电极 121a 和 121c 通过在第二绝缘膜 120 上形成的接触孔 120a 和 120b,电连接至从 TFT 116 的源极电极 116s 延伸的导线 119。同时,子像素电极(浮置子像素电极)121b 电容性耦接至控制电极 118,同时把第二绝缘膜 120 夹在中间。

通过连接至辅助电容总线 113 的屏蔽图案 412,来屏蔽子像素电极 121b 和数据总线 115 之间的空间以及子像素电极 121b 和子像素电极 121a 之间的空间。

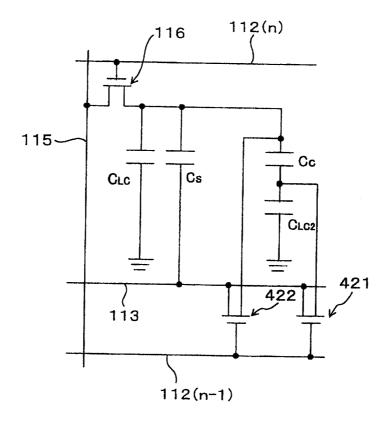

TFT 411 形成在子像素电极 121b 和子像素电极 121c 之间。该 TFT 411 的栅极电极 411g 连接至不同于连接至 TFT 116 的栅极总线 112(第 n 条栅极总线)的栅极总线 112(第 n-1 条栅极总线)。此外,源极电极 411s 和漏极电极 411d 分别通过接触孔 413a 和 413b 连接至子像素电极 121b 和 121c。

图 40 是显示上述液晶显示器中一个像素的等效电路图。在图 40 中, TFT

116 连接至第 n 条栅极总线 112 (n)。此外,如上所述,TFT 116 的源极电极 116s 直接连接至子像素电极 121a 和 121c,以及控制电极 118。附图标记  $C_{LC}$  表示子像素电极 121a 和 121c 与公共电极 133 之间的电容(液晶电容)。同时,附图标记  $C_S$  表示控制电极 118 和辅助电容总线 113 之间的电容(辅助电容)。并且,附图标记  $C_C$  表示控制电极 118 和浮置子像素电极 121b 之间的电容,而附图标记  $C_{LC2}$  表示浮置子像素电极 121b 和公共电极 133 之间的电容。

此外, TFT 411 形成在子像素电极 121b 和 121c 之间, 并且其栅极电极 411g 连接至第 n-1 条栅极总线 112 (n-1)。

在本实施例的液晶显示器中,在通过 TFT 116 将显示电压施加至子像素电极 121a 和 121c 以及控制电极 118 之前(正好是一个水平扫描期间之前), TFT 411 打开,由此,浮置子像素电极 121b 的电势等于直接连接至 TFT 116 的子像素电极 121a 和 121c 以及控制电极 118 的电势。以这种方式,归因于栅极总线 112 和数据总线 115 上流动的信号中包含的直流电压成分引起的积累在浮置子像素电极 121b 中的电荷,会流向子像素电极 121a 和 121c 以及控制电极 118。因此,可以获得抑制电荷在浮置子像素电极 121b 中的积累的效果并因此避免影像残留。

# (第一修改实例)

图 41 是显示根据第四实施例的第一修改实例的液晶显示器的平面图。 就图 41 来说,与图 38 中所示相同的部件由相同的附图标记表示,并且省略 其详细描述。

在本实例中,两个 TFT 421 和 422 位于直接连接至 TFT 116 的子像素电极 121c 和浮置子像素电极 121b 之间。这两个 TFT 421 和 422 的漏极电极相互连接。同时,这两个 TFT 421 和 422 的栅极电极 421g 和 422g 通过导线 414 连接至第 n-1 条栅极总线 112 (n-1),并且其源极电极分别连接至浮置子像素电极 121b 及子像素电极 121c。此外,TFT 421 和 422 的漏极电极通过连接部分 423 和导线 424,连接至从辅助电容总线 113 延伸出的屏蔽图案 412。

图 42 是显示上述液晶显示器中一个像素的等效电路图。在图 42 中, TFT 116 连接至第 n 条栅极总线 112 (n)。此外,该 TFT 116 的源极电极 116s 电连接至子像素电极 121a 和 121c 以及控制电极 118。附图标记 C<sub>LC</sub>表示子

像素电极 121a 和 121c 与公共电极 133 之间的电容(液晶电容)。同时,附图标记  $C_S$  表示控制电极 118 和辅助电容总线 113 之间的电容(辅助电容)。并且,附图标记  $C_C$  表示控制电极 118 和浮置子像素电极 121b 之间的电容,附图标记  $C_{LC2}$  表示浮置子像素电极 121b 和公共电极 133 之间的电容。

此外,TFT 421 和 422 连接在子像素电极 121b 和 121c 之间。TFT 421 的栅极电极连接至第 n-1 条栅极总线 112 (n-1),而其源极电极和漏极电极连接在浮置子像素电极 121b 和辅助电容总线 113 之间。同时,TFT 422 的栅极电极也连接至第 n-1 条栅极总线 112 (n-1),而其源极电极和漏极电极连接在子像素电极 121c 和辅助电容总线 113 之间。这里,假设辅助电容总线 113 保持在与相对基板上的公共电极的电势相同的电势。

在本实例的液晶显示器中,同样,在通过 TFT 116 将显示电压施加至子像素电极 121a 和 121c 以及控制电极 118 之前(正好是一个水平扫描期间之前),TFT 421 和 422 打开,由此,浮置子像素电极 121b 的电势和直接连接至 TFT 116 的子像素电极 121a 和 121c 的电势等于辅助电容总线 113 的电势。以这种方式,归因于栅极总线 112 和数据总线 115 上流动的信号中包含的直流电压成分引起的在浮置子像素电极 121b 中和在子像素电极 121a 和 121c 中的电荷的积累,会流向辅助电容总线 113。因此,可以获得抑制电荷在浮置子像素电极 121b 中的积累的效果并因此避免影像残留。

注意,在上述第一修改实例中,允许在直接连接至 TFT 116 的子像素电极 121a 和 121c 中存储的电荷通过 TFT 422 流向辅助电容总线 113。但是,如上所述,在每个帧中这些子像素电极 121a 和 121c 仅连接至数据总线 115一次。由此,在子像素电极 121a 和 121c 中积累的电荷的影响是微小的,因此,也可以省略 TFT 422。

(第五实施例)

下面,描述本发明的第五实施例。

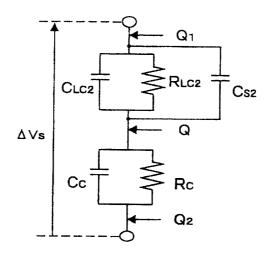

图 43 是显示本发明第五实施例的原理的像素的电路图。在图 43 中,附图标记  $C_C$  和  $R_C$  分别表示控制电极和浮置子像素电极之间的电容和电阻,以及附图标记  $C_{LC2}$  和  $R_{LC2}$  分别表示浮置子像素电极和公共电极之间的电容(液晶电容) 和电阻(液晶电阻)。

如前所述,在白色显示部分和黑色显示部分的浮置子像素电极之间产生

电势差的原因之一是液晶电容  $C_{LC2}$  的变化。由此,在第五实施例中,辅助电容  $C_{S2}$  并联连接至液晶电容  $C_{LC2}$ ,以降低浮置在子像素电极和公共电极之间的电容变化的影响。

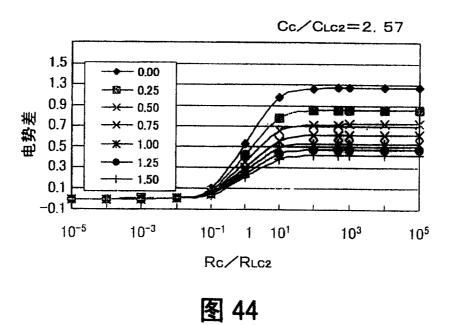

图 44 是显示在由横轴上表示的  $R_{C}/R_{LC2}$  和纵轴上表示的浮置子像素电极在白色显示部分和黑色显示部分的电势差之间的关系的坐标图。这里,在没有辅助电容  $C_{S2}$  (0.00 倍)的情况下和辅助电容  $C_{S2}$  的值为液晶电容  $C_{LC2}$  值的 0.25-1.5 倍的情况下观测该关系。注意在这里值  $C_{C}/C_{LC2}$  被设置为 2.57。

从图 44 和图 31 之间的比较可明显看出,通过并联连接辅助电容  $C_{s2}$  到液晶电容  $C_{LC2}$ ,可降低浮置子像素电极在白色显示部分和黑色显示部分之间的电势差。例如,假设辅助电容  $C_{s2}$  的值等于液晶电容  $C_{LC2}$  的值  $(C_{s2}/C_{LC2}=1.00)$ ,则导致影像残留的浮置子像素电极在白色显示部分和黑色显示部分之间的电势差,可大约降低一半。

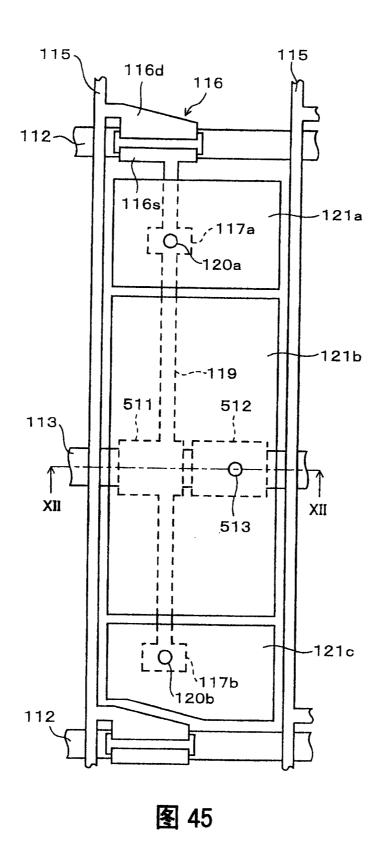

图 45 是显示经过采用上述对策之后的液晶显示器的平面图,以及图 46 是沿图 45 中的XII-XII线截取的剖面图。就图 45 和图 46 来说,与图 13、图 14A 和图 14B 中所示相同的部件由相同的附图标记表示,并且省略其详细描述。

在本实施例的液晶显示器中,控制电极 511 和辅助电容电极 512 形成在辅助电容总线 113 上。控制电极 511 通过第二绝缘膜 140 电容性耦接至浮置 子像素电极 121b。此外,控制电极 511 通过导线 119 电连接至 TFT 116 的源极电极 116s,并通过导线 119 及接触孔 120a和 120b 电连接至子像素电极 121a和 121c。此外,控制电极 511 与辅助电容总线 113 和第一绝缘膜 114 一起构成第一辅助电容。这里,假设辅助电容总线 113 保持在与相对基板上的公共电极的电势相同的电势。

辅助电容电极 512 通过在第二绝缘膜 140 上形成的接触孔 513 电连接至 浮置子像素电极 121b。此外,辅助电容电极 512 与辅助电容总线 113 和第一 绝缘膜 120 一起构成第二辅助电容 C<sub>\$2</sub>。

在本实施例中,如图 43 的等效电路图中所示,辅助电容  $C_{S2}$  与液晶电容  $C_{LC2}$  并联设置。由此,可以减少浮置子像素电极在白色显示部分和黑色显示部分之间的电势差,由此,防止影像残留的发生。

这里,也可以想到,代替设置辅助电容电极 512,而使用浮置子像素电

极 121b 和辅助电容总线 113 来形成辅助电容  $C_{S2}$ 。但是,在这种情况下,由于第一和第二绝缘膜 114 和 120 置于浮置子像素电极 121b 和辅助电容总线 113 之间,辅助电容  $C_{S2}$  的电容值会降低。因此,也降低了防止影像残留发生的效果。因此,优选如上所述的在第一绝缘膜 114 上形成辅助电容电极 512,并且将辅助电容电极 512 和浮置子像素电极 121b 电连接。

第一至第五实施例中所述的防止影像残留的方法可应用于各种类型的液晶显示器,例如 TN 液晶显示器或 VA 液晶显示器。此外,该方法不仅可应用于透射式液晶显示器,而且可应用于反射式液晶显示器和半透射式液晶显示器。

图 1A

图 1B

图 2

图 4

图 5

## 暂态结束后处于定态的 Q

$$Q_1 = (R_{LC2}/(R_{LC2}+R_C)) \times \Delta V_S \times C_{LC2}$$

$$Q_2 = (R_C/(R_{LC2}+R_C)) \times \Delta V_S \times C_C$$

$$Q = Q_2-Q_1$$

$$= -(R_{LC2} \times C_{LC2}) + (R_C \times C_C)) / R_{LC2}+R_C) \times \Delta V_S$$

## 即使去除△Vs,仍然保留在液晶层中的直流电压

$$\Delta V_{LC2} = -Q/C_{LC2}$$

$$\Delta V_{LC2} = \frac{((R_{LC2} \times C_{LC2}) - (R_C \times C_C))}{(R_{LC2} + R_C) \times C_{LC2}} \times \Delta V_S$$

## 图 11

图 14A

图 14B

47

图 18

50

52

53

图 29

|                  | 0.9   | 0.8   | 0.72  | 0.7   | 0.6   | 0.5   |

|------------------|-------|-------|-------|-------|-------|-------|

|                  | 9.00  | 4.00  | 2.57  | 2.33  | 1.50  | 1.00  |

| 10 <sup>-5</sup> | 1.00  | 1.00  | 1.00  | 1.00  | 1.00  | 1.00  |

| 10-4             | 1.00  | 1.00  | 1.00  | 1.00  | 1.00  | 1.00  |

| 10 <sup>-3</sup> | 0.99  | 1.00  | 1.00  | 1.00  | 1.00  | 1.00  |

| 10-2             | 0.90  | 0.95  | 0.97  | 0.98  | 0.98  | 0.99  |

| 10-1             | 0.09  | 0.55  | 0.70  | 0.77  | 0.82  | 0.88  |

| 1                | -4.00 | -1.50 | -0.67 | -0.25 | 0.00  | 0.25  |

| 10 <sup>1</sup>  | -8.09 | -3.55 | -2.03 | -1.27 | -0.82 | -0.36 |

| 10 <sup>2</sup>  | -8.90 | -3.95 | -2.30 | -1.48 | -0.98 | -0.49 |

| 10 <sup>3</sup>  | -8.99 | -4.00 | -2.33 | -1.50 | -1.00 | -0.50 |

| 10 <sup>4</sup>  | -9.00 | -4.00 | -2.33 | -1.50 | -1.00 | -0.50 |

| 10 <sup>5</sup>  | -9.00 | -4.00 | -2.33 | -1.50 | -1.00 | -0.50 |

60

图 35

62

图 37

64

图 39

图 42

$$\Delta V_{LC2} = \frac{(1 - (Rc/R_{LC2} \times Cc/(C_{LC2} + C_{S2})))}{(1 + Rc/R_{LC2})} \times \Delta V_{S}$$

69

图 46

| 专利名称(译)        | 液晶显示器及其防止影像残留的方法                             | 去       |            |  |  |  |

|----------------|----------------------------------------------|---------|------------|--|--|--|

| 公开(公告)号        | CN100410789C                                 | 公开(公告)日 | 2008-08-13 |  |  |  |

| 申请号            | CN200510052507.2                             | 申请日     | 2005-02-28 |  |  |  |

| [标]申请(专利权)人(译) | 富士通显示技术股份有限公司 友达光电股份有限公司                     |         |            |  |  |  |

| 申请(专利权)人(译)    | 富士通显示技术株式会社<br>友达光电股份有限公司                    |         |            |  |  |  |

| 当前申请(专利权)人(译)  | 富士通株式会社<br>友达光电股份有限公司                        |         |            |  |  |  |

| [标]发明人         | 镰田豪<br>笹林贵<br>上田一也<br>吉田秀史                   |         |            |  |  |  |

| 发明人            | 镰田豪<br>笹林贵<br>上田一也<br>吉田秀史                   |         |            |  |  |  |

| IPC分类号         | G02F1/136 G02F1/133 H01L29/786 G09G3/36      |         |            |  |  |  |

| CPC分类号         | G02F2001/134354 G02F2001/136218 G02F1/136213 |         |            |  |  |  |

| 代理人(译)         | 张龙哺                                          |         |            |  |  |  |

| 审查员(译)         | 安蕾                                           |         |            |  |  |  |

| 优先权            | 2004220263 2004-07-28 JP                     |         |            |  |  |  |

| 其他公开文献         | CN1727971A                                   |         |            |  |  |  |

| 外部链接           | Espacenet SIPO                               |         |            |  |  |  |

|                |                                              | _       |            |  |  |  |

## 摘要(译)

本发明提供一种液晶显示器及其防止影像残留的方法。其中,直接连接 至薄膜晶体管的子像素电极,位子电容性耦接至控制电极的浮置子像素 电极与栅极总线之间,以防止电荷从栅极总线注入到该浮置子像素电 极。此外,电连接至辅助电容总线的屏蔽图案形成在辅助子像素电极和 数据总线之间。该屏蔽图案避免电荷从数据总线注入到该浮置子像素电 极。