(12) 发明专利申请

(10) 申请公布号 CN 102566125 A

(43) 申请公布日 2012.07.11

(21) 申请号 201210019694.4

(22) 申请日 2008.07.22

(30) 优先权数据

10-2008-0008999 2008.01.29 KR

(62) 分案原申请数据

200810134313.0 2008.07.22

(71) 申请人 三星电子株式会社

地址 韩国京畿道水原市

(72) 发明人 郑美惠 蔡钟哲 李庸羽 金玲究

(74) 专利代理机构 北京铭硕知识产权代理有限公司 11286

代理人 韩芳

(51) Int. Cl.

G02F 1/1333(2006.01)

G02F 1/1343(2006.01)

G02F 1/1362(2006.01)

权利要求书 2 页 说明书 10 页 附图 16 页

(54) 发明名称

液晶显示器

(57) 摘要

本发明公开了一种液晶显示器，根据本发明的液晶显示器包括：第一基底和第二基底，彼此面对；像素电极，设置在第一基底上并且包括第一子像素电极和通过间隙与第一子像素电极分隔开的第二子像素电极；共电极，设置在第二基底上；屏蔽构件，设置在第一基底或第二基底上并且与第一子像素电极和第二子像素电极之间的间隙叠置；取向层，设置在像素电极和共电极中的至少一个上；液晶层，设置在第一基底和第二基底之间。

1. 一种液晶显示器，所述液晶显示器包括：

第一基底和第二基底，彼此面对；

像素电极，设置在第一基底上，并且包括第一子像素电极和第二子像素电极；

共电极，设置在第二基底上；

取向层，设置在像素电极和共电极中的至少一个上，并且包括由光反应材料制成的多个链；

液晶层，设置在第一基底和第二基底之间并且包括沿着多个方向取向的液晶分子；

导线，设置在第一基底和第二基底中的至少一个上，

其中，第一子像素电极具有第一边缘部和与第一边缘部相对的第二边缘部，第一边缘部包括第一部分和第二部分，第一部分的液晶分子沿着与第二部分的液晶分子的方向不同的方向取向，

其中，导线包括沿着第一边缘部的第一部分延伸的第一段和沿着第一边缘部的第二部分延伸的第二段，第一段与液晶分子朝向第一边缘部定向的第一部分叠置，以及

其中，第一段到第二边缘部的距离小于第二段到第二边缘部的距离。

2. 根据权利要求 1 所述的液晶显示器，其中，形成在第一子像素电极和共电极之间的液晶电容与形成在第二子像素电极和共电极之间的液晶电容不同。

3. 根据权利要求 1 所述的液晶显示器，其中，位于第一子像素电极和共电极之间的液晶分子的取向方向朝向第一部分、远离第二部分定向。

4. 根据权利要求 1 所述的液晶显示器，其中，第二边缘部包括第一部分和第二部分，其中，第一边缘部的第一部分与第二边缘部的第二部分相对设置，第一边缘部的第二部分与第二边缘部的第一部分相对设置。

5. 根据权利要求 4 所述的液晶显示器，其中，第二子像素电极具有第一边缘部和与第二子像素电极的第一边缘部相对的第二边缘部，第二子像素电极的第一边缘部和第二边缘部均包括第一部分和第二部分，第二子像素电极的第一部分与导线叠置的宽度大于第二子像素电极的第二部分与导线叠置的宽度。

6. 根据权利要求 5 所述的液晶显示器，其中，位于第二子像素电极和共电极之间的液晶分子的取向方向朝向第二子像素电极的第一部分、远离第二子像素电极的第二部分定向。

7. 根据权利要求 1 所述的液晶显示器，所述液晶显示器还包括：

第一薄膜晶体管，连接到第一子像素电极；

第二薄膜晶体管，连接到第二子像素电极。

8. 根据权利要求 7 所述的液晶显示器，所述液晶显示器还包括具有接触孔的绝缘层，其中，第一薄膜晶体管包括漏电极，第一子像素电极通过接触孔连接到所述漏电极。

9. 根据权利要求 8 所述的液晶显示器，其中，所述接触孔设置在液晶分子的取向方向彼此不同的两个区域的边界上。

10. 根据权利要求 9 所述的液晶显示器，所述液晶显示器还包括连接到第一薄膜晶体管和第二薄膜晶体管的栅极线，其中，所述漏电极从栅极线延伸到所述接触孔并且具有与栅极线垂直的第一部分和与栅极线平行的第二部分。

11. 根据权利要求 10 所述的液晶显示器，其中，所述漏电极具有两个弯曲部。

12. 根据权利要求 5 所述的液晶显示器，其中，第一子像素电极被构造为接收第一电压，第二子像素电极被构造为接收与第一电压不同的第二电压。

13. 根据权利要求 1 所述的液晶显示器，其中，液晶分子的取向方向与导线的边缘成 0° 和 90° 之间的范围内的角。

14. 根据权利要求 1 所述的液晶显示器，其中，第一子像素电极和第二子像素电极均包括四个畴。

15. 根据权利要求 1 所述的液晶显示器，其中，第一子像素电极的面积与第二子像素电极的面积不同。

16. 根据权利要求 1 所述的液晶显示器，其中，所述导线是存储电极线中的至少一条。

17. 根据权利要求 16 所述的液晶显示器，其中，所述导线包括第一部分和比第一部分宽的第二部分。

18. 根据权利要求 16 所述的液晶显示器，其中，所述导线包括台阶部分。

19. 根据权利要求 1 所述的液晶显示器，其中，第一边缘部的第二部分与所述导线叠置。

20. 根据权利要求 1 所述的液晶显示器，其中，所述导线设置在第二基底上。

21. 根据权利要求 20 所述的液晶显示器，其中，所述导线包括第一部分和比第一部分宽的第二部分。

22. 根据权利要求 1 所述的液晶显示器，其中，所述导线具有设置在第一段和第二段之间的弯曲部分。

## 液晶显示器

[0001] 本申请是申请日为 2008 年 7 月 22 日、申请号为 200810134313.0、题为“液晶显示器”的专利申请的分案申请。

### 技术领域

[0002] 本发明涉及一种液晶显示器。

### 背景技术

[0003] 液晶显示器 (LCD) 是最广泛使用的平板显示器之一, LCD 包括提供有场发生电极 (例如, 像素电极和共电极) 的一对面板以及设置在这两个面板之间的液晶 (LC) 层。当对场发生电极施加电压从而在 LC 层中产生电场时, LCD 显示图像, 其中, 产生的电场确定 LC 层中的 LC 分子的定向, 从而调节入射光的偏振。

[0004] 在垂直取向 (VA) 模式 LCD 中, 在没有电场的情况下, LC 分子的长轴垂直于上面板和下面板, 从而可以得到大的对比度和宽的基准视角。

[0005] 在 VA 模式 LCD 中, 为了得到宽视角, 可以在一个像素中形成 LC 分子的取向方向彼此不同的多个畴 (domain)。

[0006] 为了实现这个目的, 可以在至少一个场发生电极中形成至少一个切口。在该方法中, 通过使 LC 分子相对于在切口的边缘和面对所述边缘的场发生电极之间产生的边缘场垂直取向, 可以形成多个畴。

[0007] 然而, 在这种结构中, 开口率会下降。另外, 设置在开口附近的 LC 分子可以容易地相对于边缘场垂直取向, 而远离开口的设置在畴的中心部分的 LC 分子会发生随机运动, 使得响应速度变慢并且形成相反方向的畴, 这会引起出现瞬时余像。

[0008] 可选地, 可以通过向取向层照射光来控制 LC 分子的取向方向和取向角。在这种光取向方法中, 可以不必在场发生电极中形成切口, 从而可以增加开口率, 并且可以通过在光取向期间产生的预倾角来改进 LC 分子的响应时间。

[0009] 另一方面, VA 模式 LCD 的侧面可视性会低于正面可视性, 为了解决这个问题, 已经提出了将一个像素分成两个子像素并且对子像素施加不同电压。

[0010] 然而, 当将光取向方法应用到具有两个子像素的结构时, 经过光取向的 LC 分子的取向方向会与由于 LCD 的两个子像素之间的间隙中的边缘场产生的 LC 分子的取向方向不同, 从而会在相应部分中产生纹路。这种纹路会降低透射率并且出现斑点, 从而会劣化显示特性。

### 发明内容

[0011] 本发明提供了一种液晶显示器 (LCD), 在该 LCD 中, 一个像素被分为两个子像素, 并且可以减少由于光取向方法导致的纹路的产生。

[0012] 本发明的附加特征将在下面的描述中提到, 一部分从描述部分将是清楚的, 或者可以通过本发明的实践而获知。

[0013] 本发明公开了一种 LCD，该 LCD 包括：第一基底和第二基底，彼此面对；像素电极，设置在第一基底上，并且包括第一子像素电极和通过间隙与第一子像素电极分隔开的第二子像素电极；共电极，设置在第二基底上；屏蔽构件，设置在第一基底或第二基底上并且与第一子像素电极和第二子像素电极之间的间隙叠置；取向层，设置在像素电极和共电极中的至少一个上；液晶 (LC) 层，设置在第一基底和第二基底之间。

[0014] 本发明还公开了一种 LCD，该 LCD 包括：像素电极，包括第一子像素电极和第二子像素电极；共电极，面向像素电极；第一 LC 层，设置在第一子像素电极和共电极之间；第二 LC 层，设置在第二子像素电极和共电极之间；屏蔽构件，设置在像素电极下面或者共电极下面，并且与第一子像素电极和第二子像素电极之间的间隙叠置。第一 LC 层包括液晶分子分别沿着左上方向、左下方向、右上方向和右下方向取向的多个畴，第二 LC 层包括液晶分子分别沿着左上方向、左下方向、右上方向和右下方向取向的多个畴。

[0015] 应该理解，前面的概括性描述和后面的详细描述都是示例性和解释性的，意图对要求保护的本发明提供进一步的解释。

## 附图说明

[0016] 包含于此、用来提供对本发明的进一步理解并且构成本说明书的一部分的附图示出了本发明的实施例，并且与描述部分一起用来解释本发明的原理。

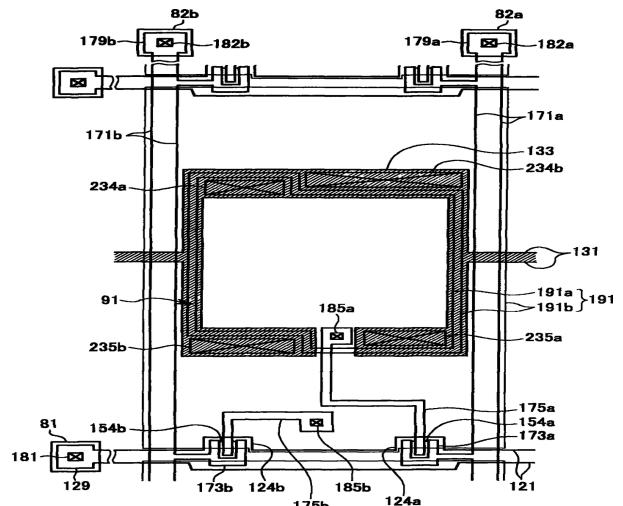

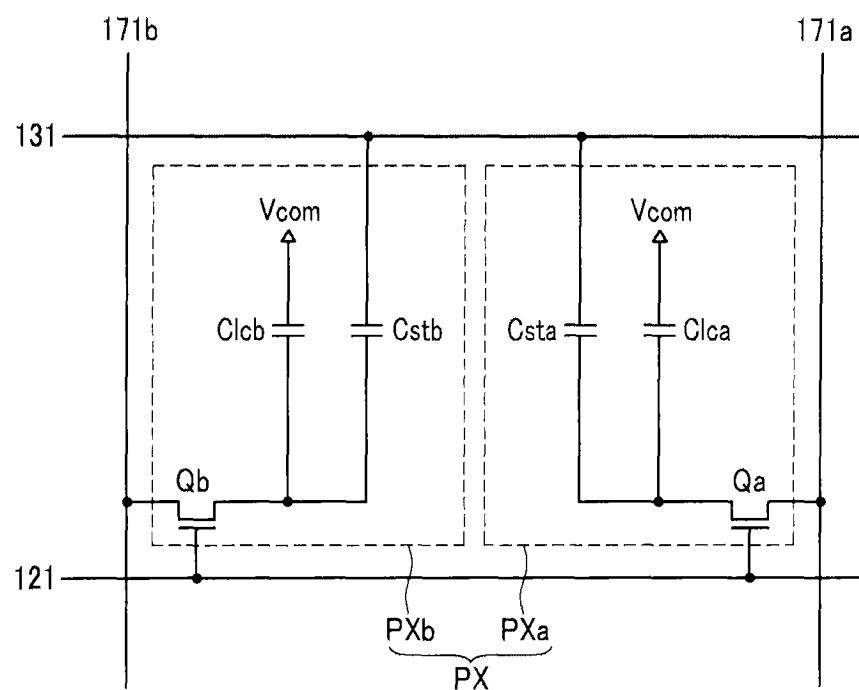

[0017] 图 1 是根据本发明示例性实施例的 LCD 的像素的等效电路图。

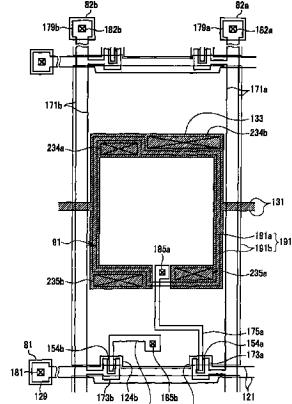

[0018] 图 2 是根据本发明示例性实施例的 LCD 的布局图。

[0019] 图 3 和图 4 是分别示出图 2 中示出的 LCD 中的像素电极和栅极导体的布局图。

[0020] 图 5 是沿着图 2 中的线 V – V 截取的 LCD 的剖视图。

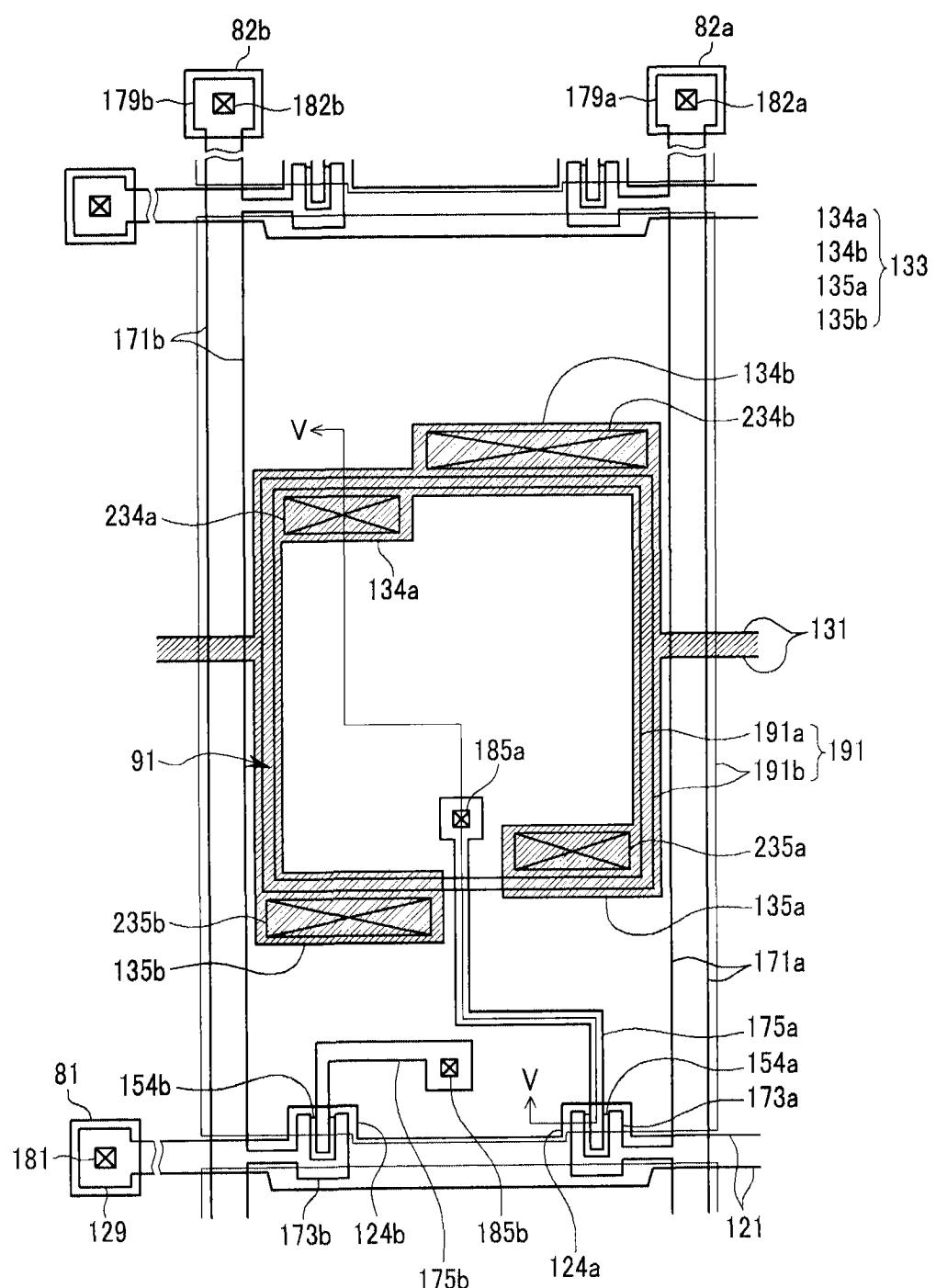

[0021] 图 6 是根据本发明另一示例性实施例的 LCD 的布局图。

[0022] 图 7 和图 8 是分别示出图 6 中的 LCD 中的像素电极和栅极导体的布局图。

[0023] 图 9 是示出图 6 中的像素电极、栅极导体和 LC 分子的取向方向的布局图。

[0024] 图 10 是根据本发明又一示例性实施例的 LCD 的布局图。

[0025] 图 11 是示出图 10 中的 LCD 中的像素电极和屏蔽构件的示意图。

[0026] 图 12 是沿着图 10 中的线 XII – XII 截取的 LCD 的剖视图。

[0027] 图 13 是根据本发明又一示例性实施例的 LCD 的布局图。

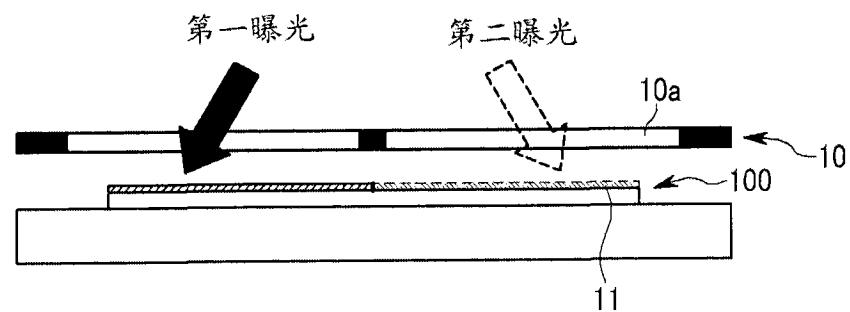

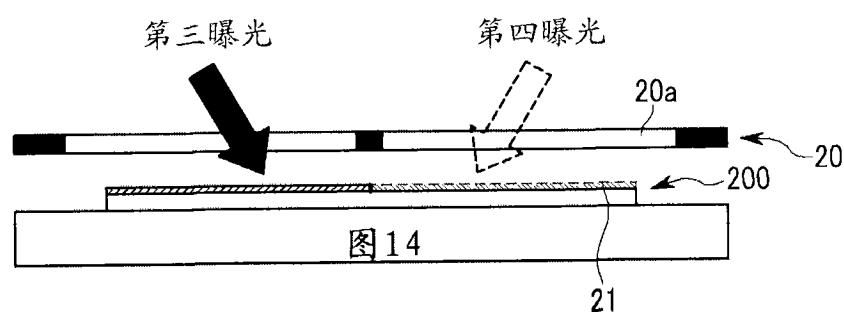

[0028] 图 14 是示出光取向情况下的两个掩模的示意图。

[0029] 图 15 是示出利用图 14 中示出的掩模来照射光的方法的示意图。

[0030] 图 16 和图 17 是示出经历光取向方法的 LC 分子的取向的示意图。

## 具体实施方式

[0031] 在下文中，参照附图来更充分地描述本发明，附图中示出了本发明的实施例。然而，本发明可以以许多不同的形式来实施，而不应该被理解为限于在此提出的实施例。相反，提供这些实施例，使得本公开是彻底的，并且将本发明的范围充分传达给本领域技术人员。在附图中，为了清晰起见，可以夸大层和区域的尺寸和相对尺寸。在附图中，相同的标号用来表示相同的元件。

[0032] 应该理解，当元件或层被称作“在”另一元件或层“上”或者“连接到”另一元件或

层时,该元件或层可以直接在另一元件或层上或者直接连接到另一元件或层,或者可以存在中间元件或层。相反,当元件被称作“直接在”另一元件或层“上”或者“直接连接到”另一元件或层时,不存在中间元件或中间层。

[0033] [示例性实施例 1]

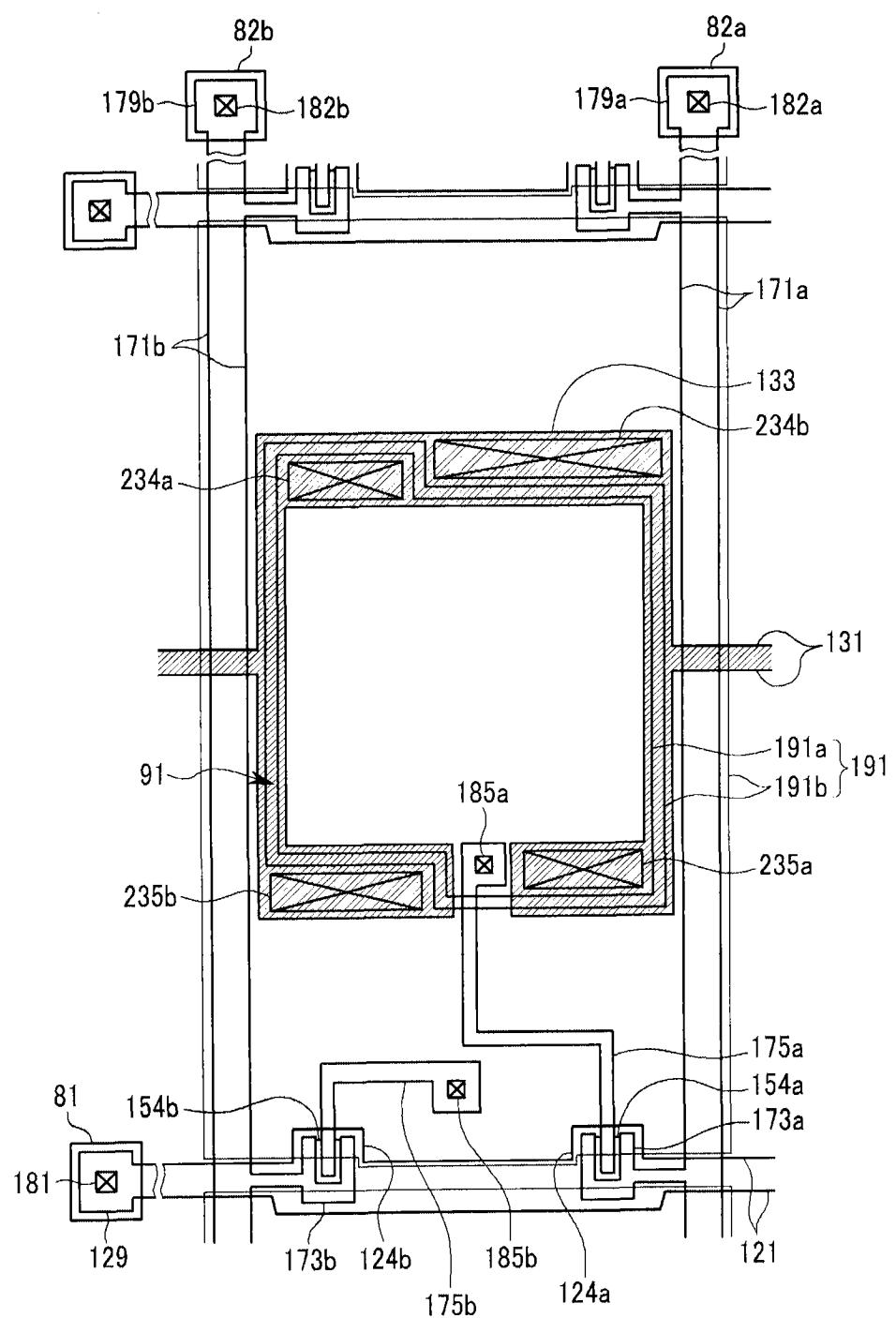

[0034] 下面将参照图 1、图 2、图 3、图 4 和图 5 来详细描述根据本发明示例性实施例的 LCD。

[0035] 图 1 是根据本发明示例性实施例的 LCD 的一个像素的等效电路图,图 2 是根据本发明示例性实施例的 LCD 的布局图,图 3 和图 4 是分别示出图 2 中的 LCD 中的像素电极和栅极导体的布局图,图 5 是沿着图 2 中的线 V - V 截取的剖视图。

[0036] 参照图 1,每个像素 PX 包括一对子像素 PXa 和 PXb,子像素 PXa 包括:开关元件 Qa,连接到栅极线 121 和相应的数据线 171a;LC 电容器 Clca,连接到开关元件 Qa;存储电容器 Csta,连接到开关元件 Qa 和存储电极线 131。子像素 PXb 包括:开关元件 Qb,连接到栅极线 121 和相应的数据线 171b;LC 电容器 Clcb,连接到开关元件 Qb;存储电容器 Cstb,连接到开关元件 Qb 和存储电极线 131。

[0037] 每个开关元件 Qa 和 Qb 可为包括控制端、输入端和输出端的三端子元件。开关元件 Qa 和 Qb 的控制端连接到栅极线 121,输入端连接到相应数据线 171a 和 171b,输出端连接到 LC 电容器 Clca 和 Clcb 以及存储电容器 Csta 和 Cstb。

[0038] 存储电容器 Csta 和 Cstb 用作 LC 电容器 Clca 和 Clcb 的辅助件,存储电容器 Csta 和 Cstb 形成在存储电极线 131 与像素电极(未示出)彼此叠置的位置,其中,在存储电极 131 和像素电极之间设置有绝缘体,对存储电极线 131 施加设置电压(例如,共电压 Vcom 等)。另外,存储电容器 Csta 和 Cstb 可以形成在像素电极与紧挨着的前一栅极线叠置的位置,其中,在像素电极和紧挨着的前一栅极线之间设置有绝缘体。

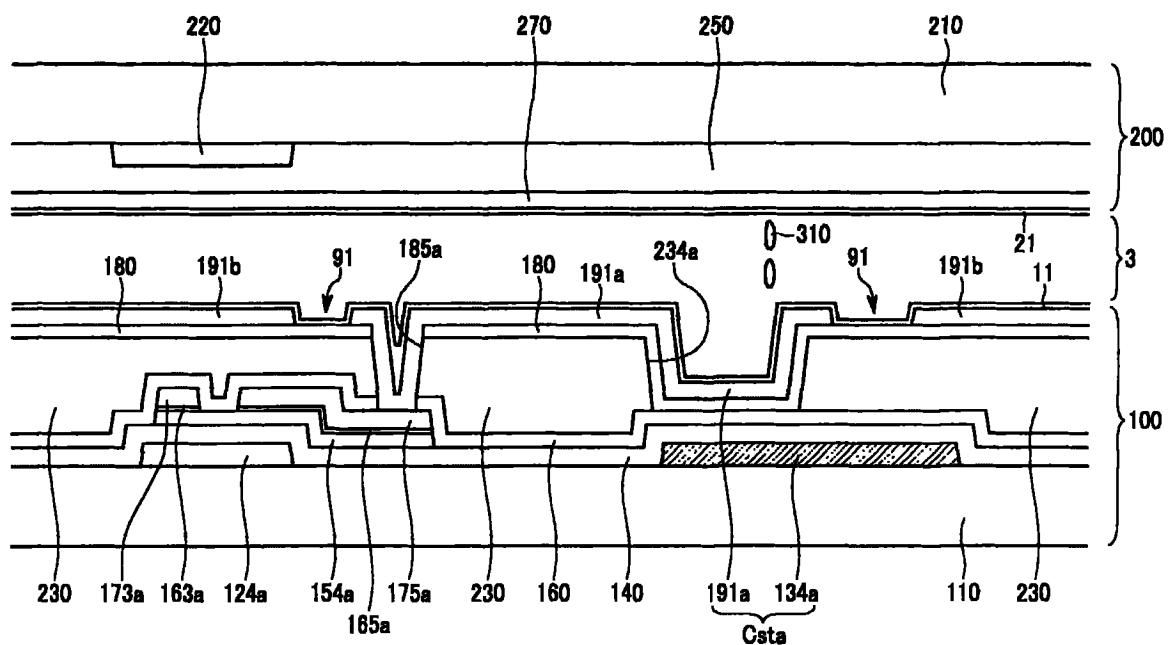

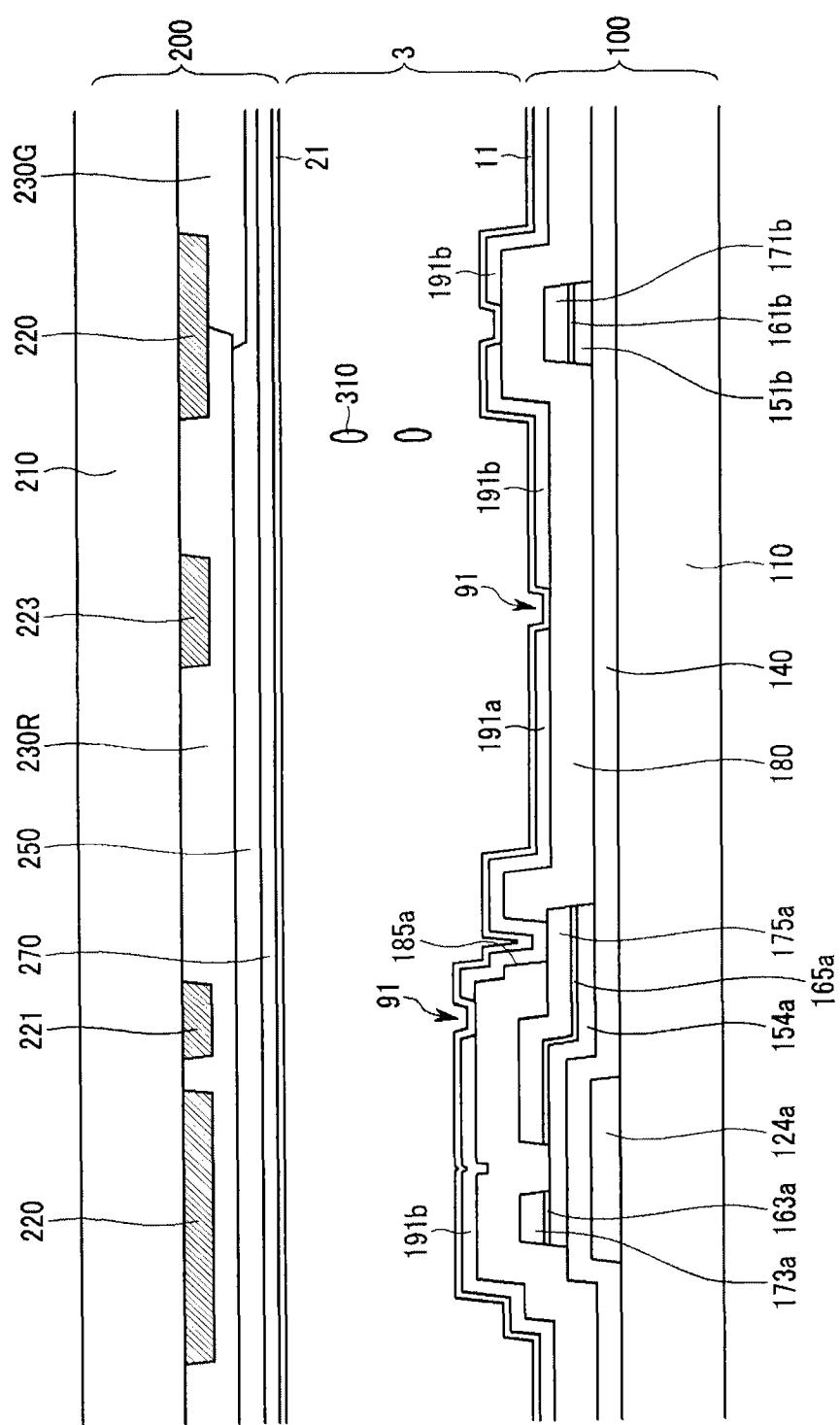

[0039] 参照图 2、图 3、图 4 和图 5,根据该示例性实施例的 LCD 包括薄膜晶体管阵列面板 100 和共电极面板 200 以及位于这两个面板之间的 LC 层 3。

[0040] 首先,将描述薄膜晶体管阵列面板 100。

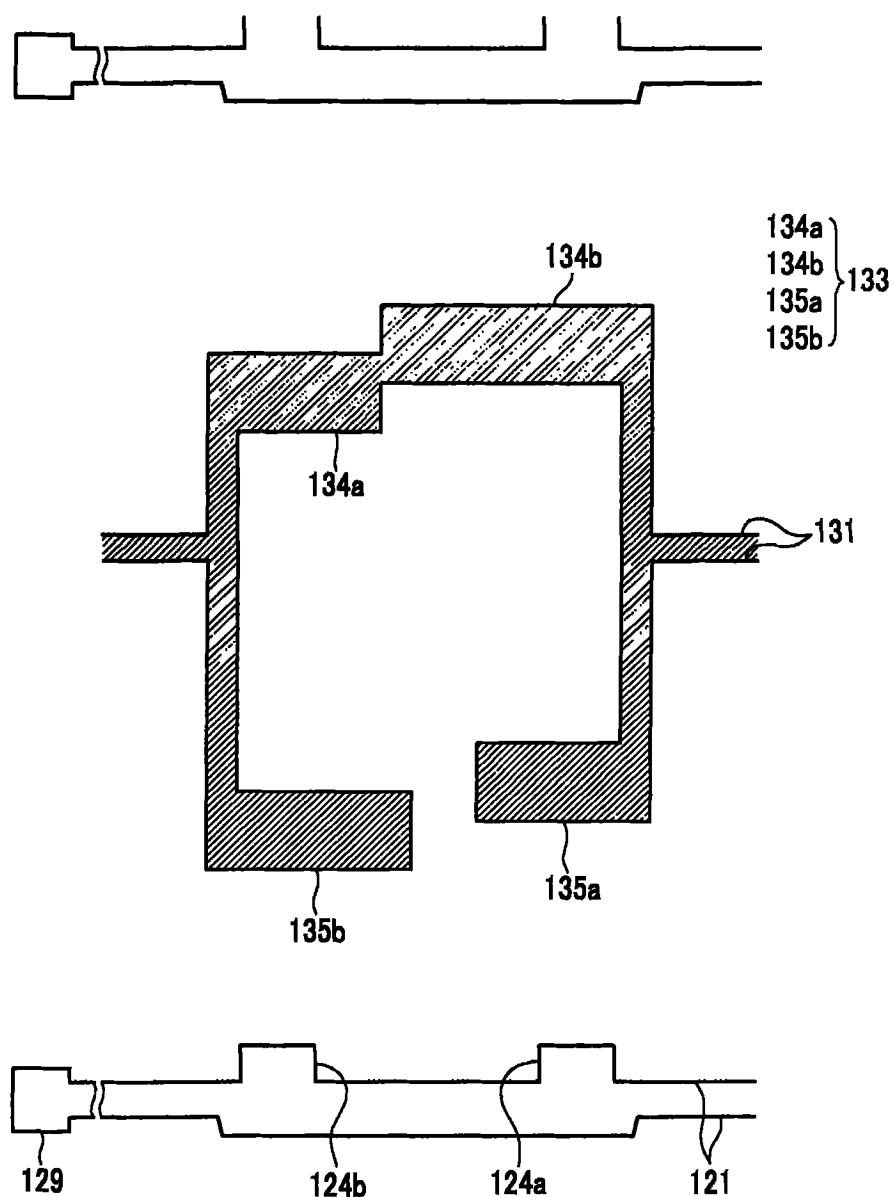

[0041] 包括多条栅极线 121 和多条存储电极线 131 的栅极导体设置在绝缘基底 110 上。

[0042] 栅极线 121 传输栅极信号并且主要在水平方向上延伸。每条栅极线 121 包括向上突出的多个第一栅电极 124a 和多个第二栅电极 124b 以及宽端部 129。

[0043] 存储电极线 131 传输共电压并且主要在水平方向上延伸。每条存储电极线 131 设置在两条栅极线 121 之间并且包括多个存储电极 133。

[0044] 参照图 2 和图 4,每个存储电极 133 可以具有包括上部、下部、右部和左部的回路形状。存储电极 133 的上部包括分别向下和向上延伸并且彼此连接的扩展部分 134a 和扩展部分 134b。存储电极 133 的下部包括分别向上和向下延伸并且没有彼此连接的扩展部分 135a 和 135b。去除具有回路形状的存储电极 133 的位于扩展部分 135a 和 135b 之间的部分。存储电极 133 的上部和下部比右部和左部宽。

[0045] 栅极绝缘层 140 设置在栅极线 121 和存储电极线 131 上。

[0046] 一对第一半导体带(未示出)和第二半导体带(未示出)设置在栅极绝缘层 140 上。第一半导体带和第二半导体带主要在垂直方向上延伸。第一半导体带包括向第一栅电极 124a 突出的第一突出部分 154a,第二半导体带包括向第二栅电极 124b 突出的第二突出

部分 154b。

[0047] 欧姆接触带（未示出）、第一欧姆接触岛 165a 和第二欧姆接触岛（未示出）设置在半导体带上。欧姆接触带包括第一突出件 163a 和第二突出件（未示出），第一突出件 163a 和第一欧姆接触岛 165a 在半导体带的第一突出部分 154a 上设置成一对并且彼此面对，第二突出件和第二欧姆接触岛在半导体带的第二突出部分 154b 上设置成一对并且彼此面对。

[0048] 第一数据线 171a、第二数据线 171b 和第一漏电极 175a、第二漏电极 175b 设置在欧姆接触带和栅极绝缘层 140 上。

[0049] 第一数据线 171a 和第二数据线 171b 在垂直方向上延伸，从而与栅极线 121 和存储电极线 131 交叉，并且传输数据电压。第一数据线 171a 包括向第一栅电极 124a 延伸的第一源电极 173a 和具有宽面积的端部 179a。第二数据线 171b 包括向第二栅电极 124b 延伸的第二源电极 173b 和具有宽面积的端部 179b。第一数据线 171a 和第二数据线 171b 可以接收不同的电压。

[0050] 第一漏电极 175a 相对于第一栅电极 124a 与第一源电极 173a 相对，第二漏电极 175b 相对于第二栅电极 124b 与第二源电极 173b 相对。第一漏电极 175a 的端部和第二漏电极 175b 的端部被第一源电极 173a 和第二源电极 173b 的弯曲部分部分地包围。

[0051] 除了第一源电极 173a 和第一漏电极 175a 之间的沟道区以及第二源电极 173b 和第二漏电极 175b 之间的沟道区之外，半导体带可以具有与第一数据线 171a、第二数据线 171b 以及第一漏电极 175a 和第二漏电极 175b 的平面形状基本相同的平面形状。

[0052] 欧姆接触带设置在半导体带和第一数据线 171a、第二数据线 171b 之间，并且可以具有与第一数据线 171a 和第二数据线 171b 的平面形状基本相同的平面形状。第一欧姆接触岛和第二欧姆接触岛设置在半导体带和第一漏电极 175a、第二漏电极 175b 之间，并且具有与第一漏电极 175a 和第二漏电极 175b 的平面形状基本相同的平面形状。

[0053] 可以由无机绝缘材料（例如，氮化硅 ( $\text{SiN}_x$ ) 或氧化硅 ( $\text{SiO}_2$ )）制成的阻挡层 160 设置在第一数据线 171a、第二数据线 171b 和第一漏电极 175a 和第二漏电极 175b 上，滤色器 230 设置在阻挡层 160 上。

[0054] 滤色器 230 可以是在平行于第一数据线 171a 和第二数据线 171b 的方向上沿着列中的像素延伸的红色滤色器、绿色滤色器或蓝色滤色器。可以交替地布置具有红色滤色器的像素、具有绿色滤色器的像素和具有蓝色滤色器的像素。

[0055] 滤色器 230 包括多个开口 234a、234b、235a 和 235b。开口 234a、234b、235a 和 235b 分别与存储电极 133 的扩展部分 134a、134b、135a 和 135b 叠置。

[0056] 钝化层 180 设置在滤色器 230 上。钝化层 180 可以由无机绝缘材料（例如，氮化硅或氧化硅）制成，钝化层 180 可以防止滤色器 230 翘起并且可以防止化学溶液（例如，蚀刻剂）流入滤色器 230。

[0057] 钝化层 180、滤色器 230 和阻挡层 160 具有分别暴露第一漏电极 175a 和第二漏电极 175b 的多个接触孔 185a 和 185b，钝化层 180 和阻挡层 160 具有分别暴露第一数据线 171a 的端部 179a 和第二数据线 171b 的端部 179b 的多个接触孔 182a 和 182b。钝化层 180、阻挡层 160 和栅极绝缘层 140 具有分别暴露栅极线 121 的端部 129 的多个接触孔 181。

[0058] 像素电极 191 和多个接触辅助件 81、82a 和 82b 设置在钝化层 180 上。

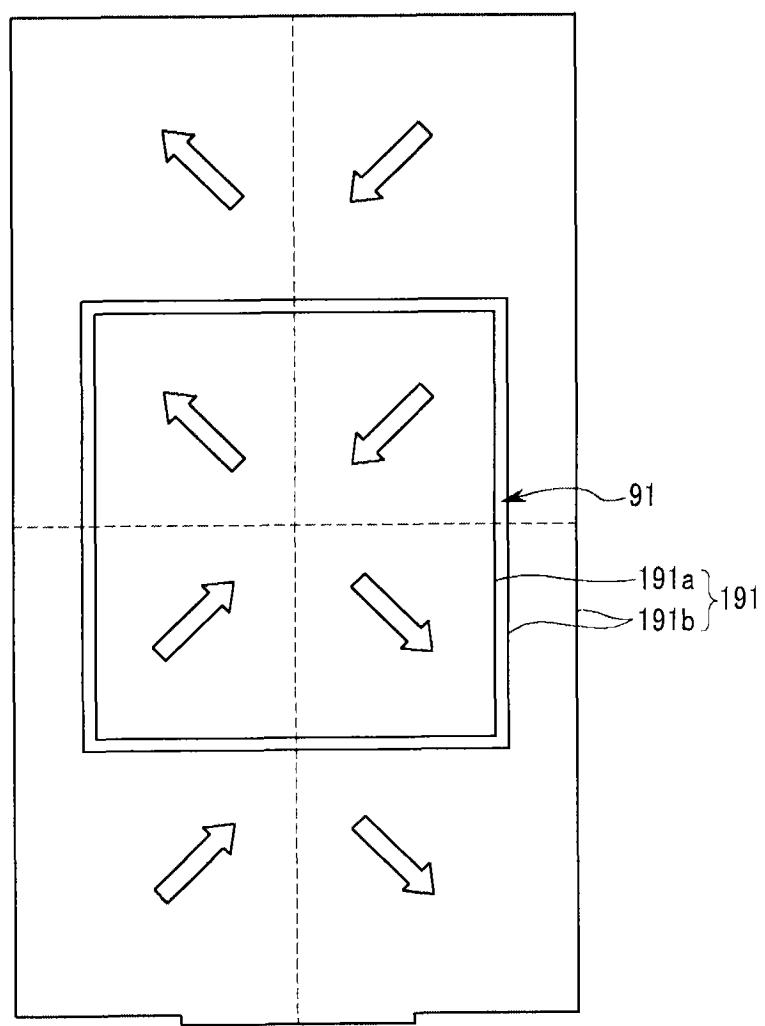

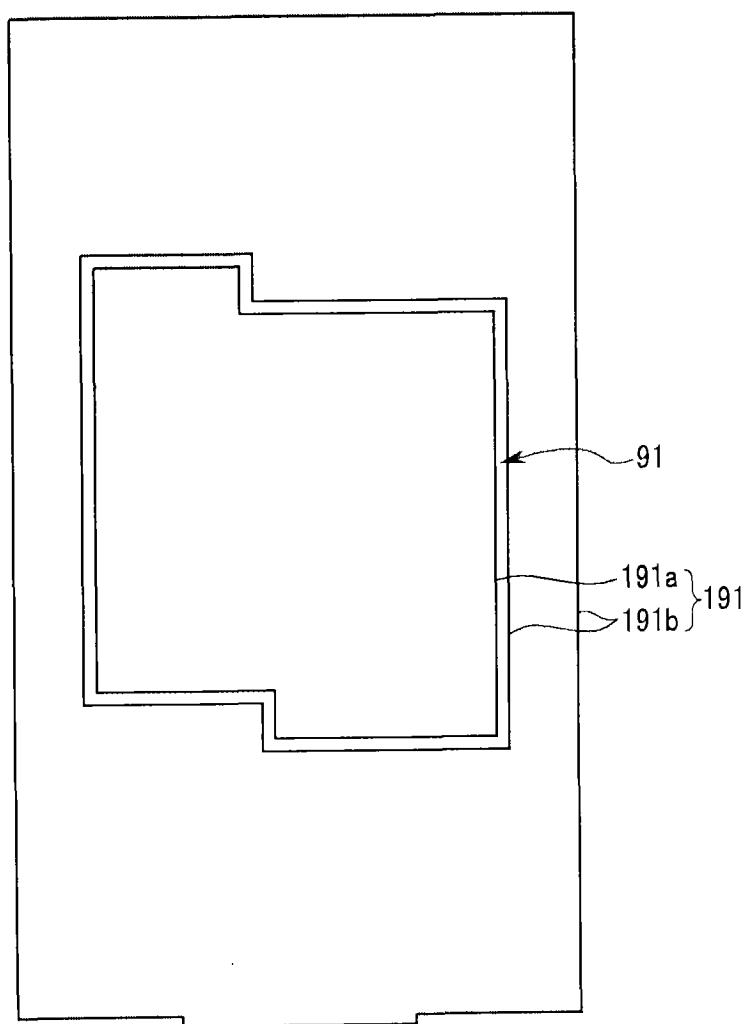

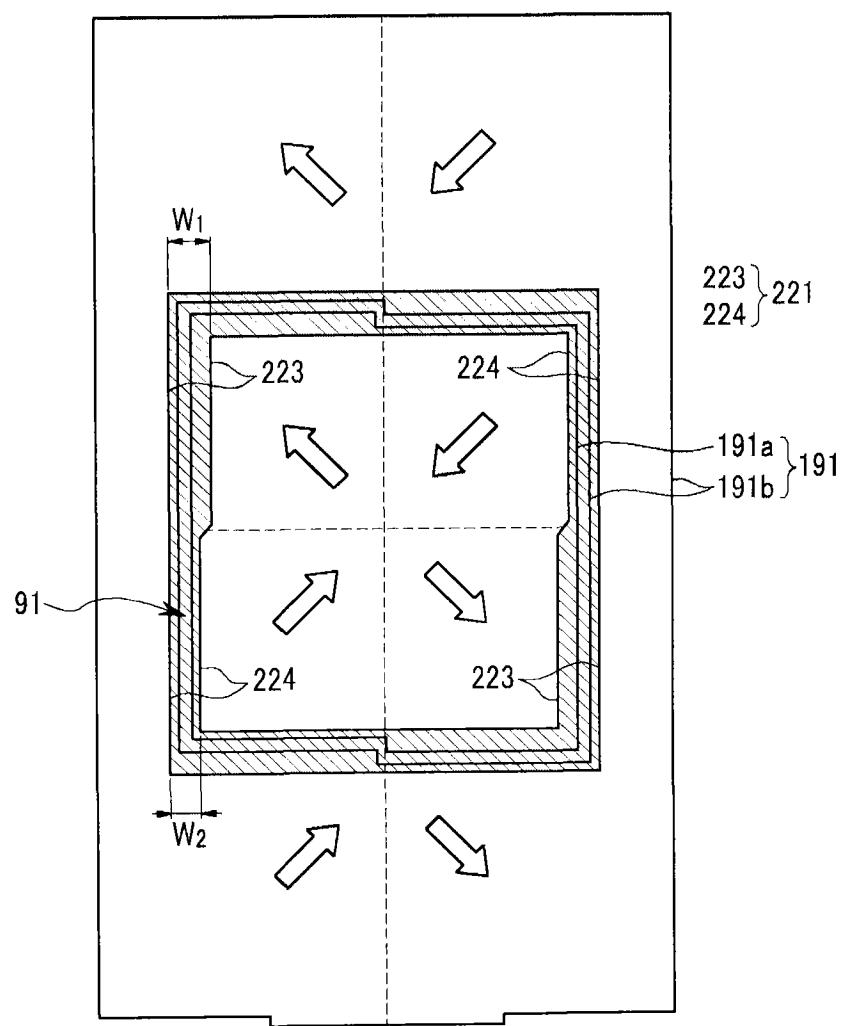

[0059] 像素电极 191 包括彼此分隔开并且其间具有间隙 91 的一对第一子像素电极 191a 和第二子像素电极 191b。如图 2 和图 3 中所示,第一子像素电极 191a 可以具有四边形形状,第二子像素电极 191b 包围第一子像素电极 191a,并且在第一子像素电极 191a 和第二子像素电极 191b 之间具有间隙 91。

[0060] 第一子像素电极 191a 和第二子像素电极 191b 之间的间隙 91 可以具有四边形回路形状,具有四边形回路形状的上述存储电极 133 与间隙 91 叠置并且用作屏蔽构件来阻挡第一子像素电极 191a 和第二子像素电极 191b 之间的光泄漏。

[0061] 另外,存储电极 133 的扩展部分 134a、134b、135a 和 135b 用作屏蔽构件来覆盖由于光取向引起的纹路,将在后面对此进行详细描述。

[0062] 另外,存储电极 133 的扩展部分 134a、135a、134b 和 135b 与第一子像素电极 191a 或者第二子像素电极 191b 叠置,来形成存储电容器 Cst。

[0063] 这就是说,第一子像素电极 191a 与存储电极 133 的扩展部分 134a 和 135a 叠置,来形成存储电容器 Csta。滤色器 230 的开口 234a 和 235a 设置在第一子像素电极 191a 与存储电极 133 的扩展部分 134a 和 135a 彼此叠置的位置,从而可以减小存储电容器 Csta 的绝缘体的厚度,这会增加存储电容。

[0064] 第二子像素电极 191b 与存储电极 133 的扩展部分 134b 和 135b 叠置,来形成存储电容器 Cstb。滤色器 230 的开口 234b 和 235b 设置在第二子像素电极 191b 与存储电极 133 的扩展部分 134b 和 135b 彼此叠置的位置,从而可以减小存储电容器 Cstb 的绝缘体的厚度,这会增加存储电容。

[0065] 第一栅电极 124a、半导体带的第一突出部分 154a、第一源电极 173a 和第一漏电极 175a 形成第一薄膜晶体管 Qa,第一薄膜晶体管 Qa 经过接触孔 185a 连接到第一子像素电极 191a。第二栅电极 124b、半导体带的第二突出部分 154b、第一源电极 173b 和第二漏电极 175b 形成第二薄膜晶体管 Qb,第二薄膜晶体管 Qb 经过接触孔 185b 连接到第二子像素电极 191b。

[0066] 按照这种方式,形成一个像素电极 191 的第一子像素电极 191a 和第二子像素电极 191b 分别连接到第一薄膜晶体管 Qa 和第二薄膜晶体管 Qb,从而第一子像素电极 191a 和第二子像素电极 191b 分别通过第一数据线 171a 和第二数据线 171b 接收不同的数据电压。可选地,第一子像素电极 191a 和第二子像素电极 191b 可以通过一条数据线在不同时间接收单独的数据电压,或者可以仅第一子像素电极 191a 连接到薄膜晶体管而第二子像素电极 191b 电容结合到第一子像素电极 191a,使得仅第一子像素电极 191a 接收数据电压,而第二子像素电极 191b 可以根据第一子像素电极 191a 的电压变化具有变化的电压。

[0067] 在这种情况下,第一子像素电极 191a 和第二子像素电极 191b 的面积比偏离大约 1 : 1,第二子像素电极 191b 大于第一子像素电极 191a。可以通过调整第一子像素电极 191a 的高度来调节第一子像素电极 191a 和第二子像素电极 191b 的面积比。这里,面积相对小的第一子像素电极 191a 的电压高于面积相对大的第二子像素电极 191b 的电压。

[0068] 按照这种方式,由于第一子像素电极 191a 和第二子像素电极 191b 的电压彼此不同,所以施加到第一子像素电极 191a 和共电极 270 之间的第一 LC 电容器 Clca 的电压与施加到第二子像素电极 191b 和共电极 270 之间的第二 LC 电容器 Clcb 的电压彼此不同,因此,第一子像素和第二子像素中的 LC 分子的倾斜角彼此不同。结果,两个子像素的亮度彼此不

同。因此,通过适当地调节第一 LC 电容器 C1ca 和第二 LC 电容器 C1cb 的电压,显示器的侧面示出的图像可以近似于显示器的前面示出的图像,这就是说,显示器的侧面的伽玛曲线可以近似接近显示器的前面的伽玛曲线,从而改进侧面可视性。

[0069] 接触辅助件 81、82a 和 82b 分别经过接触孔 181、182a 和 182b 连接到栅极线 121 的端部 129 以及数据线 171a 的端部 179a 和数据线 171b 的端部 179b。接触辅助件 81、82a 和 82b 补充栅极线 121 的端部 129、数据线 171a 的端部 179a 和数据线 171b 的端部 179b 与外部装置(例如,驱动器 IC)的粘附,并且保护端部 129、179a 和 179b。

[0070] 接着,将描述共电极面板 200 的结构。

[0071] 阻光构件 220 设置在绝缘基底 210 上,保护件 250 设置在阻光构件 220 上,共电极 270 设置在保护件 250 上。

[0072] 取向层 11 和 21 分别设置在薄膜晶体管阵列面板 100 和共电极面板 200 的相对表面上。取向层 11 和 21 是垂直取向层,取向层的表面具有根据区域而沿着不同方向倾斜的端部。

[0073] LC 层 3 设置在薄膜晶体管阵列面板 100 和共电极面板 200 之间。LC 层 3 包括具有负介电各向异性的多个 LC 分子 310。

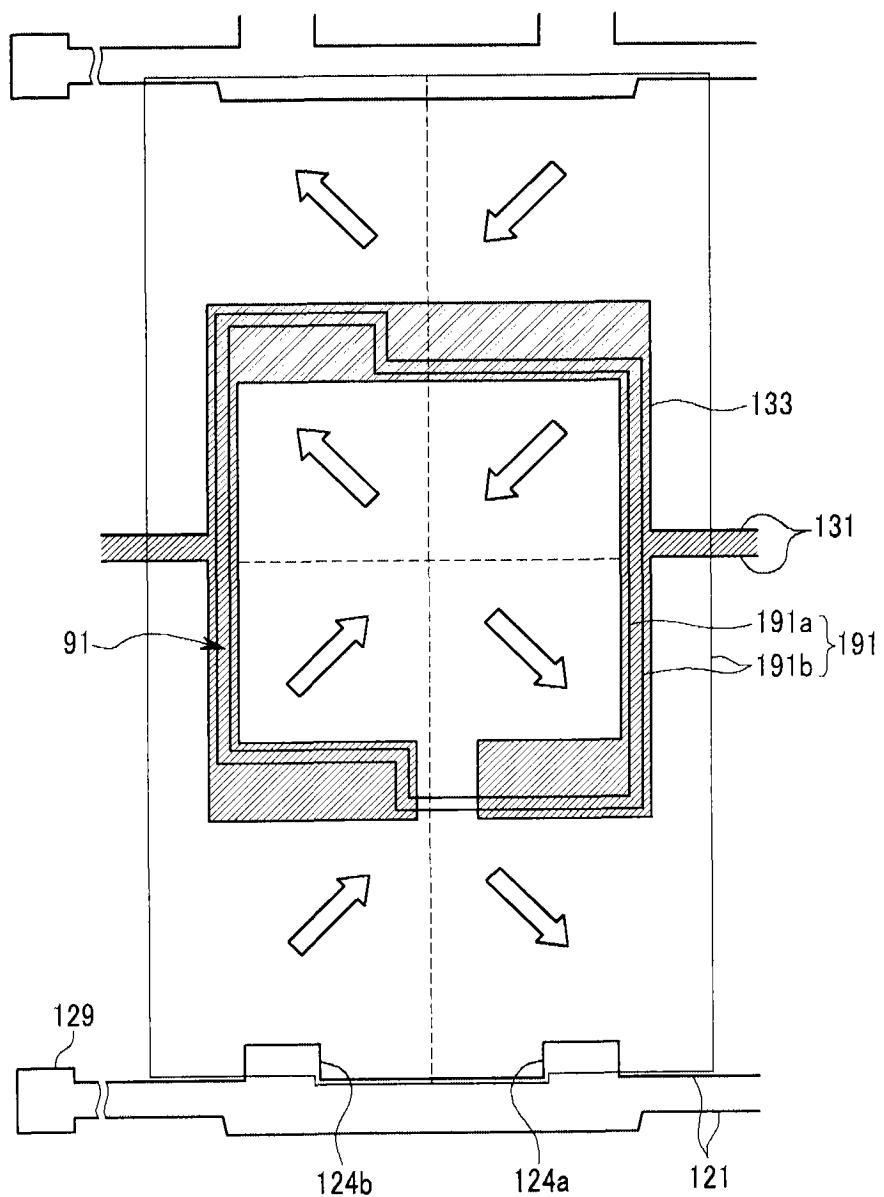

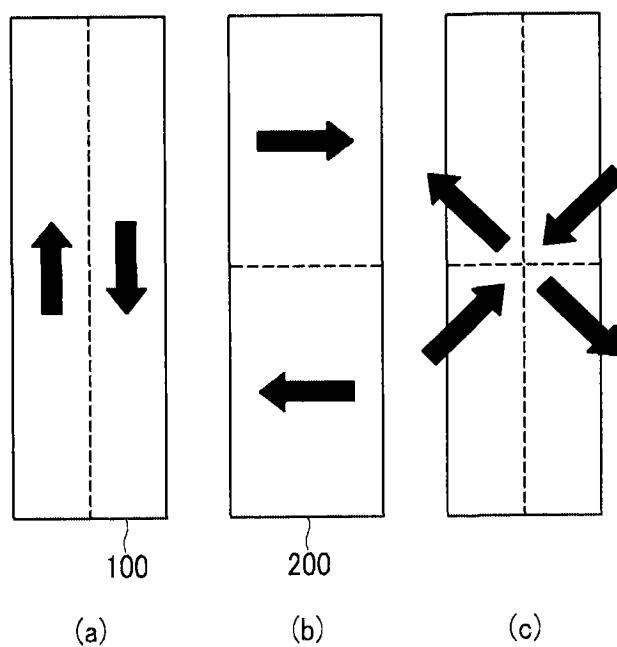

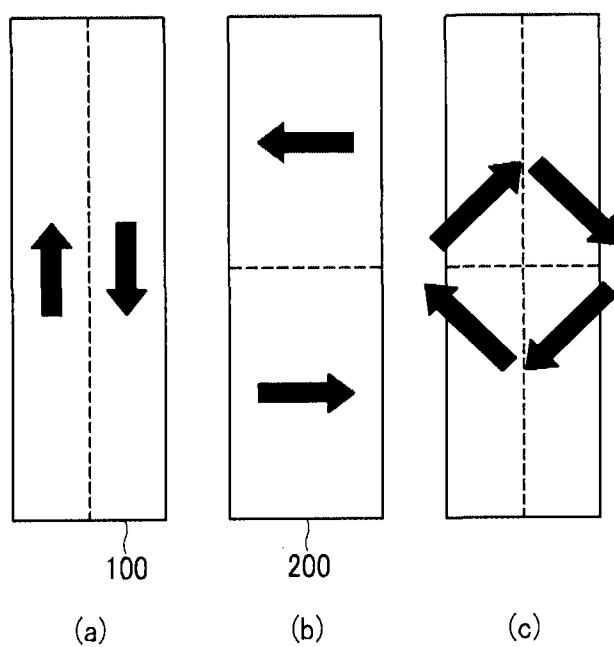

[0074] 参照图 2 和图 3,LC 层 3 的设置在第一子像素电极 191a 和共电极 270 之间的部分称作第一 LC 层,LC 层的设置在第二子像素电极 191b 和共电极 270 之间的部分称作第二 LC 层。第一 LC 层和第二 LC 层的 LC 分子 310 在四个不同方向上取向,如箭头所示。这就是说,每个子像素可以包括具有不同取向方向(例如,左上方向、左下方向、右上方向和右下方向)的 LC 分子的四个畴。这里,箭头的尾部表示 LC 分子 310 在取向之前的长轴方向,即,相对于基底的垂直方向,箭头的头部表示 LC 分子 310 的取向方向。然而,如果必要,LC 分子 310 的取向方向的数量可以为三个或少于三个、五个或者多于五个。

[0075] 可以通过将光照射到取向层 11 和 21 的光取向方法来形成这种畴。在光取向方法中,光倾斜地照射到垂直取向层,使得形成在取向层表面上的光反应链沿着光照射方向取向,当在各个方向倾斜地照射光时,可以形成多个畴。

[0076] 下面,将参照图 14、图 15、图 16 和图 17 来描述光取向方法。

[0077] 图 14 是示出光取向情况下的两个掩模的示意图,图 15 是示出通过采用图 14 中示出的掩模来照射光的方法的示意图,图 16 和图 17 是示出经历光取向方法的 LC 分子的取向的示意图。

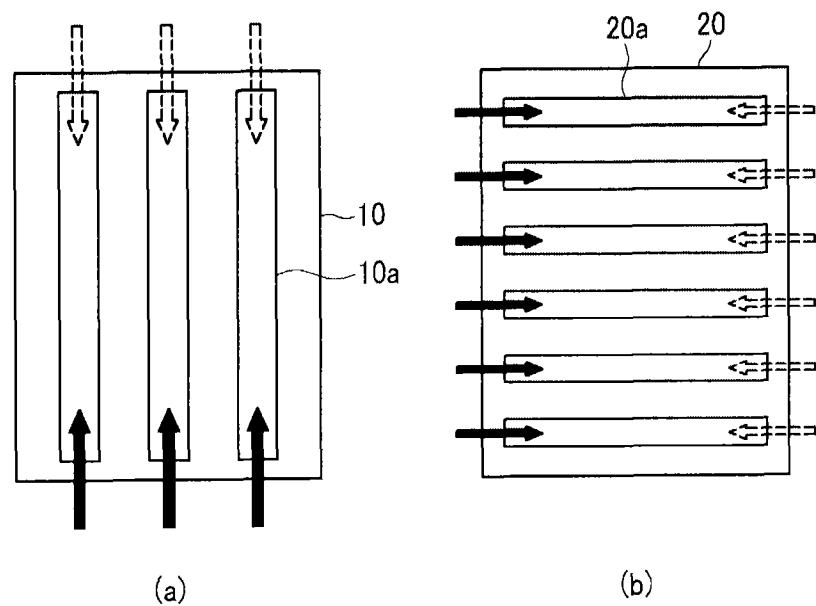

[0078] 参照图 14,在光取向情况下采用的掩模可以为包括平行于基底的长边的多个开口 10a 的第一掩模 10 或者包括垂直于基底的长边的多个开口 20a 的第二掩模 20。

[0079] 参照图 14 中的(a)和图 15 中的(a),第一掩模 10 定位在涂敷有取向层 11 的薄膜晶体管阵列面板 100 上,以倾斜角照射光(例如,紫外(UV)射线),来执行第一曝光。接着,在与第一曝光的方向相反的方向上倾斜地照射紫外(UV)射线,来执行第二曝光。

[0080] 这里,通过沿着平行于掩模 10 的开口 10a 的长轴的方向(即,图 14 中的(a)中的上下方向(箭头方向))移动来执行光照射。当不是通过沿着平行于开口 10a 的长轴的方向移动来执行光照射时,由于光衍射会导致实际被曝光的区域减少,还会减少基底和掩模之间的距离的工艺余量,并且会减小曝光角。可以通过改变基底或者照射光的装置的角度来执行将光倾斜地照射到取向层的表面上的方法。

[0081] 例如,可以从下侧向上侧用具有倾斜角的光照射像素区的左半部分,可以从上侧到下侧用具有倾斜角的光照射像素区的右半部分。因此,如图 16 中的 (a) 和图 17 中的 (a) 中所示,可以形成具有相反倾斜方向的 LC 分子的两个区域。

[0082] 类似地,参照图 14 中的 (b) 和图 15 中的 (b),第二掩模 20 在涂敷有取向层 21 的共电极面板 200 上定位,以倾斜角照射光(例如,UV 射线)来执行第三曝光。接着,在与第三曝光的方向相反的方向上倾斜地照射 UV 射线,来执行第四曝光。

[0083] 这里,通过沿着平行于掩模 20 的开口 20a 的长轴的方向(即,图 14 的 (b) 中的左右方向(箭头方向))移动来执行光照射。例如,可以从左侧到右侧用具有倾斜角的光照射像素区的上半部分,可以从右侧到左侧用具有倾斜角的光照射像素区的下半部分,因此,如图 16 中的 (b) 所示,可以形成具有相反的倾斜方向的 LC 分子的两个区域。可选地,可以从右侧向左侧用具有倾斜角的光照射像素区的上半部分,可以从左侧到右侧用具有倾斜角的光照射像素区的下半部分,因此,如图 17 中的 (b) 所示,可以形成具有相反的倾斜方向的 LC 分子的两个区域。

[0084] 按照这种方式,可以通过相对于取向层的表面倾斜地照射光来得到与沿着均匀方向擦取向层的效果相同的效果。即,根据光照射的方向来确定取向层的表面的取向方向,从而可以通过将一个像素分为多个区域并且对多个区域执行曝光来形成具有不同的预倾斜方向的 LC 分子的多个畴。

[0085] 参照图 16 和图 17,当组装具有沿着彼此相反的方向被照射的左半部分和右半部分的薄膜晶体管阵列面板 100 和具有沿着彼此相反的方向被照射的上半部分和下半部分的共电极面板 200 时,如图 16 中的 (c) 和图 17 中的 (c) 所示,可以形成分别在左下方向、左上方向、右下方向和右上方向上取向的四个畴。

[0086] 在本发明的示例性实施例中,采用光取向方法来在每个子像素中形成具有不同取向方向的四个畴。

[0087] 另一方面,与本发明的示例性实施例类似,除了光取向的取向方向之外,当一个像素包括两个子像素时,可以通过在第一子像素电极 191a 的边缘、第二子像素电极 191b 的边缘和位于第一子像素电极 191a 和第二子像素电极 191b 之间的间隙 91 附近的共电极 270 之间产生的边缘场来确定 LC 分子的取向方向。因此,因为由光取向确定的 LC 分子的取向方向与由两个子像素电极之间的间隙 91 附近产生的边缘场确定的 LC 分子的取向方向不同,所以在两个子像素电极之间的间隙 91 附近会产生由于 LC 分子的不规则布置导致的纹路。

[0088] 检测到在 LC 分子向间隙 91 倾斜的区域中产生纹路,即,在图 3 中的放置箭头的头部的区域产生纹路。参照图 3,在本示例性实施例中产生纹路的位置在第一子像素电极 191a 的左上部和右下部以及第二子像素电极 191b 的右上部和左下部。

[0089] 因此,如图 2 中所示,在本发明的示例性实施例中,作为屏蔽构件的存储电极 133 覆盖第一子像素电极 191a 的左上部和右下部、第二子像素电极 191b 的右上部和左下部以及间隙 91 的周围,来覆盖纹路。因此,可以改进透射率,并且可以防止纹路从外部显示为斑点,从而提高显示特性。

[0090] 在该示例性实施例中,用作屏蔽构件的存储电极设置在与栅极线的层相同的层上,但是不限于此,存储电极可以设置在与数据线的层相同的层上。另外,当存储电极仅用作屏蔽构件时,存储电极可以不设置在与栅极线或数据线的层相同的层上,而是可以设置

在与共电极面板 200 的阻光构件 220 的层相同的层上。另外,当存储电极设置在与阻光构件的层相同的层上时,阻光构件 220 可以设置在薄膜晶体管阵列面板 100 上。

[0091] [示例性实施例 2]

[0092] 接着,将参照图 6、图 7、图 8 和图 9 来详细描述本发明的另一示例性实施例。省略了与前面的示例性实施例重复的描述,相同的组成元件用相同的标号表示。

[0093] 图 6 是根据本发明另一示例性实施例的 LCD 的布局图,图 7、图 8 和图 9 是示出图 6 中的 LCD 中的像素电极和栅极导体的布局图。

[0094] 如前面描述的示例性实施例,该示例性实施例包括薄膜晶体管阵列面板 100 和共电极面板 200 以及形成在这两个面板之间的 LC 层 3。

[0095] 除了本示例性实施例包括与前面描述的示例性实施例的像素电极和存储电极的形状不同的像素电极 191 和存储电极 133 之外,薄膜晶体管阵列面板 100 和共电极面板 200 的沉积结构与前面描述的示例性实施例的薄膜晶体管阵列面板和共电极面板的沉积结构相同。

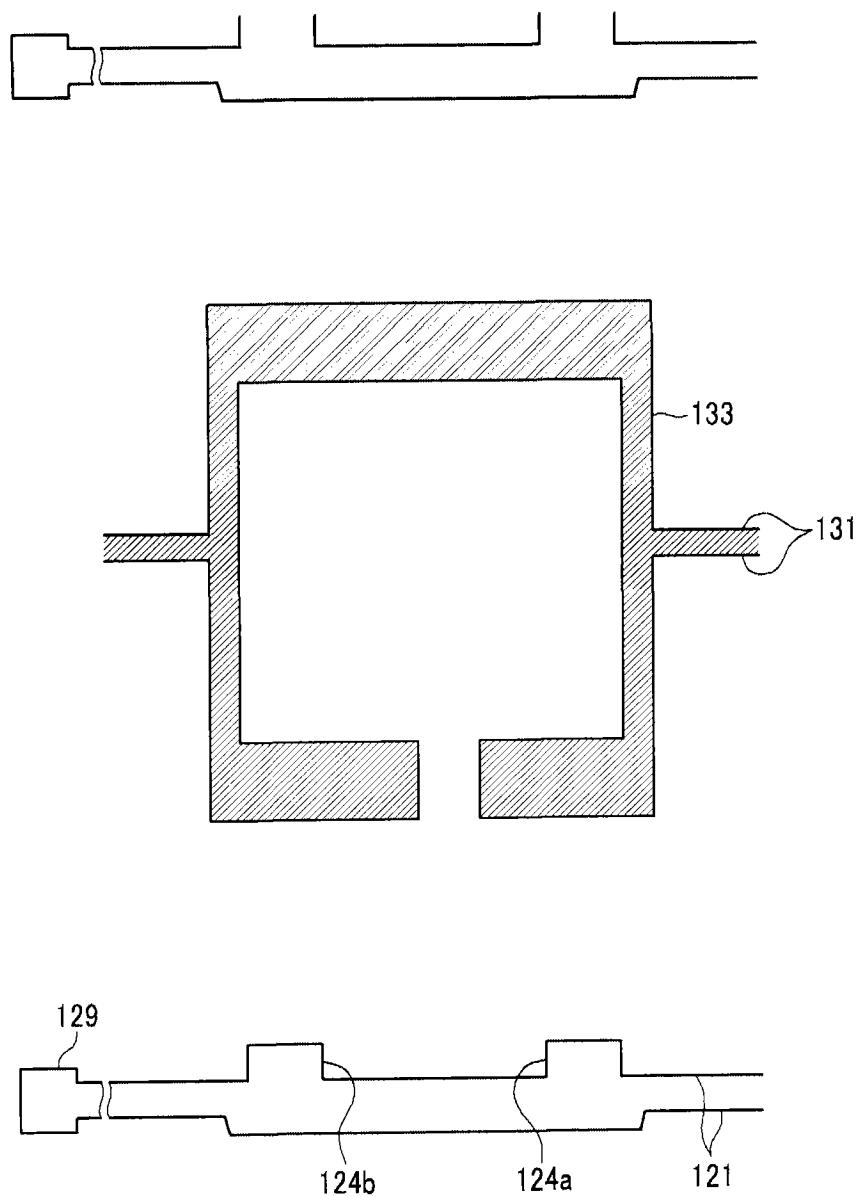

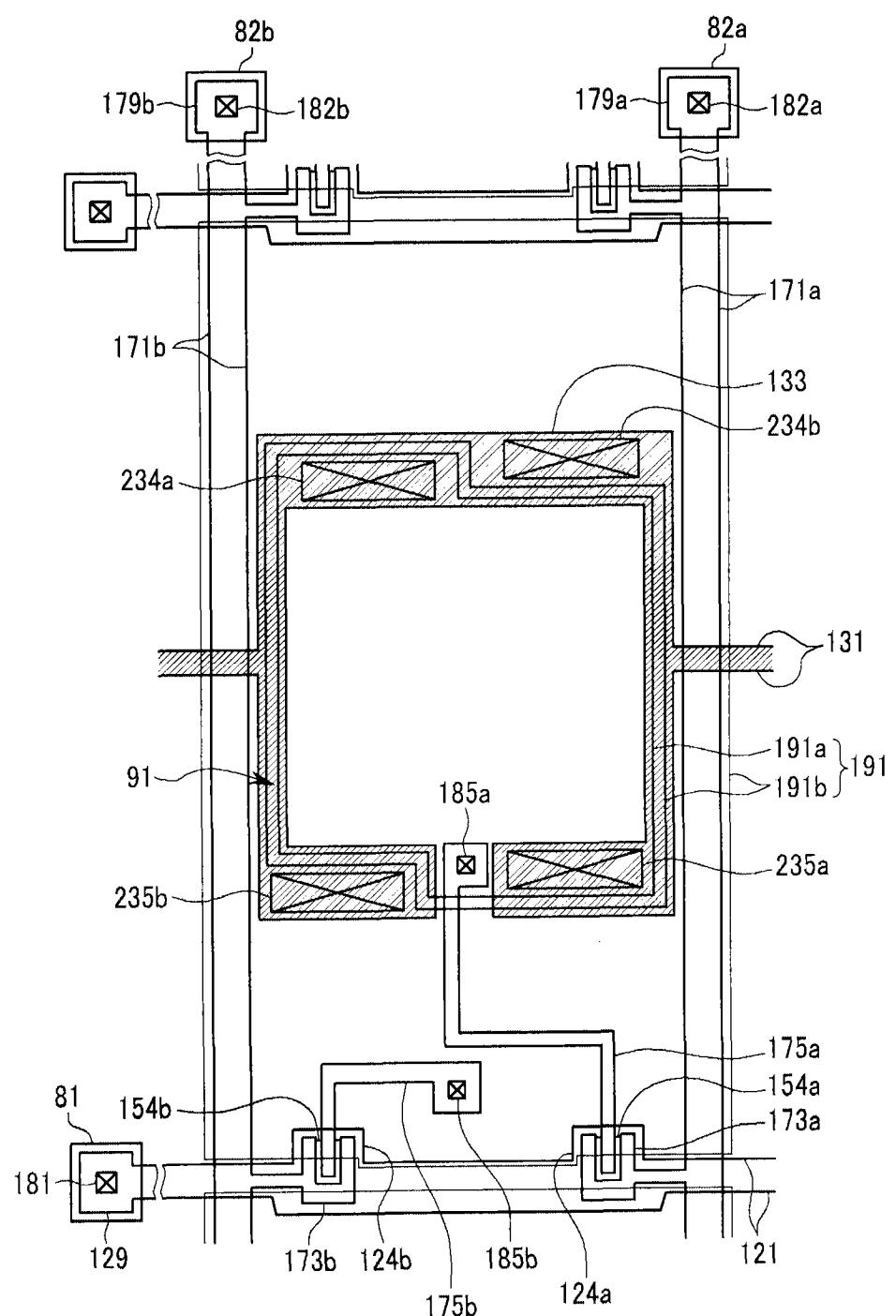

[0096] 参照图 6 和图 7,根据本示例性实施例的像素电极 191 包括一对第一子像素电极 191a 和第二子像素电极 191b,第一子像素电极 191a 和第二子像素电极 191b 被位于它们之间的间隙 91 分开。

[0097] 第一子像素电极 191a 的上边缘和下边缘具有阶梯形状。详细地讲,第一子像素电极 191a 的左上部向上延伸,右下部向下延伸。第二子像素电极 191b 包围第一子像素电极 191a。

[0098] 参照图 6 和图 8,存储电极 133 具有包括上部、下部、左部和右部的四边形回路形状。与前面描述的示例性实施例不同,存储电极 133 的上部、下部、左部和右部分别具有均匀的宽度,而不包括向上或向下延伸的部分。存储电极 133 的上部和下部比左部和右部宽,并且省略了下部中的一部分。

[0099] 参照图 6 和图 9,存储电极 133 用作屏蔽构件,来阻挡第一子像素电极 191a 和第二子像素电极 191b 之间的间隙 91 处的第一子像素电极 191a 和第二子像素电极 191b 之间的光泄漏。

[0100] 另外,存储电极 133 的上部和下部覆盖具有阶梯形状的第一子像素电极 191a 的上边缘和下边缘,使得存储电极 133 的上部和下部用作屏蔽构件来覆盖在该区域中产生的纹路。

[0101] 如前面描述的示例性实施例,当 LC 层的设置在第一子像素电极 191a 和共电极 270 之间的部分被称作第一 LC 层,LC 层的设置在第二子像素电极 191b 和共电极 270 之间的部分被称作第二 LC 层时,第一 LC 层和第二 LC 层的 LC 分子 310 沿着四个不同的方向取向,如箭头所示。即,每个子像素可以包括具有不同取向方向(例如,左上方向、左下方向、右上方向和右下方向)的 LC 分子的四个畴。这种畴可以通过如上所述的光取向方法来形成。

[0102] 如上所述,在 LC 分子的方向向间隙 91 倾斜的区域中产生纹路,即,第一子像素电极 191a 的左上部和右下部以及第二子像素电极 191b 的右上部和左下部,如图 9 中的箭头的头部所定位的。

[0103] 在本示例性实施例中,产生纹路的第一子像素电极 191a 的左上部和右下部延伸,延伸的部分被具有四边形回路形状的存储电极覆盖,来有效地覆盖纹路。

[0104] 在这种结构中,可以容易地控制滤色器 230 的开口 234a、234b、235a 和 235b 的面积比,从而可以防止视角特性不对称,可以提高透过率,并且可以通过适当地覆盖纹路来提高显示特性。另外,与前面描述的示例性实施例相比,可以提高开口率。

[0105] [示例性实施例 3]

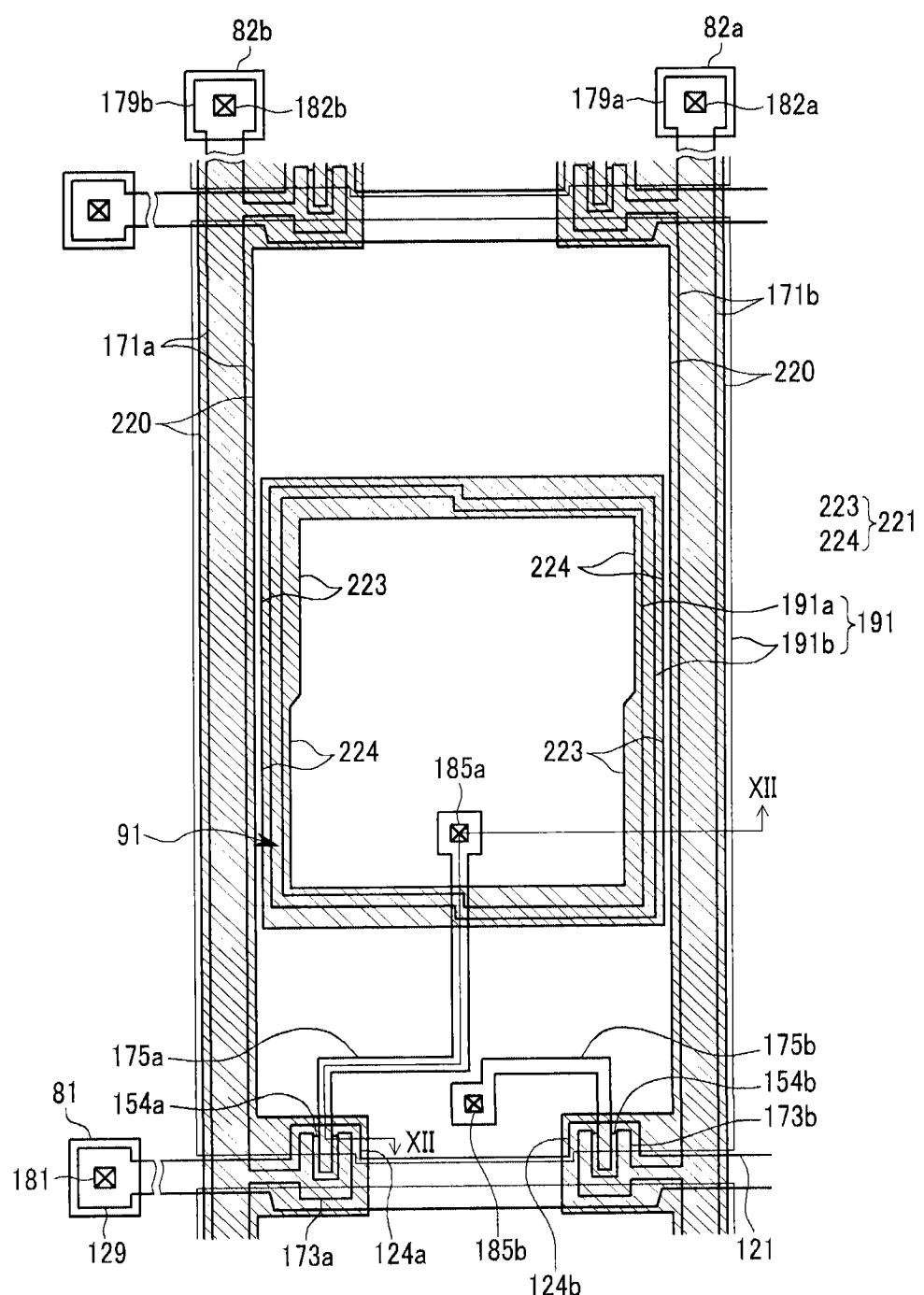

[0106] 接着,将参照图 10、图 11 和图 12 来详细描述本发明的又一示例性实施例。省略了与前面的示例性实施例重复的描述,相同的组成元件用相同的标号表示。

[0107] 图 10 是根据本发明又一示例性实施例的 LCD 的布局图,图 11 是示出图 10 中的 LCD 中的像素电极和屏蔽构件的示意图,图 12 是沿着图 10 中的线 XII-XII 截取的剖视图。

[0108] 如前面描述的示例性实施例,本示例性实施例包括薄膜晶体管阵列面板 100 和共电极面板 200 以及位于这两个面板之间的 LC 层 3。

[0109] 除了本示例性实施例中滤色器 230 设置在共电极面板 200 上之外,薄膜晶体管阵列面板 100 和共电极面板 200 的沉积结构与前面示例性实施例的薄膜晶体管阵列面板和共电极面板的沉积结构几乎相同。另外,在本示例性实施例中省略了前面示例性实施例的存储电极线 131,代替的是,与第一子像素电极 191a 和第二子像素电极 191b 之间的间隙 91 叠置的屏蔽构件 221 包含在共电极面板 200 中。

[0110] 首先,在薄膜晶体管阵列面板 100 中,包括第一栅电极 124a、第二栅电极 124b 和宽端部 129 的栅极线 121 设置在绝缘基底 110 上,栅极绝缘层 140 设置在栅极线 121 上。

[0111] 包括第一突出部分 154a 和第二突出部分 154b 的半导体带 151b 设置在栅极绝缘层 140 上,欧姆接触带 161b、第一欧姆接触岛 165a 和第二欧姆接触岛(未示出)设置在半导体带 151b 上。

[0112] 多条第一数据线 171a、多条第二数据线 171b 以及多对第一漏电极 175a 和第二漏电极 175b 设置在欧姆接触带和栅极绝缘层 140 上,钝化层 180 设置在多条第一数据线 171a、多条第二数据线 171b 以及多对第一漏电极 175a 和第二漏电极 175b 上。钝化层 180 具有分别暴露第一漏电极 175a、第二漏电极 175b 和第一数据线 171a 的端部 179a、第二数据线 171b 的端部 179b 的多个接触孔 185a、185b、182a 和 182b,钝化层 180 和栅极绝缘层 140 具有暴露栅极线 121 的端部 129 的接触孔 181。

[0113] 像素电极 191 和多个接触辅助件 81、82a 和 82b 设置在钝化层 180 上。

[0114] 像素电极 191 包括用其间的间隙 91 来彼此分开的一对第一子像素电极 191a 和第二子像素电极 191b。第一子像素电极 191a 的上边缘和下边缘可以具有阶梯形状。具体地讲,第一子像素电极 191a 的左上部向上延伸,右下部向下延伸。第二子像素电极 191b 包围第一子像素电极 191a。

[0115] 下面,将描述共电极面板 200。

[0116] 多个阻光构件 220 和多个屏蔽构件 221 设置在绝缘基底 210 上。阻光构件 220 包括与数据线 171 对应的直部分和与薄膜晶体管对应的扩展部分。每个屏蔽构件 221 具有包括上部、下部、右部和左部的四边形回路形状,并且有效地覆盖第一子像素电极 191a 和第二子像素电极 191b 之间的间隙以及第一子像素电极 191a 的阶梯形部分。

[0117] 屏蔽构件 221 的左部和右部分别包括宽部 223 和窄部 224。这里,参照图 11,宽部 223 的宽度 W1 比窄部 224 的宽度 W2 宽大约  $4 \mu m$  至  $7 \mu m$ 。按照这种方式,宽部 223 可以有效地覆盖在第一子像素电极 191a 和第二子像素电极 191b 之间的间隙 91 附近沿着垂直方

向产生的纹路。

[0118] 滤色器 230R 和 230G 设置在阻光构件 220 和屏蔽构件 221 上, 保护件 250 和共电极 270 设置在滤色器 230R 和 230G 上。

[0119] 取向层 11 和 21 分别设置在薄膜晶体管阵列面板 100 和共电极面板 200 的相对表面上, 取向层 11 和 21 具有通过光取向方法沿着各种方向倾斜的部分。

[0120] LC 分子 310 沿着各种方向取向的 LC 层 3 设置在薄膜晶体管阵列面板 100 和共电极面板 200 之间。

[0121] [示例性实施例 4]

[0122] 下面, 将参照图 13 来详细地描述本发明的又一示例性实施例。

[0123] 图 13 是根据本发明又一示例性实施例的 LCD 的布局图。

[0124] 除了第一子像素电极 191a 的上边缘的阶梯形部分与第二子像素电极 191b 的垂直中心线对齐之外, 本示例性实施例与示例性实施例 2 几乎相同。按照这种方式, 因为第一子像素电极 191a 的上边缘的阶梯形部分与第二子像素电极 191b 的垂直中心线对齐, 所以可以有效地覆盖由于不对称产生的纹路。

[0125] 本领域技术人员应该清楚的是, 在不脱离本发明的精神或范围的情况下, 可以对本发明进行各种修改和变化。因此, 如果对本发明的修改和变化落入权利要求及其等同物的范围内, 则本发明意图覆盖这些修改和变化。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8

图 9

图 10

图 11

图 12

图 13

图 14

(a)

(b)

图 15

图 16

图 17

|                |                                                                                     |         |            |

|----------------|-------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                                                               |         |            |

| 公开(公告)号        | <a href="#">CN102566125A</a>                                                        | 公开(公告)日 | 2012-07-11 |

| 申请号            | CN201210019694.4                                                                    | 申请日     | 2008-07-22 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                            |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                            |         |            |

| 当前申请(专利权)人(译)  | 三星电子株式会社                                                                            |         |            |

| [标]发明人         | 郑美惠<br>蔡钟哲<br>李庸羽<br>金玲究                                                            |         |            |

| 发明人            | 郑美惠<br>蔡钟哲<br>李庸羽<br>金玲究                                                            |         |            |

| IPC分类号         | G02F1/1333 G02F1/1343 G02F1/1362                                                    |         |            |

| CPC分类号         | G02F1/133707 G02F2001/134345 G02F2001/133742 G02F1/136213 G02F1/133788 G02F1/136209 |         |            |

| 代理人(译)         | 韩芳                                                                                  |         |            |

| 优先权            | 1020080008999 2008-01-29 KR                                                         |         |            |

| 其他公开文献         | <a href="#">CN102566125B</a>                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">SIPO</a>                                      |         |            |

## 摘要(译)

本发明公开了一种液晶显示器，根据本发明的液晶显示器包括：第一基底和第二基底，彼此面对；像素电极，设置在第一基底上并且包括第一子像素电极和通过间隙与第一子像素电极分隔开的第二子像素电极；共电极，设置在第二基底上；屏蔽构件，设置在第一基底或第二基底上并且与第一子像素电极和第二子像素电极之间的间隙叠置；取向层，设置在像素电极和共电极中的至少一个上；液晶层，设置在第一基底和第二基底之间。