(12) 发明专利

(10) 授权公告号 CN 101893800 B

(45) 授权公告日 2014.09.17

(21) 申请号 201010227534.X

审查员 胡阳

(22) 申请日 2002.06.11

(30) 优先权数据

2001-72885 2001.11.22 KR

(62) 分案原申请数据

02804752.4 2002.06.11

(73) 专利权人 三星显示有限公司

地址 韩国京畿道

(72) 发明人 宋长根

(74) 专利代理机构 北京市柳沈律师事务所

11105

代理人 张波

(51) Int. Cl.

G02F 1/139 (2006.01)

G02F 1/1333 (2006.01)

(56) 对比文件

KR 2000-0090458 A, 2001.10.18, 全文 .

权利要求书3页 说明书9页 附图13页

(54) 发明名称

用于液晶显示器的薄膜晶体管阵列板

(57) 摘要

本发明涉及一种液晶显示器，包括：第一基板；在第一基板上的像素区，划分为第一部分和第二部分；第二基板，面对第一基板；和液晶层，插置在第一基板与第二基板之间，其中在第一部分和第二部分中的每个上的液晶层划分为多个畴，多个畴的每个由施加电场时液晶分子的方向来定义，第二部分的电场值小于第一部分的电场值。

1. 一种液晶显示器，包括：

第一基板；

在所述第一基板上的像素区，划分为第一部分和第二部分；

第二基板，面对所述第一基板；和

液晶层，插置在所述第一基板与所述第二基板之间，其中在所述第一部分和所述第二部分中的每个上的所述液晶层划分为多个畴，所述多个畴中的每个由施加电场时液晶分子的方向来定义，

其特征在于：

所述第二部分的电场值小于所述第一部分的电场值，和

在所述第二部分的畴中的所述液晶分子左右倾斜，在所述第一部分的畴中的所述液晶分子上下倾斜。

2. 如权利要求 1 所述的液晶显示器，还包括多个第一导线和在所述第一基板上的像素电极。

3. 如权利要求 2 所述的液晶显示器，其中所述像素电极通过第一薄膜晶体管电连接到所述第一导线。

4. 如权利要求 2 所述的液晶显示器，还包括多个第二导线，其中所述第二导线的每个分别设置在两个相邻的第一导线之间。

5. 如权利要求 4 所述的液晶显示器，其中第二导线与所述像素电极电容耦合。

6. 如权利要求 5 所述的液晶显示器，其中所述像素电极与第二导线的一部分重叠。

7. 如权利要求 1 所述的液晶显示器，其中所述液晶层的所述畴由畴分隔元件划分。

8. 如权利要求 7 所述的液晶显示器，其中所述畴分隔元件形成在所述第一基板上。

9. 如权利要求 8 所述的液晶显示器，其中所述畴分隔元件包括多个狭缝，该多个狭缝形成在所述第一基板上的所述像素区的所述第一部分中。

10. 如权利要求 9 所述的液晶显示器，其中所述狭缝的宽度为  $2 \mu m$  至  $5 \mu m$ 。

11. 如权利要求 1 所述的液晶显示器，其中畴的所述液晶分子最初以相对于所述第一基板的垂直方向排列。

12. 如权利要求 11 所述的液晶显示器，其中所述液晶层的所述畴由畴分隔元件划分。

13. 如权利要求 12 所述的液晶显示器，其中所述畴分隔元件形成在所述第一基板上。

14. 如权利要求 13 所述的液晶显示器，其中所述畴分隔元件包括多个狭缝，该多个狭缝形成在所述第一基板上的所述像素区的所述第一部分中。

15. 如权利要求 14 所述的液晶显示器，其中所述狭缝的宽度为  $2 \mu m$  至  $5 \mu m$ 。

16. 一种液晶显示器，包括：

第一基板；

多个像素，所述像素的至少一个包括分别设置在第一基板上的相同层上的第一像素电极和第二像素电极；

第二基板，面对所述第一基板；和

液晶层，插置在所述第一基板与所述第二基板之间，其中在所述第一像素电极和所述第二像素电极中的每个上的所述液晶层划分为多个畴，所述多个畴中的每个由施加电场时液晶分子的方向来定义，

其特征在于：

所述第二像素电极产生的电场值小于所述第一像素电极产生的电场值，和

在所述第二像素电极的畴中的所述液晶分子左右倾斜，在所述第一像素电极的畴中的所述液晶分子上下倾斜。

17. 如权利要求 16 所述的液晶显示器，还包括形成在所述第一基板上的多个第一导线。

18. 如权利要求 17 所述的液晶显示器，其中所述第一像素电极通过第一薄膜晶体管电连接到所述第一导线，所述第二像素电极通过第二薄膜晶体管电连接到所述第一导线。

19. 如权利要求 17 所述的液晶显示器，其中所述第一像素电极和所述第二像素电极彼此成对地位于所述第一导线的相反侧。

20. 如权利要求 19 所述的液晶显示器，其中所述第一像素电极通过第一薄膜晶体管电连接到所述第一导线中的一条，所述第二像素电极通过第二薄膜晶体管电连接到该条第一导线。

21. 如权利要求 17 所述的液晶显示器，还包括多个第二导线，其中所述第二导线的至少一个设置在两个相邻第一导线之间。

22. 如权利要求 21 所述的液晶显示器，其中所述第二导线与所述第一像素电极和所述第二像素电极中的至少一个电容耦合。

23. 如权利要求 22 所述的液晶显示器，其中所述第二导线与相邻像素的所述第一像素电极和所述第二像素电极之一电容耦合。

24. 如权利要求 21 所述的液晶显示器，其中所述第一像素电极与所述第二导线的一部分重叠。

25. 如权利要求 24 所述的液晶显示器，其中所述第二像素电极与所述第二导线的一部分重叠，第二导线的该部分不同于与所述第一像素电极重叠的所述第二导线的一部分。

26. 如权利要求 16 所述的液晶显示器，其中所述液晶层的所述畴由畴分隔元件划分。

27. 如权利要求 26 所述的液晶显示器，其中所述畴分隔元件形成在所述第一基板上。

28. 如权利要求 26 所述的液晶显示器，其中所述畴分隔元件包括多个狭缝。

29. 如权利要求 28 所述的液晶显示器，其中所述狭缝的宽度为  $2 \mu m$  至  $5 \mu m$ 。

30. 如权利要求 16 所述的液晶显示器，其中畴的所述液晶分子最初以相对于所述第一基板的垂直方向排列。

31. 如权利要求 30 所述的液晶显示器，其中所述液晶层的所述畴由畴分隔元件划分。

32. 如权利要求 31 所述的液晶显示器，其中所述畴分隔元件形成在所述第一基板上。

33. 如权利要求 32 所述的液晶显示器，其中所述畴分隔元件包括在所述第一像素电极中的多个狭缝。

34. 如权利要求 33 所述的液晶显示器，其中所述狭缝的宽度为  $2 \mu m$  至  $5 \mu m$ 。

35. 如权利要求 16 所述的液晶显示器，其中施加到所述第一像素电极的电压高于施加到所述第二像素电极的电压。

36. 如权利要求 16 所述的液晶显示器，还包括连接到所述第二像素电极的连接电极。

37. 如权利要求 36 所述的液晶显示器，其中所述连接电极通过形成在绝缘层中的接触孔与所述第二像素电极接触。

38. 如权利要求 37 所述的液晶显示器,其中所述连接电极经由所述绝缘层与所述第一像素电极重叠。

39. 如权利要求 38 所述的液晶显示器,还包括多个第二导线,其中所述第二导线中至少一个设置在两个相邻第一导线之间。

40. 如权利要求 39 所述的液晶显示器,其中所述第二导线与所述第一像素电极和所述第二像素电极中至少一个电容耦合。

41. 如权利要求 39 所述的液晶显示器,其中所述第二导线与相邻像素的所述第一像素电极和所述第二像素电极之一电容耦合。

42. 如权利要求 41 所述的液晶显示器,其中所述第一像素电极与所述第二导线的一部分重叠。

43. 如权利要求 42 所述的液晶显示器,其中所述第二像素电极与第二导线的一部分重叠,第二导线的该部分不同于与所述第一像素电极重叠的所述第二导线的一部分。

44. 如权利要求 43 所述的液晶显示器,其中所述连接电极与所述第二导线的至少一部分重叠,该第二导线与所述第一像素电极重叠。

45. 如权利要求 16 所述的液晶显示器,其中所述第一像素电极的区域不同于所述第二像素电极的区域。

46. 如权利要求 45 所述的液晶显示器,其中所述第一像素电极的区域占据所述第一像素电极和所述第二像素电极的区域的 30% 至 70%。

47. 如权利要求 16 所述的液晶显示器,其中所述第一像素电极和第二像素电极彼此绝缘。

## 用于液晶显示器的薄膜晶体管阵列板

[0001] 本申请是申请日为 2002 年 6 月 11 日且发明名称为“用于液晶显示器的薄膜晶体管阵列板”的中国发明专利申请 No. 02804752.4 的分案申请。

### 技术领域

[0002] 本发明涉及一种用于液晶显示器的薄膜晶体管阵列板。

### 背景技术

[0003] 一般的液晶显示器具有两个带有电极的面板和夹在两面板之间的液晶层。对该电极施加电压，使得液晶层中的液晶分子重新取向，由此控制光的透射。

[0004] 液晶显示器有一个严重的缺点是窄视角。为了解决此问题，研制开发了各种扩大视角的技术。例如，已经提出在像素电极和公共电极处形成开口或凸起的预定图案的同时，可以垂直于上下面板地排列液晶分子。

[0005] 在形成开口图案的情况下，通过由于形成在像素电极和公共电极处的开口所致的边缘电场控制液晶分子的取向。

[0006] 在形成凸起图案的情形中，凸起形成在像素电极和公共电极处，通过由于凸起而变形的电场来控制液晶分子的取向。

[0007] 另外，可以在上面板的公共电极处形成凸起图案的同时，在下面板的像素电极处形成开口图案。通过由于开口和凸起所致的边缘电场来控制液晶分子的取向，同时形成多个畴。

[0008] 在这种多畴液晶显示器中，在所有方向上，每 1 : 10 对比度的视角或定义为灰色度标级间亮度转化的限制角的视角极好地达到了 80° 或更大。但是，横向伽玛曲线偏离前伽玛曲线，使得甚至与扭曲向列 (TN) 模式的液晶显示器相比，左右侧的可见度降低。例如，在用于分隔畴而形成开口部分的图案化垂直排列 (PVA) 模式中，当涉及横向面时，屏幕整体变得较亮，且颜色变成白色。在严重的情况下，当集聚图像影象时，消除了亮灰色度标等级之间的距离差。但是，随着监视器被用于多媒体的目的，监视器的可见度变得越来越重要。

### 发明内容

[0009] 本发明的一个目的在于提供一种具有极佳的横向面可见度的多畴液晶显示器。

[0010] 本发明的上述及其它目的可以通过一种具有下列特征的液晶显示器实现。左右畴内建立的电场比上下畴内的电场弱。

[0011] 根据本发明的一个方面，液晶显示器具有多个像素区。每个像素区具有多个微畴 (micro domains)。微畴包括一第一定向畴和一第二定向畴，在施加电场时，微畴中的液晶分子具有不同的平均倾斜方向。第一定向畴内的电场比第二定向畴内的电场弱一预定的值。

[0012] 从正面看时，第一定向畴中的液晶分子左右倾斜，而第二定向畴中的液晶分子上

下倾斜。第一定向畴和第二定向畴之间电场差的预定值在  $0.02/d(V/\mu m) \sim 0.5/d(V/\mu m)$  的范围内，其中的 d 为单元间隙。

[0013] 根据本发明的另一方面，液晶显示器具有一第一绝缘衬底和一沿第一方向形成在第一绝缘衬底上的第一信号线。一第二信号线沿第二方向形成在第一绝缘衬底上并以绝缘的方式与第一信号线相交。第一薄膜晶体管连结到第一和第二信号线。第二薄膜晶体管连结到与第一薄膜晶体管相连的第一和第二信号线。第一像素电极连结到第一薄膜晶体管。第二像素电极连结到第二薄膜晶体管。第二绝缘衬底面对第一绝缘衬底。在第二绝缘衬底上形成公共电极。在第一和第二衬底之间插入一液晶层。一畴分隔元件形成在第一和第二绝缘衬底的至少其一上并将第一和第二像素电极分隔成多个微畴。畴分隔离元件将第一和第二像素电极分隔成第一定向畴和第二定向畴，且第一和第二像素电极彼此电容连结。

[0014] 第 m 像素列上第 n 像素行的像素处的第一和第二薄膜晶体管连结到第 m 数据线，第 m 像素列上第 (n+1) 像素行的像素处的第一和第二薄膜晶体管连结到第 (m+1) 数据线，其中 n 和 m 是整数。第二像素电极占据 30-70% 的像素区。没有电场的情况下，液晶层中的液晶分子相对于第一和第二绝缘衬底垂直排列。

[0015] 一存储电容线形成在第一绝缘衬底上并置于第一像素电极和第二像素电极之间，由此形成一存储电容。当形成在第二像素电极和公共电极之间的液晶电容用  $C_{lcb}$  表示，形成在第二像素电极和存储电容线之间的存储电容用  $C_{stb}$  表示，并且形成在第一和第二像素电极之间的连结电容用  $C_{pp}$  表示时，由方程  $T = (C_{lcb} + C_{stb} - C_{pp}) / (C_{lcb} + C_{stb} + C_{pp})$  定义的 T 值处于 0.65-0.95 的范围。

[0016] 根据本发明的又一方面，液晶显示器具有一第一绝缘衬底和一沿第一方向形成在第一绝缘衬底上的第一信号线。第二信号线沿第二方向形成在第一绝缘衬底上并以绝缘的方式与第一信号线交叉。一薄膜晶体管连结到第一和第二信号线。像素电极连结到薄膜晶体管并具有多个狭缝。第二绝缘衬底面对第一绝缘衬底。在第二绝缘衬底上形成一公共电极。在第一和第二衬底之间插入一液晶层。一畴分隔元件形成在第一和第二绝缘衬底的至少其一上并将像素电极分隔成多个微畴。畴分隔元件把像素电极分隔成第一定向畴和第二定向畴，且第一定向畴位于狭缝区处。

[0017] 像素电极的狭缝宽度建立为  $2-5 \mu m$ ，且相邻两狭缝之间的距离建立为  $2-10 \mu m$ 。

[0018] 根据本发明的又一方面，液晶显示器具有一第一绝缘衬底和一沿第一方向形成在第一绝缘衬底上的第一信号线。一第二信号线沿第二方向形成在第一绝缘衬底上并以绝缘的方式与第一信号线交叉。薄膜晶体管连结到第一和第二信号线。像素电极连结到薄膜晶体管。第二绝缘衬底面对第一绝缘衬底。在第二绝缘衬底上形成一公共电极。在像素电极和公共电极的至少一个上形成一介电层。在第一和第二衬底间插入一液晶层。一畴分隔元件形成在第一和第二绝缘衬底中的至少其一上并将像素电极分隔成多个微畴。畴分隔元件将像素电极分隔成第一定向畴和第二定向畴，并且在第一定向畴的区域中设置介电层。

[0019] 介电层的厚度建立为  $500 \text{ \AA} \sim 1.5 \mu m$ 。开口部分形成在像素电极和公共电极处作为畴分隔元件。

[0020] 根据本发明又一方面，液晶显示器包括：第一基板；在所述第一基板上的像素区，划分为第一部分和第二部分；第二基板，面对所述第一基板；和液晶层，插置在所述第一基板与所述第二基板之间，其中在所述第一部分和所述第二部分中的每个上的所述液晶层划

分为多个畴，所述多个畴的每个由施加电场时液晶分子的方向来定义，所述第二部分的电场值小于所述第一部分的电场值。

[0021] 根据本发明又一方面，液晶显示器包括：第一基板；多个像素，所述像素的至少一个包括分别设置在第一基板上的相同层上的第一像素电极和第二像素电极；第二基板，面对所述第一基板；和液晶层，插置在所述第一基板与所述第二基板之间，其中在所述第一像素电极和所述第二像素电极中的每个上的所述液晶层划分为多个畴，所述多个畴中的每个由施加电场时液晶分子的方向来定义，所述第二像素电极产生的电场值小于所述第一像素电极产生的电场值。

## 附图说明

[0022] 通过下面结合附图进行的详细描述，可以更清晰地理解本发明和其各个方面及优点，附图中用相同的标记表示相同或类似的元件，在附图中：

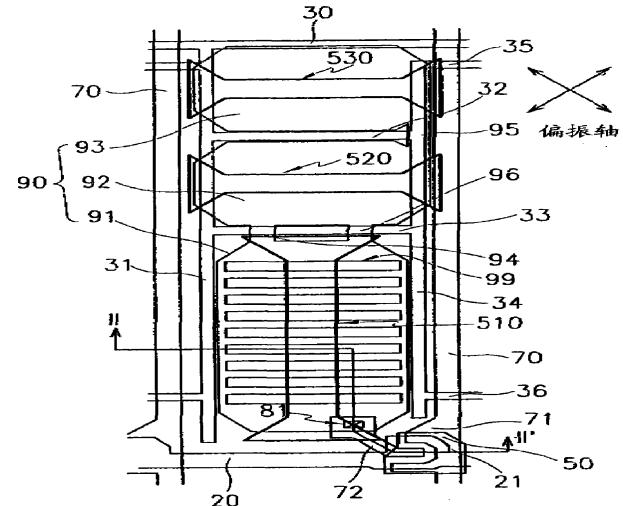

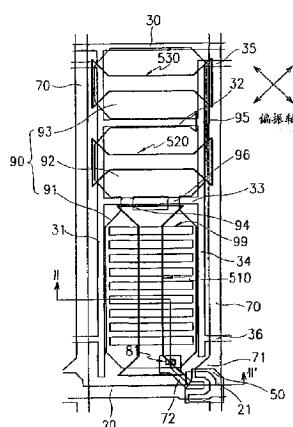

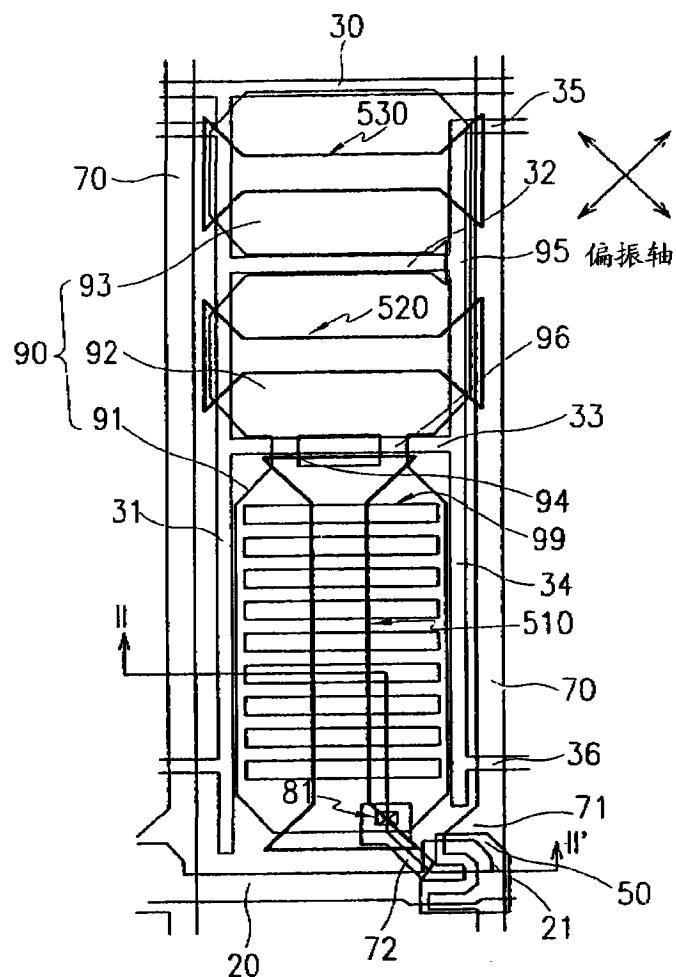

- [0023] 图 1 是根据本发明第一优选实施例的液晶显示器的平面图；

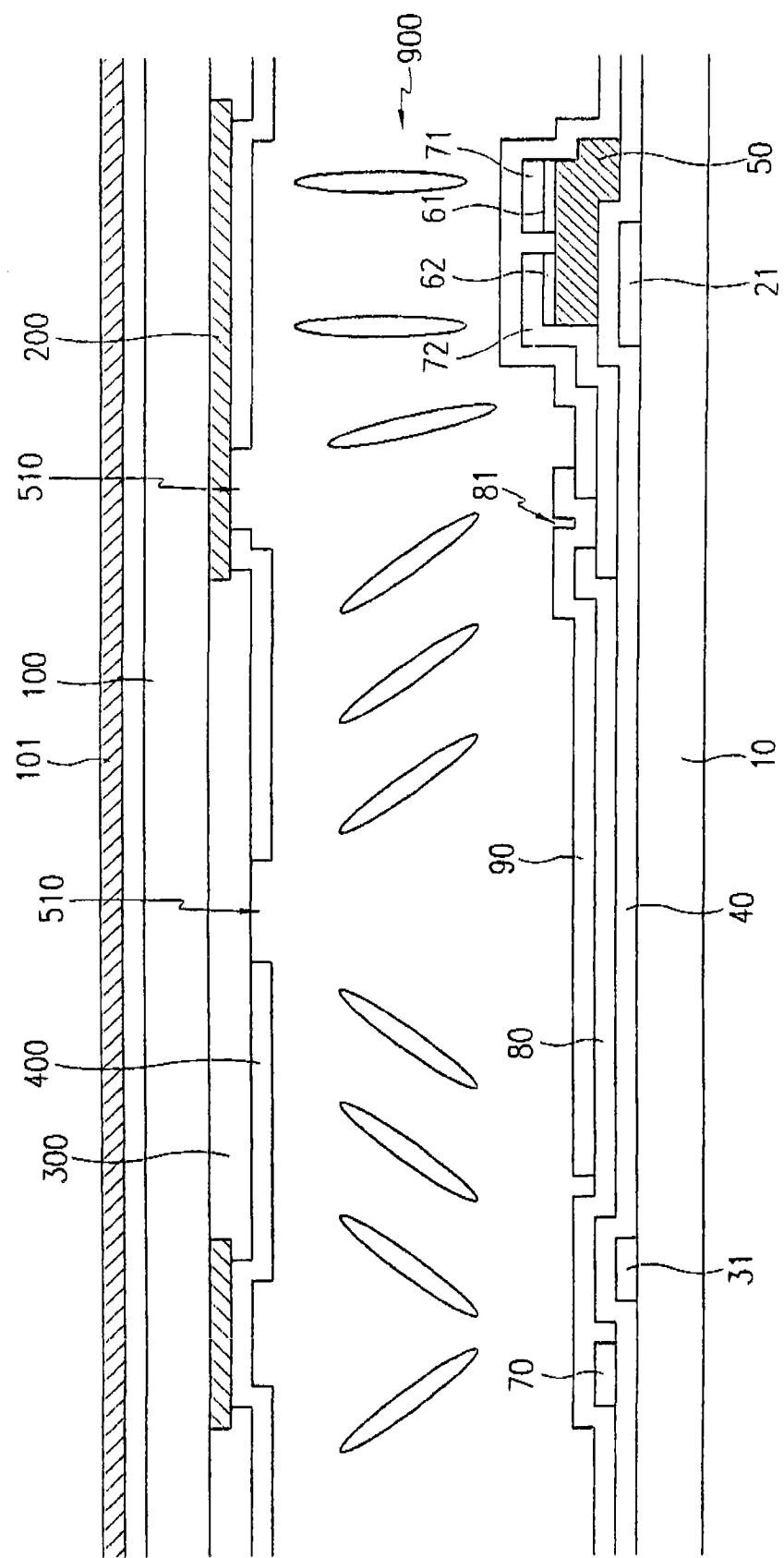

- [0024] 图 2 是液晶显示器沿图 1 中 II-II' 线的截面图；

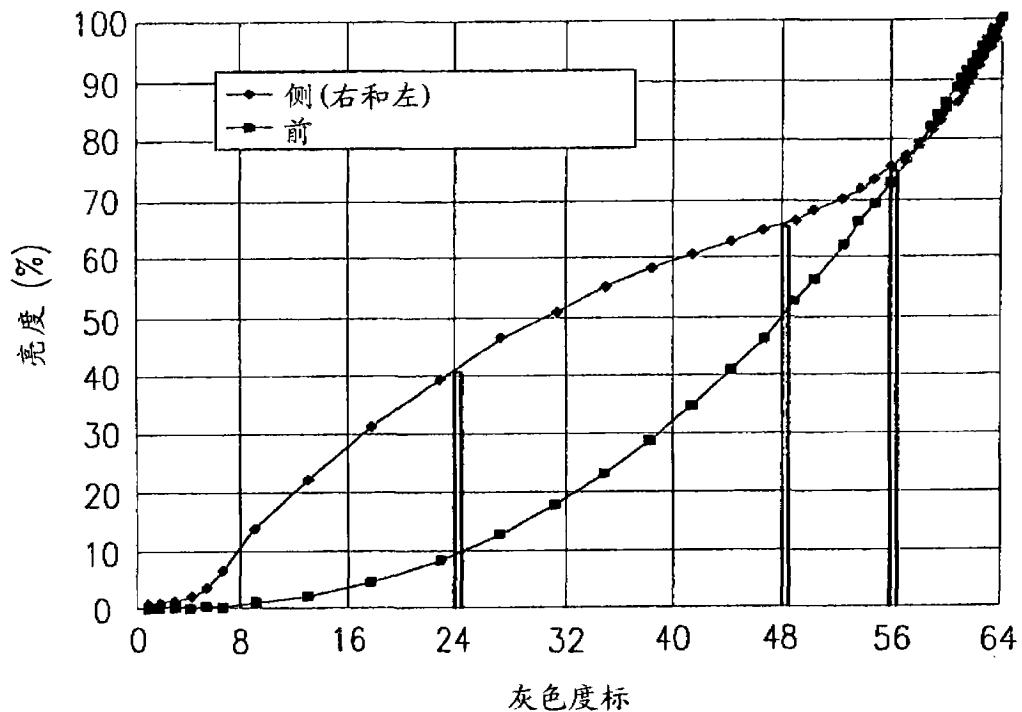

- [0025] 图 3 是测试单元正面以及其 60° 侧面处的伽玛曲线的示意图；

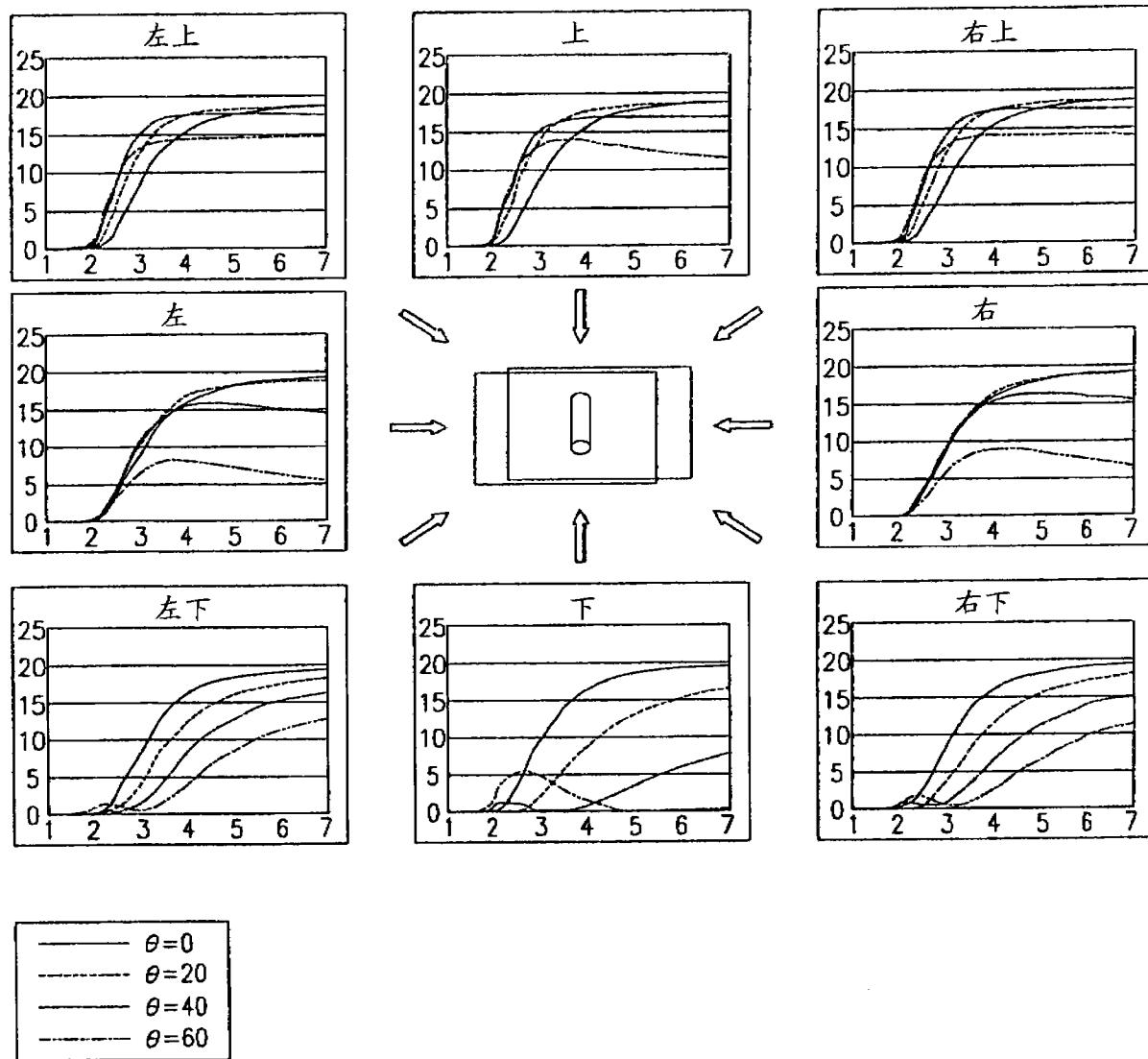

- [0026] 图 4 表示从八个方向看单畴垂直排列液晶单元时的 VT 曲线；

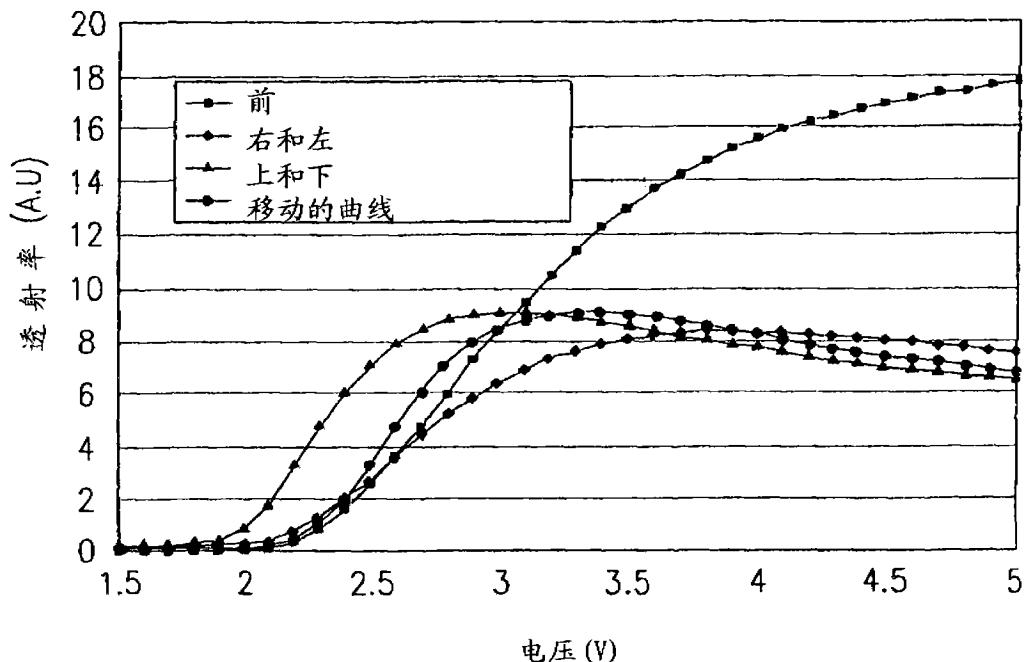

- [0027] 图 5 表示以反平行方式垂直进行摩擦时的单畴 VA 单元的正面 VT 曲线，其左右 60° 侧面处的平均 VT 曲线，其上下 60° 侧面处的平均 VT 曲线，和使上下平均曲线移动 0.3V 的曲线；

- [0028] 图 6 是根据本发明第二优选实施例的液晶显示器的平面图；

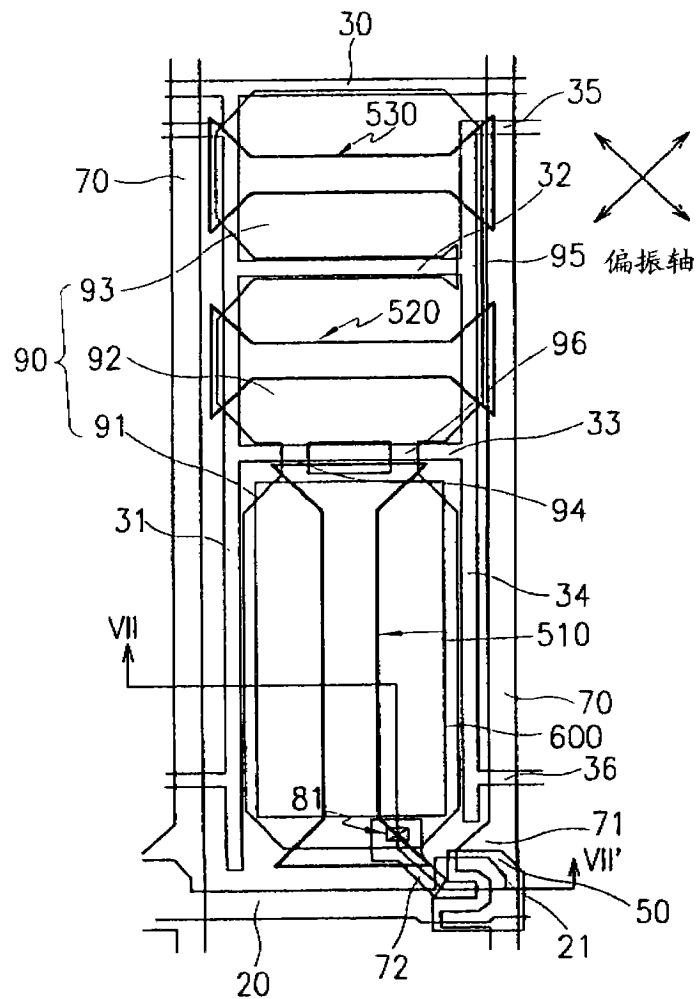

- [0029] 图 7 是液晶显示器沿图 6 中 VII-VII' 线的截面图；

- [0030] 图 8 是根据本发明第三优选实施例的液晶显示器的截面图；

- [0031] 图 9 是根据本发明第四优选实施例的液晶显示器的平面图；

- [0032] 图 10 和 11 是液晶显示器沿图 9 中 X1-X1' 线和 XII-XII' 线的截面图；

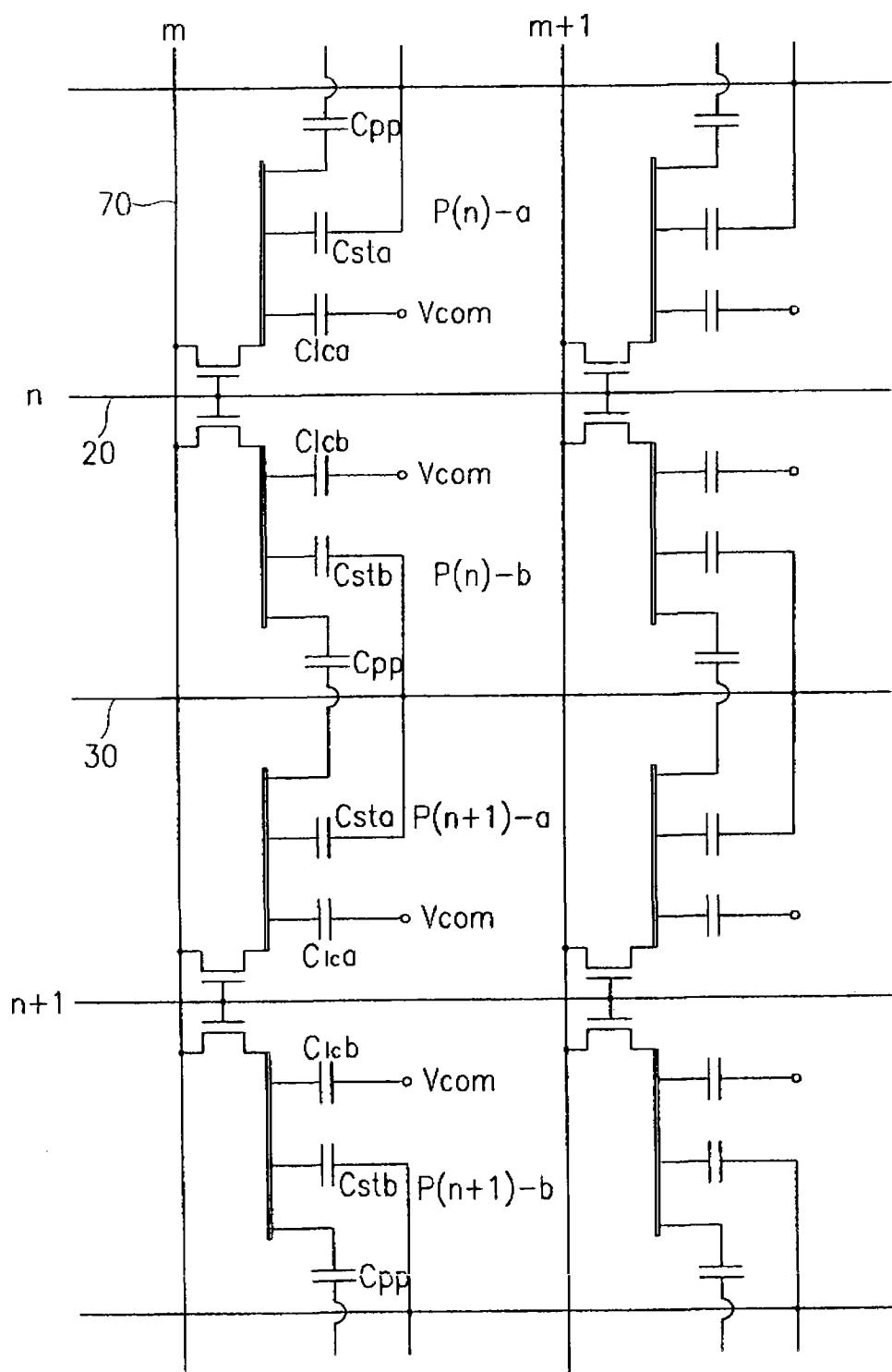

- [0033] 图 12 是具有图 9 所示薄膜晶体管阵列板的液晶显示器的等效电路图；

- [0034] 图 13 是根据本发明第五优选实施例的液晶显示器的平面图；和

- [0035] 图 14 是具有图 13 所示薄膜晶体管阵列板的液晶显示器的等效电路图。

## 具体实施方式

[0036] 下面参考附图对本发明的优选实施例进行解释。

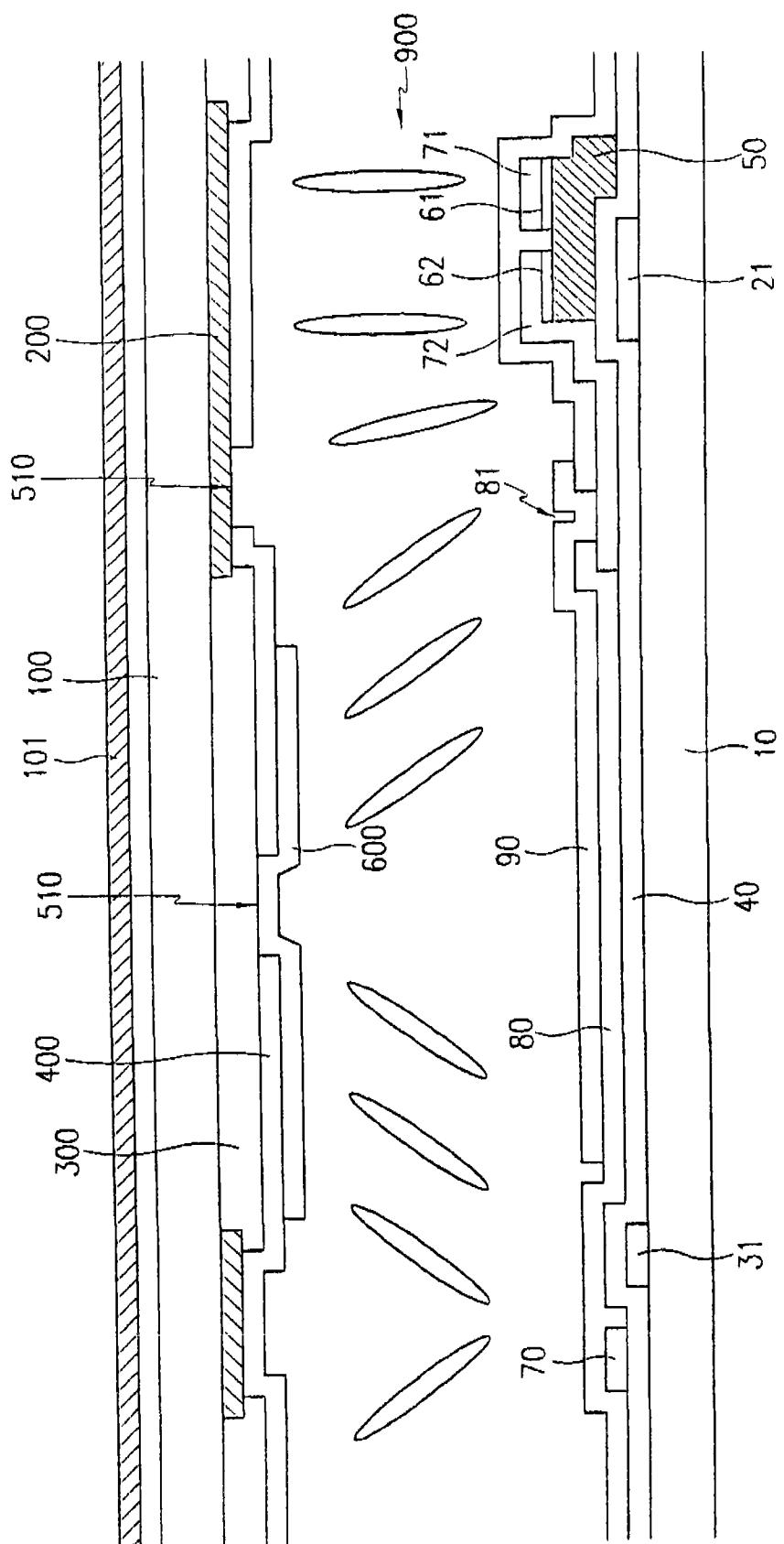

[0037] 图 1 是根据本发明第一优选实施例的液晶显示器的平面图，图 2 是液晶显示器沿图 1 中 II-II' 线的截面图。

[0038] 如图 1 和 2 所示，栅极线 20 形成在一透明绝缘衬底 10 如玻璃上并在水平方向延伸。存储电容线 30 平行于栅极线 20 延伸。栅极电极 21 从栅极线 20 伸出。第一至第四存储电容电极 31～34 以及存储电容电极连结器 35 和 36 从存储电容线 30 分支。第一存储电容电极 31 直接连结到存储电容线 30 并在垂直方向延伸。第二和第三存储电容电极 32 和 33 连结到第一存储电容电极 31 并在水平方向延伸。第四存储电容电极 34 连结到第二和第三存储电容电极 32 和 33 并在垂直方向延伸。存储电容电极连结器 35 和 36 将第四存储电容电极 34 连结到与其相邻像素的第一存储电容电极 31。在栅极线组件 20 和 21 上

以及存储电容线组件 30 ~ 36 上形成一栅极绝缘层 40，并且在栅极电极 21 上方的栅极绝缘层 40 上形成一由非晶硅制成的半导体层 50。在半导体层 50 上形成一由掺有 n 型高浓度杂质如磷 P 的非晶硅制成的欧姆接触层 61 和 62。在欧姆接触层 61 和 62 上分别形成源极电极 71 和漏极电极 72。在栅极绝缘层 40 上形成沿垂直方向延伸的数据线 70。源极电极 71 连结到数据线 70。一保护层 80 形成在数据线组件 70、71 和 72 上并具有暴露漏极电极 72 的接触孔 81。像素电极 90 形成在每个像素区的保护层 80 上并经接触孔 81 连结到漏极电极 72。像素电极 90 由一种透明导电材料如氧化铟锡 (ITO) 和氧化铟锌 (IZO) 形成。每个像素区由两条栅极线 20 和两条数据线 70 限定并被分隔成上半部和下半部。

[0039] 像素电极 90 被分成第一至第三电极部分 91 ~ 93，这些电极通过第一至第三连结器 94 ~ 96 彼此连结。第一电极部分 91 位于像素区的下半部，并具有其四个边缘被截去的矩形形状。第一电极部分 91 经接触孔 81 直接连结到漏极电极 72。第二和第三电极部分 92 和 93 位于像素区的上半部，并具有一种带四个斜切角的矩形形状。第二电极部分 92 通过第一和第二连结器 94 和 96 连结到第一电极部分 91，第三电极部分 93 通过第三连结器 95 连结到第二电极部分 92。

[0040] 在第一电极部分 91 处形成多个狭缝 99。由于狭缝 99 而在第一电极部分 91 和公共电极 400 之间产生的电场比公共电极 400 和第二电极部分 92 或第三电极部分 93 之间产生的电场弱。

[0041] 同时，第二存储电容电极 32 位于第一电极部分 91 和第二电极部分 92 之间，并且第三存储电容电极 33 位于第二电极部分 92 和第三电极部分 93 之间。第一存储电容电极 31 和第四存储电容电极 34 位于像素电极 90 和数据线 70 之间。平行于数据线延伸的第一电极部分 91 的边比其平行于栅极线延伸的边长。第二和第三电极部分 平行于数据线延伸的边短于其平行于栅极线延伸的边。第二和第三电极部分 92 和 93 与第一和第四存储电容电极 31 和 34 重叠，但第一电极部分 91 不与第一和第四存储电容电极 31 和 34 重叠。存储电容线 30 位于栅极线 20 和第三电极部分 93 之间。施加到彩色滤光板的公共电极上的电位通常被施加到存储电容线 30、存储电容电极 31 ~ 34 以及存储电容电极连结器 35 和 36。

[0042] 如上所述，当把被施加公共电位的存储电容线或存储电容电极设置在数据线和像素电极之间或设置在栅极线和像素电极之间时，数据线电位和栅极线电位对像素区的电场的影响被存储电容线和存储电容电极截断，由此形成稳定的畴。

[0043] 下面详细解释用于液晶显示器的彩色滤光板。

[0044] 具有双层结构的黑色矩阵 200 形成在透明玻璃衬底 100 上并限定像素区。黑色矩阵 200 的双层结构由铬 / 氧化铬形成。在每个像素区形成一彩色滤光片 300，在具有彩色滤光片 300 的衬底 100 的整个表面上由一种透明导电材料形成一公共电极 400。公共电极 400 在每个像素区设置有一开口图案。开口图案包括第一至第三开口部分 510、520 和 530。第一开口部分 510 在垂直方向两等分像素区的下半部，第二和第三开口部分 520 和 530 在水平方向三等分像素区的上半部。各个开口部分 510、520 和 530 的两端逐渐扩大并形成等腰三角形形状。开口部分 510、520 和 530 彼此分开。

[0045] 或者，黑色矩阵可以由一种有机材料形成，并且可在薄膜晶体管阵列板上形成彩色滤光片。

[0046] 薄膜晶体管阵列板和彩色滤光板彼此对齐并组装。在两块面板之间注入一液晶材

料 900,使得液晶分子的指向垂直于面板排列。两个偏振片 11 和 101 连结到衬底 10 和 100 的外表面,使得其偏振轴彼此垂直。

[0047] 薄膜晶体管阵列板处的像素电极 90 的电极部分 91、92 和 93 以及彩色滤光板处的公共电极 400 的第一至第三开口部分 510、520 和 530 彼此重叠,由此将像素区分隔成多个畴。由第一电极部分 91 和第一开口部分 510 分隔的畴被称作上下畴(在水平方向延伸),被第二和第三电极部分 92 和 93 以及第二和第三开口部分 520 和 530 分隔的畴称作左右畴(在垂直方向延伸)。这种特性依赖于施加电场时液晶分子的倾斜方向。各个电极部分 91 ~ 93 包括两个长边和两个短边。每个电极部分的长边平行于数据线 70 或栅极线 20 延伸,并且与偏振片的偏振轴成 45° 的角度(如图 3 所示)。在像素电极 90 的各个电极部分 91 ~ 93 的长边设置为接近数据线 70 或栅极线 20 的情况下,存储电容线 30 或存储电容电极 31 ~ 34 分布在数据线 70 和相关电极部分的长边之间或栅极线 20 和相关电极部分的长边之间。同时,优选存储电容线组件 30 ~ 34 的位置不接近像素电极 90 的电极部分 91 ~ 93 的短边。在存储电容线组件的位置接近后者的情况下,它完全被像素电极 90 覆盖,或位置离开像素电极 90 有 3 μm 或更多。原因是在数据线 70 或栅极线 20 的位置接近像素电极部分 91 ~ 93 的长边的区域中,数据线 70 或栅极线 20 的电位作用在阻碍畴形成于该区域处的方向上。相反,在数据线 70 或栅极线 20 的位置接近像素电极部分 91 ~ 93 的短边的区域中,数据线 70 或栅极线 20 的电位作用在促使畴形成于该区域的方向。

[0048] 同时,由于第一像素电极部分 91 处的狭缝 99 所致的形成在左右畴中的电场比形成在上下畴中的电场弱一预定程度。通过此结构,可以提高液晶显示器在左右侧的可见度。当液晶显示器的单元间隙用 d(m) 表示时,左右畴中形成的电场优选具有  $0.02/d(V/\mu m) \sim 0.5/d(V/\mu m)$  的值,该值小于上下畴中形成的电场。即,建立公共电极和像素电极之间的电压差,使得左右畴中的电压比上下畴中的电场弱 0.1~1V。为此目的,优选将狭缝 99 的宽度建为 2~5 微米,并且将相邻两狭缝 99 之间的距离建为 2~10 微米。

[0049] 图 3 是测试单元的正面以及其 60° 侧面处的伽玛曲线。

[0050] 如图 3 所示,测试单元正面的伽玛曲线高于其 60° 侧面处的伽玛曲线。具体地说,因为正面伽玛曲线和侧面伽玛曲线之间的宽度明显较大,所以依据同一灰色度标从正面或侧面看,产生两倍至十倍的亮度差。因为红、绿和蓝色像素的灰色度标单独地变化,所以在侧面的伽玛曲线中,红、绿和蓝色像素的变形度不同。因此,当从侧面看像素时,与从正面看同一像素的情形相比,该像素具有完全不同的颜色。例如,如图 3 所示,假设红、绿和蓝色像素表现为 56 灰色度标、48 灰色度标和 24 灰色度标,当从正面看时,红、绿和蓝色的比率设置为如下:R : G : B = 73 : 50 : 10 = 55% : 37% : 8%。相反,当从 60° 侧面看时,红、绿和蓝色的比率设置为如下:R : G : B = 75 : 66 : 41 = 41% : 36% : 23%。即,在后一种情况下,蓝色的含量增大三倍或更多,使得有关的像素看上去具有完全不同的颜色。

[0051] 在伽玛曲线如图 3 所示变形的情况下,正面低比率的颜色在侧面的比率变大。相反,正面的高比率颜色在侧面的比率变小。通过这种方式,红、绿和蓝色的比率变得彼此接近。因此,当从正面看时颜色似乎不同,而当从侧面看时,颜色敏感度差异减小。颜色整个变淡并接近白色,这称作“白色-频移”。结果,颜色表现特性变差,图象影象(picture image)变暗。白色-频移最重要的原因在于伽玛曲线在较低灰色度标处的变形严重。即使在较高灰色度标处发生伽玛变形,该变形非常小。但当在 32 或更小的较低灰色度标处发生伽玛变

形时,亮度差为两倍至十倍,并且这使得白色 - 频移显得更严重。

[0052] 图 4 表示从八个方向看单畴垂直排列的液晶单元时的 VT 曲线。

[0053] 如图 4 所示,较低灰色度标的 TV 曲线沿左方向的移动在上侧或下侧变得显著。在左侧和右侧,较低灰色度标处的曲线被升高正面曲线的相同轮廓。在左下侧和右下侧,灰色度标转化提前,VT 曲线再次沿右方向移动并上升。即,当液晶单元的观察方向和液晶分子在施加电场时的倾斜方向相同(当从液晶分子的头或尾看去)时,较低灰色度标的伽玛曲线向上变形的现象变得严重,但是当上述两种方向垂直时,变形现象可以忽略。因此,对于基于左右侧可见度的视角的有害影响,左右畴处的伽玛曲线变形很重要,并且对于基于上下侧可见度的视角的有害影响,上下畴处的伽玛曲线变形也很重要。从用户的观点出发,左右侧的视角比上下侧的视角更严重。为了补偿有害影响左右侧可见度的左右畴处的伽玛曲线变形,使左右畴内的电场强度变得比上下畴中的电场强度弱。下面将详细描述这一点。

[0054] 图 5 表示单畴 VA 单元的正面 VT 曲线,其中以反平行的方式进行垂直摩擦(液晶分子向上和向下倾斜),还表示了其左右 60° 侧面的平均 VT 曲线、其上下 60° 侧面的平均 VT 曲线以及使上下平均曲线移动 0.3V 的曲线。

[0055] 如图 5 所示,较低灰色度标时,左右侧的 VT 曲线与正面 VT 曲线接近一致,但与正面 VT 曲线相比,上下侧的 VT 曲线在较低电压时开始升高。即,与正面的阈值电压  $V_{th}$  相比,上下侧的阈值电压  $V_{th}$  降低。但是,当上下侧的 VT 曲线移动 0.3V 时,它几乎与较低灰色度标的正面 VT 曲线一致。上下侧的 VT 曲线与正面 VT 曲线一致的事实意味着上下侧的可见度与正面的可见度相同。最终为了使左右侧的可见度提高到与正面的可见度相同的程度,可以将左右畴的左右侧 VT 曲线移动预定的电压。在左右畴内的电场建得比上下畴内的电场弱的情况下,可以得到与移动左右侧 VT 曲线相同的效果。

[0056] 图 6 是根据本发明第二优选实施例的用于液晶显示器的薄膜晶体管阵列板的平面图,图 7 是薄膜晶体管阵列板沿图 6 中 VII-VII' 线的截面图。

[0057] 如图 6 和 7 所示,在本优选实施例中,除了在没有形成任何狭缝的第一像素电极部分 91 上形成一介电层 600 外,液晶显示器的其它组件和结构与第一优选实施例的相同。

[0058] 在第一像素电极部分 91 上形成介电层 600 的效果与在第一像素电极部分 91 处形成狭缝的效果相同。即,左右畴内的电场建得比上下畴内的电场弱。介电层 600 的厚度建在 500 Å -1.5 微米的范围。

[0059] 图 8 是根据本发明第三优选实施例的液晶显示器的截面图。

[0060] 如图 8 所示,在本优选实施例中,除了在第一像素电极部分 91 上不形成任何狭缝,而在公共电极 400 上形成与第一像素电极部分 91 对应的介电层 600 外,液晶显示器的其它组件和结构与第一优选实施例的相同。

[0061] 在公共电极 400 上形成介电层 600 的效果与在第一像素电极部分 91 上形成狭缝的效果相同。即,左右畴内的电场建得比上下畴内的电场弱。

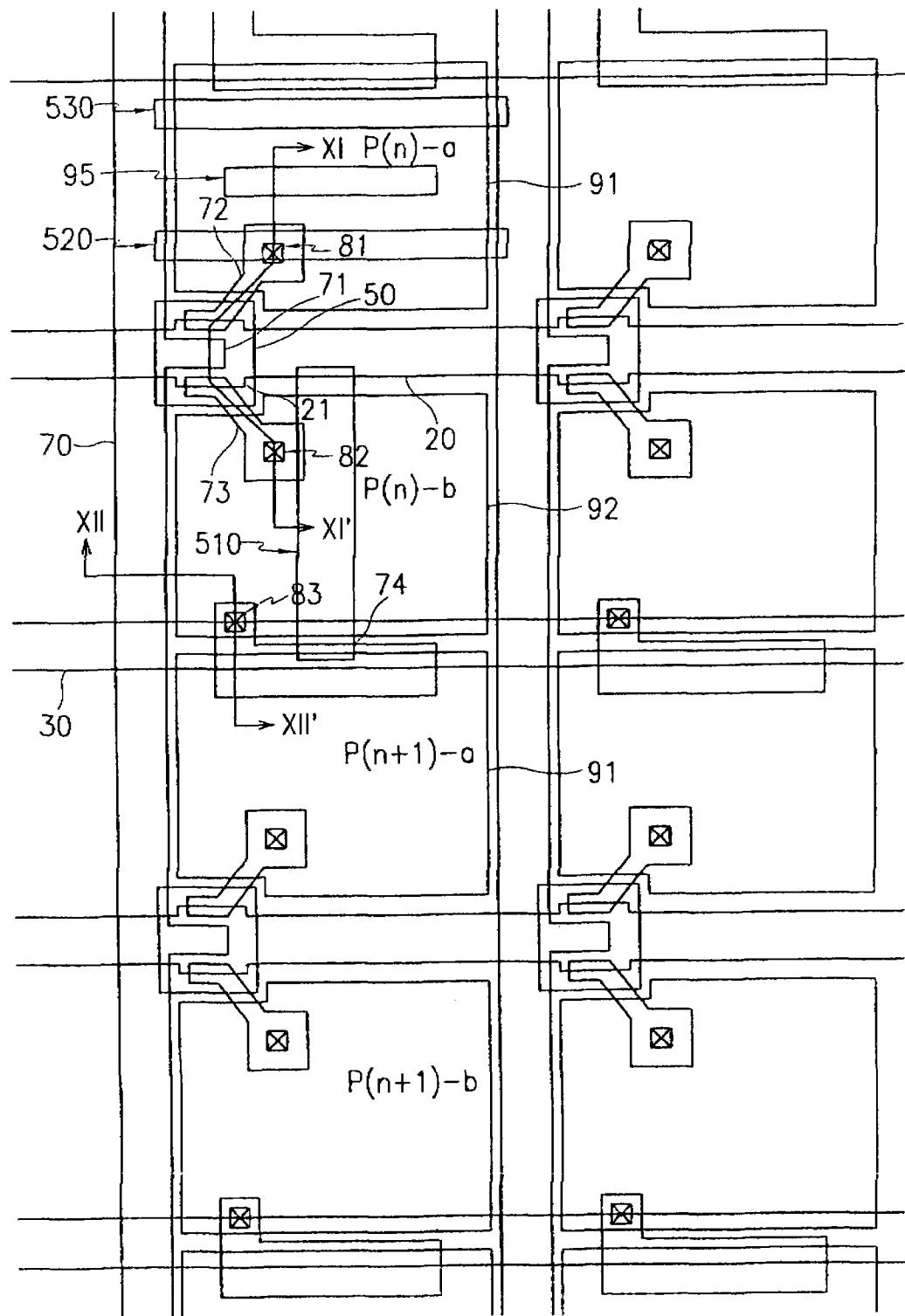

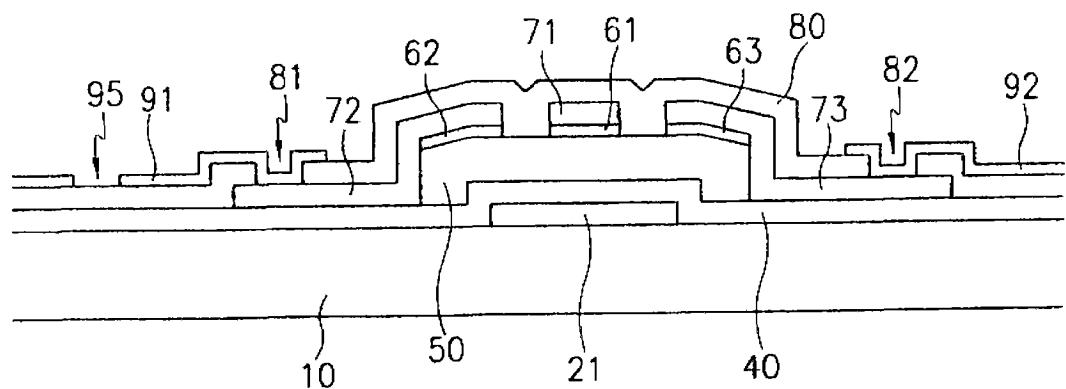

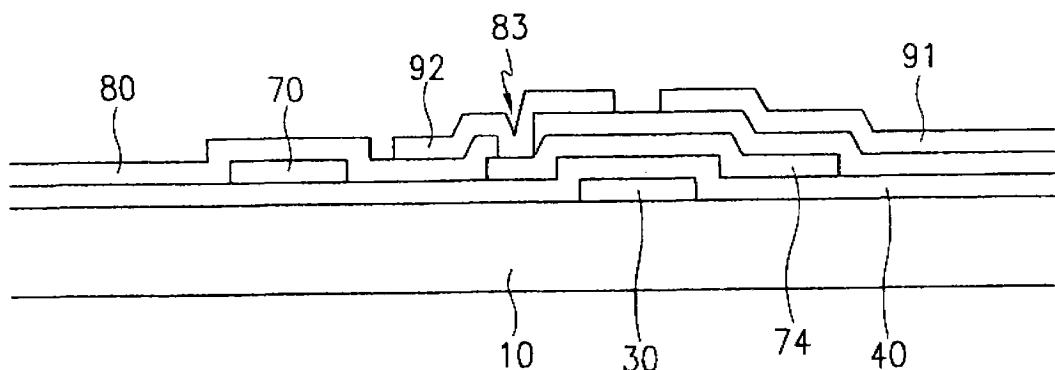

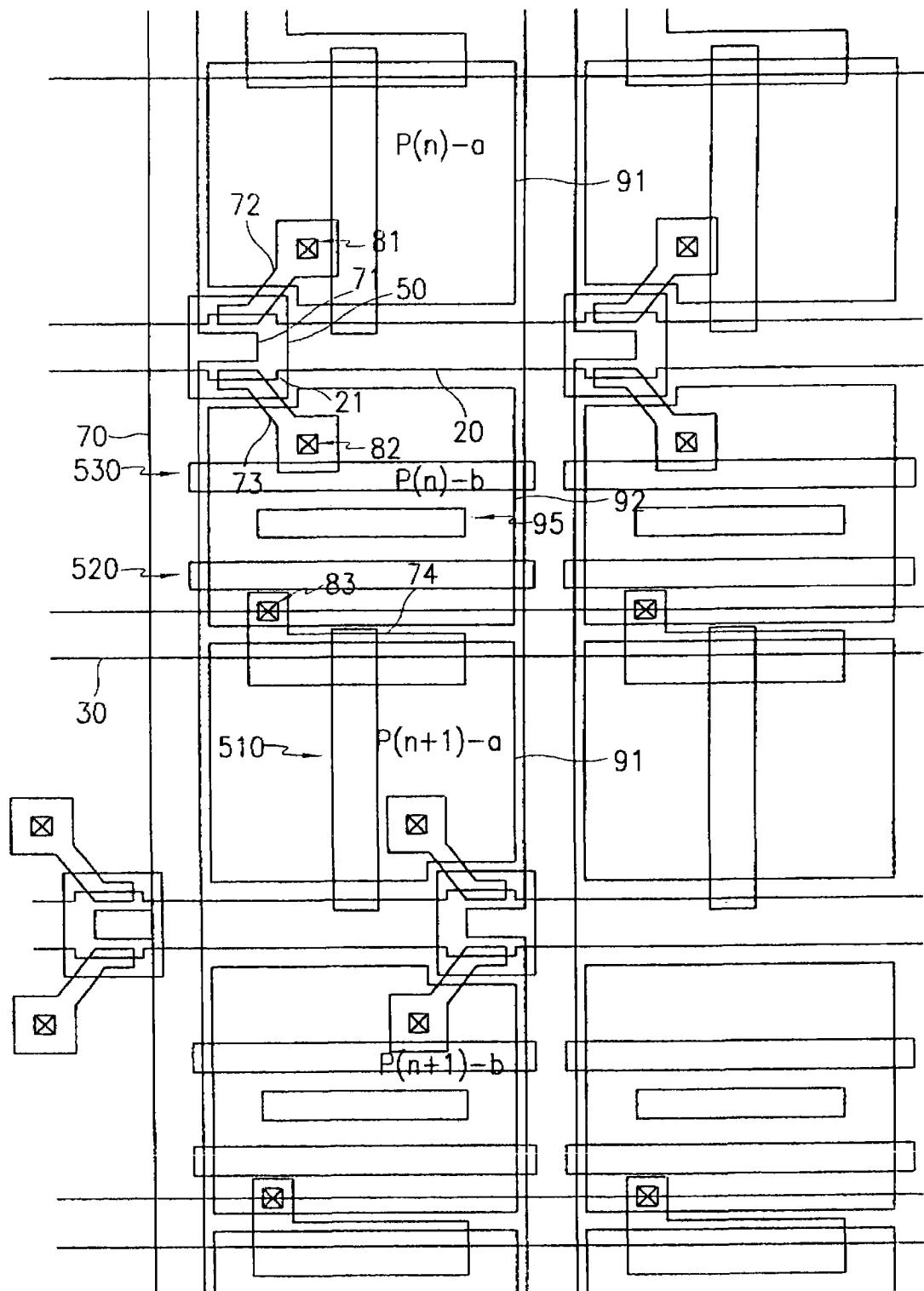

[0062] 图 9 是根据本发明第四优选实施例的液晶显示器的平面图,图 10 和 11 是液晶显示器沿图 9 中 X1-X1' 线和 XII-XII' 线的截面图,图 12 是具有图 9 所示薄膜晶体管阵列板的液晶显示器的等效电路图。

[0063] 棚极线组件和存储电容线 30 形成在一透明绝缘衬底 10 如玻璃上。

[0064] 棚极线组件包括在水平方向延伸的棚极线 20 和从棚极线 20 向上和向下伸出的棚

极电极 21。

[0065] 存储电容线 30 平行于栅极线 20 延伸。存储电容线 30 可具有分支线。

[0066] 栅极线组件和存储电容线 30 被一栅极绝缘层 40 覆盖,在栅极绝缘层 40 上形成一由非晶硅制成的半导体层 50。半导体层 50 覆盖栅极电极 21,由此形成薄膜晶体管的沟道部分。在半导体层 50 上形成一由掺有高浓度 n 型杂质例如磷的非晶硅制成的欧姆接触层 61、62 和 63。

[0067] 在欧姆接触层 61、62 和 63 以及栅极绝缘层 40 上形成一数据线组件和连结电极 74。数据线组件包括沿半导体层 50 延伸的数据线 70、连结到数据线 70 的源极电极 71 以及第一和第二漏极电极 72 和 73。源极电极 71 从数据线 70 伸出并位于栅极电极 21 之上。第一和第二漏极电极 72 和 73 分别位于源极电极 71 的两侧。第一和第二漏极电极 72 和 73 延伸到栅极线 20 周围的第一和第二像素区中。连结电极 74 部分地覆盖存储电容线 30 并且电磁互连存储电容线 30 周围被分开的第一和第二像素电极 91 和 92。欧姆接触层 61、62 和 63 只位于半导体层 50 与数据线组件重叠的区域。

[0068] 在数据线组件上形成一保护层 80。保护层 80 具有暴露第一和第二漏极电极 72 及 73 一侧端的第一和第二接触孔 81 和 82,以及暴露连结电极 74 一侧端的第三接触孔 83。

[0069] 第一和第二像素电极 91 和 92 形成在保护层 80 上,使得它们经第一和第二接触孔 81 和 82 连结到第一和第二漏极电极 72 和 73。第二像素电极 92 经第三接触孔 83 连结到连结电极 74。第一像素电极 91 与连结电极 74 重叠并产生电磁结合(电容-结合)。最终,第一和第二像素电极 91 和 92 通过连结电极 74 彼此电容-结合。像素电极 91 和 92 由一种透明导电材料如氧化铟锡(ITO)和氧化铟锌(IZO)制成。同时,第一像素电极 91 配置有在水平方向延伸的多个水平开口部分 95。在第二像素电极 92 处可以形成垂直开口部分。优选一个像素区内第一像素电极的占据比为 30-70%。

[0070] 通常对存储电容线 30 施加与像素电极 90 相对的公共电极的电位。

[0071] 同时,彩色滤光板上配置有一黑色矩阵、彩色滤光片和一公共电极。在公共电极上形成第一至第三开口部分 510、520 和 530。第一开口部分 510 在垂直方向延伸,使得其将第二像素电极 92 两等分为左右畴。第二和第三开口部分 520 和 530 将第一像素电极 91 三等分为上下畴。因此,第一像素电极 91 被第二和第三开口部分 520 和 530 以及水平开口部分 95 垂直分隔为四个畴。

[0072] 在与数据线组件相同的平面上形成连结电极 74。或者,可以在与栅极线组件相同的平面上形成连结电极 74。在后一种情况下,存储电容线 30 不应该覆盖连结电极 74。

[0073] 薄膜晶体管阵列板与彩色滤光板隔开一预定的距离,液晶材料注入在两面板之间。液晶分子的指向垂直于面板排列。一补偿膜如双轴膜连结到彩色滤光板。两个偏振片分别连结到薄膜晶体管阵列板和彩色滤光板的外表面。

[0074] 如上所述,在一个像素区中形成两个薄膜晶体管和两个像素电极,并且像素处相邻的两个像素电极通过连结电极彼此电容-连接。在此结构中,即使从左右侧看时也可得到极好的可见度。这是因为用于左右畴的第二像素电极 92 的电压保持得比第一像素电极 91 的电压低,使得左右畴内的电场比上下畴内的电场弱。

[0075] 下面将参见图 12 解释将左右畴的第二像素电极 92 的电压保持得比上下畴的第一像素电极 91 的电压低的原因。

[0076] 附图中,  $C_{1ca}$  表示形成在 a 像素电极和公共电极之间的液晶电容,  $C_{sta}$  表示形成在存储电容线和 a 像素电极之间的存储电容,  $C_{1cb}$  表示形成在 b 像素电极和公共电极之间的液晶电容,  $C_{stb}$  表示形成在存储电容线和 b 像素电极之间的存储电容,  $C_{pp}$  表示 a 像素电极和 b 像素电极之间的连结电容。

[0077] 如图 12 所示, 第一和第二薄膜晶体管连结到同一栅极线和数据线, 第一和第二像素电极分别连结到第一和第二薄膜晶体管。第一和第二像素电极彼此形成电容 - 连结 ( $C_{pp}$ ) 并在两者之间插入存储电容线 30。

[0078] 就一条数据线 70 而言, 当第 n 条栅极线 20 变为接通时, 两个薄膜晶体管 (TFT) 沟道变为接通, 使得电压施加到第一和第二像素电极  $P(n)-a$  和  $P(n)-b$ 。当  $P(n)-b$  电容 - 连结到  $P(n+1)-a$  时, 它受到后者接通状态的影响。在此连结中,  $P(n)-a$  和  $P(n)-b$  的电压可通过算术方程式 1 和 2 给出:

$$V[P(n)-a] = V_d(n) \quad (1)$$

$$V[P(n)-b] = V_d(n) + [V_d(n+1) - V'_d(n+1)] C_{pp} / (C_{1cb} + C_{stb} + C_{pp}) \quad (2)$$

[0081] 在算术方程式 1 和 2 中,  $V_d(n)$  表示施加到数据线用来驱动  $P(n)$  像素的电压,  $V_d(n+1)$  表示施加到数据线用来驱动  $P(n+1)$  像素的电压。另外,  $V'_d(n+1)$  表示施加到前面的帧处的  $P(n+1)$  像素的电压。

[0082] 如算术方程式 1 和 2 中所表述, 施加给  $P(n)-b$  像素的电压不同于施加给  $P(n)-a$  像素的电压。具体地, 在进行点反向驱动 (dot inversion driving) 或线反向驱动 (line inversion driving) 并且下一像素行表现与前一像素行相同的灰色度标的情况下 (实际上大部分像素类似于此种情况),  $V_d(n) = -V_d(n+1)$ , 并且  $V_d(n) = -V'_d(n)$  (假设公共电极电压为地电压)。因此, 算术方程式 2 可以由下列算术方程式 3 表示:

$$V[P(n)-b] = V_d(n) - 2V_d(n) C_{pp} / (C_{1cb} + C_{stb} + C_{pp}) = [(C_{1cb} + C_{stb} - C_{pp}) / (C_{1cb} + C_{stb} + C_{pp})] V_d(n) = T V_d(n) \quad (3)$$

$$[0084] \text{此处 } T = (C_{1cb} + C_{stb} - C_{pp}) / (C_{1cb} + C_{stb} + C_{pp})$$

[0085] 从算术方程式 3 可以知道, 施加给  $P(n)-b$  像素的电压低于施加给  $P(n)-a$  像素的电压。优选 T 值建立为 0.65–0.95。

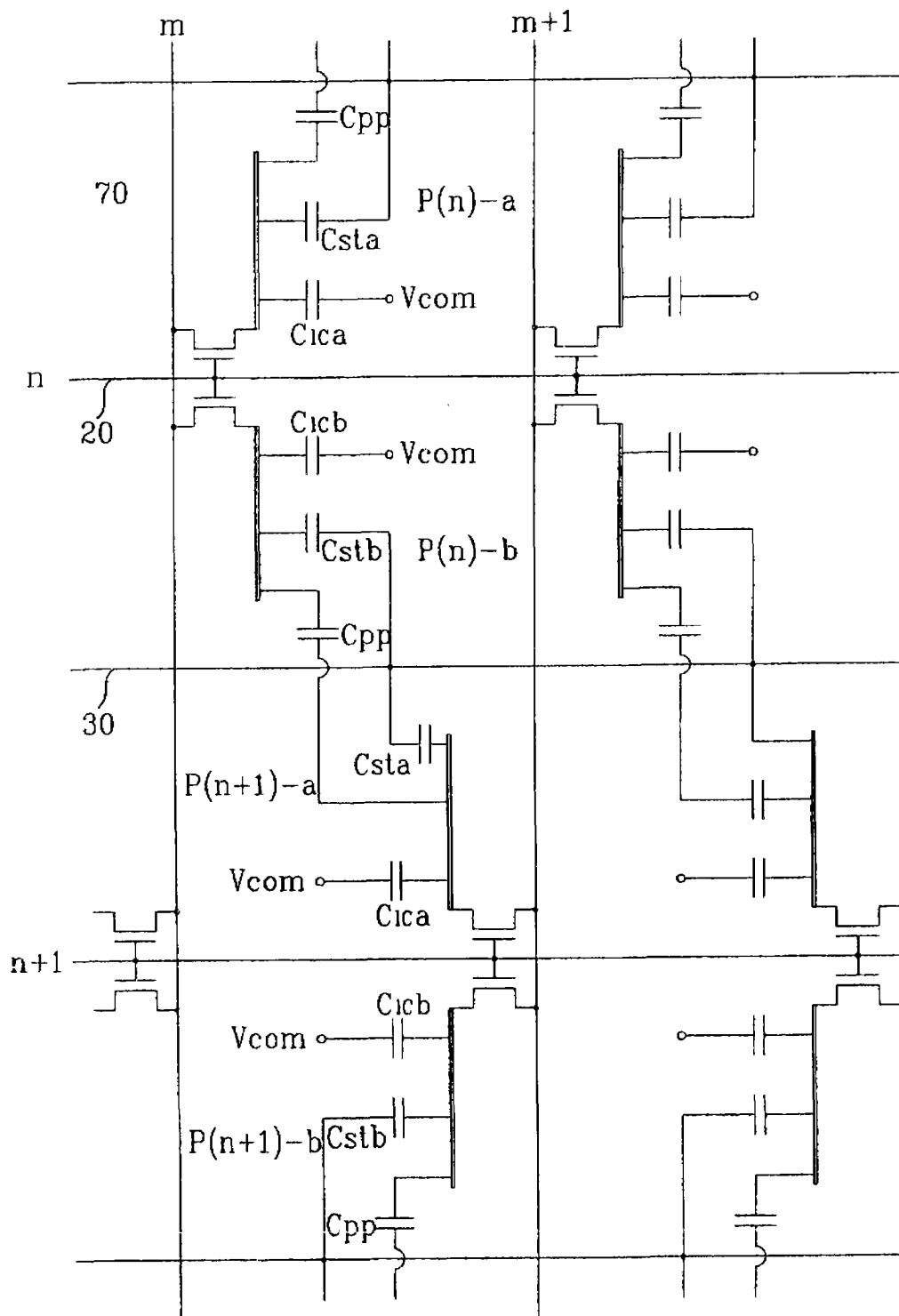

[0086] 图 13 是根据本发明第五优选实施例的用于液晶显示器的薄膜晶体管阵列板的平面图, 图 14 是具有图 13 所示薄膜晶体管阵列板的液晶显示器的等效电路图。

[0087] 在此优选实施例中, 处在一个像素列中的薄膜晶体管和像素电极交替连结到两条数据线。即,  $P(n)$  像素处的薄膜晶体管和两个像素电极 a 和 b 连结到第 m 条数据线,  $P(n+1)$  像素处的薄膜晶体管和两个像素电极 a 和 b 连结到第  $m+1$  条数据线。除了开口部分 95、510、520 和 530 的位置发生变化以外, 每个薄膜晶体管和像素电极的具体结构与第三优选实施例中的一样。即, 在第五优选实施例中, 水平开口部分 95 形成在第二像素电极 92 处。第一开口部分 510 形成在第一像素电极 91 处并将后者二等分为左右侧, 第二和第三开口部分 520 和 530 形成在第二像素电极 92 处并将后者三等分为上下侧。因此, 第一像素电极 91 形成左右畴, 而第二像素电极 92 形成上下畴。

[0088] 在上述结构中, 当进行点反向驱动时, 左右畴内的电场保持为比上下畴内的电场弱。即, 第一像素电极 91 的电位恒定地保持为低于第二像素电极 92 的电位, 使得可以提高左右侧的可见度。

[0089] 对于图 14 所示的结构,当进行点反向驱动时,对相同像素列的像素电极施加相同极性的电压,使得产生与列反向驱动相同的效果。因此,在下一像素行指示与前一像素行相同的灰色度标时(实际上,大部分像素与此情形类似), $Vd(n) = Vd(n+1)$ ,并且 $Vd(n) = -V'd(n)$ 。因此,算术方程式 2 可以由下列算术方程式 4 表示:

$$[0090] V[P(n)-b] = Vd(n)+2Vd(n)Cpp/(Clcb+Cstb+Cpp) = [(Clcb+Cstb+3Cpp)/(Clcb+Cstb+Cpp)]Vd(n) = TV_d(n) \quad (4)$$

[0091] 此处  $T = (Clcb+Cstb+3Cpp)/(Clcb+Cstb+Cpp)$ 。

[0092] 在算术方程式 4 中,b 像素的电压高于 a 像素的电压。因此,左右畴内的电场恒定地保持为弱于上下畴内的电场。

[0093] 如上所述,左右畴的电场恒定地保持为弱于上下畴的电场,使得可以提高左右侧的可见度。

[0094] 虽然已参考优选实施例对本发明进行了详细的描述,但本领域的技术人员将理解,在不脱离由权利要求限定的本发明的精神和范围的前提下,可以对本发明进行各种改型和替换。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8

图 9

图 10

图 11

图 12

图 13

图 14

|                |                                                                                                  |         |            |

|----------------|--------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于液晶显示器的薄膜晶体管阵列板                                                                                 |         |            |

| 公开(公告)号        | <a href="#">CN101893800B</a>                                                                     | 公开(公告)日 | 2014-09-17 |

| 申请号            | CN201010227534.X                                                                                 | 申请日     | 2002-06-11 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                         |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                         |         |            |

| 当前申请(专利权)人(译)  | 三星显示有限公司                                                                                         |         |            |

| [标]发明人         | 宋长根                                                                                              |         |            |

| 发明人            | 宋长根                                                                                              |         |            |

| IPC分类号         | G02F1/139 G02F1/1333 G02F1/1337 G02F1/133 G02F1/1343 G02F1/1362 G02F1/1368 G02F1/137             |         |            |

| CPC分类号         | G02F2001/133746 G02F2001/134345 G02F1/136213 G02F1/133753 G02F1/133707 G02F1/1393 G02F2001/13712 |         |            |

| 代理人(译)         | 张波                                                                                               |         |            |

| 审查员(译)         | 胡阳                                                                                               |         |            |

| 优先权            | 1020010072885 2001-11-22 KR                                                                      |         |            |

| 其他公开文献         | CN101893800A                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                   |         |            |

#### 摘要(译)

本发明涉及一种液晶显示器，包括：第一基板；在第一基板上的像素区，划分为第一部分和第二部分；第二基板，面对第一基板；和液晶层，插置在第一基板与第二基板之间，其中在第一部分和第二部分中的每个上的液晶层划分为多个畴，多个畴的每个由施加电场时液晶分子的方向来定义，第二部分的电场值小于第一部分的电场值。