(12) 发明专利

(10) 授权公告号 CN 101819365 B

(45) 授权公告日 2012.04.18

(21) 申请号 201010105205.8

审查员 商爱学

(22) 申请日 2010.01.22

(30) 优先权数据

12/590,765 2009.11.13 US

(73) 专利权人 友达光电股份有限公司

地址 中国台湾新竹

(72) 发明人 廖培钧 丁天伦 徐文浩 侯鸿龙

(74) 专利代理机构 北京律诚同业知识产权代理有限公司 11006

代理人 梁挥 祁建国

(51) Int. Cl.

G02F 1/1362 (2006.01)

G02F 1/133 (2006.01)

(56) 对比文件

CN 101216645 A, 2008.07.09,

CN 101510414 A, 2009.08.19,

US 2008204615 A1, 2008.08.28,

权利要求书 3 页 说明书 11 页 附图 12 页

(54) 发明名称

液晶显示面板及其像素列的驱动方法

(57) 摘要

本发明有关于一种液晶显示面板，此液晶显示面板包含具有第一次像素区与第二次像素区的像素，其中每一次像素区具有储存电容。每一像素具有第一栅极线提供第一栅极线信号以对第一与第二储存电容充电，以及第二栅极线于第一栅极线信号通过后提供第二栅极线信号以移动第二储存电容中的部分电荷至第三电容。第一与第二栅极线信号的频宽与时序可改变，致使提供给一列的第一栅极线信号，可作为第二栅极线信号提供给位于此列前的其中一列。

1. 一种液晶显示面板,其特征在于,包含:

多个像素,这些像素配置成多条列与多条行;以及

多条数据线,每一这些数据线用以提供数据信号至位于一行上的这些像素,其中所有或部分这些像素中的任一这些像素包含:

一第一栅极线,该第一栅极线用以提供一第一栅极线信号;

一第二栅极线,该第二栅极线用以于该第一栅极线信号通过后,提供一第二栅极线信号;

一第一次像素区;以及

一第二次像素区,其中

该第一次像素区包含一第一次像素电极电性连接至一第一电荷储存电容,该第一次像素电极配置以通过一第一开关元件从这些数据线其中一者接收数据信号,该第一开关元件包含一控制端,该控制端用于接收该第一栅极线信号,其用于控制该第一开关元件的转换;以及

该第二次像素区包含一第二次像素电极电性连接至一第二电荷储存电容,该第二次像素电极配置以通过一第二开关元件由这些数据线其中该者接收数据信号,该第二开关元件包含一控制端,该控制端用于接收该第一栅极线信号,其用于控制该第二开关元件的转换,其中该第二次像素电极还通过一第三开关元件连接至一第三电容,该第三开关元件包含一控制端,该控制端用于接收该第二栅极线信号,其用于控制该第三开关元件的转换;

这些列包含:

一第一列与一第二列,其中提供给该第二列中的这些像素的该第一栅极线信号以及提供给该第一列中的这些像素的该第一栅极线信号之间具有一重叠期间。

2. 根据权利要求 1 所述的液晶显示面板,其特征在于,提供给该第一列中的这些像素的该第二栅极线信号以及提供给该第二列中的这些像素的该第一栅极线信号之间具有一重叠期间。

3. 根据权利要求 1 所述的液晶显示面板,其特征在于,这些列包含:

一第三列位于该第二列后,其中提供给该第三列中的这些像素的该第一栅极线信号以及提供给该第一列中的这些像素的该第二栅极线信号相同。

4. 根据权利要求 1 所述的液晶显示面板,其特征在于,这些列包含:

一第三列位于该第二列后以及一第四列位于该第三列后,其中提供给该第四列中的这些像素的该第一栅极线信号以及提供给该第一列中的这些像素的该第二栅极线信号相同。

5. 根据权利要求 1 所述的液晶显示面板,其特征在于,该第一栅极线平行于该第二栅极线。

6. 根据权利要求 5 所述的液晶显示面板,其特征在于,该第一次像素区与该第二次像素区间隔,其中该第一栅极线与该第二栅极线配置在介于该第一次像素区和该第二次像素区之间的空间。

7. 根据权利要求 1 所述的液晶显示面板,其特征在于,每一这些像素还包含:

一第三次像素区;以及

一第四次像素区,其中

该第三次像素区包含一第三次像素电极电性连接至一第四电荷储存电容,该第三次像

素电极配置以通过一第四开关元件从这些数据线其中另一者接收数据信号,该第四开关元件包含一控制端,该控制端用于接收该第一栅极线信号,用于控制该第四开关元件的转换;以及

该第四次像素区包含一第四次像素电极电性连接至一第五电荷储存电容,该第四次像素电极配置以通过一第五开关元件从这些数据线其中该另一者取得数据信号,该第五开关元件包含一控制端,该控制端用于接收该第一栅极线信号,该第一栅极信号用于控制该第五开关元件的转换,其中该第四次像素电极还通过一第六开关元件连接至一第六电容,该第六开关元件包含一控制端,该控制端用于接收该第二栅极线信号,该第二栅极信号用于控制该第六开关元件的转换。

8. 根据权利要求 7 所述的液晶显示面板,其特征在于,该第五开关元件的控制端由一第三栅极线接收该第一栅极线信号,该第六开关元件的控制端从一第四栅极线接收该第二栅极线信号。

9. 一种液晶显示面板中像素列的驱动方法,该液晶显示面板包含:

多个像素,这些像素配置成多条列与多条行;

多条数据线,每一这些数据线用以提供数据信号至位于一行上的这些像素,其中所有或部分这些像素中的任一像素包含:

一第一栅极线;

一第一次像素区包含一第一次像素电极电性连接至一第一电荷储存电容;以及

一第二次像素区包含一第二次像素电极电性连接至一第二电荷储存电容,其特征在于,该方法包含:

配置一第二栅极线于每一这些像素中;

通过一第一栅极线向第一电荷储存电容和第二电荷储存电容提供一第一栅极线信号以对该第一电荷储存电容与该第二电荷储存电容充电;以及

通过一第二栅极线向第二电荷储存电容提供一第二栅极线信号以排出该第二电荷储存电容中的部分电荷,其中该第二栅极线信号提供于该第一栅极线信号通过后;

该第一次像素电极配置以通过一第一开关元件由这些数据线其中一者接收数据信号,该第一开关元件包含一控制端,该控制端用于接收该第一栅极线信号,该第一栅极线信号用于控制该第一电荷储存电容充电;以及

该第二次像素电极配置以通过一第二开关元件从这些数据线其中该者接收数据信号,该第二开关元件包含一控制端,该控制端用于接收该第一栅极线信号,该第一栅极信号用于控制该第二电荷储存电容充电,该方法还包含:

通过一第三开关元件连结该第二次像素电极至该第三电容,该第三开关元件包含一控制端,该控制端取得该第二栅极线信号以移动该第二电荷储存电容中的部分电荷至该第三电容;

这些列包含:

一第一列与一第二列,其中提供给该第二列中的这些像素的该第一栅极线信号以及提供给该第一列中的这些像素的该第一栅极线信号之间具有一重叠期间。

10. 根据权利要求 9 所述的驱动方法,其特征在于,提供给该第一列中的这些像素的该第二栅极线信号以及提供给该第二列中的这些像素的该第一栅极线信号之间具有一重叠

期间。

11. 根据权利要求 9 所述的驱动方法, 其特征在于, 这些列包含 :

一第三列位于该第二列后, 其中提供给该第三列中的这些像素的该第一栅极线信号与提供给该第一列中的这些像素的该第二栅极线信号相同。

12. 根据权利要求 9 所述的驱动方法, 其特征在于, 这些列包含 :

一第三列位于该第二列后以及一第四列位于该第三列后, 其中提供给该第四列中的这些像素的该第一栅极线信号与提供给该第一列中的这些像素的该第二栅极线信号相同。

13. 根据权利要求 9 所述的驱动方法, 其特征在于, 每一这些像素还包含 :

一第三次像素区 ; 以及

一第四次像素区, 其中

该第三次像素区包含一第三次像素电极电性连接至一第四电荷储存电容, 该第三次像素电极配置以通过一第四开关元件从这些数据线其中另一者接收数据信号, 该第四开关元件包含一控制端 ; 以及

该第四次像素区包含一第四次像素电极电性连接至一第五电荷储存电容, 该第四次像素电极配置以通过一第五开关元件由这些数据线其中该另一者取得数据信号, 该第五开关元件包含一控制端, 该方法还包含 :

通过一第六开关元件连结该第五电荷储存电容至一第六电容, 该第六开关元件包含一控制端 ;

提供该第一栅极线信号至该第四开关元件的控制端与该第五开关元件的控制端以控制对该第四电荷储存电容与该第五电荷储存电容充电 ; 以及

提供该第二栅极线信号至该第六开关元件的控制端以控制移动该第五电荷储存电容中的部分电荷至该第六电容。

14. 根据权利要求 13 所述的驱动方法, 其特征在于, 该每一像素还包含 :

一第三栅极线, 配置以提供该第一栅极线信号至该第四开关元件的控制端与该第五开关元件的控制端 ; 以及

一第四栅极线, 配置以提供该第二栅极线信号至该第六开关元件的控制端。

15. 根据权利要求 14 所述的驱动方法, 其特征在于, 这些列包含 :

一第一列 ;

一第二列位于该第一列后 ; 以及

一第三列位于该第二列后, 该方法还包含 :

提供给该第三列中的这些像素的该第一栅极线信号至位于第一列中的这些像素内的该第二栅极线。

## 液晶显示面板及其像素列的驱动方法

### 技术领域

[0001] 本发明涉及一种液晶显示面板,且特别是涉及一种驱动液晶显示面板中像素列的方法。

### 背景技术

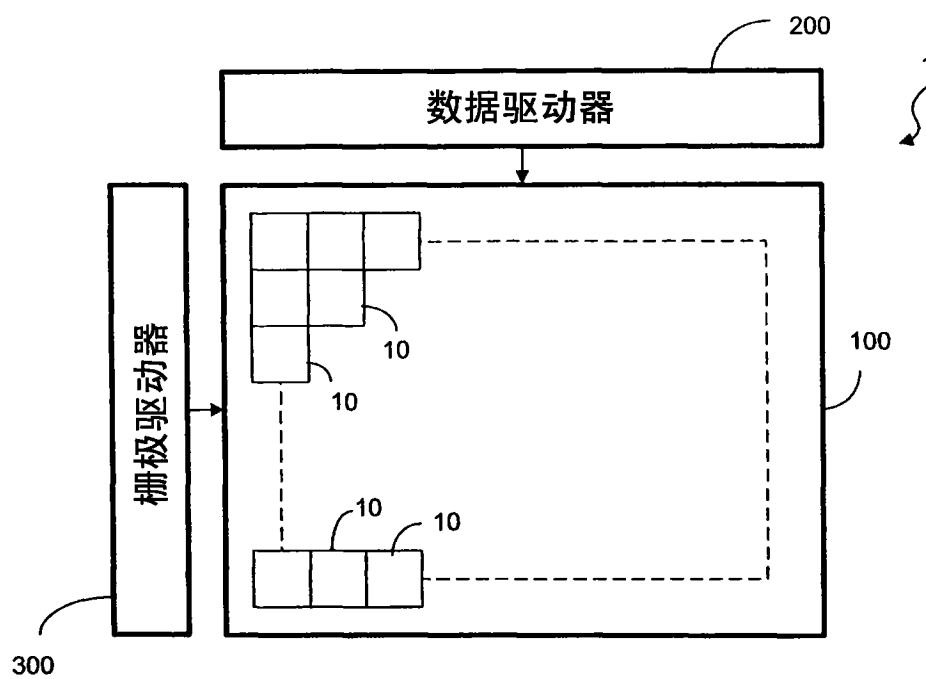

[0002] 一典型液晶显示 (liquid crystal display, LCD) 面板具有多个配置于二维阵列的像素,且上述像素以数据驱动器与栅极驱动器所驱动。如图 1 所示,于液晶显示面板 1 中的液晶显示像素 10 按照列与行排列在显像区 100 内,其中数据驱动器 200 用以提供代表数据的信号至每一行,而栅极驱动器 300 用以提供栅极线信号至每一列。在一彩色液晶显示面板中,影像通常是以红 (R)、绿 (G) 与蓝 (B) 这三种颜色呈现。如图 2 所示,每一像素 10 一般而言可分为三种颜色次像素包含红色次像素 20R、绿色次像素 20G 与蓝色次像素 20B。数据线 221 用以传输数据信号至位于一行上的红色次像素,数据线 222 用以传输数据信号至位于同一像素行上的绿色次像素,数据线 223 用以传输数据信号至位于同一像素行上的蓝色次像素,而数据线 224 用以传输数据信号至位于下一像素行上的红色次像素。栅极线 231 用以传输栅极线信号至所有位于同列上的次像素,而栅极线 232 用以传输栅极线信号至所有位于下一列上的次像素。在一半穿透反射式液晶显示面板中,每一颜色次像素可进一步分成一穿透区与一反射区。

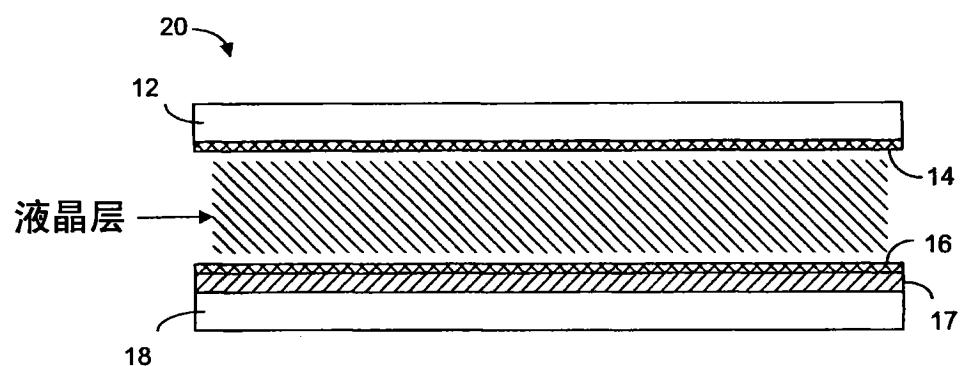

[0003] 一典型液晶显示面板以两个基板制成。如图 3 所示,液晶显示面板具有一上基板 12 与一下基板 18,以及一液晶层位于上基板 12 和下基板 18 之间。在上基板 12 上,一透明导电层 14 用作一公用电极。在每一颜色次像素 20 中,一导电层 16 配置于下基板 18 上以作为一像素电极。此液晶显示面板亦包含一电子元件层 17 以控制公用电极和像素电极之间的电压,其中公用电极通常连接至一共同接地端或一公用电压源 COM。

### 发明内容

[0004] 本发明的目的在于提供一种液晶显示器,此液晶显示器包含多个像素配置成多条列与多条行,其中所有或部分像素中的任一像素包含第一次像素区与第二次像素区,每一第一与第二次像素区均具有储存电容。其中每一像素具有第一栅极线提供第一栅极线信号以对第一与第二储存电容充电,以及第二栅极线提供第二栅极线信号以移动第二储存电容中的部分电荷至第三电容。第一与第二栅极线信号具有相同频宽,但位于栅极线信号之间的频宽与时序可变化,致使提供予一列的第一栅极线信号,可用作第二栅极线信号以提供予位于此列前的其中一列。在本发明一实施例中,在每一列中的像素具有配置以同样地接收第一与第二栅极线信号的复制像素,但此像素与其复制像素由不同的数据线接收数据信号。

[0005] 为达上述目的,本发明提供了一种液晶显示面板,其特征在于,包含:

[0006] 多个像素,这些像素配置成多条列与多条行;以及

[0007] 多条数据线,每一这些数据线用以提供数据信号至位于一行上的这些像素,其中

所有或部分这些像素中的任一这些像素包含：

- [0008] 一第一栅极线,该第一栅极线用以提供一第一栅极线信号;

- [0009] 一第二栅极线,该第二栅极线用以于该第一栅极线信号通过后,提供一第二栅极线信号;

- [0010] 一第一次像素区;以及

- [0011] 一第二次像素区,其中

- [0012] 该第一次像素区包含一第一次像素电极电性连接至一第一电荷储存电容,该第一次像素电极配置以通过一第一开关元件由这些数据线其中一者接收数据信号,该第一开关元件包含一控制端配置以接收该第一栅极线信号以供开关转换;以及

- [0013] 该第二次像素区包含一第二次像素电极电性连接至一第二电荷储存电容,该第二次像素电极配置以通过一第二开关元件由这些数据线其中该者接收数据信号,该第二开关元件包含一控制端配置以接收该第一栅极线信号以供开关转换,其中该第二次像素电极还通过一第三开关元件连接至一第三电容,该第三开关元件包含一控制端配置以接收该第二栅极线信号以供开关转换。

- [0014] 所述的液晶显示面板,其中,该第一电荷储存电容还通过一第四电容连接至该第三电容。

- [0015] 所述的液晶显示面板,其中,这些列包含:

- [0016] 一第一列与一第二列,其中提供给该第二列中的这些像素的该第一栅极线信号以及提供给该第一列中的这些像素的该第一栅极线信号之间具有一重叠期间。

- [0017] 所述的液晶显示面板,其中,提供给该第一列中的这些像素的该第二栅极线信号以及提供给该第二列中的这些像素的该第一栅极线信号之间具有一重叠期间。

- [0018] 所述的液晶显示面板,其中,这些列包含:

- [0019] 一第三列位于该第二列后,其中提供给该第三列中的这些像素的该第一栅极线信号以及提供给该第一列中的这些像素的该第二栅极线信号实质上相同。

- [0020] 所述的液晶显示面板,其中,这些列包含:

- [0021] 一第三列位于该第二列后以及一第四列位于该第三列后,其中提供给该第四列中的这些像素的该第一栅极线信号以及提供给该第一列中的这些像素的该第二栅极线信号实质上相同。

- [0022] 所述的液晶显示面板,其中,该第一栅极线实质上平行于该第二栅极线。

- [0023] 所述的液晶显示面板,其中,该第一次像素区与该第二次像素区间隔,其中该第一栅极线与该第二栅极线配置在介于该第一次像素区和该第二次像素区之间的空间。

- [0024] 所述的液晶显示面板,其中,每一这些像素还包含:

- [0025] 一第三次像素区;以及

- [0026] 一第四次像素区,其中

- [0027] 该第三次像素区包含一第三次像素电极电性连接至一第四电荷储存电容,该第三次像素电极配置以通过一第四开关元件由这些数据线其中另一者接收数据信号,该第四开关元件包含一控制端配置以接收该第一栅极线信号以供开关转换;以及

- [0028] 该第四次像素区包含一第四次像素电极电性连接至一第五电荷储存电容,该第四次像素电极配置以通过一第五开关元件由这些数据线其中该另一者取得数据信号,该第五

开关元件包含一控制端配置以接收该第一栅极线信号以供开关转换,其中该第四次像素电极还通过一第六开关元件连接至一第六电容,该第六电容包含一控制端配置以接收该第二栅极线信号以供开关转换。

[0029] 所述的液晶显示面板,其中,该第五开关元件的控制端配置以由一第三栅极线接收该第一栅极线信号,该第六开关元件的控制端配置以由一第四栅极线接收该第二栅极线信号。

[0030] 所述的液晶显示面板,其中,这些列包含:

[0031] 一第一列;以及

[0032] 一第二列,其中

[0033] 该第一栅极线信号于提供给该第一列中的这些像素的该第一栅极线信号通过后,提供给该第二列中的这些像素。

[0034] 为达上述目的,本发明还提供了一种液晶显示面板中像素列的驱动方法,该液晶显示面板包含:

[0035] 多个像素,这些像素配置成多条列与多条行;

[0036] 多条数据线,每一这些数据线用以提供数据信号至位于一行上的这些像素,其中所有或部分这些像素中的任一像素包含:

[0037] 一第一栅极线;

[0038] 一第一次像素区包含一第一次像素电极电性连接至一第一电荷储存电容;以及

[0039] 一第二次像素区包含一第二次像素电极电性连接至一第二电荷储存电容,其特征在于,该方法包含:

[0040] 配置一第二栅极线于每一这些像素中;

[0041] 通过一第一栅极线提供一第一栅极线信号以对该第一电荷储存电容与该第二电荷储存电容充电;以及

[0042] 通过一第二栅极线提供一第二栅极线信号以排出该第二电荷储存电容中的部分电荷,其中该第二栅极线信号提供于该第一栅极线信号通过后。

[0043] 所述的驱动方法,其中,

[0044] 该第一次像素电极配置以通过一第一开关元件由这些数据线其中一者接收数据信号,该第一开关元件包含一控制端配置以接收该第一栅极线信号以对该第一电荷储存电容充电;以及

[0045] 该第二次像素电极配置以通过一第二开关元件由这些数据线其中该者接收数据信号,该第二开关元件包含一控制端配置以接收该第一栅极线信号以对该第二电荷储存电容充电,该方法还包含:

[0046] 通过一第三开关元件连结该第二次像素电极至该第三电容,该第三开关元件包含一控制端配置以取得该第二栅极线信号以移动该第二电荷储存电容中的部分电荷至该第三电容。

[0047] 所述的驱动方法,其中,这些列包含:

[0048] 一第一列与一第二列,其中提供给该第二列中的这些像素的该第一栅极线信号以及提供给该第一列中的这些像素的该第一栅极线信号之间具有一重叠期间。

[0049] 所述的驱动方法,其中,提供给该第一列中的这些像素的该第二栅极线信号以及

提供给该第二列中的这些像素的该第一栅极线信号之间具有一重叠期间。

[0050] 所述的驱动方法,其中,这些列包含 :

[0051] 一第三列位于该第二列后,其中提供给该第三列中的这些像素的该第一栅极线信号与提供给该第一列中的这些像素的该第二栅极线信号实质上相同。

[0052] 所述的驱动方法,其中,这些列包含 :

[0053] 一第三列位于该第二列后以及一第四列位于该第三列后,其中提供给该第四列中的这些像素的该第一栅极线信号与提供给该第一列中的这些像素的该第二栅极线信号实质上相同。

[0054] 所述的驱动方法,其中,每一这些像素还包含 :

[0055] 一第三次像素区;以及

[0056] 一第四次像素区,其中

[0057] 该第三次像素区包含一第三次像素电极电性连接至一第四电荷储存电容,该第三次像素电极配置以通过一第四开关元件由这些数据线其中另一者接收数据信号,该第四开关元件包含一控制端;以及

[0058] 该第四次像素区包含一第四次像素电极电性连接至一第五电荷储存电容,该第四次像素电极配置以通过一第五开关元件由这些数据线其中该另一者取得数据信号,该第五开关元件包含一控制端,该方法还包含 :

[0059] 通过一第六开关元件连结该第五电荷储存电容至一第六电容,该第六开关元件包含一控制端;

[0060] 提供该第一栅极线信号至该第四开关元件的控制端与该第五开关元件的控制端以对该第四电荷储存电容与该第五电荷储存电容充电;以及

[0061] 提供该第二栅极线信号至该第六开关元件的控制端以移动该第五电荷储存电容中的部分电荷至该第六电容。

[0062] 所述的驱动方法,其中,该每一像素还包含 :

[0063] 一第三栅极线,配置以提供该第一栅极线信号至该第四开关元件的控制端与该第五开关元件的控制端;以及

[0064] 一第四栅极线,配置以提供该第二栅极线信号至该第六电容的控制端。

[0065] 所述的驱动方法,其中,这些列包含 :

[0066] 一第一列;以及

[0067] 一第二列位于该第一列后,该方法还包含 :

[0068] 提供给该第二列中的这些像素的该第一栅极线信号至位于第一列中的这些像素内的该第二栅极线。

[0069] 所述的驱动方法,其中,这些列包含 :

[0070] 一第一列;

[0071] 一第二列位于该第一列后;以及

[0072] 一第三列位于该第二列后,该方法还包含 :

[0073] 提供给该第三列中的这些像素的该第一栅极线信号至位于第一列中的这些像素内的该第二栅极线。

[0074] 为让本发明的上述和其它目的、特征、优点与实施例能更明显易懂,请参照以下实

施方式中图 4 至图 18 的说明。

### 附图说明

- [0075] 图 1 绘示现有技术中的一种典型液晶显示面板；

- [0076] 图 2 绘示现有技术中的一种典型液晶显示面板的像素内的三种颜色次像素；

- [0077] 图 3 绘示现有技术中的一种典型液晶显示面板的像素或颜色次像素的剖面图；

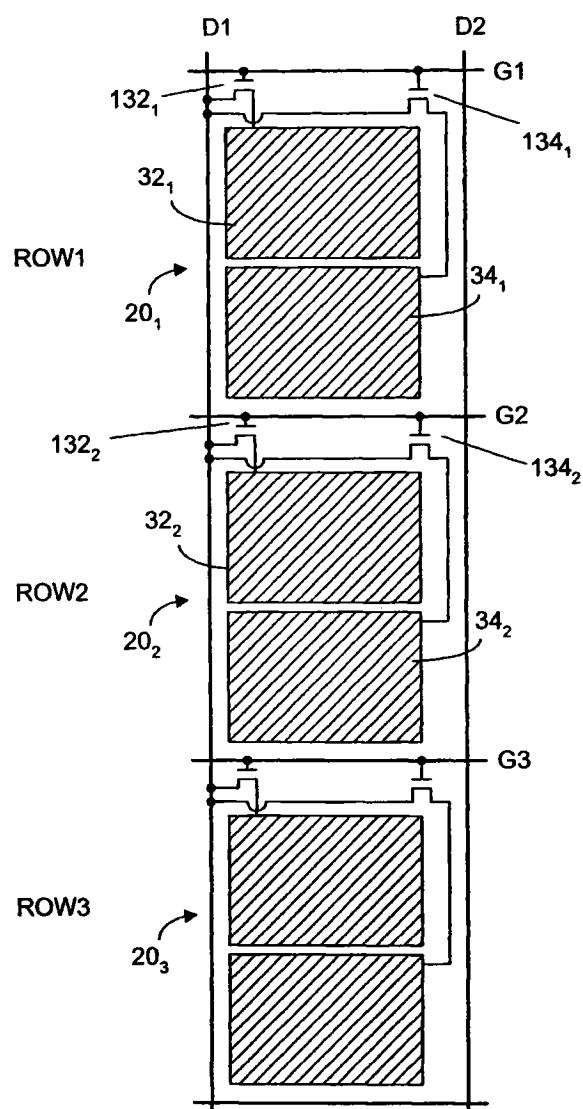

- [0078] 图 4 绘示依照本发明一实施例的一种液晶显示面板的像素或颜色次像素内的次像素电极；

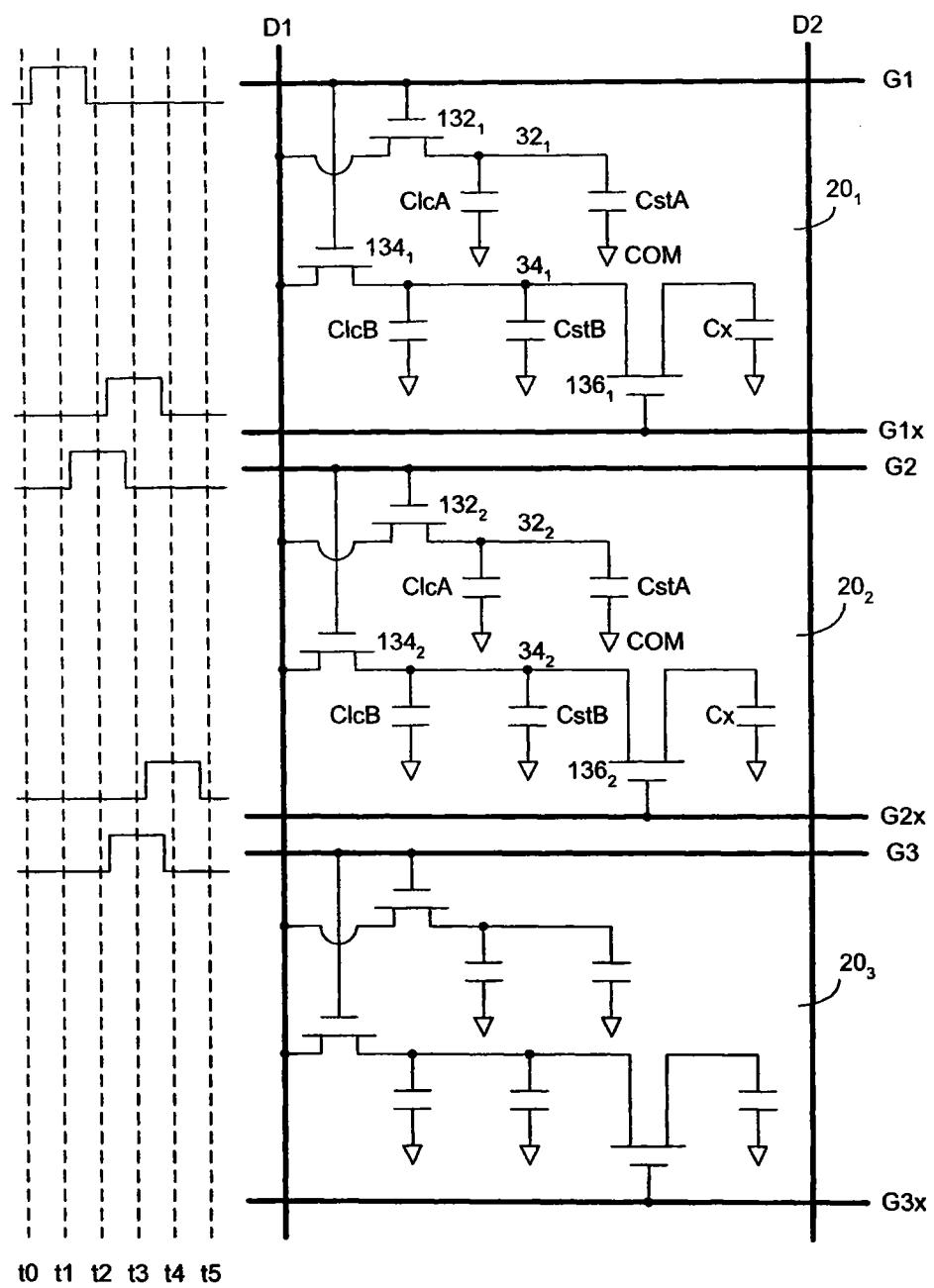

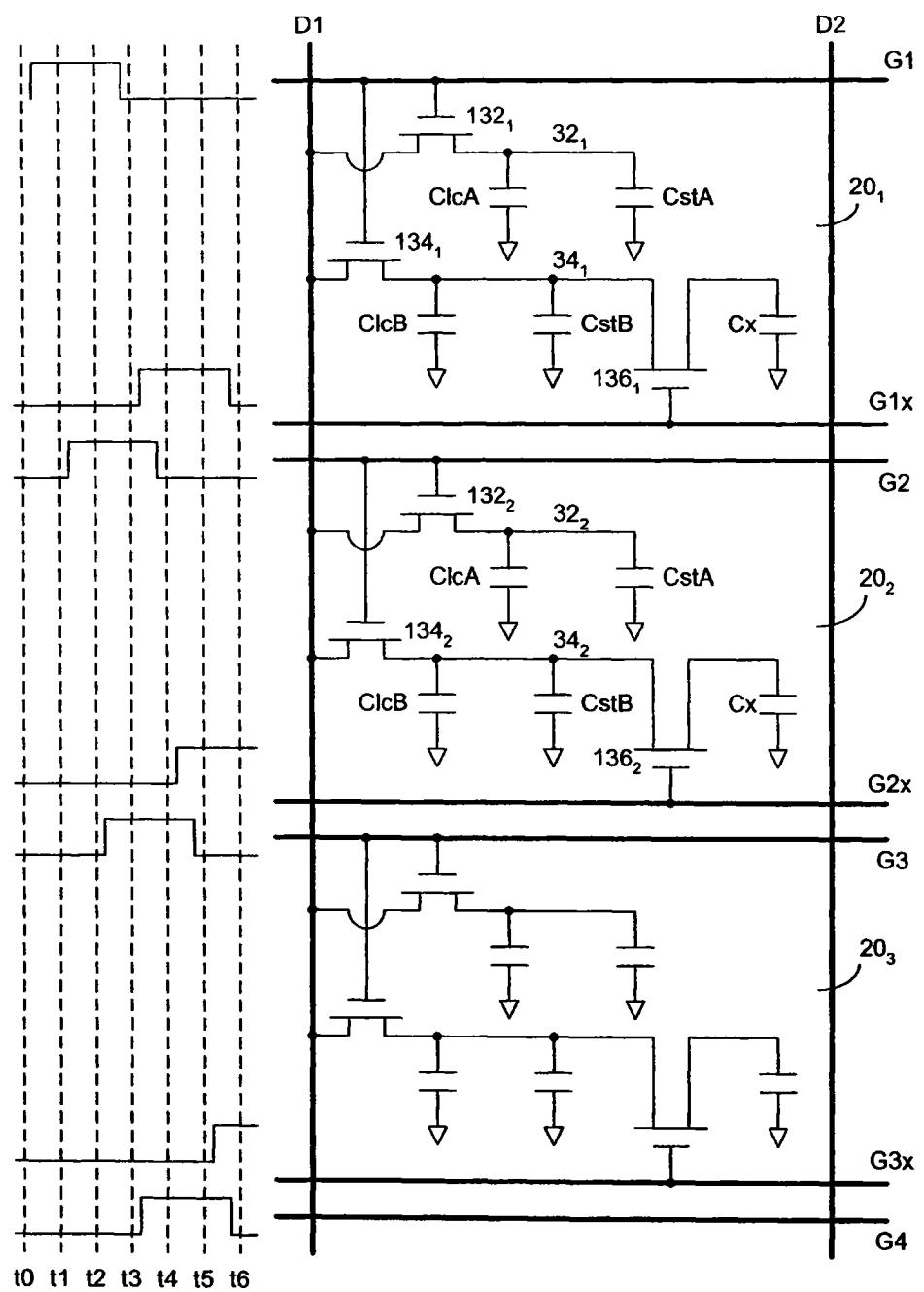

- [0079] 图 5 绘示依照本发明一实施例的一种像素或颜色次像素的等效电路图；

- [0080] 图 6 绘示依照本发明另一实施例的一种栅极线脉冲频宽；

- [0081] 图 7 绘示依照本发明另一实施例的一种像素或颜色次像素的等效电路图；

- [0082] 图 8a 绘示依照本发明一实施例的一种充电期间次像素电极间的连接方式图；

- [0083] 图 8b 绘示依照本发明一实施例的一种电荷共享期间次像素电极间的关系图；

- [0084] 图 9 绘示依照本发明一实施例的一种像素或颜色次像素的元件配置图；

- [0085] 图 10 绘示依照本发明一实施例的一种像素或颜色次像素的剖面图；

- [0086] 图 11 绘示依照本发明一实施例的一种预先充电程序的时序图；

- [0087] 图 12 绘示依照本发明图 5 的一种充电与电荷共享计划；

- [0088] 图 13 绘示依照本发明一实施例的另一种充电与电荷共享计划；

- [0089] 图 14 绘示依照本发明一实施例的再一种充电与电荷共享计划；

- [0090] 图 15a 绘示依照本发明一实施例的又一种充电与电荷共享计划；

- [0091] 图 15b 绘示依照本发明一实施例的再一种充电与电荷共享计划；

- [0092] 图 16 绘示依照本发明一实施例的又一种充电与电荷共享计划；

- [0093] 图 17 绘示依照本发明一实施例的一种颜色次像素的等效电路图；

- [0094] 图 18 绘示依照本发明一实施例的一种半栅极双数据液晶显示器的重复列。

其中，附图标记：

- |                                  |                           |

|----------------------------------|---------------------------|

| [0096] 20 <sub>1</sub> : 次像素、像素列 | 20' <sub>4</sub> : 复制像素列  |

| [0097] 20' <sub>1</sub> : 复制像素列  | 20 <sub>5</sub> : 像素列     |

| [0098] 20 <sub>2</sub> : 次像素、像素列 | 20' <sub>5</sub> : 复制像素列  |

| [0099] 20' <sub>2</sub> : 复制像素列  | 20 <sub>i</sub> : 次像素、像素列 |

| [0100] 20 <sub>3</sub> : 次像素、像素列 | 20' <sub>i</sub> : 复制像素列  |

| [0101] 20' <sub>3</sub> : 复制像素列  | 32 <sub>1</sub> : 第一次像素电极 |

| [0102] 20 <sub>4</sub> : 像素列     | 32 <sub>2</sub> : 第一次像素电极 |

| [0103] 32' <sub>2</sub> : 次像素电极  | 136 <sub>1</sub> : 开关元件   |

| [0104] 32 <sub>i</sub> : 第一次像素电极 | 136 <sub>2</sub> : 开关元件   |

| [0105] 34 <sub>1</sub> : 第二次像素电极 | 136' <sub>2</sub> : 开关元件  |

| [0106] 34 <sub>2</sub> : 第二次像素电极 | 230 : 氧化铟锡层               |

| [0107] 34' <sub>2</sub> : 次像素电极  | 240 : 数据绝缘体               |

| [0108] 34 <sub>i</sub> : 第二次像素电极 | 250 : 源极端部                |

| [0109] 132 <sub>1</sub> : 第一开关元件 | 252 : 漏极端部                |

|        |                          |                   |

|--------|--------------------------|-------------------|

| [0110] | 132 <sub>1</sub> :开关元件   | 254 :漏极端部         |

| [0111] | 132 <sub>2</sub> :第一开关元件 | 260 :高浓度 n 型非晶硅区块 |

| [0112] | 132 <sub>i</sub> :开关元件   | 262 :高浓度 n 型非晶硅区块 |

| [0113] | 134 <sub>1</sub> :第二开关元件 | 270 :栅极端部层        |

| [0114] | 134 <sub>1</sub> :开关元件   | 280 :绝缘层          |

| [0115] | 134 <sub>2</sub> :第二开关元件 | 290 :栅极端部         |

| [0116] | 134 <sub>2</sub> :开关元件   | 292 :共用配线         |

| [0117] | 134 <sub>i</sub> :开关元件   |                   |

## 具体实施方式

[0118] 有关本发明的详细说明及技术内容,配合附图说明如下,然而所附附图仅提供参考与说明用,并非用来对本发明加以限制者。

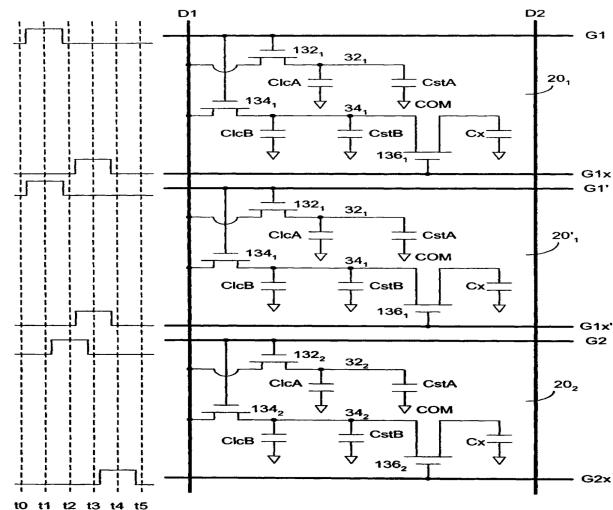

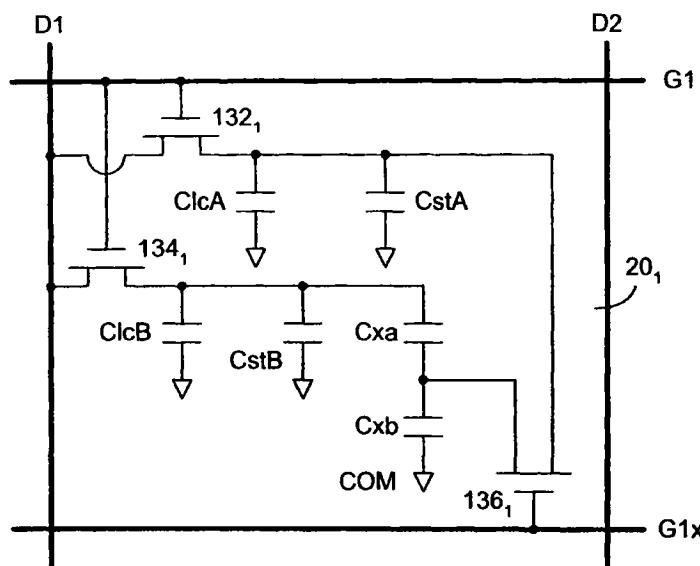

[0119] 在本发明一实施例中,一液晶显示 (liquid crystal display, LCD) 面板的像素或颜色次像素包含两个区块,其中每一区块包含区块电极和共用电极,以控制个别区块中的液晶层的配向。为了方便说明起见,次像素一词将用以表示一像素或一颜色次像素。如图 4 所示,次像素 20<sub>1</sub> 包含一第一次像素电极 32<sub>1</sub> 以划分出第一次像素区,以及一第二次像素电极 34<sub>1</sub> 以划分出第二次像素区。次像素 20<sub>2</sub> 包含一第一次像素电极 32<sub>2</sub> 以划分出第一次像素区,以及一第二次像素电极 34<sub>2</sub> 以划分出第二次像素区。次像素 20<sub>3</sub> 与其它次像素可包含类似的第一与第二次像素电极。在同一行中的次像素共用一数据线,而在同一列中的次像素共用一栅极线。如图 4 所示,次像素 20<sub>1</sub>、20<sub>2</sub>、20<sub>3</sub>、…共用一数据线 D1,而在下一行中的次像素 (图中未显示) 共用另一数据线 D2。次像素 20<sub>1</sub> 与其它位于相同列的次像素共用一栅极线 G1; 次像素 20<sub>2</sub> 与其它位于相同列的次像素共用一栅极线 G2; 以及次像素 20<sub>3</sub> 与其它位于相同列的次像素共用一栅极线 G3。

[0120] 次像素 20<sub>1</sub> 的第一次像素电极 32<sub>1</sub> 通过一第一开关元件 132<sub>1</sub> 连结至数据线 D1,而第二次像素电极 34<sub>1</sub> 通过一第二开关元件 134<sub>1</sub> 连结至数据线 D1,其中第一与第二开关元件 132<sub>1</sub> 与 134<sub>1</sub> 的控制端连接至栅极线 G1。次像素 20<sub>2</sub> 的第一次像素电极 32<sub>2</sub> 通过一第一开关元件 132<sub>2</sub> 连结至数据线 D1,而第二次像素电极 34<sub>2</sub> 通过一第二开关元件 134<sub>2</sub> 连结至数据线 D1,第一与第二开关元件 132<sub>2</sub> 与 134<sub>2</sub> 的控制端连接至栅极线 G2。

[0121] 如图 5 所示,第一次像素电极 32<sub>1</sub> 与共用电极 (COM, 请参照图 3) 形成一电容 ClcA,而第二次像素电极 34<sub>1</sub> 与共用电极形成一电容 ClcB。此外,第一次像素电极 32<sub>1</sub> 连接至一储存电容 CstA,而第二次像素电极 34<sub>1</sub> 连接至一储存电容 CstB。同样地,第一次像素电极 32<sub>2</sub> 与共用电极形成一电容 ClcA,第二次像素电极 34<sub>2</sub> 与共用电极形成一电容 ClcB,而第一次像素电极 32<sub>2</sub> 连接至一储存电容 CstA,第二次像素电极 34<sub>2</sub> 连接至一储存电容 CstB。

[0122] 如图 5 所示,第二次像素电极 34<sub>1</sub> 还通过一开关元件 136<sub>1</sub> 连接至另一电容 Cx,而第二次像素电极 34<sub>2</sub> 还通过一开关元件 136<sub>2</sub> 连接至另一电容 Cx。同样地,在每一次像素中的第二次像素电极均通过一开关元件连接至一电容 Cx。

[0123] 开关元件 136<sub>1</sub> 的控制端连接至另外的栅极线 G1x,而开关元件 136<sub>2</sub> 的控制端连接至另外的栅极线 G2x 等诸如此类连接方式。

[0124] 就目前的显示面板而言 (如:液晶显示面板),以逐一图框的方式呈现图像,如每

一图框皆由提供一连串的栅极线信号予液晶显示面板,以同时启动一列上的次像素来呈现。如图 5 所示,如栅极线 G1 的栅极线信号提供于 t0 和 t2 之间,栅极线 G2 的栅极线信号提供于 t1 和 t3 之间,以与栅极线 G3 的栅极线信号提供于 t2 和 t4 之间。确切而言,相邻列或栅极线间所提供的栅极线信号部分重叠。

[0125] 根据本发明一实施例,在每一次像素内,当开关元件 132<sub>i</sub> 与 134<sub>i</sub> 开启于栅极线 G1 提供栅极线信号时,电容 ClcA、CstA、ClcB 与 CstB 同时依据数据线 D 所提供的数据信号而充电。因此,次像素 20<sub>1</sub> 内的电容 ClcA、CstA、ClcB 与 CstB 于 t0 和 t2 之间充电。在电容 ClcA、CstA、ClcB 与 CstB 的充电完成后,部分 ClcB 与 CstB 内的电荷将于另外的栅极线提供信号时与相连结的电容 Cx 共用,从而,第二次像素电极 34<sub>i</sub> 中的电位较第一次像素电极 32<sub>i</sub> 中的电位低。由于次像素强度主要取决于像素电极和共用电极之间的电压,因此第二次像素区的次像素强度将基于电荷共用的因素而变化。

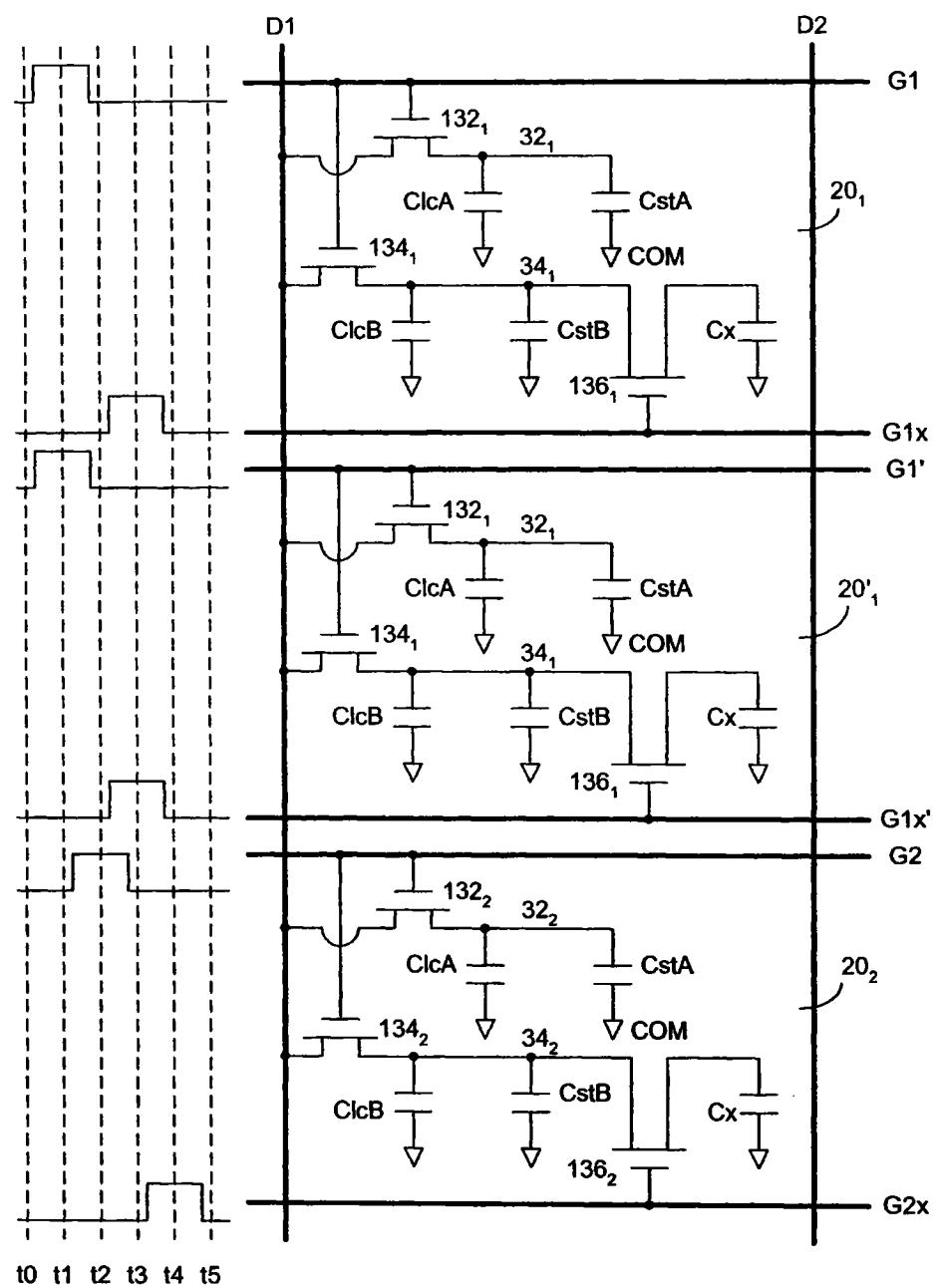

[0126] 如图 5 所示,对第一列中次像素 20<sub>1</sub> 充电通过 G1 所提供的栅极线信号以于 t0 和 t2 之间执行,对第二列中次像素 20<sub>2</sub> 充电通过 G2 所提供的栅极线信号以于 t1 和 t3 之间执行,而对第三列中次像素 20<sub>3</sub> 充电则是通过 G3 所提供的栅极线信号以于 t2 和 t4 之间执行。第一列中次像素 20<sub>1</sub> 通过 G1x 所提供的信号以于 t2 和 t4 之间开启电荷共用,第二列中次像素 20<sub>2</sub> 通过 G2x 所提供的信号以于 t3 和 t5 之间开启电荷共用,而第三列中次像素 20<sub>3</sub> 则是通过 G3x 所提供的信号以于 t4 和 t6(图中未示)之间开启电荷共享。因此, G3 内的栅极线信号可提供给 G1x 以开启次像素 20<sub>1</sub> 内的电荷共享, G4 内的栅极线信号可提供给 G2x 以开启次像素 20<sub>2</sub> 内的电荷共享, Gi+2 内的栅极线信号可提供给 Gix 以开启次像素 20<sub>i</sub> 内的电荷共享,其中 i = 1, 2, 3, ...。

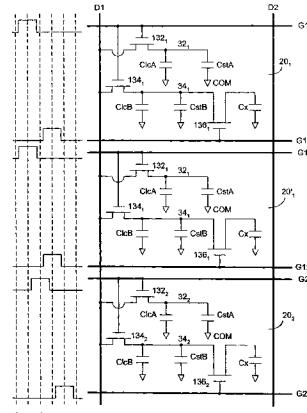

[0127] 如图 6 所示,在本发明另一实施例中,对第一列中次像素 20<sub>1</sub> 充电通过 G1 所提供的栅极线信号以于 t0 和 t3 之间执行,对第二列中次像素 20<sub>2</sub> 充电通过 G2 所提供的栅极线信号以于 t1 和 t4 之间执行,对次像素 20<sub>3</sub> 充电通过 G3 所提供的栅极线信号以于 t2 和 t5 之间执行,以及对次像素 20<sub>4</sub>(图中未示) 充电通过 G4 所提供的栅极线信号以于 t3 和 t6 之间执行。第一列中次像素 20<sub>1</sub> 通过 G1x 所提供的信号以于 t3 和 t6 之间开启电荷共享,第二列中次像素 20<sub>2</sub> 通过 G2x 所提供的信号以于 t4 和 t7(图中未示) 之间开启电荷共享。因此, G4 内的栅极线信号可提供给 G1x 以开启次像素 20<sub>1</sub> 内的电荷共享,以及 Gi+3 内的栅极线信号可提供给 Gix 以开启次像素 20<sub>i</sub> 内的电荷共享。

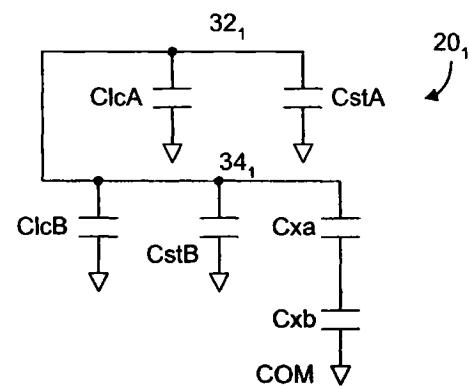

[0128] 在本发明一实施例的电容的另一配置中,通过两个串联的电容 Cxa 与 Cxb 以达成电荷共享。如图 7 所示,第一次像素电极 32<sub>1</sub> 通过一开关元件 136<sub>1</sub> 连接至电容 Cxb,而第二次像素电极 34<sub>2</sub> 则通过一电容 Cxa 连接至电容 Cxb。如图 5 与图 6 所示的本发明一实施例,开关元件 136<sub>1</sub> 的控制端连接至另外的栅极线 G1x 等诸如此类的连接方式。

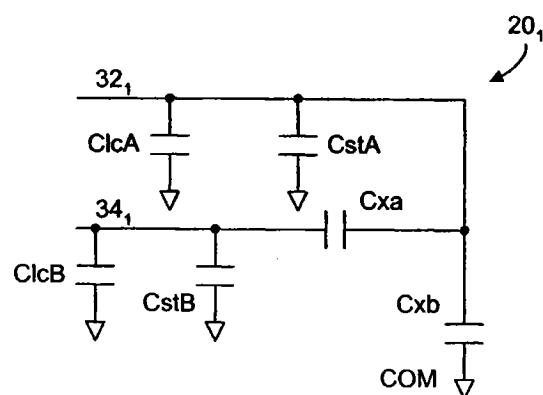

[0129] 根据本发明另一实施例,在每一次像素中,当开关元件 132<sub>i</sub> 与 134<sub>i</sub> 开启于栅极线 Gi 提供栅极线信号时,电容 ClcA、CstA、ClcB、CstB、Cxa 与 Cxb 同时依据数据线 D 所提供的数据信号而充电。因此,如图 8a 所示的第一次像素电极 32<sub>1</sub> 和第二次像素电极 34<sub>1</sub> 实质上充电至与 COM 相关的电位。如图 8b 所示,在电荷共享期间,通过第二栅极线提供第二栅极线信号以排出第二电荷储存电容 CstB 中的部分电荷,其中第二栅极线信号提供于第一栅极线信号通过后, G1x 所提供的信号致使电容 ClcA 与 CstA 分享部分电荷予电容 Cxb,因此,第一次像素电极 32<sub>1</sub> 中的电位较第二次像素电极 34<sub>1</sub> 中的电位低。

[0130] 在一画面时间里,一次像素中的第一次像素电极 32<sub>i</sub> 与第二次像素电极 34<sub>i</sub> 中的电位仅于充电期间实质上相同。在电荷共享期间之后,次像素电极 32<sub>i</sub> 和 34<sub>i</sub> 两者其中之一的电位低于另一者的电位。因此,在其中一次像素电极中液晶分子的倾斜方向和在相同次像素里的另一次像素电极中液晶分子的倾斜方向有些许的不同。次像素中液晶分子倾斜方向些许的分散将扩大液晶显示面板中的视角。

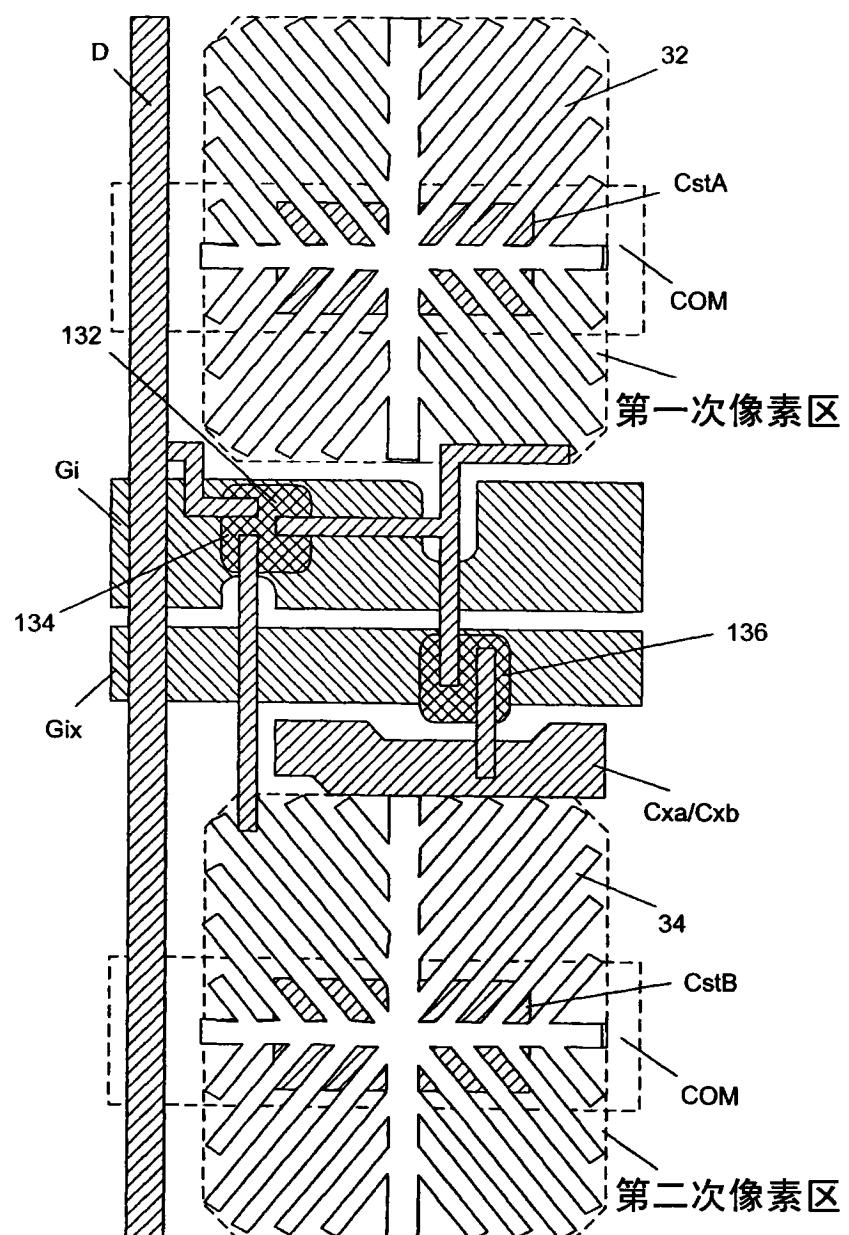

[0131] 本发明一实施例可应用于如聚合物稳定配向 (polymer stabilized alignment, PSA) 的液晶面板。一般而言,在一聚合物稳定配向液晶面板中的次像素包含两个次像素电极,分别位于大体上为长方形的两个次像素区 (请参阅美国专利公开号 No. 2008/0036931, 合并于此以供参考),每一次像素电极通常分为四个部分,每一部分均具有一由次像素电极中央分歧出的鳍状图案,因此,在每一次像素电极下的液晶分子均形成 4 个区域。与每一次像素电极相关的储存电容可配置于如次像素电极中央处附近。如图 9 所示为根据本发明一实施例中的一像素或颜色次像素的典型元件配置。如图 9 所示,次像素电极 32<sub>i</sub> 与次像素电极 34<sub>i</sub> 由一控制区段所区隔,此控制区段包含两个栅极线 G1 与 G1x,其个别连结至开关元件 132<sub>i</sub>、134<sub>i</sub> 与 136<sub>i</sub>。电荷共享电容 Cxa/Cxb 配置于薄膜晶体管 136<sub>i</sub> 与次像素 34<sub>i</sub> 的附近。此控制区段亦包含金属线以作为栅极线与共用配线。

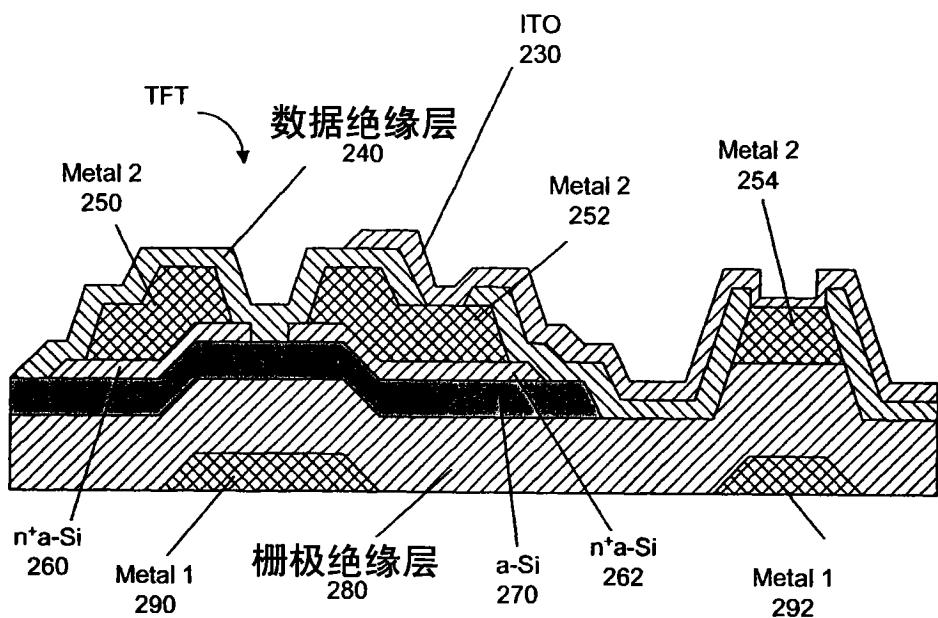

[0132] 如图 10 所示为根据本发明一实施例的次像素的剖面图。如图 10 所示,此剖面包含多条金属线 (Metal 1) 或以区块 290, 292 作为栅极线与共用配线。举例而言,金属线 290 作为一薄膜晶体管 (如图 6 所示的 132<sub>i</sub> 或 134<sub>i</sub>) 的栅极端部,而金属线 292 作为共用配线。一绝缘层 280 作为一介于金属线 290 和栅极端部层 270 (使用如非晶硅 a-Si 所形成) 之间的栅极绝缘体。在非晶硅层 270 之上为一薄膜晶体管的源极端部 250 (Metal 2) 与漏极端部 252 (Metal 2),其通过两个高浓度 n 型非晶硅区块 260 和 262 (n<sup>+</sup>a-Si) 将其与栅极端部层 270 分隔。一数据绝缘层 240 配置于薄膜晶体管与部分绝缘层 280 之上。Metal 2 层的区块 254 用以配合金属区块 292 来形成一储存电容。一氧化铟锡层 230 (ITO) 配置于部份数据绝缘层 240 上,以电性连结漏极端部 252 与 Metal 2 层的区块 254。

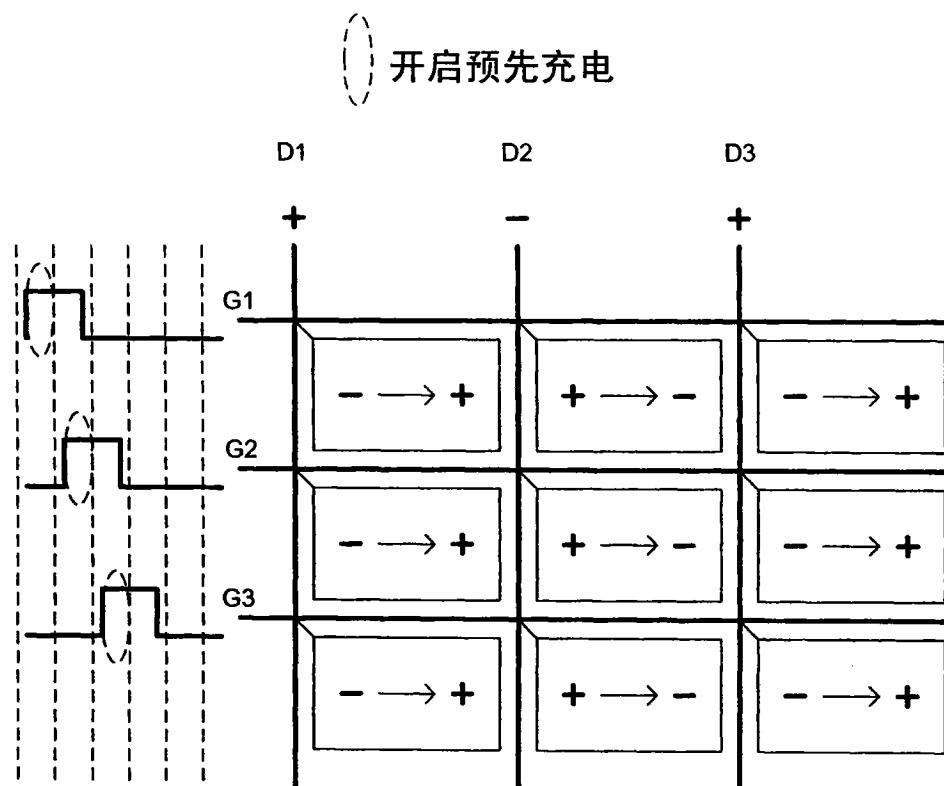

[0133] 在一高图框率或高分辨率液晶显示器中,为提高充电时间,通常会应用一预先充电方式。在一液晶显示器之中,一栅极线将于紧接于其前方的栅极线所提供的栅极线信号通过后才提供其栅极线信号,此预先充电信号通常分离且提前于用以选择一次像素的选定脉冲。若是将次像素电极及与其相关的储存电容自最低电量充电至最高电量,进而启动次像素的话,则此预先充电信号用以将一次像素由最低电量充电至介于中间值的电量。随后,选定脉冲用以将次像素充电至其最高电量。如图 5 所示,在本发明一实施例中, G1 所提供的栅极线信号部份重叠于 G2 所提供的栅极线信号,其中 G1 所提供的栅极线信号中未重叠的部分可用于一液晶显示器中的预先充电程序,此预先充电程序若采用行反转模式,则在同一画面中每一行的数据线极性均相同。如图 11 所示为在一液晶显示器中采用行反转模式的预先充电方案。

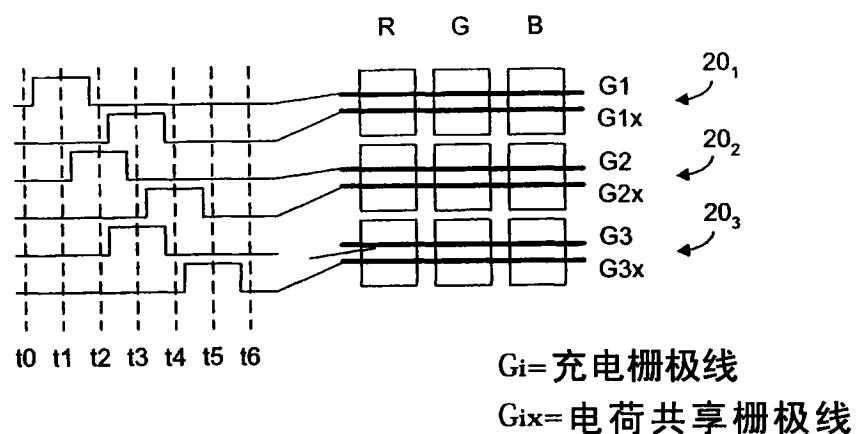

[0134] 如图 5 所示的充电与电荷共享方案,于 i 列上的次像素 20<sub>i</sub> 中使用一充电栅极线 G<sub>i</sub> 来充电,并使用另一电荷共用栅极线 G<sub>ix</sub> 来开启电荷共享。通常一像素包含三种颜色像素 R、G 与 B。图 12 所示为依照本发明一实施例绘示一种充电与电荷共享的方式。如图 5 与图 12 所示,栅极线信号宽度较现有的液晶显示器中栅极脉冲的宽度大两倍,致使当充电栅极线和电荷共用栅极线中提供给同一列上像素的栅极线信号分离时,提供给相邻列上的

栅极线信号会部份重叠。此充电与电荷共用方式可使用于一以频率 120Hz 或图框率达每秒 120 图框来驱动的液晶显示器中。

[0135] 如图 12 所示,每一像素列均具有两条栅极线,其中 Gi 用以充电而 Gi<sub>x</sub> 用以开启电荷共享。提供给相邻列之间用以充电的栅极线信号部份重叠,而提供给同列像素的充电栅极线的栅极信号不同于电荷共享栅极线的栅极信号。由图 12 中可以看出,提供给 G<sub>3</sub> 的充电栅极线信号和提供给 G<sub>1x</sub> 的电荷共享栅极线信号相同,因此,能将提供给 G<sub>3</sub> 的栅极线信号引导至栅极线 G<sub>1x</sub>,同样地,能将提供给 G<sub>(n+2)</sub> 的栅极线信号引导至栅极线 G<sub>nx</sub>。

[0136] 如图 5 与图 6 所示,每一像素列均具有两条栅极线的优点为由电容 C<sub>1cB</sub> 与 C<sub>stB</sub> 分享电荷的电容 C<sub>x</sub> 可配置于相同的次像素,其中电荷共享导线(介于 C<sub>stB</sub> 和开关元件 136 之间的导线)可完全配置于相同的次像素内。同样地,如图 7 所示,由电容 C<sub>1cA</sub> 与 C<sub>stA</sub> 分享电荷的电容 C<sub>xb</sub> 可配置于相同的次像素,其中电荷共享导线(介于 C<sub>stA</sub> 和开关元件 136 之间的导线)可完全配置于相同的次像素内。如图 5 所示的本发明一实施例,栅极线信号宽实质上较在现有的液晶显示器中栅极脉冲宽 (gate pulse width, GPW) 大两倍。如图 6 所示的本发明一实施例,栅极线信号宽实质上较在现有的液晶显示器中栅极脉冲宽大三倍。

[0137] 若每一像素列均仅具有一栅极线,且其栅极脉冲宽大于现有的液晶显示器中的栅极脉冲宽,则电荷共享导线必须跨越相邻列之间的次像素。此跨越电荷共享方式将使得像素配置更加复杂,且导致一非必要的像素间耦合效应。

[0138] 此外,如图 11 中所讨论者,预先充电的时序需求,由于相邻像素列间栅极线信号部份重叠所致。然而,充电与电荷共享的时序需求,由于同一列中的电荷共用仅能在充电完成后起始所致。因此,当仅有一栅极线用以提供每一像素列信号时,在预先充电和电荷共享之间将有一互偿。

[0139] 由于本案实施例中每一像素列均具有两条栅极线,因此可同时满足预先充电的时序需求与电荷共享的时序需求。

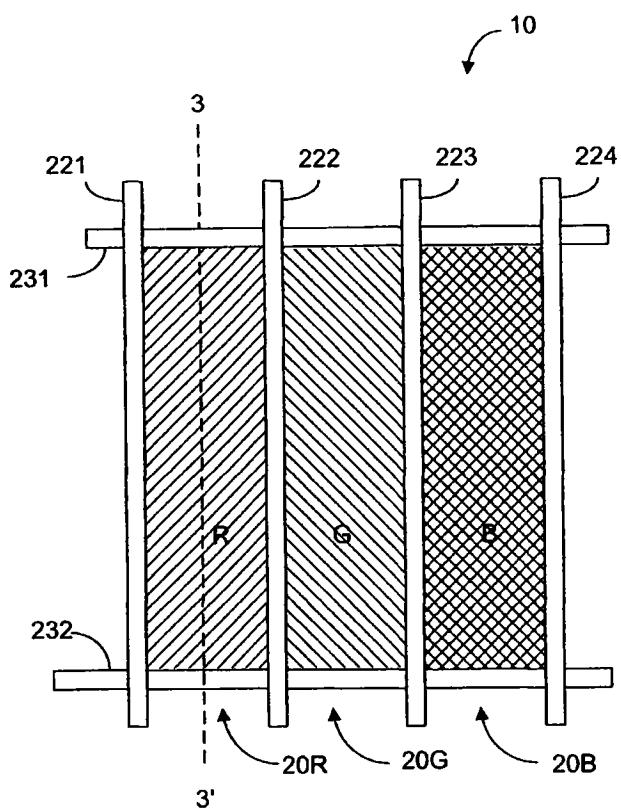

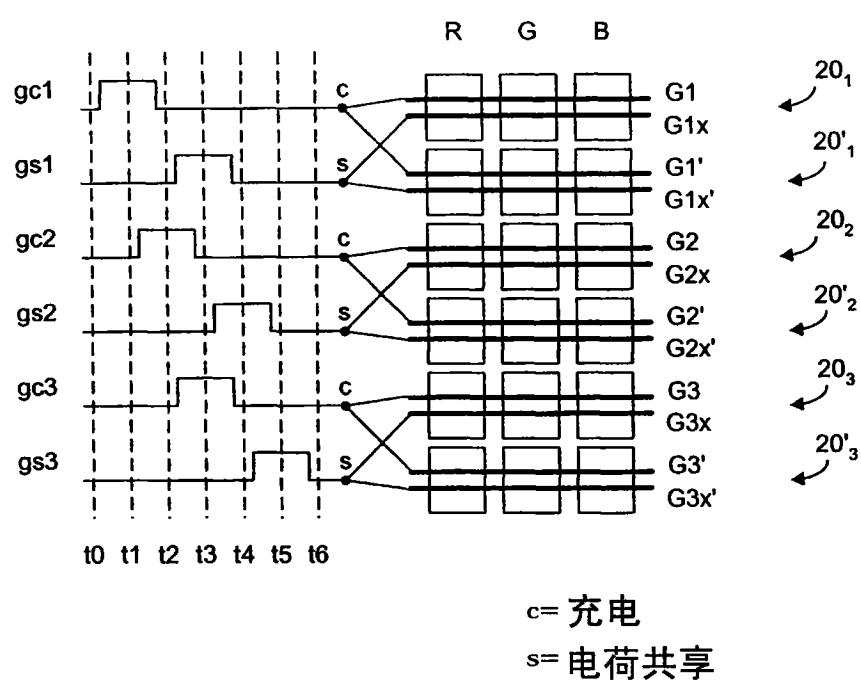

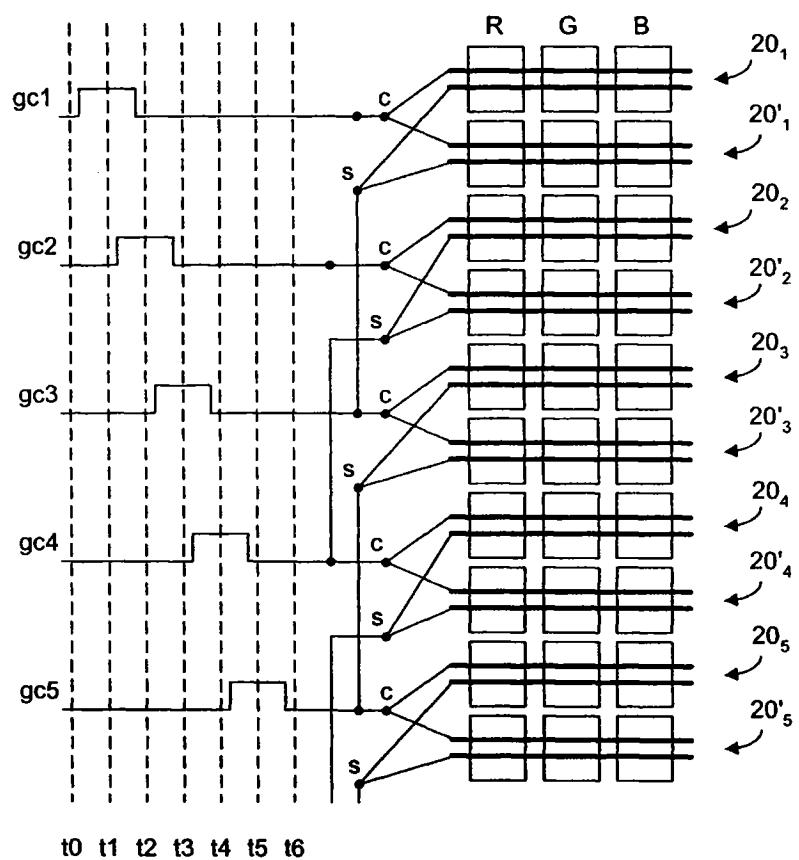

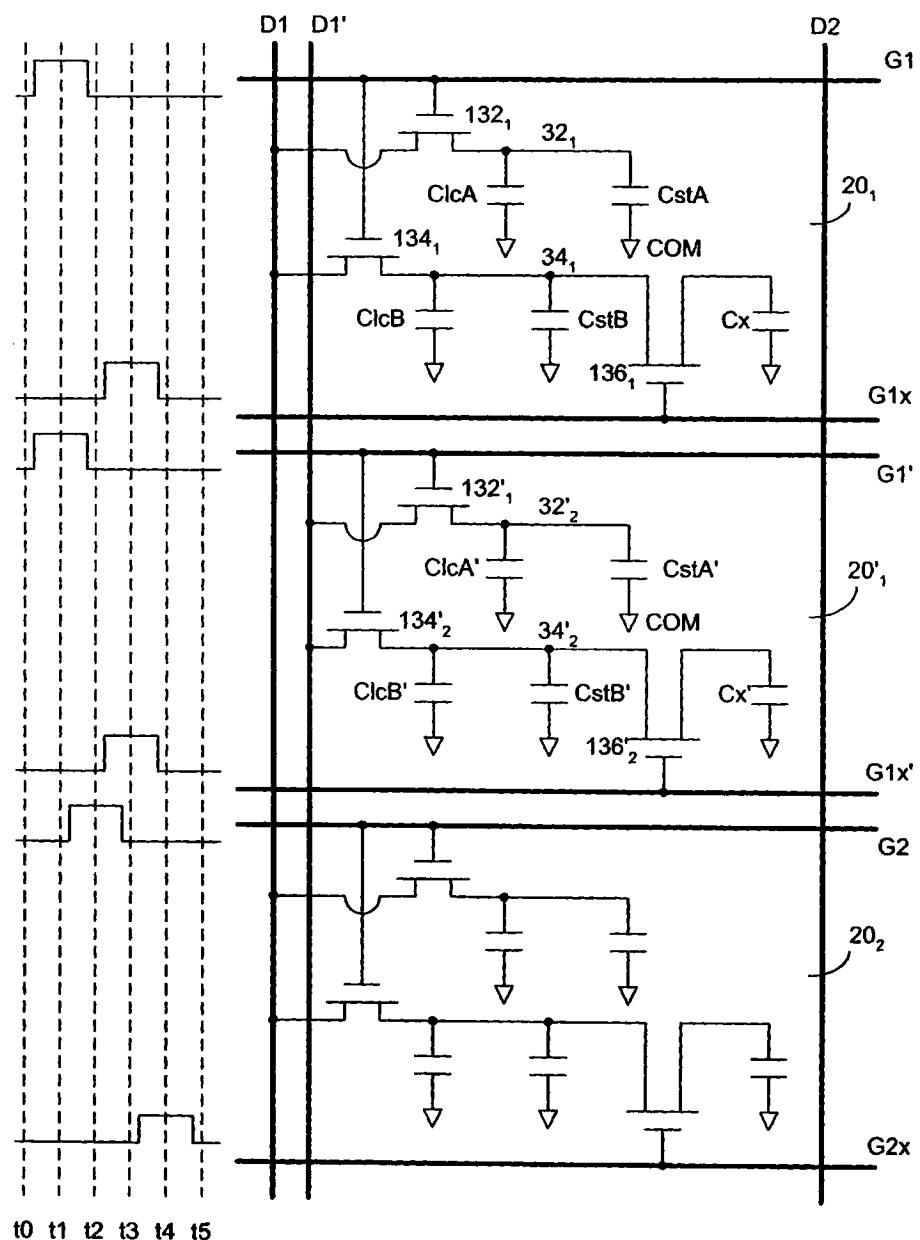

[0140] 基于一半栅极双数据 (half-gate two-data, hG-2D) 技术,类似的充电与电荷共享方式亦可用在一采用频率 240Hz 的液晶显示面板中。如图 13 所示,每一像素列均有效地划分为一上端列与一下端列,如原本通过充电栅极线 G<sub>1</sub> 与电荷共享栅极线 G<sub>1x</sub> 所驱动的像素列 20<sub>1</sub>,现在具有一通过充电栅极线 G<sub>1'</sub> 与电荷共享栅极线 G<sub>1x'</sub> 所驱动的复制像素列 20'<sub>1</sub>。在半栅极双数据驱动计划中,充电栅极线 G<sub>1</sub> 与 G<sub>1'</sub> 的栅极线信号可同时提供给像素列 20<sub>1</sub> 与 20'<sub>1</sub>,但是像素列 20<sub>1</sub> 中 G<sub>1</sub> 所提供的数据信号以及像素列 20'<sub>1</sub> 中 G<sub>1'</sub> 所提供的数据信号分别使用两条数据线(图中未示)来提供。同样地,电荷共享栅极线 G<sub>1x</sub> 与 G<sub>1x'</sub> 的栅极线信号可同时提供。用以对像素中像素列 20<sub>i</sub> 与像素列 20'<sub>i</sub> 进行充电的栅极线信号以 g<sub>ci</sub> 表示,用以将像素中像素列 20<sub>i</sub> 与像素列 20'<sub>i</sub> 的电荷共享开启的栅极线信号以 g<sub>si</sub> 表示。

[0141] 如图 13 所示的本发明一实施例,每一对相关的像素列 20<sub>i</sub> 与 20'<sub>i</sub> 均具有自己的充电栅极信号 g<sub>ci</sub> 与电荷共享栅极信号 g<sub>si</sub>。因此,在一画面时间里,将会有 n 个充电栅极信号与 n 个电荷共享栅极信号提供给 n 对相关的像素列,且可通过使用充电栅极信号以供启动电荷共享来消除 n 个电荷共享栅极信号。如图 18 所示为一半栅极双数据液晶显示器中的等效像素列电路。

[0142] 如图 14 所示,如一充电栅极信号 g<sub>c3</sub> 可同时用以对像素中的像素列 20<sub>3</sub> 与 20'<sub>3</sub> 充电以及开启像素列 20<sub>1</sub> 与 20'<sub>1</sub> 的电荷共享。同样地,一充电栅极信号 g<sub>c4</sub> 可同时用以对像

素中的像素列  $20_4$  与  $20'_4$  充电以及开启像素中的像素列  $20_2$  与  $20'_2$  的电荷共享机制。在本实施例中, 棚极线信号宽较棚极脉冲宽大两倍, 且充电棚极信号于两对列之间切换以开启电荷共享。

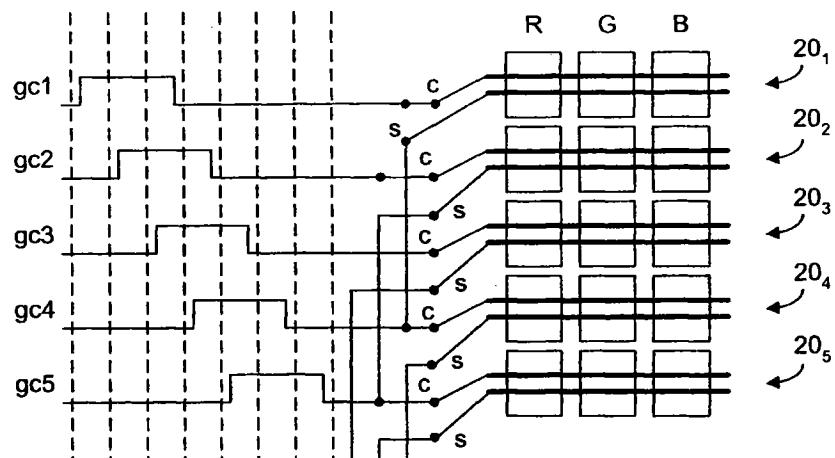

[0143] 如图 6 所示, 若棚极线信号宽更宽, 充电棚极信号将于三对或多对列之间切换以开启电荷共享。如图 15a 所示, 如一充电棚极信号  $gc4$ , 可同时用以对像素中的像素列  $20_4$  充电以及开启像素中的像素列  $20_1$  的电荷共享。同样地, 一充电棚极信号  $gc5$ , 可同时用以对像素中的像素列  $20_5$  充电以及开启像素中的像素列  $20_2$  的电荷共享。在本实施例中, 棚极线信号宽较棚极脉冲宽大三倍, 且充电棚极信号于三对列之间切换以开启电荷共享。

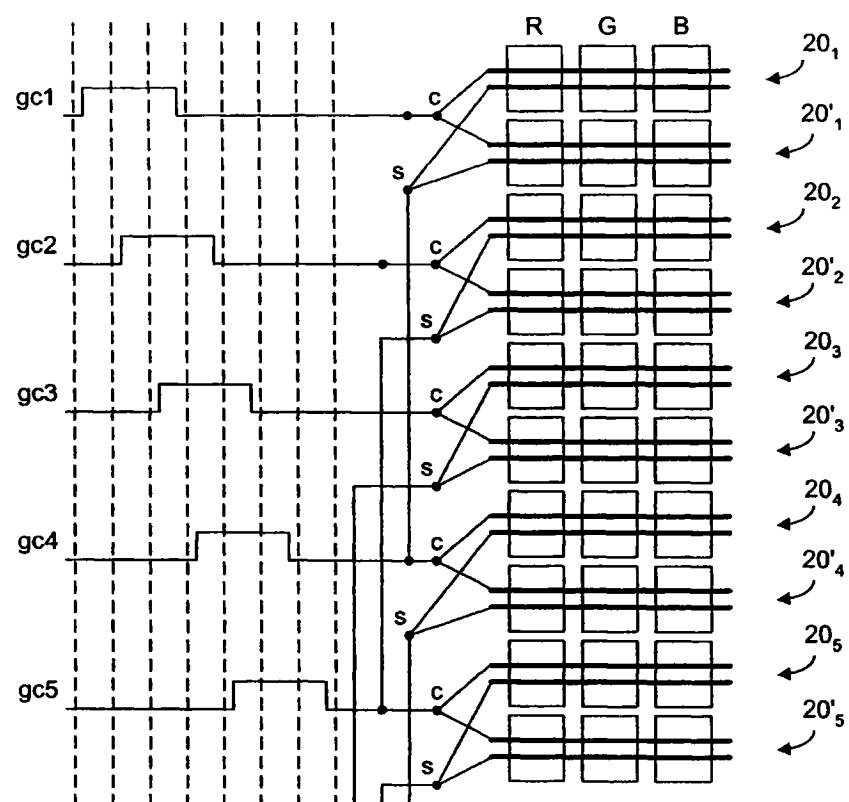

[0144] 基于一半棚极双数据技术, 一类似的充电与电荷共享方式亦可用在一采用频率 240Hz 的液晶显示面板中。如图 15b 所示, 如一充电棚极信号  $gc4$ , 可同时用以对像素中的像素列  $20_4$  与  $20'_4$  充电以及开启像素中的像素列  $20_1$  与  $20'_1$  的电荷共享。同样地, 一充电棚极信号  $gc5$ , 可同时用以对像素中的像素列  $20_5$  与  $20'_5$  充电以及开启像素中的像素列  $20_2$  与  $20'_2$  的电荷共享。在本实施例中, 棚极线信号宽较棚极脉冲宽大三倍, 且充电棚极信号于三对列之间切换以开启电荷共享。

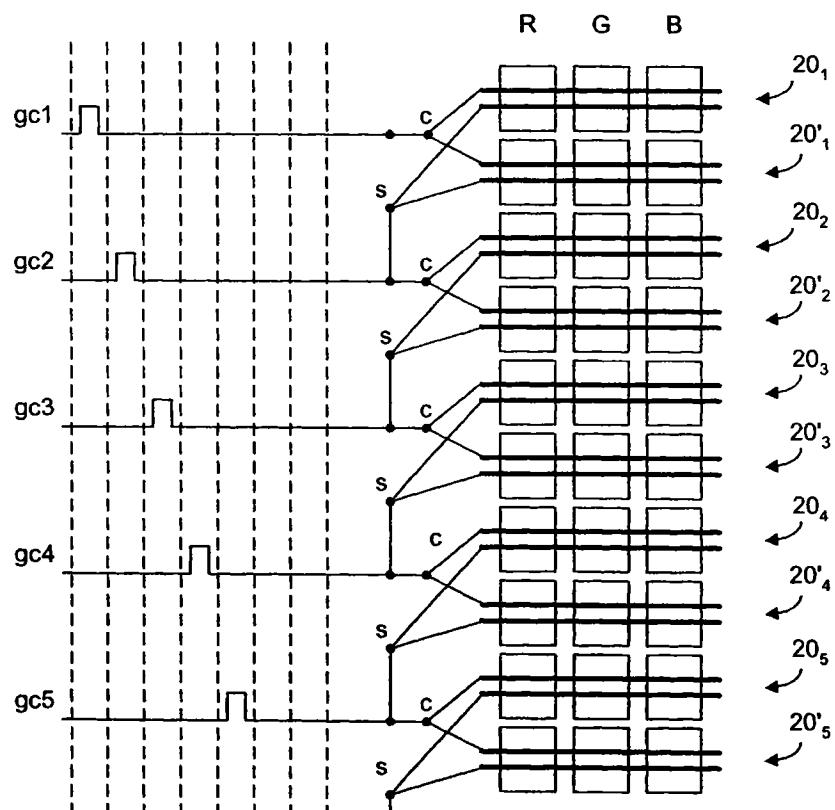

[0145] 若棚极线信号宽与棚极脉冲宽相等, 充电棚极信号仅可切换至其前一对列以开启电荷共享。如图 16 所示, 如一充电棚极信号  $gc4$ , 可同时用以对像素中的像素列  $20_4$  与  $20'_4$  充电以及开启像素中的像素列  $20_3$  与  $20'_3$  的电荷共享。同样地, 一充电棚极信号  $gc5$ , 可同时用以对像素中的像素列  $20_5$  与  $20'_5$  充电以及开启像素中的像素列  $20_4$  与  $20'_4$  的电荷共享。

[0146] 总结而论, 本发明应用一般的棚极脉冲宽或较宽的棚极脉冲宽以达成不同的实施例。由于使用一般的棚极脉冲宽, 在一应用半棚极双数据技术的频率为 240Hz 的液晶显示器中, 一棚极信号可用以同时对像素中的第  $n$  对复制像素列充电以及开启像素中的在先的第  $n-1$  对复制像素列的电荷共享, 其中复制像素列中的数据信号分别以两条数据线提供。

[0147] 由于使用两倍棚极脉冲宽 (2xGPW), 在一使用频率 120Hz 的液晶显示器中, 一棚极信号可用以同时对像素中的第  $n$  列像素充电以及开启像素中第  $n-2$  列像素的电荷共享。此外, 在一应用半棚极双数据技术的频率为 240Hz 的液晶显示器中, 类似的棚极信号可用以同时对像素中的第  $n$  对复制像素列充电以及开启像素中的第  $n-2$  对复制像素列的电荷共享, 其中复制像素列中的数据信号分别以两条数据线提供。

[0148] 由于使用三倍棚极脉冲频宽 (3xGPW), 在一使用频率 120Hz 的液晶显示器中, 一棚极信号可用以同时对像素中的第  $n$  列像素充电以及开启像素中第  $n-3$  列像素的电荷共享。此外, 在一应用半棚极双数据技术的频率为 240Hz 的液晶显示器中, 类似的棚极信号可用以同时对像素中的第  $n$  对复制像素列充电以及开启像素中的第  $n-3$  对复制像素列的电荷共享, 其中复制像素列中的数据信号分别以两条数据线提供。

[0149] 此外, 亦可使用具有较一般脉冲宽大三倍的棚极线信号, 且在同列像素中介于充电和电荷共享信号间的时序会因此而有所调整。

[0150] 在图 13 至图 16 中, 重复列中的像素  $20'_i$  可视为与像素  $20_i$  相同。因此, 如图 17 所示, 除了像素  $20_1$  中开关元件  $132_1$  与  $134_1$  配置以由数据线  $D1$  取得数据信号, 而像素  $20'_1$  中开关元件  $132'_1$  与  $134'_1$  配置以由另一数据线  $D'_1$  取得数据信号之外, 像素  $20_1$  与像素  $20'_1$  可具有实质上相同的元件。

[0151] 在一般的液晶显示器中,每一像素内的颜色次像素 R、G 与 B 如图 2 所示排列成一列。如图 2 所示,每一颜色次像素均具有各自的数据线。在一三栅极液晶显示器中,每一像素中的颜色次像素 R、G 与 B 排列成一行,且每一颜色次像素均具有各自的栅极线,因此每一像素列将具有三条栅极线。在一半源极驱动 (half-source driver, HSD) 型液晶显示器中,每一像素内的颜色次像素 R、G 与 B 排列成一列,与现有的液晶显示器类似,但是次像素的 R、G 与 B 数据线分组成对,致使每一像素的其中一数据线需移至次像素的另一边。当数据线移至次像素的另一边后,将在介于两相邻的颜色次像素之间留下一空间或空置区,此区域可用以设置电荷共享导线的布线,因此,将没必要为了设置电荷共享导线而缩小次像素电极间的宽度。基于上述原由,本发明可用在半源极驱动型液晶显示器中而无须牺牲像素的开口率 (aperture ratio, AR)。

[0152] 在一聚合物稳定配向型液晶显示器中,充电栅极线  $G_i$  与电荷共享栅极线  $G_{ix}$  可设置在一非重叠且非交错配置中 (请参照如图 9)。在图 9 中,栅极线  $G_i$  实质上平行于栅极线  $G_{ix}$ , 且此两者配置在一介于第一次像素区 132、134 与第二次像素区 136 之间的空间中。

[0153] 本发明的其它实施例亦可使用于分辨率达 1920x1080 的 FHD 型液晶显示器中,以及分辨率达 3840x2160 的 4k2k 型显示器中。

[0154] 值得注意的是,本发明所列举的各式实施例虽然用于彩色液晶显示器内的颜色次像素,但亦可用于单色液晶显示器中,举例而言,此液晶显示器可为一透射型显示器。本发明亦可用于半穿透反射式显示器或反射式显示器中。

[0155] 当然,本发明还可有其它多种实施例,在不背离本发明精神及其实质的情况下,熟悉本领域的技术人员当可根据本发明做出各种相应的改变和变形,但这些相应的改变和变形都应属于本发明所附的权利要求的保护范围。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8a

图 8b

图 9

图 10

图 11

图 12

图 13

图 14

图 15a

图 15b

图 16

图 17

图 18

|                |                                                                                                                                                   |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示面板及其像素列的驱动方法                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">CN101819365B</a>                                                                                                                      | 公开(公告)日 | 2012-04-18 |

| 申请号            | CN201010105205.8                                                                                                                                  | 申请日     | 2010-01-22 |

| [标]申请(专利权)人(译) | 友达光电股份有限公司                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | 友达光电股份有限公司                                                                                                                                        |         |            |

| 当前申请(专利权)人(译)  | 友达光电股份有限公司                                                                                                                                        |         |            |

| [标]发明人         | 廖培钧<br>丁天伦<br>徐文浩<br>侯鸿龙                                                                                                                          |         |            |

| 发明人            | 廖培钧<br>丁天伦<br>徐文浩<br>侯鸿龙                                                                                                                          |         |            |

| IPC分类号         | G02F1/1362 G02F1/133                                                                                                                              |         |            |

| CPC分类号         | G09G2310/0251 G09G2300/0443 G09G2300/0447 G09G2300/0852 G09G3/3659 G09G2320/028<br>G02F1/136213 G02F1/133707 G02F1/13624 G09G3/3648 G09G2310/0205 |         |            |

| 优先权            | 12/590765 2009-11-13 US                                                                                                                           |         |            |

| 其他公开文献         | <a href="#">CN101819365A</a>                                                                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                                                                    |         |            |

### 摘要(译)

本发明有关于一种液晶显示面板，此液晶显示面板包含具有第一次像素区与第二次像素区的像素，其中每一次像素区具有储存电容。每一像素具有第一栅极线提供第一栅极线信号以对第一与第二储存电容充电，以及第二栅极线于第一栅极线信号通过后提供第二栅极线信号以移动第二储存电容中的部分电荷至第三电容。第一与第二栅极线信号的频宽与时序可改变，致使提供给一列的第一栅极线信号，可作为第二栅极线信号提供给位于此列前的其中一列。