(12) 发明专利

(10) 授权公告号 CN 101354512 B

(45) 授权公告日 2012. 11. 14

(21) 申请号 200810134339.5

CN 1372241 A, 2002. 10. 02,

(22) 申请日 2008. 07. 24

US 2005/0036091 A1, 2005. 02. 17,

(30) 优先权数据

审查员 贾杨

74127/07 2007. 07. 24 KR

(73) 专利权人 三星电子株式会社

地址 韩国京畿道

(72) 发明人 刘惠兰 朴乘范 严允成 朴振远

都熙旭 金勋

(74) 专利代理机构 北京市柳沈律师事务所

11105

代理人 邵亚丽

(51) Int. Cl.

G02F 1/1362 (2006. 01)

G09G 3/36 (2006. 01)

(56) 对比文件

US 2007/0165149 A1, 2007. 07. 19,

CN 1979274 A, 2007. 06. 13,

权利要求书 2 页 说明书 17 页 附图 17 页

(54) 发明名称

液晶显示器及其驱动方法

(57) 摘要

提供了一种 LCD 和驱动该 LCD 的方法。该 LCD 包括：在第一方向上延伸的第一和第二栅极线；与第一栅极线隔离并与第一栅极线交叉的数据线；包括第一和第二子像素电极的像素电极，该像素电极被布置在于第一方向上具有长侧边的像素中；连接到第一栅极线、数据线和第一子像素电极的第一薄膜晶体管 (TFT)；连接到第一栅极线、数据线和第二子像素电极的第二 TFT；以及连接到第二栅极线、第二子像素电极和电荷共享电容的第三 TFT，该电荷共享电容共享施加到第二子像素电极的数据电压。

1. 一种液晶显示器 (LCD), 包括 :

在第一方向上延伸的第一栅极线和第二栅极线 ;

数据线, 其与第一栅极线隔离并与第一栅极线交叉 ;

像素电极, 包括第一子像素电极和第二子像素电极, 所述像素电极被布置在于第一方向上具有长侧边的像素中 ;

第一薄膜晶体管 (TFT), 其连接到第一栅极线、数据线和第一子像素电极 ;

第二 TFT, 其连接到第一栅极线、数据线和第二子像素电极 ;

第三 TFT, 其连接到第二栅极线、第二子像素电极和电荷共享电容, 该电荷共享电容共享施加到第二子像素电极的数据电压 ; 以及

第三栅极线, 其被布置为平行于第一栅极线和第二栅极线并位于两者之间。

2. 如权利要求 1 所述的液晶显示器, 其中栅极导通信号被顺序地和重叠地施加到第一栅极线、第三栅极线和第二栅极线。

3. 如权利要求 1 所述的液晶显示器, 还包括存储线, 其被布置为与第一栅极线和第二栅极线平行,

其中, 所述电荷共享电容包括第三 TFT 的漏电极和存储线。

4. 一种液晶显示器 (LCD), 包括 :

液晶面板组件, 包括 :

在第一方向上延伸的第一栅极线和第二栅极线,

数据线, 其与第一栅极线隔离并与第一栅极线交叉,

像素电极, 其包括第一子像素电极和第二子像素电极, 该像素电极被布置在于第一方向上具有长侧边的像素中,

第一薄膜晶体管 (TFT), 其连接到第一栅极线、数据线和第一子像素电极,

第二 TFT, 其连接到第一栅极线、数据线和第二子像素电极,

第三 TFT, 其连接到第二栅极线、第二子像素电极和电荷共享电容, 该电荷共享电容共享施加到第二子像素电极的数据电压, 以及

第三栅极线, 其被布置为平行于第一栅极线和第二栅极线并位于两者之间,

信号控制器, 其提供具有相位差的第一扫描开始信号和第二扫描开始信号 ; 以及

栅极驱动器, 其通过第一扫描开始信号和第二扫描开始信号使能, 以便顺序地输出第一栅极导通信号和第二栅极导通信号到所述液晶面板组件。

5. 如权利要求 4 所述的液晶显示器, 还包括存储线, 其被布置为与第一栅极线和第二栅极线平行,

其中所述电荷共享电容包括第一电荷共享电容和第二电荷共享电容, 其中第一电荷共享电容包括第三 TFT 的漏电极和存储线, 而第二电荷共享电容包括第三 TFT 的漏电极和第一子像素电极。

6. 如权利要求 4 所述的液晶显示器, 其中 H 是第一栅极导通信号和第二栅极导通信号被分别施加到第一栅极线和第二栅极线的一段时间, 并且

其中所述第一扫描开始信号和第二信号扫描开始信号具有  $2H$  的相位差。

7. 如权利要求 4 所述的液晶显示器, 其中 H 是第一栅极导通信号和第二栅极导通信号被分别施加到第一栅极线和第二栅极线的一段时间, 并且

其中所述第一扫描开始信号和第二扫描开始信号具有  $2.5H$  的相位差。

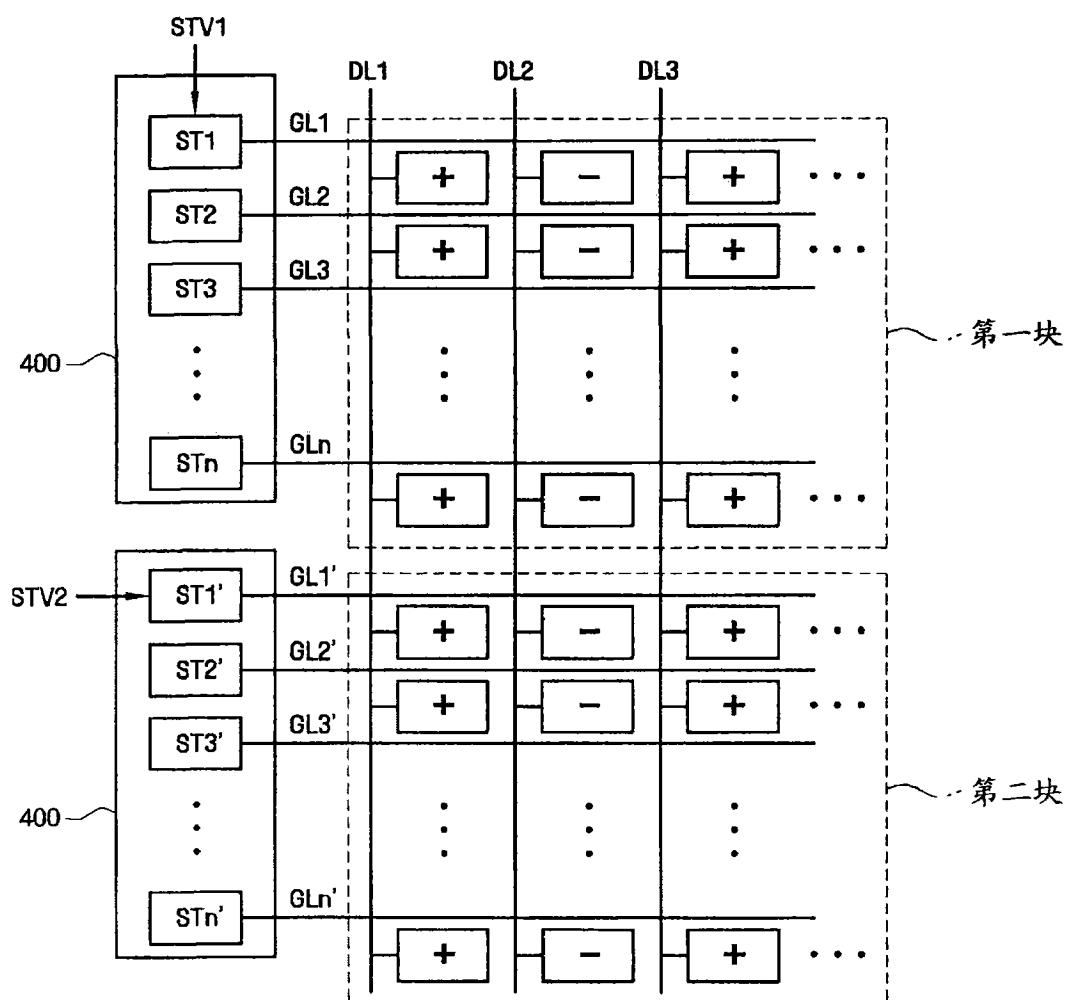

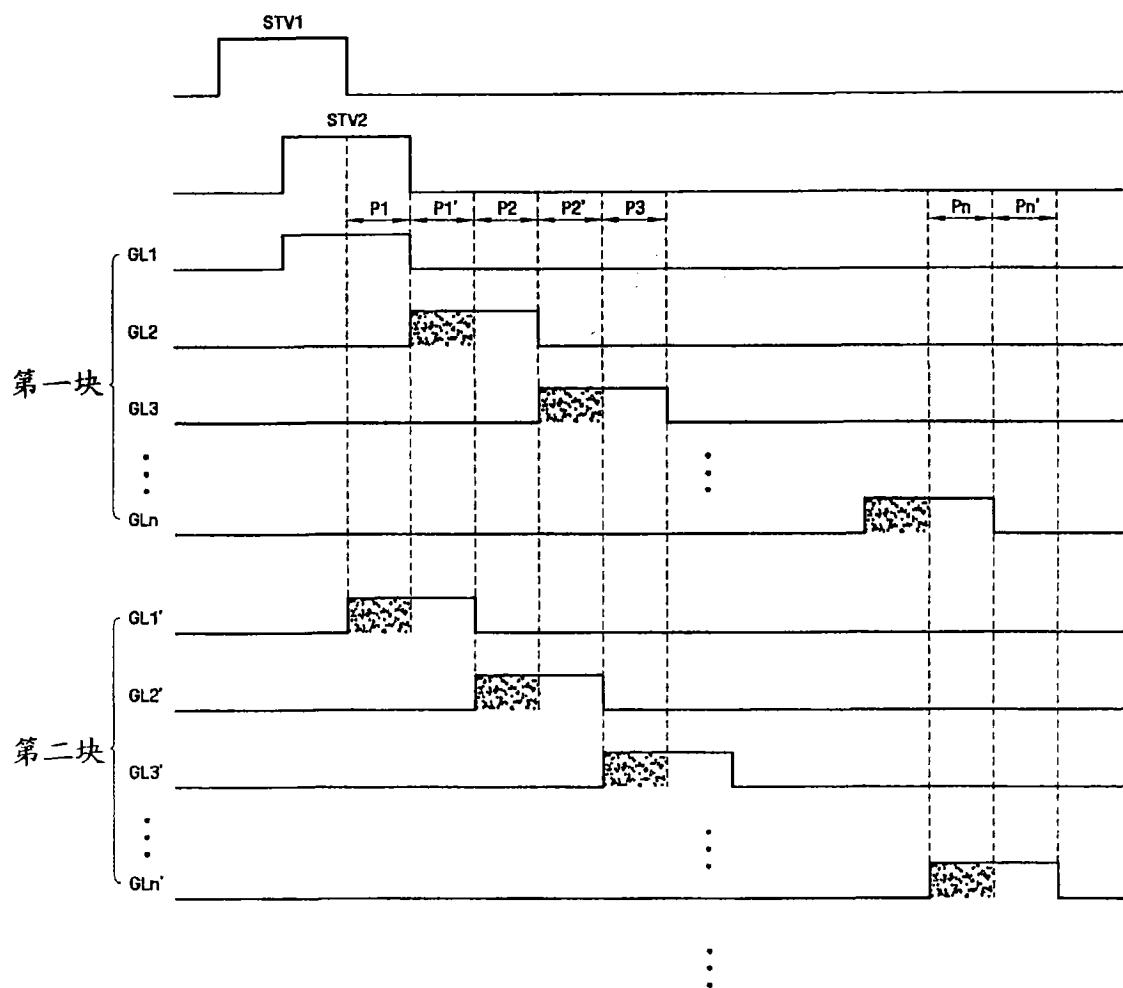

8. 如权利要求 4 所述的液晶显示器, 其中所述液晶面板组件被分为第一块和第二块,

其中第一栅极导通信号被顺序地施加到在第一块中的栅极线, 并且

其中第二栅极导通信号被顺序地施加到在第二块中的栅极线。

9. 如权利要求 8 所述的液晶显示器, 其中  $H$  是第一栅极导通信号和第二栅极导通信号被分别施加到第一栅极线和第二栅极线的一段时间, 并且

其中所述第一扫描开始信号和第二扫描开始信号具有  $0.5H$  的相位差。

## 液晶显示器及其驱动方法

### 背景技术

[0001] 本发明涉及一种显示设备及其驱动方法,更具体而言,涉及液晶显示器 (LCD) 及其驱动方法。

### 技术领域

[0002] LCD 是广泛使用的平板显示器。LCD 可以包括两个基片以及布置在其间的液晶 (LC) 层,其中所述基片包括场生成电极,诸如像素电极和公共电极。LCD 通过施加电压到场生成电极以在 LC 层中产生电场来显示图像,该电场改变 LC 层中的 LC 分子的朝向 (orientations),以调整入射光的偏振 (polarization)。

[0003] 垂直校准 (vertical alignment, VA) 模式 LCD 具有高对比率和宽参考视角,其中在垂直校准模式中,LC 分子被校准,从而在没有电场的情况下,它们的长轴 (long axes) 与基片垂直。参考视角被定义为对比率等于 1 : 10 的视角,或者被定义为在灰度 (gray) 之间亮度反转 (inversion in luminance) 的限制角度。

[0004] VA 模式 LCD 的宽视角可以通过,例如,在场生成电极中具有切口 (cutouts) 和在场生成电极上具有突起 (protrusions) 来实现。所述切口和突起能够改变 LC 分子的倾斜方向。由于切口和突起,LC 分子可以具有不同的倾斜方向,这可以加宽参考视角。

[0005] 但是,VA 模式 LCD 具有与正面可视性相比较差的侧面 (lateral) 可视性。例如,具有切口的图案 (patterned) VA (PVA) 模式的 LCD 可以显示在其侧面 (sides) 变得更亮的图像,因此导致差的侧面可视性。

[0006] 此外,随着 LCD 的分辨率增加,有必要增加数据线和数据驱动芯片的数量。因此,生产成本可能会增加,生产小的 LCD 可能会很难。

### 发明内容

[0007] 本发明提供了一种具有改善的侧面可视性和更低生产成本的 LCD。

[0008] 本发明也提供了一种驱动 LCD 的方法,该方法可以改善侧面可视性和减少生产成本。

[0009] 本发明的其它特征将会在以下的说明书中被描述,并将从说明书部分地变得明显,或者可以通过实施本发明而被习得。

[0010] 本发明公开了一种 LCD,其包括:在第一方向上延伸的第一栅极线和第二栅极线;与第一栅极线隔离并与第一栅极线交叉的数据线;包括第一子像素电极和第二子像素电极的像素电极,该像素电极被布置在于第一方向上具有长侧边 (long side) 的像素中;连接到第一栅极线、数据线和第一子像素电极的第一薄膜晶体管 (TFT);连接到第一栅极线、数据线和第二子像素电极的第二 TFT;以及连接到第二栅极线、第二子像素电极和电荷共享电容的第三 TFT,该电荷共享 (charge-sharing) 电容共享被施加到第二子像素电极的数据电压。

[0011] 本发明还公开了一种 LCD,其包括:液晶面板组件;信号控制器,其提供具有相位

差的第一扫描开始信号和第二扫描开始信号；以及栅极驱动器，其被第一扫描开始信号和第二扫描开始信号使能，以顺序地输出第一栅极导通（gate-on）信号和第二栅极导通信号到液晶面板组件。这里，液晶面板组件包括：在第一方向上延伸的第一栅极线和第二栅极线；与第一栅极线隔离并与第一栅极线交叉的数据线；包括第一子像素电极和第二子像素电极的像素电极，该像素电极被布置在于第一方向上具有长侧边的像素中；连接到第一栅极线、数据线和第一子像素电极的第一薄膜晶体管（TFT）；连接到第一栅极线、数据线和第二子像素电极的第二 TFT；以及连接到第二栅极线、第二子像素电极和电荷共享电容的第三 TFT，该电荷共享电容共享被施加到第二子像素电极的数据电压。

[0012] 本发明还公开了一种驱动 LCD 的方法，该方法包括：提供具有相位差的第一扫描开始信号到第二扫描开始信号；顺序地输出第一栅极导通信号和第二栅极导通信号到多条栅极线，该第一栅极导通信号和第二栅极导通信号分别被第一扫描开始信号和第二扫描开始信号使能；对连接到每条栅极线的像素电极预充电，该像素电极包括一对子像素电极；以数据电压对这对子像素电极进行充电；以及共享数据电压，从而子像素电极对的每个子像素电极具有不同的电压。

[0013] 可以理解，上述总的说明和以下具体的说明是示例性和解释性的，旨在提供如权利要求所述的本发明的更进一步的解释。

## 附图说明

[0014] 所包括的附图提供对本发明的进一步理解，并结合在和组成本说明书的一部分，解释本发明的实施例，以及用作解释本发明原理的说明。

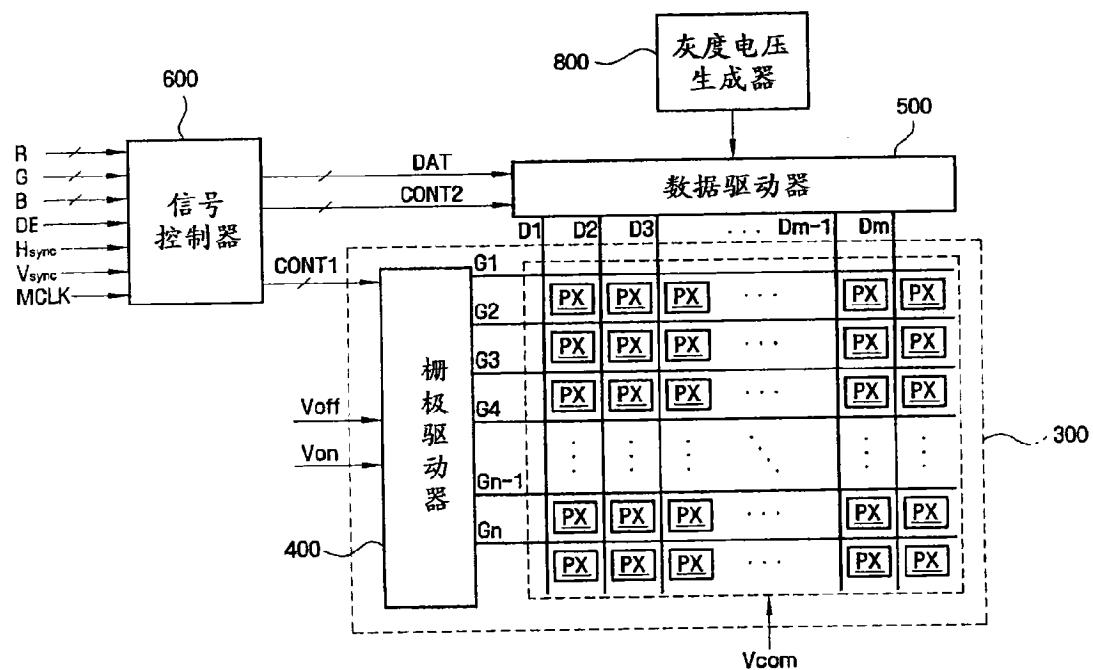

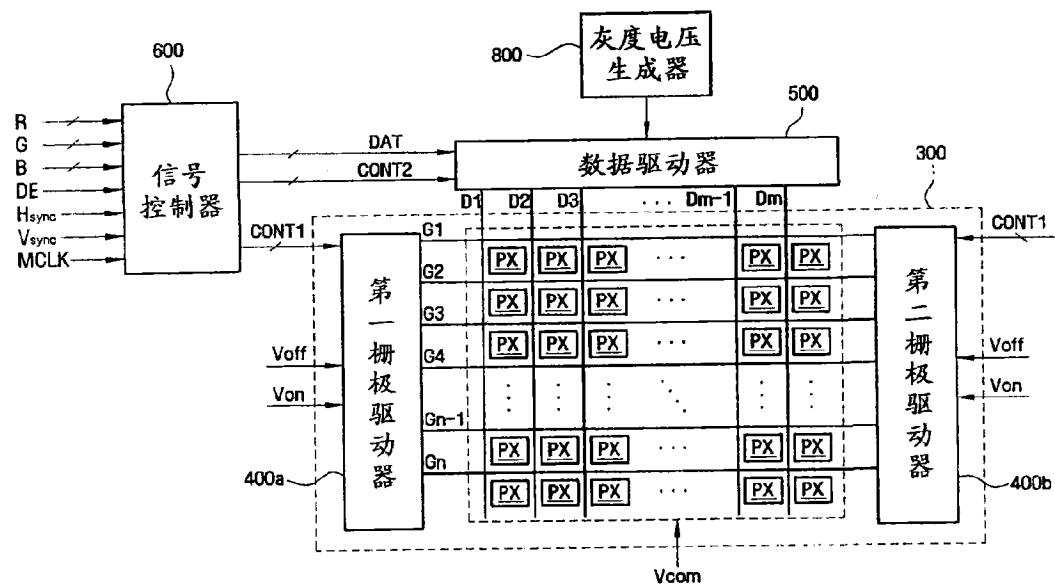

[0015] 图 1 和图 2 是根据本发明的示例性实施例的 LCD 的框图。

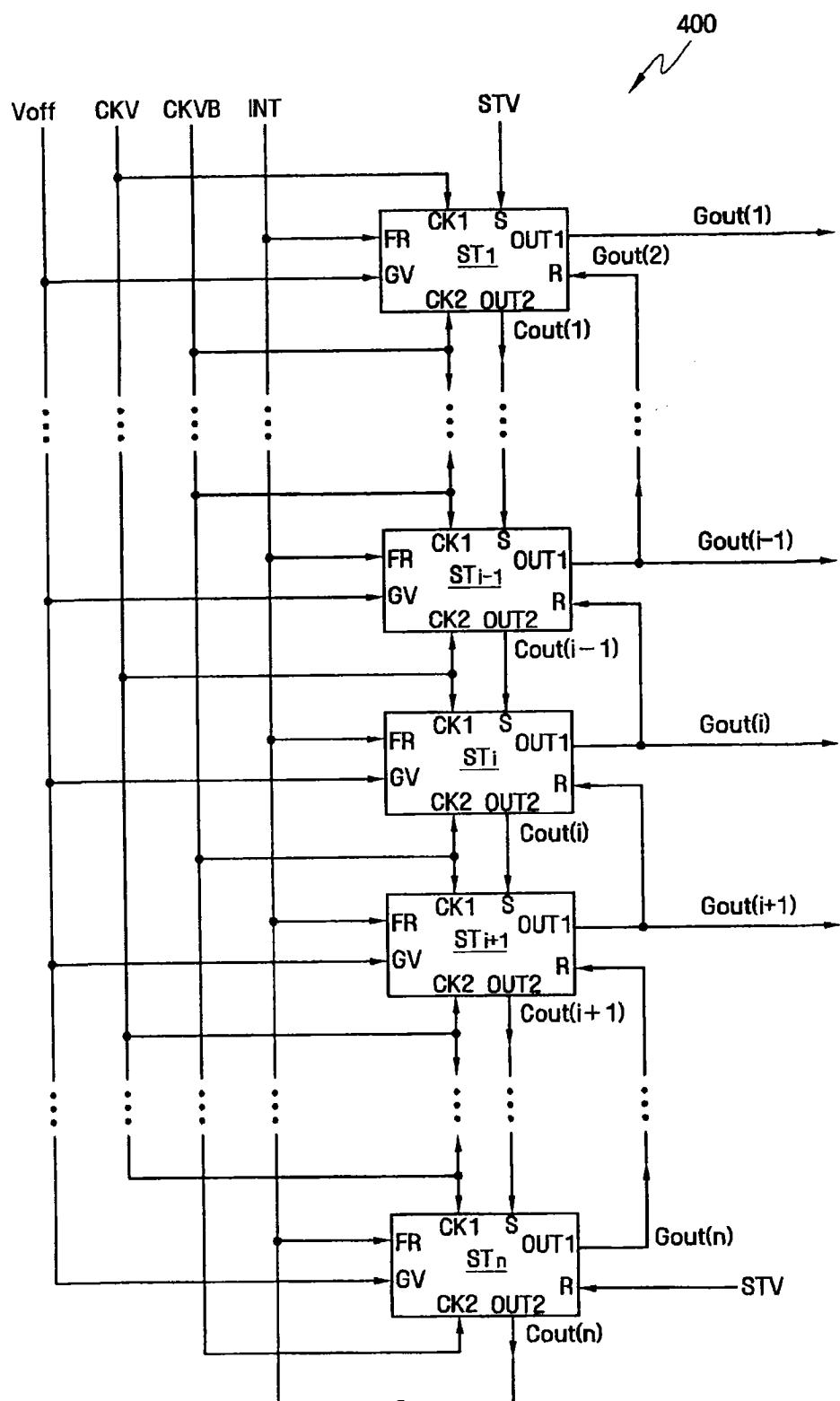

[0016] 图 3 是图 1 中示出的栅极驱动器的框图。

[0017] 图 4 是图 8 中示出的栅极驱动器的级的电路图。

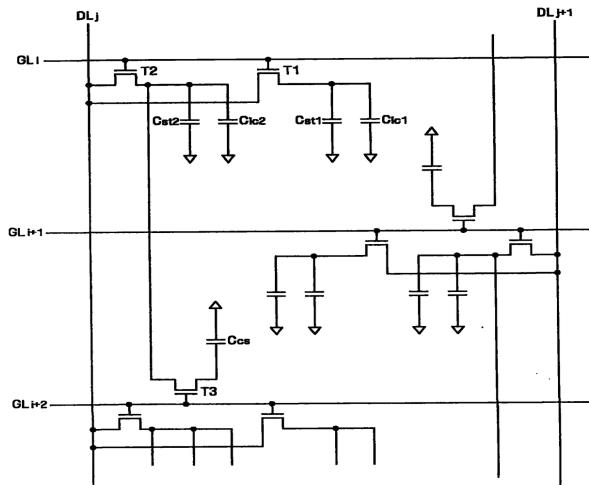

[0018] 图 5 是图 1 的 LCD 的等效电路图。

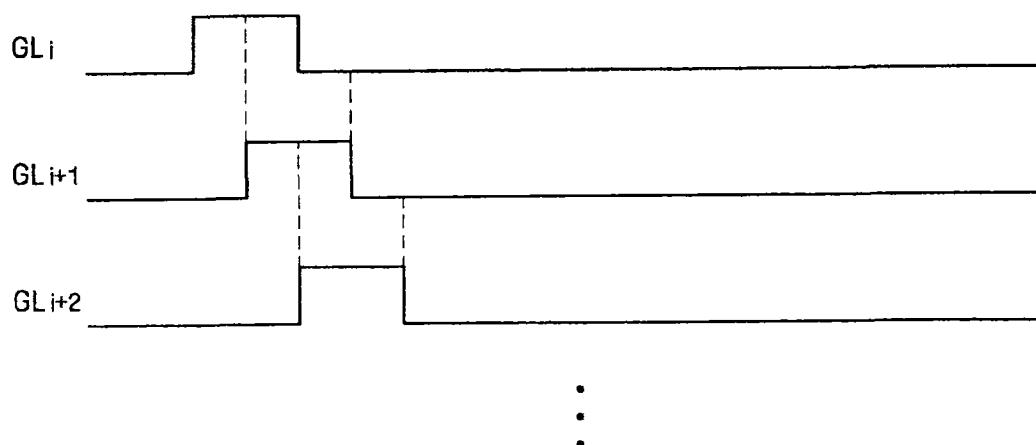

[0019] 图 6 是示出图 1 所示的栅极驱动器的操作的时序图。

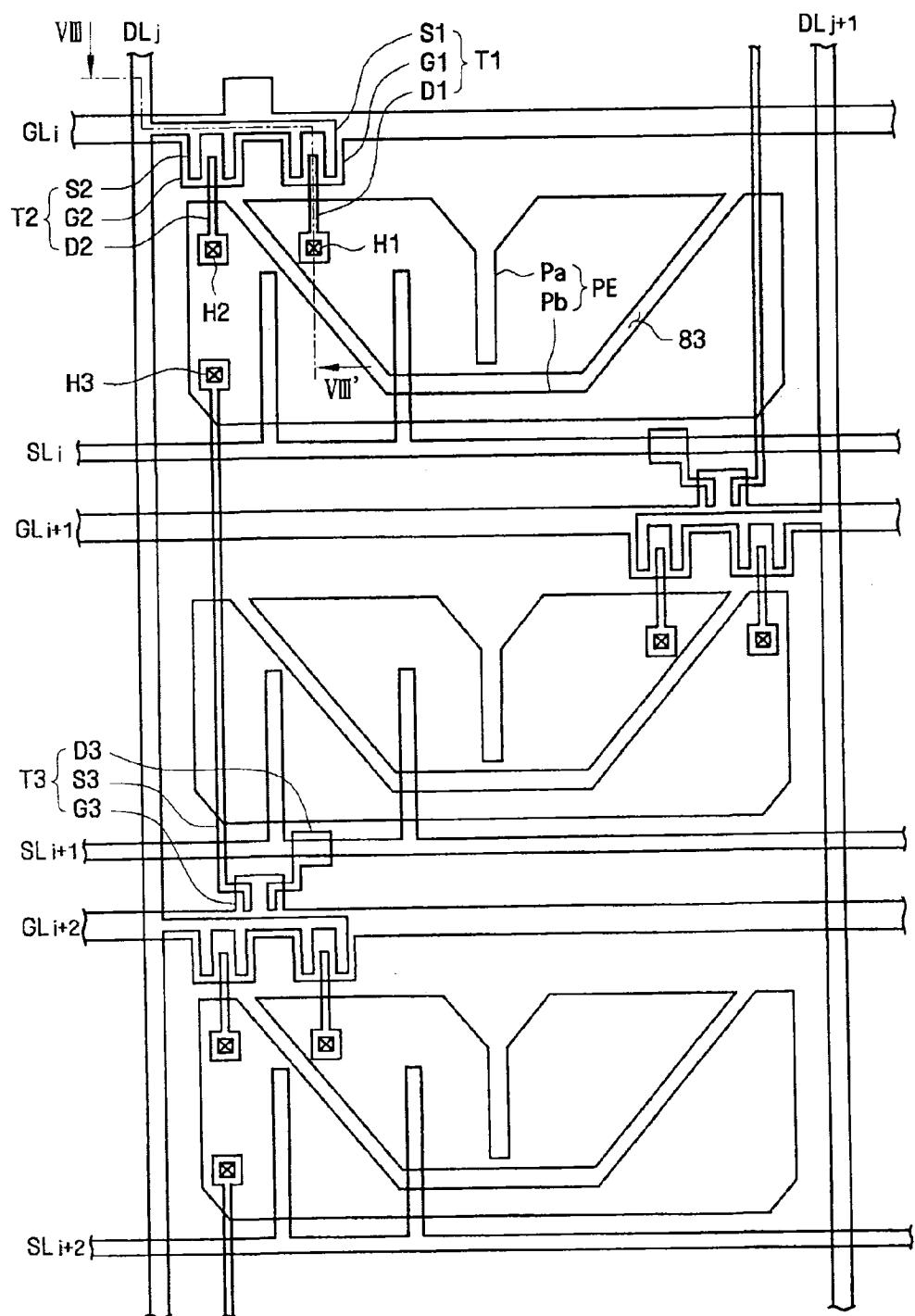

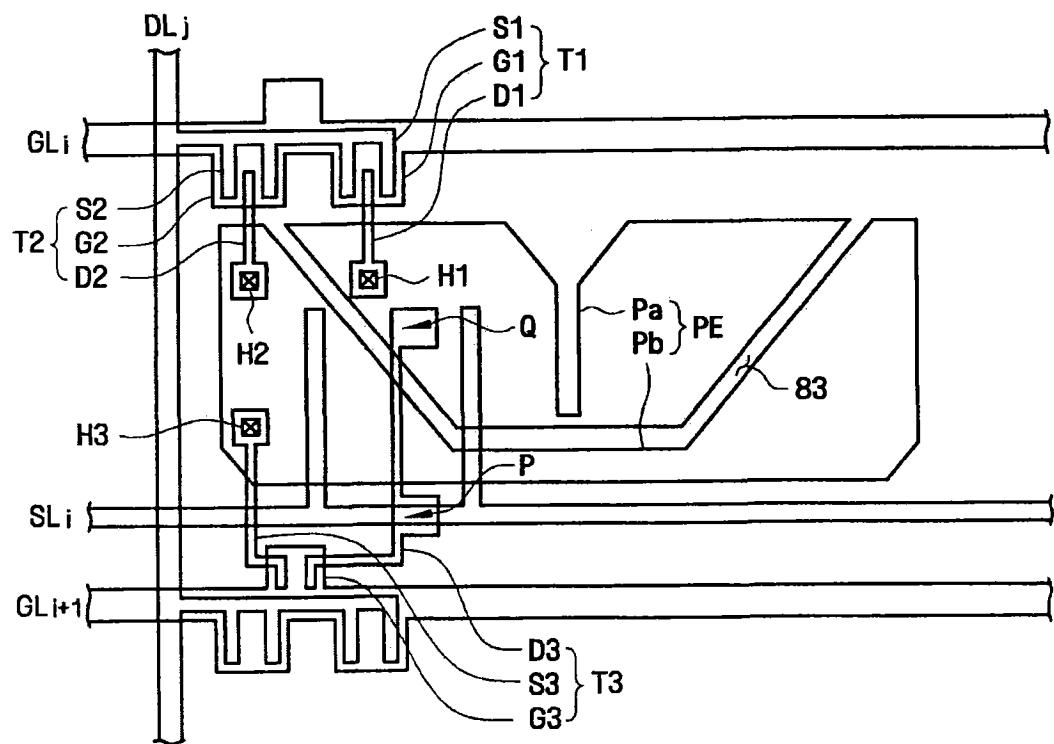

[0020] 图 7 是根据本发明的示例性实施例的 LCD 的下层（lower）显示面板的布局。

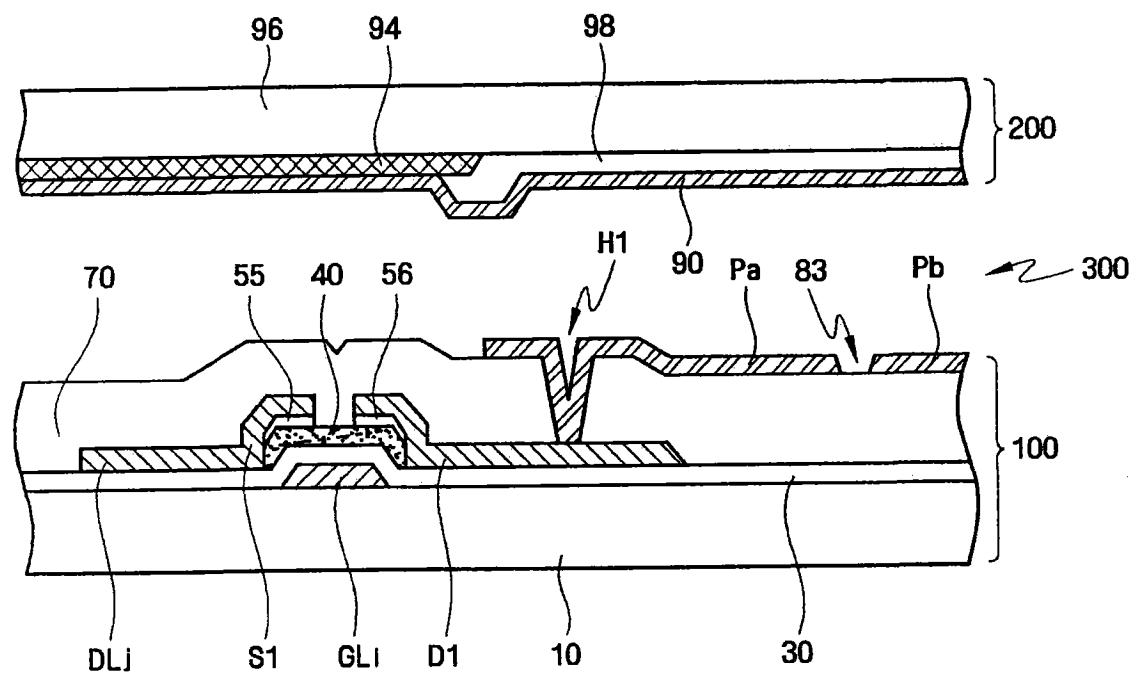

[0021] 图 8 是图 7 的下部显示面板沿 VIII-VIII' 线的横截面示意图。

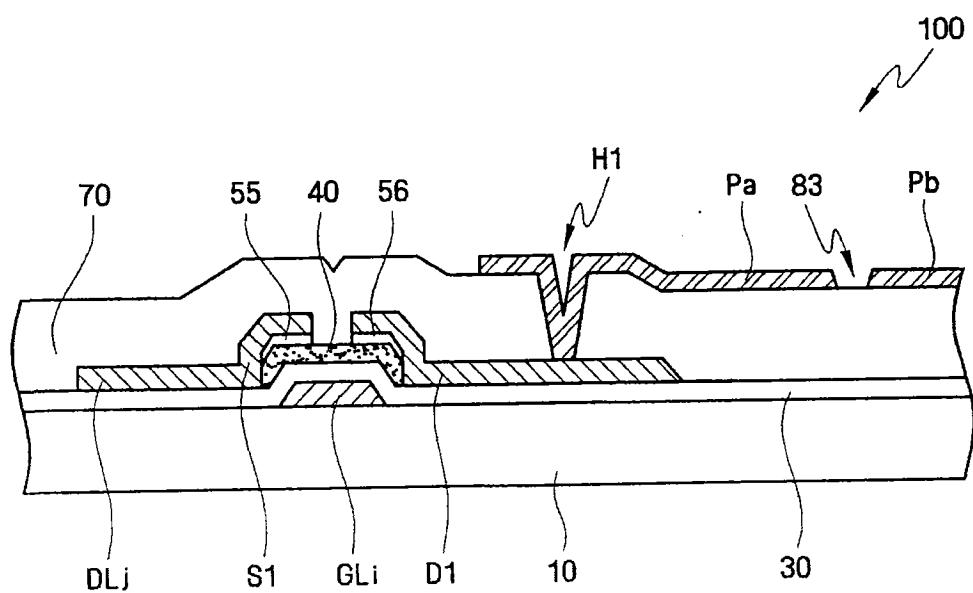

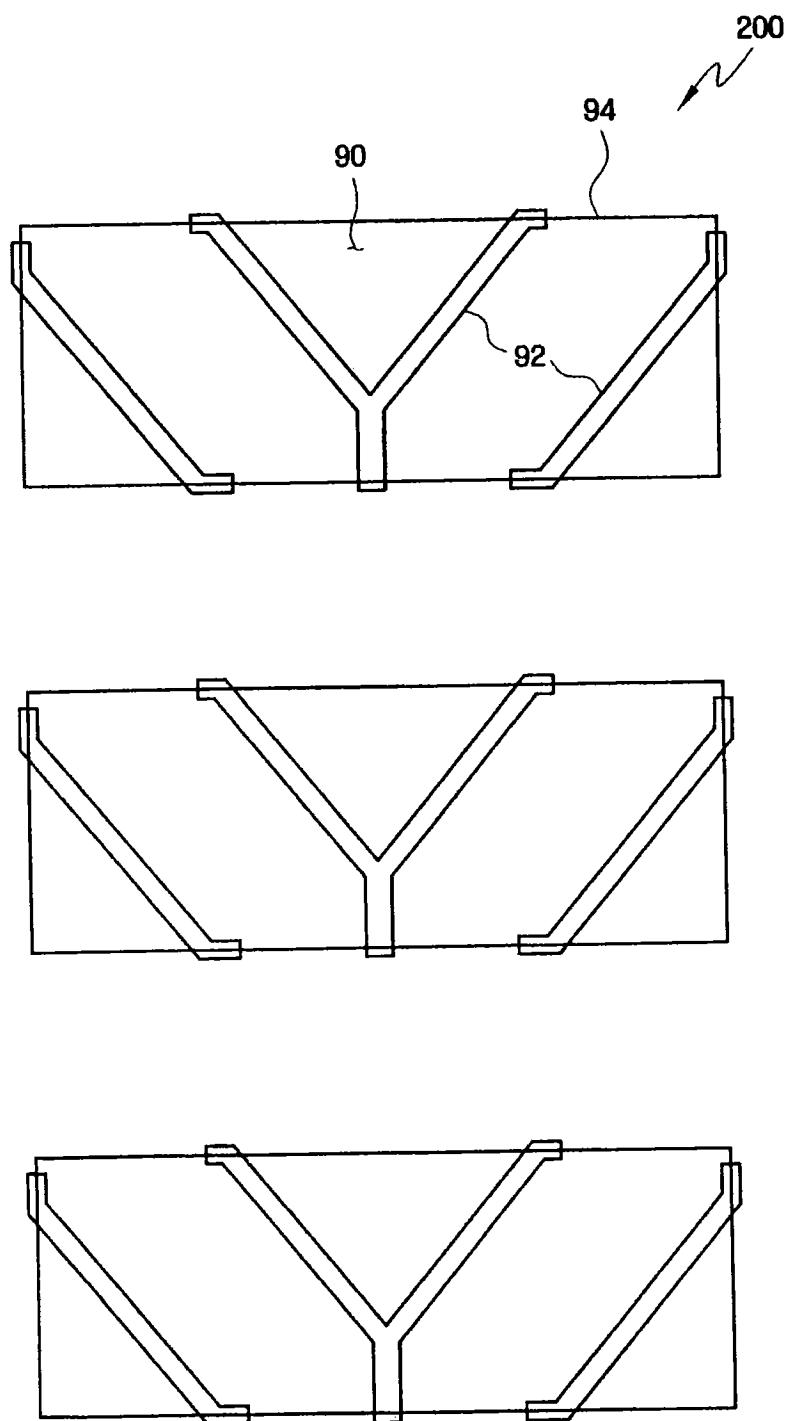

[0022] 图 9 是根据本发明的示例性实施例的 LCD 的上部（upper）显示面板的布局。

[0023] 图 10 是根据本发明的示例性实施例的包括图 7 的下部显示面板和图 9 的上部显示面板的 LCD 的布局图。

[0024] 图 11 是图 10 的 LCD 沿 XI-XI' 线的横截面示意图。

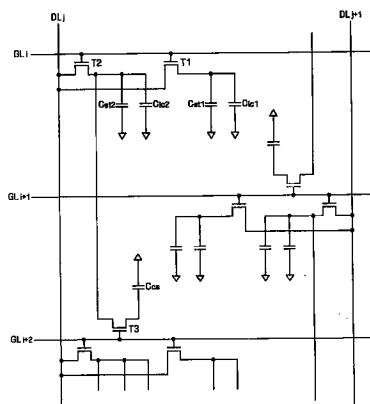

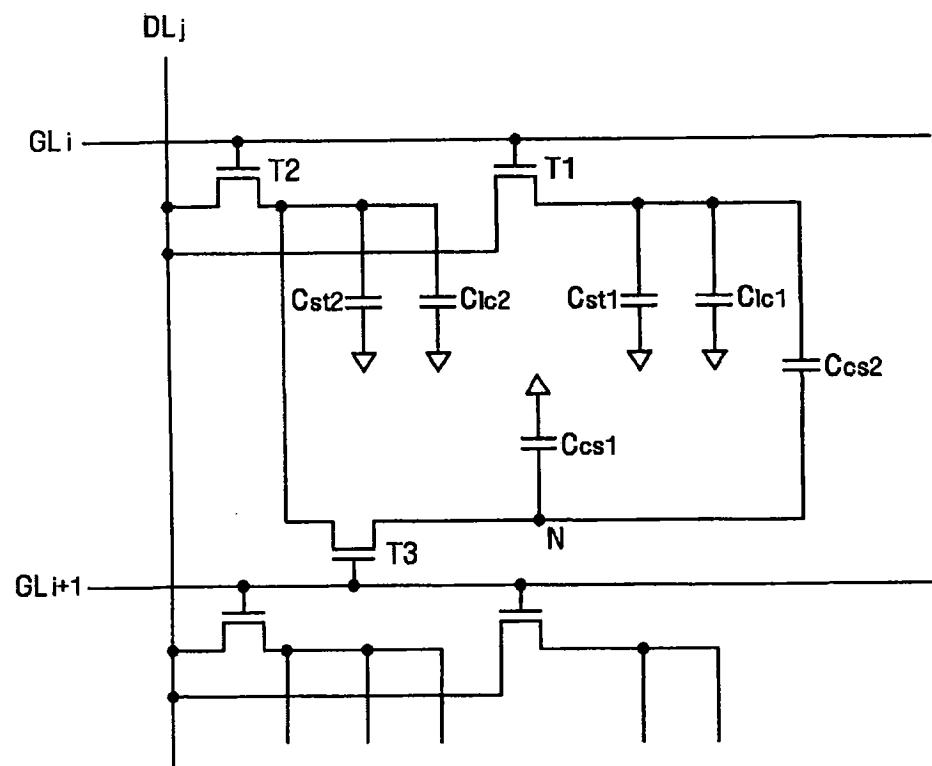

[0025] 图 12 是根据本发明的另一个示例性实施例的 LCD 的等效电路图。

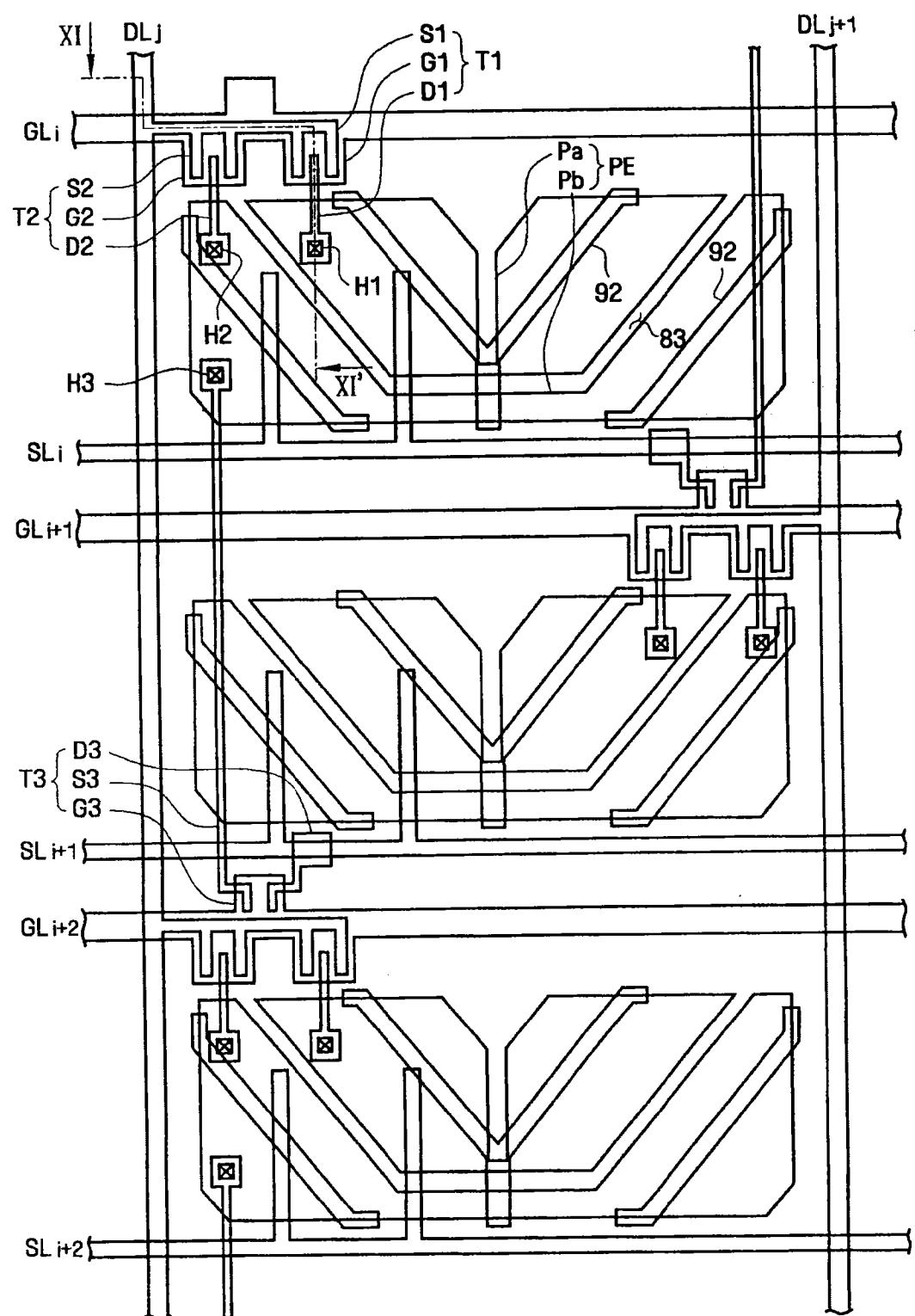

[0026] 图 13 是根据本发明的另一个示例性实施例的 LCD 的下部显示面板的布局。

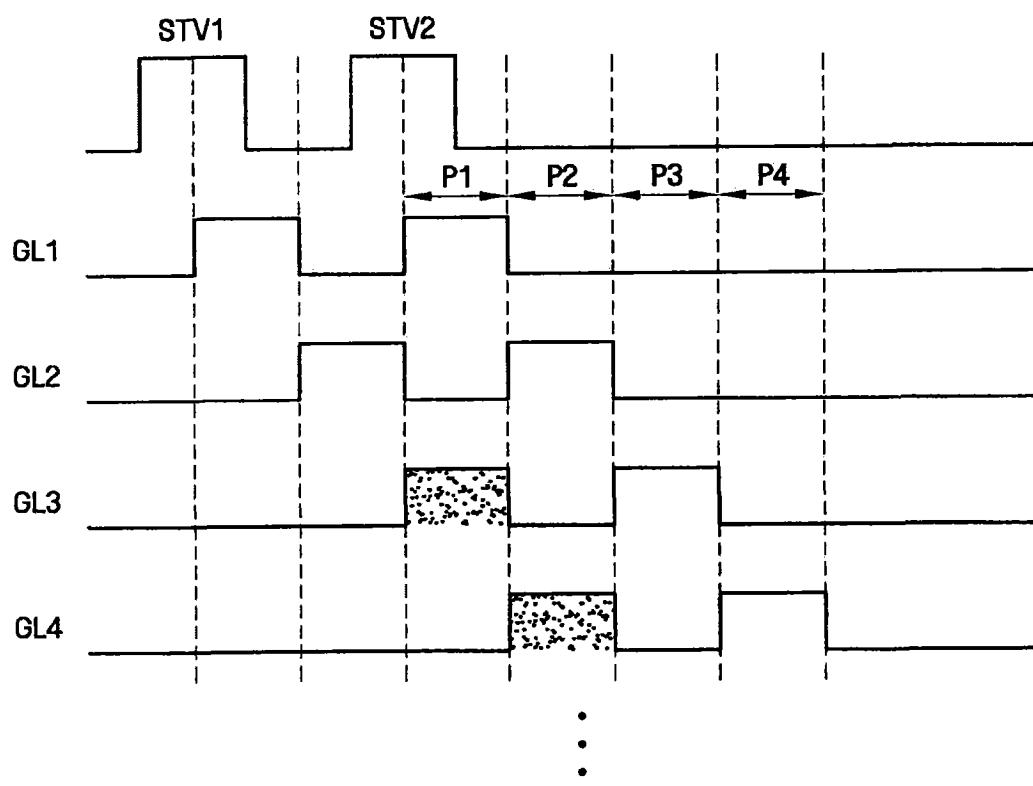

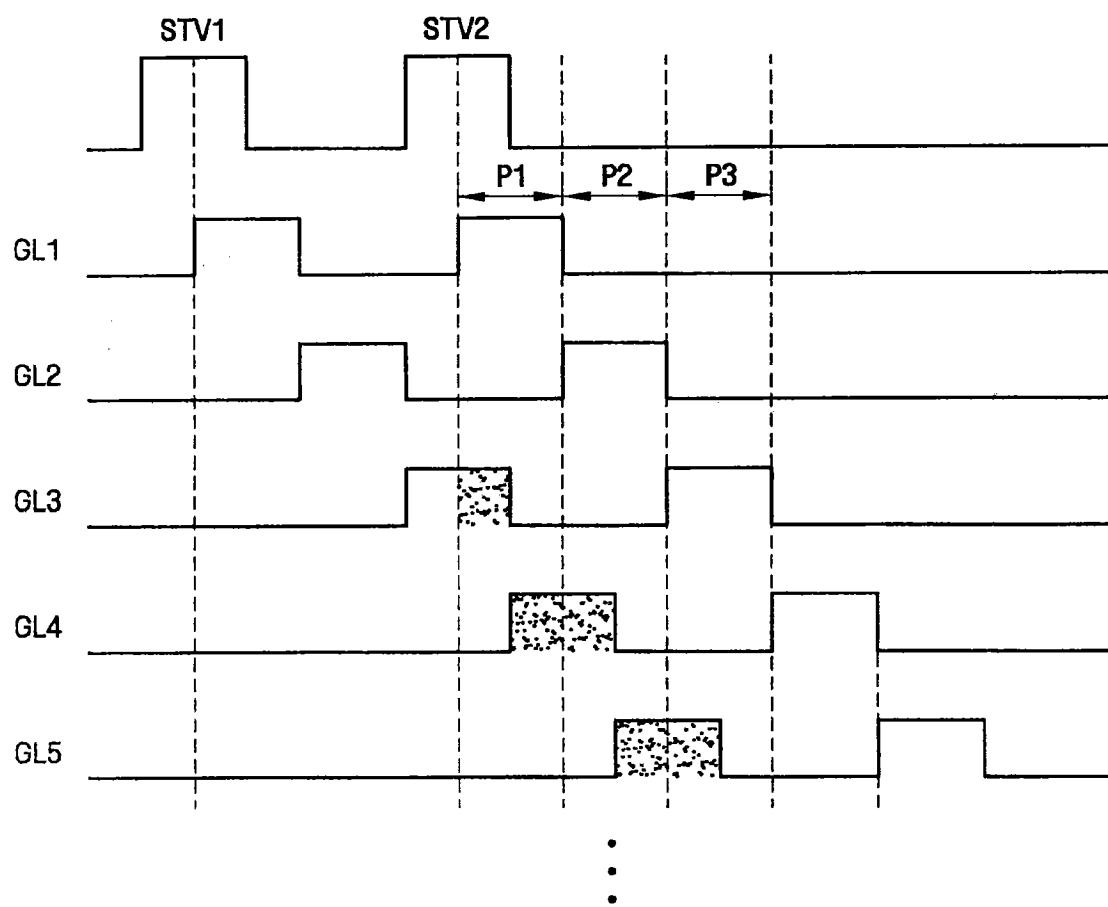

[0027] 图 14 是根据本发明的一个示例性实施例的用于表示栅极信号的时序图。

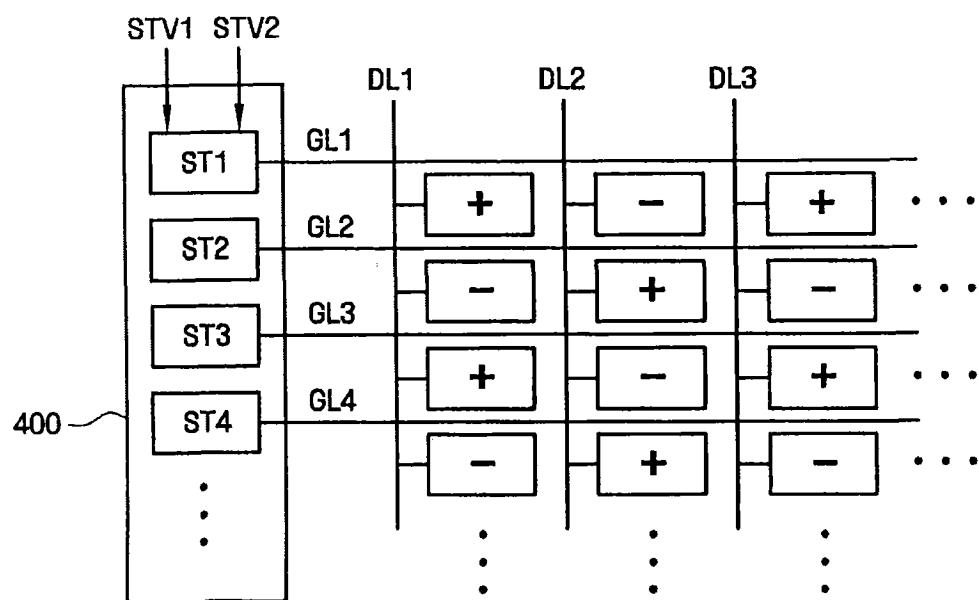

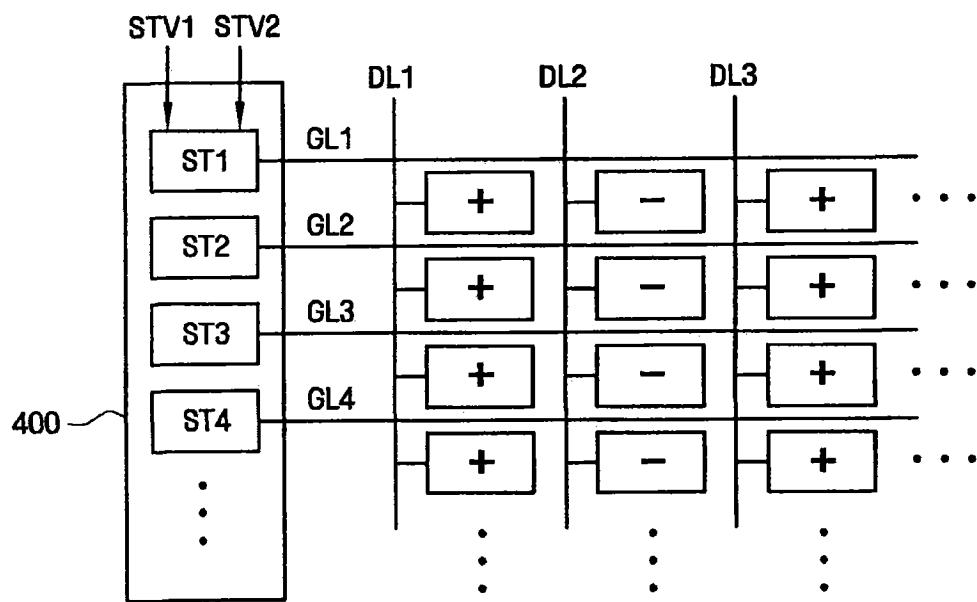

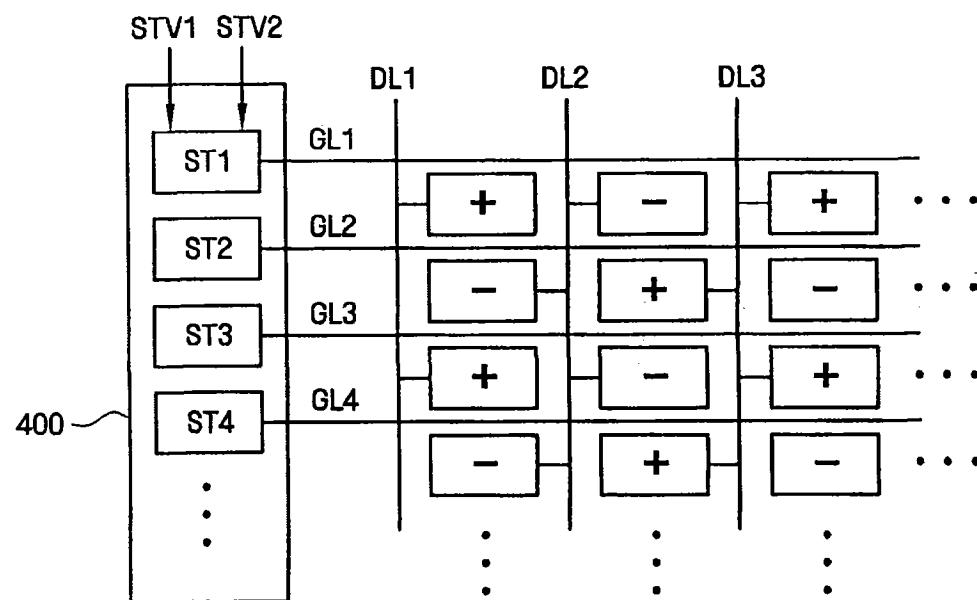

[0028] 图 15、图 16 和图 17 是表示根据图 14 的时序图操作的 LCD 的示意图。

[0029] 图 18 是根据本发明的另一个示例性实施例的用于表示栅极信号的时序图。

[0030] 图 19 是根据本发明的另一个示例性实施例的表示 LCD 的示意图。

[0031] 图 20 是用于表示施加到图 19 的 LCD 的栅极信号的时序图。

[0032] 具体实施方法

[0033] 以下将参考附图更详细地描述本发明，在附图中示出了用于本发明的实施例。本发明可以用许多不同的形式实施，且不应被认为是限于这里所描述的实施例。而且，提供这些实施例这样本发明就变得完整，并对本领域技术人员来说，将完全覆盖本发明的范围。在图中，为了清楚起见，可以扩大层和区域的大小和相对大小。图中相似的附图标号指示相同的元件。

[0034] 应该理解，当一个元件被称为“在……之上”、“连接到”或者“链接到”另一个元件，这可以是直接在……之上，直接连接到，或者直接链接到另一个元件，或者可以有中间元件在其之间。相反，当一个元件被称为“直接在…之上”、“直接连接到”或者“直接链接到”另一个元件时，没有中间元件存在。如在这里所使用的，术语“和 / 或”包括相关显示项的一个或多个的任何和全部组合。

[0035] 应该理解，尽管术语第一、第二和第三等可以被应用于此以描述各种元件、成分、区域、层和 / 或部分，这些元件、成分、区域、层和 / 或部分可以不限于这些术语。这些术语仅用于区别一个元件、成分、区域、层和 / 或部分。因此，以下描述的第一元件、成分、区域、层或部分可以被描述为第二元件、成分、区域、层或部分，而不脱离本发明的教义。

[0036] 这里使用的术语仅是为了描述本发明的特定实施例，而不旨在限制本发明。如在这里所使用，单数形式“一”、“一个”和“该”旨在包括复数形式，除非该文本另外清楚说明。进一步将理解，当在本说明中使用术语“包括”和 / 或“包含”时，指示所述的存在，但并不预先包括其它特征、区域、整数、步骤、操作、元件和 / 或成分中的一个或多个中的存在或添加。

[0037] 为了描述的简便可以在这里使用空间相关的术语，如“位于…之下”、“在…以下”、“下部”、“以上”、“上部”等，以描述图中所示的一个元件或特征与另一个元件或特征的关系。将理解，空间相关的术语旨在包括使用中或操作中的装置的不同方向。例如，如果图中的装置被反过来，被描述为在其它元件或特征“之下”或“下面”的元件将会变成在其它元件或特征“之上”。因此，示例性术语“之下”可以包括上面和下面两种方向。然后装置可以被重新定向（旋转 90 度或对着其它方向），且相应地，这里使用的空间相关描述符被解释。

[0038] 除非另外定义，这里使用的所有的术语（包括技术术语和科学术语）具有本发明所属领域普通技术人员所共同理解的意思。还应当理解，这些术语，如在通常使用的字典中所定义的，应当被理解为具有与其在相应领域和本公开文本中的意思一致的意思，且不应被理解为理想化或过于正式的意思，除非在这里特别定义。

[0039] 参考交叉部分的图示来描述本发明的实施例，该图示是本发明的理想化实施例的示意图。同样地，不期望由于，例如，制造技术和 / 或容差而导致图解的形状的变化。因此，本发明的实施例不应被解释为限于在这里所描述的特定形状，但可以被理解为包括由于，例如，制造而导致的形状上的变化。例如，典型地，被图示为或描述为平面的区域可以具有粗糙和 / 或非线形特征。而且，在这里所描述的尖角可以使圆的。因此，在图中描述的区域在本质上是示意性的，且其形状不旨在描述区域的精确形状，且不旨在限于本发明的范围。

[0040] 以下将参考附图详细描述根据本发明的示例性实施例的液晶显示器（“LCD”）。

[0041] 参考图 1 和图 2，根据本发明的示例性实施例的 LCD 包括液晶面板组件 300、数据驱动器 500 和连接到液晶面板组件 300 的栅极驱动器 400（或者一对栅极驱动器 400a 和 400b）、连接到数据驱动器 500 的灰度电压生成器 800、用于控制栅极驱动器 400（或者栅极

驱动器 400a 和 400b) 和数据驱动器 500 的信号控制器 600。

[0042] 液晶面板组件 300 包括多个显示信号线和连接到显示信号线并以矩阵形式配置的像素 PX。这里,液晶面板组件 300 可以包括互相面对的下部显示面板和上部显示面板,并且液晶层插入两者之间。

[0043] 显示信号线被布置在下部显示面板上,并包括传输栅极信号的多条栅极线 G1 到 Gn 和传输数据信号的多条数据线 D1 到 Dm。栅极线 G1 到 Gn 在横向方向上延伸并且相互平行,而数据线 D1 到 Dm 在纵向方向上延伸并且相互平行。

[0044] 每个像素 PX 包括开关装置、液晶电容和存储电容。开关装置连接到栅极线 G1 到 Gn 中的一条和数据线 D1 到 Dm 中的一条。液晶电容连接到开关装置。存储电容并联到开关装置。这里,存储电容可以省略。

[0045] 像素 PX 的开关装置 Q 包括布置在下部显示面板上的薄膜晶体管 (TFT),并且它是一个三端部分 (three-end portion) 装置,包括连接到栅极线 G1 到 Gn 之一的控制端部分、连接到数据线 D1 到 Dm 之一的输入端部分和连接到液晶电容的输出端部分。

[0046] 栅极驱动器 400 (或者是栅极驱动器 400a 或 400b) 连接到栅极线 G1 到 Gn,并将从外部电路施加的由栅极导通电压 Von 和栅极截止 (gate-off) 电压 Voff 组成的栅极信号施加到栅极线 G1 到 Gn。具体地,参考图 1,数据驱动器 400 位于液晶面板组件 300 的一侧,并连接到所有的栅极线 G1 到 Gn。参考图 2,数据驱动器 400a 和 400b 分别位于液晶面板组件 300 的左侧和右侧,并且连接到栅极线 G1 到 Gn。在大 LCD 的情况下,一个栅极驱动器 400 不足以施加栅极导通电压 Von 或栅极截止电压 Voff 到栅极线 G1 到 Gn 的末端 (ends)。因此,一对栅极驱动器 400a 和 400b 可以分别连接到栅极线 G1 到 Gn 的两端。栅极驱动器 400 (或者栅极驱动器 400a 和 400b) 可以被作为集成电路集成到液晶面板组件 300 的下部显示面板中。

[0047] 灰度电压生成器 800 生成与像素 PX 的透明度相关的灰度电压。灰度电压被提供给每个像素 PX。灰度电压可以包括相对于公共电压 Vcom 的正极性电压和负极性电压。

[0048] 数据驱动器 500 连接到液晶面板组件 300 的数据线 D1 到 Dm,并将由灰度电压产生器 800 产生的灰度级电压施加到像素 PX 作为数据电压。这里,如果灰度电压生成器 800 被设计为仅提供参考灰度电压,而不是提供用于所有灰度的电压,则数据驱动器 500 通过划分该参考灰度电压来生成所有的灰度的多个参考电压,并选择参考电压之一作为数据电压。

[0049] 栅极驱动器 400 (或者栅极驱动器 400a 和 400b) 或者数据驱动器 500 可以和显示信号线 G1 到 Gn 和 D1 到 Dm、以及例如 TFT 的开关装置一起,被集成到液晶面板组件 300。或者,栅极驱动器 400 (或者栅极驱动器 400a 和 400b) 或者数据驱动器 500 可以设置在软性印制电路薄膜 (未示出) 上,所得的结构可以被设置在液晶面板组件 300 上作为带载封装 (tape carrier package)。

[0050] 信号控制器 600 控制栅极驱动器 400 (或者栅极驱动器 400a 和 400b) 和数据驱动器 500。

[0051] 信号控制器 600 接收输入图像信号 (R、G、B) 和输入控制信号,以控制输入图像信号的显示,例如,来自外部图形控制器 (未示出) 的垂直同步信号 Vsync、水平同步信号 Hsync、主时钟控制信号 MCLK,以及数据使能信号 DE。信号控制器 600 根据液晶面板组件

300 的操作条件,适当地处理输入图像信号和输入控制信号,生成栅极控制信号 CONT1 和数据控制信号 CONT2,将栅极控制信号 CONT1 发送到栅极驱动器 400(或者栅极驱动器 400a 和 400b),并将数据控制信号 CONT2 和处理的图像信号 DAT 发送到数据驱动器 500。

[0052] 棚极控制信号 CONT1 包括扫描初始信号 STV 以初始化扫描,以及至少一个时钟信号以控制何时输出栅极导通电压 Von。栅极控制信号 CONT1 还可以包括输出使能信号 OE 以定义栅极导通信号 Von 的持续时间 (duration)。这里,包含在栅极控制信号 CONT1 中的时钟信号可以被用作选择信号 SE。

[0053] 数据控制信号 CONT2 包括水平同步信号 STH 以通知数据驱动器 500 对于一组像素的数据传输的开始、载入信号 LOAD 以指示数据驱动器 500 将数据电压施加到数据线 D1 到 Dm、以及数据时钟信号 HCLK。数据控制信号 CONT2 还可以包括反转信号 RVS 以相对于公共电压 Vcom 反转数据电压的极性。

[0054] 响应于由信号控制器 600 传输的数据控制信号 CONT2,数据驱动器 500 接收用于像素 PX 的图像信号 DAT,选择用于图像数据 DAT 的灰度电压,将图像信号 DAT 转为数据电压,并将该数据电压施加到对应于像素 PX 的数据线 D1 到 Dm 中的一条。

[0055] 响应于由信号控制器 600 传输的栅极控制信号 CONT1,栅极驱动器 400(或者栅极驱动器 400a 和 400b) 将栅极导通电压 Von 施加到多条栅极线 G1 到 Gn 中的一条,这样连接到被施加了栅极导通信号 Von 的栅极线的开关装置被导通。因此,经由数据线施加的数据电压通过开关装置被施加到像素 PX。

[0056] 施加到像素 PX 的数据电压和公共电压 Vcom 之间的差值被表示为在 LC 电容上充电的电压,其被称为像素电压。LC 层中的液晶分子的朝向取决于像素电压的大小,且 LC 分子的分子朝向确定了穿过 LC 层的光的偏振。一个或多个偏振器 (polarizer) 传输被偏振的光。

[0057] 在根据本发明的示例性实施例的 LCD 中,当栅极导通电压被施加到栅极线时,数据电压被施加到像素 PX 的一对子像素,然后,当栅极导通电压被施加到临近的栅极线时,由于电荷共享过程,被施加到一对子像素中的一个的数据电压降低。由于不同的数据电压被分别施加到子像素对中的每一个,包括子像素的像素 PX 的伽马曲线 (gamma curve) 可以通过合成所述子像素的伽马曲线来获得。由于电荷共享过程,通过确定每个子像素的数据电压,能够改善侧面可视性,所以从 LCD 前面 (front) 获得的合成伽马曲线类似于 LCD 前面的参考伽马曲线,并且从 LCD 的任一侧 (side) 获得的合成伽马曲线尽可能地类似于参考伽马曲线。

[0058] 以下参考图 3 和图 4 详细描述栅极驱动器 400(或者栅极驱动器 400a 和 400b)。由于图 1 的栅极驱动器 400 基本上与图 2 的栅极驱动器 400a 和 400b 相同,为了简洁将描述图 1 的栅极驱动器 400。此外,在本示例性实施例中,将描述栅极驱动器作为集成电路被集成到液晶面板组件的下部显示面板的情况。

[0059] 参考图 3,数据驱动器 400 包括多个级联级 (cascade-connected stage) ST1 到 STn。每一级可以具有被布置在 LC 面板组件上的非晶硅 (a-Si) 薄膜晶体管 (TFT),以输出每个栅极信号。

[0060] 除了最后一级 STn 的每一级 ST1 到 STi+1 分别输出输出栅极信号 Gout(1) 到 Gout(i+1)。栅极截止电压 Voff、时钟信号 CKV、时钟条 (bar) 信号 CKVB 和初始信号 INT 被

平行输入到每一级 ST1-STn。所述初始信号 INT 可以从时钟生成器提供。

[0061] 每级 ST1-STn 可以具有第一时钟端 CK1、第二时钟端 CK2、设置端 S、重置端 R、电源端 GV、帧重置端 FR、栅极输出端 OUT1 和进位输出 (carryoutput) 端 OUT2。

[0062] 例如,前一级 Sti-1 的进位 (carry) 信号 Cout(i-1) 被输入到连接到第 i 条栅极线的级 Sti 的设置端 S,并且下一级 Sti+1 的栅极信号 Gout(i+1) 被输入到级 Sti 的重置端 R。第一时钟信号 CKV 和第一时钟条信号 CKVB 被分别输入到第一时钟端 CK1 和第二时钟端 CK2,且栅极截止信号 Voff 被输入到电源端 GV。初始信号 INT 或最后一级 Stn 的进位信号 Cout(n) 被输入到帧重置端 FR。栅极输出端 OUT1 输出栅极信号 Gout(i),而进位信号输出端 OUT2 输出进位信号 Cout(i)。

[0063] 但是,扫描开始信号 STV 被输入到第一级 ST1 的设置端 S,而不是从前一级输出的进位信号,并且扫描开始信号 STV 被输入到最后一级 STn 的重置端,而不是从下一级输出的栅极信号。

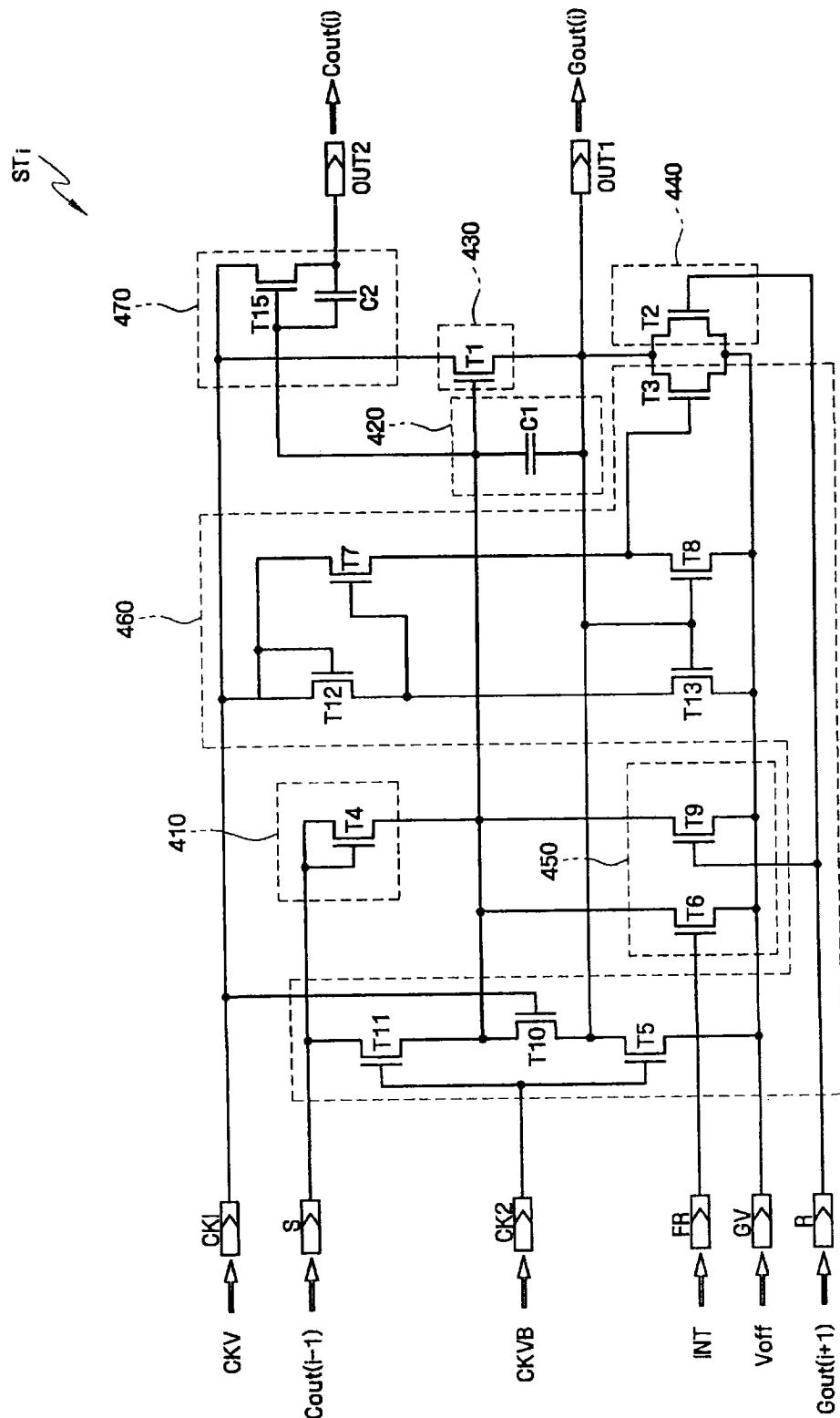

[0064] 以下将参考图 4,详细描述图 3 中示出的示例性的级 STi。

[0065] 参考图 4,级 STi 包括缓存器单元 410、充电单元 420、上拉单元 430、进位信号生成器 470、下拉单元 440、放电单元 450 和保持单元 460。

[0066] 缓冲单元 410 包括晶体管 T4,其具有互相连接的漏极和栅极,并提供前一级 Sti-1 的进位信号 Cout(i-1) 到充电单元 420、进位信号生成器 470 和上拉单元 430。这里,前一级 STi-1 的进位信号 Cout(i-1) 通过级 STi 的设置端 S 被输入。

[0067] 充电单元 420 包括电容 C1,其第一端连接到在缓存器单元 410 中的晶体管 T4 的源极、上拉单元 430 及放电单元 450,其第二端连接到栅极输出端 OUT1。充电单元 420 被提供以前一级 STi-1 的进位信号 Cout(i-1) 并由该进位信号充电。

[0068] 上拉单元 430 包括晶体管 T1,其漏极连接到第一时钟端 CK1,其栅极连接到充电单元 420 中的电容 C1 的第一端,而其源极连接到电容 C1 的第二端和栅极输出端 OUT1。当充电单元 420 的电容 C1 被充电时,晶体管 T1 被导通,从而通过第一时钟端 CK1 施加的第一时钟信号 CKV 通过栅极输出端 OUT1 被作为栅极信号 Gout(i) 提供。

[0069] 进位信号生成器 470 包括晶体管 T15,其漏极连接到第一时钟端 CK1,其源极连接到栅输出端 OUT1,而其栅极连接到缓存器 410,并且进位信号生成器 470 还包括连接到栅极和源极的电容 C2。电容 C2 被提供以前一级 STi-1 的进位信号 Cout(i-1),并被充电。当电容 C2 被充电时,晶体管 T15 被导通,这样时钟信号 CKV 通过进位输出端 OUT2 作为进位信号 Cout(i) 输出。

[0070] 下拉单元 440 包括晶体管 T2,其漏极连接到晶体管 T1 的源极和电容 C1 的第二端,其源极连接到电源端 GV,而其栅极连接到重置端 R。下拉单元 440 被通过重置端 R 施加的下一级 STi+1 的栅极信号 Gout(i+1) 导通,并将栅极信号 Gout(i) 下拉至栅极截止信号 Voff。

[0071] 放电单元 450 包括晶体管 T9,其栅极连接到重置端 R,其漏极连接到电容 C1 的第一端,其源极连接到电源端 GV,以响应于下一级 STi+1 的栅极信号 Gout(i+1) 来给充电单元 420 放电。放电单元 450 还包括晶体管 T6,其栅极连接到帧重置端 FR,其漏极连接到电容 C1 的第一端,其源极连接到电源端 GV,以响应于初始信号 INT 来给充电单元 420 放电。因此,响应于下一级 STi+1 的栅极信号 Gout(i+1),或响应于初始信号 INT,放电单元 450 将电容 C1 放电至栅极截止电压 Voff 以截止上拉单元 430。

[0072] 当栅极信号  $Gout(i)$  发生由低到高的转变时, 维持单元 460 维持高电平状态。在栅极信号  $Gout(i)$  发生由低到高的转变后, 维持单元 460 在一帧期间将栅极信号  $Gout(i)$  维持在低电平, 而不考虑时钟信号  $CKV$  和时钟条信号  $CKVB$  的电压电平。

[0073] 首先, 在栅极信号  $Gout(i)$  发生由低到高的转变的情况下, 晶体管  $T8$  和  $T13$  被导通。被导通的晶体管  $T13$  截止了晶体管  $T7$ , 以阻止高电平的时钟信号  $CKV$  被提供给晶体管  $T3$ , 而被导通的晶体管  $T8$  截止了晶体管  $T3$ 。因此, 栅极信号  $Gout(i)$  被维持在高电平。

[0074] 接下来, 在栅极信号  $Gout(i)$  发生由高到低的转变后, 晶体管  $T8$  和  $T13$  被截止。如果时钟信号  $CKV$  在高电平, 被导通的晶体管  $T7$  和  $T12$  导通了晶体管  $T3$  以便将栅极信号  $Gout(i)$  维持在低电平。此外, 晶体管  $T10$  被导通以使晶体管  $T1$  的栅极维持低电平状态, 从而高电平的时钟信号  $CKV$  没有被输出到栅极输出端  $OUT1$ 。因此, 时钟条信号  $CKVB$  处于高电平, 且晶体管  $T5$  和  $T11$  被导通。被导通的晶体管  $T5$  将栅极信号  $Gout(i)$  维持在低电平, 而被导通的晶体管  $T11$  将电容  $C1$  的第一端维持在低电平。因此, 在一帧的时间期间内, 栅极信号  $Gout(i)$  被维持在低电平。

[0075] 或者, 级  $STi$  可以不包括进位信号生成器 470。在这种情况下, 通过设置端  $S$ , 级  $STi$  可以通过设置终端  $S$  接收到前一级  $STi-1$  的栅极信号  $Gout(i)$  来进行操作, 而不是进位信号  $Cout(i-1)$ 。

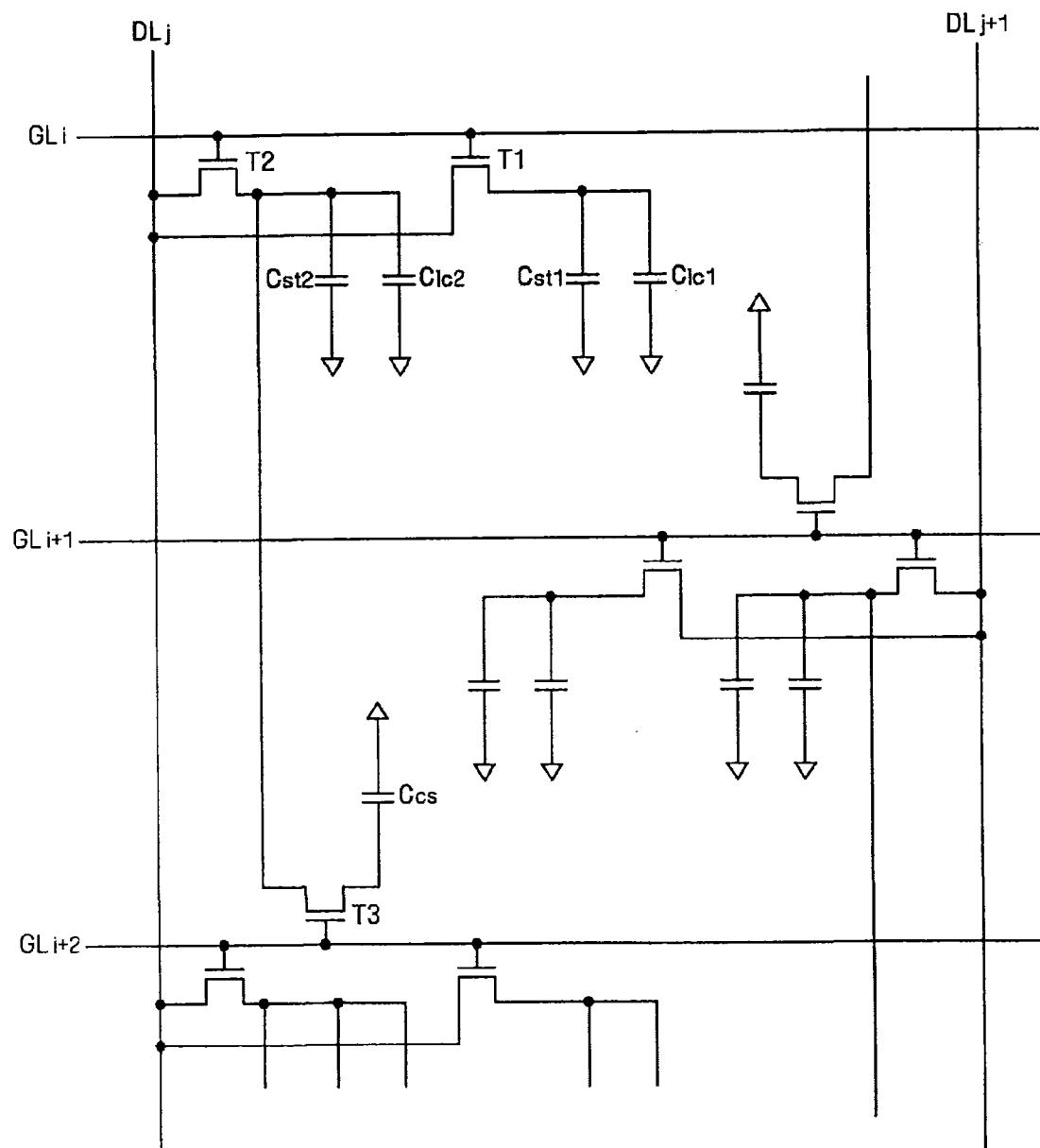

[0076] 参考图 5, 根据本发明的示例性实施例的 LCD 包括传输栅极信号的多条栅极线  $GLi$ 、 $GLi+1$  和  $GLi+2$ , 以及与栅极线  $GLi$ 、 $GLi+1$  和  $GLi+2$  交叉并传输数据信号的多条数据线  $DLj$  和  $DLj+1$ 。

[0077] 第一薄膜晶体管 (TFT)  $T1$  和第二 TFT  $T2$  被布置在第  $i$  条栅极线  $GLi$  和第  $j$  条数据线  $DLj$  交叉的地方, 且第三 TFT  $T3$  连接到第  $(i+2)$  条栅极线  $GLi+2$ 。

[0078] 第一 TFT  $T1$  包括连接到第  $i$  条栅极线  $GLi$  的栅极、连接到第  $j$  条数据线  $DLj$  的源极、以及连接到第一液晶 (LC) 电容  $Clc1$  和第一存储电容  $Cst1$  的漏极。第二 TFT  $T2$  包括连接到第  $i$  条栅极线  $GLi$  的栅极、连接到第  $j$  条数据线  $DLj$  的源极、以及连接到第二 LC 电容  $Clc2$  和第二存储电容  $Cst2$  的漏极。第三 TFT  $T3$  包括连接到第  $i+2$  条栅极线  $GLi+2$  的栅极、连接到第二 TFT  $T2$  的漏极的源极和连接到电荷共享电容  $Ccs$  的漏极。

[0079] 下部显示面板的每个像素具有像素电极, 其包括连接到第一 TFT  $T1$  的漏极的第一子像素电极和连接到第二 TFT  $T2$  的漏极的第二子像素电极。公共电极布置在面向下部显示面板的上部显示面板上。

[0080] 第一 LC 电容  $Clc1$  包括连接到第一 TFT  $T1$  的第一子像素电极、公共电极、以及布置在第一子像素电极和公共电极之间的液晶层。第一存储电容  $Cst1$  包括第一子像素电极、布置在下部显示面板上的存储线、以及位于第一子像素电极和存储线之间的绝缘物质。

[0081] 第二 LC 电容  $Clc2$  包括连接到第二 TFT  $T2$  的第二子像素电极、公共电极、以及布置在第二子像素电极和公共电极之间的液晶层。第二存储电容  $Cst2$  包括第二子像素电极、布置在下部显示面板上的存储线、以及位于第二子像素电极和存储线之间的绝缘物质。

[0082] 电荷共享电容  $Ccs$  包括第三 TFT  $T3$  的漏极、布置在下部显示面板上的存储线、以及位于漏极和存储线之间的绝缘物质。这里, 电荷共享电容  $Ccs$  降低了连接到第二 TFT  $T2$  的第二子像素电极的数据电压。在示例性实施例中, 可以通过将第三 TFT  $T3$  的漏极与第一 TFT  $T1$  的第一子像素电极重叠 (overlapping) 来形成额外的电荷共享电容。额外的电荷共

享电容升高了连接到第一 TFT T1 的第一子像素电极的数据电压。

[0083] 参考图 5 和图 6,当栅极导通电压被施加到第 i 条栅极线 GLi 时,相同的数据电压分别经由第一 TFTT1 和第二 TFTT2 从第 j 条数据线 DLj 施加到布置在第 i 行的第一和第二子像素电极。即,连接到第 i 行的第一 LC 电容 Clc1 和第二 LC 电容 Clc2 被以相同的数据电压充电。随后,当栅极截止电压被施加给第 i 条栅极线 GLi,第一个子像素电极没有被连接到第二子像素电极。即,在相同的数据电压被施加给第一和第二子像素电极后,第一和第二子像素电极处于浮动 (floating) 状态。

[0084] 当栅极导通电压被施加给 i+1 条栅极线 GLi+1 时,相同的数据电压经由连接到第 i+1 条栅极线 GLi+1 的一对开关装置被分别施加到布置在第 i+1 行的一对子像素电极。在第 i 个栅极截止电压之前,第 i+1 个栅极导通电压可以被施加。在这种情况下,当数据电压被施加给布置在第 i 行的一对子像素电极时,布置在第 i+1 行的一对子像素电极可以用数据电压进行预充电。这里,预充电过程是顺序地和重叠地将栅极导通电压施加到多条栅极线 GLi、GLi+1 和 GLi+2 的驱动方法。这里,“重叠地”是指栅极导通电压以重叠的方式被施加,这样在栅极导通电压被初始施加到前一栅极之后、并在栅极导通电压被施加到前一栅极线结束之前,栅极导通电压被施加给下一条栅极线。在示例性实施例中,像素基本上为矩形形状,其具有长于纵向长度的横向长度,因此即使栅极线的数量增加,也可以以足够的速度驱动 LCD。但是本发明不限于此,并且第 i+1 个栅极导通电压可以在第 i 个栅极截止电压之后被施加。随后,当第 i+1 个栅极截止电压被施加给第 i+1 条栅极线 GLi+1 时,连接到第 i+1 条栅极线 GLi+1 的一对子像素电极没有彼此连接,因此处于浮动状态。

[0085] 当栅极导通电压被施加给第 i+2 条栅极线 GLi+2 时,相同的数据电压经由连接到第 i+2 条栅极线 GLi+2 的一对开关装置被分别施加到布置在第 i+2 行的一对子像素电压。第 i+2 个栅极导通电压可以在第 i+1 个栅极截止电压之前被施加。

[0086] 此外,当栅极导通电压被施加给第 i+2 条栅极线 GLi+2 时,连接到第二 TFT T2 的第二子像素电极的数据电压经由第三 TFT T3 与电荷共享电容 Ccs 共享。这是因为第三 TFT T3 的源极连接到与第二 TFT T2 相连的第二子像素电极,且第三 TFT T3 的漏极连接到电荷共享电容 Ccs。因此,布置在第 i 行且分别连接到第一 TFT T1 和第二 TFT T2 的第一和第二子像素电极具有不同的数据电压。具体地说,由于连接到第二 TFT T2 的第二子像素电极的数据电压经由第三 TFT T3 与电荷共享电容 Ccs 共享,因此第二子像素电极的数据电压降低。

[0087] 当布置在像素中的第一和第二子像素电极具有不同的数据电压时,则可以改善侧面可视性。一对灰度电压集 (sets) 被施加到第一和第二子像素电极,所述灰度电压集具有从一条 (a piece of) 图像信息获得的不同伽马曲线。因此,通过合成第一和第二子像素电极的伽马曲线可以获得包括所述第一和第二子像素的像素电极的伽马曲线。通过确定各个子像素的灰度电压能够改善侧面可视性,从而从 LCD 前面获得的合成伽马曲线类似于 LCD 前面的参考伽马曲线,并且从 LCD 的任一侧获得的合成伽马曲线尽可能地类似于参考伽马曲线。

[0088] 随后,当栅极截止电压被施加到第 i+2 条栅极线 GLi+2 时,连接到第 i+2 条栅极线 GLi+2 的一对子像素电极没有彼此连接,从而处于浮动状态。此外,与布置在第 i 行的第二 TFT T2 相连接的第二子像素电极没有连接到电荷共享电容 Ccs,从而处于浮动状态。

[0089] 以下将参考图 7、图 8、图 9、图 10 和图 11 详细描述根据本发明的示例性实施例的 LCD 的结构。根据本发明的示例性实施例的 LCD 包括 TFT 阵列位于其上的下部显示面板、面向下部显示面板的上部显示面板、以及插入位于下部显示面板和上部显示面板之间的液晶层。

[0090] 以下将参考图 7 和图 8 详细说明根据本发明的示例性实施例的 LCD 的下部显示面板的结构。图 7 是根据本发明的示例性实施例的 LCD 的下部显示面板的布局，而图 8 是图 7 的下部显示面板沿 VIII-VIII' 线的横截面示意图。

[0091] 参考图 7 和图 8，布置在绝缘基片上的栅极线 GLi、GLi+1 和 GLi+2 可以包括，例如，透明玻璃。栅极线 GLi、GLi+1 和 GLi+2 在水平方向延伸，并且传输栅极信号。以突起形式的第一栅电极 G1 和第二栅电极 G2 连接到第 i+2 条栅极线 GLi+2。栅极线 GLi、GLi+1 和 GLi+2 以及第一、第二和第三栅电极 G1、G2 和 G3 被共同称为栅极互连 (gate interconnections)。

[0092] 存储线 SLi、SLi+1 和 SLi+2 布置在绝缘基片 10 上，并且沿水平方向延伸穿过 (extend across) 像素区域。存储线 SLi、SLi+1 和 SLi+2 包括突起，所述突起可以重叠第一和第二子像素电极 Pa 和 Pb。存储线 SLi、SLi+1 和 SLi+2 的形状和排列可以以各种方式进行修改。公共电压 Vcom 可以被施加到存储线 SLi、SLi+1 和 SLi+2。

[0093] 在示例性实施例中，栅极互连 GLi、GLi+1、GLi+2、G1、G2 和 G3 以及存储线 SLi、SLi+1 和 SLi+2 可以包括铝 (Al) 或铝基金属材料，如铝合金，银或银基金属材料，如银合金，铜 (Cu) 或铜基金属材料，如铜合金、钼 (Mo) 或钼基金属材料，如钼合金、铬 (Cr)、钛 (Ti) 或钽 (Ta)。在示例性实施例中，栅极互连 GLi、GLi+1、GLi+2、G1、G2 和 G3 以及存储线 SLi、SLi+1 和 SLi+2 可以包括多层结构，该多层结构包括具有不同物理性质的两个导电层 (未示出)。在示例性实施例中，所述两个导电层中的一个可以包括低电阻金属，例如，铝或铝基金属材料、银或银基金属材料、或者铜或铜基金属材料，从而降低信号延迟或电压降低的可能性。在另一个示例性实施例中，其它的导电层可以包括这样的材料，例如钼或钼基金属材料、铬、钛或钽，该材料包括与例如氧化铟锡 (ITO) 或氧化铟锌 (IZO) 良好的接触特性。在另一个示例性实施例中，栅极互连 GLi、GLi+1、GLi+2、G1、G2 和 G3 以及存储线 SLi、SLi+1 和 SLi+2 可以是双层，包括铬层 (作为下层) 和铝层 (作为上层)，或包括铝层 (作为下层) 和钼层 (作为上层)。但是，本发明不限于此。即，在示例性实施例中，栅极互连 GLi、GLi+1、GLi+2、G1、G2 和 G3 以及存储线 SLi、SLi+1 和 SLi+2 可以包括不同于这里所列出的材料的各种材料和导电材料。

[0094] 栅极绝缘层 30 可以包括在栅极互连 GLi、GLi+1、GLi+2、G1、G2 和 G3 上以及在存储线 SLi、SLi+1 和 SLi+2 上的氮化硅 (SiNx)。

[0095] 在示例性实施例中，半导体层 40 可以包括在栅极绝缘层 30 上的氢化非晶硅或多晶硅。在示例性实施例中，半导体层 40 可以具有各种形状，例如岛形或线形。在示例性实施例中，例如，半导体层 40 可以具有岛形。当半导体层 40 具有线形时，它们可以被布置在数据线 DLj 之下。

[0096] 一对欧姆接触层 55 和 56 可以包括在半导体层 40 上的、掺杂 (doped with) 高浓度 n- 型杂质的硅化物或 n+ 氢化非晶硅。在示例性实施例中，欧姆接触层 55 和 56 可以具有各种形状，例如岛形或线形。当欧姆接触层 55 和 56 可以包括岛形时，它们可以被布置在第一漏极 D1 和第一源极 S1 之下。当欧姆接触层 55 和 56 具有线形时，它们可以被布置在数据

线 DL<sub>j</sub> 和 DL<sub>j+1</sub> 之下。

[0097] 数据线 DL<sub>j</sub> 和 DL<sub>j+1</sub> 以及第一、第二和第三漏极 D<sub>1</sub>、D<sub>2</sub> 和 D<sub>3</sub> 被布置在欧姆接触层 55 和 56 和栅极绝缘层 30 上。

[0098] 数据线 DL<sub>j</sub> 和 DL<sub>j+1</sub> 沿纵向延伸并与栅极线 GL<sub>i</sub>、GL<sub>i+1</sub> 和 GL<sub>i+2</sub> 交叉以定义像素。第一和第二源极 S<sub>1</sub> 和 S<sub>2</sub> 从第 j 条数据线 DL<sub>j</sub> 分出 (branch)，并分别向第一和第二漏极 D<sub>1</sub> 和 D<sub>2</sub> 延伸。位于半导体层 40 上的第一漏极 D<sub>1</sub> 相对于第一栅极 G<sub>1</sub> 与第一源极 S<sub>1</sub> 分开并与之相对 (opposite)。位于半导体层 40 上的第二漏极 D<sub>2</sub> 考虑到第二栅极 G<sub>2</sub> 与第二源极 S<sub>2</sub> 分开并与之相对。第一和第二漏极 D<sub>1</sub> 和 D<sub>2</sub> 包括条纹图案 (pattern) 和从条纹图案扩展的扩展图案。条纹图案在半导体层 40 上。扩展图案具有大面积和第一和第二接触孔 H<sub>1</sub> 和 H<sub>2</sub>。这里，第一和第二接触孔分别重叠第一和第二子像素电极 Pa 和 Pb。

[0099] 第三源极 S<sub>3</sub> 从被第二子像素电极 Pb 重叠的第三接触孔 H<sub>3</sub> 延伸到第三栅极 G<sub>3</sub> 的上部 (upper portion)。第三漏极 D<sub>3</sub> 从第三栅极 G<sub>3</sub> 的上部向第 i+1 条存储线 SL<sub>i+1</sub> 的上部延伸。位于半导体层 40 上的第三漏极 D<sub>3</sub> 相对于第三栅极 G<sub>3</sub> 与第三源极 S<sub>3</sub> 分开并与之相对。

[0100] 数据线 DL<sub>j</sub> 和 DL<sub>j+1</sub>、第一、第二和第三源极 S<sub>1</sub>、S<sub>2</sub> 和 S<sub>3</sub>、以及第一、第二和第三漏极 D<sub>1</sub>、D<sub>2</sub> 和 D<sub>3</sub> 被共同称为数据互连。

[0101] 在示例性实施例中，数据互连 DL<sub>j</sub>、DL<sub>j+1</sub>、S<sub>1</sub>、S<sub>2</sub>、S<sub>3</sub>、D<sub>1</sub>、D<sub>2</sub> 和 D<sub>3</sub> 可以包括高熔点金属，如铬、钼或钼基金属材料、钽或钛。在另一示例性实施例中，数据互连 DL<sub>j</sub>、DL<sub>j+1</sub>、S<sub>1</sub>、S<sub>2</sub>、S<sub>3</sub>、D<sub>1</sub>、D<sub>2</sub> 和 D<sub>3</sub> 可以具有多层结构，该多层结构包括下层 (未示出) 和上层 (未示出)，该下层包括高熔点金属，该上层包括低电阻材料。多层结构的例子包括双层结构，该双层结构具有下层 Cr 薄膜和上层 Al 薄膜，或下层 Al 薄膜和上层 Mo 薄膜，以及三层结构，该三层结构包括下层 Mo 薄膜、中间层 Al 薄膜和上层 Mo 薄膜。

[0102] 第一源极 S<sub>1</sub> 至少部分地与半导体层 40 重叠。第一漏极 D<sub>1</sub> 相对于第一栅极 G<sub>1</sub> 面向第一源极 S<sub>1</sub> 并与之相对，并至少部分地与半导体层 40 重叠。这里，欧姆接触 55 和 56 被插入下面的 (underlying) 半导体层 40 和上面的 (overlying) 第一源极 S<sub>1</sub> 之间，以及下面的半导体层 40 和上面的第一漏极 D<sub>1</sub> 之间，以降低它们之间的接触电阻。

[0103] 第二源极 S<sub>2</sub> 至少部分地与半导体层 40 重叠。第二漏极 D<sub>2</sub> 相对于第二栅极 G<sub>2</sub> 面向第二源极 S<sub>2</sub> 并与之相对，并至少部分地与半导体层 40 重叠。这里，欧姆接触被插入下面的半导体层和在上面的第二源极 S<sub>2</sub> 之间，以及下面的半导体层和在上面的第二漏极 D<sub>2</sub> 之间，以降低它们之间的接触电阻。

[0104] 钝化层 70 被布置在数据互连 DL<sub>j</sub>、DL<sub>j+1</sub>、S<sub>1</sub>、S<sub>2</sub>、S<sub>3</sub>、D<sub>1</sub>、D<sub>2</sub> 和 D<sub>3</sub> 上，以及在源极和漏极之间暴露的半导体层部分上。在示例性实施例中，钝化层 70 可以包括氮化硅或氧化硅基的无机材料、具有良好平面性质的光感有机材料、low-k 电介质材料如 a-Si:C:O 或 a-Si:O:F，其可以使用等离子体增强的化学气相沉积 (PECVD) 方法来形成。在示例性实施例中，钝化层 70 可以包括双层结构，其由下层无机层和上层有机层构成，以便提供极好的有机层性质，并且有效地保护半导体层 40 的暴露部分。

[0105] 钝化层 70 具有第一、第二和第三接触孔 H<sub>1</sub>、H<sub>2</sub> 和 H<sub>3</sub>，其分别暴露第一、第二和第三漏极 D<sub>1</sub>、D<sub>2</sub> 和 D<sub>3</sub>。

[0106] 像素电极 PE 根据像素形状被布置在钝化层 70 上。像素电极 PE 可以具有基本上

矩形的形状,该矩形形状具有长于纵向长度的横向长度。像素电极包括第一和第二子像素电极 Pa 和 Pb。第一子像素电极 Pa 经由第一接触孔 H1 连接到第一漏极 D1,而第二子像素电极 Pb 经由第二和第三接触孔 H2 和 H3 分别连接到第二和第三漏极 D2 和 D3。在示例性实施例中,第一和第二子像素电极 Pa 和 Pb 可以包括透明导电材料,如 ITO 或 IZO,或可以包括反射导电材料,如铝。

[0107] 第一和第二子像素电极 Pa 和 Pb 经由第一和第二接触孔 H1 和 H2 分别连接到第一和第二漏极 D1 和 D2,因此每一个分别由第一和第二漏极 D1 和 D2 提供数据电压。在示例性实施例中,分别向第一和第二漏极 D1 和 D2 传输数据电压的第一和第二源极 S1 和 S2 互相连接,因此从第 j 条数据线 DLj 施加到第一和第二子像素电极 Pa 和 Pb 的数据电压基本相同。

[0108] 电场在被提供以数据电压的第一和第二子像素电极 Pa 和 Pb 与上部显示面板的公共电极之间生成,该电场决定在第一和第二子像素电极 Pa 和 Pb 与公共电极之间的 LC 层中的液晶分子的朝向。

[0109] 组成像素区域的第一和第二子像素电极 Pa 和 Pb 以间隙 83 相互分开,并形成基本上矩形的形状,该矩形形状具有长于纵向长度的横向长度。第一子像素电极 Pa 是 V- 形的 (V-shaped) 并位于像素区域的中间。第二子像素电极 Pb 被配置在像素区域中与第一子像素电极 Pa 不同的部分。这里,间隙 83 包括与偏振片 (polarizing plate) 的传输轴 (或与栅极线 GLi、GLi+1 和 GLi+2) 成大约 45 度角的间隙、以及与偏振片的传输轴 (或与栅极线 GLi、GLi+1 和 GLi+2) 成大约 -45 度角的间隙。因此,邻近间隙 83 的第一和第二子像素电极 Pa 和 Pb 的边缘与栅极线 GLi、GLi+1 和 GLi+2 形成 45 度或 -45 度角 (以下称为倾斜方向)。多个第一域分割器 (domain divider) (未示出) 可以在倾斜方向上被布置在第一和第二子像素电极 Pa 和 Pb 中。在示例性实施例中,多个第一域分割器可以是切口或突起。当电场被施加到 LC 层时,像素电极 PE 的显示区域可以根据 LC 层中 LC 分子的朝向被分割为多个域。间隙 83 和多个第一域分割器将像素电极 PE 分割成许多域。这里,域是由于在图 7 的像素电极 PE 和图 9 的公共电极 90 之间形成的电场而在相同方向上统一倾斜的 LC 分子组所定义的区域。

[0110] 如上所述,当栅极导通电压被施加到第 i 条栅极线 GLi 时,相同数据电压被从第 j 条数据线 DLj 施加到邻近第 i 条栅极线 GLi 的第一和第二子像素电极 Pa 和 Pb。随后,当栅极导通电压被施加到第 i+2 条栅极线 GLi+2 时,第二子像素电极 Pb 的数据电压通过第三 TFT T3 与第三漏极 D3 共享。电荷共享电容被布置在第三漏极 D3 与布置在第三漏极 D3 下的第 i+1 条存储线 SLi+1 之间。因此,第二子像素电极 Pb 的数据电压降低,并且第一子像素电极 Pa 的数据电压升高。

[0111] 在示例性实施例中,校准 LC 分子的校准层 (未示出) 可以被布置在第一和第二子像素电极 Pa 和 Pb 上,并且在钝化层 70 上。

[0112] 以下将参考图 9、图 10 和图 11 详细描述根据本发明的示例性实施例的 LCD 装置的上部显示面板的结构。

[0113] 参考图 9、图 10 和图 11,黑色矩阵 (black matrix) 94、滤色器 (color filter) 98,例如,红色、绿色和蓝色滤光器,以及公共电极 90 被布置在具有透明材料如玻璃的绝缘基片 96 上。公共电极 90 可以包括透明和导电材料,如 ITO 或 IZO。黑色矩阵对应栅极线 GLi、

GLi+1 和 GLi+2、数据线 DLj、DLj+1、以及开关装置 T1、T2 和 T3。黑色矩阵可以具有任何不同形状,只要它可以防止在第一和第二子像素电极 Pa 和 Pb 及开关装置 T1、T2 和 T3 的附近发生光线泄露。

[0114] 公共电极 90 面向第一和第二子像素电极 Pa 和 Pb, 并包括多个第二域分割器 92。多个第二域分割器可以是切口或突起。这里, 第二域分割器 92 包括与偏振片的传输轴 (或与栅极线 GLi、GLi+1 和 GLi+2) 成大约 -45 度或 45 度角的倾斜部分。在示例性实施例中, 为简短起见, 将以第二域由切口组成的情形进行说明。

[0115] 布置在公共电极 90 中的第二域分割器 92 的倾斜部分与第一和第二子像素电极 Pa 和 Pb 之间的间隙 83 (可以) 交替 (alternate with)。

[0116] 在示例性实施例中, 用于校准 (align) 液晶层 150 的液晶分子的校准层 (未示出) 可以被布置在公共电极 90 上。

[0117] 根据本发明的示例性实施例的基本 LCD 结构可以通过以下方式形成: 纵向互相对准下部显示面板 100 和上部显示面板 200, 并将它们与插在其间的液晶材料相连。除了上述基本 LCD 结构之外, LCD 还可以包括附加的元件, 如偏振片和背光组件。在示例性实施例中, 偏振片可以被布置在基本 LCD 结构的相对侧, 使得偏振片之一的传输轴与栅极线 GLi、GLi+1 和 GLi+2 平行, 且另一偏振片的传输轴与栅极线 GLi、GLi+1 和 GLi+2 垂直。

[0118] 当电场被施加到下部显示面板和上部显示面板之间时, 每个域的 LC 分子以与间隙 83 或第二域分割器 92 垂直的方向倾斜。因此, 每个域中的 LC 分子以相对于偏振片的传输轴或栅极线 GLi、GLi+1 和 GLi+2 成大约 45 度或 -45 度角倾斜。在间隙 83 或第二域分割器 92 的每一个中形成的侧面电场促进了每个域中液晶分子的校准。

[0119] 上述示例性实施例示出了与第 i+2 条栅极线 GLi+2 相连的第三 TFT T3, 但在预充电过程没有被施加到第 i 条栅极线 GLi 和第 i+1 条栅极线 GLi+1 时, 第三 TFT T3 可以替代地连接到第 i+1 条栅极线 GLi+1。

[0120] 以下, 将参考图 12、图 13、图 14、图 15、图 16、图 17、图 18、图 19 和图 20 说明根据本发明的示例性实施例的 LCD。具有如前一个示例性实施例的图 1、图 2、图 3、图 4、图 5、图 6、图 7、图 8、图 9、图 10 和图 11 所述相关的相同或类似功能的组件以相同的参考标号来表示, 且不再重复对其说明。

[0121] 图 12 是根据本发明的另一个示例性实施例的 LCD 的等效电路图。

[0122] 参考图 12, LCD 包括传输栅极信号的多条栅极线 GLi 和 GLi+1, 及与栅极线交叉并传输数据信号的多条数据线 DLj。

[0123] 第一薄膜晶体管 (TFT) T1 和第二 TFT T2 被配置在第 i 条栅极线 GLi 和第 j 条数据线 DLj 交叉的地方, 并且第三晶体管 TFT T3 连接到第 i+1 条栅极线 GLi+1。

[0124] 第一 TFT T1 包括连接到第 i 条栅极线 GLi 的栅极、连接到第 j 条数据线 DLj 的源极、及连接到第一 LC 电容 Clc1 和第一存储电容 Cst1 的漏极。第二 TFT T2 包括连接到第 i 条栅极线 GLi 的栅极、连接到第 j 条数据线 DLj 的源极、及连接到第二 LC 电容 Clc2 和第二存储电容 Cst2 的漏极。第三 TFT T3 包括连接到第 i+1 条栅极线 GLi+1 的栅极、连接到第二 TFT T2 的漏极的源极、及连接到第一电荷共享电容 Ccs1 和第二电荷共享电容 Ccs2 的漏极。

[0125] 下部显示面板的每个像素具有像素电极, 该像素电极包括连接到第一 TFT T1 的漏

极的第一子像素电极和连接到第二 TFT T2 的漏极的第二子像素电极。公共电极被布置在面向下部显示面板的上部显示面板上。

[0126] 第一LC电容Clc1包括连接到第一TFT T1的第一子像素电极、公共电极、及插入第一子像素电极和公共电极之间的LC层。第一存储电容Cst1包括第一子像素电极、布置在下部显示面板上的存储线、以及插入第一子像素电极和存储线之间的绝缘材料(dielectric material)。

[0127] 第二LC电容Clc2包括连接到第二TFT T2的第二子像素电极、公共电极、以及插入第二子像素电极和公共电极之间的LC层。第二存储电容Cst2包括第二子像素电极、布置在下部显示面板上的存储线、以及插入第二子像素电极和存储线之间的绝缘材料。

[0128] 第一电荷共享电容Ccs1包括第三TFT T3的漏极。布置在下部显示面板上的存储线、以及插入漏极和存储线之间绝缘材料。

[0129] 第二电荷共享电容Ccs2包括第三TFT T3的漏极,第一子像素电极、以及插入漏极和第一子像素电极之间的绝缘材料。

[0130] 当栅极导通电压被施加到第i条栅极线GLi时,相同数据电压通过第一和第二TFT T1和T2从第j条数据线DLj分别施加到布置在第i行的第一和第二子像素。即,连接到第i行的第一和第二LC电容Clc1和Clc2以相同数据电压进行充电。随后,当栅极截止电压被施加到第i条栅极线GLi时,第一子像素电极没有连接到第二子像素电极。即,在相同数据电压被施加到第一和第二子像素电极之后,第一和第二子像素电极处于浮动状态。

[0131] 当栅极导通电压被施加到第i+1条栅极线GLi+1时,相同数据电压经由连接到第i+1条栅极线GLi+1的一对开关装置被分别施加到布置在第i+1行中的一对子像素电极。第i+1个栅极导通电压可以在第i个栅极截止电压之前被施加。在这种情况下,当数据电压被施加到布置在第i行的一对子像素电极时,布置在第i+1行的一对子像素电极可以用数据电压进行预充电。这里,预充电过程是将栅极导通电压顺序地和重叠地施加到多条栅极线GLi和GLi+1的驱动方法。在示例性实施例中,像素具有基本上矩形的形状,该矩形形状的具有长于纵向长度的横向长度,因此即使栅极线的数量增加,LCD也可以以足够的速度驱动。但是,本发明不限于此,第i+1个栅极导通电压可以在第i个栅极截止电压之后被施加。在示例性实施例中的预充电过程将在下面更具体的描述。随后,当栅极截止电压被施加到第i+1条栅极线GLi+1时,连接到第i+1条栅极线GLi+1的一对子像素电极没有互相连接,从而处于浮动状态。

[0132] 这里,当栅极导通电压被施加到第i+1条栅极线GLi+1时,连接到第二TFT T2的第二子像素电极的数据电压经由第三TFT T3与第一和第二电荷共享电容Ccs1和Ccs2共享。这时由于第三TFT T3的源极连接到第二子像素电极,该第二子像素电极连接到第二TFT T2,且第三TFT T3的漏极连接到第一和第二电荷共享电容Ccs1和Ccs2。因此,布置在第i行中并分别连接到第一和第二TFT T1和T2的第一和第二子像素电极具有不同的数据电压。

[0133] 具体来说,当栅极导通电压被施加到第i条栅极线GLi时,数据电压通过第一和第二TFT T1和T2被施加。在数据电压具有相对于公共电压Vcom的正极电平的情况下,公共电压Vcom被施加到第一电荷共享电容Ccs1的第一端,因此第一和第二电荷共享电容Ccs1和Ccs2之间的节点N的电压低于数据电压。随后,当栅极截止电压被施加到第i条栅极线

GLi 且栅极导通电压被施加到第  $i+1$  条栅极线 GLi+1 时,由于连接到第二 TFT T2 的第二子像素电极的数据电压相对高于节点 N 的电压,电流从第二子像素电极经由第三 TFT T3 流向第一和第二电荷共享电容 Ccs1 和 Ccs2。因此,第二子像素电极的数据电压降低,而节点 N 和第一子像素电极的电压升高。在数据电压具有相对于公共电压 Vcom 的负极电平的情况下,第一和第二子像素电极数据电压反过来改变 (change vice versa)。因此,第一子像素电极与公共电极之间的电压绝对值始终高于第二子像素与公共电极之间的电压绝对值。

[0134] 当布置在像素中的第一和第二子像素电极具有不同的数据电压时,侧面可视性可以被改善。具有从一条图像信息获得的不同伽马曲线的一对灰度电压集被施加到第一和第二子像素电极。因此,用于包括第一和第二子像素的像素电极的伽马曲线可以通过合成所述第一和第二子像素电极的伽马曲线来获得。通过确定各个子像素的灰度电压,能够改善侧面可视性,从而从 LCD 前端获得的合成伽马曲线类似于用于 LCD 前端的参考伽马曲线,而且从 LCD 的任一侧获得的合成伽马曲线尽可能地类似于参考伽马曲线。

[0135] 随后,当栅极截止电压被施加到第  $i+1$  条栅极线 GLi+1 时,连接到第  $i+1$  条栅极线 GLi+1 的一对子像素电极没有彼此连接,从而处于浮动状态。此外,连接到位于第  $i$  条栅极线 GLi 的第一和第二子像素电极没有彼此连接,从而处于浮动状态。

[0136] 以下将参考图 13 描述根据本发明的示例性实施例的 LCD 的结构。LCD 包括其上布置有 TFT 阵列的下部显示面板、面向下部显示面板的上部显示面板、以及在插入下部显示面板和上部显示面板之间的液晶层。

[0137] 图 13 是根据本发明的另一个示例性实施例的 LCD 的下部显示面板的布局。具有如前一个示例性实施例的图 1、图 2、图 3、图 4、图 5、图 6、图 7、图 8、图 9、图 10 和图 11 所述相关的相同或类似功能的组件以相同的参考标号表示,且不再重复对其描述。以下将结合前一个及当前示例性实施例之间的区别来给出解释。

[0138] 参考图 13,栅极线 GLi 和 GLi+1 被布置在绝缘基片上。栅极线 GLi 和 GLi+1 沿水平方向延伸并传输栅极信号。突起形式的第一和第二栅极 G1 和 G2 连接到第  $i$  条栅极线 GLi。突起形式的第三栅极连接到第  $i+1$  条栅极线 GLi+1。栅极线 GLi 和 GLi+1 及第一和第二栅极 G1 和 G2 被共同称为栅极互连。

[0139] 第三源极 S3 从被第二子像素电极 Pb 重叠的第三接触孔 H3 延伸到第三栅极 G3 的上部。第三漏极 D3 从第三栅极 G3 的上部经由第  $i$  条存储线 SLi 的上部延伸到第一子像素电极 Pa 的下部。布置在半导体层 40 上的第三漏极 D3 相对于第三栅极 G3 与第三源极 S3 分开并与之相对。第一电荷共享电容 Ccs1 形成在第三漏极 D3 和第  $i$  条存储线 SLi 重叠的区域 P。第二电荷共享电容 Ccs2 形成在第三漏极 D3 和第一子像素电极 Pa 重叠的区域 Q。

[0140] 当栅极导通电压被施加到第  $i$  条栅极线 GLi 时,相同的数据电压从第  $j$  条数据线 DLj 施加到邻近第  $i$  条栅极线 GLi 的第一和第二子像素电极 Pa 和 Pb。随后,当栅极导通电压被施加到第  $i+1$  条栅极线 GLi+1 时,第二子像素电极 Pb 的数据电压经由第三 TFT T3 与第三漏极 D3 共享。因此,第二子像素电极 Pb 的数据电压降低,而第一子像素电极 Pa 的数据电压升高。

[0141] 以下,将参考图 14、图 15、图 16、图 17、图 18、图 19 和图 20 描述根据本发明的示例性实施例的 LCD 的各种驱动方法。

[0142] 首先,将参考图 14、图 15、图 16 和图 17 描述驱动根据本发明的示例性实施例的

LCD 的方法。

[0143] 参考图 12、图 14 和图 15，包括多个级 ST1、ST2、ST3 和 ST4 的栅极驱动器 400 被以一定间隔施加的第一扫描开始信号 STV1 和第二扫描开始信号 STV2 使能，以向栅极线 GL1、GL2、GL3 和 GL4 顺序地输出高电平的第一和第二栅极信号（以下称为第一和第二栅极导通信号）。具体来说，栅极驱动器 400 被第一扫描开始信号 STV1 使能，以向第一栅极线 GL1 传输第一栅极导通信号。栅极驱动器 400 被第二扫描开始信号 STV2 使能，以向第一栅极线 GL1 传输第二栅极导通信号。第一扫描开始信号 STV1 和第二扫描开始信号 STV2 具有大约 2H 的相位差。这里，1H 是栅极导通信号被施加到并维持在每条栅极线 GL1、GL2、GL3 和 GL4 的一段时间。

[0144] 当第一栅极导通信号被传输到第二栅极线 GL2 时，第一栅极截止信号被传输到第一栅极线 GL1。当第二栅极导通信号被传输到第二栅极线 GL2 时，第二栅极截止信号被传输到第一栅极线 GL1。当第一和第二栅极导通信号被传输到第二栅极线 GL2 时，在连接到第一栅极线 GL1 的像素中存储的电荷经由连接到第二栅极线 GL2 的第三 TFT T3 被共享。对于其它栅极线，电荷共享过程以相同的方式发生。

[0145] 传输到每条栅极线 GL1、GL2、GL3 和 GL4 的第一栅极导通信号是用来对连接到每条栅极线 GL1、GL2、GL3 和 GL4 的像素进行预充电的信号，而第二栅极导通信号是对连接到每条栅极线 GL1、GL2、GL3 和 GL4 的像素以与其相对应的数据电压进行充电的信号。

[0146] 在第二栅极导通信号被传输到第一栅极线 GL1 的第一时间段 P1 期间，第一栅极导通信号被传输到第三栅极线 GL3。即，在第一时间段 P1 期间，连接到第一栅极线 GL1 的像素经由数据线 DL1、DL2 和 DL3 以数据电压进行充电。同时，连接到第三栅极线 GL3 的像素以数据电压进行预充电。对于其它的栅极线，预充电过程以相同的方式发生。

[0147] 这样，像素之间的电荷共享和预充电可以使用第一扫描开始信号 STV1 和第二扫描开始信号 STV2 来容易地执行。当第二栅极导通信号被施加到第 i 像素行时，在第 i+2 像素行中发生预充电。此外，当第一和第二栅极导通信号被施加到第 i+1 像素行时，在第 i 像素行中发生电荷共享。

[0148] 如图 15 所示，由于第一扫描开始信号 STV1 和第二扫描开始信号 STV2 之间存在相位差，可以使用点反转驱动方法。此外，如图 16 所示，可以使用列反转驱动方法。另外，如图 17 所示，当源极从每条数据线向左侧和右侧分出时，列反转驱动可以和点反转驱动具有相同的效果。这被称为像点的 (dot-like) 列反转驱动方法。

[0149] 以下，将参考图 18 具体描述驱动根据本发明的另一个示例性实施例的 LCD 的方法。图 18 是表示根据本发明的另一个示例性实施例的栅极信号的时序图。具有如前一个示例性实施例的图 14、图 15、图 16、和图 17 所述相关的相同或类似功能的组件以相同的参考标号表示，且不再重复对其描述。以下将结合前一个及当前示例性实施例之间的区别来给出解释。

[0150] 第一扫描开始信号 STV1 和第二扫描开始信号 STV2 具有大约 2.5H 的相位差。这里，1H 是栅极导通信号被施加到并维持在每条栅极线 GL1、GL2、GL3 和 GL4 的一段时间。

[0151] 当第一栅极导通信号被传输到第二栅极线 GL2 时，第一栅极截止信号被传输到第一栅极线 GL1。当第二栅极导通信号被传输到第二栅极线 GL2 时，第二栅极截止信号被传输到第一栅极线 GL1。当第一和第二栅极导通信号被传输到第二栅极线 GL2 时，在连接到第一

栅极线 GL1 的像素中存储的电荷经由连接到第二栅极线 GL2 的第三 TFT T3 被共享。对于其它的栅极线，电荷共享过程以相同的方式发生。

[0152] 传输到每条栅极线 GL1、GL2、GL3 和 GL4 的第一栅极导通信号是用来对连接到每条栅极线 GL1、GL2、GL3 和 GL4 的像素进行预充电的信号，而第二栅极导通信号是对连接到每条栅极线 GL1、GL2、GL3 和 GL4 的像素以数据电压进行充电的信号。

[0153] 在第二栅极导通信号被传输到第一栅极线 GL1 的第一时间段 P1 期间，第一栅极导通信号被传输到第三和第四栅极线 GL3 和 GL4。即，在第一时间段 P1 期间，连接到第一栅极线 GL1 的像素经由数据线 DL1、DL2 和 DL3 以数据电压进行充电。同时，连接到第三和第四栅极线 GL3 和 GL4 的像素以数据电压进行预充电。对于其它的栅极线，预充电过程以相同的方式发生。

[0154] 这样，像素之间的电荷共享和预充电可以使用第一扫描开始信号 STV1 和第二扫描开始信号 STV2 来容易地执行。当第二栅极导通信号被施加到第 i 像素行时，在第 i+2 和第 i+3 像素行中发生预充电。此外，当第一和第二栅极导通信号被施加到第 i+1 像素行时，在第 i 像素行中发生电荷共享。

[0155] 由于第一和第二扫描开始信号 STV1 和 STV2 之间的相位差基本上是 2.5H，可以使用点反转驱动方法（如图 16 所示）或像点的列反转驱动方法（如图 18 所示）。

[0156] 以下，将参考图 19 和图 20 具体描述驱动根据本发明的另一个示例性实施例的 LCD 的方法。具有如前一个示例性实施例的图 14、图 15、图 16、和图 17 所述相关的相同或类似功能的组件以相同的参考标号表示，且不再重复对其描述。

[0157] 参考图 19 和图 20，液晶面板组件被分为上部和下部，分别称为第一块和第二块。对应于第一块的栅极驱动器 400 由第一扫描开始信号 STV1 使能，并向栅极线 GL1、GL2、GL3 和 GL4 顺序地输出高电平的栅极信号（以下称为栅极导通信号）。对应于第二块的栅极驱动器 400 由第二扫描开始信号 STV2 使能，并向栅极线 GL1'、GL2'、GL3' 和 GL4' 顺序地输出高电平的栅极信号（以下称为栅极导通信号）。栅极驱动器 400 由第一扫描开始信号 STV1 使能，并向第一块的第一栅极线 GL1 传输栅极导通信号。栅极驱动器 400 也由第二扫描开始信号 STV2 使能，并向第二块的第一栅极线 GL1' 传输栅极导通信号。第一扫描开始信号 STV1 和第二扫描开始信号 STV2 具有大约 0.5H 的相位差。这里，1H 是栅极导通信号被施加到并维持在每条栅极线 GL1、GL2、GL3、GL4、GL1'、GL2'、GL3' 和 GL4' 的一段时间。

[0158] 在第一块中，当栅极导通信号被传输到第二栅极线 GL2 时，栅极截止信号被传输到第一栅极线 GL1。当栅极导通信号被传输到第二栅极线 GL2，在连接到第一栅极线 GL1 的像素中存储的电荷经由连接到第二栅极线 GL2 的第三 TFT T3 被共享。

[0159] 在第二块中，当栅极导通信号被传输到第二栅极线 GL2' 时，栅极截止信号被传输到第一栅极线 GL1'。当栅极导通信号被传输到第二栅极线 GL2'，在连接到第一栅极线 GL1' 的像素中存储的电荷经由连接到第二栅极线 GL2' 的第三 TFT T3 被共享。

[0160] 对于其它的栅极线，电荷共享过程以相同的方式发生。此外，当栅极导通信号被传输到额外的伪 (dummy) 栅极线或传输到下一帧中的第二块的第一栅极线 GL1' 时，在连接到第一块的最后第 n 条栅极线 GLn 的像素中存储的电荷可以被共享。此外，当栅极导通信号被传输到额外的伪栅极线时，在连接到第二块的最后第 n 条栅极线 GLn' 的像素中存储的电荷可以被共享。

[0161] 传输到每条栅极线 GL1、GL2、GL3、GL4、GL1'、GL2'、GL3' 和 GL4' 的栅极导通信号的前端 (front-end) 是对连接到每条栅极线 GL1、GL2、GL3、GL4、GL1'、GL2'、GL3' 和 GL4' 的像素进行预充电的信号, 而传输到每条栅极线 GL1、GL2、GL3、GL4、GL1'、GL2'、GL3' 和 GL4' 的栅极导通信号的后端 (back-end) 是对连接到每条栅极线 GL1、GL2、GL3、GL4、GL1'、GL2'、GL3' 和 GL4' 的像素以与之相对应的数据电压进行充电的信号。

[0162] 在栅极导通信号的后端被传输到第一块的第一栅极线 GL1 的第一时间段 P1 期间, 栅极导通信号被传输到第二块的第一栅极线 GL1'。即, 在第一时间段 P1 期间, 连接到第一栅极线 GL1 的像素经由数据线 DL1、DL2 和 DL3 以数据电压进行充电。同时, 连接到第一栅极线 GL1' 的像素以数据电压进行预充电。

[0163] 在栅极导通信号的后端被传输到第二块的第一栅极线 GL1' 的第一时间段 P1' 期间, 栅极导通信号被传输到第一块的第二栅极线 GL2。即, 在第一时间段 P1' 期间, 连接到第一栅极线 GL1' 的像素经由数据线 DL1、DL2 和 DL3 以数据电压进行充电。同时, 连接到第二栅极线 GL2 的像素以数据电压进行预充电。

[0164] 对于其它的栅极线, 预充电过程可以以相同的方式发生。

[0165] 这样, 像素之间的电荷共享和预充电可以使用第一扫描开始信号 STV1 和第二扫描开始信号 STV2 来容易地执行。当栅极导通信号的后端被施加到第一块的第 i 像素行时, 在第二块的第 i 像素行中发生预充电。当栅极导通信号的后端被施加到第二块的第 i 像素行时, 在第一块的第 i+1 像素行中发生预充电。此外, 当栅极导通信号被施加到第一块的第 i+1 像素行时, 在第 i 像素行中发生电荷共享。当栅极导通信号被施加到第二块的第 i+1 像素行时, 在第 i 像素行中发生电荷共享。

[0166] 由于第一和第二扫描开始信号 STV1 和 STV2 之间的相位差基本上是 0.5H, 可以使用点反转驱动方法 (如图 16 所示) 或像点的列反转驱动方法 (如图 18 所示)。

[0167] 在示例性实施例中, 液晶面板组件被分为两块, 但本发明不限于此。液晶面板组件可以被分为两块或更多个块。

[0168] 根据本发明的示例性实施例, 通过将像素电极分为一对子像素电极并通过电荷共享过程充以施加到每个子像素电极的数据电压, 有可能改善侧面可视性。此外, 像素具有基本上矩阵的形状, 该矩阵形状具有长于纵向长度的横向长度, 这可以减少数据线和数据驱动芯片的数量并降低产品成本。用来驱动 LCD 的充足时间可以使用预充电过程来获得, 即使栅极线的数量增加。

[0169] 本领域的技术人员将清楚, 在不偏离本发明的精神和范围的前提下, 可以对本发明进行各种修改和变化。因此, 本发明意在提供所附权利要求书及其等效物的范围。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8

图 9

图 11

图 12

图 13

图 14

图 15

图 16

图 17

图 18

图 19

图 20

|                |                                                                                                                           |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器及其驱动方法                                                                                                               |         |            |

| 公开(公告)号        | <a href="#">CN101354512B</a>                                                                                              | 公开(公告)日 | 2012-11-14 |

| 申请号            | CN200810134339.5                                                                                                          | 申请日     | 2008-07-24 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                  |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                  |         |            |

| 当前申请(专利权)人(译)  | 三星电子株式会社                                                                                                                  |         |            |

| [标]发明人         | 刘惠兰<br>朴乘范<br>严允成<br>朴振远<br>都熙旭<br>金勋                                                                                     |         |            |

| 发明人            | 刘惠兰<br>朴乘范<br>严允成<br>朴振远<br>都熙旭<br>金勋                                                                                     |         |            |

| IPC分类号         | G02F1/1362 G09G3/36                                                                                                       |         |            |

| CPC分类号         | G09G2300/0443 G09G3/3677 G09G3/36 G09G3/3659 G02F2001/134354 G02F1/13624 G02F1/1393<br>G09G3/3614 G09G2330/023 G11C19/184 |         |            |

| 代理人(译)         | 邵亚丽                                                                                                                       |         |            |

| 审查员(译)         | 贾杨                                                                                                                        |         |            |

| 优先权            | 1020070074127 2007-07-24 KR                                                                                               |         |            |

| 其他公开文献         | CN101354512A                                                                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                                            |         |            |

### 摘要(译)

提供了一种LCD和驱动该LCD的方法。该LCD包括：在第一方向上延伸的第一和第二栅极线；与第一栅极线隔离并与第一栅极线交叉的数据线；包括第一和第二子像素电极的像素电极，该像素电极被布置在于第一方向上具有长侧边的像素中；连接到第一栅极线、数据线和第一子像素电极的第一薄膜晶体管(TFT)；连接到第一栅极线、数据线和第二子像素电极的第二TFT；以及连接到第二栅极线、第二子像素电极和电荷共享电容的第三TFT，该电荷共享电容共享施加到第二子像素电极的数据电压。