[19] 中华人民共和国国家知识产权局

[51] Int. Cl.

G09G 3/36 (2006.01)

## [12] 发明专利说明书

专利号 ZL 02157817.6

[45] 授权公告日 2008 年 10 月 29 日

[11] 授权公告号 CN 100429691C

[22] 申请日 2002.12.19 [21] 申请号 02157817.6

[30] 优先权

[32] 2001.12.19 [33] KR [31] P2001 - 81433

[32] 2002.6.29 [33] KR [31] P2002 - 37740

[73] 专利权人 乐金显示有限公司

地址 韩国首尔

[72] 发明人 尹相昌 宋鸿声

[56] 参考文献

JP2001 - 42287A 2001.2.16

US6160535A 2000.12.12

CN1317778A 2001.10.17

US5436747A 1995.7.25

US5311205A 1994.5.10

WO0148546A1 2001.7.5

审查员 王 超

[74] 专利代理机构 北京律诚同业知识产权代理有限公司

代理人 徐金国 陈 红

权利要求书 3 页 说明书 24 页 附图 15 页

[54] 发明名称

液晶显示器

[57] 摘要

本发明涉及液晶显示器，包括液晶显示板，其上设有由 n 条选通线和 m + 1 条数据线交叉限定的以 n 行乘以 m 列的矩阵形式排列的液晶盒，其中，n, m 为大于 1 的正整数，而且液晶盒中的薄膜晶体管按每 i 行交替一次的方式交替地连接到左右相邻的数据线其中之一上，其中 i 为大于 1 的正整数；栅极驱动器，其用于驱动选通线；数据驱动器，用于驱动数据线并且包括多路复用器阵列和数模转换器阵列，多路复用器阵列用于确定输入像素数据的输出通道并且根据极性每 i 行反转一次的控制信号确定输入的像素数据的输出通道并且向输出通道其中之一添加空白数据，数模转换器阵列把像素数据和空白数据转换成像素信号和空白信号，其极性按照数据线和帧进行反转。

1. 液晶显示器，包括：

液晶显示板，所述液晶显示板上设有由  $n$  条选通线和  $m+1$  条数据线交叉限定的以  $n$  行乘以  $m$  列的矩阵形式排列的液晶盒，其中  $n, m$  为大于 1 的正整数，而且所述液晶盒中的薄膜晶体管按每  $i$  行交替一次的方式交替地连接到与该液晶盒左右相邻的数据线其中之一上，其中  $i$  为大于 1 的正整数，其中，连接至其左侧的数据线的液晶盒所处的行称为第一类水平行，连接至其右侧数据线的液晶盒所处的行称为第二类水平行；

栅极驱动器，其用于驱动选通线；

数据驱动器，其用于驱动数据线，所述数据驱动器包括多路复用器阵列和数模转换器阵列，所述多路复用器阵列用于根据控制信号确定输入的象素数据的输出通道并且向输出通道其中之一添加一个空白数据，所述控制信号的极性每所述  $i$  行反转一次，并且所述多路复用器阵列把象素数据和空白数据输出给数模转换器阵列，所述数模转换器阵列用于把象素数据和空白数据转换成象素信号和空白信号，所述象素信号和空白信号的极性按照数据线和帧反转，

其中多路复用器阵列在驱动第一类水平行中的液晶盒的第一水平周期内，使象素数据的输出通道保持与其输入通道相同，并向最后一个输出通道提供空白数据，而在驱动第二类水平行的液晶盒的第二水平周期内，使象素数据产生一个通道的移位并将移位后的数据发送给输出通道而且把空白数据发送给第一输出通道。

2. 根据权利要求 1 所述的液晶显示器，其中数据驱动器进一步包括：

移位寄存器阵列，其发送连续的采样信号；

锁存器阵列，其根据采样信号通过特定数量的通道锁存象素数据，并且同时把这些数据输出和发送到多路复用器阵列；和

缓冲器阵列，其缓冲来自数模转换器阵列的象素信号和空白信号，并把这些信号分别送到数据线中。

3. 液晶显示器，包括：

液晶显示板，所述液晶显示板上设有由  $n$  条选通线和  $m+1$  条数据线交叉限定的以  $n$  行乘以  $m$  列的矩阵形式排列的液晶盒，其中  $n, m$  为大于 1 的正整

数，其中所述液晶盒中的薄膜晶体管以每  $i$  行交替一次的方式交替地连接至与该液晶盒左右相邻的数据线其中之一，其中  $i$  为大于 1 的正整数，其中，连接至其左侧的数据线的液晶盒所处的行称为第一类水平行，连接至其右侧的数据线的液晶盒所处的行称为第二类水平行；

栅极驱动器，其用于驱动选通线；

数据驱动器，其用于把输入的象素数据和空白数据转换成象素信号和空白信号，其中所述象素信号和空白信号的极性按照数据线和帧反转，而且数据驱动器把所述象素信号和空白信号传送到数据线；和

定时控制器，其用于控制栅极驱动器和数据驱动器，并且用于响应控制信号向第一通道和最后一个通道中之一添加空白数据并且将空白数据与象素数据一起提供给数据驱动器，其中所述控制信号的极性每所述  $i$  行反转一次，

其中定时控制器在驱动位于所述第一类水平行中的液晶盒的第一水平周期内，向数据驱动器发送象素数据和添加至最后一个通道的空白数据，并且所述定时控制器在驱动位于所述第二类水平行中的液晶盒的第二水平周期内向数据驱动器提供延迟一个通道之后的象素数据和添加到第一通道中的空白数据。

4. 根据权利要求 3 所述的液晶显示器，其中定时控制器包括：

控制信号发生器，其产生控制栅极驱动器和数据驱动器的第一控制信号，并且产生极性按照每所述  $i$  行反转一次的第二控制信号；

象素数据排列器，用于排列输入的象素数据以在数据使能周期通过多条第一总线输出所述排列后的象素数据，并且通过第一总线中的最后一条总线提供空白数据；

延迟器，用于将象素数据和通过所述第一总线中最后一条总线传输的空白数据延迟一个通道；和

多路复用器，响应第二控制信号通过多条第二总线使通过第一总线输入的空白数据和象素数据按原位提供或是把通过第一总线输入并且延迟一个通道的象素数据与空白数据组合在一起以通过第二总线提供组合后的数据，

其中在驱动位于第一类水平行的液晶盒的第一水平周期内，多路复用器通过第二总线使经第一总线输入的空白数据和象素数据按原位提供，以及在驱动位于第二类水平行的液晶盒的第二水平周期内，多路复用器使得通过第一总

---

线中除了最后一条总线之外的其它条第一总线输入的象素数据产生一个通道的移位以通过第二总线中除第二总线中第一条之外的其它总线提供移位后的象素数据，以及所述多路复用器还用于通过第二总线中的第一条总线提供空白数据。

## 液晶显示器

### 技术领域

本发明涉及一种液晶显示装置，尤其涉及一种能够降低功耗且又能改善画质的液晶显示器。

### 背景技术

通常，液晶显示器(LCD)用一电场控制具有介电各向异性(dielectric anisotropy)的液晶的透光率以显示图像。为此，LCD 包括一液晶显示板和一驱动电路，液晶显示板具有以矩阵形式排列的液晶盒，而驱动电路用来驱动该液晶显示板。

在液晶显示板中，液晶盒根据象素信号控制透光率来显示图像。驱动电路包括：一栅极驱动器（gate driver），它用来驱动选通线（gate lines）；一数据驱动器，它用来驱动数据线；一定时控制器，它把一定时控制信号和一象素数据提供给栅极驱动器和数据驱动器；一供电电源。

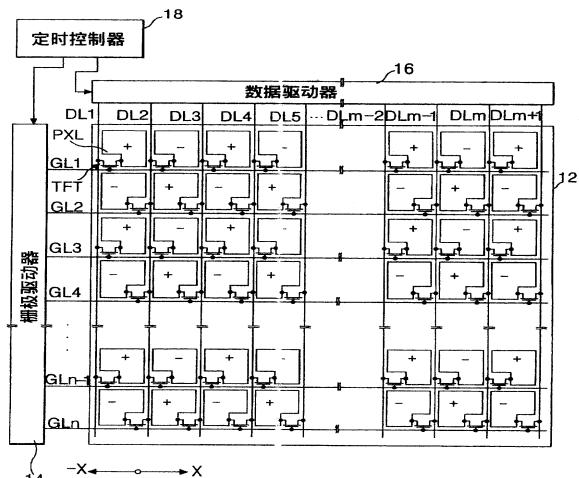

例如，如图 1 所示，液晶显示器包括：一液晶显示板 2，它具有以矩阵形式排列的液晶盒 Clc；一栅极驱动器 4，它用来驱动液晶显示板 2 的选通线 GL1 至 GLn；一数据驱动器 6，它用来驱动液晶显示板 2 的数据线 DL1 至 DLm。

在图 1 中，液晶显示板 2 包括一液晶盒 Clc 和薄膜晶体管(TFT's)，每一个薄膜晶体管设置在 n 条选通线 GL1 至 GLn 与 m 条数据线 DL1 至 DLm 之间的交叉部分上。响应于来自选通线 GL1 至 GLn 的一个扫描信号，TFT 把来自数据线 DL1 至 DLm 的视频信号加到液晶盒 Clc 上。液晶盒 Clc 能够等效表达为含一相对的公共电极和一接至 TFT 的象素电极的液晶电容 Clc，该公共电极与象素电极之间有液晶。

栅极驱动器 4 按将一扫描信号依次加到选通线 GL1 至 GLn 上，以驱动接至相应选通线的 TFT。

当把一选通信号加到选通线 GL 上时，在一个水平(horizontal)处理期内，

数据驱动器 6 把象素数据转换为模拟象素信号，用以把一水平线的视频信号加到数据线 DL1 至 DLm 上。这种情况下，数据驱动器借助来自伽马电压发生器（图中未示）的伽马电压把象素数据转换为象素信号以提供它们。

为了防止液晶变质并且提高图像显示画质，以一反向驱动方法（inversion driving method）如一帧反转系统（frame inversion system）、一行（或列）反转系统或一点反转系统来驱动这样一种液晶显示器。

在帧反转系统中，液晶盒的极性在一帧内是相同的，而在帧改变时反向。这种帧反转系统的问题在于各帧会产生闪烁。

在行反转系统中，通过分别如图 2A 和图 2B 所示的水平线和各帧使液晶盒的极性反向。这样一种行反转系统的问题在于，水平方向上的液晶盒之间存在串扰，使得水平带状图案（horizontal stripe pattern）中出现闪烁。

在列反转系统中，通过分别如图 3A 和图 3B 所示的垂直线和各帧使液晶盒的极性反向。这样一种列反向驱动系统的问题在于，垂直方向上的液晶盒之间存在串扰，使得垂直带状图案（vertical stripe pattern）中出现闪烁。

在点反转系统中，如图 4A 和图 4B 所示，液晶盒的极性与水平会垂直相邻的液晶盒极性相反，并且在各帧反向。

换句话说，在点反转系统中，把一些象素信号供给每一个液晶盒，如图 4A 所示，其正（+）极性和负（-）极性随着从左上液晶盒到右液晶盒和到下液晶盒的顺序在奇数帧处交替出现；把另一些象素信号供给每一个液晶盒，如图 4B 所示，其负（-）极性和正（+）极性随着从左上液晶盒到右液晶盒和到下液晶盒的顺序在偶数帧处交替出现。

这样一种点反向驱动系统令其弥补了垂直方向上和水平方向上相邻液晶盒之间出现的闪烁，由此与其他反转系统相比，能够产生更优质的画质。

但是，这种点反向驱动系统的缺点在于，由于从数据驱动器供给数据线的象素信号极性应当在水平方向上和垂直方向上反向，所以象素信号的变化量，即象素信号的频率高于其他反转系统，从而导致功耗增大。

## 发明内容

因此，本发明的目的在于提供一种液晶显示器，它能够在 N 个（这里，N 为一个正数）点(dots)反转系统中驱动液晶显示板时显著降低功耗，又改善

其画质。

为了实现本发明的这些和其他目的，一种根据本发明一个方面的液晶显示器包括：一液晶显示板，它具有由  $n$  条选通线和  $m+1$  条数据线交叉限定的以  $n$  行乘以  $m$  列的矩阵形式排列的液晶盒，其中  $n, m$  为大于 1 的正整数，并且所述液晶盒中的薄膜晶体管按每  $i$  行交替一次的方式连接到与该液晶盒左右相邻的数据线其中之一上，其中  $i$  为大于 1 的正整数，其中连接至其左侧的数据线的液晶盒所处的行称为第一类水平行，连接至其右侧数据线的液晶盒所处的行称为第二类水平行；一栅极驱动器，它用来驱动选通线；一数据驱动器，它用来驱动数据线，并且所述数据驱动器包括一多路复用器阵列和一数模转换器阵列，该多路复用器阵列用于响应于其极性每所述  $i$  行反转一次的控制信号来确定输入的象素数据的输出通道(channel)并且向输出通道其中之一添加一个空白数据，并且所述多路复用器阵列把象素数据和空白数据输出给数模转换器阵列，该数模转换器阵列用来将象素数据和空白数据转换为象素信号和空白信号，所述象素信号和空白信号的极性按照数据线和帧反转，其中当在驱动第一类水平行中的液晶盒的第一水平周期内，多路复用器 MUX 阵列把象素数据的输出通道保持得与输入通道相同，把空白数据提供给最后一个输出通道，并且当在驱动第二类水平行的液晶盒的第二水平周期内，将象素数据移位一个通道并且将移位后的象素数据发送至输出通道并且把空白数据提供给第一输出通道。

在这种液晶显示器中，数据驱动器还包括：一移位寄存器阵列，它提供一连续的采样信号；一锁存器阵列，它根据该采样信号，用一特定的通道数连续锁存该象素数据，从而将它们同时输出和送至多路复用器阵列；一缓冲器阵列，它对来自数模转换器的象素信号和空白信号进行缓存，从而将它们分别送至数据线。

根据本发明的另一种液晶显示器，包括：一液晶显示板，所述液晶显示板上设有由  $n$  条选通线和  $m+1$  条数据线交叉限定的以  $n$  行乘以  $m$  列的矩阵形式排列的的液晶盒，其中  $n, m$  为大于 1 的正整数，其中所述液晶盒中的薄膜晶体管以每  $i$  行交替一次的方式交替地连接至与该液晶盒左右相邻的两条数据线其中之一，其中  $i$  为大于 1 的正整数，其中，连接至其左侧的数据线的液晶盒所处的行称为第一类水平行，连接至其右侧的数据线的液晶盒所处的行称为

第二类水平行；一栅极驱动器，它用来驱动选通线；一数据驱动器，用于把输入的象素数据和空白数据转换为象素信号和空白信号，其中所述象素信号和空白信号的极性按照数据线和帧反转，而且数据驱动器将象素信号和空白信号传送至数据线；一定时控制器，它用来控制栅极驱动器和数据驱动器，并且用于响应于控制信号向第一通道和最后一个通道之一添加空白数据，并且将空白数据连同象素数据一起提供给数据驱动器，其中所述控制信号的极性按照每所述 i 行反转一次，其中在驱动位于所述第一类水平行中的液晶盒的第一水平周期内，定时控制器向数据驱动器提供象素数据和添加到最后一个通道中的空白数据；而在驱动位于所述第二类水平行中的液晶盒的第二水平周期内，定时控制器向数据驱动器提供延迟一个通道之后的象素数据和添加到第一通道中的空白数据。

这种液晶显示器中，定时控制器包括：一控制信号发生器，它产生控制栅极驱动器和数据驱动器的第一控制信号，并且产生极性按照每所述 i 行反转一次的第二控制信号；象素数据排列器 (arranger)，它排列输入的象素数据，以在数据使能周期内通过多条第一总线输出所述排列后的象素数据，并且通过第一总线中的最后一条总线提供空白数据；延迟器，用于将象素数据和通过第一总线中最后一条总线所传送的空白数据延迟一个通道；一多路复用器，它响应于该第二控制信号，通过多条第二总线使通过第一总线输入的空白数据和象素数据按原位提供，或者把通过第一总线输入并且延迟一个通道的象素数据和空白数据组合在起来以通过第二总线传送组合后的数据，其中在驱动位于第一类水平行的液晶盒的第一水平周期内，多路复用器通过第二总线使通过第一总线输入的空白数据和象素数据按原位提供，而在驱动位于第二类水平行中的液晶盒的第二水平周期内，将通过第一总线中除最后一条总线之外的其它条第一总线输入的象素数据移位一个通道以通过第二总线中除第一条总线之外的其它条第二总线提供移位后的象素数据，并且所述多路复用器还通过第二总线中的第一条总线提供空白数据。

## 附图说明

根据参照附图对本发明各实施例的以下详细描述，本发明的这些和其他目的将很明显，在这些附图中：

图 1 是一示意图，它示出一传统液晶显示器的结构；

图 2A 和图 2B 是用来解释液晶显示器的行反向驱动系统的图；

图 3A 和图 3B 是用来解释液晶显示器的列反向驱动系统的图；

图 4A 和图 4B 是用来解释液晶显示器的点反向驱动系统的图；

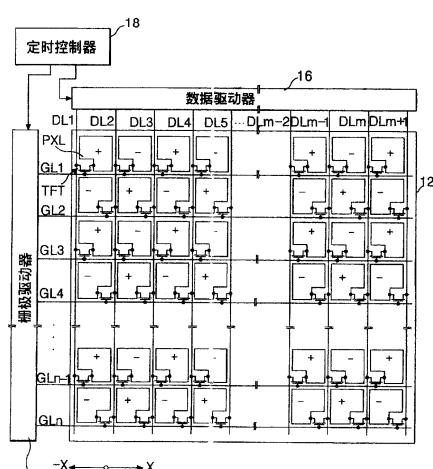

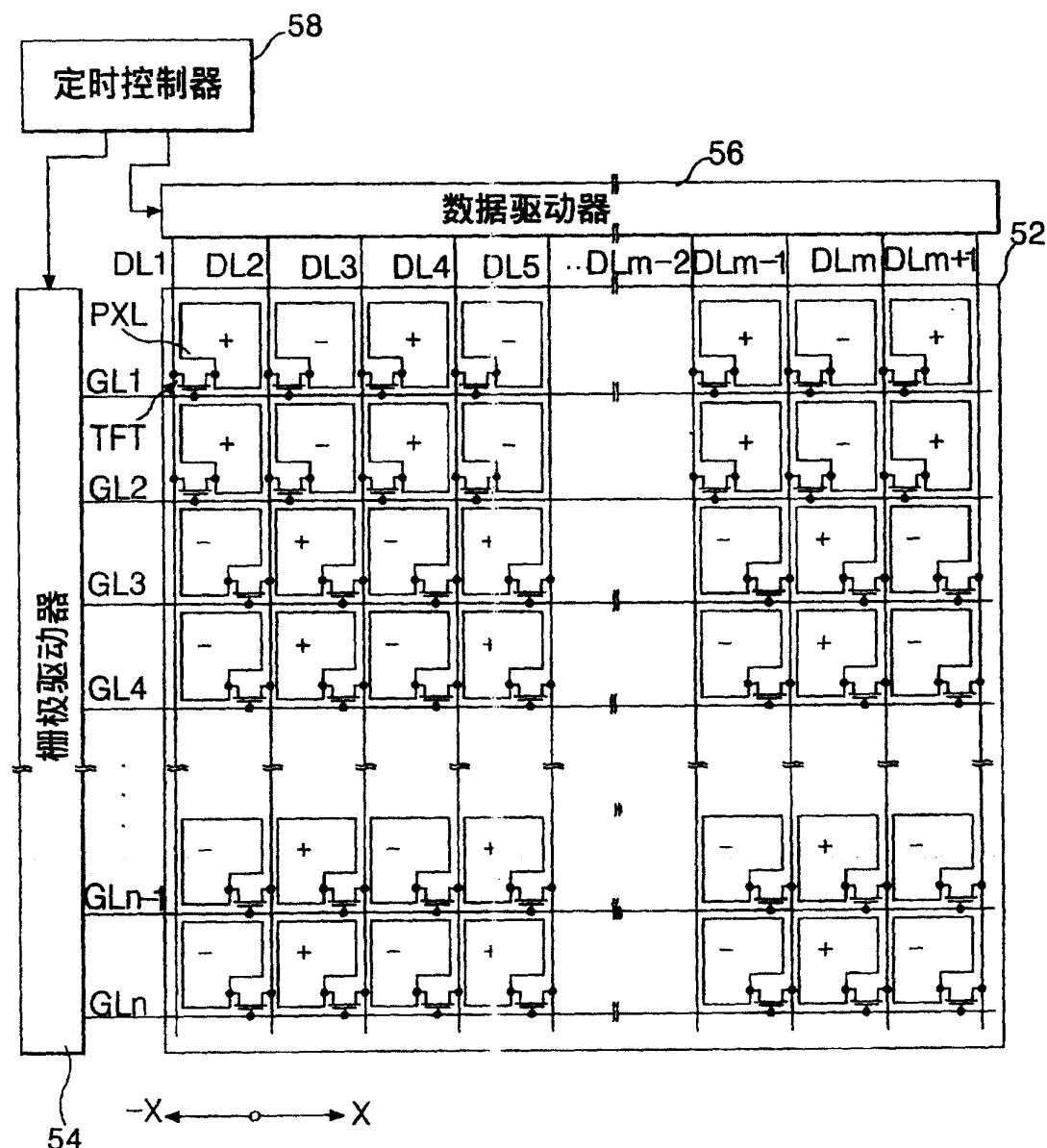

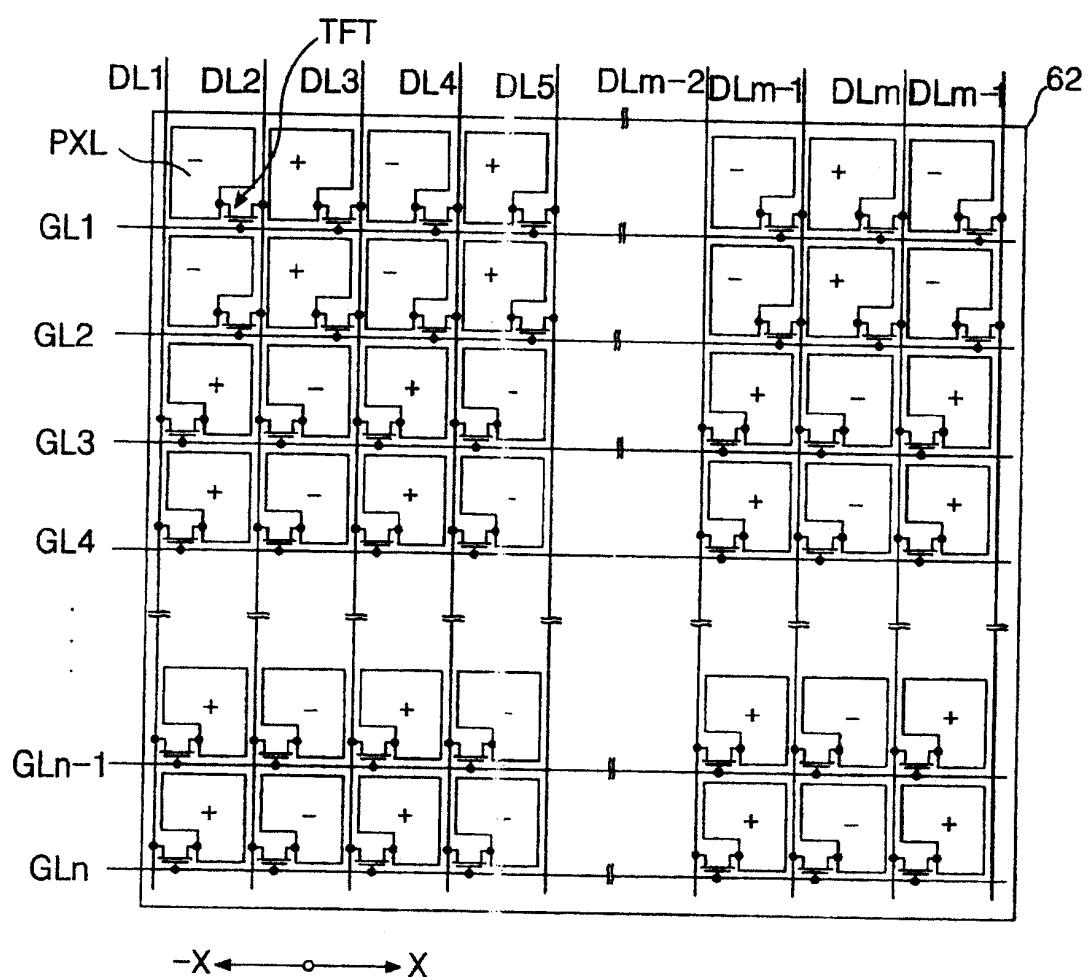

图 5 是一示意图，它示出根据本发明一个实施例的液晶显示器结构；

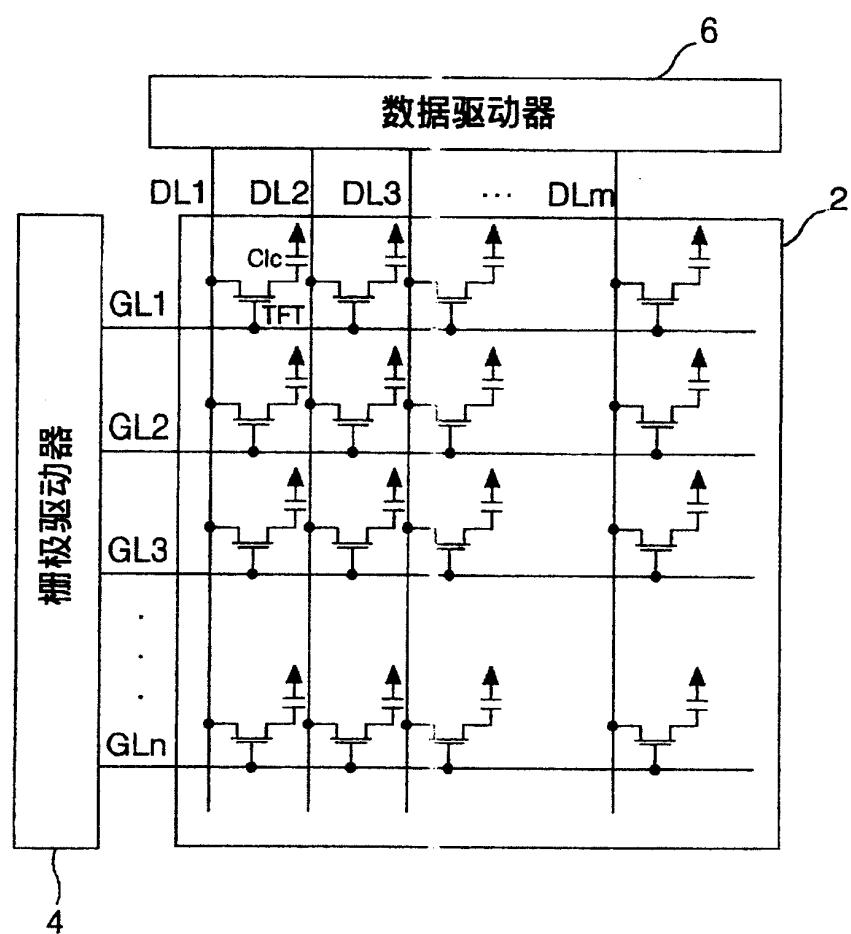

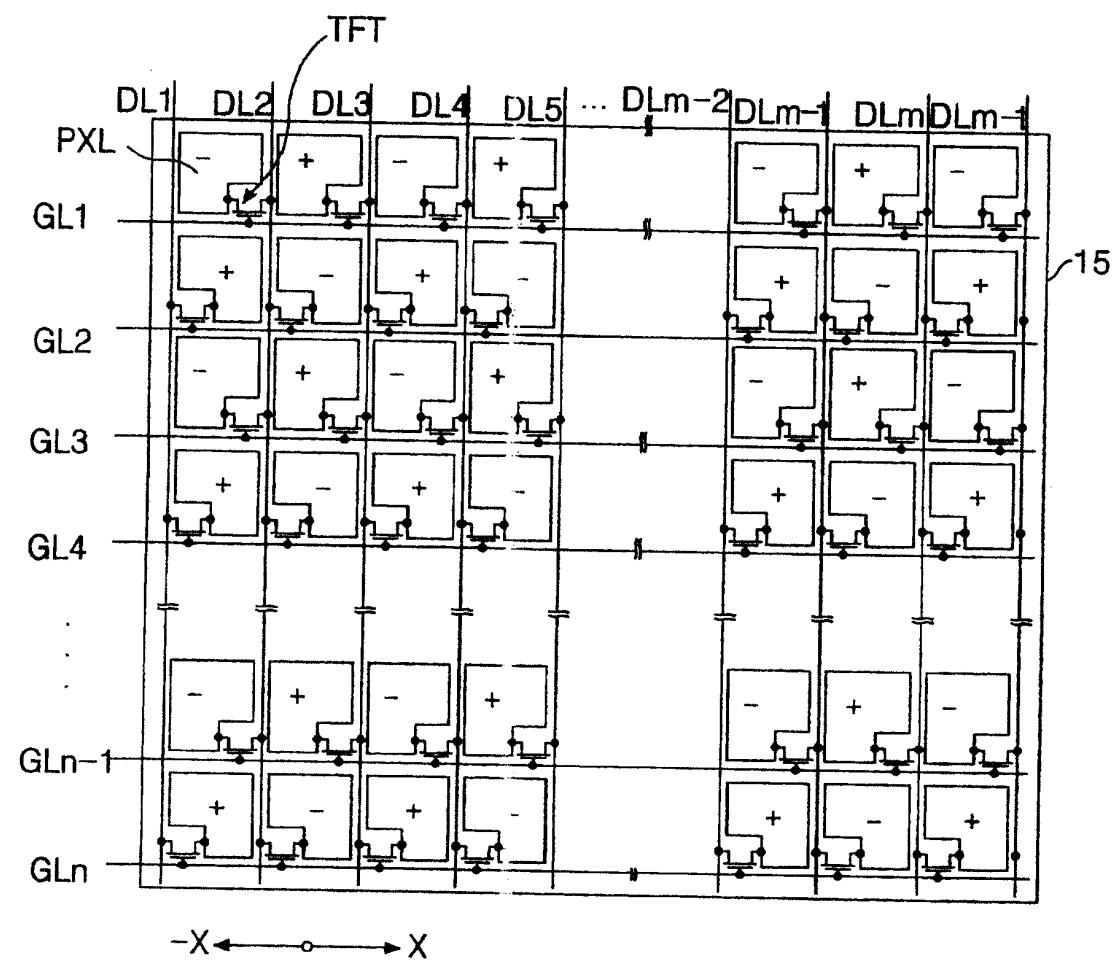

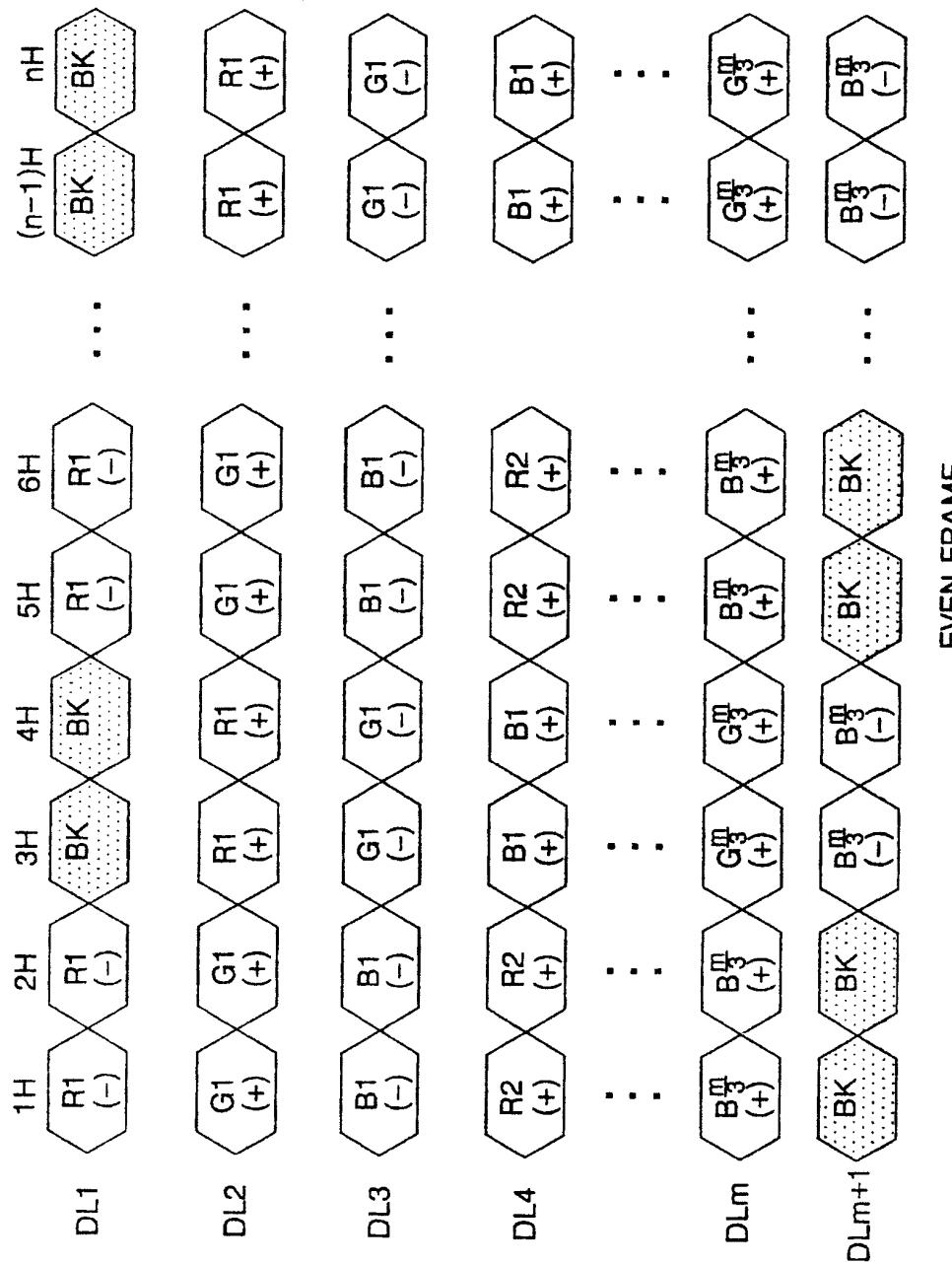

图 6 是一示意图，它示出用于本发明的另一种液晶显示板的结构；

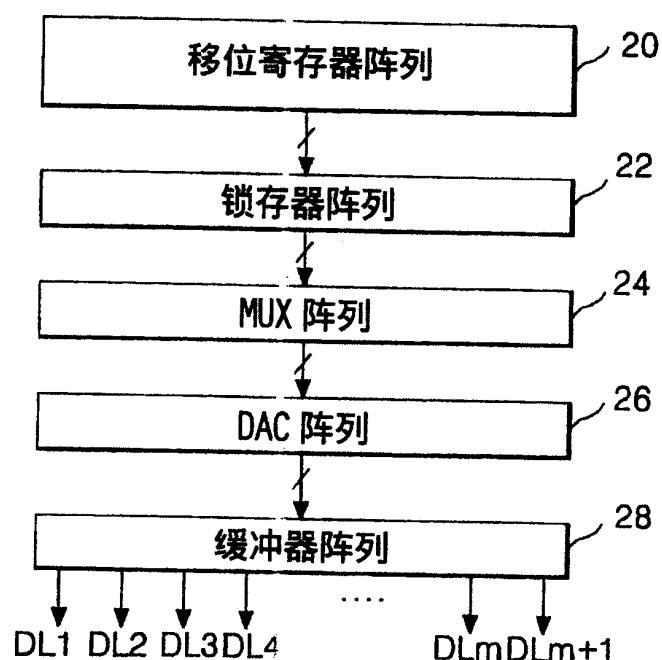

图 7 是一详细的方框图，它示出图 5 所示数据驱动器的结构；

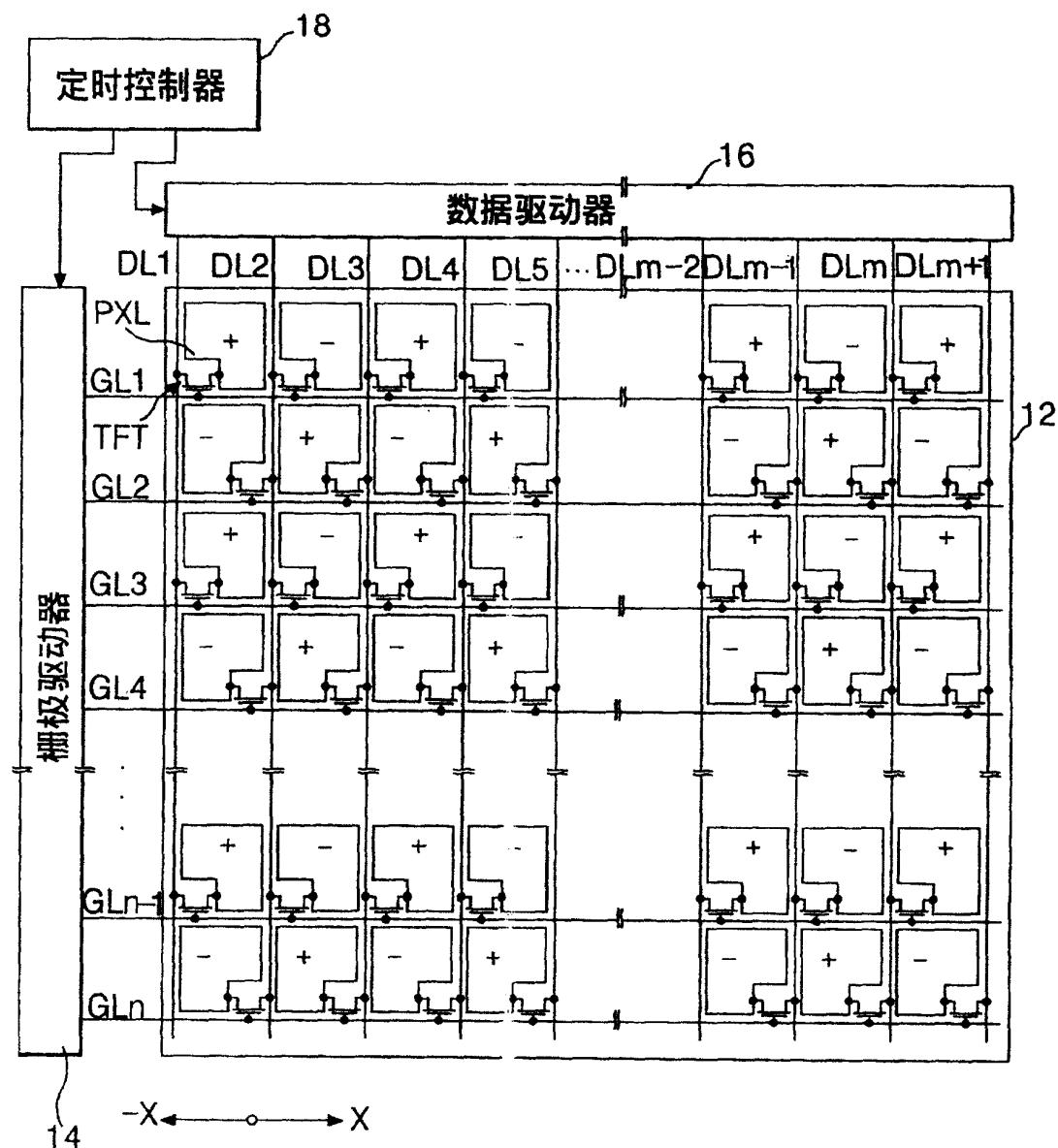

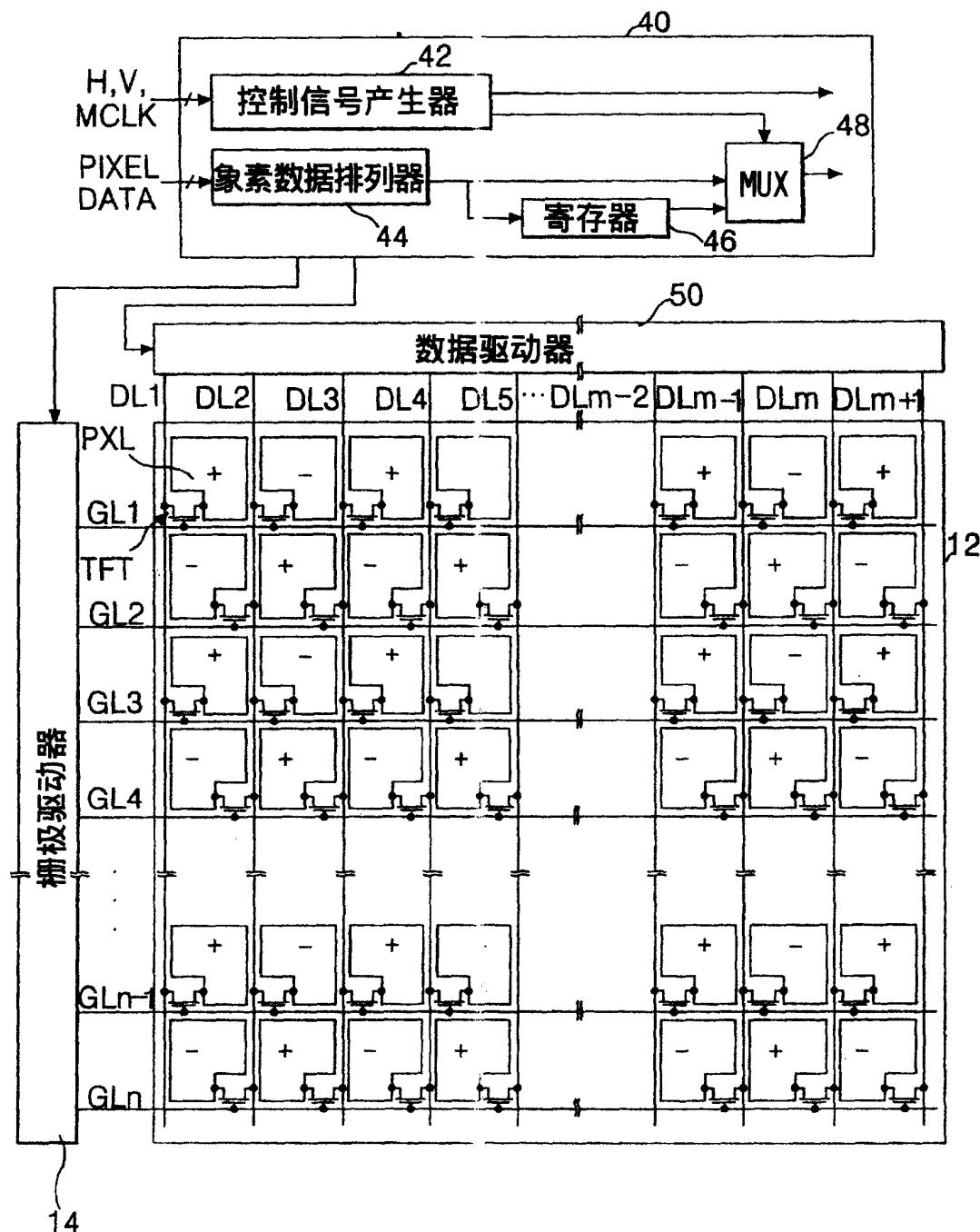

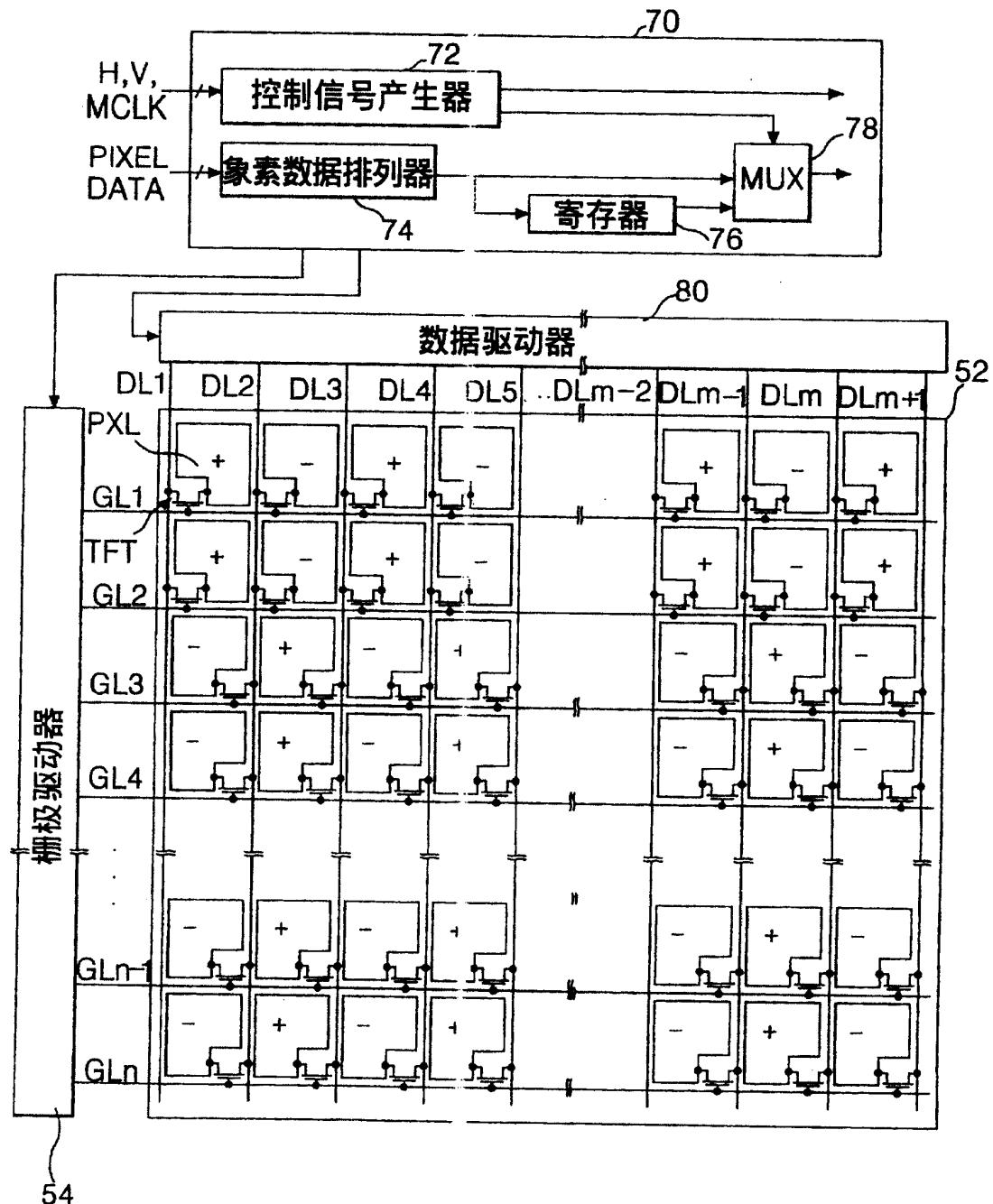

图 8 是一示意图，它示出根据本发明另一个实施例的液晶显示器结构；

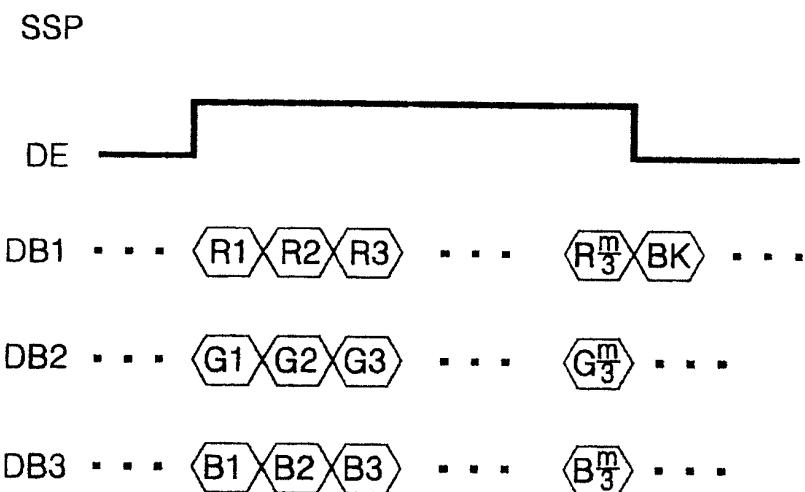

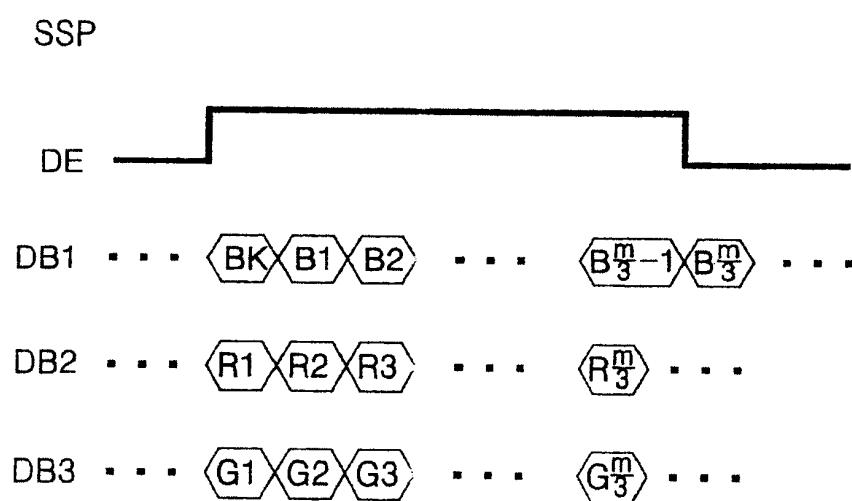

图 9A 和 9B 是图 8 所示定时控制器三总线系统的数据输出波形图；

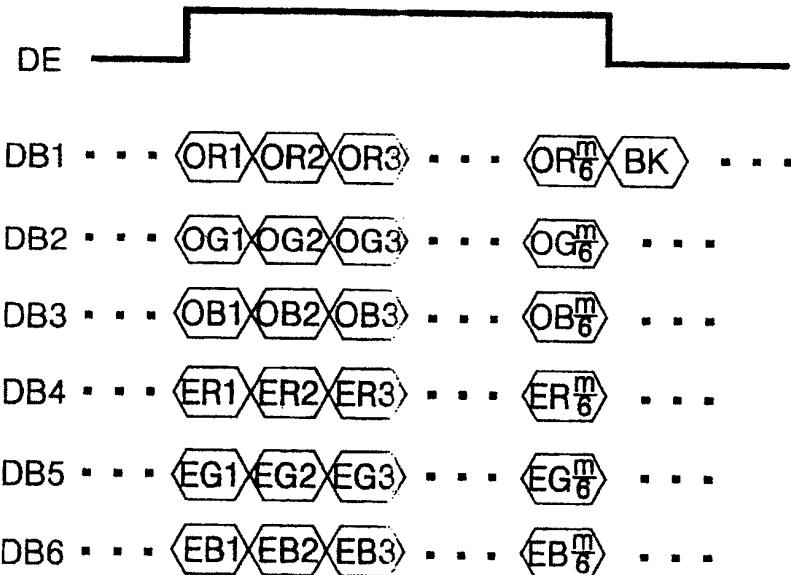

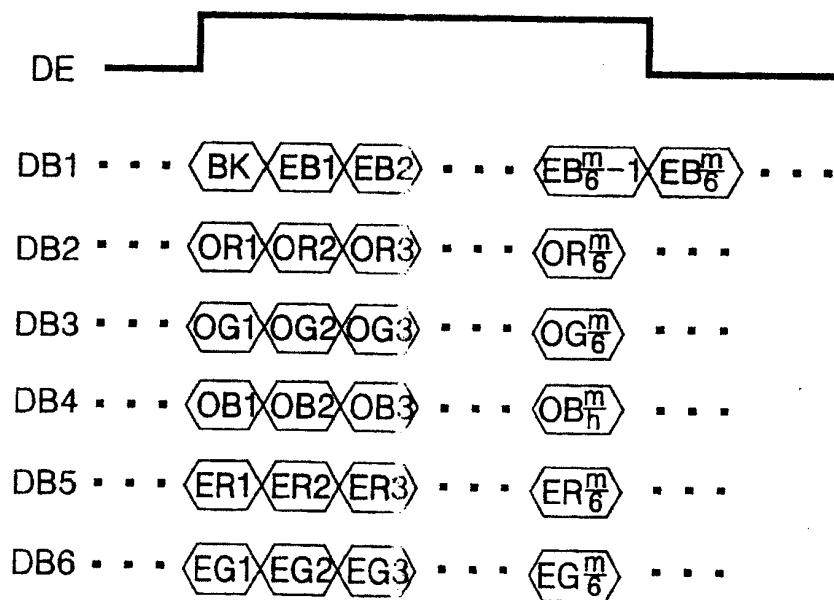

图 10A 和 10B 是图 8 所示定时控制器六总线系统的数据输出波形图；

图 11 是一示意图，它示出根据本发明又一实施例的垂直 2 点反向驱动的液晶显示器结构；

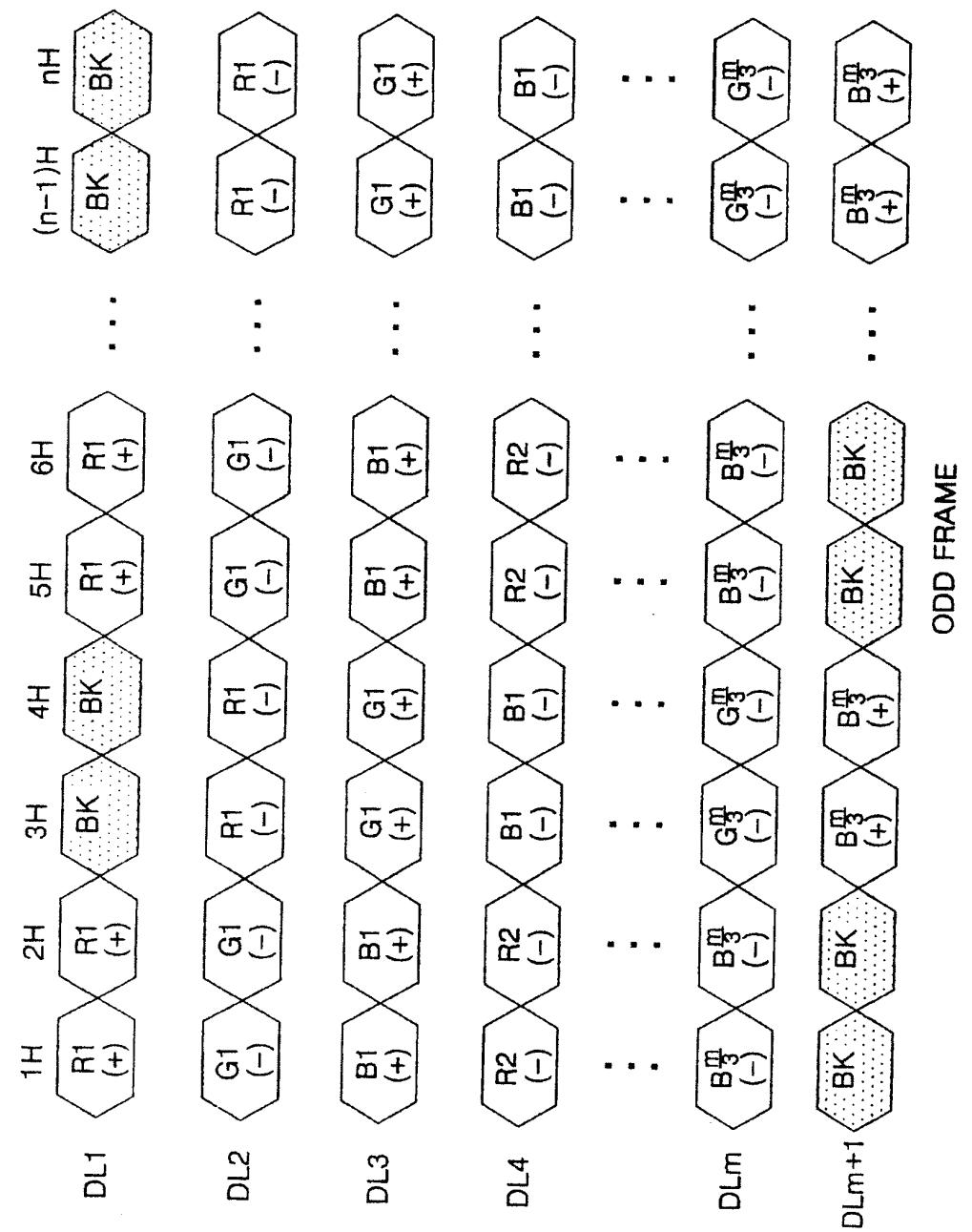

图 12 是一示意图，它示出用于本发明的液晶显示板另一种结构；

图 13A 和 13B 是示出用于图 11 所示液晶板的象素信号和空白信号的图；

图 14 是一示意图，它示出根据本发明再一实施例的垂直 2 点反向驱动的液晶显示器结构。

## 具体实施方式

参见图 5 至 14，其中详细解释了本发明的优选实施例。

参见图 5，其中示出了根据本发明一个实施例的液晶显示器。

图 5 所示的液晶显示器包括：液晶显示板 12，它具有以矩阵形式排列的液晶盒；栅极驱动器 14，它用来驱动液晶显示板 12 的选通线 GL1 至 GLn；数据驱动器 16，它用来驱动液晶显示板 12 的数据线 DL1 至 DLm+1；定时控制器 18，它用来控制栅极驱动器 14 和数据驱动器 16。

液晶显示板 12 包括 N 条选通线 GL1 至 GL 和 M+1 条数据线 DL1 至 DLm+1，数据线与选通线 GL1 至 GLn 交叉并彼此绝缘隔离。液晶板 12 还包括一液晶盒 PXL 和一薄膜晶体管，它们设置在选通线 GL1 至 GLn 与数据线 DL1 至 DLm+1 交叉部分所限定的每一个区域上。响应于来自选通线 GL1 至 GLn 的扫描信号，该 TFT 把象素信号从数据线 DL1 至 DLm+1 送至液晶盒 PXL。响应于该象素信号，液晶盒 PXL 通过驱动位于公共电极（图中未示）

之间的液晶来控制透光率。

特别是，薄膜晶体管和液晶盒 PXL 沿数据线 DL 方向以 Z 字形依次排列设置。换句话说，包括在同一列中的液晶盒 PXL 和 TFT's 通过水平线接至另外相邻的数据线。

例如，在图 5 所示液晶显示板 12 的情况下，接至奇数选通线 GL1, GL3, GL5.....的奇数水平线上的 TFT's 和液晶盒 PXL 分别接至其左侧相邻的第 1 至第 m 数据线 DL1 至 DLm。因此，通过 TFT，把来自其左侧相邻数据线 DL 的象素信号加到奇数水平线上的液晶盒 PXL 上。

另一方面，接至偶数选通线 GL2,GL4,GL6.....的偶数水平线上的 TFT's 和液晶盒 PXL 分别接至其右侧相邻的第 2 至第 (m + 1) 数据线 DL2 至 DLm+1。因此，通过 TFT，把来自其右侧相邻数据线 DL 的象素信号加到偶数水平线上的液晶盒 PXL 上。

另外，在图 6 所示的液晶显示板 15 中，接至奇数选通线 GL1, GL3, GL5.....的奇数水平线上的 TFT's 和液晶盒 PXL 分别接至其右侧相邻的第 2 至第 (m + 1) 数据线 DL2 至 DLm+1。因此，通过 TFT，把来自其右侧相邻数据线 DL 的象素信号加到奇数水平线上的液晶盒 PXL 上。

另一方面，接至偶数选通线 GL2,GL4,GL6.....的偶数水平线上的 TFT's 和液晶盒 PXL 分别接至其左侧相邻的第 1 至第 m 数据线 DL1 至 DLm。因此，通过 TFT，把来自其左侧相邻数据线 DL 的象素信号加到偶数水平线上的液晶盒 PXL 上。

定时控制器 18 产生控制栅极驱动器 14 和数据驱动器 16 的定时控制信号，并且把象素数据信号送至数据驱动器 16。定时控制器 18 产生的选通定时控制信号包括：一栅极起始脉冲 GSP；一栅极移位时钟信号 GSC；一选通输出使能（enable）信号 SOE 等。定时控制器 18 产生的数据定时控制信号包括：一源极起始脉冲 SSP；一源极移位时钟信号 SSC；一源极输出使能(enable) 信号 SOE；极性控制信号 POC 等。

利用定时控制信号，栅极驱动器 14 把扫描信号顺序加至选通线 GL1 至 GLn。因此，响应于扫描信号，栅极驱动器 14 通过水平线驱动薄膜晶体管。

当一扫描信号加至选通线 GL 时，数据驱动器 16 将象素数据转换为模拟象素信号，将一条水平线的象素信号通过水平处理周期加至数据线 DL1 至

DL<sub>m+1</sub>。这种情况下，借助来自伽马电压发生器（图中未示）的伽马电压，数据驱动器 16 将象素数据转换为象素信号以传送它们。

另外，数据驱动器 16 以其中象素信号的极性逐条数据线 DL 反向的列反向驱动系统的方式施加象素信号。换句话说，数据驱动器 16 以奇数数据线 DL<sub>1</sub>、DL<sub>3</sub>、……与偶数数据线 DL<sub>2</sub>、DL<sub>4</sub>、……上极性相反的方式施加象素信号，送至数据线 DL 的象素信号极性逐帧反向。

这种情况下，由于液晶盒 PXL 在加有列反转系统提供的象素信号的数据线 DL<sub>1</sub> 至 DL<sub>m+1</sub> 周围以 Z 字形排列，随意用点反转系统驱动液晶盒 PXL。

特别是，数据驱动器 16 在各水平处理周期内交替改变象素信号的输出通道，把正确的象素信号供给以 Z 字形沿数据线 DL<sub>1</sub> 至 DL<sub>m+1</sub> 排列的液晶盒 PXL。

在把象素信号供给接至右侧数据线 DL<sub>1</sub> 至 DL<sub>m+1</sub> 的液晶盒 PXL 的情况下，数据驱动器 16 把 m 个有效象素信号供给 m 条数据线 DL<sub>1</sub> 至 DL<sub>m</sub>，把空白信号供给 m+1 条数据线 DL<sub>m+1</sub>。与此不同的是，在把象素信号供给接至左侧数据线 DL<sub>1</sub> 至 DL<sub>m+1</sub> 的液晶盒 PXL 的情况下，数据驱动器 16 通过把 m 个有效象素信号向右侧转移一个通道，将它们供给 2 至 m+1 条数据线 DL<sub>2</sub> 至 DL<sub>m+1</sub>，把空白信号供给第 1 条数据线 DL<sub>1</sub>。

例如，如图 5 所示，当液晶盒 PXL 驱动接至右侧数据线 DL<sub>1</sub> 至 DL<sub>m+1</sub> 的奇数水平线时，数据驱动器 16 把 m 个有效信号供给第 1 至第 m 数据线 DL<sub>1</sub> 至 DL<sub>m</sub>，另外将空白信号供给第(m+1)数据线 DL<sub>m+1</sub>。而当液晶盒 PXL 驱动接至左侧数据线 DL<sub>1</sub> 至 DL<sub>m+1</sub> 的偶数水平线时，数据驱动器 16 把 m 个有效信号供给第 2 至第 (m + 1) 数据线 DL<sub>2</sub> 至 DL<sub>m+1</sub>，并且将空白信号供给第 1 数据线。

与此不同的是，如图 6 所示，当液晶盒 PXL 驱动接至左侧数据线 DL<sub>1</sub> 至 DL<sub>m+1</sub> 的奇数水平线时，数据驱动器 16 通过把 m 个有效信号向右侧转移一个通道，把它们供给第 2 至第 (m + 1) 数据线 DL<sub>2</sub> 至 DL<sub>m+1</sub>，并且将空白信号供给第 1 数据线。而当液晶盒 PXL 驱动接至左侧数据线 DL<sub>1</sub> 至 DL<sub>m+1</sub> 的偶数水平线时，数据驱动器 16 把 m 个有效信号供给第 1 至第 m 数据线 DL<sub>1</sub> 至 DL<sub>m</sub>，另外将空白信号供给第 (m+1) 数据线 DL<sub>m+1</sub>。

因此，画质通过以点反转系统驱动的液晶盒 PXL 得以改善，而由于数据

驱动器 16 通过列反转系统提供象素信号，所以其功耗比用点反转系统提供象素信号时有显著降低。

图 7 是一方框图，它示出图 5 所示数据驱动器 16 的一种详细结构。

参见图 7，数据驱动器 16 包括：移位寄存器阵列 20，它用来按序施加采样信号；锁存器阵列 22，它响应于采样信号，锁存和输出象素数据；多路复用器（MUX）阵列 24，它确定从锁存器阵列 22 中输入的象素数据路径；数模转换器（DAC）阵列 26，它用来把来自 MUX 阵列 24 的象素数据转换为模拟象素信号；缓冲器阵列 28，它用来缓存和输出来自 DAC 阵列 26 的象素信号。

包括在移位寄存器阵列 20 中的多个移位寄存器，响应于一源极采样时钟信号 SSC，对来自定时控制器 18 的源极起始脉冲 SSP 作按序移位，将其作为一采样信号输出。

包括在锁存器阵列 22 中的多个锁存器，响应于来自移位寄存器阵列 20 的采样信号，通过某一单元借助来自定时控制器 18 的采样象素数据按序进行锁存，然后响应于来自定时控制器 18 的源极输出使能（enable）信号（SOE），锁存器阵列 22 同时输出锁存的象素阵列。

MUX 阵列 24 响应于来自定时控制器 18 的控制信号，在各水平处理周期内选择来自锁存器阵列 22 的象素数据路径。特别是，在奇数（或偶数）水平处理周期内，当驱动接至右侧数据线 DL1 至 DL<sub>m</sub>+1 的液晶盒 PXL 时，MUX 阵列 24 输出通道没有变化的所输入的象素数据，并且将空白数据供给最后一个通道。与此不同的是，在偶数（或奇数）水平处理周期内，当驱动接至左侧数据线 DL1 至 DL<sub>m</sub>+1 的液晶盒 PXL 时，MUX 阵列 24 通过向右转移一个通道来输出所输入的象素数据，并且将空白数据供给第一通道。

为此，MUX 阵列 24 包括  $m$  个 MUX，每一个 MUX 接收两个相邻锁存器的输出信号，以根据来自定时控制器 18 的控制信号有选择地输出。这里，除了一种极性锁存器中的第一和第  $m$  锁存器之外，其他锁存器的输出由两个相邻的 MUX 共用。在各水平处理周期内，供给 MUX 阵列 24 的控制信号极性反向。

借助于来自伽马电压发生器（图中未示）的正负伽马电压，包括在 DAC 阵列 26 中的多个 DAC 把来自 MUX 阵列 24 的象素数据和空白数据转换

成象素信号和空白信号，以输出它们。特别是，响应于来自定时控制器 18 的极性控制信号 POL，DAC 阵列 26 把奇数象素数据和偶数象素数据转换为极性相反的象素信号，为列反向驱动而输出它们。

缓冲器阵列 28 缓存来自 DAC 阵列 26 的象素信号和空白信号，然后将它们输出至数据线 DL1 至 DLm+1。

因此，将其极性逐数据线和逐帧反向的象素信号送至数据线 DL1 至 DLm+1。在奇数（或偶数）水平处理周期内，把有效的象素信号送至第一至第 m 数据线 DL1 至 DLm，并且把空白信号送至第 m+1 数据线 DLm+1，而在偶数或奇数水平处理周期内，把空白信号送至第 1 数据线 DL1，并且把有效的象素信号送至第 2 至第 m+1 数据线 DL2 至 DLm+1。随后，可以用点反转系统驱动沿数据线 DL1 至 DLm+1 以 Z 字形排列的液晶盒。因此，由于数据驱动器 16 受列反转系统的驱动而液晶盒受点反转系统的驱动，所以可以显著降低功耗。

图 8 表示根据本发明另一个实施例的液晶显示器。

图 8 所示的液晶显示器具有与图 7 所示液晶显示器相同的部件，不过定时控制器 40 和数据驱动器 50 的功能不同。

这种液晶显示器 12 使设置在选通线 GL1 至 GLn 与数据线 DL1 至 DLm+1 之间交叉部分所限定的每一个区域上的液晶盒 PXL 和 TFT 以一矩阵图案方式排列。

TFT 和液晶盒 PXL 沿数据线 DL1 至 DLm+1 以一 Z 字形排列，它们的位置依次从右到左或者从左到右。换句话说，包括在同一列中的液晶盒和 TFT 通过水平线交替接至另一条相邻的数据线。

例如，液晶显示板 12 接至奇数或偶数水平线的 TFT，而液晶盒 PXL 分别接至第 1 至其左侧相邻的第 m 数据线 DL1 至 DLm。另一方面，偶数水平线的液晶盒 PXL 和 TFT 分别接至其右侧相邻的第 2 至第 (m+1) 数据线 DL2 至 DLm+2。

利用来自定时控制器 40 的选通定时控制信号，栅极驱动器 14 按序将扫描信号加至选通线 GL1 至 GLn。因此，响应于这些扫描信号，栅极驱动器 14 通过水平线驱动各 TFT。

在各水平处理周期内，当将扫描信号加至选通线 GL 时，数据驱动器 50

把所输入的象素数据转换为模拟象素信号，以将一条水平线的象素信号加到数据线 DL1 至 DLm+1 上。这种情况下，借助来自伽马（gamma）电压发生器（图中未示）的伽马电压，数据驱动器 50 把象素数据转换为象素信号，从而输出它们。

另外，数据驱动器 50 通过列反向驱动系统施加象素信号，在该系统中，数据线 DL1 至 DLm+1 使象素信号反向。换句话说，数据驱动器 50 把具有相反极性的象素信号加至奇数数据线 DL1、DL3、……和偶数数据线 DL2、DL4、……，供给数进行 DL1 至 DLm+1 的象素信号继续逐帧反向。这种情况下，由于液晶盒 PXL 基于在列反向驱动系统中供有象素信号的数据线 DL1 至 DLm+1 而以 Z 字形排列，所以液晶盒受点反转系统的驱动。

尤其是，为了将正确的象素信号供给沿数据线 DL1 至 DLm+1 以 Z 字形排列的液晶盒 PXL，在奇数（或偶数）水平处理周期内，数据驱动器 50 把空白信号供给第 1 数据线 DL1，把有效象素信号供给第 2 至第 (m+1) 数据线 DL2 至 DLm+1。而在偶数（或奇数）水平处理周期内，将有效象素信号供给第 1 至第 m 数据线 DL1 至 DLm，把空白信号供给第 (m+1) 数据线 DLm+1。

定时控制器 40 产生用来控制栅极驱动器 14 和数据驱动器 40 驱动的控制信号，并且将一象素数据加至数据驱动器 50。定时控制器 40 所产生的选通定时控制信号包括：栅极起始脉冲 GSP；栅极移位时钟信号 GSC；选通输出使能（enable）信号 GOE 等。定时控制器 40 所产生的数据定时控制信号包括：源极起始脉冲 SSP；源极移位时钟信号 SSC；源极输出使能(enable) 信号 SOE；极性（polarity）控制信号 POL 等。

特别是，在奇数（或偶数）水平处理周期内，定时控制器 40 通过某一单元依次提供一条水平线的 m 个象素数据，另外把空白数据作为第 (m+1) 个象素数据提供。响应于来自移位寄存器阵列 20 的采样信号，包括在锁存器阵列 22 中的多个锁存器通过某一单元借助来自定时控制器 18 的采样象素数据按序进行锁存，然后响应于来自定时控制器 18 的源极输出使能(enable) 信号(SOE)，锁存器阵列 22 同时输出锁存的象素阵列。而在偶数（或奇数）水平周期内，提供由一个通道延迟的 m 个象素数据，另外把空白信号作为第一象素数据提供。

为了进行这种驱动，定时控制器 40 包括：一控制信号发生器 42，它用

为了进行这种驱动，定时控制器 40 包括：一控制信号发生器 42，它用来产生控制信号；一像素数据排列器 44，它排列和输出输入的像素数据；一寄存器 46，它用来延迟从像素数据排列器 44 输出的像素数据中最后一个像素数据；一 MUX48，它用来有选择地结合来自像素数据排列器 44 的像素数据和来自寄存器 46 延迟后的像素数据。

利用水平同步信号 H、垂直同步信号 V、主时钟信号 MCLK 等，控制信号发生器 42 产生控制栅极驱动器 14 的选通定时控制信号和控制数据驱动器 50 的数据定时控制信号。另外，控制信号发生器 42 产生一 MUX48 控制信号。这种情况下，利用水平同步信号 H，控制信号发生器 42 产生表示奇数水平周期和偶数水平周期的控制信号，也就是说，其极性在水平处理周期内反向以便将其供给 MUX48。

像素数据排列器 44 根据一数据传输总线层级排列输入的像素数据并且输出它们。例如，像素数据排列器 44 通过三条总线同时输出 R、G、B 像素数据，或者通过六条总线同时输出奇数 R、G、B 像素数据和偶数 R、G、B 像素数据。把通过这些总线中最后一条总线之外的其他总线输出的像素数据送至 MUX48，把通过该最后一条总线输出的像素数据一般送至 MUX48 和寄存器 46。而且，像素数据排列器 44 在允许数据输出时间段之间存在的空白时间段内对空白数据 BK 采样，用以在允许数据输出时间段内输出。

寄存器 46 暂时存储通过从选告诉数据排列器 44 中输出的像素数据最后一条总线传输的像素数据，并且用将它们延迟一个通道。

MUX48 在奇数（或偶数）水平处理周期内，响应于该控制信号，从像素数据排列器 44 中输入，经三条总线或者六条总线输出 n 个像素数据和空白数据、第(m+1)数据。

而且，MUX48 在偶数（或奇数）水平处理周期内，响应于该控制信号，把通过第一或第二总线从像素数据排列器 44 输入的像素数据移位输出给第二或第三总线。或者，它将通过第一至第五总线输入的像素数据进行移位处理，以输出给第二至第六总线。

经过寄存器 46 一个通道延迟的最后一条总线即第三或第六总线的像素数据输出至第一总线。这种情况下，在偶数（或奇数）水平处理时间段内，把在空白时间段内存储在寄存器 46 中的空白数据作为第一总线的第一数据传

图 9A 和 9B 是在奇数（或偶数）水平处理周期和偶数（或奇数）水平处理周期内经三条总线从定时控制器 40 供给数据驱动器 50 的空白数据和象素数据的时序图。

参见图 9A，在奇数（或偶数）水平处理周期内，定时控制器 40 把一个空白数据 BK 和  $m/3$  个红色象素数据 R1、R2、R3、……、R $m/3$  经第一总线 DB1、 $m/3$  个绿色象素数据 G1、G2、G3、……、G $m/3$  经第二总线 DB2 和  $m/3$  个蓝色象素数据 B1、B2、B3、……、B $m/3$  经第三总线 DB3 送至数据驱动器 50，在这种方式下，在允许数据信号 DE 的允许输出时间段内，定时控制器 40 通过第一至第三总线 DB1 至 DB3，把  $m$  个有效象素数据 R、G 和 B 供给数据驱动器 50。在该允许输出时间段之后，定时控制器 40 继续提供空白数据 BK。

因此，数据驱动器 50 输入来自定时控制器 40 的一个空白数据 BK 和  $m$  个有效象素数据 R、G、B。数据驱动器 50 把所输入的  $m$  个有效象素数据 R、G、B 转换成模拟象素信号，以将其送至第一之第  $m$  数据线 DL1 至 DL $m$ ，并且同时把一个空白数据 BK 转换成模拟空白色号以将其送至第  $(m+1)$  数据线 DL $m + 1$ 。

参见图 9B，在偶数（或奇数）水平处理周期内，定时控制器 40 通过把  $m/3$  个红色象素数据 R1、R2、R3、……、R $m/3$  转移到第二总线 DB2、把  $m/3$  个绿色象素数据 G1、G2、G3、……、G $m/3$  转移到第三总线 DB3，将它们送至数据驱动器 50。而且定时控制器 40 通过第一总线 DB1，把延迟一个通道的  $m/3$  个蓝色象素数据 B1、B2、B3、……、B $m/3$  和一个空白数据送至数据驱动器 50。这种方式下，在允许数据信号 DE 的允许输出时间段内，定时控制器 40 通过第一至第三总线 DB1 至 DB3，把移动了一个通道的一个空白数据 BK 和  $m-1$  个有效象素数据 R、G、B 供给数据驱动器 50，并且在该允许输出时间段之后，定时控制器 40 还提供移动了一个通道的最后一个有效象素数据 D $m/3$ 。

因此，数据驱动器 50 输入来自定时控制器 40 的一个空白数据 BK 和  $m$  个有效象素数据 R、G、B。而且，数据驱动器 50 把移动了一个通道的所输入的  $m$  个有效象素数据 R、G、B 转换为模拟象素信号，以将其供给第二至第  $(m+1)$  条数据线 DL2 至 DL $m + 2$ ，同时将一个空白数据 BK 转换为模

拟空白信号，以将其供给第一数据线 DL1。

图 10A 和 10B 是在奇数（或偶数）水平处理周期和偶数（或奇数）水平处理周期内经六条总线从定时控制器 40 供给数据驱动器 50 的空白数据和象素数据的时序图。

参见图 10A，在奇数（或偶数）水平处理周期内，定时控制器 40 把一个空白数据 BK 和  $m/6$  个奇数红色象素数据 OR1、OR2、OR3、……、OR $m/6$  经第一总线 DB1  $m/6$  个奇数绿色象素数据 OG1、OG2、OG3、……、OG $m/6$  经第二总线 DB2 送至数据驱动器 50， $m/6$  个奇数蓝色象素数据 OB1、OB2、OB3、……、OB $m/6$  经第三总线 DB3 送至数据驱动器 50，而 6 个偶数红色象素数据 ER1、ER2、ER3、……、ER $m/6$  经第四总线 DB4 送至数据驱动器 50， $m/6$  个偶数绿色象素数据 EG1、EG2、EG3、……、EG $m/6$  经第五总线 DB5 送至数据驱动器 50， $m/6$  个偶数蓝色象素数据 EB1、EB2、EB3、……、EB $m/6$  经第六总线 DB6 送至数据驱动器 50。

这种方式下，在允许数据信号 DE 的允许输出时间段内，定时控制器 40 通过第一至第六总线 DB1 至 DB6 把  $m$  个有效象素数据 R、G、B 至数据驱动器 50。在该允许输出时间段之后，定时控制器 40 继续（sequentially）传送空白数据 BK。

因此，数据驱动器 50 输入一个空白数据 BK 和  $m$  个有效象素数据 R、G、B。而且，数据驱动器 50 把  $m$  个有效象素数据 R、G、B 转换为模拟象素信号，以将其供给第一至第  $m$  条数据线 DL1 至 DL $m$ ，同时将一个空白数据 BK 转换为模拟空白信号，以将其供给第  $(m+1)$  数据线 DL $m+1$ 。

参见图 10B，在偶数（或奇数）水平处理周期内，定时控制器 40 通过把  $m/6$  个奇数红色象素数据 OR1、OR2、OR3、……、OR $m/6$  移位到第二总线 DB2、把  $m/6$  个奇数绿色象素数据 OG1、OG2、OG3、……、OG $m/6$  移到第三总线 DB3、把  $m/6$  个奇数蓝色象素数据 OB1、OB2、OB3、……、OB $m/6$  移位到第四总线 DB4、把  $m/6$  个偶数红色象素数据 ER1、ER2、ER3、……、ER $m/6$  移位到第五总线 DB5、把  $m/6$  个偶数绿色象素数据 EG1、EG2、EG3、……、EG $m/6$  移位到第六总线 DB6，将它们送至数据驱动器 50。

而且，定时控制器 40 还把  $m/6$  个偶数蓝色象素数据 EB1、EB2、EB3、……、EB $m/6$  和延迟了一个通道的一个空白数据 BK 经第一总线 DB1

送至数据驱动器 50。这种方式下，在允许数据输出时间段内，定时控制器 40 通过第一至第六总线 DB1 至 DB6 把移位一通道的一个空白数据 BK 和  $m-1$  个有效象素数据 R、G、B 送至数据驱动器 50。在该允许输出时间段之后，定时控制器 40 继续传送移位一通道的最后一个有效象素数据  $Dm/6$ 。

因此，数据驱动器 50 输入一个空白（blank）数据 BK 和  $m$  个有效象素数据 R、G 和 B。而且数据驱动器 50 将所输入的经过一个通道移位的  $m$  个有效象素数据 R、G 和 B 转换成向第 2 条数据线 DL2 至第  $(m+1)$  条数据线  $DLm+1$  传送的模拟象素信号，同时将一个空白数据 BK 转换成向第一条数据线 DL1 传送的模拟空白信号。

同样，在借助定时控制器 40 的水平周期传送  $m$  个有效象素数据的同时，传送第一或最后一个象素数据的空白数据。而且数据驱动器 50 把  $m$  个有效象素数据和一个空白数据转换成列反转系统的象素信号和空白信号，并将它们送到液晶板 12 和 15。因此，可以用点反转系统驱动液晶板 12 和 15。

另一方面，当在点反转系统中驱动液晶板 12 和 15 时，若在 window Shut Down（视窗关机）时显示一个特定的点图案，那么会出现闪烁。这是因为其他图案的频率为 60Hz 的垂直驱动频率，而相反地，该特定点图案的频率为 30Hz，从而发生 30Hz 频率的闪烁。

为了防止这种闪烁，通过采用垂直双点反转系统使闪烁的频率达到 60Hz。在这种情况下，闪烁的频率变得与垂直驱动频率相一致，从而使人感觉不出闪烁。

参见图 11，该图表示按照本发明另一个实施例所述采用垂直双点反转系统驱动的液晶显示器。

图 11 中所示的液晶显示器包括：液晶显示板 52、栅极驱动器 54、数据驱动器 56 和定时控制器 58，其中液晶显示板 52 带有设置成矩阵形式的液晶盒，栅极驱动器 54 用于驱动液晶显示板 52 上的选通线 GL1-GLn，数据驱动器 56 用于驱动液晶显示板 52 上的数据线 DL1-DLm+1，而定时控制器 58 用于控制栅极驱动器 54 和数据驱动器 56。

液晶显示板 52 包括  $N$  条选通线 GL1-GLn，和  $M + 1$  条与选通线 GL1-GLn 交叉并彼此绝缘的数据线 DL1-DLm+1。而且液晶板 52 还包括液晶盒 PXL 和薄膜晶体管，所述液晶盒 PXL 和薄膜晶体管设置在由选通线

GL<sub>1</sub>-GL<sub>n</sub> 和数据线 DL<sub>1</sub>-DL<sub>m+1</sub> 交叉形成的每个区上。TFT 响应来自选通线 GL<sub>1</sub>-GL<sub>n</sub> 的扫描信号并通过数据线 DL<sub>1</sub>-DL<sub>m+1</sub> 把象素信号送到液晶盒 PXL 上。液晶盒 PXL 响应象素信号并通过驱动位于共用电极（未示出）之间的液晶来控制透光率。

特别是，薄膜晶体管和液晶盒 PXL 沿数据线 DL 方向以 Z 字形每隔两条水平线依次排列设置。换句话说，包括在同一列中的液晶盒 PXL 和 TFT's 通过两条水平线交替接至另外相邻的数据线。

例如，如图 11 所示，把与第 (4K-3) 和第 (4K-2) 条选通线 GL<sub>1</sub>、GL<sub>2</sub>、GL<sub>5</sub>、GL<sub>6</sub>... 相连的第 (4K-3) (在此， K 是正数) 和第 (4K-2) 条水平线上的 TFT 和液晶盒 PXL 在靠近其左侧的位置分别连接到第 1 到第 m 条数据线 DL<sub>1</sub>-DL<sub>m</sub> 上。因此，第 (4K-3) 和第 (4K-2) 条水平线上的液晶盒 PXL 将通过 TFT 由来自靠近左侧数据线 DL 的象素信号充电。

另一方面，把与第 (4K-1) 和第 (4K) 条选通线 GL<sub>3</sub>、GL<sub>4</sub>、GL<sub>7</sub>、GL<sub>8</sub>... 相连的第 (4K-1) 和 (4K) 条水平线上的 TFT 和液晶盒 PXL 在靠近其右侧的位置分别连接到第 2 至第 (m+1) 条数据线 DL<sub>2</sub>-DL<sub>m+1</sub> 上。因此，第 (4K-1) 和第 (4K) 条水平线上的液晶盒 PXL 将通过 TFT 由来自靠近右侧数据线 DL 的象素信号充电。

此外，在图 12 所示的液晶显示板 15 中，把与第 (4K-3) 和第 (4K-2) 条选通线 GL<sub>1</sub>、GL<sub>2</sub>、GL<sub>5</sub>、GL<sub>6</sub>... 相连的第 (4K-3) 和第 (4K-2) 条水平线上的 TFT 和液晶盒 PXL 在靠近其右侧的位置分别连接到第 2 到第 m + 1 条数据线 DL<sub>2</sub>-DL<sub>m+1</sub> 上。因此，第 (4K-3) 和第 (4K-2) 条水平线上的液晶盒 PXL 将通过 TFT 由来自靠近右侧数据线 DL 的象素信号充电。

另一方面，把与第 (4K-1) 和第 (4K) 条选通线 GL<sub>3</sub>、GL<sub>4</sub>、GL<sub>7</sub>、GL<sub>8</sub>... 相连的第 (4K-1) 和 (4K) 条水平线上的 TFT 和液晶盒 PXL 在靠近其左侧的位置分别连接到第 1 至第 m 条数据线 DL<sub>1</sub>-DL<sub>m</sub> 上。因此，第 (4K-1) 和第 (4K) 条水平线上的液晶盒 PXL 将通过 TFT 由来自靠近左侧数据线 DL 的象素信号充电。

定时控制器 58 产生控制选通线 54 和数据驱动器 56 的定时控制信号，并将象素数据信号送到数据驱动器 56。在定时控制器 58 中产生的栅极定时控制信号包括栅极起动脉冲 GSP、栅极移位时钟信号 GSC、栅极输出使

能 (enable) 信号 GOE 等。在定时控制器 58 中产生的数据定时控制信号包括源极起动脉冲 SSP、源极移位时钟信号 SSC、源极输出使能 (enable) 信号 SOE、极性 (polarity) 控制信号 POC 等。

栅极驱动器 54 利用栅极定时控制信号，按序向选通线 GL1-GLn 传送扫描信号。所以，栅极驱动器 54 可响应扫描信号并通过水平线来驱动薄膜晶体管。

数据驱动器 56 把象素数据转换成模拟象素信号，并且在扫描信号送到选通线 GL 中时，通过水平周期把一条水平线的象素信号送到数据线 DL1-DLm+1 中。在这种情况下，数据驱动器 56 借助于来自伽马电压发生器（图中未示）的伽马电压把象素数据转换成象素信号并传输这些信号。

此外，数据驱动器 56 以列反转驱动系统的方式提供象素信号，即通过数据线 DL 使象素信号的极性反向。换句话说，数据驱动器 56 向奇数数据线 DL1、DL3、...，和偶数数据线 DL2、DL4、... 传送具有相反极性的象素信号，而且传送到数据线 DL 中的象素信号的极性是通过帧频反向的。

在这种情况下，由于液晶盒 PXL 交替地连接到与之相邻的不同数据线上，所以，在用列反转系统向数据线 DL1-DLm + 1 传送象素信号的基础上，可用垂直双点反转系统驱动液晶盒 PXL。

特别是，数据驱动器 56 通过两个水平周期交替地改变象素信号的输出通道，从而可通过两条水平线向沿数据线 DL1-DLm+1 交替改变其位置的液晶盒 PXL 传送正确的象素信号。

在将象素信号传送到与右侧数据线 DL1-DLm+1 相连接的液晶盒 PXL 的情况下，数据驱动器 56 向 m 条数据线 DL1-DLm 传送 m 个有效象素信号，并且向第 m+1 条数据线 DLm+1 传送空白信号。与此不同的是，在向与左侧数据线 DL1-DLm+1 相连接的液晶盒 PXL 传送象素信号的情况下，数据驱动器 56 通过使信号右移一个通道来向 2 到 m+1 条数据线 DL2-DLm+1 传送 m 个有效象素信号，和向第 1 条数据线 DL1 传送空白信号。

例如，如图 11 所示，当液晶盒 PXL 驱动与右侧数据线 DL1-DLm+1 相连的第 (4K-3) 和第 (4K-2) 条水平线时，数据驱动器 56 向第 1 到第 m 条数据线 DL1-DLm 传送 m 个有效象素信号，此外还向第 (m+1) 条数据线 DLm + 1 传送空白信号。而且当液晶盒 PXL 驱动与左侧数据线 DL1-DLm

+1 相连的第 (4K-1) 和第 (4K) 条水平线时, 数据驱动器 56 通过使信号右移一个通道而向第 2 到第 (m+1) 条数据线 DL2-DLm+1 传送 m 个有效象素信号并向第 1 条数据线传送空白信号。

与此不同的是, 如图 12 所示, 当液晶盒 PXL 驱动与左侧数据线 DL1-DLm+1 相连的 (4K-3) 和第 (4K-2) 条水平线时, 数据驱动器 56 通过使信号右移一个通道而向第 2 到第 (m+1) 条数据线 DL2 -DLm + 1 传送 m 个有效象素信号, 此外还向第 1 条数据线传送空白信号。而且当液晶盒 PXL 驱动与左侧数据线 DL1-DLm+1 相连的第 (4K-1) 和第 (4K) 条水平线时, 数据驱动器 56 向第 1 到第 m 条数据线 DL1-DLm 传送 m 个有效象素信号并向第 (m+1) 数据线 DLm+1 传送空白信号。

这种数据驱动器 56 的实物 (materialized) 结构与图 7 中所示相同。然而, 唯一不同的是, MUX 阵列 24 通过两个水平周期改变了象素数据的通道。在此省略了对与上述结构和工作情况一致的更详细的说明。

参见图 7, 锁存器阵列 22 根据移位寄存器阵列 20 的采样信号锁存并输出来自定时控制器 58 的象素数据。

MUX 阵列 24 根据来自定时控制器 58 的控制信号, 通过两个水平周期改变来自锁存器阵列 22 的象素数据路线。特别是, 当驱动与右侧数据线 DL1-DLm+1 连接的液晶盒 PXL 时, 和在第 (4K-3) 和 (4K-2) { 或是第 (4K-1) 和 (4K) } 水平周期期间没有改变通道的情况下, MUX 阵列 24 将输出已输入的象素数据, 并且向最后一个通道传送空白数据。与此不同的是, 当驱动与左侧数据线 DL1-DLm+1 连接的液晶盒 PXL 时, 和在第 (4K-1) 和 (4K) { 或是第 (4K-3) 和 (4K-2) } 水平周期内, MUX 阵列 24 通过使数据右移一个通道而输出已输入的象素数据, 并且向第一通道传送空白数据。

为此, 输入到 MUX 阵列 24 的控制信号通过两个水平周期形成极性反转。

DAC 阵列 26 响应列反转极性控制信号 POL, 把来自 MUX 阵列 24 的象素数据和空白数据转换成使相邻通道的信号极性相反的象素信号和空白信号, 并输出这些信号。

缓冲器阵列 28 把象素信号和空白信号从 DAC 阵列 26 分别送到数据线 DL1-DLm+1。

因此, 如图 13A 和 13B 所示, 向数据线 DL1-DLm+1 传送的象素信号

和空白信号的极性是经数据线和帧频转换的信号。

图 13A 和 13B 表示的是在奇数帧和偶数帧中施加到图 11 所示液晶板的数据线 DL1-DLm+1 中的象素信号和空白信号。

参照图 13A，在第 (4K-3) 和 (4K-2) 水平周期内，把奇数帧中红、绿和蓝色的象素信号 R、G 和 B 传送到第 1 到第 m 条数据线 DL1-DLm 上，同时将空白信号 BK 送到第 (m+1) 条数据线 DLm+1 上。而且，将  $m/3$  个红、绿、和蓝色象素信号 (R、G 和 B) 中的每一个传送到第 2 到第 (m+1) 条数据线 DL2-DLm+1 中，而且同时在第 (4K-1) 和第 (4K) 水平周期 2H、3H、… n-1H、nH 内将空白信号 BK 送到的第一条数据线 DL1 上。

在这种奇数帧间隔 (interval) 内，总是将具有正极性的象素信号送到奇数数据线 DL1、DL3、…、DLm+1 上，而将具有负极性的象素信号送到偶数数据线上。因此，可以用垂直双点反转系统驱动在两条水平线上位置交替的液晶盒 PXL。

参照图 13B，在第 (4K-3) 和 (4K-2) 水平周期 (period) 内，将偶数帧中红、绿和蓝色象素信号 (R、G 和 B) 传送到第 2 至第 (m+1) 条数据线 DL2-DLm+1 上，同时，将空白信号 BK 送到第 1 条数据线 DL1 上。而且，将  $m/3$  个红、绿和蓝色象素信号 (R、G 和 B) 中的每一个传送到第 1 到第 m 条数据线 DL1-DLm，而且同时在第 (4K-1) 和第 (4K) 水平周期 2H、3H、… n-1H、nH 内将空白信号 BK 送到的第 (n+1) 条数据线 DLm+1 上。

在这种偶数帧间隔内，与上述奇数帧相反，总是把具有负极性的象素信号送到奇数数据线 DL1、DL3、…、DLm+1 上，而把具有正极性的象素信号送到偶数数据线上。因此，可以用垂直双点反转系统驱动在两条水平线上位置交替的液晶盒 PXL。

图 14 表示根据本发明另一个实施例所述垂直双点反转的液晶显示器。

除了定时控制器 70 和数据驱动器 80 的功能不同之外，图 14 中所示的液晶显示器具有与图 11 所示的液晶显示器相同的元件。

液晶显示板 52 上的液晶盒 PXL 和 TFT 设置在选通线 GL1-GLn 和数据线 DL1-DLm+1 之间的交叉区上，并布置成矩阵图形。

TFT 和液晶盒 PXL 设置成 Z 字形，它们的位置采用由两条水平线沿着数据线 DL1-DLm+1 从右向左转的形式或是从左向右转的形式。换句话说，包

含在同一列中的液晶盒和 TFT 每隔两条水平线交替地连接到与之相邻的不同数据线上。

例如，把与第(4K-3)和第(4K-2) { 或是第(4K-1)和第(4K)} 条选通线相连接的第(4K-3)和第(4K-2) { 或是第(4K-1)和第(4K)} 条水平线上的液晶盒 PXL 和 TFT 分别连接到靠近其左侧的第 1 到第 m 条数据线 DL1-DLm 上。因此，第(4K-3) 和第(4K-2) { 或是第(4K-1)和第(4K)} 条水平线上的液晶盒 PXL 通过 TFT 由来自靠近其左侧的数据线 DL 的象素信号充电。

另一方面，把与第(4K-1)和第(4K) { 或是第(4K-3)和第(4K-2)} 条选通线相连接的第(4K-1)和第(4K) { 或是第(4K-3)和第(4K-2)} 条水平线上的液晶盒 PXL 和 TFT 分别连接到靠近其右侧的第 2 条数据线 DL2 到第 m+1 条数据线 DLm+1 上。因此，第(4K-1)和第(4K) { 或是第(4K-3)和第(4K-2)} 条水平线上的液晶盒 PXL 通过 TFT 由来自靠近其右侧的数据线 DL 的象素信号充电。

栅极驱动器 54 利用来自定时控制器 70 的栅极定时控制信号按序向选通线 GL1-GLn 传送扫描信号。

数据驱动器 80 把输入的象素数据转换成模拟象素信号，以便在向选通线 GL 传送扫描信号时，通过水平周期向数据线 DL1-DLm+1 传送一条水平线的象素信号。在这种情况下，数据驱动器 80 借助于来自伽马电压发生器(图中未示)的伽马电压把象素数据转换成象素信号并传送该信号。

此外，数据驱动器 80 通过列反转驱动系统传送象素信号，在所述列反转驱动系统中通过数据线 DL1-DLm+1 使象素信号反转。换句话说，数据驱动器 80 向奇数数据线 DL1、DL3、… 和偶数数据线 DL2、DL4、… 传送极性相反的象素信号，而送到数据线 DL1-DLm+1 上的象素信号的极性通过帧频反转。在这种情况下，由于是以用列反转驱动系统向数据线 DL1-DLm+1 传送象素信号为基础，通过两条水平线交替地把液晶盒 PXL 连接到与之相邻的不同数据线上，所以可以通过垂直双点反转系统驱动液晶盒。

特别是，为了向沿数据线 DL1-DLm+1 设置成 Z 字形的液晶盒 PXL 传送准确的象素信号，数据驱动器 80 在第(4K-3)和第(4K-2) { 或是第(4K-1)和第(4K)} 水平周期内，向第 1 条数据线 DL1 传送空白信号，而向第 2 到第(m+1) 条数据线 DL2-DLm+1 发送有效象素信号。而且在(4K-1)和(4K) { 或是(4K-3) 和(4K-2)} 水平周期内，向第 1 到第 m 条数据线 DL1-DLm 传送有效象素

信号，和向第 (m+1) 条数据线 DLm+1 传送空白信号。

定时控制器 70 产生用于控制栅极驱动器 54 和数据驱动器 80 驱动的控制信号，并且向数据驱动器 80 提供象素数据。在定时控制器 70 中产生的栅极定时控制信号包括栅极起动脉冲 GSP、栅极移位时钟信号 GSC、栅极输出使能 (enable) 信号 GOE 等。在定时控制器 70 中产生的数据定时控制信号包括源极起动脉冲 SSP、源极移位时钟信号 SSC、源极输出使能 (enable) 信号 SOE、极性控制信号 POL 等。

特别是，定时控制器 70 通过第(4K-3)和第(4K-2) { 或是第(4K-1)和第(4K)} 水平周期内的特定单元按顺序传送一条水平线的 m 个象素数据，此外，把空白数据作为第 (m+1) 个象素数据发送。而且，在第(4K-1)和(4K) { 或是(4K-3) 和(4K-2)} 水平周期内，使传送的 m 个象素数据具有一个通道的滞后，而另外把空白信号作为第一个象素数据发送。

对于这种驱动而言，定时控制器 70 包括用于产生控制信号的控制信号发生器 72，用于传送和输出所输入的象素数据的象素数据传送器 74，用于使从象素数据传送器 74 输出的象素数据的最后一个象素数据延迟的寄存器 76，和用于选择性地把来自象素数据传送器 74 的象素数据和来自寄存器 76 的延迟象素数据相结合的 MUX78。

在使用水平同步信号 H、垂直同步信号 V 和主时钟信号 MCLK 等信号时，控制信号发生器 72 产生控制栅极驱动器 54 的栅极定时控制信号和控制数据驱动器 80 的数据定时控制信号。此外，控制信号发生器 72 产生 MUX78 控制信号。在这种情况下，控制信号发生器 72 在使用水平同步信号 H 时，产生表示第(4K-3)和第(4K-2)水平周期和第(4K-1)和(4K)水平周期的控制信号（也就是说，信号极性通过两个水平周期而反转），并将该信号送到 MUX78 中。

象素数据传送器 74 传送输入的象素数据并根据数据传输总线的层级 (hierarchy) 输出这些数据。例如，象素数据传送器 74 通过三条总线同步输出 R、G 和 B 象素数据，或者是通过六条总线同步输出奇数 R、G、B 象素数据和偶数 R、G、B 象素数据。把通过不包括最后一条总线的其他总线输出的象素数据（这些总线接到 MUX78）和通过最后一条总线输出的象素数据，同时送到 MUX78 和寄存器 76 中。而且，象素数据传送器 74 对存在于数据

使能(enable)间隔之间空白间隔内的空白数据 BK 进行采样并以数据使能间隔的形式输出。

寄存器 76 临时存储从象素数据传送器 74 输出的象素数据中通过最后一条总线传输的象素数据，并使这部分数据延迟一个通道。

在第(4K-3)和第(4K-2){或是第(4K-1)和第(4K)}水平周期内，MUX78 响应控制信号并通过三条总线或六条总线把从象素数据传送器输入的 m 个象素数据和空白数据、第(m+l)个数据输出。

而且，在第(4K-1)和第(4K) {或是第(4K-3)和第(4K-2)} 水平周期内，MUX78 响应控制信号，把通过第一或第二总线输入的象素数据从象素数据传送器 74 移位并输出到第二或第三总线中。或者，把通过第一至第五总线输入的象素数据移位并输出到第二至第六总线上。而且，最后一条总线的象素数据由寄存器 76 延迟一个通道，即，把第三或是第六总线输出到第一总线。在这种情况下，在第(4K-1)和第(4K) {或是第(4K-3)和第(4K-2)} 水平周期内，在空白间隔内存储到寄存器 76 中的空白数据将作为第一条总线中的第一数据发送。

在具有这种结构的定时控制器 70 中，在(4K-3)和第(4K-2){或是第(4K-1)和第(4K)}水平周期以及第(4K-1)和第(4K) {或是第(4K-3)和第(4K-2)} 水平周期内，通过第三或第六总线传送到数据驱动器 80 上的象素数据和空白数据与上述图 9A-图 10B 中所述相同。

参照图 9A，在第(4K-3)和第(4K-2) {或是第(4K-1)和第(4K)} 水平周期内，定时控制器 70 通过第一总线 DB1 向数据驱动器 80 传送一个空白数据 BK 和 m/3 个红色象素数据 R1、R2、R3…、Rm/3，通过第二总线 DB2 传送 m/3 个绿色象素数据 G1、G2、G3、…Gm/3，和通过第三总线 DB3 传送 m/3 个蓝色象素数据 B1、B2、B3…、Bm/3。通过这种方式，定时控制器 70 在数据使能(enable)信号 DE 的使能间隔内通过第一到第三总线 DB1-DB3 向数据驱动器 80 传送 m 个有效象素数据 R、G 和 B。而且，定时控制器 70 按照后面的使能(enable)周期顺序传送空白数据 BK。

因此，数据驱动器输入一个空白数据 BK 和 m 个有效象素数据 R、G、B。而且，数据驱动器 80 把 m 个有效象素数据 R、G、B 转换成向第一到第 m 条数据线 DL1-DLm 发送的模拟象素信号，同时把一个空白数据 BK 转换成

向第 (m+1) 条数据线 DLm+1 发送的模拟空白信号。

参照图 9B，在第(4K-1)和第(4K) { 或是第(4K-3)和第(4K-2) } 水平周期内，定时控制器 70 通过把 m/3 个红色象素数据 R1、R2、R3…Rm/3 移位到第二总线 DB2，把 m/3 个绿色象素数据 G1、G2、G3…、Gm/3 移位到第三总线 DB3 而把这些信号发送到数据驱动器 80 中。而且，定时控制器 70 通过第一总线向数据驱动器 80 发送延迟一个通道的 m/3 个蓝色象素数据 B1、B2、B3…、Bm/3 和一个空白数据 BK。通过这种方式，定时控制器 70 在数据使能 (enable) 信号 DE 的使能间隔内，通过第一到第三总线 DB1-DB3 向数据驱动器 80 发送移位一个通道的一个空白数据 BK 和 m-1 个有效象素数据 R、G、B。而且，定时控制器 70 进一步包括按照后序的使能周期顺序发送移位一个通道的最后一个有效象素数据 Dm/3 。

因此，数据驱动器 80 输入一个空白数据 BK 和 m 个有效象素数据 R、G、B。而且，数据驱动器 80 把输入的移位一个通道的 m 个有效象素数据 R、G、B 转换成向第 2 到第 (m+1) 数据线 DL2-DLm+2 发送的模拟象素信号，同时把一个空白数据 BK 转换成向第一条数据线 DLI 发送的模拟空白信号。

参照图 10A，在第(4K-3)和第(4K-2) { 或是第(4K-1)和第(4K) } 水平周期内，定时控制器 70 通过第一总线 DB1 向数据驱动器 80 传送一个空白数据 BK 和 m/6 个奇数红色象素数据 OR1、OR2、OR3、…、ORM/6，通过第二总线 DB2 传送 m/6 个奇数绿色象素数据 OG1、OG2、OG3、…、OGM/6，通过第三总线 DB3 传送 m/6 个奇数蓝色象素数据 OB1、OB2、OB3、…、OBM/6，通过第四总线 DB4 传送 m/6 个偶数红色象素数据 ER1、ER2、ER3、…、ERM/6，通过第五总线传送 m/6 偶数绿色象素数据 EG1、EG2、EG3、…、EGM/6，通过第六总线 DB6 传送 m/6 个偶数蓝色象素数据 EB1、EB2、EB3、…、EBM/6。

通过这种方式，定时控制器 70 在数据使能 (enable) 信号 DE 的使能间隔内通过第一到第六总线 DB1-DB6 向数据驱动器 80 传送 m 个有效象素数据 R、G 和 B。而且，定时控制器 70 按照后面的使能周期继续 (sequentially) 传送空白数据 BK。

因此，数据驱动器 80 输入一个空白数据 BK 和 m 个有效象素数据 R、G、B。而且，数据驱动器 80 把 m 个有效象素数据 R、G、B 转换成向第一到第 m 条数据线 DL1-DLm 发送的模拟象素信号，同时把一个空白数据 BK 转换成

向第 (m+1) 条数据线 DL<sub>m+1</sub> 发送的模拟空白信号。

参照图 10B，在第(4K-1)和第(4K) { 或是第(4K-3)和第(4K-2)} 水平周期内，定时控制器 70 通过把 m/6 个奇数红色象素数据 OR1、OR2、OR3…OR<sub>m/6</sub> 移位到第二总线 DB2，把 m/6 个奇数绿色象素数据 OG1、OG2、OG3…、OG<sub>m/6</sub> (原文有错) 移位到第三总线 DB3，把 m/6 个奇数蓝色象素数据 OB1、OB2、OB3、… OB<sub>m/6</sub> 移位到第四总线 DB4，把 m/6 个偶数红色象素数据 ER1、ER2、ER3… ER<sub>m/6</sub> 移位到第五总线 DB5，把 m/6 个偶数绿色象素数据 EG1、EG2、EG3…EG<sub>m/6</sub> 移位到第六总线 DB6 而把这些信号发送到数据驱动器 80 中。

而且，定时控制器 70 通过第一总线向数据驱动器 80 发送延迟 (delay) 一个通道的 m/6 个偶数蓝色象素数据 EB1、EB2、EB3…、EB<sub>m/6</sub> 和一个空白数据 BK。通过这种方式，定时控制器 70 在数据使能 (enable) 周期内，通过第一到第六总线 DB1-DB6 向数据驱动器 80 发送移位一个通道的一个空白数据 BK 和 m-1 个有效象素数据 R、G、B。而且，定时控制器 70 进一步按照后序的使能周期继续发送移位一个通道的最后一个有效象素数据 D<sub>m/6</sub>。

因此，数据驱动器 80 输入经移位一个通道的一个空白数据 BK 和 m 个有效象素数据 R、G、B。而且，数据驱动器 80 把输入的移位一个通道的 m 个有效象素数据 R、G、B 转换成向第 2 到第 (m+1) 数据线 DL<sub>2</sub>-DL<sub>m+2</sub> 发送的模拟象素信号，同时把一个空白数据 BK 转换成向第一条数据线 DL<sub>1</sub> 发送的模拟空白信号。

同样，通过定时控制器 70 中的两个水平周期可以把第一或最后一个象素数据的空白数据与 m 个有效象素数据一起发送。而且数据驱动器 80 把 m 个有效象素数据和一个空白数据转换成列反转系统的象素信号和空白信号，并将这些信号发送到液晶板 52 中。因此，可用垂直双点反转系统来驱动液晶板 52。

另一方面，在本发明的实施例中，所解释的仅仅是通过水平线或是通过两条水平线把液晶显示盒交替地连接到彼此不同的相邻数据线上的情况，然而，也可以通过三条水平线或多条水平线把液晶盒交替地相互连接。

如上所述，按照本发明所述的液晶显示器具有通过 i (i 为正数) 条水平线交替连接到与之相邻的不同数据线上的液晶盒，所述液晶盒沿数据线设置成

曲折形。此外，按照本发明所述的液晶显示器，其所提供的象素信号的极性由列反转系统确定，所以可以用  $i$  点反转系统来驱动液晶盒。而且，按照本发明所述的液晶显示器，其在每  $i$  个水平周期内同时发出  $m$  个有效象素信号和作为第一或最后一个象素数据的空白信号，从而可将正确的象素信号传送到沿曲折线布置的液晶盒中。

最后，按照本发明的液晶显示器，与  $i$  点反转系统相比，不仅明显地降低了能耗而且提高了图象质量，这是因为它可在列反转系统的能耗下，用  $i$  点反转系统驱动。

尽管以上通过附图中所示的实施例对本发明进行了说明，但是很显然，对于熟悉本领域的技术人员来说，本发明并不限于这些实施例，而是可以在不脱离本发明构思的情况下做出各种改进和变型。因此，本发明的范围将由所附权利要求及其等同物确定。

图 1

|   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|

| + | + | + | + | + | + | + | + | + |

| - | - | - | - | - | - | - | - | - |

| + | + | + | + | + | + | + | + | + |

| - | - | - | - | - | - | - | - | - |

| + | + | + | + | + | + | + | + | + |

| - | - | - | - | - | - | - | - | - |

| + | + | + | + | + | + | + | + | + |

| - | - | - | - | - | - | - | - | - |

图 2A

|   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - | - |

| + | + | + | + | + | + | + | + | + |

| - | - | - | - | - | - | - | - | - |

| + | + | + | + | + | + | + | + | + |

| - | - | - | - | - | - | - | - | - |

| + | + | + | + | + | + | + | + | + |

| - | - | - | - | - | - | - | - | - |

| + | + | + | + | + | + | + | + | + |

图 2B

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| + | - | + | - | + | - | + | - |

| + | - | + | - | + | - | + | - |

| + | - | + | - | + | - | + | - |

| + | - | + | - | + | - | + | - |

| + | - | + | - | + | - | + | - |

| + | - | + | - | + | - | + | - |

| + | - | + | - | + | - | + | - |

| + | - | + | - | + | - | + | - |

图 3A

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| - | + | - | + | - | + | - | + |

| - | + | - | + | - | + | - | + |

| - | + | - | + | - | + | - | + |

| - | + | - | + | - | + | - | + |

| - | + | - | + | - | + | - | + |

| - | + | - | + | - | + | - | + |

| - | + | - | + | - | + | - | + |

| - | + | - | + | - | + | - | + |

图 3B

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| + | - | + | - | + | - | + | - |

| - | + | - | + | - | + | - | + |

| + | - | + | - | + | - | + | - |

| - | + | - | + | - | + | - | + |

| + | - | + | - | + | - | + | - |

| - | + | - | + | - | + | - | + |

| + | - | + | - | + | - | + | - |

| - | + | - | + | - | + | - | + |

图 4A

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| - | + | - | + | - | + | - | + |

| + | - | + | - | + | - | + | - |

| - | + | - | + | - | + | - | + |

| + | - | + | - | + | - | + | - |

| - | + | - | + | - | + | - | + |

| + | - | + | - | + | - | + | - |

| - | + | - | + | - | + | - | + |

| + | - | + | - | + | - | + | - |

图 4B

图 5

图 6

16

图 7

图 8

图 9A

图 9B

SSP

图 10A

SSP

图 10B

图 11

图 12

图 13A

图 13B

图 14

|                |                                                                                                                                                                       |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">CN100429691C</a>                                                                                                                                          | 公开(公告)日 | 2008-10-29 |

| 申请号            | CN02157817.6                                                                                                                                                          | 申请日     | 2002-12-19 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | LG. 菲利浦LCD株式会社                                                                                                                                                        |         |            |

| 当前申请(专利权)人(译)  | 乐金显示有限公司                                                                                                                                                              |         |            |

| [标]发明人         | 尹相昌<br>宋鸿声                                                                                                                                                            |         |            |

| 发明人            | 尹相昌<br>宋鸿声                                                                                                                                                            |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G02F1/1362 G09G3/20                                                                                                                                |         |            |

| CPC分类号         | G09G2320/0247 G09G2310/065 G09G3/3688 G09G2310/027 G09G3/3607 G09G2330/021 G09G2320/0209 G02F1/136286 G09G2310/0297 G09G3/3614 G09G2310/0275 G09G3/3648 G09G2300/0426 |         |            |

| 代理人(译)         | 徐金国<br>陈红                                                                                                                                                             |         |            |

| 审查员(译)         | 王超                                                                                                                                                                    |         |            |

| 优先权            | 1020010081433 2001-12-19 KR<br>1020020037740 2002-06-29 KR                                                                                                            |         |            |

| 其他公开文献         | <a href="#">CN1427391A</a>                                                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                                                                                        |         |            |

#### 摘要(译)

本发明涉及液晶显示器，包括液晶显示板，其上设有由n条选通线和m+1条数据线交叉限定的以n行乘以m列的矩阵形式排列的液晶盒，其中，n，m为大于1的正整数，而且液晶盒中的薄膜晶体管按每i行交替一次的方式交替地连接到左右相邻的数据线其中之一上，其中i为大于1的正整数；栅极驱动器，其用于驱动选通线；数据驱动器，用于驱动数据线并且包括多路复用器阵列和数模转换器阵列，多路复用器阵列用于确定输入象素数据的输出通道并且根据极性每i行反转一次的控制信号确定输入的象素数据的输出通道并且向输出通道其中之一添加空白数据，数模转换器阵列把象素数据和空白数据转换成象素信号和空白信号，其极性按照数据线和帧进行反转。