## [12] 发明专利说明书

[21] ZL 专利号 01124568.9

[45] 授权公告日 2005 年 1 月 19 日

[11] 授权公告号 CN 1185530C

[22] 申请日 2001.8.10 [21] 申请号 01124568.9

[30] 优先权

[32] 2000. 8. 10 [33] JP [31] 242170/2000

[71] 专利权人 索尼株式会社

地址 日本东京

[72] 发明人 桥本诚 佐藤拓生

审查员 焦丽宁

[74] 专利代理机构 中国国际贸易促进委员会专利

商标事务所

代理人 王永刚

权利要求书 5 页 说明书 10 页 附图 7 页

[54] 发明名称 薄膜半导体器件与液晶显示单元及

其制作方法

[57] 摘要

薄膜半导体器件包括多个彼此交叉的信号和栅极互连。置于交叉点处的像素至少有像素电极、薄膜晶体管和为薄膜晶体管遮光的光屏蔽带。光屏蔽带由第一导电层制成，它至少有一部分用作栅极互连。栅极由不同于第一导电层的第二导电层制成。用作栅极互连的第一导电层经接触孔与每个像素区中构成栅极的第二导电层电连接。这样就改善了用作有源矩阵液晶显示单元驱动衬底的薄膜半导体器件的像素孔径率。

1. 一种薄膜半导体器件，包括：

多个信号互连和与所述信号互连交叉的多个栅极互连，以及置于所述信号和栅极互连交叉点处的像素，所述信号和栅极互连以及所述像素都设置在绝缘衬底上；

其中每个所述像素至少包含像素电极、驱动所述像素电极的薄膜晶体管、以及为所述薄膜晶体管遮挡外部光的光屏蔽带；以及

所述薄膜晶体管的源极与所述信号互连之一相连，所述薄膜晶体管的漏极与所述像素电极相连，而所述薄膜晶体管的栅极与所述栅极互连之一相连；

其特征在于：

所述光屏蔽带由第一导电层制成，且所述光屏蔽带的至少一部分被用作所述栅极互连；

所述栅极是由不同于所述第一导电层的第二导电层制成的；以及

在每个像素区中，用作所述栅极互连的所述第一导电层与构成所述栅极的所述第二导电层电连接。

2. 权利要求 1 的薄膜半导体器件，其特征在于，构成所述栅极的所述第二导电层在每个像素区中都是彼此隔开的，所述第二导电层的每个隔开的部分都与每个像素区中用作所述栅极互连的所述第一导电层电连接。

3. 权利要求 1 的薄膜半导体器件，其特征在于，构成所述栅极互连的所述第一导电层在每个像素区中都是彼此隔开的，所述第一导电层的每个隔开的部分都与每个像素区中构成所述栅极的所述第二导电层电连接。

4. 权利要求 1 的薄膜半导体器件，其特征在于，所述光屏蔽带是由从上面和下面遮挡所述薄膜晶体管的两个导电层组成的，所述两个导电层之一用作所述栅极互连的所述第一导电层。

5. 权利要求 1 的薄膜半导体器件，其特征在于，所述光屏蔽带

是由从上面或下面遮挡所述薄膜晶体管的单个导电层组成的，所述单个导电层用作所述栅极互连的所述第一导电层。

6. 权利要求 1 的薄膜半导体器件，其特征在于，每个所述像素包含辅助电容，它是由电介质夹于一对上、下电极之间而成的，以保存经所述薄膜晶体管由所述信号互连写入所述像素电极的信号电荷；

所述这对上、下电极之一是由构成所述栅极的同一所述第二导电层制成的。

7. 一种液晶显示单元，包括：

一对彼此相连的衬底，其间保持规定的间隙，在所述间隙中保持液晶；

其中一个衬底具有多个信号互连和与所述信号互连交叉的多个栅极互连以及置于所述信号与栅极互连的交叉点处的像素，而另一个衬底具有对着各像素的电极；

每个所述像素至少包含像素电极、驱动所述像素电极的薄膜晶体管、以及为所述薄膜晶体管遮挡外部光的光屏蔽带；以及

所述薄膜晶体管的源极与所述信号互连之一相连，所述薄膜晶体管的漏极与所述像素电极相连，而所述薄膜晶体管的栅极与所述栅极互连之一相连；

其特征在于：

所述光屏蔽带由第一导电层制成，且所述光屏蔽带的至少一部分被用作所述栅极互连；

所述栅极是由不同于所述第一导电层的第二导电层制成的；

在每个像素区中，用作所述栅极互连的所述第一导电层与构成所述栅极的所述第二导电层电连接。

8. 权利要求 7 的液晶显示单元，其特征在于，构成所述栅极的所述第二导电层在每个像素区中都是彼此隔开的，所述第二导电层的每个隔开的部分都与每个像素区中用作所述栅极互连的所述第一导电层电连接。

9. 权利要求 7 的液晶显示单元，其特征在于，构成所述栅极互

连的所述第一导电层在每个像素区中都是彼此隔开的，所述第一导电层的每个隔开的部分都与每个像素区中构成所述栅极的所述第二导电层电连接。

10. 权利要求 7 的液晶显示单元，其特征在于，所述光屏蔽带是由从上面和下面遮挡所述薄膜晶体管的两个导电层组成的，所述两个导电层之一用作所述栅极互连的所述第一导电层。

11. 权利要求 7 的液晶显示单元，其特征在于，所述光屏蔽带是由从上面或下面遮挡所述薄膜晶体管的单个导电层组成的，所述单个导电层用作所述栅极互连的所述第一导电层。

12. 权利要求 7 的液晶显示单元，其特征在于，所述每个像素包含辅助电容，它是由电介质夹于一对上、下电极之间而成的，以保存经所述薄膜晶体管由所述信号互连写入所述像素电极的信号电荷；以及

所述这对上、下电极之一是由构成所述栅极的同一所述第二导电层制成的。

13. 一种制作薄膜半导体器件的方法，所述半导体器件包括：多个信号互连和与所述信号互连交叉的多个栅极互连，以及置于所述信号和栅极互连交叉点处的像素，所述信号和栅极互连以及所述像素都设置在绝缘衬底上；其中每个所述像素至少包含像素电极、驱动所述像素电极的薄膜晶体管、以及为所述薄膜晶体管遮挡外部光的光屏蔽带；所述薄膜晶体管的源极与所述信号互连之一相连，所述薄膜晶体管的漏极与所述像素电极相连，而所述薄膜晶体管的栅极与所述栅极互连之一相连；

其特征在于：

所述光屏蔽带由第一导电层制成，且所述光屏蔽带的至少一部分被用作所述栅极互连；

所述栅极是由不同于所述第一导电层的第二导电层制成的；以及

在每个像素区中，用作所述栅极互连的所述第一导电层与构成所述栅极的所述第二导电层电连接。

14. 权利要求 13 的制作薄膜半导体器件的方法，其特征在于，构成所述栅极的所述第二导电层在每个像素区中都是彼此隔开的，所述第二导电层的每个隔开的部分都与每个像素区中用作所述栅极互连的所述第一导电层电连接。

15. 权利要求 13 的制作薄膜半导体器件的方法，其特征在于，构成所述栅极互连的所述第一导电层在每个像素区中都是彼此隔开的，所述第一导电层的每个隔开的部分都与每个像素区中构成所述栅极的所述第二导电层电连接。

16. 权利要求 13 的制作薄膜半导体器件的方法，其特征在于，所述光屏蔽带是由从上面和下面遮挡所述薄膜晶体管的两个导电层组成的，所述两个导电层之一用作所述栅极互连的所述第一导电层。

17. 权利要求 13 的制作薄膜半导体器件的方法，其特征在于，所述光屏蔽带是由从上面或下面遮挡所述薄膜晶体管的单个导电层组成的，所述单个导电层用作所述栅极互连的所述第一导电层。

18. 权利要求 13 的制作薄膜半导体器件的方法，其特征在于，每个所述像素包含辅助电容，它是由电介质夹于一对上、下电极之间而成的，以保存经所述薄膜晶体管由所述信号互连写入所述像素电极的信号电荷；以及

所述这对上、下电极之一是由构成所述栅极的同一所述第二导电层制成的。

19. 一种制作液晶显示单元的方法，所述液晶显示单元包括：一对彼此相连的衬底，其间保持规定的间隙，和置于所述间隙中的液晶；其中一个衬底具有多个信号互连和与所述信号互连交叉的多个栅极互连和置于所述信号与栅极互连的交叉点处的像素，而另一个衬底具有对着各像素的电极；每个所述像素至少包含像素电极、驱动所述像素电极的薄膜晶体管、以及为所述薄膜晶体管遮挡外部光的光屏蔽带；所述薄膜晶体管的源极与所述信号互连之一相连，所述薄膜晶体管的漏极与所述像素电极相连，而所述薄膜晶体管的栅极与所述栅极互连之一相连；

其特征在于：

所述光屏蔽带由第一导电层制成，且所述光屏蔽带的至少一部分被用作所述栅极互连；

所述栅极是由不同于所述第一导电层的第二导电层制成的；以及

在每个像素区中，用作所述栅极互连的所述第一导电层与构成所述栅极的所述第二导电层电连接。

20. 权利要求 19 的制作液晶显示单元的方法，其特征在于，构成所述栅极的所述第二导电层在每个像素区中都是彼此隔开的，所述第二导电层的每个隔开的部分都与每个像素区中用作所述栅极互连的所述第一导电层电连接。

21. 权利要求 19 的制作液晶显示单元的方法，其特征在于，构成所述栅极互连的所述第一导电层在每个像素区中都是彼此隔开的，所述第一导电层的每个隔开的部分都与每个像素区中构成所述栅极的所述第二导电层电连接。

22. 权利要求 19 的制作液晶显示单元的方法，其特征在于，所述光屏蔽带是由从上面和下面遮挡所述薄膜晶体管的两个导电层组成的，所述两个导电层之一用作所述栅极互连的所述第一导电层。

23. 权利要求 19 的制作液晶显示单元的方法，其特征在于，所述光屏蔽带是由从上面或下面遮挡所述薄膜晶体管的单个导电层组成的，所述单个导电层用作所述栅极互连的所述第一导电层。

24. 权利要求 19 的制作液晶显示单元的方法，其特征在于，所述每个像素包含辅助电容，它是由电介质夹于一对上、下电极之间而成的，以保存经所述薄膜晶体管由所述信号互连写入所述像素电极的信号电荷；以及

所述这对上、下电极之一是由构成所述栅极的同一所述第二导电层制成的。

## 薄膜半导体器件与液晶显示单元及其制作方法

### 技术领域

本发明涉及到薄膜半导体器件与液晶显示单元及其制作方法。尤其是，本发明关系到集成在半导体薄膜上的薄膜晶体管的栅极互连结构与光屏蔽结构。

### 背景技术

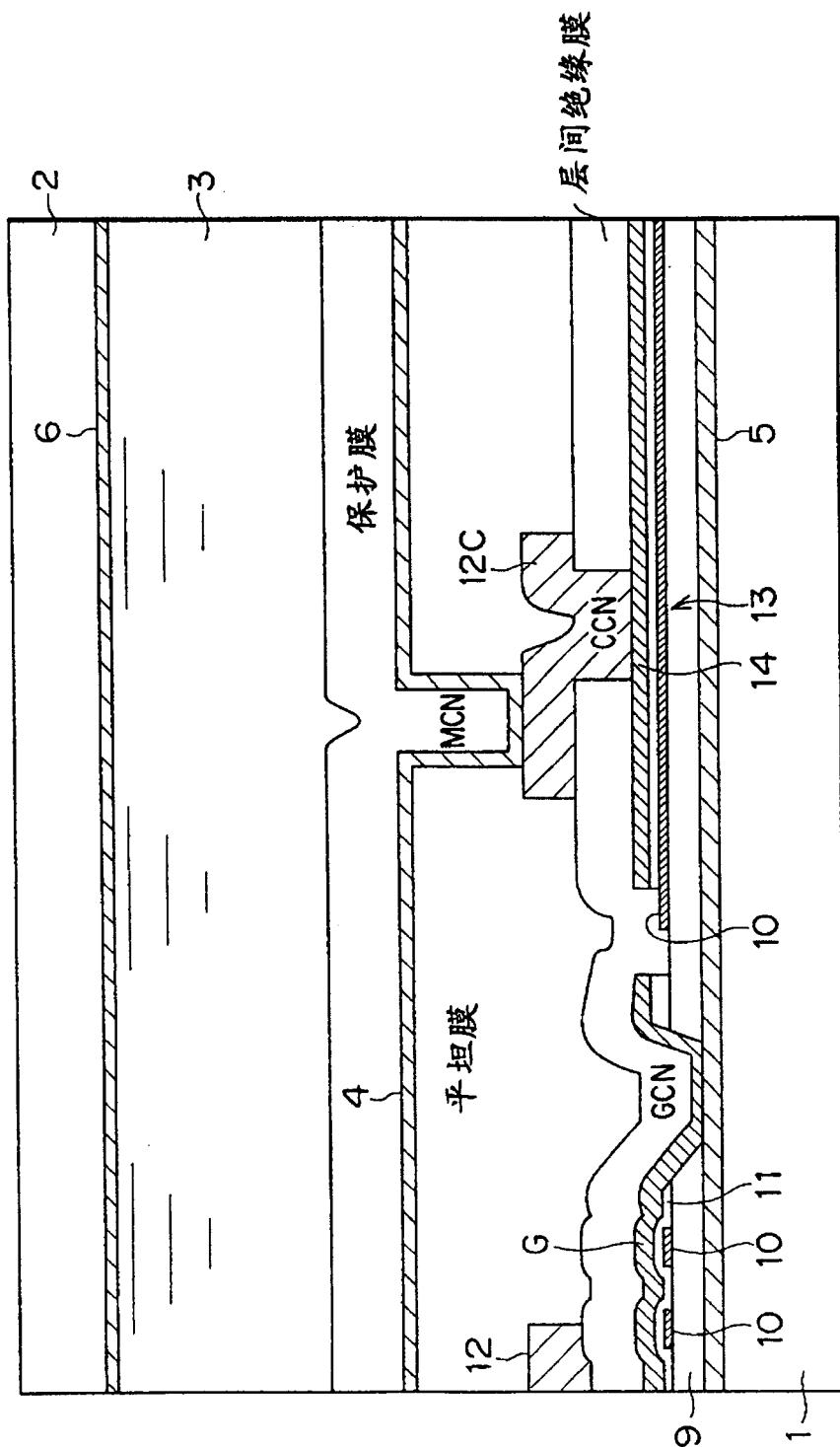

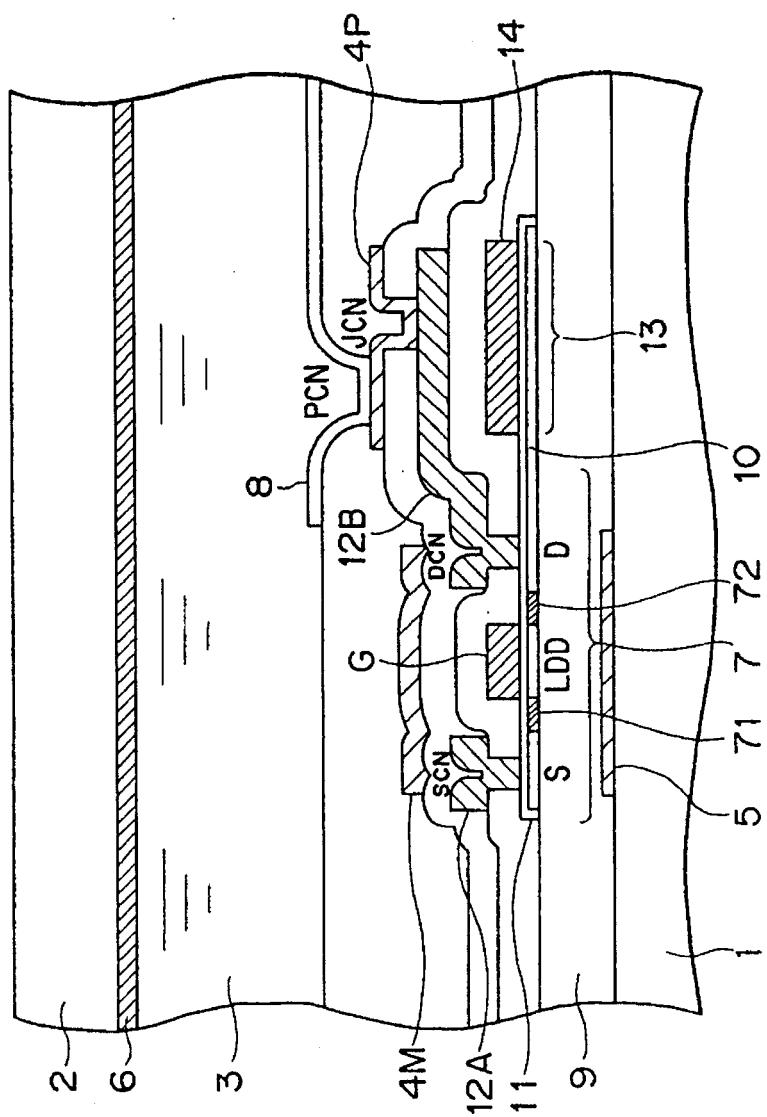

在其上集成有薄膜晶体管与像素电极的半导体薄膜被广泛地用作驱动液晶显示单元的衬底。尤其是，装在投影仪液晶显示单元中的薄膜半导体器件，具有遮挡投影仪液晶源强光的光屏蔽结构是很重要的。图 5 表示这样的液晶显示单元的一个实例。如图所示，液晶显示单元用薄膜晶体管来驱动每个像素电极 8。此薄膜晶体管典型地由高温多晶硅 TFT 构成；然而，也可由低温多晶硅 TFT 或非晶硅 TFT 构成。图中所示的液晶显示单元公开在，例如，日本专利公开 Hei 2000-131716 号中。如图所示，液晶显示单元包括带有作为像素晶体管的 TFT 7 的衬底 1（承载 TFT 的石英）和对衬底 2，液晶 3 夹于衬底 1 和对衬底 2 之间。对衬底 2 带有对电极 6。

参见图 5，在衬底 1 的上层部分有像素电极 8，下层部分带有 TFT（薄膜晶体管，此处为顶栅结构）。TFT 7 用作驱动像素电极 8 的开关元件。TFT 7 具有由第一层多晶硅制成的半导体薄膜 10 作为有源层。在半导体薄膜 10 上经  $\text{SiO}_2$  制成的栅绝缘膜制作栅极 G。栅极 G 由第二层多晶硅制成。在栅极的两边，TFT 7 具有源区 S 和漏区 D。LDD 区 71 和 72 分别制作在源区和漏区的端部。引出电极 12A 和 12B 分别与源区 S 和漏区 D 相连。每个引出电极 12A 和 12B 都是由铝基材料例如铝制成的。引出电极 12A 经接触孔 SCN 与 TFT 7 的源区 S 电连接，引出电极 12B 经接触孔 DCN 与 TFT 7 的漏区 D 电连接。

半导体薄膜 10 包含辅助电容（Cs）13。辅助电容（Cs）13 是将

构成栅绝缘膜 11 的例如  $\text{SiO}_2$  制成的介质膜置于构成 TFT 7 的半导体薄膜 10 的第一层多晶硅与构成栅极 G 的半导体薄膜 14 的第二层多晶硅之间而成的。

光屏蔽层 4M 和 4P 制作在带有像素电极 8 的上层部分与带有 TFT 7 的下层部分之间的中间层中。光屏蔽层 4M 和 4P 设在对着 TFT 7 的对衬底 2 侧，即在受光侧，因此，称为“上部光屏蔽层”。这就是说，此处的上部光屏蔽层是由遮光屏蔽层（mask shield layer）4M 和焊盘屏蔽层（pad shield layer）4P 构成的。借助于上面的两个光屏蔽层（遮光屏蔽层 4M 和焊盘屏蔽层 4P）以及与上部光屏蔽层重叠的引出电极 12A 和 12B（此处每个都是由铝制成的），整个像素区除了其开孔以外都被遮挡而免受来自对衬底 2 侧的光照。遮光屏蔽层 4M 和焊盘屏蔽层 4P 每个都是由导电材料制成的，例如，一种金属如钛。遮光屏蔽层 4M 沿像素的行方向（横向）为连续图形，它至少遮挡一部分外来的光。焊盘屏蔽层 4P 为对每个像素的分立图形，用作与像素电极 8 的接触。更具体地讲，像素电极 8 经接触孔 PCN 与焊盘屏蔽层 4P 相连。焊盘屏蔽层 4P 经接触孔 JCN 与引出电极 12B 相连。引出电极 12B，如上所述，经接触孔 DCN 与 TFT 7 的漏区 D 相连。由于设置了遮光屏蔽层 4M 和焊盘屏蔽层 4P 以及与屏蔽层 4M 和 4P 重叠的引出电极 12A 和 12B，整个像素区除了其开孔以外都被遮挡而免受来自对衬底侧的光照。

另一方面，在像素晶体管部分与对衬底 2 相反的一侧制作有光屏蔽层 5。这个光屏蔽层称为“下部光屏蔽层”。这样，至少遮挡了外面的光对像素晶体管 7 的源和漏区的端部以及在源和漏端部形成的 LDD 区 71 和 72 的照射。一般说来，下部光屏蔽层 5 由难熔金属的硅化物如硅化钨制成，厚 200 nm。

为满足当前对高亮度投影仪的强烈要求，已要求改进图 5 所示类型液晶板的透光性。与此同时，要求图 5 所示液晶板即使在投影仪光源的大量光照下也能保持高质量的图象。为使图 5 所示类型的液晶板满足这些市场要求，已采用方法（1）用增大像素的孔径率来改善透光

性，以及方法（2）用增大辅助电容（Cs）面积来保持高质量的图象。然而，方法（1）和（2）实质上是互相矛盾的。即，如果增大辅助电容（Cs），像素孔径率减小。同时采用方法（1）和（2）的原因是基于这样一个事实，即，像素的布局是有余量的。然而，液晶投影仪高清晰度的发展趋势，很难实现使像素的布局有这样的余量，因而在相关技术的像素结构基础上，不可能达到较高的像素孔径率。

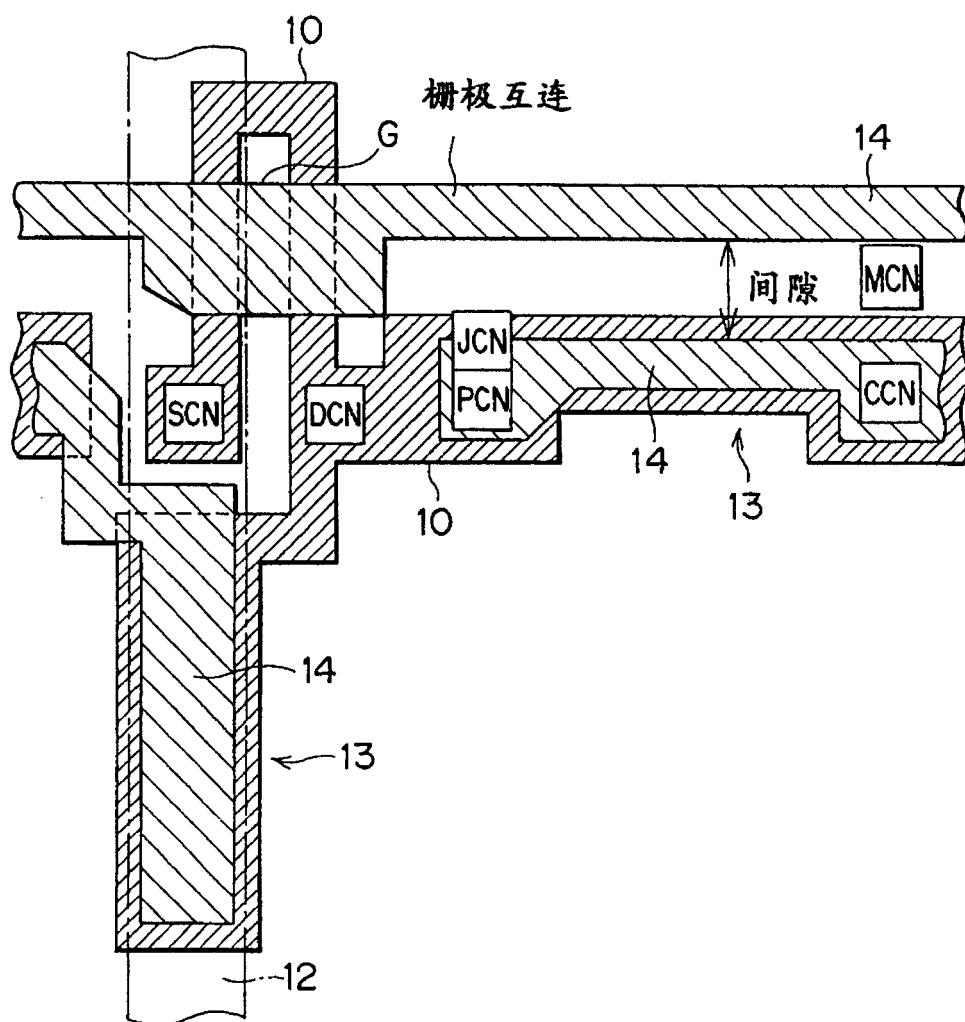

图 6 为图 5 所示现有技术液晶显示单元，特别是液晶显示单元一个像素区域的示意平面图。如图所示，液晶显示单元包括多个信号互连 12 以及与信号互连 12 交叉的栅极互连。像素则置于沿列向（纵向）伸展的信号互连与沿行向（横向）伸展的栅极互连的交叉点处。如上所述，像素包含像素电极、驱动像素电极的薄膜晶体管、以及为薄膜晶体管遮挡外部光的光屏蔽带（光屏蔽层）。薄膜晶体管具有作为有源层的半导体薄膜 10。半导体薄膜 10 的源区经接触孔 SCN 与信号互连 12 相连；其漏区经接触孔 DCN 与像素电极（未示出）相连；其栅极 G 由栅极互连的一部分构成。此外，栅极互连还由不同于半导体薄膜 10（由第一层多晶硅制成）的半导体薄膜 14（由第二层多晶硅制成）制成。像素也包含辅助电容 13。辅助电容具有这样的叠层结构，与栅极绝缘膜相同的介电薄膜夹于半导体薄膜 10（第一层多晶硅）和半导体薄膜 14（第二层多晶硅）之间。构成辅助电容 13 下电极的半导体薄膜 10 与薄膜晶体管的漏极呈相同的电位，而构成辅助电容 13 上电极的半导体薄膜 14 经接触孔 CCN 与铝制的上部引出电极（未示出）相连。引出电极还经接触孔 MCN 与上部的遮挡屏蔽层相连。像素电极（未示出）经接触孔 PCN、JCN 和 DCN 与薄膜晶体管的漏区 D 相连。如图所示，栅极 G 由半导体薄膜 14（第二层多晶硅）制成，它沿横向伸展形成栅极互连。半导体薄膜 14 的一部分取作辅助电容 13 的上电极，其电位不同于栅极互连。因此，虽然栅极互连与辅助电容 13 的上电极都是由同一大气薄膜 14 制成的，但要求它们彼此间是电绝缘的，在其间设有规定的间隙（GAP）。这就是说，在这种像素结构中，由于栅极互连与辅助电容 13 的上电极被安排成彼此平行的，其间

必须提供有间隙（GAP），其结果使像素的孔径率减小。为改善像素的孔径率，这是容易理解的，将栅极互连与辅助电容 13 的上电极分层制作是有效的；然而，图 6 所示现有技术的结构对于考察栅极互连和辅助电容 13 上电极的这种布局是无效的。

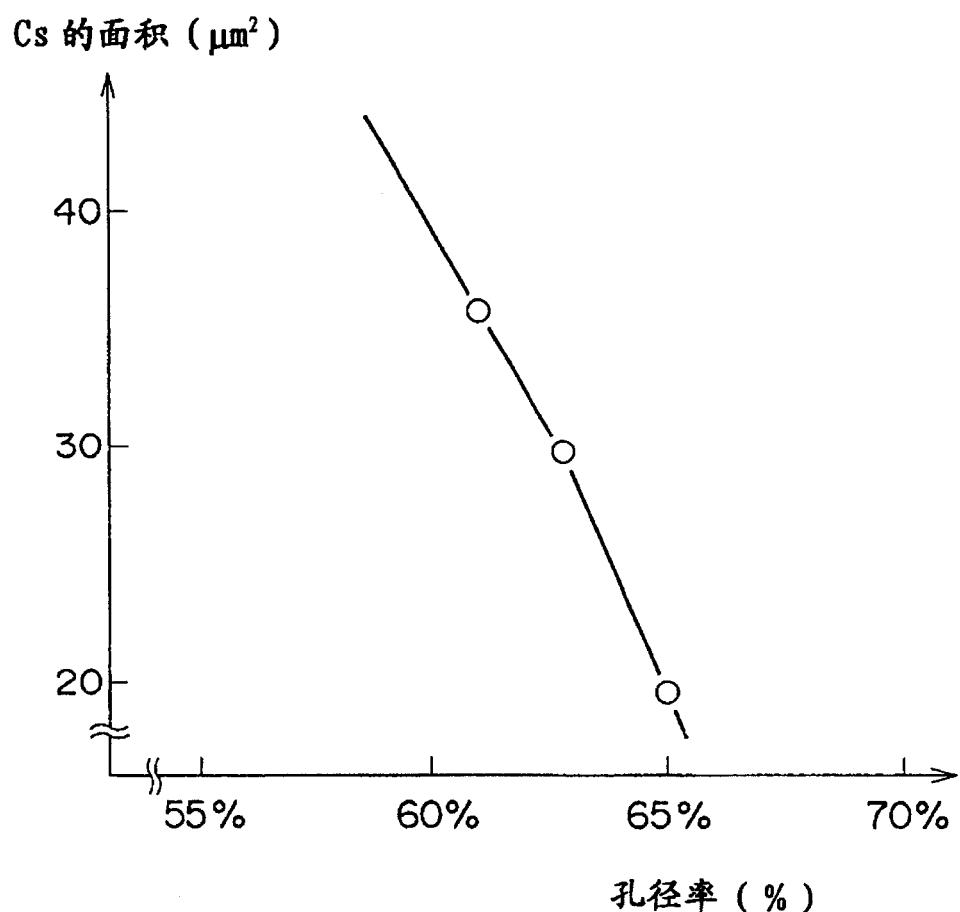

图 7 表示在图 6 所示现有技术结构的像素孔径率与辅助电容（Cs）面积之间的关系。随着像素孔径率的增大，辅助电容面积则被牺牲而大为减小。这是由于栅极互连和辅助电容上电极（辅助电容互连）是由同一层制成的且彼此平行。栅极互连与辅助电容互连这样的平行布局，使得在保证辅助电容面积时很难改善孔径率。

#### 发明内容

本发明的一个目的是改善用作有源矩阵型液晶显示单元驱动衬底的薄膜半导体器件的像素孔径率。

为达到上述目的，按照本发明，这里配备的半导体薄膜器件包括：多个信号互连和多个与信号互连交叉的栅极互连、以及置于信号与栅极互连交叉点处的像素，信号与栅极互连以及像素都置于一绝缘衬底上；其中每个像素都至少包含一个像素电极、一个驱动像素电极的薄膜晶体管、以及为薄膜晶体管遮挡外部光的光屏蔽带；薄膜晶体管的源极与信号互连之一相连，薄膜晶体管的漏极与像素电极相连，而薄膜晶体管的栅极与栅极互连之一相连。这种薄膜半导体器件的特点是，光屏蔽带由第一导电层制成，至少光屏蔽带的一部分被用作栅极互连；栅极是由不同于第一导电层的第二导电层制成的；用作栅极互连的第一导电层与每个像素区中构成栅极的第二导电层是电连接的。

优选地，每个像素区构成栅极的第二导电层是彼此隔开的，第二导电层每个隔开的部分都与每个像素区中用作栅极互连的第一导电层电连接。

优选地，每个像素区构成栅极互连的第一导电层是彼此隔开的，第一导电层每个隔开的部分都与每个像素区中构成栅极的第二导电层电连接。

优选地，光屏蔽带是由两个导电层组成的，以从上面和下面遮挡

薄膜晶体管，两个导电层之一被用作栅极互连的第一导电层。

优选地，光屏蔽带是由单个导电层组成的，以从上面或下面遮挡薄膜晶体管，单个导电层被用作栅极互连的第一导电层。

优选地，每个像素都包含辅助电容，它是由夹在一对上、下电极之间的电介质构成的，以保存由信号互连经薄膜晶体管写入像素电极的信号电荷；并且这对上、下电极之一就是由构成栅极的同一层第二导电层制作的。

采取这些结构，为薄膜晶体管遮挡外部光的光屏蔽带由第一导电层构成，且至少部分光屏蔽带被用作栅极互连。另一方面，栅极是由不同于第一导电层的第二导电层构成的，并与每个像素区中的光屏蔽带电连接。由于使用上述的光屏蔽层作为栅极互连，因而不需要用同一层制作栅极互连和辅助电容互连。例如，用下部光屏蔽层作为栅极互连，由构成栅极的同一层制作的辅助电容互连就可与栅极互连重叠。由于无须保证由同一层制成的栅极互连与辅助电容互连之间的间隙，像素孔径率可相应得到改善。

#### 附图说明

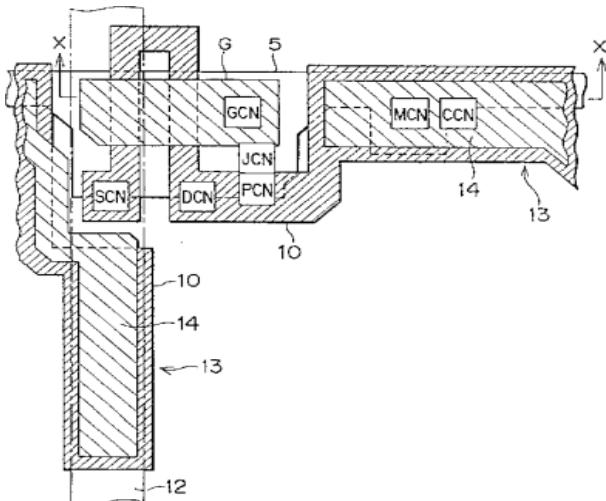

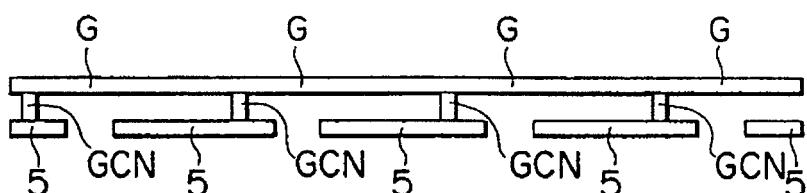

图 1 为本发明液晶显示单元的示意平面图；

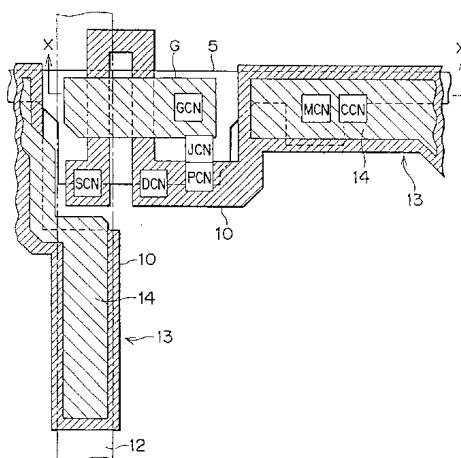

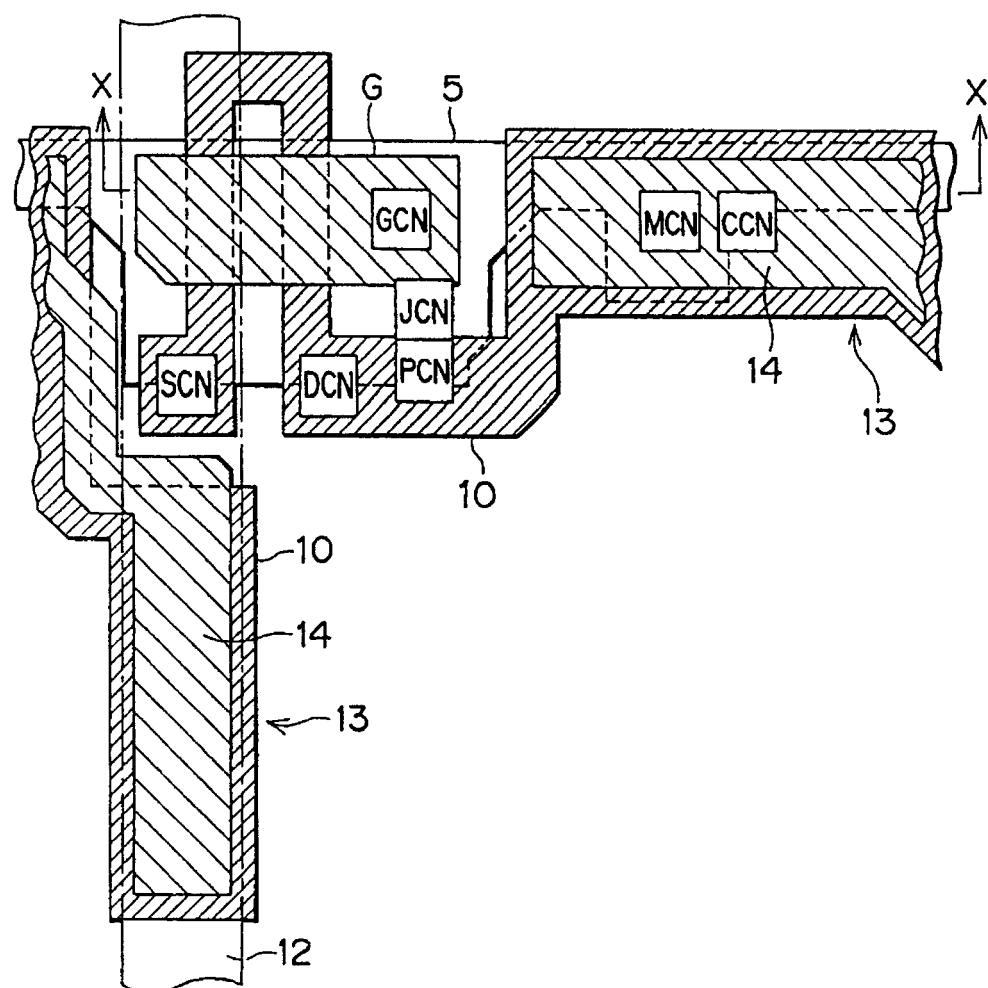

图 2 为图 1 所示液晶显示单元的示意平面图；

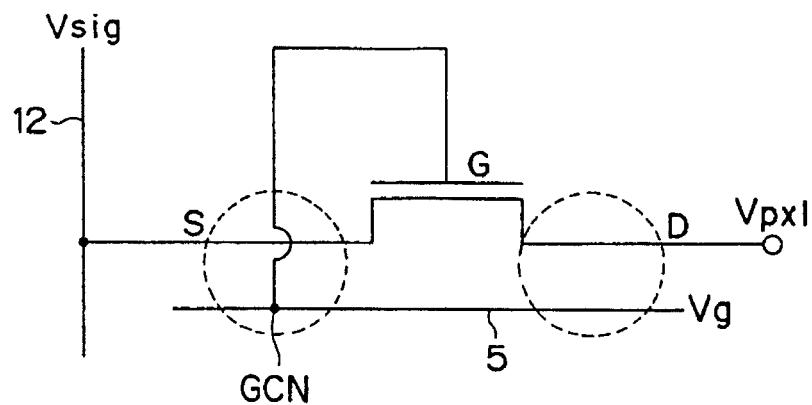

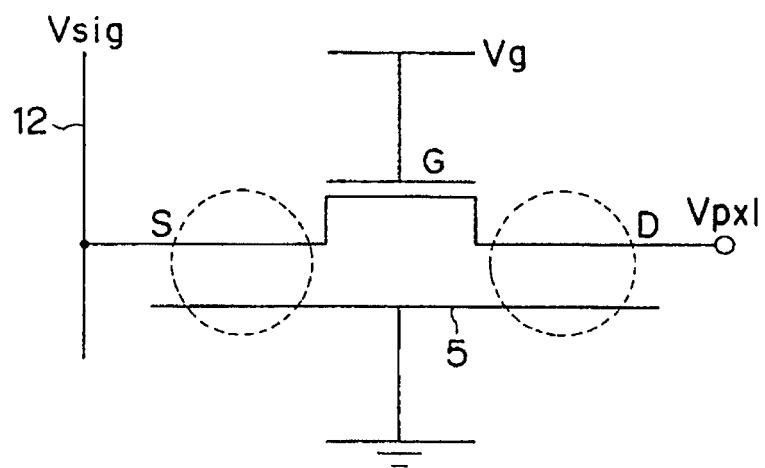

图 3A 和 3B 每个都是一个像素区域的等效电路图，其中图 3A 表示图 1 和 2 所示液晶显示单元的电路，图 3B 表示参考实例的电路；

图 4A~4D 为一组示意图，每个都表示在本发明的液晶显示单元中，像素电极与光屏蔽层之间的电连接关系；

图 5 是表示现有技术的液晶显示单元一个实例的剖面图；

图 6 为图 5 所示现有技术的液晶显示单元的平面图；

图 7 是表示像素孔径率与辅助电容面积的关系曲线。

#### 具体实施方式

下面将参照附图来详细描述本发明的优选实施方案。图 1 为本发明液晶显示单元的一个实例，特别是液晶显示单元一个像素区的示意平面图。此图具体表示在液晶显示单元驱动衬底侧的薄膜半导体器件

的平面结构。此薄膜半导体器件包含，在绝缘衬底上的多个信号互连 12 以及与信号互连 12 交叉的多个栅极互连和置于信号与栅极互连的交叉点处的像素。应注意，在图中只示出了一个像素，它置于沿纵向伸展的一条信号互连 12 与沿横向伸展的一条栅极互连的交叉点处。每个像素至少包含一个像素电极（未示出）、一个驱动像素电极的薄膜晶体管、以及为薄膜晶体管遮挡外部光的光屏蔽层（光屏蔽带）5。薄膜晶体管包含制作在下部光屏蔽层 5 上作为器件区的半导体薄膜 10（由第一层多晶硅制成）。薄膜晶体管的源极经接触孔 SCN 与信号互连 12 相连。薄膜晶体管的漏极经接触孔 DCN、JCN 和 PCN 与像素电极（未示出）相连。薄膜晶体管的栅极 G 与栅极互连相连。注意，栅极 G 是由置于半导体薄膜 10（由第一层多晶硅制成）上面的另一个半导体薄膜 14（由第二层多晶硅制成）制成的。

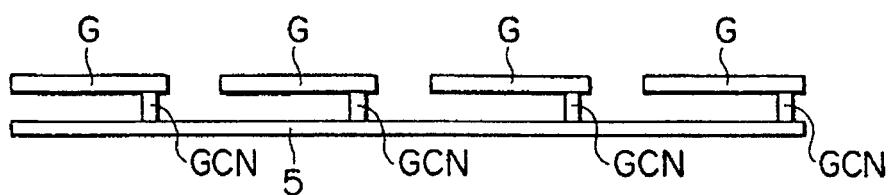

按照本发明的特点，光屏蔽层 5 是由第一导电层制成的，光屏蔽层 5 至少有一部分被用作栅极互连；栅极 G 是由不同于第一导电层的第二导电层（即，重掺杂的半导体薄膜 14）制成的；第一导电层用作栅极互连，而构成栅极 G 的第二导电层（半导体薄膜 14）经每个像素区的接触孔 GCN 彼此电连接。总之，按照本发明构成栅极 G 的层不同于构成栅极互连的层，栅极 G 和栅极互连二者都经每个像素区中的接触孔 GCN 彼此形成三维连接。作为本发明的另一个特点，每个像素构成栅极 G 的第二导电层（半导体薄膜 14）都是彼此隔开的，第二导电层每个隔开的部分（栅极 G）都与每个像素区中用作栅极互连的第一导电层（光屏蔽层 5）电连接。

除了上述的薄膜晶体管和像素电极外，像素还包含辅助电容 13。辅助电容 13 用来保存由信号互连 12 经薄膜晶体管写入像素电极的信号电荷，以保持图象质量。辅助电容 13 具有叠层结构，是将电介质夹于一对上、下电极之间而成的。辅助电容 13 的上电极是由构成栅极 G 的同一层第二导电层（半导体薄膜 14）制成的。辅助电容 13 的下电极是由同一层半导体薄膜 10 制成的。辅助电容 13 的电介质是由夹于一对上、下电极 14 和 10 之间的同一栅绝缘膜构成的。从图中显然可

以看到，辅助电容 13 可与构成栅极互连的光屏蔽层 5 重叠。结果，按照本发明的结构，像素孔径率可比相关技术的结构大为增加。由不同的层，即光屏蔽层 5 来代替构成栅极 G 的那部分栅极互连，可实现本发明的这样一种结构。更具体地，栅极互连由例如 WSi 制的下部光屏蔽层 5 制成，而栅极 G 由如相关技术结构的半导体薄膜 14（由第二层多晶硅制成）制成。栅极互连和栅极 G 经接触孔 GCN 彼此电连接。另一方面，辅助电容 13 的上电极由形成栅极的同一层半导体薄膜 14（由第二层多晶硅制成）构成。由于构成栅极互连的层不同于构成辅助电容 13 上电极（辅助电容互连）的层，辅助电容 13 可制作在构成栅极互连的光屏蔽层 5 上，因而大为改善像素的孔径率。

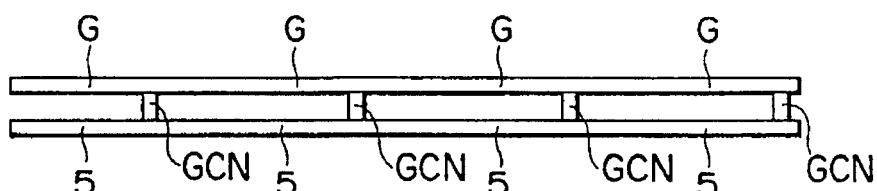

图 2 为沿图 1 X-X 方向所取的液晶显示单元结构的剖面图。参照此图，液晶显示单元包含一对保持一定间隙彼此相连的衬底 1 和 2，液晶 3 置于间隙中。如上所述，一个衬底 1 具有多个信号互连 12 以及与信号互连 12 交叉的多个栅极互连，像素置于信号与栅极互连间的交叉点处。另一个衬底（对衬底）2 有一个对着各像素的电极（对电极）6。

下部光屏蔽层 5 制作在下部衬底 1 的表面上，薄膜晶体管与辅助电容 13 也经绝缘膜 9 制作在其上。薄膜晶体管为顶栅结构，其栅极 G 经栅绝缘膜 11 置于双重结构的半导体薄膜 10 上。如上所述，每个像素区的栅极 G 是彼此隔开的，每个栅极 G 经接触孔 GCN 与用作栅极互连的光屏蔽层 5 电连接。另一方面，辅助电容 13 由下部半导体薄膜 10、上部半导体薄膜 14、以及夹于其间的栅绝缘膜 11 组成。由图可以明显地看到，辅助电容 13 的上电极和栅极 G 都由同一个半导体薄膜 14（由第二层多晶硅制成）制成。如上述配置的薄膜晶体管和辅助电容 13 盖以层间绝缘膜。信号互连 12 与引出电极 12C 制作在层间绝缘膜上。每个信号互连 12 与引出电极 12C 都是由铝制成的，其表面盖以平坦膜。上部光屏蔽层 4 制作在平坦膜上。这样，按照此实施方案，为薄膜晶体管遮挡外部光的光屏蔽带由两个导电层组成，以从上部和下部遮挡薄膜晶体管，而两个导电层之一用作栅极互连的第一导

电层。作为选择，光屏蔽带也可由单个导电层组成以从上部或下部遮挡薄膜晶体管，而此单个导电层被用作栅极互连的第一导电层。在此实施方案中，辅助电容 13 的上电极经接触孔 CCN 与引出电极 12C 电连接。引出电极 12C 还经接触孔 MCN 与上部光屏蔽层 4 电连接。由于这种连接，规定的电位施加至辅助电容 13 的上电极。上部屏蔽层 4 盖以保护膜，在其上制作像素电极（未示出）。

参照图 2 来描述本发明液晶显示单元的制作方法。液晶显示单元包含一对彼此相连的衬底 1 和 2，其间有规定的间隙，液晶 3 置于间隙中。为制作这样的液晶显示单元，在衬底 1 上制作多个信号互连 12 和多个与信号互连交叉的栅极互连，以及置于信号与栅极互连交叉点处的像素，在另一个衬底 2 上制作对着各像素的电极 6。在每个像素区中至少制作一个像素电极、一个驱动像素电极的薄膜晶体管、以及为薄膜晶体管遮挡外部光的光屏蔽带 5。薄膜晶体管的源极与信号互连 12 相连，其漏极与像素电极相连，其栅极 G 与栅极互连相连。对于这种情形，光屏蔽带 5 是由第一导电层制成的，且光屏蔽带至少有一部分用作栅极互连。栅极 G 是由不同于第一导电层的第二导电层 14 制成的。用作栅极互连的第一导电层经每个像素区中的接触孔 GCN 与构成栅极 G 的第二导电层 14 电连接。在此实施方案中，光屏蔽带由两个导电层组成，以从上部和下部遮挡薄膜晶体管，而其中一个光屏蔽带 5 用作栅极互连的第一导电层。在每个像素区中，辅助电容 13 是将栅极绝缘膜 11 作为电介质置于一对上、下电极（10, 14）之间制成的，以保存由信号互连 12 写入像素电极的信号电荷。这对上、下电极之一是由构成栅极 G 的同一层第二导电层 14 制成的。

图 3A 和 3B 都是示意图，每个都表示一个像素的等效电路，其中图 3A 表示本发明的液晶显示单元的电路，图 3B 表示参考实例的电路。在图 3B 所示的参考实例中下部屏蔽层 5 未作为栅极互连的一部分，且接为地电位。在这样的结构中，因金属光屏蔽层 5 而在 LDD 区产生寄生晶体管，如虚线的圆圈所示。由于光屏蔽层 5 的电位是固定的，即通常为地电位，以使寄生晶体管通常为关断的。为防止上述的不便，

不可能使 LDD 区的杂质浓度减小规定值以上。然而，随着增大光量的趋势，已要求将 LDD 区的杂质浓度减小至现有杂质浓度的 1/3，以改善图象质量。

在图 3A 所示的结构中，虽然像参考实例那样因金属光屏蔽层而产生寄生晶体管，光屏蔽层 5 的电位经接触孔 GCN 通常保持等于栅极电位值。因此，由虚线所圈的寄生晶体管的通/断完全与真实的薄膜晶体管同步。所以，可大为降低 LDD 区的杂质浓度，因而改善图象质量。此外，供给信号互连 12 的图象信号 Vsig 由薄膜晶体管 TFT 的源极 S 经漏区 D 写入像素电极。在图中，写入像素的电位由符号 Vpx1 表示，施加于薄膜晶体管栅极 G 的电位由符号 Vg 表示。

图 4A~4D 为一组示意图，每个都表示栅极 G 与用作栅极互连的光屏蔽层 5 的连接关系。图 4A 示意地表示图 1 所示实施方案的连接关系，其中每个像素区的像素电极 G 是彼此隔开的，而构成栅极互连的光屏蔽层 5 则伸展穿过各个像素。每个隔开的栅极 G 经相应的接触孔 GCN 与下部光屏蔽层 5 电连接。由金属薄层、半导体薄膜层等彼此重叠而成的多层结构产生了使衬底形变量增大的副作用。这对液晶显示板的组装有不利的影响。尤其是，已表明沿显示板的横向连续形成的由半导体薄膜（由第二层多晶硅制成）构成的栅极互连成了衬底形变的一大原因。与之对照，按照本发明，如图 4A 所示意性表示的，由第二层多晶硅构成的每个像素区的栅极 G 是彼此隔开的，这就使得衬底的形变量可以减小。而且，由于栅极 G 没有像相关技术结构那样被用作互连，栅极 G 的厚度也可以做得很薄。这就进一步有效地降低了衬底的形变量。

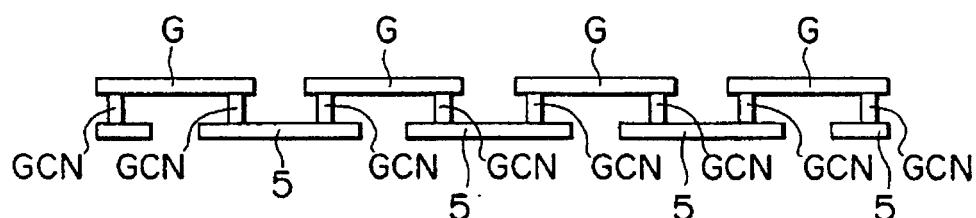

在图 4B 所示的连接关系中，不仅栅极 G 而且下部光屏蔽层 5 都构成栅极互连，对每个像素区它们都是彼此隔开的。隔开的栅极 G 和下部光屏蔽层 5 经每个像素的两个接触孔 GCN 彼此依次电连接。由于下部光屏蔽层 5 也是彼此隔开的，就可能进一步降低衬底的形变量。

在图 4C 所示的连接关系中，每个像素区的光屏蔽层 5 是彼此隔开的，但栅极 G 伸展穿过各个像素。在图 4D 所示的连接关系中每个

栅极 G 和下部光屏蔽层 5 都伸展穿过各个像素，栅极 G 和下部光屏蔽层 5 二者都经每个像素区的接触孔 GCN 彼此相连。由于这种结构，即便是上下两个导电层有一个断开了，另一个导电层也能保证导电，因而能防止发生失效。

如上所述，按照本发明，使用光屏蔽层作为栅极互连可改善像素孔径率。还可实现双栅结构，其中作为薄膜晶体管有源层的半导体薄膜从上面和下面置于用作栅极互连的光屏蔽层与栅极之间，因而增大了薄膜晶体管的设计余地。例如，双栅结构有效地降低了 LDD 区的杂质浓度，因而相应地降低了薄膜晶体管的漏光。而且，将每个像素区的栅极或用作栅极互连的光屏蔽层彼此隔开，能够抑制衬底的形变。

虽然用具体条件描述了本发明的优选实施方案，这样的描述只是为了进行说明，应知可做出各种更改与变动而没有背离下面权利要求的构思或范围。

图 1

图 2

图 3A

图 3B

图 4A

图 4B

图 4C

图 4D

图 5

图 6

图 7

|                |                                                                |         |            |

|----------------|----------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 薄膜半导体器件与液晶显示单元及其制作方法                                           |         |            |

| 公开(公告)号        | <a href="#">CN1185530C</a>                                     | 公开(公告)日 | 2005-01-19 |

| 申请号            | CN01124568.9                                                   | 申请日     | 2001-08-10 |

| [标]申请(专利权)人(译) | 索尼公司                                                           |         |            |

| 申请(专利权)人(译)    | 索尼株式会社                                                         |         |            |

| 当前申请(专利权)人(译)  | 索尼株式会社                                                         |         |            |

| [标]发明人         | 桥本诚<br>佐藤拓生                                                    |         |            |

| 发明人            | 桥本诚<br>佐藤拓生                                                    |         |            |

| IPC分类号         | G02F1/1345 G02F1/136 G02F1/1362 G02F1/1368 G09F9/30 H01L29/786 |         |            |

| CPC分类号         | G02F1/136213 G02F1/136209 G02F1/136286 G02F1/136227 G02F1/1368 |         |            |

| 代理人(译)         | 王永刚                                                            |         |            |

| 优先权            | 2000242170 2000-08-10 JP                                       |         |            |

| 其他公开文献         | <a href="#">CN1338658A</a>                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                 |         |            |

### 摘要(译)

薄膜半导体器件包括多个彼此交叉的信号和栅极互连。置于交叉点处的像素至少有像素电极、薄膜晶体管和为薄膜晶体管遮光的光屏蔽带。光屏蔽带由第一导电层制成，它至少有一部分用作栅极互连。栅极由不同于第一导电层的第二导电层制成。用作栅极互连的第一导电层经接触孔与每个像素区中构成栅极的第二导电层电连接。这样就改善了用作有源矩阵液晶显示单元驱动衬底的薄膜半导体器件的像素孔径率。